Apparatus used for debugging programmable chip and field programmable gate array chip

A chip and debugging host technology, applied in the field of hardware programmable, can solve the problems of high cost, difficulty in changing the circuit in seconds, and increase of product cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

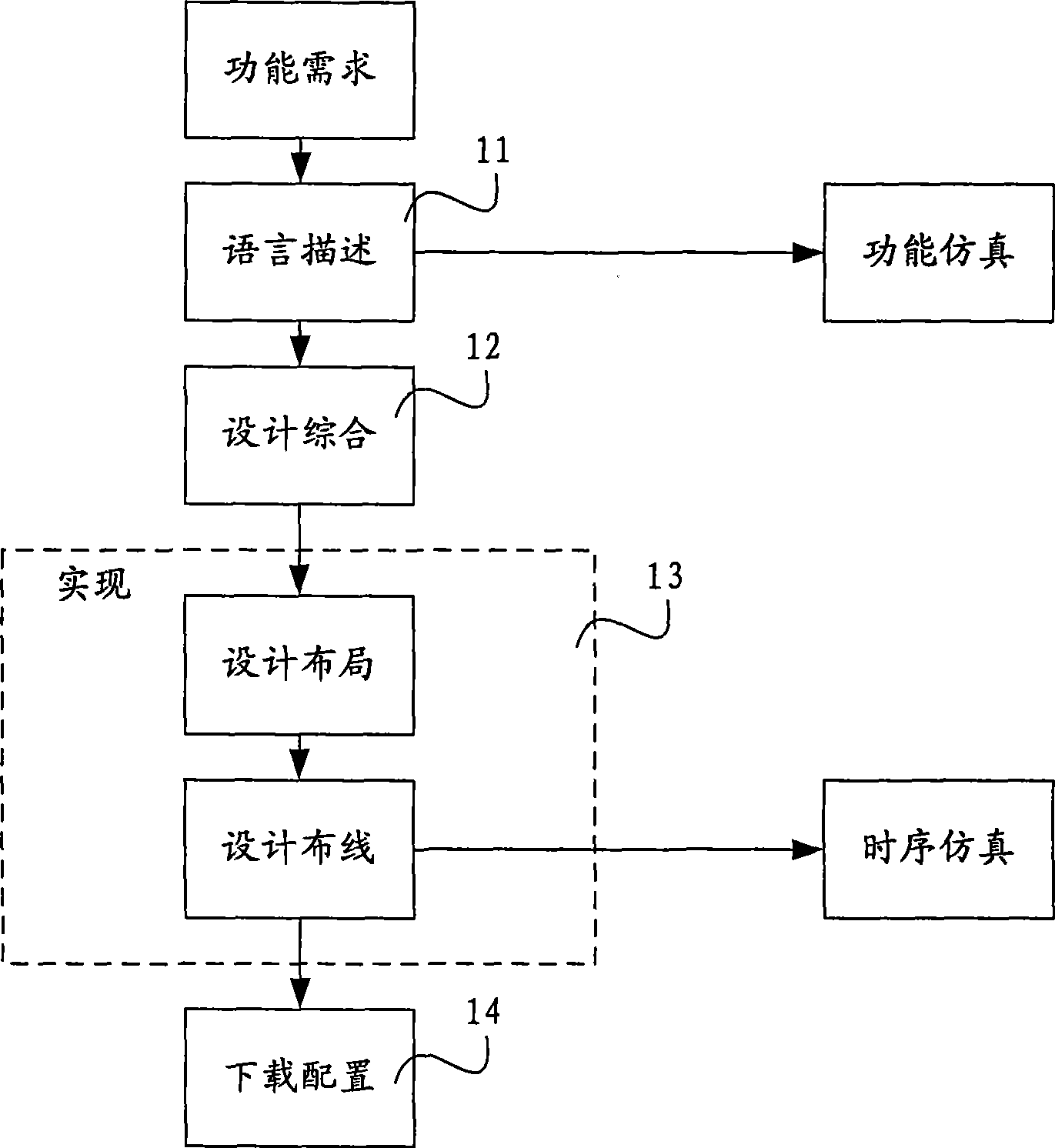

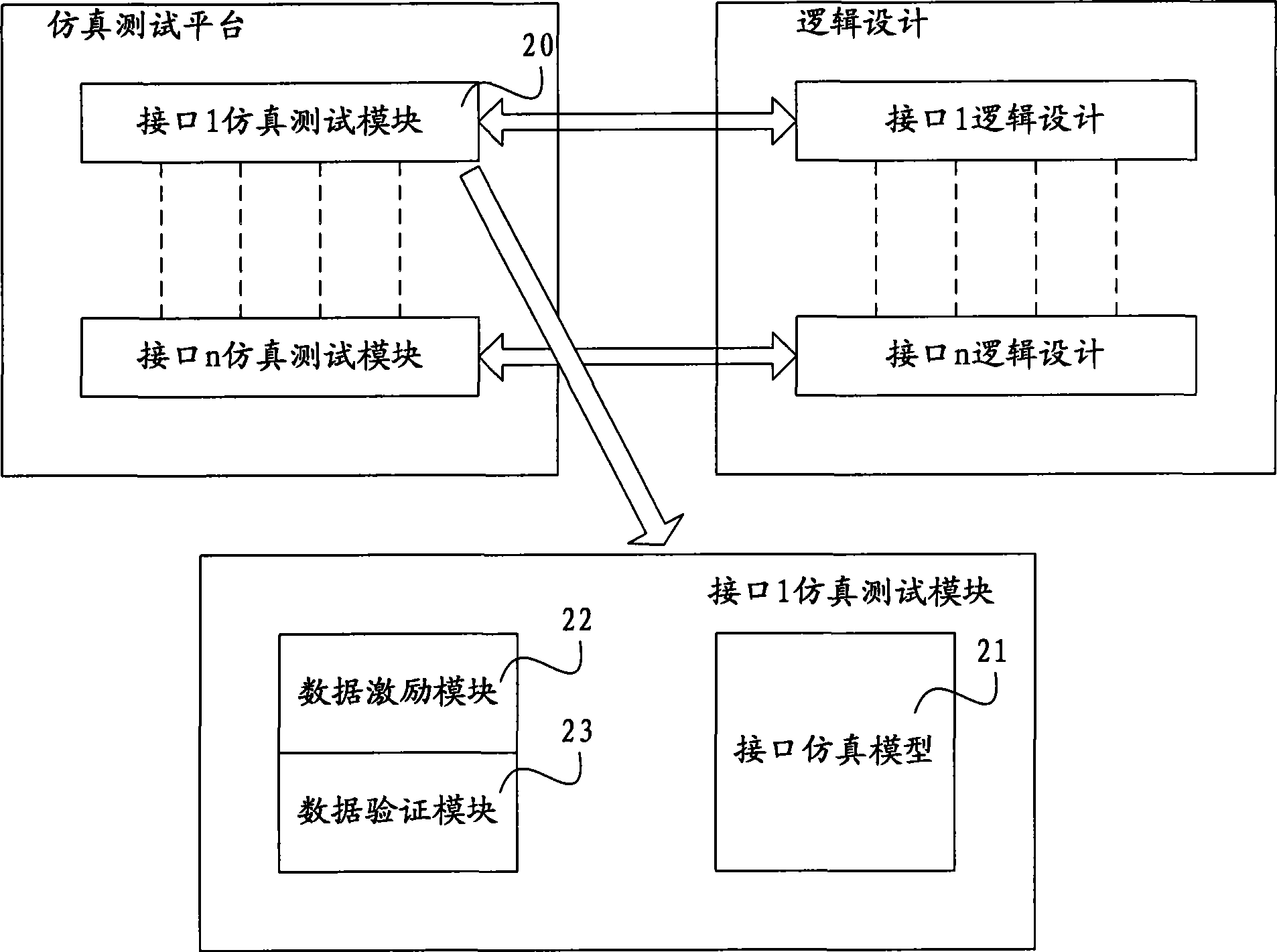

Method used

Image

Examples

Embodiment Construction

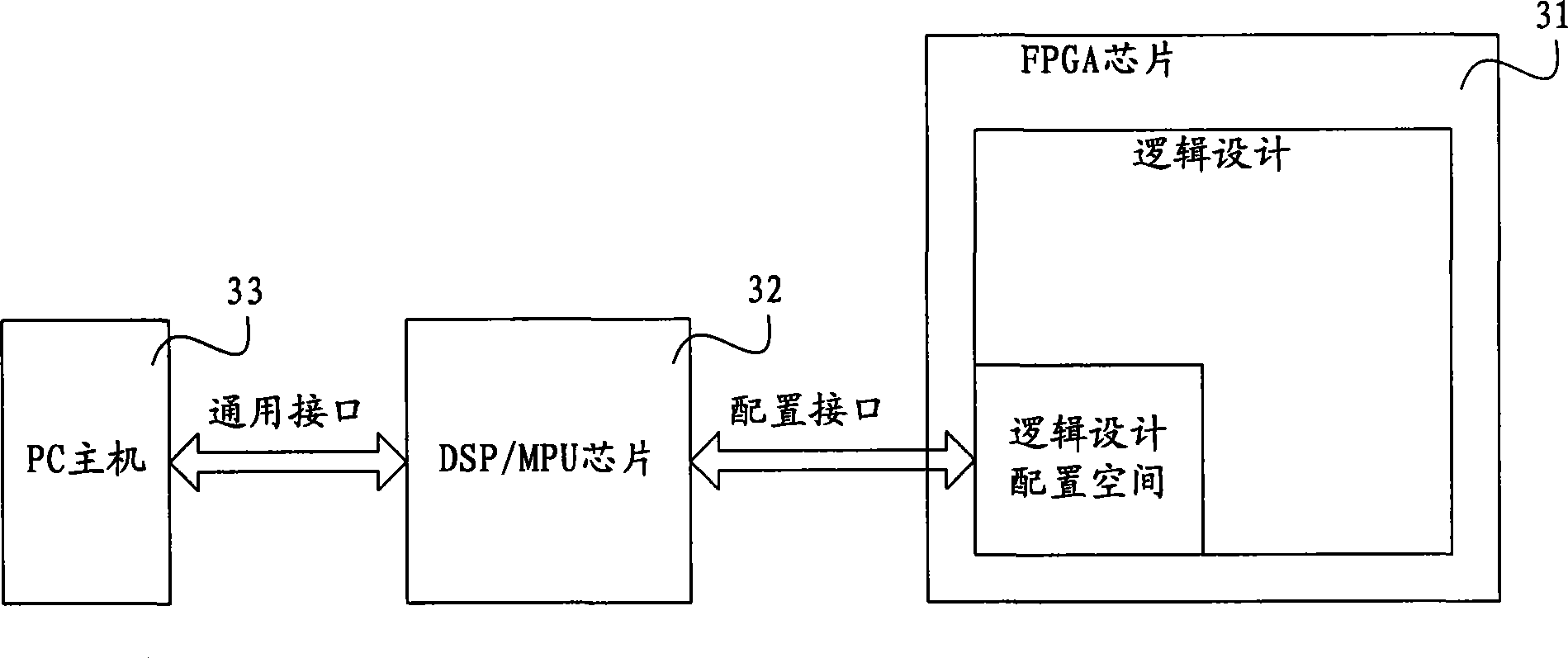

[0072] Figure 4It is a schematic structural diagram of Embodiment 1 of the device for debugging a programmable chip of the present invention. The device for debugging the programmable chip includes: a physical layer 41 , a decoding operation module 42 , an encoding operation module 43 , a command operation module 44 and a debugging interface 45 . The physical layer 41 is connected with the debugging host 46 outside the FPGA chip, and is used for carrying out command data interaction with the debugging host 46; the decoding operation module 42 is used for decoding the command data received by the physical layer 41; The encoding operation module 43 is used to combine the command information containing the signal state information into command data, and send it to the debugging host 46 through the physical layer 41; the command operation module 44 is used to decode according to the decoding operation module 42 to obtain The command information of the command information is used...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com