Look-up tables for delay circuitry in field programmable gate array (fpga) chipsets

A chipset and gate array technology, applied in logic circuits using specific components, logic circuits using basic logic circuit components, CAD circuit design, etc., can solve the problem of expensive FPGA units and achieve the effect of saving space and reducing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The innovative teachings of the present invention will be described with particular reference to various exemplary embodiments. It should be understood, however, that this class of embodiments provides only a few examples of the many advantageous uses of the innovative teachings of the present invention. In general, statements made in the specification of the present application do not necessarily limit any of the various claimed aspects of the invention. Additionally, some statements may apply to some inventive features but not to others. In the drawings, like reference numerals are used throughout the several views to designate like or similar elements.

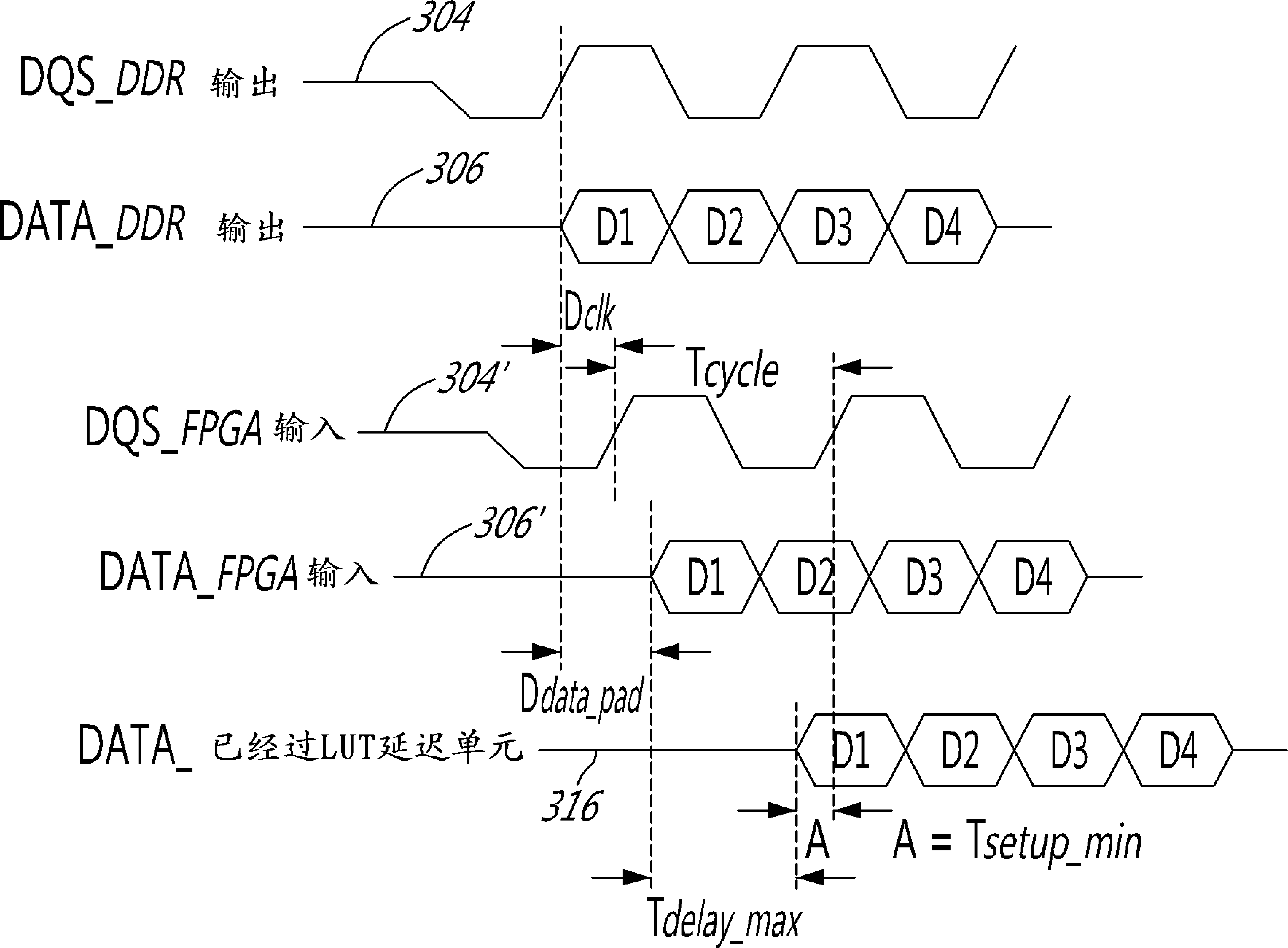

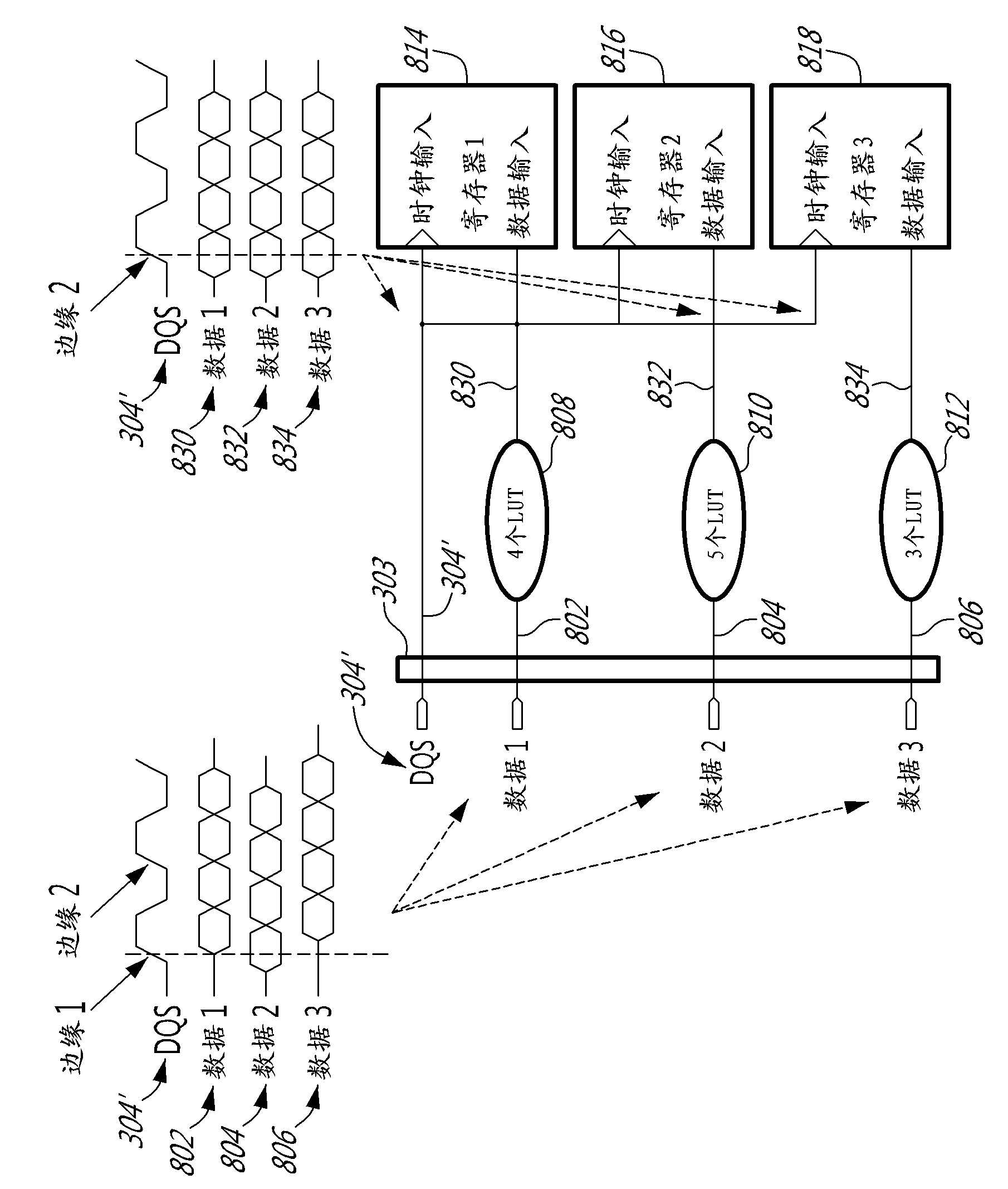

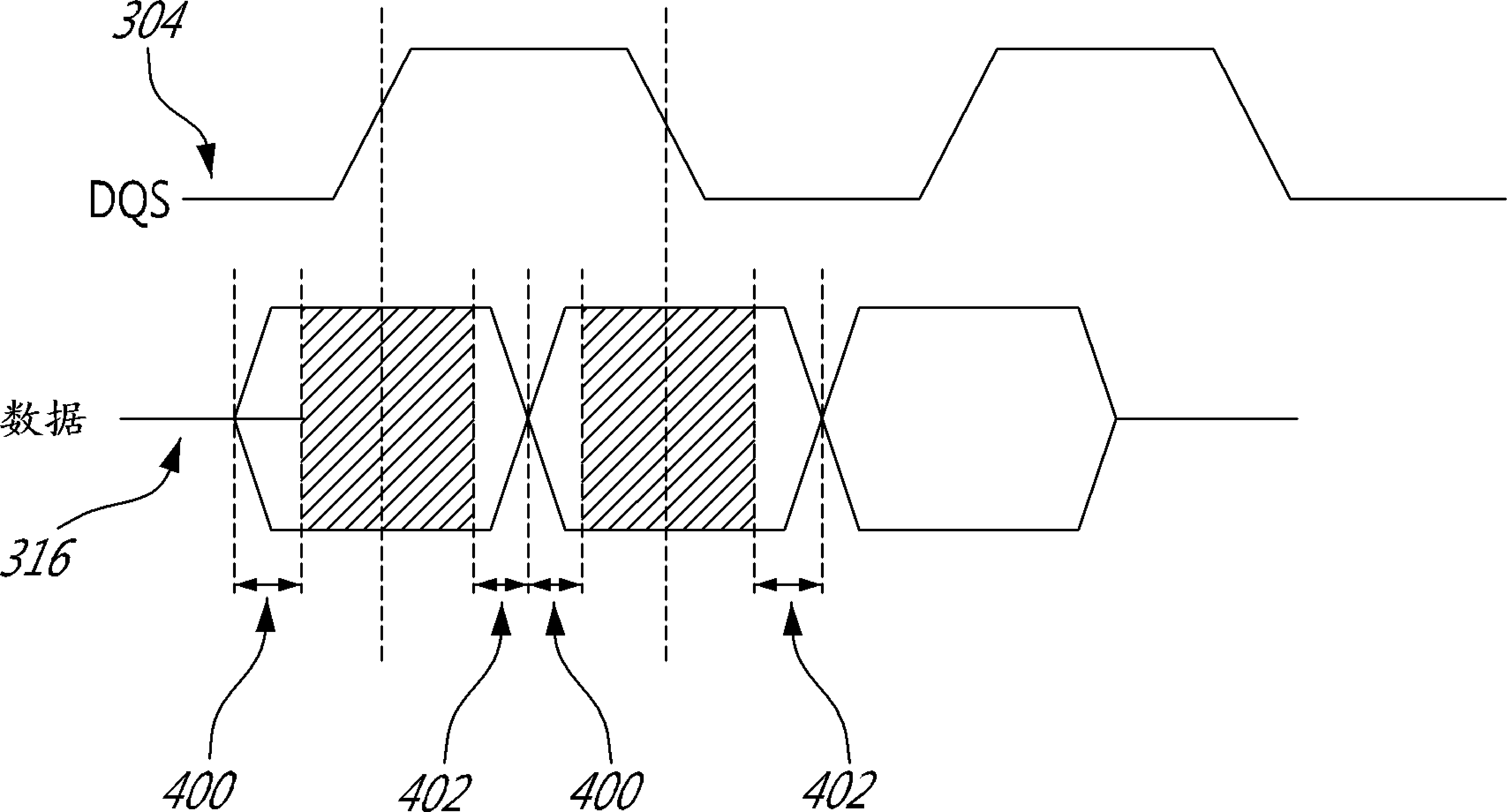

[0024] When the FPGA chipset samples the data signal, the phase relationship between the data signal and the corresponding clock signal must meet a series of requirements imposed by the FPGA chipset itself. If the data signal phase is not adjusted and somehow properly synchronized with the phase of the clock signal...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com