On site programmable gate array on-chip programmable system based on DW8051 core

A programming system and gate array technology, applied in the field of on-chip programmable systems, can solve problems such as uneven technology, low operating speed of programmable systems, poor system anti-interference and stability, and achieve strong flexibility and configurability , Improve the running speed and enhance the effect of anti-interference

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

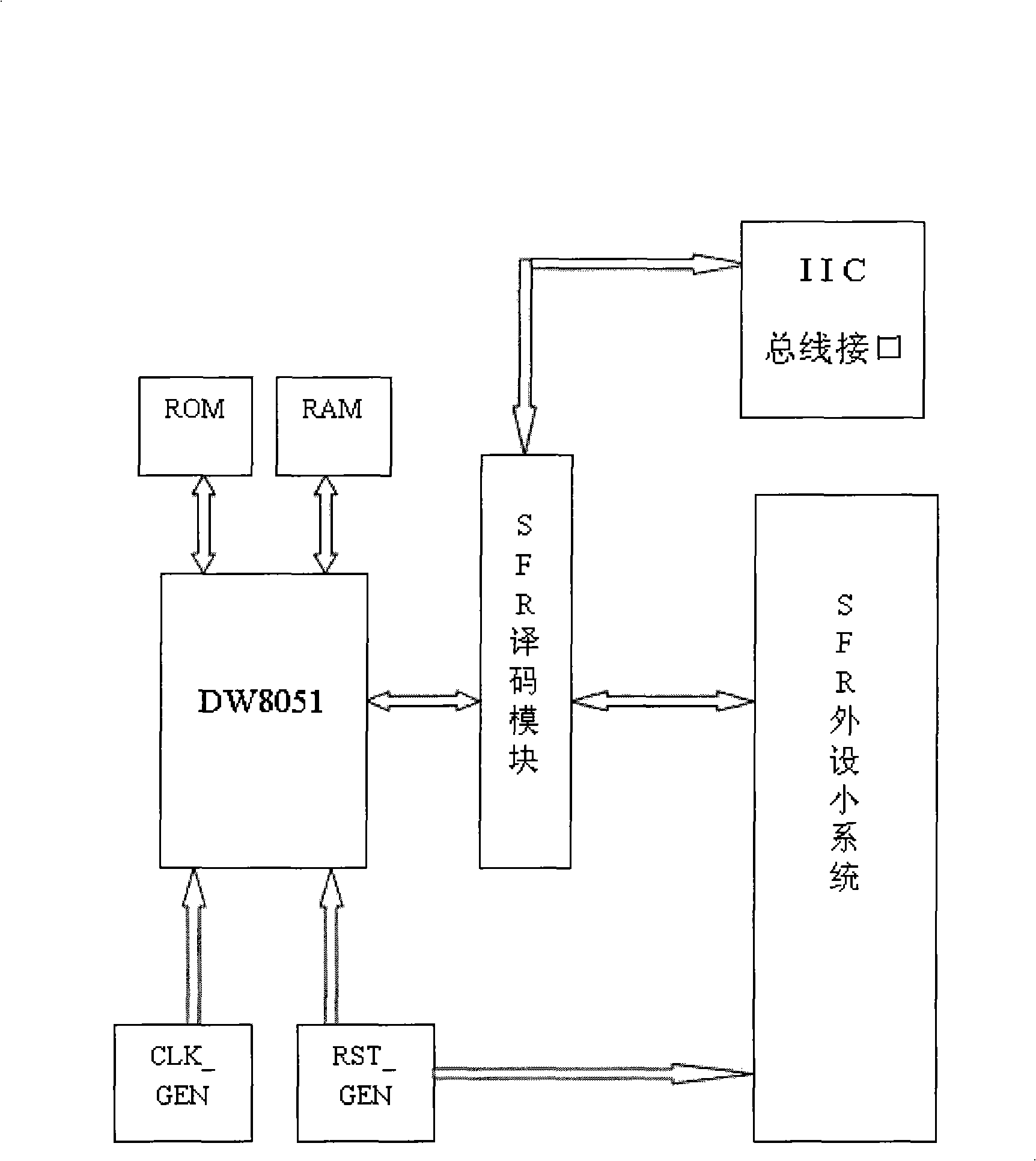

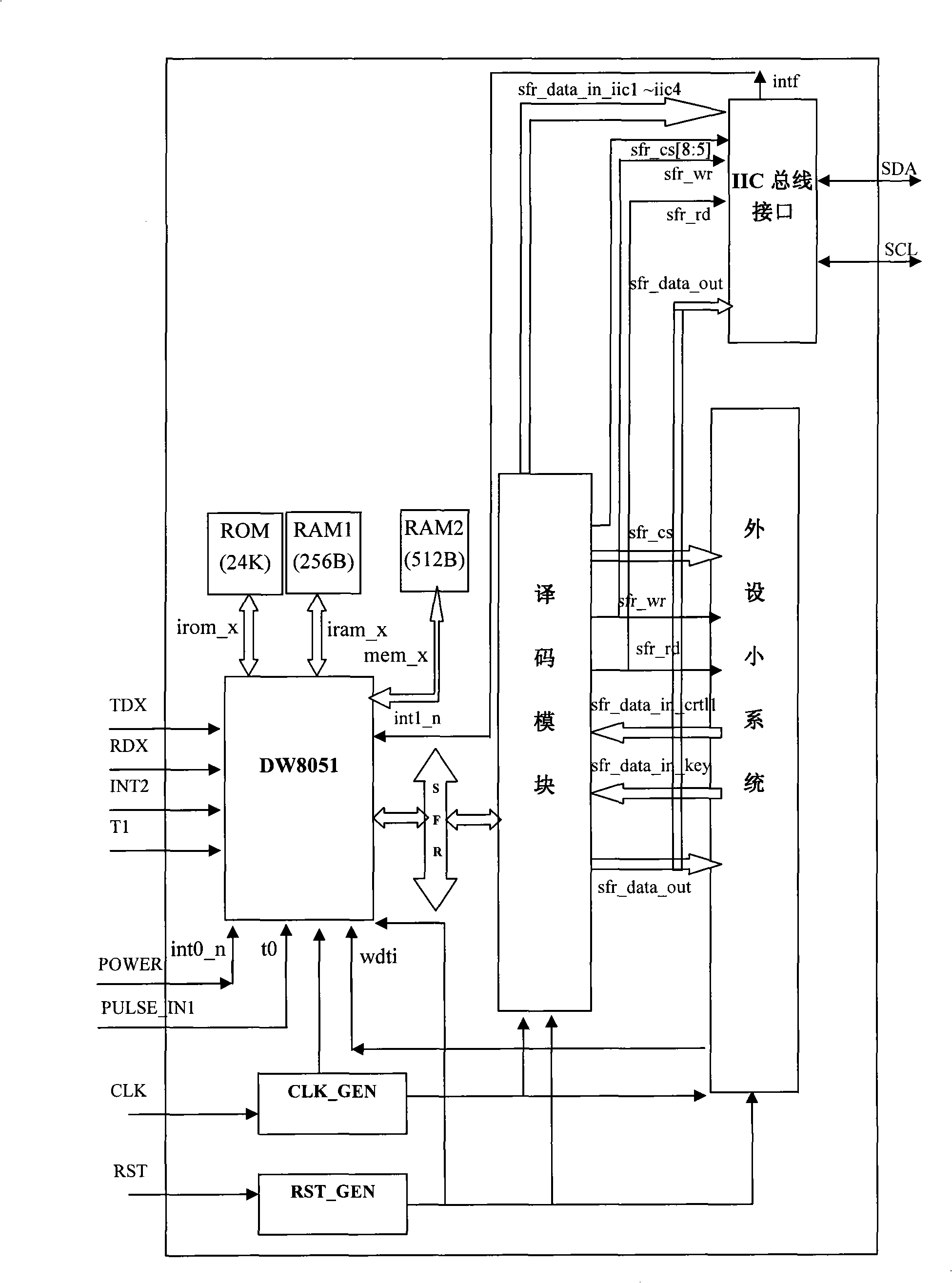

[0017] Such as figure 1 As shown, the entire system of the present invention is based on the DW8051 core provided by Synopsys, and includes three parts: memory design, external signal interface design, and design for providing clock and reset signals for the entire system.

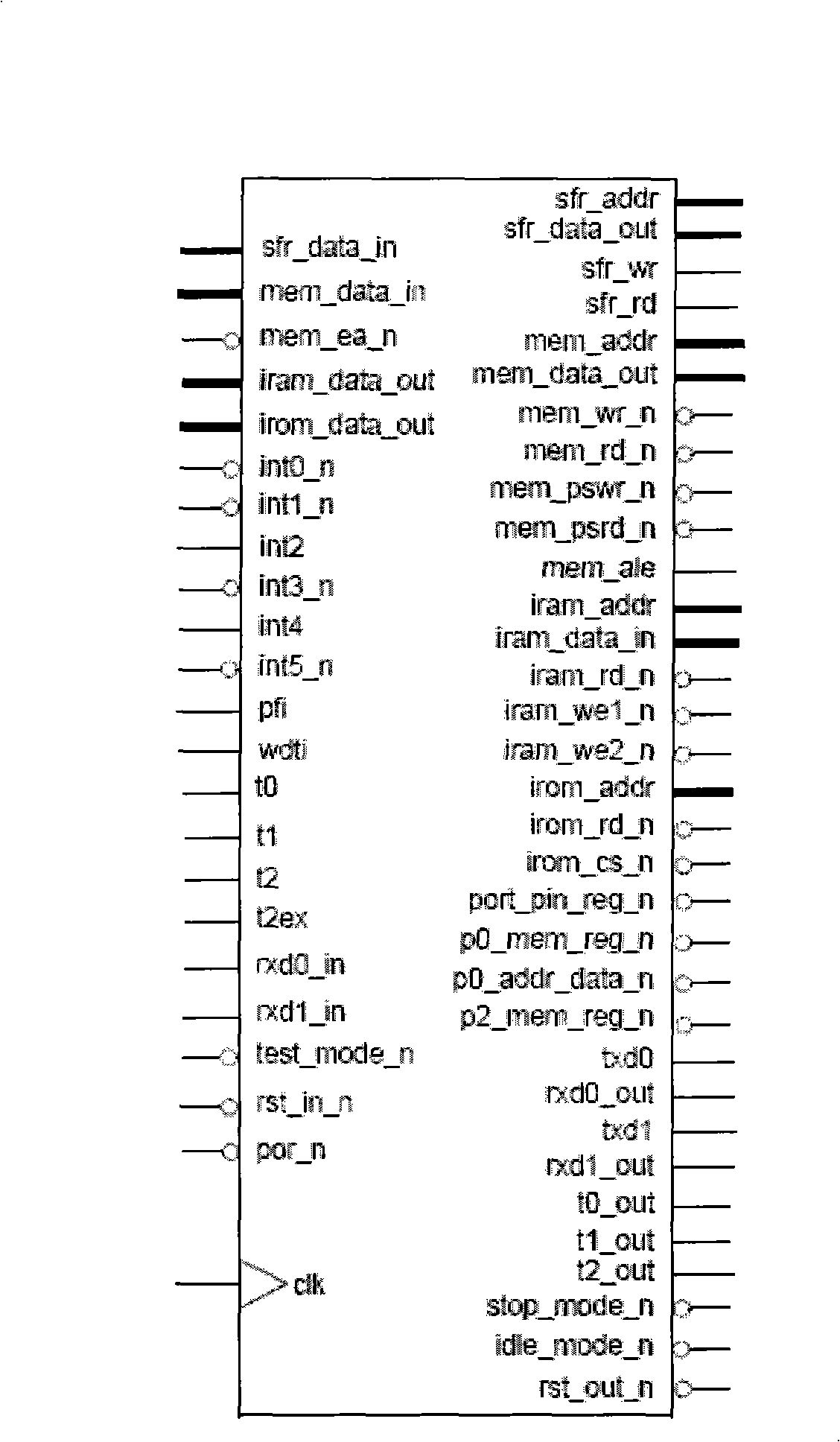

[0018] figure 2 It is the input and output signal diagram of DW8051 macro unit. It contains four independent addressing paths, namely SFR bus, mem bus (external RAM bus), iram bus (internal RAM bus) and irom bus (program memory bus); two serial communication ports UART0 and UART1; 7 or 13 external interrupt sources programmed and configured; three timers / counters; and some lead-out ports indicating the internal execution status of the system.

[0019] The memory circuit includes ROM (Read Only Memory) and RAM (Random Access Memory), which are essential for the operation of DW8051. The external interface circuit part includes three small modules: SFR (Special Function Register, special function register...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com