Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

64 results about "Special function register" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A Special Function Register (or Special Purpose Register, or simply Special Register) is a register within a microprocessor, which controls or monitors various aspects of the microprocessor's function.

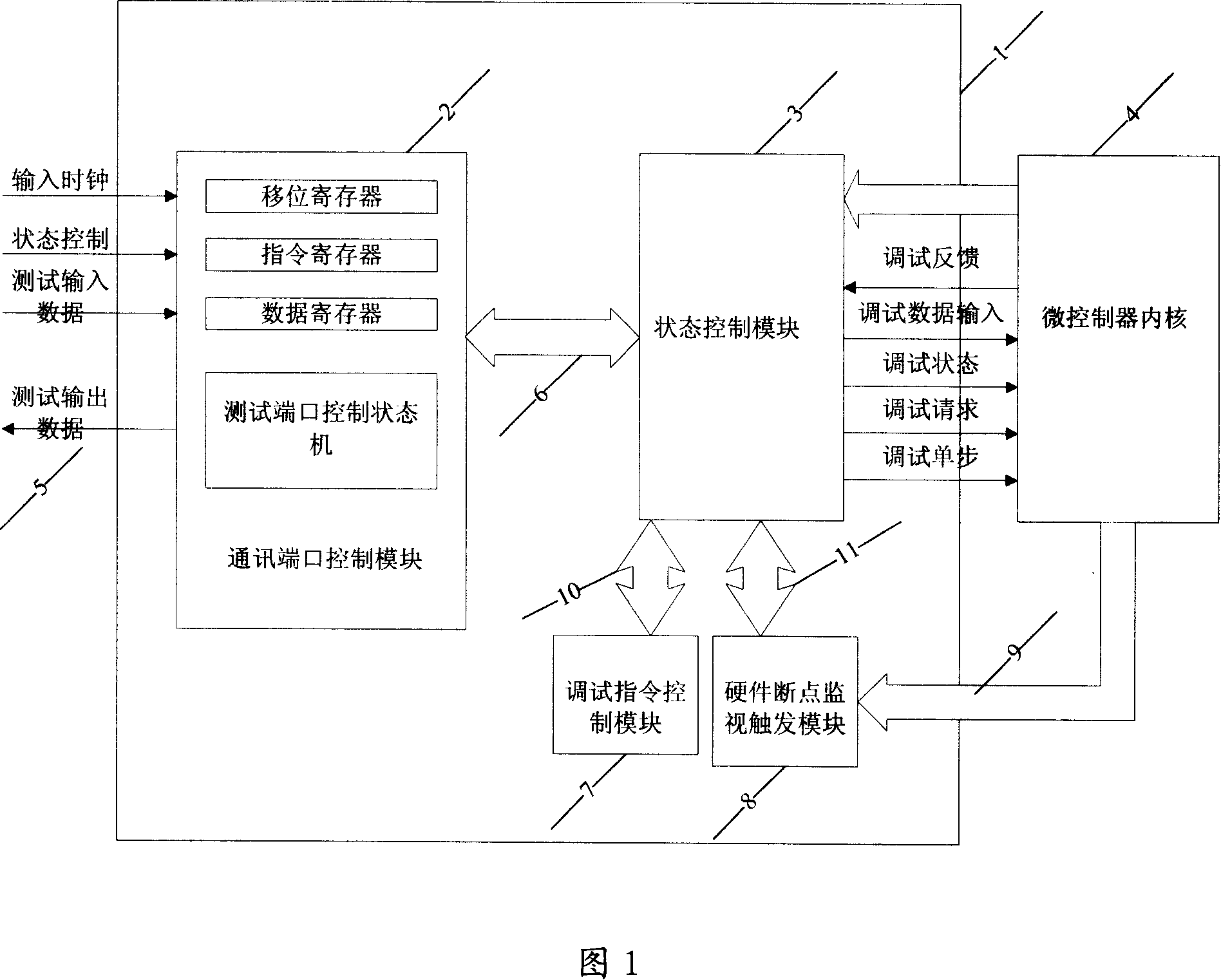

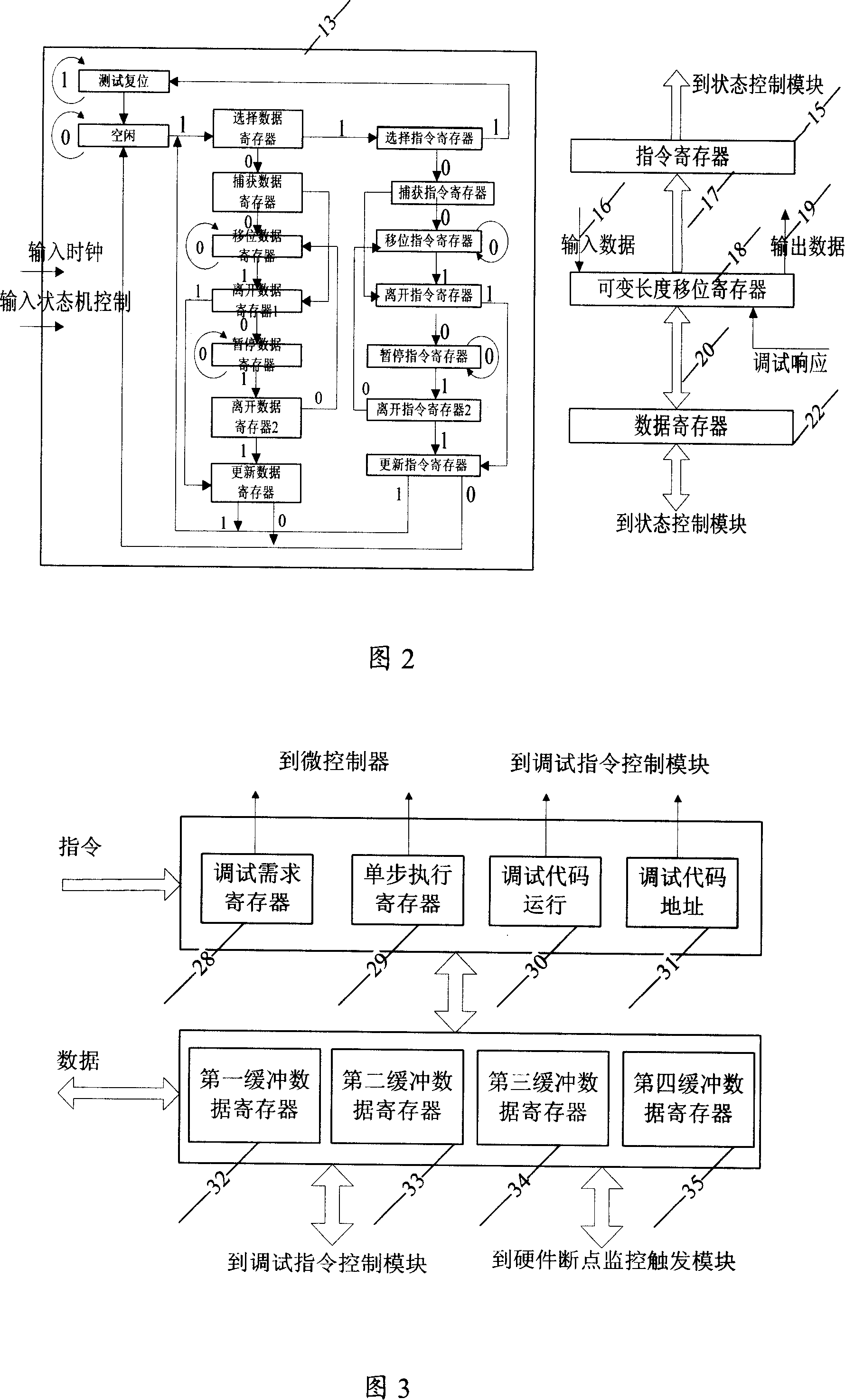

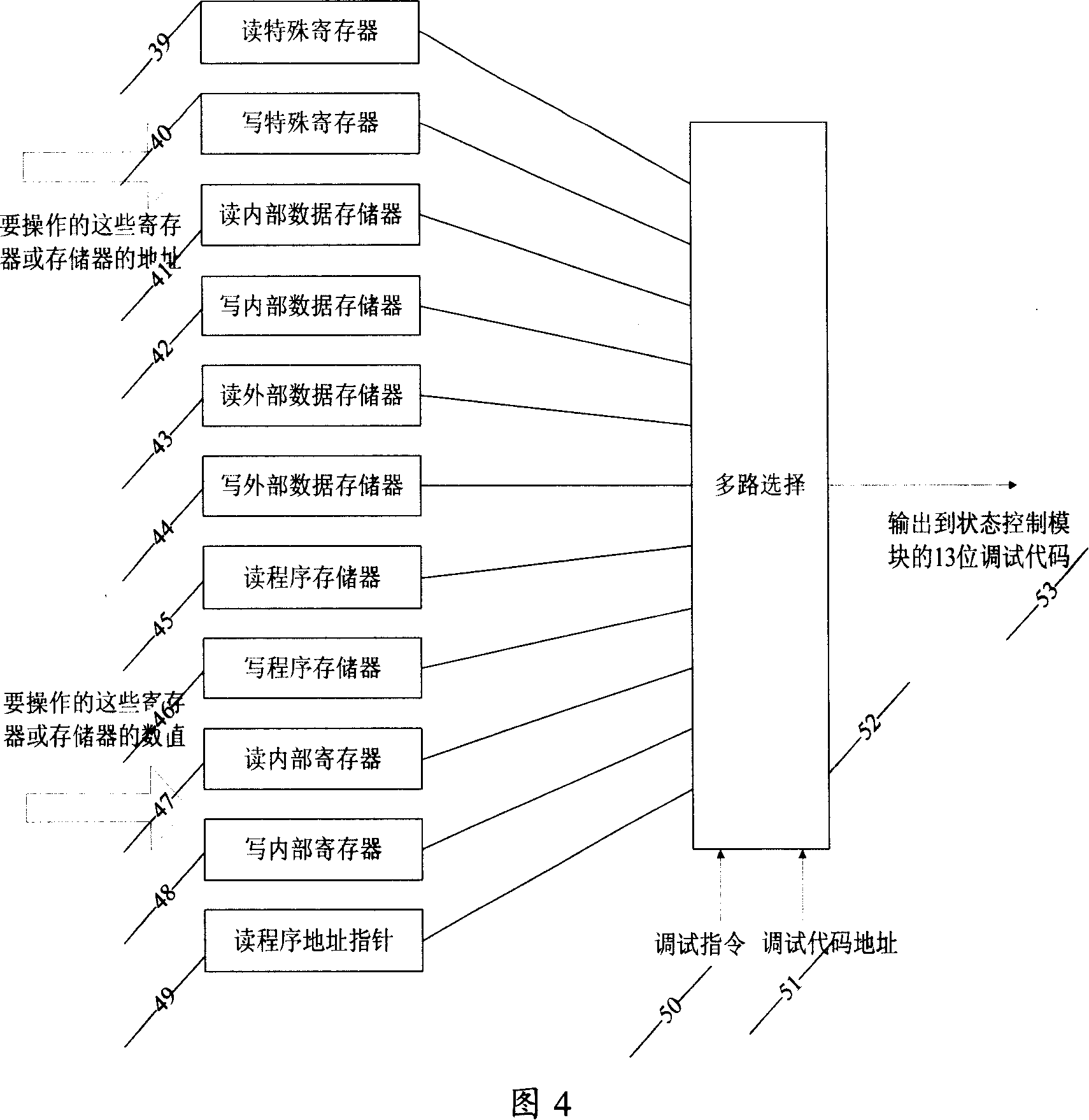

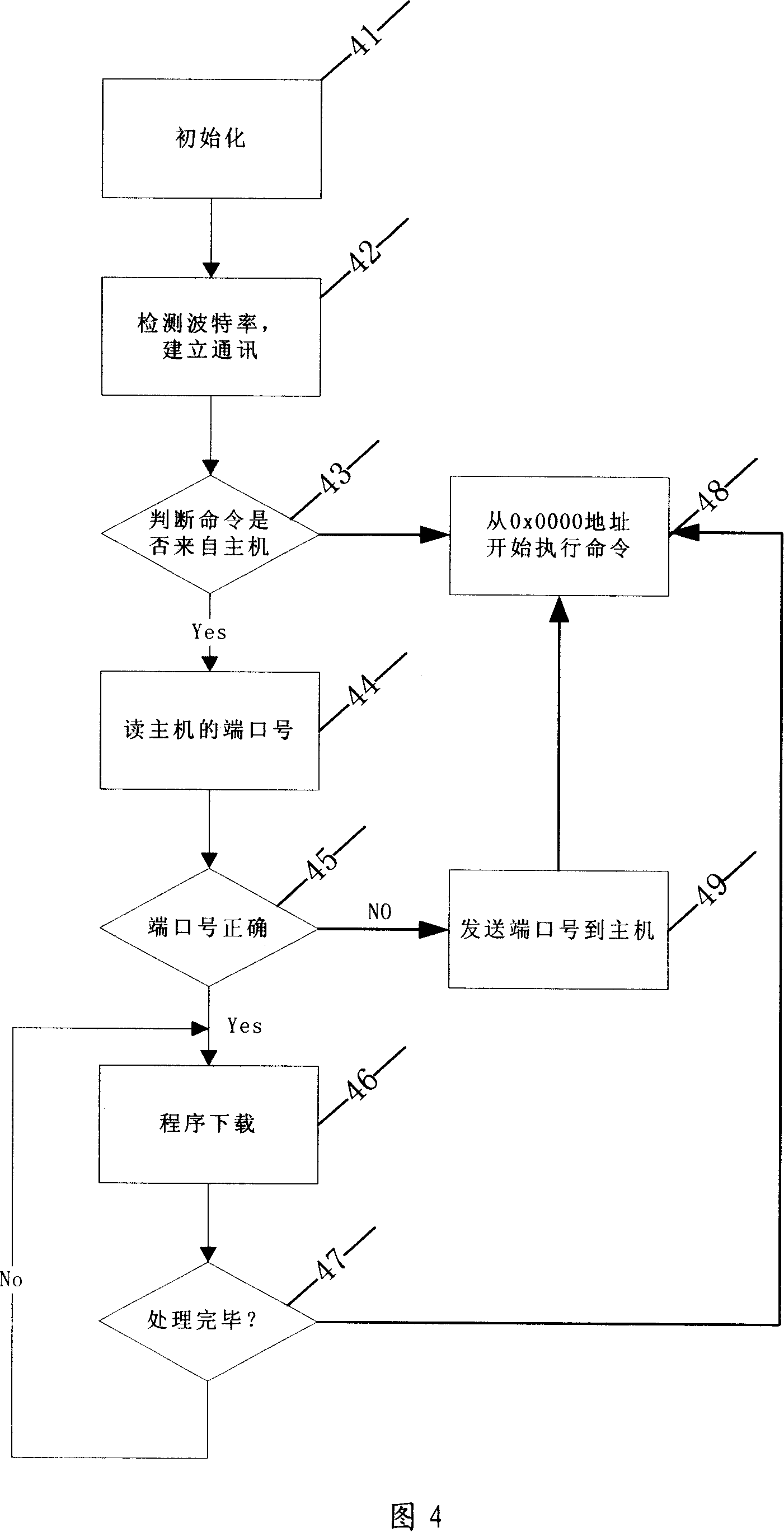

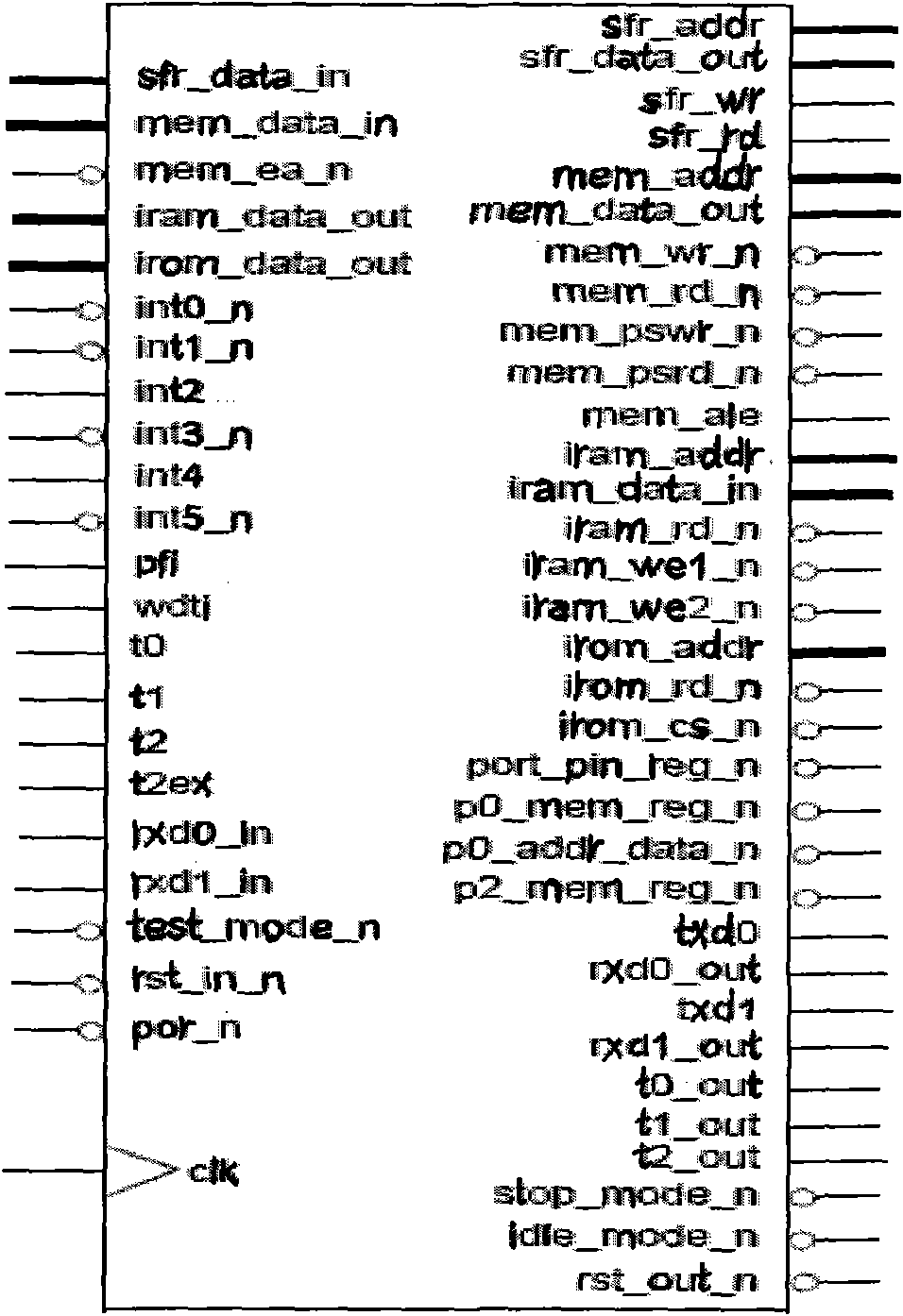

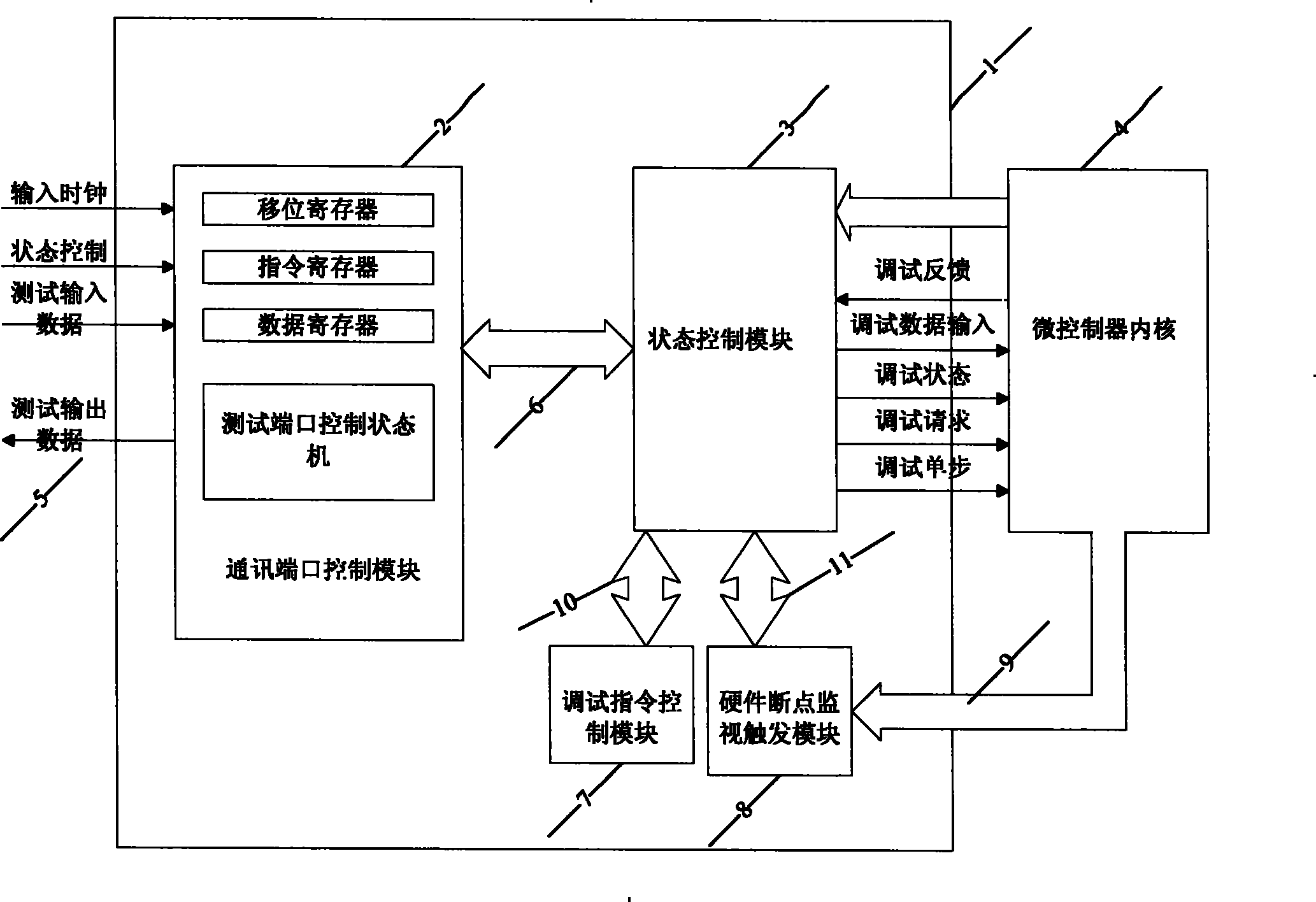

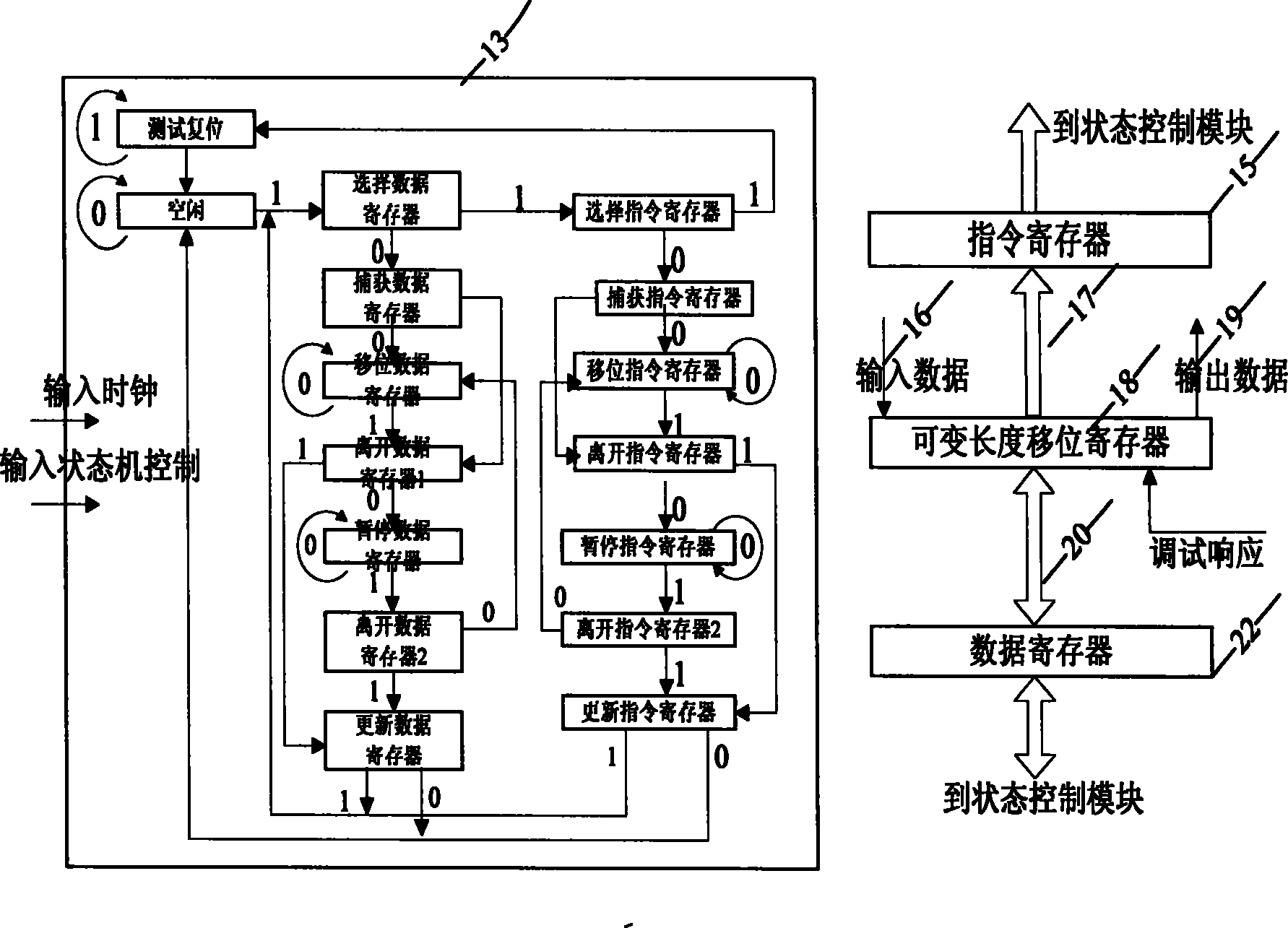

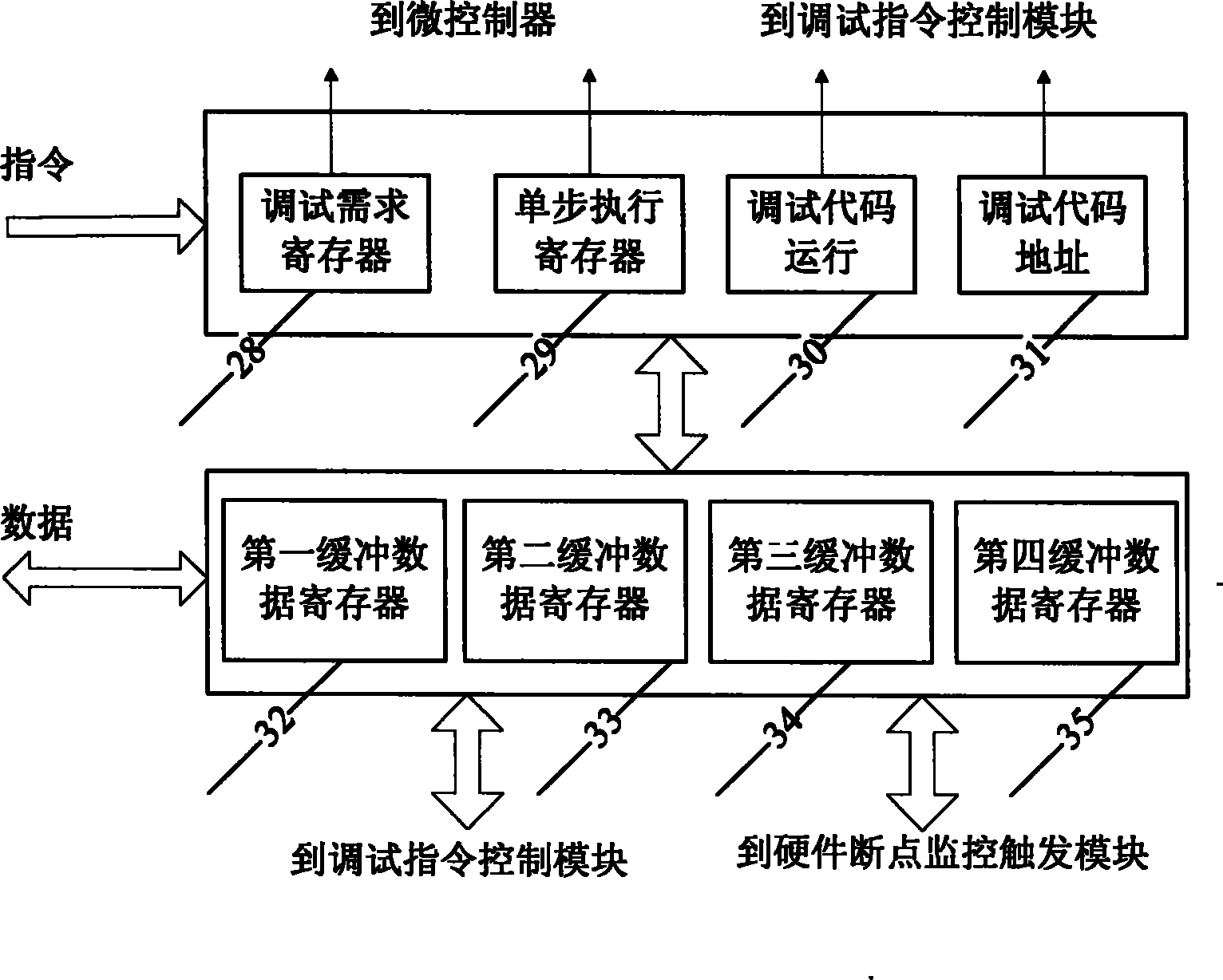

Microcontroller built-in type on-line simulation debugging system

InactiveCN101154183AImproved debugging capabilitiesRealize real-time monitoringSoftware testing/debuggingSpecific functionData memory

The invention provides a microcontroller flush bonding on-line simulation debugging system, comprising a communication port control module, a state control module, a debugging command control module and a hardware breakpoint monitoring trigger module; the modules are collected into a chip through a special debugging command transmitted by a mainboard to control the work of the whole on-line simulation debugging system; complex boundary scan to the inside of the chip through a standard test boundary scan can be finished; the microcontroller chip is controlled according to an outer command to be converted into a debugging mode from a normal mode; a program can be downloaded and numerated from any position in a memorizer of the microcontroller through the debugging communication interface of the mainboard to support the target system single-step debugging and support software breakpoints and hardware breakpoints; the contents of a specific function register, a data memorizer and a program memorizer of the inside of the chip are checked and altered real-time; address bus and data bus are monitored, and the functions of real-time logical tracing, etc. are realized. The invention is of clear and simple structure, high-efficient operating effect and precise real-time monitoring.

Owner:SHANGHAI EASTSOFT MICROELECTRONICS

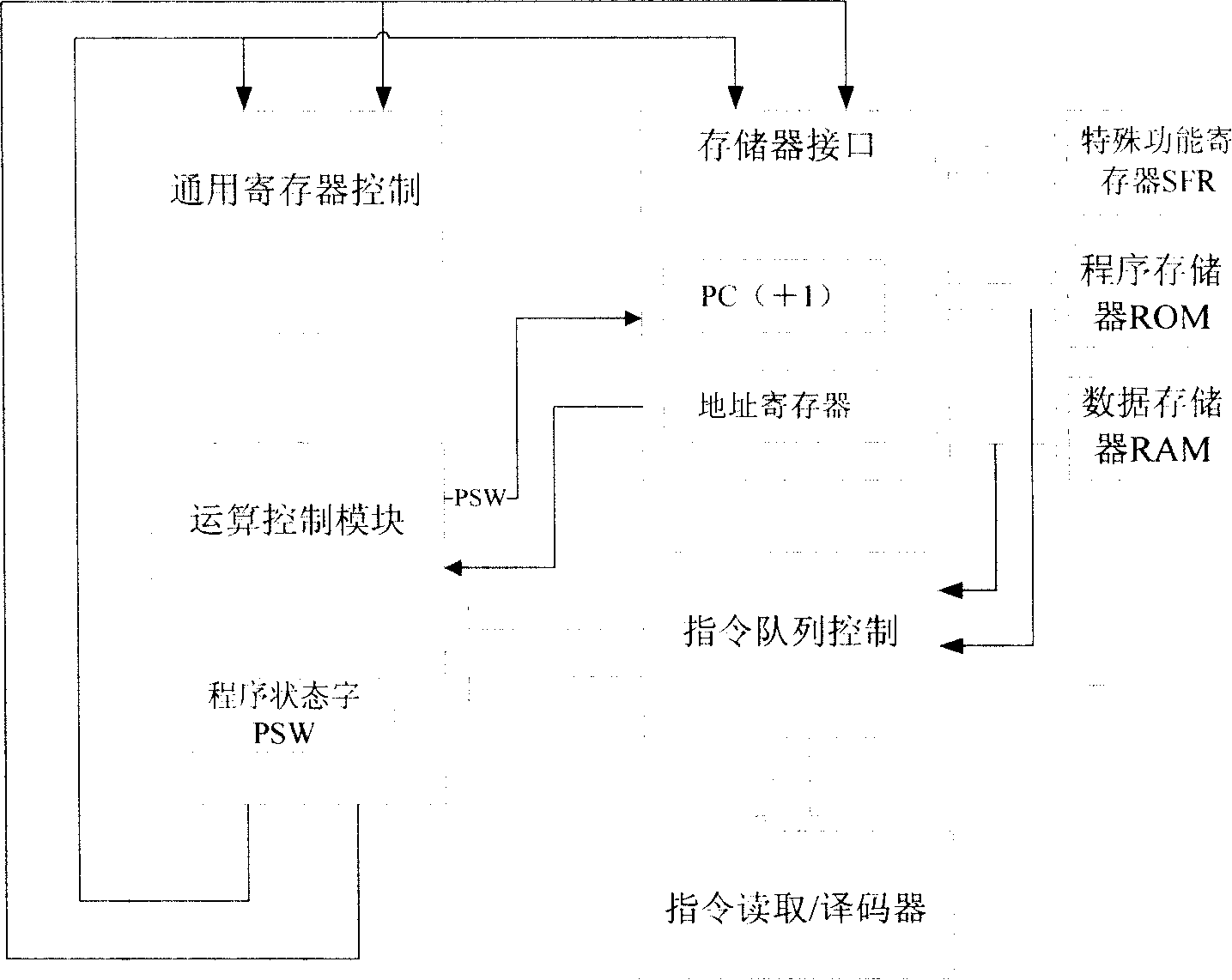

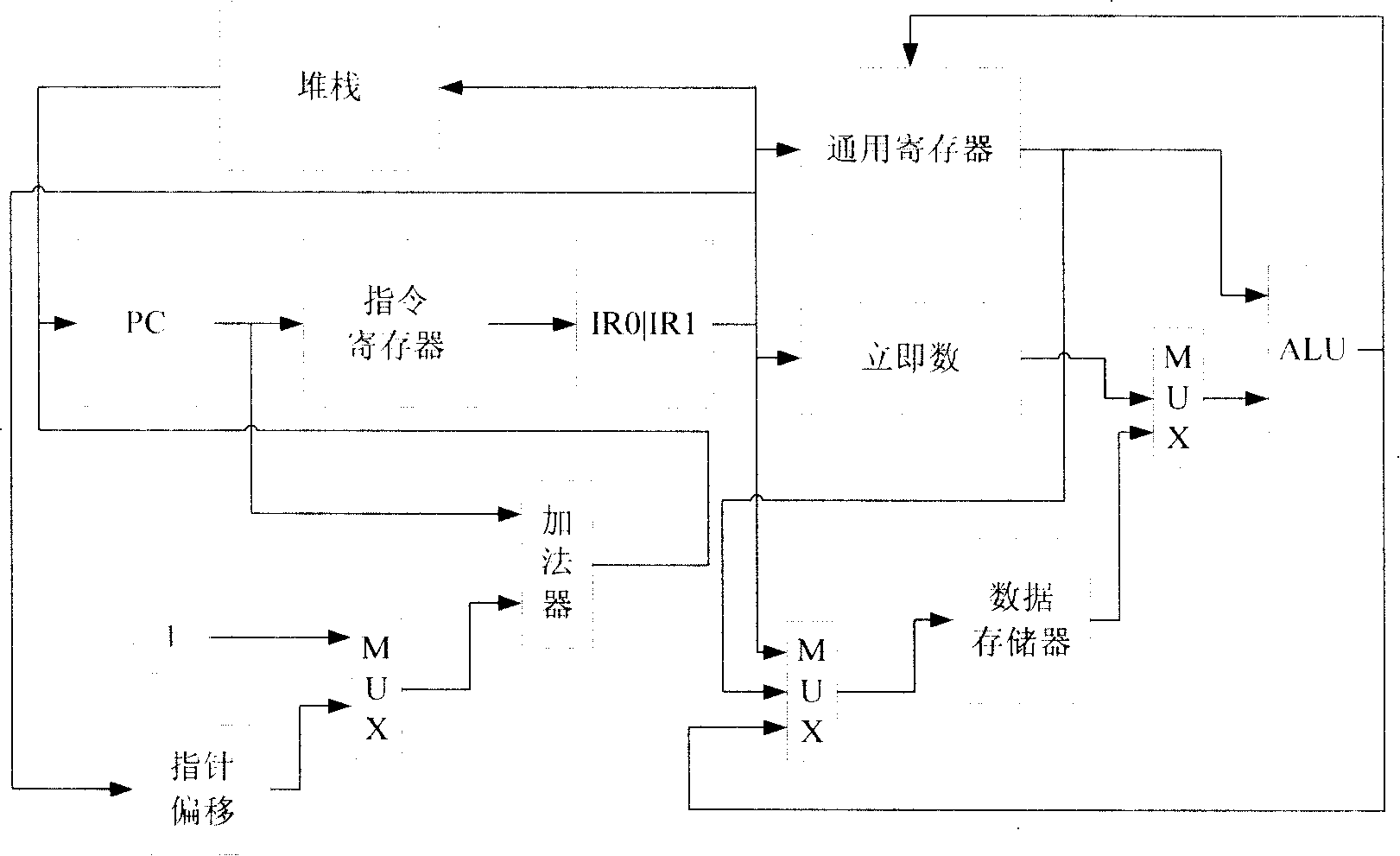

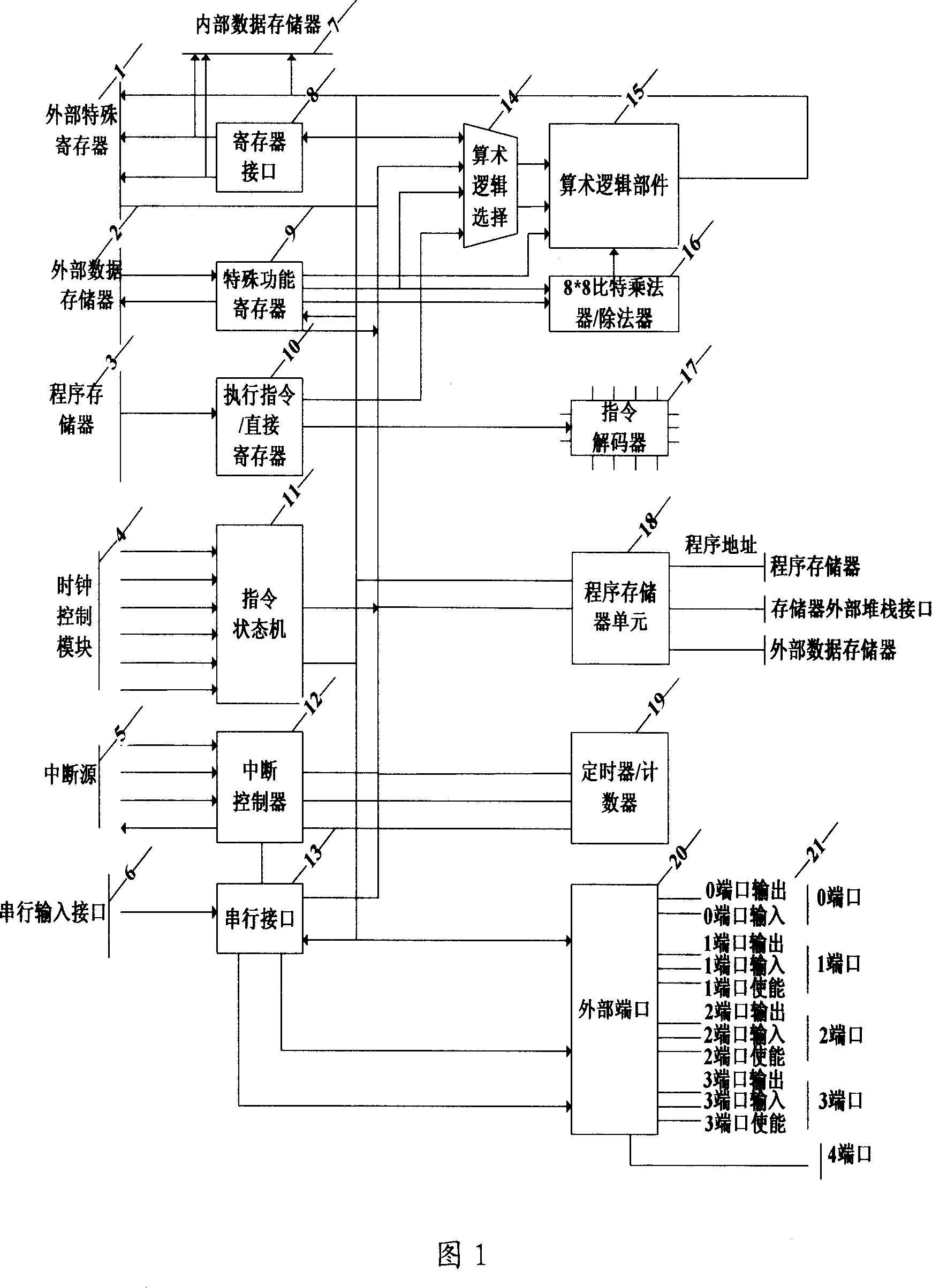

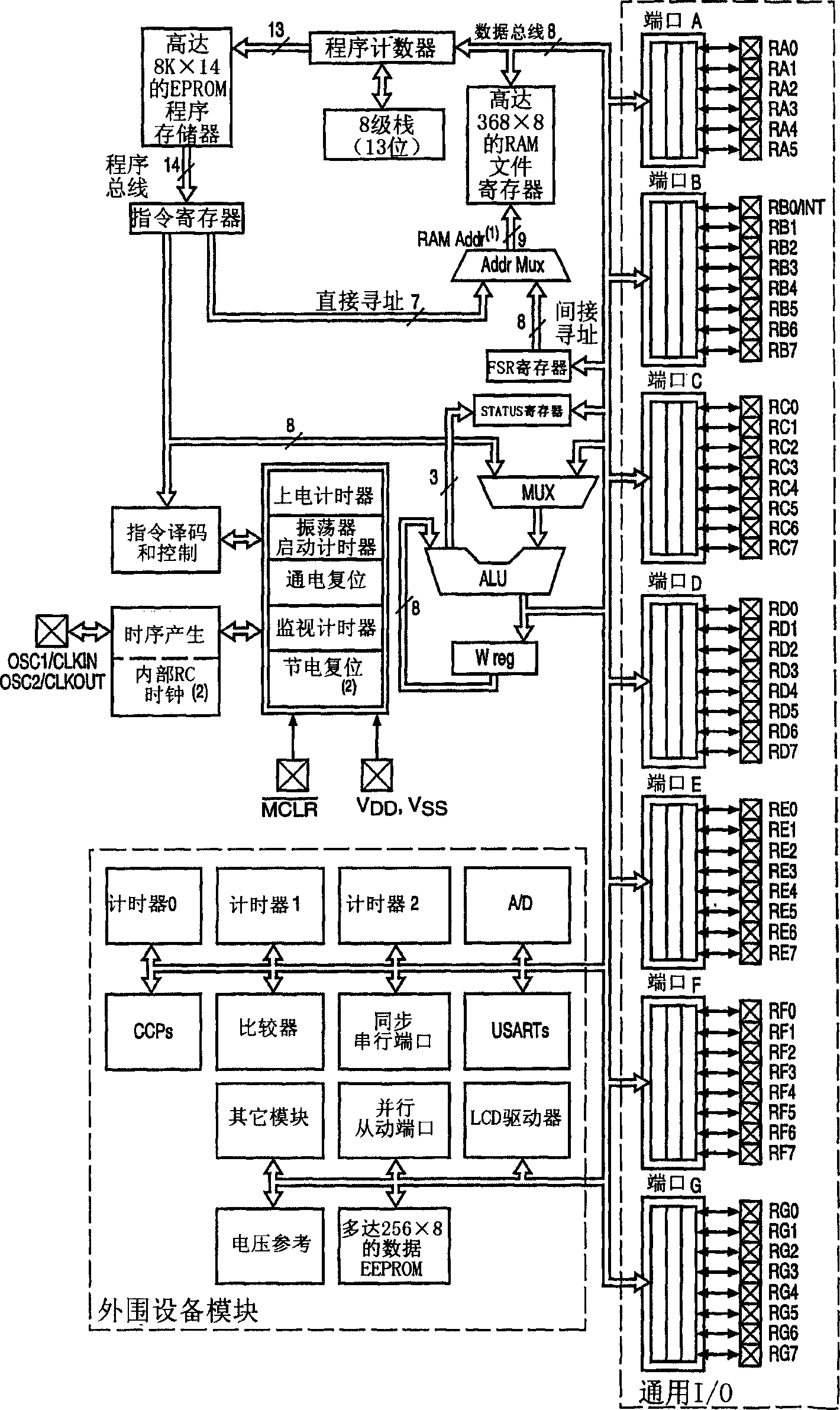

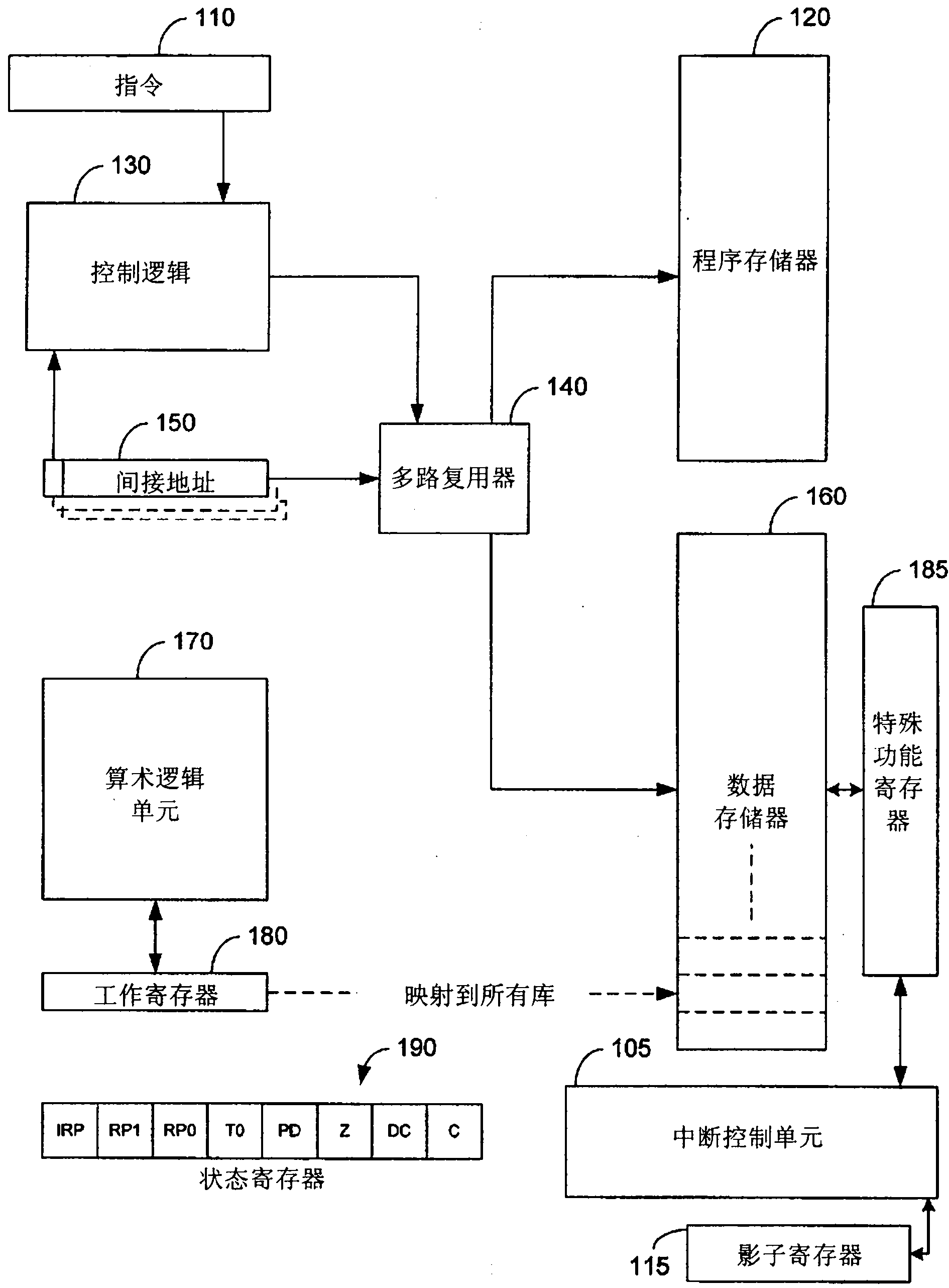

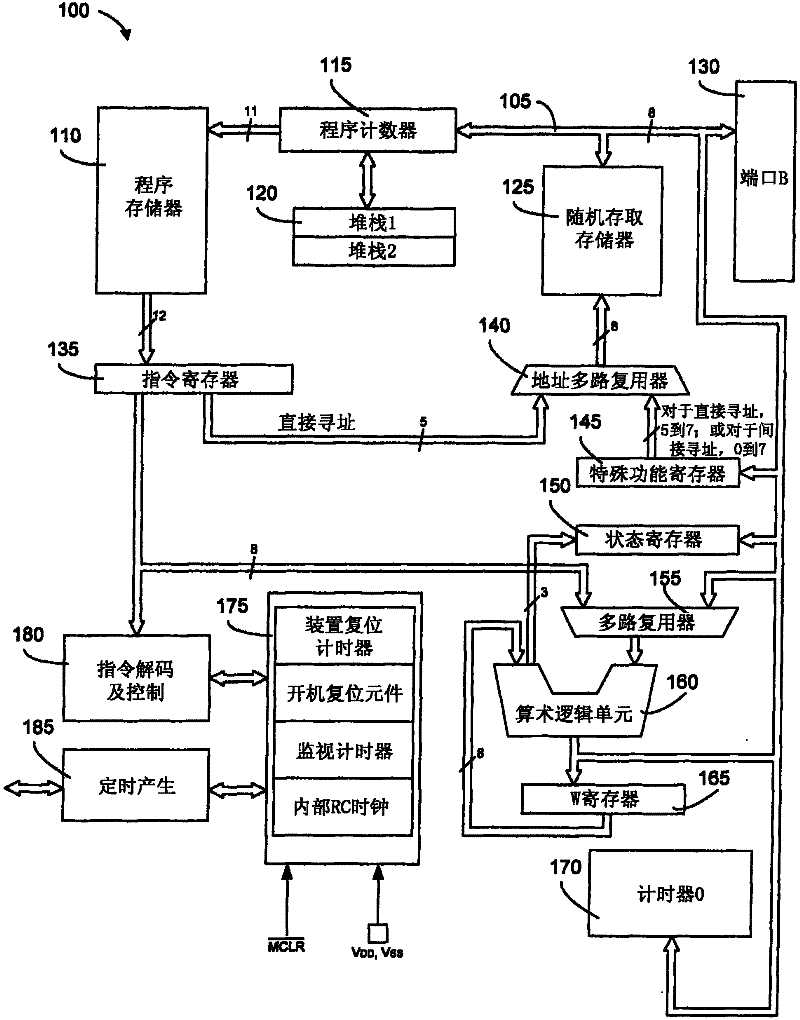

Microprocessor structure based on sophisticated vocabulary computerarchitecture

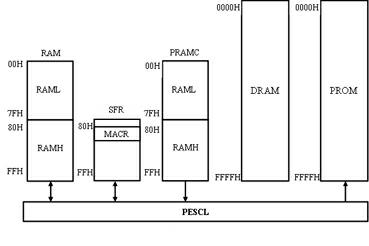

ActiveCN101178644AProcessing speedRich commandConcurrent instruction executionArchitecture with single central processing unitSpecial function registerMemory interface

The invention relates to a micro-processor architecture based on a complicated instruction set computer structure, comprising a program memory, a random data memory, a particular function register, a data buffer register, a common register, a data bus and an address bus, a memory interface, an operation and control module, an instruction reading and decoder and an instruction array control module. The data bus is divided into a separated eight-byte program data bus and an eight-byte inner random data bus. The invention is applicable to various embedded SOC systems for real time control, and can be widely applied in electric products such as home appliance, civilian use communication and car electronic.

Owner:SHANGHAI EASTSOFT MICROELECTRONICS

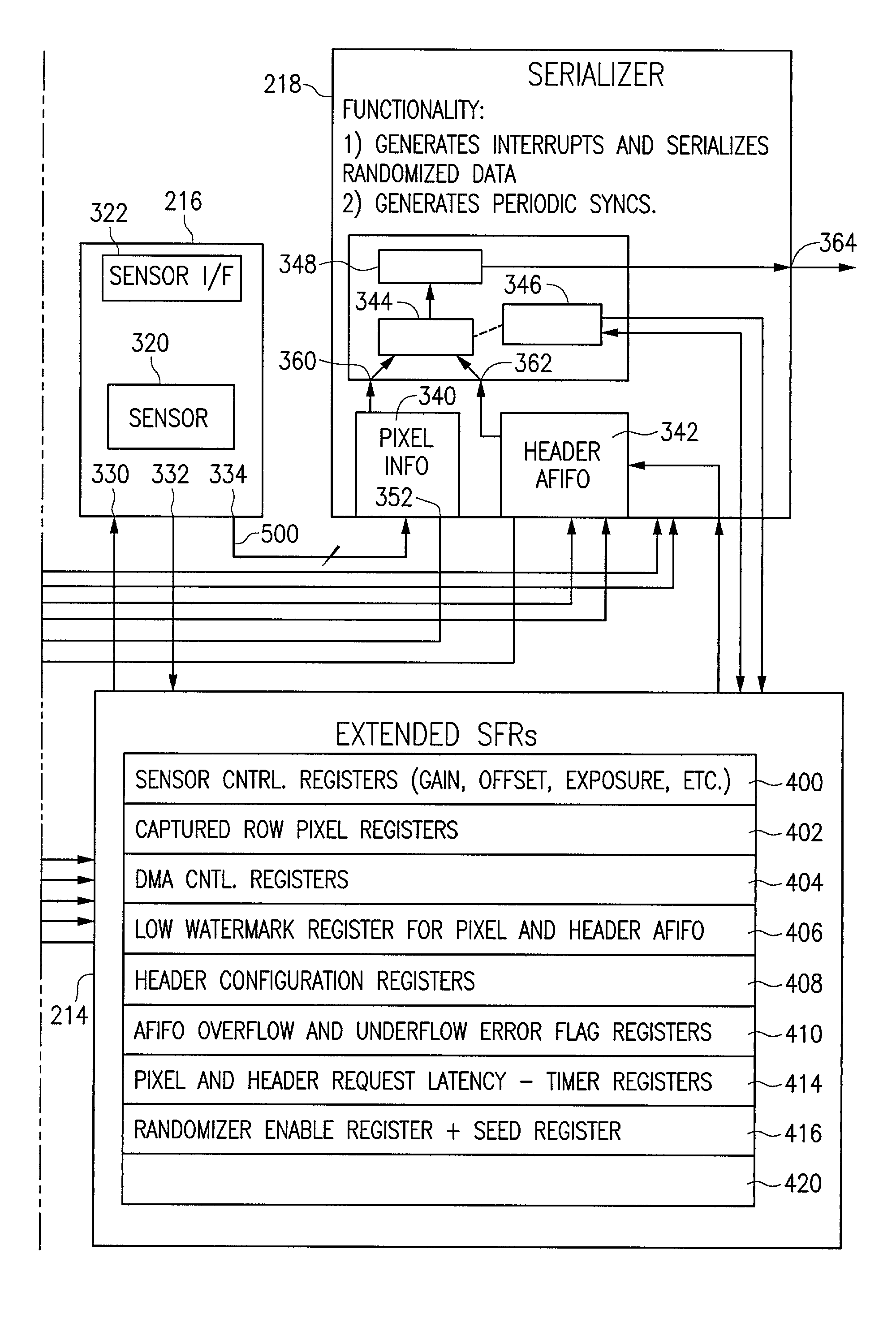

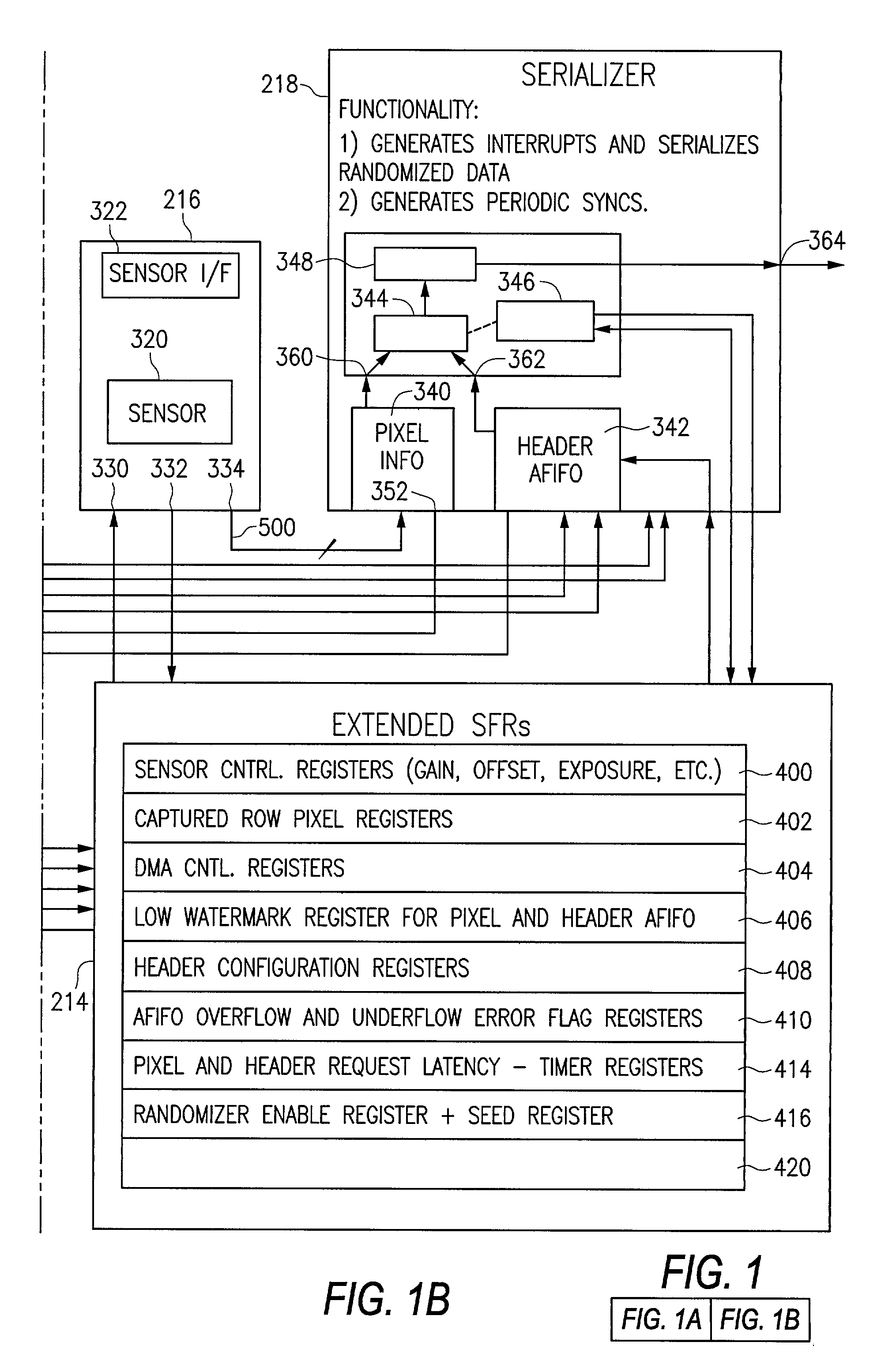

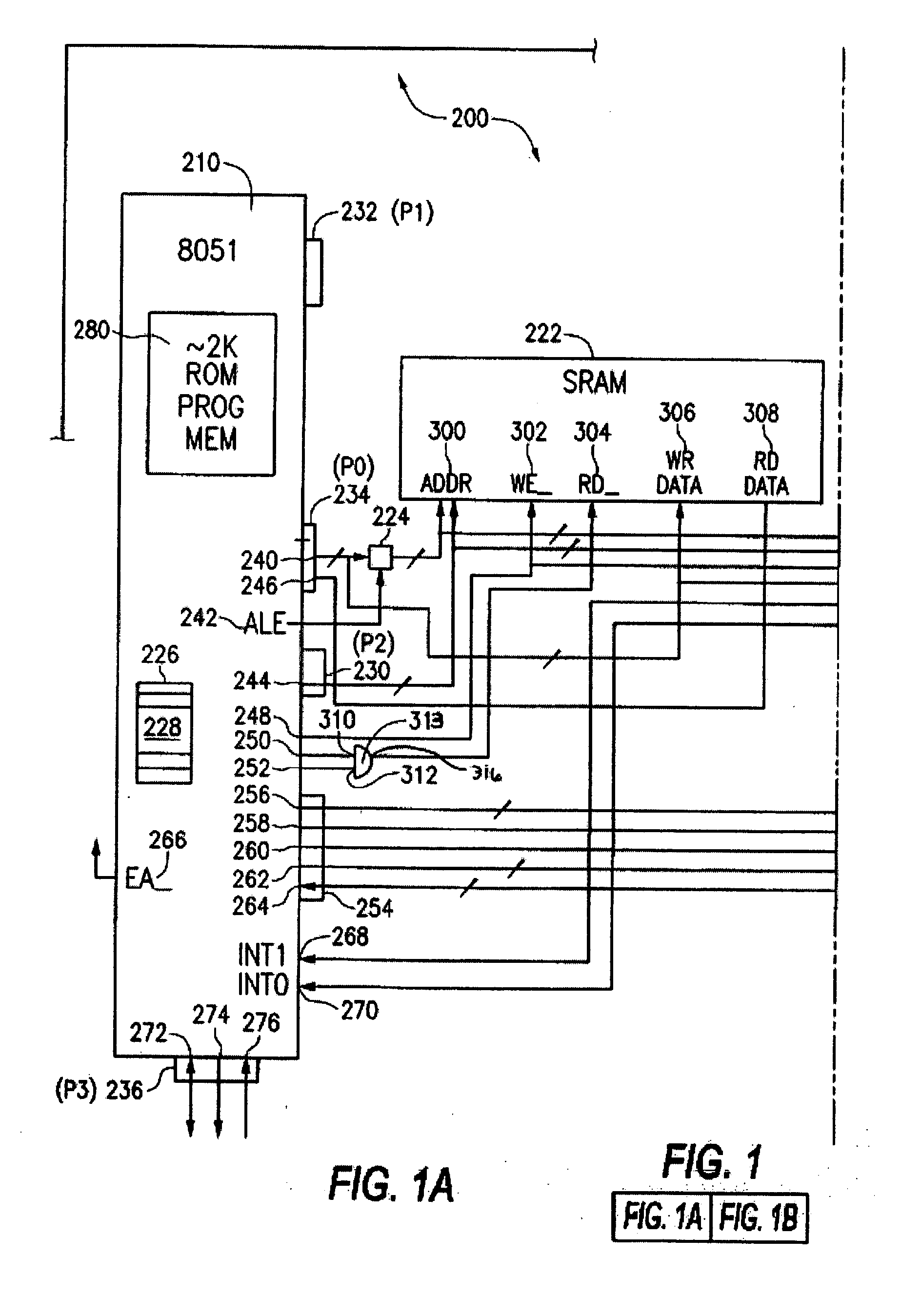

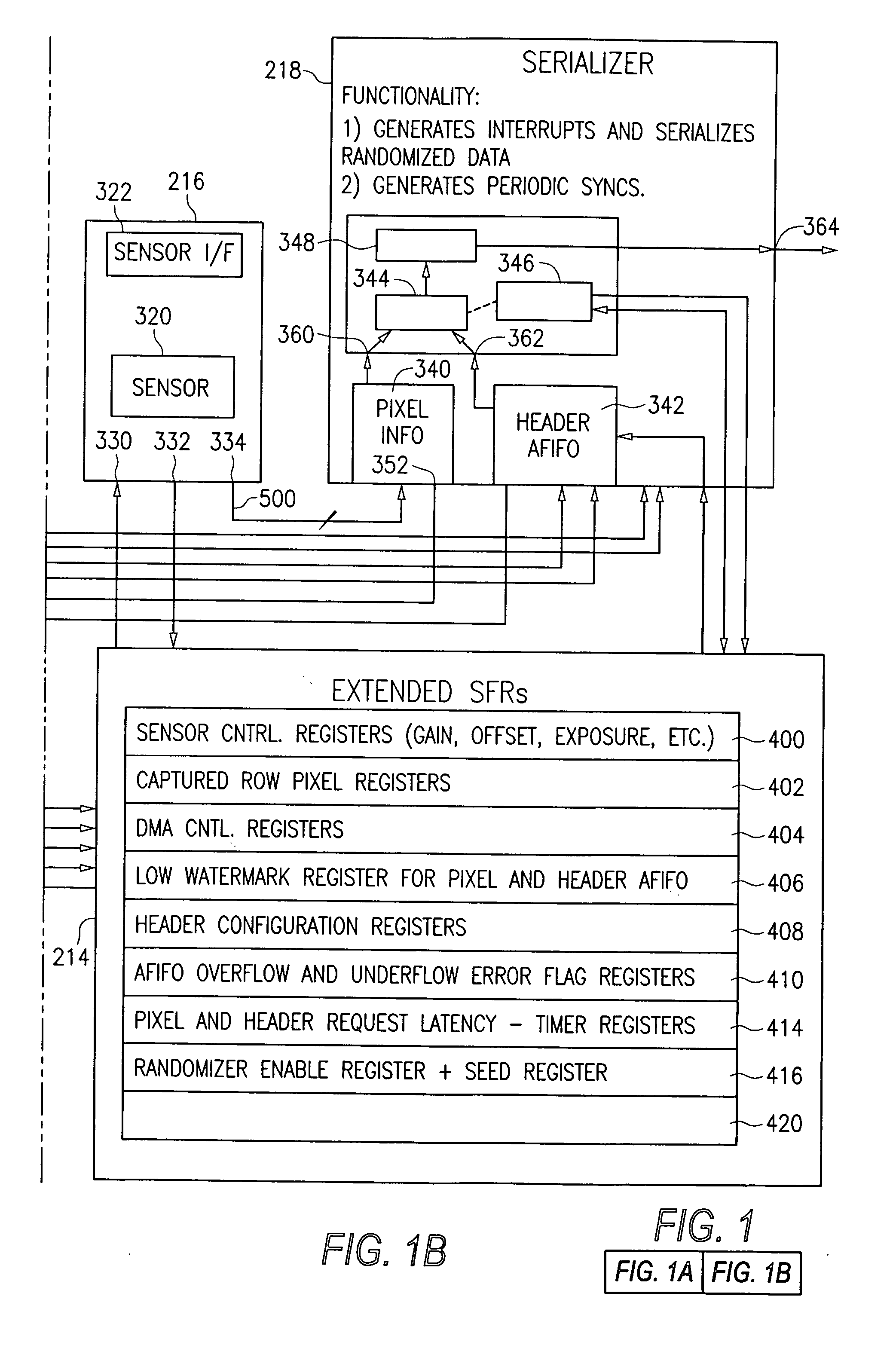

Integrated CMOS imager and microcontroller

ActiveUS7106367B2Television system detailsTelevision system scanning detailsCMOSSpecial function register

Owner:MICRON TECH INC

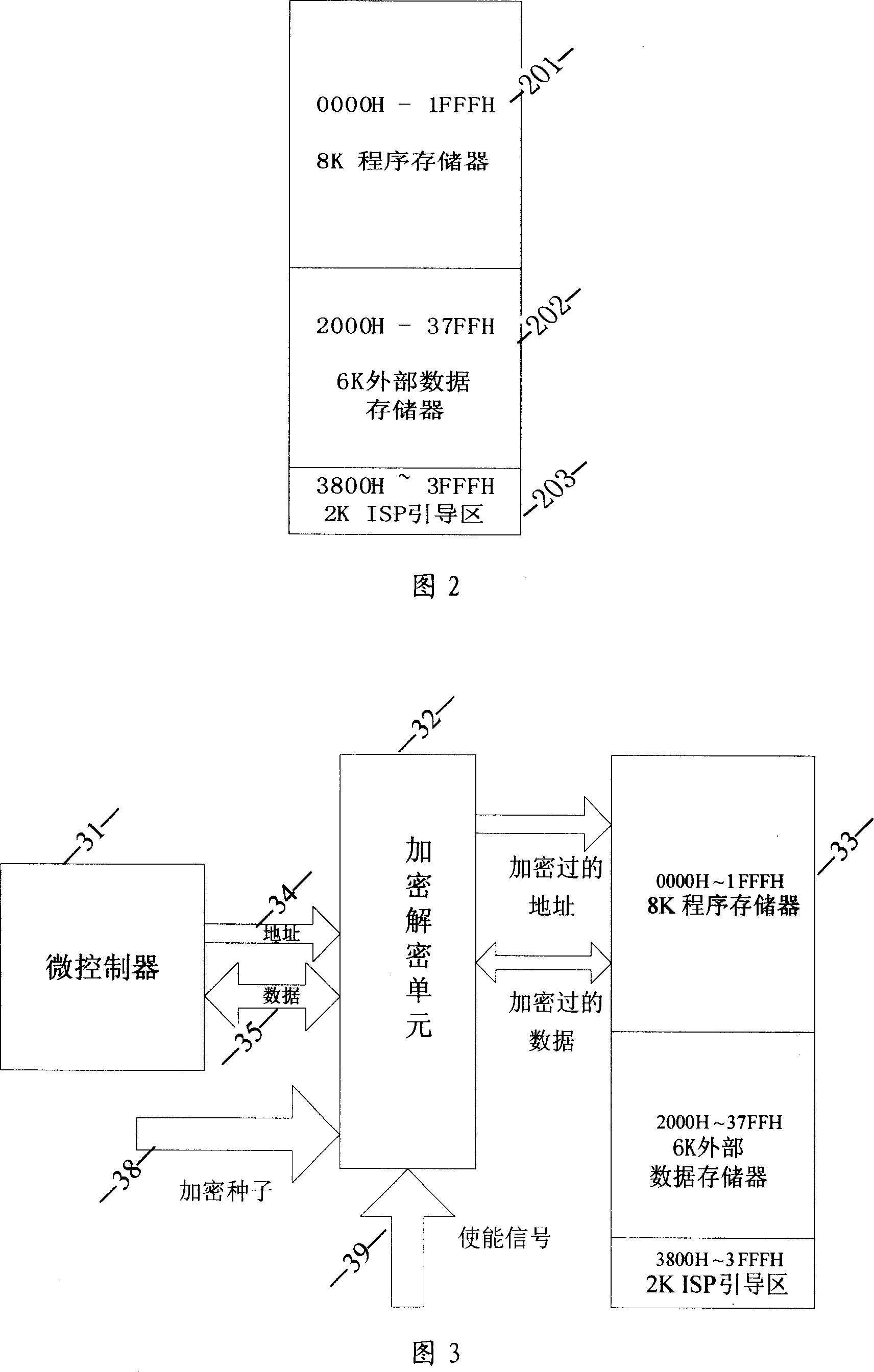

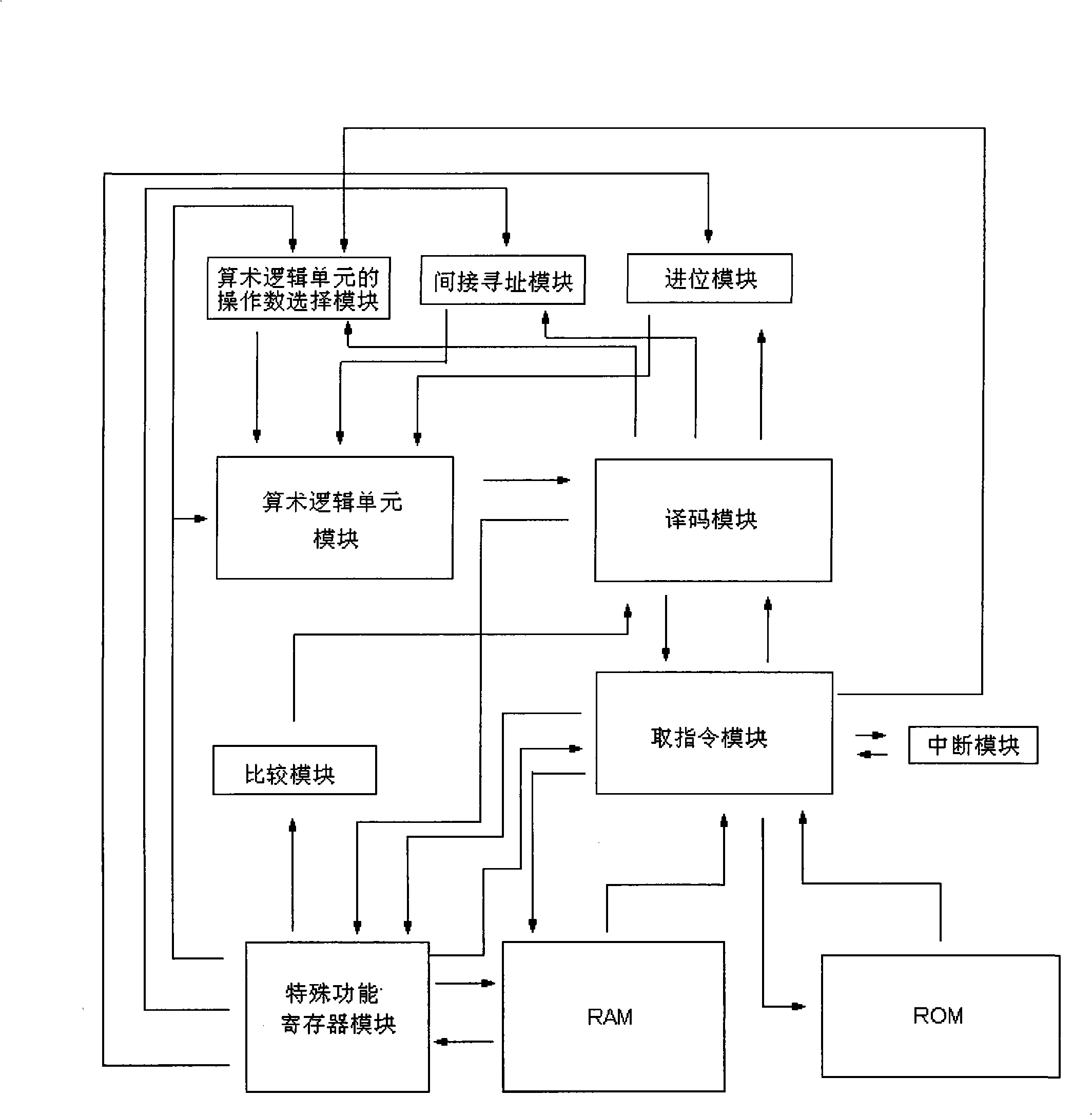

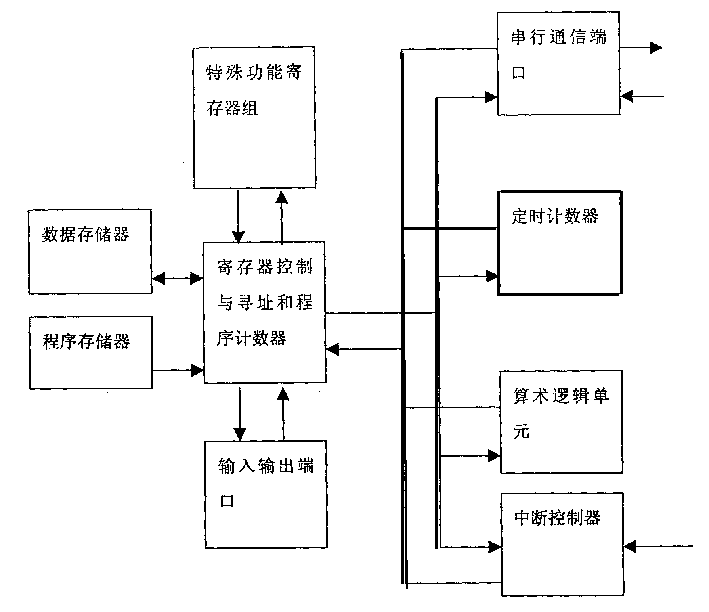

Eight-digit compatible C51 instruction set microcontroller

ActiveCN101154212AReduced operating power consumptionReduce power consumptionEnergy efficient ICTUnauthorized memory use protectionSpecial function registerProcessor register

The invention relates to a 8 bit compatible C51 index microcontroller which comprises a 8 bit high speed arithmetic logic component module, an arithmetic logic selection module, a 8x8 bit multiplication / division device, an internal data storage, a register interface module, a special function register, an index execution / direction register, an index state device, a breaking controller module, an index decoder, a program storage unit, a timer / counter module, an external port module, two serial interface modules, three 16 bit timers and one 16 bit watchdog timer; when the internal index is operated, the clock cycle used for each machine cycle is increased from the original twelve clock cycles to two clock cycles, the index operation speed can reach to six times of the prior 51 singlechip, the operation power consumption can be largely reduced, the function is complete, the performance is ideal, a wide application foreground can be obtained.

Owner:SHANGHAI EASTSOFT MICROELECTRONICS

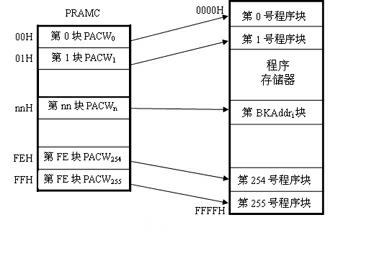

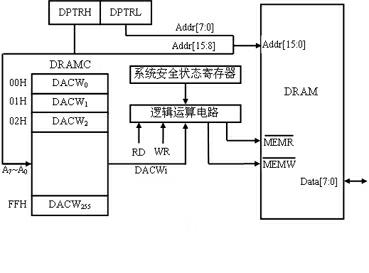

External program security access architecture based on system on chip (SoC) and control method

ActiveCN102184366AMake sure to pass throughEffective protectionDigital data protectionPlatform integrity maintainanceMode controlSecure state

The invention relates to an external program security access control system based on a system on chip (SoC) and an access control method. The system consists of an internal buffer memory, an extended external program memory area security attribute control memory, a memory operating mode control register, a program execution security control logic circuit, an external data memory and a programmemory, wherein the memory operating mode control register is positioned in a special function register area SFR area of the SoC, the address thereof is 8FH; the respective memories and the register are connected with a central processing unit (CPU) by an address bus, a data bus and a control bus. By connecting the address bus, the data bus and the control bus to the CPU, under the control of program execution security control logic circuit, the classified security management of the external program memory is realized; the execution, access and monitoring of instructions and the sensitive data on the premise that a security state meets a requirement are guaranteed; the progressive starting and transfer of a trusted root of an information system are realized.

Owner:ZHENGZHOU XINDA JIEAN INFORMATION TECH

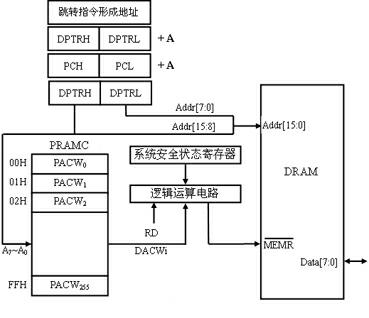

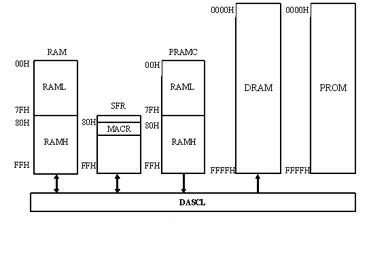

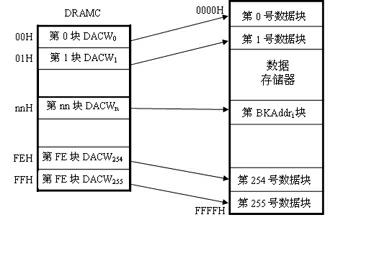

External data security memory architecture based on system on chip (SoC) and access control method

ActiveCN102184365AEffective protectionIncrease profitDigital data protectionPlatform integrity maintainanceMode controlStructure of Management Information

The invention relates to an external data security access system based on a system on chip (SoC) and a memory control method. The structure consists of an internal buffer memory, an extended external program memory area security attribute control memory, a memory operating mode control register, a data access security control logic circuit, an external data memory and a program memory, wherein the memory operating mode control register is positioned in a special function register area of the SoC; the respective memories and the register are connected with a central processing unit (CPU) by an address bus, a data bus and a control bus; and the CPU sets an operating mode of an external data memory area security attribute control memory by the memory operating mode control register, configures the SoC to operate in a security static or dynamic access control mode of the external data memory, and carries out classified security management on the external data memory, so that the overall monitoring of data which is memorized in the external data memory in life cycles of generation, usage, correction, filling and clearing is guaranteed, a function of firewalls among the data with different security levels is realized, and requirements of the SoC on the security protection of sensitive data are met.

Owner:ZHENGZHOU XINDA JIEAN INFORMATION TECH

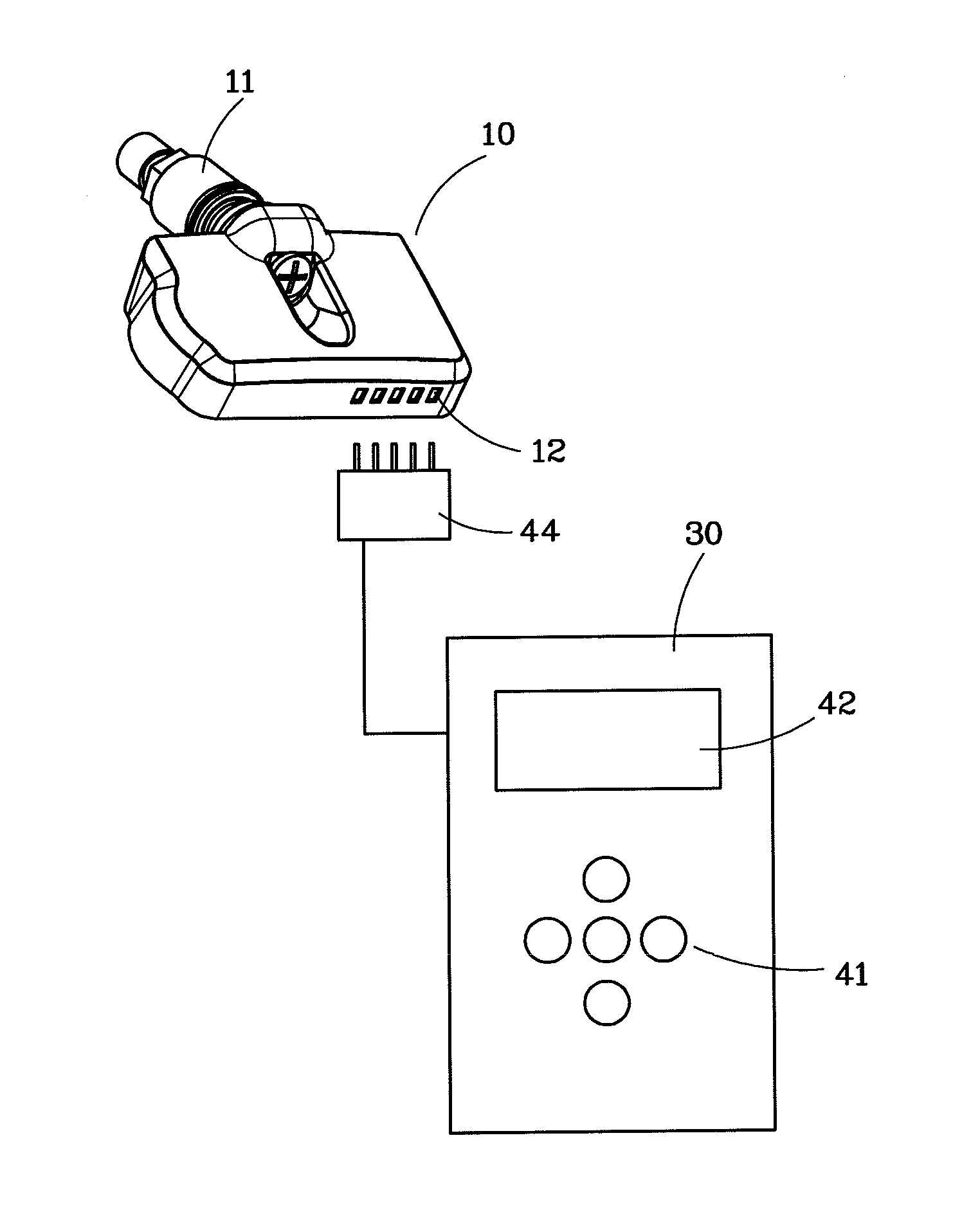

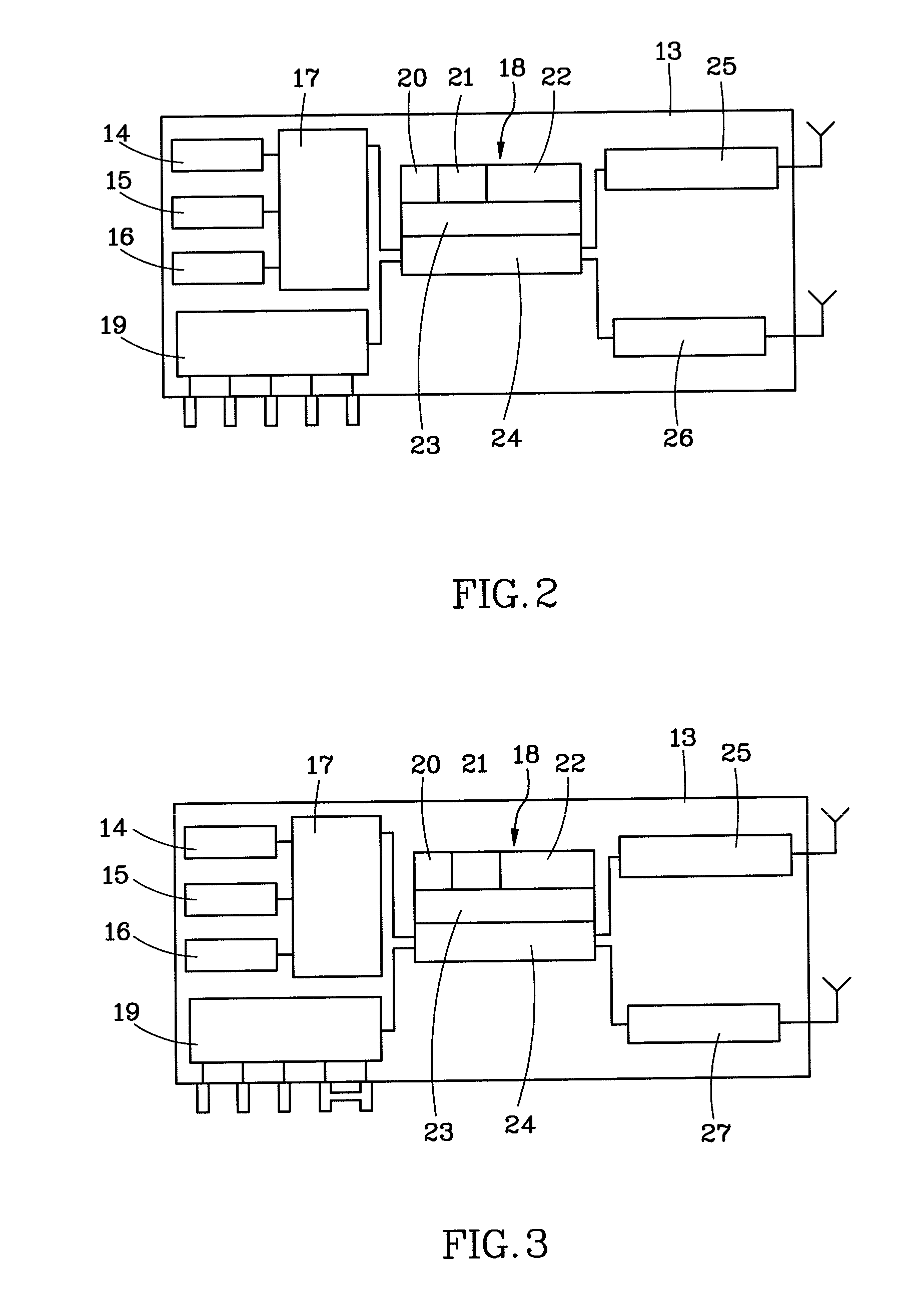

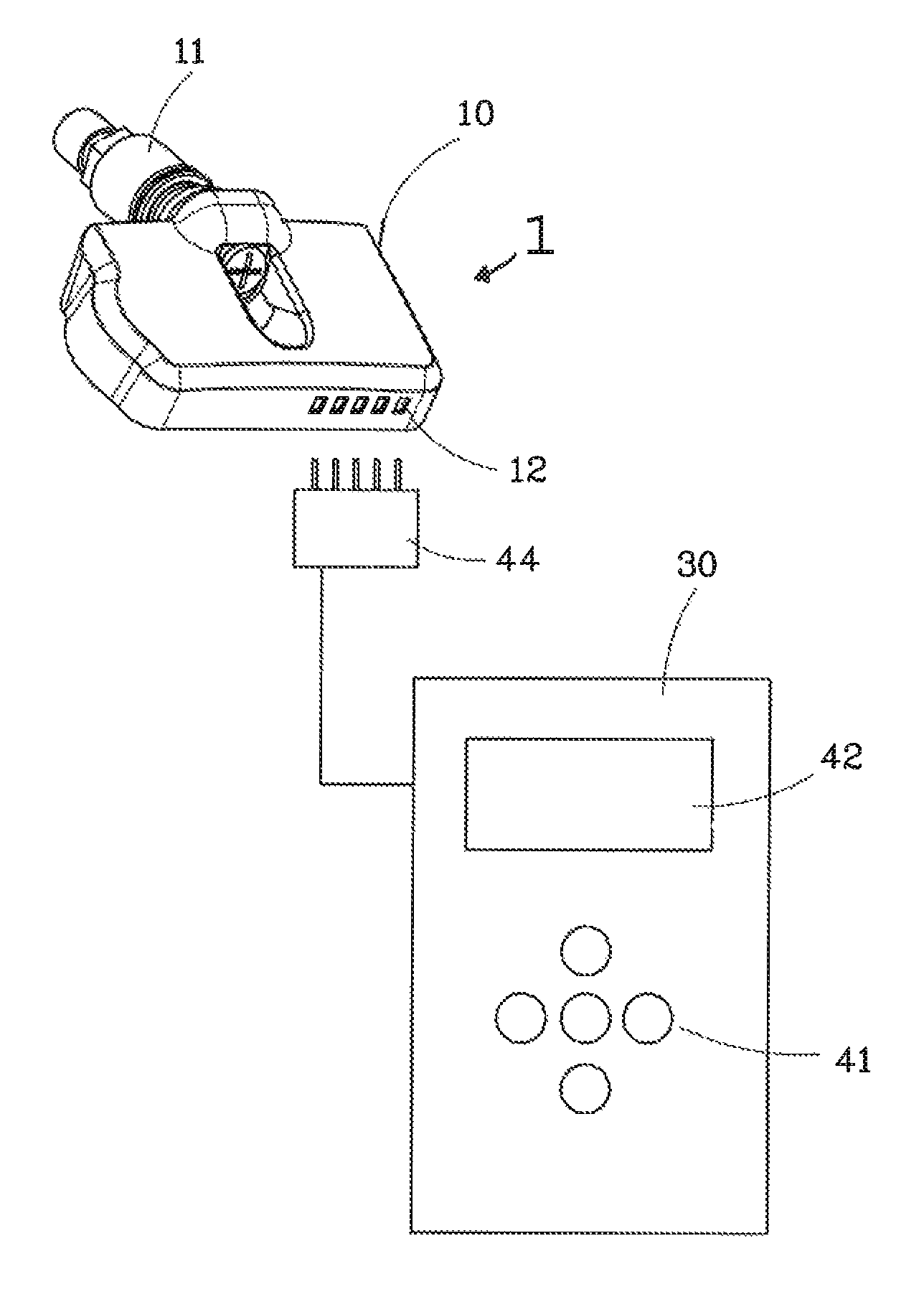

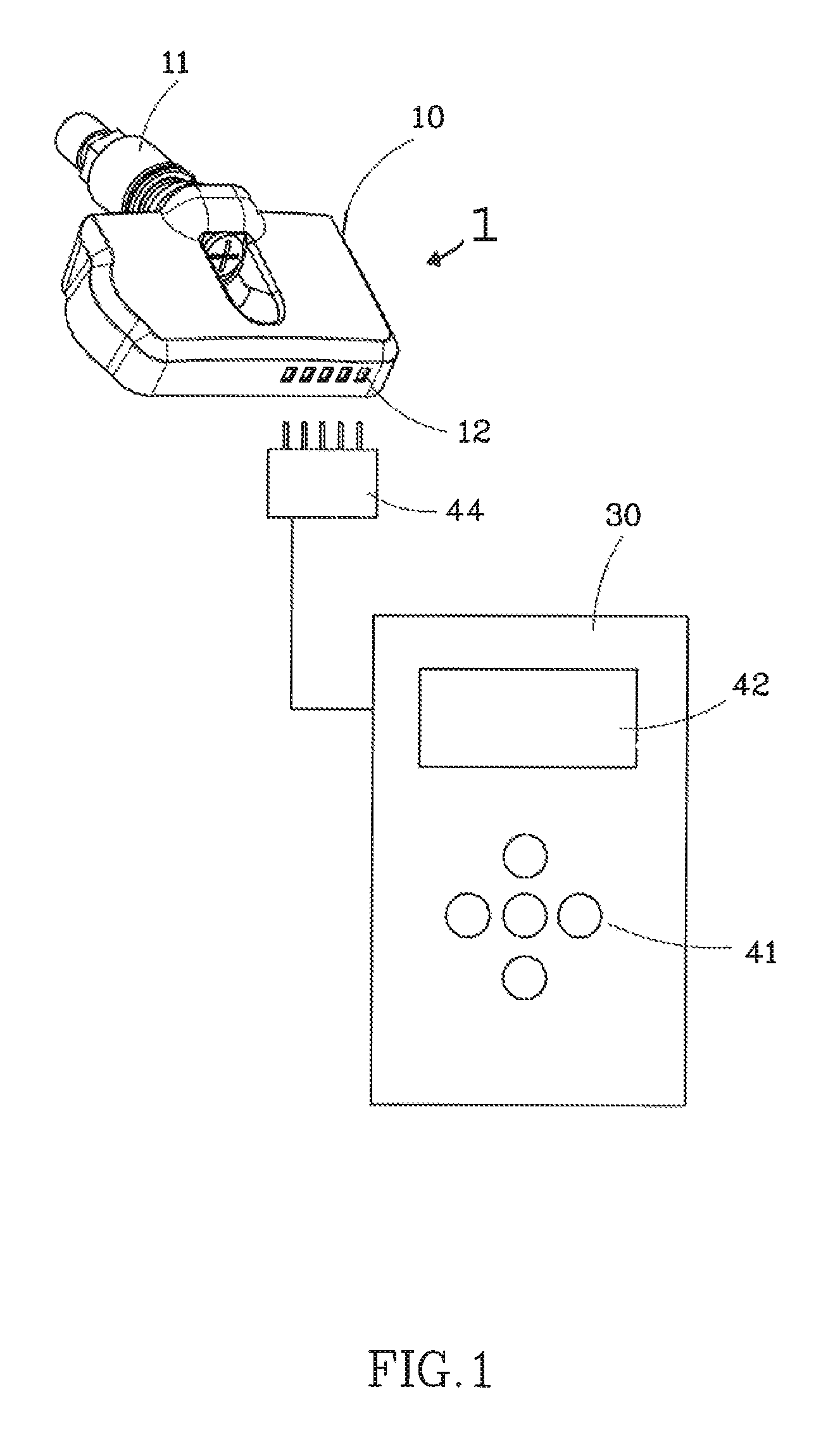

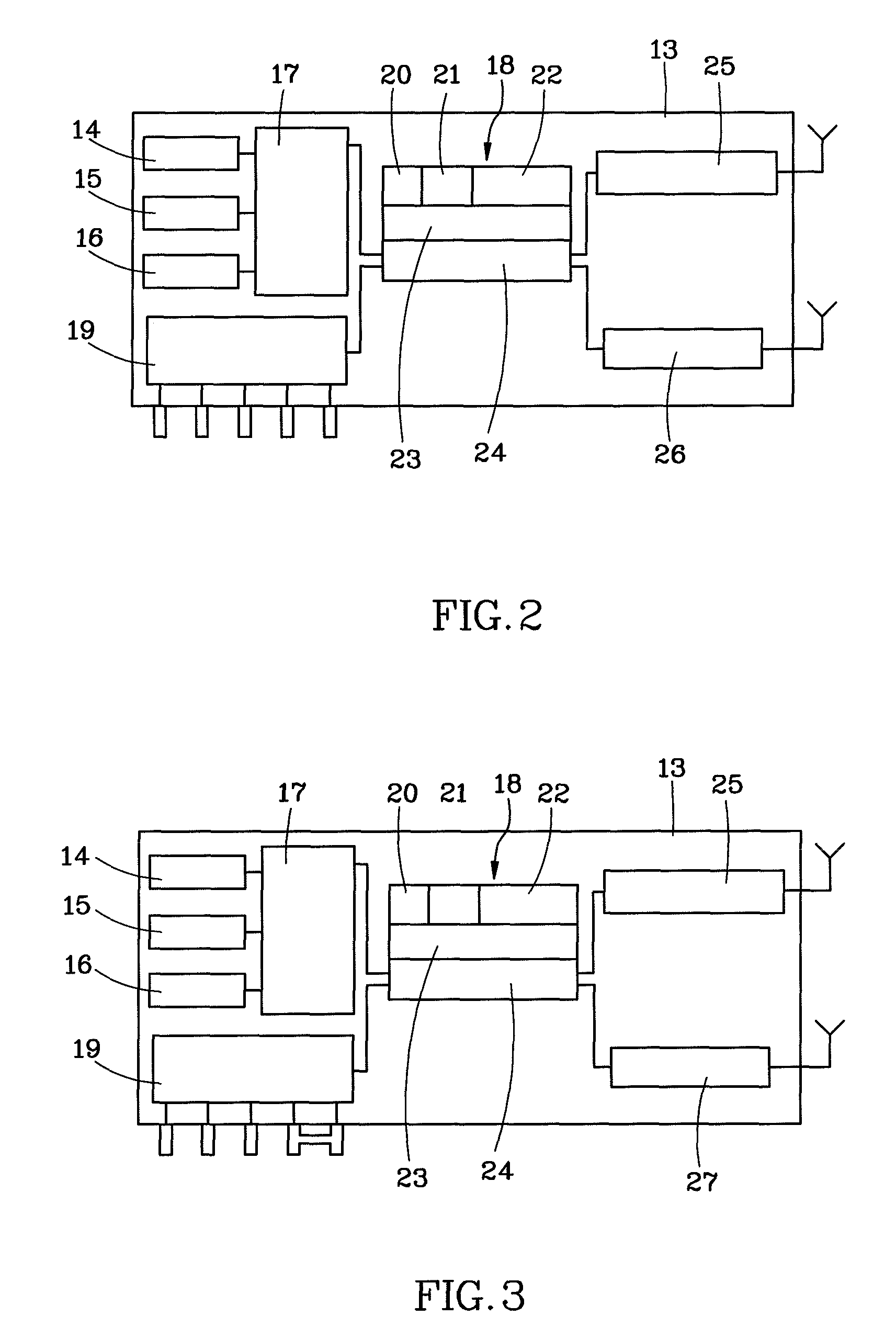

Blank tire pressure monitoring device and its setup method

A blank tire pressure monitoring device includes a housing having an air valve at one end and connection terminals at an opposite end, a circuit board mounted in the housing and carrying a pressure sensor, a temperature sensor, an acceleration sensor, an analog-digital converter electrically connected with the pressure sensor, the temperature sensor and the acceleration sensor, a general purpose I / O terminal unit electrically connected with the connection terminals of the housing; an embedded microcontroller module electrically connected with the general purpose I / O terminal unit and the analog-digital converter and having built therein a flash memory, a microcontroller core and a special-function register controller, a LF receiver electrically connected to the embedded microcontroller module, and a transmitter electrically connected to the embedded microcontroller module; and a method is still also disclosed for setting up a blank tire pressure monitoring device.

Owner:CUB ELECPARTS

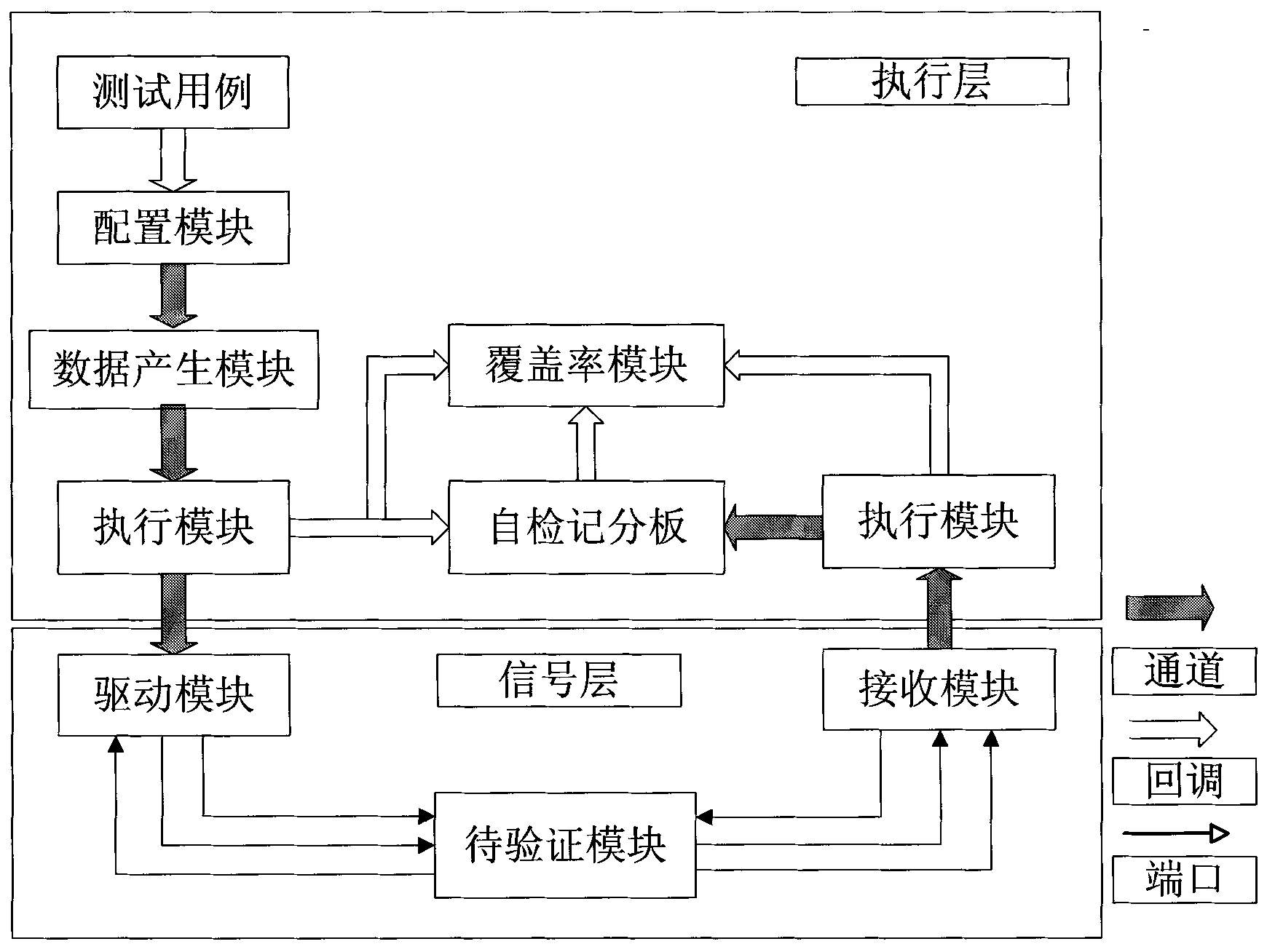

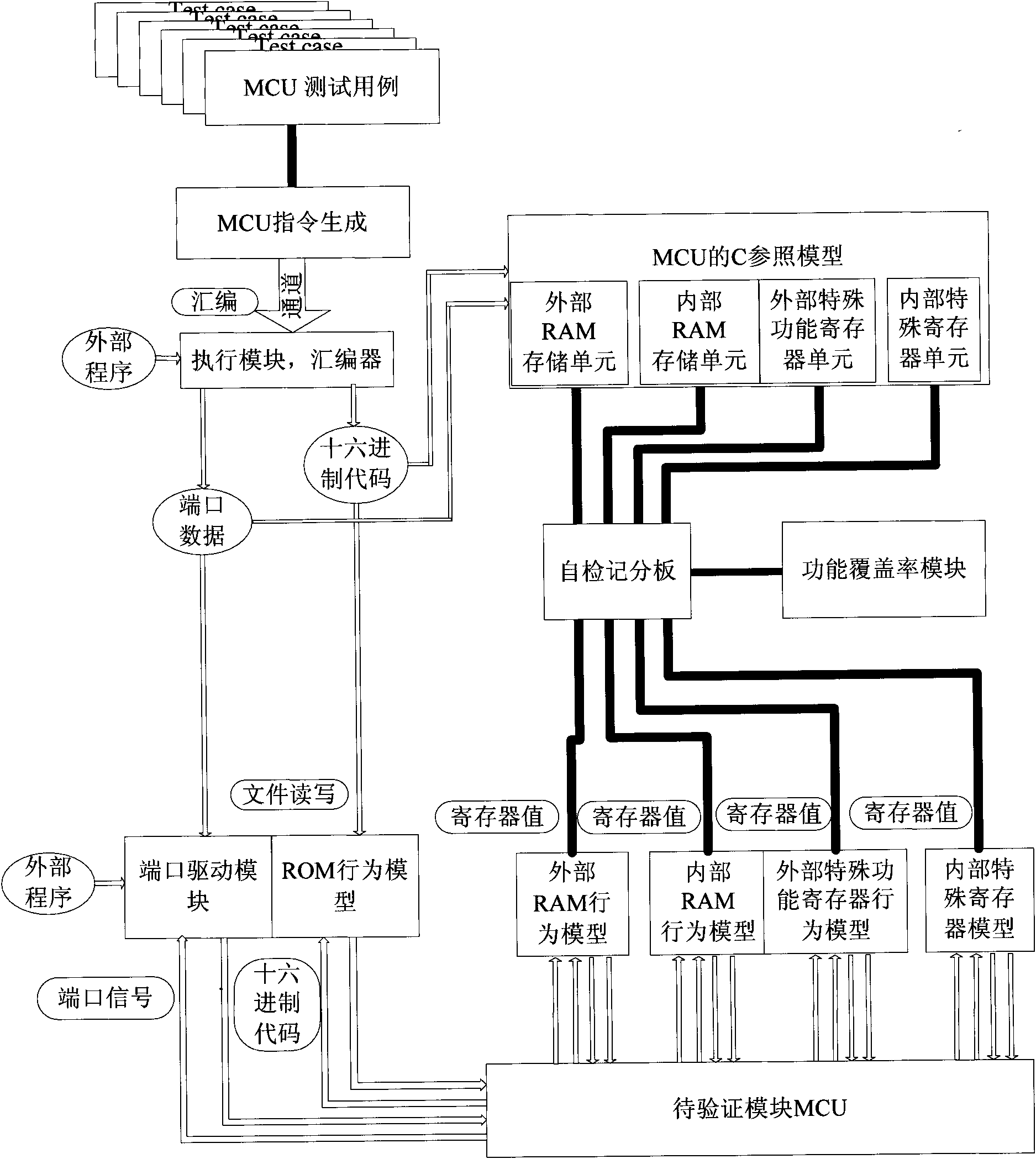

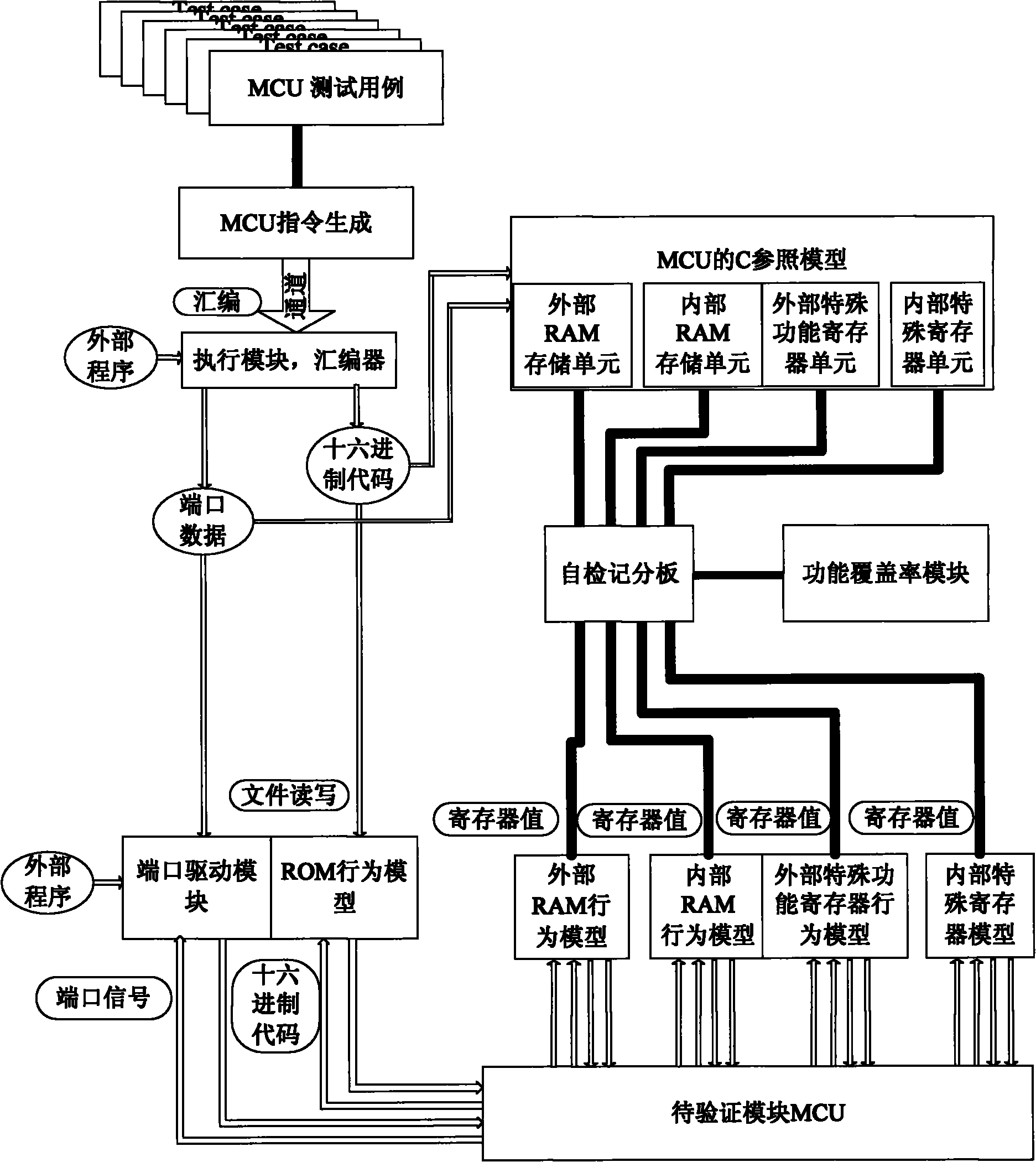

Method for realizing microprogrammed control unit (MCU) verification platform based on verification methodology of verification methodology manual (VMM)

InactiveCN102096628ASimple migration and verificationExtended fully automated checksSoftware testing/debuggingComputer architectureSpecial function register

The invention discloses a method for realizing a microprogrammed control unit (MCU) verification platform based on the verification methodology of a verification methodology manual (VMM). The method comprises the following steps of: inputting all usable application program codes or generating a constraint random instruction by using the platform; realizing a model C of an MCU and providing values of all memory units and special function registers, and calling through a direct program interface (DPI); automatically performing self-checking according to a memory unit model serving as a reference; and describing various functional coverage models and providing a functional coverage result. By the method, a portable, reusable, extensible and fully automatic check MCU verification platform with a hierarchical structure can be established.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

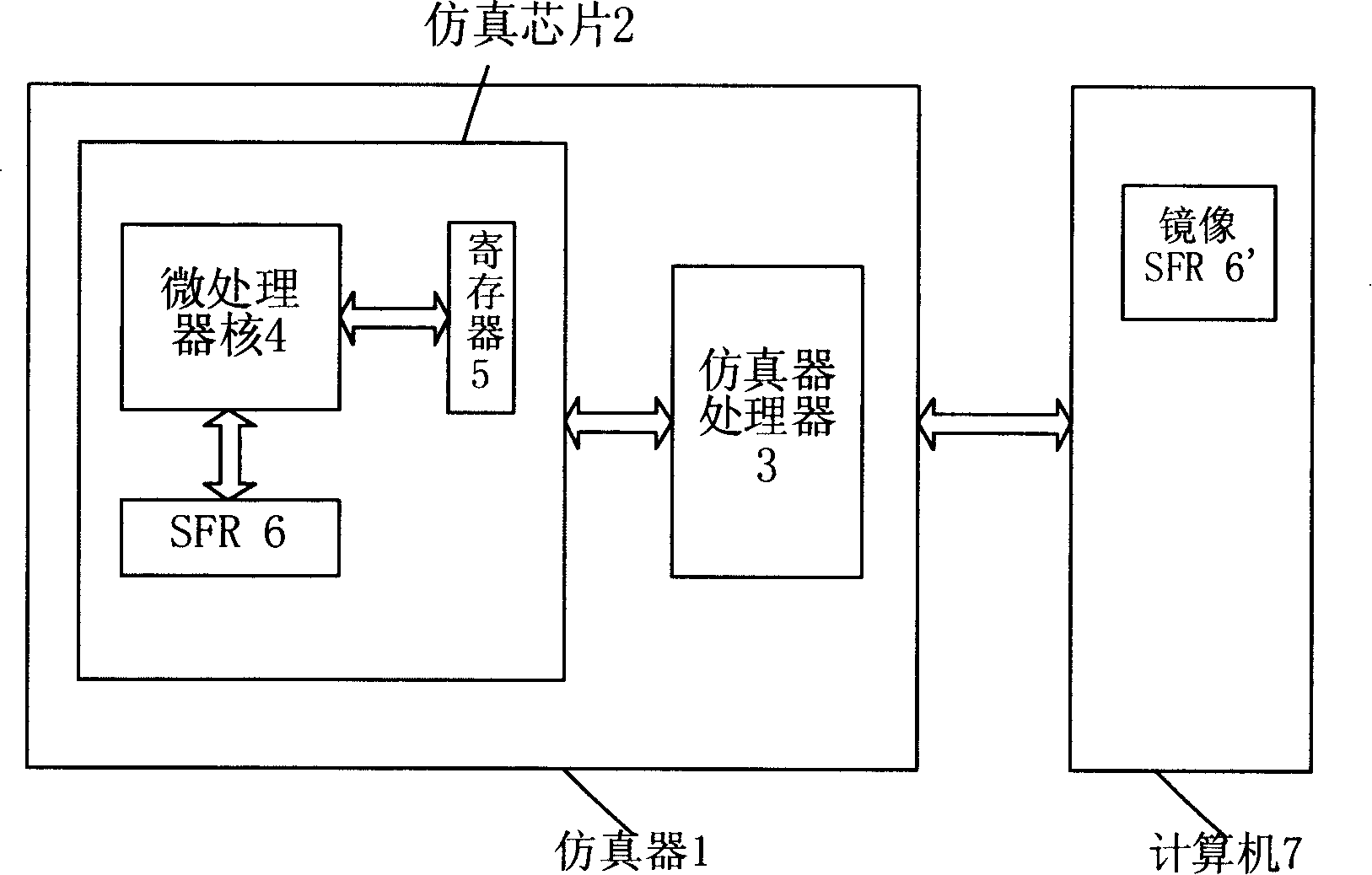

Simulator for simulating register with specific function

InactiveCN101206614AWill not affect operationImprove debugging efficiencySoftware testing/debuggingMonitoring statusSpecial function register

The present invention discloses a simulator simulating special function register, comprising a simulation chip and a simulator processor. A general register is arranged inside the simulation chip, and when the simulator is in monitoring state, a microprocessor core of the simulation chip can automatically store a current reading / writing operation FIFO count pointer value of a SFR realized in the FIFO mode into the register. After the microprocessor core of the simulation chip executes reading / writing operation to the SFR, the microprocessor core can automatically update the value in the register. The simulator processor can automatically read the value stored in the register. The simulator processor can send commands or commands and data to the simulation chip, and the microprocessor core carries out reading / writing operation to the SFR. The present invention provides reliable and convenient means for debugging the SFR of the type, and can effectively improve the debugging efficiency of user programs.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

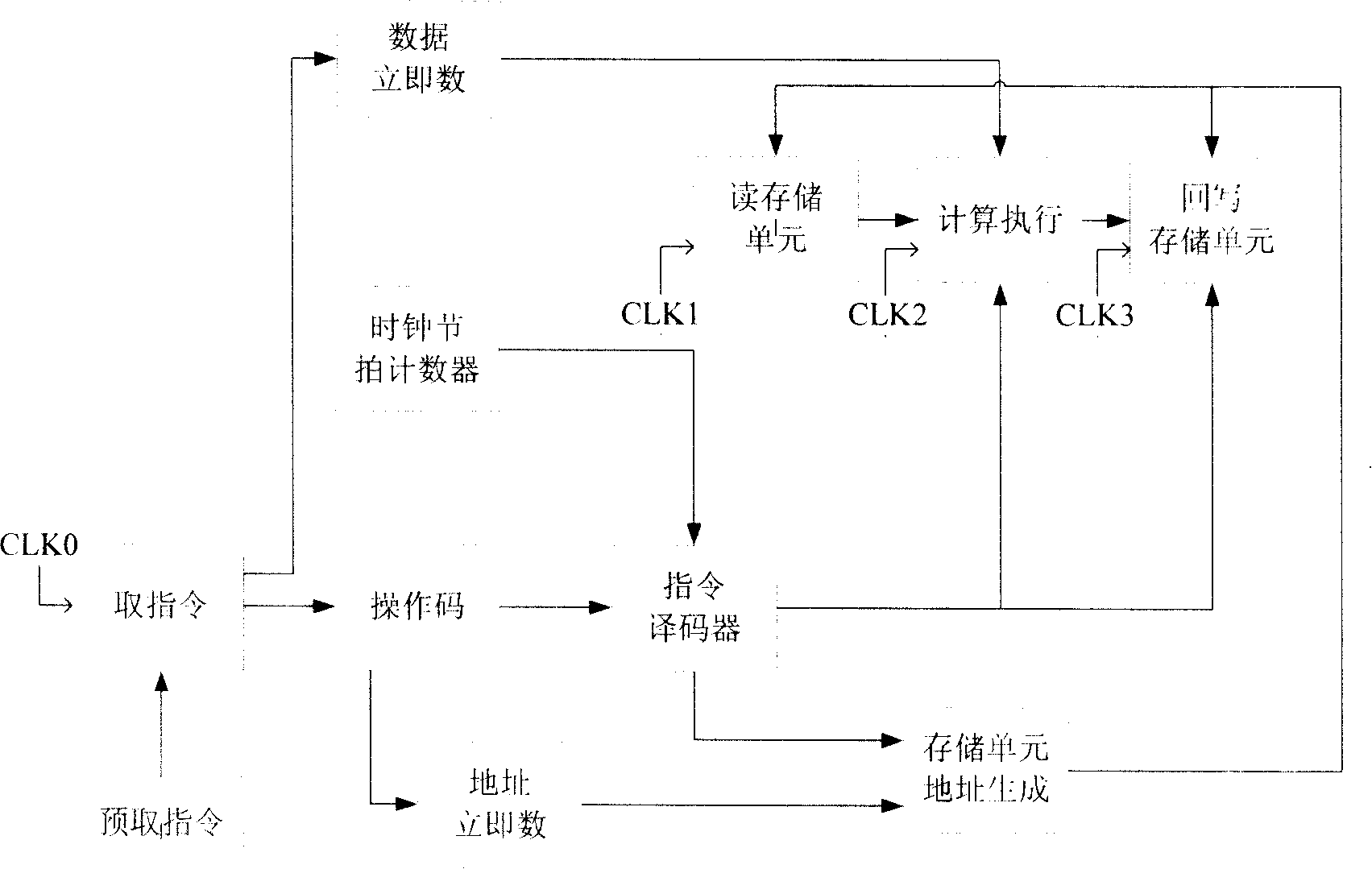

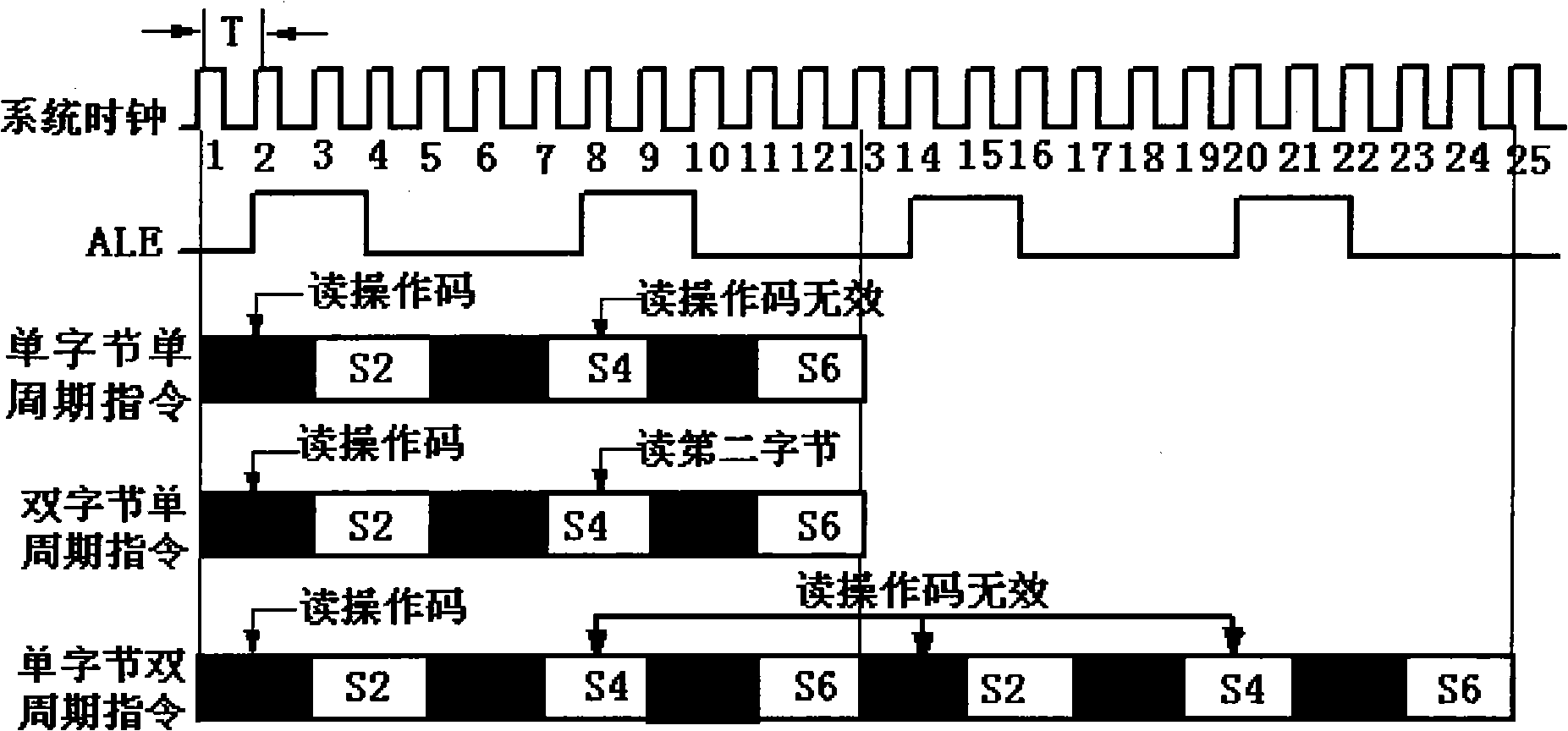

Singlechip adopting RISC structure

InactiveCN101339498ARun fastGood value for moneyConcurrent instruction executionArithmetic logic unitComputer architecture

The invention discloses a singlechip that supports MCS-51 instruction set, which comprises a ROM, an instruction fetching module, a RAM, an arithmetic logic unit, a special function register and a decoding module, and the like, adopts the way of an instruction with equal length, and adds a 3 lever pipeline function. The ROM is used for storing the application program of a user; the instruction fetching module provides the value of a program counter PC to the ROM and reads the application program from the ROM, thereby finishing the instruction fetching of the pipeline operation in a first phase, and then decomposes the application program into the operation code and operand which are transmitted to the decoding module; after the interruption module receives the interruption signal, the interruption response signal is returned. The decoding module fetches the operation code and operand to be implemented from the instruction fetching module, determines the control signal to other modules according to the operation code, and then finish a second phase and a third phase of the pipeline operation. On the condition that the instruction system of the MCS-51 series single-chip remains unchanged, the speed for the operation of the instruction can be improved effectively.

Owner:EAST CHINA NORMAL UNIV

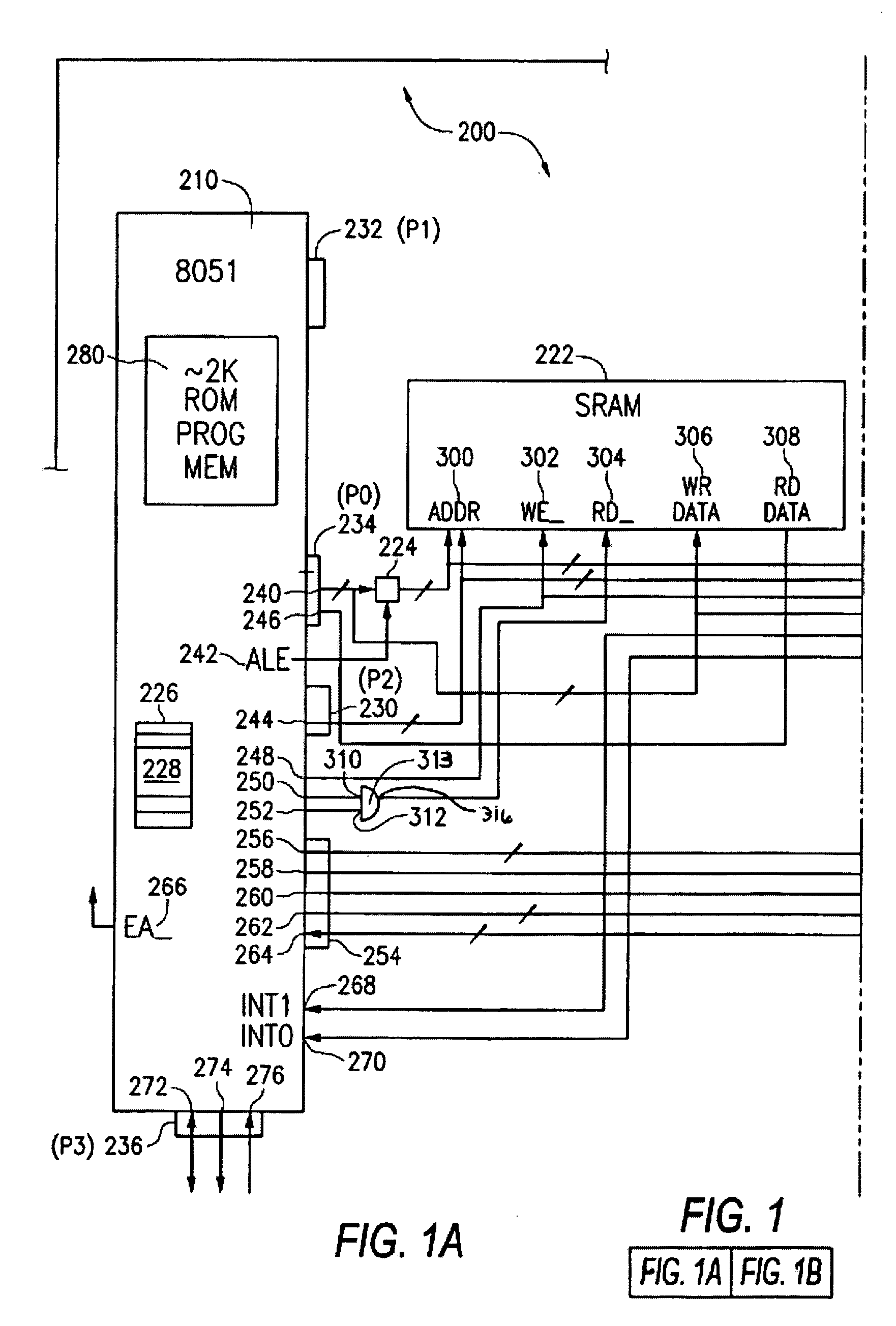

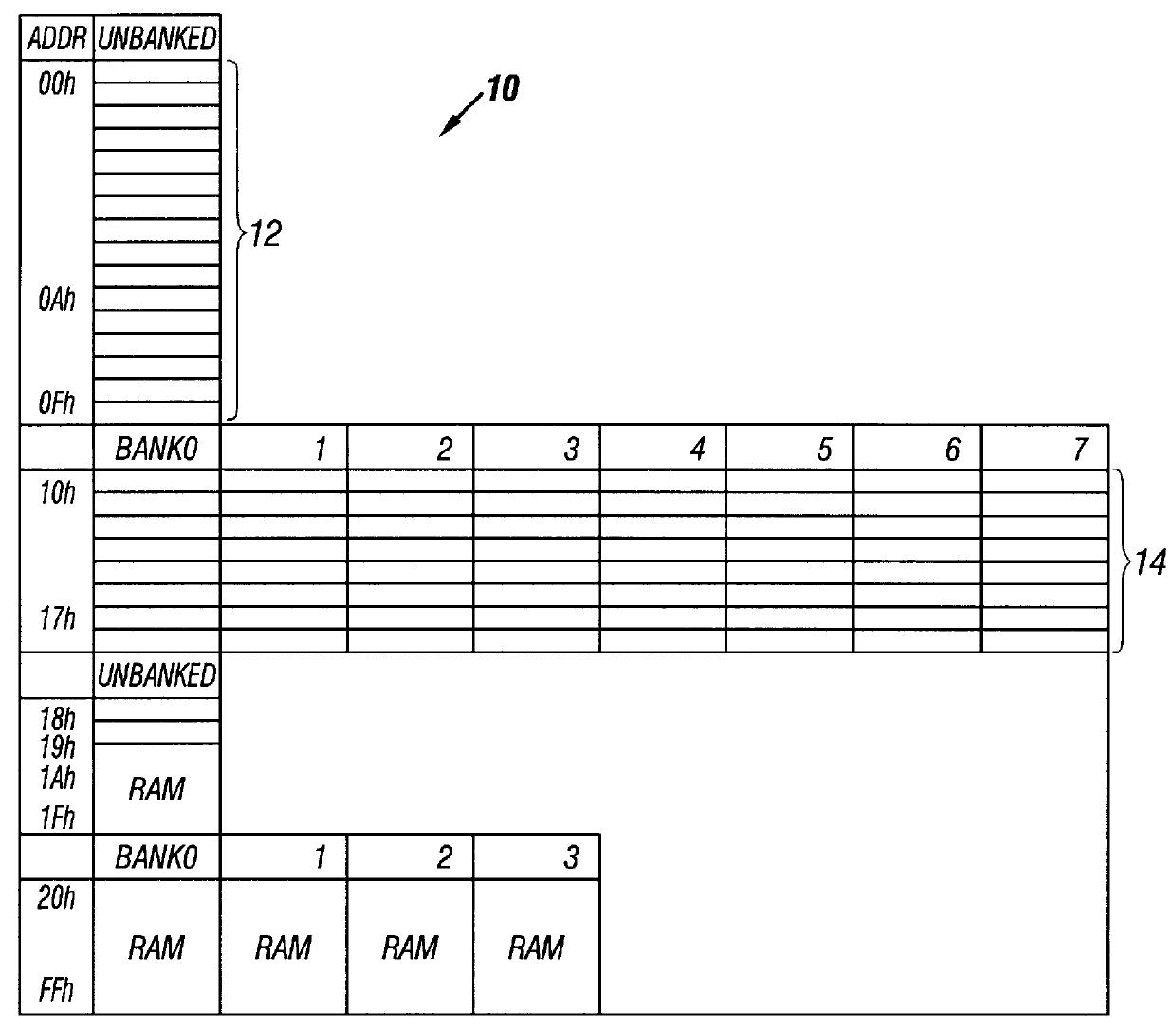

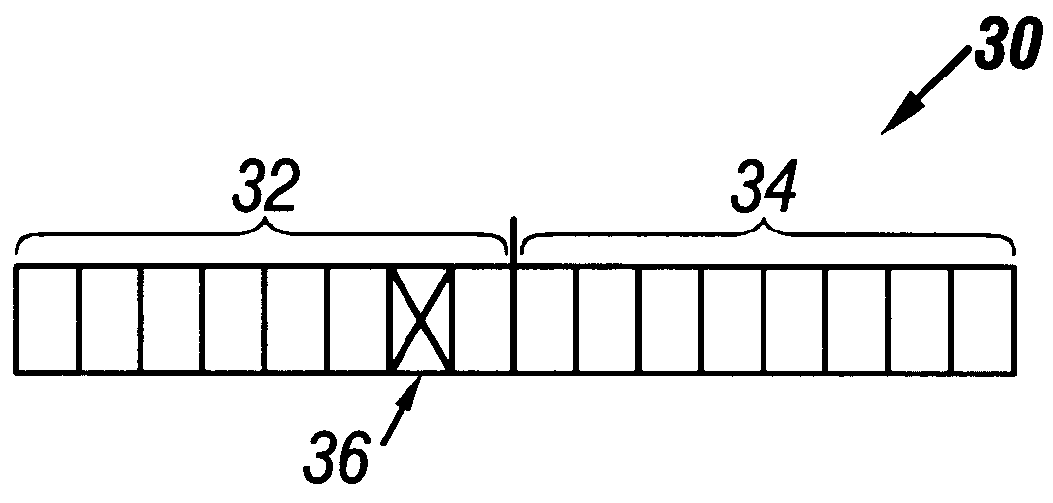

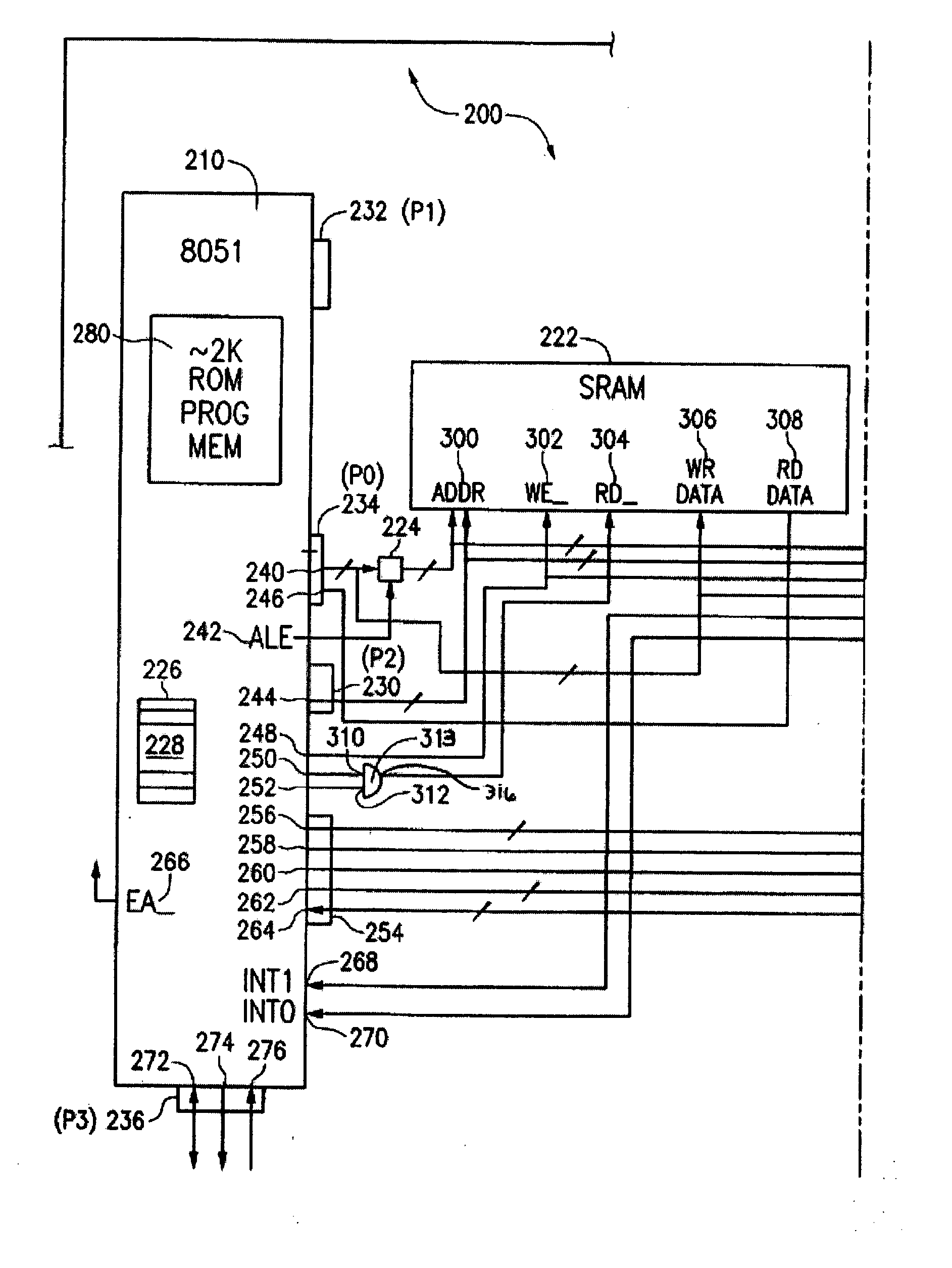

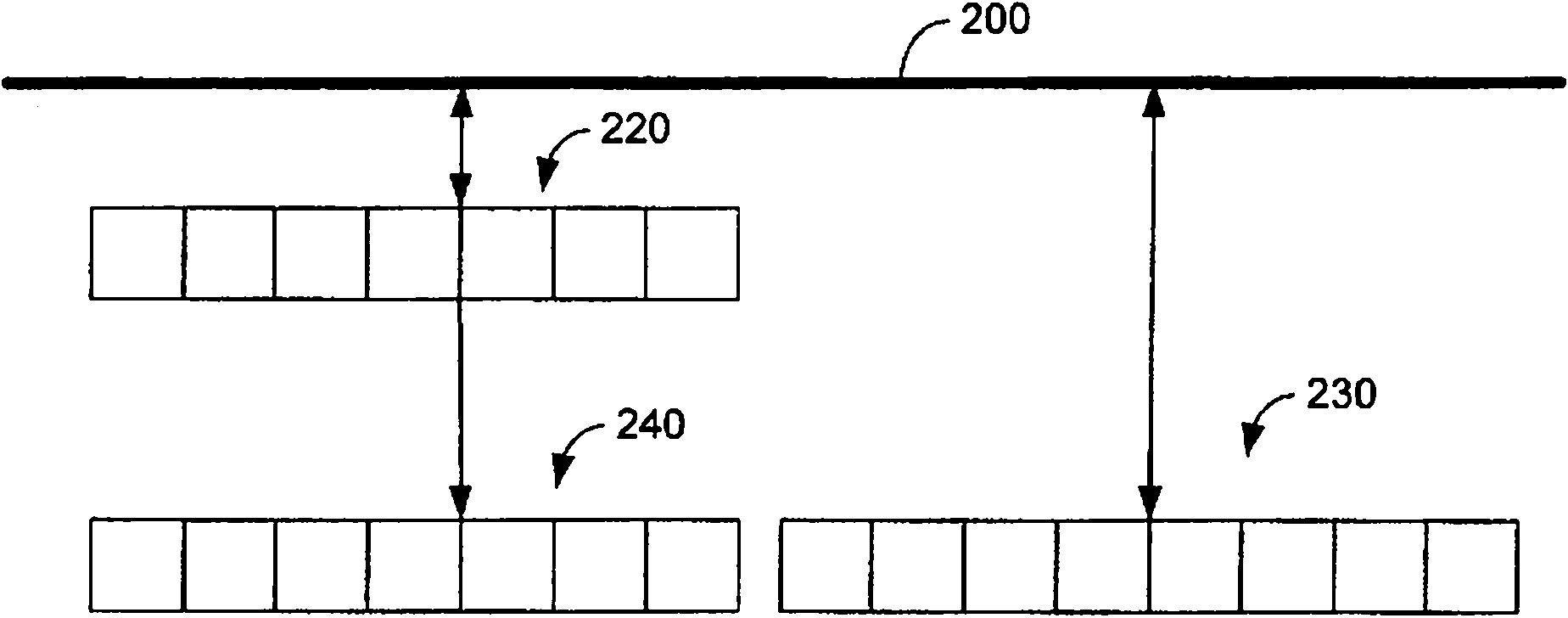

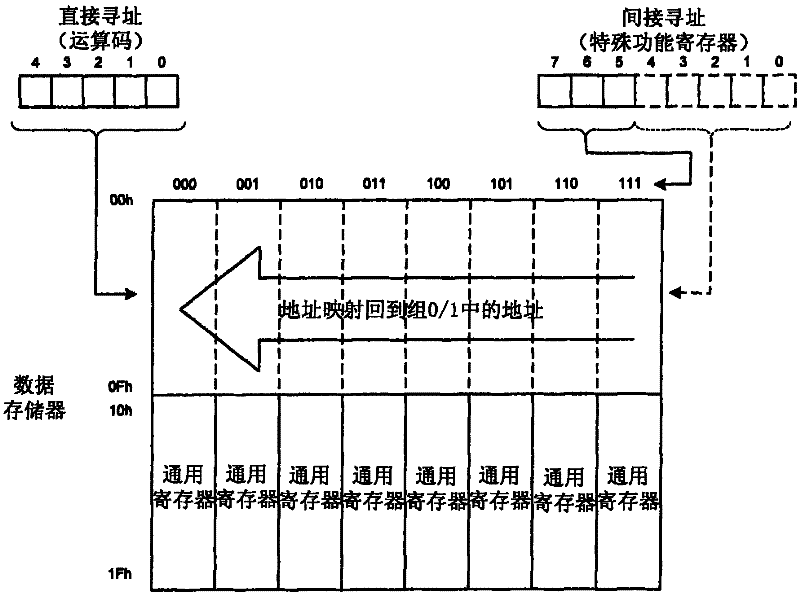

Force page zero paging scheme for microcontrollers using data random access memory

InactiveUS6055211ARegister arrangementsCircuit arrangementsController architectureStatic random-access memory

A microcontroller architecture that adds a dedicated bit in the op-code decode field to force data access to take place on page 0 of the random access memory (RAM) for that instruction. This allows the user to have any page selected and still have direct access to the special function registers or the register variables which are located on page 0 of the RAM. The setting of the dedicated bit will not affect the current operation of the microcontroller nor will the setting of the bit modify the currently selected address stored in the op-code instruction currently being executed by the microcontroller.

Owner:MICROCHIP TECH INC

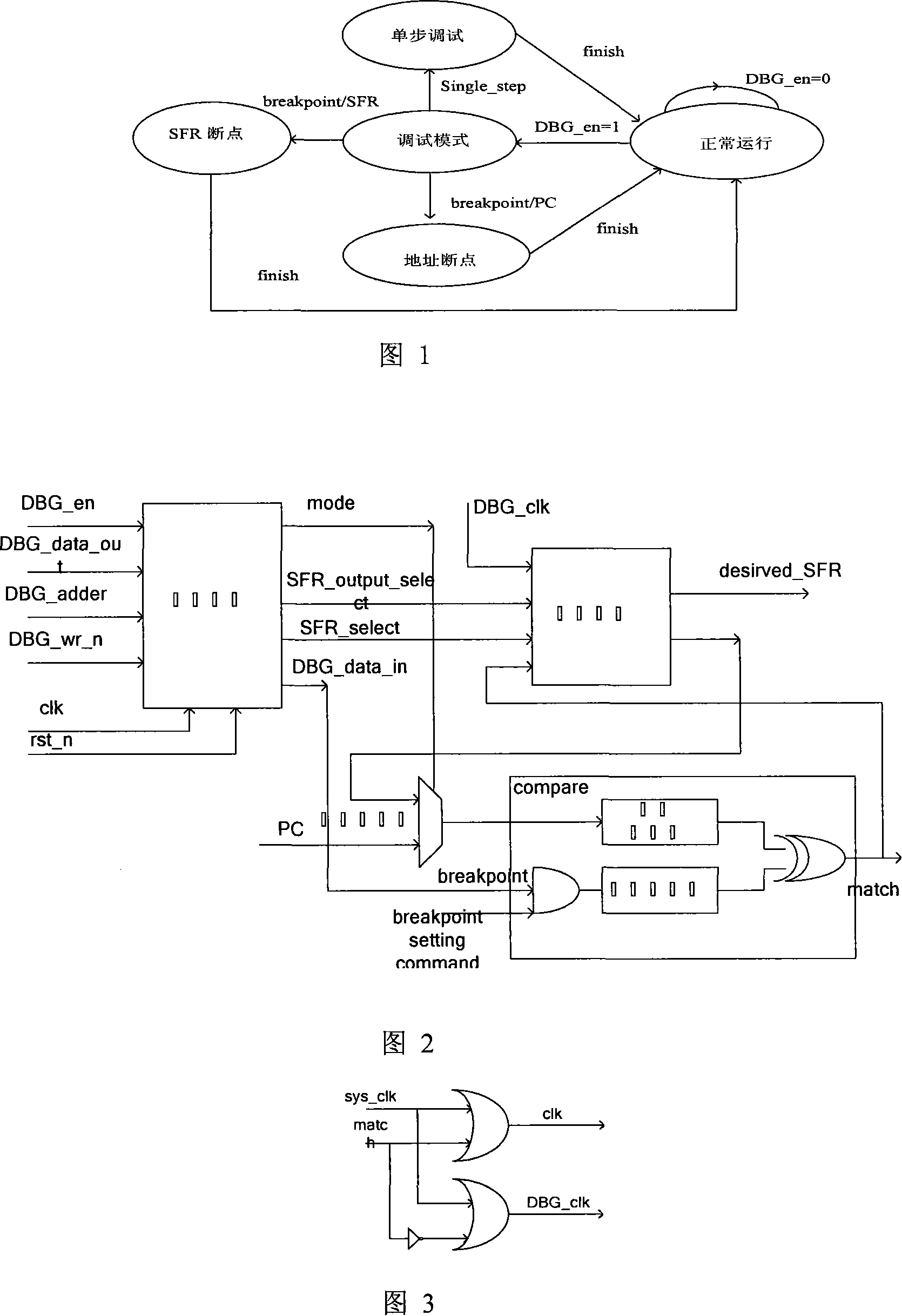

Enhancement type microprocessor piece on-chip dynamic state tracking method with special function register breakpoints

InactiveCN101178685AMeet staging requirementsSoftware testing/debuggingSpecial function registerProcessor register

The invention relates to a dynamic tracing method on the strengthening type card of a register breakpoint with particular function. The invention can set a certain positions or a register with particular functions to be breakpoints during the procedure executing process by unattached debugs module with SFR breakpoint function which is arranged on a strengthening type piece and is integrated in a microprocessor, then traces, records and outputs the information of the inside register at the breakpoints in real-time. The invention realizes to switch the debugging mode and the normal running mode though adding debugging signal. The method of the invention can be applied in the 8051 serials microprocessor field and also can be applied in other microprocessor fields.

Owner:SHANGHAI UNIV +2

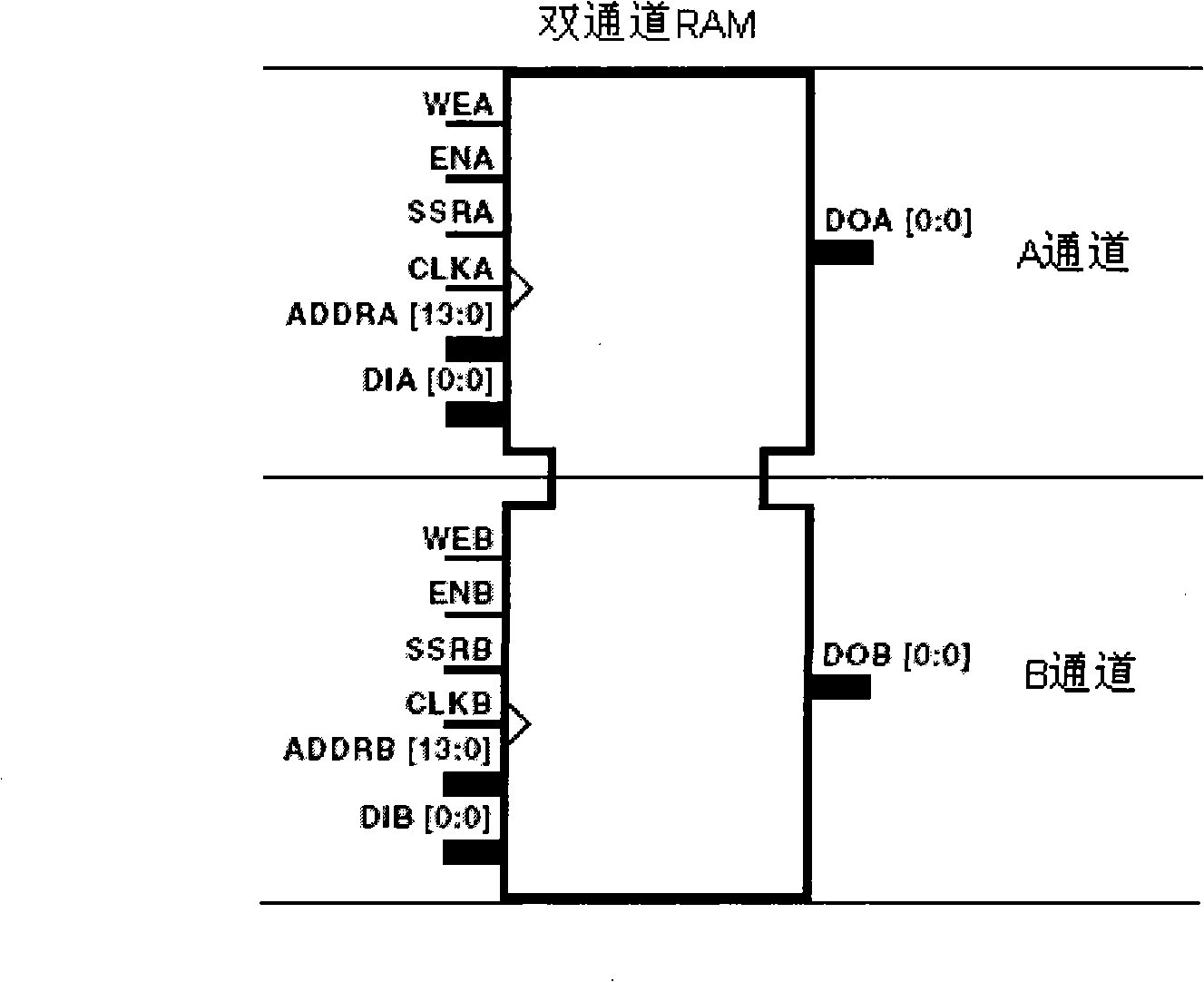

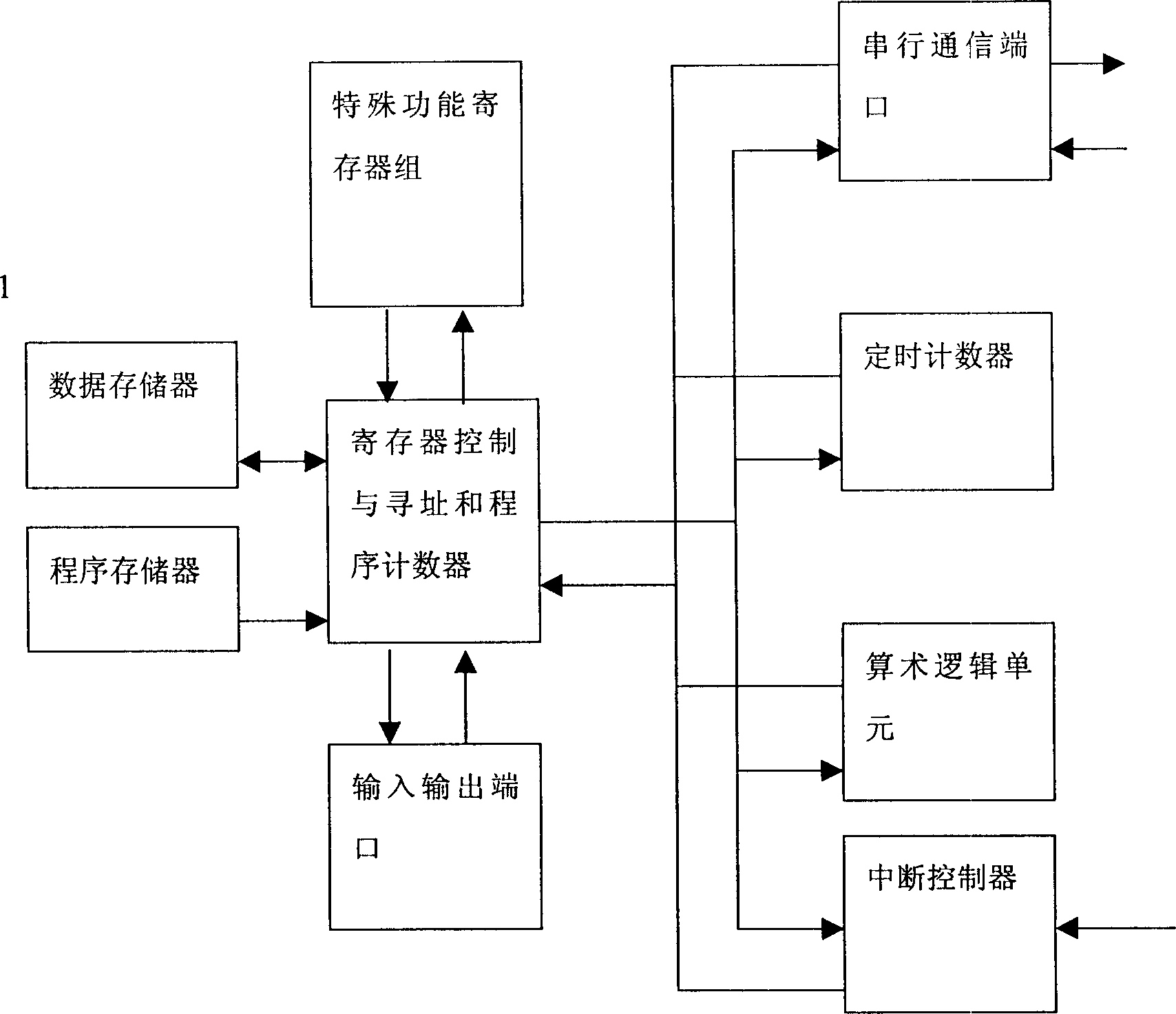

Micro controller IP nucleus

InactiveCN1508672AMicrocontrol arrangementsMemory systemsArithmetic logic unitSpecial function register

The invention refers to a kind of micro-control technology, especially a microcontroller IP core which has 8 bits, MCS51 instructions structure, which includes data memory, program memory, special function resister group, resister control and addressing, program counter, I / O ports, series communication port, timing counter, arithmetic logic unit, interruption controller. The character lies in: the instruction in 8 bits, MCS51 instructions structure is accomplished in 4 or 8 clock periods.

Owner:成都三零嘉微电子有限公司

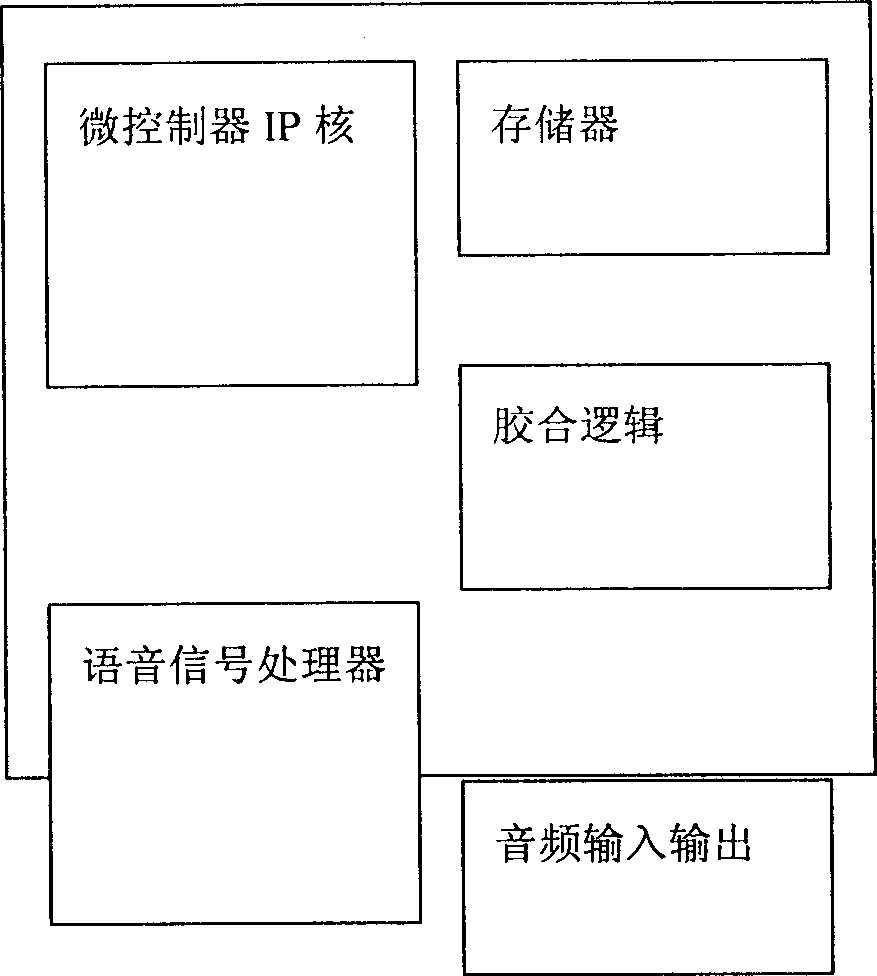

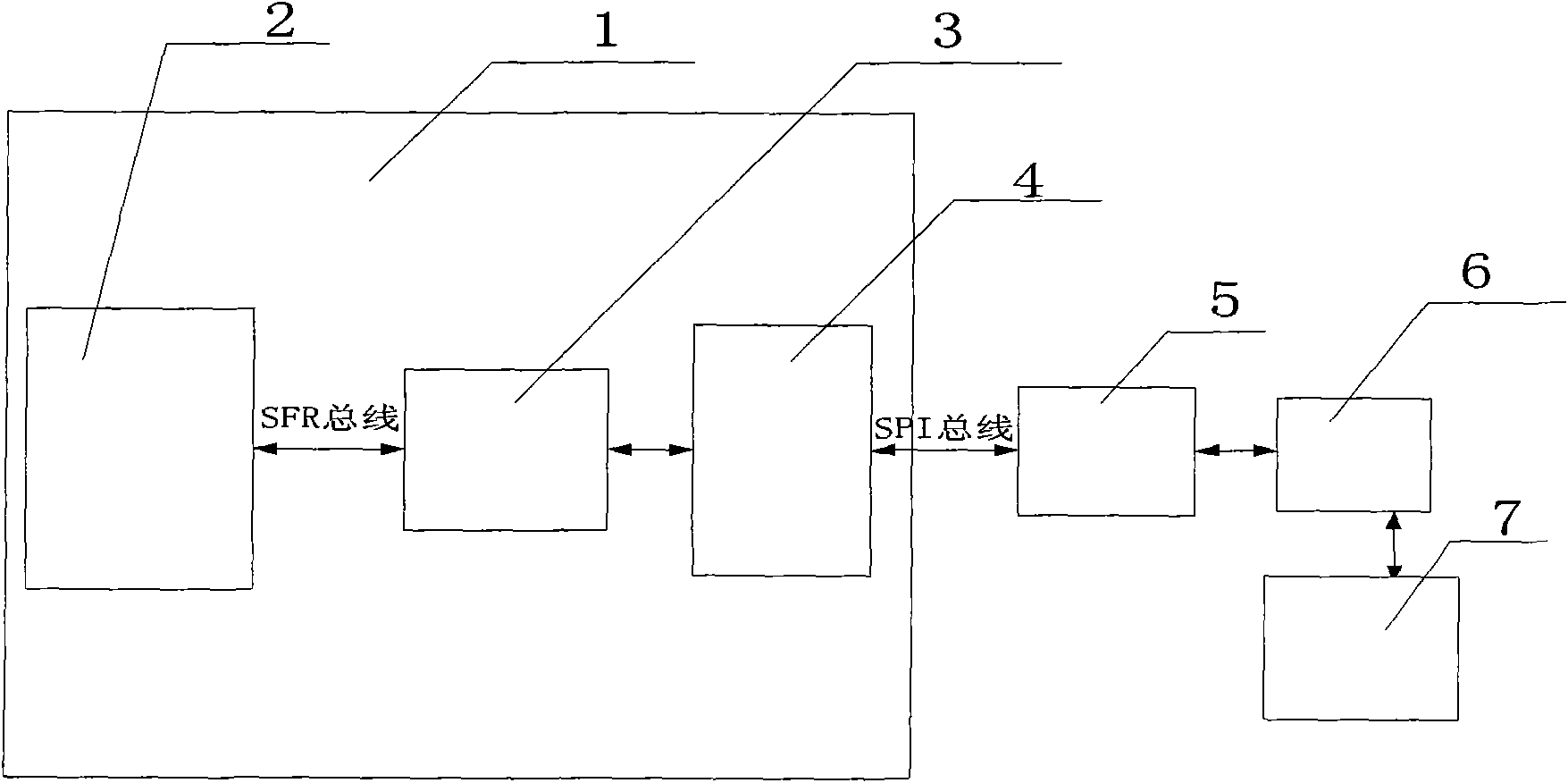

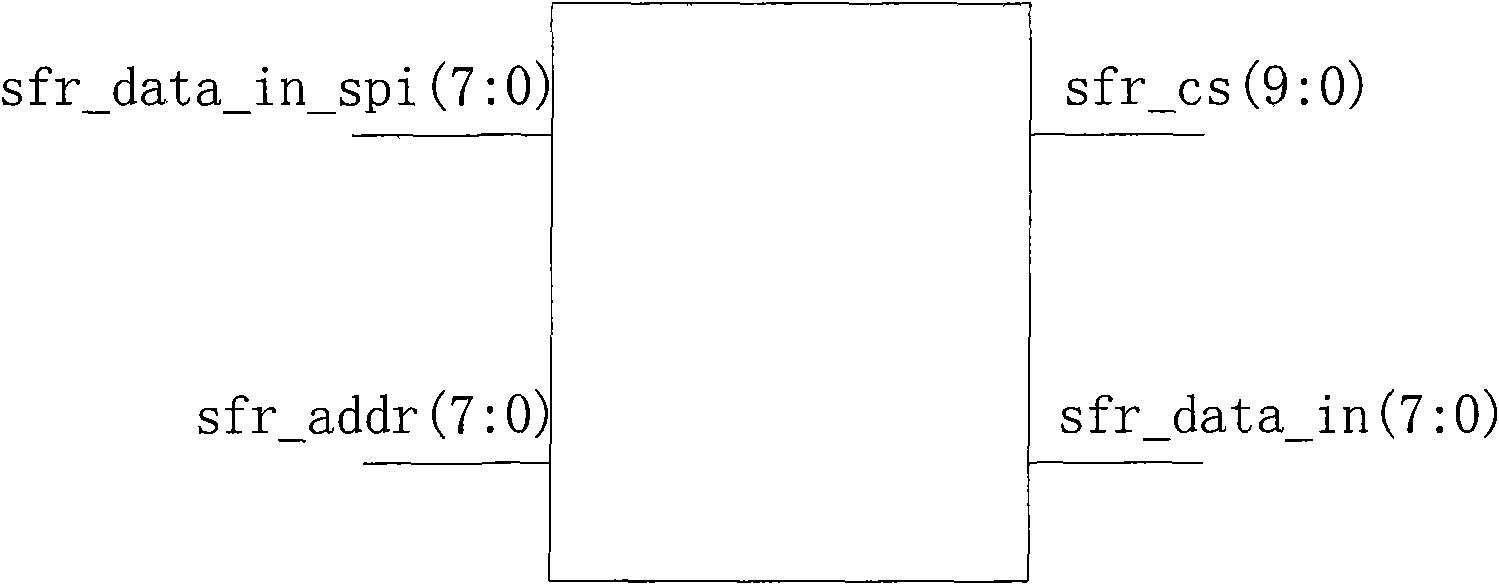

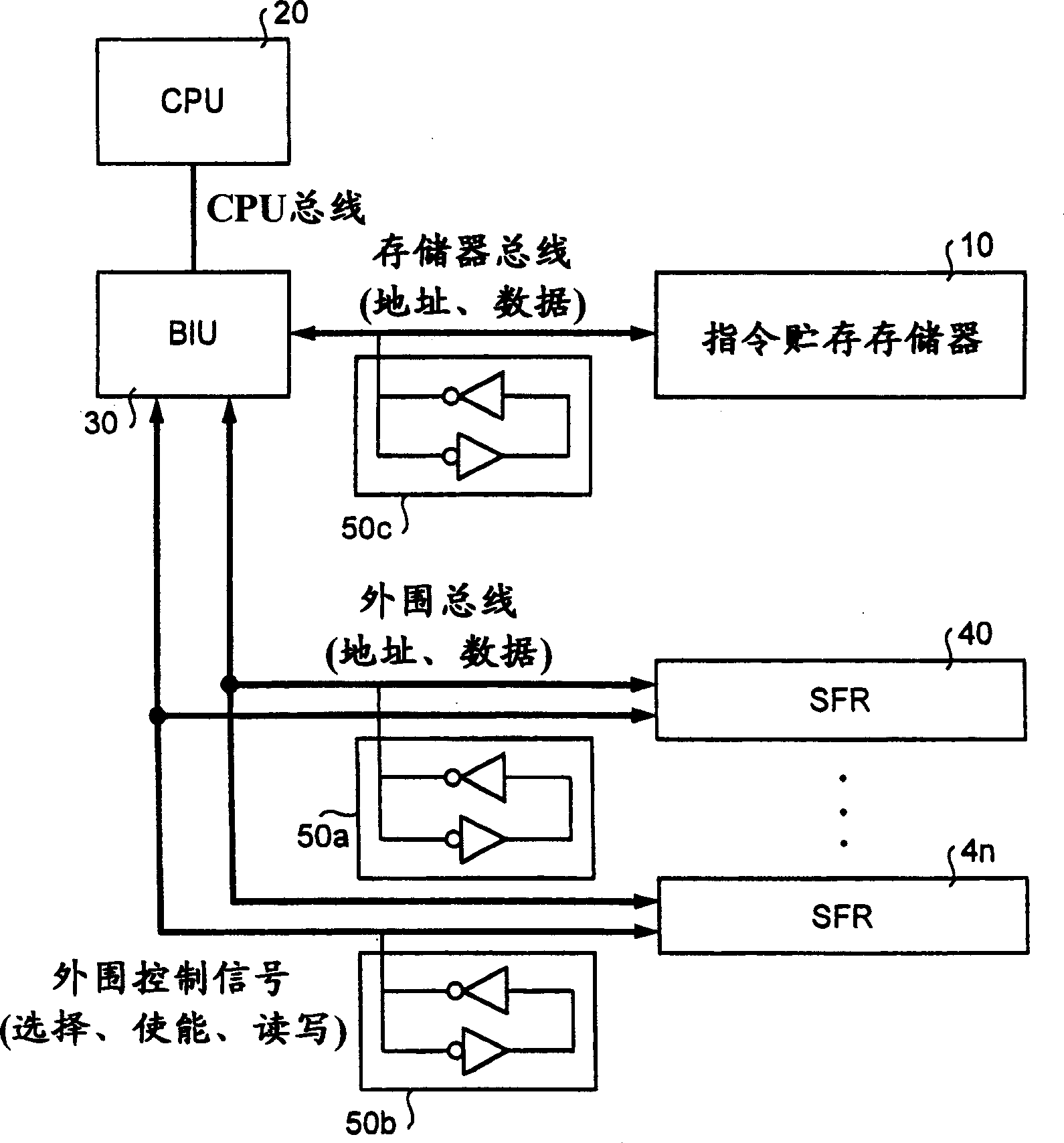

Method for connecting system on programmable chip to Ethernet

InactiveCN101651673AEasy to implementShorten development timeData switching by path configurationCode moduleSpecial function register

The invention relates to a method for connecting a system on programmable chip to an Ethernet, belonging to the technical field of electronic information. The method comprises the following steps: a DW8051 core is downloaded onto an FPGA chip to form a processor which is connected with an SFR decoding module through an SFR bus; the SFR coding module is connected with an SPI module which carries out data communication with a network chip through an SPI bus; the network chip transmits the data to the Ethernet or receives the data from the Ethernet through a network interface. The FPGA chip is aCyclone II EP2C20 chip of American ALTERA Company; the DW8051 core is a code module; the SFR coding module is a special functional register decoding module; the SPI module is a serial peripheral interface module; the model of the network chip is a W5100 chip of the Korea Wiznet Company. The model of the network interface is a common Ethernet interface RJ45. The method of the invention does not need to use hardware to describe an Ethernet networking module with complex language; the hardware is realized simply and conveniently, which shortens the development time of the products.

Owner:SHANDONG UNIV

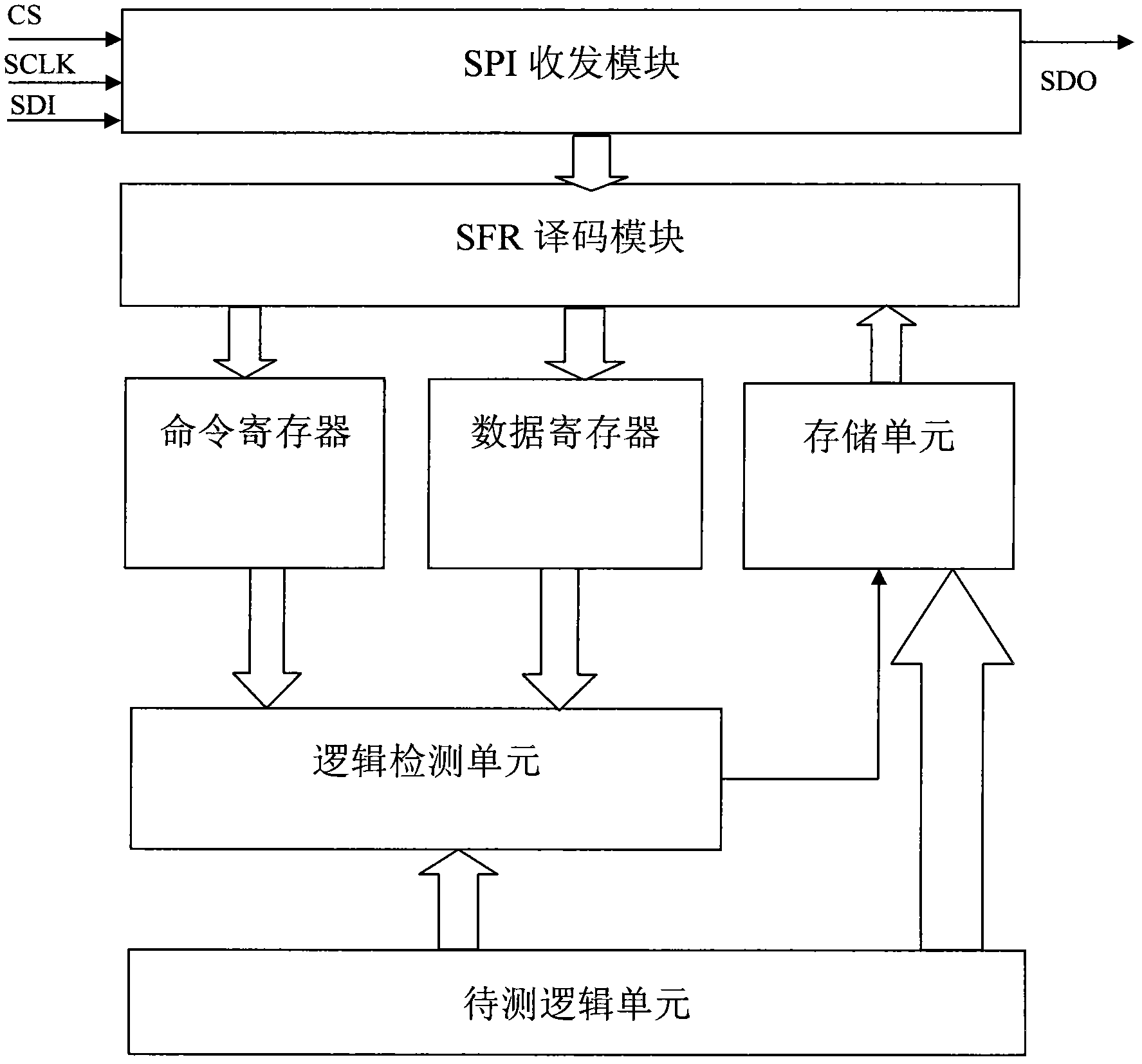

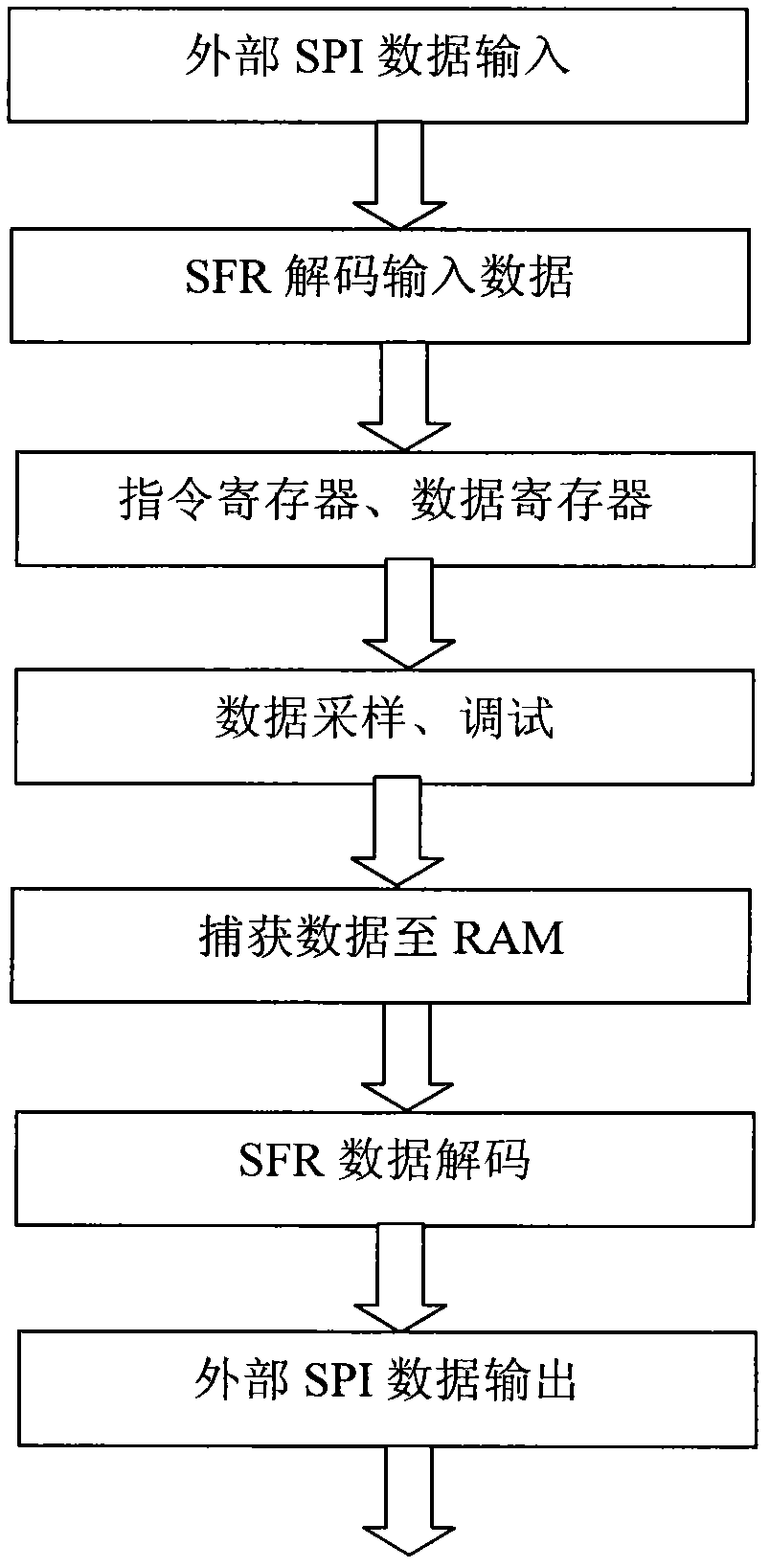

System and method for debugging FPGA (field programmable gate array) in real time

InactiveCN102841305AHigh speed designDigital circuit testingSpecial function registerField-programmable object array

The invention discloses a system for debugging FPGA (field programmable gate array) in real time, comprising an SPI (serial peripheral interface) transceiving module, an SFR (special function register) decoding module, a data storing unit and a logic detection unit, wherein the SPI transceiving module is used for receiving external data to form a detection command and detection data and sending an internal detection result and internal storage data; the SFR decoding module is used for decoding a register command with special functions; the data storing unit is used for storing specified sampled data; and the logic detection unit is used for being connected with at least one group of logic units to be detected and carrying out real-time verification to obtain a verification result; and the modules and the units are sequentially connected for carrying out data communication. A real-time debugging method of the system comprises the following steps that: the SPI transceiving module receives data of a monitoring system, the data received by the SPI transceiving module is converted into a detection instruction or detection data by virtue of the SFR module, is stored by the data storing unit and then is sent to the logic detection unit, the logic detection unit judges the logic units to be detected, and judgement data and result are stored and then are transmitted by the SPI transceiving module. The system disclosed by the invention takes an SPI bus protocol as a protocol used for realizing data interaction between a basic debugging device and equipment, and high-speed product debugging and verifying design and dynamic check debugging are realized.

Owner:BEIJING UPTOPS DESIGN TECH

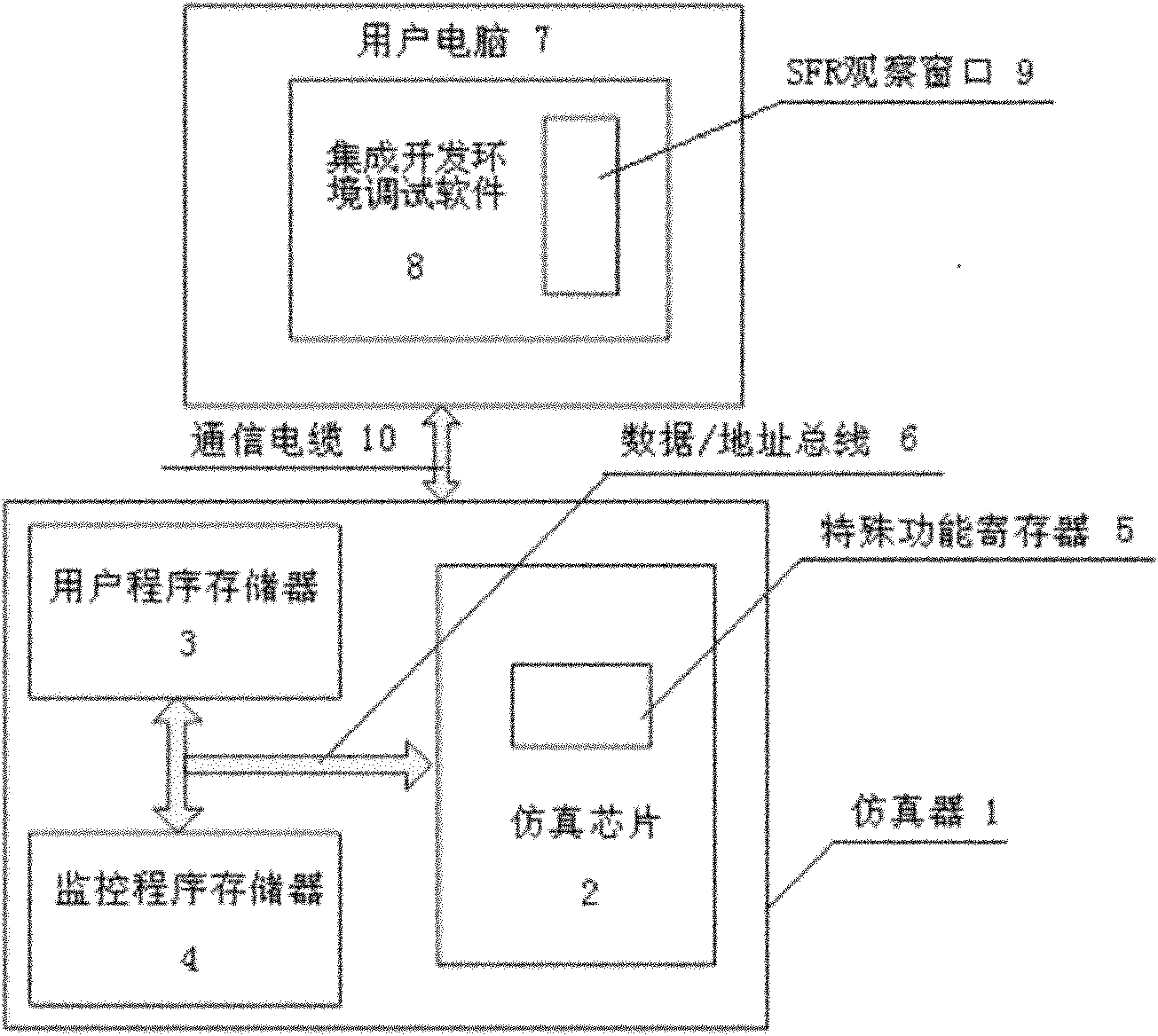

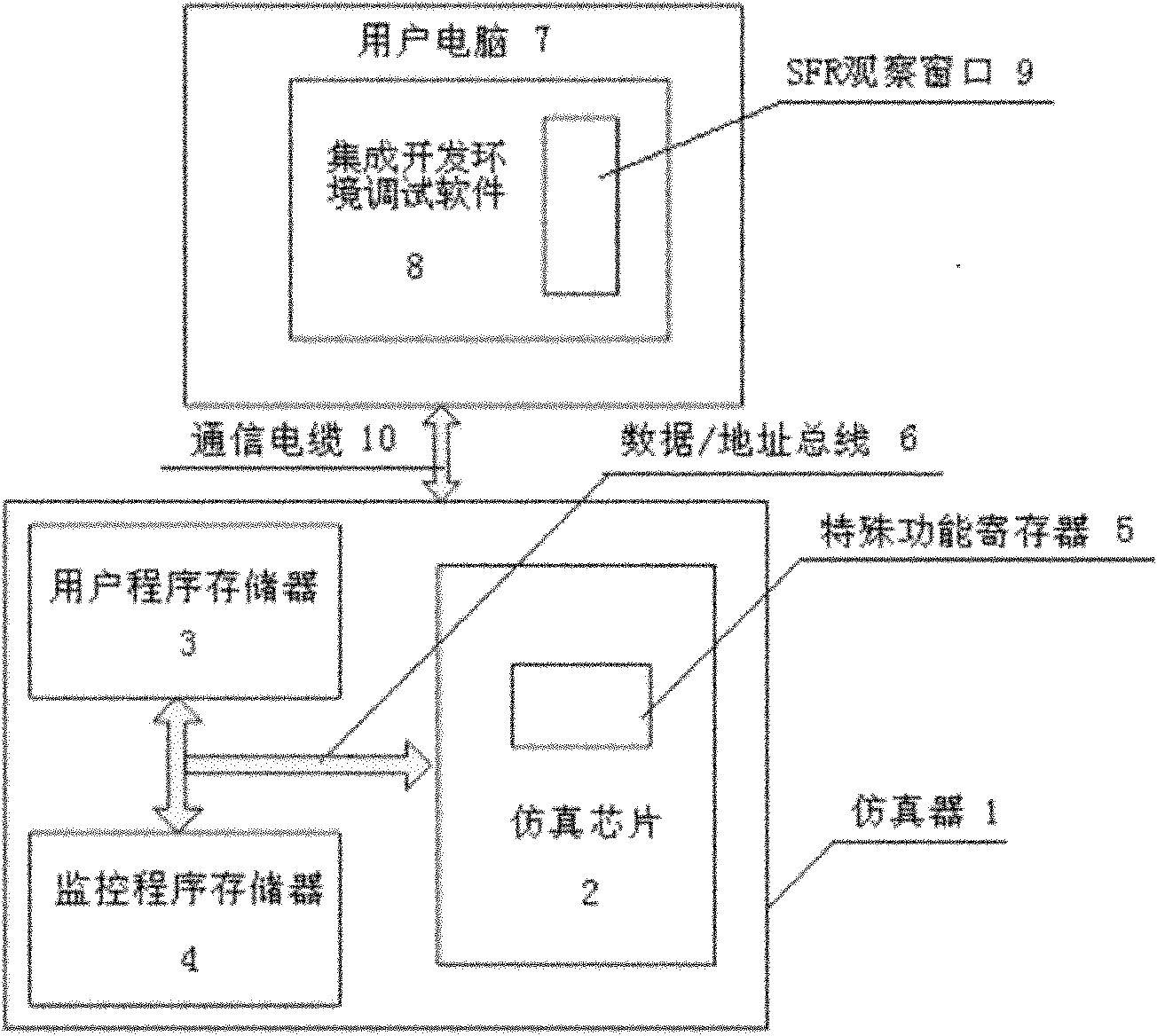

Simulation debugging system for special function register

InactiveCN102467444AGuaranteed Observation OperationsOperation will not affectSoftware testing/debuggingSpecial function registerProcessor register

The invention discloses a simulation debugging system for a special function register (SFG). All sub-SFRs are displayed in an SFR observing window in a list form. Integrated development environment debugging software continuously reads numerical values of the sub-SFRs in the SFR which is realized by a first in first out (FIFO) way, and the number of reading times is the number of all the sub-SFRs in the SFR. The integrated development environment debugging software displays the group of numerical values of the sub-SFRs in a numerical value list in the SFR observing window. After a user modifies the numerical value of a certain sub-SFR in the numerical value list, the integrated development environment debugging software continuously writes a new integral group of numerical values of the sub-SFRs into the SFR which is realized in the FIFO way, and the number of writing times is the number of the sub-SFRs in the SFR which is realized in the FIFO way. By the simulation debugging system, the numerical value of each sub-SFR in the SFR can be observed / modified in the SFR observing window without influencing subsequent operation on the SFR in the running of a user program.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

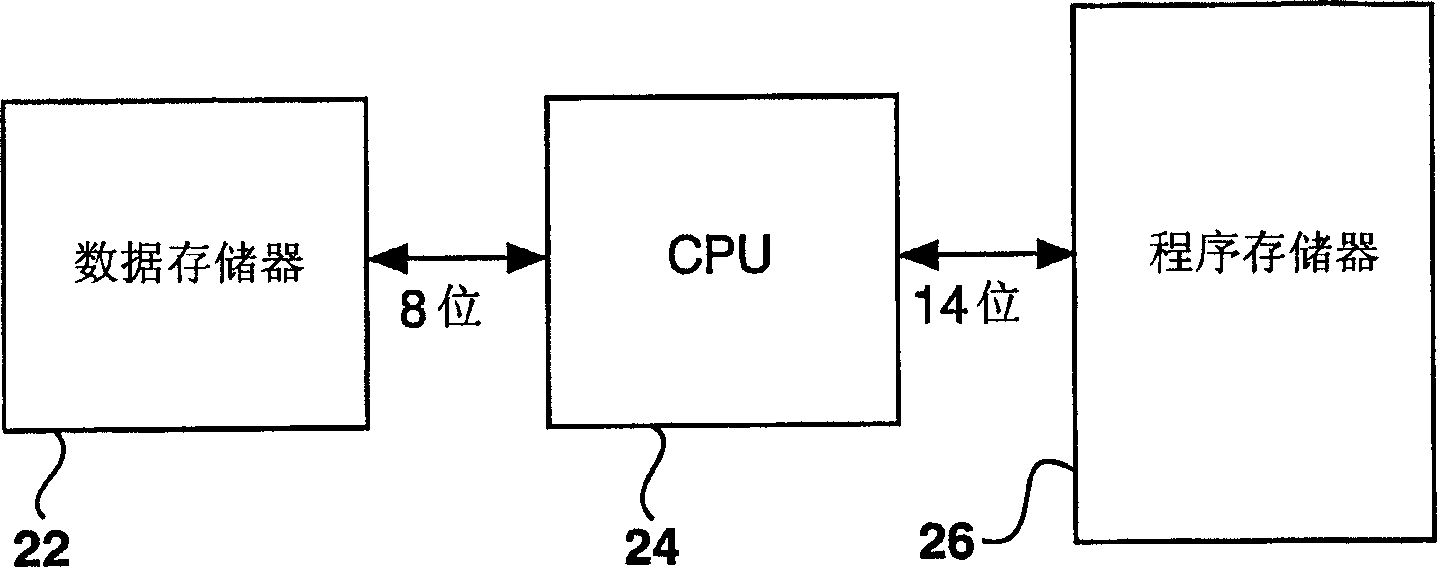

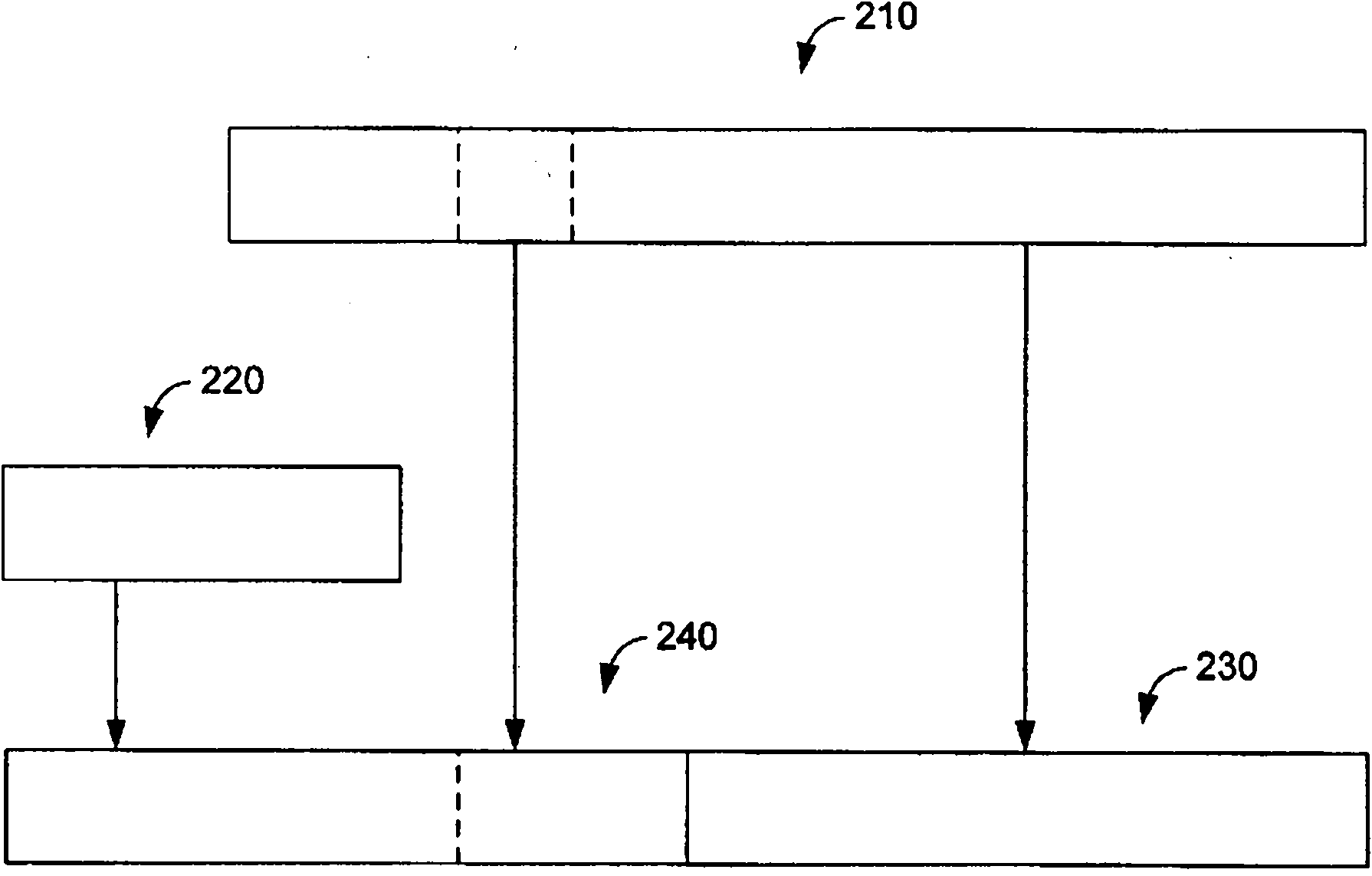

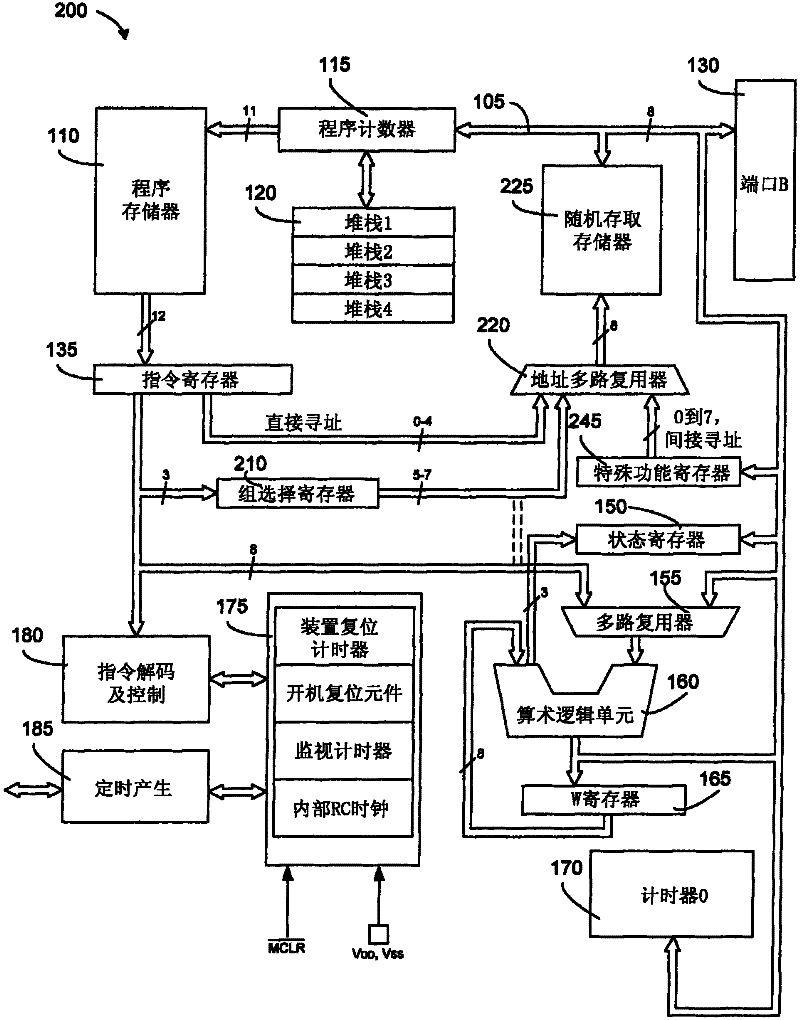

Microcontroller instruction set

ActiveCN1898641AShorten learning curveEasy programmingMemory systemsMachine execution arrangementsComputer architectureSpecial function register

The invention provides a microcontroller apparatus with an instruction set for manipulating the behavior of the microcontroller. The invention provides an apparatus and system that enables a linearized address space that makes modular emulation possible. Direct or indirect addressing is possible through register files or data memory. Special function registers, including the Program Counter (PC) and Working Register (W), are mapped in the data memory. An orthogonal (symmetrical) instruction set makes possible any operation on any register using any addressing mode. Consequently, two file registers to be used in some two operand instructions. This allows data to be moved directly between two registers without going through the W register. Thus, increasing performance and decreasing program memory usage.

Owner:MICROCHIP TECH INC

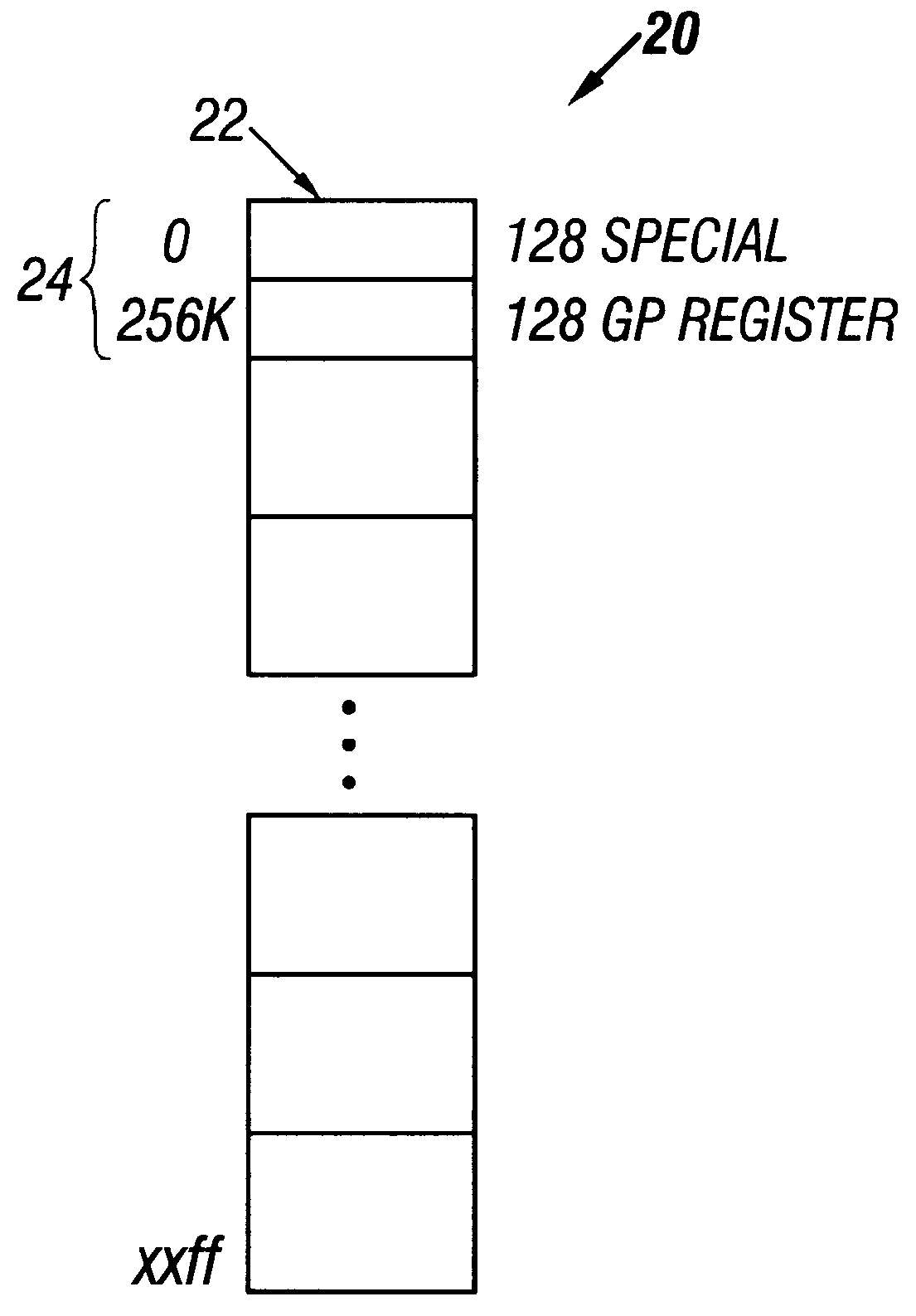

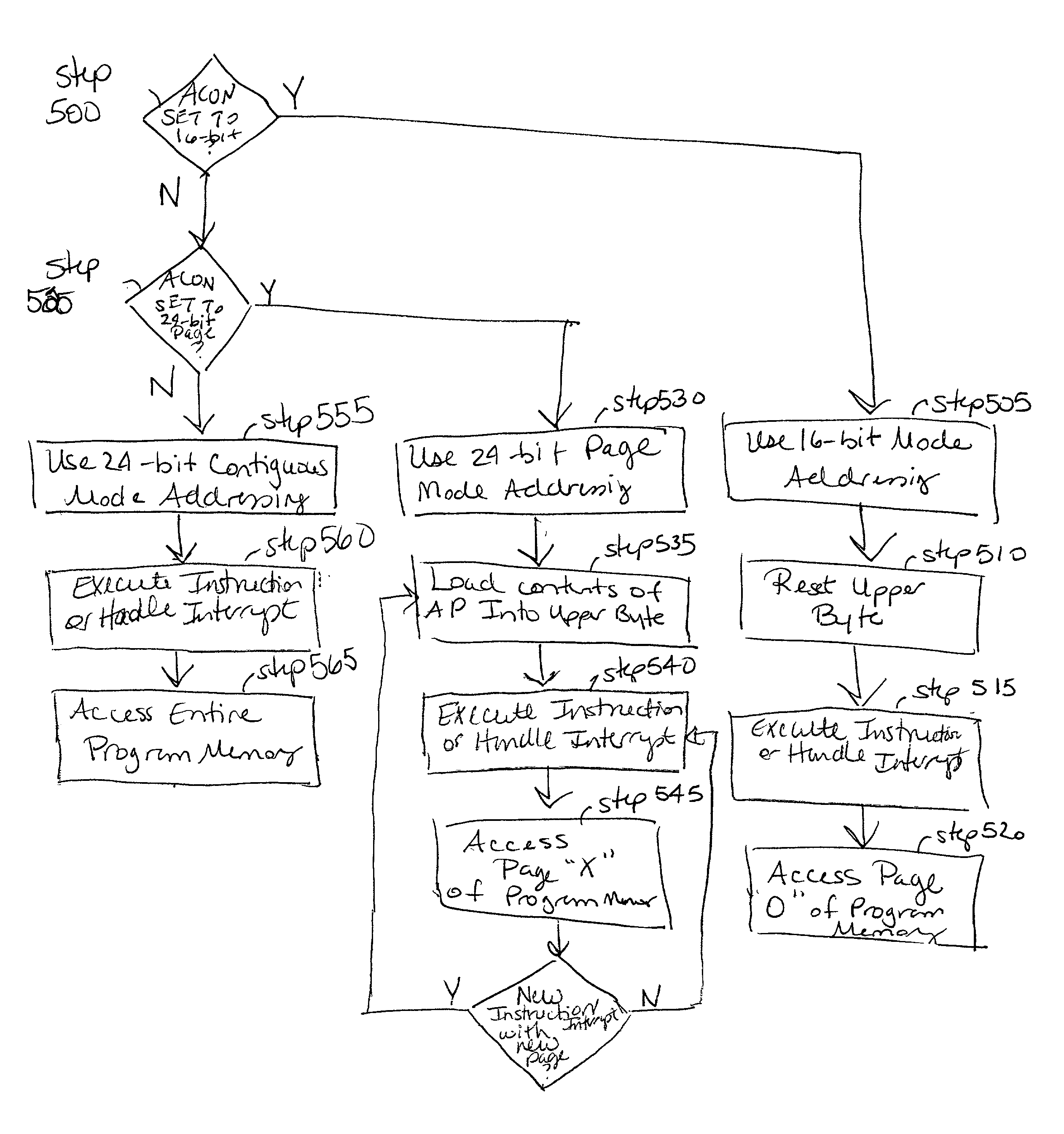

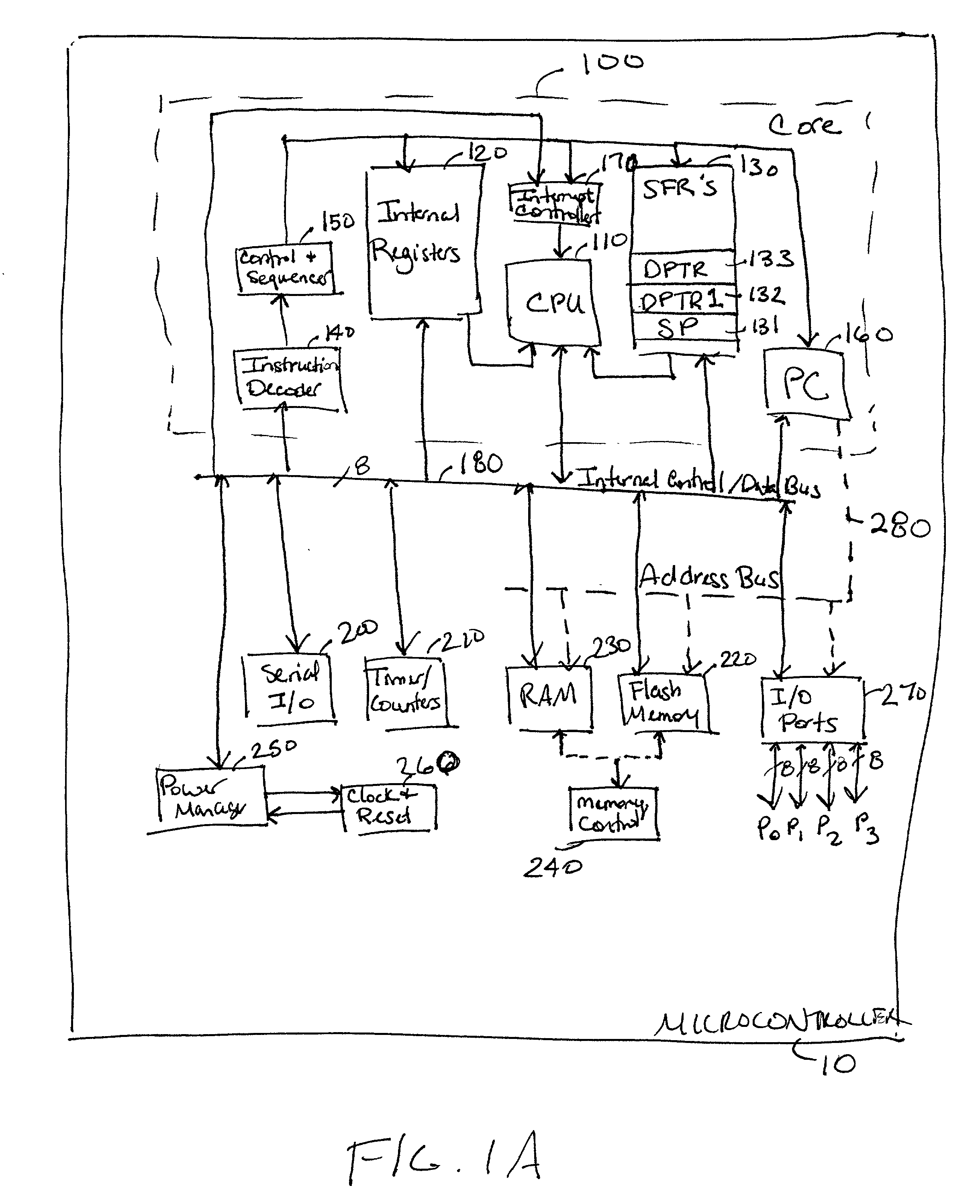

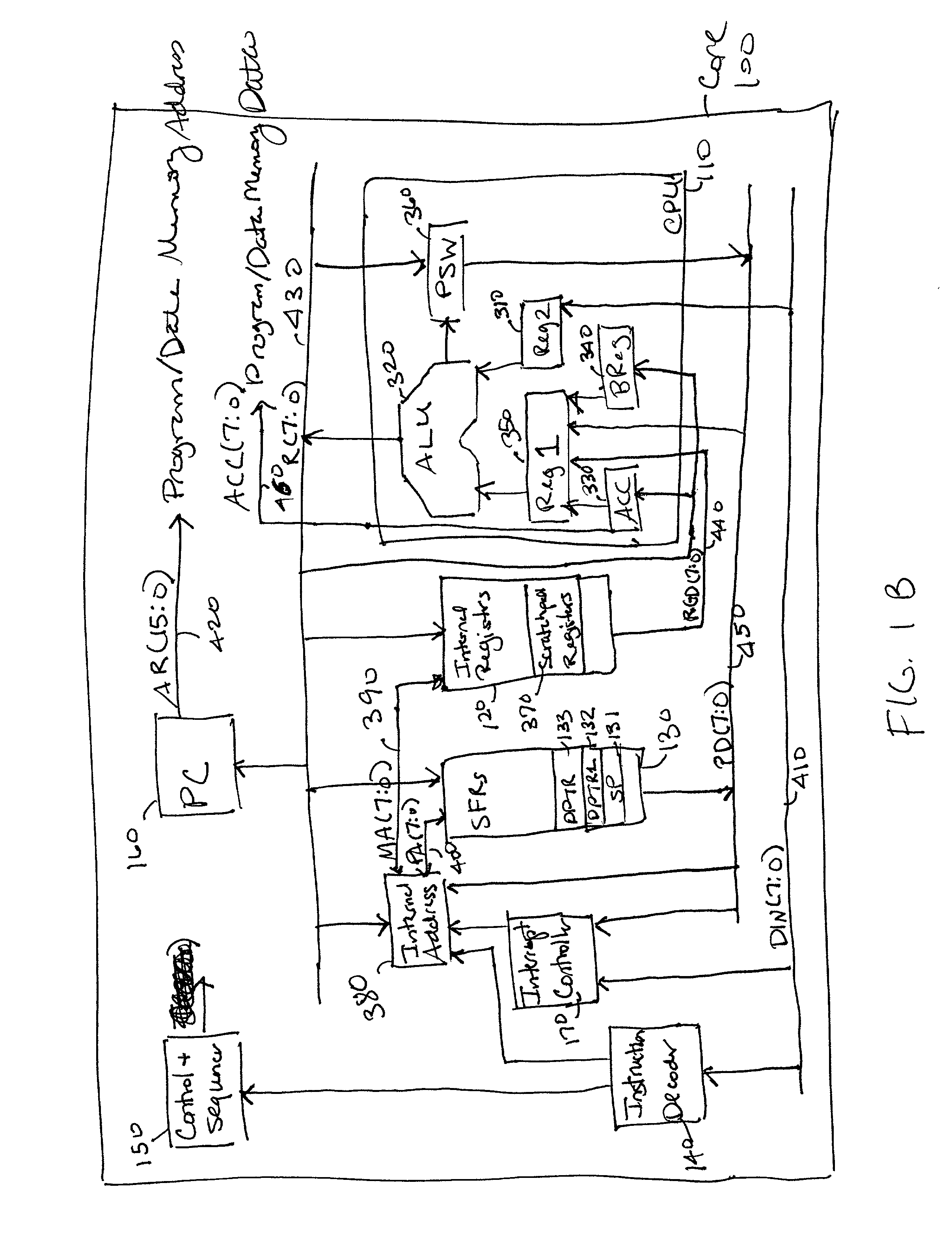

Method and apparatus for 24-bit memory addressing in microcontrollers

InactiveUS20020156991A1Architecture with single central processing unitMemory systemsMemory address24-bit

The present invention provides an 8-bit microcontroller capable of supporting expanded addressing capability in one of three address modes. The microcontroller operates in either the traditional 16-bit address mode, a 24-bit paged address mode or in a 24-bit contiguous address mode based on the setting of a new Address Control (ACON) Special Function Register (SFR). The 24-bit paged address mode is binary code compliant with traditional compilers for the standard 16-bit address range, but allows for up to 16M bytes of program memory and 16M bytes of data memory to be supported via a new Address Page (AP) SFR, a new first extended data pointer (DPX) SFR and a new second extended data pointer (DPX1) register. The 24-bit contiguous mode requires a 24-bit address compiler that supports contiguous program flow over the entire 24-bit address range via the addition of an operand and / or cycles to either basic instructions.

Owner:MAXIM INTEGRATED PROD INC

Blank tire pressure monitoring device and its setup method

A blank tire pressure monitoring device includes a housing having an air valve at one end and connection terminals at an opposite end, a circuit board mounted in the housing and carrying a pressure sensor, a temperature sensor, an acceleration sensor, an analog-digital converter electrically connected with the pressure sensor, the temperature sensor and the acceleration sensor, a general purpose I / O terminal unit electrically connected with the connection terminals of the housing; an embedded microcontroller module electrically connected with the general purpose I / O terminal unit and the analog-digital converter and having built therein a flash memory, a microcontroller core and a special-function register controller, a LF receiver electrically connected to the embedded microcontroller module, and a transmitter electrically connected to the embedded microcontroller module; and a method is still also disclosed for setting up a blank tire pressure monitoring device.

Owner:CUB ELECPARTS

Integrated CMOS imager and microcontroller

ActiveUS20060192876A1Television system detailsTelevision system scanning detailsCMOSSpecial function register

A method and apparatus providing a CMOS imager with an integrated controller on a common integrated circuit substrate. Also integrated on the common substrate are, a serializer circuit including a dynamic arbiter under the control of the microcontroller core and a set of extended special function registers through which data is passed to allow the microcontroller to control the CMOS imager and the serializer circuit.

Owner:MICRON TECH INC

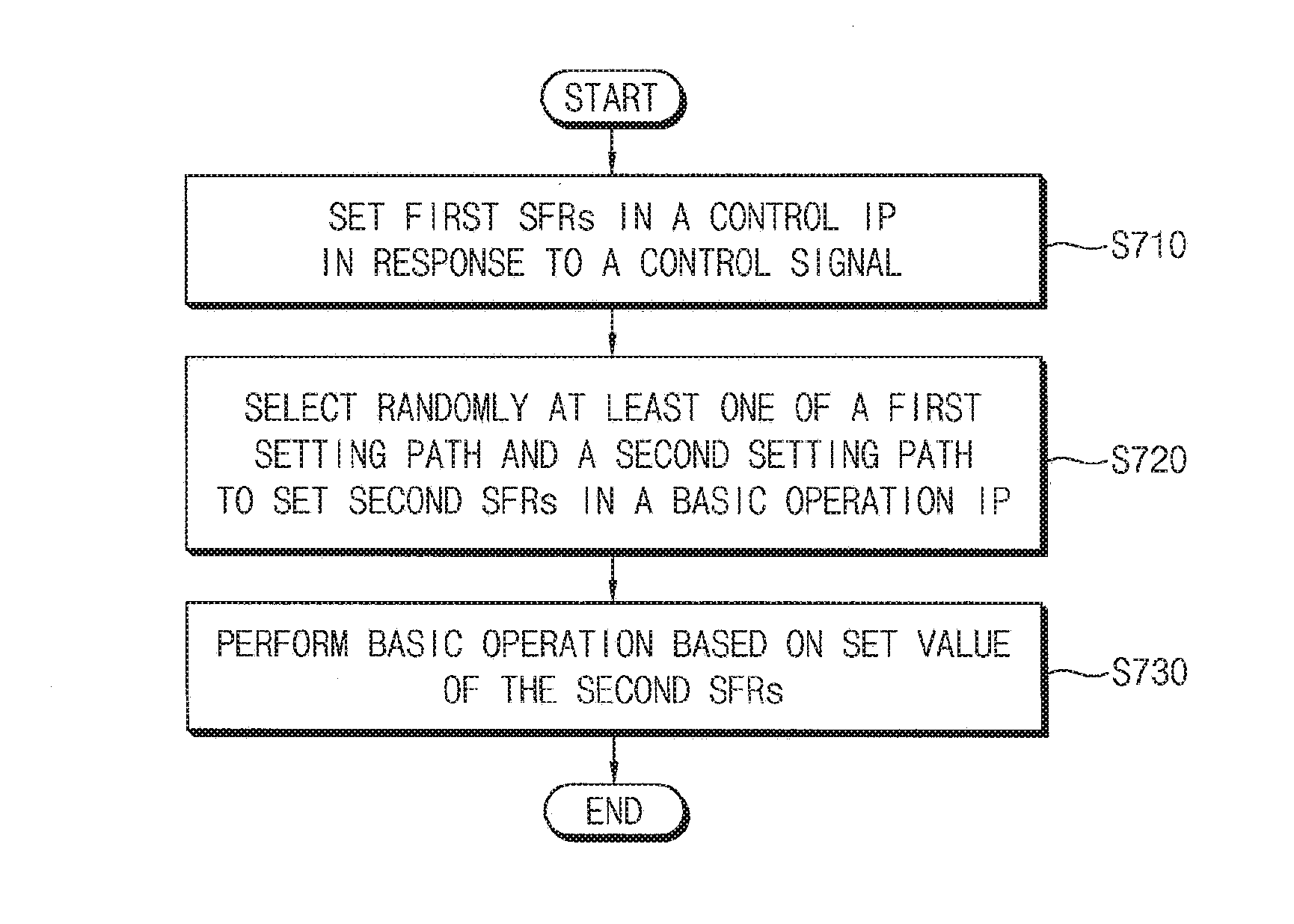

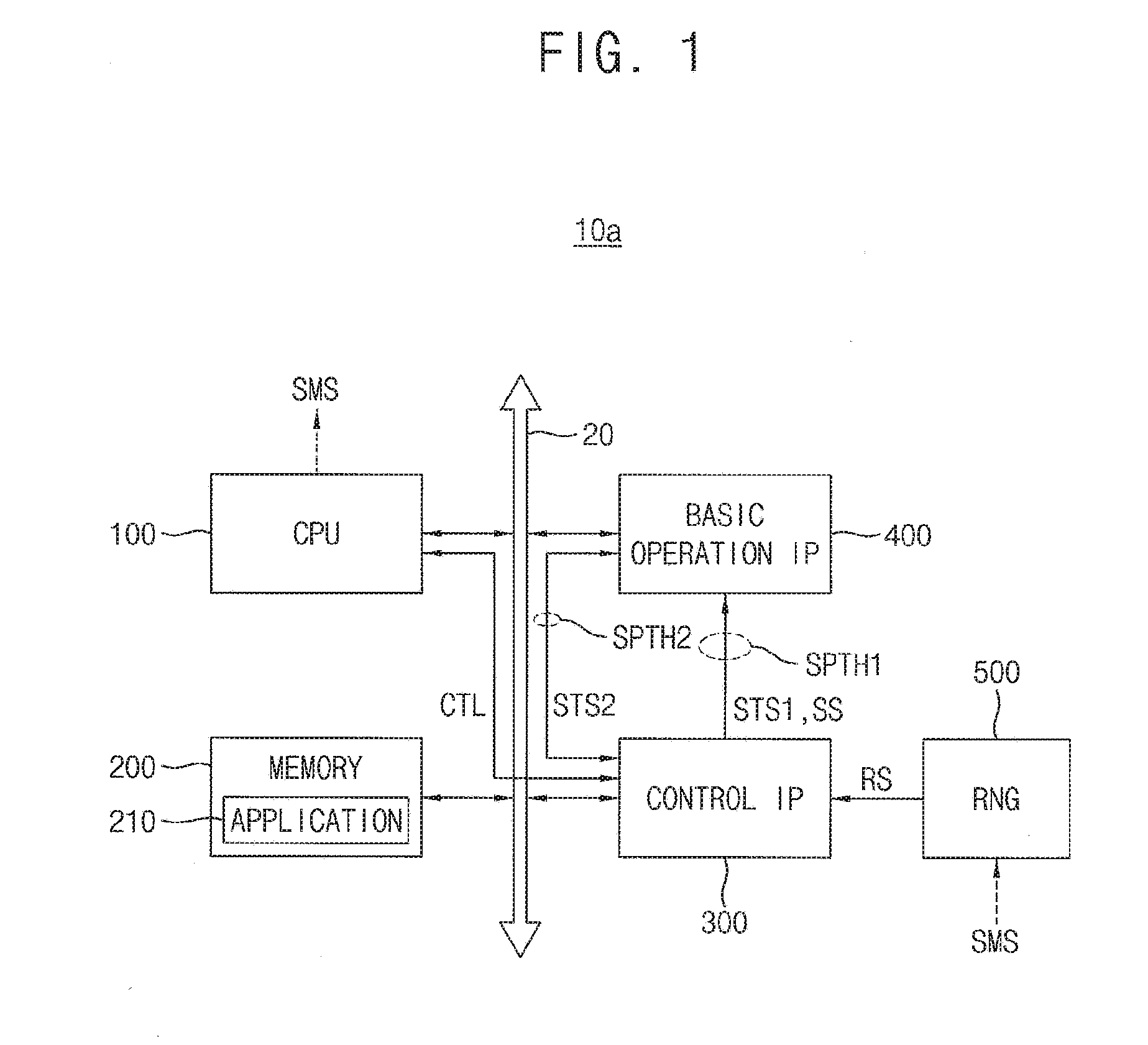

Electronic device against side channel attacks

ActiveUS20170046537A1Random number generatorsInternal/peripheral component protectionSpecial function registerIntellectual property

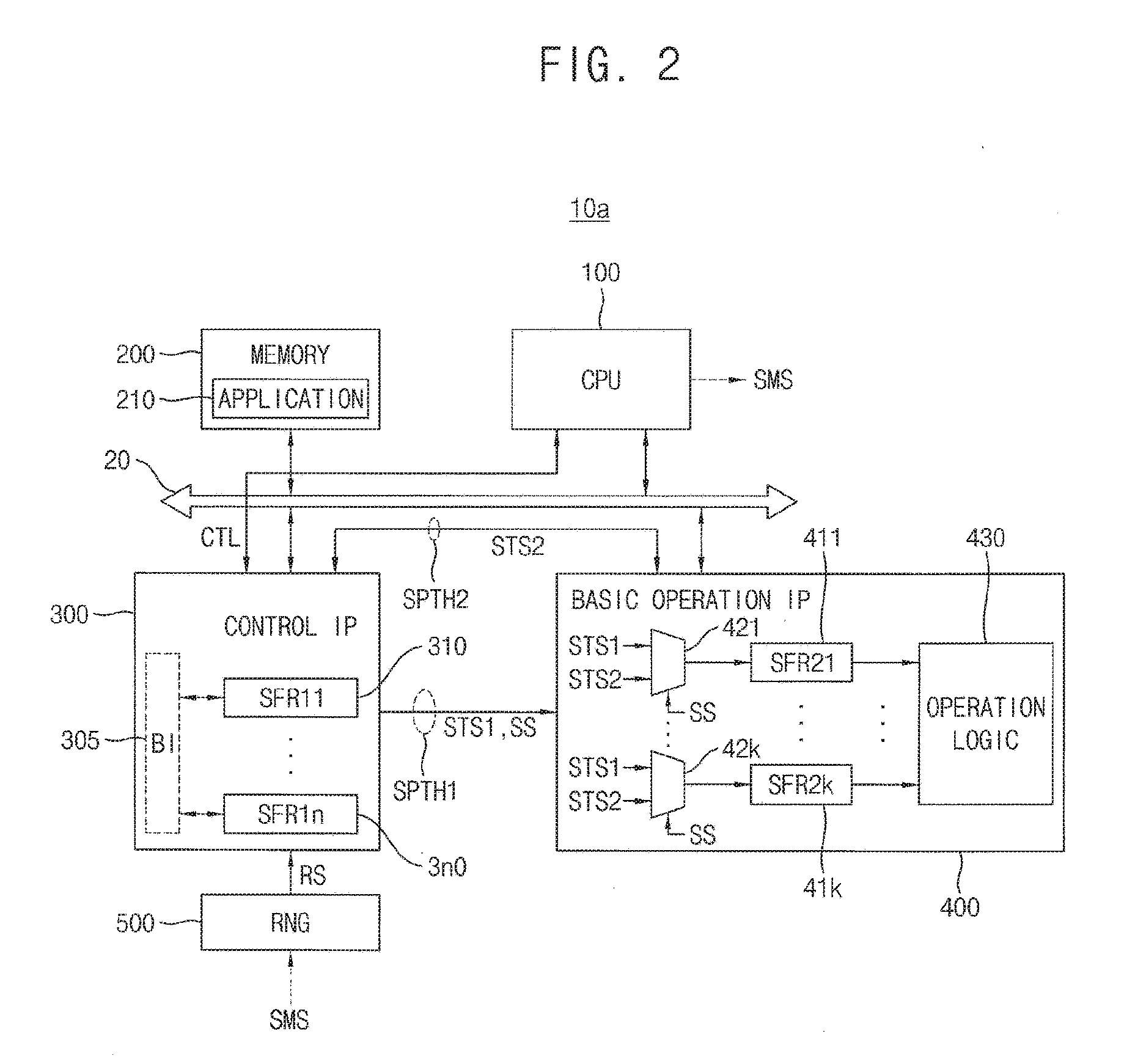

An embodiment includes an electronic device, comprising: a control intellectual property (IP) including a plurality of first special function registers (SFRs); a basic operation IP including a plurality of second SFRs and coupled to the control IP through a first path and a second path; and a random number generator configured to generate a random signal; wherein the control IP is configured to: select one of the first path and the second path based on the random signal; and set the second SFRs using the selected path.

Owner:SAMSUNG ELECTRONICS CO LTD

A Microcontroller Embedded Online Simulation Debugging System

InactiveCN101154183BImproved debugging capabilitiesRealize real-time monitoringSoftware testing/debuggingAddress busData memory

A micro-controller embedded online simulation debugging system, including a communication port control module, a state control module, a debugging command control module, and a hardware breakpoint monitoring and triggering module. The above-mentioned modules are controlled inside the chip through the special debugging command set sent by the host The entire online simulation debugging system works; it can complete the complex boundary scan of the chip through the standard test boundary scan, control the microcontroller chip from the normal mode to the debugging mode according to the external command, and through the debugging communication interface with the host, the program can be from Download or read from any location in the memory of the microcontroller, support single-step debugging of the target system, support software and hardware breakpoints, view or modify the contents of special function registers, data memory and program memory inside the chip in real time, monitor address bus and data bus , to achieve real-time logic tracking and other functions. The structure is clear and simple, the operation effect is efficient, and the real-time monitoring is accurate.

Owner:SHANGHAI EASTSOFT MICROELECTRONICS

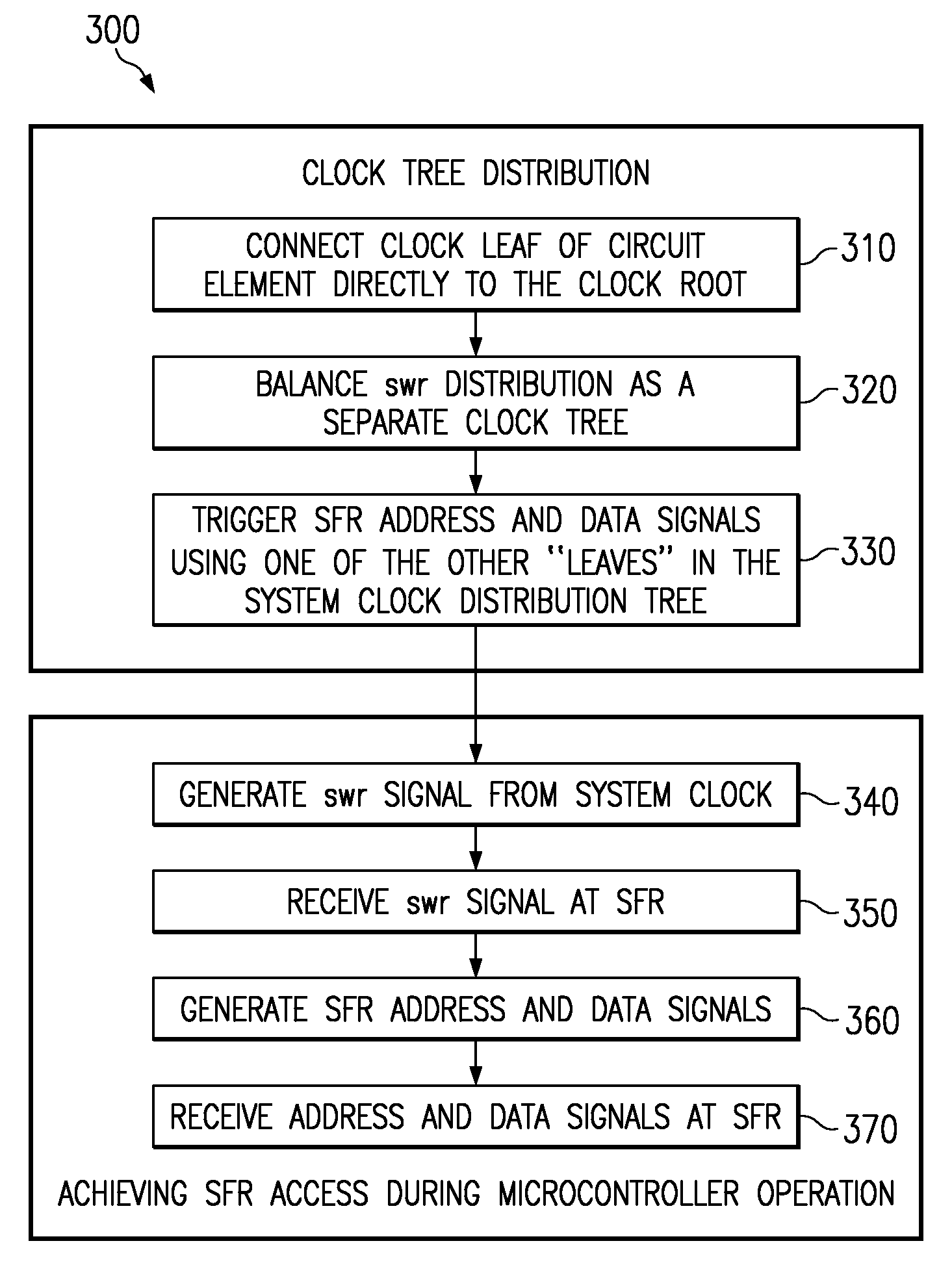

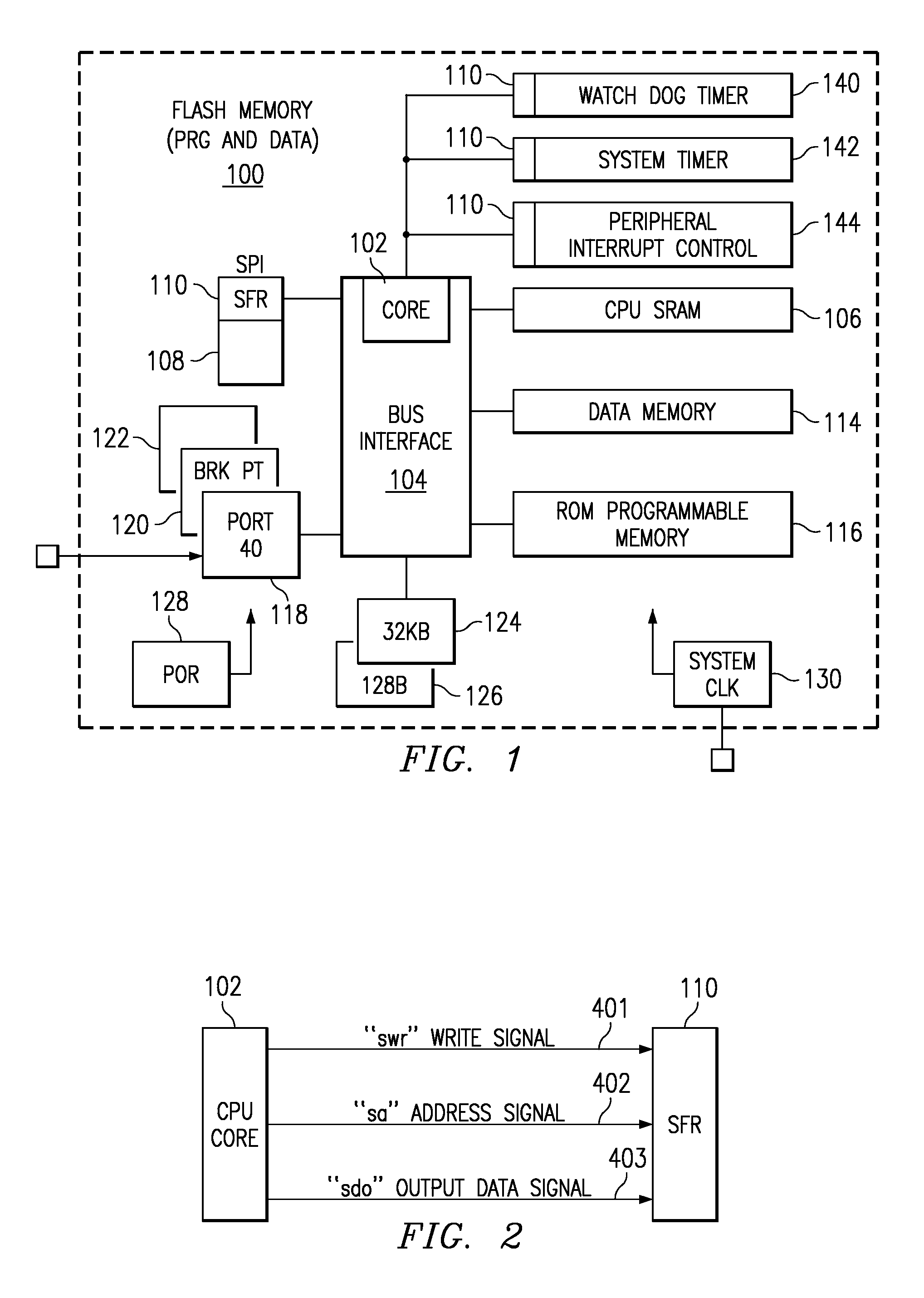

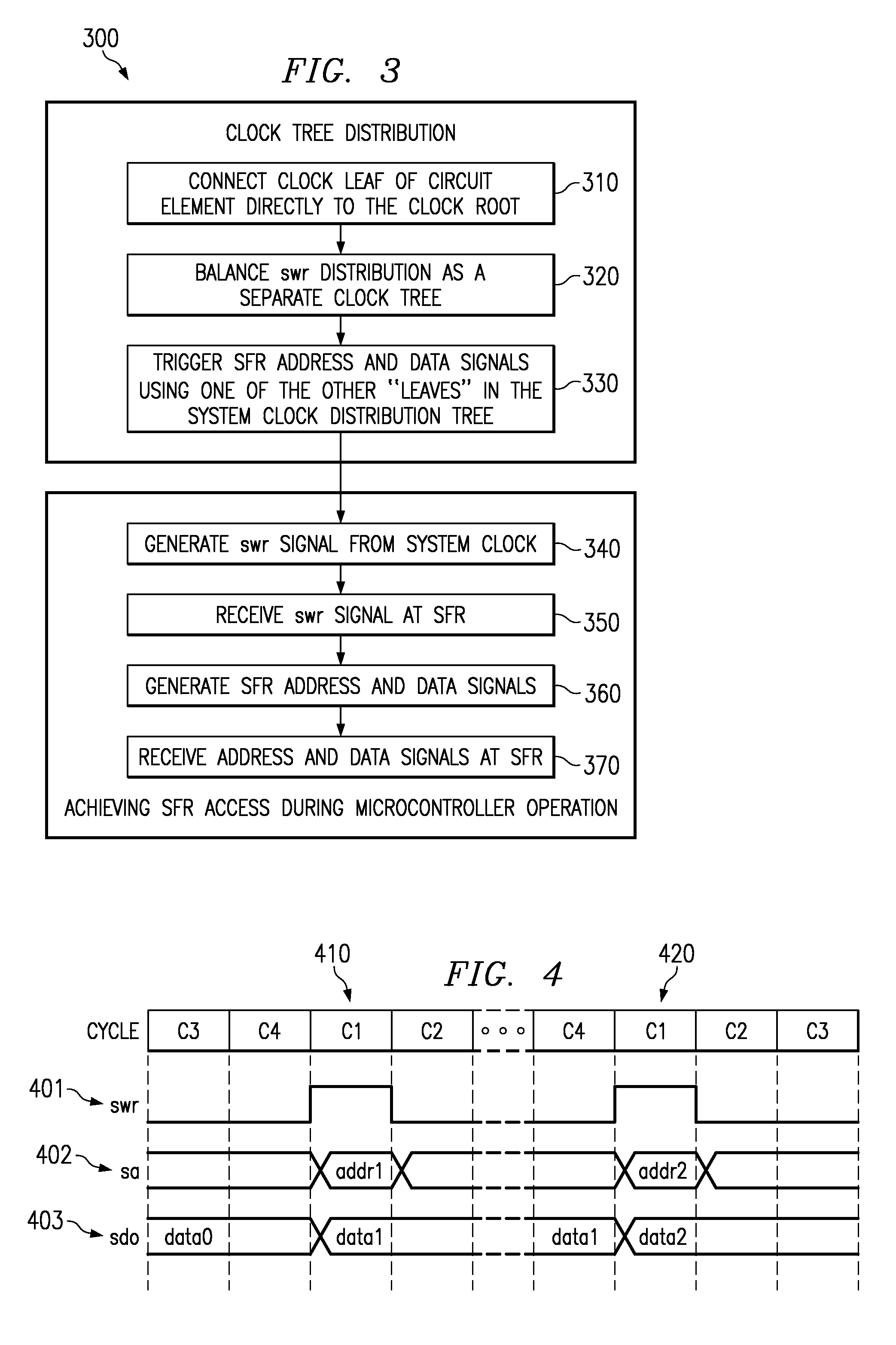

System and method for providing a write strobe signal to a receiving element before both an address and data signal

InactiveUS7065669B2Improve system speedMinimum delayGenerating/distributing signalsMemory systemsSpecial function registerProcessor register

Owner:TEXAS INSTR INC

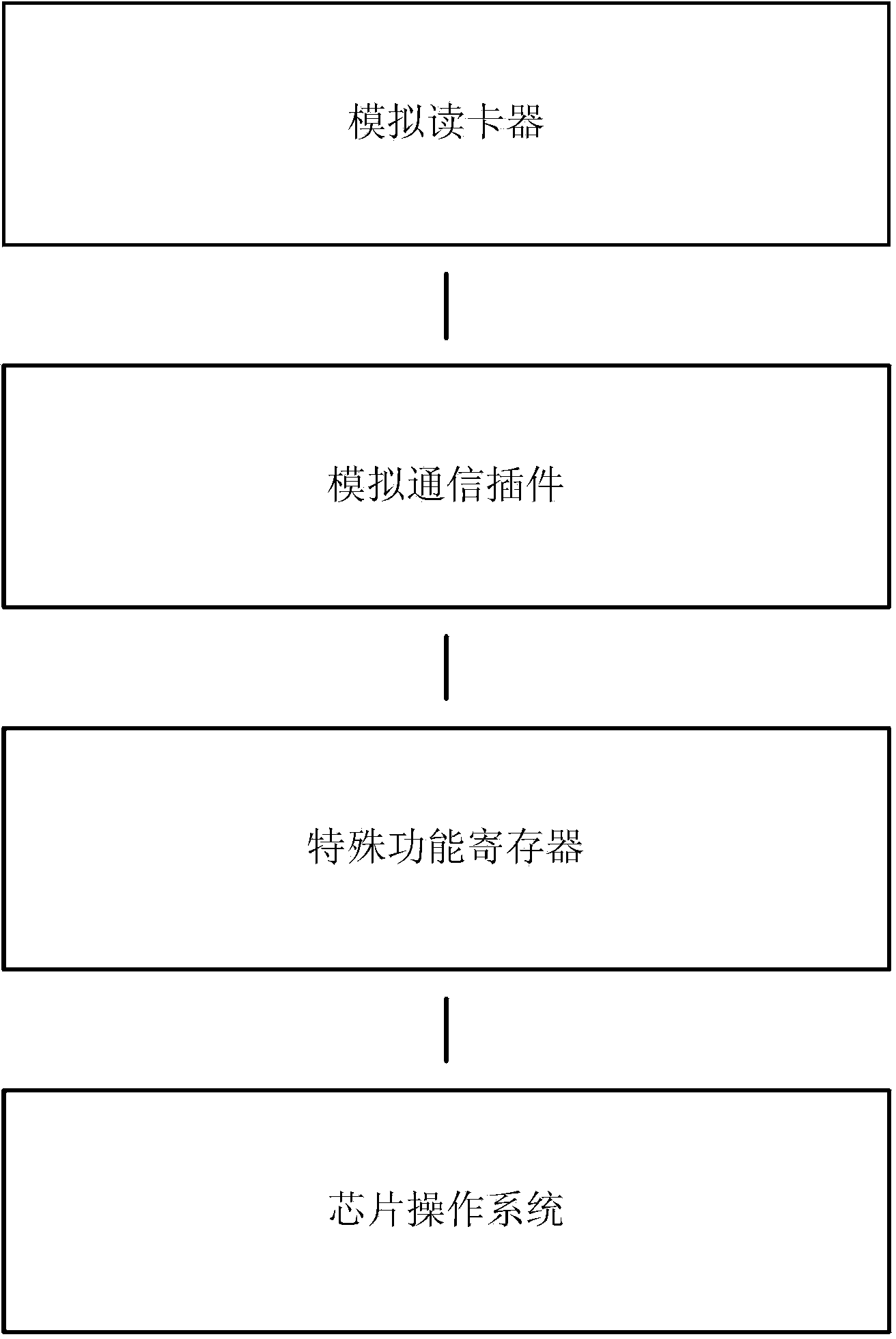

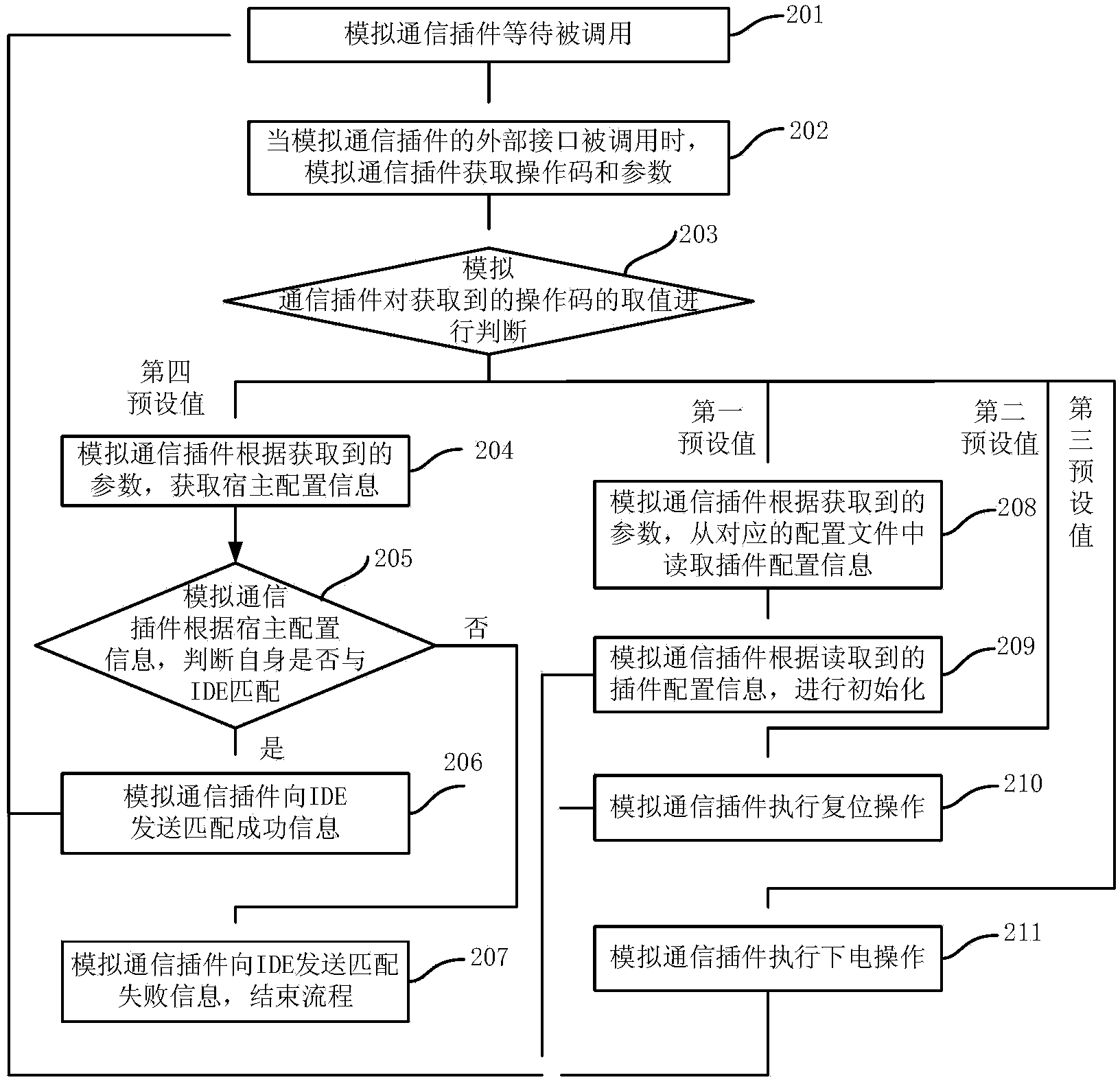

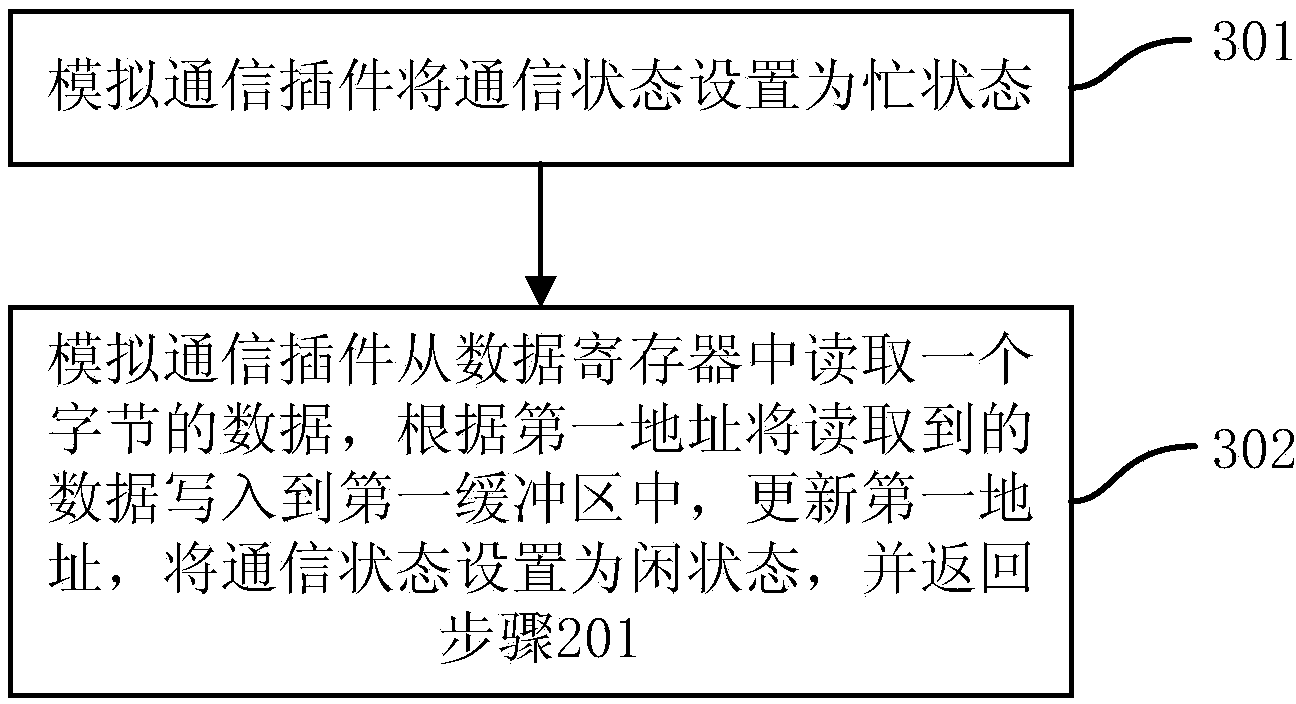

Analog communication plug-in and working method thereof

ActiveCN103559074AImprove real-time performanceImprove reliabilityMemory adressing/allocation/relocationSoftware simulation/interpretation/emulationOperational systemCommunications system

The invention discloses an analog communication plug-in and a working method thereof. The analog communication plug-in is applied to an analog communication system comprising a chip operating system, a special function register, the analog communication plug-in and an analog card reader, the analog communication plug-in is loaded when an IDE (integrated drive electronics) is started and used for establishing communication between the chip operating system and the analog card reader, and the analog card reader is used for receiving and processing data from the chip operating system and transmitting the data to the chip operating system. Analog communication between the chip operating system and the analog card reader is realized by calling an external interface of the analog communication plug-in, setting a data register and reading and writing the data register, instantaneity and reliability of analog communication are improved, the problem of debugging resource shortage in the prior art is solved, the development cycle of a protocol stack is shortened, the development cost of the protocol stack is saved, and development efficiency is improved.

Owner:FEITIAN TECHNOLOGIES

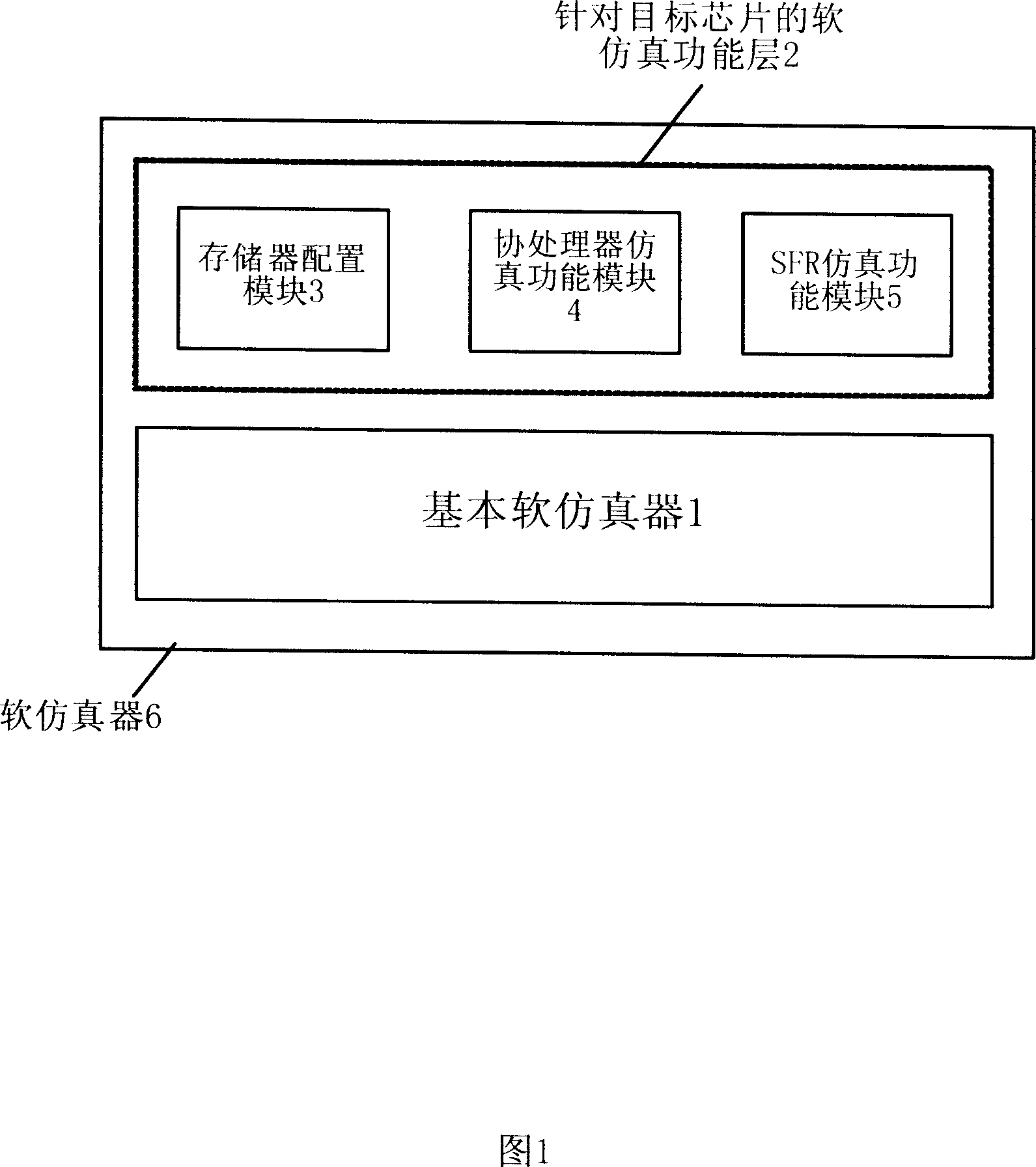

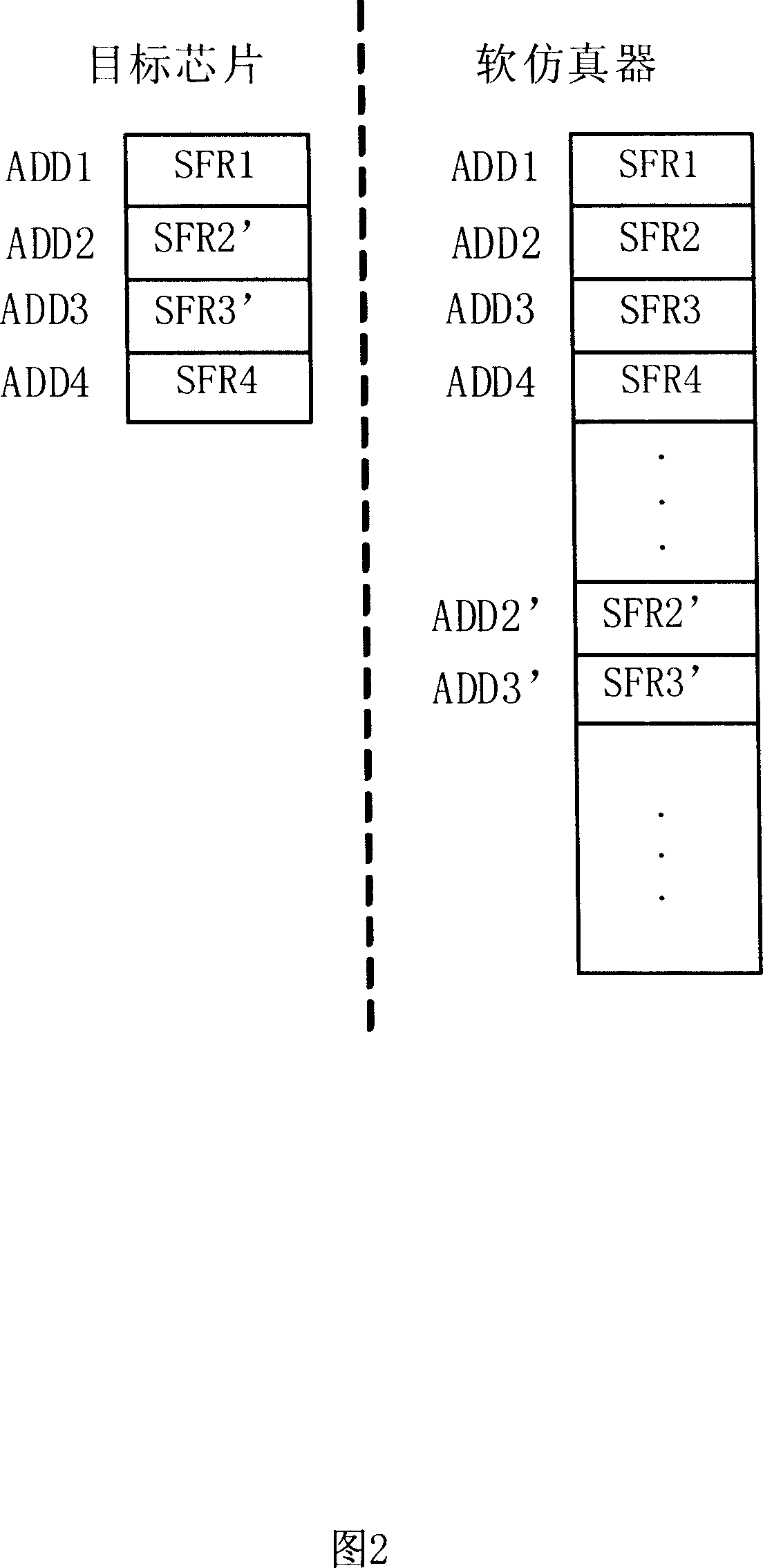

Manufacturing method of soft emulator

InactiveCN101000577AFast to marketLow costSoftware testing/debuggingSpecial function registerProcessor register

A method for preparing soft simulator includes adding a special function register simulation module in soft simulator when special function register in object chip is collided to special function register address in basic soft simulator, expanding out special function register function with collision in said module, intercepting operation down before basic soft simulator by said module when special function register of these address is operated by software then remapping and connecting operation onto expanded out special function register.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

Enhanced microprocessor or microcontroller

An n-bit microprocessor device has an n-bit central processing unit (CPU); a plurality of special function registers and general purpose registers which are memory-mapped to a plurality of banks, with at least two 16-bit indirect memory address registers which are accessible by the CPU across all banks; a bank access unit for coupling the CPU with one of the plurality of banks; a data memory coupled with the CPU; and a program memory coupled with the CPU, wherein the indirect address registers are operable to access the data memory or program memory and wherein a bit in each of the indirect memory address registers indicates an access to the data memory or to the program memory.

Owner:MICROCHIP TECH INC

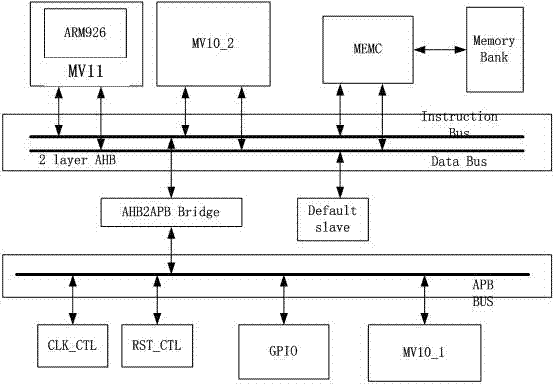

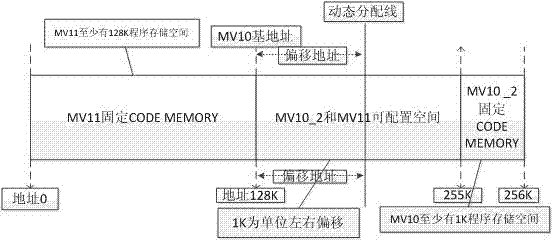

Dynamic allocation method for instruction memory cell for multi-core heterogeneous system

InactiveCN102566973AOptimizationProgram controlMemory systemsInstruction memorySpecial function register

The invention relates to a dynamic allocation method for an instruction memory cell for a multi-core heterogeneous system, which includes the steps: setting a special function register on hardware of the multi-core heterogeneous system, enabling the special function register to dynamically allocate the shared instruction memory cell for the multi-core heterogeneous system by means of software programming, and enabling an instruction memory cell occupied by each processor to be adjusted according to the size of application programs at the start of operation of the system. The method can be applied to an MV12 multi-core heterogeneous system, and can be also applied to the field of the multi-core heterogeneous system comprising 8051 series microprocessors.

Owner:SHANGHAI UNIV

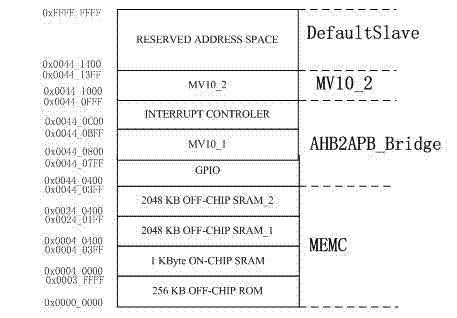

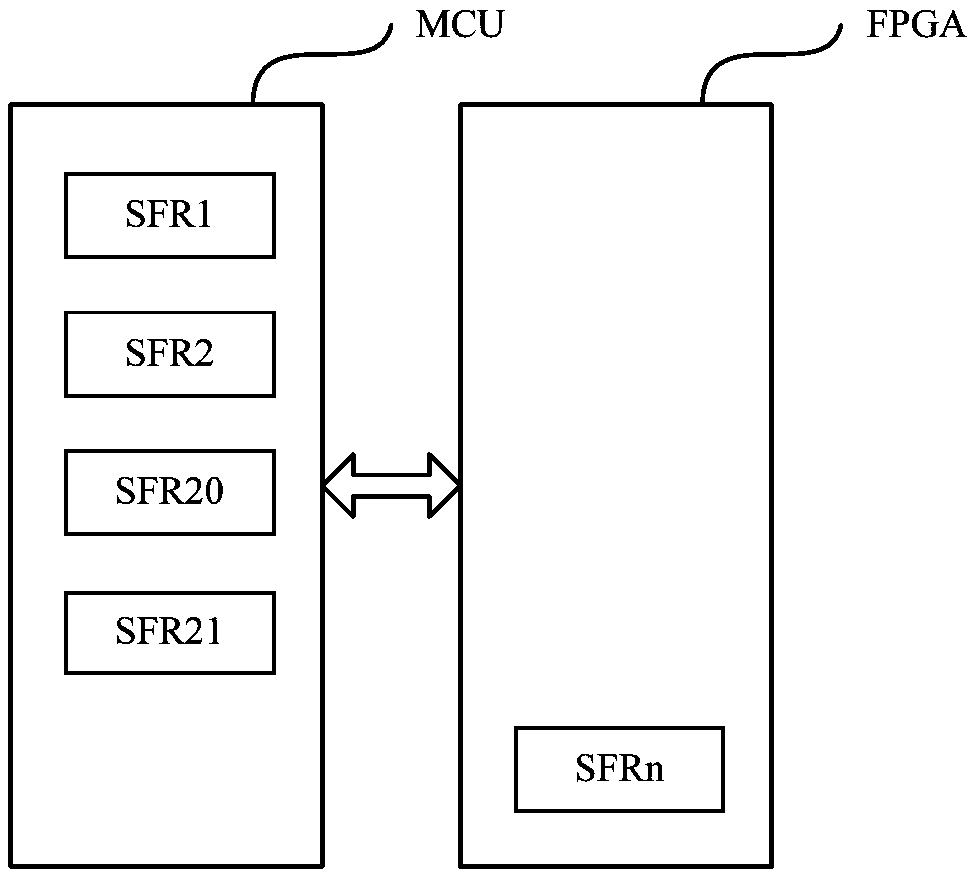

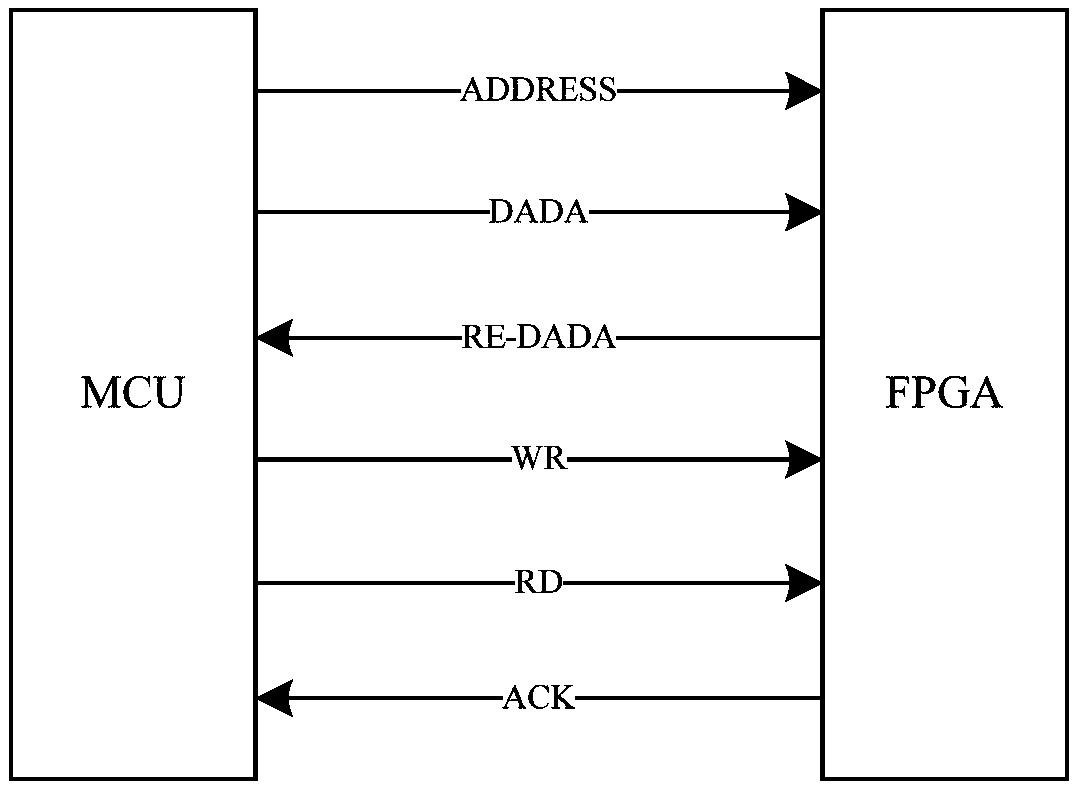

A SoC system

PendingCN109542840AIncrease the number ofFunction increaseArchitecture with single central processing unitElectric digital data processingFpga field programmable gate arraySpecial function register

The invention provides a SoC system, which comprises a field programmable gate array FPGA and a micro control unit MCU. The MCU comprises a special function register SFR unit; The MCU is connected with the FPGA for mapping the spare address in the SFR unit into the FPGA and extending the SFR in the FPGA. The FPGA is added to that present application, Based on the programmable principle of FPGA, The free address in SFR unit is mapped to FPGA to form a new usable SFR in FPGA, which expands the number and function of SFR in MCU system, can allow the SoC system to expand SFR according to the actual application requirements, and makes the programming and control function of SoC system stronger and more flexible.

Owner:京微齐力(深圳)科技有限公司

Microcontrollers with Special Grouped Instructions

An instruction set for a microcontroller with a data memory divided into a plurality of memory banks wherein the data memory has more than one memory bank of the plurality of memory banks that form a block of linear data memory to which no special function registers are mapped, a bank select register which is not mapped to the data memory for selecting a memory bank, and with an indirect access register mapped to at least one memory bank, wherein the instruction set includes a plurality of instructions operable to directly address all memory locations within a selected bank, at least one instruction that provides access to the bank select register, and at least one instruction performing an indirect address to the data memory using the indirect access register.

Owner:MICROCHIP TECH INC

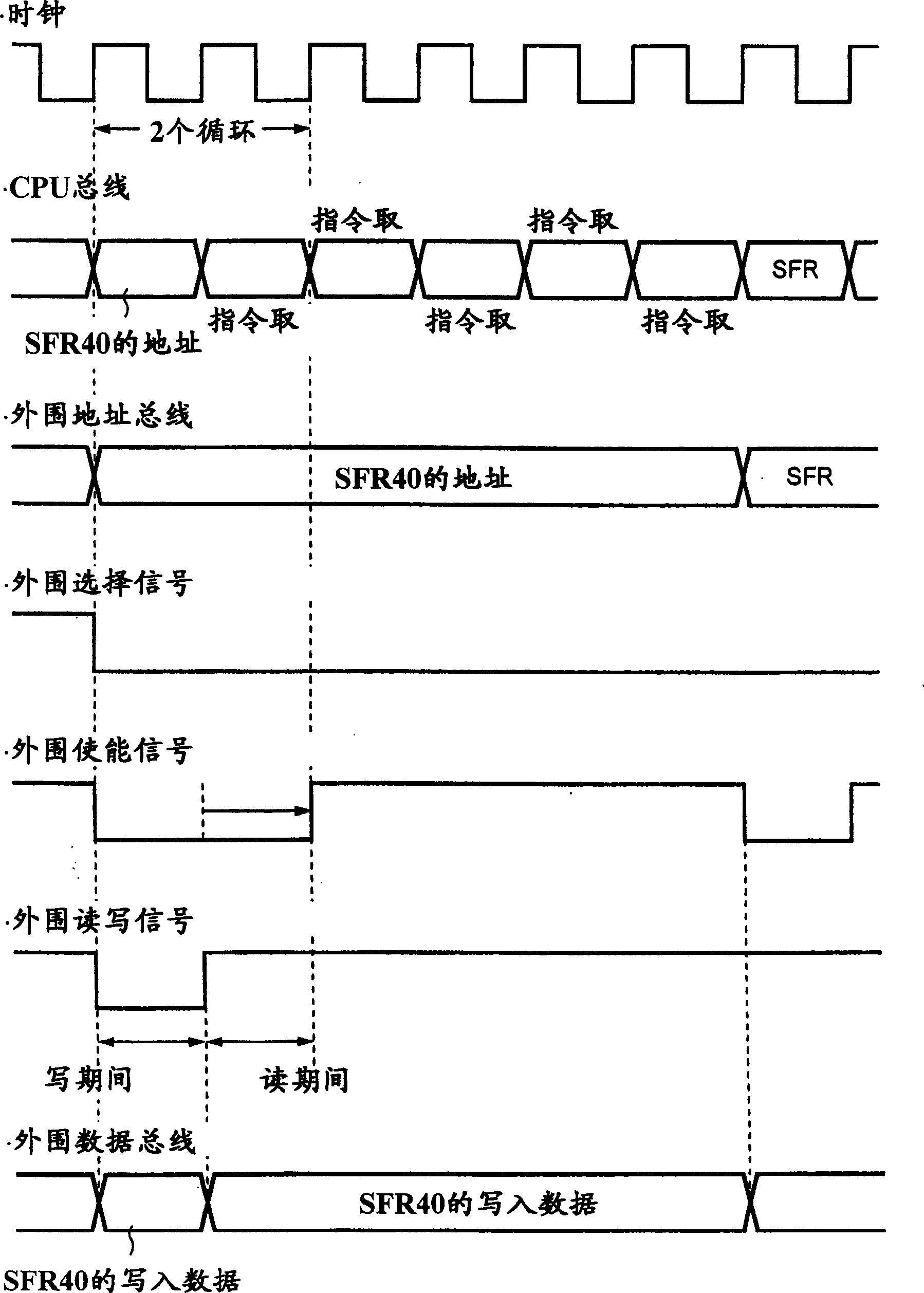

Microcomputer

A CPU of a microcomputer according to the present invention executes a write operation for setting data in a special function register (SFR) while a peripheral enable signal is asserted, and then asserts the peripheral enable signal for one more cycle. By doing so, a peripheral read / write signal becomes effective and the SFR outputs the data set during the write operation onto a peripheral data bus. Therefore, it is possible to check whether the data is successfully written in the SFR within a shorter period of time by automatically executing a read instruction immediately after a write instruction is executed.

Owner:RENESAS TECH CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com