Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

241 results about "Watchdog timer" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A watchdog timer (sometimes called a computer operating properly or COP timer, or simply a watchdog) is an electronic timer that is used to detect and recover from computer malfunctions. During normal operation, the computer regularly resets the watchdog timer to prevent it from elapsing, or "timing out". If, due to a hardware fault or program error, the computer fails to reset the watchdog, the timer will elapse and generate a timeout signal. The timeout signal is used to initiate corrective action or actions. The corrective actions typically include placing the computer system in a safe state and restoring normal system operation.

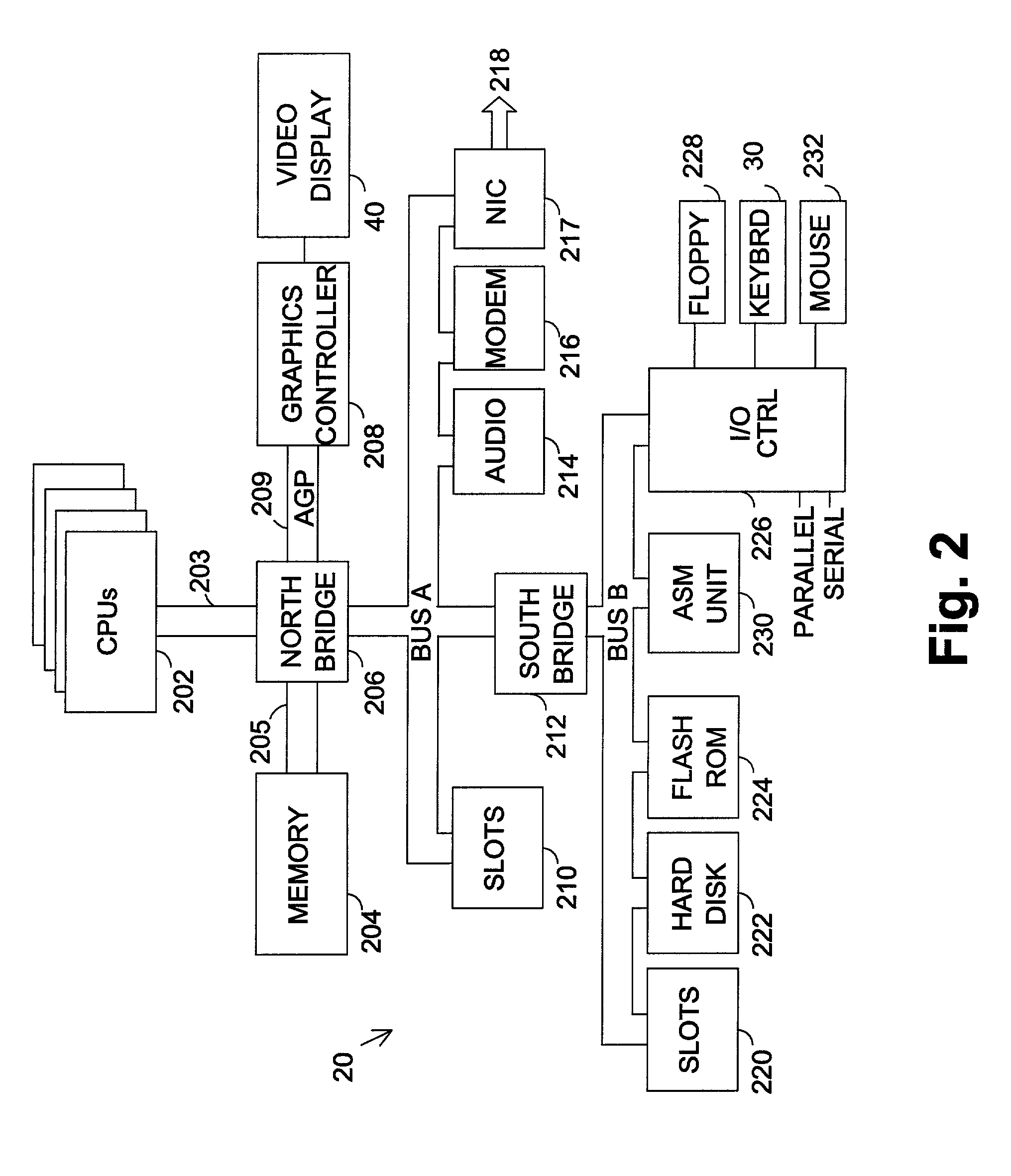

Maintenance unit architecture for a scalable internet engine

InactiveUS20050080891A1Error detection/correctionDigital computer detailsManagement unitOperational system

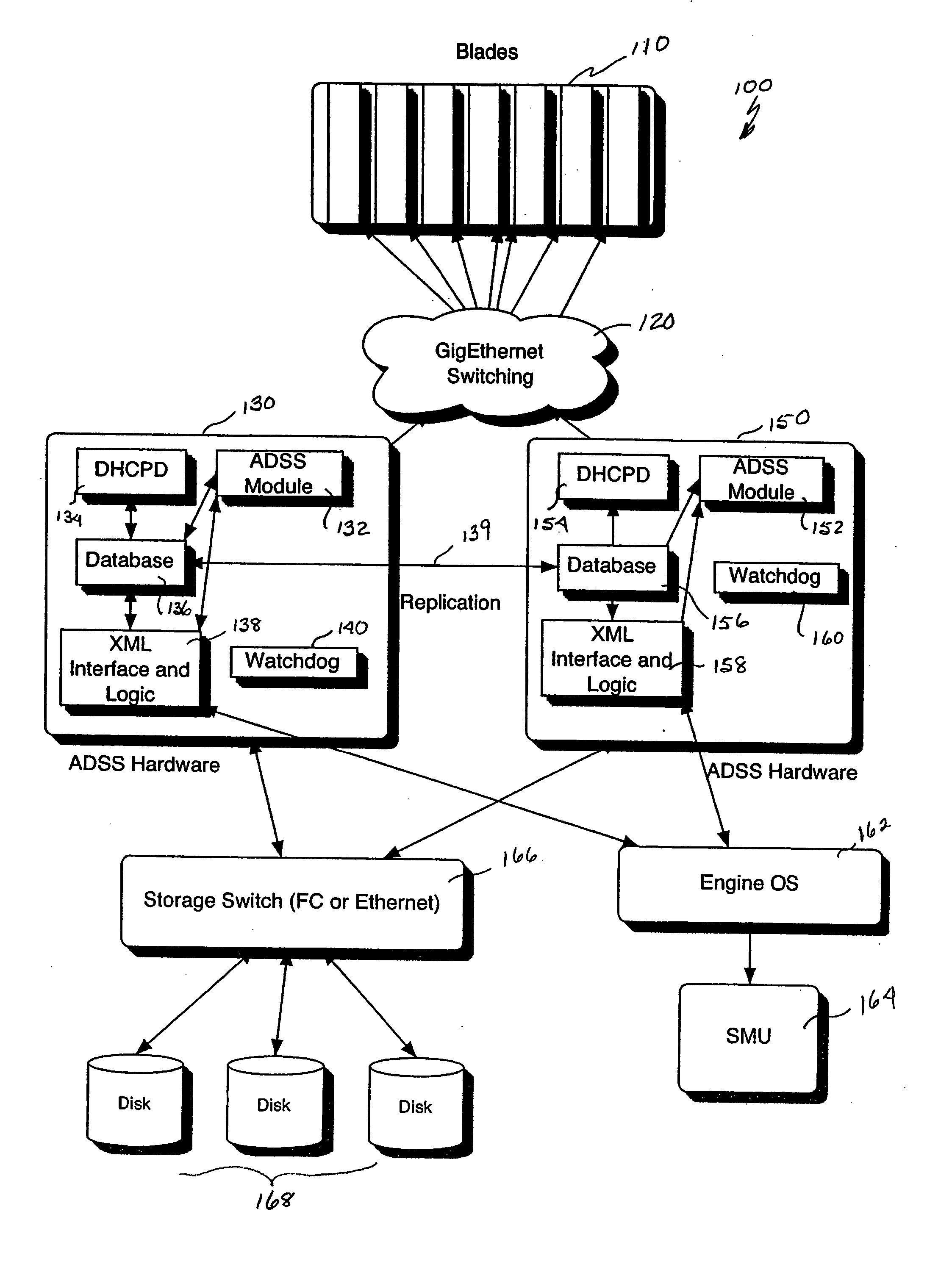

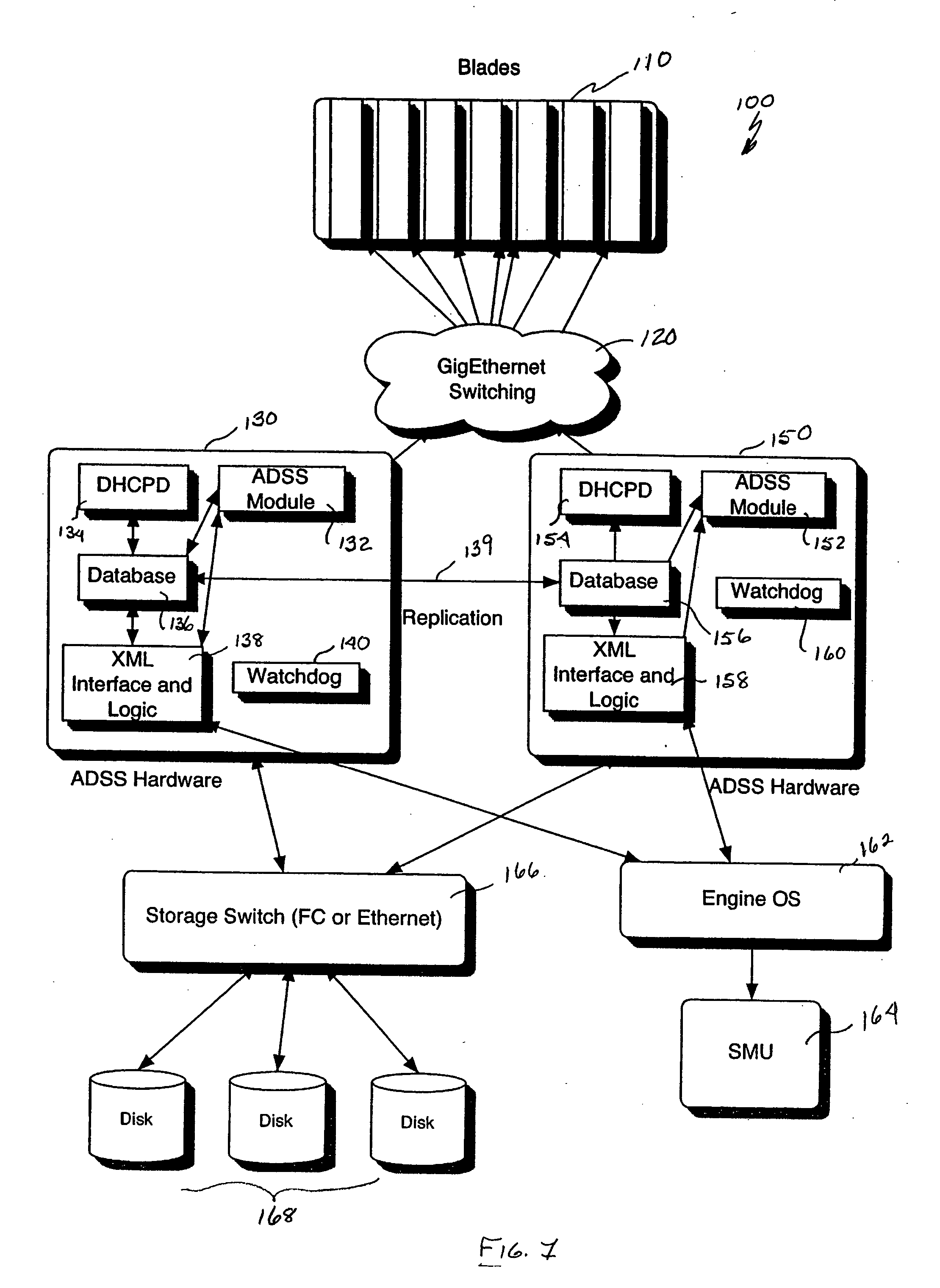

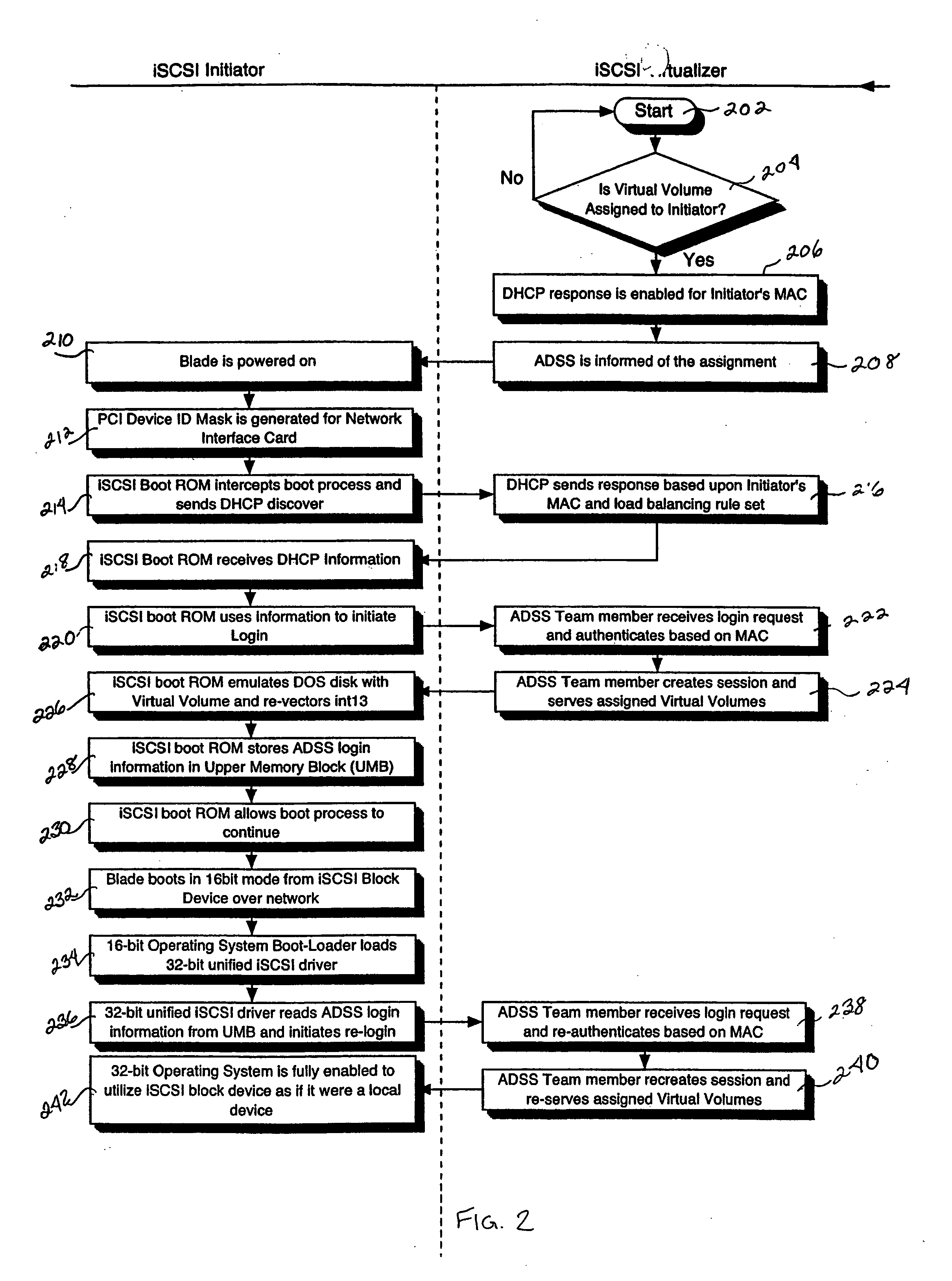

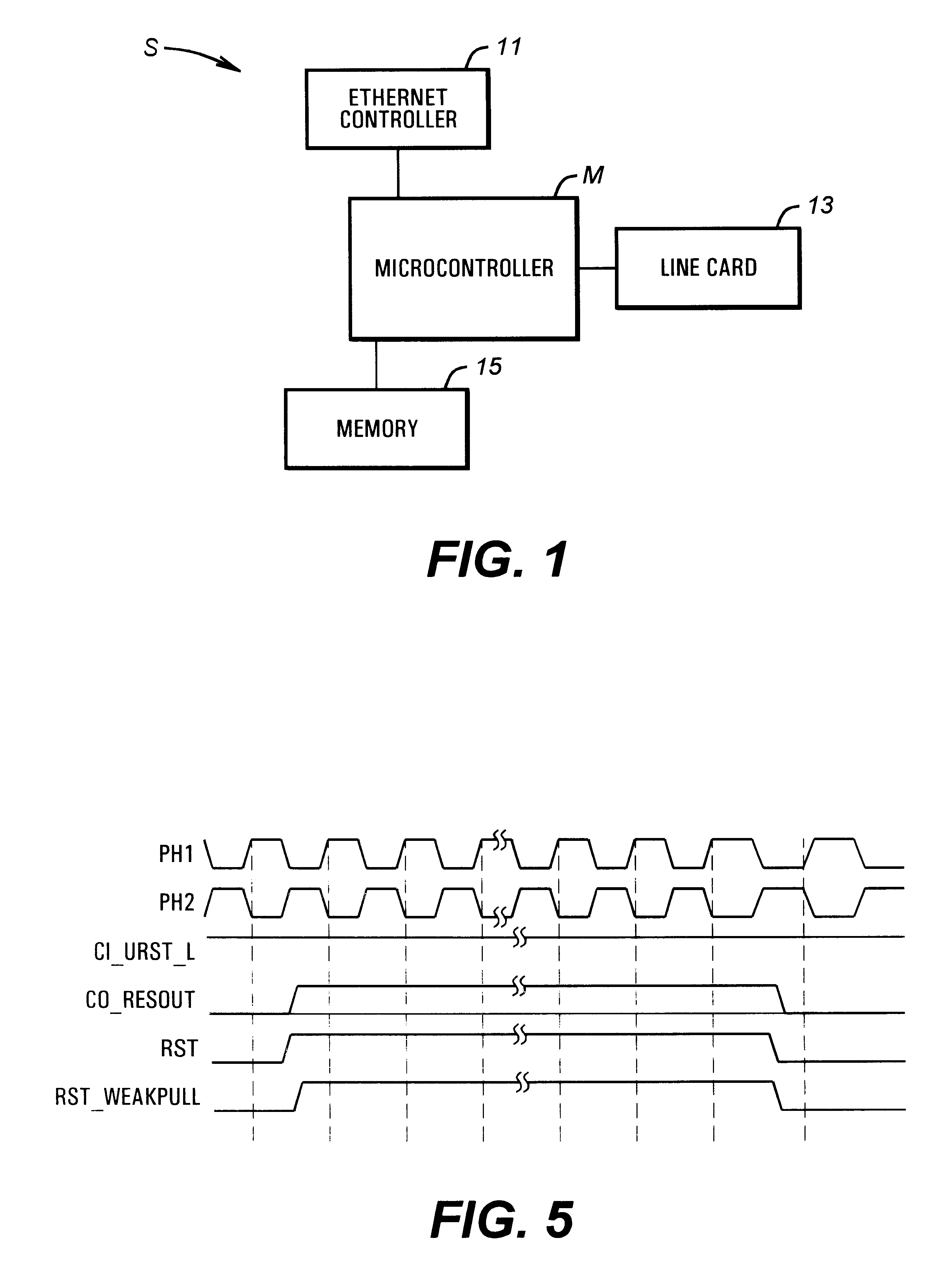

A scalable Internet engine that dynamically reassigns server operations in the event of a failure of an ADSS (Adaptive Data Storage System) server. A first and a second ADSS server mirror each other and include corresponding databases with redundant data, domain host control protocol servers, XML interfaces and watchdog timers. The ADSS servers are communicatively coupled to at least one engine operating system and a storage switch; the storage switch being coupled to at least one storage element. The second ADSS server detects, via a heartbeat monitoring algorithm, the failure of the first ADSS server and automatically initiates a fail over action to switch over functions to the second ADSS server. The architecture also includes a supervisory data management arrangement that includes a plurality of reconfigurable blade servers coupled to a star configured array of data management units.

Owner:RPX CORP

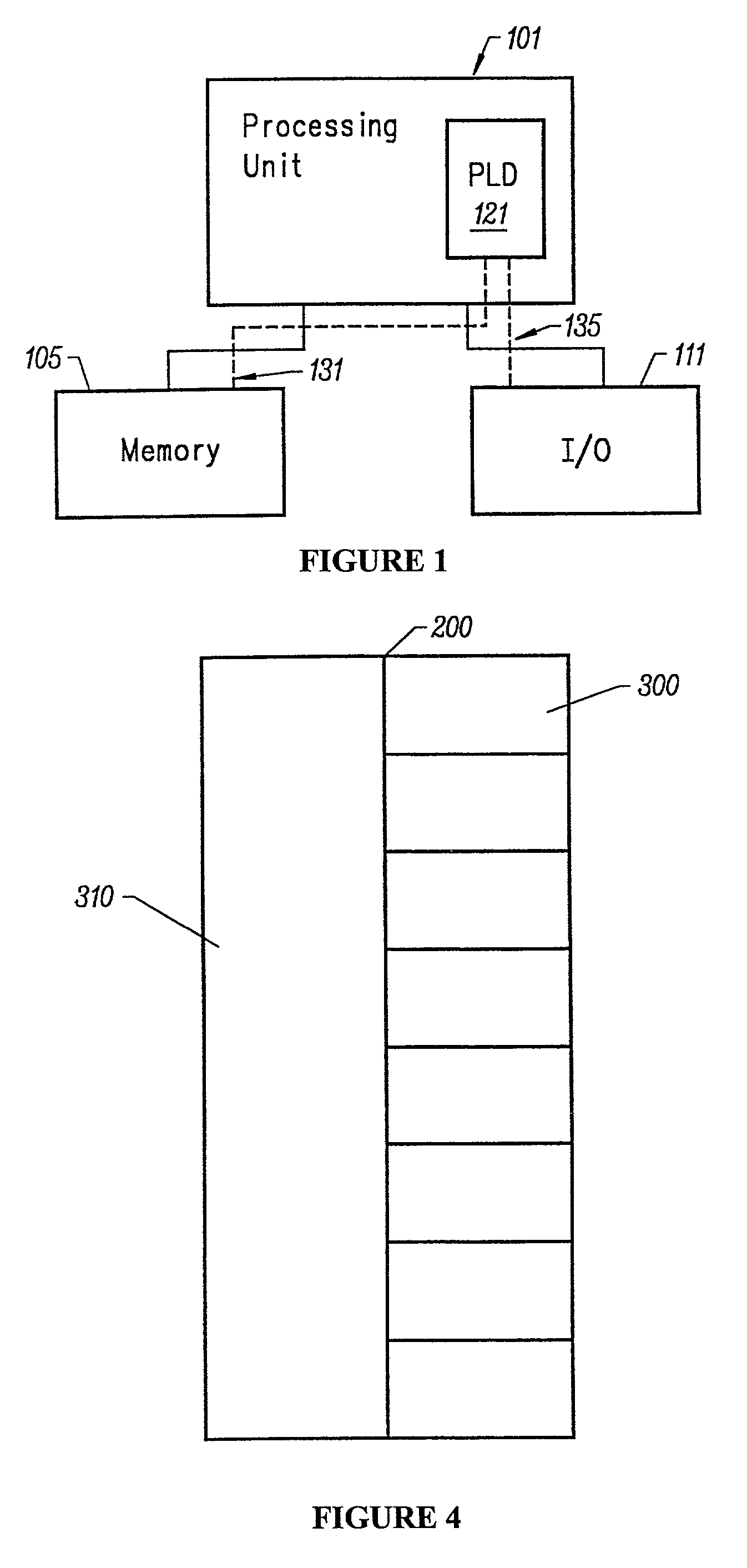

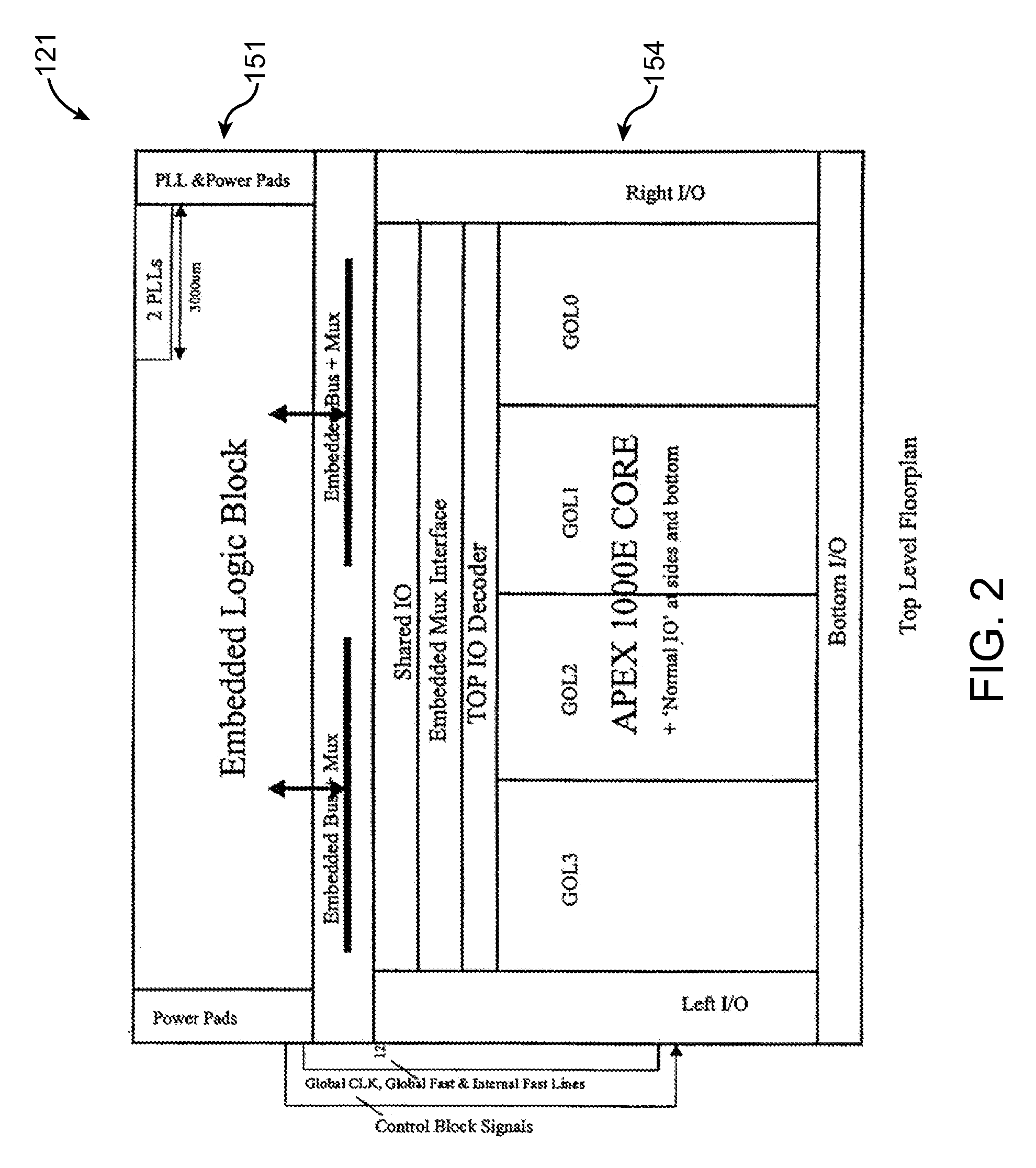

Embedded processor with watchdog timer for programmable logic

InactiveUS7340596B1Digital computer detailsData resettingProgrammable logic deviceProcessor register

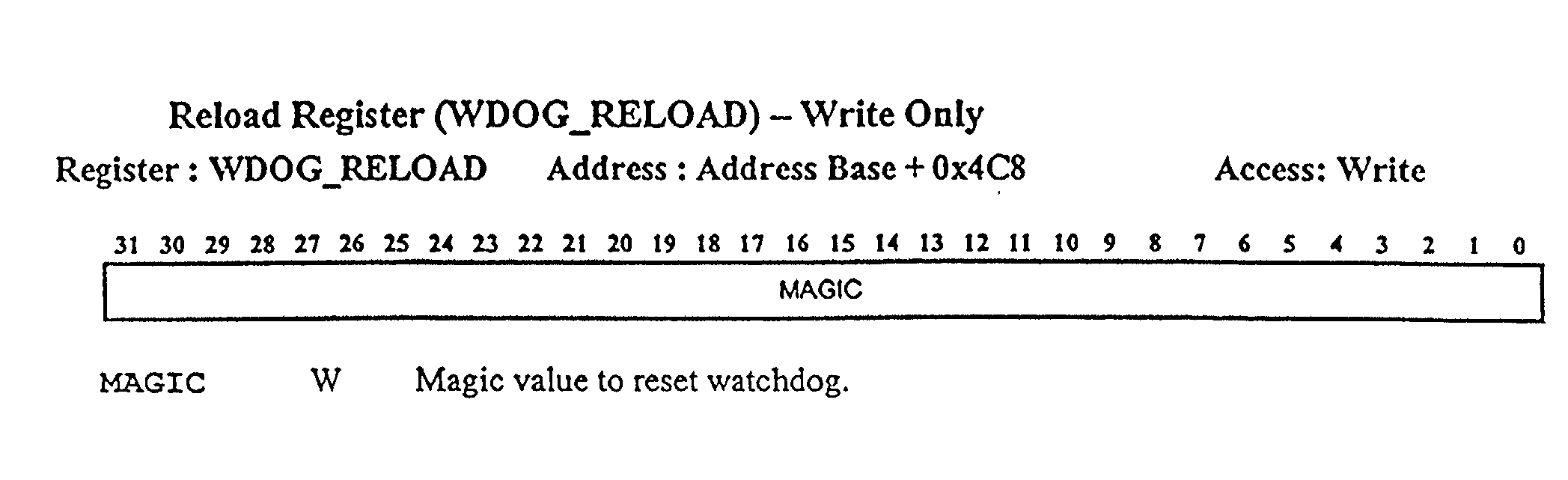

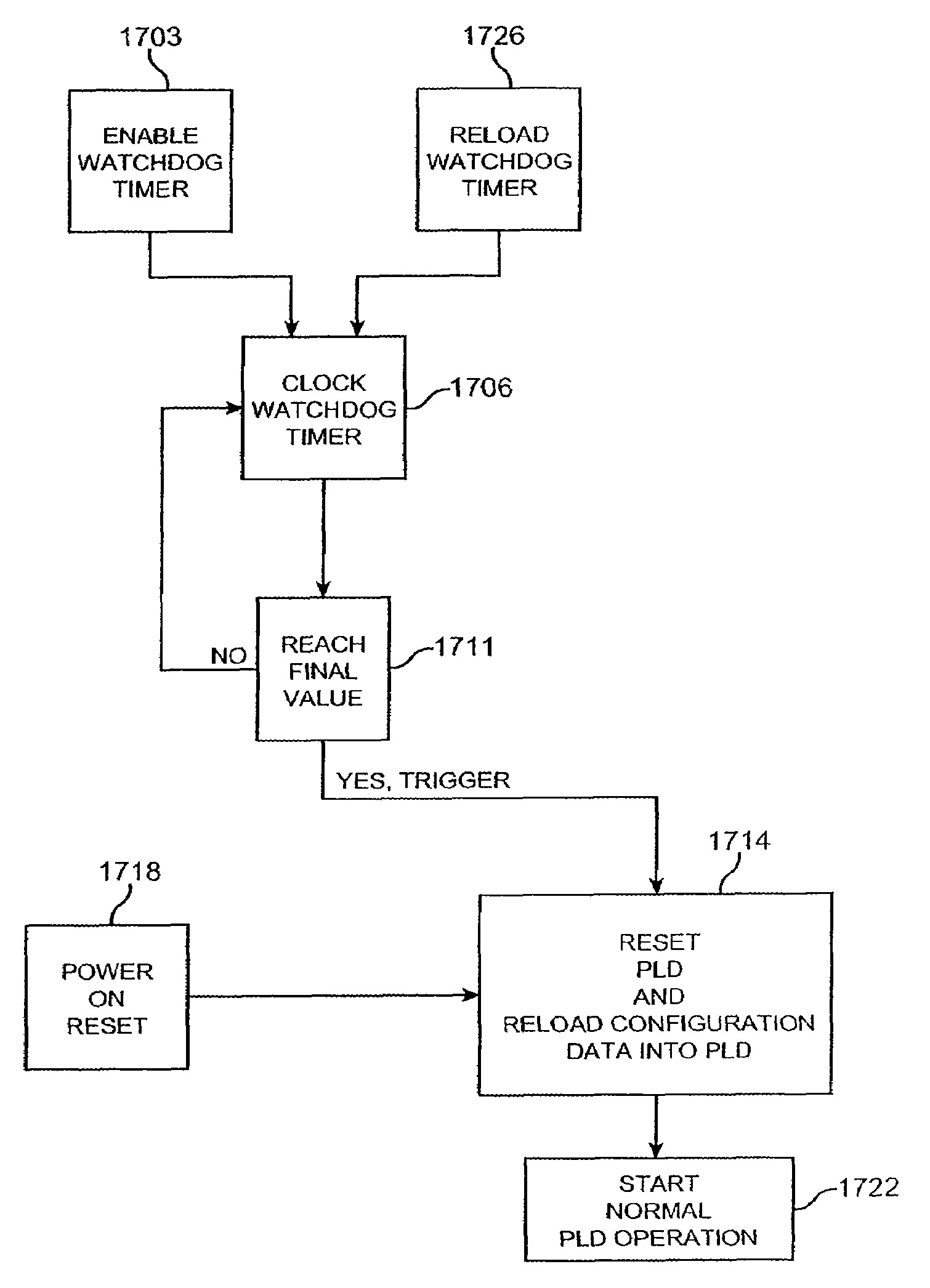

A programmable logic integrated circuit has an embedded processor with a watchdog timer circuit. The watchdog timer circuit is used to detect software or hardware failures. In one implementation, the watchdog timer circuit includes a counter register that advances (e.g., incremented or decremented) with each clock. To prevent the watchdog timer circuit from becoming triggered, the watchdog timer circuit should be reset or reloaded by software. For example, the count register may be reset to a value to start the count over. If the count register is allowed to count to a final or maximum value, the watchdog timer circuit will become triggered, generating a triggered signal that causes the programmable logic integrated circuit to be reset. A reset causes a reloading of the configuration data used to program the programmable logic and embedded processor portions of the integrated data. The configuration data may be stored in an external nonvolatile storage memory.

Owner:ALTERA CORP

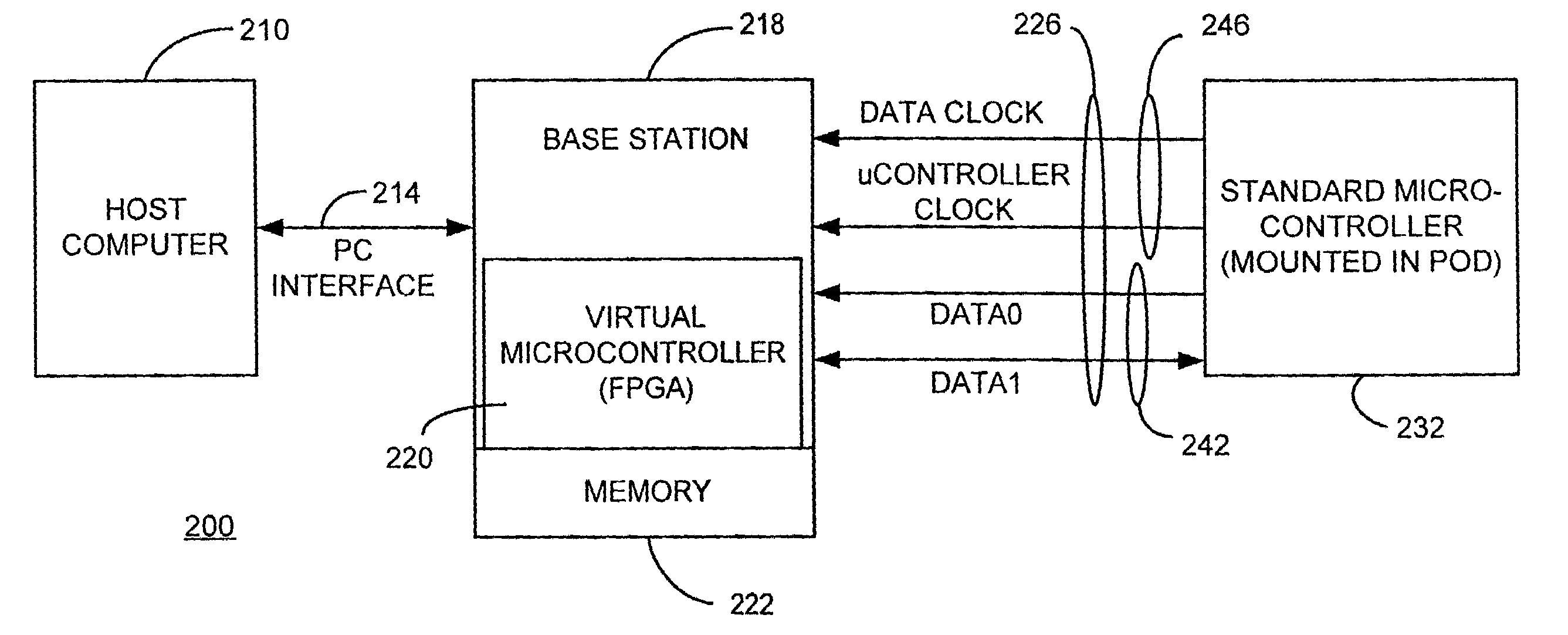

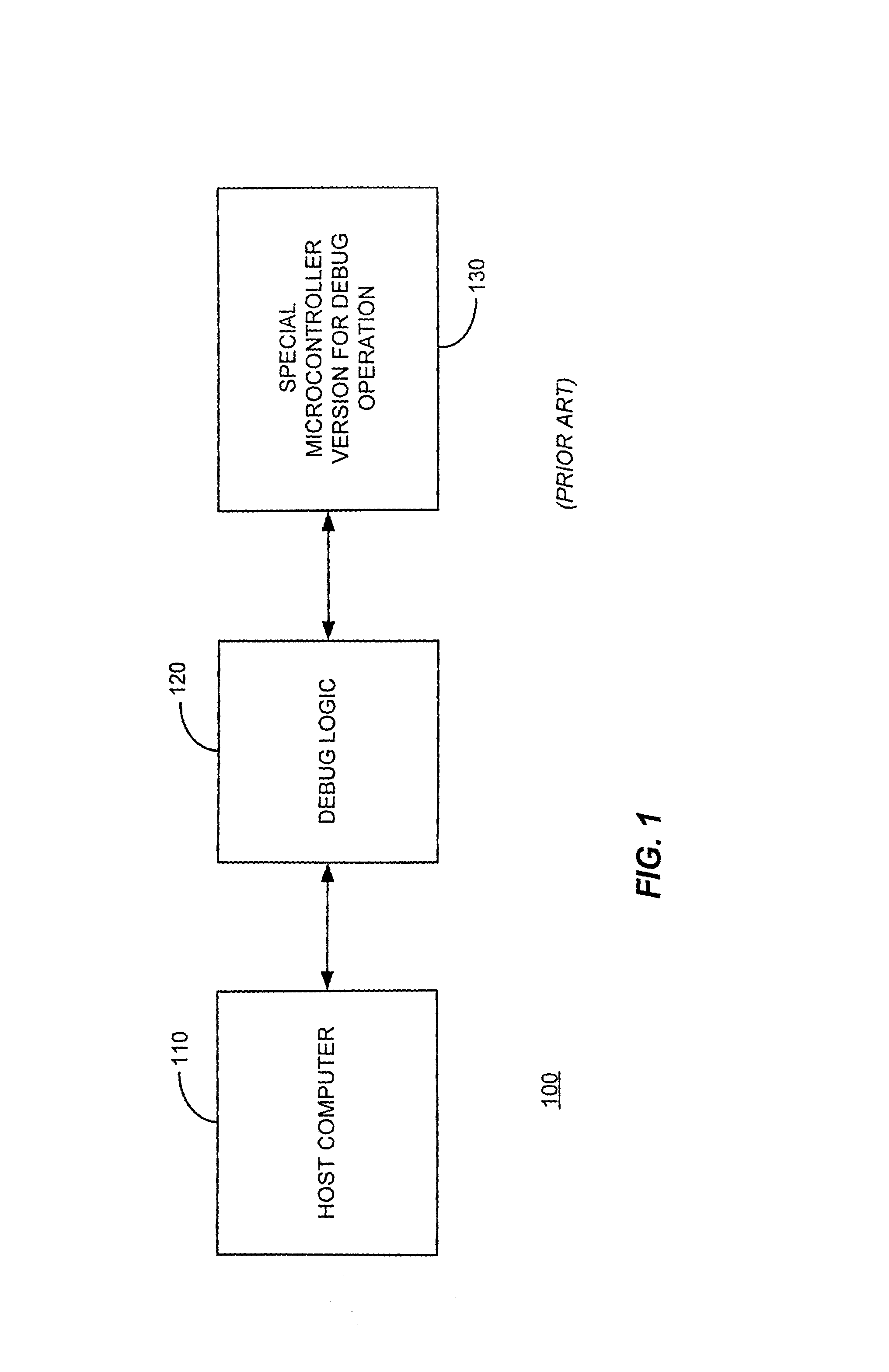

In-circuit emulator with gatekeeper for watchdog timer

ActiveUS7162410B1Easy to operate and debugDebug operationError detection/correctionSoftware simulation/interpretation/emulationMicrocontrollerIn-circuit emulator

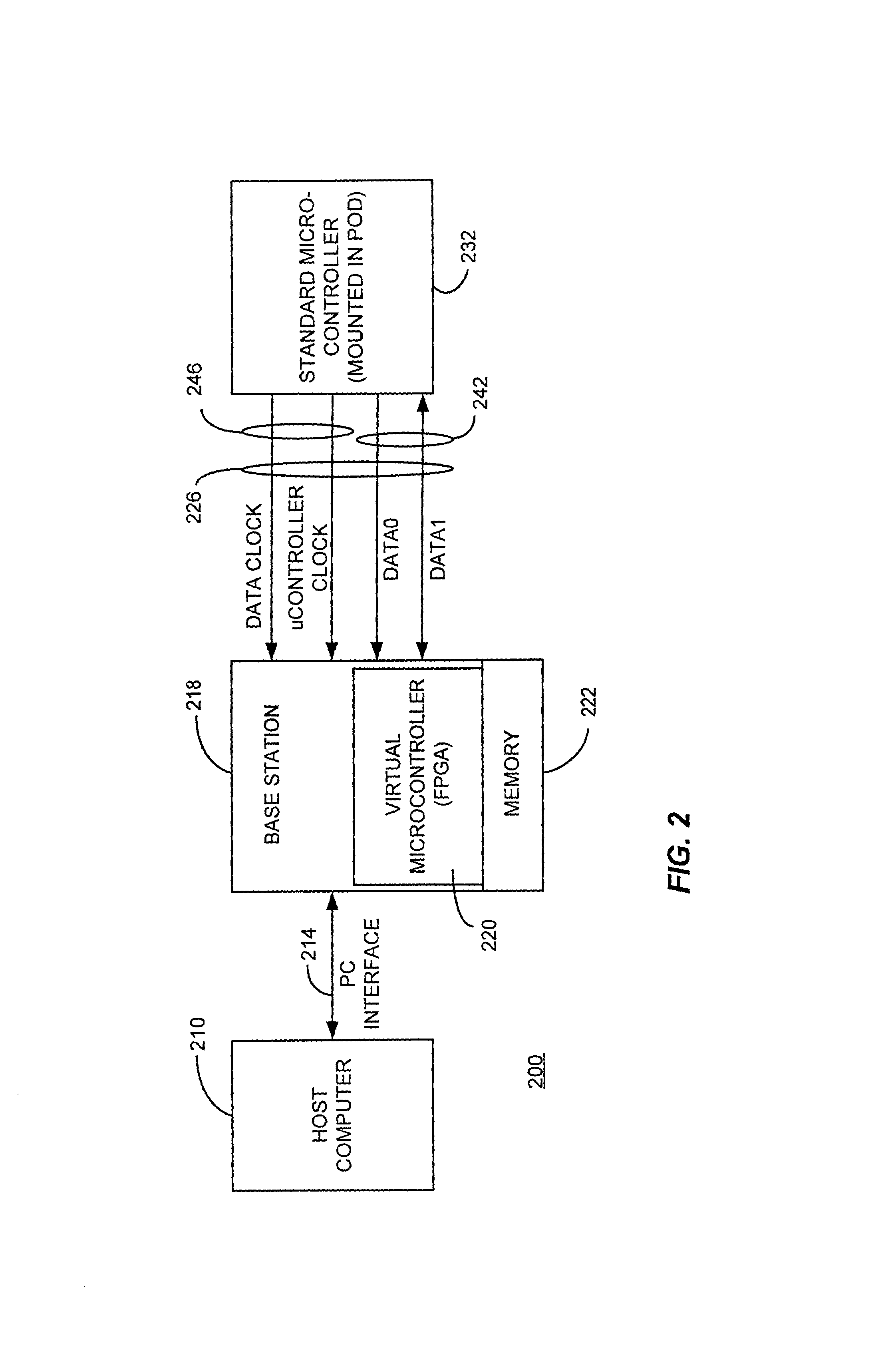

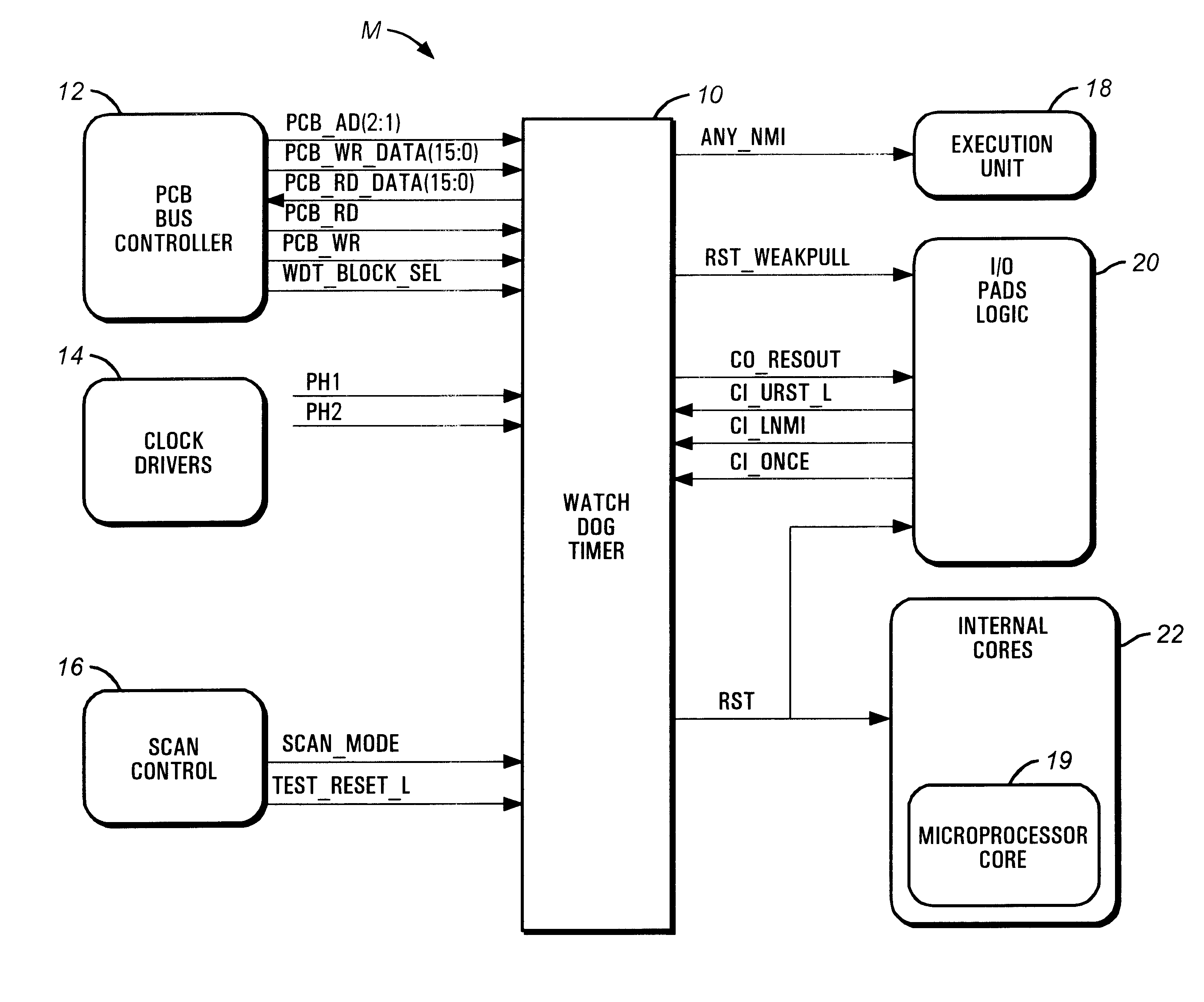

A watchdog timer control using a gatekeeper in an In-Circuit Emulation system. The In-Circuit Emulation system has a microcontroller operating in lock-step synchronization with a virtual microcontroller. When a watchdog event occurs, the gatekeeper, forming a part of the virtual microcontroller, crowbars the reset line of the virtual microcontroller as well as the real microcontroller. This freezes the state of the virtual microcontroller so that debug operations can be carried out. The gatekeeper operates with its own gatekeeper clock independent of the microcontroller clock. When a watchdog event occurs, the gatekeeper clock is rerouted to the virtual microcontroller to facilitate debug operations of the virtual microcontroller.

Owner:MONTEREY RES LLC

System and method for concurrent WLAN and WPAN wireless modes from a single device

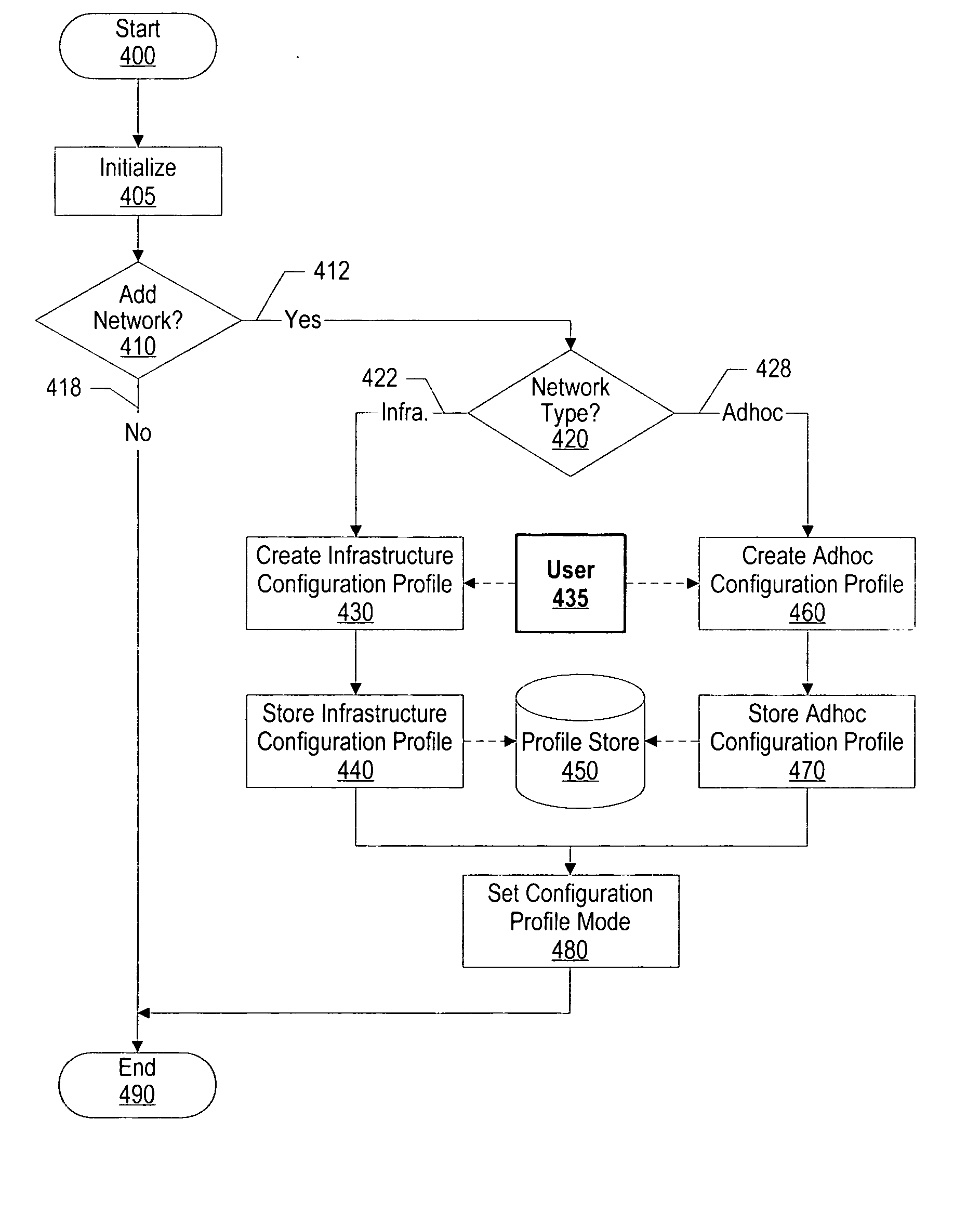

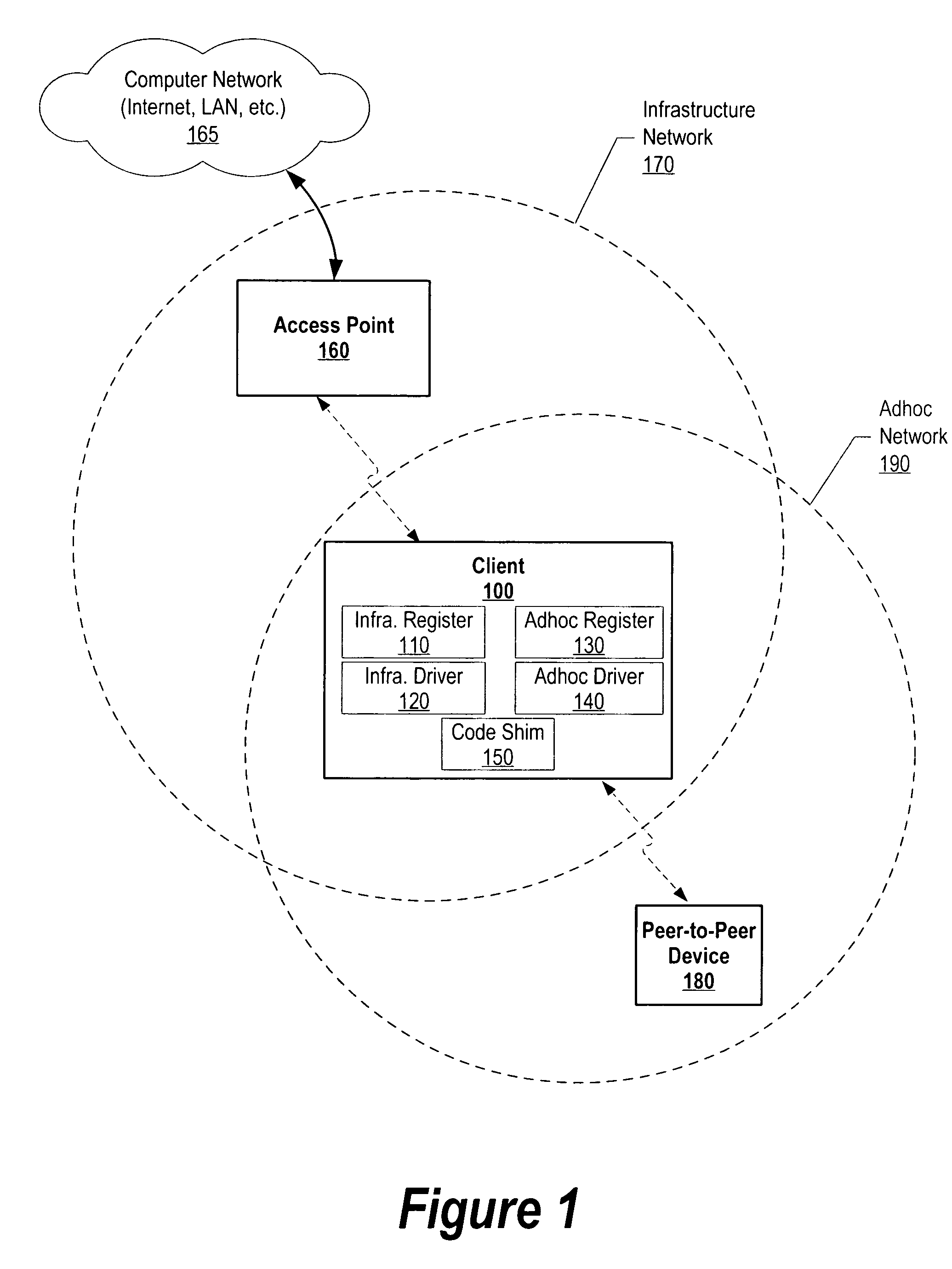

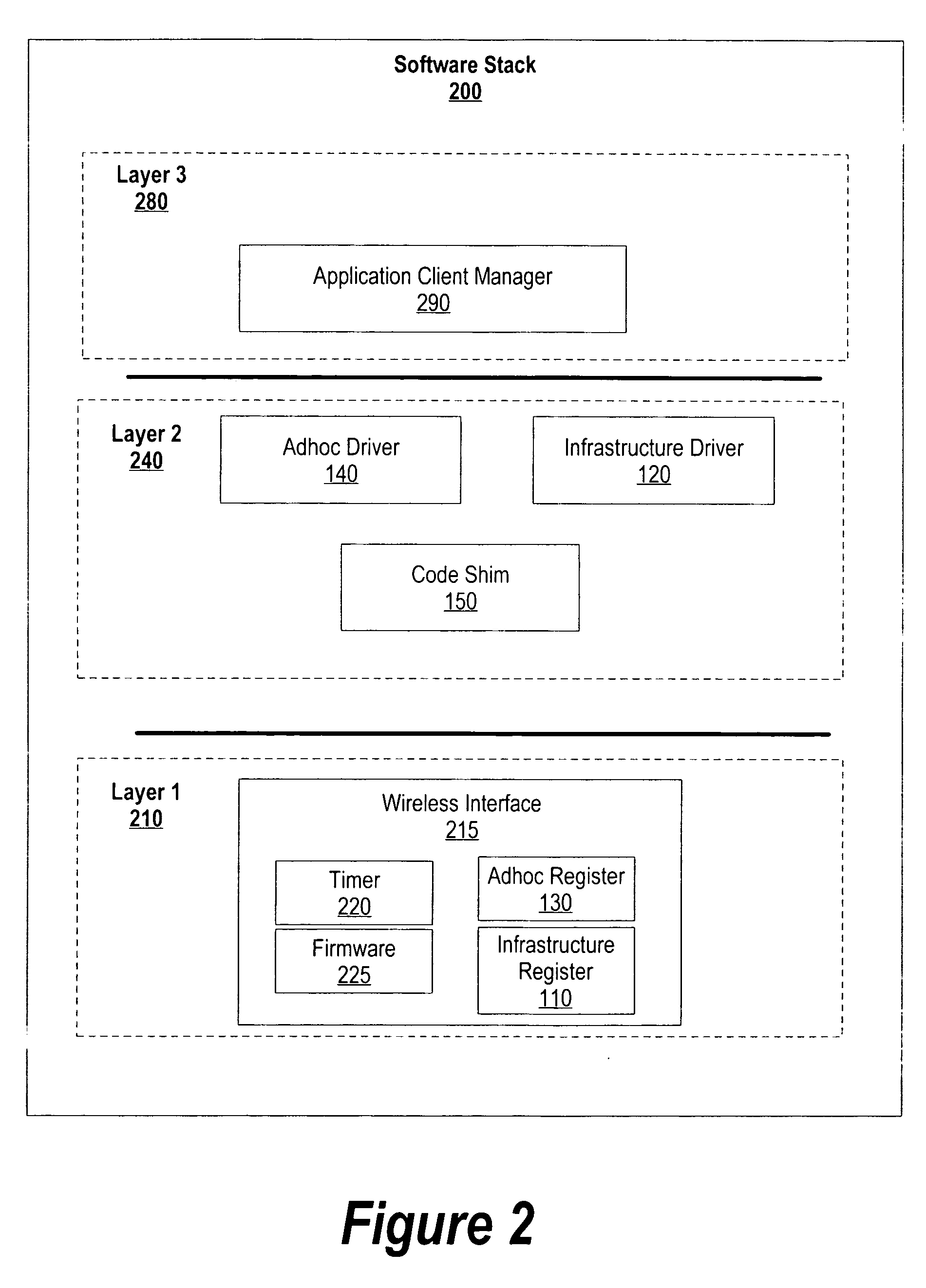

A system and method for concurrent WLAN and WPAN wireless modes from a single device is presented. A client uses a Wi-Fi device's infrastructure mode to communicate in a WLAN environment and, during idle WLAN times, uses the Wi-Fi device's adhoc mode to communicate in a WPAN environment. The Wi-Fi device uses a watchdog timer to switch between infrastructure mode and adhoc mode. When the client's Wi-Fi device switches to infrastructure mode, the client's Wi-Fi device uses an infrastructure register and an infrastructure device driver to transfer data over the WLAN environment. Likewise, when the client's Wi-Fi device switches to adhoc mode, the client's Wi-Fi device uses an adhoc register and an adhoc device driver to transfer data over the WLAN environment. The client uses a code shim to act as a virtual device driver at times when either the infrastructure device driver or the adhoc device driver is inactive.

Owner:LENOVO PC INT

Application-level software watchdog timer

InactiveUS7000100B2Error detection/correctionData resettingCommunication interfaceOperational system

A software implementation of an application watchdog, comprising a restart service operating in the user mode and a watchdog driver operating in the kernel mode of a computer operating system. The driver incorporates a system thread configured to monitor a plurality of user applications operating in the user mode. The driver provides a first IOCTL signal interface for communicating control signals between the watchdog driver and one of the user applications and a second IOCTL signal interface for communicating control signals between the watchdog driver and the restart service. A communication interface exists for coordinating timer events with the operating system scheduler. If the system thread does not receive a message from one of said applications within an allotted period of time, the timer event alerts the watchdog driver that the allotted time has elapsed and the watchdog driver signals the restart service to restart that application.

Owner:HEWLETT PACKARD DEV CO LP

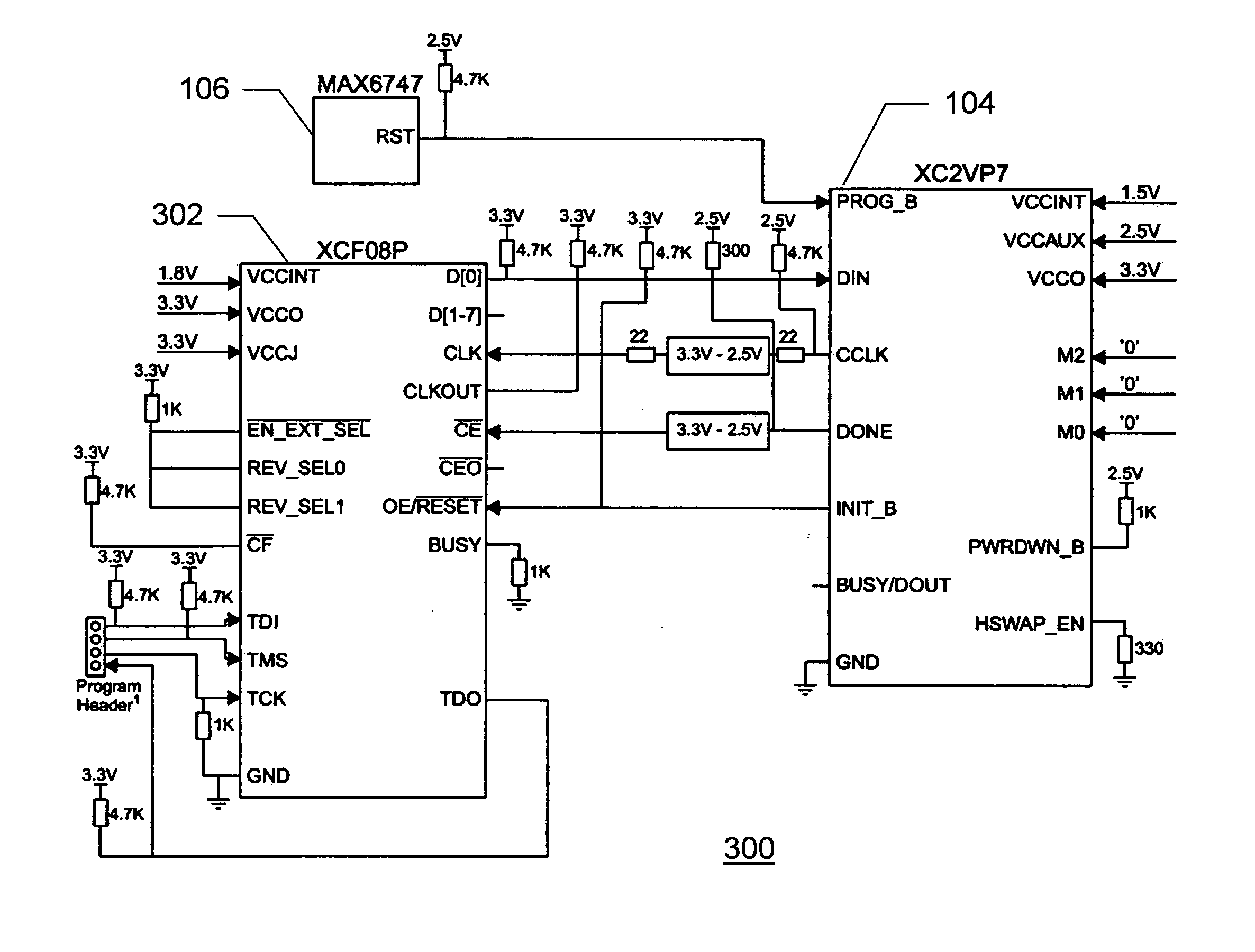

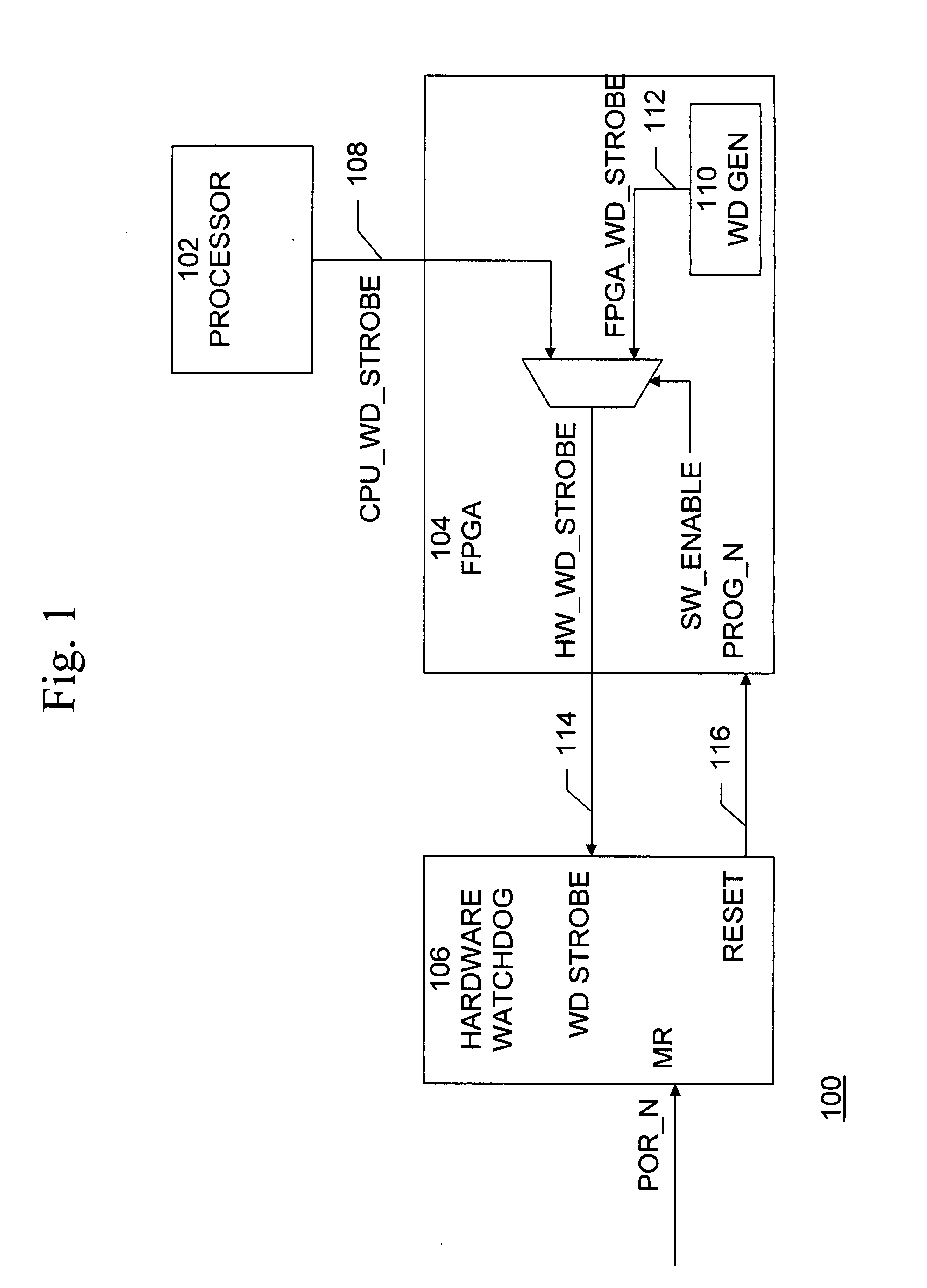

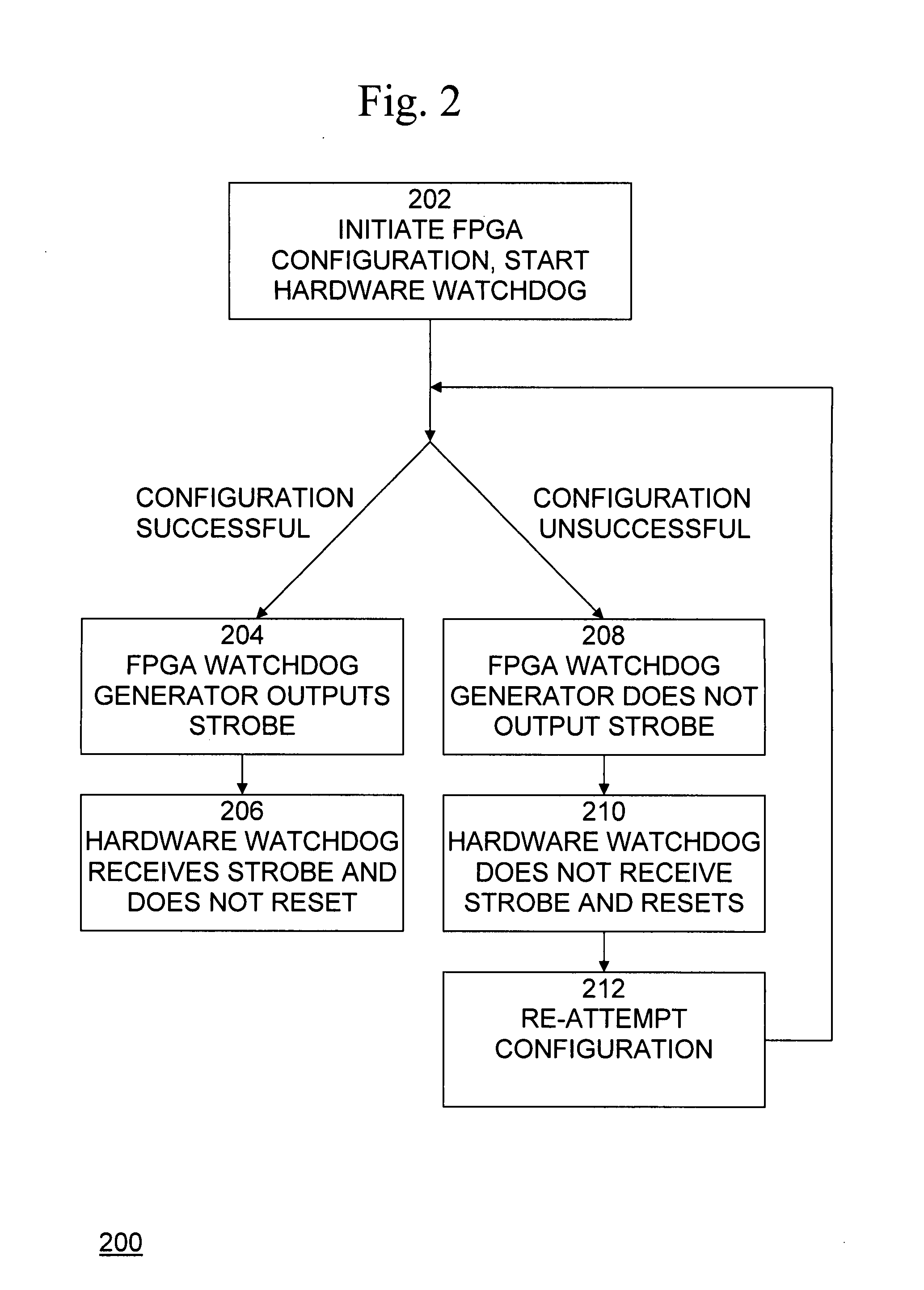

FPGA configuration protection and control using hardware watchdog timer

InactiveUS20090085603A1Low costSave spaceElectronic circuit testingDigital computer detailsSignal generatorEmbedded system

An apparatus and method provides automatic reconfiguration of an FPGA, such as in case of lost configuration or configuration error, and software-controlled reconfiguration may be provided that does not require the use of additional devices. An apparatus for FPGA configuration protection comprises watchdog signal generator circuitry in the FPGA configured to output a watchdog signal when the FPGA is properly configured and watchdog circuitry configured to receive the watchdog signal and to initiate reconfiguration of the FPGA if the watchdog signal is not received for or within a predetermined time. The circuitry in the FPGA may be configured to receive a signal from a processor and to output the watchdog signal when the signal from the processor is received.

Owner:FUJITSU LTD

Embedded processor with watchdog timer for programmable logic

InactiveUS7350178B1Data resettingAerodynamics improvementProcessor registerProgrammable logic device

Owner:ALTERA CORP

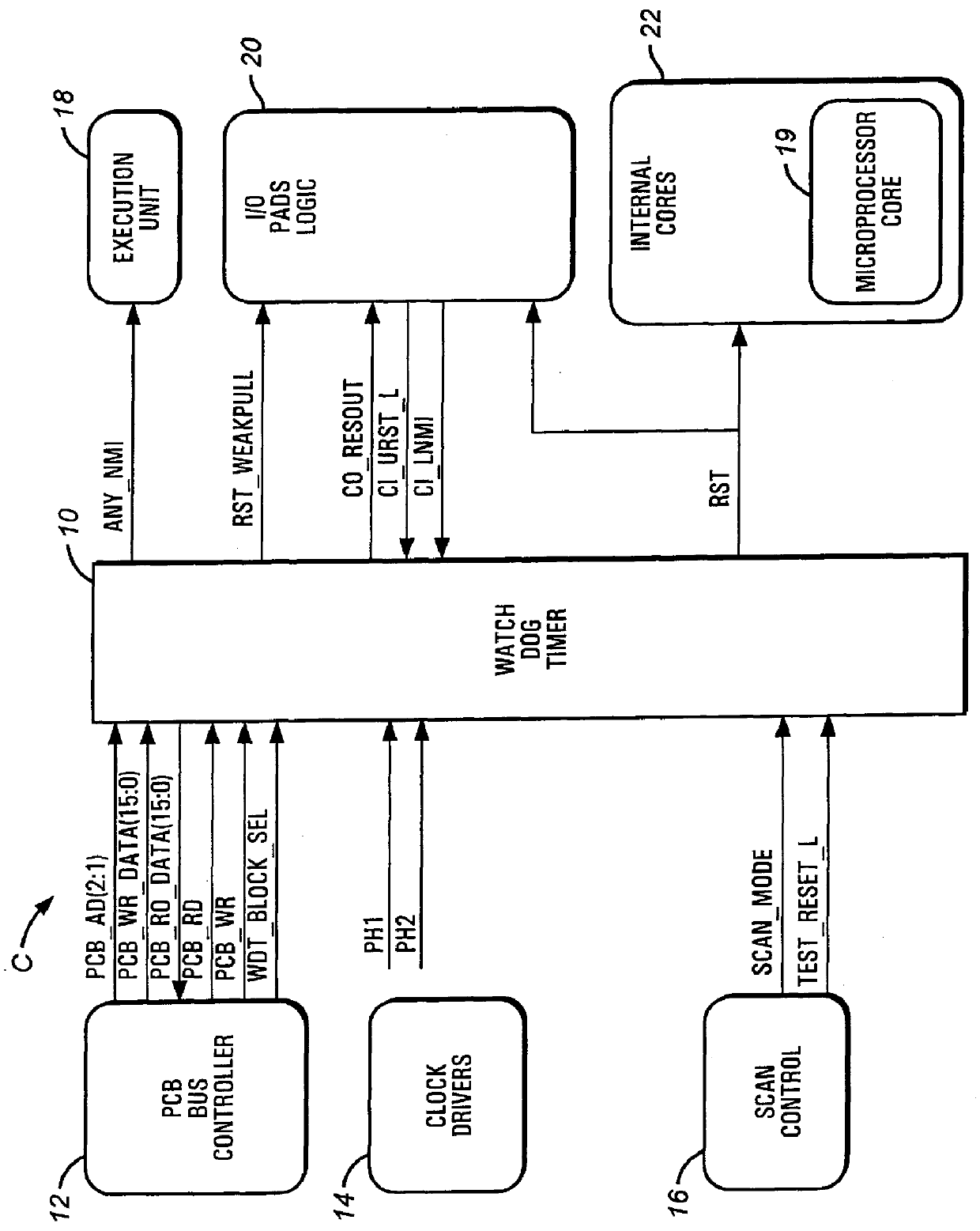

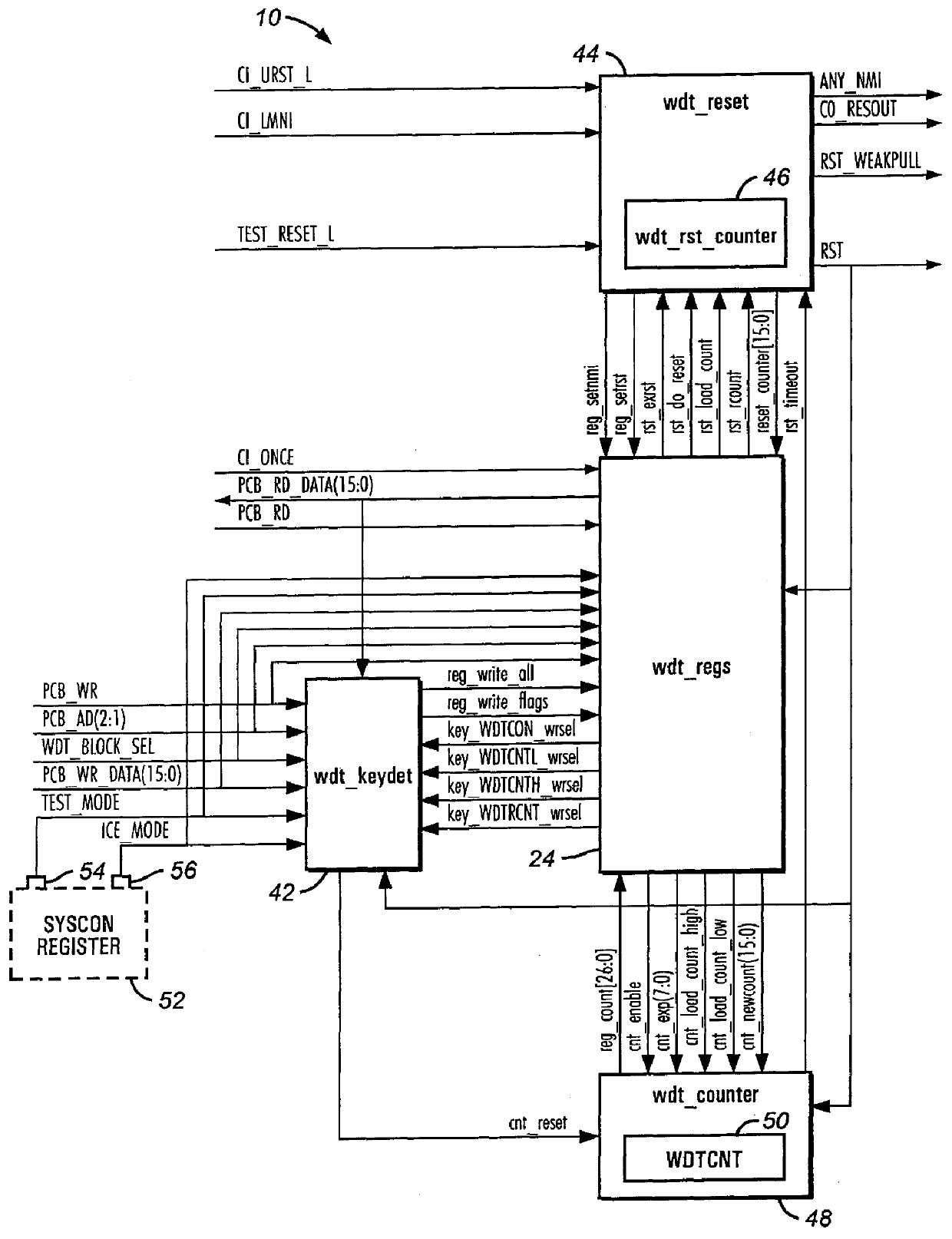

Test mode programmable reset for a watchdog timer

A processor-oriented device provides a watchdog timer having a test mode programmable reset. When the device is placed in a test mode by pulling a test mode hardware pin during a reset of the timer and then an appropriate write key is provided to the timer, a watchdog timer reset count is writeable, allowing for a programmable duration for a watchdog timer reset. The watchdog timer reset count may be a reset duration value maintained by a watchdog timer reset counter. Based on both a test mode signal from watchdog timer test mode enable logic and a write key, watchdog timer reset write enable logic enables writes to the watchdog timer reset count.

Owner:ADVANCED MICRO DEVICES INC

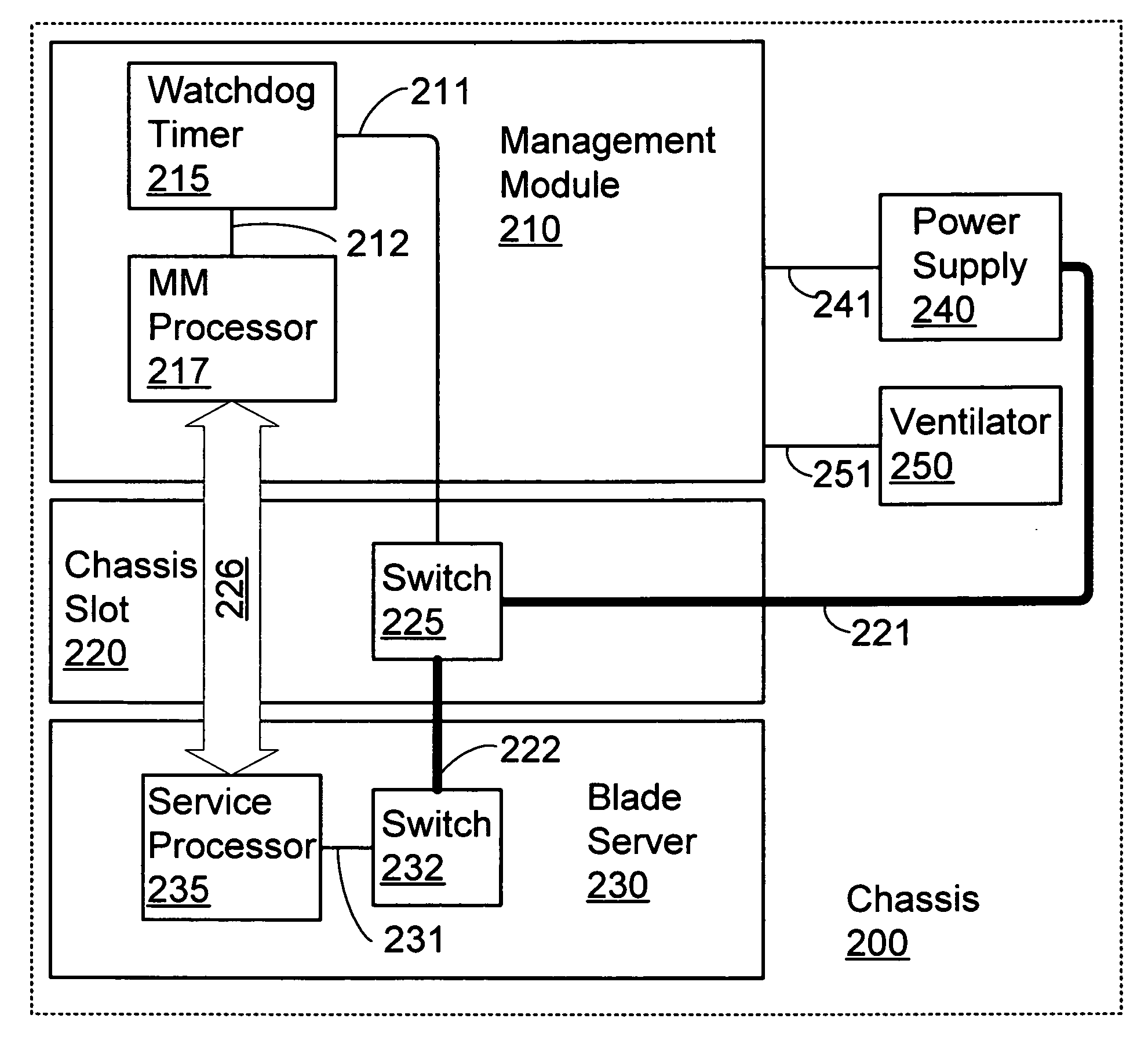

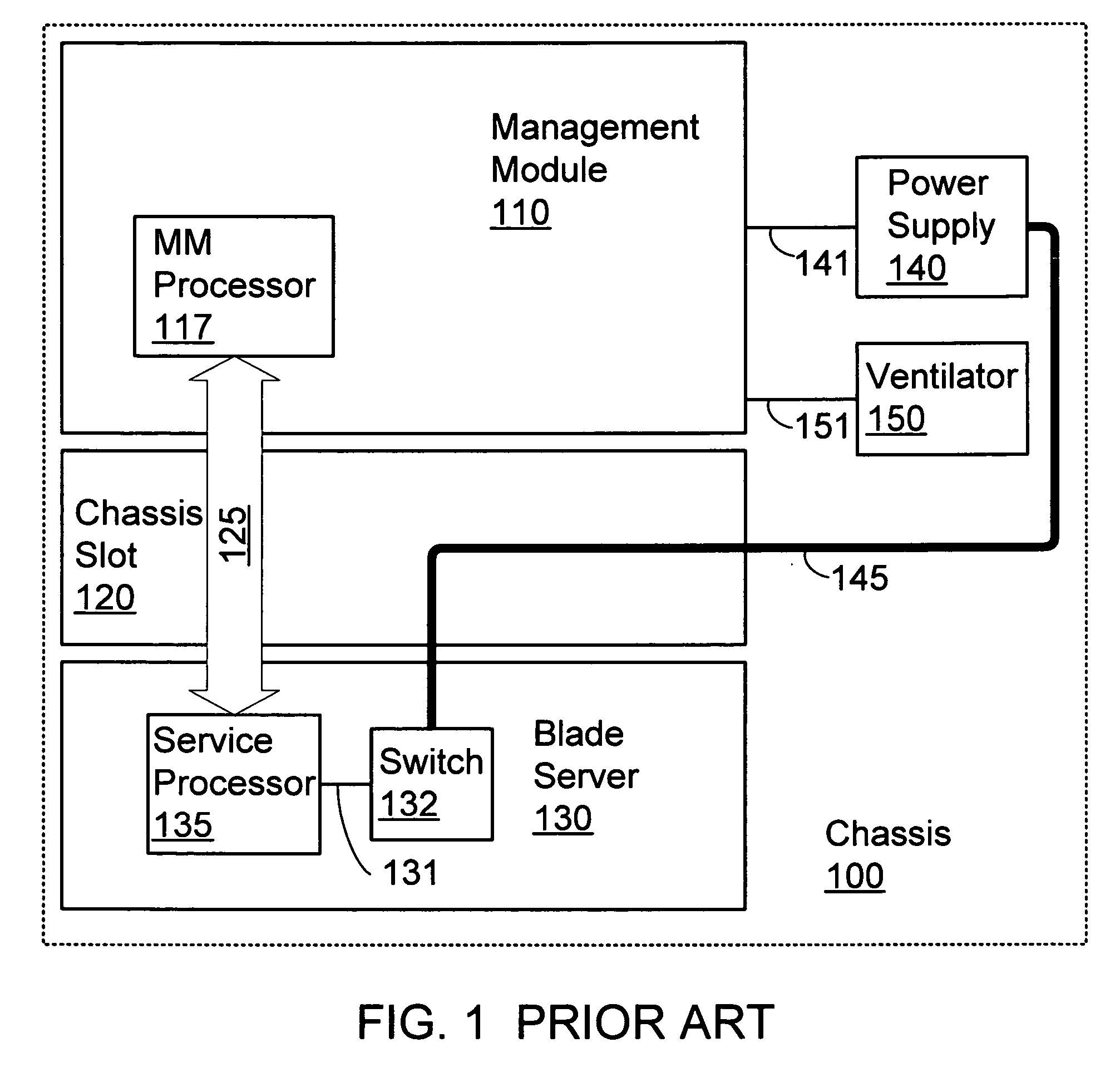

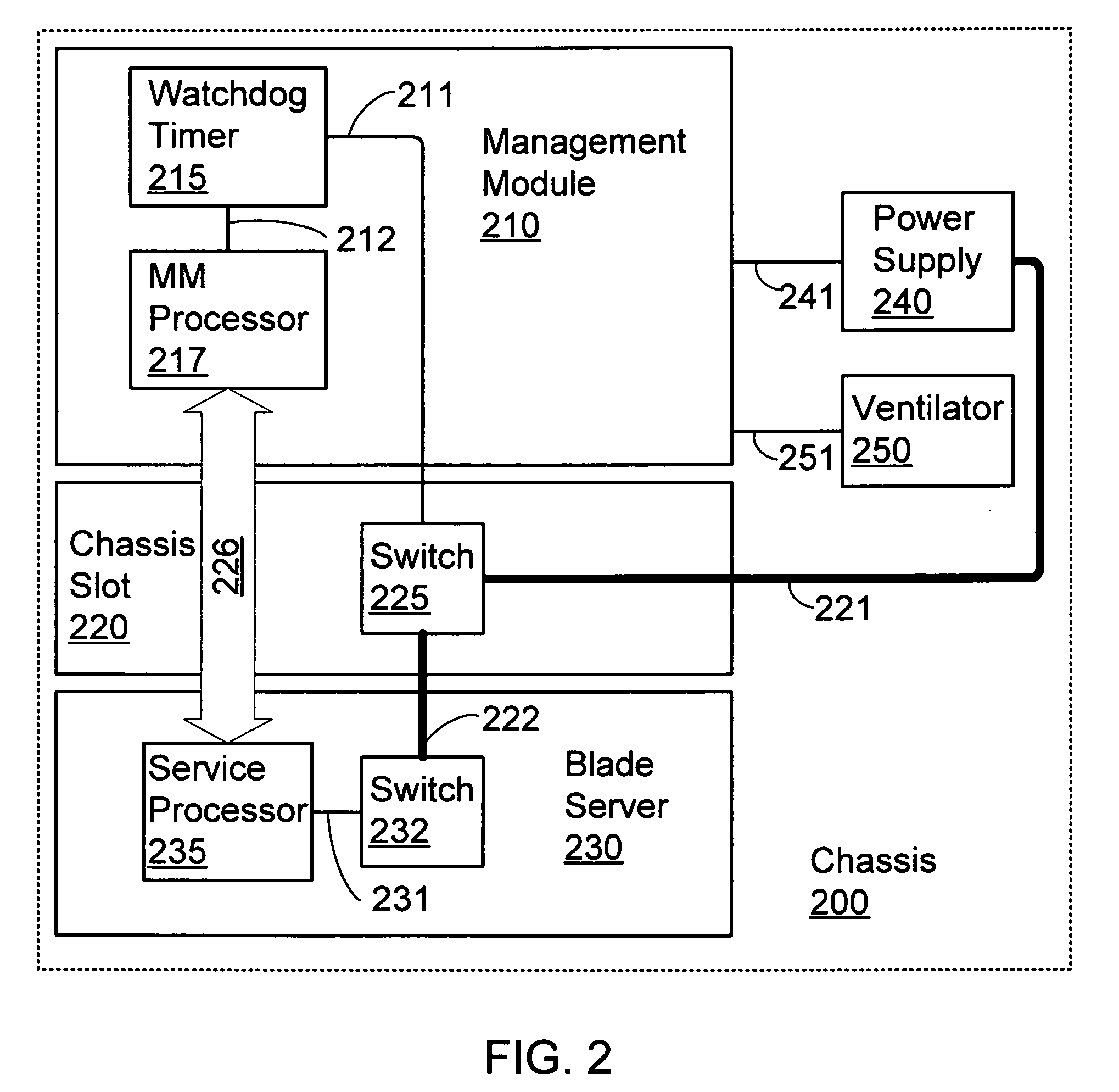

Method and apparatus for enforcing of power control in a blade center chassis

InactiveUS20070047195A1Guaranteed uptimeAvoid failureVolume/mass flow measurementDigital computer detailsEmbedded systemBlade server

A mechanism for changing ownership over the physical power to a blade server in a blade center chassis that prevents a malfunctioning blade from jeopardizing other components in the chassis. When the management module is not present, control over power to the blade is switched to a service processor on the blade. This arbitration of control over power to a blade is accomplished by implementing a watchdog timer mechanism. The management module is responsible for tickling the watchdog timer when the present in the chassis and operating normally. This mechanism provides the management module with control over power. If the management module malfunctions or is removed, control over power is switched to the local service processor on the blade server as soon as the watchdog timer is not tickled.

Owner:IBM CORP

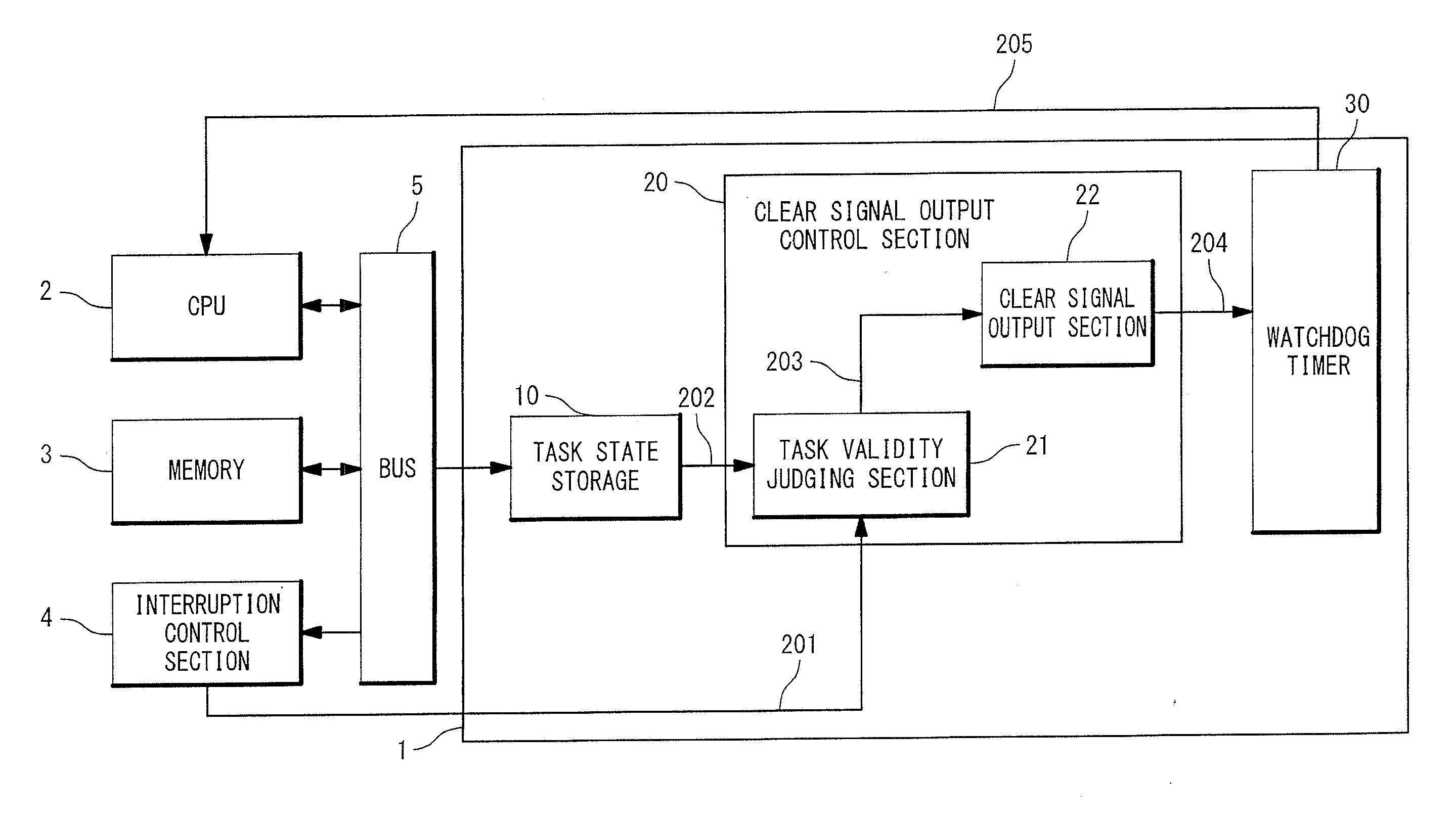

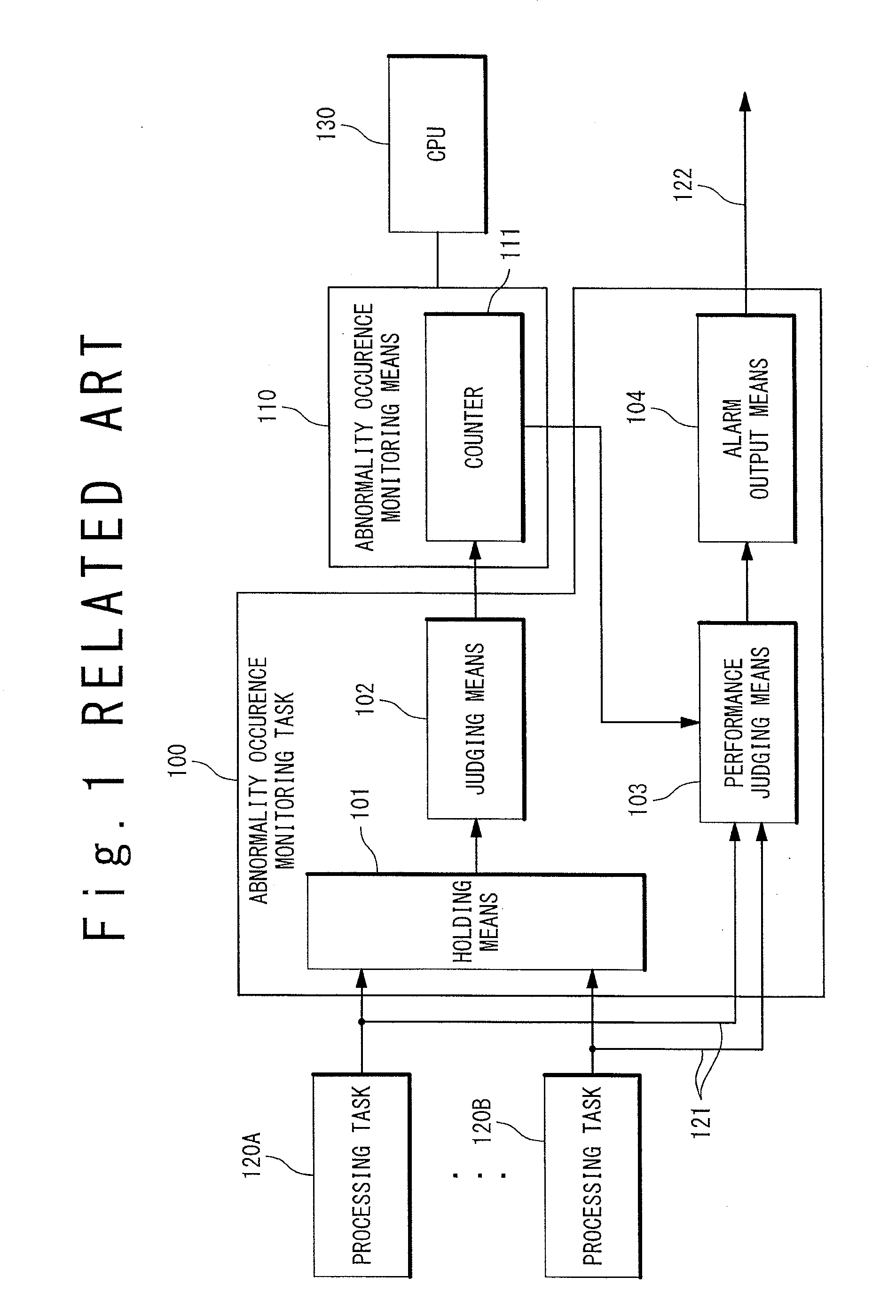

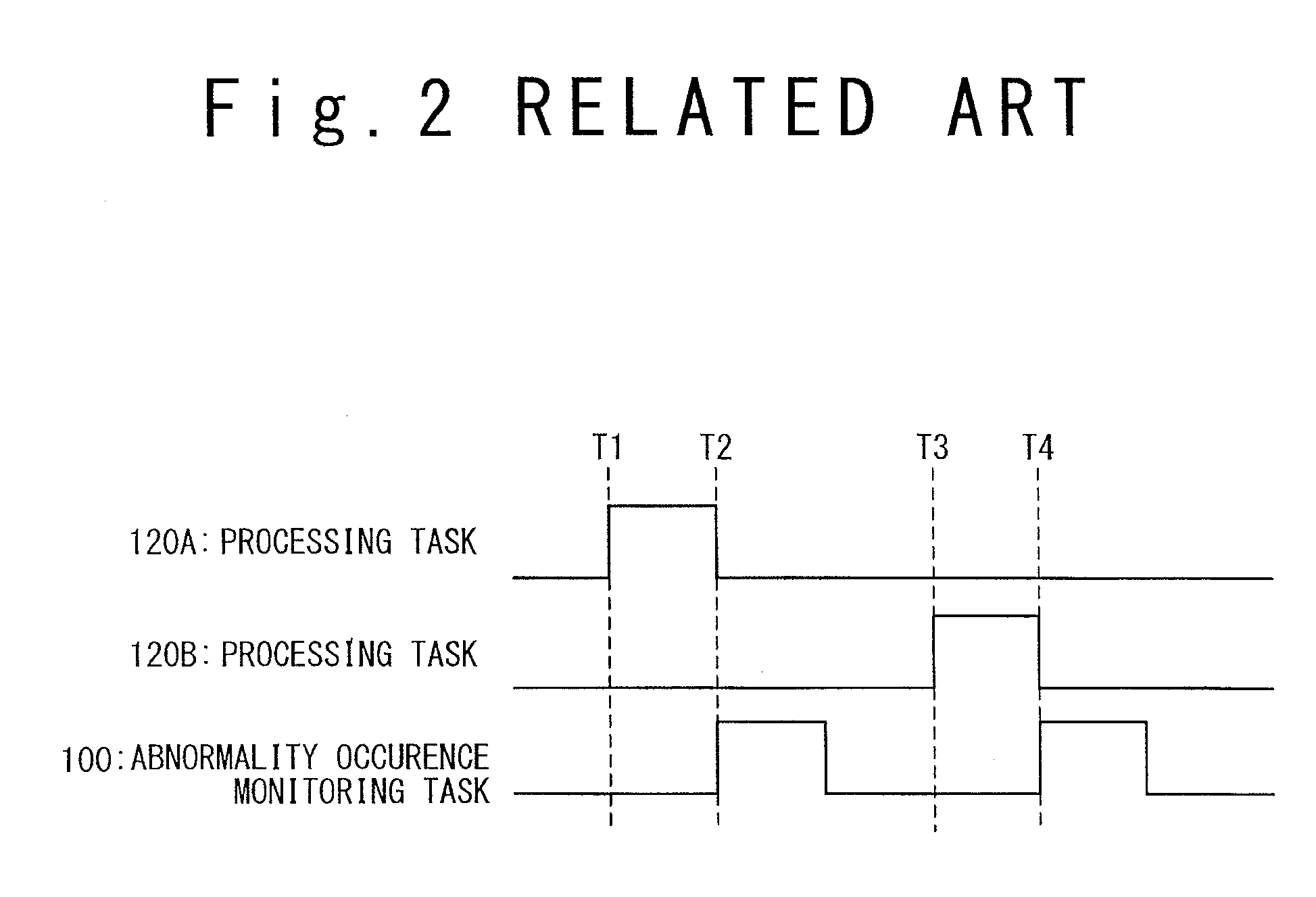

Semiconductor device and abnormality detecting method

A semiconductor device comprises: a task state storage configured to store an executing state of a processing task of software executed by a CPU and to output an executing state signal to show the executing state of the processing task; a task validity judging section configured to acquire an interruption signal corresponding to the processing task based on a control of the CPU and the execution state signal, and to output a valid signal when the processing task is executed validly; a clear signal output section configured to output a clear signal in response to the valid signal; and a watchdog timer configured to clear a timer count value when the clear signal is acquired within a prescribed time and to output a reset signal when the clear signal is not acquired within the prescribed time.

Owner:RENESAS ELECTRONICS CORP

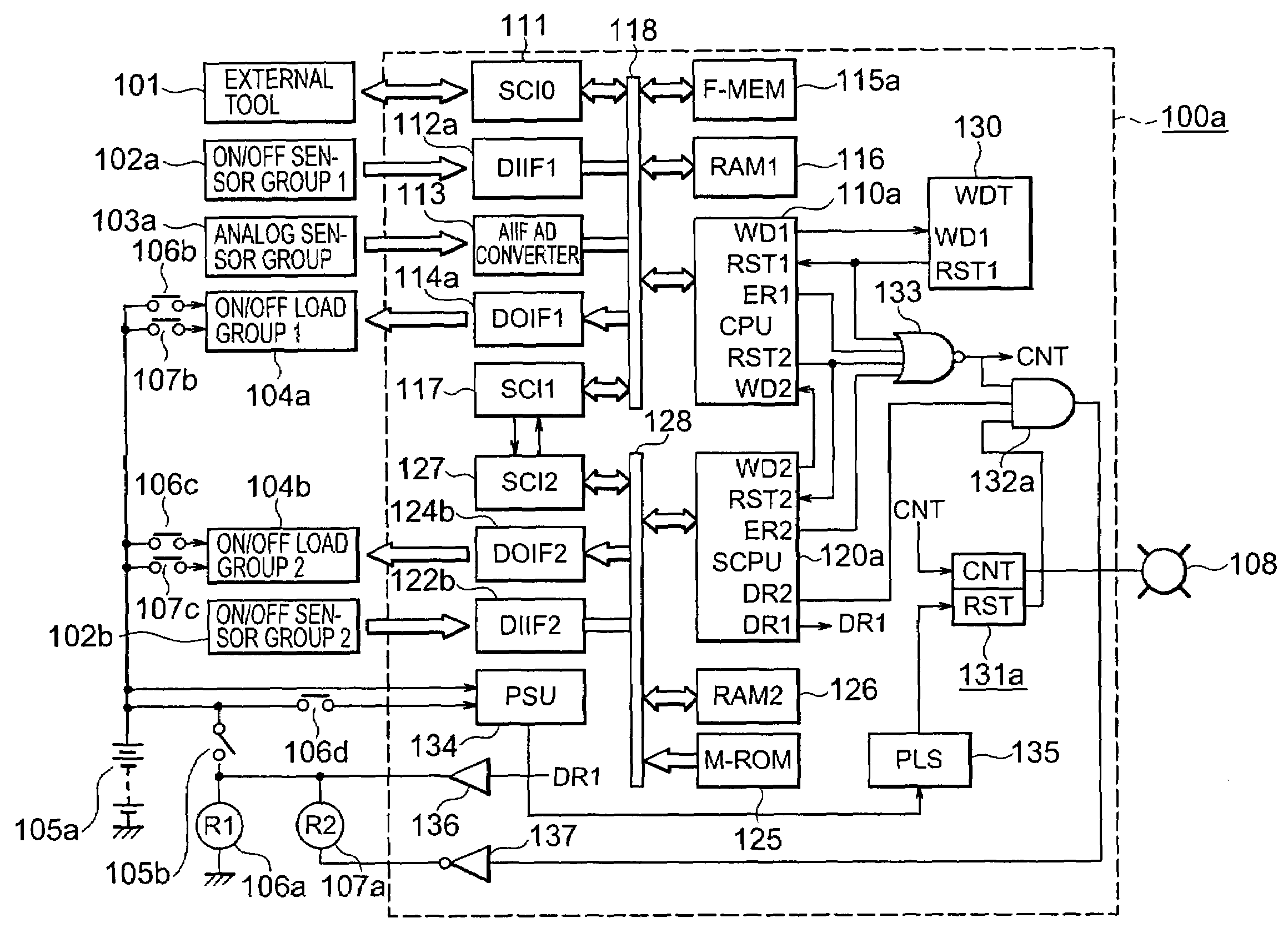

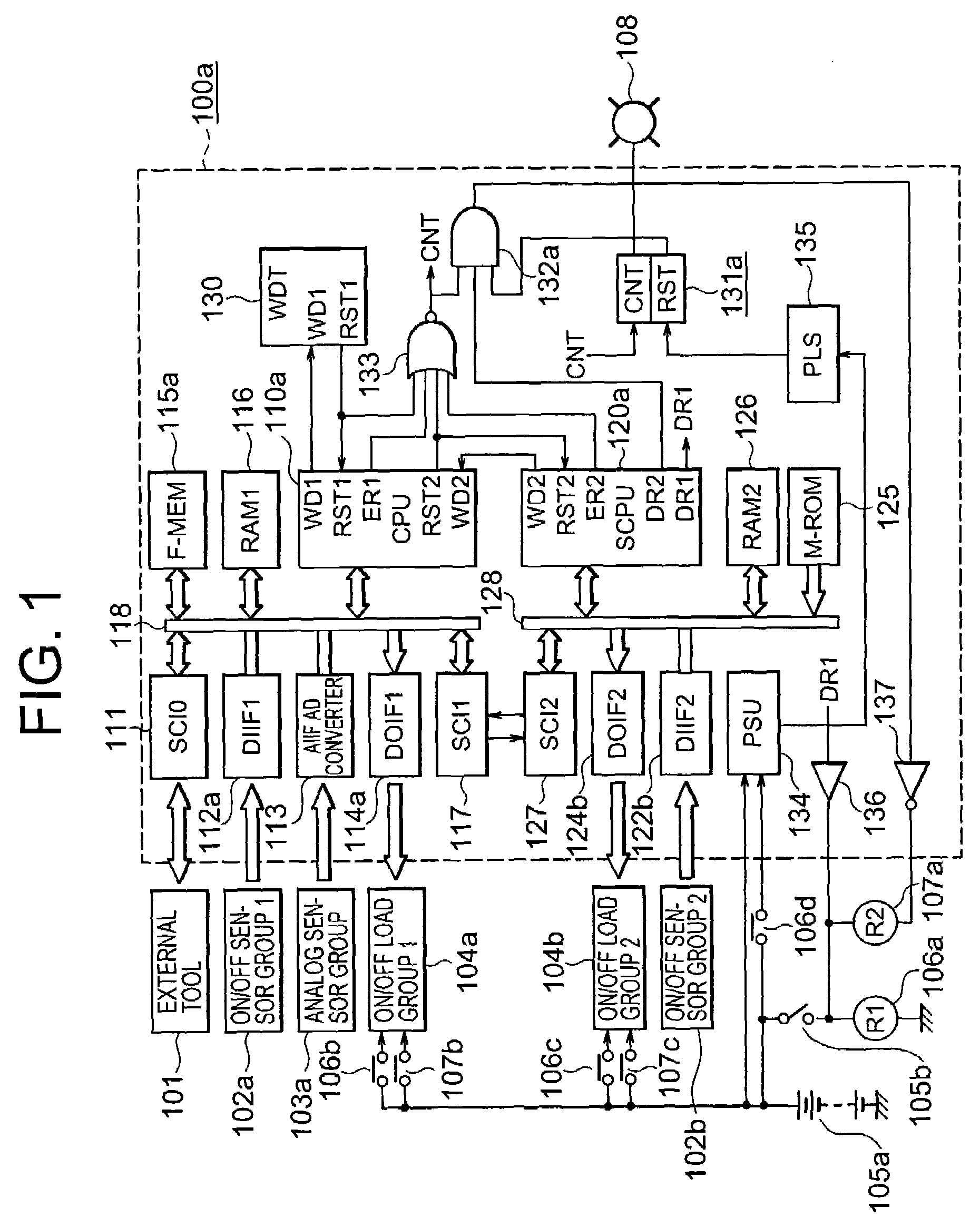

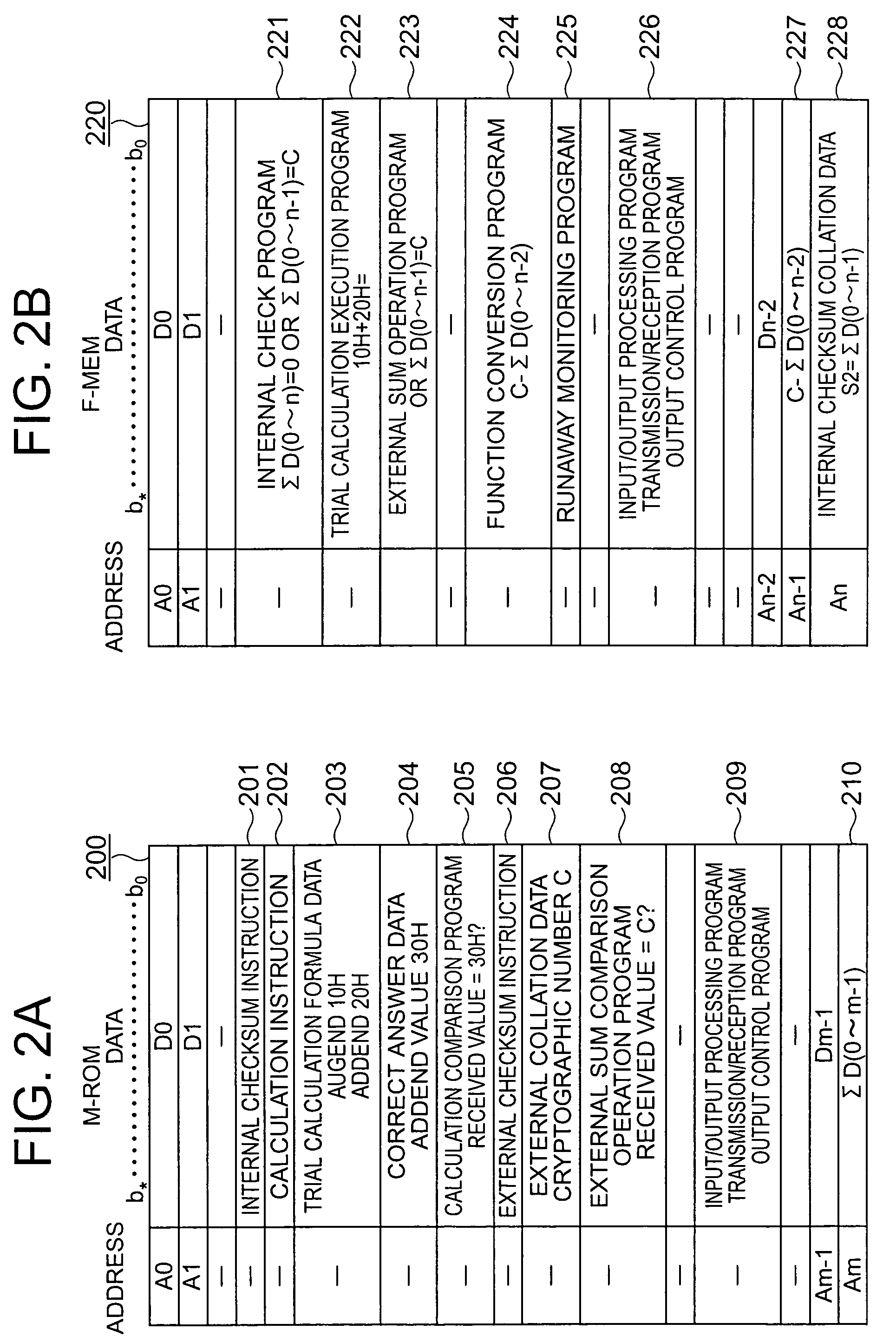

On-vehicle electronic control device

ActiveUS7251551B2Improve performance reliabilityVehicle testingElectrical controlElectricityChecksum

An on-vehicle electronic control device includes an auxiliary microprocessor and subjects a microprocessor allocated to a main part of control to an external diagnosis, thereby improving reliability of performance. A microprocessor including a nonvolatile program memory into which a control program is written is serially connected to an auxiliary microprocessor including an auxiliary nonvolatile program memory. The microprocessor and the auxiliary microprocessor function in cooperation to control on-vehicle electric load groups in response to input signals from on-vehicle sensor groups and on-vehicle analog sensor group. The nonvolatile program memory and the microprocessor are subjected to runaway monitoring performed by a watchdog timer and to an external checksum diagnosis performed periodically by the auxiliary microprocessor. If an anomaly occurs in the runaway monitoring, the external checksum diagnosis, and a checksum interval, parts of electric loads are cut off of power supply by load power relay.

Owner:MITSUBISHI ELECTRIC CORP

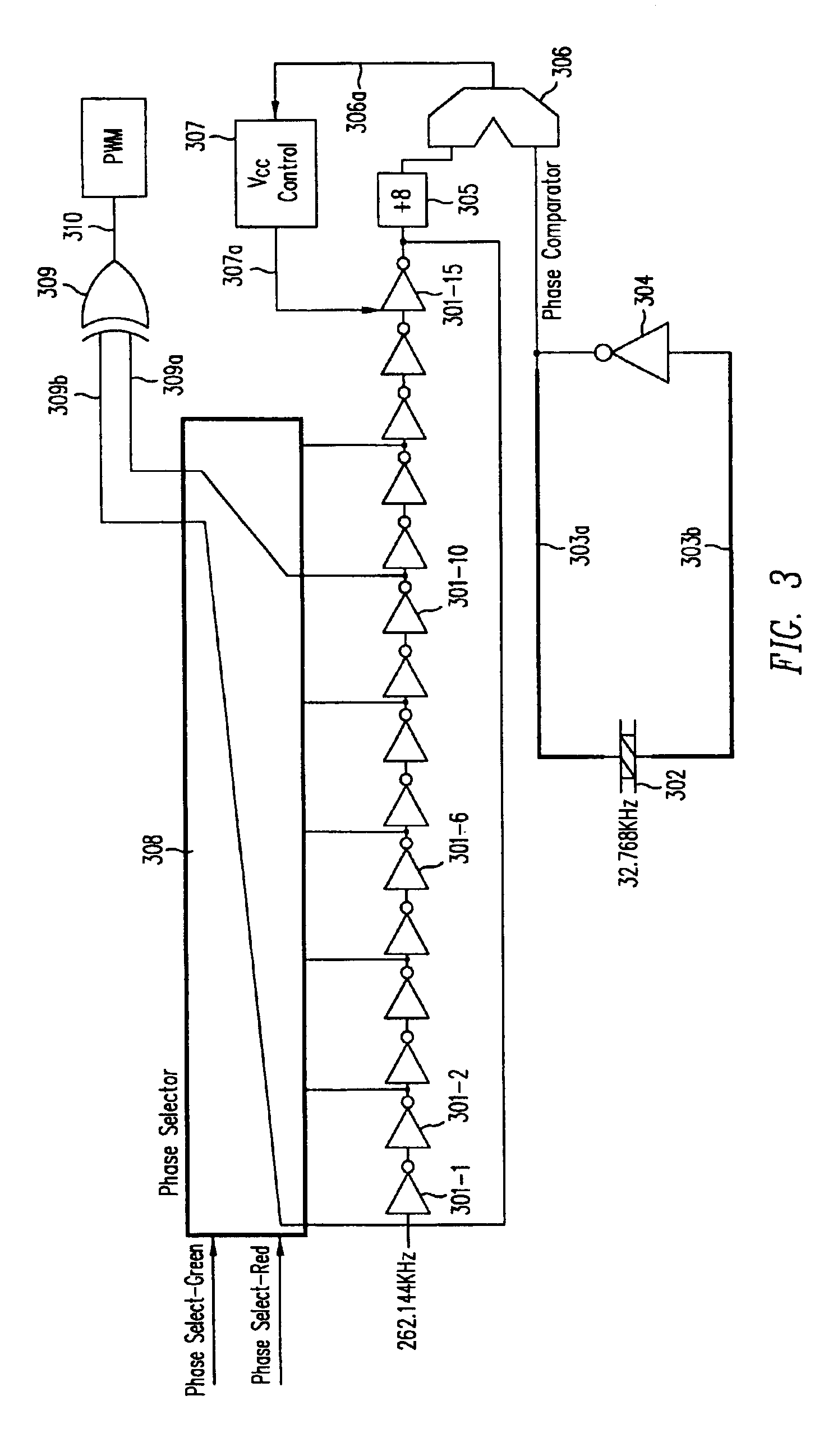

Emulator support mode for disabling and reconfiguring timeouts of a watchdog timer

InactiveUS6145103AEasy to appreciateEasy to predictSoftware testing/debuggingSoftware simulation/interpretation/emulationMicrocontrollerProcessor register

A microcontroller-based device according to the present invention provides a watchdog timer having an emulator support mode for disabling and reconfiguring time-outs. When the watchdog timer is placed in the emulator support mode, the watchdog timer is inhibited from counting. In a disclosed embodiment, the watchdog timer is inhibited from counting by deasserting a count enable signal. A watchdog time-out is thus prevented from occurring during the emulator support mode. Also, during the emulator support mode, the watchdog timer control register is writable, allowing the emulator to disable a watchdog timer, enable the timer, or program a new time-out value for the timer. The watchdog timer control register is writable regardless of the state of the enable bit of the timer. Further, in the emulator support mode, a watchdog timer current count becomes readable and writable at a predetermined register address above the watchdog timer control register subsequent to a write of a write key sequence to the watchdog timer control register. By writing and reading the predetermined register address location, the emulator is able to define and monitor a condition as the watchdog timer is approaching its timeout value. By monitoring a condition as the watchdog timer approaches its timeout value, a software debugger may better predict and appreciate the behavior of a microcontroller-based device prior to a watchdog time-out. In a disclosed embodiment, the watchdog timer current count is readable and writable through a watchdog timer count high register and a watchdog timer count low register.

Owner:LAWRENCE LIVERMORE NAT SECURITY LLC +1

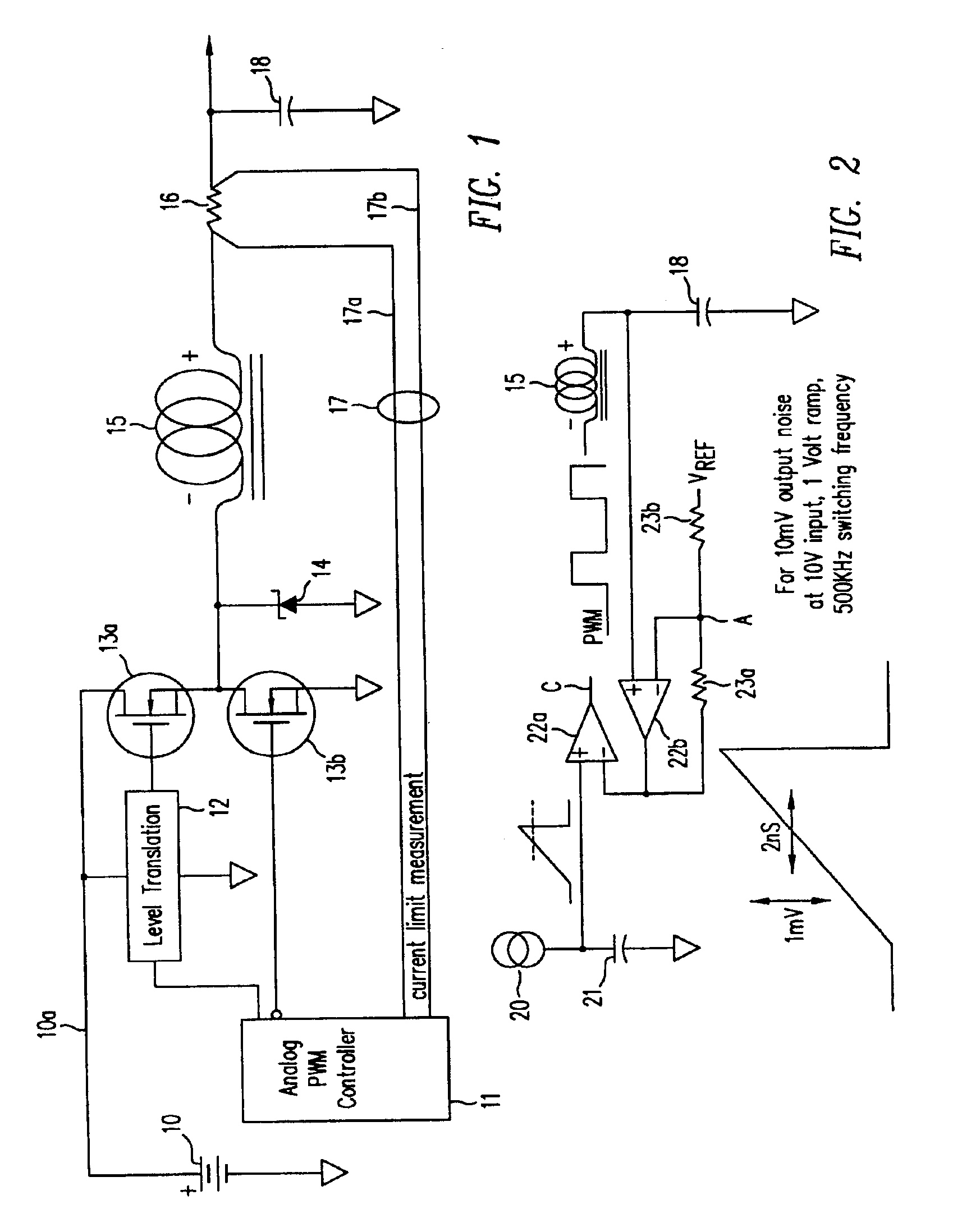

Switching power converter controller with watchdog timer

Switching power converter controller providing control of plurality of switching power converters which provide power to a host microprocessor. A watchdog timer included in the switching power converter controller is configured to countdown a timer unless it receives a reset signal from the host microprocessor. The switching power converter controller is configured to assert a reset command for the host microprocessor if the watchdog timer expires and to not de-assert the reset command until the plurality of switching power converters are operating as desired.

Owner:EXAR CORP

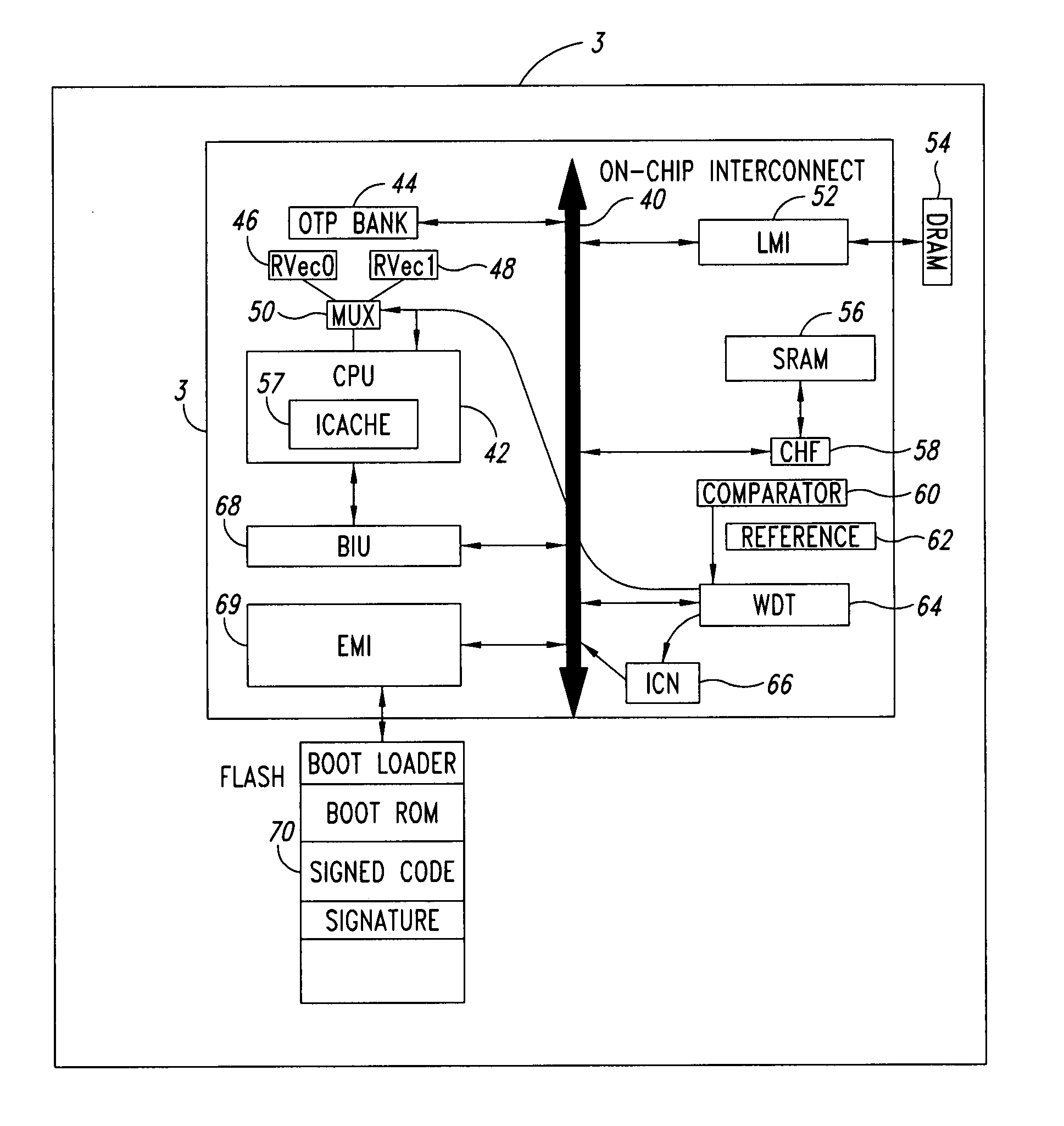

Multiple purpose integrated circuit

ActiveUS20070283140A1Minimizes silicon areaSimplifying design cycleDigital computer detailsUnauthorized memory use protectionInternal memoryHash function

An integrated circuit is operable to execute boot loader code and a boot code from external memory. To provide security so that the CPU does not execute malicious codes, the circuit resets in a restricted mode in which only certain functional units may be connected. In the restricted mode the CPU is only able to fetch boot code from an external memory for transfer to an internal memory. A hash function operates on the fetched boot code to determine whether it is authentic and, if it is determined that the code is authentic the circuit is reset to an unrestricted mode to continue executing from the boot code now stored in the internal memory. Further security is provided by a watchdog timer function which resets the circuit if the boot code is not determined to be authentic within a threshold period of time.

Owner:STMICROELECTRONICS (RES & DEV) LTD

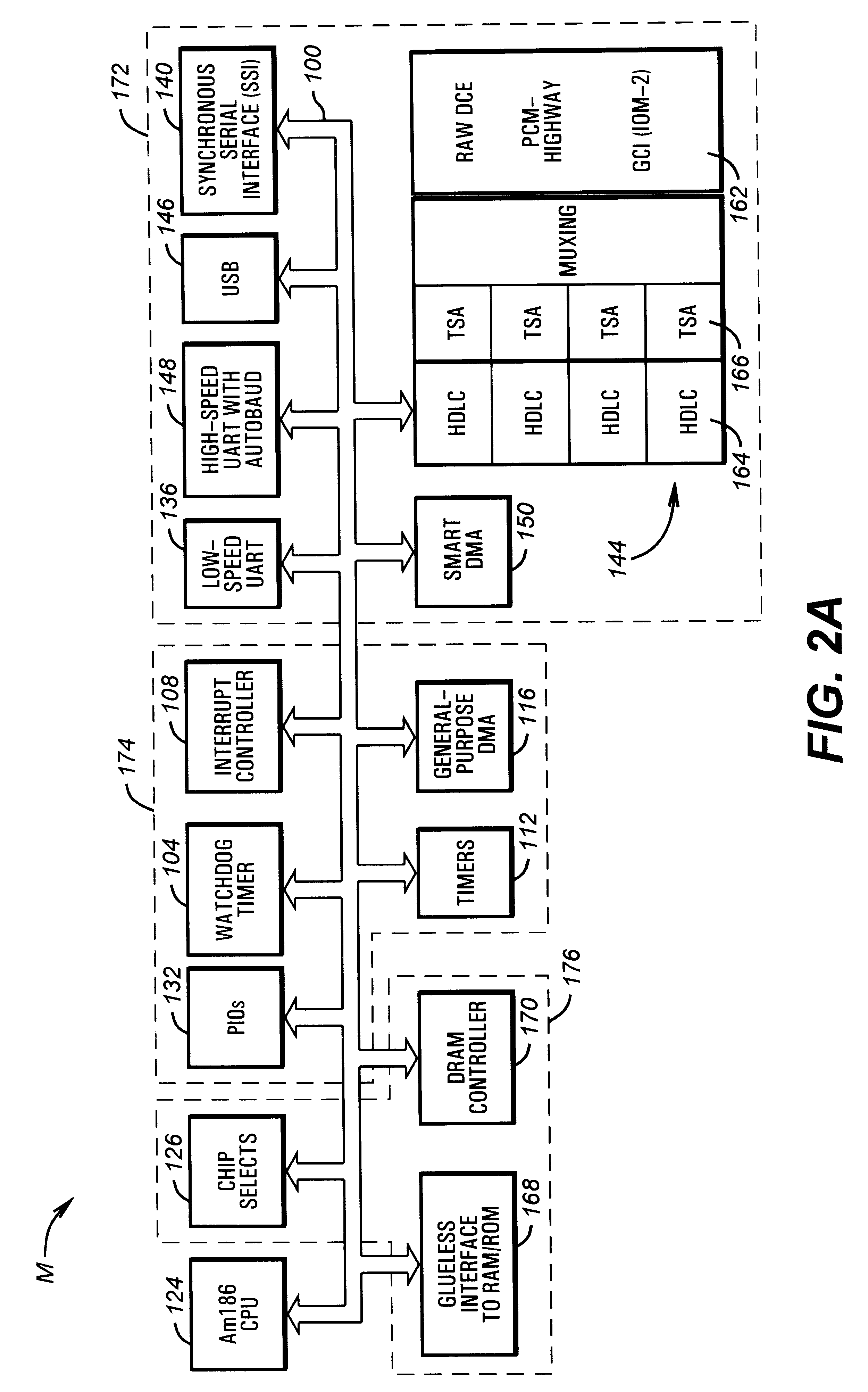

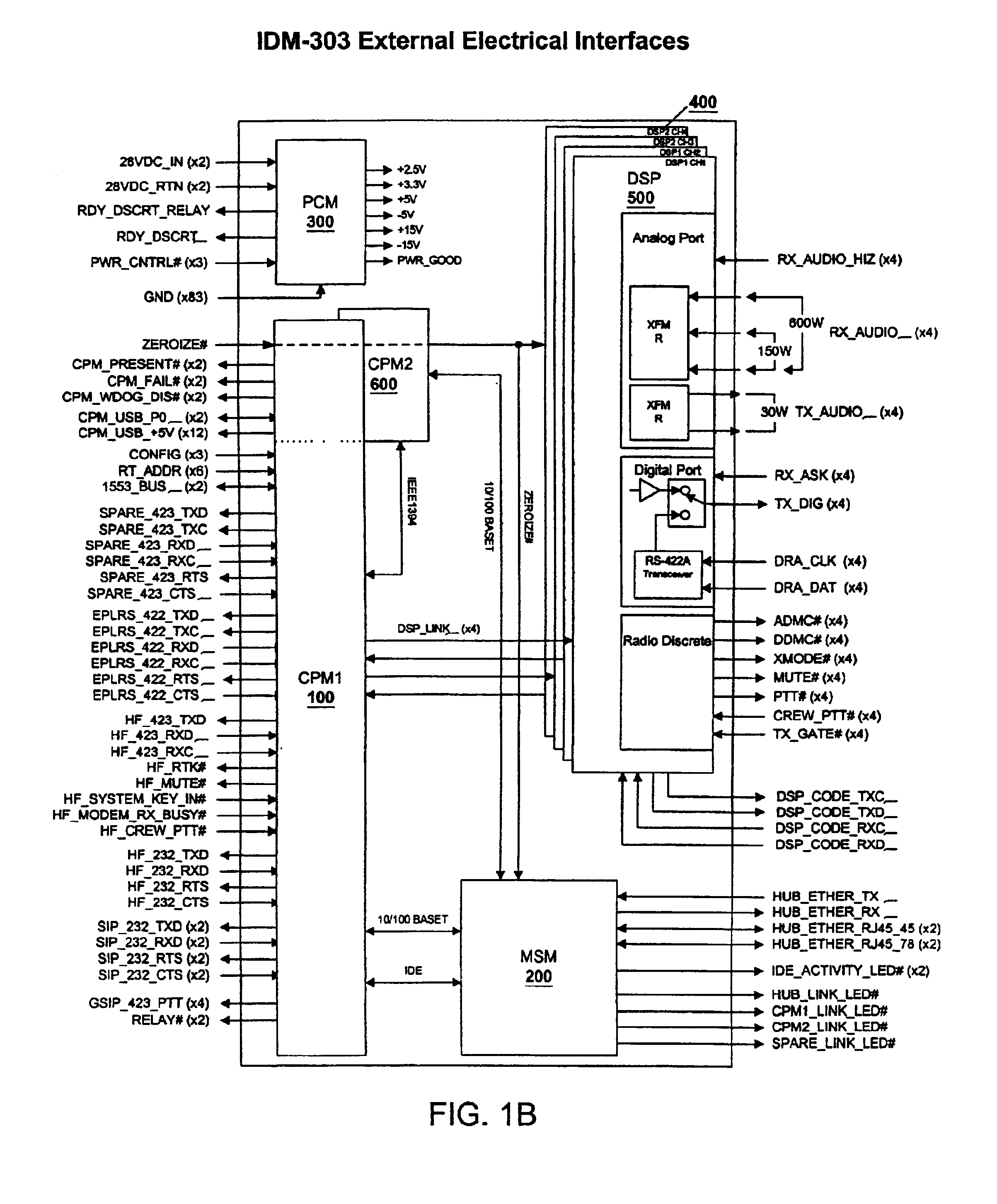

Data modem

InactiveUS6839792B2Maximum flexibilityMinimal costTelephonic communicationGenerating/distributing signalsMass storageModem device

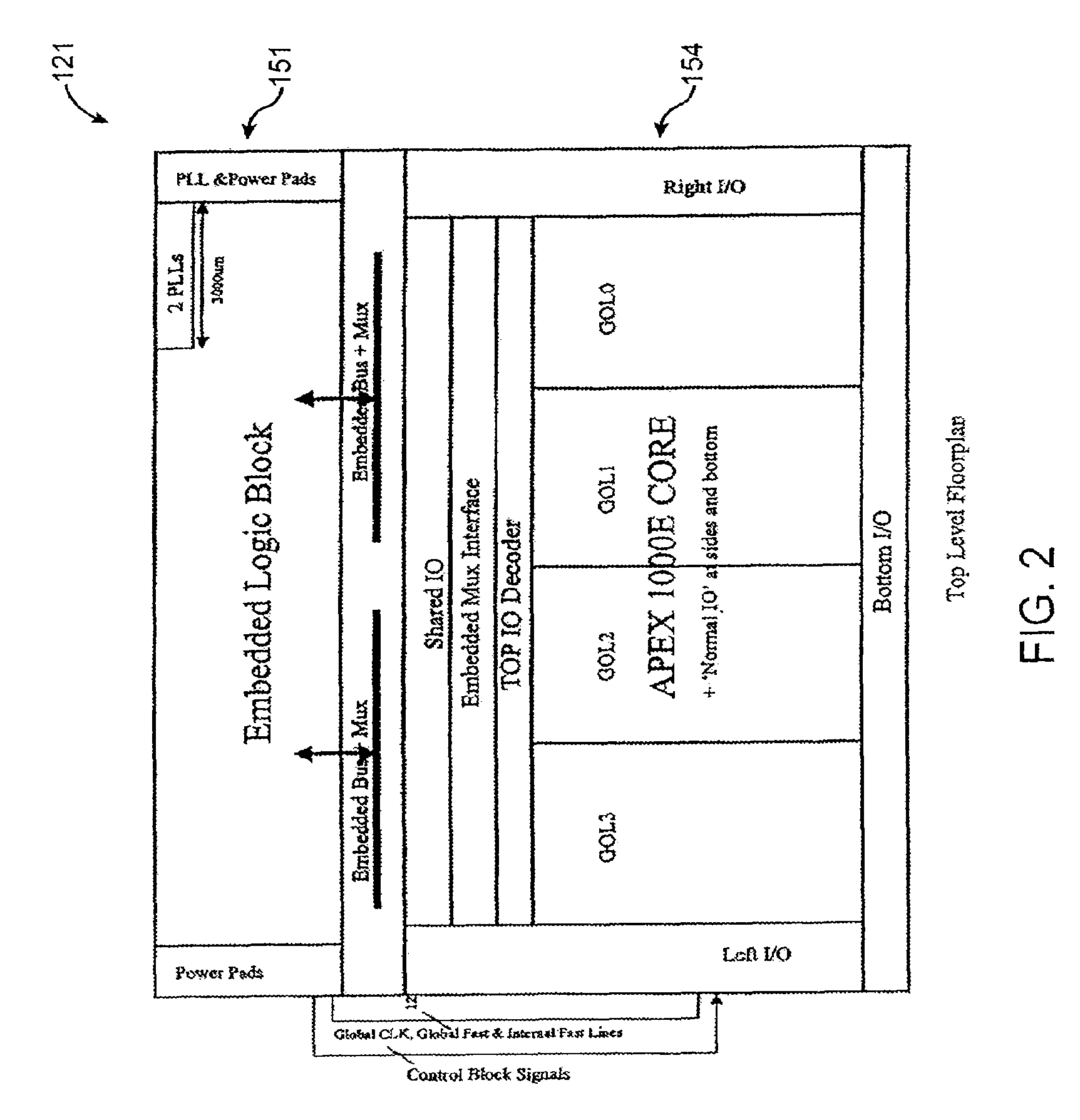

An improved data modem (IDM) and method includes a communication processor module, a mass storage module, a power converter module, and one or more DSP modules. The communication processor module utilizes commercial off-the-shelf components as well as programmable logic devices (EPLD), which are programmed to provide a watchdog timer, programmable interrupt controller, flash page addressing, ISA bus decoder and controller, and various circuits and logic.

Owner:ELBIT SYSTEMS OF AMERICA LLC

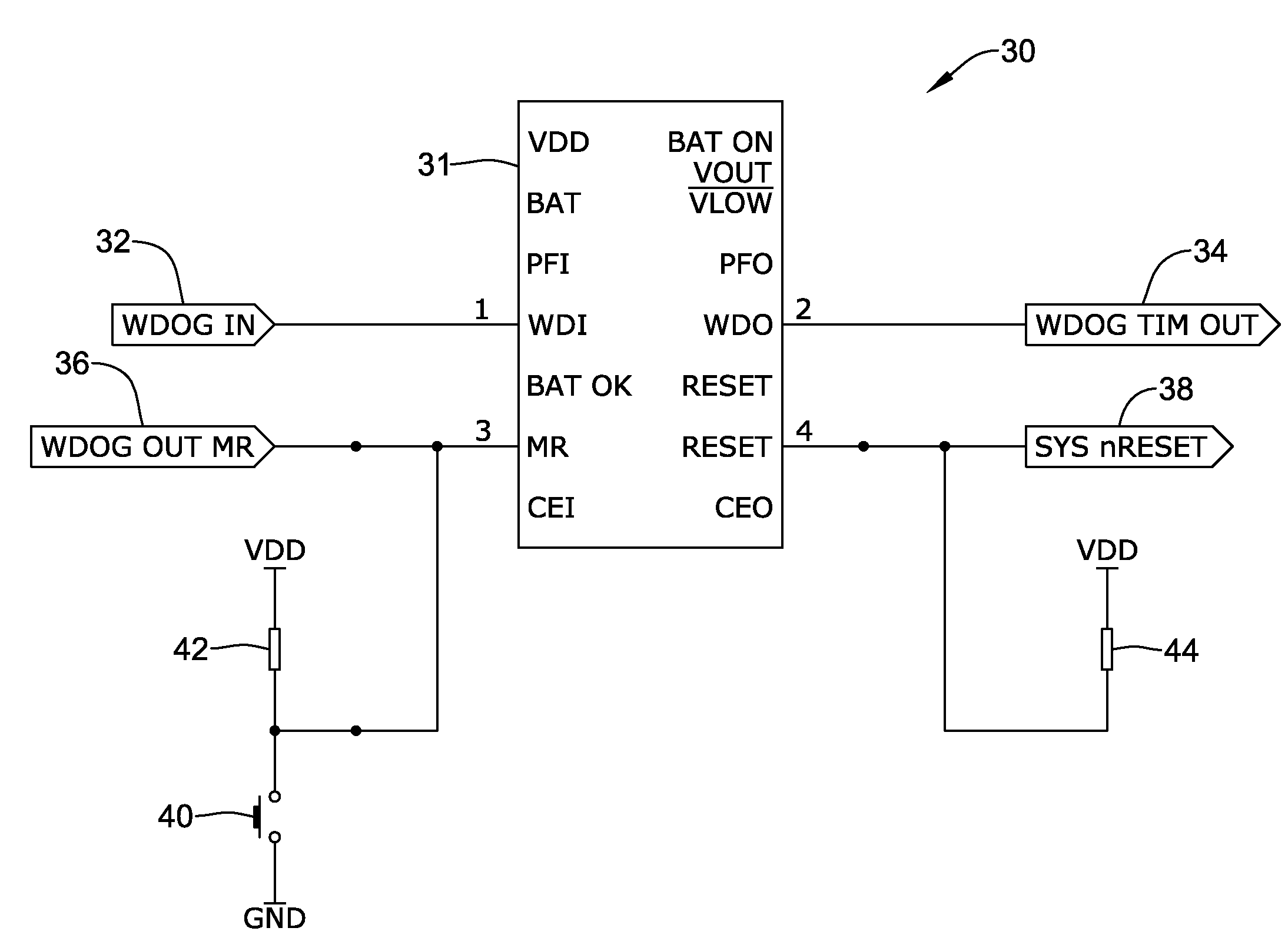

Microprocessor supervision in a special purpose computer system

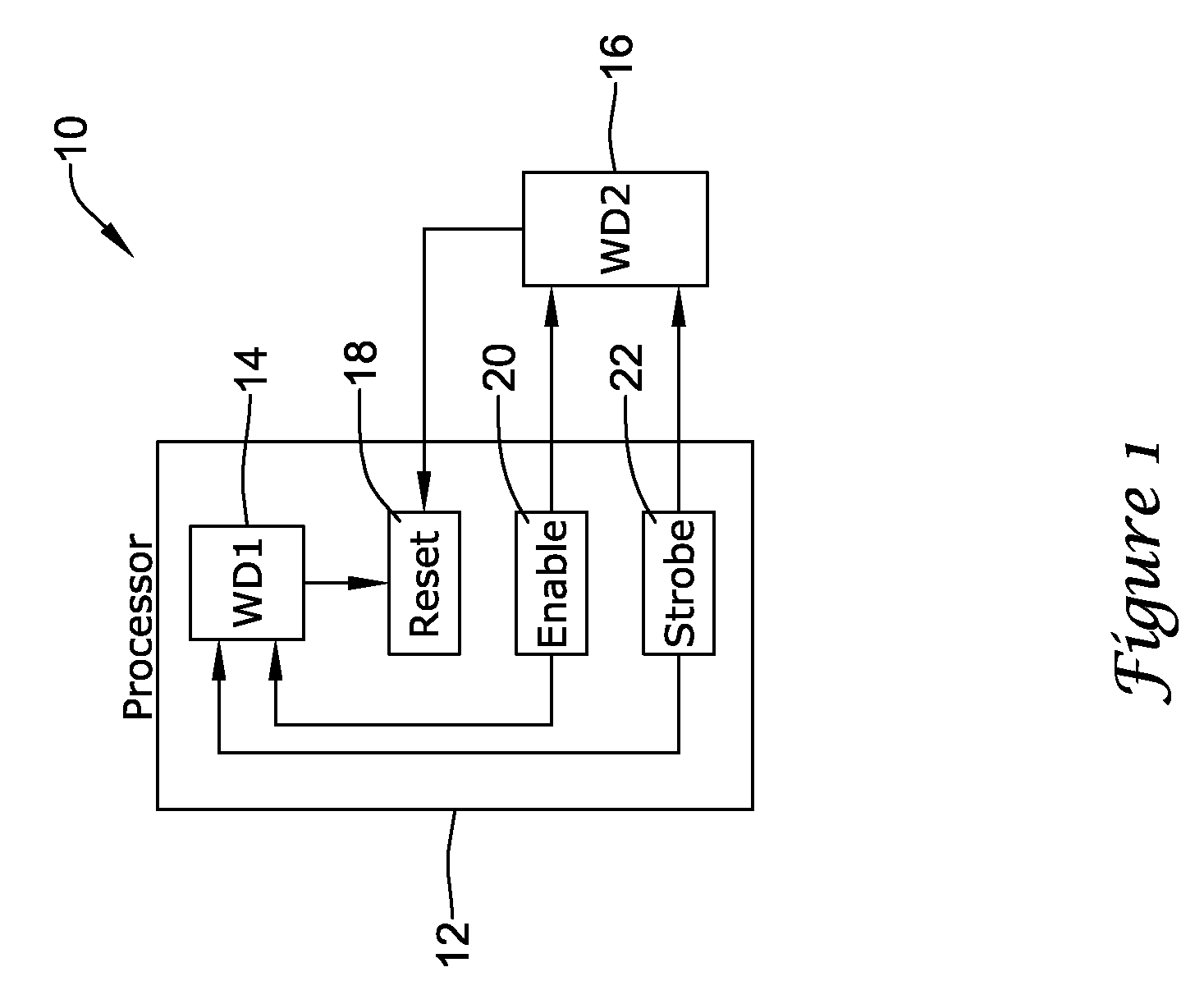

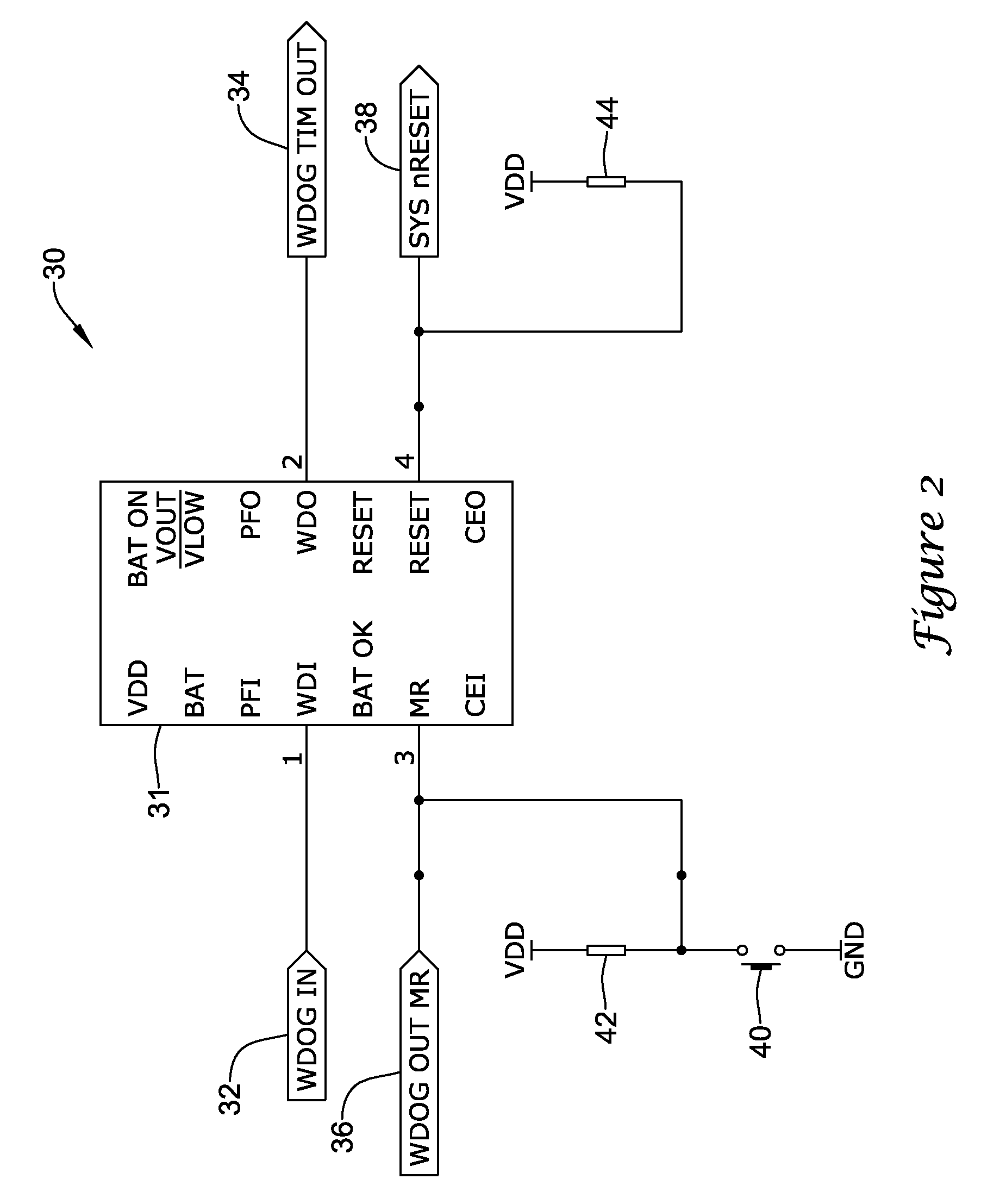

Devices and methods for microprocessor supervision in a special purpose computer system are provided. One illustrative embodiment includes a first watchdog timer internal to the microprocessor and a second watchdog timer external to the microprocessor. In some cases, the internal watchdog timer may be initiated prior to or during the operating system startup and the external watchdog timer may be initiated after the operating system is up and running. The internal watchdog timer may have a relatively longer timer duration than the external watchdog timer, but is not required in all embodiments. In some embodiments, the internal watchdog timer may monitor the microprocessor's startup sequence and the internal watchdog timer and / or external watchdog timer may monitor the microprocessor when the operating system is up and running. If the microprocessor faults at any time during startup or while the operating system is up and running, the internal and / or external watchdog timer may trigger a microprocessor reset.

Owner:HONEYWELL INT INC

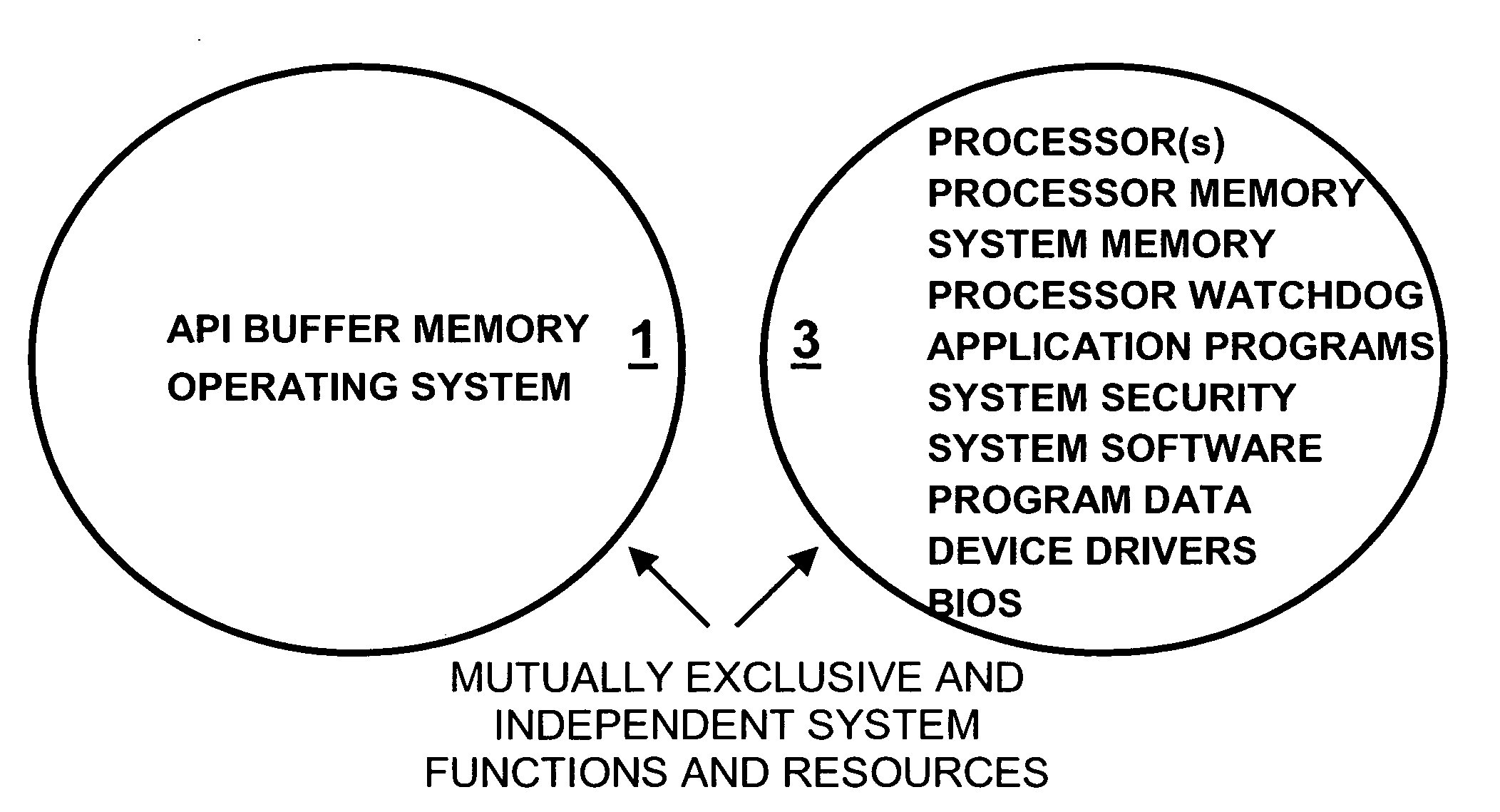

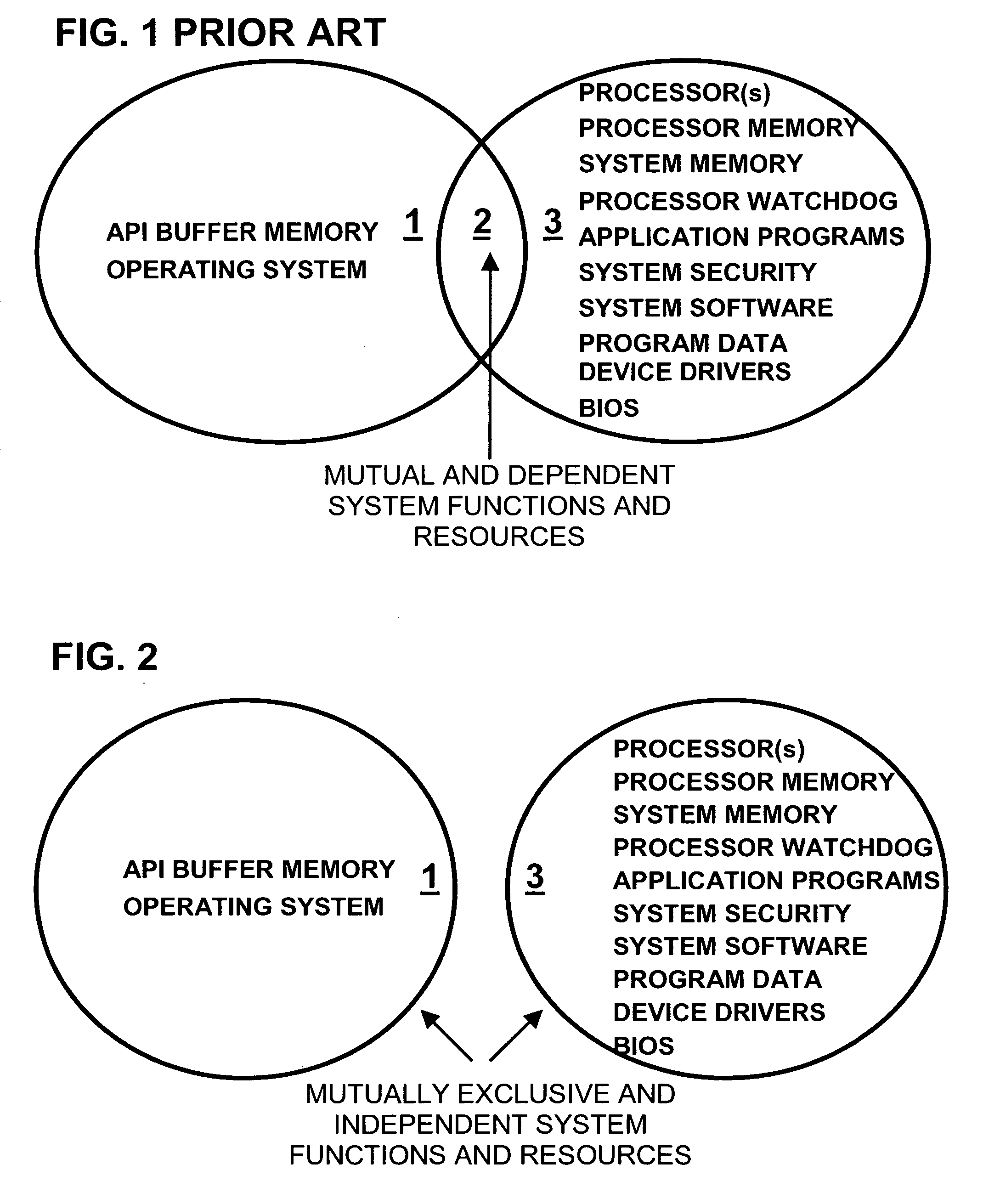

Controller and resource management system and method with improved security for independently controlling and managing a computer system

InactiveUS20050228916A1Improve securityImprove reliabilityDigital data processing detailsUnauthorized memory use protectionOperational systemResource Management System

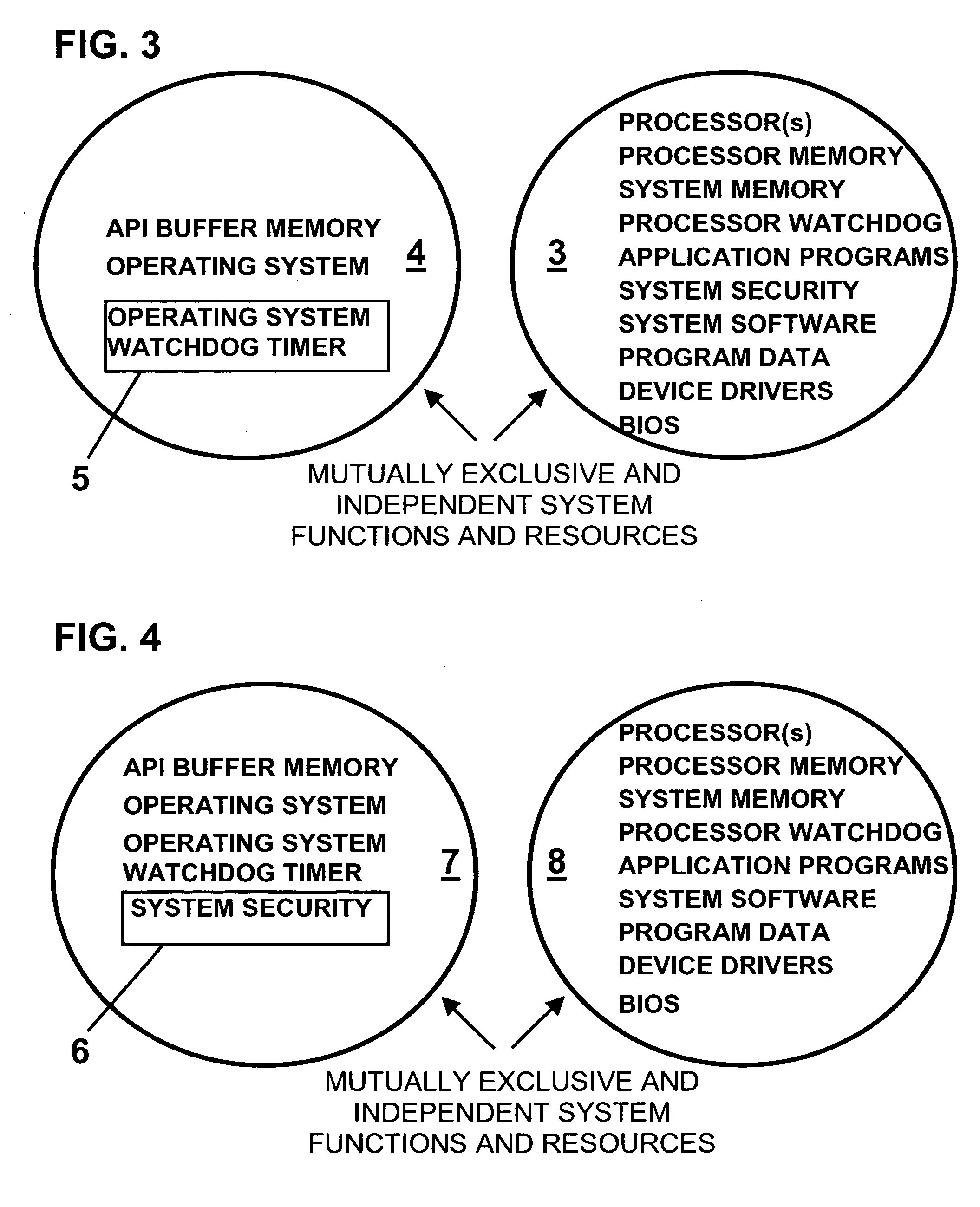

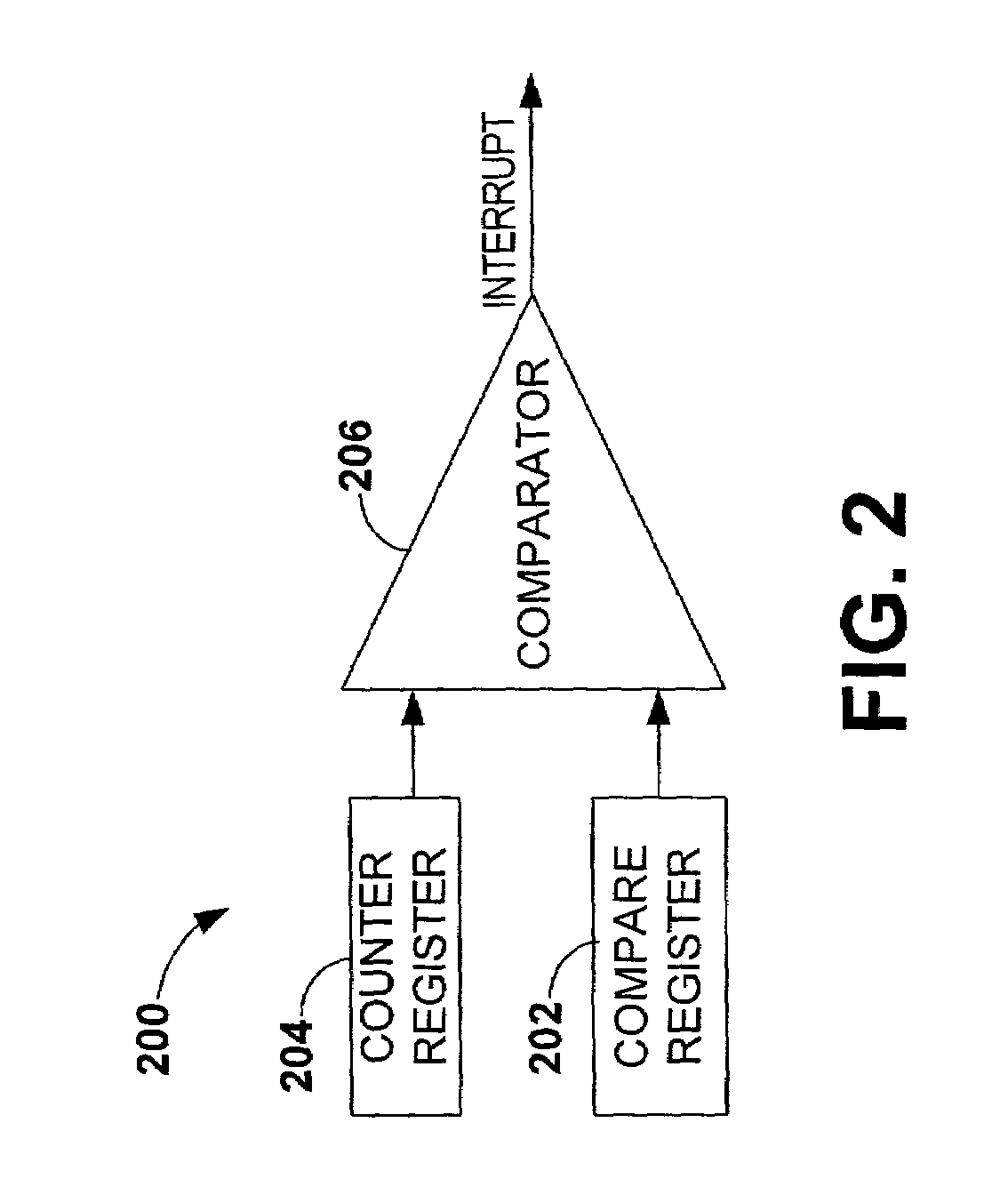

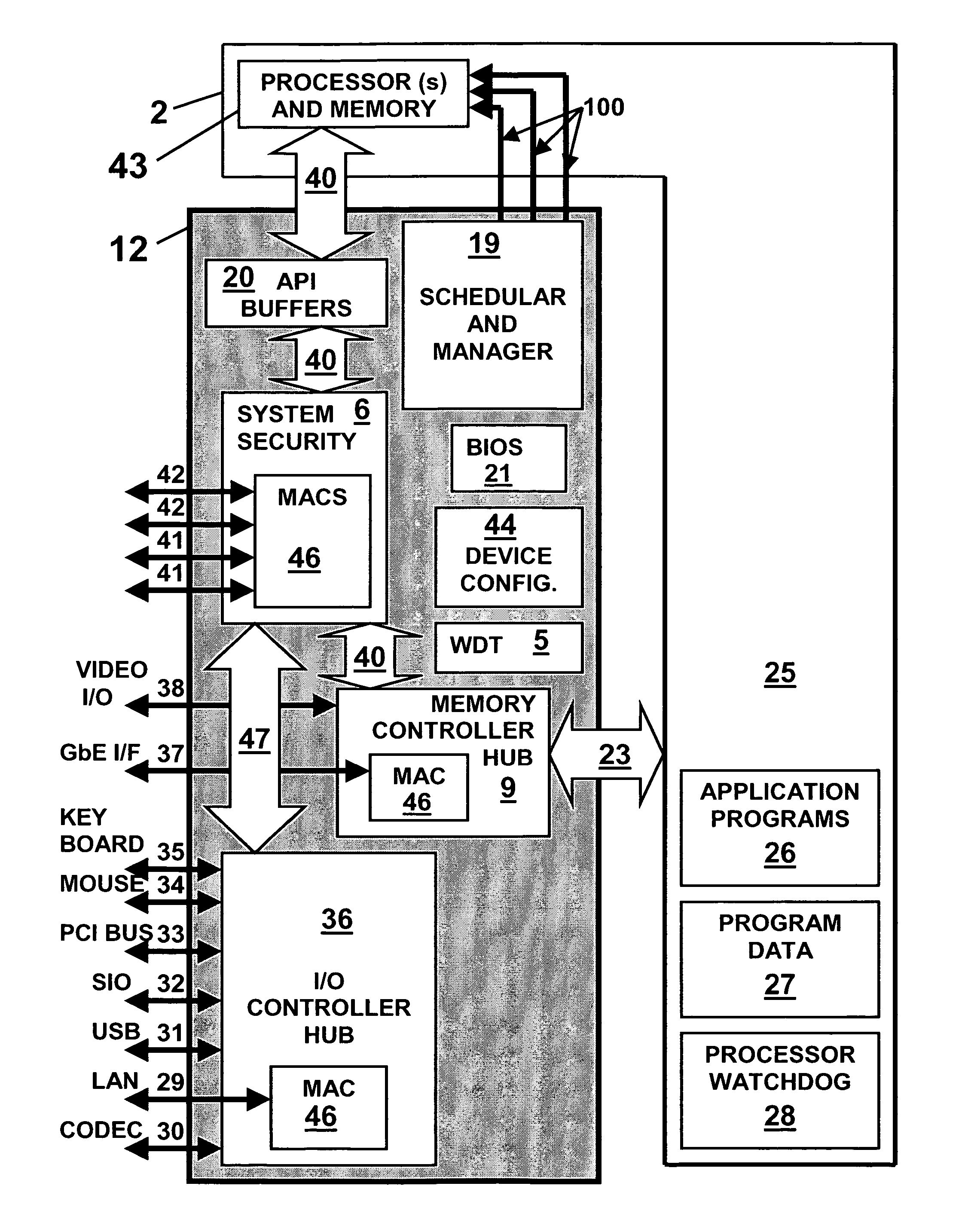

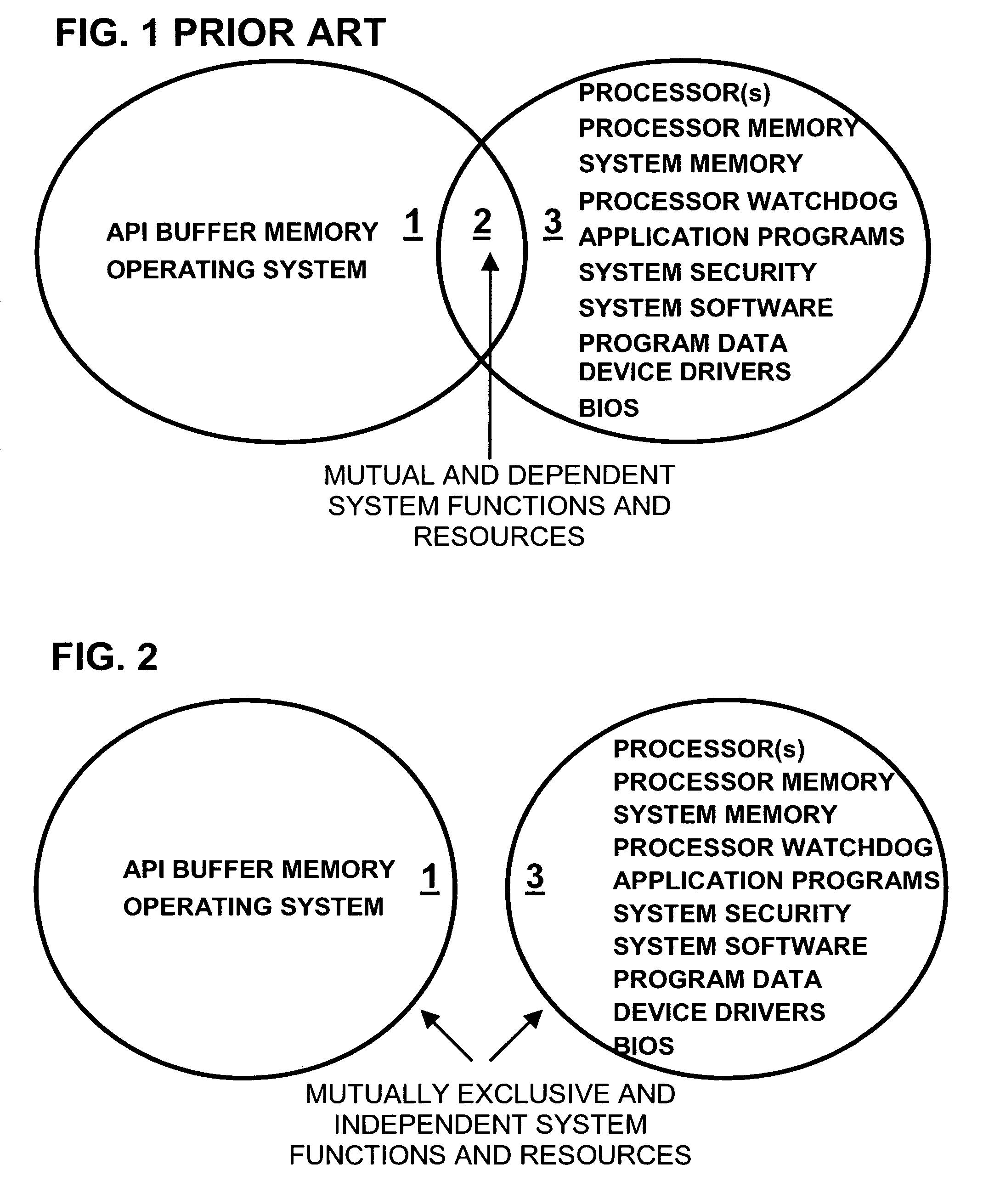

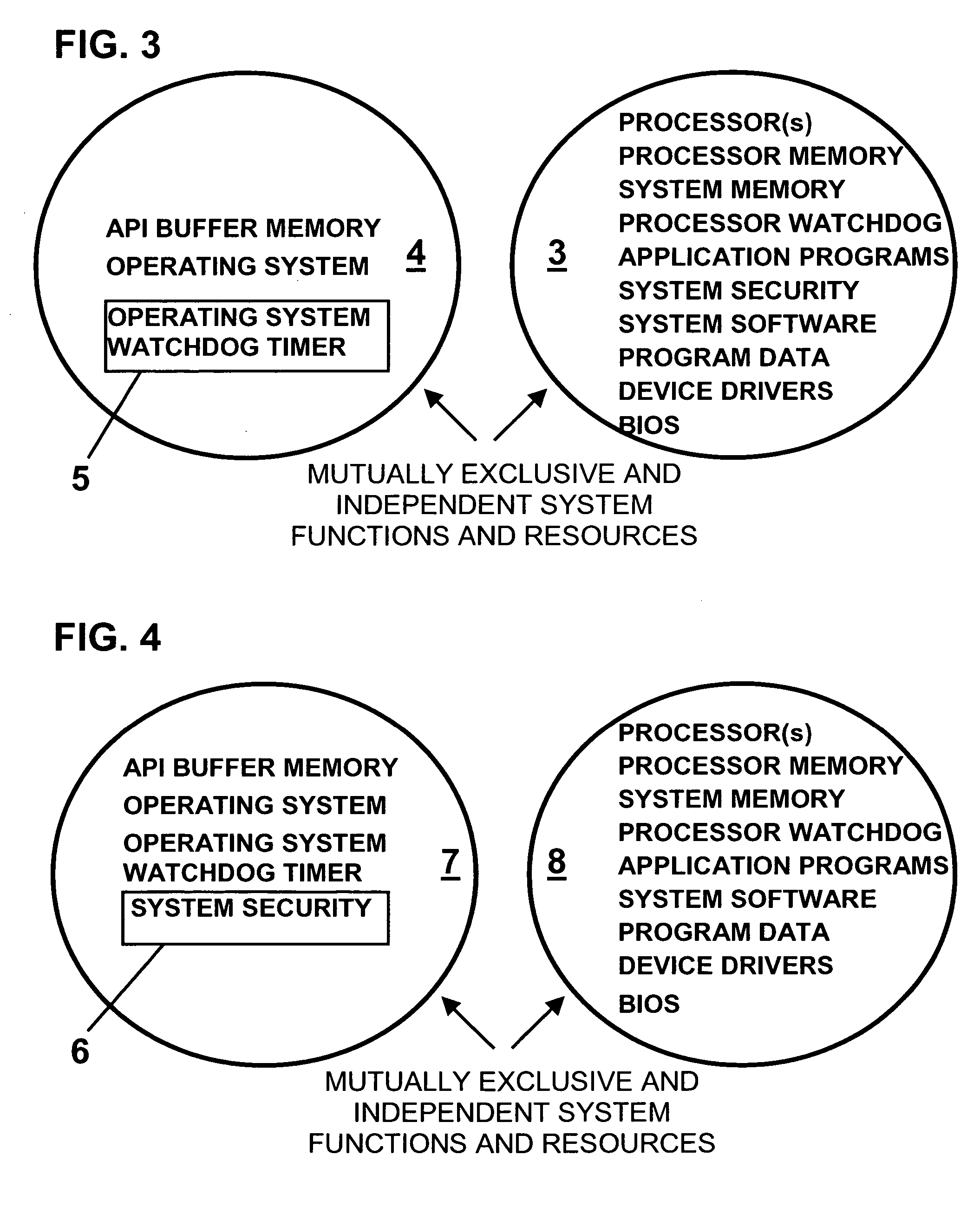

A controller and resource management system and method with improved security for independently controlling and managing a computer system is provided. Control, management and security protection is provided while functioning: conceptually, logically, functionally, operatively, physically and electrically independent of computer system resources, including processors. All computer system resources, including processors are operatively dependent on the present invention; processors do not execute operating system instructions. Data transferred between the computer system and processors is communicable through the controller and resource management system for improved security. The present invention comprising: Buffer memory, BIOS, device drivers, event handler, system security, scheduler, memory manager, I / / O controller, configuration manager, independent watchdog timer and networking interfaces. One method whereby the invention is implemented in hardware for improved security is provided; another method whereby information is communicable between multiple controller and resource management systems, or micronodes©, independently of computer system resources, including processors is also provided.

Owner:BRYTE COMP TECH

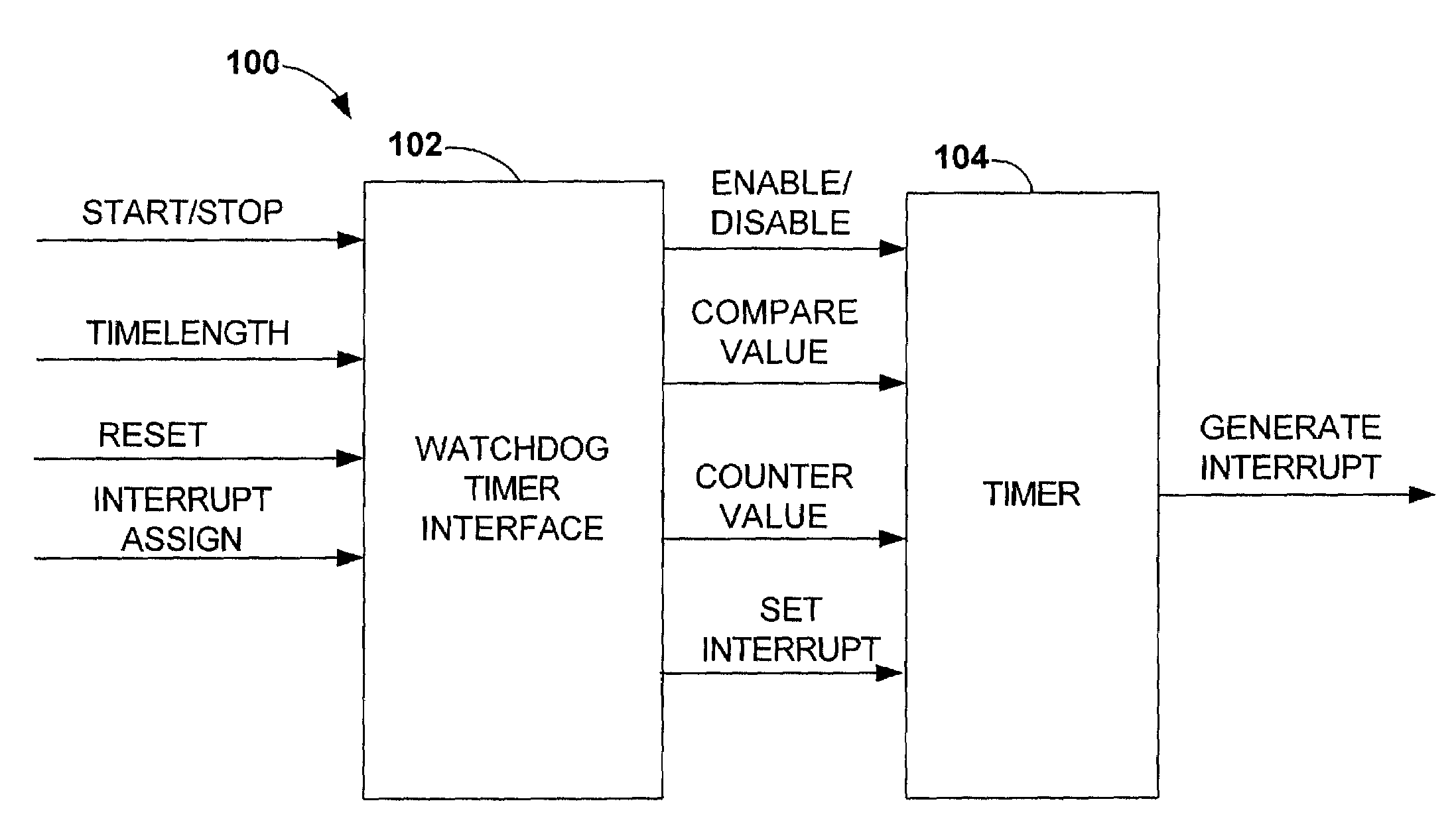

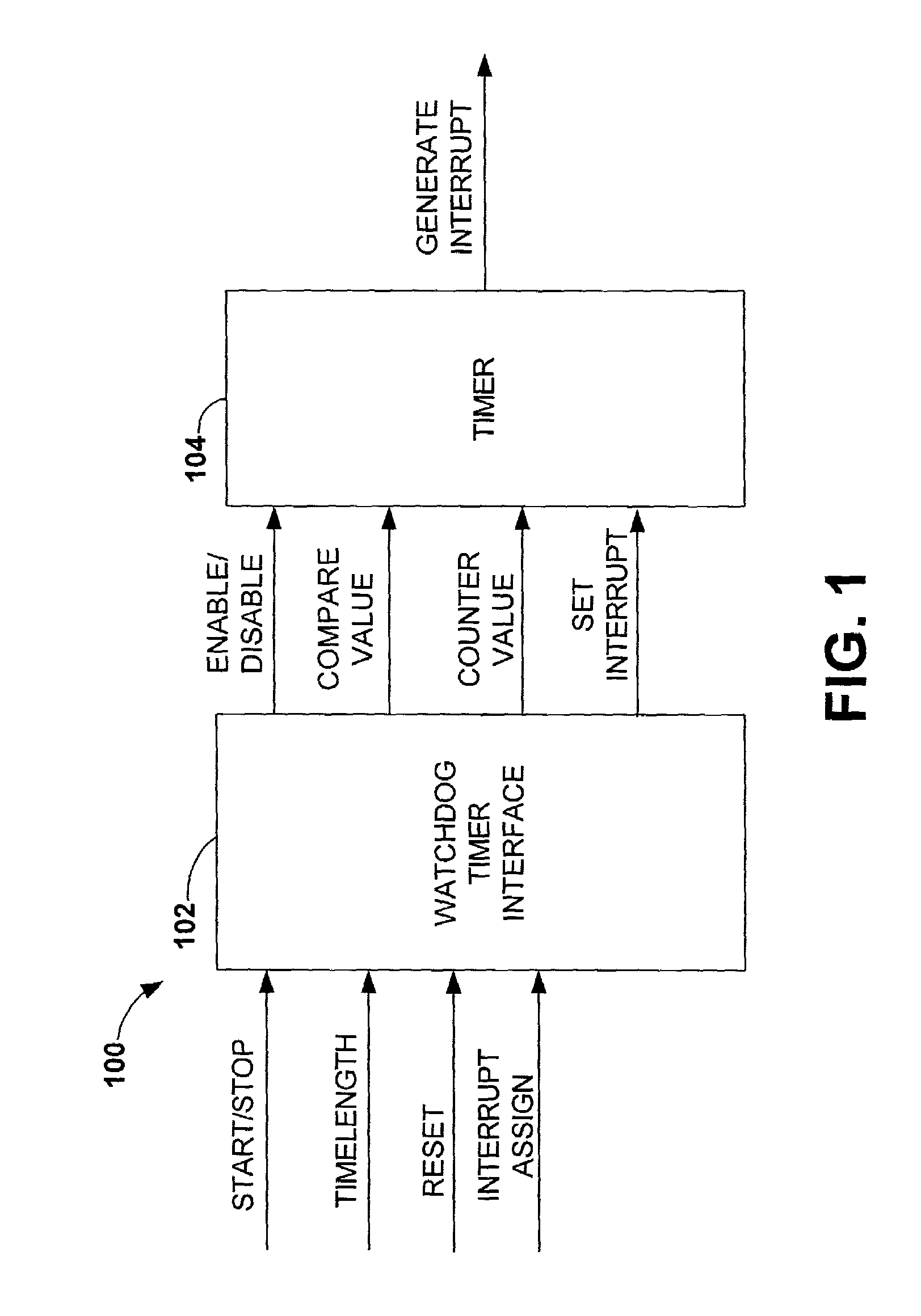

Watchdog timer using a high precision event timer

ActiveUS7689875B2Easy to detectFacilitate handling errorHardware monitoringHardware architectureHigh Precision Event Timer

A system and method for detecting and handling errors in a computer system are disclosed. The invention is configurable to permit selecting of timelength or time out values, assigned interrupts to be generated and error recover procedures so that failures of system events can be promptly detected and recovered from. The watchdog timer is started with a timelength or time out value and generates an interrupt (i.e., is triggered) if the period of time set as the timelength passes without receiving a reset. The watchdog timer interface interacts and controls the hardware based timer to obtain this watchdog timer functionality. The hardware based timer is generally a high precision timer that exists in hardware architecture for a computer system and is usable by system software. The watchdog timer interface controls and sets various parameters and / or registers of the hardware based timer in order to provide the desired functionality of a watchdog timer. Thus, another software component can call and interact with the watchdog timer interface for a system event and view the watchdog timer interface as a watchdog timer (i.e., the operation of the hardware based timer is transparent).

Owner:MICROSOFT TECH LICENSING LLC

Hardware interlock mechanism using a watchdog timer

InactiveUS20030097587A1Error detection/correctionVolume/mass flow measurementMicrocontrollerComputerized system

An integrated circuit, a computer system and a method of operating an computer system are disclosed. The method includes receiving a request for an authentication, at a microcontroller and requesting security data from a security device. The method also includes receiving the security data from the security device, at the microcontroller and evaluating the security data. The method also includes approving the authentication if the security data is evaluated as acceptable.

Owner:GLOBALFOUNDRIES INC

Hardware interlock mechanism using a watchdog timer

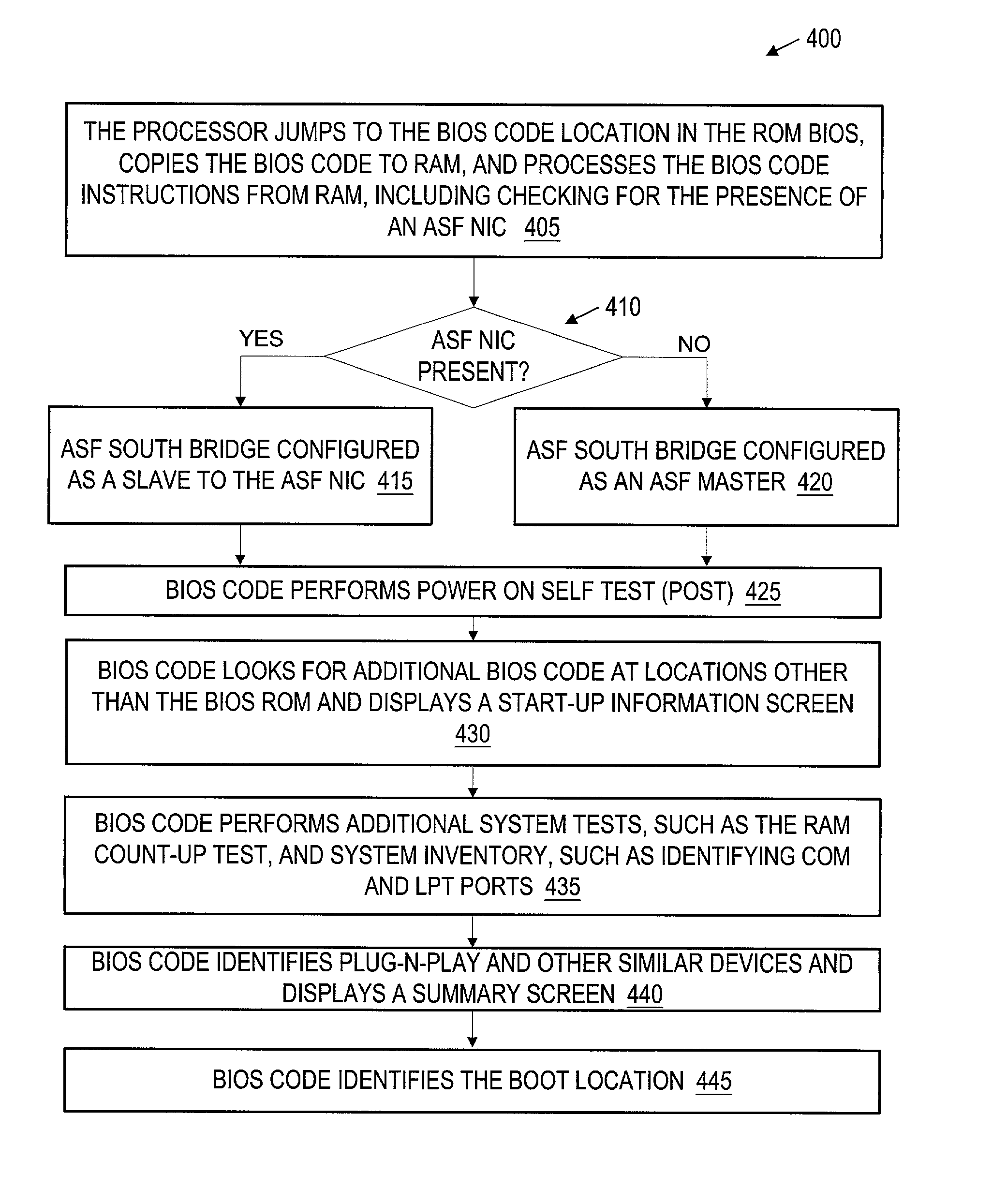

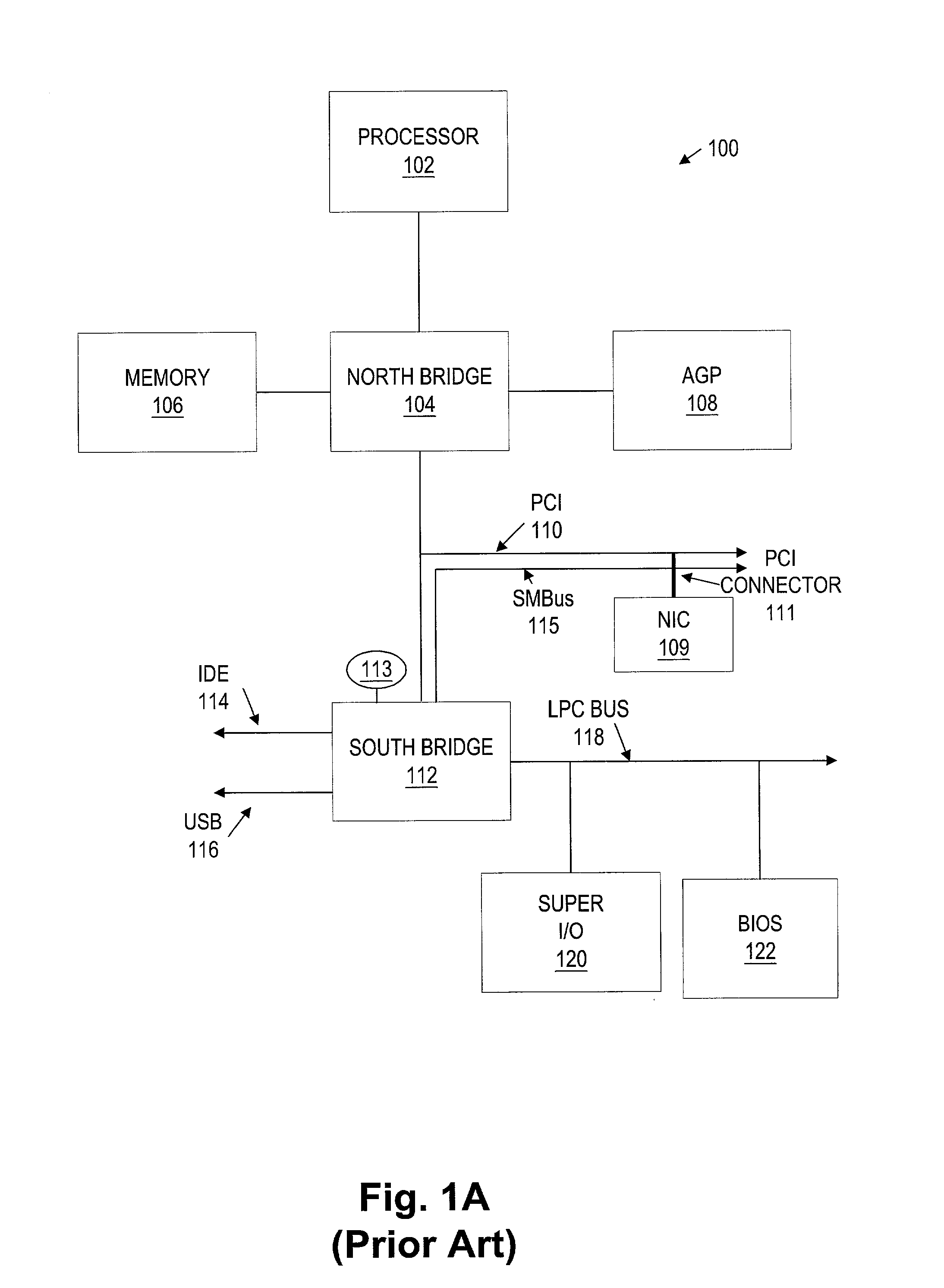

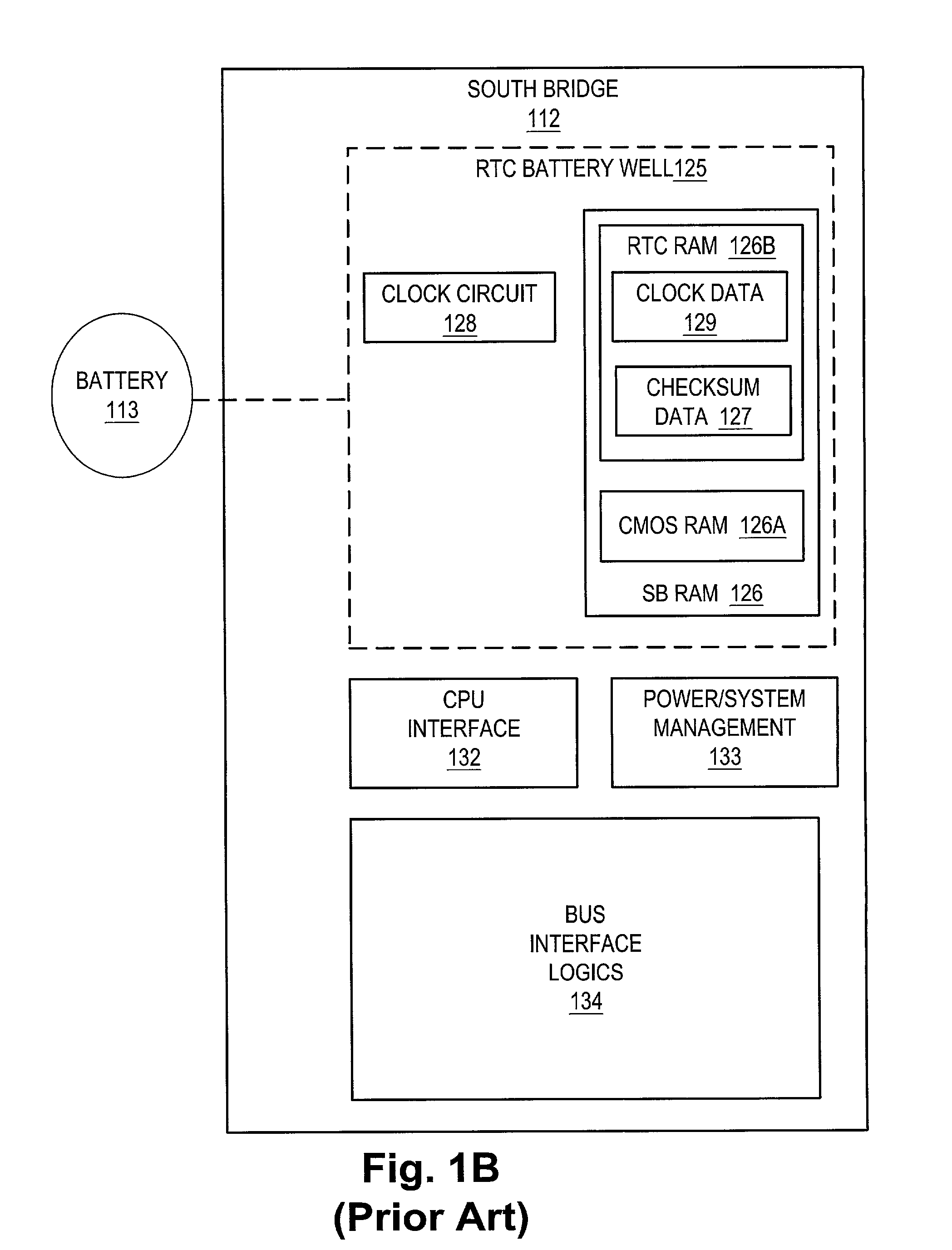

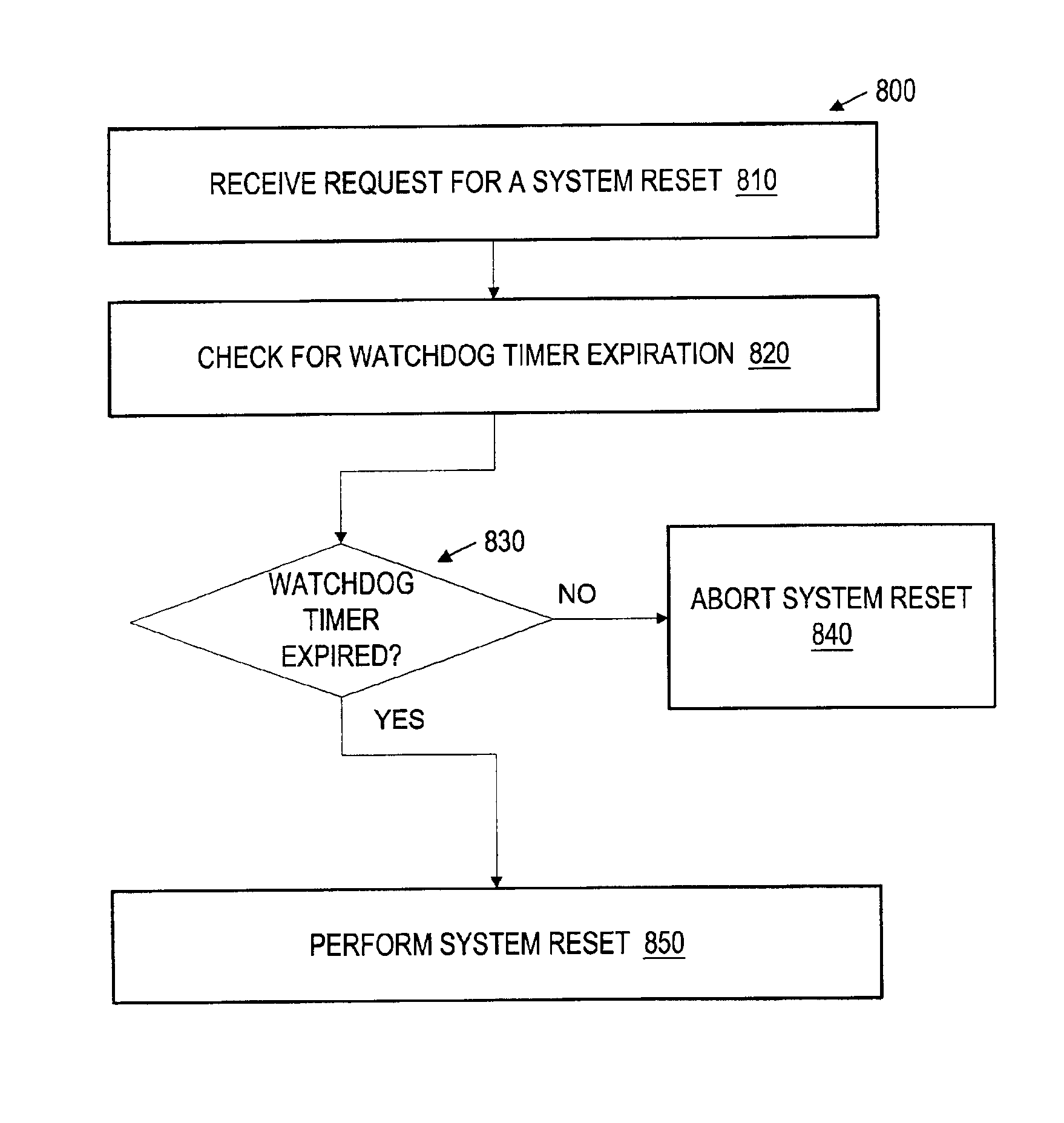

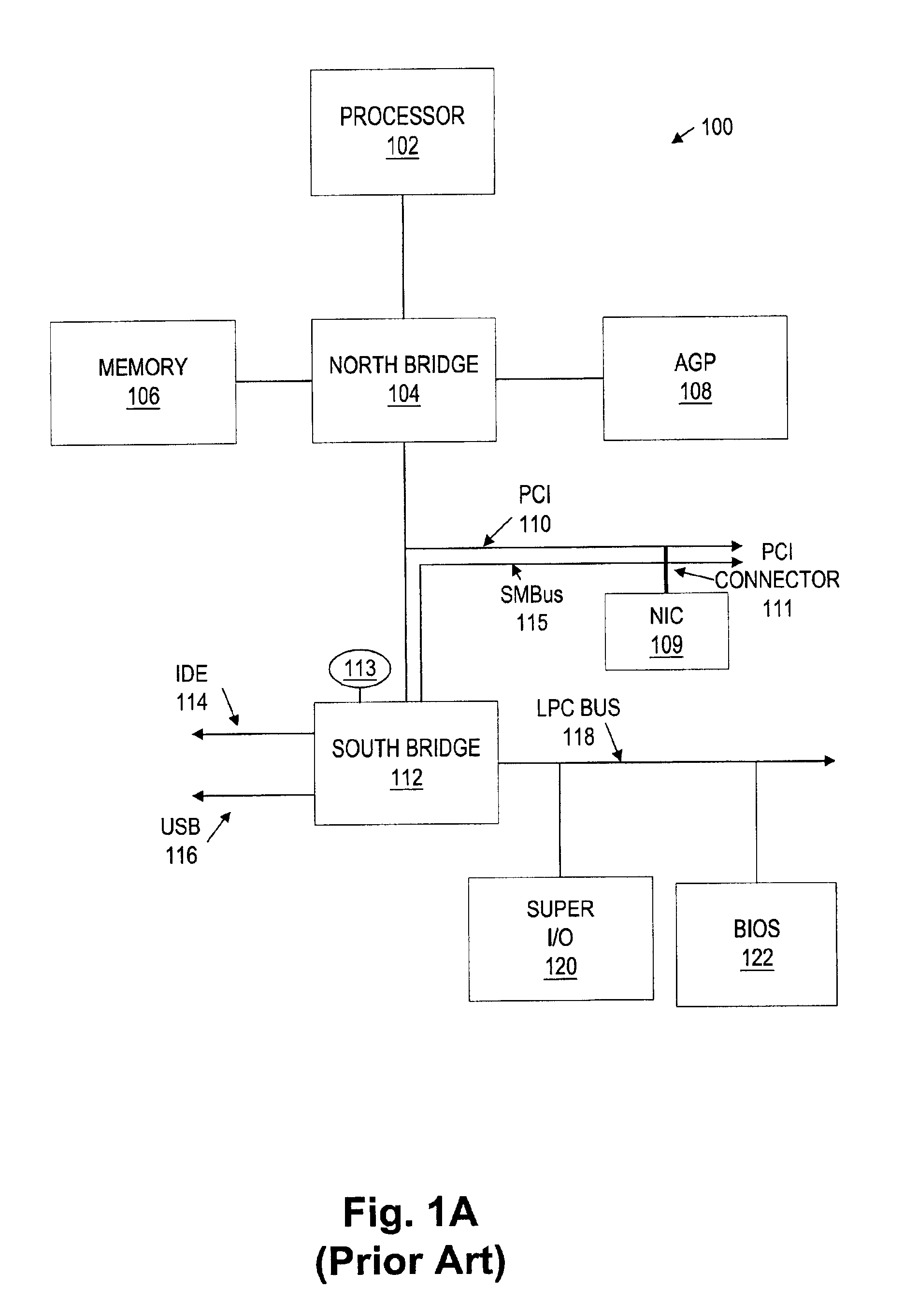

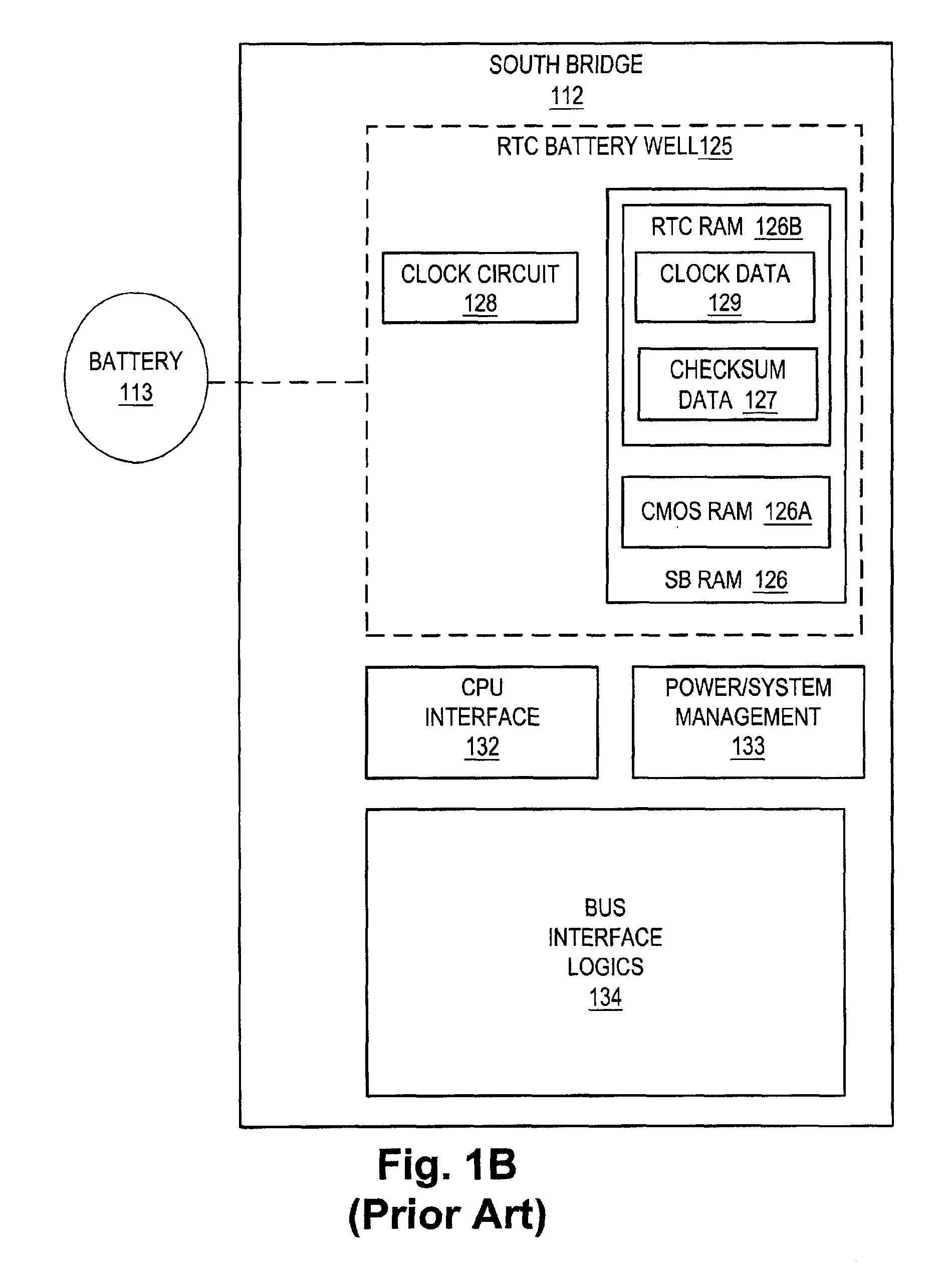

InactiveUS6892332B1Speed initializationReduce dependenceError detection/correctionComputerized systemBus interface

An integrated circuit, a client computer system, and a method for using a watchdog timer as a check before changing the system state of a computer system. The integrated circuit includes a first bus interface logic for coupling to a first external bus, a watchdog timer, and logic configured to receive a request for a system reset. The watchdog timer is coupled to receive a reset input upon a predetermined change in a system state. The watchdog timer is further configured to provide an indication in response to an expiration of the watchdog timer. The logic is configured to query the watchdog timer for the expiration of the watchdog timer in response to receiving the request for the system reset.

Owner:GLOBALFOUNDRIES INC

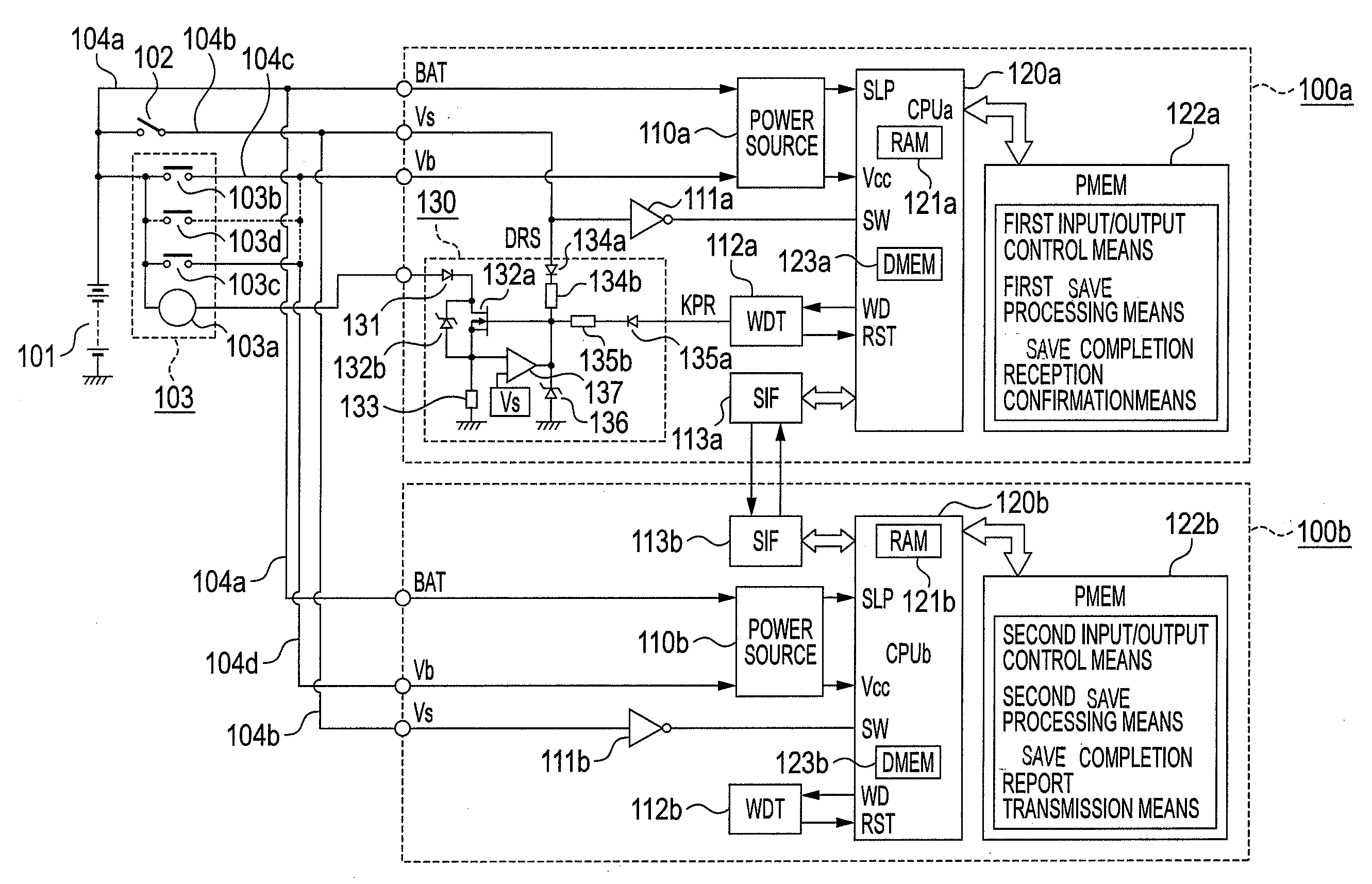

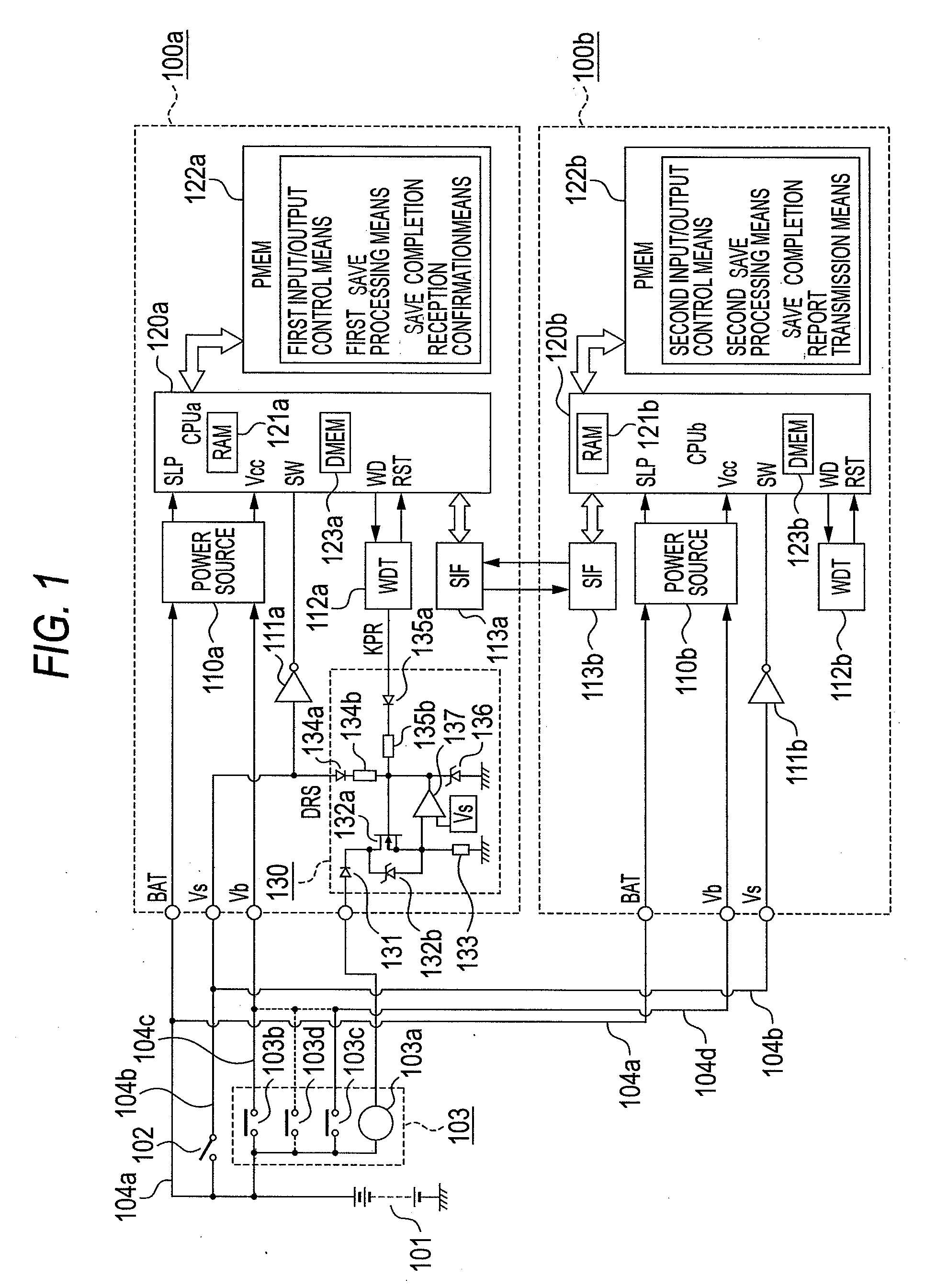

Power feed control circuit for on-vehicle electronic control apparatuses

InactiveUS20080238192A1Small sizeLow priceElectric devicesLoad balancing in dc networkPower switchingEngineering

First and second on-vehicle electronic control apparatuses which communicate with each other through serial communication interface circuits are fed with powers through an output contact of a power source relay from an on-vehicle battery, an electromagnetic coil of the power source relay is energized through a transistor when a power source switch has been closed, first and second microprocessors are activated upon closure of the output contact, a first watchdog timer generates a self-holding command signal and keeps an operating state of the power source relay when intervals of a watchdog signal which is generated by the first microprocessor are normal, and the self-holding command signal is stopped to deenergize the power source relay, when the first and second on-vehicle electronic control apparatuses have completed their save processing steps in accordance with opening of the power source switch.

Owner:MITSUBISHI ELECTRIC CORP

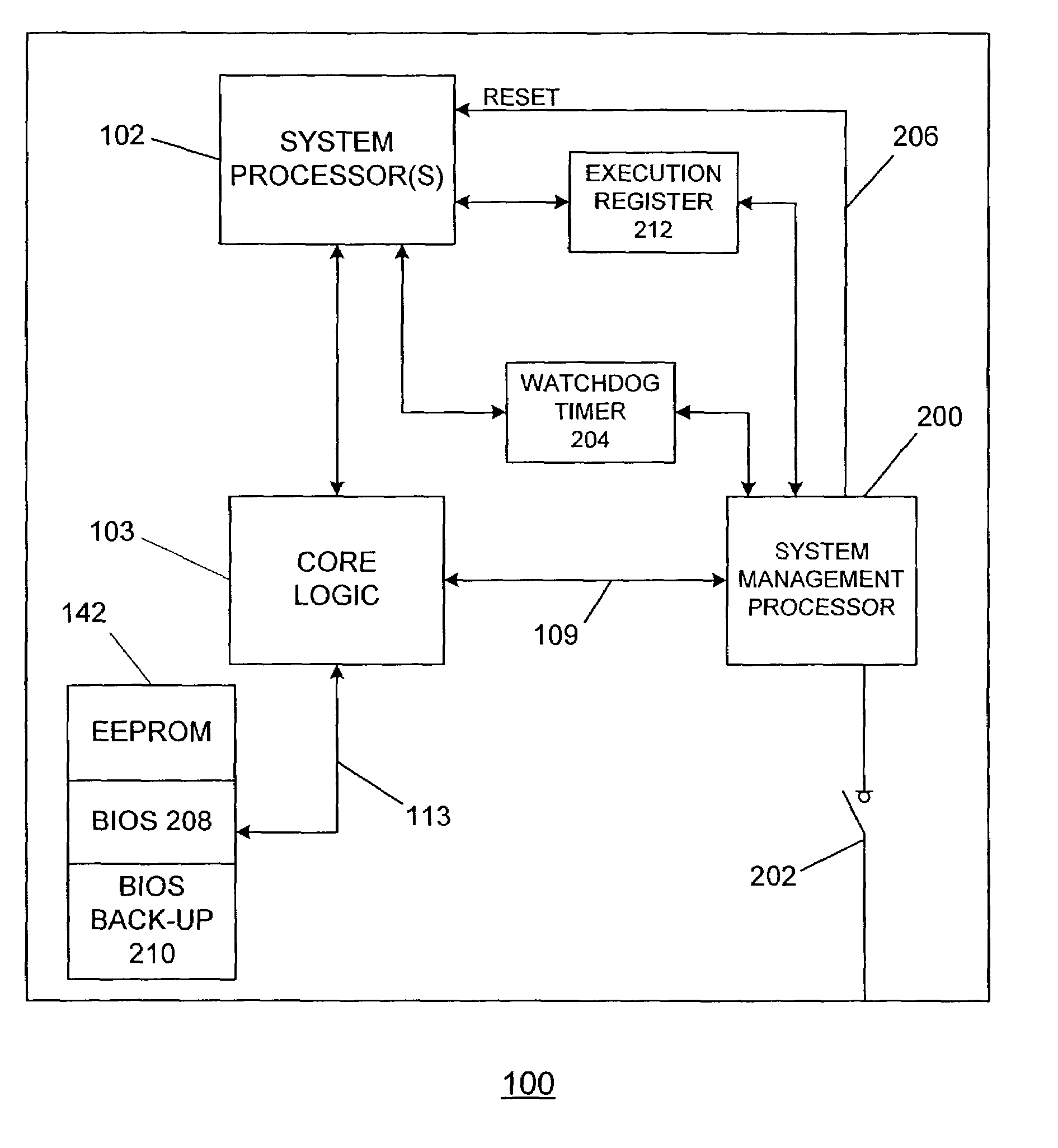

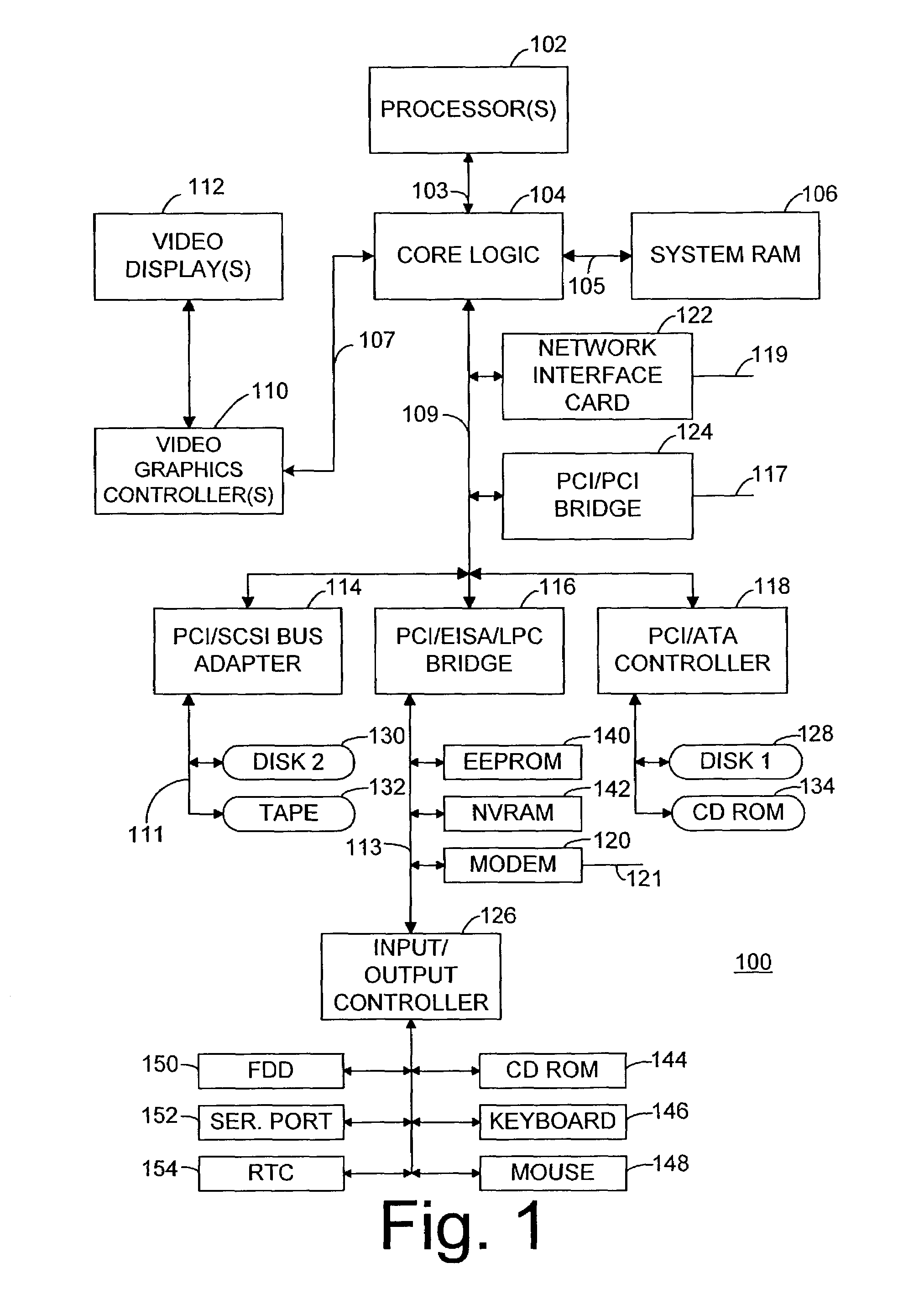

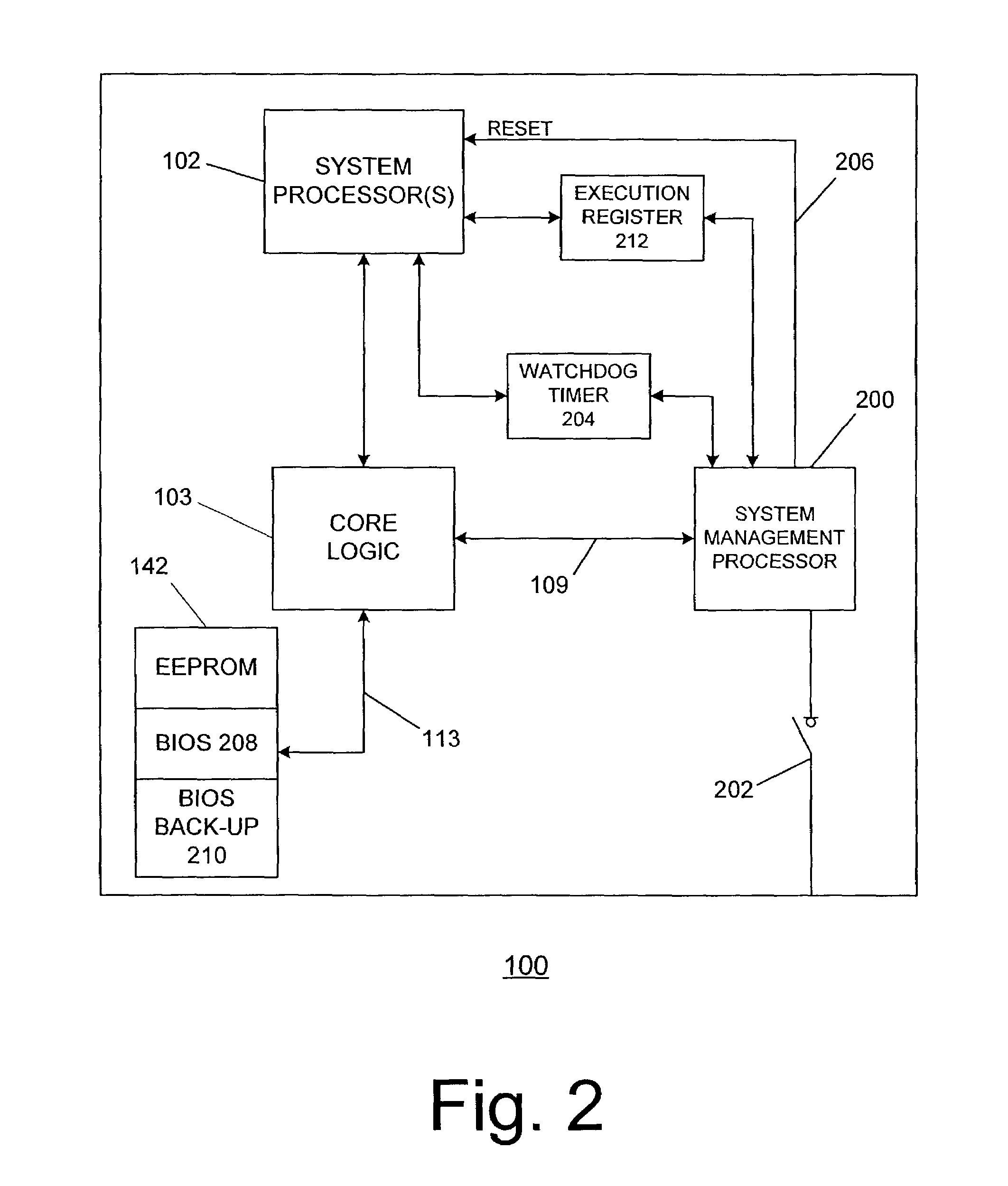

Method and apparatus for recovering from corrupted system firmware in a computer system

InactiveUS7024550B2Digital computer detailsProgram loading/initiatingData integritySystems management

The disclosed embodiments relate generally to providing increased data integrity in computer systems and, more particularly, to using a system management processor to overcome a computer system failure because of corrupted programming. A system management processor detects an attempted boot by host computer system and starts a watchdog timer. If the system BIOS or other firmware fails to execute, the watchdog timer expires and the system management processor places the system processor(s) in a reset state. The system management processor provides the address of a back-up BIOS or firmware and releases the system processor(s) from the reset state. The system processor(s) are redirected to the back-up BIOS or firmware and the computer system is able to boot.

Owner:SAMSUNG ELECTRONICS CO LTD

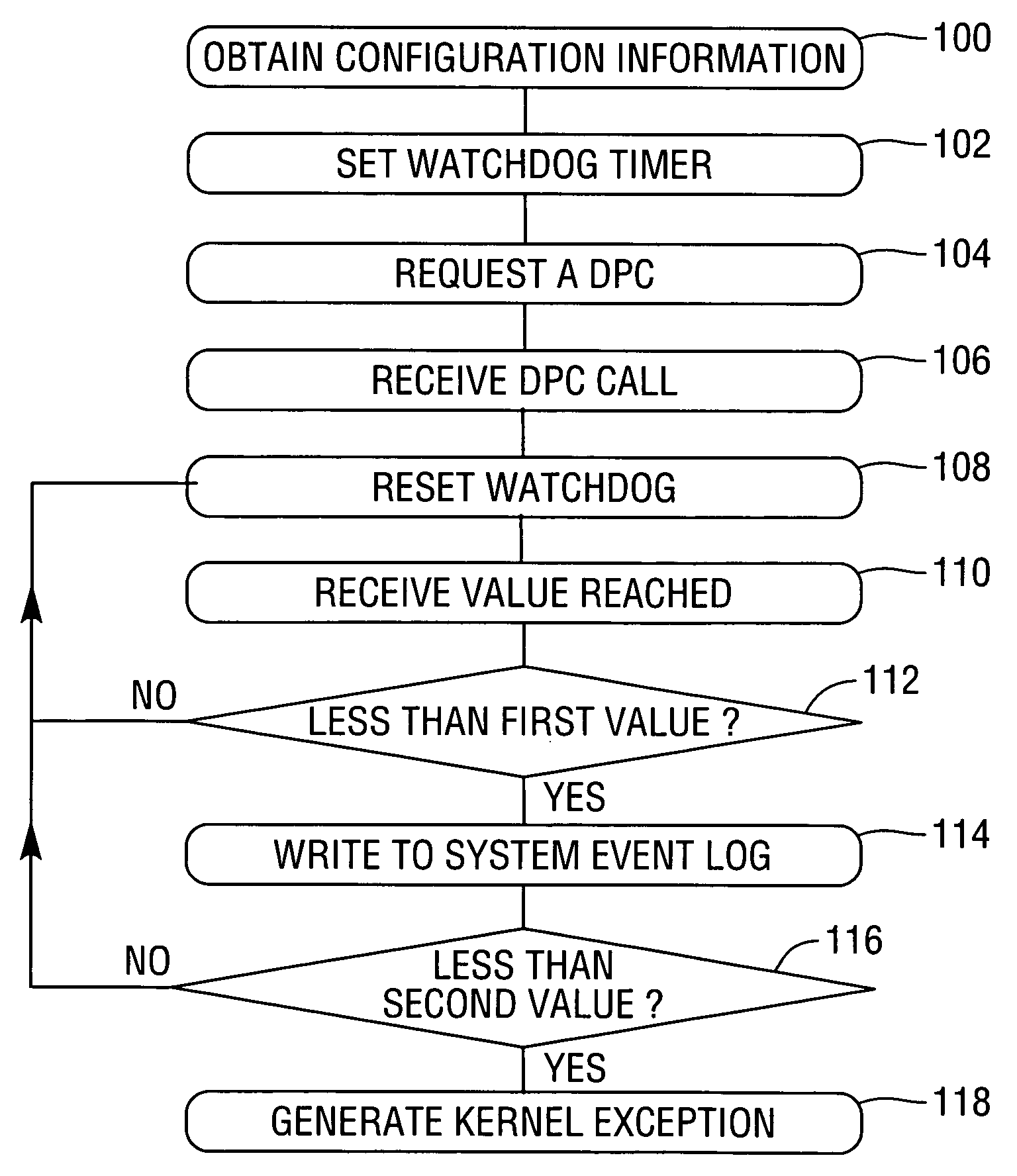

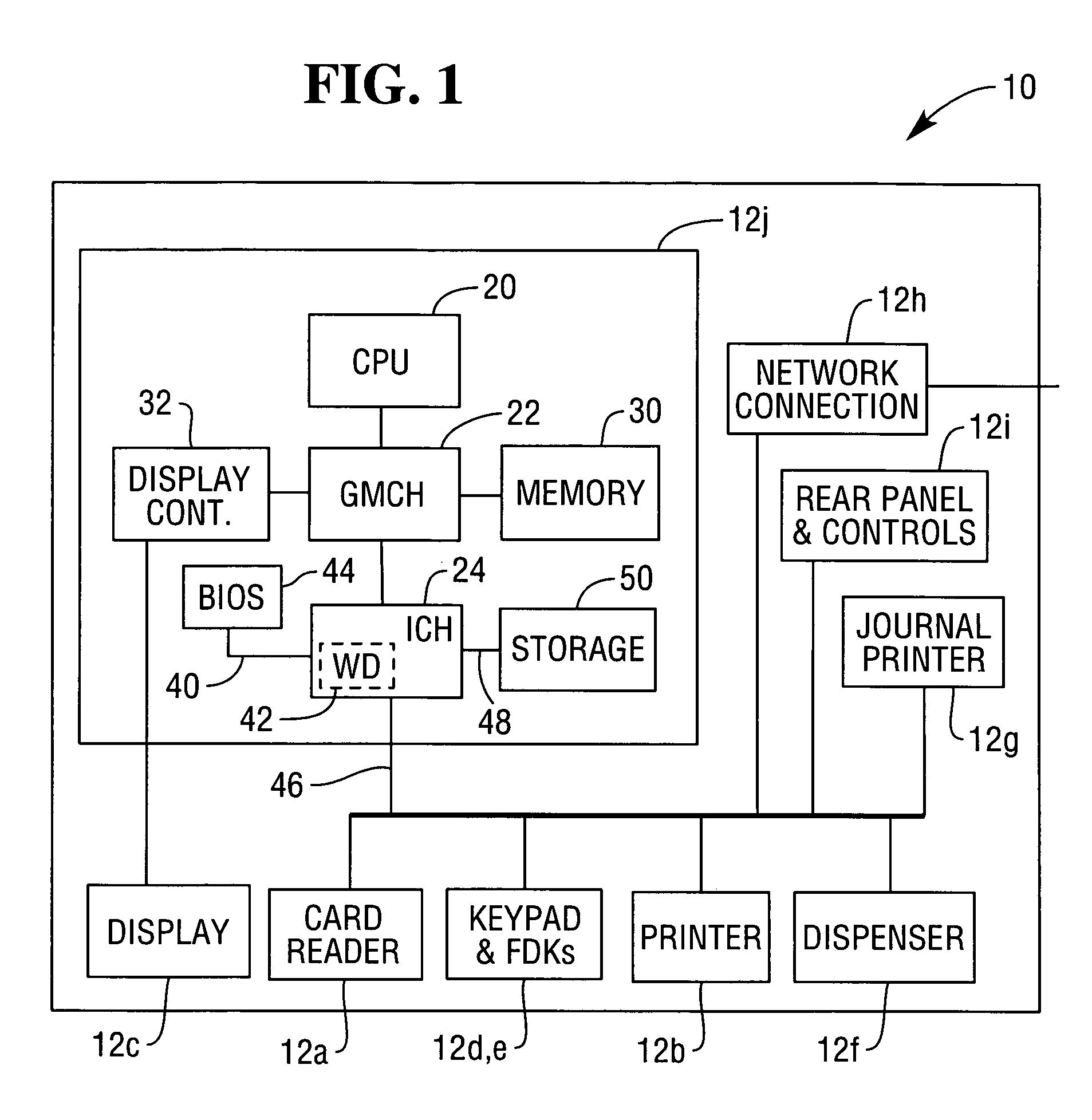

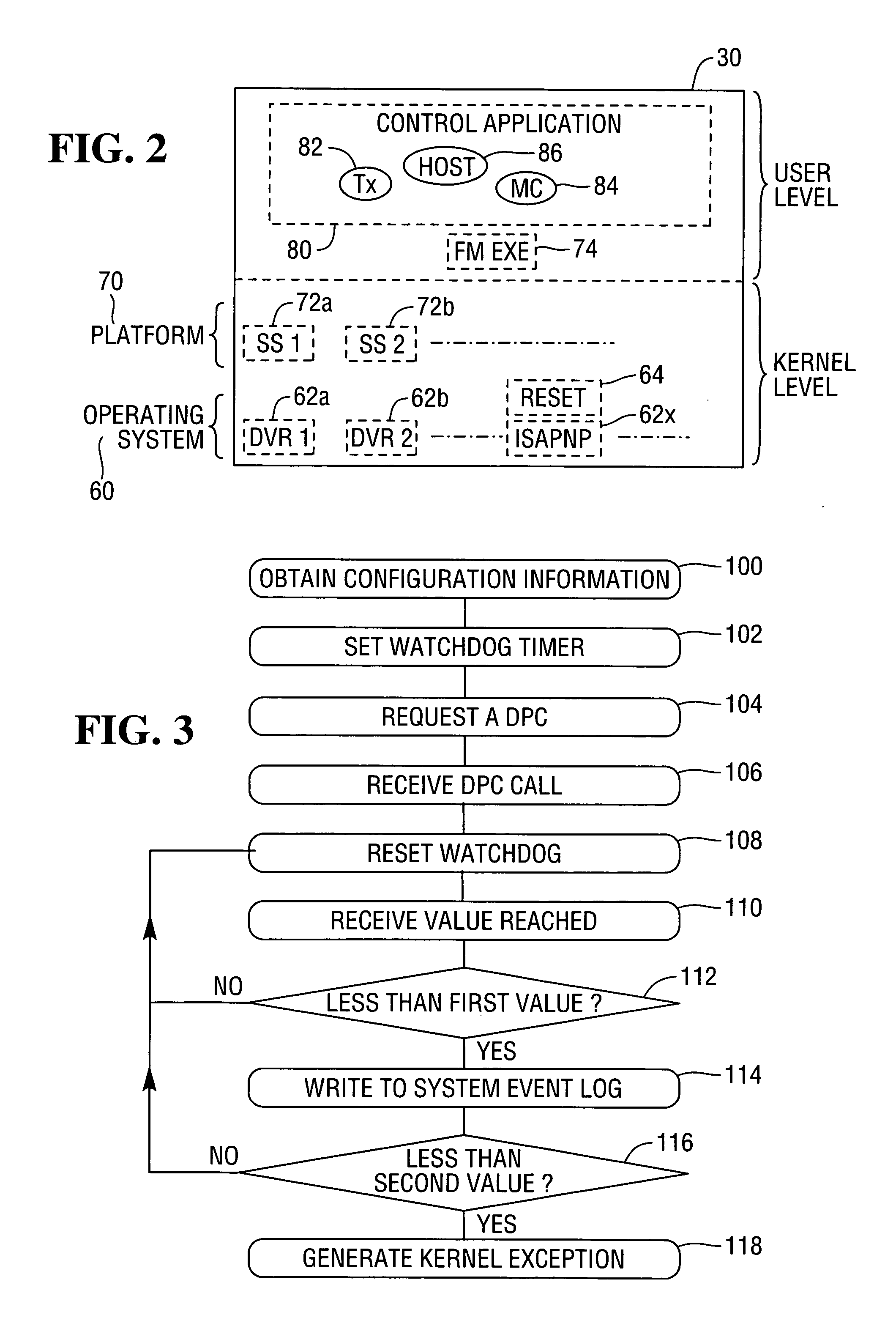

Self-service terminal

InactiveUS20090204856A1Enable detectionPayment architectureApparatus for meter-controlled dispensingSelf-serviceEmbedded system

A self-service terminal comprises a watchdog timer coupled to a clock; and a reset driver for resetting the watchdog timer. The reset driver is operable to monitor a count reached by the watchdog timer, and to instigate a diagnostic action, such as writing information to a system event log, in the event that the count reaches a first predefined number.

Owner:NCR CORP

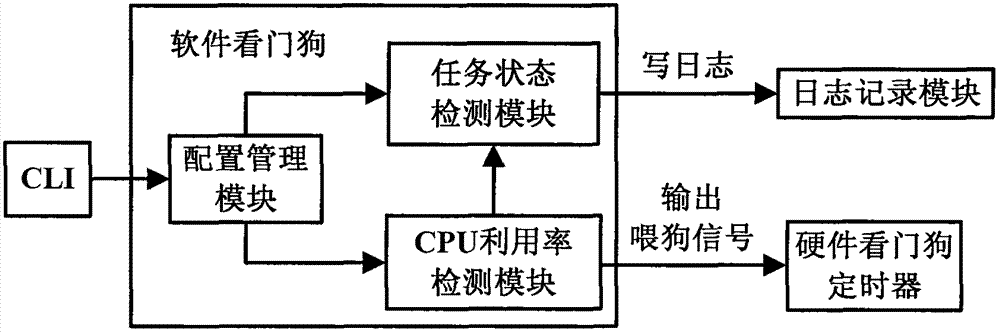

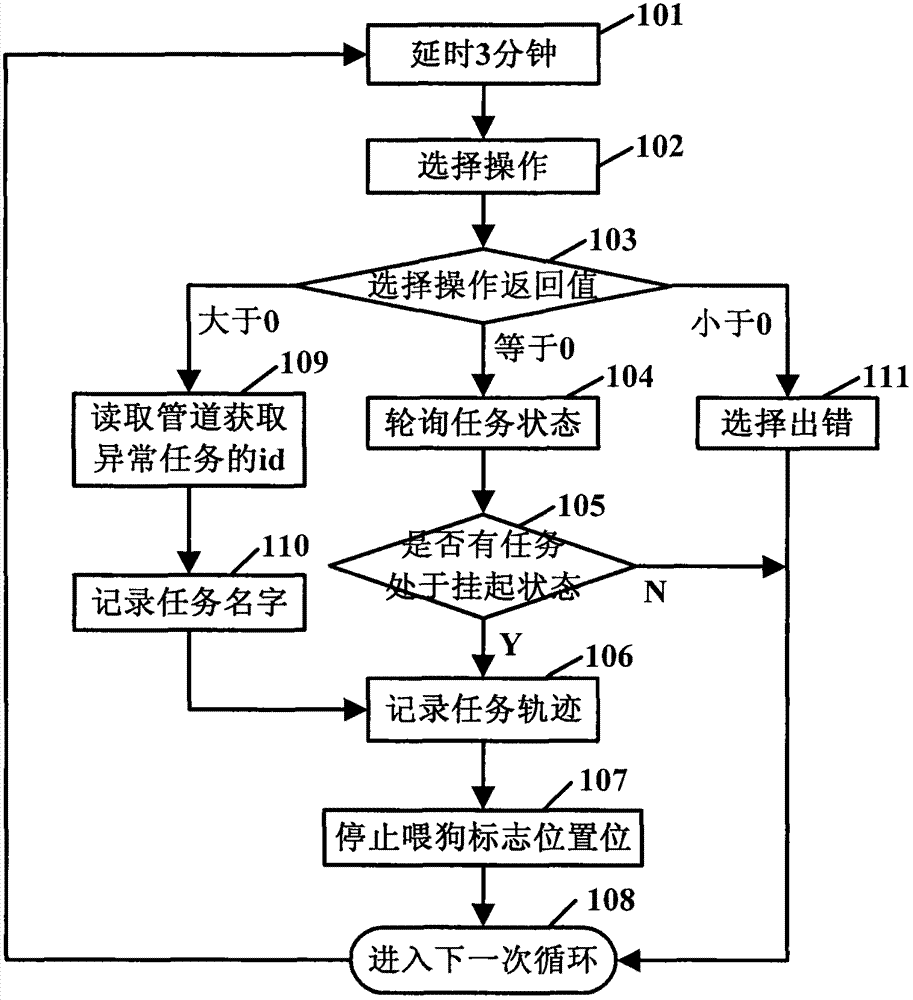

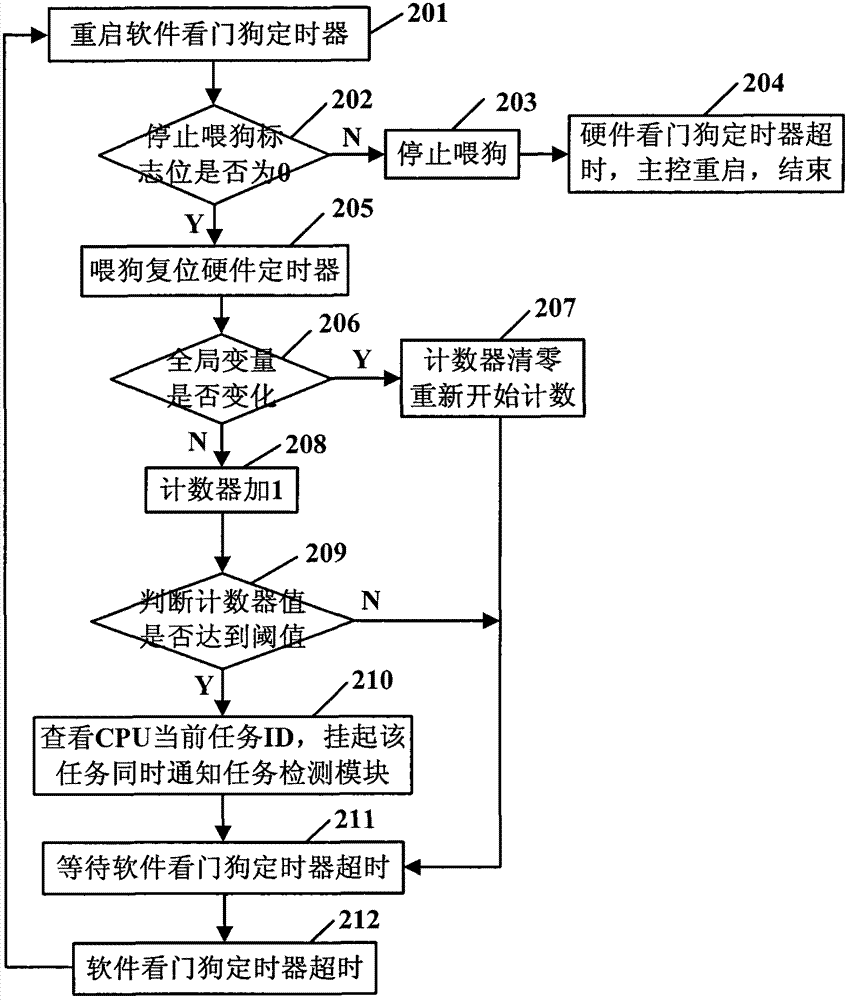

Device and method for detecting and recording abnormity on basis of watchdog in PON (Passive Optical Network) access system

ActiveCN102761439AReduce lossesFacilitate viewing phenomena and locating faultsElectromagnetic transmissionData switching networksCommand-line interfacePolling system

The invention discloses a device and a method for detecting and recording abnormity on the basis of a watchdog in a PON (Passive Optical Network) access system. The device comprises a hardware watchdog, a software watchdog, a log recording module and a CLI (Command-Line Interface), wherein the software watchdog comprises a configuration management module, a task state detection module and a CPU (Central Processing Unit) utilization ratio detection module; the task state detection module is connected with the log recording module and used for polling the task sate of the system; the CPU utilization ratio detection module is connected with the hardware watchdog and used for detecting the CPU utilization ratio of the system; the task state detection module is communicated with the CPU utilization ratio detection module through a pipeline communication mode; the software watchdog is used for outputting a reset signal to a hardware watchdog timer at regular time; and when abnormity is detected, a zone bit is set, zero clearing is stopped by the log recording module after the abnormal information is recorded by the log recording module, a master control panel is reset, and changeover is triggered. According to the invention, a master panel is automatically reset to recover a system service when the master control panel is abnormal, and the abnormal data is recorded before resetting, which is beneficial to positioning faults.

Owner:FENGHUO COMM SCI & TECH CO LTD

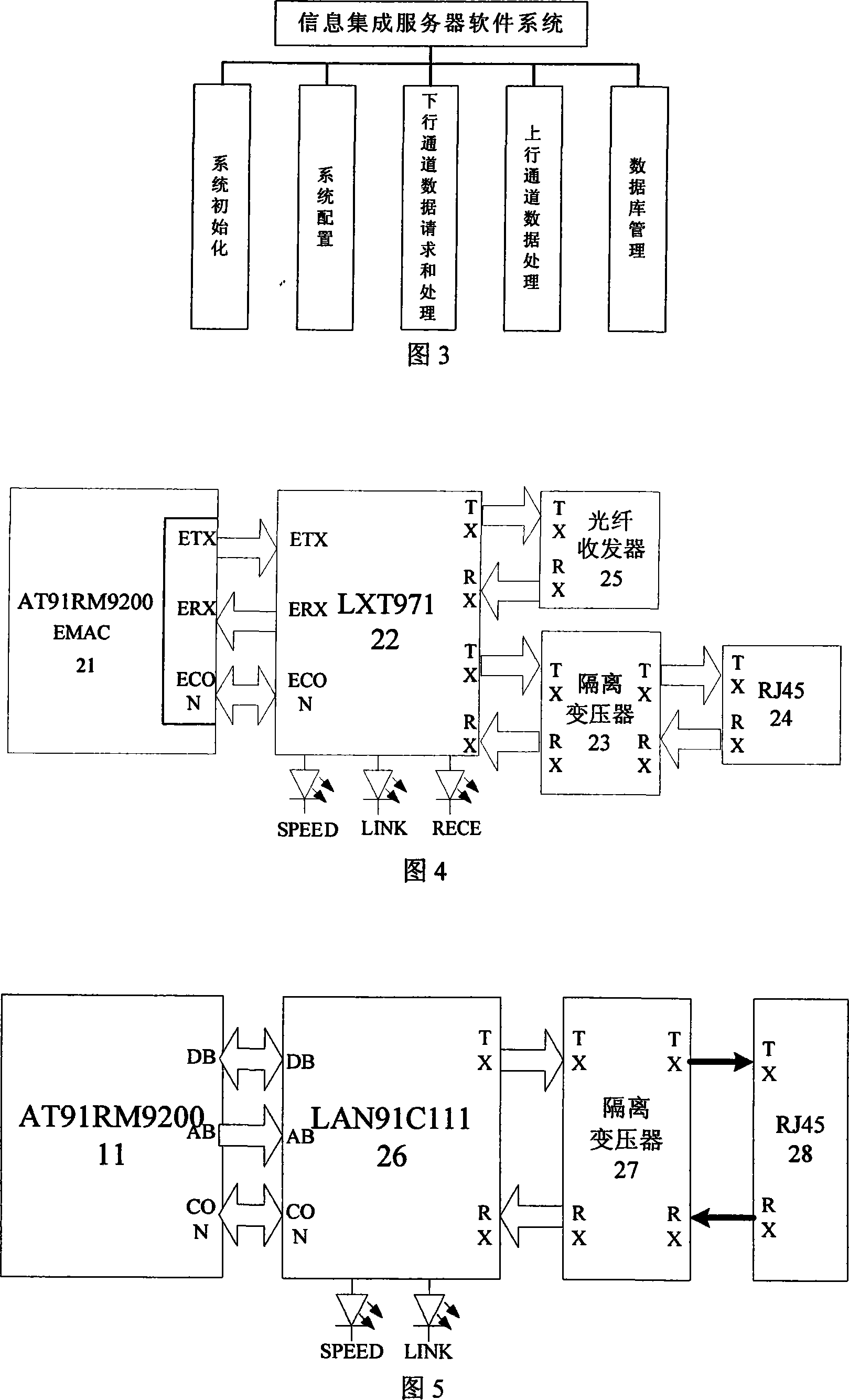

Embedded transformer station information integrated server

InactiveCN101163017ASupport remote operationSupport controlData switching detailsCircuit arrangementsProgrammable read-only memoryTransformer

The invention relates to an embedded substation information integration server, which is composed of a core processing module (1), an ethernet communication interface module (2), a CAN bus communication interface module (3), a serial communication interface module (4) and a switching value input-output module (5), and wherein, the core processing module (1) is composed of a processor AT91RM9200 (11), a synchronous dynamic random access memory (12), a parallel flash memory (13), a NAND flash memory (14), an electrically erasable programmable read-only memory AT24C512 (15), a real-time clock (16), a watchdog timer (17), a complex programmable logic device XC95144 (18) and peripheral auxiliary circuits, which jointly construct a basic embedded system. The invention applies uniform network and specification systems to develop the embedded substation information integration server which has the advantages of high performance, high openness, high reliability and low cost and realizes the interconnection and interoperation among the devices of different manufacturers, thus providing a data service platform for the integration, sharing and comprehensive processing of information.

Owner:SOUTHEAST UNIV

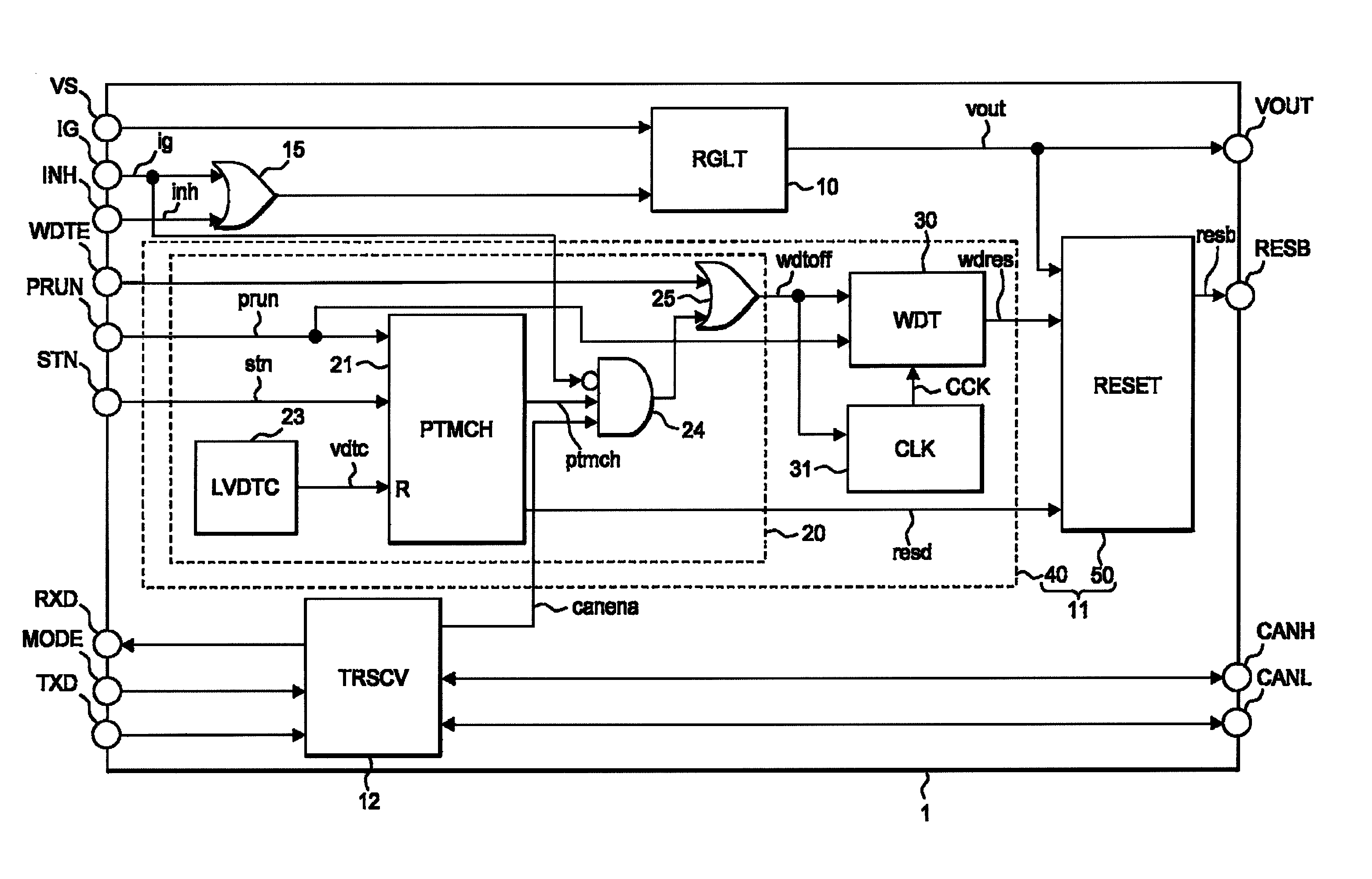

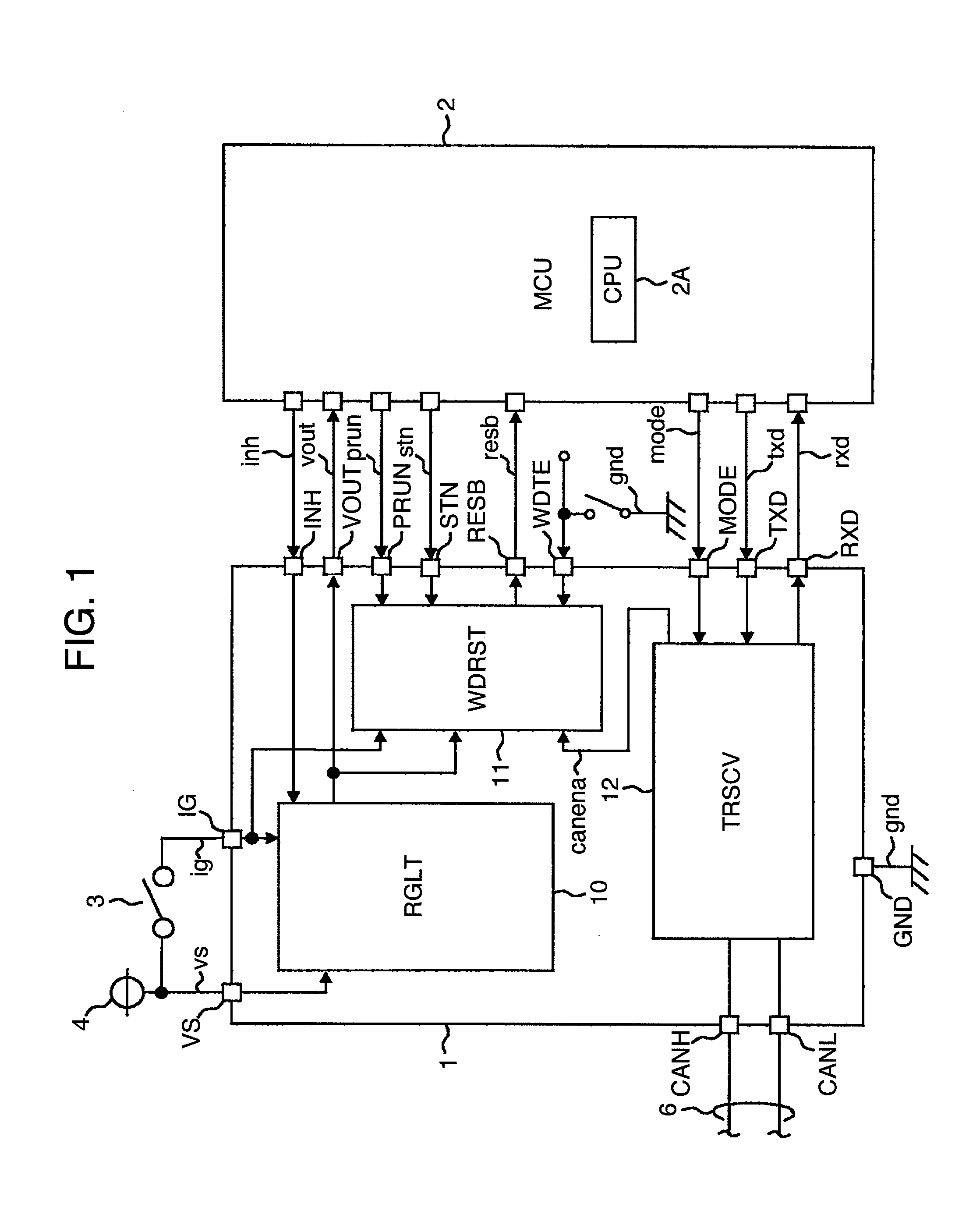

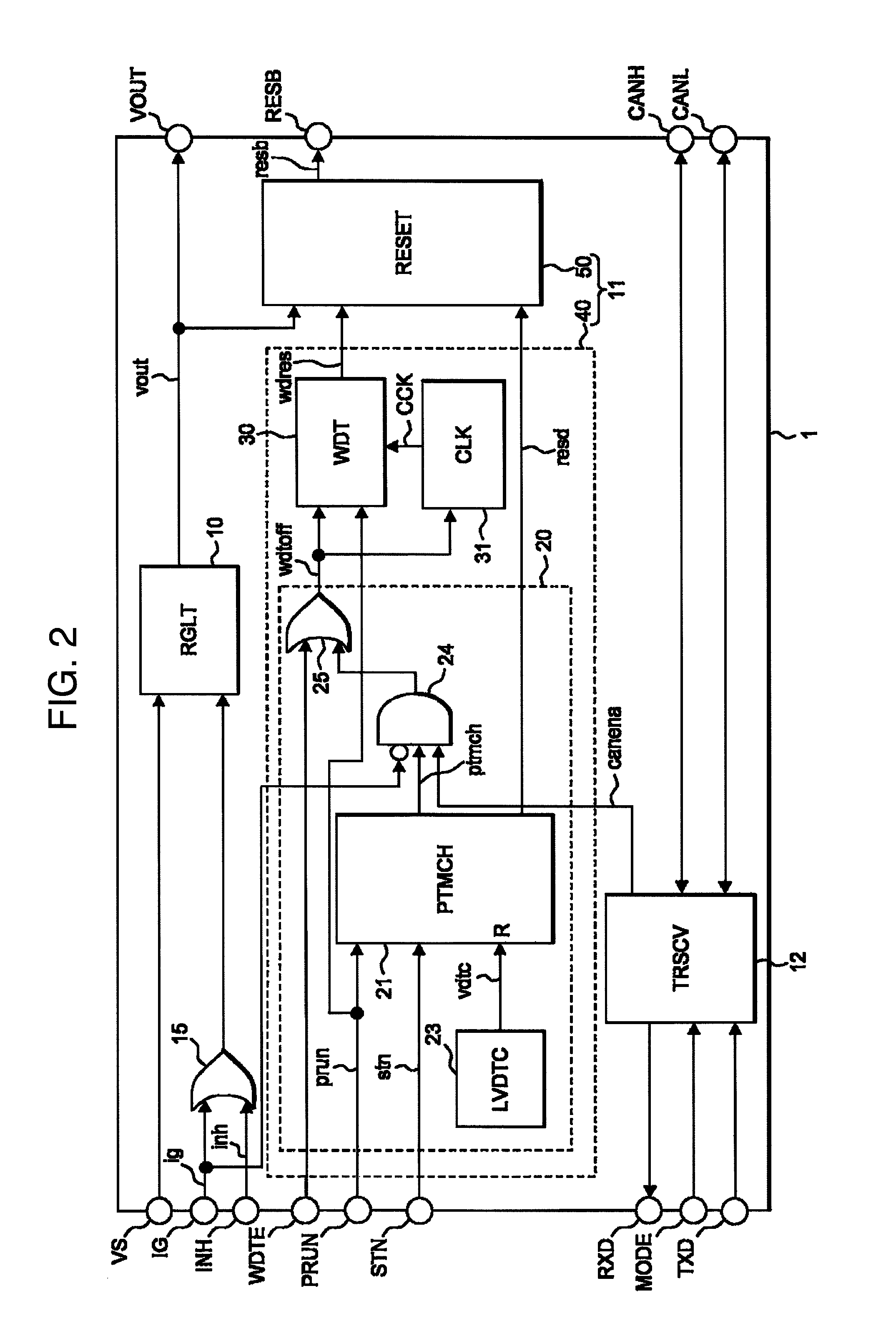

Watchdog circuit, power IC and watchdog monitor system

ActiveUS20130198539A1Promote recoveryReadily and quickly recover to its operable stateEnergy efficient ICTError detection/correctionMicrocomputerData signal

A watchdog timer circuit for use in microcomputer monitor systems is disclosed. This circuit includes a timer circuit responsive to receipt of a count clock signal for counting it up, and a timer control circuit which loads an externally inputted data signal (stn) in sync with a timer refresh instruction (prun) and holds therein a sequentially loaded latest multi-bit data signal as reference data. When the reference data agrees with a predefined pattern and simultaneously another prespecified condition is met, the timer control circuit interrupts the clock signal counting operation of the timer circuit. During interruption of the counting operation, when the reference data does not agree with the predefined pattern or when the above-stated another prespecified condition becomes unsatisfied, the control circuit allows the timer circuit to restart the clock signal counting operation.

Owner:RENESAS ELECTRONICS CORP

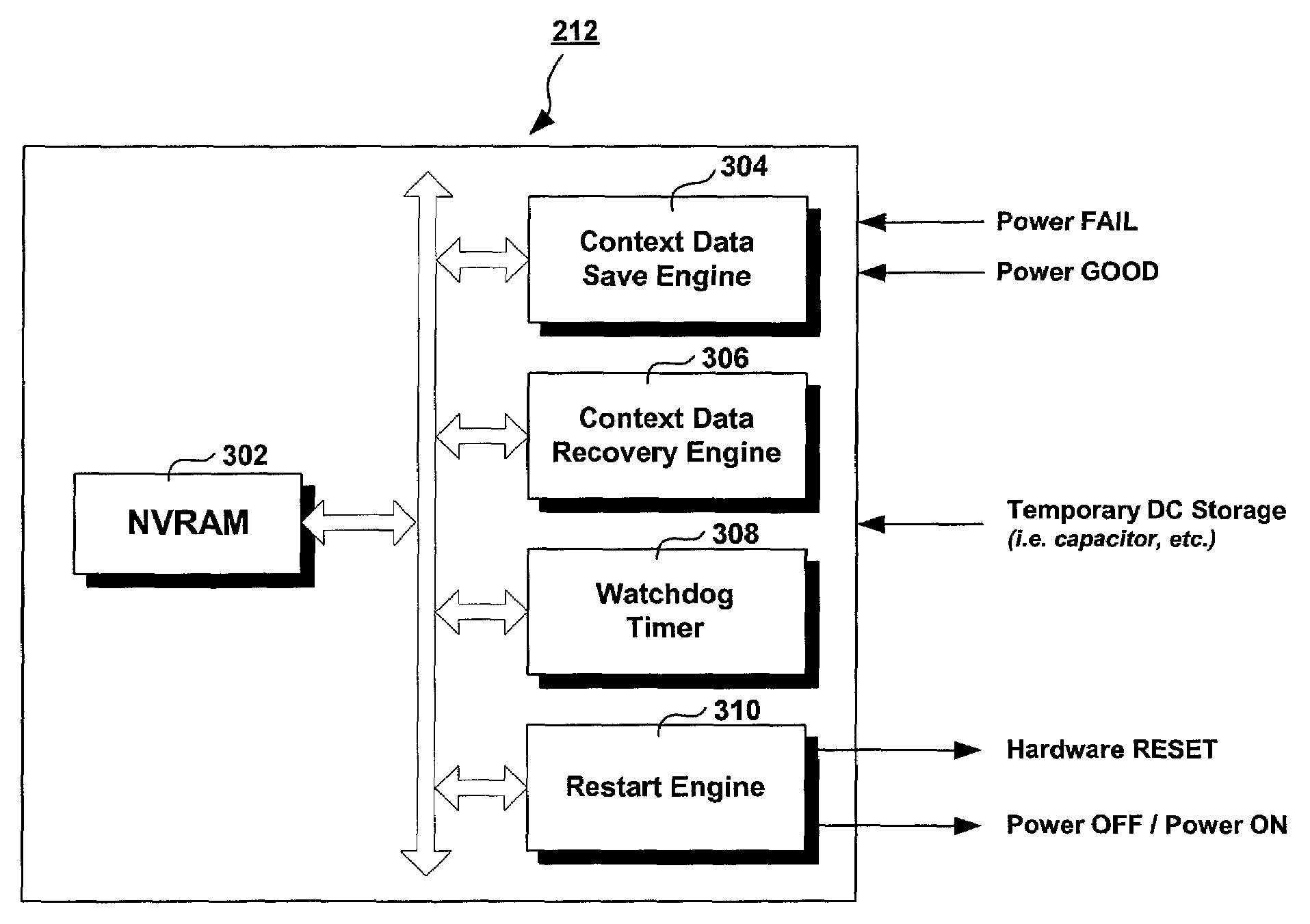

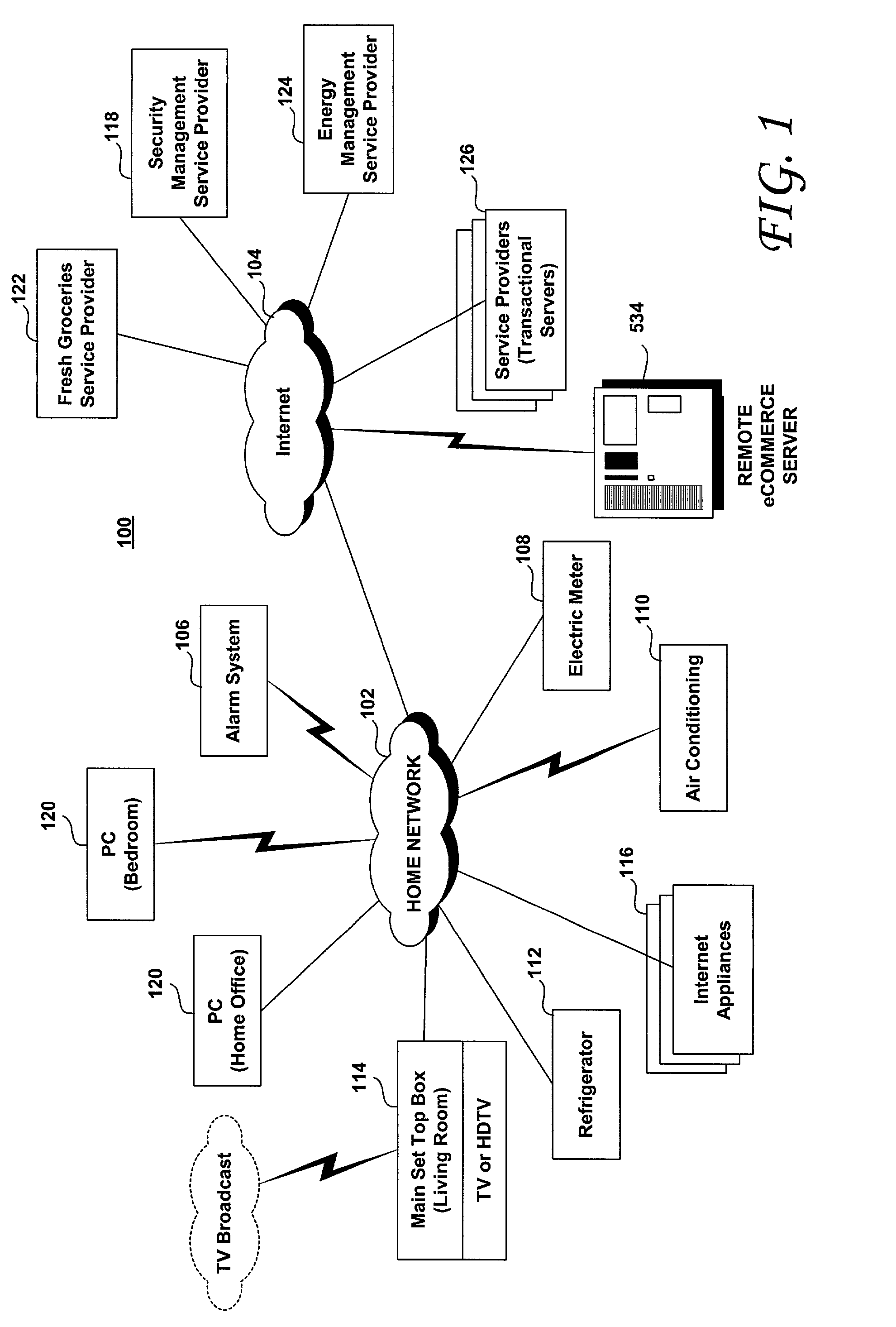

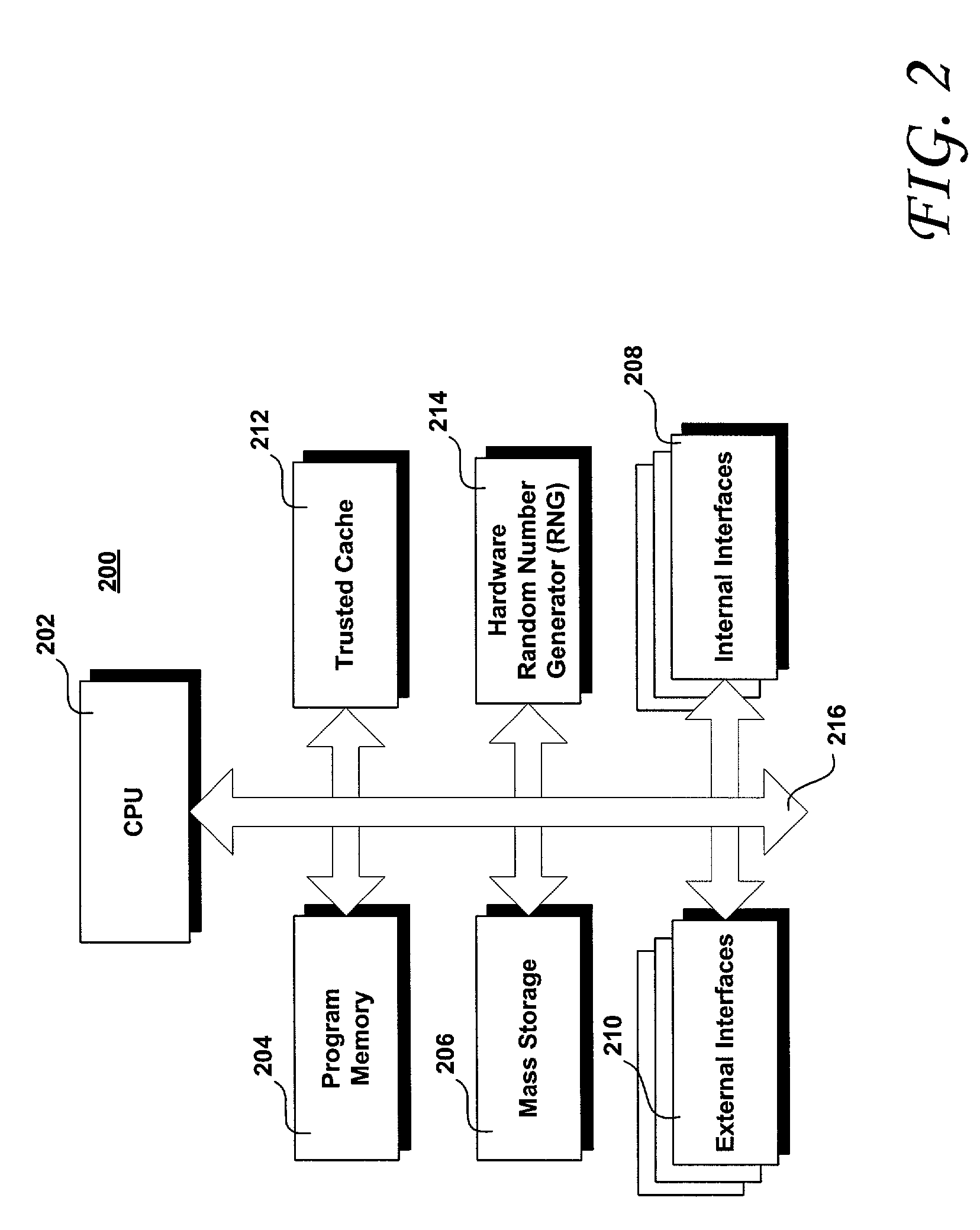

Controller having a restart engine configured to initiate a controller restart cycle upon receipt of a timeout signal from a watchdog timer

InactiveUS7051332B2Multiprogramming arrangementsBuying/selling/leasing transactionsElectronic controllerPrivate network

An electronic controller for conducting trusted lightweight e-commerce transactions. A trusted transactional cache and the associated transactional protocol allow e-commerce transactions to be committed to a remote server extremely quickly and with little network overhead. The end-to-end transactions are completed is just a few seconds or less. The invention operates equally well on robust private networks as on unpredictable Internet or wireless networks. The transaction is automatically completed following a temporary communication failure with the central site or following a temporary local controller failure. The invention can advantageously be used in embedded Internet products such as fixed or mobile Internet kiosks, transactional terminals, and Internet Appliances.

Owner:MUDALLA TECH INC THOITS LOVE HERSHBERGER & MCLEAN

Controller and resource management system and method with improved security for independently controlling and managing a computer system

InactiveUS7249381B2Digital data processing detailsUnauthorized memory use protectionOperational systemResource Management System

A controller and resource management system and method with improved security for independently controlling and managing a computer system is provided. Control, management and security protection is provided while functioning: conceptually, logically, functionally, operatively, physically and electrically independent of computer system resources, including processors. All computer system resources, including processors are operatively dependent on the present invention; processors do not execute operating system instructions. Data transferred between the computer system and processors is communicable through the controller and resource management system for improved security. The present invention comprising: Buffer memory, BIOS, device drivers, event handler, system security, scheduler, memory manager, I / / O controller, configuration manager, independent watchdog timer and networking interfaces. One method whereby the invention is implemented in hardware for improved security is provided; another method whereby information is communicable between multiple controller and resource management systems, or micronodes©, independently of computer system resources, including processors is also provided.

Owner:BRYTE COMP TECH

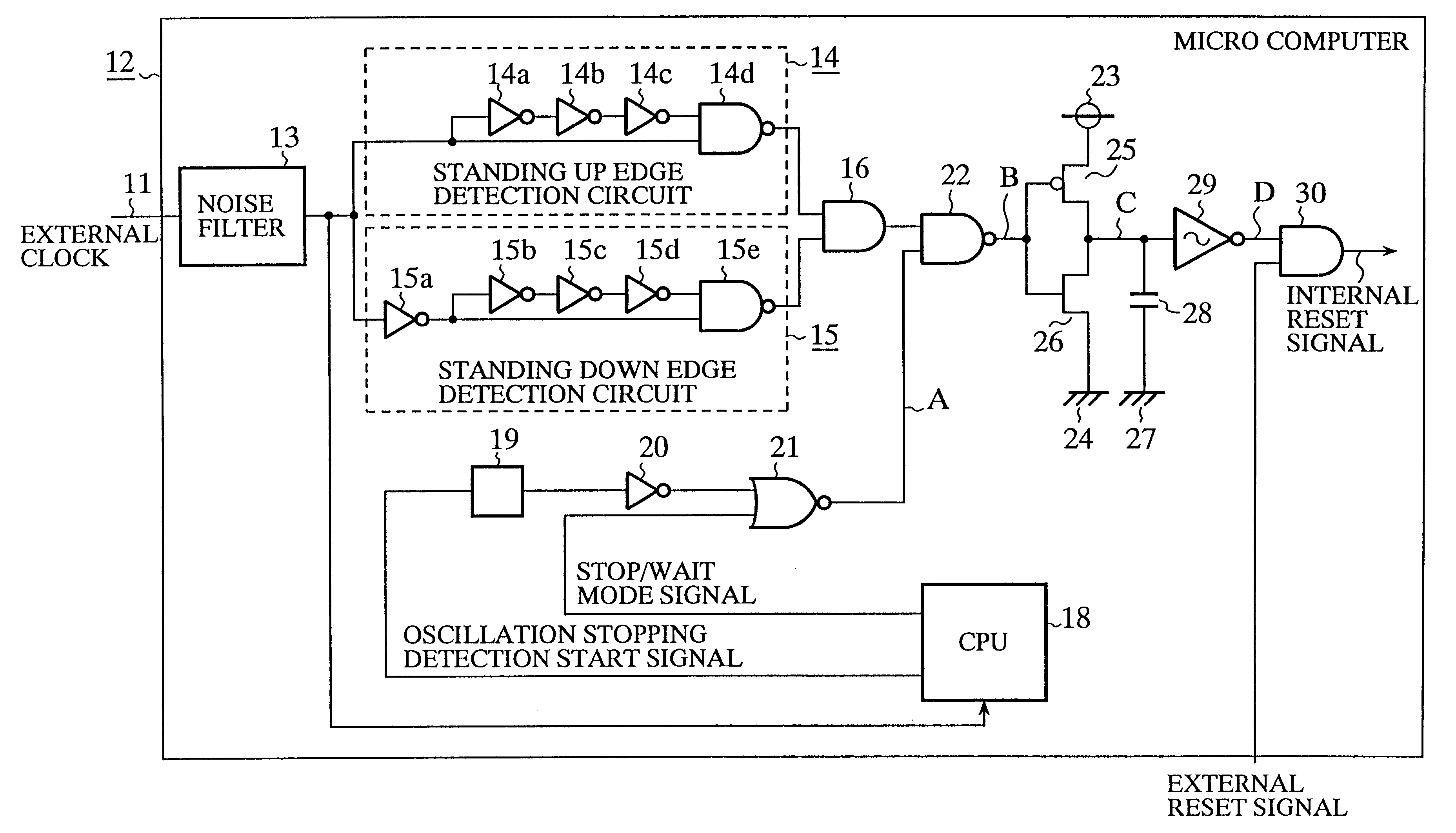

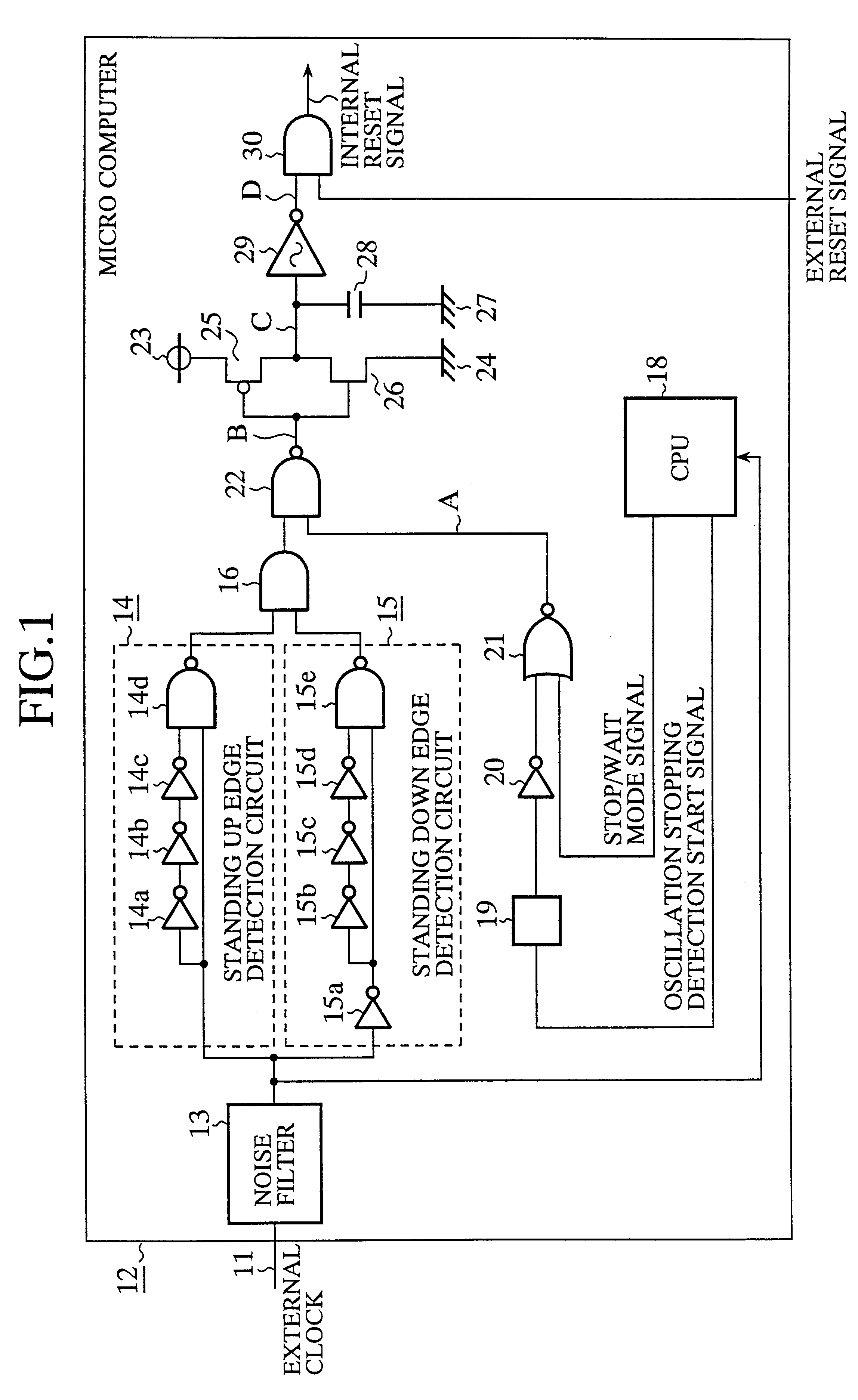

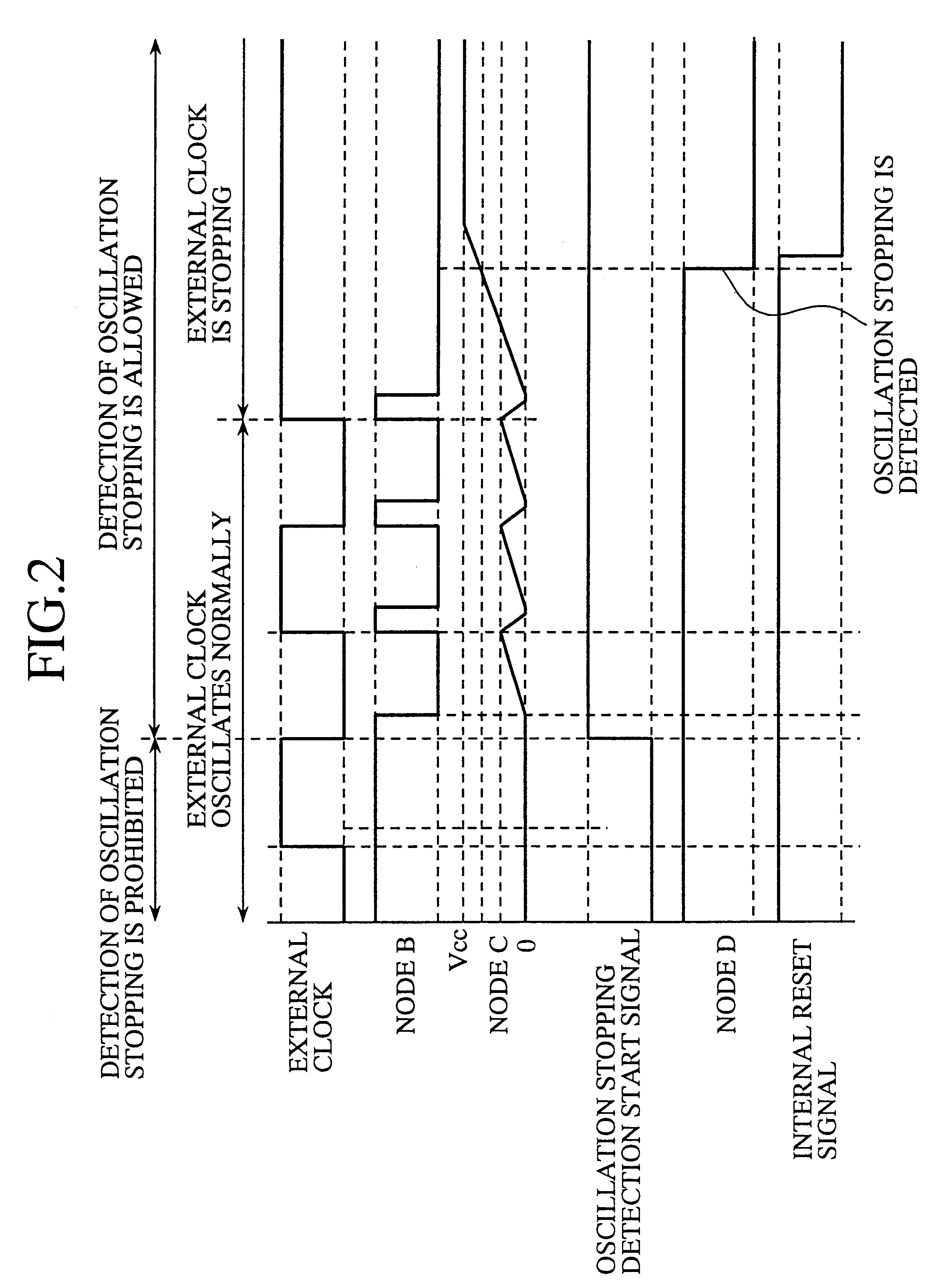

Detector of an oscillation stopping and an apparatus for executing a treatment after the detection of an oscillation stopping

A detector of an oscillation stopping, which detects the stopping of the oscillation of external clock 11, without increasing the load of CPU 45 in the micro computer 40, and generates a signal to reset the micro computer or exchanges the system clock from the external clock to an inner clock.In an embodiment, one shot pulse is generated for every standing up and / or down edge of the external clock. A capacitor of the charge-discharge circuit is charged and discharged at every one shot pulse. The voltage of the charge-discharge circuit is watched by a Schmitt circuit. When the voltage of the charge-discharge circuit exceeds a predetermined voltage, a signal for resetting the micro computer is generated.In another embodiment, an inner clock oscillation circuit, comprised of a ring oscillator, for example, is actuated, when the voltage of the charge / discharge circuit exceeds a predetermined voltage, and the system clock of the micro computer is exchanged to the inner clock from the external clock.In another embodiment, an interruption signal is sent to the CPU of the micro computer to execute an appropriate treatment after the stopping of the clock oscillation, when the voltage of the charge / discharge circuit exceeds a predetermined voltage.In another embodiment, a watchdog timer monitors the malfunction of the micro computer. It is judged whether the accident is a stopping of the oscillation of the clock or a malfunction of the micro computer. The treatment after the stopping of the clock is executed, according to the reason of the accident.

Owner:MITSUBISHI ELECTRIC SYST LSI DESIGN +1

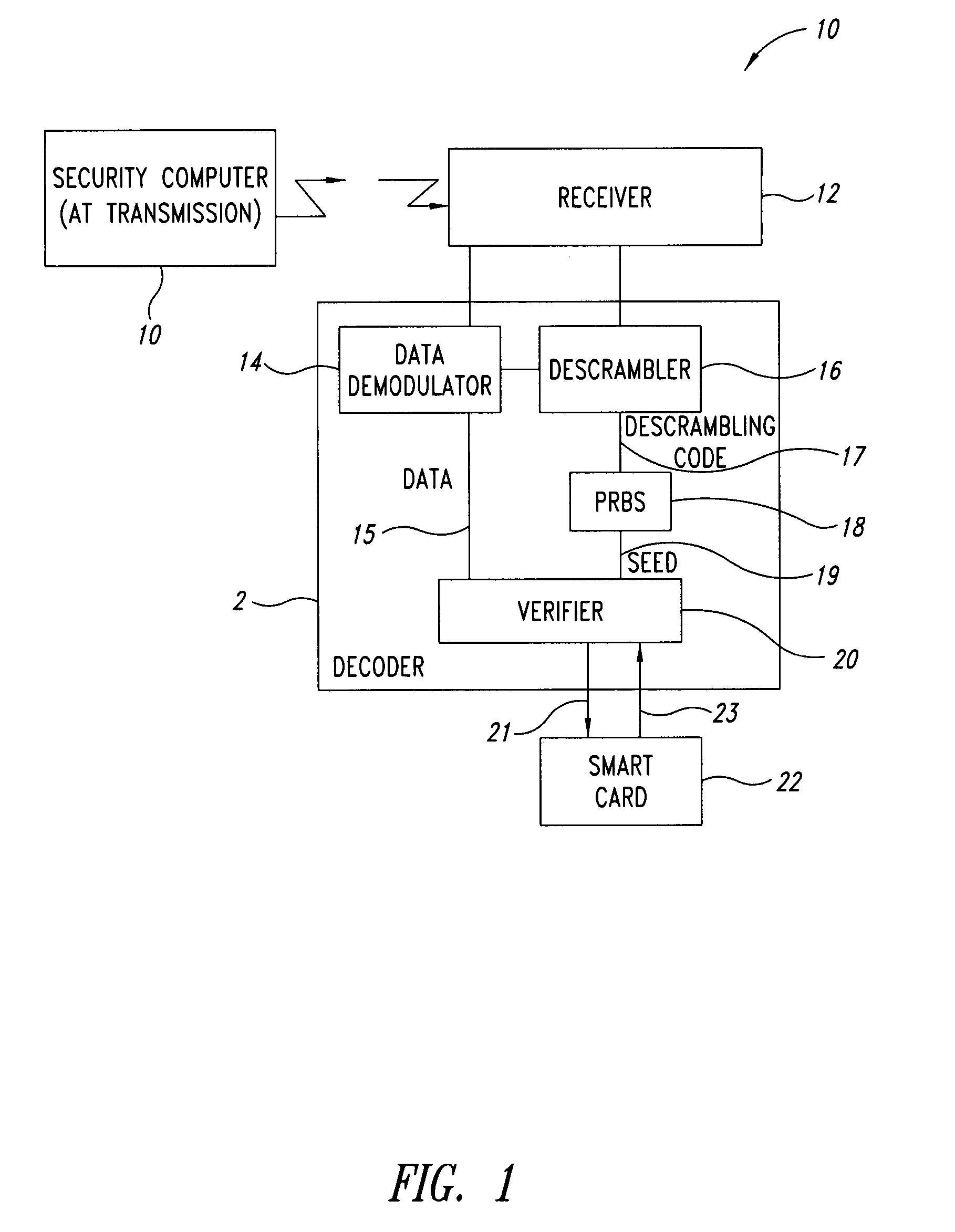

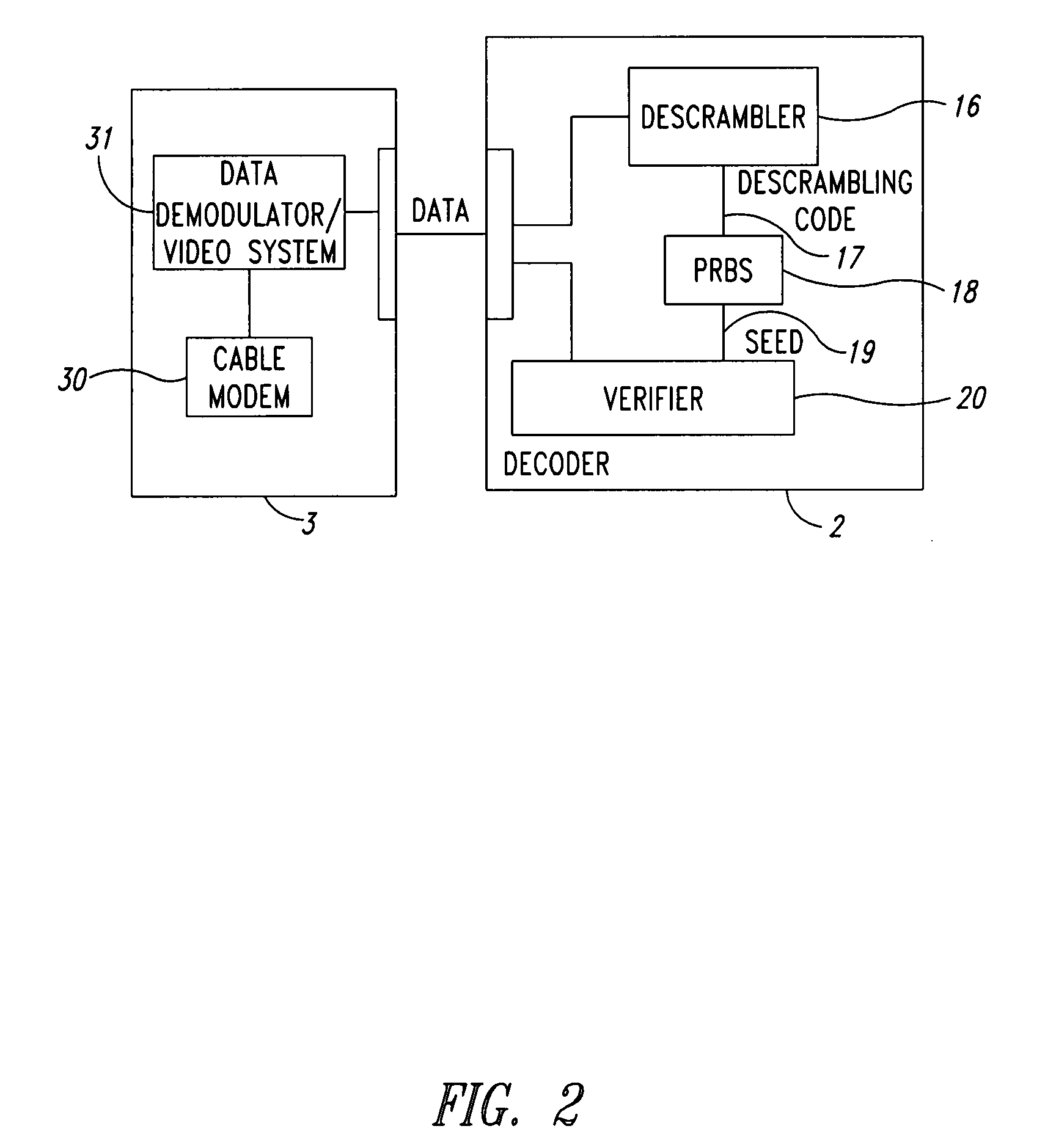

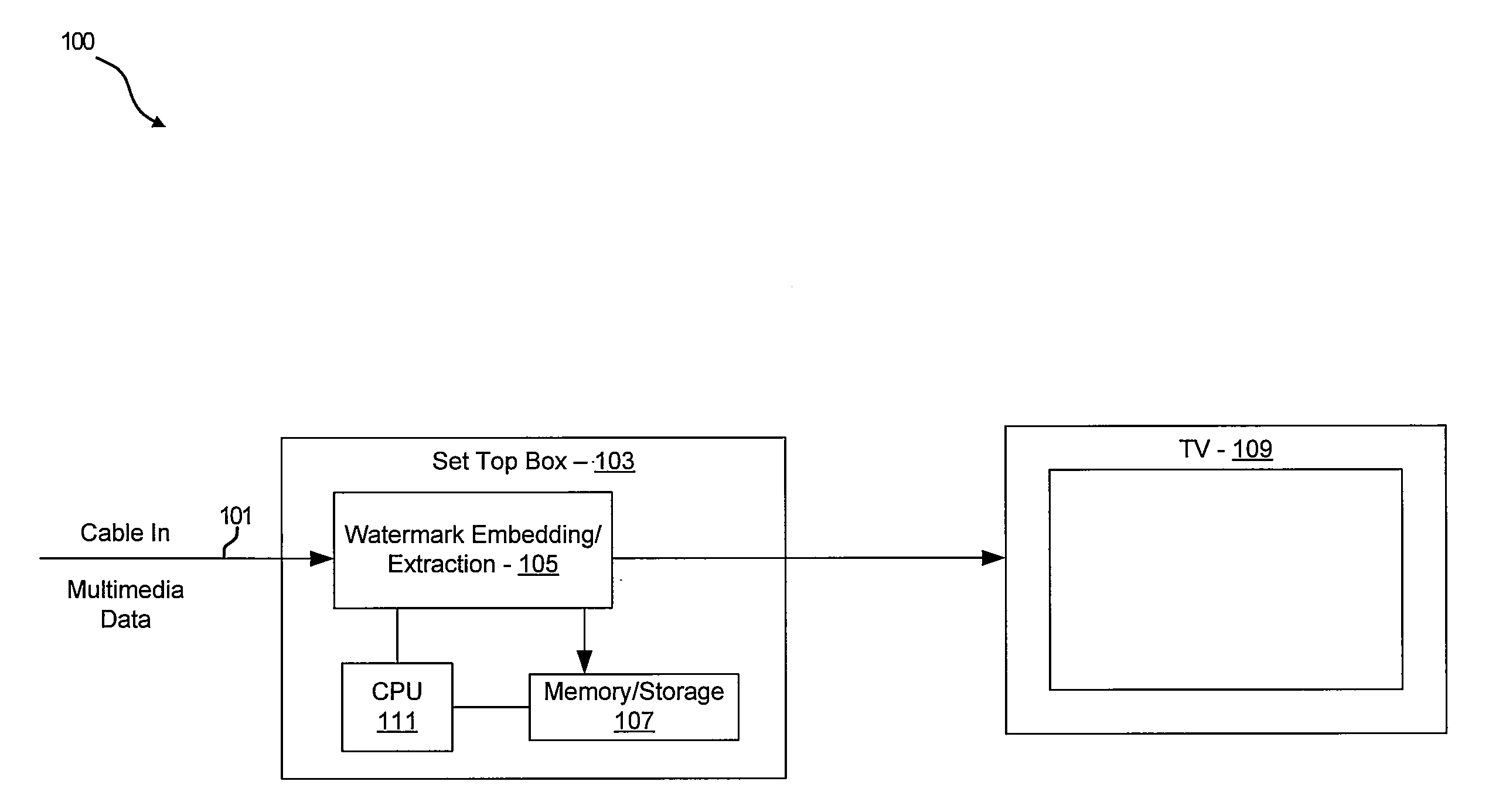

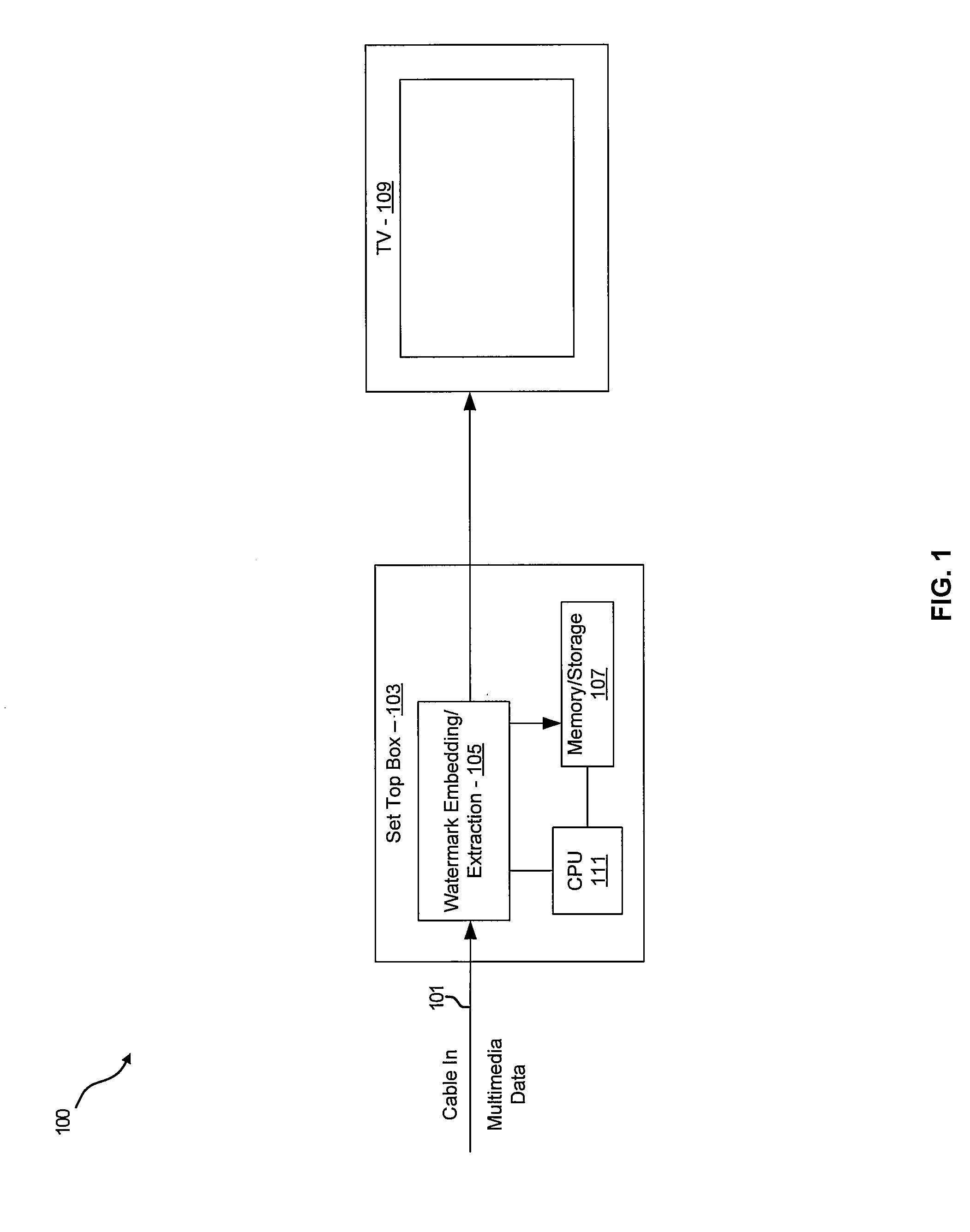

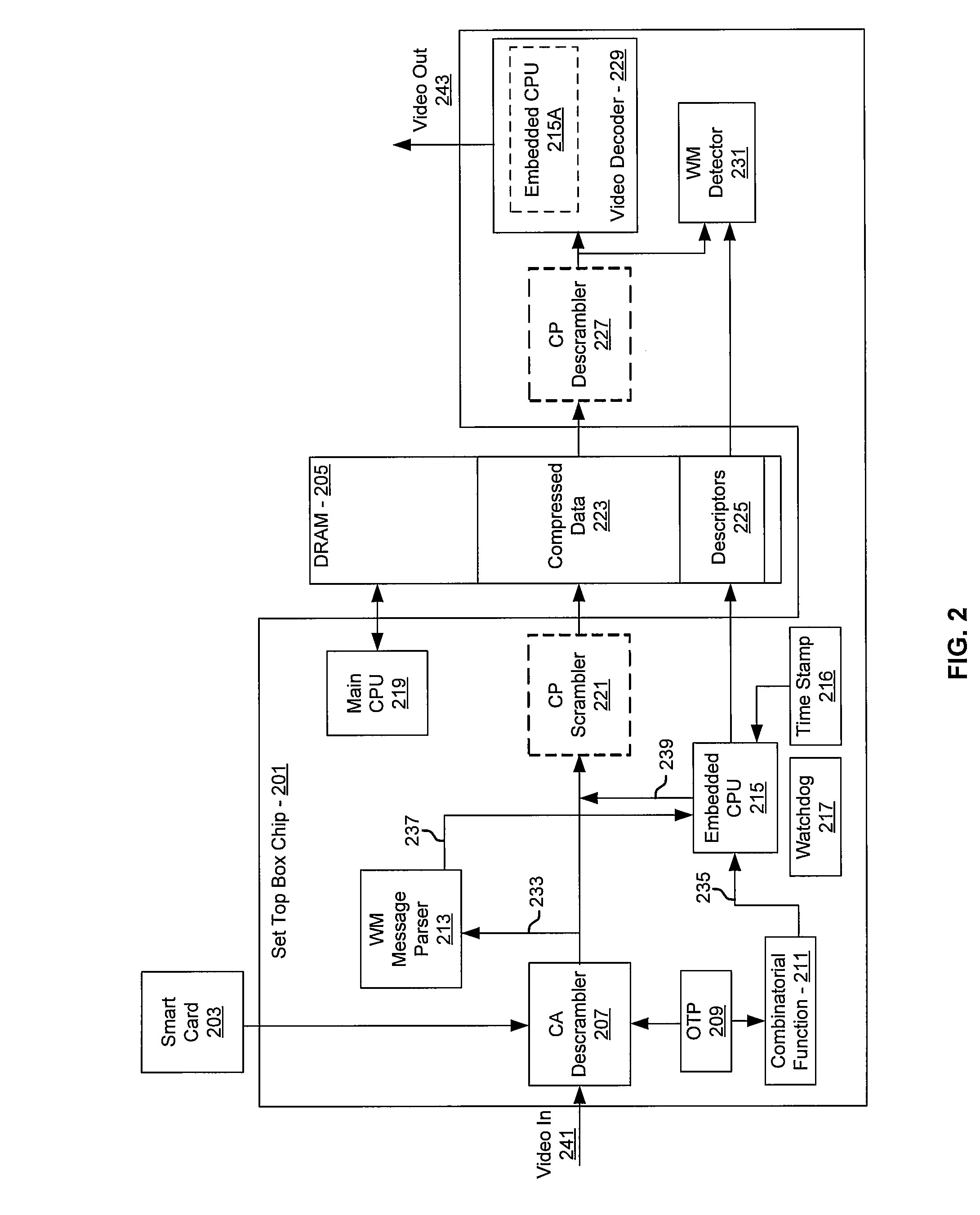

Method and system for robust watermark insertion and extraction for digital set-top boxes

ActiveUS20090150676A1Television system detailsBroadcast systems characterised by watermarksFunctional encryptionUnique identifier

Methods and systems for robust watermark insertion and extraction for digital set-top boxes are disclosed and may include descrambling, detecting watermarking messages in a received video signal utilizing a watermark message parser, and immediately watermarking the descrambled video signal utilizing an embedded CPU. The embedded CPU may utilize code that may be signed by an authorized key, encrypted externally to the chip, decrypted, and stored in memory in a region off-limits to other processors. The video signal may be watermarked in a decompressed domain. The enabling of the watermarking may be verified utilizing a watchdog timer. The descriptors corresponding to the watermarking may be stored in memory that may be inaccessible by the main CPU. The watermark may comprise unique identifier data specific to the chip and a time stamp, and may be encrypted utilizing an on-chip combinatorial function.

Owner:AVAGO TECH INT SALES PTE LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com