Method for realizing microprogrammed control unit (MCU) verification platform based on verification methodology of verification methodology manual (VMM)

A verification methodology and verification platform technology, applied in the field of verification and testing of 8-bit MCUs, can solve problems such as low efficiency, lack of quantitative indicators, and inability to guarantee verification quality, and save verification time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

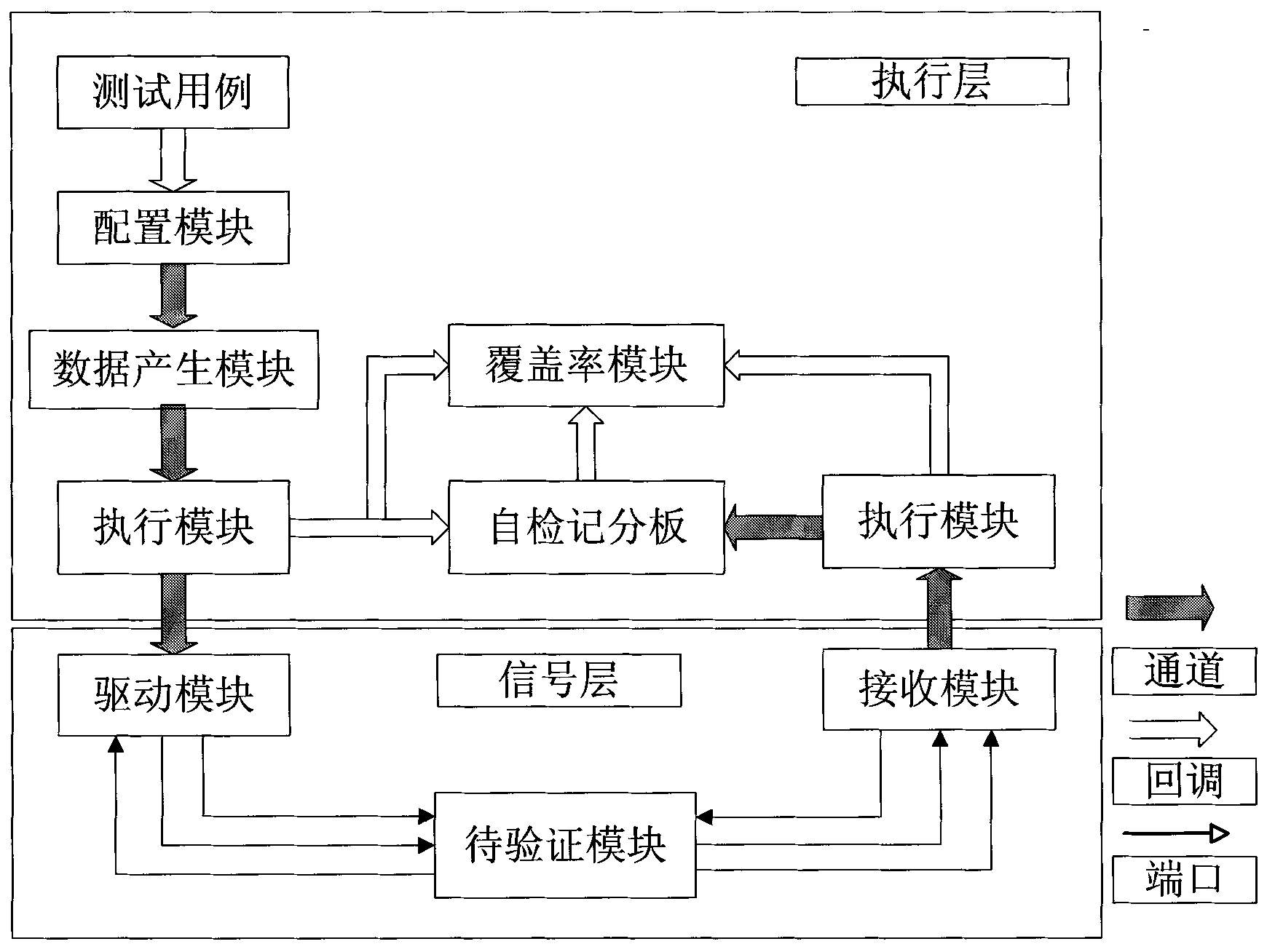

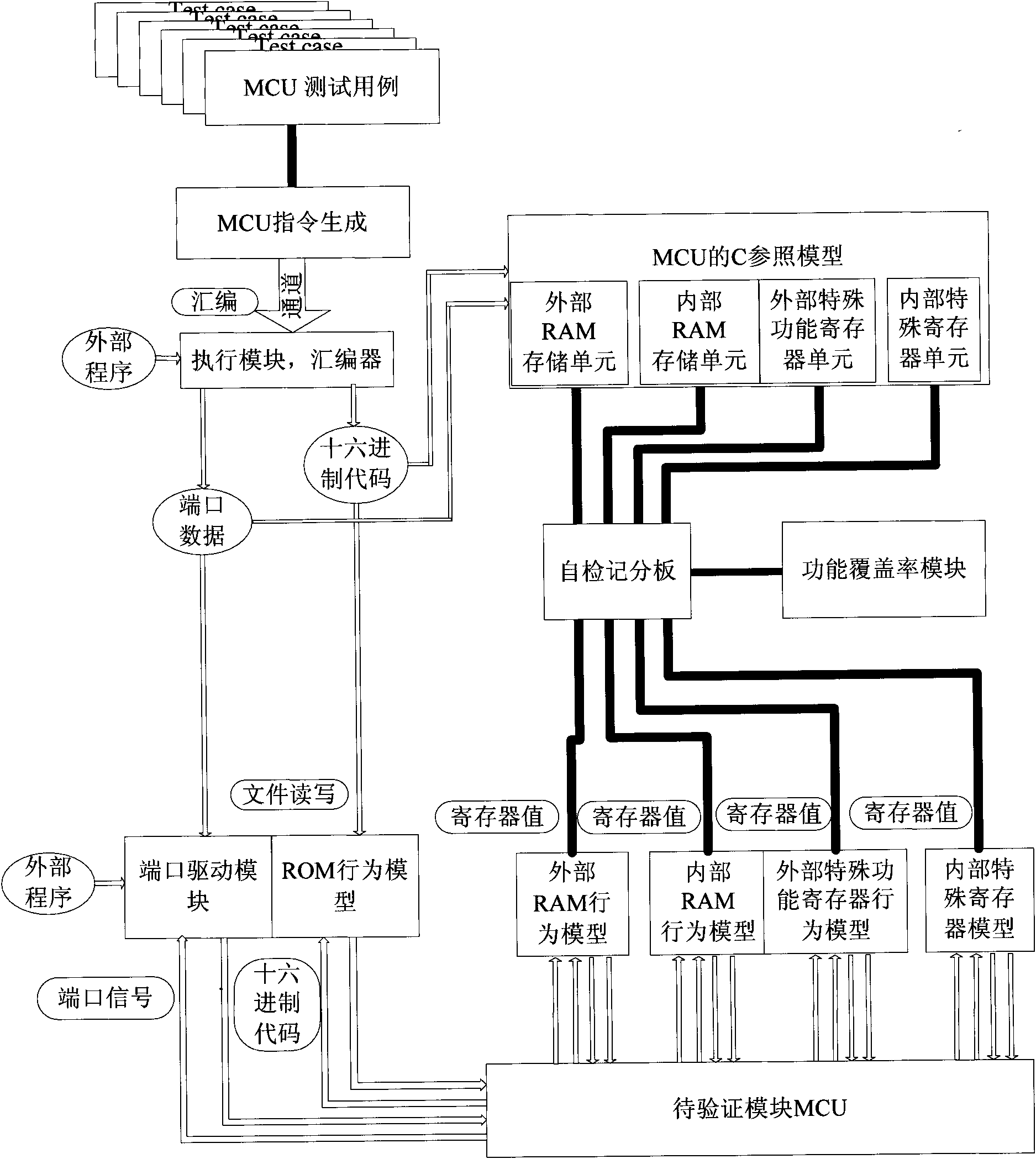

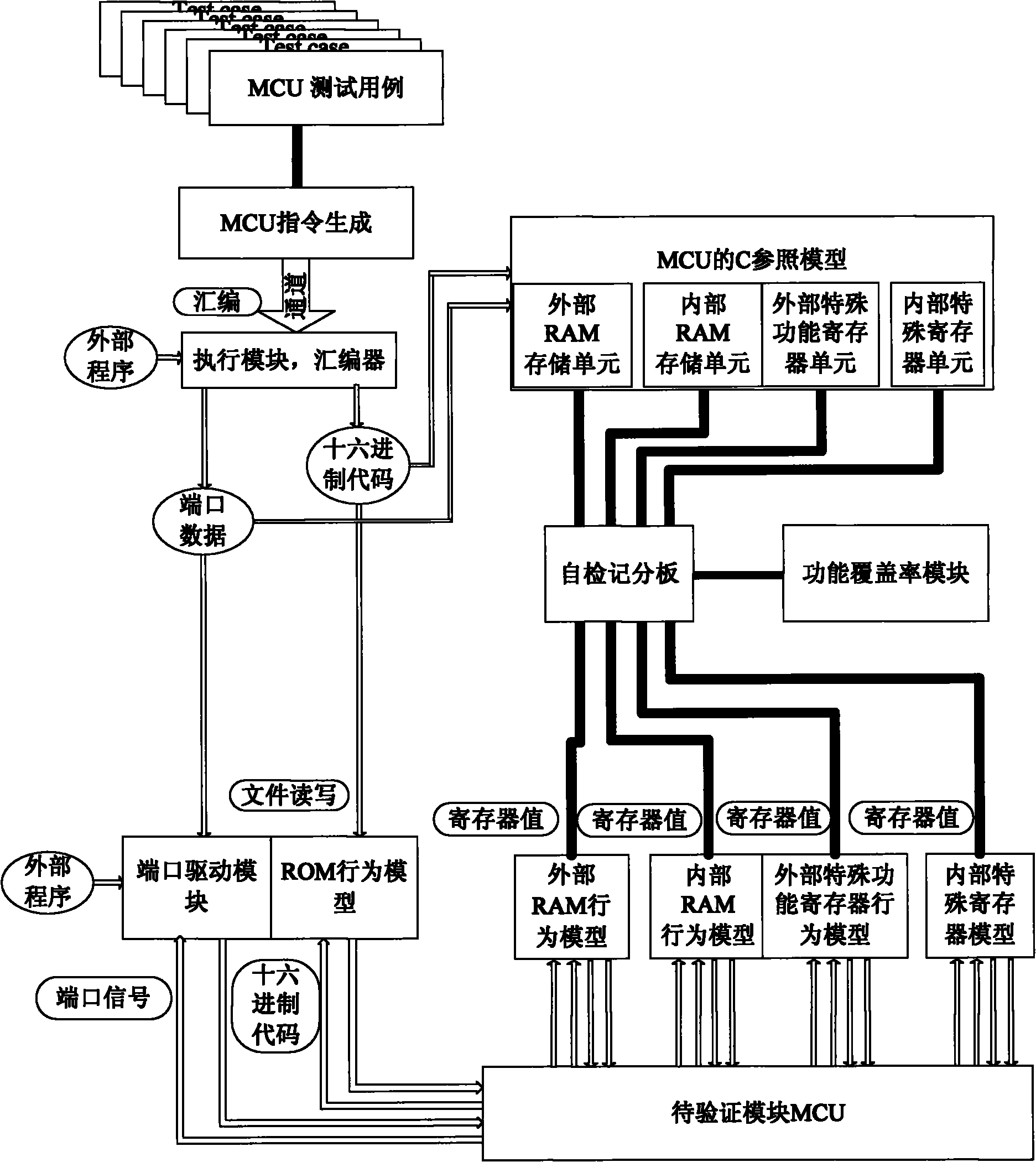

[0018] As SystemVerilog has become the P1800 specification of IEEE (Institute of Electrical and Electronics Engineers), more and more projects have begun to adopt SystemVerilog-based verification methodology to obtain more reuse scalability, more comprehensive functional coverage, and more reasonable Hierarchical verification structure.

[0019] As the complexity of the design continues to increase, more resources need to be devoted to verification. Not only is verification required to cover all functions, but also a large number of exceptions can be given to check the corresponding exception processing status of the module to be verified. Under traditional testing methods, the above requirements are often difficult to achieve. In addition, the design is constantly reused, and the verification also hopes to reuse similar verification modules, which leads to a hierarchical verification method. The VMM verification methodology provides a verification method based on SystemVeril...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com