Microcomputer

A technology of microcomputer and register, which is applied in computing, general-purpose stored program computer, program control design, etc., and can solve the problems of long time consumption and increasing ROM

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

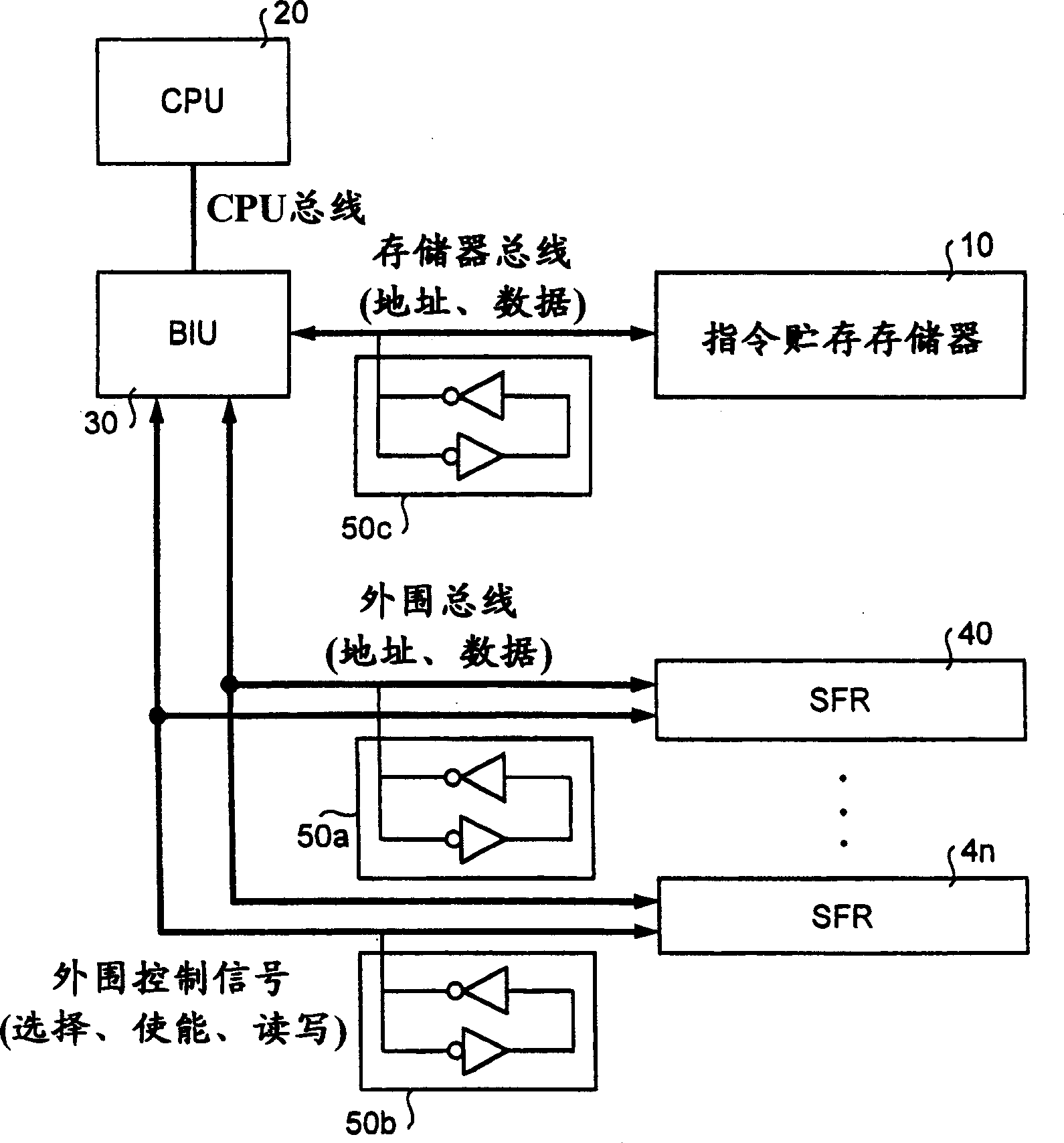

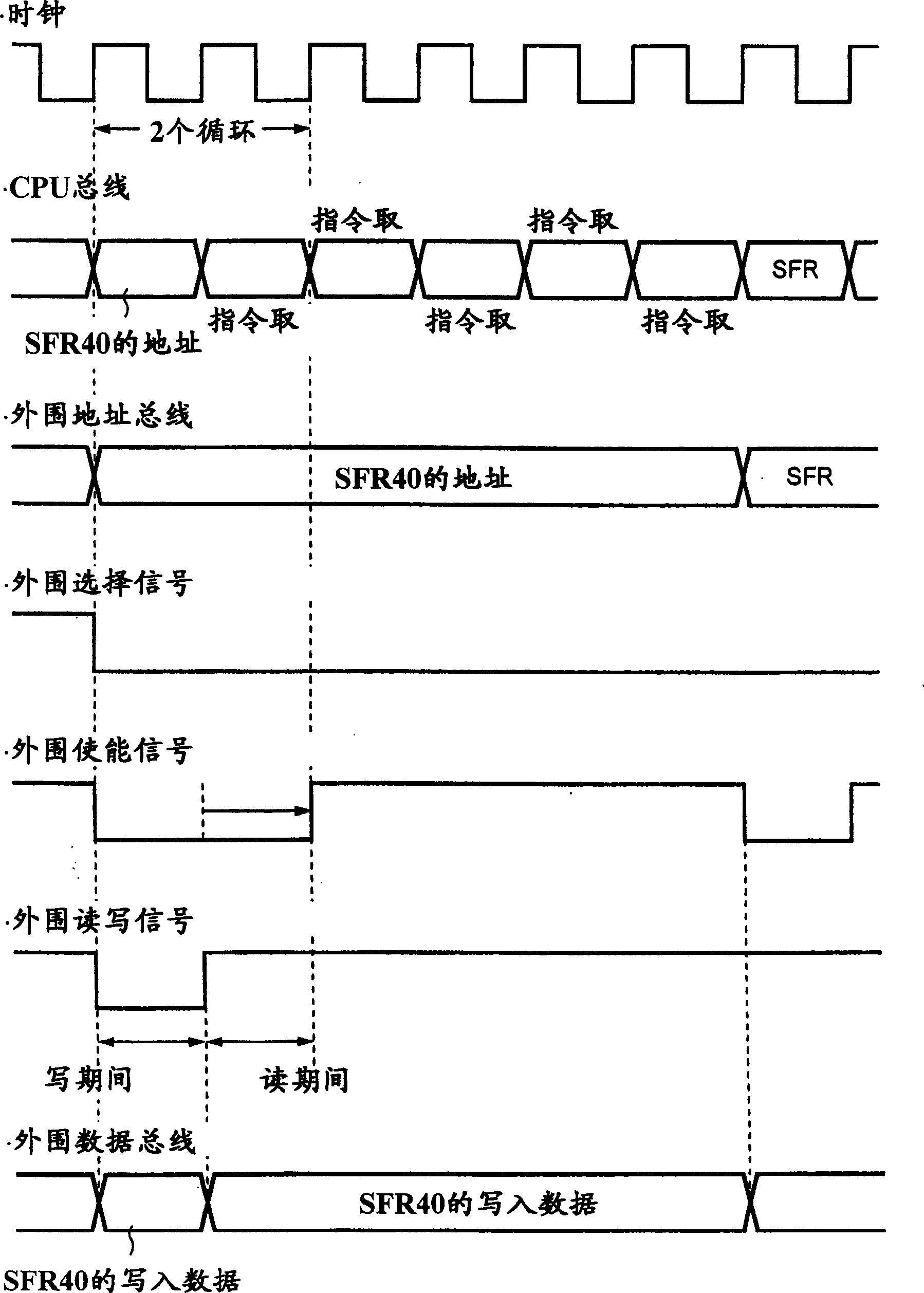

[0026] Figure 1 ~ Figure 2 The embodiment 1 of the present invention will be described. figure 1 It is a block diagram showing the structure of a microcomputer according to the first embodiment of the present invention. The microcomputer of the first embodiment includes an instruction storage memory 10, a CPU 20, a BIU 30, a plurality of peripheral modules (n in this case), operation mode setting registers SFR40-4n of these peripheral modules, and latch circuits 50a-c.

[0027] The instruction storage memory 10 is composed of ROM and RAM, and stores programs executed by the CPU 20, that is, instructions executed by the CPU 20.

[0028] SFR40 to 4n are operation mode setting registers of peripheral modules such as timers, A / D converters, and D / A converters. SFR40~4n are allocated to specific address space.

[0029] The CPU 20 reads the instructions of the instruction storage memory 10 via the BIU 30, and executes arithmetic processing and the like based on the instructions. In ad...

Embodiment 2

[0039] image 3 Example 2 of the present invention will be described. image 3 It is a block diagram showing the structure of a microcomputer according to the second embodiment of the present invention. In the microcomputer of the second embodiment, figure 1 A test register 60, a latch circuit 50d, and a comparator 70 are added to the illustrated microcomputer. Components having the same functions as those of the first embodiment are given the same reference numerals, and redundant descriptions are omitted.

[0040]The test register 60 is connected to the BIU 30 through a dedicated data bus, and writes the same data and the data written when one of the SFRs 40 to 4n is written. That is, when the CPU 20 writes data to the SFRs 40 to 4n via the BIU 30, it outputs the same data to the peripheral data bus and the dedicated data bus, and the test register 60 writes data on the dedicated data bus.

[0041] The latch circuit 50d is connected to the dedicated data bus and holds the data...

Embodiment 3

[0049] Figure 4 Example 3 of the present invention will be described. In the second embodiment, by comparing the data of the operation mode setting register read from the peripheral data bus with the data of the test register read from the dedicated data bus, the confirmation of the data written in the operation mode setting register is performed. However, a dedicated data bus for writing data to the test register 60 becomes necessary, resulting in an increase in wiring.

[0050] In the third embodiment, in order to improve such a problem, the peripheral bus connected to the operation mode setting register is connected to the test register, and the data written in the operation mode setting register is confirmed.

[0051] Figure 4 It is a block diagram showing the structure of a microcomputer according to the third embodiment of the present invention. In the microcomputer in the third embodiment, the test register 60 is connected to the peripheral bus, and the outputs of the S...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap