Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

185 results about "Cmos compatible" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

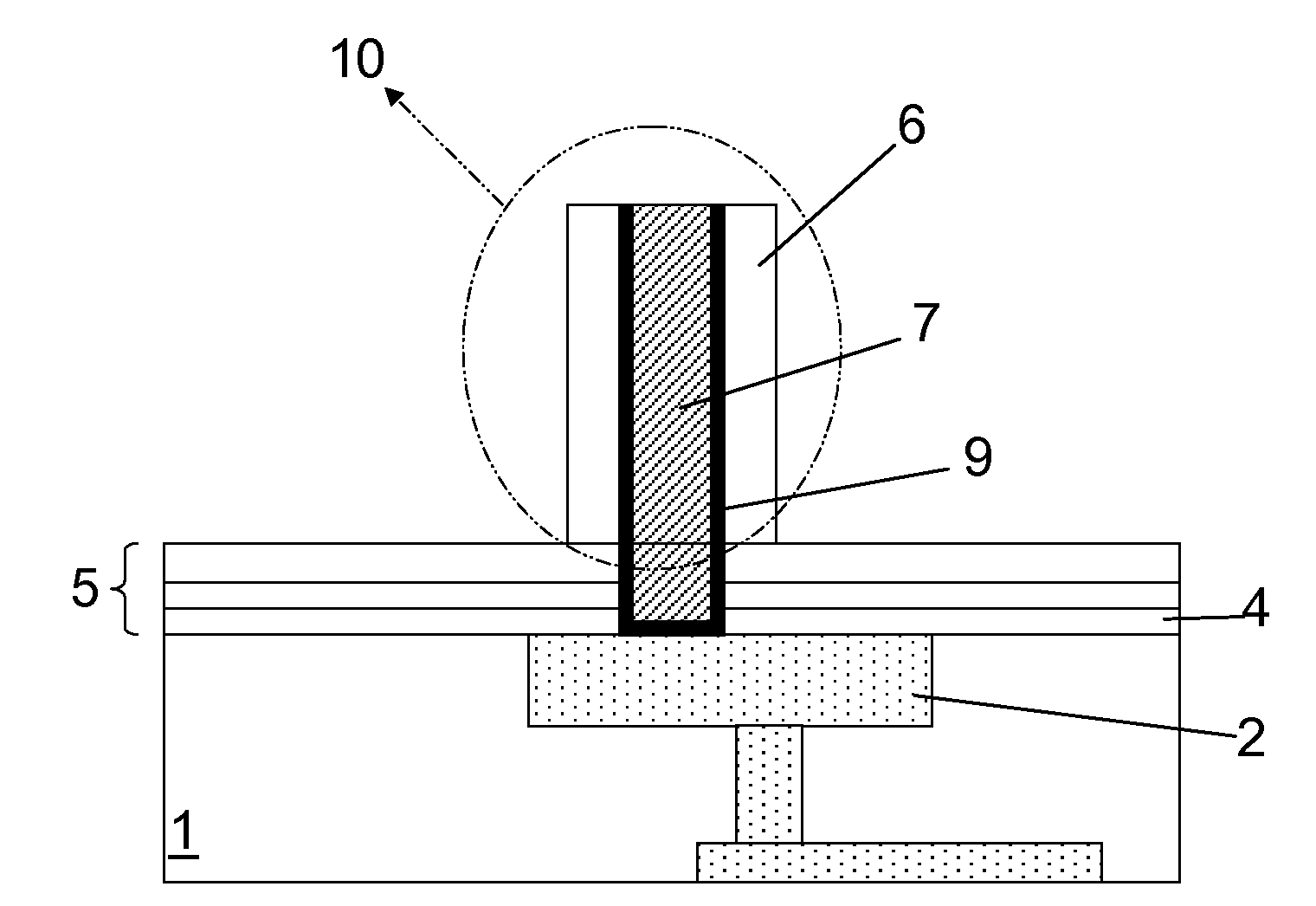

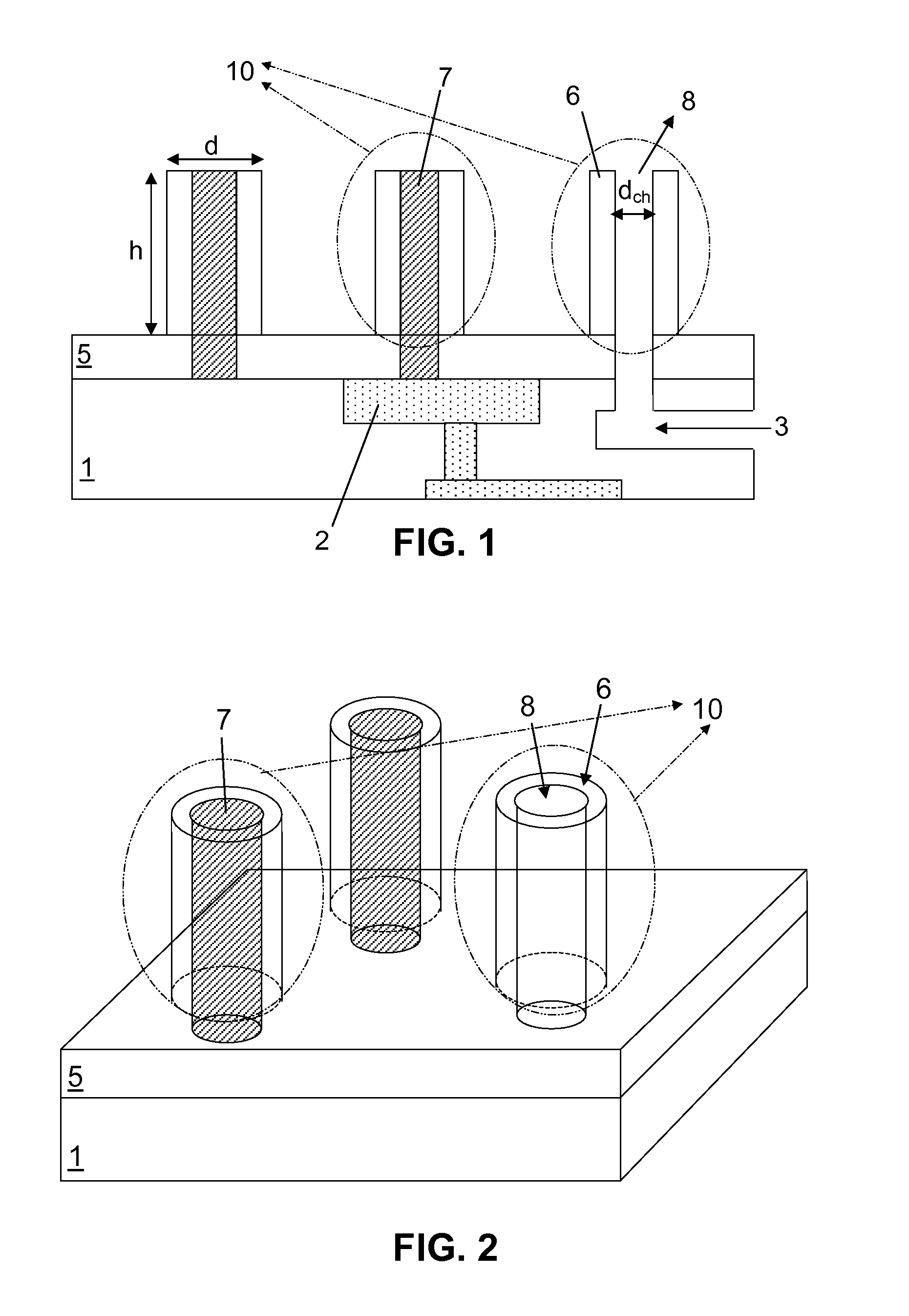

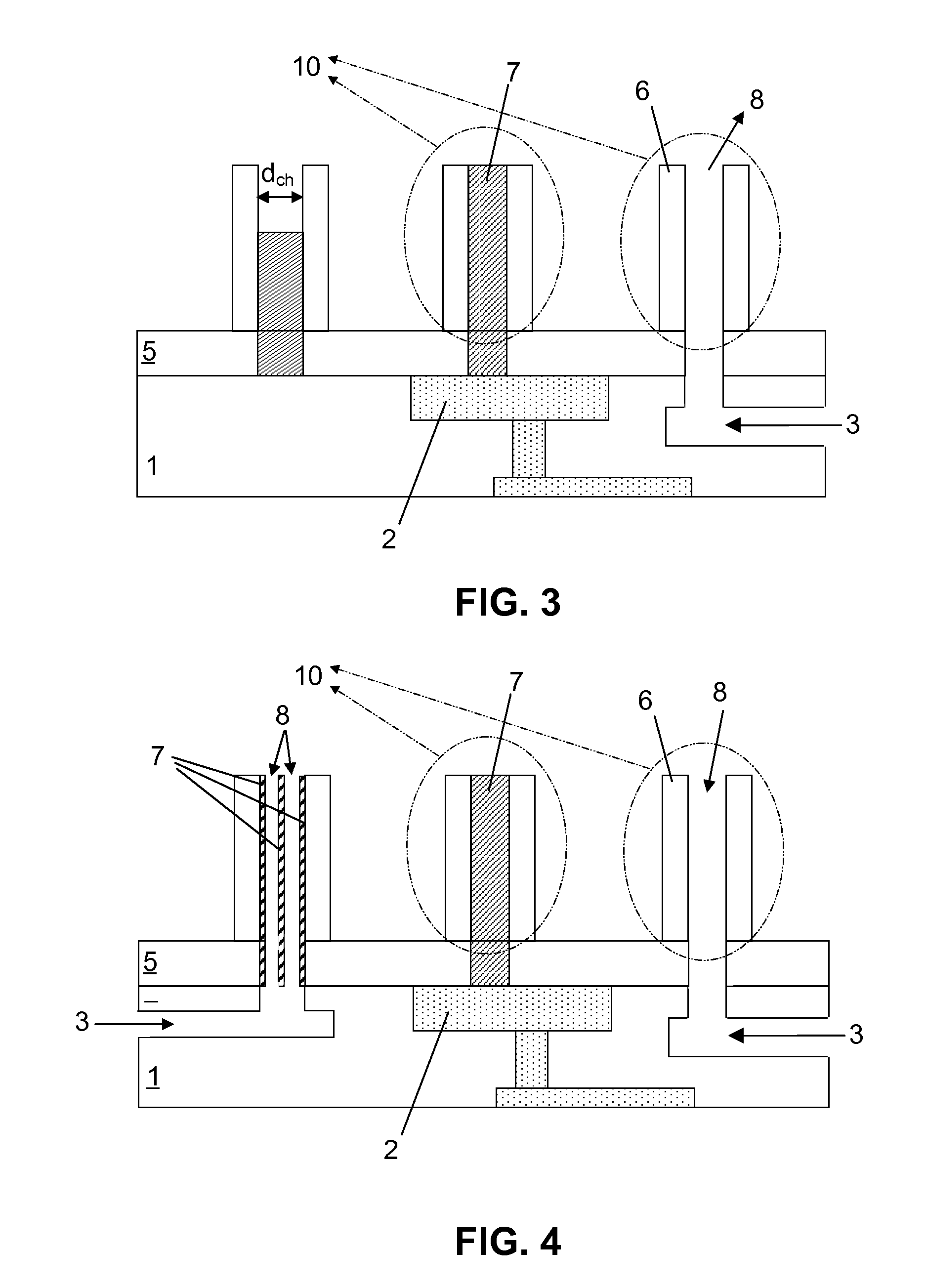

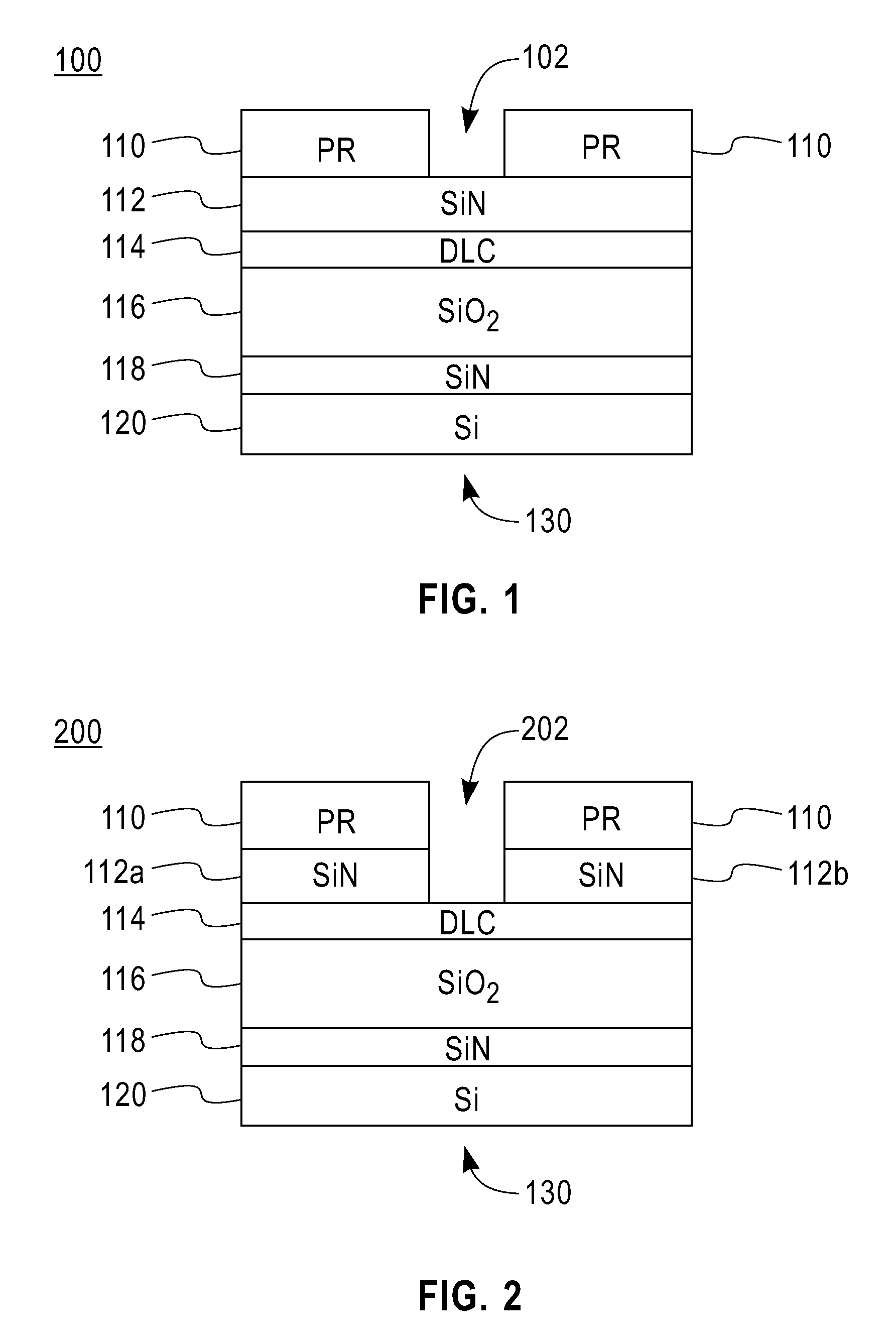

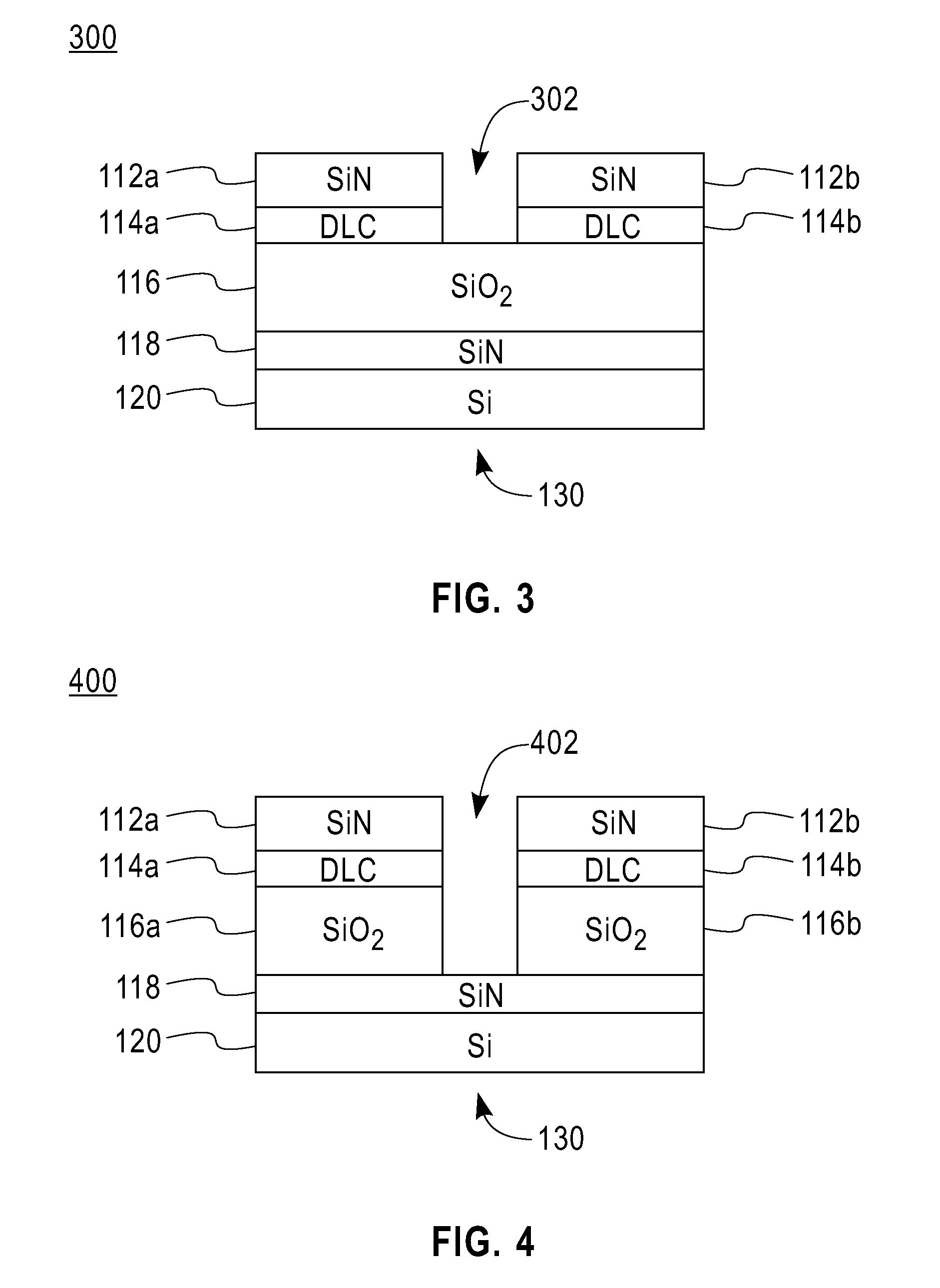

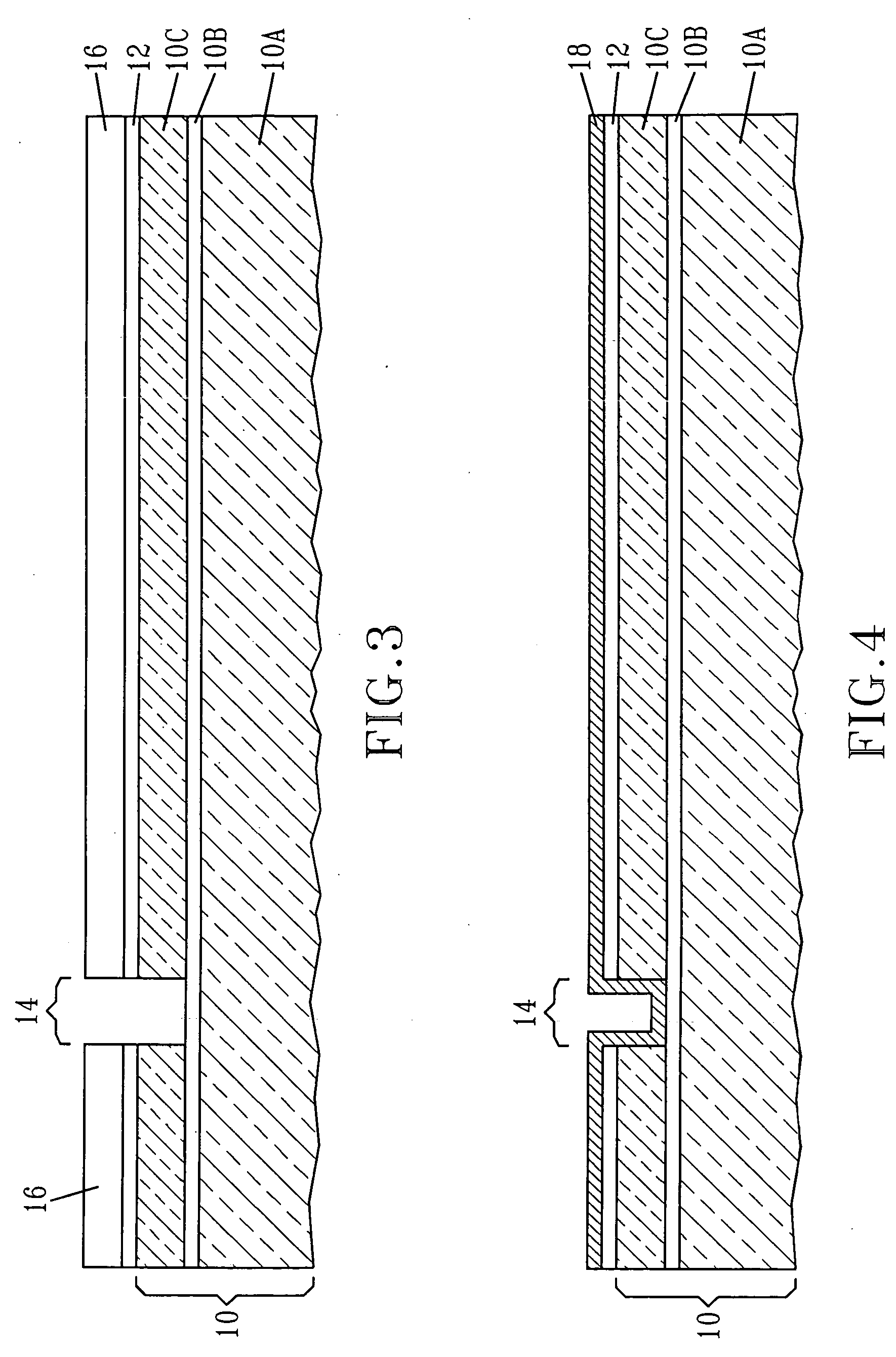

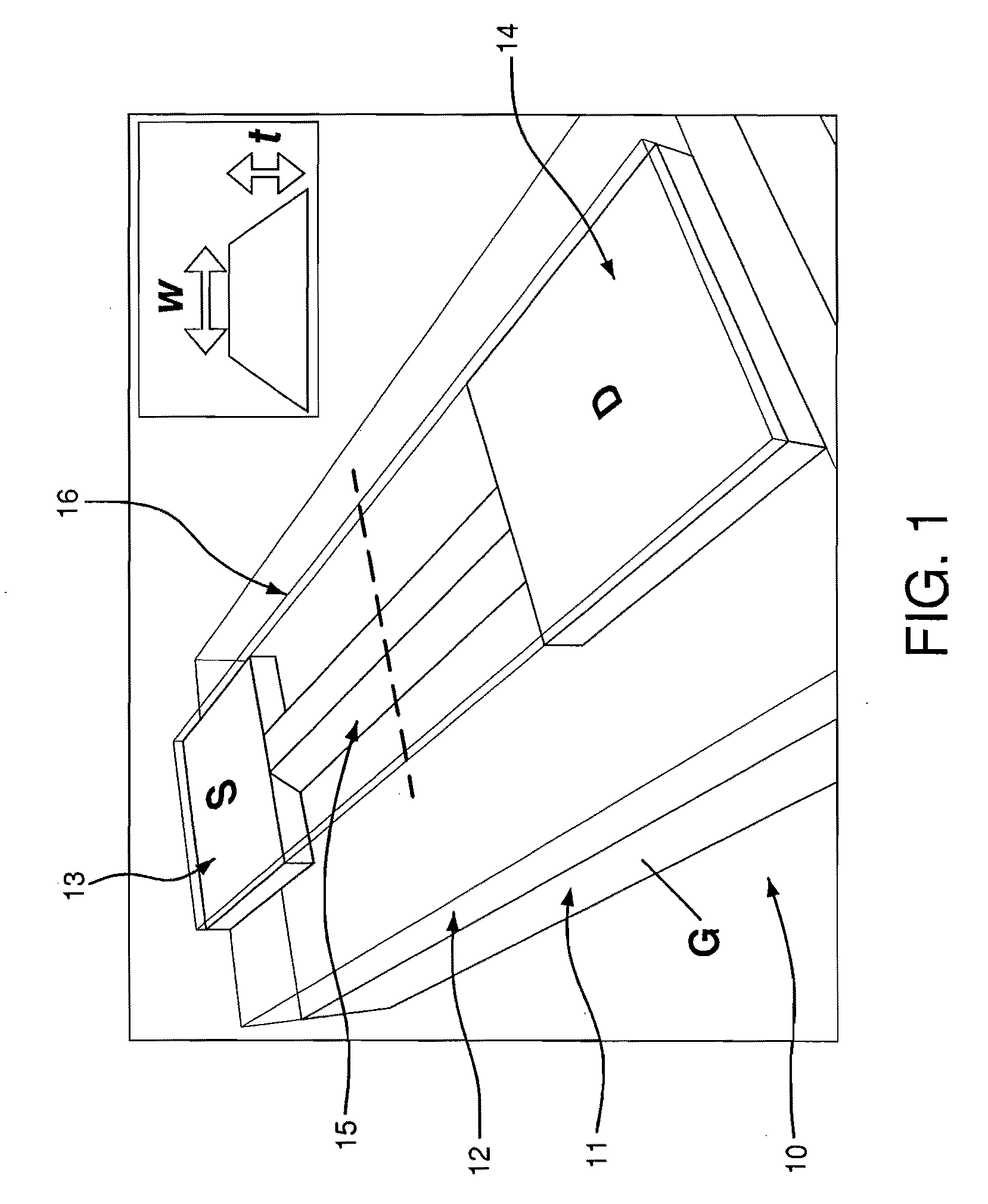

Low temperature bi-CMOS compatible process for MEMS RF resonators and filters

InactiveUS20090108381A1Impedence networksSemiconductor/solid-state device detailsMetal interconnectOxygen plasma

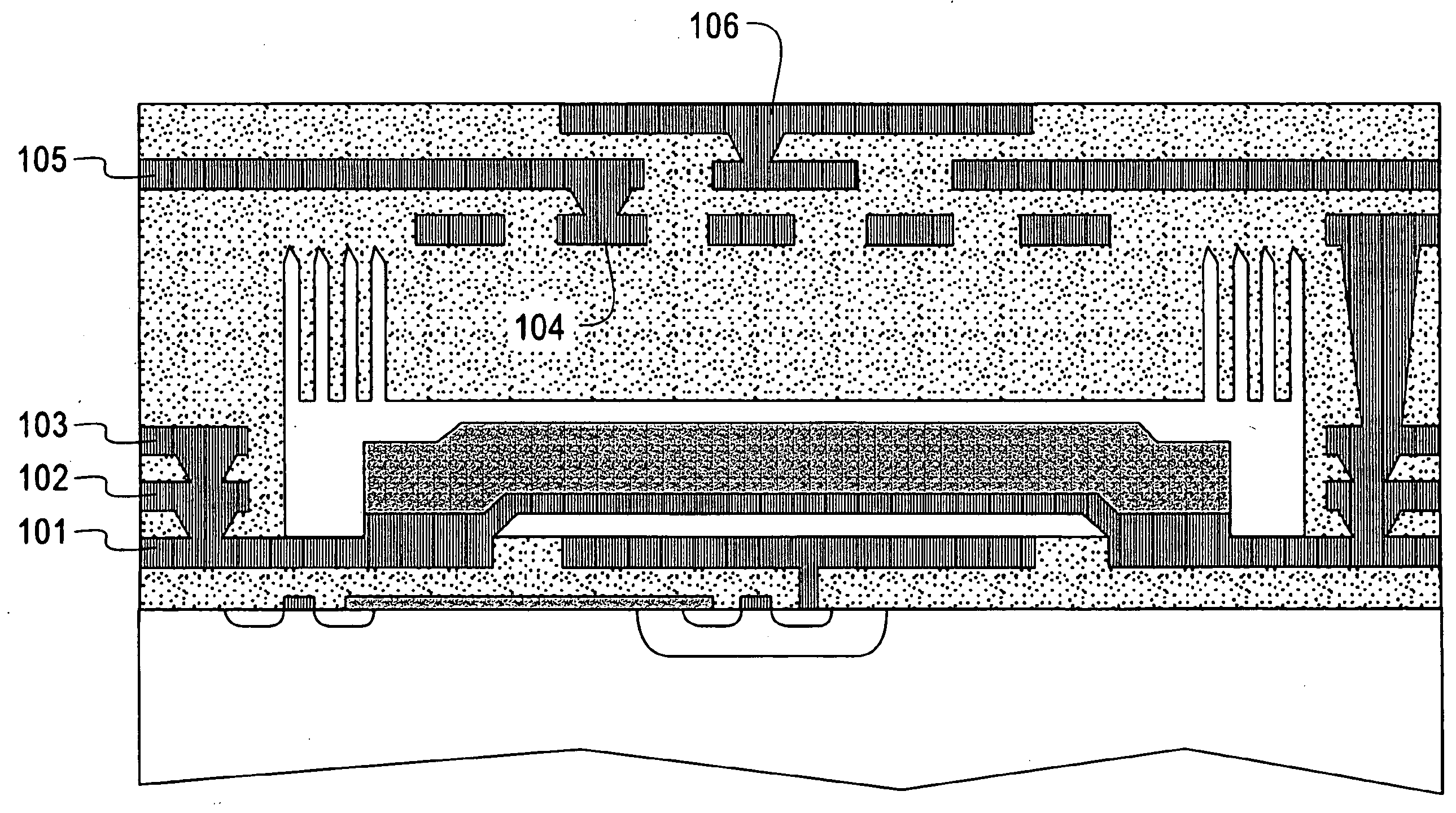

A method of formation of a microelectromechanical system (MEMS) resonator or filter which is compatible with integration with any analog, digital, or mixed-signal integrated circuit (IC) process, after or concurrently with the formation of the metal interconnect layers in those processes, by virtue of its materials of composition, processing steps, and temperature of fabrication is presented. The MEMS resonator or filter incorporates a lower metal level, which forms the electrodes of the MEMS resonator or filter, that may be shared with any or none of the existing metal interconnect levels on the IC. It further incorporates a resonating member that is comprised of at least one metal layer for electrical connection and electrostatic actuation, and at least one dielectric layer for structural purposes. The gap between the electrodes and the resonating member is created by the deposition and subsequent removal of a sacrificial layer comprised of a carbon-based material. The method of removal of the sacrificial material is by an oxygen plasma or an anneal in an oxygen containing ambient. A method of vacuum encapsulation of the MEMS resonator or filter is provided through means of a cavity containing the MEMS device, filled with additional sacrificial material, and sealed. Access vias are created through the membrane sealing the cavity; the sacrificial material is removed as stated previously, and the vias are re-sealed in a vacuum coating process.

Owner:IBM CORP

Semiconductor photonic nano communication link apparatus

InactiveUS7603016B1Eliminate needNanoopticsSemiconductor lasersElectro-absorption modulatorPhotonics

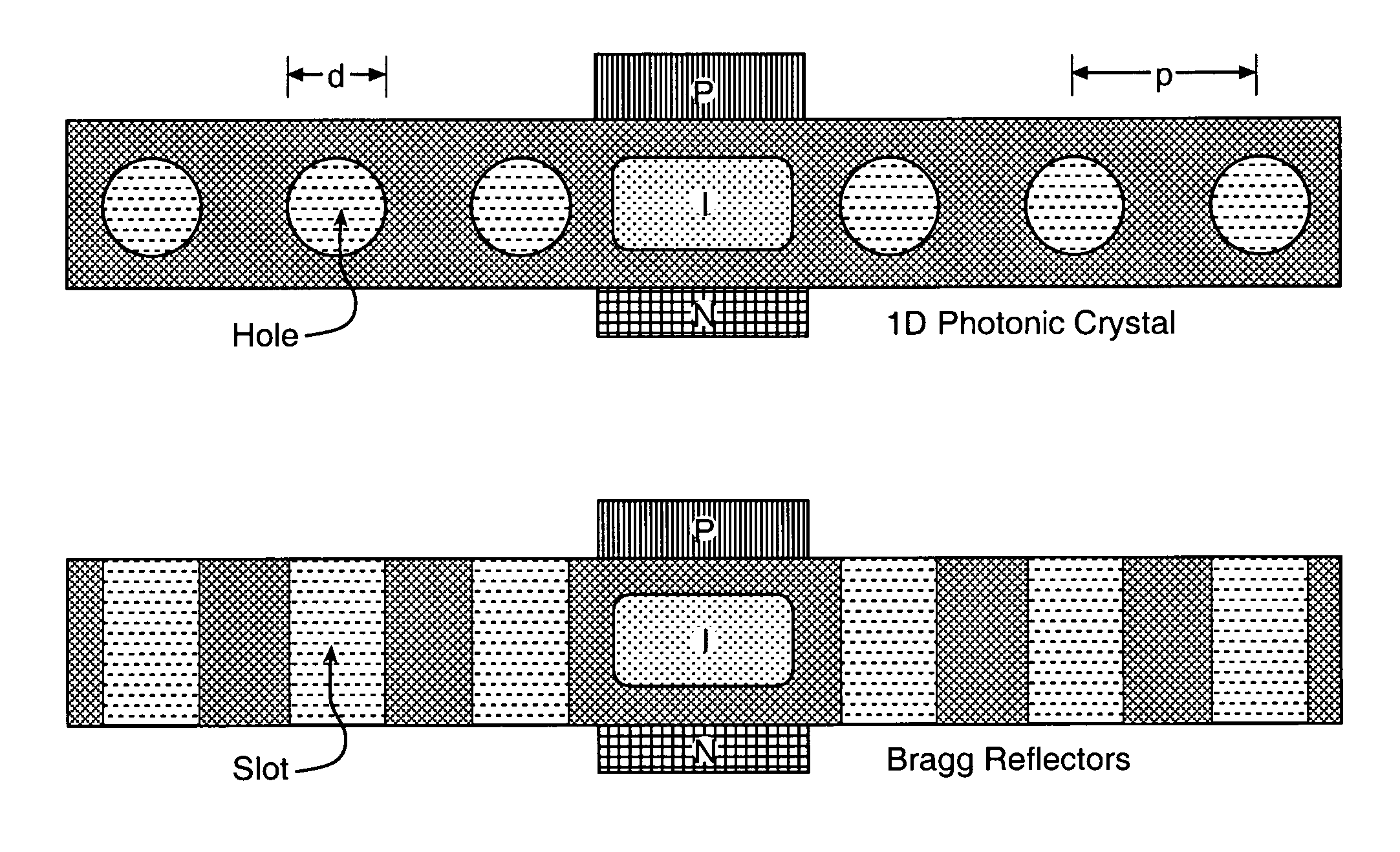

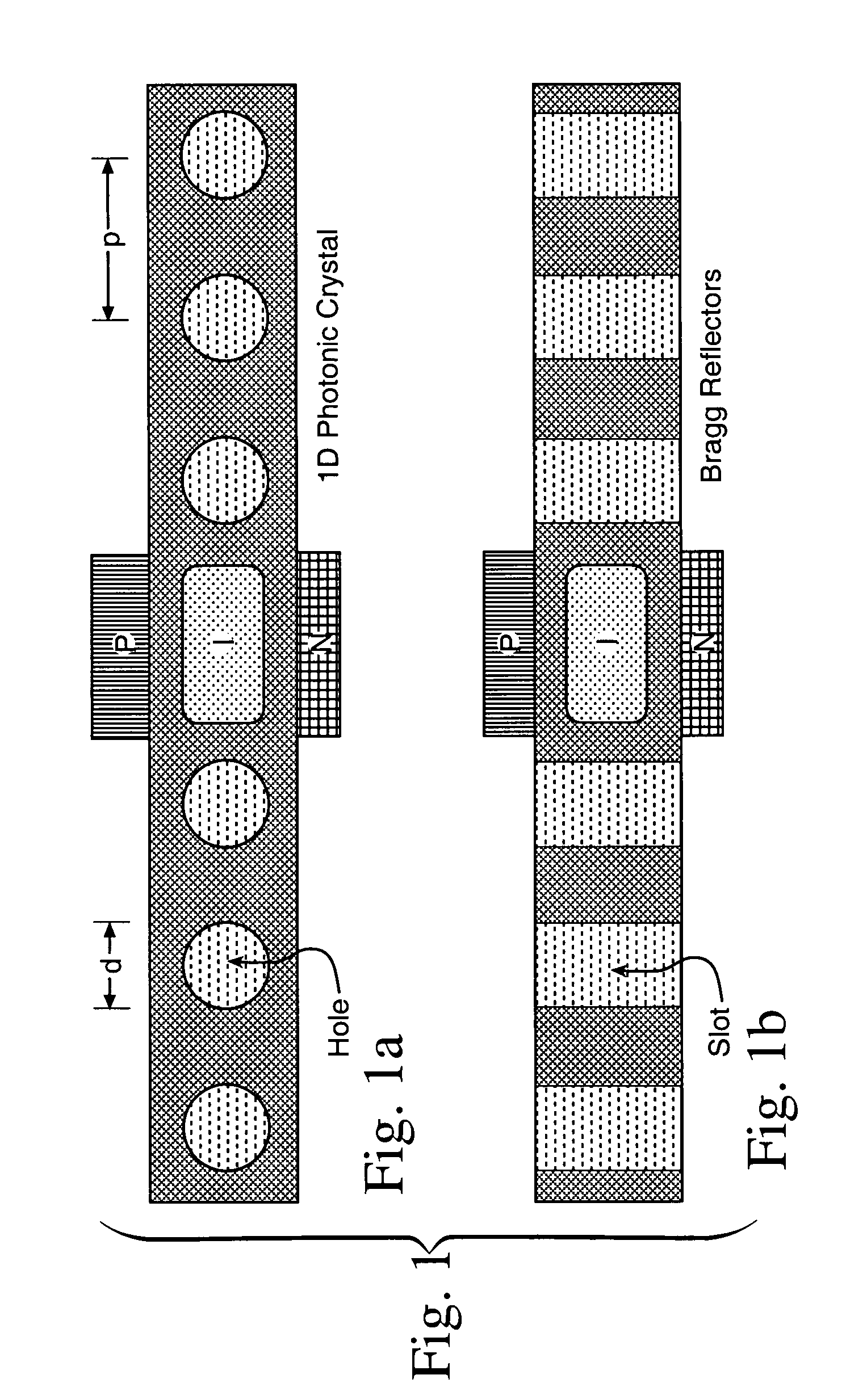

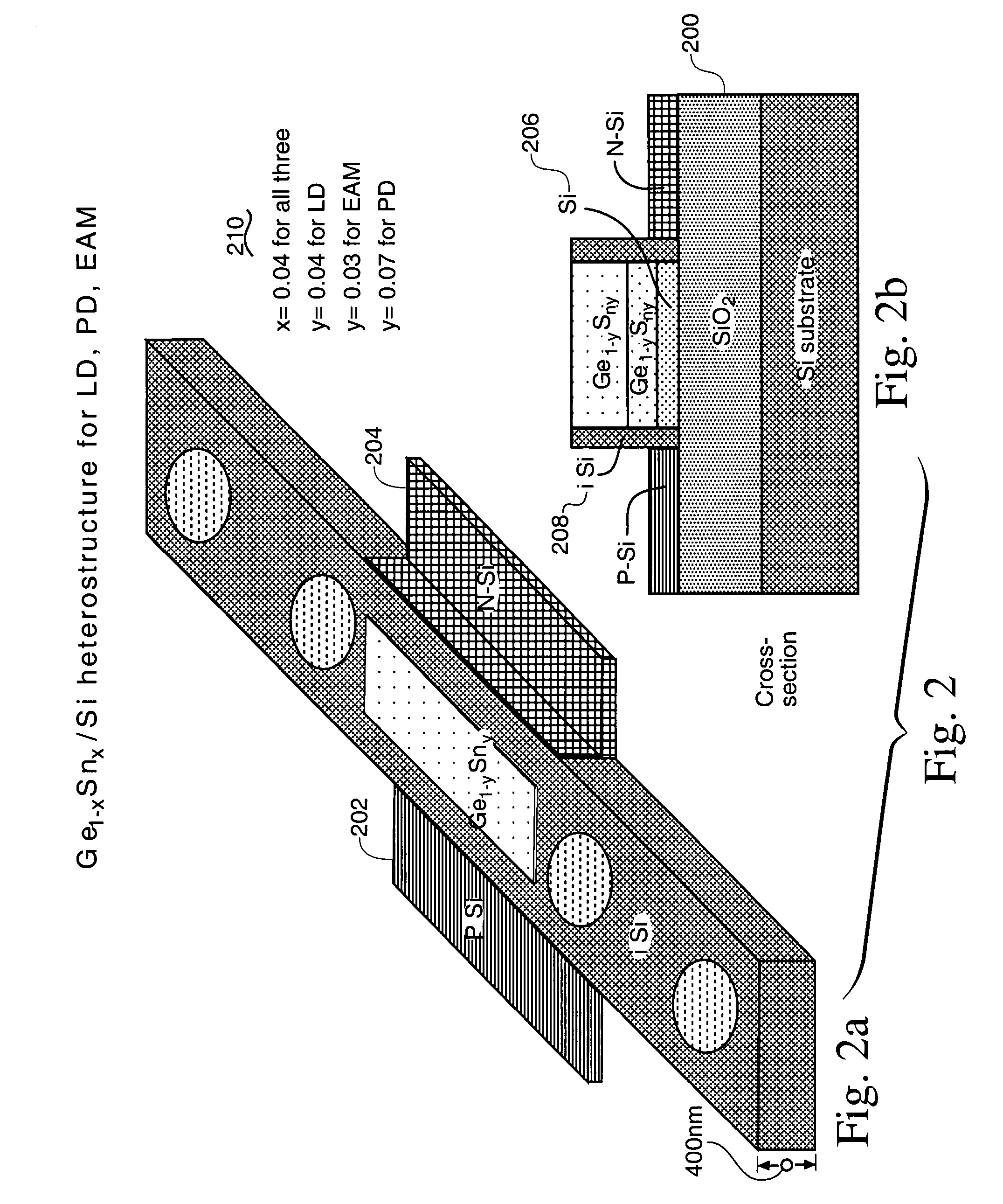

A CMOS compatible ten-gigabit-per-second region nano-waveguide included photonic communication link apparatus of low energy use per transmitted bit. An embodiment of the link includes an electrically pumped laser, an electro absorption modulator and a photodetector for the 1.5 to 2.0 micrometer infrared spectral region; omission of the separate electro absorption modulator is additionally disclosed. Each of these three nano-scale elements preferably includes active semiconductor crystal material situated in a preferably Silicon resonator within a nano-strip waveguide. The resonator is defined by dispersed resonator mirrors having tapered separation distance one dimensional photonic crystal lattice apertures of oxide holes or slots. Each of the three devices may be a semiconductor heterodiode pumped or controlled by laterally disposed wings enclosing the resonator to form a lateral PIN heterodiode for current injection or high E-field generation depending on bias and composition conditions selected.

Owner:US SEC THE AIR FORCE THE

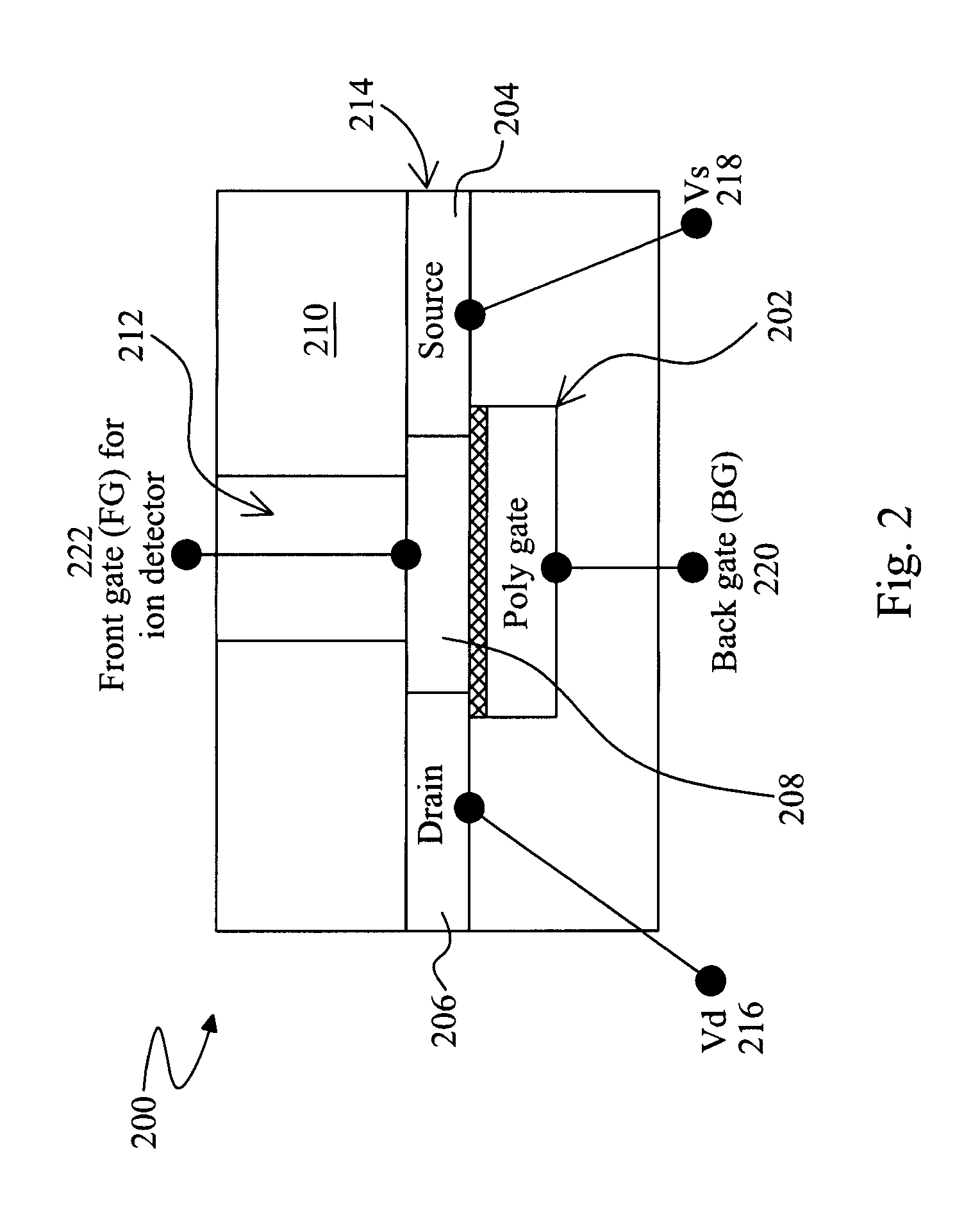

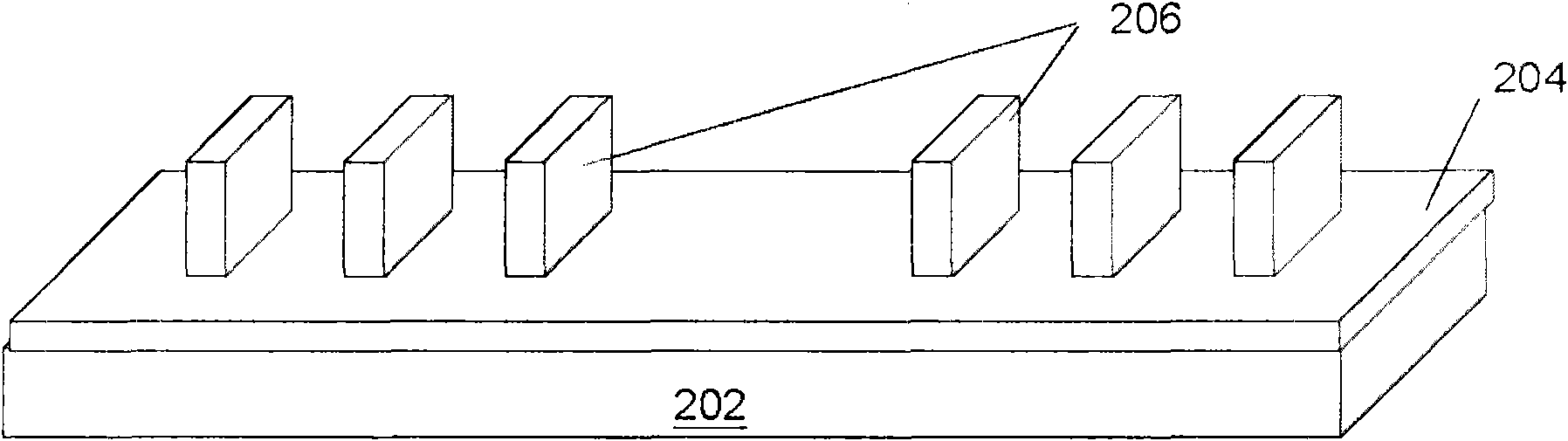

CMOS compatible biofet

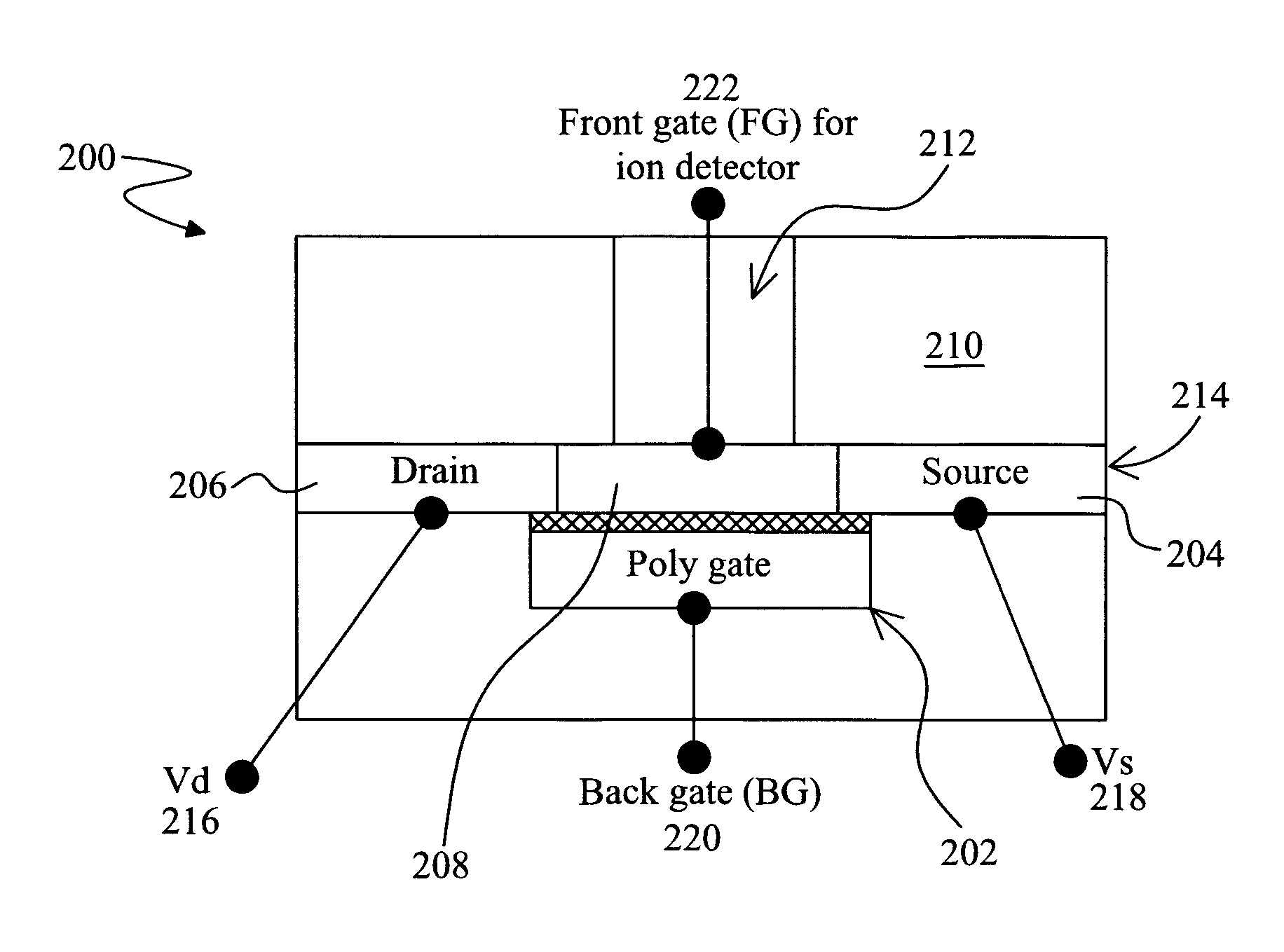

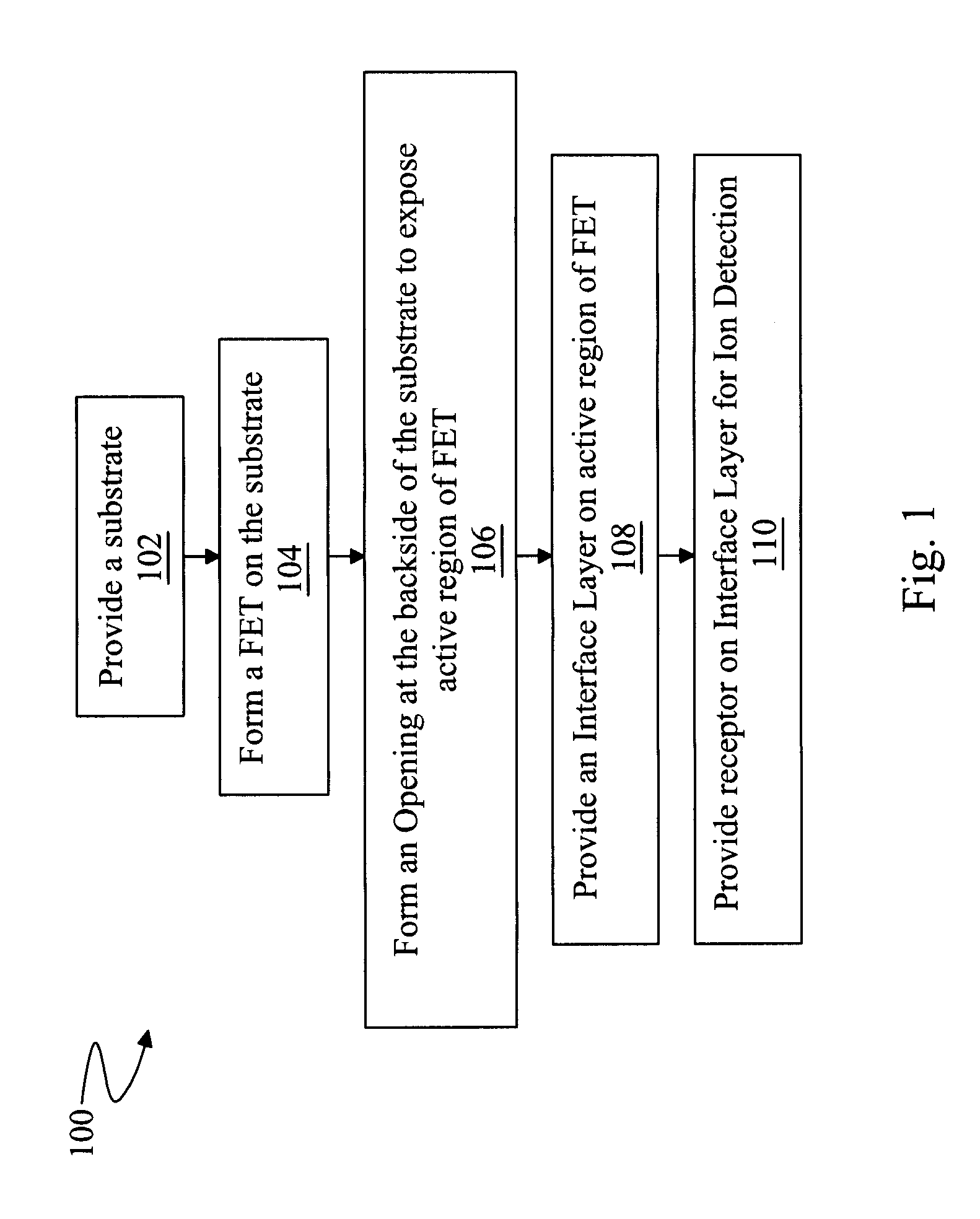

The present disclosure provides a bio-field effect transistor (BioFET) and a method of fabricating a BioFET device. The method includes forming a BioFET using one or more process steps compatible with or typical to a complementary metal-oxide-semiconductor (CMOS) process. The BioFET device may include a substrate; a gate structure disposed on a first surface of the substrate and an interface layer formed on the second surface of the substrate. The interface layer may allow for a receptor to be placed on the interface layer to detect the presence of a biomolecule or bio-entity.

Owner:TAIWAN SEMICON MFG CO LTD

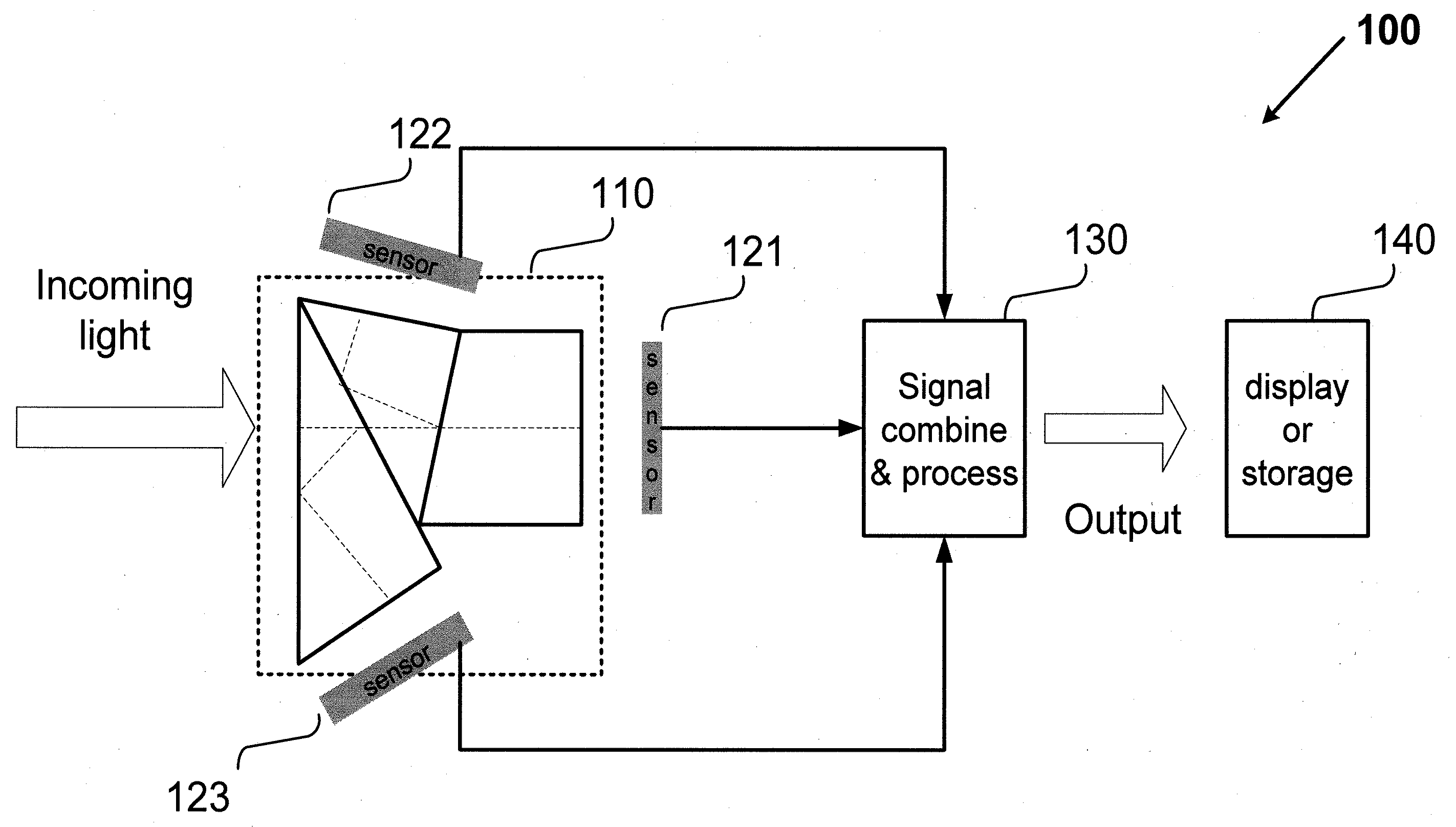

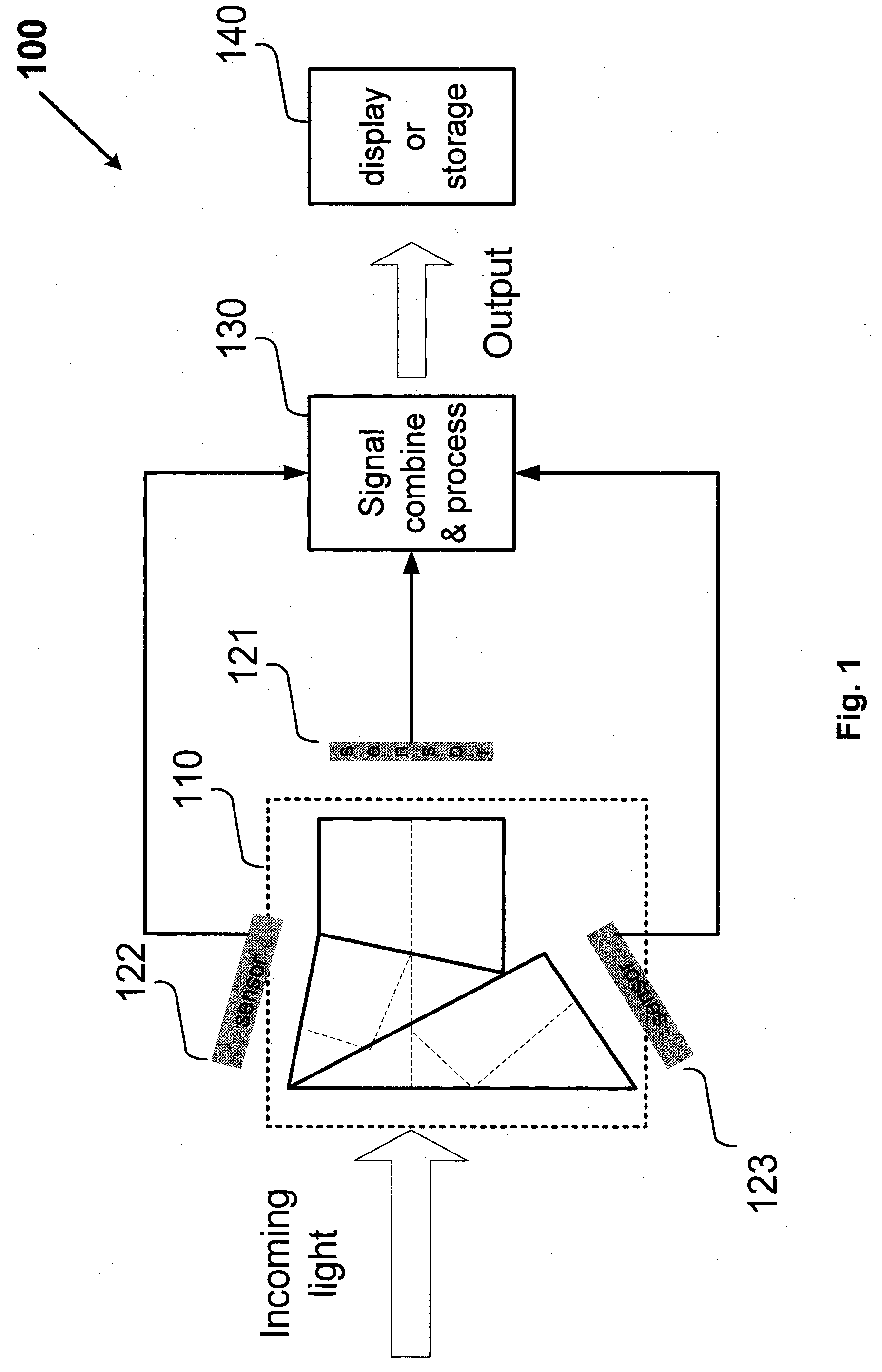

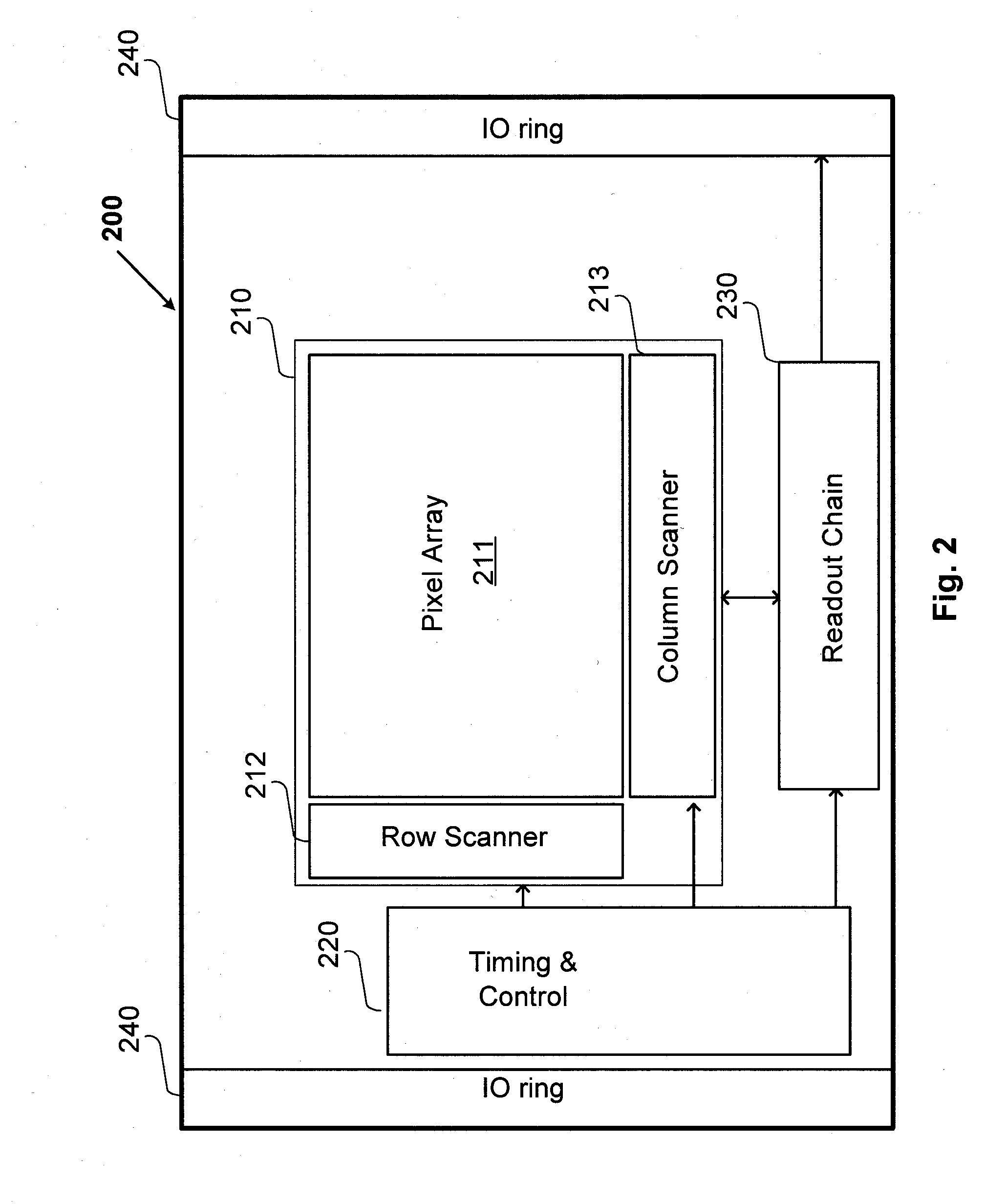

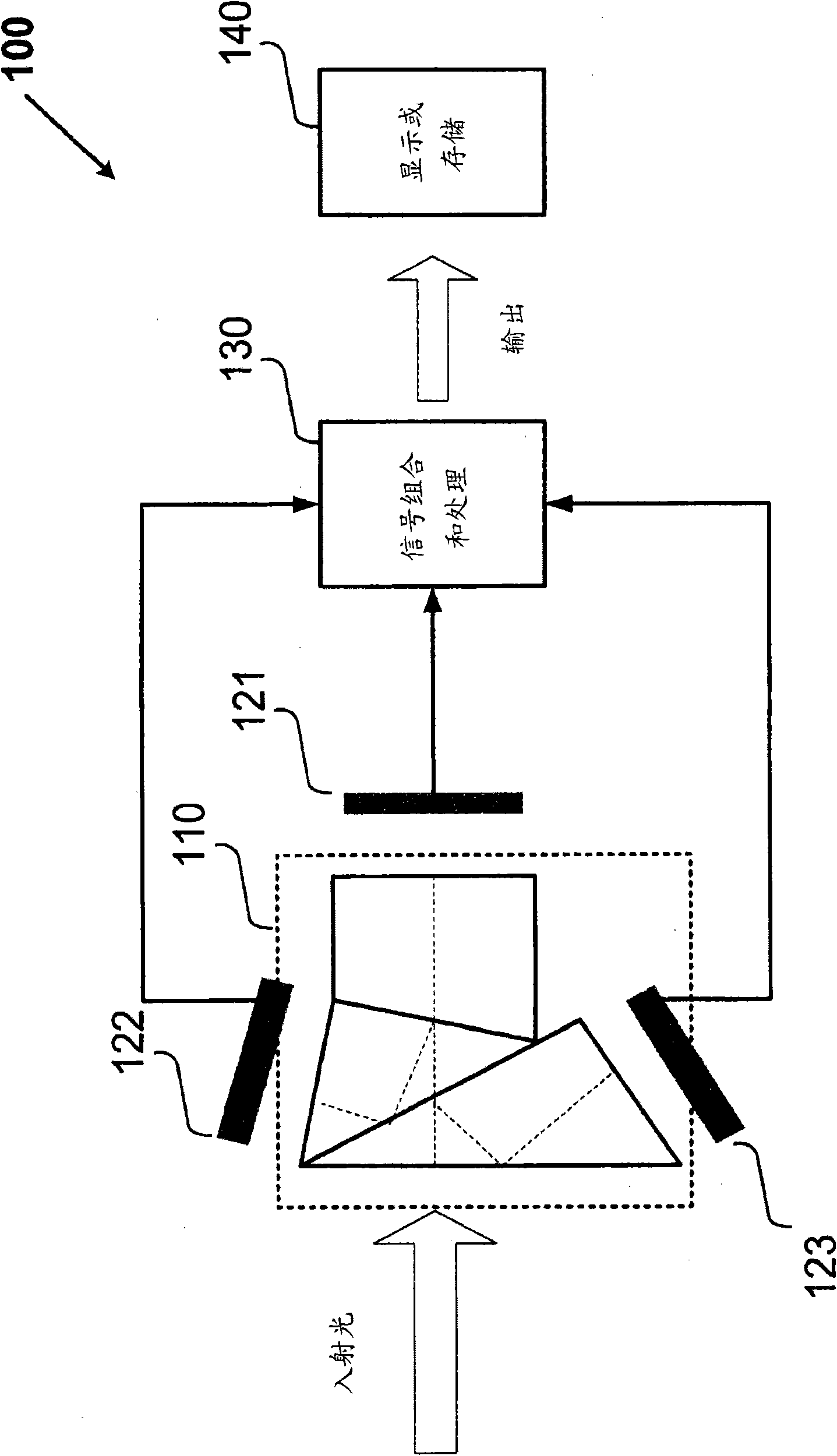

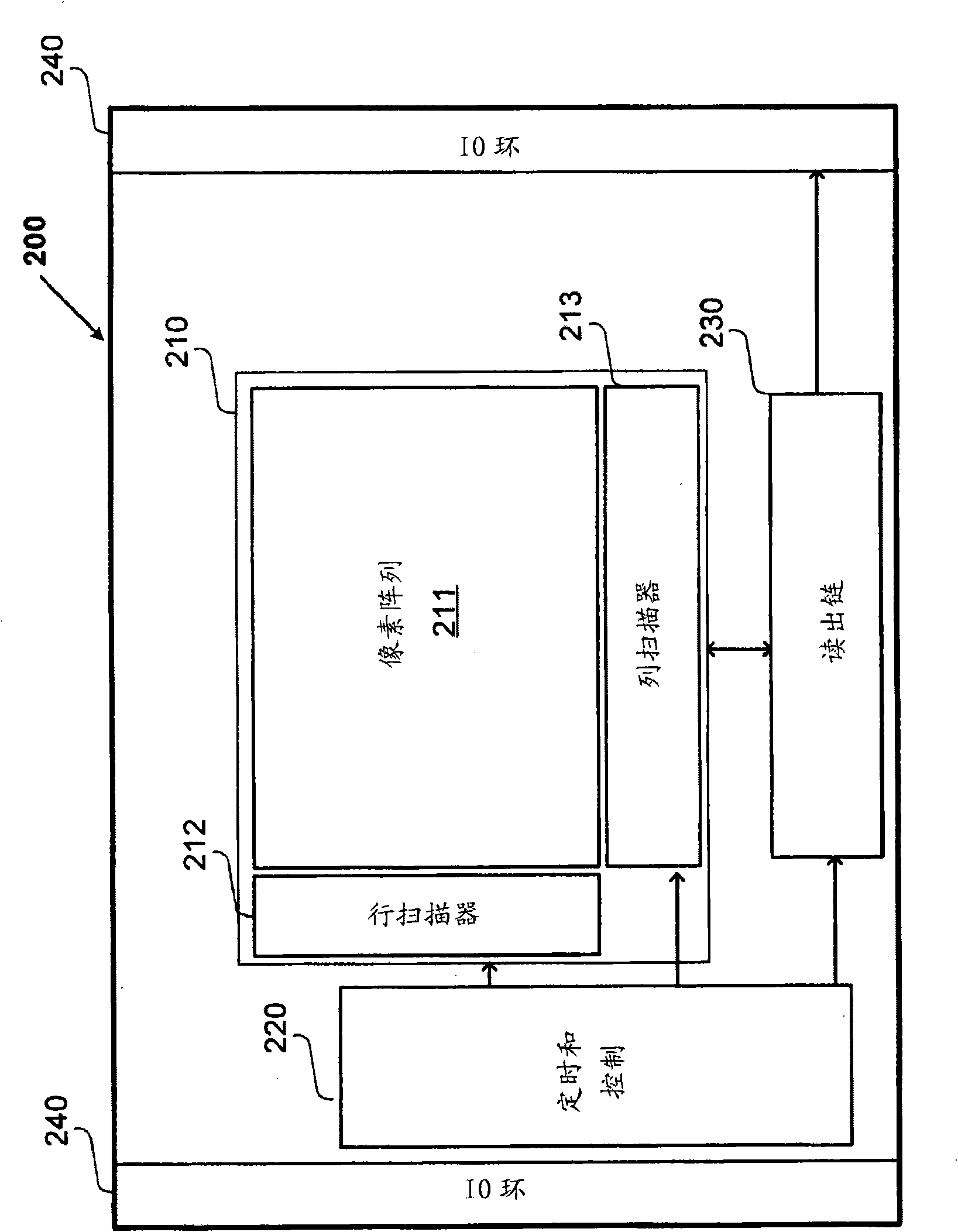

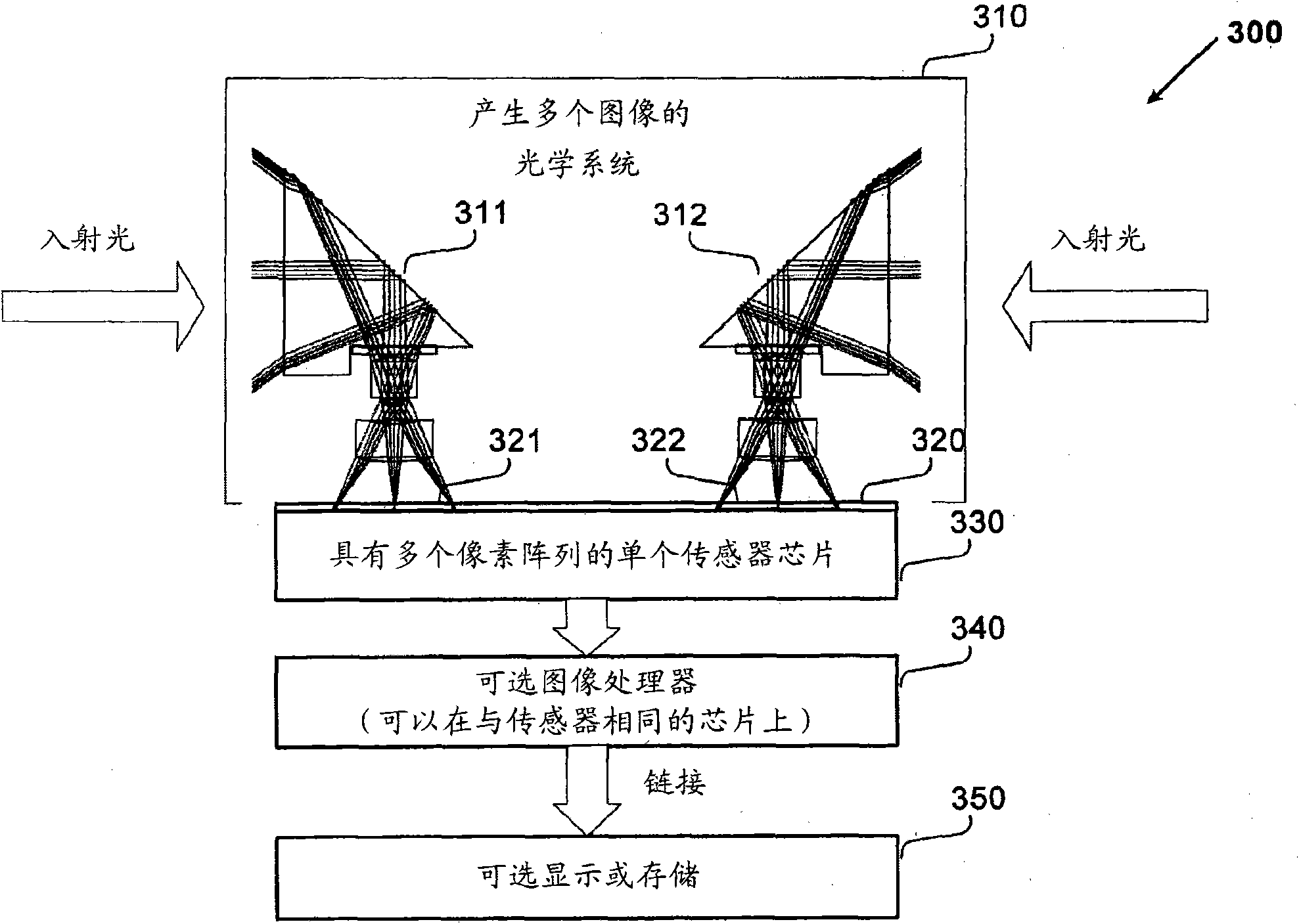

Camera system with multiple pixel arrays on a chip

ActiveUS20090135245A1Compact designEasy to makeTelevision system detailsPulse modulation television signal transmissionTelecommunications linkDigital storage

A camera system uses one or more image sensor IC chips each having multiple pixel arrays on the same semiconductor substrate (i.e., “multiple pixel arrays on a chip”). In one embodiment, such a camera system includes: (a) optical components that create multiple images in close physical proximity of each other (e.g., within a few millimeters or centimeters); and (b) a single sensor substrate (“chip”) containing multiple 2-dimensional pixel arrays that are aligned to capture these multiple images, so as to convert the multiple images into electrical signal. The pixel arrays can be manufactured using a CCD or a CMOS compatible process. For manufacturing reasons, such a chip is typically two centimeters or less on a side. However, large chips can also be made. Optional electronic components for further signal processing of the captured images may be formed either on the sensor chip (i.e., in a “system-on-a-chip” implementation), or in a separate back-end application specific integrated circuit (ASIC). In addition, digital storage components, display elements, and wired or wireless communication links may also be included in any suitable combination to allow review and further processing of the captured images.

Owner:CAPSO VISION INC

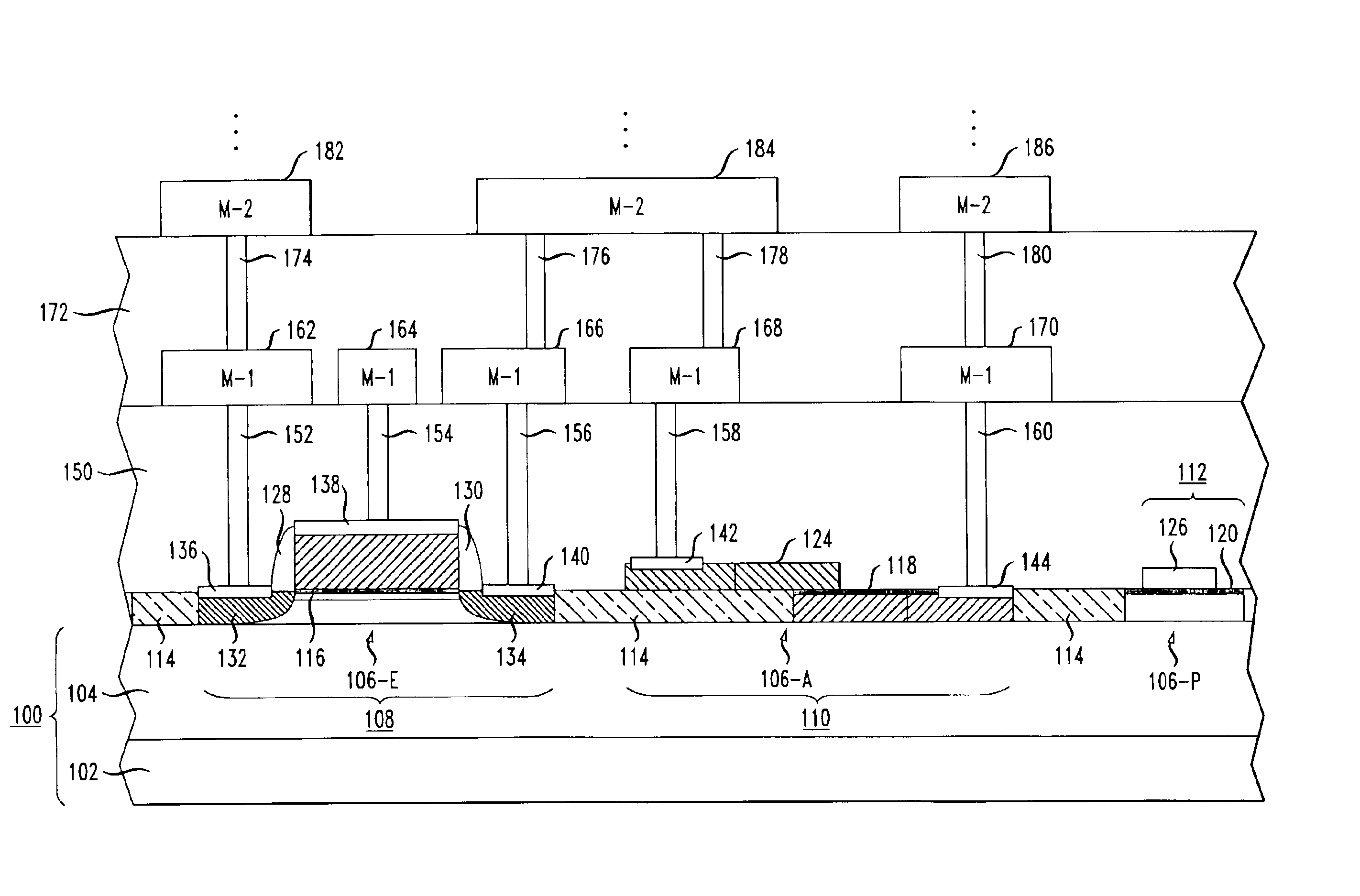

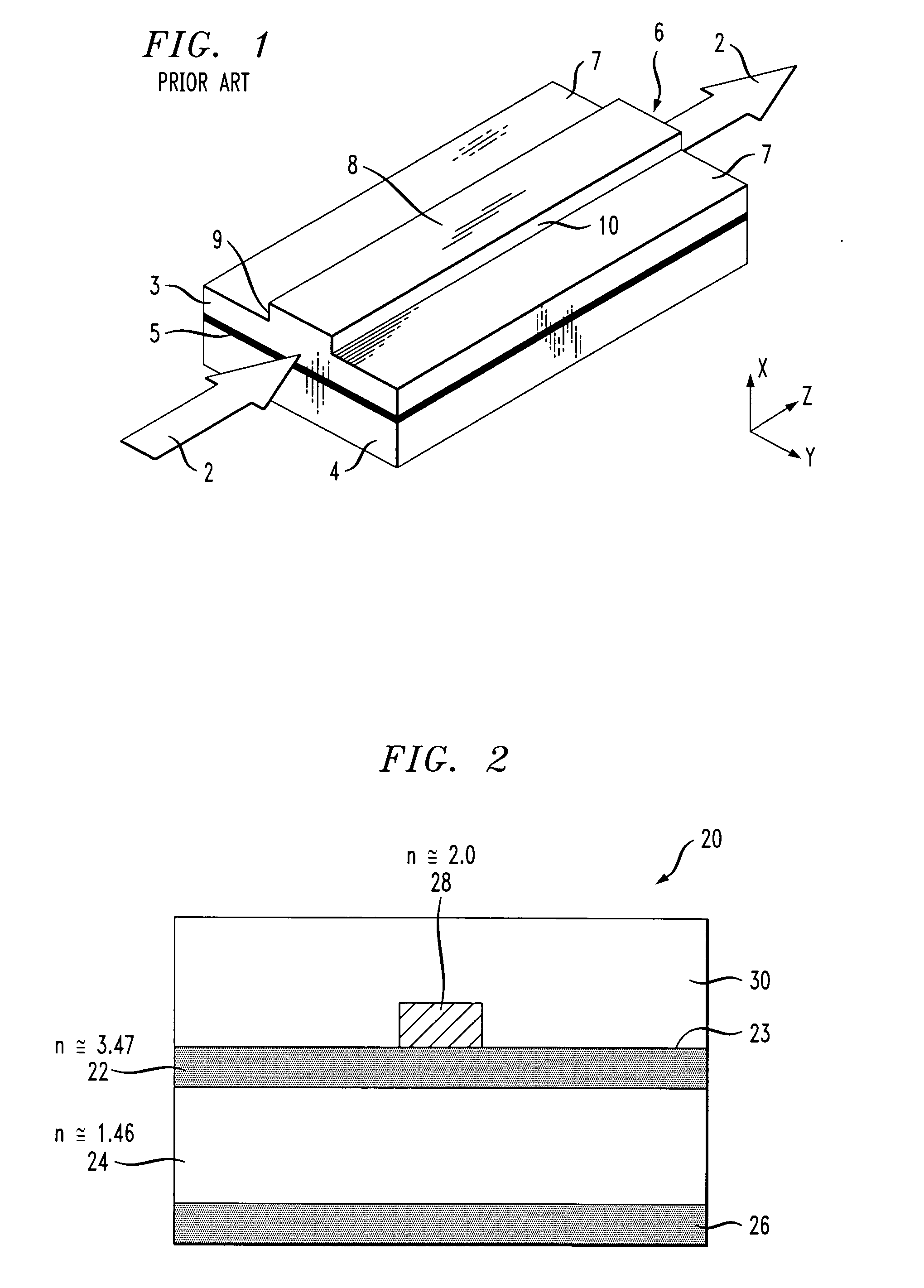

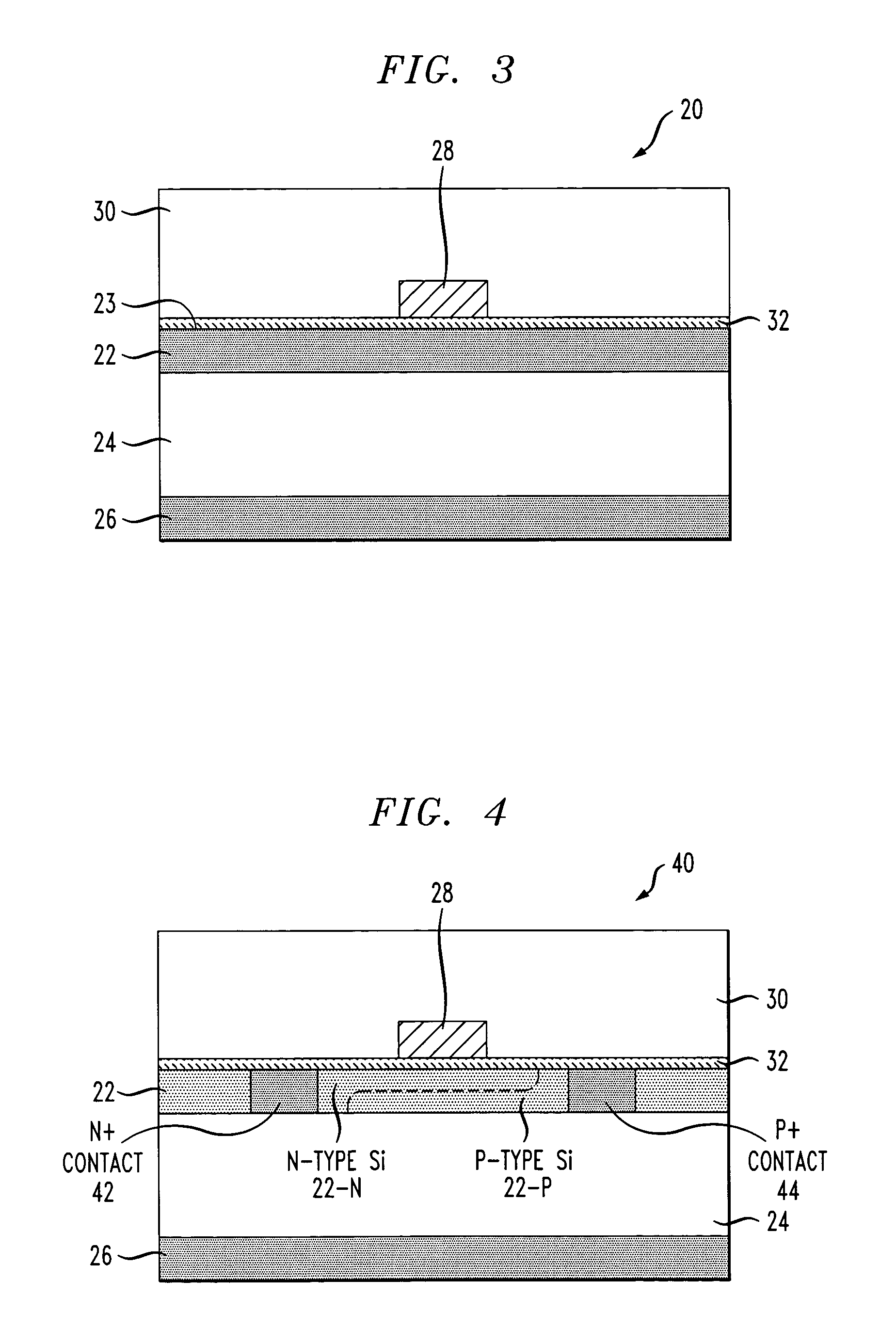

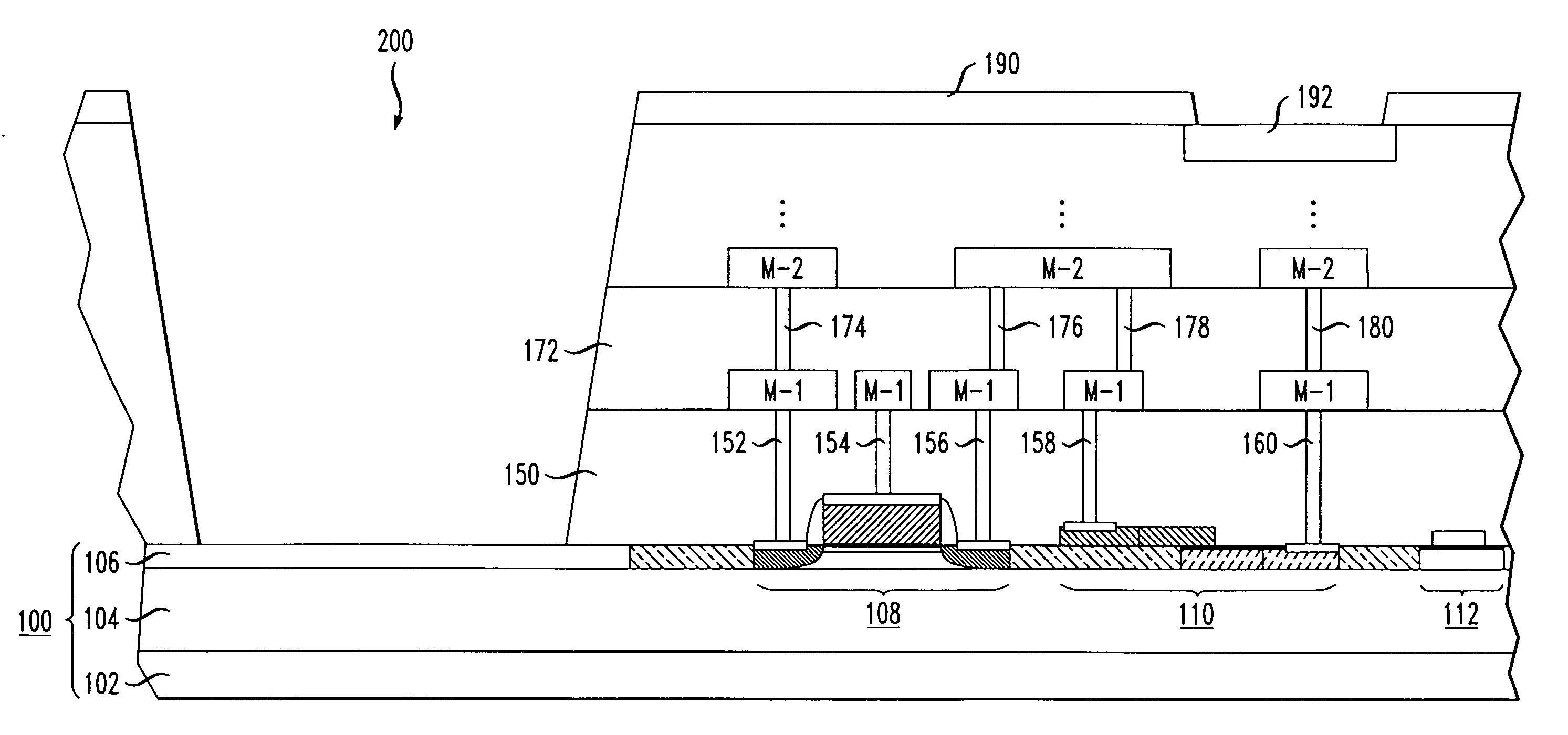

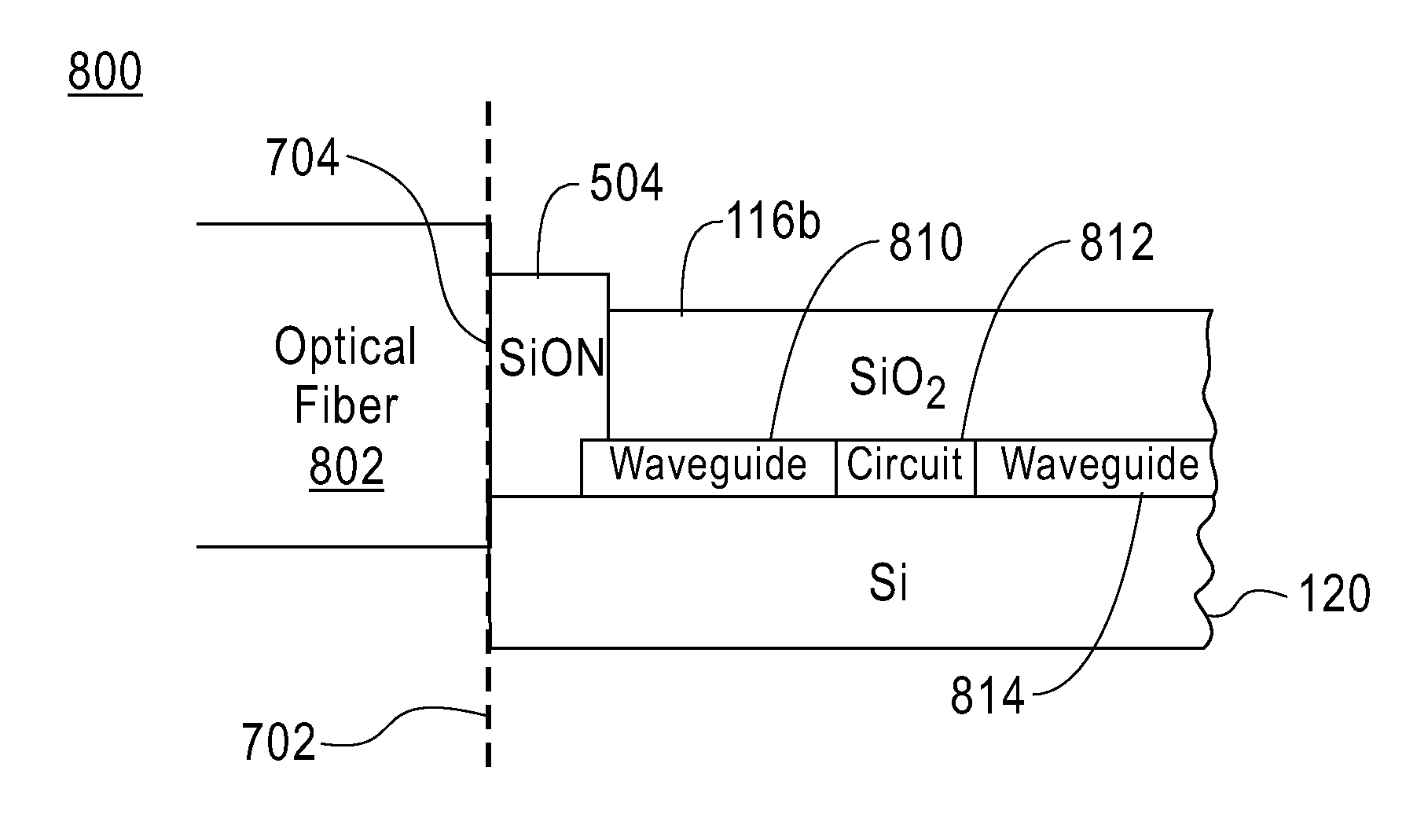

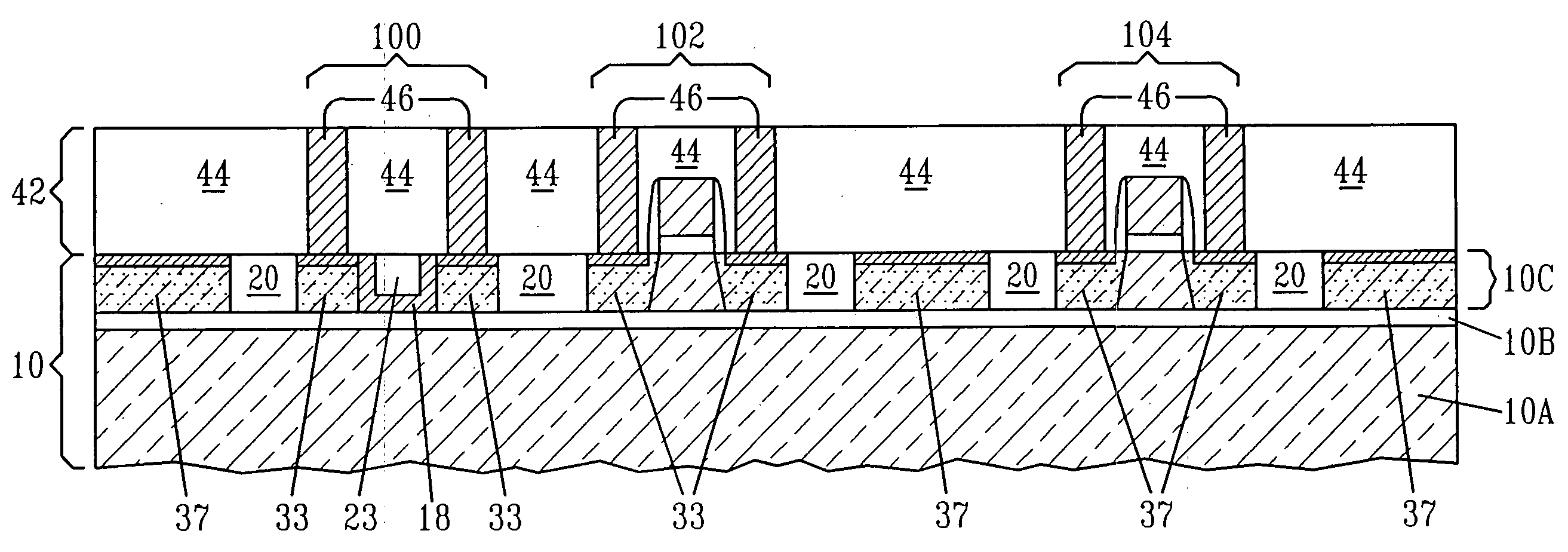

CMOS-compatible integration of silicon-based optical devices with electronic devices

ActiveUS6968110B2Reduce the possibilityReduce yieldTransistorCladded optical fibreCMOSElectrical devices

A conventional CMOS fabrication technique is used to integrate the formation of passive optical devices and active electro-optic devices with standard CMOS electrical devices on a common SOI structure. The electrical devices and optical devices share the same surface SOI layer (a relatively thin, single crystal silicon layer), with various required semiconductor layers then formed over the SOI layer. In some instances, a set of process steps may be used to simultaneously form regions in both electrical and optical devices. Advantageously, the same metallization process is used to provide electrical connections to the electrical devices and the active electro-optic devices.

Owner:CISCO TECH INC

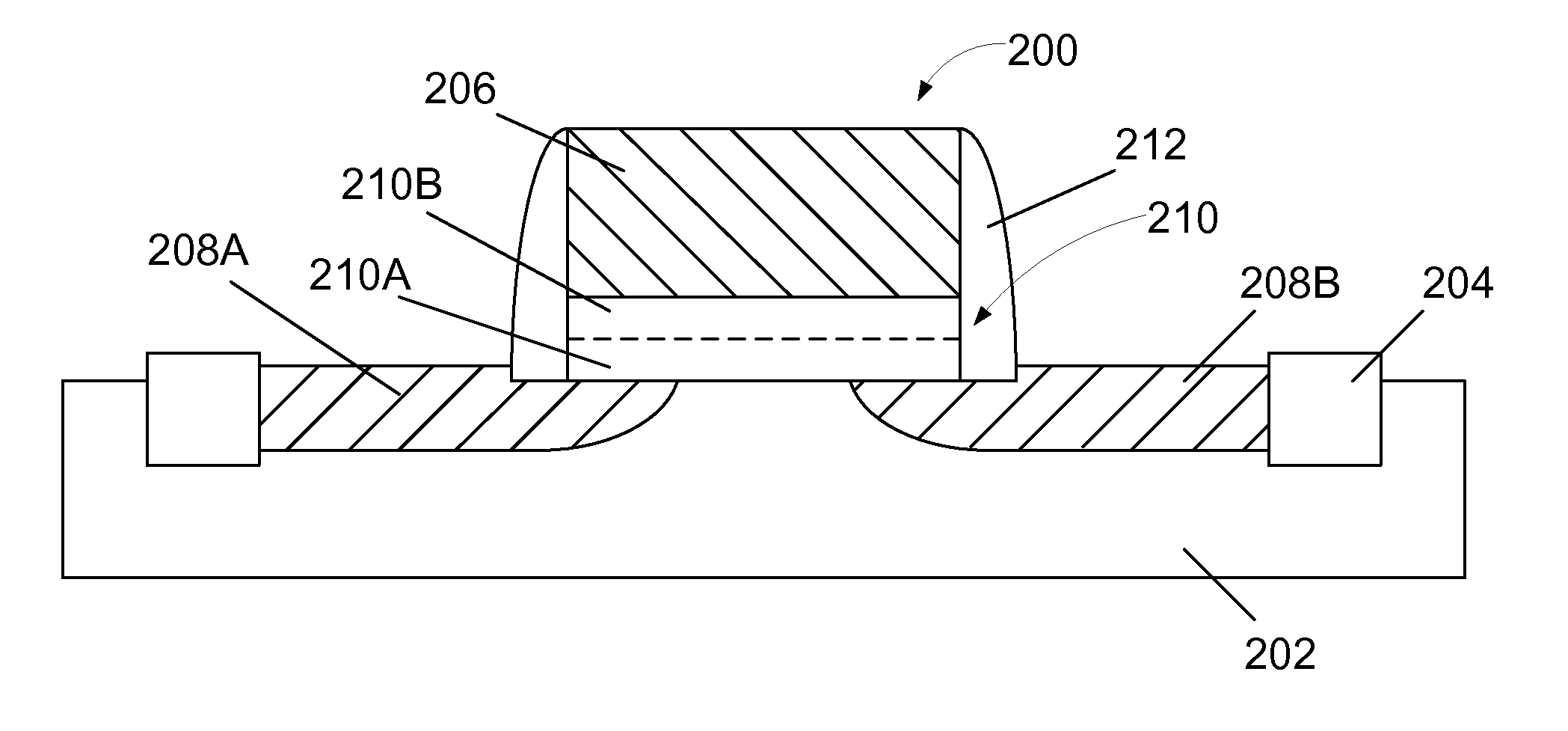

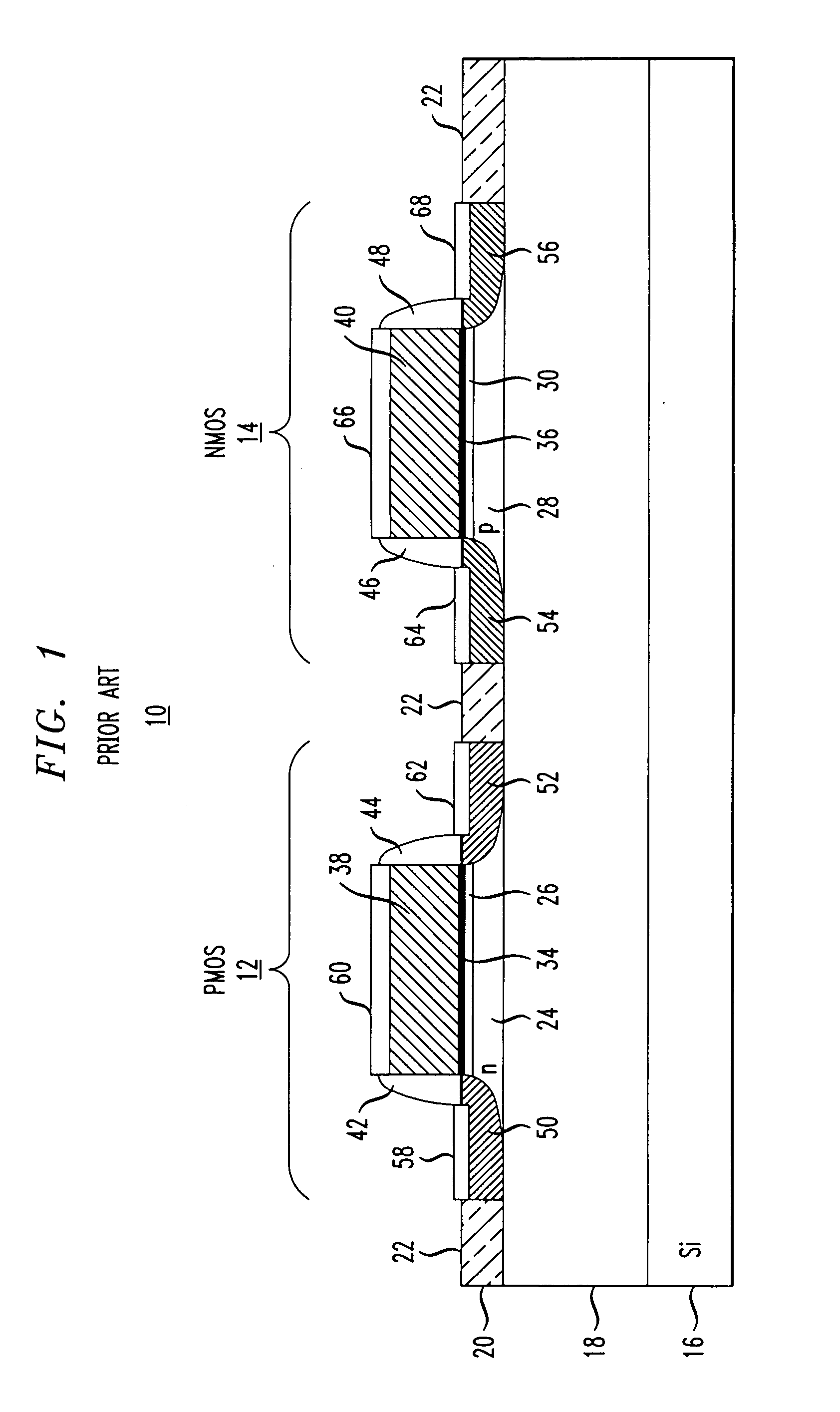

CMOS compatible low band offset double barrier resonant tunneling diode

InactiveUS20050056827A1Good I-V characteristicRaise the ratioTransistorNanoinformaticsCMOSElectrical resistance and conductance

Three configurations of double barrier resonant tunneling diodes (RTD) are provided along with methods of their fabrication. The tunneling barrier layers of the diode are formed of low band offset dielectric materials and produce a diode with good I-V characteristics including negative differential resistance (NDR) with good peak-to-valley ratios (PVR). Fabrication methods of the RTD start with silicon-on-insulator substrates (SOI), producing silicon quantum wells, and are, therefore, compatible with main stream CMOS technologies such as those applied to SOI double gate transistor fabrication. Alternatively, Ge-on-insulator or SiGe-on-insulator substrates can be used if the quantum well is to be formed of Ge or SiGe. The fabrication methods include the formation of both vertical and horizontal silicon quantum well layers. The vertically formed layer may be oriented so that its vertical sides are in any preferred crystallographic plane, such as the 100 or 110 planes.

Owner:AGENCY FOR SCI TECH & RES +1

Camera system with multiple pixel arrays on chip

ActiveCN101926171AAllow browsingTelevision system detailsPulse modulation television signal transmissionElectronic componentApplication-specific integrated circuit

A camera system uses one or more image sensor IC chips each having multiple pixel arrays on the same semiconductor substrate (i.e., ''multiple pixel arrays on a chip''). In one embodiment, such a camera system includes: (a) optical components that create multiple images in dose physical proximity of each other (e.g., within a few millimeters or 10 centimeters); and (b) a single sensor substrate (''chip'') containing multiple 2 -dimensional pixel arrays that are aligned to capture these multiple images, so as to convert the multiple images into electrical signal. The pixel arrays can be manufactured using a CCD or a CMOS compatible process. Such a chip is typically two centimeters or less on a side. Optional electronic components for further signal processing of the captured images may be formed either on the sensor chip (i.e., in a ''system-on-a-chip'' implementation), or in a separate back-end application specific integrated circuit (ASIC).

Owner:CAPSO VISION INC

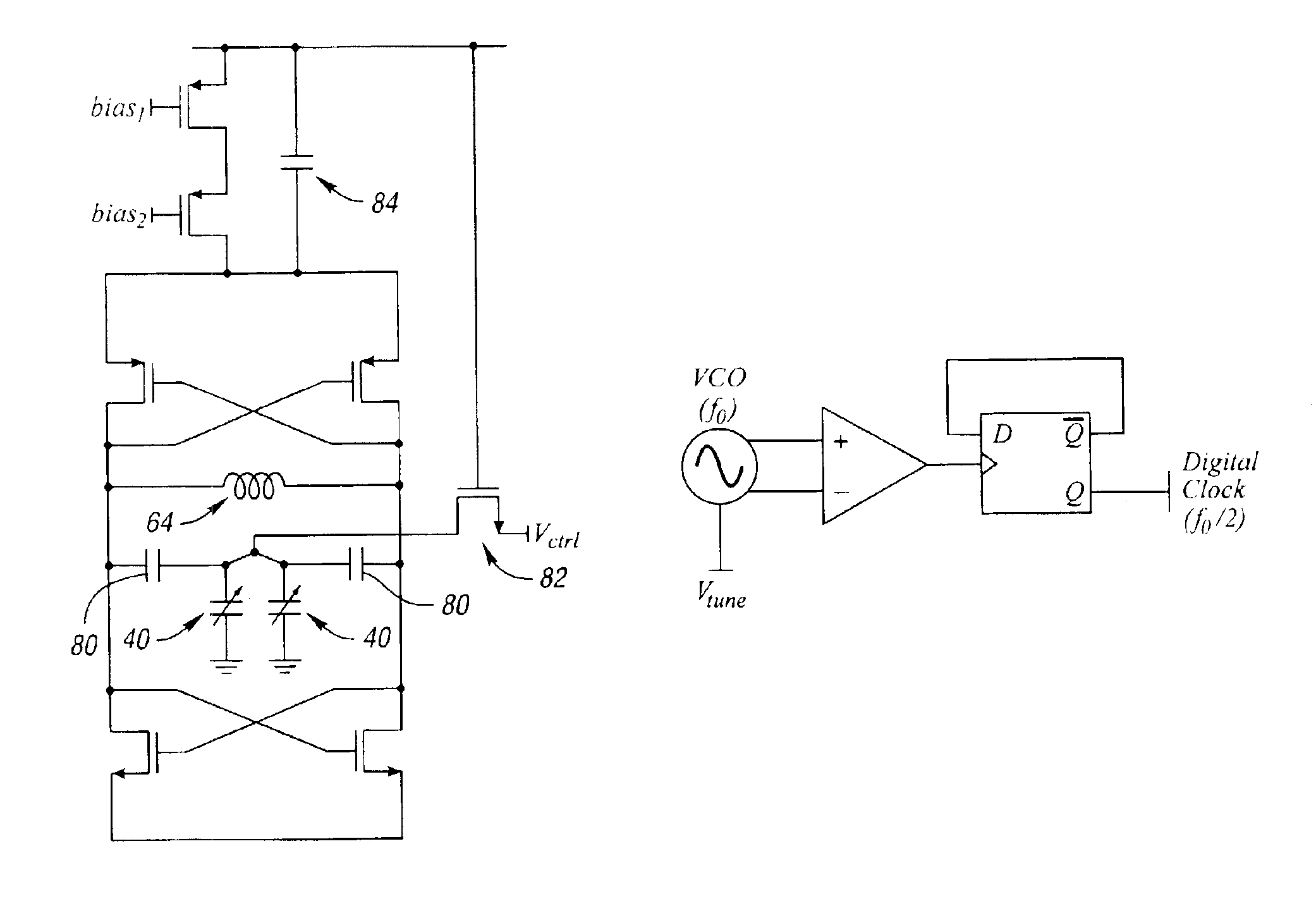

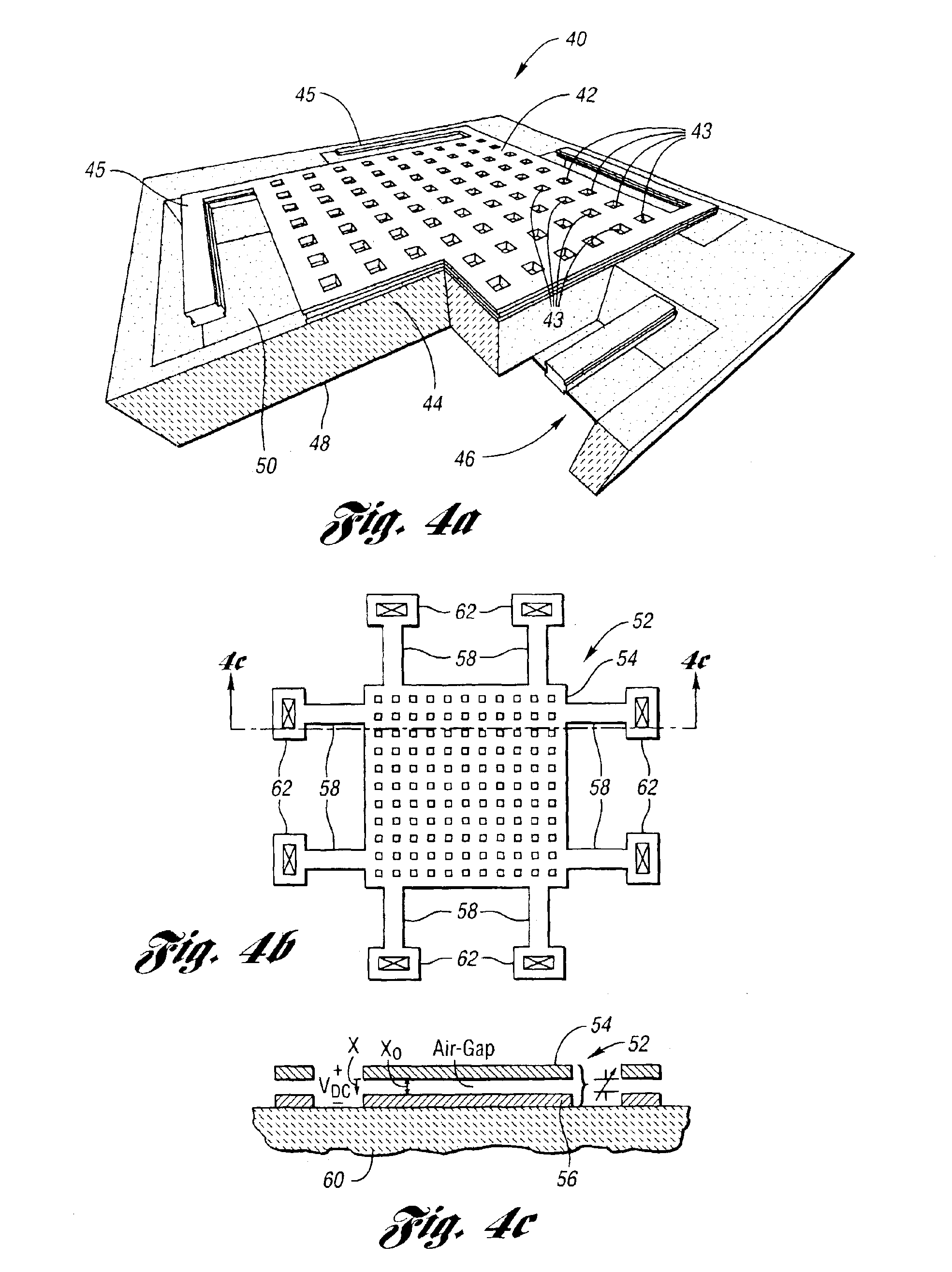

MEMS-based, computer systems, clock generation and oscillator circuits and LC-tank apparatus for use therein

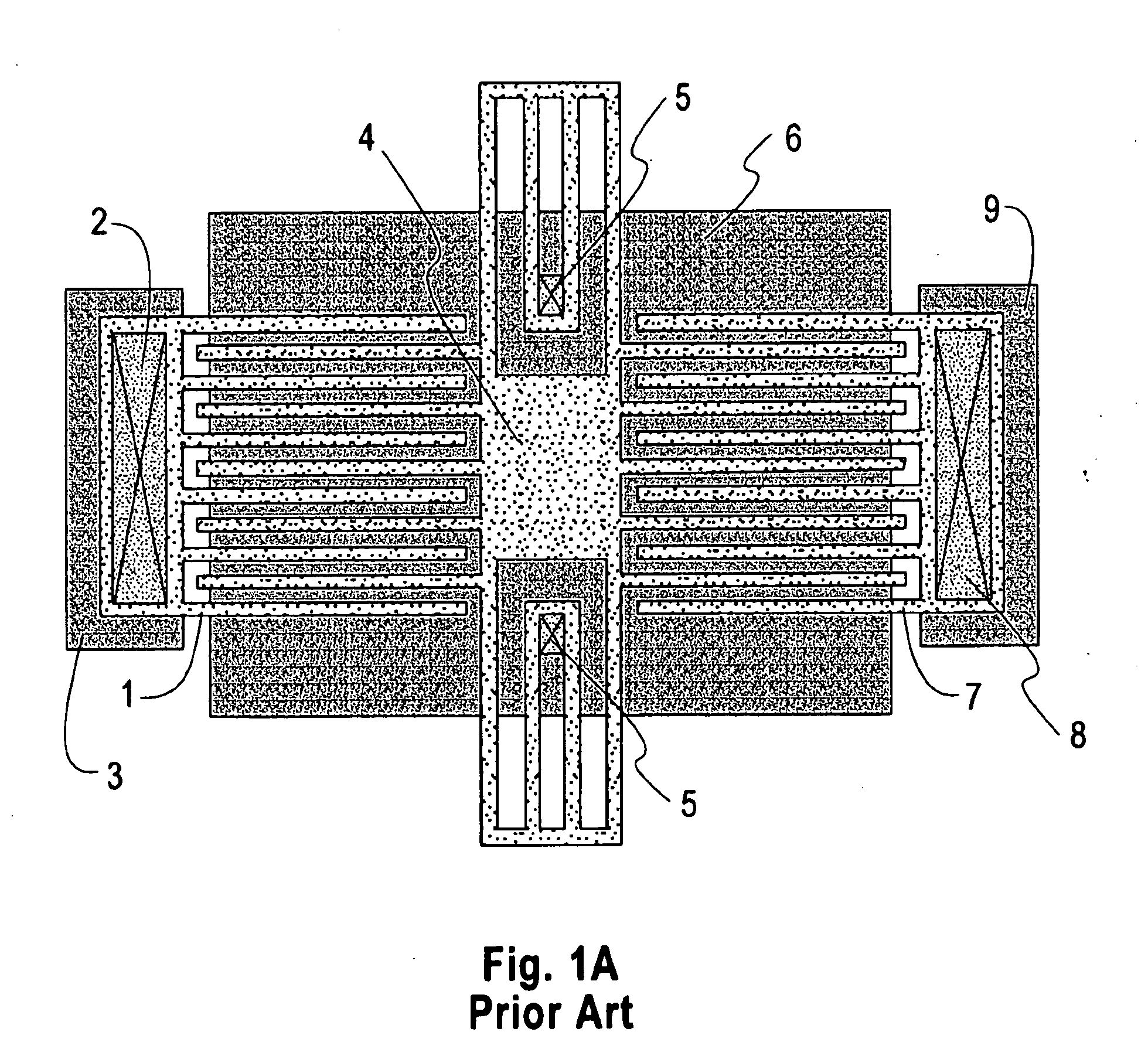

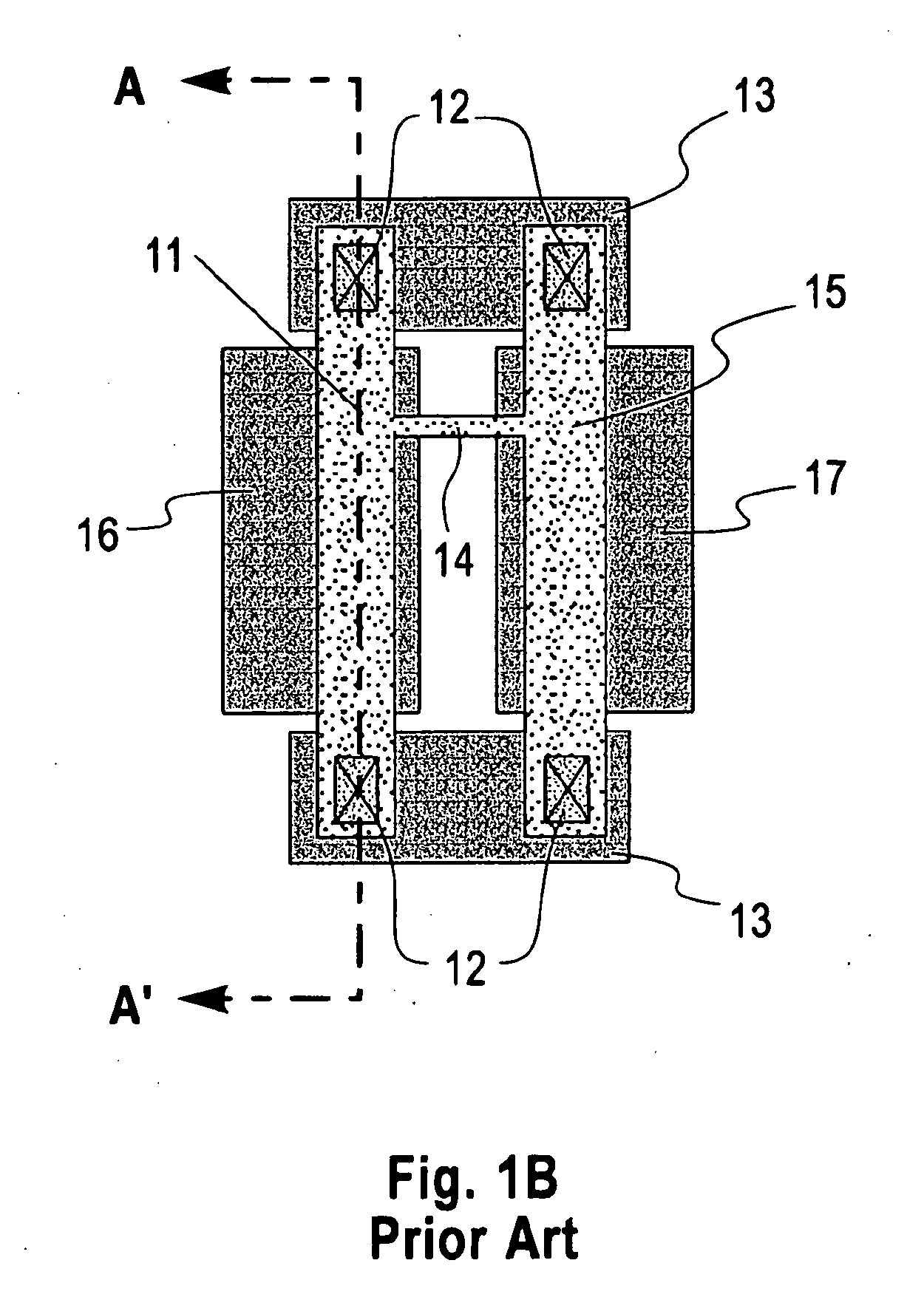

InactiveUS6972635B2Reduce flicker noiseReduce phase noiseAngle modulation by variable impedenceMultiple-port networksEngineeringVaricap

MEMS-based, computer system, clock generation and oscillator circuits and LC-tank apparatus for use therein are provided and which are fabricated using a CMOS-compatible process. A micromachined inductor (L) and a pair of varactors (C) are developed in metal layers on a silicon substrate to realize the high quality factor LC-tank apparatus. This micromachined LC-tank apparatus is incorporated with CMOS transistor circuitry in order to realize a digital, tunable, low phase jitter, and low power clock, or time base, for synchronous integrated circuits. The synthesized clock signal can be divided down with digital circuitry from several GHz to tens of MHz—a systemic approach that substantially improves stability as compared to the state of the art. Advanced circuit design techniques have been utilized to minimize power consumption and mitigate transistor flicker noise upconversion, thus enhancing clock stability.

Owner:RGT UNIV OF MICHIGAN

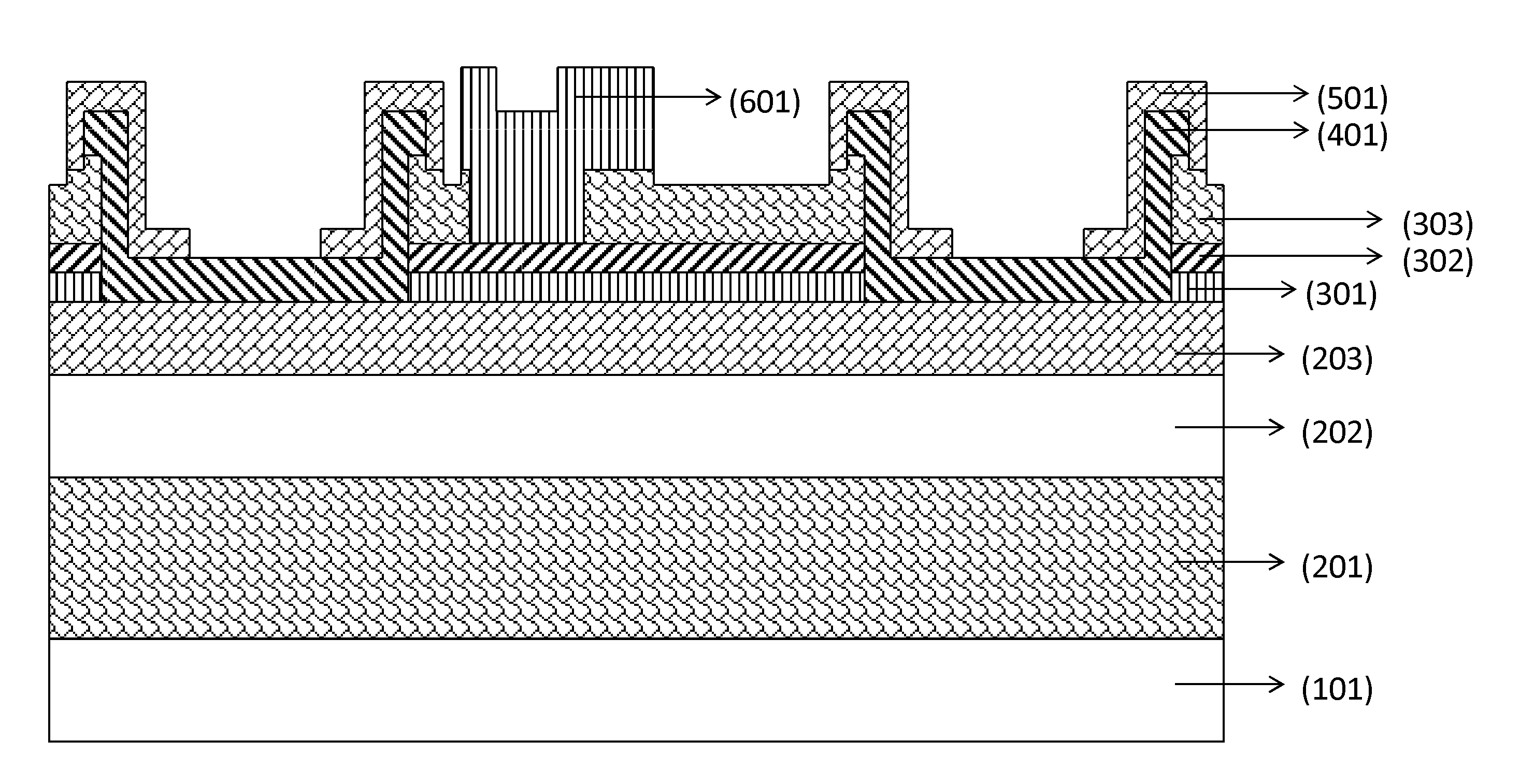

CMOS compatible method for manufacturing a HEMT device and the HEMT device thereof

ActiveUS20120319169A1Semiconductor/solid-state device detailsSolid-state devicesOhmic contactDielectric layer

A method for manufacturing a III-nitride HEMT having a gate electrode and source and drain ohmic contacts is provided, comprising providing a substrate; forming a stack of III-nitride layers on the substrate; forming a first passivation layer comprising silicon nitride overlying and in contact with an upper layer of the stack of III-nitride layers, wherein the first passivation layer is deposited in-situ with the stack of III-nitride layers; forming a dielectric layer overlying and in contact with the first passivation layer; forming a second passivation layer comprising silicon nitride overlying and in contact with the dielectric layer wherein the second passivation layer is deposited at a temperature higher than 450° C. by LPCVD or MOCVD or any equivalent technique; and thereafter forming the source and drain ohmic contacts and the gate electrode.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

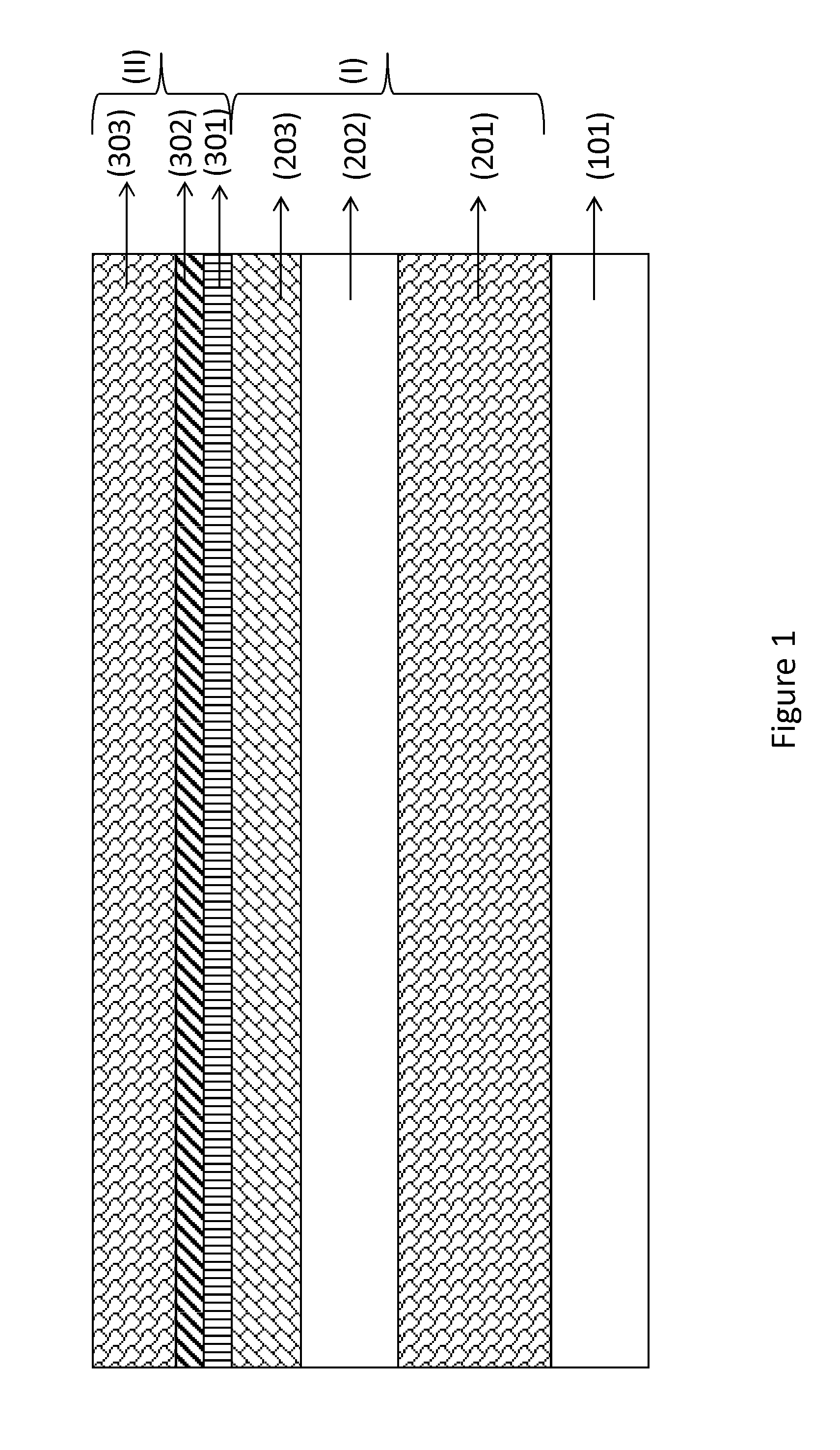

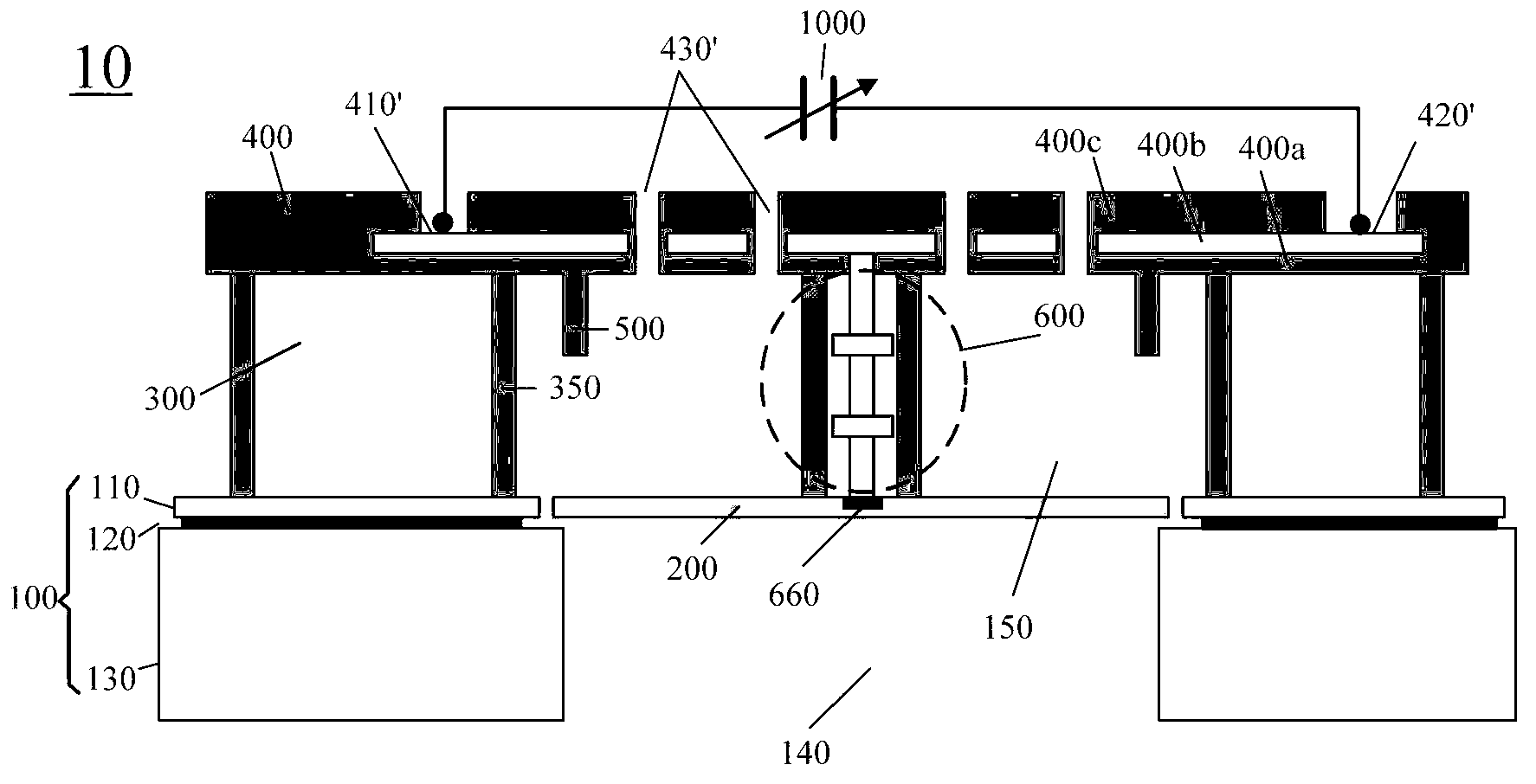

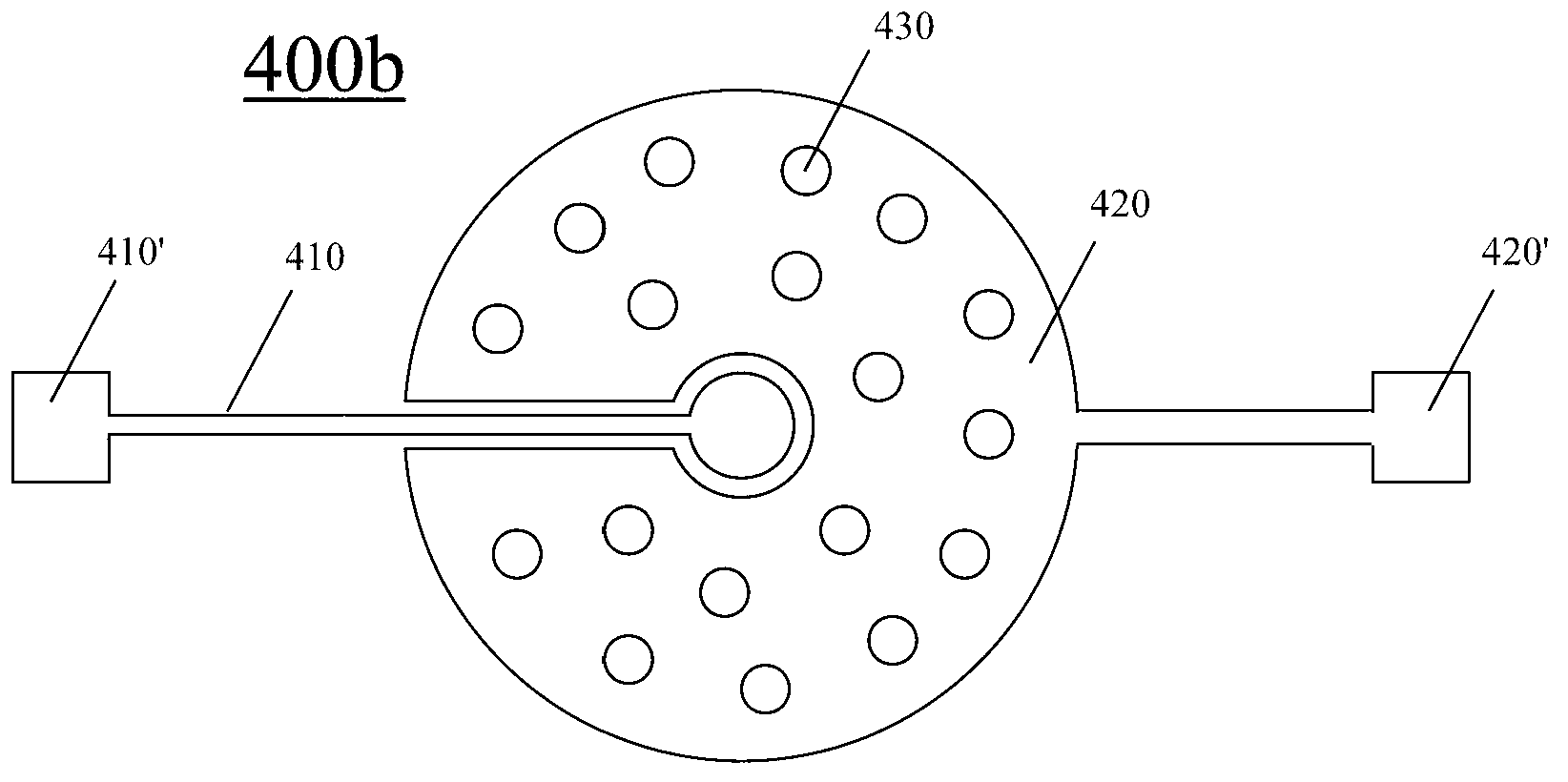

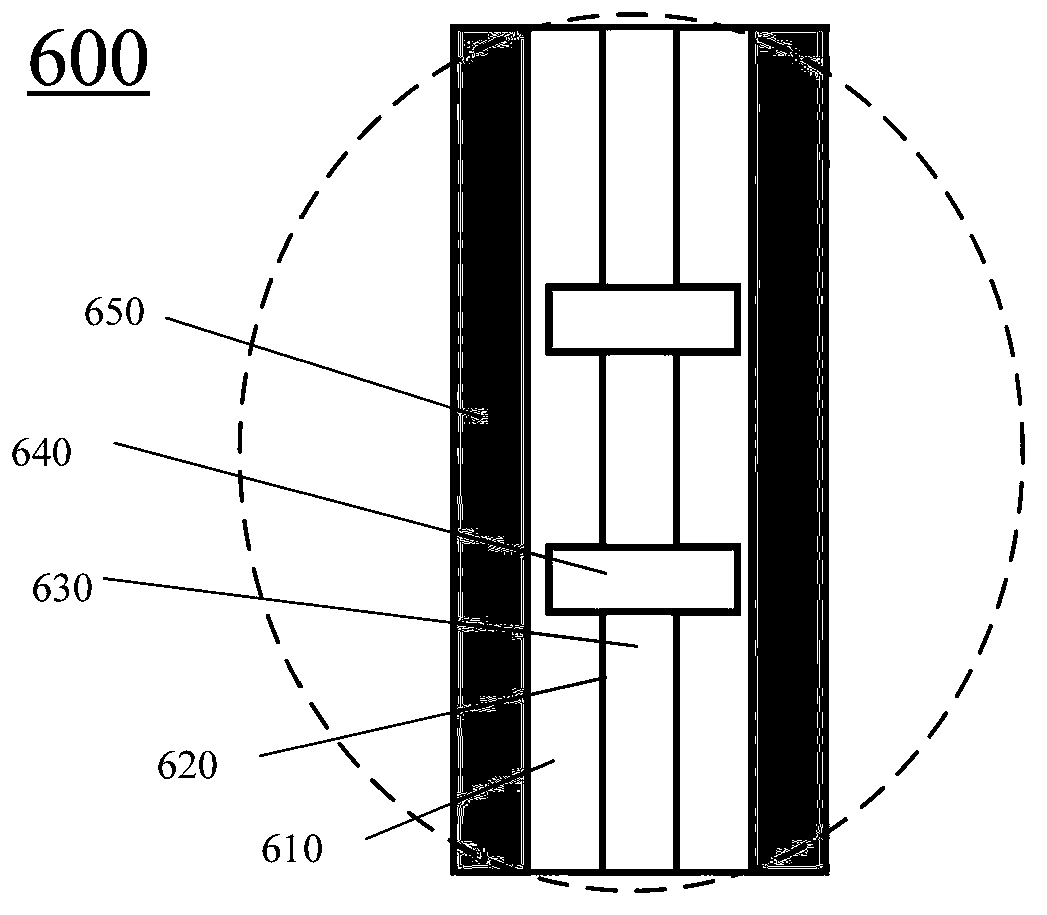

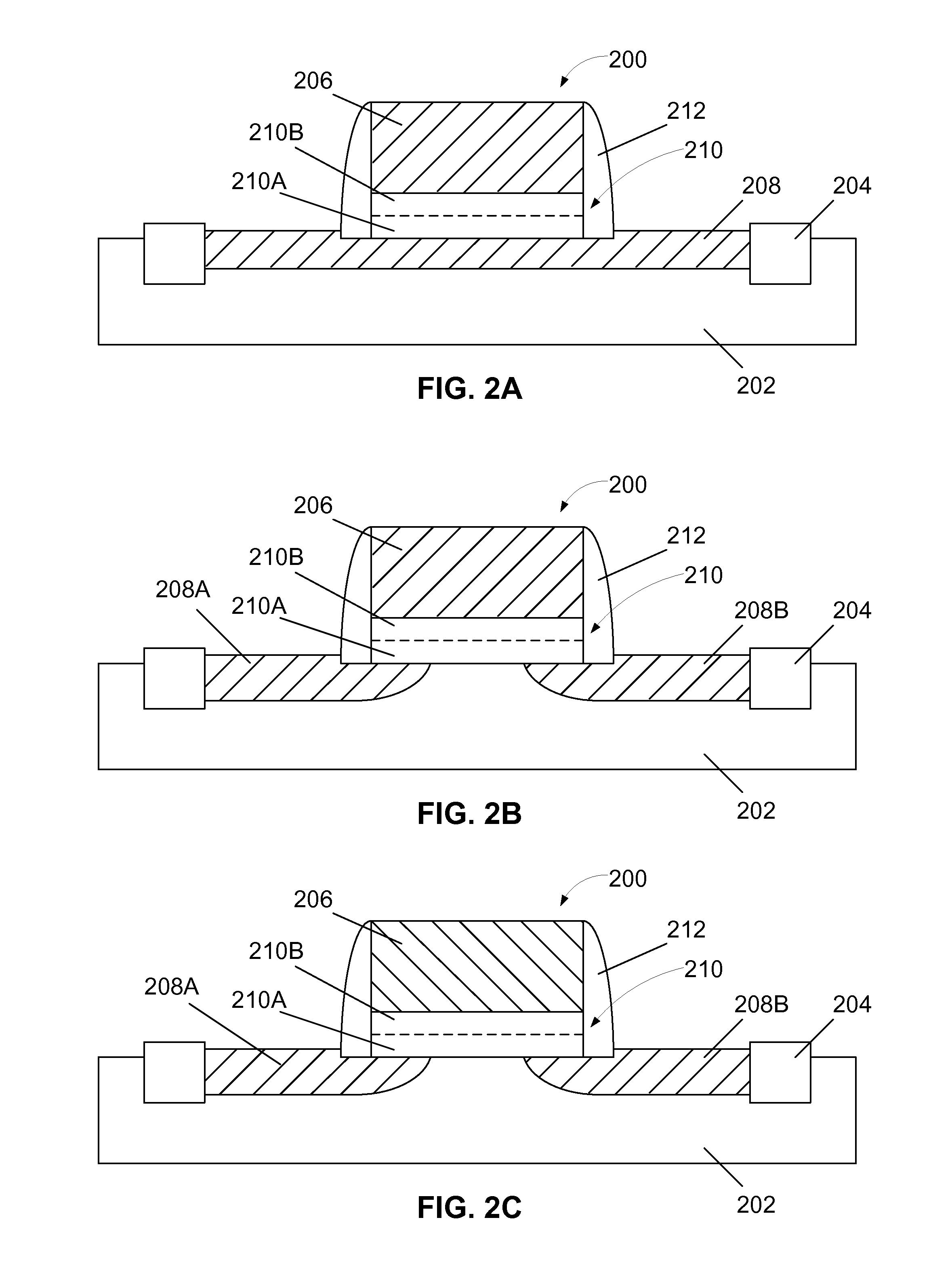

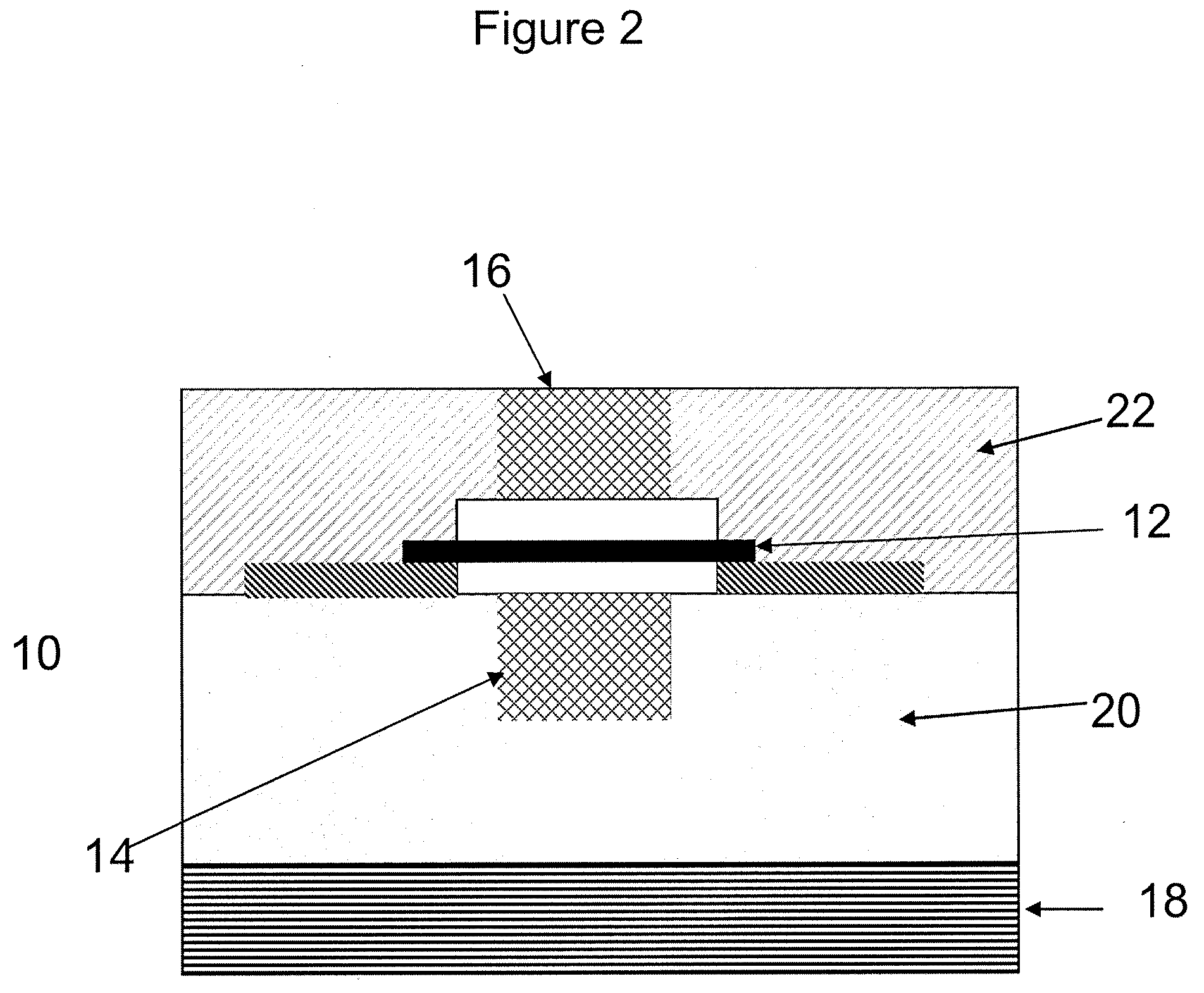

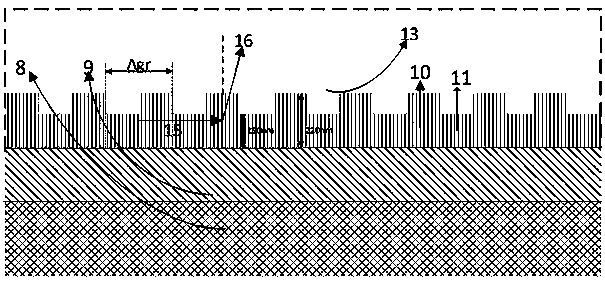

CMOS compatible MEMS microphone and method for manufacturing the same

The present invention relates to a CMOS compatible MEMS microphone, comprising: an SOI substrate, wherein a CMOS circuitry is accommodated on its silicon device layer; a microphone diaphragm formed with a part of the silicon device layer, wherein the microphone diaphragm is doped to become conductive; a microphone backplate including CMOS passivation layers with a metal layer sandwiched and a plurality of through holes, provided above the silicon device layer, wherein the plurality of through holes are formed in the portions thereof opposite to the microphone diaphragm, and the metal layer forms an electrode plate of the backplate; a plurality of dimples protruding from the lower surface of the microphone backplate opposite to the diaphragm; and an air gap, provided between the diaphragm and the microphone backplate, wherein a spacer forming a boundary of the air gap is provided outside of the diaphragm or on the edge of the diaphragm; wherein a back hole is formed to be open in substrate underneath the diaphragm so as to allow sound pass through, and the microphone diaphragm is used as an electrode plate to form a variable capacitive sensing element with the electrode plate of the microphone backplate.

Owner:GOERTEK MICROELECTRONICS CO LTD

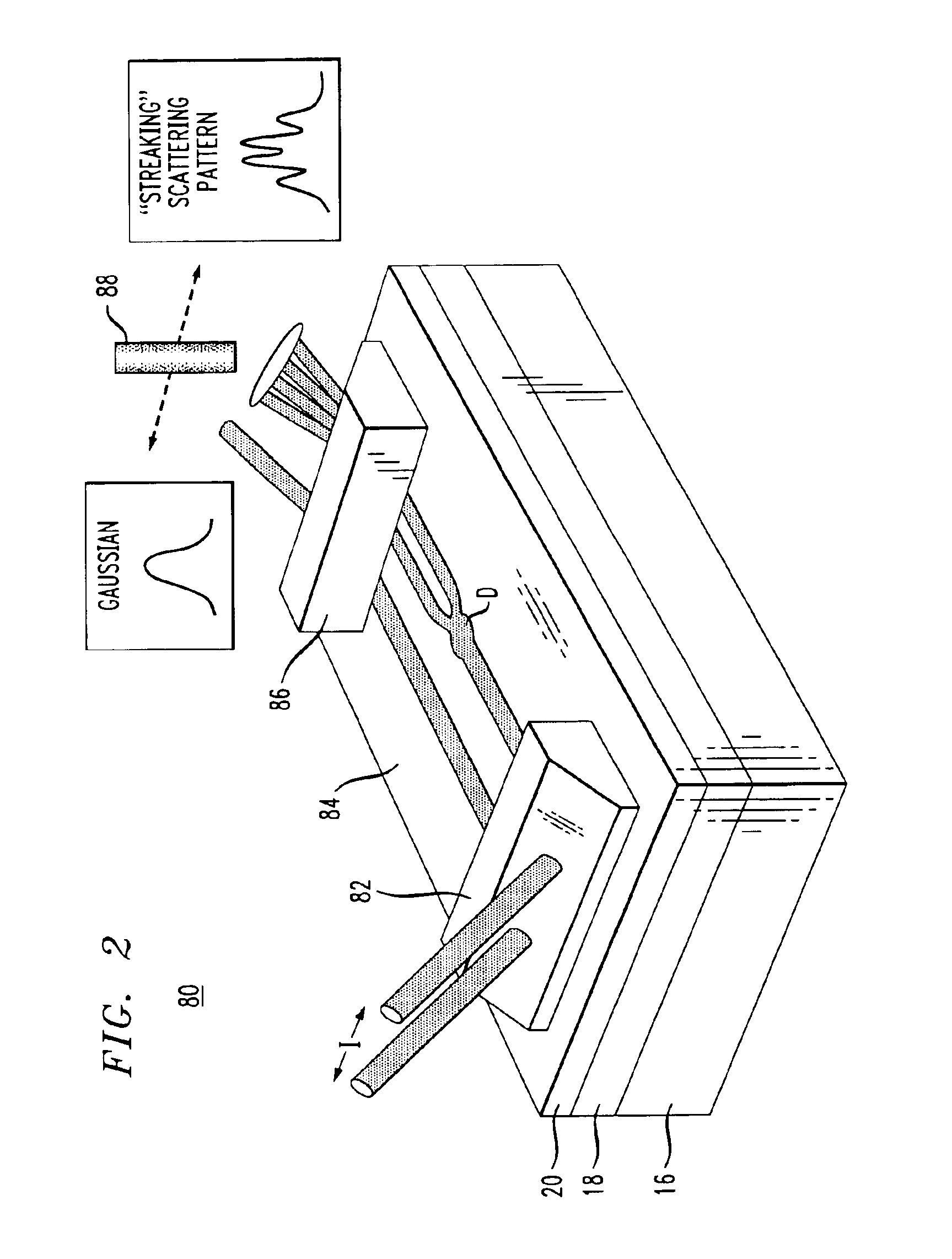

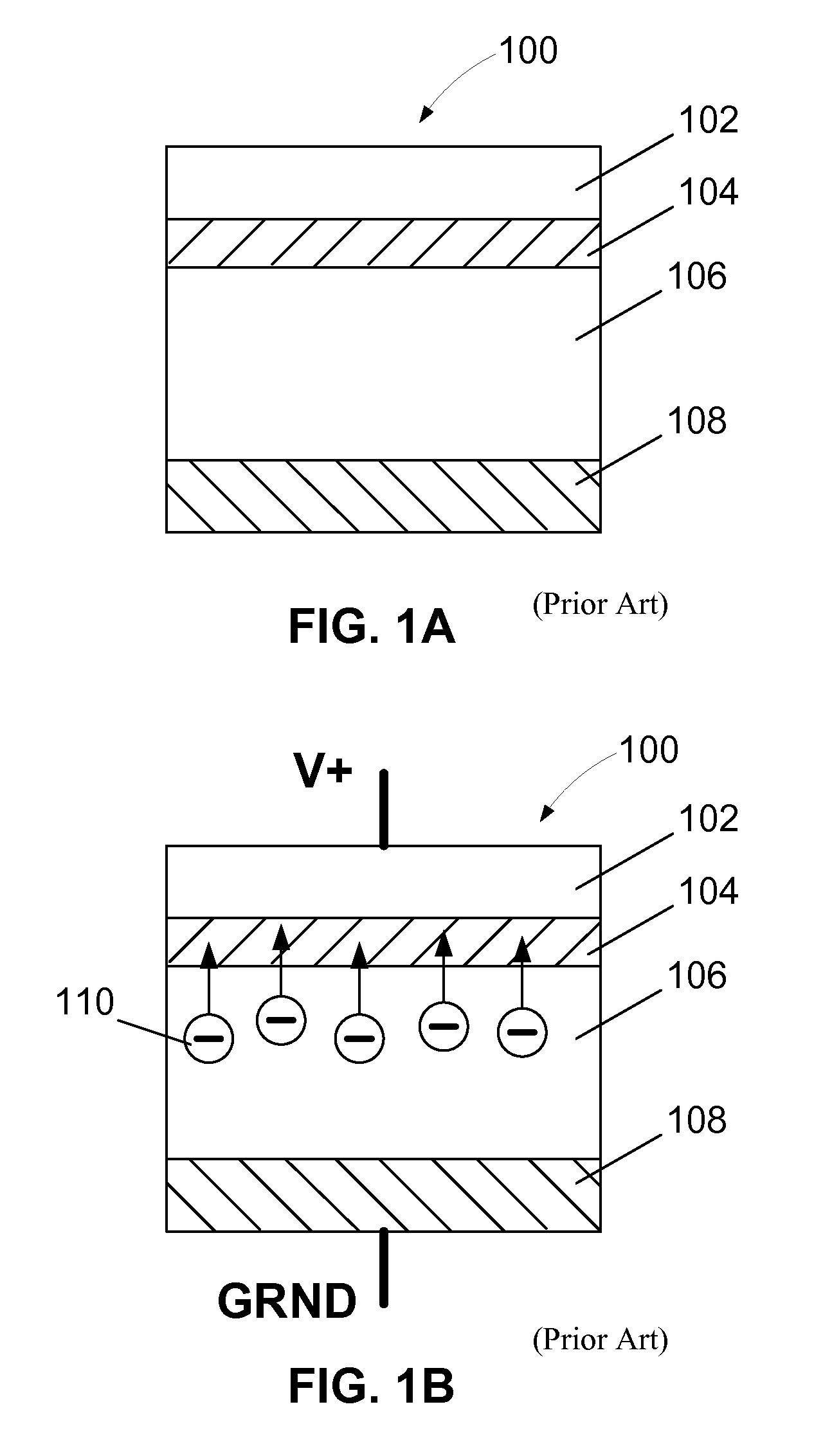

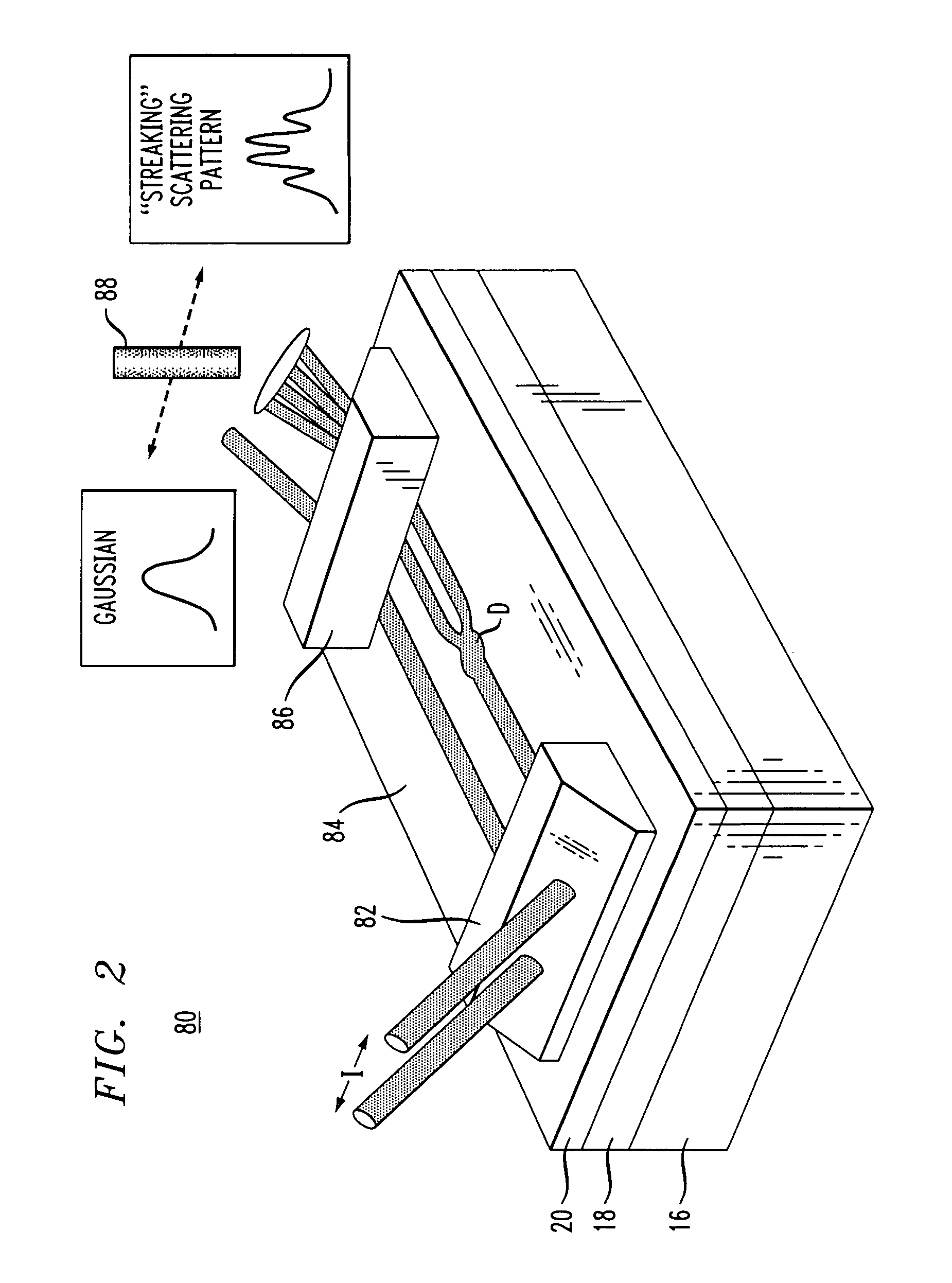

Ultra low-loss CMOS compatible silicon waveguides

InactiveUS20060133754A1Reduce lossReduce light lossOptical waveguide light guideNon-linear opticsBand shapeScattering loss

A low loss optical waveguiding structure for silicon-on-insulator (SOI)-based arrangements utilizes a tri-material configuration including a rib / strip waveguide formed of a material with a refractive index less than silicon, but greater than the refractive index of the underlying insulating material. In one arrangement, silicon nitirde may be used. The index mismatch between the silicon surface layer (the SOI layer) and the rib / strip waveguide results in a majority of the optical energy remaining within the SOI layer, thus reducing scattering losses from the rib / strip structure (while the rib / strip allows for guiding along a desired signal path to be followed). Further, since silicon nitirde is an amorphous material without a grain structure, this will also reduce scattering losses. Advantageously, the use of silicon nitride allows for conventional CMOS fabrication processes to be used in forming both passive and active devices.

Owner:CISCO TECH INC +1

Fabrication of RRAM Cell Using CMOS Compatible Processes

InactiveUS20120241710A1Well formedSolid-state devicesSemiconductor/solid-state device manufacturingDopantRandom access memory

Generally, the subject matter disclosed herein relates to the fabrication of an RRAM cell using CMOS compatible processes. A resistance random access memory device is disclosed which includes a semiconducting substrate, a top electrode, at least one metal silicide bottom electrode formed at least partially in the substrate, wherein at least a portion of the at least one bottom electrode is positioned below the top electrode, and at least one insulating layer positioned between the top electrode and at least a portion of the at least one bottom electrode. A method of making a resistance random access memory device is disclosed that includes forming an isolation structure in a semiconducting substrate to thereby define an enclosed area, performing at least one ion implantation process to implant dopant atoms into the substrate within the enclosed area, after performing the at least one ion implantation process, forming a layer of refractory metal above at least portions of the substrate, and performing at least one heat treatment process to form at least one metal silicide bottom electrode at least partially in the substrate, wherein at least a portion of the at least one bottom electrode is positioned below at least a portion of a top electrode of the device.

Owner:NANYANG TECH UNIV +1

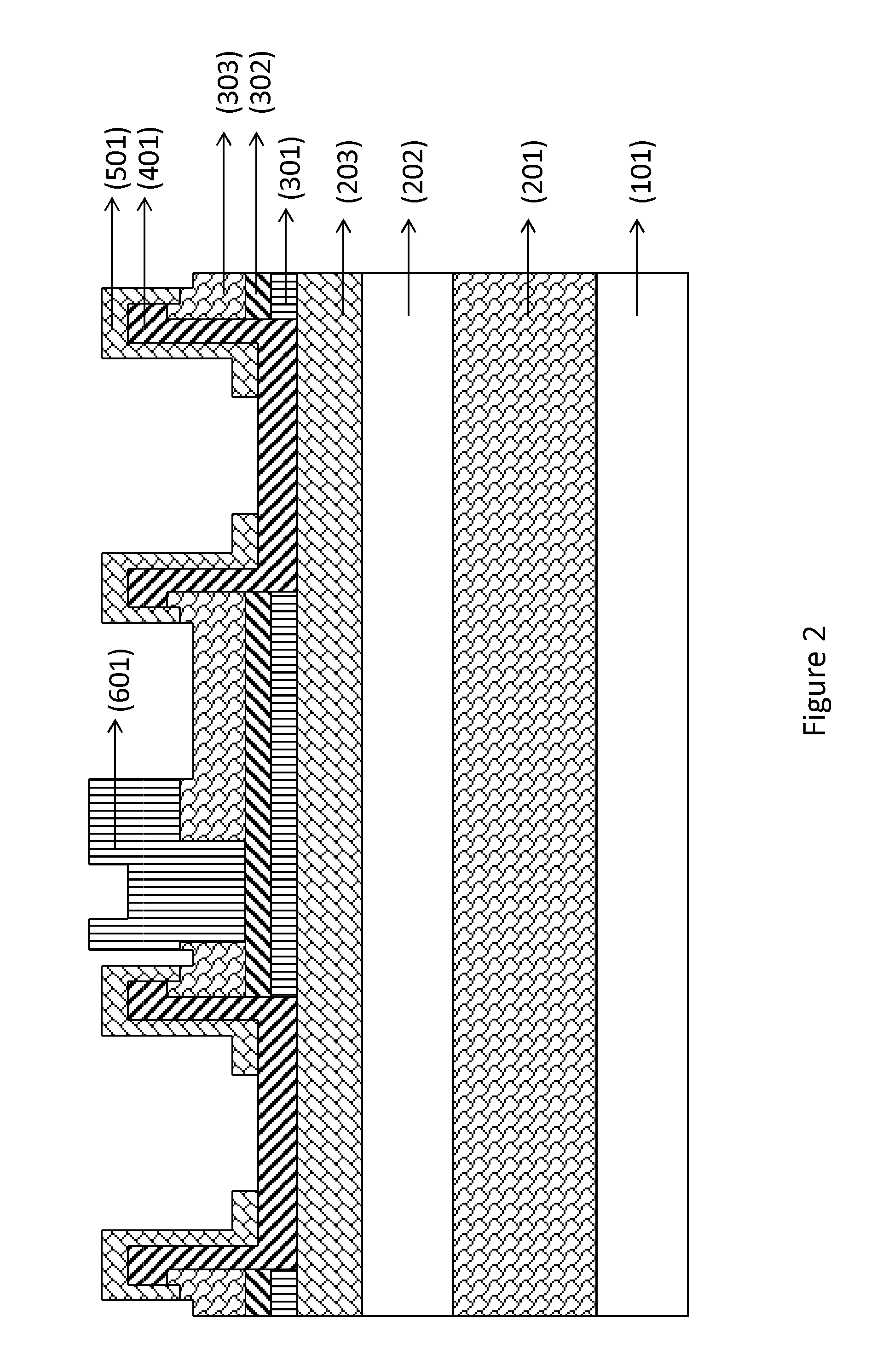

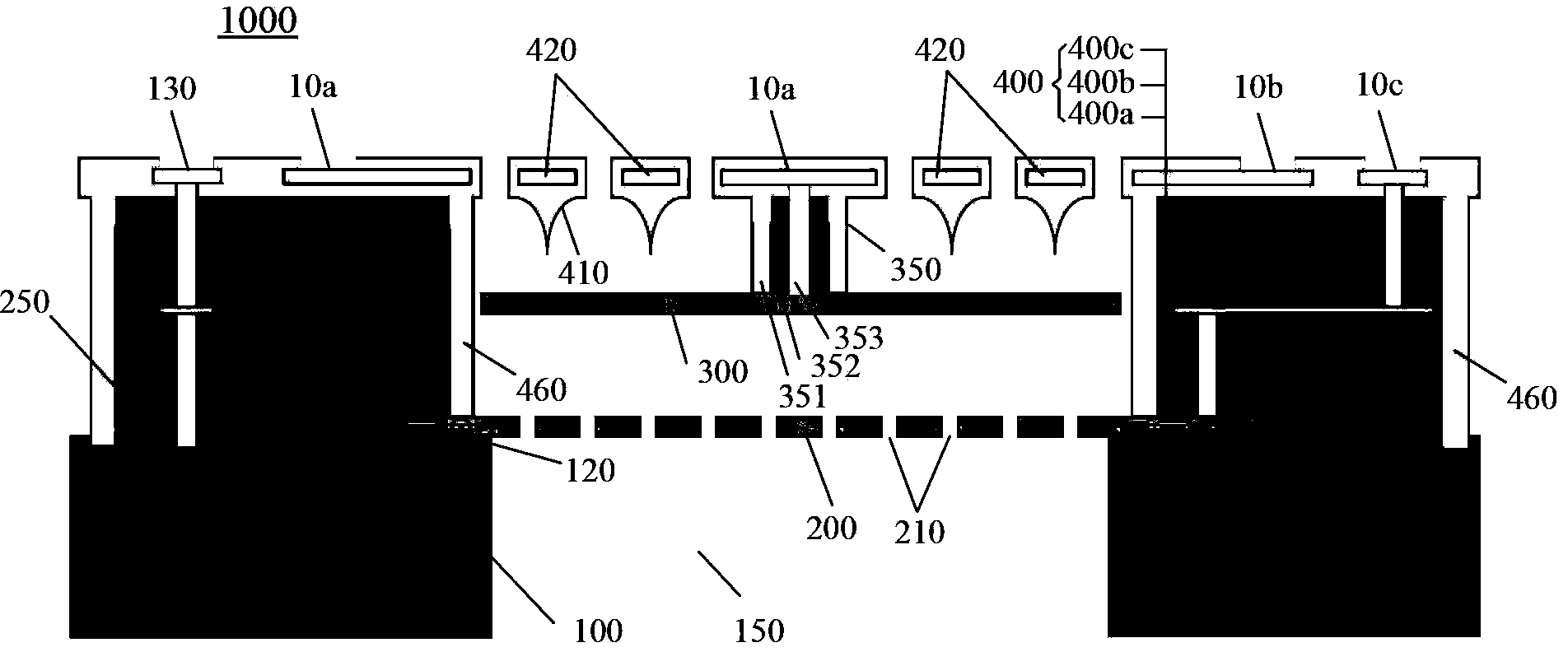

CMOS compatible silicon differential condenser microphone and method for manufacturing the same

ActiveCN103563399AImprove signal-to-noise ratioSemiconductor electrostatic transducersElectrostatic transducer microphonesCMOSEngineering

A CMOS compatible silicon differential condenser microphone and a method for manufacturing the same are provided. The microphone(1000) comprises a silicon substrate(100), wherein a CMOS circuitry is accommodated thereon; a first rigid conductive perforated backplate(200) supported on the silicon substrate with an insulating layer(120) inserted therebetween; a second rigid perforated backplate(400) formed above the first backplate, including CMOS passivation layers(400a, 400c) and a metal layer(400b) sandwiched between the CMOS passivation layers as an electrode plate of the second plate, wherein an air gap, with a spacer forming its boundary, is provided between the opposite perforated areas of the first backplate and the second backplate; a compliant diaphragm(300) provided between the first backplate and the second backplate, wherein a back hole(150) is formed to be open in the silicon substrate underneath the first backplate so as to allow sound pass through, and the diaphragm and the first backplate form a first variable condenser, the diaphragm and the second backplate form a second variable condenser, and the first variable condenser and the second variable condenser form differential condensers.

Owner:GOERTEK MICROELECTRONICS CO LTD

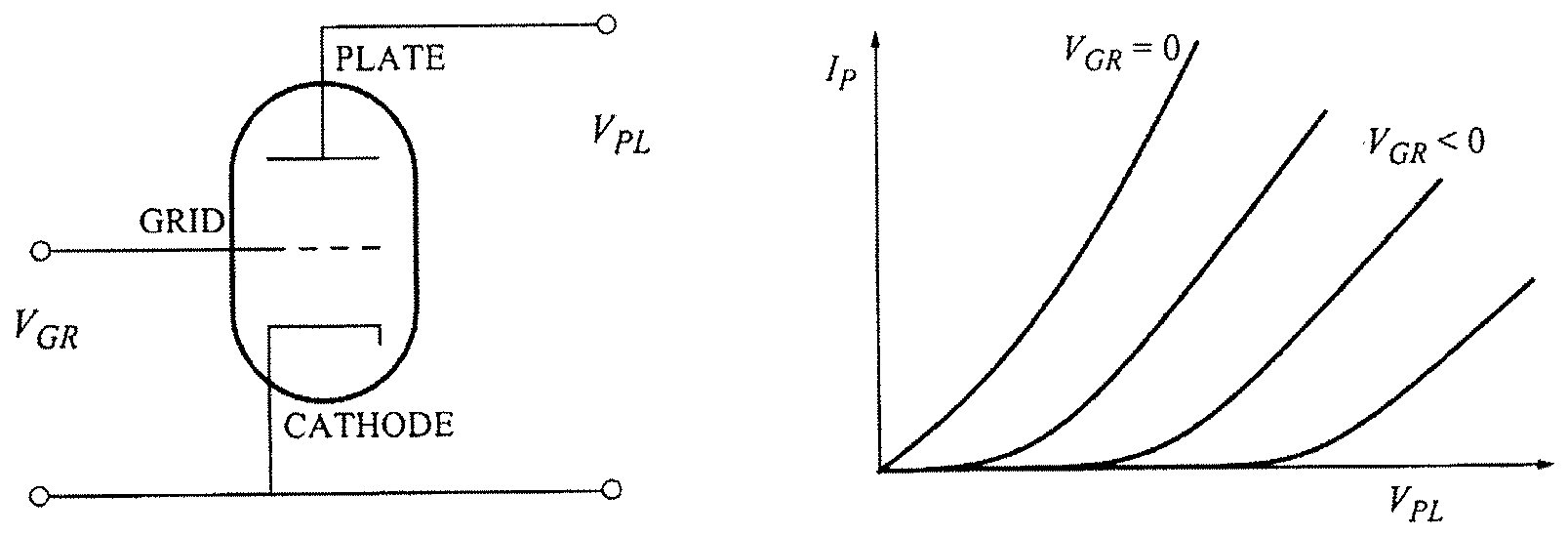

Triodes using nanofabric articles and methods of making the same

Vacuum microelectronic devices with carbon nanotube films, layers, ribbons and fabrics are provided. The present invention discloses microelectronic vacuum devices including triode structures that include three-terminals (an emitter, a grid and an anode), and also higher-order devices such as tetrodes and pentodes, all of which use carbon nanotubes to form various components of the devices. In certain embodiments, patterned portions of nanotube fabric may be used as grid / gate components, conductive traces, etc. Nanotube fabrics may be suspended or conformally disposed. In certain embodiments, methods for stiffening a nanotube fabric layer are used. Various methods for applying, selectively removing (e.g. etching), suspending, and stiffening vertically- and horizontally-disposed nanotube fabrics are disclosed, as are CMOS-compatible fabrication methods. In certain embodiments, nanotube fabric triodes provide high-speed, small-scale, low-power devices that can be employed in radiation-intensive applications.

Owner:NANTERO

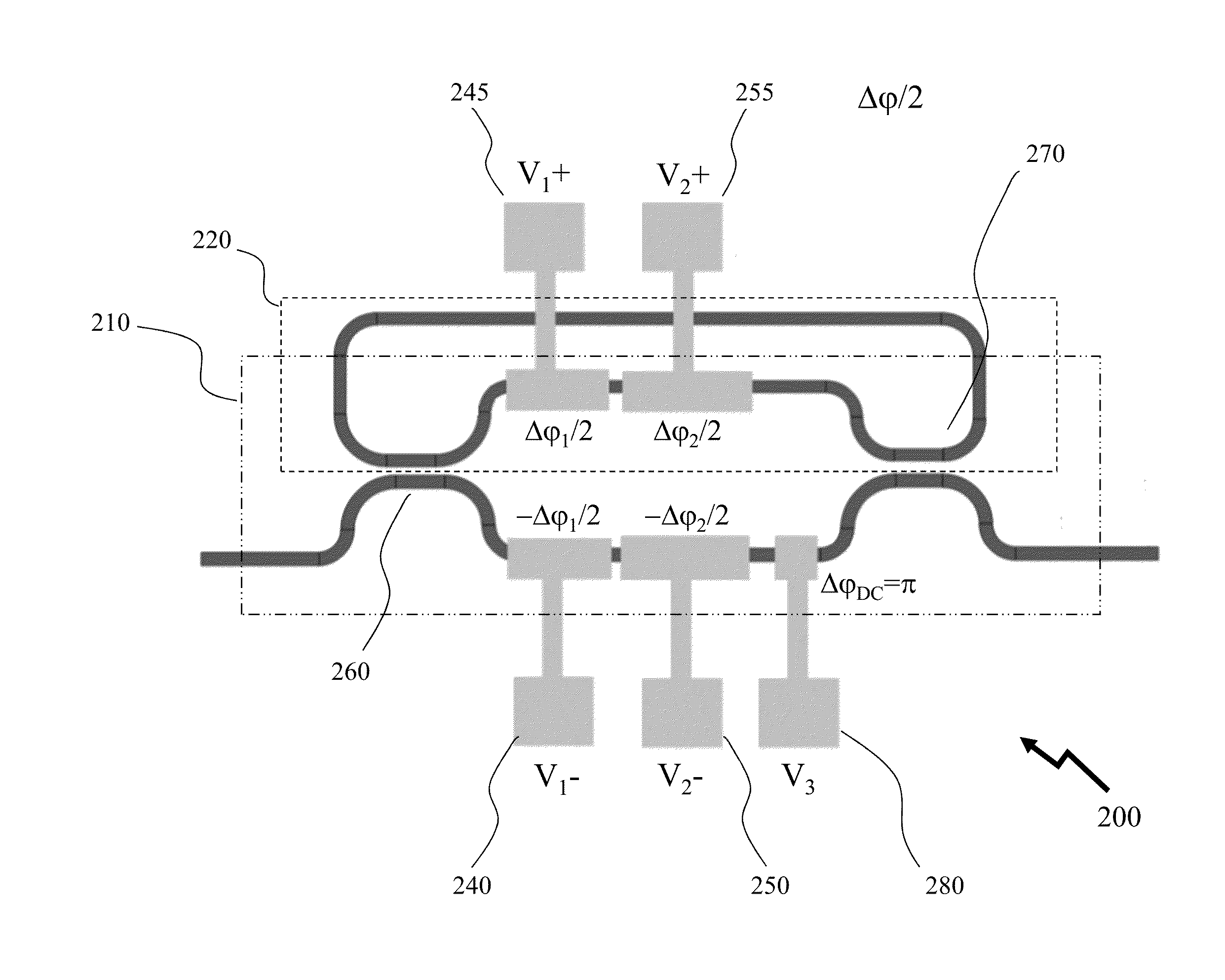

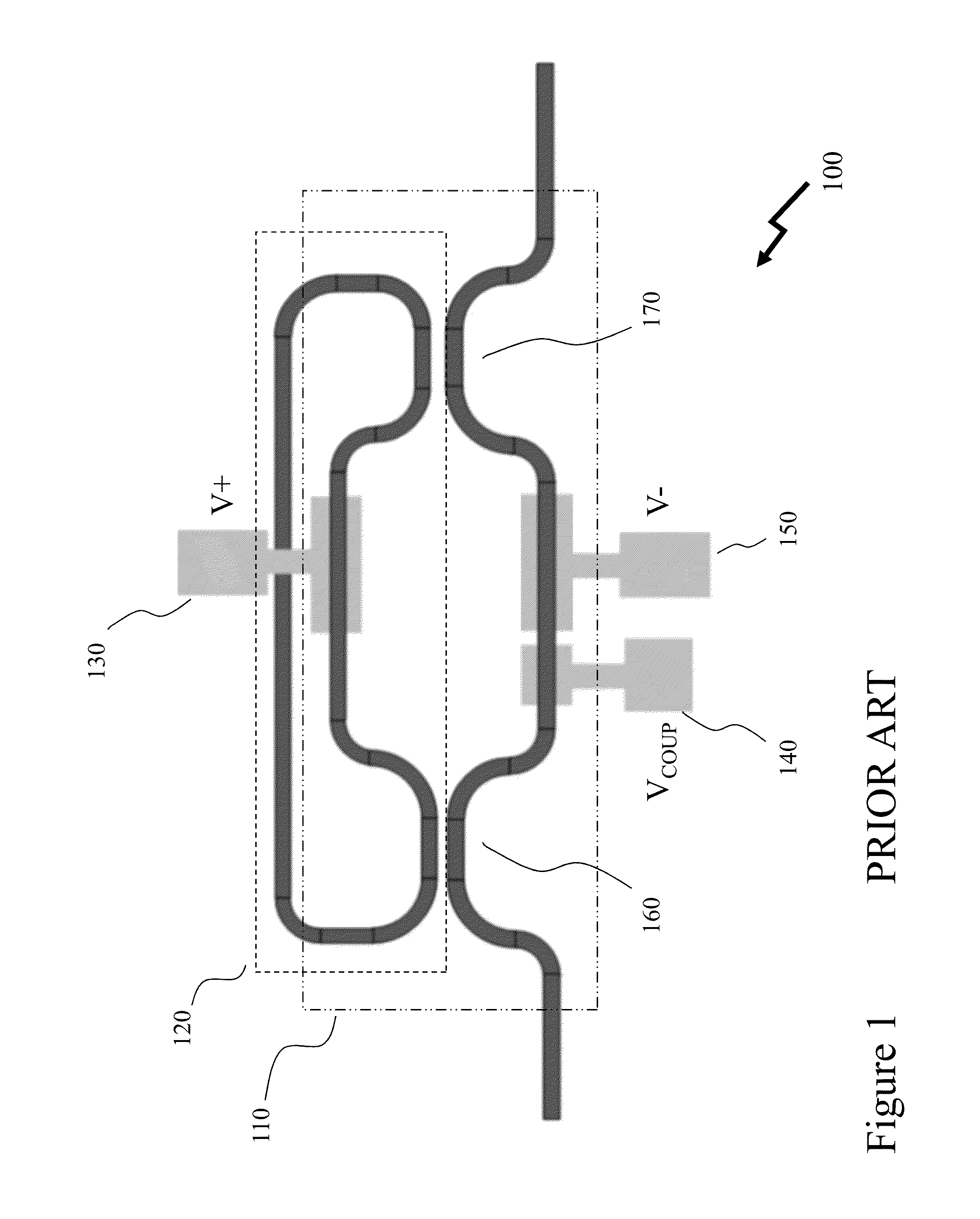

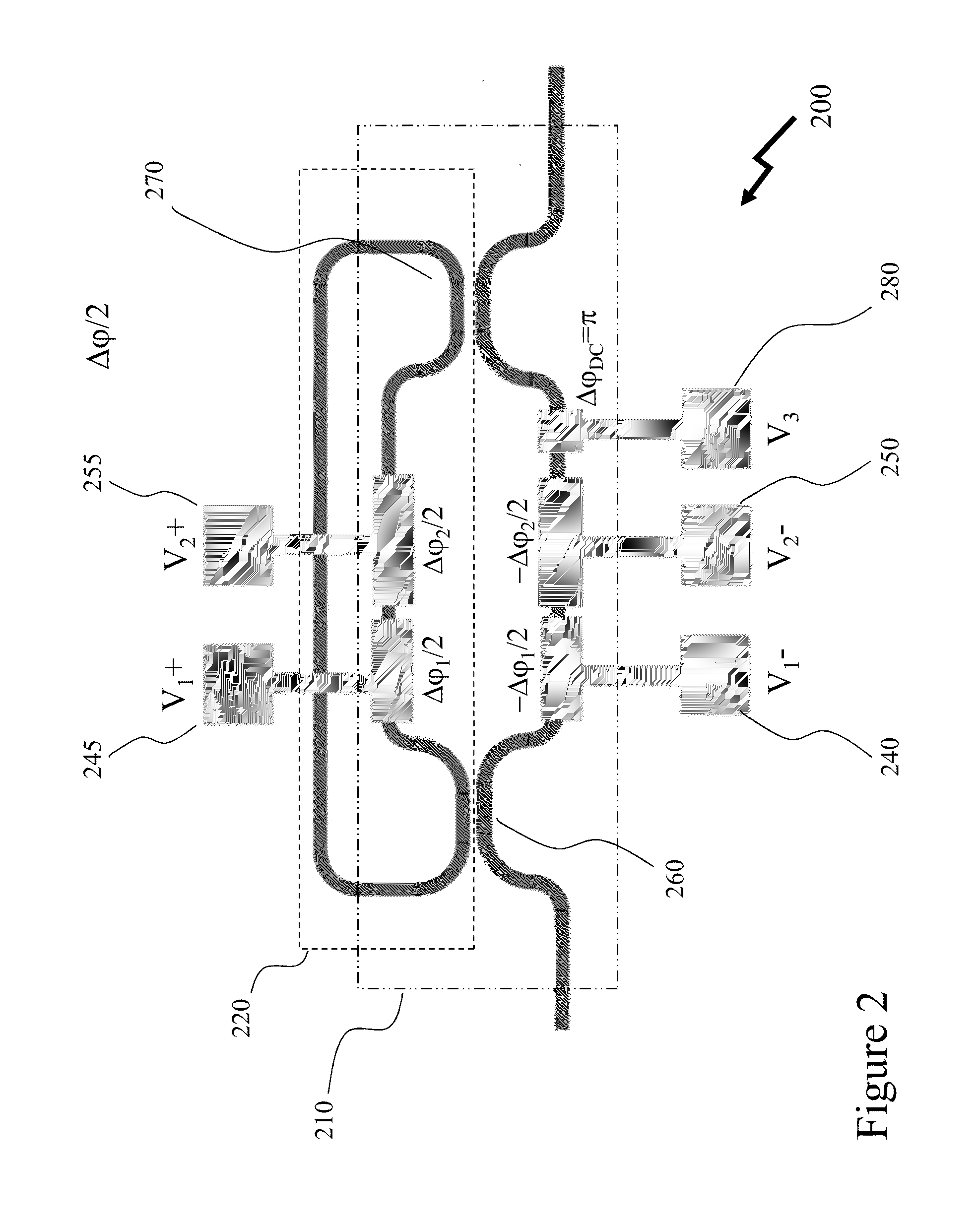

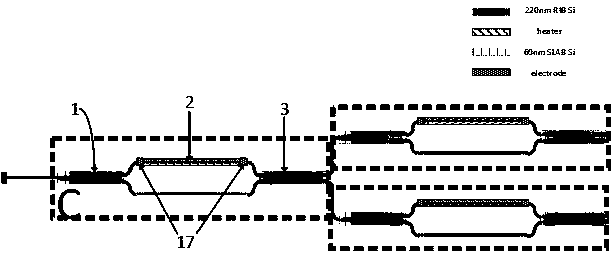

Methods and devices for photonic m-ary pulse amplitude modulation

CMOS compatible SOI photonic integrated circuits (PICs) offer a low cost and promising solution to future short reach optical links operating beyond 100 Gb / s. A key building block in these optical links is the external optical modulator. Amongst, the PIC geometries for external modulators are those based upon ring resonators and Mach-Zehnder interferometers (MZI) where whilst the latter have been reported with increased thermal stability and fabrication tolerances, the former have demonstrated lower loss and lower driving voltages leading to a more energy efficient approach. Multi-segmented electrode structure based PAM optical modulator can potentially replace the analog digital-to-analog circuits (DACs) which are commonly used to achieve the multilevel electrical driving signal. Accordingly, it would be beneficial to combine the benefits of ring resonators to provide PAM-N modulators. It would be further beneficial for such PAM-N ring resonator modulators to exploit multi-segmented electrode structures to remove the requirements for high speed DACs.

Owner:MCGILL UNIV

CMOS-compatible integration of silicon-based optical devices with electronic devices

InactiveUS20050236619A1Reduce the possibilityReduce yieldSolid-state devicesRadiation controlled devicesCMOSElectrical devices

A conventional CMOS fabrication technique is used to integrate the formation of passive optical devices and active electro-optic devices with standard CMOS electrical devices on a common SOI structure. The electrical devices and optical devices share the same surface SOI layer (a relatively thin, single crystal silicon layer), with various required semiconductor layers then formed over the SOI layer. In some instances, a set of process steps may be used to simultaneously form regions in both electrical and optical devices. Advantageously, the same metallization process is used to provide electrical connections to the electrical devices and the active electro-optic devices.

Owner:CISCO TECH INC

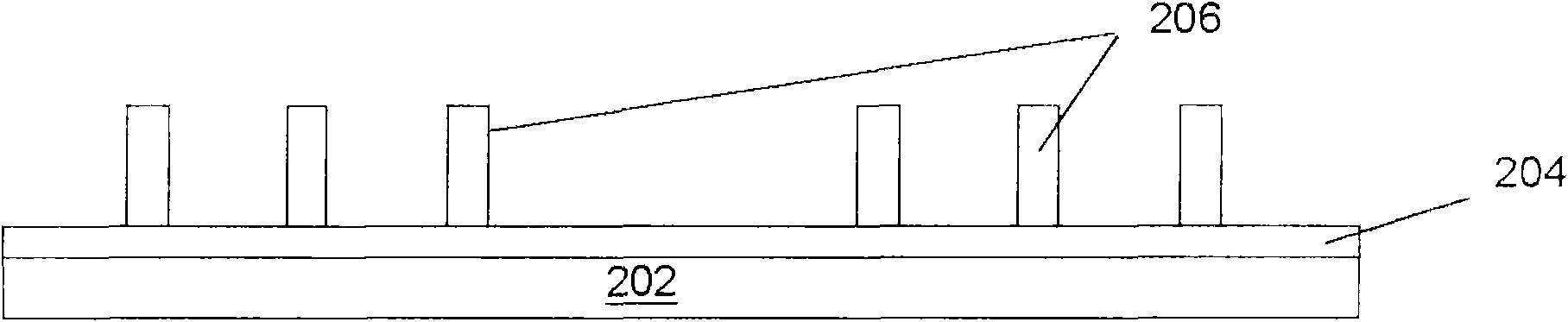

CMOS Compatible Microneedle Structures

ActiveUS20080319298A1Accurate placementMicroneedlesSemiconductor/solid-state device manufacturingEngineeringElectron

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW) +1

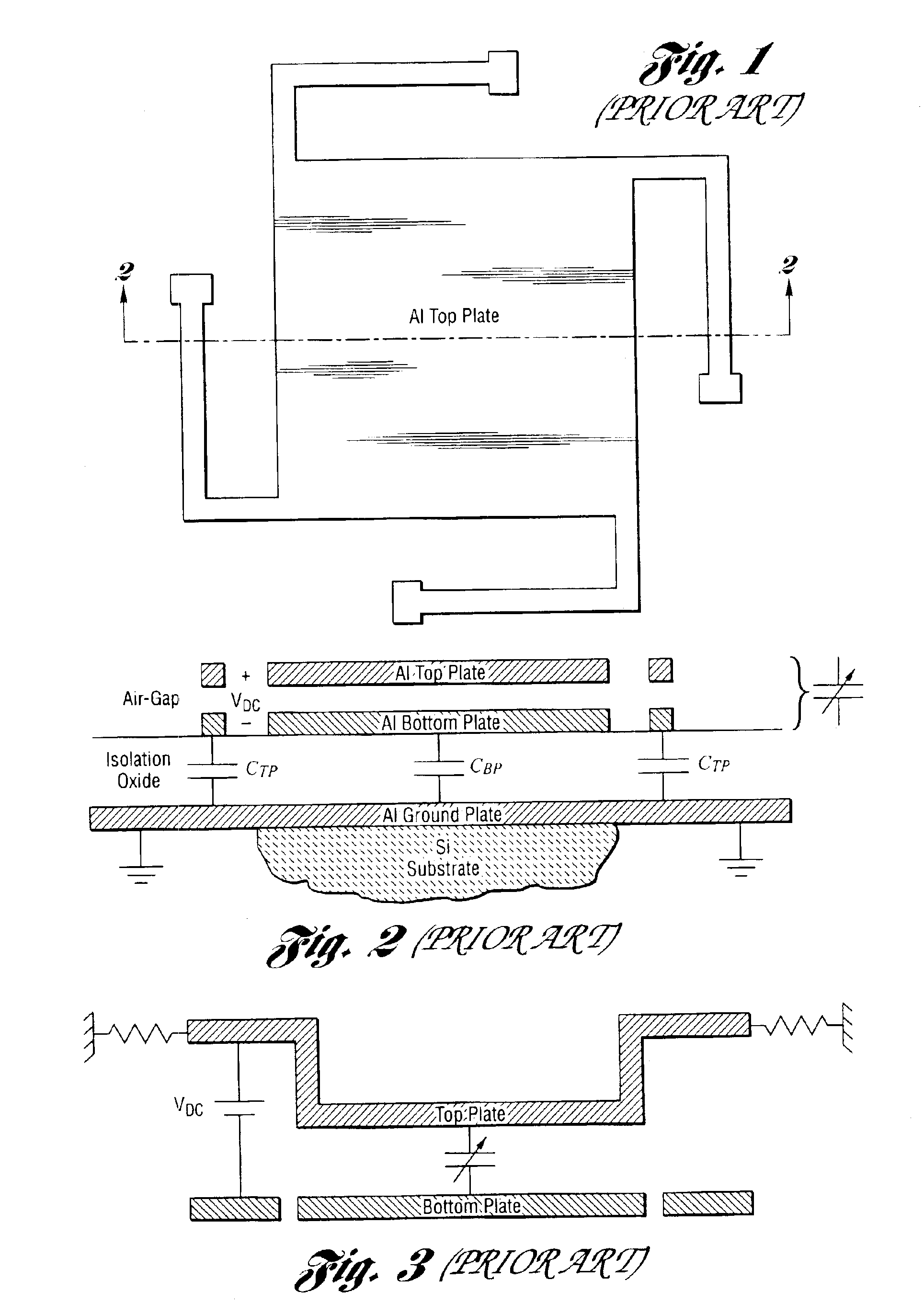

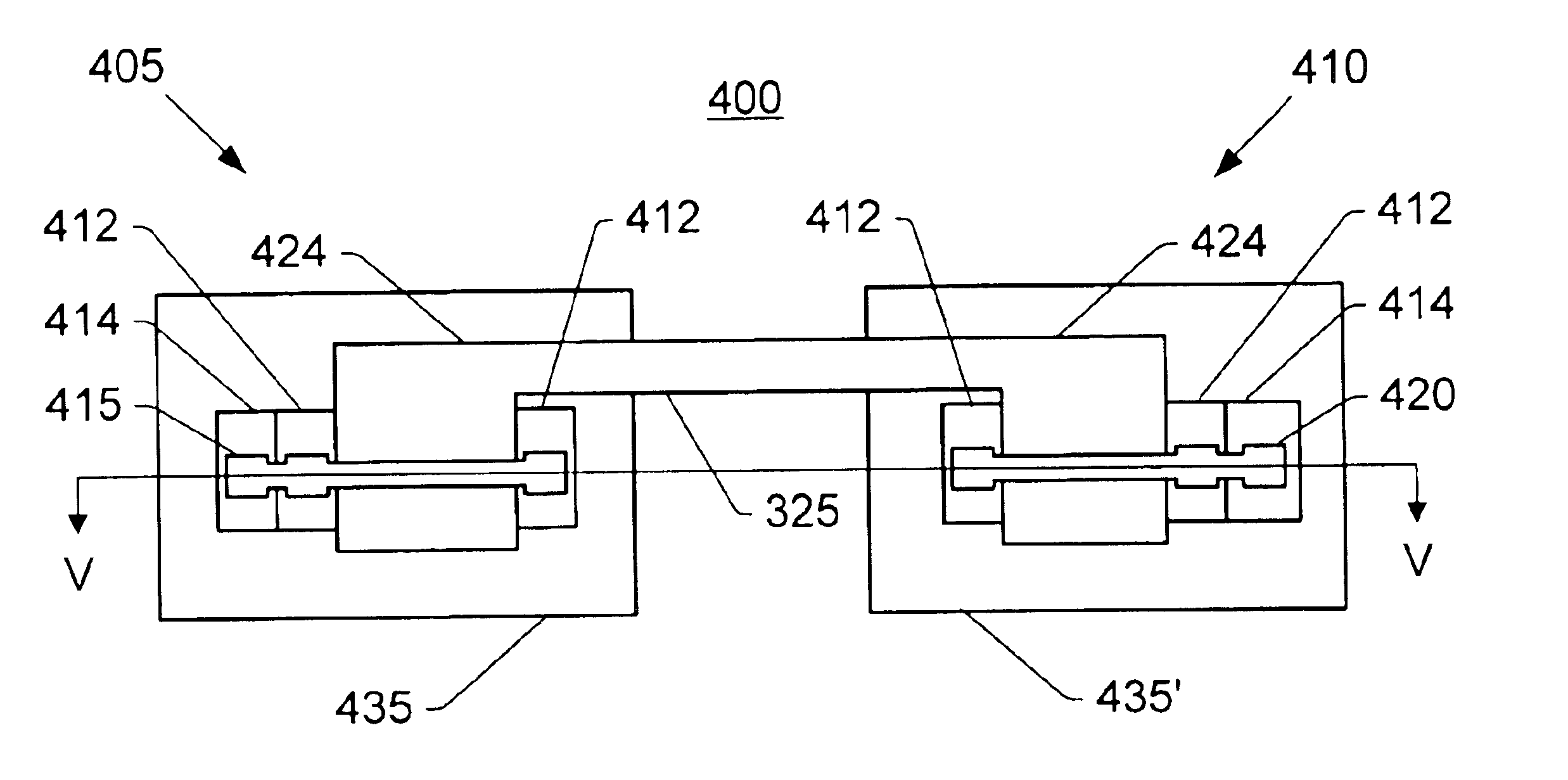

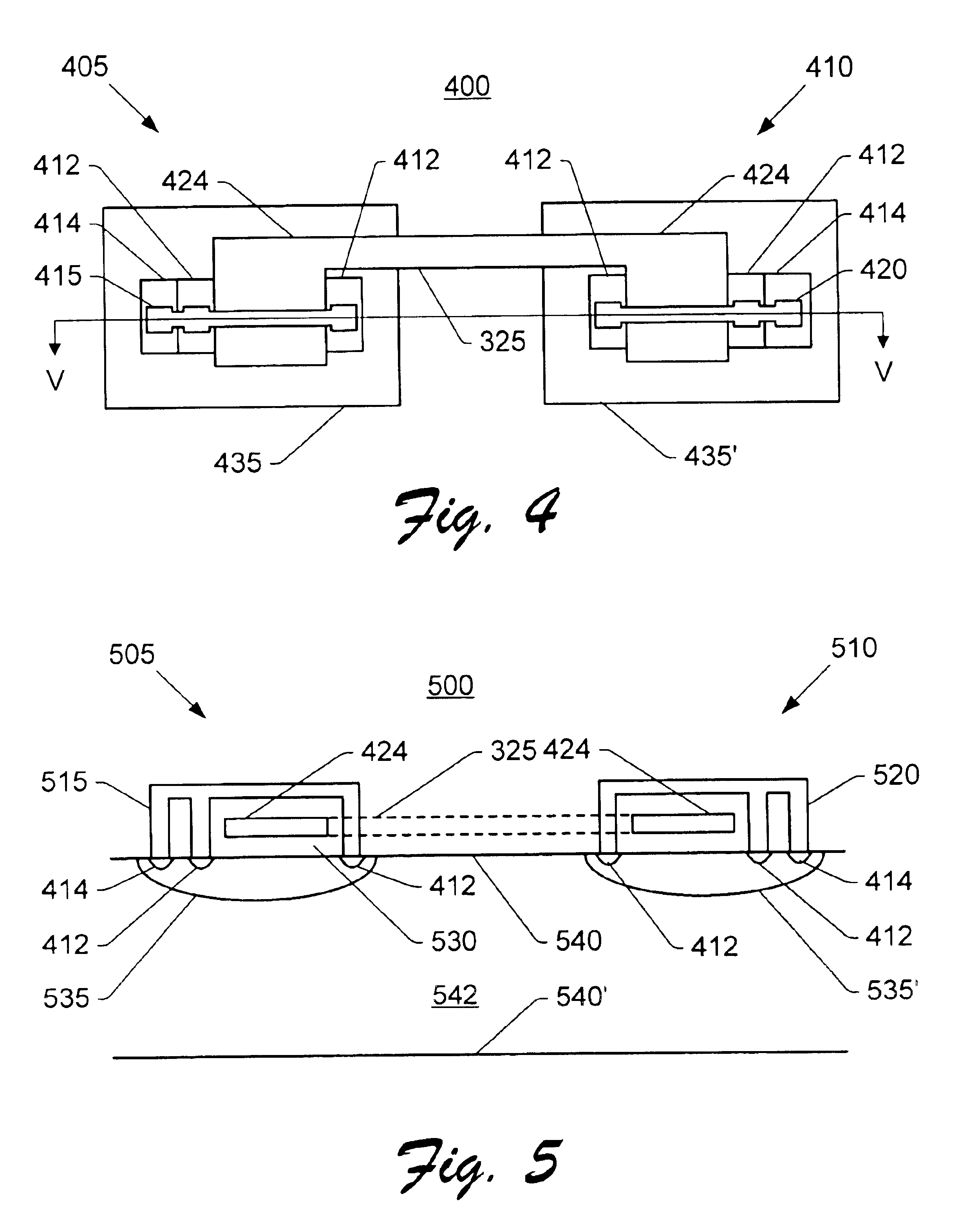

High-voltage CMOS-compatible capacitors

A high-voltage stacked capacitor includes a first capacitor and a second capacitor. Each capacitor includes a first plate comprising a first semiconductive body and a second plate comprising a floating electrode. The first and second semiconductor bodies are electrically isolated from each other. The floating electrode includes an intercapacitor node configured to self-adjust to a value less than a working voltage impressed on the stacked capacitor.

Owner:SYNOPSYS INC

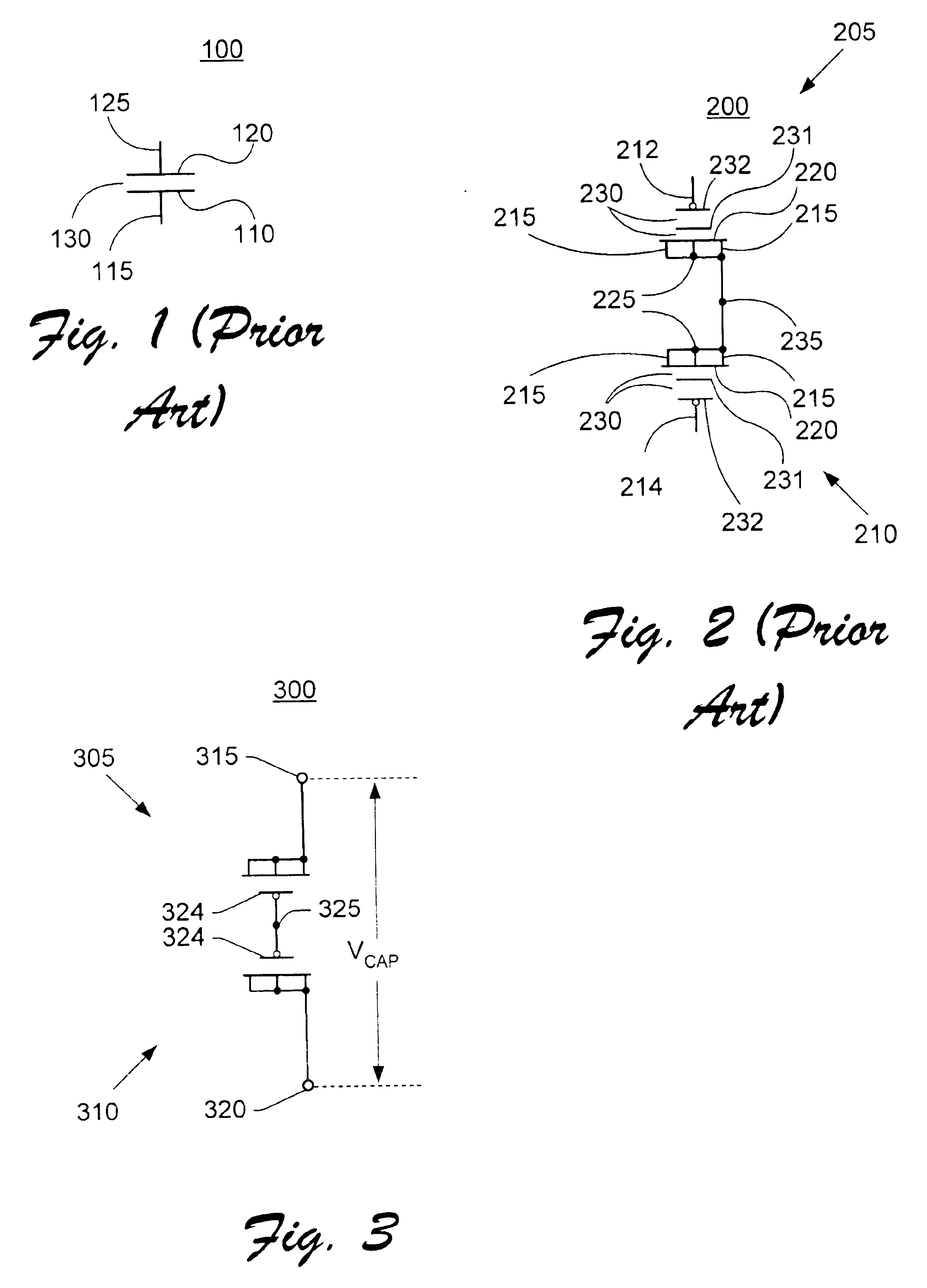

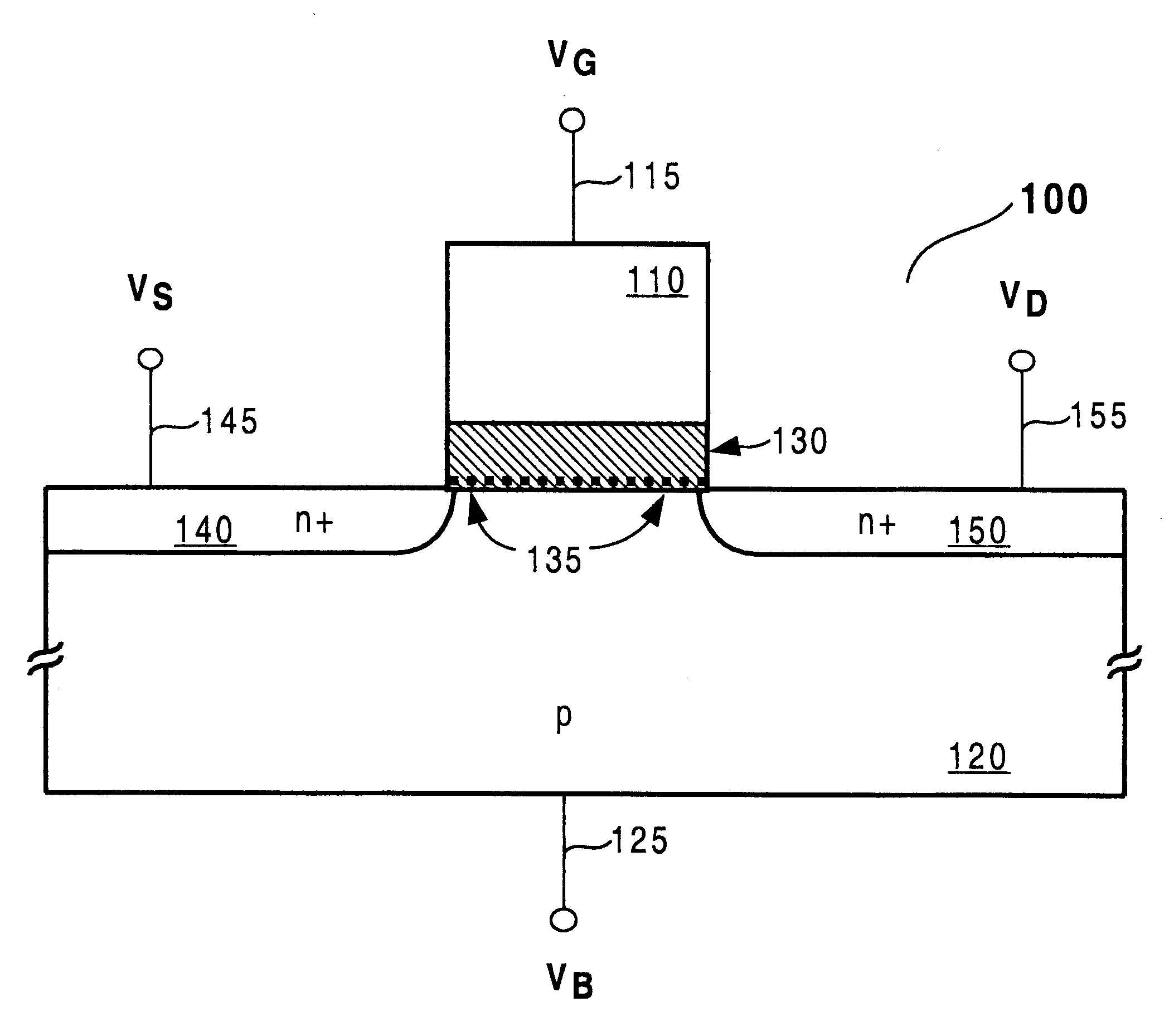

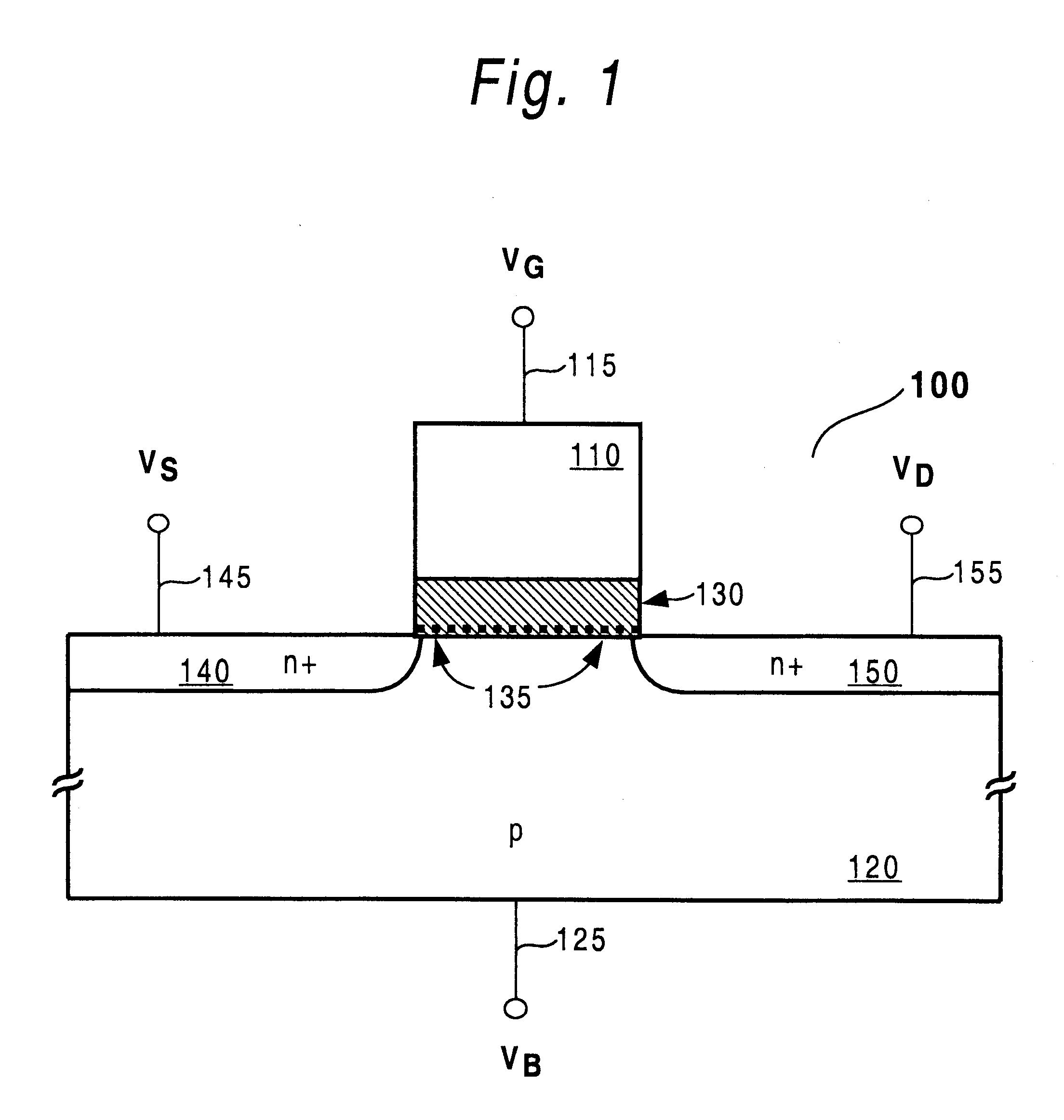

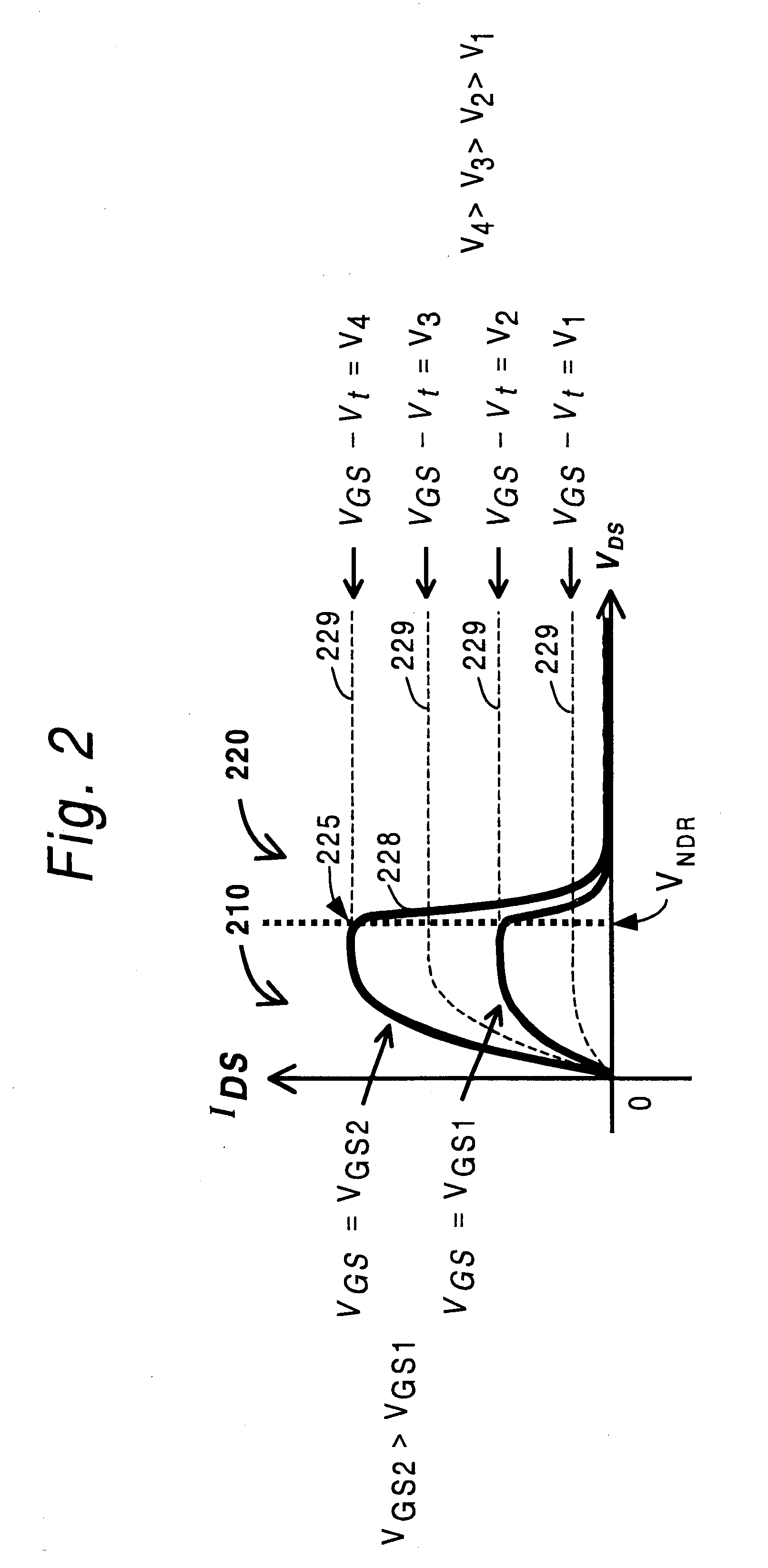

CMOS compatible process for making a tunable negative differential resistance (NDR) device

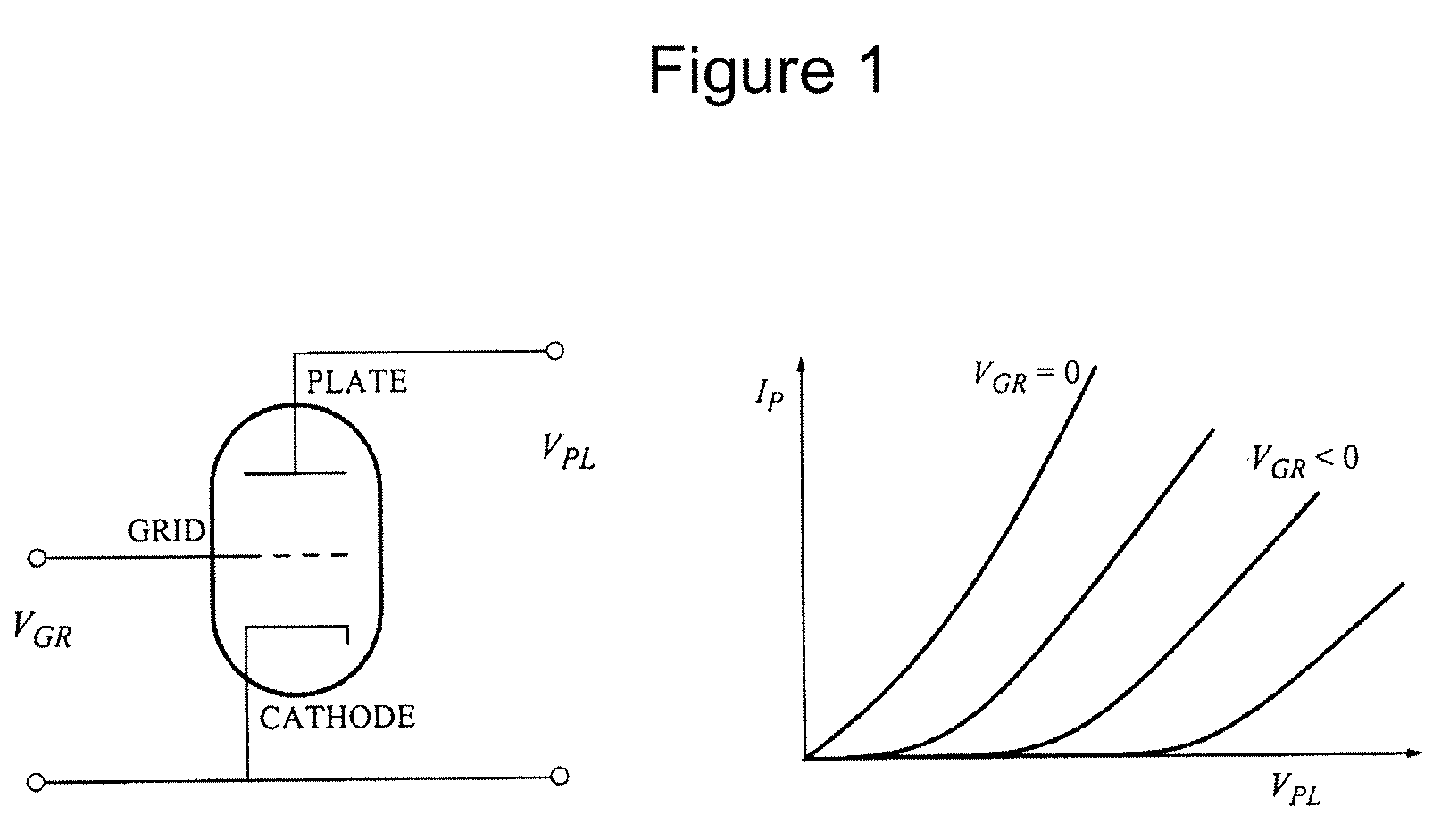

InactiveUS6596617B1Improve performance and functionalityNegative differential resistance (NDR) characteristicTransistorSemiconductor/solid-state device manufacturingCMOSMetal insulator

A method of making an n-channel metal-insulator-semiconductor field-effect transistor (MISFET) that exhibits negative differential resistance in its output characteristic (drain current as a function of drain voltage) is disclosed. By implanting ions into a substrate that is later thermally oxidized, a number of temporary charge trapping sites can be established above a channel region of a transistor. The channel is also heavily doped, so that a strong electrical field can be generated to accelerate hot carriers into the temporary charge trapping sites. The insulating layer formed during the oxidation step is made sufficiently thick to prevent quantum tunnelingo of the hot carriers into a gate electrode. Other suitable and conventional processing steps are used to finalize completion of the fabrication of the NDR device so that the entire process is compatible and achieved with CMOS processing techniques.

Owner:SYNOPSYS INC

CMOS compatible integrated dielectric optical waveguide coupler and fabrication

ActiveUS7738753B2Efficient preparationPerformance is not affectedSemiconductor/solid-state device manufacturingNanoopticsDielectricRefractive index

Owner:GLOBALFOUNDRIES U S INC

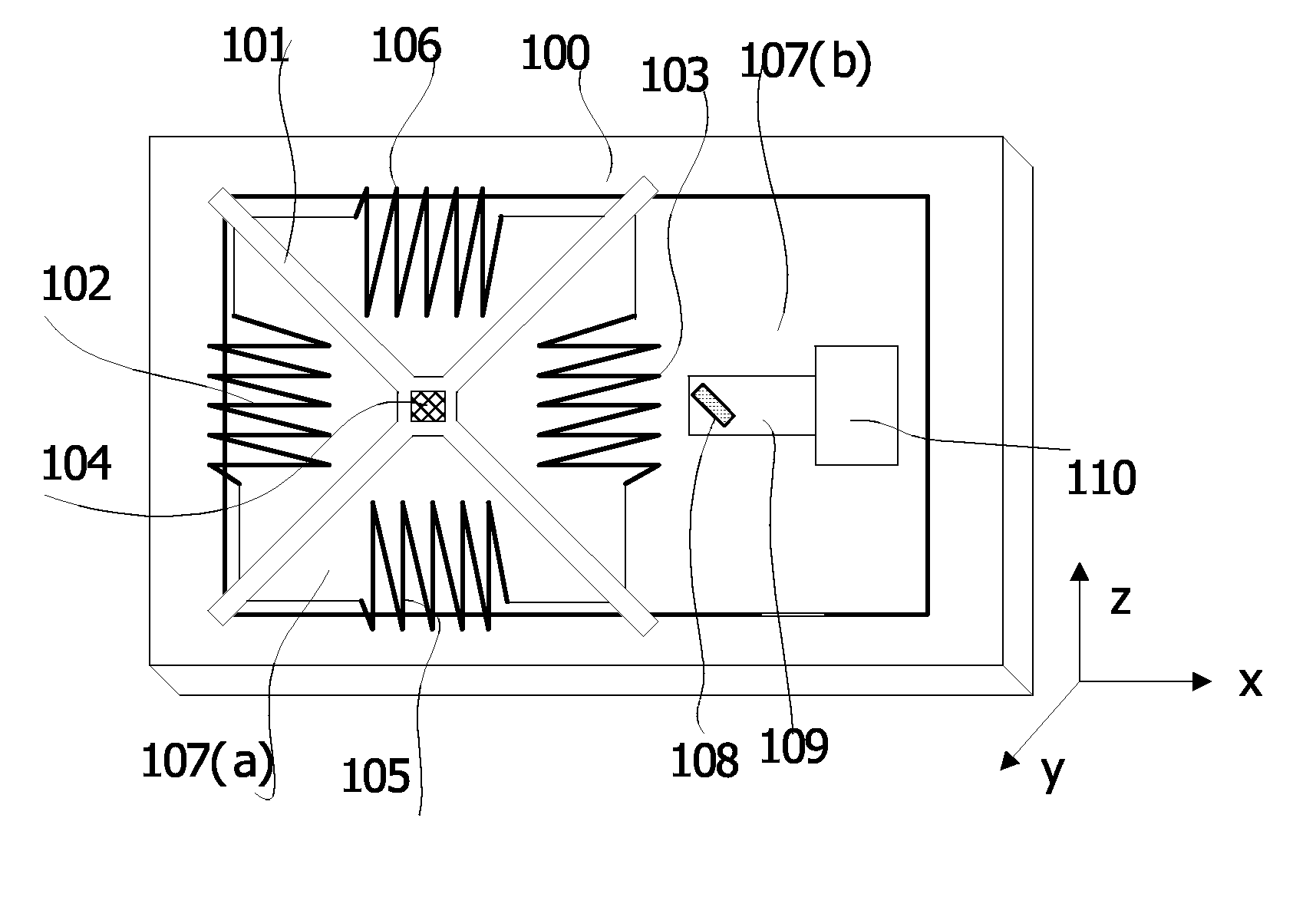

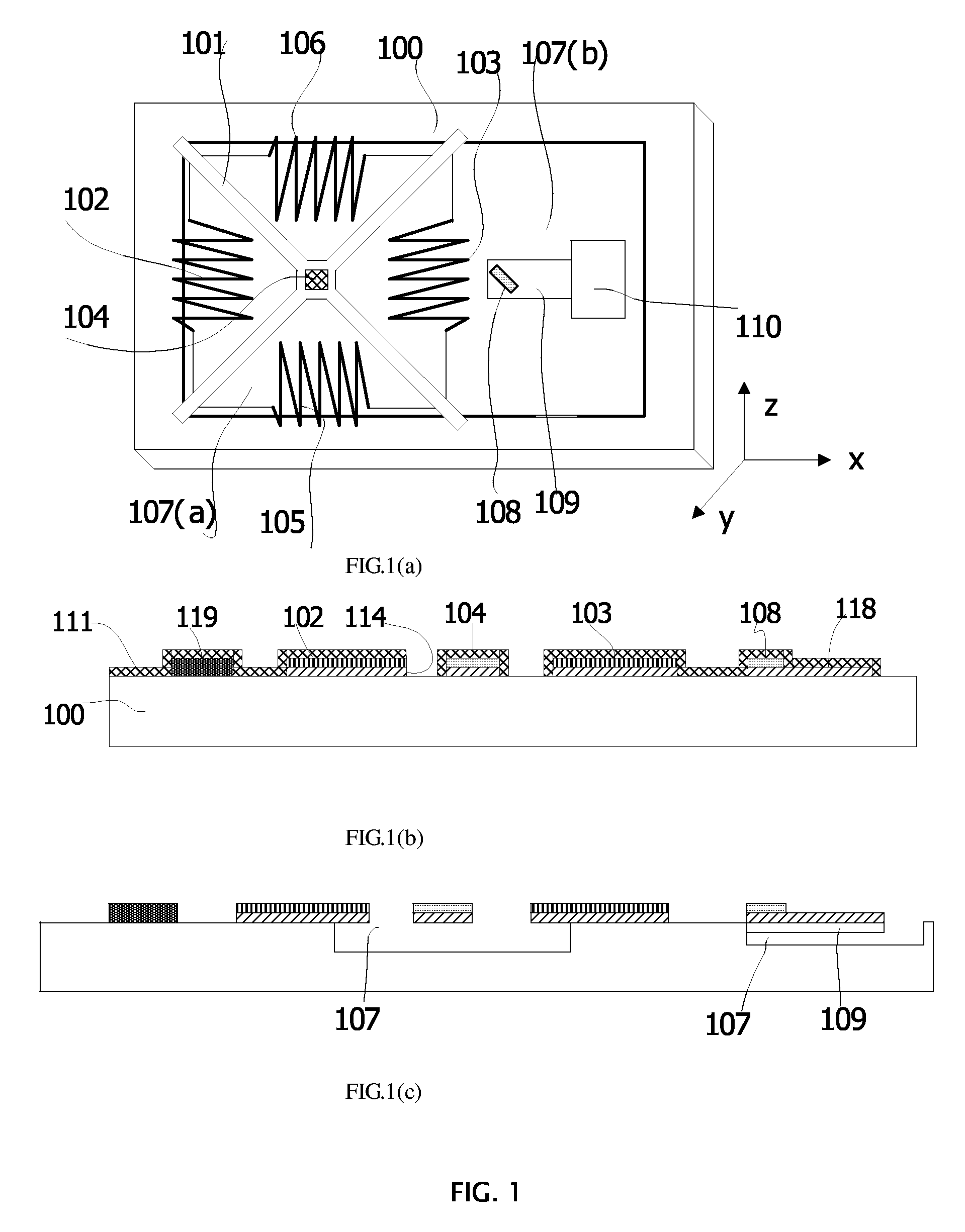

Ultra-small Profile, Low Cost Chip Scale Accelerometers of Two and Three Axes Based on Wafer Level Packaging

Several micro-machined, ultra-profile two-axis and three-axis accelerometers are fabricated by CMOS-compatible process, which makes them suitable for volume production. The x, y axis signal is based on natural thermal convection, and z-axis signal may be based on thermal convention or piezoresistive in nature. The bulk MEMS (Micro-Electro-Mechanical-Systems) process is based on Deep Reactive Ion Etching (DRIE). After the front-end fabrication process, the accelerometers are packaged at wafer level by glass frit and / or anodic bonding, which lowers the device cost.

Owner:WUHAN FINEMEMS

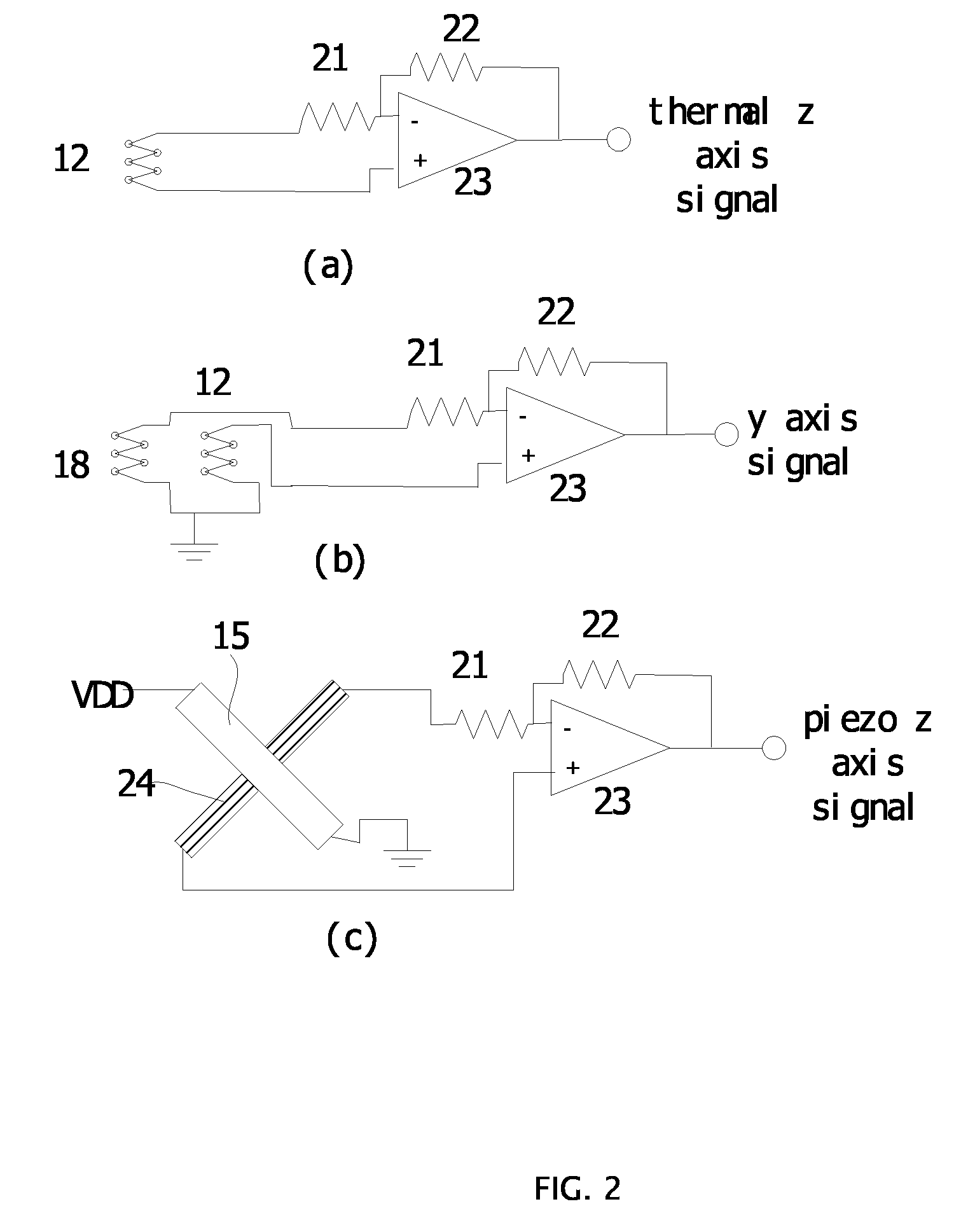

Method of fabrication of a FINFET element

The present disclosure provides a FinFET element and a method of fabricating a FinFET element. The FinFET element includes a germanium-FinFET element (e.g., a multi-gate device including a Ge-fin). In one embodiment, the method of fabrication the Ge-FinFET element includes forming silicon fins on a substrate and selectively growing an epitaxial layer including germanium on the silicon fins. A Ge-condensation process may then be used to selectively oxidize the silicon of the Si-fin and transform the Si-fin to a Ge-fin. The method of fabrication provided may allow use of SOI substrate or bulk silicon substrates, and CMOS-compatible processes to form the Ge-FinFET element.

Owner:TAIWAN SEMICON MFG CO LTD

CMOS compatible shallow-trench efuse structure and method

InactiveUS20070120218A1Easy to integrateMinimizing implementation costSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureEngineering

A semiconductor structure including at least one e-fuse embedded within a trench that is located in a semiconductor substrate (bulk or semiconductor-on-insulator) is provided. In accordance with the present invention, the e-fuse is in electrical contact with a dopant region that is located within the semiconductor substrate. The present invention also provides a method of fabricating such a semiconductor structure in which the embedded e-fuse is formed substantially at the same time with the trench isolation regions.

Owner:GOOGLE LLC

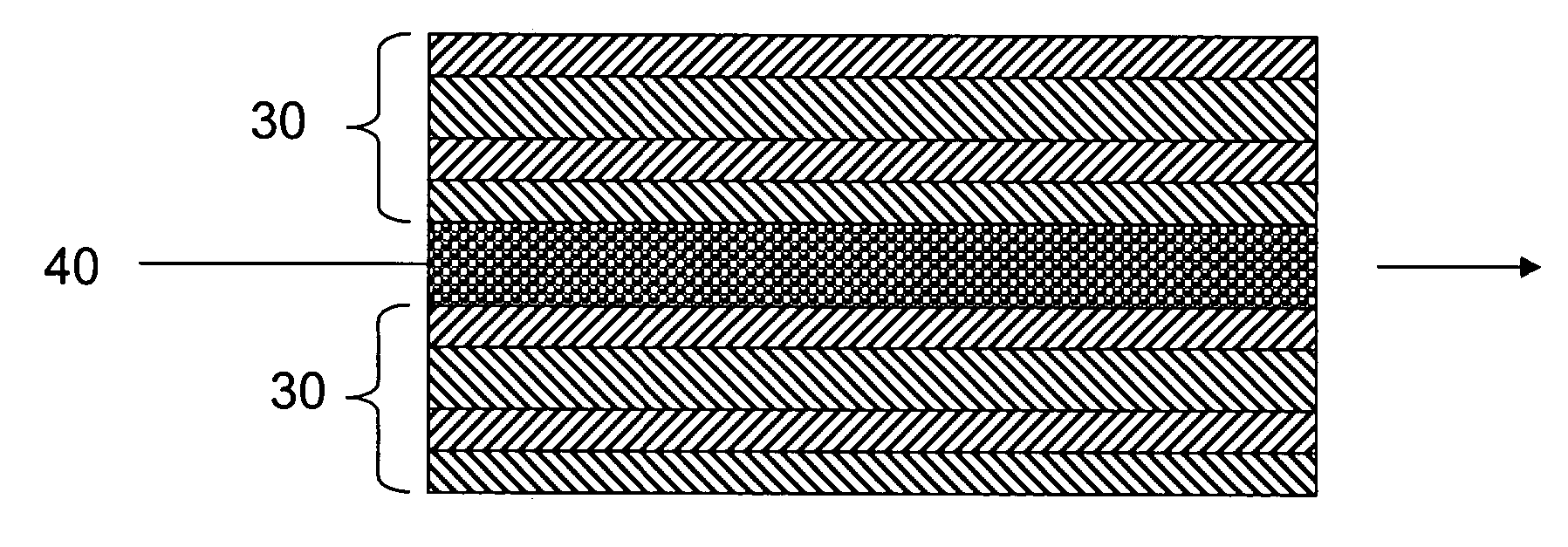

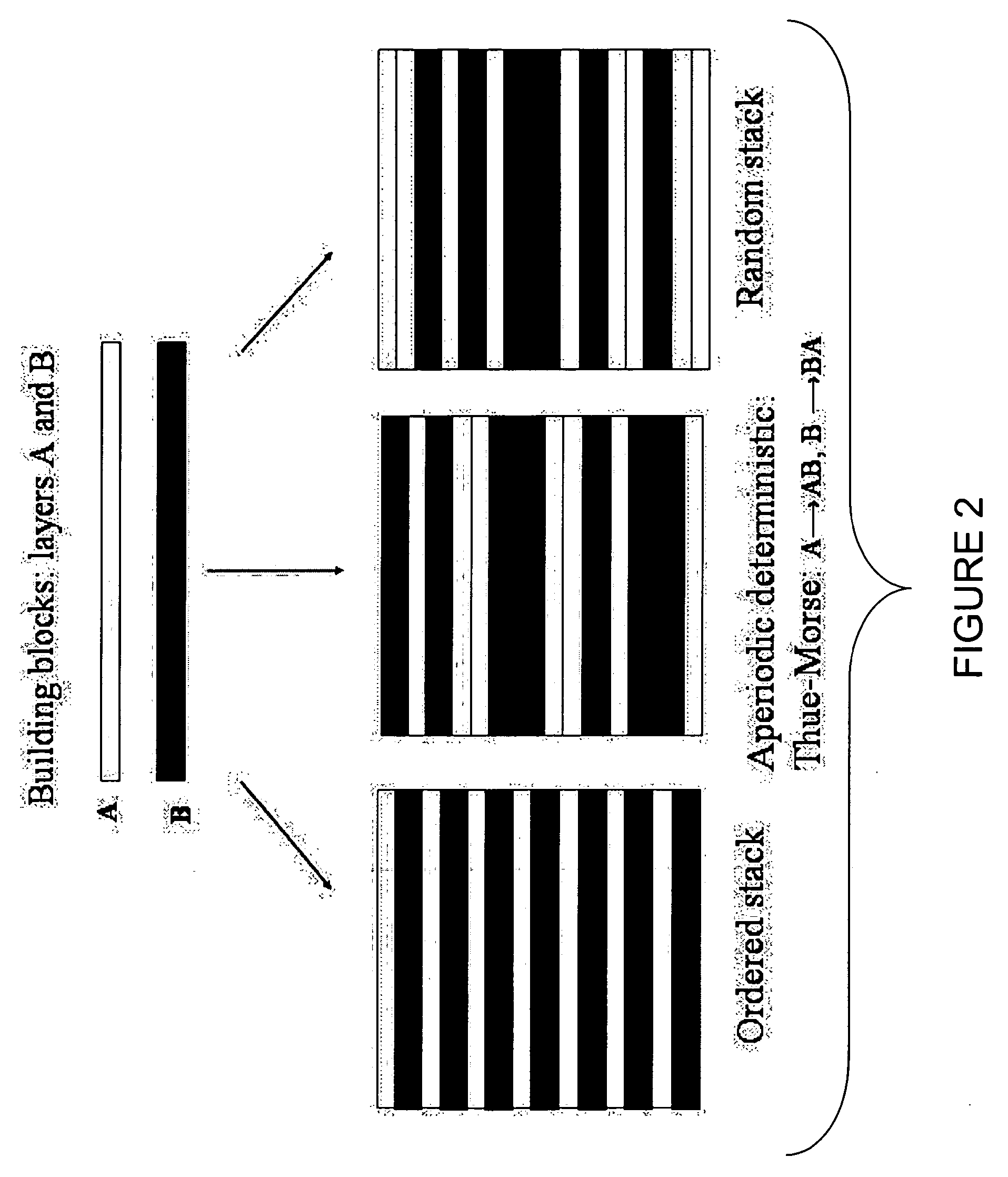

CMOS-compatible light emitting aperiodic photonic structures

A fabrication method and materials produce high quality aperiodic photonic structures. Light emission can be activated by thermal annealing post growth treatments when thin film layers of SiO2 and SiNx or Si-rich oxide are used. From these aperiodic structures, that can be obtained in different vertical and planar device geometries, the presence of aperiodic order in a photonic device provides strong group velocity reduction (slow photons), enhanced light-matter interaction, light emission enhancement, gain enhancement, and / or nonlinear optical properties enhancement.

Owner:MASSACHUSETTS INST OF TECH

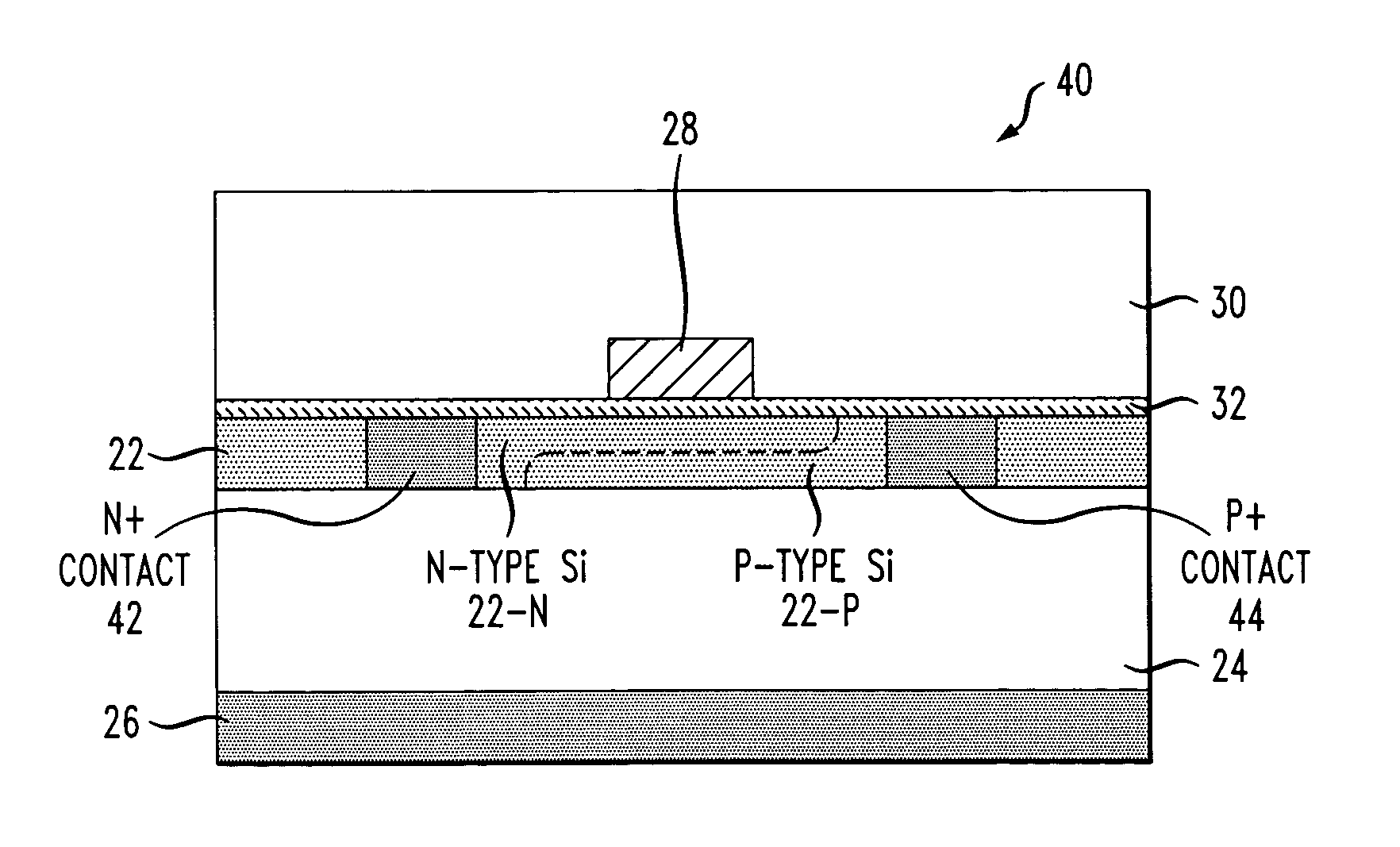

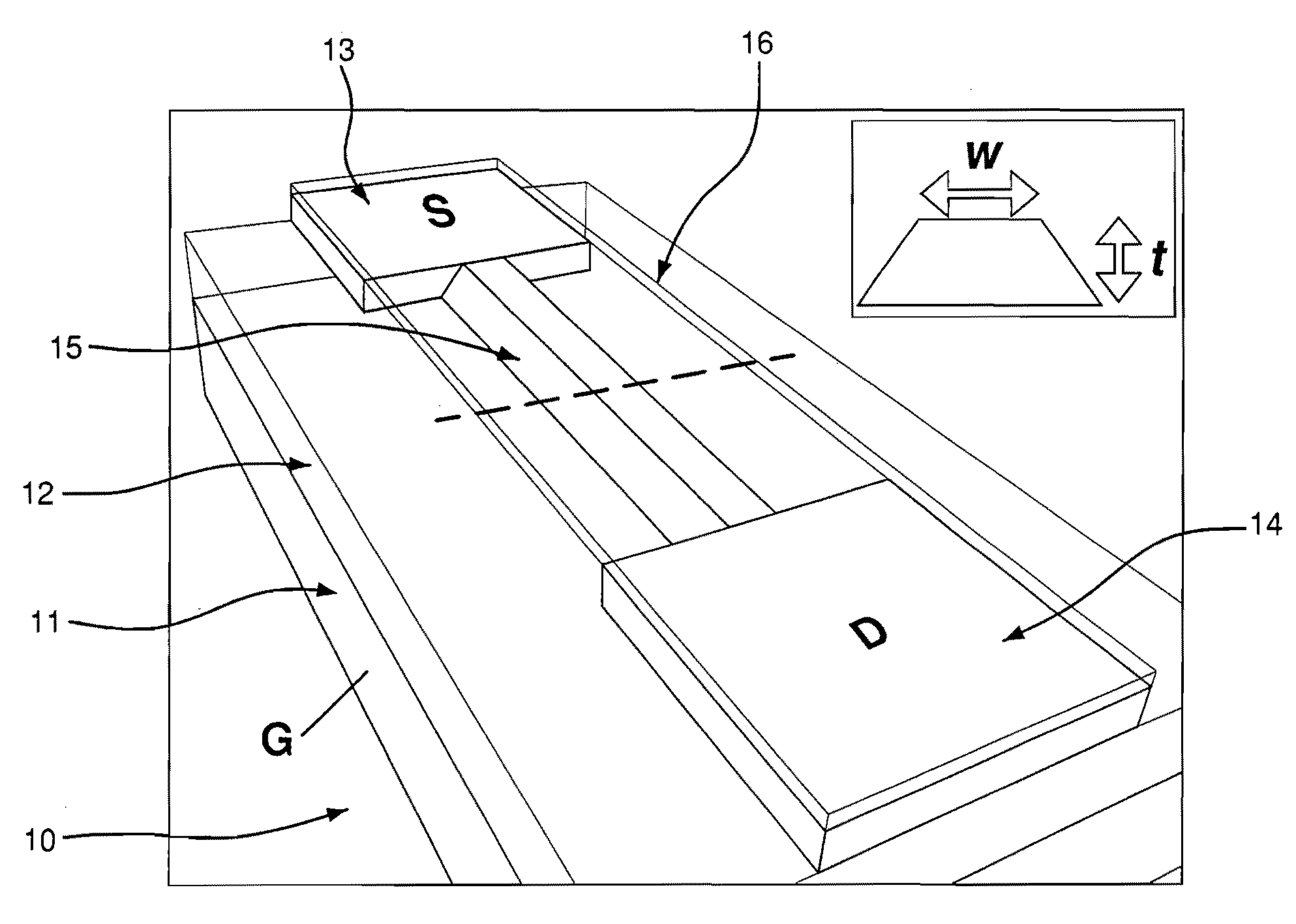

Systems and Methods for CMOS-Compatible Silicon Nano-Wire Sensors with Biochemical and Cellular Interfaces

ActiveUS20100297608A1High sensitivityIncrease the areaMicrobiological testing/measurementNanoinformaticsSemiconductor materialsConducting pathway

The systems and methods described herein include a sensor for suitable for sensing chemical and biological substances. The sensor comprises a semiconductor layer formed in or on a substrate and a channel having nano-scale dimensions formed in the semiconductor layer, where the structure creates an electrically conducting pathway between a first contact and a second contact on the semiconductor layer. In certain preferred embodiments, the nano-scale channel has a trapezoidal cross-section with an effective width and exposed lateral faces, where the effective width is selected to have same order of magnitude as a Debye length (LD) of the semiconductor material of which the semiconductor layer is formed.

Owner:YALE UNIV

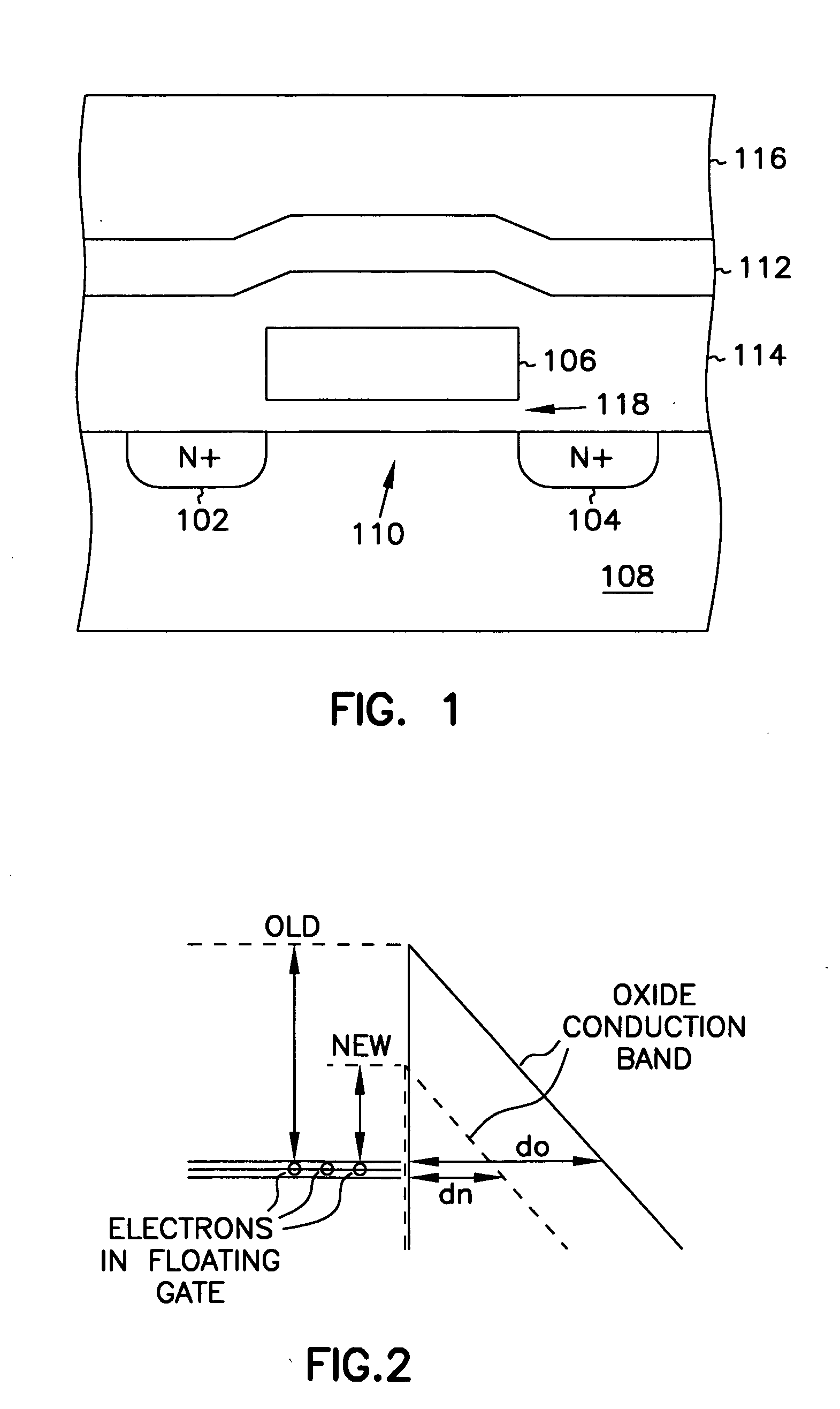

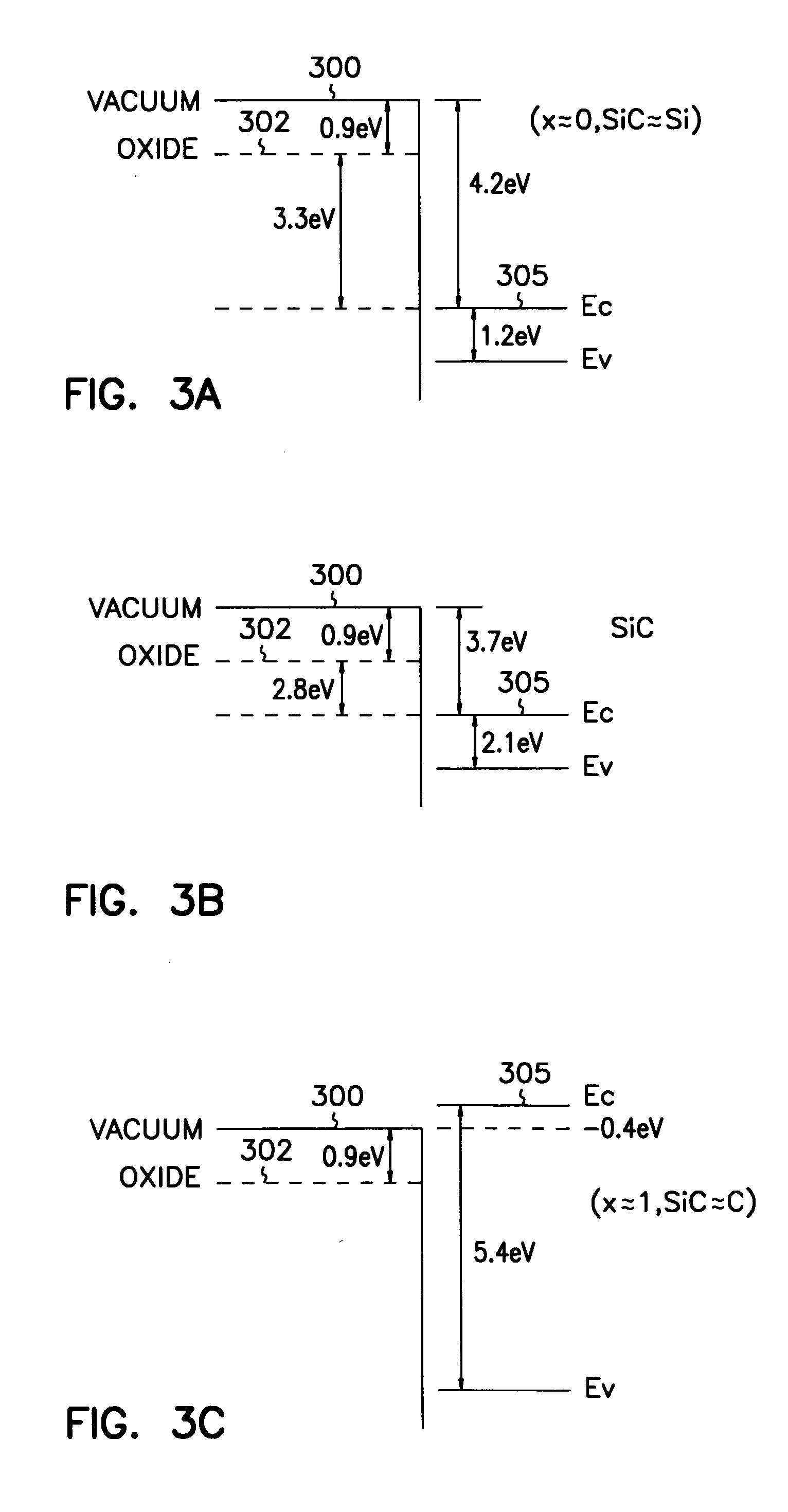

Transistor with variable electron affinity gate and methods of fabrication and use

InactiveUS20050146934A1Reduced barrier energyIncreases tunneling probabilityTransistorRead-only memoriesCharge retentionPhotodetector

A CMOS-compatible FET has a reduced electron affinity polycrystalline or microcrystalline SiC gate that is electrically isolated (floating) or interconnected. The SiC material composition is selected to establish the barrier energy between the SiC gate and a gate insulator. In a memory application, such as a flash EEPROM, the SiC composition is selected to establish a lower barrier energy to reduce write and erase voltages and times or accommodate the particular data charge retention time needed for the particular application. In a light detector or imaging application, the SiC composition is selected to provide sensitivity to the desired wavelength of light. Unlike conventional photodetectors, light is absorbed in the floating gate, thereby ejecting previously stored electrons therefrom. Also unlike conventional photodetectors, the light detector according to the present invention is actually more sensitive to lower energy photons as the semiconductor bandgap is increased.

Owner:MICRON TECH INC

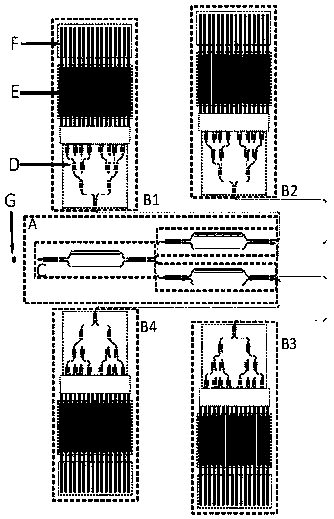

Single wavelength multiline scanning system based on thermo-optic switches and silicon optical phased array

The invention discloses a single wavelength multiline scanning system based on thermo-optic switches and a silicon optical phased array. MZ-MMI thermo-optic switches form a channel selection module through cascading, and the output end is connected with the optical phased array unit modules of different grating period coupled grating arrays. Each optical phased array unit module comprises a beam splitter module formed by the cascaded 1x2MMI, a waveguide connection module, a thermo-optic phase shifter array and a coupled grating array. The cascaded thermo-optic switches are applied to select and switch different optical phased array modules, different grating periods of coupled grating arrays are applied for radiation in the aspect of device, beam elevation control is realized in the aspectof effect and the frequency band resource can be greatly saved. Besides, the silicon-based optoelectronic device has the characteristics of being small in size and compatible with the CMOS technologyso that manufacturing is easy and large-scale integration can be realized. The size of the whole set of system is far less than that of other radar scanning systems, and full coverage scanning of thebeams on the hemispherical surface can be realized by only using single wavelength.

Owner:ZHEJIANG UNIV

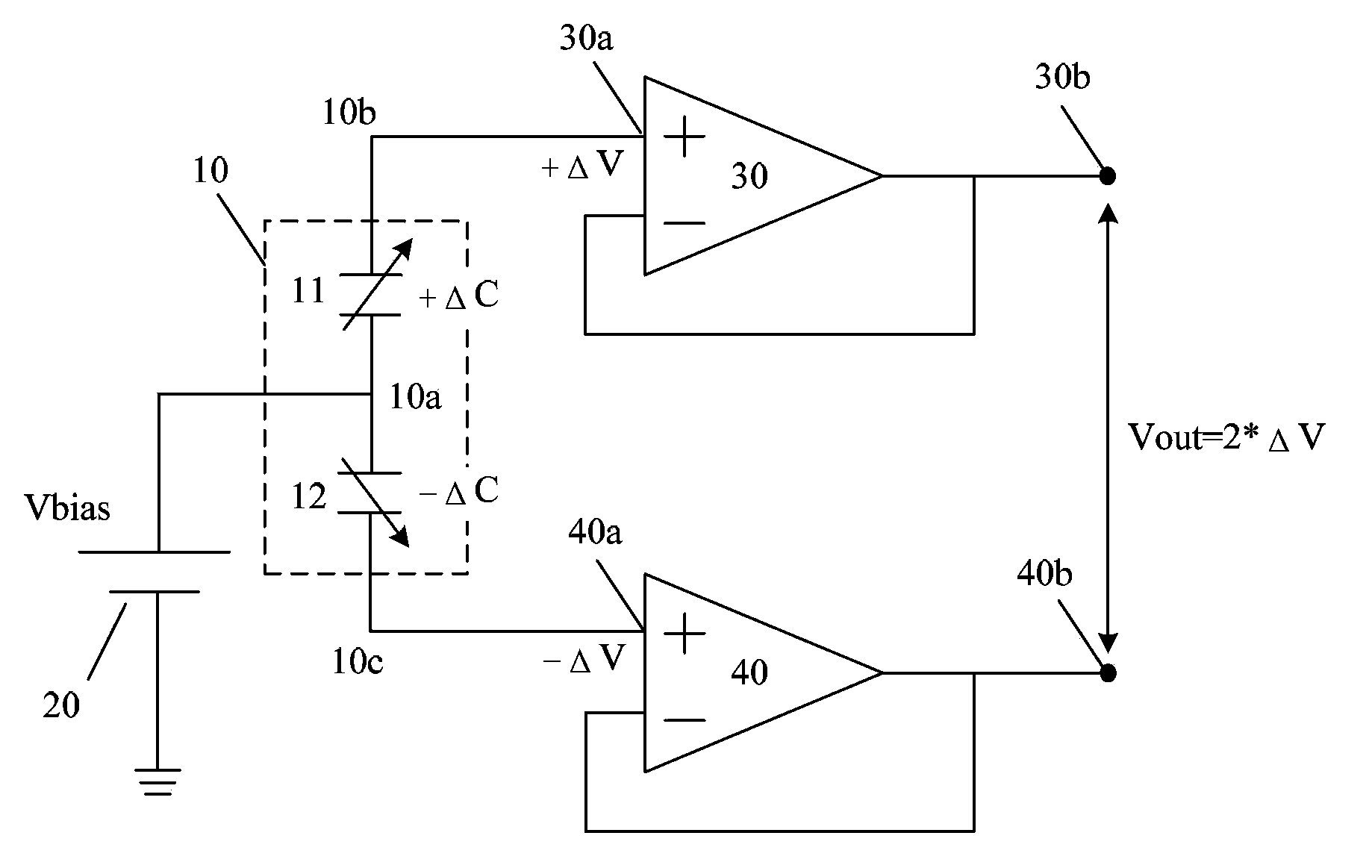

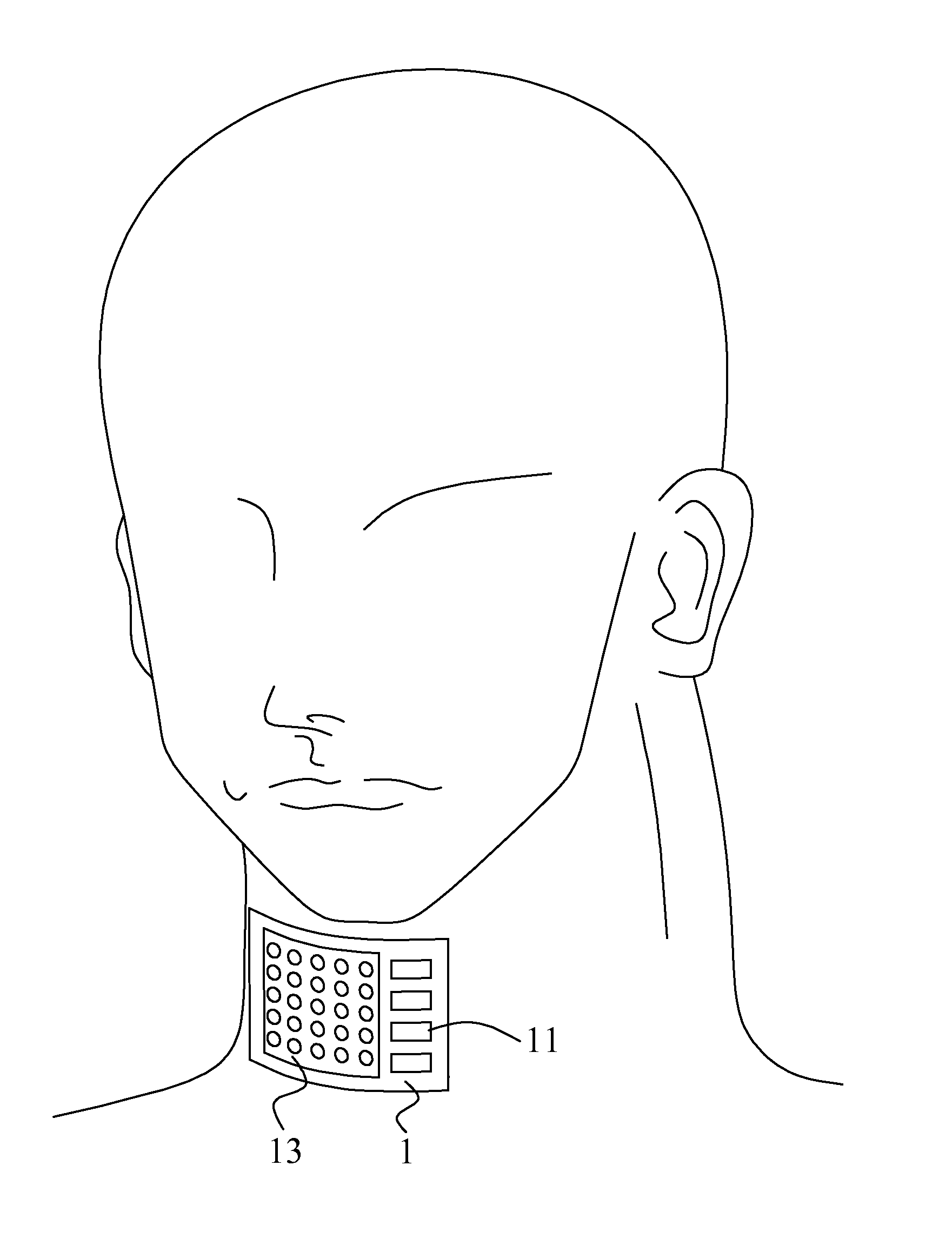

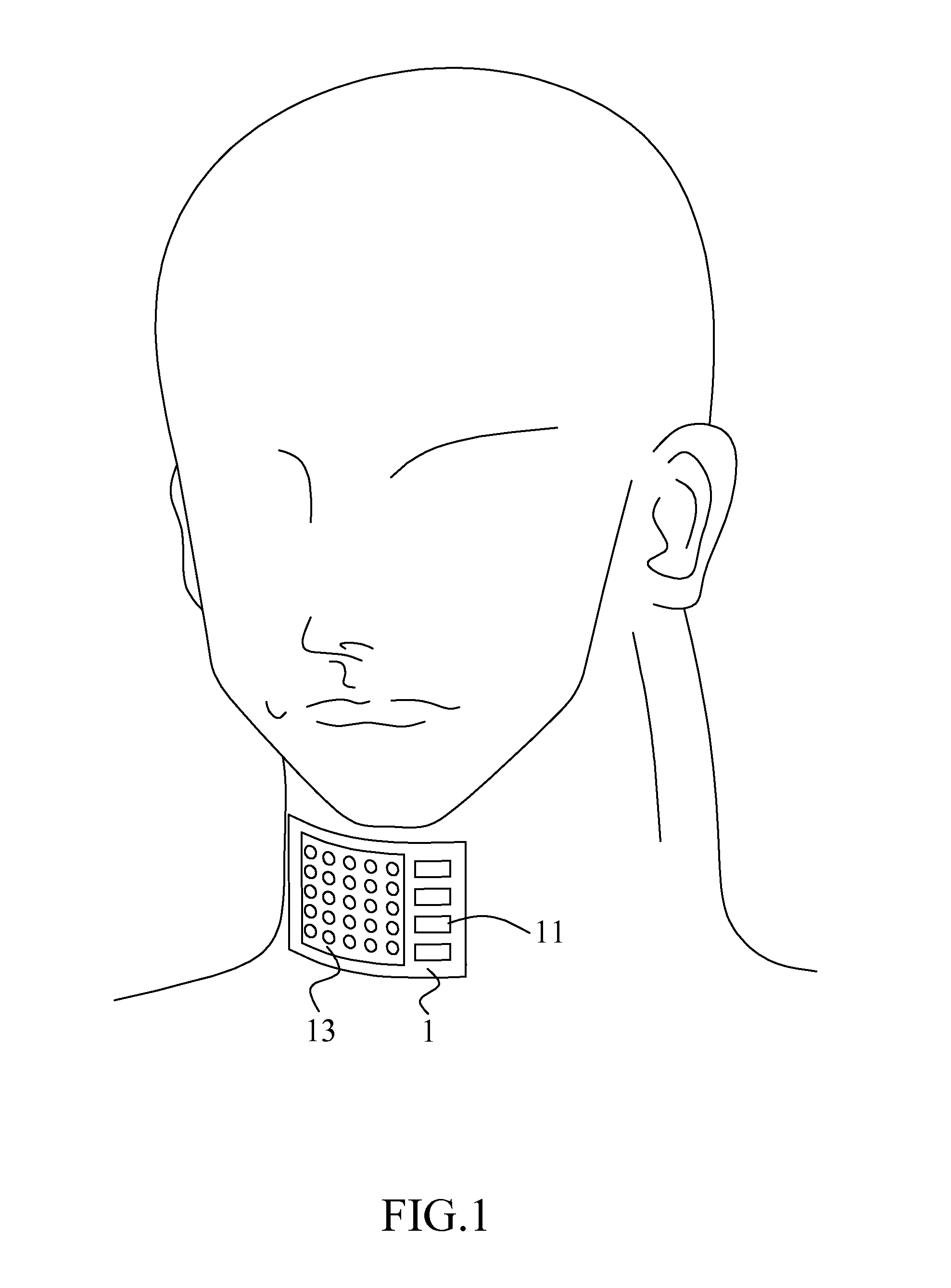

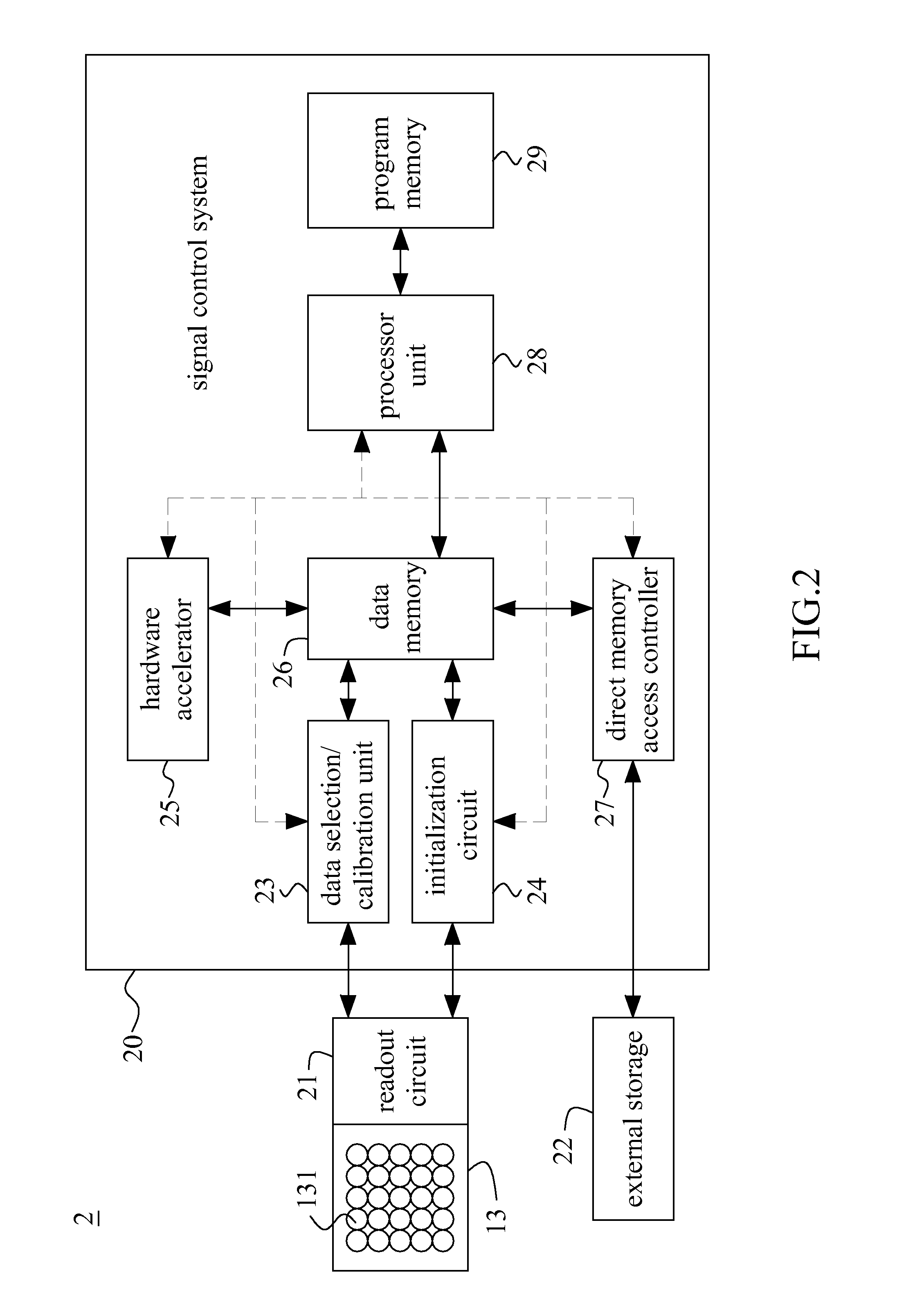

SMART NON-INVASIVE ARRAY-BASED HEMODYNAMIC MONITORING SYSTEM on CHIP AND METHOD THEREOF

A non-invasive array-based hemodynamic monitoring system on chip is disclosed. The non-invasive array-based hemodynamic monitoring system on chip comprises a CMOS MEMS pressure sensor array, a readout circuit, and a signal control system. The CMOS MEMS pressure sensor array is configured to sense a pulse wave of a blood vessel. The readout circuit is coupled with each of the CMOS compatible MEMS pressure sensors and is configured to read the pulse wave and transformed the pulse wave into a voltage signal. The signal control system is coupled with each of the readout circuit, and is configured to estimate a wave velocity according to the voltage signal.

Owner:NAT TAIWAN UNIV

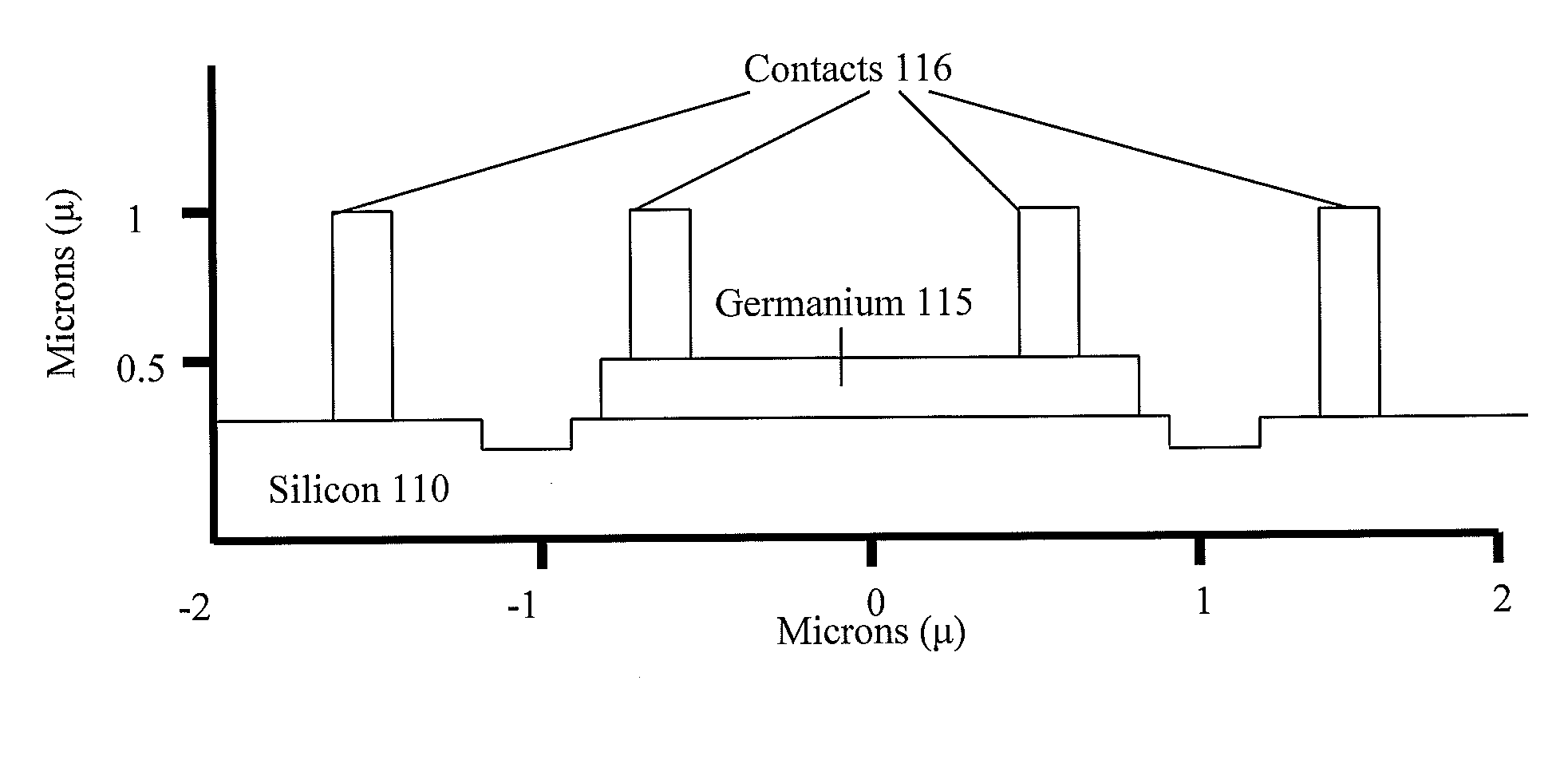

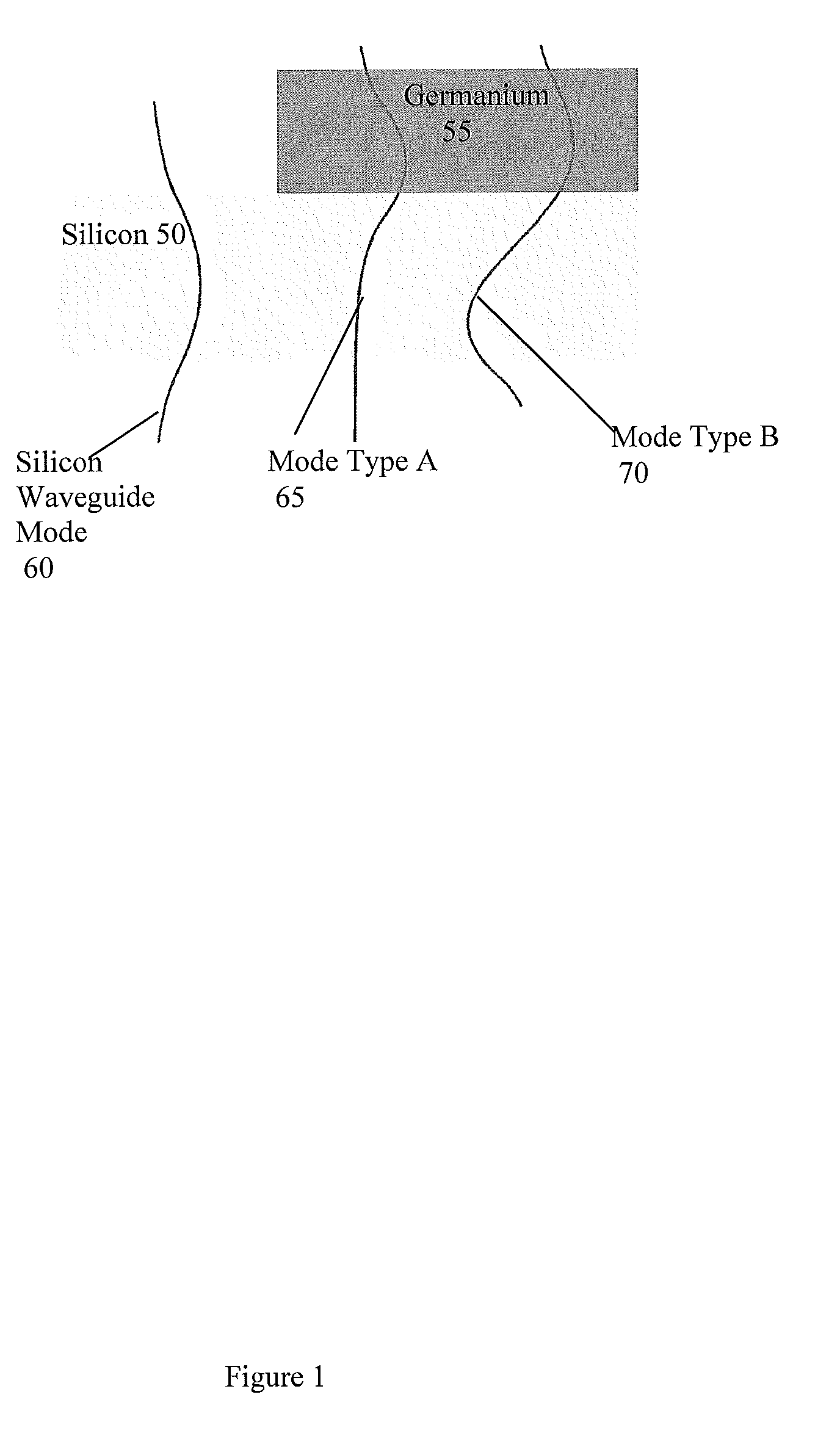

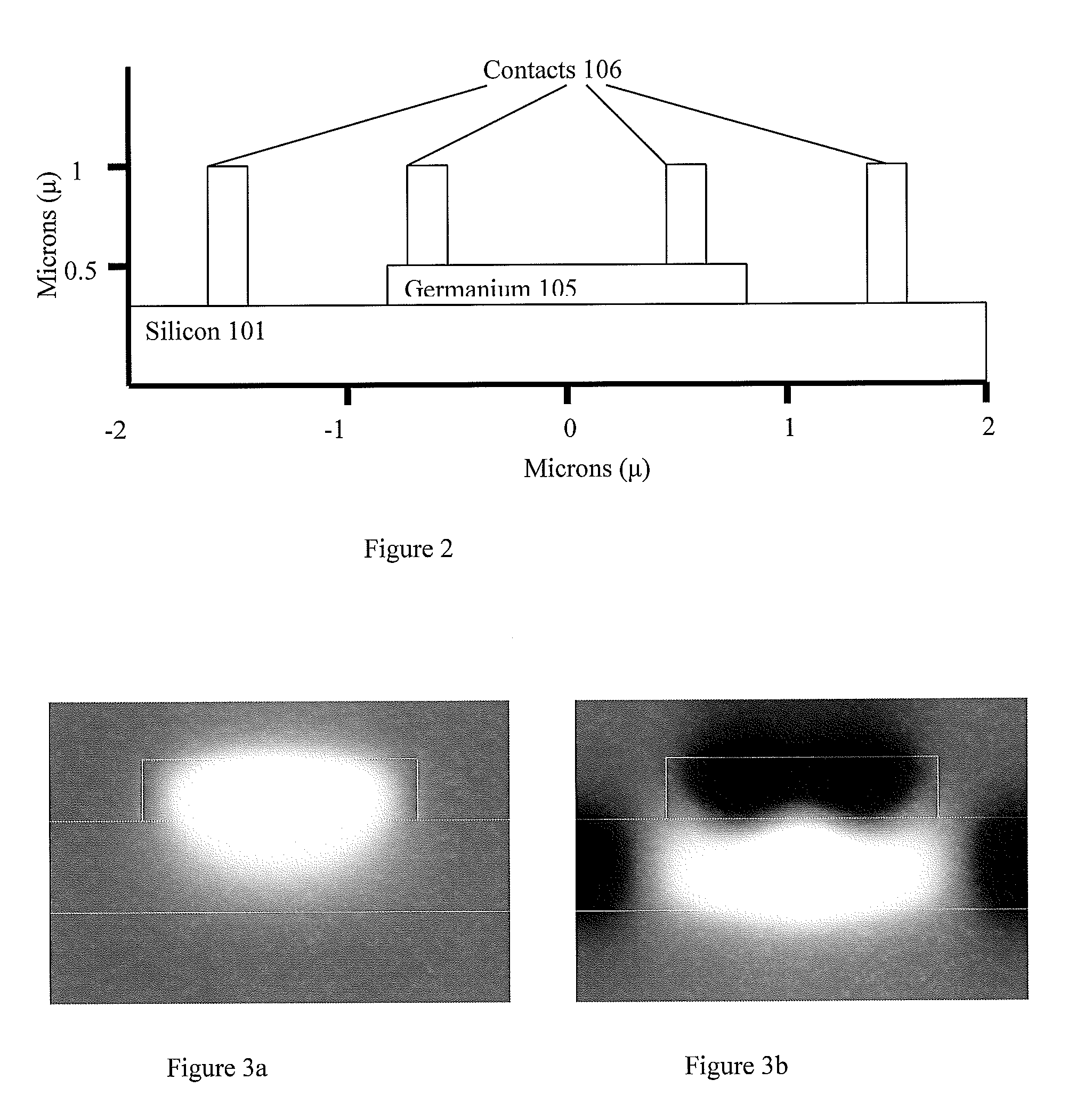

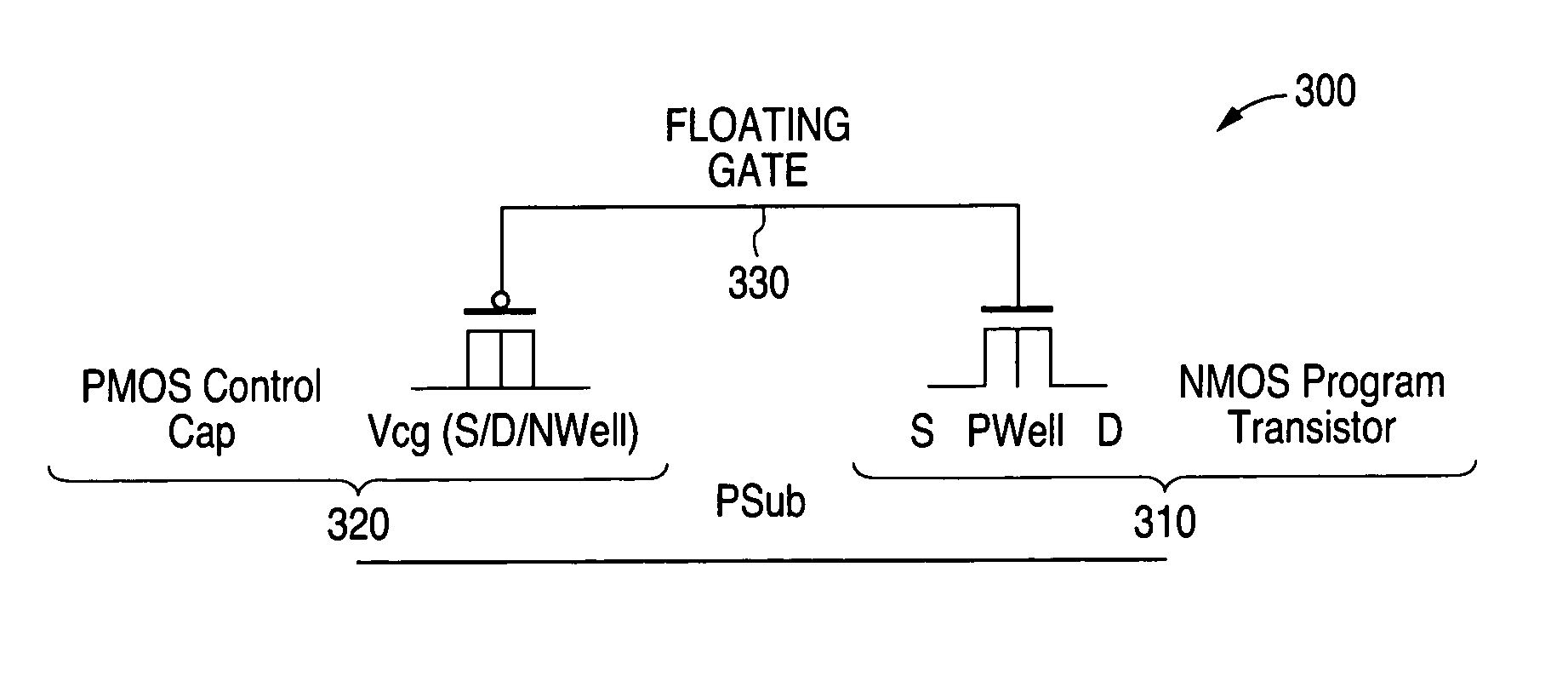

Design of CMOS Integrated Germanium Photodiodes

ActiveUS20080193076A1Easy to optimizeSmall and compactGlass making apparatusLaser detailsWaveguide photodiodeWaveguide

A CMOS processing compatible germanium on silicon integrated waveguide photodiode. Positioning contacts in predicted low optical field regions, establishing side trenches in the silicon layer along the length of the photodiode reduces optical losses. Novel taper dimensions are selected based on the desirability of expected operational modes, reducing optical losses when light is injected from the silicon layer to the germanium layer. Reduced vertical mismatch systems have improved coupling between waveguide and photodiode. Light is coupled into and / or out of a novel silicon ring resonator and integrated waveguide photodiode system with reduced optical losses by careful design of the geometry of the optical path. An integrated waveguide photodiode with a reflector enables transmitted light to reflect back through the integrated waveguide photodiode, improving sensitivity. Careful selection of the dimensions of a novel integrated waveguide microdisk photodiode system results in reduced scattering. Improved sensitivity integrated waveguide photodiodes comprise integrated heaters.

Owner:CISCO TECH INC

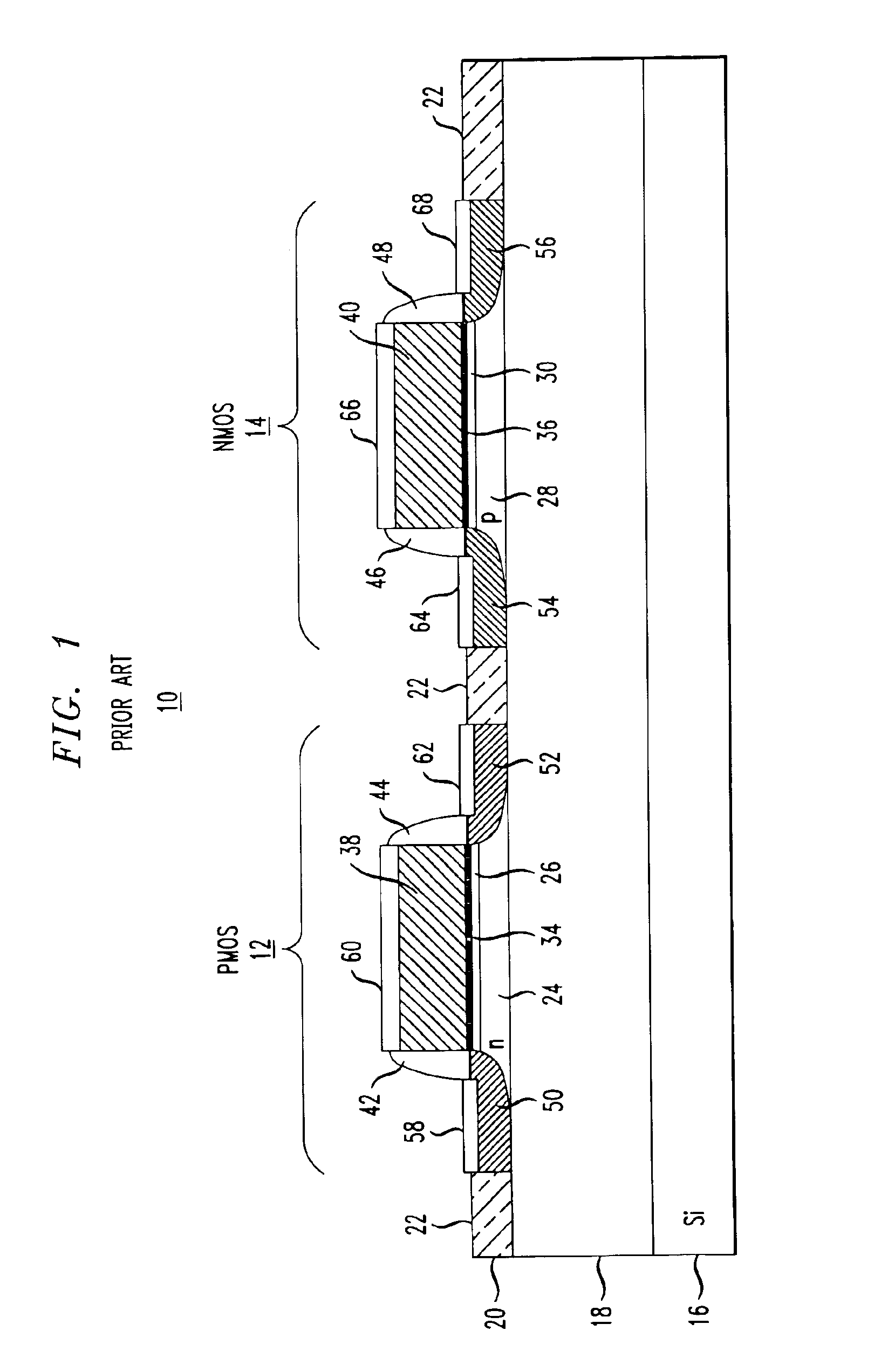

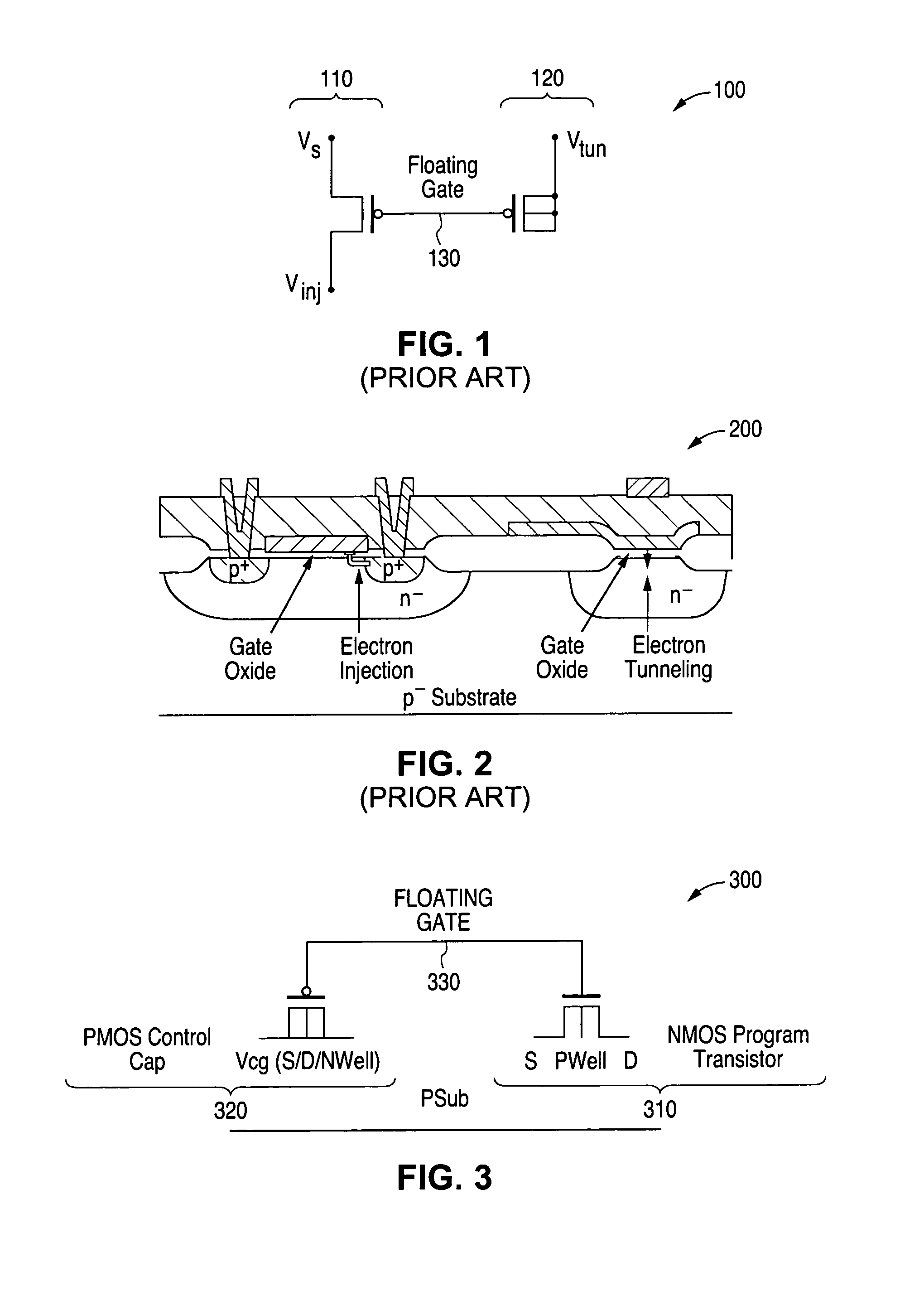

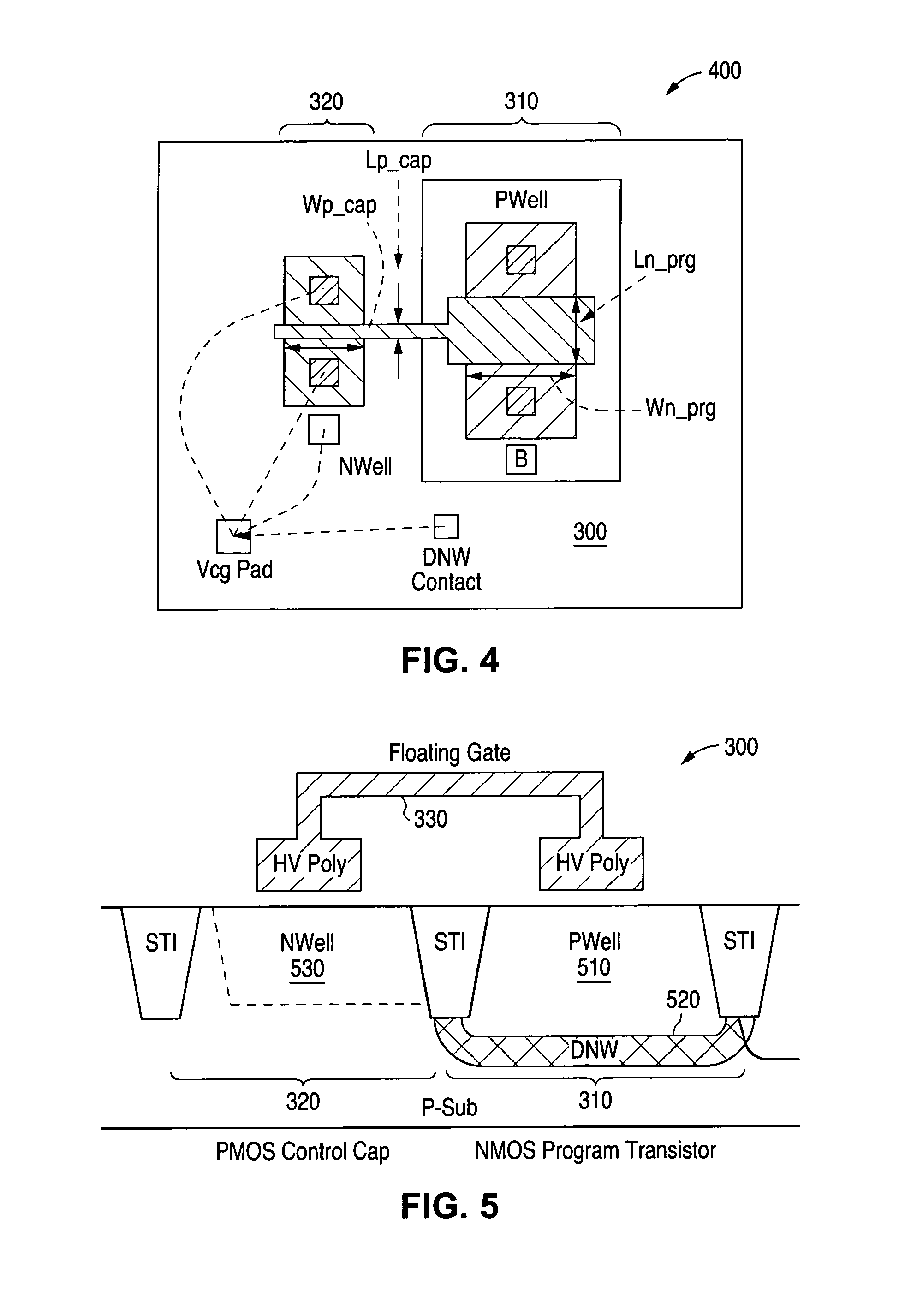

System and method for providing a CMOS compatible single poly EEPROM with an NMOS program transistor

A system and method is disclosed for providing a CMOS compatible single poly electrically erasable programmable read only memory (EEPROM) with memory cells that comprise an NMOS program transistor. In a first embodiment the memory cells of the EEPROM comprise a PMOS control capacitor. In a second embodiment the memory cells of the EEPROM comprise an NMOS control capacitor. A well bias voltage is applied to the NMOS program transistor instead of a gate bias voltage. The well bias voltage enables the injection of (1) channel hot electrons, (2) second hot electrons initiated by the channel hot electrons, and (3) drain impact ionization hot electrons into a floating gate of the NMOS program transistor.

Owner:NAT SEMICON CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com