Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

294 results about "Analog chip" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

An analog chip is a set of miniature electronic analog circuits formed on a single piece of semiconductor material.

Semiconductor device

InactiveUS20070289771A1Guarantee signal qualityAchieving stabilization of a power sourceSemiconductor/solid-state device detailsCross-talk/noise/interference reductionHigh densityAnalog chip

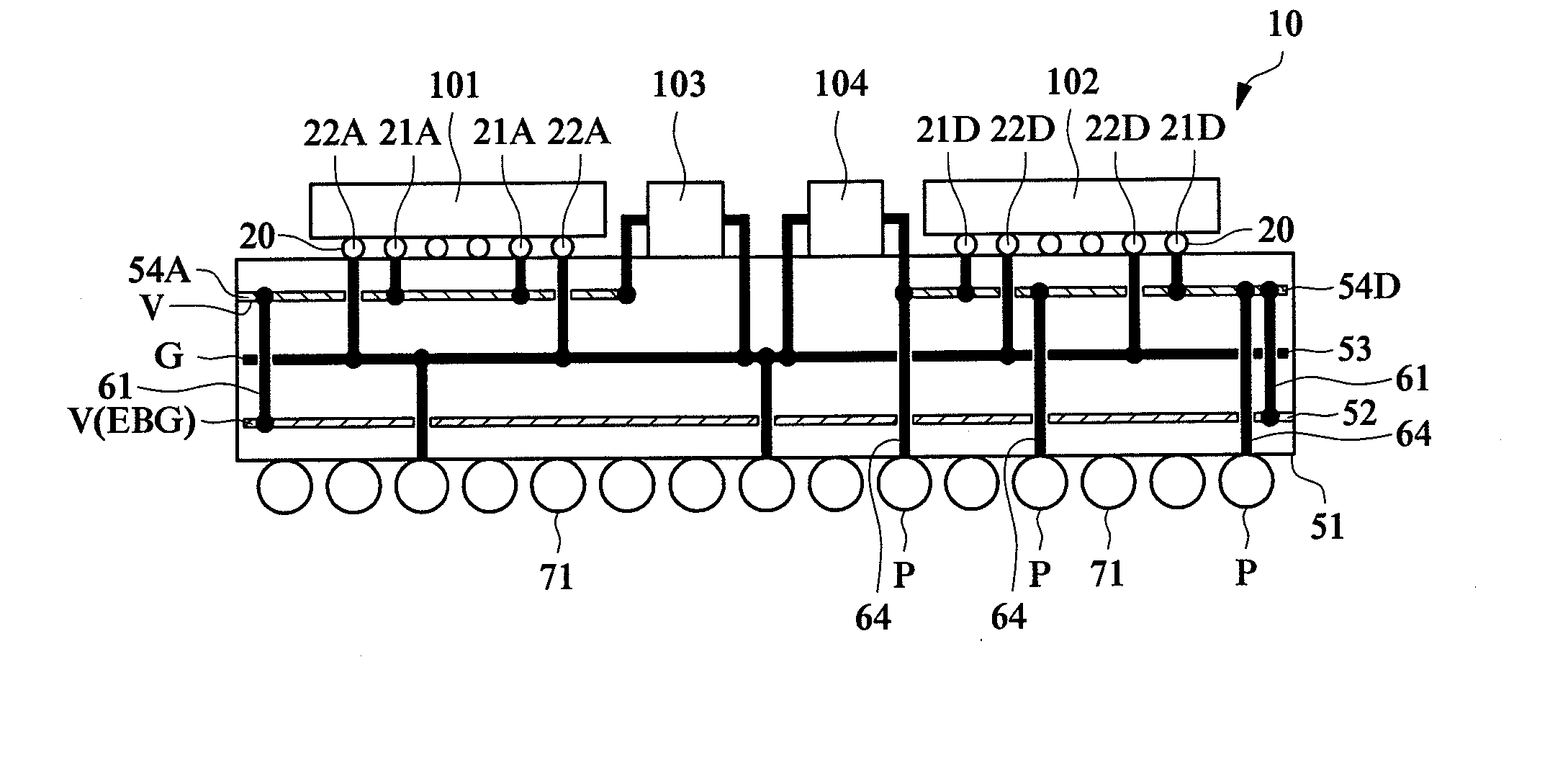

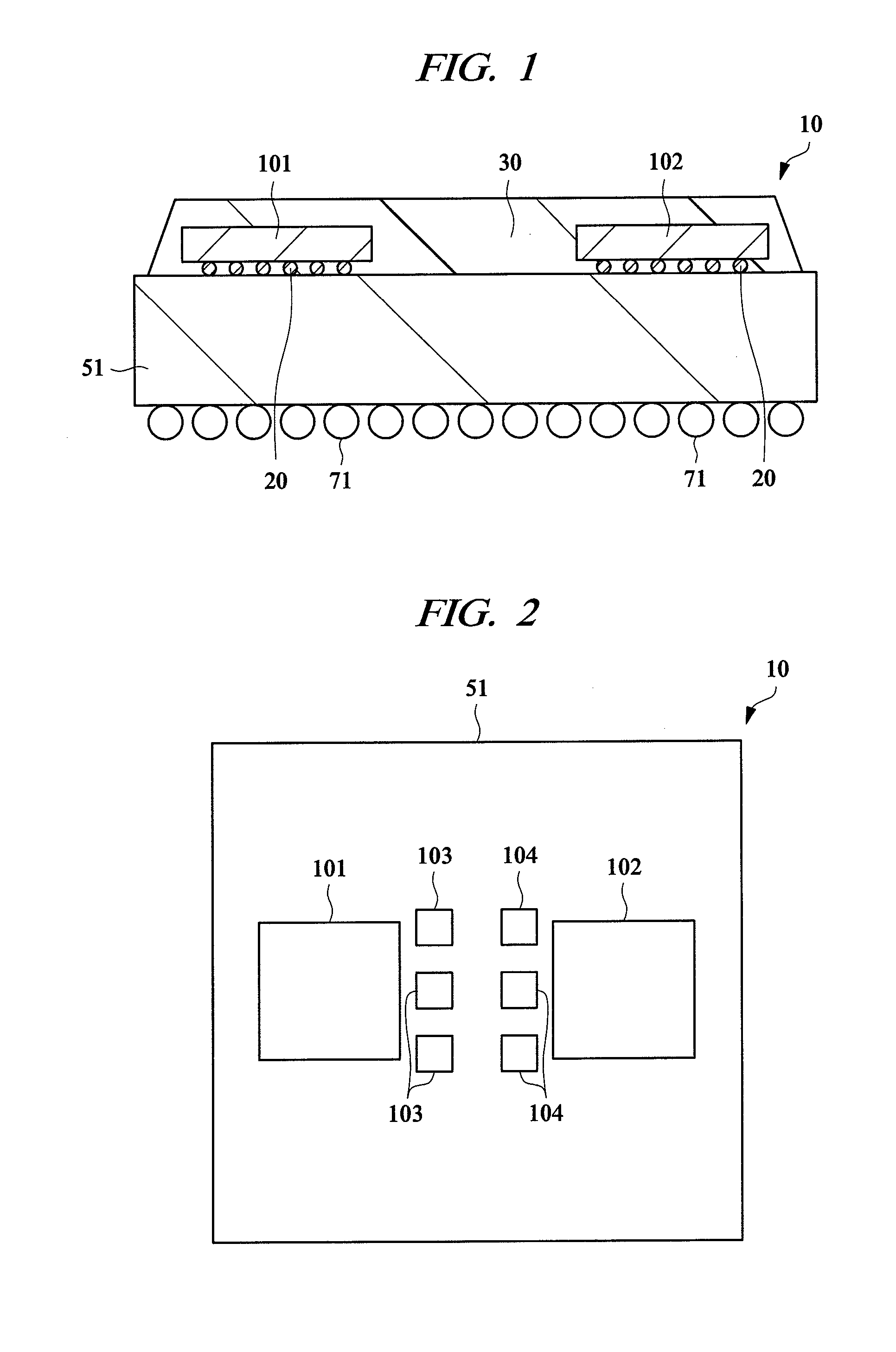

The present invention realizes high density mounting along with achieving power source sharing by a digital semiconductor element and an analog semiconductor element in a semiconductor device. An power layer for analog is connected to one end of an EBG layer, a power layer for digital is connected to the other end of the EBG layer, ground terminals for the respective elements are connected to a common ground layer, and a ground layer for separating the power layer for analog and the EBG layer from each other is disposed between the power layer for analog and the EBG layer. Thereby, high density mounting is achieved along with reducing interference of power source to an analog chip.

Owner:RENESAS ELECTRONICS CORP

Multi-functional integrated circuit chip testing machine

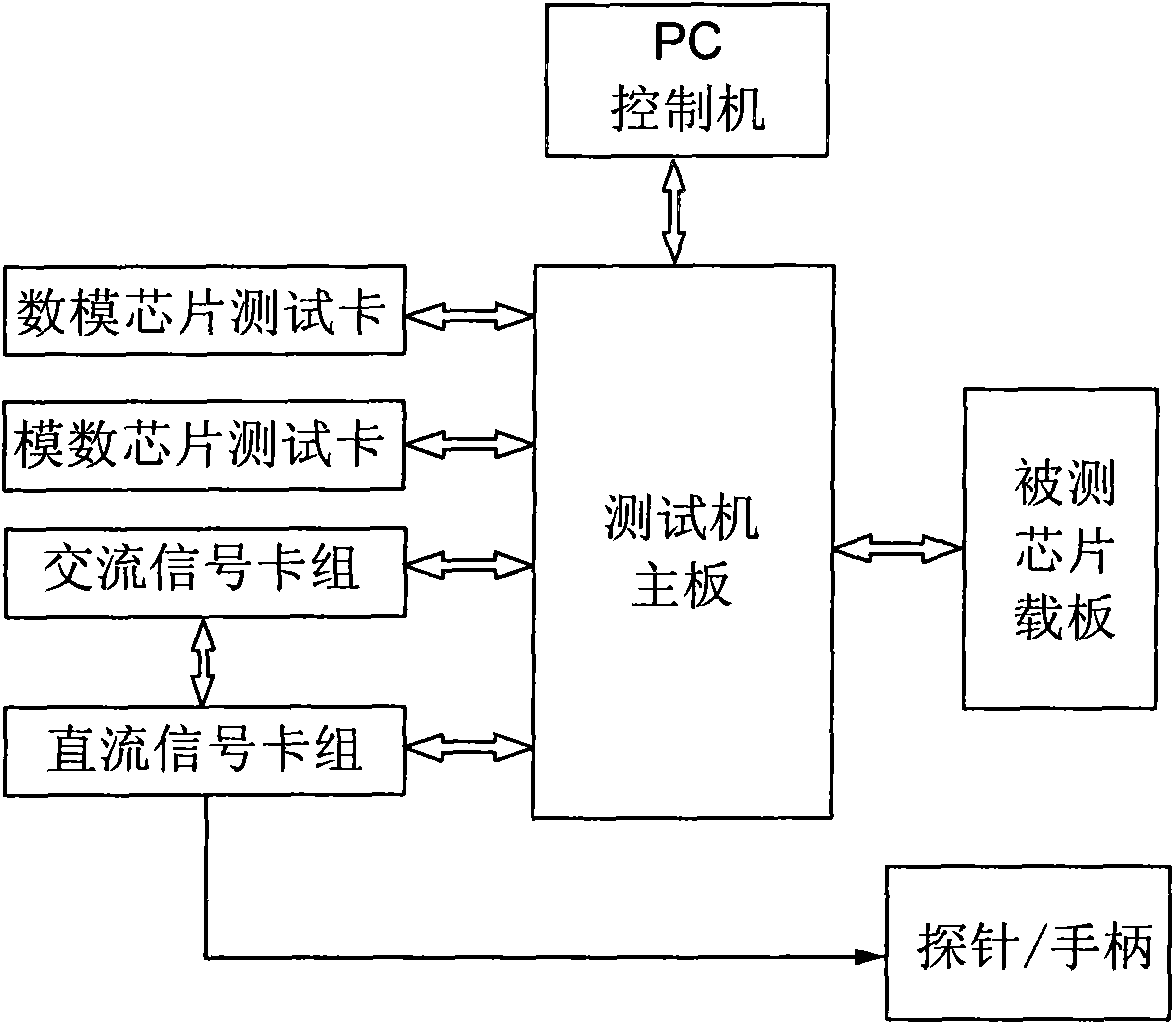

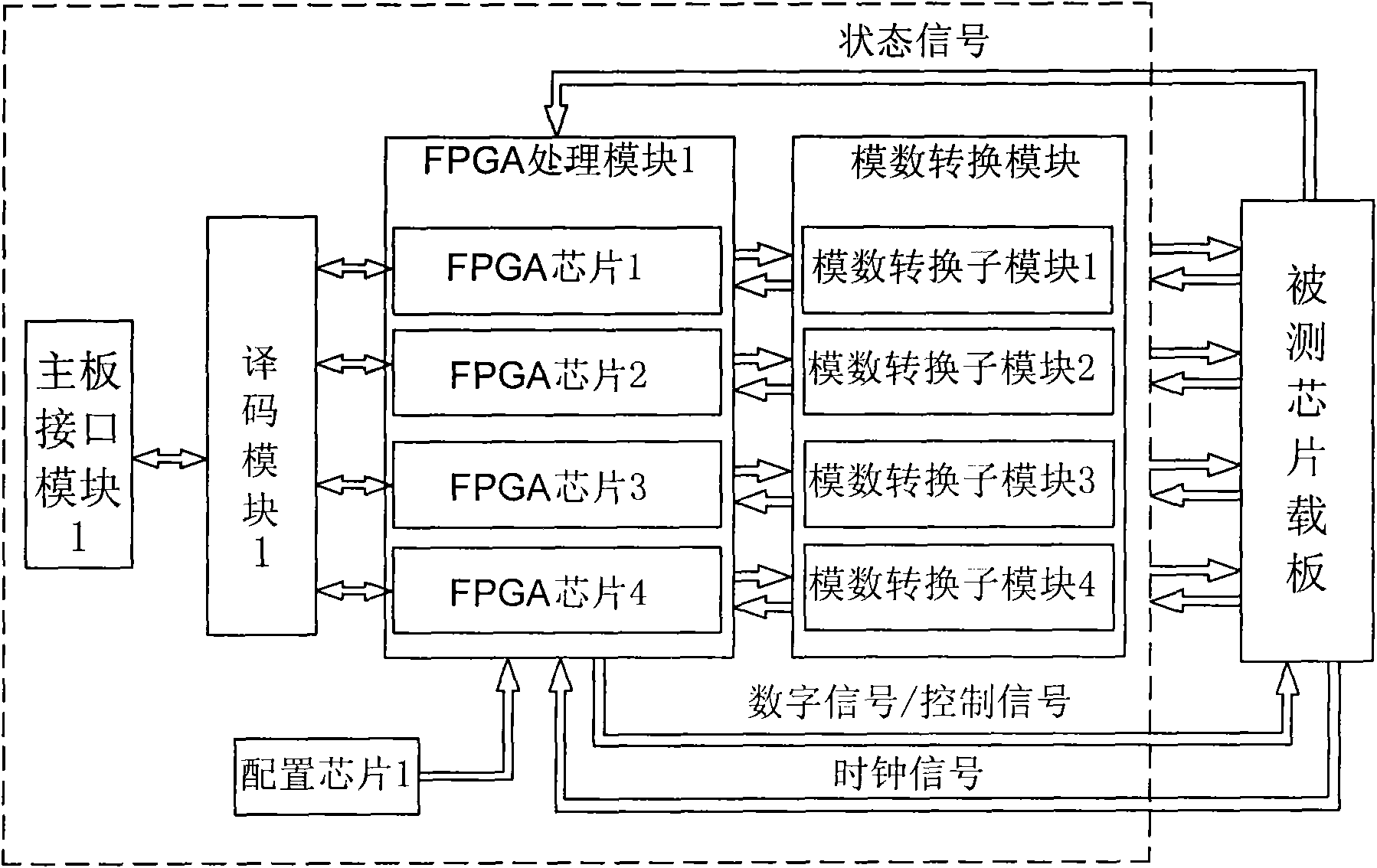

ActiveCN101587167AExpand the scope of testingAdd test functionElectronic circuit testingAnalog chipIc production

The present invention relates to a multi-functional integrated circuit chip testing machine which comprises the following components: a casing, an inner testing machine mainboard, an AC signal card group and a DC signal card group. The AC signal card group and the DC signal card group are connected with each other and are respectively installed on the testing machine mainboard. The testing machine mainboard is respectively connected with a PC controlled and a tested chip carrier plate. The multi-functional integrated circuit chip testing machine is technically characterized in that the testing machine mainboard is also installed with a digital / analog chip testing card and an analog / digital chip testing card. The multi-functional integrated circuit chip testing machine of the invention is reasonably designed, realizes the test function to different types of integrated circuit chip, reduced device investment of the integrated circuit manufacturer and saves the operation and maintenance cost of the device. Furthermore the multi-functional integrated circuit chip testing machine of the invention has the characteristics of wide testing range, stable performance, high testing speed, high efficiency, flexible and convenient using, etc.

Owner:天津津能易安泰科技有限公司

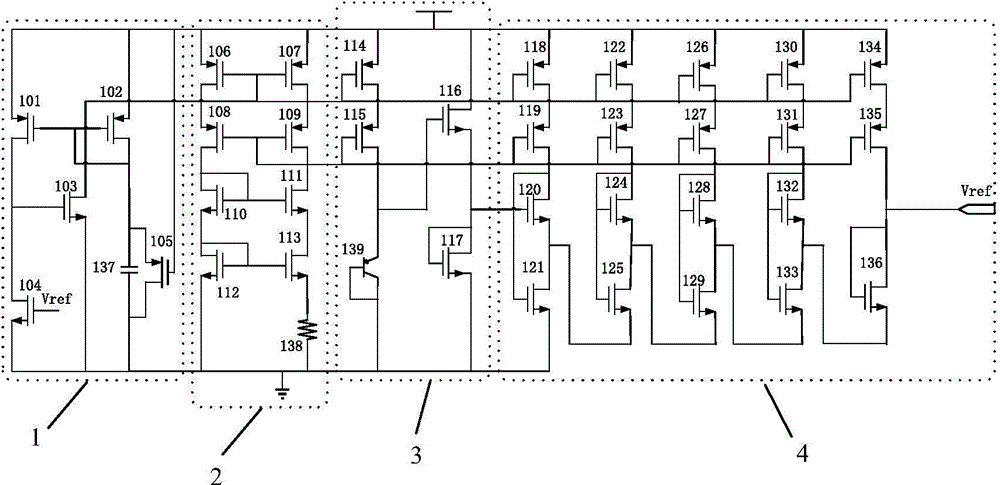

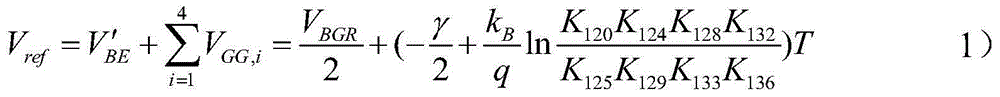

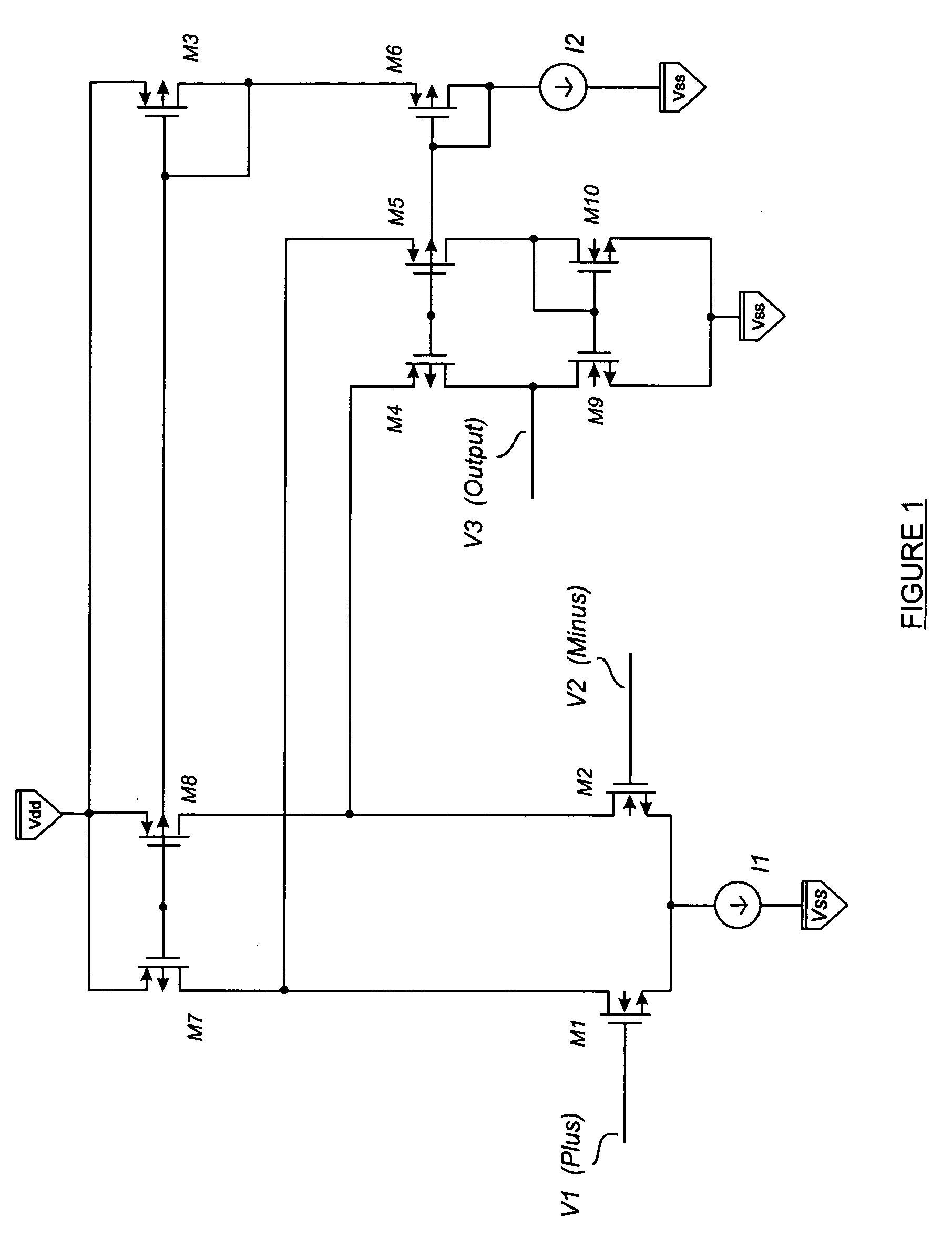

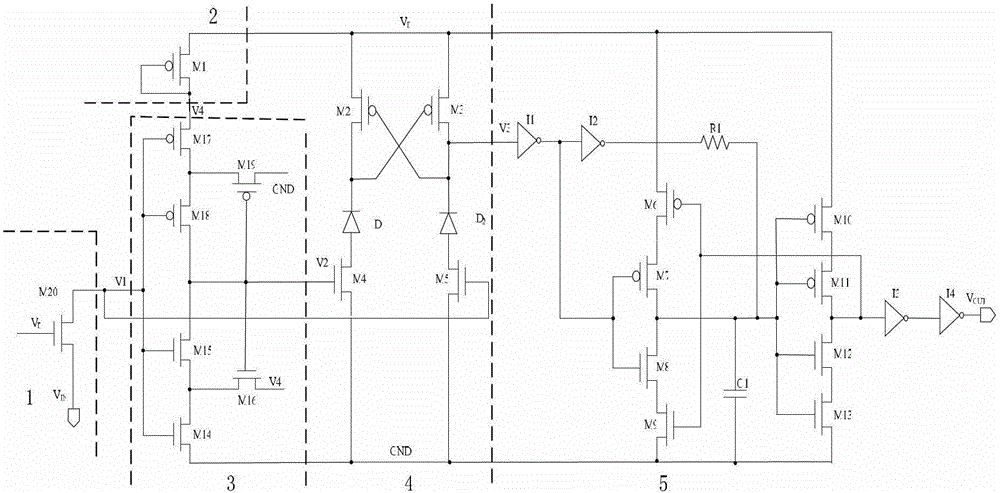

Low-power-consumption sub-threshold type CMOS band gap reference voltage circuit

ActiveCN104950971AReduce power consumptionLow working voltageElectric variable regulationReference currentEngineering

The invention belongs to the technical field of simulation integrated circuits, and discloses a low-power-consumption sub-threshold type CMOS band gap reference voltage circuit. The circuit comprises a start circuit, a reference current source generation circuit, a voltage division circuit and a reference voltage output circuit. The start circuit is used for enabling a reference voltage source to get rid of a zero degeneracy point and to work under specific work voltage. The reference current source generation circuit is used for generating current to provide bias for a rear end circuit, and MOS transistors in the rear end circuit all work in a sub-threshold region. The voltage division circuit is used for enabling an output circuit to reach required technical indexes and generating a negative temperature coefficient. The reference voltage output circuit is used for generating voltage with a positive temperature coefficient and making the output voltage Vref have the zero temperature characteristic. The low-power-consumption sub-threshold type CMOS band gap reference voltage circuit has the advantages of being low in work voltage, low in power consumption and low in temperature coefficient.

Owner:NAT UNIV OF DEFENSE TECH

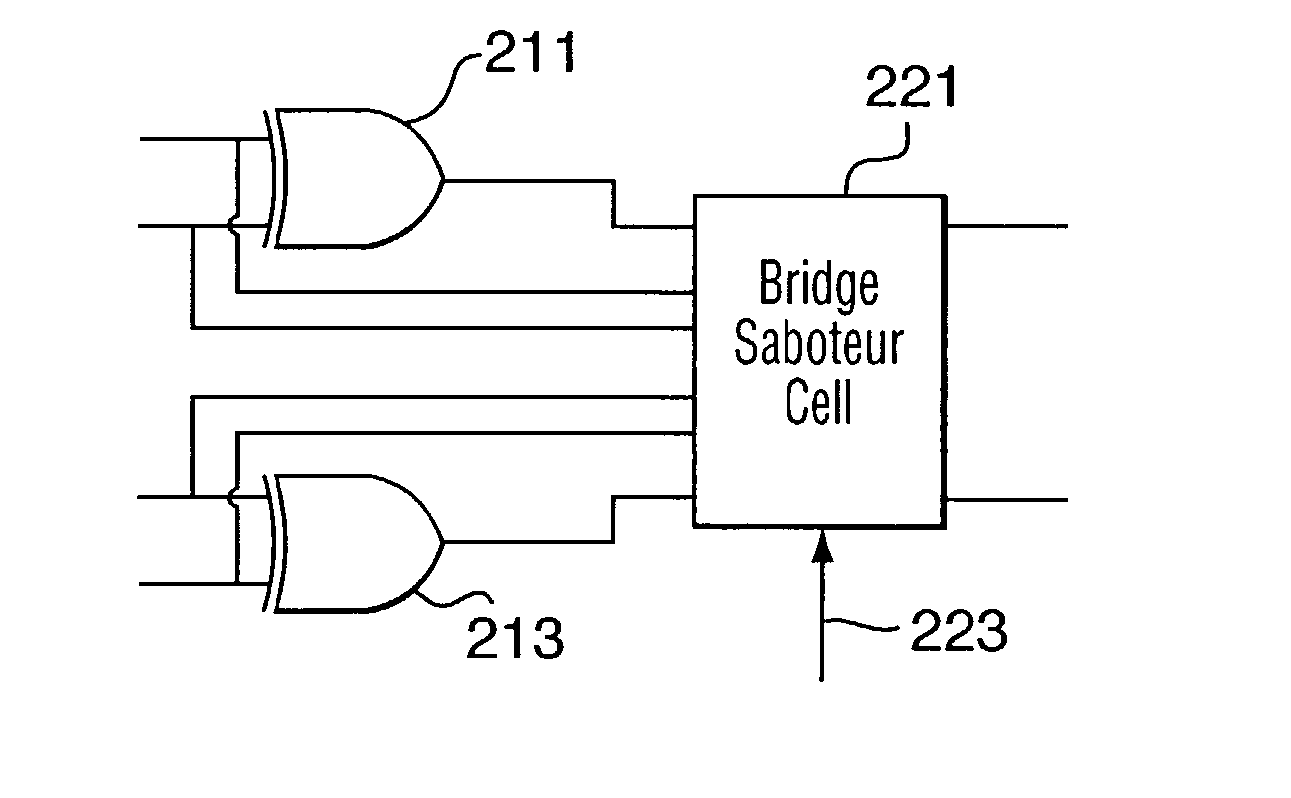

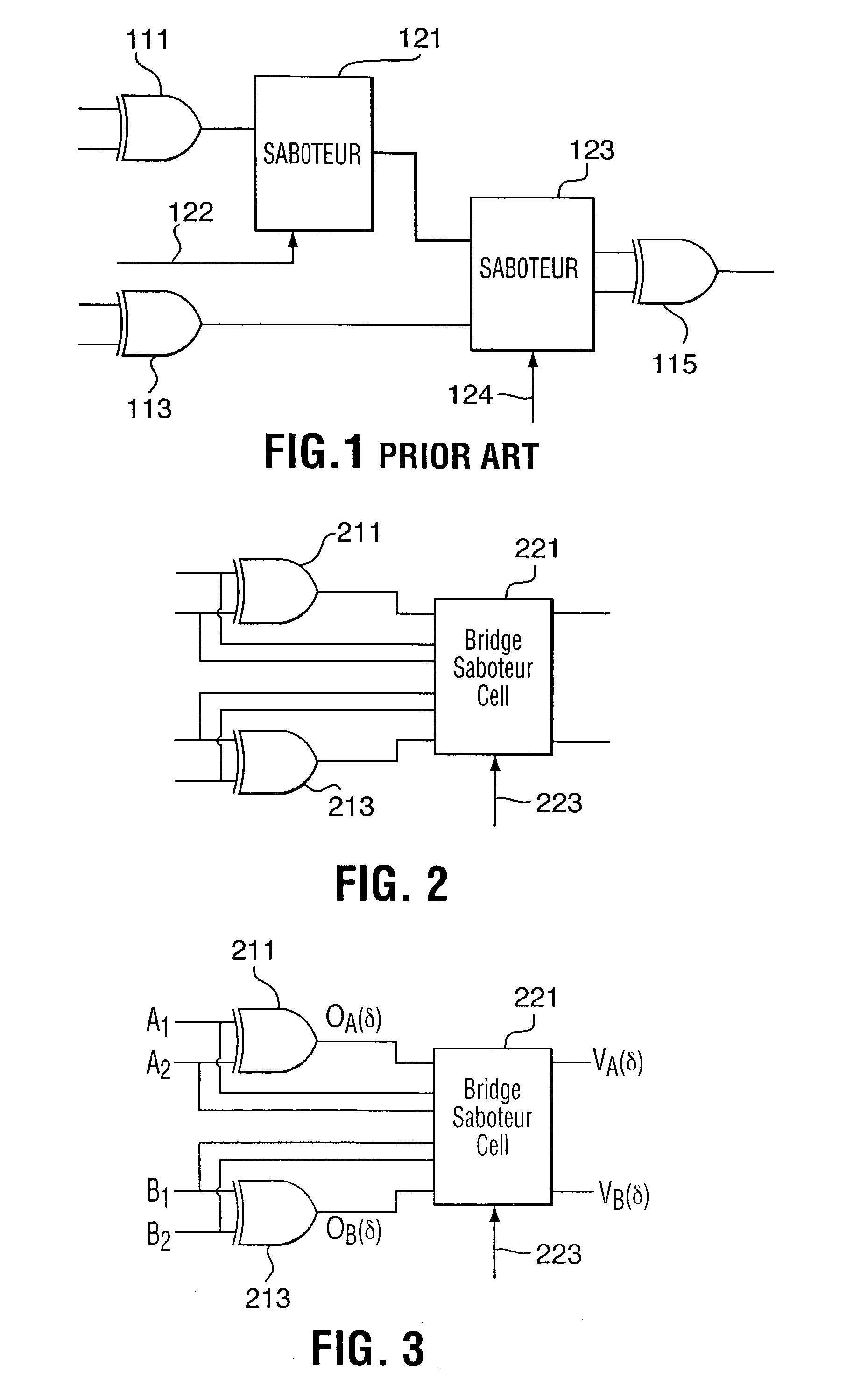

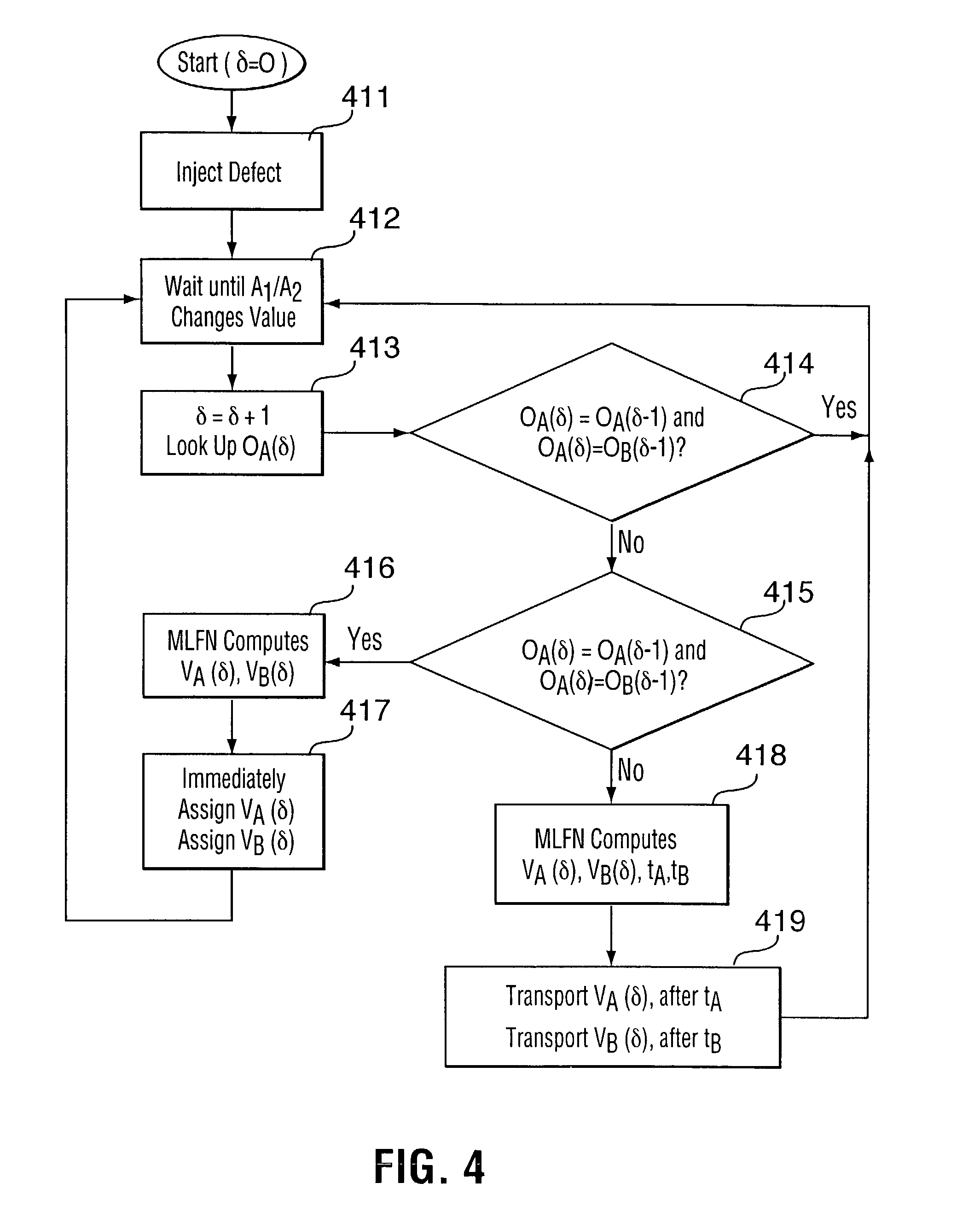

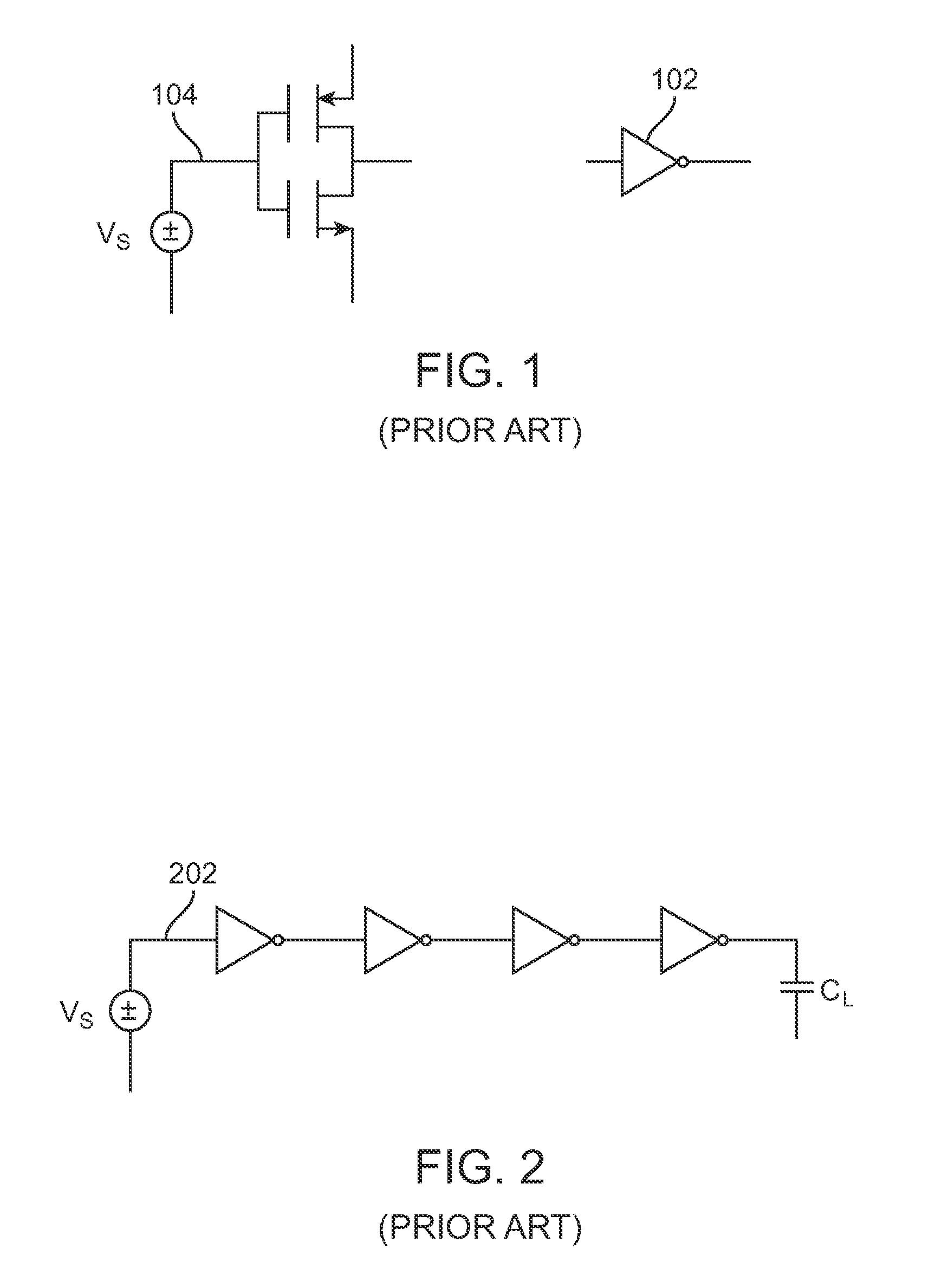

Method and apparatus for modeling and simulating the effects of bridge defects in integrated circuits

A bridge fault modeling and simulation apparatus including a neural network simulates the effects of bridge defects in complementary metal oxide semiconductor integrated circuits. The apparatus includes a multilayer feedforward neural network (MLFN), implemented within the framework of a very high speed integrated circuit hardware description language (VHDL) saboteur. The saboteur is placed between logic cells in the IC simulation. The apparatus computes exact bridged node voltages and propagation delay times with due attention to surrounding circuit elements. It results in faster simulation and achieves excellent accuracy.

Owner:HER MAJESTY THE QUEEN AS REPRESENTED BY THE MINIST OF NAT DEFENCE OF HER MAJESTYS CANADIAN GOVERNMENT

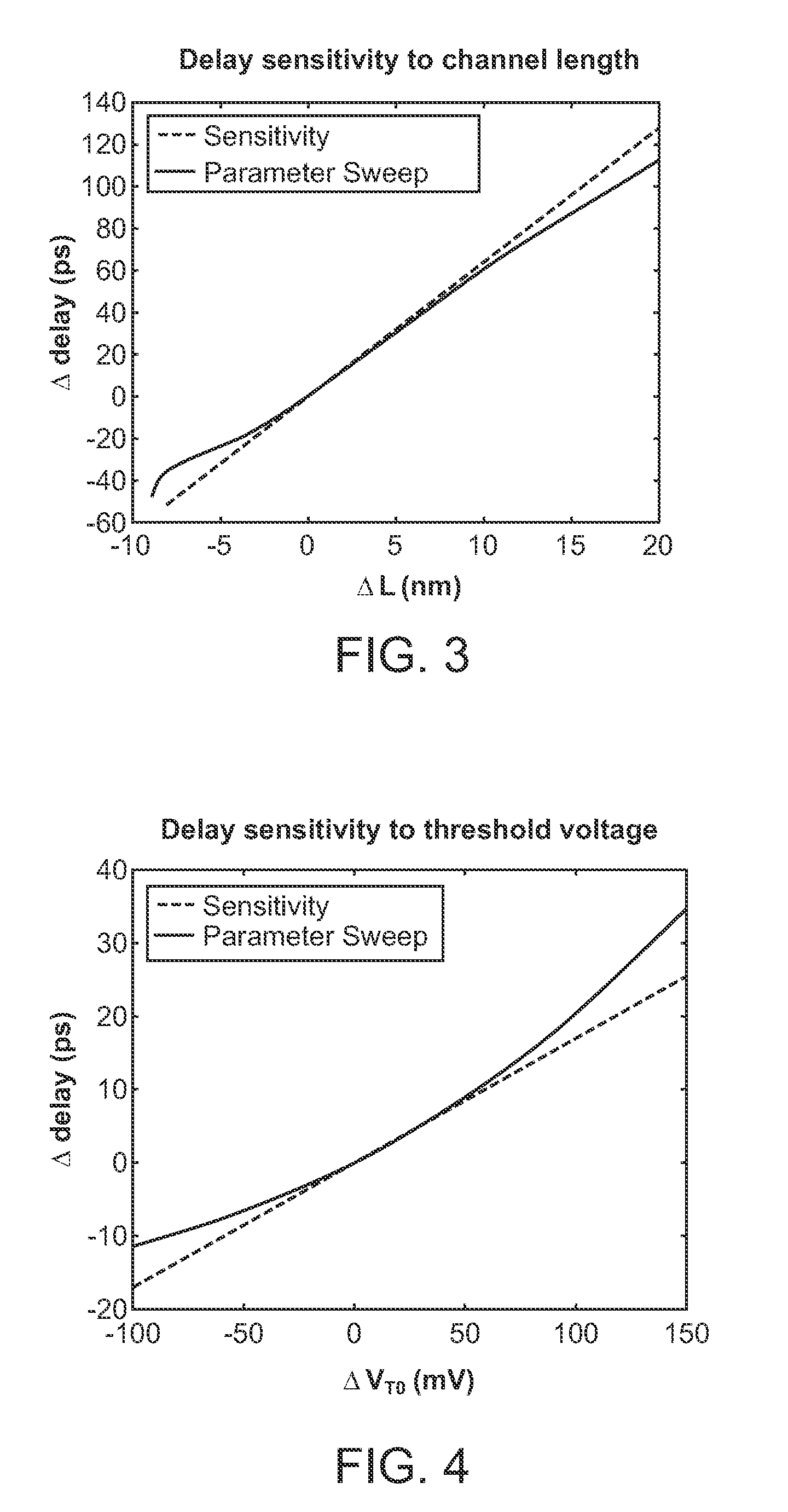

Parametric perturbations of performance metrics for integrated circuits

ActiveUS20090228250A1Simple methodComputation using non-denominational number representationComputer aided designAnalog chipNominal condition

A method of simulating parametric variations in an integrated circuit (IC) includes: specifying an IC model, wherein the IC model includes one or more parameters for variation about a nominal condition; calculating parametric perturbations about the nominal condition; and saving one or more values for the parametric perturbations in a computer-readable medium. Calculating the parametric perturbations includes: simulating the nominal condition for the IC; determining perturbation values for the IC model about the nominal conditions, wherein the perturbation values include linear time-varying matrices and parametric right-hand sides, determining a performance metric for the IC and a performance sampling vector for sampling the performance metric about the nominal condition from the perturbation values; and determining voltage-sensitivity values and performance-sensitivity values from the perturbation values and the performance-sampling vector.

Owner:CADENCE DESIGN SYST INC

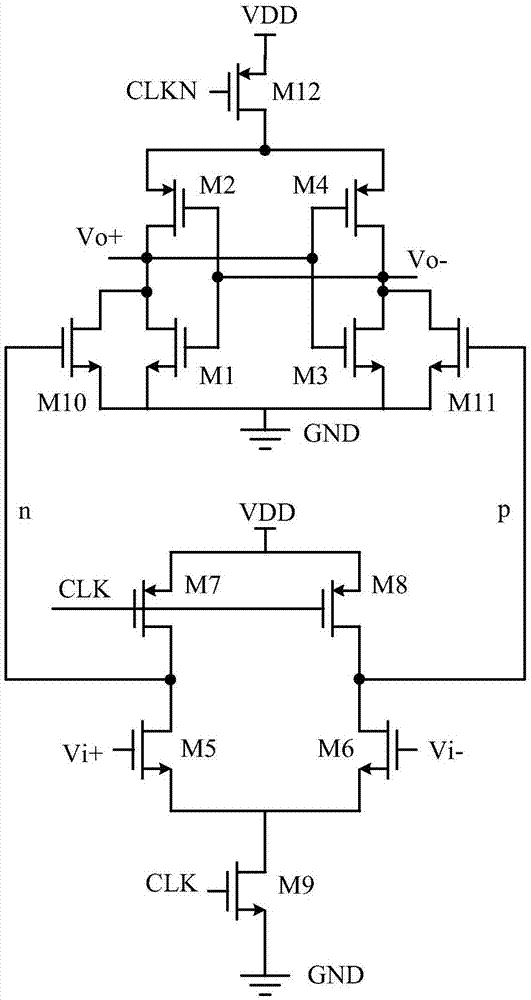

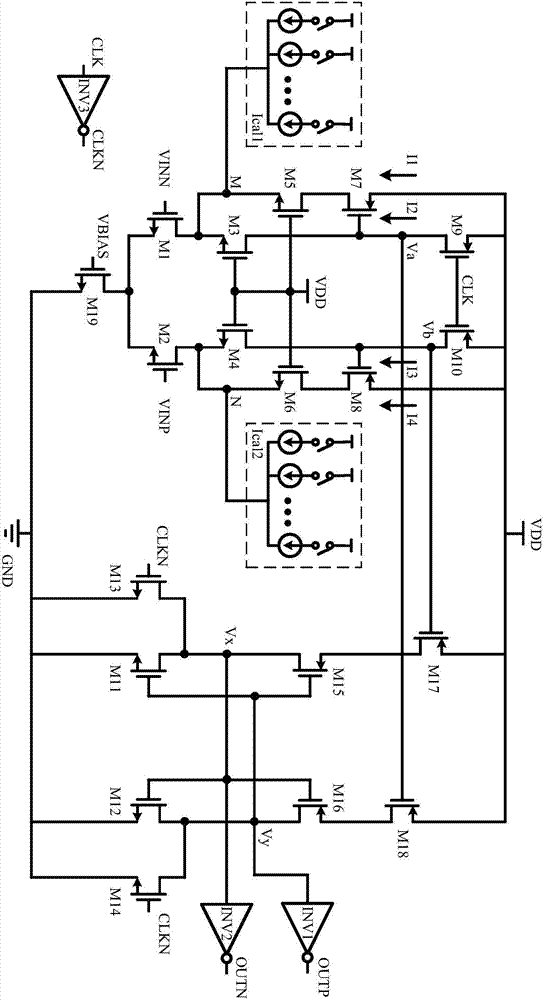

High-speed low-kickback-noise dynamic comparer and circuit

InactiveCN107888171AReduce reset timeShorten the working cycleMultiple input and output pulse circuitsUltrasound attenuationDynamic noise

The invention discloses a dynamic comparator with high speed and low kick noise, which belongs to the field of analog integrated circuits. Its structure includes: pre-amplification stage, current compensation branch for suppressing kickback noise, positive feedback regeneration stage composed of N-channel transistor and P-channel transistor cross-coupling unit, current between pre-amplification stage and positive feedback regeneration stage A control unit, a reset control unit, an offset calibration unit, and an inverter output driver stage. The two current compensation branches that suppress the kickback noise compensate the current attenuation of the main channel to ensure a constant working current of the input pair tube, thereby suppressing the influence of the kickback noise on the input signal, thereby increasing the size of the input pair tube and reducing offset voltage, increasing the response speed. Compared with the traditional comparator, the invention satisfies the requirement of high speed and low power consumption, and exhibits excellent kickback noise suppression ability.

Owner:SHANGHAI RES INST OF MICROELECTRONICS SHRIME PEKING UNIV

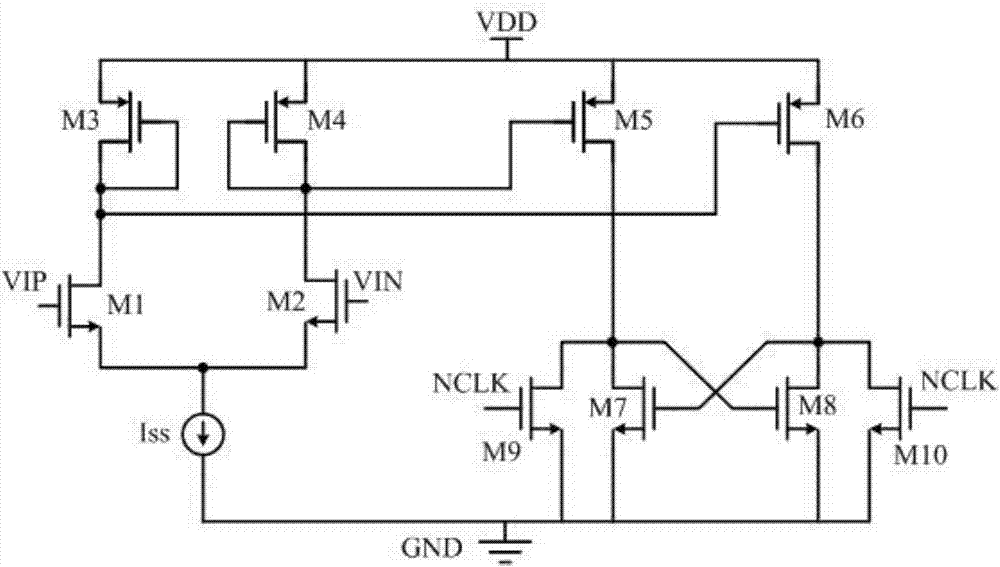

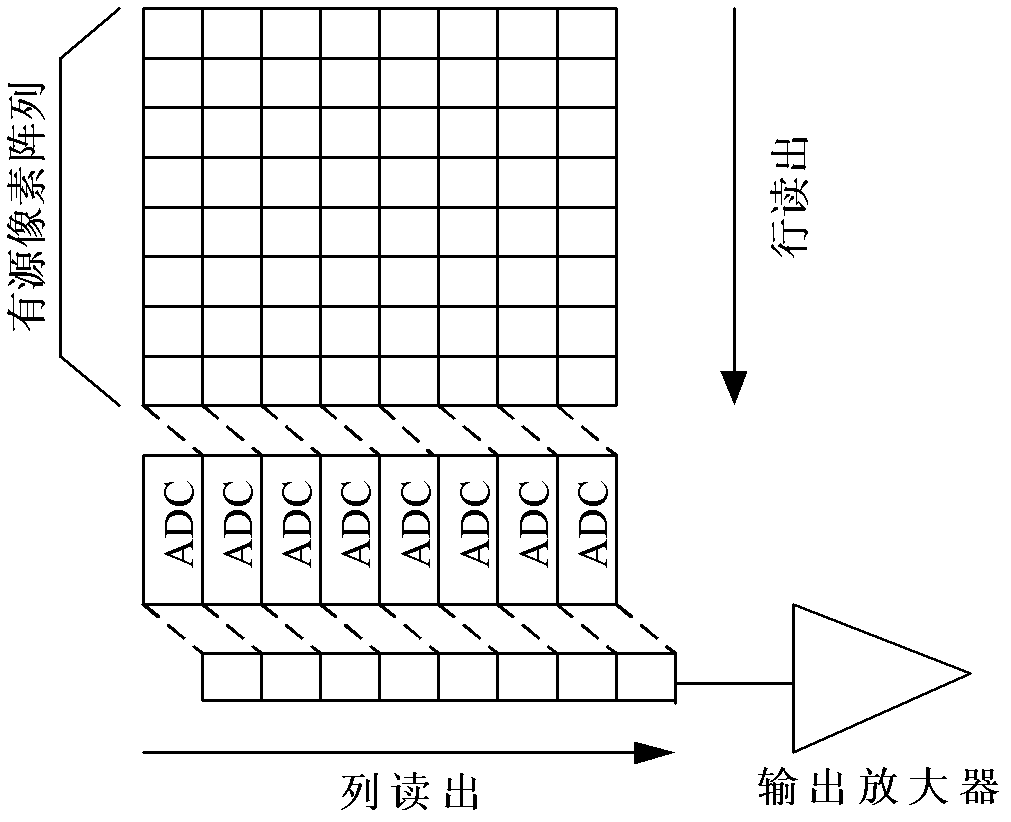

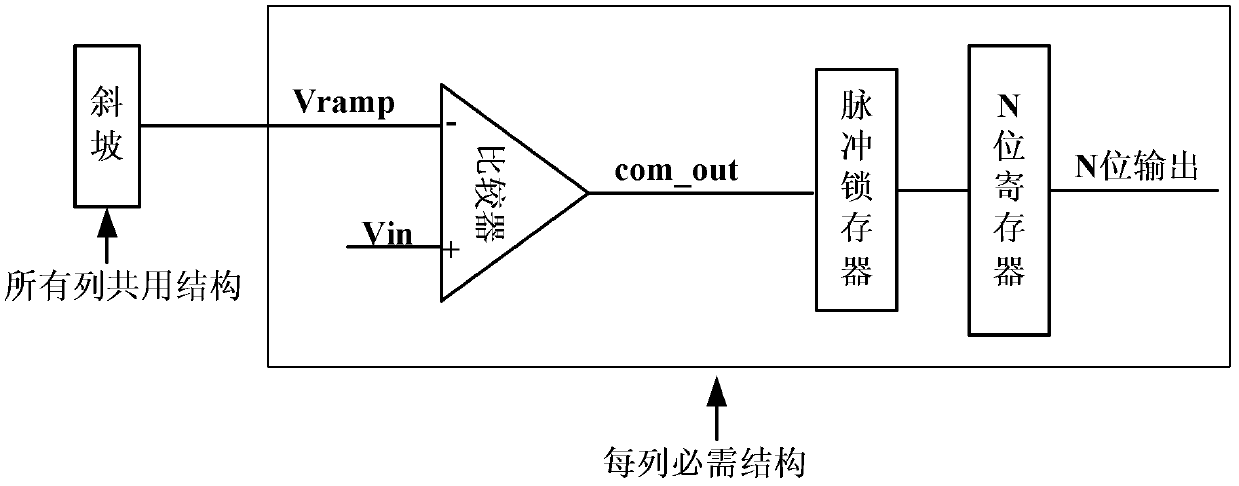

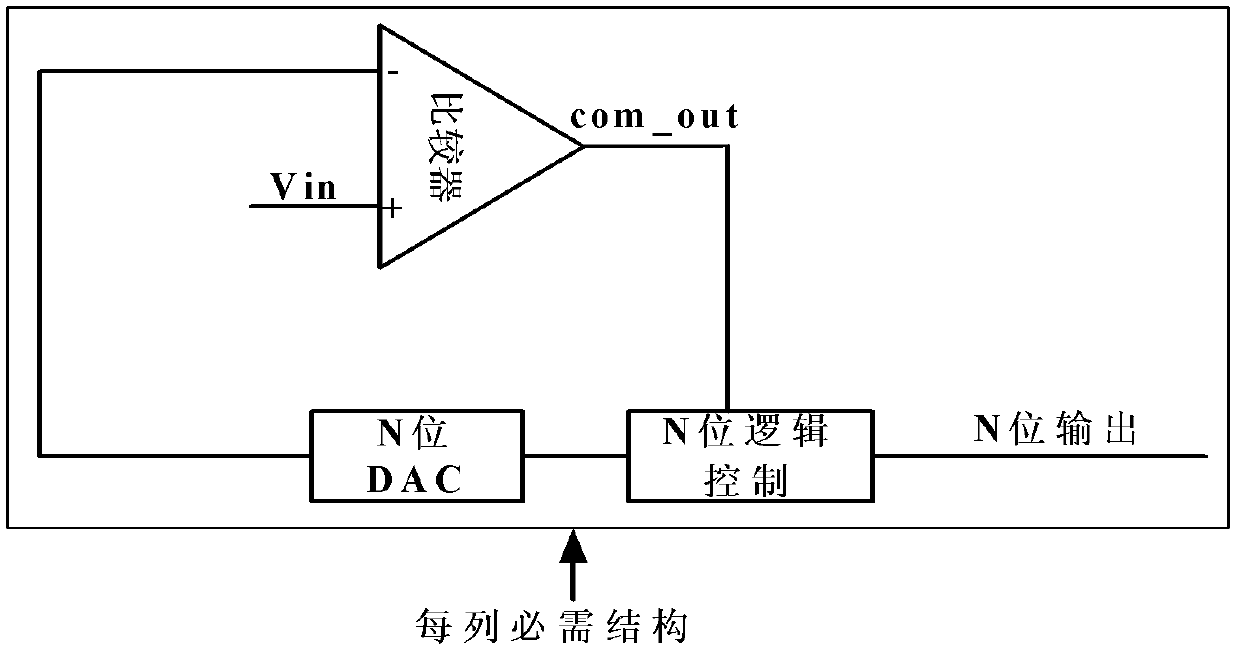

Realization device of column-level analog-to-digital converter (ADC) in complementary metal-oxide semiconductor (CMOS) image sensor

InactiveCN102611854AIncrease conversion rateHigh speedAnalogue/digital conversionTelevision system detailsComputer hardwareDigital converter

The invention relates to the field of analog integrated circuit design. In order to provide an analog-to-digital converter (ADC) structure which has a simple structure and a short conversion cycle, and achieve the purpose of improving the dynamic scope of a sensor, the technical adopts the following technical scheme that: a realization device of a column-level ADC in complementary metal-oxide semiconductor (CMOS) image sensor comprises a single-slope ADC, a successive approximation ADC and two slope signal generators; the single-slope ADC, the successive approximation ADC and a group of six switches form a unit, and each column in a sensor pixel array is provided with the unit; and two slope signal generators are shared by each column of the sensor pixel array. The realization device of the column-level ADC in the CMOS image sensor is mainly applied in the design and manufacturing of the semi-conductor image sensor.

Owner:TIANJIN UNIV

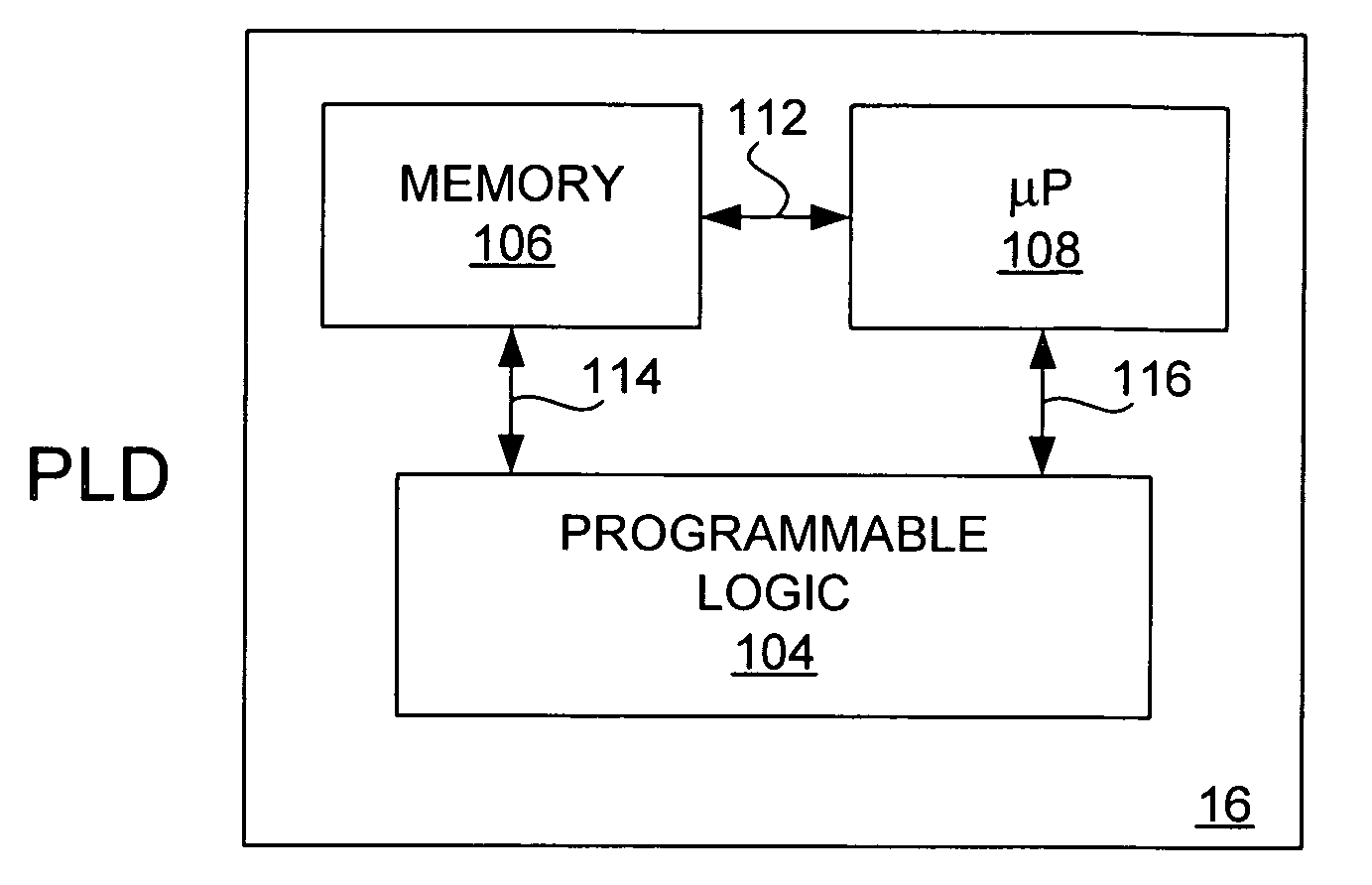

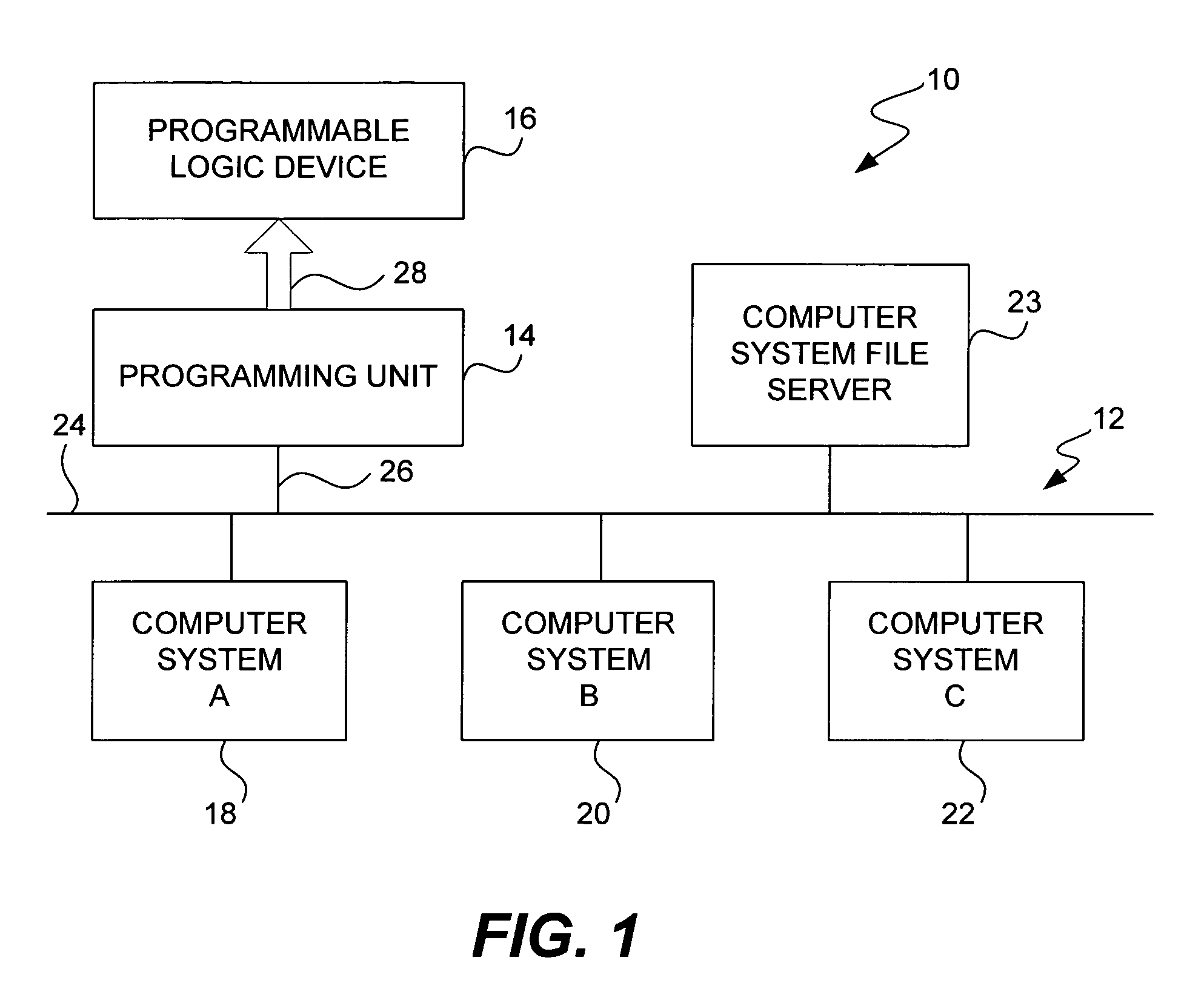

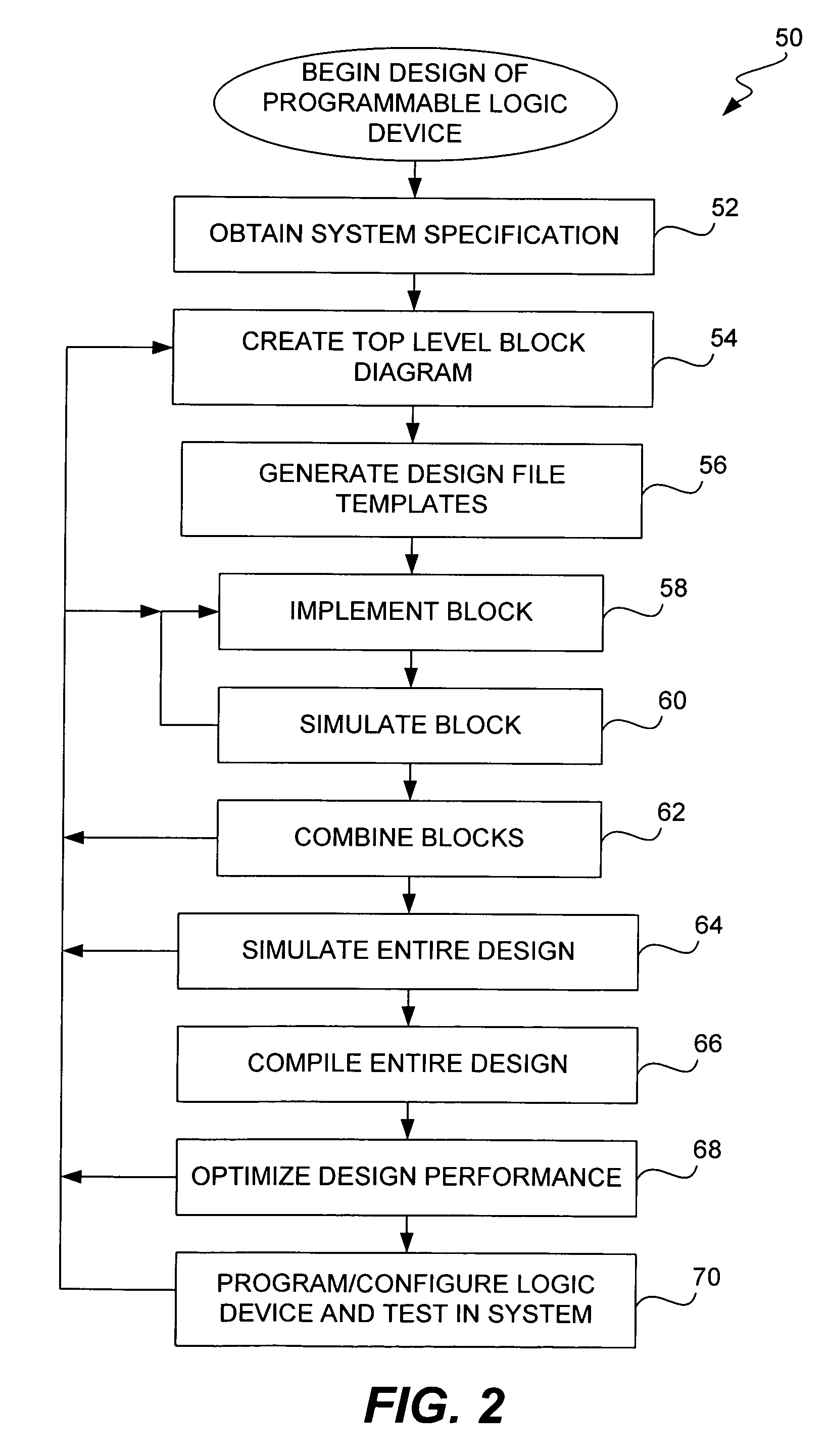

Embedded microprocessor for integrated circuit testing and debugging

ActiveUS7539900B1Less-expensive to placeFast testElectrical testingFunctional testingMemory chipProgrammable logic device

A technique for embedding a microprocessor into an integrated circuit allows on-chip testing and debugging. The microprocessor present on the chip tests and debugs the rest of the chip. Both testing and debugging of a programmable logic device use an embedded microprocessor. Testing is performed by the device manufacturer using a test system. Debugging is performed by a user using a host computer. A PLD includes programmable logic, an embedded microprocessor and separate memory. Testing or debugging routines, patterns, simulations, etc., are downloaded onto the memory. The microprocessor executes the test or debug routine and uploads results to the test system or host computer. The technique is applicable any integrated circuit that can include an embedded microprocessor and associated memory, such as a PLD, an ASIC, a memory chip, or an analog chip.

Owner:TAHOE RES LTD

Method and apparatus for calibrating analog circuits using statistical techniques

ActiveUS20060125563A1Regard to overcoming effectsCharge amplifiersAmplifier modifications to reduce temperature/voltage variationEngineeringAnalog chip

The performance of precision analog integrated electronic circuits is directly related to the degree of matching between electrical circuit elements. Any residual mismatch of circuit elements after manufacturing must be calibrated out using numerous techniques such as adjusting potentiometers, trimming capacitors, modifying binary-weighted resistor strings, etc. Prior art matching techniques entail the use of large area circuit elements or a large number of elements arranged in a prescribed manner on the surface of a silicon die to minimize the residual calibration. The present invention utilizes a multiplicity of circuit elements that are interconnected in distinct groups to achieve a higher degree of element matching and the ensuing benefits thereof. The elements are interconnected to yield a prescribed minimum mismatch error.

Owner:ELDER J SCOTT

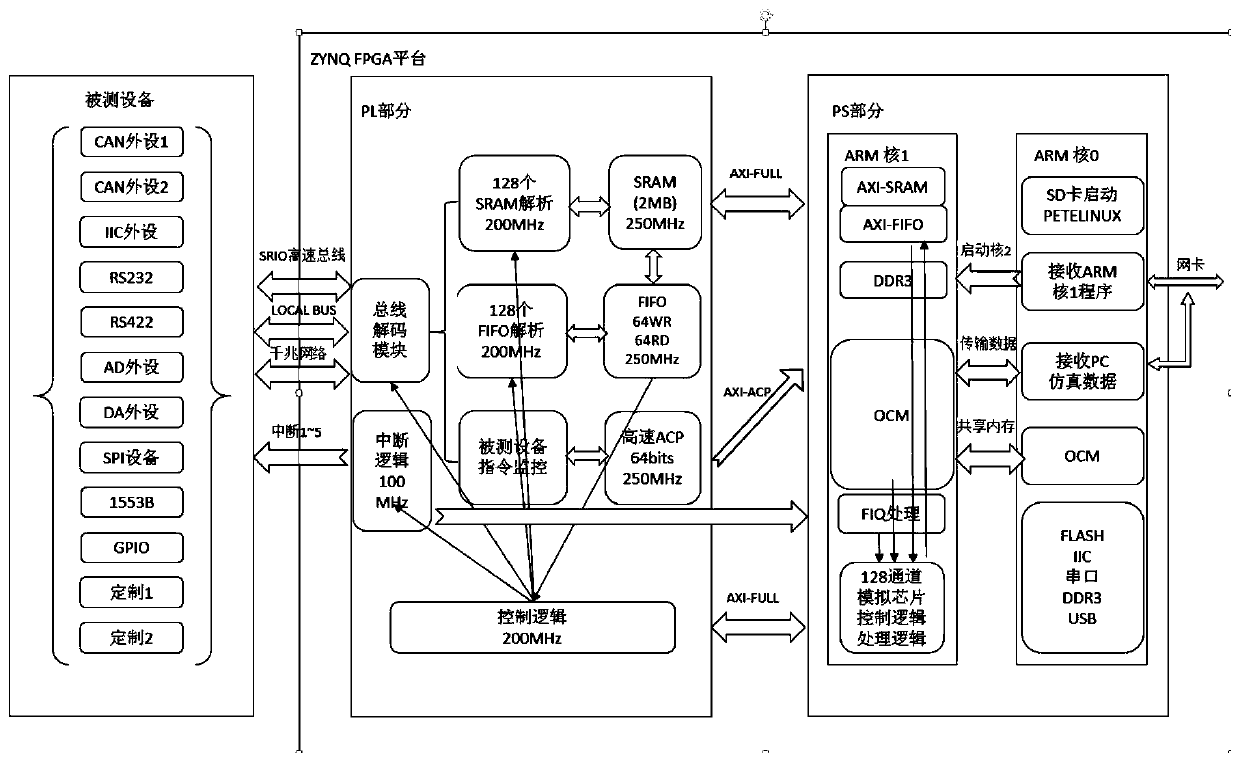

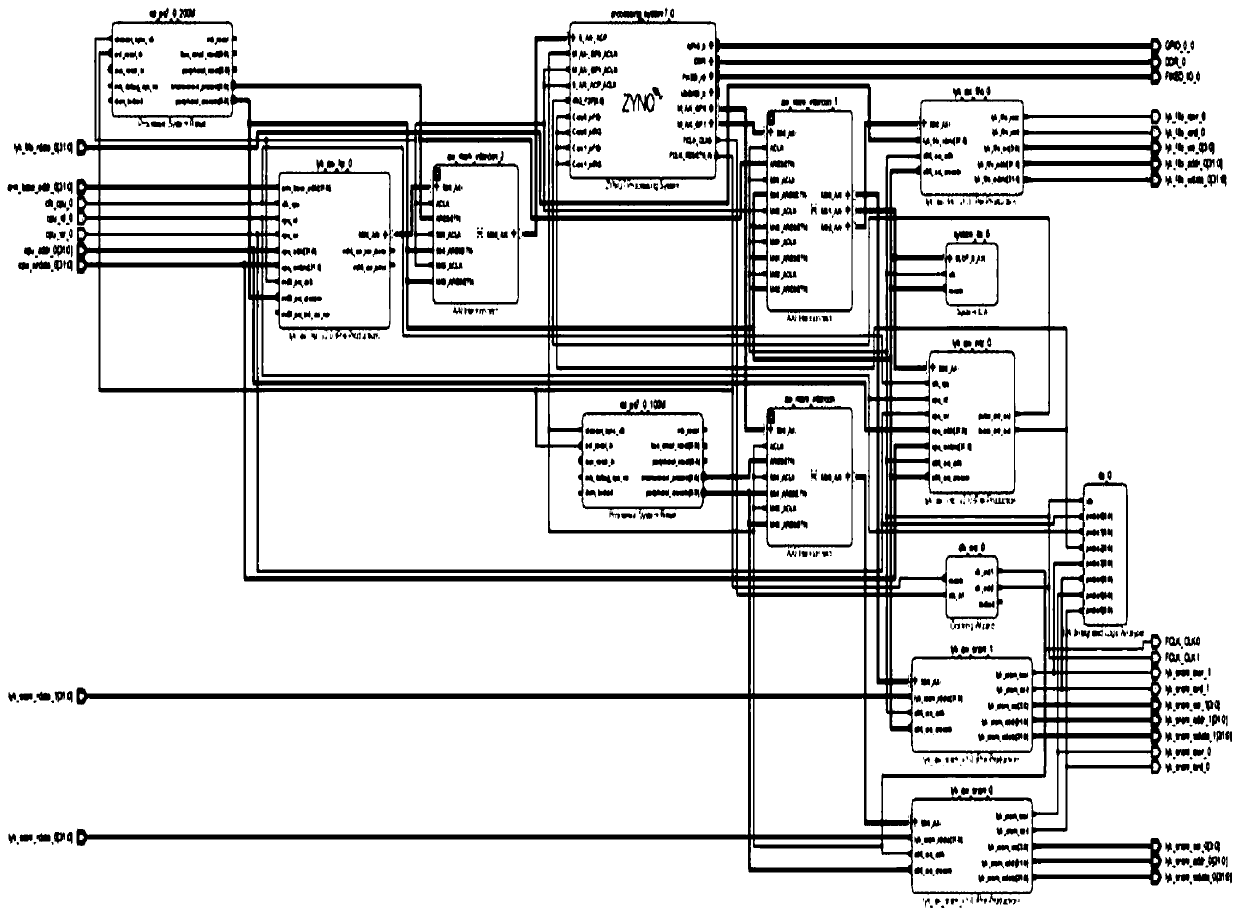

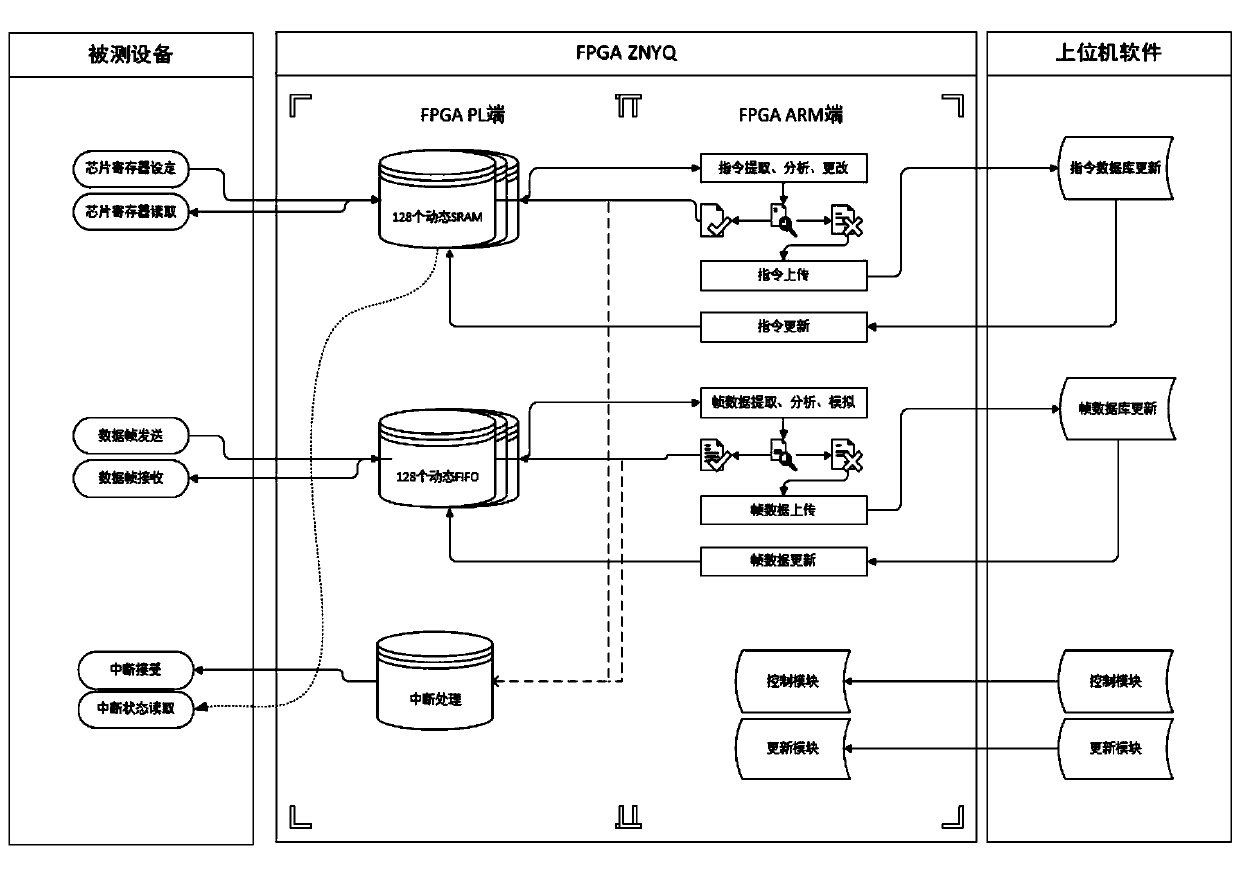

Hardware real-time simulation multi-channel multi-type communication protocol chip system, method and medium

ActiveCN109818790AHigh degree of simulationSame characteristicsBus networksData conversionReal-time dataReal-time simulation

The invention provides a hardware real-time simulation multi-channel multi-type communication protocol chip system and method and a medium, and the system comprises a system interaction module which is used for completing the connection with a tested system and monitoring the control instruction of the tested system in real time; A PL logic module in the FPGA which is used for finishing hardware acceleration of the protocol chip; An ARM1 module in the FPGA which is used for realizing a multi-protocol chip function; The FPGA internal ARM0 module which is used for realizing interaction with an upper computer and realizing multi-protocol chip control and data interaction; And the upper computer software platform module which is used for realizing function customization of a multi-protocol chip and real-time data monitoring and control of an analog chip. A user can carry out customized simulation according to different chip manuals, control over information such as a chip register is completed through C codes, customized updating is completed through a system software platform, and convenience and flexibility are achieved.

Owner:VISION MICROSYST SHANGHAI

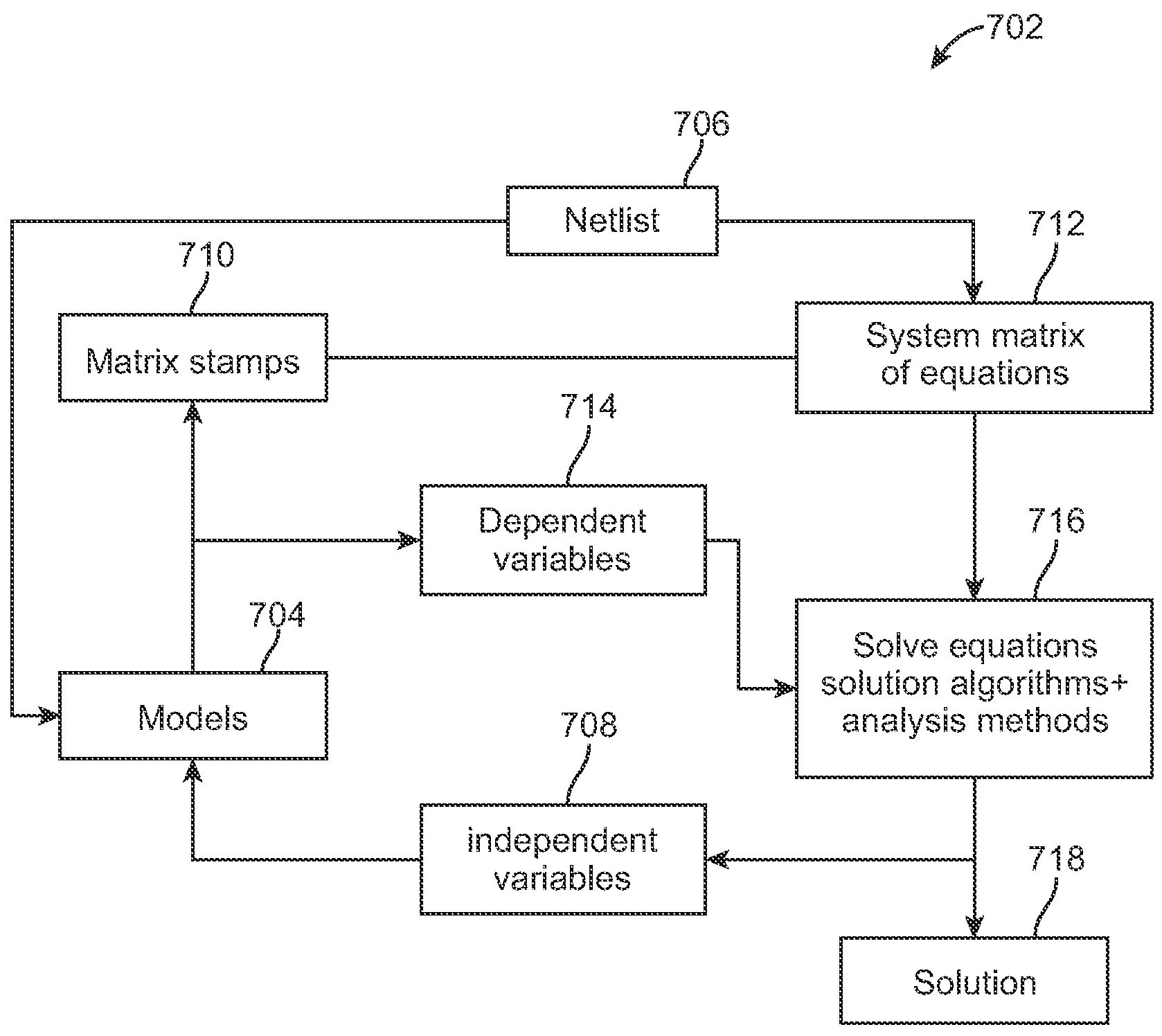

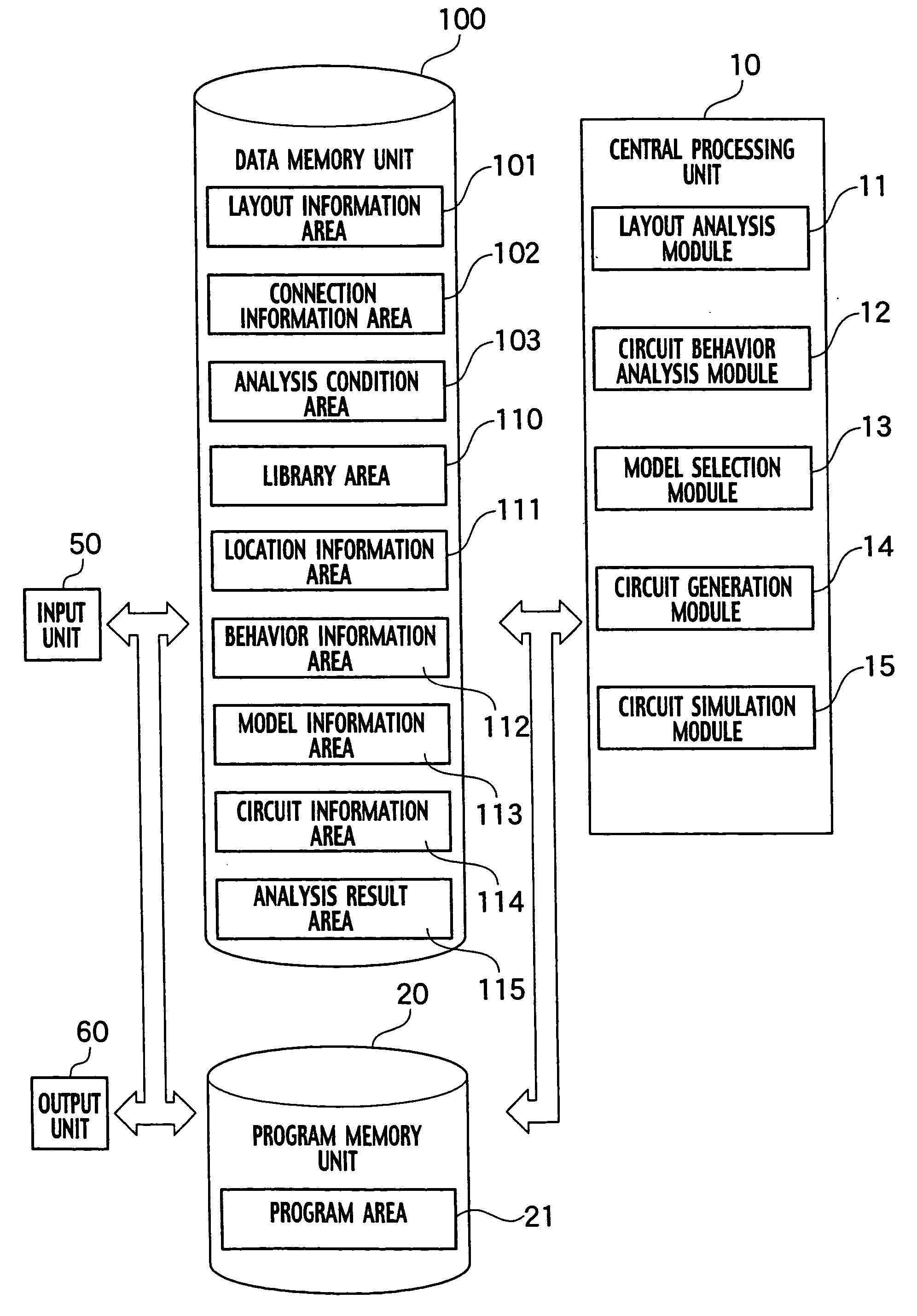

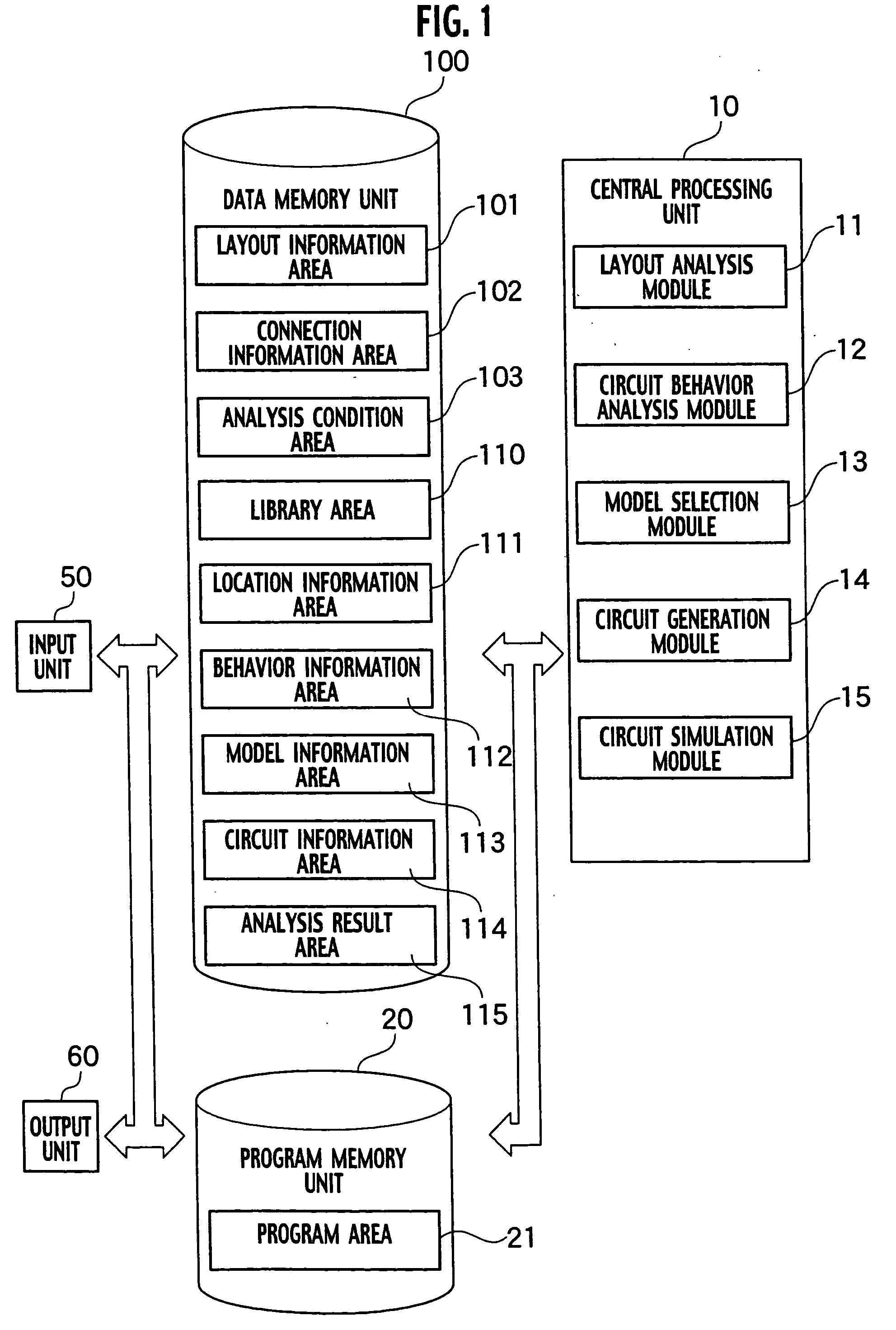

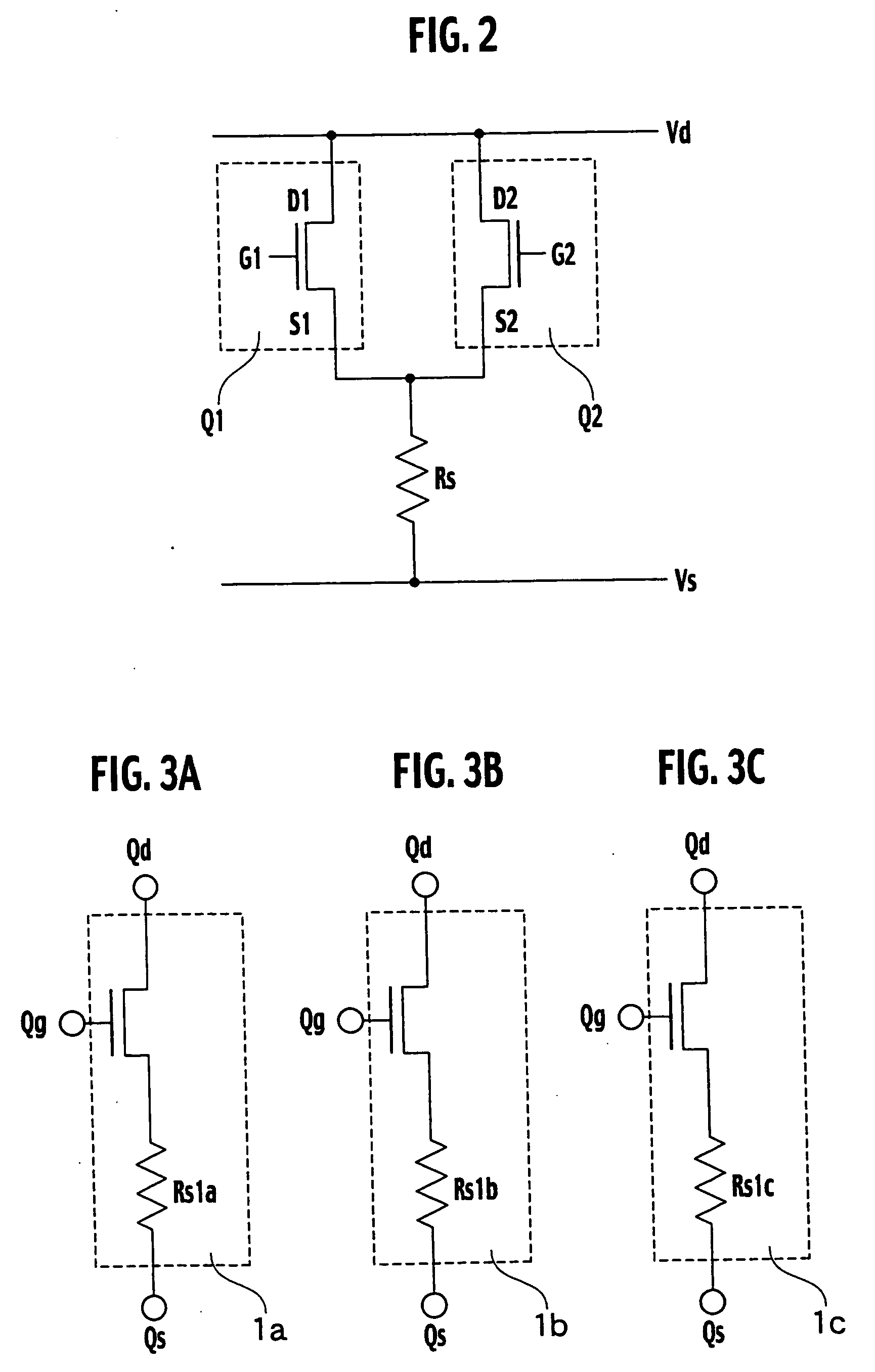

Circuit simulation system with simulation models assigned based on layout information and connection information

InactiveUS20050197816A1Solid-state devicesAnalogue computers for electric apparatusElement modelInformation analysis

A circuit simulation system for simulating an integrated circuit includes a circuit behavior analysis module analyzing behavior information of a circuit element of the integrated circuit based on connection information; a model selection module selecting a circuit element model corresponding to the circuit element from the library area based on location information and behavior information of the circuit element; a circuit generation module generating a to-be-analyzed circuit using the selected circuit element model; and a circuit simulation module executing the to-be-analyzed circuit simulation.

Owner:KK TOSHIBA

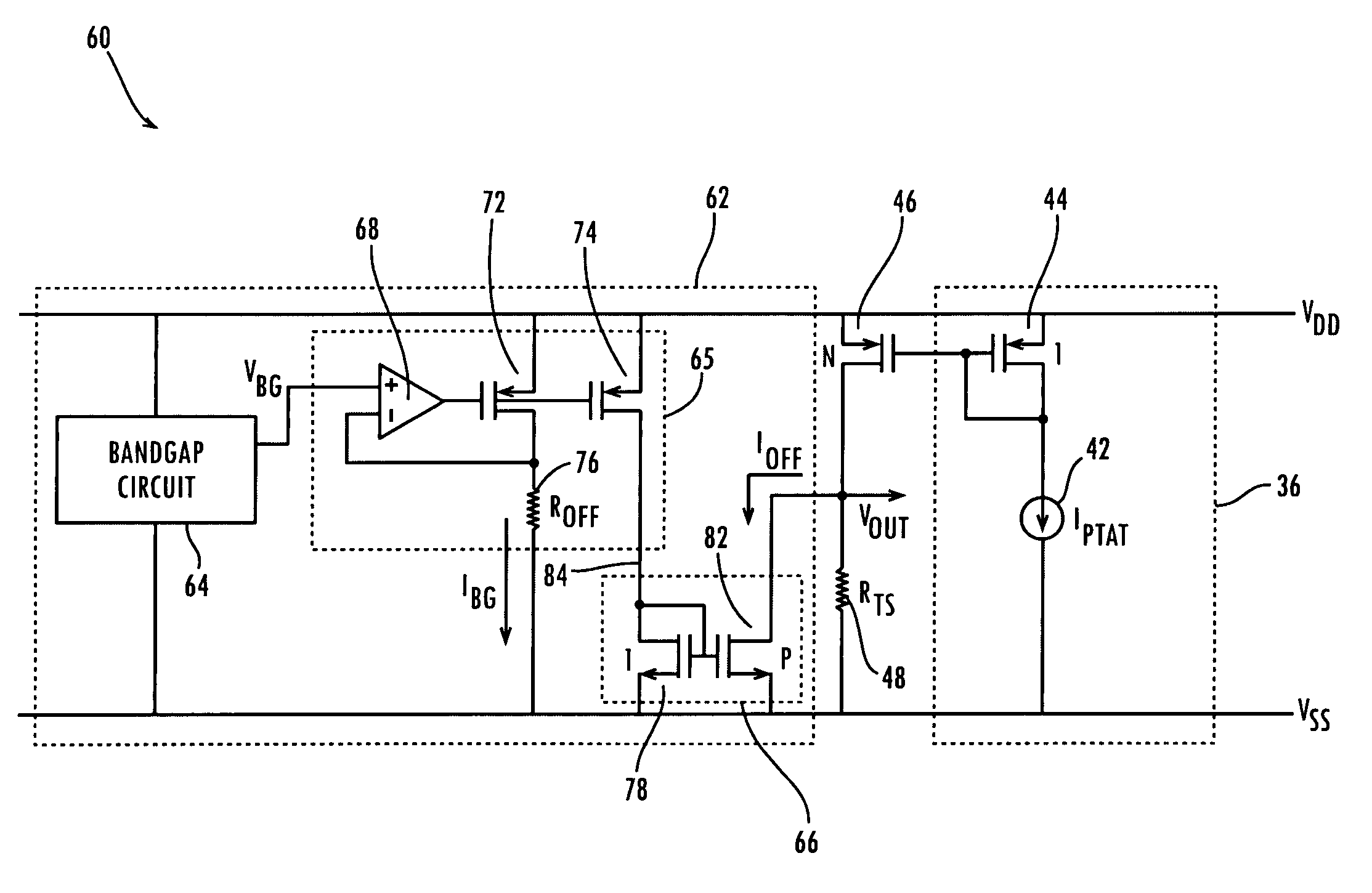

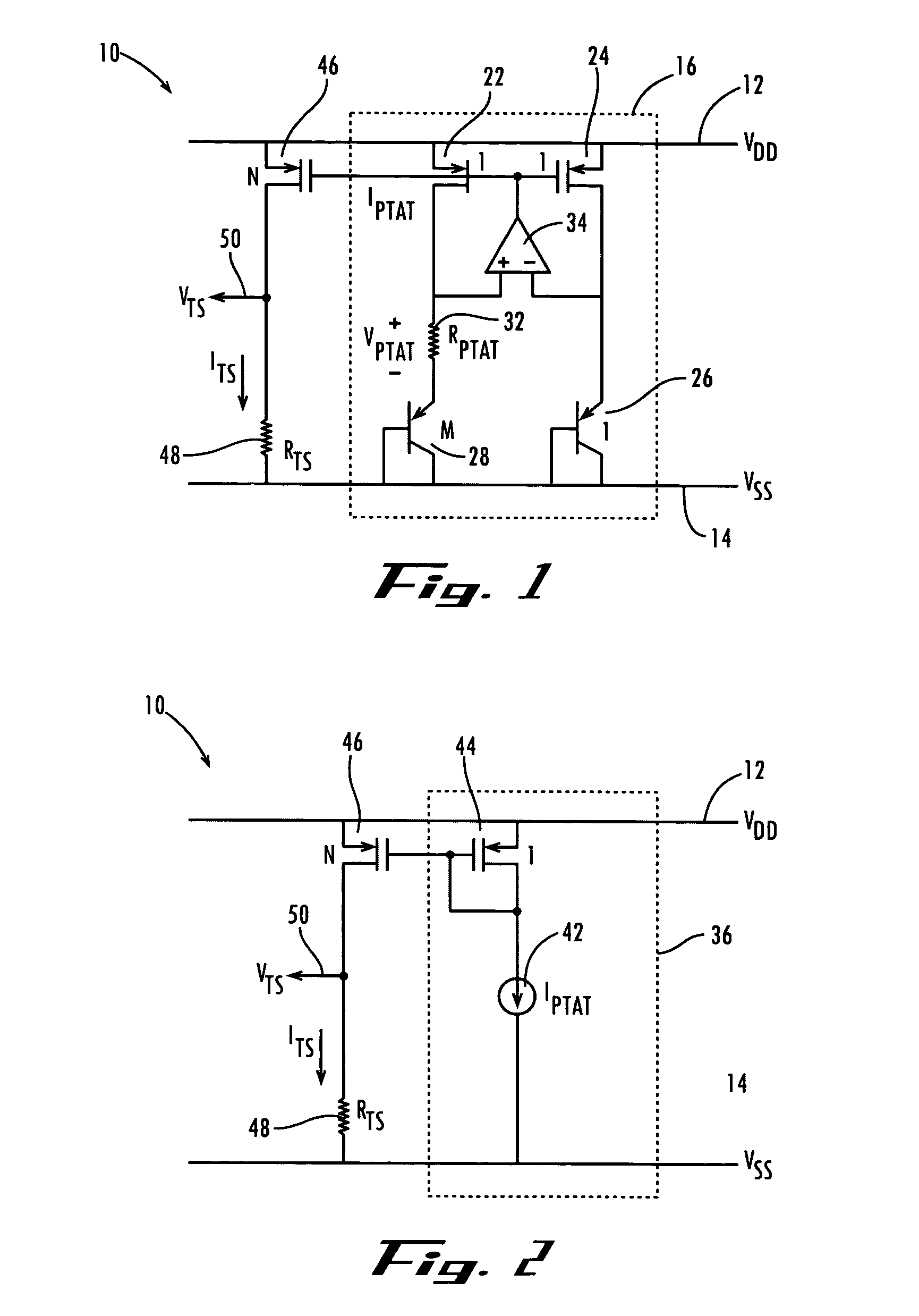

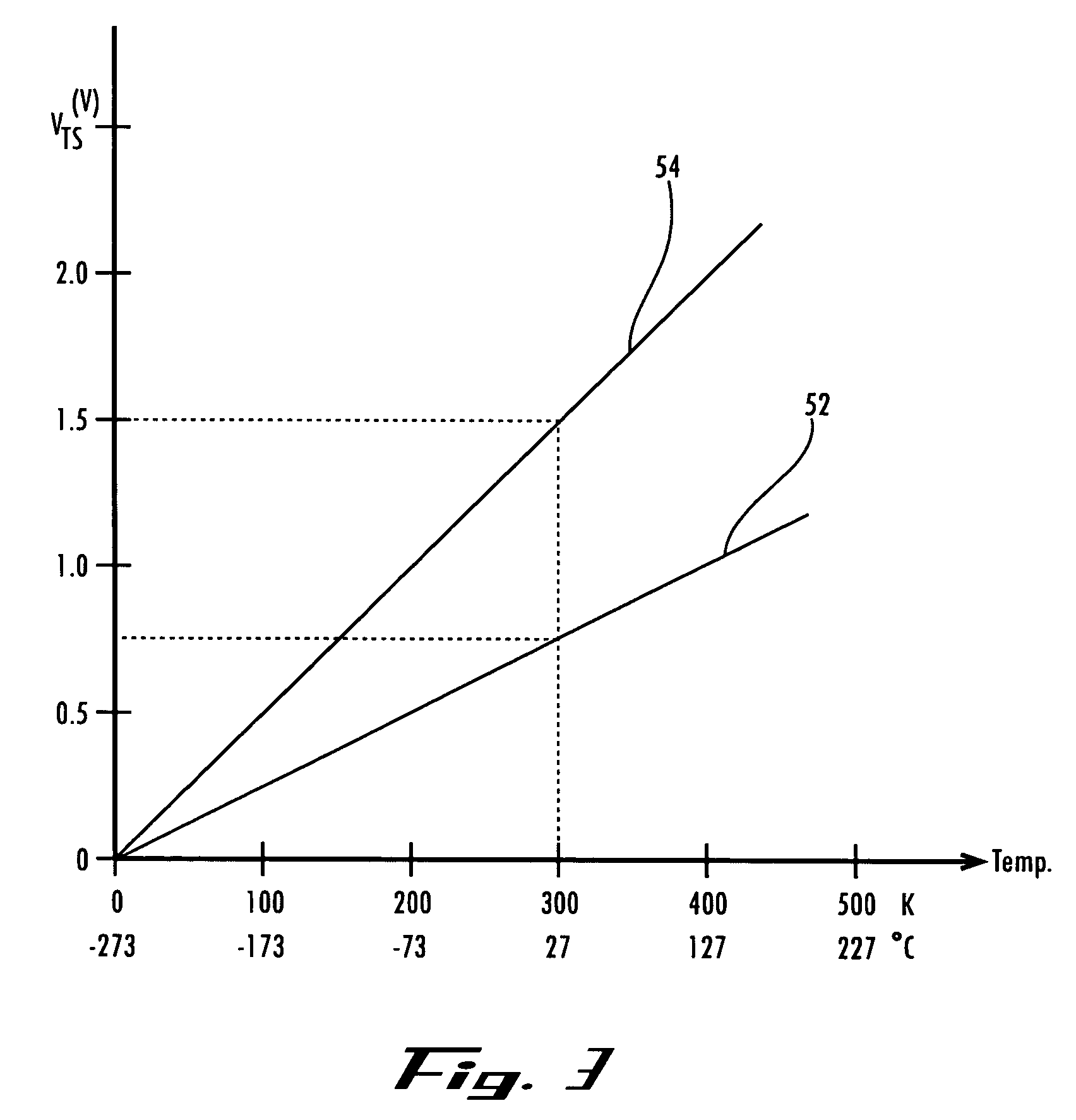

Linear integrated circuit temperature sensor apparatus with adjustable gain and offset

InactiveUS7439601B2Thermometers using electric/magnetic elementsPhotovoltaicsEngineeringVoltage response

Embodiments of the invention include a temperature sensor apparatus, method and system for providing an output voltage response that is linear to the temperature of the integrated circuit to which the temperature sensor belongs and / or the integrated circuit die on which the temperature sensor resides. The output voltage of the temperature sensor has an adjustable gain component and an adjustable voltage offset component that both are adjustable independently based on circuit parameters. The temperature sensor includes a conventional bandgap circuit, which generates an internal PTAT (proportional to absolute temperature) current to produce a bandgap reference voltage, and a current mirror arrangement that provides a scaled current that is proportional to the bandgap circuit's PTAT current. Conventionally, the scaled PTAT current is sourced through an output resistor to provide the output voltage of the temperature sensor. The inventive temperature sensor includes an offset circuit that diverts a portion of current from the scaled PTAT current before the current is sourced through the output resistor. Thus, the inventive temperature sensor subtracts an offset voltage from the output voltage, which offset voltage represents the desired voltage offset component. The offset circuit includes a bandgap circuit arrangement, a voltage to current converter arrangement, and a current mirror arrangement that are configured to provide a voltage offset that is adjustable based on independent circuit parameters such as resistor value ratios and transistor device scaling ratios. The gain component of the inventive temperature also is based on similar independent circuit parameters.

Owner:AVAGO TECH INT SALES PTE LTD

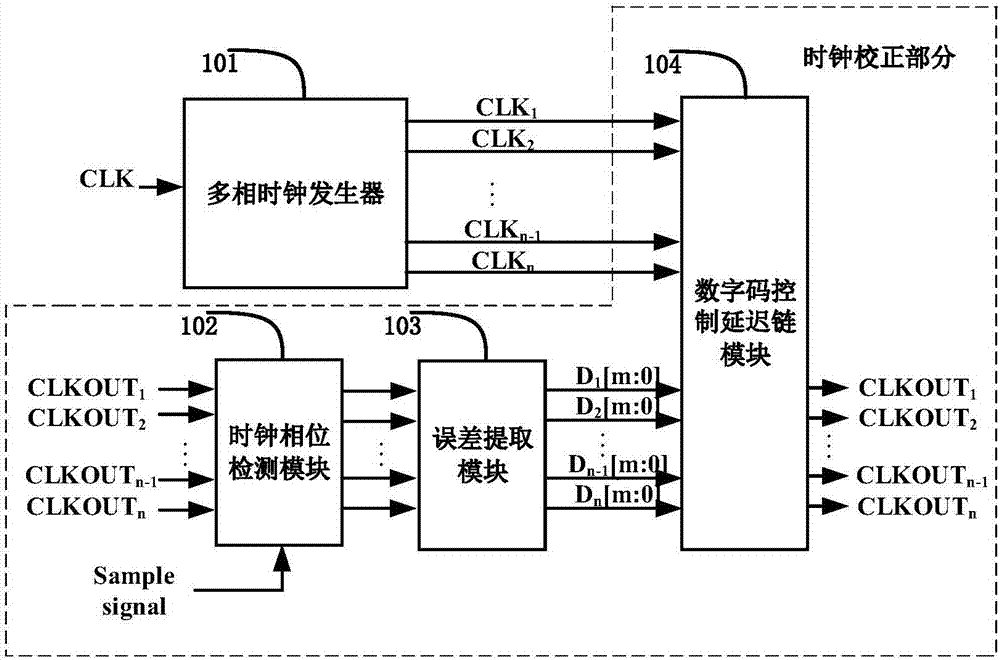

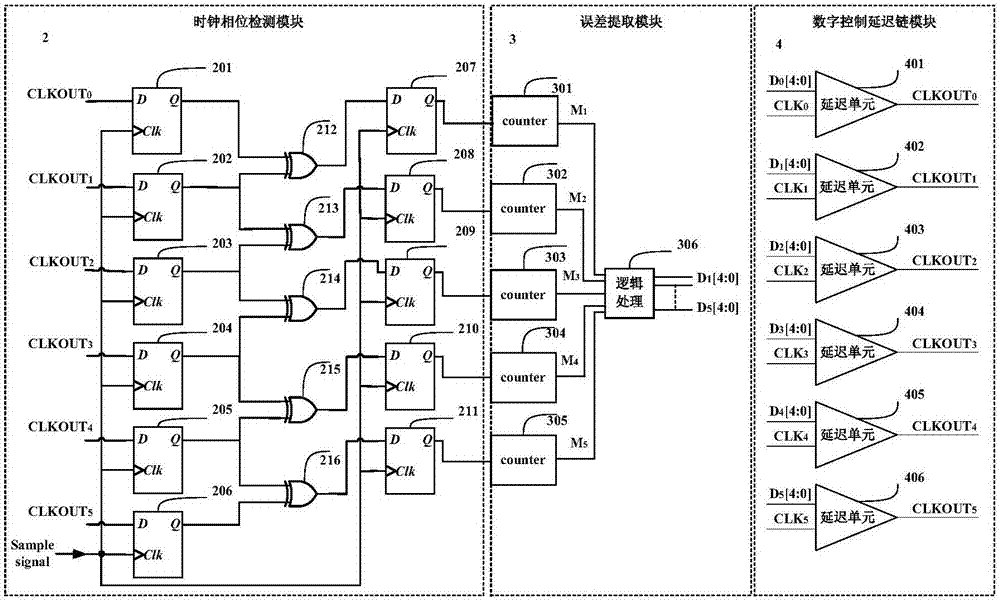

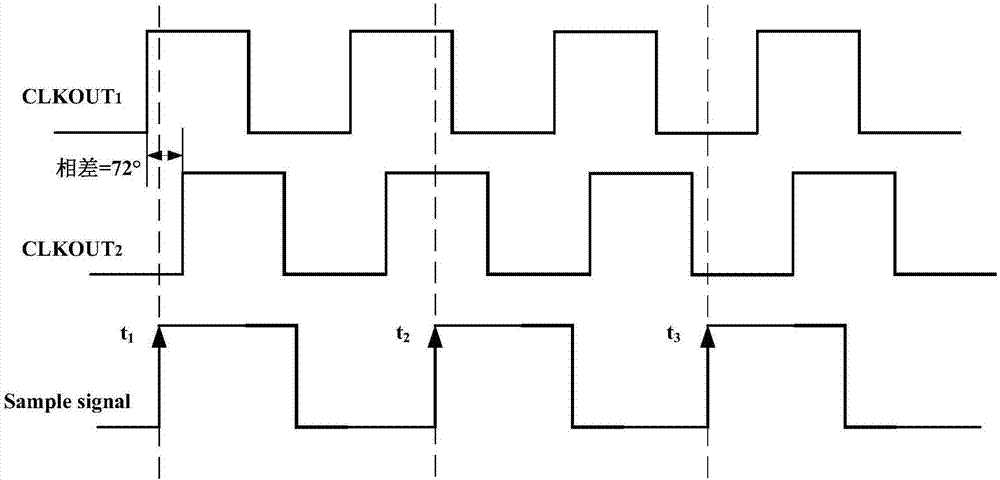

High-precision multi-phase clock correcting circuit

InactiveCN106899290AReduce areaReduce power consumptionPulse automatic controlClock correctionClock phase

The invention discloses a high-precision multi-phase clock correcting circuit, belonging to the field of analog integrated circuit technology, and particularly relating to a multi-phase clock phase error correction circuit. The high-precision multi-phase clock correcting circuit disclosed by the invention aims to solve the problem that the existing traditional multi-phase clock generator has clock delay errors due to non-ideal effects; a traditional multi-phase clock generation circuit generates a multi-phase clock by using a multi-level delay chain, and errors are caused by the mismatch between the delay units; and the high-precision multi-phase clock correcting circuit is beneficial to reduce the power consumption and save the chip area, is high in clock phase detection precision and easy to implement, is high in adjustment precision of the clock delay units, adopts the code values of digital codes to correspond to the delay size, ensures that the clock accuracy of the clock correction module depends on the feedback adjustment accuracy and the detection accuracy of the clock phase errors, and ensures that the high-precision multi-phase clock can be achieved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

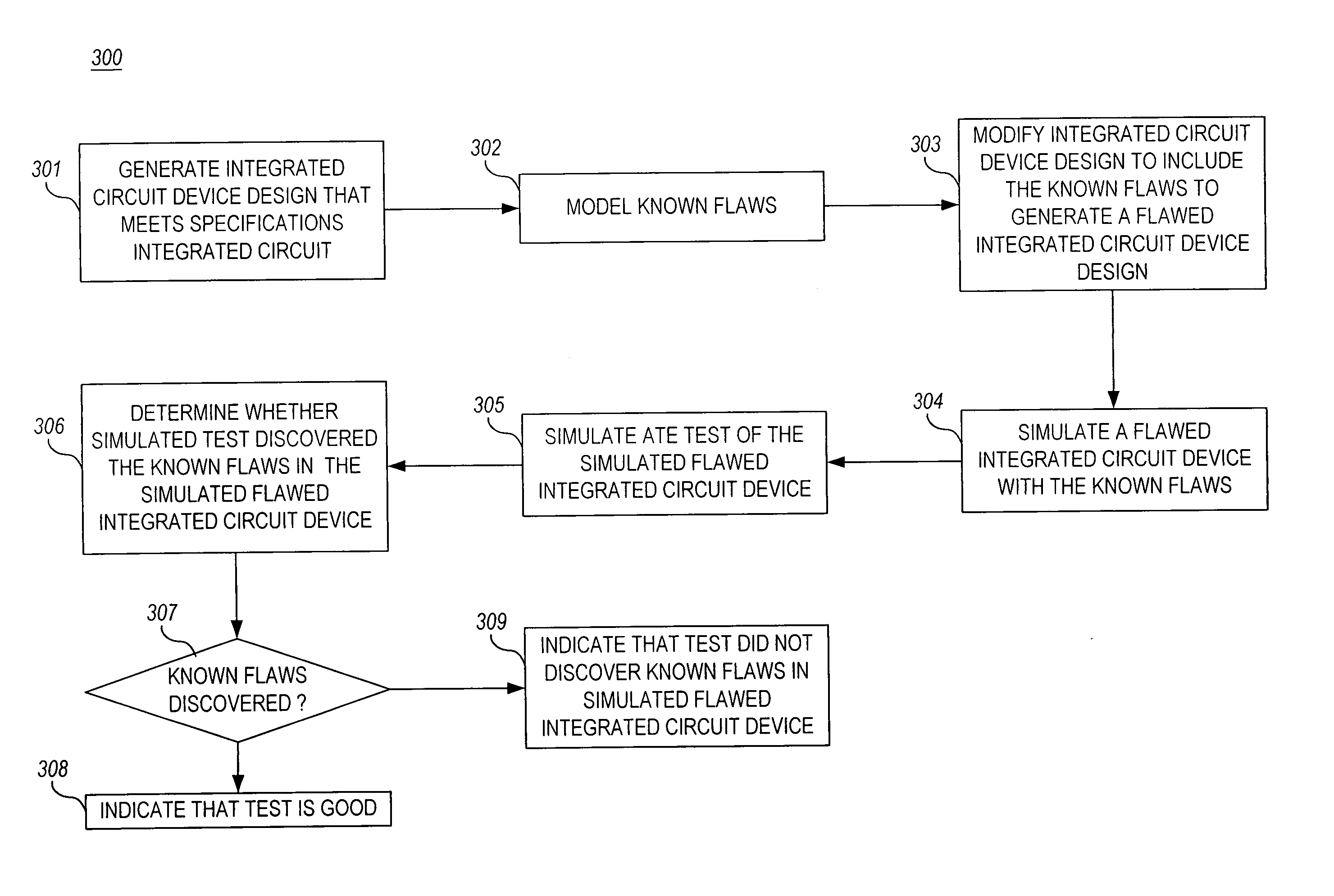

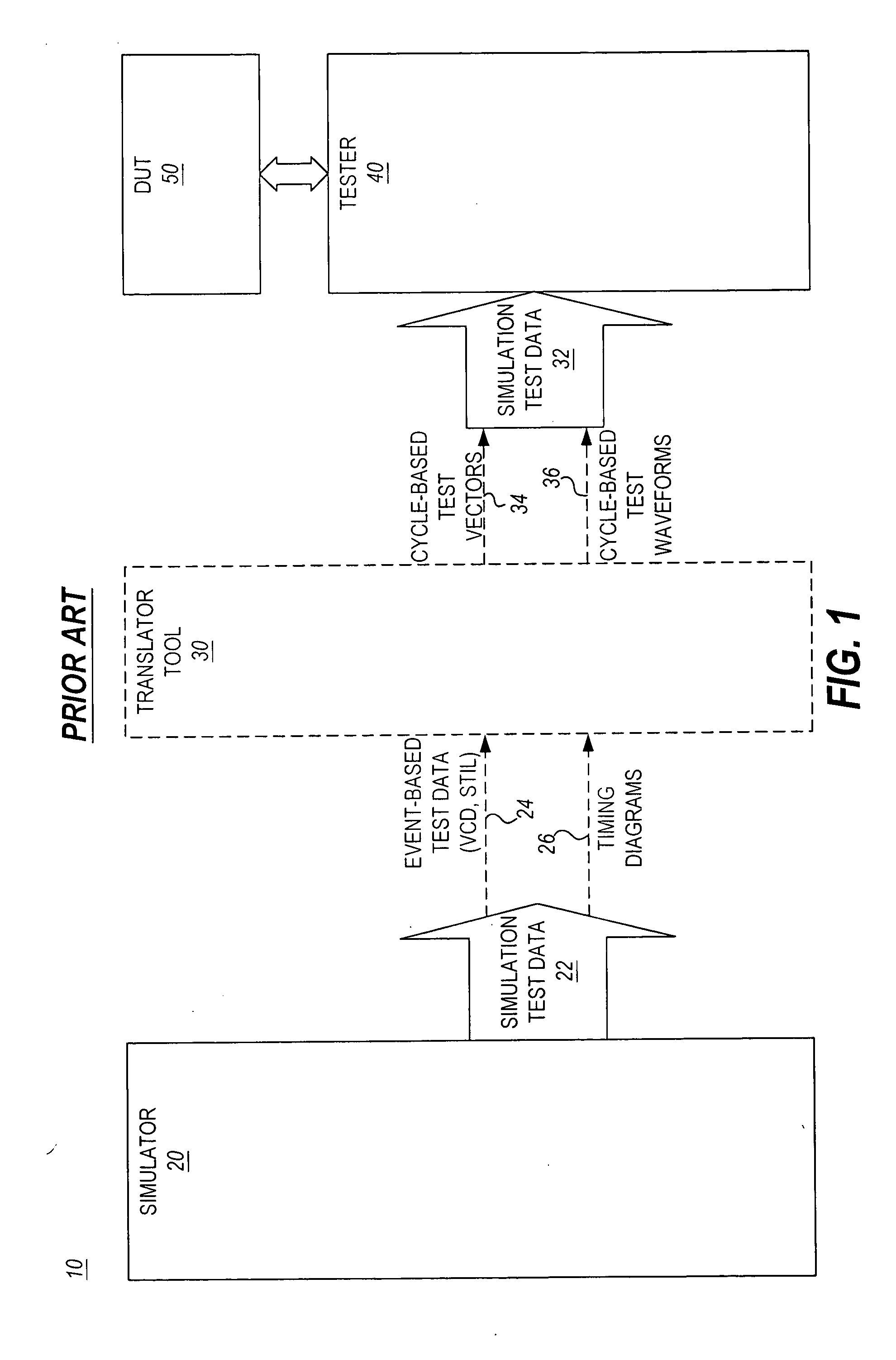

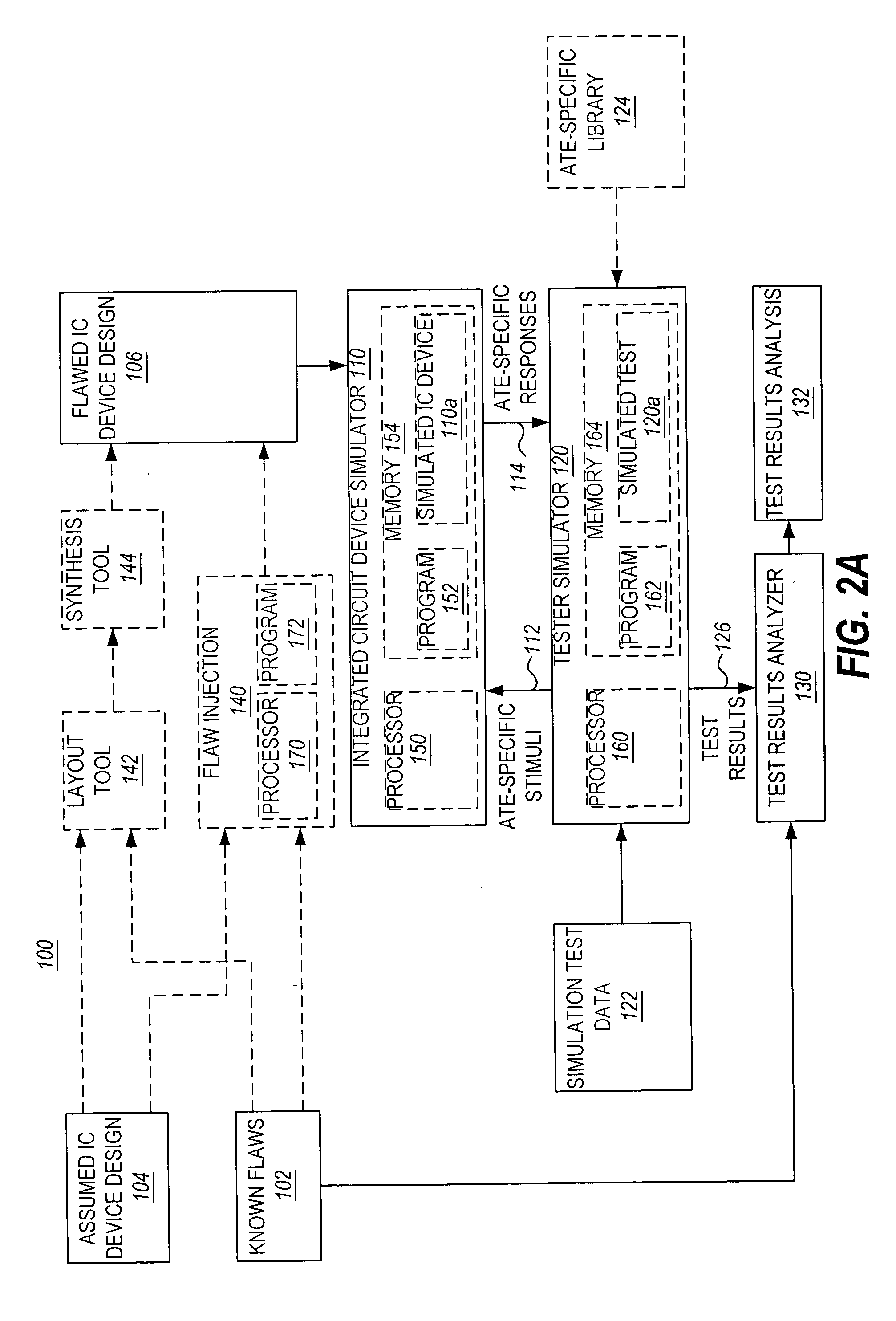

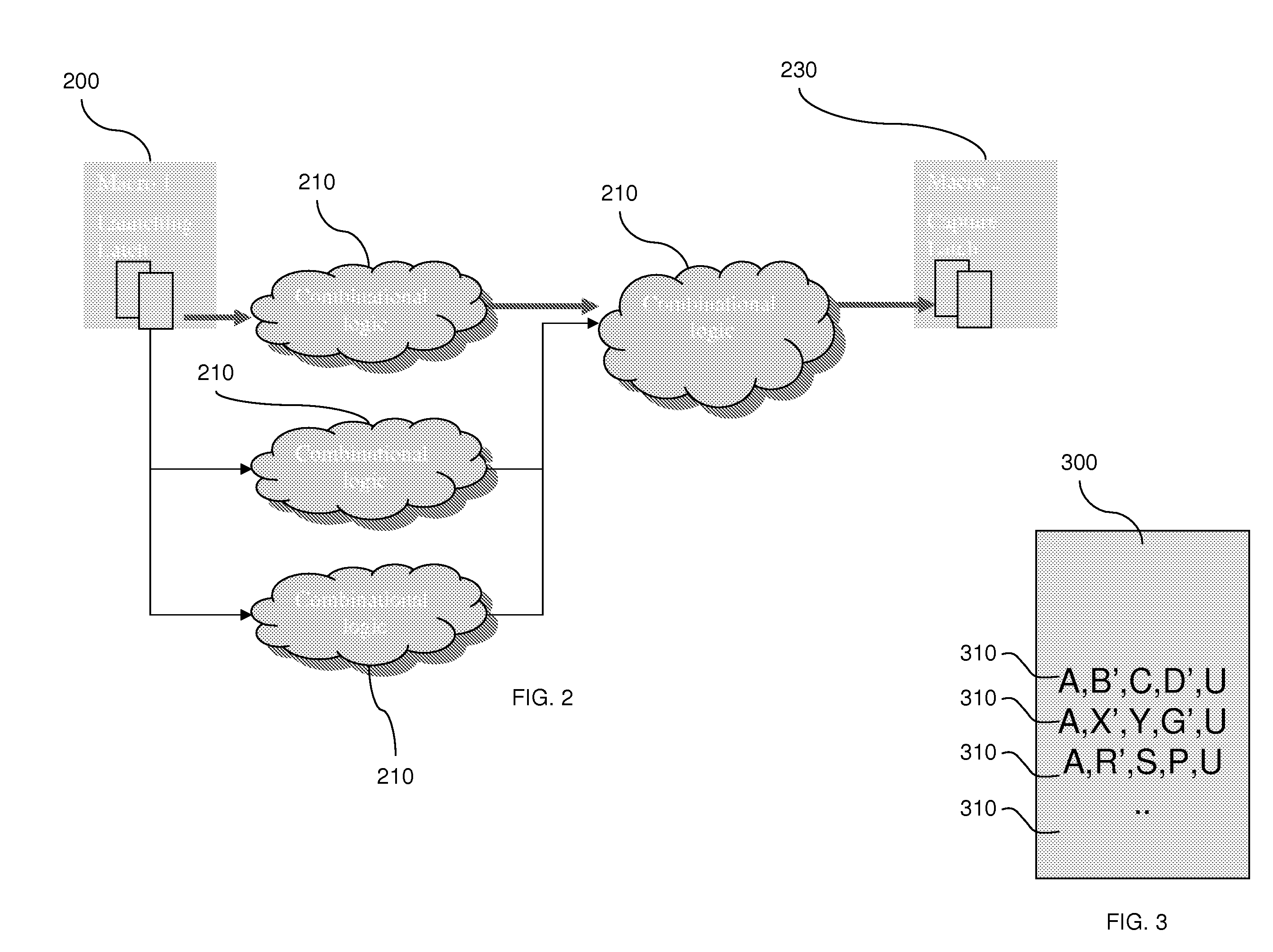

Verification of integrated circuit tests using test simulation and integrated circuit simulation with simulated failure

ActiveUS20050229121A1Convenient verificationElectronic circuit testingAnalogue computers for electric apparatusEngineeringAnalog chip

A method and apparatus for verifying an integrated circuit device test for testing an integrated circuit device on an automated tester is presented. An integrated circuit device simulator simulates a flawed integrated circuit device that models one or more known flaws, or physical defects, in an assumed good integrated circuit device design. A tester simulator simulates the integrated circuit device test which sends stimuli to, and receives responses from, the simulated flawed integrated circuit device. A test analyzer then determines whether the simulated test of the simulated flawed integrated circuit device detected the flaws in the simulated flawed integrated circuit device and properly failed the simulated flawed integrated circuit device.

Owner:ADVANTEST CORP

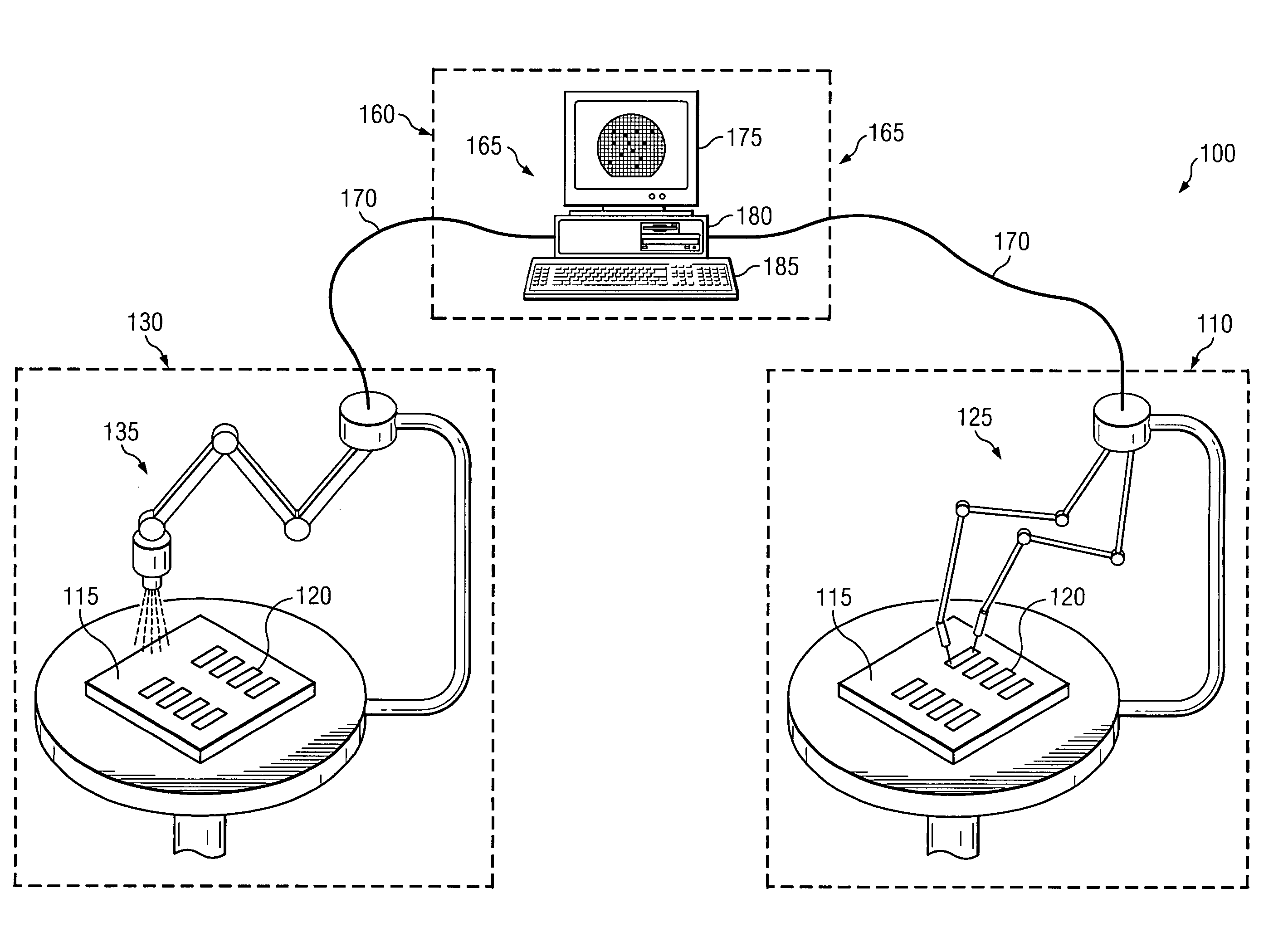

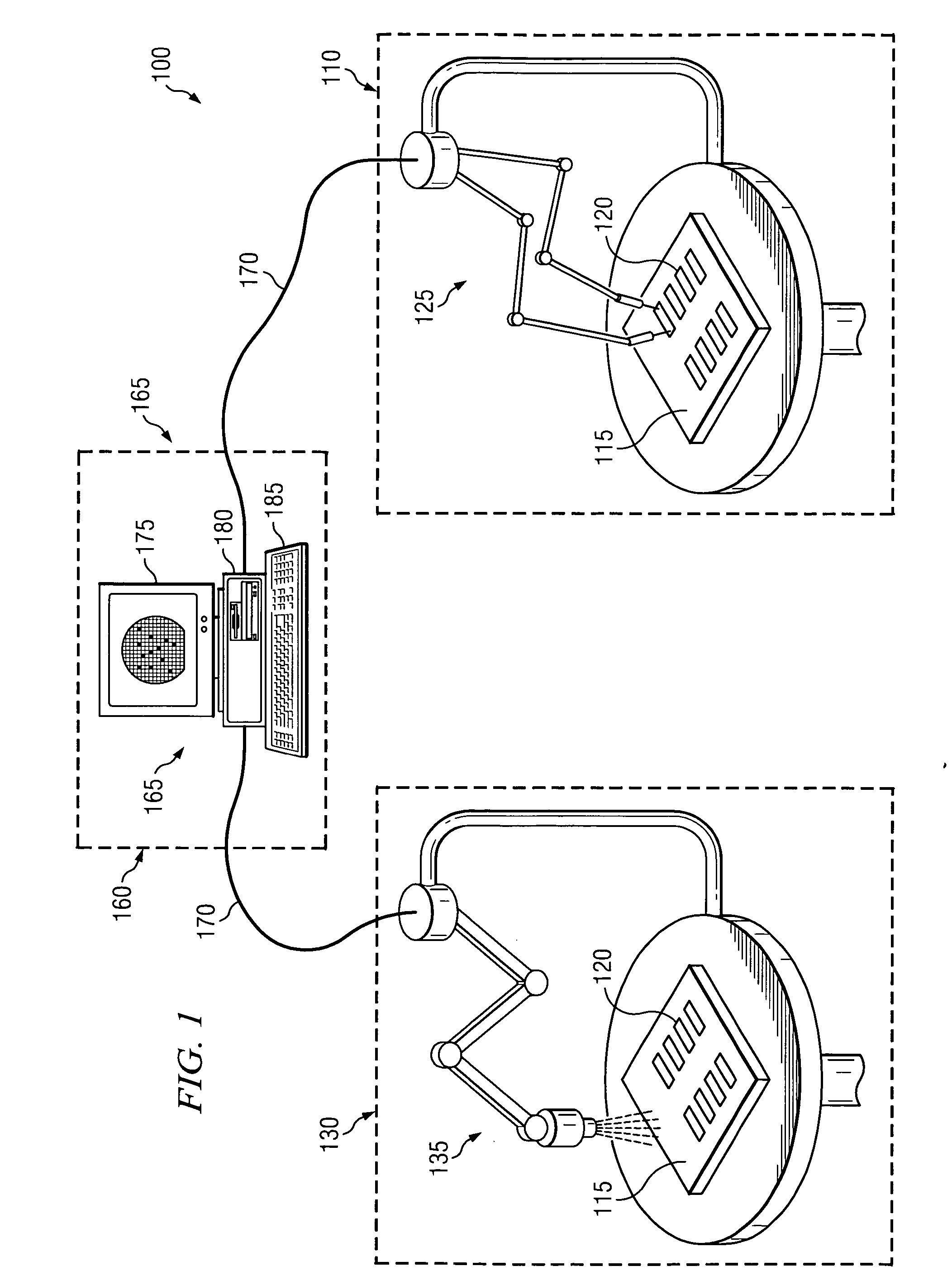

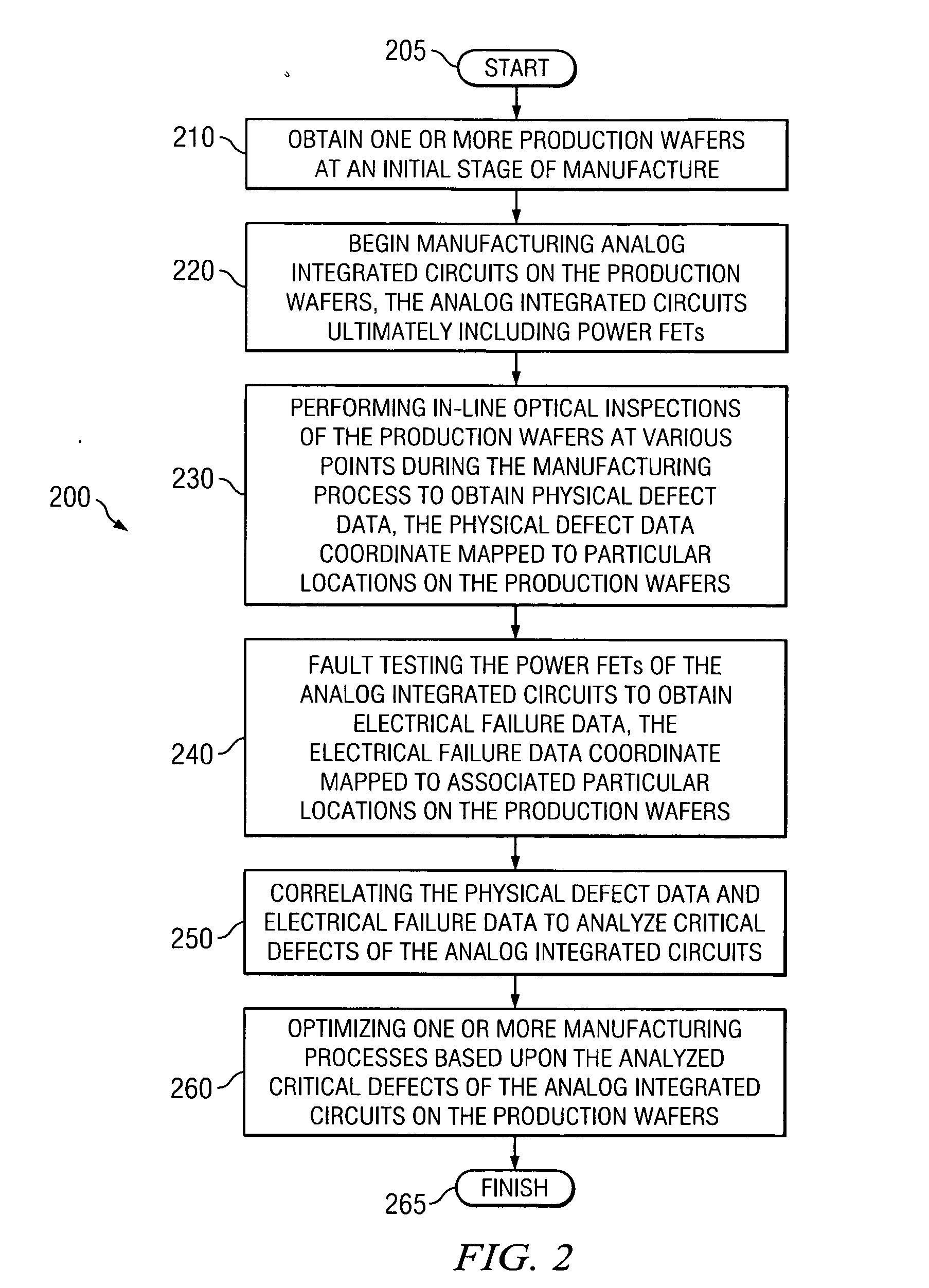

Method for analyzing critical defects in analog integrated circuits

The present invention provides a method for analyzing critical defects in analog integrated circuits. The method for analyzing critical defects, among other possible steps, may include fault testing a power field effect transistor (120) portion of an analog integrated circuit (115) to obtain electrical failure data. The method may further include performing an in-line optical inspection of the analog integrated circuit (115) to obtain physical defect data, and correlating the electrical failure data and physical defect data to analyze critical defects.

Owner:TEXAS INSTR INC

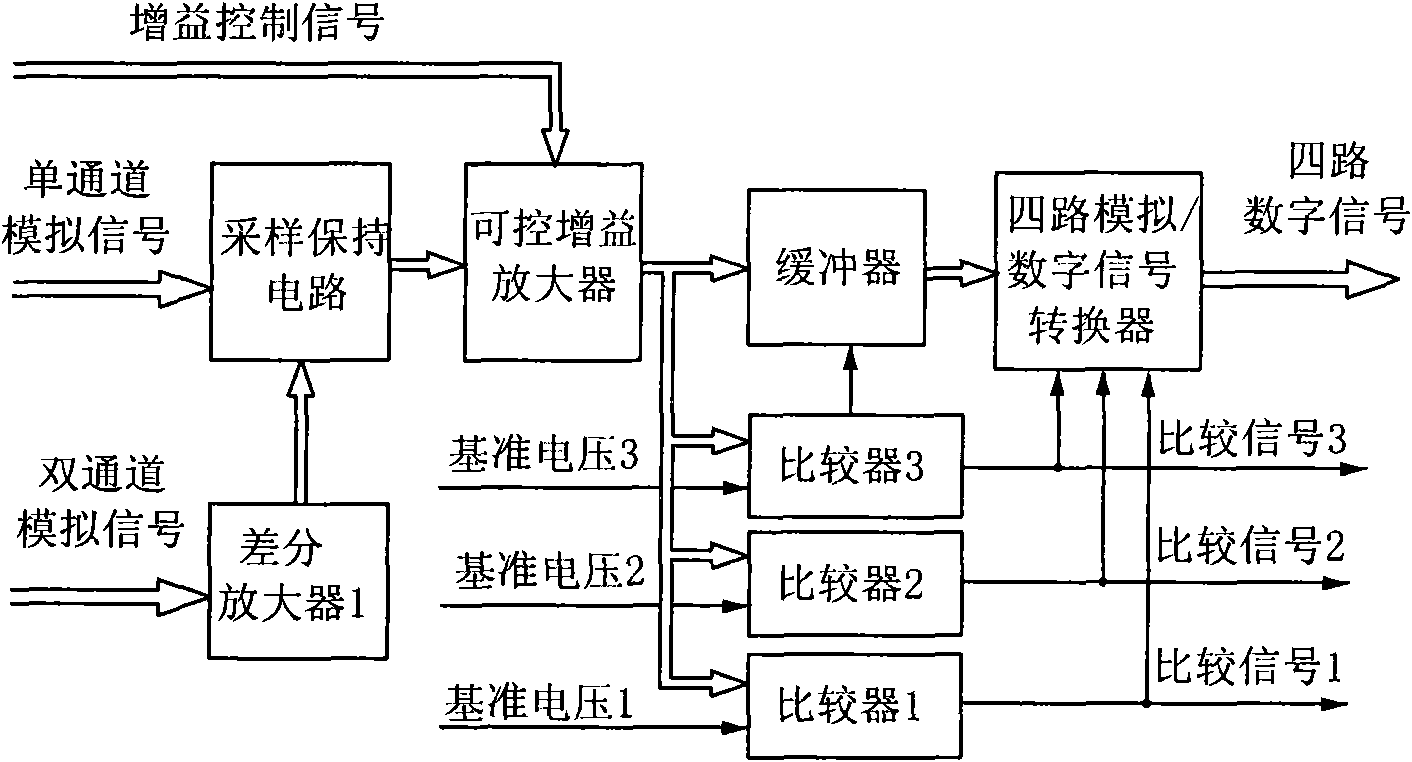

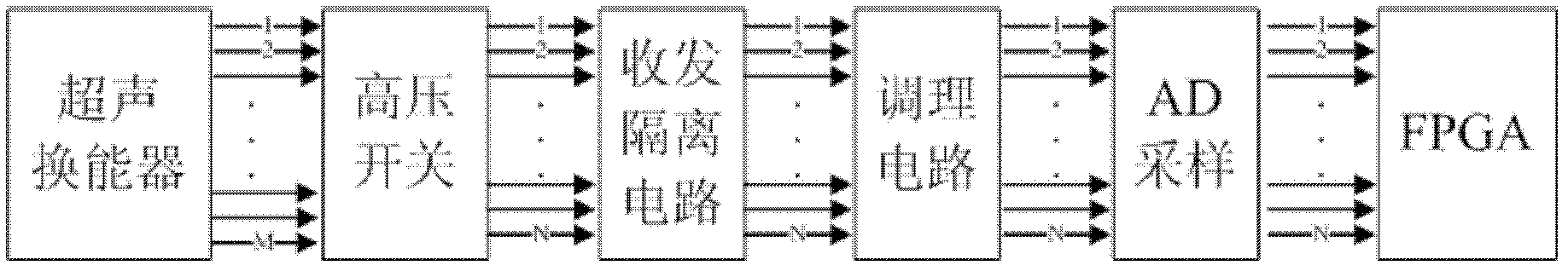

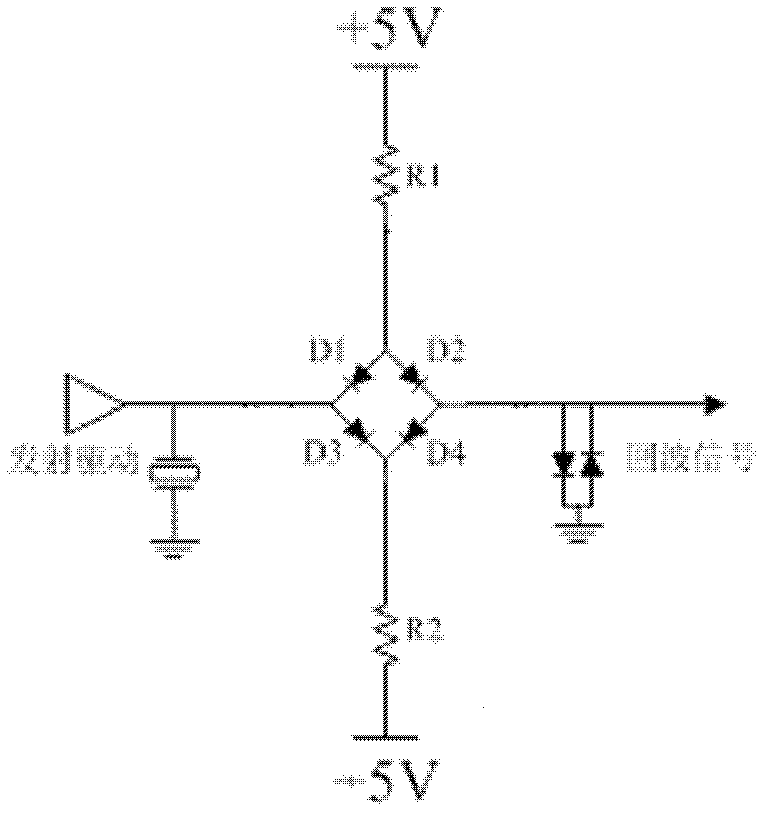

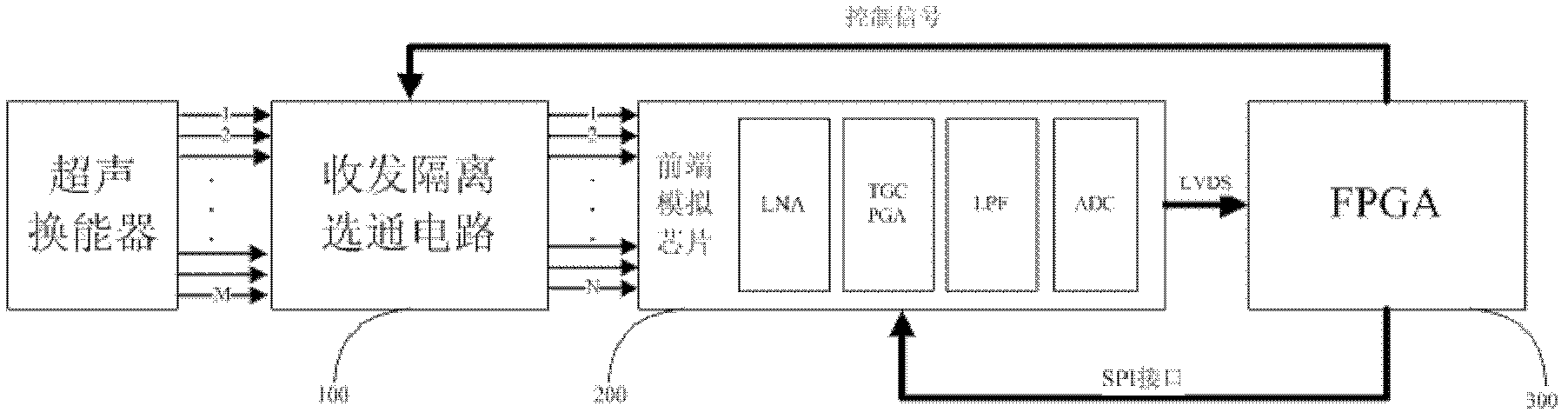

Portable ultrasonic imaging system receiving front-end device

InactiveCN103033807APortableGood for serial-to-parallel conversionWave based measurement systemsUltrasound imagingElectrical resistance and conductance

The invention provides a portable ultrasonic imaging system receiving front-end device which is used for receiving and processing echo signals input by an ultrasonic transducer. The portable ultrasonic imaging system receiving front-end device is characterized by comprising sending and receiving isolated gate circuits which are connected in series sequentially, a front-end analog chip and a field programmable gata array (FPGA) main control unit. Optimized diode bridge circuits are adopted in the sending and receiving isolated gate circuits and the sending and receiving isolated gate circuits are controlled by the FPGA main control unit, each optimized sending and receiving isolated diode bridge circuit is connected with a transducer array element directly, wherein the optimized diode bridge circuits are provided with two inductances which are in a serial connection with the direct circuit bias access, and the specific circuit is characterized in that one ends, connected with the diode bridge, of a first bias resistance (R1) and a second bias resistance (R2) of the diode bridge circuit are respectively serially connected with a first inductance (L1) and a second inductance (L2), wherein the ranges of the first inductance and the second inductance are from several microhenries to hundreds of microhenries, and the portable ultrasonic imaging system receiving front-end device is powered by a single power supply.

Owner:INST OF ACOUSTICS CHINESE ACAD OF SCI

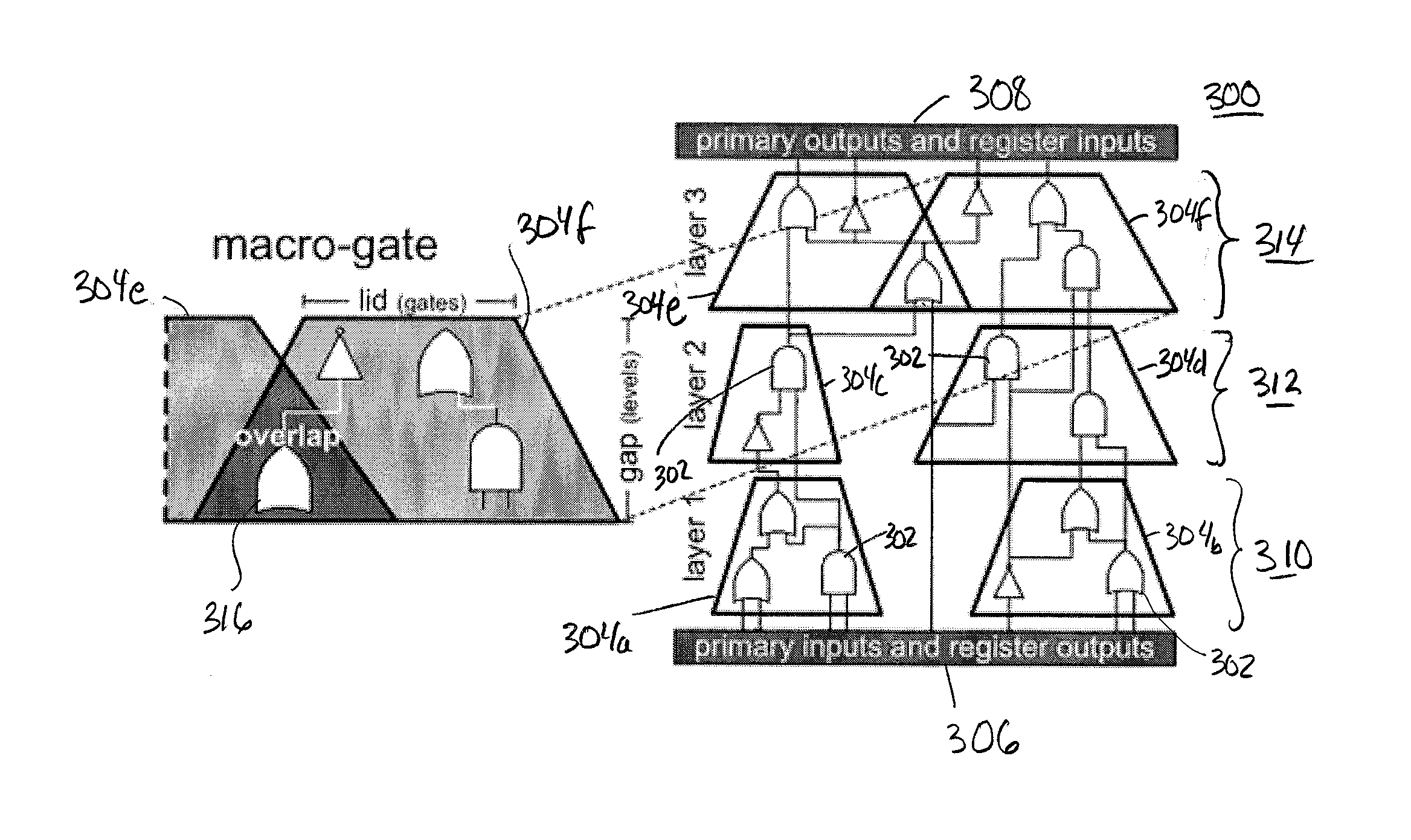

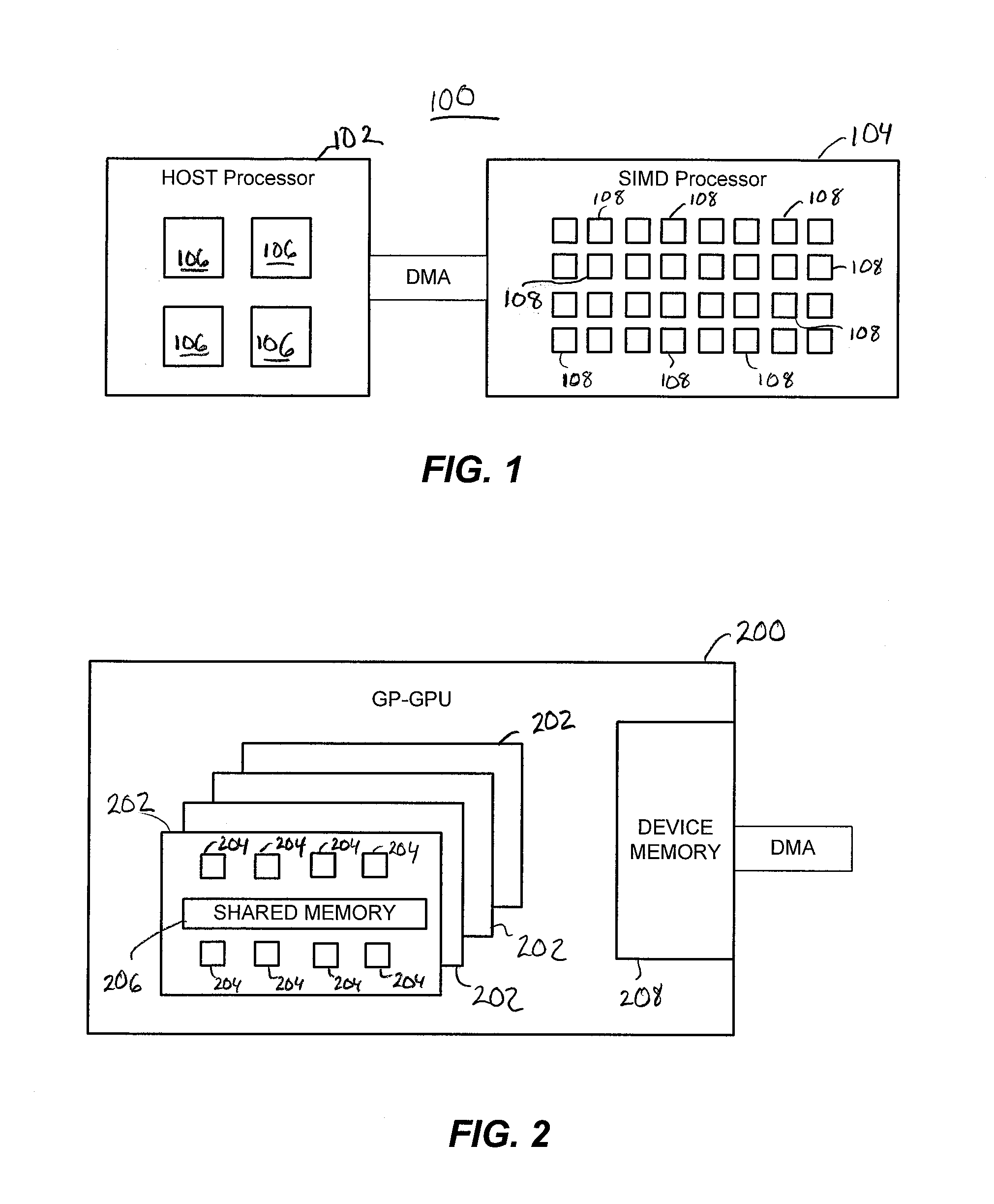

Gate-Level Logic Simulator Using Multiple Processor Architectures

ActiveUS20110257955A1CAD circuit designSpecial data processing applicationsSimd processorCluster group

Techniques for simulating operation of a connectivity level description of an integrated circuit design are provided, for example, to simulate logic elements expressed through a netlist description. The techniques utilize a host processor selectively partitioning and optimizing the descriptions of the integrated circuit design for efficient simulation on a parallel processor, more particularly a SIMD processor. The description may be segmented into cluster groups, for example macro-gates, formed of logic elements, where the cluster groups are sized for parallel simulation on the parallel processor. Simulation may occur in an oblivious as well as event-driven manner, depending on the implementation.

Owner:RGT UNIV OF MICHIGAN

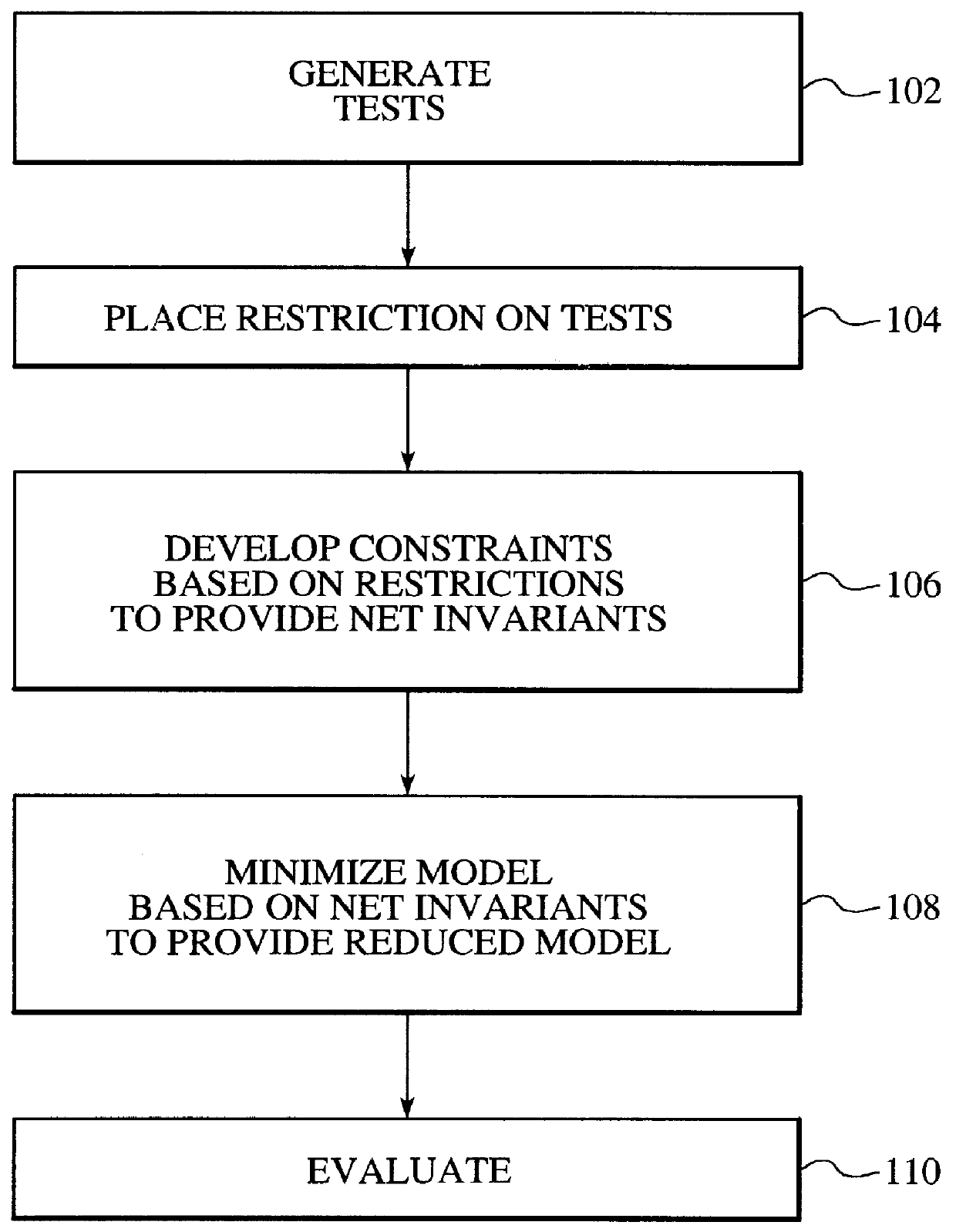

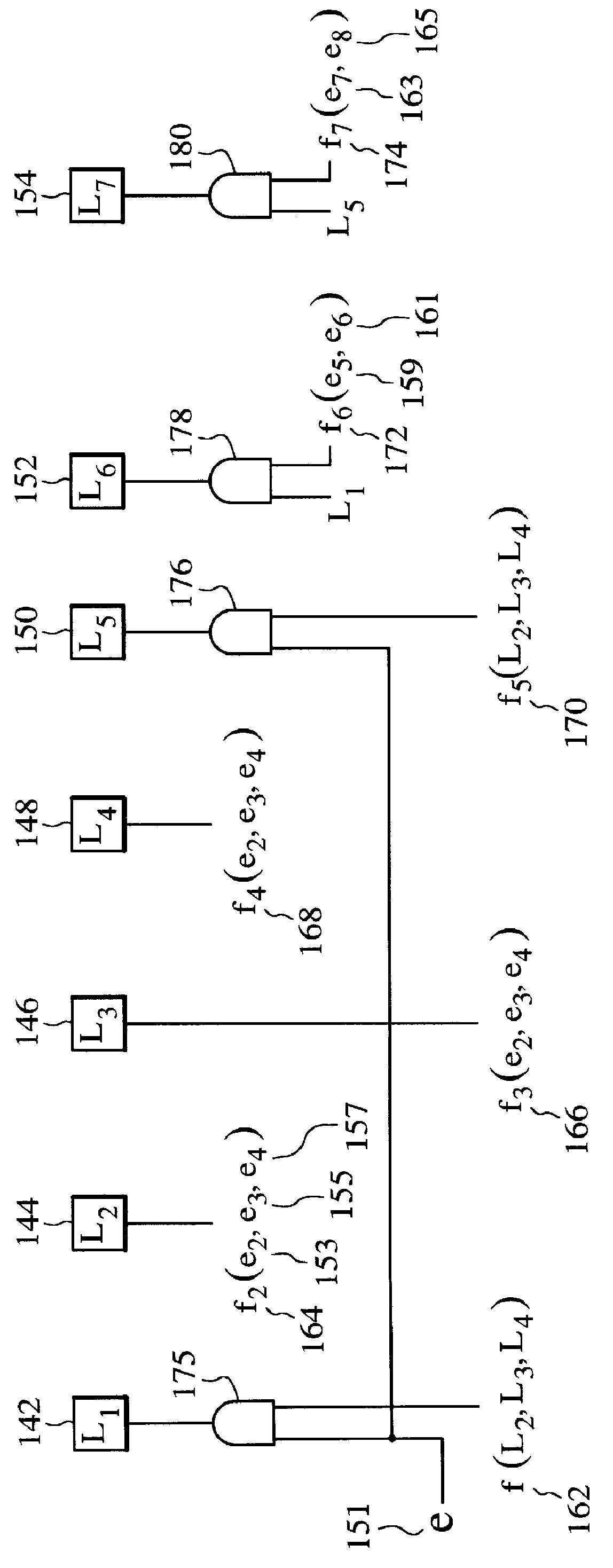

System and method for model size reduction of an integrated circuit utilizing net invariants

InactiveUS6049662AReduce the amount requiredImprove simulation speedDigital circuit testingAnalogue computers for electric apparatusReduced modelMinimization algorithm

The present invention provides a system and method for verifying an integrated circuit model. The model includes a plurality of net variables. The system and method comprises generating a plurality of tests for simulating the integrated circuit, precalculating a reduced model based upon the generated tests, and evaluating the reduced model. In a preferred embodiment, the present invention includes restricting the test that are generated. Then net invariants for the integrated circuit are generated by translating the restricted plurality of tests to a smaller set of possible values for the net variables. Thereafter, a minimization algorithm or procedure is utilized to minimize the logic used in the particular system based upon the latch constraints. This system produces a reduced model which reduces the amount of the integrated circuit that must be simulated thereby increasing the simulation speed thereof. Accordingly, the present invention integrates an event-driven simulation and a cycle simulation in such a manner that the saving can be proportional to the size of the reduction of the model. In many environments this reduction is significant because it allows for a significant reduction in space which has a clear bearing on the verification process.

Owner:IBM CORP

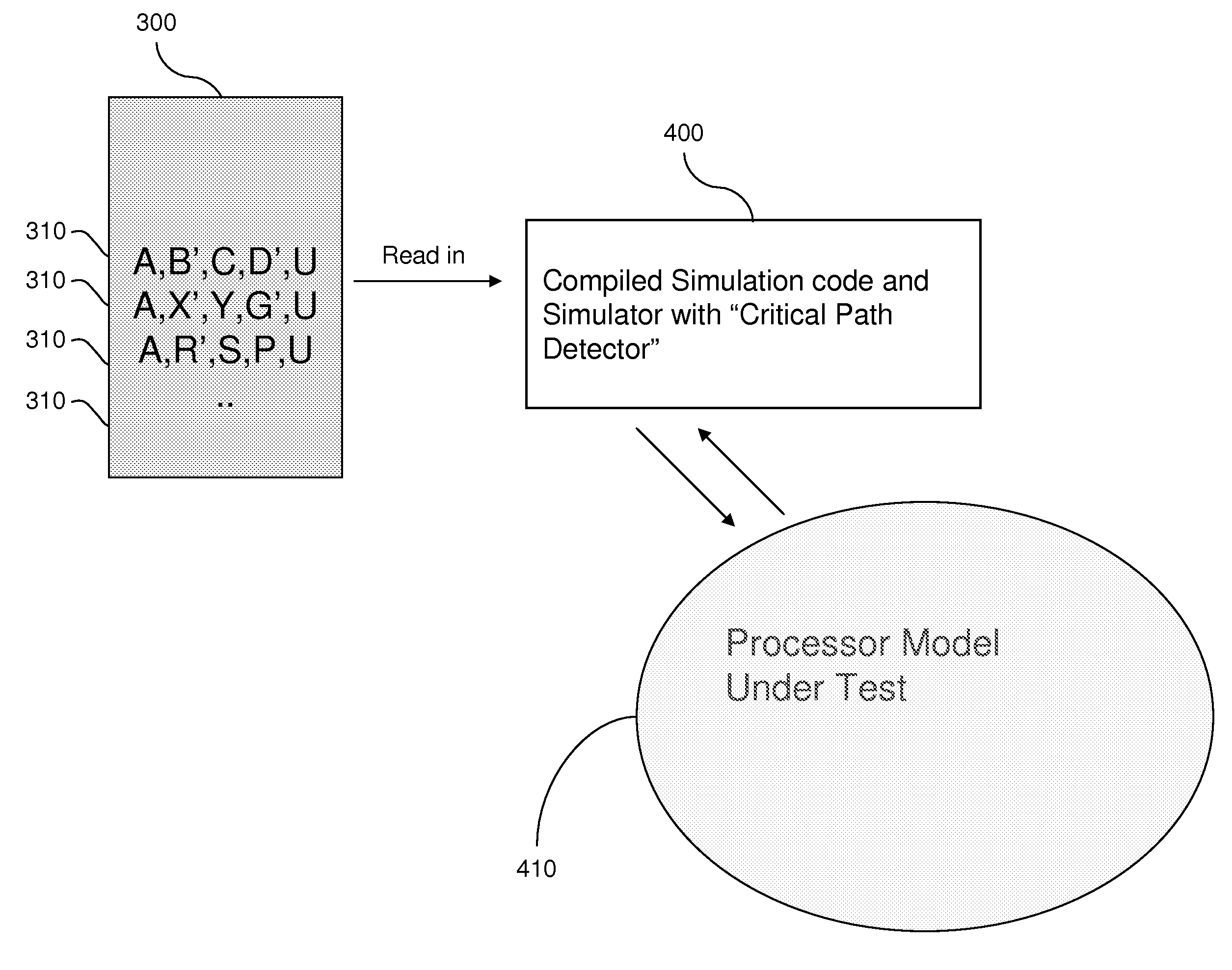

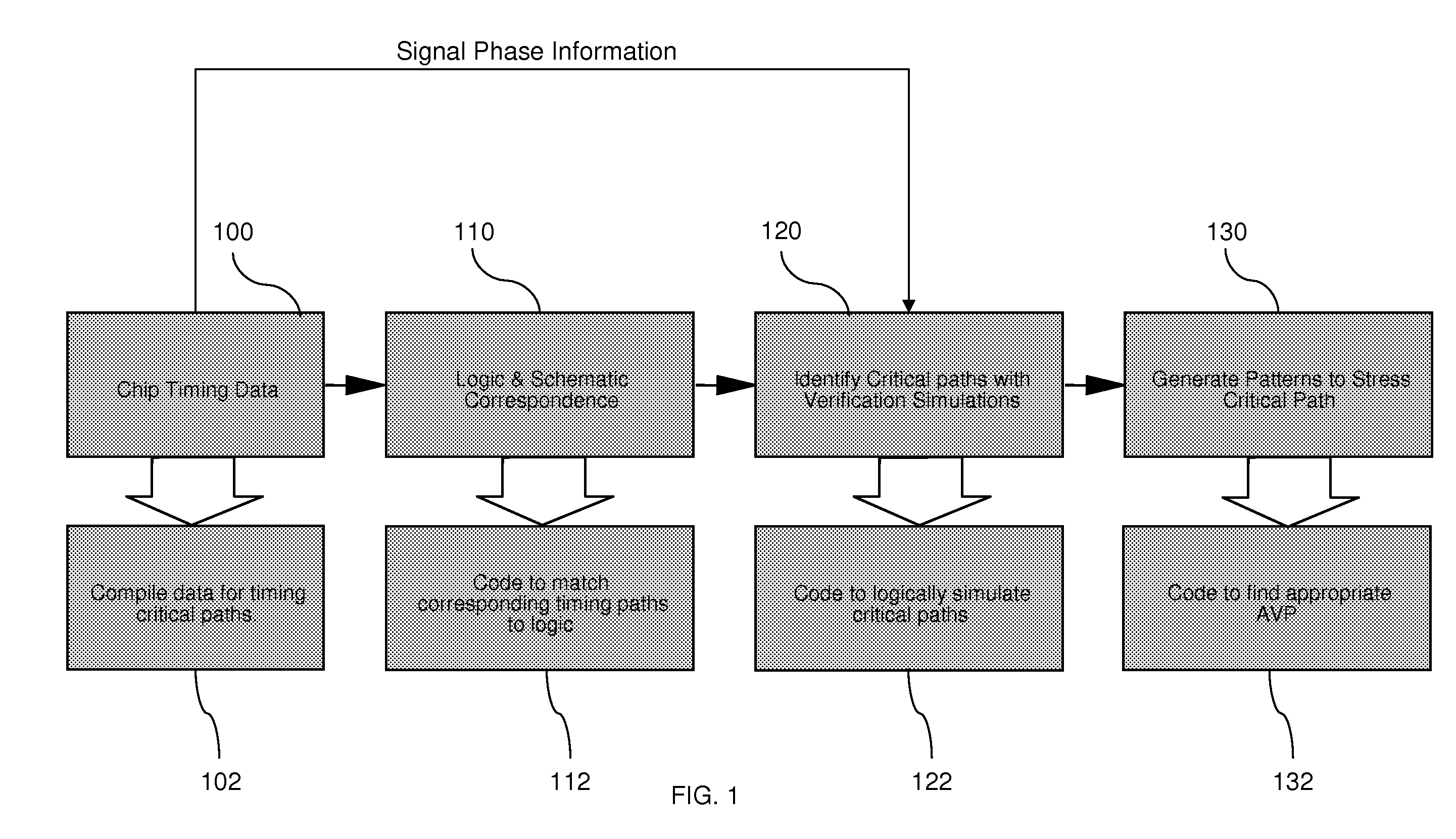

Method to identify and generate critical timing path test vectors

InactiveUS20080263489A1Shorten test timeEasy to integrateElectrical testingComputer aided designFunctional testingCritical path method

A method of testing critical paths in integrated circuits begins by simulating at least one operation of an integrated circuit chip design to produce chip timing data. Next, critical paths of the integrated circuit chip design are identified based on the chip timing data. The method applies functional test signals to simulations of the critical paths and monitors the number of times each of the functional test signals propagate from the beginning to the end of each of the critical paths. This allows the method to identify stress producing test signals as those that propagate along the critical paths more than other test signals. These stress producing test signals are applied to integrated circuit chip hardware manufactured according to the integrated circuit chip design to stress test the hardware.

Owner:IBM CORP

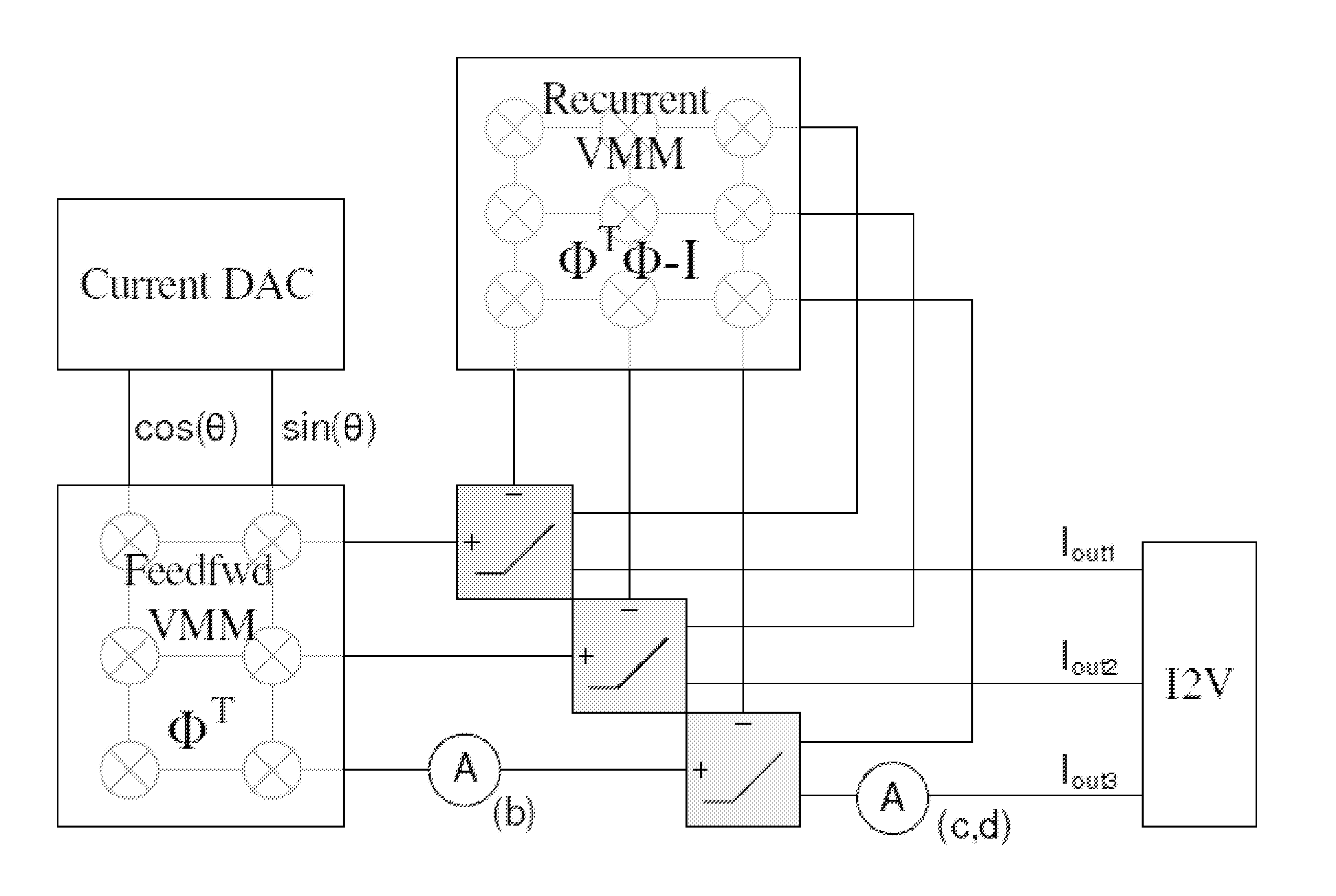

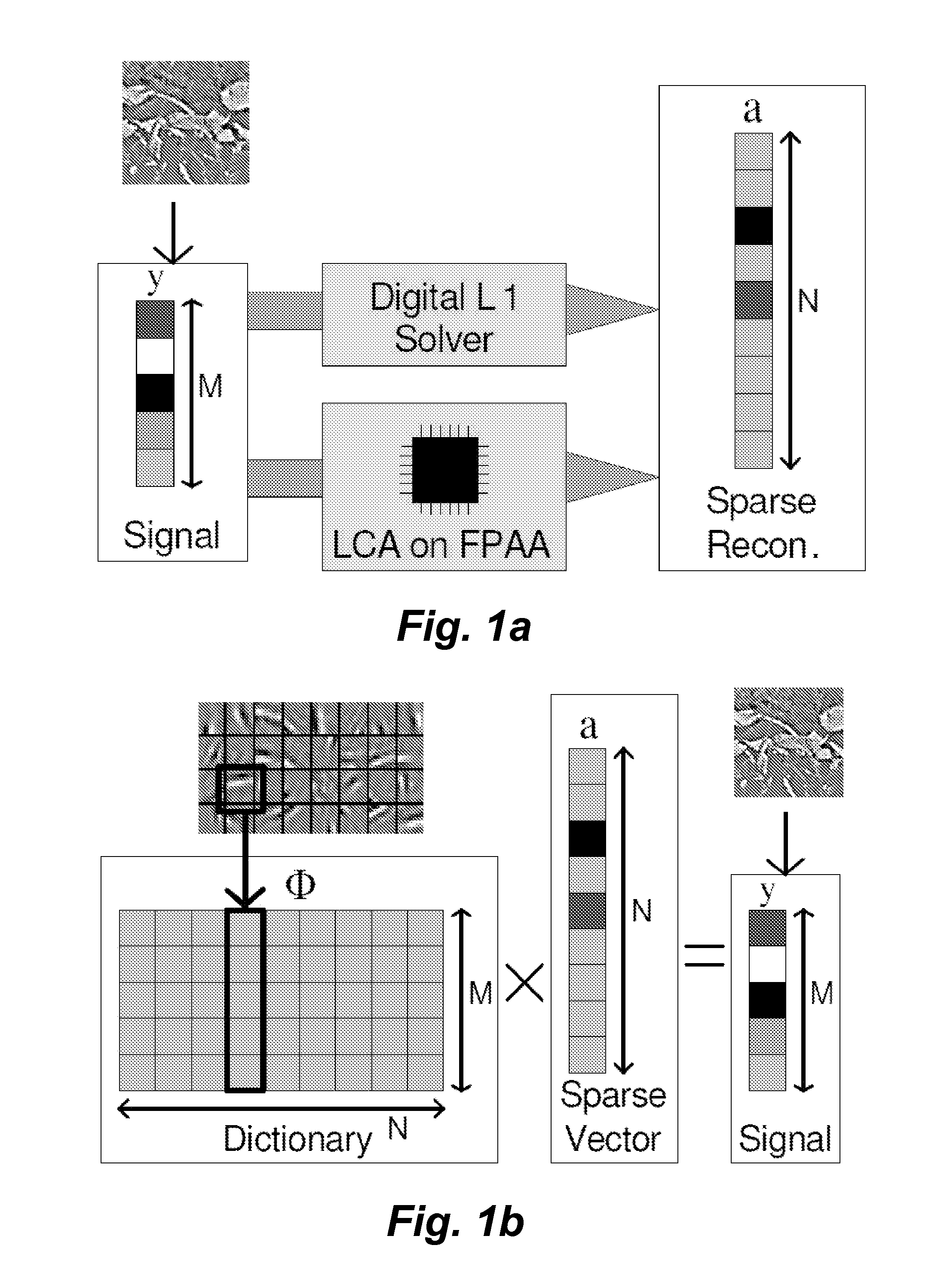

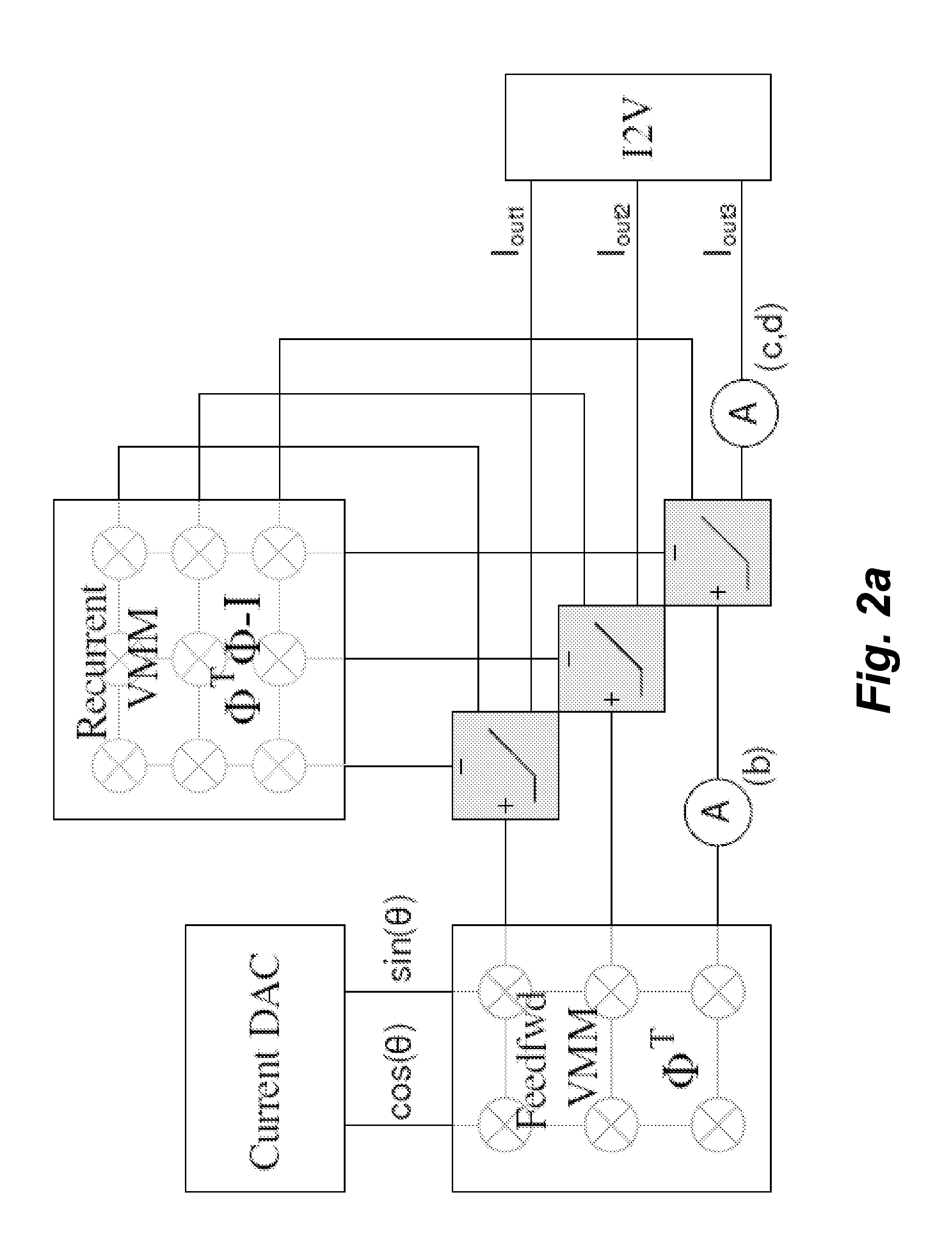

Analog programmable sparse approximation system

InactiveUS20130318020A1Reduce energy consumptionLower computational expenseDigital computer detailsDigital dataSub thresholdAnalog chip

A system and device for solving sparse algorithms using hardware solutions is described. The hardware solution can comprise one or more analog devices for providing fast, energy efficient solutions to small, medium, and large sparse approximation problems. The system can comprise sub-threshold current mode circuits on a Field Programmable Analog Array (FPAA) or on a custom analog chip. The system can comprise a plurality of floating gates for solving linear portions of a sparse signal. The system can also comprise one or more analog devices for solving non-linear portions of sparse signal.

Owner:GEORGIA TECH RES CORP

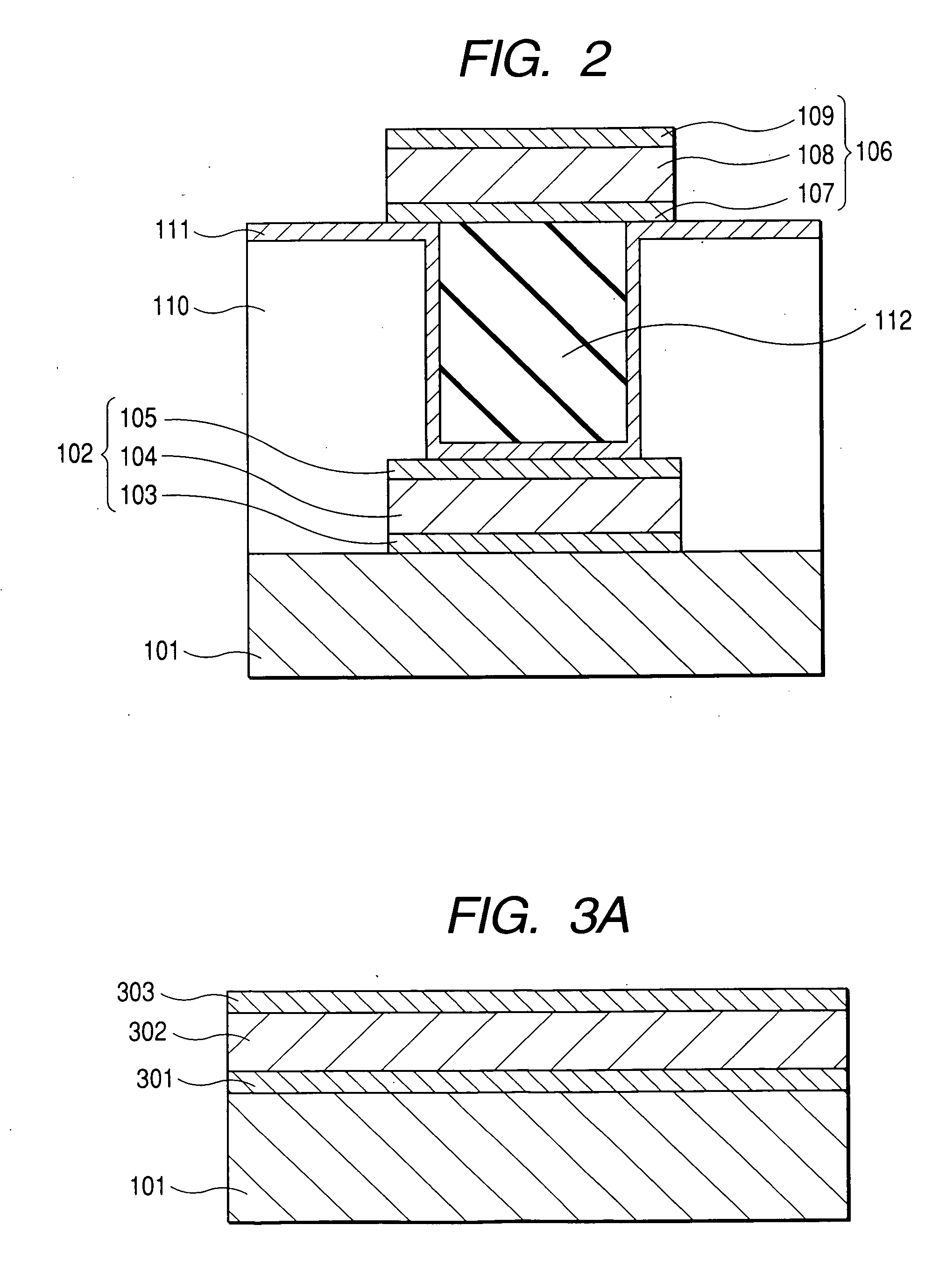

Integrated semiconductor device and method of manufacturing the same

InactiveUS20060125048A1Low temperature coefficientLow densitySolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering

An integrated semiconductor device comprising an analog integrated circuit or mixed signal integrated circuit having a capacitor, wherein the dielectric film of the capacitor is a laminated film consisting of a first dielectric film essentially composed of aluminum oxide and a second dielectric film essentially composed of crystallized niobium oxide. This integrated semiconductor device is small in size and has a low temperature coefficient and high reliability. The niobium oxide is crystallized to increase its dielectric constant and reduce its loss. To reduce the temperature coefficient, the film thickness ratio of the aluminum oxide layer to the niobium oxide layer is set to 0.2 to 1, preferably 0.4 to 0.7.

Owner:HITACHI LTD

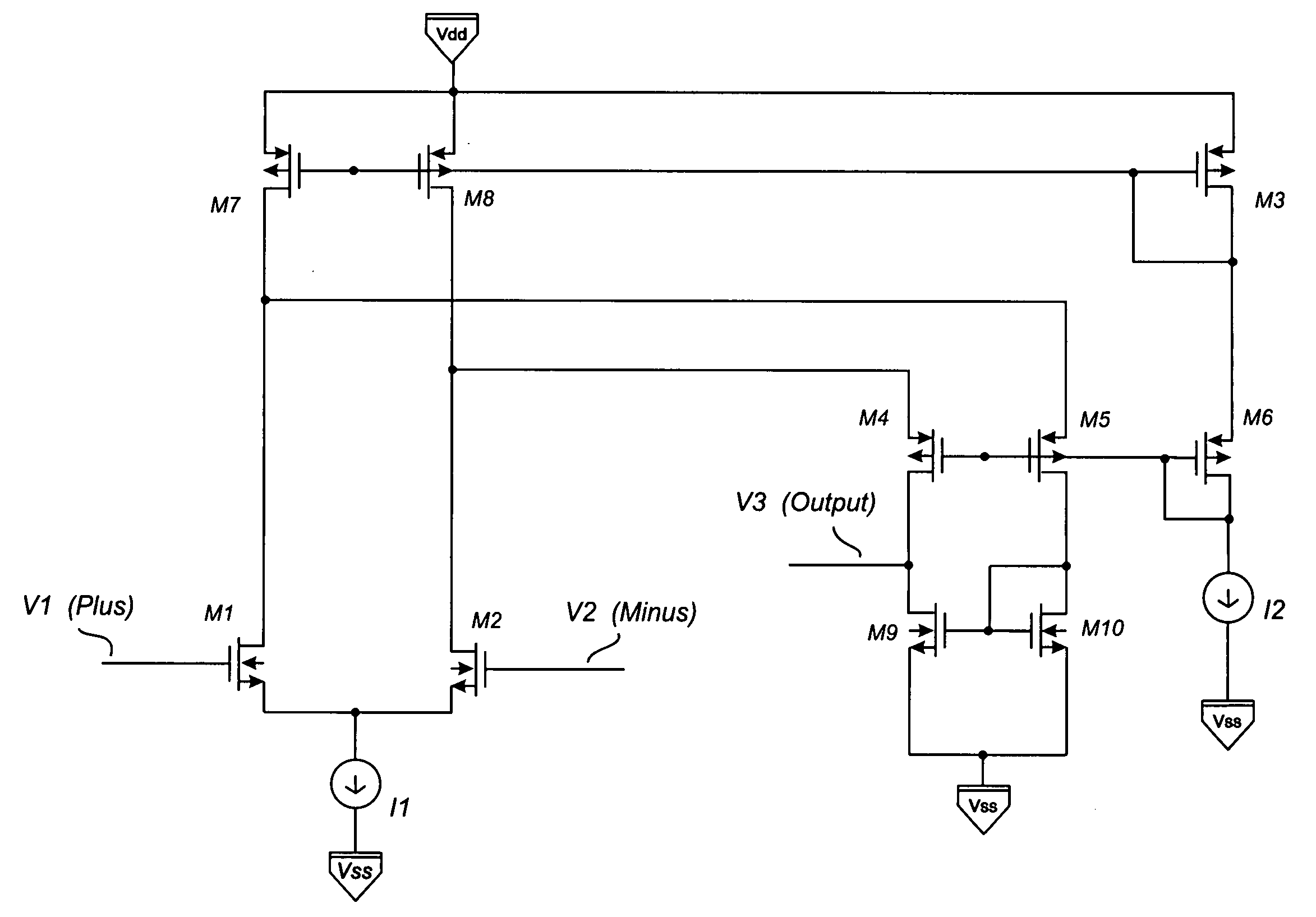

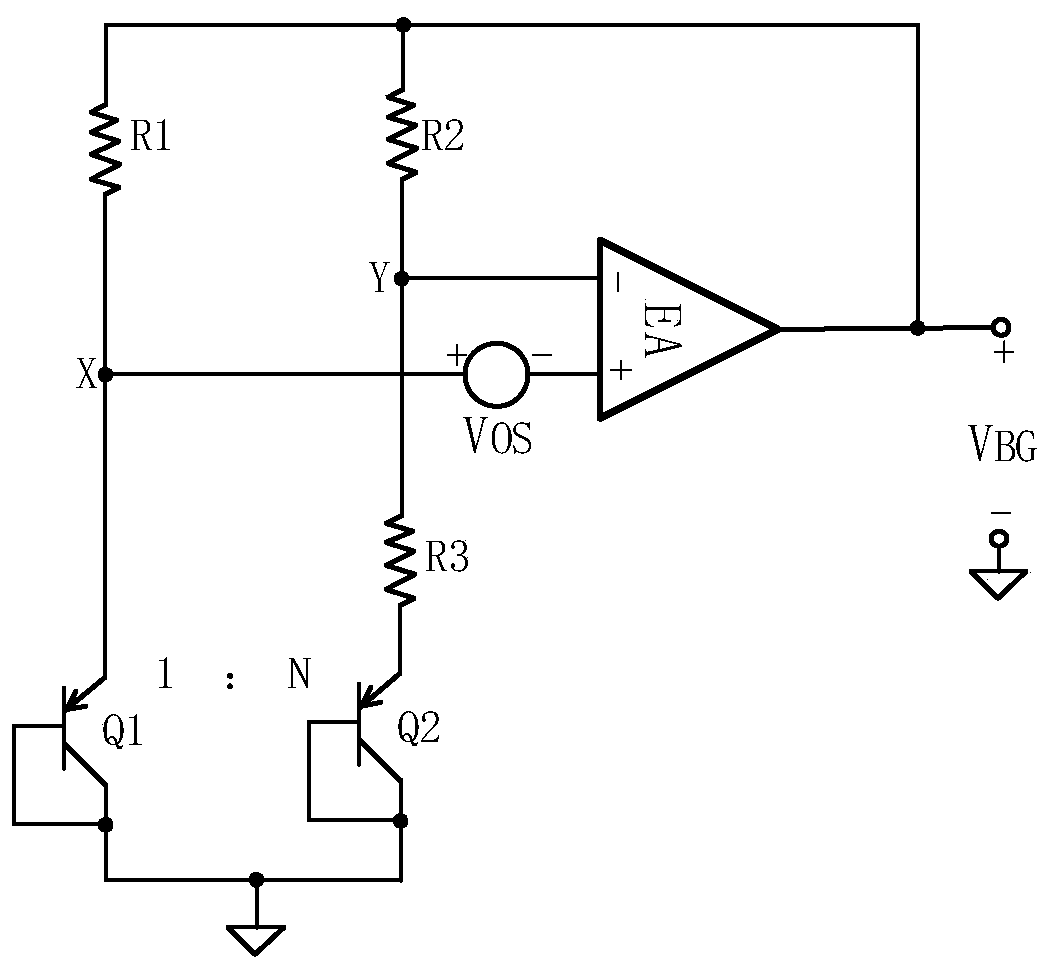

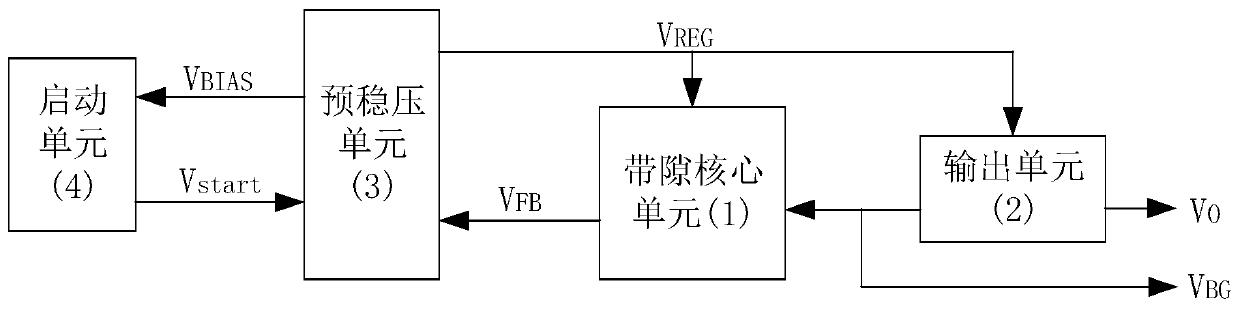

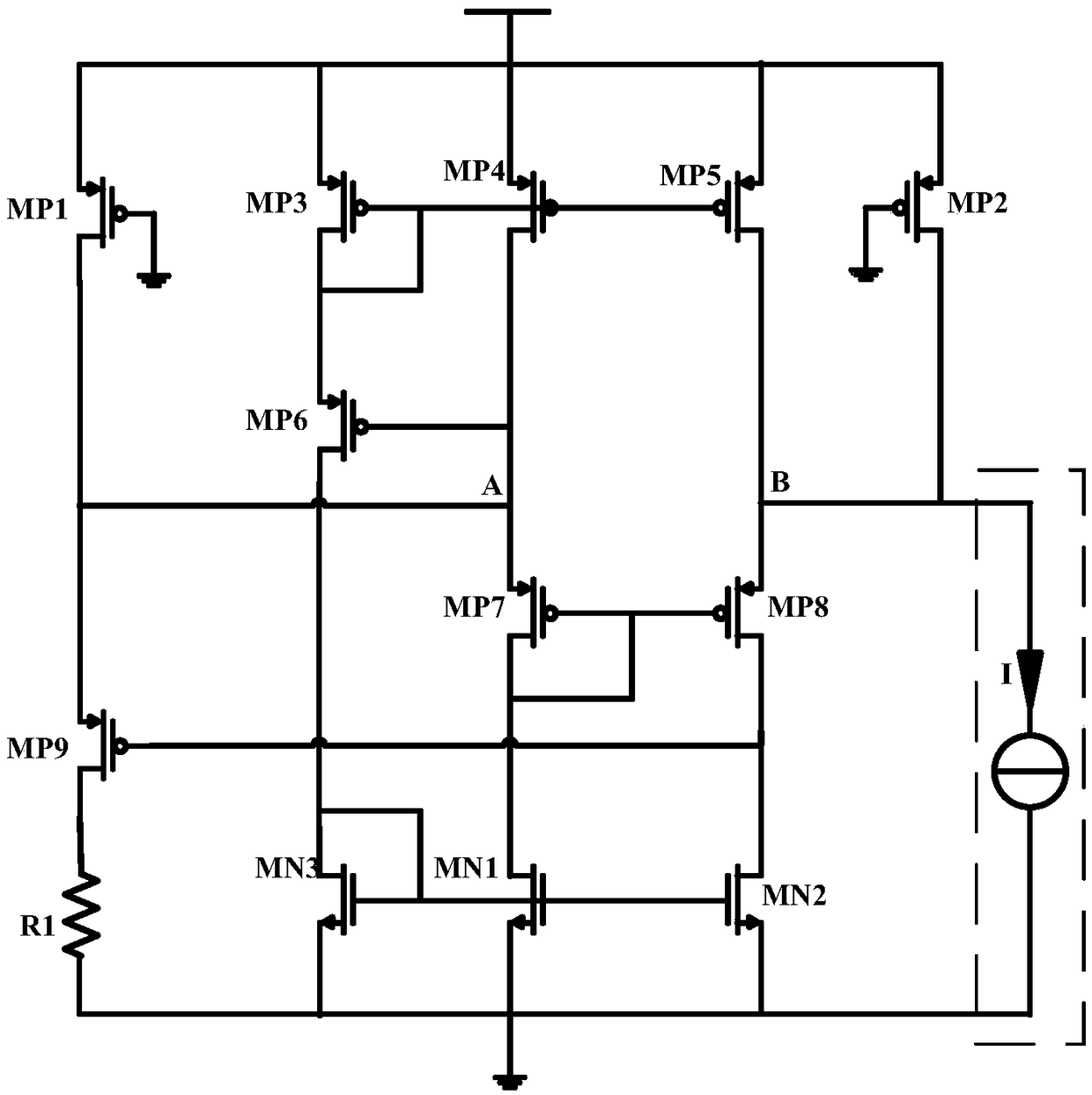

Operational amplifier-free band-gap reference circuit with pre-voltage-stabilizing structure

ActiveCN111240394AHigh inhibition ratioReduce the impactElectric variable regulationHemt circuitsAnalog chip

The invention discloses an operational-amplifier-free band-gap reference circuit with a pre-voltage-stabilizing structure, and solves the problems in the prior art that the power supply rejection ratio is low and the offset voltage is high. The operational-amplifier-free band-gap reference circuit comprises a band-gap core unit (1), an output unit (2), a voltage pre-stabilizing unit (3) and a starting unit (4). The band-gap core unit generates a negative temperature coefficient voltage VBE and a positive temperature coefficient voltage delta VBE; the output unit generates band-gap voltage VBGand zero temperature coefficient voltage VO; the pre-voltage-stabilizing unit generates stable pre-adjusting voltage VREG by detecting feedback voltage VFB and supplies power to the band-gap core unit. The starting unit detects the bias voltage VBIAS outputted by the pre-voltage-stabilizing unit and outputs a starting signal Vstart to the pre-voltage-stabilizing unit. The pre-voltage-stabilizing structure is adopted so that the power supply rejection ratio of reference voltage is increased; the operational amplifier structure is not adopted, and the influence of offset voltage on reference voltage is weakened. The circuit is simple in structure and can be used for an analog integrated circuit.

Owner:XIDIAN UNIV

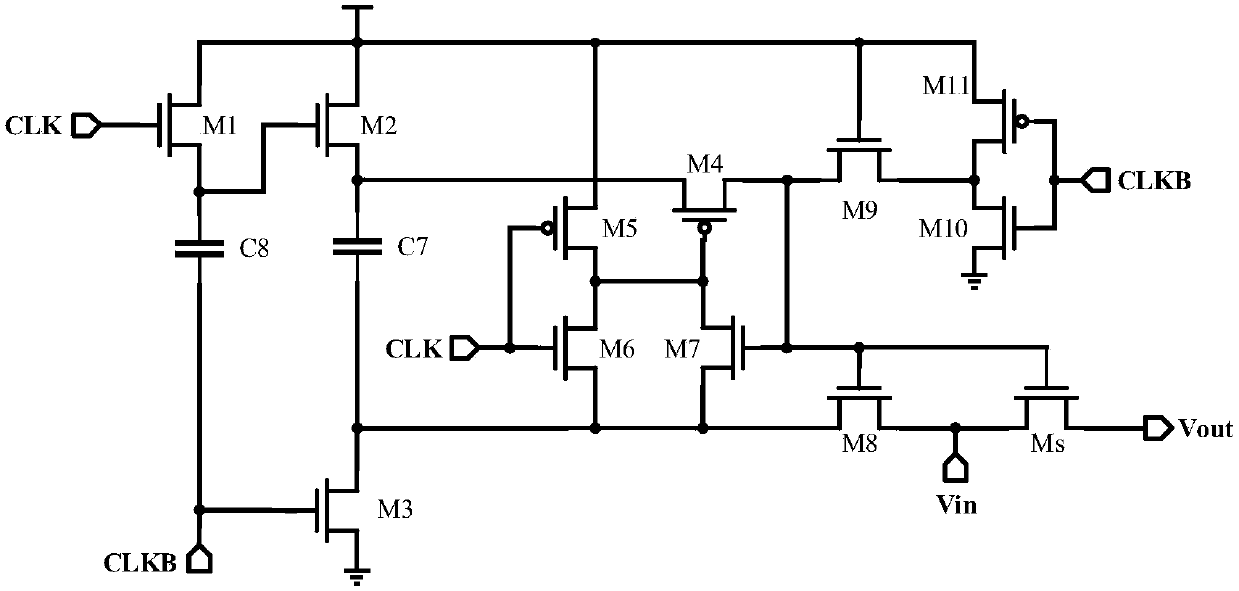

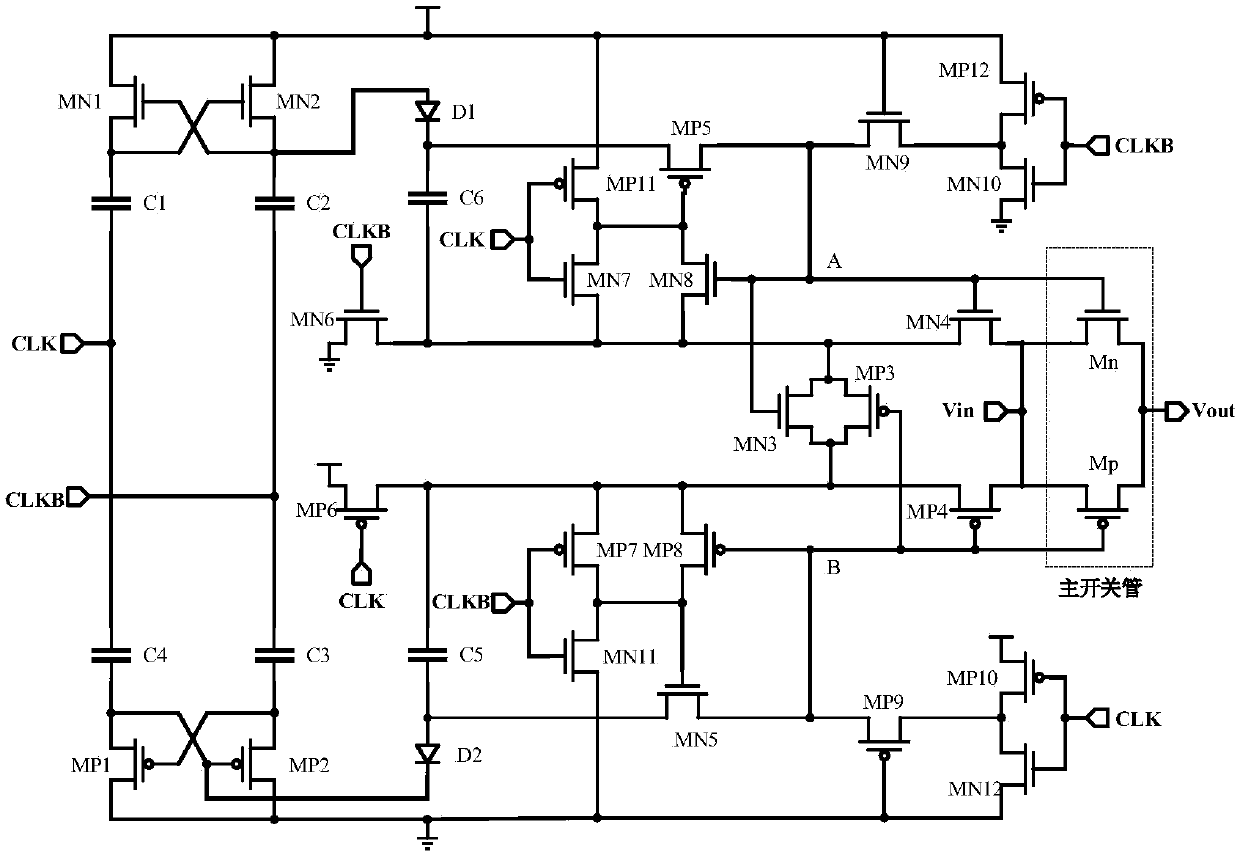

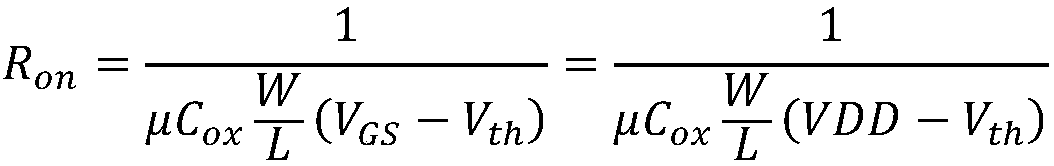

Grid voltage bootstrap switch circuit

The invention provides a grid voltage bootstrap switch circuit, and belongs to the field of analog integrated circuits. A charge pump circuit is used for charging a fifth capacitor and a sixth capacitor to make the stored charge amounts be constant, a grid voltage boosting circuit and a grid voltage reducing circuit are used for changing the grid voltages of an NMOS switch tube and a PMOS switch tube to maintain the grid voltages as constant values, and a switching circuit is used for controlling the charging of the charge pump circuit and the opening and closing of the grid voltage boosting circuit and the grid voltage reducing circuit. The grid voltage bootstrap switch circuit provided by the invention uses the NMOS switch tube and the PMOS switch tube to connect input signals to the output at the same time, thereby reducing the on-resistance of the switch; by using a parallel connection mode of the NMOS switch tube and the PMOS switch tube, the channel charge injection effects of the NMOS switch tube and the PMOS switch tube caused by clock changes cancel each other, and the clock feedthrough effects cancel each other as well, thereby improving the linearity of the switch; and by using a diode to charge the capacitor, the circuit does not have an overvoltage device, thus improving the reliability of the circuit.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

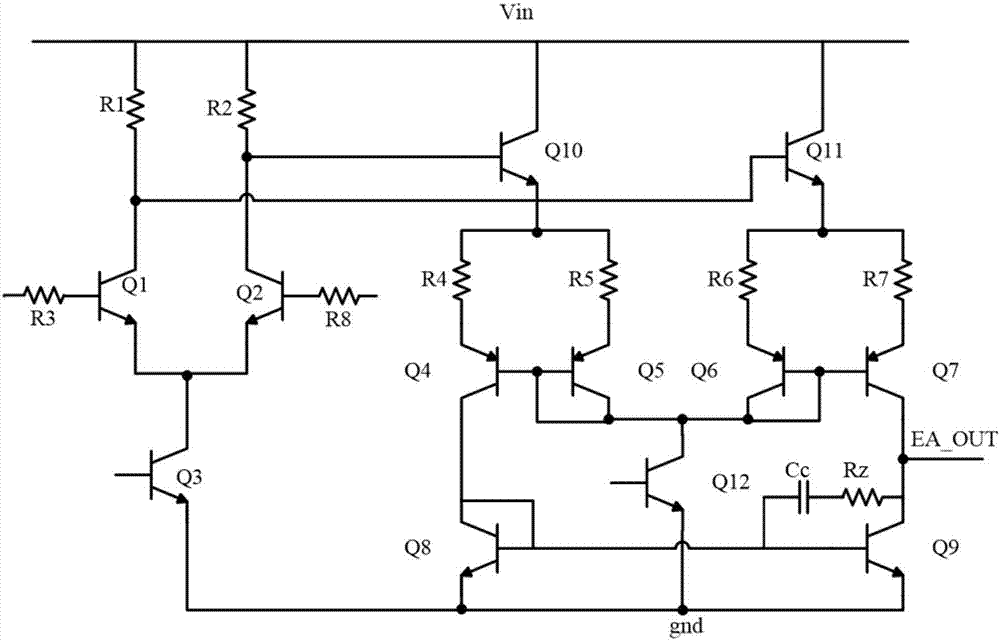

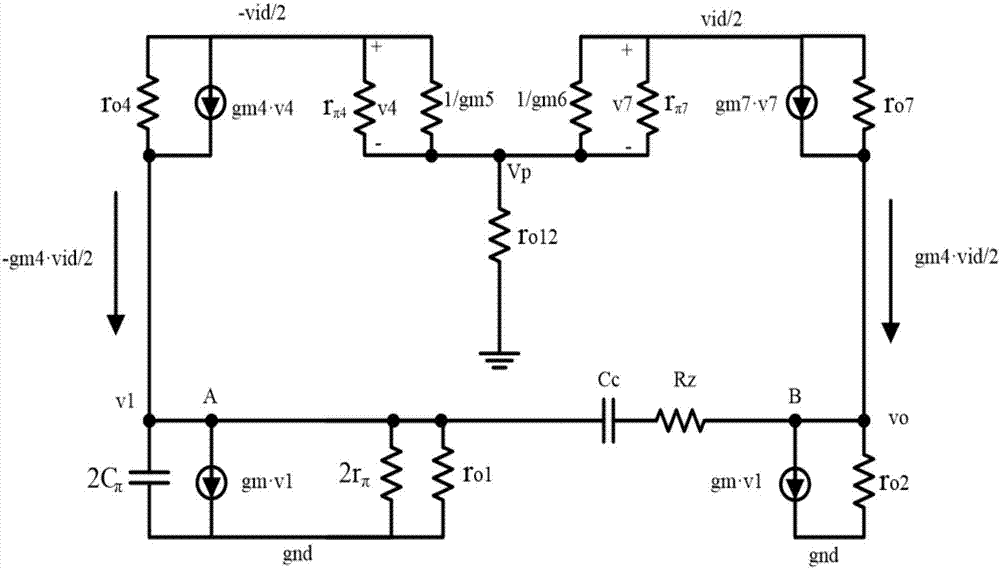

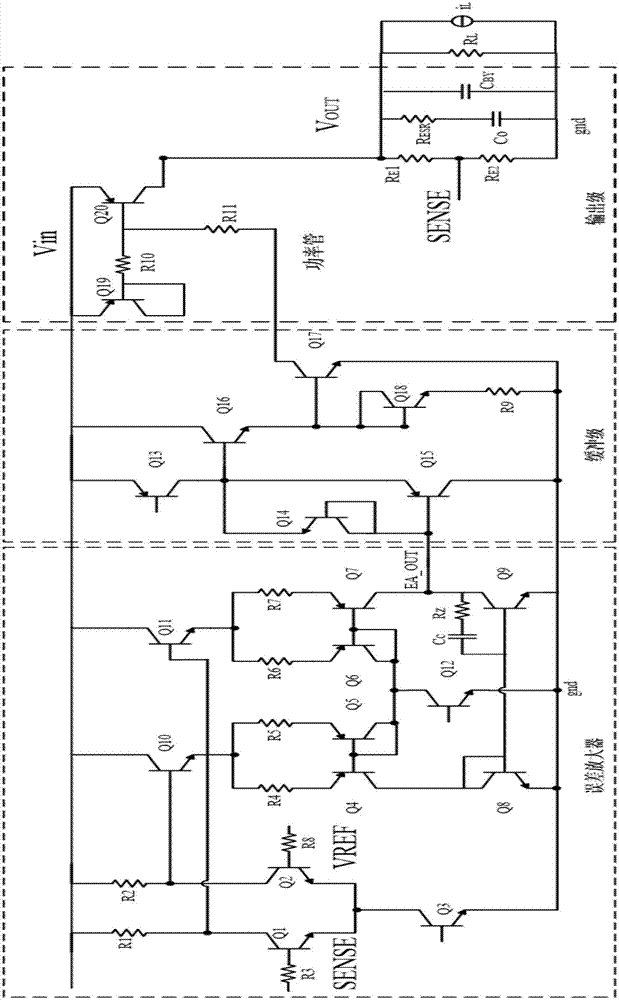

Frequency compensation scheme for LDO regulator to drive large current loads

InactiveCN107505971AWide gain bandwidthImprove rippleElectric variable regulationCapacitanceFrequency stabilization

The invention belongs to the field of analog integrated circuits, and specifically provides a frequency compensation scheme for an LDO regulator to drive large current loads. In the scheme, two-stage operational amplifiers having approximate monopole points, a buffer stage and an output stage. Capacitor compensation is introduced innovatively, so that a two-stage error amplifier originally having two low frequency pole points becomes an approximate monopole point system, and the position of the pole point can be manually controlled. According to the scheme, the pole point is set as a secondary pole point high in frequency, and after an output capacitance and parasitic resistor (ESR) is introduced in a parasitic zero point, the pole point is appropriately compensated. The output pole points changing with loads are still main pole points, and by reasonably selecting filtering capacitance of an output end, the generated zero point is located at the maximum loop gain GBW frequency. The inside parasitic zero point is located at high frequency due to the specific circuit structure. Finally, the whole low-pressure-difference linear voltage stabilizer achieves frequency stability in the full current load change range, and the phase margin is more than 50 degrees.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

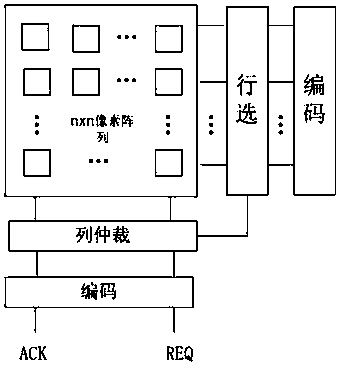

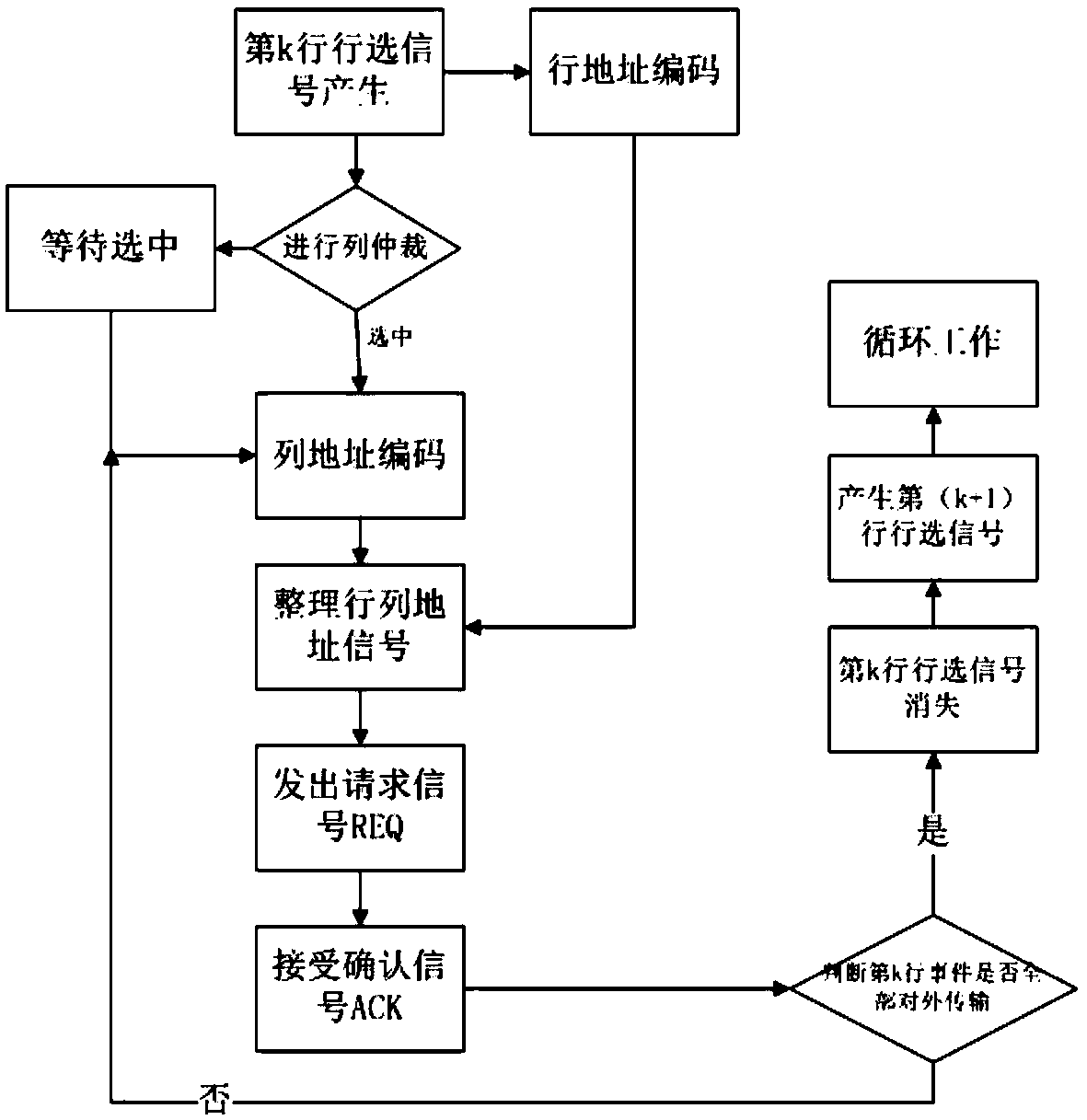

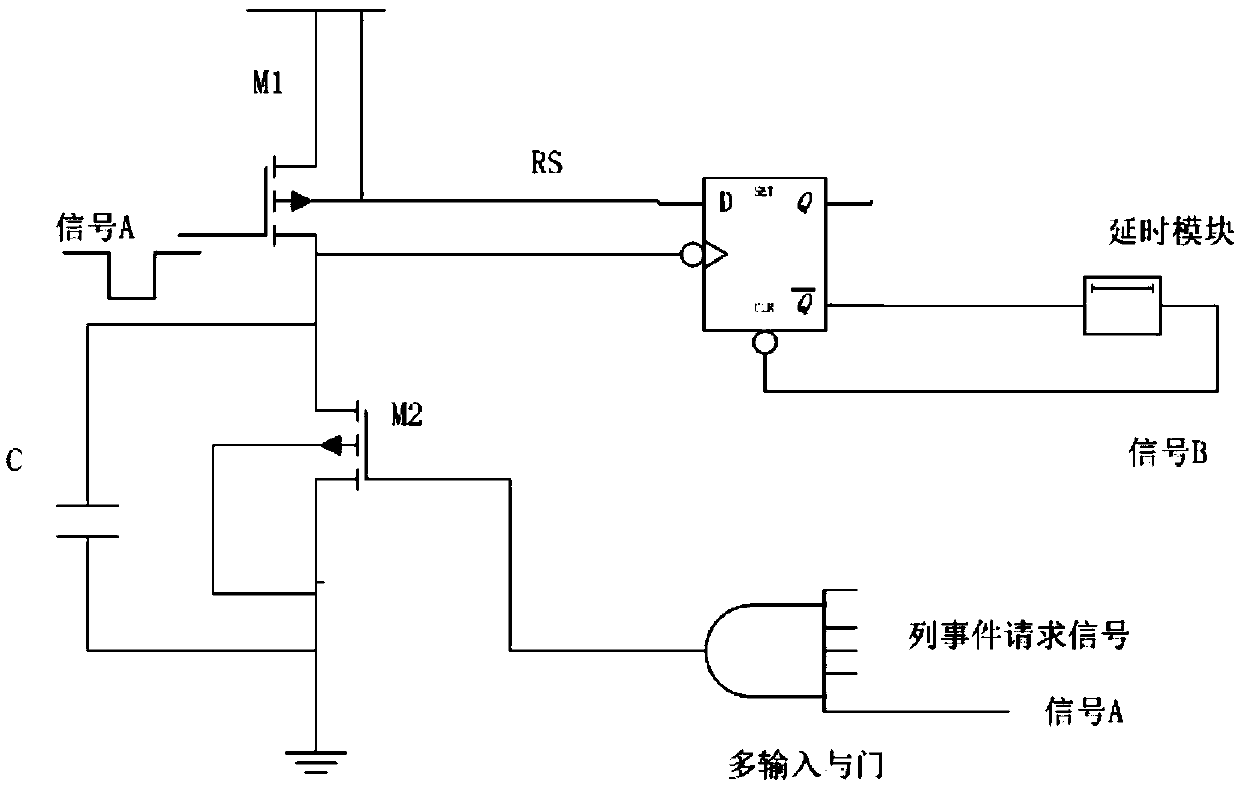

Row selection column arbitration AER image sensor event transmission device and row selection column arbitration AER image sensor event transmission method

ActiveCN109547716AReduce Arbitration TimeIncrease transfer rateTelevision system detailsColor television detailsSelf adaptiveIntegrated circuit

The invention relates to the field of analog integrated circuit design, is used for omitting a row arbitration structure and reducing arbitration time, can save row selection time through row selection signals adaptive to duration, further reduces delay and improves work speed. For such purpose, a technical scheme used in the invention is that a row selection column arbitration AER image sensor event transmission device and a row selection column arbitration AER image sensor event transmission method are provided, the device and the method are realized through a pixel array, a row selection module, a column arbitration module and a row and column coding module, events are generated through pixel array sensitization, when the row selection module generates the k row row-selection signals, the row and column coding module performs address coding and judges the number of the k row events, then, the column arbitration module performs column request signal arbitration, and the row and column coding module performs row and column address coding for the signals selected, tidies the row and line address signals and sends out a request signal. The method and the device provided by the invention are mainly used for design and manufacturing occasions of the analog integrated circuit.

Owner:TIANJIN UNIV

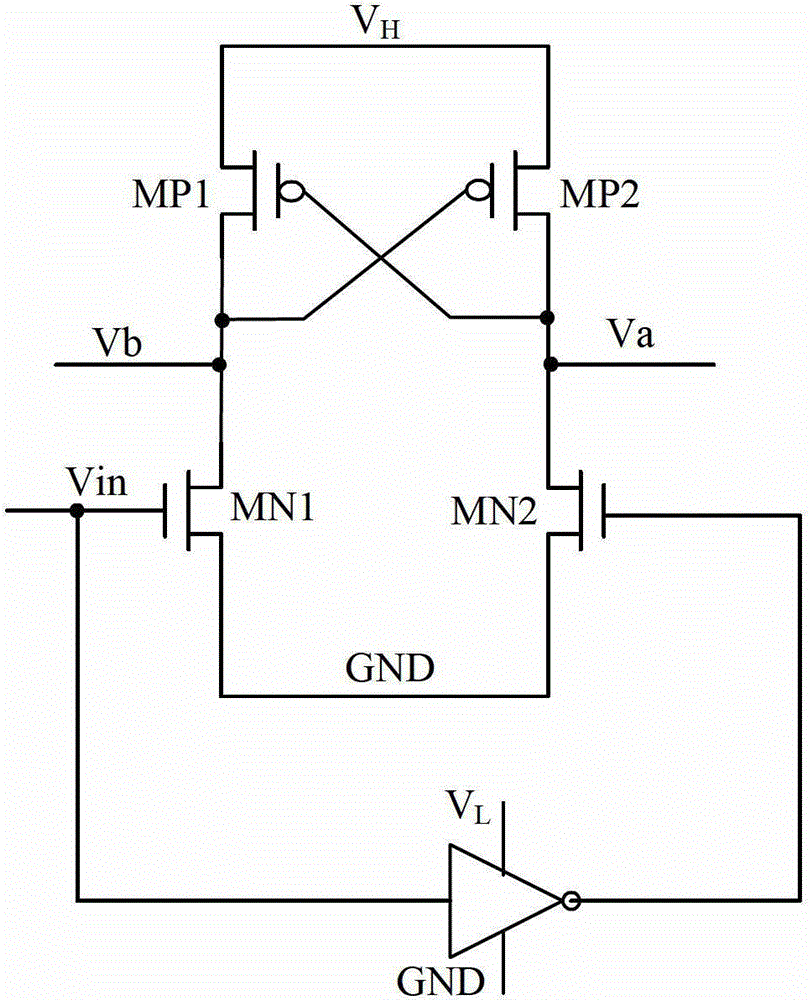

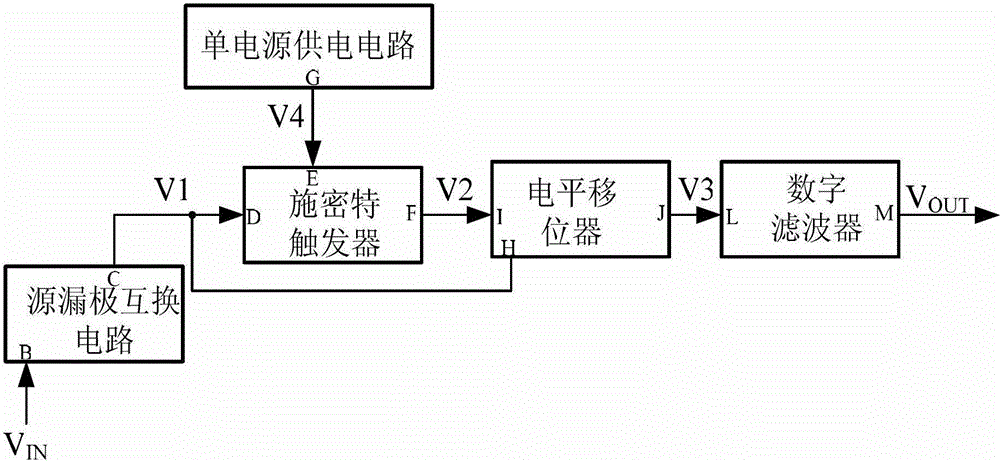

Single power electric level shift circuit with digital filtering function

ActiveCN103066989AReduce power consumptionSimplify routing issuesLogic circuits coupling/interface using field-effect transistorsSchmitt triggerEngineering

The invention discloses a single power electric level shift circuit with a digital filtering function. The single power electric level shift circuit with the digital filtering function mainly resolves the problems that an existing electric level shift circuit is too large in static power consumption, fluctuating in output voltage and difficult in multi-power-signal transmission. The electric level shift circuit comprises source drain interchange circuits (1), a single power supply circuit (2), a schmitt trigger (3), an electric level shifter (4) and a digital filter (5). The source drain interchange circuits (1) output voltage signal V1 and are respectively connected on the schmitt trigger (3) and the electric level shifter (4). The single power supply circuit (2) provides voltage control signal V4 for the schmitt trigger (3). The schmitt trigger (3) provides voltage control signal V2 for the electric level shifter (4). The electric level shifter (4) provides voltage signal V3 for the digital filter (5). The digital filter (5) outputs voltage signal V OUT. According to the single power electric level shift circuit with the digital filtering function, the stability of output voltage is improved, the static power consumption is reduced, the accuracy of electric level transformation is improved and sharp plus interference waves are removed by filtering. The single power electric level shift circuit with the digital filtering function can be used for an analogue integrated circuit.

Owner:XIDIAN UNIV

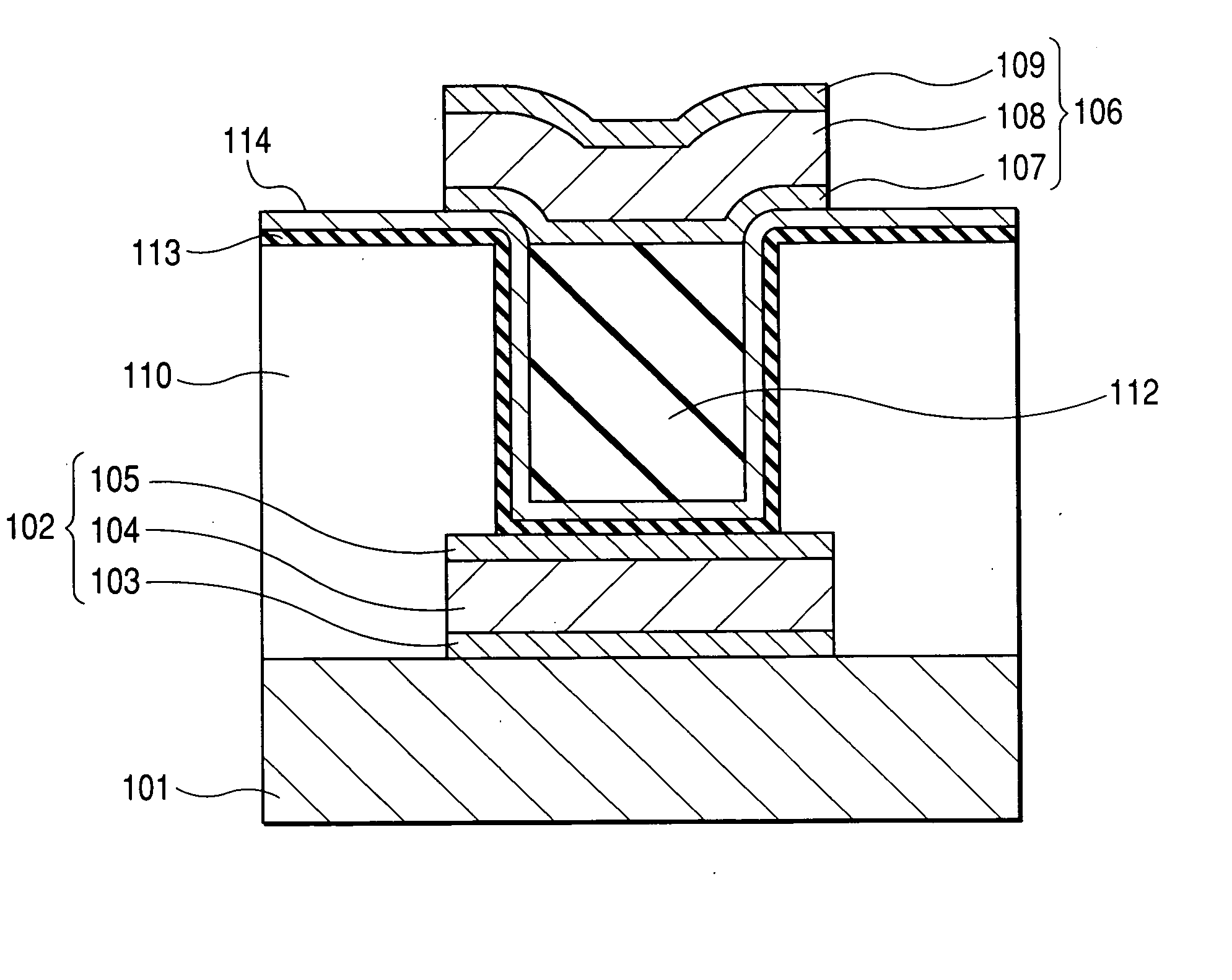

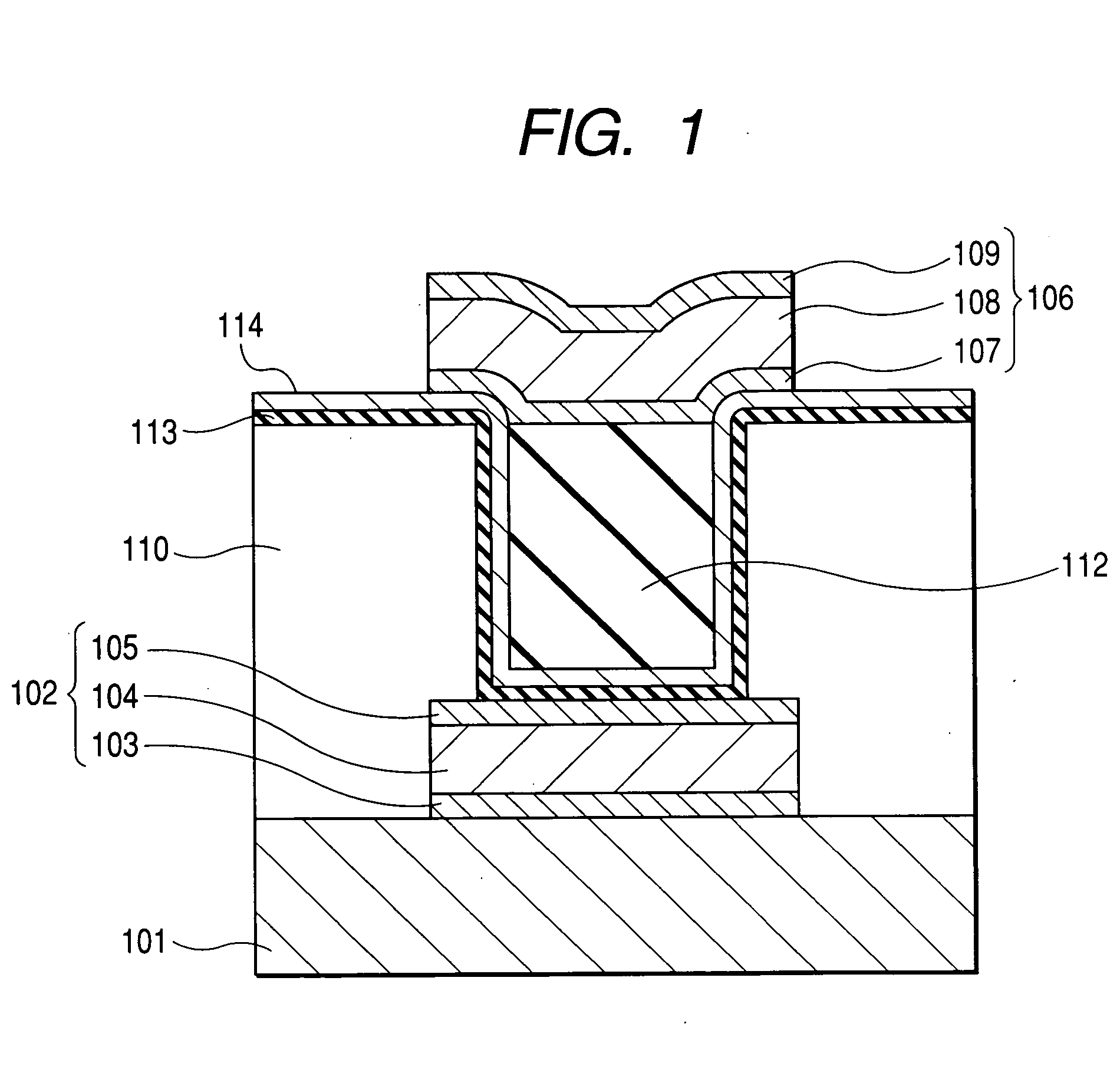

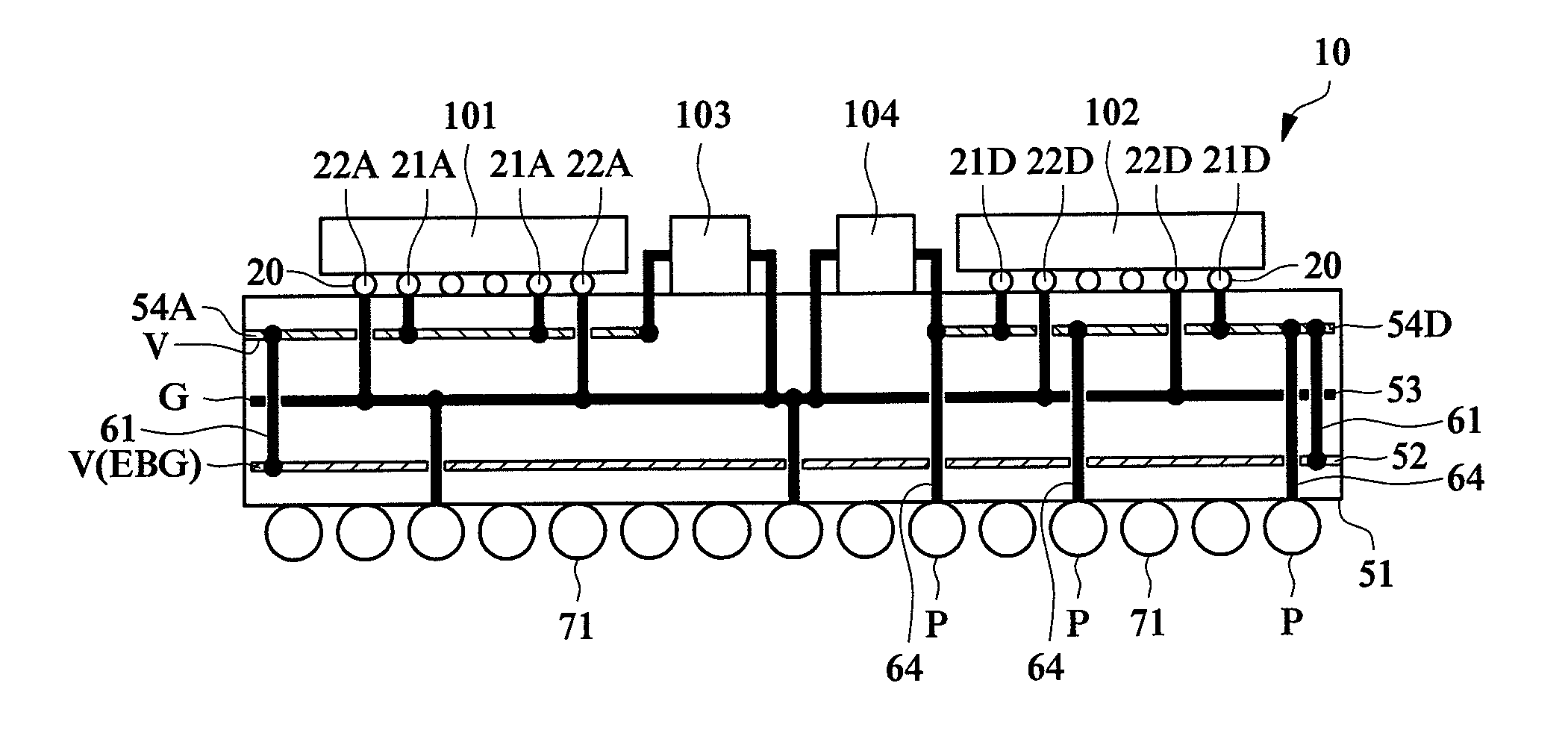

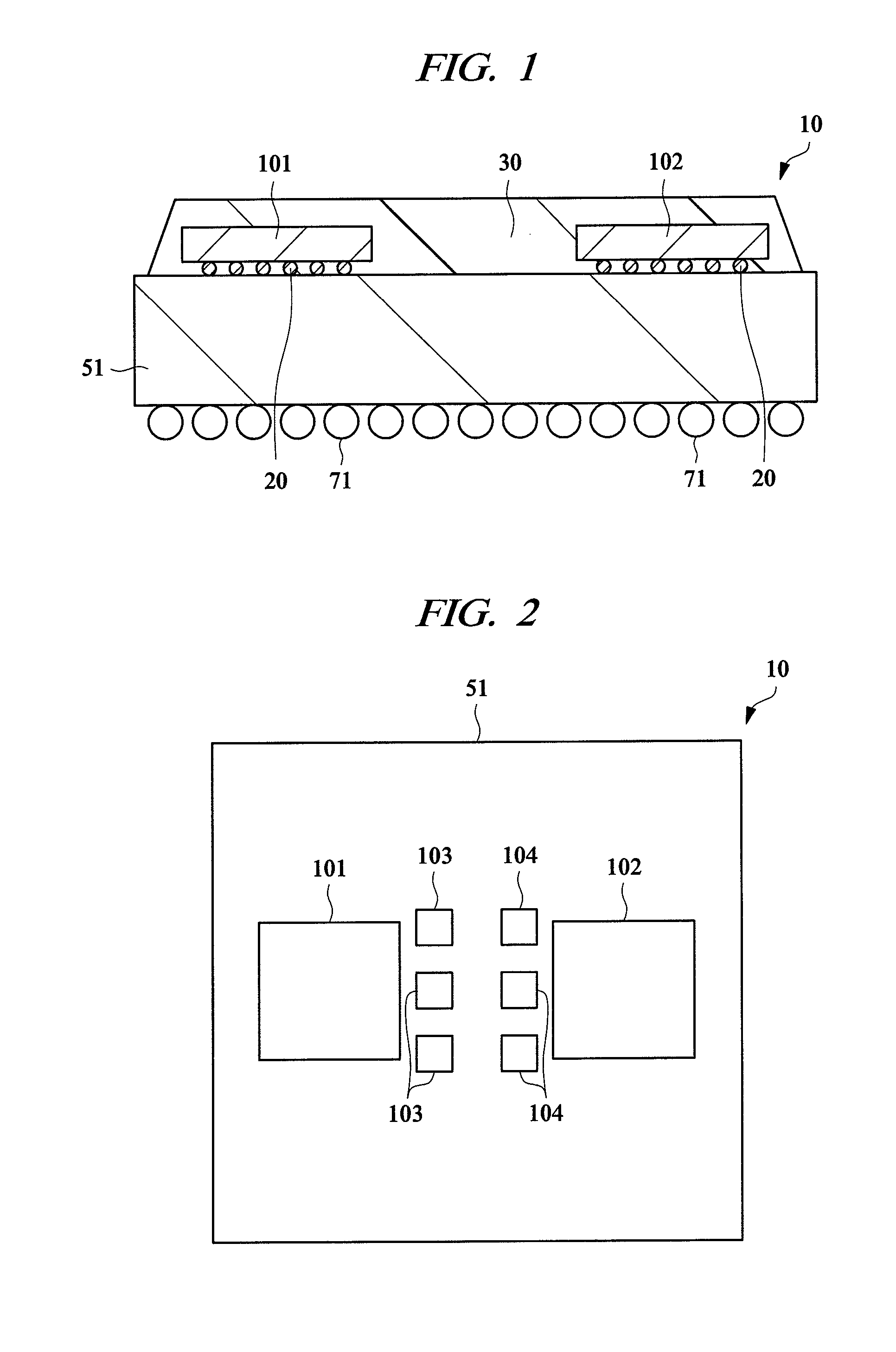

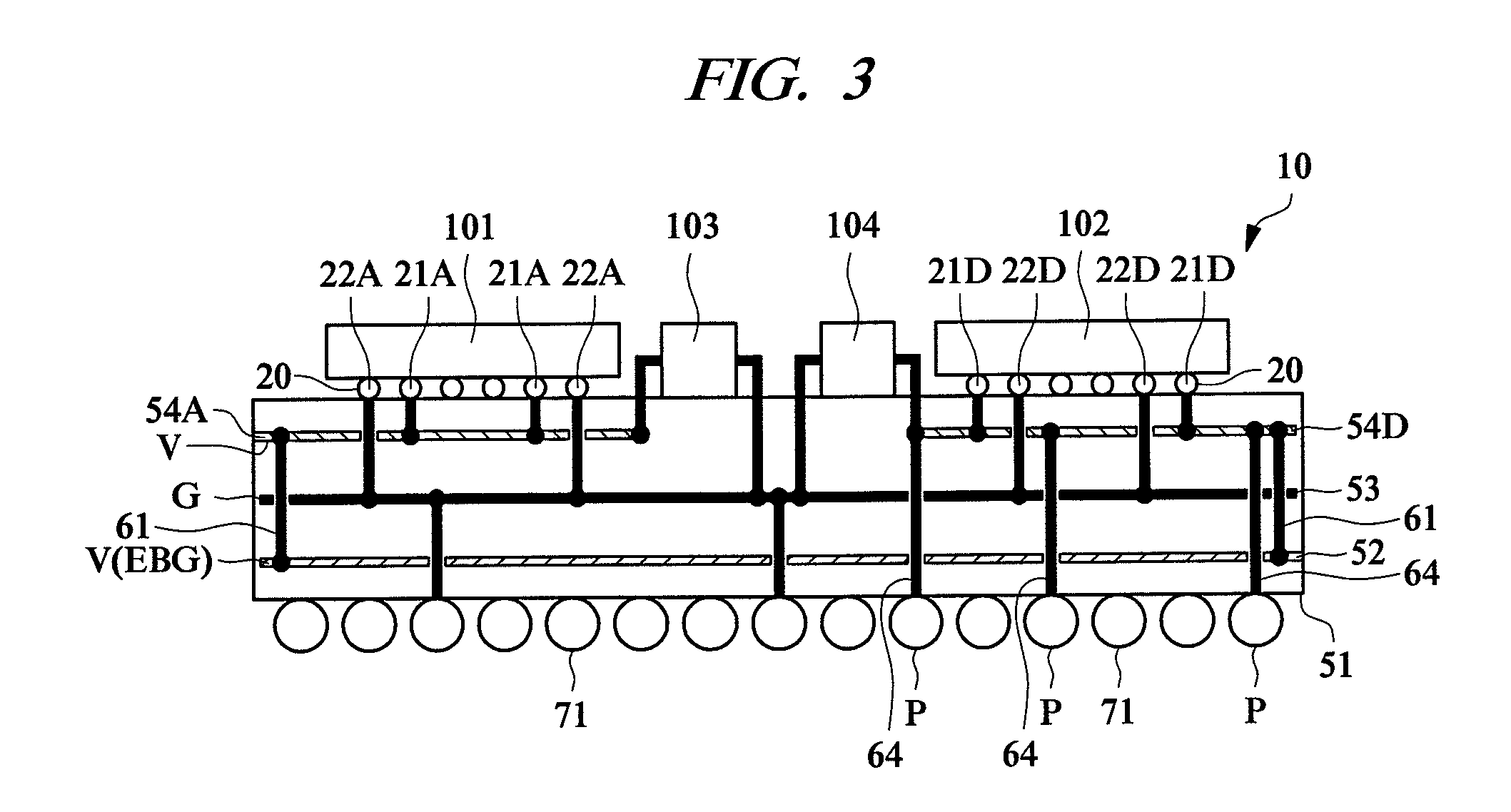

Semiconductor device including a digital semiconductor element and an analog semiconductor element in a common semiconductor device

InactiveUS7939907B2Guarantee signal qualityAchieving stabilization of a power sourceCross-talk/noise/interference reductionSemiconductor/solid-state device detailsPower semiconductor deviceHigh density

High density mounting and power source sharing are achieved by a digital semiconductor element and an analog semiconductor element provided in a common semiconductor device. A power layer for analog operation is connected to one end of an EBG (Electromagnetic Band Gap) layer, a power layer for digital operation is connected to the other end of the EBG layer, ground terminals for the respective elements are connected to a common ground layer, and a ground layer for separating the power layer for analog operation and the EBG layer from each other is disposed between the power layer for analog operation and the EBG layer. Thereby, high density mounting is achieved along with reducing interference of the power source to an analog chip.

Owner:RENESAS ELECTRONICS CORP

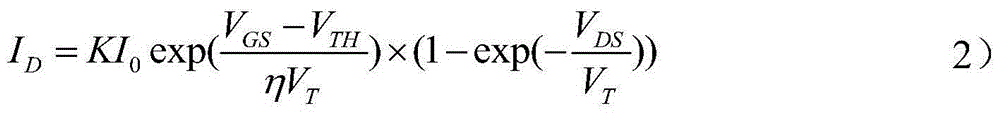

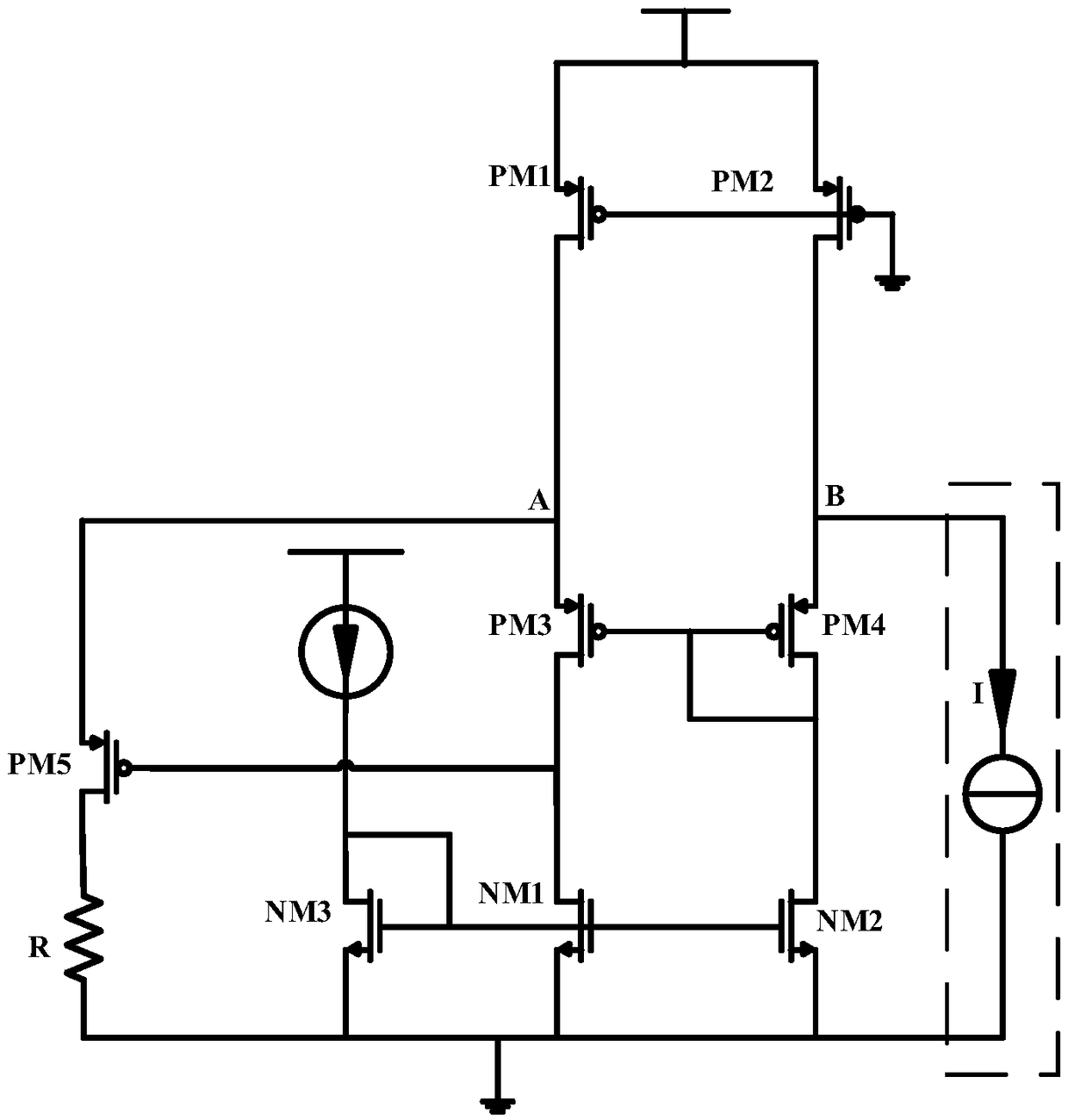

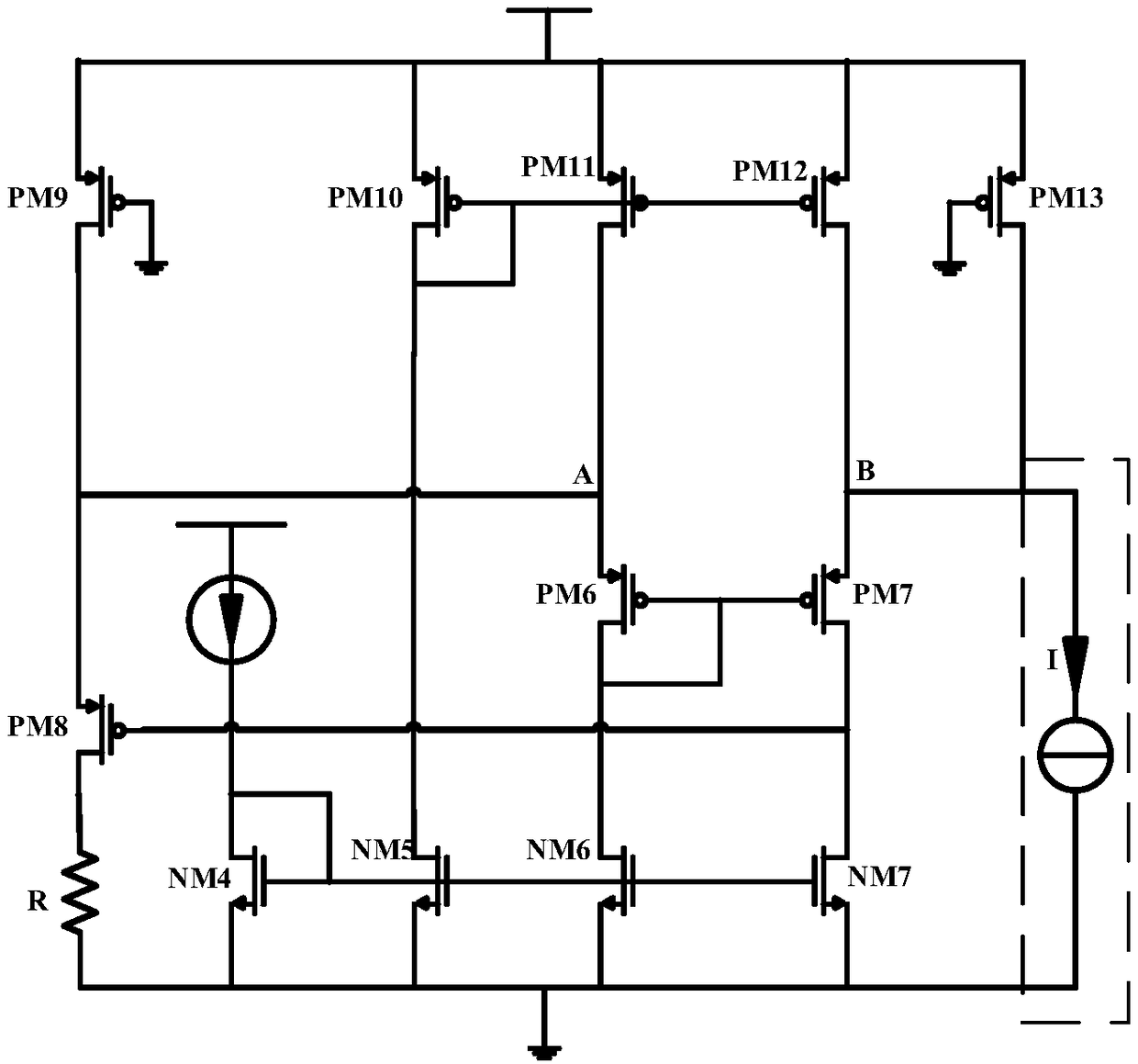

High-precision current detection circuit working in sub-threshold region

ActiveCN108845175AReduce churnReduce power consumptionCurrent measurements onlyElectrical resistance and conductanceSub threshold

A high-precision current detection circuit working in a sub-threshold region belongs to the technical field of analog simulated circuits. The circuit comprises a sampling unit, a detection unit and adynamic bias unit, the sampling unit is used to sample a current to be detected, the current to be detected passes a second PMOS to cause change of the drain-end voltage of the second PMOS, the detection unit copies the current of the second PMOS via a first PMOS, the current to be detected is responded to the voltage between the two ends of a first resistor to realize current detection, and the dynamic bias unit transmits the current to be detected to the detection unit without loss. Voltage feedback and current feedback are introduced to ensure that voltage of the point A changes dynamicallywith voltage of the point B, the MOS is controlled to work in the sub-threshold region, power consumption is reduced, current loss is reduced, and the detection precision is improved.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

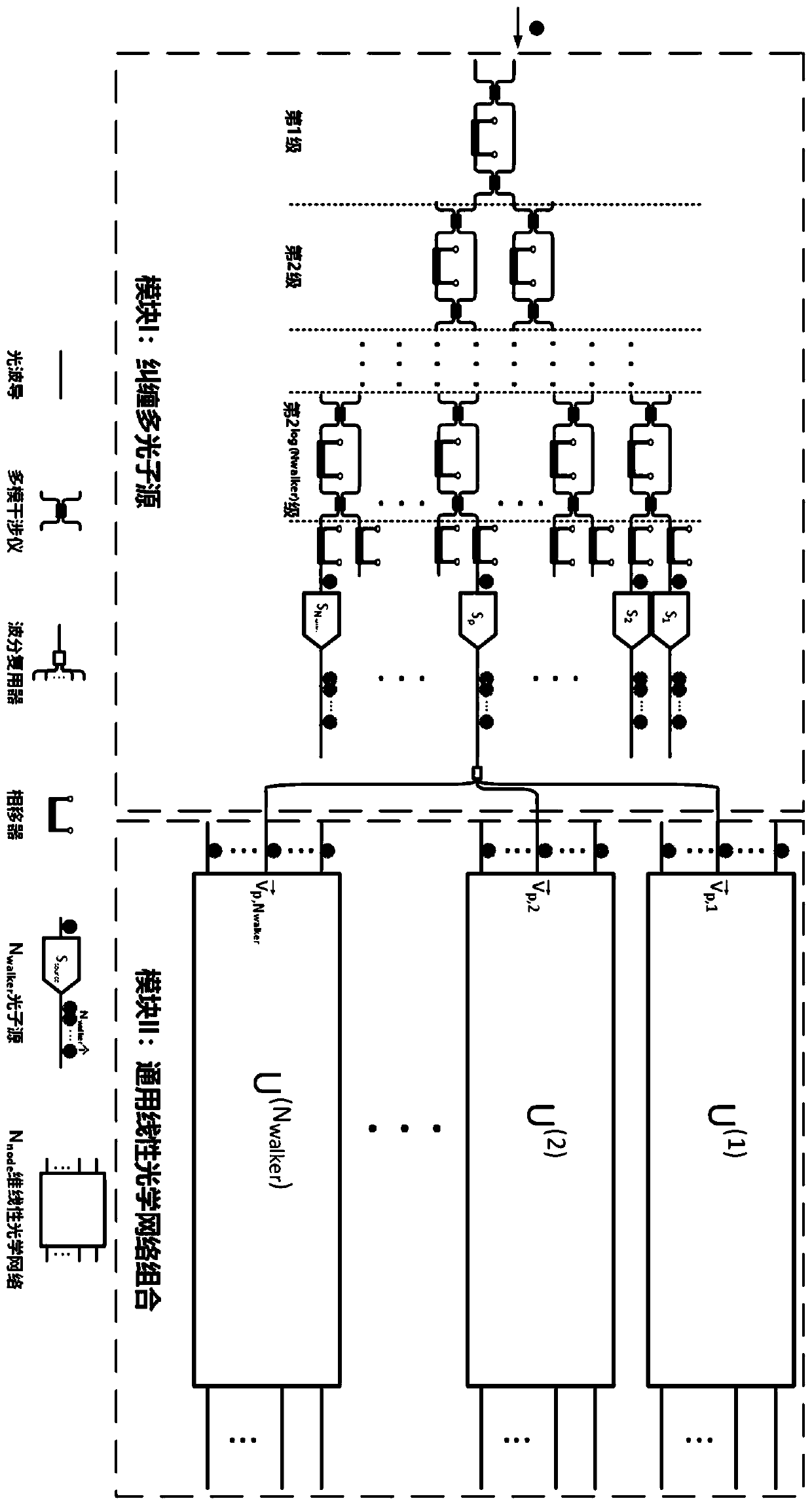

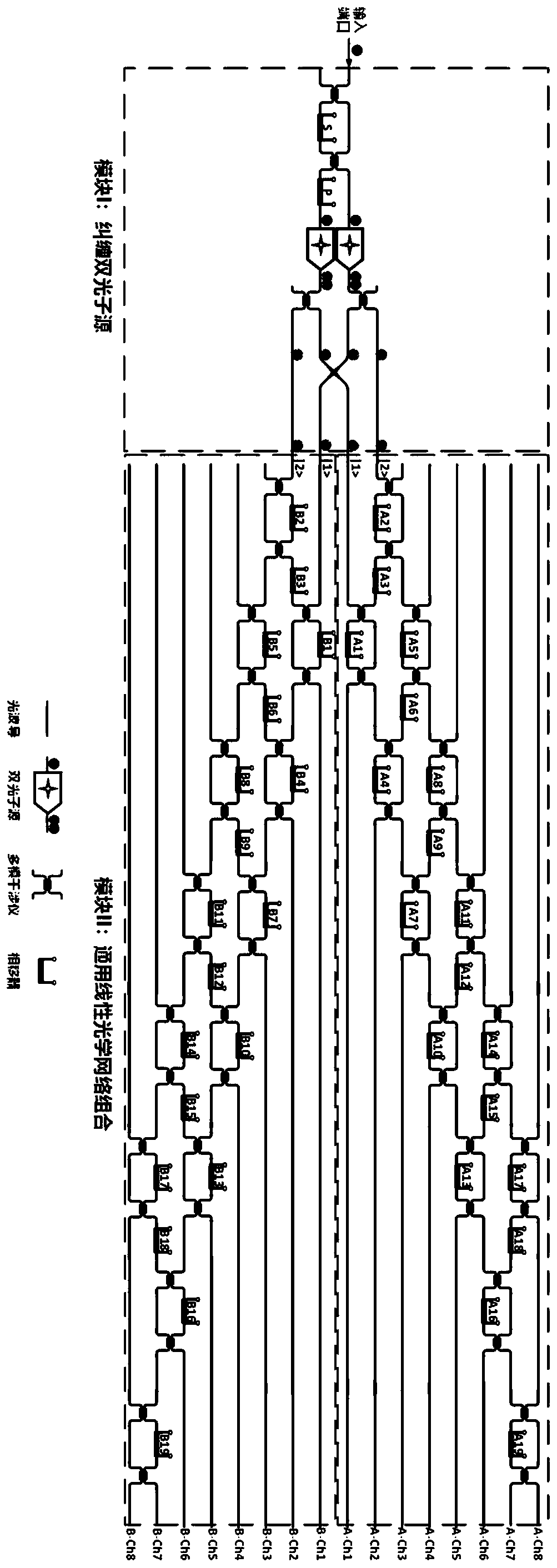

Universal quantum walk analog chip structure based on integrated optics

ActiveCN111478735AQuantum computersKey distribution for secure communicationParticle physicsAnalog chip

The invention discloses a universal quantum walk analog chip structure based on integrated optics. A multi-photon source capable of preparing a multi-photon path entangled state and a linear optical network capable of achieving unitary transformation are organically combined and used in cooperation, and the corresponding relation among the on-chip multi-photon path entangled state, the unitary transformation, the quantum walking state of multi-particle quantum walking and the walking process is established. Optical unitary transformation is realized by regulating and controlling a multi-photonpath entangled state prepared by a multi-photon source and a universal linear optical network; the chip structure can carry out general quantum walk simulation with configurable elements such as evolution Hamiltonian quantity, evolution time, initial evolution state, particle properties (such as particle isotropy and particle exchange symmetry) and the like of multi-particle quantum walk.

Owner:NAT UNIV OF DEFENSE TECH

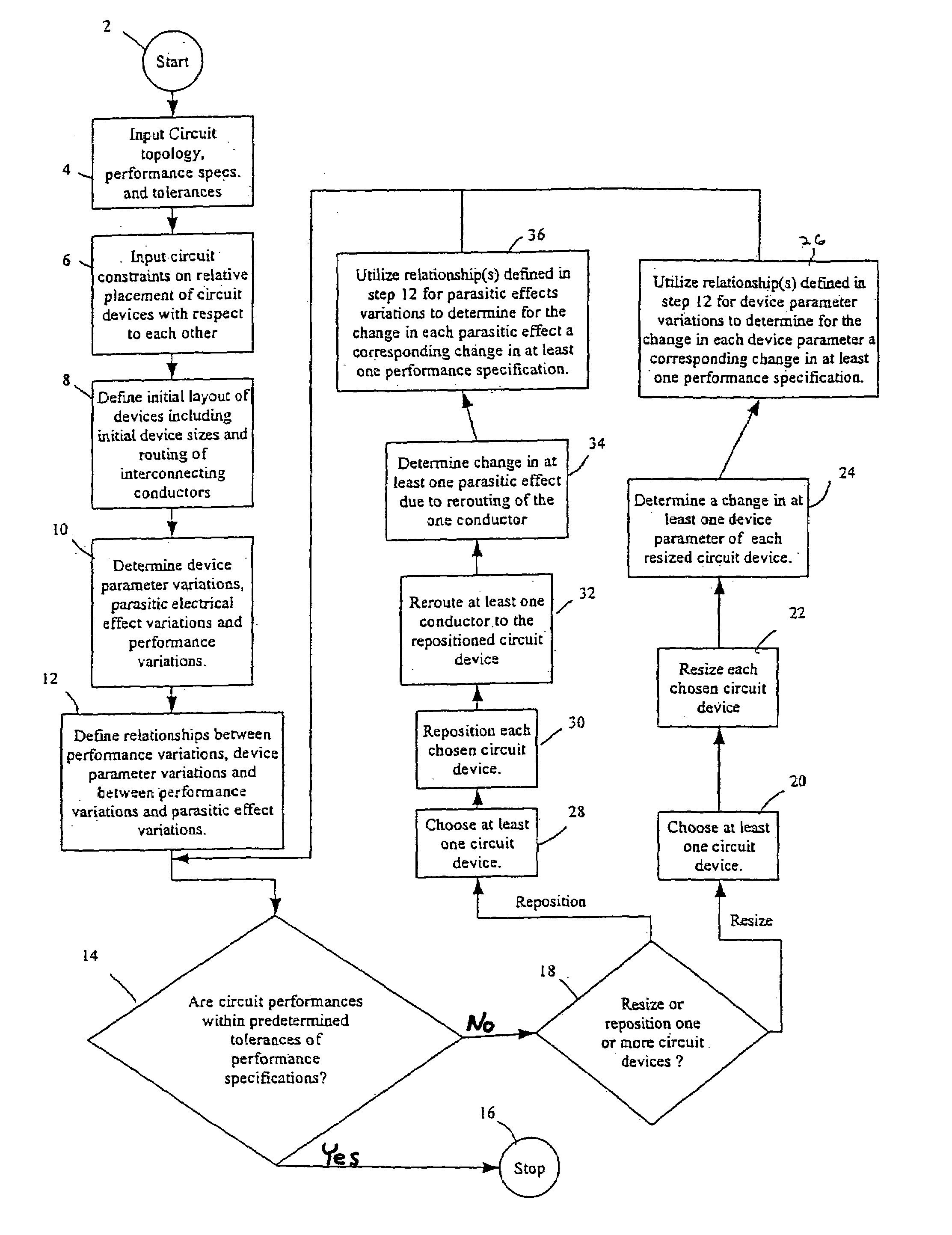

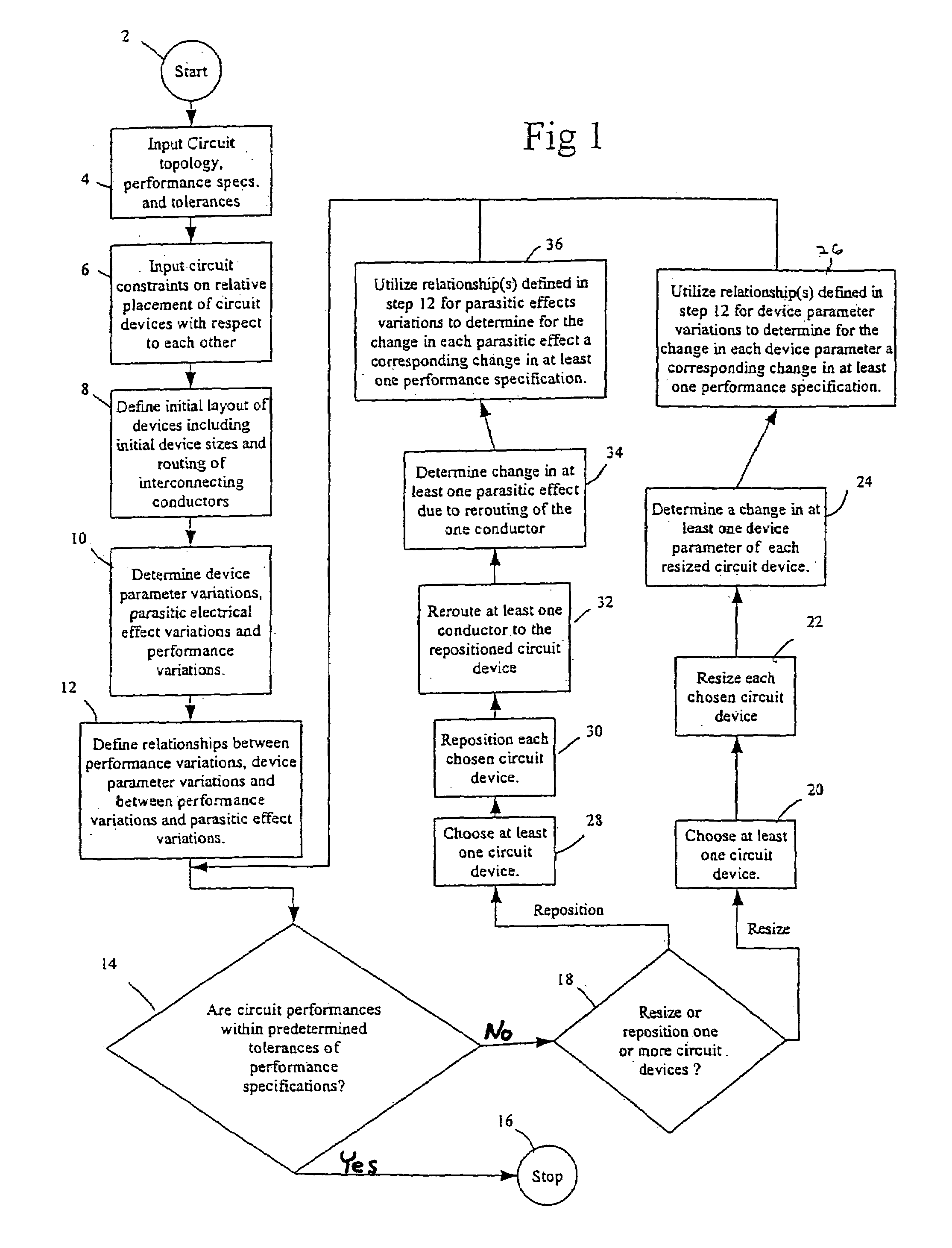

Analog integrated circuit layout design

ActiveUS7139987B2CAD circuit designSoftware simulation/interpretation/emulationIntegrated circuit layoutPerformance specification

In an automated integrated circuit design, if the performances of a layout of circuit devices are not within predetermined tolerances of performance specifications, at least one of the circuit devices is resized or repositioned and an updated value of a device parameter for each resized or repositioned circuit device is determined. A difference between the initial and updated value of each device parameter is then determined and each difference is combined with a ratio formed from changes in the value of one of the device parameters and changes in the value of one of the performances affected by the device parameter. The result of this combination is then combined with the initial value of the performance to determine an updated value therefor.

Owner:CADENCE DESIGN SYST INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com