Realization device of column-level analog-to-digital converter (ADC) in complementary metal-oxide semiconductor (CMOS) image sensor

An image sensor, column-level technology, applied in the field of analog integrated circuit design, can solve the problems of short SAADC conversion cycle, increased design difficulty, long conversion cycle, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

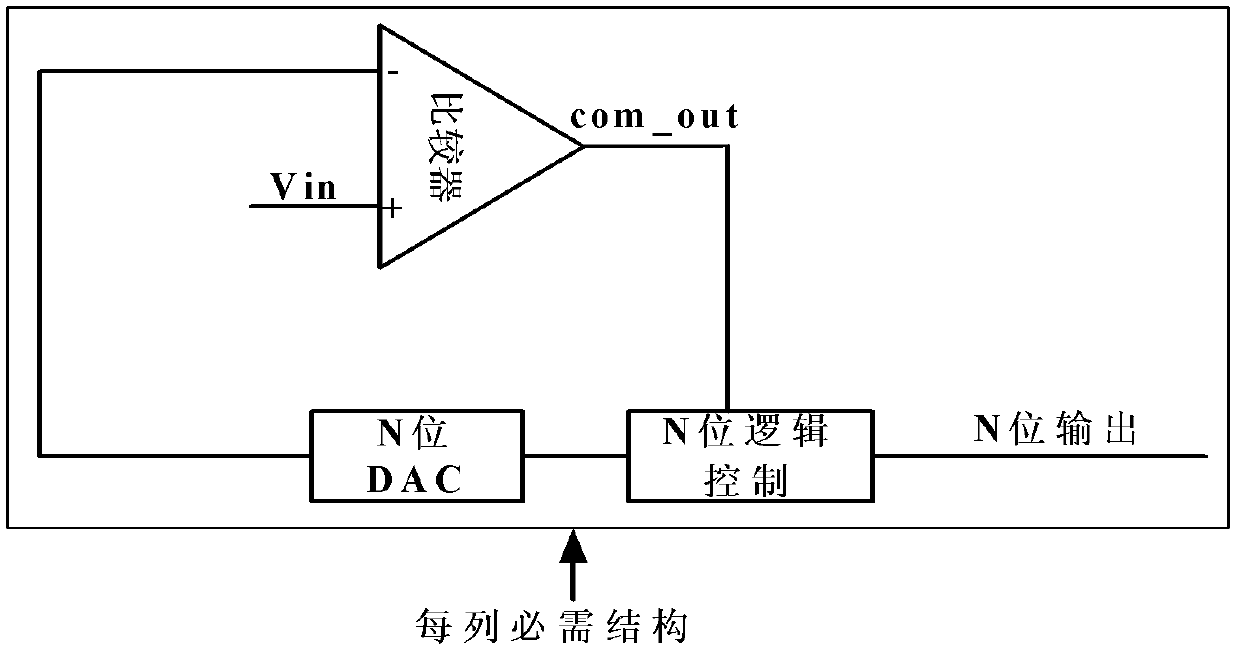

[0018] by Figure 4 The scheme shown is an example. All columns share two ramps. The binary code value that generates ramp 1 is one bit more than the binary code value that generates ramp 2. The signals generated by ramp 1 and ramp 2 pass through the sample and hold circuit and the voltage buffer ( buffer) are respectively connected to the high and low reference voltages required by the DAC in the SA ADC of each column. The circuit structure required for each column is similar to SA ADC, but switches S4, S5, sampling capacitors C1, C2 and two buffers are added. There are two switches at the negative end of the comparator in each column. When performing high M-bit conversion, the negative terminal of the comparator is connected to the ramp signal generated by ramp 1; when performing low N-M bit conversion, the negative terminal is connected to the signal generated by the DAC in SAADC. So the SS ADC shares a comparator with the SAADC.

[0019] It works as follows:

[0020] Th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com