Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

80results about How to "Simplify process complexity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

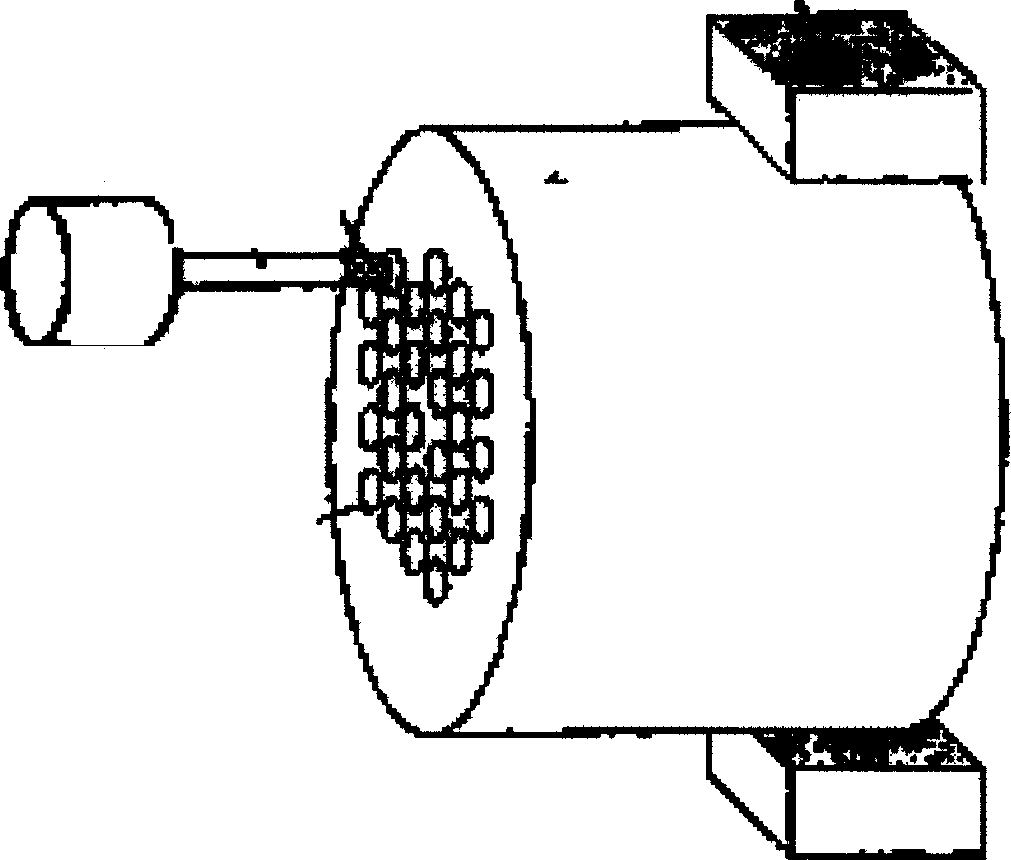

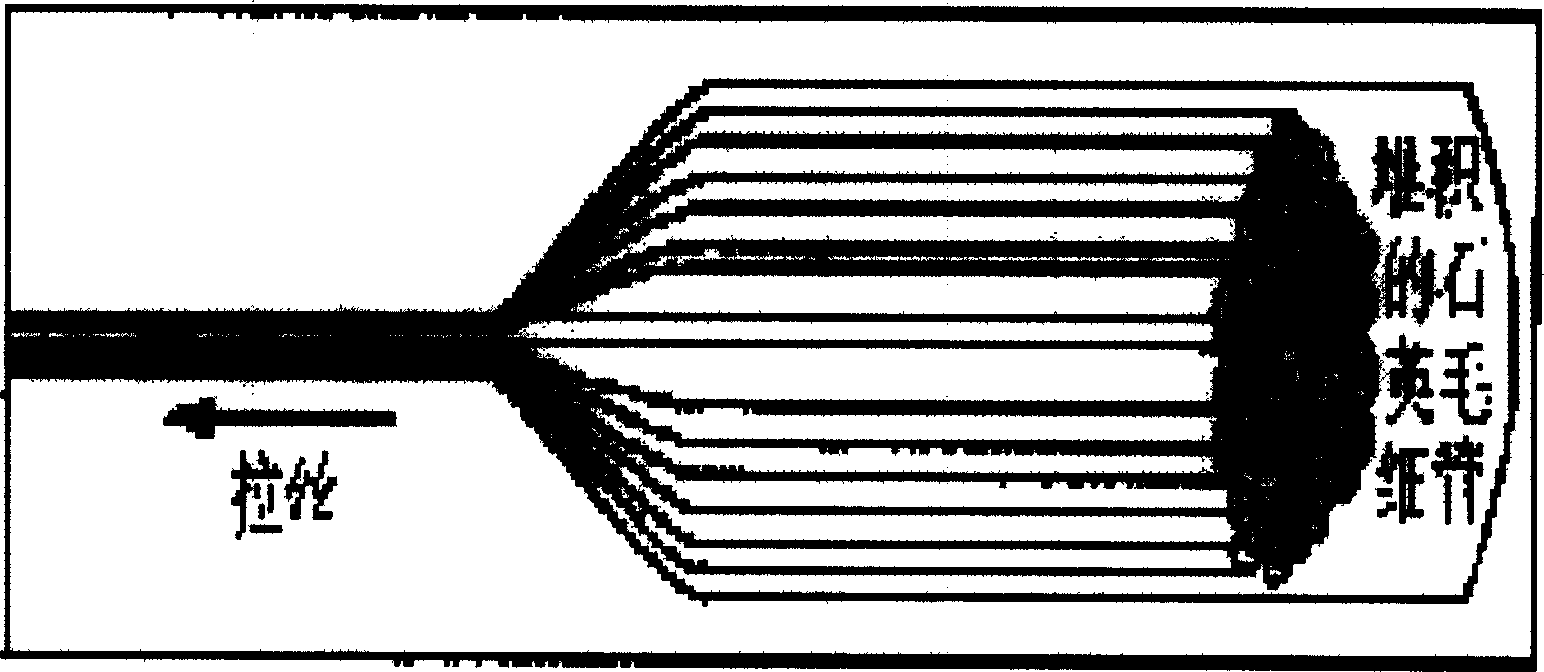

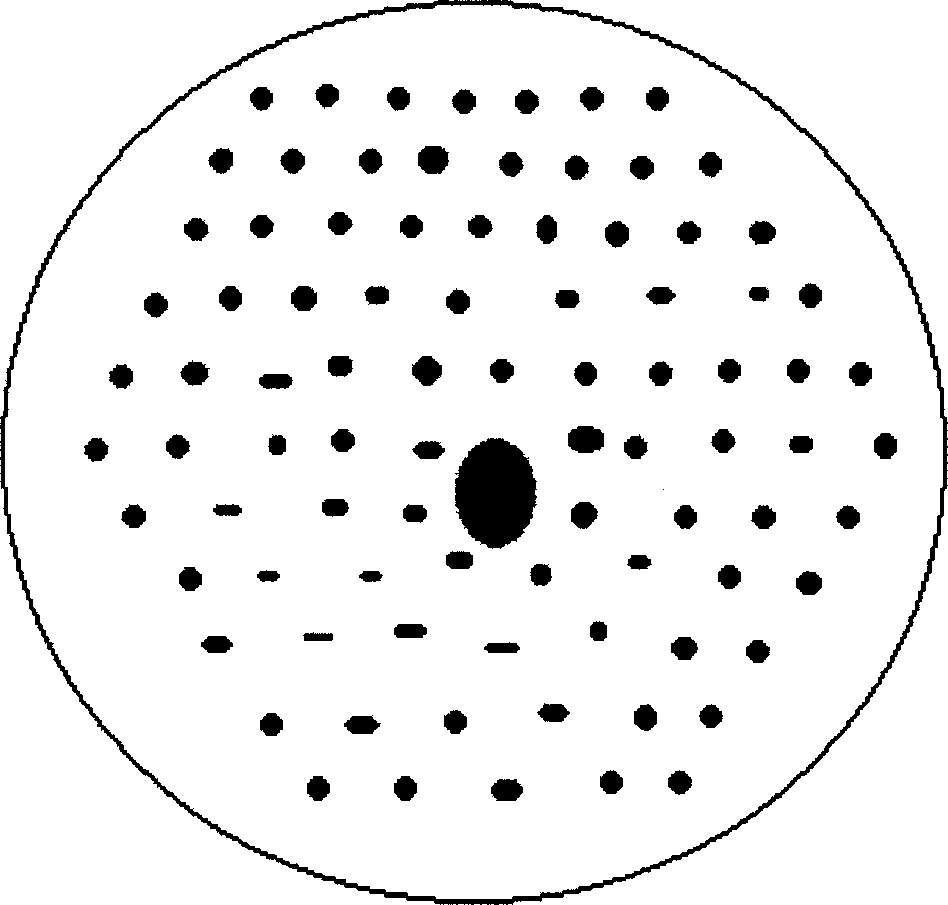

Method for preparing photon crystal optical fibre and apparatus therefor

ActiveCN1583617ASimple preparation procedureReduce lossGlass making apparatusGlass productionAtmospheric pressureMaterials science

The method is: Put many glass pipe in order to form a specific structure (photon crystal optical fibre prefab stick) in the glass cannula. The thin glass pipe is longer then the others. The equipment controls the pressure of photon-crystal optical fibre prefab stick. In another word is to vacuum the glass cannula, to input the thin glass pipe of 10 -1 mbar air.

Owner:FENGHUO COMM SCI & TECH CO LTD

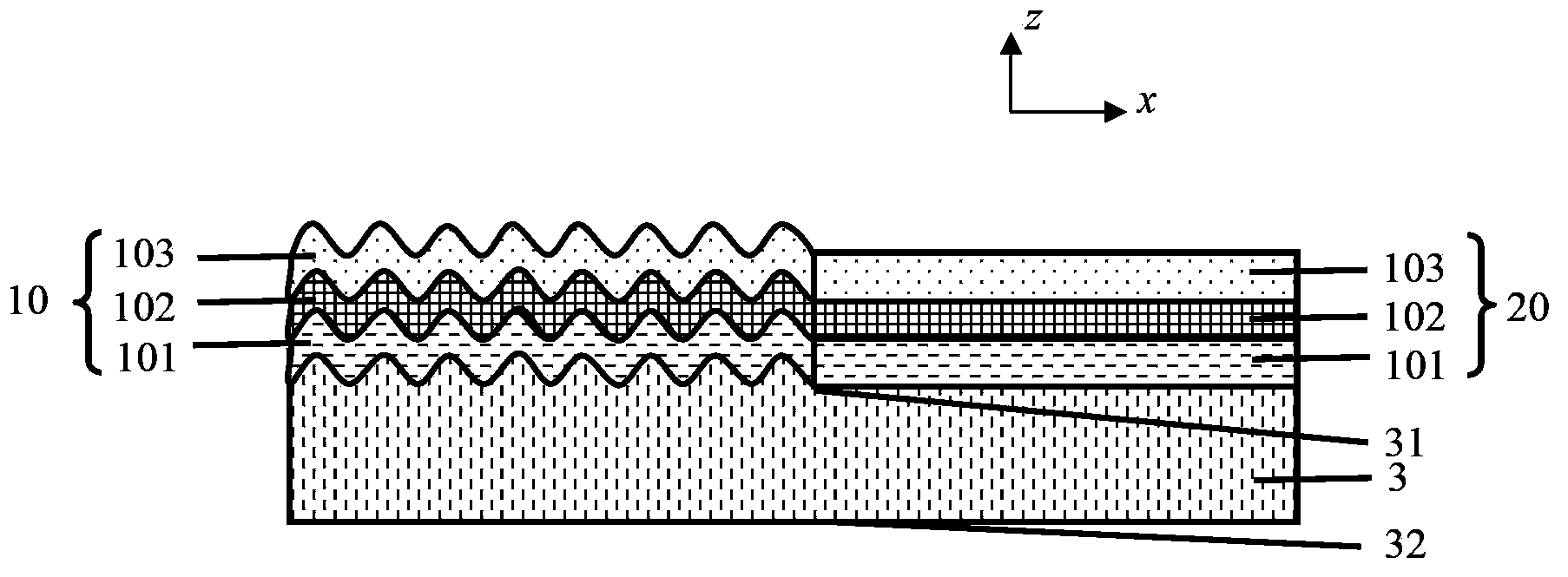

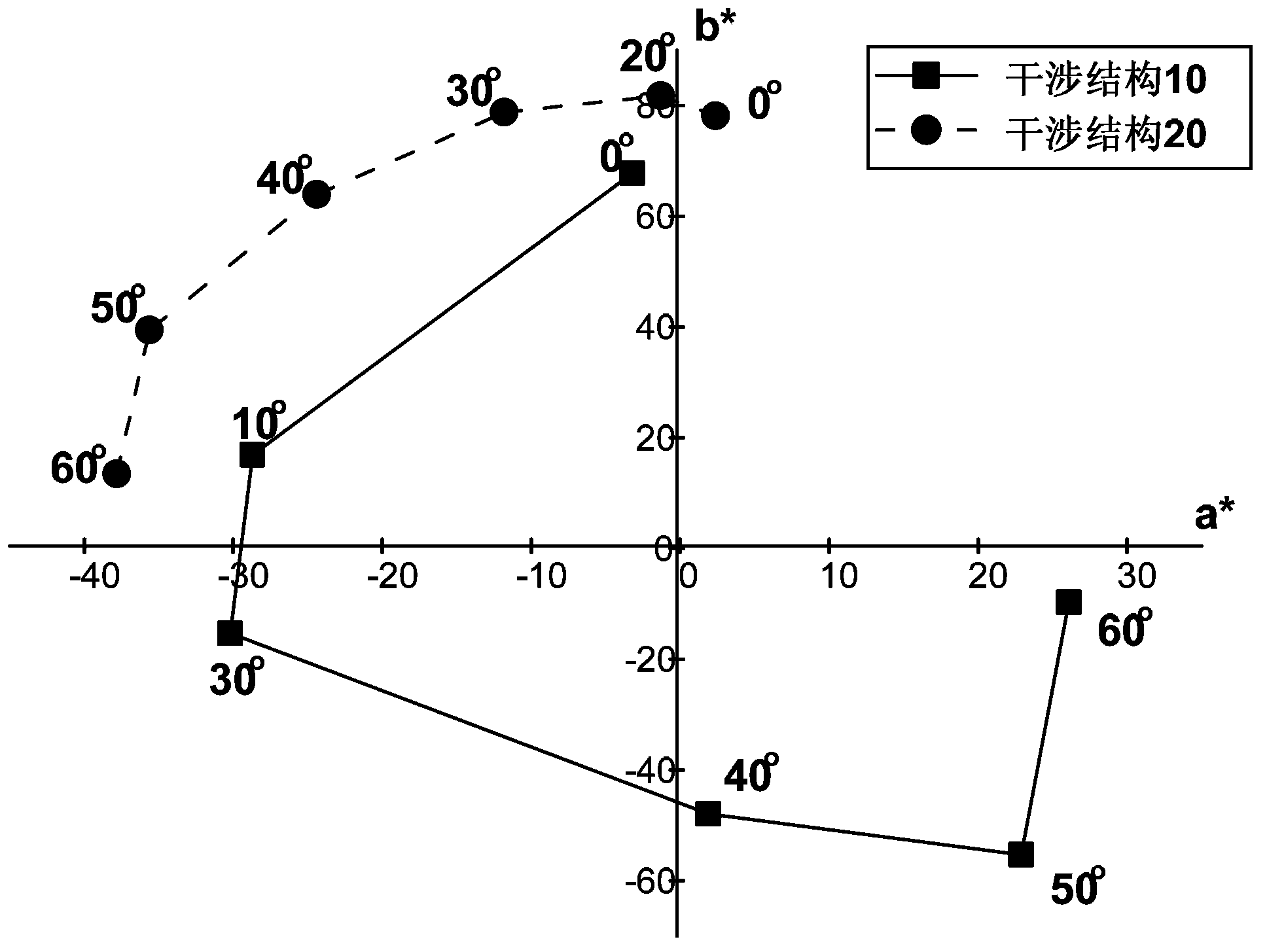

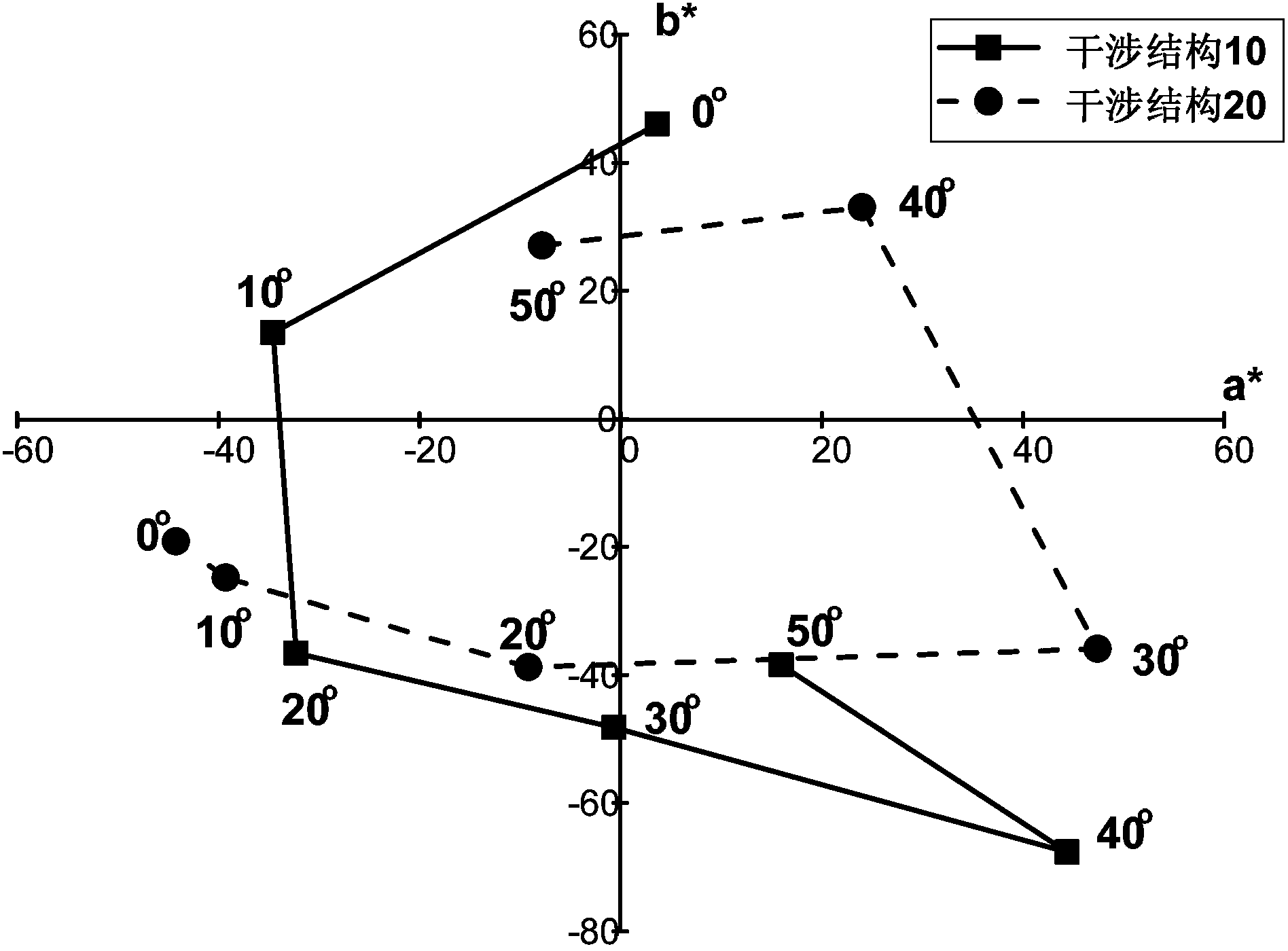

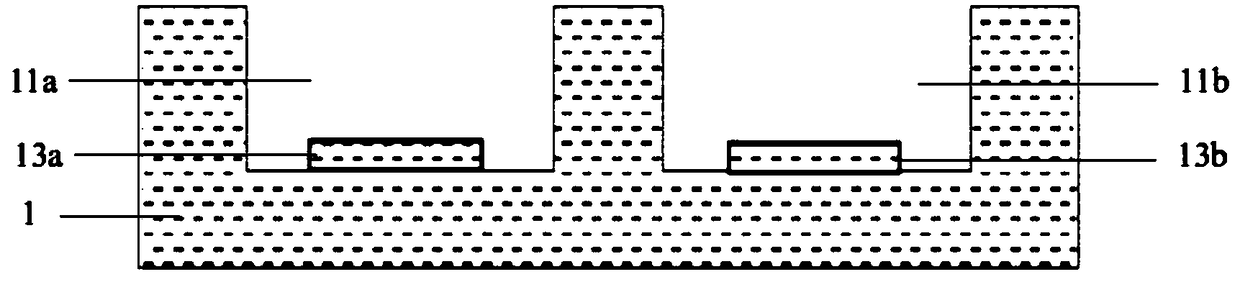

Optical anti-fake element and production method thereof

ActiveCN103448411AGood optical performanceHigh precisionDiffraction gratingsInformation cardsWavelengthMedia layer

The invention provides an optical anti-fake element and a production method thereof, aiming to overcome defects that processes in the prior art are complicated and it's difficult to realize color matching due to difficulty in accurately controlling thickness of coating layers of two types of coating structures in the prior art. The optical anti-fake element comprises a substrate (1) consisting of a first surface (31) and a second surface (32). Part of the first surface (31) is of a sub-wavelength micro-relief structure while another part thereof is of a flat surface structure; a first medium layer, a second medium layer and a third medium layer are sequentially superposed on the sub-wavelength micro-relief structure and the flat surface structure; colors of the sub-wavelength micro-relief structure and the flat surface structure are the same when observed in specific viewing angle, and are different when observed in other angles.

Owner:ZHONGCHAO SPECIAL SECURITY TECH +1

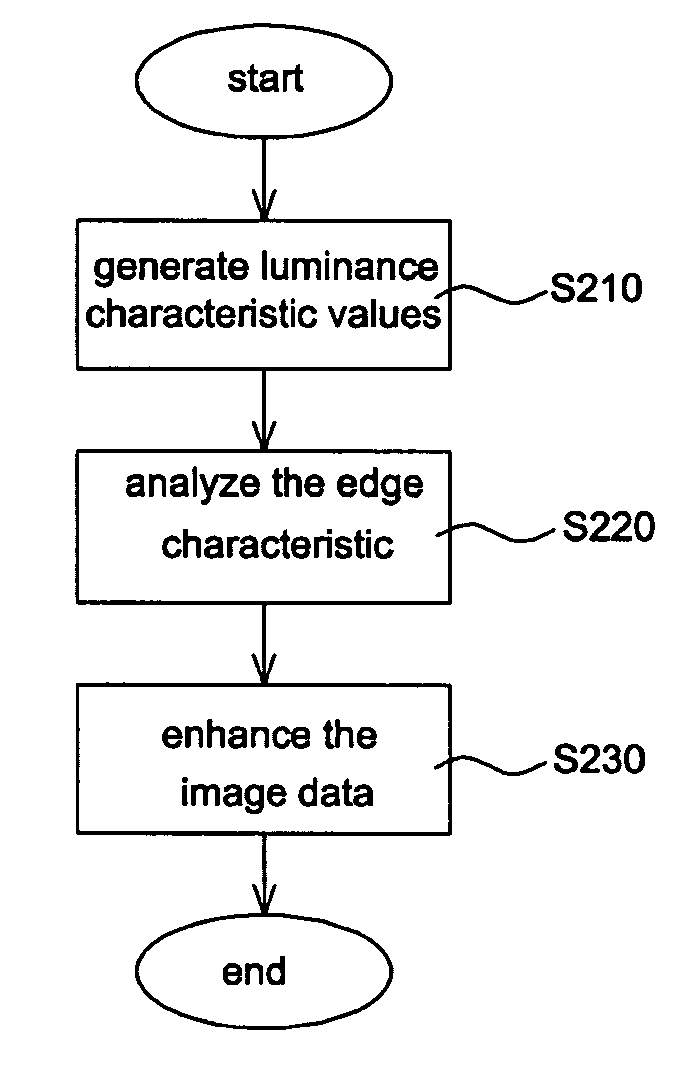

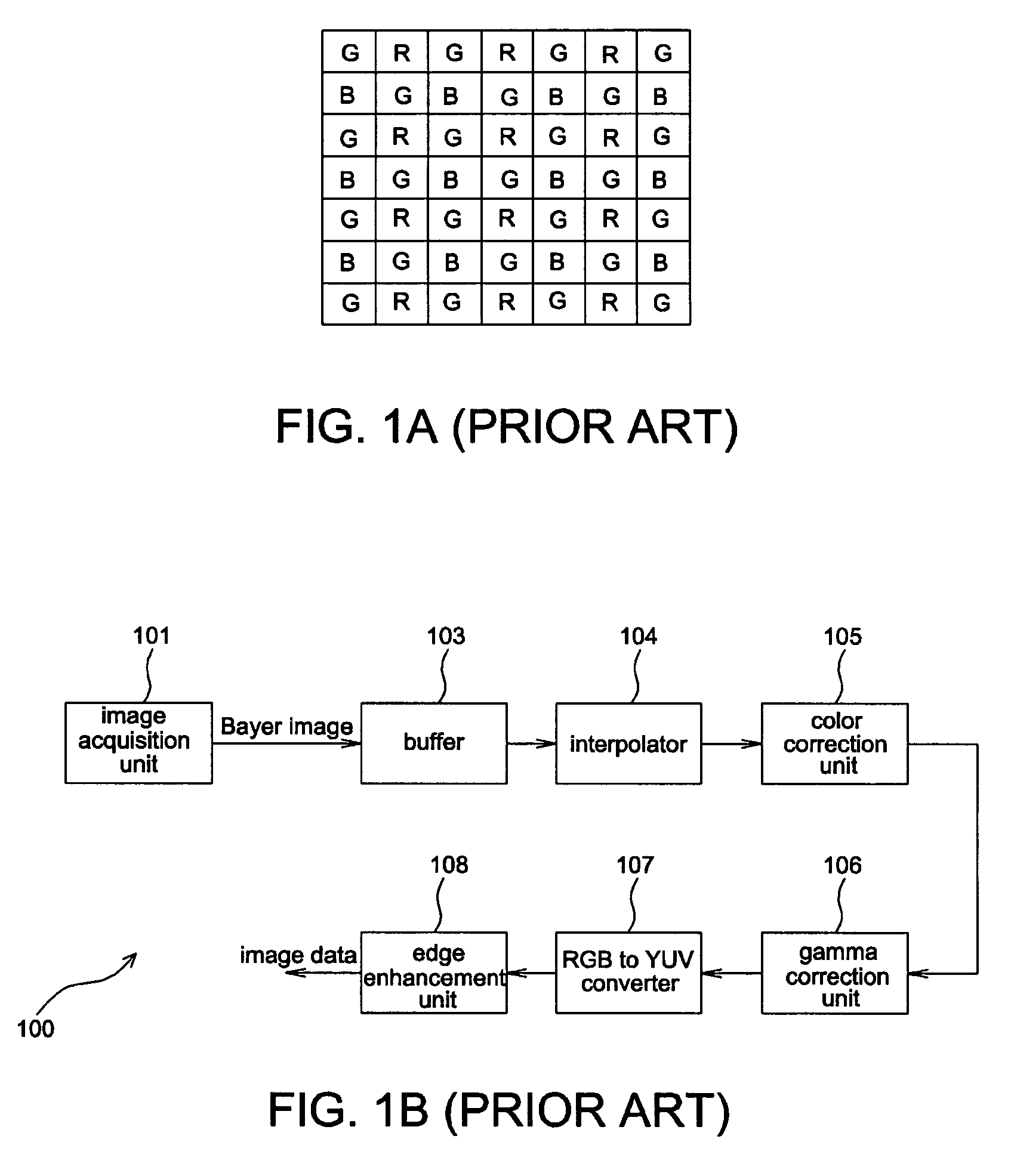

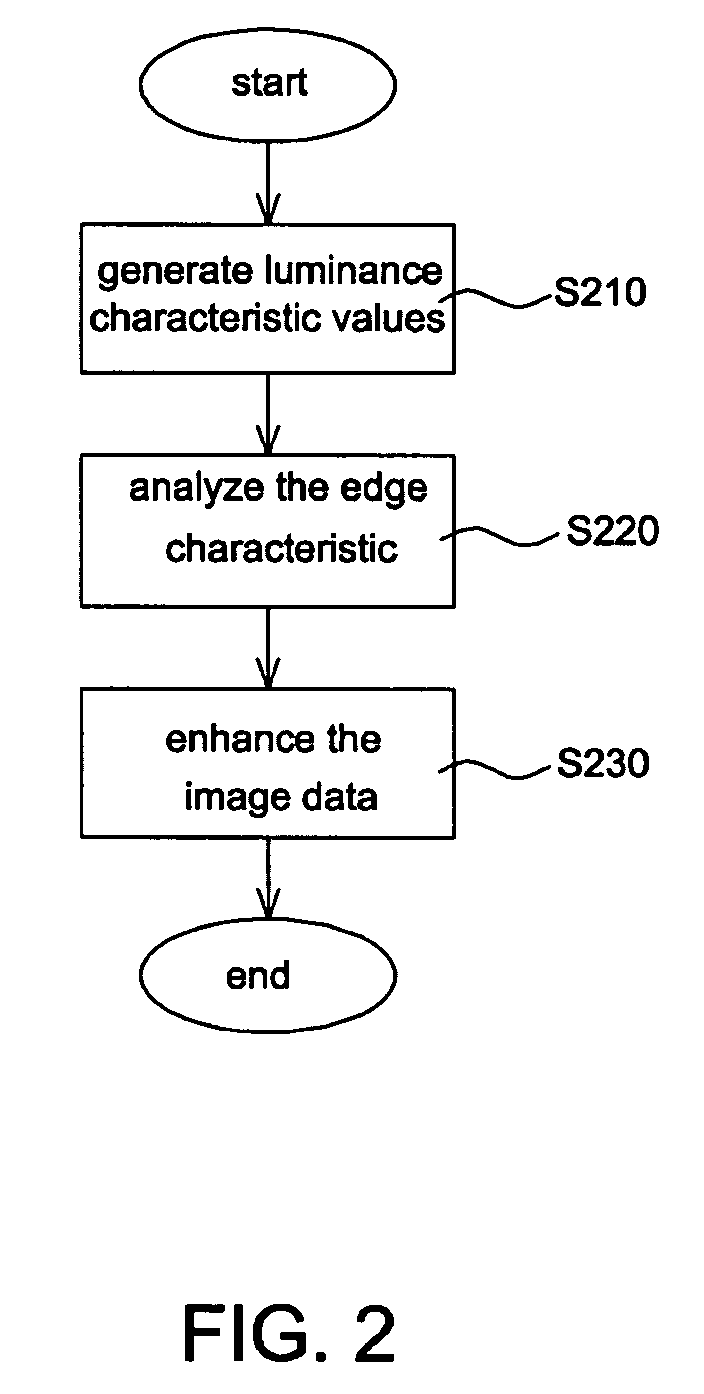

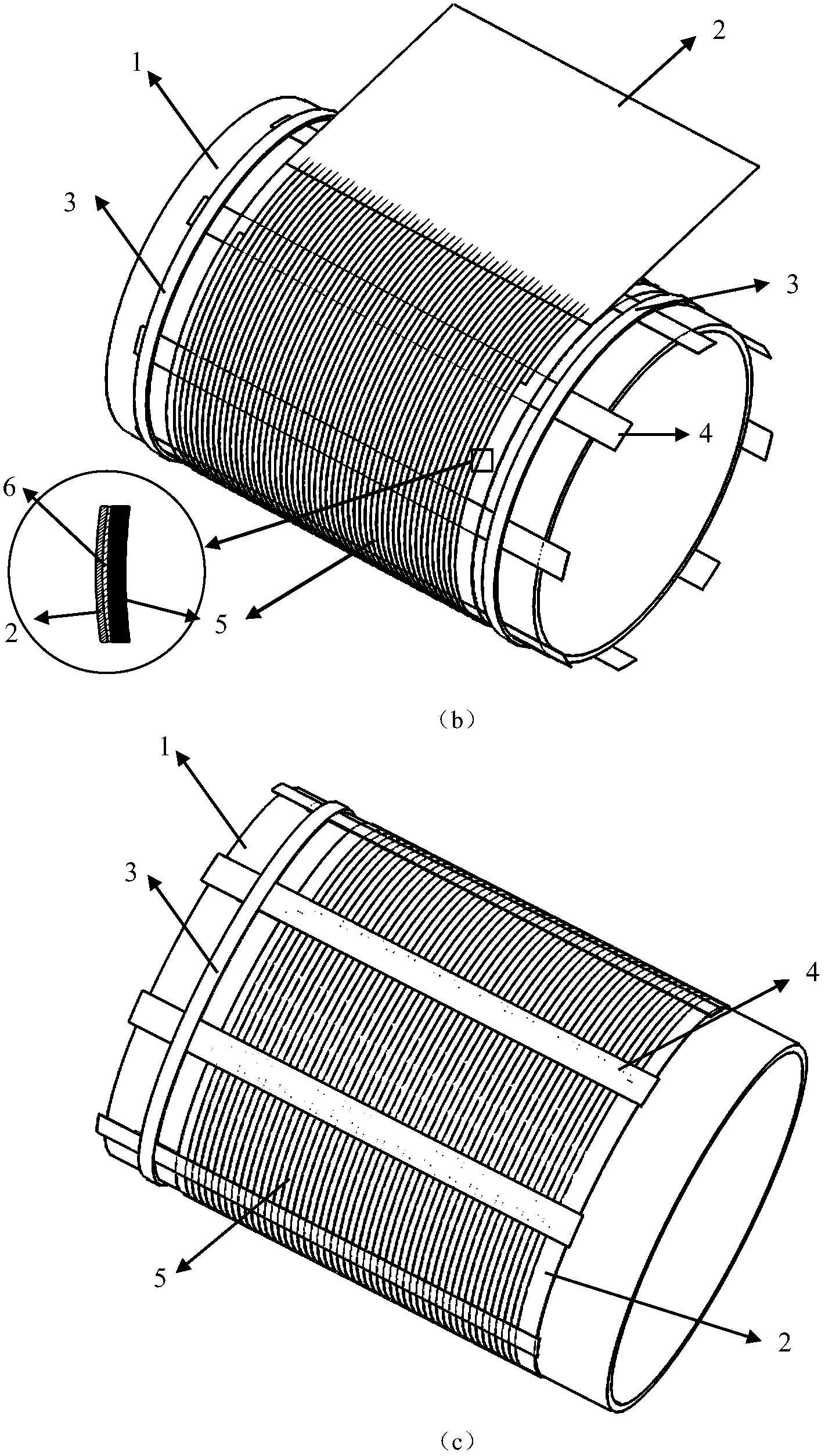

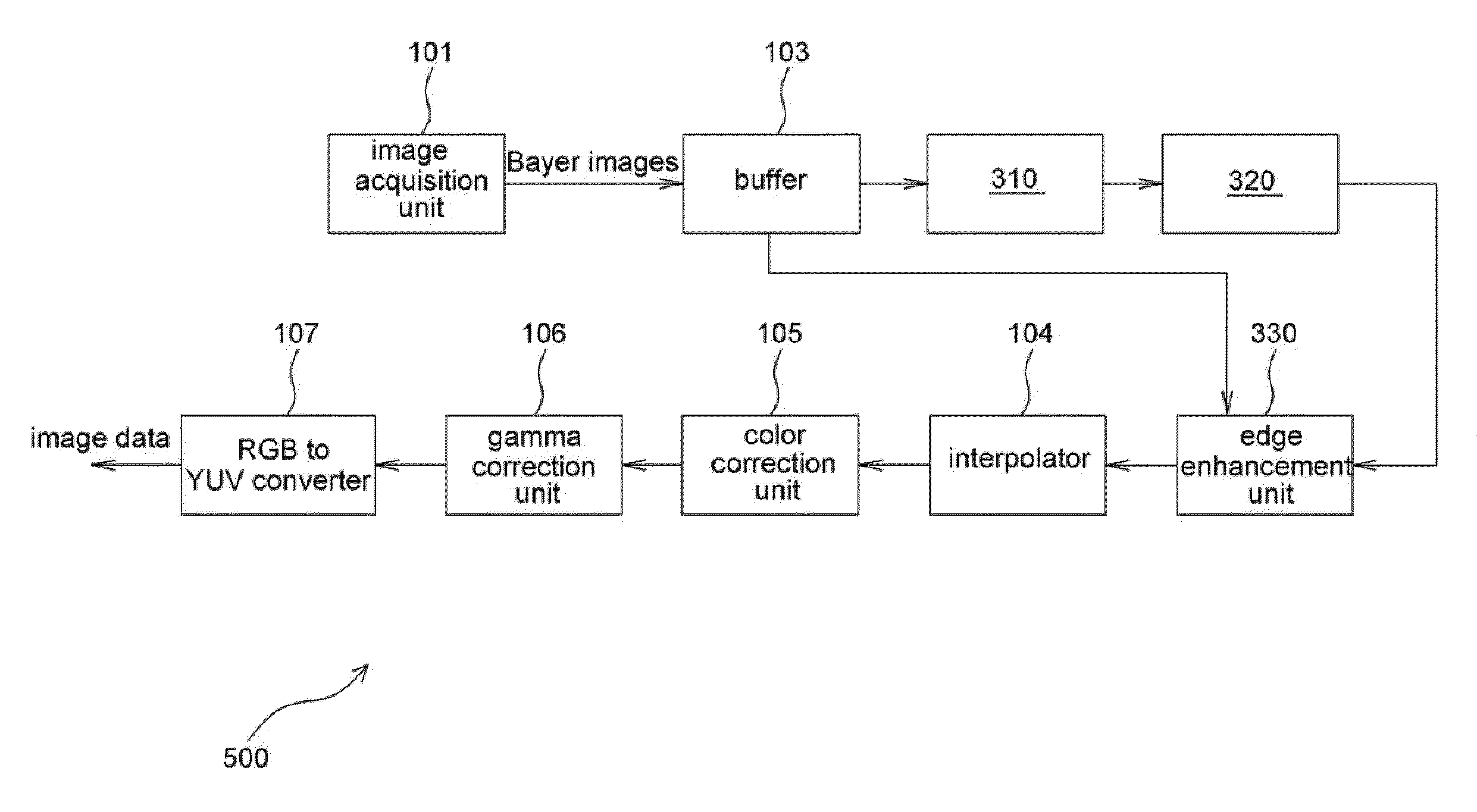

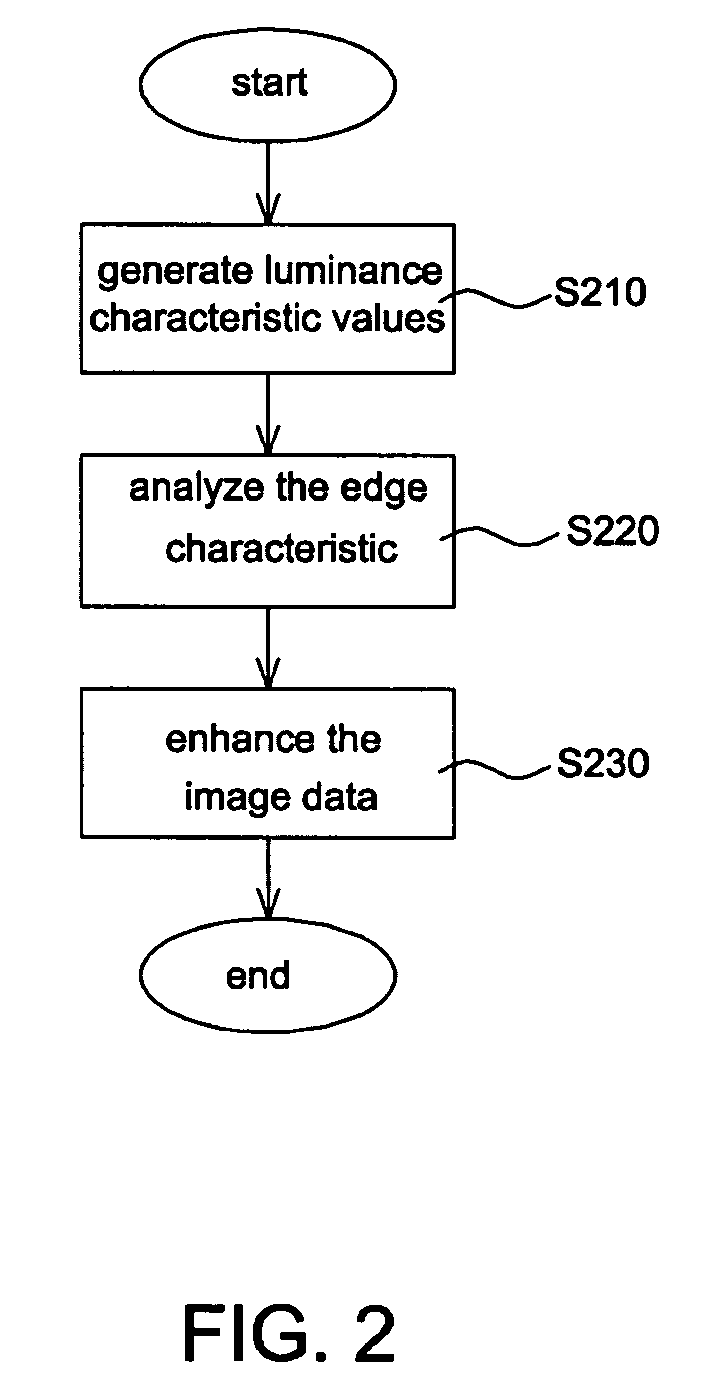

Edge enhancement method and apparatus for Bayer images, and color image acquisition system

ActiveUS20060250655A1Save memory access spaceSave spaceImage enhancementTelevision system detailsColor imageImaging processing

An edge enhancement method and apparatus for Bayer images are provided. The apparatus stores the raw Bayer image data into a line buffer. After having directly read the raw Bayer image data from the buffer, the apparatus computes luminance characteristic values, analyzes the edge characteristic and then outputs the edge characteristic values. According to the edge characteristic values, the edges in the raw Bayer image data are enhanced. The apparatus simplifies the processing complexity of the rear-stage circuit by directly enhancing the edges in the Bayer image, and is easily combined with the post image processing mechanism. Conventionally, the raw Bayer image is converted to the RGB image or the YUV image and then the edge enhancement operation is performed. The invention reduces the computing volume and memory size. Also, performing the edge enhancement operation in advance helps to identify the interpolation direction and ease the annoying noise.

Owner:ICATCH TECH INC

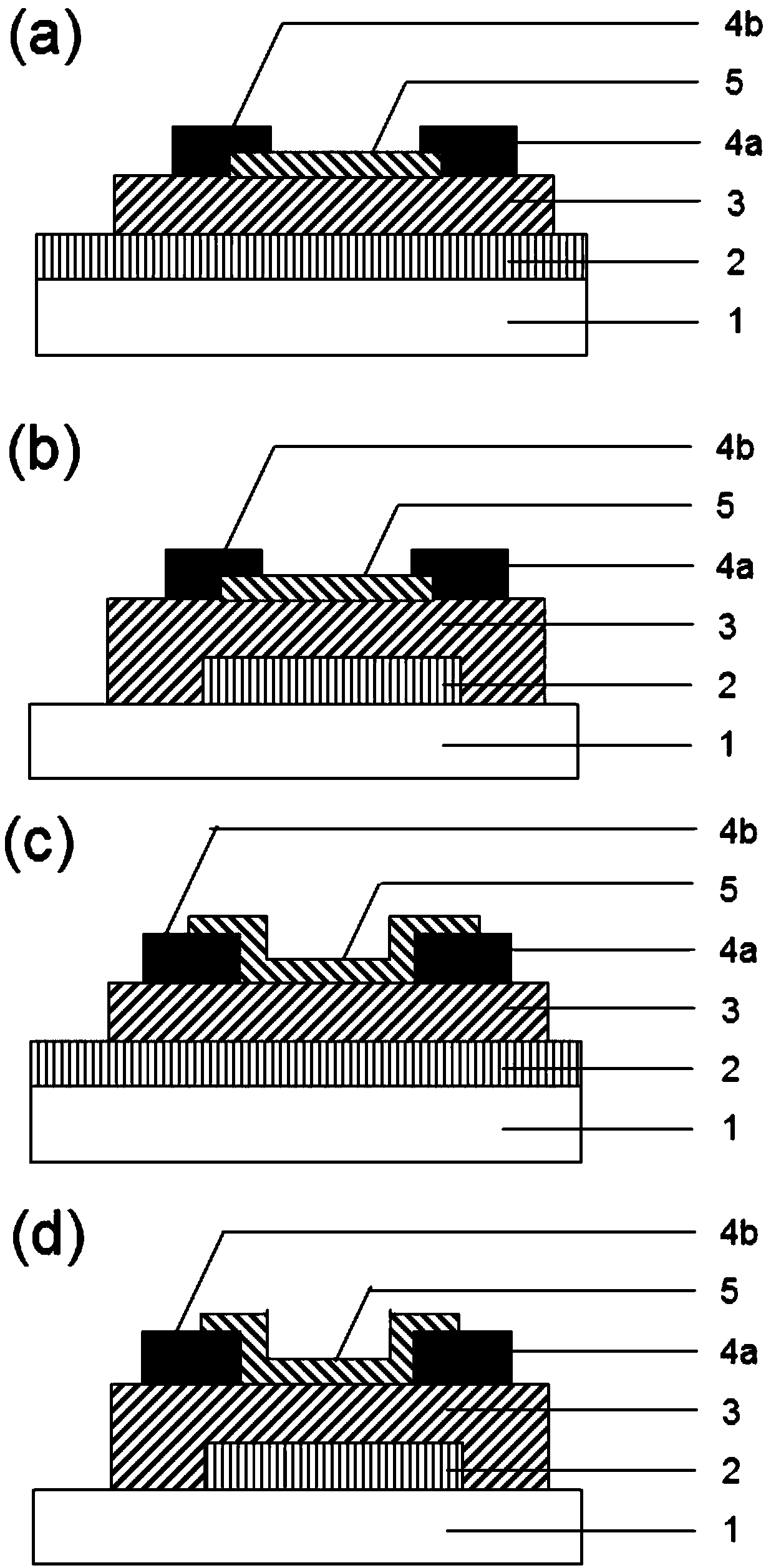

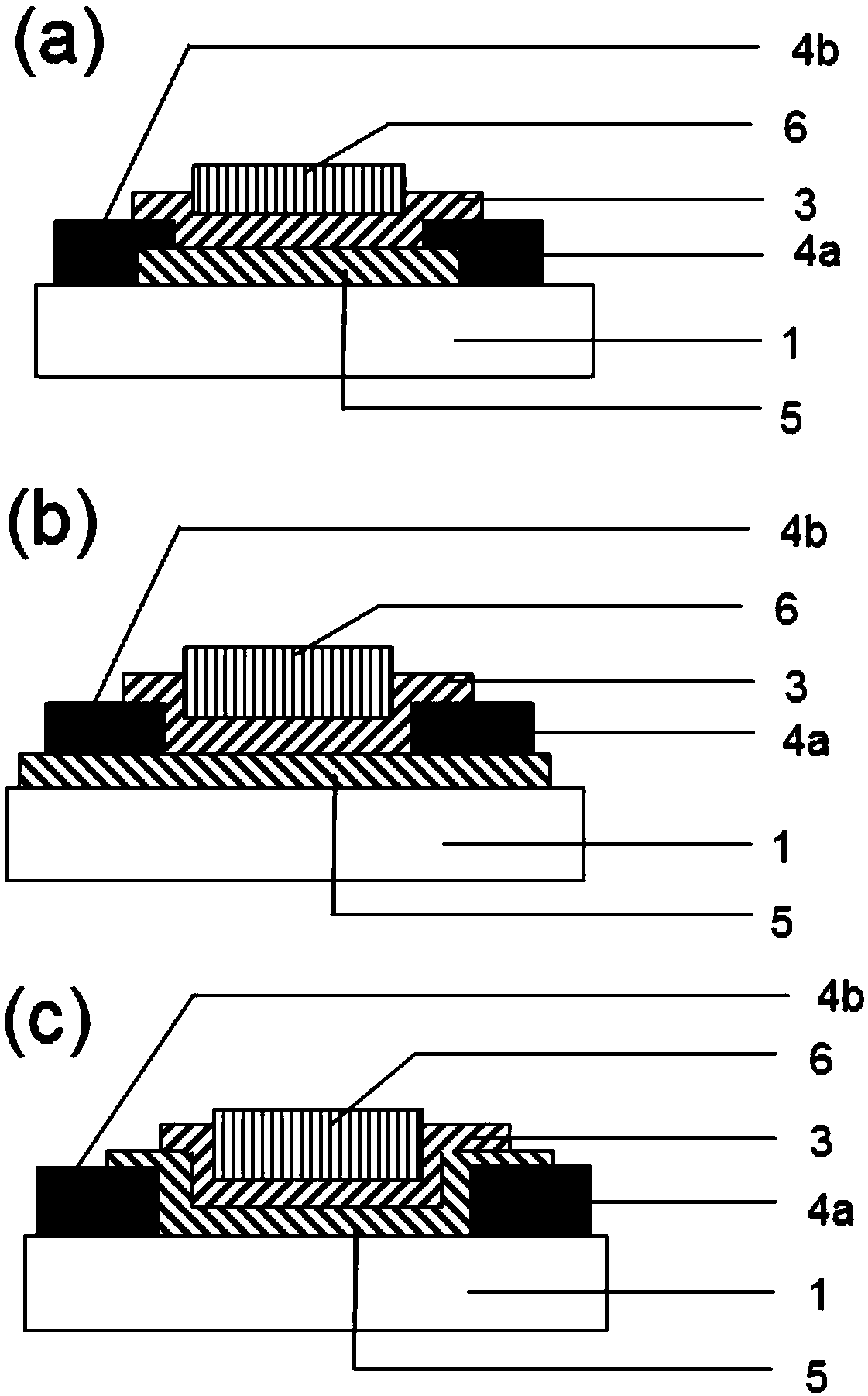

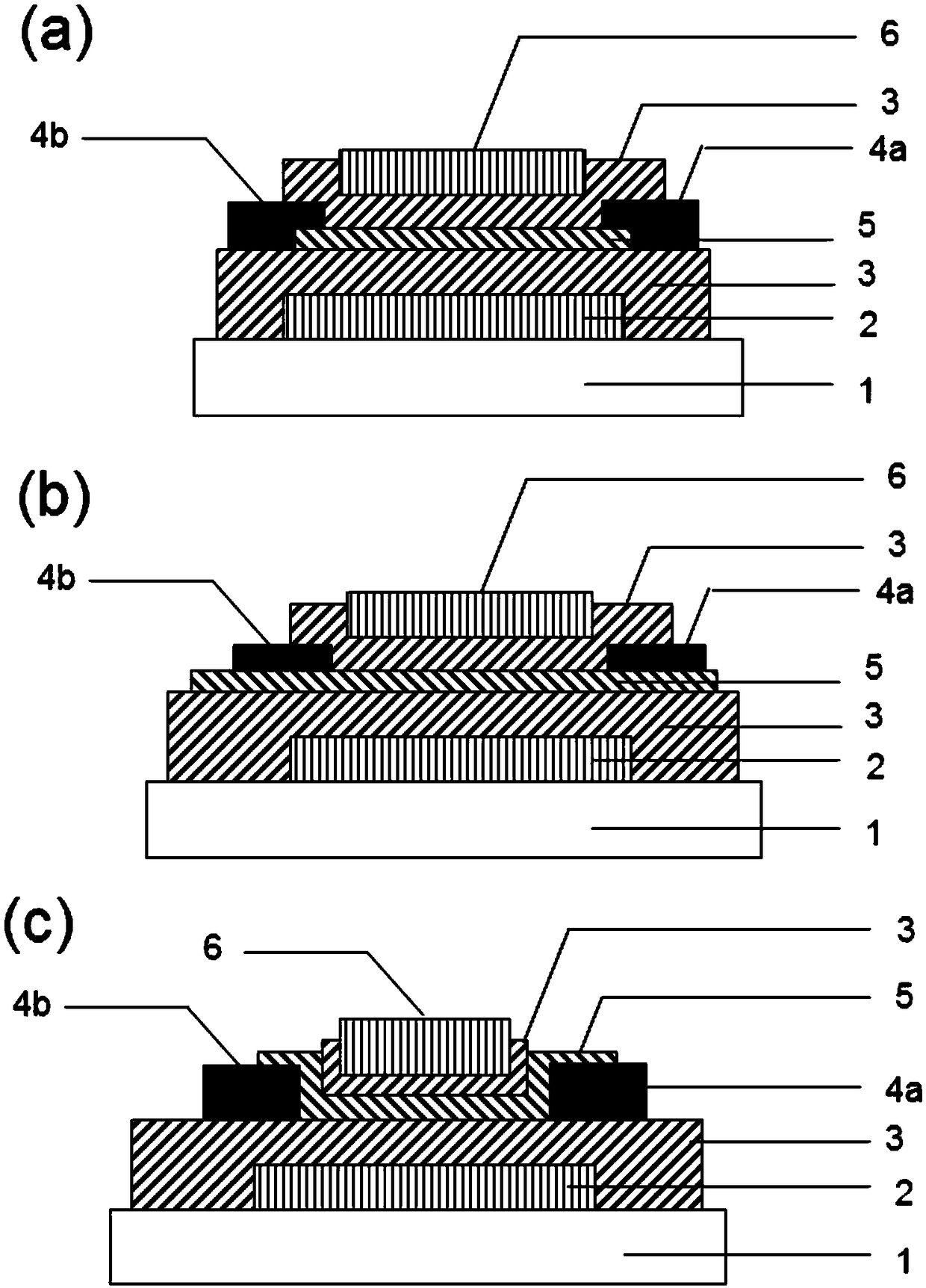

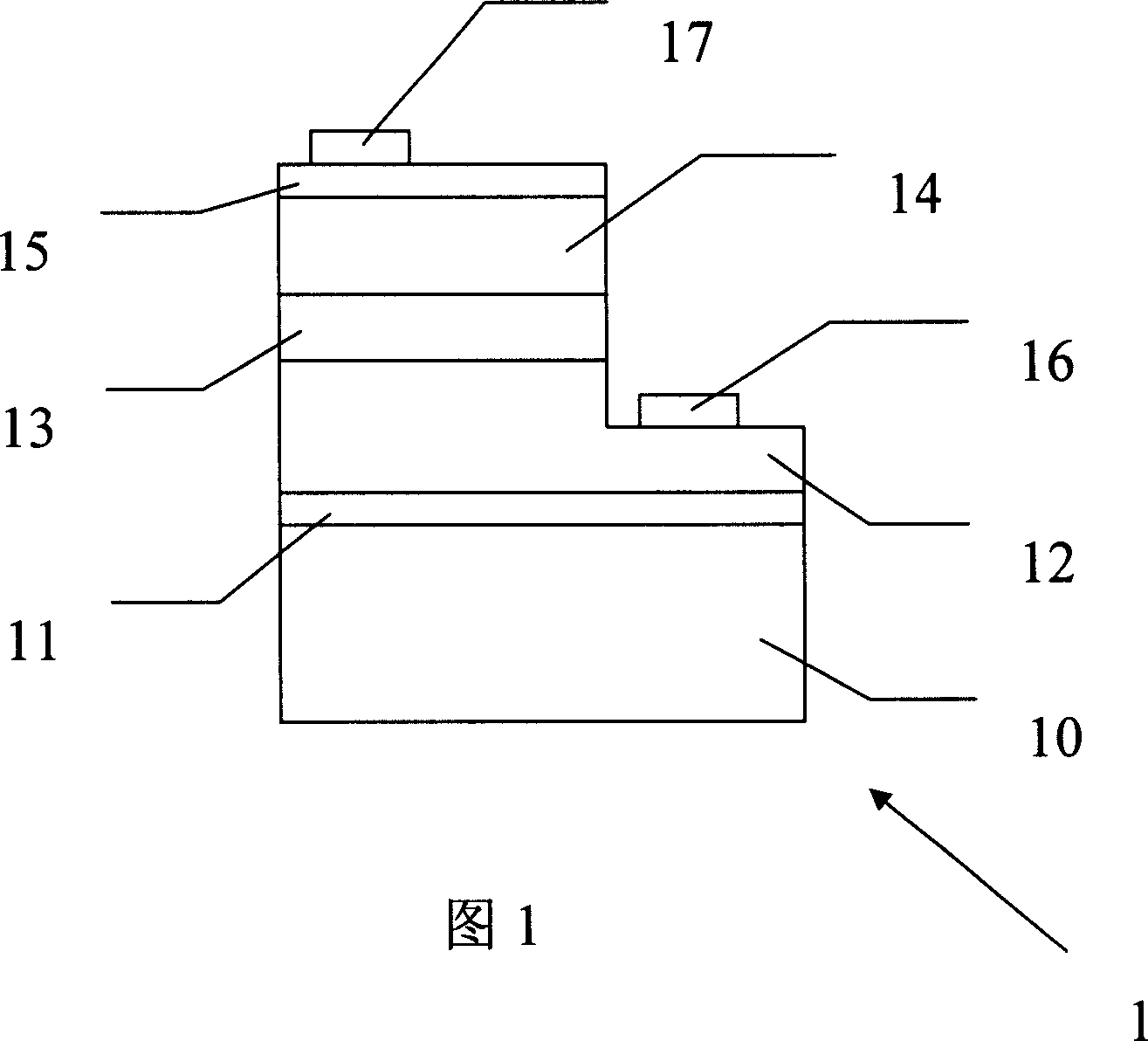

Oxide film transistor and manufacturing method thereof

ActiveCN108807546AAvoid pollutionLow working voltageTransistorSemiconductor/solid-state device manufacturingSolid state electrolyteOxide thin-film transistor

The invention discloses an oxide film transistor comprising an insulation substrate, a gate medium layer, a grid electrode arranged on one side of the gate medium layer, a source electrode and a drainelectrode arranged on the other side of the gate medium layer, and a channel layer between the source electrode and the drain electrode; the gate medium is a solid electrolyte with proton conductivecharacteristics, and a grid electrode bias pulse can be applied to regulate a transistor threshold voltage; the oxide film transistor can be either of the following structure types: a bottom gate topcontact type, a bottom gate bottom contact type, a top gate top contact type, a top gate bottom contact type, and a bottom gate and top gate combined type. The oxide film transistor can effectively reduce the work voltage; the grid electrode bias voltage can be applied to regulate the device threshold voltage according to needs, thus simplifying the process complexity, and reducing the process cost.

Owner:NINGBO INST OF MATERIALS TECH & ENG CHINESE ACADEMY OF SCI

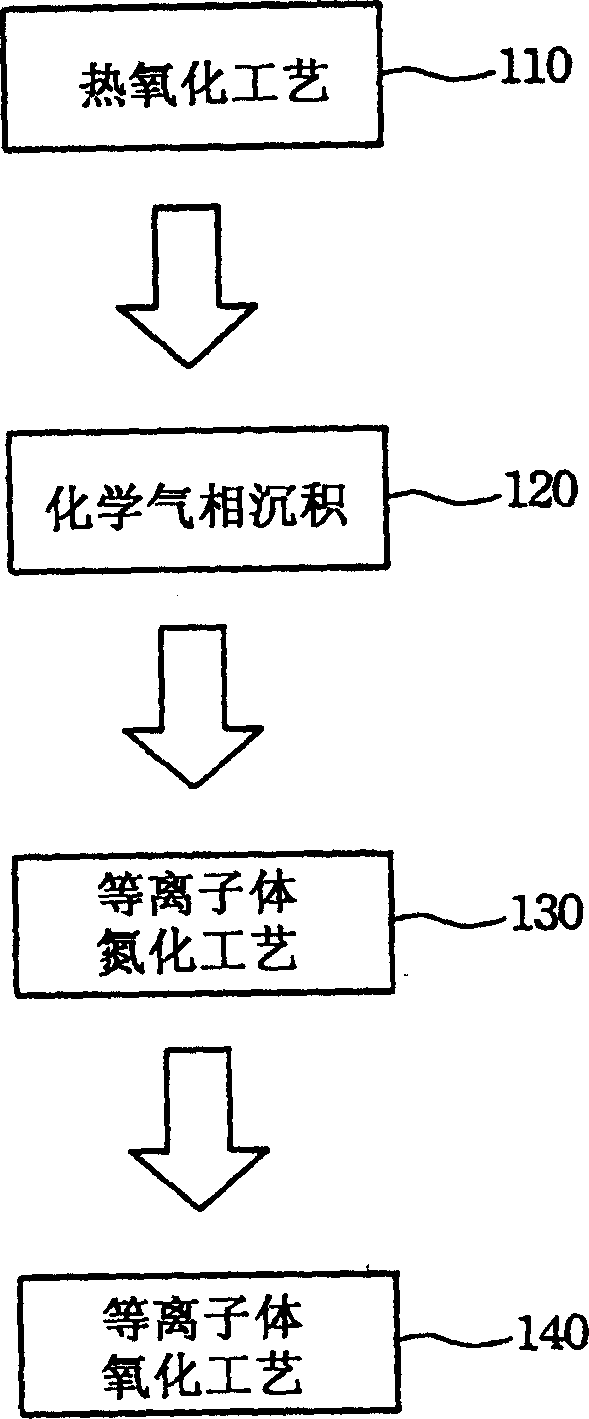

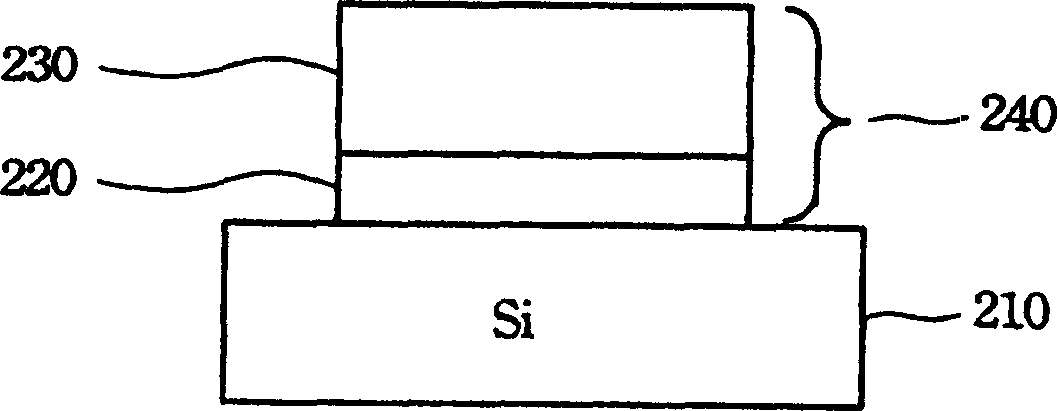

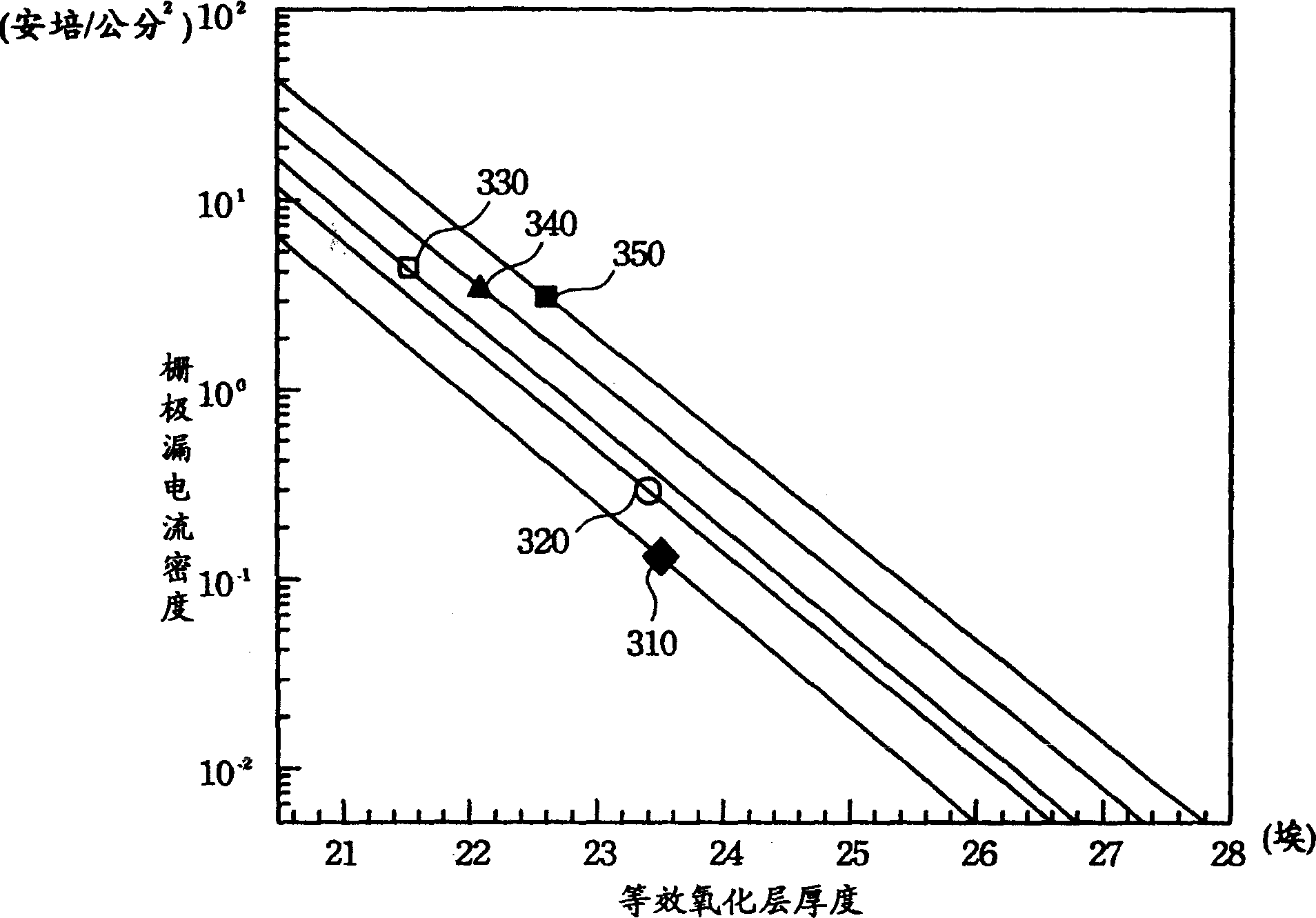

Process for making super-thin silicon nitride / silicon oxide grid electrode dielectric layer

InactiveCN1464530AReduce hydrogen contentImprove featuresSemiconductor/solid-state device manufacturingRemote plasmaSurface oxidation

The invention discloses a process for manufacturing ultra-thin silicon nitride / silicon oxide grid electrode dielectric layer, characterized by that, first forming a surface oxidation layer on a silicon substrate by silicon oxidation, then depositing silicon nitride layer on the surface oxidation layer, and nitrogenizing and oxidizing the silicon nitride using plasma body. The thermal oxidation silicon substrate is carried out by oxidizing the silicon substrate using oxygen or N#-[2]O, so as to form silicon oxide layer or silicon nitride layer. The deposition silicon nitride uses rapid heating chemical vapor deposition or remote plasma body to reinforce the chemical vapor deposition silicon nitride layer. Plasma body nitridation uses N#-[2] plasma body, and plasma body oxidation uses oxygen plasma body or N#-[2] plasma body to oxidizing the silicon nitride layer.

Owner:TAIWAN SEMICON MFG CO LTD

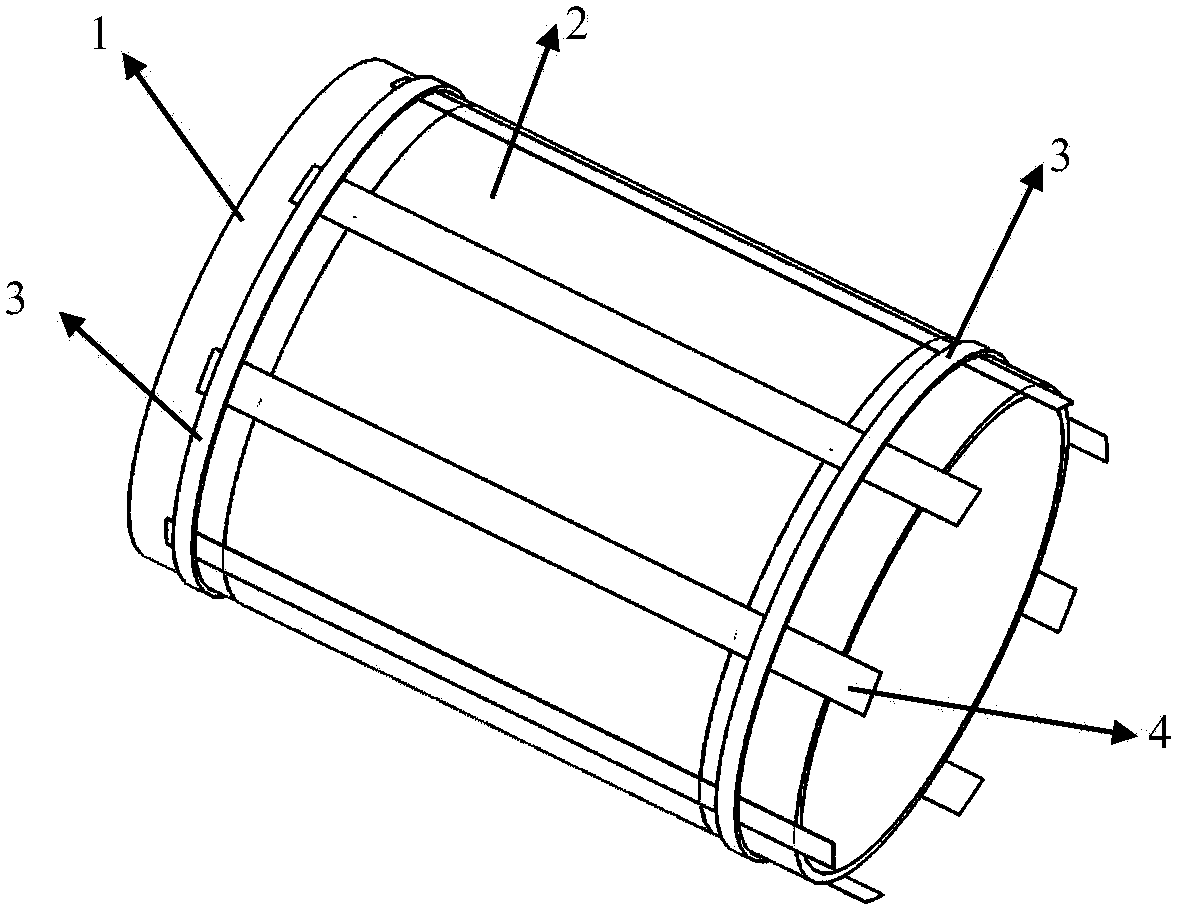

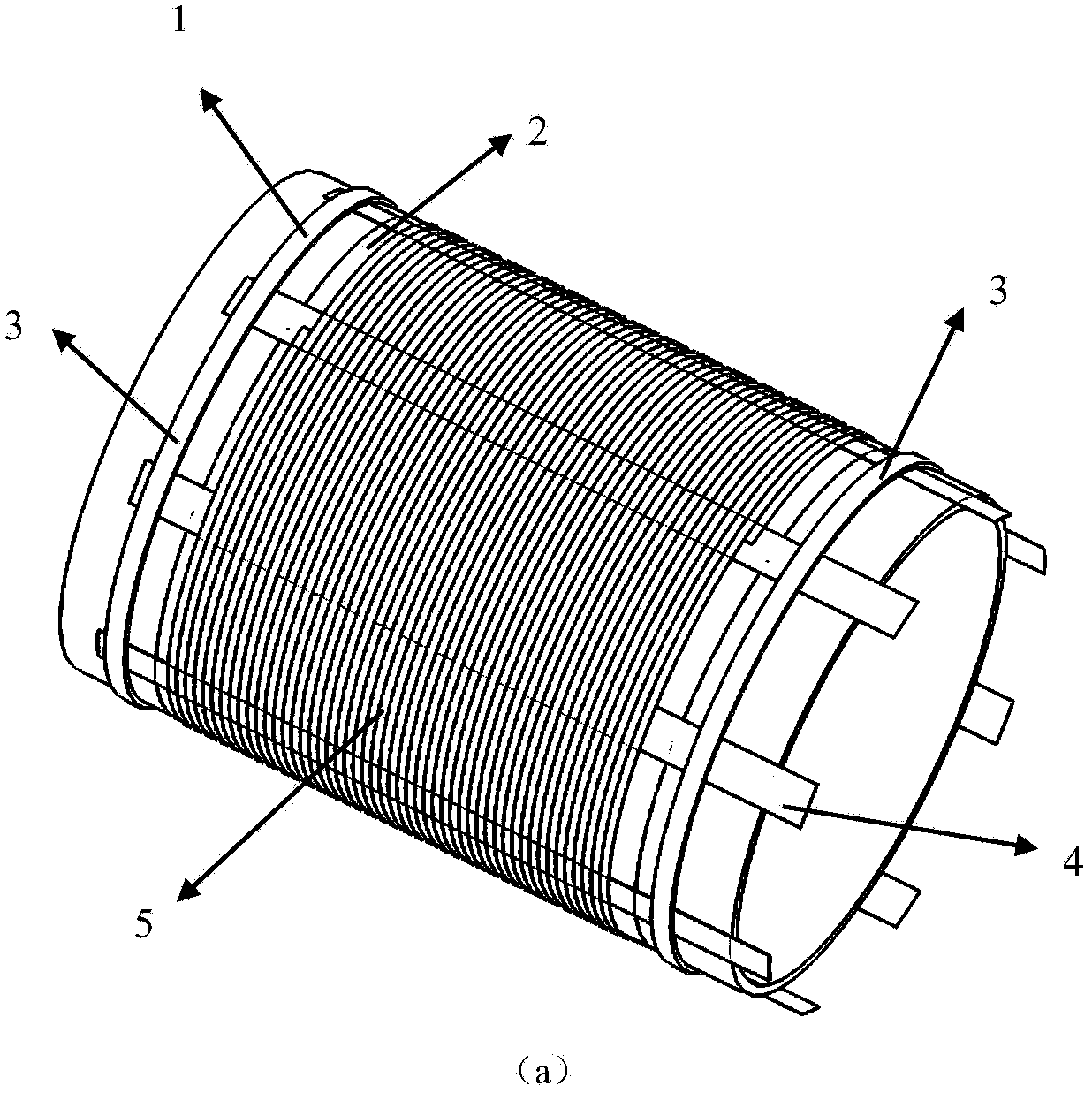

High temperature superconductor coil and winding technology thereof

InactiveCN103714936AAvoid failureGuaranteed insulation performanceSuperconductors/hyperconductorsSuperconductor devicesHigh-temperature superconductivitySuperconducting Coils

Owner:HUAZHONG UNIV OF SCI & TECH +1

Edge enhancement method and apparatus for Bayer images, and color image acquisition system

ActiveUS7659930B2Save spaceSimplify process complexityTelevision system detailsImage enhancementColor imageImaging processing

An edge enhancement method and apparatus for Bayer images are provided. The apparatus stores the raw Bayer image data into a line buffer. After having directly read the raw Bayer image data from the buffer, the apparatus computes luminance characteristic values, analyzes the edge characteristic and then outputs the edge characteristic values. According to the edge characteristic values, the edges in the raw Bayer image data are enhanced. The apparatus simplifies the processing complexity of the rear-stage circuit by directly enhancing the edges in the Bayer image, and is easily combined with the post image processing mechanism. Conventionally, the raw Bayer image is converted to the RGB image or the YUV image and then the edge enhancement operation is performed. The invention reduces the computing volume and memory size. Also, performing the edge enhancement operation in advance helps to identify the interpolation direction and ease the annoying noise.

Owner:ICATCH TECH INC

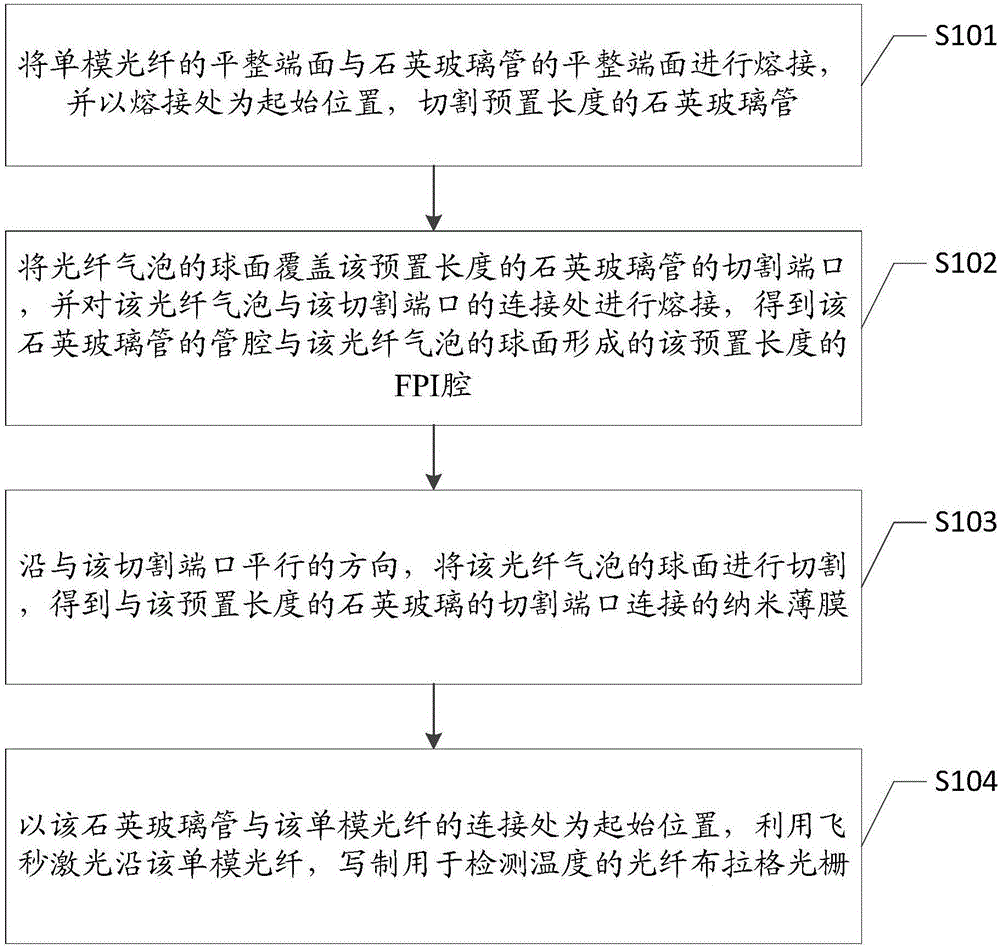

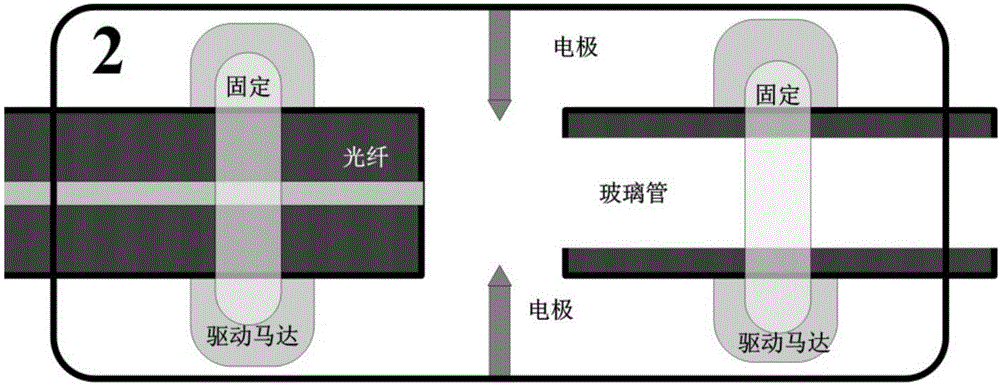

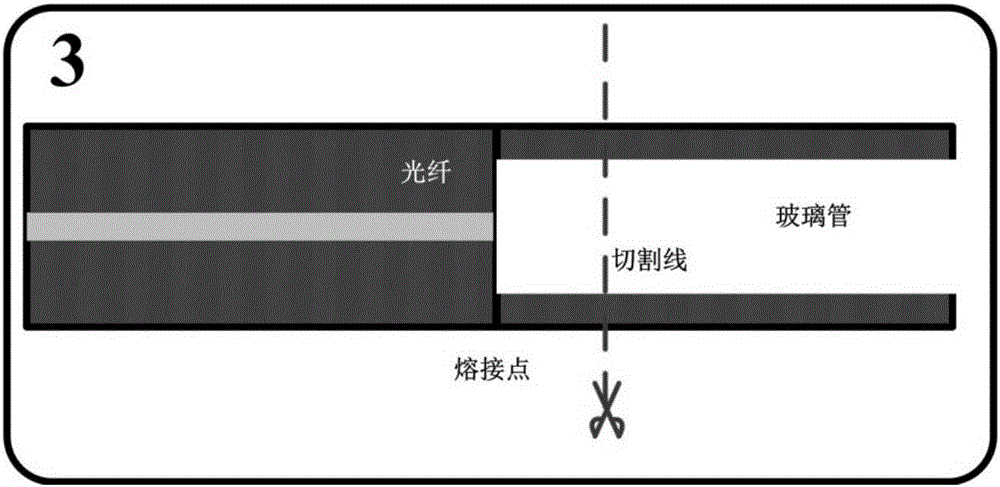

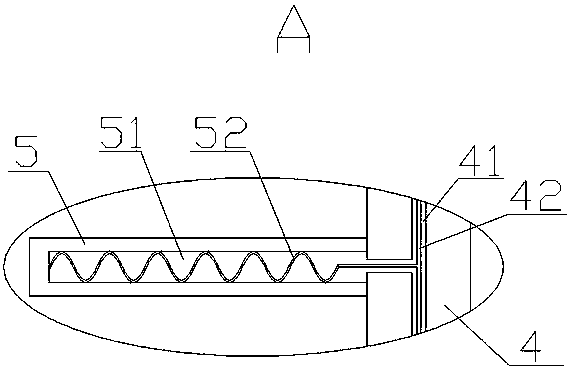

Method for preparing temperature-pressure sensor, temperature-pressure sensor structure and temperature-pressure measuring system and method

ActiveCN106643908ASimplify process complexitySimplify installation complexityConverting sensor output opticallyFiber Bragg gratingEngineering

The invention provides a method for preparing a temperature-pressure sensor, a temperature-pressure sensor structure and a temperature-pressure measuring system and method. The method for preparing a temperature-pressure sensor comprises the following steps: fusion splicing the flat end face of a single-mode fiber and the flat end face of a quartz glass tube and cutting the quartz glass tube at a position a preset length close to a fusion splicing port, covering the cutting port of the quartz glass tube with the preset length with the spherical surface of a fiber bubble, fusion splicing the joint of the fiber bubble and the cutting port, cutting the spherical surface of the fiber bubble along a direction in parallel with the cutting port in order that the quartz glass tube with the preset length and the spherical surface of the fiber bubble form a Fabry-Perot interference cavity with the preset length, and making a fiber bragg grating for temperature detection in the single-mode fiber connected with the Fabry-Perot interference cavity by using laser. The method simplifies the process complexity and installation complexity of the temperature-pressure sensor, improves pressure detection accuracy, and enhances the reliability of a temperature and measurement system.

Owner:SHENZHEN UNIV

EVA (ethylene-vinyl acetate) precoating packaging adhesive film and preparation method thereof

InactiveCN104762023AIncrease production speedSimplify process complexityNon-macromolecular adhesive additivesFilm/foil adhesivesPolymer scienceAdhesive

The invention provides an EVA (ethylene-vinyl acetate) precoating packaging adhesive film and a preparation method thereof. The adhesive film is composed of three layers, wherein the middle layer is a BOPP (biaxially-oriented polypropylene) film layer, and the upper and lower layers are respectively an EVA adhesive layer. The EVA adhesive layer is prepared from 100 parts of ethylene-vinyl acetate copolymer, 0.5-1 part of crosslinking agent, 0.1-2 parts of antioxidant, 0.01-0.02 part of light stabilizer and 0.02-0.04 part of tackifier. A precoating technique is adopted to produce the EVA packaging adhesive film, i.e. the EVA adhesive layers are coated to the upper and lower surfaces of the BOPP film layer to constitute the EVA packaging adhesive film, thereby greatly enhancing the production rate and simplifying the technique complexity degree under the support of the BOPP film. The bonding firmness between the EVA adhesive layer and BOPP film layer is enhanced, and the shock strength and environmental stress crack resistance of the adhesive film are enhanced.

Owner:ANHUI GUOFENG PLASTIC

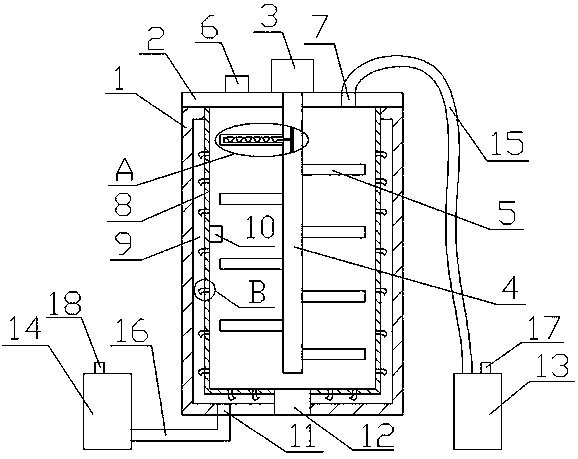

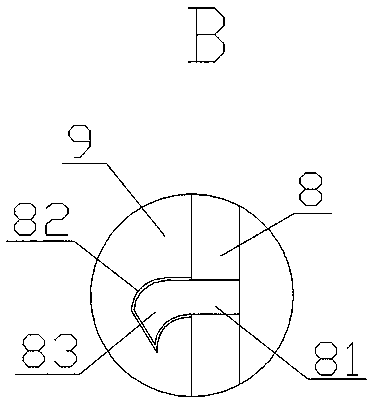

Traditional Chinese medicinal material washing and treating device

InactiveCN107855316ASimplify process complexityImprove cleaning efficiencyCleaning using liquidsHeating arrangementWater dischargeProcess complexity

The invention discloses a traditional Chinese medicinal material washing and treating device which comprises a barrel. A barrel cover is arranged over the barrel, a motor is arranged in the center ofthe upper surface of the barrel cover, a heating control device is arranged on one side of the motor, a water inlet is formed in the position, located on the other side, of the barrel cover, a rotating shaft is connected to the lower end of the motor and is fixedly provided with blades, a screen drum is fixed into the barrel, and a liquid cavity is formed between the screen drum and the barrel; and an ultrasonic wave transmitting device is further arranged on the inner wall of the screen drum, discharging openings which are through are formed in the screen drum and the middle of the bottom ofthe barrel, a water discharging opening communicated with the liquid cavity is formed in the bottom end of the barrel, and a water inlet device and a water outlet device are arranged in the exterior of the barrel. By means of the washing and treating device, the effect of removing impurities in traditional Chinese medicinal materials can be remarkably improved, the washing efficiency is high, operation is easy, washing and drying treatment can be integrated together, a mechanical structure and the traditional Chinese medicinal material treating process complexity are simplified, and the use and popularization value is achieved.

Owner:许五妮

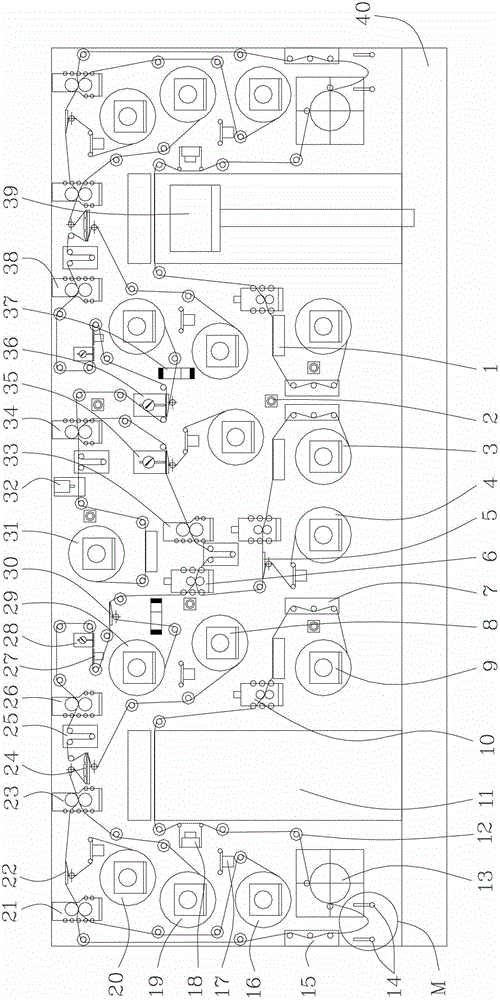

Method and device for continuous laminating of flexible thin film with multilayer structure

ActiveCN102717576AGuaranteed mechanical strengthAccurateLamination ancillary operationsControlling laminationComposite filmEngineering

The invention discloses a method for continuous laminating of flexible thin films with a multilayer structure, comprising the steps of: (1) carrying out die cutting and waste stripping treatment on a first flexible thin film and a second flexible thin film to make a protective layer on one side of each thin film be stripped and to cut rectangular incisions arranged in an array on a useful layer in the middle of each thin film; (2) taking a third flexible thin film as an intermediate layer for laminating, stripping a protective layer on one side first, then laminating the surface stripped with the first flexible thin film in the preparation stage to obtain a flexible film with a four-layer structure; and (3) stripping a protective layer on the other side of the third flexible thin film and laminating the surface stripped with the second flexible thin film in the preparation stage to obtain a composite film with a five-layer structure. The invention further discloses a device for continuous laminating of flexible thin films with a multilayer structure. With the laminating device and the technological method thereof provided by the invention, half-cut die cutting and accurate counterpoint laminating of flexible thin films with a multilayer structure can be realized effectively.

Owner:HUAZHONG UNIV OF SCI & TECH

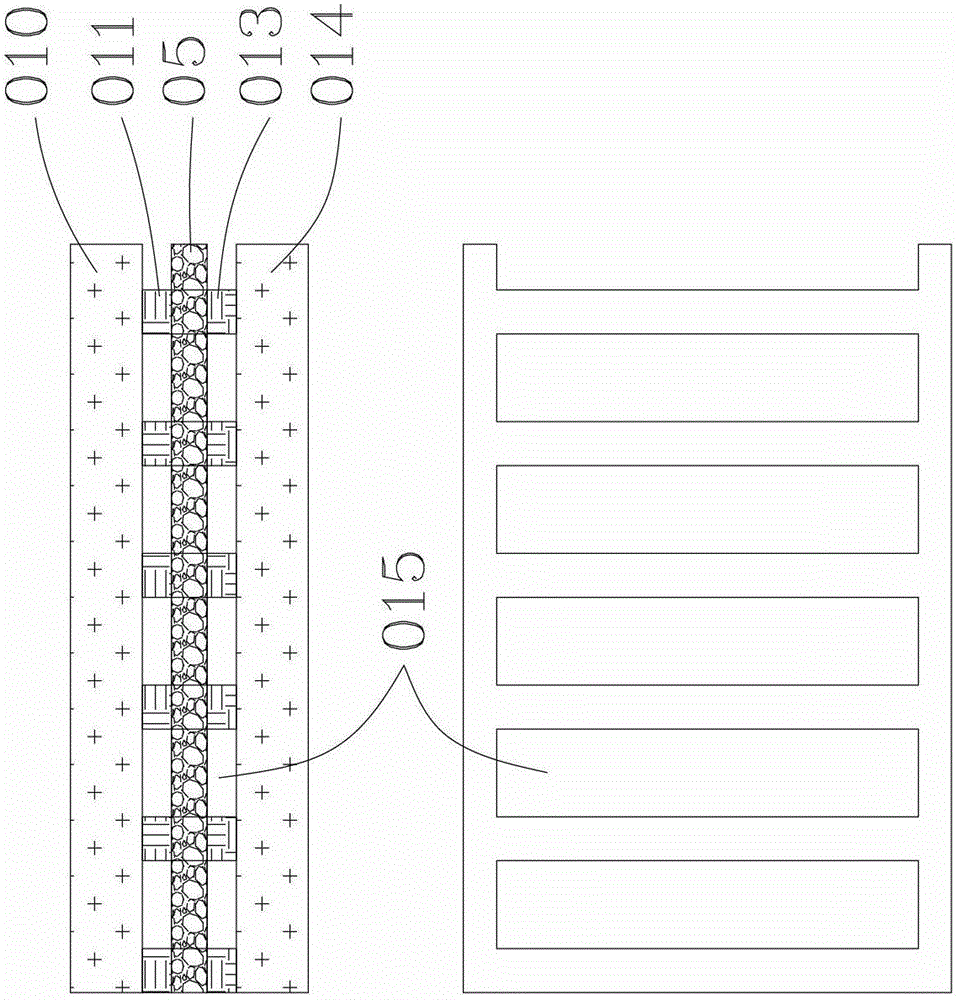

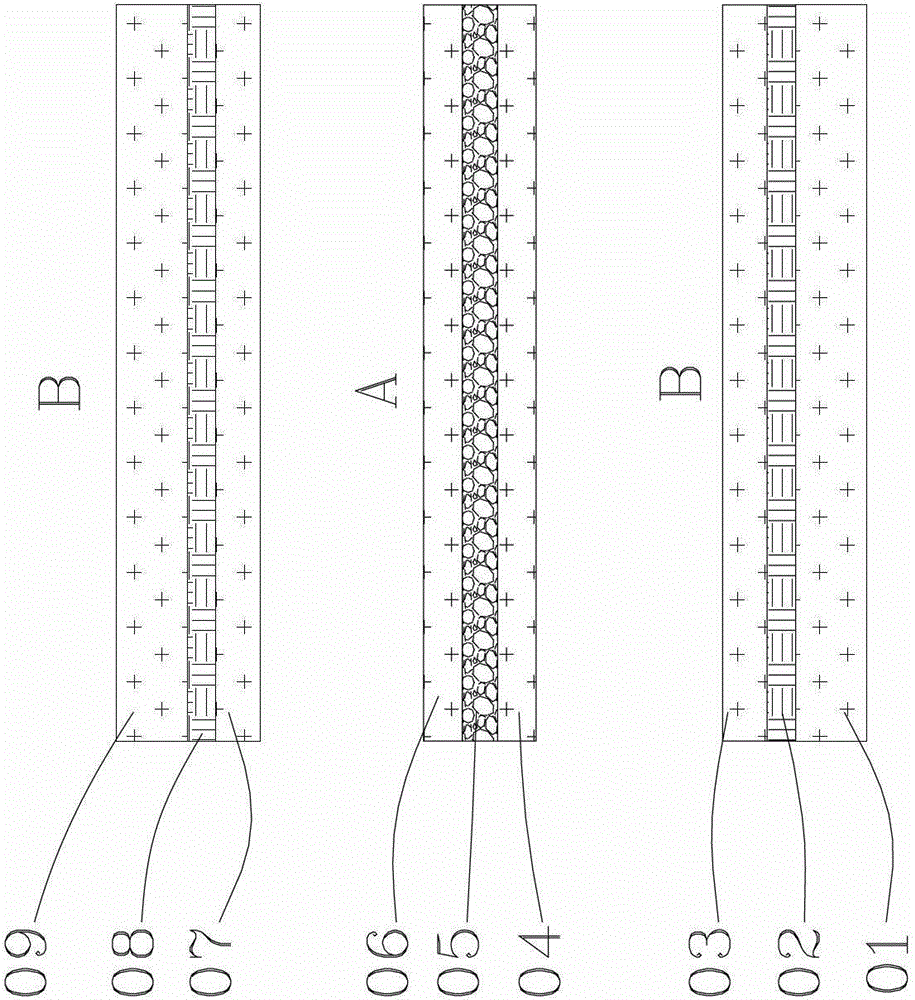

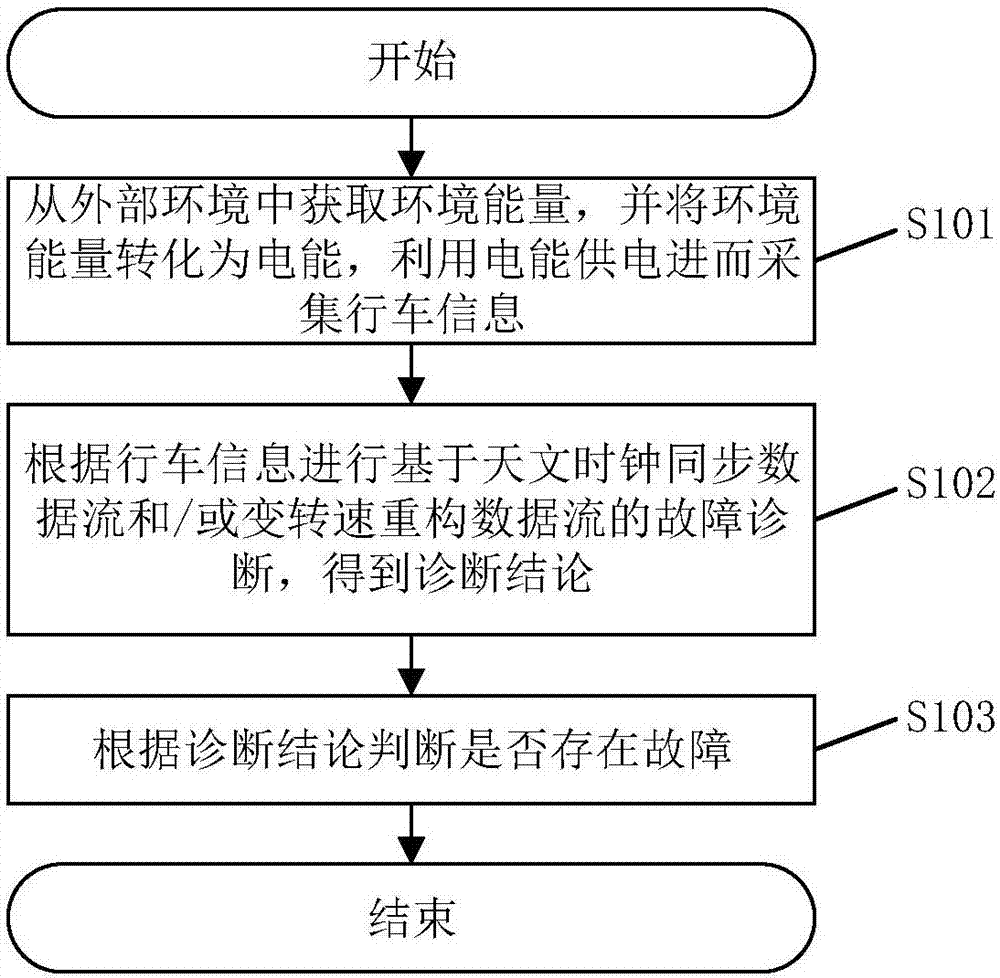

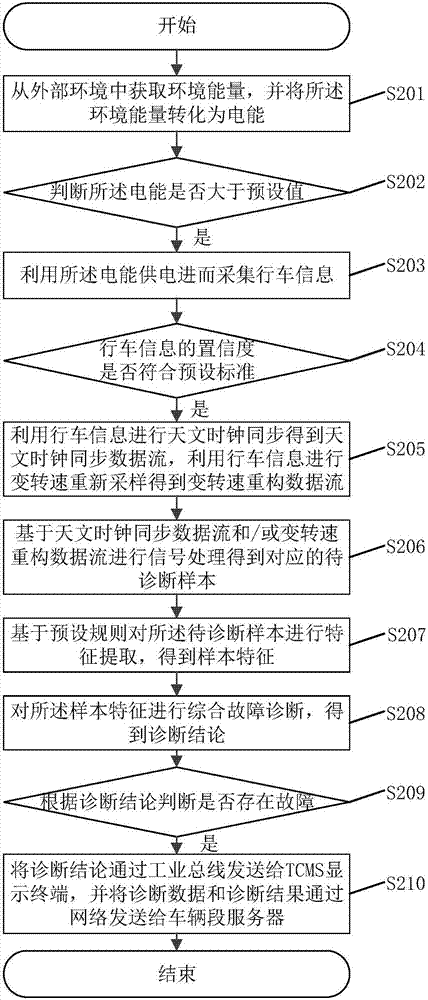

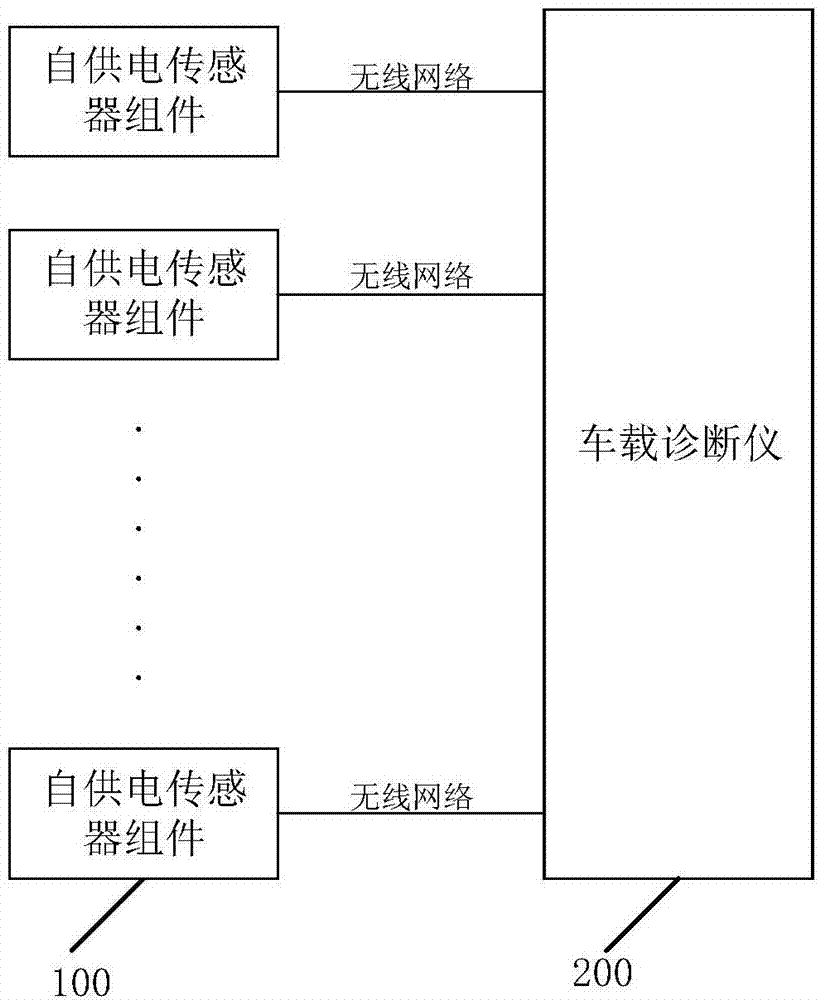

Method for acquiring and transmitting fault signals of rail traffic vehicles

PendingCN107966308AQuick installationSolve the problem that needs to be connected to the power supply by wireRailway vehicle testingAstronomical clockData stream

The invention discloses a method for acquiring and transmitting fault signals of rail traffic vehicles. The method comprises the following steps: acquiring environment energy from an external environment, and converting the environment energy into electric energy; supplying power by using the electric energy and then acquiring traveling information, and carrying out fault diagnosis according to the traveling information on the basis of astronomical clock synchronous data stream and / or variable speed reconstructed data stream to obtain a diagnosis, wherein the traveling information comprises temperature information and accelerated speed information of a diagnosis object of a vehicle traveling portion; and judging whether faults exist or not according to the diagnosis. By the method, the process complexity of product loading can be greatly simplified, and rapid retrofitting of an existing vehicle is implemented. The invention further discloses a device for acquiring and transmitting fault signals of rail traffic vehicles. The device has the foregoing beneficial effects.

Owner:TANGZHI SCI & TECH HUNAN DEV CO LTD

Manufacturing method of hollow nanotube structure

InactiveCN102616730AReduce manufacturing costIncrease optionalityDecorative surface effectsNanotechnologyNanowireNanometre

The invention discloses a manufacturing method of a hollow nanotube structure, comprising the following steps: preparing a substrate; forming a crystal seed layer on the substrate first, then generating a nanowire with a predetermined dimension on the crystal seed layer at relatively low temperature by using hydrothermal method; forming an outer coating layer on the surface of the nanowire; selectively etching the top of the outer coating layer to expose the top of the nanowire; and removing the whole nanowire and keeping the hollow outer coating layer to form a plurality of hollow nanotubes. The method is beneficial to simplify the nanotube technology, improve the dimension precision of the nanotubes and improve the photoelectric properties of elements.

Owner:NAT CHENG KUNG UNIV

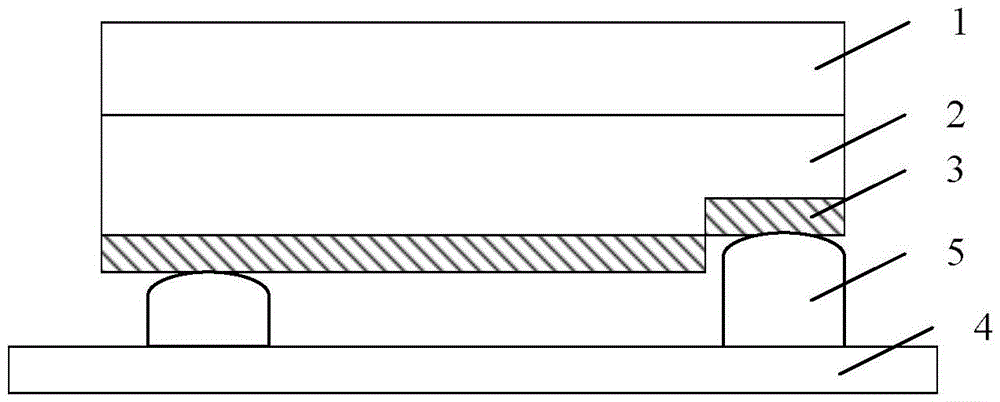

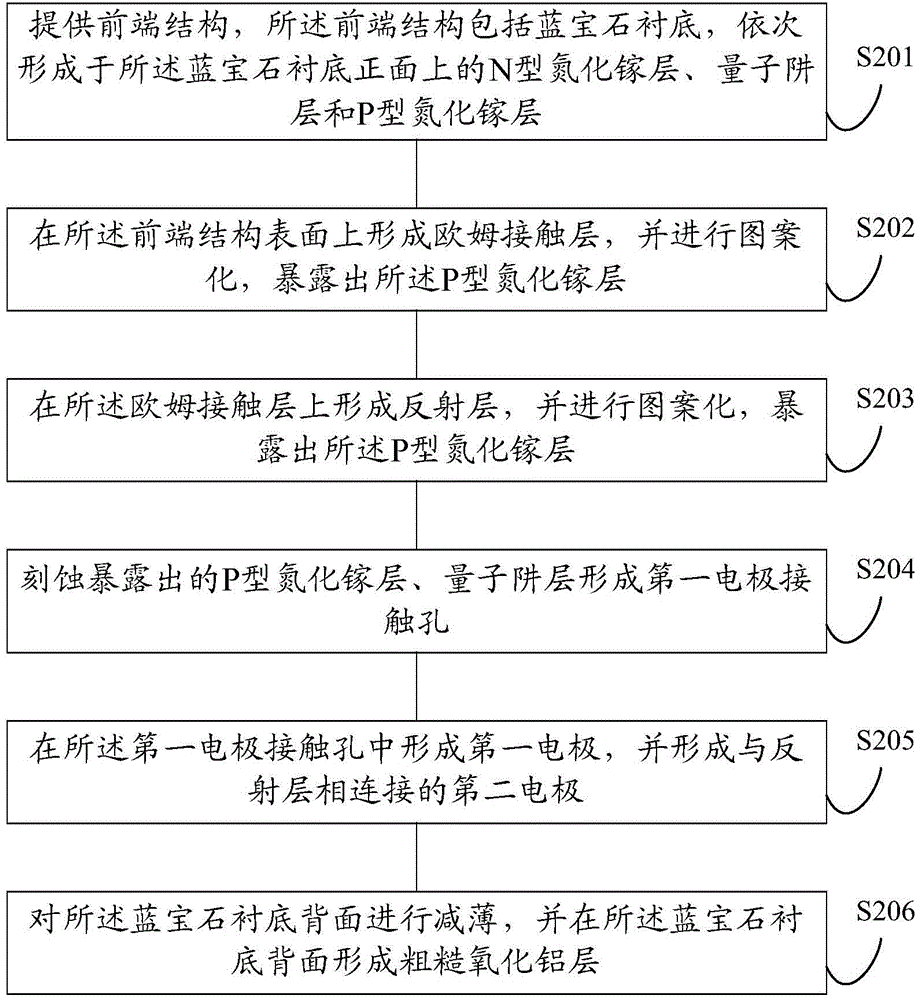

Flip LED chip and manufacturing method thereof

InactiveCN104868021ASurface roughening light extraction efficiencyImprove light extraction efficiencySemiconductor devicesGallium nitrideRough surface

The invention discloses a flip LED chip and a manufacturing method thereof. A front-end structure containing a sapphire substrate, an N type gallium nitride layer, a quantum well layer, and a P type gallium nitride layer is provided, wherein the N type gallium nitride layer, the quantum well layer, and the P type gallium nitride layer are formed on the front side of the sapphire substrate; an ohmic contact layer and a reflecting layer are formed on the front-end structure; a first electrode connecting the N type gallium nitride layer and a second electrode connecting the reflecting layer are formed; and reduction processing is carried out on the back side of the sapphire substrate and a rough aluminium oxide layer is formed. Compared with the prior art, because of the aluminium oxide layer with the rough surface and the material consistent with the substrate material, an effect of improvement of the luminous efficiency based on surface roughening is realized; and defects of great influence on the front side and high cost in the prior art can be overcome. Therefore, the preparation cost is low; the process complexity is low; and the large-scale mass production can be realized easily.

Owner:ENRAYTEK OPTOELECTRONICS

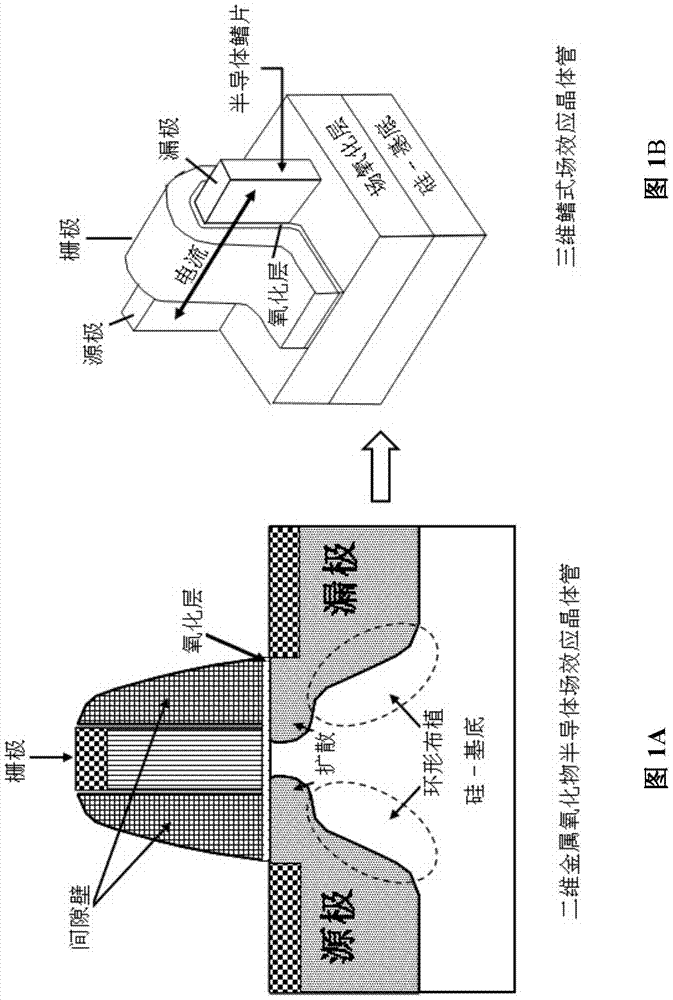

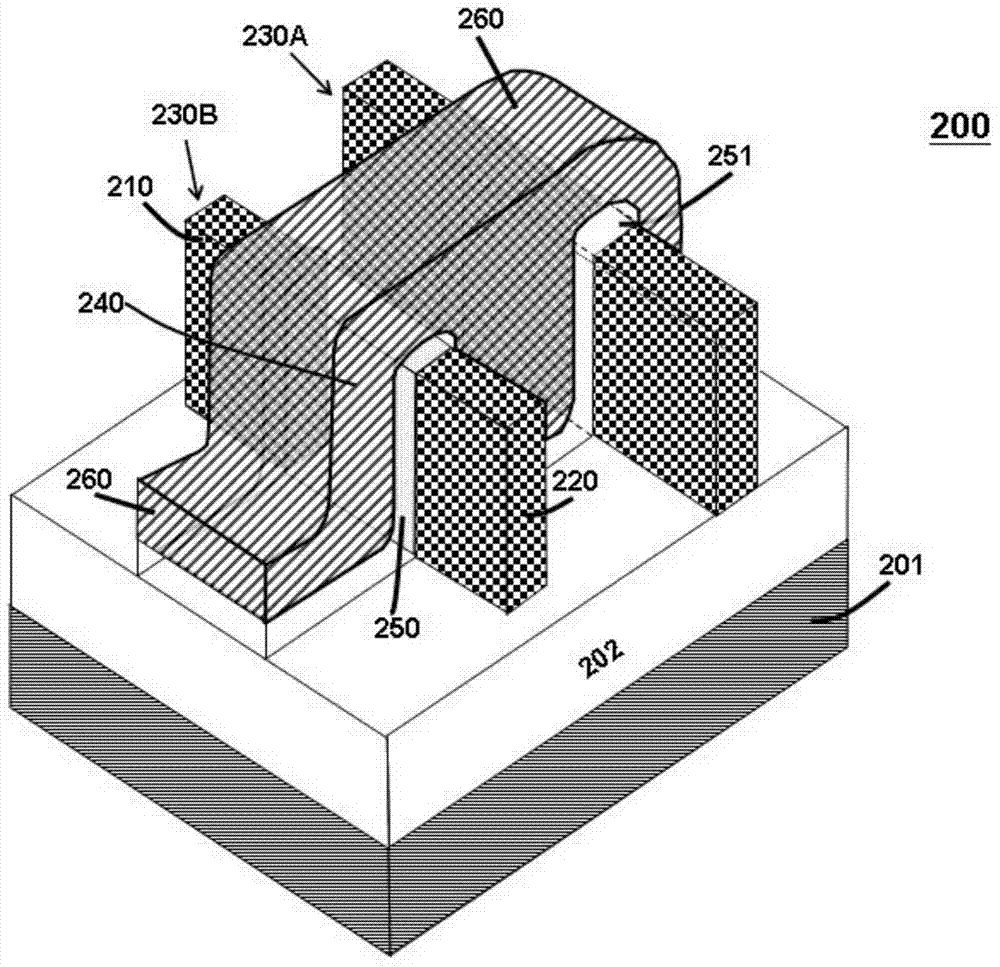

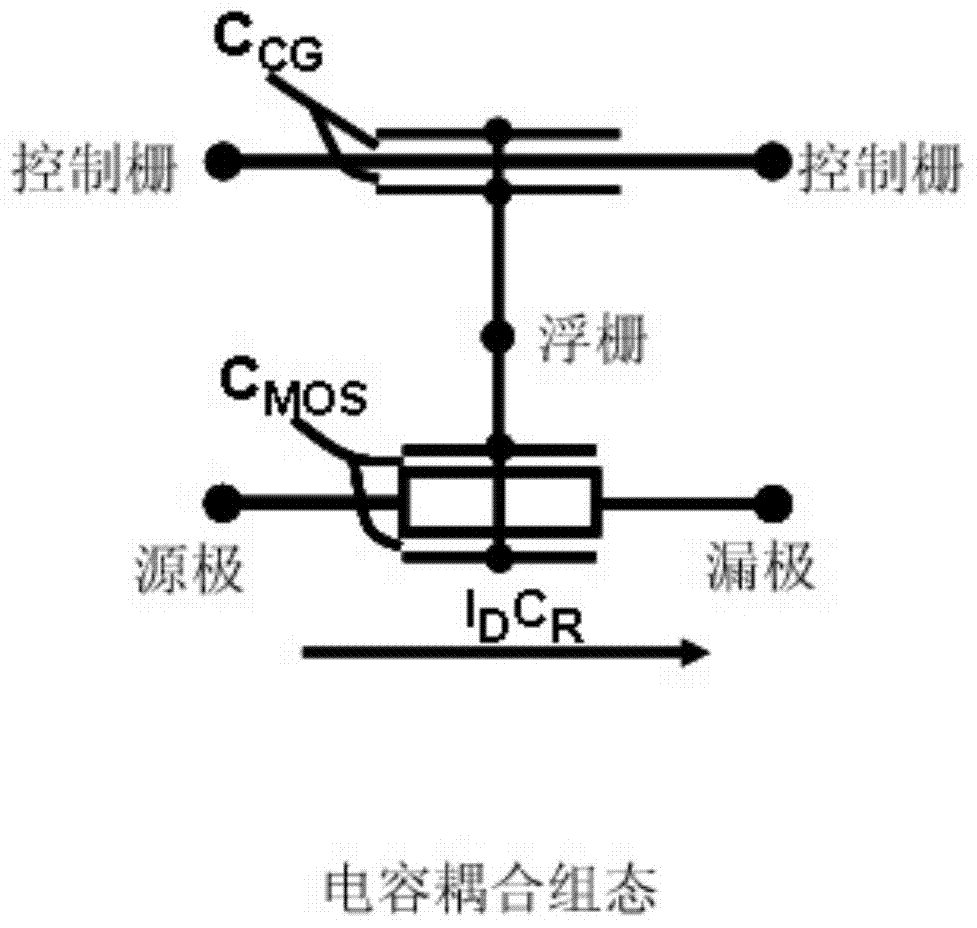

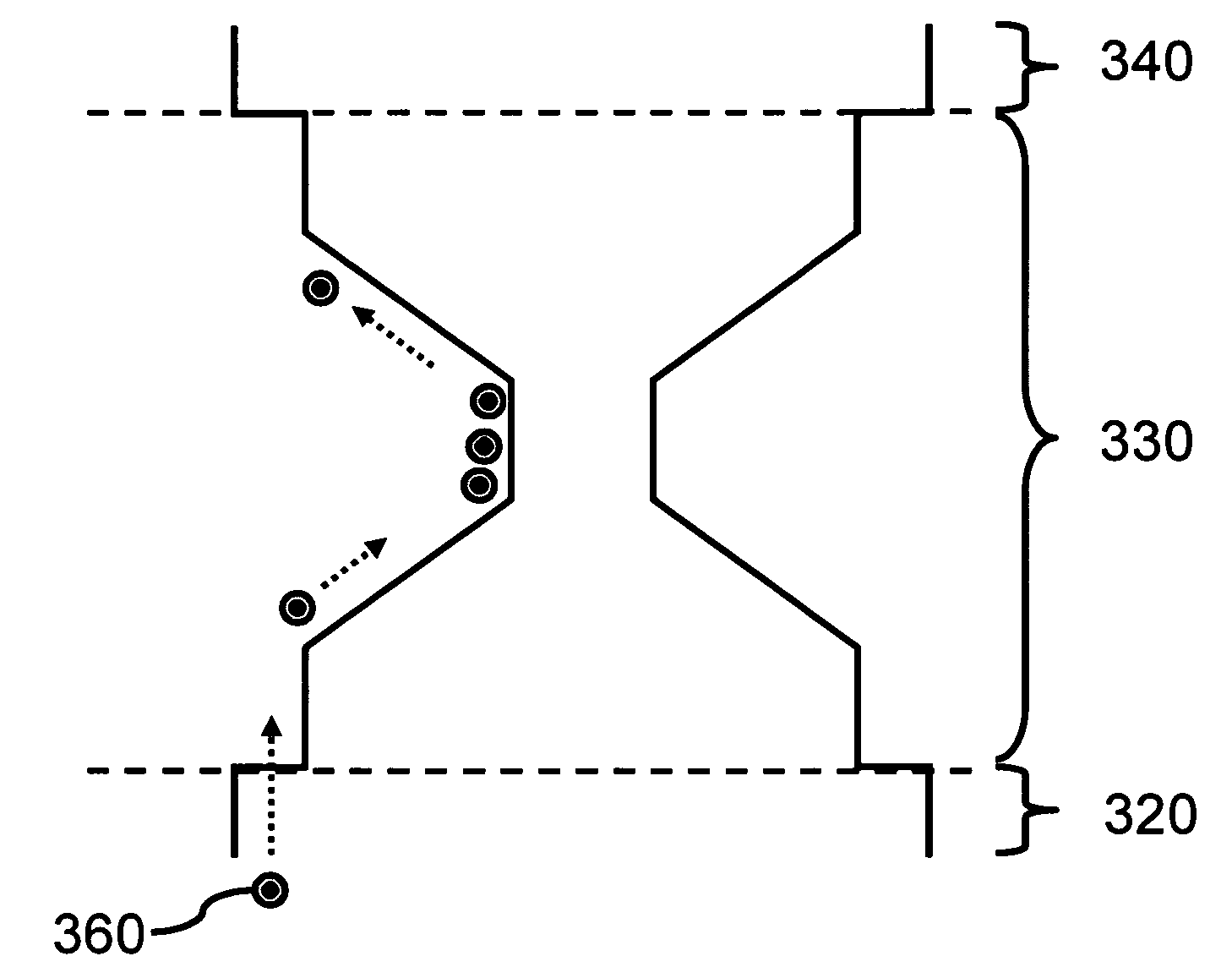

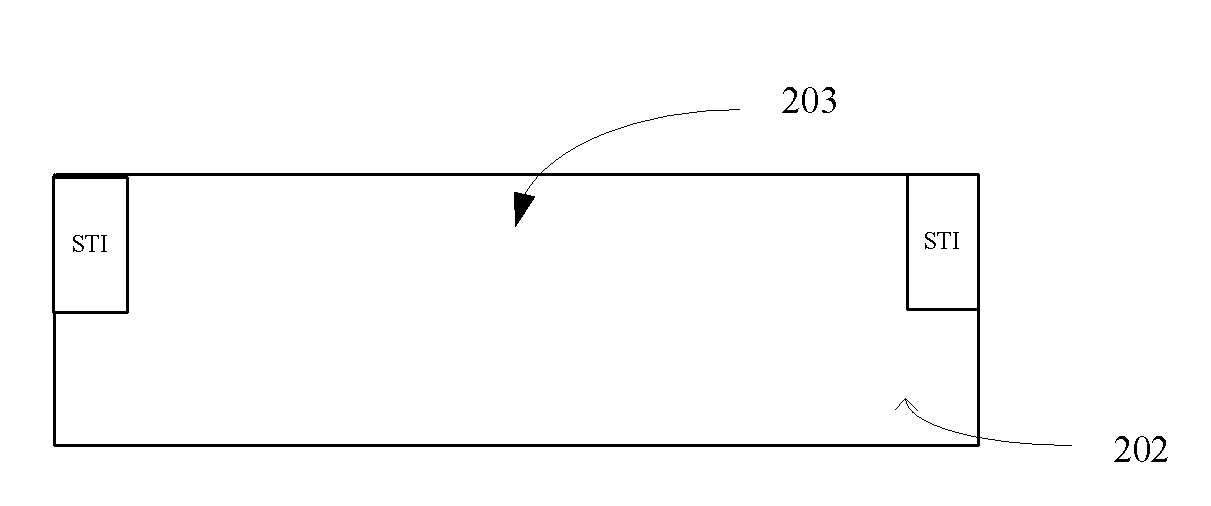

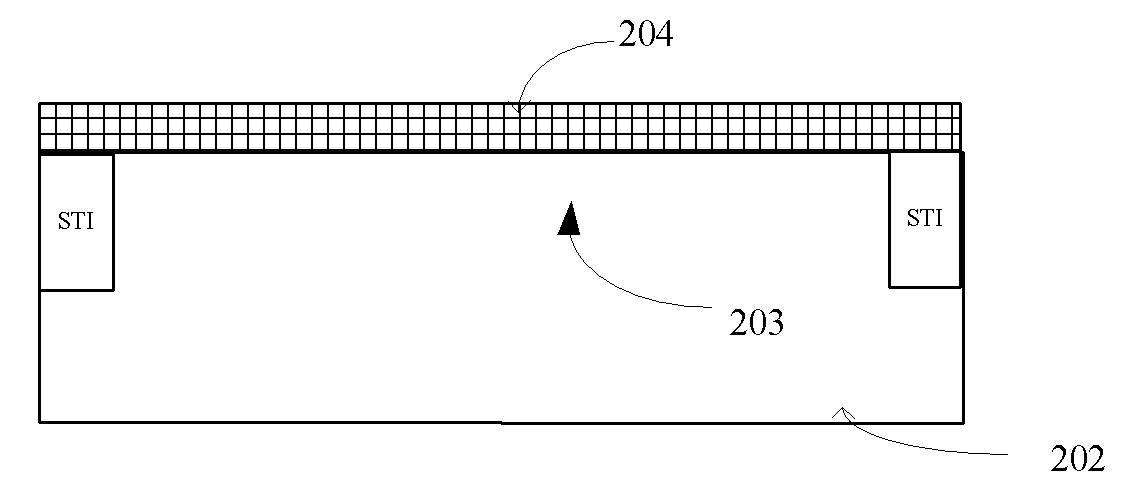

3-D single floating gate non-volatile memory device

ActiveCN103715198ALow costSimplify process complexitySolid-state devicesSemiconductor devicesDielectricMOSFET

A 3-D Single Floating Gate Non-Volatile Memory (SFGNVM) device based on the 3-D fin Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET) is disclosed. The disclosed Non-Volatile Memory (NVM) device consists of a pair of semiconductor fins and one floating metal gate. The floating metal gate for storing electrical charges to alter the threshold voltage of the fin MOSFET crosses over the pair of semiconductor fins on top of coupling and tunneling dielectrics above the surfaces of the two semiconductor fins. One semiconductor fin with the same type impurity forms the control gate of the non-volatile memory device. The other semiconductor fin is doped with opposite type of impurity in the channel regions under the metal floating gate and with the same type of impurity in the source and drain regions on the sides of the crossed metal floating gate.

Owner:XINLIJIA INTEGRATED CIRCUIT (HANGZHOU) CO LTD

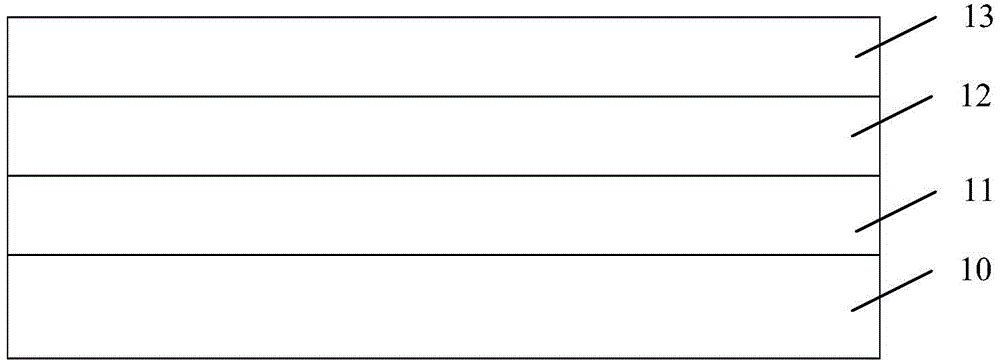

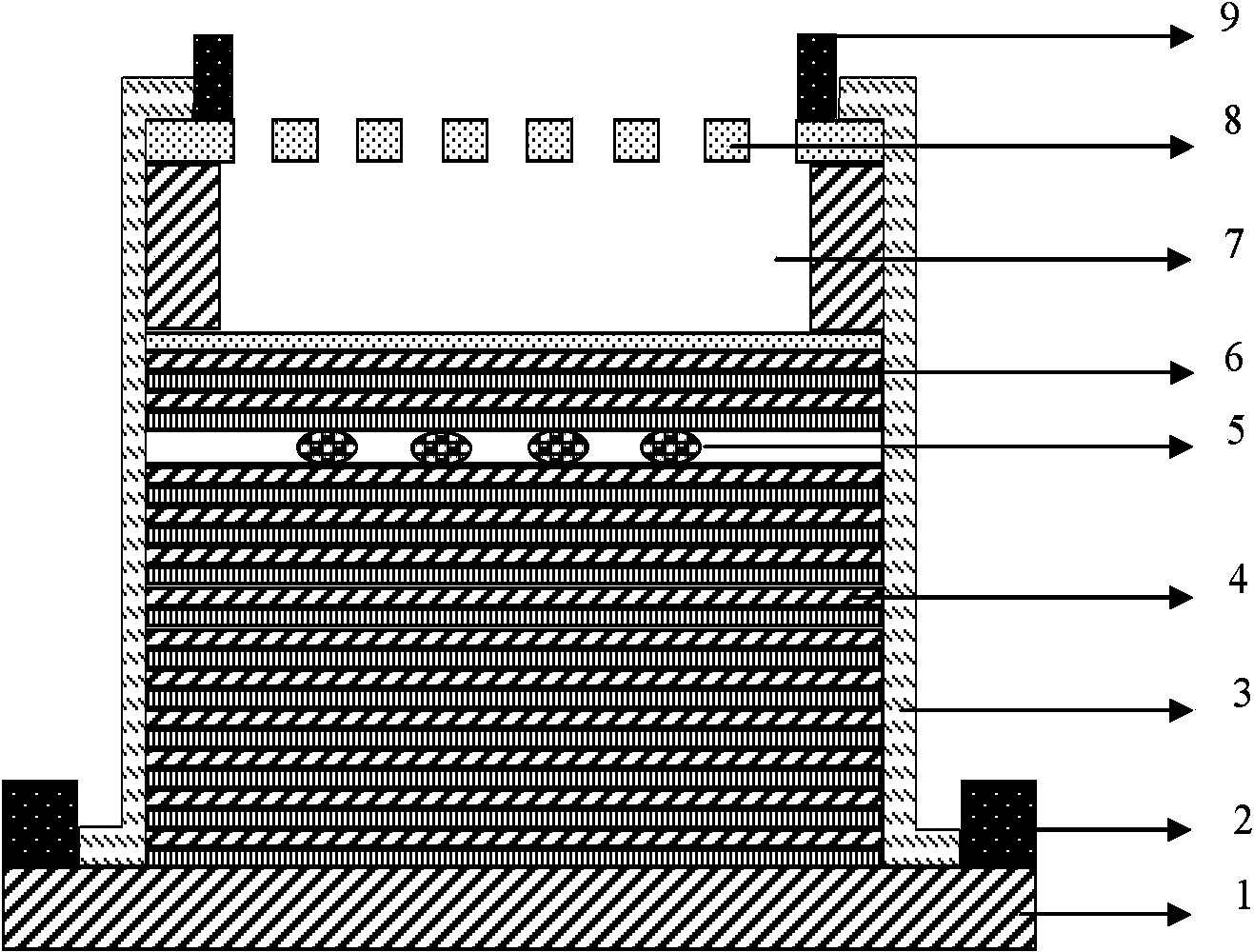

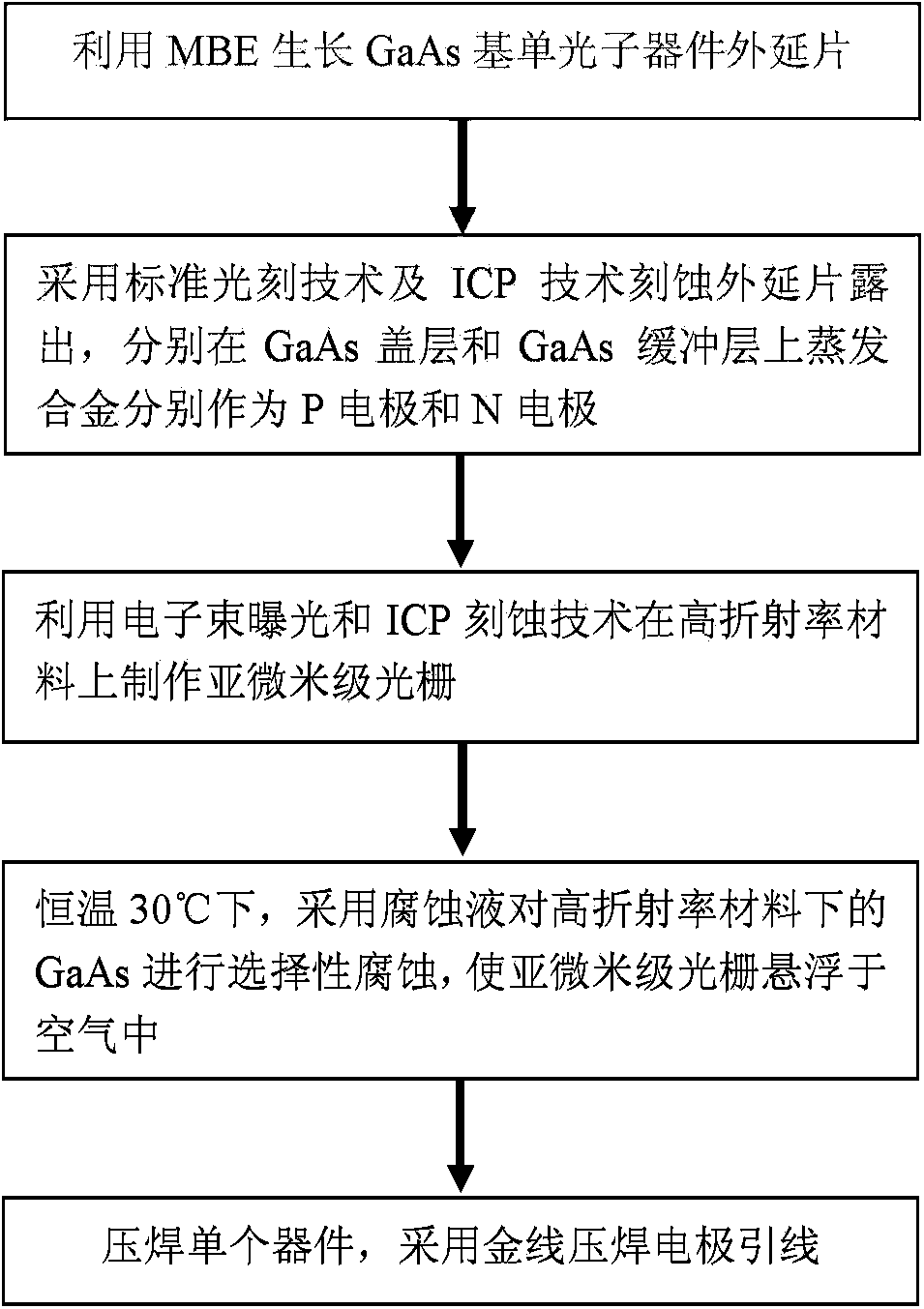

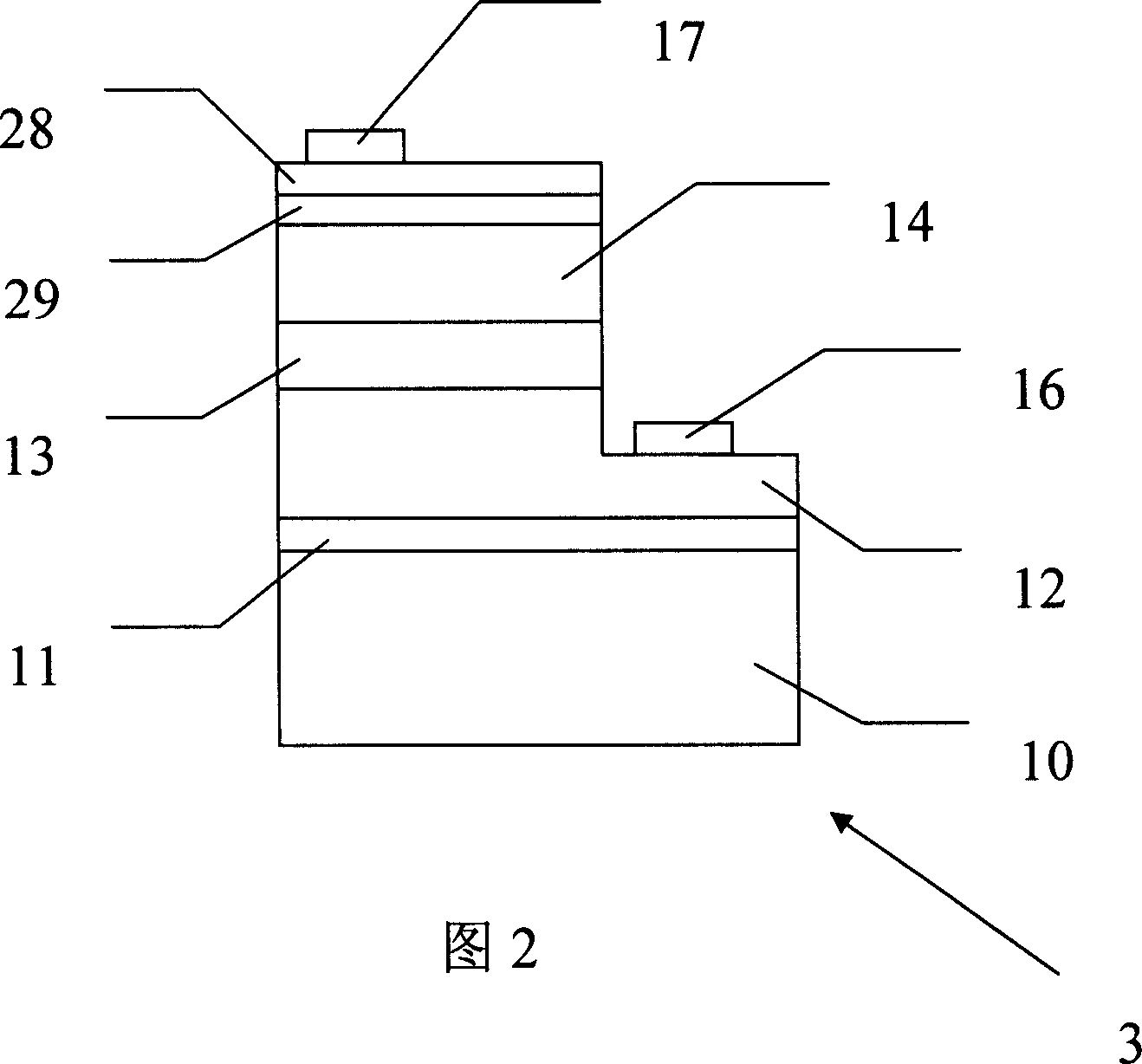

Single photon emitter and manufacturing method thereof based on high refractive index contrast grating structure

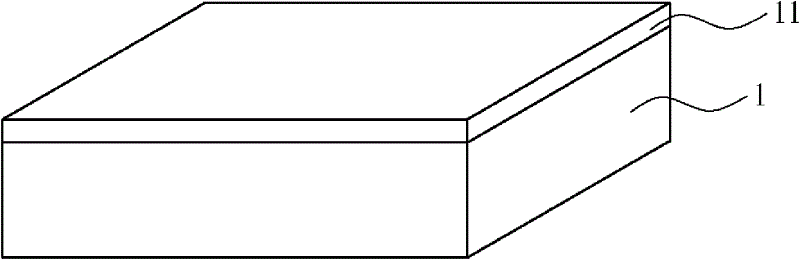

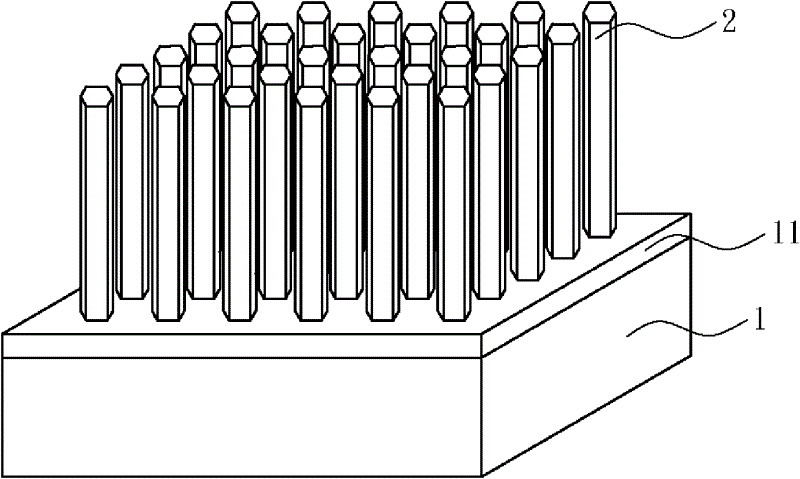

ActiveCN103532010AReduce difficultySave growth source materialLaser detailsSemiconductor lasersPhysicsQuantum dot

The invention discloses a single photon emitter and a manufacturing method thereof based on a high refractive index contrast grating structure. The single photon emitter comprises a GaAs substrate, wherein an epitaxial wafer is prepared on the GaAs substrate, and comprises a GaAs buffer layer (1), DBR (Distributed Bragg Reflector) layers (4) and (6), an InAs quantum dot active area (5) and a high refractive index contrast grating (a low refractive index material (7) and a high refractive index material (8)) sequentially from the bottom up. The GaAs buffer layer is etched and exposed on the epitaxial wafer by adopting a standard photetching technology and an ICP (Inductively Coupled Plasma) technology to serve as an N-type ohmic contact layer, and then alloys are evaporated on the high refractive index material and the GaAs buffer layer respectively to serve as a P-type electrode and an N-type electrode. The submicron grating is manufactured on the high refractive index material by utilizing electron beam exposure and the ICP etching technology; a material of the lower layer of the grating is selectively corroded by utilizing a corrosive liquid; and a low refractive index air layer is obtained.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Method for fabricating solid electrolytic capacitors

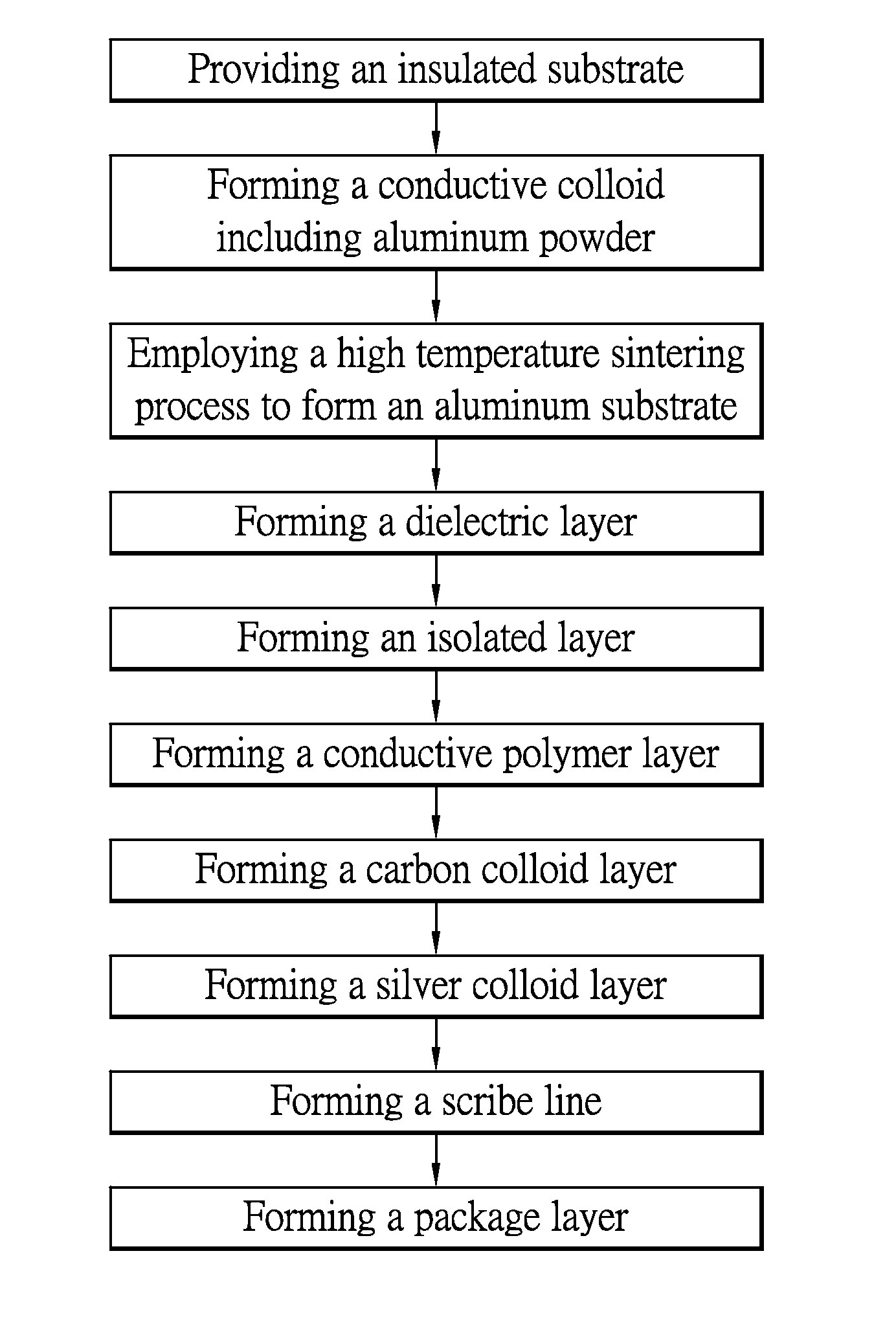

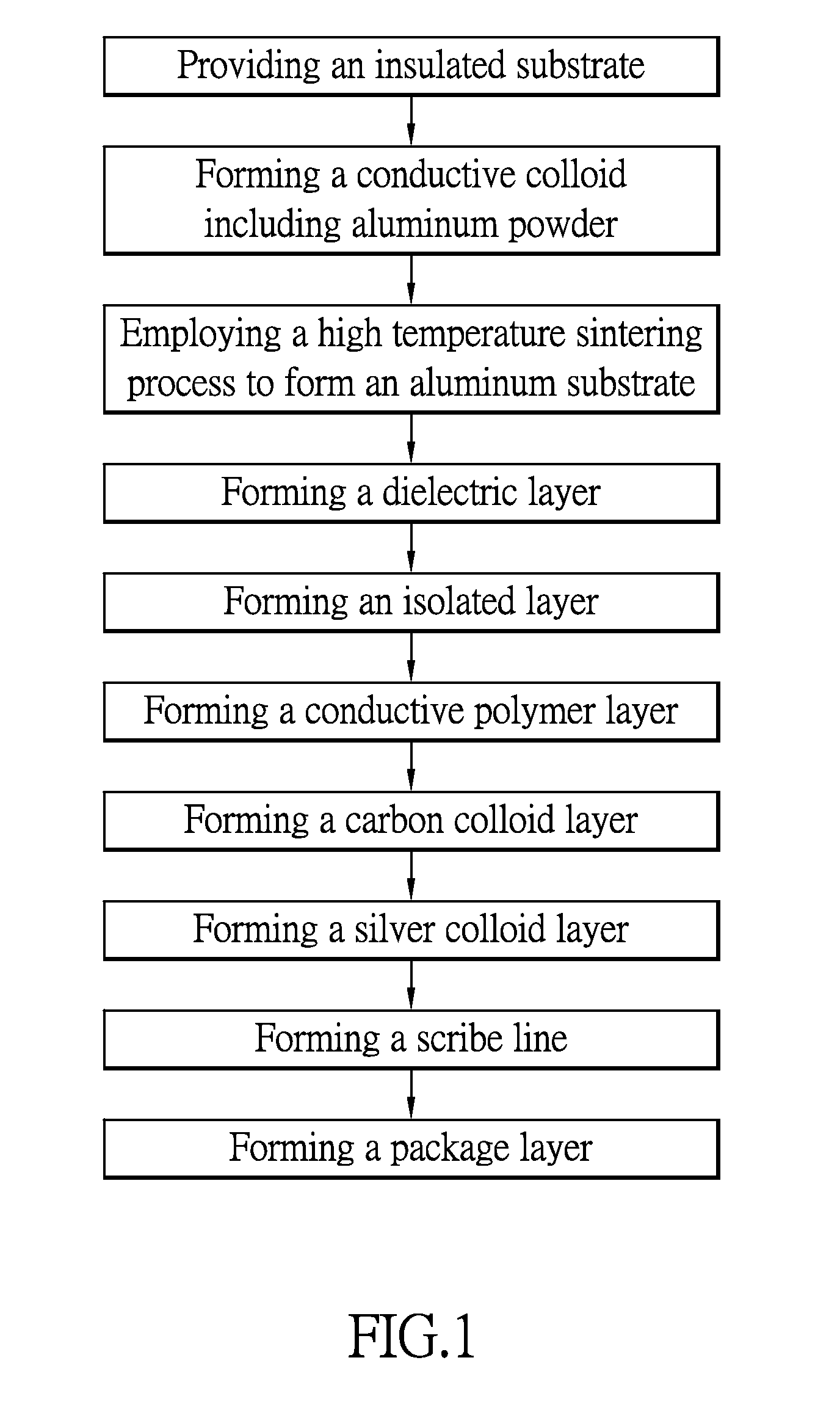

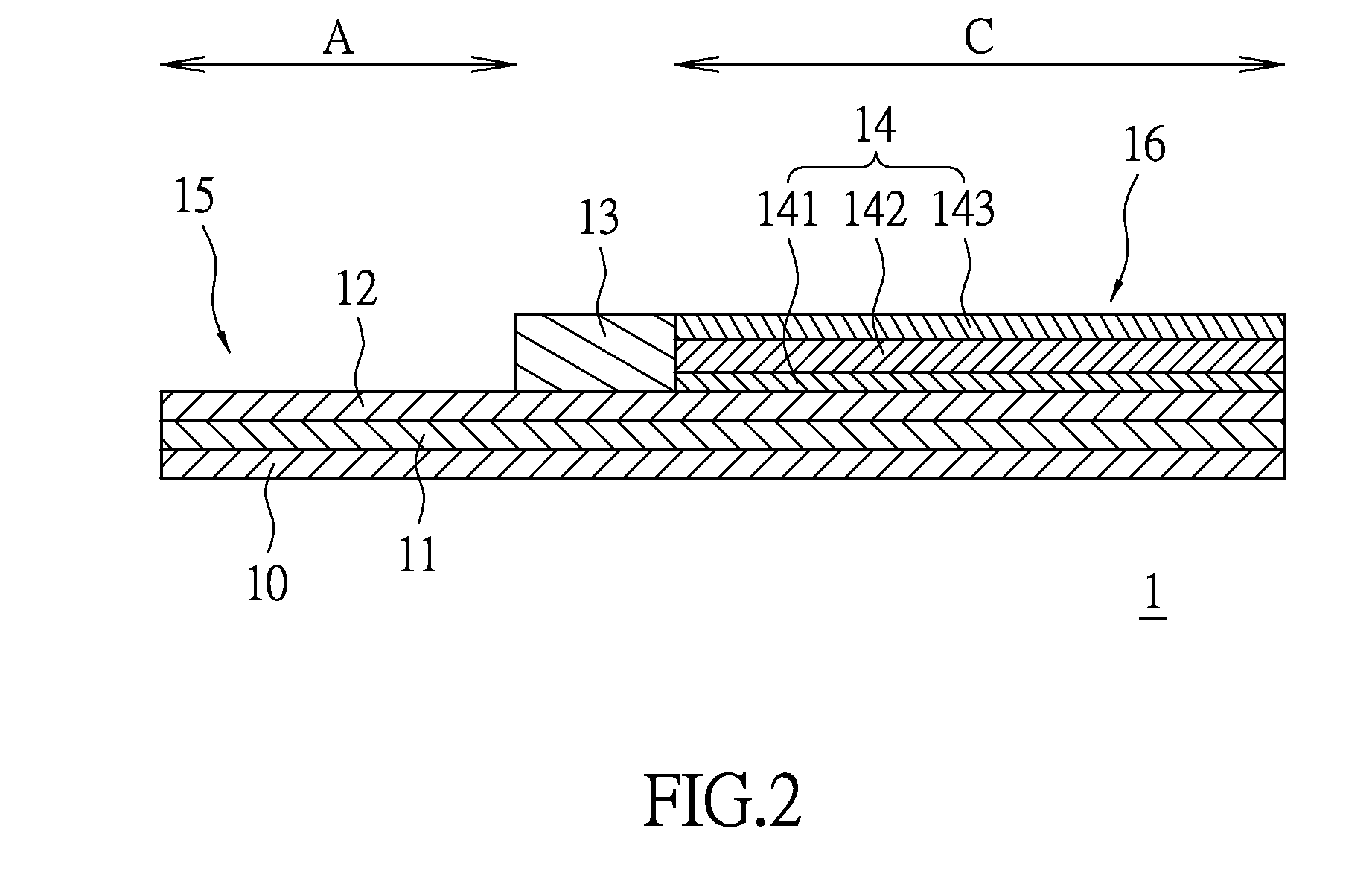

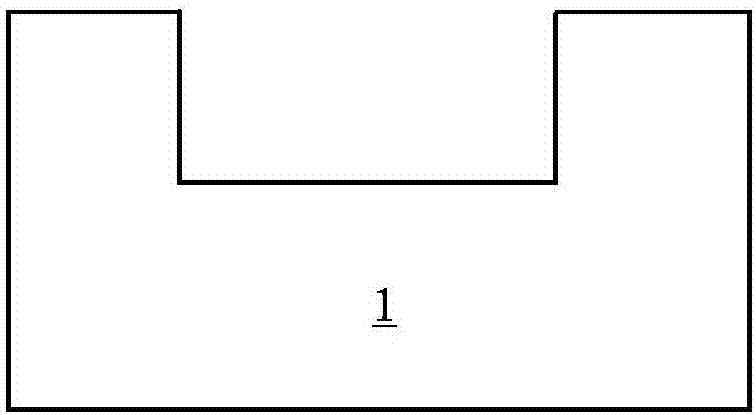

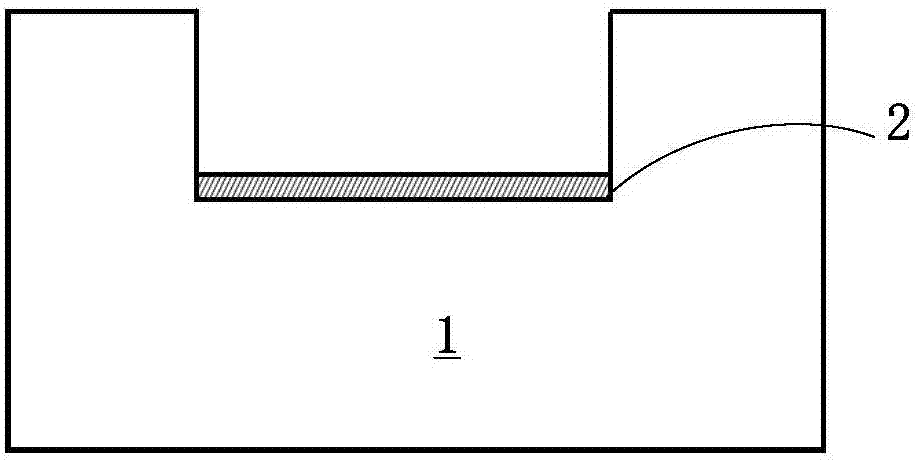

ActiveUS20140259580A1Simplify process complexityReduce manufacturing costSolid electrolytic capacitorsCapacitor dielectric layersMetallurgyIsolation layer

The instant disclosure relates to an improved method for the production of solid electrolytic capacitor, comprising the following steps. First, provide an insulating substrate. Next, form a plurality of conducting gels including aluminum powder on the insulating substrate. Thirdly, execute a high-temperature sintering process to metalize the conducting gels to form a plurality of aluminum plates. Next, form a dielectric layer on every aluminum plate. Then form an isolation layer on every dielectric layer to define an anodic region and a cathodic region. Lastly, form a conductive layer on the dielectric layer of every cathodic region, thus defining a solid electrolytic capacitor unit.

Owner:APAQ TECH

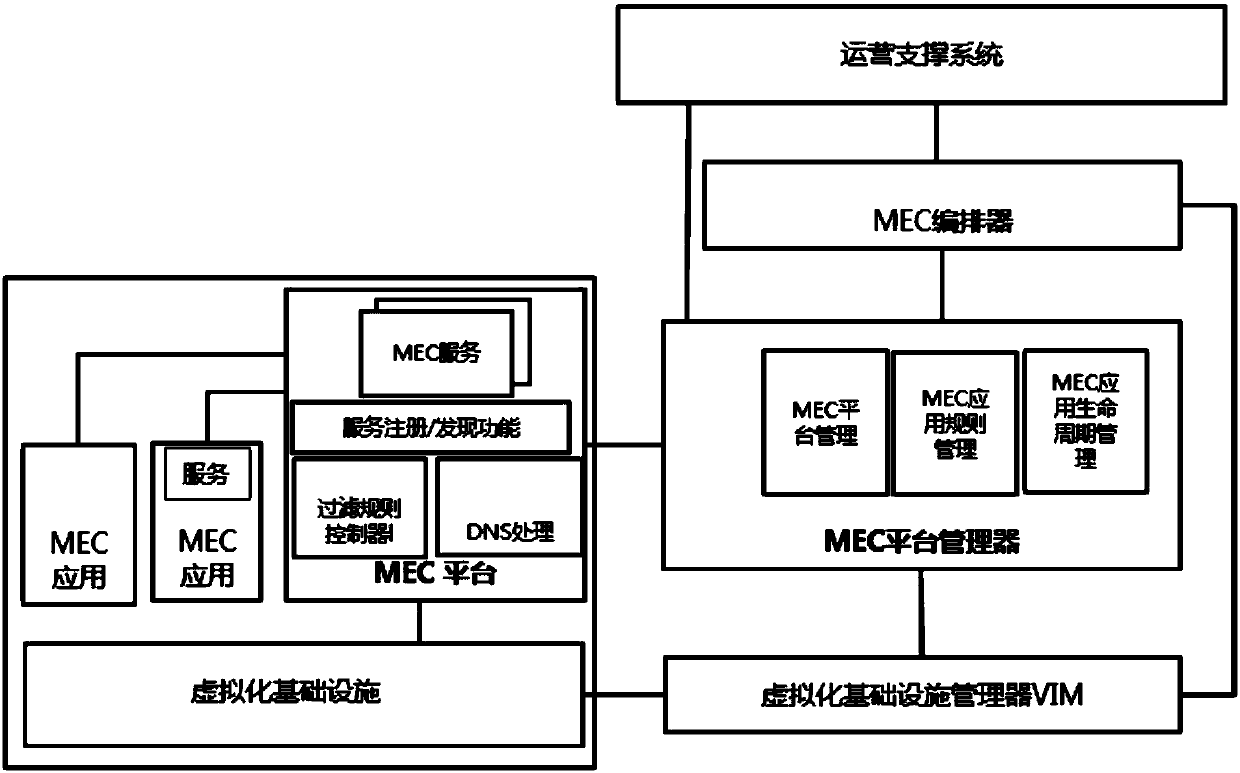

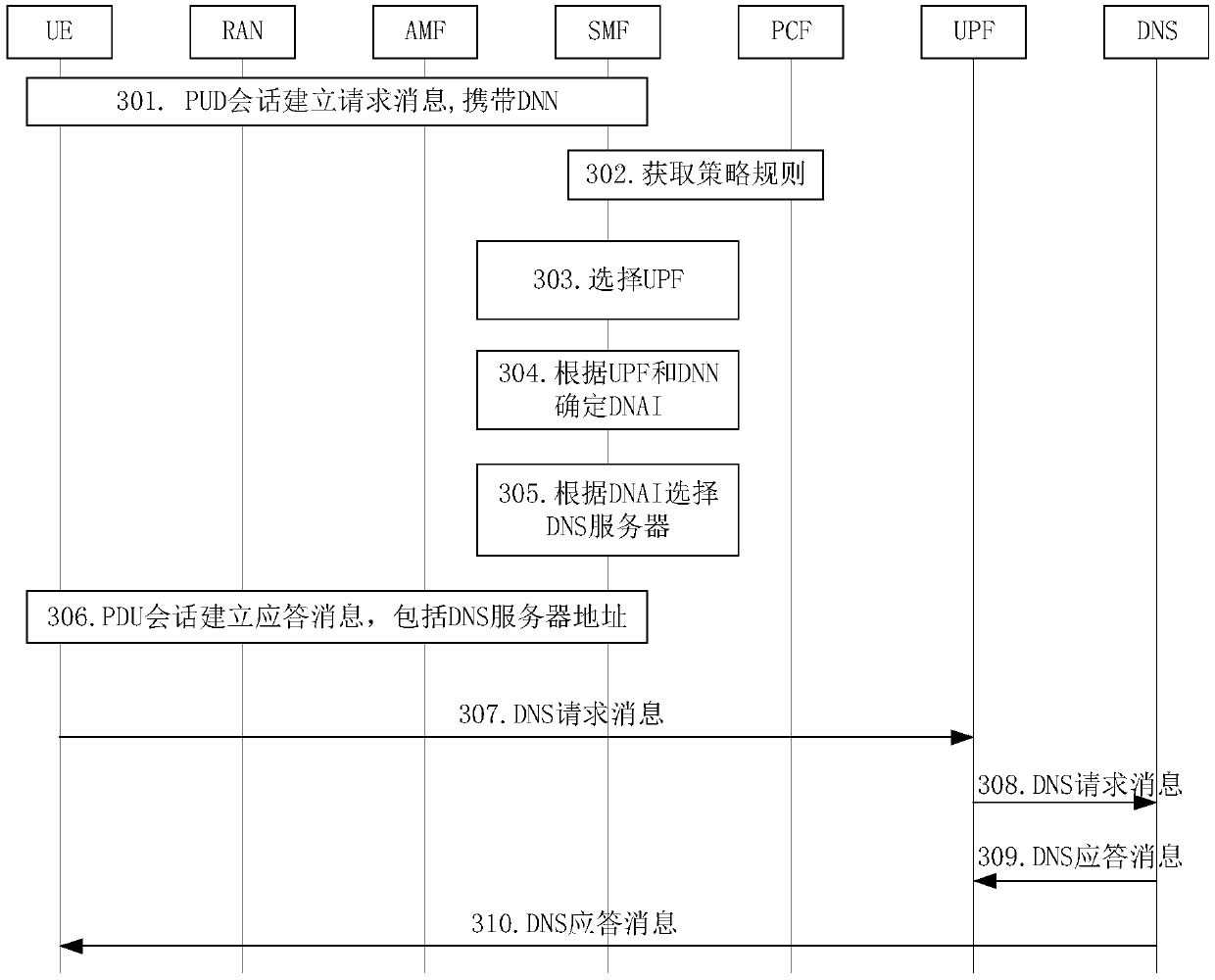

Domain name server distribution method and device

ActiveCN111385369AImprove processing efficiencySimplify process complexityTransmissionNetwork data managementDomain nameSession management

The invention provides a domain name system DNS server distribution method, device and system, and the method comprises that: a session management function SMF receives a session establishment requestmessage sent by terminal UE, and the request message comprises the name of a data network to be accessed by the UE; the SMF acquires a first DNS server IP address according to the data network name and the geographic position of the UE; and the SMF sends a session establishment response message to the UE, wherein the response message comprises the first DNS server IP address. The scheme is mainlyused in a 3GPP core network, and the 3GPP core network can dynamically allocate a DNS server located in a local data network to the UE according to the position of the local network accessed by the UE.

Owner:HUAWEI TECH CO LTD

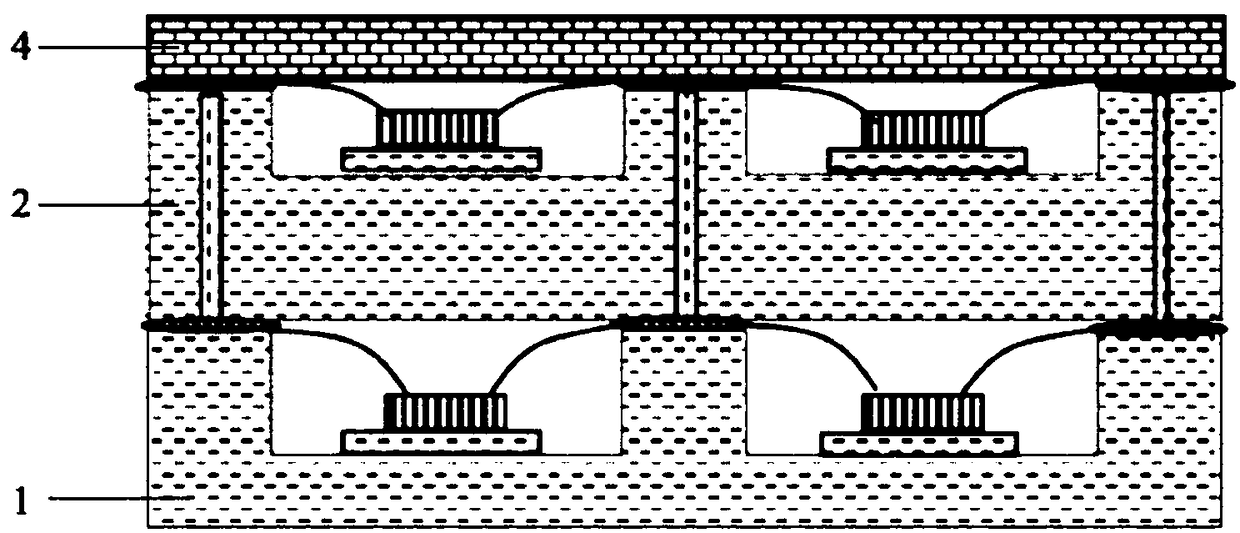

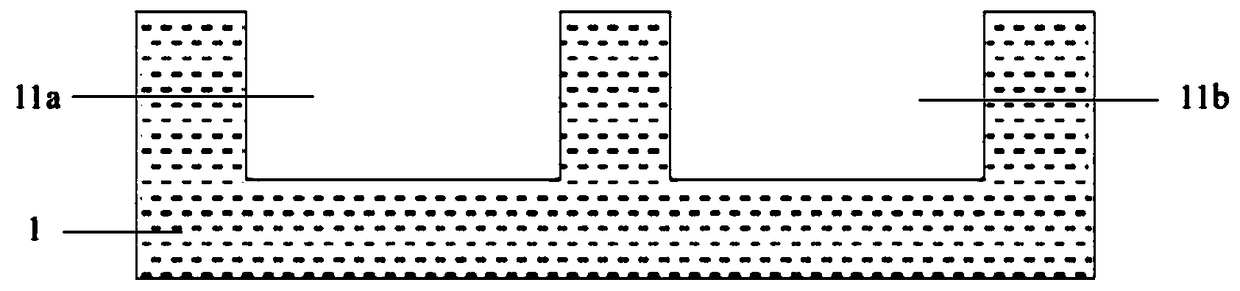

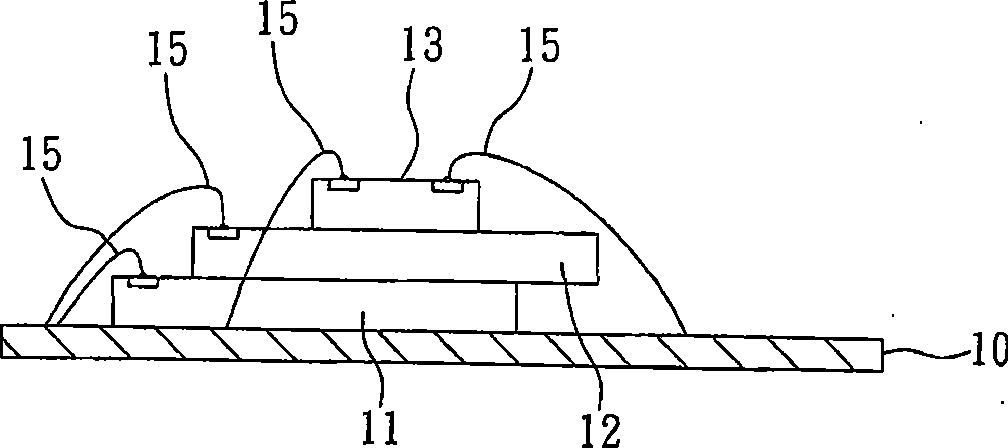

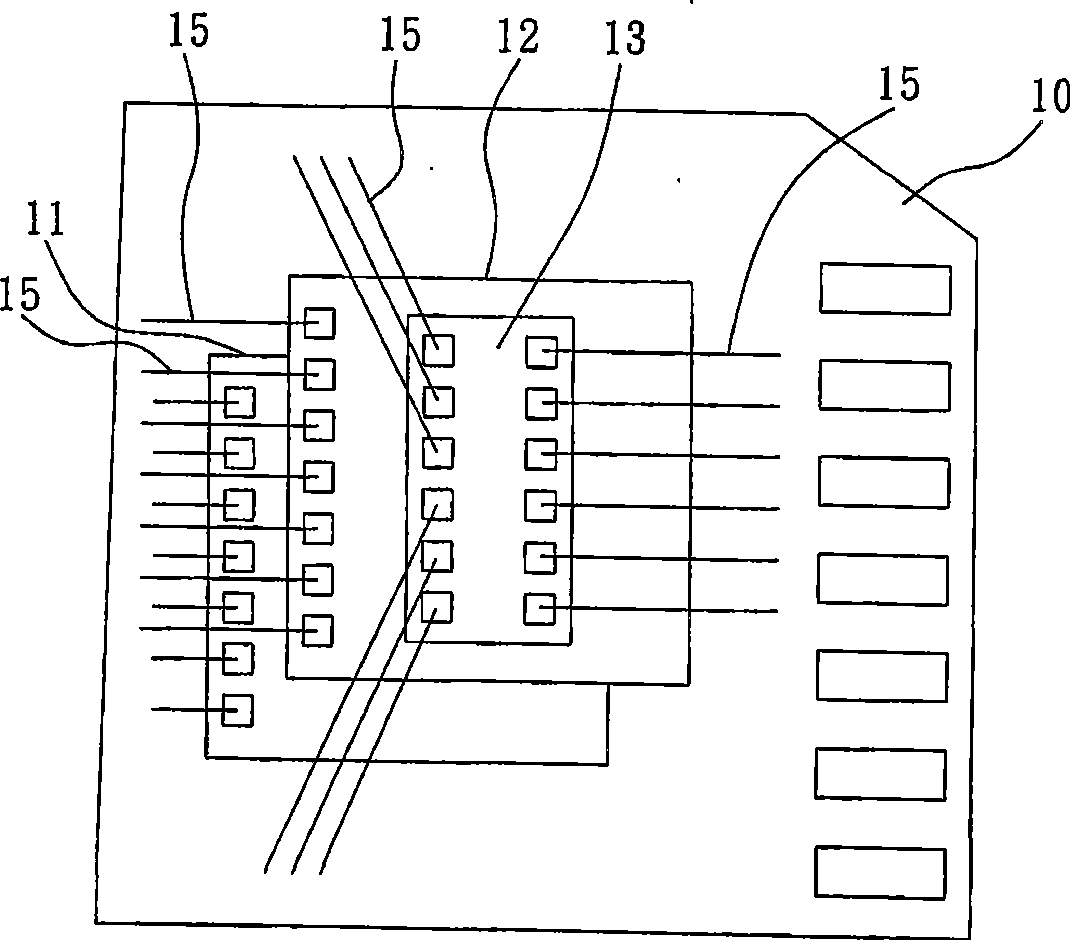

Multi-chip package interconnection structure and multi-chip package interconnection method

PendingCN109326580AHighly integratedImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesHigh densityMicrowave

The invention discloses a multi-chip package interconnection structure, which comprises a first substrate and a second substrate which are superposed, wherein a plurality of first cavities are arranged on the first substrate; a plurality of first chips are arranged in the first cavities; the first surface of the first substrate is provided with a first pad; the first pad is electrically connectedto the first chips; a plurality of second cavities are formed in the second substrate; a plurality of second chips are arranged in the second cavities; the upper surface of the second substrate is provided with a second pad; the second pad is electrically connected to the second chips; the first pad and the second pad are electrically connected by a conductive medium penetrating the second substrate. The multi-chip package interconnection structure disclosed by the invention adopts a direct soldering method to realize the vertical interconnection of the substrates, so that multi-chip package is high in integration degree, good in reliability, simple in process and low in cost; microwave radio frequency signal insertion loss does not exceed 0.5 dB, which can solve the problem of high-density vertical interconnection of the substrates; and the multi-chip package interconnection structure is widely used in a multi-chip package system of a radio frequency microwave circuit.

Owner:中国科学院苏州纳米技术与纳米仿生研究所南昌研究院

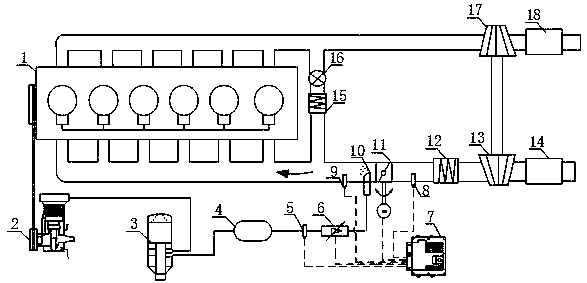

Intelligent pneumatic supercharging device with adjustable injection pressure

InactiveCN108843445AFast response timeFine pressure regulationInternal combustion piston enginesEngine controllersClosed loopEngineering

The invention relates to an intelligent pneumatic supercharging device with the adjustable injection pressure. The intelligent pneumatic supercharging device with the adjustable injection pressure comprises a compressed air tank (4), an electronic control unit (7), a nozzle (10) and a pneumatic supercharging valve (11), wherein the nozzle (10) is arranged on the pneumatic supercharging valve (11)and faces the engine inlet direction; an outlet of the compressed air tank (4) is connected with the nozzle (10); a pressure adjusting valve (6), or a proportional electromagnetic valve, or an electric ball valve is arranged on a pipeline for connecting the compressed air tank (4) and the nozzle (10); a pressure sensor I (5) is arranged at the outlet of the compressed air tank (4); the pressure sensor I (5) and the pneumatic supercharging valve (11) are electrically connected with the electronic control unit (7); and the pressure adjusting valve (6), or the proportional electromagnetic valve,or the electric ball valve is electrically connected with the electronic control unit (7). The more-refined air inlet pressure closed-loop adjustment is realized, the optimal air inflow under the current working condition is provided for an engine, and the control quality is improved.

Owner:DONGFENG COMML VEHICLE CO LTD

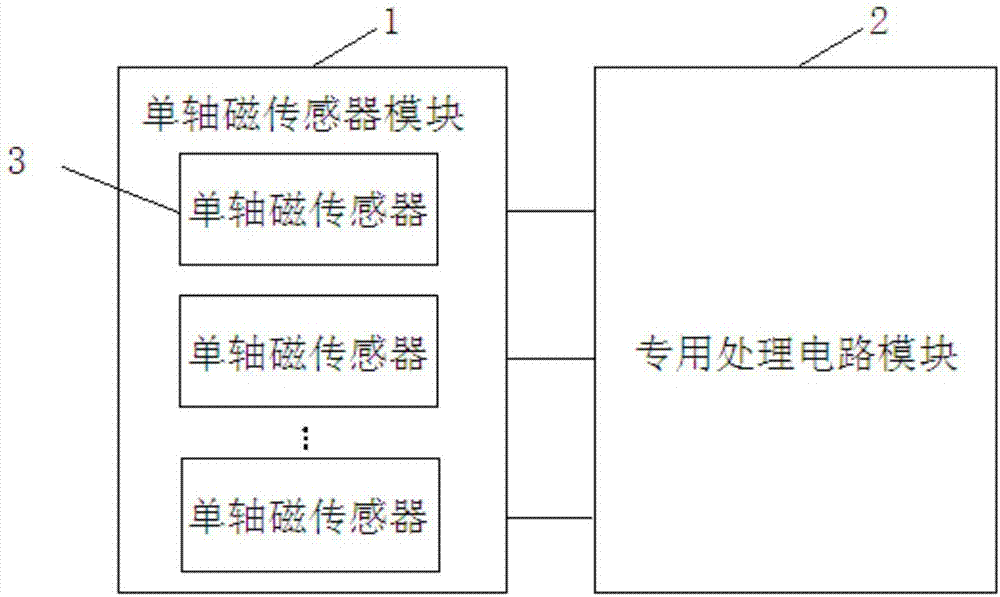

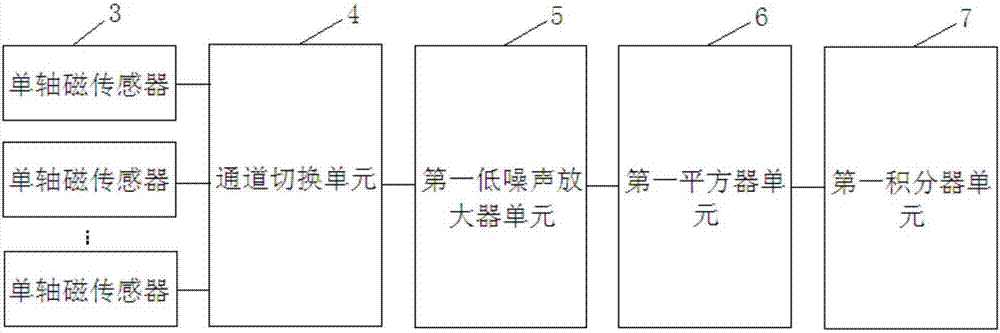

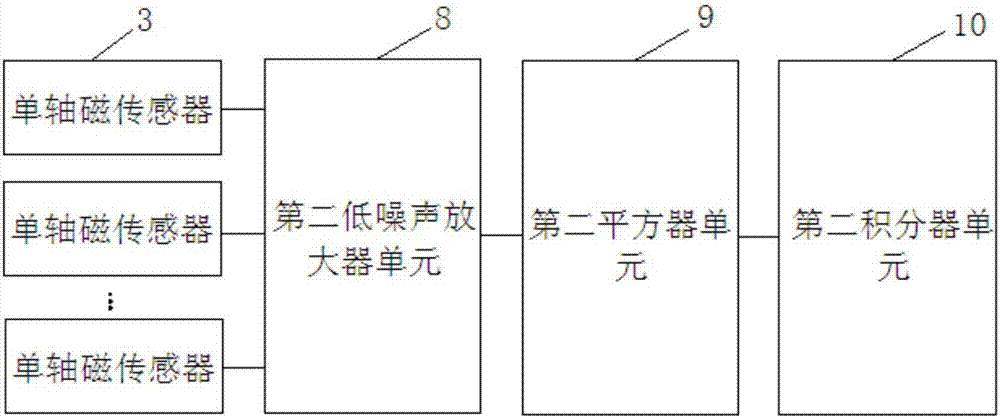

Magnetic switch circuit for outputting vector length of magnetic field

InactiveCN107884726AReduce design difficultySimplify process complexityMagnitude/direction of magnetic fieldsMagnetic switchApplication-specific integrated circuit

The present invention provides a magnetic switch circuit for outputting a vector length of a magnetic field, and relates to the field of magnetic field intensity detection circuit. The circuit comprises: an uniaxial magnetic sensor module comprising a plurality of uniaxial magnetic sensors, each uniaxial magnetic sensor being configured to output first preprocessing signals in a corresponding preset direction; an application specific integrated circuit connected with the uniaxial magnetic sensor module and configured to receive each first preprocessing signal and perform vector modulus processing and vector modulus solution and processing to obtain magnetic vector signals and a corresponding magnetic field vector length and output the magnetic vector signals and the corresponding magneticfield vector length. The magnetic switch circuit for outputting the vector length of the magnetic field measures one magnetic field intensity in each direction on the application specific integrated circuit and achieves vector modulus processing and vector modulus solution and processing on the application specific integrated circuit to obtain an accurate magnetic vector length, reduce the designdifficulty of the magnetic sensors in a traditional technology, simplify the process complexity of the magnetic sensors and effectively improve the yield rate.

Owner:QST CORP

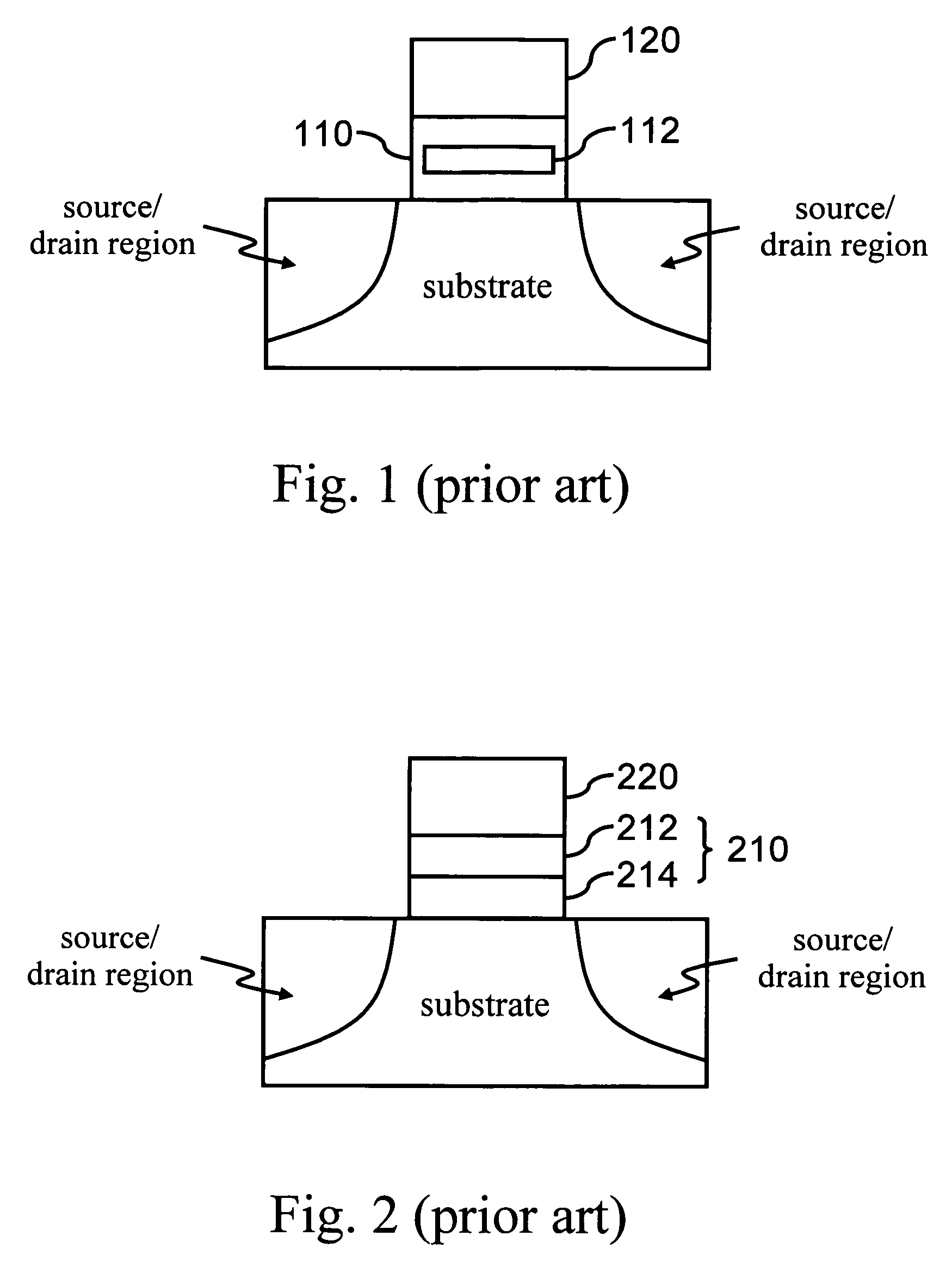

Non-volatile memory device and fabricating method thereof

InactiveUS7663177B2High energy gapSimplify process complexityTransistorSemiconductor/solid-state device manufacturingTrappingEngineering

A non-volatile memory device and fabricating method thereof are provided. In the deposition to form a tunneling dielectric layer, a composite charge trapping layer and a block dielectric layer, an ingredient of a depositing material or the depositing material is adjusted to form a grading energy level structure, such that carriers are trapped or erased more easily in accordance with a variation in grading energy level. Therefore, the carriers are stored more effectively and the probability that the electric leakage occurs is reduced substantially.

Owner:IND TECH RES INST

Buffering layer of ternary nitride for nitride luminescent assembly and its production

The invention consists of the base board, the ternary nitride buffer layer formed on the base board, the first conducting nitride semiconductor layer formed on the ternary nitride buffer layer, the luminescent layer formed on the first conducting nitride semiconductor layer, and the second conducting nitride semiconductor layer formed on the luminescent layer. The manufacturing method of the ternary nitride buffer layer is: at first preset temperature the first gas reaction source containing first group III element whose melting point is under the first preset temperature is put through; the group III element is deposited on the base board; at the second preset temperature the second gas reaction source containing group III element and the third gas reaction source containing nitride element are put through to make reaction with first group III element formed on the base board; the second preset temperature is not less than the melting point of first group III element.

Owner:EPISTAR CORP

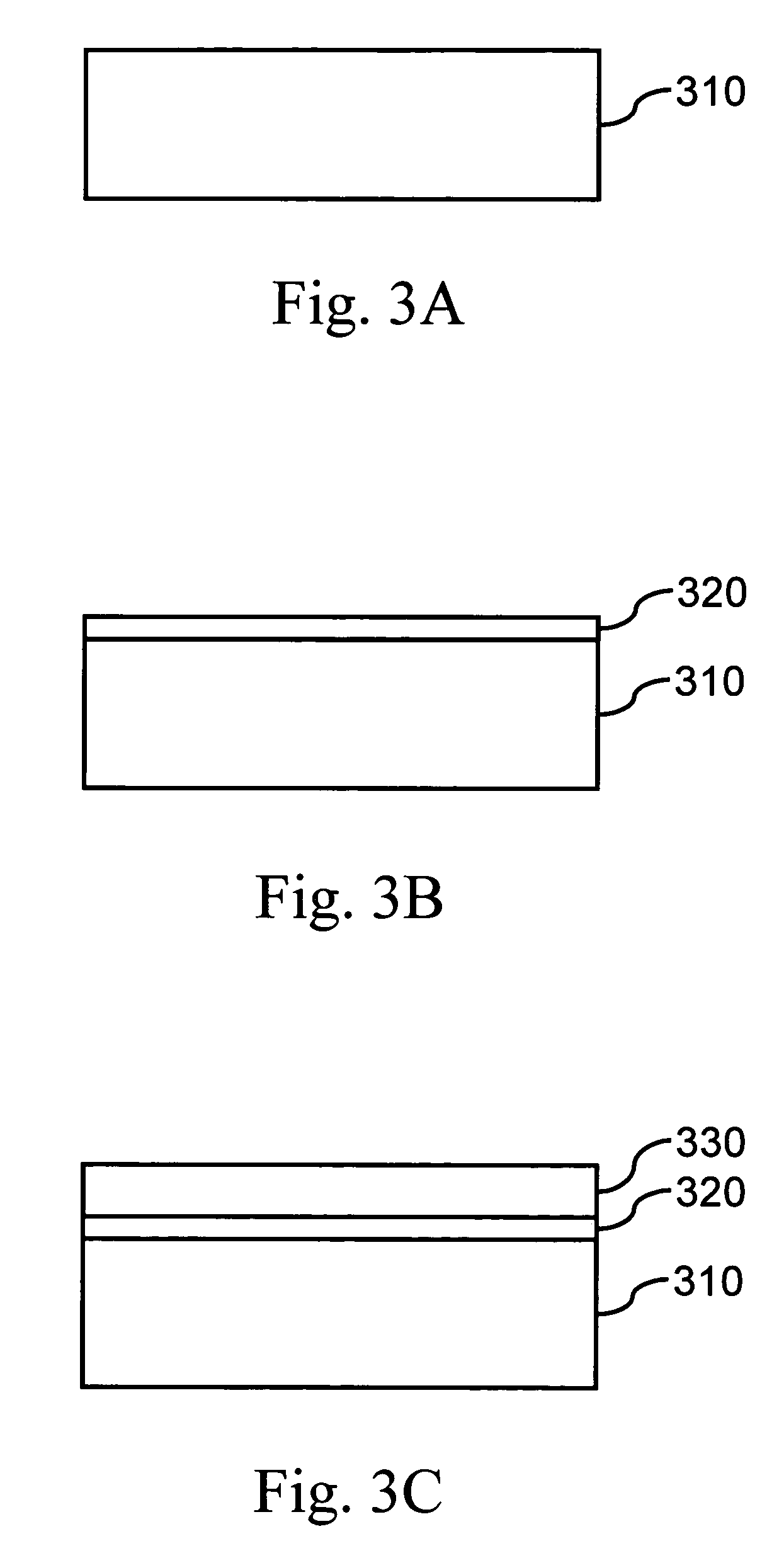

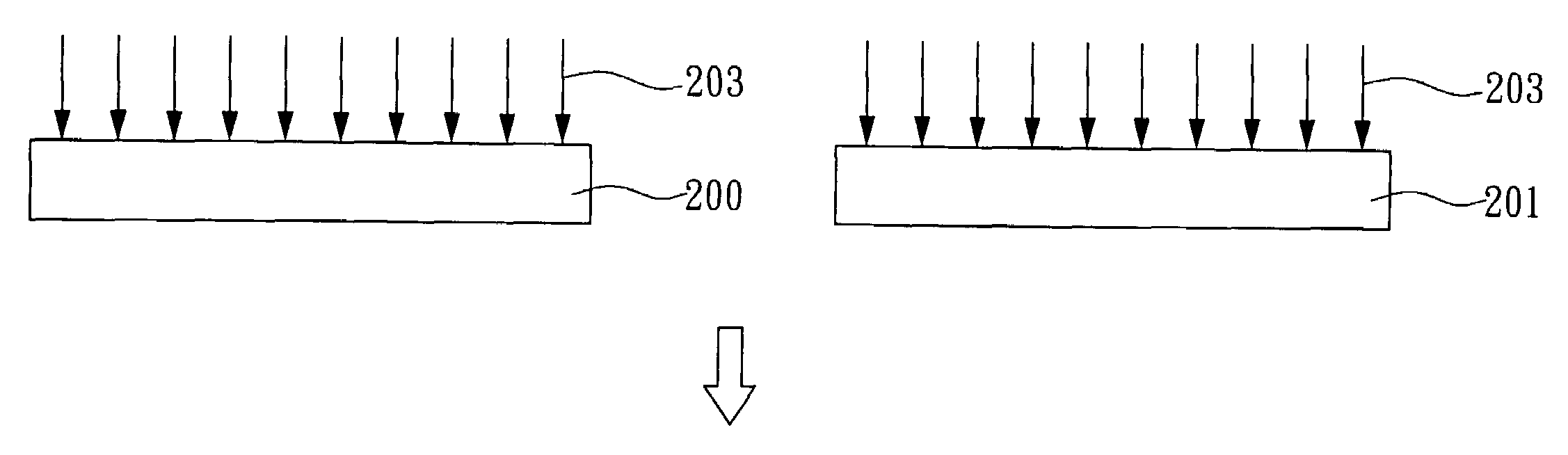

Method for manufacturing bonded wafer with ultra-thin single crystal ferroelectric film

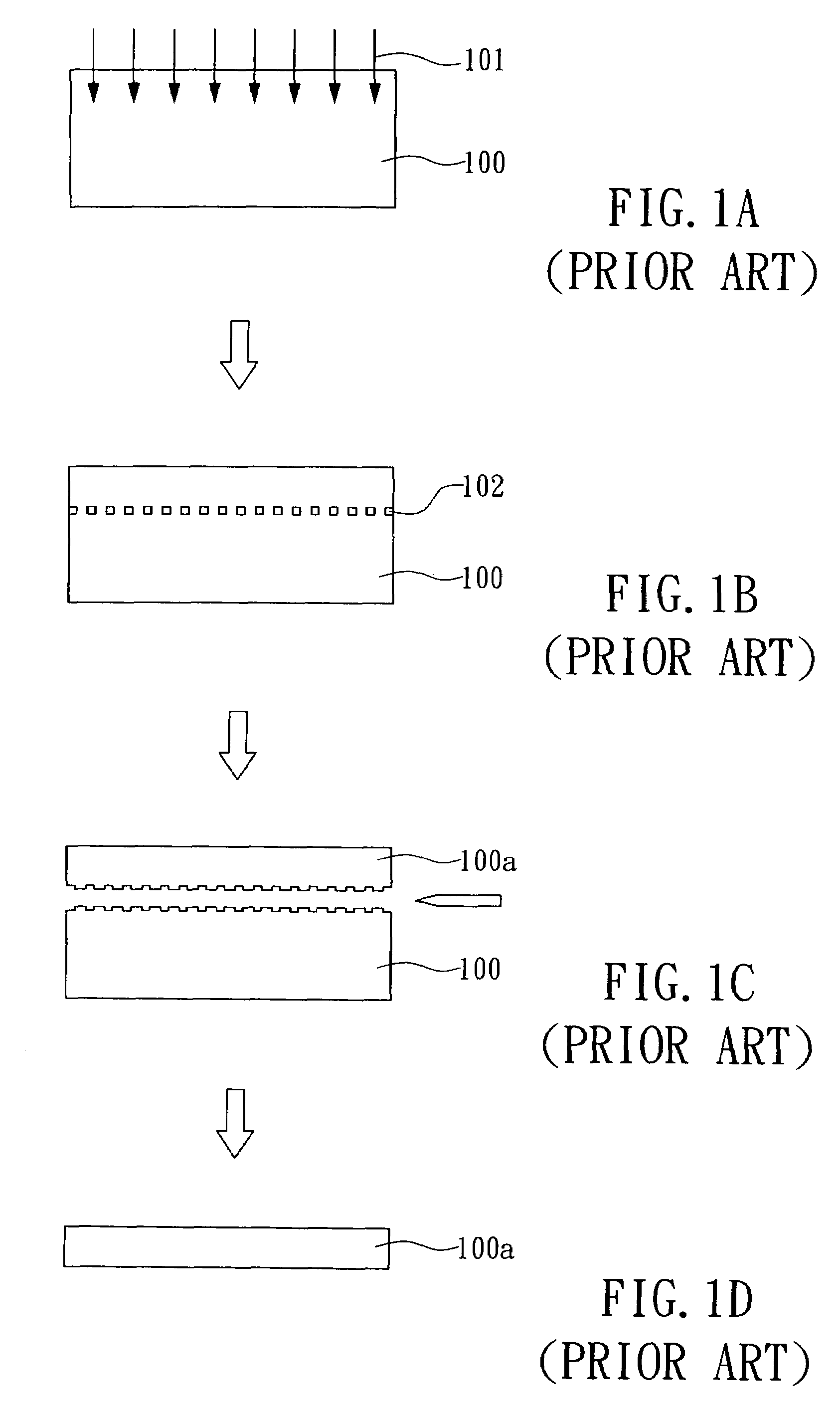

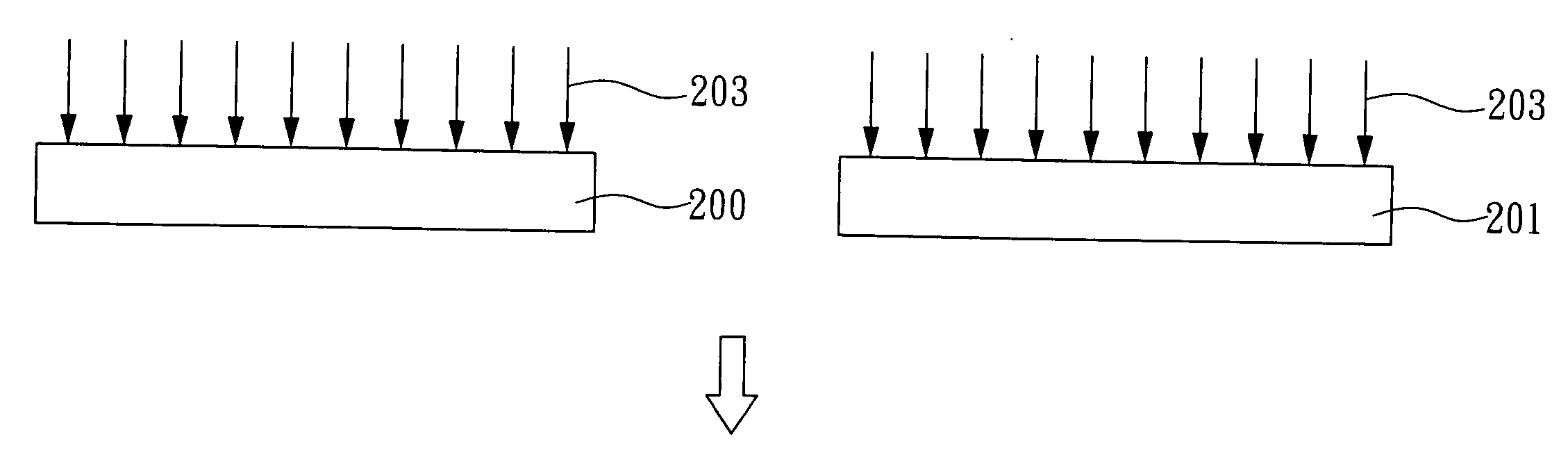

InactiveUS7329364B2Low costImprove business competitivenessPolycrystalline material growthAfter-treatment detailsWaferingBonding process

A method for manufacturing a bonded wafer with ultra-thin single crystal ferroelectric film is provided, comprising the following steps: providing a single crystal ferroelectric wafer and a carrier wafer while activating the surfaces of the single crystal ferroelectric wafer and the carrier wafer; bonding the activated surface of the single crystal ferroelectric wafer to the activated surface of the carrier wafer; and thinning the single crystal ferroelectric wafer for forming an ultra-thin single crystal ferroelectric film. Wherein, the thinning process in the aforesaid preferred embodiment is the method of polishing, grinding, chemical mechanical polishing, or etching. And the bonding force generated in the bonding process is strong enough to resist the shearing force.

Owner:IND TECH RES INST

Method for manufacturing bonded wafer with ultra-thin single crystal ferroelectric film

InactiveUS20060090691A1Easily brokenReduce process yieldPolycrystalline material growthAfter-treatment detailsWaferingBonding process

A method for manufacturing a bonded wafer with ultra-thin single crystal ferroelectric film is provided, comprising the following steps: providing a single crystal ferroelectric wafer and a carrier wafer while activating the surfaces of the single crystal ferroelectric wafer and the carrier wafer; bonding the activated surface of the single crystal ferroelectric wafer to the activated surface of the carrier wafer; and thinning the single crystal ferroelectric wafer for forming an ultra-thin single crystal ferroelectric film. Wherein, the thinning process in the aforesaid preferred embodiment is the method of polishing, grinding, chemical mechanical polishing, or etching. And the bonding force generated in the bonding process is strong enough to resist the shearing force.

Owner:IND TECH RES INST

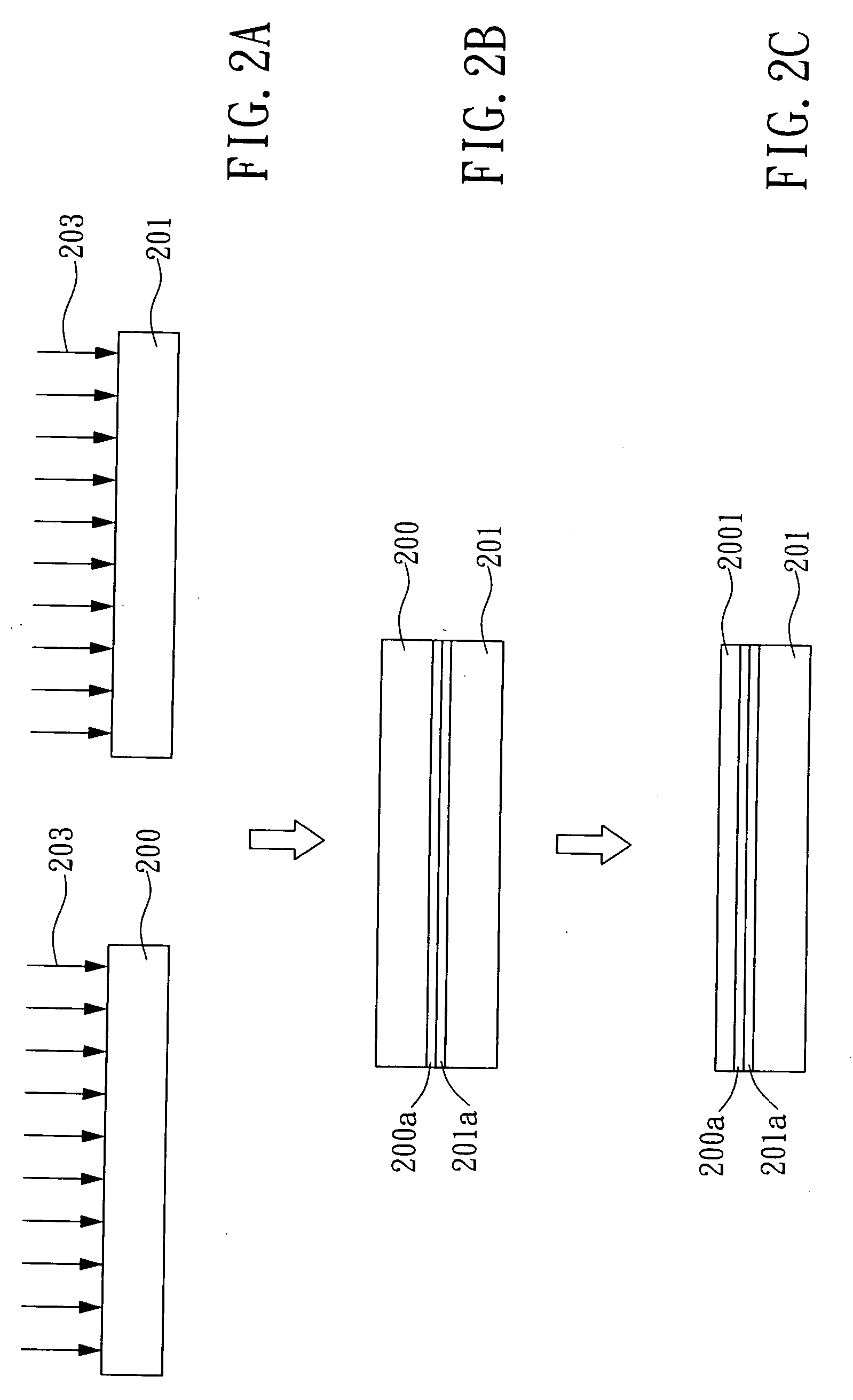

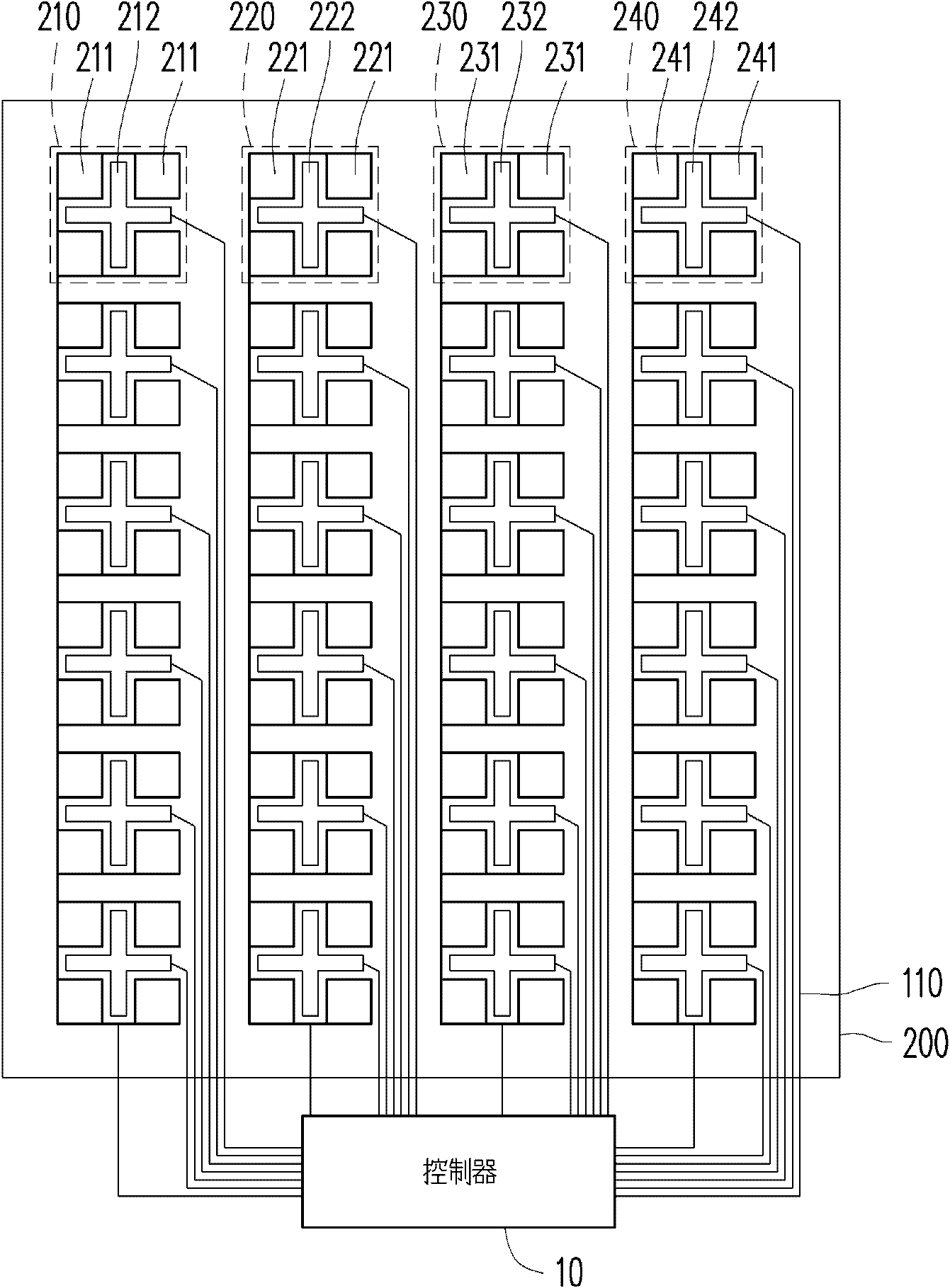

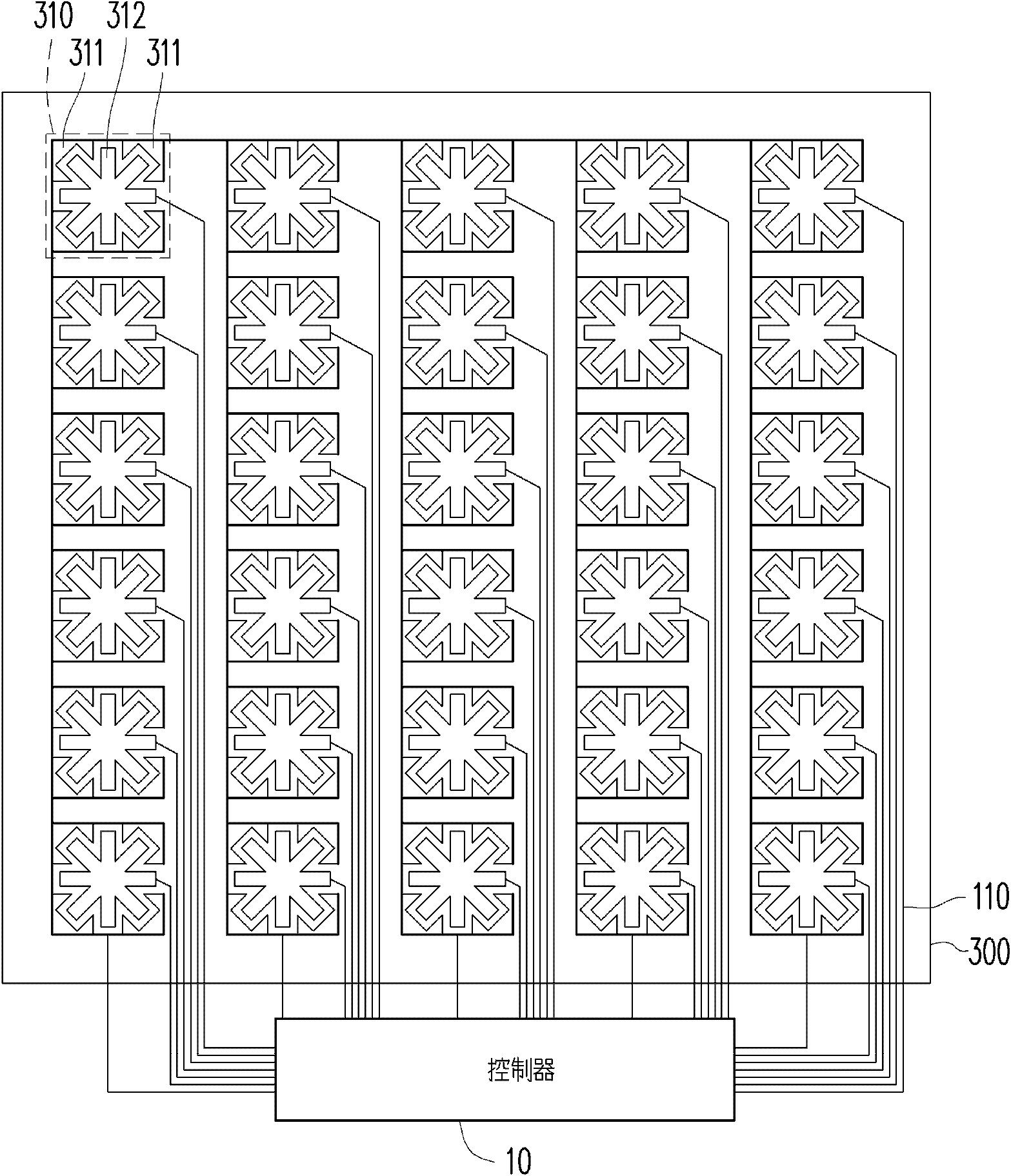

Layout structure of capacitive touch panel

ActiveCN102760016ASimplify the number of masks and process complexityLow manufacturing costInput/output processes for data processingTouch panelProcess complexity

The invention discloses a layout structure of a capacitive touch panel, which comprises a plurality of electrical paths and a plurality of touch units, wherein the touch units respectively comprise at least one receiving electrode and at least one driving electrode; the receiving electrodes and the driving electrodes are allocated in the same conducting layer; the receiving electrodes and the driving electrodes are insulated with each other; the receiving electrodes are connected to a controller by different electrical paths, and the driving electrodes are electrically connected with each other. According to the invention, the light cover quantity and process complexity are simplified, and the manufacturing cost is further lowered.

Owner:NOVATEK MICROELECTRONICS CORP

A LED flip chip and a manufacturing method thereof

InactiveCN109103316AReduce absorption ratioIncrease the average reflectanceSemiconductor devicesMultiple quantumGallium nitride

The invention relates to the technical field of semiconductors and in particular provides an LED flip chip and a manufacturing method thereof. The method comprises the steps of: A) providing a substrate on which an N-type gallium nitride layer, multiple quantum well layers and a P-type gallium nitride layer are sequentially formed; B, forming an ohmic contact layer on the surface of the substrate;C, forming a mirror dielectric layer on the ohmic contact layer; D, forming a mirror metal layer; E, etching the exposed P-type gallium nitride layer and the quantum well layers to form an N-electrode contact hole; F, forming an isolation layer; G, forming an N electrode in thr N electrode contact hole and forming a P electrode on a mirror metal layer covering the exposed ohmic contact layer; H,thinning the back surface of the sapphire substrate and forming a coarse alumina lay on the back surface of the sapphire substrate. The manufacturing method of the invention can improve the light emitting efficiency of the LED flip chip, thereby improving the photoelectric conversion efficiency of the LED flip chip, avoiding the influence on the front side of the chip and reducing the manufacturing cost.

Owner:DONGGUAN SINOWIN OPTO ELECTRONICS

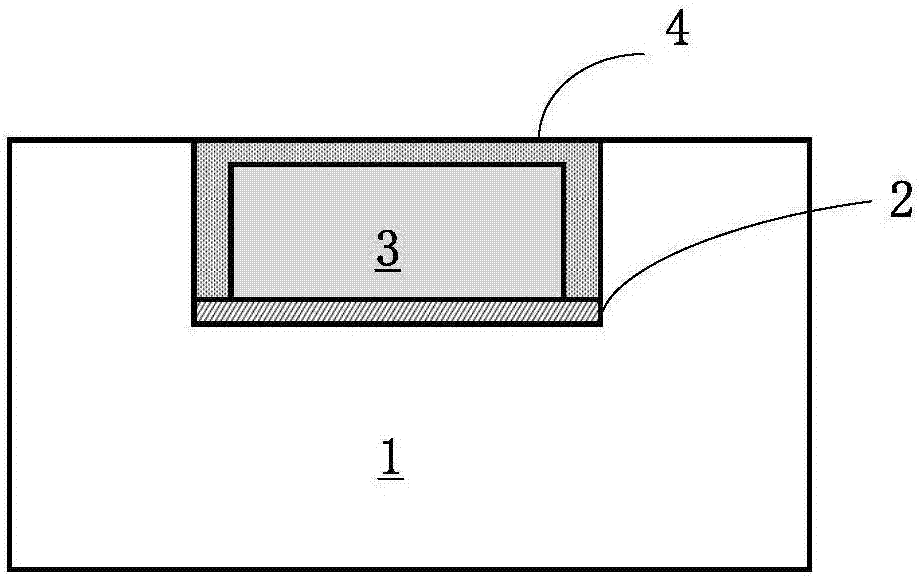

Chip packaging method and packaging structure

ActiveCN107393836ASimplify process complexityReduce thicknessSemiconductor/solid-state device detailsSolid-state devicesPlastic packagingEngineering

The invention provides a chip packaging method and a packaging structure. The chip packaging method comprises the steps of forming a cavity in a base body; and then installing a chip in the cavity, wherein the base body encapsulates the installed chip to serve as a protective shell of the installed chip. Therefore, a traditional plastic packaging process is not needed to be adopted to form a plastic package body for protecting the chip, and the technical complexity of the chip packaging structure is simplified efficiently. In addition, the base body also serves as a carrier of the installed chip, so that the chip is not needed to be installed at a pre-formed lead frame; and a bonding wire is not required to be adopted and convex points are not needed to be formed on the chip in the process of leading out a chip electrode, so that the technical difficulty is not only further simplified, but also the thickness of the chip packaging structure can be reduced efficiently.

Owner:SILERGY SEMICON TECH (HANGZHOU) CO LTD

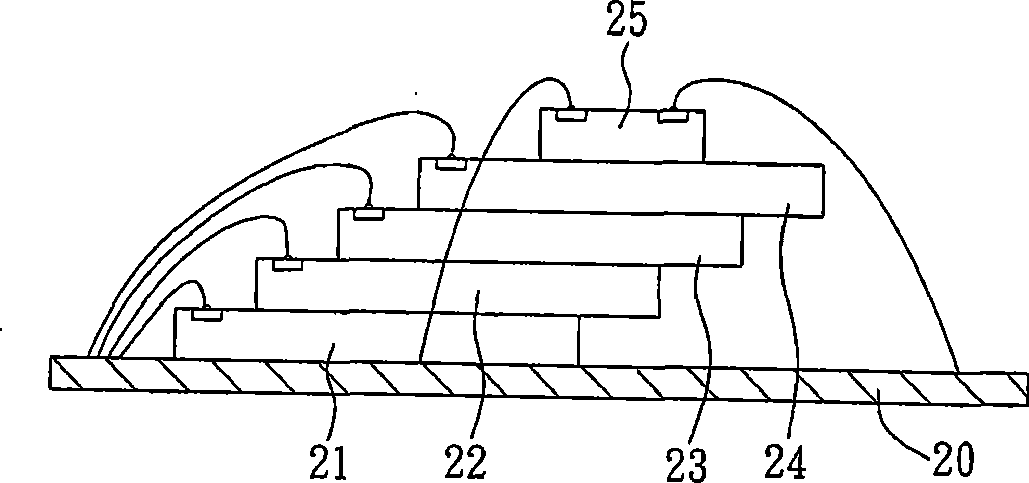

Multi-chip stacking structure and preparation thereof

ActiveCN101452861AIncrease the number of stacked layersAvoiding the problem of increasing structural heightSemiconductor/solid-state device detailsSolid-state devicesState of artChip stacking

The invention discloses a multichip stacking structure and a method for manufacturing the same. The multichip stacking structure comprises a first chip set which is provided with a plurality of first chips and is connected with a chip bearing piece in a stepped mode; the first chip of the topmost layer of the first chip set is connected with a second chip so that the first chip and the second chip are in electric connection with the chip bearing piece through a welding wire; adhesive film over wire technology (Film over Wire, FOW) is utilized to stack a third chip alternated with an insulating adhesive film on the first chip and the second chip so that the insulating adhesive film covers part of the welding wire end of the first chip of the topmost layer of the first chip set and at least one part of the second chip and is in electric connection with the third chip and the chip bearing piece through the welding wire, thereby solving the problem that when the second chip with planar dimension far less than that of the first chip is directly stacked on the first chip in the prior art, the height of the whole structure and the difficulty of wire welding operation are increased.

Owner:SILICONWARE PRECISION IND CO LTD

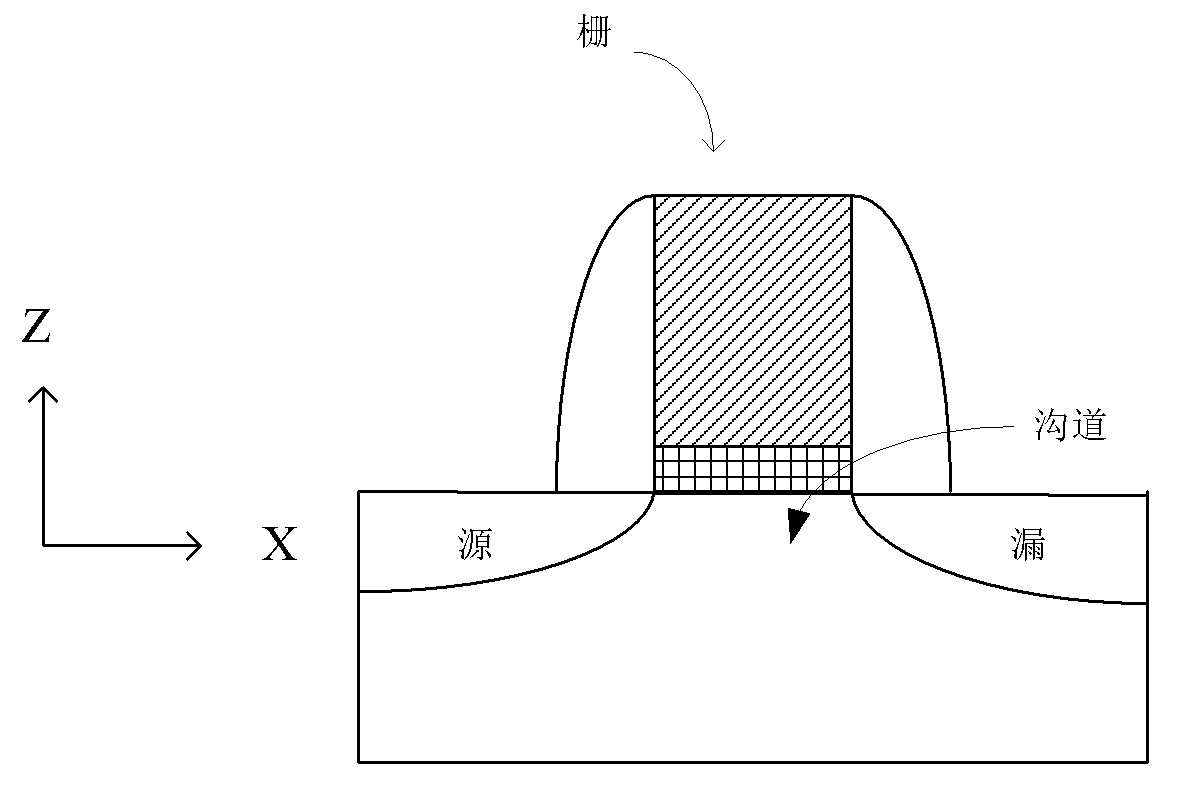

Method for introducing strain to channel and device manufactured by the same

ActiveCN102593001AStrong process flexibilitySimplify process complexitySemiconductor/solid-state device manufacturingSemiconductor devicesOxide semiconductorPolycrystalline silicon

The invention relates to a method for introducing strain to a channel of a MOS (Metal Oxide Semiconductor) device and a device manufactured by the method. The method comprises the following steps of: providing a semiconductor substrate; forming a channel on the semiconductor substrate; forming a first grid dielectric layer on the channel; forming a polycrystalline silicon grid electrode layer on the first grid dielectric layer; doping or injecting a first element in the polycrystalline silicon grid electrode layer; removing parts of the first grid dielectric layer and the polycrystalline silicon grid electrode layer so as to form a first grid electrode structure; forming a source drain extending zone in the channel; forming side walls on both sides of the first grid electrode structure; forming a source drain electrode in the channel; and annealing so that polycrystalline silicon doped or injected with the first element generates crystal lattice variation in a high-temperature crystallization process, thus generating first strain in the polycrystalline silicon grid electrode layer, and introducing the first stress to the channel through a grid medium layer. The method has stronger process flexibility, simpler process complication and no additional process cost.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com