Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

85results about How to "Improved resistance to electromigration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

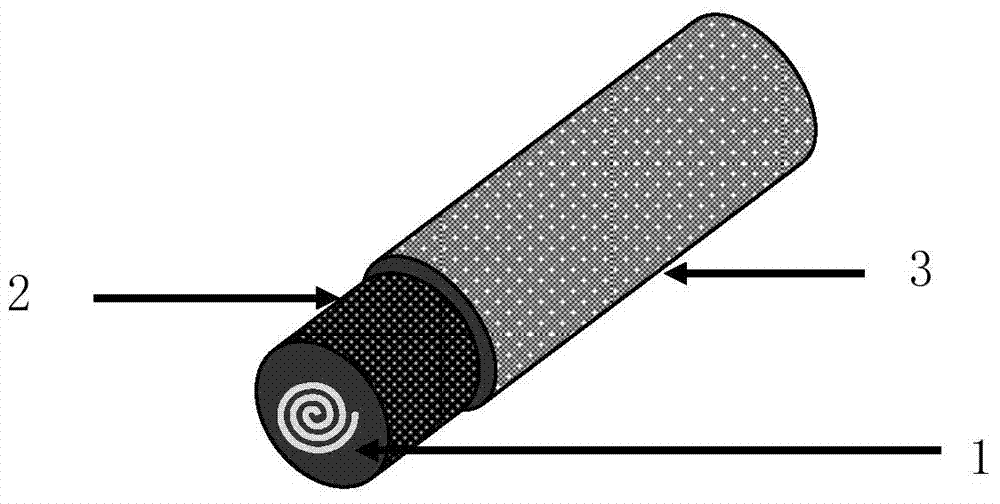

Full-carbon coaxial line and manufacturing method thereof

InactiveCN103943925AStable structureFast heat conductionCarbon-silicon compound conductorsWaveguidesElectrical conductorCoaxial line

The invention discloses a full-carbon coaxial line and a manufacturing method of the full-carbon coaxial line, and belongs to the technical field of integrated circuits. Graphene serves as a monatomic layer thickness, is coiled into a cylinder and form an inner conductor of the coaxial line with a small radius (can be as small as the nm level), and the inner conductor of the coaxial line transfers currents. Meanwhile, a signal layer or multiple layers of graphene serve(s) as an outer conductor of the coaxial line to form a boundary of electromagnetic waves in a space, and graphite oxide serves as medium materials between the inner conductor and the outer conductor to limit and guide oriented transmission of electromagnetic wave energy. The coaxial line is quite small in size and applicable to radio-frequency and microwave integrated circuits.

Owner:PEKING UNIV

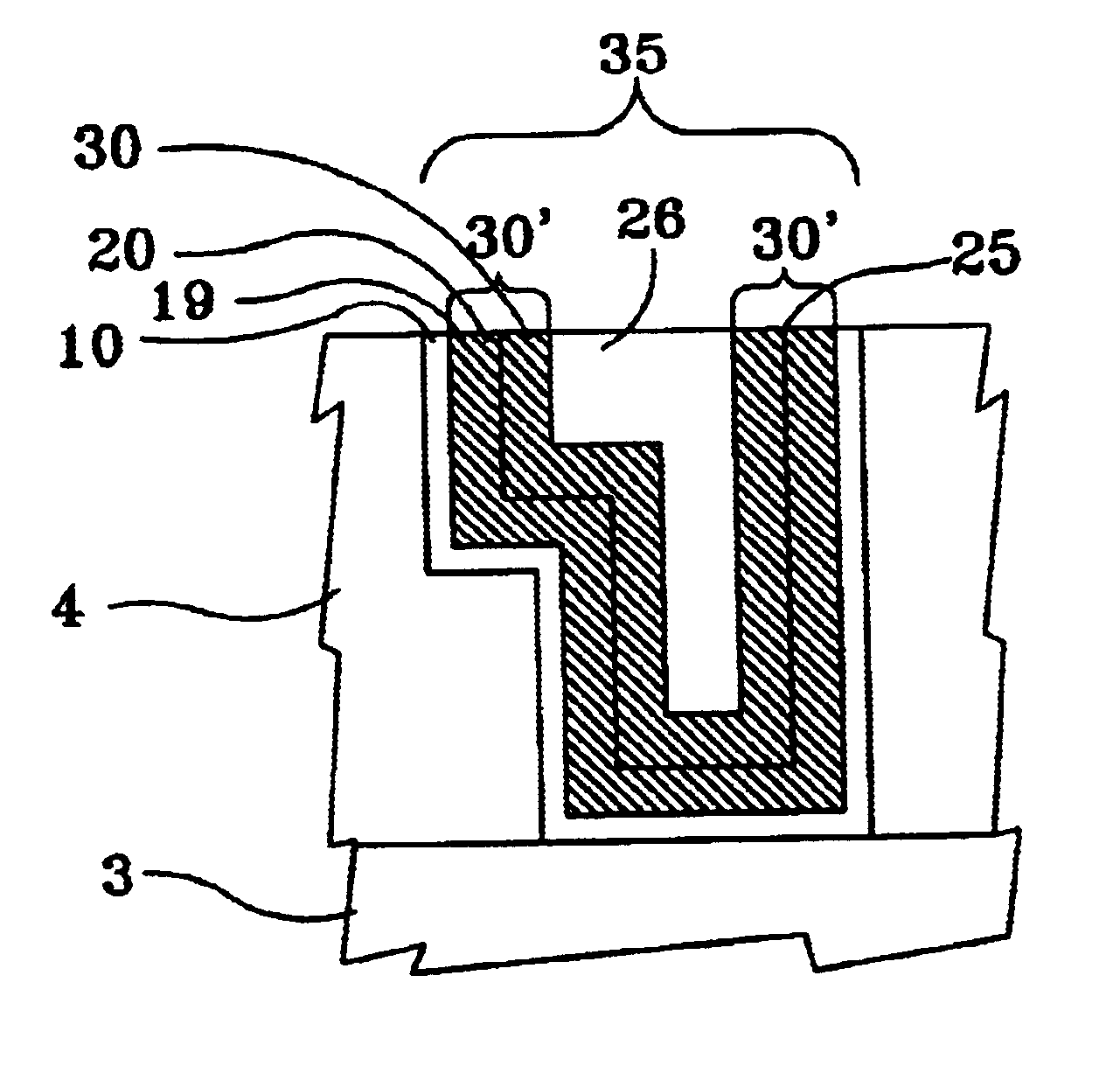

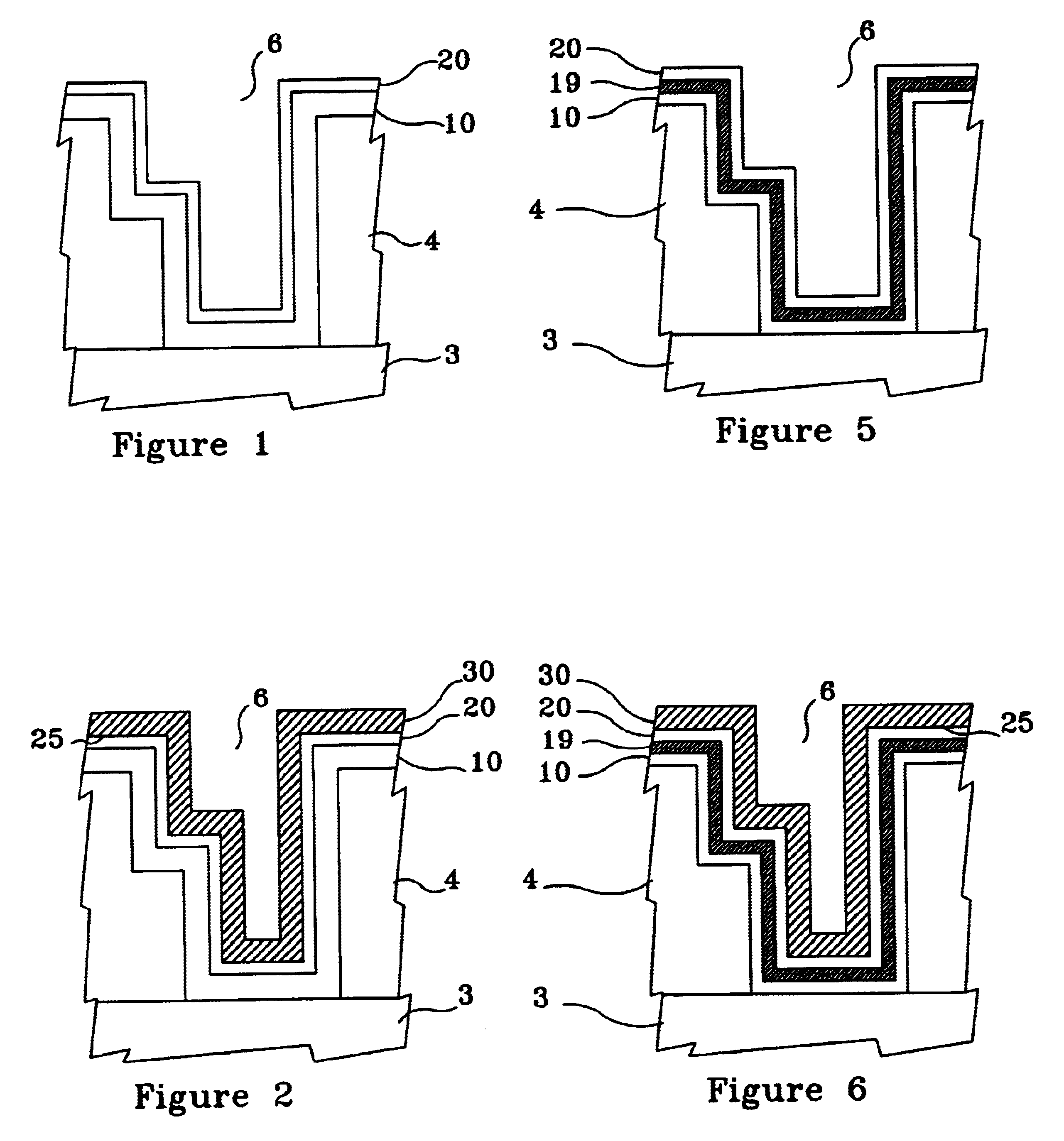

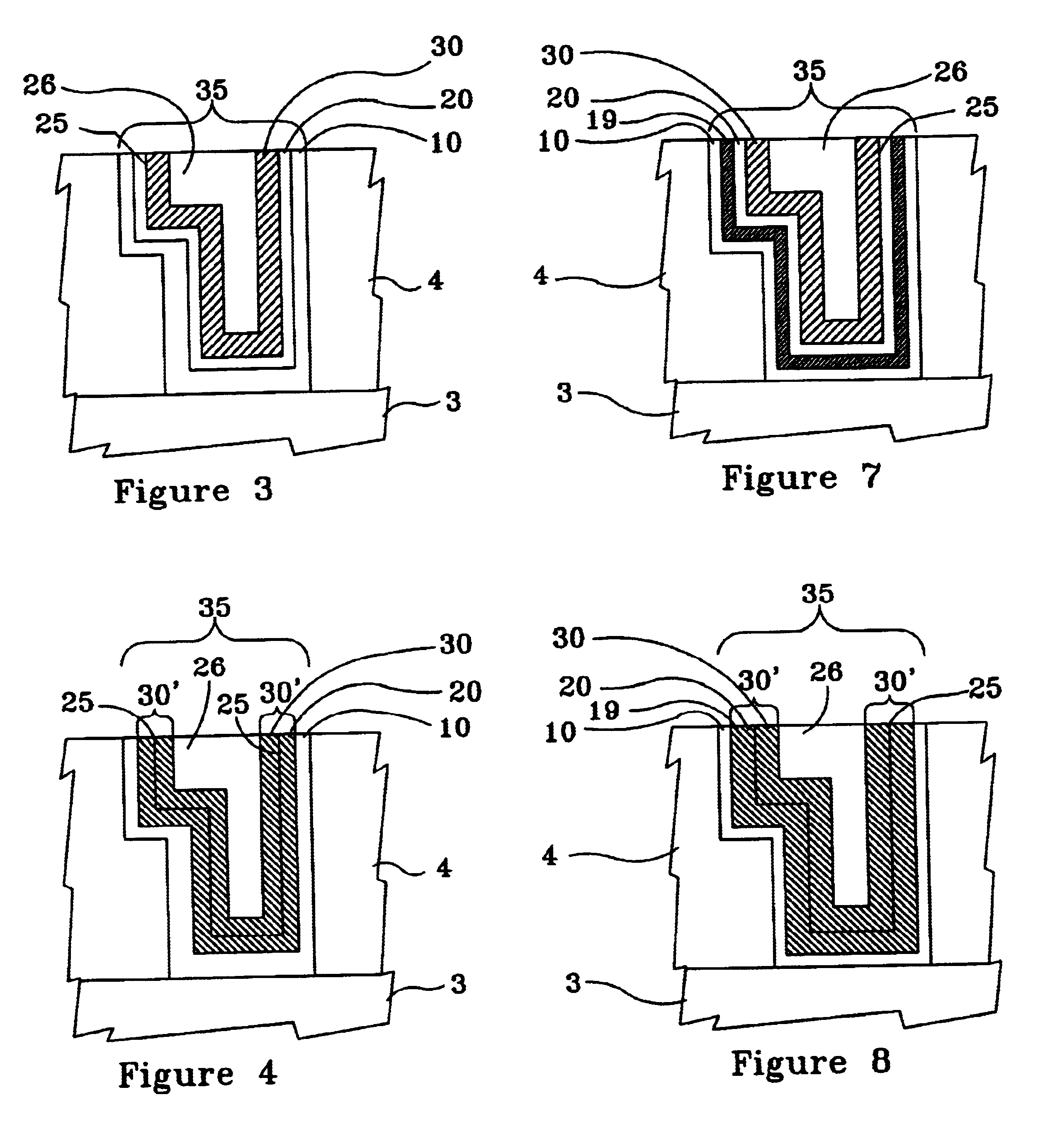

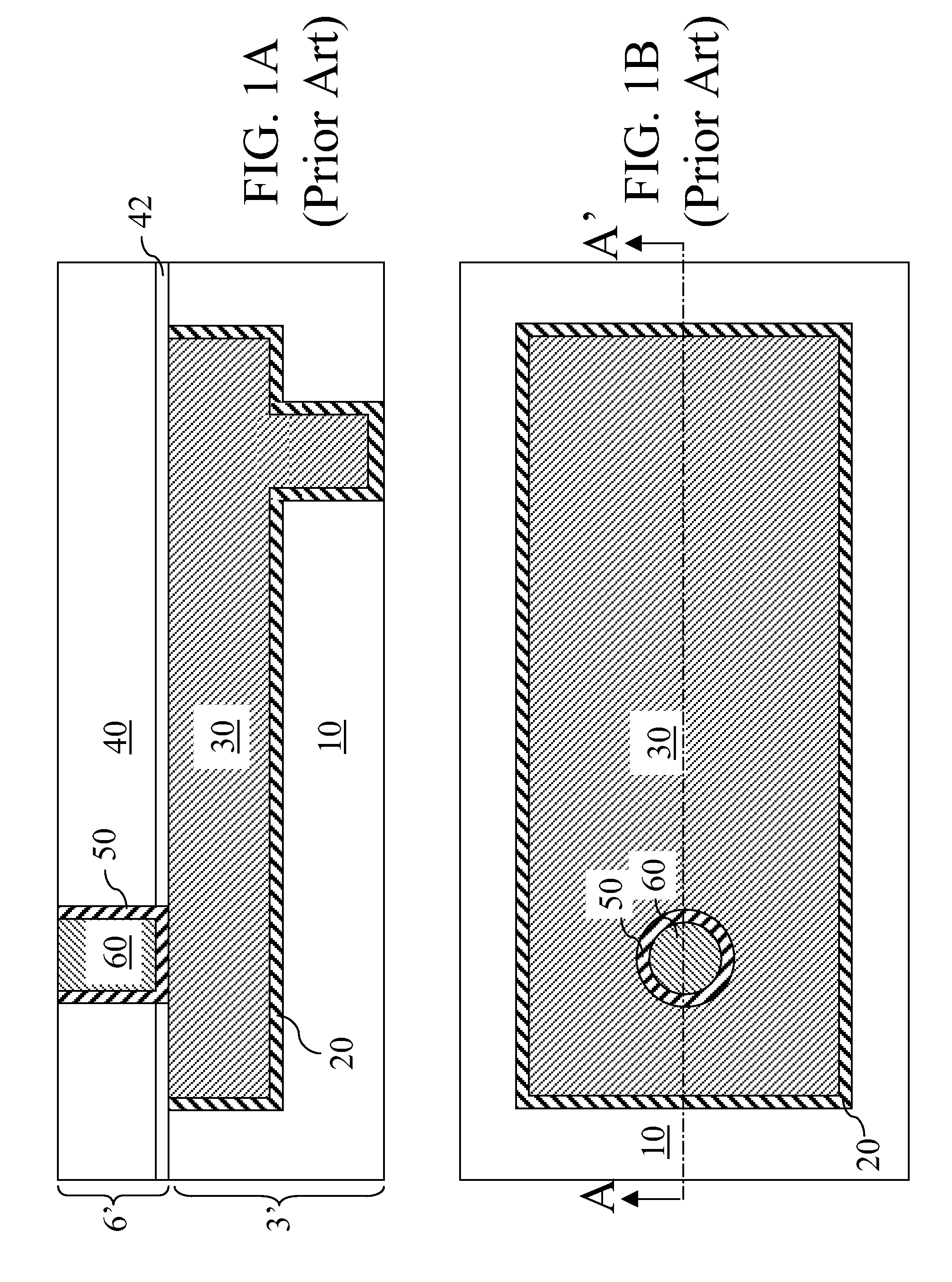

Method of reducing electromigration in a copper line by electroplating an interim copper-zinc alloy thin film on a copper surface and a semiconductor device thereby formed

InactiveUS6660633B1Improves Cu interconnect reliabilityReduce manufacturing costElectrolysis componentsSolid-state devicesCopper interconnectChemical solution

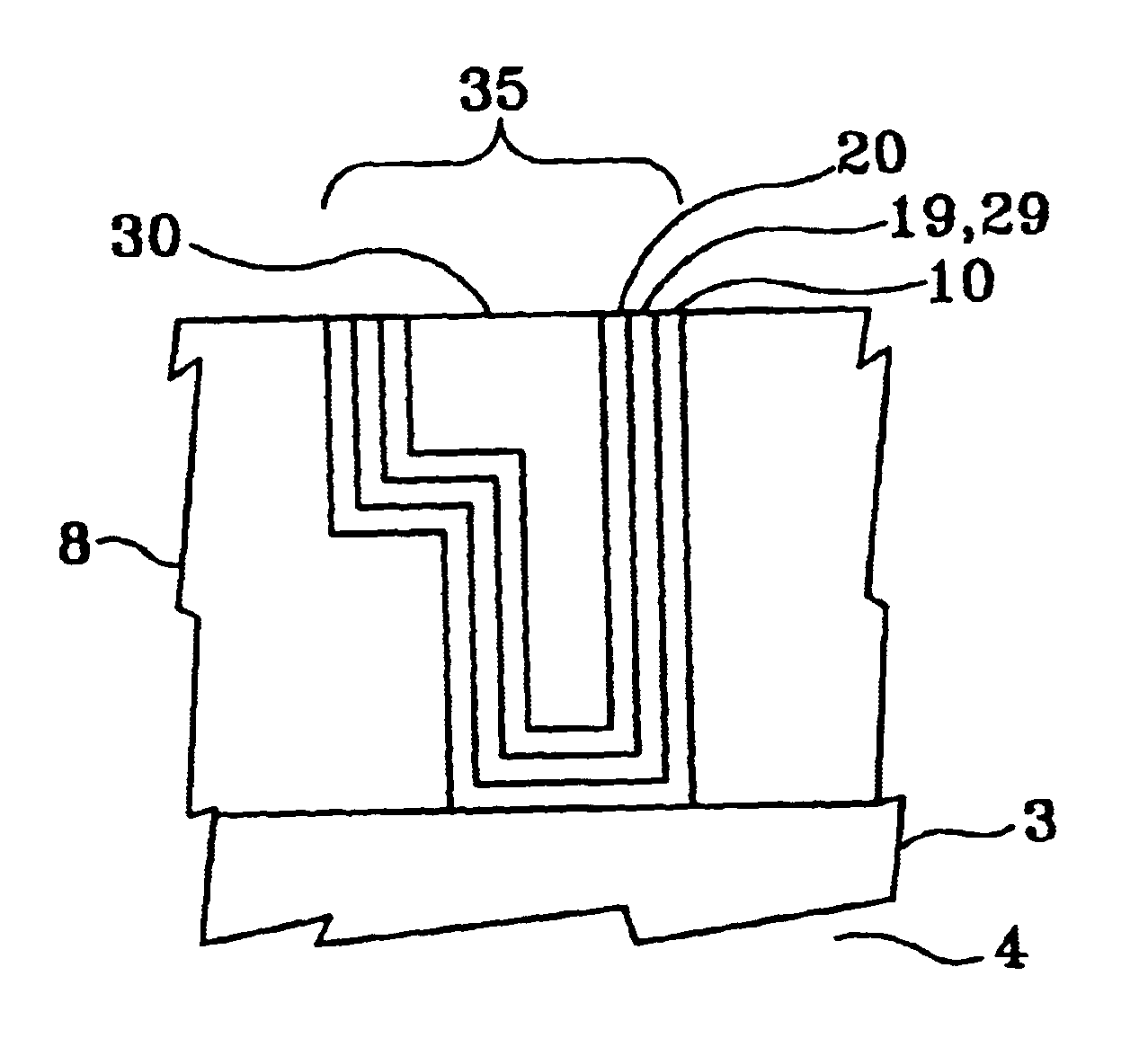

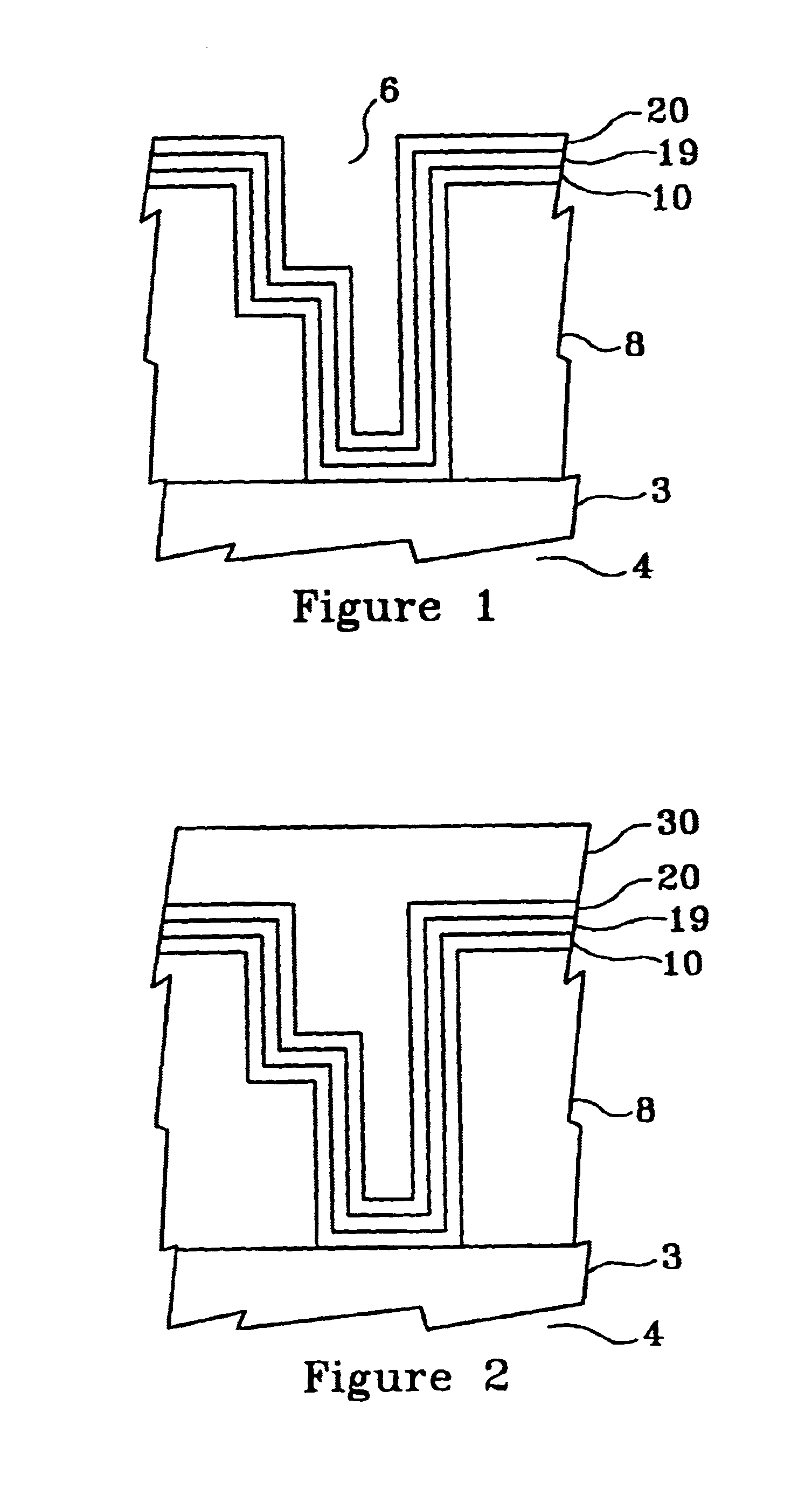

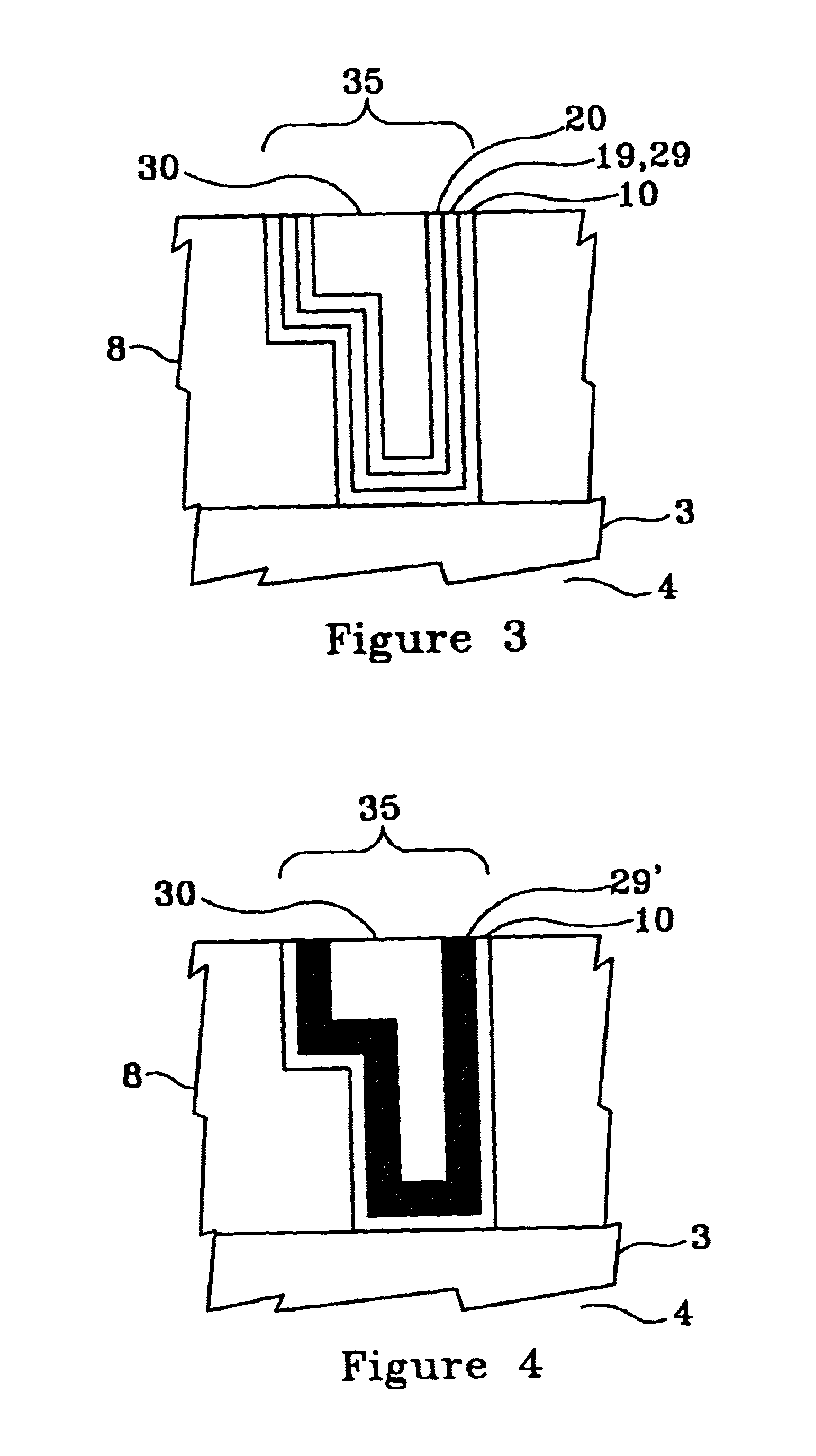

A method of fabricating a semiconductor device, having an interim reduced-oxygen Cu-Zn alloy thin film (30) electroplated on a blanket Cu surface (20) disposed in a via (6) by electroplating, using an electroplating apparatus, the Cu surface (20) in a unique chemical solution containing salts of Zn and Cu, their complexing agents, a pH adjuster, and surfactants; and annealing the interim electroplated Cu-Zn alloy thin film (30); filling the via (6) with further Cu (26); annealing and planarizing the interconnect structure (35); and a semiconductor device thereby formed. The reduction of electromigration in copper interconnect lines (35) is achieved by decreasing the drift velocity in the copper line (35) / via (6), thereby decreasing the copper migration rate as well as the void formation rate, by using an interim conformal Cu-rich Cu-Zn alloy thin film (30) electroplated on a Cu surface (20) from a stable chemical solution, and by controlling the Zn-doping thereof, which improves also interconnect reliability and corrosion resistance.

Owner:GLOBALFOUNDRIES US INC

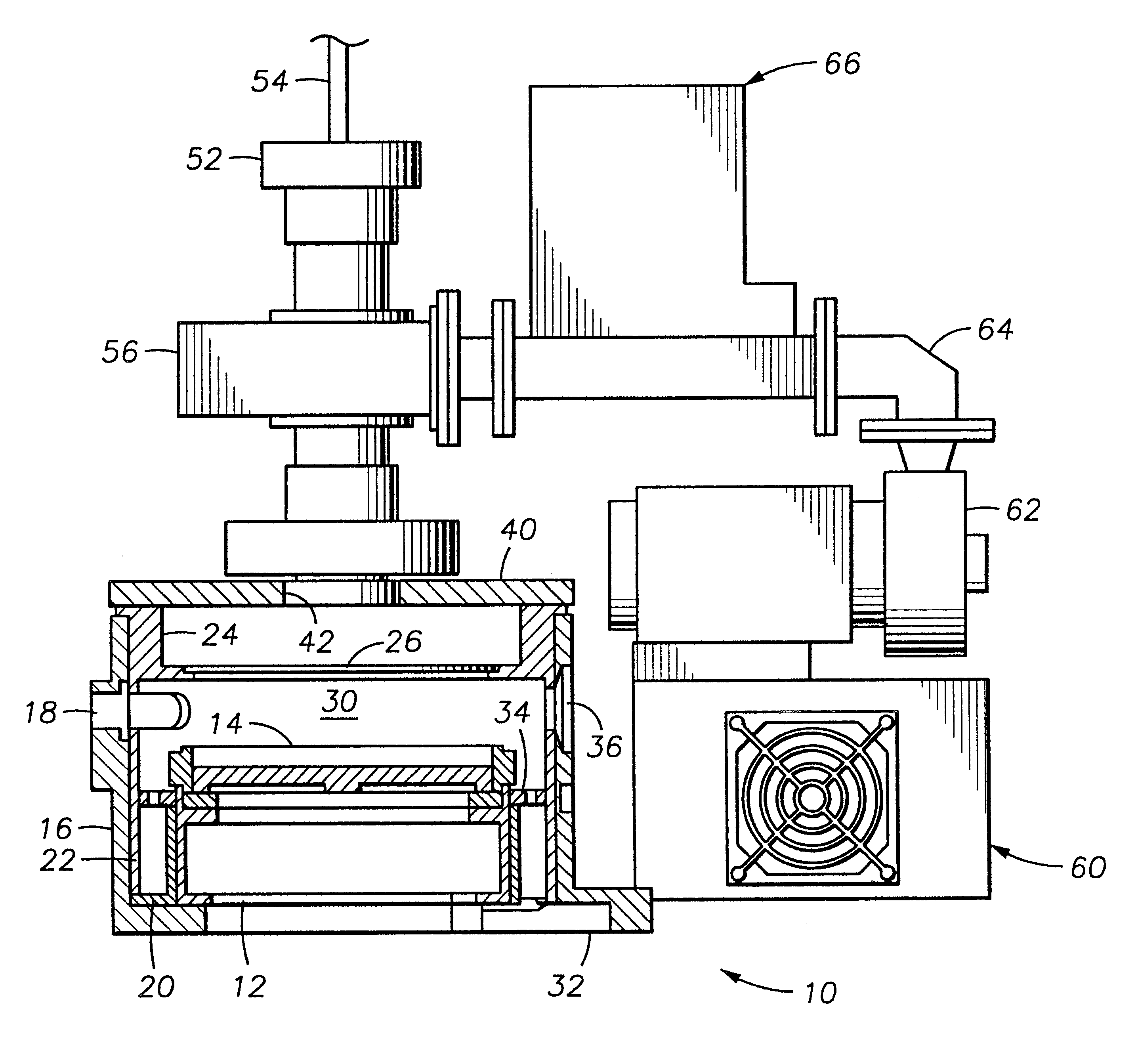

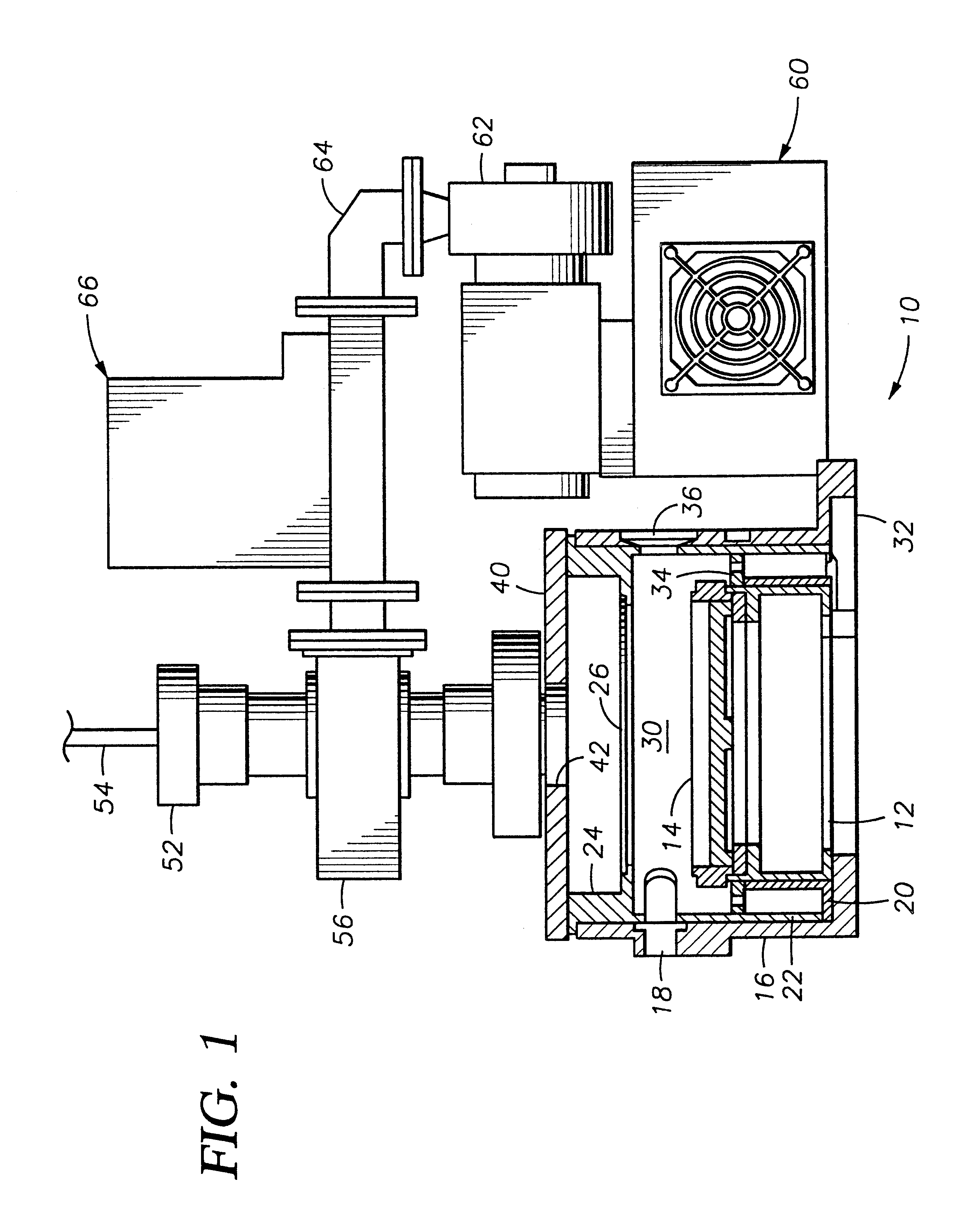

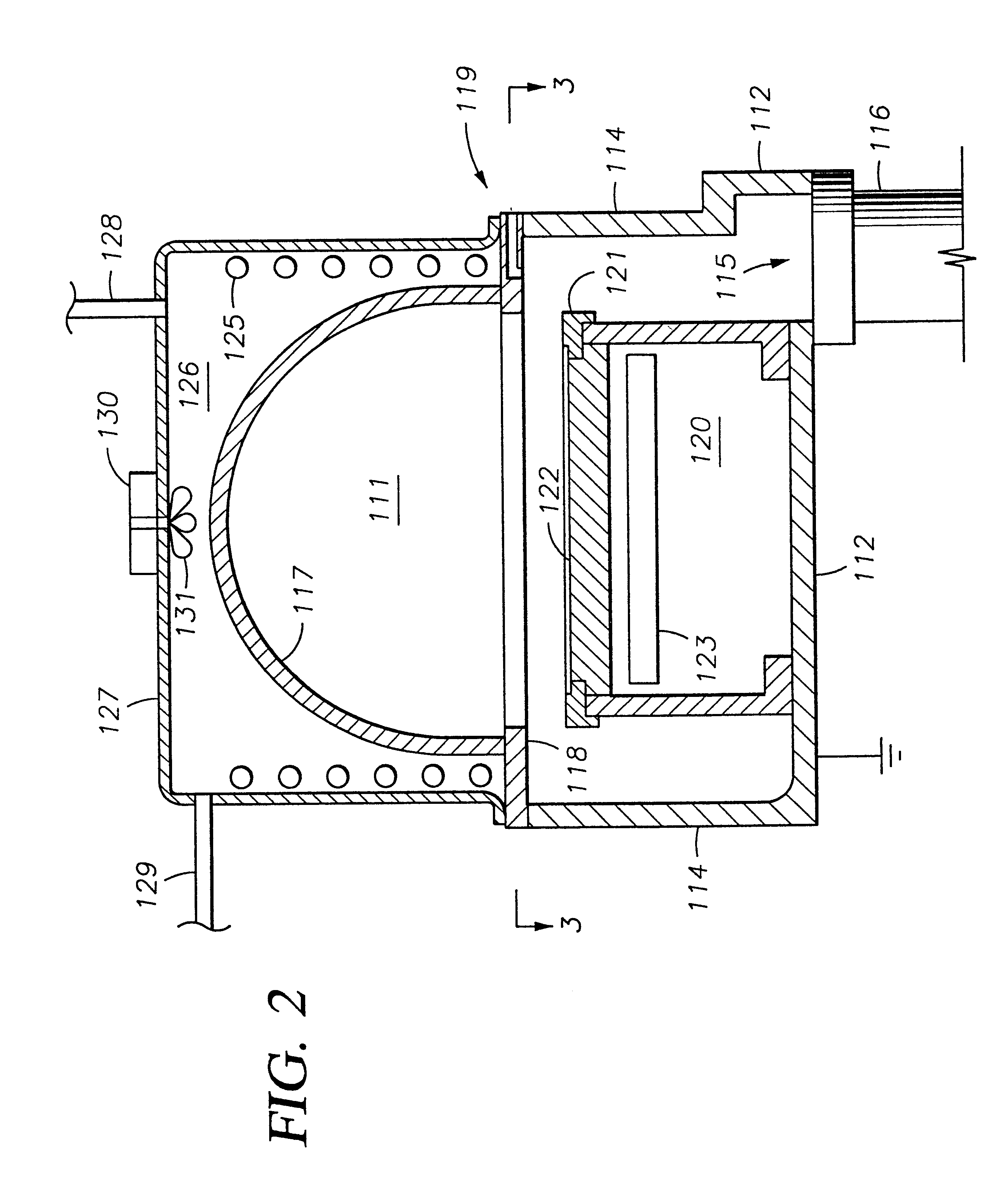

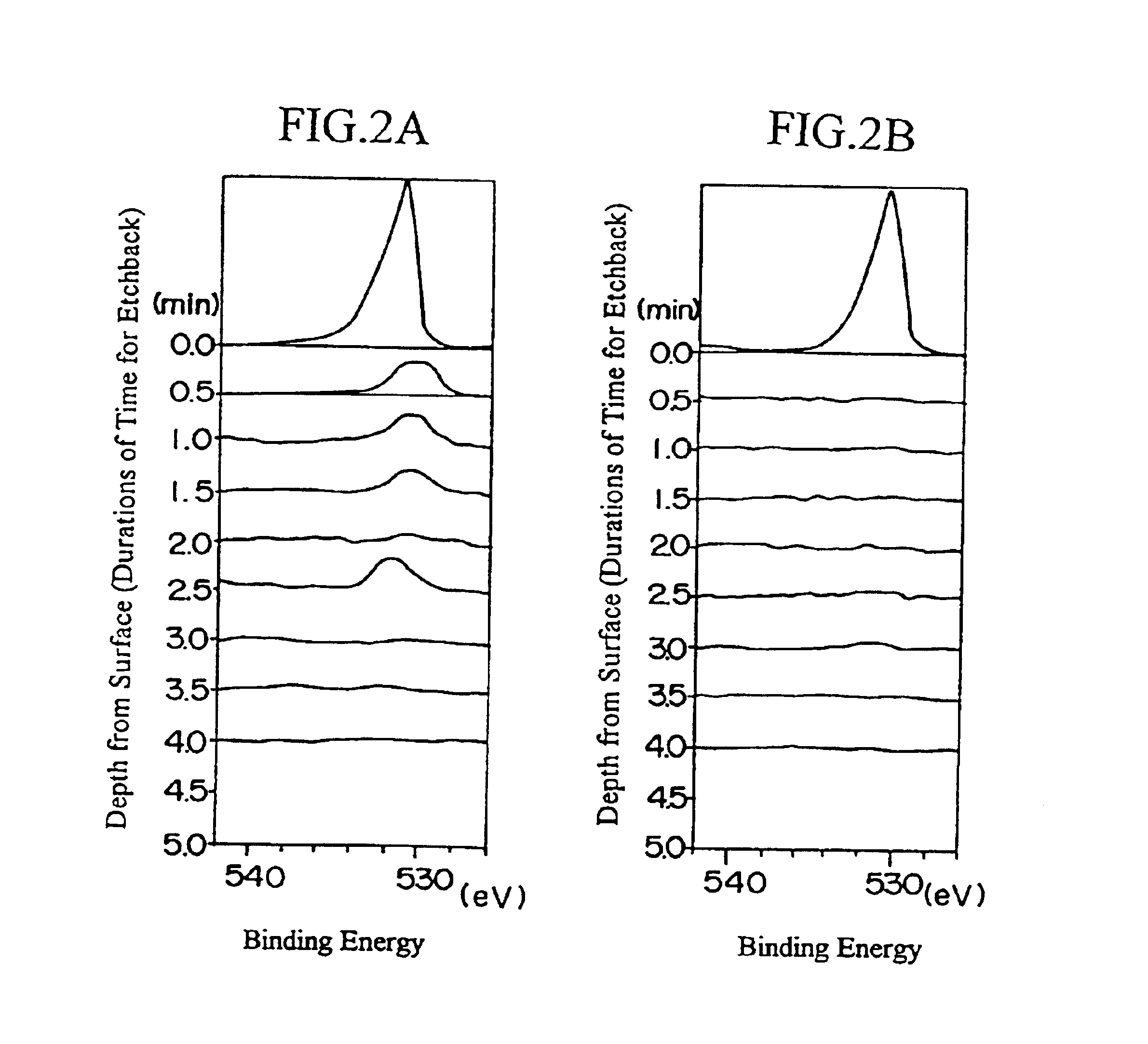

Reactive preclean prior to metallization for sub-quarter micron application

InactiveUS6693030B1Reduce the amount requiredImproved resistance to electromigrationVacuum evaporation coatingSputtering coatingRemote plasmaHydrogen

The present invention generally provides a precleaning process prior to moralization for submicron features on substrates. The method includes cleaning the submicron features with radicals from a plasma of a reactive gas such as oxygen, a mixture of CF4 / O2, or a mixture of He / NF3, wherein the plasma is preferably generated by a remote plasma source and the radicals are delivered to a chamber in which the substrate is disposed. Native oxides remaining in the submicron features are preferably reduced in a second step by treatment with radicals from a plasma containing hydrogen. Following the first or both precleaning steps, the features can be filled with metal by available moralization techniques which typically include depositing a barrier / liner layer on exposed dielectric surfaces prior to deposition of aluminum, copper, or tungsten. The precleaning and moralization steps can be conducted on available integrated processing platforms.

Owner:APPLIED MATERIALS INC

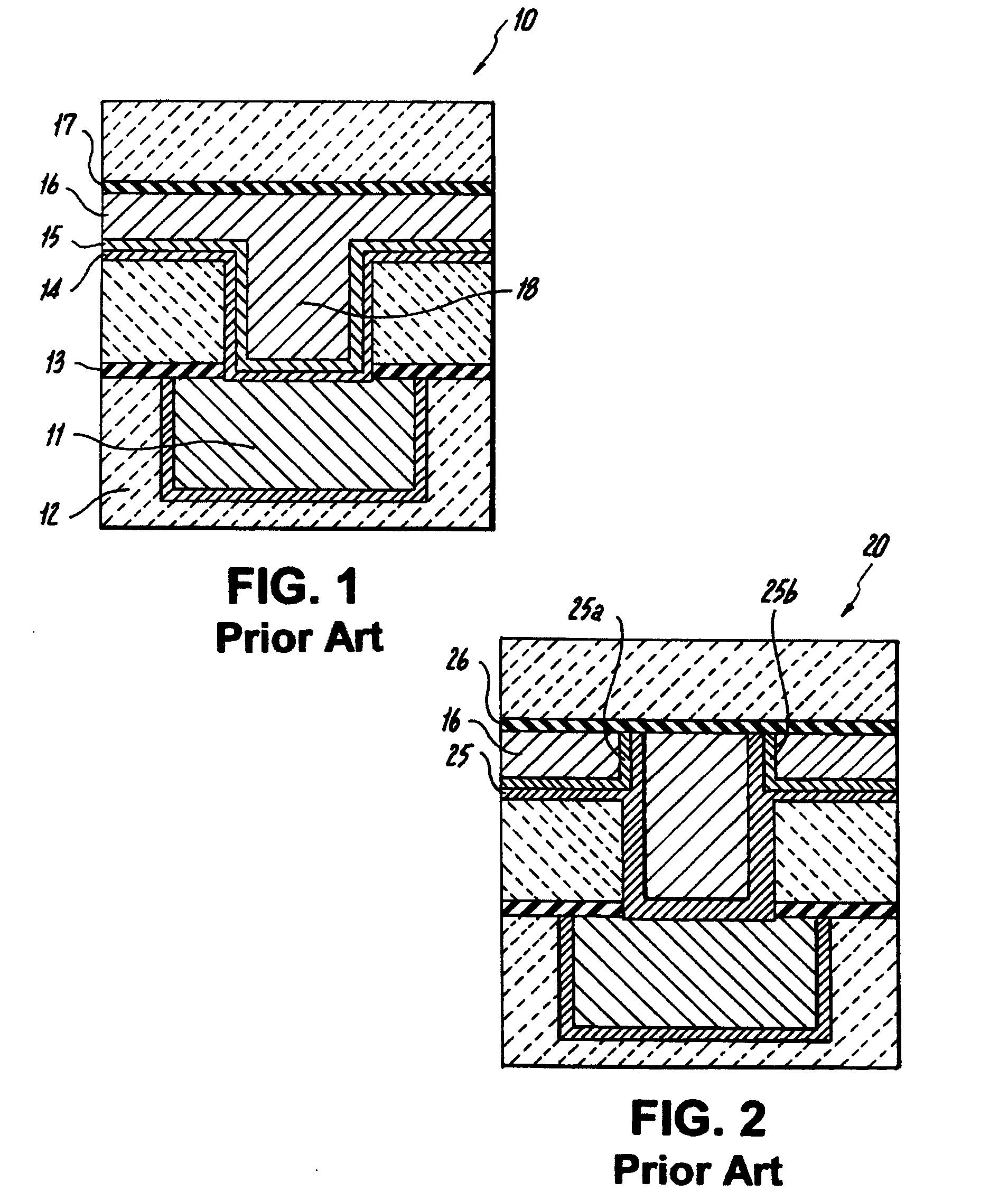

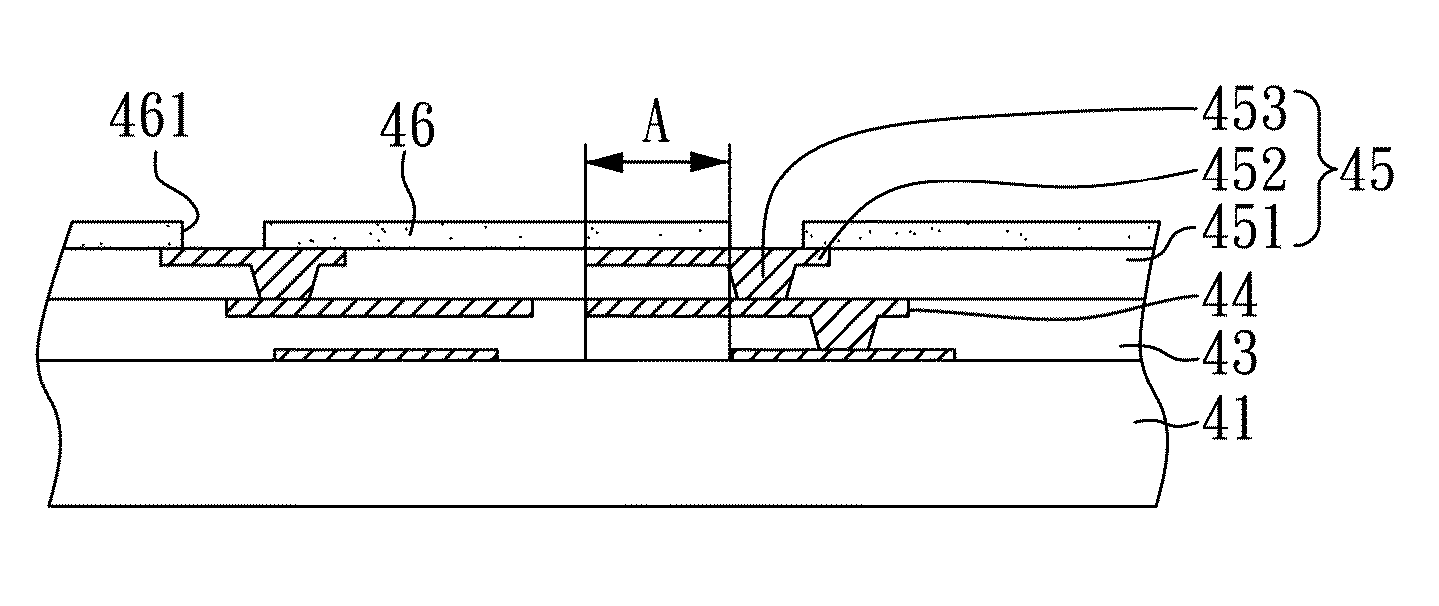

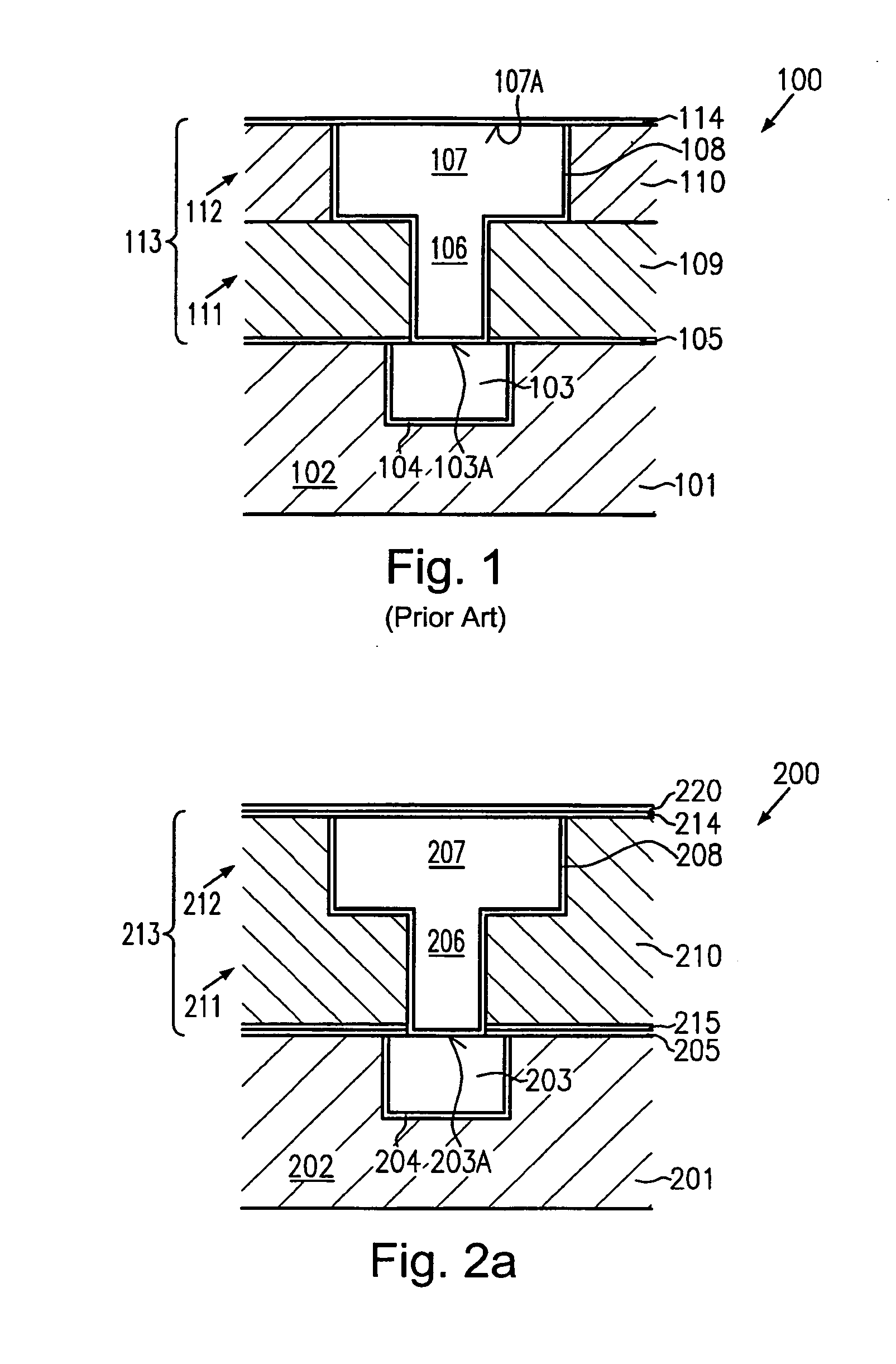

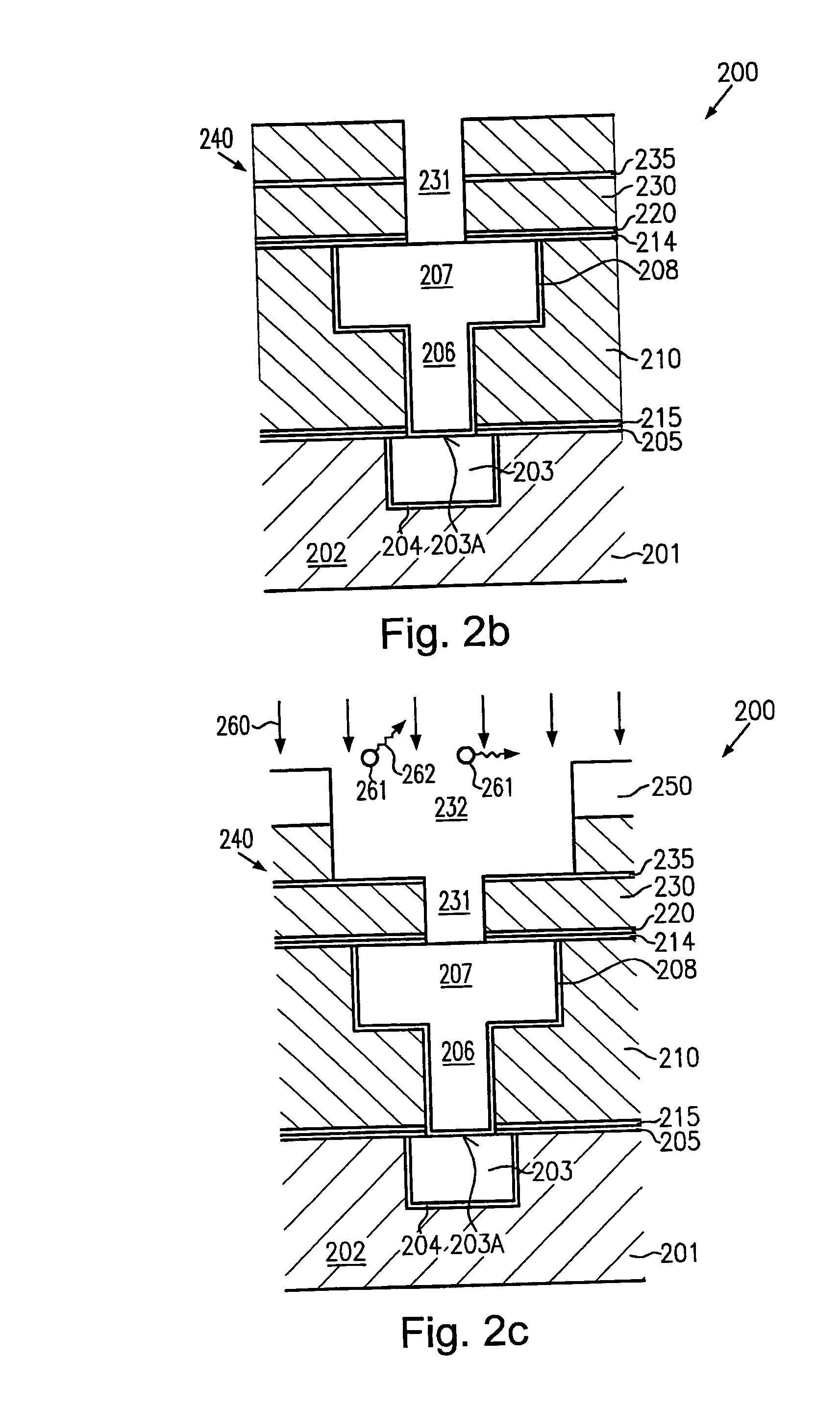

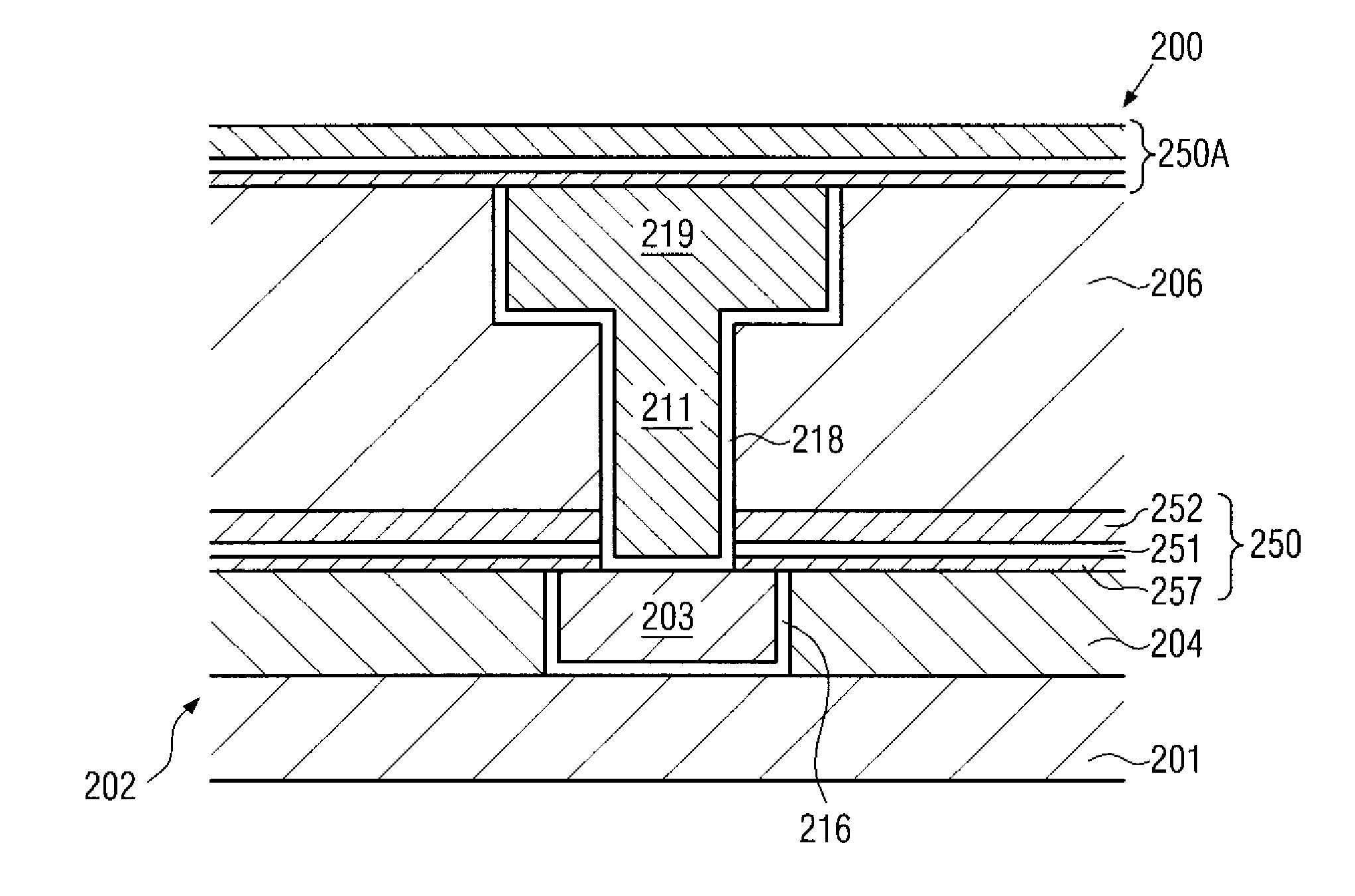

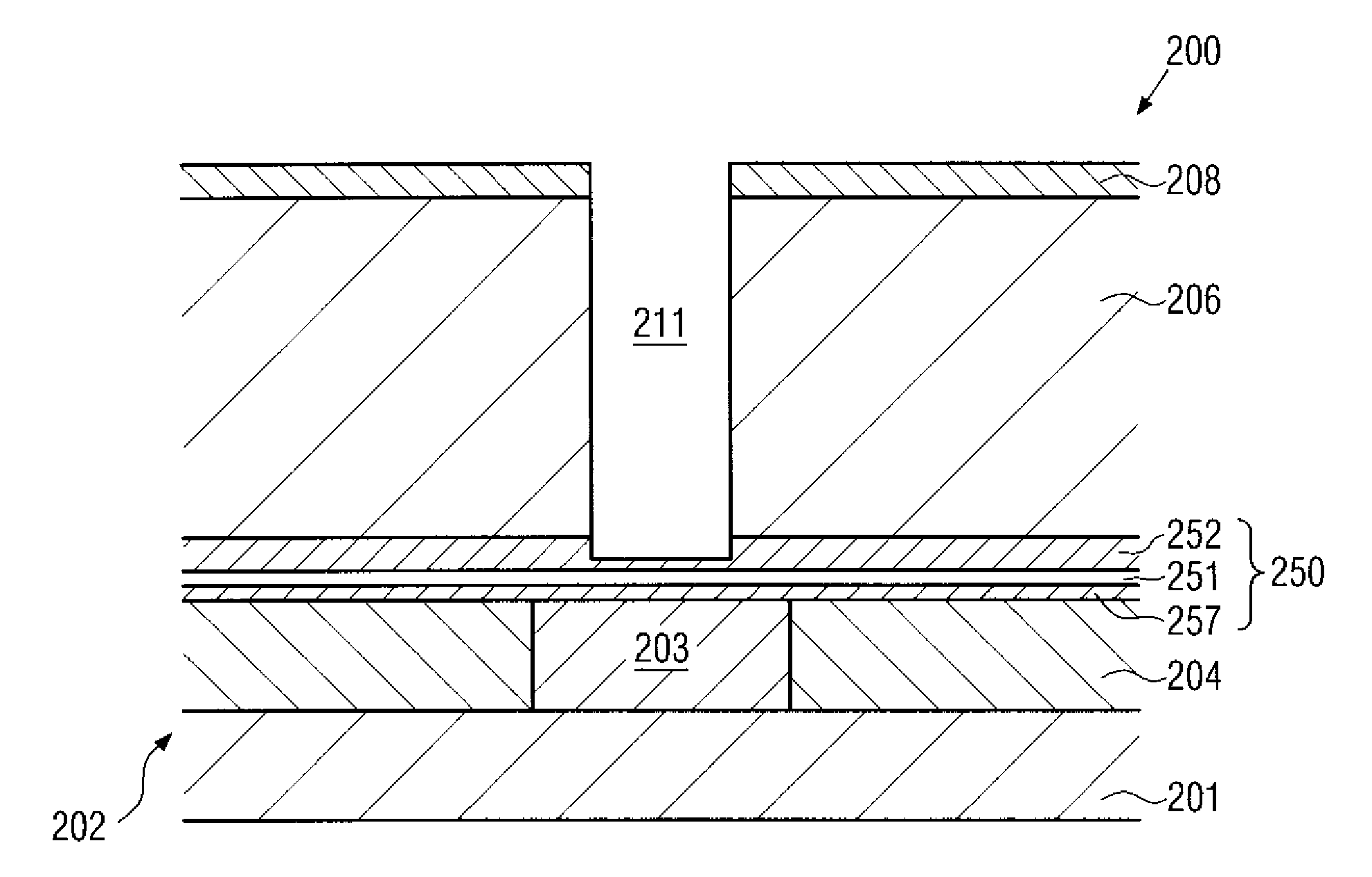

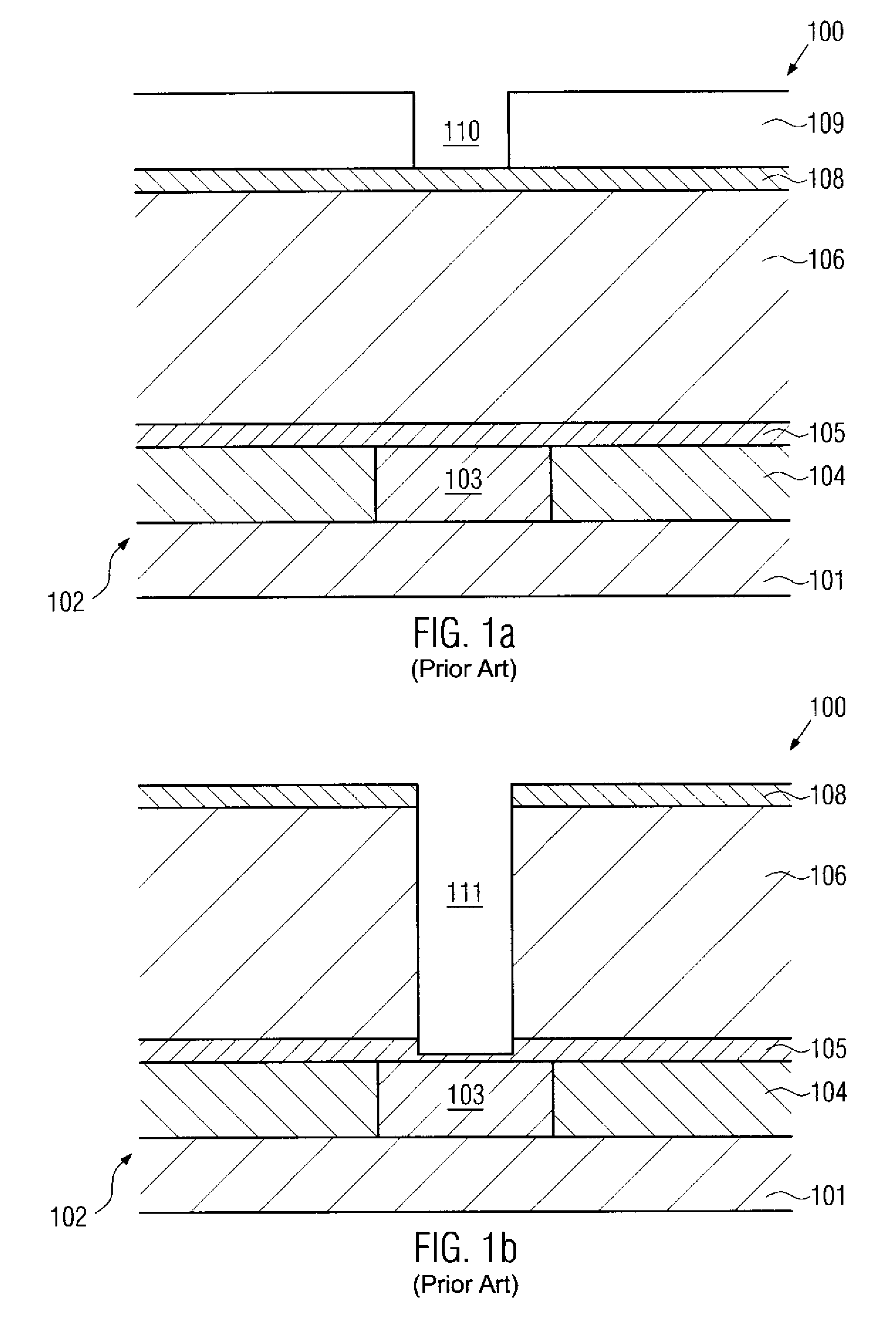

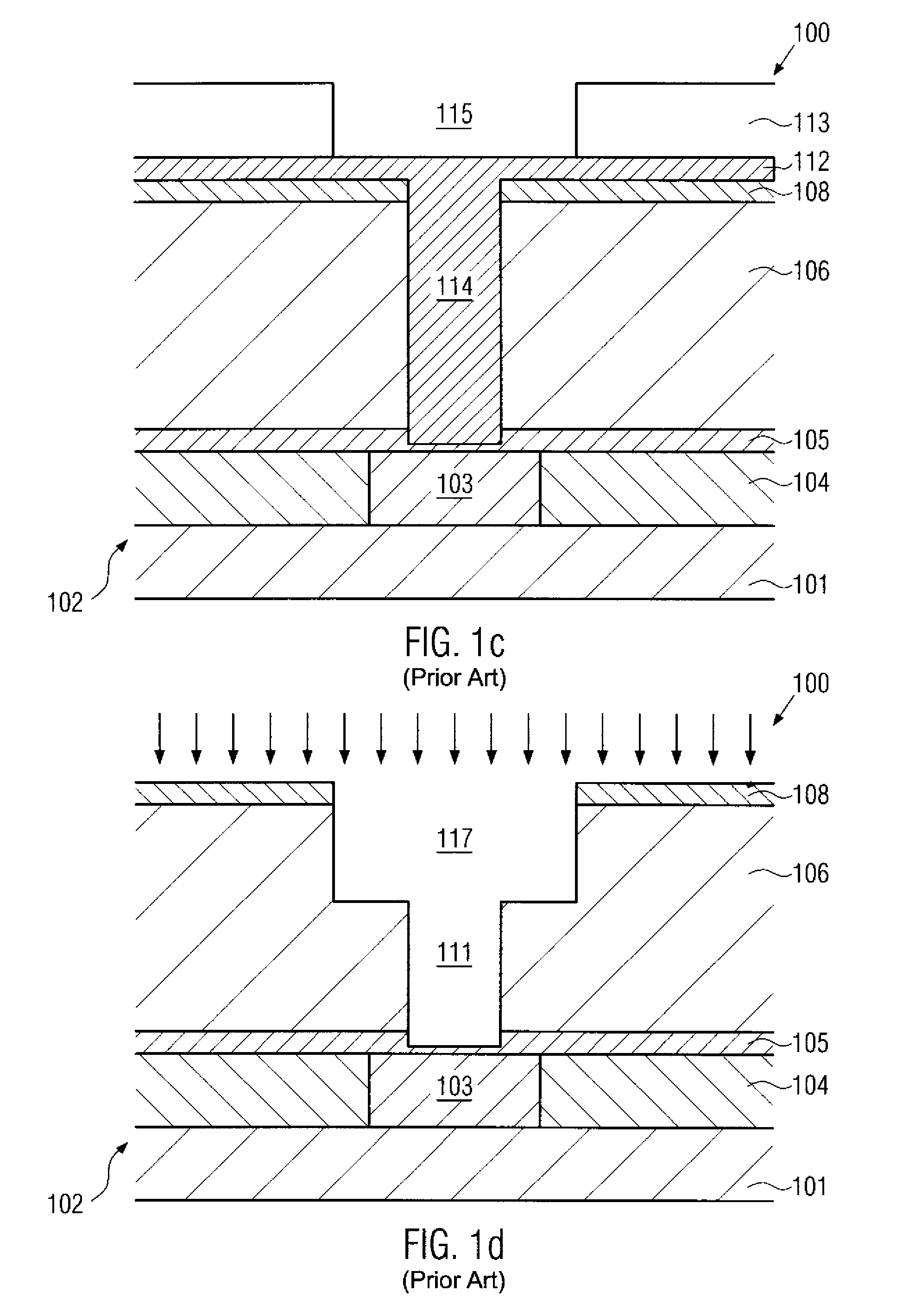

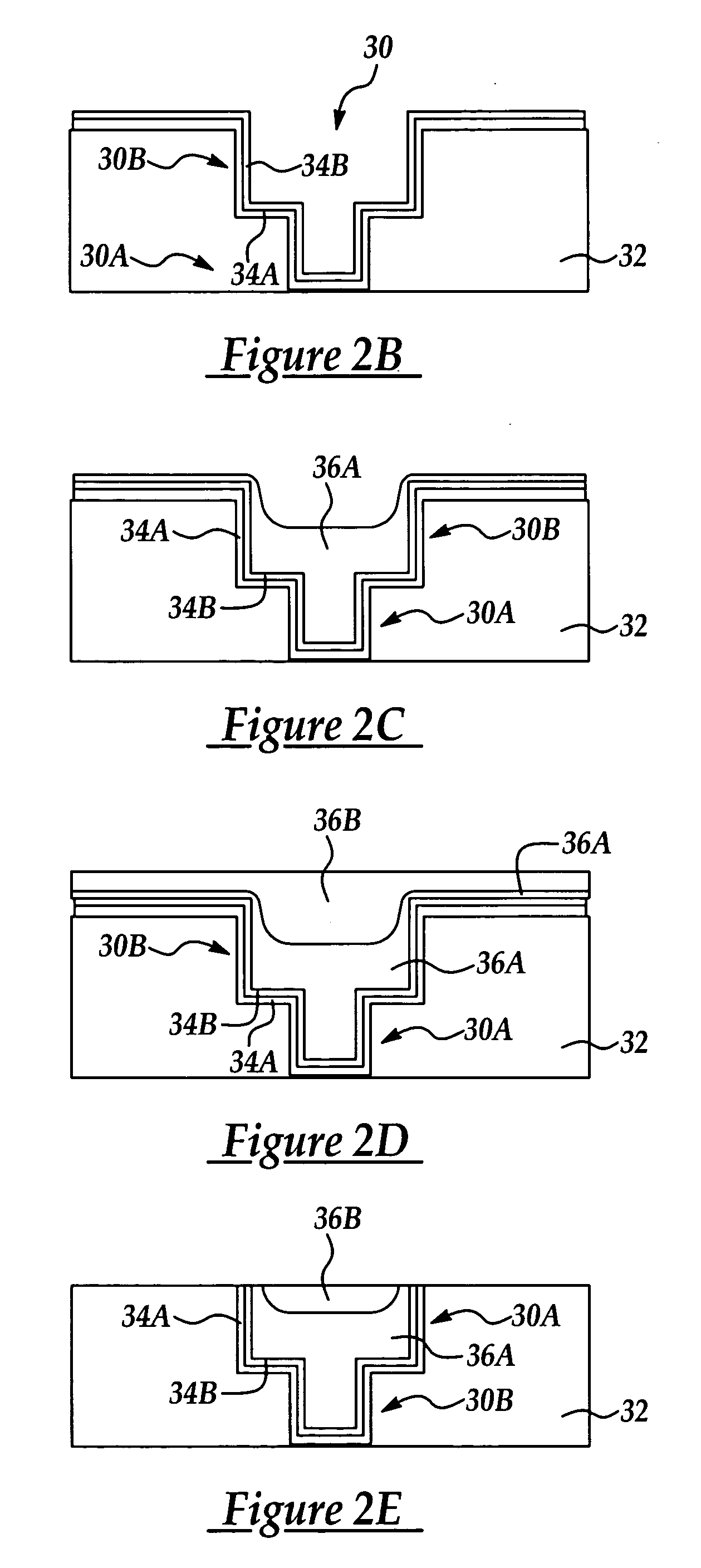

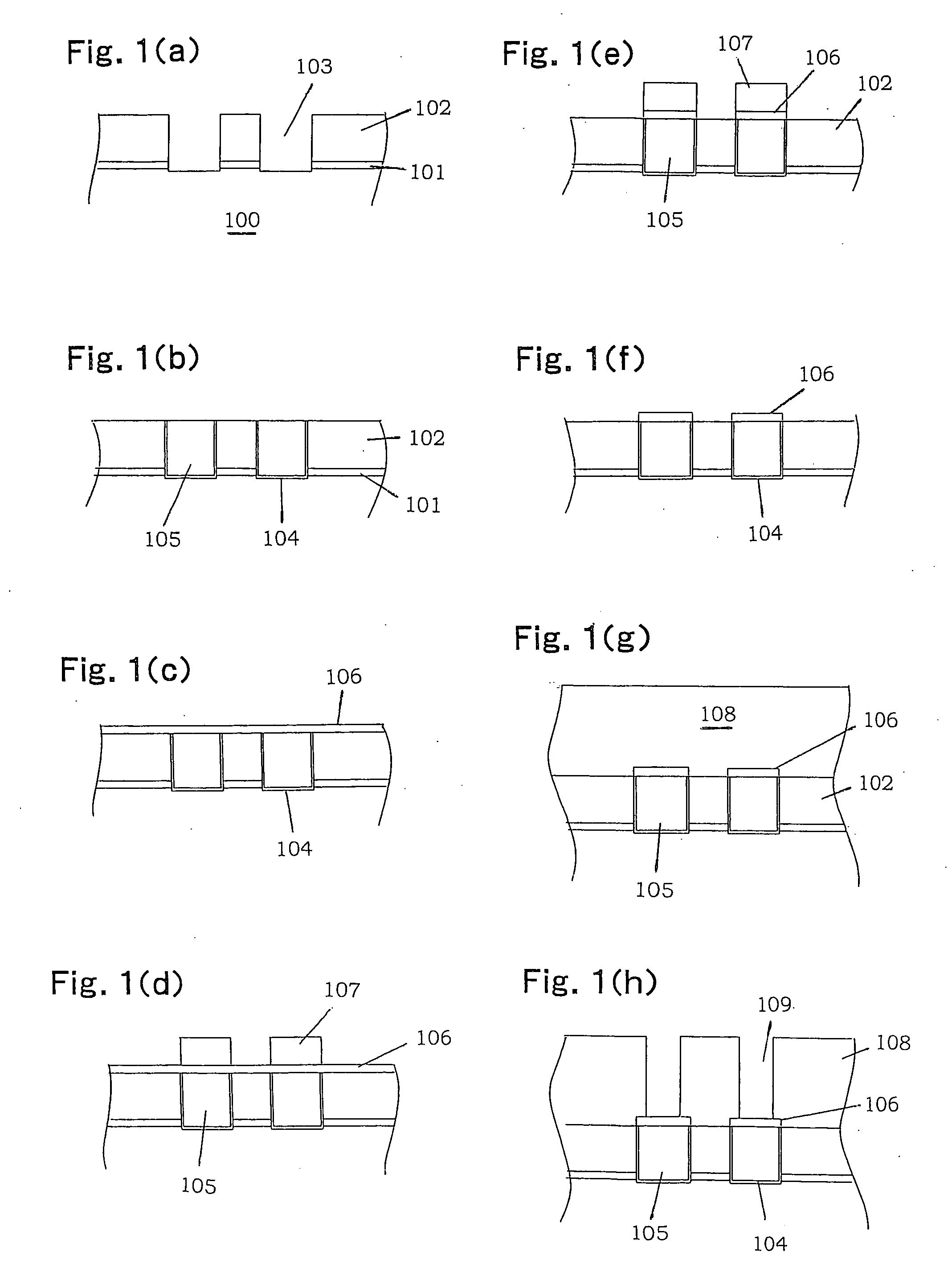

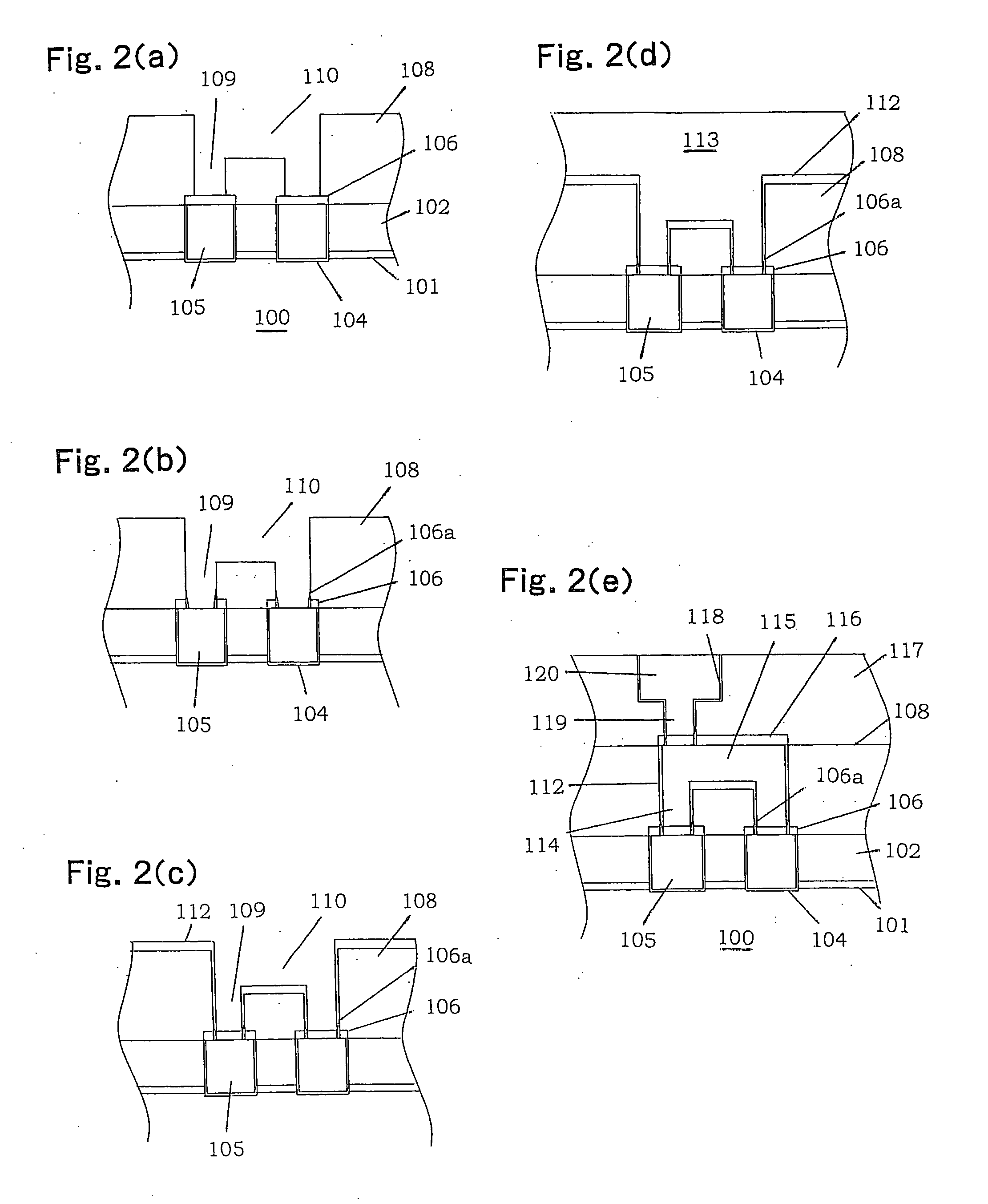

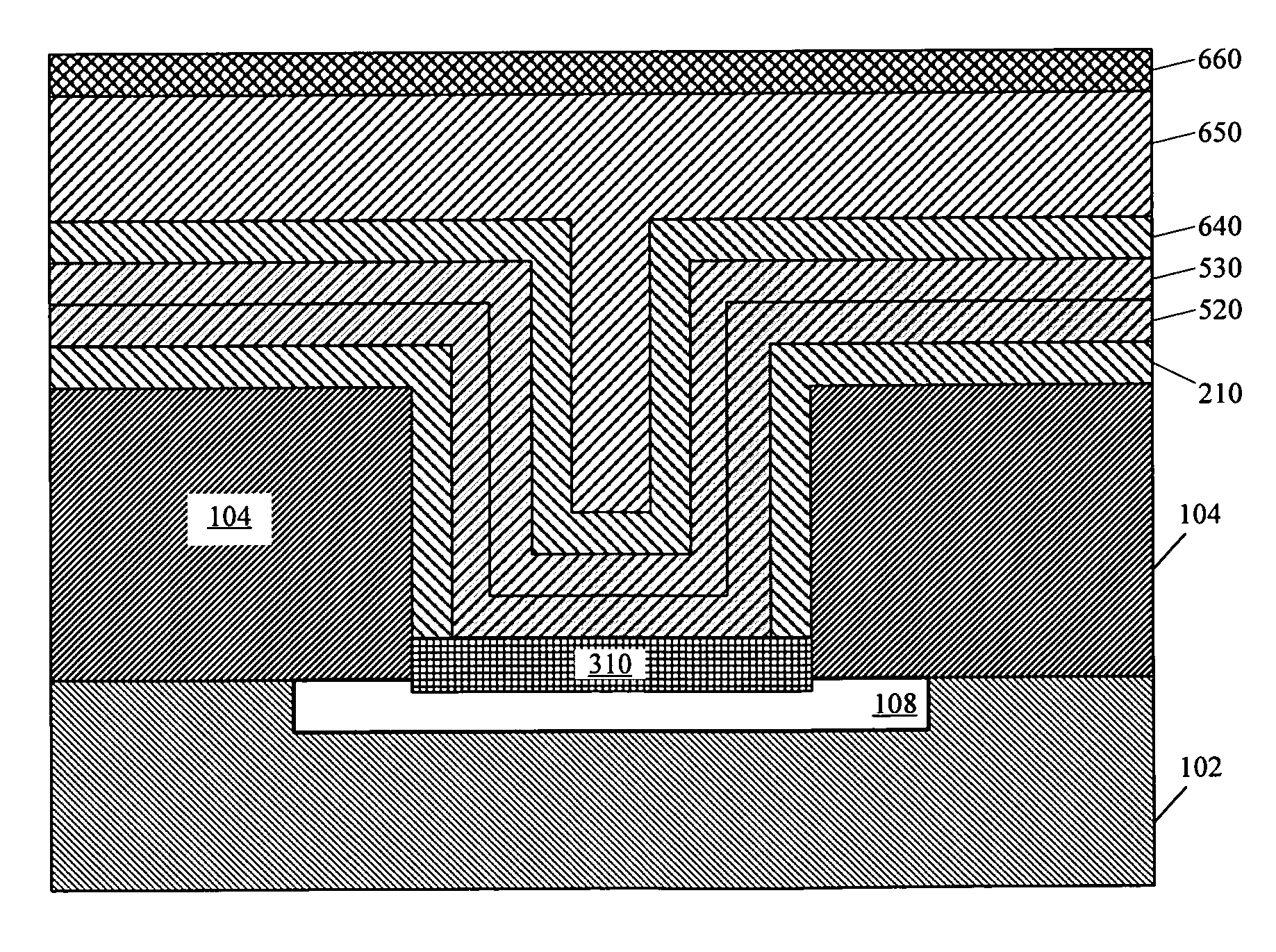

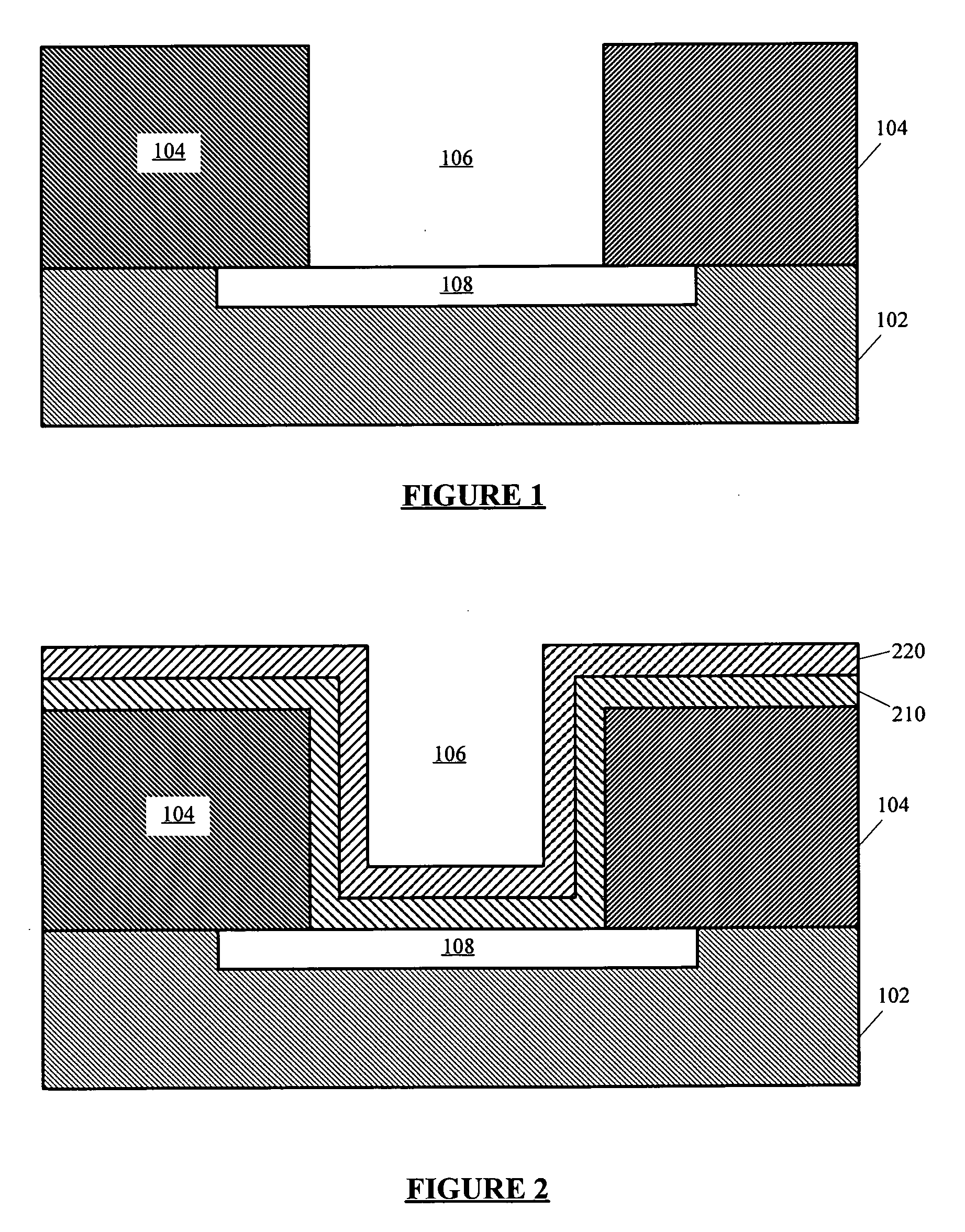

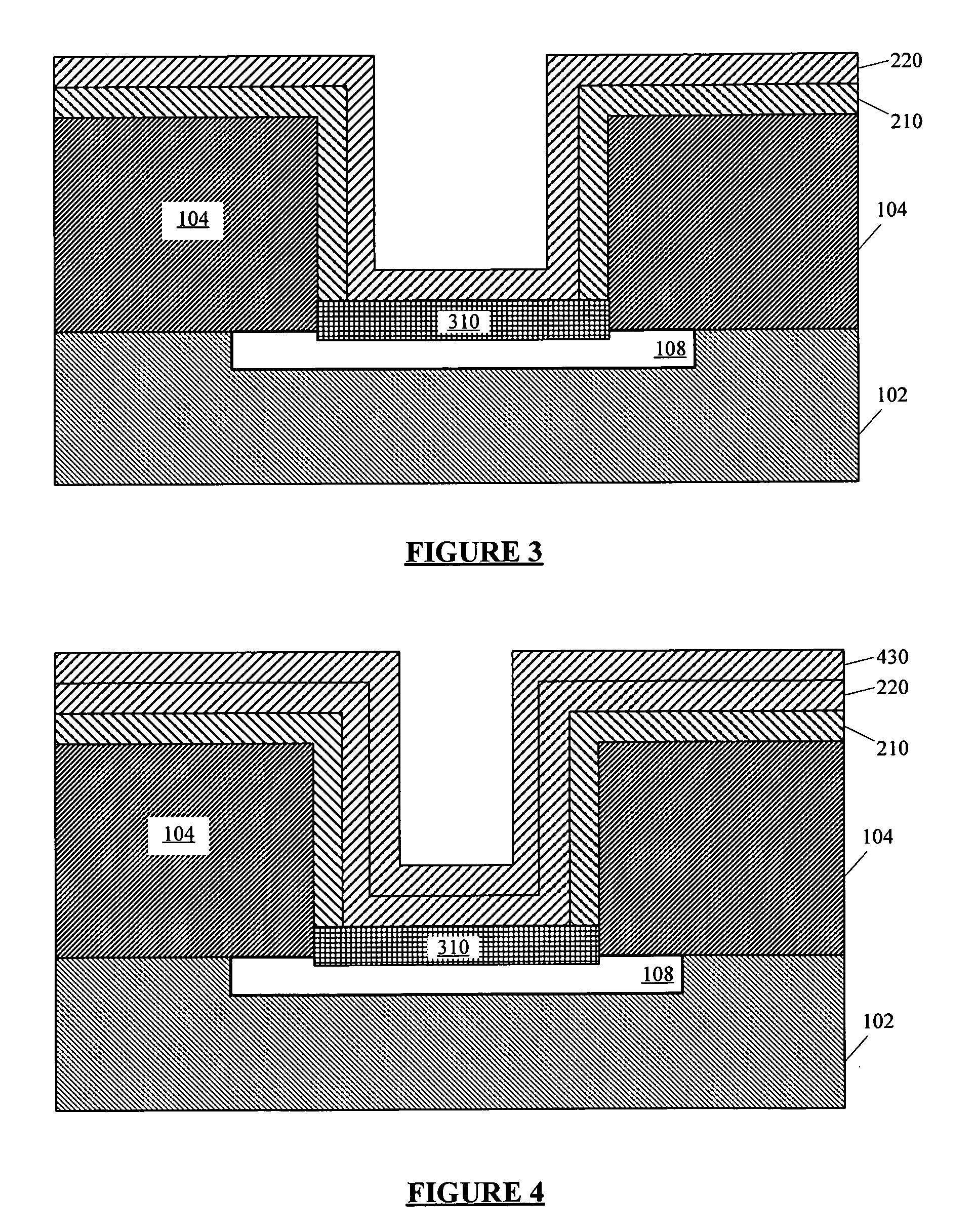

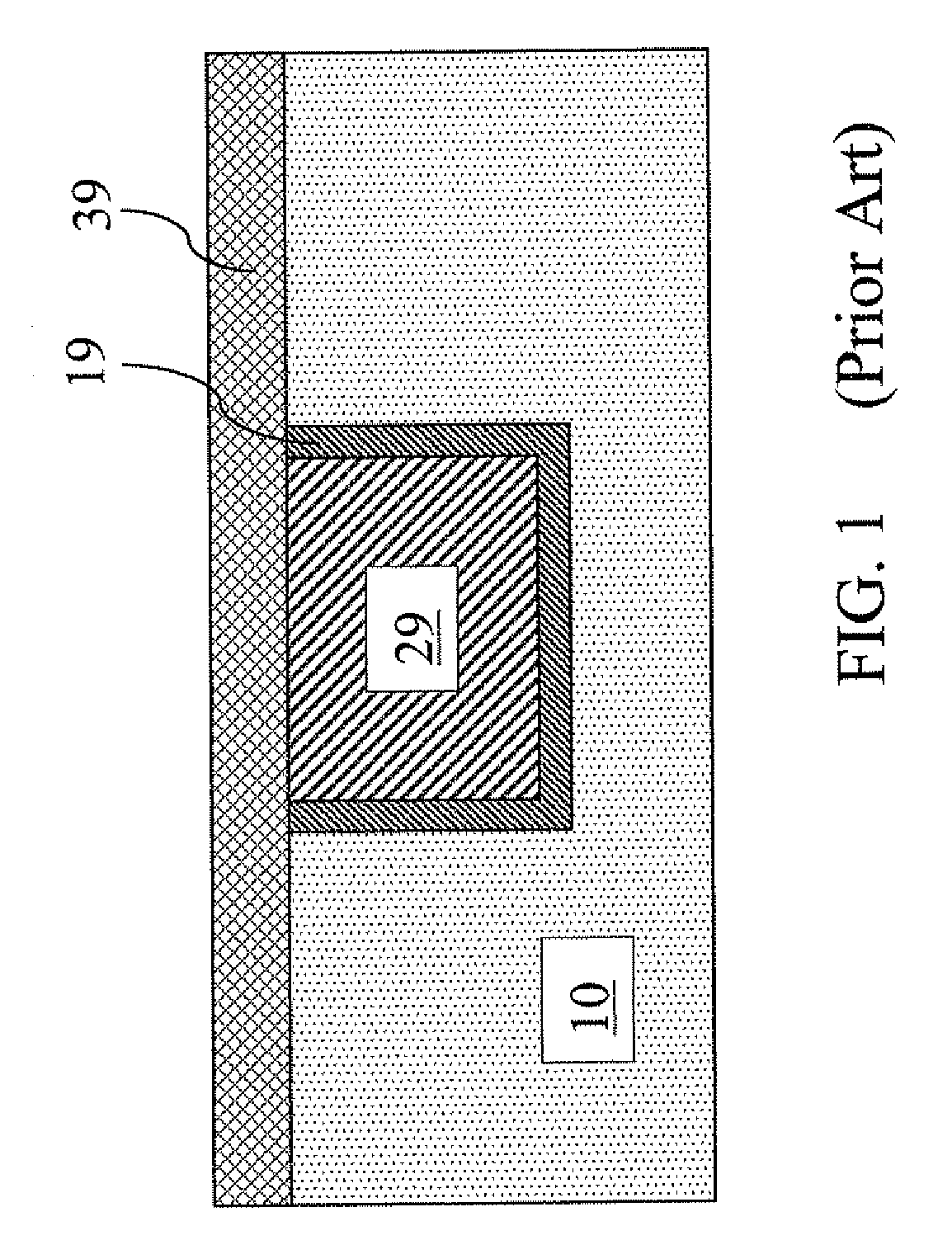

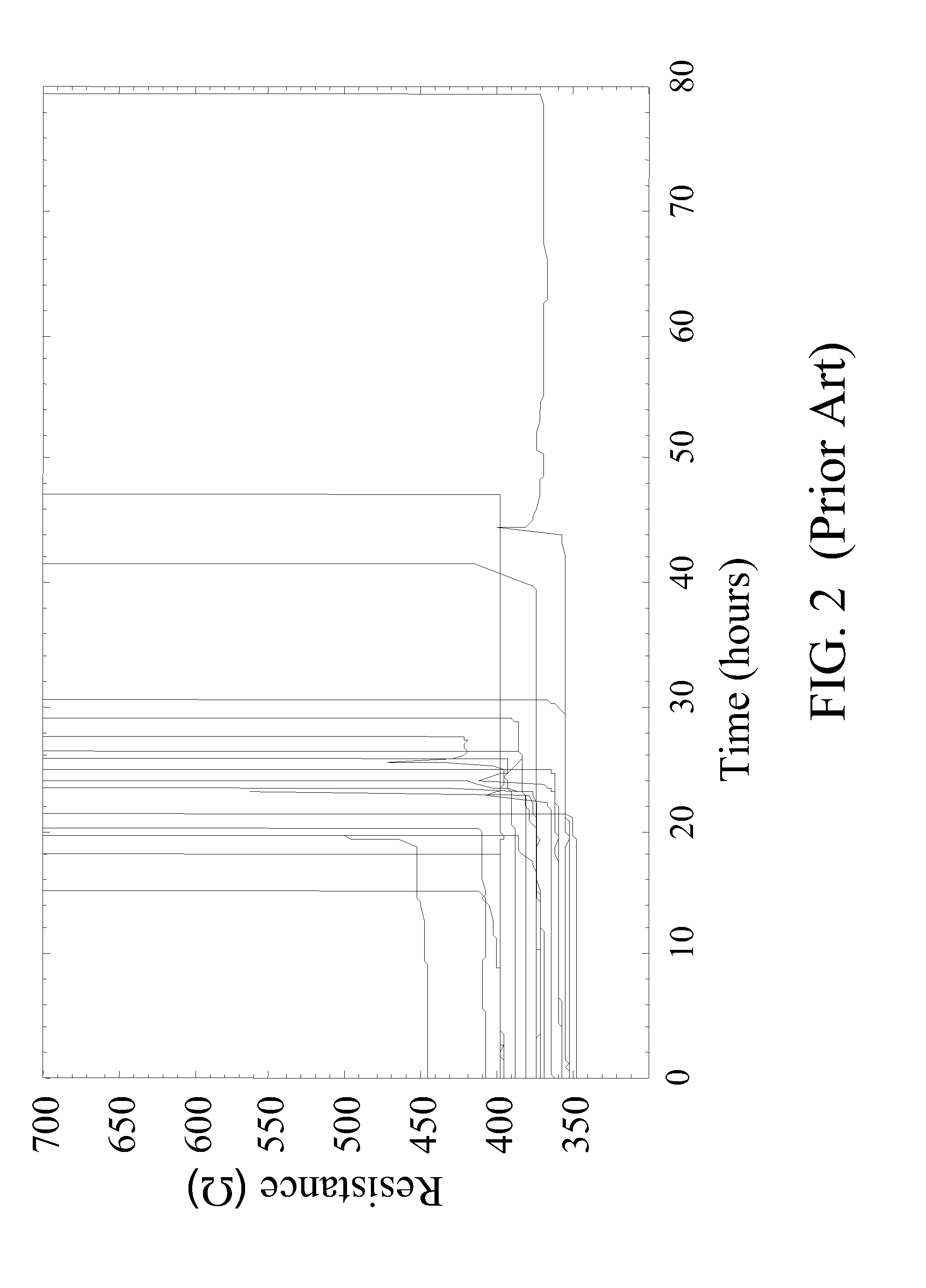

Partial inter-locking metal contact structure for semiconductor devices and method of manufacture

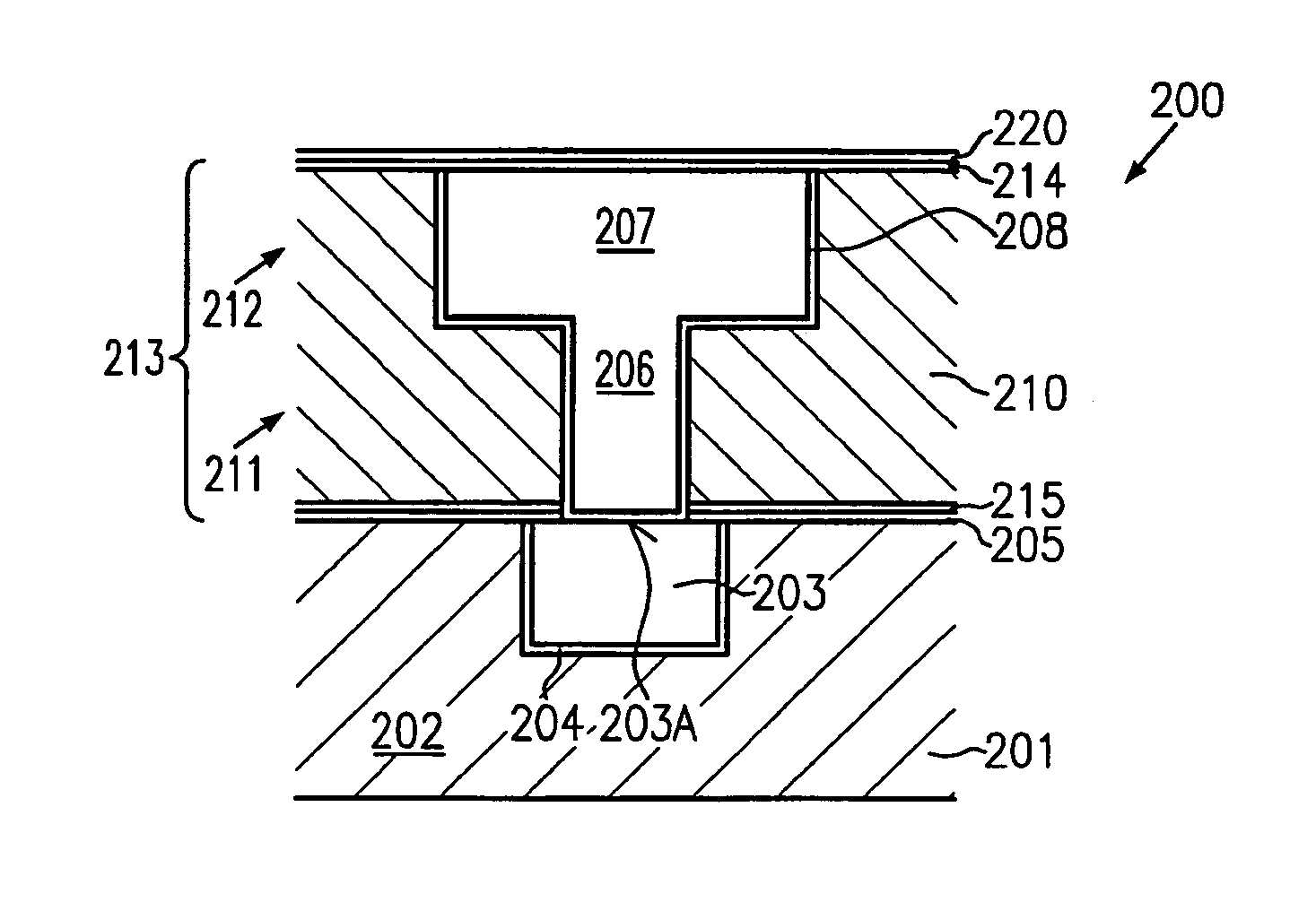

InactiveUS20050112957A1Improves Structural IntegrityHigh wiring densitySemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

A structure and method of fabricating a “Lego”-like interlocking contact for high wiring density semiconductors is characterized in that the barrier liner formed in the contact via extends only partially upwards into the adjacent wire level. As a consequence, current crowding and related reliability problems associated with conventional prior art interconnect structures is avoided and structural integrity of the contact via (metal stud) structure is enhanced. The novel “crown” shape of the Lego-like interlocking contact structure that is fabricated to extend in an upward direction may be employed for other integrated circuit applications including forming capacitor (e.g., MIMCAP) and heat sink structures due to its increased surface area.

Owner:IBM CORP

Tungsten liner for aluminum-based electromigration resistant interconnect structure

InactiveUS20090230555A1Improved resistance to electromigrationIncrease resistanceSemiconductor/solid-state device detailsSolid-state devicesMetal interconnectCompound (substance)

An underlying interconnect level containing underlying W vias embedded in a dielectric material layer are formed on a semiconductor substrate. A metallic layer stack comprising, from bottom to top, a low-oxygen-reactivity metal layer, a bottom transition metal layer, a bottom transition metal nitride layer, an aluminum-copper layer, an optional top transition metal layer, and a top transition metal nitride layer. The metallic layer stack is lithographically patterned to form at least one aluminum-based metal line, which constitutes a metal interconnect structure. The low-oxygen-reactivity metal layer enhances electromigration resistance of the at least one aluminum-based metal line since formation of compound between the bottom transition metal layer and the dielectric material layer is prevented by the low-oxygen-reactivity metal layer, which does not interact with the dielectric material layer.

Owner:GLOBALFOUNDRIES INC

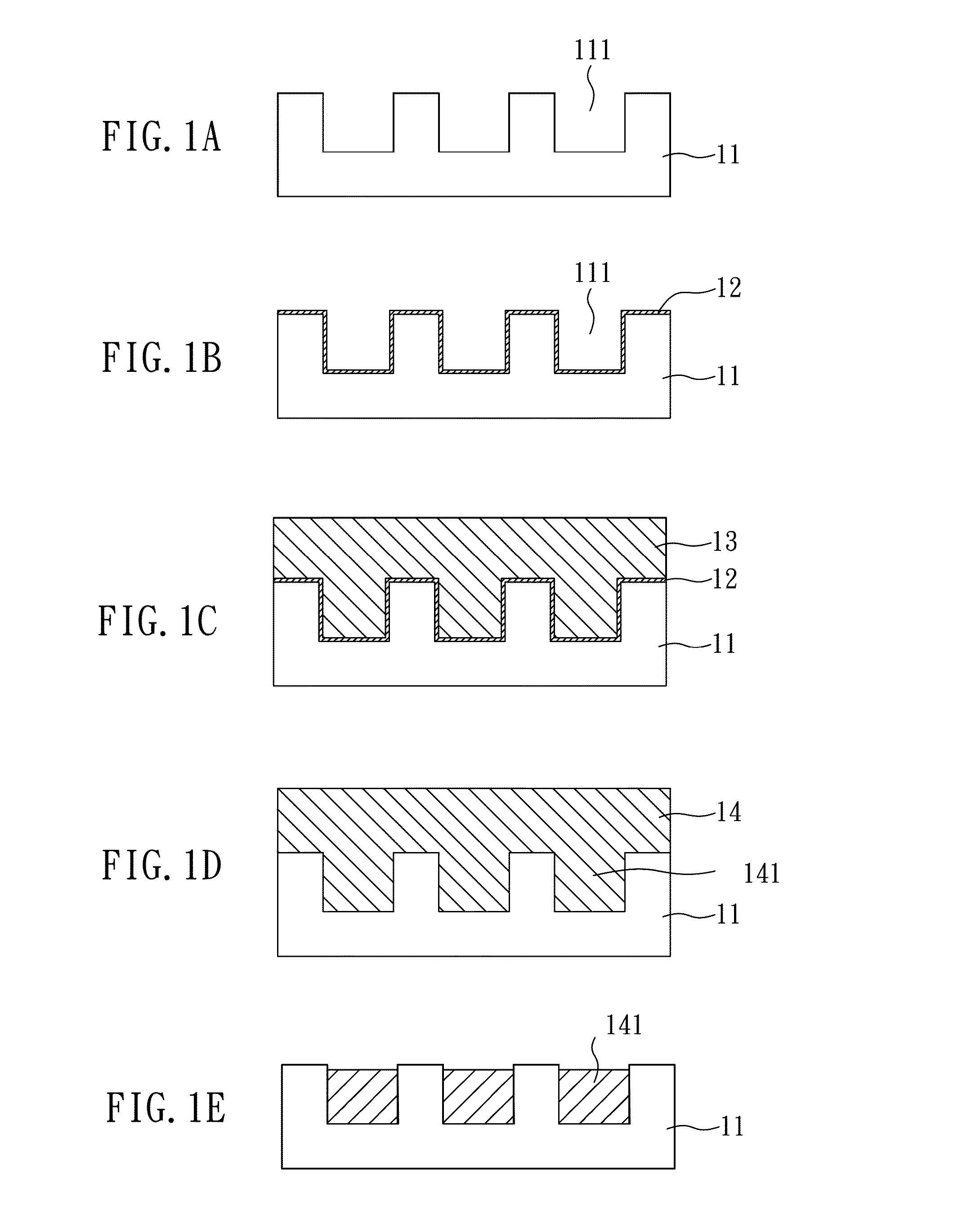

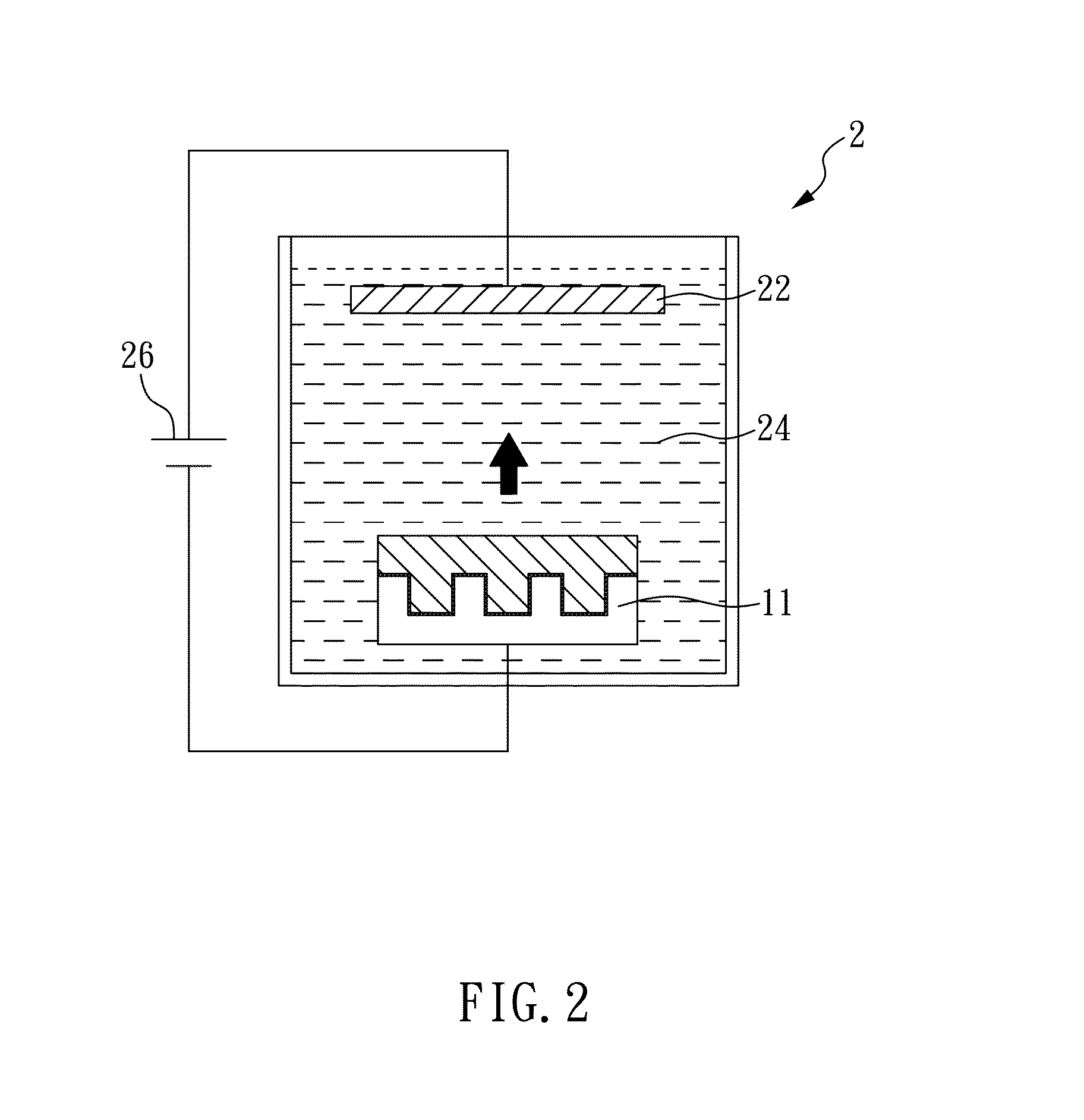

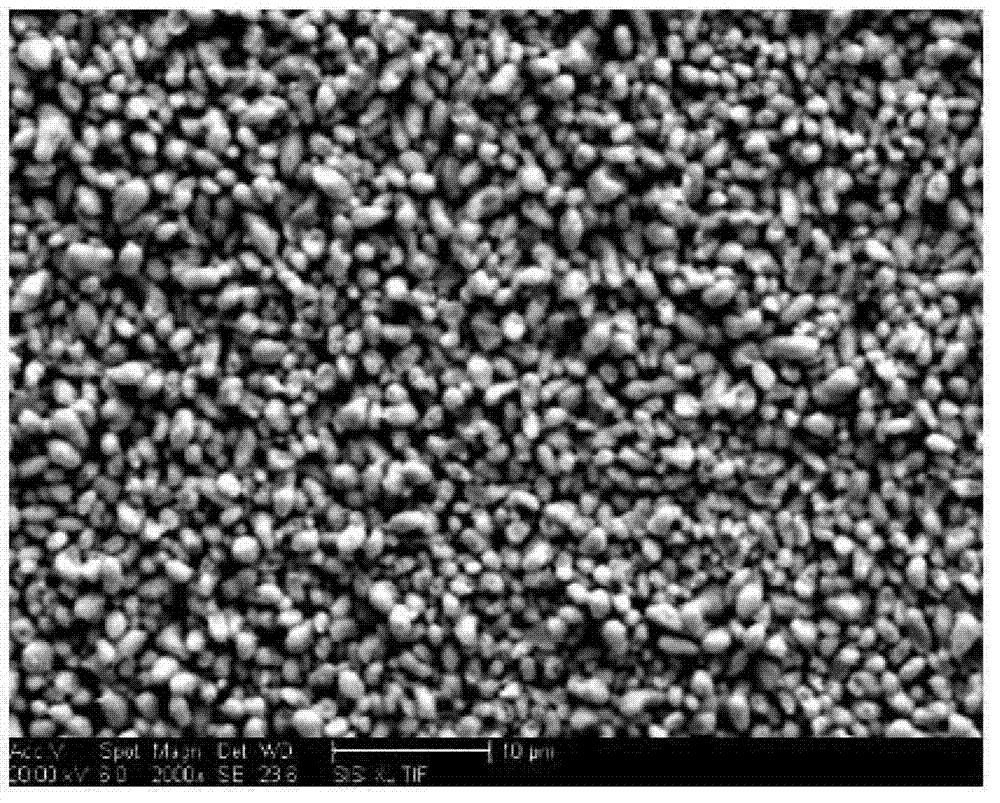

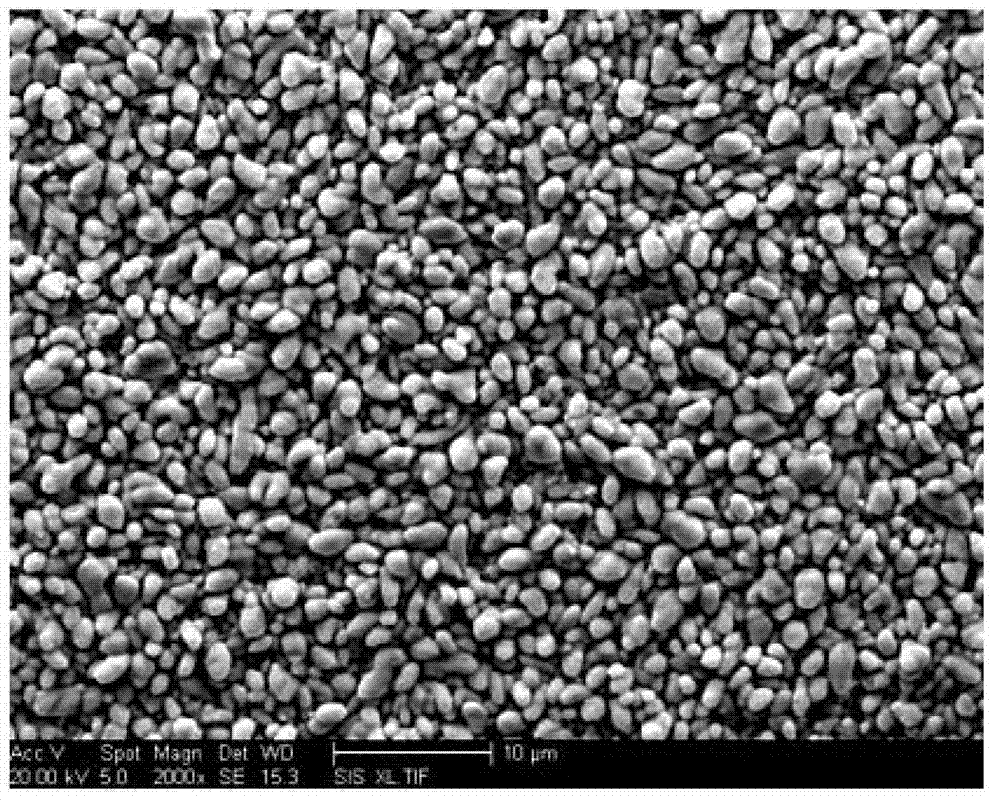

Circuit board with twinned cu circuit layer and method for manufacturing the same

ActiveUS20140103501A1Low production costHigh densitySemiconductor/solid-state device detailsSolid-state devicesEngineeringCopper

A circuit board with twinned Cu circuit layer and a method for manufacturing the same are disclosed, wherein the method comprises the following steps: (A) providing a substrate with a first circuit layer formed thereon, wherein the first circuit layer comprises a conductive pad; (B) forming a first dielectric layer on the surface of the substrate; (C) forming plural openings in the first dielectric layer, wherein each opening penetrates through the first dielectric layer and communicates with the conductive pad to expose the conductive pad; (D) forming a Cu seeding layer in the openings; (E) forming a nano-twinned Cu layer in the openings with an electroplating process; and (F) annealing the substrate to transfer the material of the Cu seeding layer into nano-twinned Cu, wherein the nano-twinned Cu layer and the transferred Cu seeding layer are formed into a second circuit layer.

Owner:NAT CHIAO TUNG UNIV

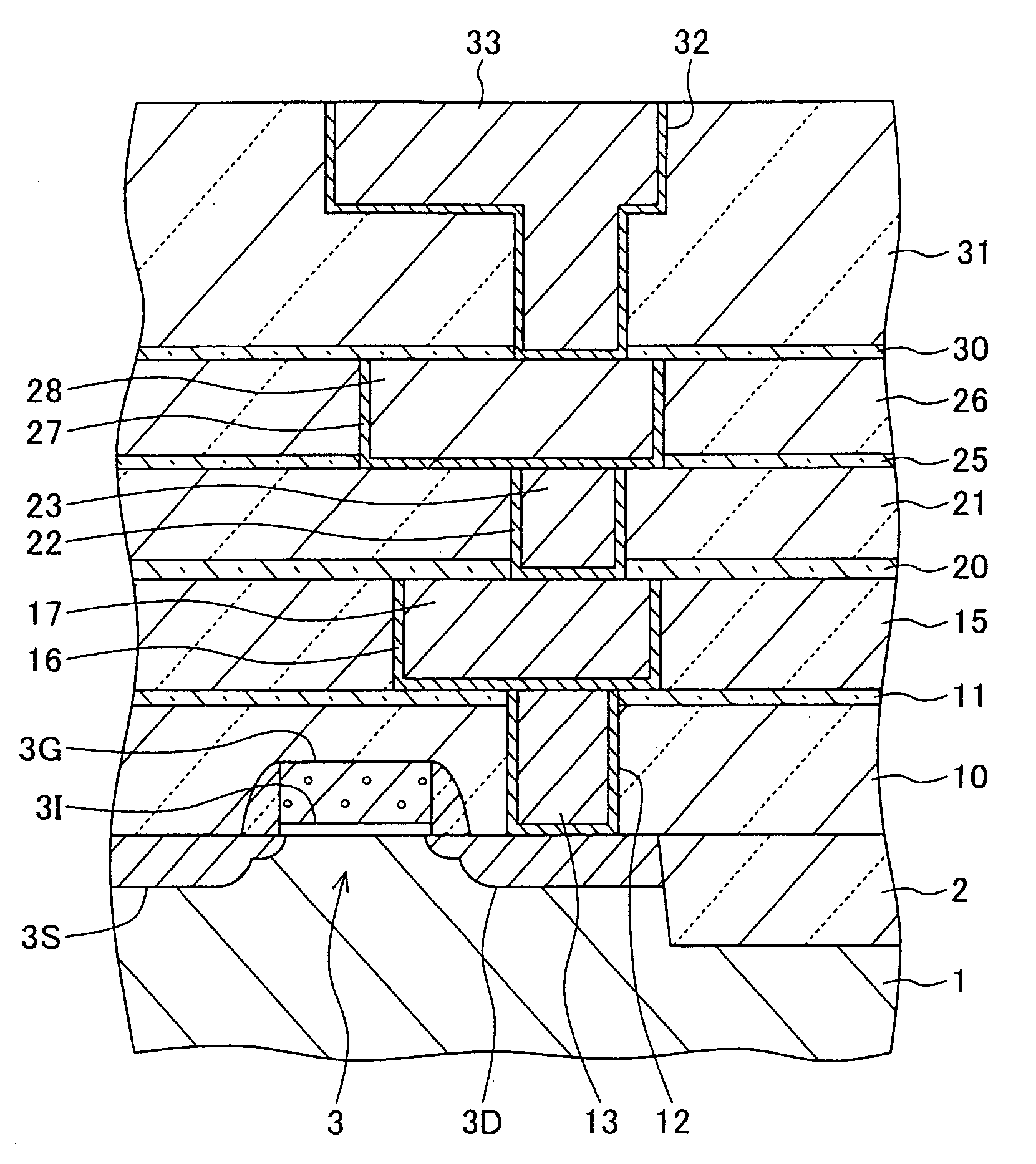

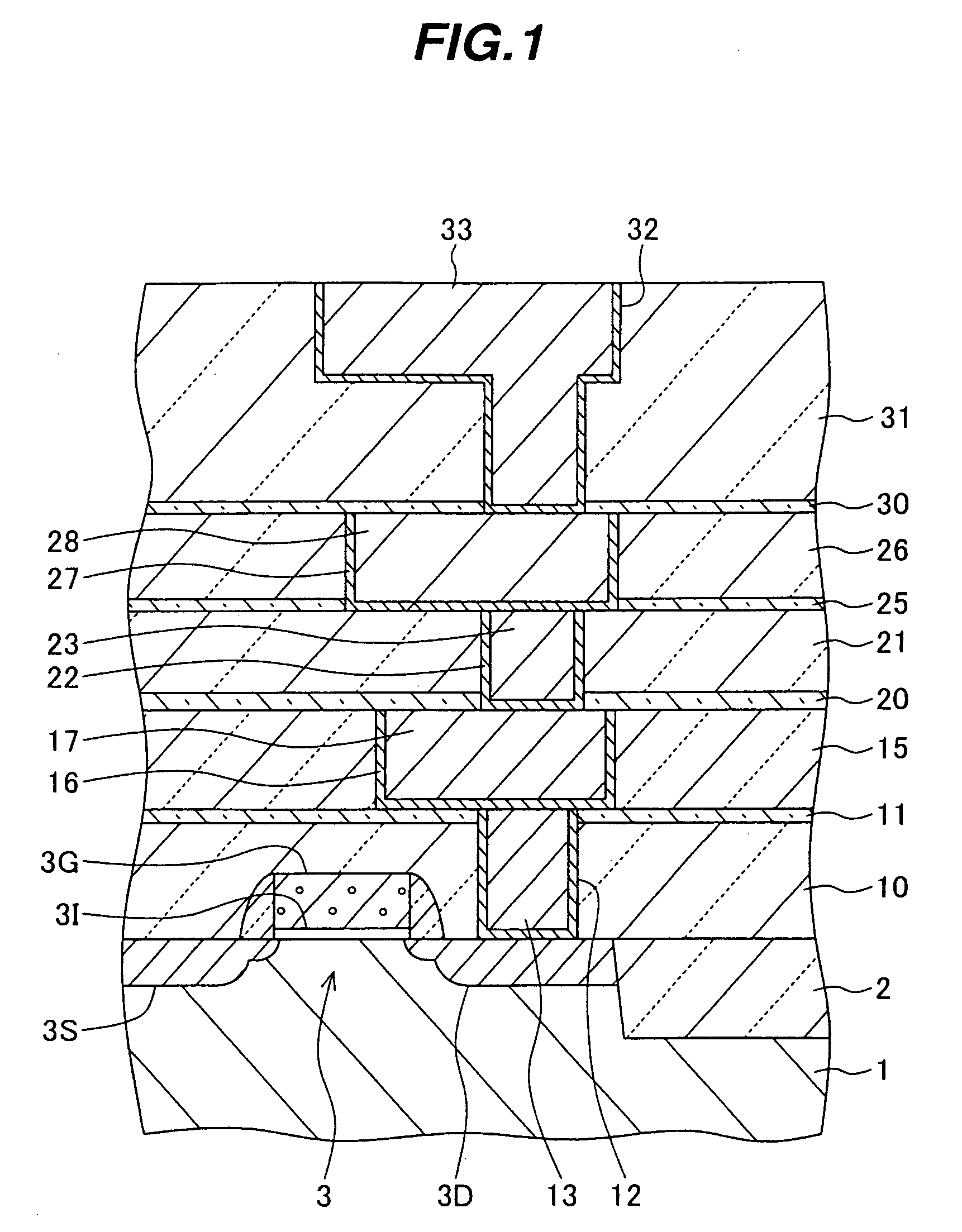

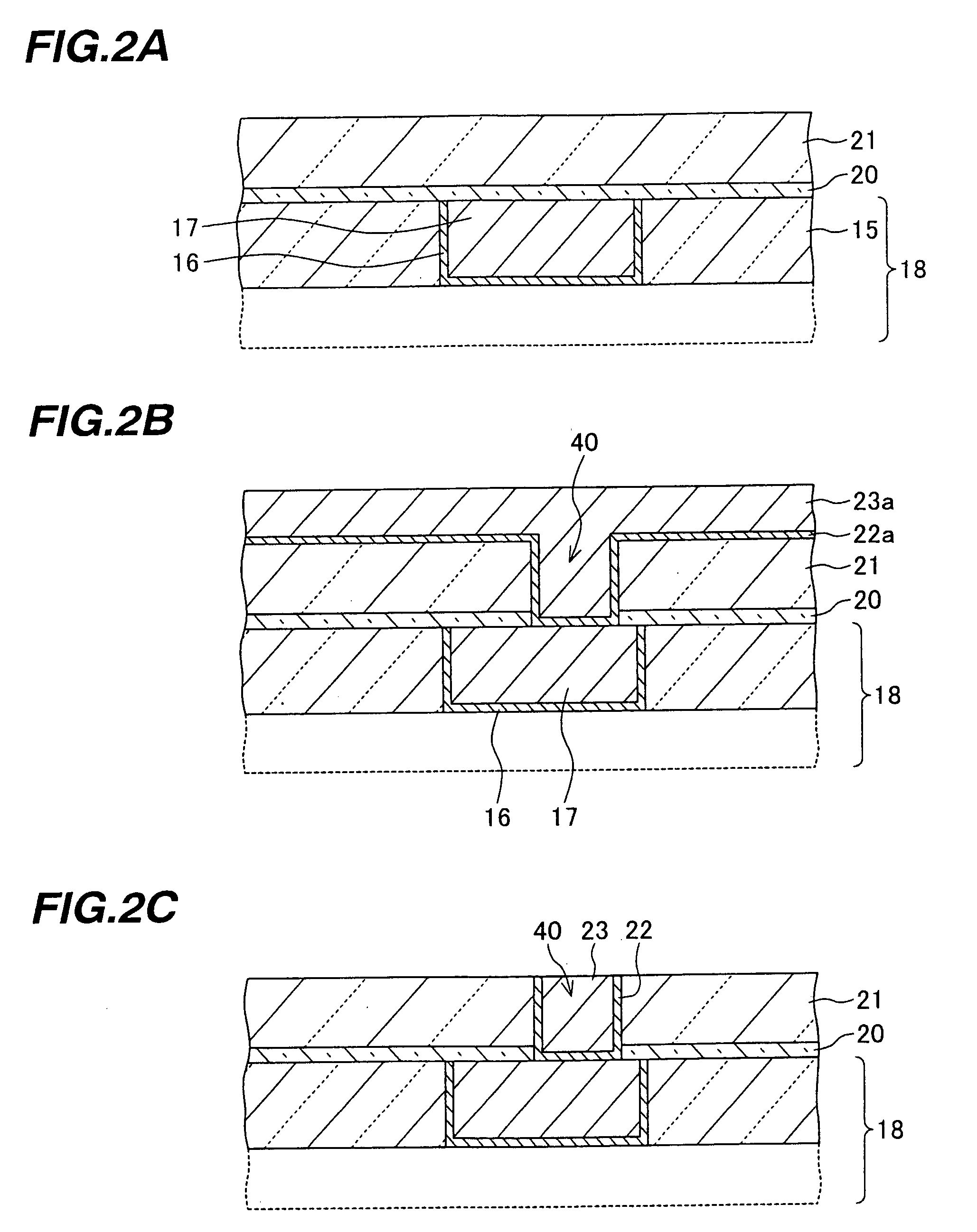

Semiconductor device having copper wiring and its manufacture method

ActiveUS20060012046A1Sufficient stressmigrationImproved resistance to electromigrationSemiconductor/solid-state device detailsSolid-state devicesDevice materialSulfur

A first interlayer insulating film made of insulting material is formed over an underlying substrate. A via hole is formed through the first interlayer insulating film. A conductive plug made of copper or alloy mainly consisting of copper is filled in the via hole. A second interlayer insulating film made of insulating material is formed over the first interlayer insulating film. A wiring groove is formed in the second interlayer insulating film, passing over the conductive plug and exposing the upper surface of the conductive plug. A wiring made of copper or alloy mainly consisting of copper is filled in the wiring groove. The total atom concentration of carbon, oxygen, nitrogen, sulfur and chlorine in the conductive plug is lower than the total atom concentration of carbon, oxygen, nitrogen, sulfur and chlorine in the wiring.

Owner:FUJITSU LTD

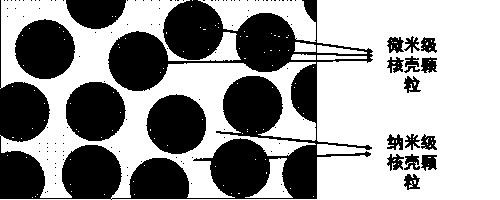

Multi-scale micro-nano particle composite soldering paste for field of electronic packaging and preparation method of multi-scale micro-nano particle composite soldering paste

ActiveCN109664049ASolve the disadvantages of poor oxidation resistance and difficulty in preservationSolve uneven distributionWelding/cutting media/materialsSoldering mediaMicro nanoActive agent

The invention provides the multi-scale micro-nano particle composite soldering paste for the field of electronic packaging and a preparation method and an application process of the multi-scale micro-nano particle composite soldering paste. The novel composite soldering paste is formed by mixing metal powder and a soldering flux, the metal powder is composed of 30 to 70 nm in particle size and 3 to 7 microns, 15 to 25 microns of Cu @ Ag particles, 40 to 60 nm of Ni @Ag particles and 1 to 2 microns of Ag particles, the scaling powder is composed of solvent isopropanol, an active agent stearicacid, a film-forming agent mixed rosin, polyethylene glycol, a modifier triethanolamine and a surfactant octylphenol polyoxyethylene ether, the existence of Cu @ Ag particles in the composite solder paste is reduced relative to the cost of the nano-silver solder paste, the electromigration resistance can be improved, the Ag particles can protect the integrity of the Cu @ Ag core-shell structure, under a high-frequency induction process condition, the magnetism of the Ni @ Ag particles ni enables the particle distribution to be more uniform, the density is improved, and the electric conductionheat conduction performance is improved. The method is low in cost, simple and controllable in process and high in efficiency, the problems that an existing device pasting material is high in cost, low in service temperature, long in process time and the like are solved.

Owner:哈尔滨景成创业投资管理有限公司

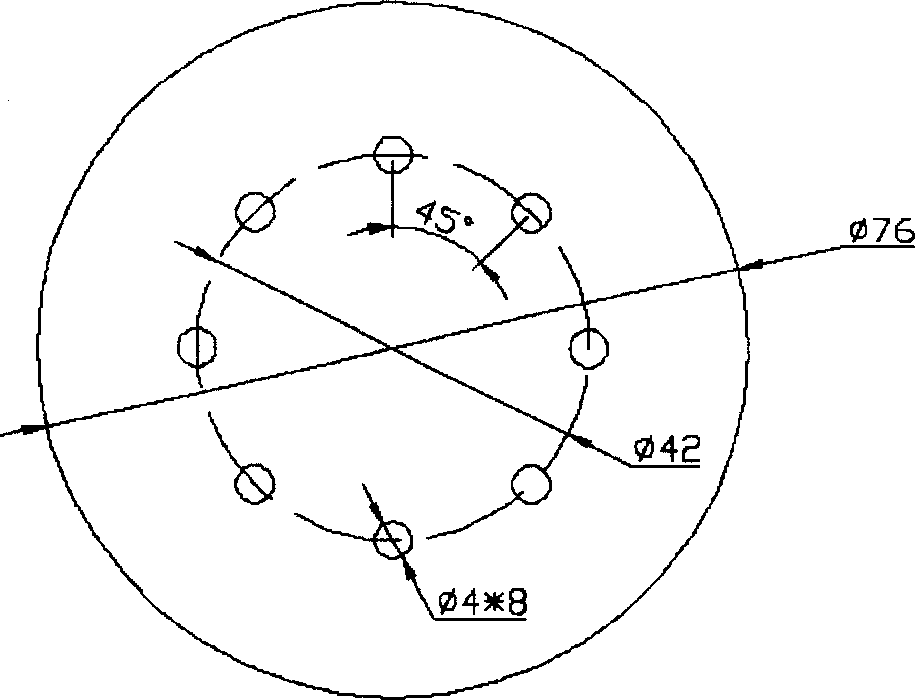

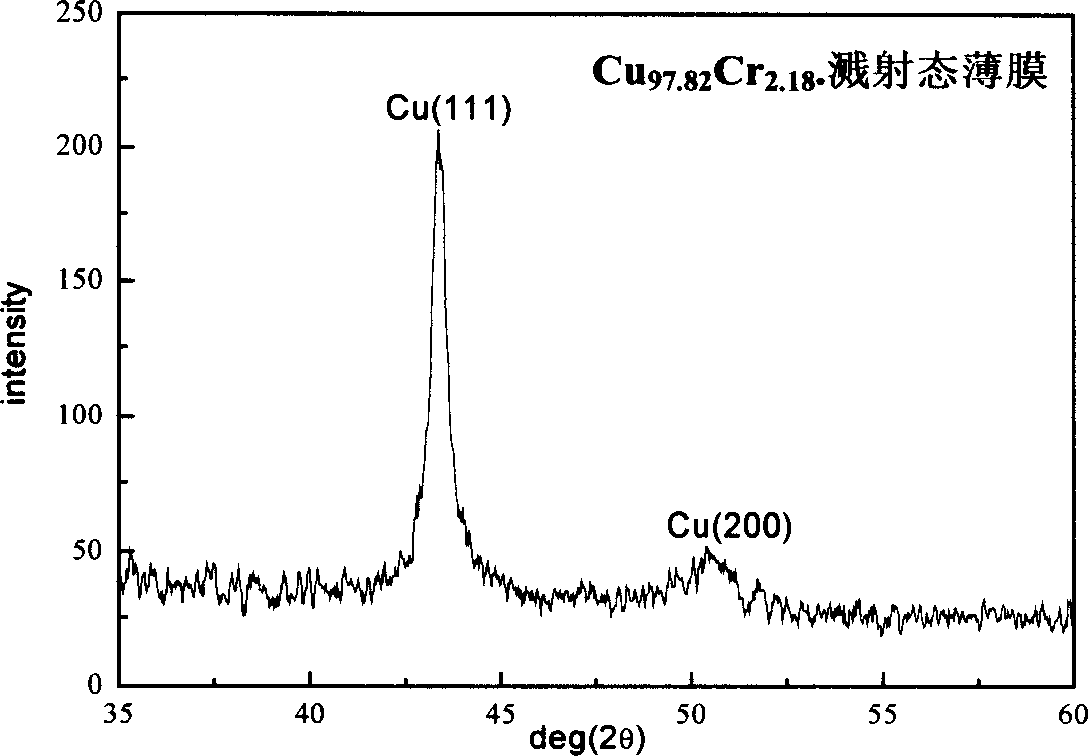

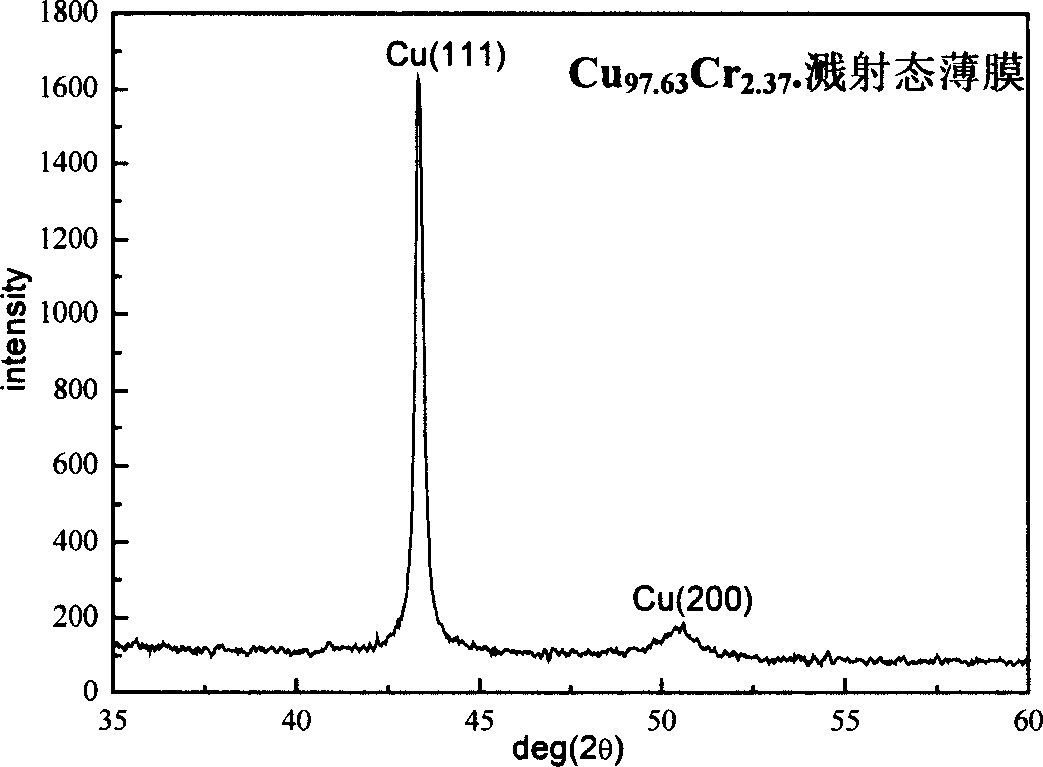

Single-target magnetic control sputtering process for Cu1-xCrx alloy film

InactiveCN1807675AImproved resistance to electromigrationHigh purityVacuum evaporation coatingSputtering coatingSputteringSmall hole

The invention discloses a single target magnetron sputtering Cu1-xCrx alloy film producing method in the film technique domain, which is characterized by the following steps: working brass plate for copper target according to requirement of sputter instrument; drilling circular of different amount and different diameter or taper eyelet on target radius of sputtering area of copper target according to sputtering parameter of sputtering apparatus; annexing fender sheet of target material; working chrome metal for small stick according to size and form and fitting tightly for eyelet; cleaning copper fender sheet, target material, foundation base then putting in sputtering apparatus; choosing sputtering power; adjusting sputtering target position and sputtering parameter; preparing chrome copper alloy film (Cu1-xCrx, xú¢1. 19-2. 37, x as atomic percentage). The invention saves original material, improves film pureness and production efficiency.

Owner:SHANGHAI JIAO TONG UNIV

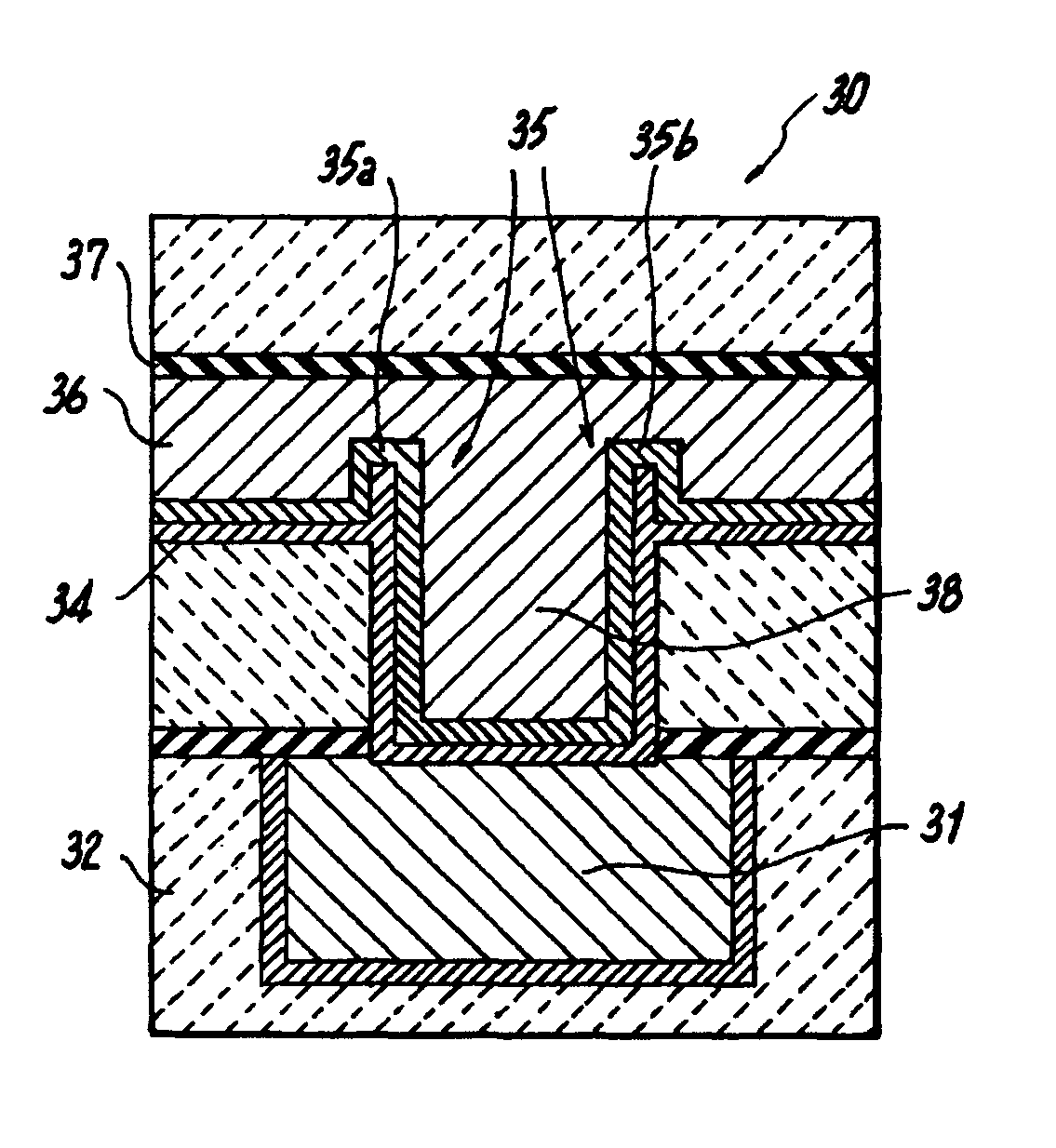

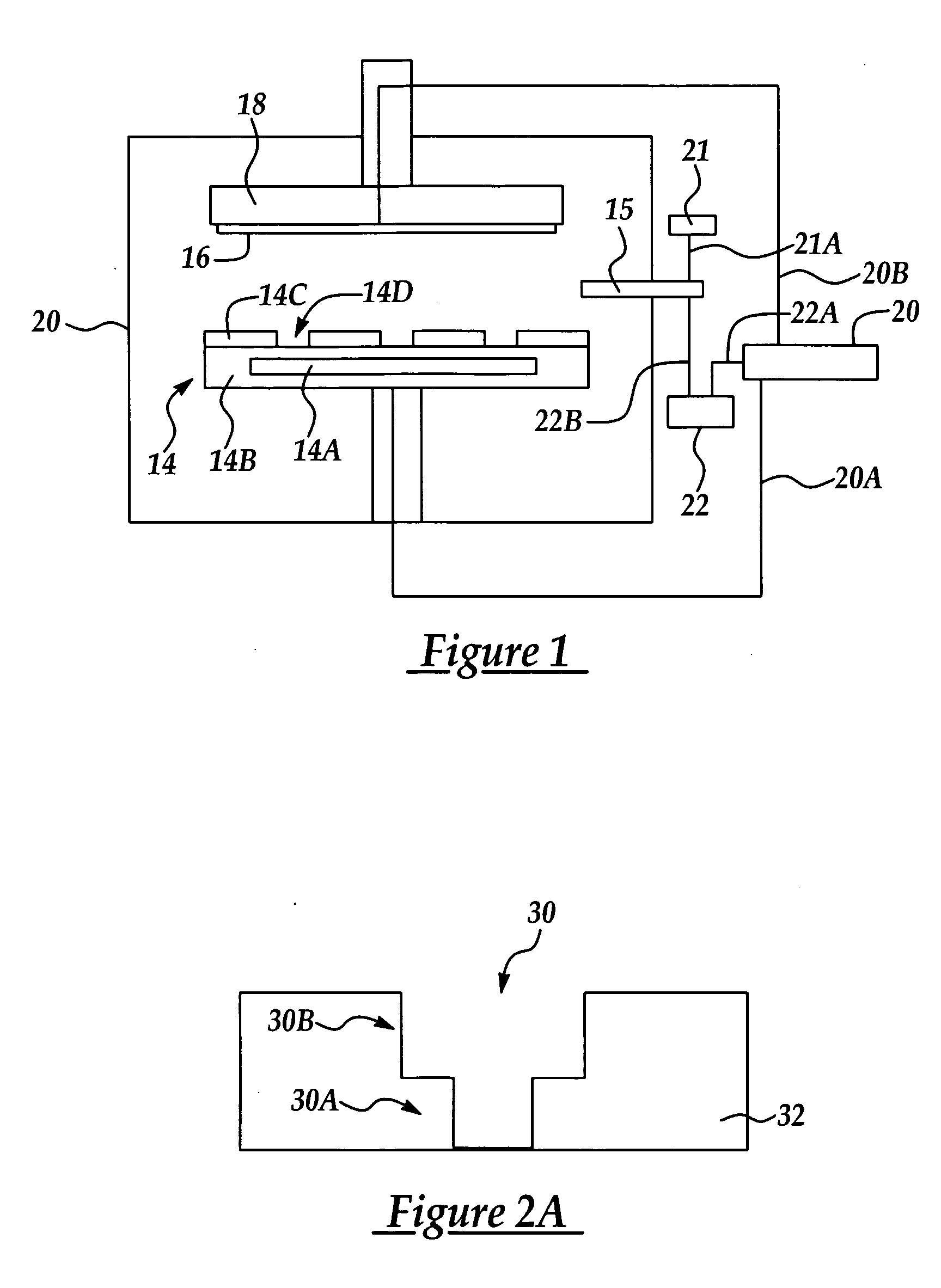

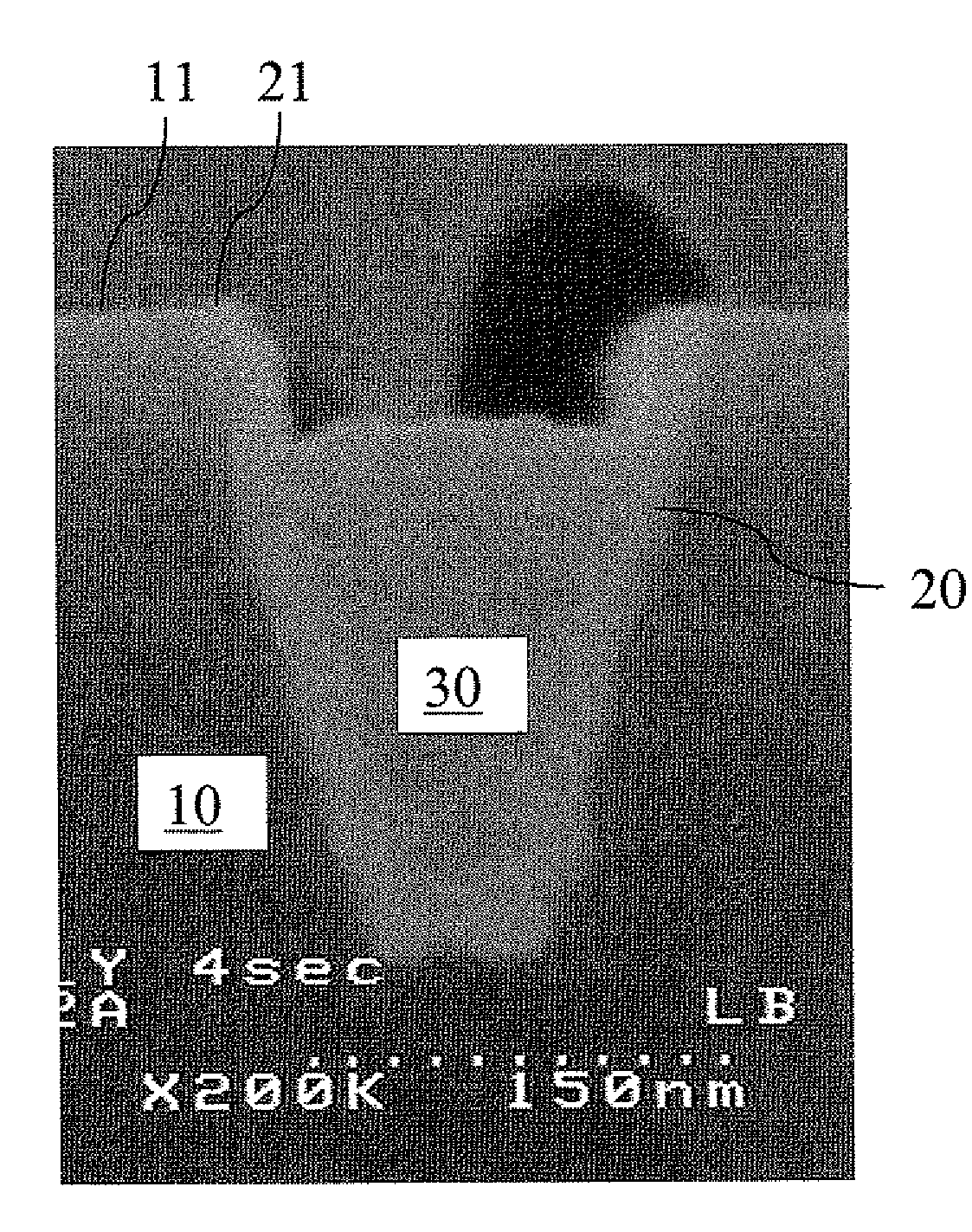

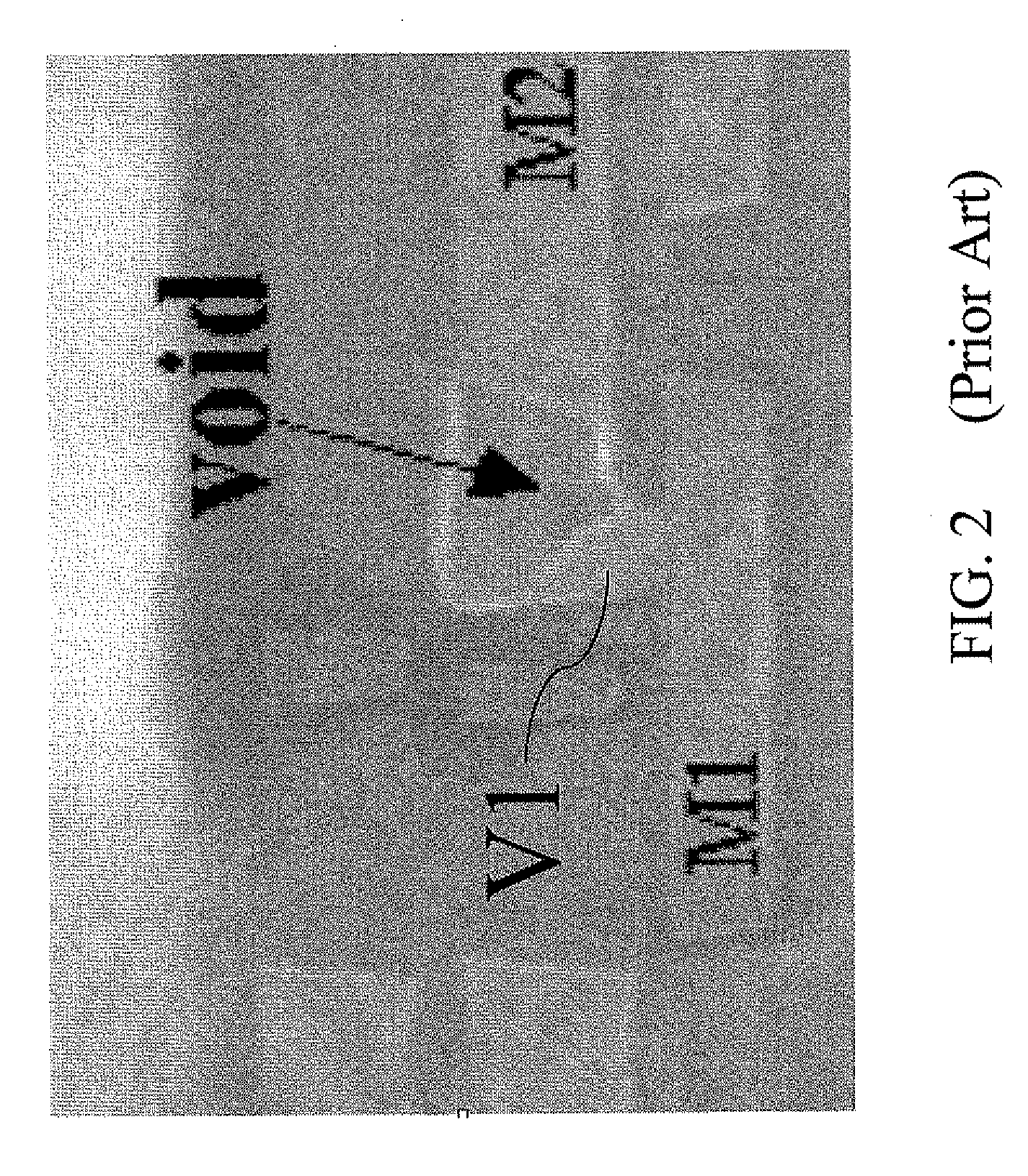

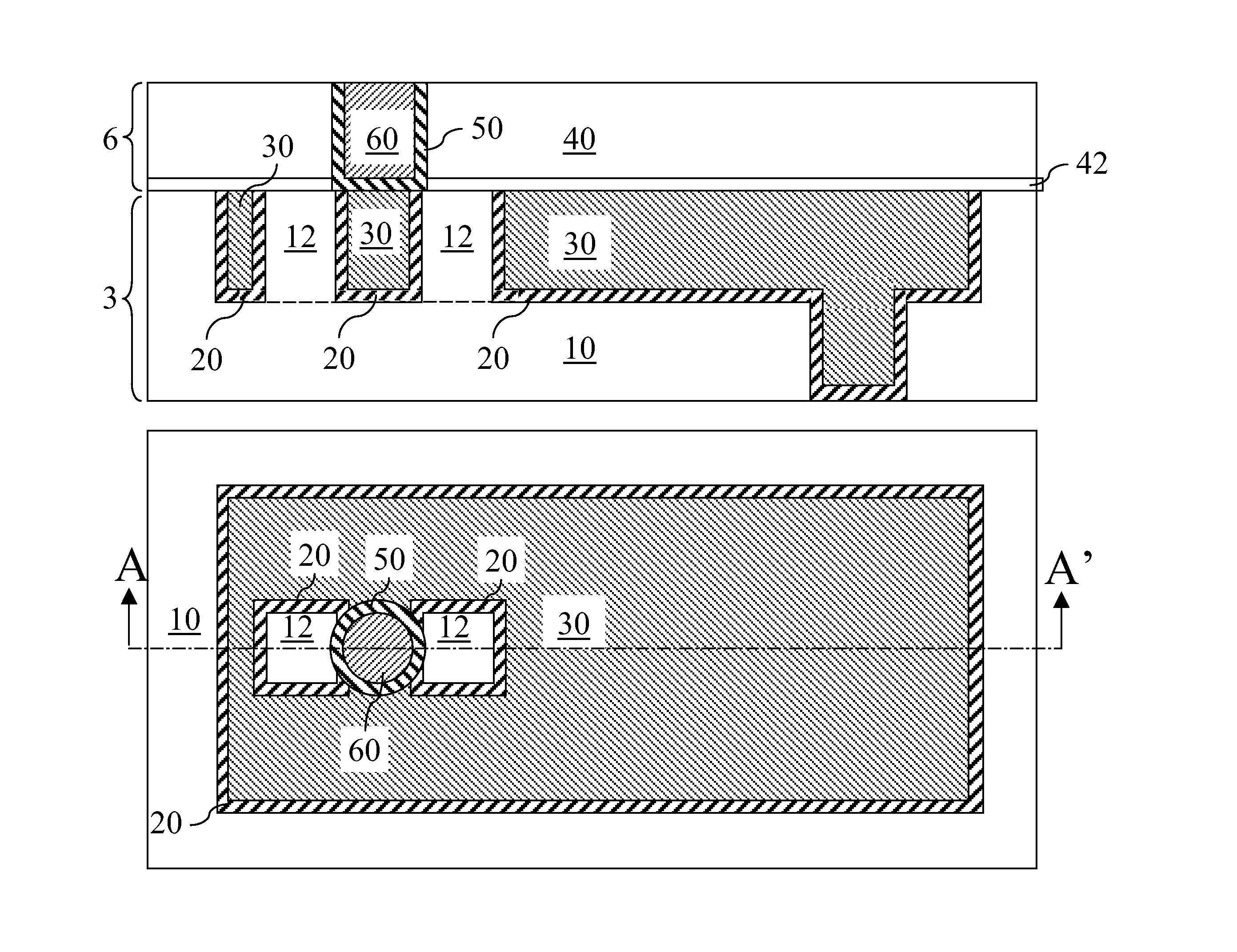

Method of reducing electromigration by forming an electroplated copper-zinc interconnect and a semiconductor device thereby formed

InactiveUS6717236B1Reduce electromigrationImprove corrosion resistanceTransistorElectrolysis componentsCopper interconnectChemical solution

A method of reducing electromigration in a dual-inlaid copper interconnect line (3) by filling a via (6) with a Cu-rich Cu-Zn alloy (30) electroplated on a Cu surface (200 from a stable chemical solution, and by controlling the Zn-doping thereof, which also improves interconnect reliability and corrosion resistance, and a semiconductor device thereby formed. The method involves using a reduced-oxygen Cu-Zn alloy as fill (30) for the via (6) in forming the dual-inlaid interconnect structure (35). The alloy fill (30) is formed by electroplating the Cu surface (20) in a unique chemical solution containing salts of Zn and Cu, their complexing agents, a pH adjuster, and surfactants, thereby electroplating the fill (30) on the Cu surface (20); and annealing the electroplated Cu-Zn alloy fill (30); and planarizing the Cu-Zn alloy fill (30), thereby forming the dual-inlaid copper interconnect line (35).

Owner:GLOBALFOUNDRIES US INC

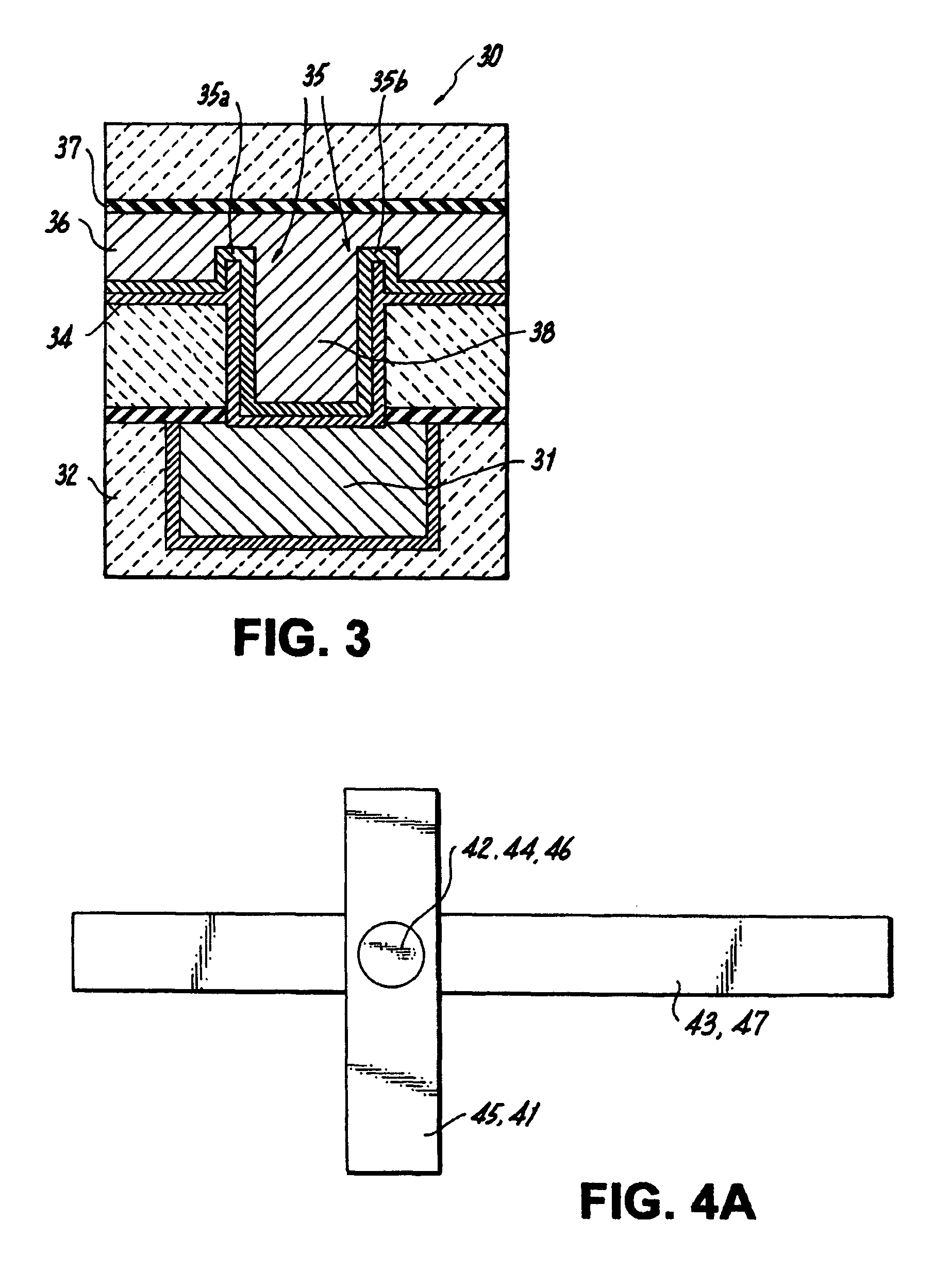

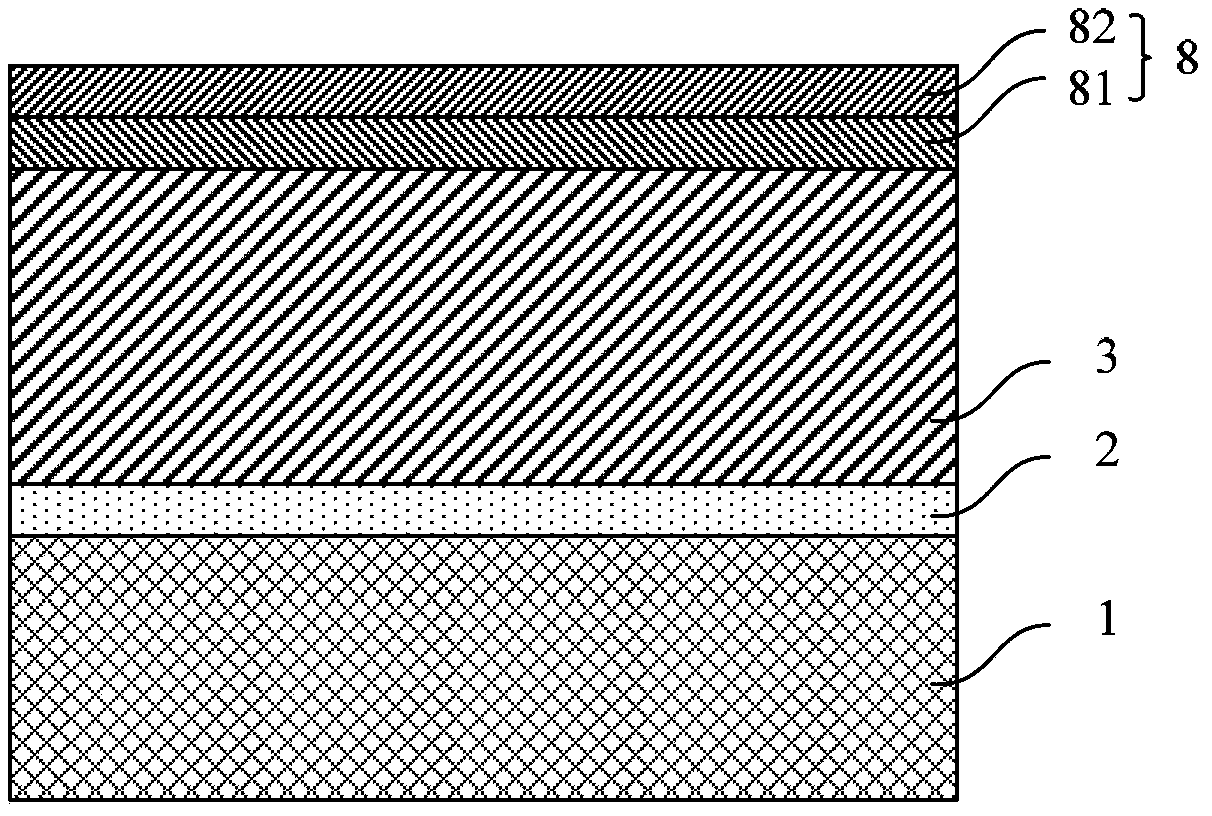

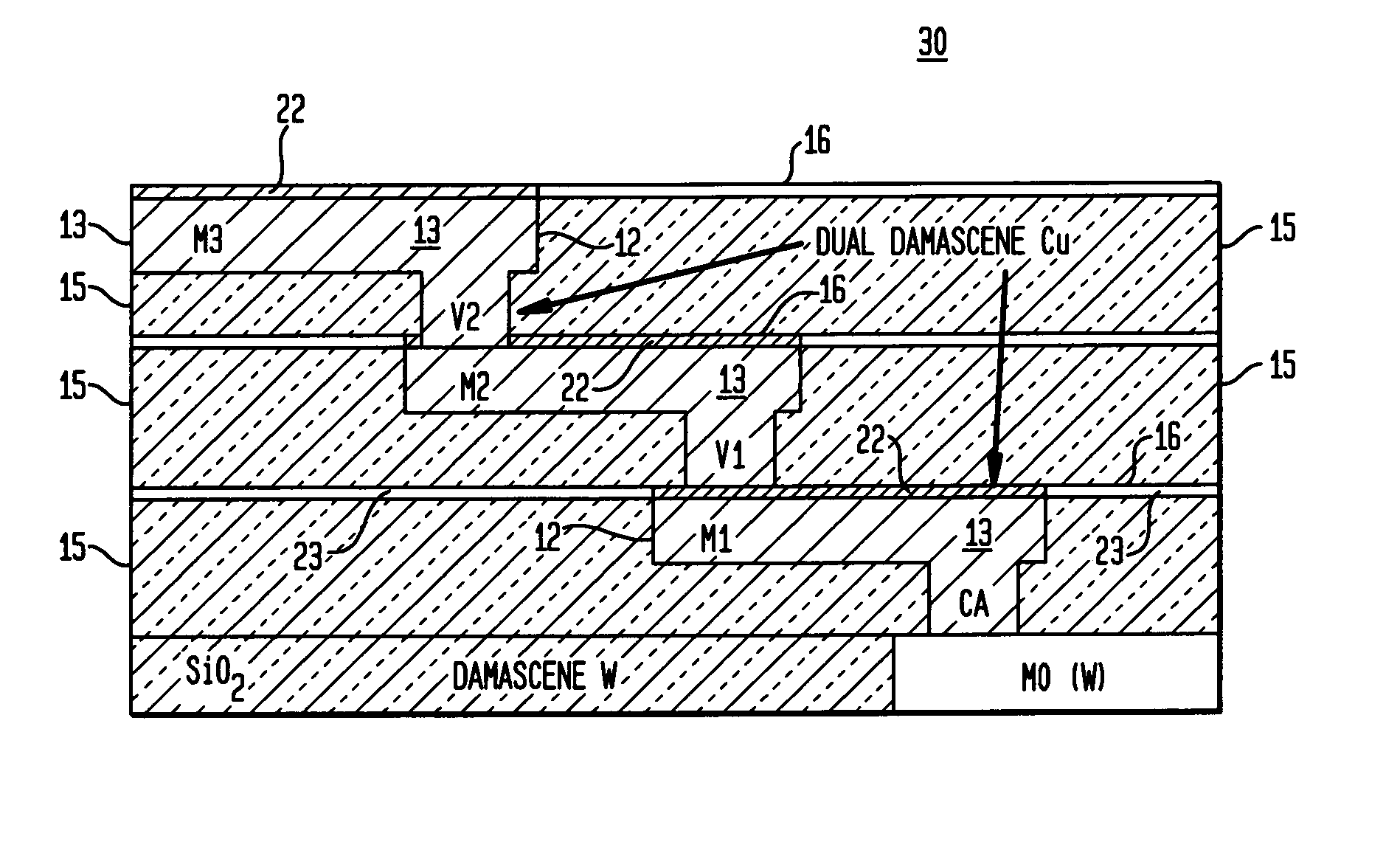

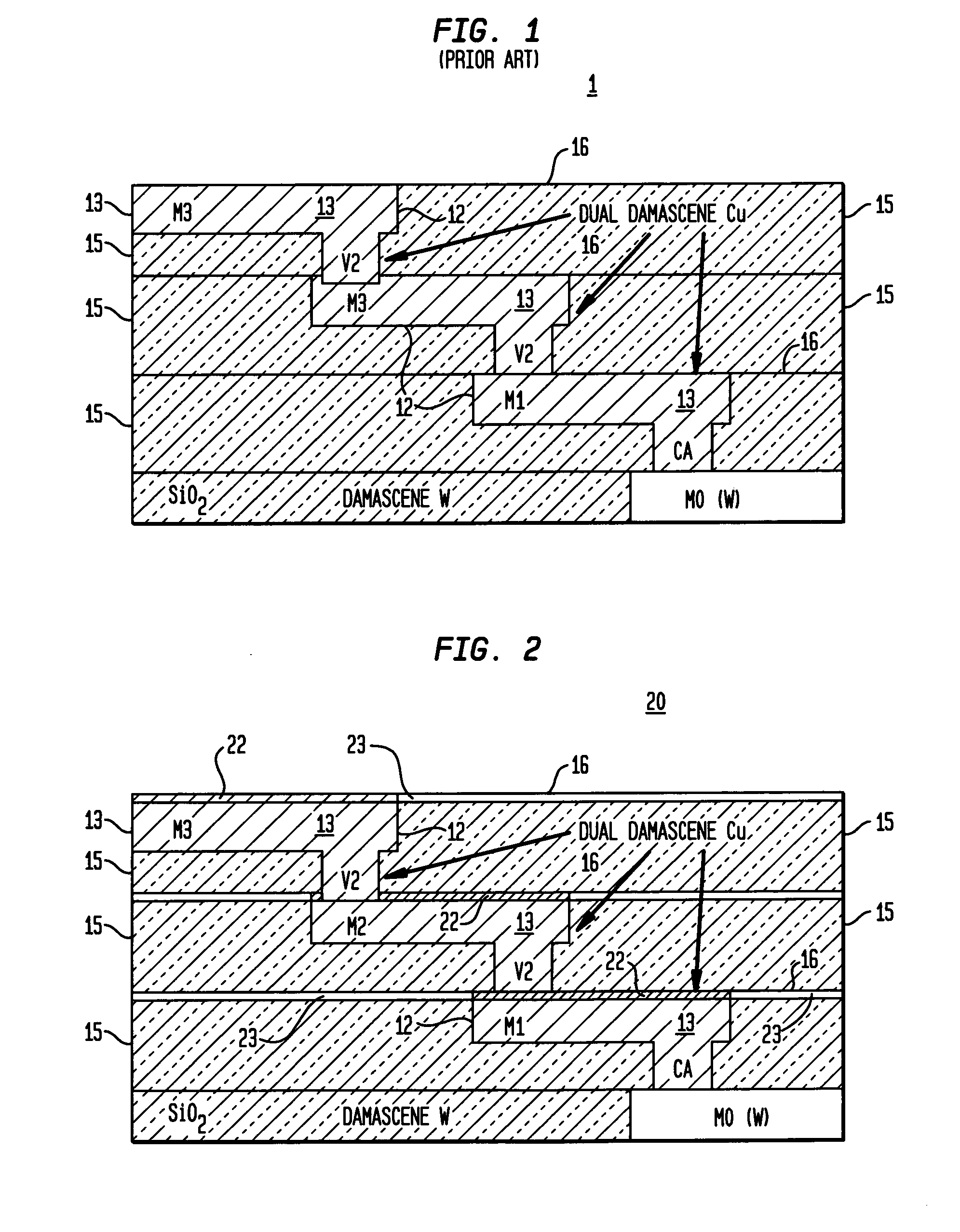

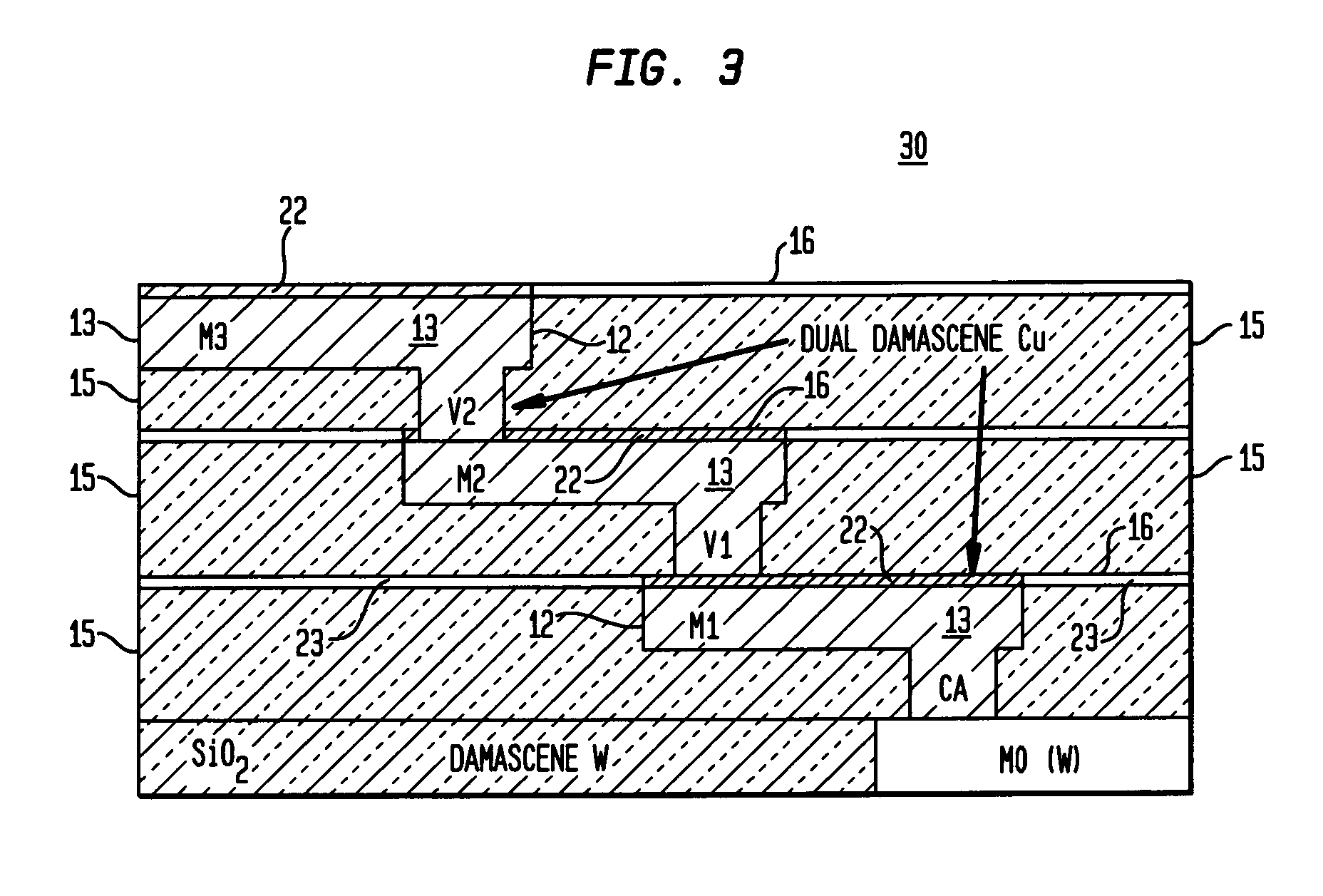

Semiconductor device including a low-k metallization layer stack for enhanced resistance against electromigration

InactiveUS20060043588A1Low dielectric constantImproved resistance to electromigrationSemiconductor/solid-state device detailsSolid-state devicesSilicon dioxideSemiconductor

A technique is disclosed which enables the formation of a metallization layer being substantially comprised of a low-k dielectric material, wherein a compressive stress layer provides enhanced electromigration behavior of the metallization layer. In particular embodiments, a compressive silicon dioxide layer may be formed on or in the vicinity of a dielectric barrier layer and a metallization layer based on SiCOH.

Owner:ADVANCED MICRO DEVICES INC

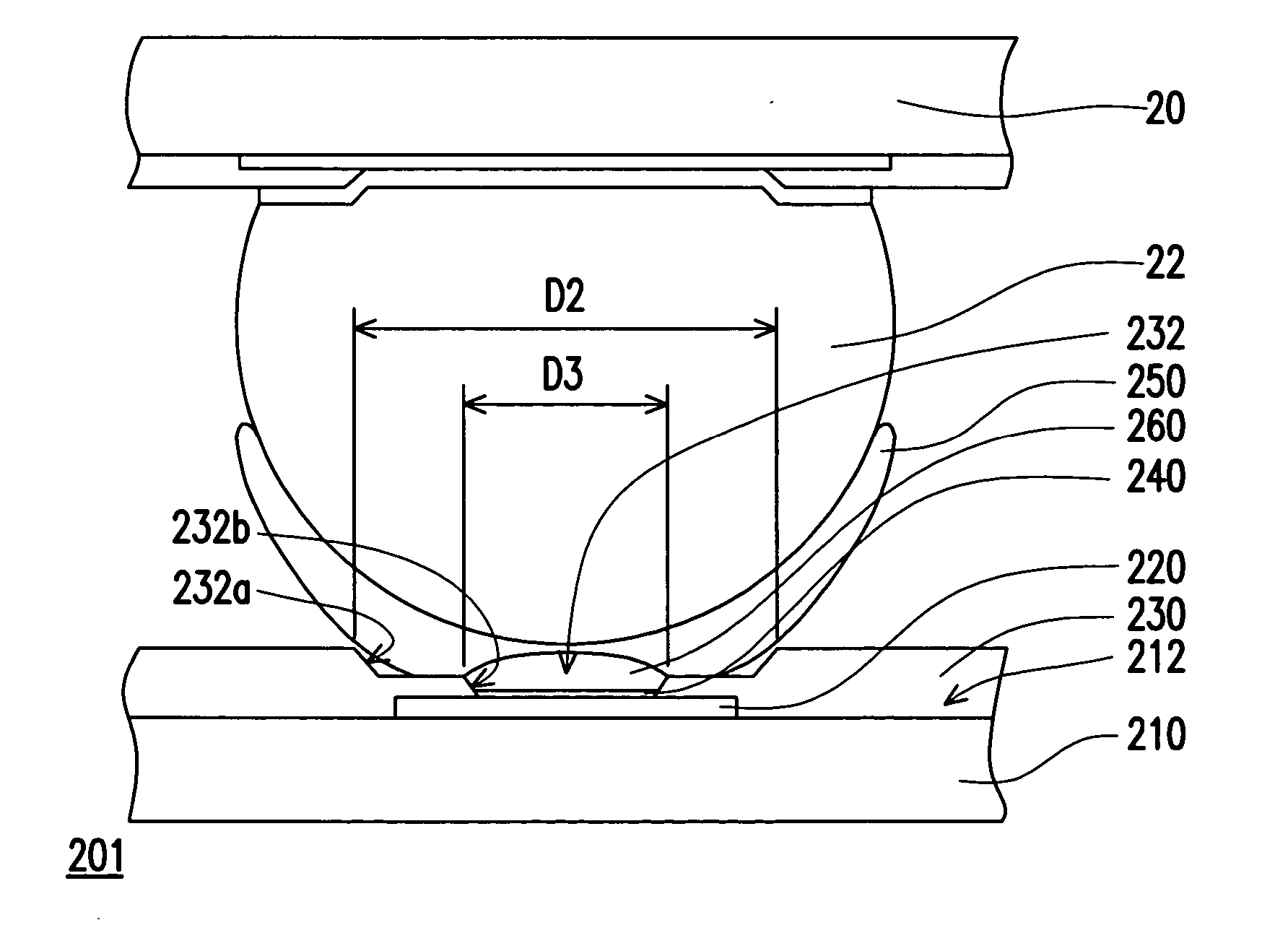

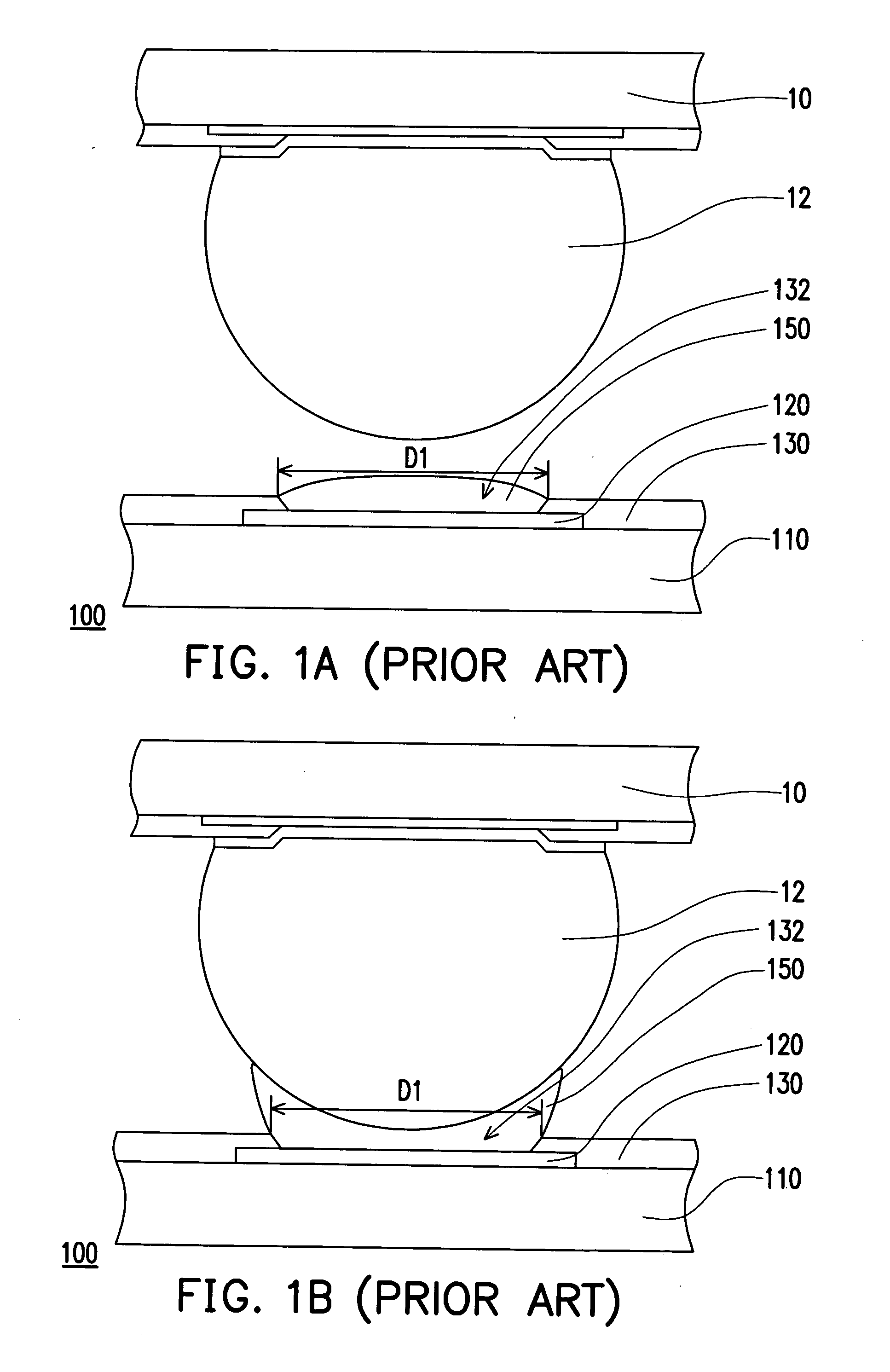

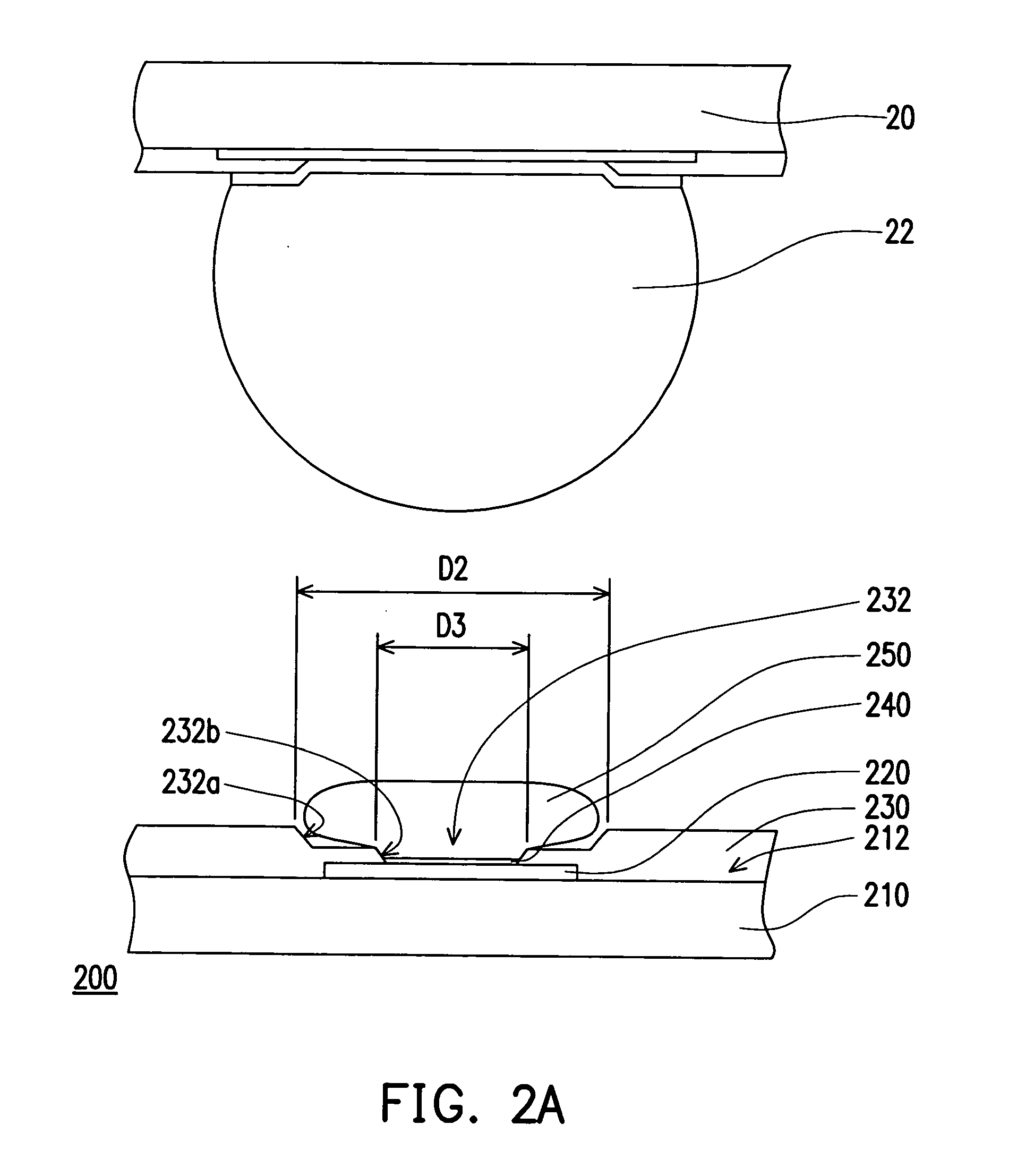

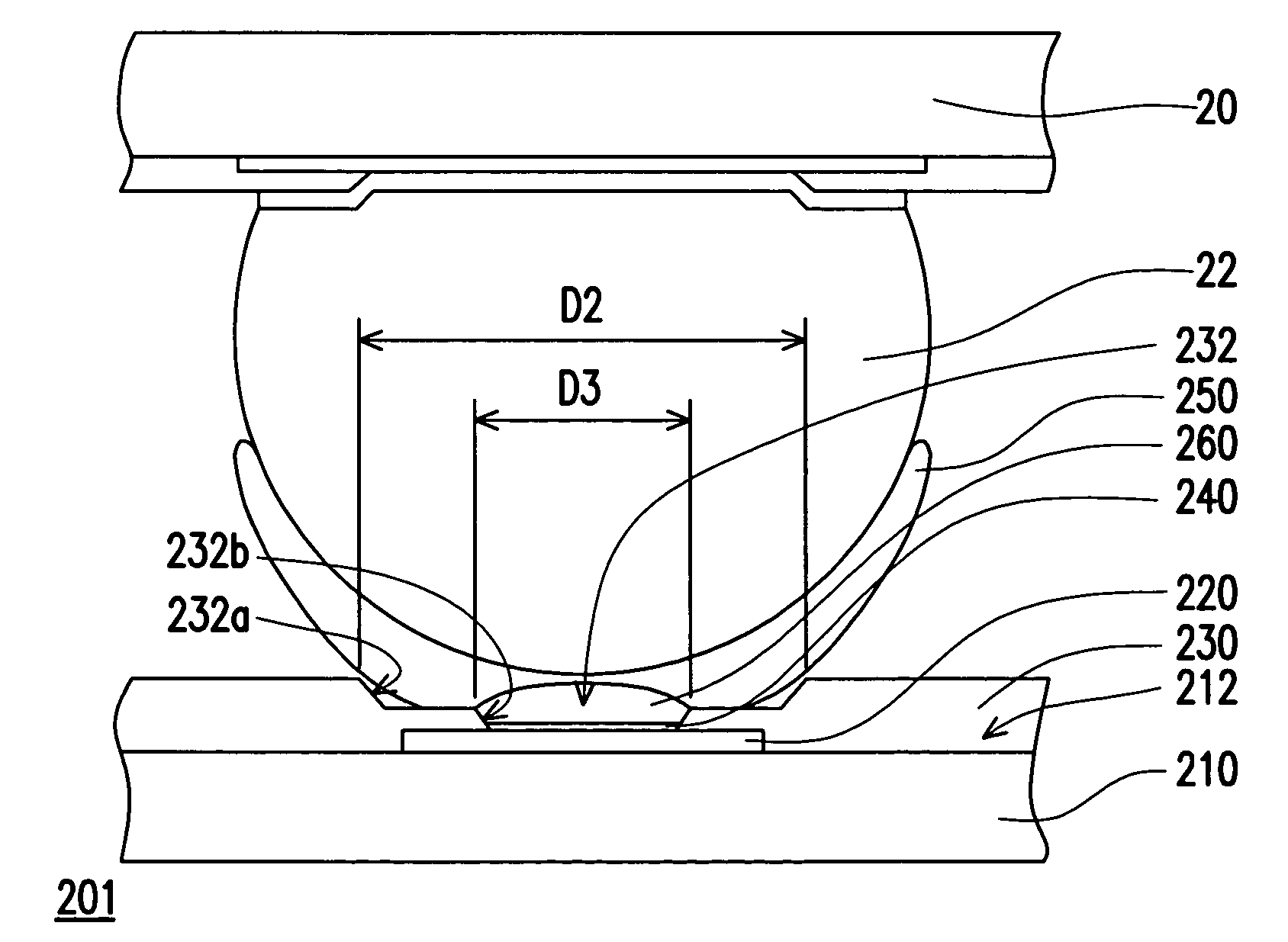

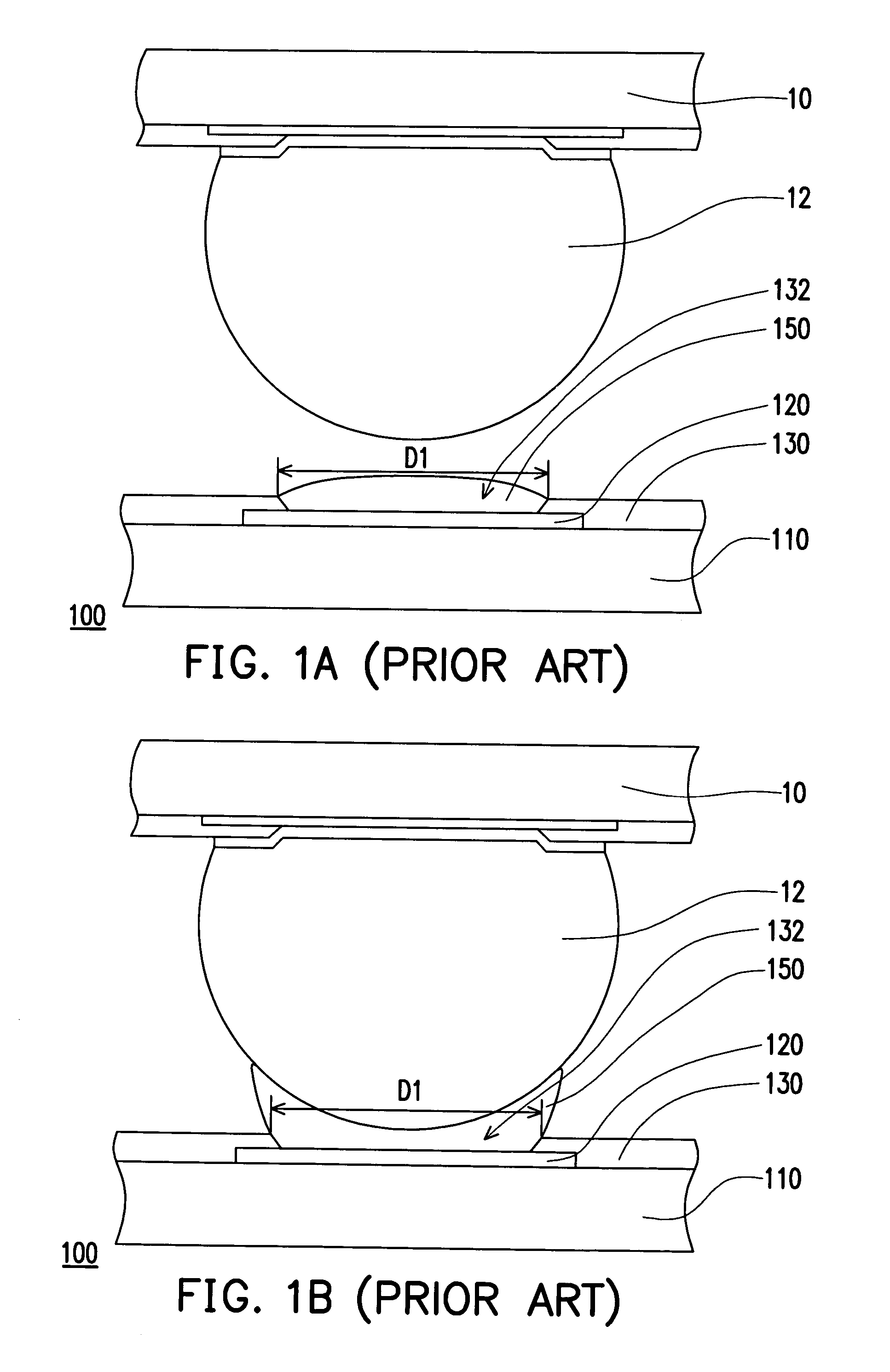

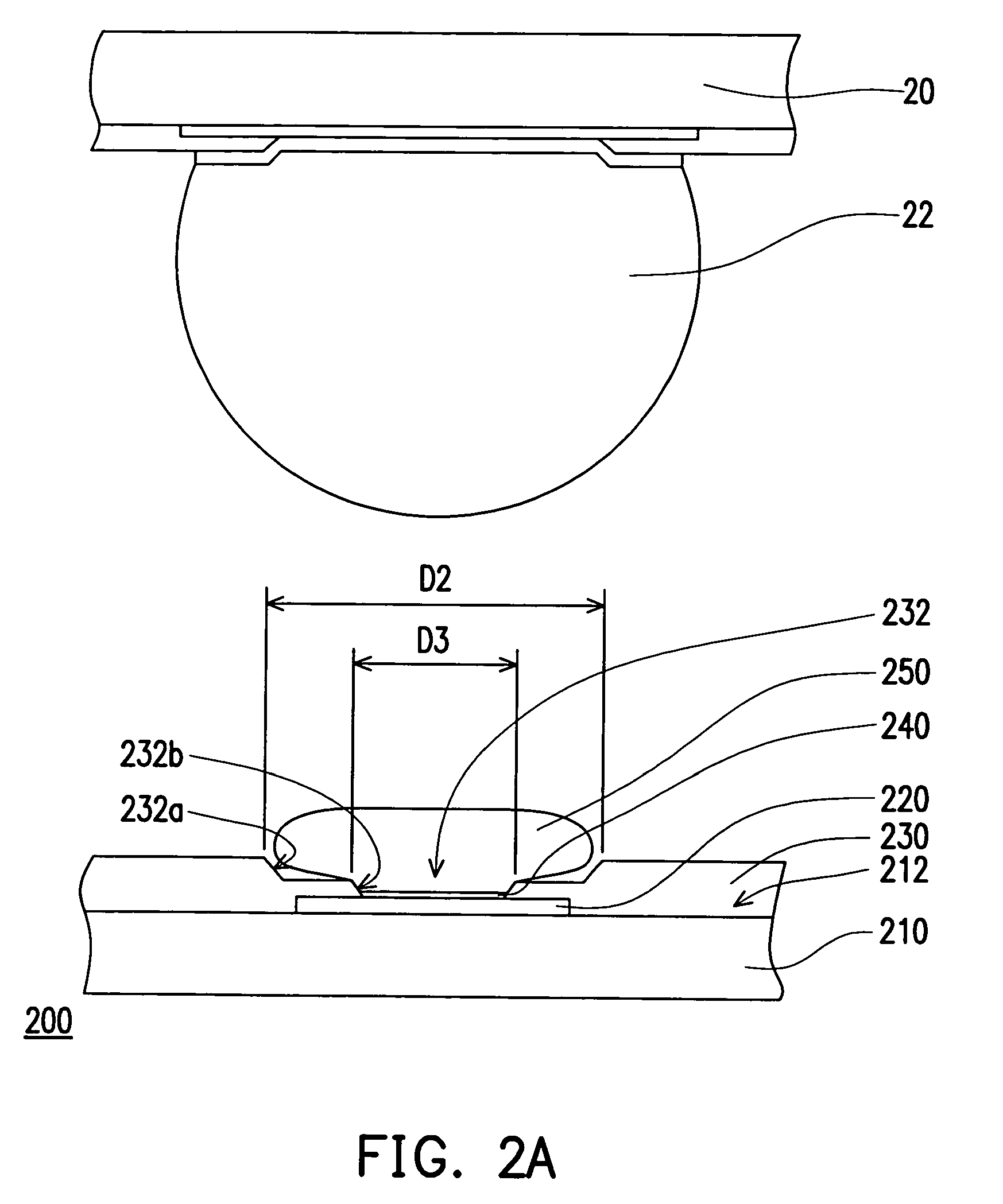

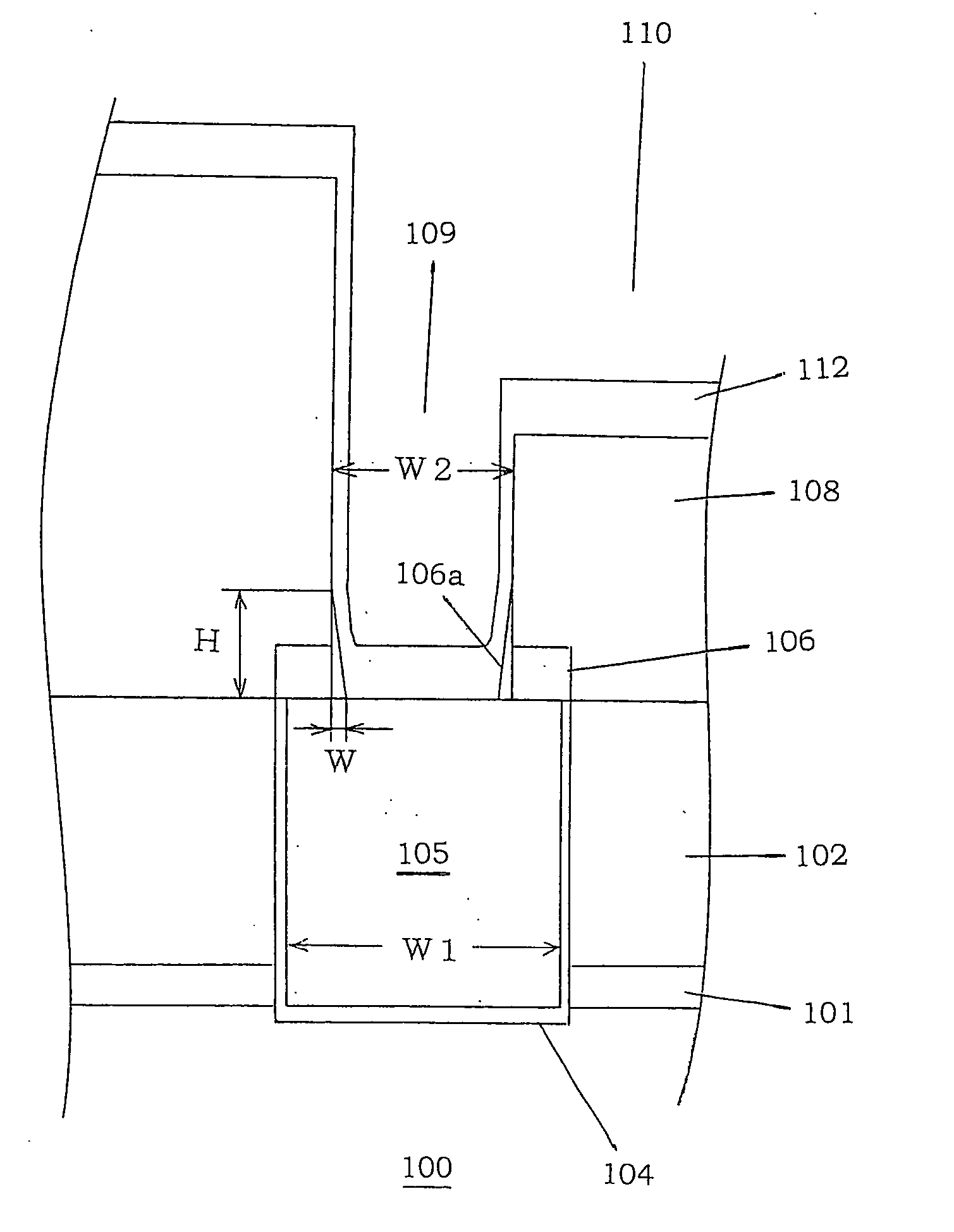

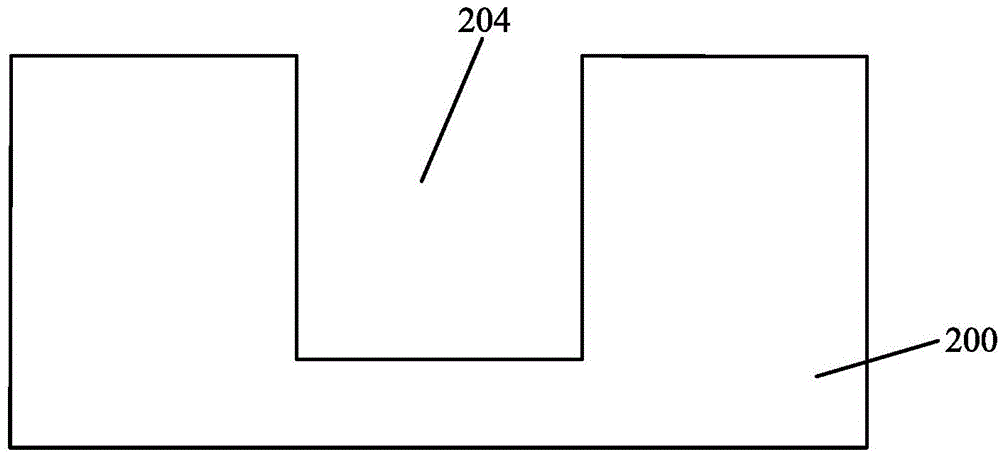

Circuit carrier

ActiveUS20050184371A1Improve connection strengthIncreasing reliability and qualityPrinted circuit assemblingFinal product manufactureSolder maskContact pad

The present invention provides a circuit carrier for connecting to at least a bump. The circuit carrier comprises a substrate, at least a contact pad on a surface of the substrate and a solder mask layer covering the substrate. The solder mask has at least a stepped opening that exposes a portion of the contact pad. The stepped opening includes at least a first opening and a second opening and the size of the first opening is larger than that of the second opening. The stepped opening of the solder mask layer can contain more pre-solder paste, thus increasing the bonding strength between the bump and the contact pad.

Owner:VIA TECH INC

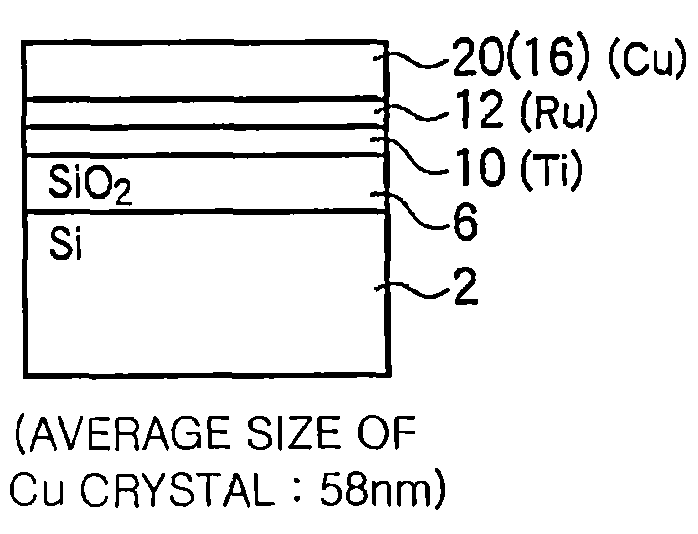

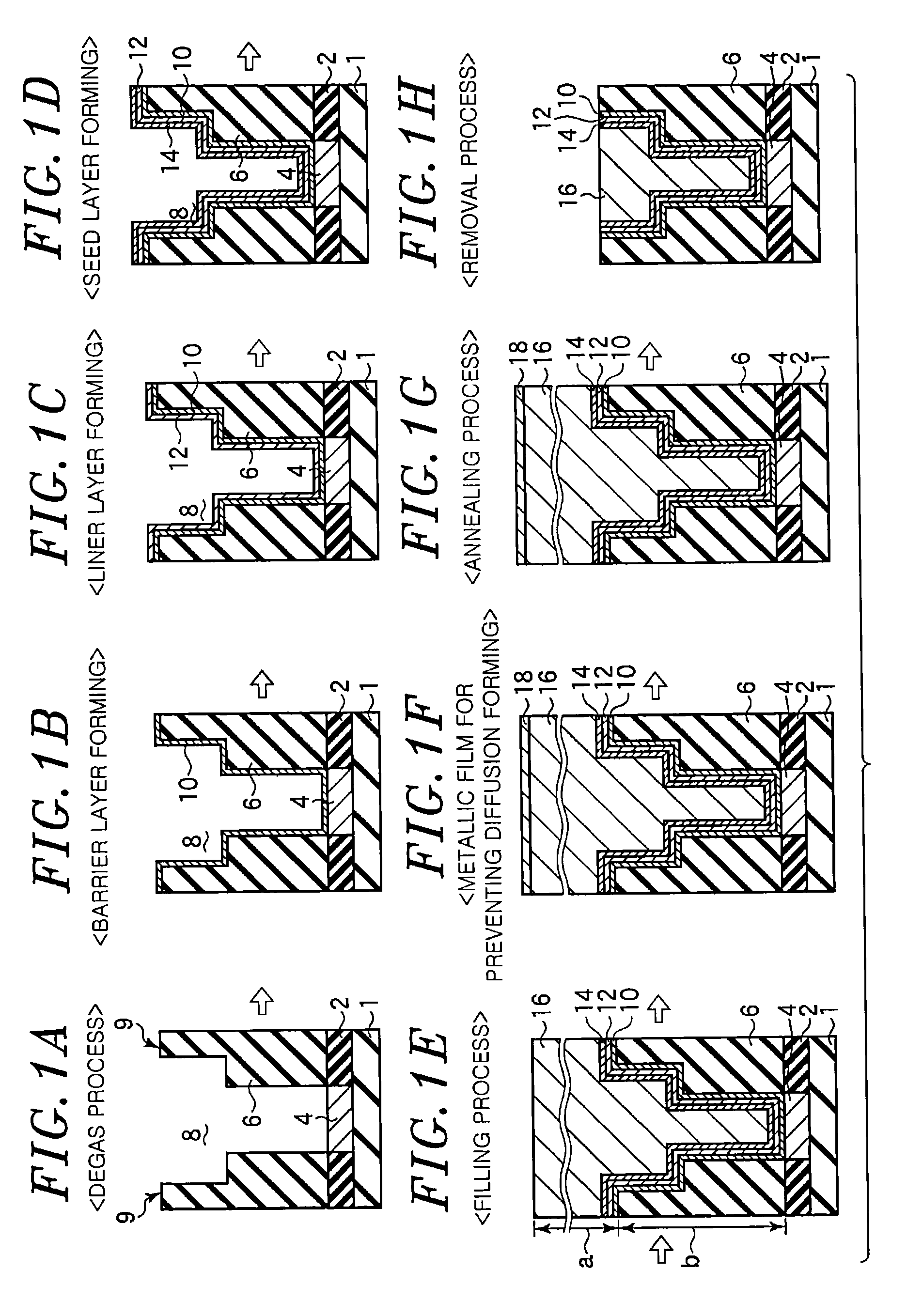

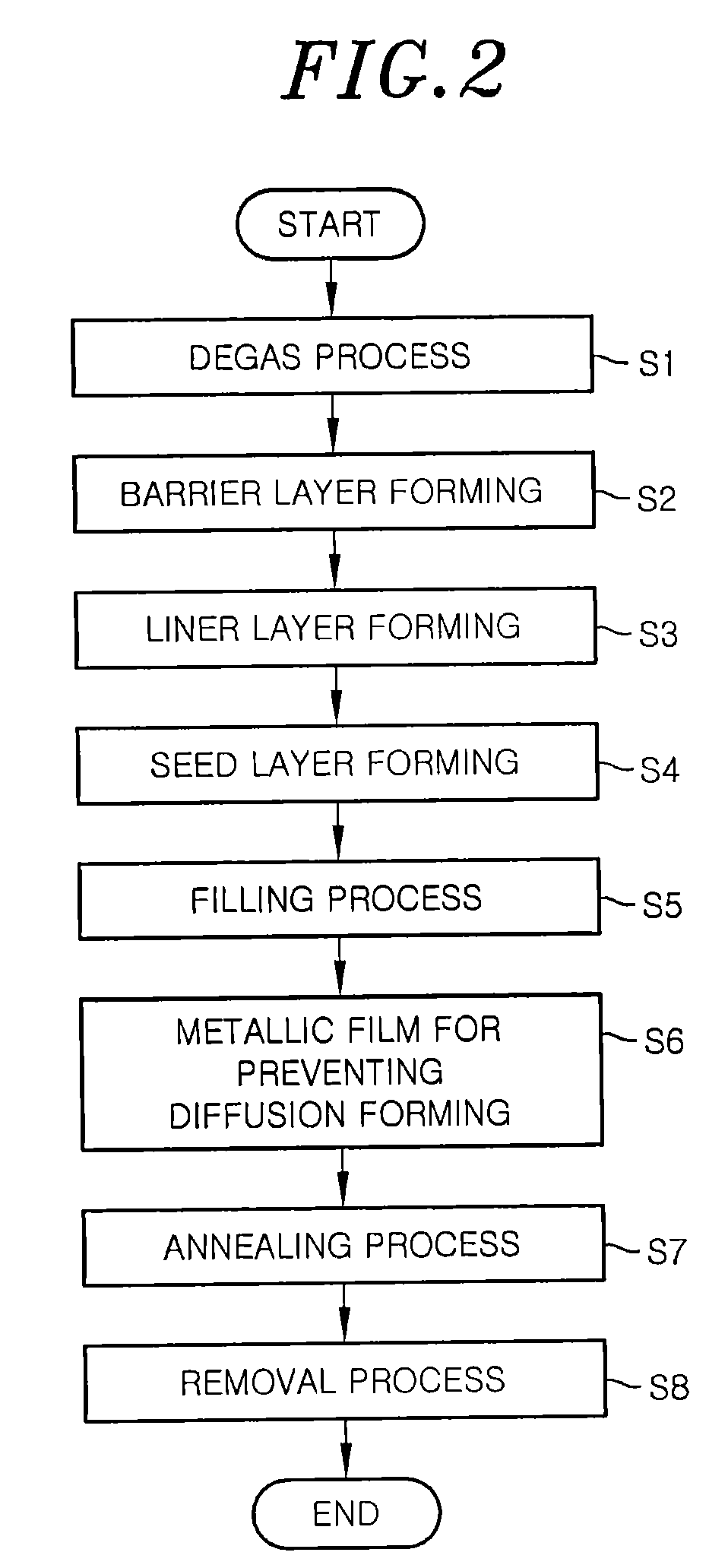

Thin film forming method

InactiveUS20130252417A1Improve adhesionImproved resistance to electromigrationSemiconductor/solid-state device detailsVacuum evaporation coatingTarget surfaceMaterials science

A thin film forming method in which a thin film is formed on a surface of a target object to be processed to fill a recess formed in the surface of the target object includes the steps of forming a metal layer for filling on the surface of the target object to fill the recess formed in the surface of the target object and forming a metal film for preventing diffusion on an entire surface of the target object to cover the metal layer for filling. The thin film forming method further includes the step of annealing the target object having the metal film for preventing diffusion formed thereon.

Owner:TOKYO ELECTRON LTD

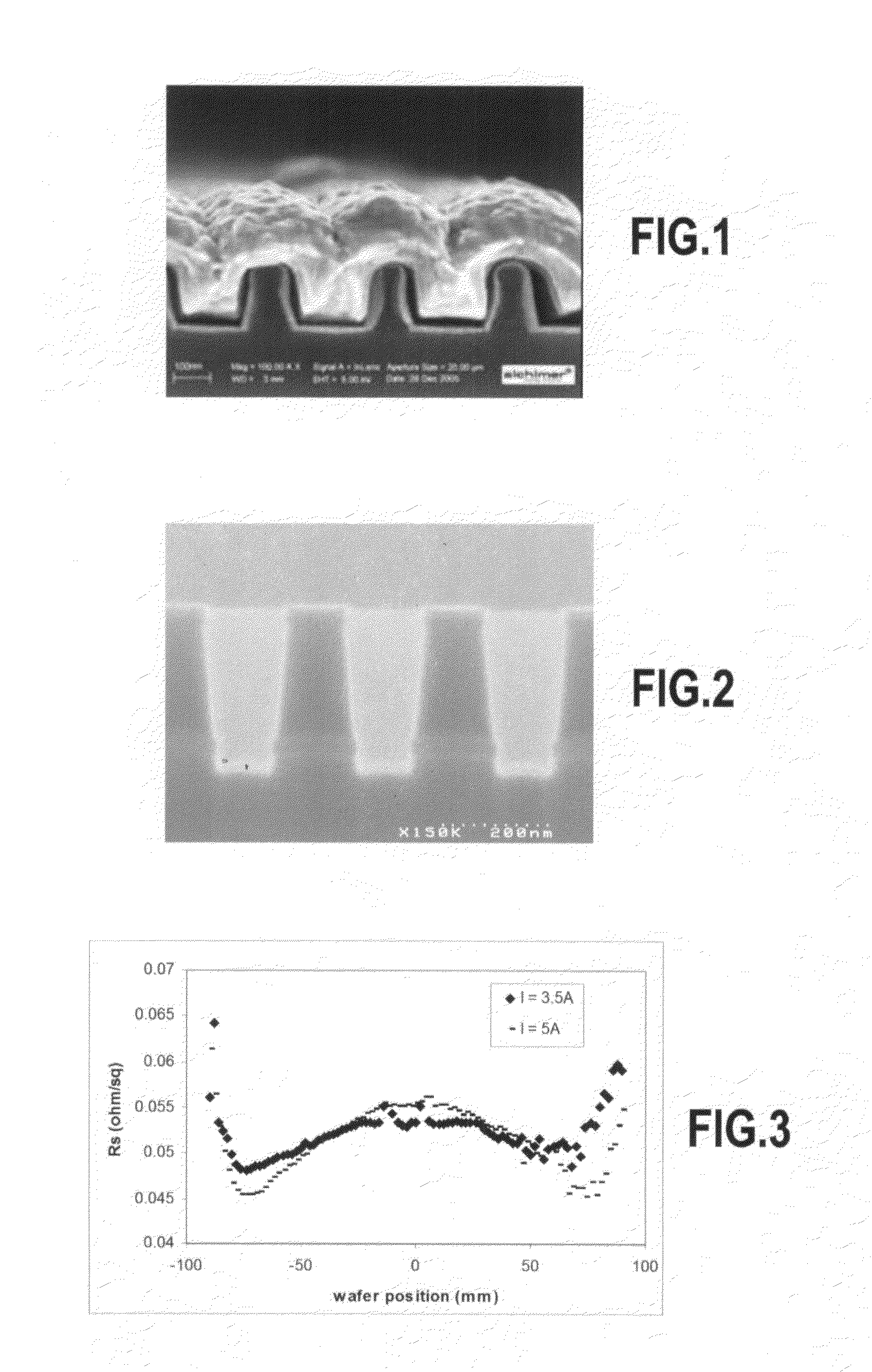

Method and compositions for direct copper plating and filing to form interconnects in the fabrication of semiconductor devices

ActiveUS7579274B2Low resistivityStrong adhesionGarmentsSemiconductor/solid-state device manufacturingCopper platingElectrolysis

Owner:ALCHIMER SA

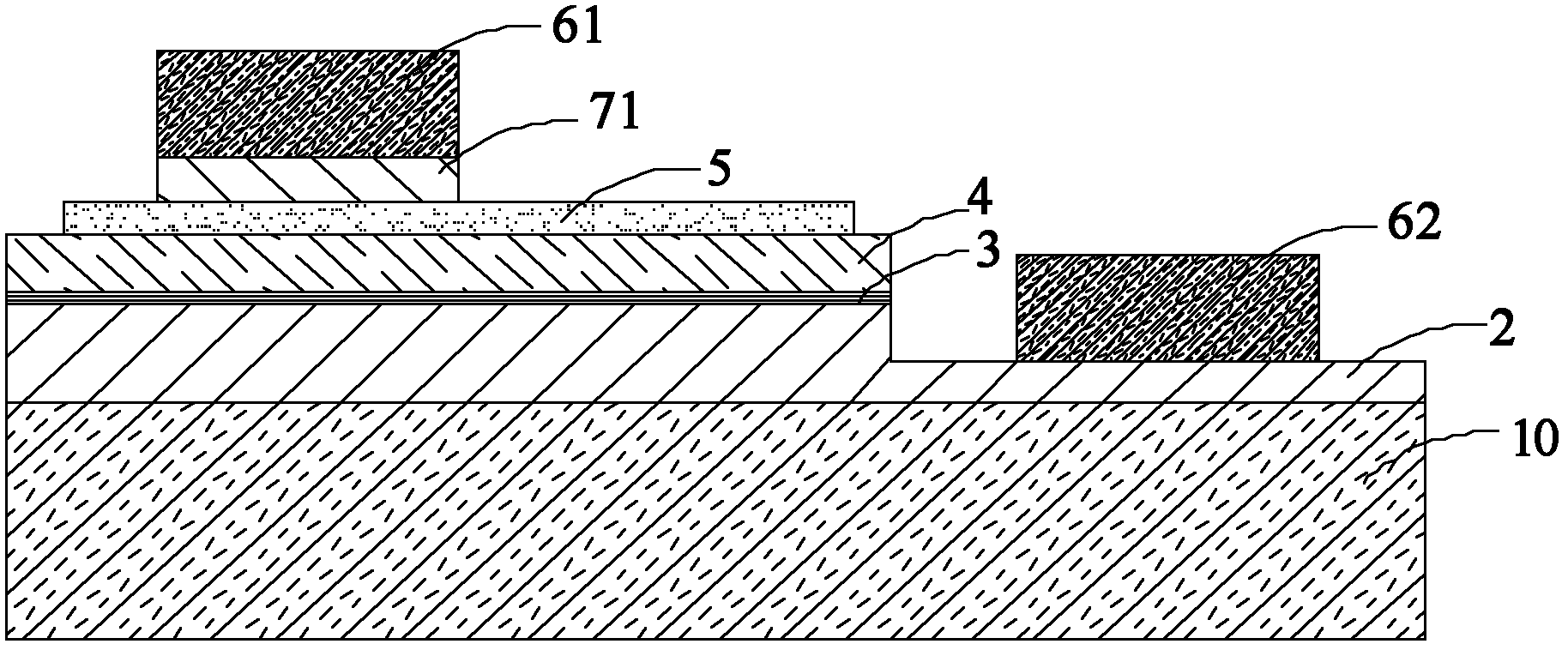

Circuit carrier

ActiveUS7126211B2Improve connection strengthIncreasing reliability and qualityPrinted circuit assemblingFinal product manufactureContact padSolder mask

The present invention provides a circuit carrier for connecting to at least a bump. The circuit carrier comprises a substrate, at least a contact pad on a surface of the substrate and a solder mask layer covering the substrate. The solder mask has at least a stepped opening that exposes a portion of the contact pad. The stepped opening includes at least a first opening and a second opening and the size of the first opening is larger than that of the second opening. The stepped opening of the solder mask layer can contain more pre-solder paste, thus increasing the bonding strength between the bump and the contact pad.

Owner:VIA TECH INC

An etch stop layer for a metallization layer with enhanced adhesion, etch selectivity and hermeticity

ActiveUS20070099010A1Increase moistureEnhanced oxygen diffusion blocking effectLiquid surface applicatorsSemiconductor/solid-state device detailsOxygenCopper

By providing a barrier layer stack including a thin SiCN layer for enhanced adhesion, a silicon nitride layer for confining a copper-based metal region (thereby also effectively avoiding any diffusion of oxygen and moisture into the copper region), and a SiCN layer, the total relative permittivity may still be maintained at a low level, since the thickness of the first SiCN layer and of the silicon nitride layer may be moderately thin, while the relatively thick silicon carbide nitride layer provides the required high etch selectivity during a subsequent patterning process of the low-k dielectric layer.

Owner:ADVANCED MICRO DEVICES INC

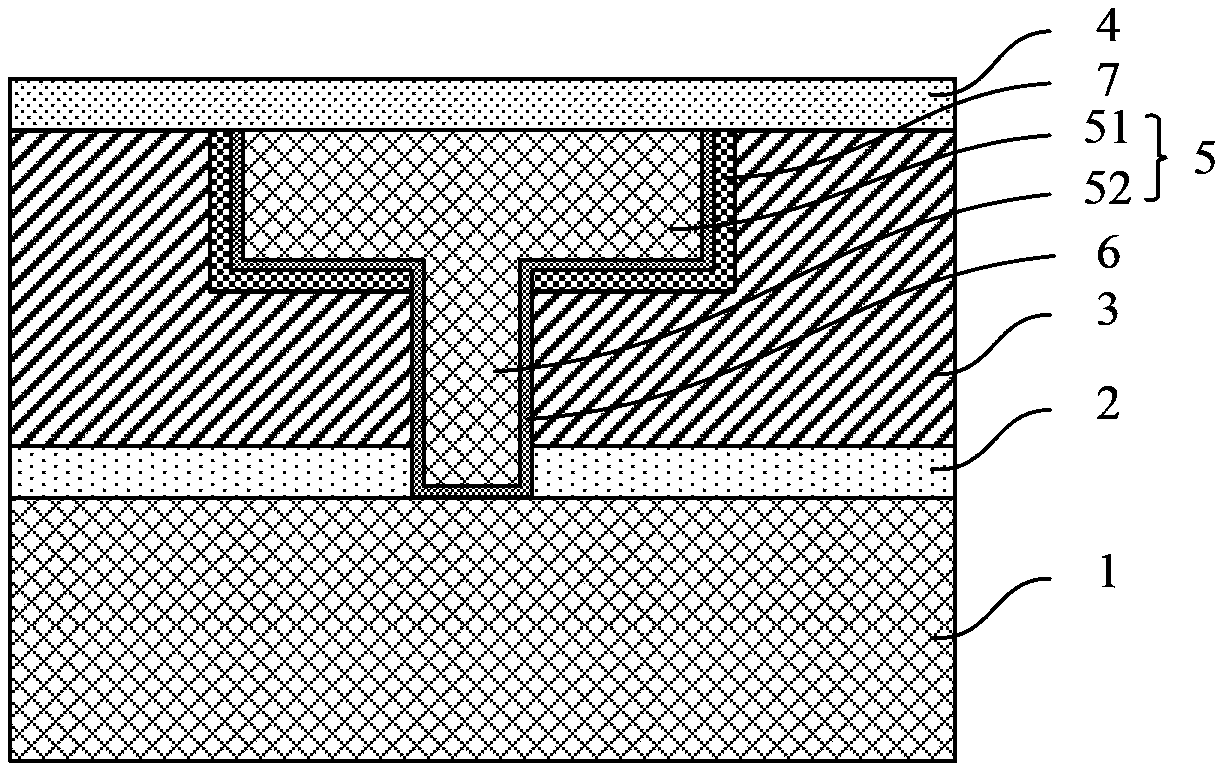

Double-nested copper interconnection structure and fabrication method thereof

ActiveCN104112734AInhibited DiffusionImprove adhesionSemiconductor/solid-state device detailsSolid-state devicesInterconnectionDiffusion barrier

The invention provides a double-nested copper interconnection structure and a fabrication method thereof. In the double-nested copper interconnection structure, the metal diffusion barrier layer on the surface of a metal connection line is surrounded by a nitrogen-doped layer, or the metal diffusion barrier layer of the partial surface of the metal connection line and a conductive plug that located in an interlayer dielectric layer is surrounded by a nitrogen-doped layer. The nitrogen-doped layer is obtained through nitrogen or ammonia gas plasma treatment. The nitrogen-doped layer can be used to improve the adhesive power between the interlayer dielectric layer and metal, and the mechanical strength between the nitrogen-doped layer and a second cap layer is higher, so that the adhesive power between copper and the second cap layer can be further improved, the electromigration resistance of devices can be improved, and the nitrogen-doped layer can also be used to further prevent copper from being diffused into the interlayer dielectric on the basis of the metal diffusion barrier layer to prevent the short-circuit phenomenon from occurring on the devices.

Owner:SEMICON MFG INT (SHANGHAI) CORP

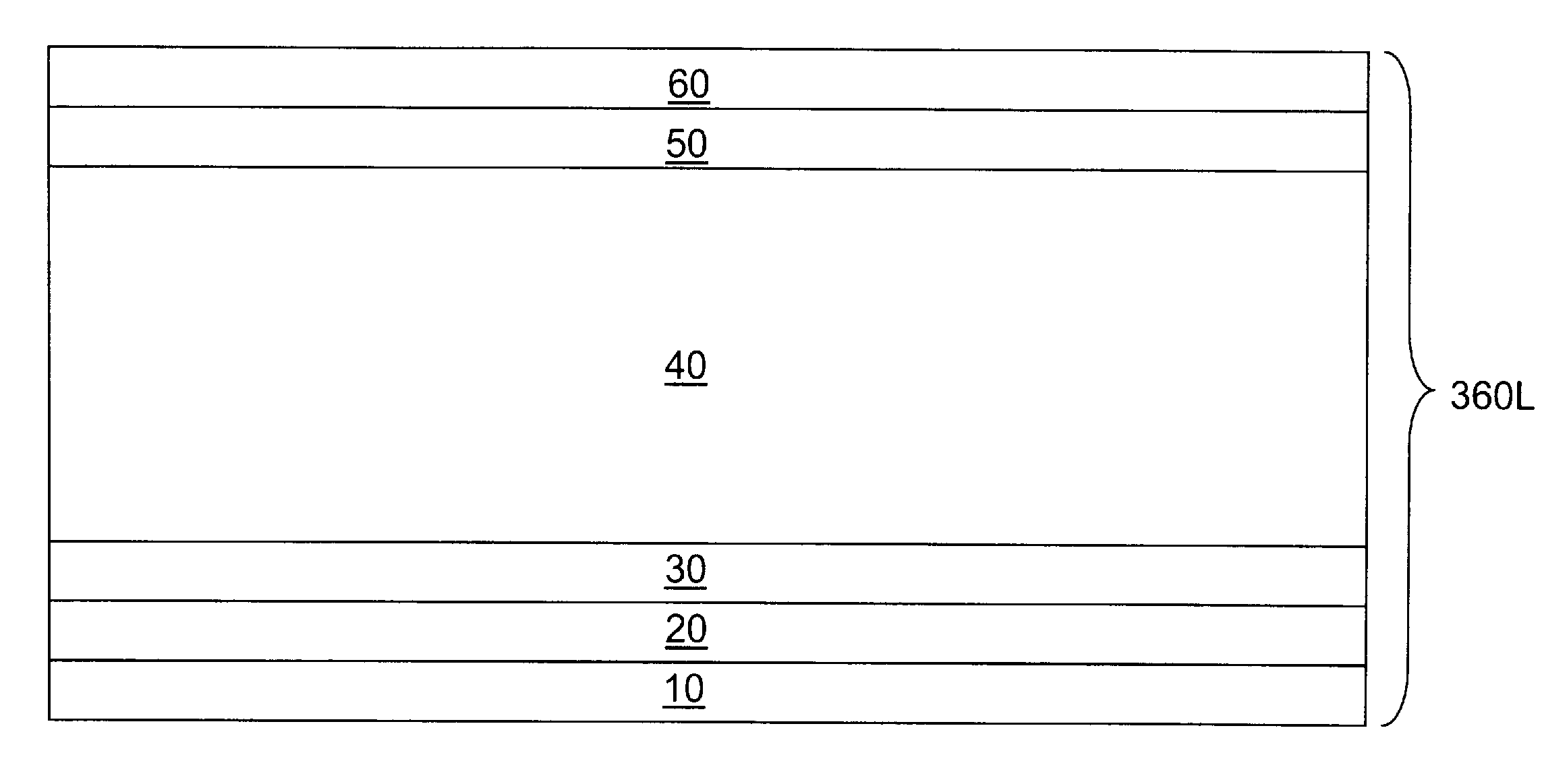

Etch stop layer for a metallization layer with enhanced adhesion, etch selectivity and hermeticity

ActiveUS7867917B2Improve integrityEffective limitLiquid surface applicatorsSemiconductor/solid-state device detailsOxygenCopper

By providing a barrier layer stack including a thin SiCN layer for enhanced adhesion, a silicon nitride layer for confining a copper-based metal region (thereby also effectively avoiding any diffusion of oxygen and moisture into the copper region), and a SiCN layer, the total relative permittivity may still be maintained at a low level, since the thickness of the first SiCN layer and of the silicon nitride layer may be moderately thin, while the relatively thick silicon carbide nitride layer provides the required high etch selectivity during a subsequent patterning process of the low-k dielectric layer.

Owner:ADVANCED MICRO DEVICES INC

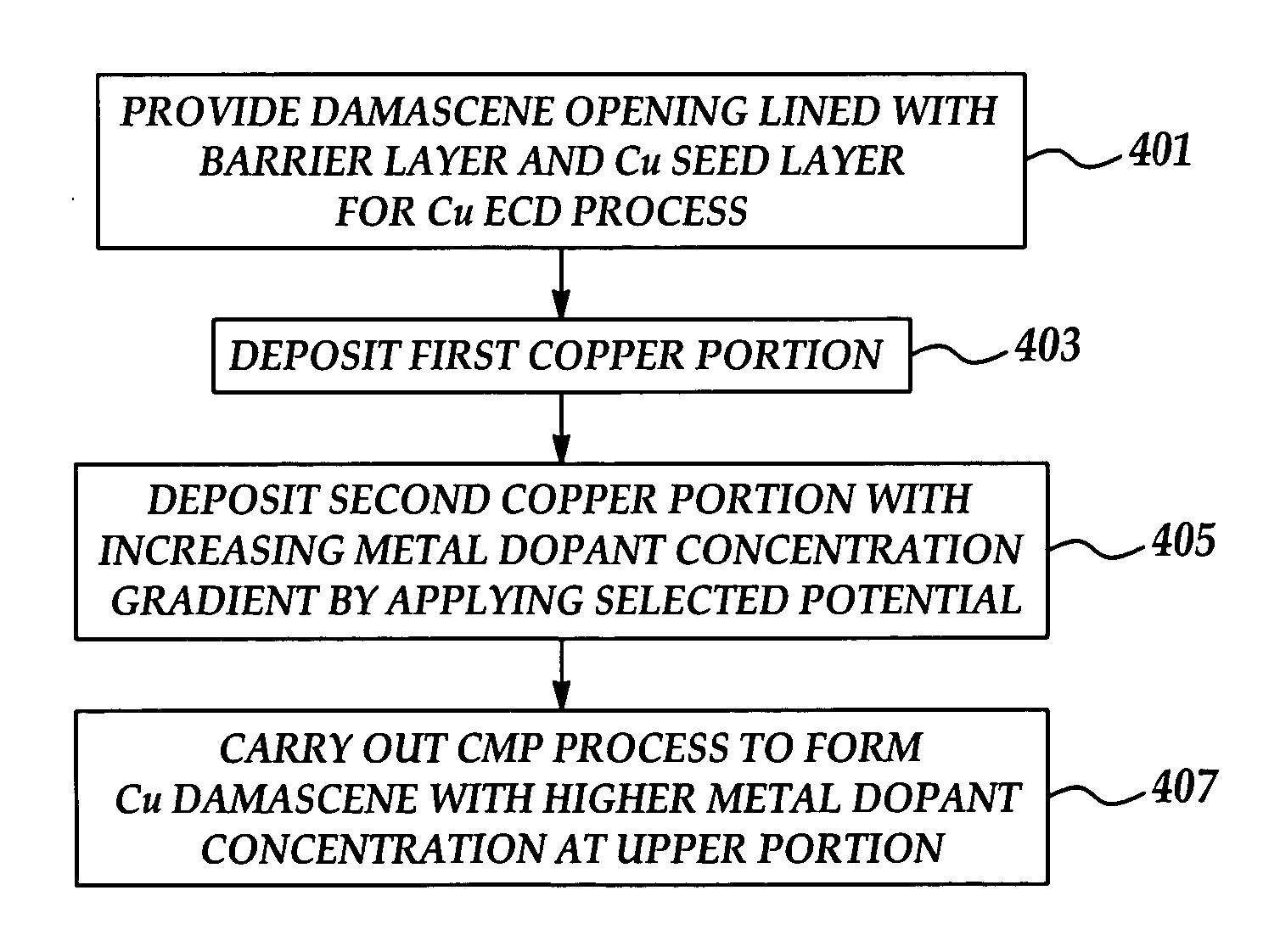

Metal interconnect features with a doping gradient

InactiveUS20060027460A1Improved resistance to electromigrationIncrease resistanceAnodisationSemiconductor/solid-state device manufacturingMetal interconnectElectromigration

A metal filled damascene structure with improved electromigration resistance and method for forming the same, the method including providing a semiconductor process wafer comprising damascene openings; and, depositing metal and at least one metal dopant according to an ECD process to from a metal filled damascene comprising a doped metal alloy portion.

Owner:TAIWAN SEMICON MFG CO LTD

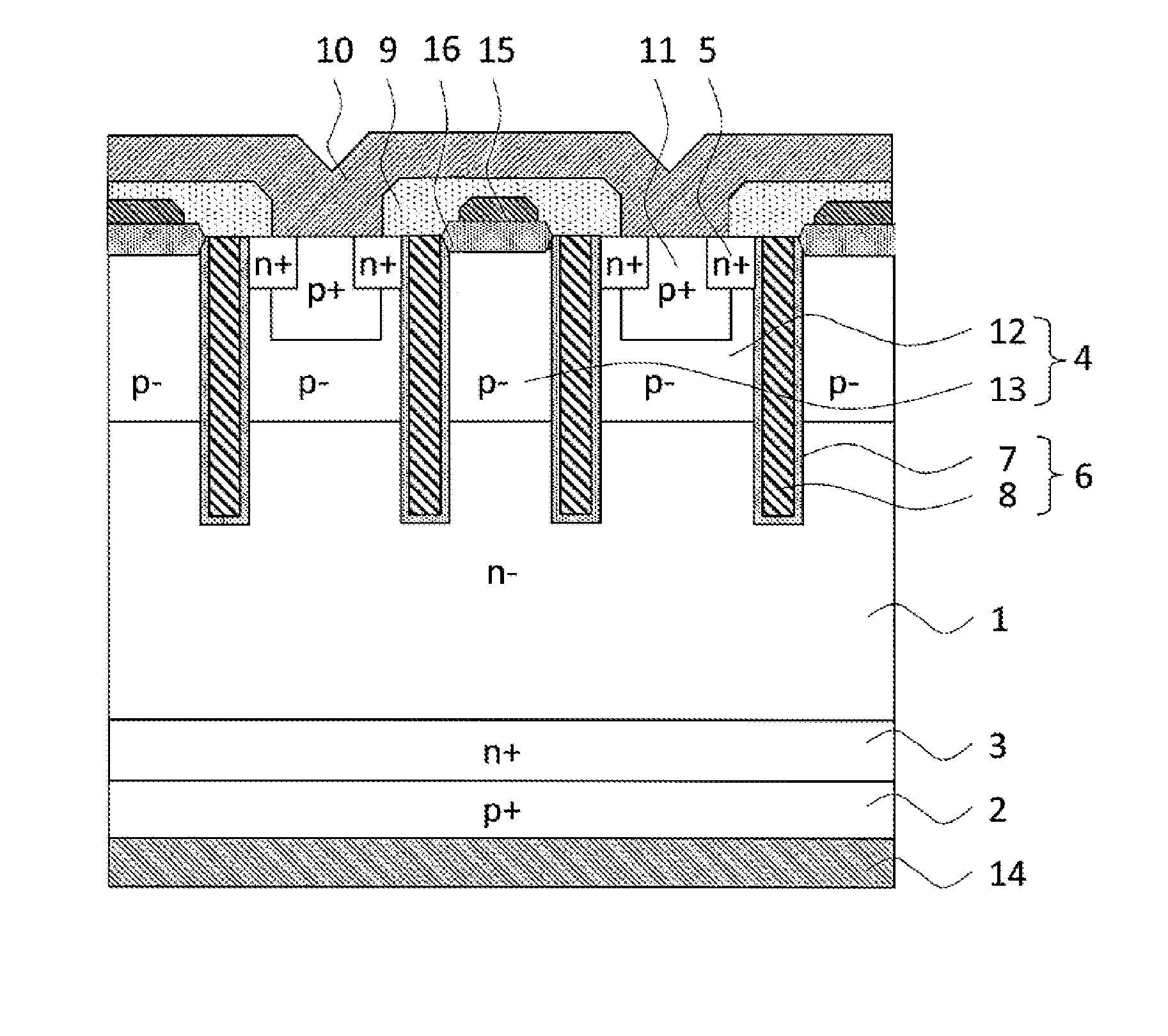

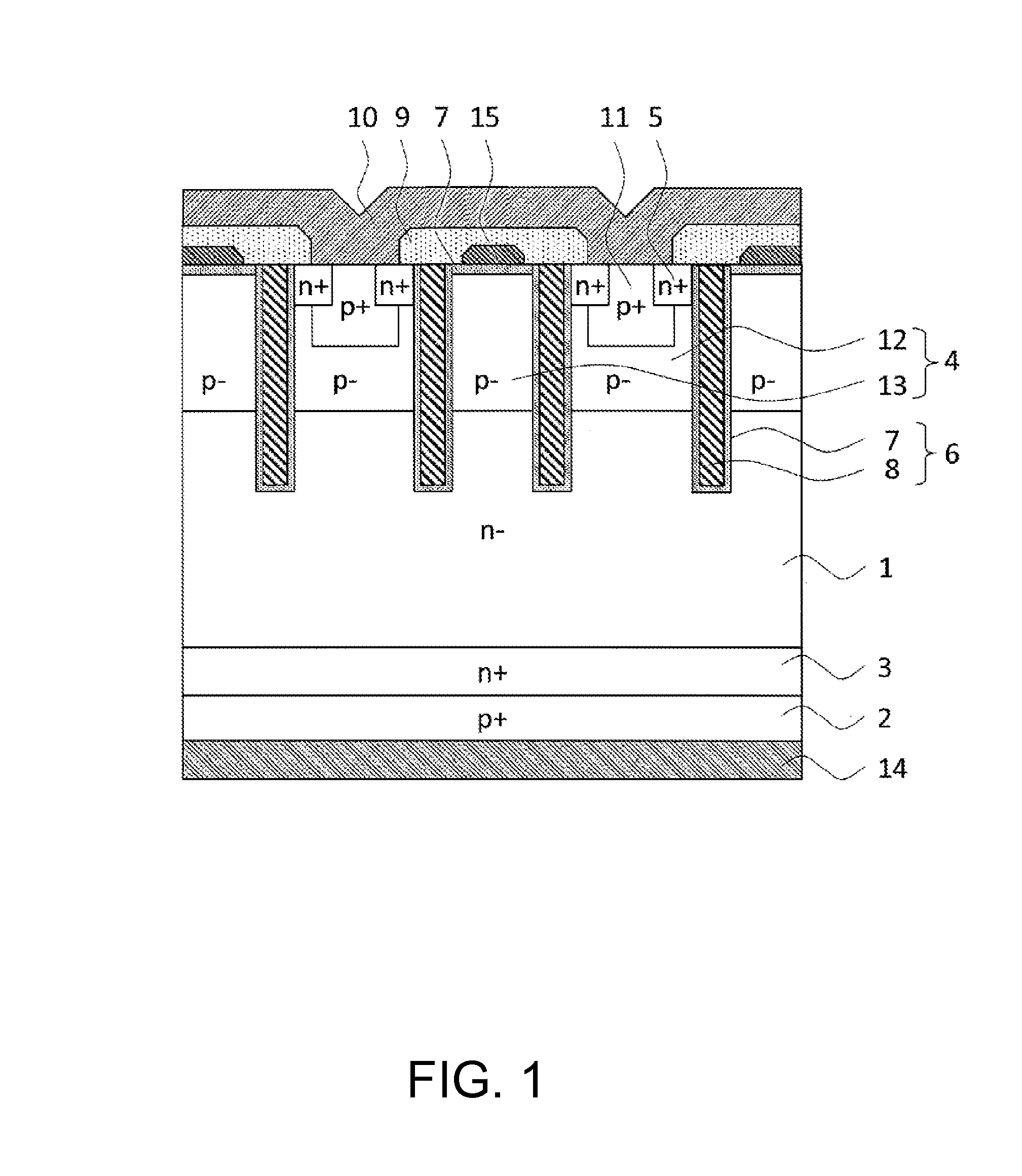

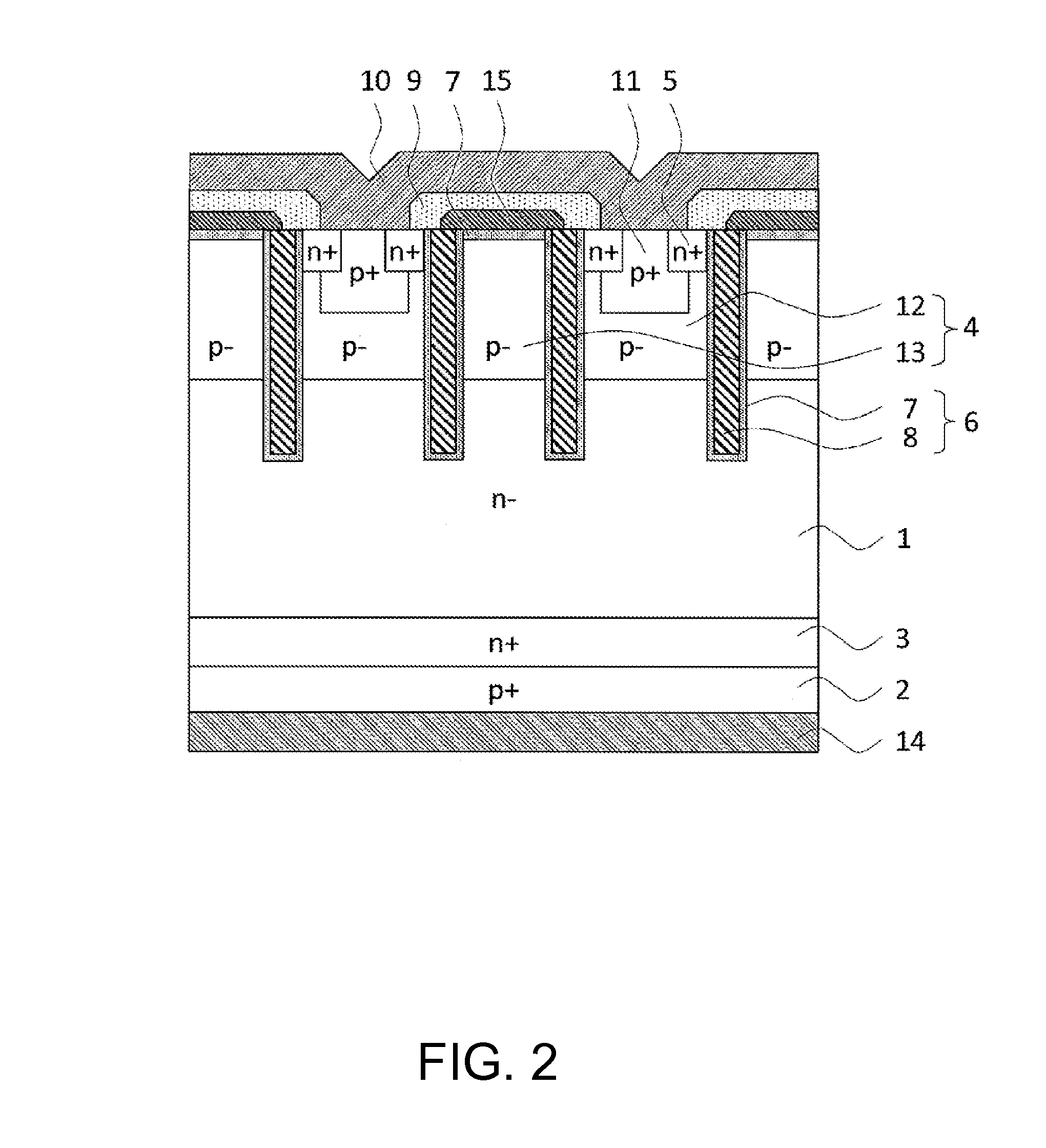

Semiconductor device

ActiveUS20160211354A1Reduce gate-collector capacitanceFast switching speedTransistorSolid-state devicesPower semiconductor deviceEngineering

A shield electrode is formed above a floating p region in a semiconductor layer and connected to a gate electrode in a trench. The shield electrode is composed of a material having an electrical resistivity lower than that of the gate electrode.

Owner:FUJI ELECTRIC CO LTD

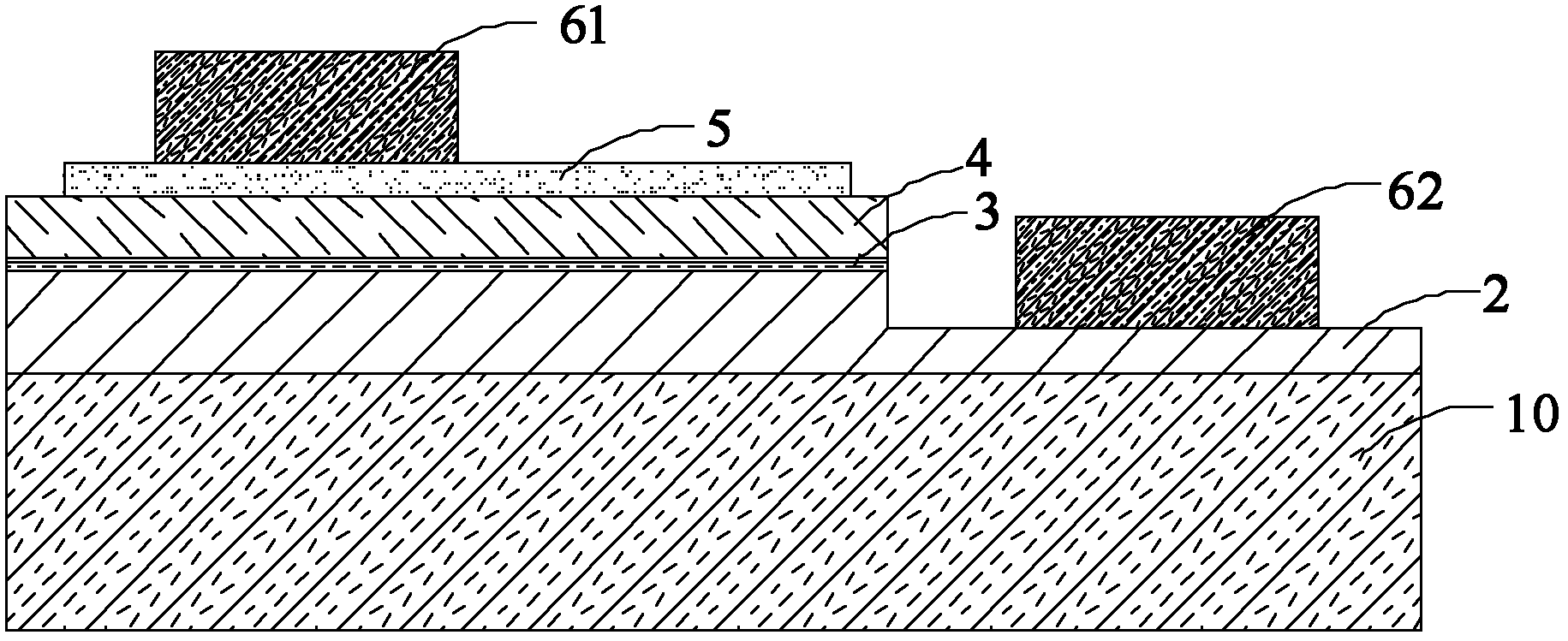

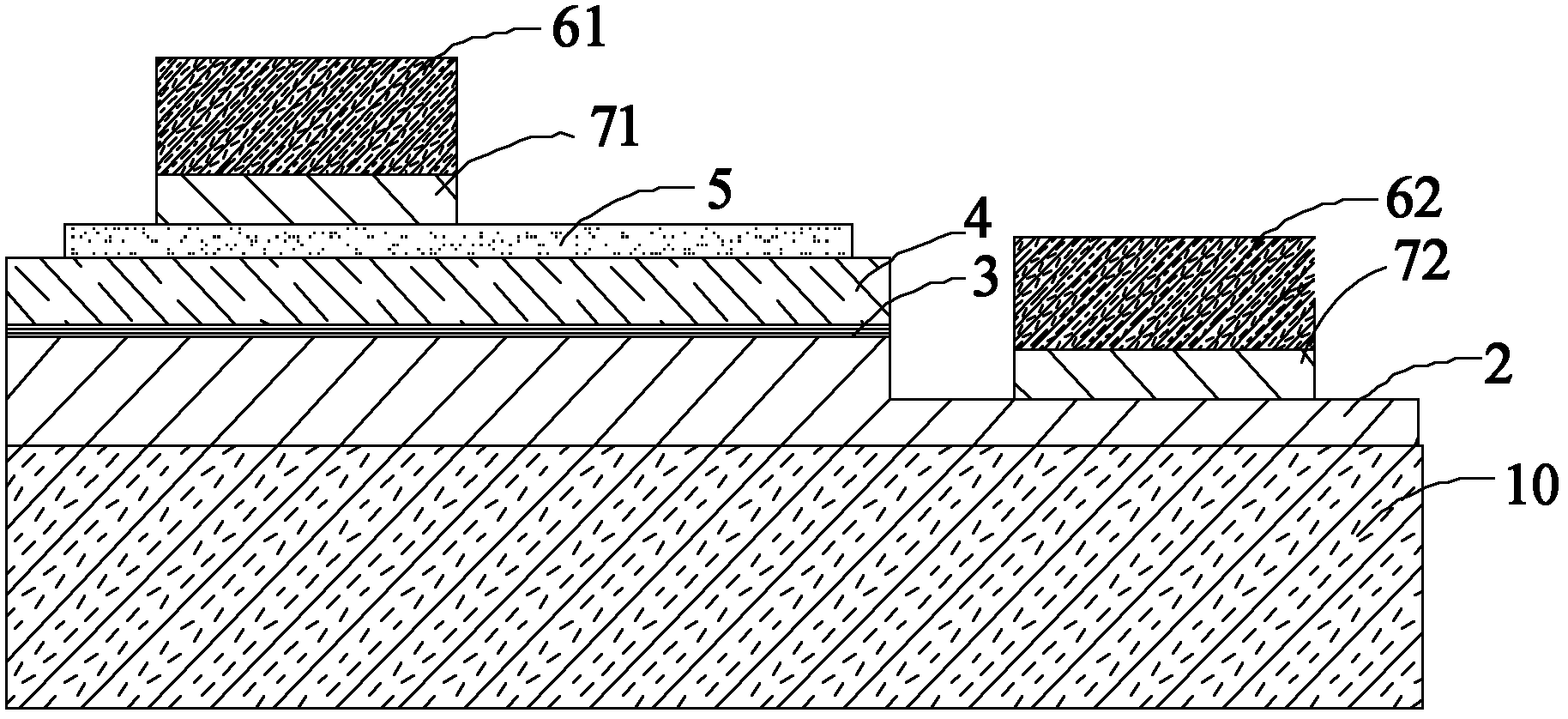

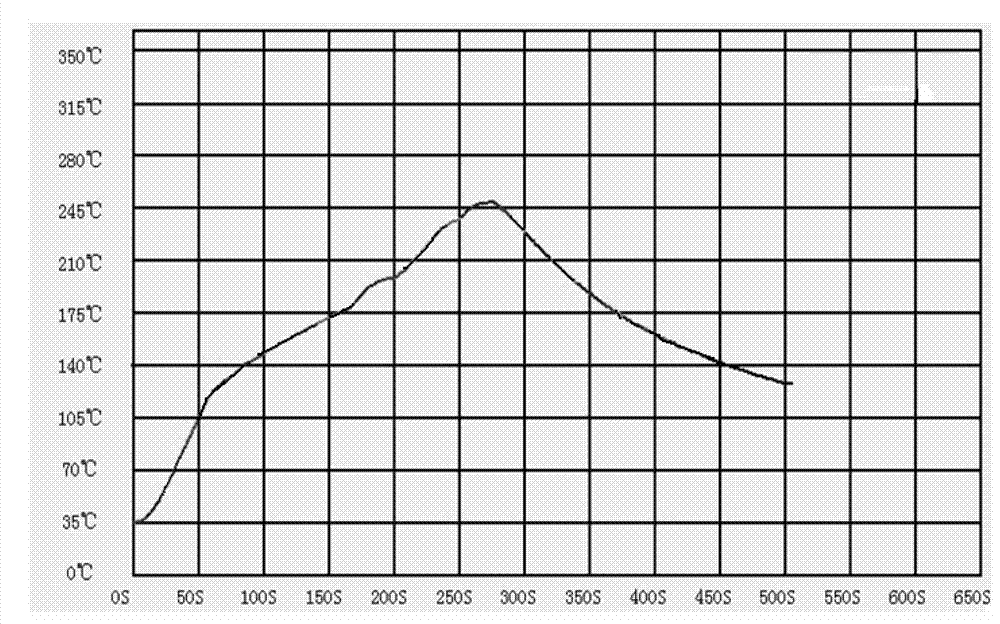

Semiconductor light emitting diode (LED) device and formation method thereof

ActiveCN102664227AImprove thermal stabilityExtended service lifeSemiconductor devicesThermal stabilityActive layer

Owner:HANGZHOU SILAN AZURE

Wire structure and forming method of the same

InactiveUS20060264030A1Excellent electromigration resistanceStress migrationSemiconductor/solid-state device detailsSolid-state devicesCompound (substance)Electrical conductor

A wire structure, comprising: a first insulating layer having a lower layer trench formed in an outer surface thereof; a first diffusion preventing film formed on an inner surface of the lower layer trench; a lower layer wire filled in the lower layer trench through the first diffusion preventing film; an interlayer diffusion preventing film formed on the lower layer wire, the interlayer diffusion preventing film made of a high melt point metal or a high melt point metal compound; a second insulating layer formed over the first insulating layer and the interlayer diffusion preventing film, a second insulating layer having a via hole that penetrates through the second insulating layer and the interlayer diffusion preventing film so as to reach the lower layer wire; a conductive second diffusion preventing film formed on an inner surface of the via hall; a conductor filled in the via hole through the second diffusion preventing film, and an adhering film made of the material that forms the interlayer diffusion preventing film, wherein the adhering film is formed so as to extend from an upper surface of the lower layer wire to a side surface of the second insulating layer within the via hall.

Owner:SHARP KK

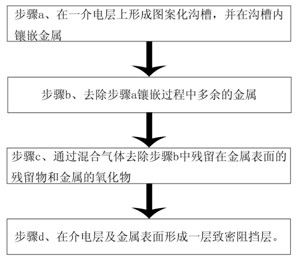

Surface treatment method for improving copper interconnection reliability

ActiveCN102420173AImprove bindingImprove performanceSemiconductor/solid-state device manufacturingCopper interconnectNitrogen

The invention discloses a surface treatment method for improving copper interconnection reliability. The surface treatment method comprises the following steps of: a. forming a patterned groove on a dielectric layer and embedding metal in the patterned groove; b. removing residual metal in the embedding process in the step a; and c. removing residues and metal oxides on the surface by mixed gas. The invention has the benefits that oxides on the surface of a copper metal layer and residues in the chemical mechanical polishing process can be removed, thereby an atomic-scale cleaning surface is obtained; in addition, the bonding force of the cleaning surface and a nitride-containing barrier layer on the lower layer of the cleaning surface is improved, so that the copper interconnected electromigration resistant performance is improved, the stress resistant performance is improved and the dielectric breakdown life of a dielectric layer is prolonged; meanwhile, the damage to the dielectric layer in the prior art can be reduced and the improvement on the integrated performance of a chip is facilitated.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

On-chip Cu interconnection using 1 to 5 nm thick metal cap

ActiveUS20060160350A1Improve corrosion resistanceImproved resistance to electromigrationSemiconductor/solid-state device detailsSolid-state devicesDielectricSolubility

Disclosed is a procedure to coat the free surface of Cu damascene lines by a 1-5 nm thick element prior to deposition of the inter-level dielectric or dielectric diffusion barrier layer. The coating provides protection against oxidation, increases the adhesion strength between the Cu and dielectric, and reduces interface diffusion of Cu. In addition, the thin cap layer further increases electromigration Cu lifetime and reduces the stress induced voiding. The selective elements can be directly deposited onto the Cu embedded within the under layer dielectric without causing an electric short circuit between the Cu lines. These chosen elements are based on their high negative reduction potentials with oxygen and water, and a low solubility in and formation of compounds with Cu.

Owner:GLOBALFOUNDRIES US INC

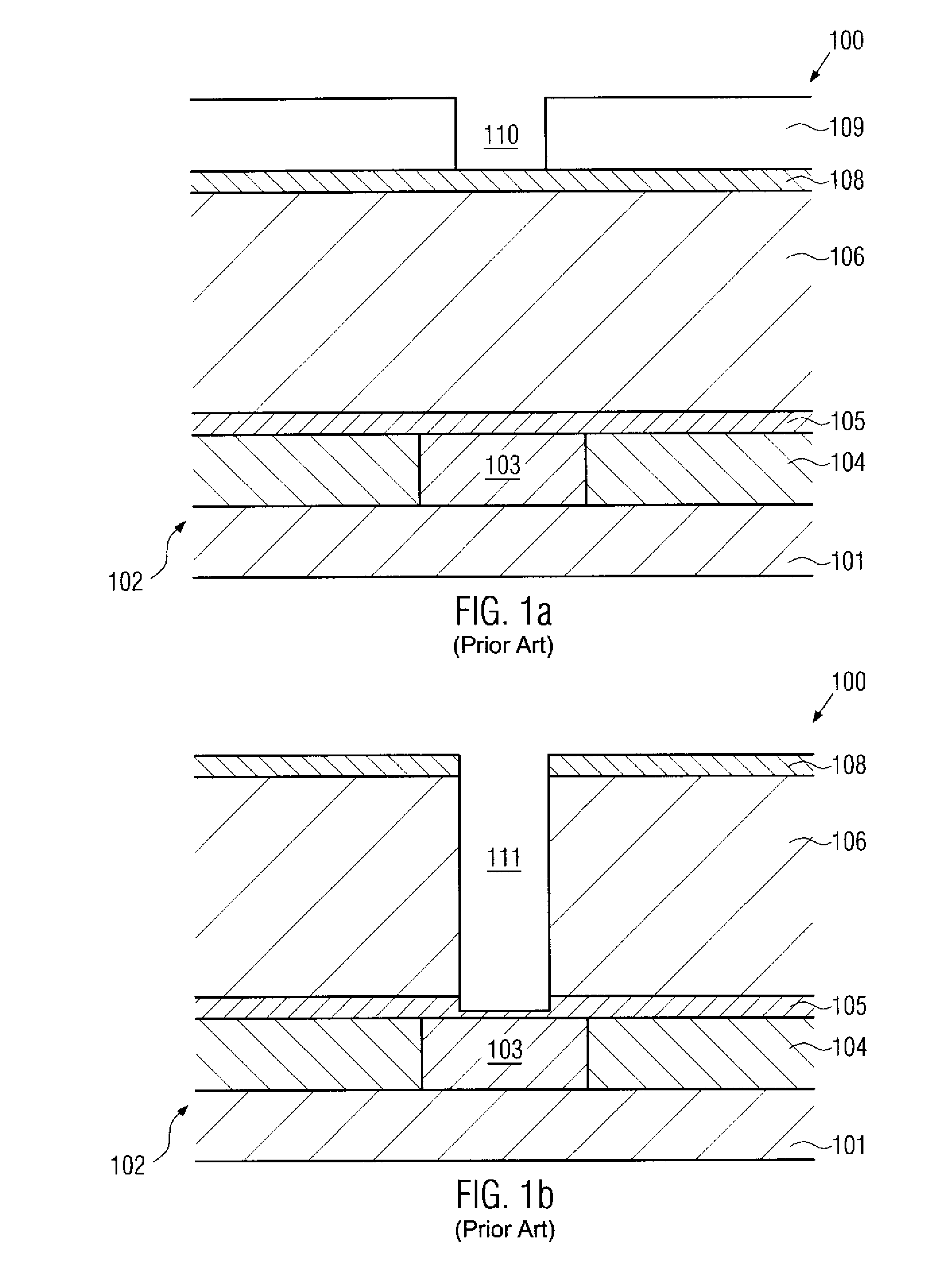

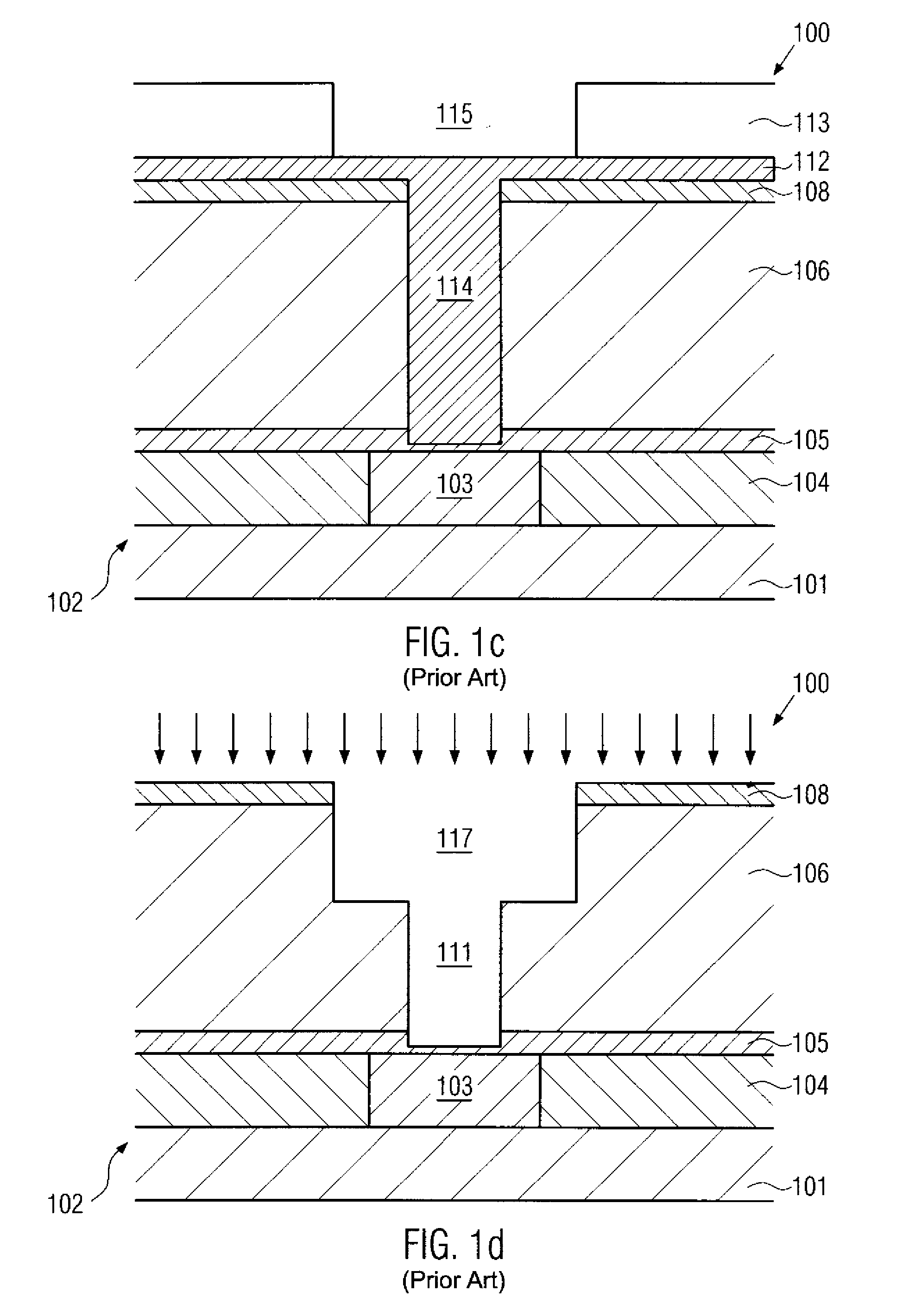

Submicron contact fill using a CVD TiN barrier and high temperature PVD aluminum alloy deposition

ActiveUS20060076680A1Increased electro-migration resistanceImprove electrical characteristicsSemiconductor/solid-state device detailsSolid-state devicesAlloy depositionChemical vapor deposition

A submicron contact opening fill using a chemical vapor deposition (CVD) TiN liner / barrier and a high temperature, e.g., greater than about 385° C., physical vapor deposition (PVD) aluminum alloy layer that substantially fills the submicron contact.

Owner:MICROCHIP TECH INC

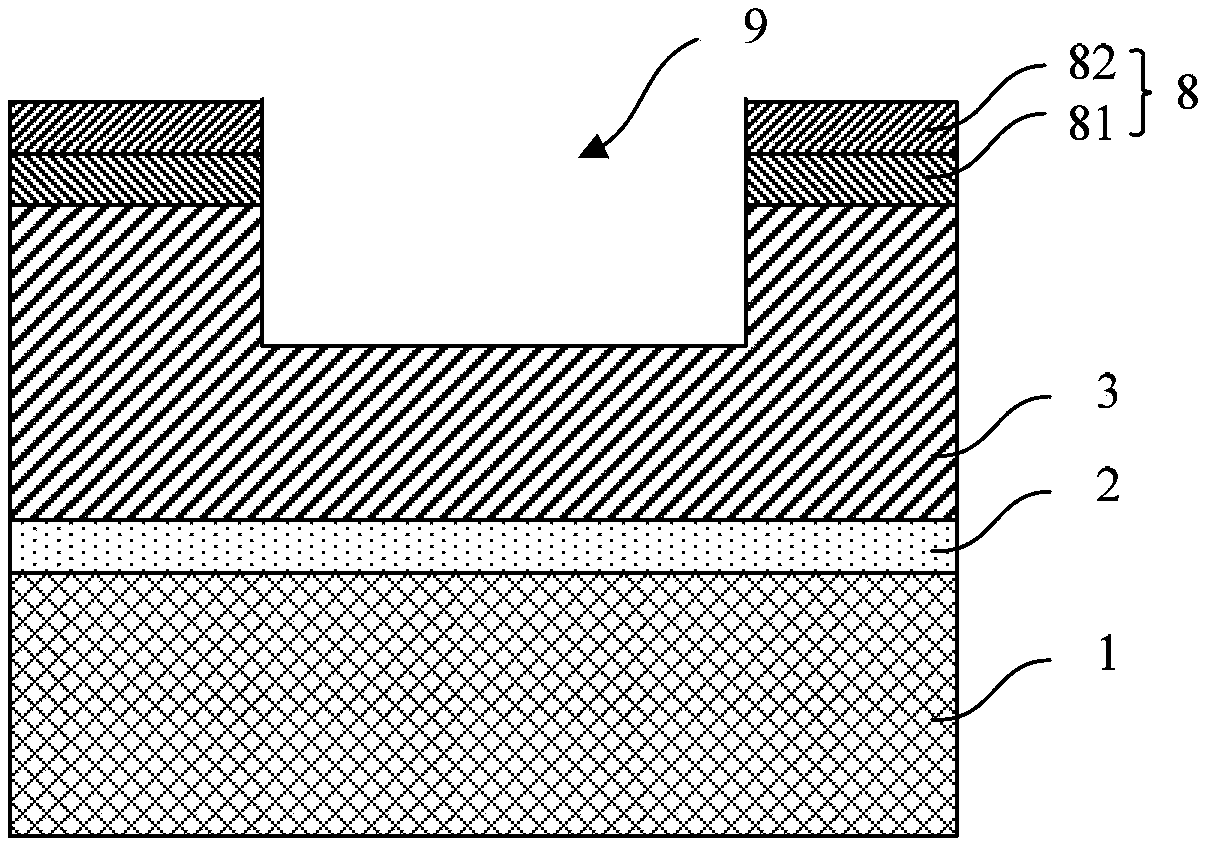

Electromigration resistant interconnect structure

InactiveUS20090039512A1Improved resistance to electromigrationReduce parasitic resistanceSemiconductor/solid-state device detailsSolid-state devicesDielectric layerElectromigration

A line trench is formed in a dielectric layer that may contain an interlayer dielectric material. A metal liner is formed on the sidewalls and the bottom surface of the line trench. A conductive metal is deposited within a remaining portion of the line trench at least up to a top surface of the dielectric layer and planarized to form a metal line in the line trench. The metal line is recessed by a recess etch below the top surface of the dielectric layer. A dielectric line cap or a metallic line cap is formed by deposition of a dielectric cap layer or a metallic cap layer, followed by planarization of the dielectric or metallic cap layer. The dielectric line cap or the metallic line cap applies a highly compressive stress on the underlying metal line, which increases electromigration resistance of the metal line.

Owner:IBM CORP

Electromigration resistant via-to-line interconnect

ActiveUS8114768B2Increase resistanceExtended service lifeSemiconductor/solid-state device detailsSolid-state devicesMetal interconnectElectromigration

Owner:GLOBALFOUNDRIES U S INC

Semiconductor structure and formation method thereof

ActiveCN105336670AImprove surface chemical activityLower resistanceSemiconductor/solid-state device detailsSolid-state devicesSemiconductor structureAmorphous silicon

A semiconductor structure and a formation method thereof are disclosed. The formation method of the semiconductor structure comprises the following steps of providing a substrate and forming a through hole in the substrate; forming amorphous silicon layers on a through hole bottom and a sidewall surface; forming a barrier layer on an amorphous silicon layer surface, wherein the barrier layer preferentially orients a crystal plane (111); and forming a metal layer on a barrier layer surface, wherein the metal layer fills in the through hole and the metal layer preferentially orients the crystal plane (111). In the invention, after the amorphous silicon layers are formed on the silicon through hole bottom and the sidewall surface, the barrier layer and the metal layer which preferentially orient the crystal plane (111) are formed on the amorphous silicon layer surface so that an electromigration resistance capability of the metal layer is increased; a resistance of the metal layer is reduced; an electromigration resistance capability of the semiconductor structure is increased; an RC delayed effect of the semiconductor structure is reduced and electric performance of the semiconductor structure is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Lead-free solder for electronic packaging

InactiveCN102962599AHigh melting pointImprove wettabilityWelding/cutting media/materialsSoldering mediaElectronic packagingMechanical property

The invention relates to a lead-free solder for electronic packaging. The invention solves the technical problems that: the cost of the conventional high-silver solder is higher, and the mechanical property of the conventional low-silver solder is poor. According to percentage by weightmass, the lead-free solder for electronic packaging is composed of Ag, Cu, Ni, Bi, Sb, Ti and the balance of Sn. By designing and optimizing the solder ingredients, the lead-free solder for electronic packaging, which has excellent properties and is low in cost, is obtained. The addition of a variety of elements takes the complementation between the elements into consideration, consequently, while the properties of a certain element are improved, the other adverse affection is reduced, and thereby therefore the comprehensive properties of the solder are effectively enhanced.

Owner:HARBIN UNIV OF SCI & TECH

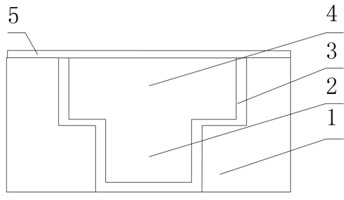

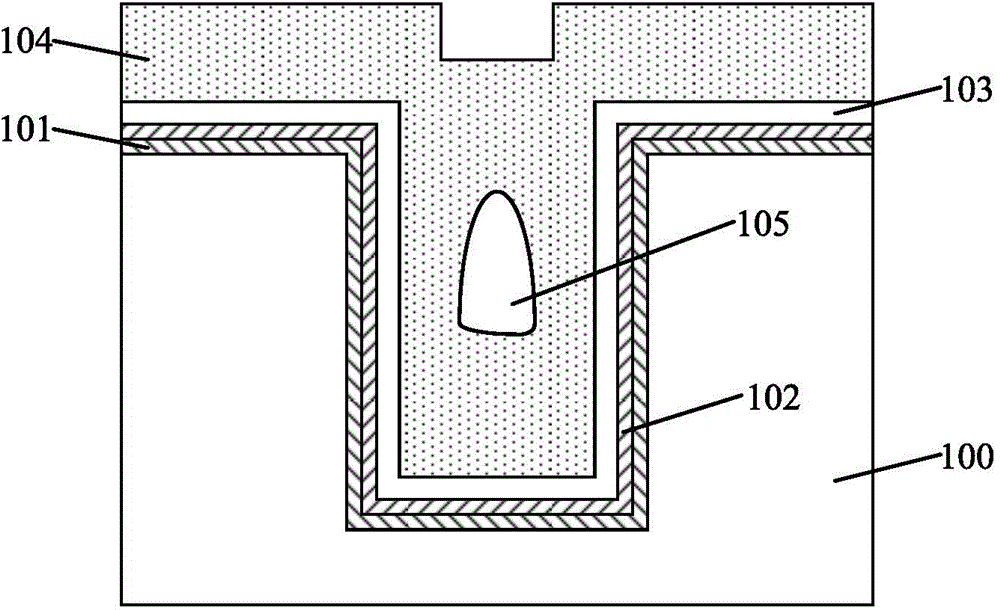

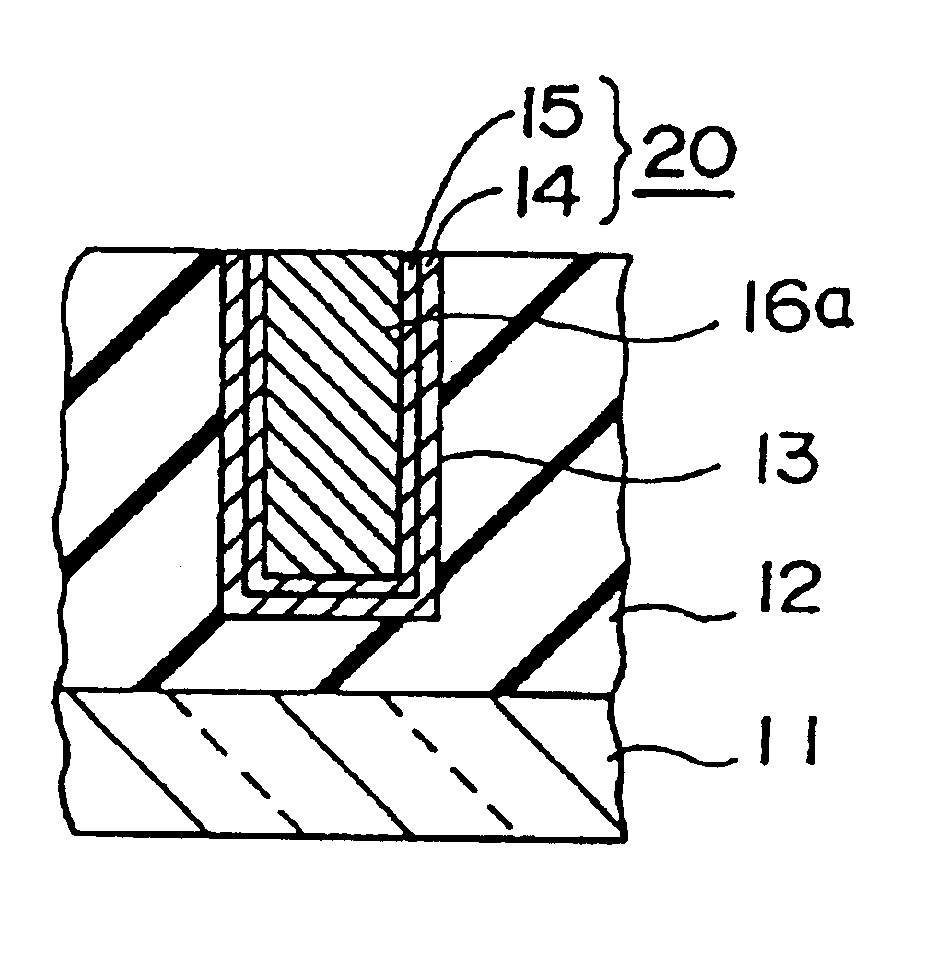

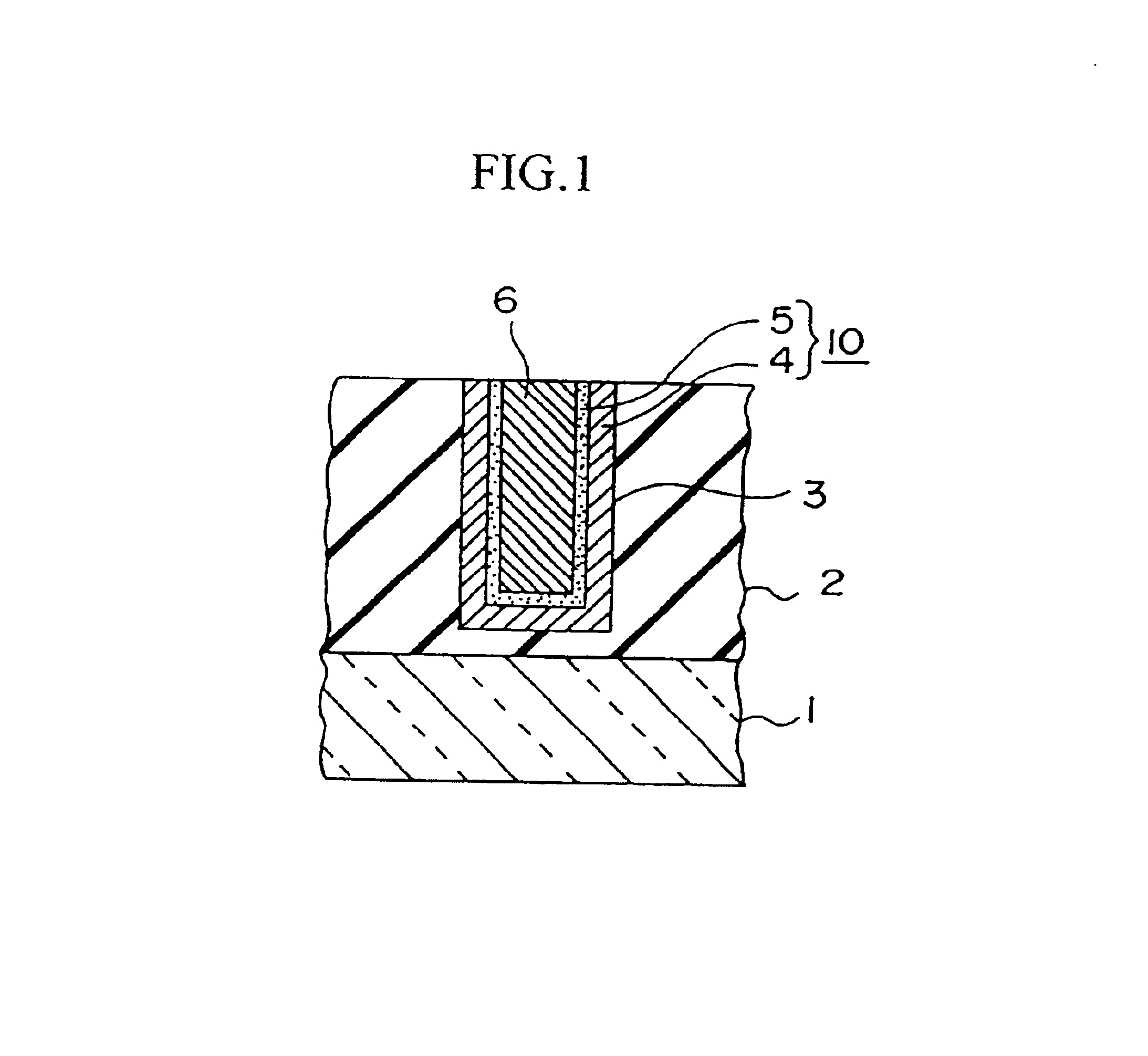

Embedded electroconductive layer structure

InactiveUS6891269B1Improved resistance to electromigrationReduce incubation timeSemiconductor/solid-state device detailsSolid-state devicesGrowth promotingMetal

An embedded electroconductive layer is disclosed which comprises an opening part or a depressed part 3 formed in an insulating film 2 on a substrate 1, a barrier layer for covering the opening part or the depressed part, a metal growth promoting layer 5 on the barrier layer, and an electroconductive layer 6 embedded in the opening part or the depressed part via the barrier layer 4 and the metal growth promoting layer 5.

Owner:FUJITSU SEMICON LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com