Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

403results about How to "Improve electrical characteristics" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

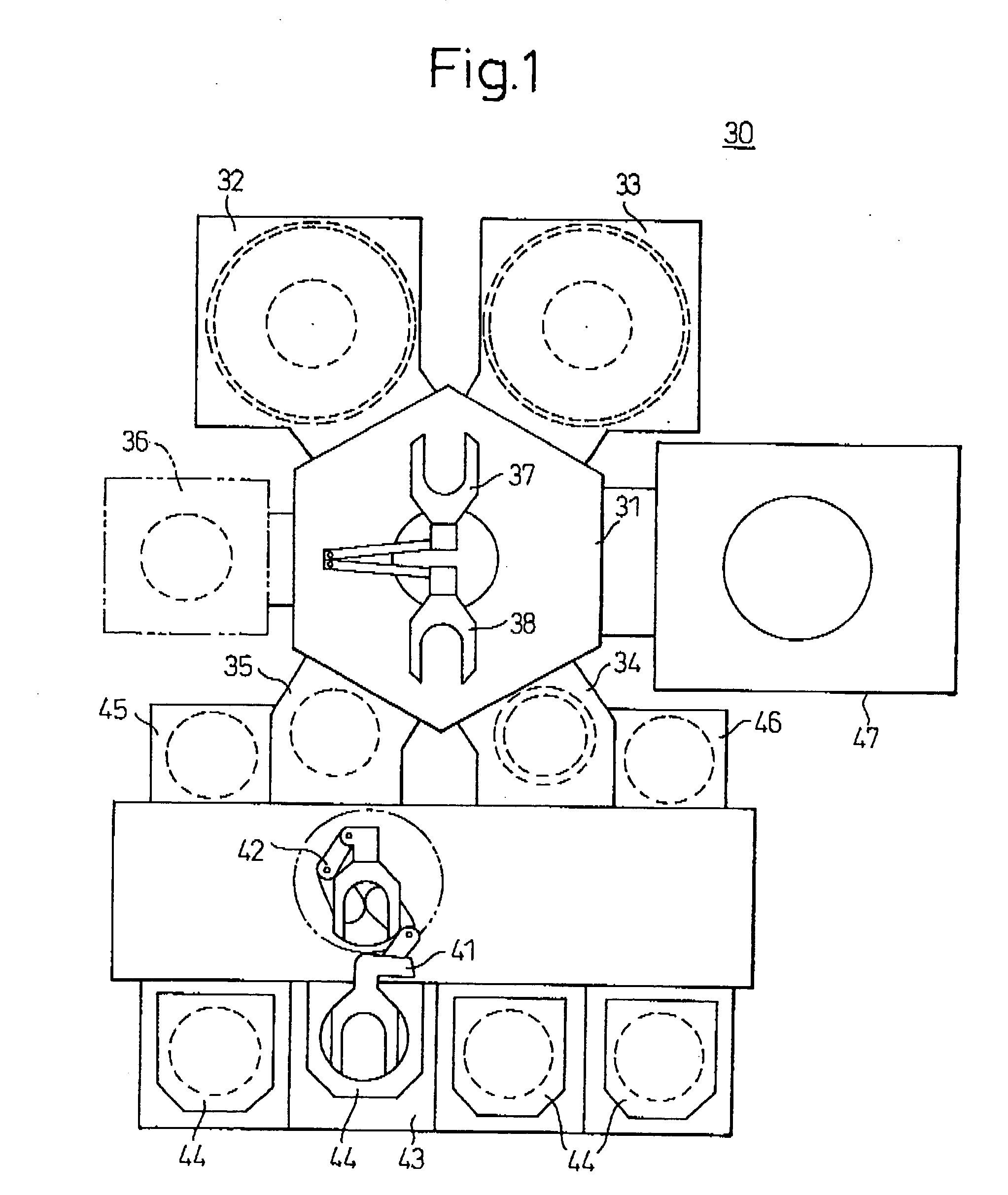

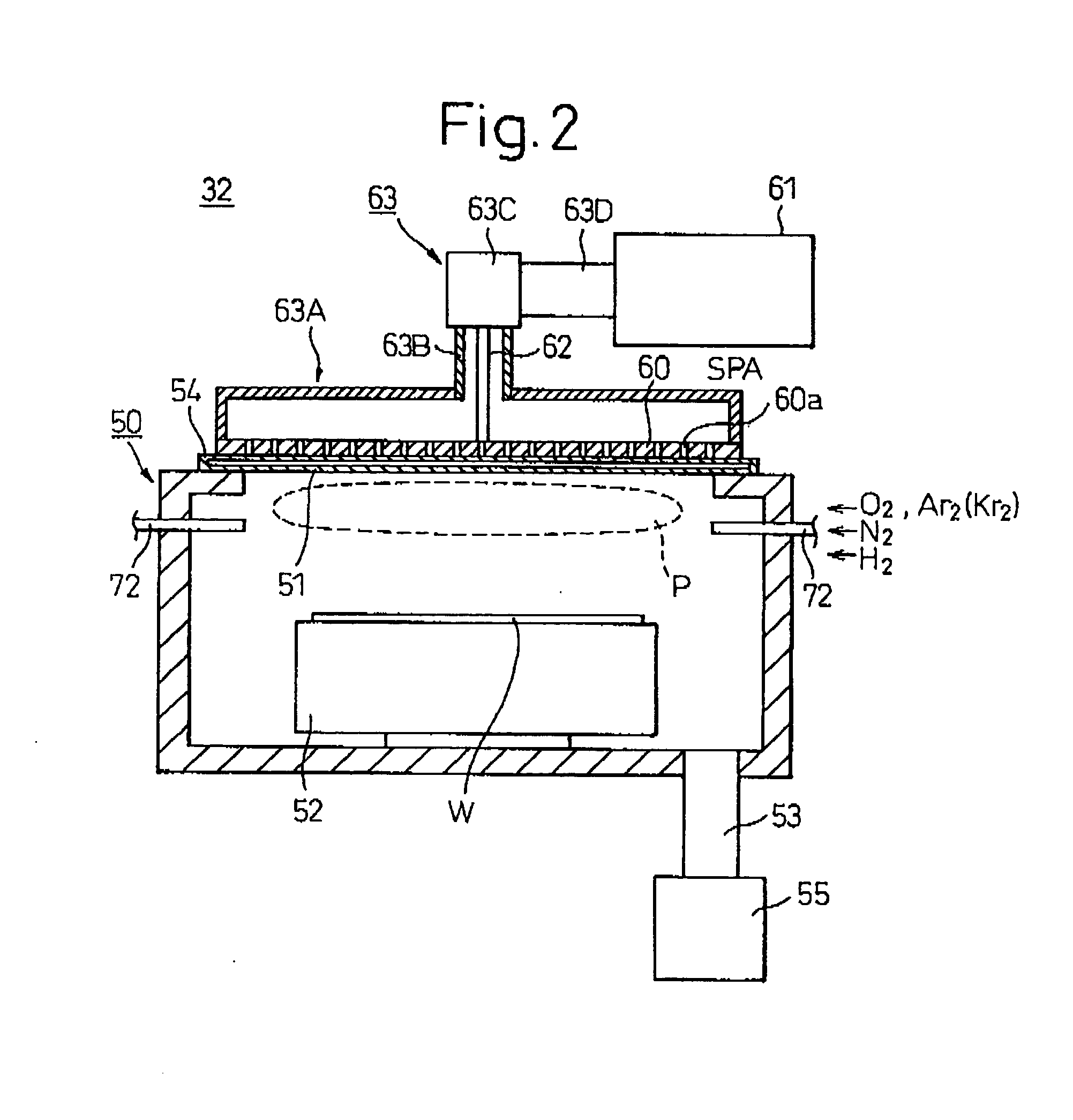

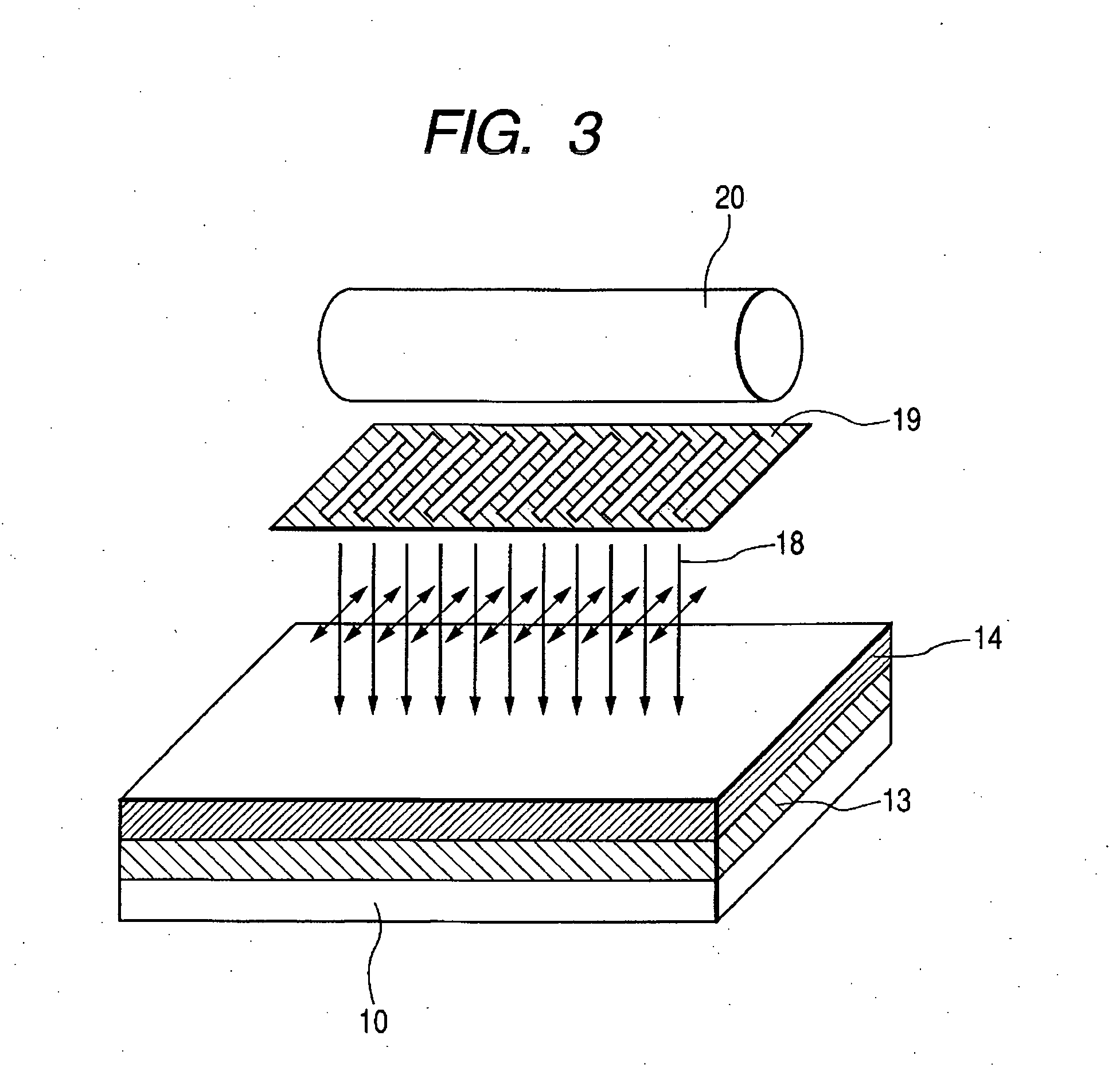

Method of producing electronic device material

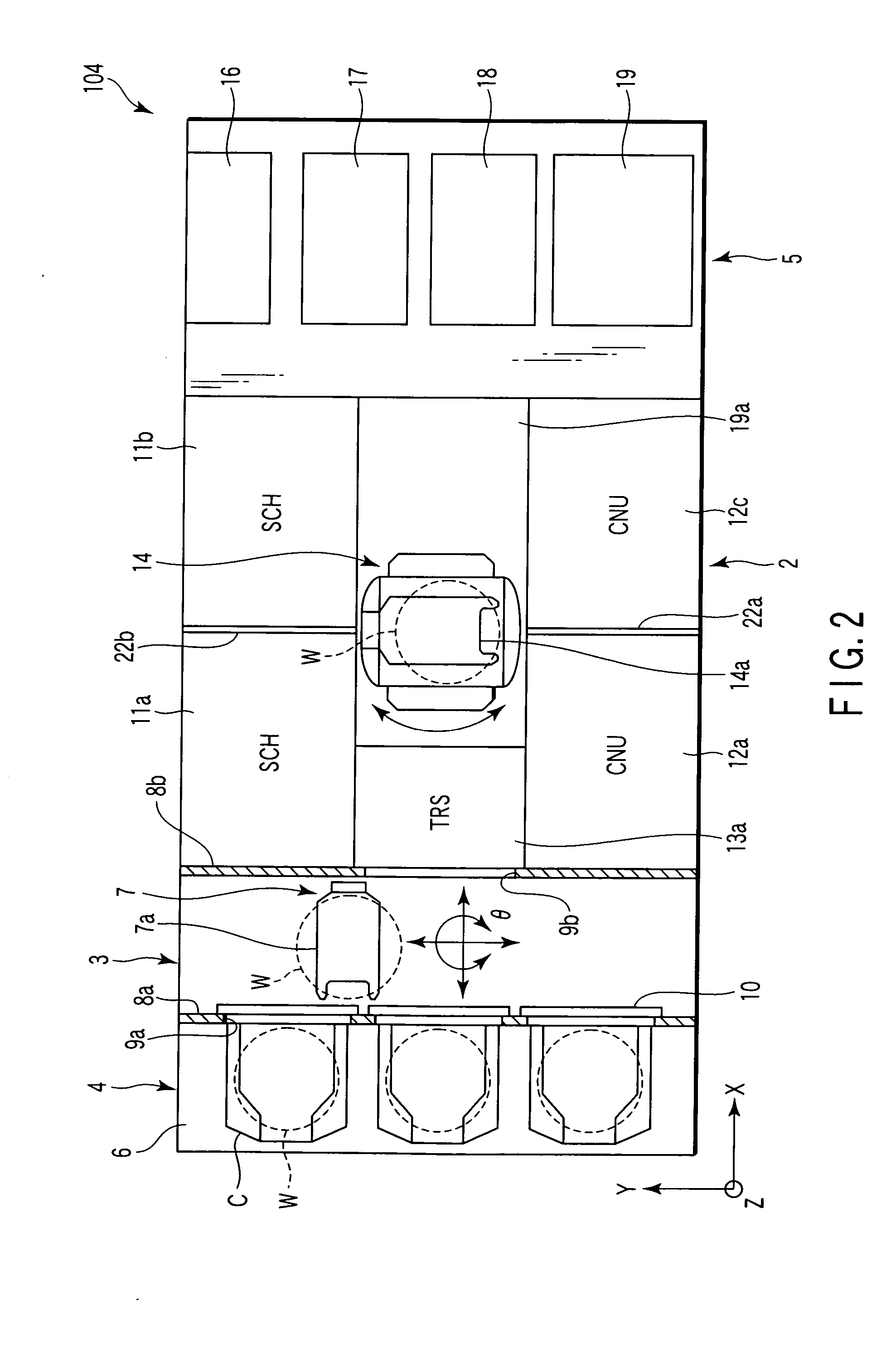

InactiveUS20040048452A1High densityLow electron temperatureElectric discharge tubesSemiconductor/solid-state device manufacturingDevice materialEngineering

A process for producing an electronic device material of a high quality MOS-type semiconductor comprising an insulating layer and a semiconductor layer excellent in the electrical characteristic. The process includes: a step of CVD-treating a substrate to be processed comprising single-crystal silicon as a main component, to thereby form an insulating layer; and a step of exposing the substrate to be processed to a plasma which has been generated from a process gas on the basis of microwave irradiation via a plane antenna member having a plurality of slots, to thereby modify the insulating film by using the thus generated plasma.

Owner:TOKYO ELECTRON LTD

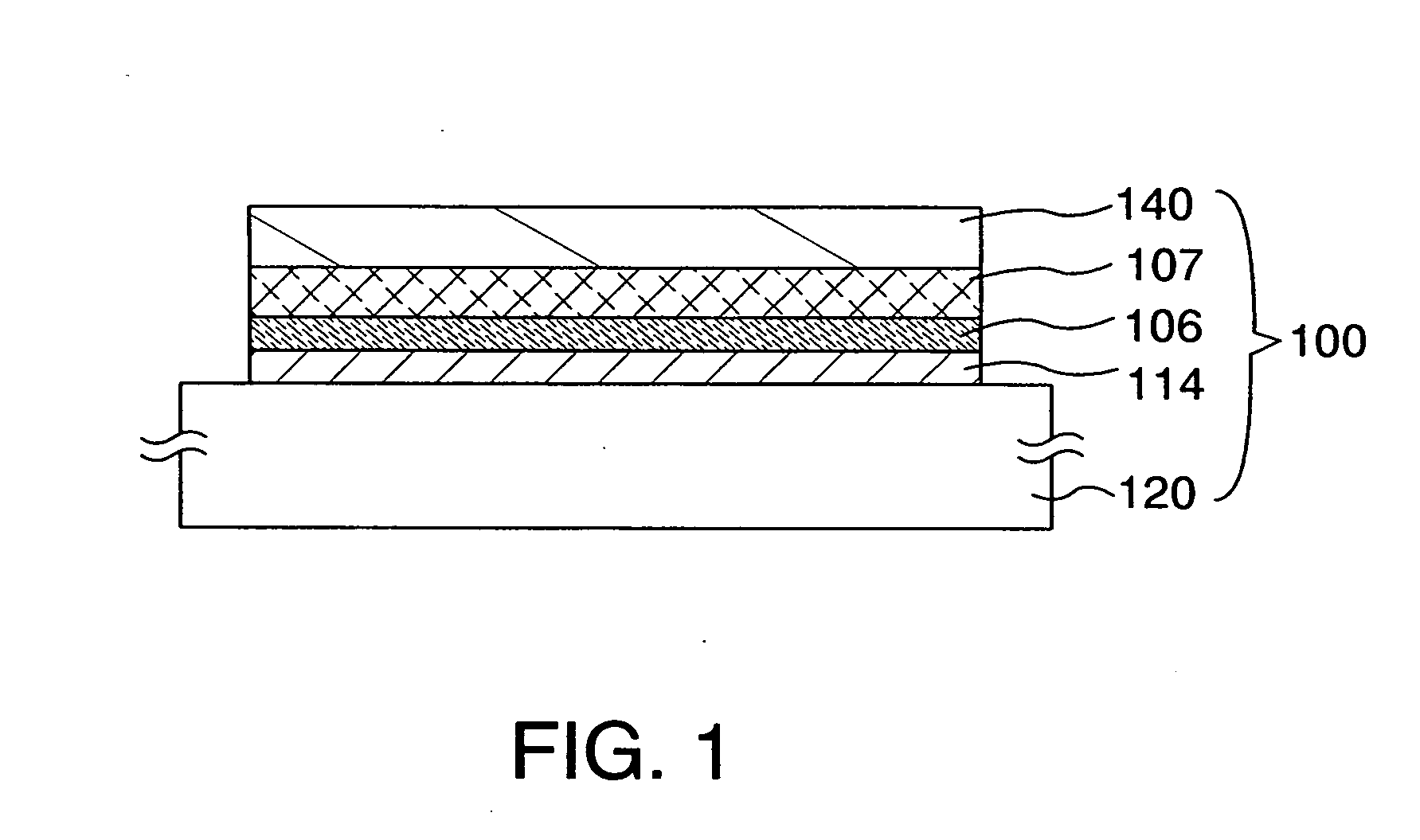

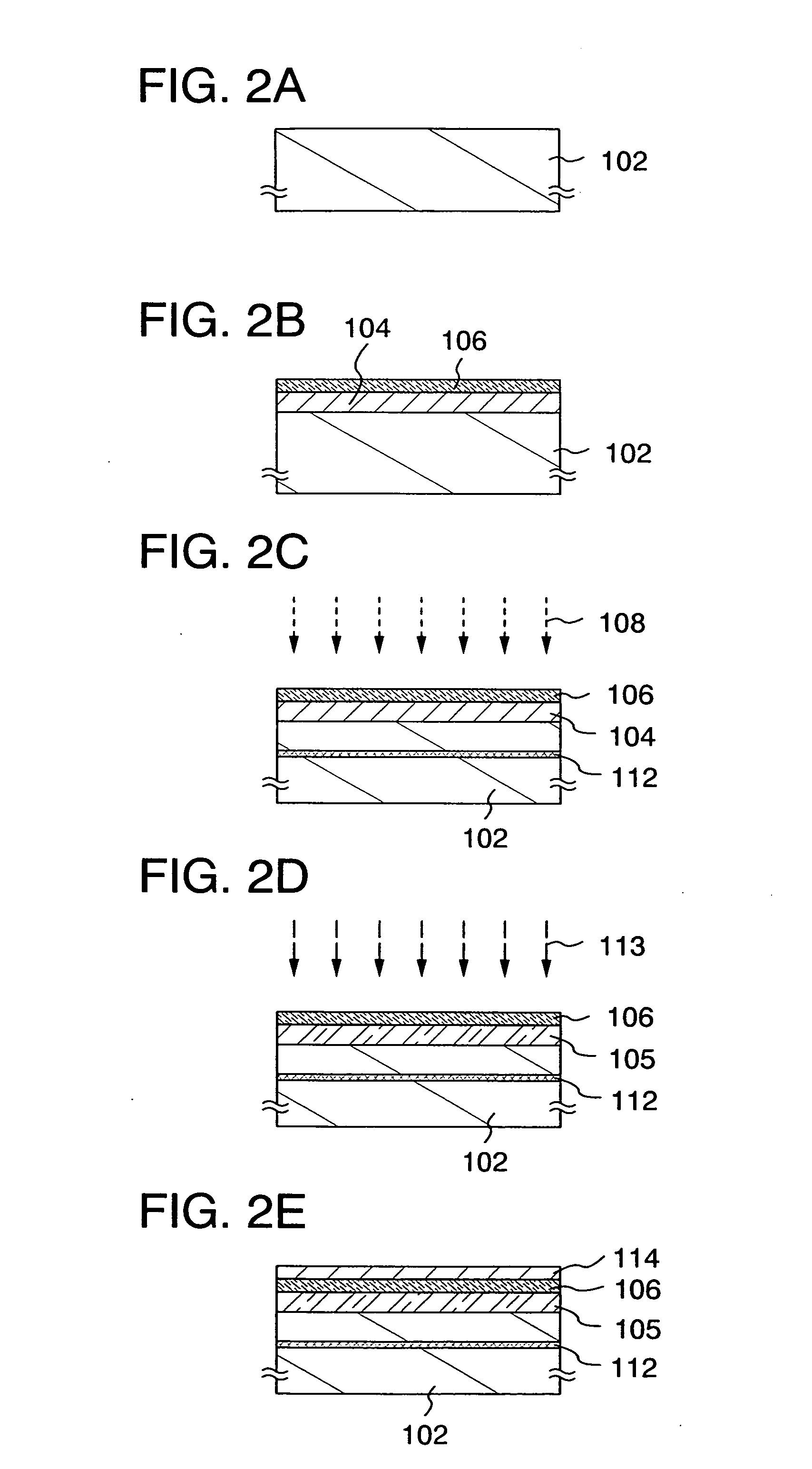

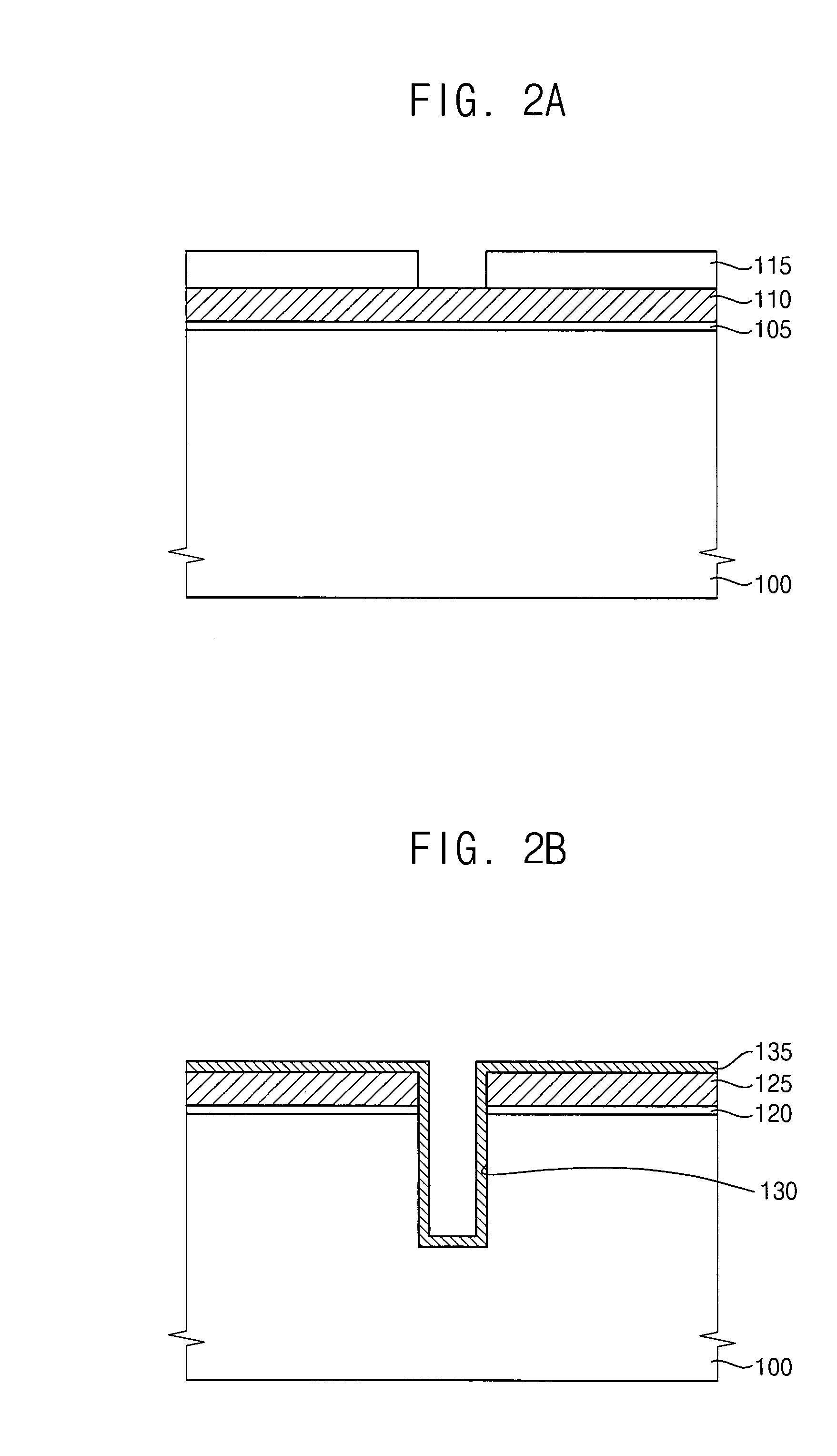

Semiconductor substrate and maehtod for manufacturing the same

InactiveUS20080315351A1Improve electrical characteristicsEasy to manufactureTransistorSolid-state devicesNitrogenSingle crystal

A semiconductor device and a method for manufacturing thereof are provided. The method includes a step of forming a first insulating film containing silicon and oxygen as its composition over a single-crystal semiconductor substrate, a step of forming a second insulating film containing silicon and nitrogen as its composition over the first insulating film, a step of irradiating the second insulating film with first ions to form a separation layer in the single-crystal semiconductor substrate, a step of irradiating the second insulating film with second ions so that halogen is contained in the first insulating film, and a step of performing heat treatment to separate the single-crystal semiconductor substrate with a single-crystal semiconductor film left over the supporting substrate.

Owner:SEMICON ENERGY LAB CO LTD

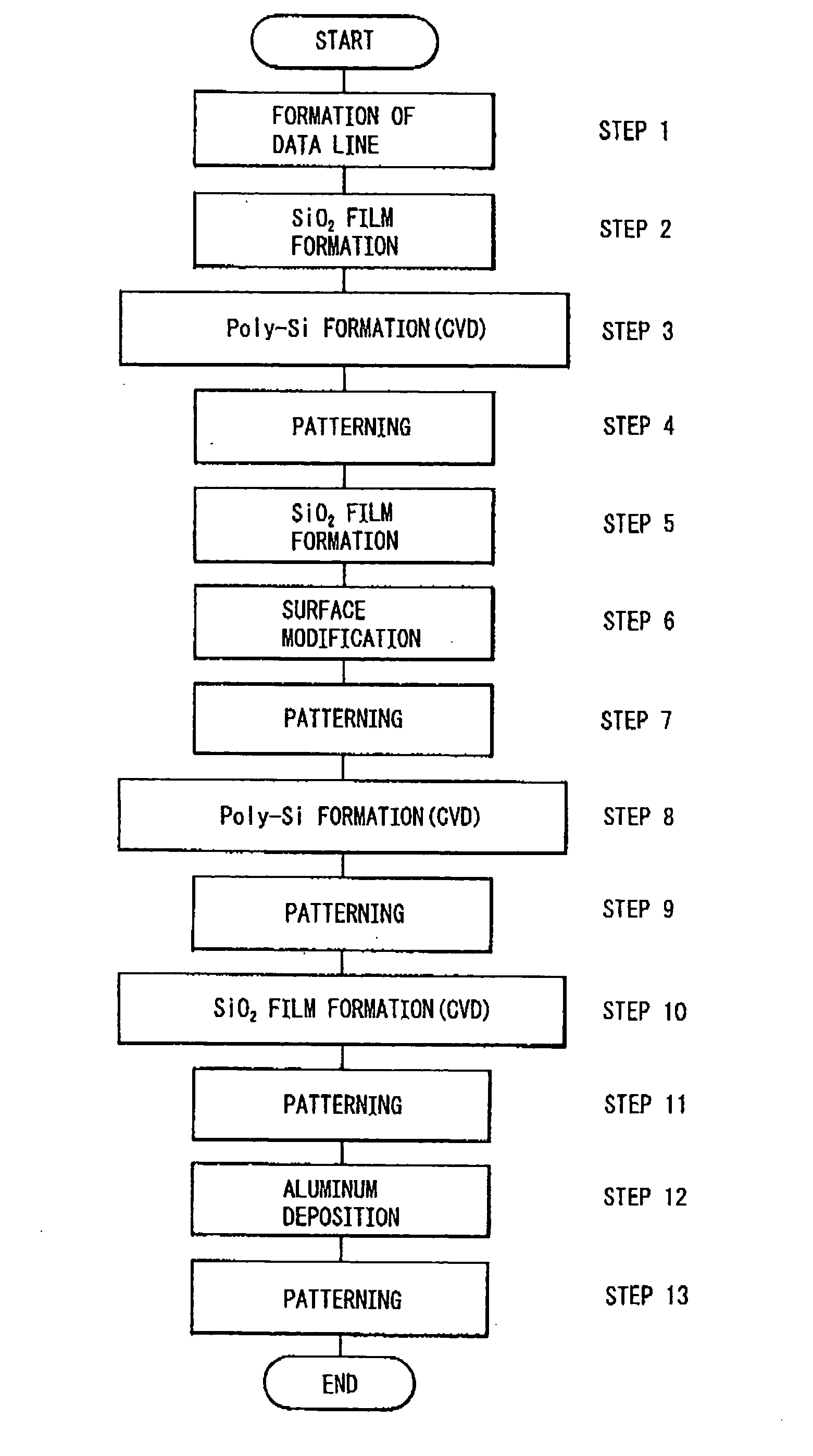

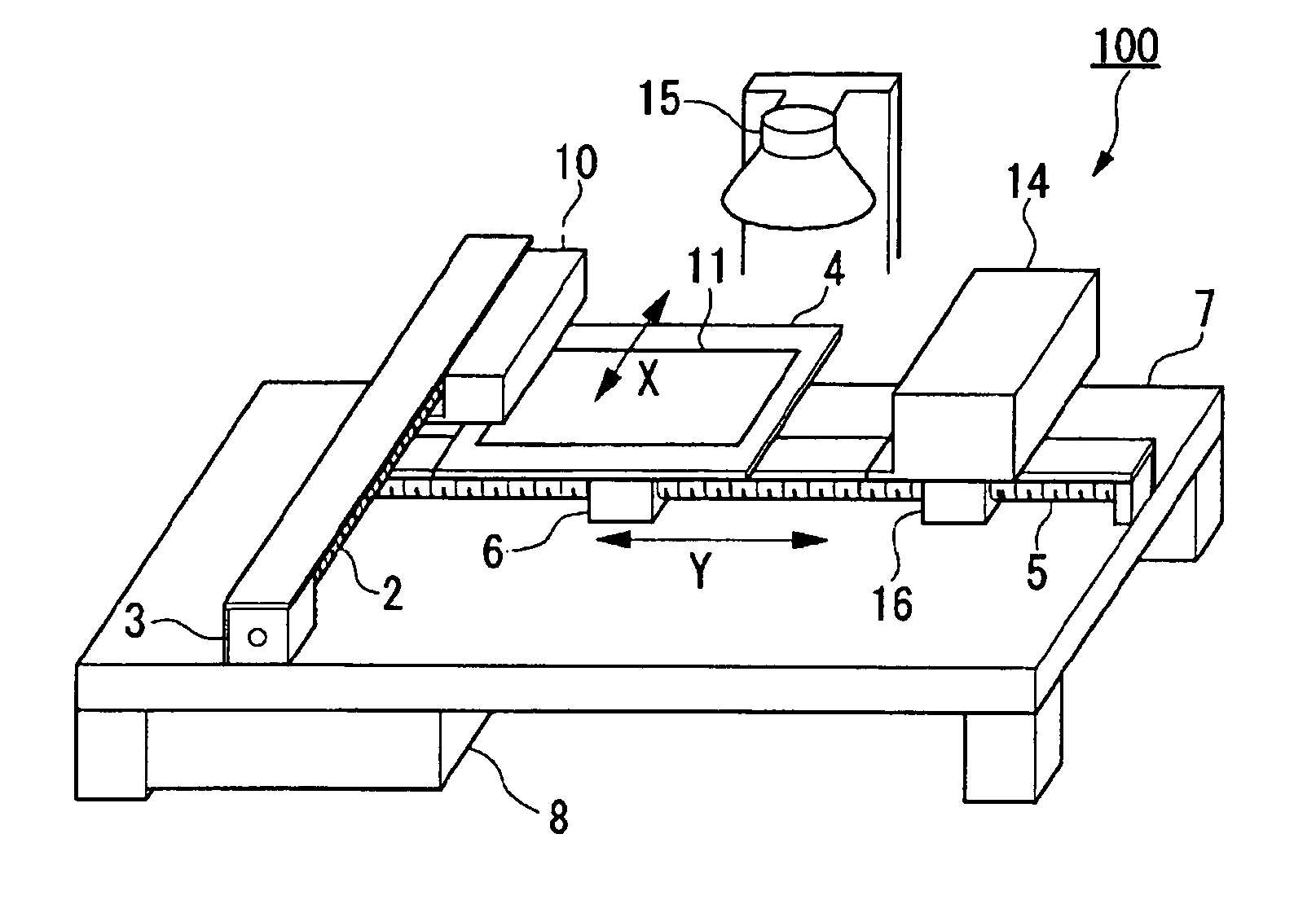

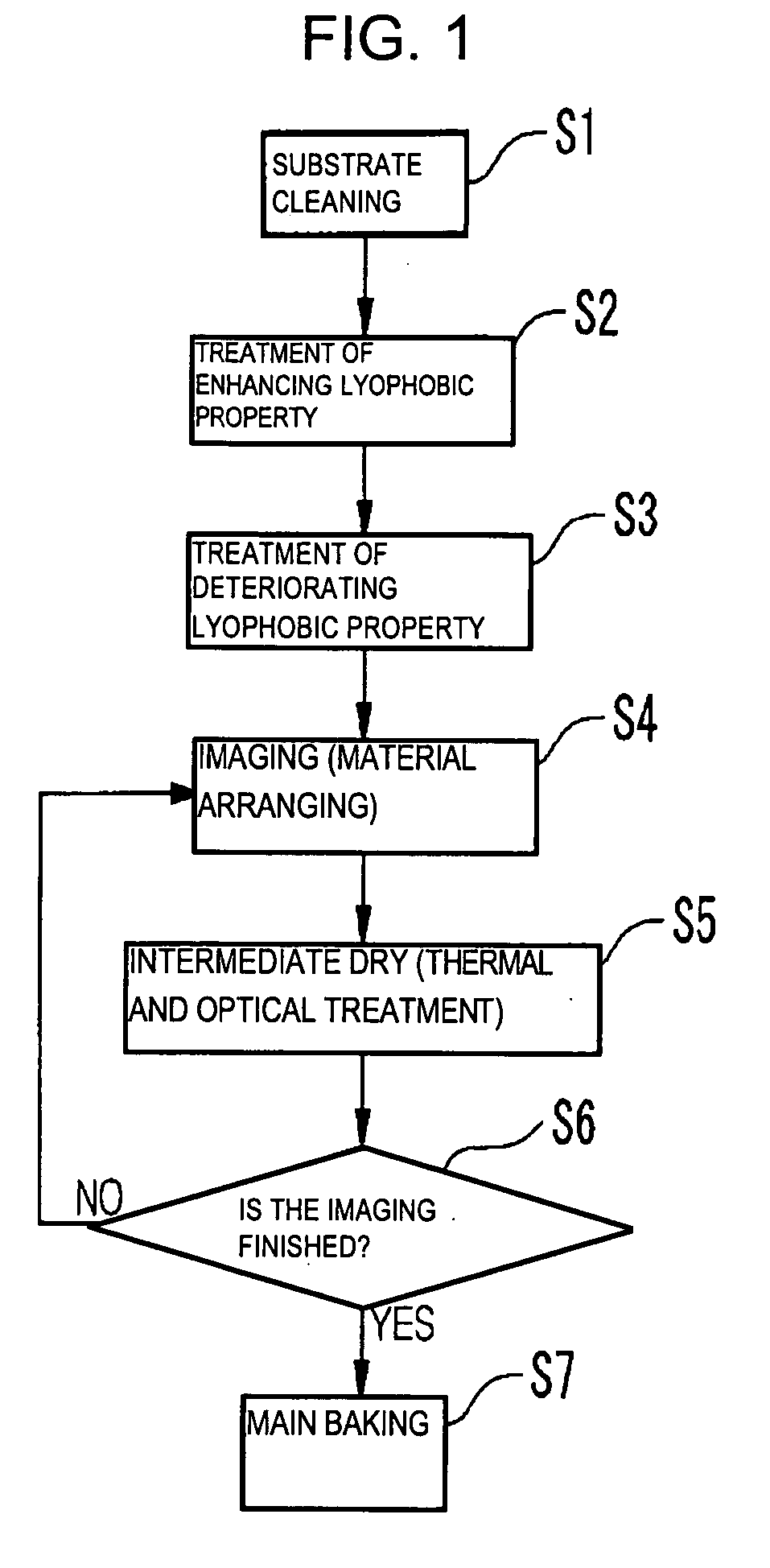

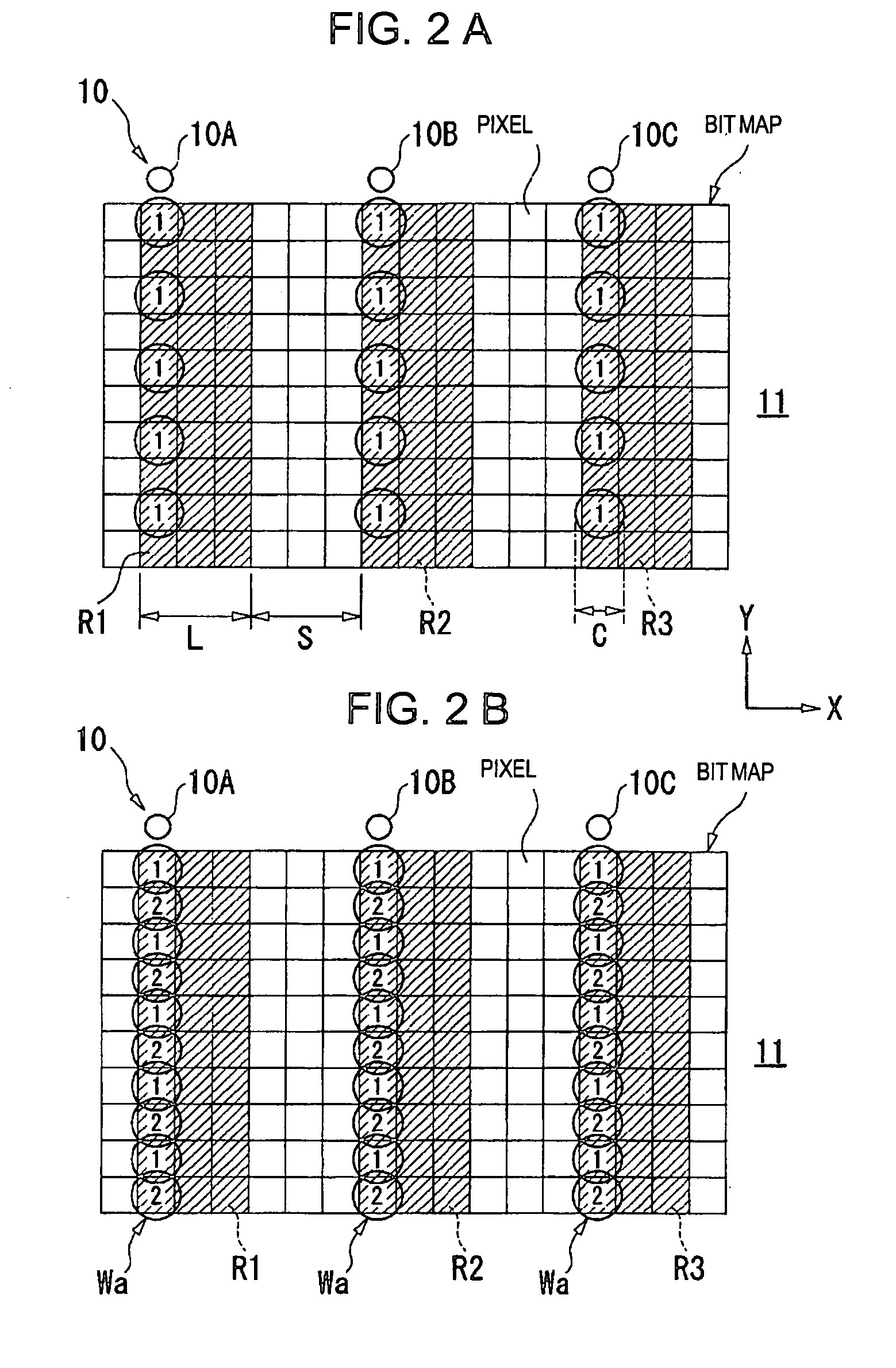

Pattern forming method, pattern forming apparatus, device manufacturing method, conductive film wiring, electro-optical device, and electronic apparatus

InactiveUS20050031836A1Without lack of uniformity in appearanceImprove electrical characteristicsTransistorSolid-state devicesEngineeringElectron

Owner:SEIKO EPSON CORP

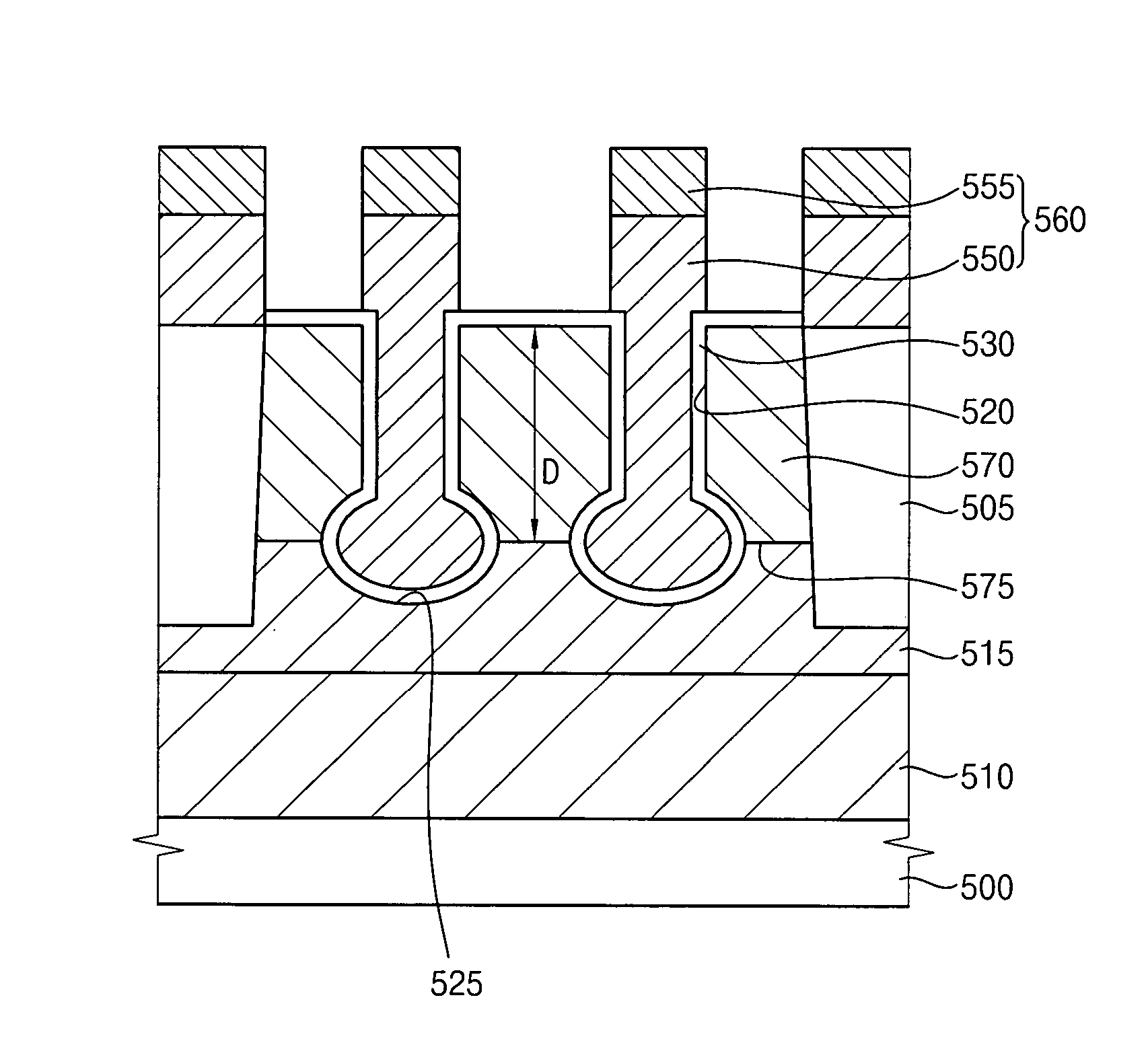

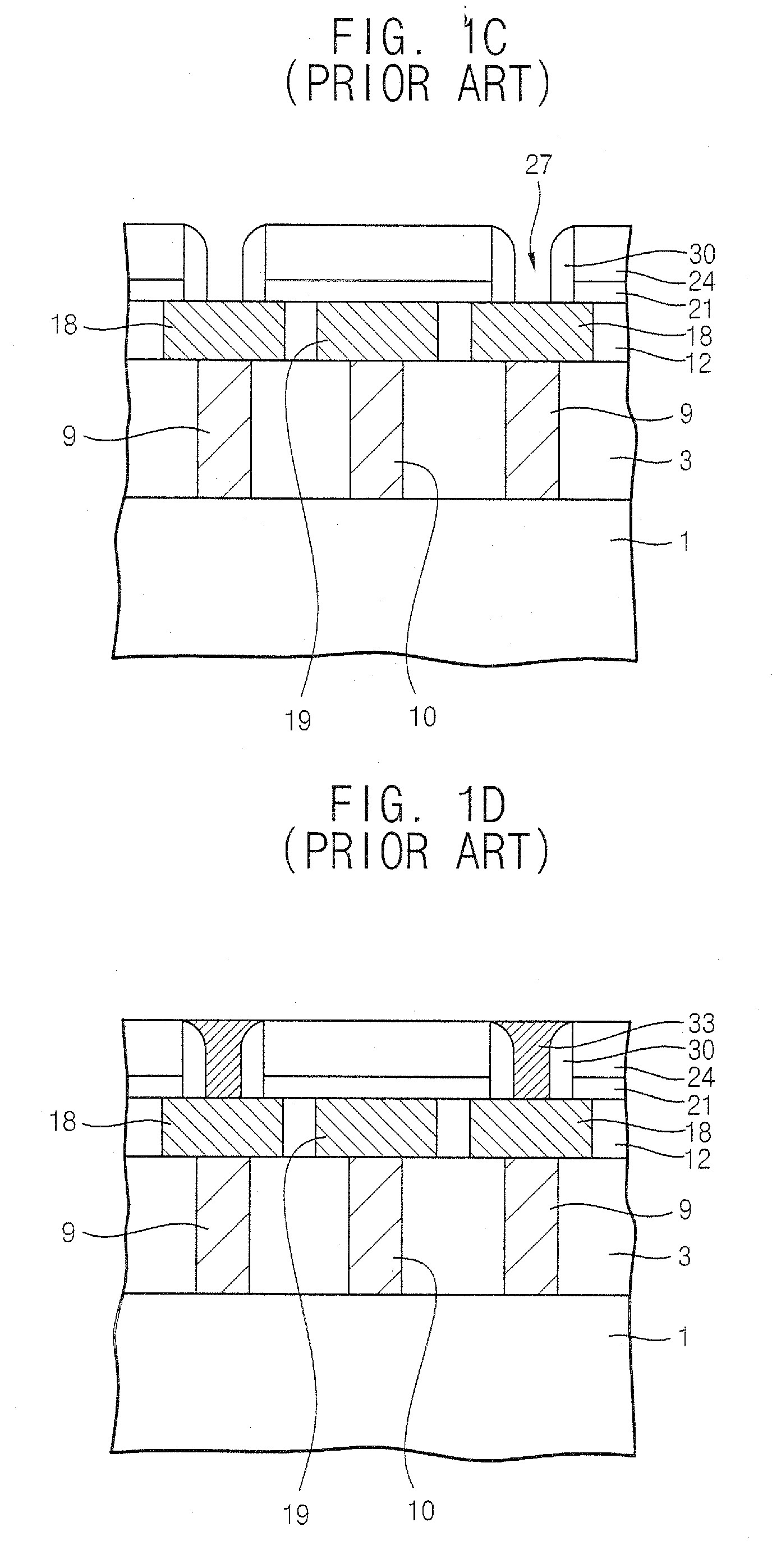

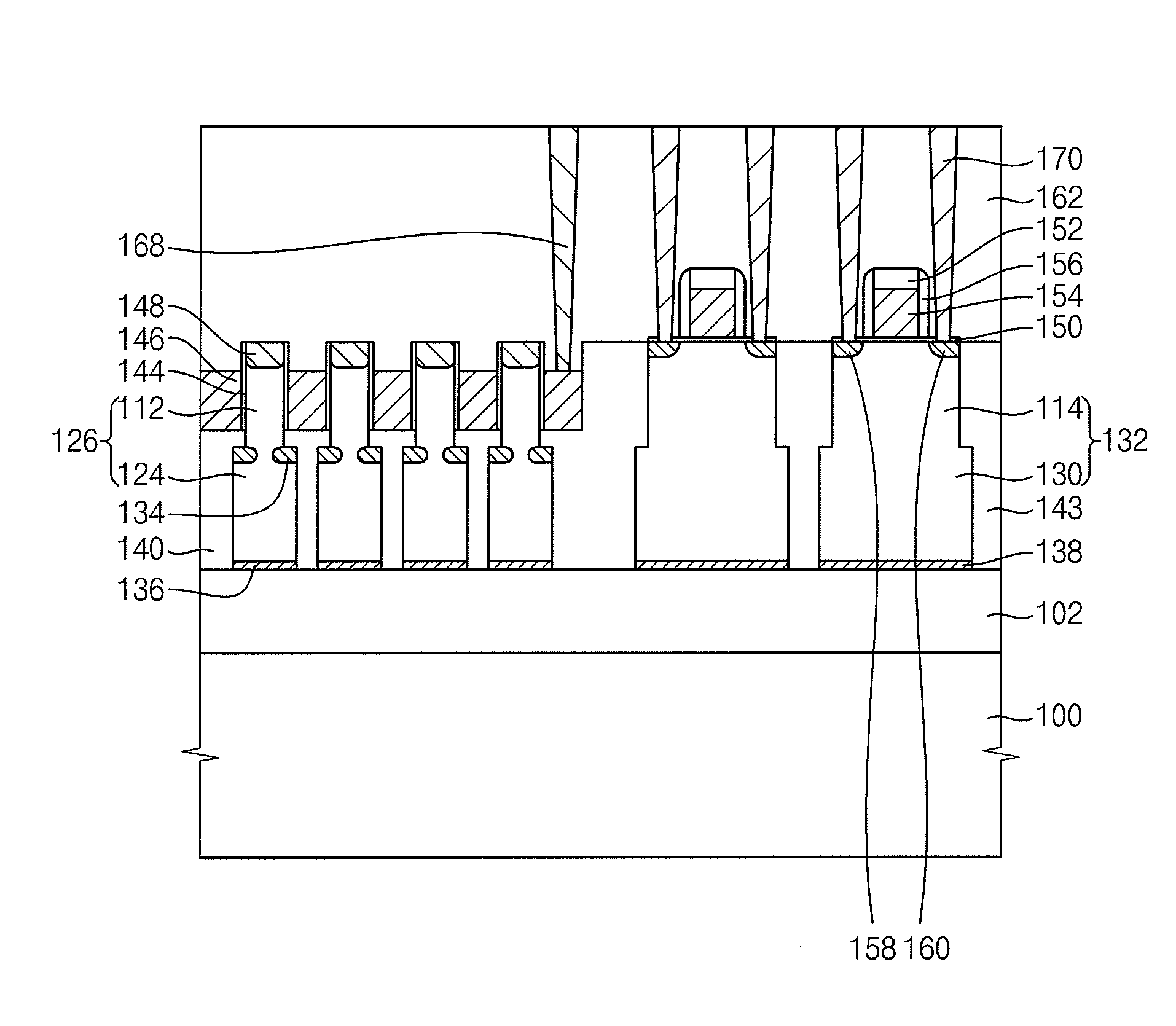

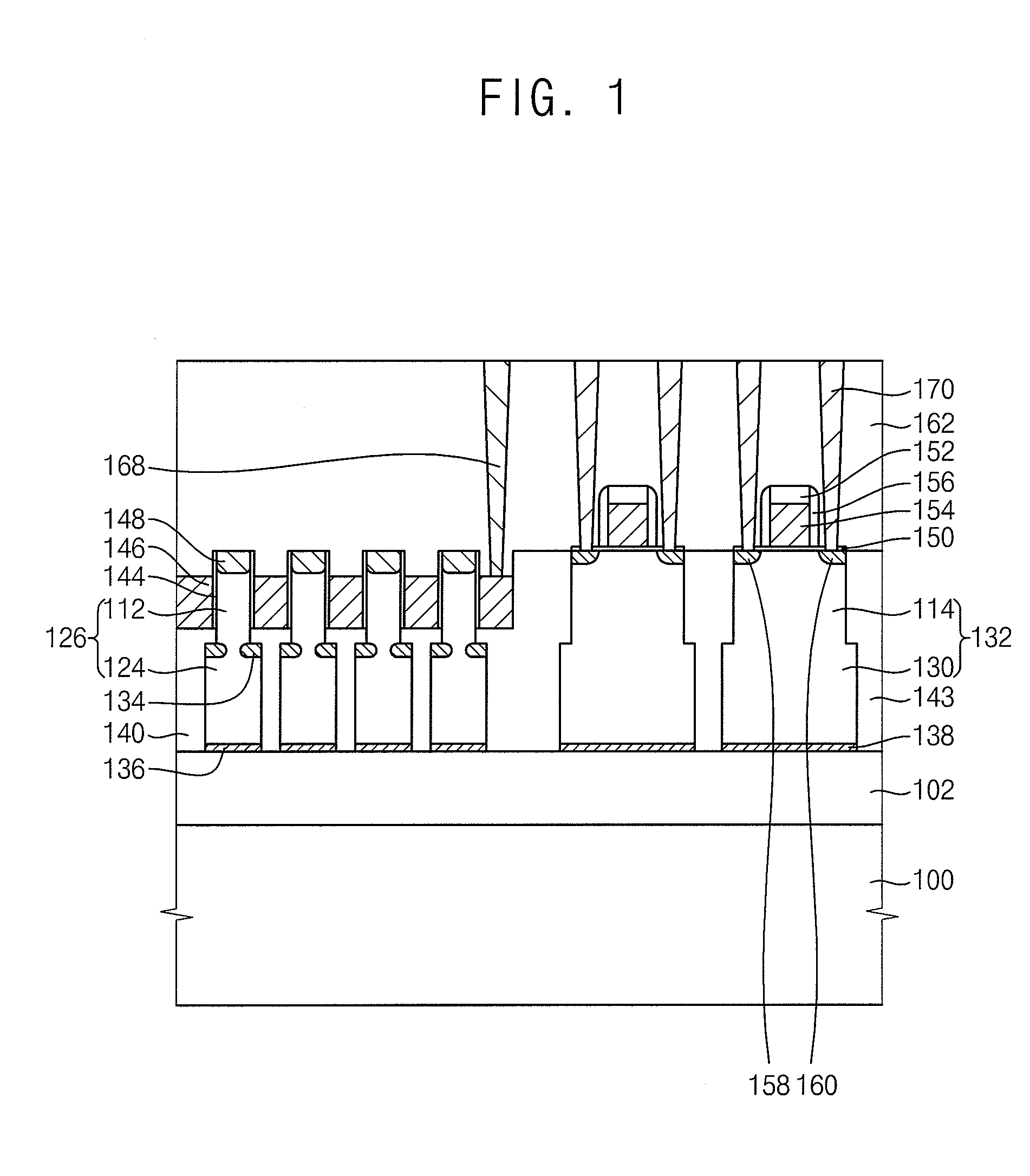

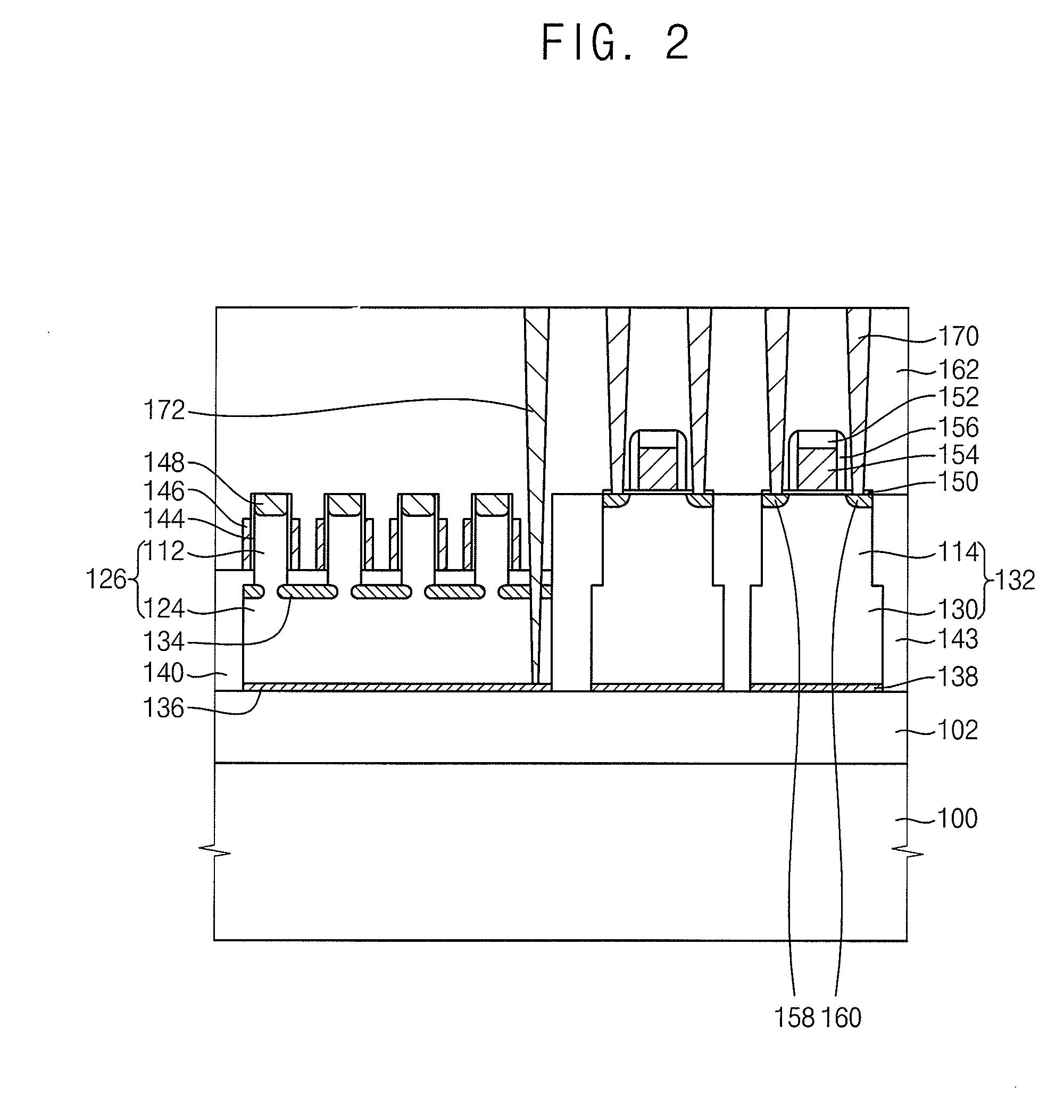

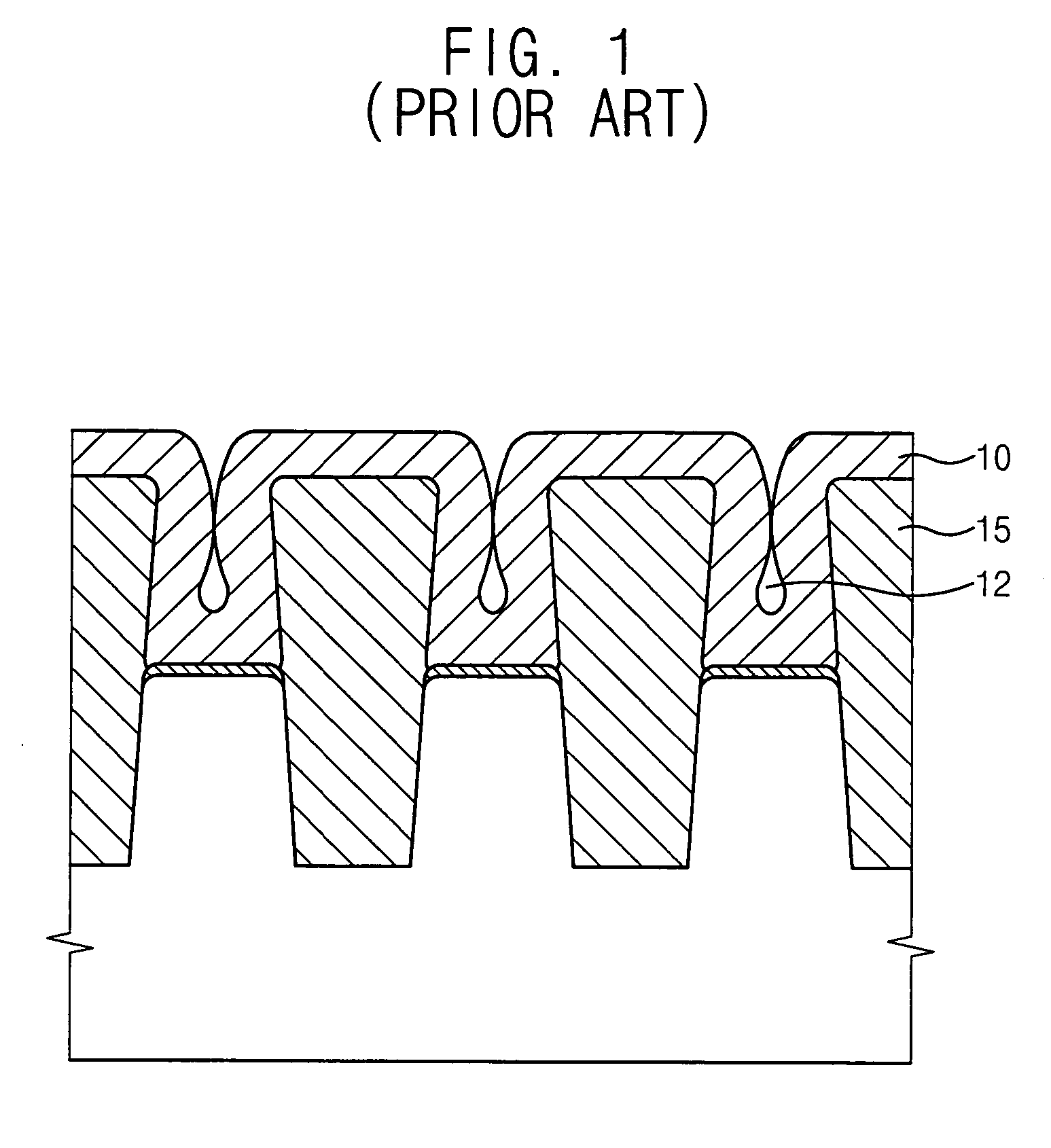

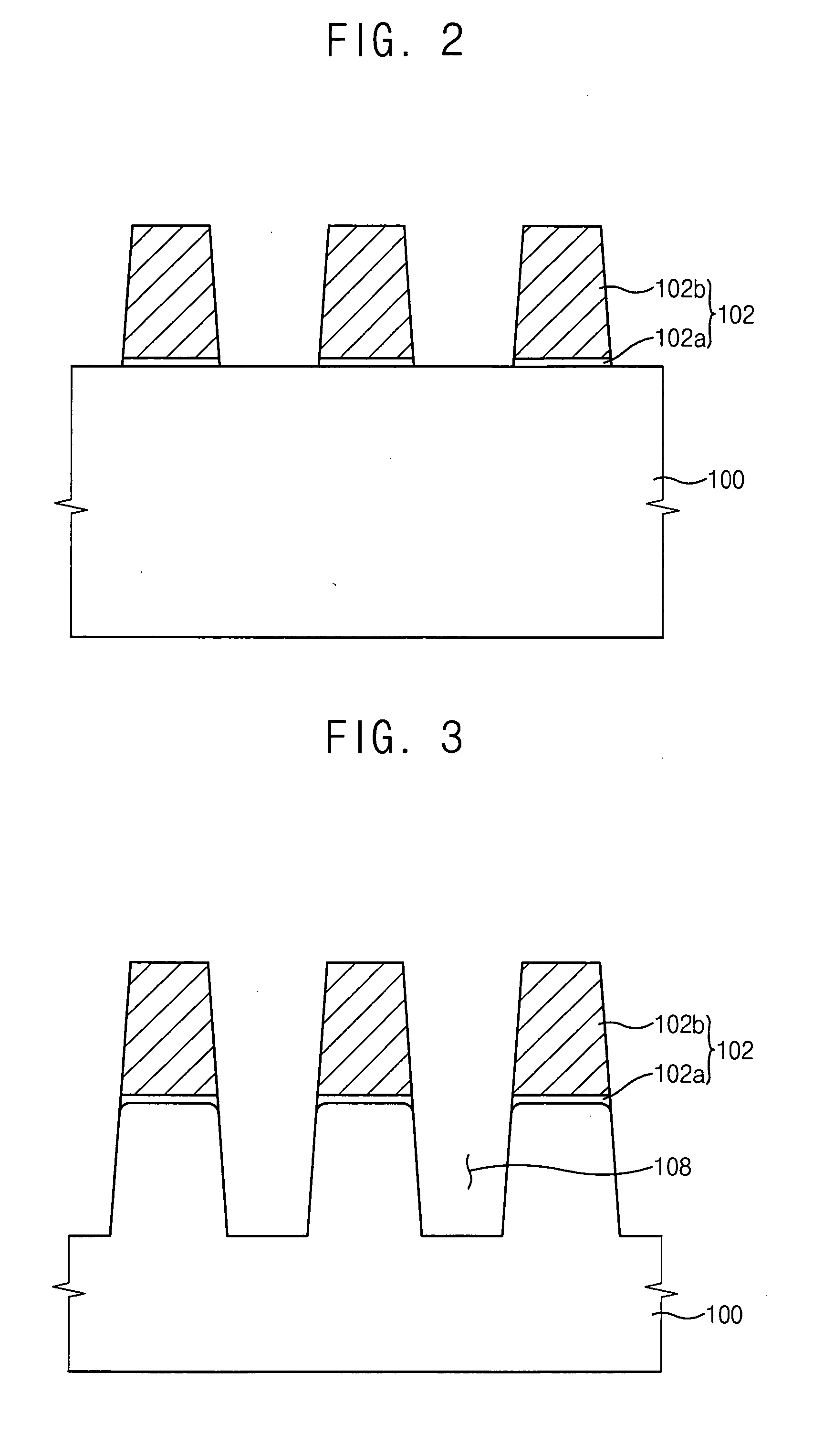

Method of forming a recess structure, recessed channel type transistor and method of manufacturing the recessed channel type transistor

InactiveUS20060113590A1Reduce widthReduce leakage currentSemiconductor devicesInsulation layerIsolation layer

An isolation layer having a first depth is formed from an upper face of a substrate. Source / drain regions including junctions are formed in the substrate. Each of the junctions has a second depth substantially smaller than the first depth. A first recess is formed in the substrate by a first etching process. A protection layer pattern is formed on a sidewall of the first recess. A second recess is formed beneath the first recess. The second recess has a width substantially larger than that of the first recess. The second recess is formed by a second etching process using an etching gas containing an SF6 gas, a Cl2 gas and an O2 gas. A gate insulation layer is formed on surfaces of the first and the second recesses. The second recess having an enlarged shape may reduce a width of the junction between the gate electrode and the isolation layer so that a leakage current generated through the junction may decrease.

Owner:SAMSUNG ELECTRONICS CO LTD

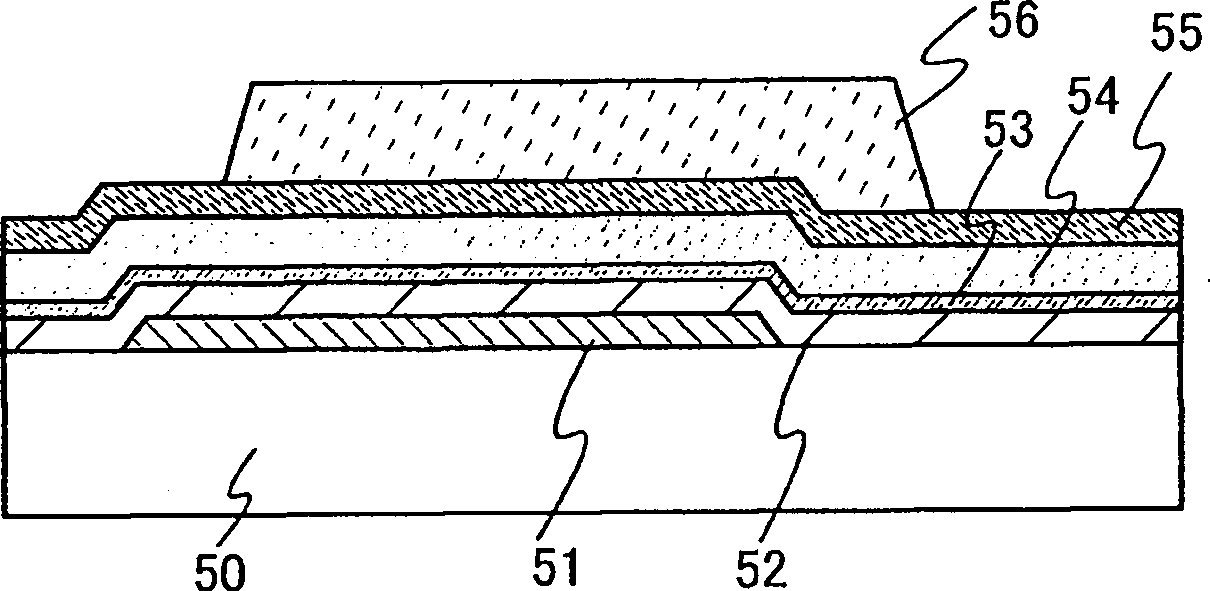

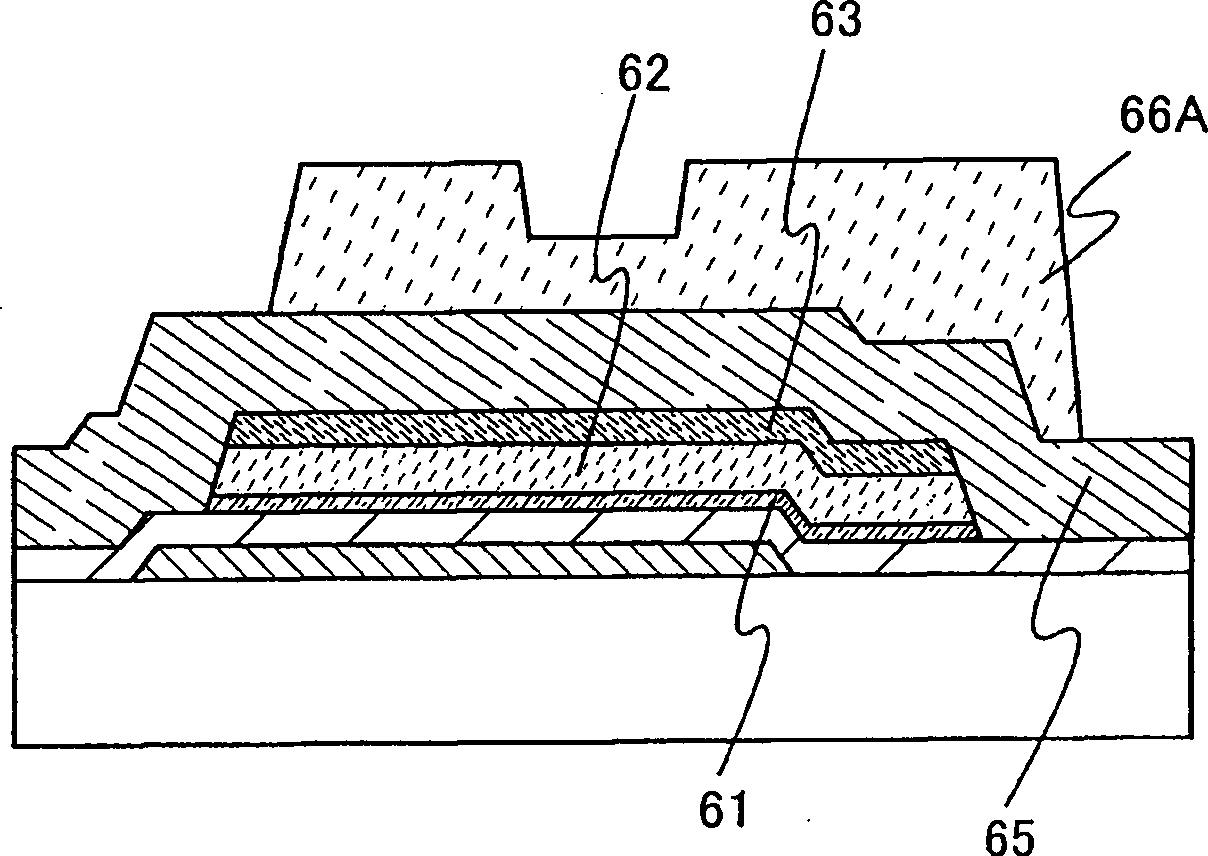

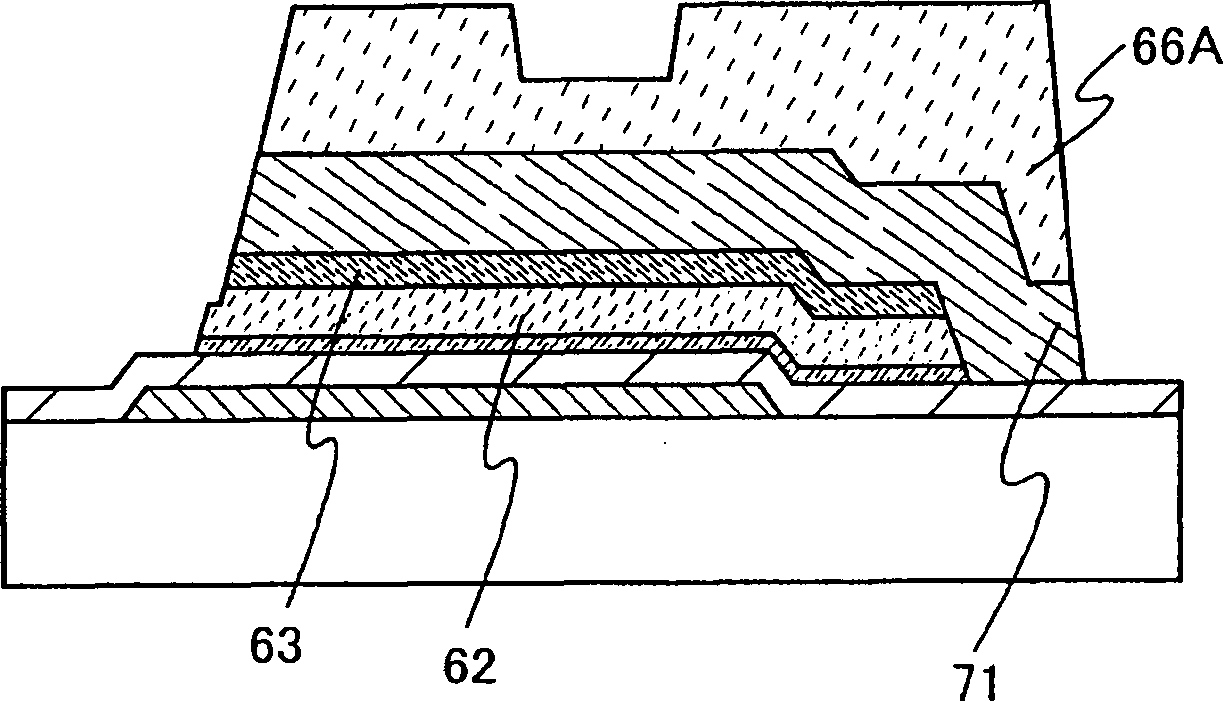

Semiconductor device fabrication method

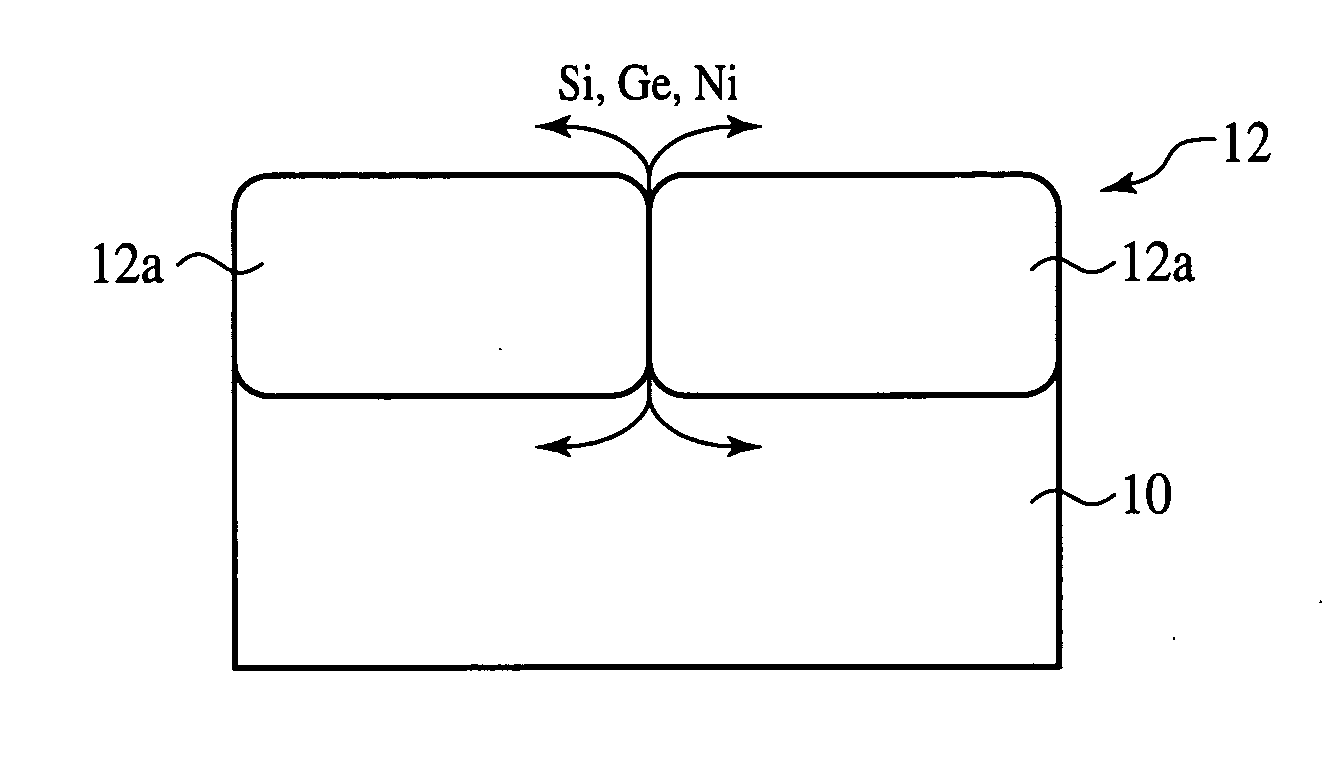

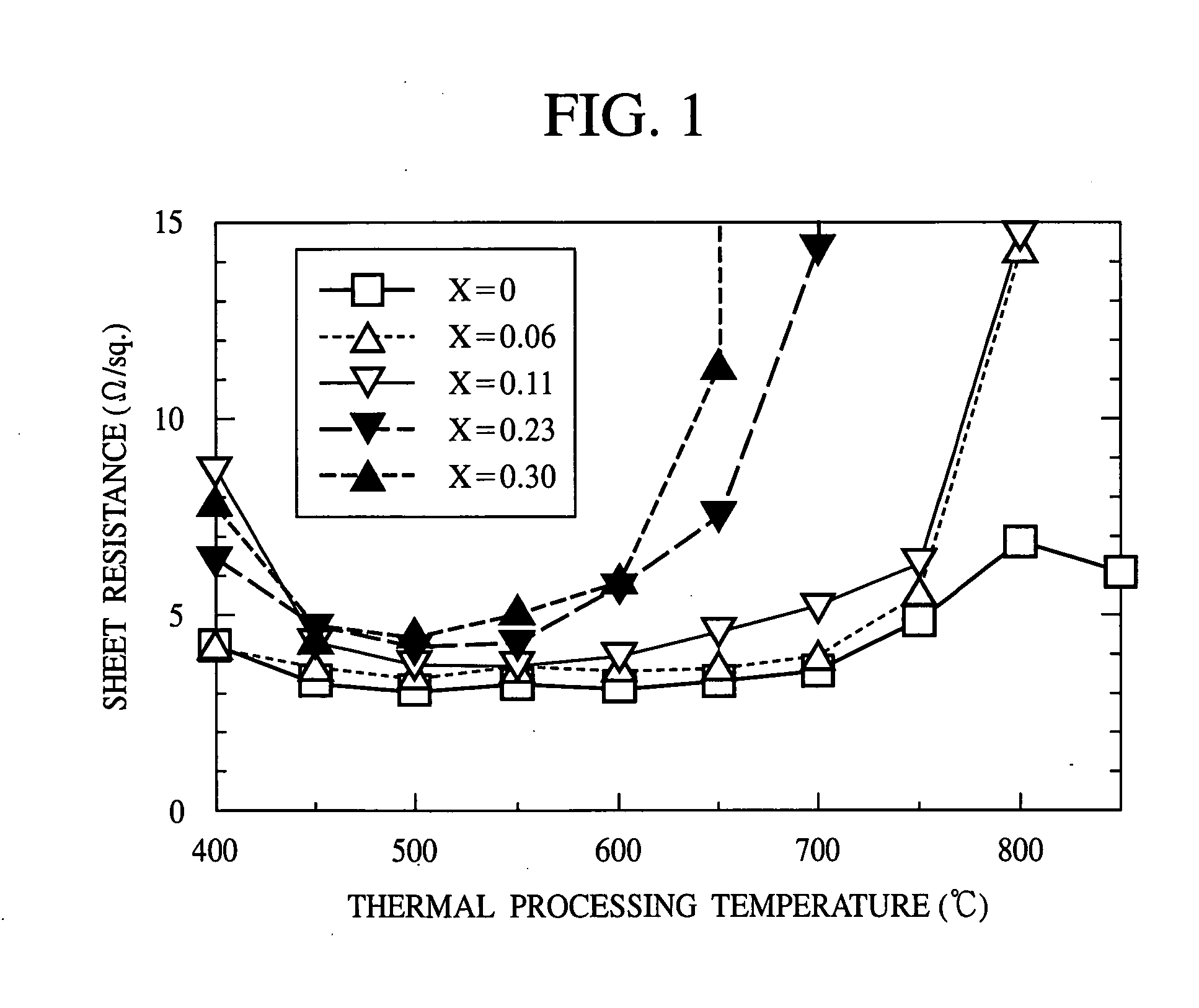

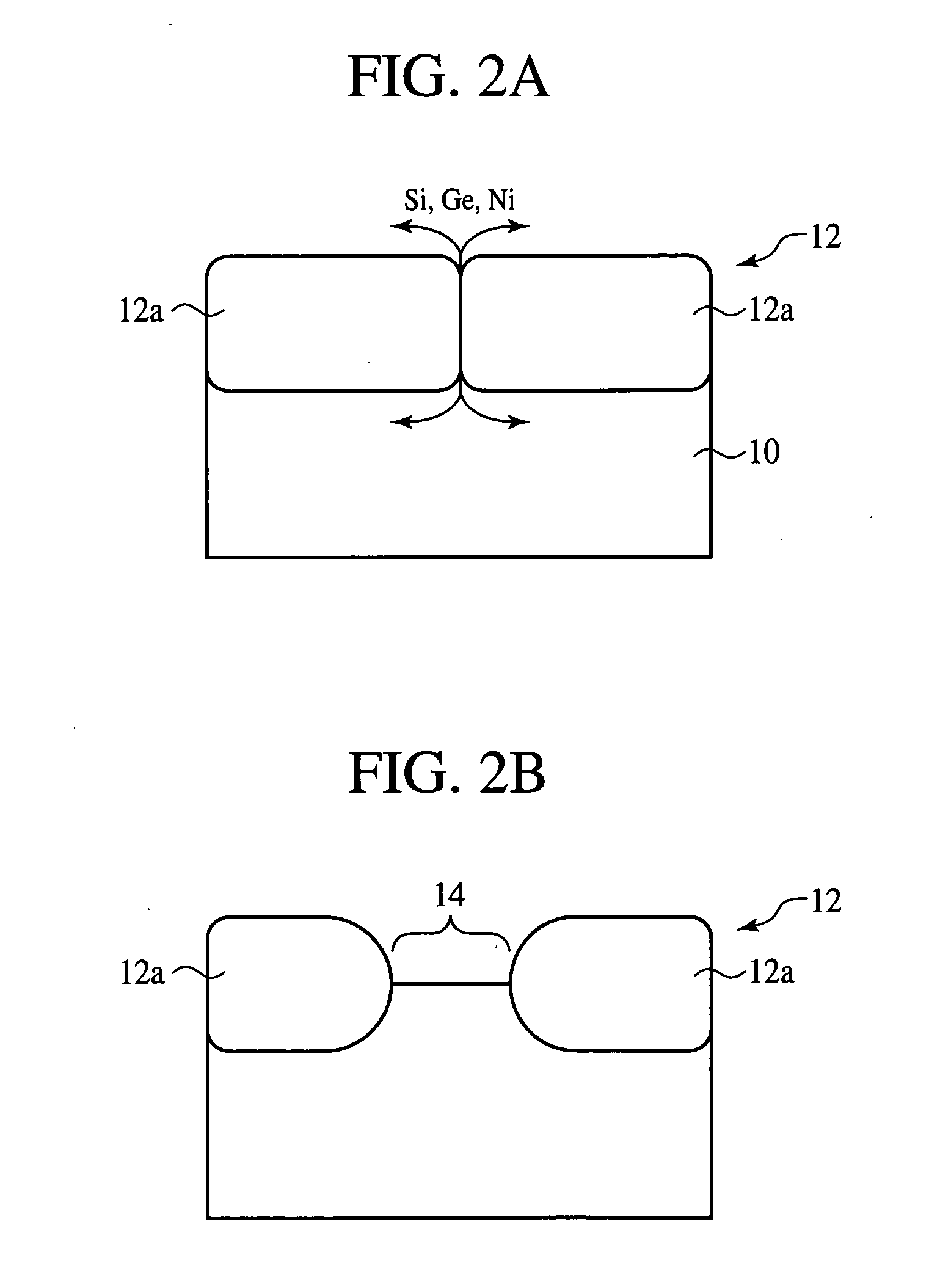

ActiveUS20060281288A1Improve electrical characteristicsReduce sheet resistanceTransistorSemiconductor/solid-state device manufacturingSemiconductorGrain boundary

The semiconductor device fabrication method comprising the step of forming a gate electrode 54p on a semiconductor substrate 34; the step of forming a source / drain diffused layer 64p in the semiconductor substrate 34 on both sides of the gate electrode 54p; the step of burying a silicon germanium layer 100b in the source / drain diffused layer 64p; the step of forming an amorphous layer at an upper part of the silicon germanium layer 101; the step of forming a nickel film 66 on the amorphous layer 101; and the step of making thermal processing to react the nickel film 66 and the amorphous layer 101 with each other to form a silicide film 102b on the silicon germanium layer 100b. Because of no crystal boundaries in the amorphous layer 101 to react with the nickel film 66, the silicidation homogeneously goes on. Because of no crystal faces in the amorphous layer 101, the Ni(Si1-xGex)2 crystals are prevented from being formed in spikes. Thus, even when the silicon germanium layer 100b is silicided by using a thin nickel film 66, the sheet resistance can be low, and the junction leak current can be suppressed.

Owner:FUJITSU LTD

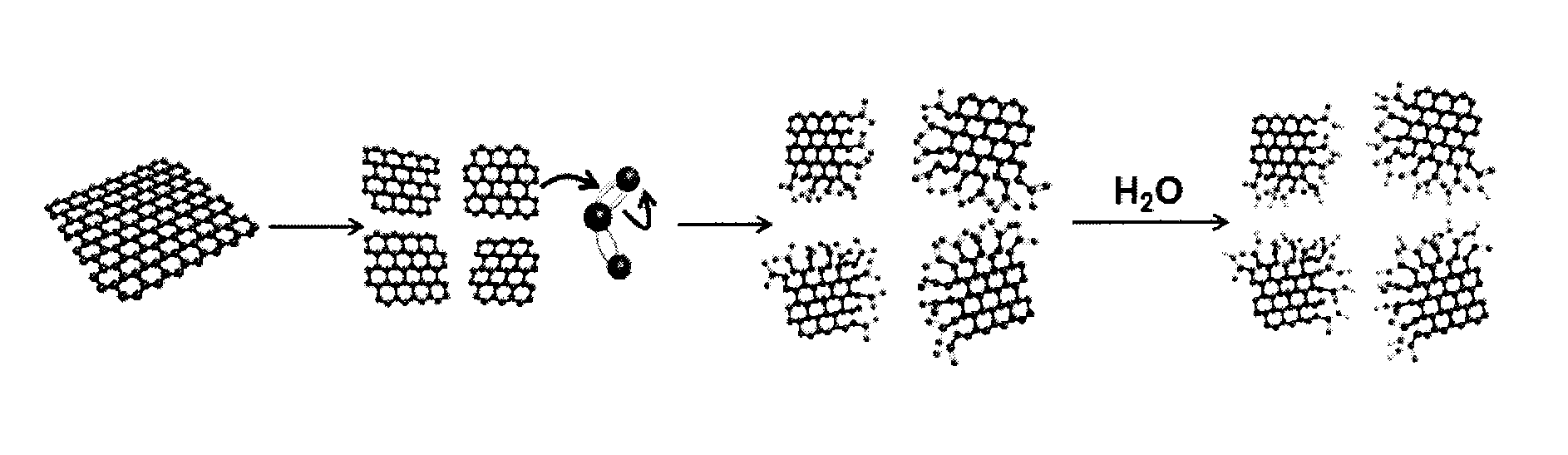

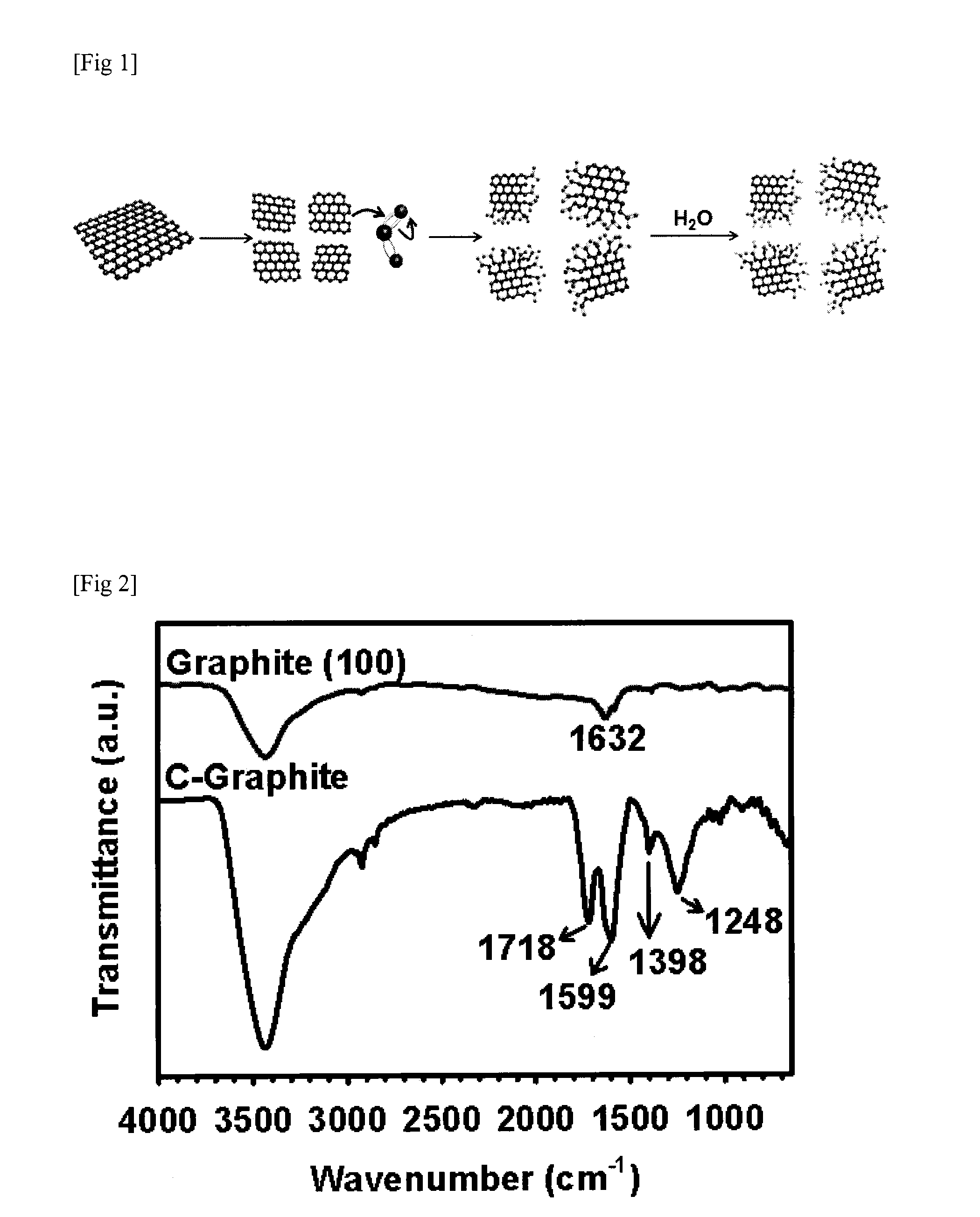

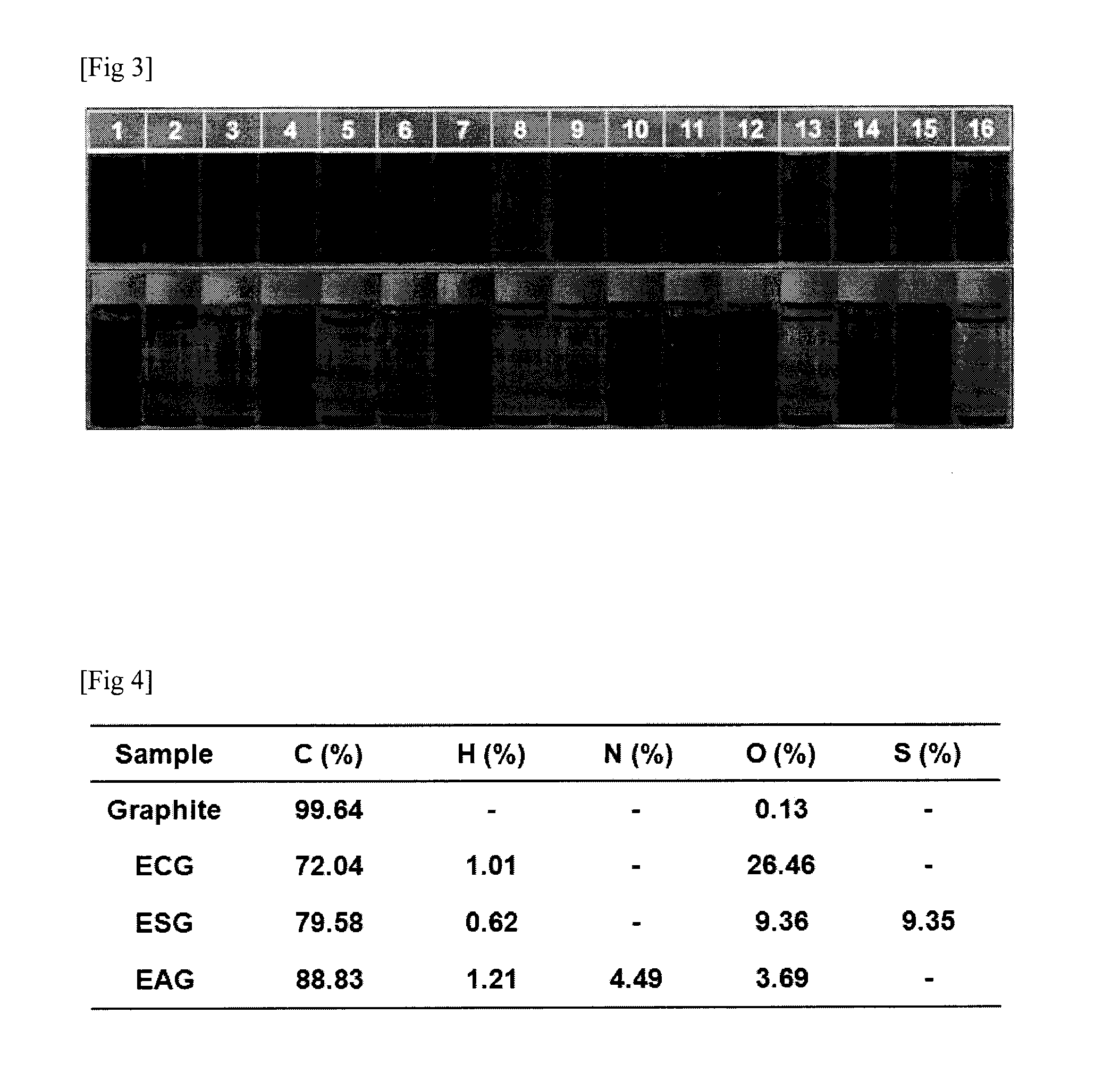

Edge-functionalized graphitic material through mechanochemical process and manufacturing method thereof

InactiveUS20130018204A1High degree of commercializationRaise the potentialMaterial nanotechnologyOrganic compound preparationGas phaseMaterials science

Disclosed is an edge-functionalized graphitic material manufactured by using a mechanochemical process. The edge-functionalized graphitic material is manufactured by pulverizing graphite in the presence of a variety of atmospheric agents in the form of gas phase, liquid phase, or solid phase. The edge-functionalized graphitic material, which is a precursor applicable into various fields, is expected to replace the prior art oxidized graphite.

Owner:DEOKYANG ECO LTD

Method of manufacturing a variable resistance structure and method of manufacturing a phase-change memory device using the same

ActiveUS20070020799A1Improve electrical characteristicsExcellent electrical propertiesSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerPhase-change memory

In methods of manufacturing a variable resistance structure and a phase-change memory device, after forming a first insulation layer on a substrate having a contact region, a contact hole exposing the contact region is formed through the first insulation layer. After forming a first conductive layer on the first insulation layer to fill up the contact hole, a first protection layer pattern is formed on the first conductive layer. The first conductive layer is partially etched to form a contact and to form a pad on the contact. A second protection layer is formed on the first protection layer pattern, and then an opening exposing the pad is formed through the second protection layer and the first protection layer pattern. After formation of a first electrode, a phase-change material layer pattern and a second electrode are formed on the first electrode and the second protection layer.

Owner:SAMSUNG ELECTRONICS CO LTD

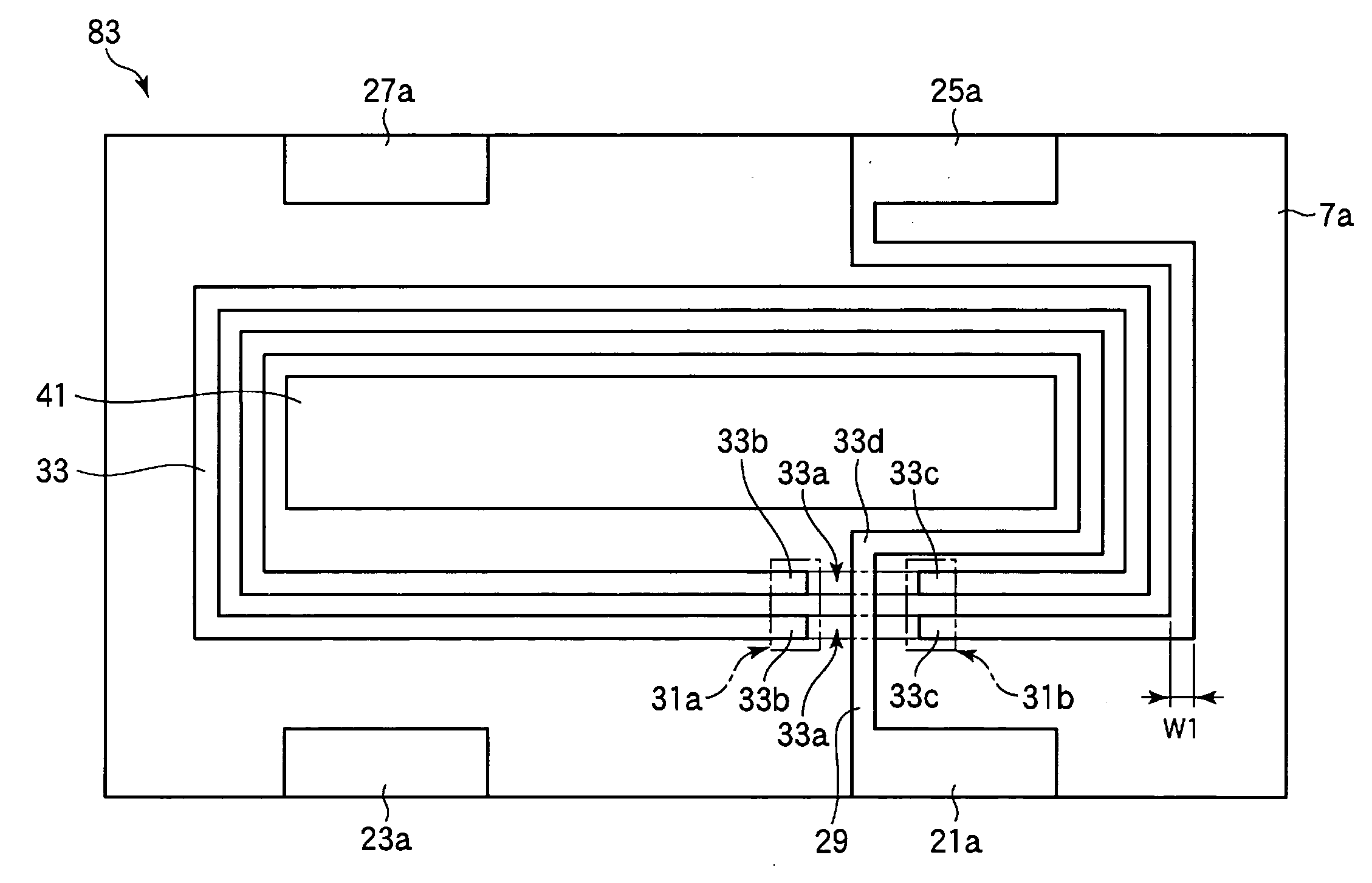

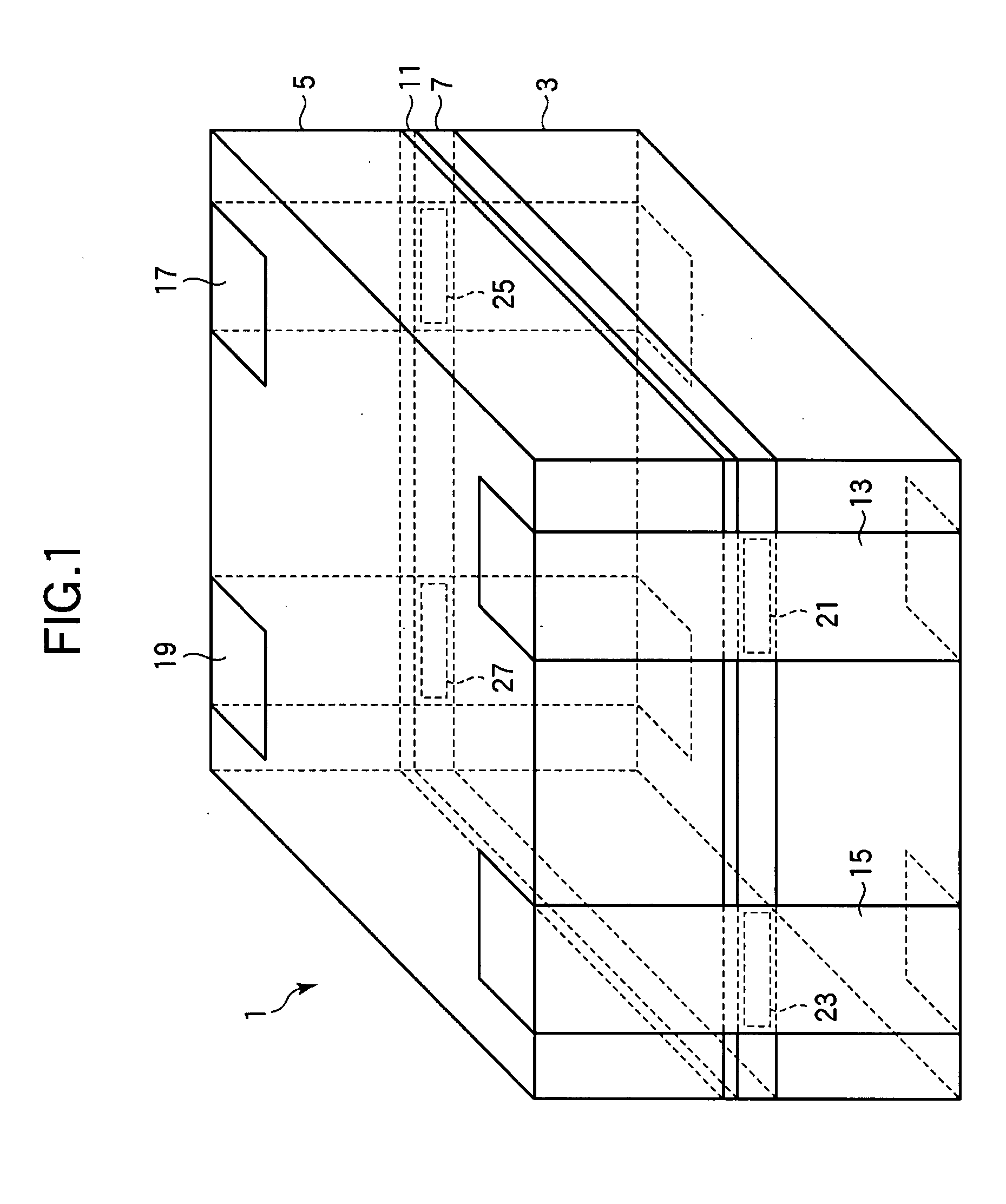

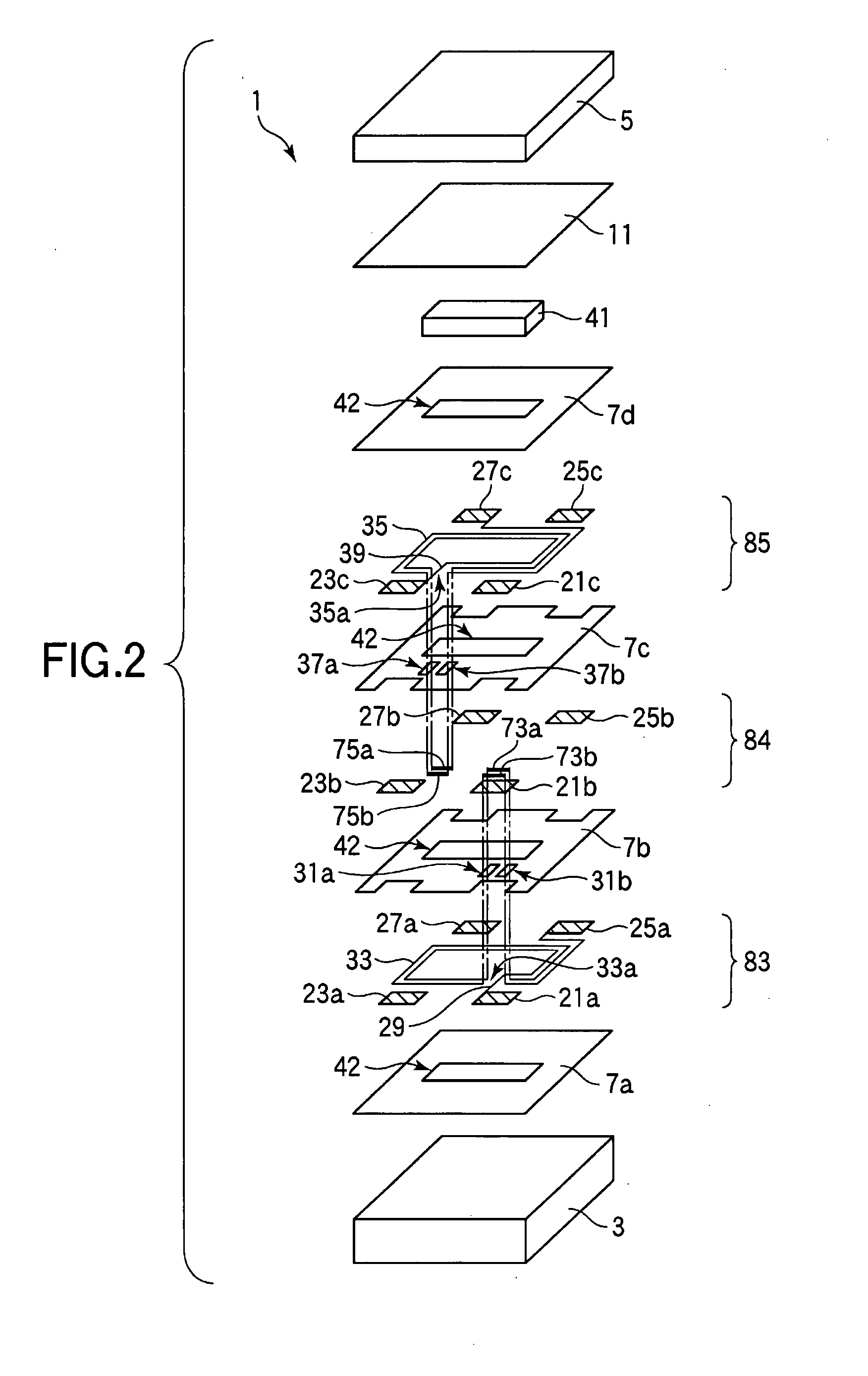

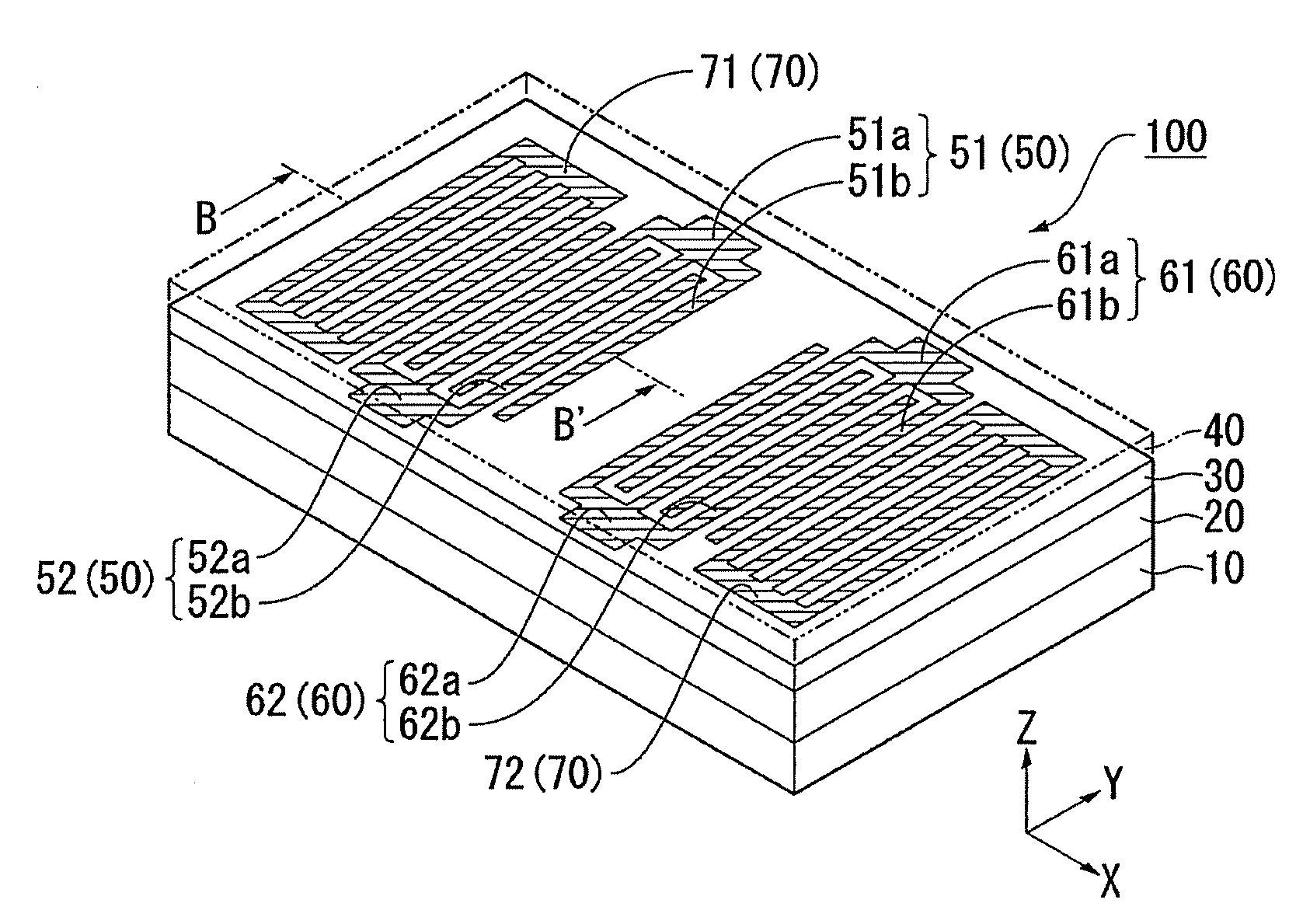

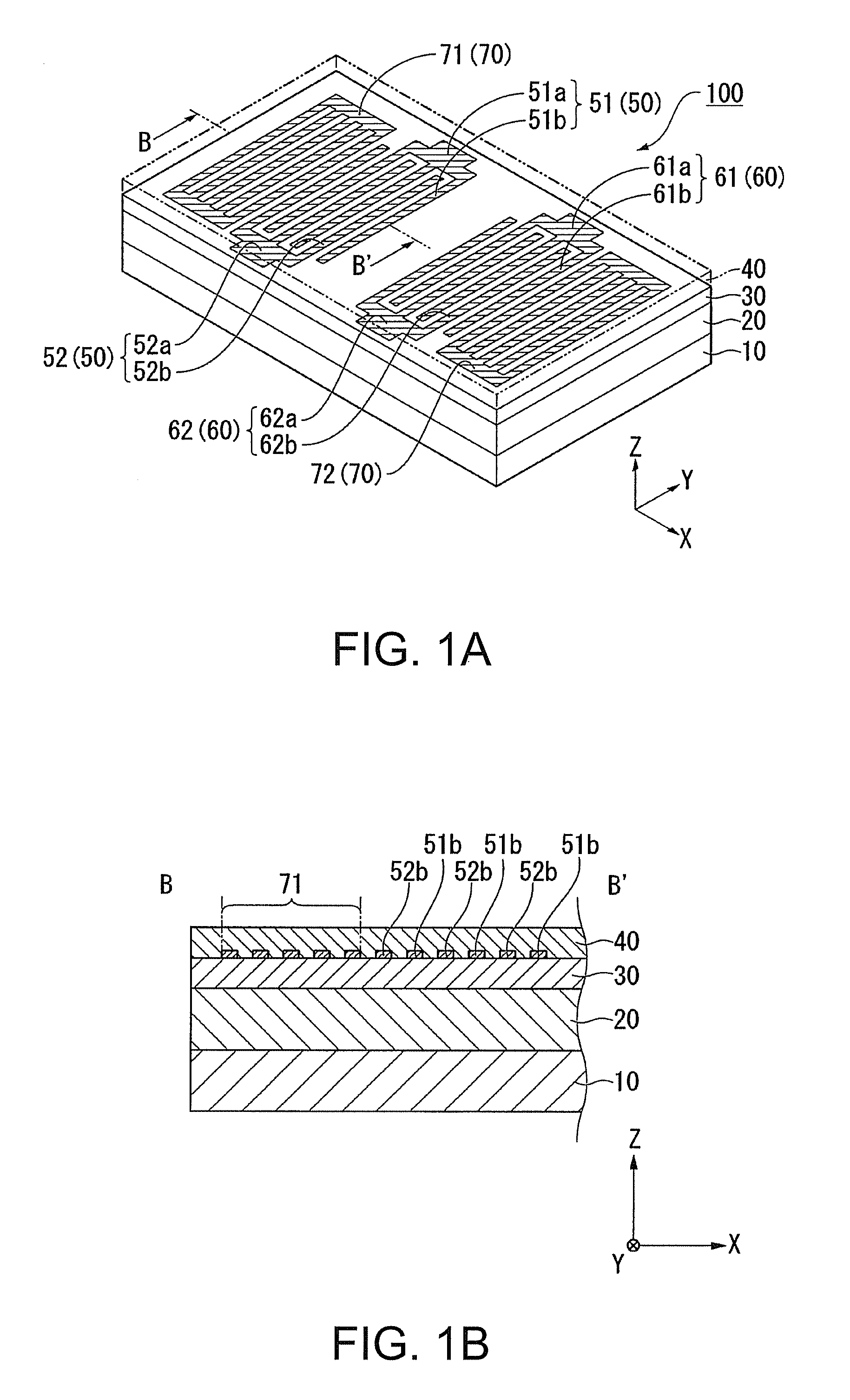

Coil component

ActiveUS20080129439A1Improve electrical characteristicsImpedence networksTransformers/inductances coils/windings/connectionsElectrical conductorSurface mounting

The invention relates to surface-mount type coil components having a mounting surface for mounting them on a printed circuit board or hybrid IC (HIC) and provides a coil component having high electrical characteristics. A common mode filter includes a coil conductor formed in a spiral shape, cut ends which are parts of the coil conductor cut to face each other, and bridge conductors formed so that an insulation film is interposed between the coil conductor and the same to connect the cut ends to each other.

Owner:TDK CORPARATION

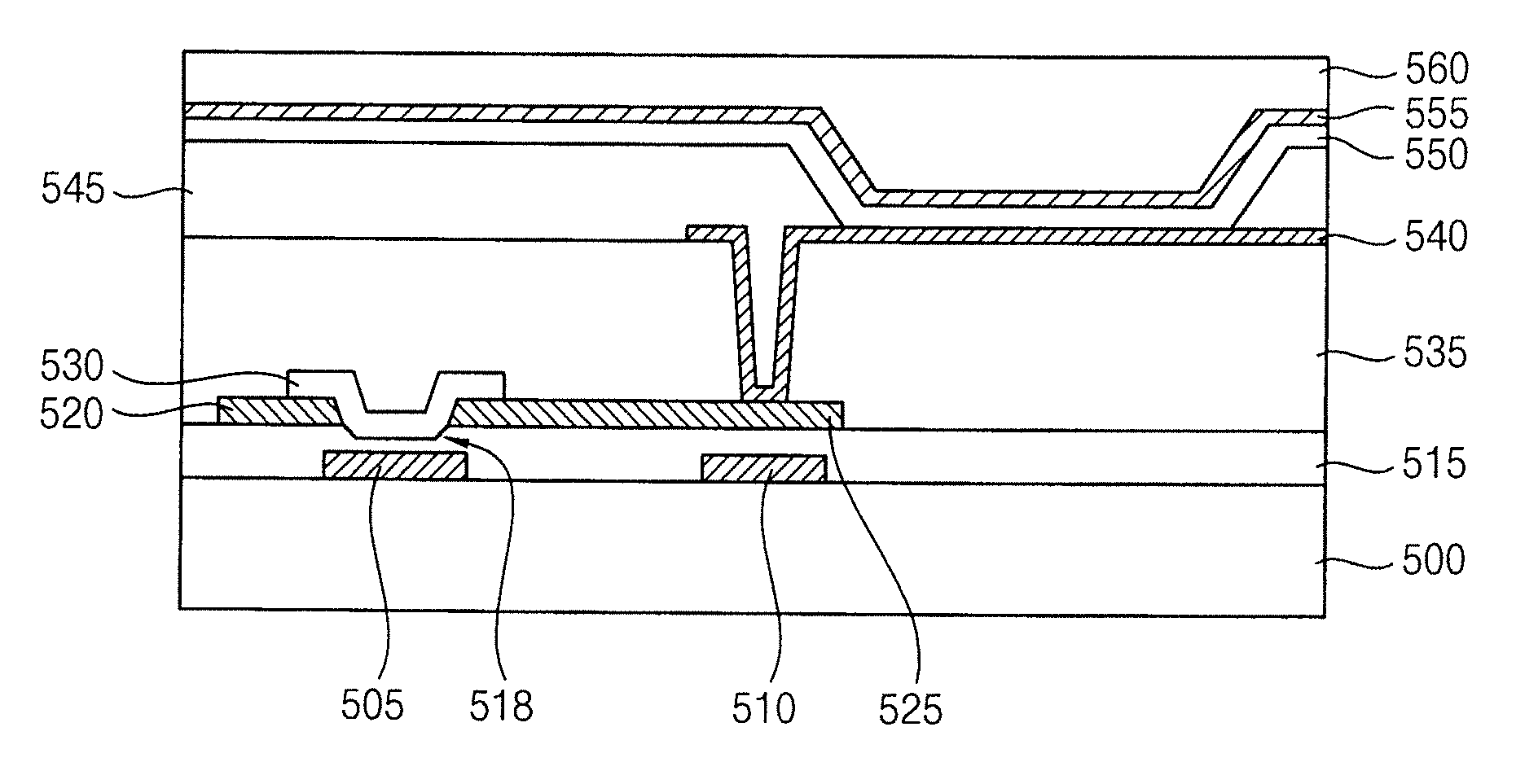

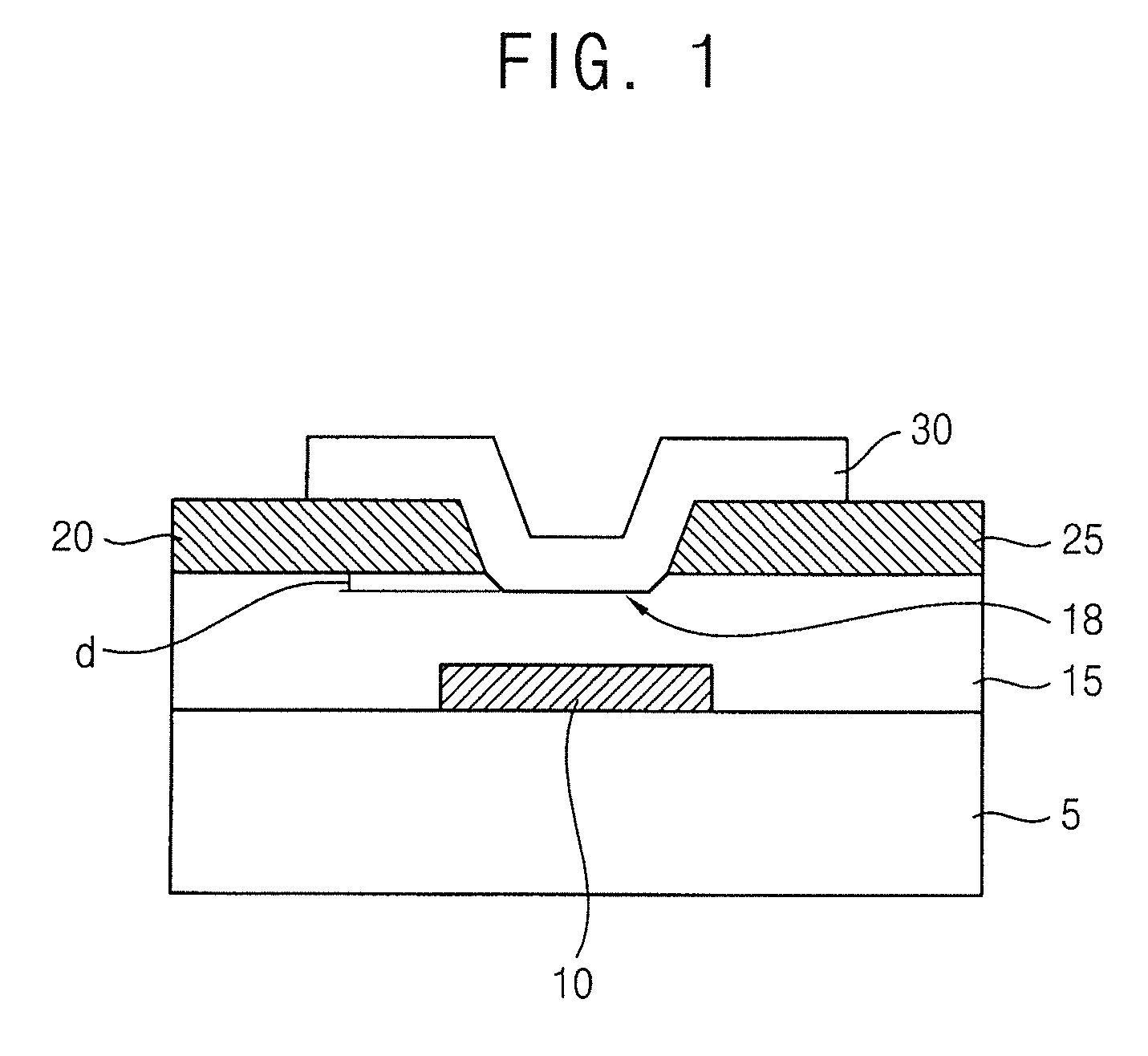

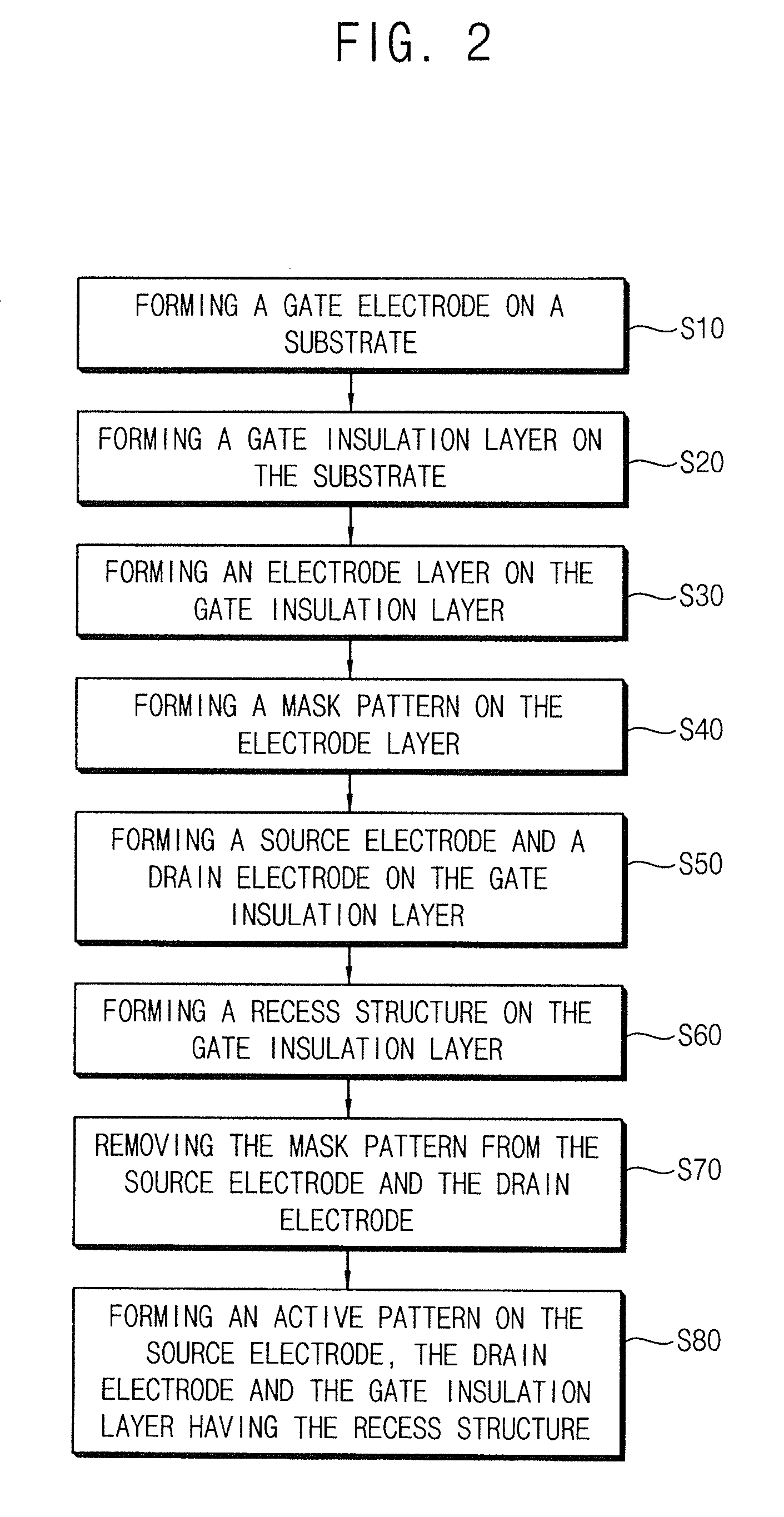

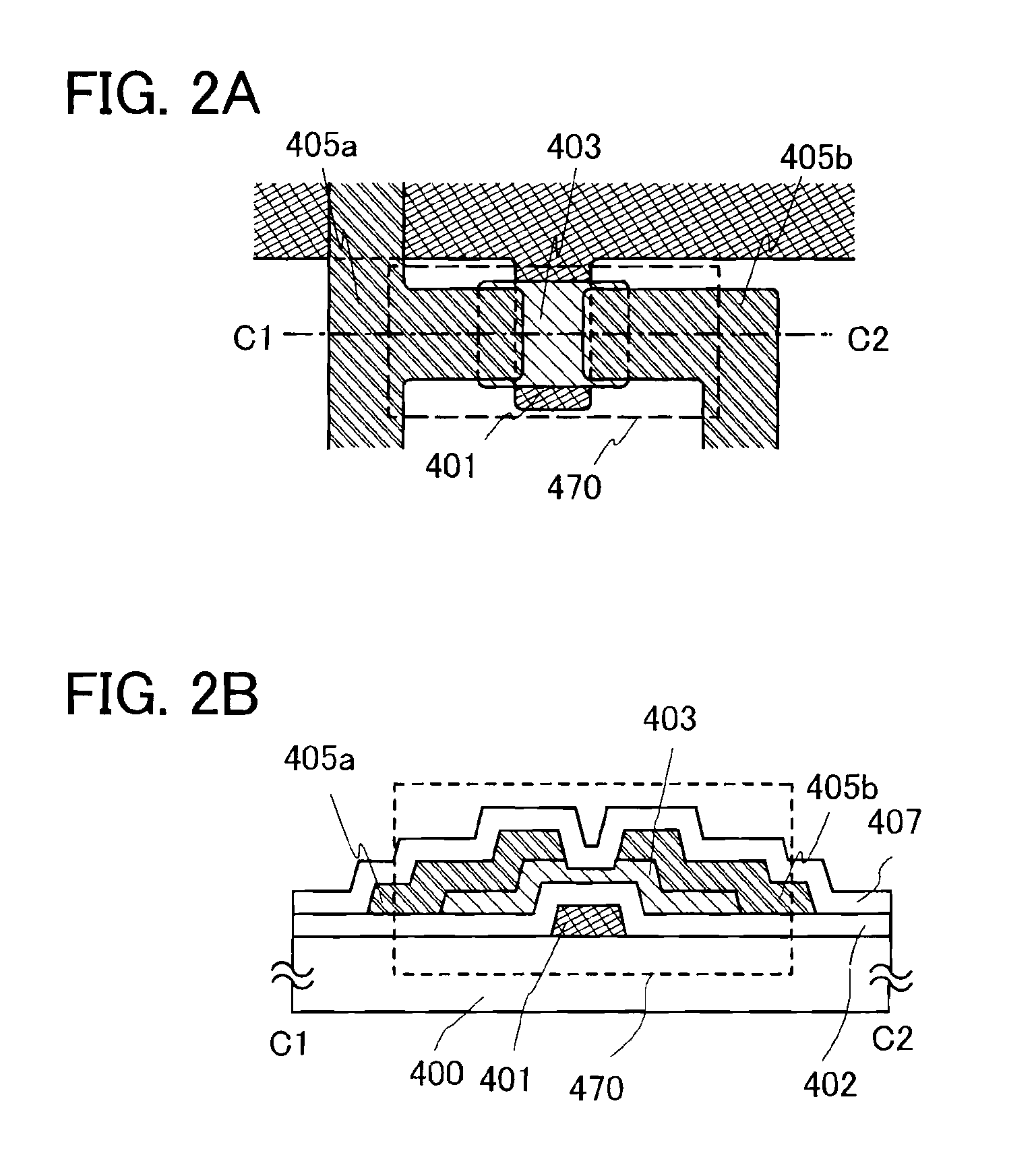

Oxide semiconductor devices, methods of manufacturing oxide semiconductor devices, display devices having oxide semiconductor devices, methods of manufacturing display devices having oxide semiconductor devices

InactiveUS20120292610A1Improve electrical characteristicsIncrease charge mobilityTransistorSolid-state devicesInsulation layerDisplay device

An oxide semiconductor device includes a gate electrode on a substrate, a gate insulation layer on the substrate, the gate insulation layer having a recess structure over the gate electrode, a source electrode on a first portion of the gate insulation layer, a drain electrode on a second portion of the gate insulation layer, and an active pattern on the source electrode and the drain electrode, the active pattern filling the recess structure.

Owner:SAMSUNG DISPLAY CO LTD

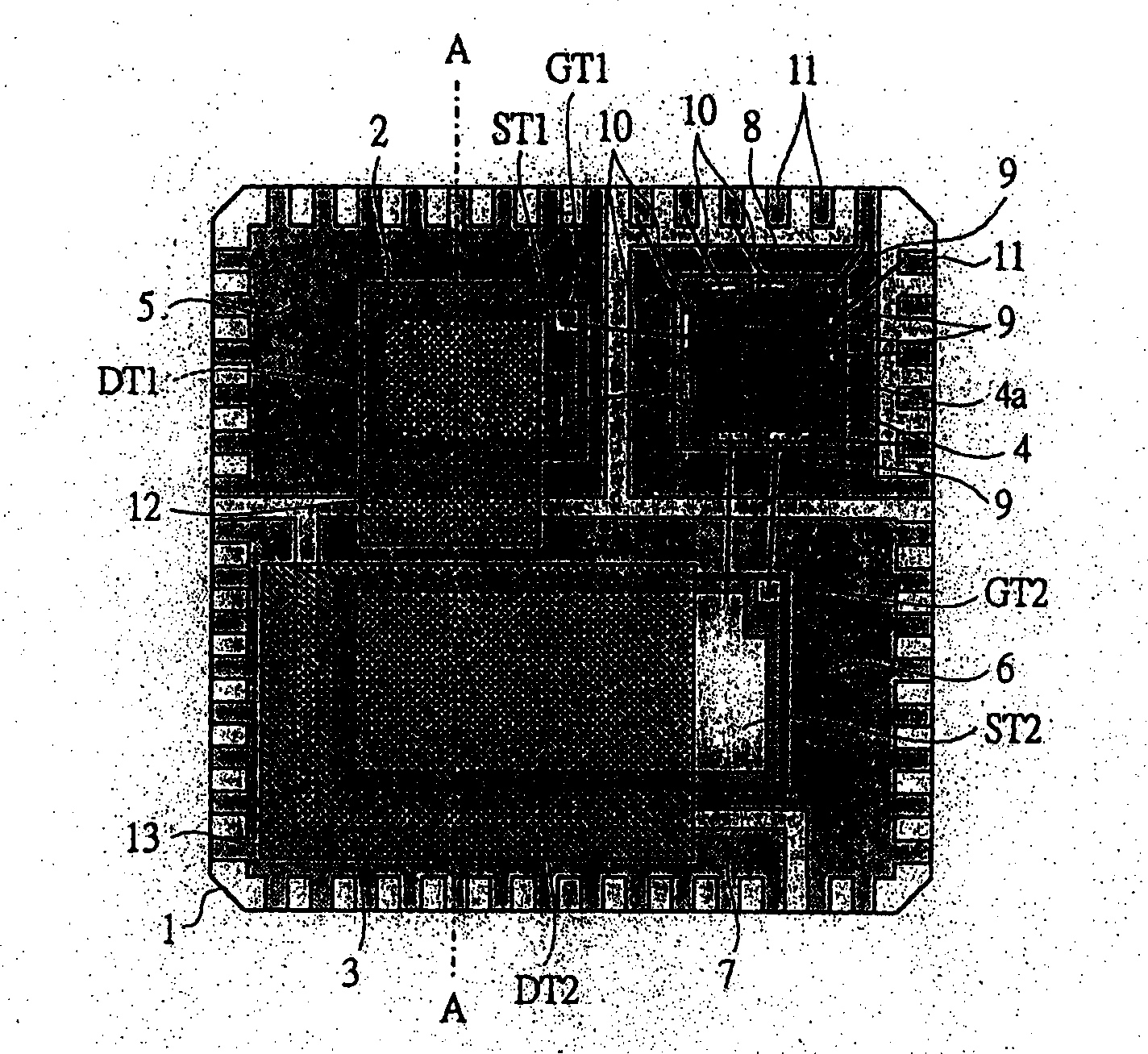

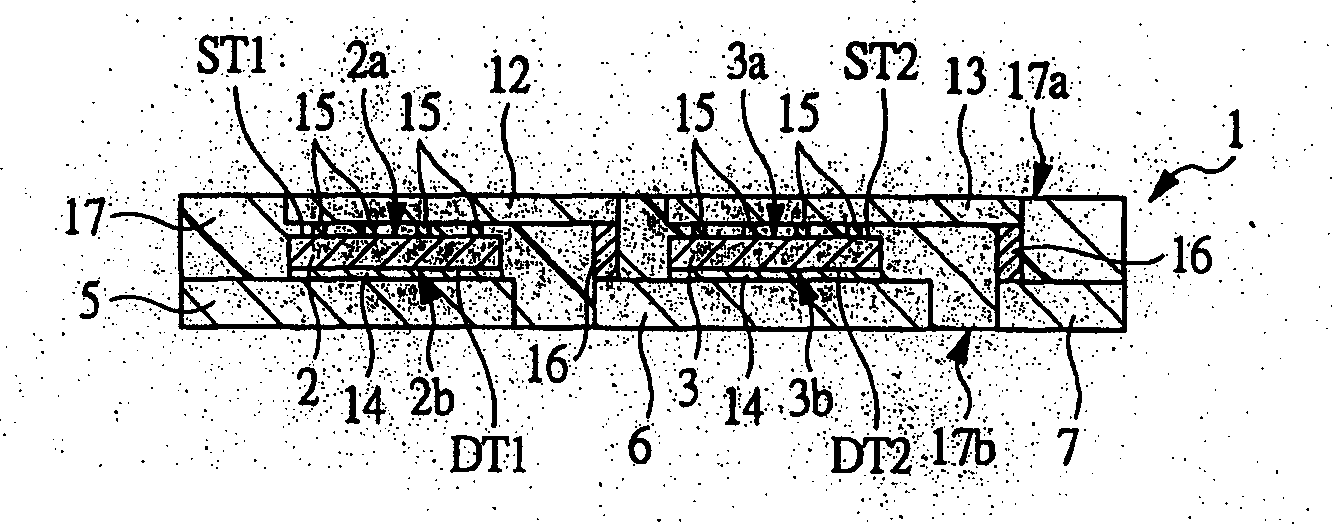

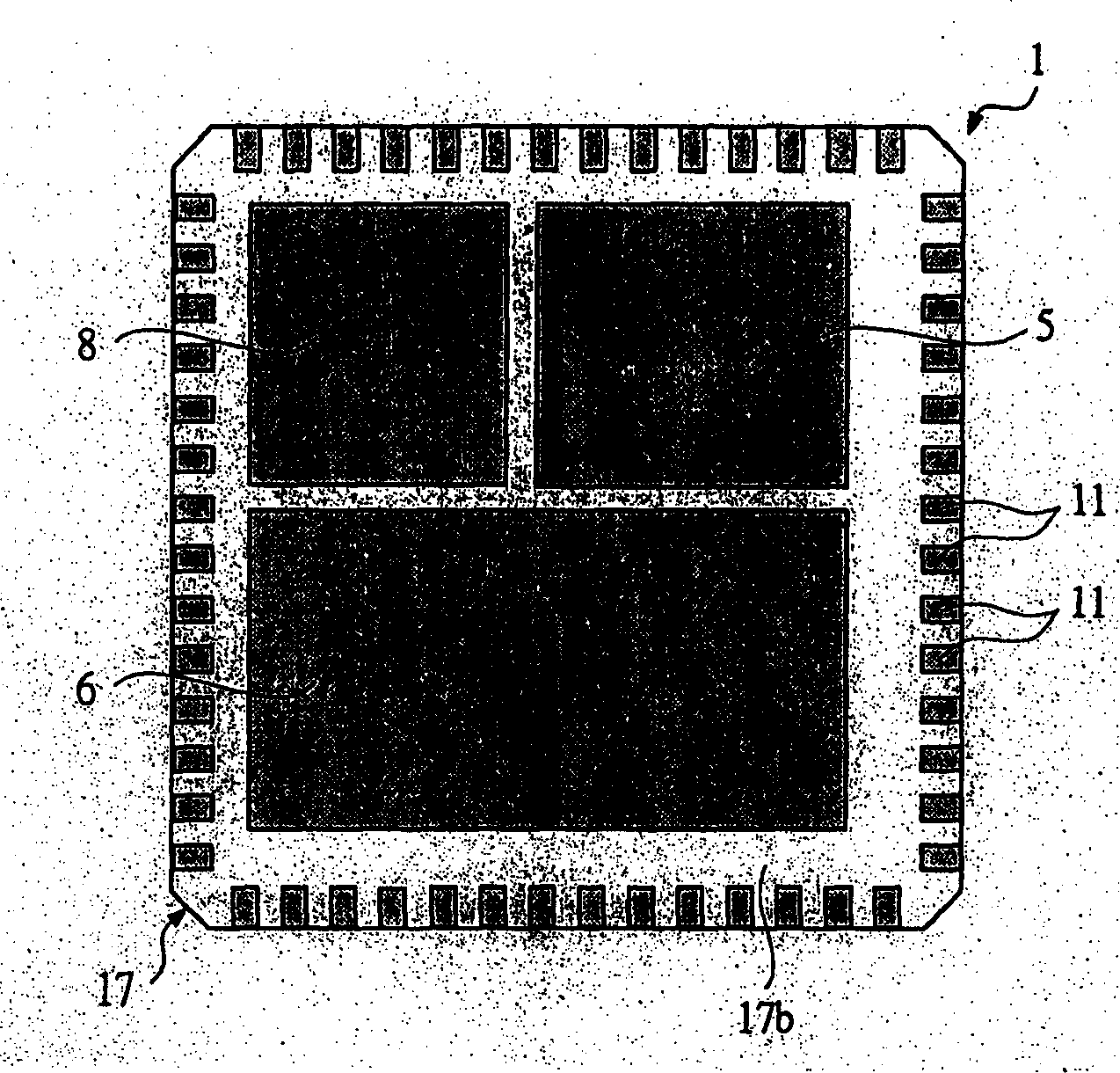

Semiconductor device

InactiveCN1649146AImprove electrical characteristicsImprove cooling effectSemiconductor/solid-state device detailsSolid-state devicesControl powerSemiconductor chip

In the semiconductor device, a control power MOSFET chip 2 is disposed on the input-side plate-like lead 5 , and the drain terminal DT 1 is formed on the rear surface of the chip 2 , and the source terminal ST 1 and gate terminal GT 1 are formed on the principal surface of the chip 2 , and the source terminal ST 1 is connected to the plate-like lead for source 12 . Furthermore, a synchronous power MOSFET chip 3 is disposed on the output-side plate-like lead 6 , and the drain terminal DT 2 is formed on the rear surface of the chip 3 and the output-side plate-like lead 6 is connected to the drain terminal DT 2 . Furthermore, source terminal ST 2 and gate terminal GT 2 are formed on the principal surface of the synchronous power MOSFET chip 3 , and the source terminal ST 2 is connected to the plate-like lead for source 13 . The plate-like leads for source 12 and 13 are exposed, and therefore, it is possible to increase the heat dissipation capability of the MCM 1.

Owner:RENESAS ELECTRONICS CORP

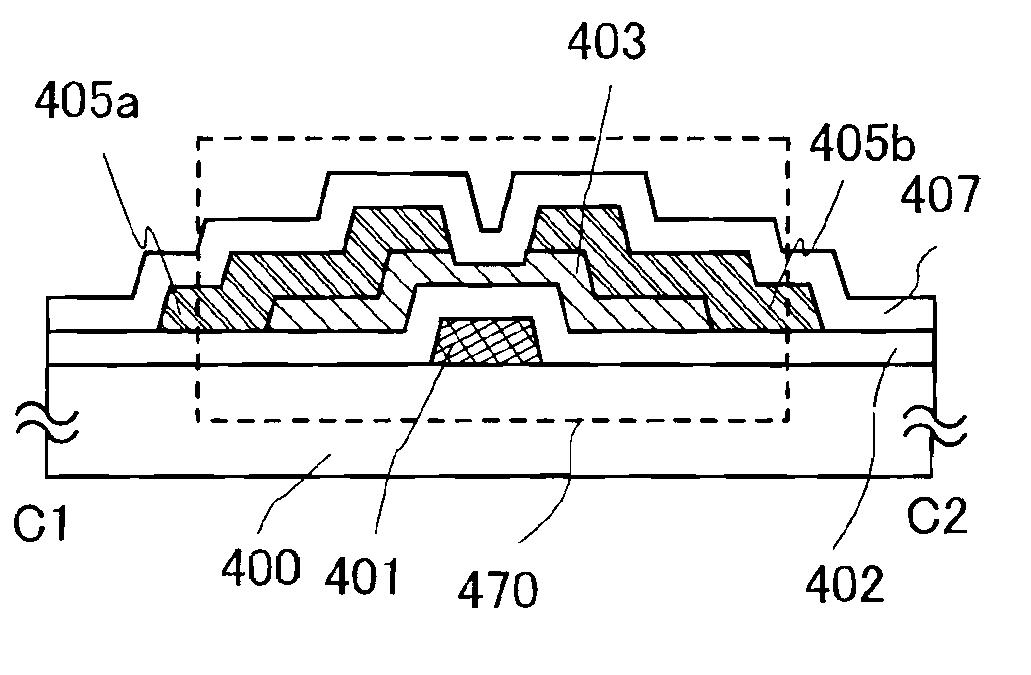

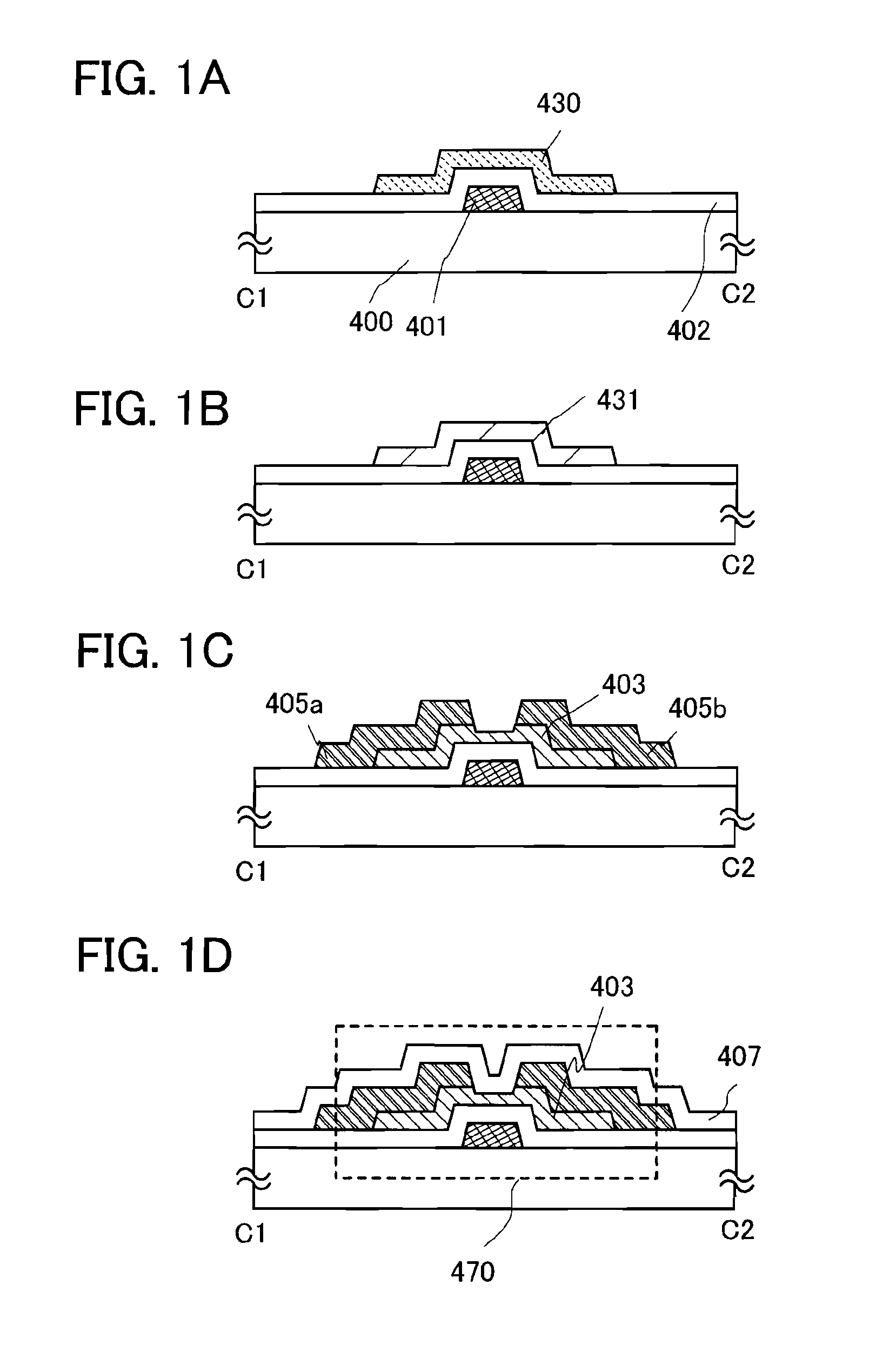

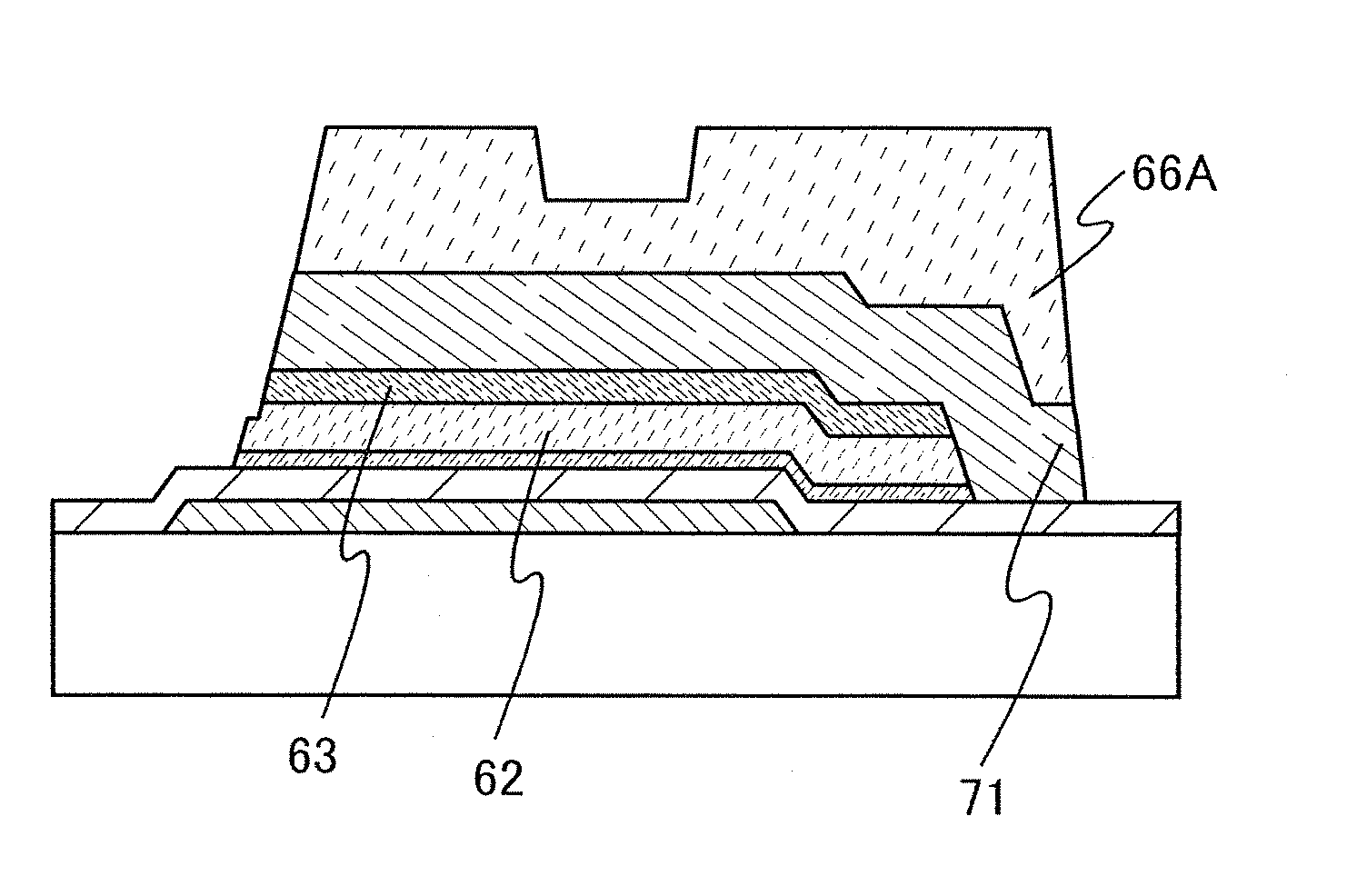

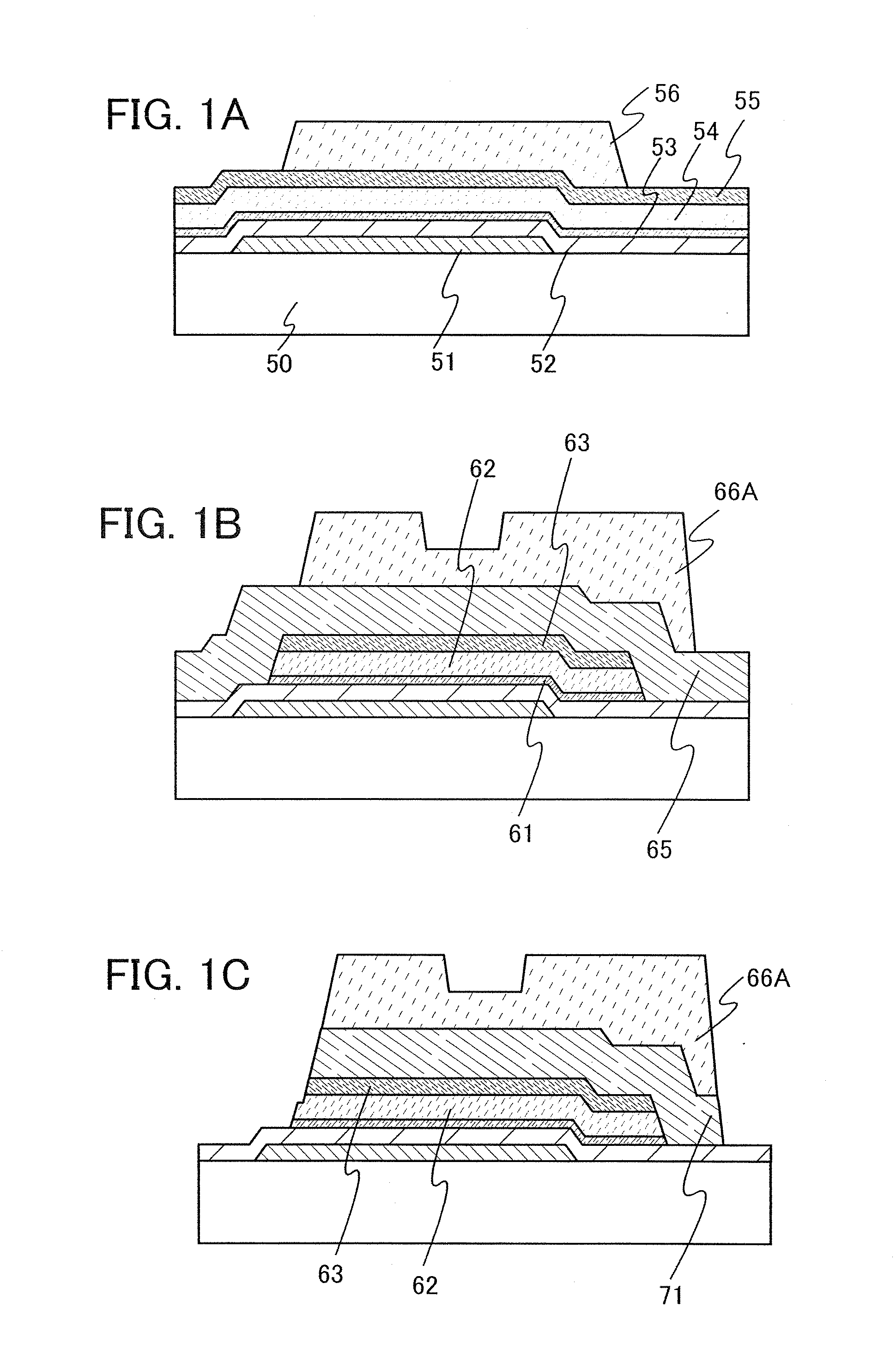

Method for manufacturing semiconductor device

ActiveUS20110008931A1Stable electrical characteristicsImprove electrical characteristicsElectroluminescent light sourcesSolid-state devicesEngineeringMoisture

A highly reliable semiconductor device which includes a thin film transistor having stable electric characteristics, and a manufacturing method thereof. In the manufacturing method of the semiconductor device which includes a thin film transistor where a semiconductor layer including a channel formation region is an oxide semiconductor layer, heat treatment which reduces impurities such as moisture to improve the purity of the oxide semiconductor layer and oxidize the oxide semiconductor layer (heat treatment for dehydration or dehydrogenation) is performed. Not only impurities such as moisture in the oxide semiconductor layer but also those existing in a gate insulating layer are reduced, and impurities such as moisture existing in interfaces between the oxide semiconductor layer and films provided over and under and in contact with the oxide semiconductor layer are reduced.

Owner:SEMICON ENERGY LAB CO LTD

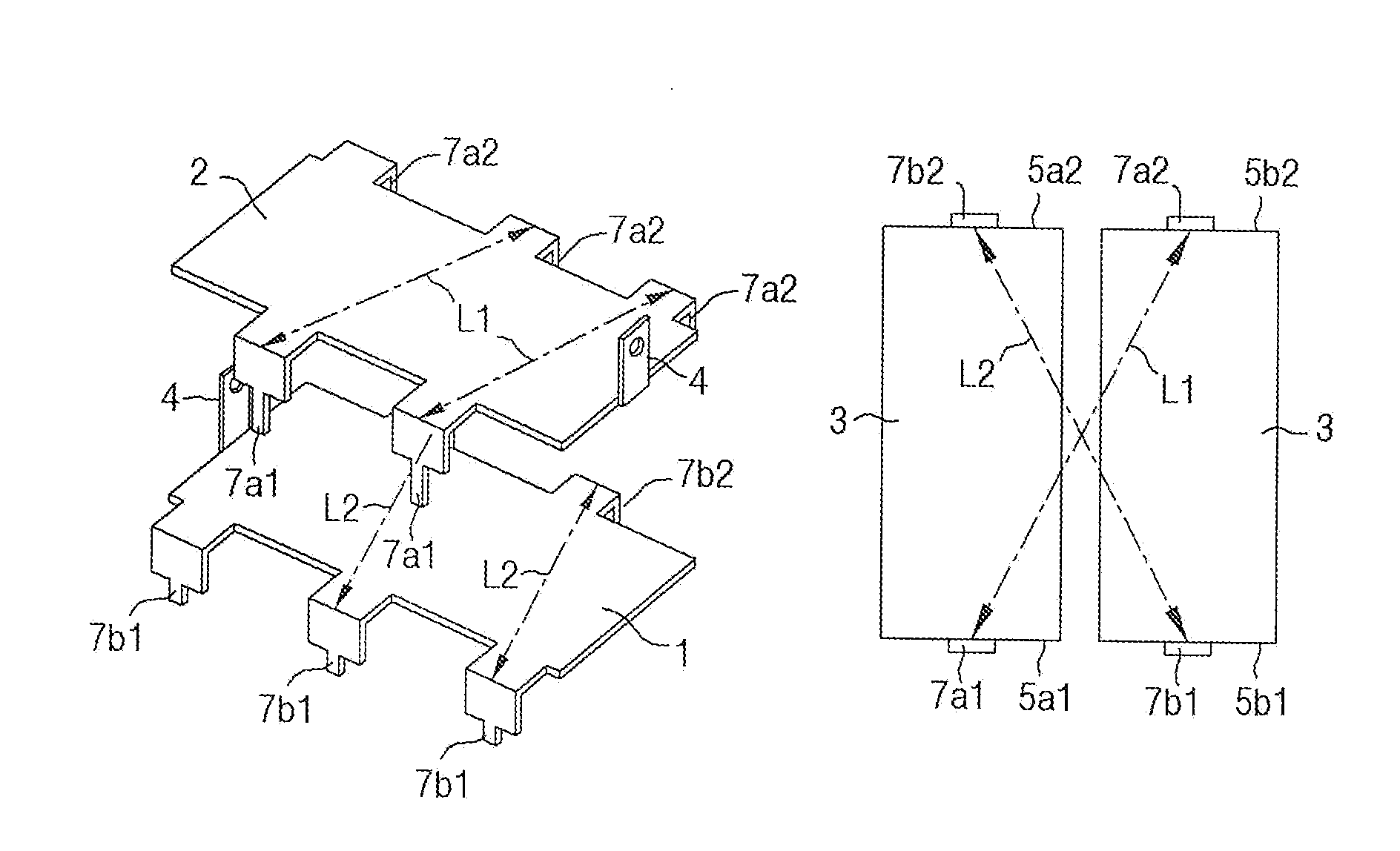

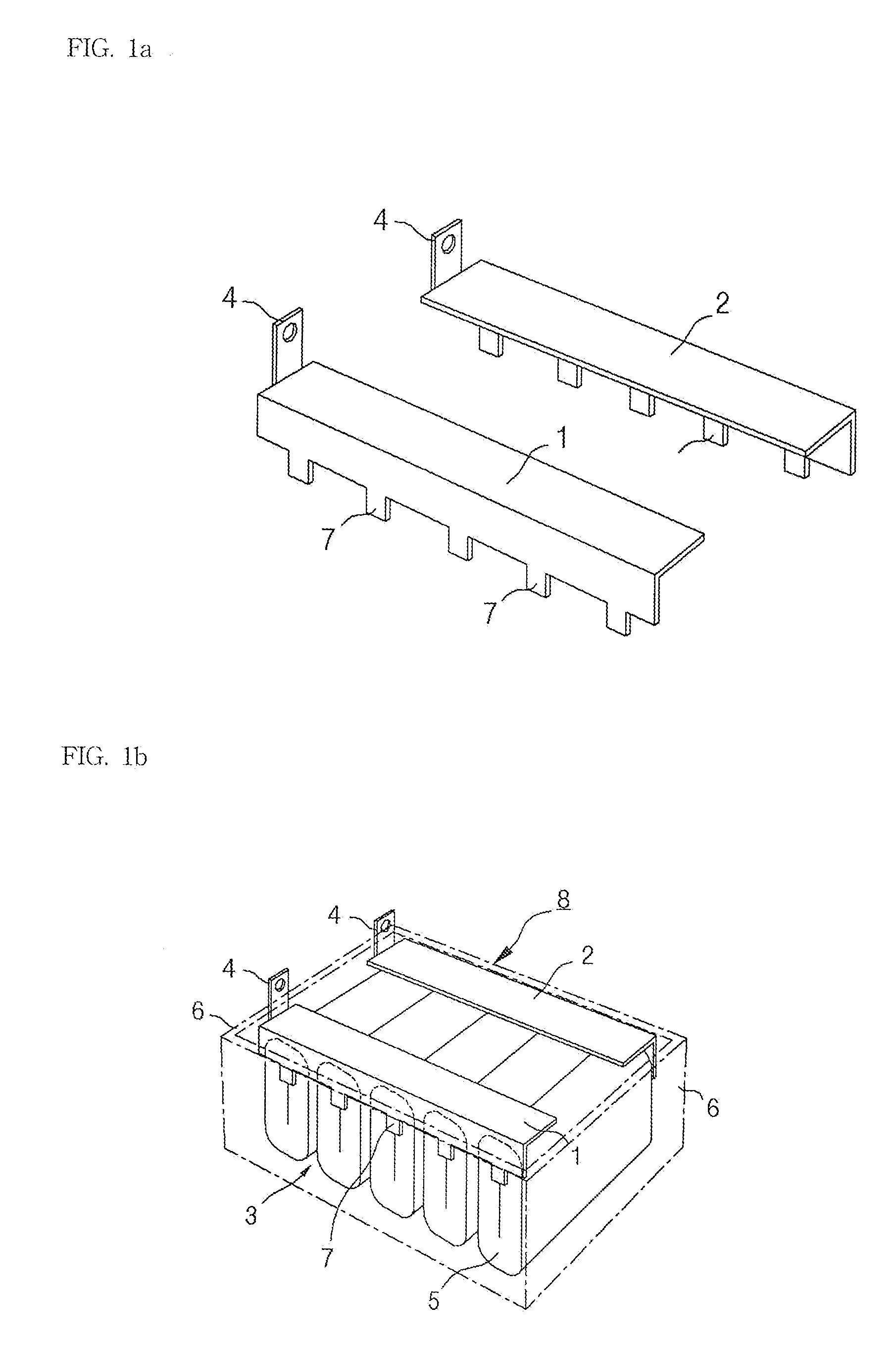

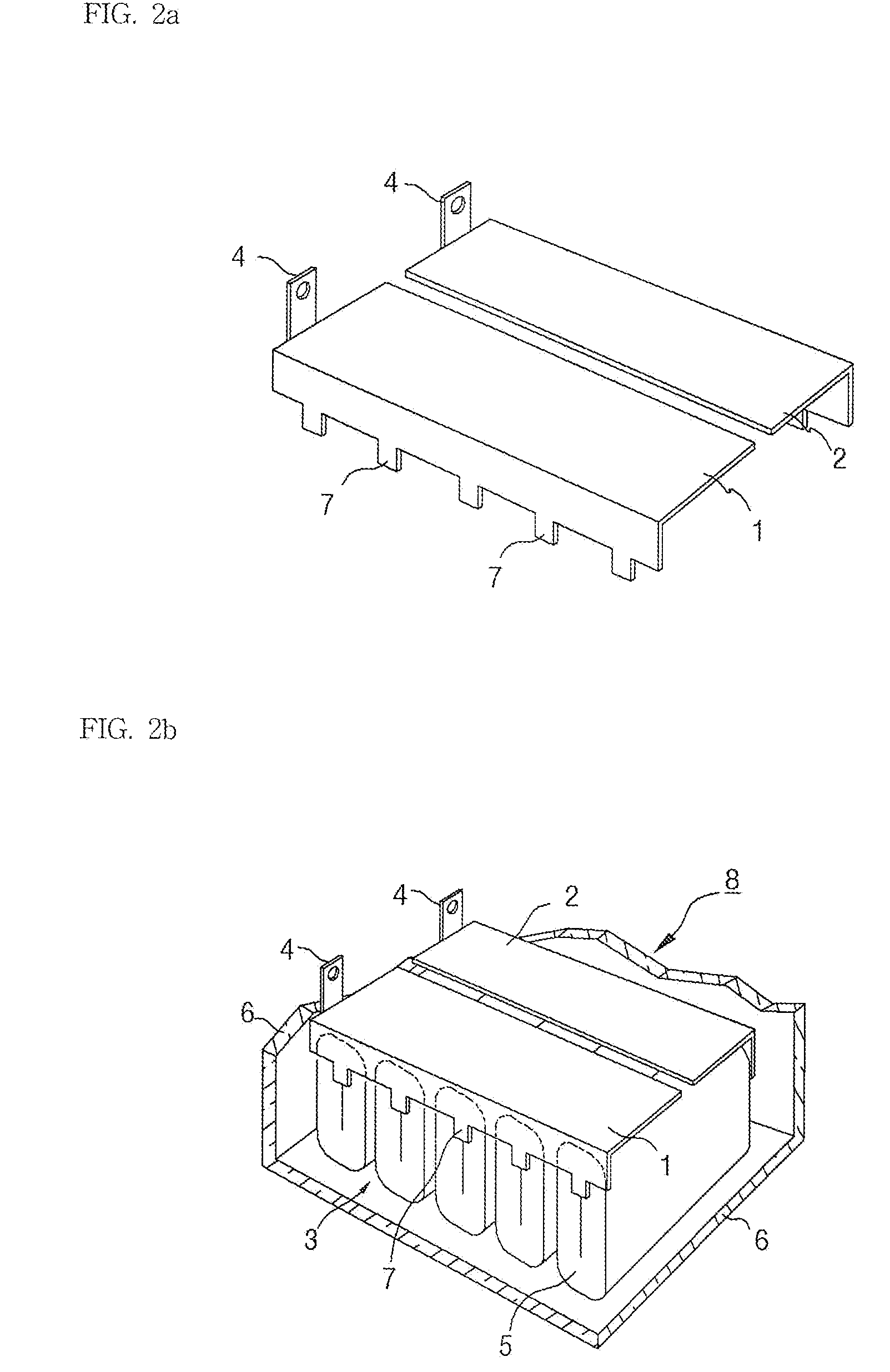

Method for Connecting Bus Bar on Capacitor and Product Fabricated by the Same

ActiveUS20100000089A1Improve electrical characteristicsImprove reliabilityLine/current collector detailsFixed capacitor electrodesCapacitanceDiagonal

Disclosed are a method for connecting a bus bar of a capacitor, improving temperature characteristics and reliability of the capacitor by reducing inductance and impedance such that heat generation is restrained during use of the capacitor, and a product fabricated by the same.A pair of bus bars are insulatedly connected to sprayed surfaces on both sides of a plurality of capacitor devices, in such a manner that lead frames arranged alternately on a first bus bar are connected in contact with the sprayed surfaces facing in a diagonal direction, of neighboring capacitor devices. Other lead frames arranged alternately on a second bus bar are connected to the sprayed surfaces facing in another diagonal direction across the above diagonal direction in an X-shape. Then, the pair of bus bars are assembled to be insulated from each other and overlapped at one side of the capacitor device.

Owner:NUINTEK

Semiconductor device and method for manufacturing the same

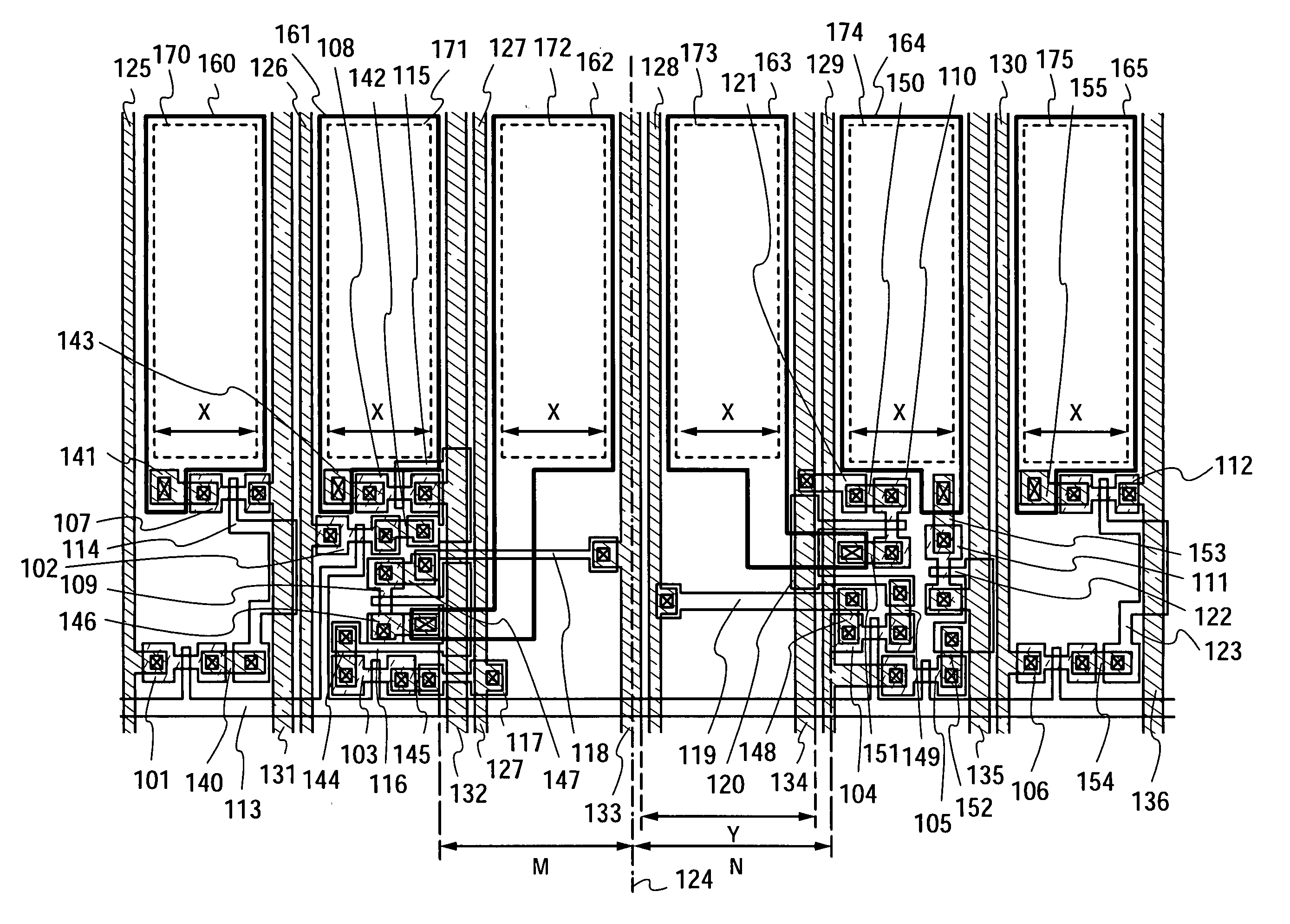

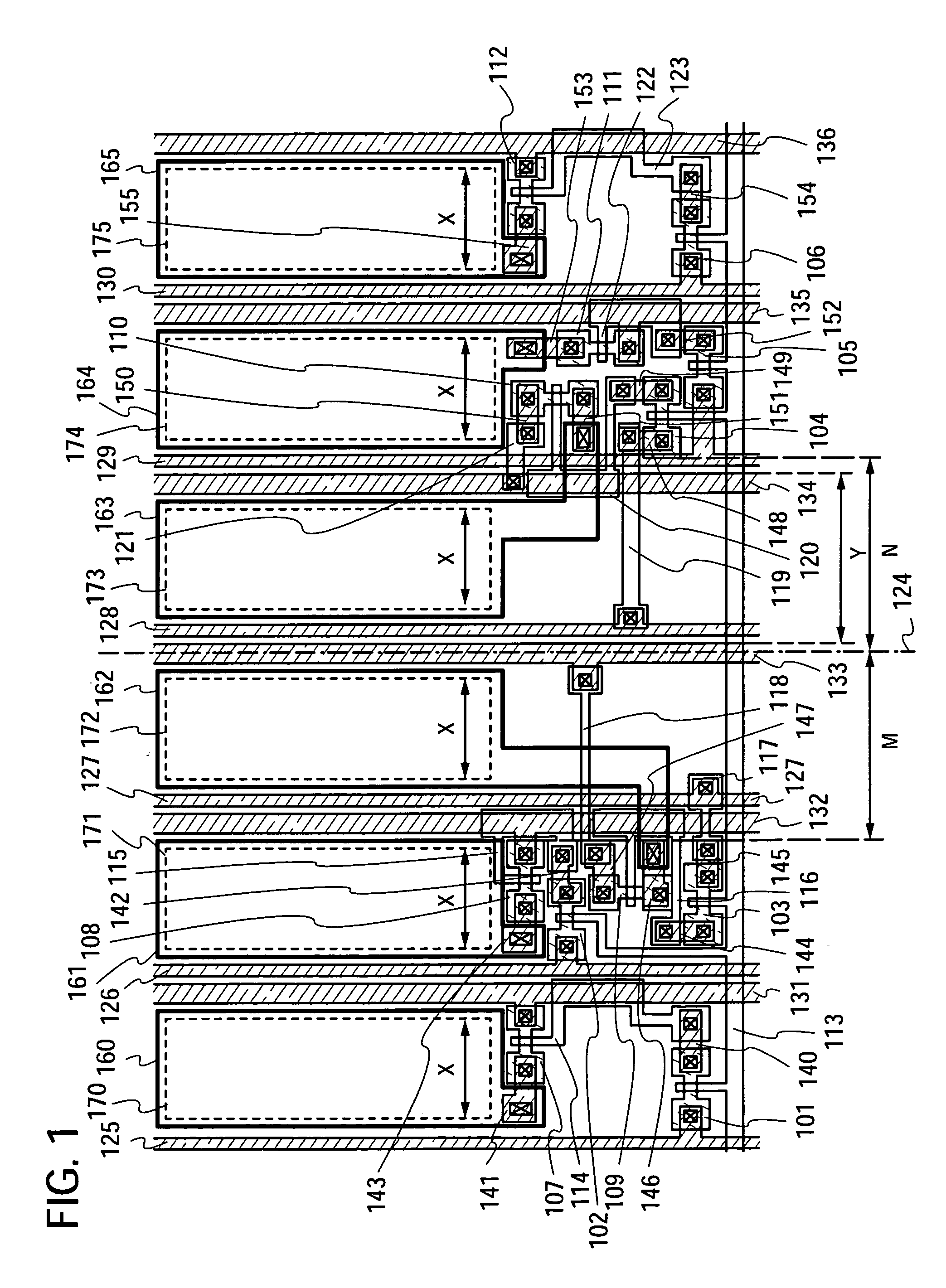

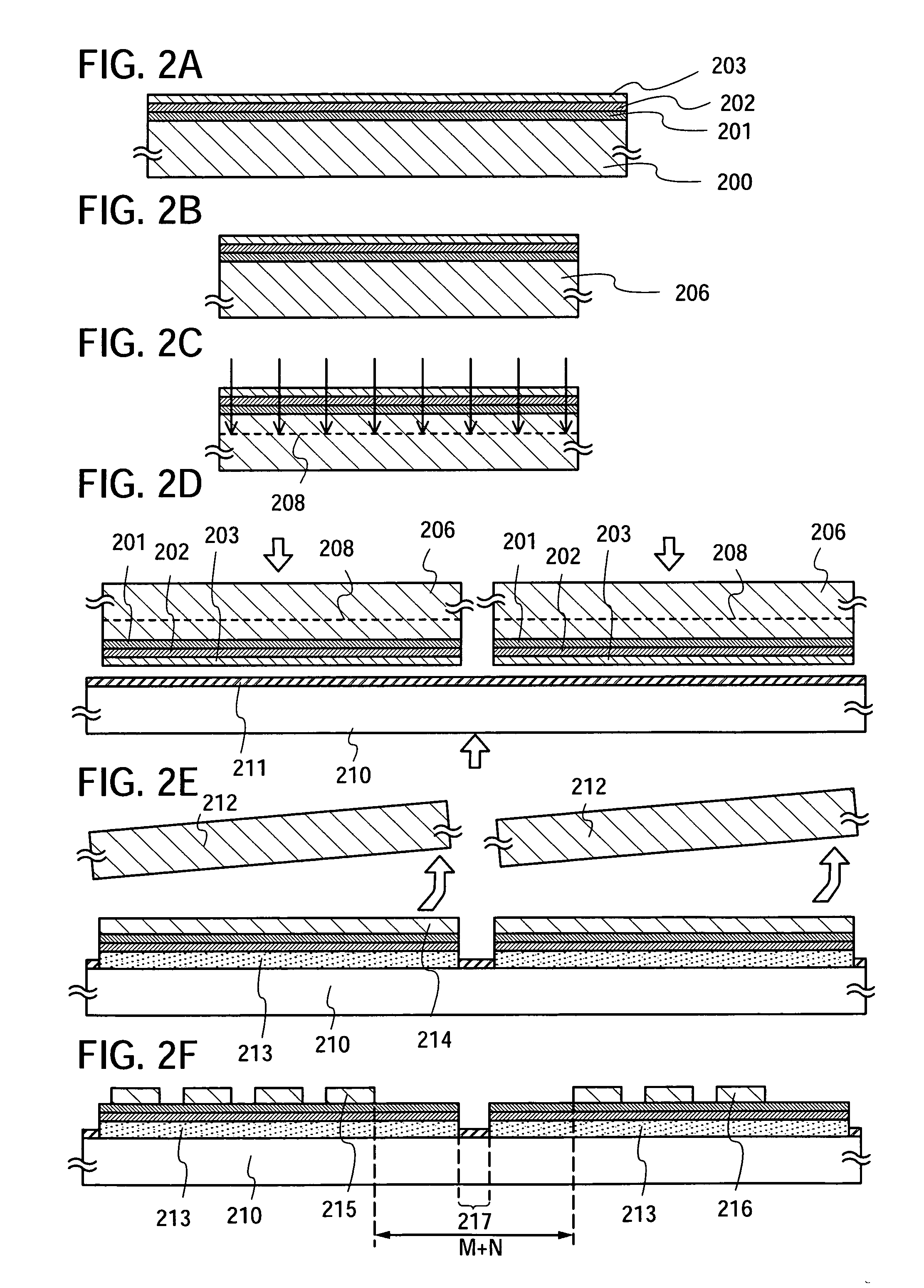

InactiveUS20080283848A1Suitable for mass productionIncrease the areaTransistorElectroluminescent light sourcesSingle crystalSemiconductor

A plurality of rectangle semiconductor substrates are attached to a single mother glass substrate. A pixel structure is determined so that even if a gap or a an overlapping portion is generated in a boundary between a plurality of semiconductor substrates, a single-crystal semiconductor layer does not overlap with the gap or the overlapping portion. Two TFTs are located in a first unit cell including the first light emitting element, four TFTs are located in a second unit cell including the second light emitting element, and no TFT is located in a third unit cell including the third light emitting element. A boundary line is between the third unit cell and a fourth unit cell.

Owner:SEMICON ENERGY LAB CO LTD

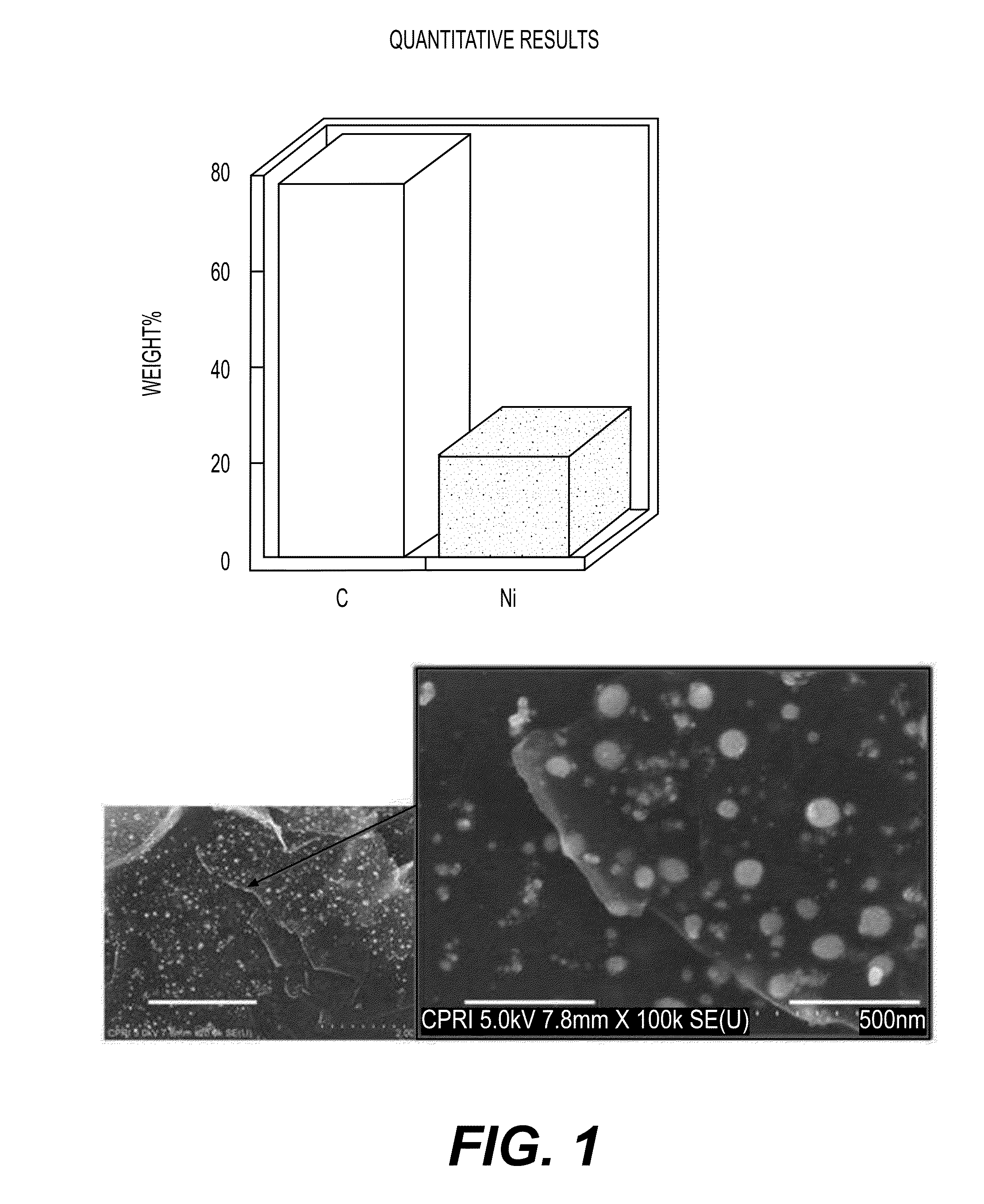

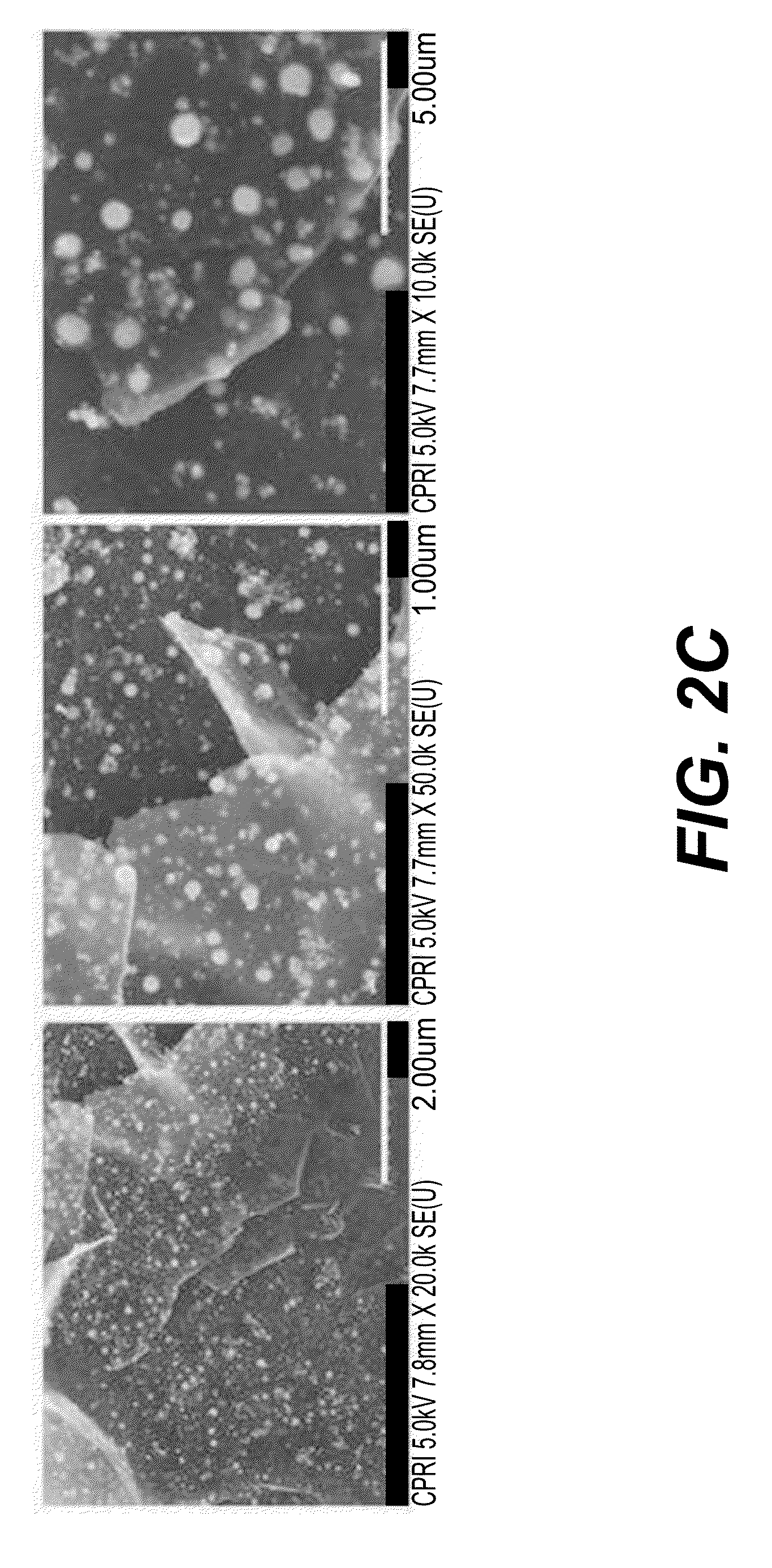

Graphene-nano particle composite having nanoparticles crystallized therein at a high density

InactiveUS20150179294A1Improve mechanical propertiesImprove electrical characteristicsSynthetic resin layered productsConductive materialNanoparticle ComplexHigh density

The present invention relates to a graphene-nanoparticle composite having a structure in which nanoparticles are crystallized at a high density in a carbon-based material, for example, graphene, and, more particularly, to a graphene-nanoparticle composite capable of remarkably improving physical properties such as contact characteristics between basal planes of graphene and conductivity since nanoparticles are included as a large amount of 20 to 50% by weight, based on 100% by weight of graphene, and a method of preparing the same.

Owner:CHEORWON PLASMA RES INST

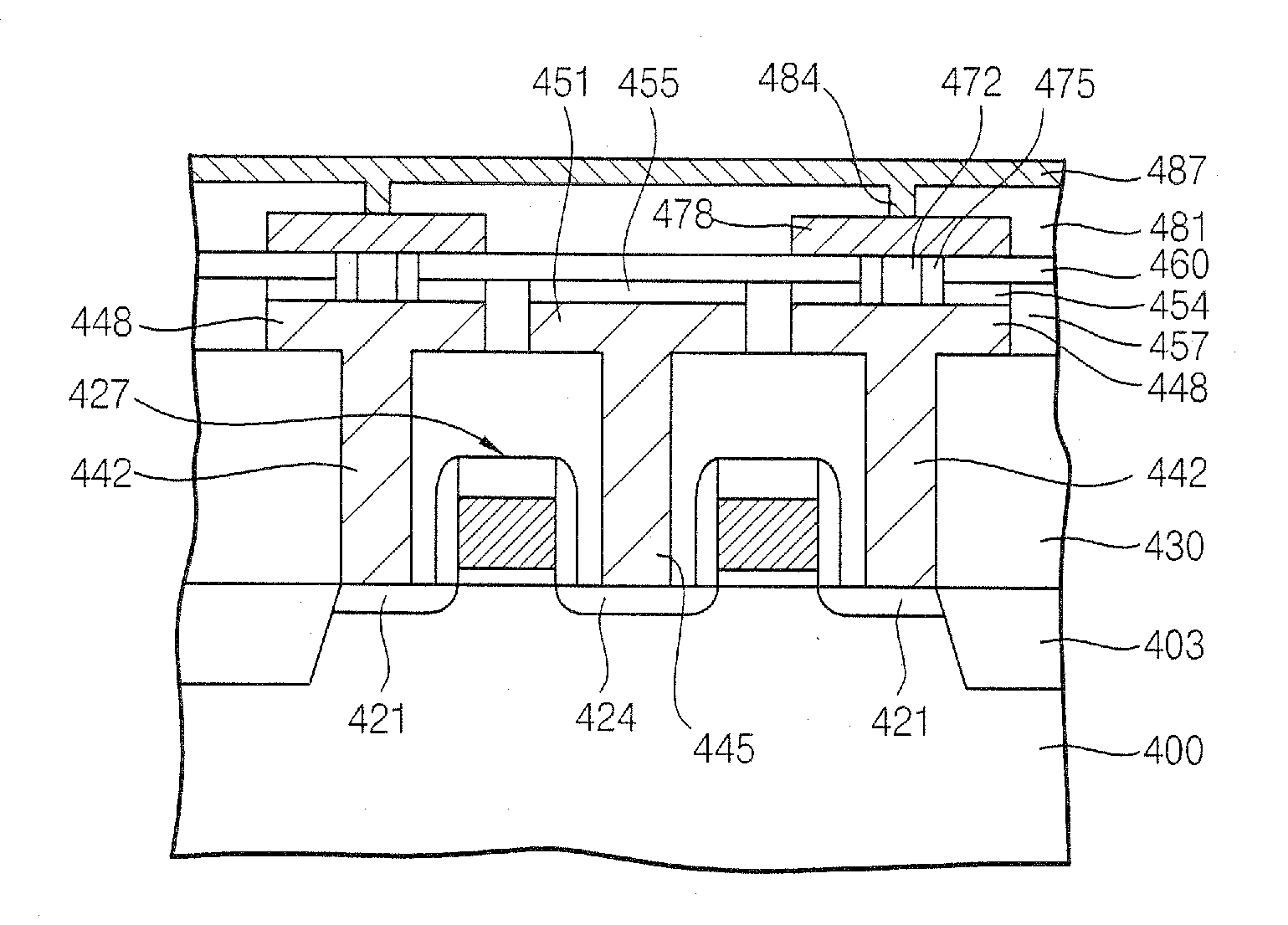

Method of manufacturing semiconductor devices

ActiveUS20100203695A1Reduce resistanceImprove electrical characteristicsSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerDevice material

A semiconductor device includes an insulation layer disposed on a substrate having a first area and a second area, a first wiring disposed on the insulation layer in the first area, a first active structure disposed on the first wiring, a first gate insulation layer enclosing the first upper portion, a first gate electrode disposed on the first gate insulation layer, a first impurity region disposed at the first lower portion, and a second impurity region disposed at the first upper portion. The first wiring may extend in a first direction. The first active structure includes a first lower portion extending in the first direction and a first upper portion protruding from the first lower portion. The first gate electrode may extend in a second direction. The first impurity region may be electrically connected to the first wiring.

Owner:SAMSUNG ELECTRONICS CO LTD

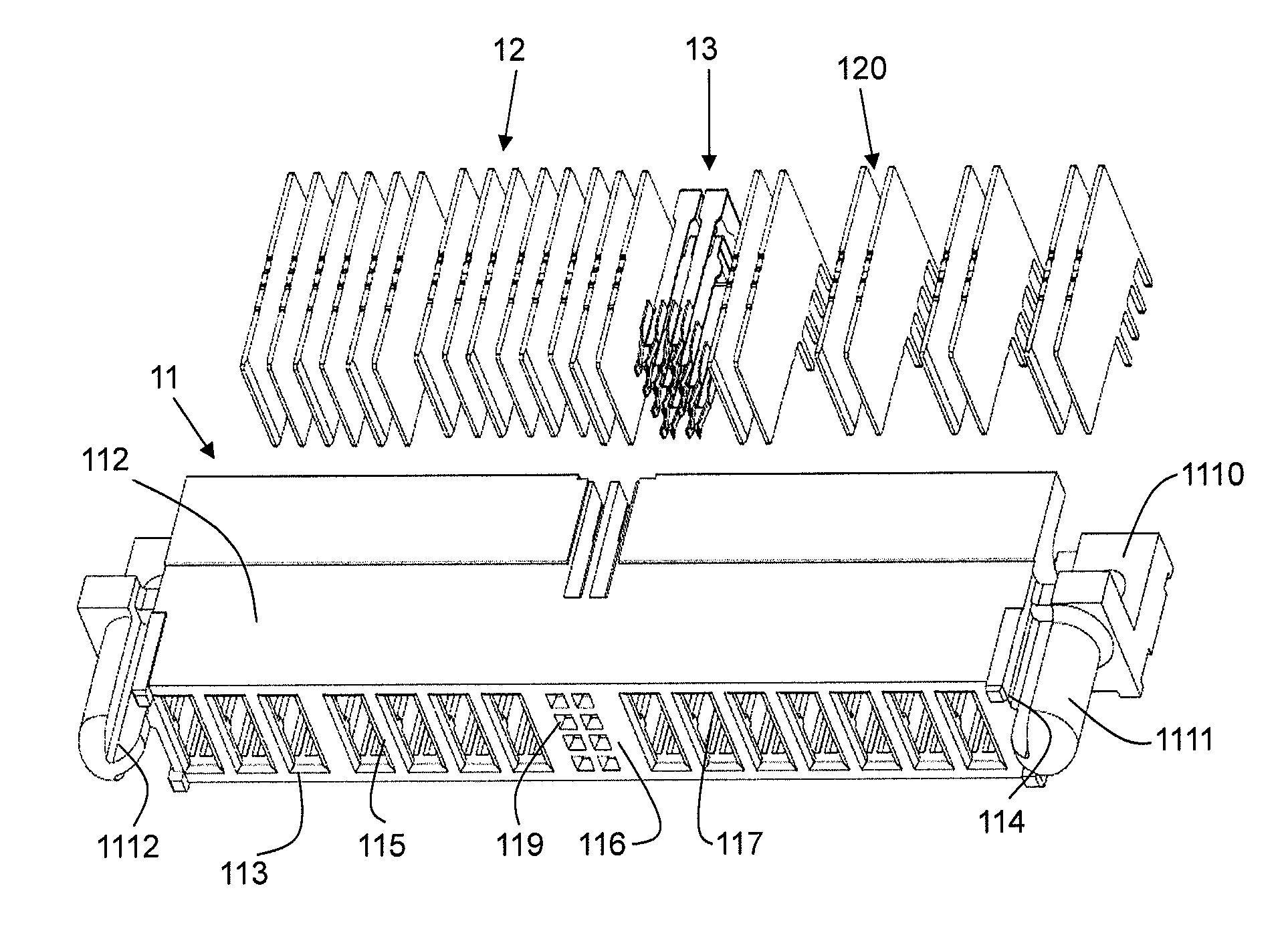

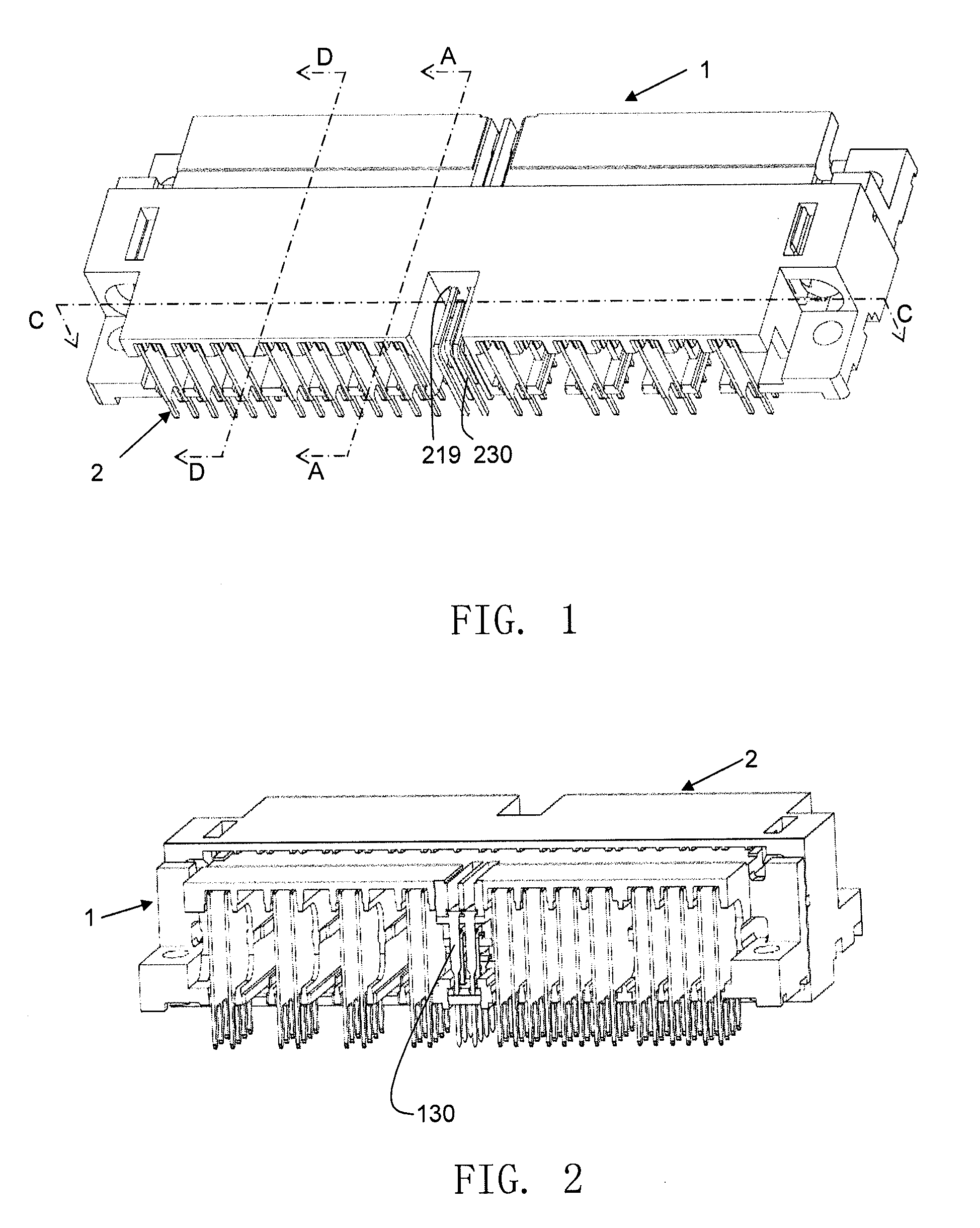

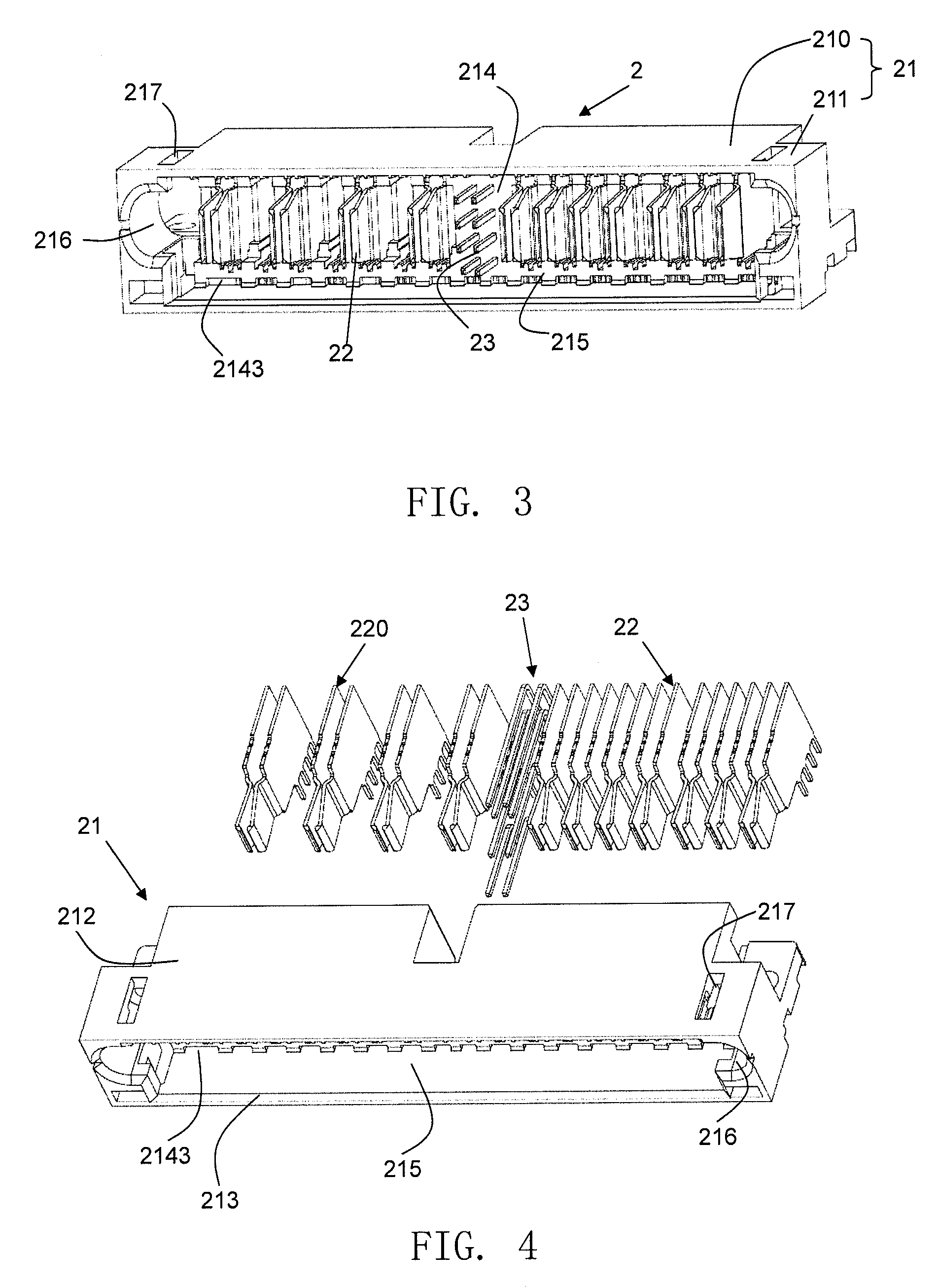

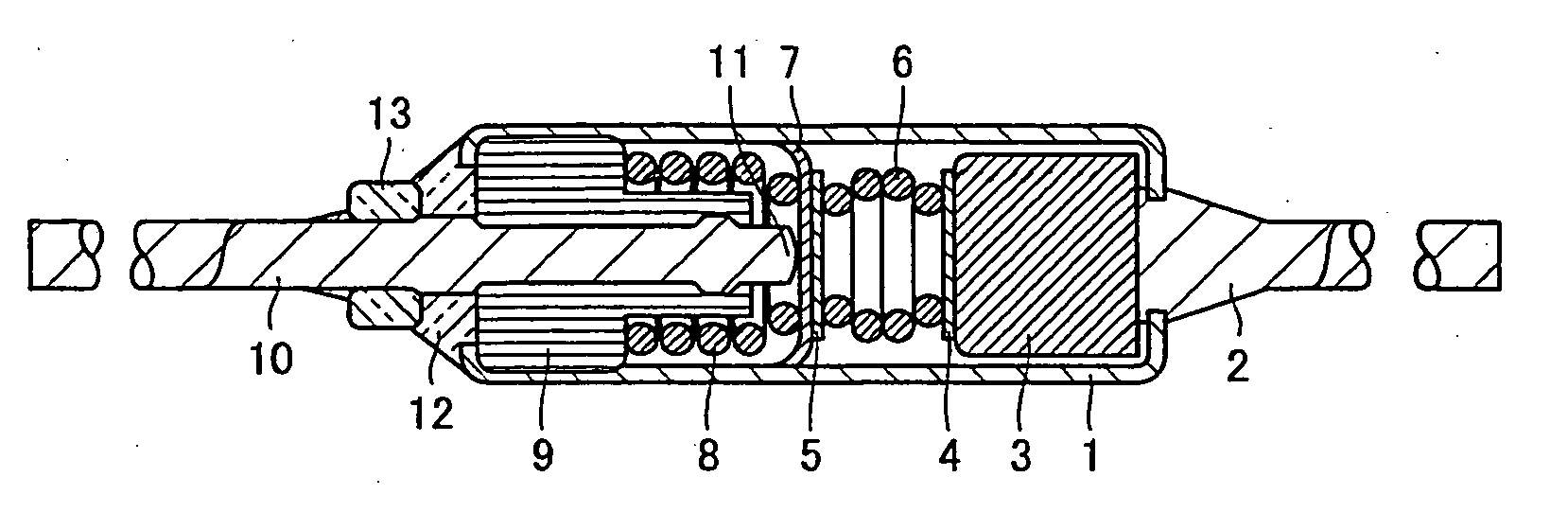

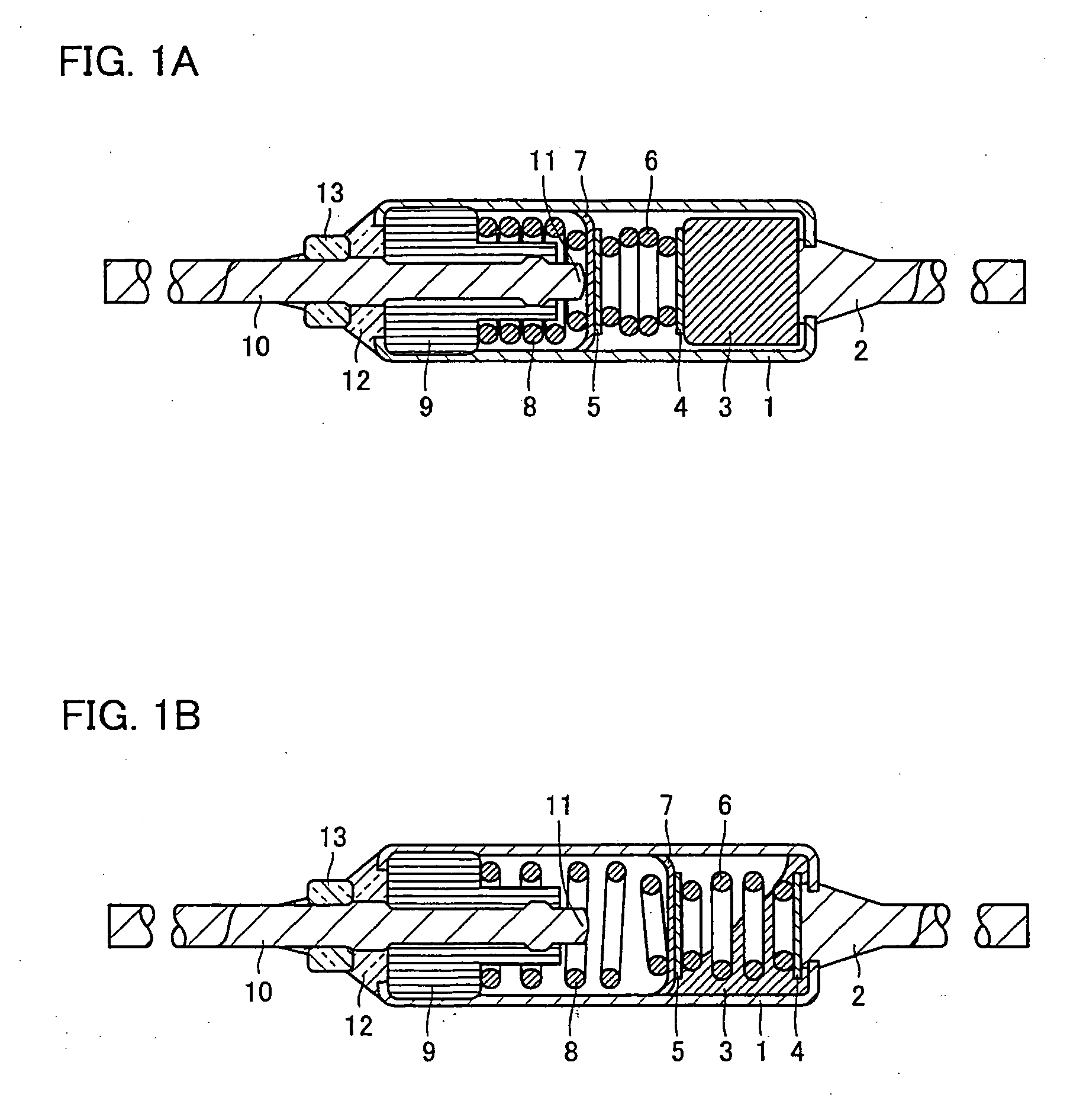

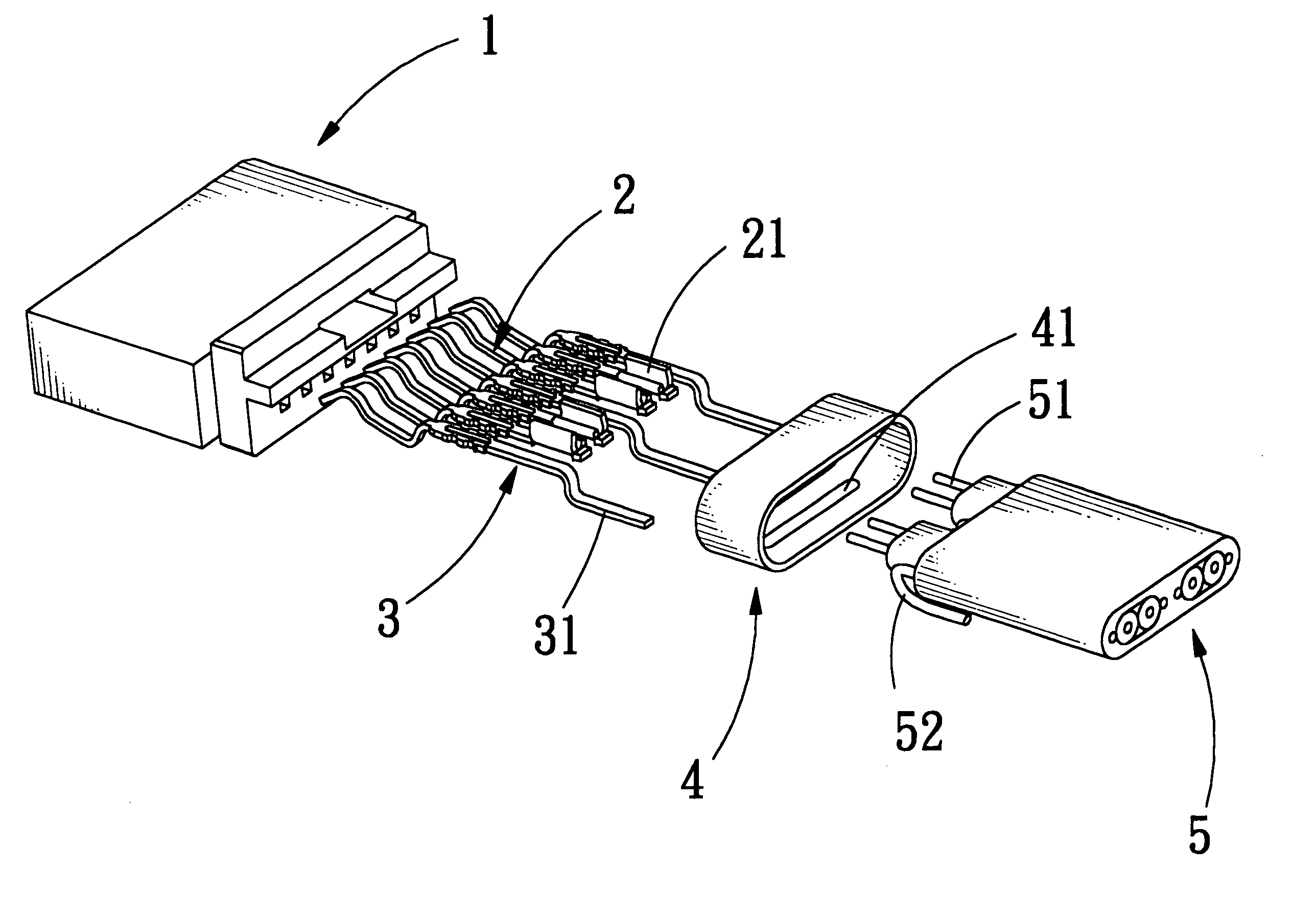

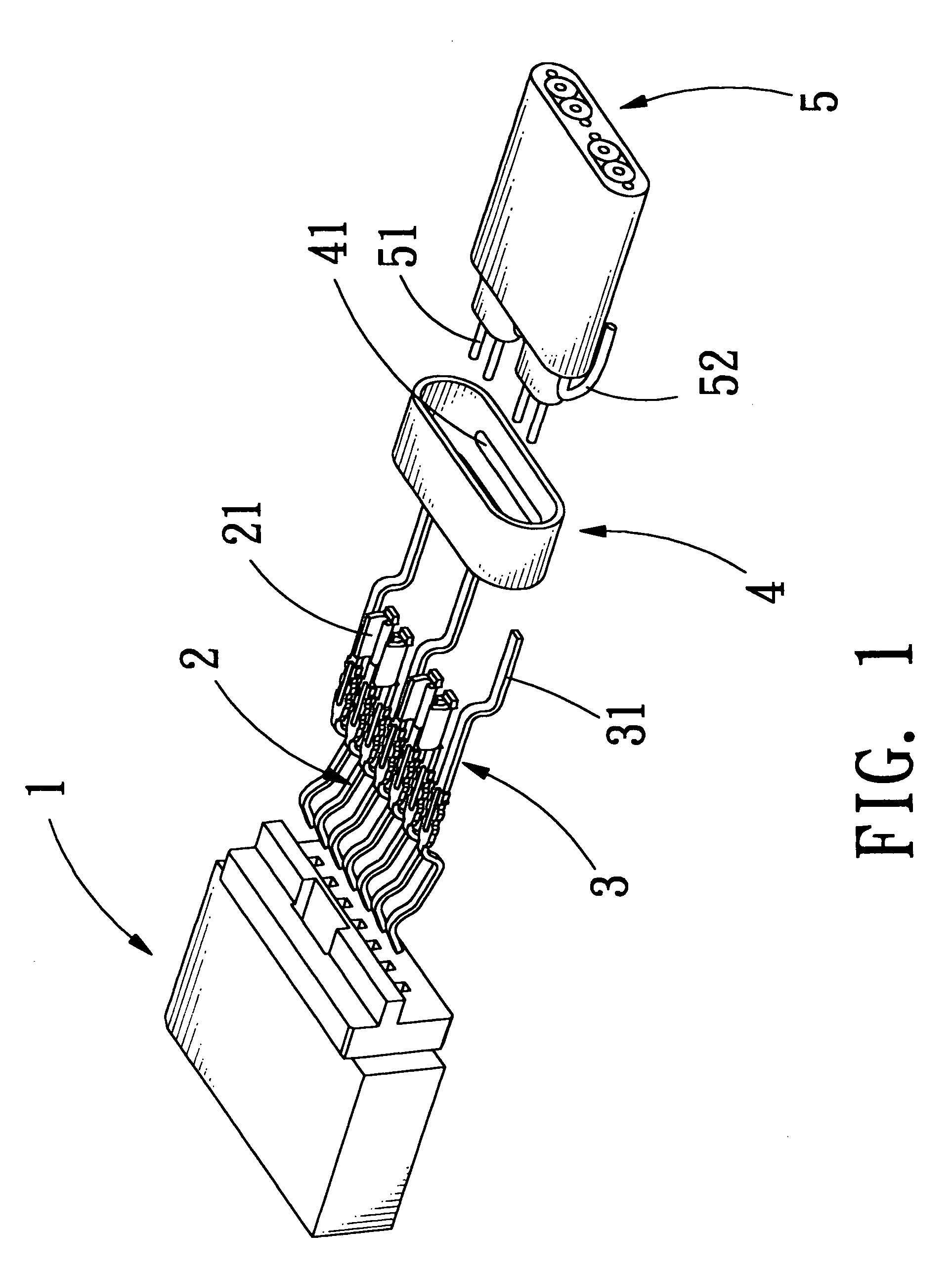

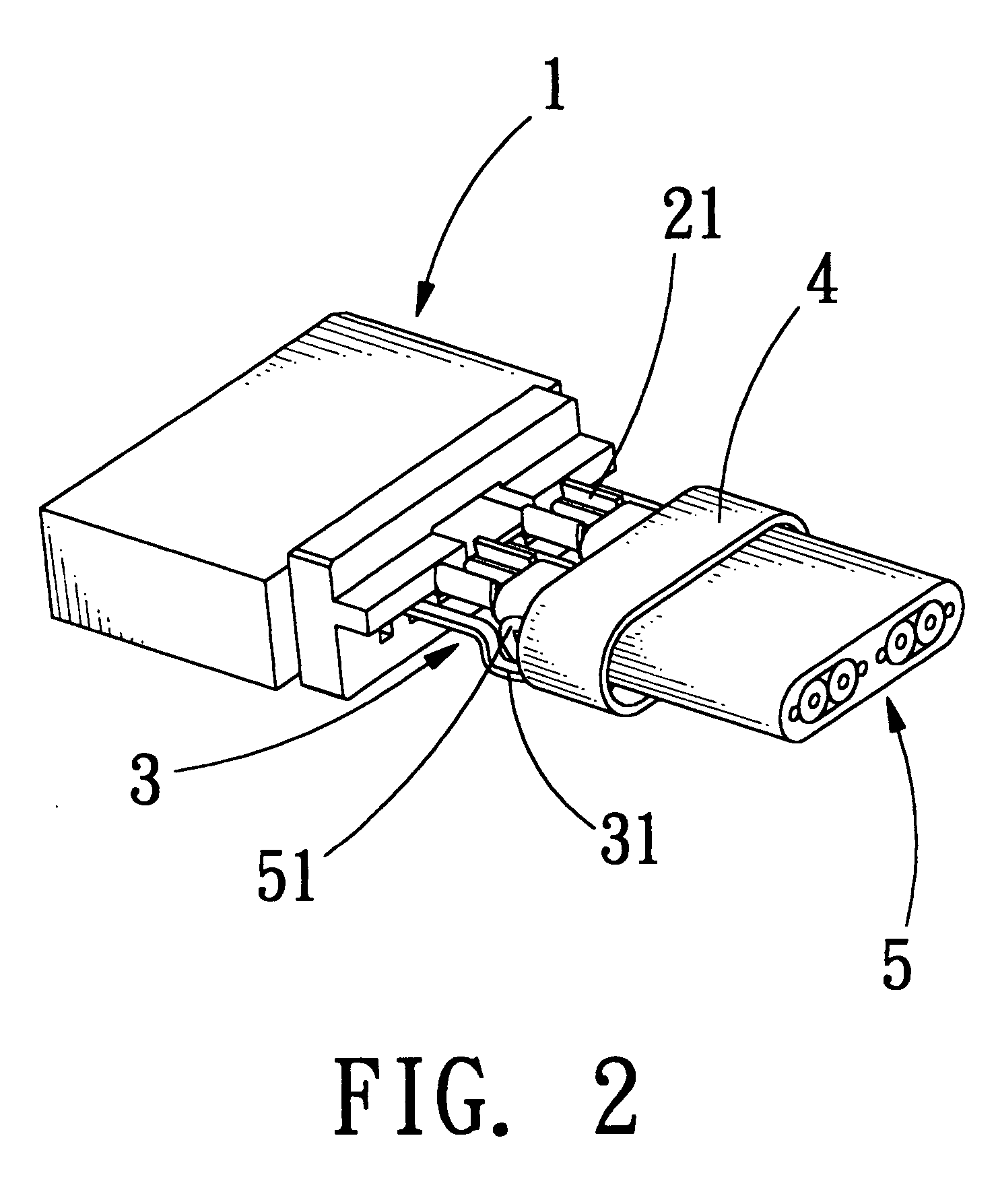

Power connector assembly

InactiveUS7666025B2Increase heat dissipation structureImproved terminalIncorrect coupling preventionTwo-part coupling devicesEngineeringElectrical and Electronics engineering

A power connector assembly is provided which comprises a plug connector and a mating receptacle connector. The plug connector includes an insulative plug housing having a plurality of passageways divided by division walls and a plurality of plug terminals accommodated in the corresponding passageways of the plug housing. The receptacle connector includes an insulative receptacle housing having a receiving space for receiving a part of the plug housing inserted therein and a plurality of receptacle terminals accommodated in the receptacle housing for mating with the plug terminals. Airflow channels are formed between the outer surface of the part of the plug housing in the receiving space and the inner surface of the receiving space for dissipation of heat.

Owner:ALLTOP ELECTRONICS SU ZHOU

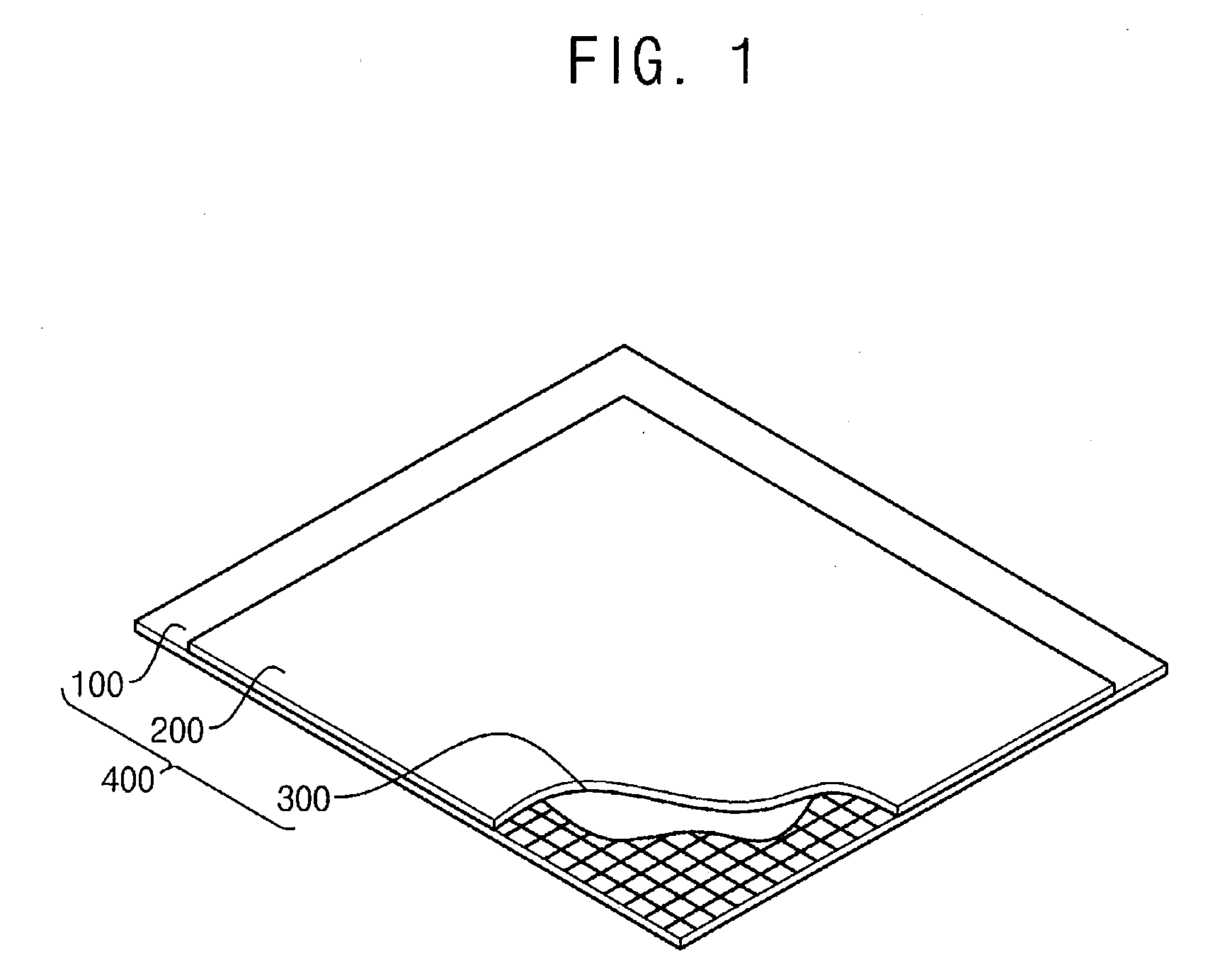

Electrophoretic display device and method for manufacturing thereof

InactiveUS20090078938A1Improve featuresImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceEngineering

It is an object to provide an electrophoretic display device having a thin film transistor which has highly reliable electric characteristics, lightweight, and flexibility. A gate insulating film is formed over a gate electrode, a microcrystalline semiconductor film which functions as a channel formation region is formed over the gate insulating film, a buffer layer is formed over the microcrystalline semiconductor film, a pair of source and drain regions are formed over the buffer layer, a pair of the source and drain electrodes in contact with the source and drain regions are formed. Then, the inverted-staggered thin film transistor is interposed between the flexible substrates, and the thin film transistor is provided with electrophoretic display element which is electrically connected by the pixel electrode. Then, the electrophoretic display electrode is surrounded by the partition layer so as to cover the end portion of the pixel electrode and provided over the pixel electrode.

Owner:SEMICON ENERGY LAB CO LTD

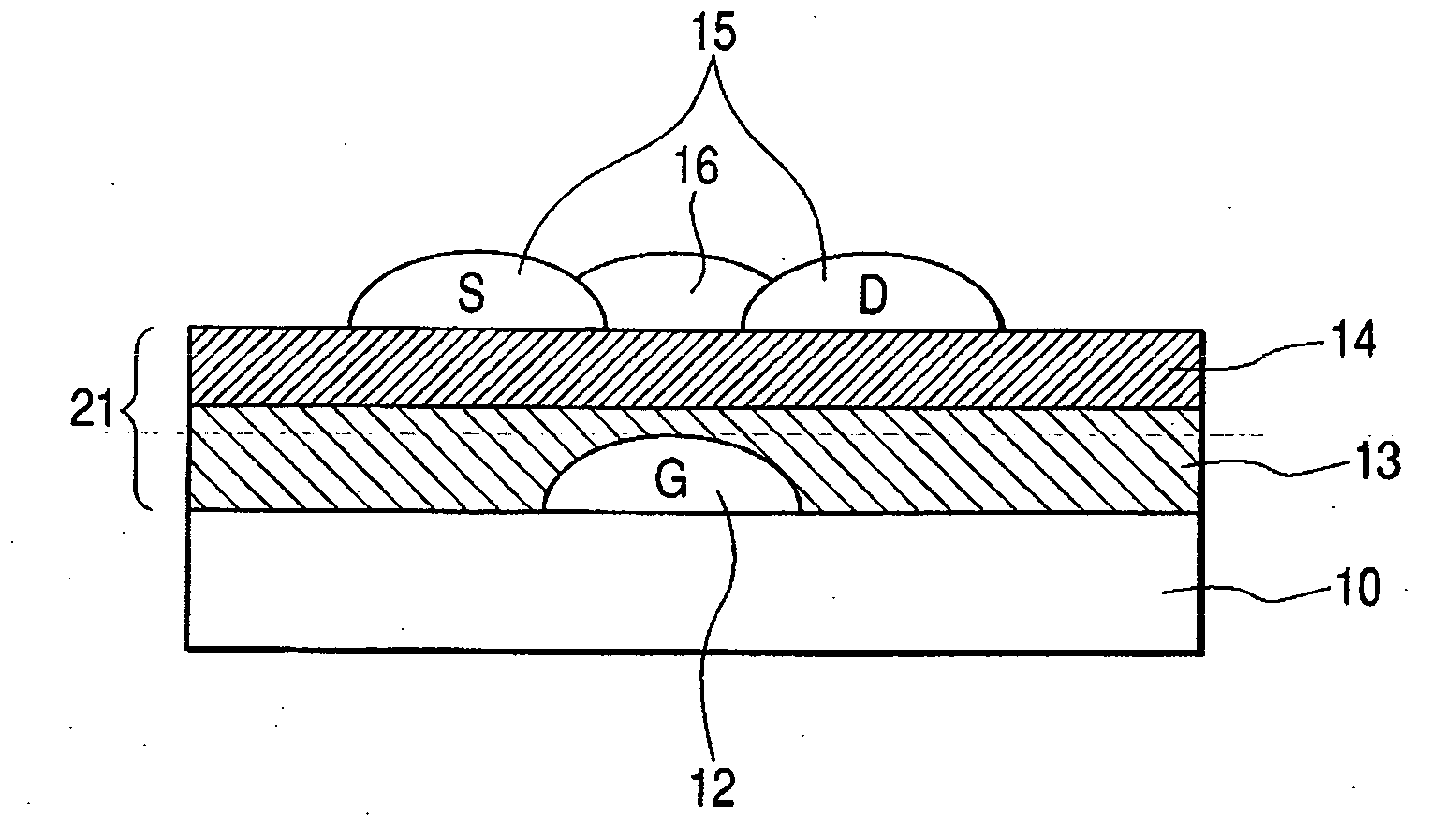

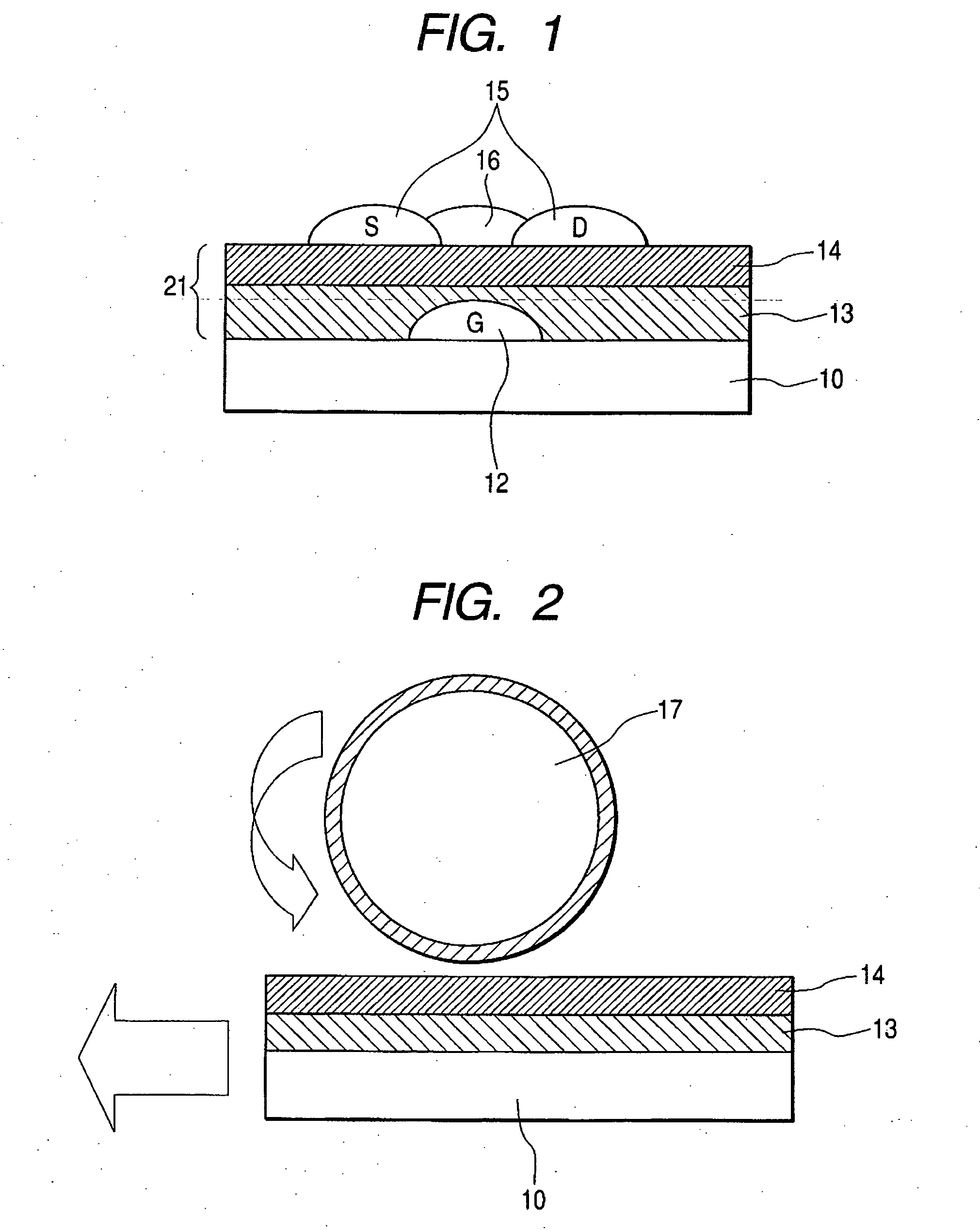

Organic transistor and manufacturing method thereof

InactiveUS20060157692A1Channel shortImprove electrical characteristicsSolid-state devicesSemiconductor/solid-state device manufacturingBottom gateEngineering

There is provided an organic transistor having a bottom gate structure, composed of a substrate, a gate electrode, a gate insulating layer, source and drain electrodes and an organic semiconductor layer, wherein the gate insulating layer is formed so as to have a low surface energy in a portion thereof in proximity to the source and drain electrodes and a relatively high surface energy in a portion in proximity to the gate electrode, and consist of different compositions in a layer thickness direction, whereby an organic transistor has a short channel and high electric characteristics; as well as a method of manufacturing the organic semiconductor.

Owner:CANON KK

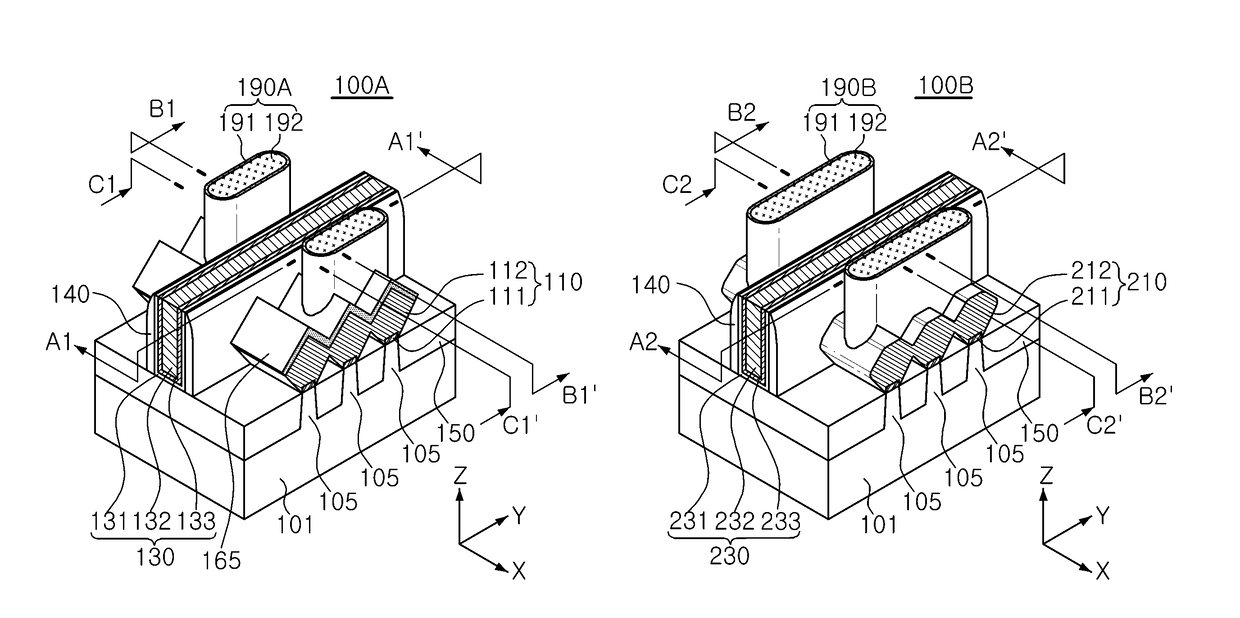

Semiconductor device

ActiveUS20180130886A1Improve electrical characteristicsImprove reliabilityTransistorSemiconductor/solid-state device detailsDevice materialMetal silicide

A semiconductor device includes: a substrate having an active region; a gate structure disposed in the active region; source / drain regions respectively formed within portions of the active region disposed on both sides of the gate structure; a metal silicide layer disposed on a surface of each of the source / drain regions; and contact plugs disposed on the source / drain regions and electrically connected to the source / drain regions through the metal silicide layer, respectively. The metal silicide layer is formed so as to have a monocrystalline structure.

Owner:SAMSUNG ELECTRONICS CO LTD

Temperature sensing material type thermal use

ActiveUS20050179516A1Improve electrical characteristicsReduce deformationHeating/cooling contact switchesEmergency protective devicesMaterial typeEngineering

In the present invention, a physical and chemical property of thermosensitive material is noted in selecting and using thermosensitive material to provide a noble and improved thermal fuse using thermosensitive material. To achieve this object, the present thermal fuse includes: a thermosensitive material formed of thermoplastic resin fusing at a prescribed temperature; a cylindrical enclosure accommodating the thermosensitive material; a first lead member attached at one opening of the enclosure, forming a first electrode; a second lead member attached at the other opening of the enclosure, forming a second electrode; a movable conductive member accommodated in the enclosure and engaged with the thermosensitive material; and a spring member accommodated in the enclosure, and pressed against and thus acting on the movable conductive member. When the thermosensitive material fuses at an operating temperature an electrical circuit between the first and second electrodes is switched.

Owner:SCHOTT JAPAN CORP

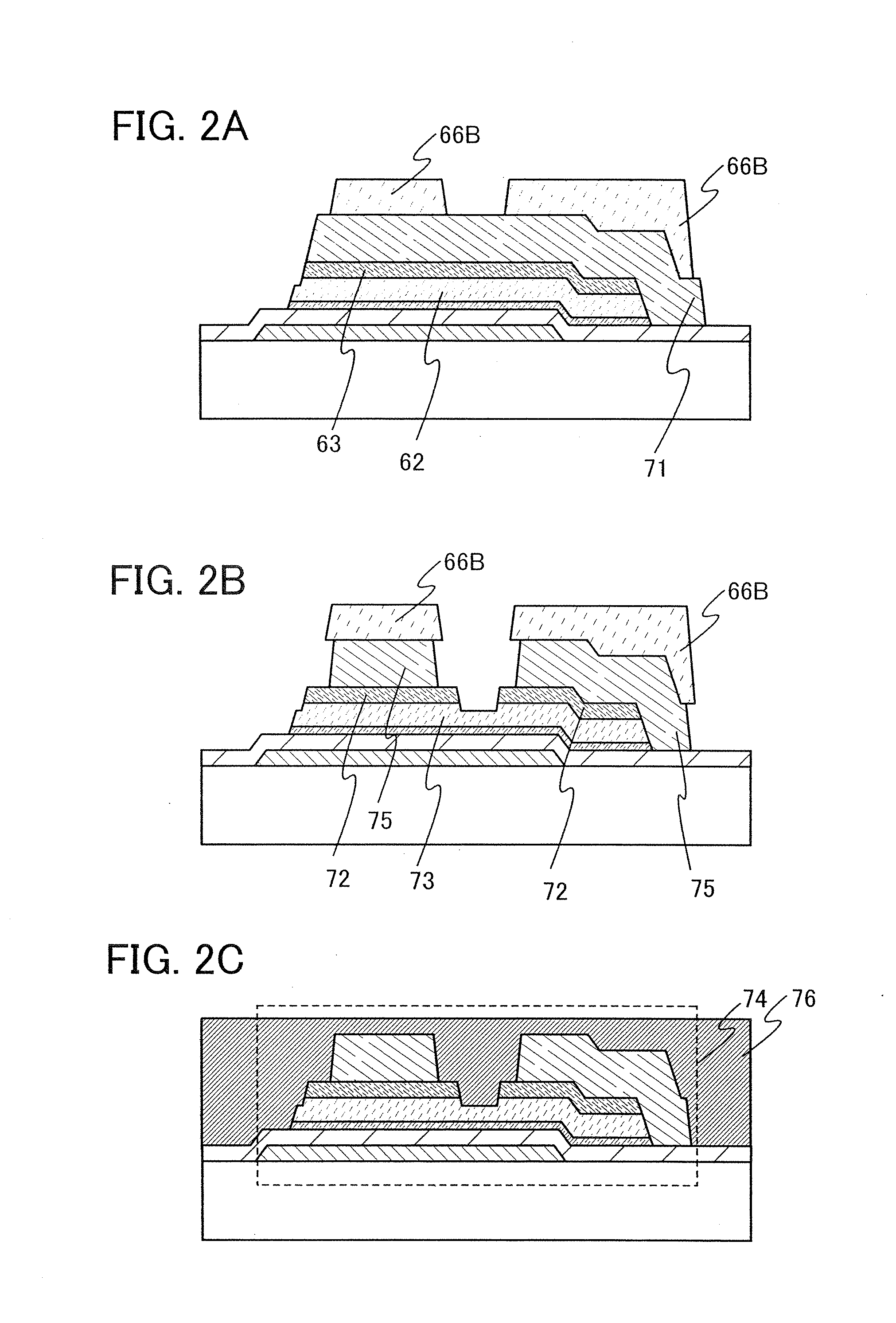

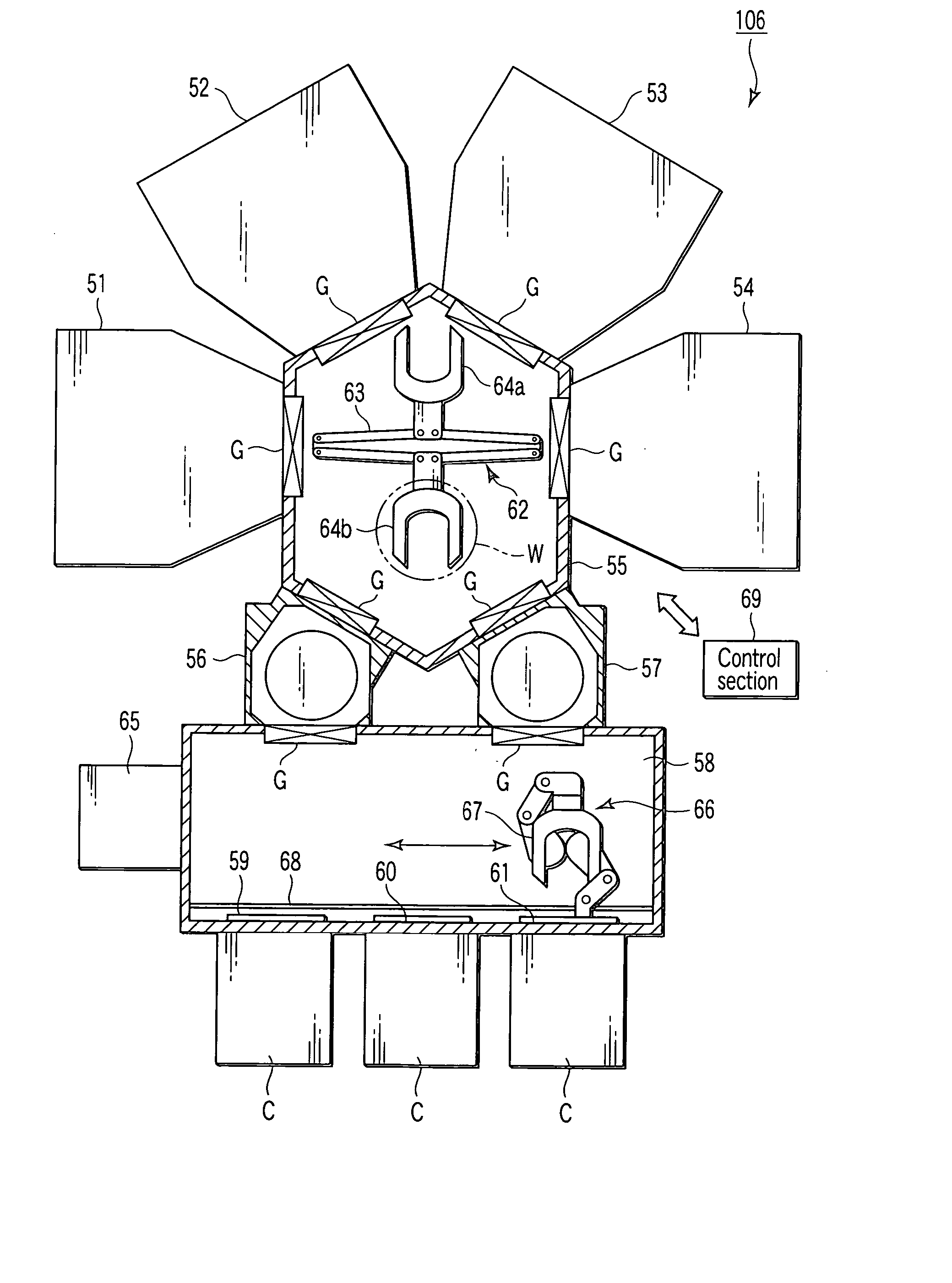

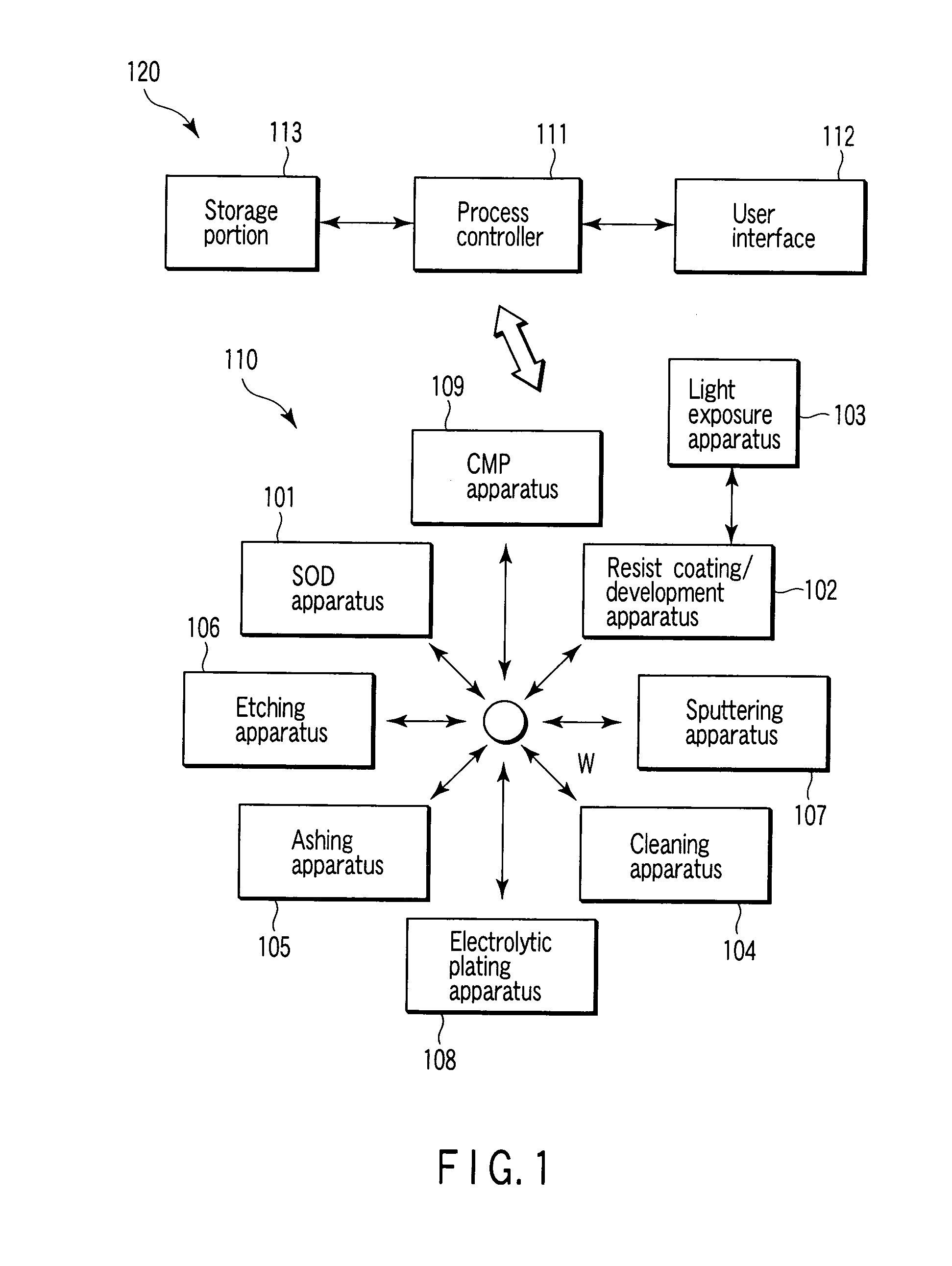

Process For Fabricating Semiconductor Device

InactiveUS20080057728A1Improve electrical characteristicsImprove reliabilitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingDevice materialEngineering

In a semiconductor device manufacturing method, an etching mask (75b) having a predetermined opening pattern is formed on an etching target film (74) disposed on a target object. Then, an etching process is performed on the etching target film (74) through the opening pattern of the etching mask (75b) within a first process chamber, thereby forming a groove or hole (78a) in the etching target film. Then, the target object treated by the etching process is transferred from the first process chamber to a second process chamber, within a vacuum atmosphere. Then, a silylation process is performed on a side surface of the groove or hole (78a), which is an exposed portion of the etching target film (74), within the second process chamber.

Owner:TOKYO ELECTRON LTD

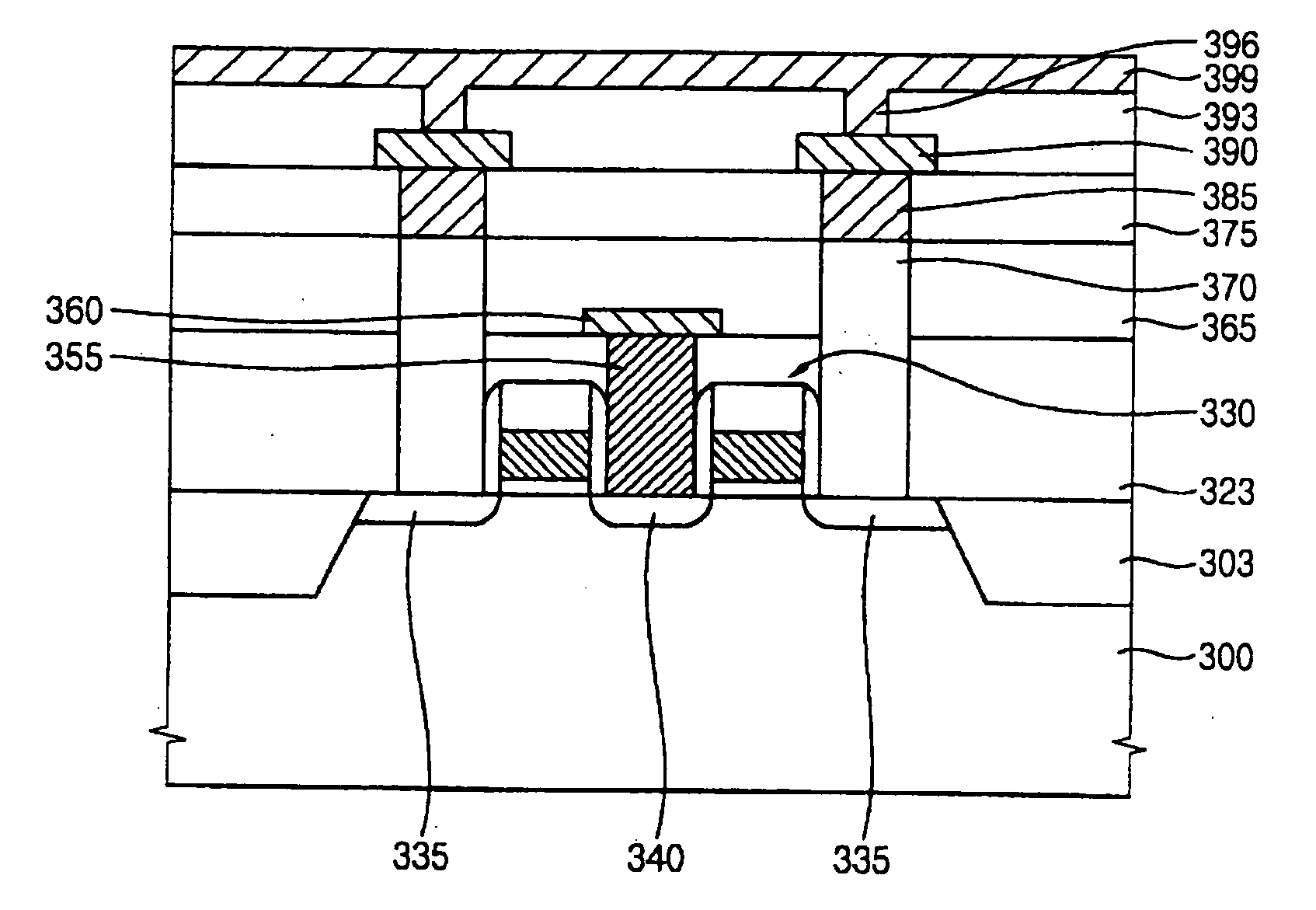

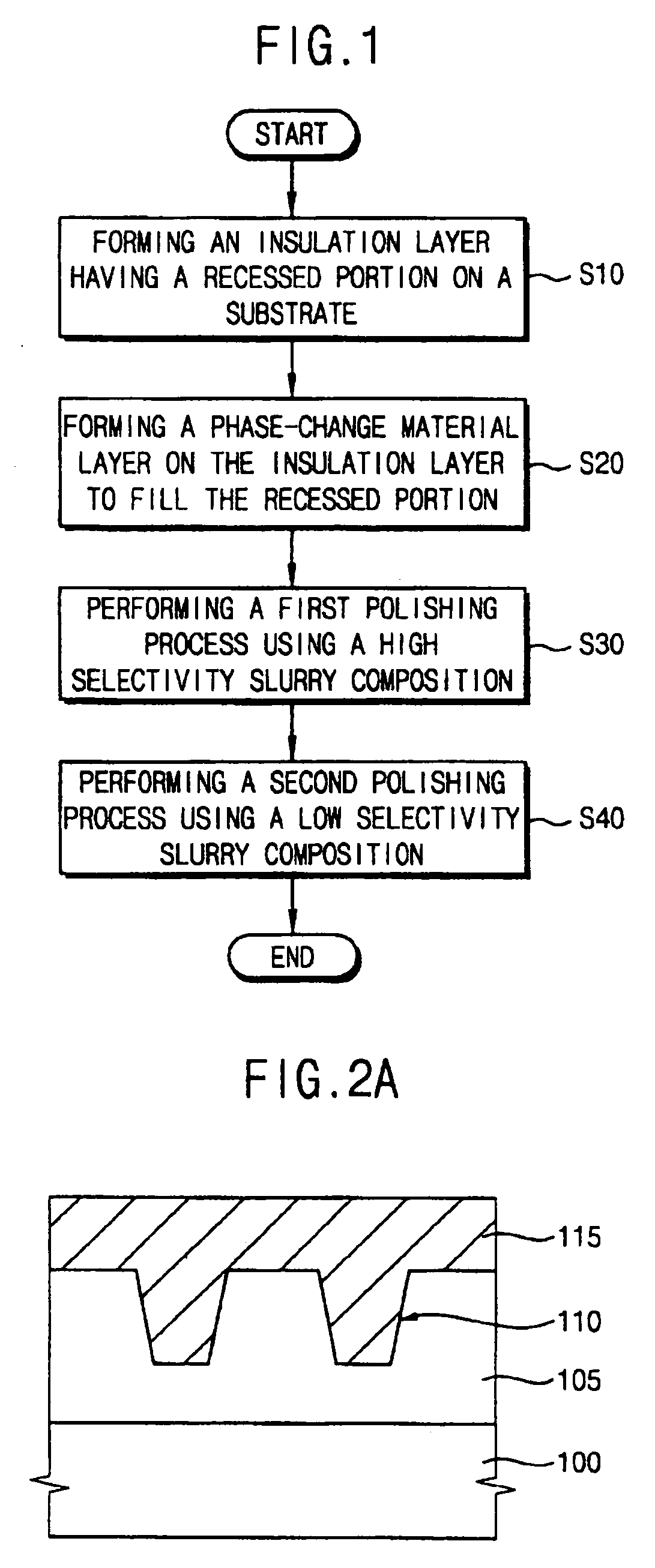

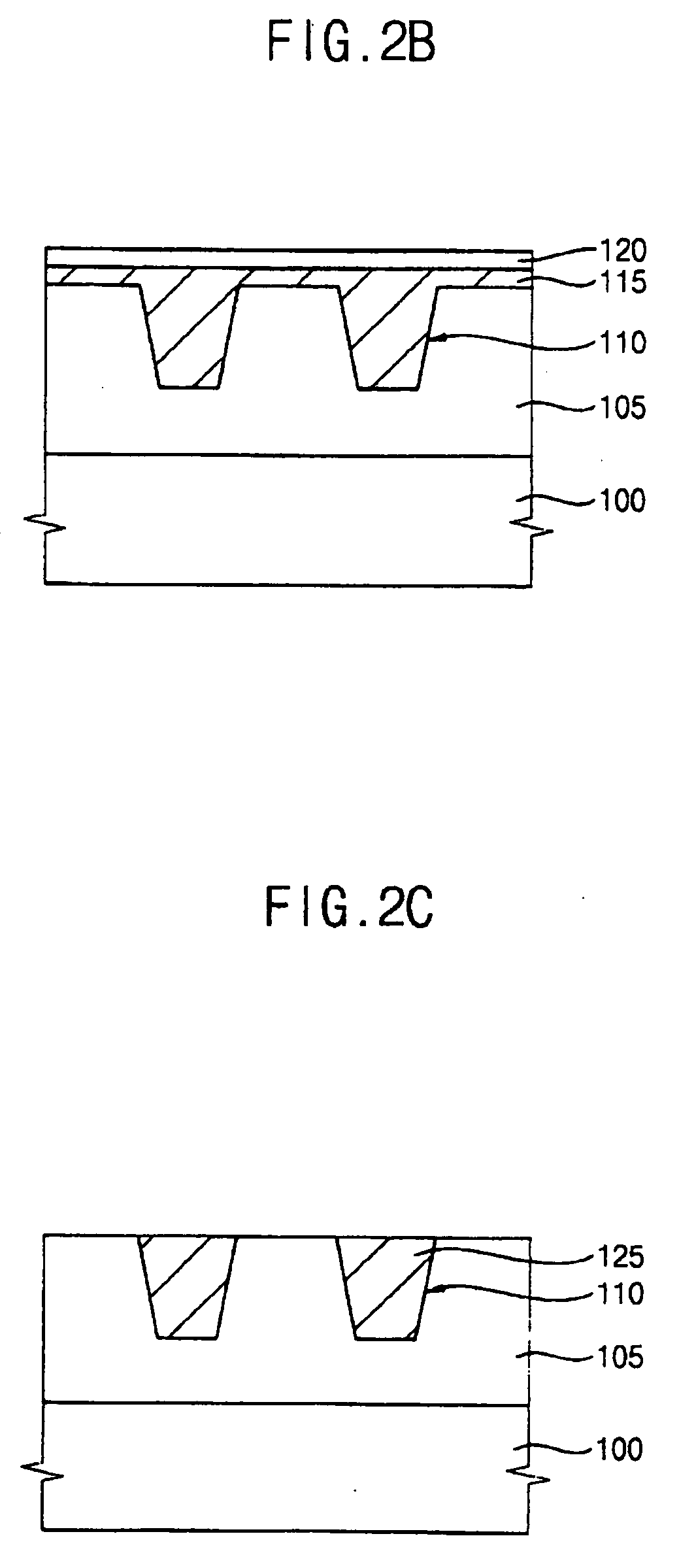

Methods of forming a phase-change material layer pattern, methods of manufacturing a phase-change memory device and related slurry compositions

ActiveUS20090149006A1High selectivityLow selectivitySolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerPhase-change memory

In methods of forming a phase-change material layer pattern, an insulation layer having a recessed portion may be formed on a substrate, and a phase-change material layer may be formed on the insulation layer to fill the recessed portion. A first polishing process may be performed on the phase-change material layer using a first slurry composition to partially remove the phase-change material layer, the first slurry composition having a first polishing selectivity between the insulation layer and the phase-change material layer. A second polishing process may be performed on the phase-change material layer using a second slurry composition to form a phase-change material layer pattern in the recessed portion, the second slurry composition having a second polishing selectivity substantially lower than the first polishing selectivity.

Owner:SAMSUNG ELECTRONICS CO LTD

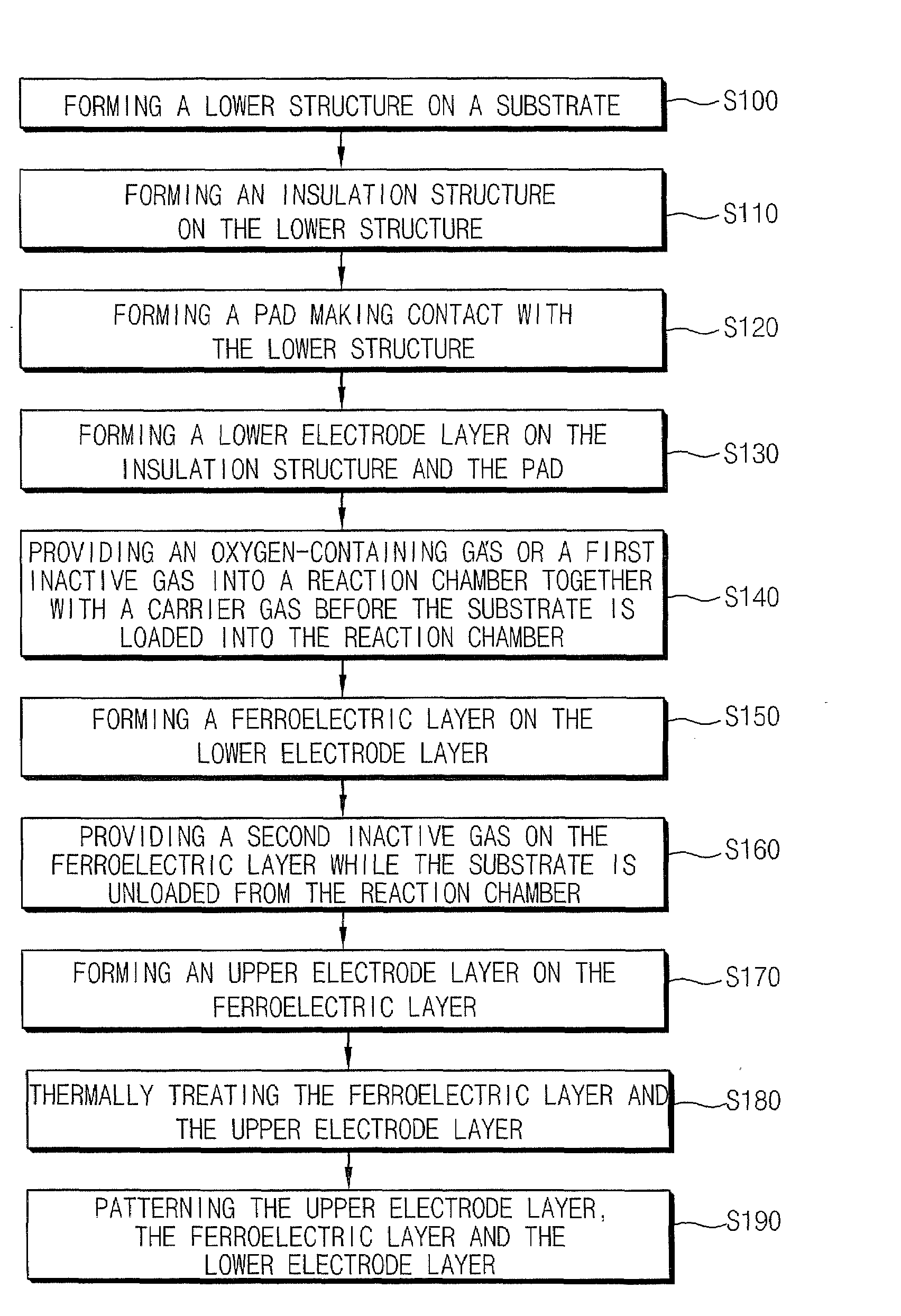

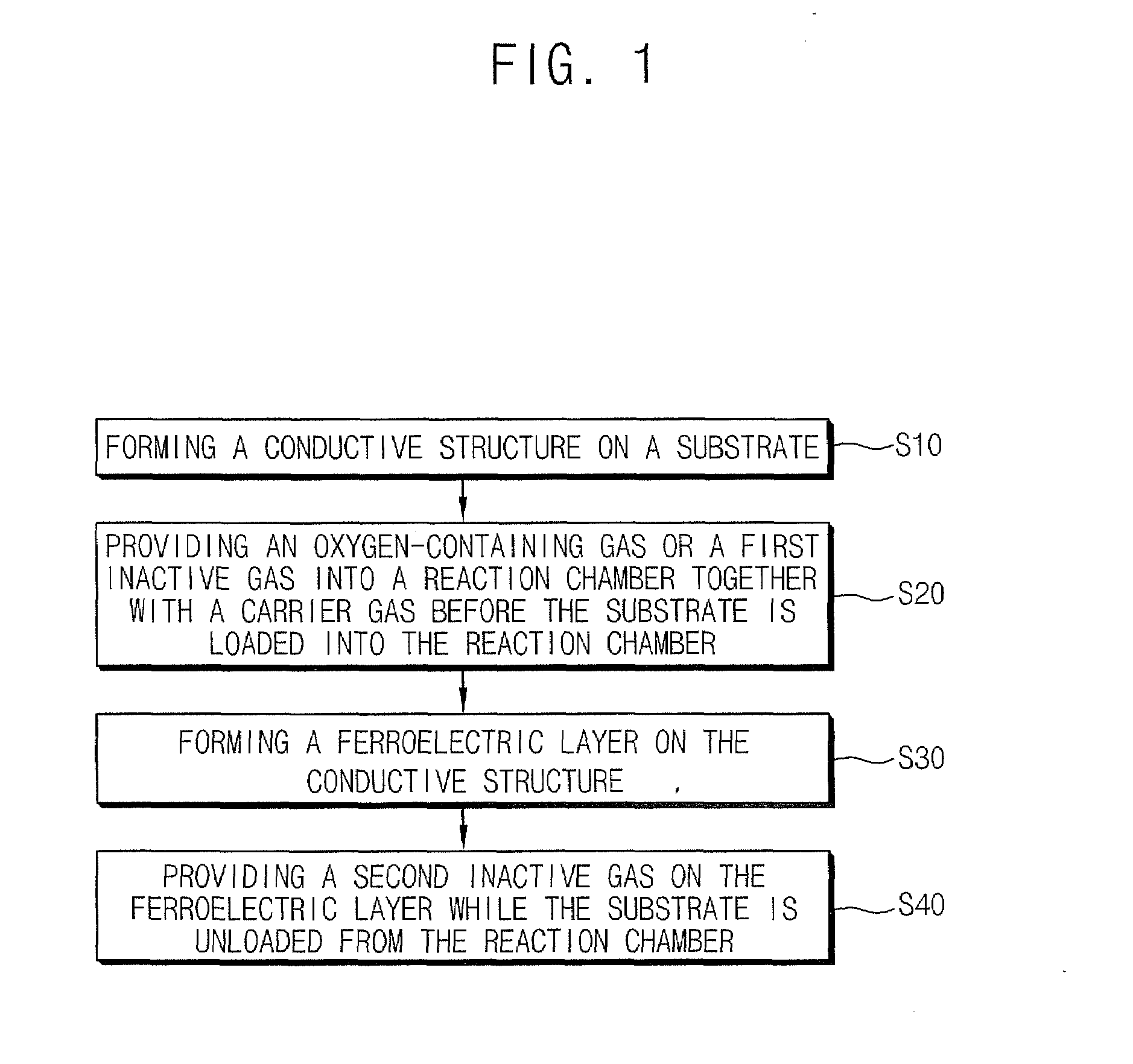

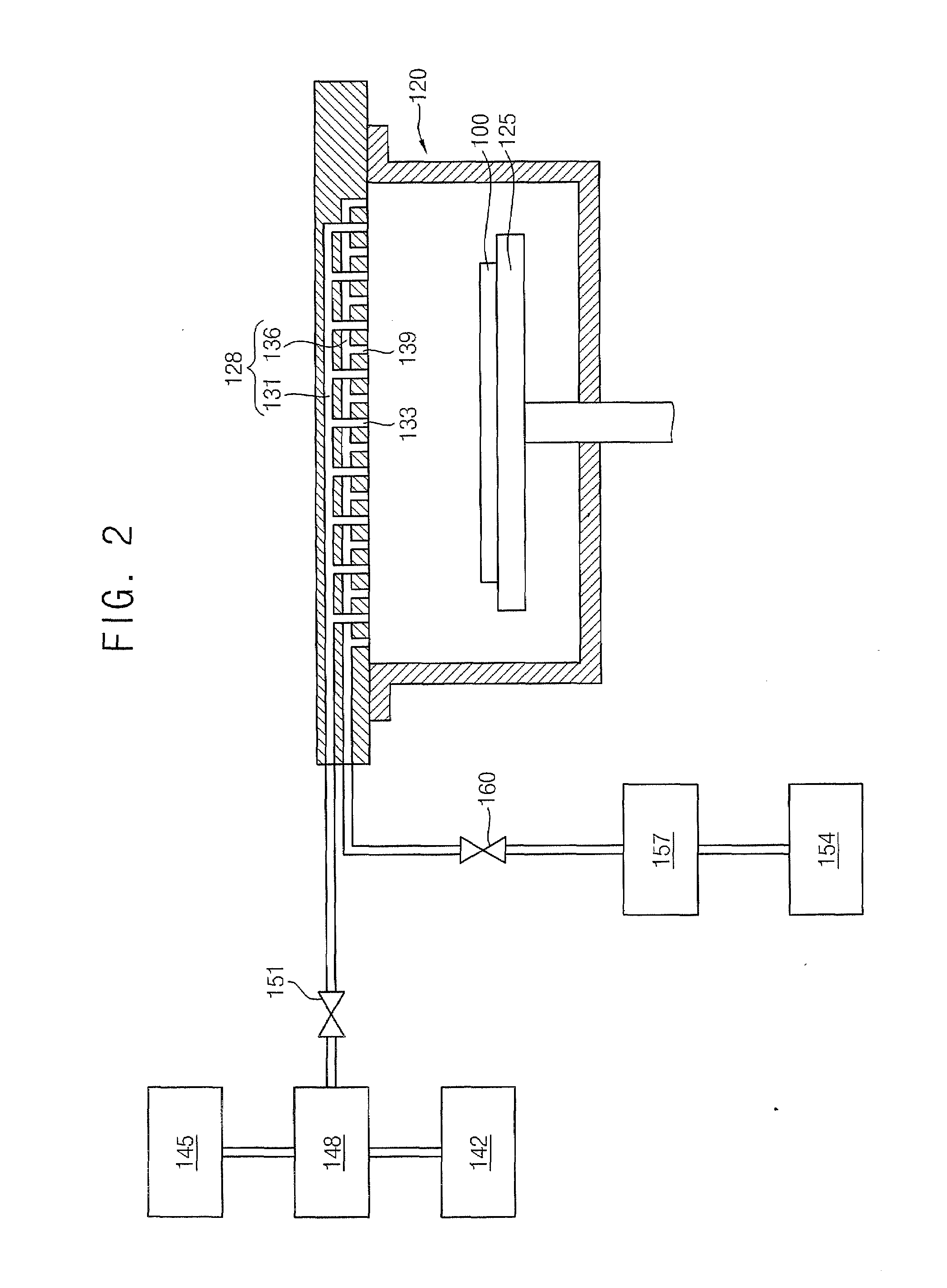

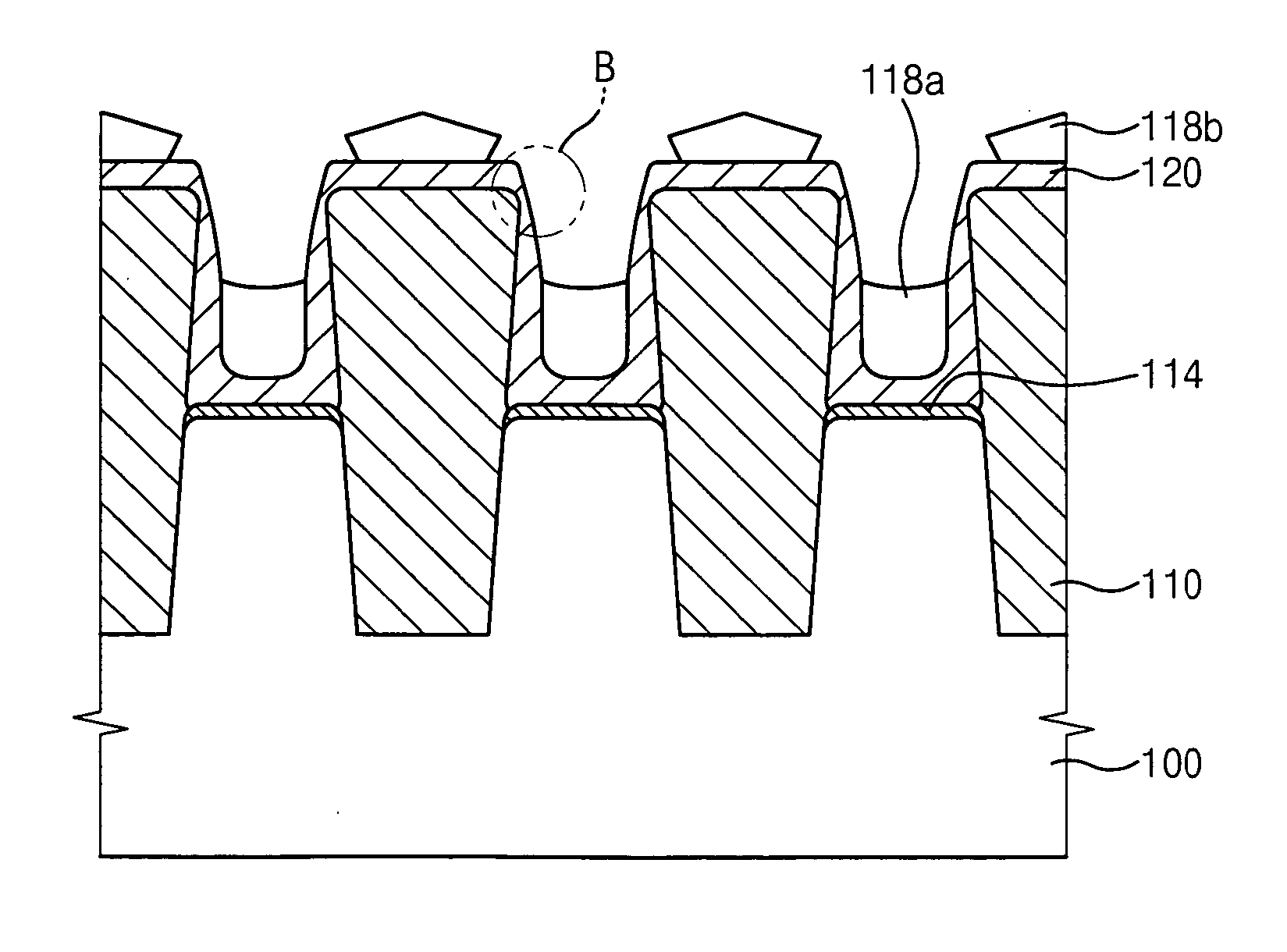

Methods of fabricating ferroelectric devices

ActiveUS20080020489A1Improved ferroelectricImprove electrical characteristicsSolid-state devicesSemiconductor/solid-state device manufacturingOptoelectronicsImpurity

A method of fabricating a ferroelectric device includes forming a ferroelectric layer on a substrate in a reaction chamber. An inactive gas is provided into the reaction chamber while unloading the substrate therefrom to thereby substantially inhibit formation of an impurity layer on the ferroelectric layer.

Owner:SAMSUNG ELECTRONICS CO LTD

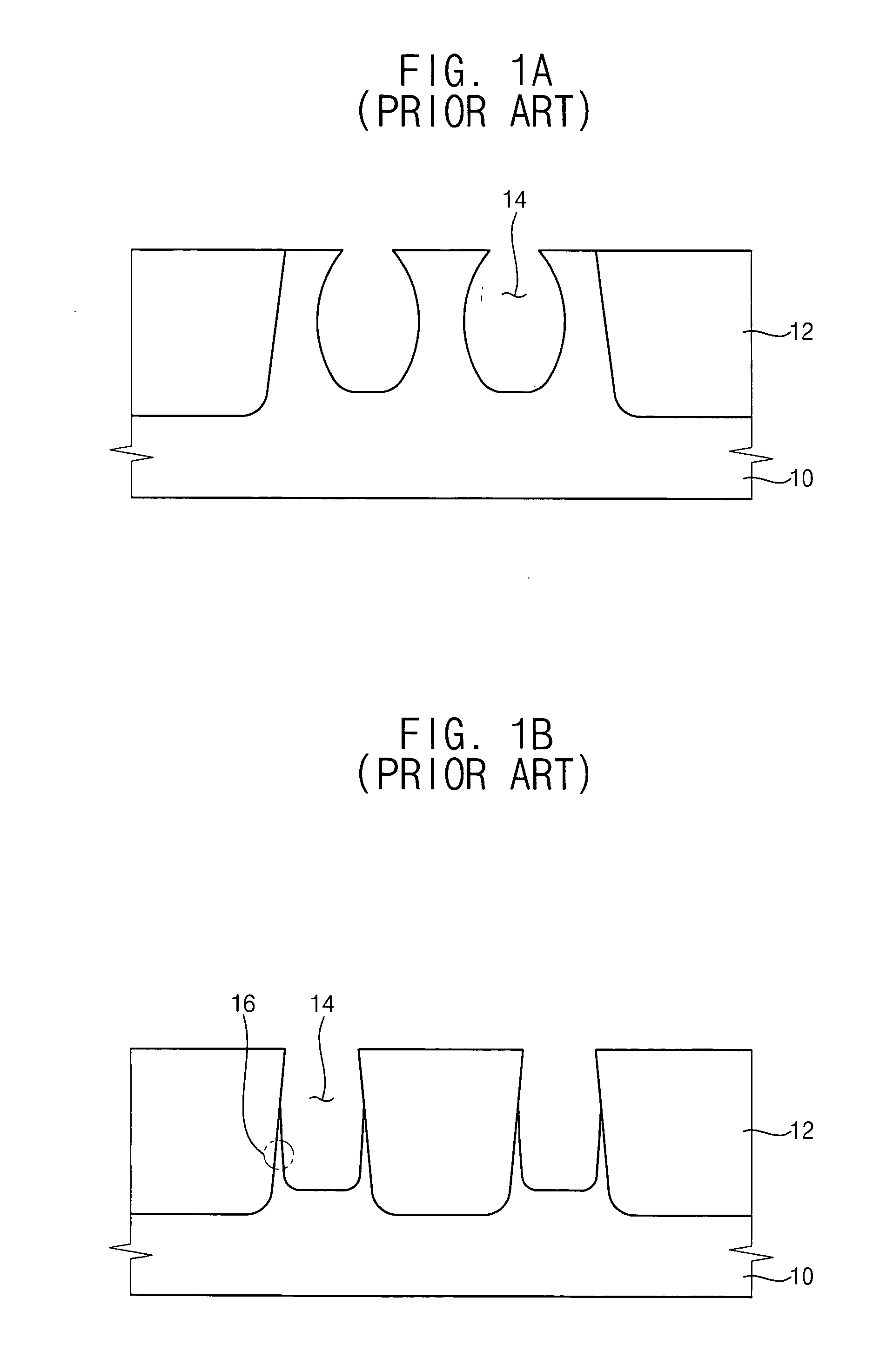

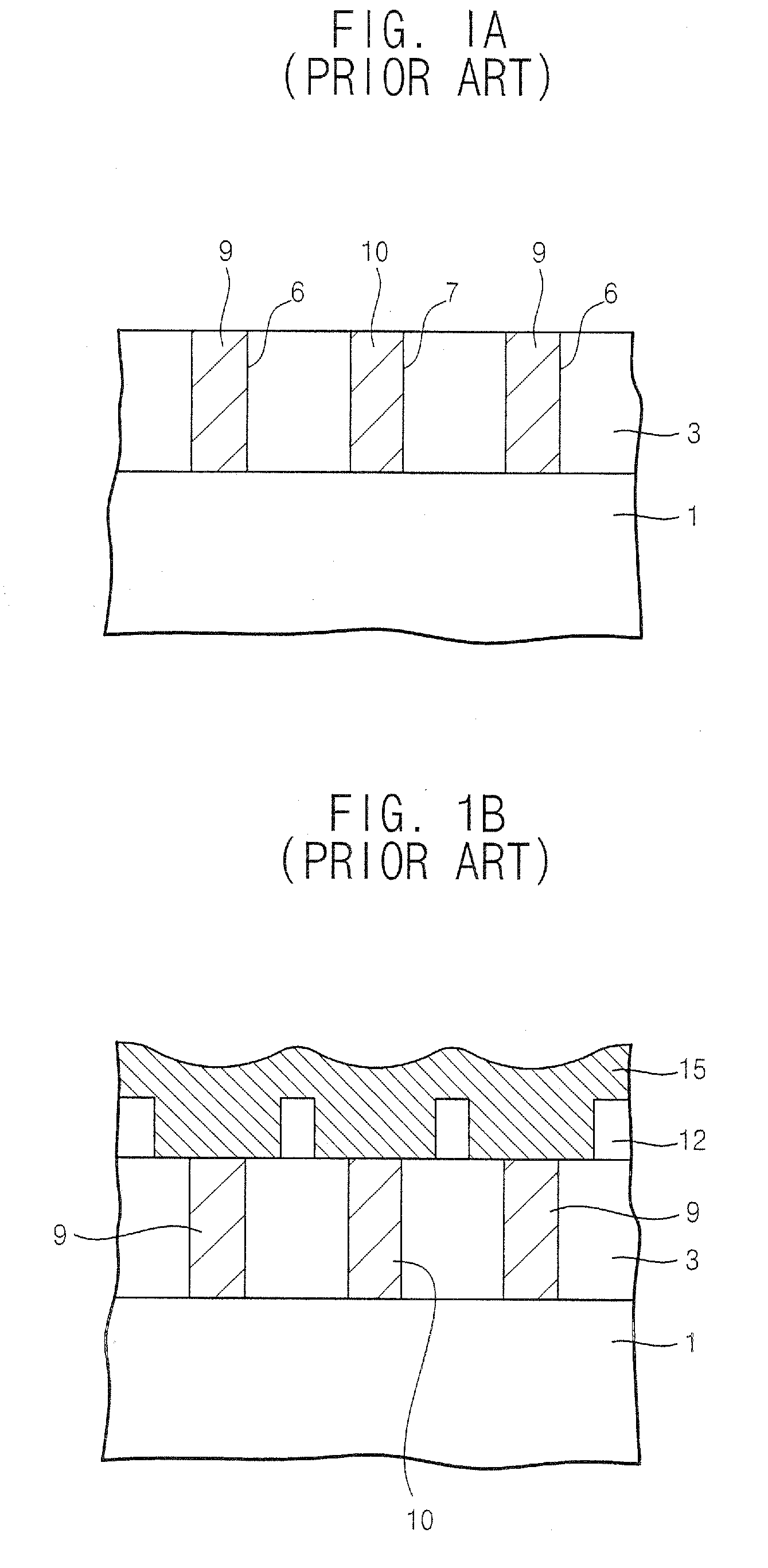

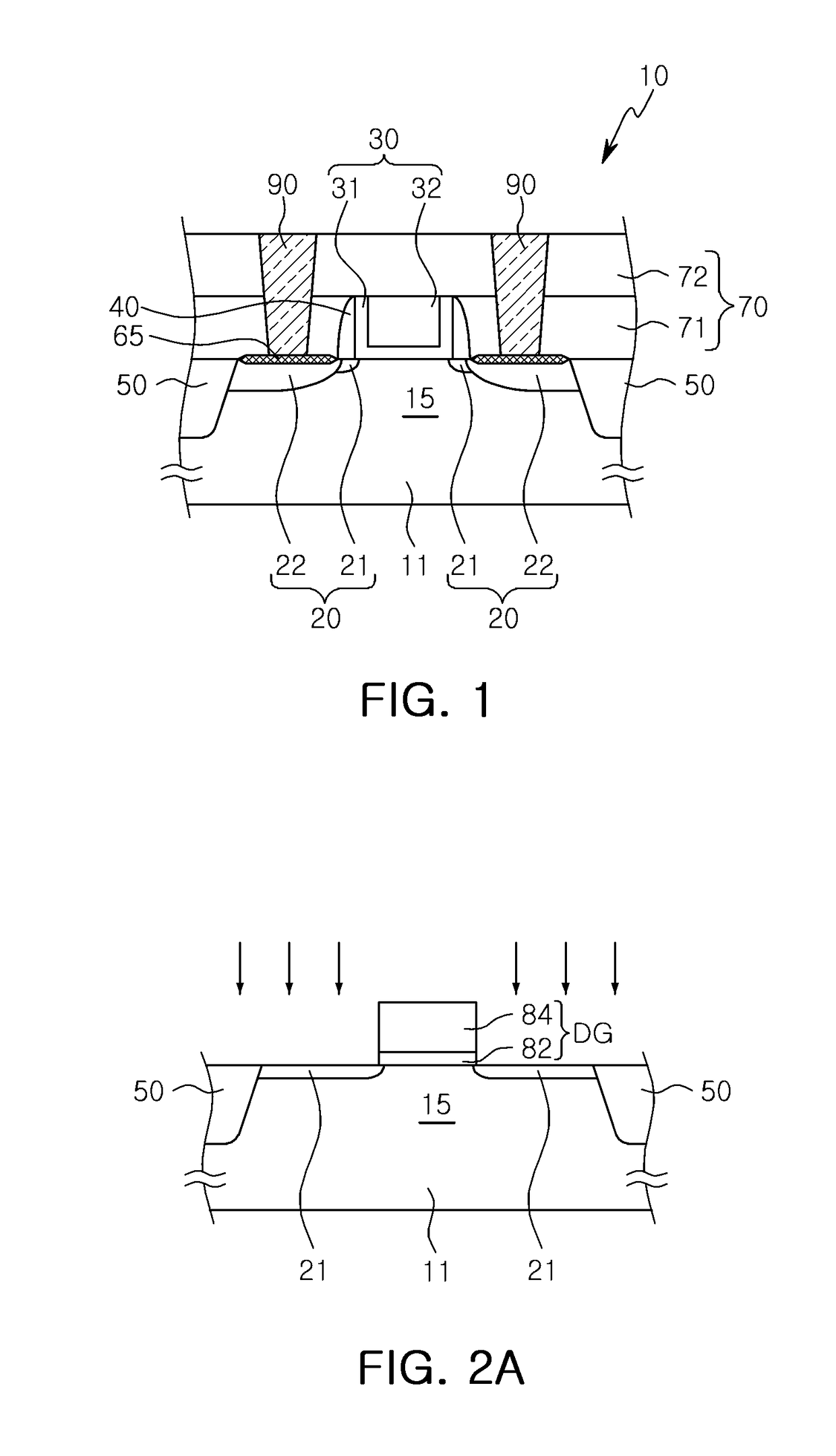

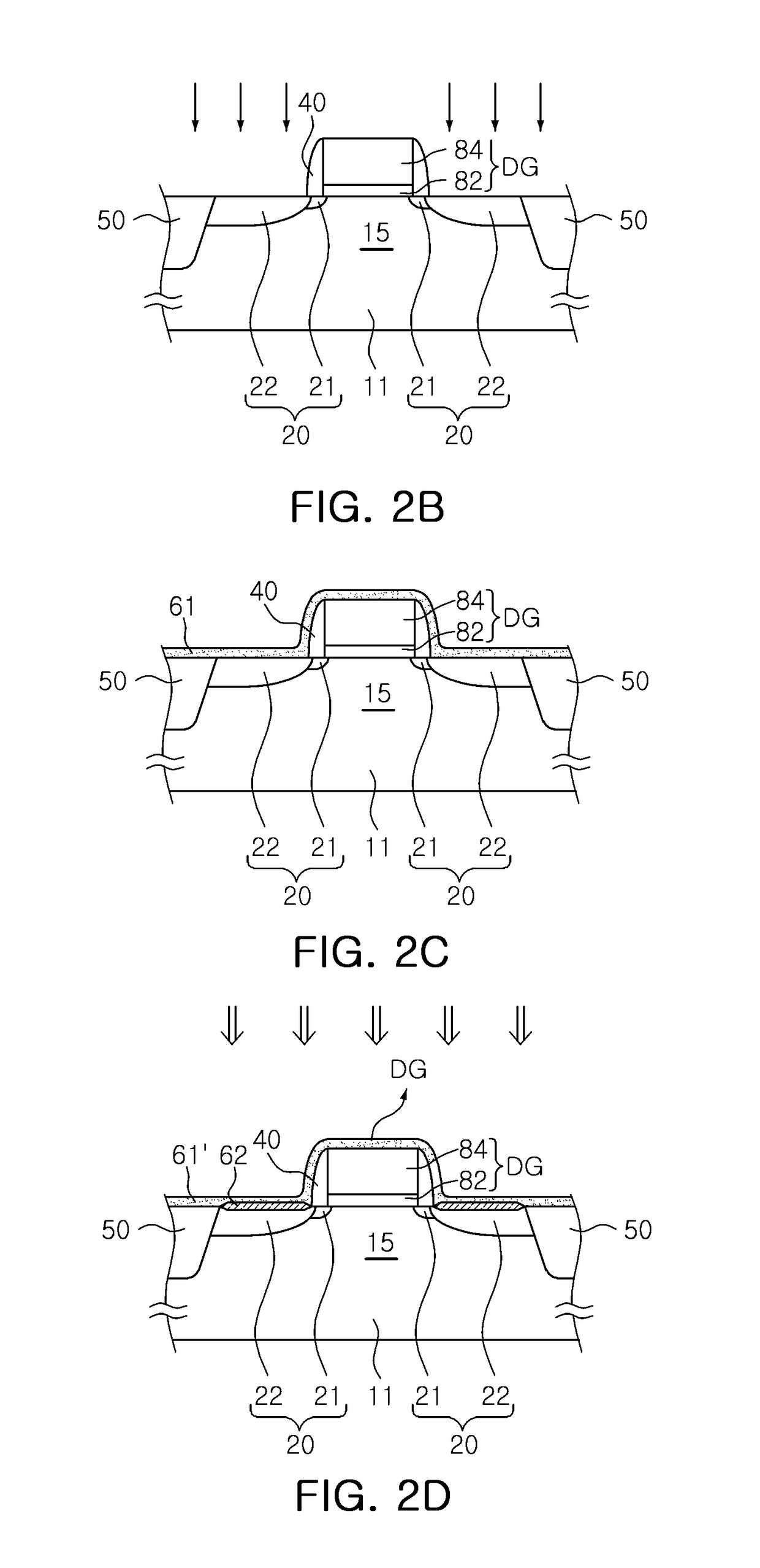

Method of manufacturing a semiconductor device

InactiveUS20050287763A1Improve electrical characteristicsImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering

In a method of manufacturing a semiconductor device, an isolation pattern is formed on a substrate. The isolation pattern includes an opening that exposes a portion of the substrate. A preliminary polysilicon layer is formed on the substrate and the isolation pattern to partially fill up the opening. A sacrificial layer is formed on the preliminary polysilicon layer. The sacrificial layer is partially etched to expose a portion of the preliminary polysilicon layer formed on a shoulder portion of the isolation pattern. A first polysilicon layer is formed by etching the exposed portion of the preliminary polysilicon layer to enlarge an upper width of the opening. After the etched sacrificial layer is removed, a second polysilicon layer is formed on the first polysilicon layer to fill up the enlarged opening. Because the upper width of the opening is larger than the lower width, no seam or void would be generated in the second polysilicon layer, therefore improving the electrical characteristics and reliability of the device.

Owner:SAMSUNG ELECTRONICS CO LTD

Grounding structure of an electrical connector

InactiveUS20050176300A1Improve electrical characteristicsEasy to connect partsCoupling protective earth/shielding arrangementsConnection contact member materialElectricityEngineering

The present invention relates to a grounding structure of an electrical connector suitable for high frequency transmitting. The high frequency connector mainly has a connecting part being combined with a plurality of grounding lines to improve the electrical characteristics of the high frequency connector when it transmits a signal. Wherein, the connecting part further comprises a wing portion and a protrusion portion; thereby the connecting part can engage the grounding terminals with the grounding line of the cable to form electrical contact. Furthermore, one end of the connecting part is extended directly and comprises predetermined grounding terminals, such that the grounding line can be directly connected to connecting part; such as, the electrical connector can have better electrical characteristics and the grounding line can directly be coupled to the grounding terminals without the soldering process by using aforesaid structure, meanwhile, the entire assembly process and the relative cost can be lessened.

Owner:ING SHANG LUN

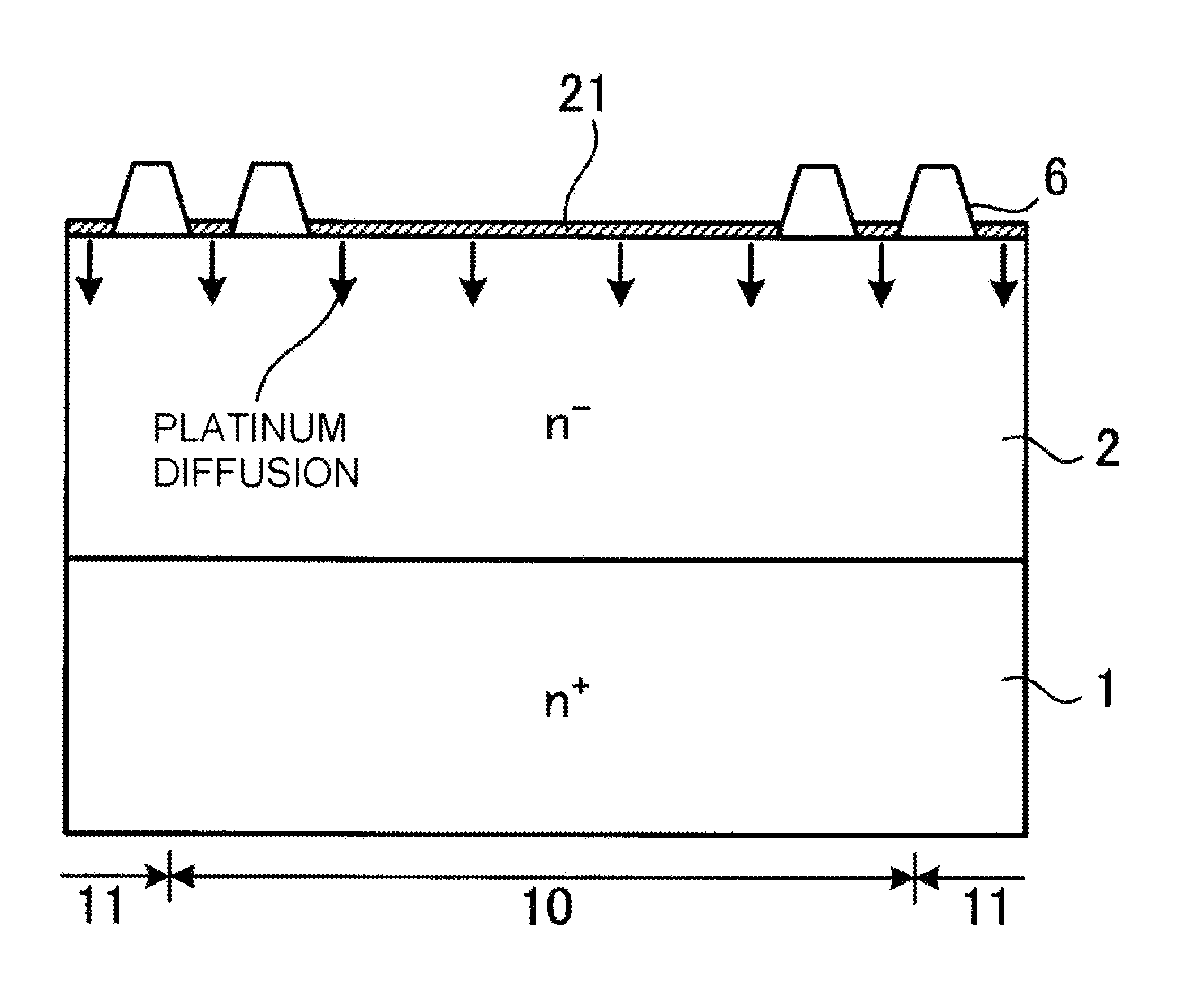

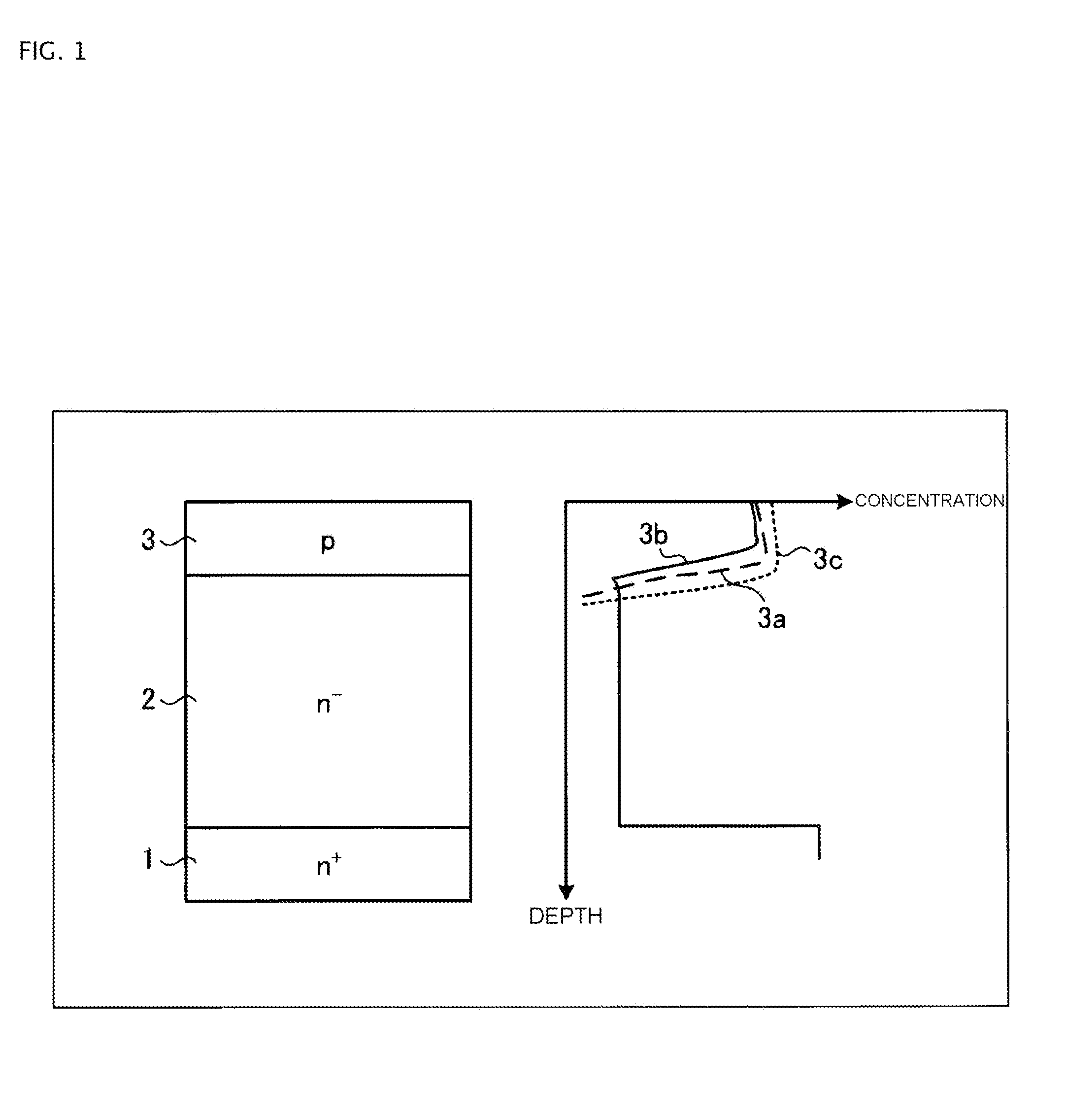

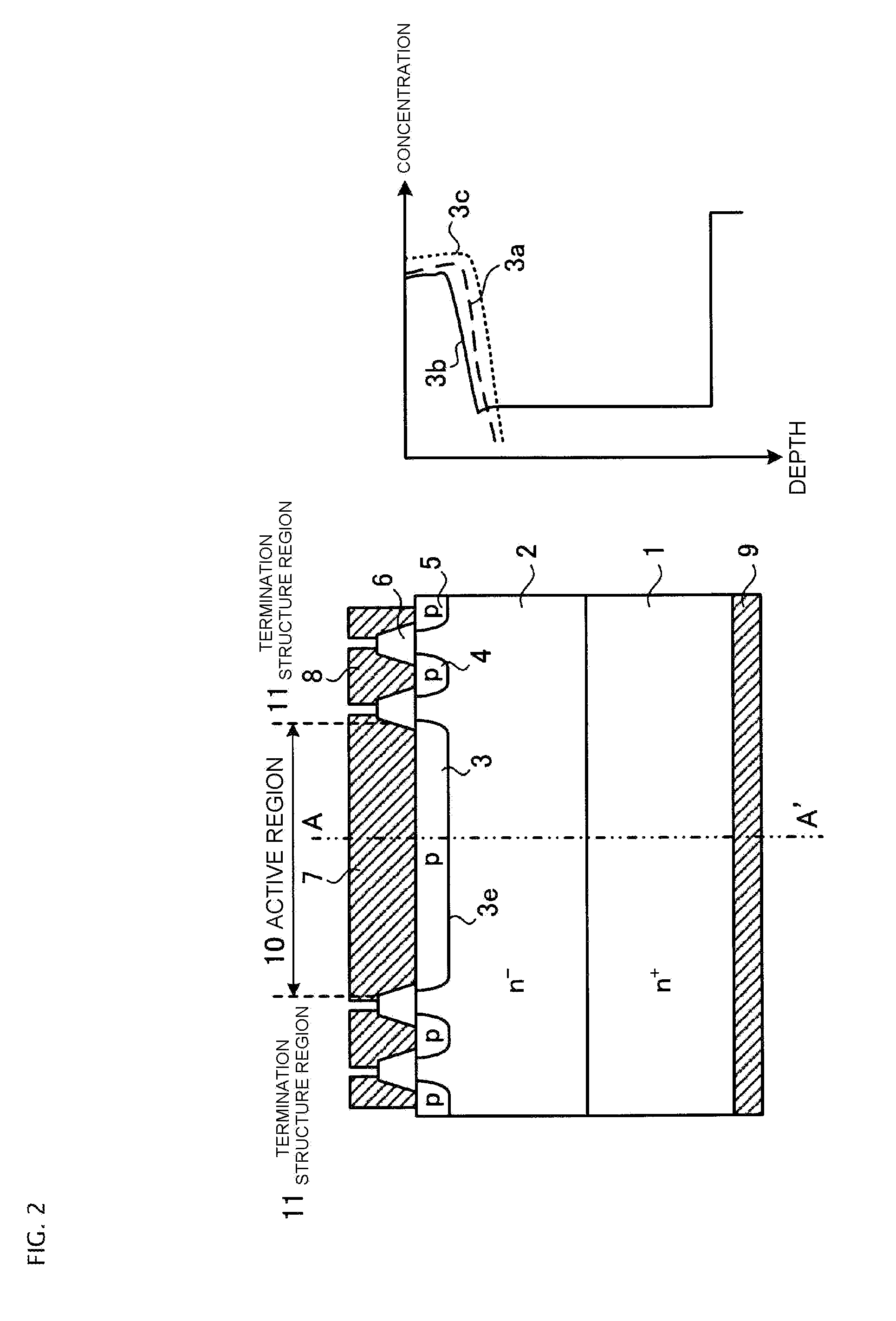

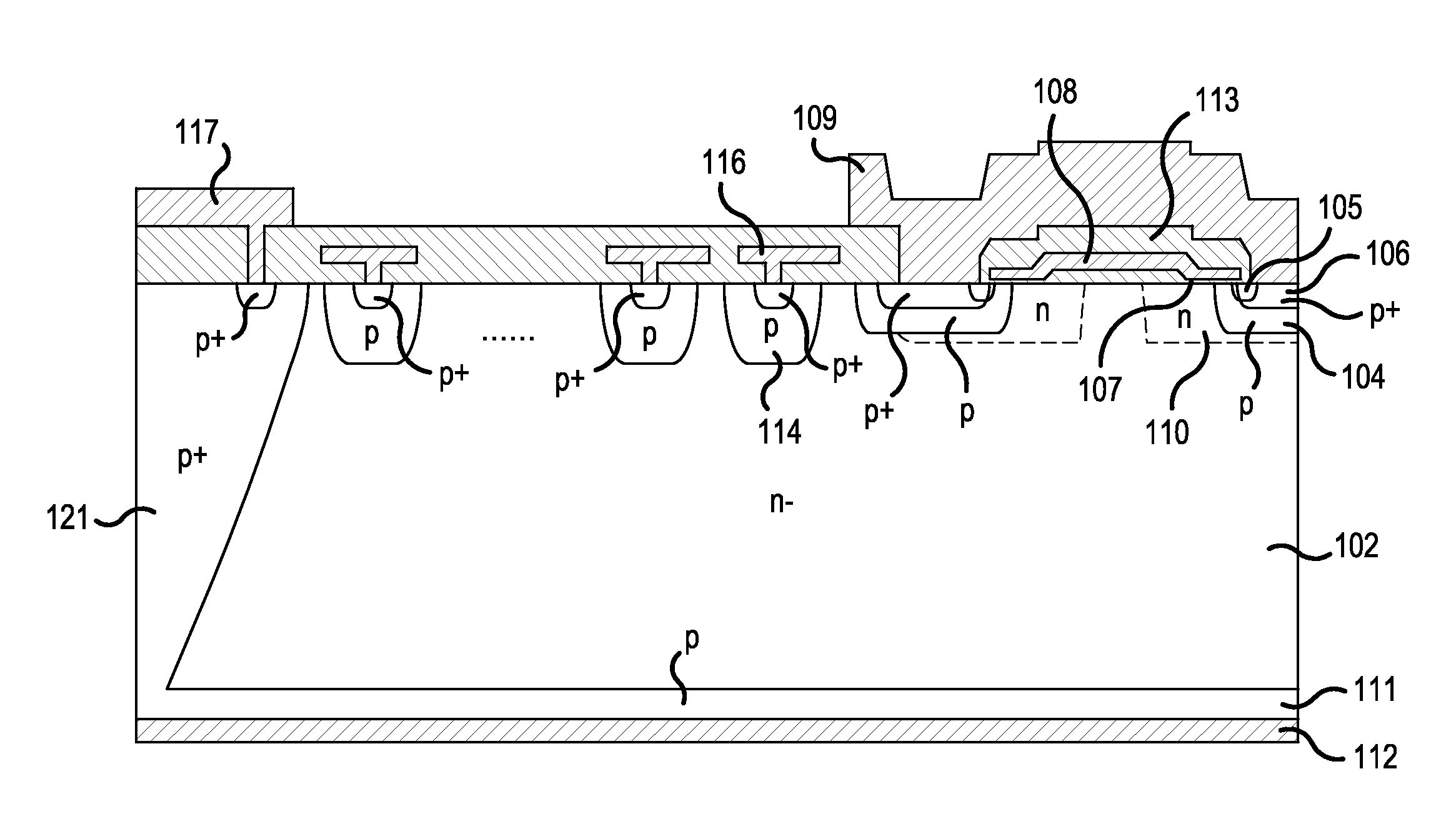

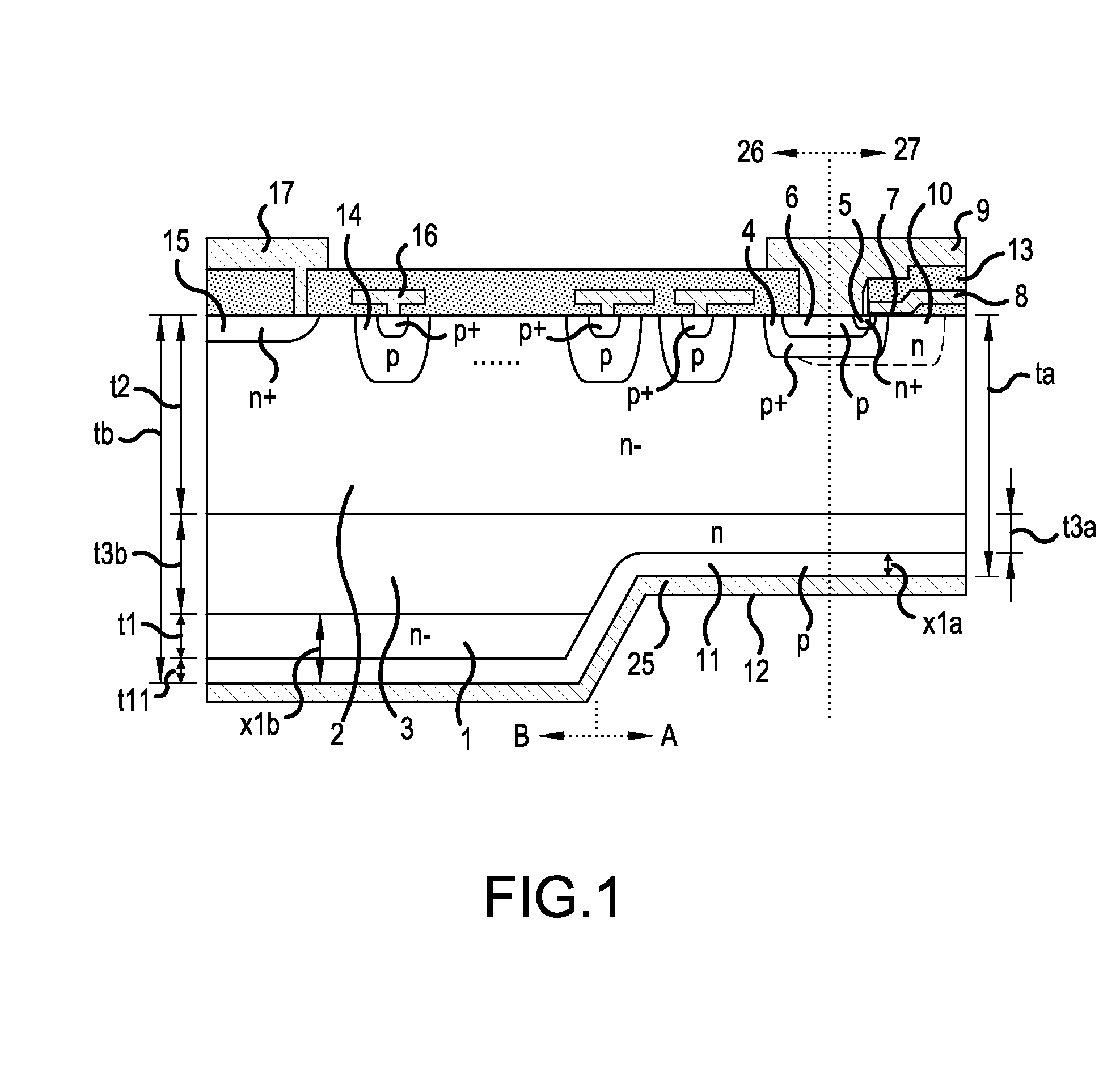

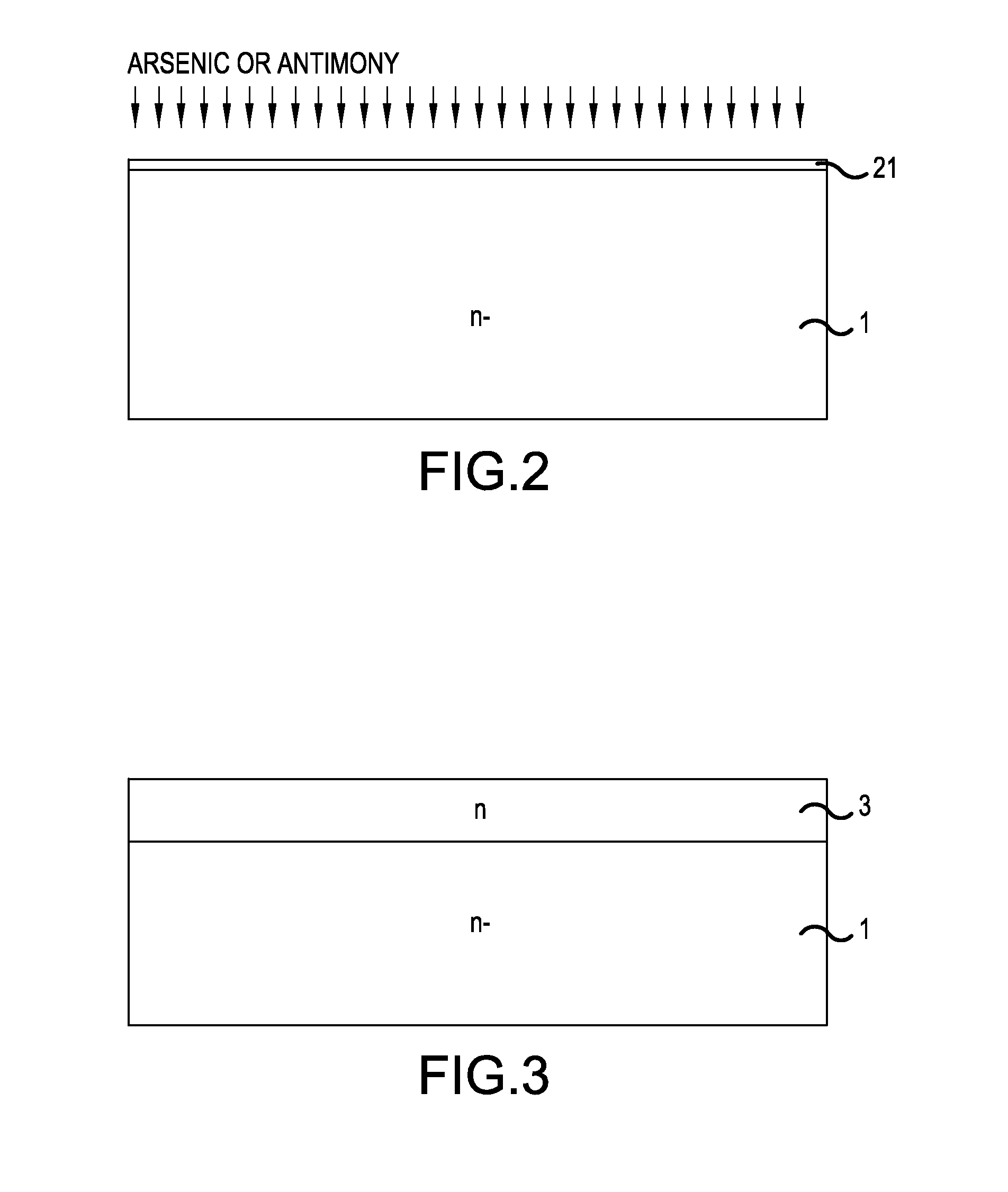

Semiconductor device and semiconductor device manufacturing method

ActiveUS20140070369A1Improve controllabilityControl depthSemiconductor/solid-state device manufacturingDiodeAcceptorDevice material

A simplified manufacturing process stably produces a semiconductor device with high electrical characteristics, wherein platinum acts as an acceptor. Plasma treatment damages the surface of an oxide film formed on a n− type drift layer deposited on an n+ type semiconductor substrate. The oxide film is patterned to have tapered ends. Two proton irradiations are carried out on the n− type drift layer with the oxide film as a mask to form a point defect region in the vicinity of the surface of the n− type drift layer. Silica paste containing 1% by weight platinum is applied to an exposed region of the n− type drift layer surface not covered with the oxide film. Heat treatment inverts the vicinity of the surface of the n− type drift layer to p-type by platinum atoms which are acceptors. A p-type inversion enhancement region forms a p-type anode region.

Owner:FUJI ELECTRIC CO LTD

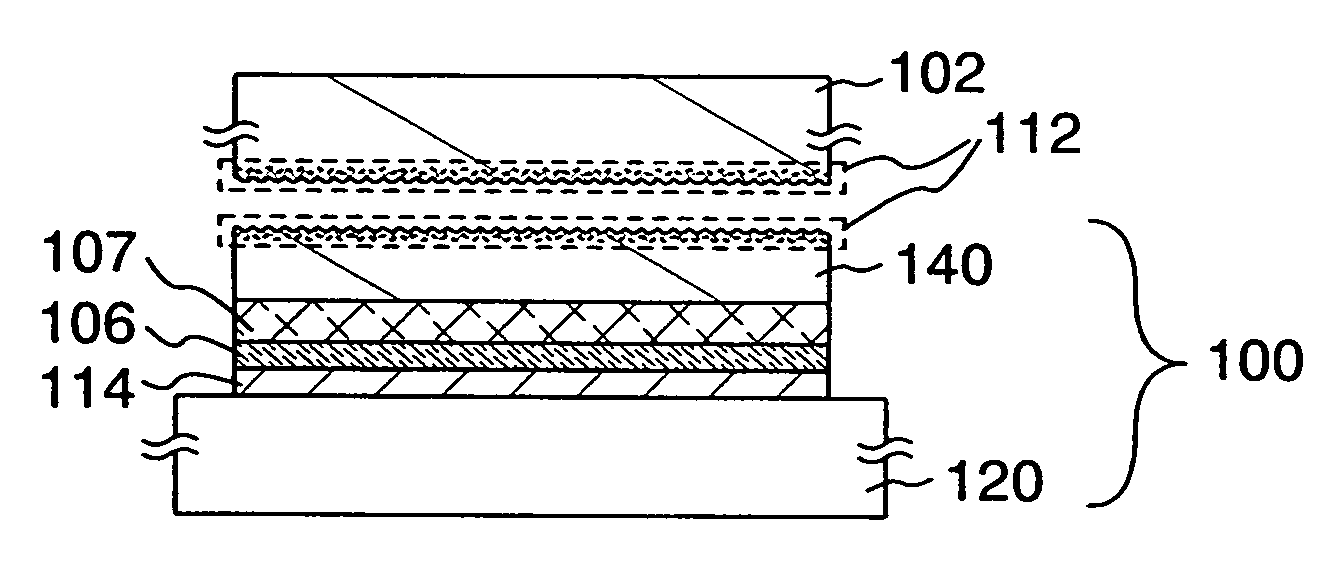

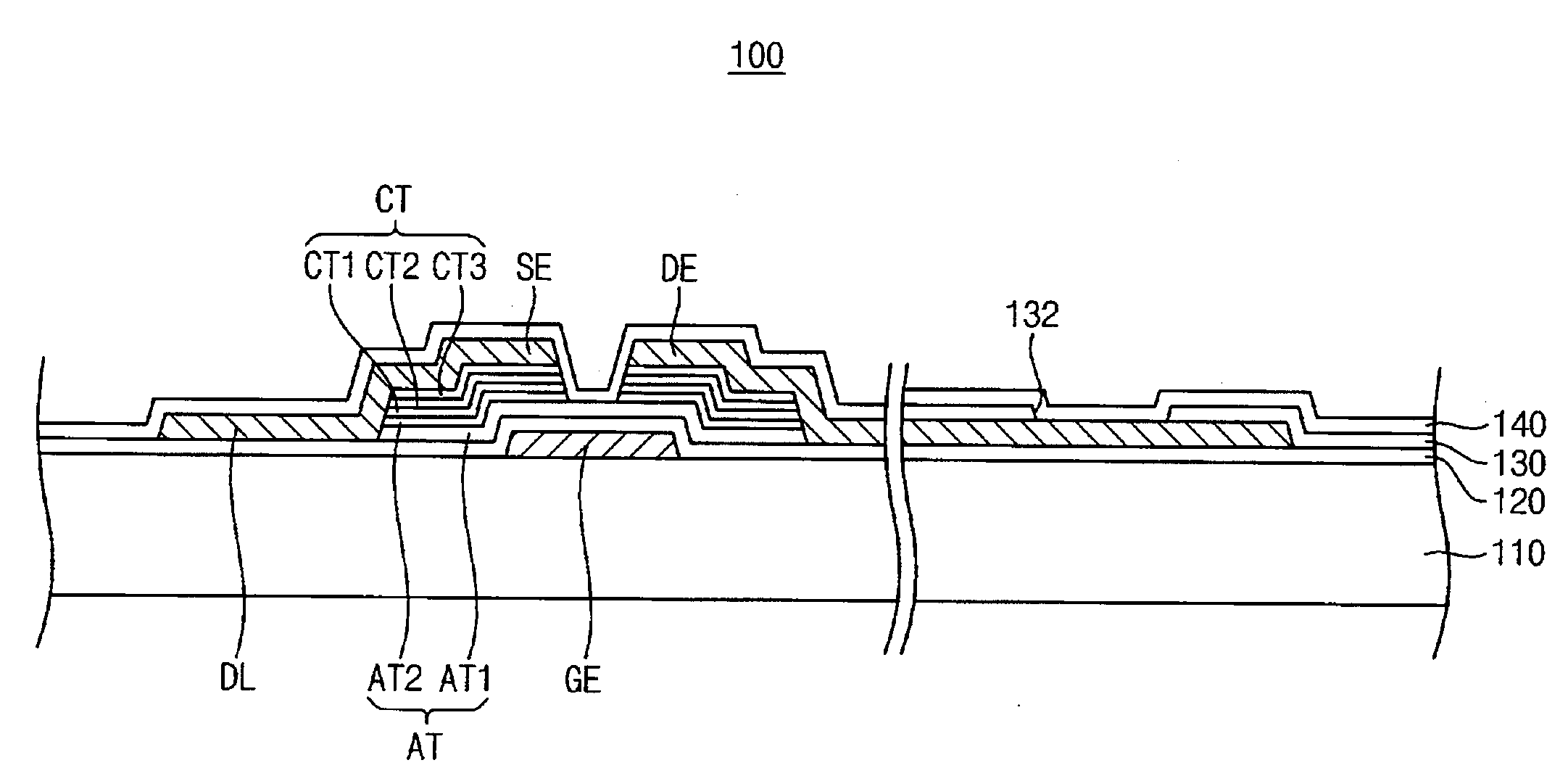

Thin-film transistor, method of manufacturing the same, liquid crystal display panel having the same and electro-luminescence display panel having the same

InactiveUS20100062574A1Improve electrical characteristicsPrevent oxidationSolid-state devicesSemiconductor/solid-state device manufacturingLiquid-crystal displayEngineering

A TFT includes a gate electrode, an active layer, a source electrode, a drain electrode, and a buffer layer. The gate electrode is formed on the substrate; the active layer is formed on the gate electrode. The source and drain electrodes, formed on the active layer, are separated by a predetermined distance. The buffer layer is formed between the active layer and the source and drain electrodes. The buffer layer has a substantially continuously varying content ratio corresponding to a buffer layer thickness. The buffer layer is formed to suppress oxidation of the active layer, and reduce contact resistance.

Owner:SAMSUNG DISPLAY CO LTD

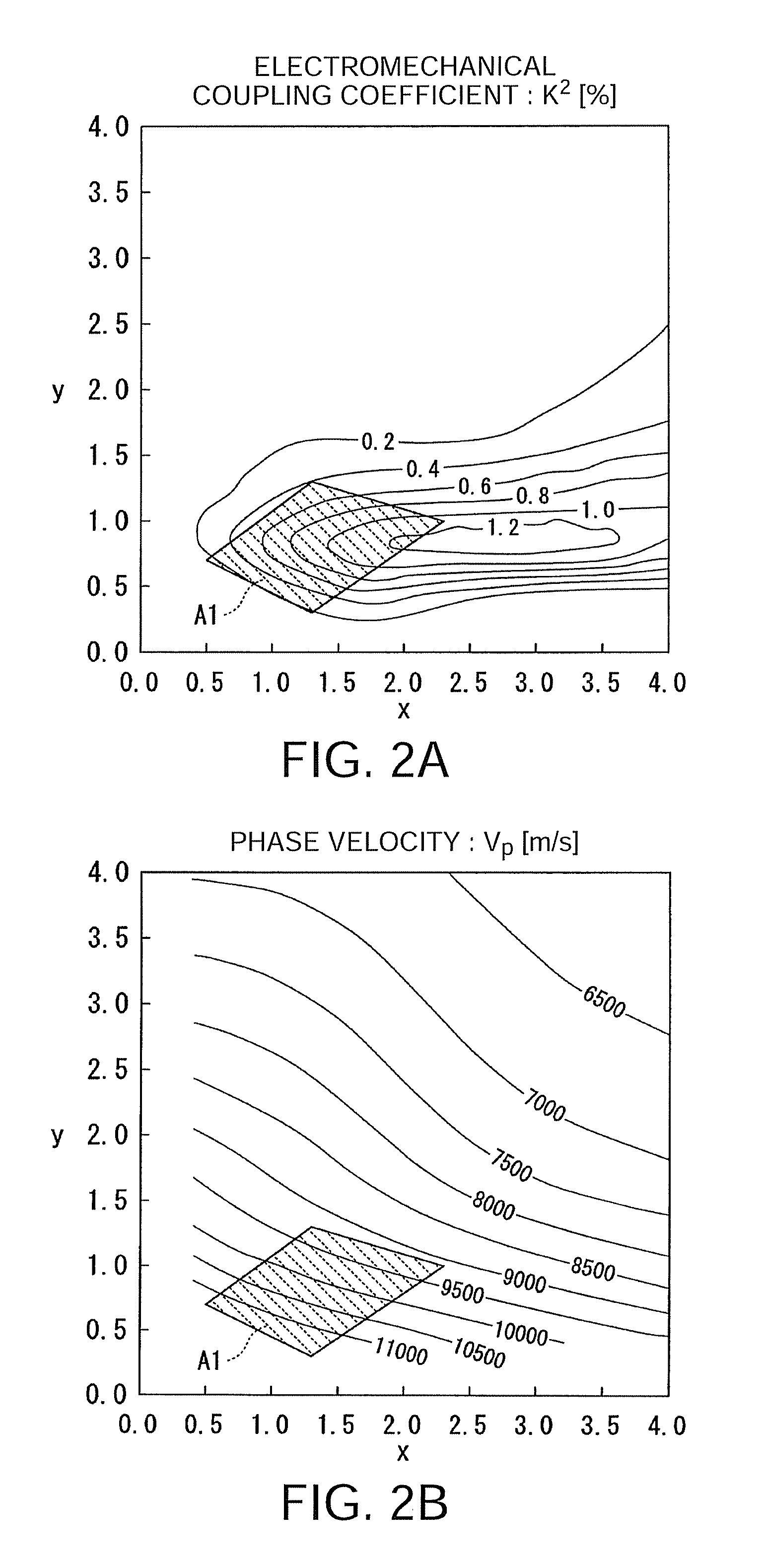

Surface acoustic wave element

ActiveUS20100038993A1Increase working frequencyGood weather resistancePiezoelectric/electrostriction/magnetostriction machinesImpedence networksSilicon oxideSurface acoustic wave

A surface acoustic wave element includes: a diamond layer; an alumina nitride layer provided on the diamond layer; a silicon oxide layer provided on the alumina nitride layer; and a pair of electrodes provided between the alumina nitride layer and the silicon oxide layer, the electrodes applying a voltage to the alumina nitride layer. If a thickness of the alumina nitride layer is represented by H1, a thickness of the silicon oxide layer is represented by H2, a wavelength of a surface acoustic wave is represented by λ, x is defined as x=2πH1 / λ, and y is defined as y=2πH2 / λ, (x, y) meets all of the following formulas 1 to 4 below. That is, the formula 1 is y≦0.750×x+0.325; the formula 2 is y≦−0.300×x+1.690; the formula 3 is y≧−0.500×x+0.950; and the formula 4 is y≧0.700×x−0.610.

Owner:SEIKO EPSON CORP

Electrophoretic display device and method for manufacturing thereof

InactiveCN101393370AImprove electrical characteristicsImprove reliabilitySolid-state devicesNon-linear opticsElectrophoresisDisplay device

It is an object to provide an electrophoretic display device having a thin film transistor which has highly reliable electric characteristics, lightweight, and flexibility. A gate insulating film is formed over a gate electrode, a microcrystalline semiconductor film which functions as a channel formation region is formed over the gate insulating film, a buffer layer is formed over the microcrystalline semiconductor film, a pair of source and drain regions are formed over the buffer layer, a pair of the source and drain electrodes in contact with the source and drain regions are formed. Then, the inverted-staggered thin film transistor is interposed between the flexible substrates, and the thin film transistor is provided with electrophoretic display element which is electrically connectedby the pixel electrode. Then, the electrophoretic display electrode is surrounded by the partition layer so as to cover the end portion of the pixel electrode and provided over the pixel electrode.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and semiconductor device manufacturing method

InactiveUS20150060938A1Easy maintenanceReduce the amount requiredTransistorSemiconductor/solid-state device manufacturingEngineeringSemiconductor

An n− type drift region, an n-type field stop region, and an n− type FZ wafer are provided in an n− type wafer. An edge termination structure portion is provided in a chip outer peripheral portion of regions of the n− type wafer, surrounding an active region inside a chip inner portion. A thickness of the chip inner portion is less than a thickness of the chip outer peripheral portion owing to a groove. A p-type collector region is in contact with the n− type FZ wafer and n-type field stop region. A collector electrode is in contact with the p-type collector region. A second distance between the collector electrode and the n-type field stop region in the edge termination structure portion is greater than a first distance between the collector electrode and the n-type field stop region in the active region.

Owner:FUJI ELECTRIC CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com