Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

184results about How to "Improve programmability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

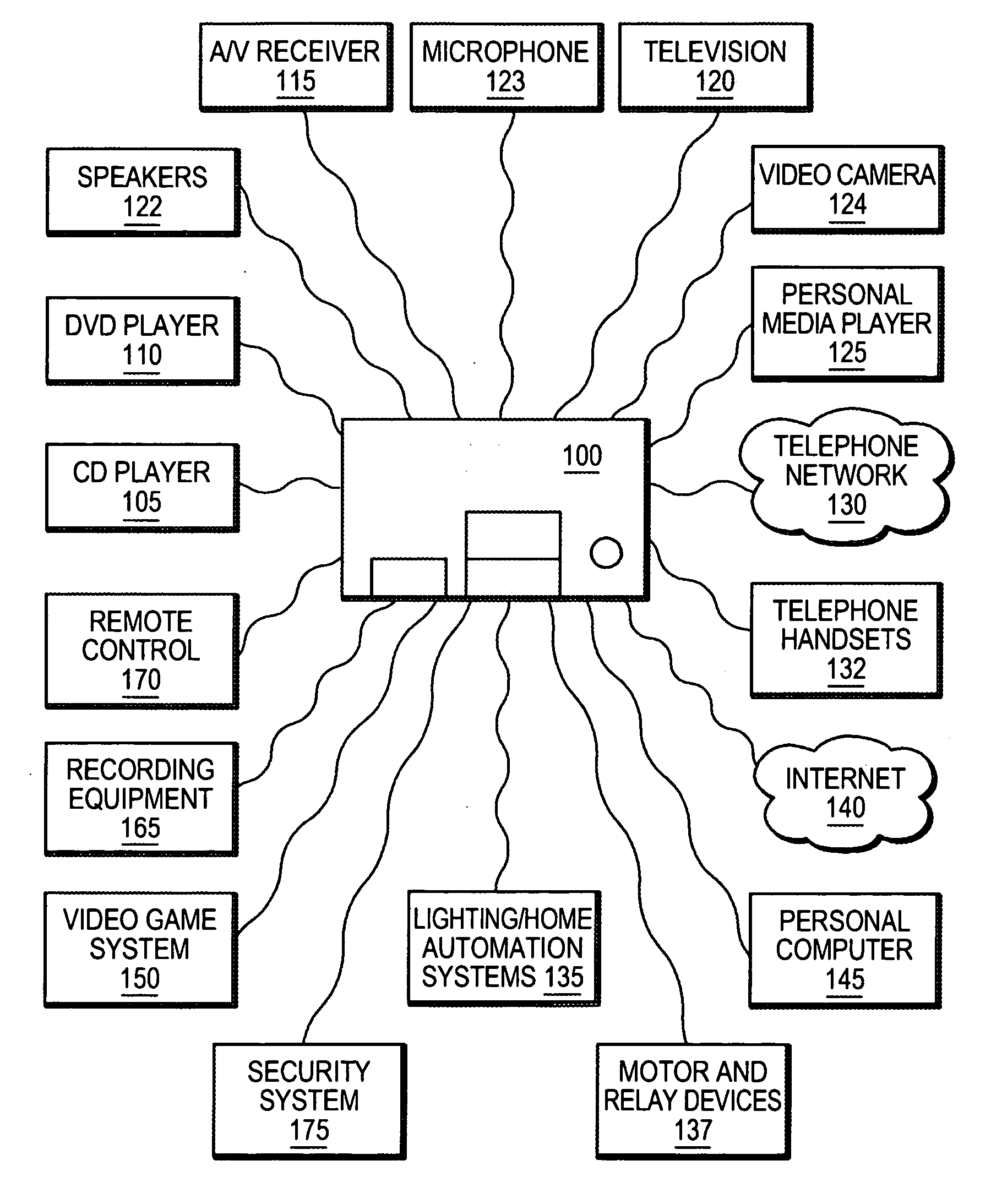

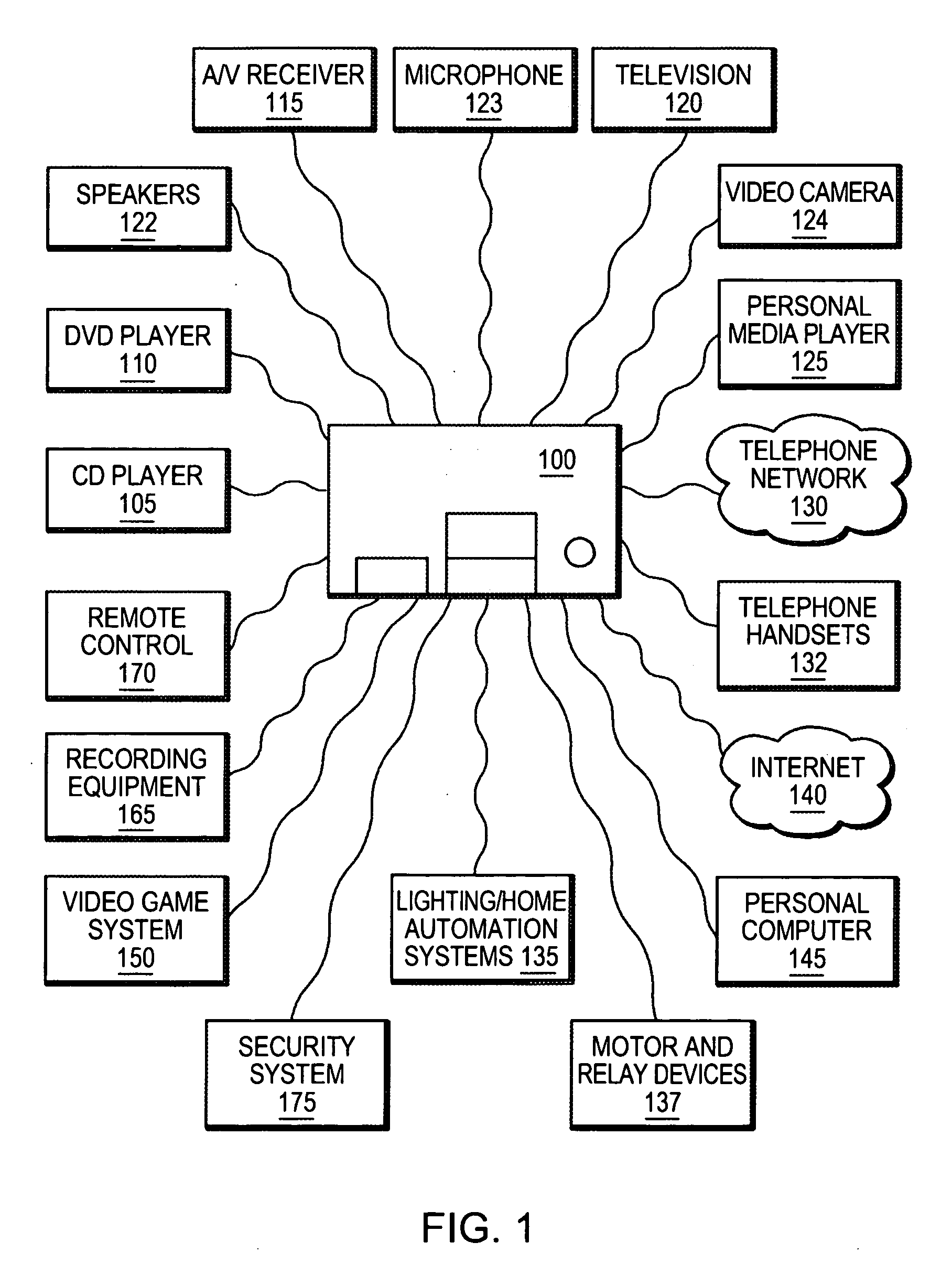

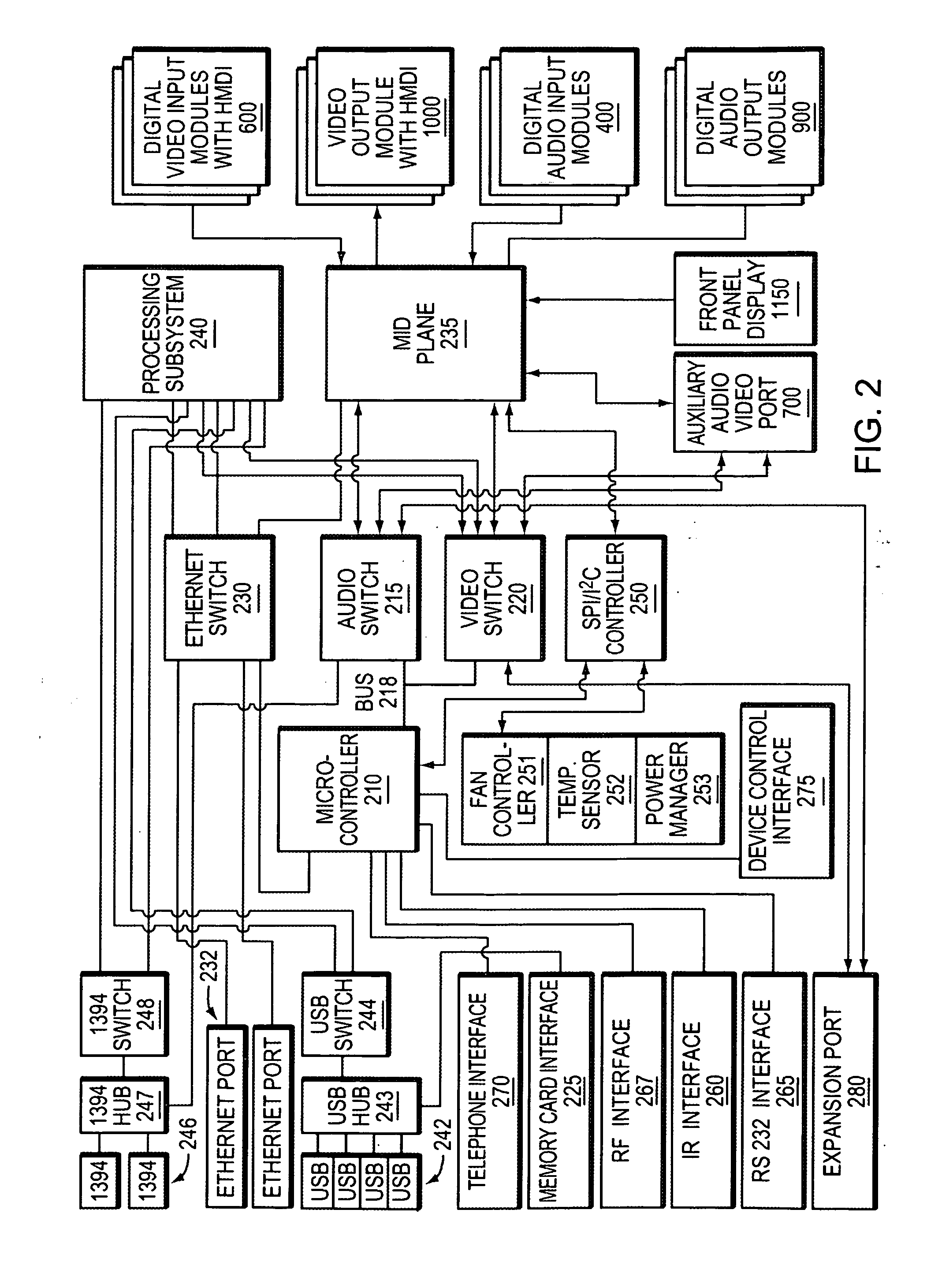

Programmable multimedia controller with programmable services

ActiveUS20070142022A1Easy to useEfficient modificationLink editingTransmission systemsControl systemProgrammable logic device

An integrated multimedia, entertainment, communications and control system. The system is based on a general purpose computer and is capable of interfacing with, controlling or managing a wide variety of audio, video, telecommunications, data communications or other devices. The system includes a programming environment for creating services or user experiences that may incorporate features or functionalities of several devices that are conventionally operated as separate, standalone devices.

Owner:SAVANT SYST INC

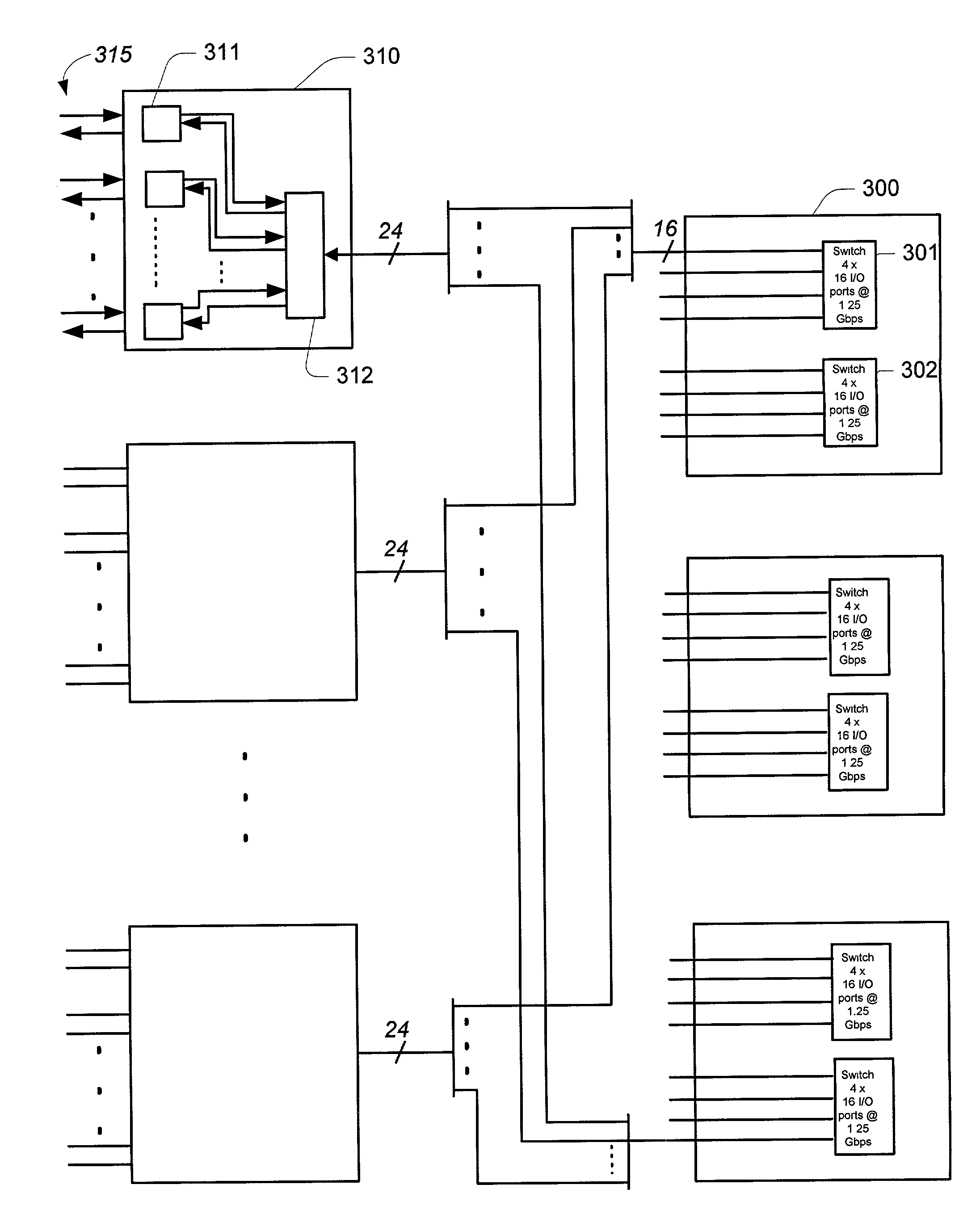

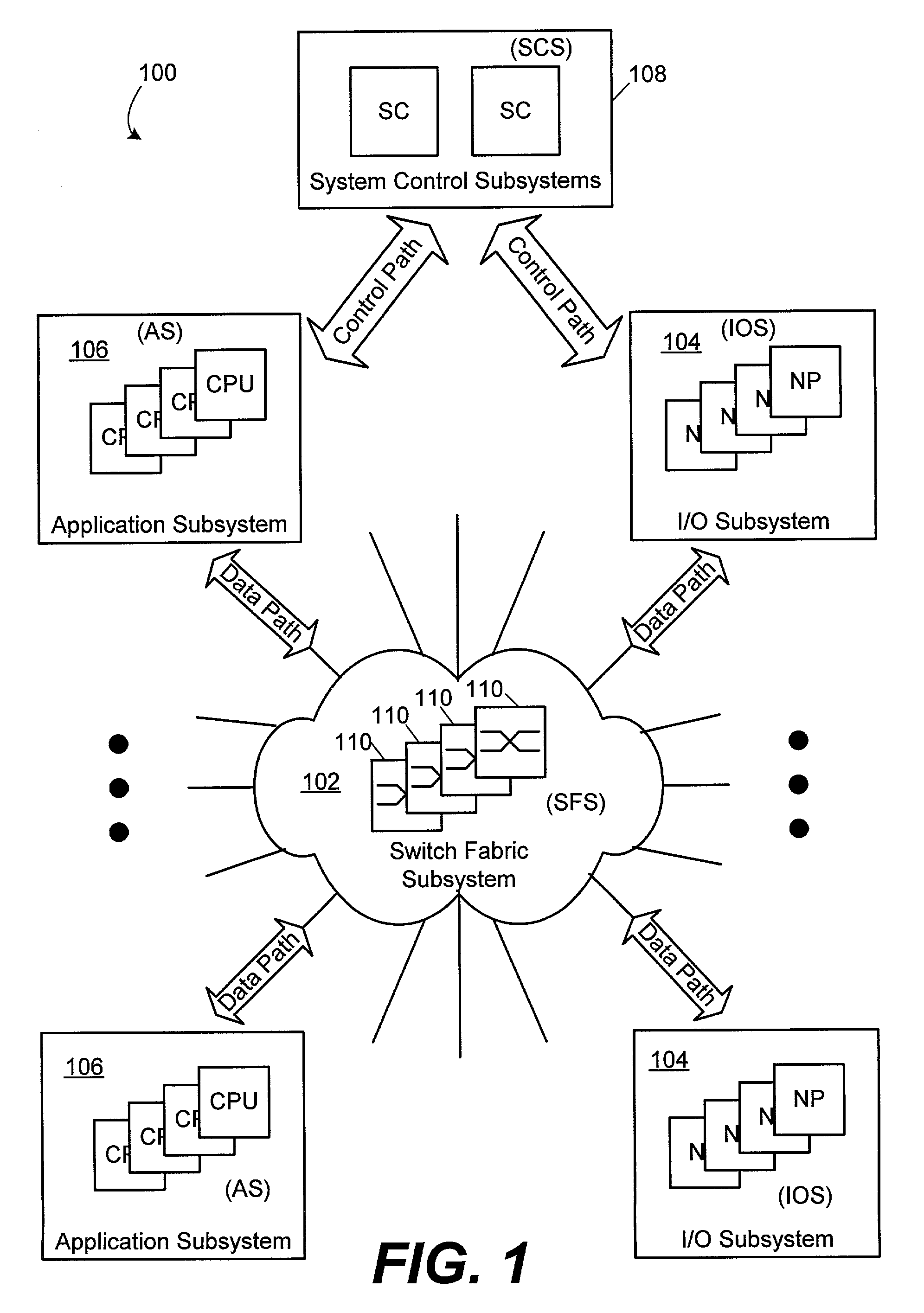

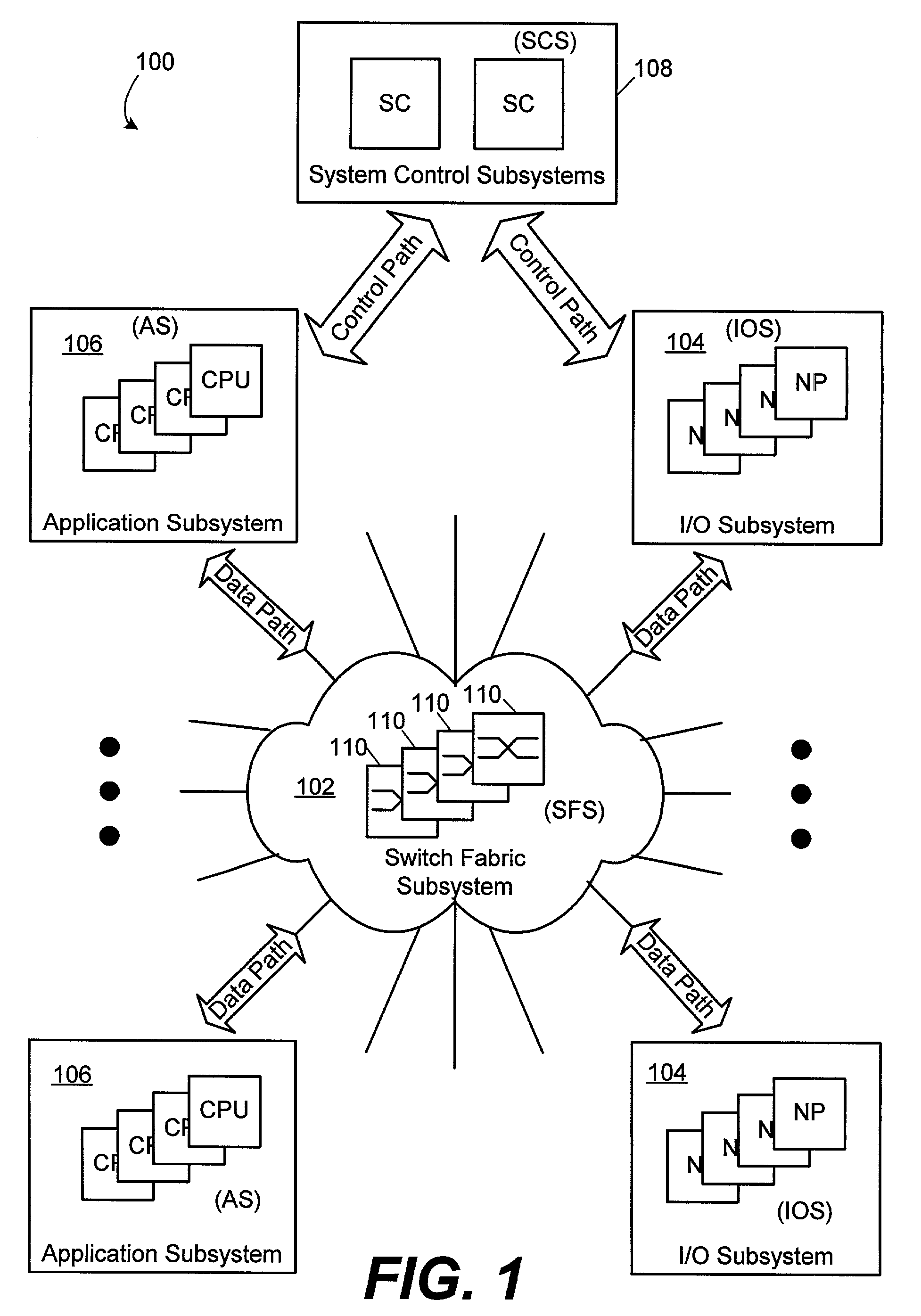

System and method for expansion of computer network switching system without disruption thereof

InactiveUS7406038B1Easily maintainableEasy to upgradeError preventionTransmission systemsTraffic volumeSwitched fabric

A switch fabric system comprises a first chassis for receiving a plurality of line cards each having a plurality of ports and at least two switch fabric cards wherein each line card comprises a plurality of link ports for linking the line card with the switch fabric card. Each switch fabric card provides a switching bandwidth. The system comprises a management unit for managing the traffic on the switch fabric cards wherein the management unit removes the traffic from one switch fabric card if the one switch fabric card is to be removed while the other switch fabric card operates and transfers the traffic to the other switch fabric card.

Owner:SAICO INFORMATION TECH WUHAN

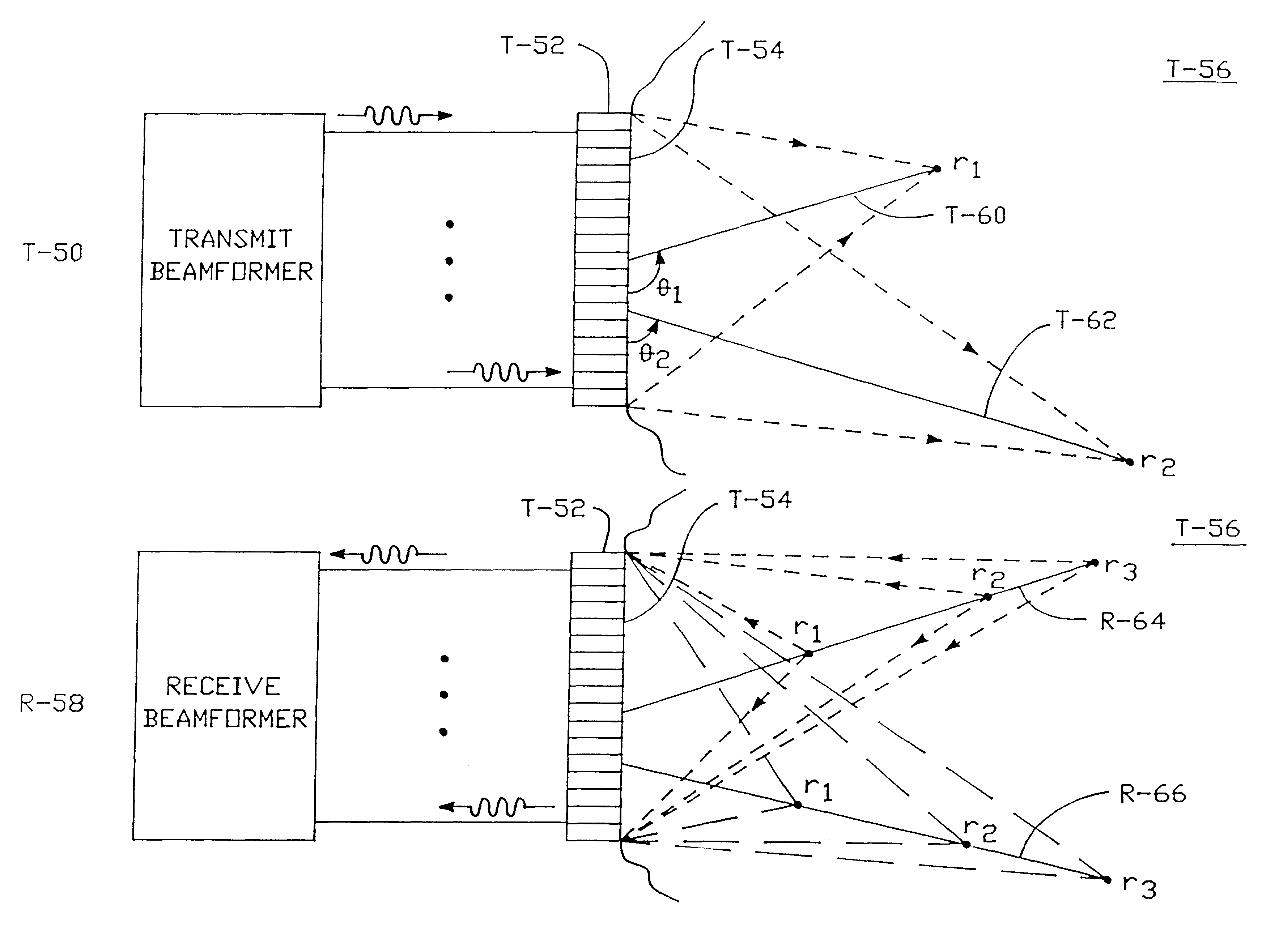

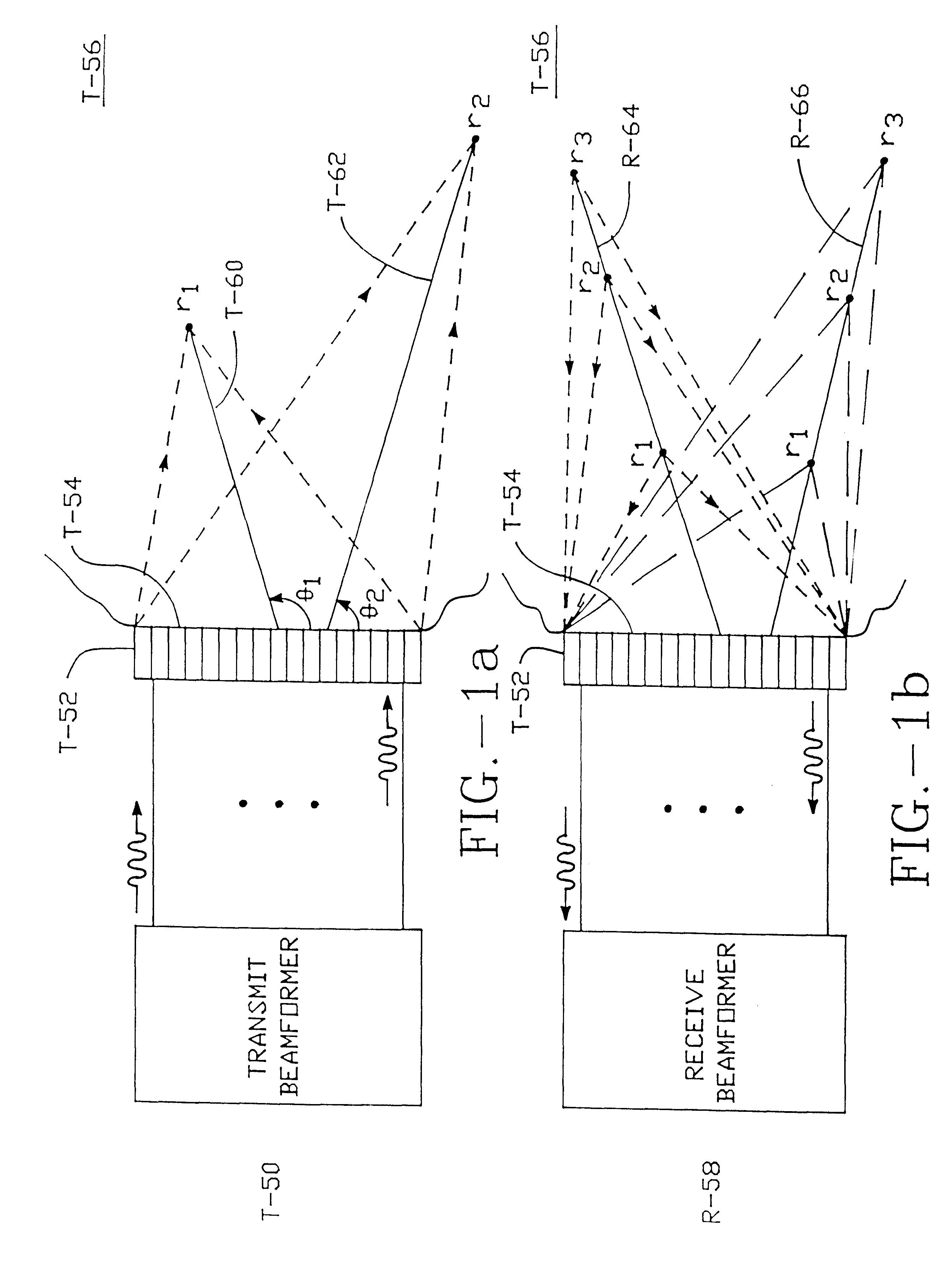

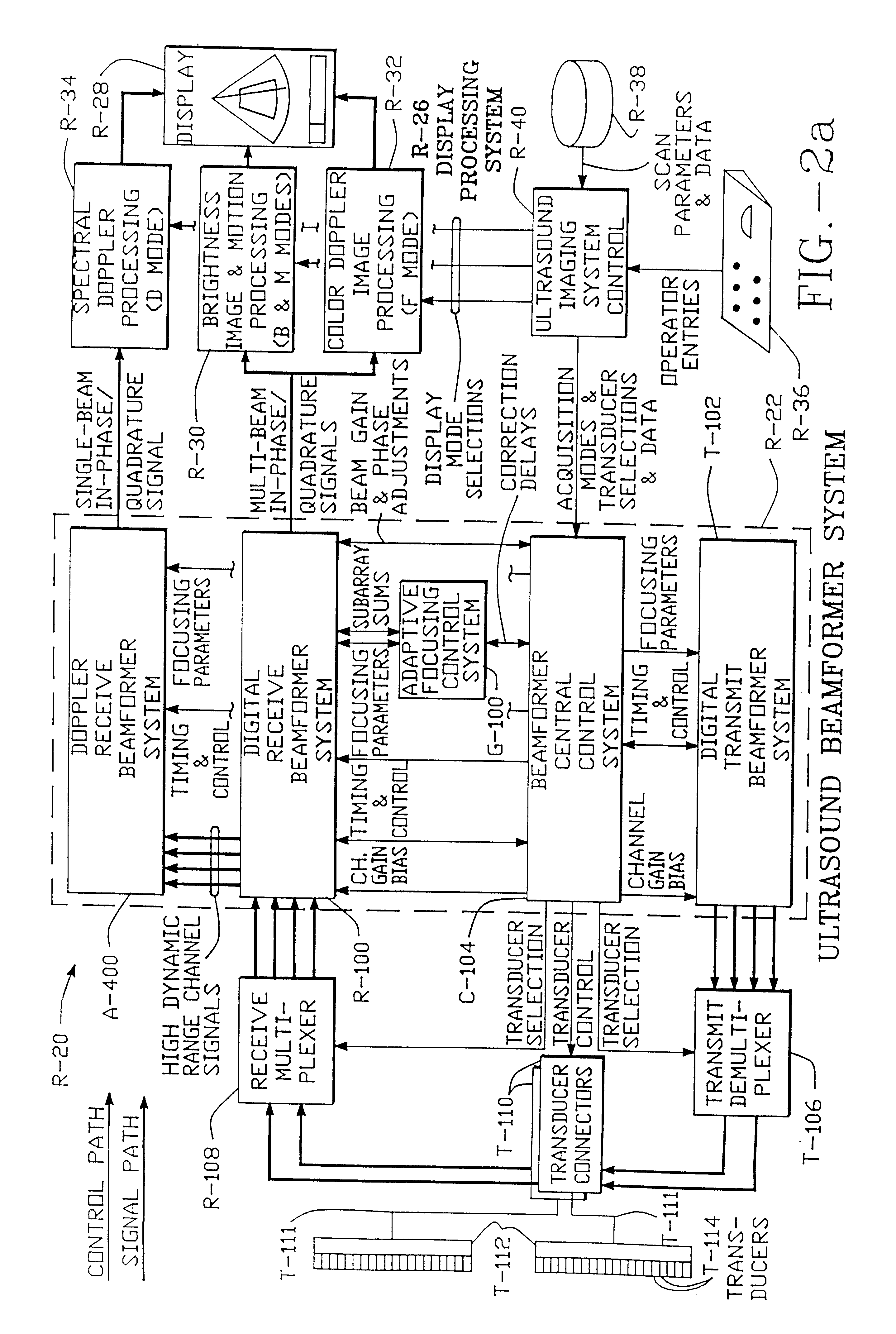

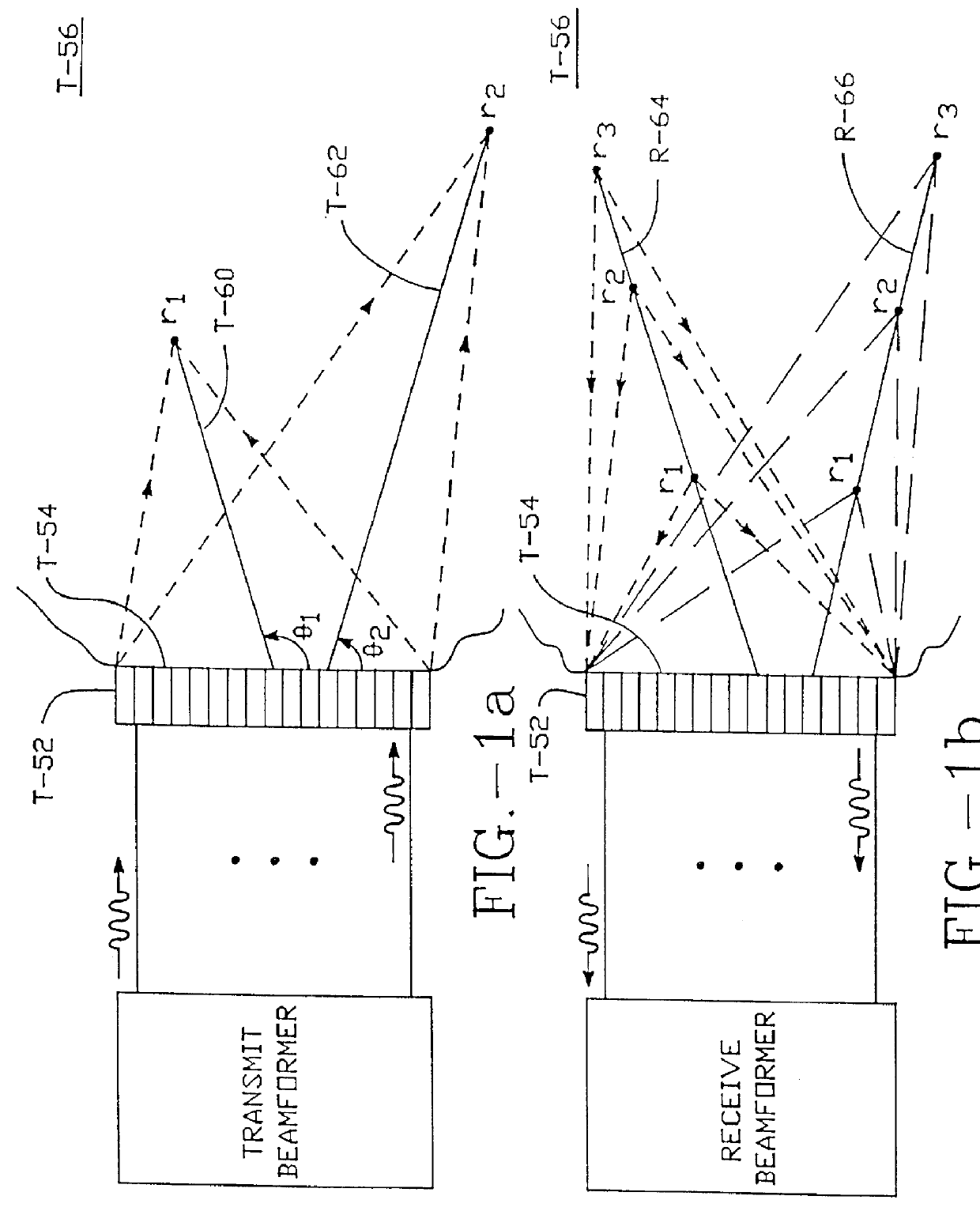

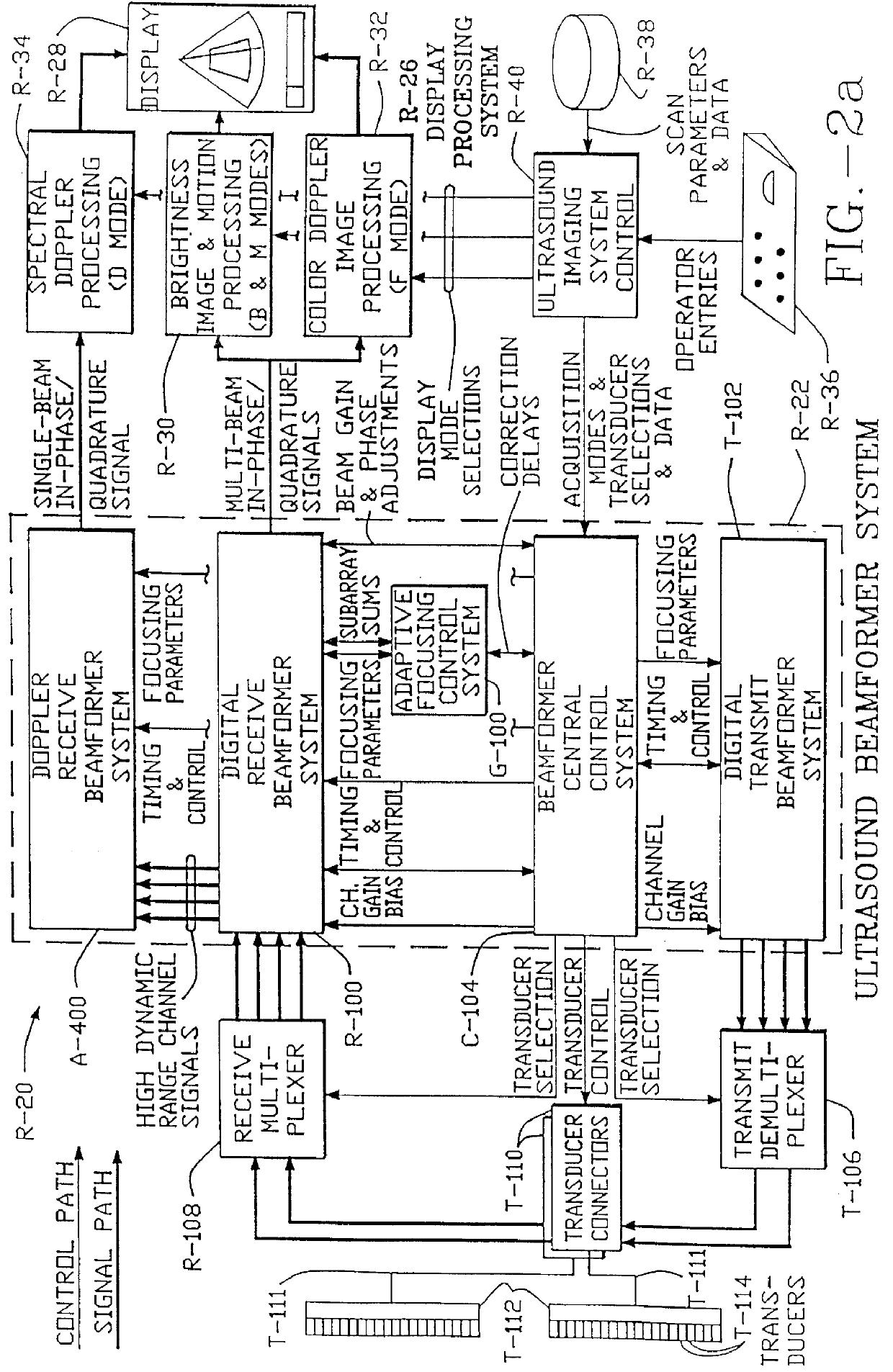

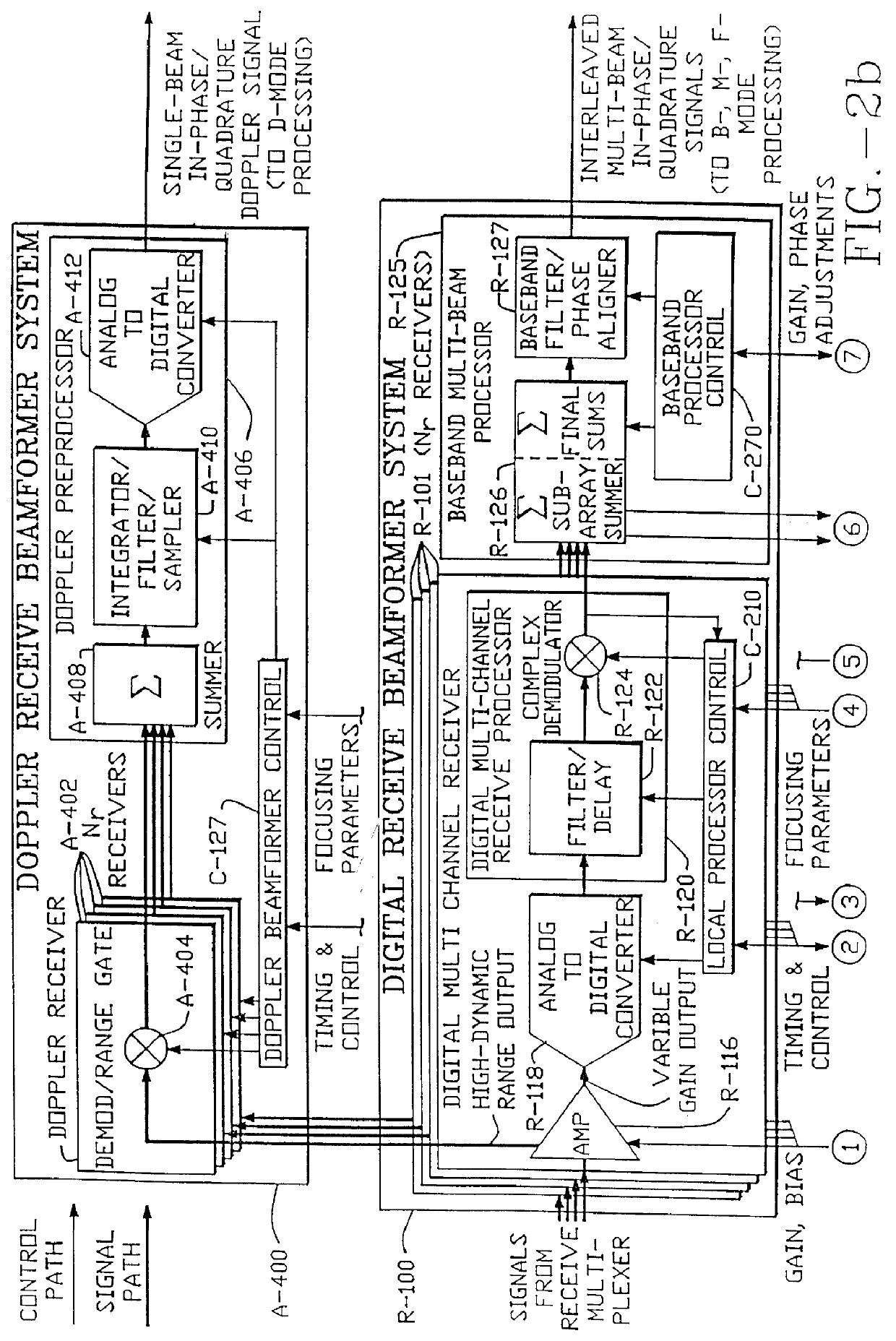

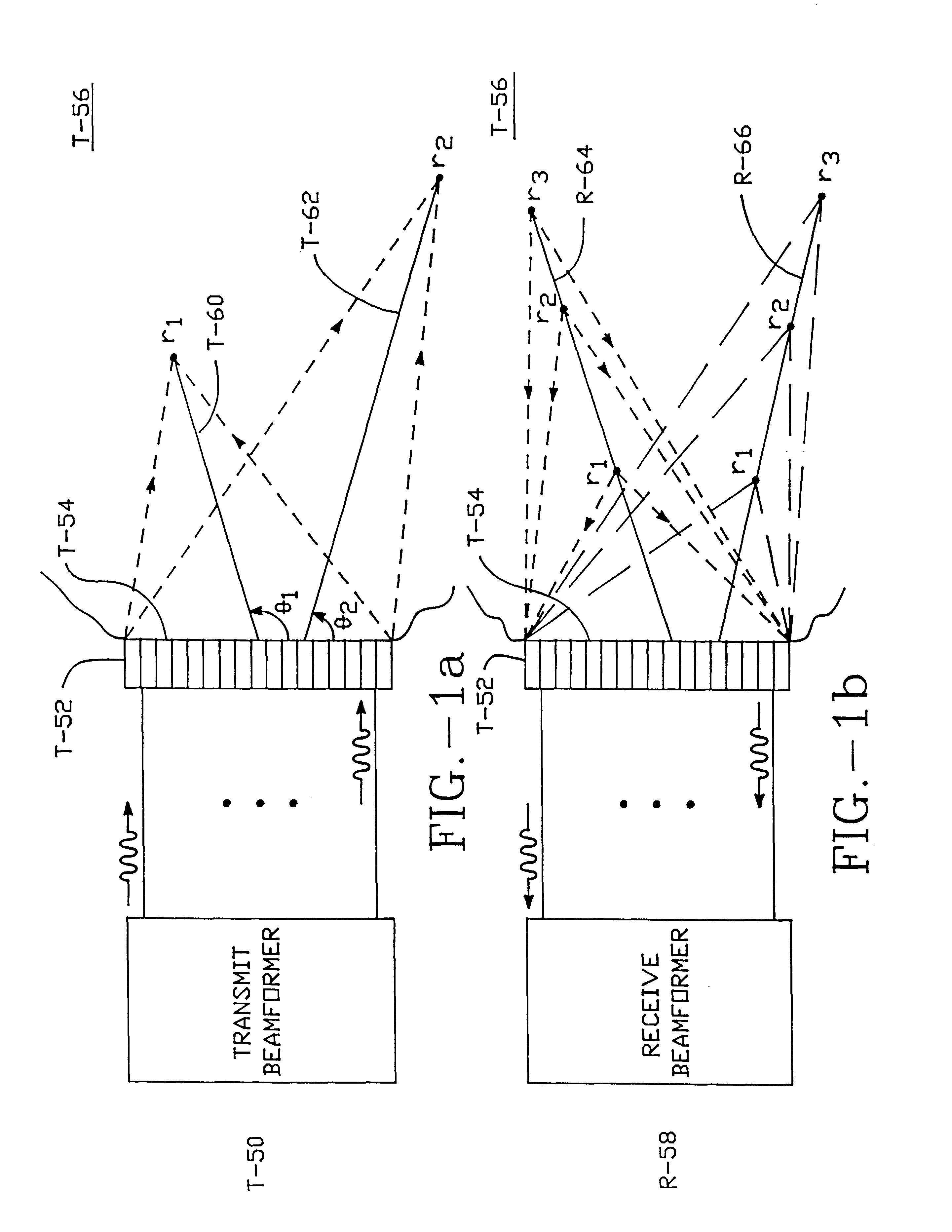

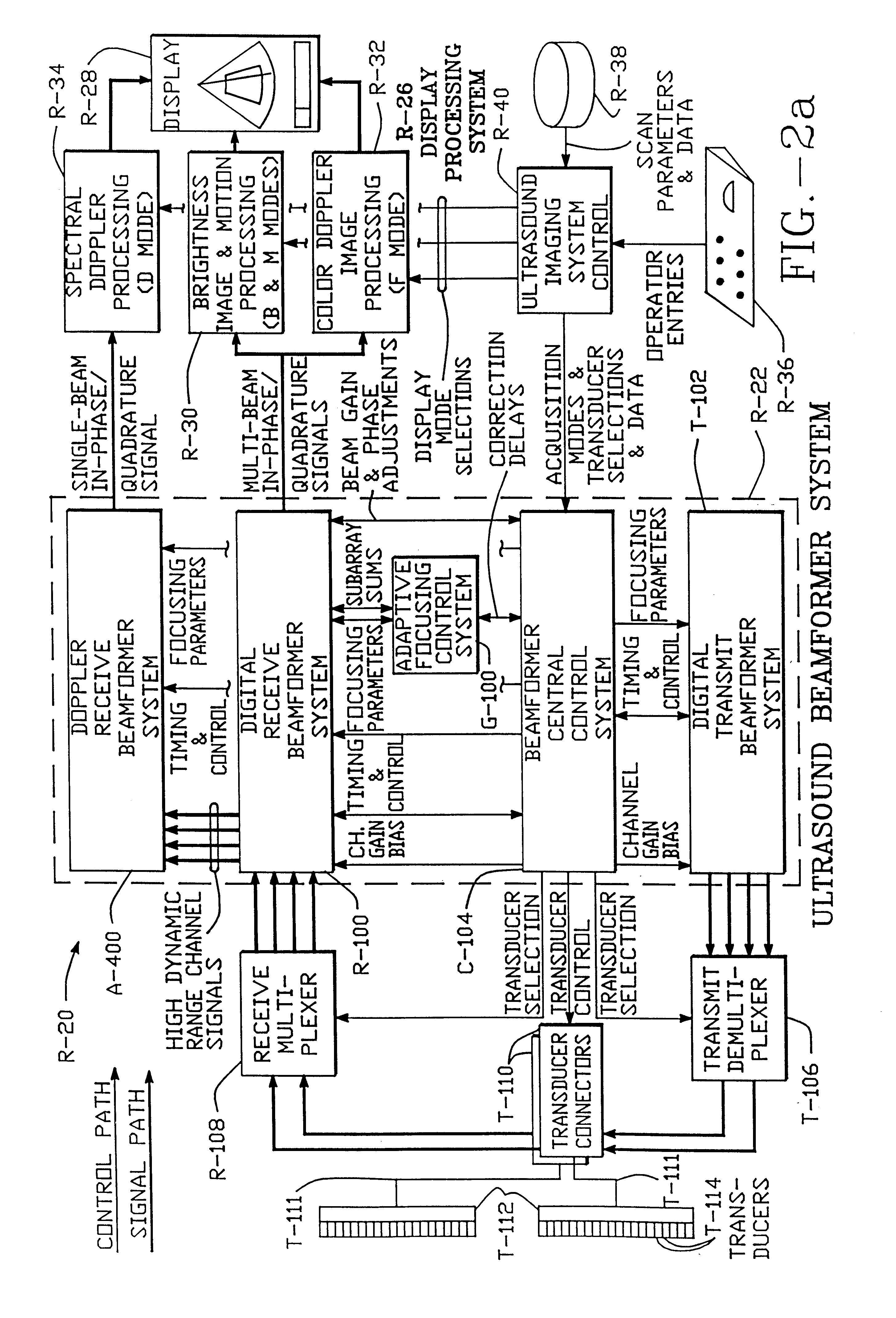

Method and apparatus for transmit beamformer system

InactiveUS6363033B1Improve programmabilityMaximum flexibilityUltrasonic/sonic/infrasonic diagnosticsProcessing detected response signalTrade offsApodization

A digital transmit beamformer system with multiple beam transmit capability has a plurality of multi-channel transmitters, each channel with a source of sampled, complex-valued initial waveform information representative of the ultimate desired waveform to be applied to one or more corresponding transducer elements for each beam. Each multi-channel transmitter applies beamformation delays and apodization to each channel's respective initial waveform information digitally, digitally modulates the information by a carrier frequency, and interpolates the information to the DAC sample rate for conversion to an analog signal and application to the associated transducer element(s). The beamformer transmitters can be programmed per channel and per beam with carrier frequency, delay, apodization and calibration values, For pulsed wave operation, pulse waveform parameters can be specified to the beamformer transmitters on a per firing basis, without degrading the scan frame rate to non-useful diagnostic levels. Waveform parameters can be specified to the transmitters by an external central control system which is responsible for higher level flexibility, such as scan formats, focusing depths and fields of view. The transmit pulse delay specified per-channel to each transmitter is applied in at least two components: a focusing time delay component and a focusing phase component. The carrier frequency can be specified for each transmit beam, to any desired frequency within a substantially continuous predefined range of frequencies, and a beam-interleaved signal processing path permits operation in any of several predefined processing modes, which define different parameter sets in a trade-off among (1) the number of beams produced; (2) per-beam initial waveform sample interval; and (3) transmit frequency.

Owner:ACUSON

Method and apparatus for transmit beamformer system

InactiveUS6104673AImprove abilitiesImprove programmabilityUltrasonic/sonic/infrasonic diagnosticsProcessing detected response signalSoftware engineeringCarrier signal

A digital transmit beamformer system with multiple beam transmit capability has a plurality of multi-channel transmitters, each channel with a source of sampled, complex-valued initial waveform information representative of the ultimate desired waveform to be applied to one or more corresponding transducer elements for each beam. Each multi-channel transmitter applies beamformation delays and apodization to each channel's respective initial waveform information digitally, digitally modulates the information by a carrier frequency, and interpolates the information to the DAC sample rate for conversion to an analog signal and application to the associated transducer element(s). The beamformer transmitters can be programmed per channel and per beam with carrier frequency, delay, apodization and calibration values. For pulsed wave operation, pulse waveform parameters can be specified to the beamformer transmitters on a per firing basis, without degrading the scan frame rate to non-useful diagnostic levels. Waveform parameters can be specified to the transmitters by an external central control system which is responsible for higher level flexibility, such as scan formats, focusing depths and fields of view. The transmit pulse delay specified per-channel to each transmitter is applied in at least two components: a focusing time delay component and a focusing phase component. The carrier frequency can be specified for each transmit beam, to any desired frequency within a substantially continuous predefined range of frequencies, and a beam-interleaved signal processing path permits operation in any of several predefined processing modes, which define different parameter sets in a trade-off among (1) the number of beams produced; (2) per-beam initial waveform sample interval; and (3) transmit frequency.

Owner:ACUSON

Method and apparatus for transmit beamformer system

InactiveUS6172939B1Improve abilitiesImprove programmabilityUltrasonic/sonic/infrasonic diagnosticsProcessing detected response signalEngineeringTrade offs

A digital transmit beamformer system with multiple beam transmit capability has a plurality of multi-channel transmitters, each channel with a source of sampled, complex-valued initial waveform information representative of the ultimate desired waveform to be applied to one or more corresponding transducer elements for each beam. Each multi-channel transmitter applies beamformation delays and apodization to each channel's respective initial waveform information digitally, digitally modulates the information by a carrier frequency, and interpolates the information to the DAC sample rate for conversion to an analog signal and application to the associated transducer element(s). The beamformer transmitters can be programmed per channel and per beam with carrier frequency, delay, apodization and calibration values. For pulsed wave operation, pulse waveform parameters can be specified to the beamformer transmitters on a per firing basis, without degrading the scan frame rate to non-useful diagnostic levels. Waveform parameters can be specified to the transmitters by an external central control system which is responsible for higher level flexibility, such as scan formats, focusing depths and fields of view. The transmit pulse delay specified per-channel to each transmitter is applied in at least two components: a focusing time delay component and a focusing phase component. The carrier frequency can be specified for each transmit beam, to any desired frequency within a substantially continuous predefined range of frequencies, and a beam-interleaved signal processing path permits operation in any of several predefined processing modes, which define different parameter sets in a trade-off among (1) the number of beams produced; (2) per-beam initial waveform sample interval; and (3) transmit frequency.

Owner:ACUSON

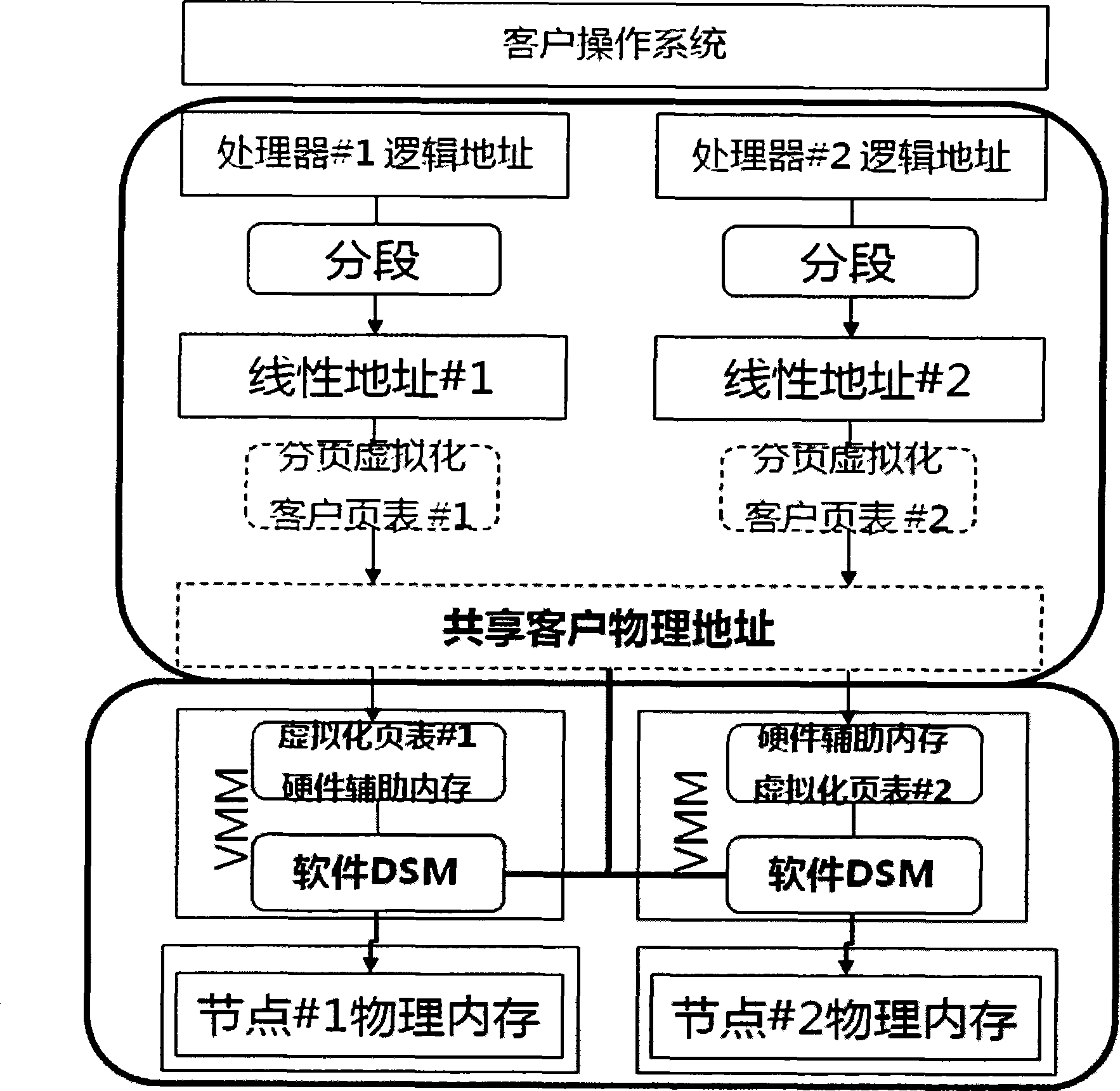

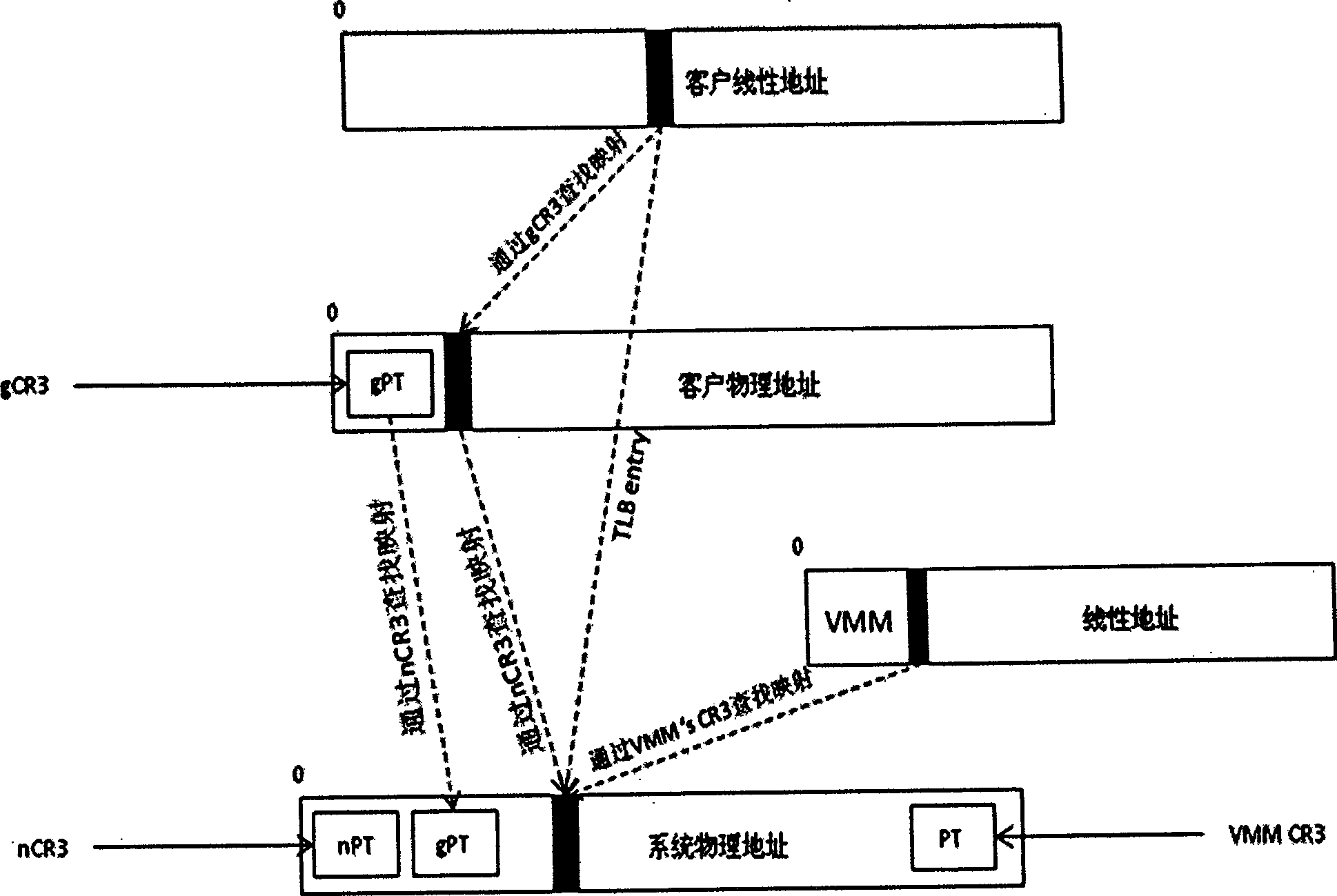

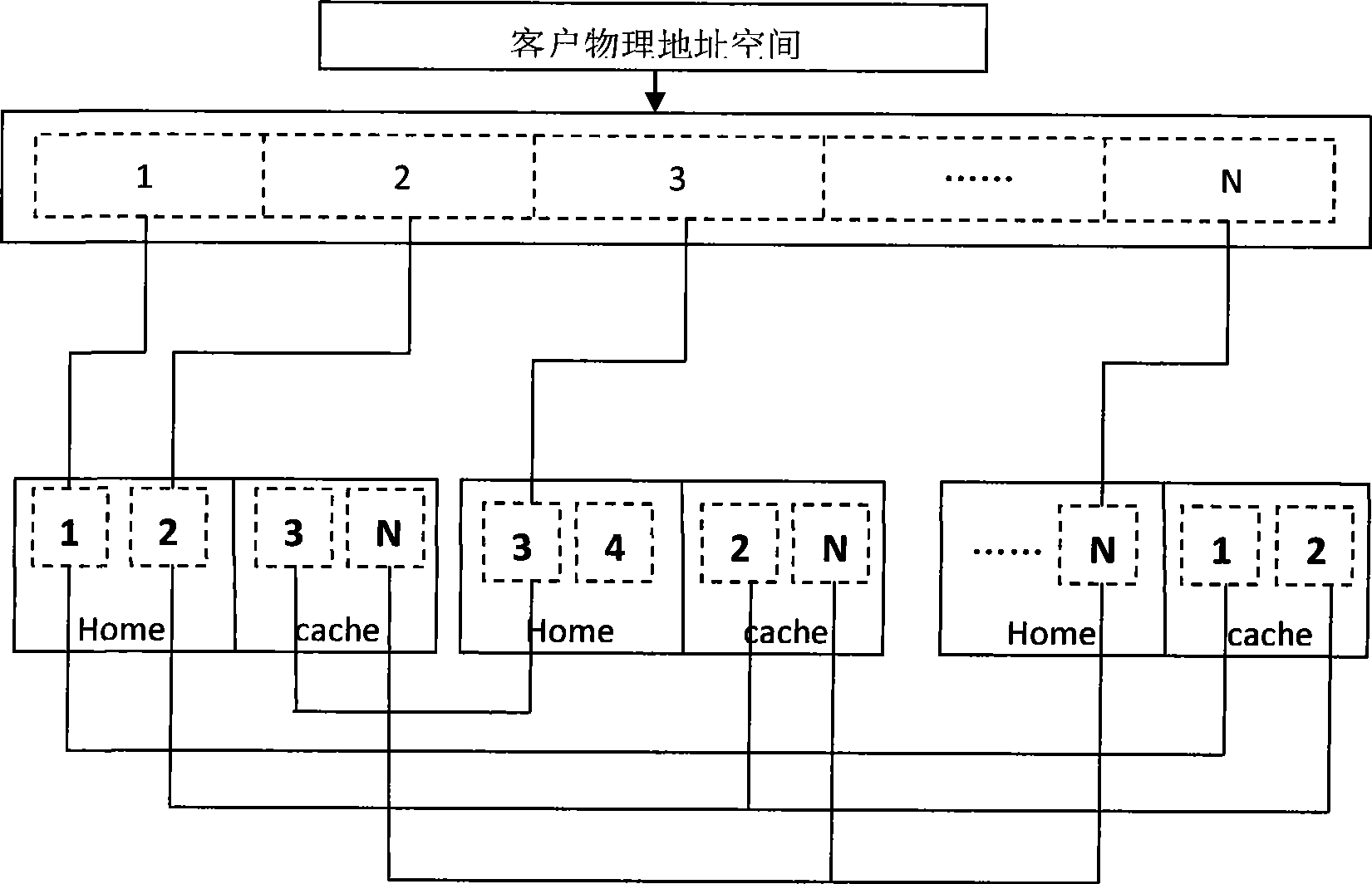

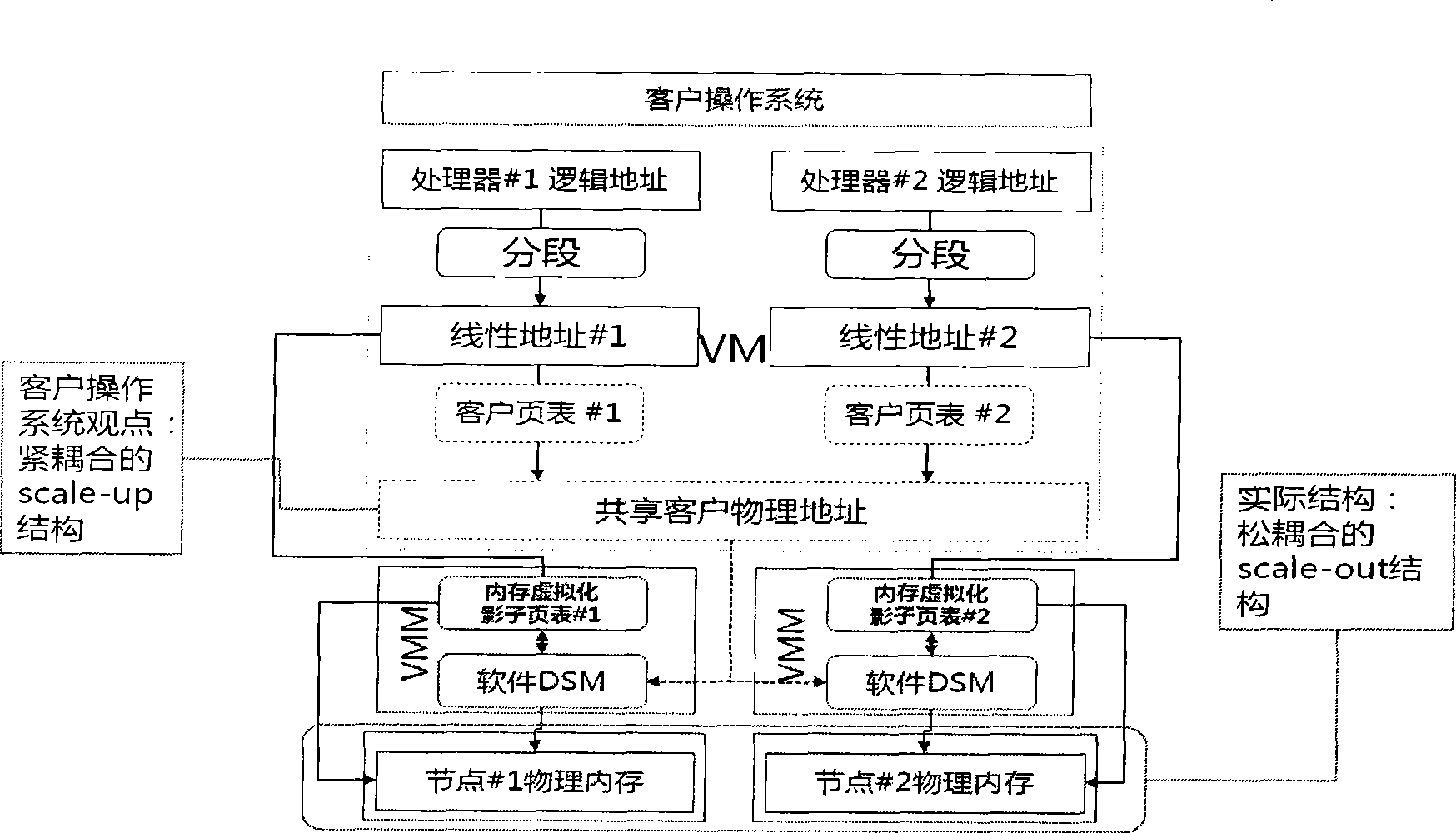

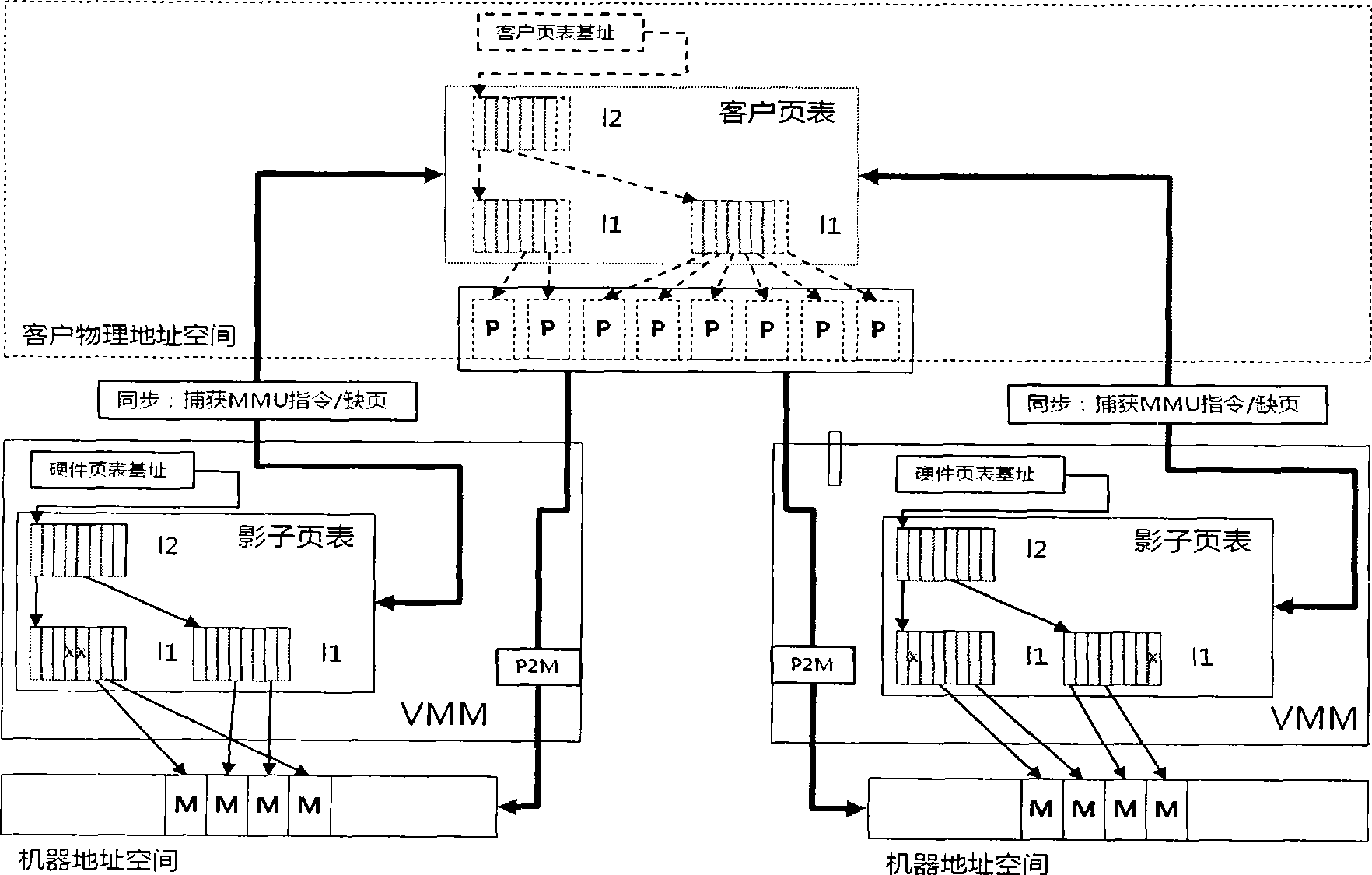

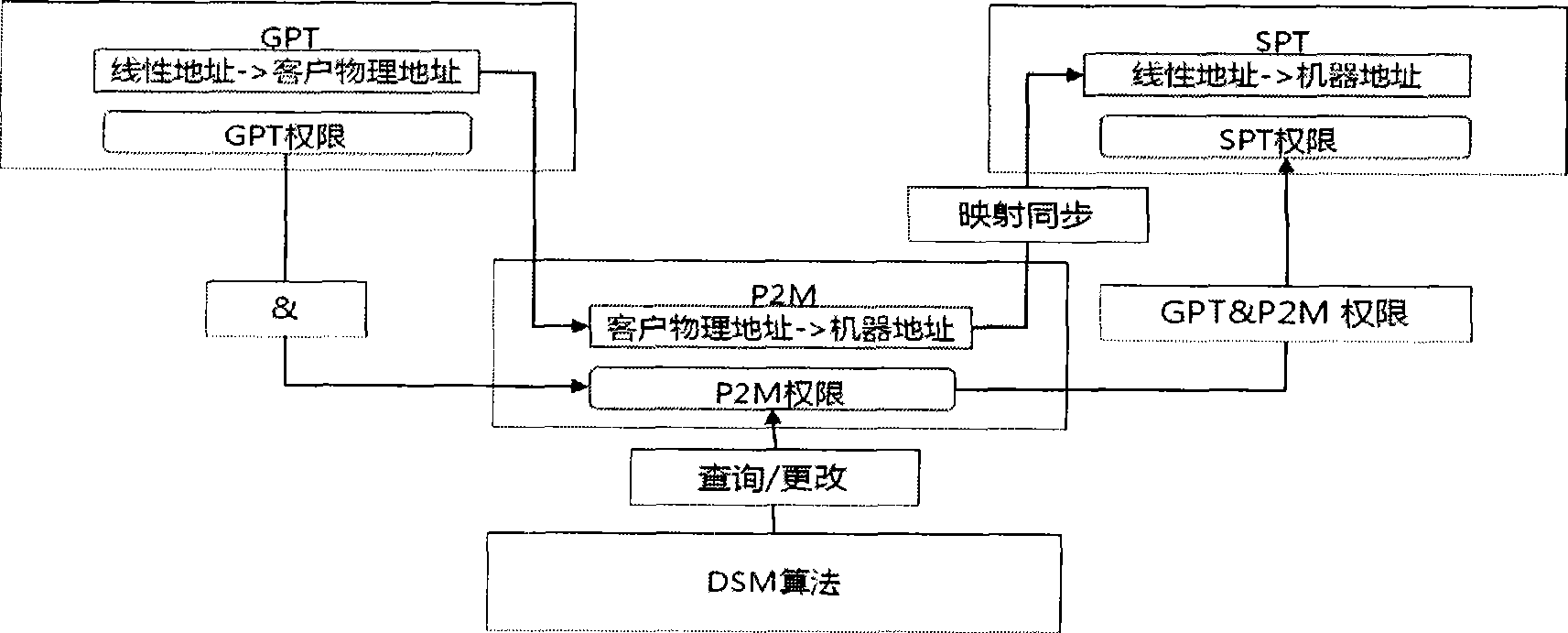

NUMA structure implementing method based on distributed internal memory virtualization

InactiveCN101477496AGuaranteed correctnessImprove manageabilityMemory adressing/allocation/relocationUnauthorized memory use protectionInternal memoryVirtualization

The invention discloses a realization method for NUMA (Non-Uniform Memory Access) structure based on distributed hardware-assisted memory virtualization. The method comprises the following four steps: step one, preparation stage; step two, normal work stage; step three, NUMA processing local request stage; and step four, NUMA processing remote request stage. The invention adopts the latest hardware-assisted memory virtualization technology and the distributed shared storage algorithm, provides a NUMA-structure shared single physical address space, and realizes the transparent and unified management to the multi-host memory resource by a guest operation system, so as to reduce the complexity of the application programming and increase the usability of system resource. Furthermore, the invention has the advantages of favorable use and development prospects.

Owner:HUAWEI TECH CO LTD

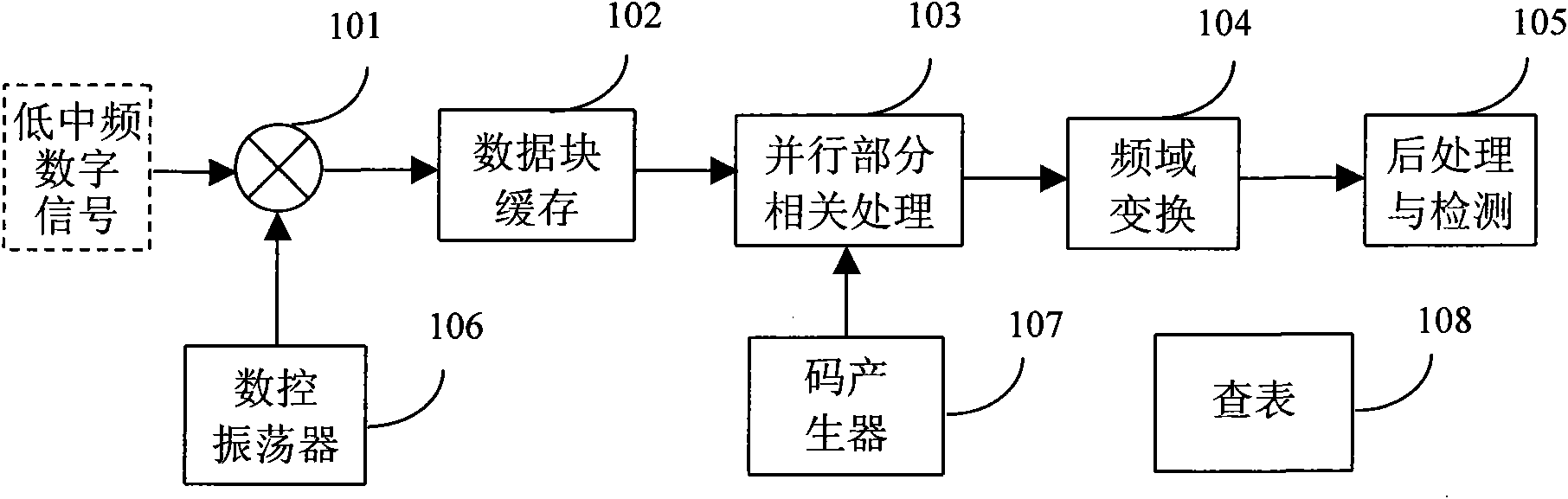

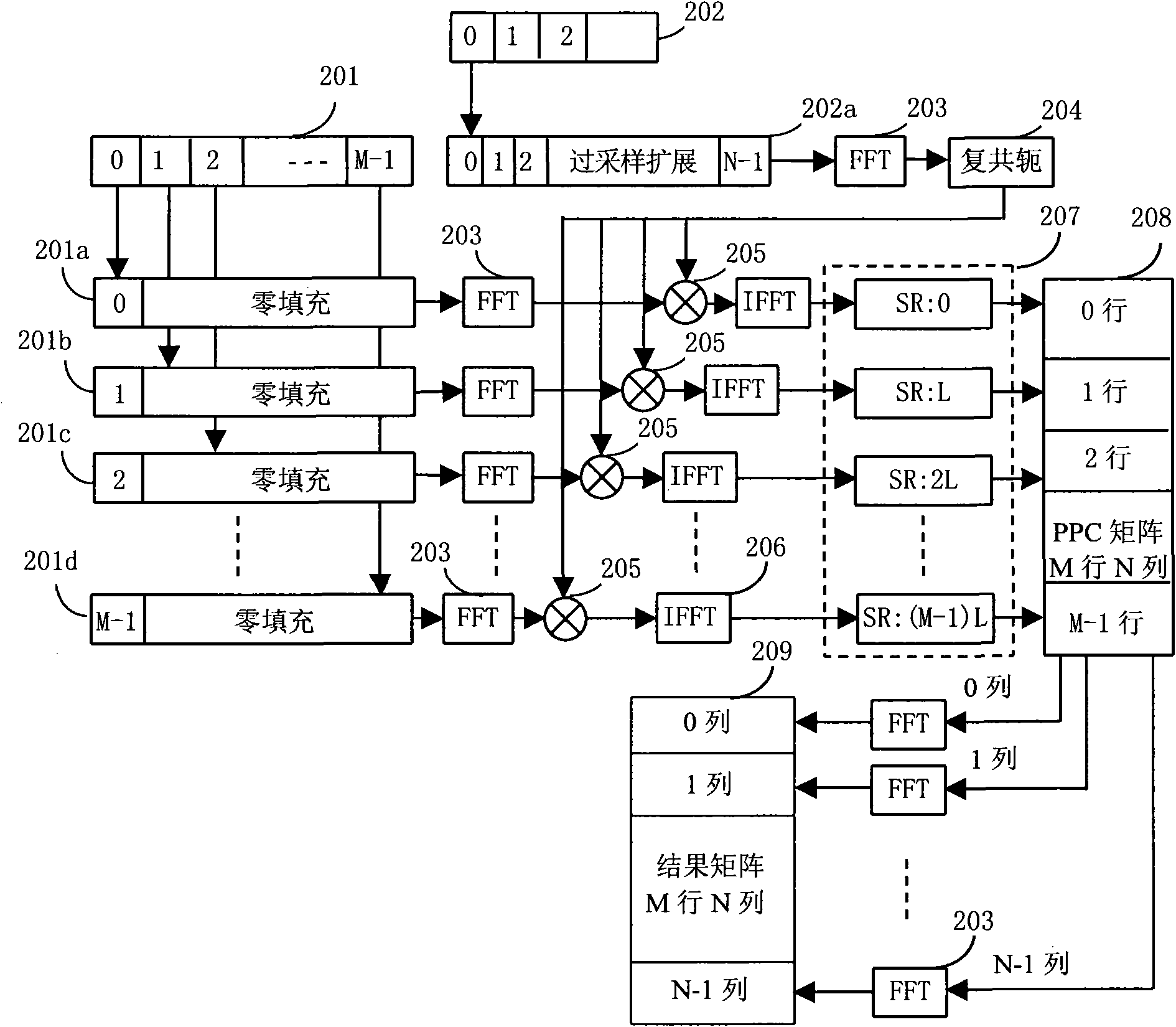

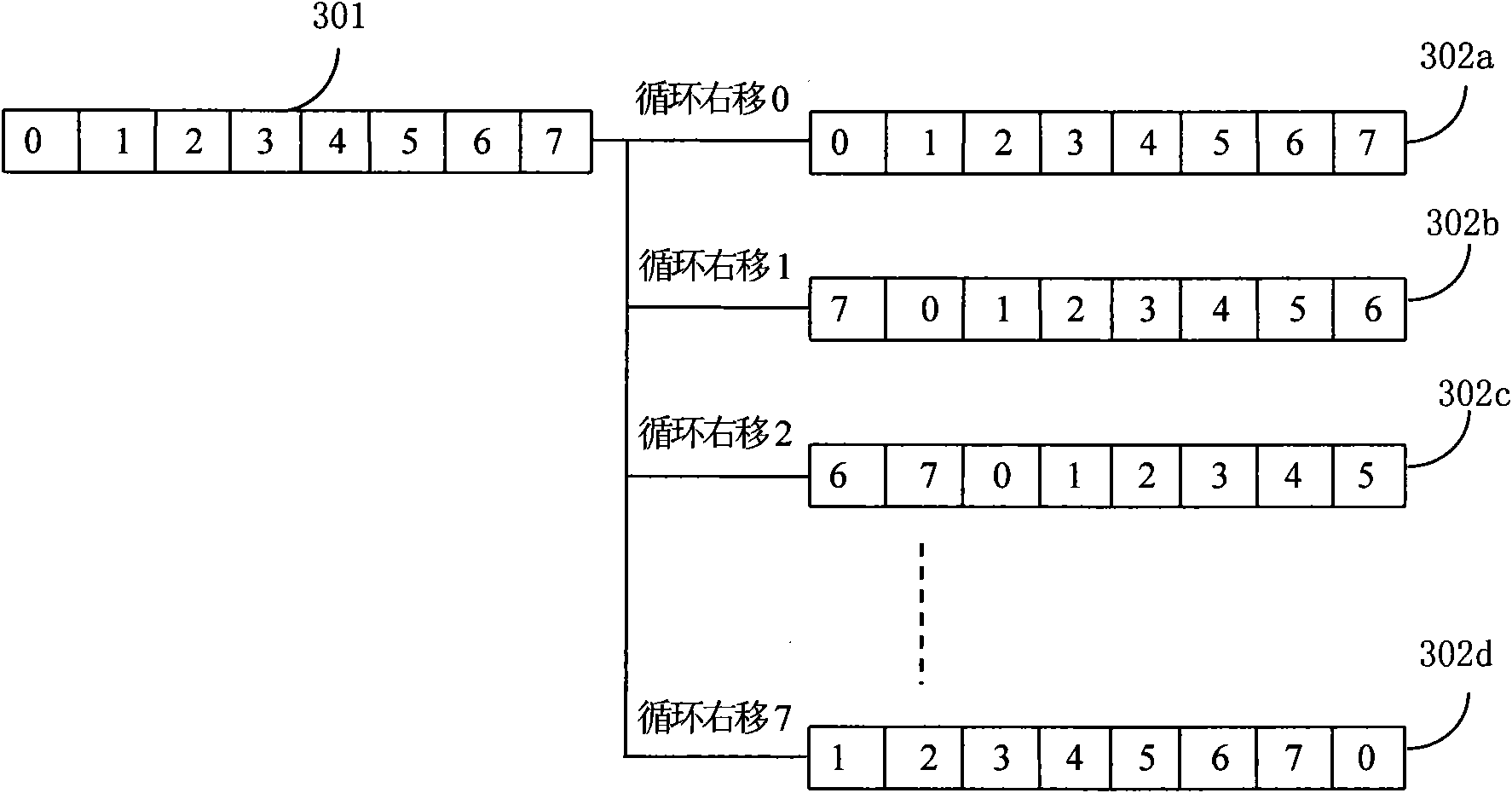

GPS signal large-scale parallel quick capturing method and module thereof

ActiveCN101625404ALow costCapture flexibleBeacon systemsTransmissionData segmentIntermediate frequency

The invention discloses a GPS signal large-scale parallel quick capturing method, which comprises the following steps: configuring a large-scale parallel quick capturing module firmware comprising submodules of multiplier, data block cache, parallel part correlative processing, frequency domain transformation, postprocessing and digital controlled oscillator, code generator and the like in a system CPU; through the calling computation, converting low-medium frequency digital signals into baseband signals in a processing procedure to combine a data block; performing zeroing extension of the length and the data block on each equational data section in the data block; then based on FFT transformation computation, performing parallel part correlative PPC processing on each extended data section and local spreading codes, and performing FFT transformation on each line of a formed PPC matrix to obtain a result matrix; and performing coherent or incoherent integration on a plurality of result matrixes formed by processing a plurality of data blocks to increase the processing gain, improve the capturing sensitivity, roughly determine the code phase and the Doppler frequency of GPS signals, and achieve two-dimensional parallel quick capturing of the GPS signals. The method has high processing efficiency and high capturing speed, and can be applied to various GPS positioning navigation aids.

Owner:杭州中科微电子有限公司

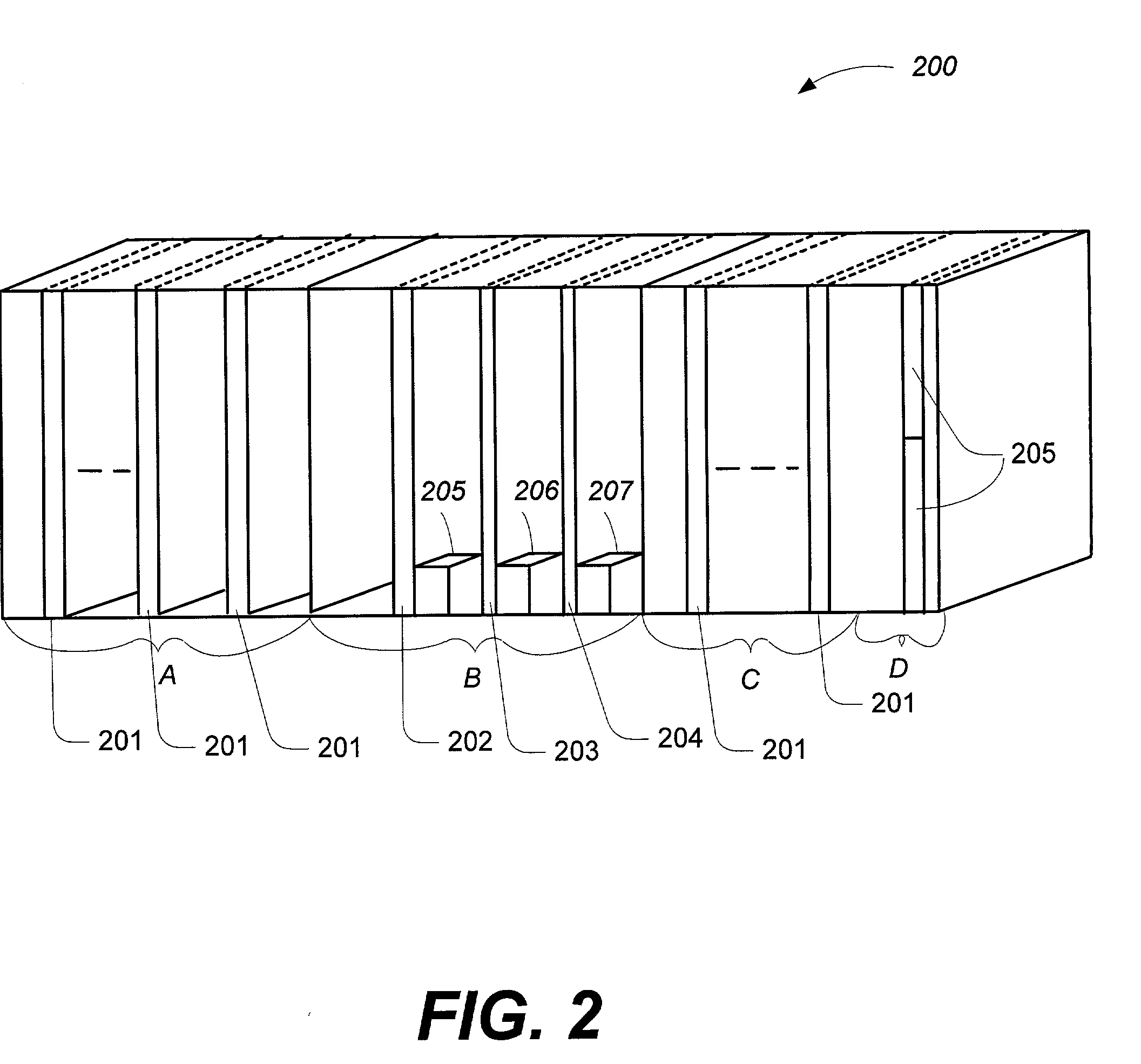

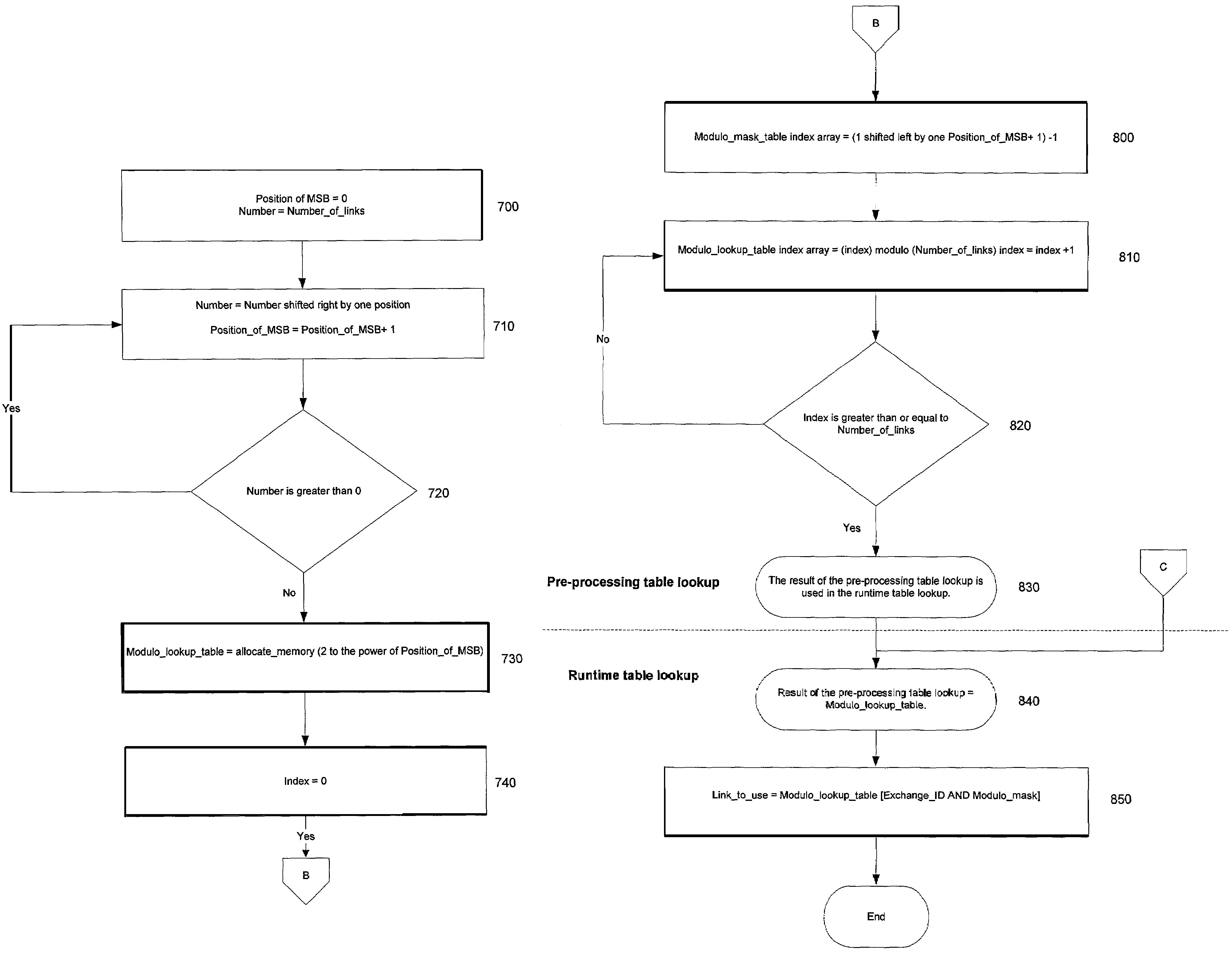

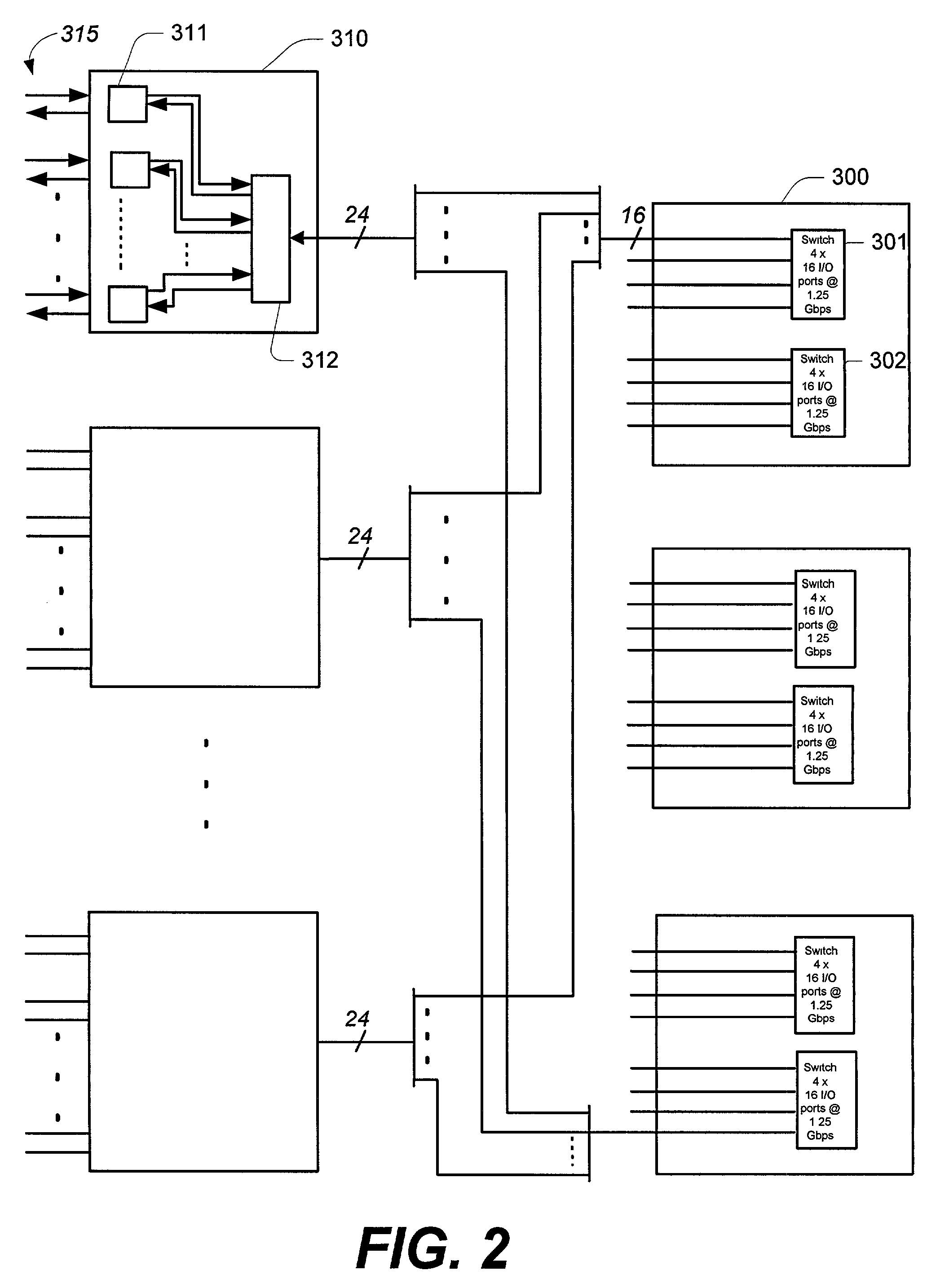

System and method for linking a plurality of network switches

InactiveUS7307995B1Easy maintenanceMinimal and no downtimeData switching by path configurationData streamCoupling

A method of linking at least two network switches is disclosed, wherein each network switch switches data traffic of a plurality of devices, through a plurality of couplings. The method comprises the steps of generating a data stream including an identifier to be sent from a first to a second network switch, generating a number identifying one of the couplings from the identifier, and using the identified coupling for transfer of the data stream.

Owner:SAICO INFORMATION TECH WUHAN

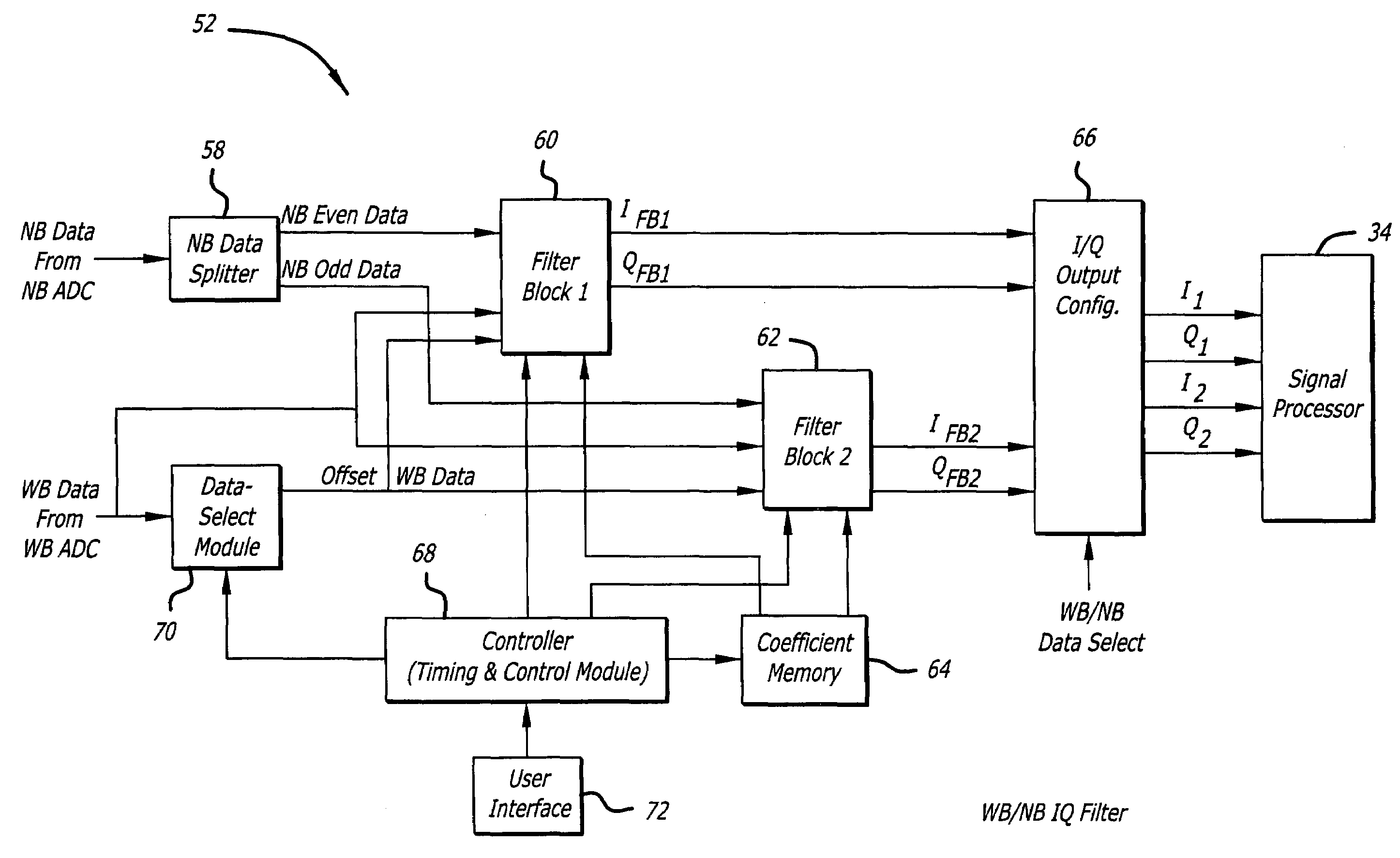

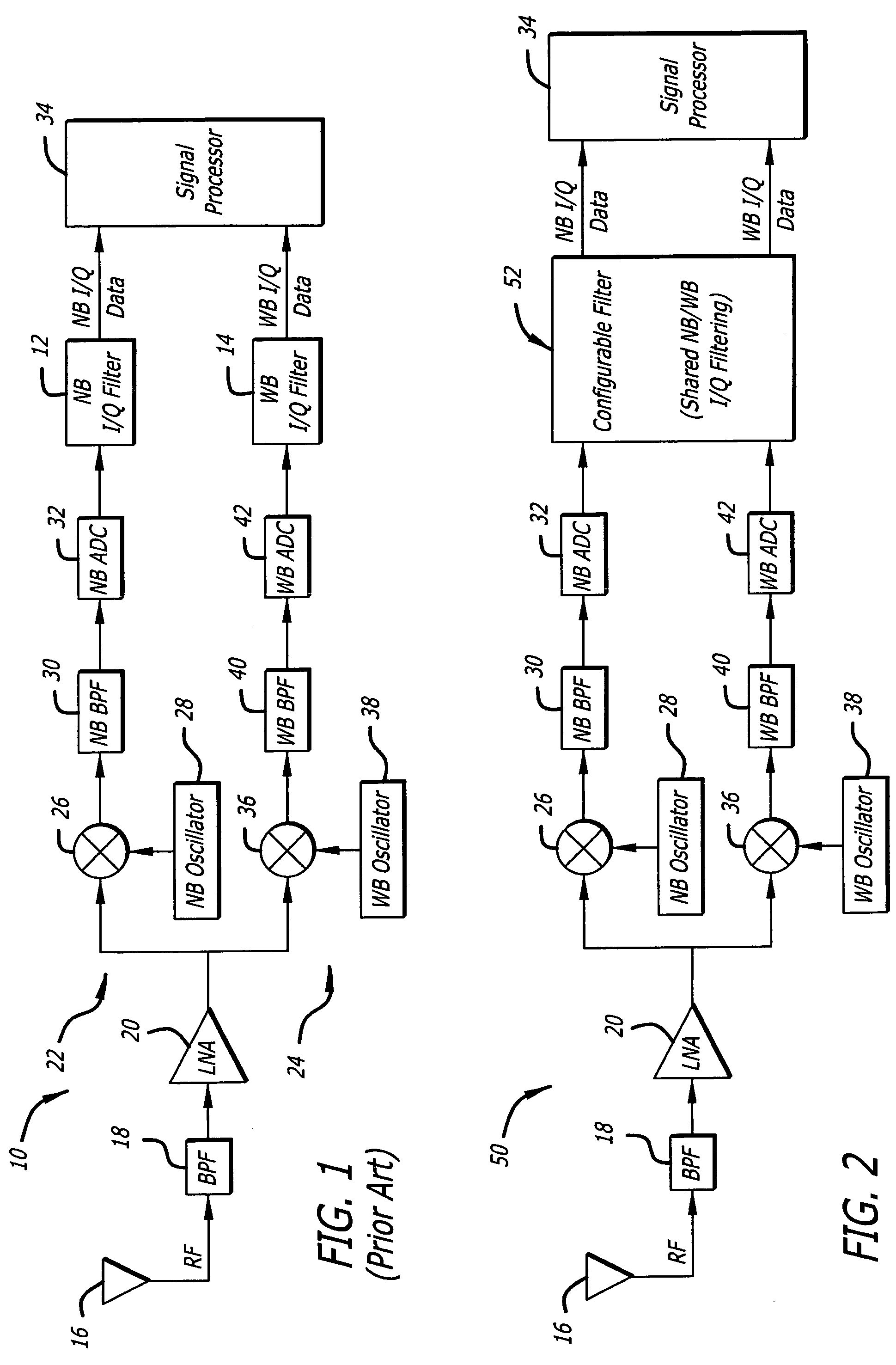

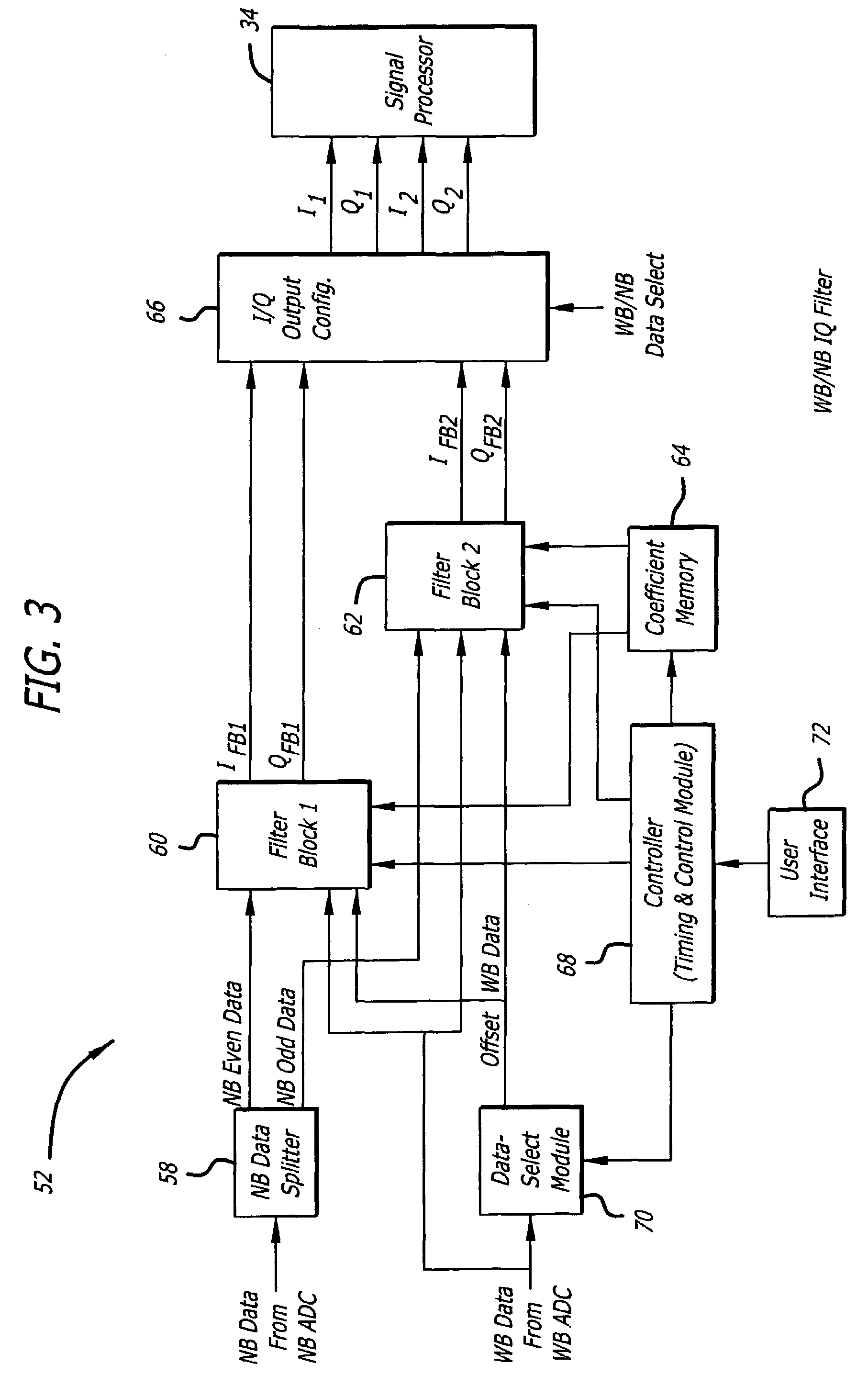

Configurable filter and receiver incorporating same

ActiveUS7526052B2Selectively affecting filter responseFacilitates coefficientModulated-carrier systemsSimultaneous amplitude and angle demodulationMultiplexerControl signal

An efficient configurable signal filter. The filter includes a first mechanism for receiving a first signal of a first type and a second signal of a second type. A second mechanism selectively filters the first signal during a first mode of operation, and filters the second signal during a second mode of operation. A third mechanism generates control signals. A fourth mechanism automatically configures the second mechanism to operate in the first mode of operation or the second mode of operation based on the control signals. In a specific embodiment, the first type of signal is characterized by a first rate, and the second type of signal is characterized by a second rate. The first signal and the second signal are digital ADC outputs. The second mechanism includes plural filter blocks, each having one or more Multiply-Accumulate (MAC) pipes. Each of the one or more MAC pipes include one or more MAC blocks that are each associated with a coefficient memory data structure of a coefficient memory. The third mechanism or a user selects coefficients from each memory data structure to apply to each MAC block, thereby selectively affecting filter response. The control signals direct multiplexers or switches to configure the MAC pipes in a serial configuration or a parallel configuration corresponding to the first mode of operation or the second mode of operation, respectively.

Owner:RAYTHEON CO

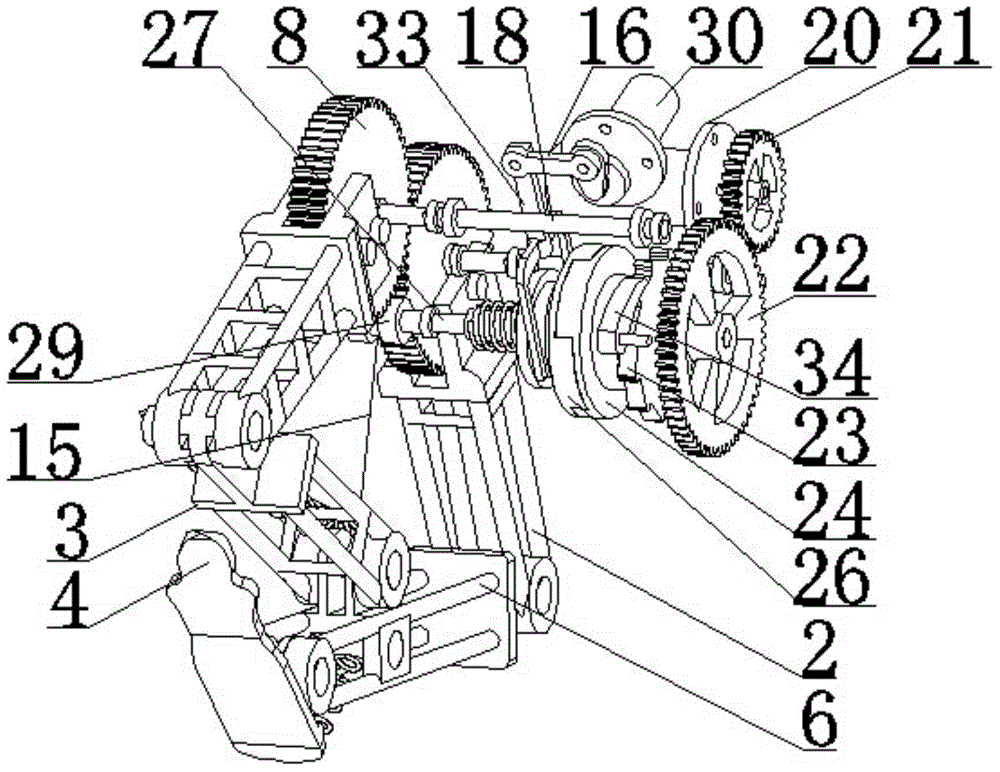

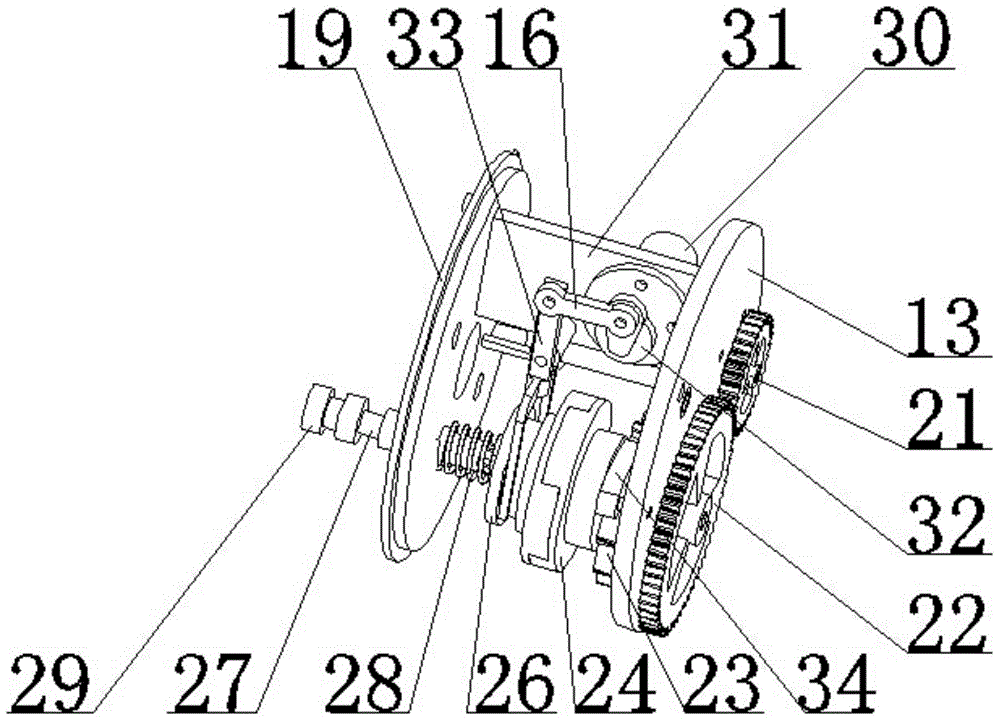

Bionic jumping and walking mechanism

The invention discloses a bionic jumping and walking mechanism. Existing robot can only move on the flat terrain and can not be adapted to the complicated terrain environment in the natural world. According to the bionic jumping and walking mechanism, the jumping mechanism is driven and locked or unlocked through a spring locking and unlocking mechanism, a main motor drives a fourth straight gear, an input shaft is supported by a gearbox through a bearing, the fourth straight gear, a ratchet wheel and a clutch fixed block are all fixed to the input shaft, the ratchet wheel is meshed with a pawl, a clutch movable block is connected with an output shaft through a spline, the clutch movable block and the clutch fixed block are embedded together, a base of a shifting fork driving motor is fixed to the gearbox, a second crank is fixedly connected to an output shaft of the shifting fork driving motor, the two ends of a second connecting rod are hinged to the second crank and the end of a shifting fork respectively, the middle of the shifting fork is hinged to a supporting shaft of a motor supporting frame, and a U-shaped fork body of the shifting fork is embedded in an annular groove of the clutch movable block. According to the bionic jumping and walking mechanism, jumping angle adjustment, jumping height adjustment, continuous jumping, automatic resetting and walking can be achieved so that the bionic jumping and walking mechanism can be adapted to the complicated environment.

Owner:ZHEJIANG SCI-TECH UNIV

Implementing method for distributed internal memory virtualization technology

InactiveCN101477495AImprove manageabilityImprove programmabilityMemory adressing/allocation/relocationSoftware simulation/interpretation/emulationInternal memoryVirtualization

The invention provides a realization method for distributed memory virtualization technology. The method mainly adopts the latest virtualization technology of combing hardware and software together, conducts virtualization and integration to the memory resource distributed in a multi-host combining with distributed shared storage algorithm, provides a shared single physical address space for an upper grade guest operation system, and realizes the management and the use of the guest operation system to the distributed memory. The invention carried out innovation on the basis of the current mature technology, is simple to implement, and has excellent use and development prospects.

Owner:HUAWEI TECH CO LTD

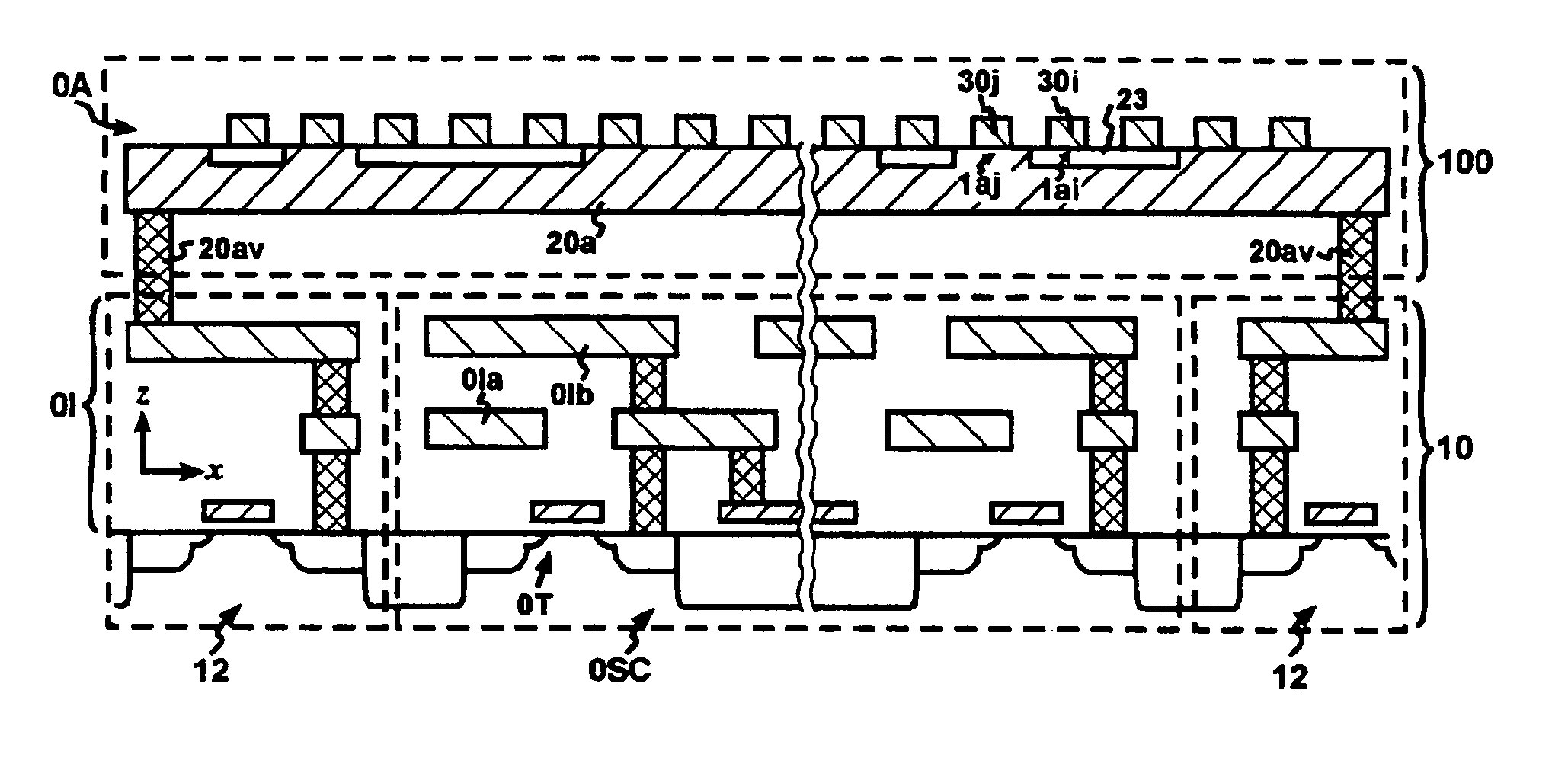

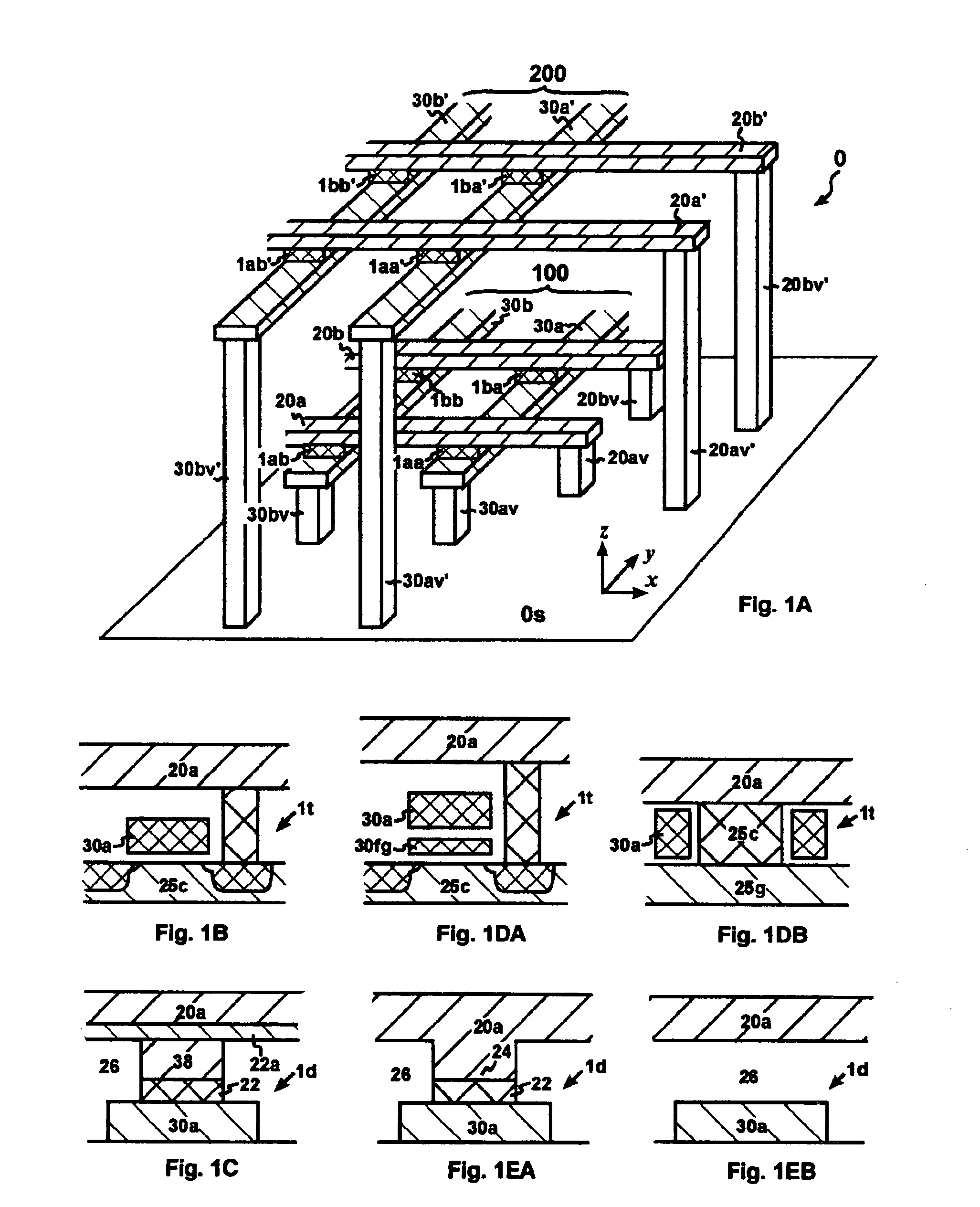

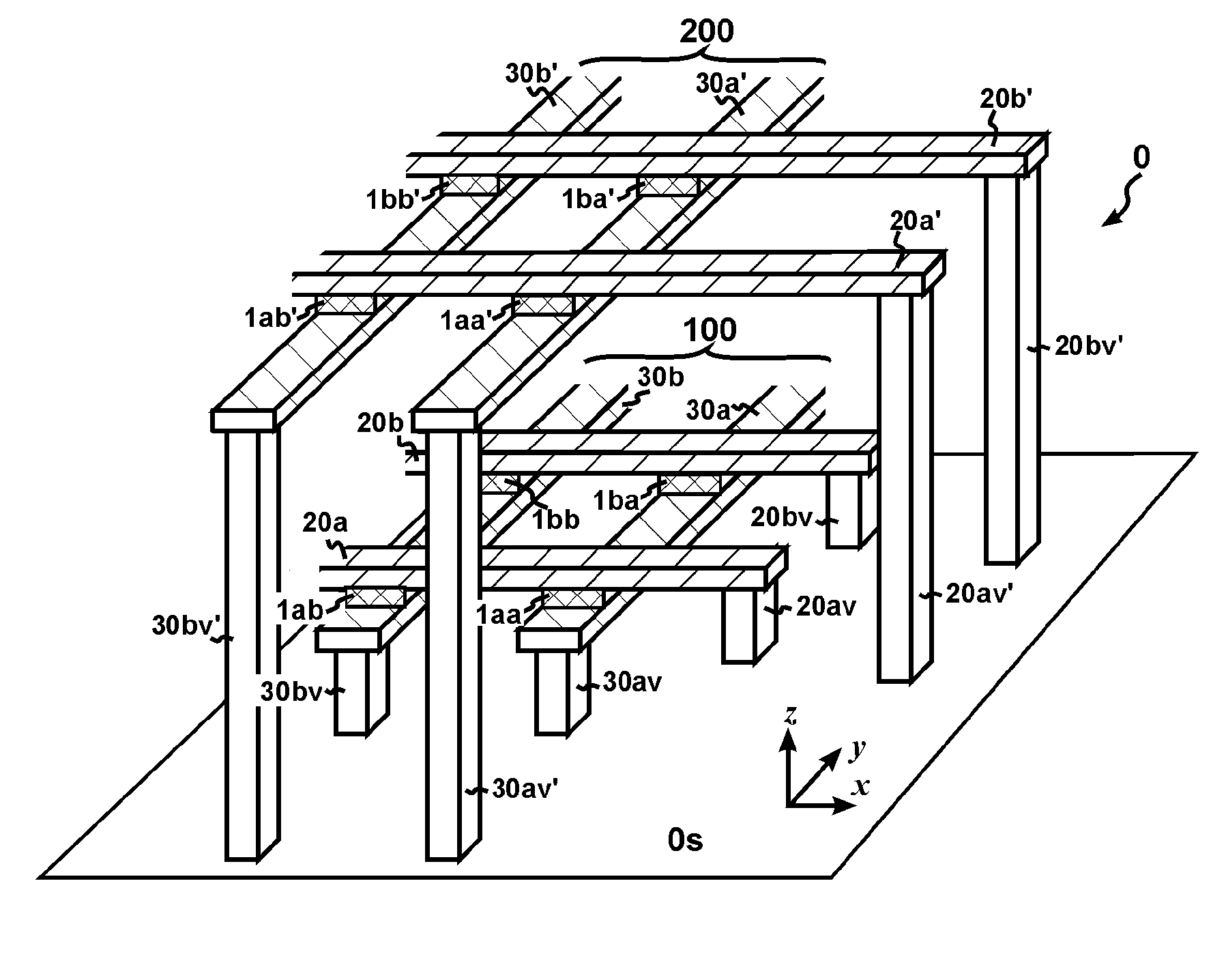

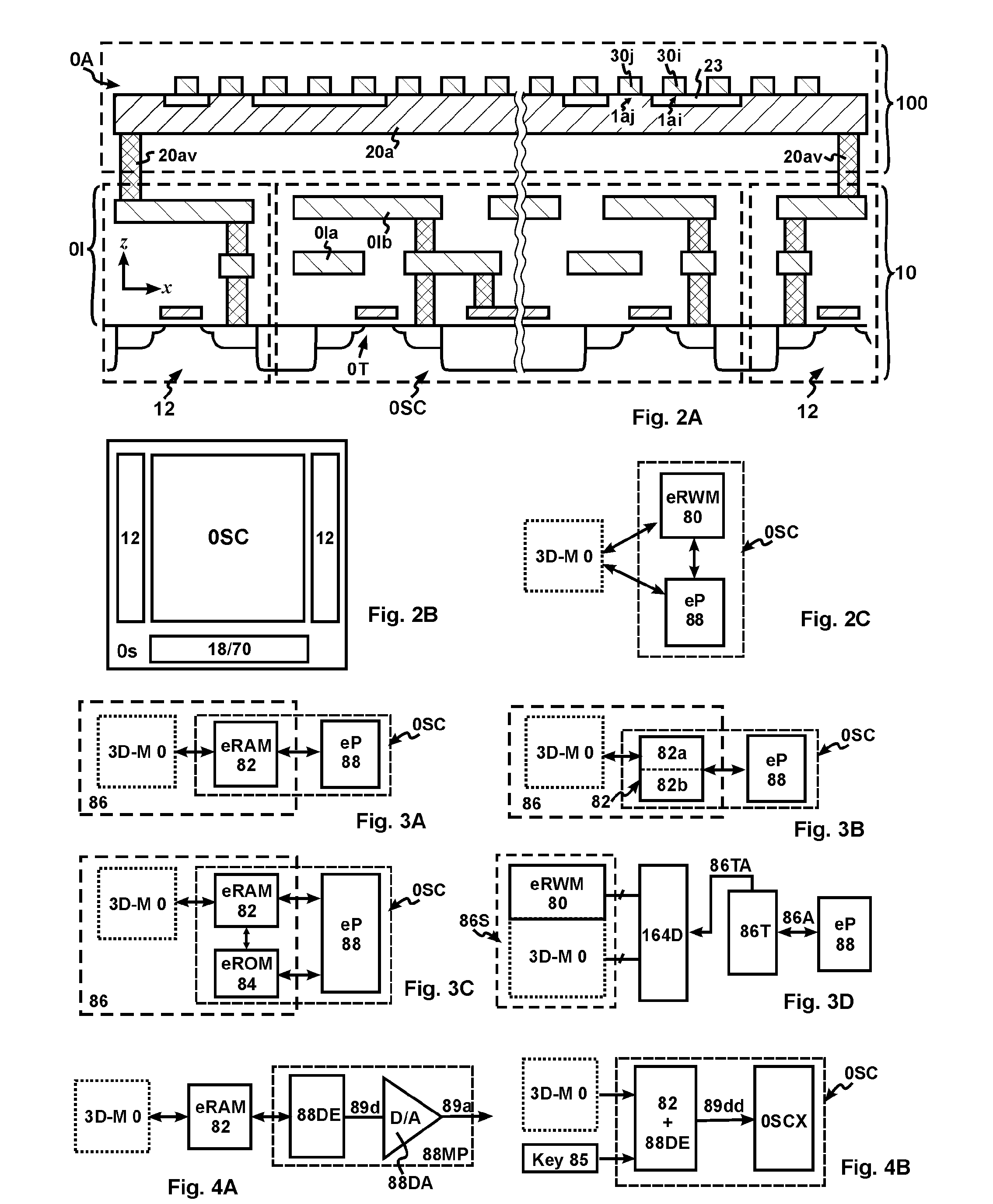

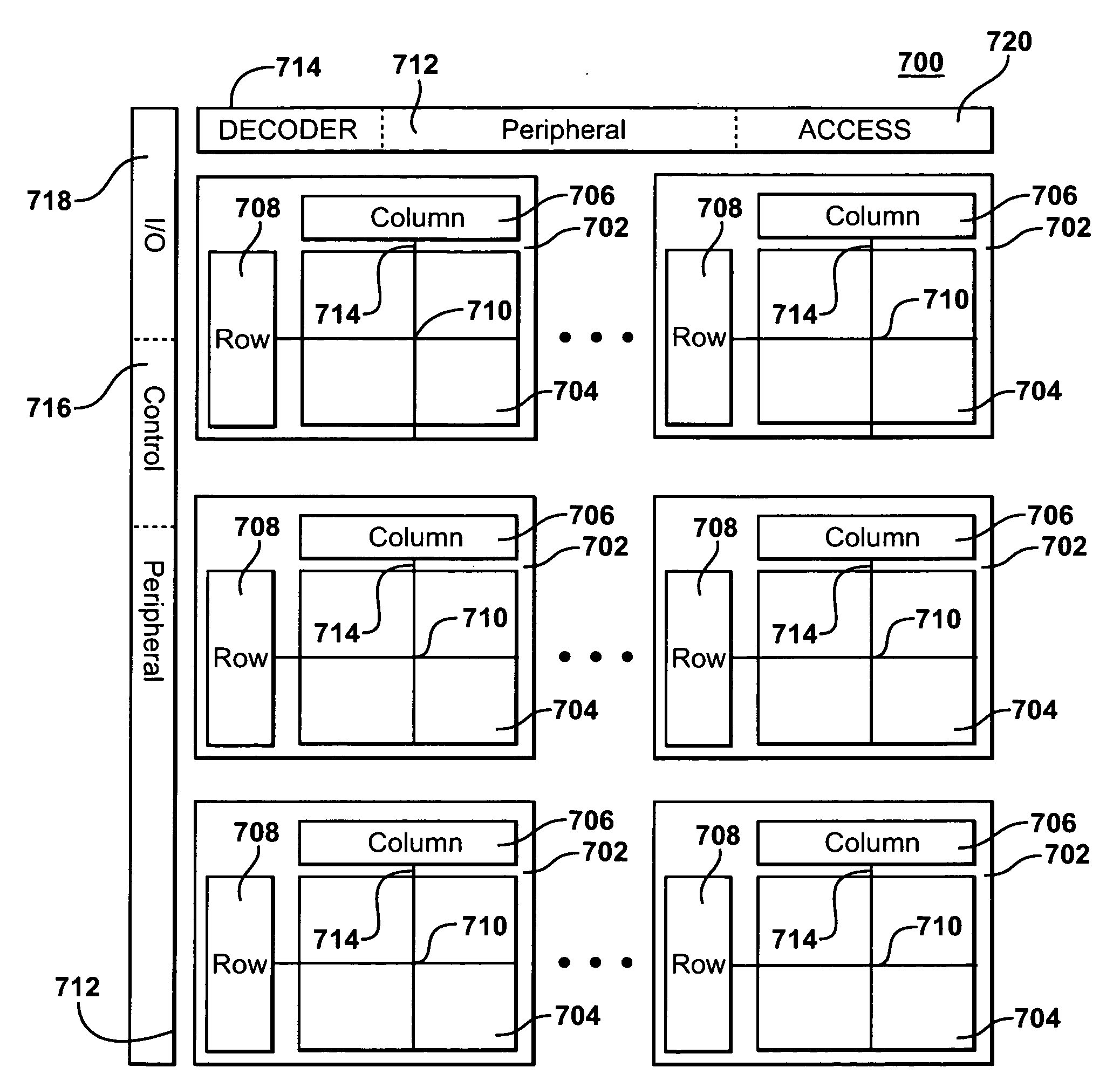

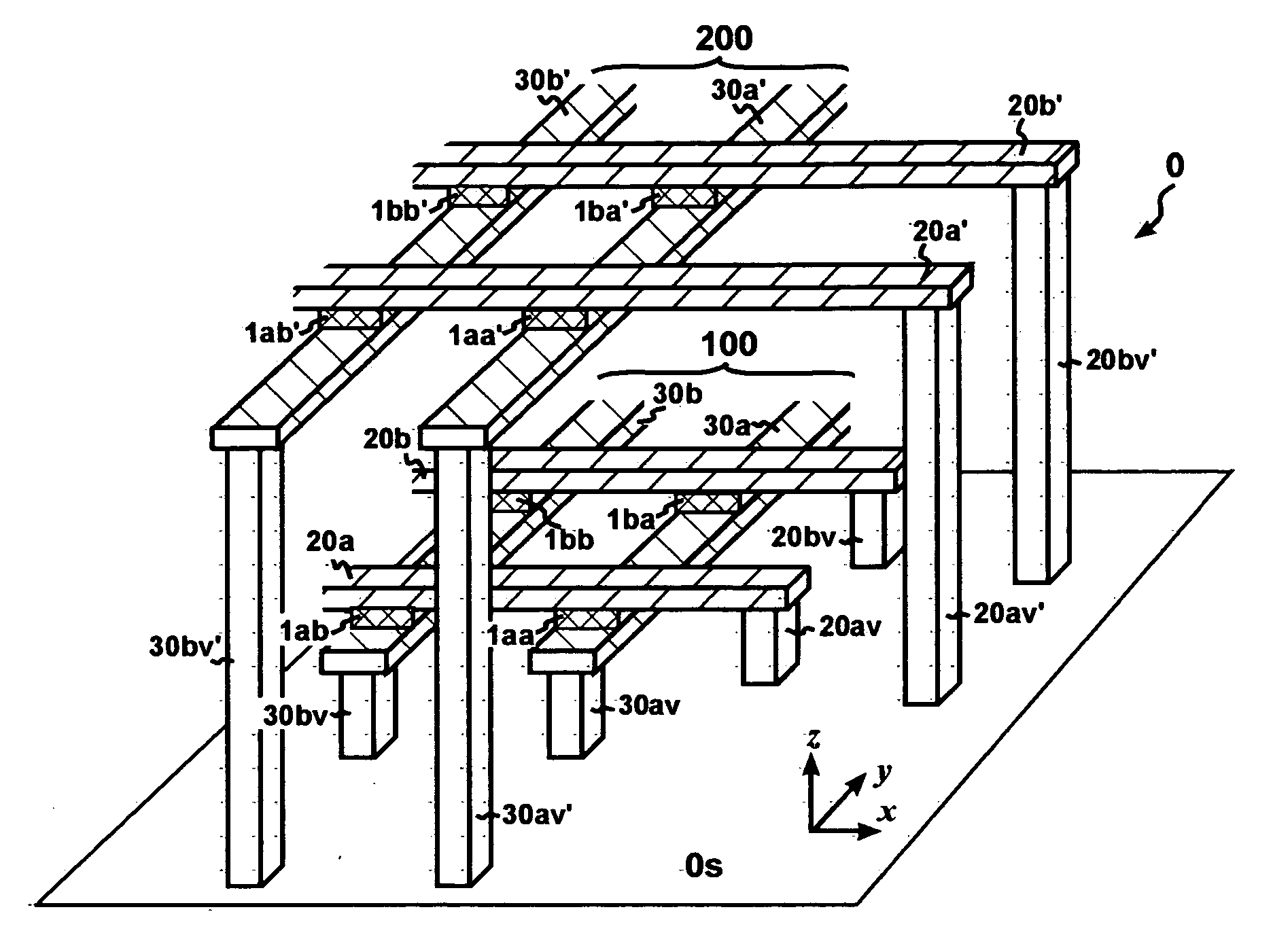

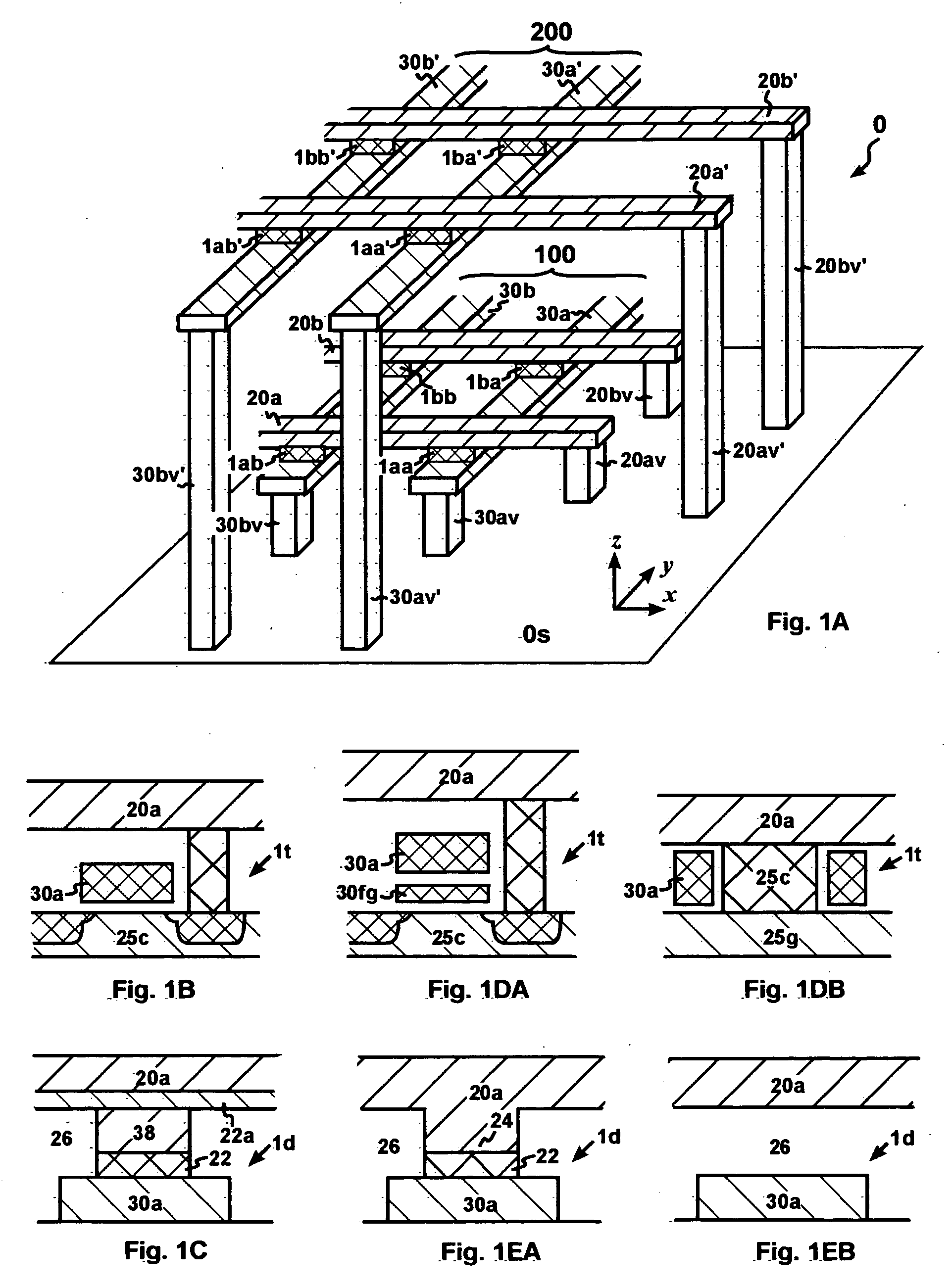

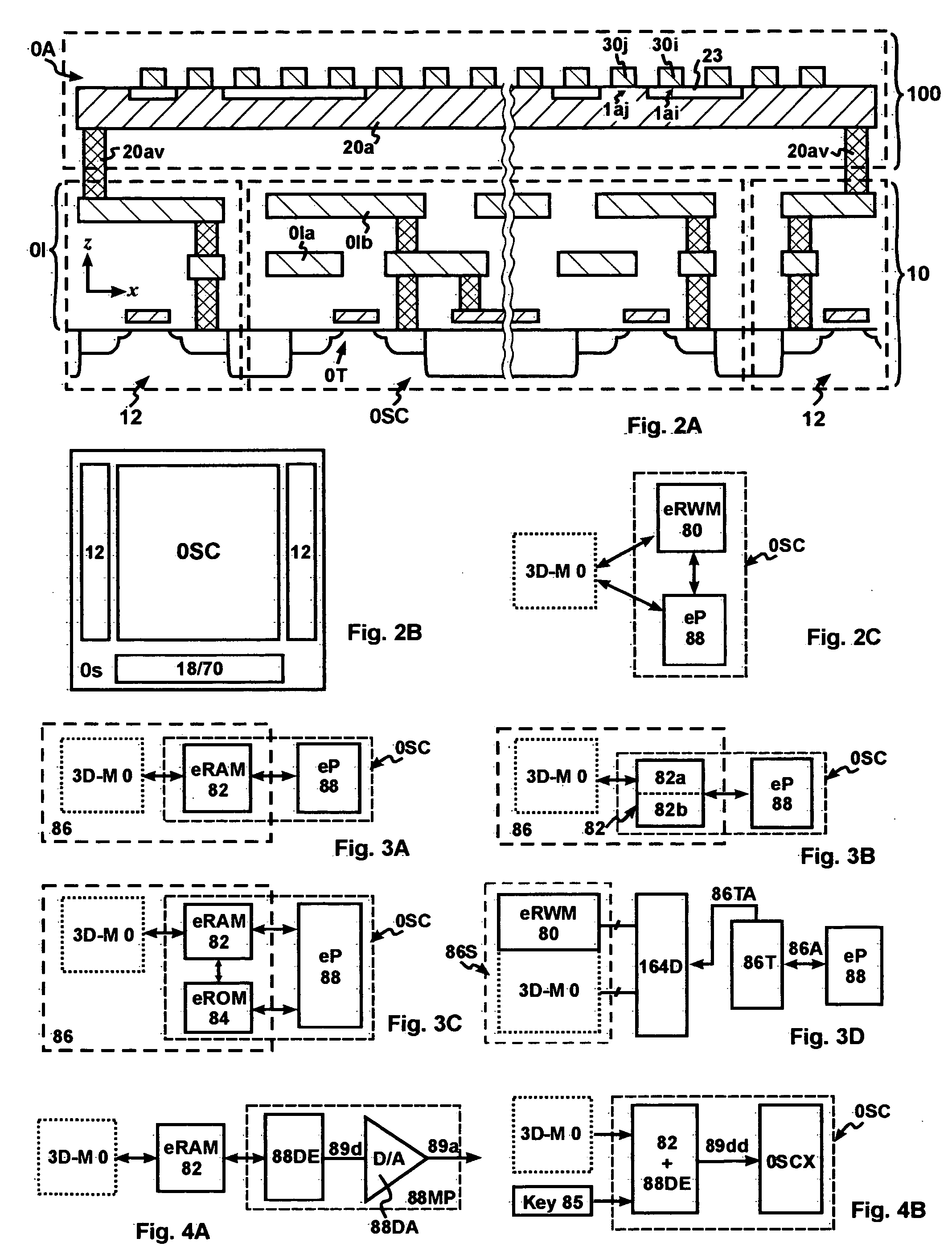

Electrically programmable three-dimensional memory

InactiveUS6861715B2Improve EP-3DM integratibilityImprove EP-3DMTransistorThyristorComputer scienceData security

One greatest advantage of the three-dimensional memory (3D-M) is its integratibility. In a electrically programmable three-dimensional integrated memory (EP-3DiM), an electrically programmable 3D-M (EP-3DM) is integrated with an embedded RWM and / or an embedded processor. Collectively, the EP-3DiM excels in speed, density / cost, programmability and data security.

Owner:ZHANG GUOBIAO

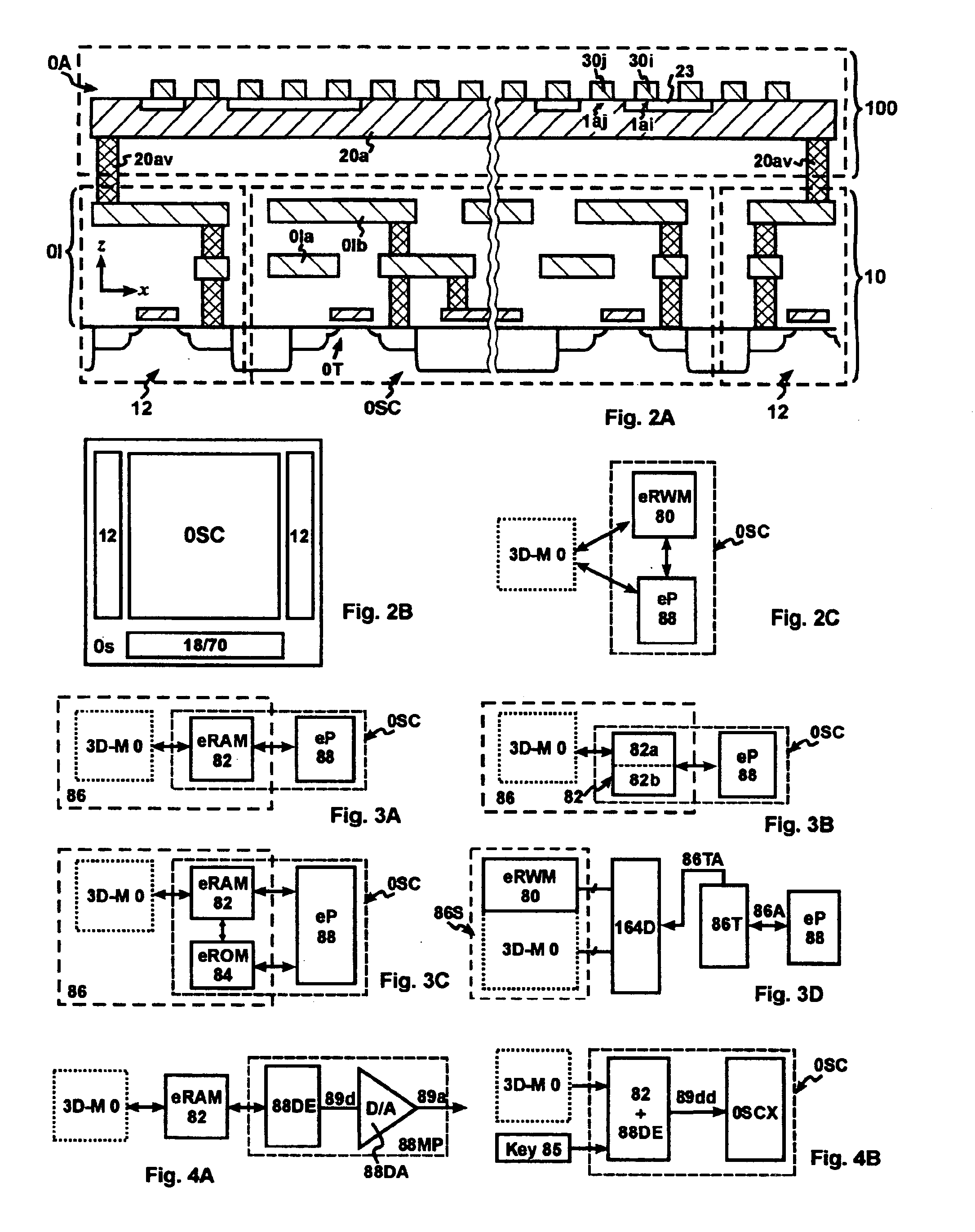

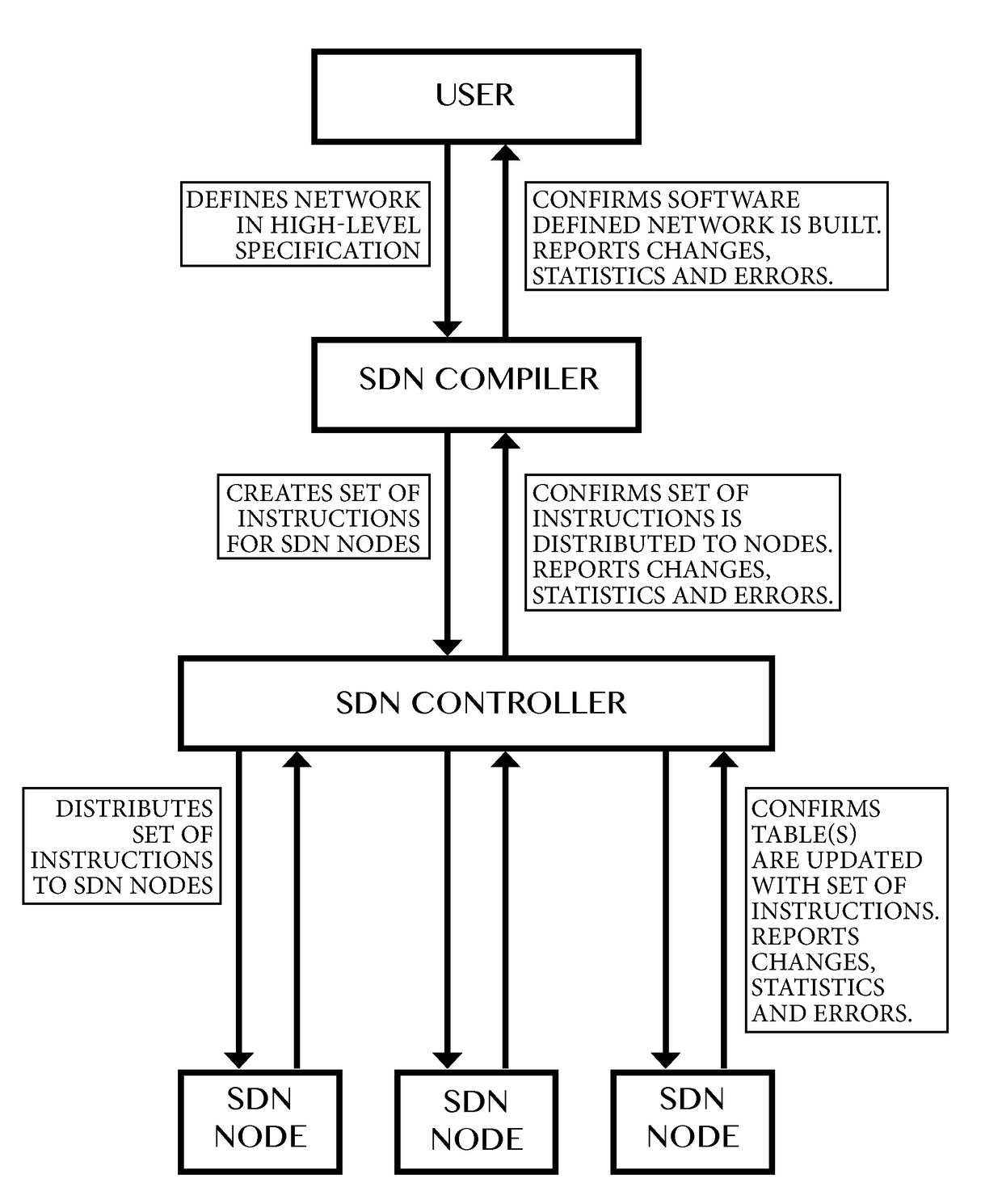

Compiler for and method of software defined networking, storage and compute performing operations

ActiveUS20170302530A1Increasing network programmabilityTightly coupledData switching networksMultiplexingDepth mapping

Method of and a compiler for controlling a network based on a logical network model. The network has physical nodes and logical nodes. The physical nodes are interconnected by physical links in accordance with a physical network layout. The logical network model has logical nodes indicated with a logical node name which refers to at least one physical node in the network. The method uses a depth-mapping relation defining how the logical nodes are mapped to the physical nodes. The method includes creating logical links between the logical nodes in dependence on the physical paths between the physical nodes and on the depth-mapping relation. The method uses edge-relationships between logical link, logical path, physical link, physical path and depth-mapping relations. Logical paths in the logical network are transformed into a physical path comprising of physical links between the physical nodes through recursive calculation and forwarding instructions are created for the physical nodes, in dependence on the edge-relationships and point-of-attachment names between physical links and physical nodes. A user of a compiler may specify additional operations other than switching, multiplexing or de-multiplexing to be performed at a logical node on packet or signal. Said packet or signal may be identified with a logical identifier identifying at least one logical link or logical path, and said additional operation may be specified at a logical node, providing programmability of additional operations in said logical network model. Said additional operations will, if possible, be performed by physical or virtual resources represented by physical nodes.

Owner:WOLTING HLDG

Three-Dimensional Memory Cells

InactiveUS20070170520A1Easy to integrateImprove manufacturing yieldTransistorSolid-state devicesComputer scienceRead-only memory

Owner:ZHANG GUOBIAO

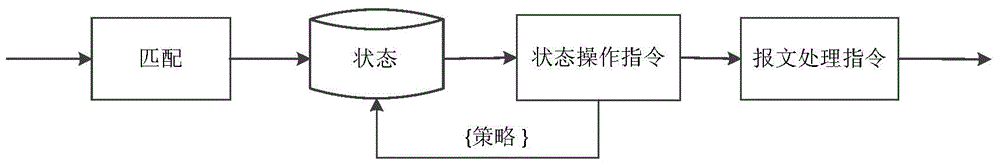

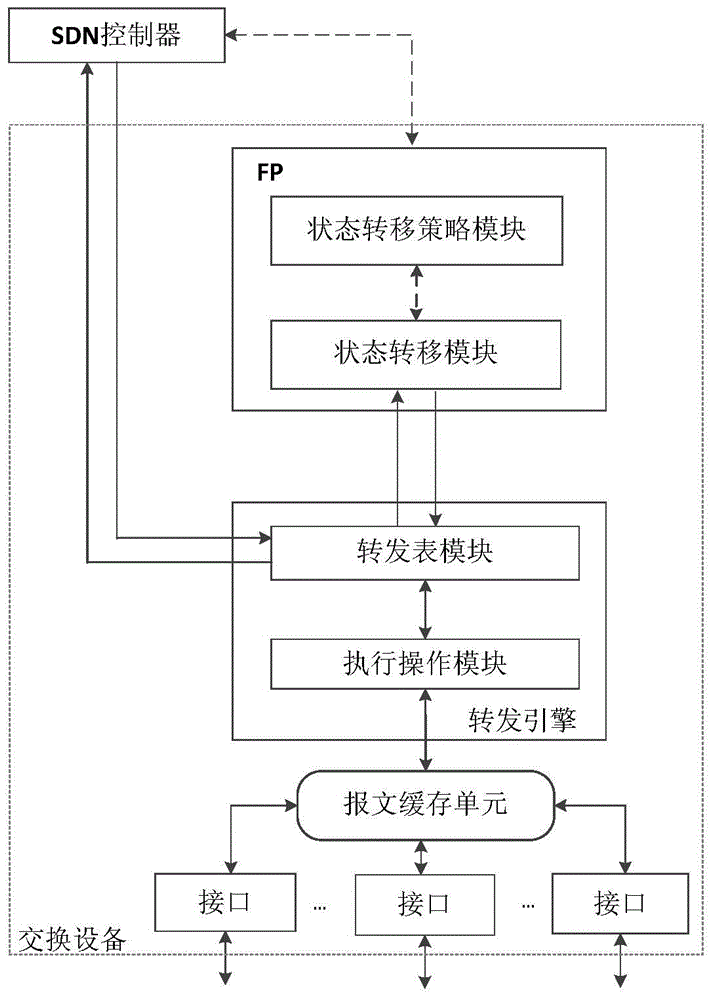

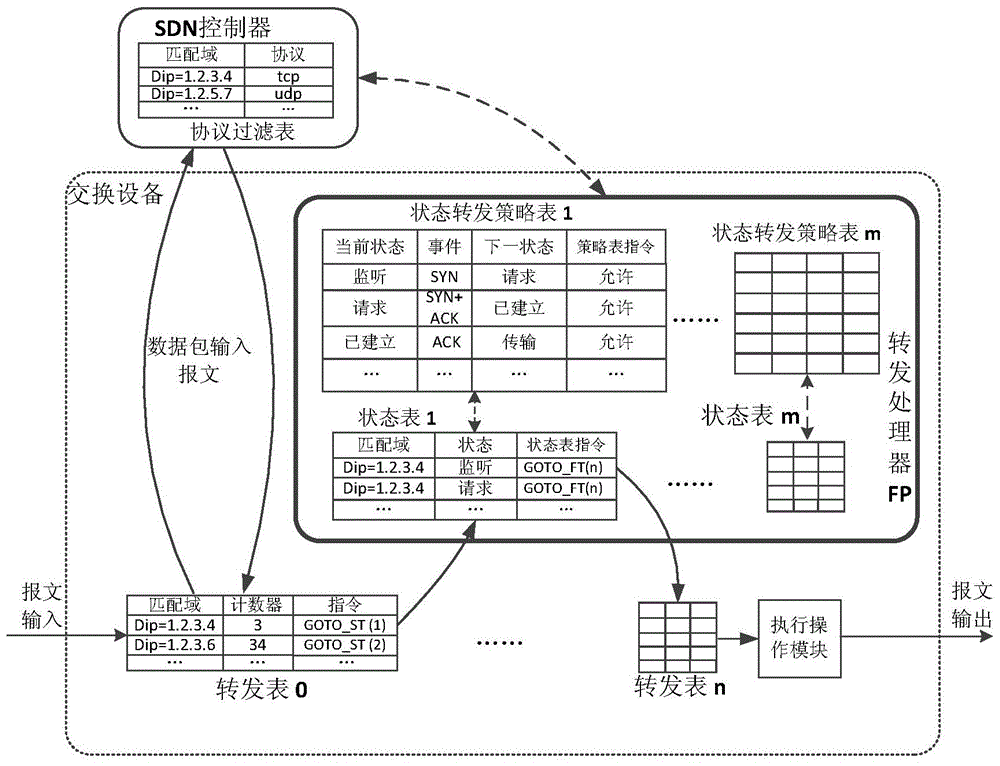

Software-defined networking (SDN) data plane strip state exchange device, SDN exchange system and SDN data plane strip state forwarding and processing method

ActiveCN104836753AHave full controlFlexible expansion of processing actionsData switching networksProcessing InstructionData stream

The present invention discloses a SDN data plane strip state exchange device, a SDN exchange system and a SDN data plane strip state forwarding and processing method. The SDN data plane strip state exchange device comprises a SDN data plane strip state forwarding processor which comprises the state processing modules and the strategy modules arranged for a plurality of application protocols, wherein the state processing modules are used to maintain the data plane data packets, the data flows, the states of the connection or a network and determine the control instructions and the message processing instructions according to the processing strategies provided by the strategy modules; and a forwarding engine which analyzes the received data message headers, sends the messages to the corresponding state processing modules according to the information matching forwarding tables of the data message headers, and queries the forwarding tables to forward the data flows according to the control instructions returned by the state processing modules. According to the present invention, the data messages, the data flows, the state information of the connection and the network can be processed on a SDN data plane.

Owner:TSINGHUA UNIV

Logic drive based on multichip package using interconnection bridge

ActiveUS20200111734A1Lower the barrierReduce expensesSemiconductor/solid-state device detailsSolid-state devicesMemory chipComputer architecture

A multi-chip package comprising: an interconnection substrate comprising an interconnection bridge embedded in the interconnection substrate, and an interconnection scheme comprising a first interconnection metal layer, a second interconnection metal layer over the first interconnection layer and the interconnection bridge, and a polymer layer between the first and second interconnection metal layers, wherein the interconnection bridge is embedded in the interconnection scheme and has sidewalls surrounded by the polymer layer; a semiconductor IC chip over the interconnection substrate and across over an edge of the interconnection bridge; a memory chip over the interconnection substrate and across over an edge of the interconnection bridge, wherein the interconnection bridge comprises a plurality of metal interconnects configured for a data bus coupling the semiconductor IC chip to the memory chip, wherein a bitwidth of the data bus between the semiconductor IC chip and the memory chip is greater than or equal to 512.

Owner:ICOMETRUE CO LTD

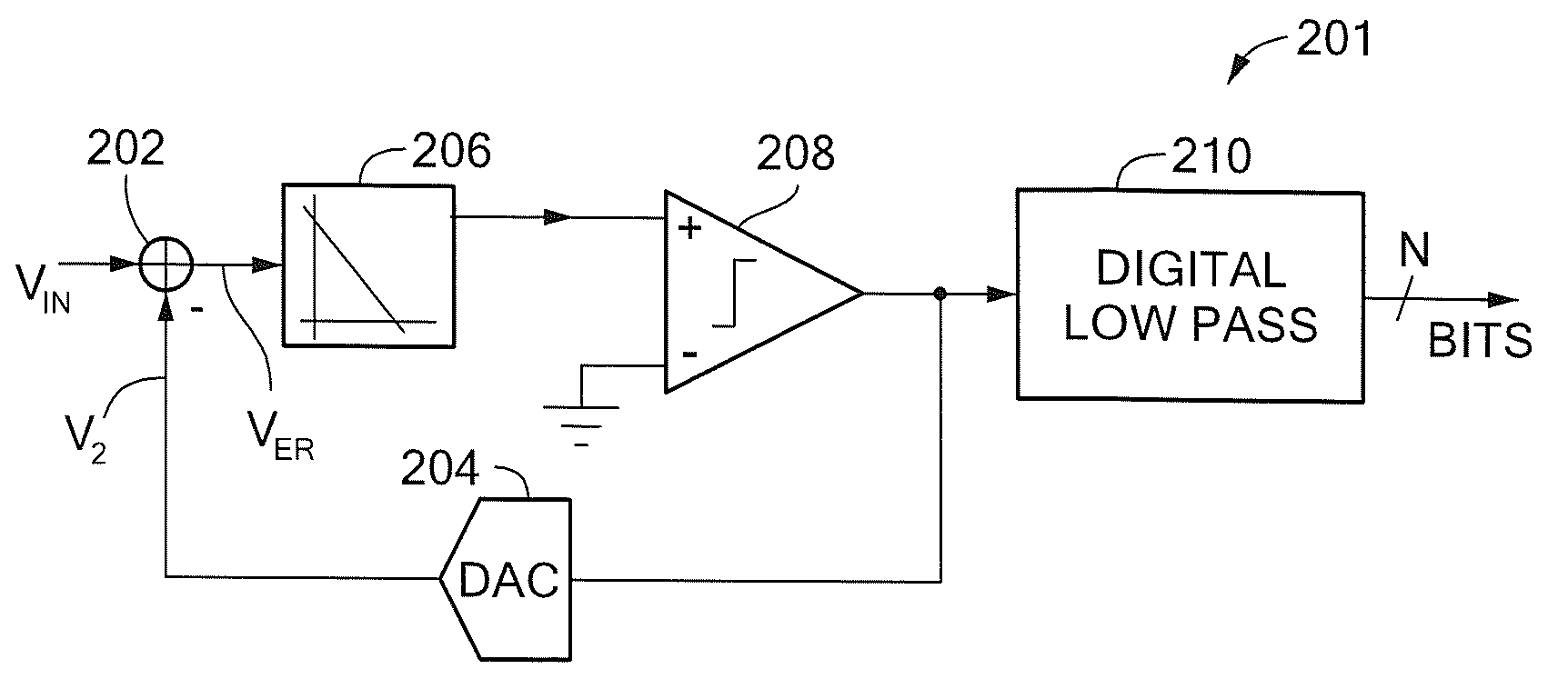

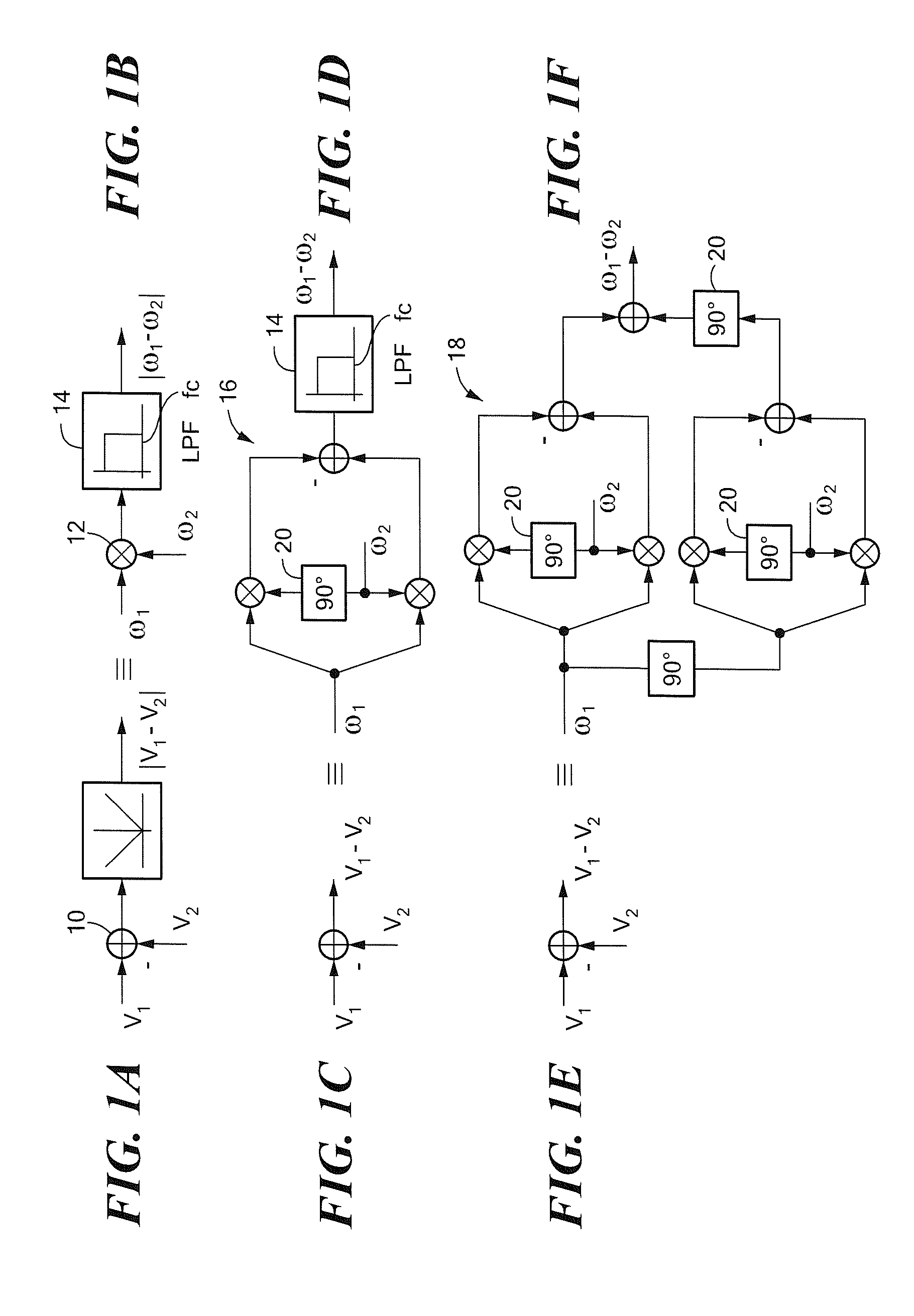

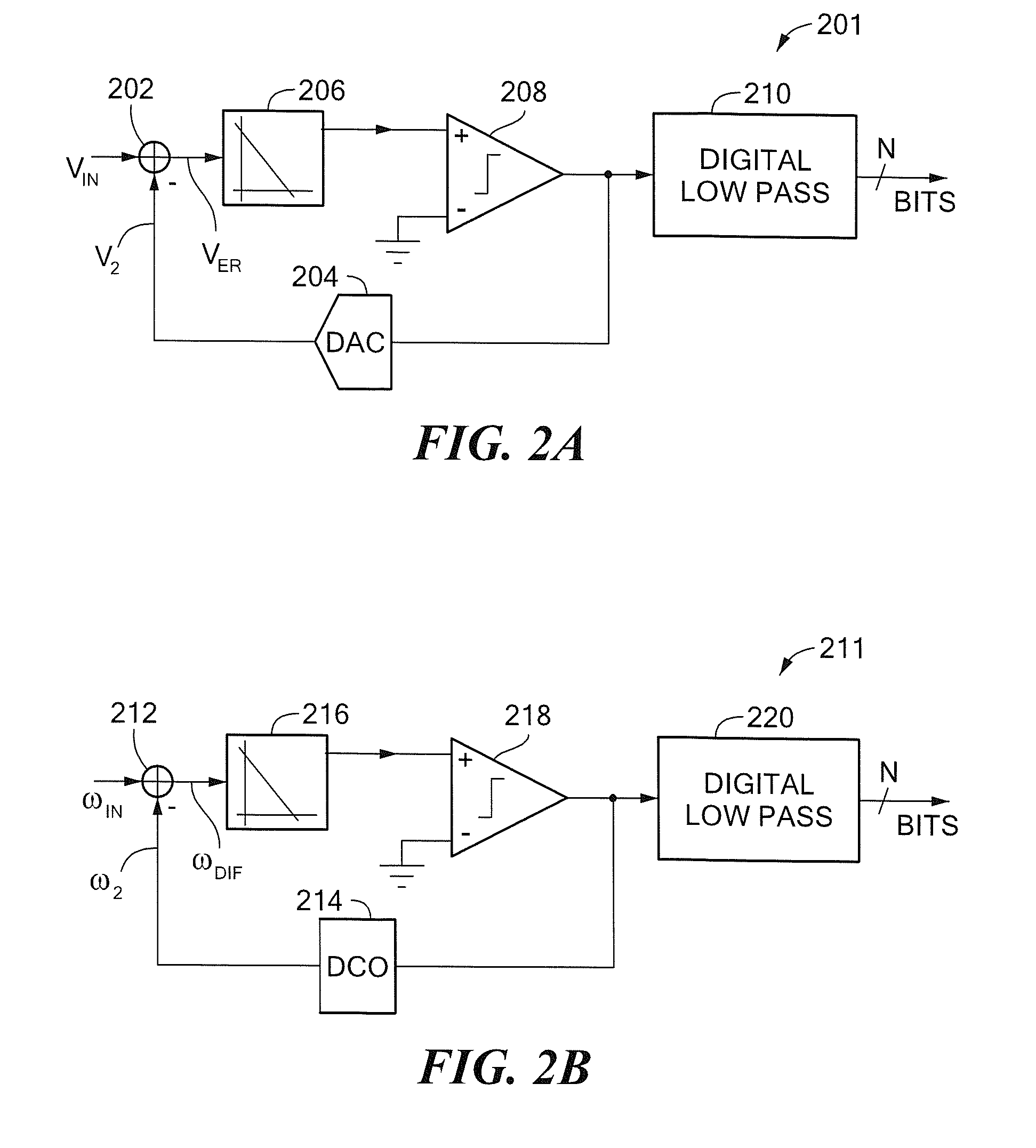

Architectures for universal or software radio

InactiveUS20080240301A1Wide fractional bandwidthImprove time resolutionSpatial transmit diversityPulse automatic controlAcquisition timeSpectrum analyzer

A system and technique for providing to flexible, programmable frequency estimators and spectrum analyzers that can operate over extremely large bandwidths and yet provide high spectral resolution are described. The acquisition time and hardware complexity of one technique scale as O(N), where N denotes the number of frequency bins acquired. Embodiments are disclosed in which architectures are implemented using exponentially-tapered transmission lines and filter cascades.

Owner:MASSACHUSETTS INST OF TECH

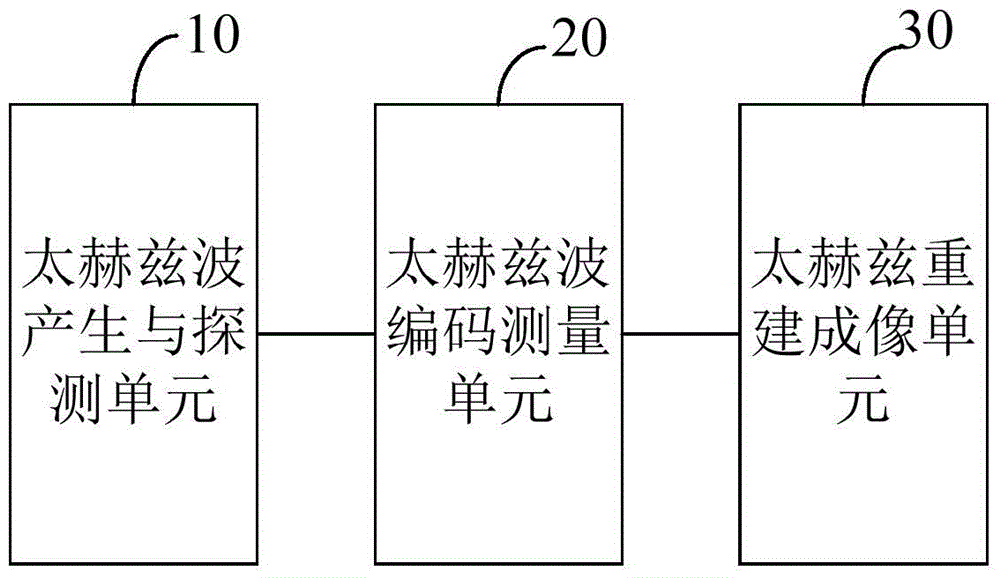

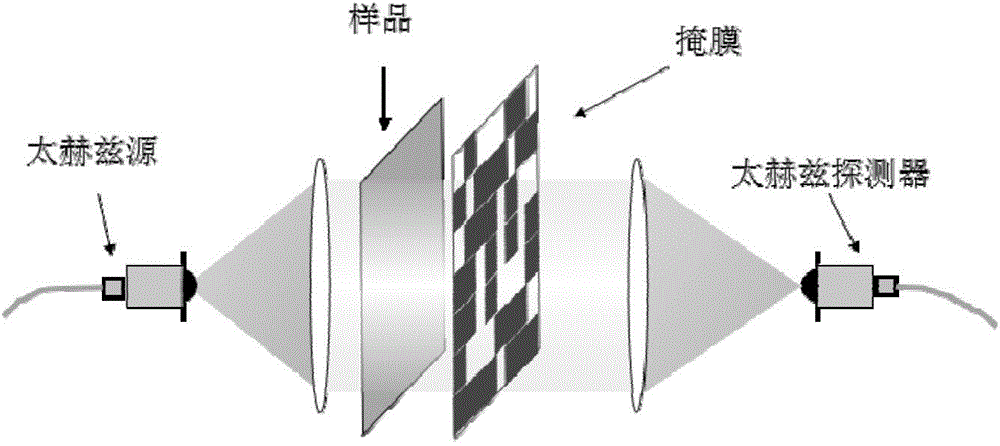

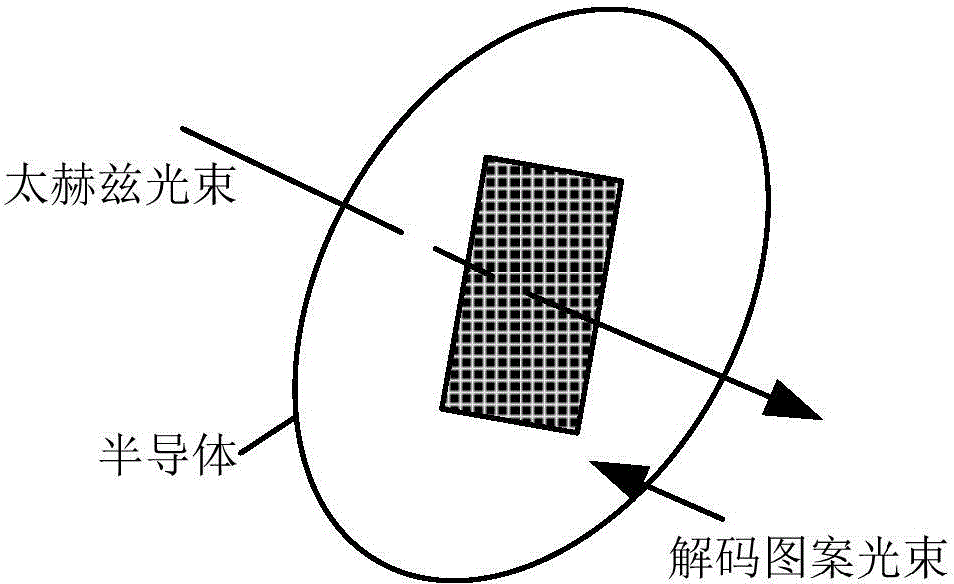

Terahertz compressive imaging system and method

ActiveCN105527242AFully digitalHigh speedMaterial analysis by optical meansLight beamReconstruction algorithm

The invention discloses a terahertz compressive imaging system and method. The system comprises 1, a terahertz generation and detection unit which comprises a laser source, a terahertz emitter and a terahertz detector, 2, a terahertz wave coding measurement unit which comprises a light splitter lens, a semiconductor mask plate and a digital projection device, wherein the digital projection device produces encoded pattern light beams, the light beams act on the semiconductor mask plate to cause semiconductor carrier distribution and the semiconductor mask plate allows the specific terahertz wave to go through the mask plate and keeps congruity of the specific terahertz wave and the light beam pattern so that terahertz wave spatial modulation is realized and a semiconductor mask plate coding function is realized, and 3, a terahertz reconstruction imaging unit which is used for recovering the original image through a reconstruction algorithm so that terahertz imaging is realized. Through combination of digital light processing projection and semiconductor photo-induced carrier characteristics, terahertz wave light-controlled modulation is realized. The system has the advantages of complete digitization, fast rate, high programmable capability, low cost and integration easiness.

Owner:SHENZHEN INST OF ADVANCED TECH

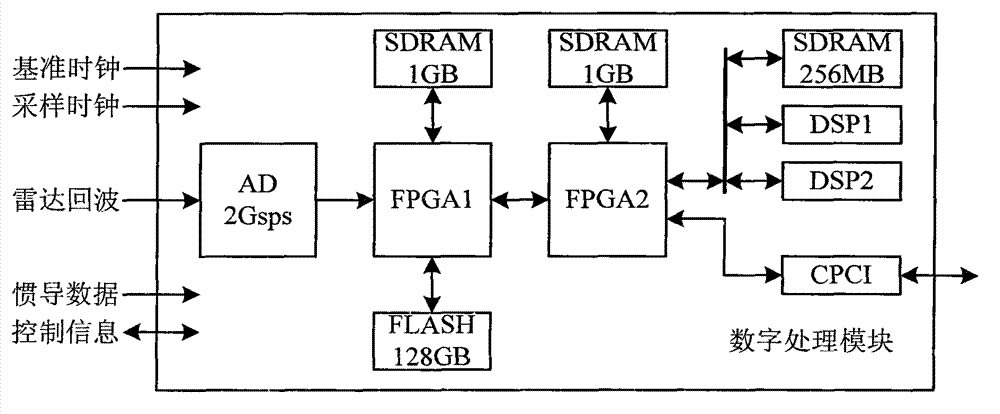

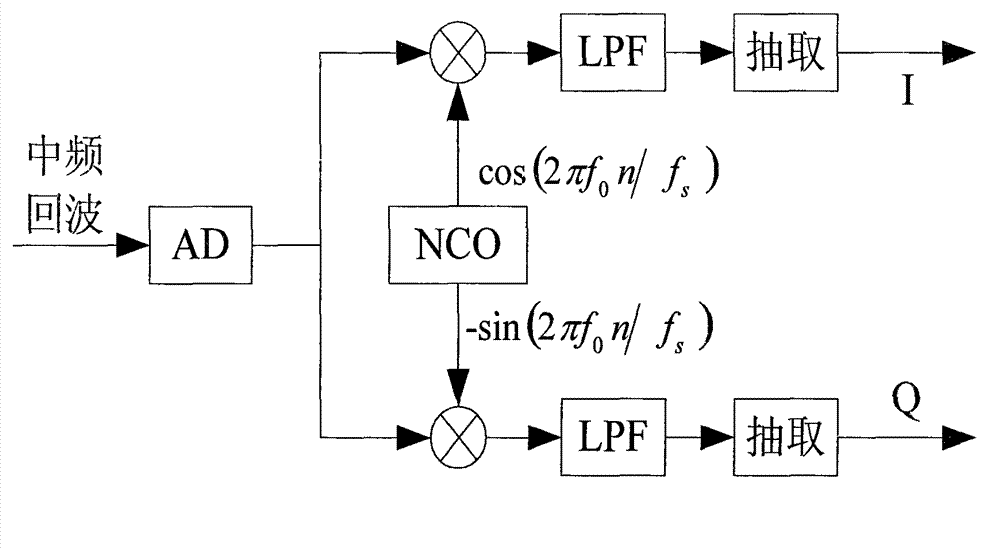

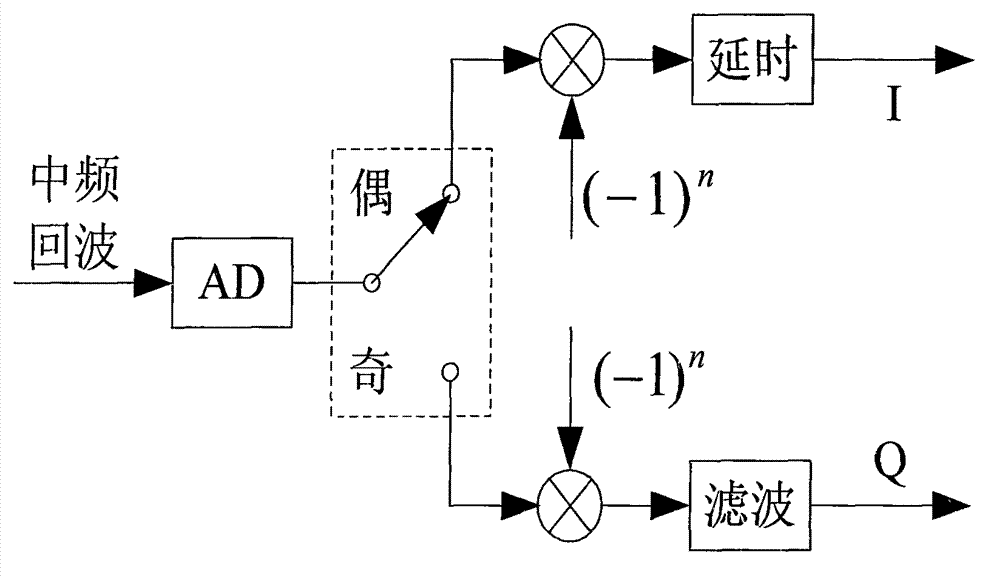

Design method of miniature synthetic aperture radar (SAR) digital down converter based on rapidly-moving finite impulse response (FIR) filter

InactiveCN103095220AGood orthogonalityImprove consistencyDigital technique networkMulti-frequency-changing modulation transferenceDigital down converterSynthetic aperture radar

The invention discloses a design method of a miniature synthetic aperture radar (SAR) digital down converter based on a rapidly-moving finite impulse response (FIR) filter. The steps includes utilizing a parallel processing method to process eight input data in a clock period, enabling an internal clock of a field programmable gate array (FPGA) to run at 250 megahertz, enabling a sampling rate in the miniature SAR to reach 2 G sps, utilizing a miniature SAR parameter to optimize an implementation structure of the traditional digital down converter, designing two FIR filters from Q way parallel filters in the optimized structure according to a work frequency of 250 megahertz and coefficient of an odd member position of an existing low pass filter, optimizing the digital down converter of the rapidly moving FIR filter design and finally designing a miniature SAR digital processing hardware module which is used for processing data of the digital down converter. According to requirements of the miniature SAR, the design method of the SAR digital down converter based on the rapidly-moving FIR filter utilizes the FPGA to achieve the high-speed and direct digital down converter module, takes high sampling rate in account, optimizes and screens out an optimal structure and improves digitization degree and performance of radar.

Owner:XIDIAN UNIV

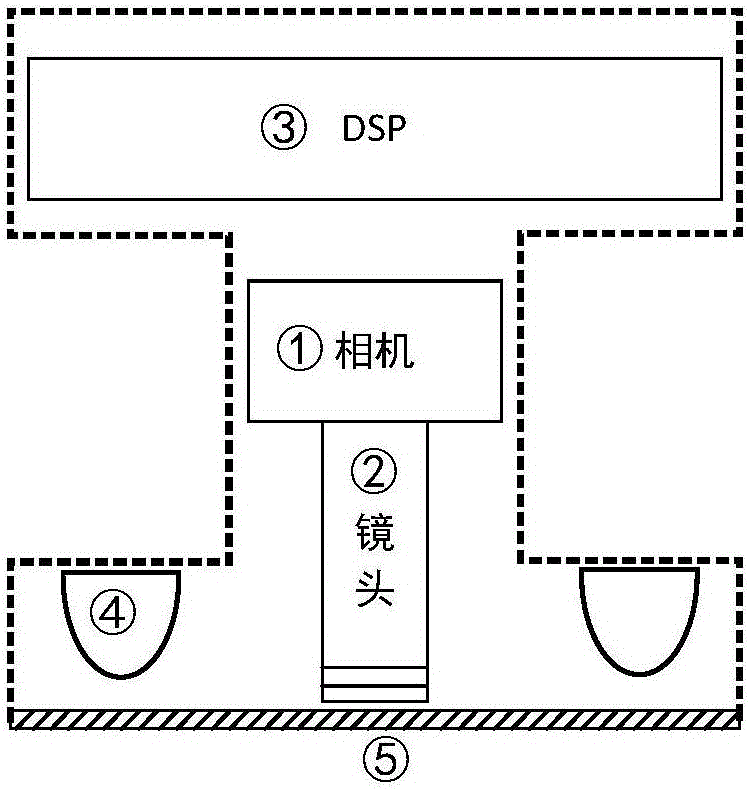

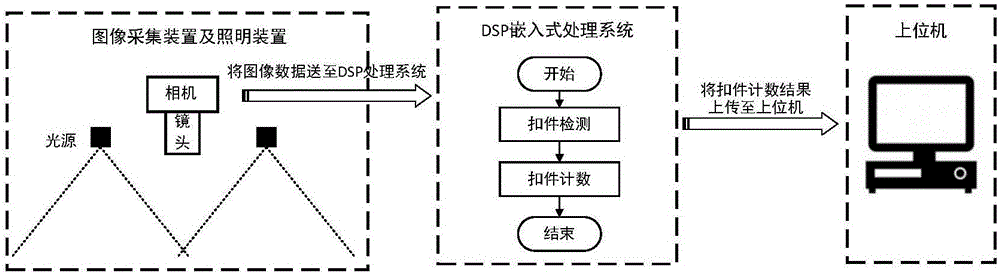

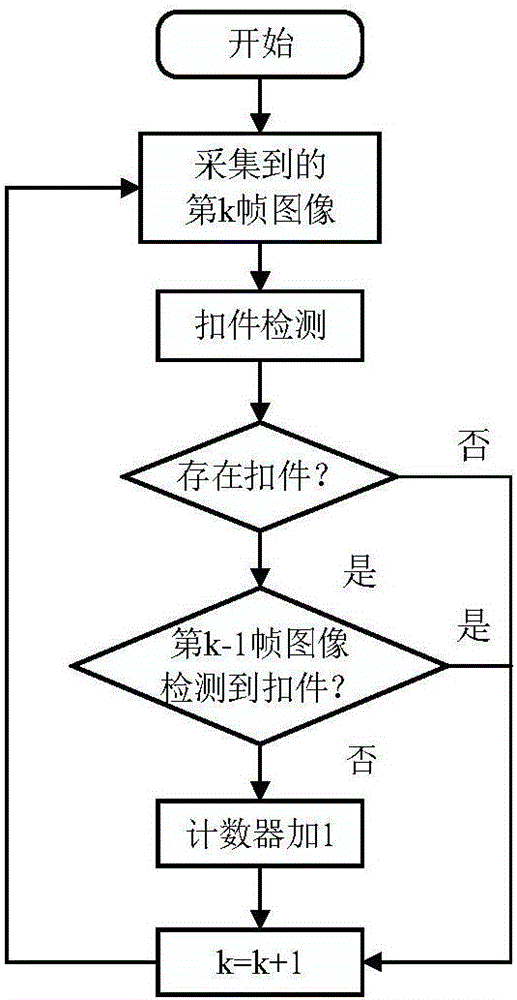

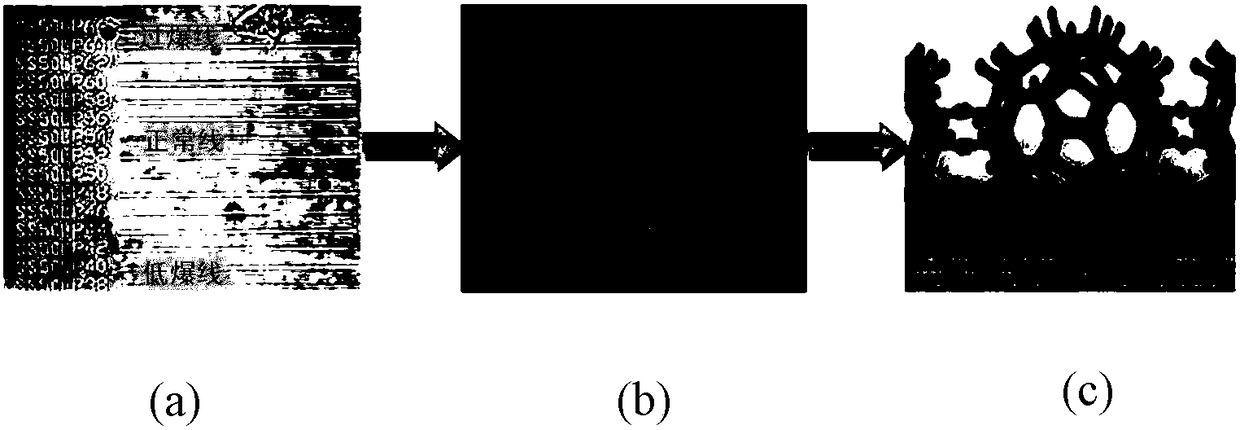

High-speed rail fastener detection and counting method and system based on machine vision

InactiveCN106709911AHigh positioning accuracyGood value for moneyImage enhancementImage analysisMachine visionGps positioning system

The invention relates to a high-speed rail fastener detection and counting method and a high-speed rail fastener detection and counting system based on machine vision. The high-speed rail fastener detection and counting system comprises image acquisition equipment, a DSP embedded processing system and two LED lighting devices, and designs a rapid fastener detection method based on area and width characteristics of a fastener. Compared with a fastener positioning methods adopting a photoelectric encoder, a photoelectric ranging sensor, a GPS positioning system and the like, the fastener positioning method based on machine vision has the advantages of high positioning precision, no accumulative error, simple structure, easy establishment, high cost performance and the like. A fastener counting result obtained by the high-speed rail fastener detection and counting system is uploaded to an upper computer, a rail geometric parameter fault position obtained by a rail geometric parameter measurement sensor is marked, the maintenance position is provided for railway maintenance personnel quickly and precisely, and the high-speed rail fastener detection and counting method and the high-speed rail fastener detection and counting system are of great significance to safety early warning of the railway.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

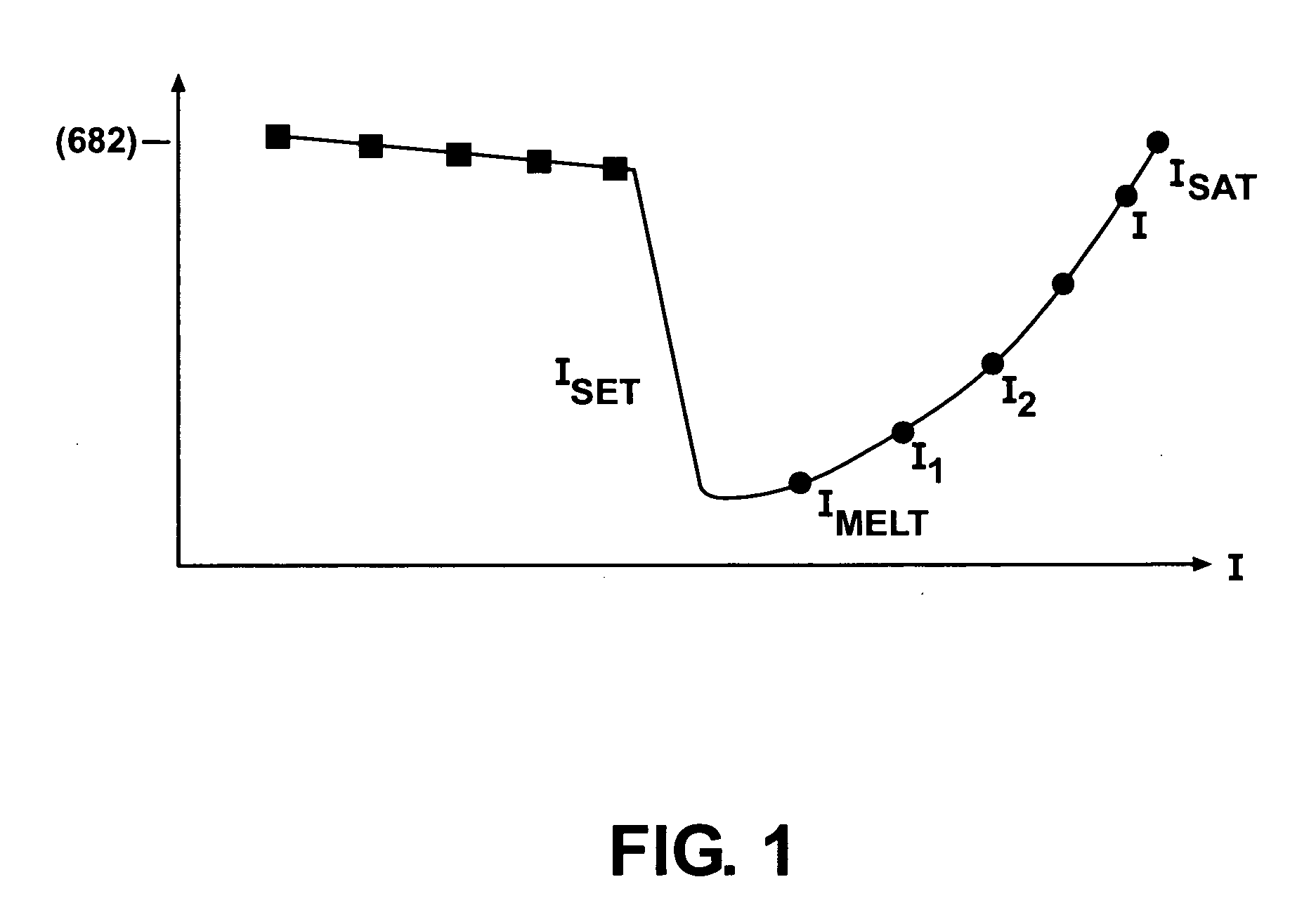

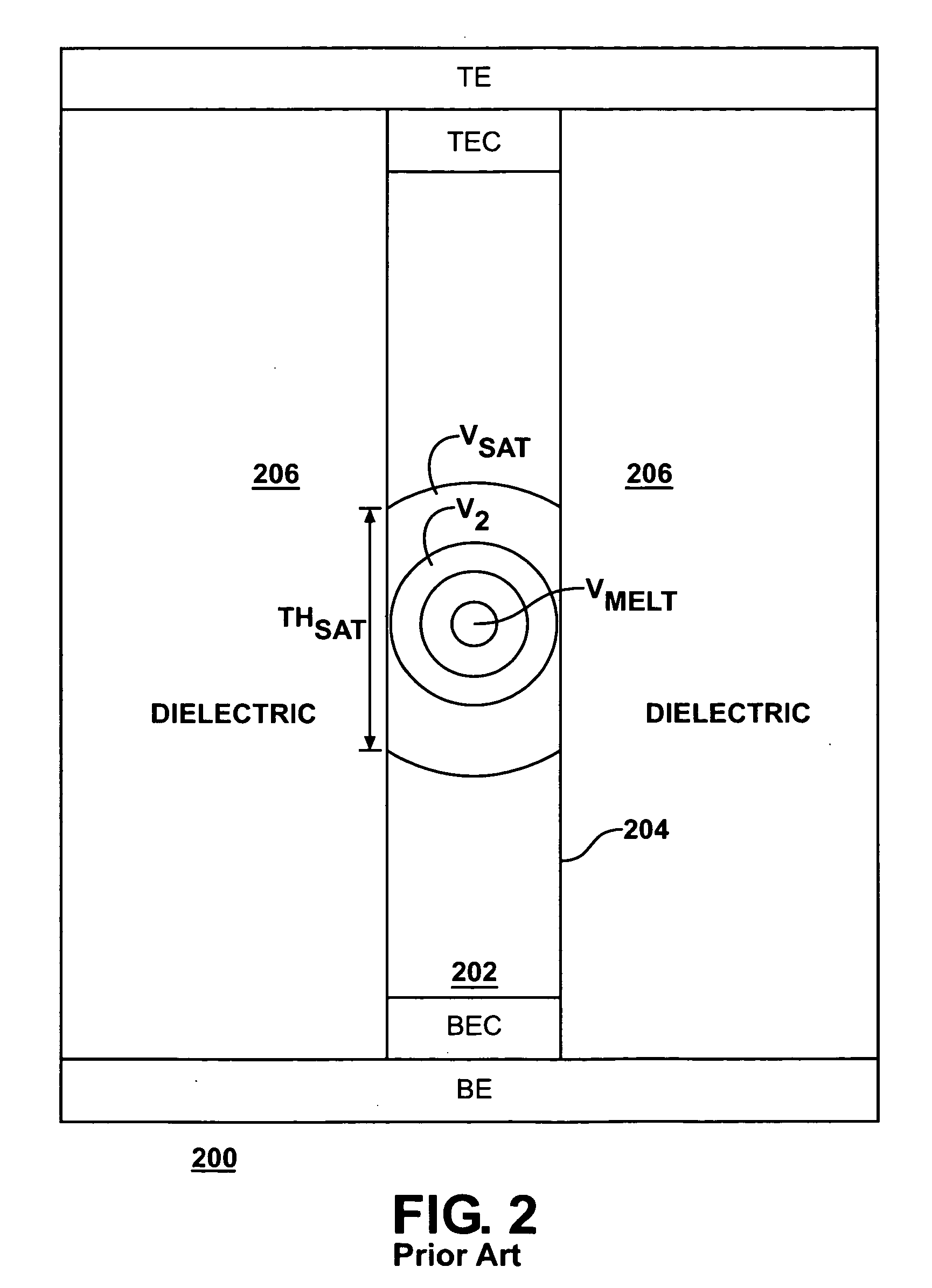

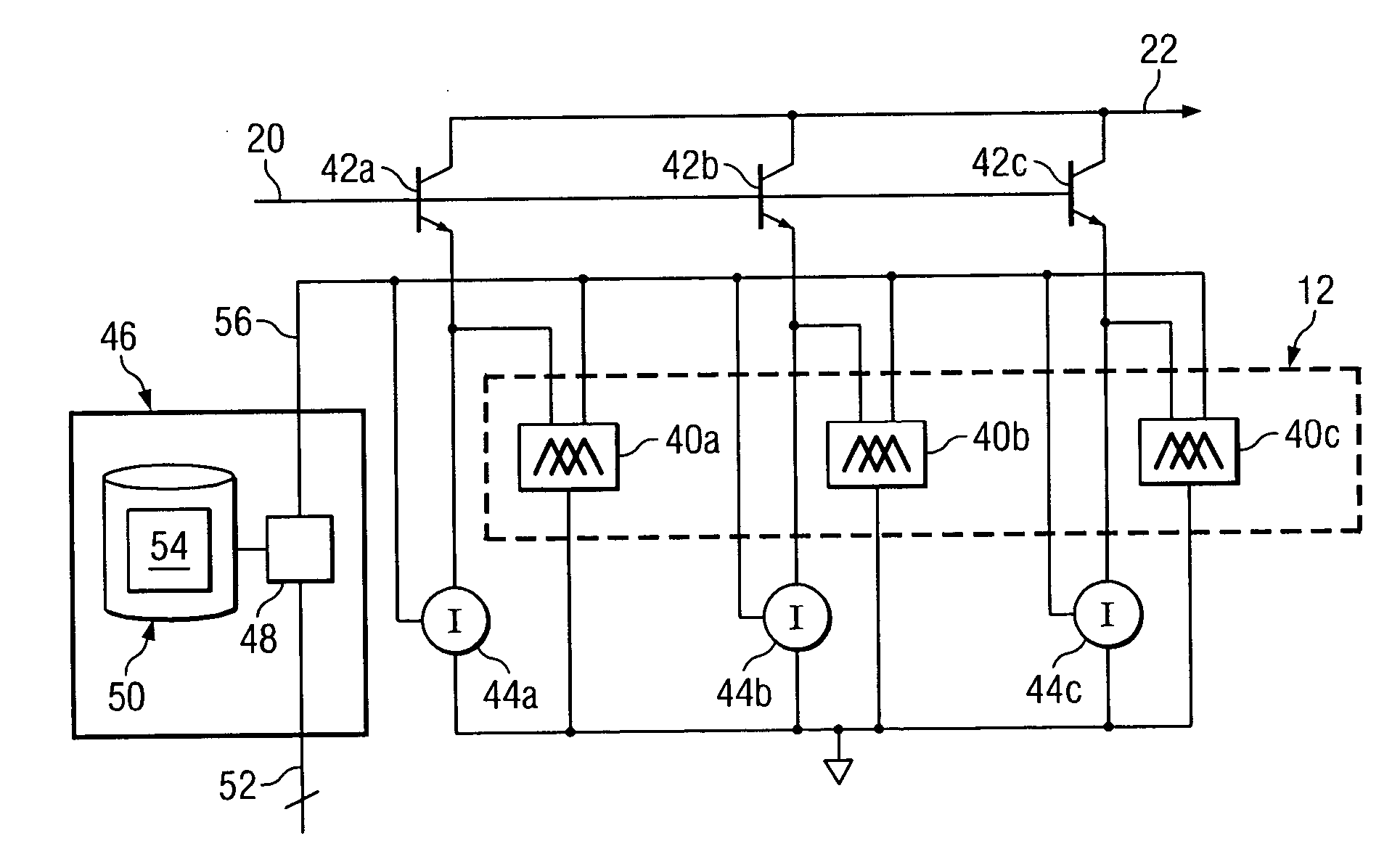

Apparatus and method for memory

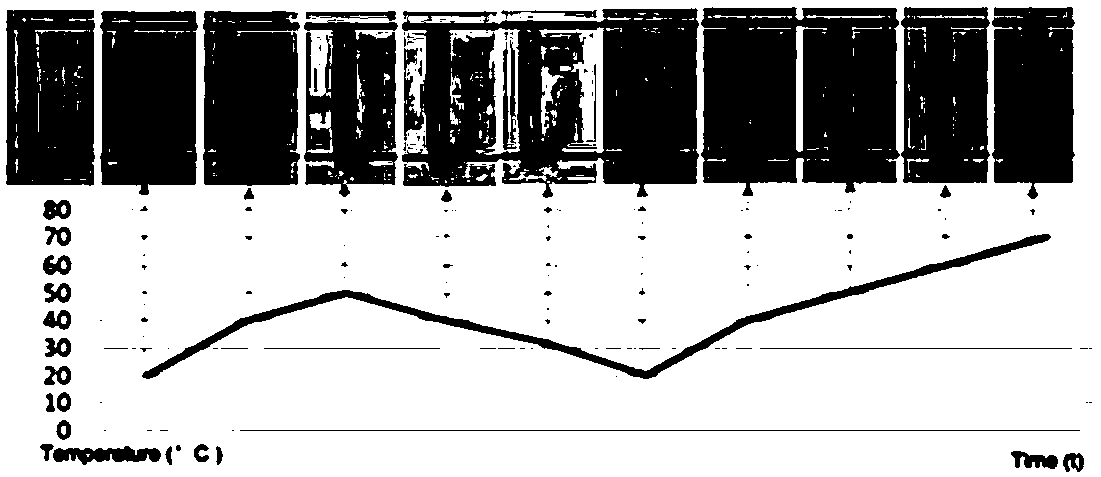

InactiveUS20100059729A1Improve programmabilityMaximize the effectSolid-state devicesSemiconductor/solid-state device manufacturingThermal conductivityElectric current

A programmable resistance memory includes a volume of programmable resistance material formed between and coupled to two electrodes. The volume of programmable resistance material includes a region of enhanced programmability that is positioned to maximize the effect of a programming current. The region of enhanced programmability is positioned at a distance from regions of high thermal conductivity, such as areas in close proximity to electrodes.

Owner:OVONYX

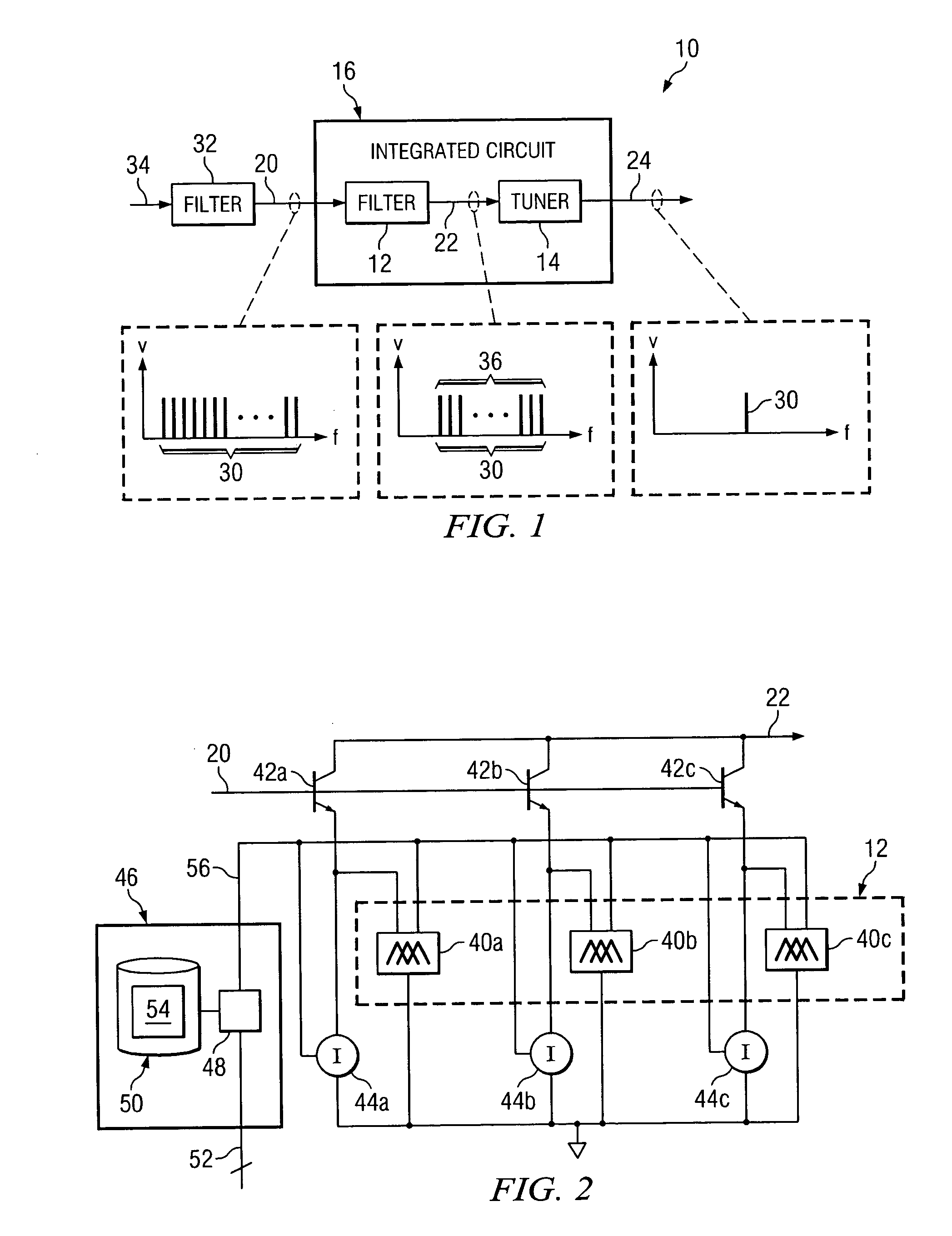

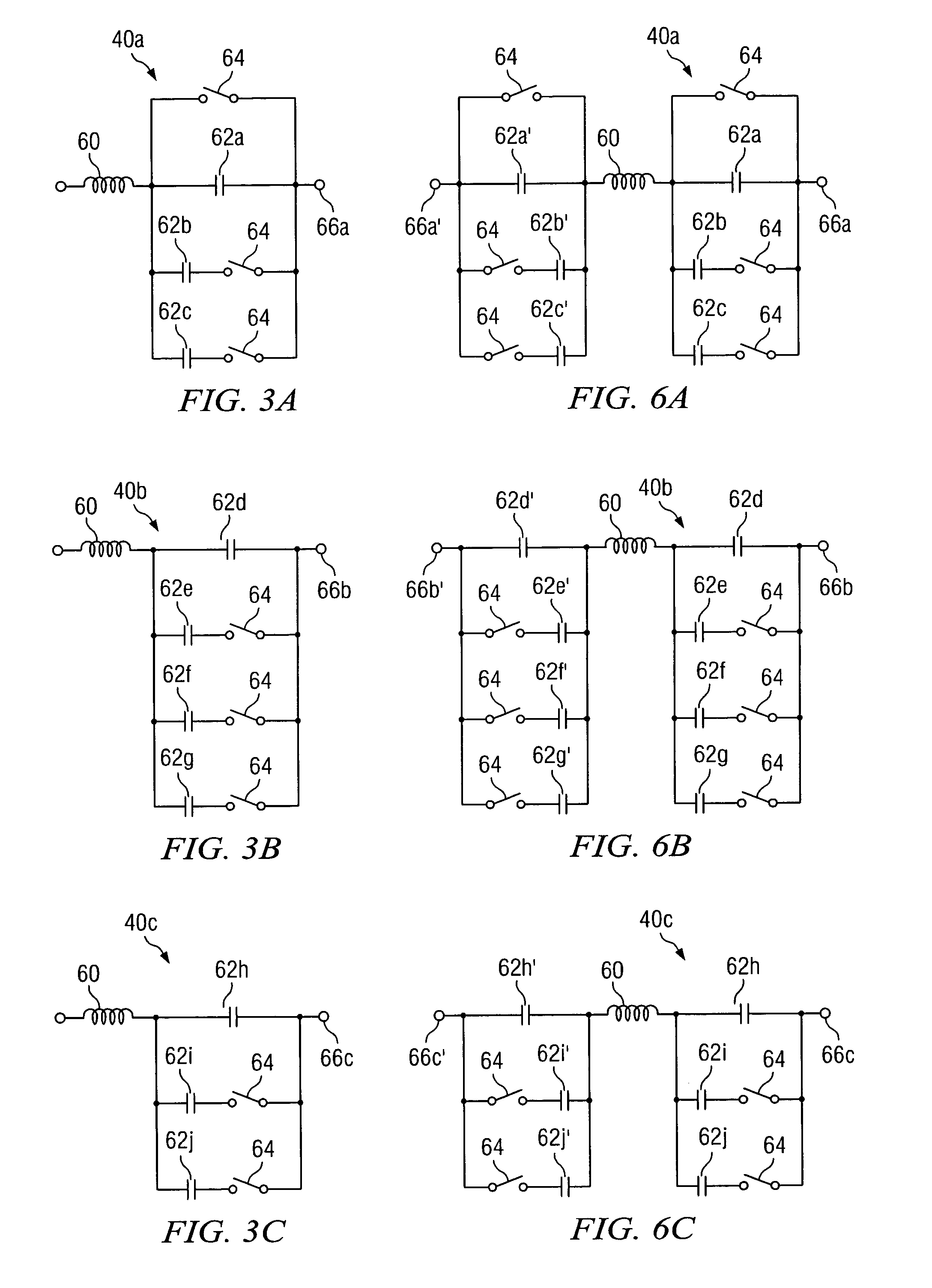

Integrated channel filter and method of operation

ActiveUS20050088254A1Disadvantages and reduced eliminatedProblems reduced eliminatedMultiple-port networksTelevision system detailsEngineeringIntegrated circuit

A system includes a filter and a tuner formed on an integrated circuit. The filter receives an input signal comprising a first number of channels and communicates an intermediate output signal comprising a second number of channels less than the first number of channels. The tuner is coupled to the filter and receives the intermediate output signal and communicates an output signal comprising a third number of channels less than the second number of channels.

Owner:CSR TECH INC

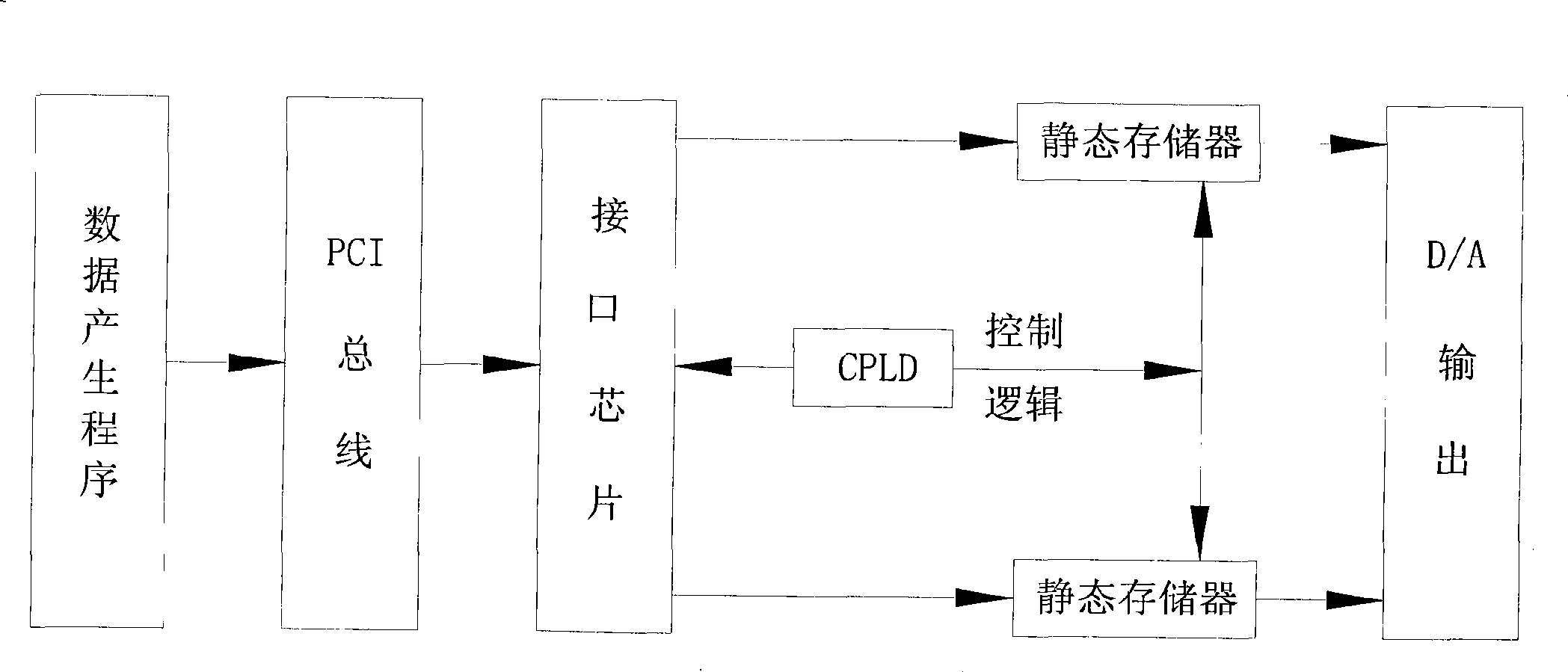

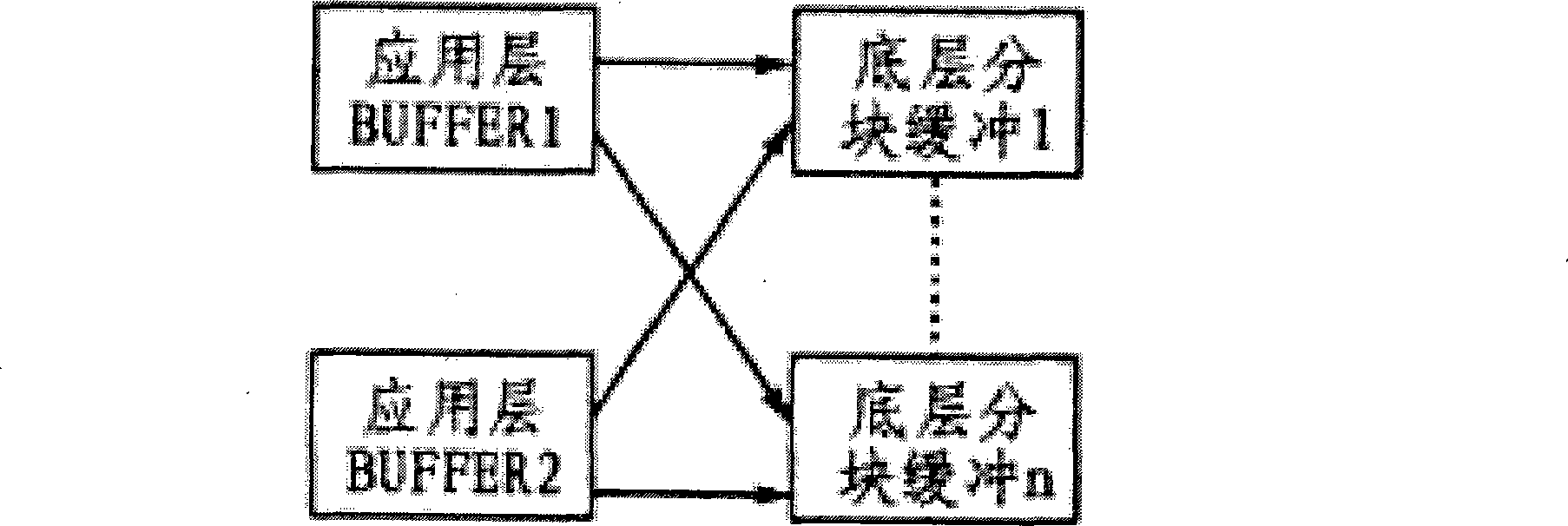

Optional waveform generator based on PCI bus

InactiveCN101425103AQuick switchGuaranteed continuitySpecial data processing applicationsParallel computingControllability

The invention relates to an arbitrary waveform generator based on a PCI bus, which comprises the PCI bus being a local bus not attached to some a concrete processor. Structurally, the PCI is a primary bus which is inserted between a CPU and an original system bus, management on the layer is concretely realized by a bridge circuit, and an interface between top and bottom is realized to coordinate data transportation. An application layer buffer zone can continuously exchange data. The process of the data transportation is sponsored by an application layer program, but is executed by a chip PLX9054 of a PCI bridge interface, application layer software can carry out data generation and allocation in the process, and the whole transportation process is completed by direct memory access (DMA) and interruption. By utilizing the buffer zone to fast exchange the data, the arbitrary waveform generator can fast carry out data exchange, efficiently ensures the continuity of space signals and the fast switch of multiple signals, and has the advantages in multiple aspects such as flexibility, rapidness, changeability, controllability, high accuracy, and the like.

Owner:成都飞机工业(集团)电子科技有限公司

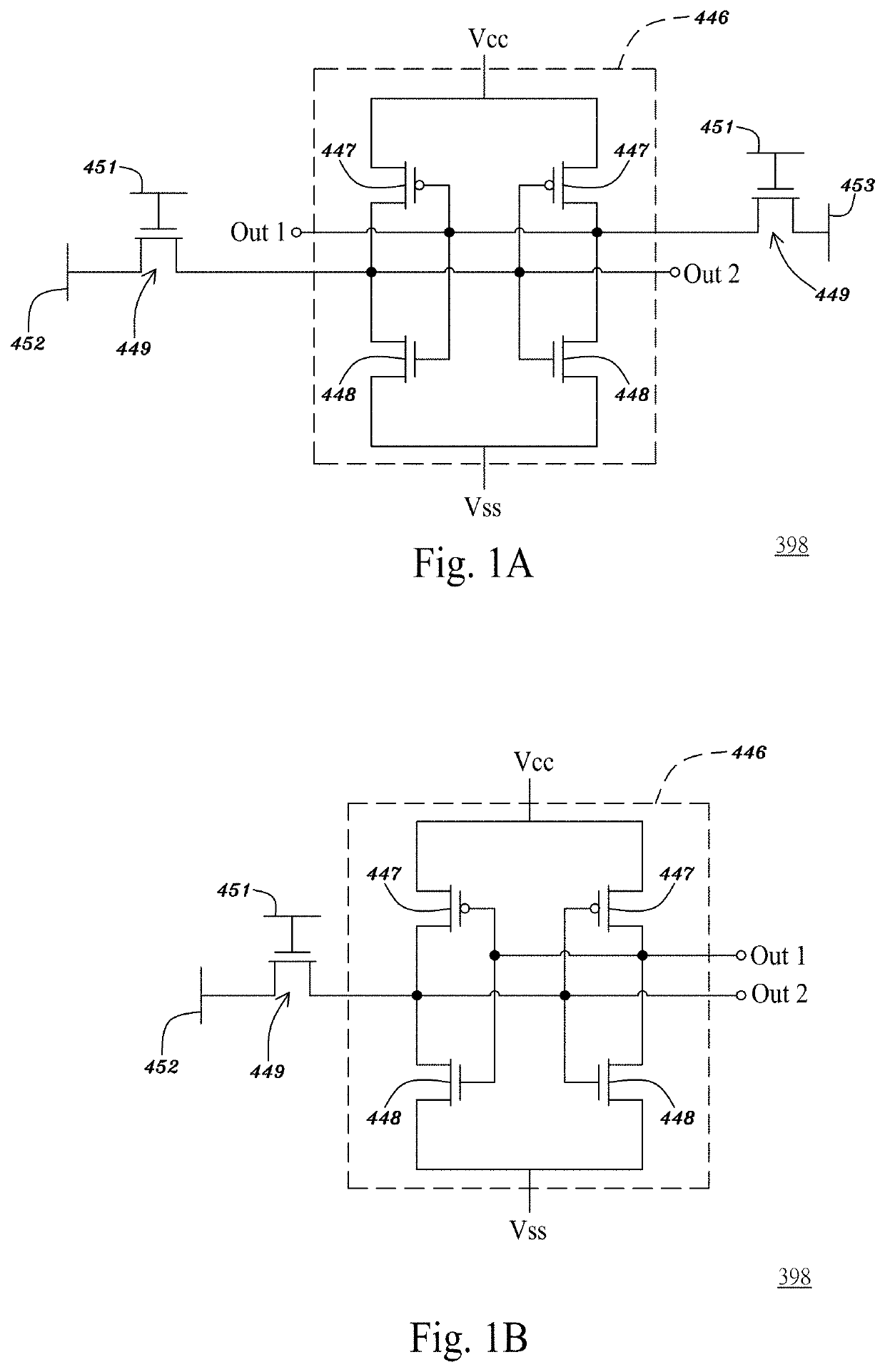

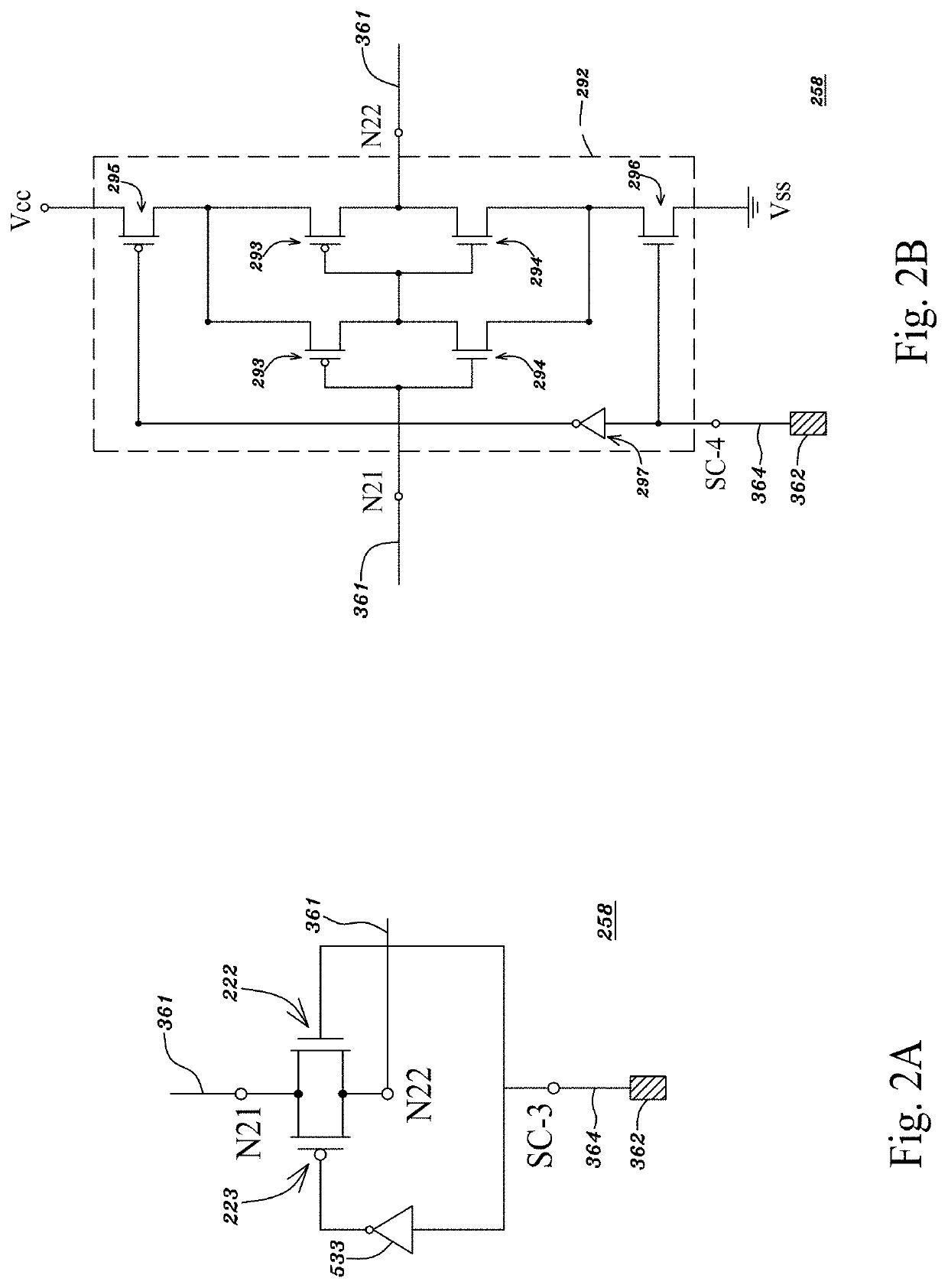

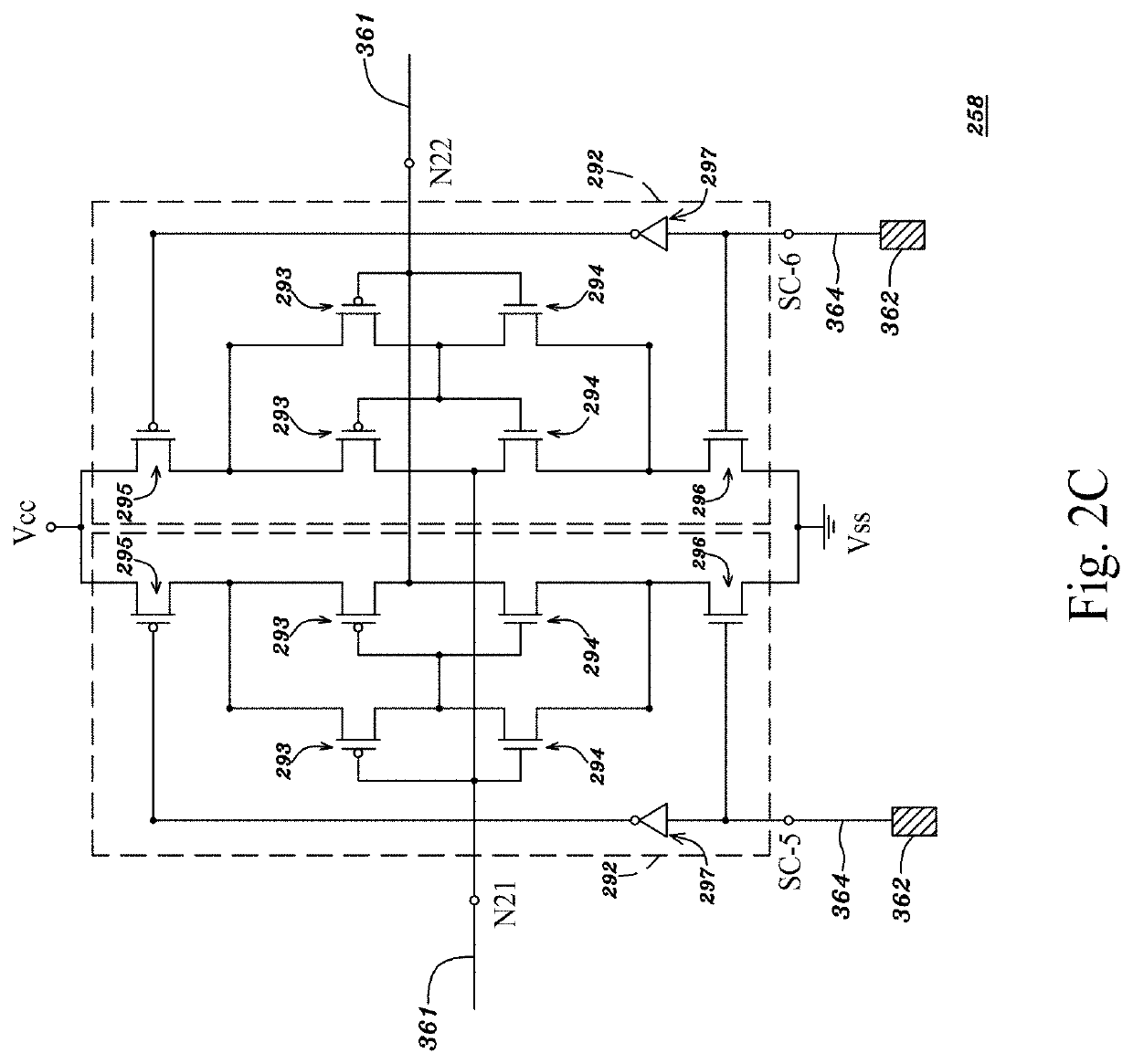

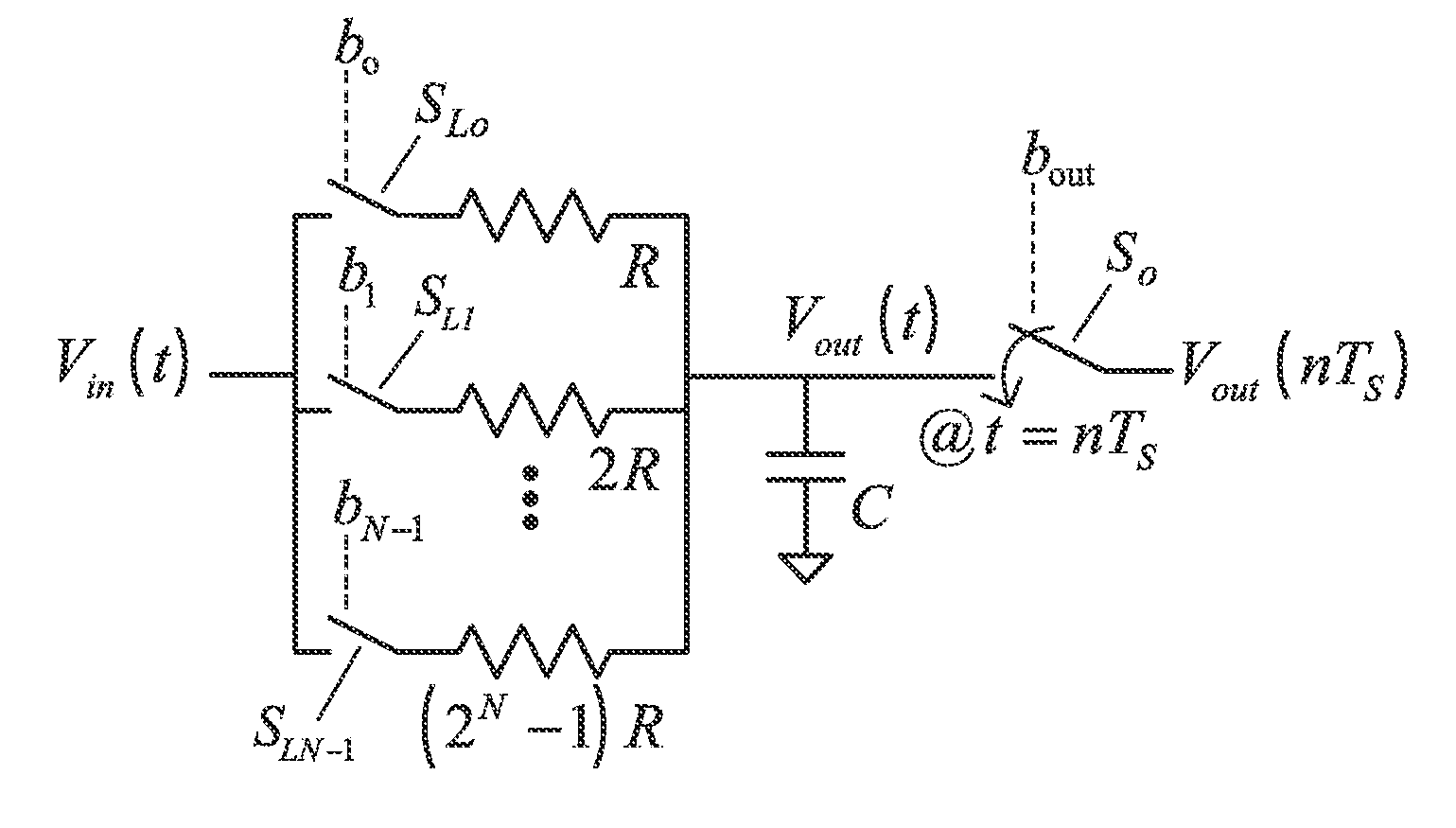

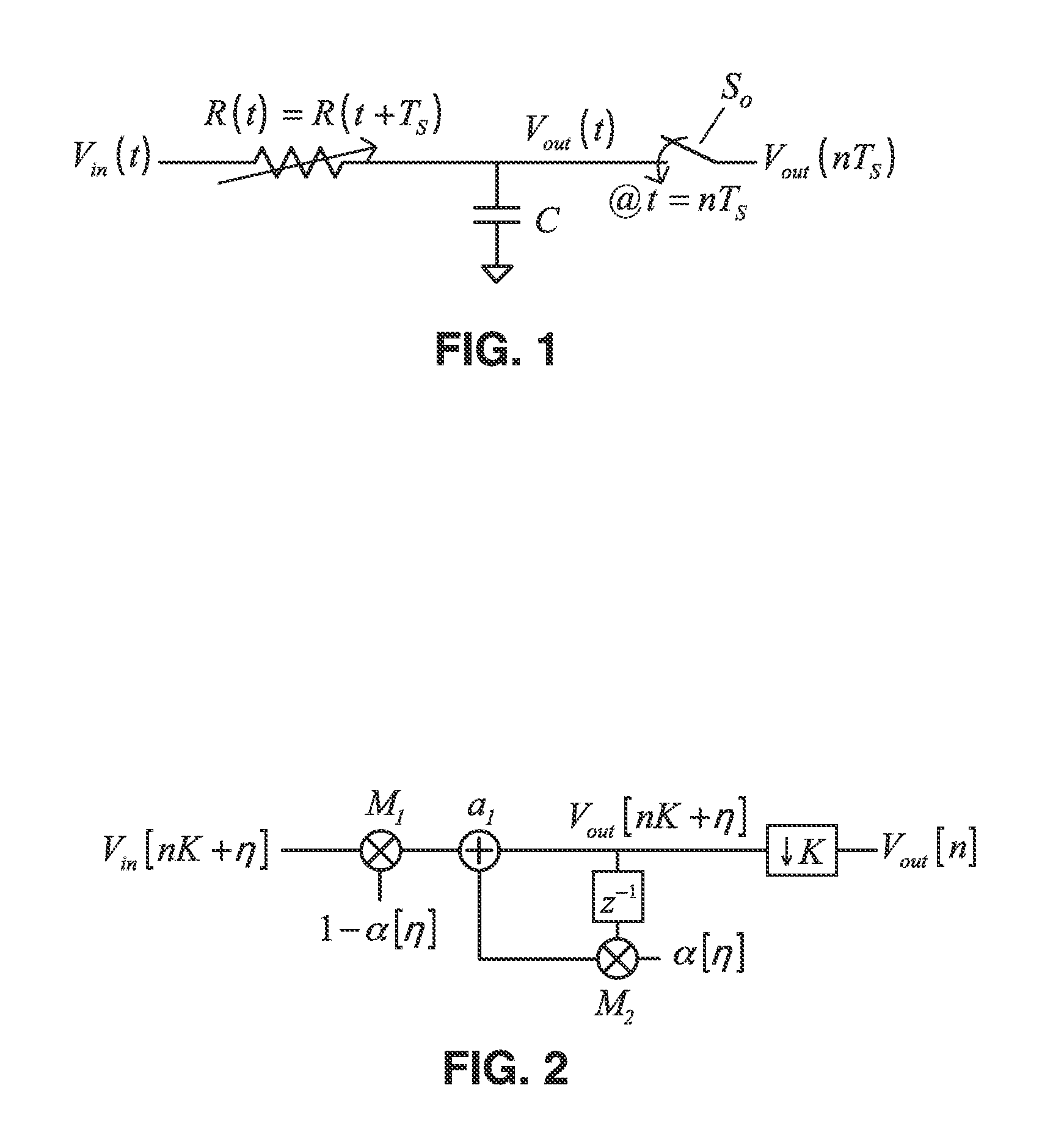

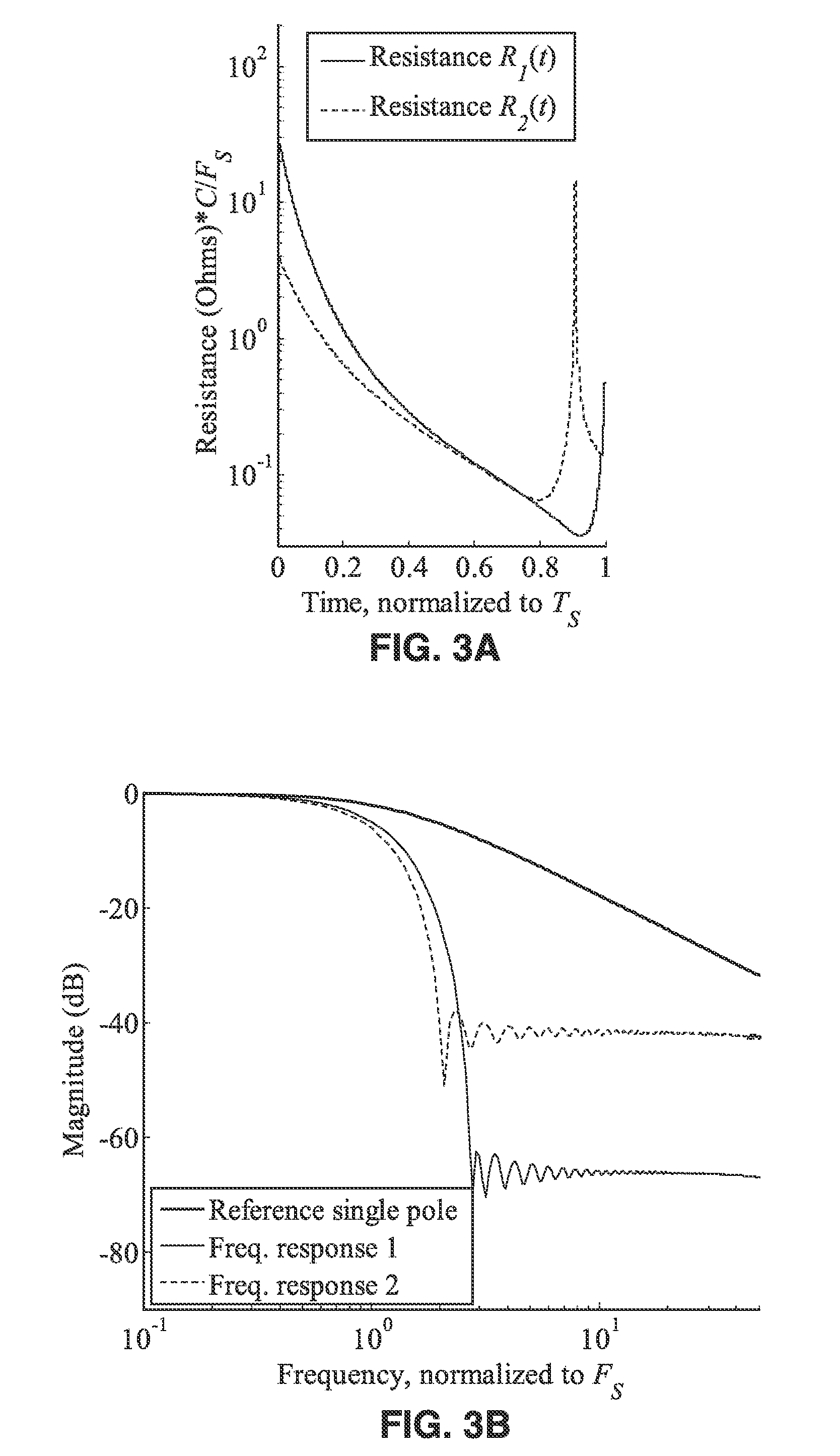

Sharp programmable filters using periodically time-varying components

ActiveUS20140333373A1Easy to implementLower power consumption levelsMultiple-port networksTime-varying networkElectrical resistance and conductanceCapacitance

A method and apparatus for selective programmable filtering using analog circuits with time-varying components (e.g., resistances, capacitances) is presented. An analog front end receives an electronic signal and filters said signal by a passive or active continuous-time filter, having a combination of equivalent memory-less (e.g., resistive) and memory (e.g., capacitive or inductive) elements. A variable resistor circuit allows switching through a range of values to control one or more of the equivalent resistances of the passive or active continuous-time filter. The variable resistors are controlled using a control circuit to periodically modulate the resistances in the continuous-time filter between periodic sampling instances, such as during analog to digital conversion. Such periodic modulation of the resistances in the continuous-time filter allows for the programming and enhancement of the selectivity of said filter.

Owner:RGT UNIV OF CALIFORNIA

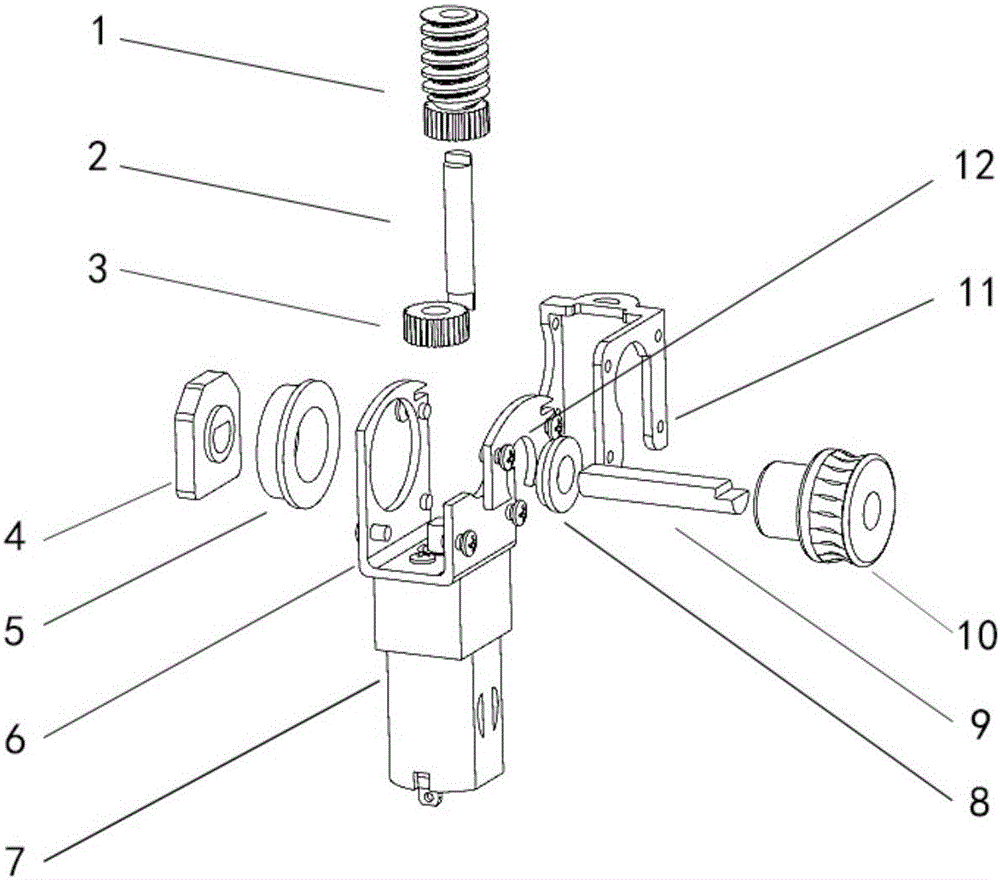

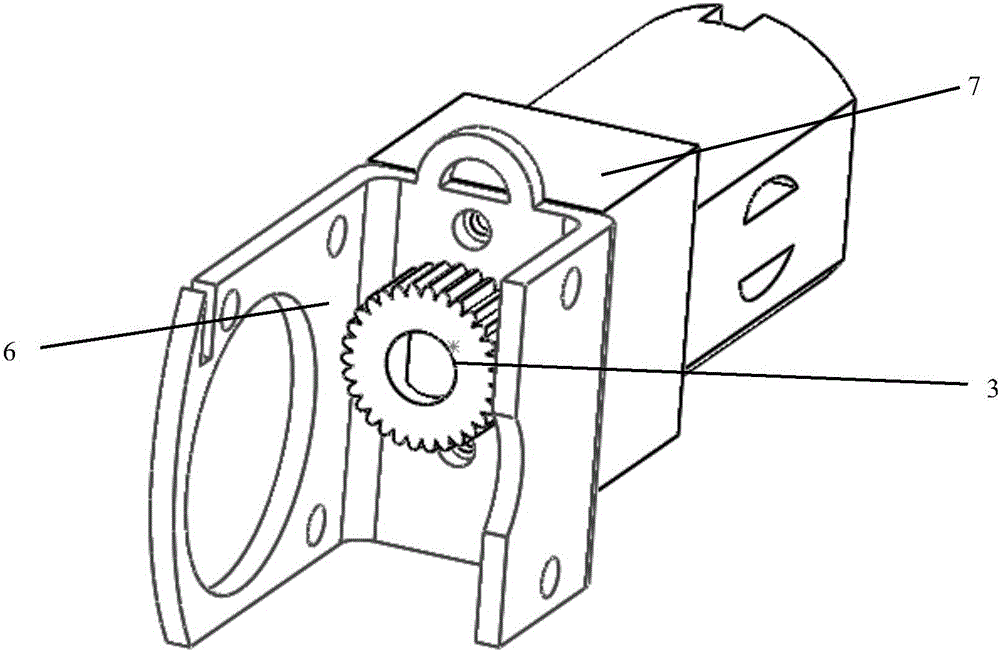

Knuckle movement module of five-finger dextrous hande based on worm wheel and worm mechanism

InactiveCN105881536AMechanically compactLightweightProgramme-controlled manipulatorGripping headsGear wheelSpatial structure

The invention designs a knuckle movement module of a five-finger dextrous hand based on the structural features and kinetic characteristics of a worm wheel and worm mechanism. Movement functions of all fingers are satisfied, additionally, the space structure of knuckles can be optimized to the maximum, the used worm wheel and worm mechanism has a self-locking function, and therefore, the designed knuckle movement module of the five-finger dextrous hand can achieve the poweroff self-locking function, so that the grasping ability of the dextrous hand is increased, and the movement and grasping requirements of the five-finger dextrous hand are satisfied. A worm wheel and worm speed reducer which is used as a driving unit of the knuckle module is mainly composed of a worm wheel, a worm, a gear, a shaft, a bearing, a box body and accessories and can be divided into three basic structures including the box body, a worm wheel and worm gear set and the combination of the bearing and the shaft, wherein the box body is a base of all parts in the worm wheel and worm mechanism and is an important part for supporting and fixing shaft components, guaranteeing correct positions of all transmission parts and supporting loads which act on the speed reducer; the worm wheel and worm gear set is used for transferring output power of a motor and changing the direction of the output power; the combination of the bearing and the shaft is mainly used for transferring power, supporting operation and improving the efficiency.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

Copolymer gel, 4D micro-nano printing material, and printing test method

ActiveCN108546312AExcellent photocurabilityNo residueDiagnosticsMicrobiological testing/measurementCross-linkMicro nano

The invention discloses a copolymer gel, a 4D micro-nano printing material, and a printing test method. The copolymer gel comprises: reactants comprising a functional monomer N-isopropyl acrylamide and acrylic acid; a cross-linking agent DPEPA; a photosensitizer triethanolamine; and a photoinitiator EMK. According to the present invention, the hydrogel-based 4D micro-nano printing material especially has good photocuring performance and good heterogeneous swelling property to two-photon 780 nm femtosecond laser, can print complex three-dimensional micro-nano structures with submicron precisionin photoresists without supporting materials, and can achieve the controlled deformation from three-dimensional to three-dimensional by designing the local difference in the structure under the stimulation of the pH value, the organic solvent and the temperature.

Owner:PEKING UNIV

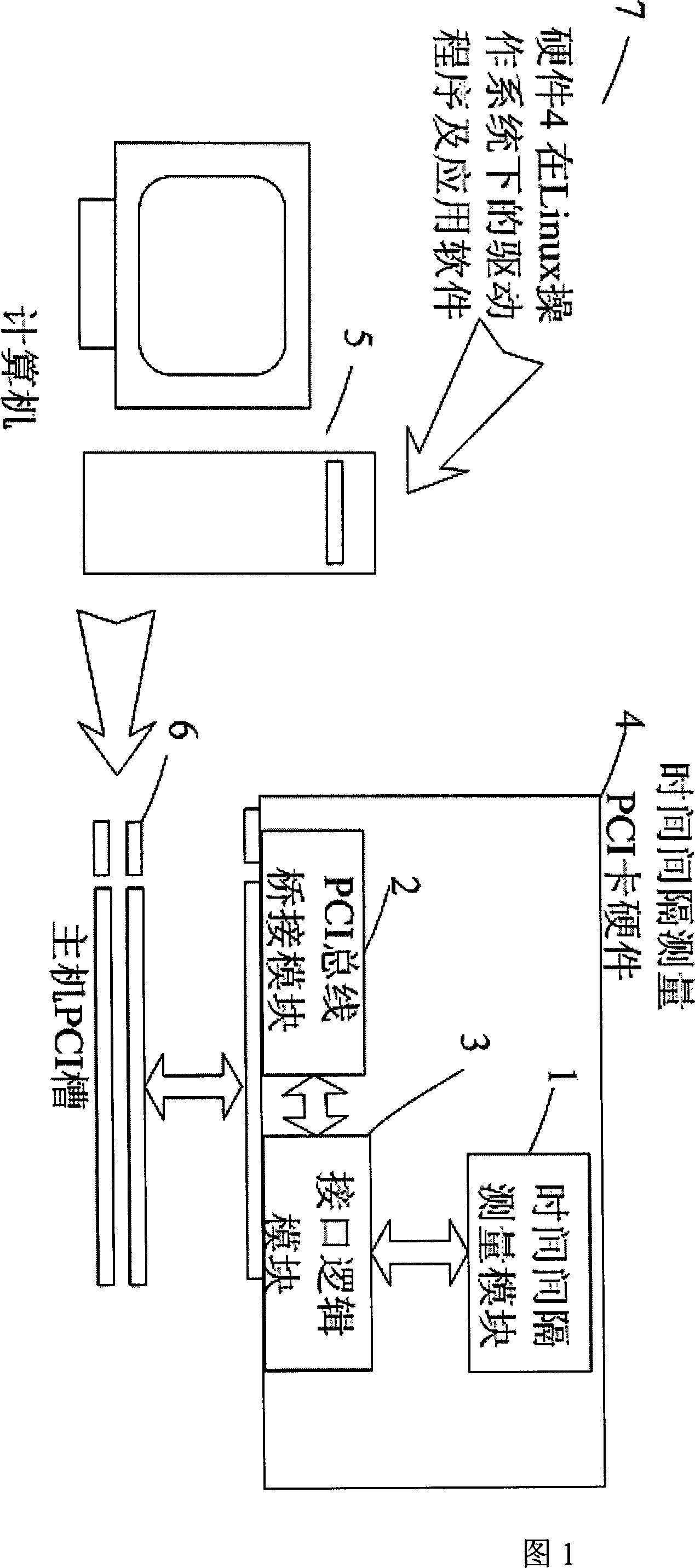

High precision time interval measurement PCI card

InactiveCN101013304AMature technologyFast transmissionElectric unknown time interval measurementOperational systemGNU/Linux

A high-precision timing interval measurement PCI card belongs to the measurement technology field. Hardware (4) includes PCI bus bridging module (2) with the core PCI9054, high-precision timing interval measurement module (1) with the core TDC-GP1, and core interface logic module (3) with the core XC3S400 FPGA; the hardware (4) comprising the timing interval measurement module (1), PCI bus bridging module (2), and interface logic module (3) is inserted in the PCI slots (6) of the computer (5), and under the control of the Linux operating system drivers and application software (7), it achieves high-precision timing interval measurement. The advantages are that it has high transmission speed, meeting the high-speed timing interval measurement application; and strong programmability, with good portability; strong functional scalability, and according to different applications, designing corresponding application software to facilitate the application in other areas.

Owner:AUTOMATION RES & DESIGN INST OF METALLURGICAL IND

Self-testing printed circuit board comprising electrically programmable three-dimensional memory

InactiveUS20040262731A1Minimal impactImprove system performanceSemiconductor/solid-state device detailsSolid-state devicesElectricityCircuit under test

The electrically programmable three-dimensional memory (EP-3DM) can be used to carry the test data and / or test-data seeds for the circuit-under-test (CUT). When integrated with the CUT, EP-3DM has minimum impact to the layout of the CUT. Apparently, CUT with integrated EP-3DM supports IC self-test. Moreover, with a large bandwidth with the CUT, EP-3DM-based IC self-test enables at-speed test.

Owner:ZHANG GUOBIAO

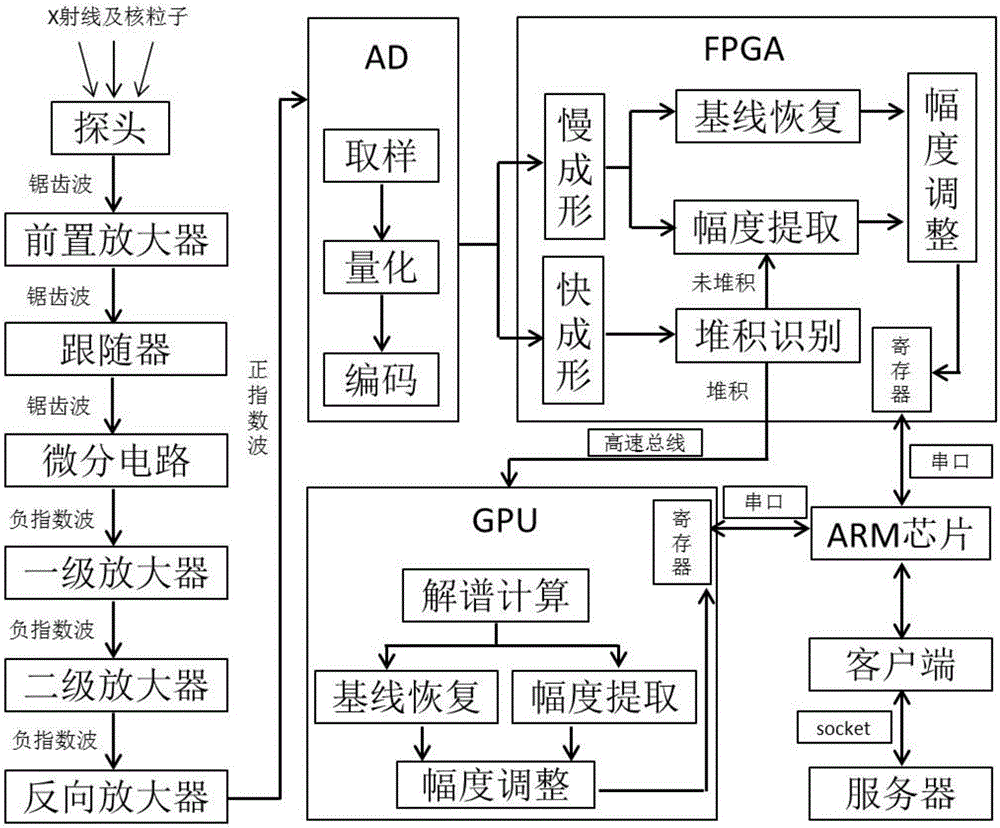

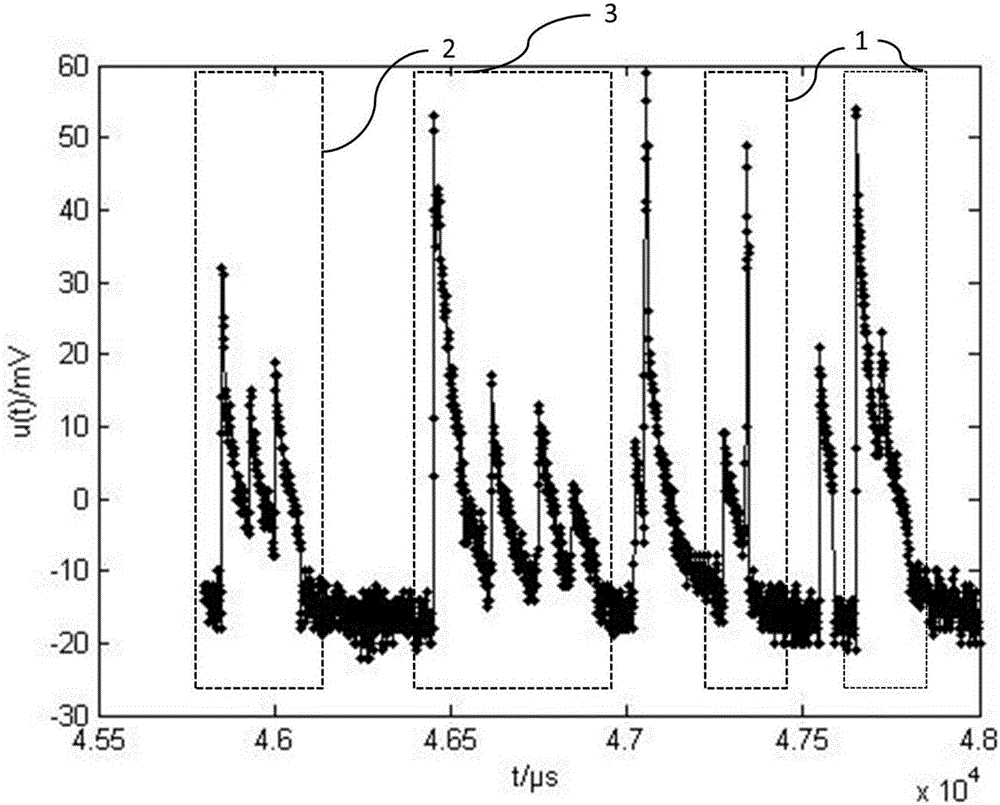

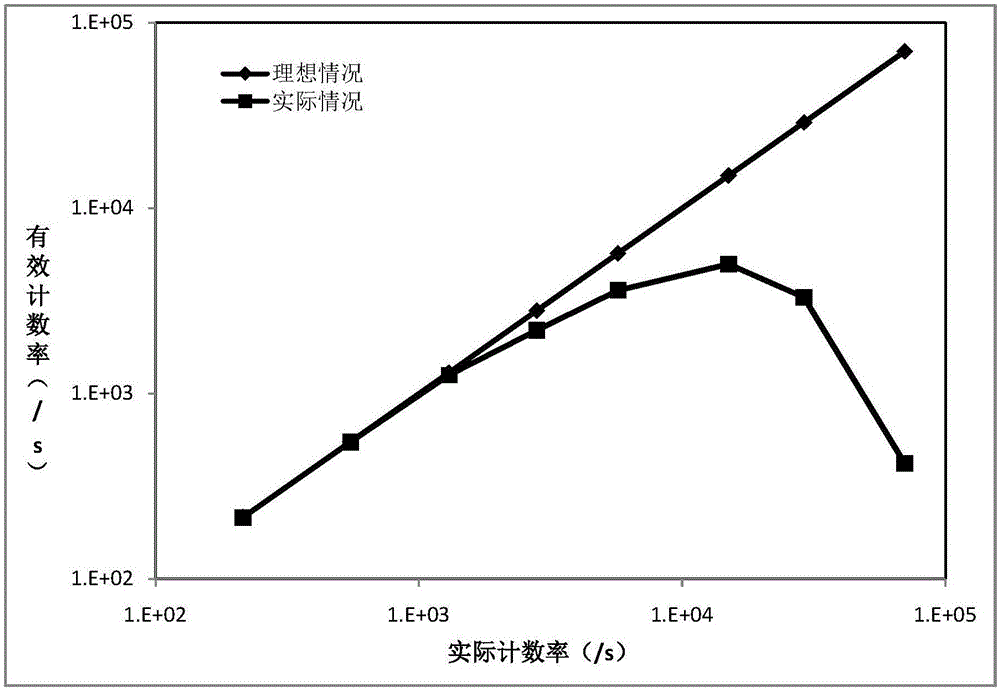

High-speed collection board based on electronic filtering technology, and collection processing method

ActiveCN106325159AIncrease profitImprove programmabilityProgramme controlComputer controlAudio power amplifierData transmission

The invention discloses a high-speed collection board based on electronic filtering technology, and a collection processing method. The collection board comprises an ARM chip, a client, a server, a pre-amplifier, a follower, a differentiating circuit, a first stage amplifier, a second stage amplifier, a reverse amplifier, an analog-digital converter, an FPGA and a GPU, wherein the pre-amplifier, the follower, the differentiating circuit, the first stage amplifier, the second stage amplifier, the reverse amplifier, the analog-digital converter, the FPGA and the GPU are sequentially connected. The FPGA and the GPU are connected to the client through a serial port and the ARM chip, and the client transmits an instruction to the FPGA or the GPU, and controls the processing process of a pulse signal. The client and the server carry out the bidirectional communication through a network. The collection board makes the most of the GPU to support floating calculation, and is high in programmability. The collection board achieves the multi-thread calculation, and is high in calculation speed. The collection board is high in data transmission speed. In order to solve a problem of pulse accumulation, the method provides the reliable hardware basis. The collection board can overcome the technical difficulty of pulse accumulation, improves the utilization rate of the pulse signals, and finally improves the detection precision of a system.

Owner:杭州率通电子科技有限公司

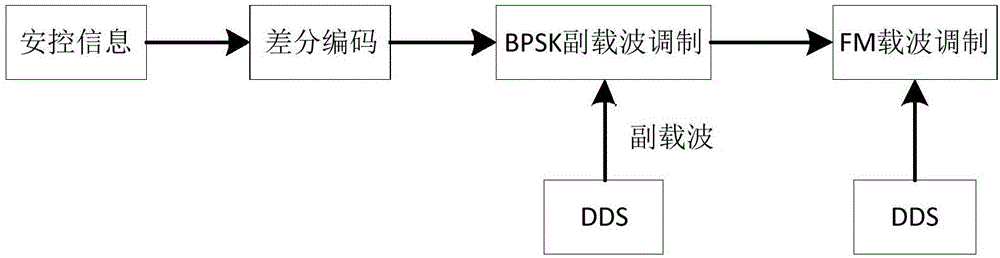

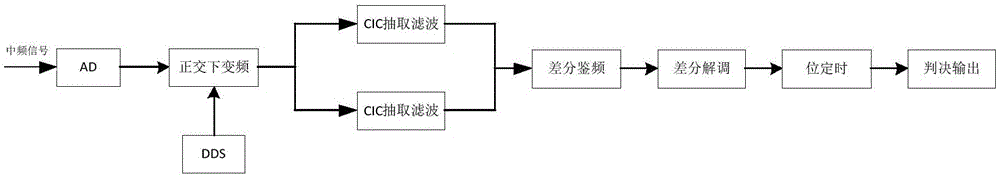

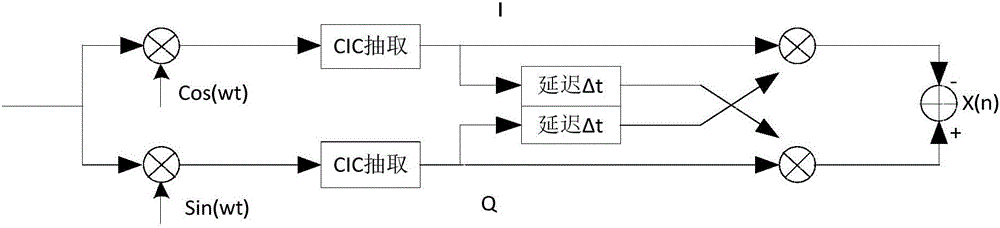

PCM/DPSK/FM modulation and demodulation module and method

InactiveCN106789787AShort development cycleImprove programmabilityModulated-carrier systemsPulse-code modulationCoded element

The invention discloses a PCM / DPSK / FM modulation and demodulation module and method. The module comprises a modulation module and a demodulation module. The modulation module carries out pulse coding modulation on sending information codes, carries out DPSK subcarrier modulation on pulse coding modulation signals and carries out FM modulation on the DPSK modulation signals, thereby finally obtaining double-modulation signals. The demodulation module carries out down-conversion and extraction processing on received signals and carries out FM demodulation on the signals of which rate is reduced, thereby saving hardware resources; the signals output by an FM demodulation module enter a DPSK demodulation module; front and rear code element phase comparison is carried out on the DPSK modulation signals, thereby demodulating modulation information; and finally the DPSK demodulation signals enter a bit timing module, thereby obtaining the optimum judgment point and demodulating the sending information. According to the module and the method, a bit error rate is greatly reduced, and the system performance is improved.

Owner:NANJING UNIV OF SCI & TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com