Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

56results about How to "Data retention time is long" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

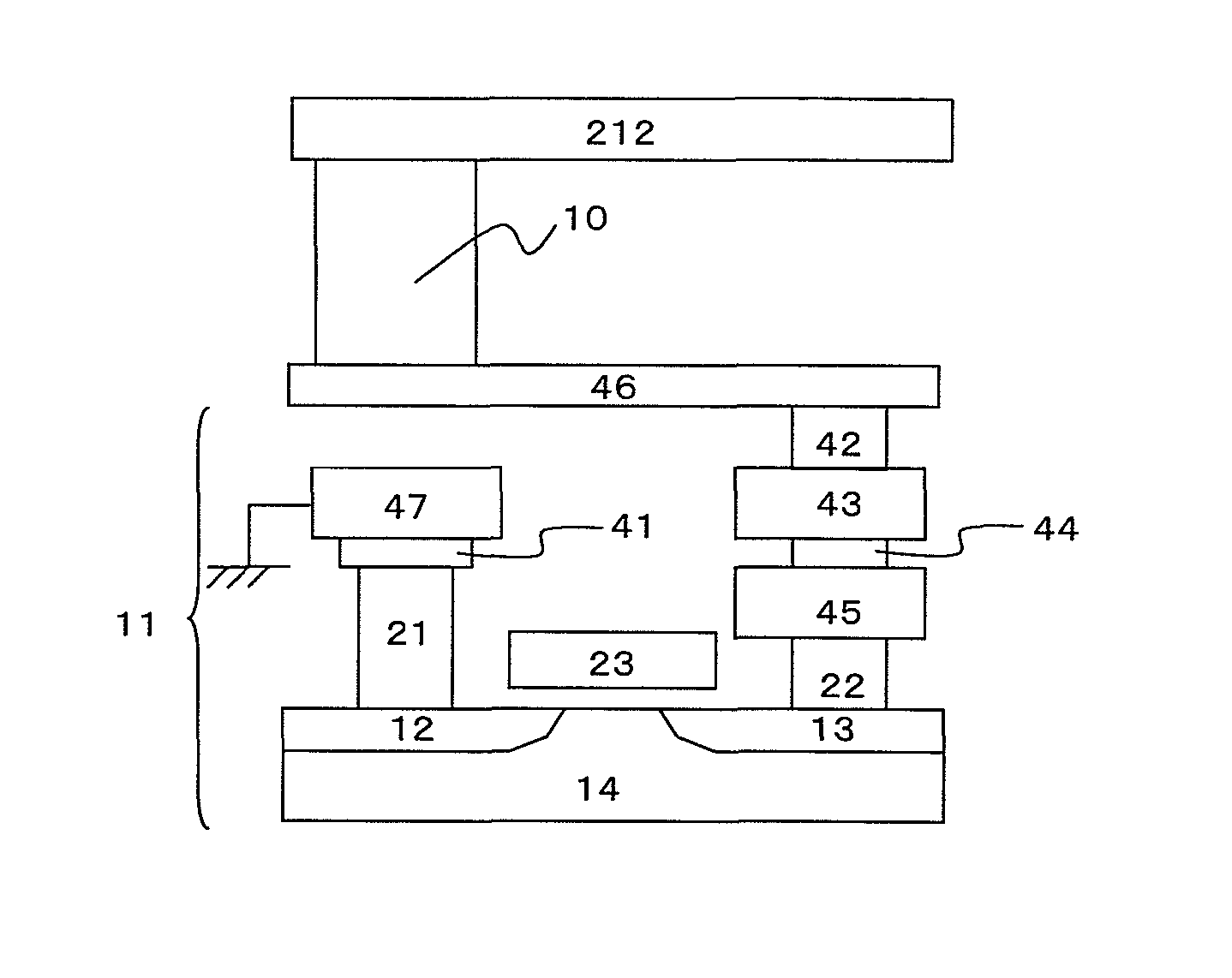

Power storage device and power storage system

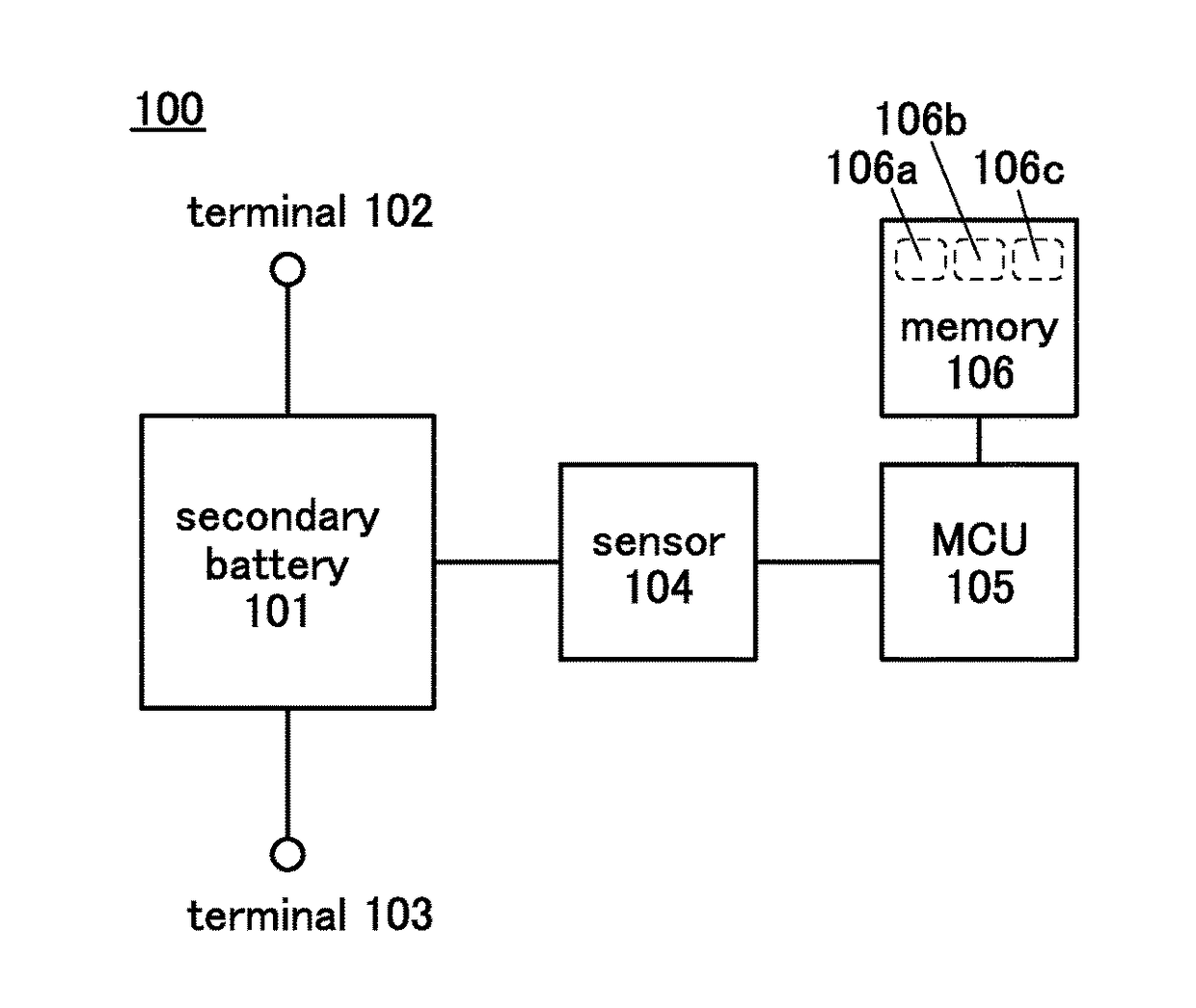

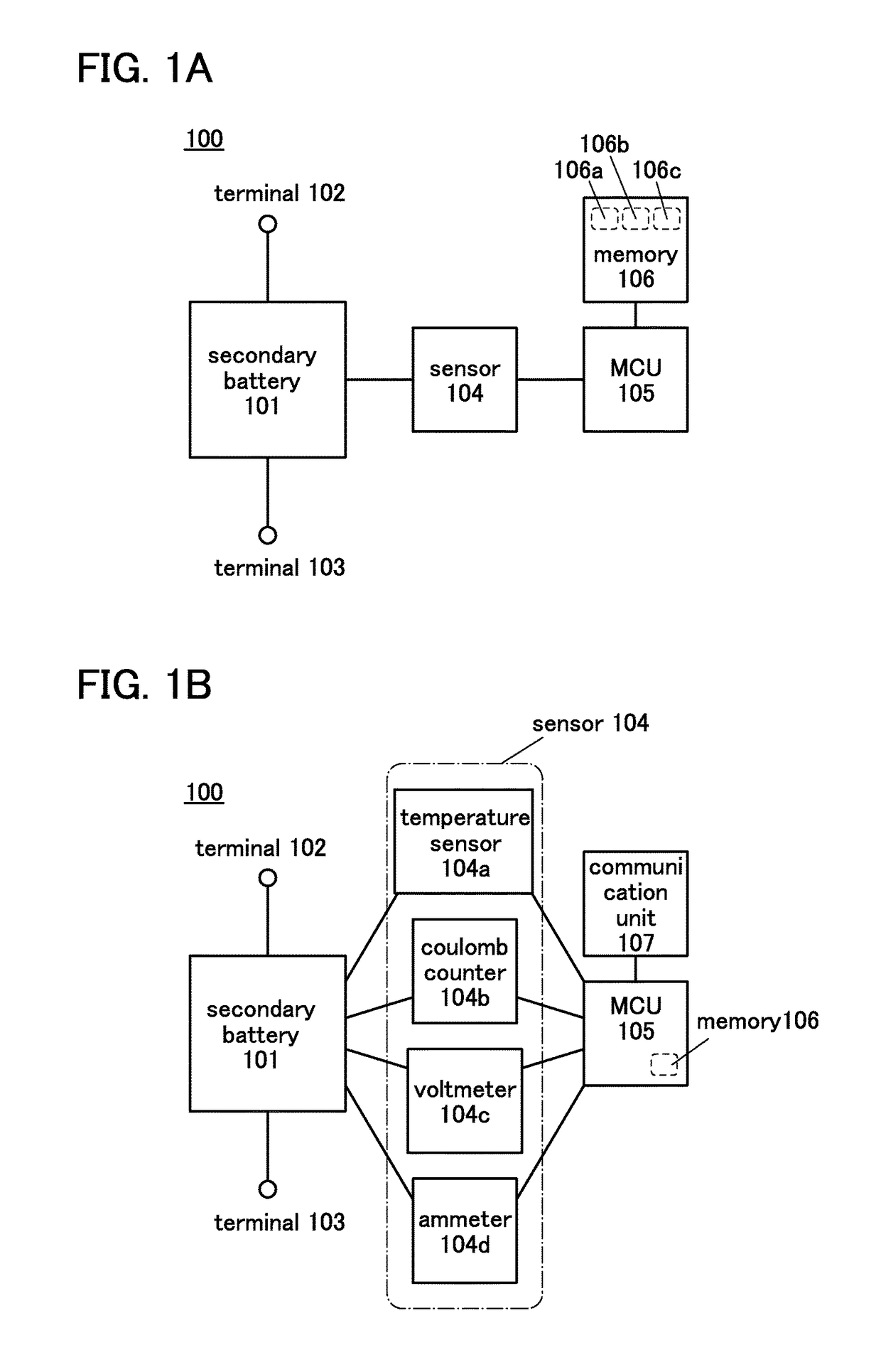

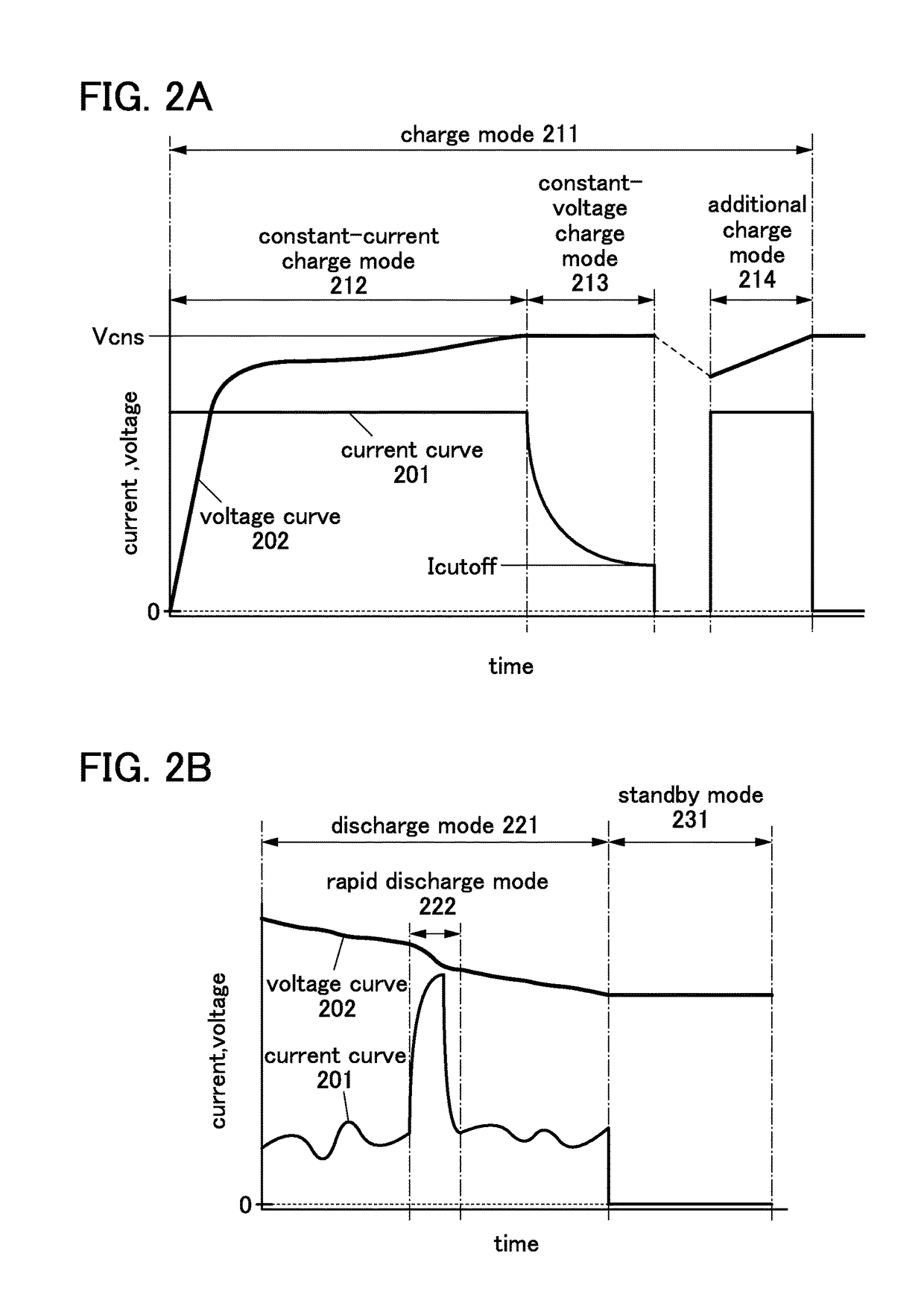

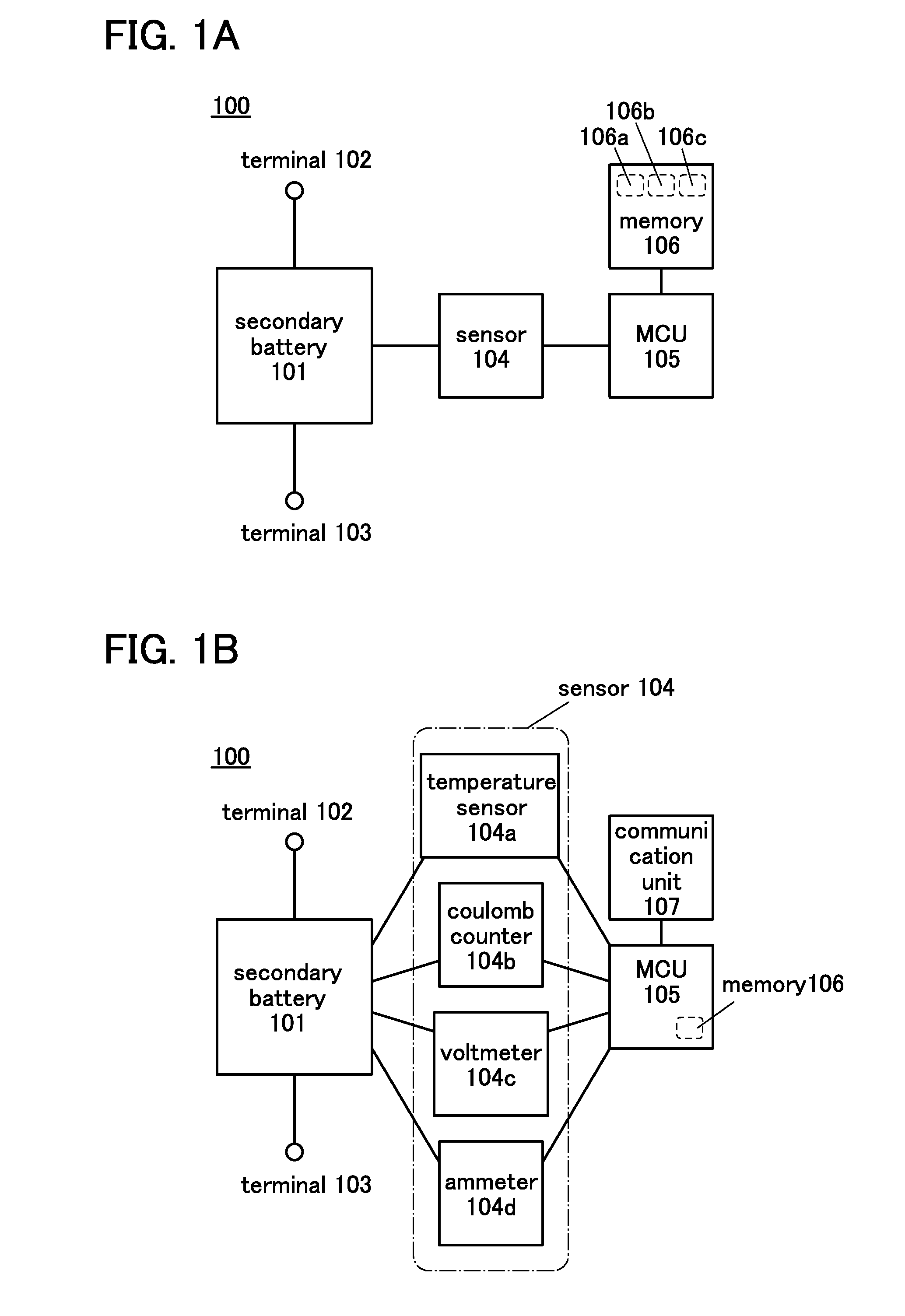

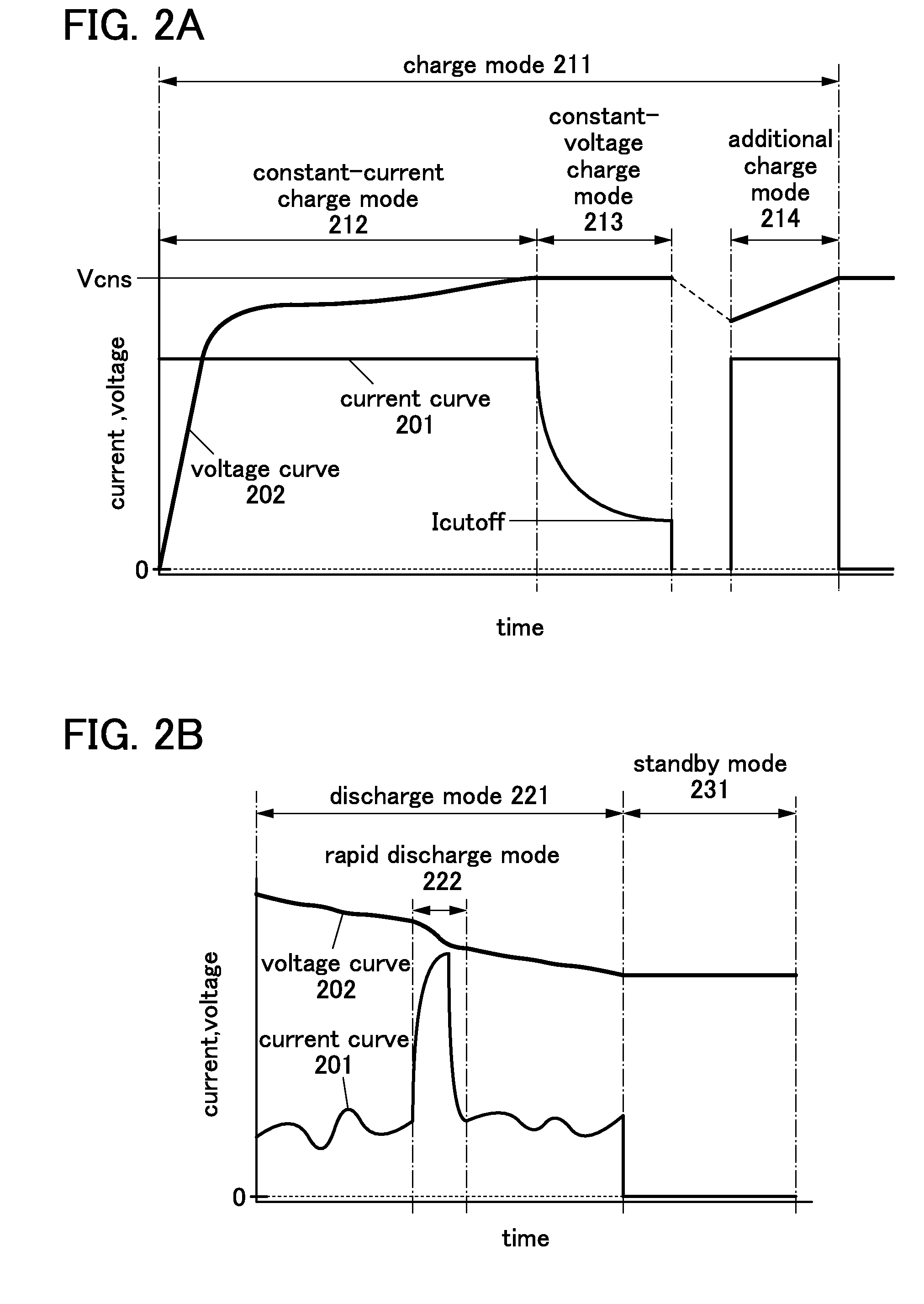

ActiveUS9614258B2Easy to analyzeData retention time is longBatteries circuit arrangementsElectrical testingMicrocontrollerElectrical battery

To provide a power storage device, an operation condition of which is easily analyzed. A secondary battery includes a sensor that is a measurement unit, a microcontroller unit that is a determination unit, and a memory that is a memory unit. With the sensor, conditions of the secondary battery such as the remaining battery power, the voltage, the current, and the temperature are measured. The microcontroller unit performs arithmetic processing of the measurement results and determines the operation condition of the secondary battery. Further, the microcontroller unit stores the measurement result in the memory in accordance with the operation condition of the secondary battery.

Owner:SEMICON ENERGY LAB CO LTD

Power storage device and power storage system

ActiveUS20140184165A1Improve battery performanceLarge capacityBatteries circuit arrangementsSecondary cellsMicrocontrollerVoltage

To provide a power storage device, an operation condition of which is easily analyzed. A secondary battery includes a sensor that is a measurement unit, a microcontroller unit that is a determination unit, and a memory that is a memory unit. With the sensor, conditions of the secondary battery such as the remaining battery power, the voltage, the current, and the temperature are measured. The microcontroller unit performs arithmetic processing of the measurement results and determines the operation condition of the secondary battery. Further, the microcontroller unit stores the measurement result in the memory in accordance with the operation condition of the secondary battery.

Owner:SEMICON ENERGY LAB CO LTD

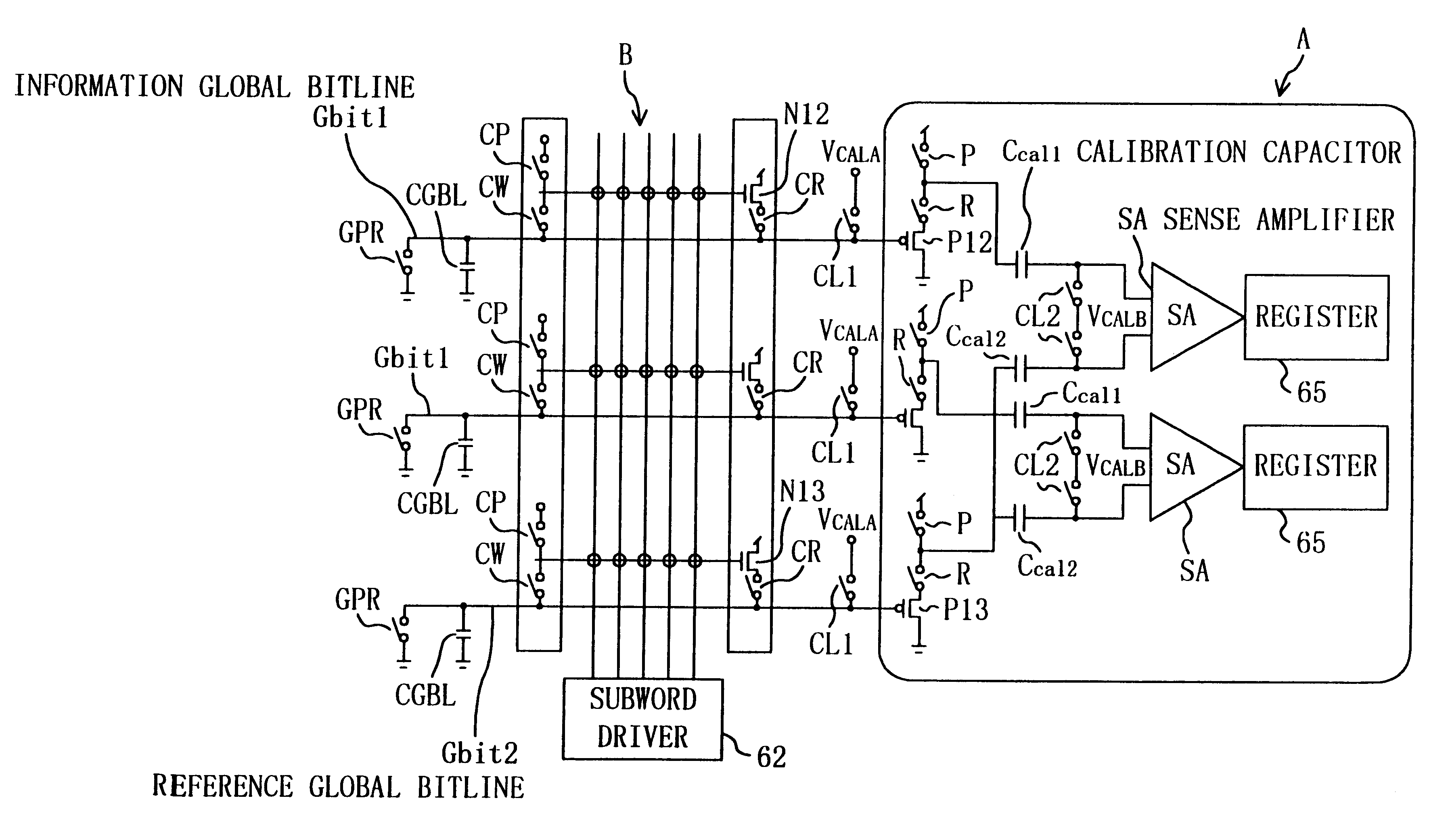

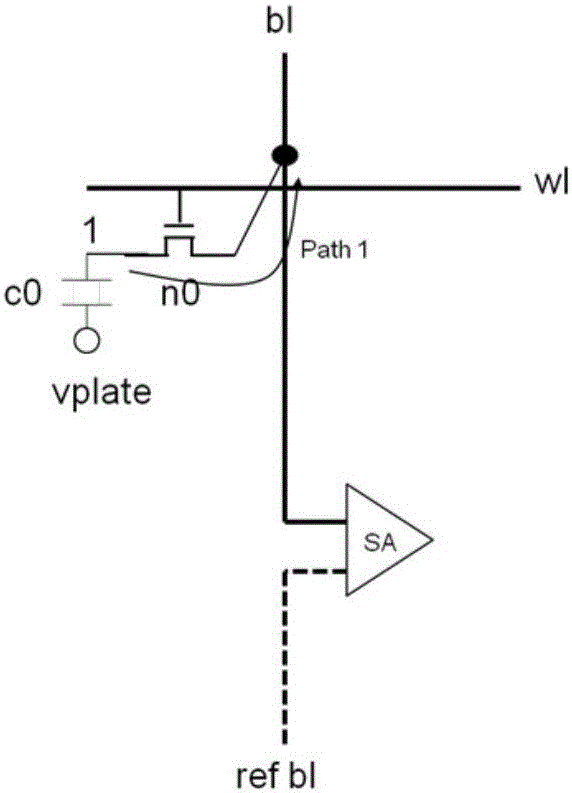

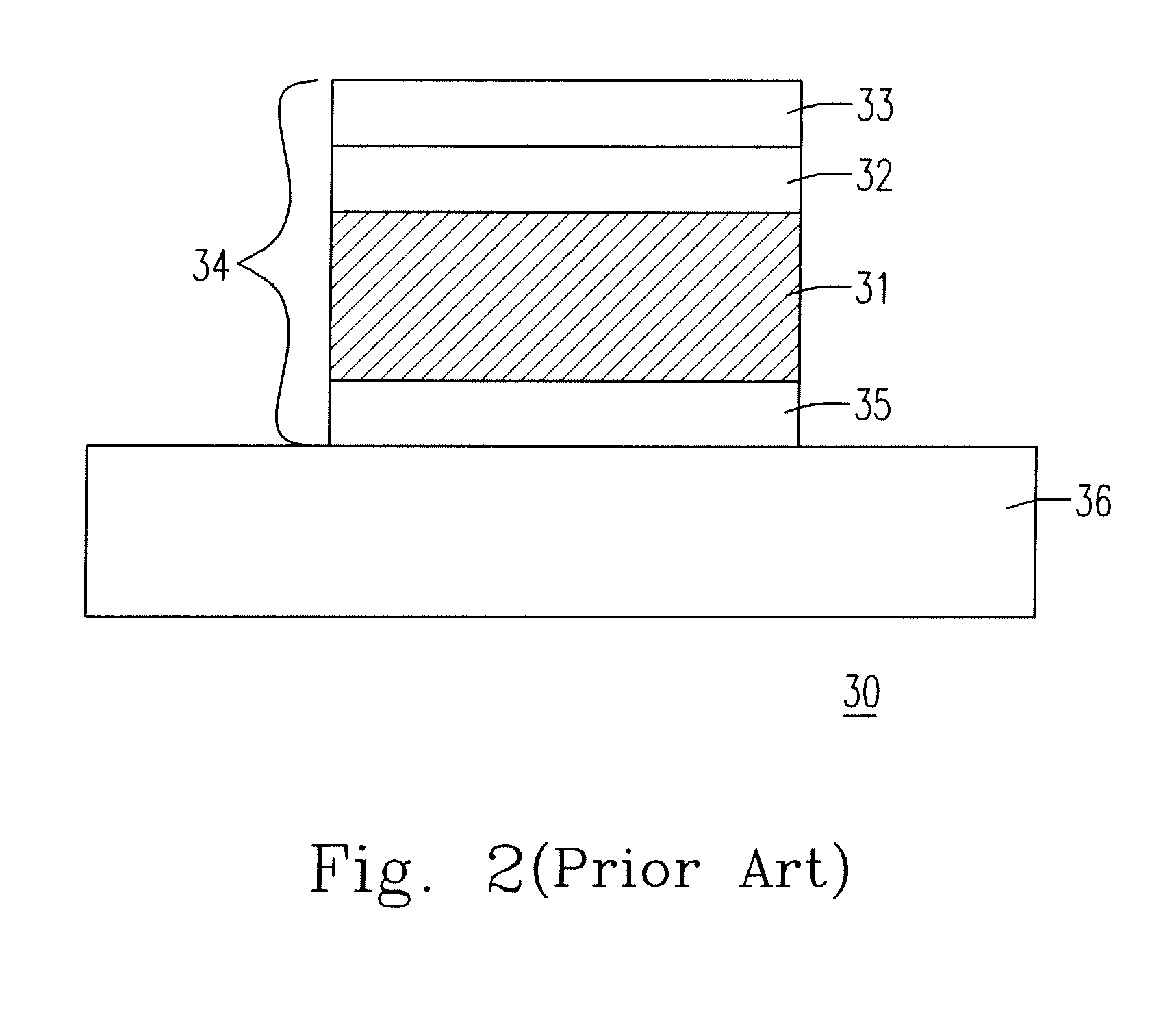

Semiconductor memory

InactiveUS6275434B1Avoid yield lossData retention time is longTransistorSolid-state devicesBit lineRefresh cycle

Owner:PANASONIC CORP

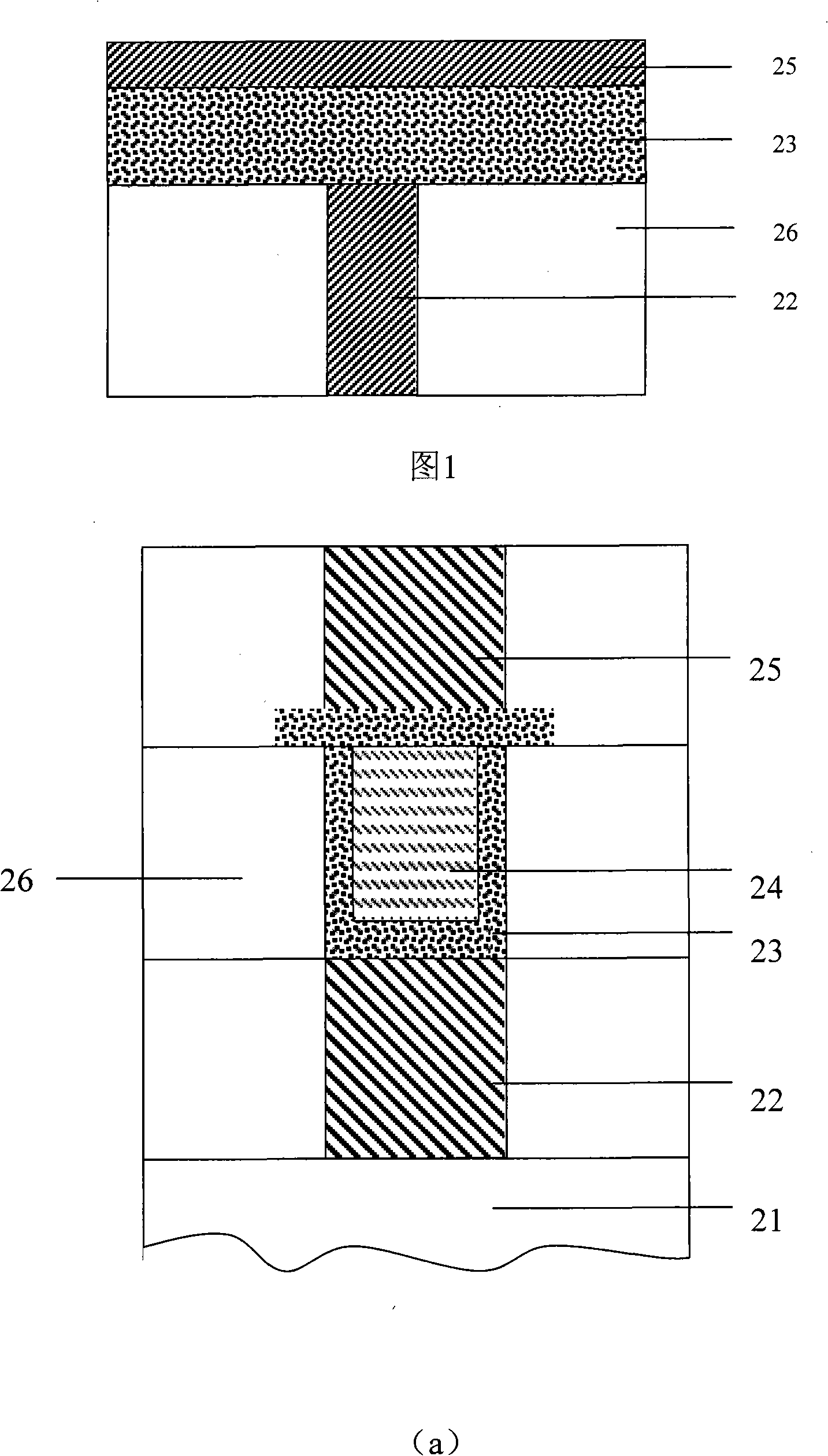

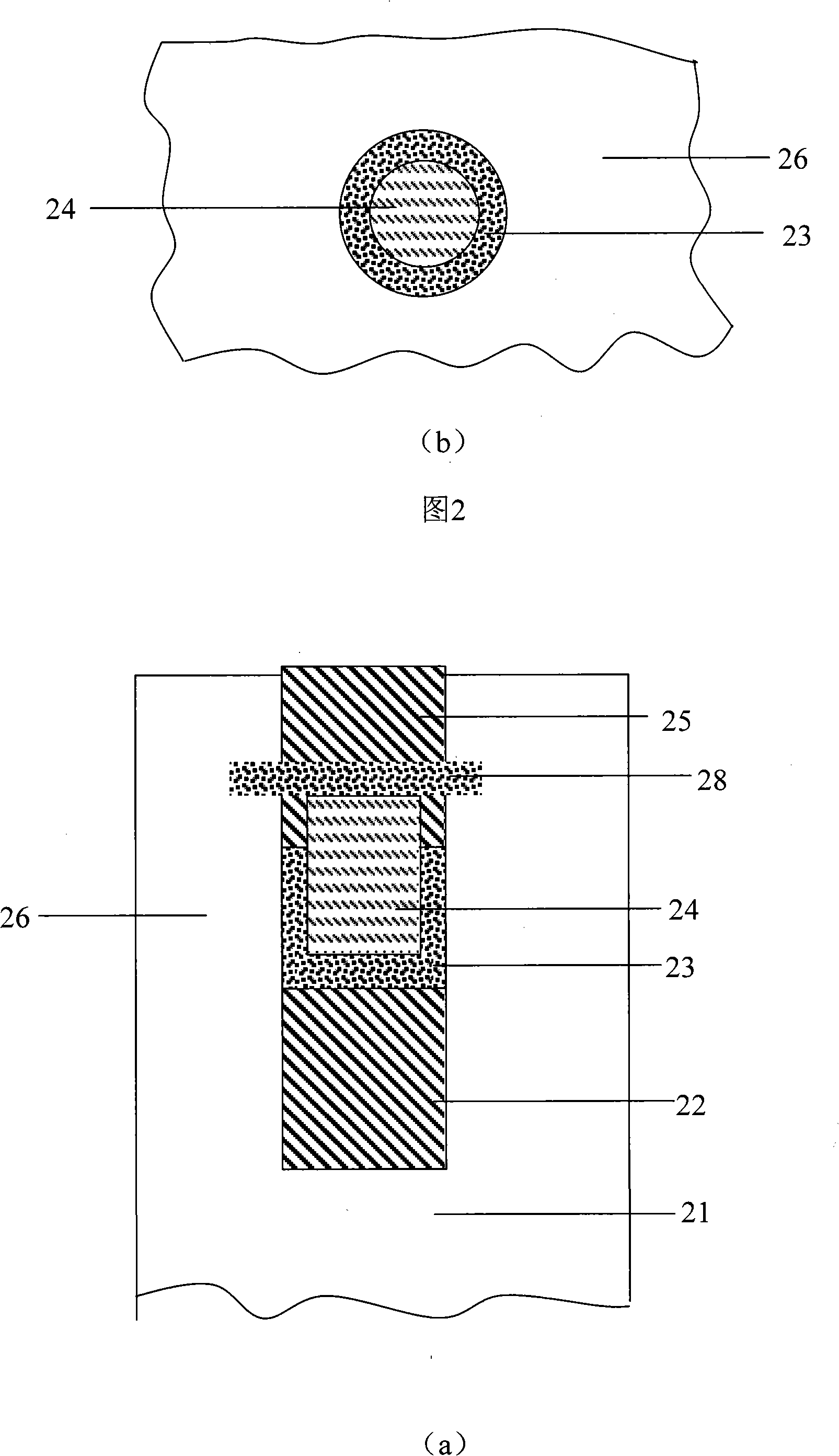

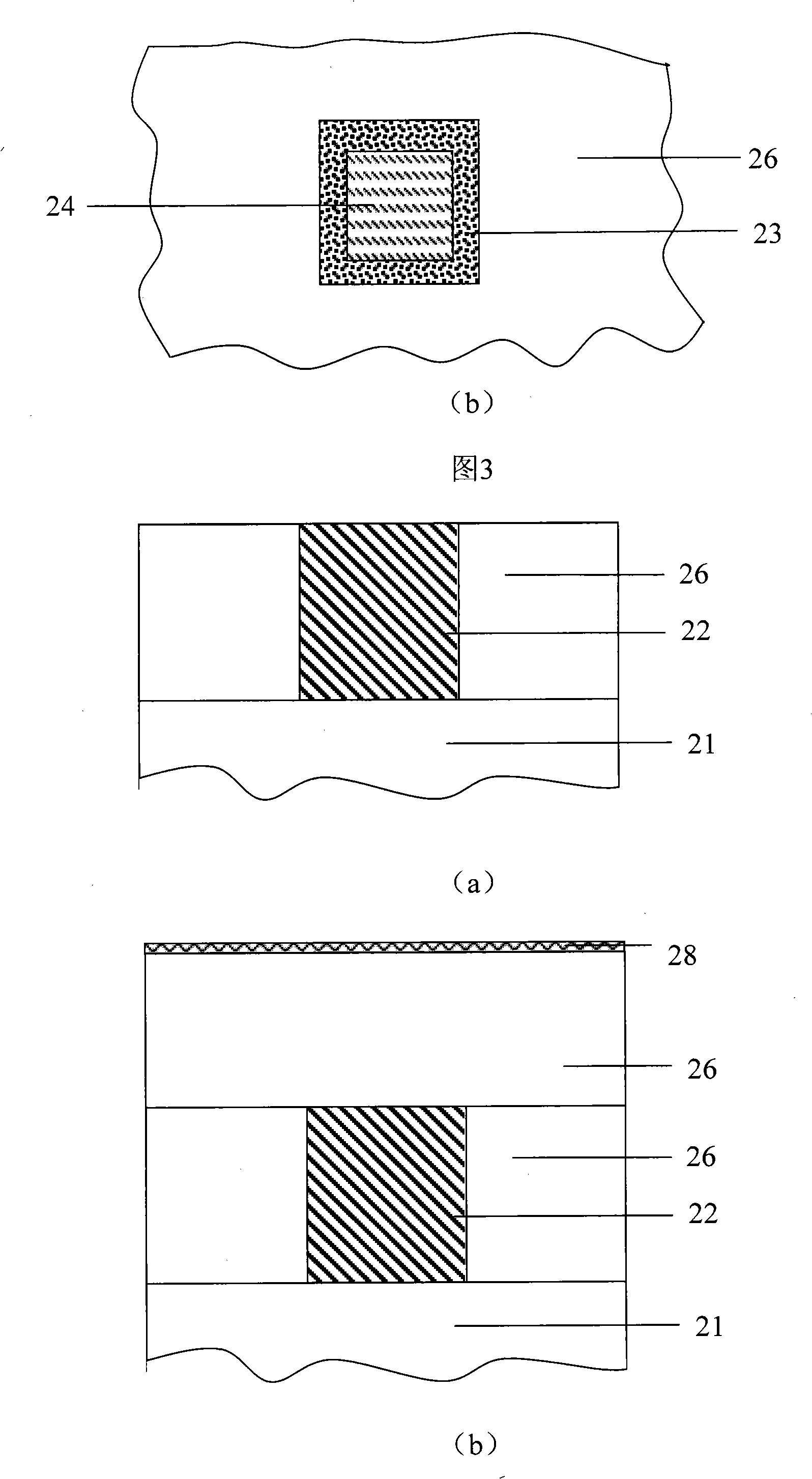

A tube phase change memory unit structure and its making method

ActiveCN101267017AImprove utilization efficiencyData retention time is longSolid-state devicesRead-only memoriesElectrical resistance and conductancePhase-change memory

The invention relates to a tube-like phase-change memory single structure and making method, the phase-change memory single structure comprises a top electrode, a bottom electrode and a memory part. The single structure has basic characters that: phase-change material distributes at lateral wall of a hole, the phase-change is implemented in the hole in reading and writing operation through heating own by using small sectional area and big resistance of the phase-change material, and tubular is formed at two ends of ring phase-change material through adding phase-change material insulating layer as closure, thus improving use efficiency of heat in the reading and writing operation, the memory part is a tubular structure enclosed by the phase-change material up and down, and is filled with metal, insulation materials or high resistivity material. The memory structure of the invention can reduce operating current, and has small-power, high heat utilization ratio and good data retention performance, and the invention can improve the consistency of resistance value of device of chip.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

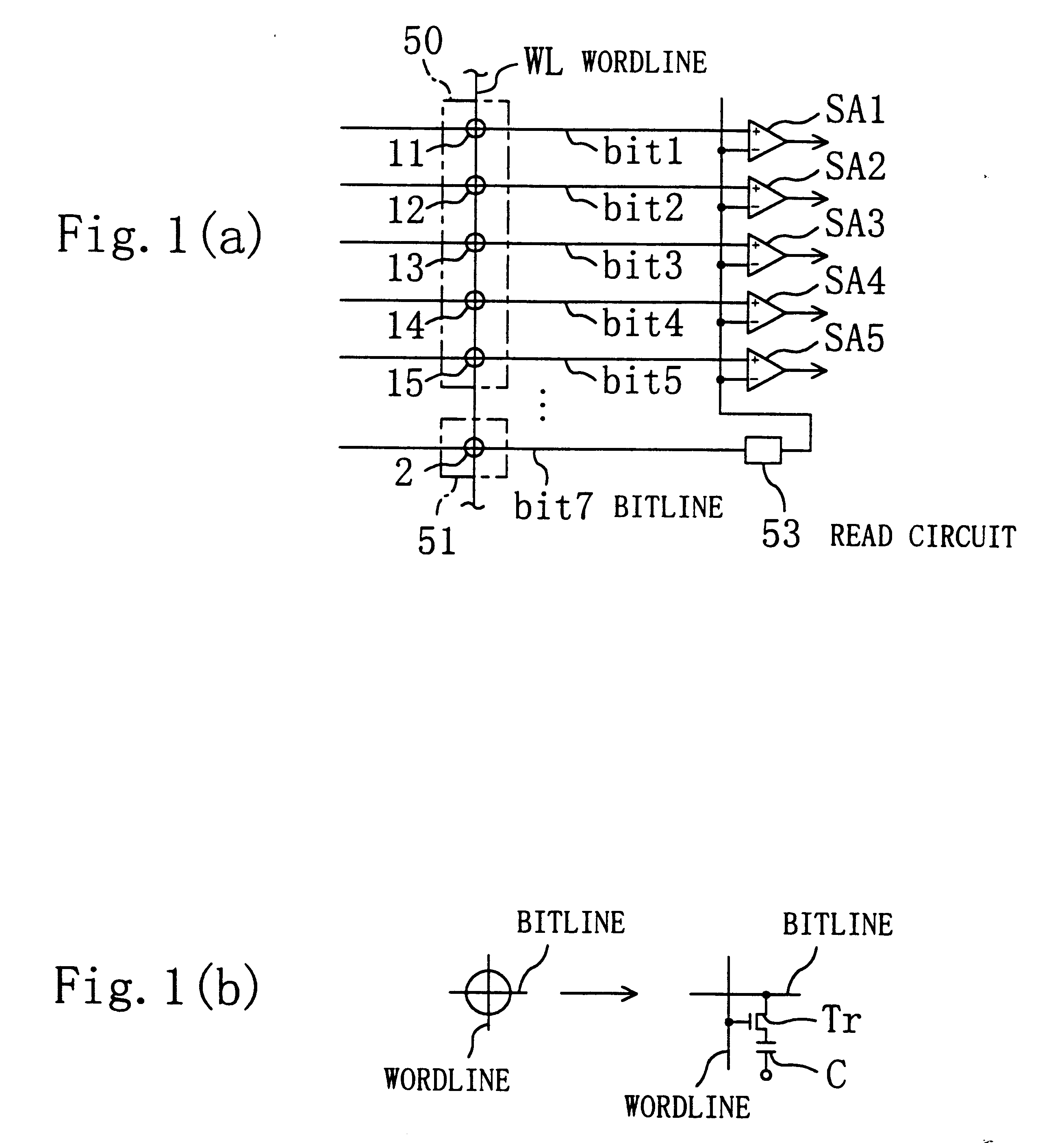

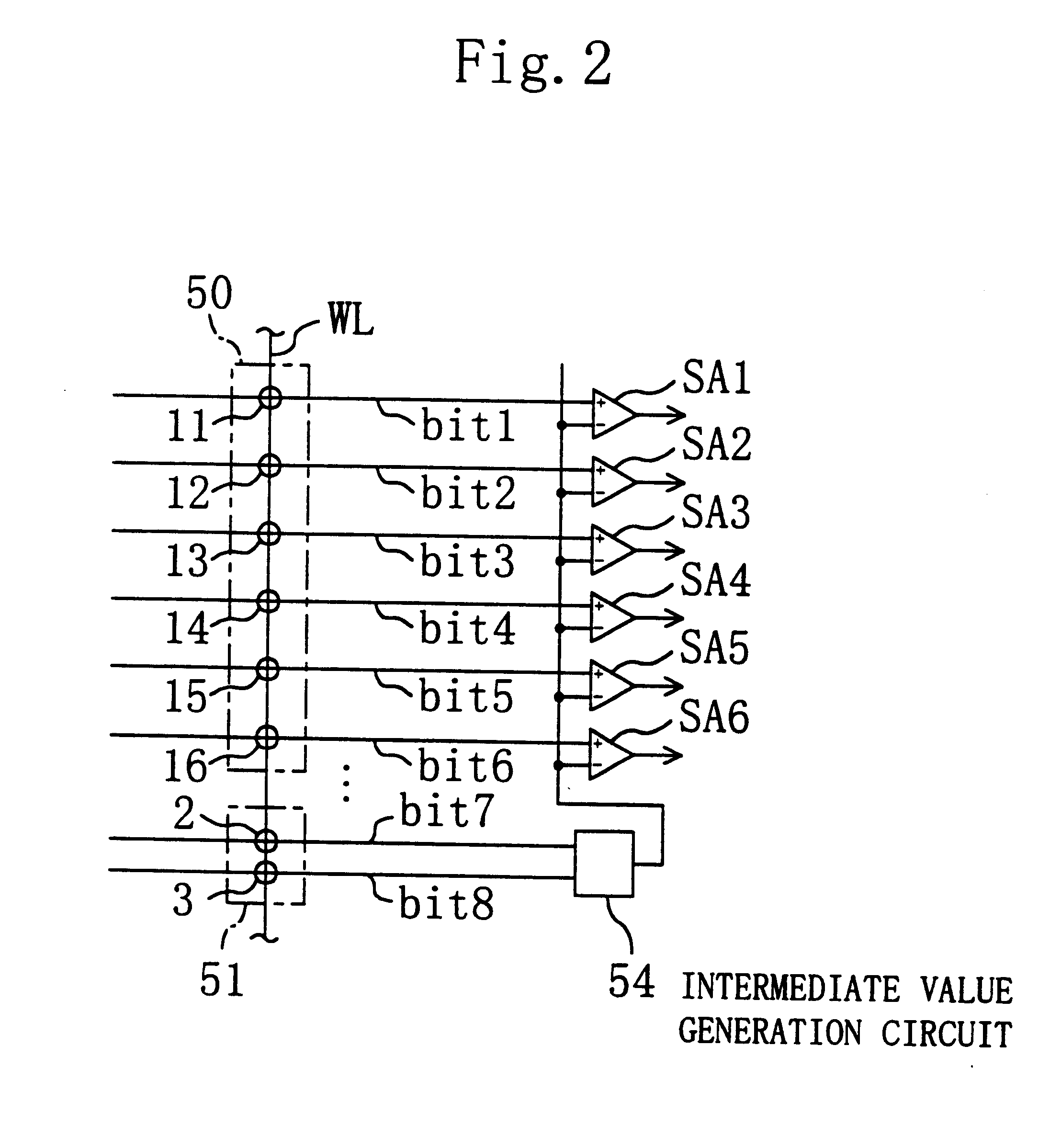

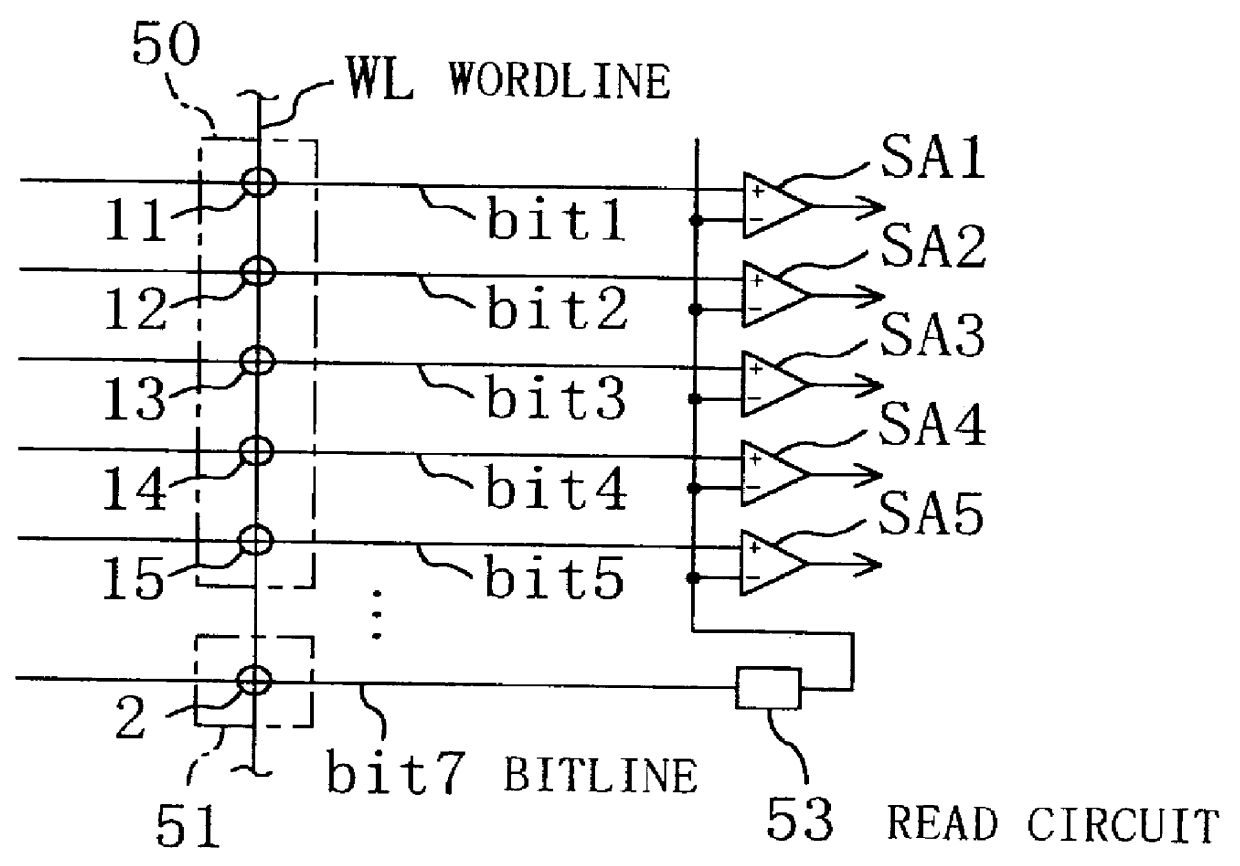

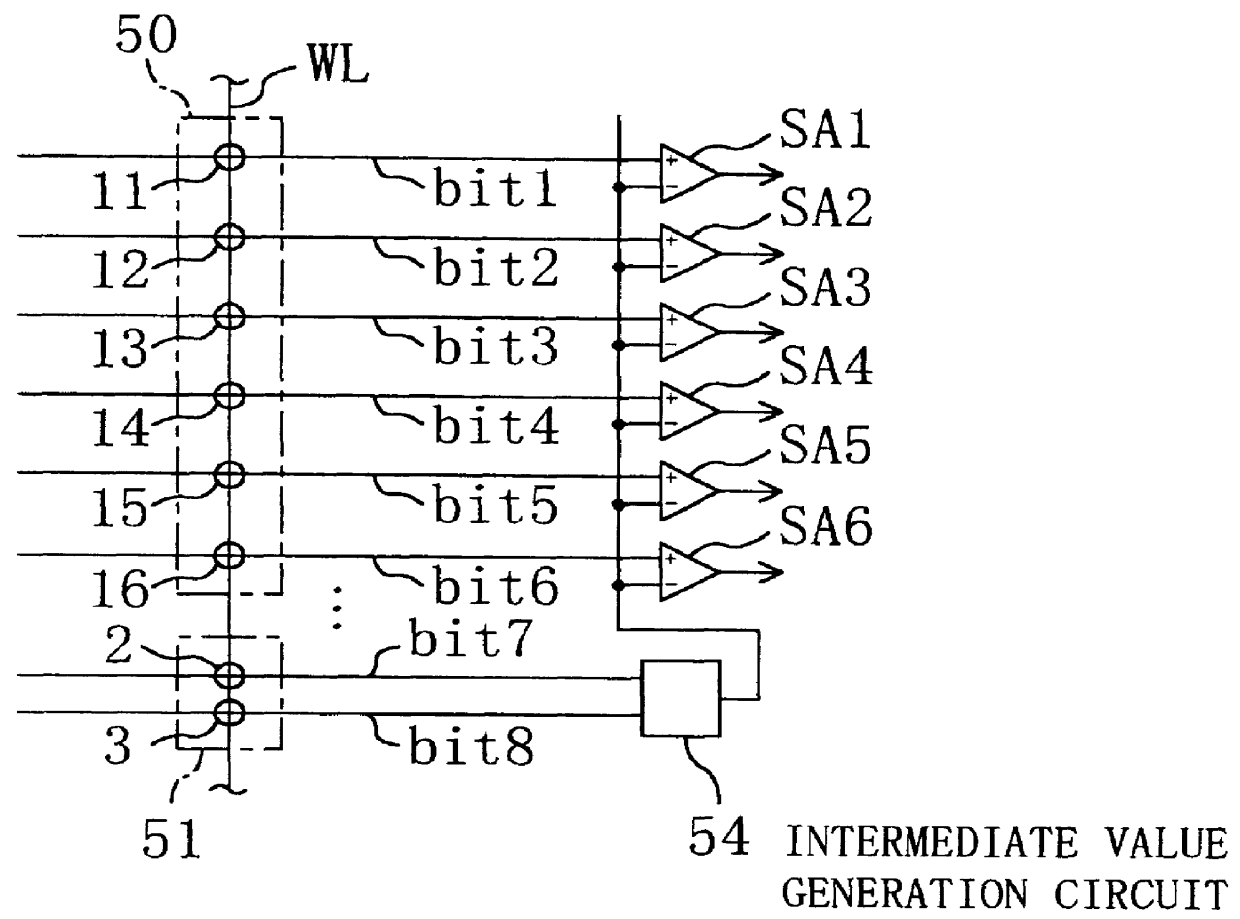

Semiconductor memory

InactiveUS6091655AAvoid yield lossData retention time is longTransistorSolid-state devicesBit lineRefresh cycle

A plurality of information memory cells and a single reference memory cell are coupled to a single word line. The reference memory cell stores reference information equivalent to a reference potential to information readout. Pieces of information, stored in the information memory cells, are fed, over respective bit lines, to first input terminals of sense amplifiers. The reference information, stored in the reference memory cell, is fed, over a bit line, to second input terminals of the sense amplifiers. When the potential of signal charges stored in the information memory cells falls due to leakage current, the potential of a signal charge stored in the reference memory cell correspondingly falls due to leakage current. This prolongs a length of time taken for a difference between these potentials to reach a sense limit, thereby achieving a longer data retention time. As a result of such arrangement, even when there occurs a small current leakage from memory cells, it is possible to secure a long data retention time thereby making it possible to obtain a long refresh cycle period.

Owner:PANASONIC CORP

Resistive radom access memory device, method for manufacturing the same, and method for operating the same

ActiveUS20130128653A1Improve memory performanceFast switching speedSolid-state devicesSemiconductor/solid-state device manufacturingRandom access memoryEngineering

A resistive random access memory device, a method for manufacturing the resistive random access memory device, and a method for operating the resistive random access memory device are disclosed. The resistive random access memory device includes a resistive switching memory element including two electrodes and a layer of variable-resistance material between the two electrodes, wherein the layer of variable-resistance material exhibits bipolar resistive switching behavior; and a Schottky diode including a metal layer and a p-doped semiconductor layer which contact each other, wherein the metal layer of the Schottky diode is coupled to one of the two electrodes of the resistive switching memory element. The present disclosure provides the resistive random access memory device operating in bipolar resistive switching scheme.

Owner:PEKING UNIV

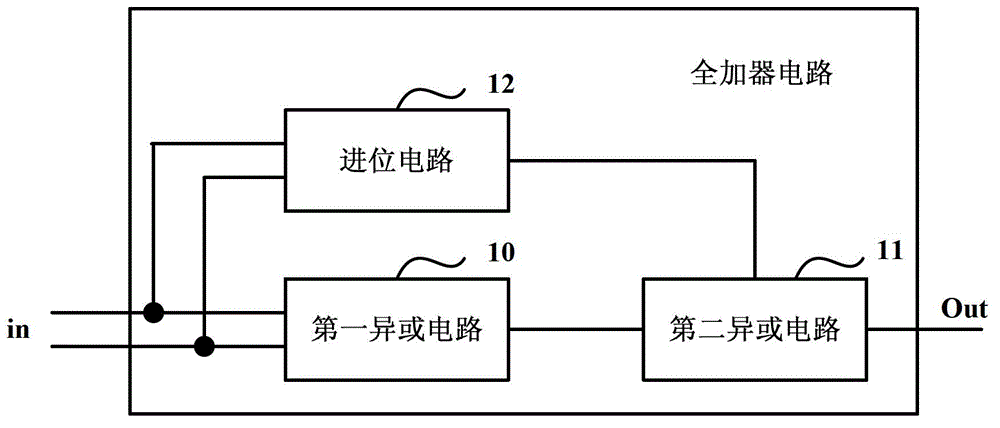

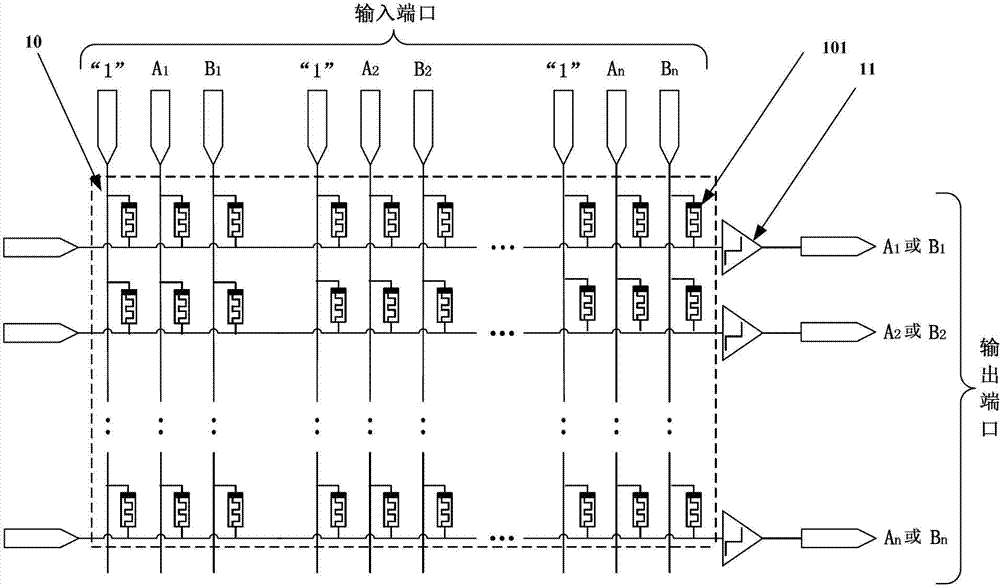

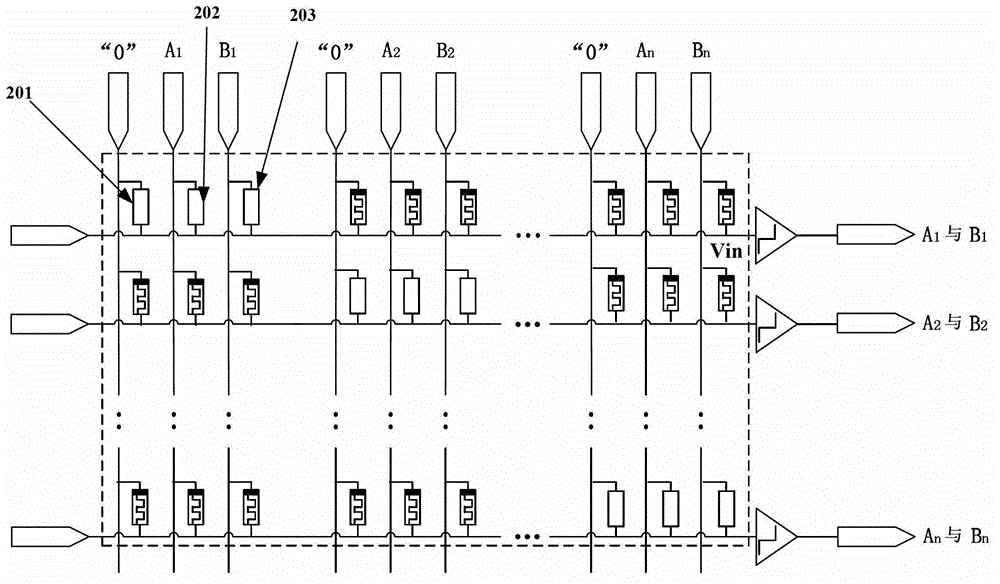

Full adder circuit and chip

ActiveCN102882513AData retention time is longData Retention Time SavingsLogic circuits characterised by logic functionMemristorComputer engineering

The embodiment of the invention discloses a full adder circuit and a chip. The circuit comprises a first xor circuit, a second xor circuit and a carry circuit; the input end of the first xor circuit is used as the signal input end of the full adder circuit; a group of input ends of the second xor circuit are connected with the output end of the first xor circuit, the other group of input ends of the second xor circuit are used as the carry input ends of the full adder circuit, and the output end of the second xor circuit is used as the signal output end of the full adder circuit; the input end of the carry circuit is used as the signal input end of the full adder circuit, and the output end of the carry circuit is connected with the carry input end of the full adder circuit; and at least one of the first xor circuit, the second xor circuit and the carry circuit comprises a resistance-variable memristor array. In the embodiment of the invention, the area occupied by the full adder circuit is reduced, and meanwhile, the programmable performance of the full adder circuit is achieved.

Owner:PEKING UNIV

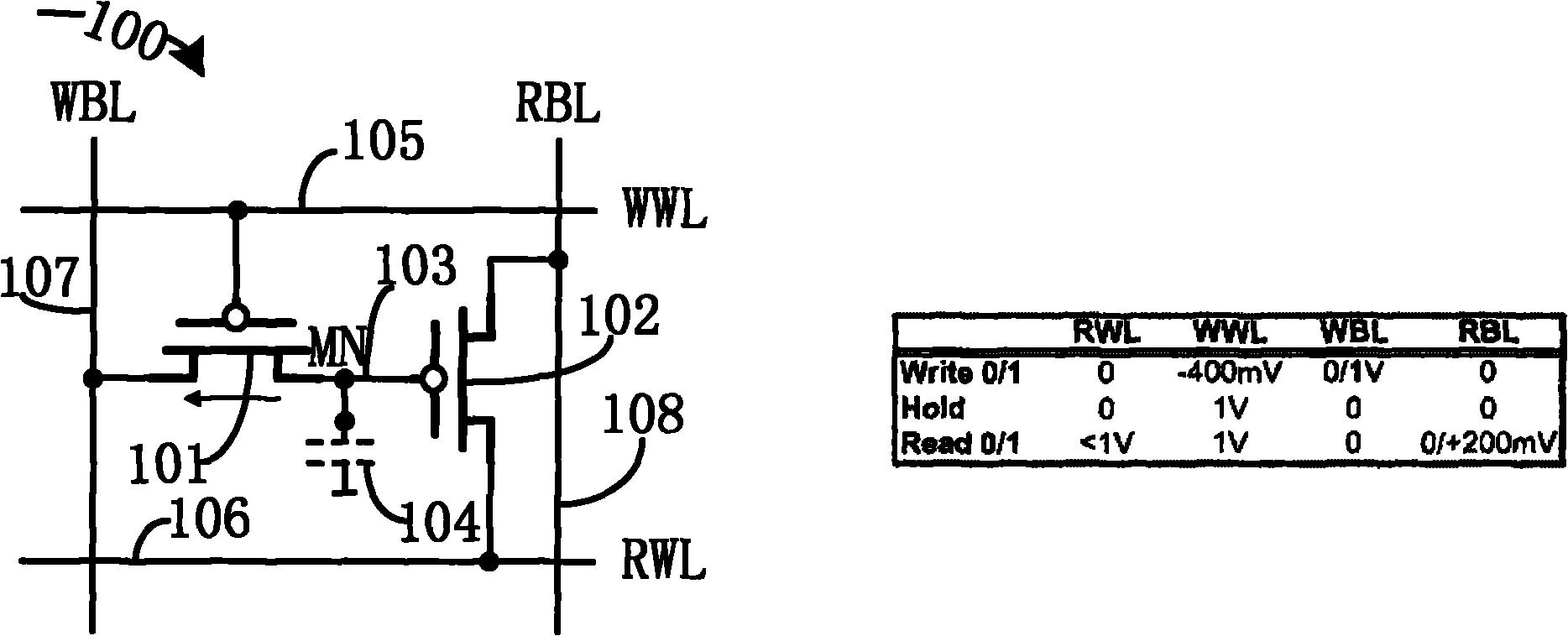

EDRAM (Enhanced Dynamic Random Access Memory) unit of gain unit, memory and operating method

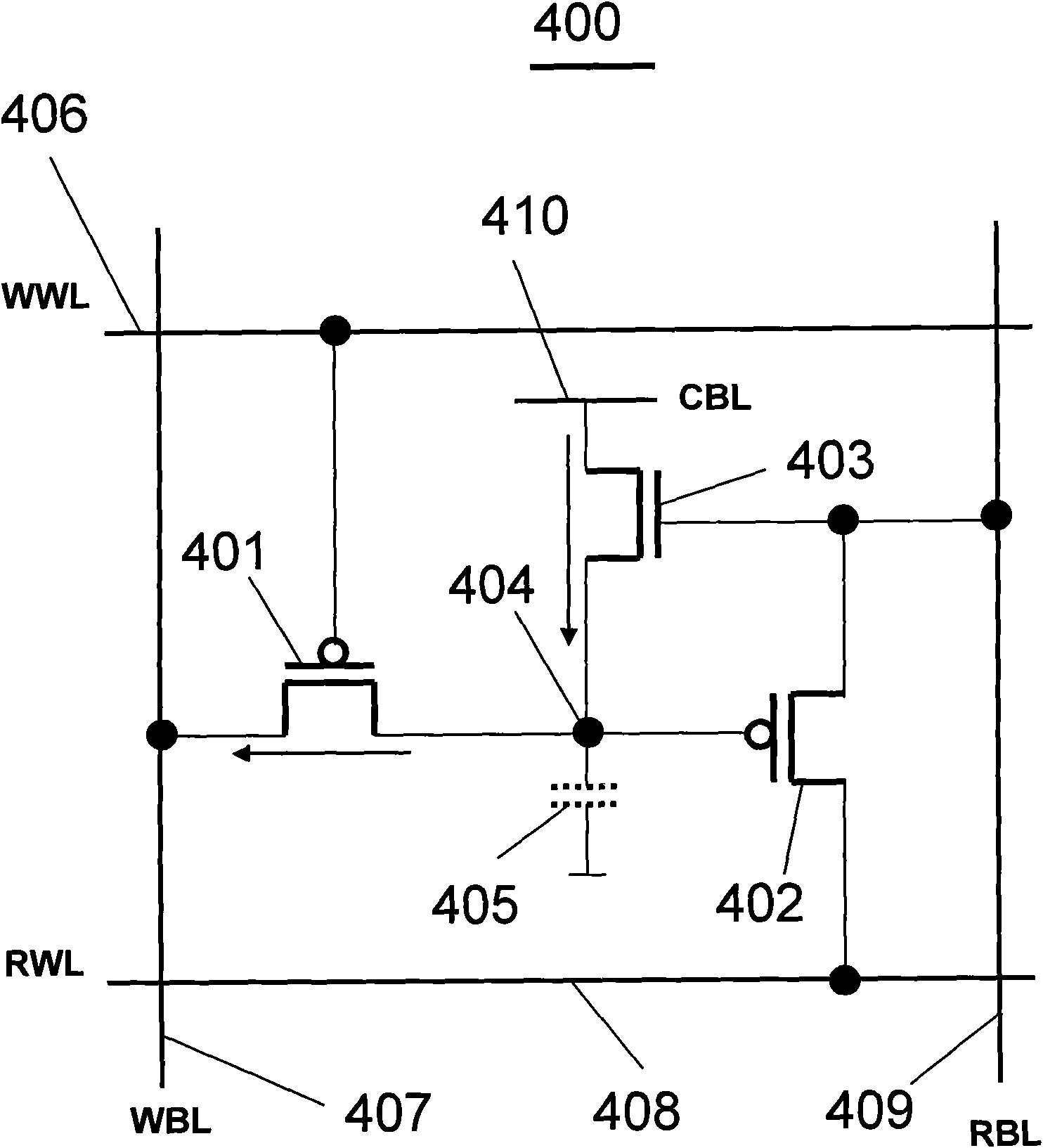

InactiveCN102081962AImprove reading speedData retention time is longDigital storageWrite bitHigh Readings

The invention belongs to the technical field of dynamic random access memories and in particular relates to an EDRAM (Enhanced Dynamic Random Access Memory) unit of a gain unit, a memory and an operating method thereof. Based on a writing MOS (Metal Oxide Semiconductor) transistor, a reading MOS transistor, a writing word line, a writing bit line, a reading word line, a reading bit line and an equivalent parasitic capacitor, the EDRAM unit of the gain unit provided by the invention is obtained by increasing a coupling complementary MOS transistor and a shared bit line which is connected to a fixed voltage such that the EDRAM unit of the gain unit has the characteristics of long data retention time and low refreshing frequency; and the memory formed by the EDRAM unit of the gain unit has the characteristics of high reading speed and low power consumption.

Owner:FUDAN UNIV

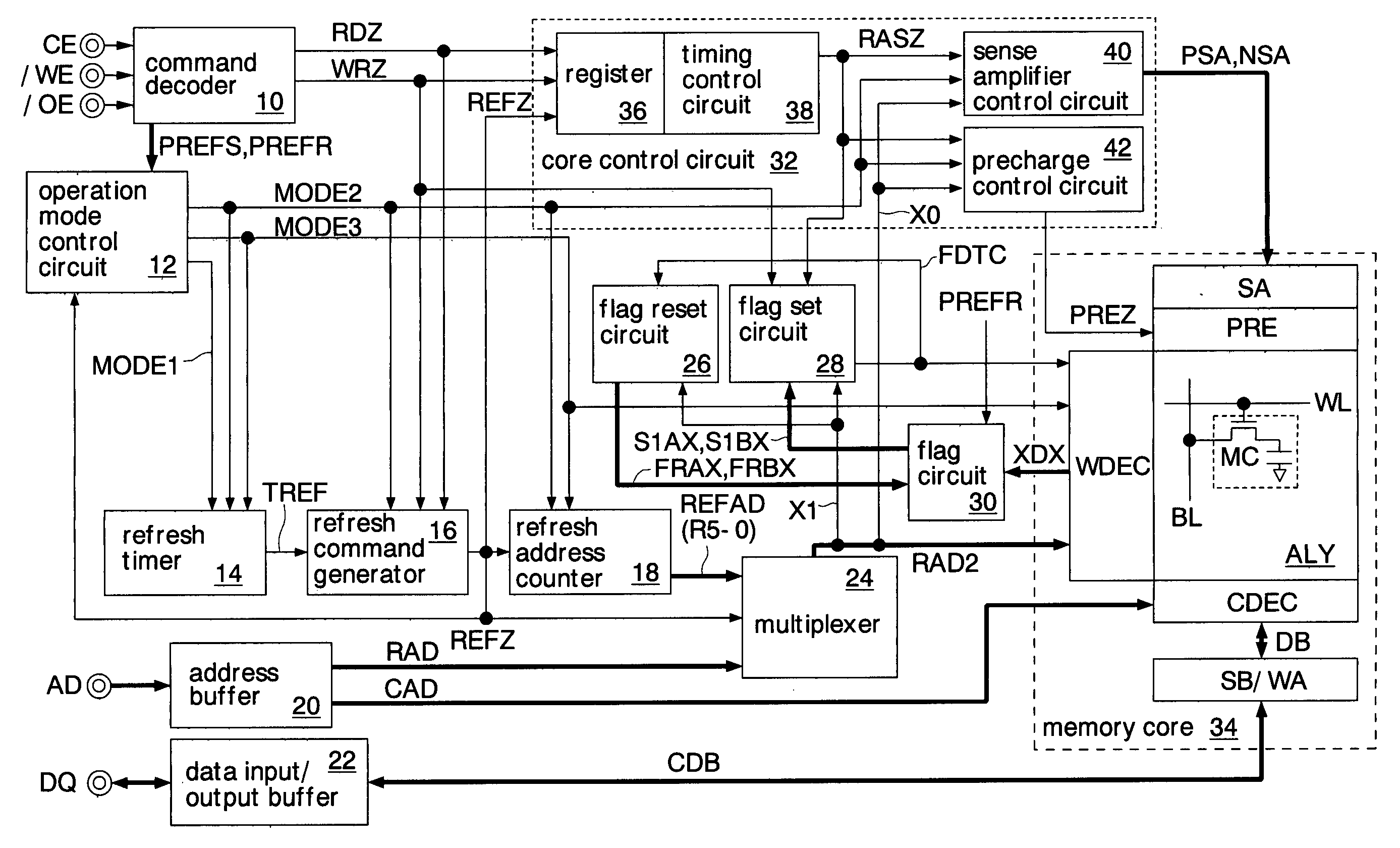

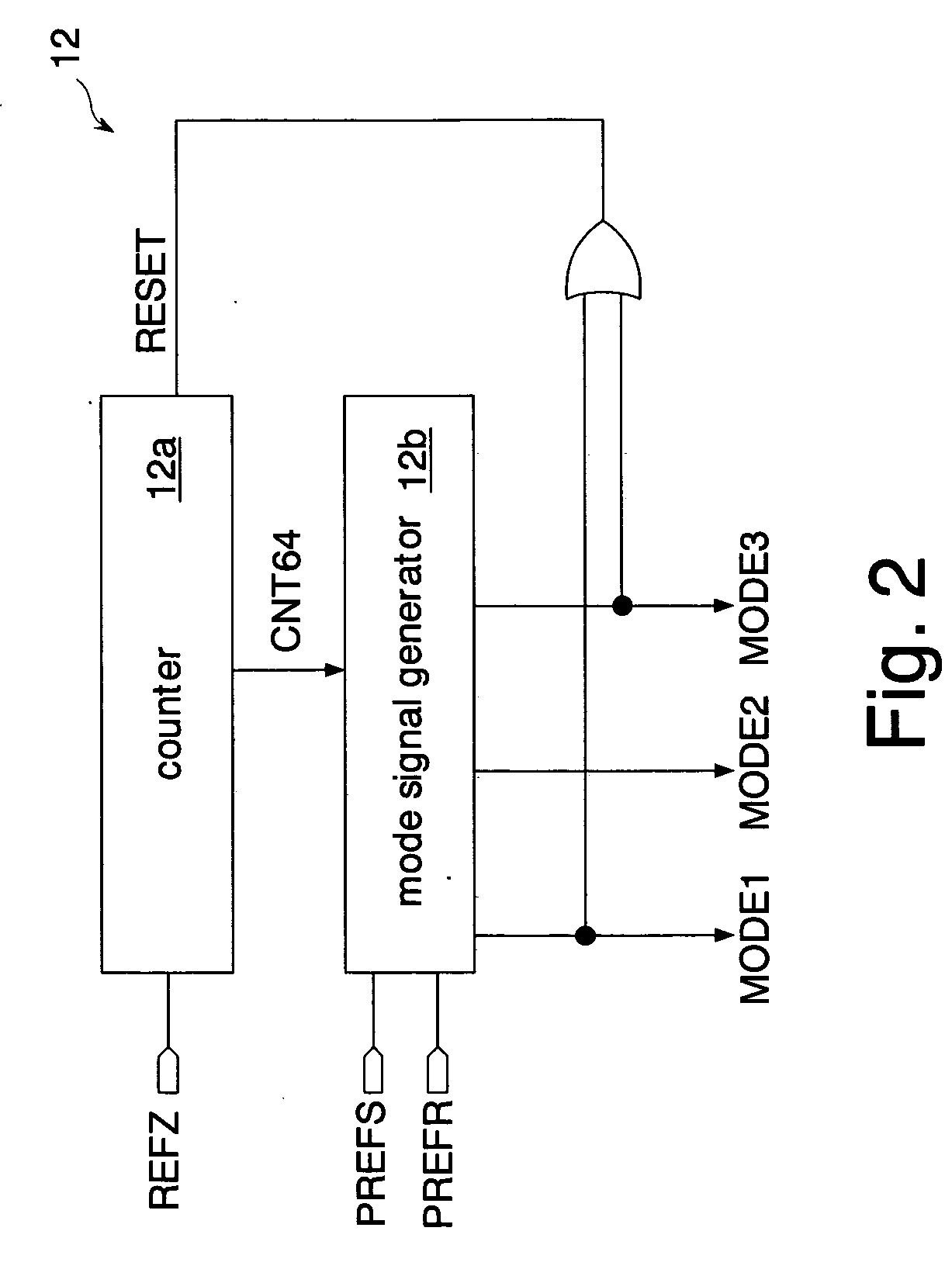

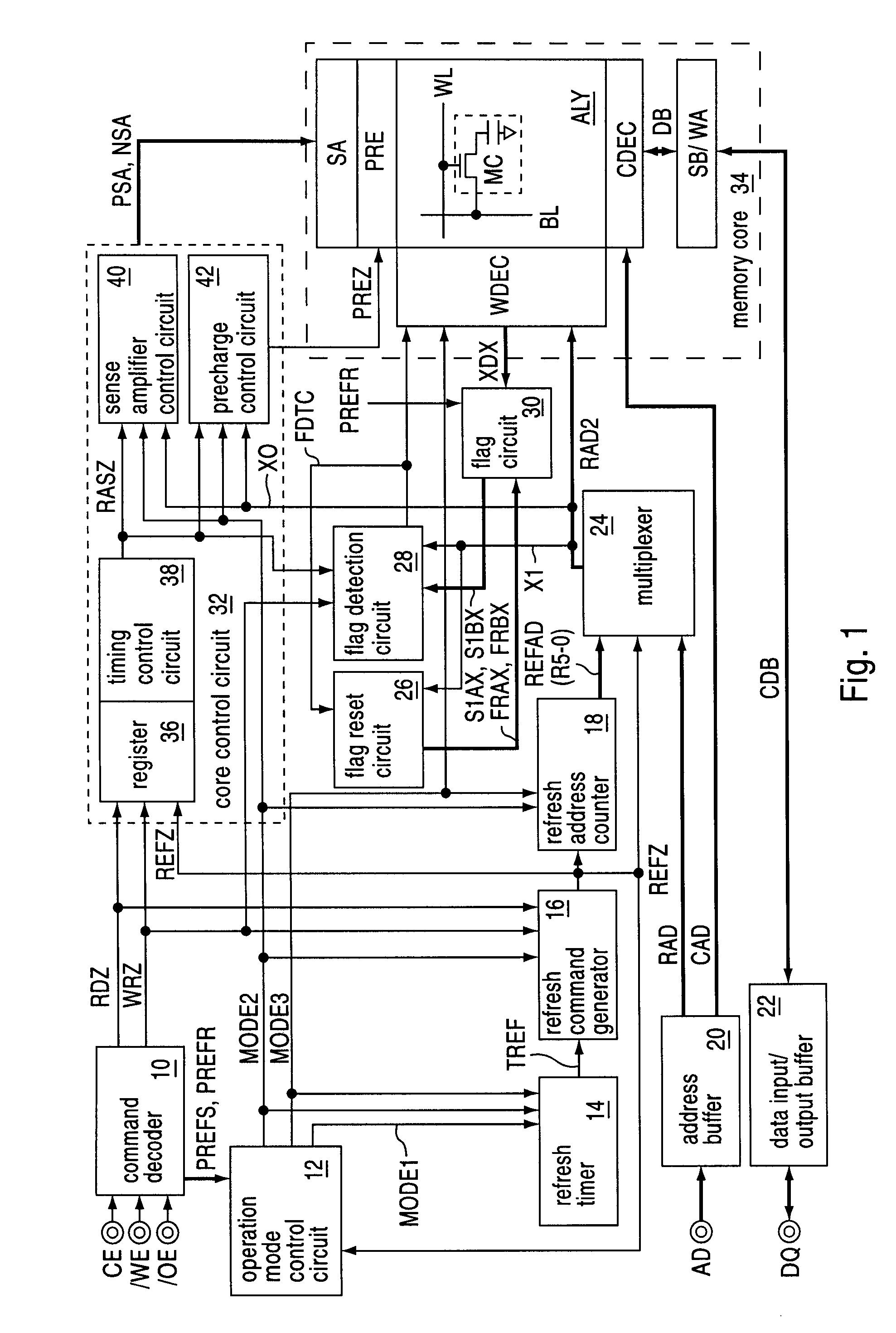

Semiconductor memory

Flags are formed to respectively correspond to memory cell groups each including volatile memory cells. Each flag indicates as a set state that the memory cells store data in a second memory mode. In a changing operation of changing from a first memory mode in which data is independently retained by each memory cell to a second memory mode in which same data are retained in the memory cells of each memory cell group, each flag is reset in response to the first access to the corresponding memory cell group. Therefore, only the first access is made in the second memory mode in each memory cell group. The memory cells are accessed in a mode according to the flag in the changing operation, thereby allowing a system managing the semiconductor memory to freely access the memory cells even during the changing operation. Consequently, a practical changing time can be eliminated.

Owner:SOCIONEXT INC

Semiconductor memory with single cell and twin cell refreshing

InactiveUS7154799B2Reduce power consumptionQuick changeDigital storageComputer architectureSemiconductor

Flags are formed to respectively correspond to memory cell groups each including volatile memory cells. Each flag indicates as a set state that the memory cells store data in a second memory mode. In a changing operation of changing from a first memory mode in which data is independently retained by each memory cell to a second memory mode in which same data are retained in the memory cells of each memory cell group, each flag is reset in response to the first access to the corresponding memory cell group. Therefore, only the first access is made in the second memory mode in each memory cell group. The memory cells are accessed in a mode according to the flag in the changing operation, thereby allowing a system managing the semiconductor memory to freely access the memory cells even during the changing operation. Consequently, a practical changing time can be eliminated.

Owner:SOCIONEXT INC

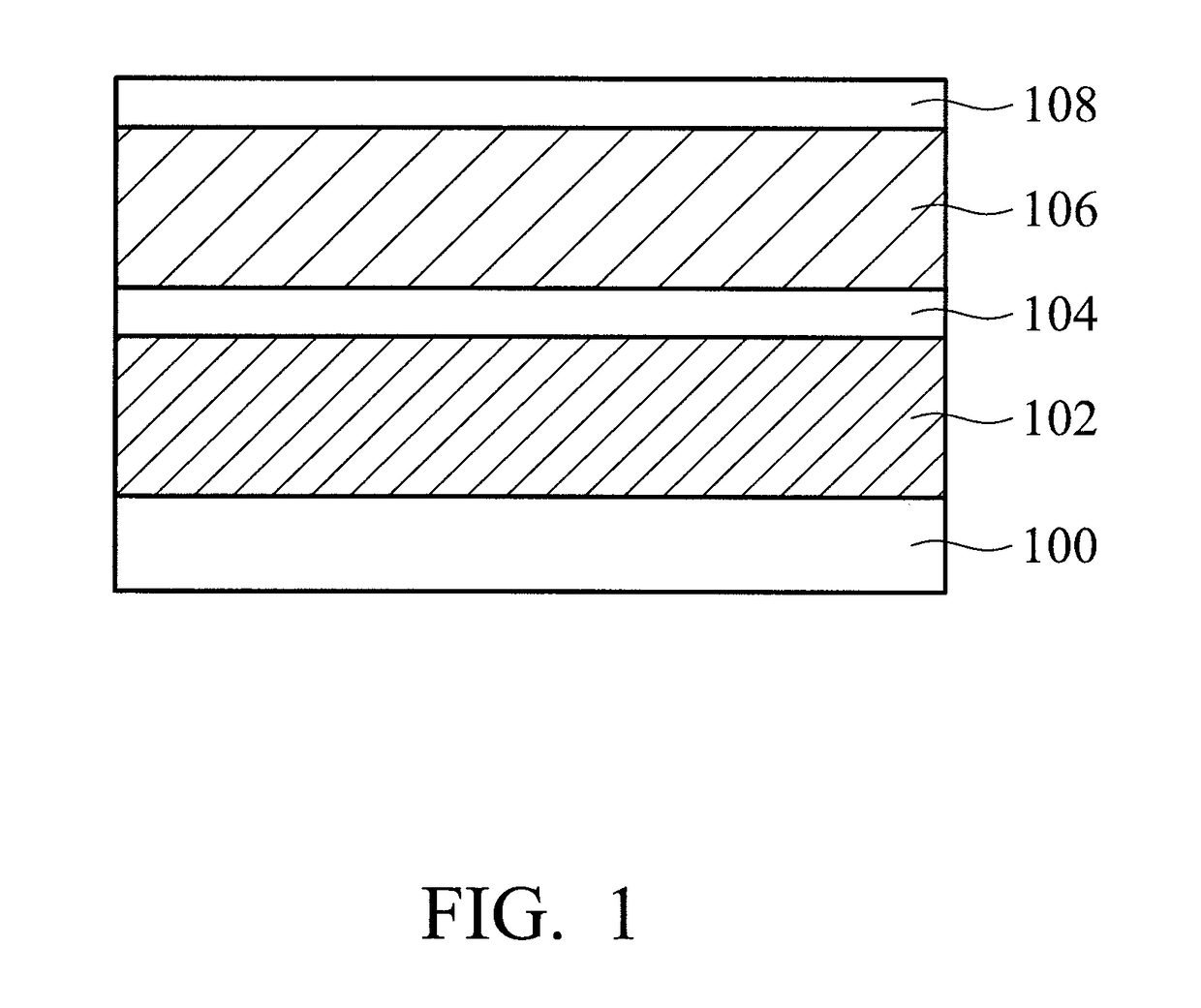

RRAM device and method for manufacturing the same

ActiveUS9716223B1Short timeLong enduranceSolid-state devicesBulk negative resistance effect devicesResistive switchingEngineering

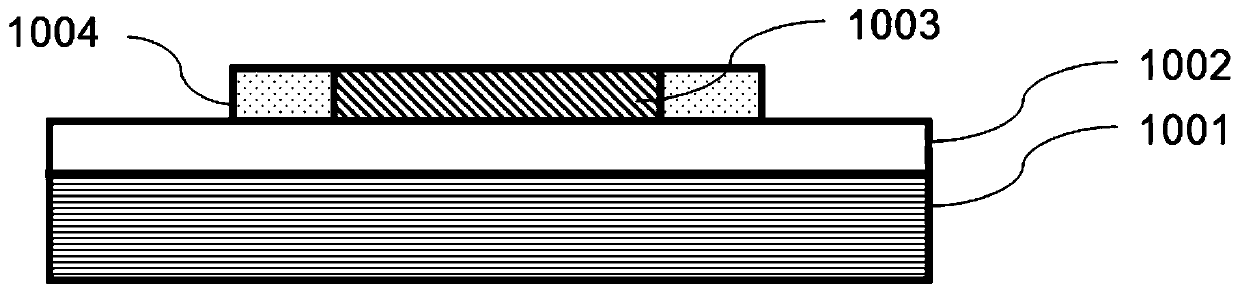

A resistive random access memory device includes a bottom electrode, a plurality of memory stacks separately formed over the bottom electrode, a third oxygen diffusion barrier layer formed between the memory stacks, and a top electrode formed over the plurality of memory stacks and the third oxygen diffusion barrier layer. Each of the plurality of memory stacks includes a resistive switching layer formed over the bottom electrode, a first oxygen diffusion barrier layer formed over the resistive switching layer, a conductive oxygen reservoir layer formed over the first oxygen diffusion barrier layer, and a second oxygen diffusion barrier layer formed over the conductive oxygen reservoir layer.

Owner:WINBOND ELECTRONICS CORP

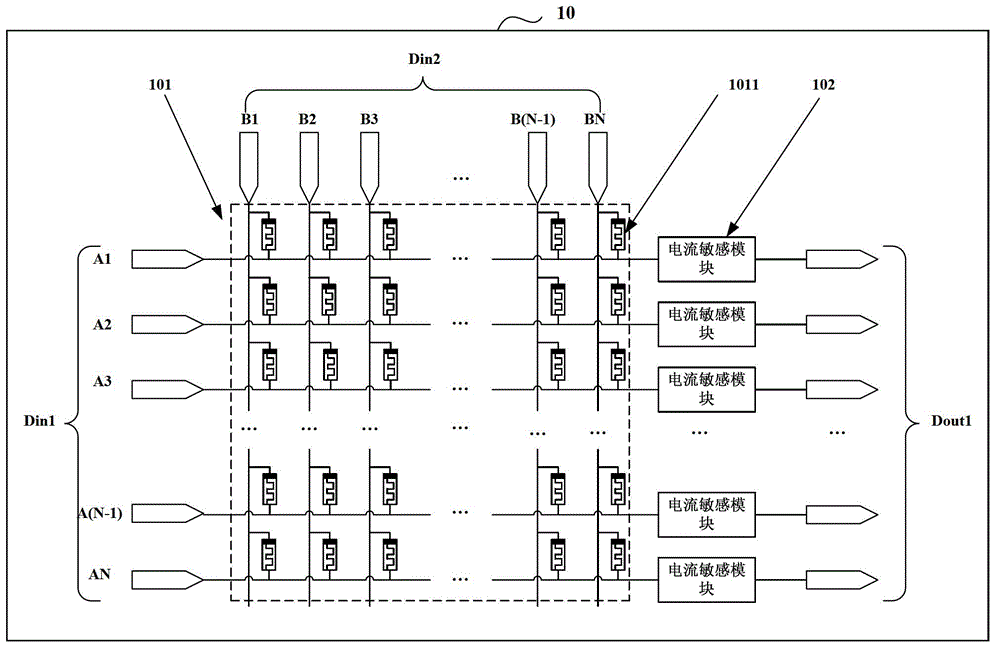

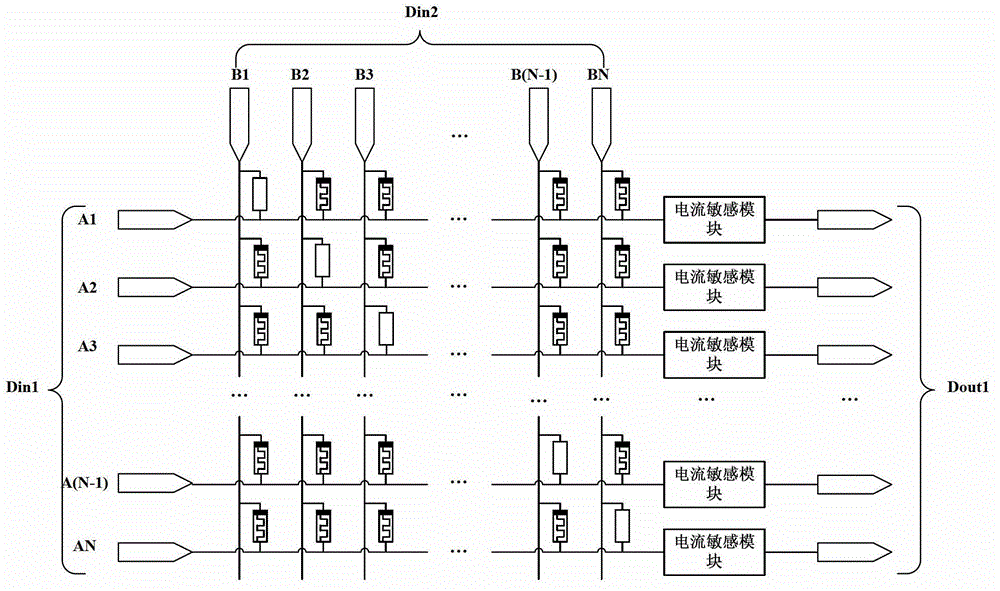

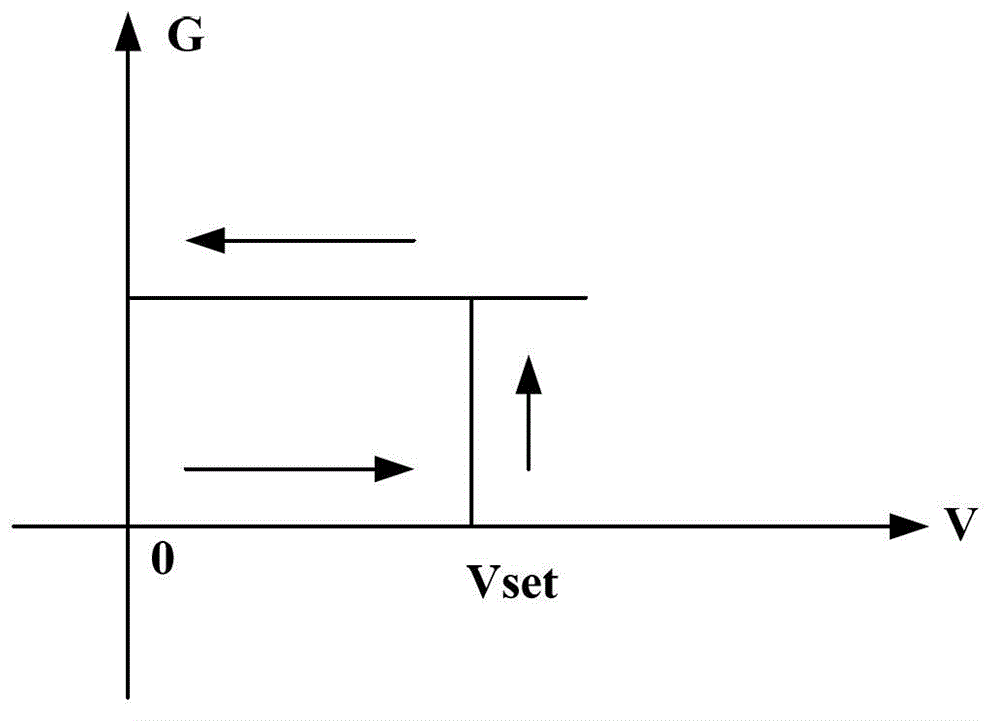

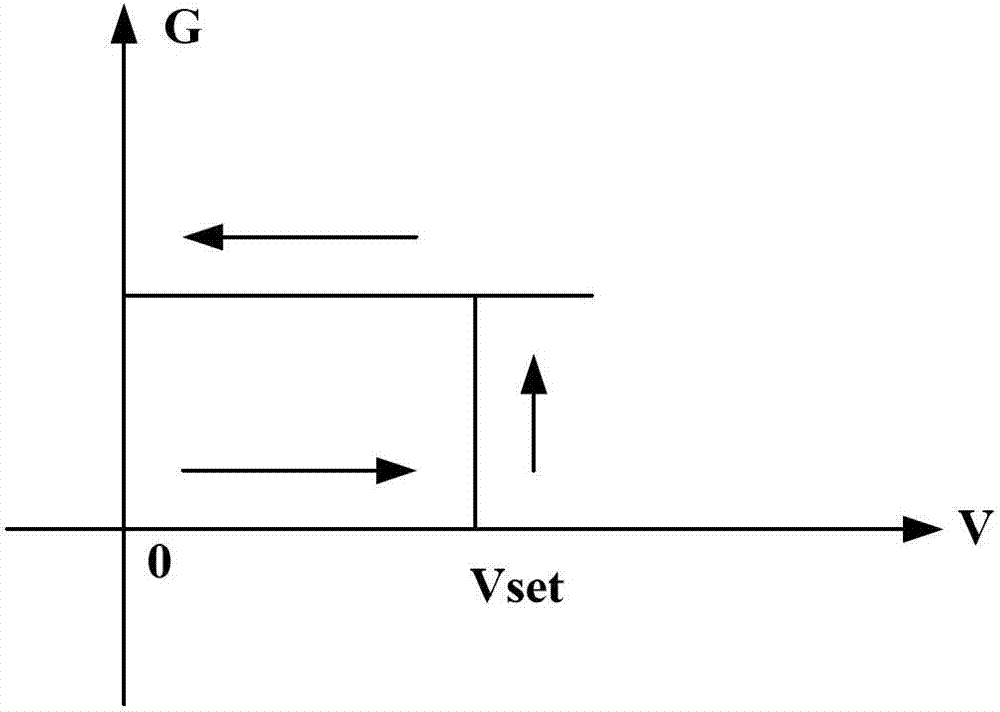

OR logic circuit and chip

ActiveCN102891679AData retention time is longData Retention Time SavingsLogic circuits characterised by logic functionComparatorLogic circuitry

The inventive embodiment discloses an OR logic circuit and a chip. The circuit comprises a resistance random memristor array and comparators, wherein the forward input ends of resistance random memristors on the same column in the resistance random memristor array are connected, so that the forward input ends of the resistance random memristors on the same column serves as a signal input end or an auxiliary signal input end of the OR logic circuit; the auxiliary signal input end is connected with a high level during work; the reverse input ends of the resistance random memristors on the same column in the resistance random memristor array are connected with the input end of one comparator, so that the output end of the comparator serves as a signal output end of the OR logic circuit; and the output end of the comparator outputs a high level or a low level when the voltage received by the input end of the comparator is larger or smaller than a threshold voltage. In the embodiment of the invention, the OR logic circuit can realize the programmable performance while saving the occupation area of the OR logic circuit.

Owner:PEKING UNIV

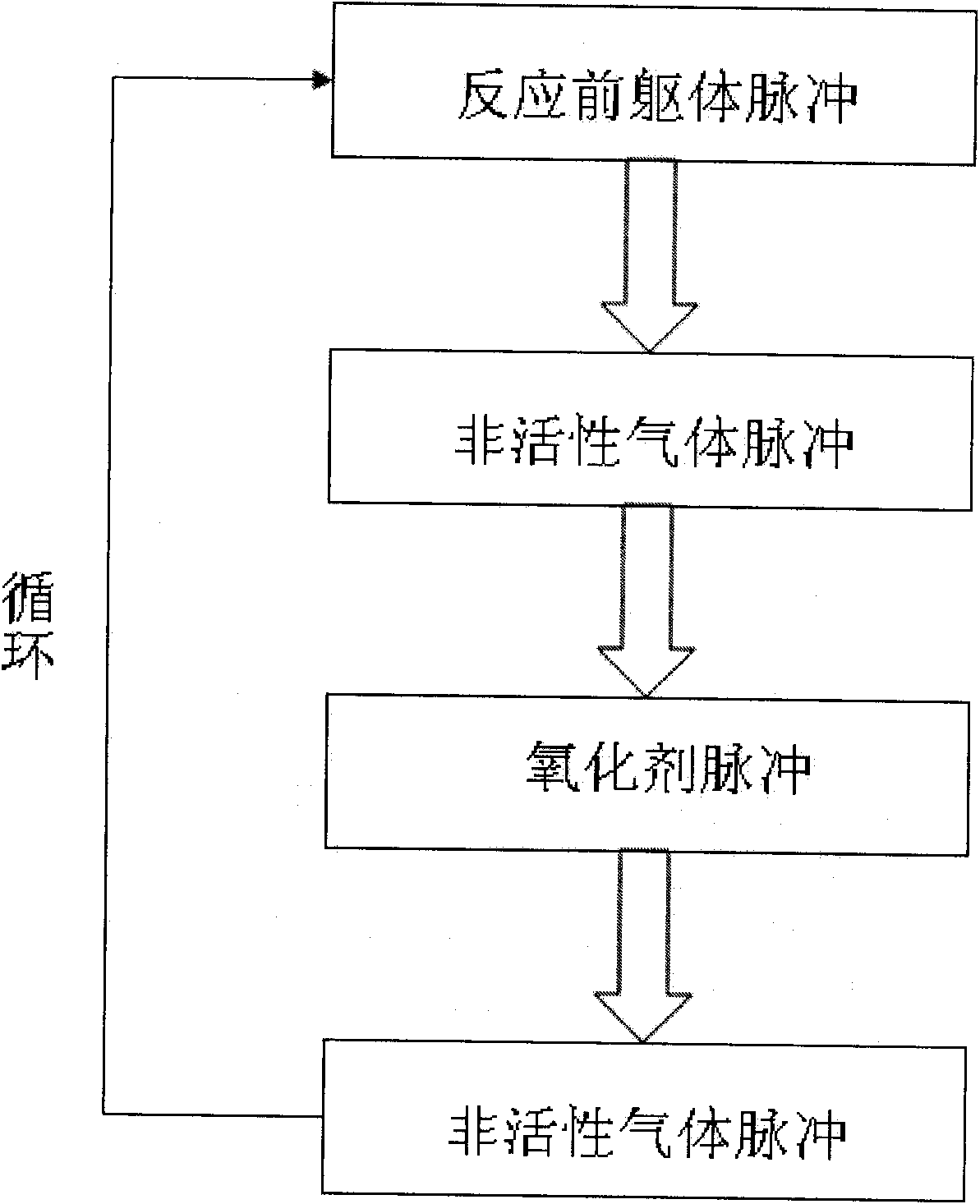

Resistance random memory based on columbium oxide film and preparation method thereof

InactiveCN101673803AImprove compatibilityPrecise thickness controlElectrical apparatusDigital storageContinuous scanningInsulation layer

The invention relates to a resistance random memory based on a columbium oxide film and a preparation method thereof, belonging to the technical field of memories. The memory unit comprises a substrate and a metal-insulation layer-metal (MIM) structure unit, wherein a top electrode of the MIM structure unit is metal films, such as titanium nitride and the like, the insulation layer is a columbiumoxide film, and a lower electrode adopts Pt or Au. The MIM structure in the invention represents excellent transformation and memory properties between high and low resistance states under the continuous scanning excitation of direct-current voltage. Further, the invention also provides the preparation method of the memory unit. The method comprises the preparation of a substrate material, the lower electrode, a dielectric film and an upper electrode and the like.

Owner:FUDAN UNIV

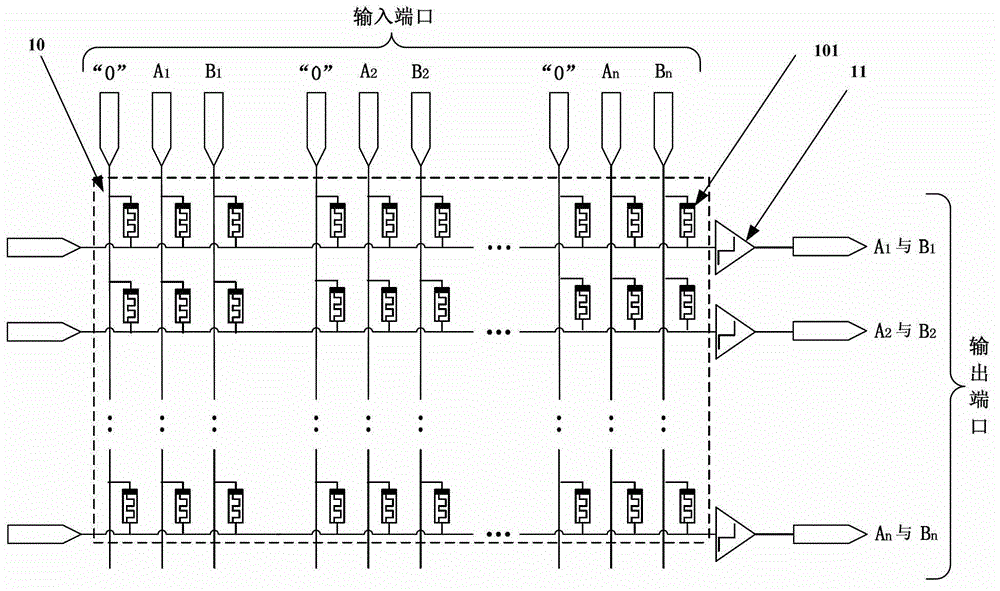

AND logic circuit and chip

ActiveCN102882514AImprove scalabilityImprove storage densityLogic circuits characterised by logic functionLogic circuitryComparator

The embodiment of the invention discloses an AND logic circuit and a chip. The circuit comprises a resistance change memristor array and comparators; the non-inverting input ends of the same line of resistance change memristors in the resistance change memristor array are connected with one another, so that the non-inverting input ends of the same line of the resistance change memristors serve as a signal input end or an auxiliary signal input end of the AND logic circuit; the auxiliary signal input end is connected to a low level when working; inverting input ends of the same row of resistance change memristors in the resistance change memristor array are connected with the input end of a comparator, so that the output end of the comparator serves as a signal output end of the AND logic circuit; when the voltage received by the input end of the comparator is greater than a threshold voltage, the output end of the comparator outputs a high level; and when the voltage received by the input end of the comparator is lower than the threshold voltage, the output end of the comparator outputs the low level. By the embodiment of the invention, the area occupied by the AND logic circuit is saved and simultaneously the programmable performance of the AND logic circuit is realized.

Owner:PEKING UNIV

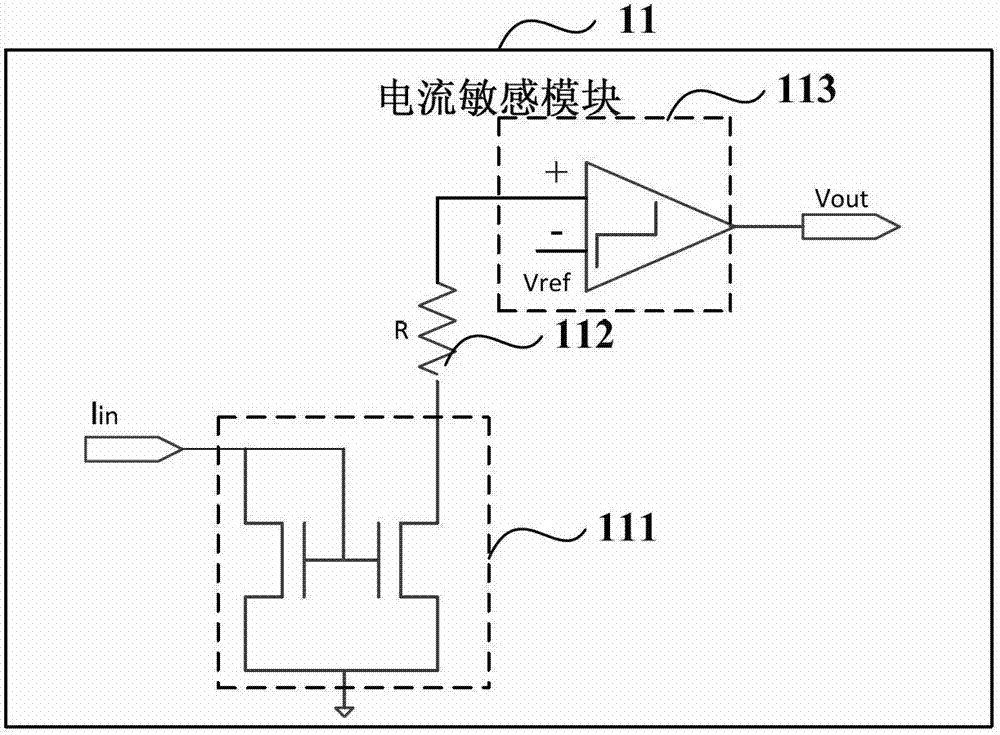

Phase inverter circuit and chip

InactiveCN102891678AData retention time is longData Retention Time SavingsLogic circuitsPower flowComputer module

The embodiment of the invention discloses a phase inverter circuit and a chip. The phase inverter circuit comprises a resistive memristor matrix and a current sensitive module; normal phase input ends of the same line of resistive memristors in the resistive memristor matrix are connected to ensure that the normal phase input ends of the same line of resistive memristors are used as signal input ports; inverted phase input ends of the same line of resistive memristors in the resistive memristor matrix are connected to ensure that the output end of the current sensitive module is used as a signal output port; and the input end of the current sensitive module is connected to low level in the working process, and when the current received by the input end of the current sensitive module is larger than threshold current, the output end of the current sensitive module outputs low level; and when the current received by the input end of the current sensitive module is lower than the threshold current, the output end of the current sensitive module outputs high level. According to the embodiment of the invention, the area occupied by the phase inverter circuit is saved, and meanwhile, the programmable performance of the phase inverter circuit is achieved.

Owner:PEKING UNIV

Resistive random access memory device

A resistive random access memory device is provided, which includes a bottom electrode, a resistive switching layer disposed on the bottom electrode, an oxidizable layer disposed on the resistive switching layer, a first oxygen diffusion barrier layer disposed between the oxidizable layer and the resistive switching layer, and a second oxygen diffusion barrier layer disposed on the oxidizable layer.

Owner:WINBOND ELECTRONICS CORP

Shift register circuit and chip

ActiveCN102881333AData retention time is longData Retention Time SavingsDigital storageShift registerNegative phase

The embodiment of the invention discloses a shift register circuit and a chip. The circuit comprises a resistance changing memristor matrix and a current sensitive module, wherein positive phase input ends of the same column of resistance changing memristors in the resistance changing memristor matrix are connected, so that the positive phase input ends of the same column of resistance changing memristors are served as signal input ports; negative phase input ends of the same column of resistance changing memristors in the resistance changing memristor matrix are connected with the input end of the current sensitive module, so that the output end of the current sensitive module is served as a signal output port; the input end of the current sensitive module is connected to low electric level during operation; when the current received by the input end of the current sensitive module is more than threshold current, the output end of the current sensitive module outputs high electric level; and when the current received by the input end of the current sensitive module is less than the threshold current, the output end of the current sensitive module outputs low electric level. In the embodiment of the invention, the occupied area of the shift register circuit is saved and the programmable performance of the shift register circuit is achieved.

Owner:PEKING UNIV

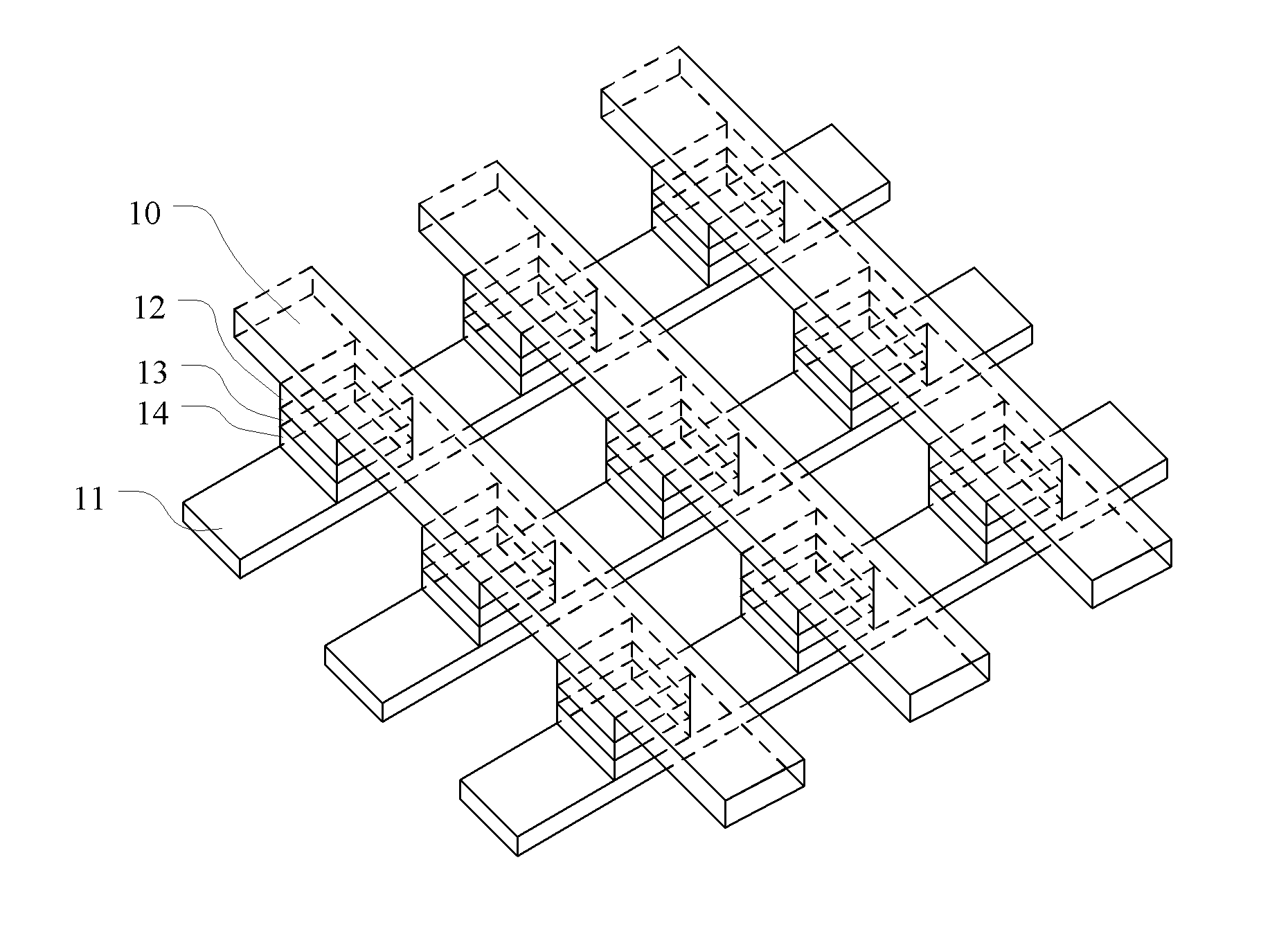

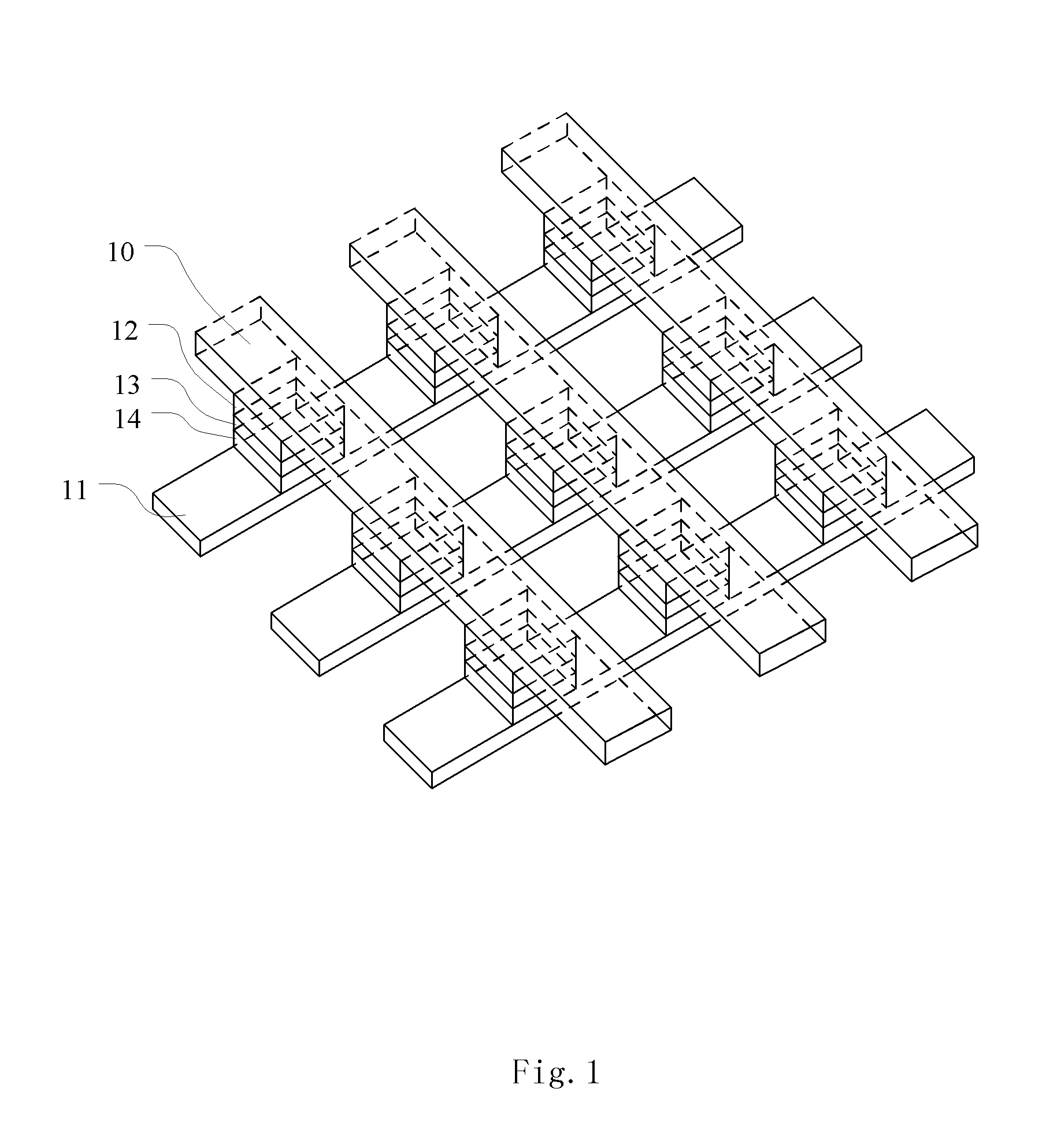

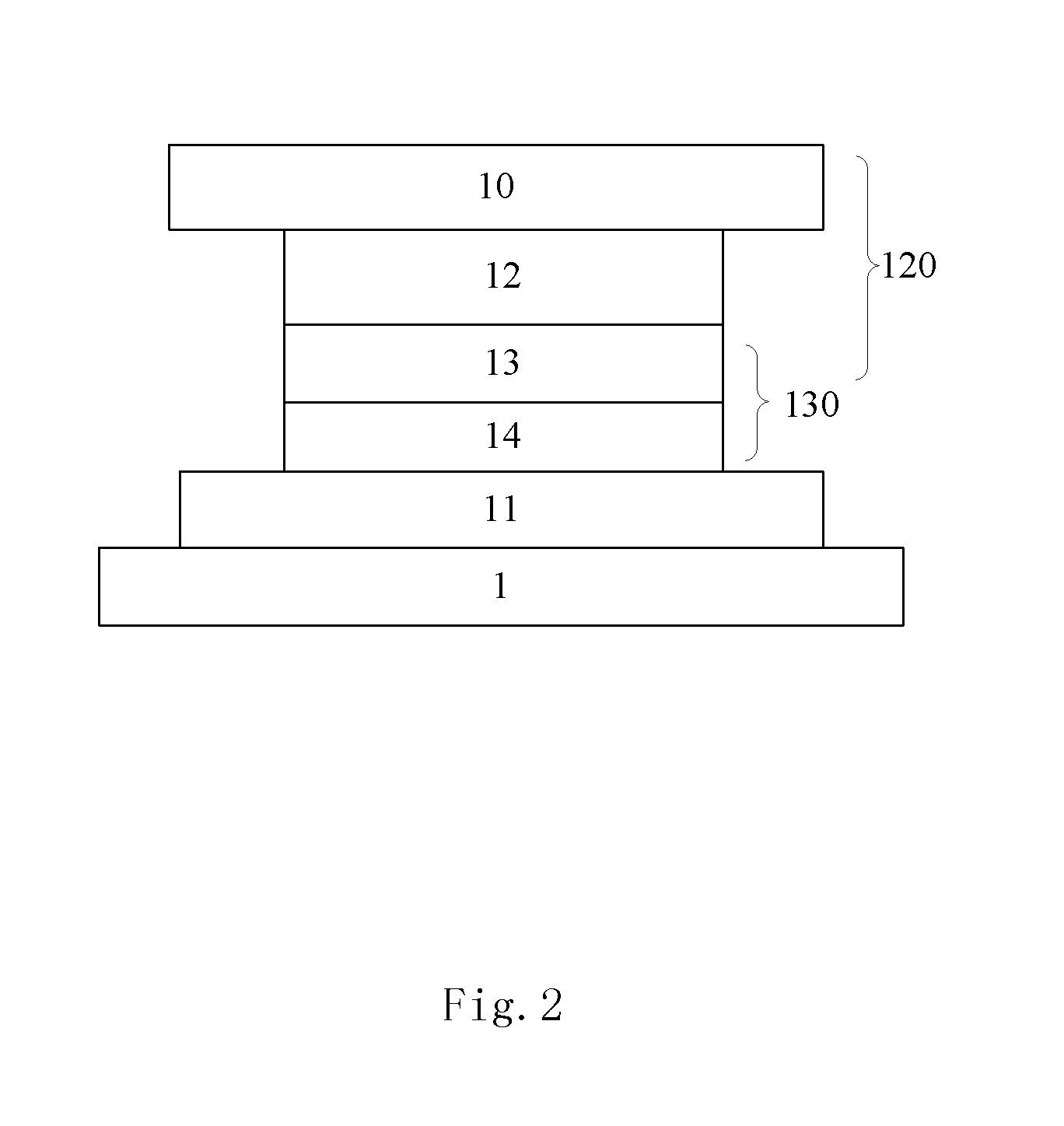

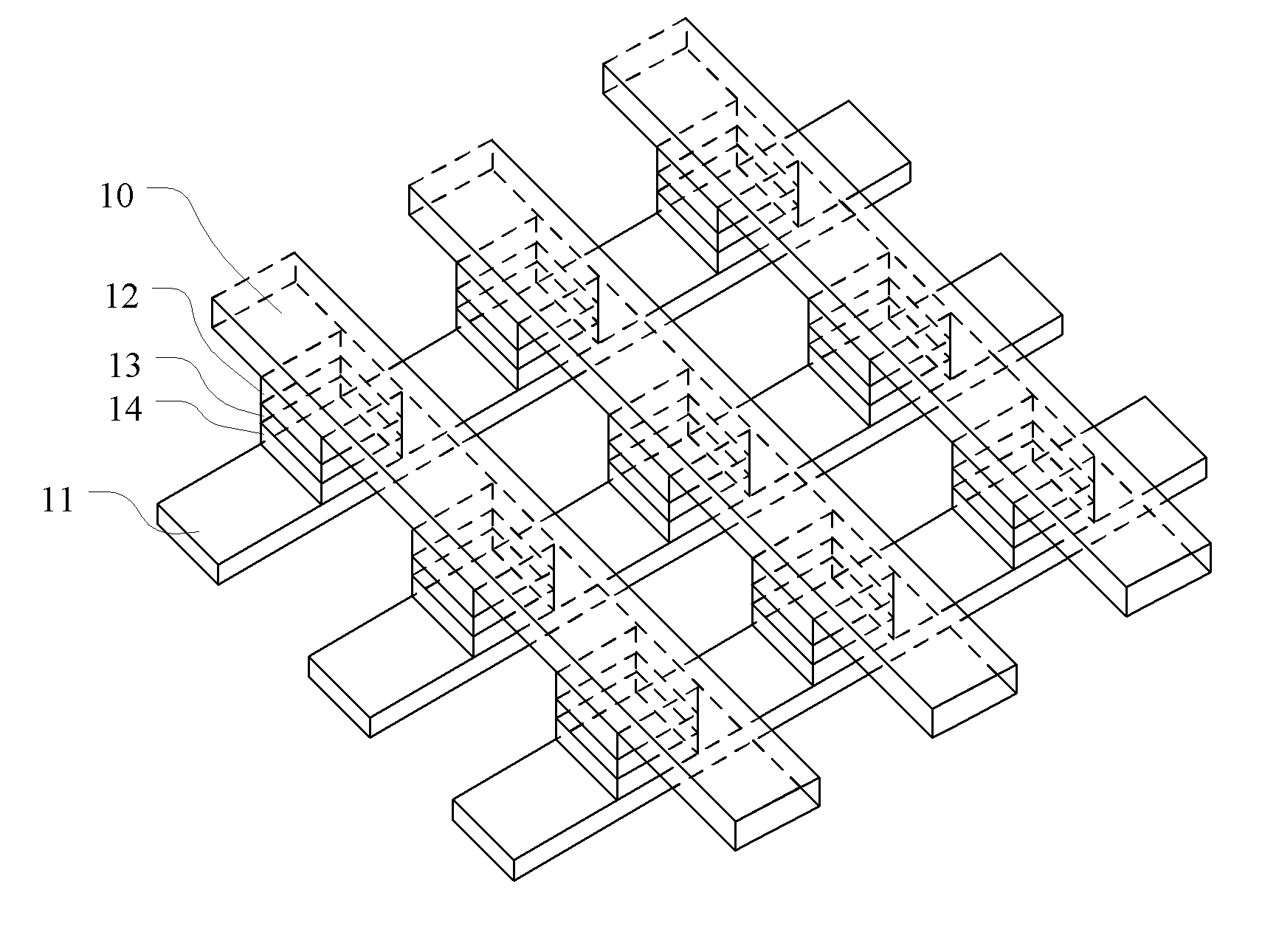

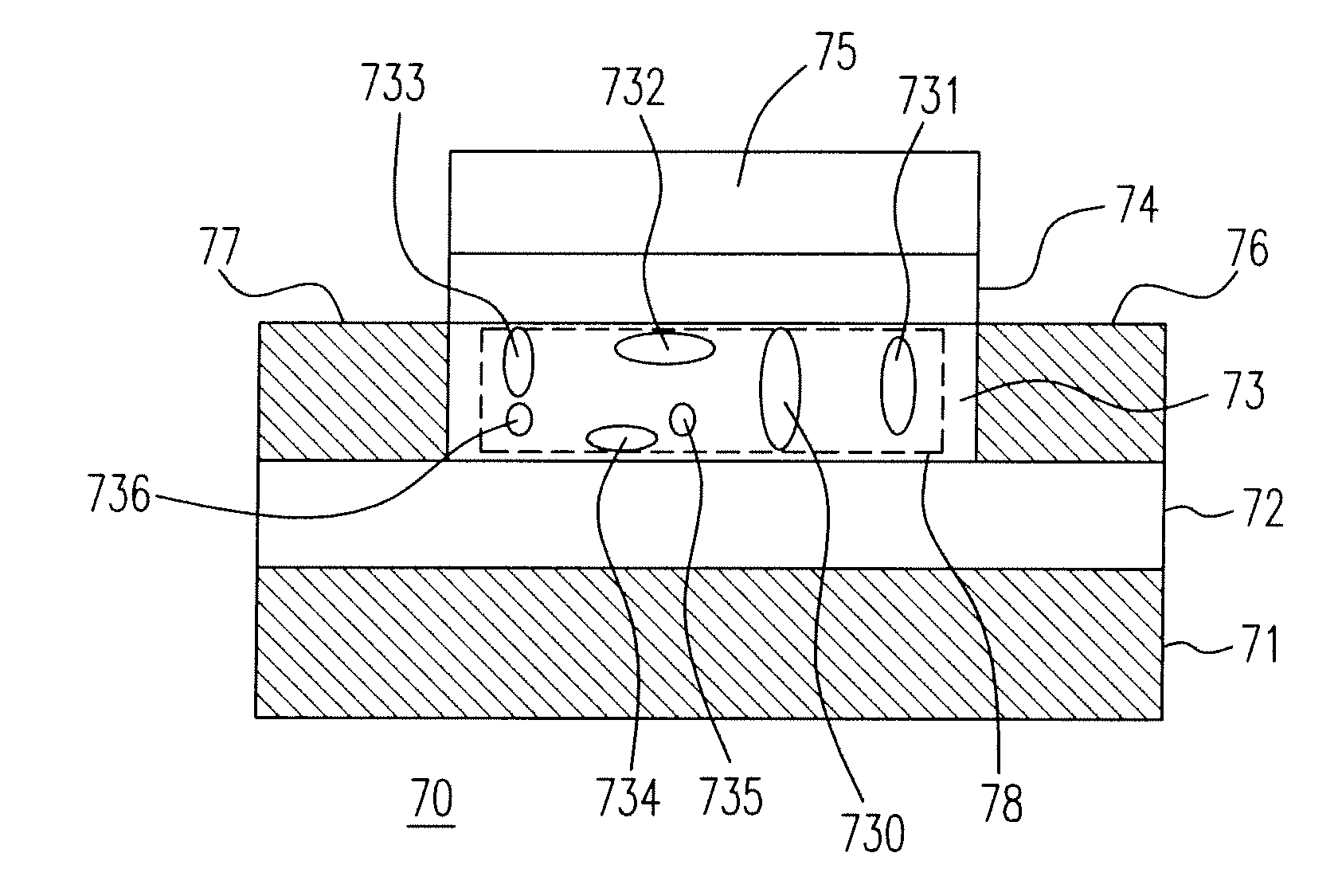

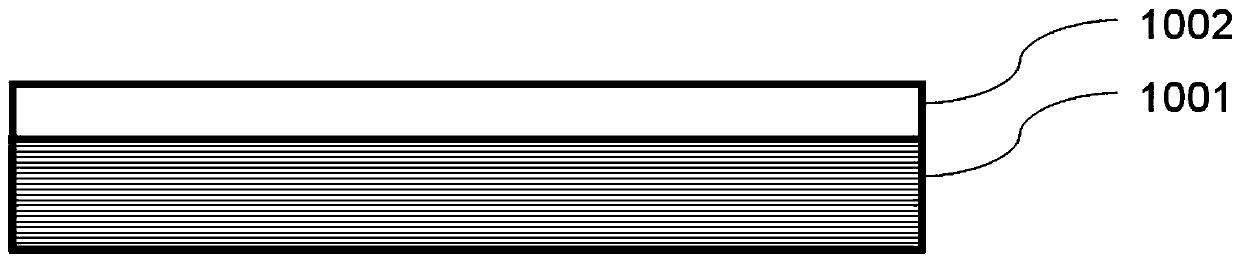

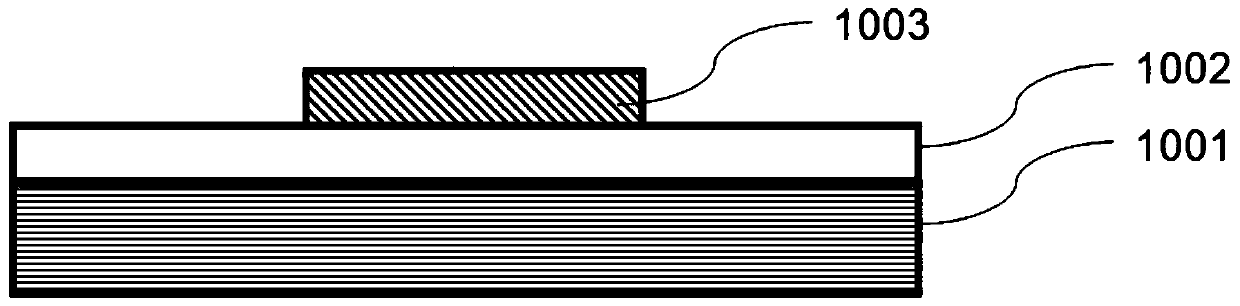

Semi-floating gate memory based on two-dimensional material and preparation method thereof

ActiveCN111490045AWith ultra-thin characteristicsReduce volumeSolid-state devicesSemiconductor devicesBottom gateEngineering physics

The invention belongs to the technical field of semiconductor memories, and particularly relates to a semi-floating gate memory based on a two-dimensional material and a preparation method thereof. The semi-floating gate memory comprises an L-shaped bottom gate, a barrier layer covering the surface of the bottom gate, and an L-shaped semi-floating gate layer which is a first type of two-dimensional material, and the top of the L-shaped semi-floating gate layer is flush with the top of the bottom gate; the semi-floating gate memory further comprises a semi-closed tunneling layer at the bottom of the semi-floating gate, wherein the semi-closed tunneling layer is a second type of two-dimensional material, and the upper surface of the semi-closed tunneling layer is flush with the top of the semi-floating gate; the semi-floating gate memory further comprises a channel layer which covers the semi-floating gate and the semi-closed tunneling layer and is made of a third type two-dimensional material, and the upper surface of the channel layer is flush with the top of the barrier layer; the semi-floating gate memory further comprises a source electrode and a drain electrode which are on thesurface of the channel and are a fourth type of two-dimensional material. The first type of two-dimensional material and the third type of two-dimensional material form a diode, and the first type oftwo-dimensional material, the third type of two-dimensional material, the barrier layer and the bottom gate form a grid-control diode. The device is good in reliability and high in data erasing and writing speed, and the data retention time can be prolonged; in addition, the device is small in size and suitable for being used in ultrathin electronic equipment.

Owner:FUDAN UNIV +1

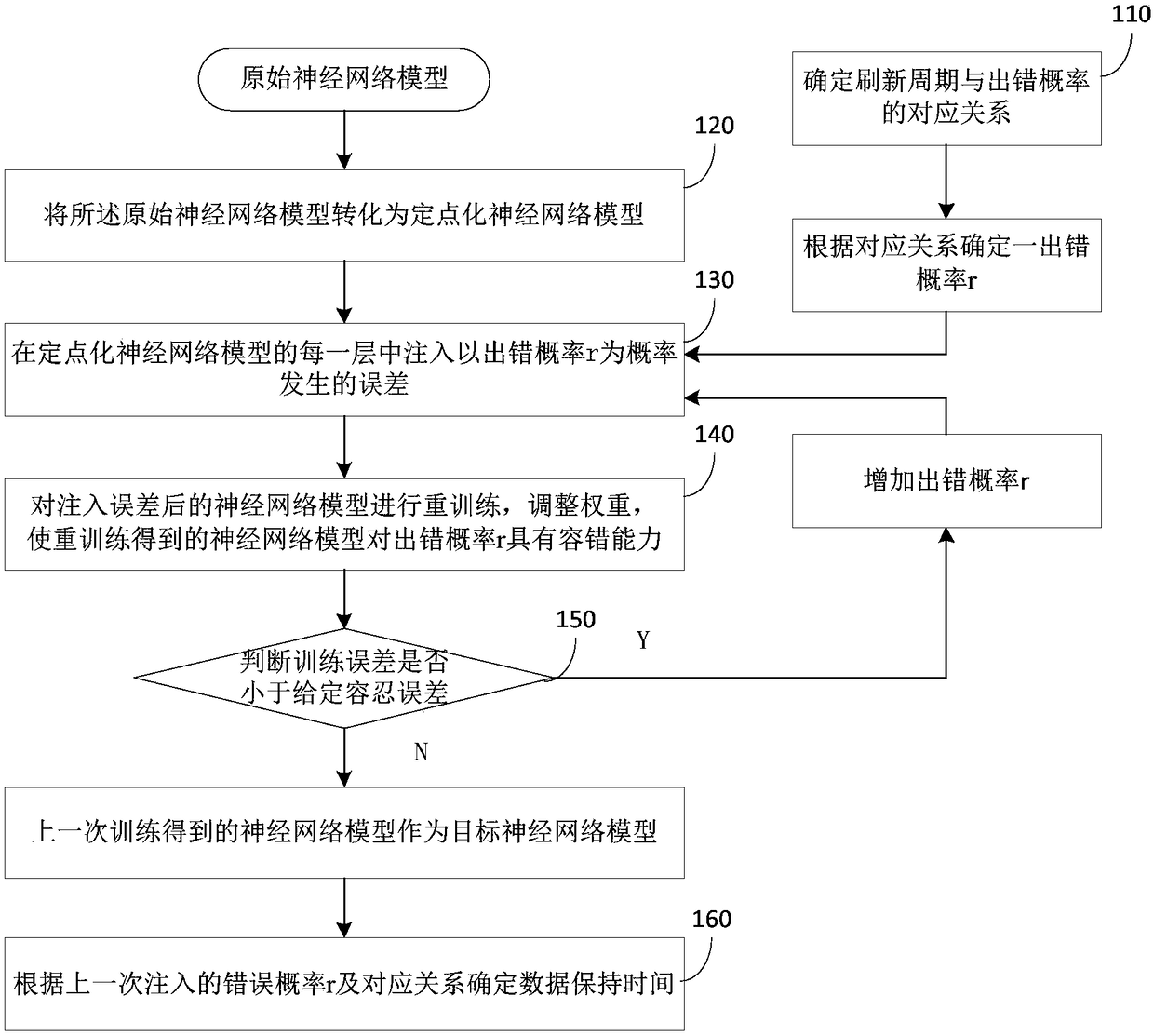

Method and system for reducing eDRAM (Embedded Dynamic Random Access Memory) refreshing energy consumption in neural network chip

ActiveCN108647782AReduce refresh energy consumptionData retention time is longDigital storagePhysical realisationSimulationNetwork model

The invention provides a method and system for reducing eDRAM (Embedded Dynamic Random Access Memory) refreshing energy consumption in a neural network chip. The method comprises the steps of trainingan original neural network model, and determining a target neural network model with the maximum fault-tolerant capability, and data hold time of an eDRAM corresponding to the target neural network model; scheduling each layer of the target neural network model, and determining a computing mode of each layer and data survival time of each layer under the lowest computing energy consumption; and setting the target neural network model to be performed on the neural network chip according to the computing model of each layer, for storage subareas of each layer, if effective data is not stored inthe storage subareas or the data survival time of each layer is shorter than the data holder time, not refreshing the storage subareas. According to the method, the unnecessary refreshing operation can be removed to the greatest extent, and the eDRAM refreshing energy consumption in the neural network chip is greatly reduced.

Owner:TSINGHUA UNIV

Flexible resistive random access memory and preparation method

InactiveCN106920877AHigh mechanical strengthImprove bending strengthElectrical apparatusGraphicsThin-film memory

The invention discloses a flexible resistive random access memory and a preparation method. The flexible resistive random access memory comprises a bottom electrode, a memory functional layer and a top electrode which are prepared on a flexible substrate in sequence, wherein the bottom electrode, the memory functional layer and the top electrode form a sandwich structure; and the material of the memory functional layer is rare earth oxide. The preparation method comprises the following steps of (1) forming a bottom electrode layer on the flexible substrate; (2) forming a pattern required by the memory device on the bottom electrode through a photoetching process; (3) forming a rare earth oxide thin film memory functional layer on the pattern; (4) forming a top electrode layer on the memory functional layer; and (5) removing photoresist to form a complete device unit. The flexible resistive random access memory disclosed by the invention has the advantage of maintaining memory performance stability when the flexible resistive random access memory is bent for a certain radius and bent for multiple times, so that the flexible resistive random access memory is applicable to a flexible memory technology.

Owner:GENERAL RESEARCH INSTITUTE FOR NONFERROUS METALS BEIJNG

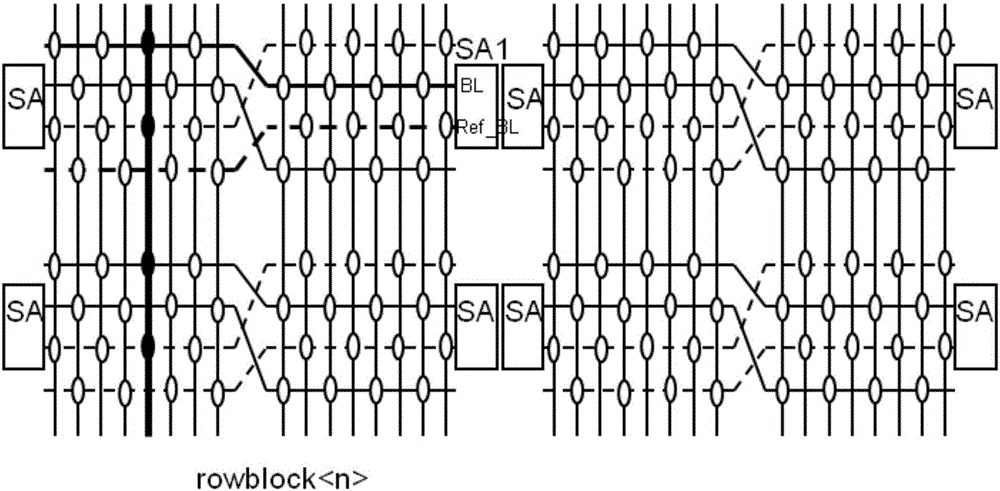

Dynamic storage based on open bit line structure

ActiveCN105895147AData Retention Time EnhancementSolve the problem that it cannot be applied to the current mainstream open bit line structure dynamic memory in the industryDigital storageHigh energyComputer module

The invention relates to a dynamic storage based on an open bit line structure. The dynamic storage comprises a decoder circuit, a sense amplifier and a plurality of dual-storage units, wherein the decoder circuit comprises a first decoding unit and a second decoding unit which have the same structure, an input end of a first XOR gate circuit is connected with an external address signal RA<0>, the other input end of the first XOR gate circuit is connected with a cfg_dualcell signal, and an output end of a first phase inverter controls a bit line Wl of one dual-storage unit in a storage unit array module to be opened; and an input end of a second XOR gate circuit is connected with an inverted signal / RAI<0> of the external address signal RA<0>, the other input end of the second XOR gate circuit is connected with the cfg_dualcell signal, and an output end of a second phase inverter controls the other bit line Wl of one dual-storage unit in the storage unit array module to be opened. According to the dynamic storage, the technical problems of high energy consumption and low reliability are overcome, and the data hold time of the dynamic storage is remarkably improved.

Owner:XI AN UNIIC SEMICON CO LTD

Resistive random access memory device, method for manufacturing the same, and method for operating the same

ActiveUS9047937B2Small footprintImprove memory performanceSolid-state devicesDigital storageRandom access memoryEngineering

A resistive random access memory device, a method for manufacturing the resistive random access memory device, and a method for operating the resistive random access memory device are disclosed. The resistive random access memory device includes a resistive switching memory element including two electrodes and a layer of variable-resistance material between the two electrodes, wherein the layer of variable-resistance material exhibits bipolar resistive switching behavior; and a Schottky diode including a metal layer and a p-doped semiconductor layer which contact each other, wherein the metal layer of the Schottky diode is coupled to one of the two electrodes of the resistive switching memory element. The present disclosure provides the resistive random access memory device operating in bipolar resistive switching scheme.

Owner:PEKING UNIV

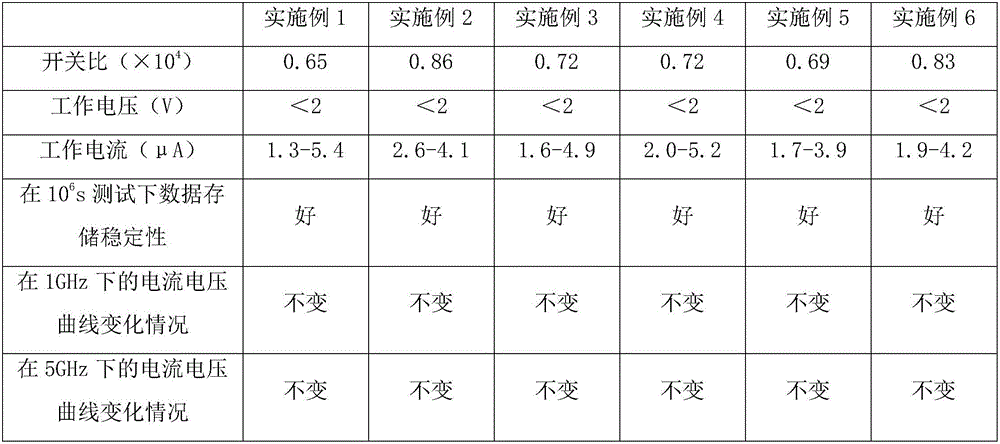

Preparation method of flexible biological memristor for neurosynaptic bionics

The invention relates to a preparation method of a flexible biological memristor for neurosynaptic bionics. The preparation method comprises the following steps: coating a mixed solution on a conductive layer to obtain a composite silk fibroin membrane, treating the composite silk fibroin membrane with ethanol or methanol, and preparing an electrode layer on the composite silk fibroin membrane toobtain the flexible biological memristor, wherein the mixed solution mainly consists of silk fibroin, metal ions and water, and the metal ions are Ag<+>, Ca<2+>, Fe<2+>, Fe<3+> or Li<+>. The preparation method of the flexible biological memristor for neurosynaptic bionics disclosed by the invention is simple and easy to operate, is capable of effectively preparing the biological memristor which ishigh in sensitivity, low in working voltage, relatively large in switch ratio, stable in signal transmission and long in data retention time, and has the characteristics of neurosynaptic bionics, thestability, durability and consistency of device can be remarkably improved, and the flexible biological memristor is low in power consumption, wide in application range and good application prospectand is suitable for large-scale production.

Owner:DONGHUA UNIV +1

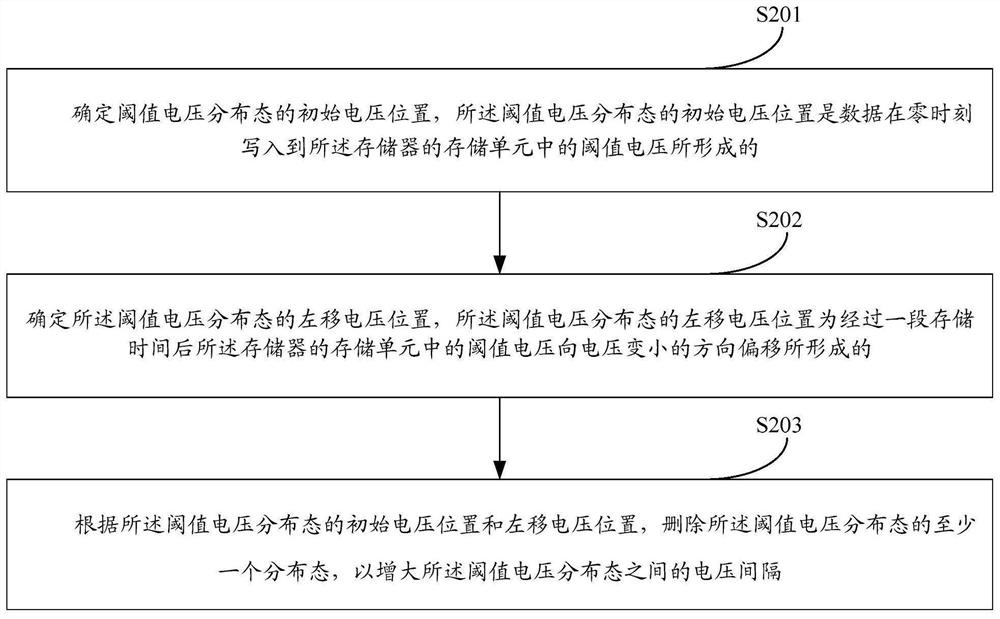

Error correction method, error correction device and data refreshing method of memory

ActiveCN113380315AIncrease the voltage intervalKeep errors downStatic storageEnergy efficient computingControl theoryData retention

The embodiment of the invention provides an error correction method and device for a memory. The method comprises the steps of: determining initial voltage positions of threshold voltage distribution states, and determining left-shift voltage positions of the threshold voltage distribution states; and deleting at least one distribution state of the threshold voltage distribution states according to the initial voltage positions and the left-shift voltage positions of the threshold voltage distribution states so as to increase the voltage interval between the threshold voltage distribution states. Therefore, in the embodiment of the invention, by determining the initial voltage positions and the left-shift voltage positions of the threshold voltage distribution states, whether data retention error occurs in a memory can be determined; and after data retention error occurs, at least one distribution state of the threshold voltage distribution states is deleted, and the voltage interval between the threshold voltage distribution states is increased, so that the data retention error is reduced, and the data retention time of a storage unit is prolonged.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Indium phosphide resistance variable material-based resistive random access memory and preparation method thereof

InactiveCN106803534ALarge storage windowData retention time is longElectrical apparatusStatic random-access memorySingle crystal

The present invention provides an indium phosphide resistance variable material-based resistive random access memory and a preparation method thereof. The resistive random access memory comprises a platinum bottom electrode, an indium phosphide resistance variable material doped with S and Fe and a silver top electrode, and the preparation method comprises the steps of taking an insulating inorganic material of which the surface is deposited with platinum metal as a substrate, adopting a pulse laser technology to deposit an indium phosphide thin film on the surface of the substrate to form the indium phosphide resistance variable material, and then covering a hard mask on the surface of the indium phosphide resistance variable material, adopting a magnetron sputtering technology to deposit a silver electrode layer, and removing the mask to obtain the indium phosphide resistance variable material-based resistive random access memory. According to the present invention, an indium phosphide single crystal wafer and a preparation method of the indium phosphide single crystal wafer of utilizing the pulse laser technology to deposit the indium phosphide thin film, are limited, so that the consistency and stability of the indium phosphide resistance variable material in the resistive random access memory are guaranteed, and the resistive random access memory has the characteristics of being wide in storage window, long in data hold time and high in durability.

Owner:DONGGUAN JIAQIAN NEW MATERIAL TECH CO LTD

Memory Formed By Using Defects

InactiveUS20110032765A1Reduce power consumptionHigh densityTransistorSemiconductor/solid-state device testing/measurementPower flowSilicon on insulator

A non-volatile memory is provided. The non-volatile memory comprises at least a silicon-on-insulator transistor including a substrate; an insulating layer disposed on the substrate; an active region disposed on the insulating layer; and an energy barrier device disposed in the active region and outputting a relatively small current when the non-volatile memory is read.

Owner:NAT TAIWAN UNIV

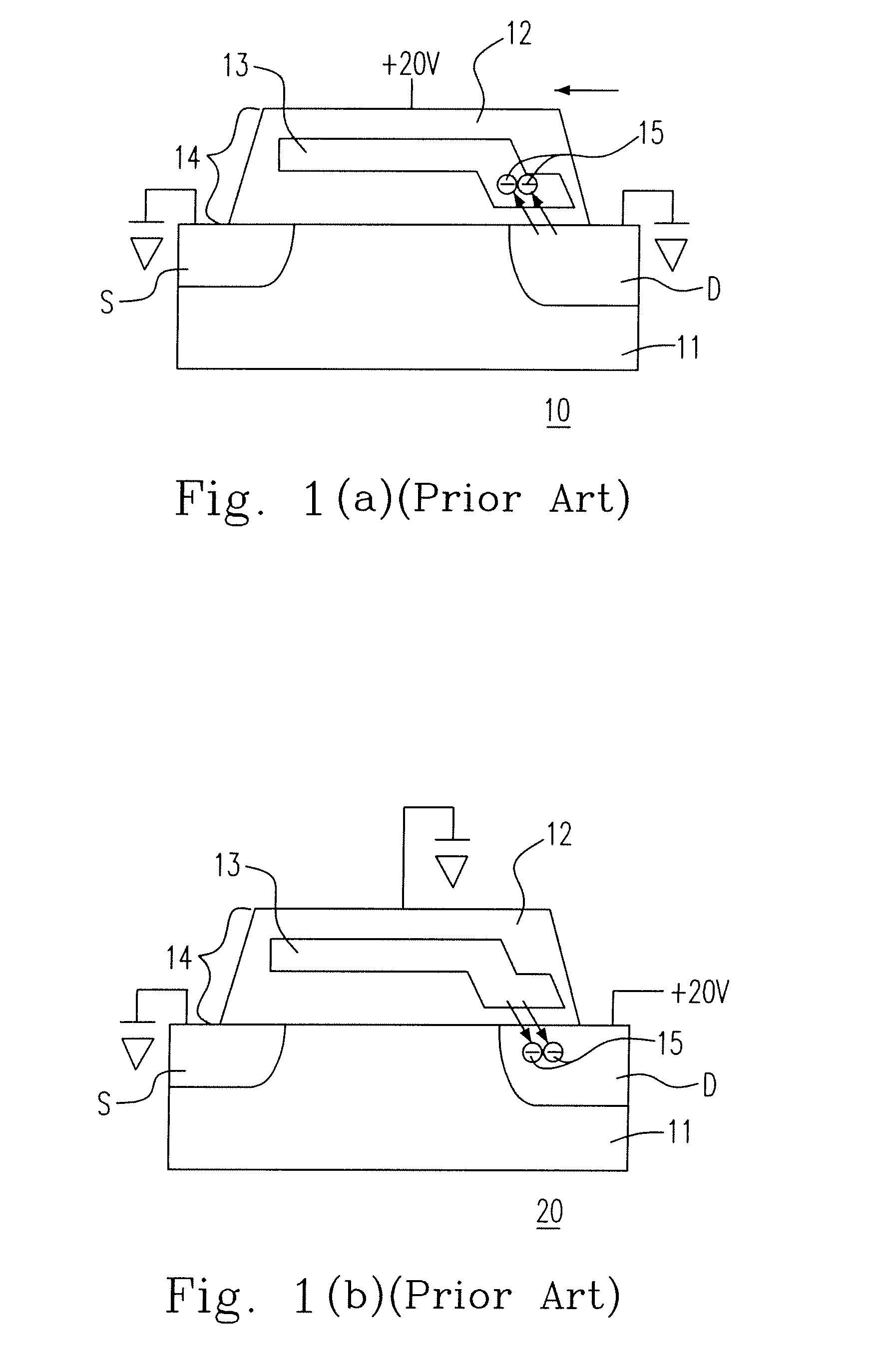

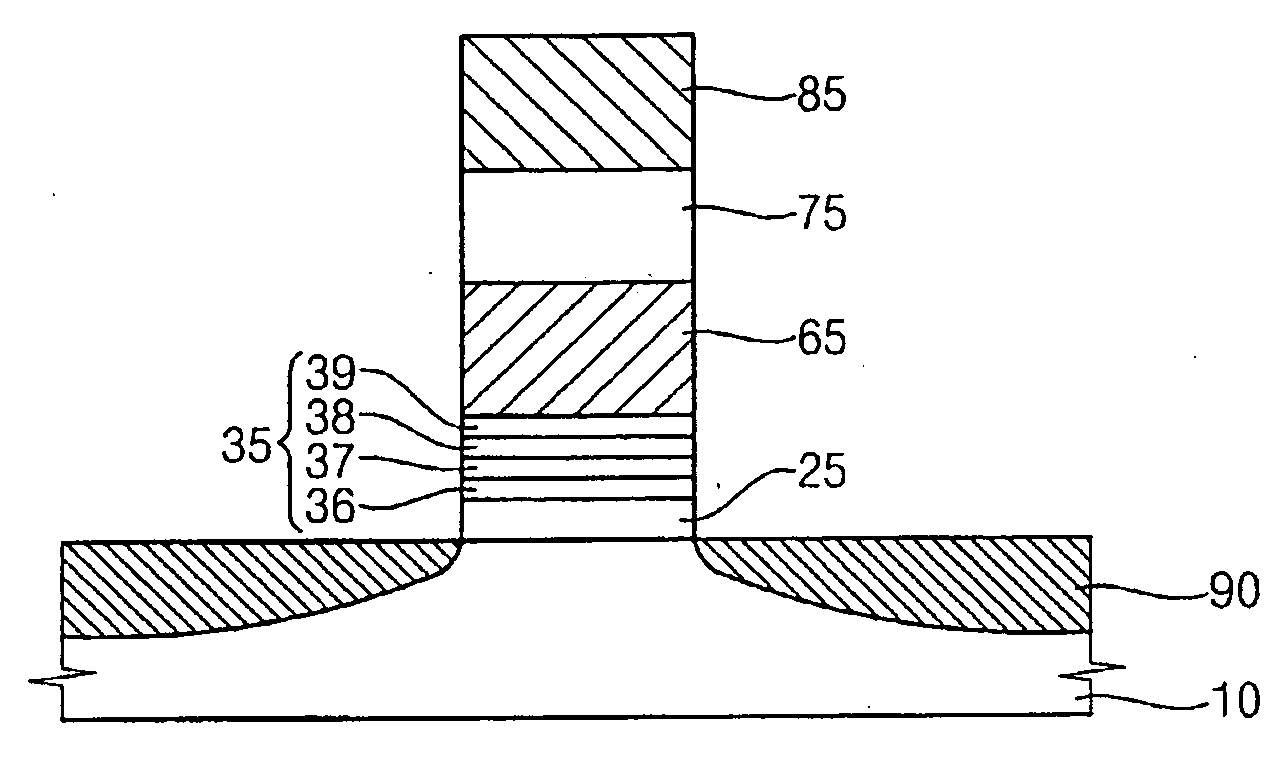

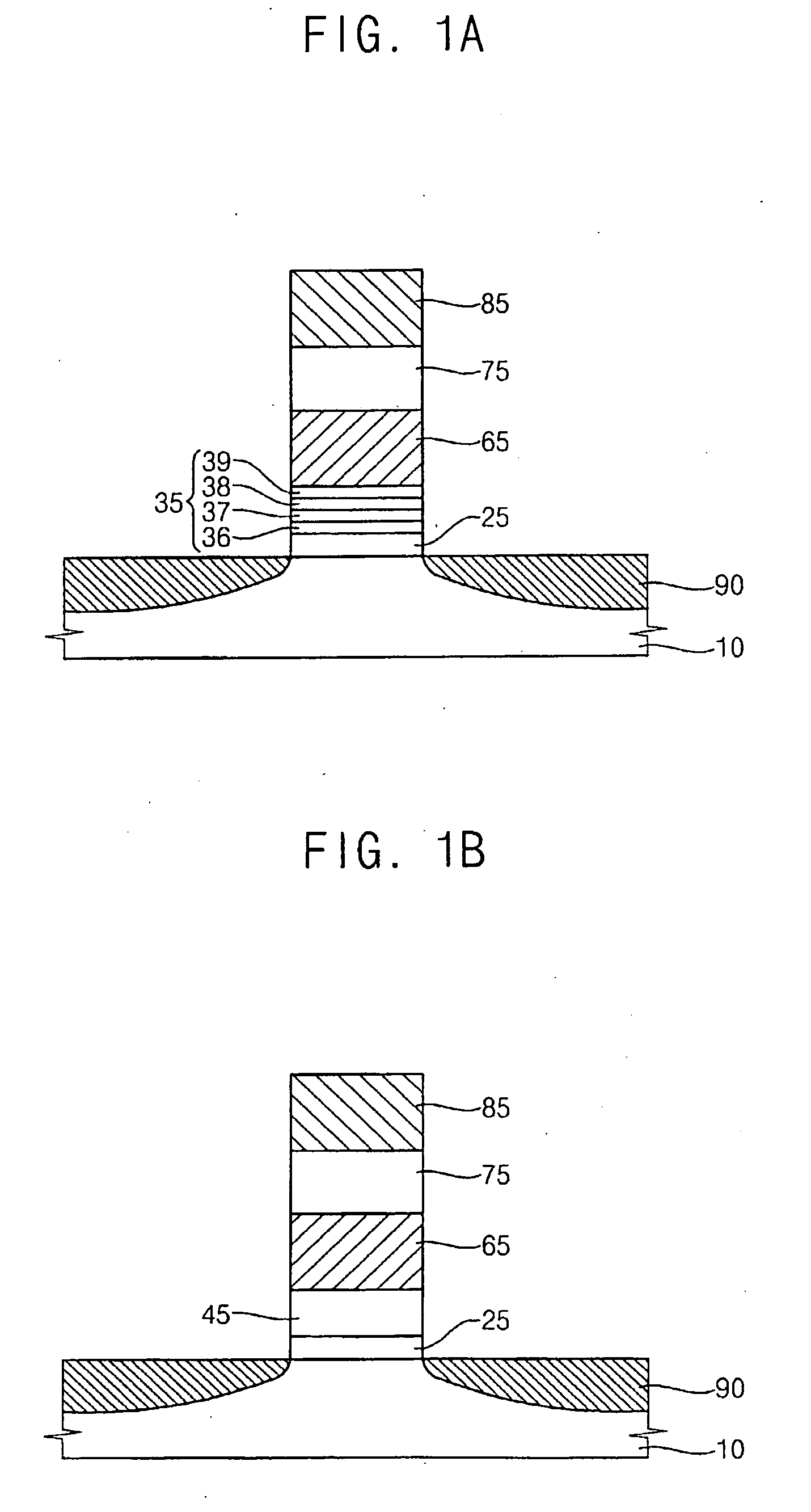

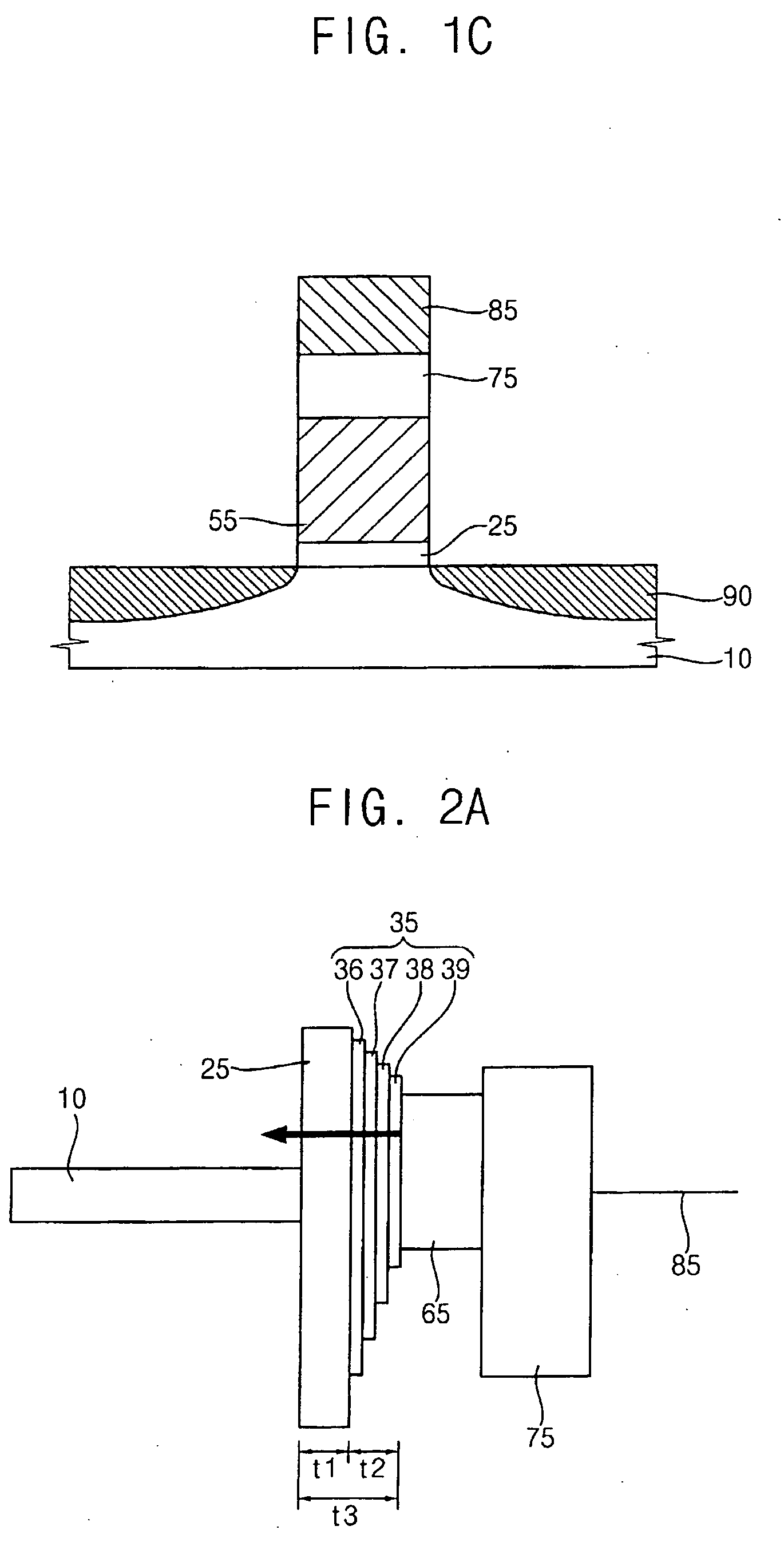

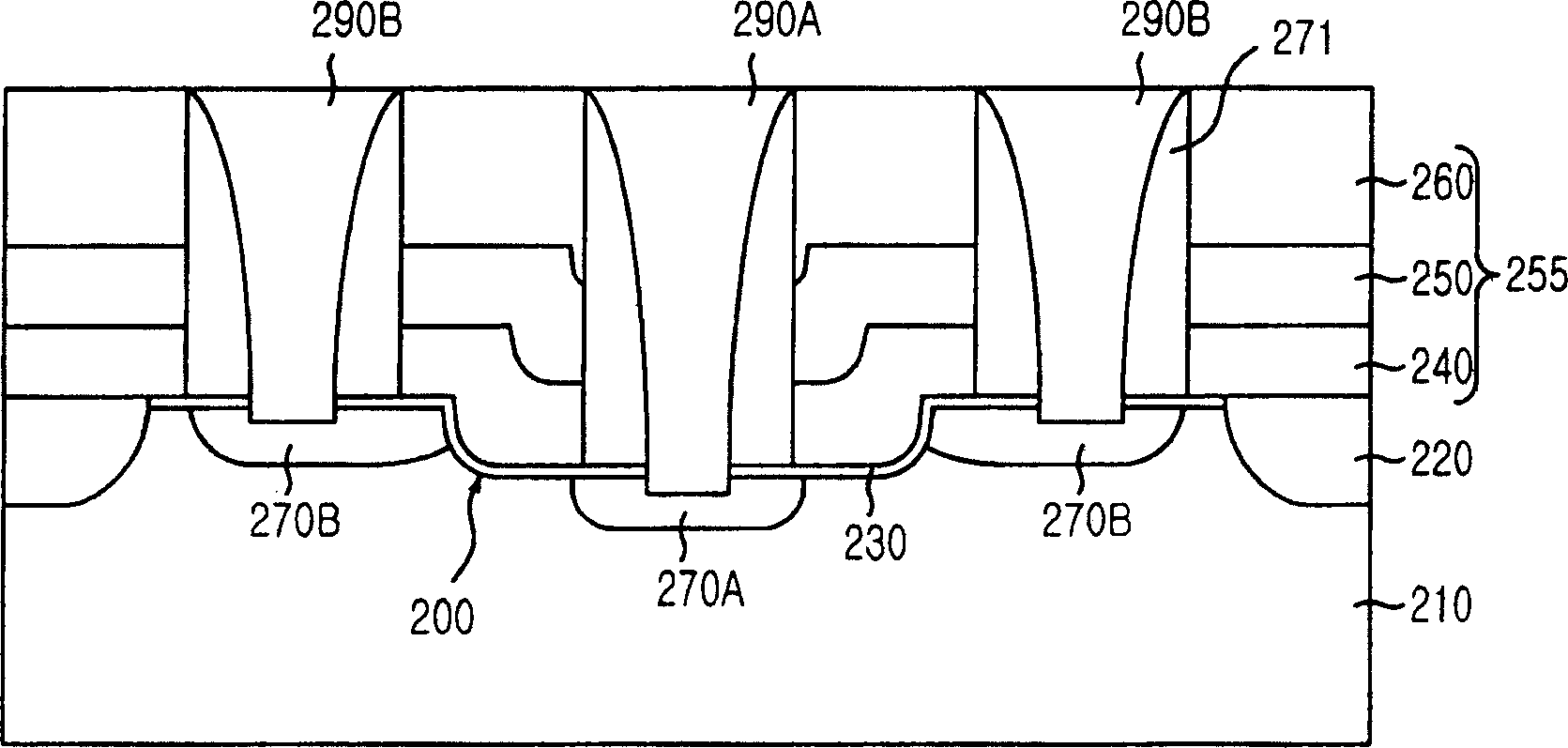

Memory devices and methods of manufacturing the same

InactiveUS20080164508A1Faster data programming/erasing speedSmall energy band gapTransistorSolid-state devicesInsulation layerTrapping

The memory device includes a first tunnel insulation layer pattern on a semiconductor substrate, a second tunnel insulation layer pattern having an energy band gap lower than that of the first tunnel insulation layer pattern on the first tunnel insulation layer pattern, a charge trapping layer pattern on the second tunnel insulation layer pattern, a blocking layer pattern on the charge trapping layer pattern, and a gate electrode on the blocking layer pattern. The memory device further includes a source / drain region at an upper portion of the semiconductor substrate, The upper portion of the semiconductor substrate is adjacent to the first tunnel insulation layer pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

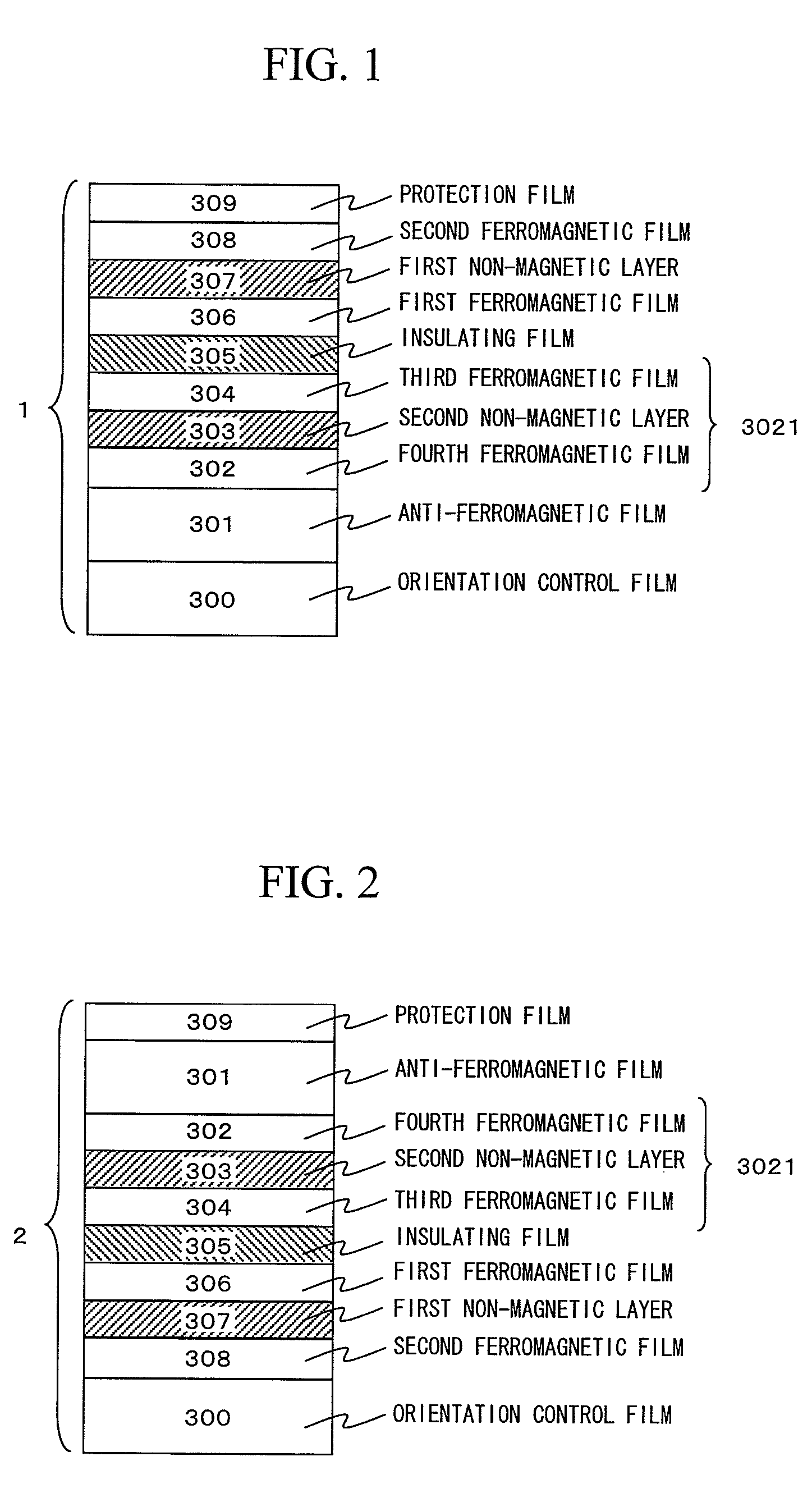

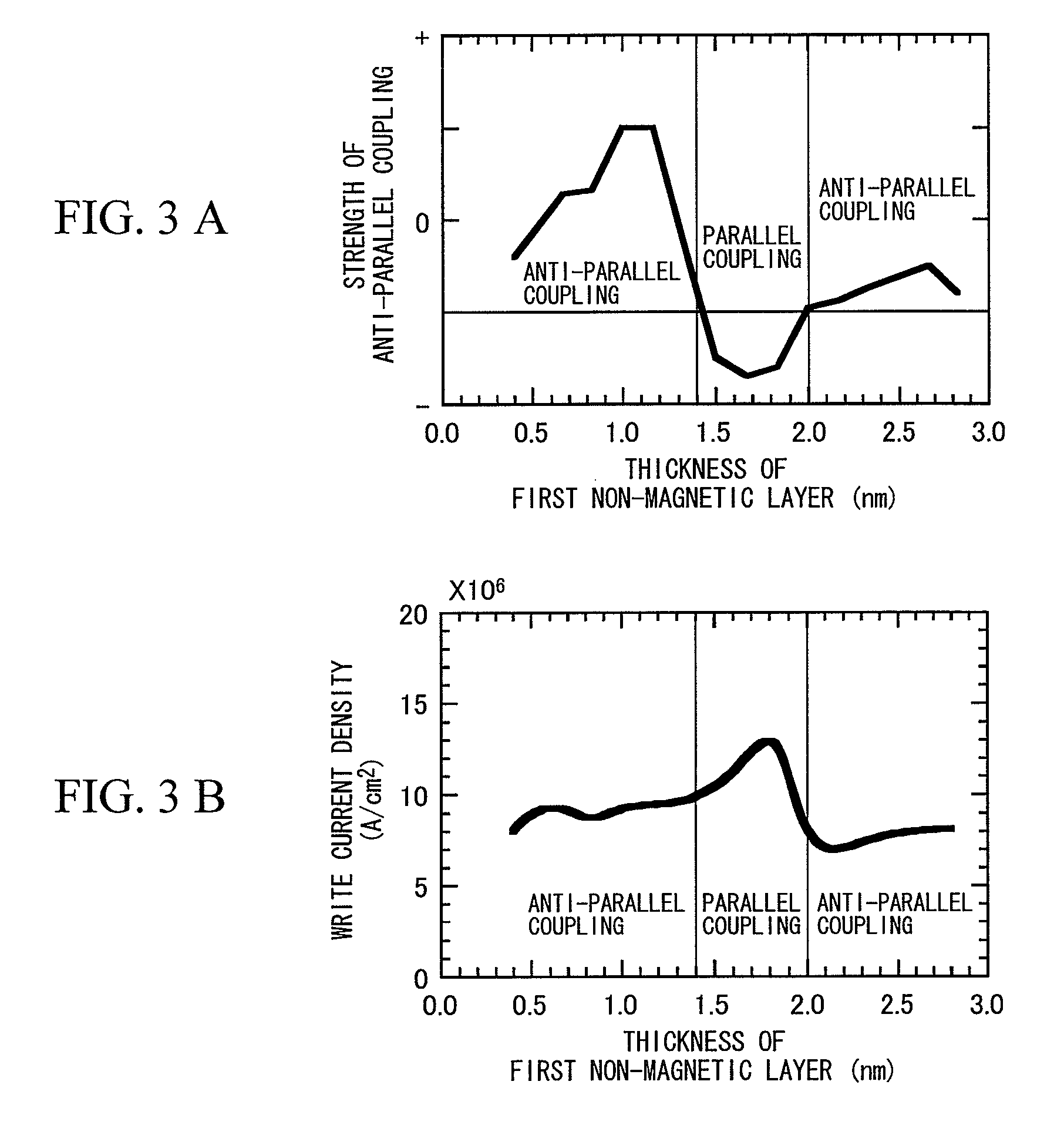

Tunnel magnetic resistance device, and magnetic memory cell and magnetic random access memory using the same

ActiveUS7894244B2Improve thermal stabilityData retention time is longNanomagnetismMagnetic-field-controlled resistorsSpin-transfer torqueRandom access memory

Provided is a high-speed, super-low-power-consumption nonvolatile memory with a high thermal stability. A nonvolatile magnetic memory is equipped with high-output tunnel magnetic resistance devices to each of which a free layer with a high thermal stability is applied, while a writing method by spin transfer torque is applied to the memory. The tunnel magnetic resistance device has a free layer including a first ferromagnetic film and the second ferromagnetic film each of which has a body center cubic structure and each of which contains Co, Fe and B. The free layer, additionally, includes a first non-magnetic layer. The tunnel magnetic resistance device has a layered structure formed of the free layer and a pinned layer with a MgO insulating film with a (100) orientation rock-salt structure interposed in between.

Owner:TOHOKU UNIV

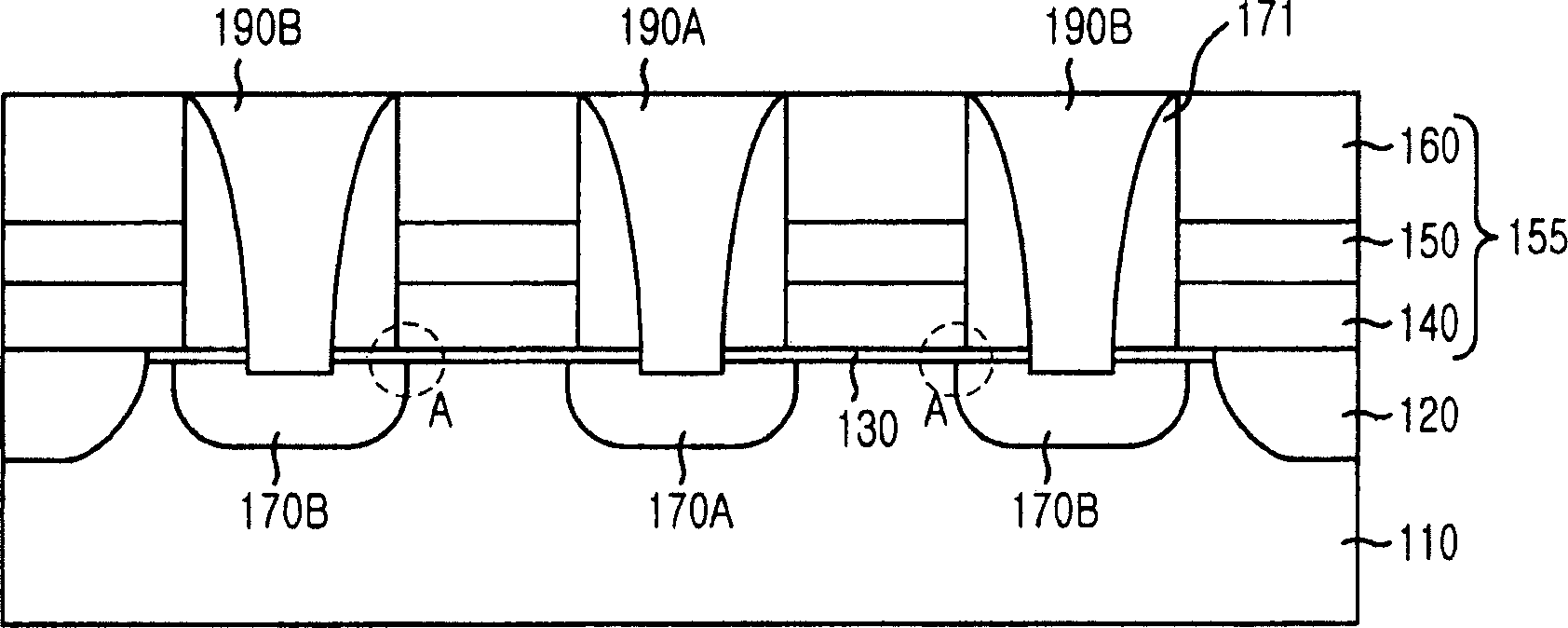

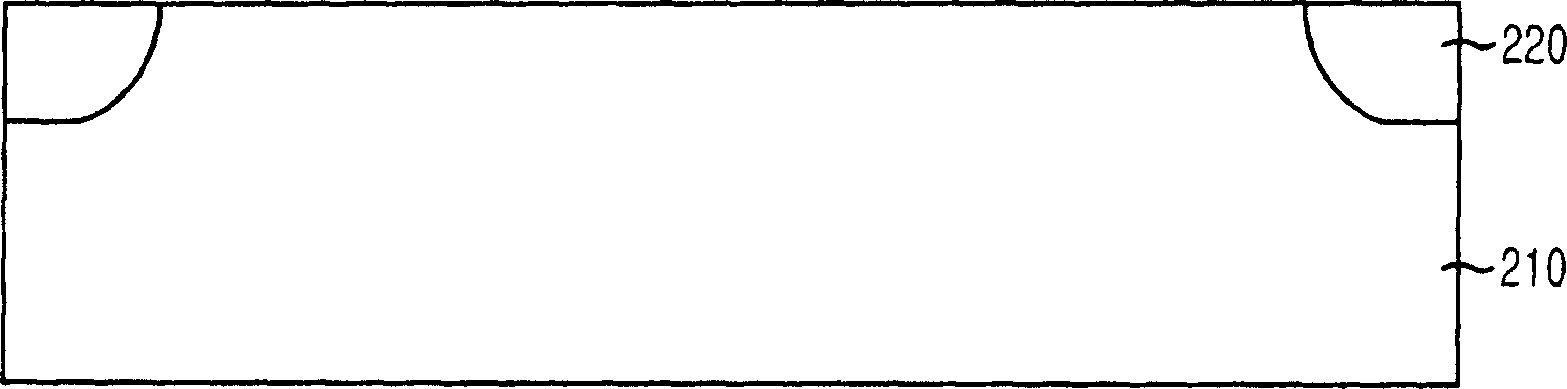

Memory device and method for fabricating the same

InactiveCN1728387AReduced Junction Leakage CurrentData retention time is longTransistorSolid-state devicesBit lineCell region

Disclosed are a memory device and a method for fabricating the same. The memory device includes: a substrate provided with a trench; a bit line contact junction formed beneath the trench; a plurality of storage node contact junctions formed outside the trench; and a plurality of gate structures each being formed on the substrate disposed between the bit line contact junction and one of the storage node contact junctions. Each sidewall of the trench becomes a part of the individual channels and thus, channel lengths of the transistors in the cell region become elongated. Accordingly, the storage node contact junctions have a decreased level of leakage currents, thereby increasing data retention time.

Owner:SK HYNIX INC

Memory based on flexible two-dimensional semiconductor channel quantum dots and preparation method thereof

InactiveCN109801920AHigh switching ratioRealize the function of multi-value storageSolid-state devicesSemiconductor devicesSemiconductor materialsGas phase

The invention belongs to the technical field of memories and in particular to a nonvolatile memory based on flexible two-dimensional semiconductor channel quantum dots and a preparation method thereof. The nonvolatile memory, by using zero-dimensional quantum dots as a charge trapping layer and using a two-dimensional semiconductor as a device channel on a substrate based on a flexible material, realizes a high switching ratio and a multi-value storage function by means of the tunneling of charges. The preparation method of the present invention comprises preparing metal oxide by atomic layerdeposition, preparing a two-dimensional material by mechanical stripping or chemical vapor deposition, and preparing quantum dots by spin-coating. The method can prepare a novel nonvolatile memory with a high switching ratio and a multi-value storage function, opens up a new field where two-dimensional semiconductor materials and zero-dimensional quantum dots are combined, and has a broad application prospect.

Owner:FUDAN UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com