Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

69 results about "Sidewall roughness" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

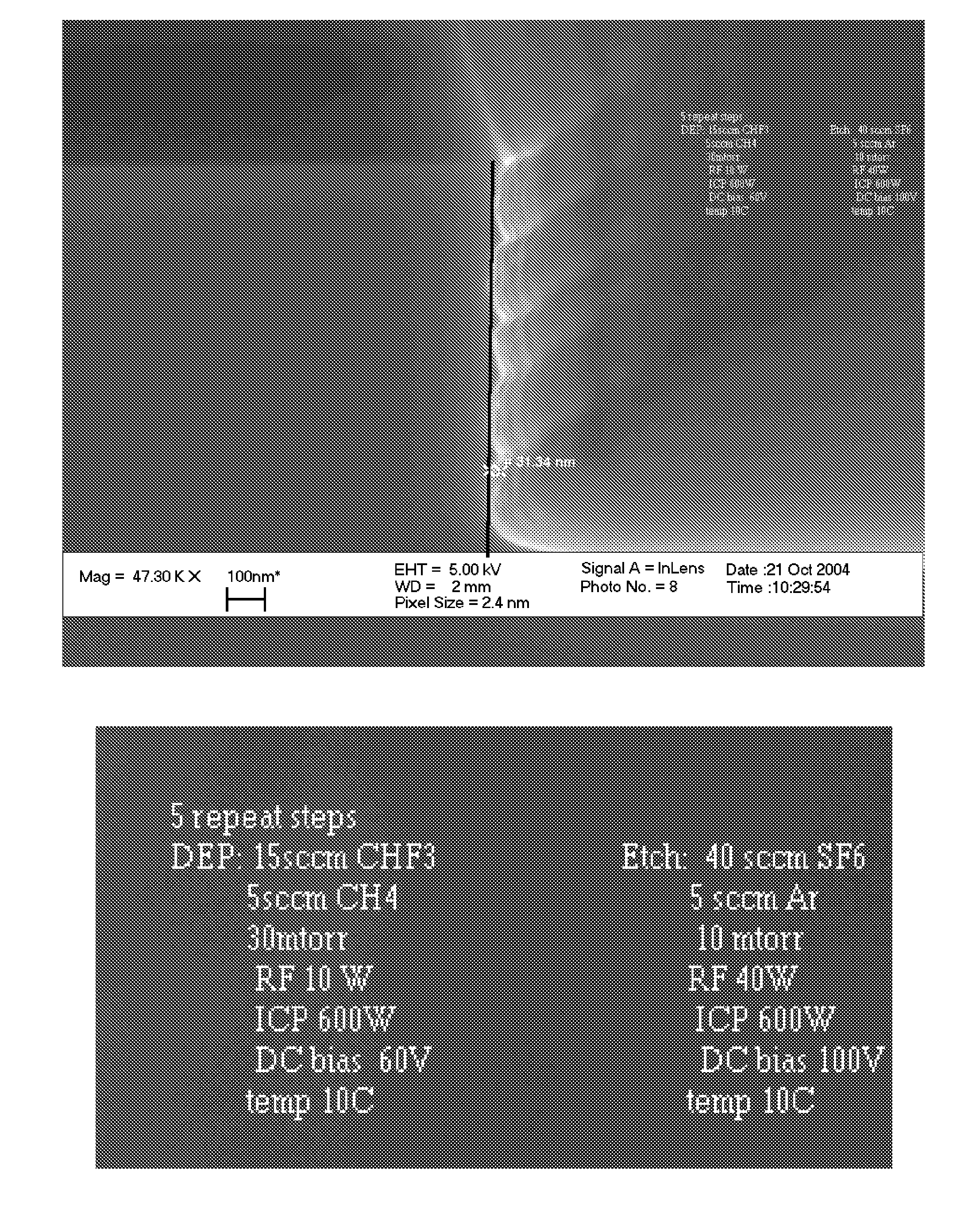

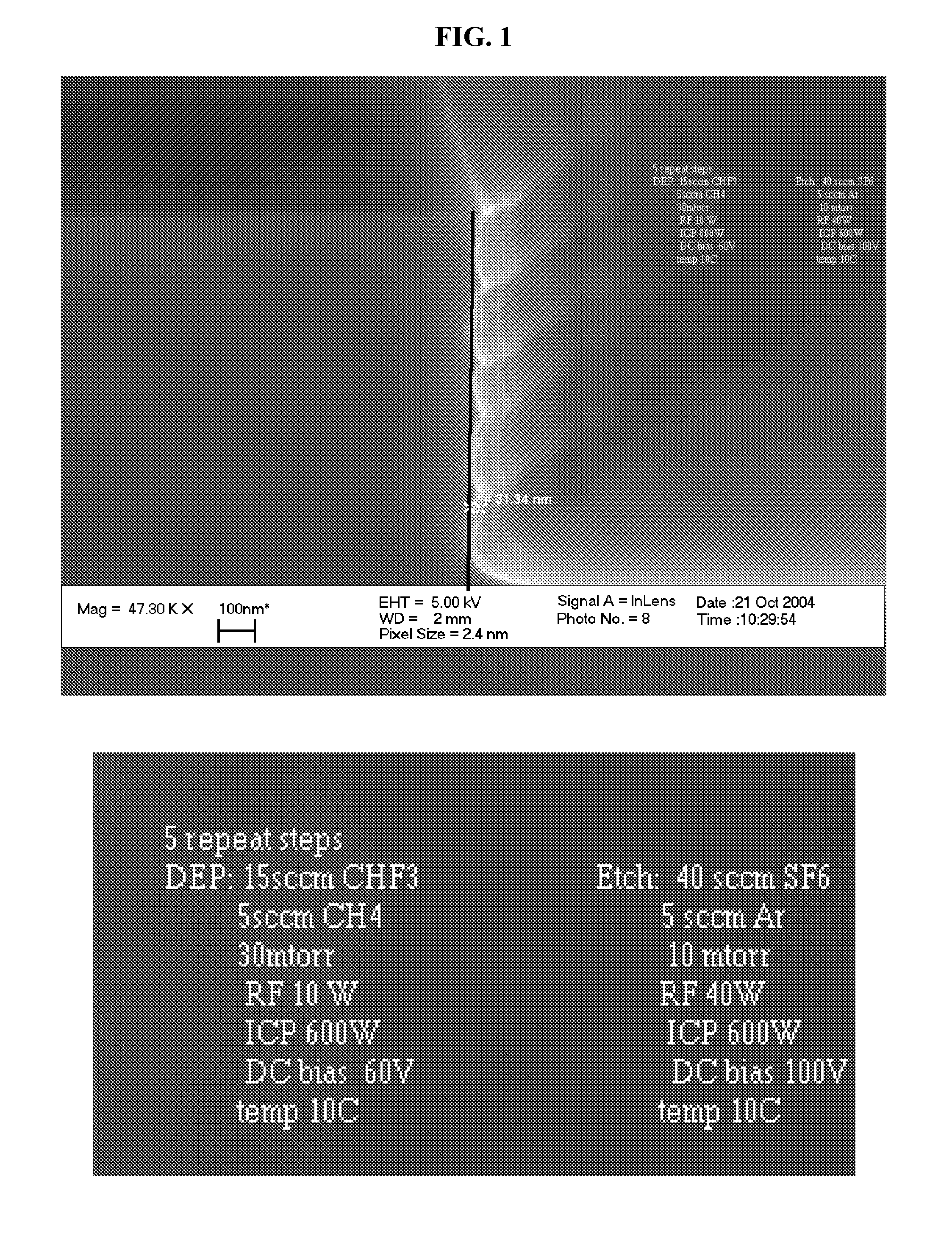

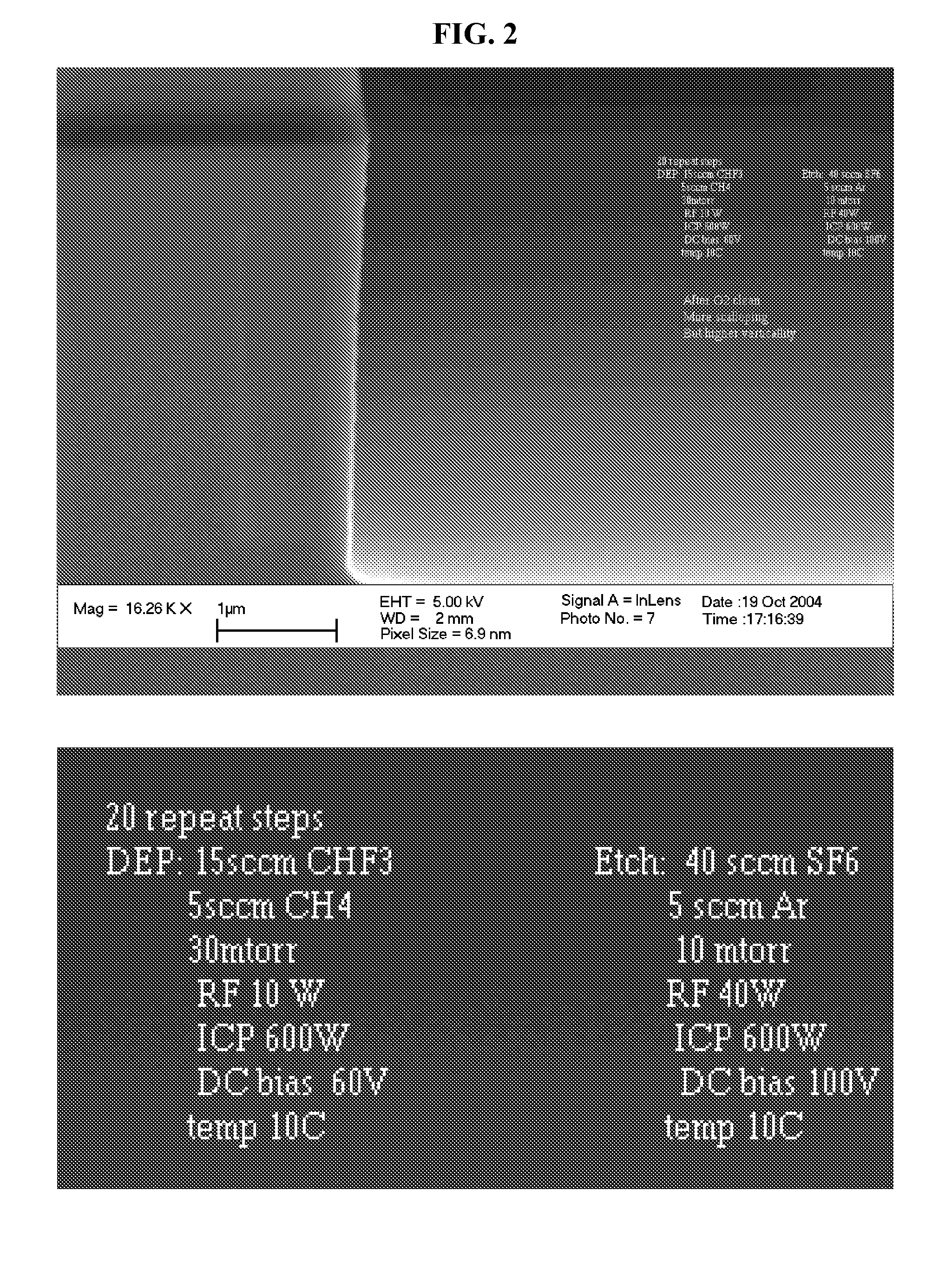

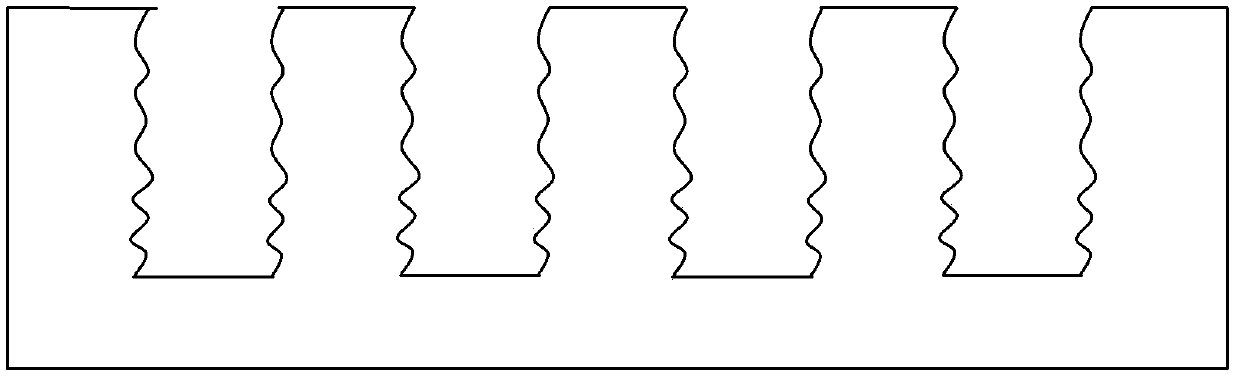

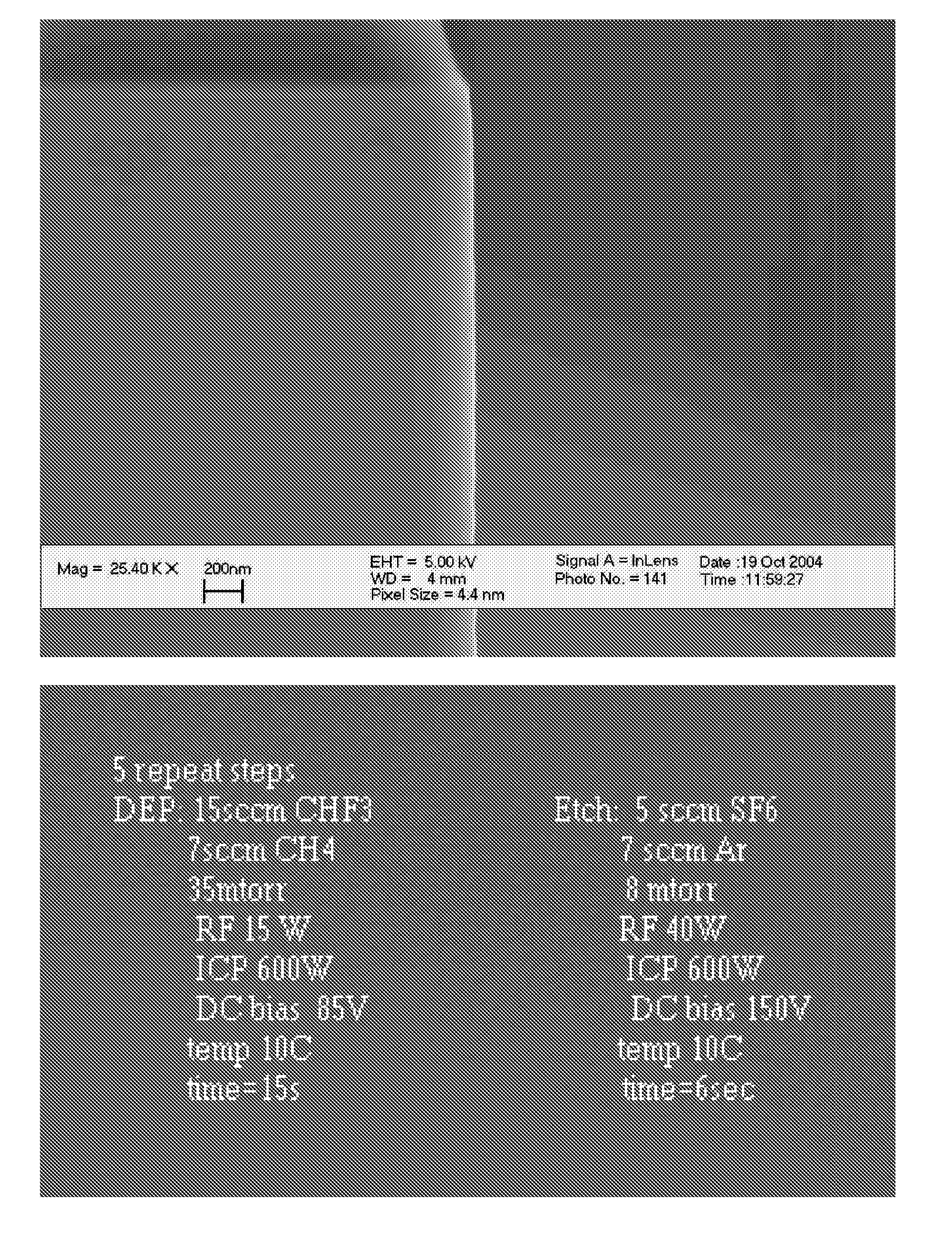

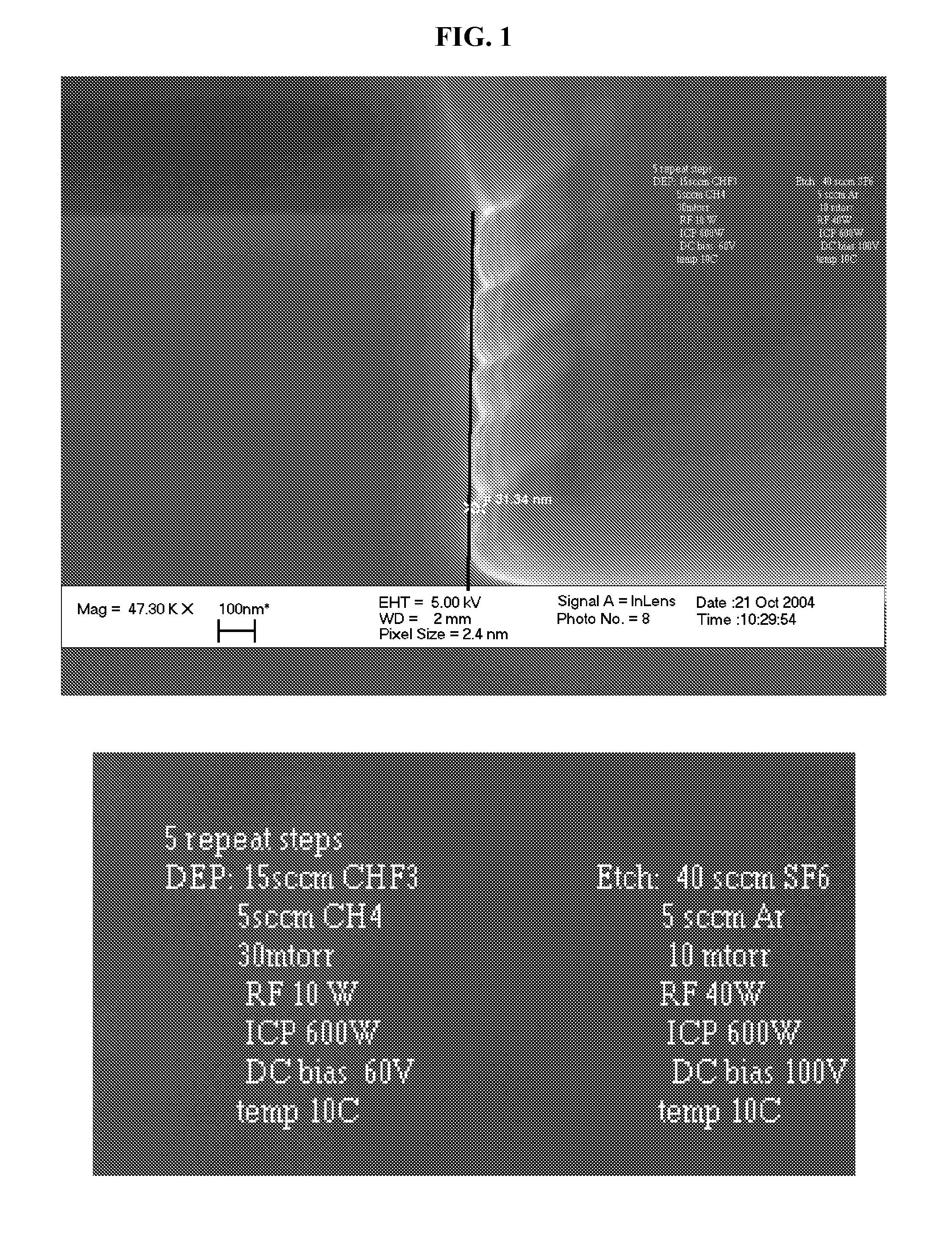

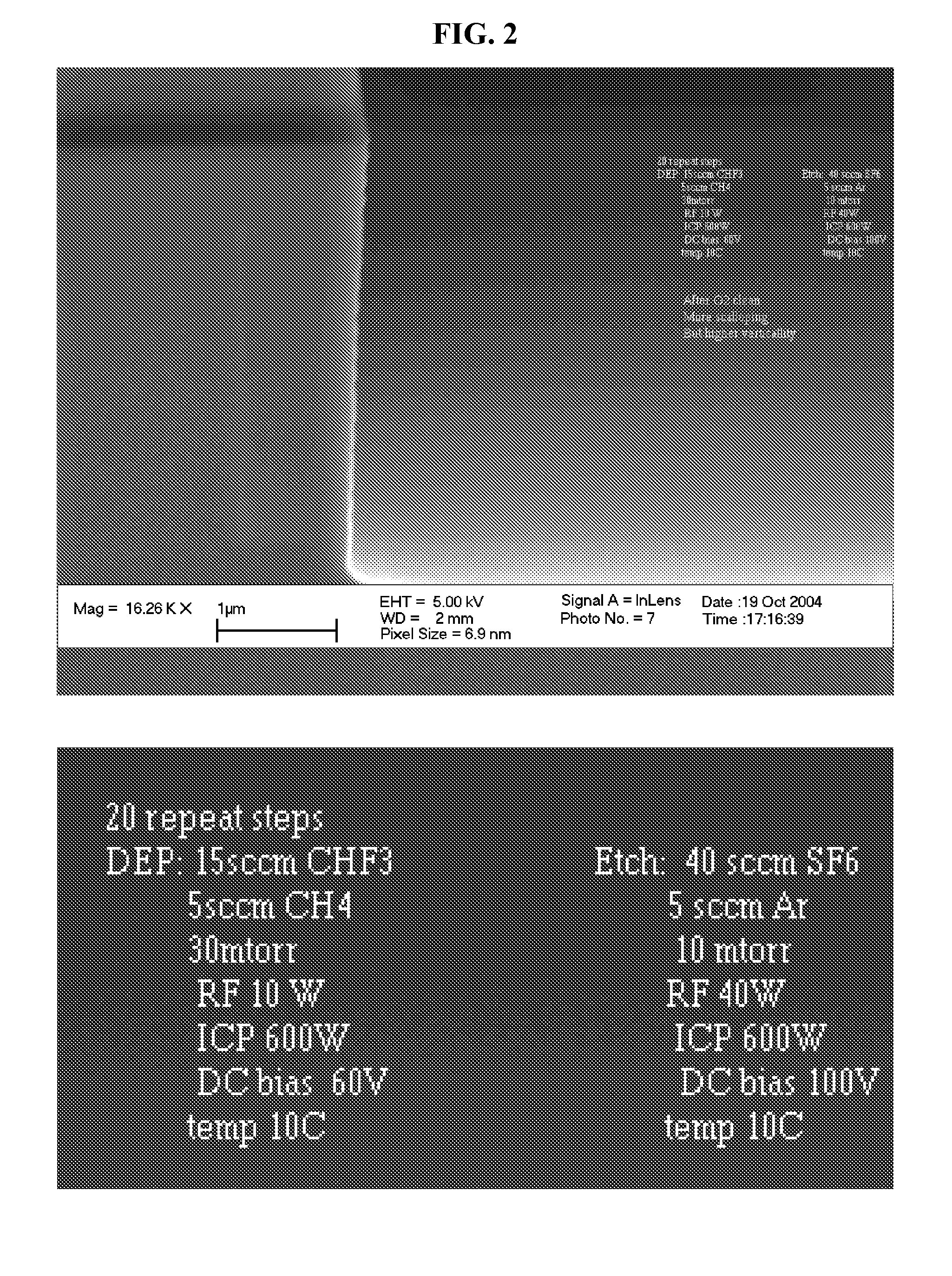

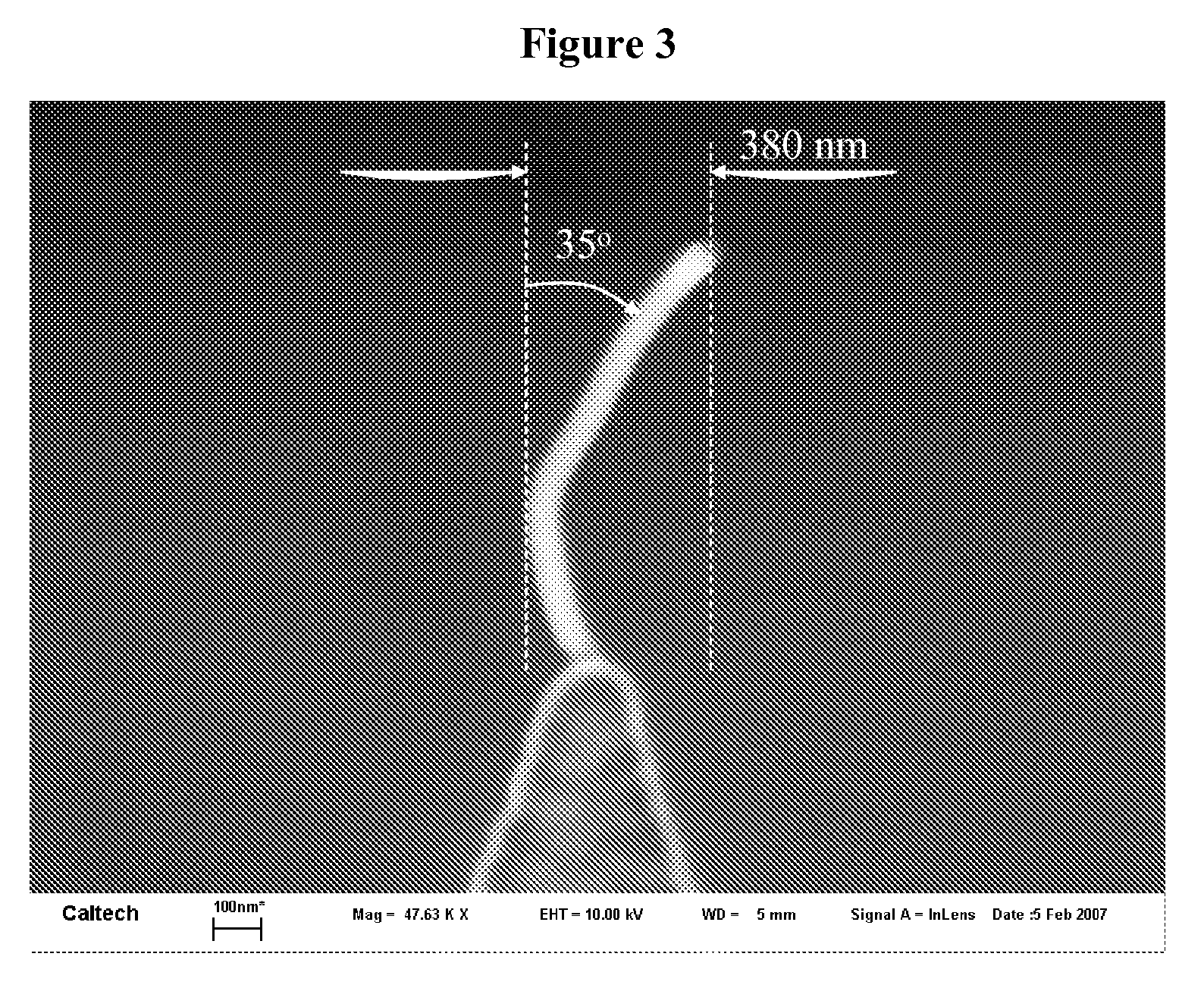

Etching radical controlled gas chopped deep reactive ion etching

ActiveUS20070015371A1Decorative surface effectsSemiconductor/solid-state device manufacturingInductively coupled plasmaChemical measurement

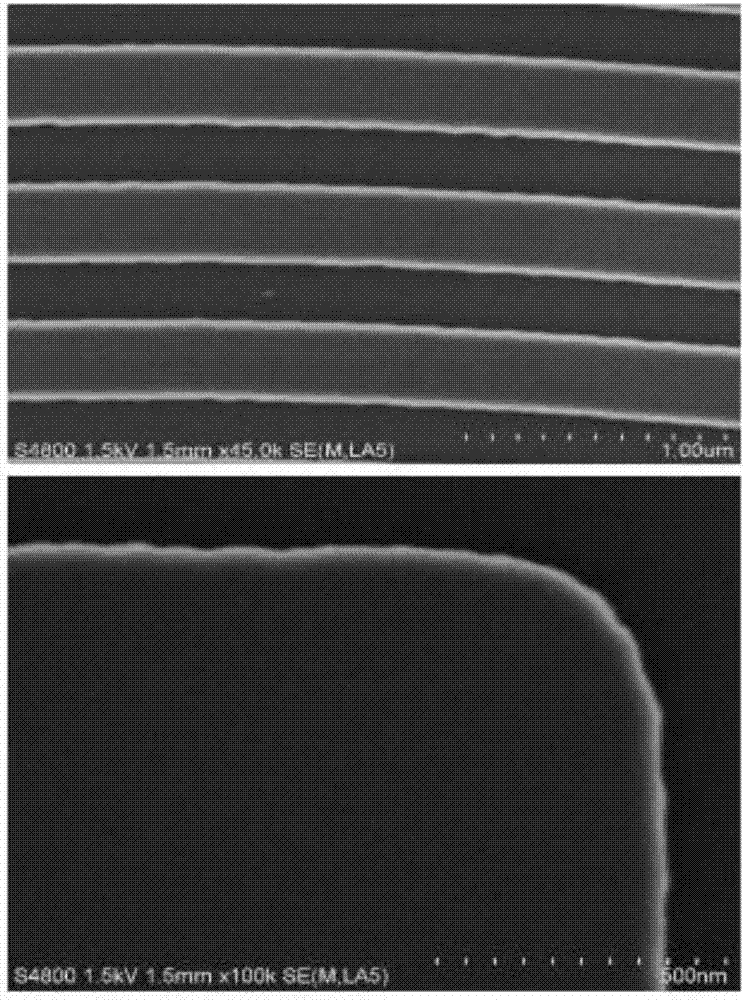

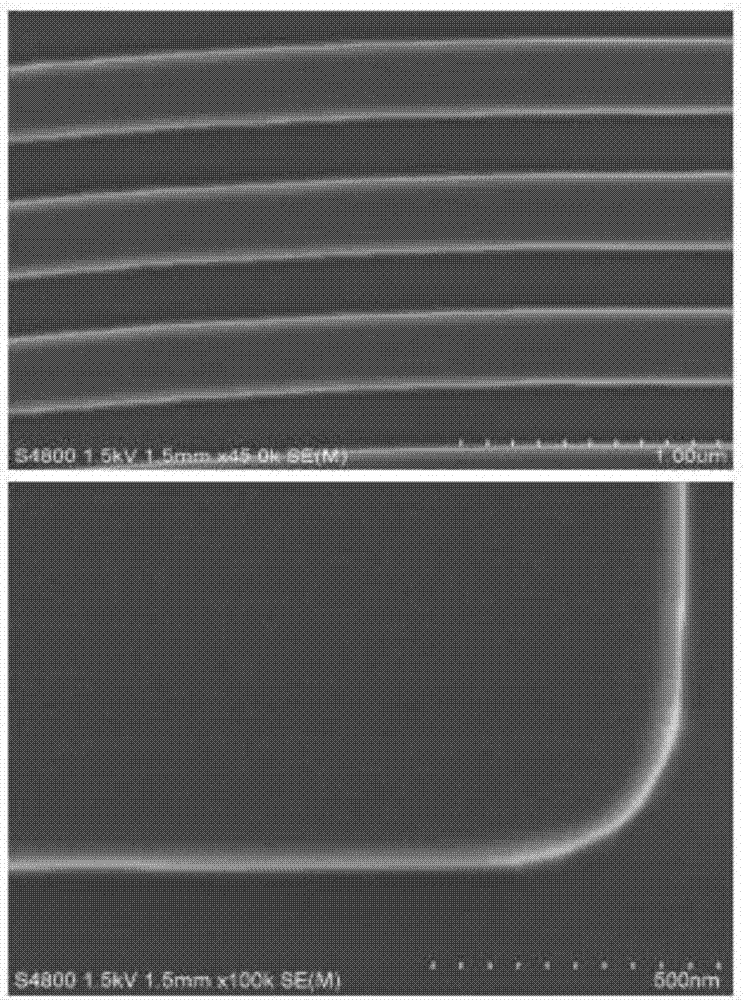

A method for silicon micromachining techniques based on high aspect ratio reactive ion etching with gas chopping has been developed capable of producing essentially scallop-free, smooth, sidewall surfaces. The method uses precisely controlled, alternated (or chopped) gas flow of the etching and deposition gas precursors to produce a controllable sidewall passivation capable of high anisotropy. The dynamic control of sidewall passivation is achieved by carefully controlling fluorine radical presence with moderator gasses, such as CH4 and controlling the passivation rate and stoichiometry using a CF2 source. In this manner, sidewall polymer deposition thicknesses are very well controlled, reducing sidewall ripples to very small levels. By combining inductively coupled plasmas with controlled fluorocarbon chemistry, good control of vertical structures with very low sidewall roughness may be produced. Results show silicon features with an aspect ratio of 20:1 for 10 nm features with applicability to nano-applications in the sub-50 nm regime. By comparison, previous traditional gas chopping techniques have produced rippled or scalloped sidewalls in a range of 50 to 100 nm roughness.

Owner:RGT UNIV OF CALIFORNIA

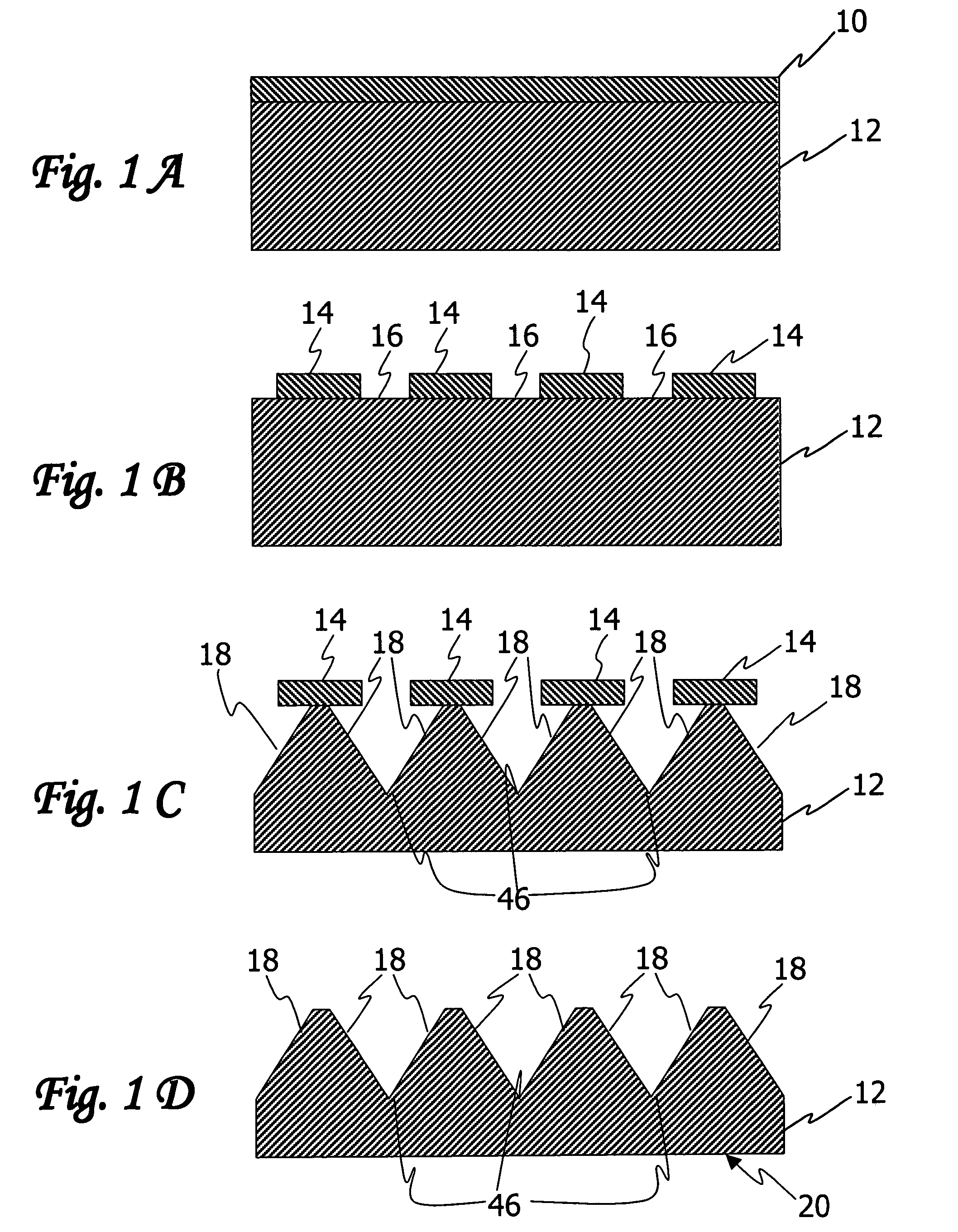

Articles Comprising Nanoscale Patterns With Reduced Edge Roughness and Methods of Making Same

In accordance with the invention, an article comprising a nanoscale surface pattern, such as a grating, is provided with a nanoscale patterns of reduced edge and / or sidewall roughness. Smooth featured articles, can be fabricated by nanoimprint lithography using a mold having sloped profile molding features. Another approach uses a mold especially fabricated to provide smooth sidewalls of reduced roughness, and a third approach adds a post-imprint smoothing step. These approaches can be utilized individually or in various combinations to make the novel articles.

Owner:PRINCETON UNIV

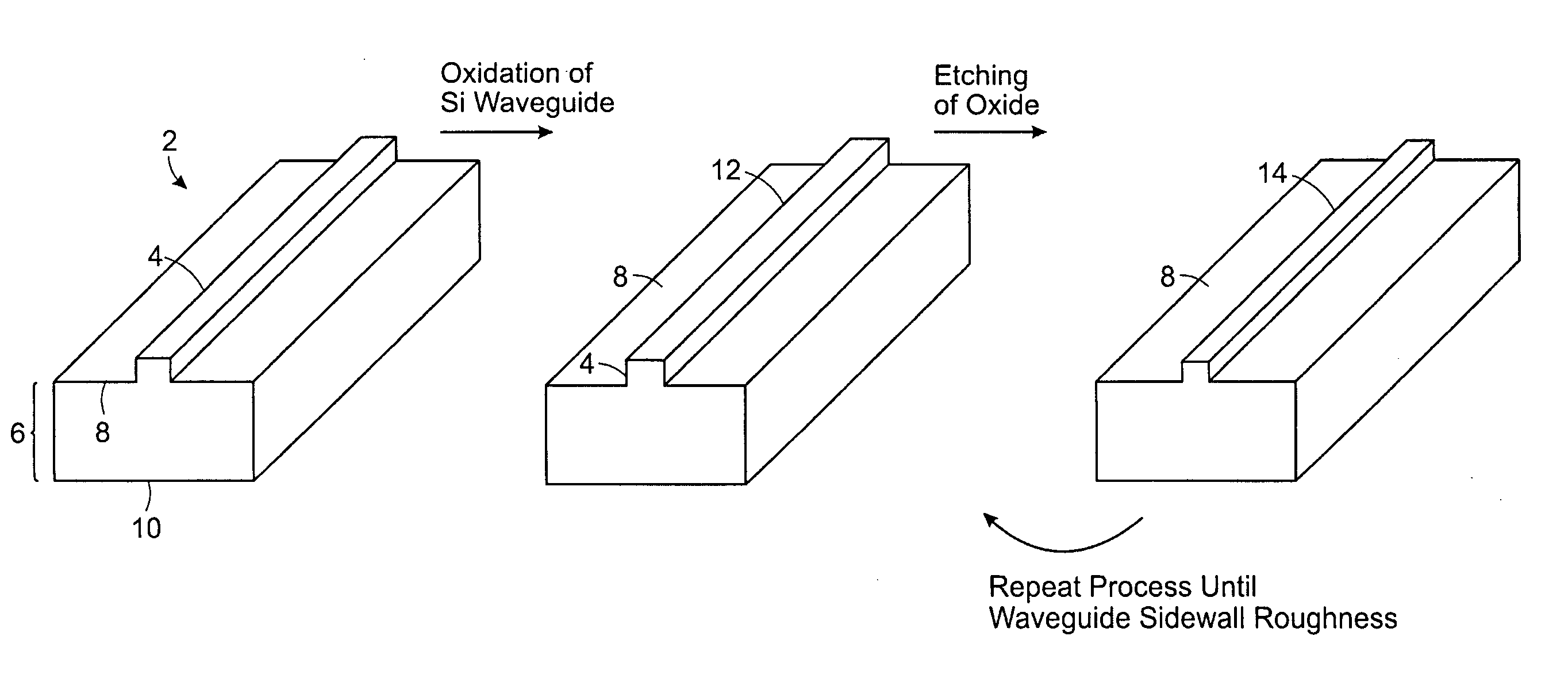

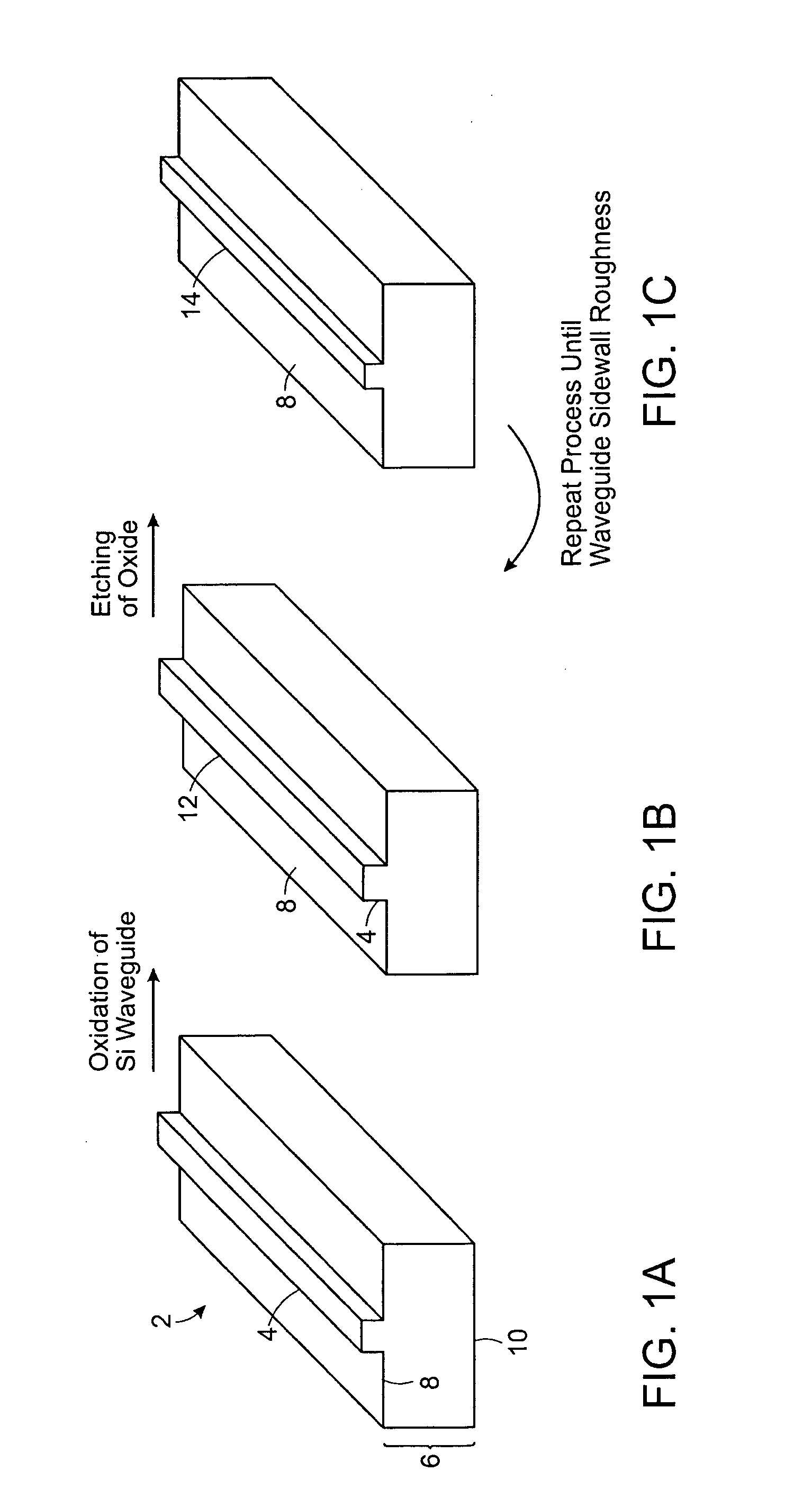

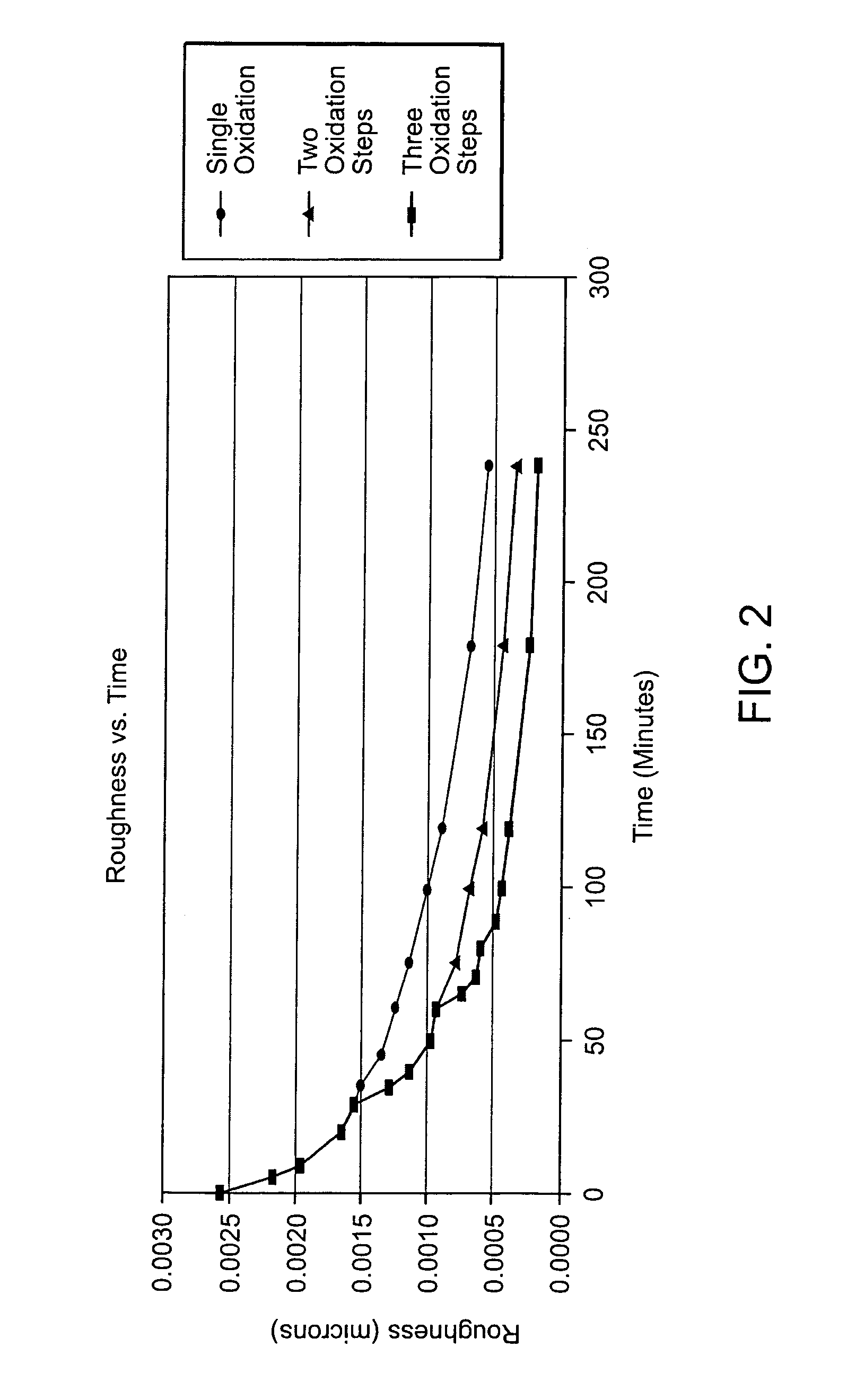

Multiple oxidation smoothing method for reducing silicon waveguide roughness

ActiveUS7123805B2Shorten the timeReduce volumeSemiconductor/solid-state device manufacturingOptical waveguide light guideSidewall roughnessPhysical chemistry

Owner:MASSACHUSETTS INST OF TECH

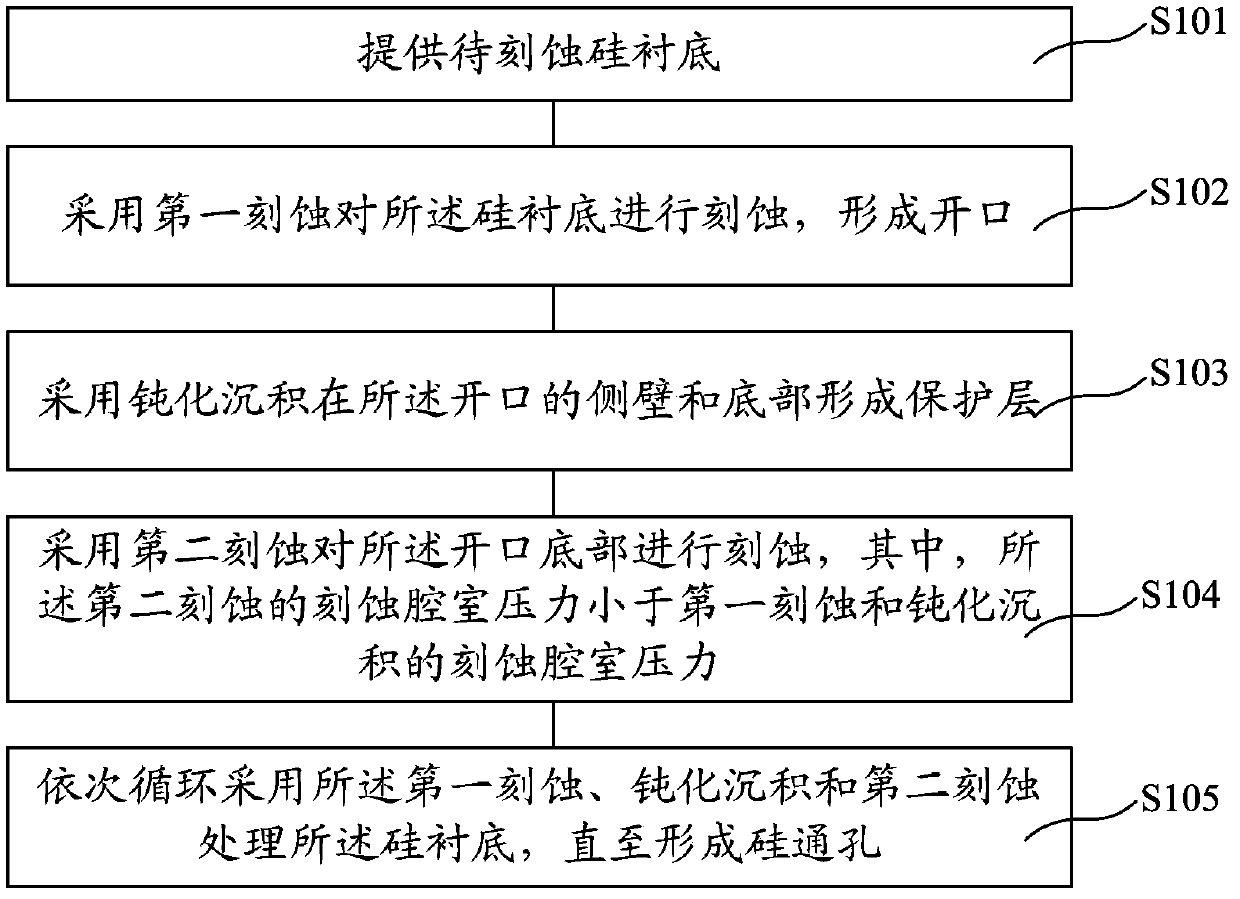

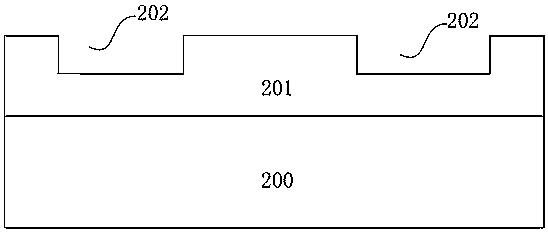

Through-silicon-via etching method

InactiveCN103390581AEfficient removalImprove efficiencySemiconductor/solid-state device manufacturingEtchingSidewall roughness

A through-silicone-via etching method comprises steps as follows: providing a to-be-etched silicon substrate; etching the silicon substrate through first etching to form an opening; forming protecting layers on the side wall and the bottom of the opening through passivation deposition; etching the bottom of the opening through second etching, wherein the pressure of an etching chamber of the second etching is smaller than that of etching chambers of the first etching and the passivation deposition; and treating the silicon substrate sequentially and circularly through the first etching, the passivation deposition and the second etching until a through-silicone-via is formed. The roughness of the side wall of the formed through-silicone-via is low.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

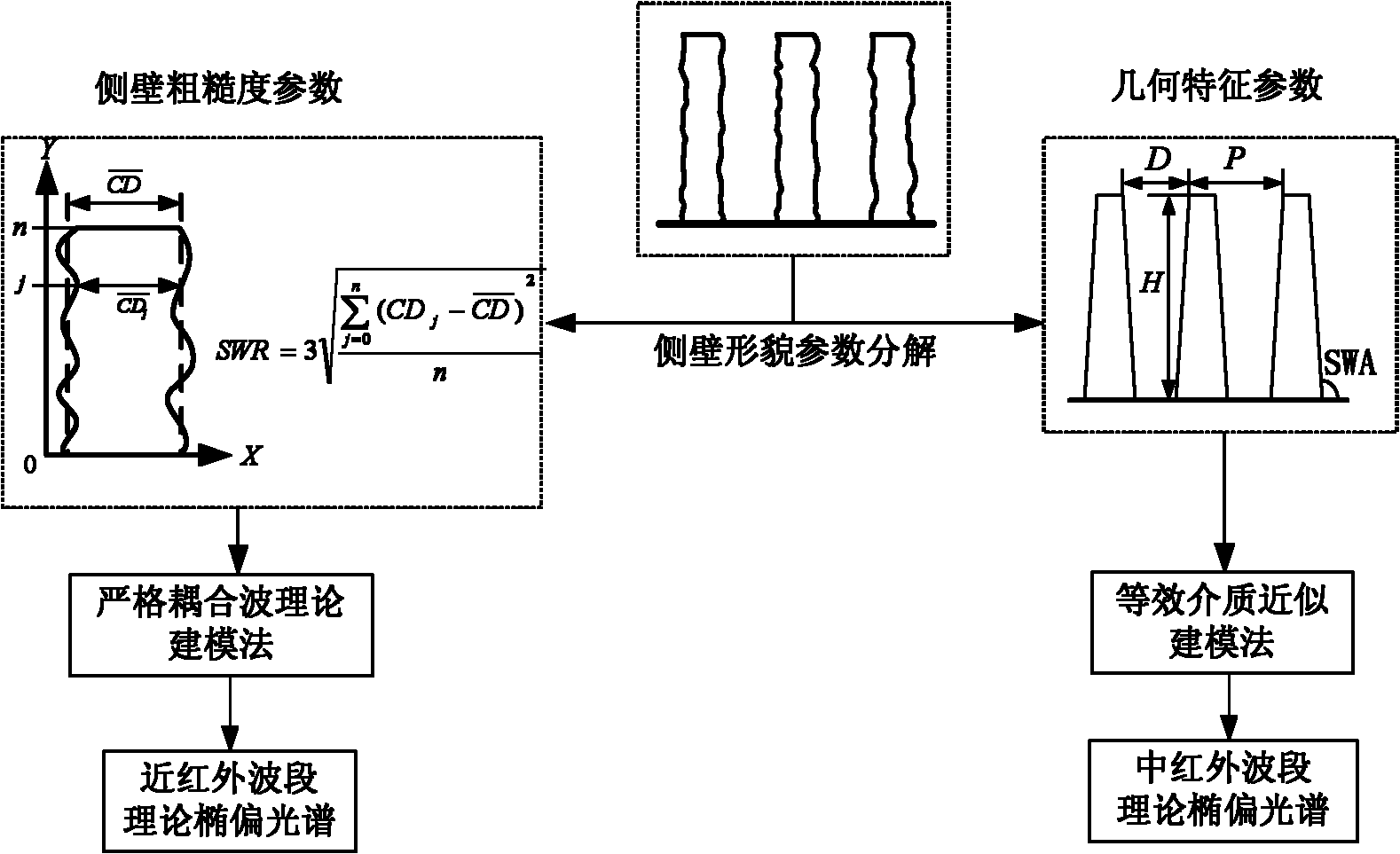

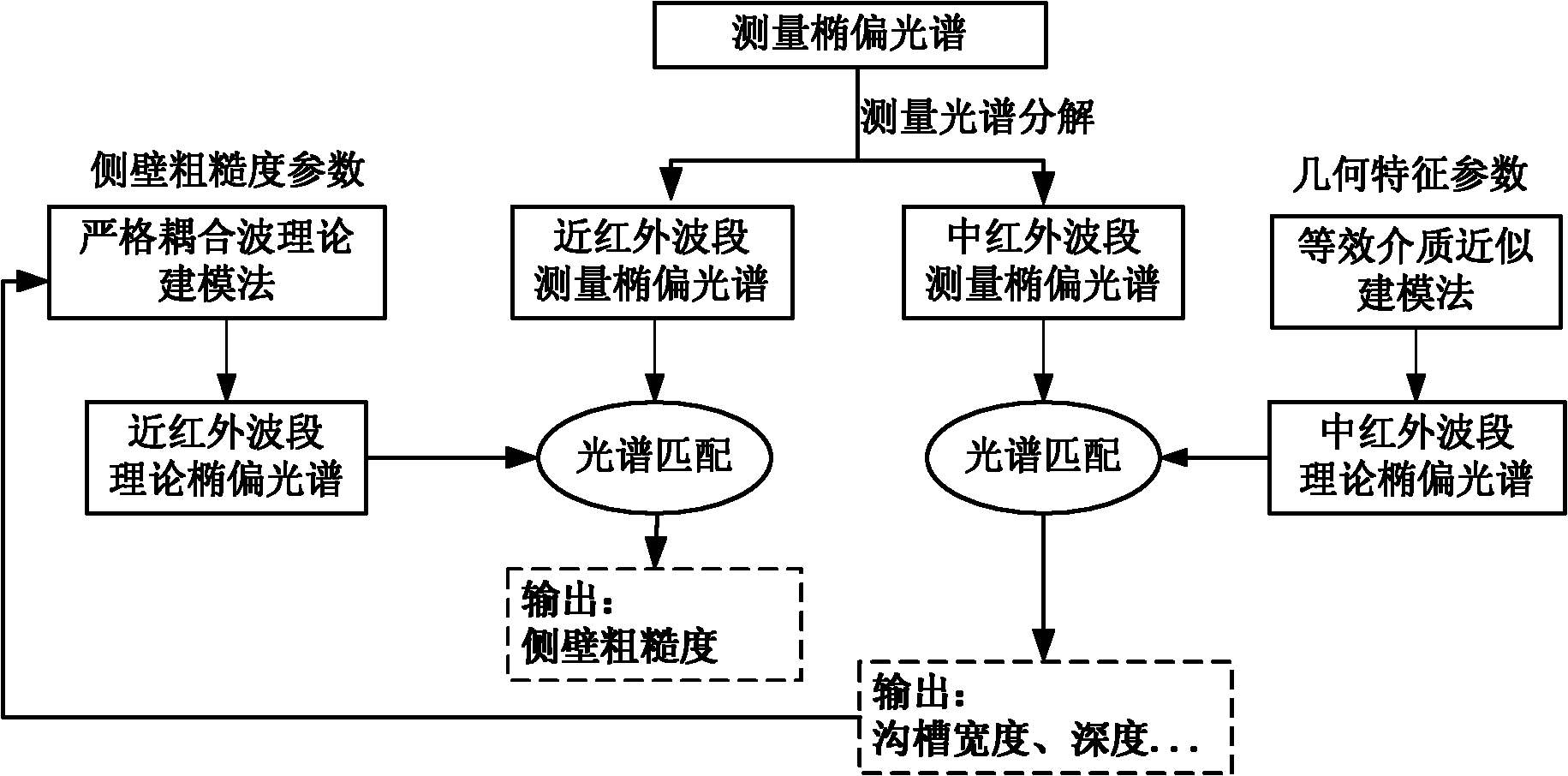

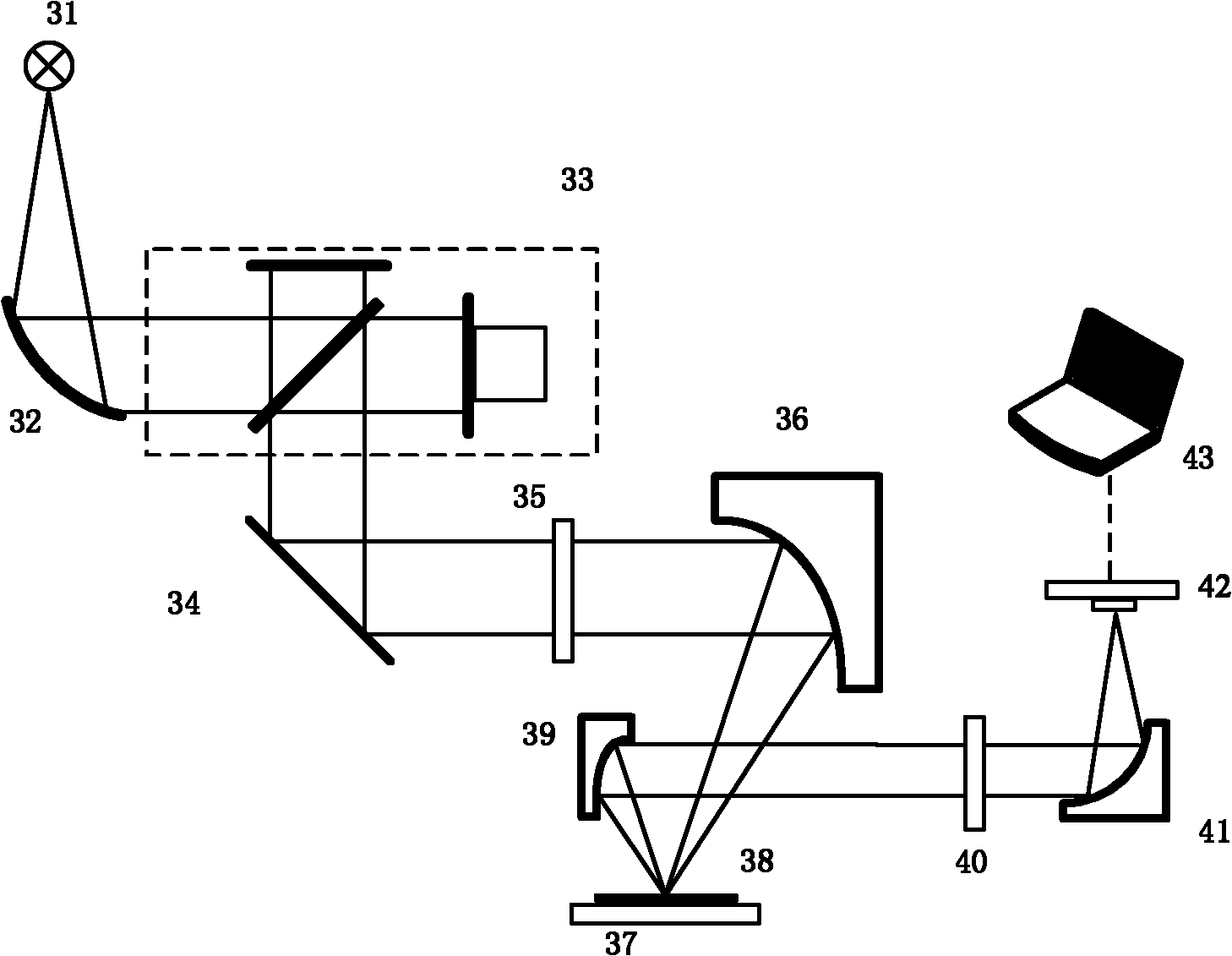

Method and device for rapidly measuring sidewall appearance of micro-nano deep groove structure

ActiveCN102082108ARealize onlineQuick measurementSemiconductor/solid-state device testing/measurementUsing optical meansMicro nanoMiddle infrared

The invention discloses a method and device for rapidly measuring sidewall appearance of a micro-nano deep groove structure, which can simultaneously and rapidly measure the parameters of the sidewall appearance of the micro-nano deep groove structure, such as line width, groove depth, sidewall angle, sidewall roughness and the like. The method comprises the steps of: projecting elliptical polarized lights, which is obtained by polarizing light beams with the wavelengths ranging from near infrared waveband to middle infrared waveband, onto the surface of a structure to be measured; collecting zero-level diffraction signals on the surface of the structure to be measured, and calculating to obtain a measured infrared spectroscopic ellipsometry of the micro-nano deep groove structure; calculating theoretical spectroscopic ellipsometries in the near infrared waveband and the middle infrared waveband respectively by using a wavelength allocation modeling method, matching the theoretical spectroscopic ellipsometries with the infrared spectroscopic ellipsometry measured in the experiment by using a stepwise spectral inversion method, and sequentially extracting the groove structure parameter and the roughness parameter. The device comprises an infrared light source, first, second, third and fourth off-axis parabolic mirrors, a Michelson's interferometer, a planar reflector, a polarizer, a sample bench, an analyzer, a detector and a computer; and the method is a noncontact, nondestructive low-cost method for rapidly measuring the sidewall appearance.

Owner:HUAZHONG UNIV OF SCI & TECH

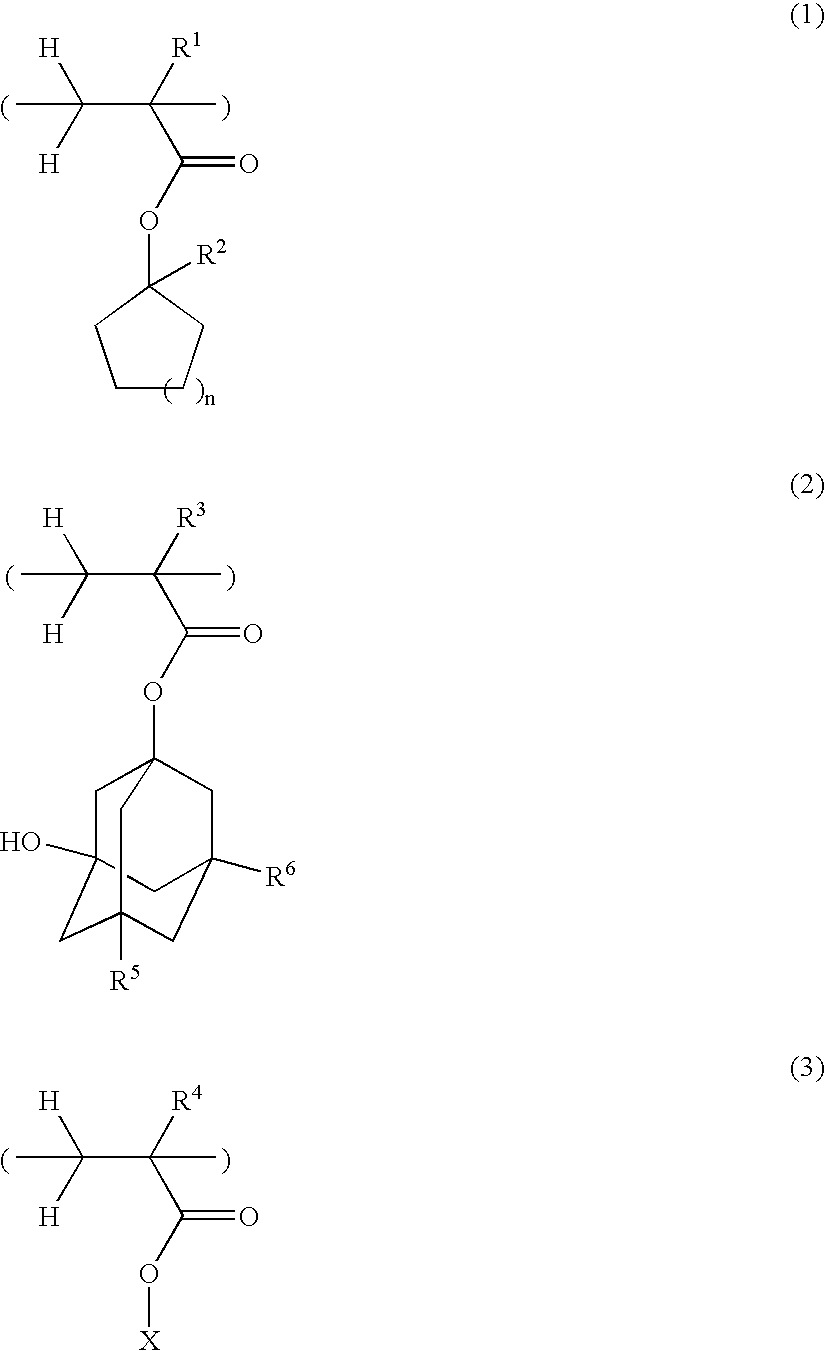

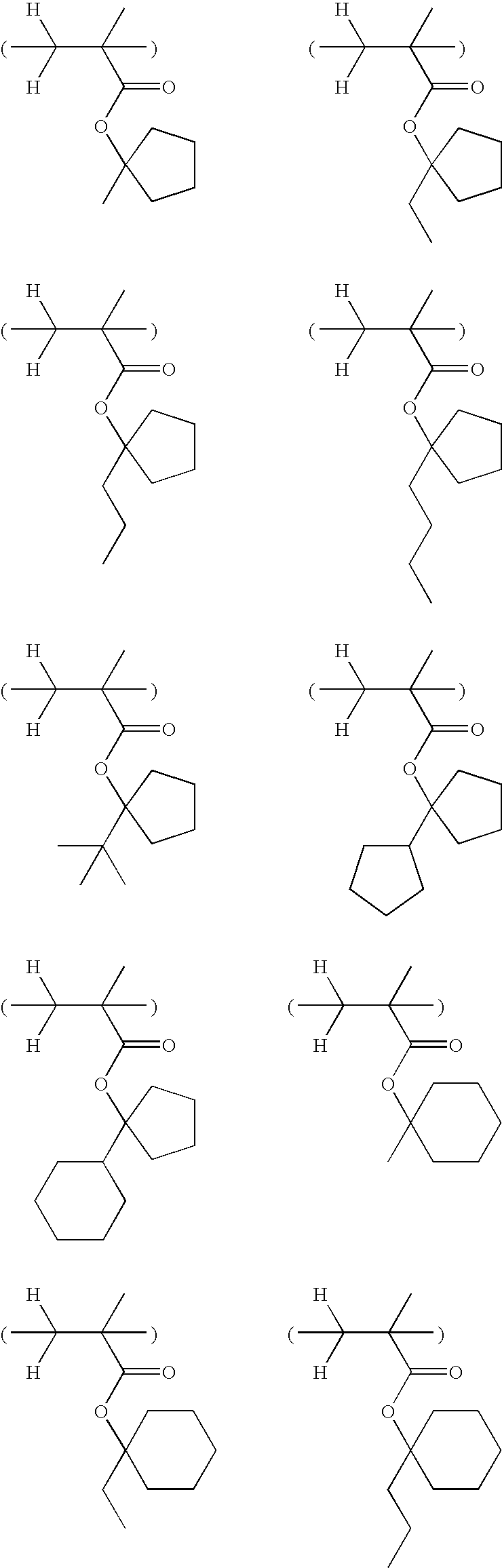

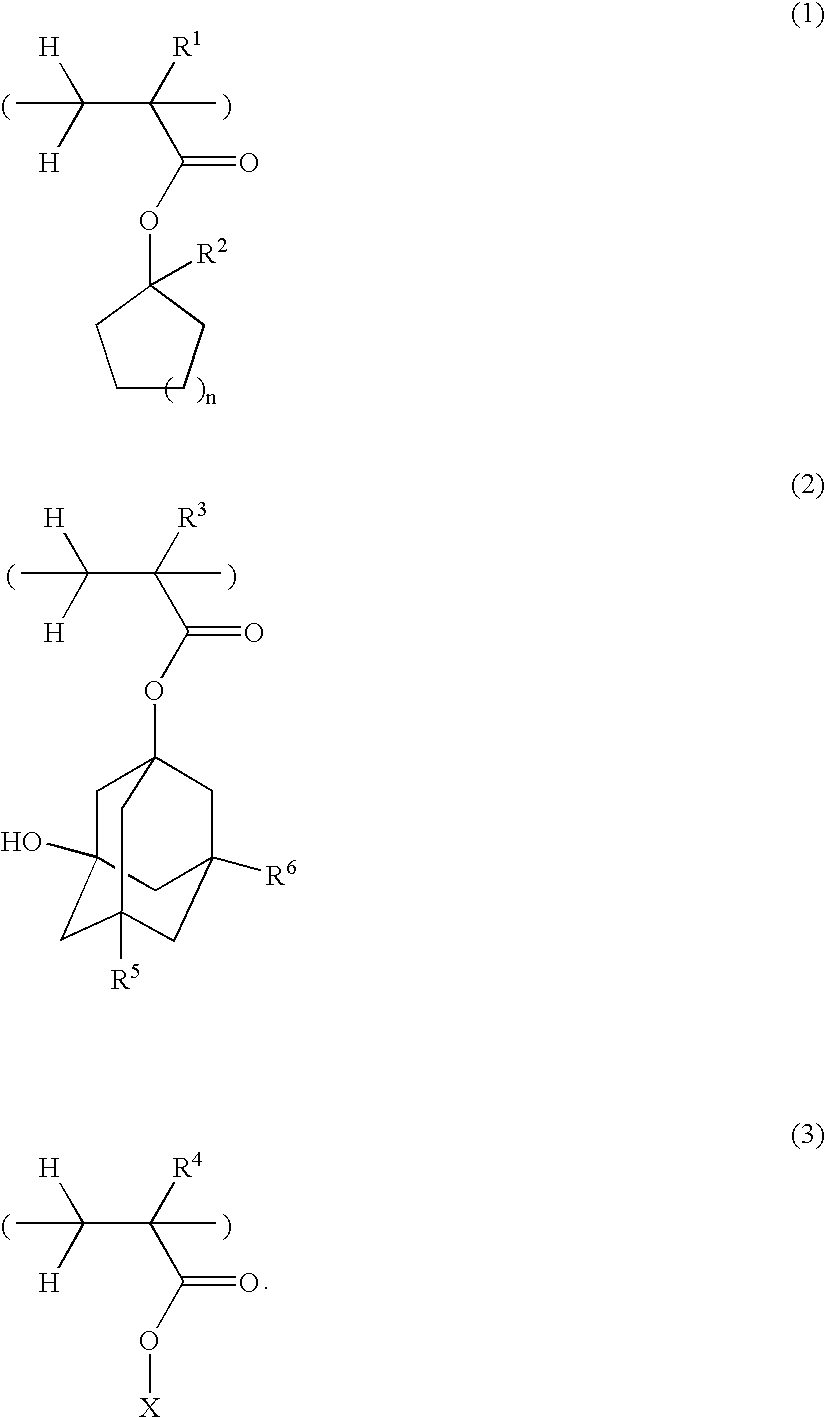

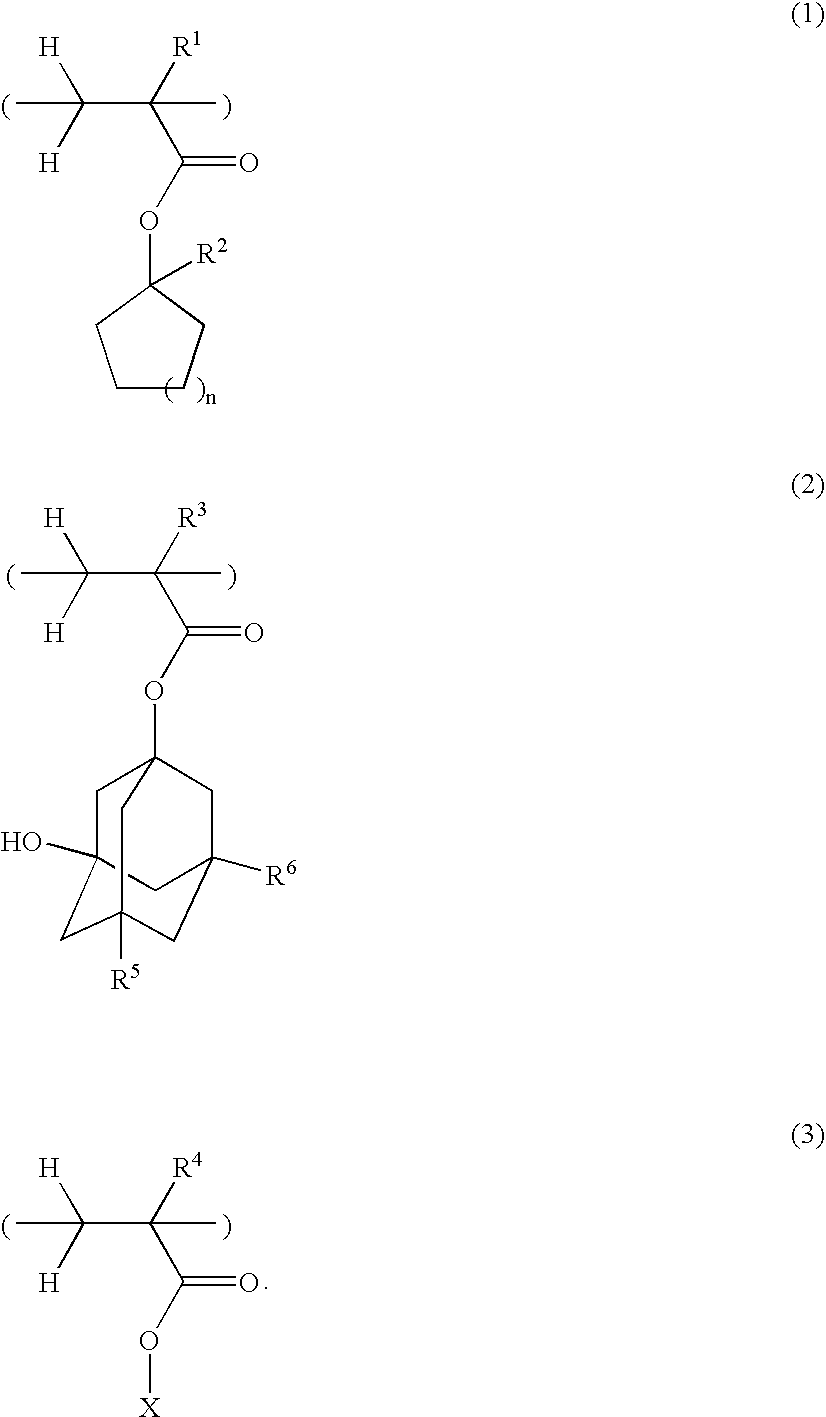

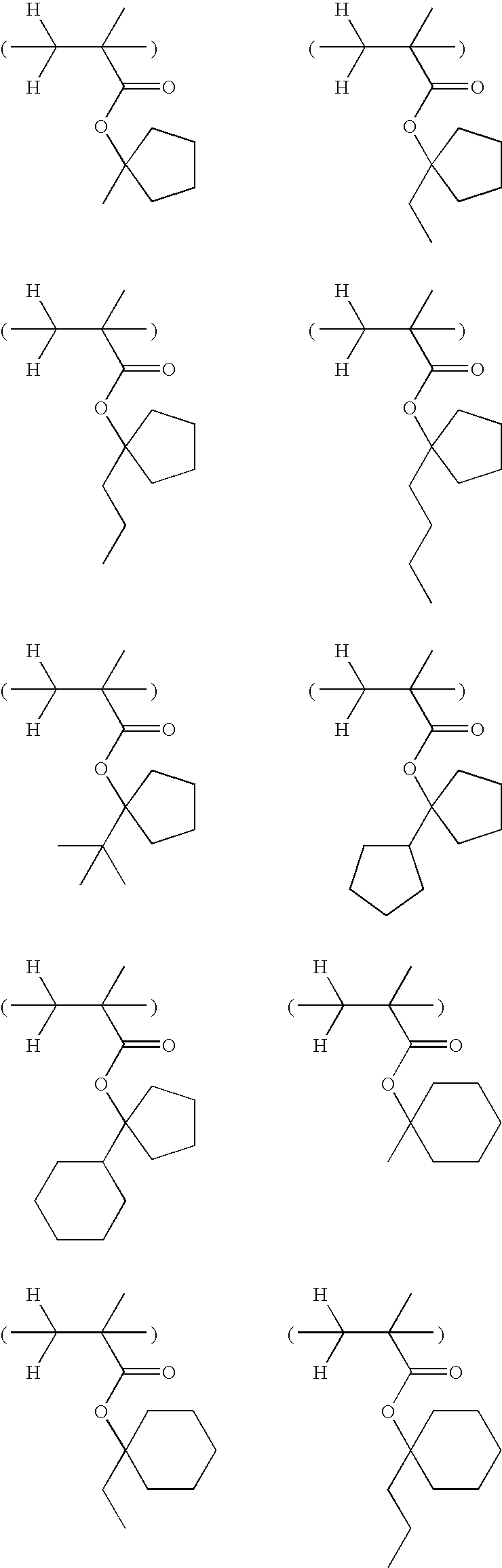

Polymer, resist material and patterning processing

ActiveUS20050089796A1Improved coating propertiesRadiation applicationsPhotomechanical apparatusPolymer scienceHigh energy

Provided is a polymer useful as a base resin of a resist material featuring a high resolution, patterns with less sidewall roughness, practically acceptable etching resistance, and a substantial margin allowed for heat treatment temperature after exposure. The polymer has a weight-average molecular weight of from 1,000 to 50,000 and comprises at least one repeating unit of formula (1) below, at least one repeating unit of formula (2) below and at least one repeating unit of formula (3) below. A resist material comprising the polymer is also provided. In addition, provided is a pattern formation process comprising steps of applying the resist material onto a substrate, heating the film, exposing the heated film through a photomask to high energy radiation or electron beam, heating the exposed film and then developing with a developer.

Owner:SHIN ETSU CHEM IND CO LTD

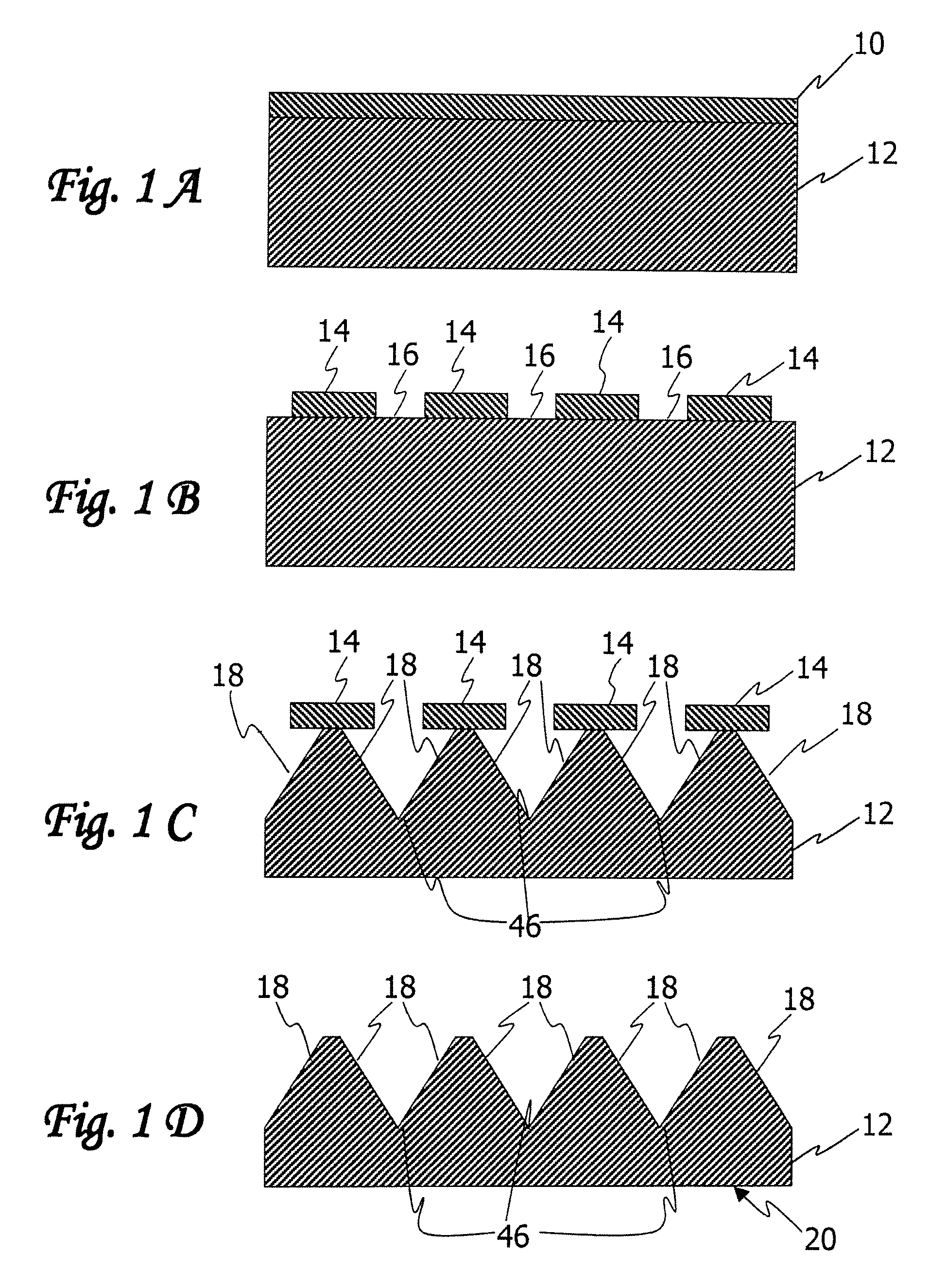

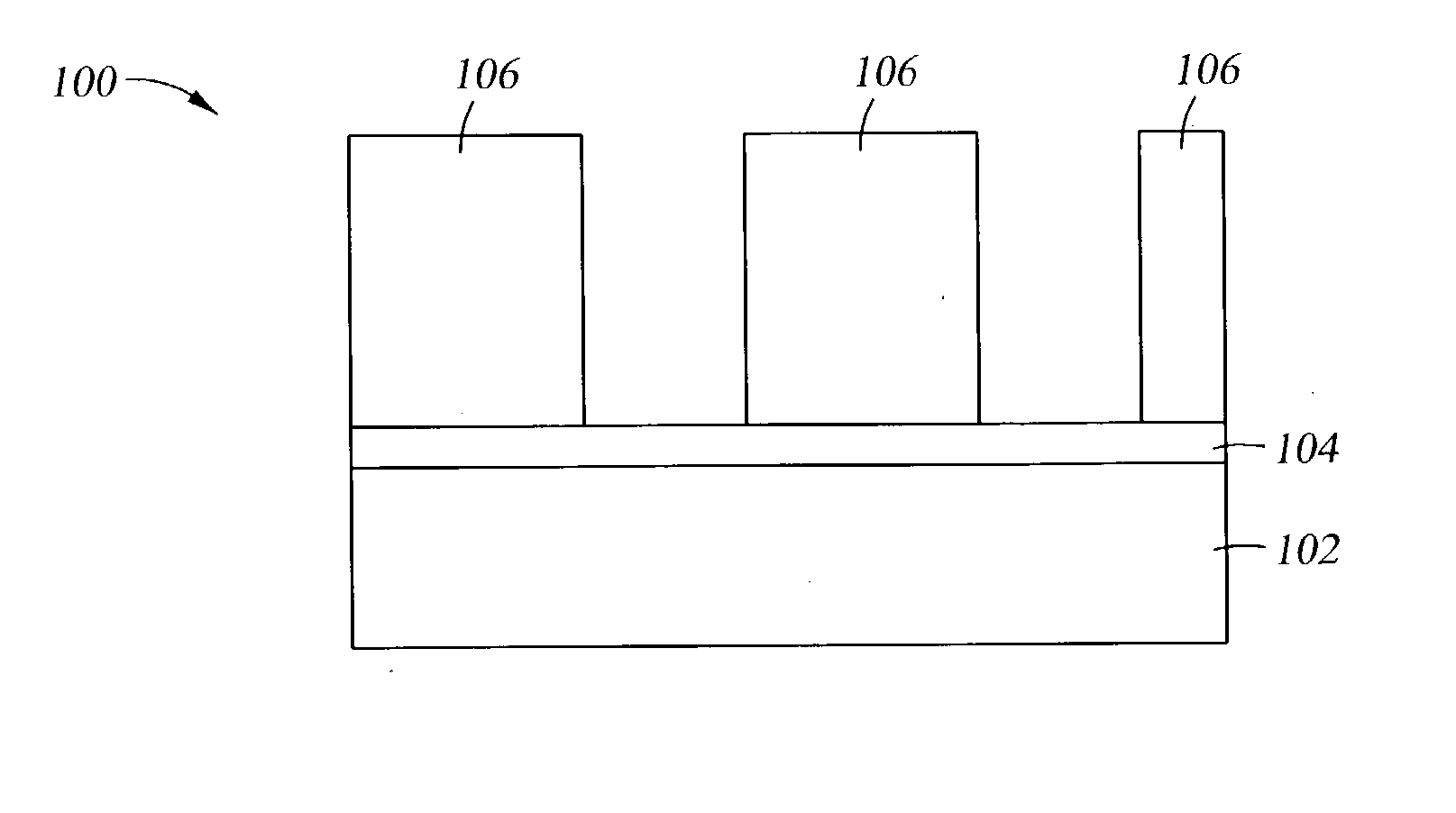

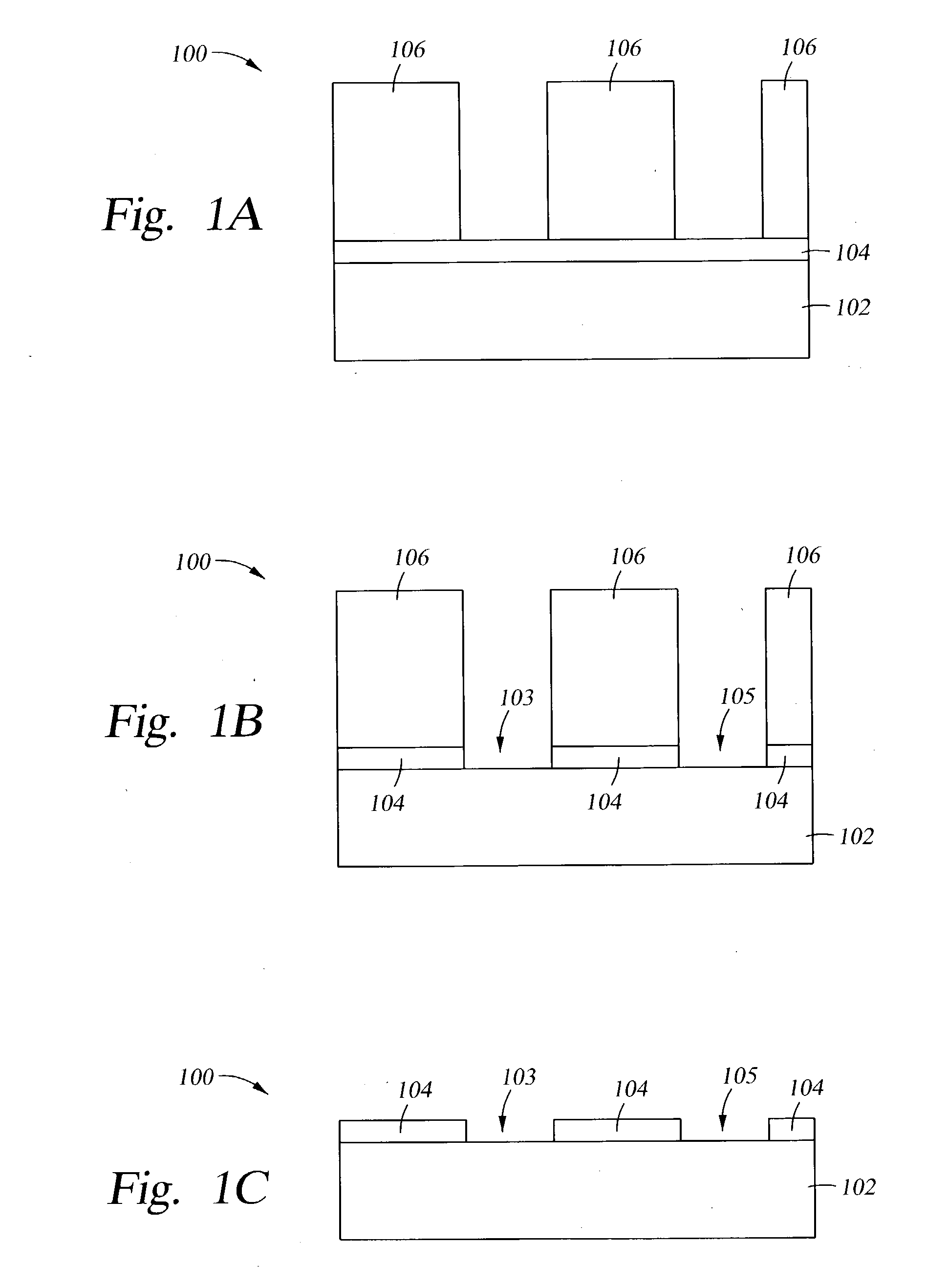

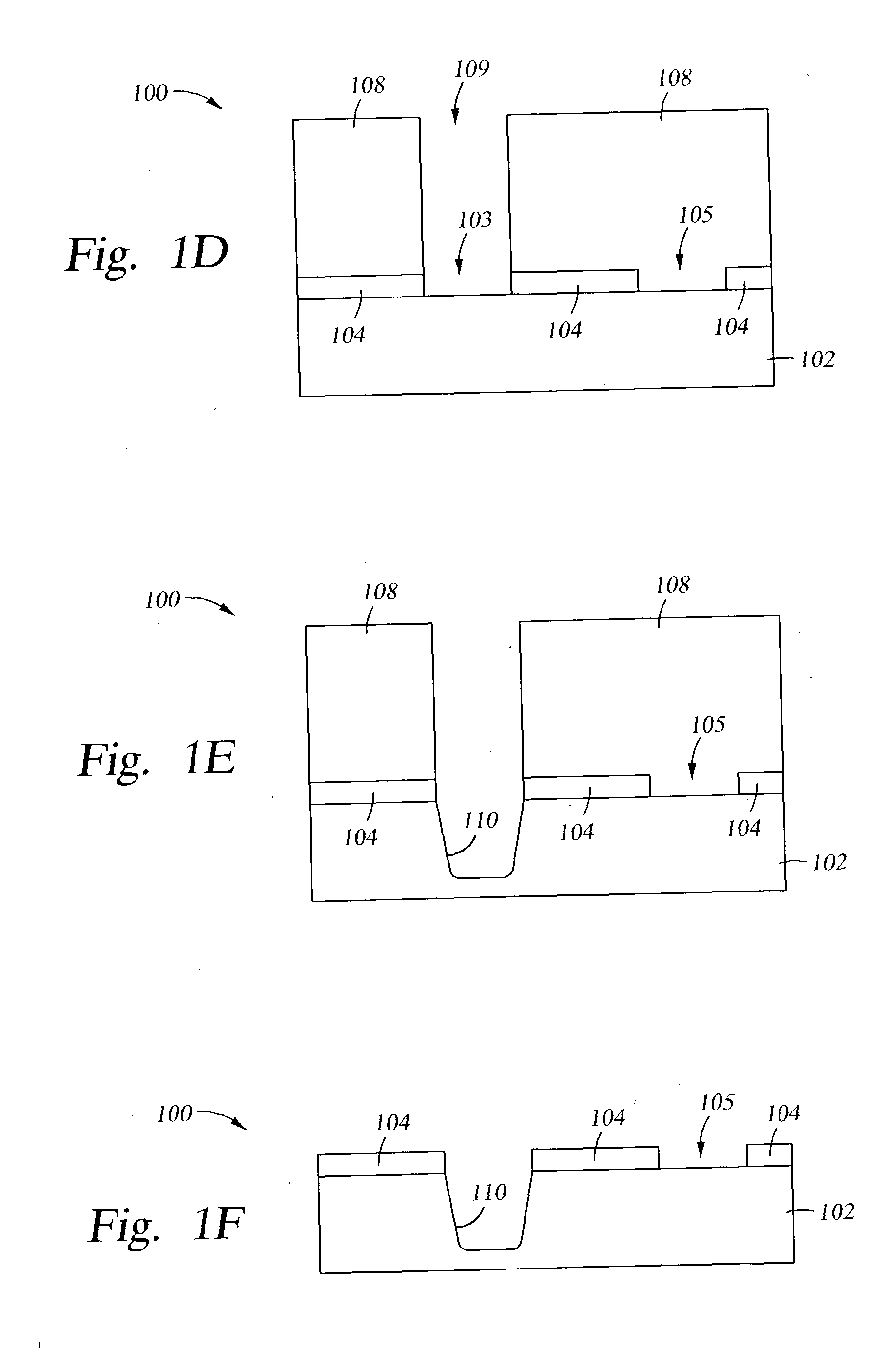

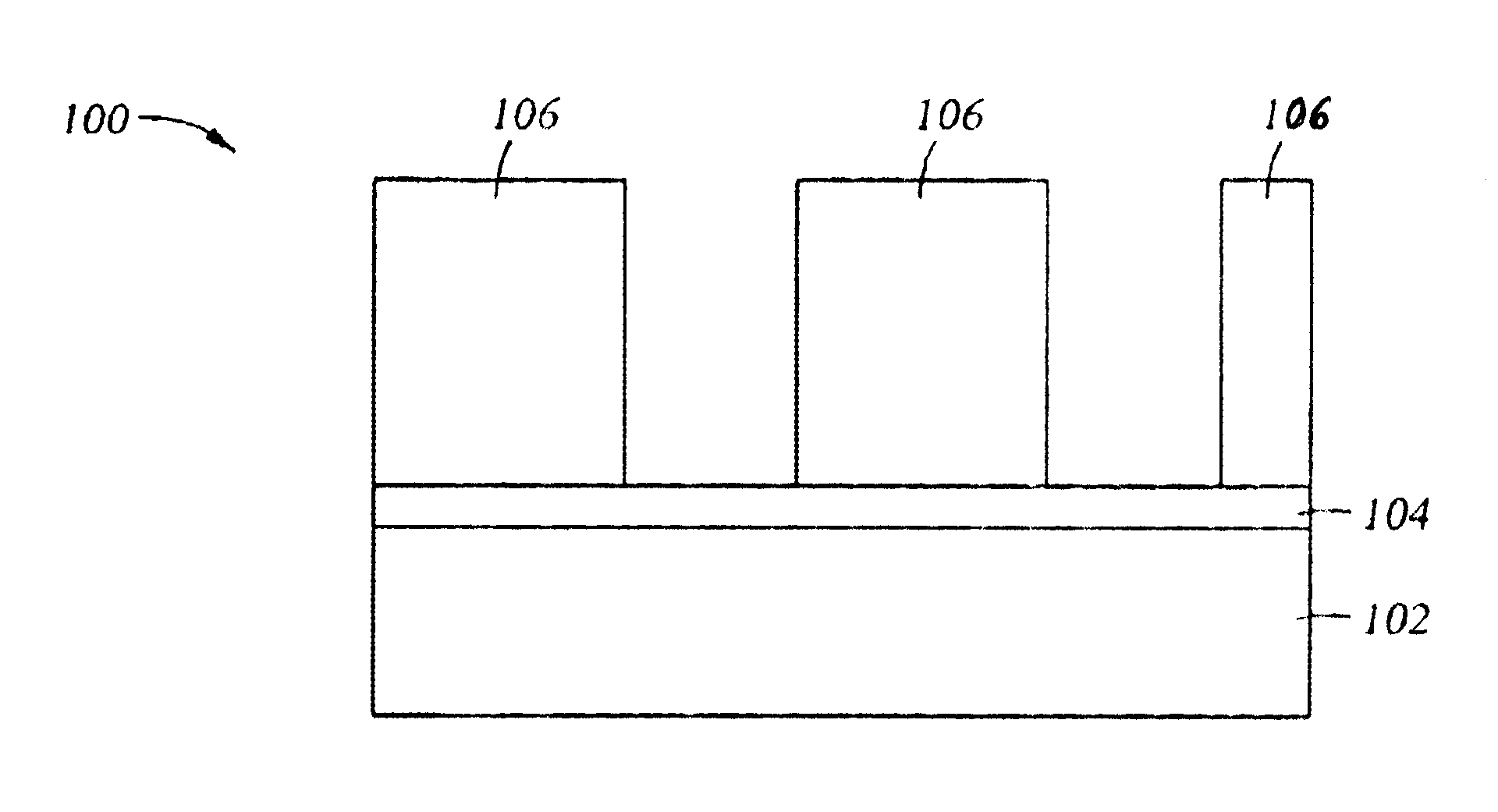

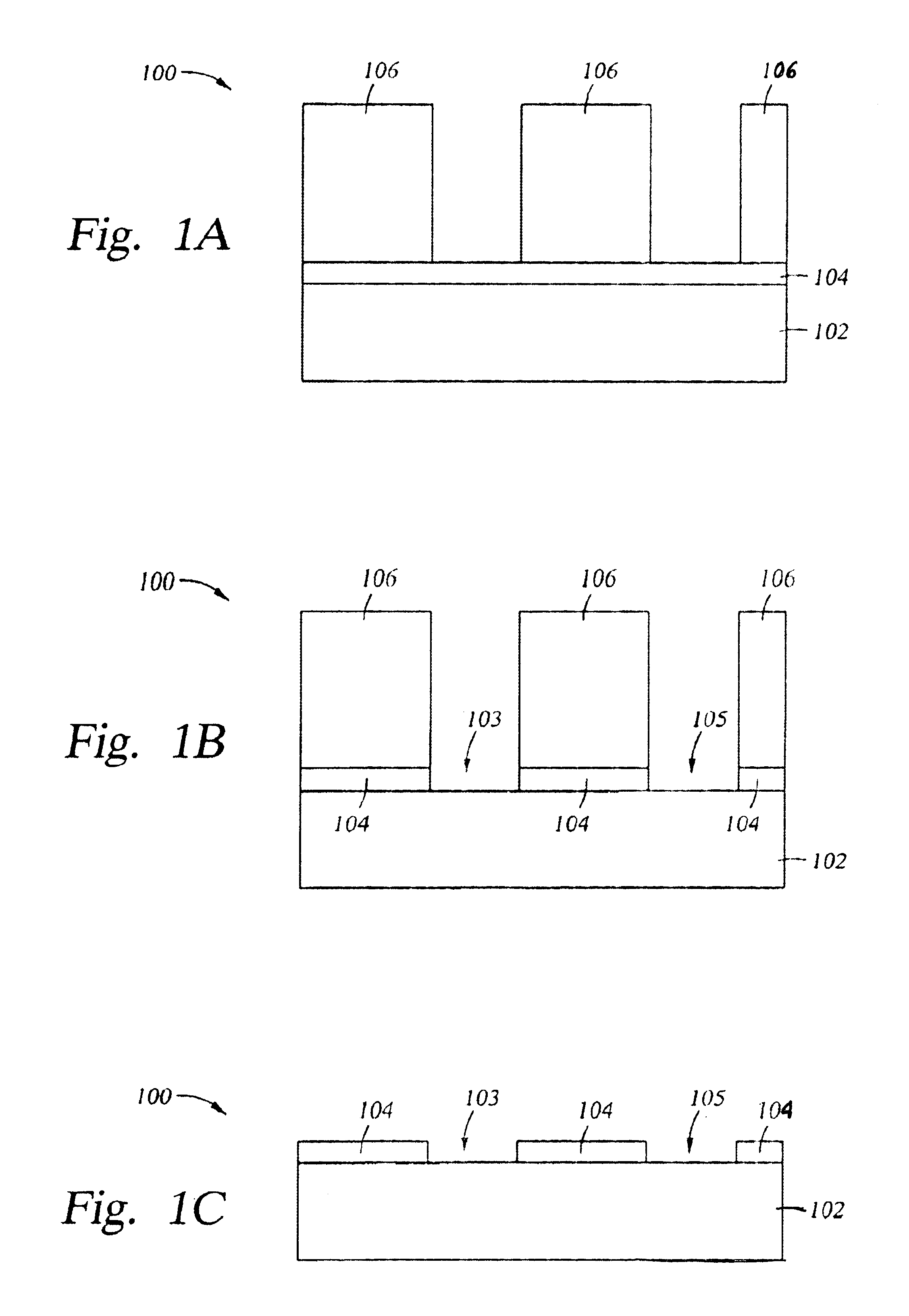

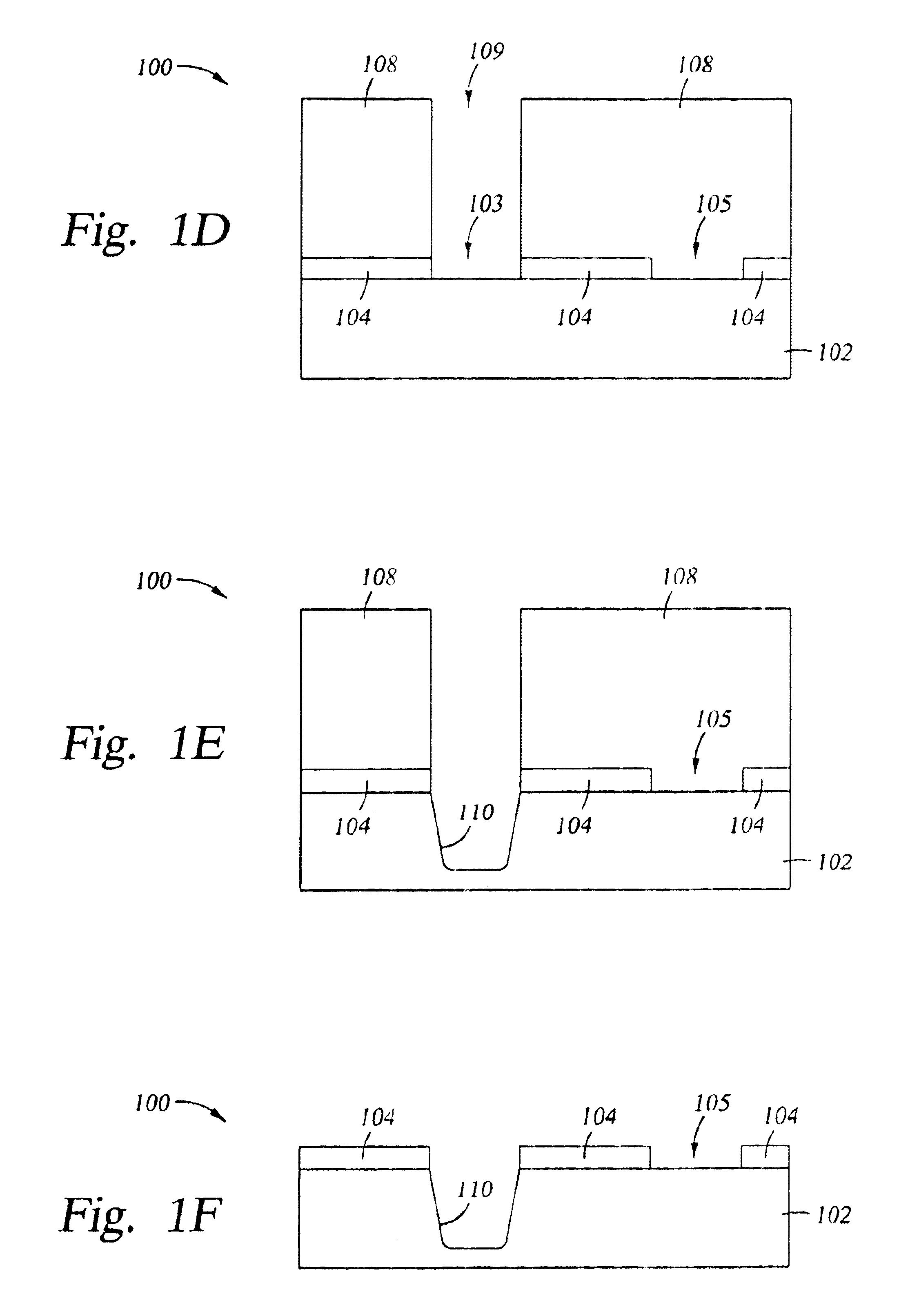

Method of etching variable depth features in a crystalline substrate

InactiveUS20040053505A1Decorative surface effectsSemiconductor/solid-state device manufacturingSidewall roughnessSemiconductor

Disclosed herein is an easy and well-integrated method of etching features to different depths in a crystalline substrate, such as a single-crystal silicon substrate. The method utilizes a specialized masking process and takes advantage of a highly selective etch process. The method provides a system of interconnected, variable depth reservoirs and channels. The plasma used to etch the channels may be designed to provide a sidewall roughness of about 200 nm or less. The resulting structure can be used in various MEMS applications, including biomedical MEMS and MEMS for semiconductor applications.

Owner:APPLIED MATERIALS INC

Method of etching variable depth features in a crystalline substrate

InactiveUS6900133B2Easy and well-integratedDecorative surface effectsSemiconductor/solid-state device manufacturingSidewall roughnessSemiconductor

Disclosed herein is an easy and well-integrated method of etching features to different depths in a crystalline substrate, such as a single-crystal silicon substrate. The method utilizes a specialized masking process and takes advantage of a highly selective etch process. The method provides a system of interconnected, variable depth reservoirs and channels. The plasma used to etch the channels may be designed to provide a sidewall roughness of about 200 nm or less. The resulting structure can be used in various MEMS applications, including biomedical MEMS and MEMS for semiconductor applications.

Owner:APPLIED MATERIALS INC

Low-power laser-induced TIG electric arc-based additive manufacturing method of stainless steel structural member and manufacturing system

ActiveCN109909616ACases to prevent spot depositsHigh precisionLaser beam welding apparatusArc stabilitySidewall roughness

The invention provides a low-power laser-induced TIG electric arc-based additive manufacturing method of a stainless steel structural member and a manufacturing system. According to the method, a low-power laser and a TIG electric arc are taken as a composite heat source, an included angle relationship among a welding gun, the laser and a substrate is arranged according to a welding environment, astainless steel welding wire is fed into a molten pool through an additional wire feeding device, is stably melted and spread on the treated substrate, surfacing is carried out according to a plannedroute, and a stainless steel workpiece with a required structure is formed by accumulating layer-by-layer. According to the method and the system, the process of electric arc additive manufacturing is effectively improved through the addition of the low-power laser, the electric arc stability is increased, the irregular flowing of the molten pool is reduced, the roughness of a side wall of an additive wall body is effectively improved, the forming quality is improved, the processing allowance is reduced, and the utilization rate of a material is increased; and the method and the system have the characteristics of high efficiency and energy saving, and speediness, high precision, short period, low cost and the like are achieved when the complicated large-scale member is manufactured by themethod and the system.

Owner:DALIAN UNIV OF TECH

Method of making an article comprising nanoscale patterns with reduced edge roughness

In accordance with the invention, an article comprising a nanoscale surface pattern, such as a grating, is provided with a nanoscale patterns of reduced edge and / or sidewall roughness. Smooth featured articles, can be fabricated by nanoimprint lithography using a mold having sloped profile molding features. Another approach uses a mold especially fabricated to provide smooth sidewalls of reduced roughness, and a third approach adds a post-imprint smoothing step. These approaches can be utilized individually or in various combinations to make the novel articles.

Owner:PRINCETON UNIV

Method of forming isolation film in semiconductor device

The present invention relates to a method for forming an isolation film in a semiconductor device. After a trench for isolation is formed, a polymer film is stripped by a post cleaning process using BFN. A pre-treatment cleaning process using only SC-1 is performed and a sidewall oxidization process is then carried out. It is therefore possible to improve fail of the roughness of the trench sidewall and to easily strip polymer. Furthermore, since a conventional PET process is omitted, an isolation film manufacturing process is simplified. It is also possible to prohibit out-diffusion of dopants injected into a semiconductor substrate through a pre-treatment cleaning process using CLN N before the sidewall oxidization process. Incidentally, by forming a slope at the top corner of the trench, it is possible to prevent a gate oxide film thinning phenomenon that the gate oxide film thinner than a desired thickness is deposited at the trench corner. It is also possible to improve electrical properties of a device since an active region as much as a target critical dimension is secured.

Owner:MICRON TECH INC +1

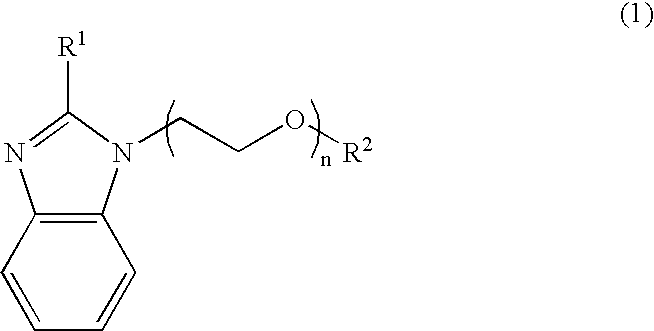

Polymer, resist material and patterning processing

ActiveUS7157207B2Improved coating propertiesRadiation applicationsSemiconductor/solid-state device manufacturingPolymer scienceHigh energy

Provided is a polymer useful as a base resin of a resist material featuring a high resolution, patterns with less sidewall roughness, practically acceptable etching resistance, and a substantial margin allowed for heat treatment temperature after exposure. The polymer has a weight-average molecular weight of from 1,000 to 50,000 and comprises at least one repeating unit of formula (1) below, at least one repeating unit of formula (2) below and at least one repeating unit of formula (3) below. A resist material comprising the polymer is also provided. In addition, provided is a pattern formation process comprising steps of applying the resist material onto a substrate, heating the film, exposing the heated film through a photomask to high energy radiation or electron beam, heating the exposed film and then developing with a developer

Owner:SHIN ETSU CHEM IND CO LTD

Etching method of silicon chip grooves for optical waveguide

ActiveCN105589131AReduce transmission lossGood resistance to dry etchingOptical light guidesScattering lossSilicon oxide

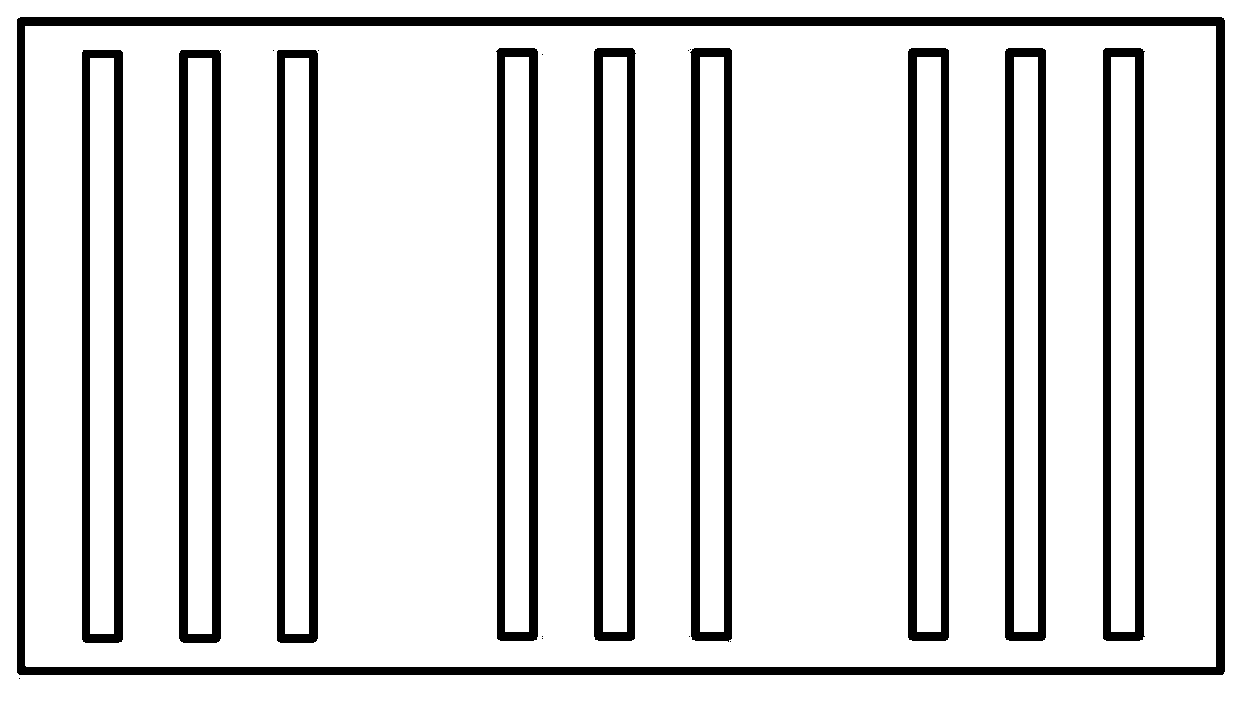

The invention discloses an etching method of silicon chip grooves for an optical waveguide. The method includes: S1: a dielectric layer and a shielding layer are deposited on the surface of a silicon substrate in sequence, the dielectric layer is a silicon oxide layer or a silicon nitride layer, and the shielding layer is a polysilicon layer or an amorphous silicon layer; S2: shielding patterns of photoresist are formed on the surface of the shielding layer by employing a silicon groove processing photoetching mask; S3: the first etching of the shielding layer is performed by employing a dry method plasma etching process; S4: the polysilicon layer or the amorphous silicon layer after the first etching is regarded as the shielding layer, and the second etching of the dielectric layer is performed; S5: the shielding patterns of the photoresist are formed on the surface of the bare silicon substrate by employing a reverse mask of the silicon groove processing photoetching mask, and the third etching is performed; and S6: the residual dielectric layer is regarded as the shielding layer for silicon etching to obtain the required silicon grooves. According to the method, the roughness of sidewalls of the silicon grooves can be greatly improved, and the scattering loss and the transmission loss of the silicon-based optical waveguide are reduced.

Owner:CHINA ELECTRONICS TECH GRP NO 23 RES INST

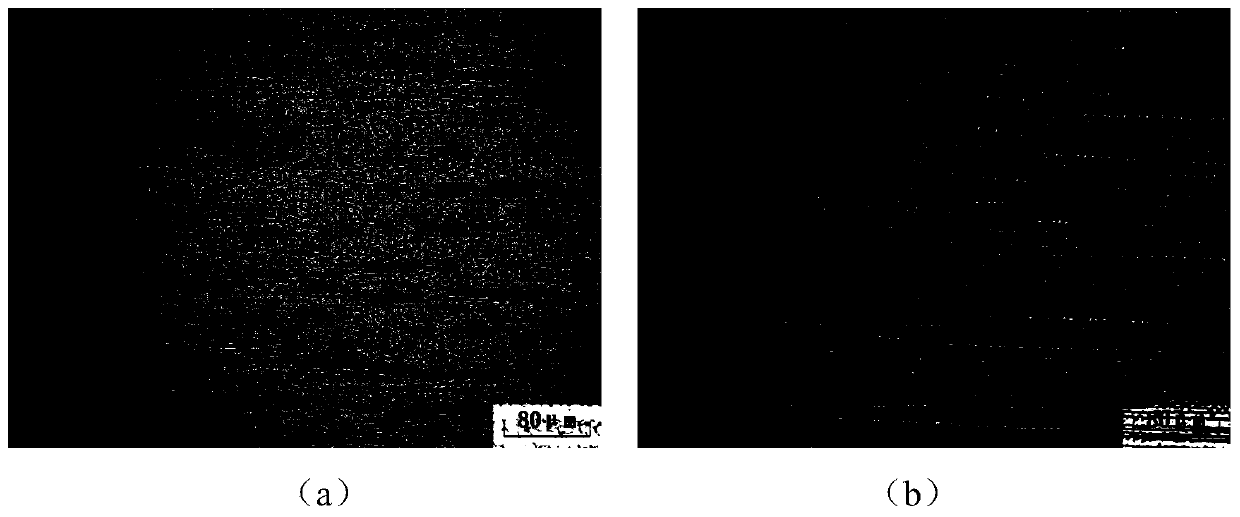

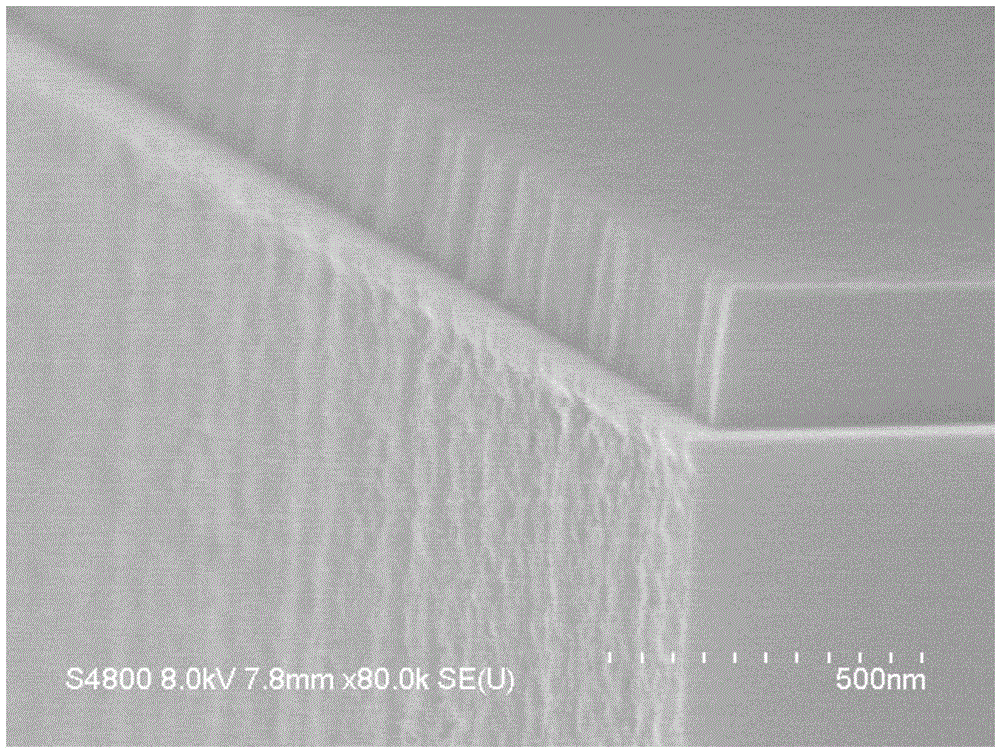

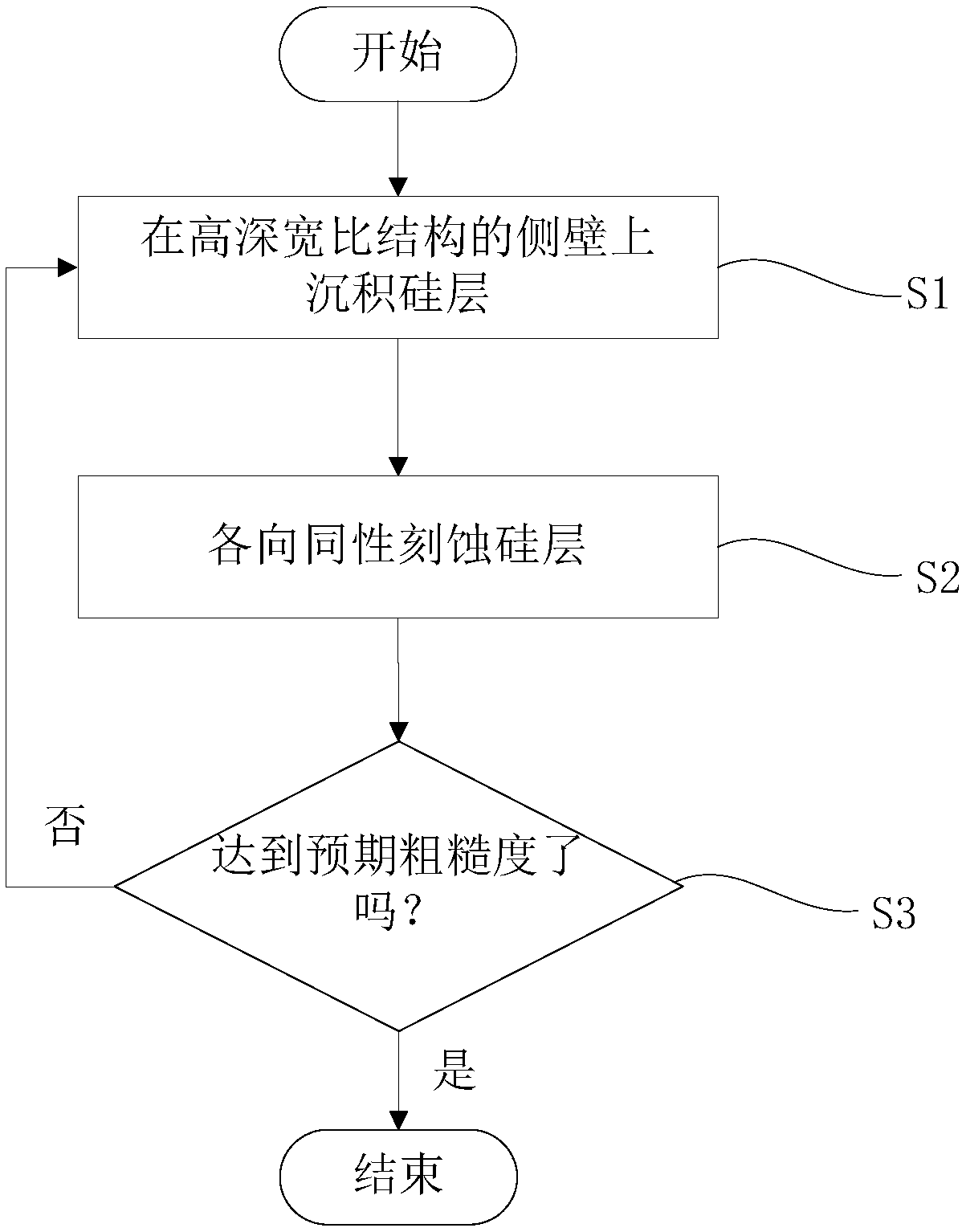

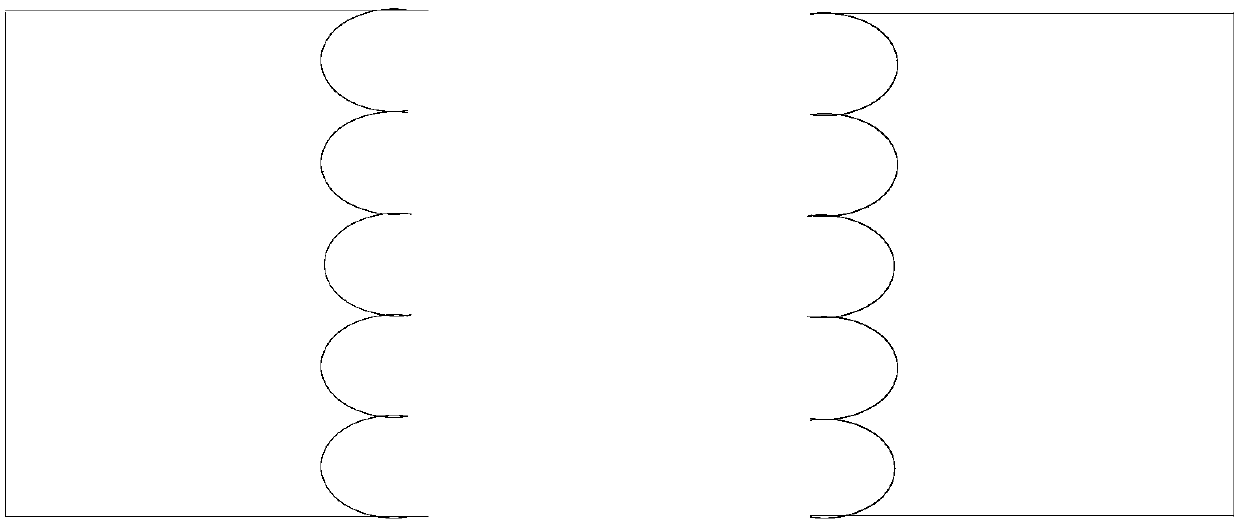

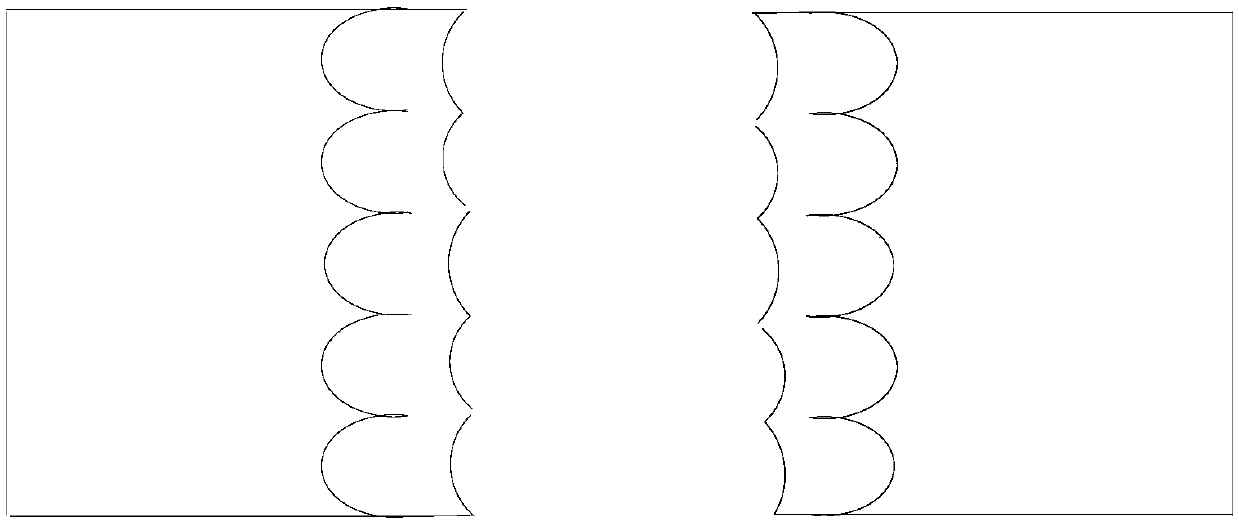

Method for improving roughness of side wall formed through deep silicon etching

InactiveCN107611027AIncrease roughnessMeet design needsDecorative surface effectsSemiconductor/solid-state device manufacturingSidewall roughnessSilicon etching

The invention discloses a method for improving the roughness of a side wall formed through deep silicon etching. The method comprises the following steps of a deposition step: depositing a silicon layer with a certain thickness on a side wall, formed by etching, with a high-aspect-ratio structure; an etching step: carrying out isotropic etching on the silicon layer; and a judgement step: judging whether the roughness of the side wall reaches a default value or not, if the roughness of the side wall does not reach the default value, returning to the deposition step and repeating a cycle from the deposition step to the etching step, and if the roughness of the side wall reaches the default value, ending the process. The roughness of the side wall formed through deep silicon etching can be effectively improved through circularly executing the deposition step and the etching step, the shape and form with higher smoothness can be obtained, meanwhile, the size of the formed high-aspect-ratiostructure is prevented from deviating from a default size, and the design requirements of a device are met.

Owner:JIANGSU LEUVEN INSTR CO LTD

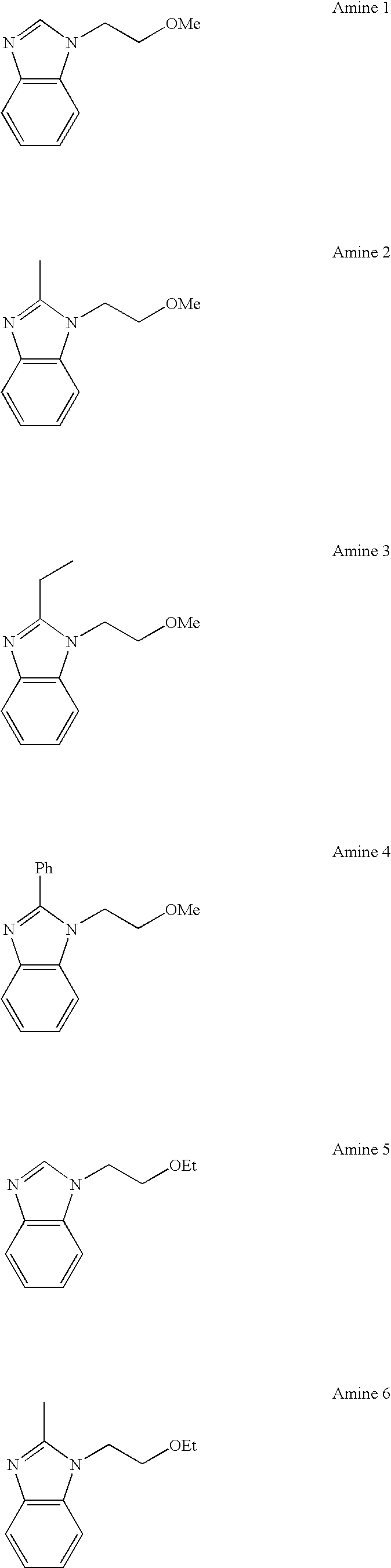

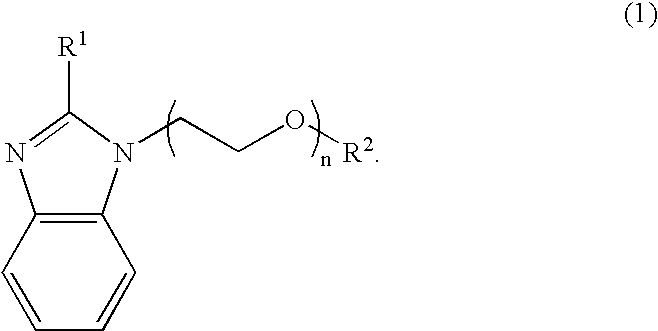

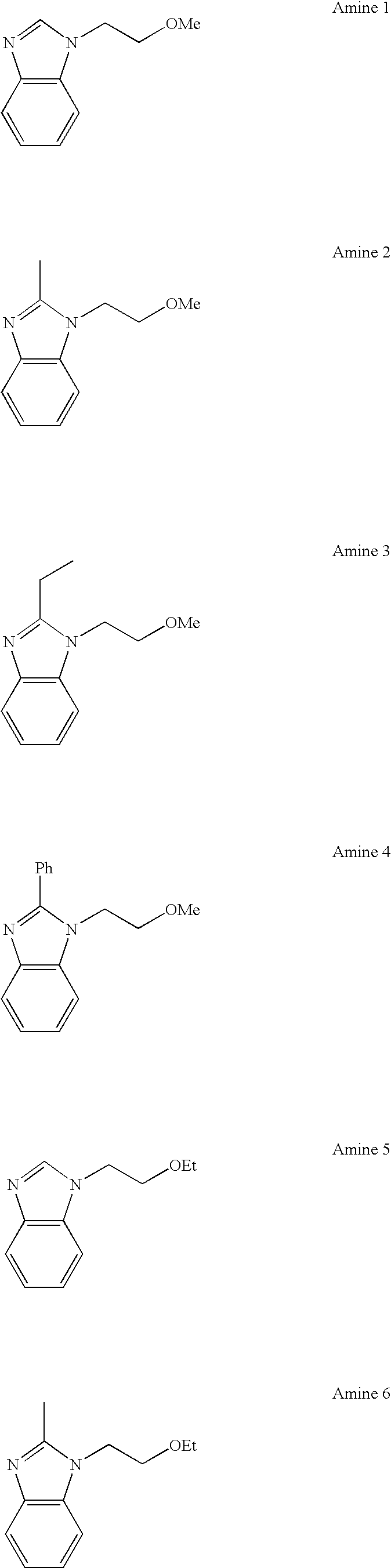

Nitrogen-containing organic compound, resist composition and patterning process

ActiveUS7252925B2High resolutionMinimized roughnessOrganic chemistryPhotosensitive materialsResistImage resolution

Resist compositions comprising nitrogen-containing organic compounds having a benzimidazole structure and a specific ether chain moiety have an excellent resolution, form precisely configured patterns with minimized roughness of sidewalls and are useful in microfabrication using electron beams or deep-UV light.

Owner:SHIN ETSU CHEM CO LTD

Etching radical controlled gas chopped deep reactive ion etching

ActiveUS8546264B2Decorative surface effectsSemiconductor/solid-state device manufacturingInductively coupled plasmaPolymer

A method for silicon micromachining techniques based on high aspect ratio reactive ion etching with gas chopping has been developed capable of producing essentially scallop-free, smooth, sidewall surfaces. The method uses precisely controlled, alternated (or chopped) gas flow of the etching and deposition gas precursors to produce a controllable sidewall passivation capable of high anisotropy. The dynamic control of sidewall passivation is achieved by carefully controlling fluorine radical presence with moderator gasses, such as CH4 and controlling the passivation rate and stoichiometry using a CF2 source. In this manner, sidewall polymer deposition thicknesses are very well controlled, reducing sidewall ripples to very small levels. By combining inductively coupled plasmas with controlled fluorocarbon chemistry, good control of vertical structures with very low sidewall roughness may be produced. Results show silicon features with an aspect ratio of 20:1 for 10 nm features with applicability to nano-applications in the sub-50 nm regime. By comparison, previous traditional gas chopping techniques have produced rippled or scalloped sidewalls in a range of 50 to 100 nm roughness.

Owner:RGT UNIV OF CALIFORNIA

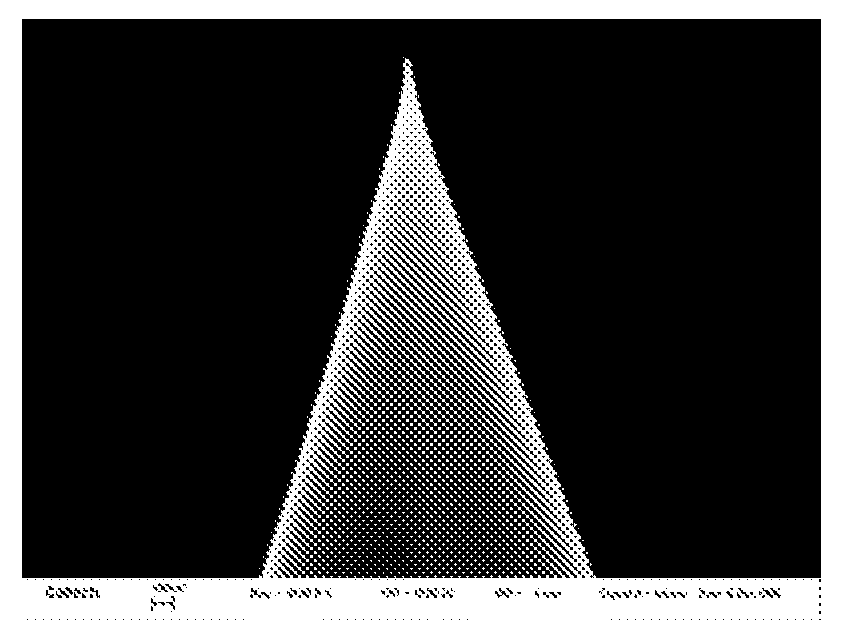

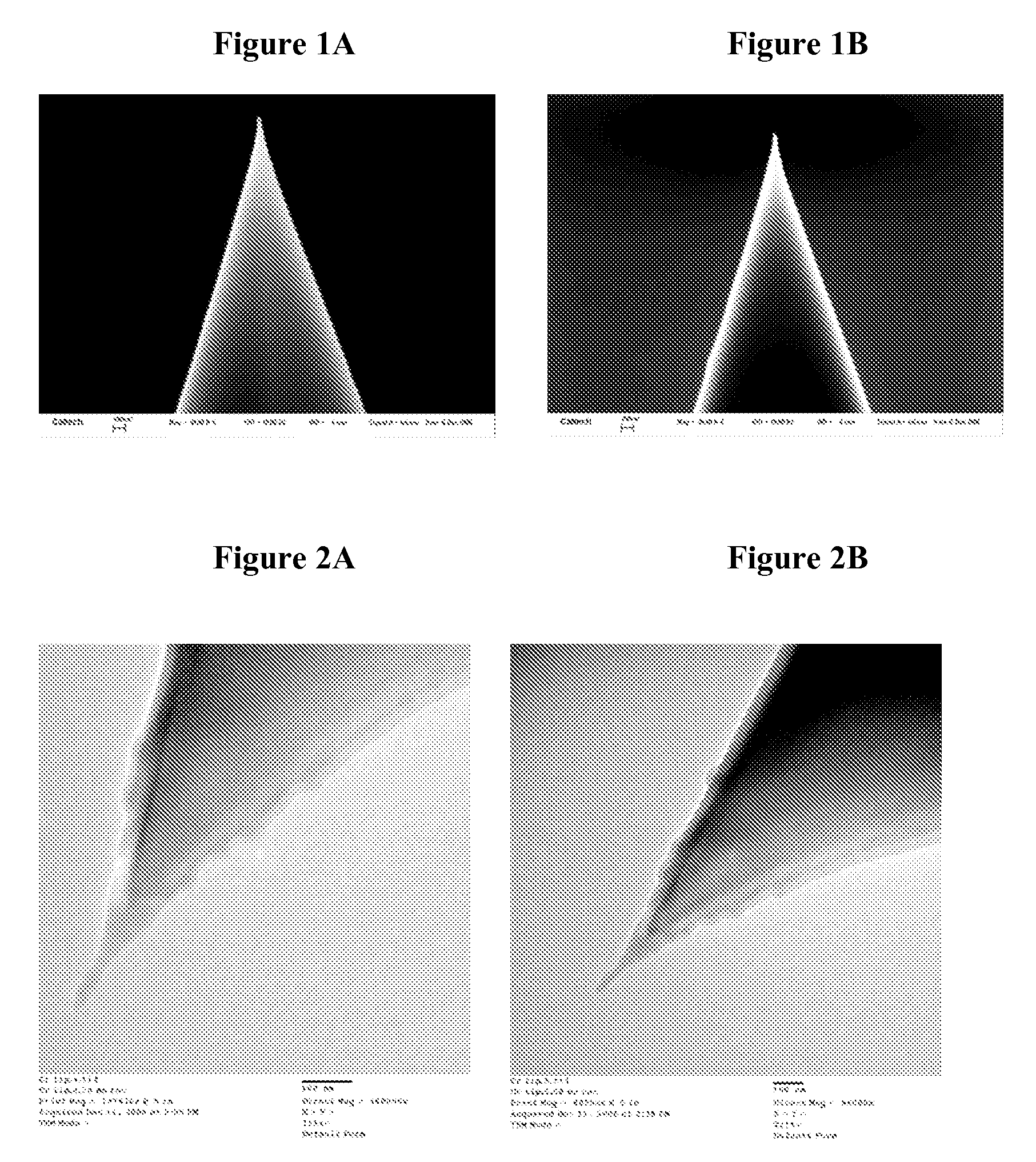

Probe tips

InactiveUS20080216565A1Small apex radiusUniform coatingNanosensorsScanning probe microscopySidewall roughnessCritical dimension

Probe tips comprising tips and coatings are described. The tips and coatings may be selected to provide various probe-tip features, including, but not limited to, high reproducibility, high reliability, low cost, ultra-sharpness, high conductivity and / or simultaneous critical dimension imaging and sidewall roughness analysis.

Owner:CERES DONATO +2

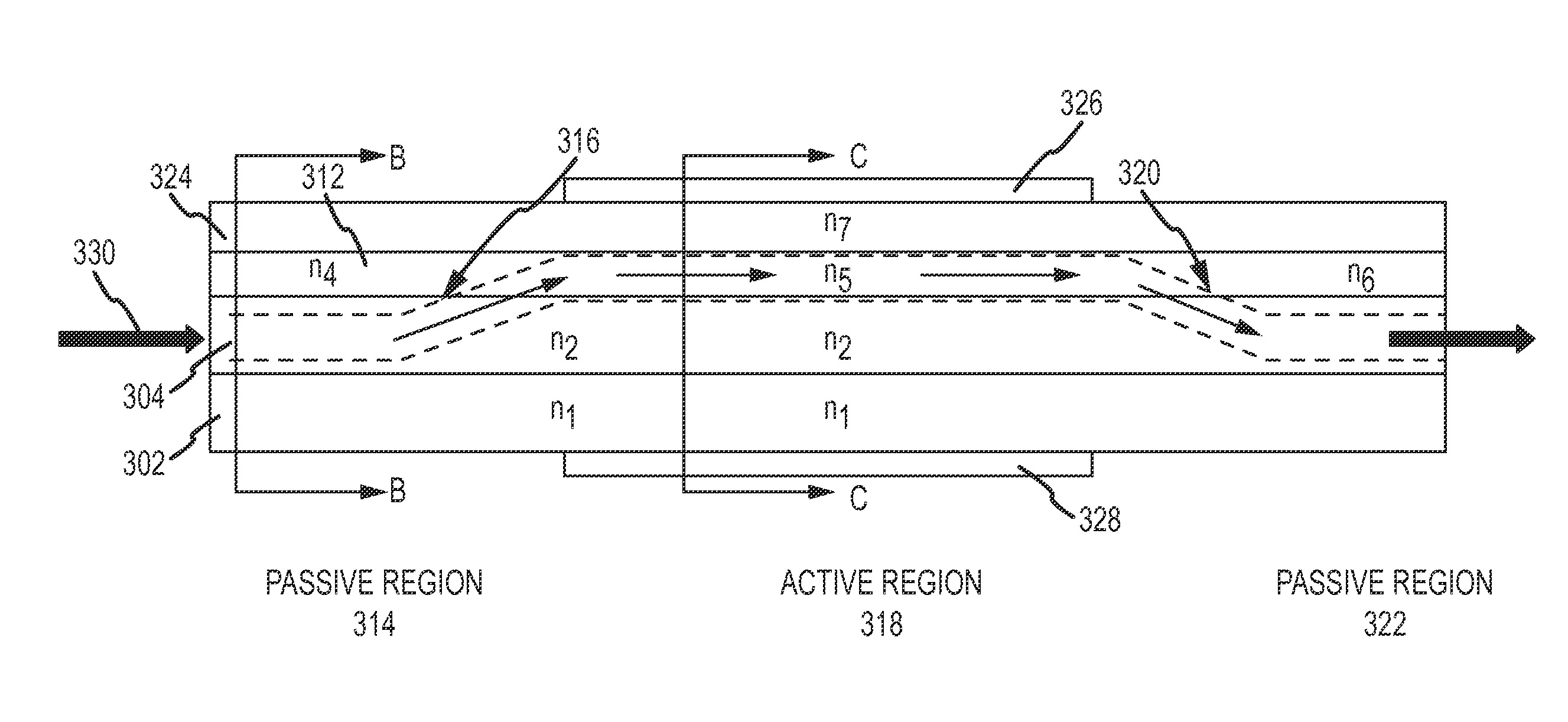

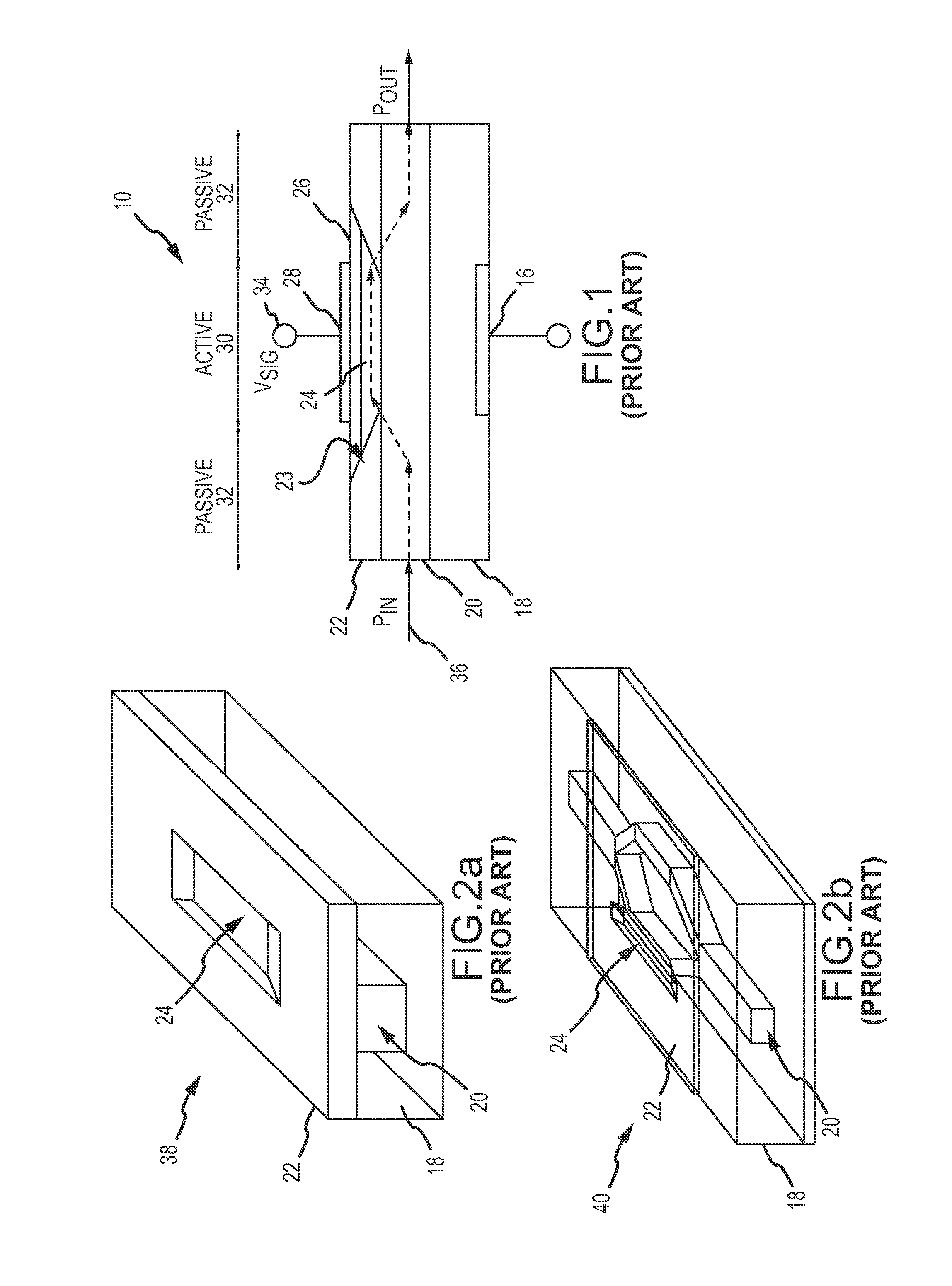

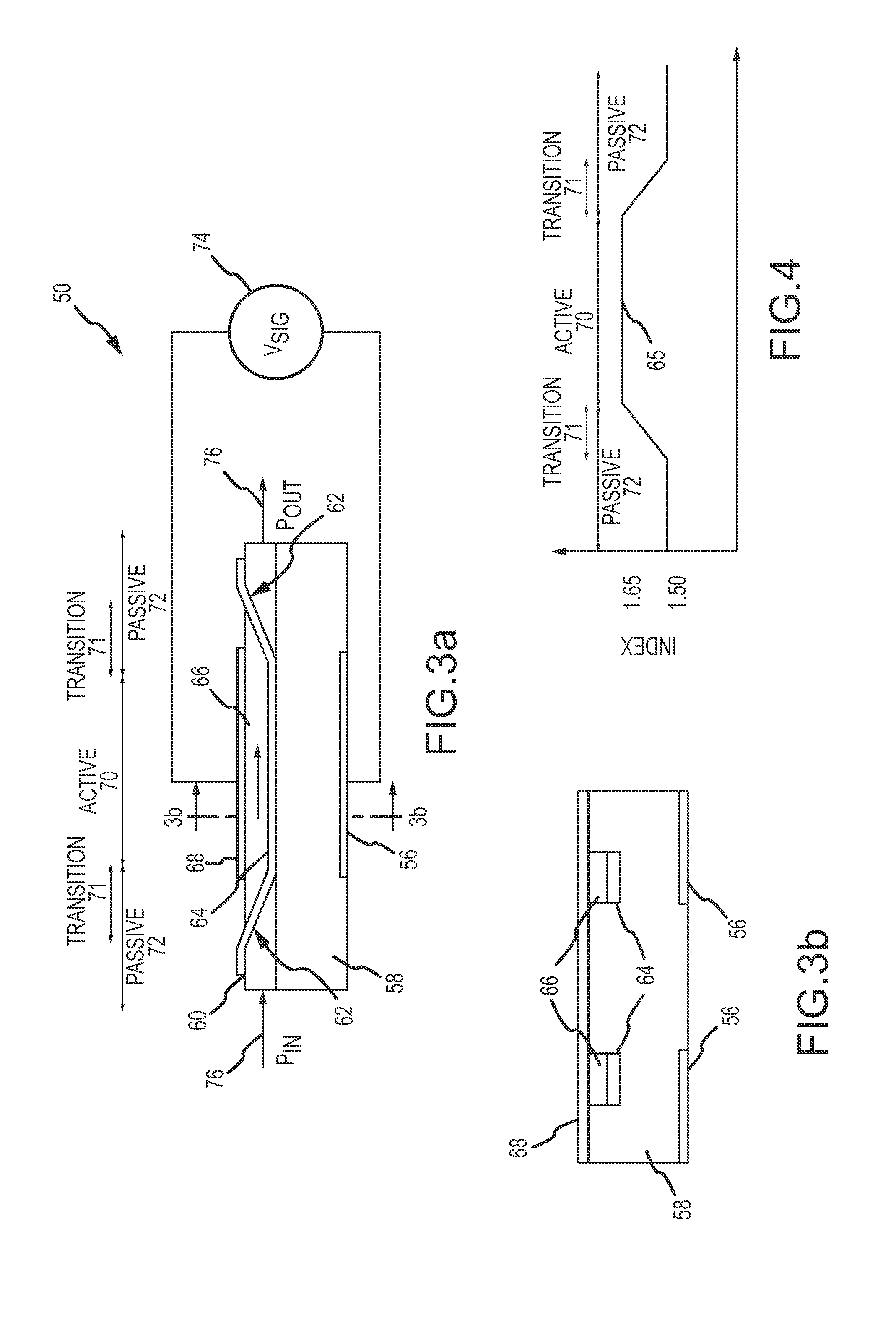

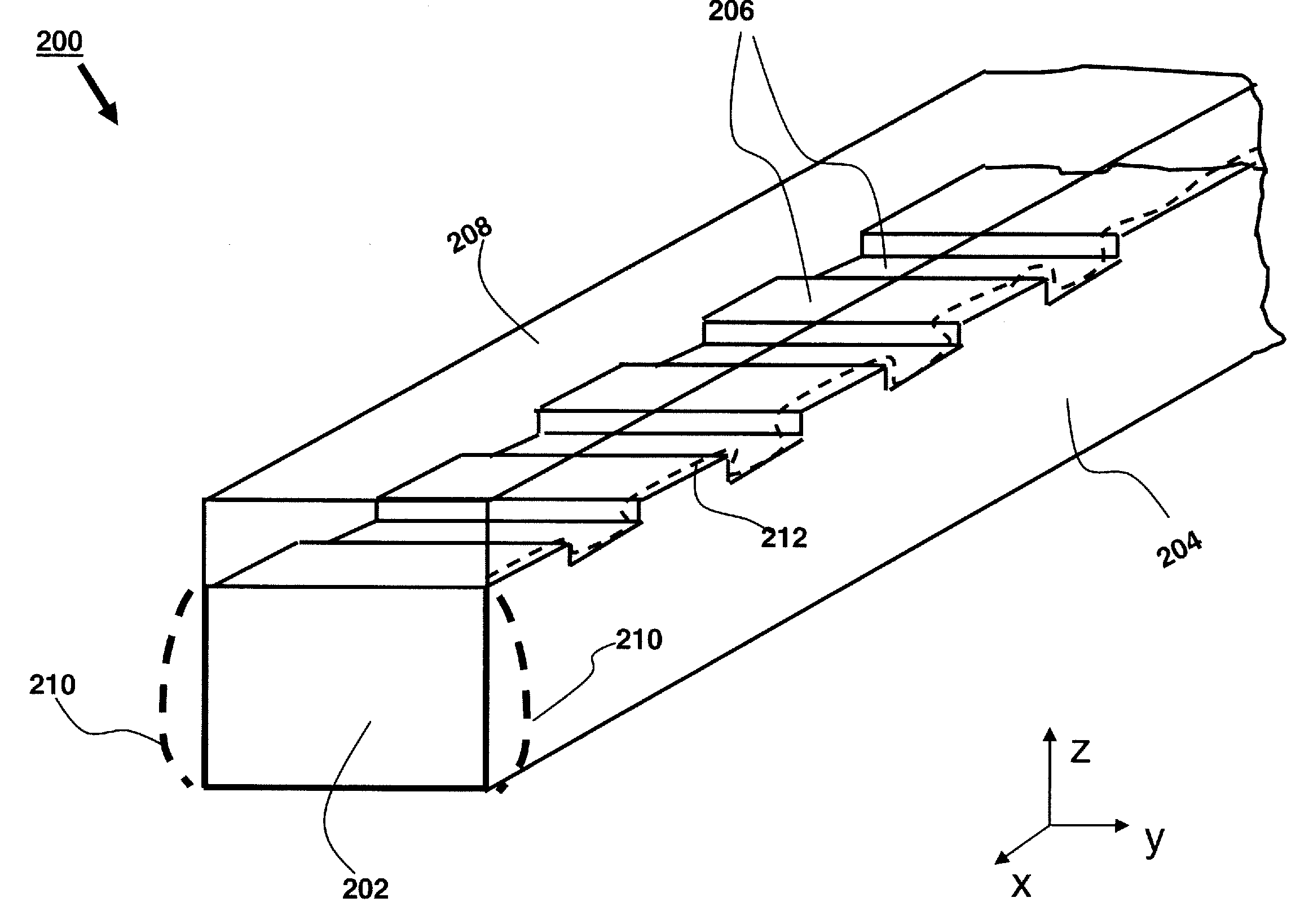

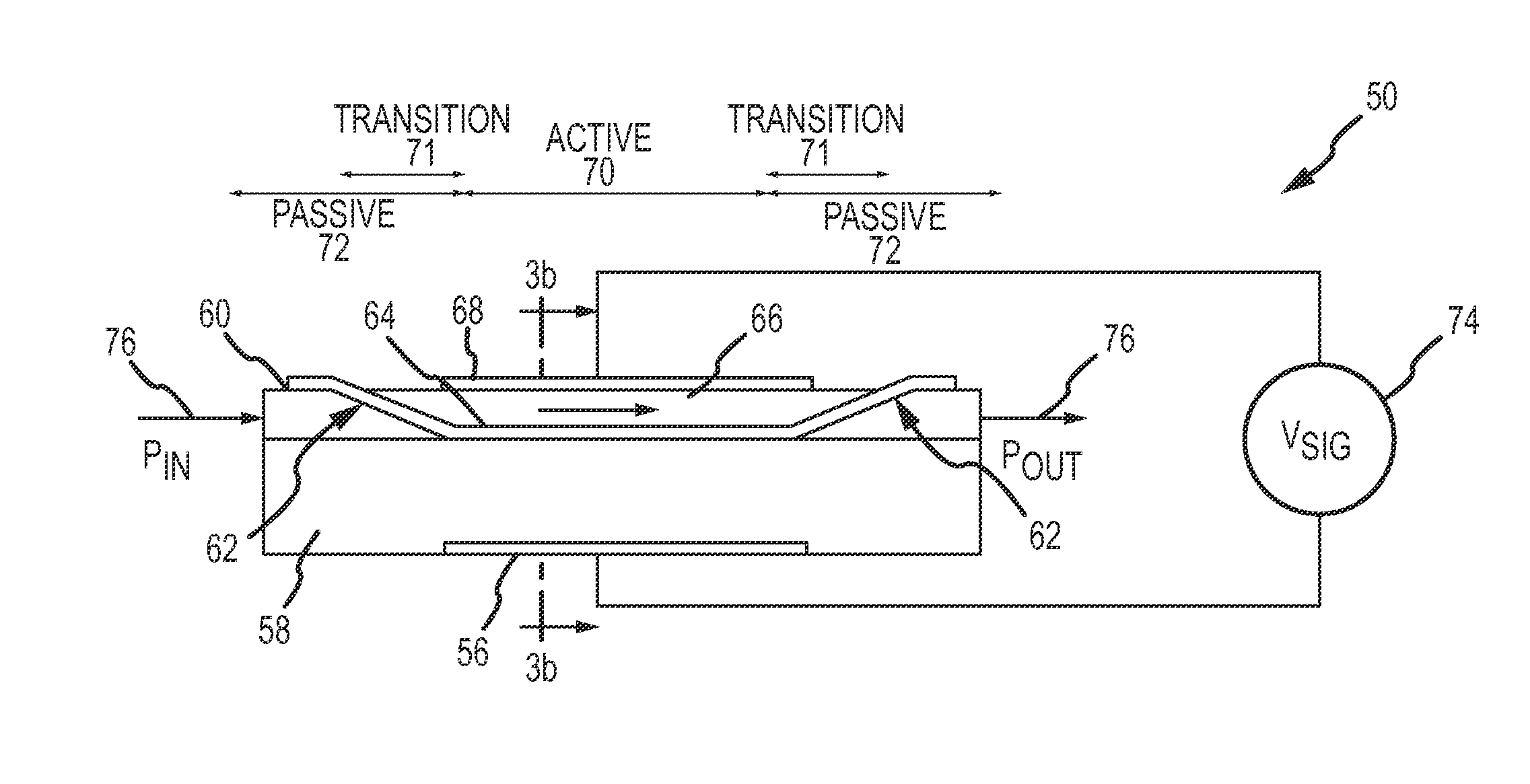

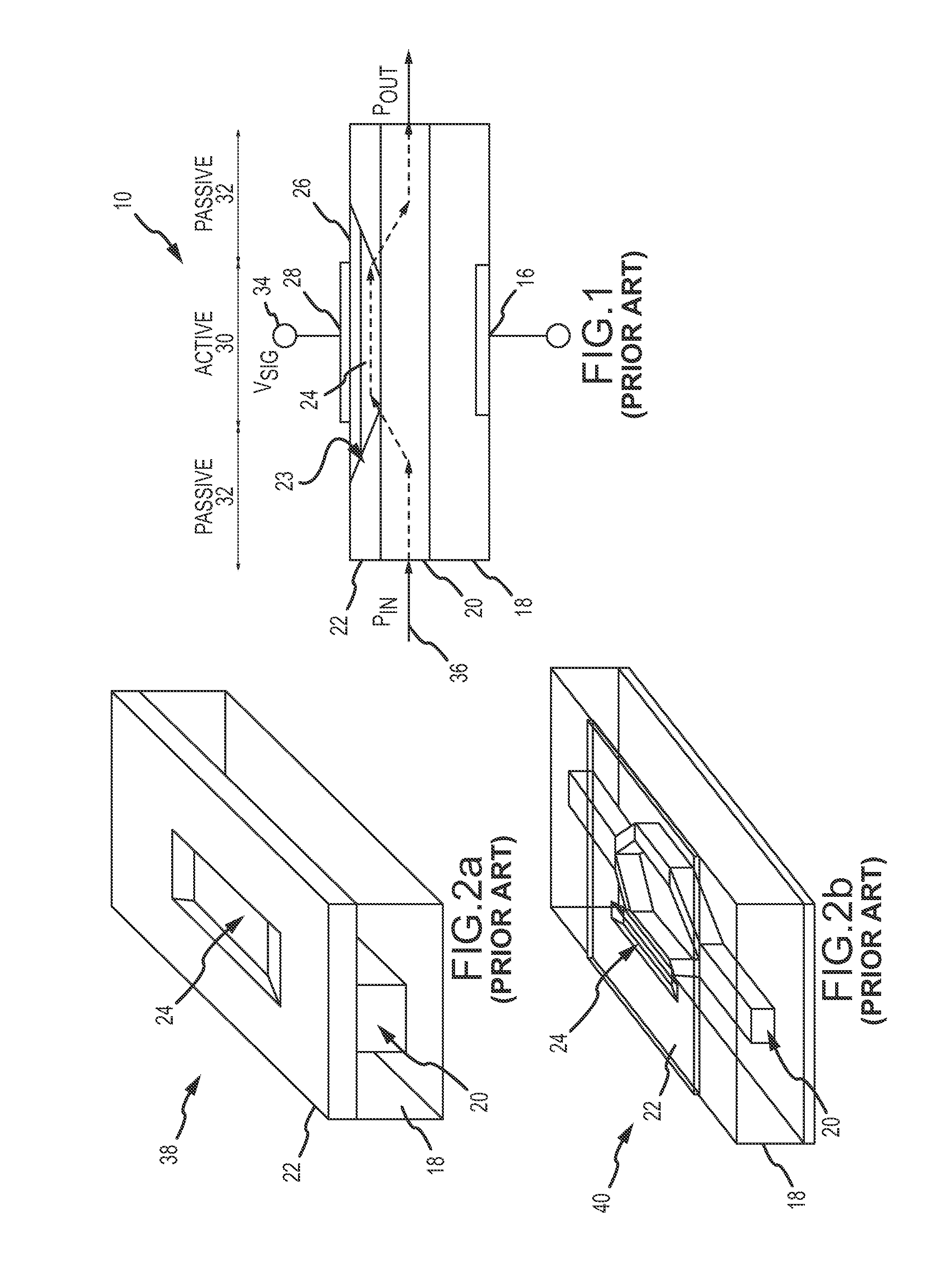

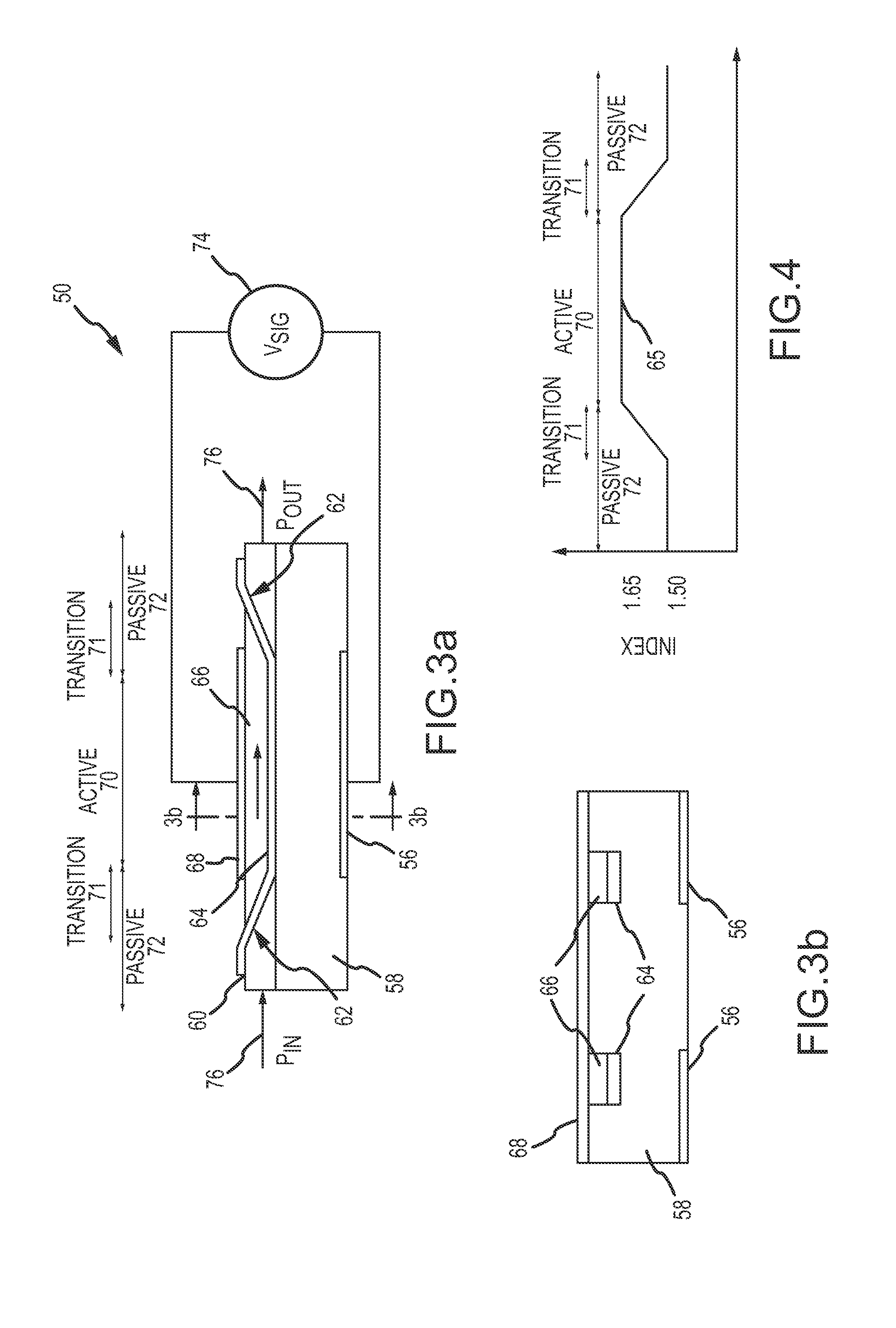

Hybrid strip-loaded electro-optic polymer/sol-gel modulator

InactiveUS7912327B2Higher electric field/optical field overlap factorReduced insertion lossOptical waveguide light guideNon-linear opticsSidewall roughnessHYDROSOL

Owner:THE ARIZONA BOARD OF REGENTS ON BEHALF OF THE UNIV OF ARIZONA

Photolithography method capable of reducing line roughness

InactiveCN103777466AReduce roughnessReduce volatilitySemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusGraphicsFine line

The invention discloses a photolithography method capable of reducing line roughness. The method comprises the following steps: forming a structural material layer and hard mask layers on a substrate; forming electronic beam photoresist on the hard mask layers, then forming electronic beam photoresist graphics by executing electronic beam overexposure, wherein the exposure dose is increased so as to improve the roughness; taking the electronic beam photoresist graphics as the mask, forming hard mask graphics by etching; taking the hard mask graphics as the mask, and etching the structural material layer so as to formed the needed fine lines. In this method, a plurality of hard mask layers made of different materials is adopted and photolithography conditions are reasonably adjusted at the same time so as to prevent the roughness degree of the sidewall of the electronic beam photoresist from being transmitted to the structural material layer under the hard mask layers, thus the line roughness is effectively reduced, the technology stability is improved, and the fluctuation of device performance is reduced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

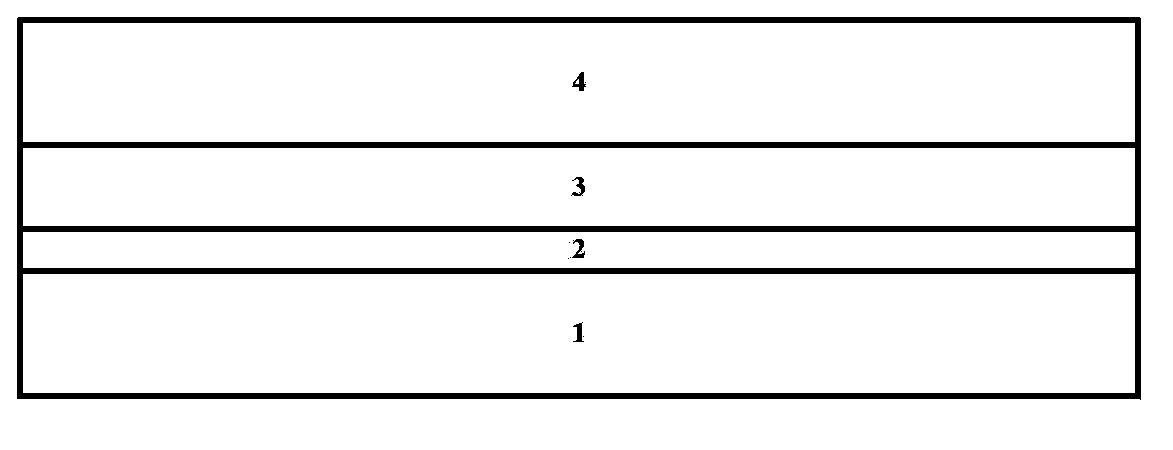

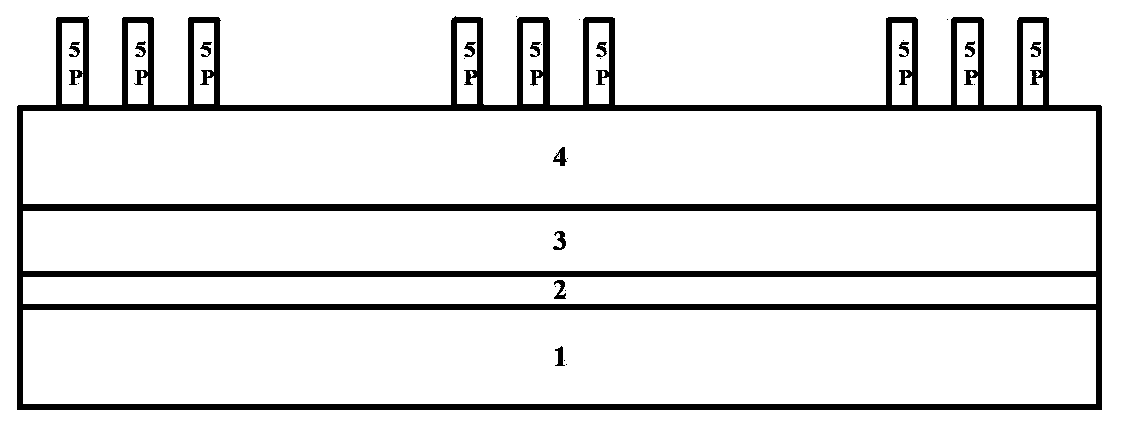

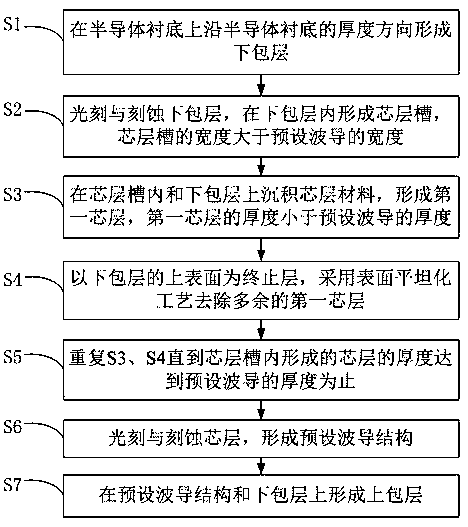

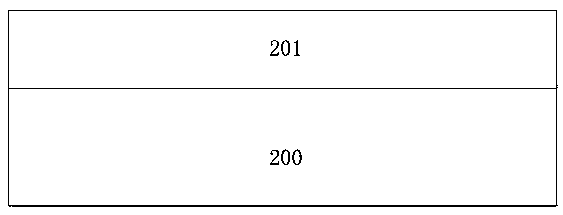

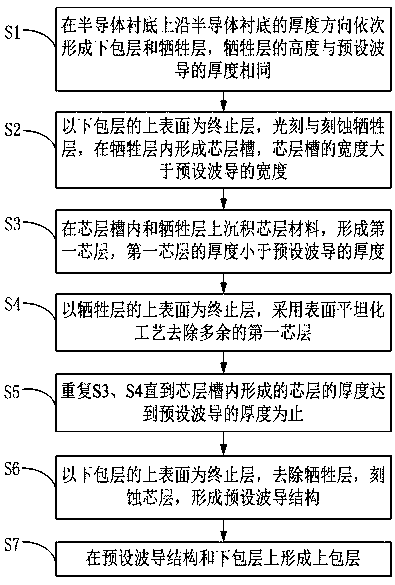

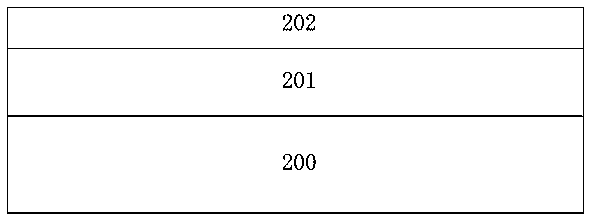

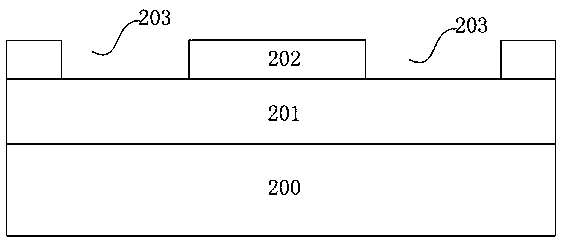

Groove-digging preparation method for thick-film silicon nitride waveguide

The invention discloses a groove-digging preparation method for a thick-film silicon nitride waveguide. The preparation method comprises the following steps: forming a lower cladding on a semiconductor substrate in a thickness direction of the semiconductor substrate; photoetching and etching the lower cladding, and forming a core layer groove in the lower cladding, wherein the core layer groove is wider than a preset waveguide; depositing a core layer material in the core layer groove and on the lower cladding, thus forming a first core layer, wherein the first core layer is thinner than thepreset waveguide; taking the upper surface of the lower cladding as a stop layer, and removing redundant first core layer by adopting a surface planarization technology; repeating the steps until thethickness of the core layer formed in the core layer groove reaches the thickness of the preset waveguide; photoetching and etching the core layer, thus forming a preset waveguide structure; and forming an upper cladding on the preset waveguide structure and the lower cladding. The scheme of the invention solves a high stress problem caused by a thin film which is too thick; meanwhile, shape of the waveguide is optimized, roughness of the side wall is reduced, steep degree of the waveguide is increased, and loss of the waveguide is reduced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

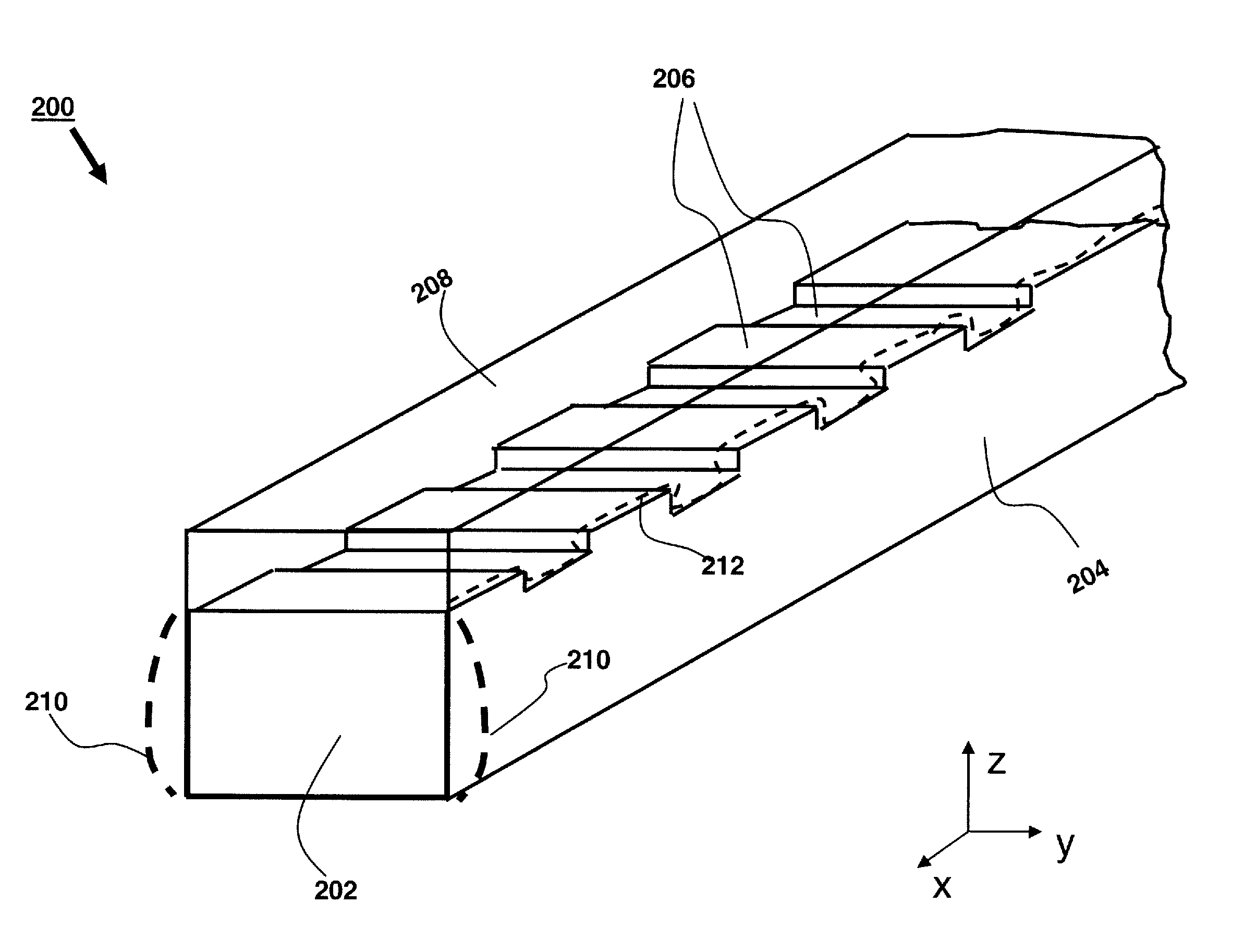

Waveguide device and method for making same

ActiveUS7256667B1Improve welfarePhotomechanical apparatusSemiconductor/solid-state device manufacturingOptical frequenciesWave shape

A monolithic micromachined waveguide device or devices with low-loss, high-power handling, and near-optical frequency ranges is set forth. The waveguide and integrated devices are capable of transmitting near-optical frequencies due to optical-quality sidewall roughness. The device or devices are fabricated in parallel, may be mass produced using a LIGA manufacturing process, and may include a passive component such as a diplexer and / or an active capping layer capable of particularized signal processing of the waveforms propagated by the waveguide.

Owner:SANDIA NAT LAB

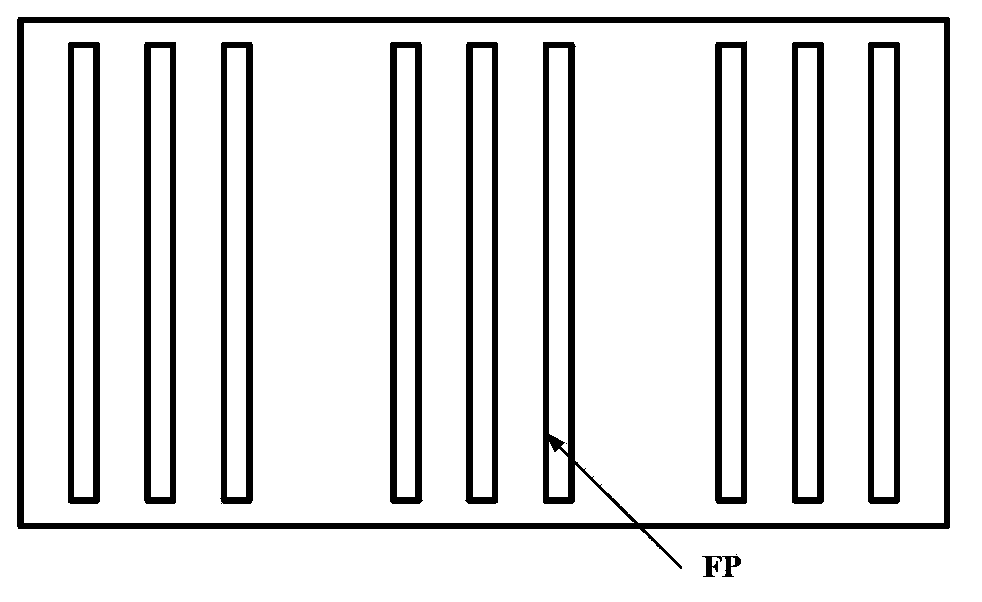

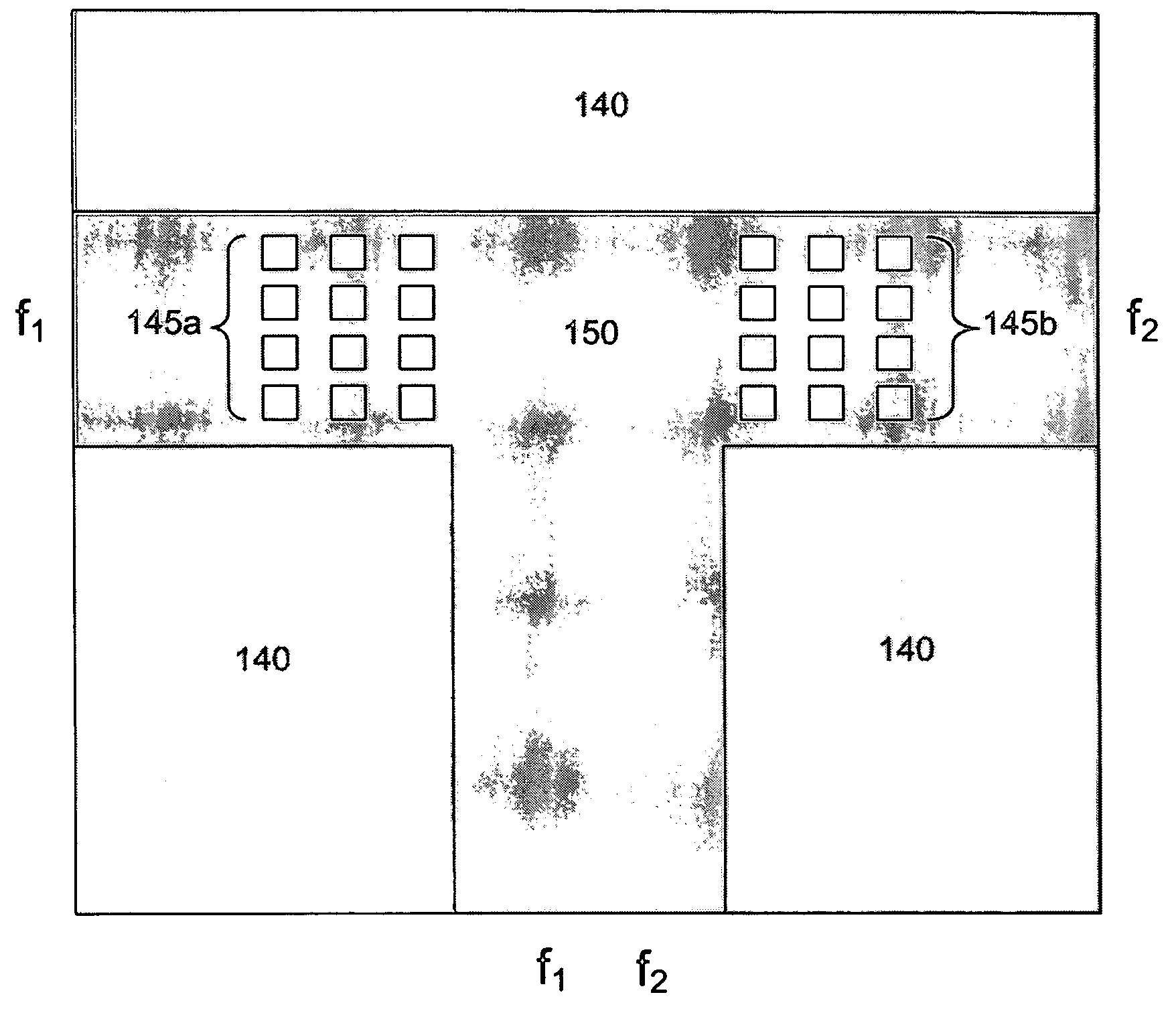

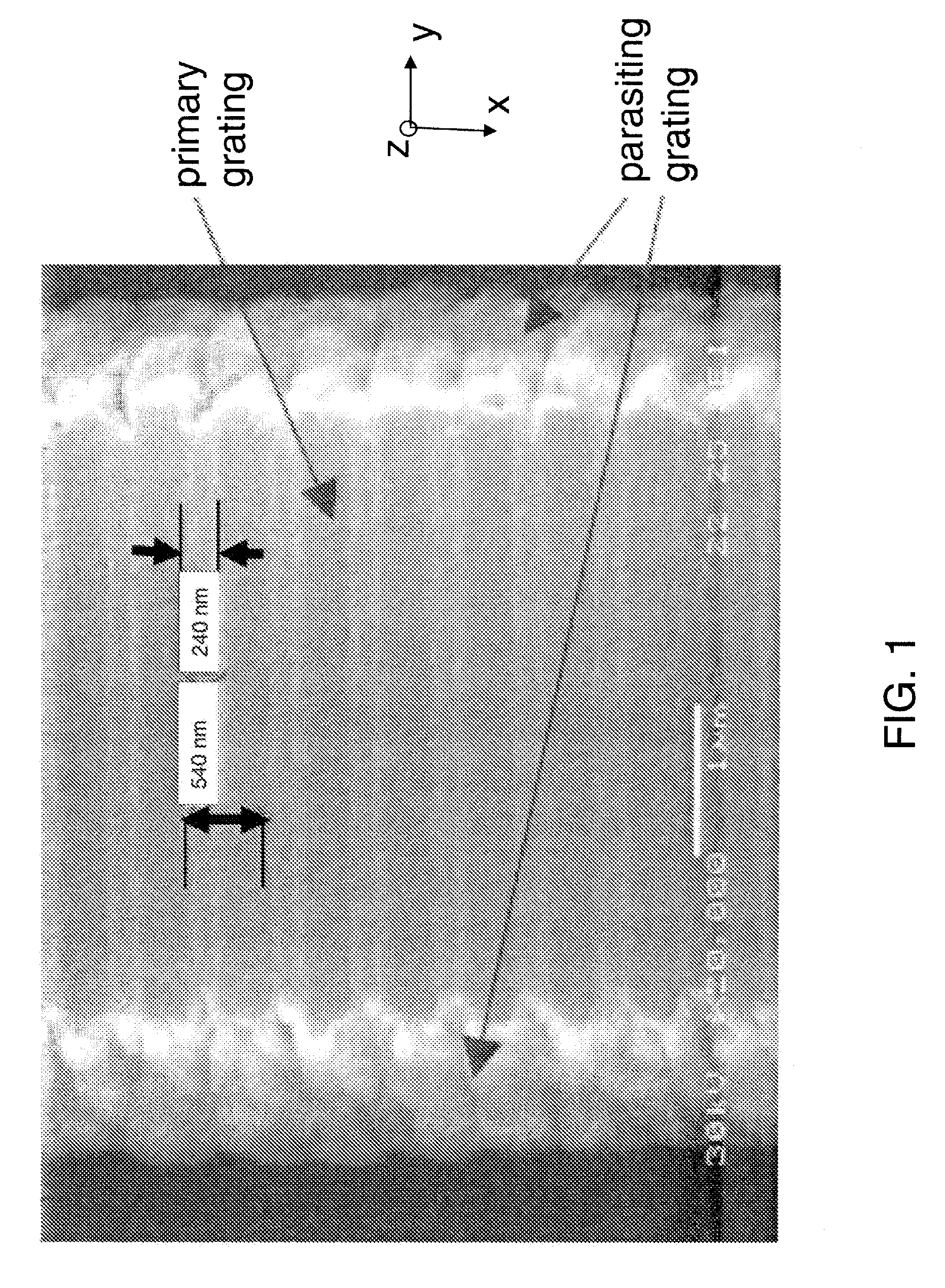

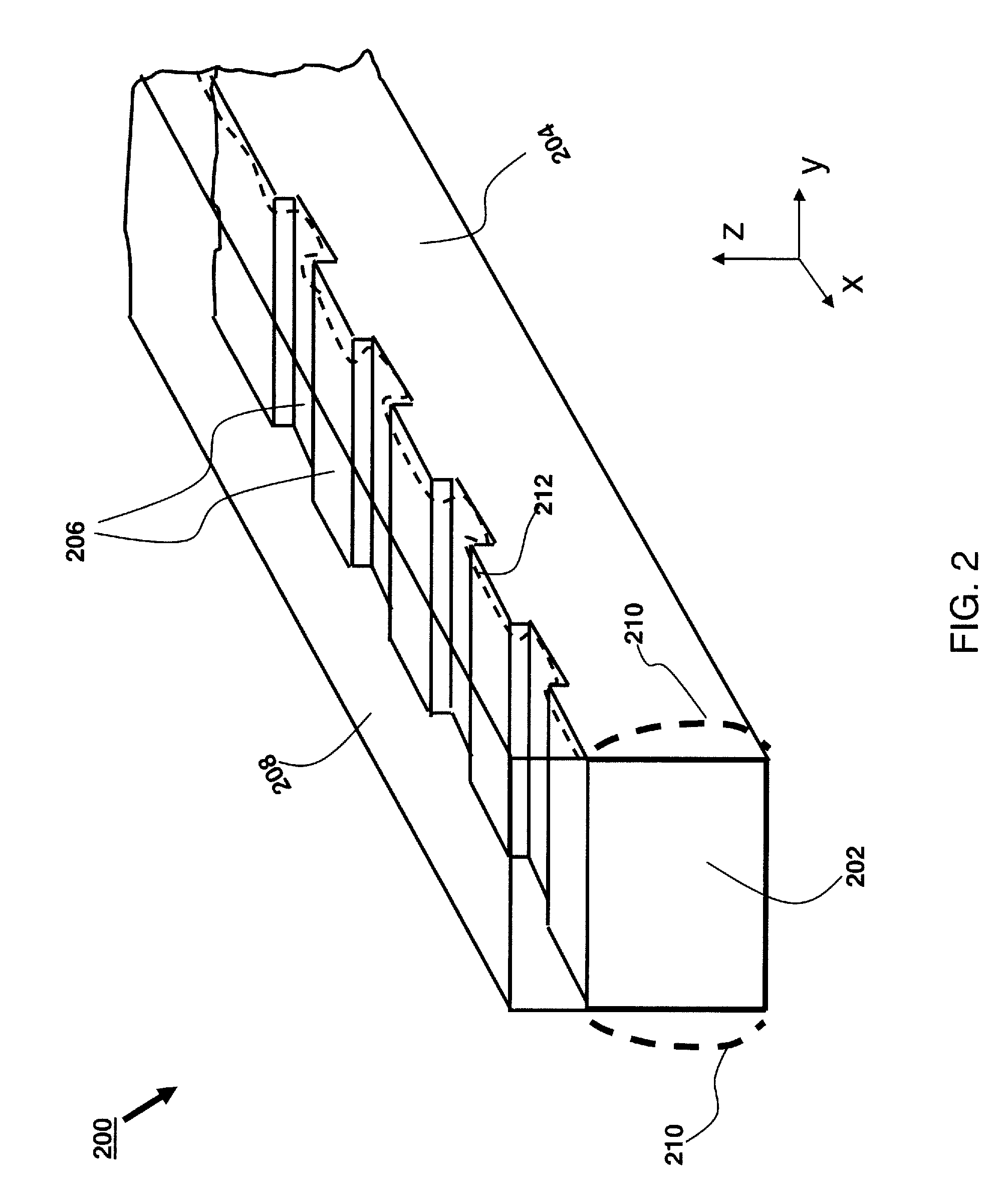

Device fabrication with planar bragg gratings suppressing parasitic effects

ActiveUS20100303411A1Suppressing unwanted parasitic grating effectsAvoid spreadingOptical articlesNanoopticsResistAnti-reflective coating

The present invention relates to various methods of fabricating Planar Bragg Gratings (PBG) in a doped waveguide in a Planar Lightwave Circuit (PLC) device, suppressing unwanted parasitic grating effects during fabrication of the device. One approach to reduce parasitic gratings is to use a hard mask before the waveguide photolithography and etch, that results in a steeper sidewall angle that reduces or eliminates the parasitic grating effect. Another method of reducing parasitic grating effect is to deposit a layer of developable Bottom Anti Reflective Coating (BARC) prior to depositing the photo resist for waveguide etch. A third method of resisting parasitic gratings comprises using a planarizing undoped silica layer as a barrier layer on top of the core. During subsequent high temperature annealing germanium outdiffuses laterally into the cladding. The net effect is an optical waveguide with improved lateral uniformity because germanium diffusion smoothes out the sidewall roughness created during the waveguide reactive ion etch process. The undoped silica (SiO2) layer on top of the grating also serves the purpose of significantly reducing germanium outdiffusion from the core in the upward direction.

Owner:OPTASENSE

Hybrid Strip-Loaded Electro-Optic Polymer/Sol-Gel Modulator

InactiveUS20100014800A1Improve extinctionReduced insertion lossOptical waveguide light guideNon-linear opticsHYDROSOLWaveguide

A hybrid strip-loaded EO polymer / sol-gel modulator in which the sol-gel core waveguide does not lie below the active EO polymer waveguide increases the higher electric field / optical field overlap factor Γ and reduces inter-electrode separation d thereby lowering the modulator's half-wave drive voltage Vπ, reducing insertion loss and improving extinction. The strip-loaded modulator comprises an EO polymer layer that eliminates optical scattering caused by sidewall roughness due to etching. Light does not encounter rough edges as it transitions to and from the sol-gel and EO polymer waveguides. This reduces insertion loss.

Owner:THE ARIZONA BOARD OF REGENTS ON BEHALF OF THE UNIV OF ARIZONA

Method for preparing thick film silicon nitride waveguide

ActiveCN110456450AReduce lossEasy to adjust the thicknessOptical waveguide light guideSidewall roughnessHigh stress

The invention discloses a method for preparing a thick film silicon nitride waveguide, comprising the steps of: sequentially forming a lower cladding layer and a sacrificial layer on a semiconductor substrate, wherein the height of the sacrificial layer is the same as the thickness of a preset waveguide; photoetching and etching the sacrificial layer to form a core layer groove by using an upper surface of the lower cladding layer as a termination layer, wherein the width of the core layer groove is greater than the width of the preset waveguide; depositing a core layer material in the core layer groove and on the sacrificial layer to form a first core layer; removing the excess first core layer by using a surface planarization process and by using the upper surface of the sacrificial layer as the termination layer; repeating the above step until the thickness of the core layer formed in the core layer groove reaches the thickness of the preset waveguide; removing the sacrificial layerand etching the core layer to form a preset waveguide structure by using the upper surface of the lower cladding layer as the termination layer; and forming an upper cladding layer on the preset waveguide structure on the lower cladding layer. By adopting the scheme, the high stress problem caused by the excess thickness of the thin film is solved, and the shape of the waveguide is optimized to reduce the sidewall roughness.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

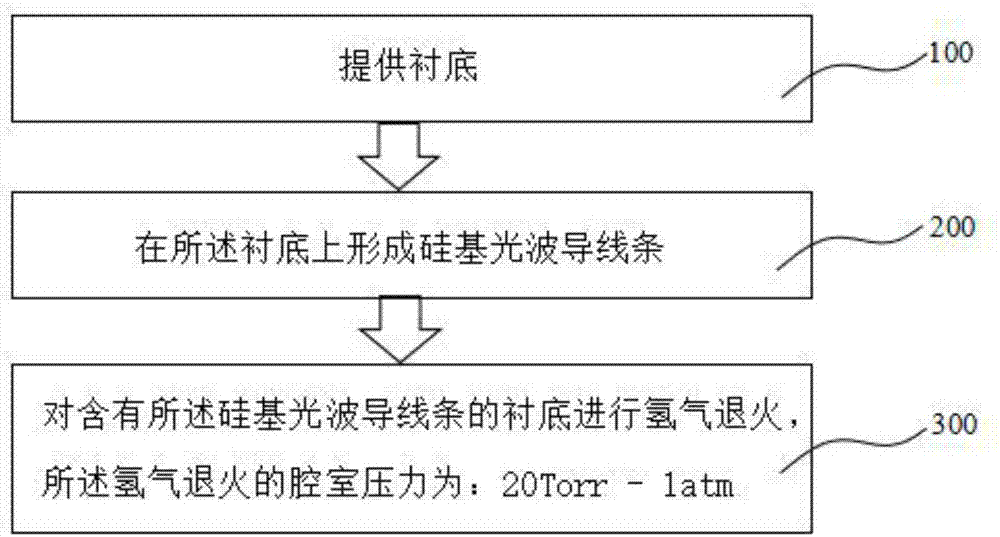

Method for reducing silicon-based optical waveguide sidewall roughness

ActiveCN107132617AReduced sidewall roughnessKeep shapeOptical waveguide light guideSidewall roughnessWaveguide

The invention belongs to the semiconductor integration technology field and discloses a method for reducing silicon-based optical waveguide sidewall roughness. The method for reducing the silicon-based optical waveguide sidewall roughness comprises steps of providing a substrate, forming a silicon-based optical waveguide line on the substrate, performing hydrogen annealing on the substrate containing the silicon-based optical waveguide line, wherein pressure of a chamber, on which hydrogen annealing is performed, is 20Torr-latmn. The method for reducing silicon-based optical waveguide sidewall roughness solves a problem that the silicon-based optical waveguide sidewall roughness is too big. The method of the invention is simple, can better maintain the features and sizes of the silicon-based optical waveguide lines and achieves a technical effect that the silicon-based optical waveguide sidewall roughness can be reduced under chamber pressure of 20Torr-latm.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Method for reducing roughness of photoresist during electron beam lithography

ActiveCN103676491AReduce roughnessReduce volatilitySemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusSidewall roughnessElectron-beam lithography

The invention discloses a method for reducing roughness of photoresist during electron beam lithography. The method comprises the steps of forming a structural material layer and a first hard mask layer on a substrate; forming a second hard mask layer on the first hard mask layer; forming an electron beam photoresist pattern on the second hard mask layer; etching the second hard mask layer to form a second hard mask pattern with the electron beam photoresist pattern as a mask; etching the first hard mask layer to form a first hard mask pattern with the second hard mask pattern as a mask; and etching the structural material layer to form a required line with the first hard mask pattern and the second hard mask pattern as masks. According to the method, multiple hard mask layers with different materials and multiple etching operations are adopted, and the roughness of the side wall of the electron-beam photoresist is prevented from being transmitted to the lower structural material layer, so that the line roughness is effectively reduced, the process stability is improved and the fluctuations of device performance are reduced.

Owner:SOI MICRO CO LTD

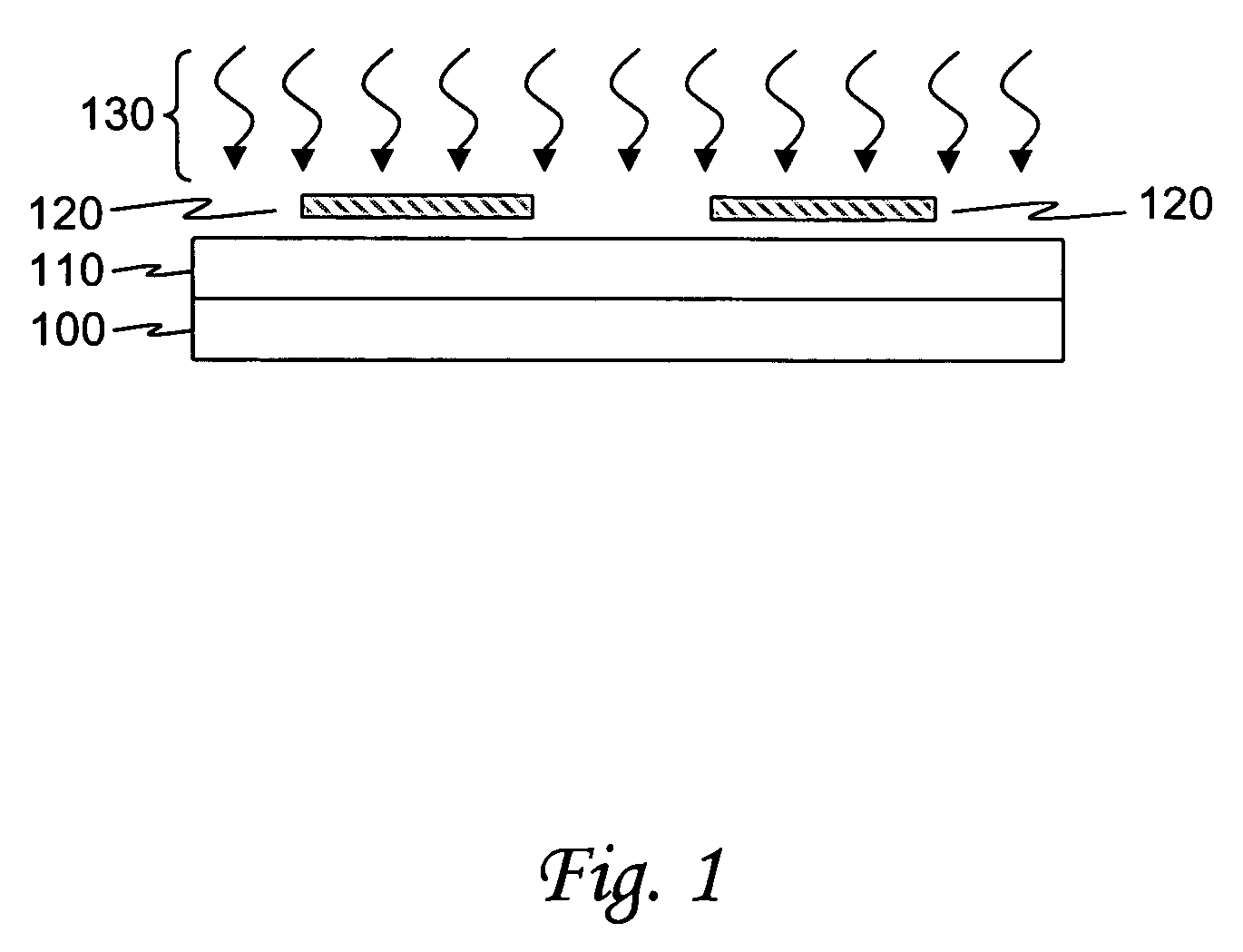

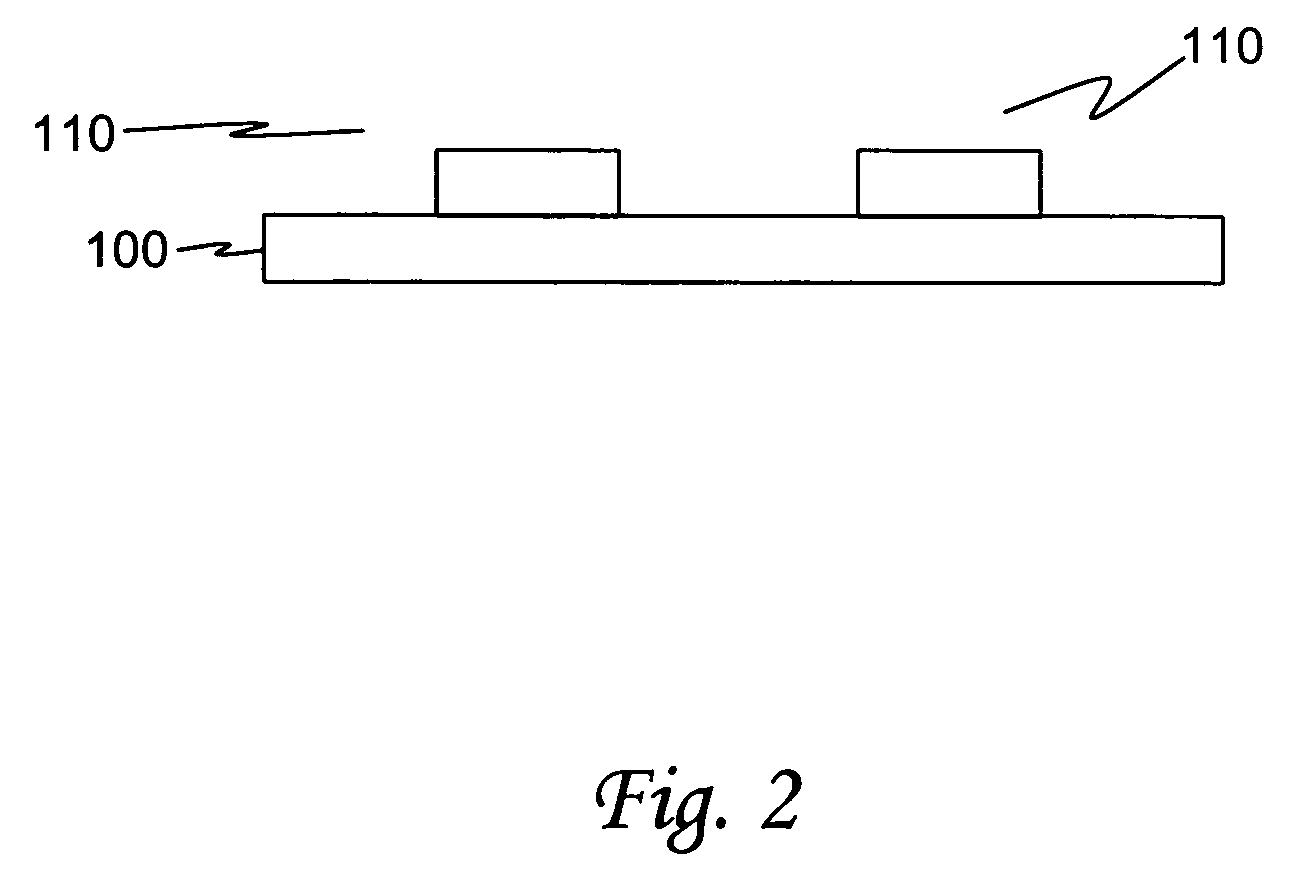

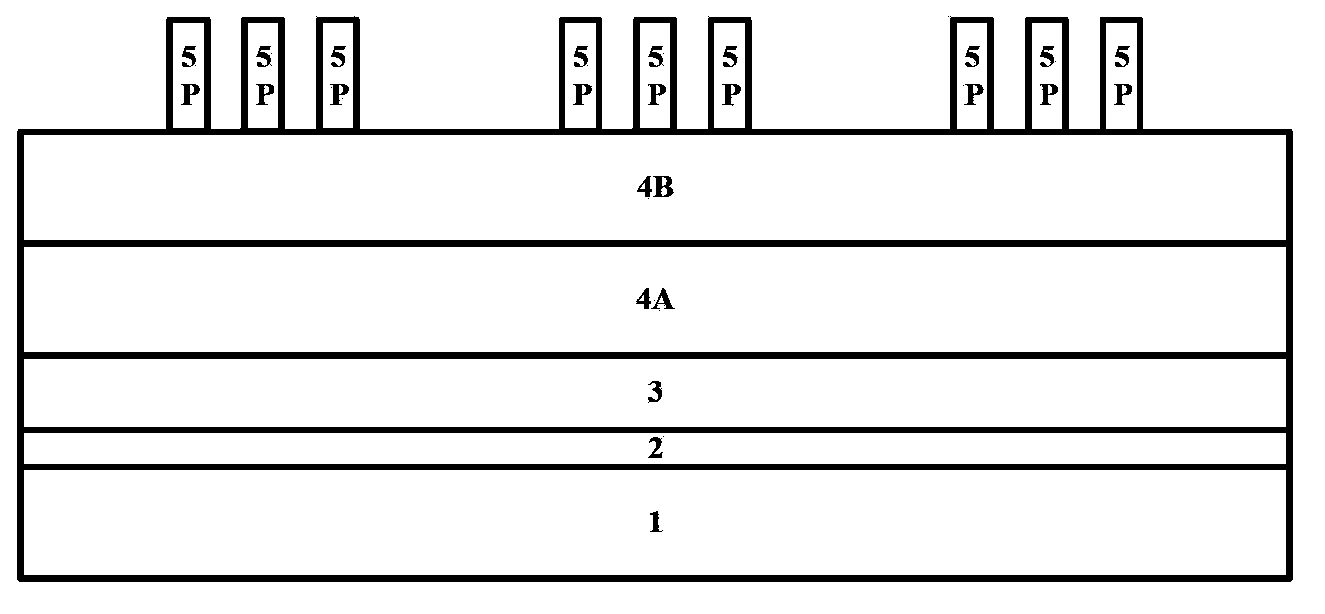

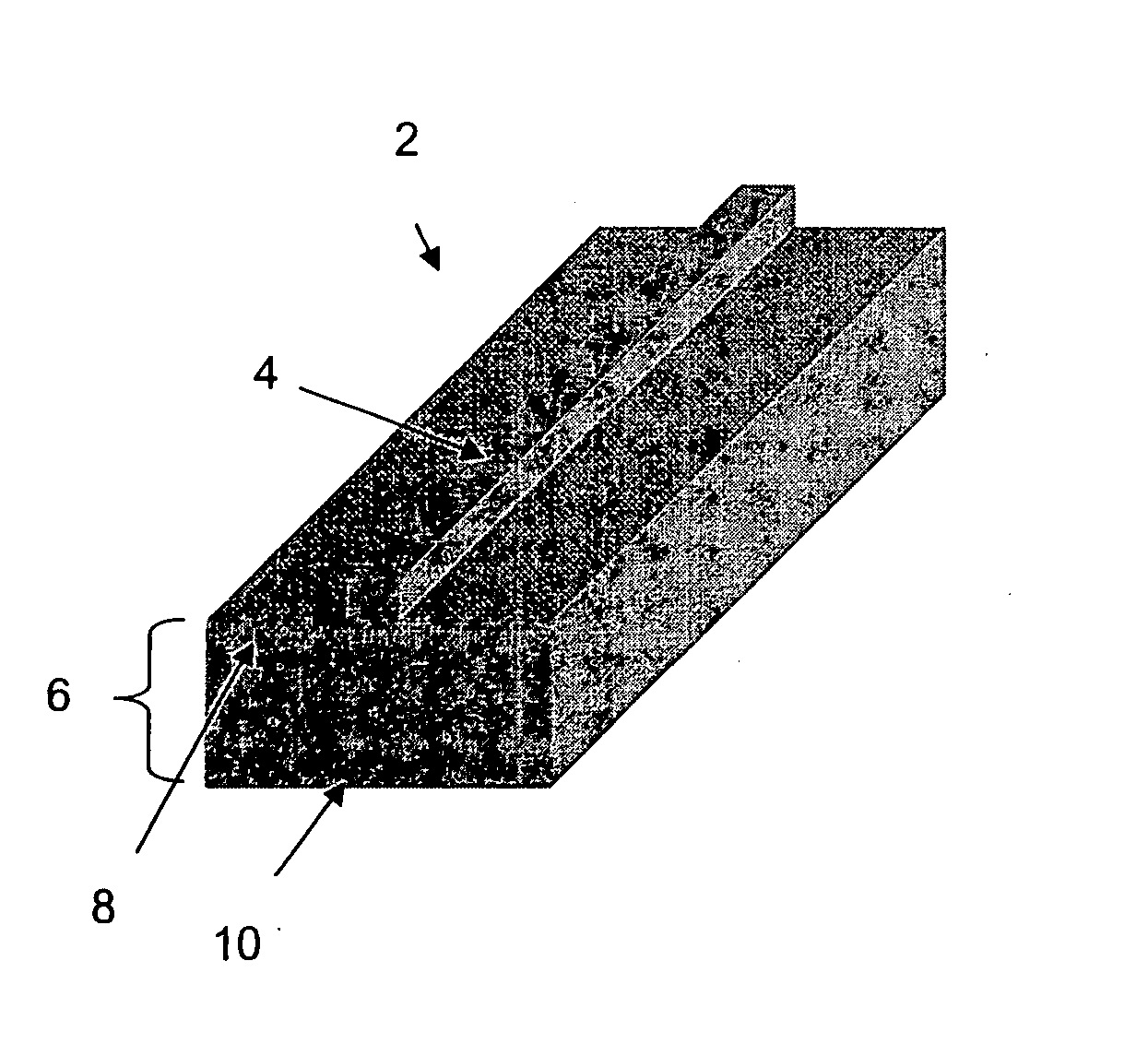

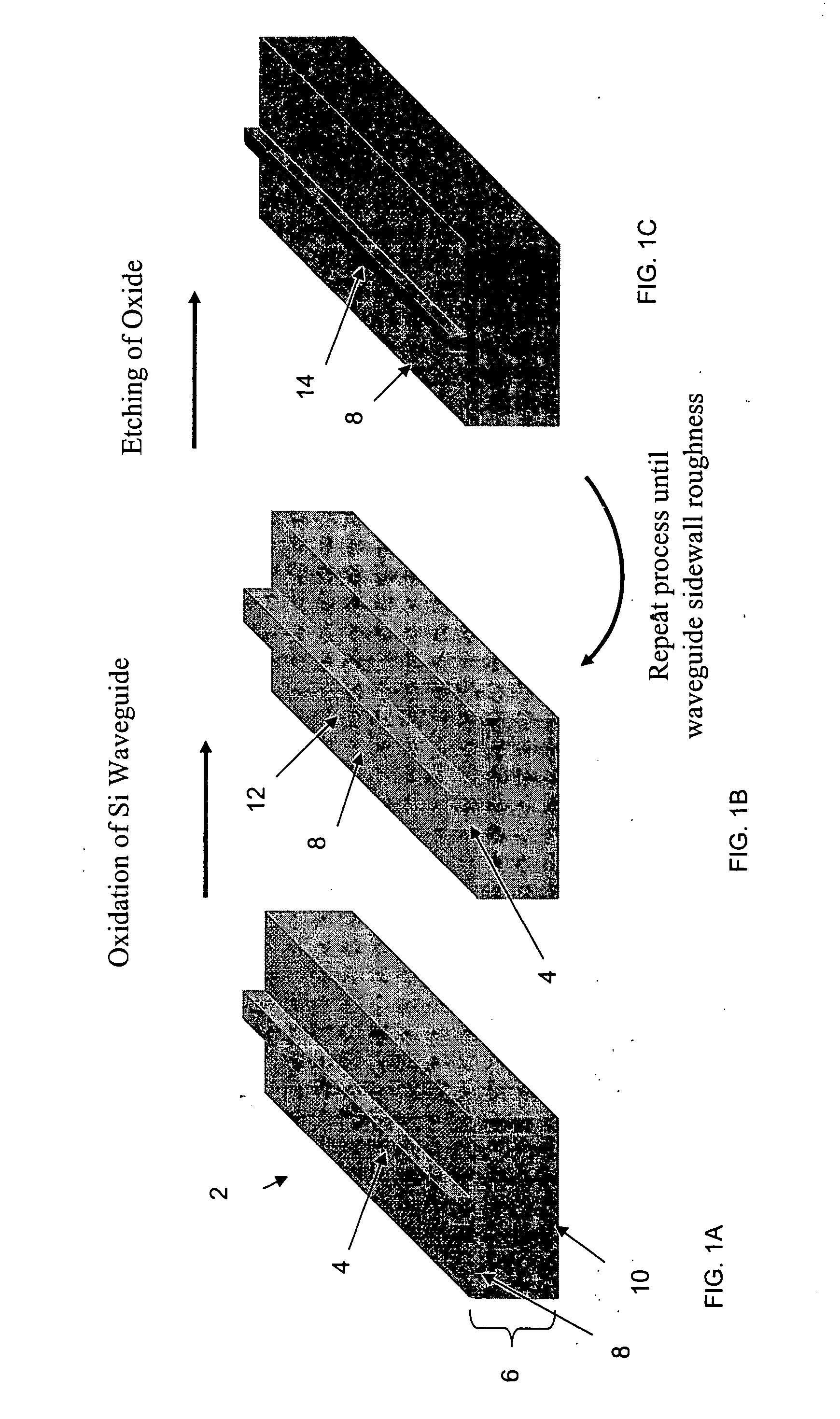

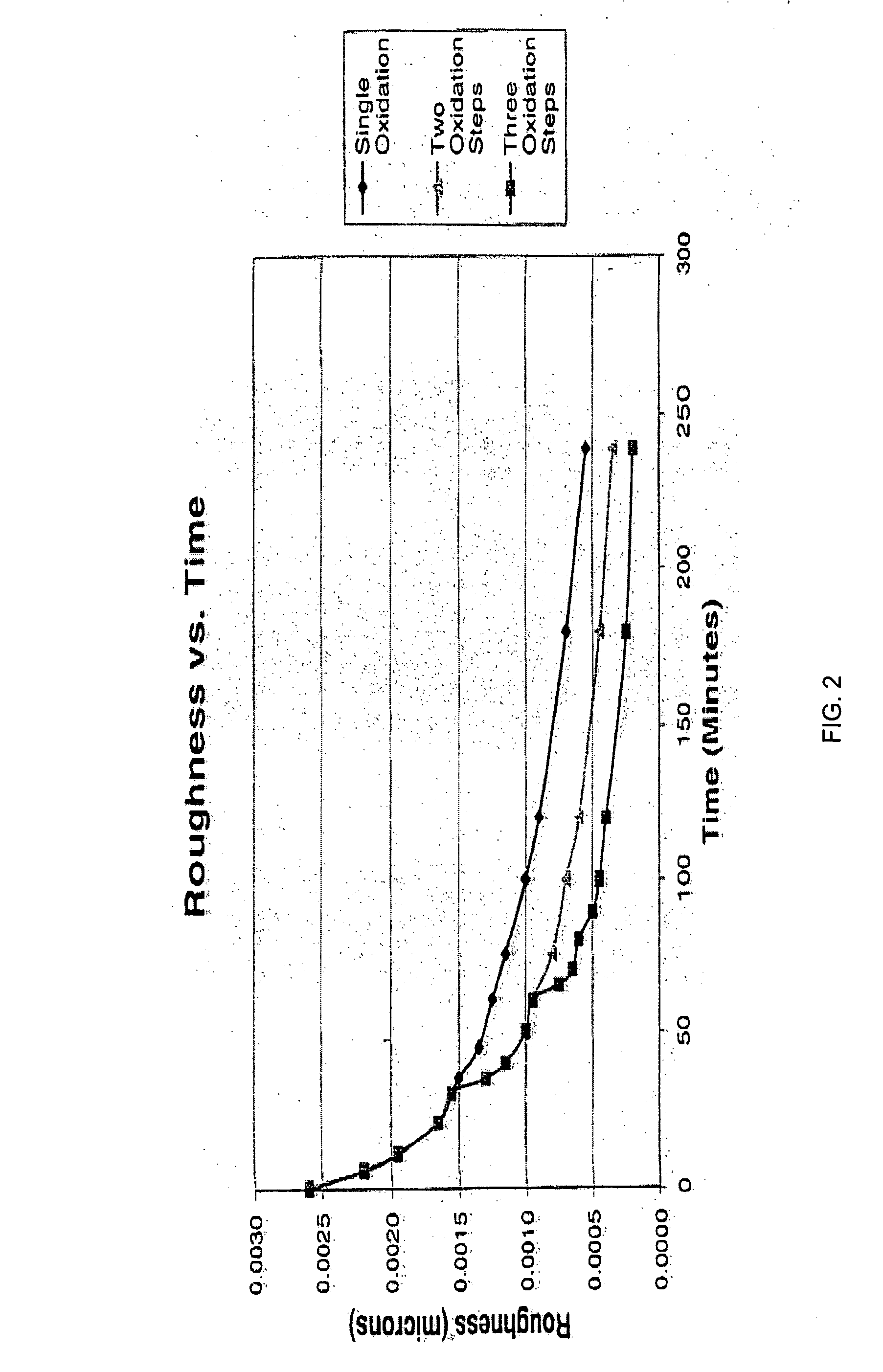

Multiple oxidation smoothing method for reducing silicon waveguide roughness

ActiveUS20050013575A1Reducing waveguide roughnessImprove transfer rateSemiconductor/solid-state device manufacturingOptical waveguide light guideDiffusionLight guide

The light-guiding structure includes a waveguide structure that comprises a substrate and a low refractive index underclad material. The waveguide structure is oxidized to form an oxidized layer on a surface of the waveguide structure. The oxidized layer is isotropically etched after the reaction-limited oxidation regime is approaching the diffusion-limited regime and repeatedly oxidized and etched so that the waveguide structure is continuously oxidized in the reaction-limited regime, reducing the overall time of oxidation and volume of oxidized material so that the waveguide structure has its sidewall roughness reduced efficiently enabling high transmission rates of guided light.

Owner:MASSACHUSETTS INST OF TECH

Fine line preparation method

ActiveCN103779190AReduce roughnessReduce volatilitySemiconductor/solid-state device manufacturingOriginals for photomechanical treatmentFine lineSidewall roughness

The invention discloses a fine line preparation method which comprises the steps of forming a structural material layer and hard mask layers on a substrate, forming electron beam photoresist on the hard mask layers and performing electron beam exposure to form an electron beam photoresist pattern, carrying out etching with the use of the electron beam photoresist pattern as a mask to form a hard mask pattern, and etching the structural material layer with the use of the hard mask pattern as a mask to form a needed fine line. According to the method of the invention, a plurality of hard mask layers of different materials are adopted and etching reaction conditions are reasonably adjusted, the roughness of the side wall of the electron beam photoresist is prevented from being transferred to the lower structural material layer, the line roughness is effectively reduced, the process stability is improved, and the fluctuation of device performance is reduced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Device fabrication with planar bragg gratings suppressing parasitic effects

ActiveUS8358889B2Suppressing unwanted parasitic grating effectsAvoid spreadingOptical articlesNanoopticsResistAnti-reflective coating

Owner:OPTASENSE

Nitrogen-containing organic compound, resist composition and patterning process

ActiveUS20050095533A1High resolutionMinimized roughnessOrganic chemistryPhotosensitive materialsResistImage resolution

Resist compositions comprising nitrogen-containing organic compounds having a benzimidazole structure and a specific ether chain moiety have an excellent resolution, form precisely configured patterns with minimized roughness of sidewalls and are useful in microfabrication using electron beams or deep-UV light.

Owner:SHIN ETSU CHEM IND CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com