Photolithography method capable of reducing line roughness

A roughness and line technology, applied in the field of semiconductor integrated circuit manufacturing, can solve the problems of unobtainable lines, insufficient height, loss, etc., and achieve the effect of reducing roughness, improving stability, and reducing fluctuations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

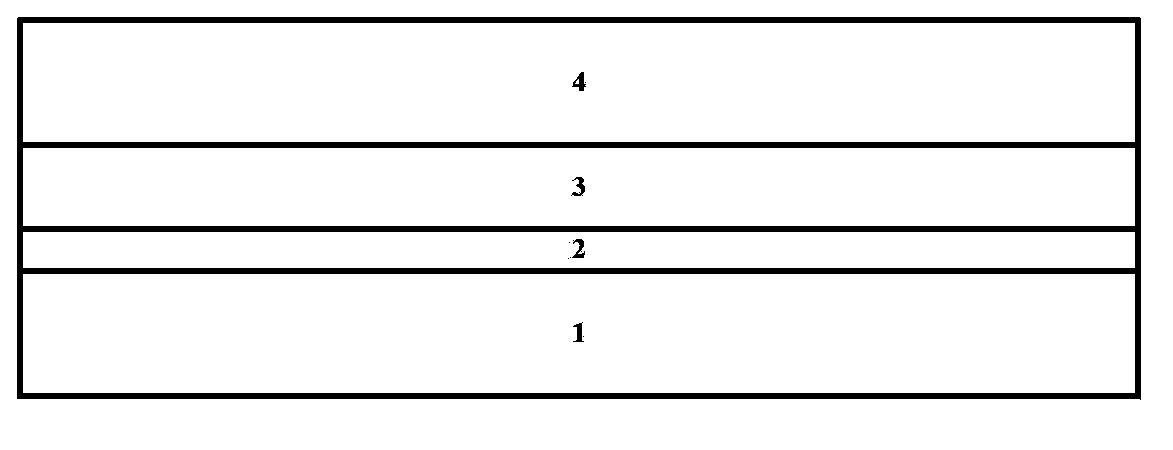

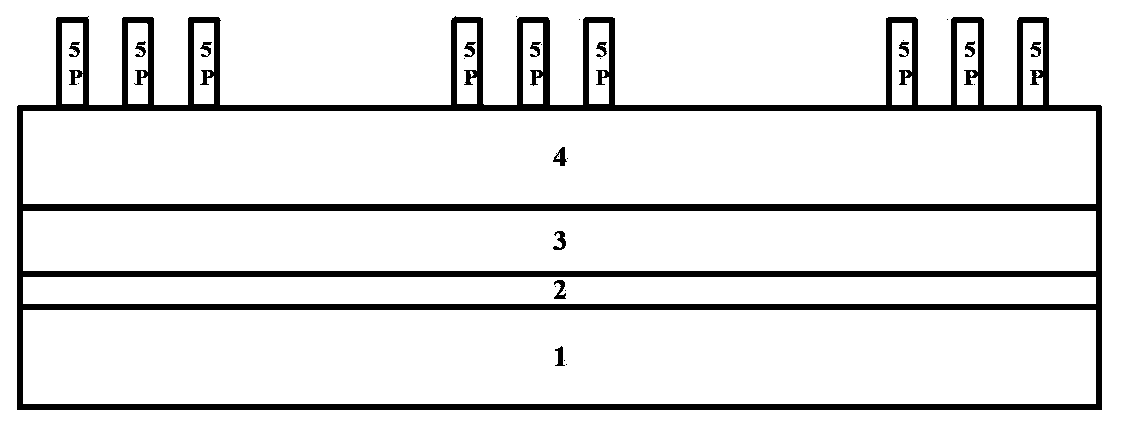

[0020] The features and technical effects of the technical solution of the present invention will be described in detail below with reference to the accompanying drawings and in combination with exemplary embodiments. It should be pointed out that similar reference numerals represent similar structures, and the terms "first", "second", "upper", "lower", "thick", "thin" and the like used in this application can be used for Modify various device structures. These modifications do not imply a spatial, sequential or hierarchical relationship of the modified device structures unless specifically stated.

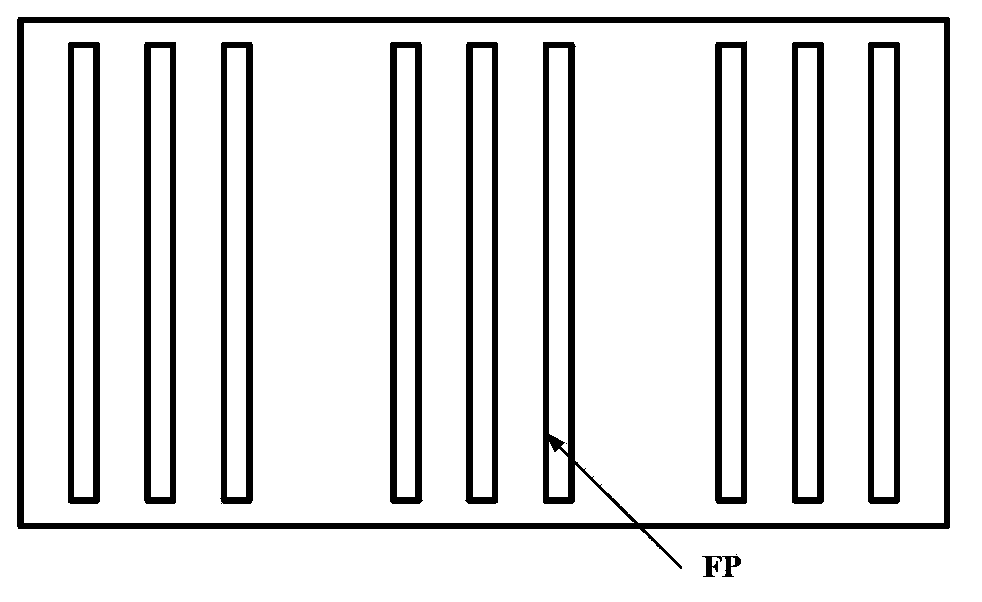

[0021] Reference attached figure 1 , shows a schematic diagram of an e-beam lithography layout for small linewidth features such as gate electrode layers, local interconnect layers, etc. In the present invention, the fine pattern FP is defined as a pattern that is beyond the capability of ordinary optical exposure and needs to be exposed by electron beams, and lines with a patte...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com