Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

39 results about "Hot holes" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Nonvolatile semiconductor memory device

ActiveUS6972997B2Improve performanceImprove reliabilityTransistorSolid-state devicesElectron flowImpact ionization

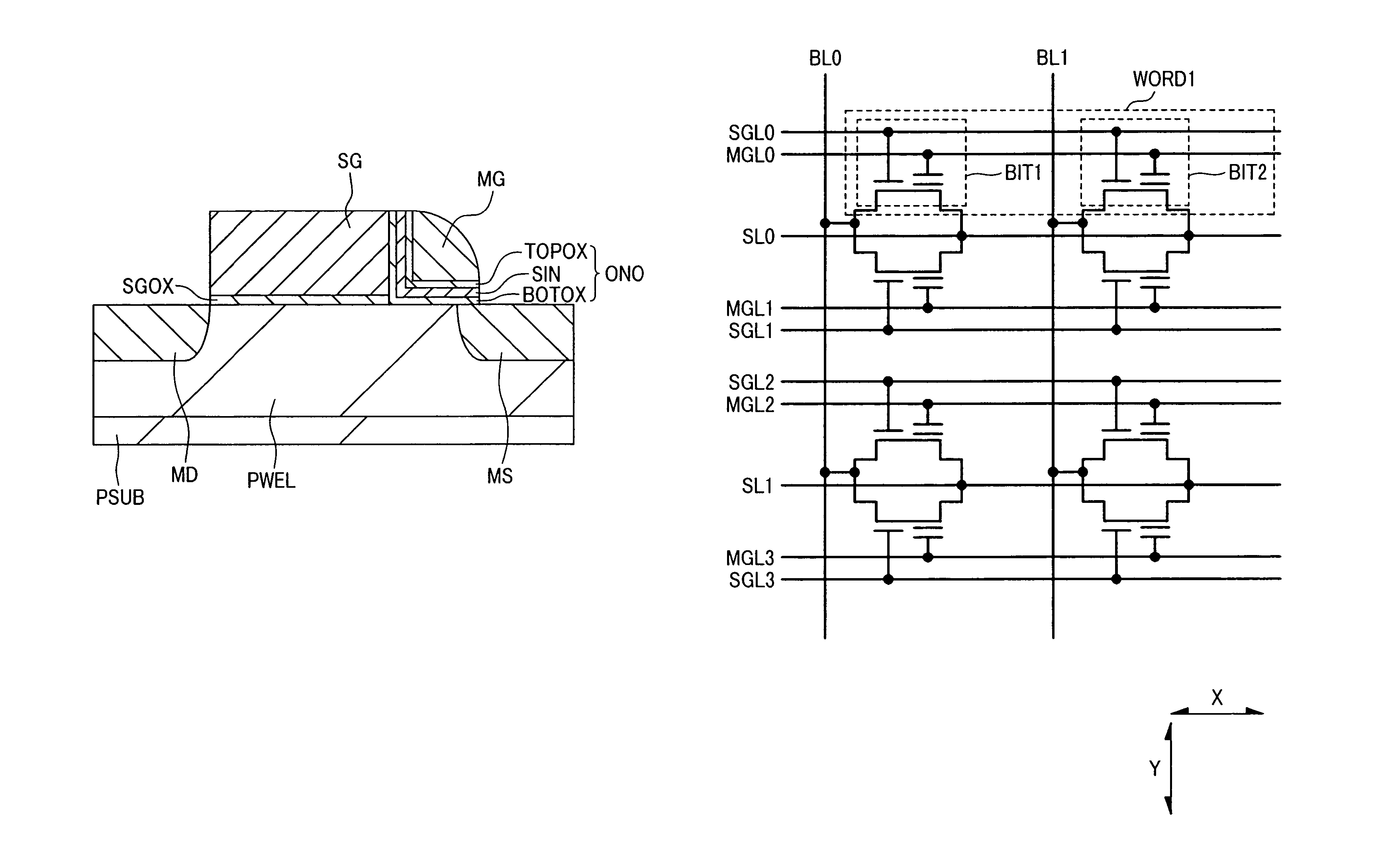

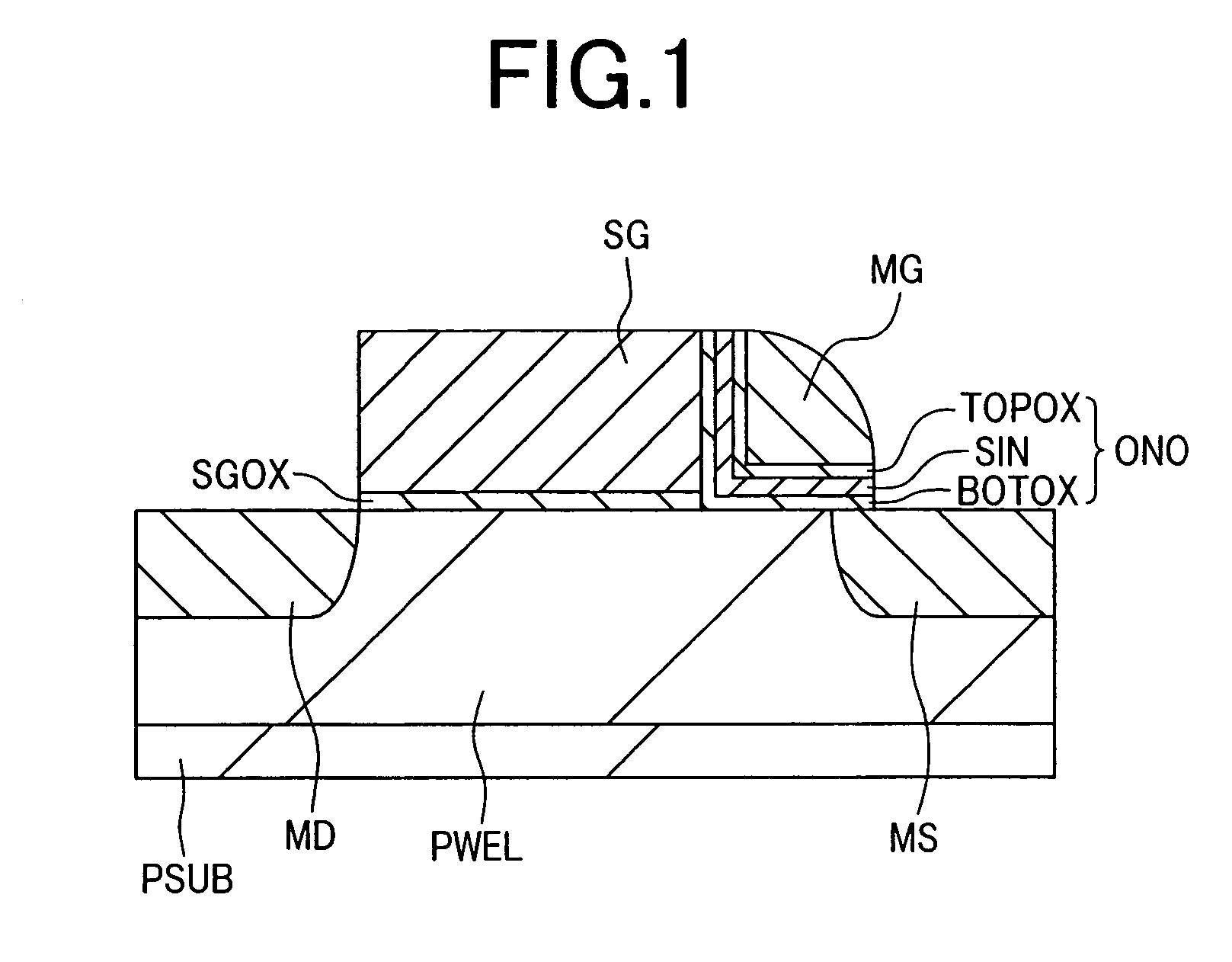

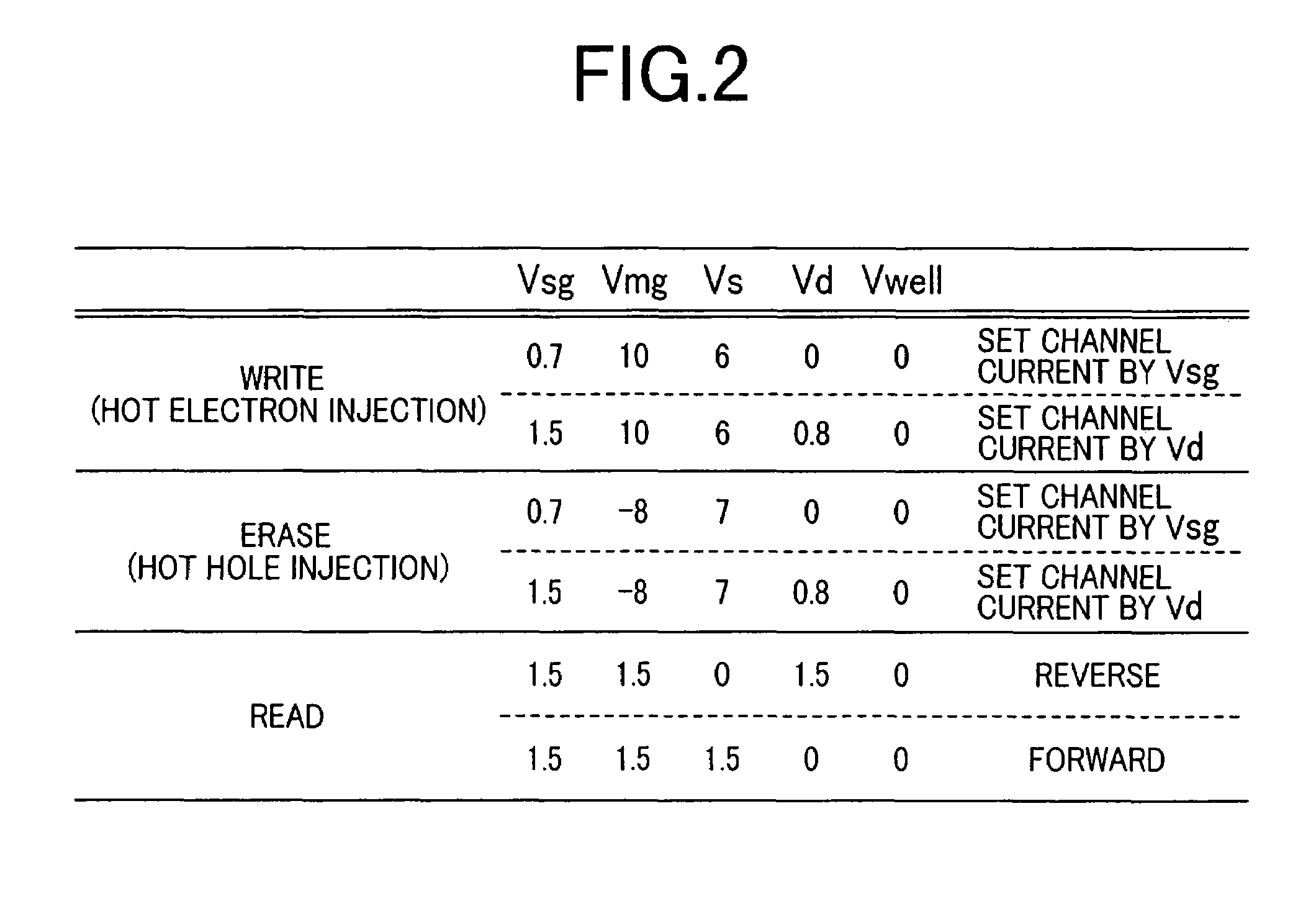

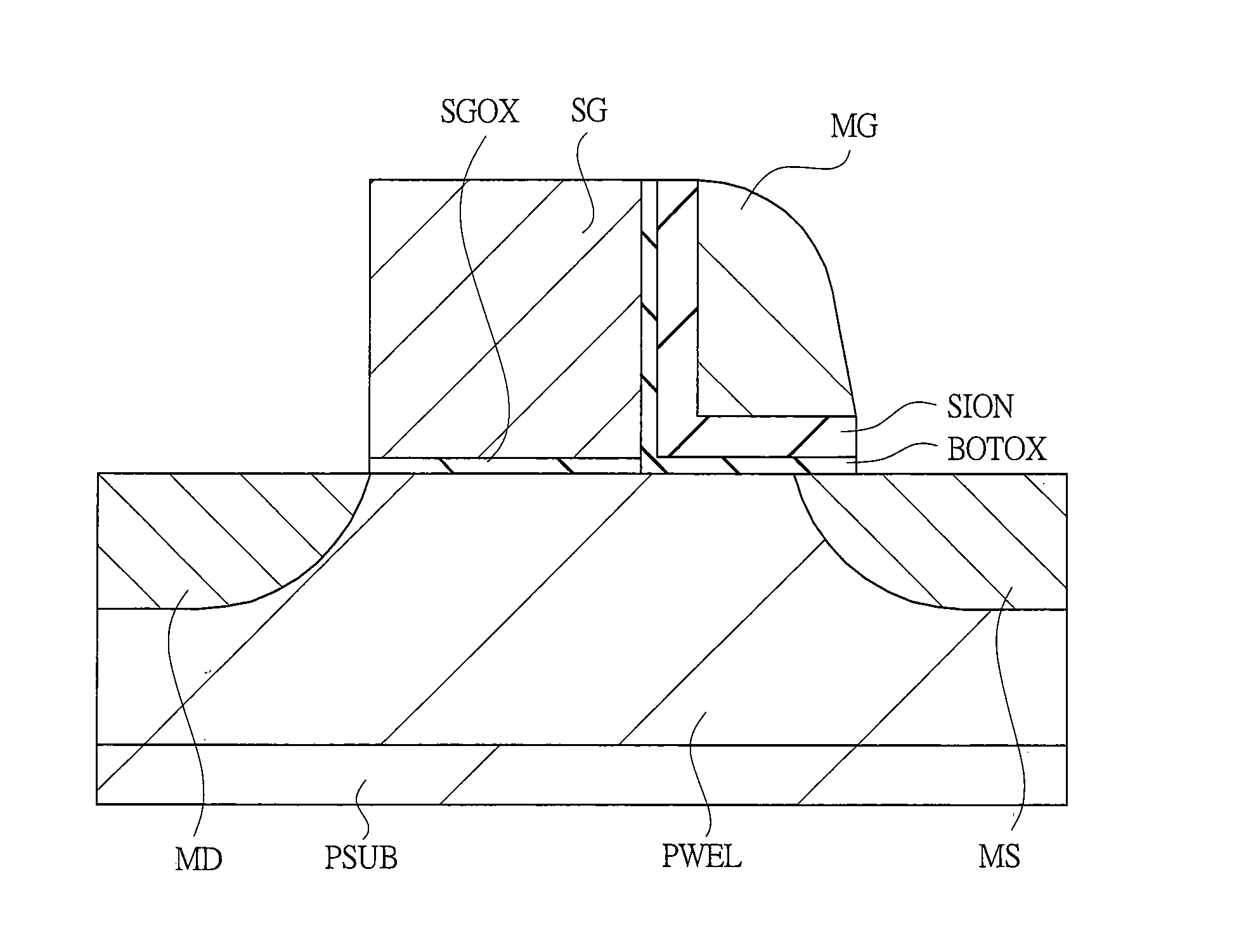

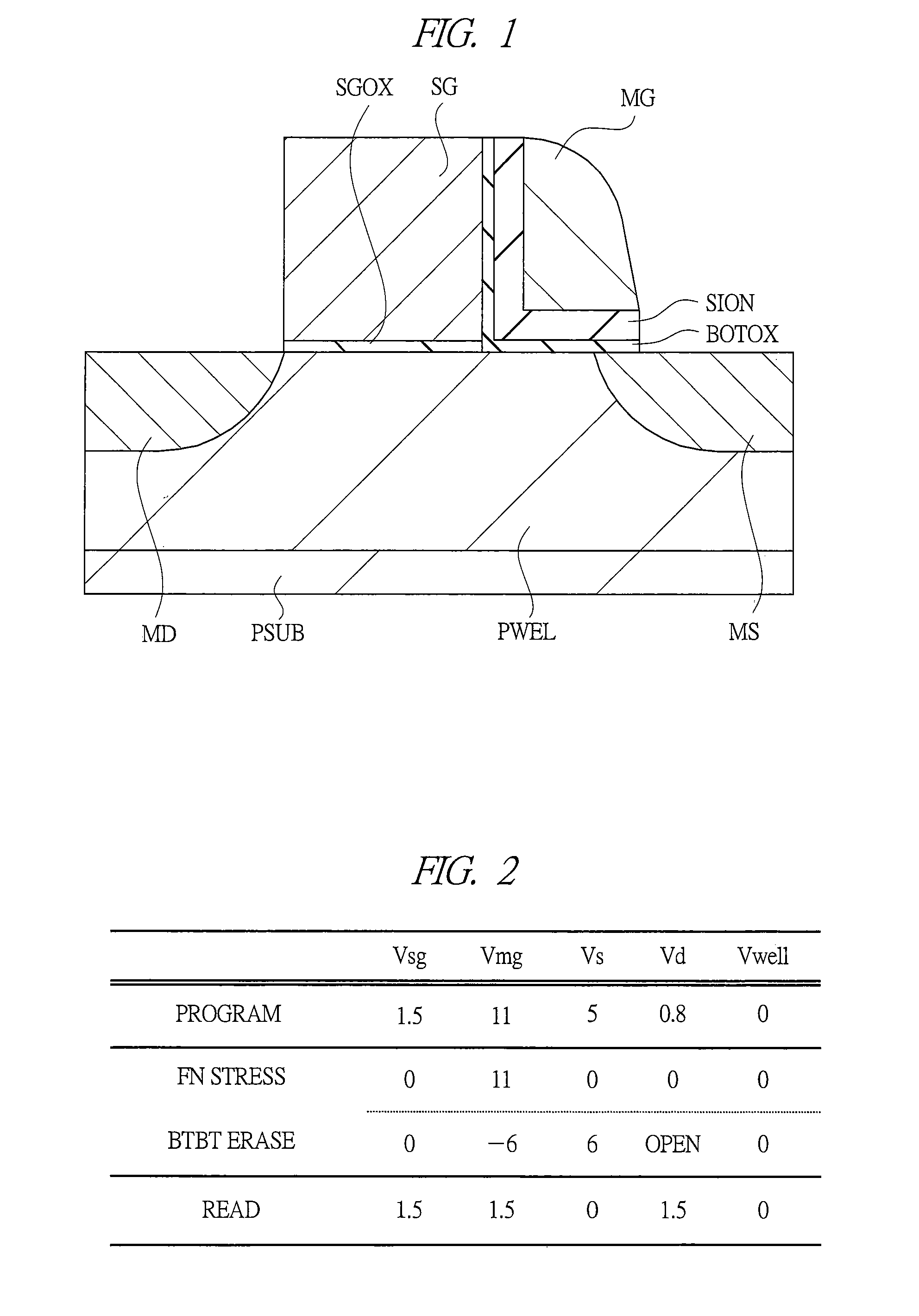

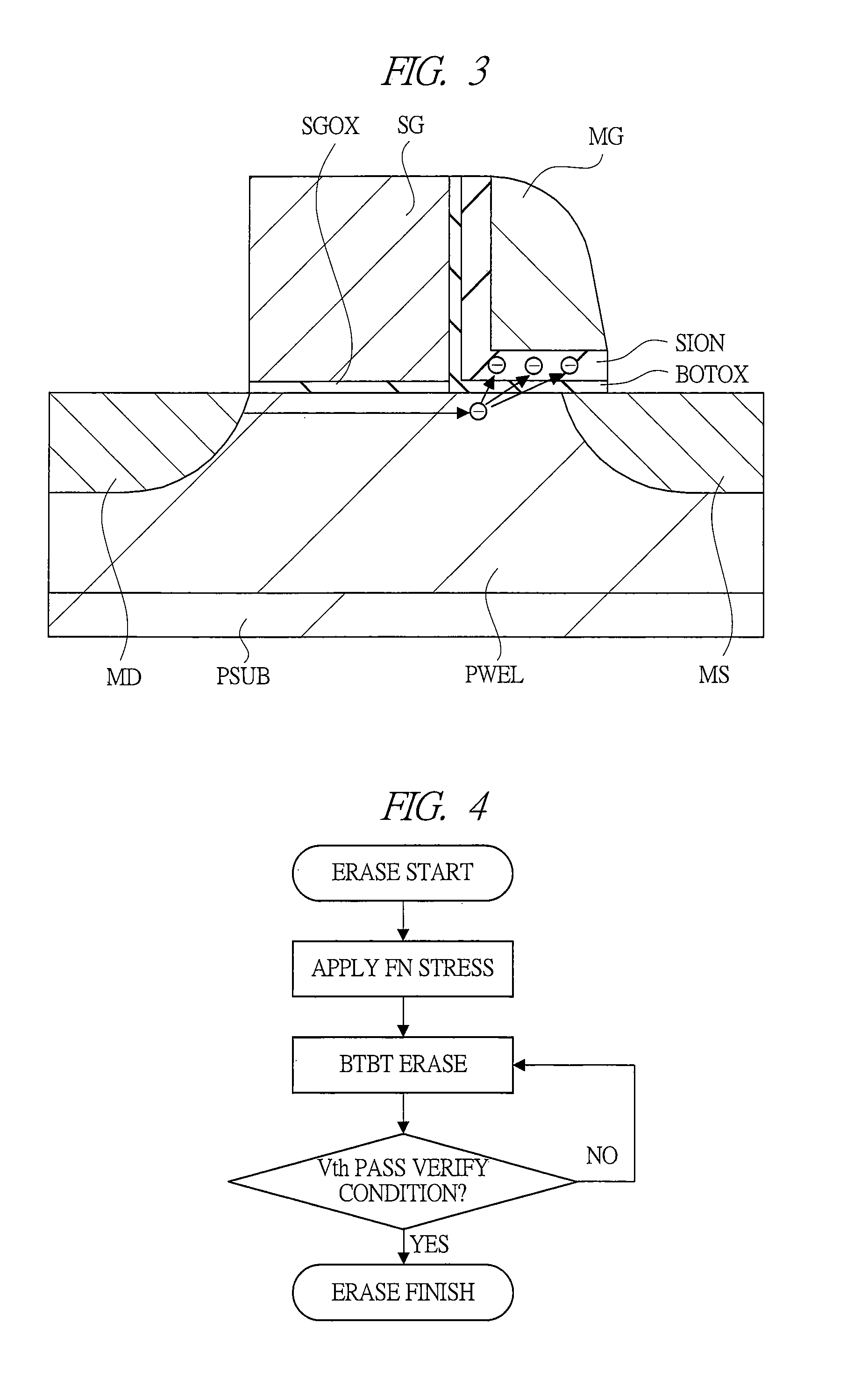

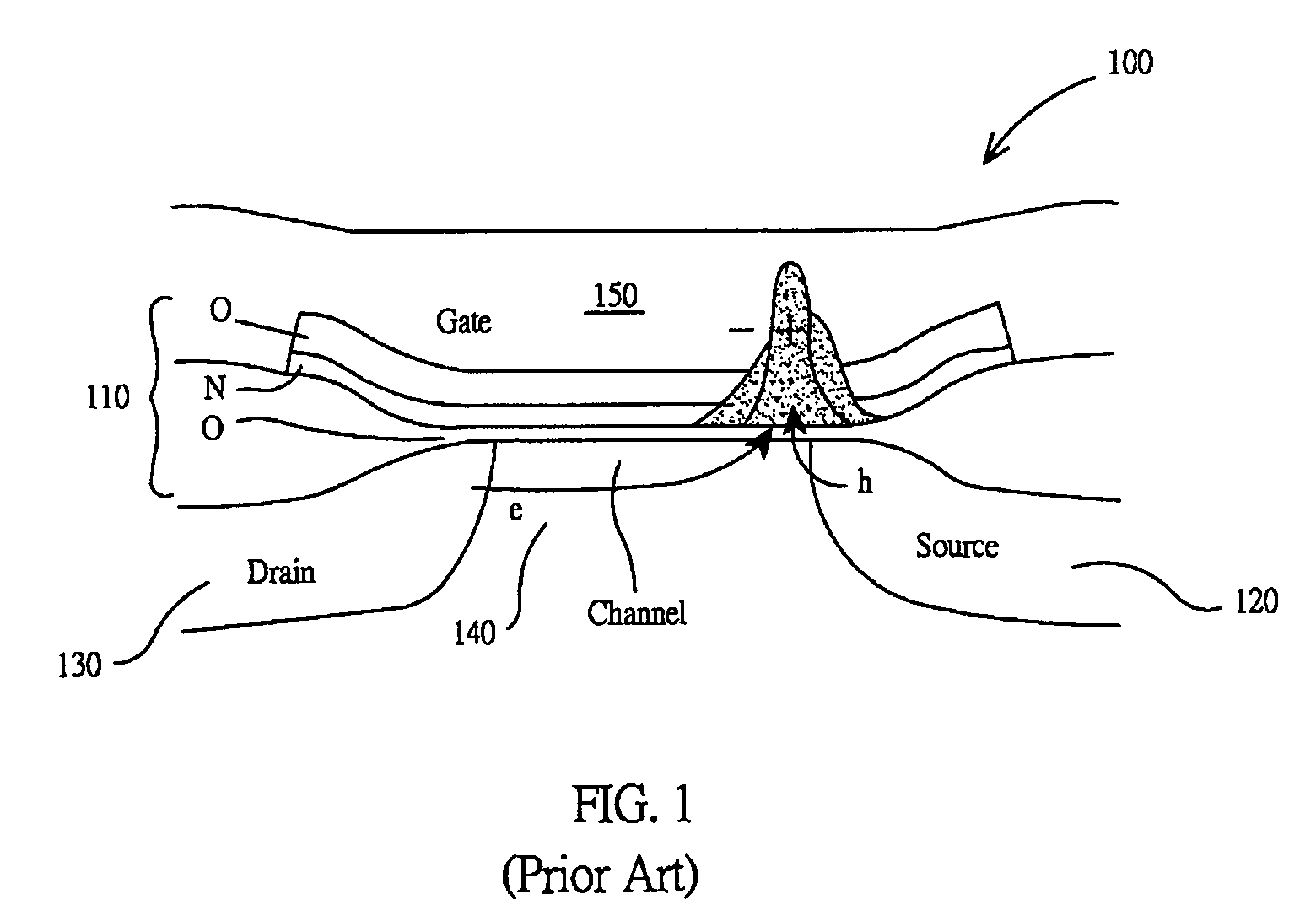

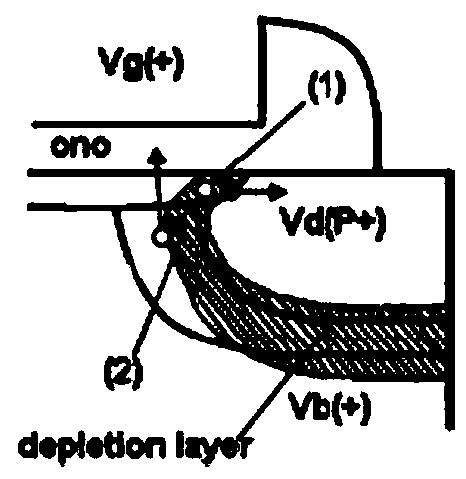

Characteristics of a nonvolatile semiconductor memory device are improved. The memory cell comprises: an ONO film constituted by a silicon nitride film SIN for accumulating charge and by oxide films BOTOX and TOPOX disposed thereon and thereunder; a memory gate electrode MG disposed at an upper portion thereof; a select gate electrode SG disposed at a side portion thereof through the ONO film; a gate oxide film SGOX disposed thereunder. By applying a potential to a select gate electrode SG of a memory cell having a source region MS and a drain region MD and to the source region MS and by accelerating electrons flowing in a channel through a high electric field produced between a channel end of the select transistor and an end of an n-type doped region ME disposed under the memory gate electrode MG, hot holes are generated by impact ionization, and the hot holes are injected into a silicon nitride film SIN by a negative potential applied to the memory gate electrode MG, and thereby an erase operation is performed.

Owner:TESSERA ADVANCED TECH

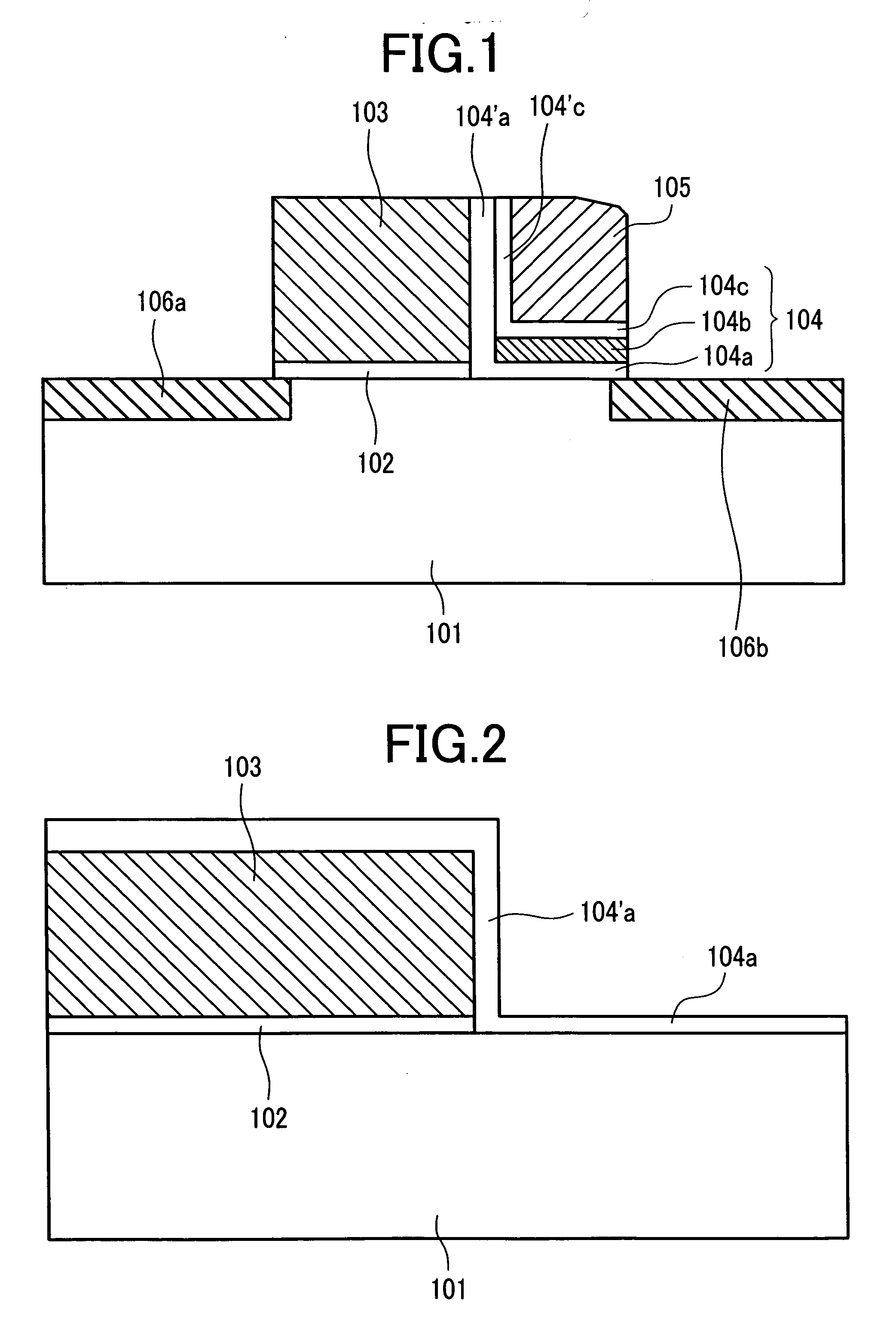

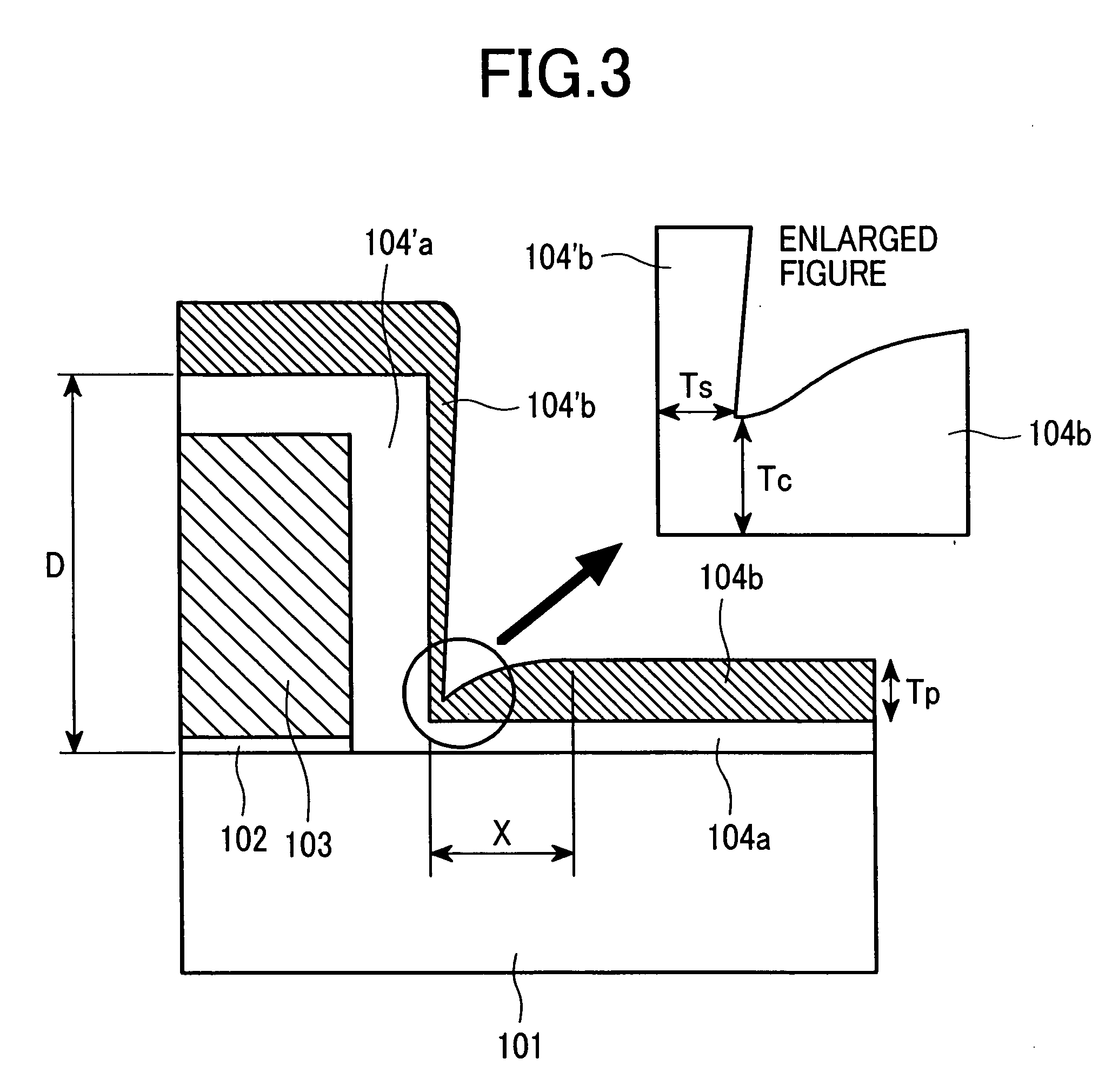

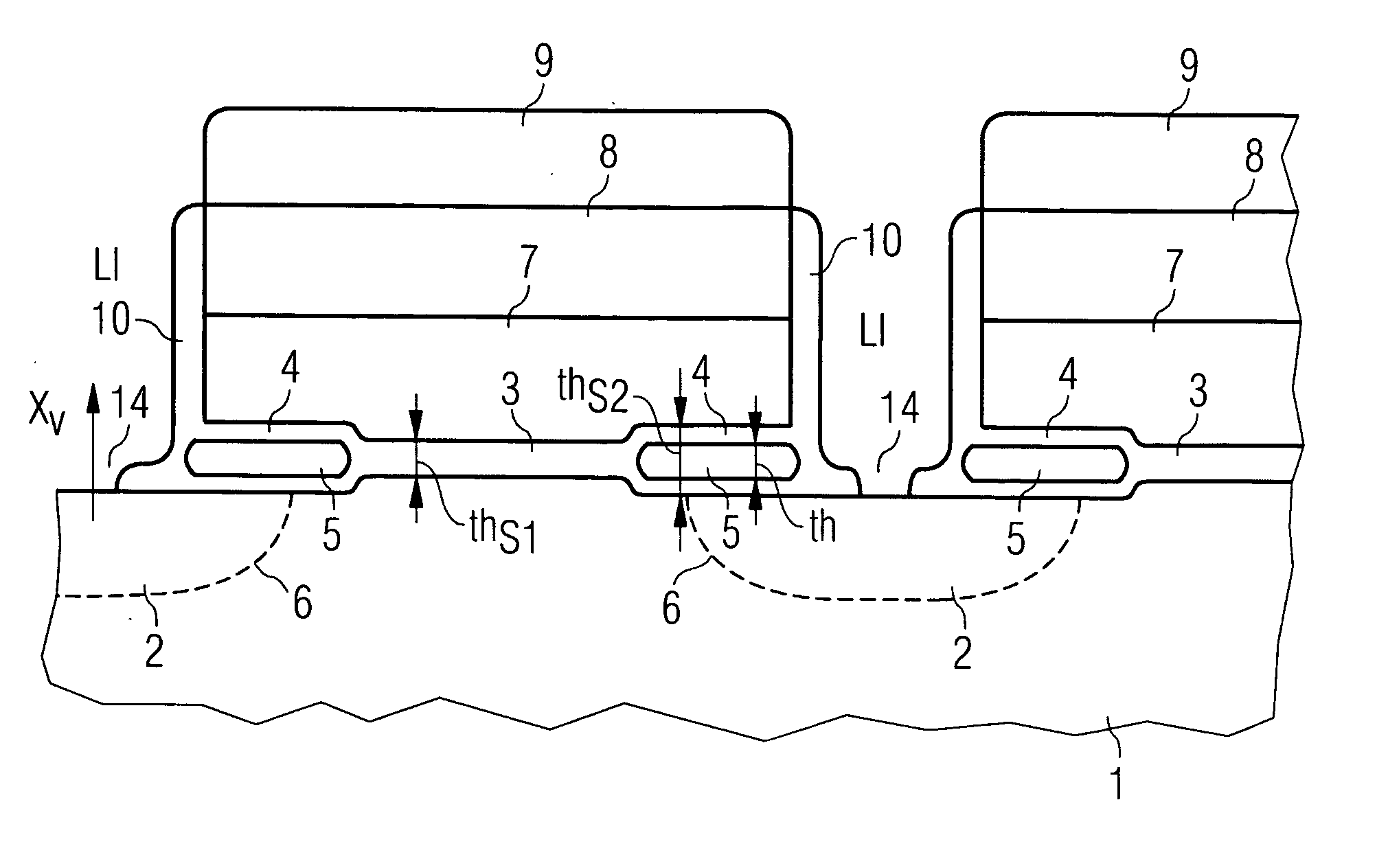

Nonvolatile semiconductor memory device and manufacturing method thereof

ActiveUS20050199940A1Reduce the impactReduce in quantityTransistorSolid-state devicesReactive plasmaSputter deposition

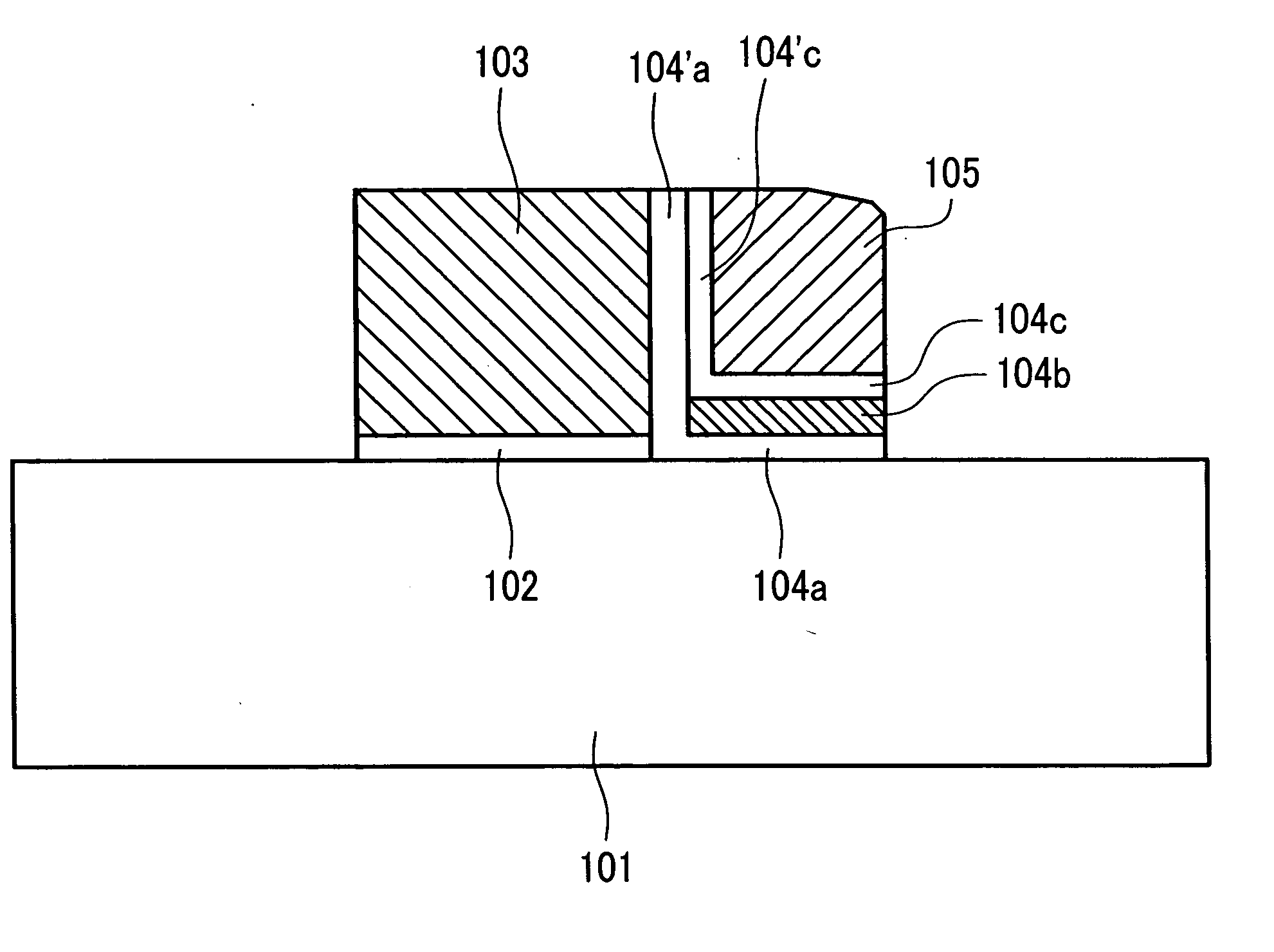

A MONOS nonvolatile memory of a split gate structure, wherein writing and erasing are performed by hot electrons and hot holes respectively, is prone to cause electrons not to be erased and to remain in an Si nitride film on a select gate electrode sidewall and that results in the deterioration of rewriting durability. When long time erasing is applied as a measure to solve the problem, drawbacks appear, such as the increase of a circuit area caused by the increase of the erasing current and the deterioration of retention characteristics. In the present invention, an Si nitride film is formed by the reactive plasma sputter deposition method that enables oriented deposition and the Si nitride film on a select gate electrode sidewall is removed at the time when a top Si oxide film is formed.

Owner:RENESAS ELECTRONICS CORP

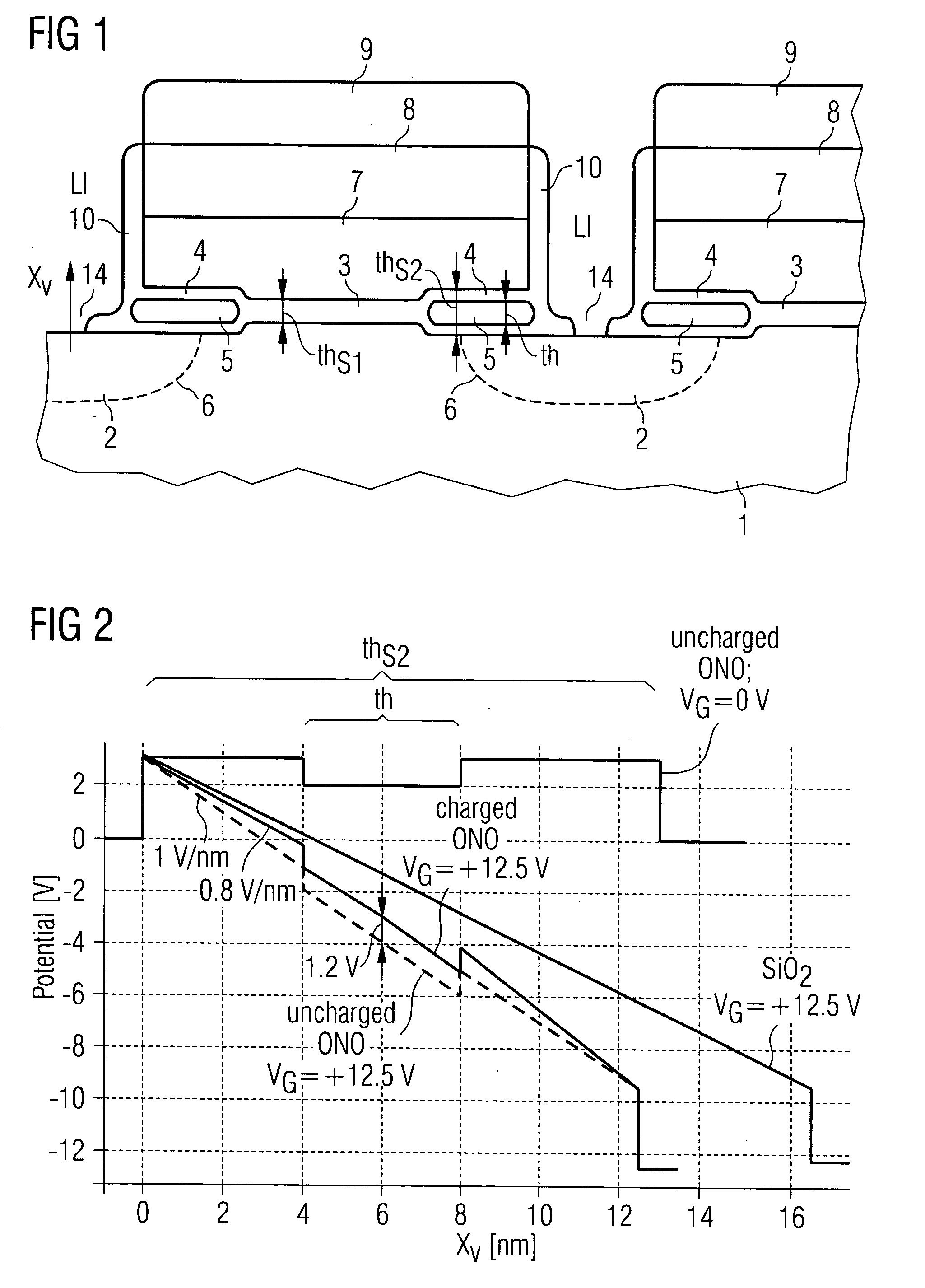

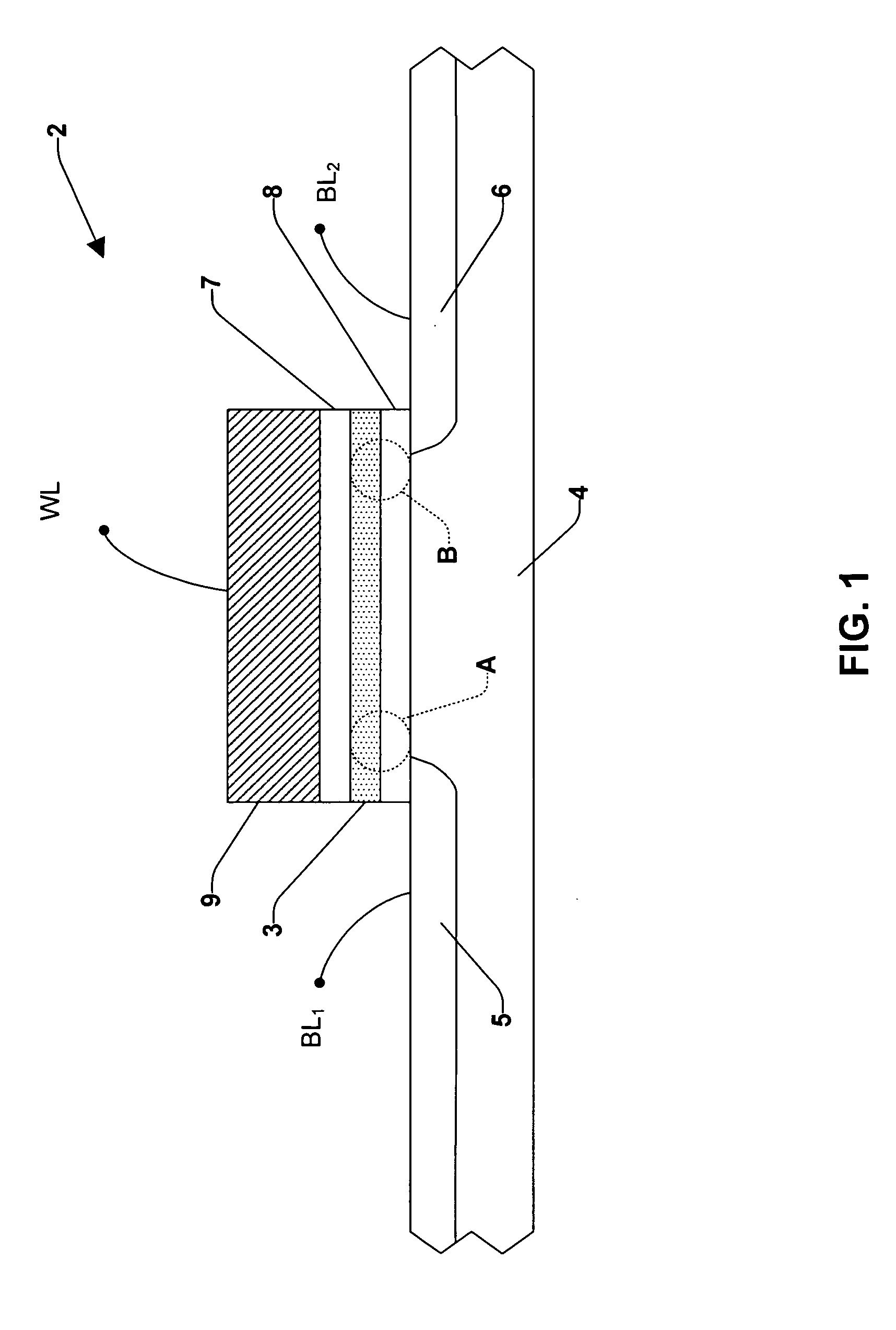

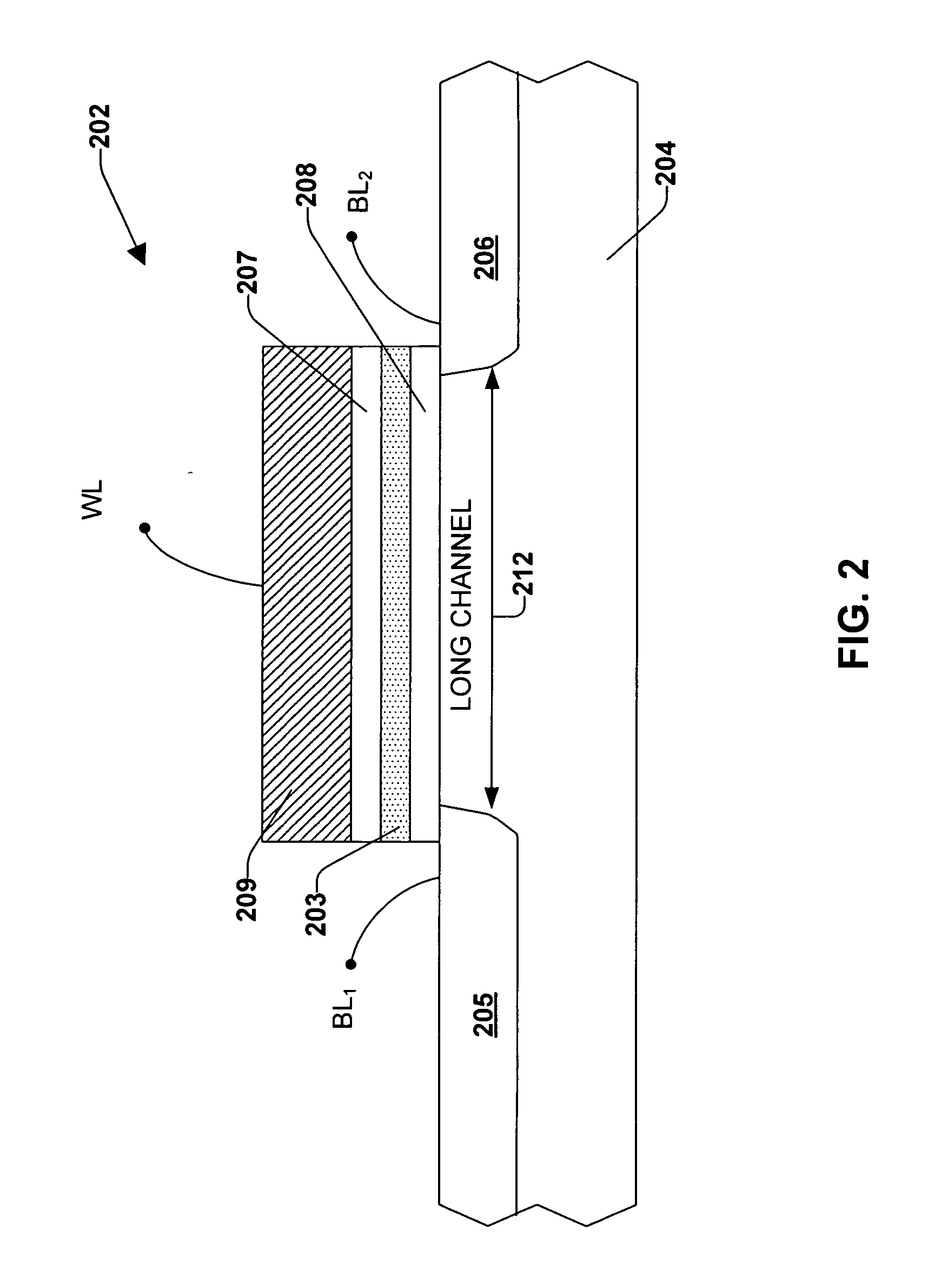

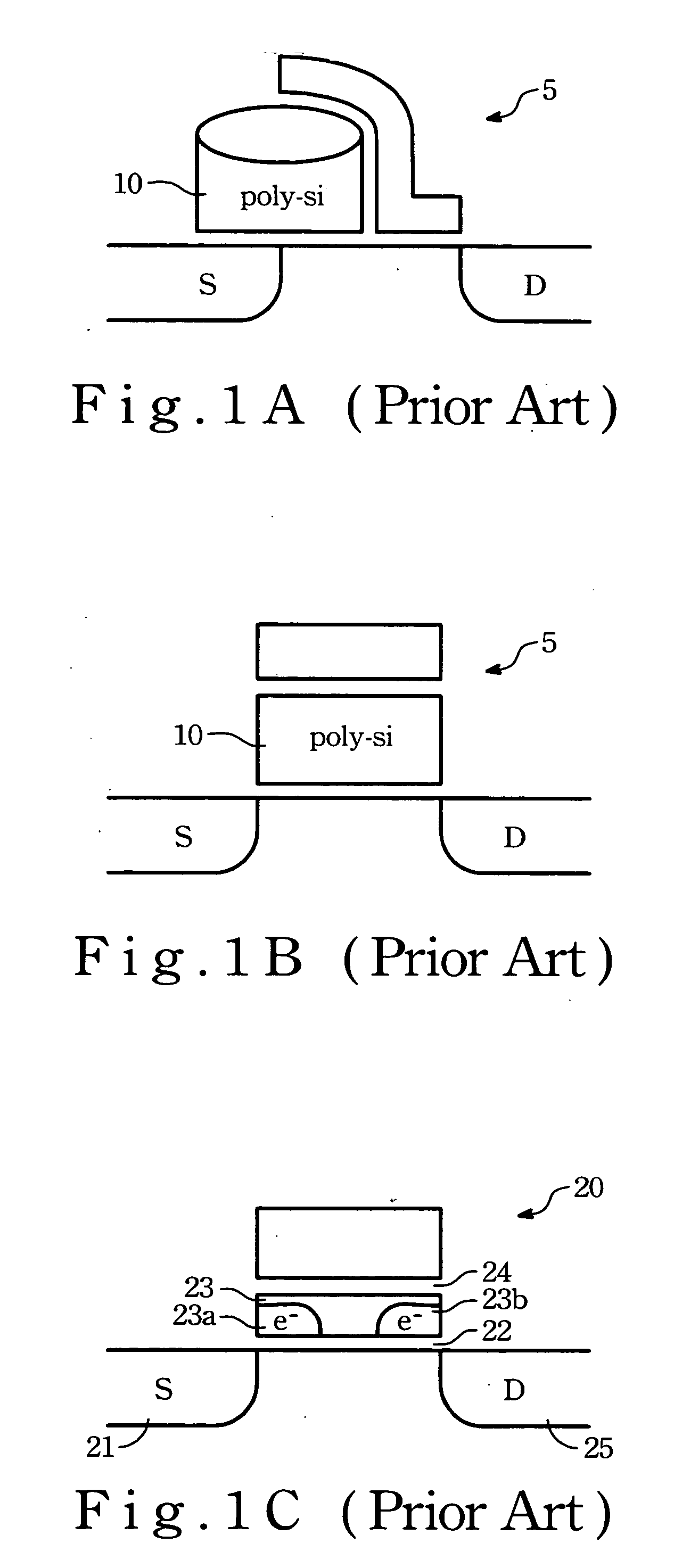

Charge-trapping memory device and methods for operating and manufacturing the cell

InactiveUS20050104117A1Reduce the total amount of chargingReduce degradationTransistorSolid-state devicesGate dielectricFowler nordheim

The charge-trapping layer comprises two strips above the source and drain junctions. The thicknesses of the charge-trapping layer and the gate dielectric are chosen to facilitate Fowler-Nordheim-tunnelling of electrons into the strips during an erasure process. Programming is performed by injection of hot holes into the strips individually for two-bit storage.

Owner:POLARIS INNOVATIONS

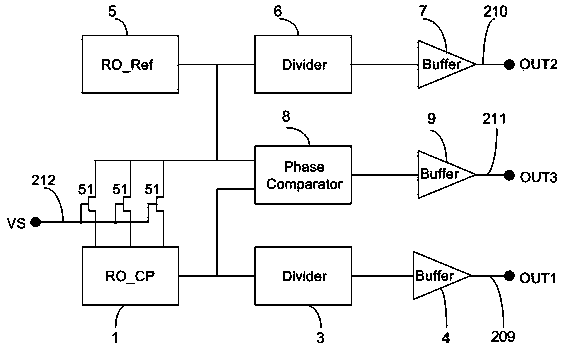

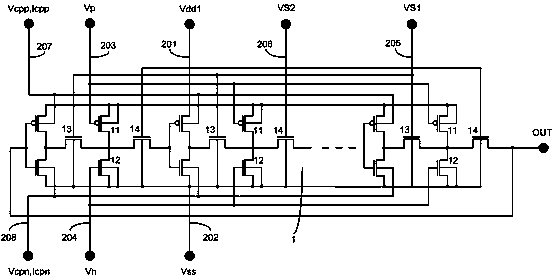

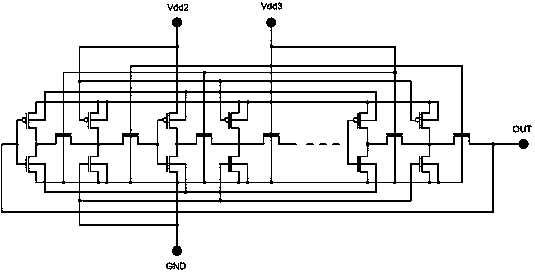

Multifunctional test circuit of integrated circuit stress degradation and test method thereof

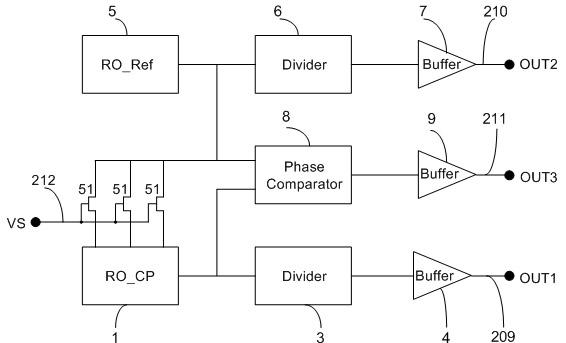

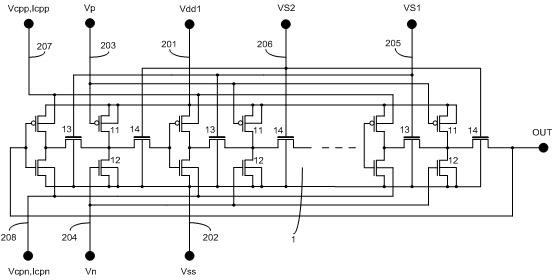

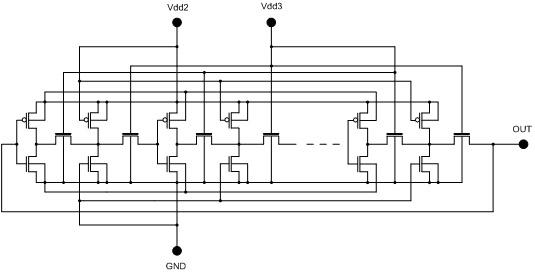

The invention belongs to a integrated circuit reliability test technology field and especially relates to a multifunctional test circuit of integrated circuit stress degradation and a test method thereof. A core part of the test circuit takes an annular oscillator as a basis. Several auxiliary transistors, switch transistors and control terminals are added. By using the circuit and the method of the invention, a negative bias temperature instability, a positive bias temperature instability, hot hole injection or hot electron injection stress can be applied to pMOSFETs or nMOSFETs in a ring vibration inverter respectively; a ring oscillator is in a normal oscillation and stress oscillation state; the pMOSFETs or nMOSFETs of the inverter in the ring oscillator is in a measuring state of a charge pump. The degradation of the MOSFETs in the ring vibration inverter can be shown through changes of a ring oscillator oscillation frequency after the stress and can be shown through the changes of a CP current (Icpp or Icpn) of the pMOSFETs or nMOSFETs in the ring oscillator.

Owner:FUDAN UNIV

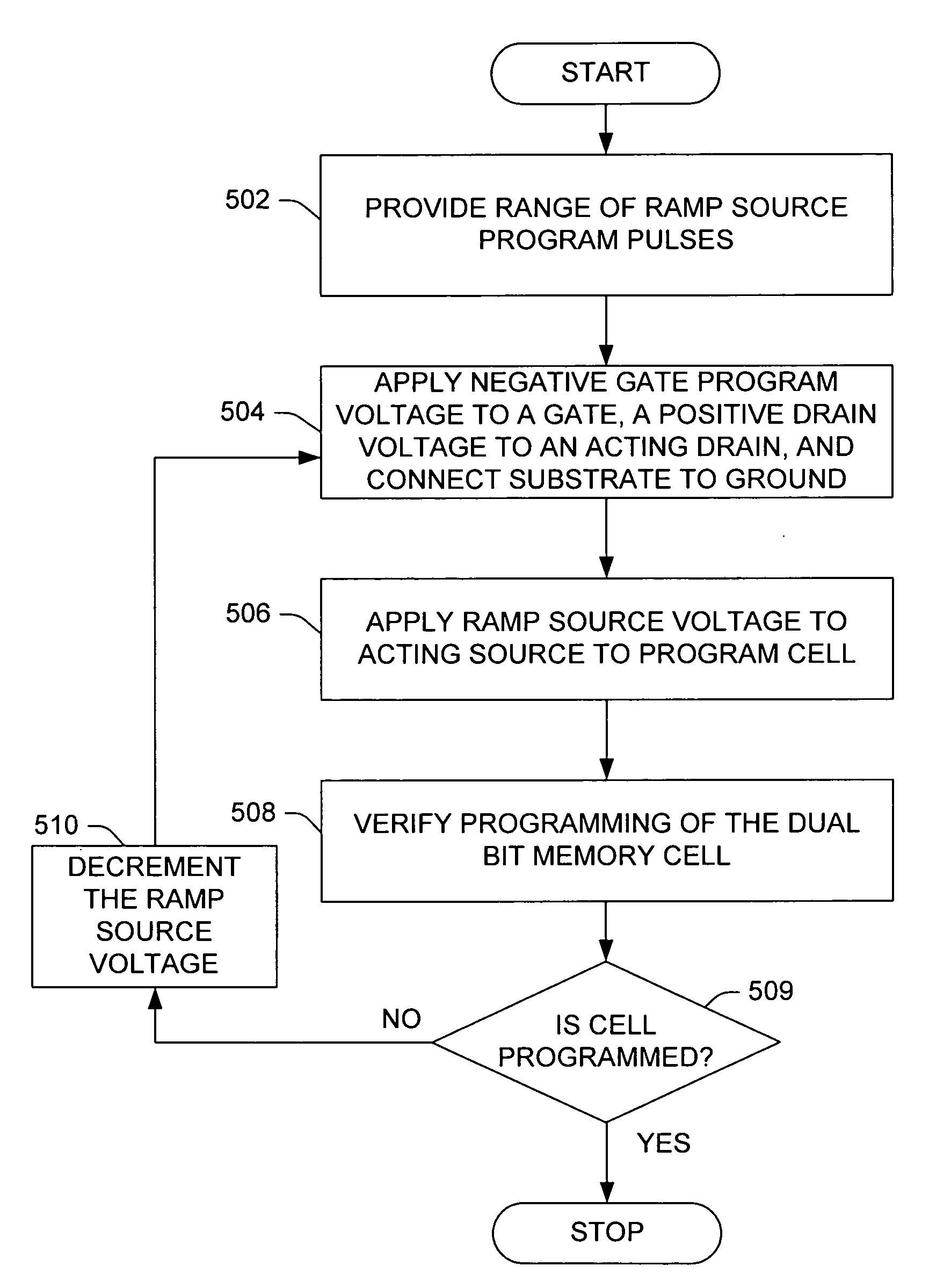

Ramp source hot-hole programming for trap based non-volatile memory devices

ActiveUS6934190B1Lower threshold voltageThe equipment is easy to operateRead-only memoriesDigital storageHot holesComputer science

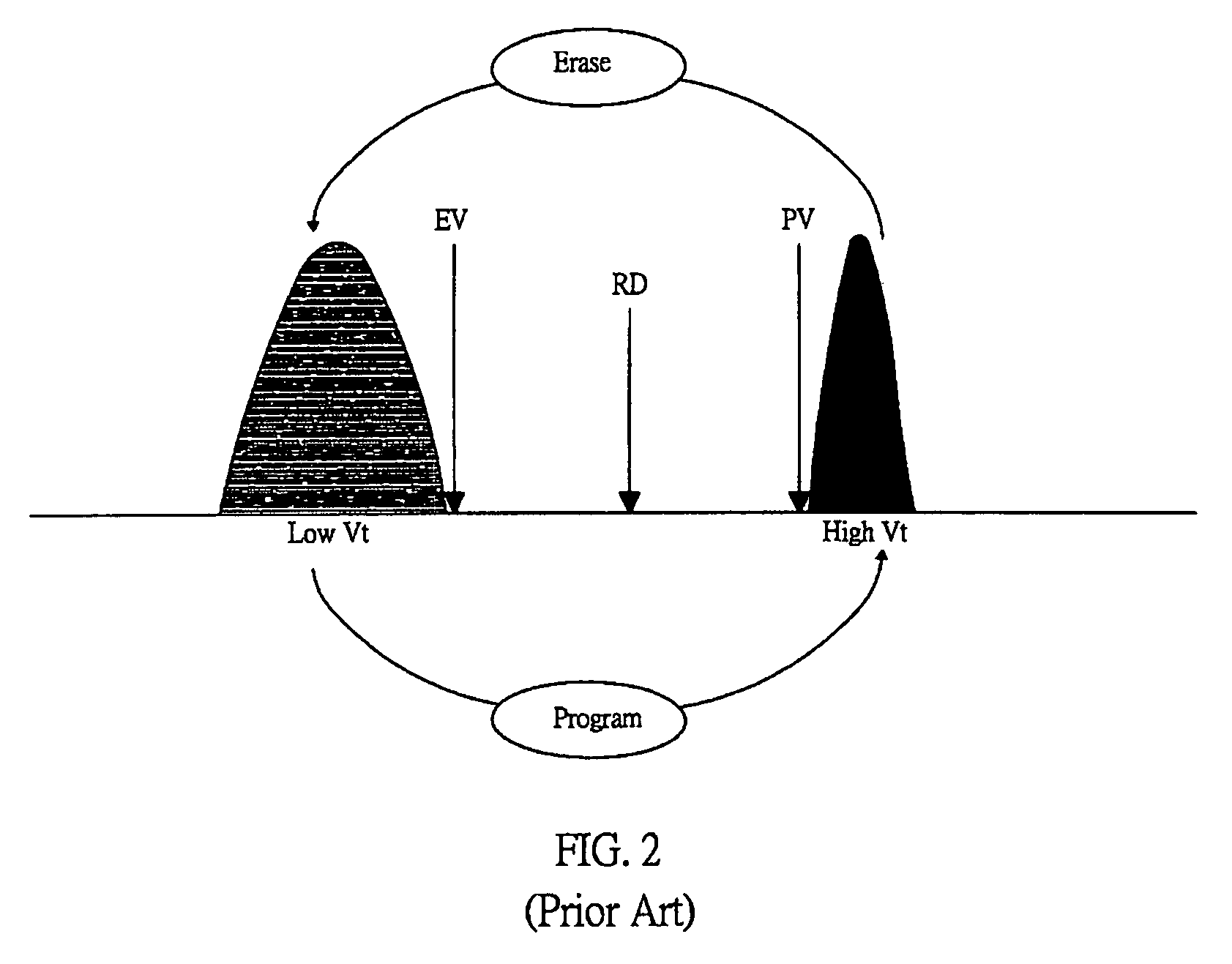

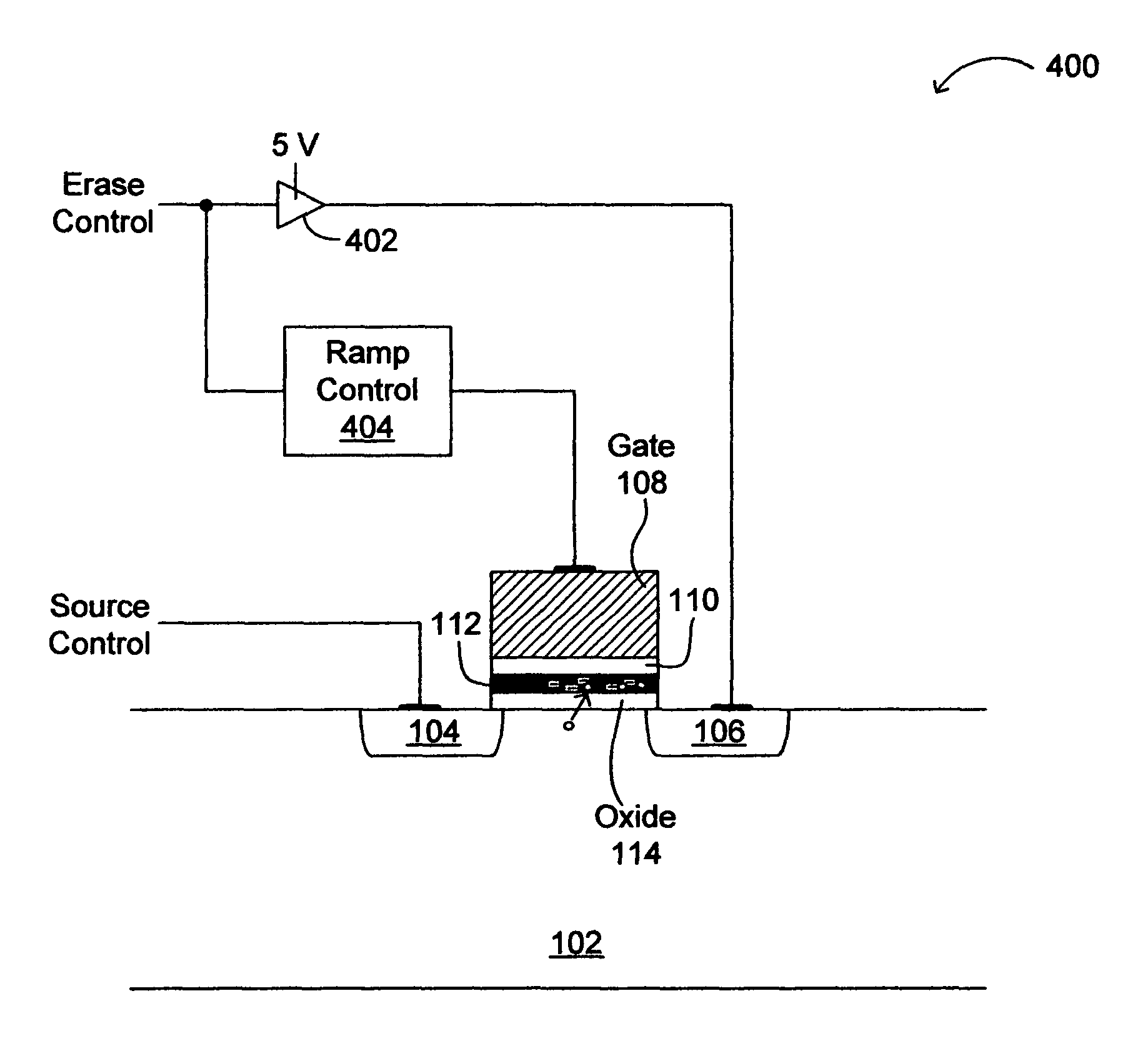

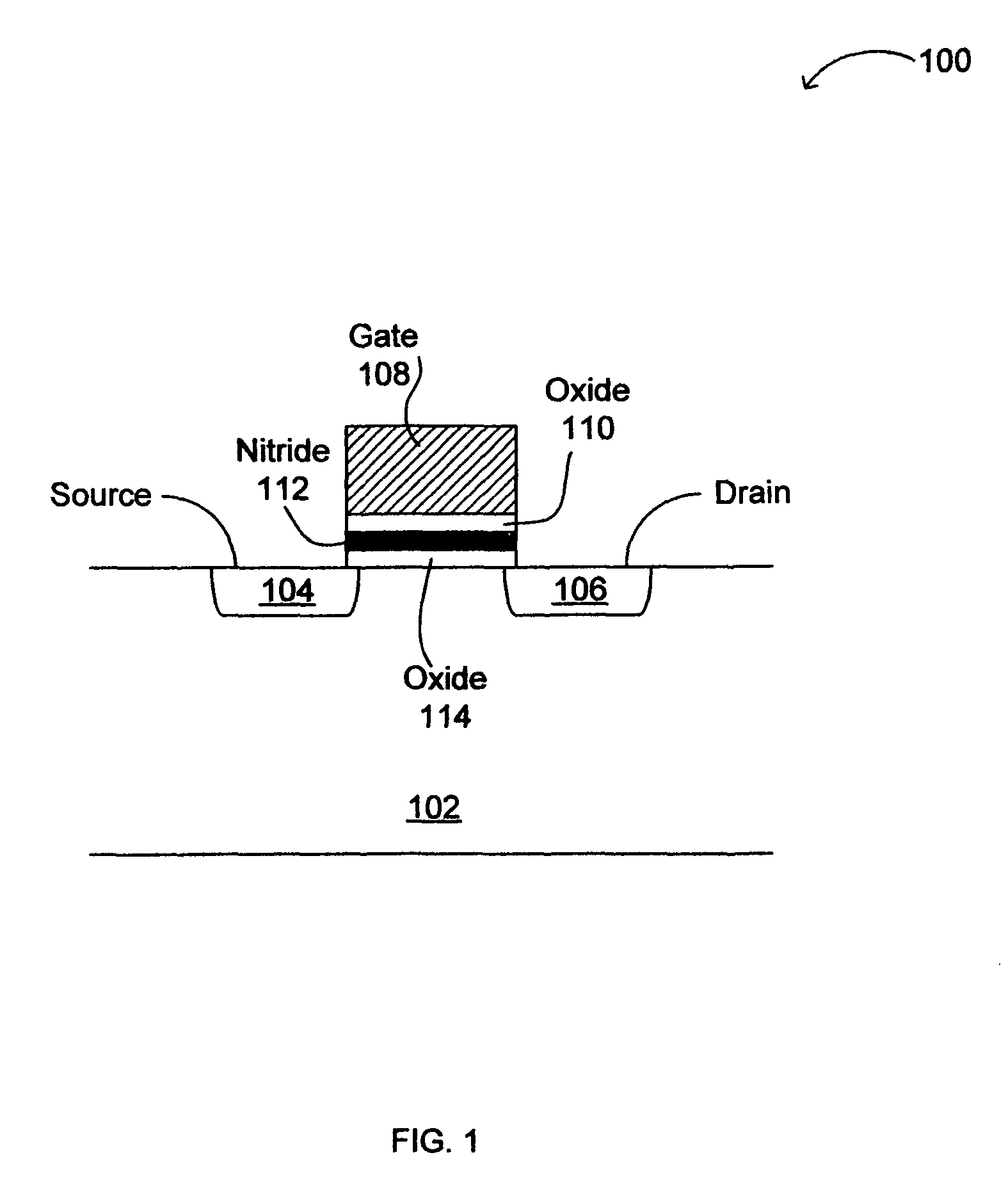

Methods of operating dual bit memory devices including programming with a range of values are provided. The present invention employs a range of ramp source program pulses to iteratively perform a program operation that employs hot hole injection. The range is related to channel lengths of individual dual bit memory cells within the memory device. To program a bit of a particular dual bit memory cell, a negative gate program voltage is applied to its gate, a positive drain voltage is applied to its acting drain, and its substrate is connected to ground. Additionally, a ramp source voltage of the range of ramp source program pulses is concurrently applied to an acting source of the dual bit memory cell. A verification operation is then performed and the programming is repeated with a decremented ramp source voltage on verification failure.

Owner:MONTEREY RES LLC

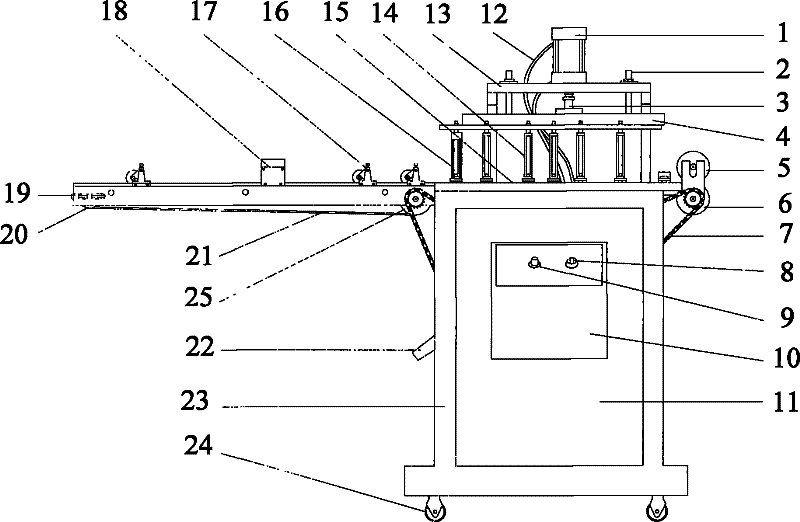

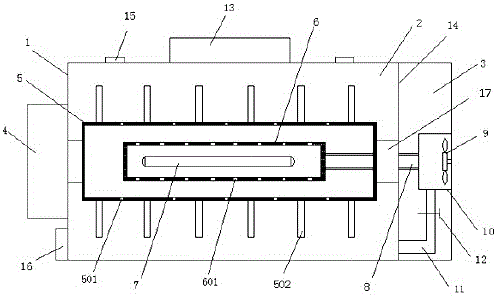

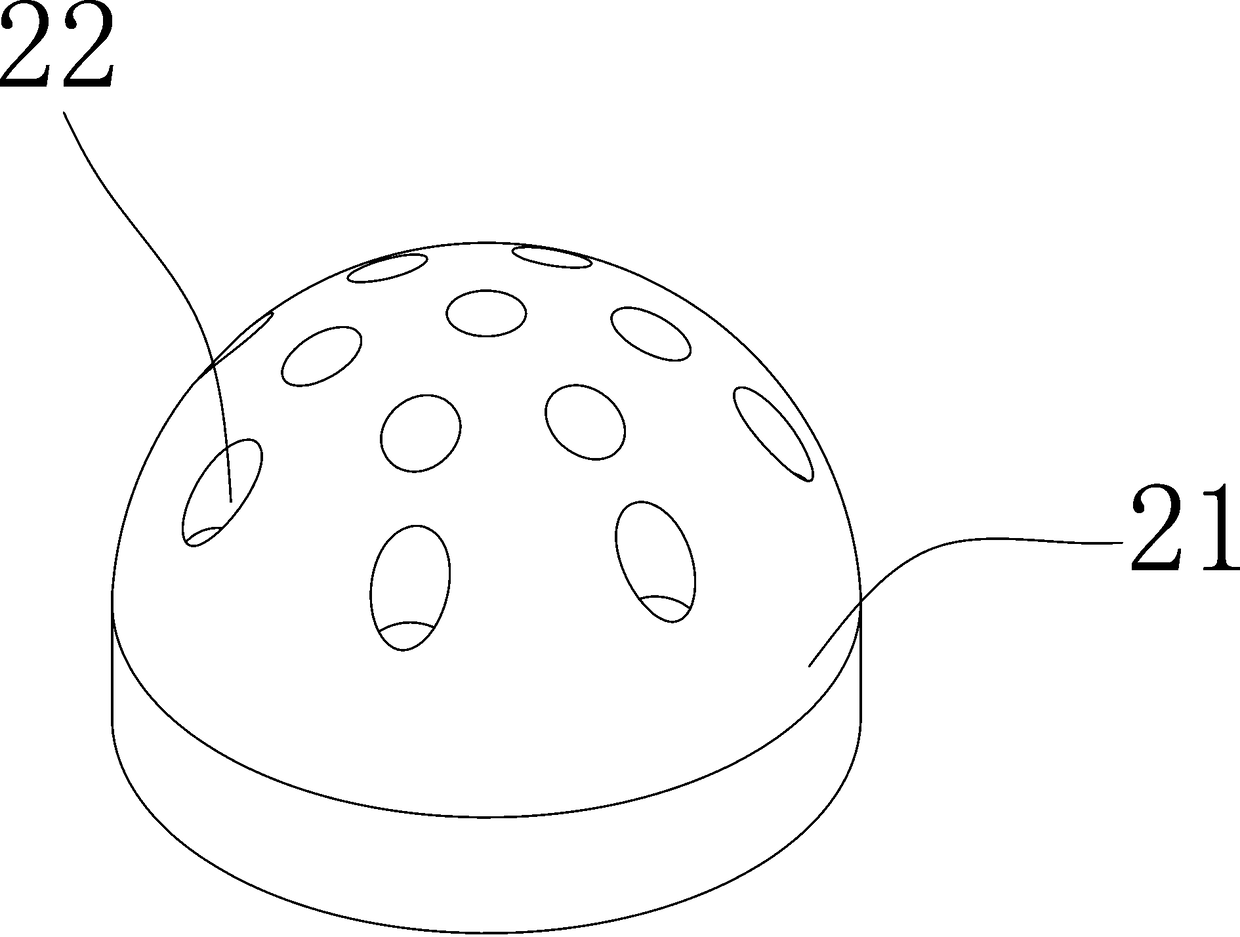

A non-woven fabric punching forming device

InactiveCN102284974AIncrease productivityEliminate the influence of human factorsMetal working apparatusPunchingEngineering

The invention relates to a non-woven fabric punching and forming device, which includes a pneumatic punching device, a knife die device, an electric transmission device and a motor box, the pneumatic punching device is arranged on the upper part of the device, and the knife die device is connected to the pneumatic punching device The lower part of the die cutter device is supported and connected on the top platform of the motor box, and the electric transmission device is arranged on the upper part of the motor box. Compared with the prior art, the present invention replaces the manual section cutting and manual ironing, and completes the punching at the same time as the section cutting, which improves the production efficiency and ensures the punching quality of the product. In addition, the punching knife edge is hidden in the In the positioning hole, it will not pose a safety hazard to the operator, ensuring production safety.

Owner:上海新必工贸有限公司

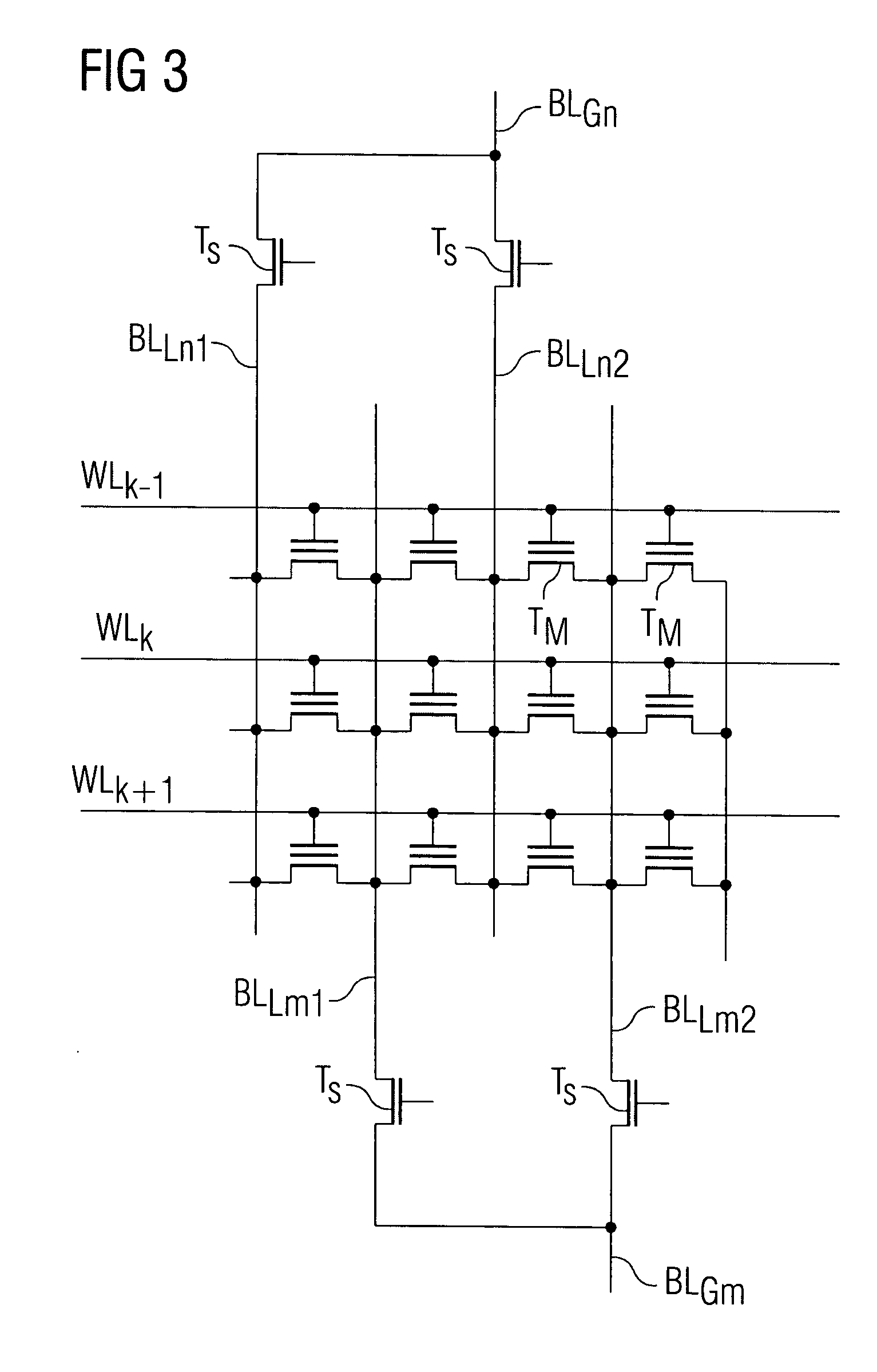

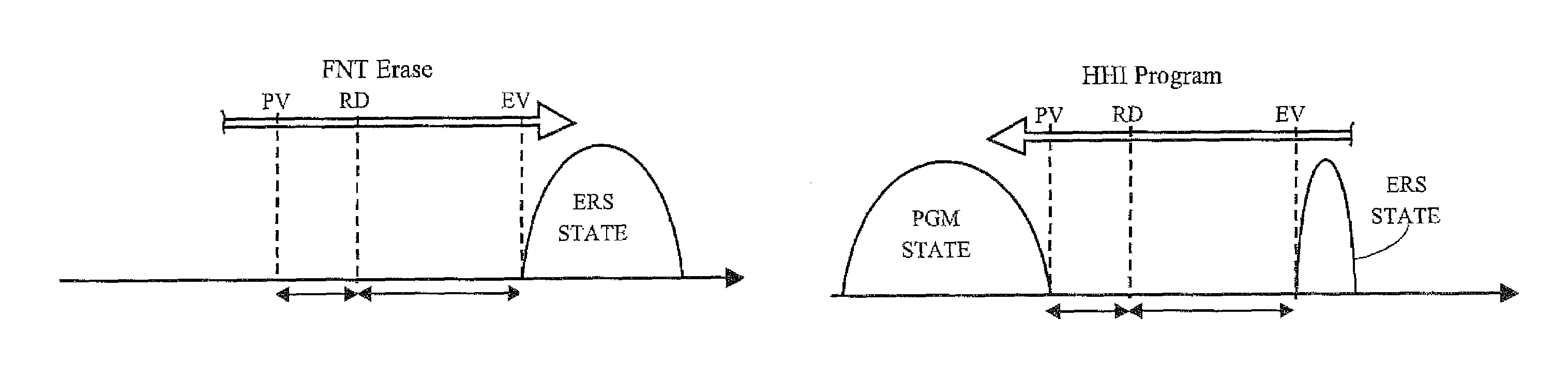

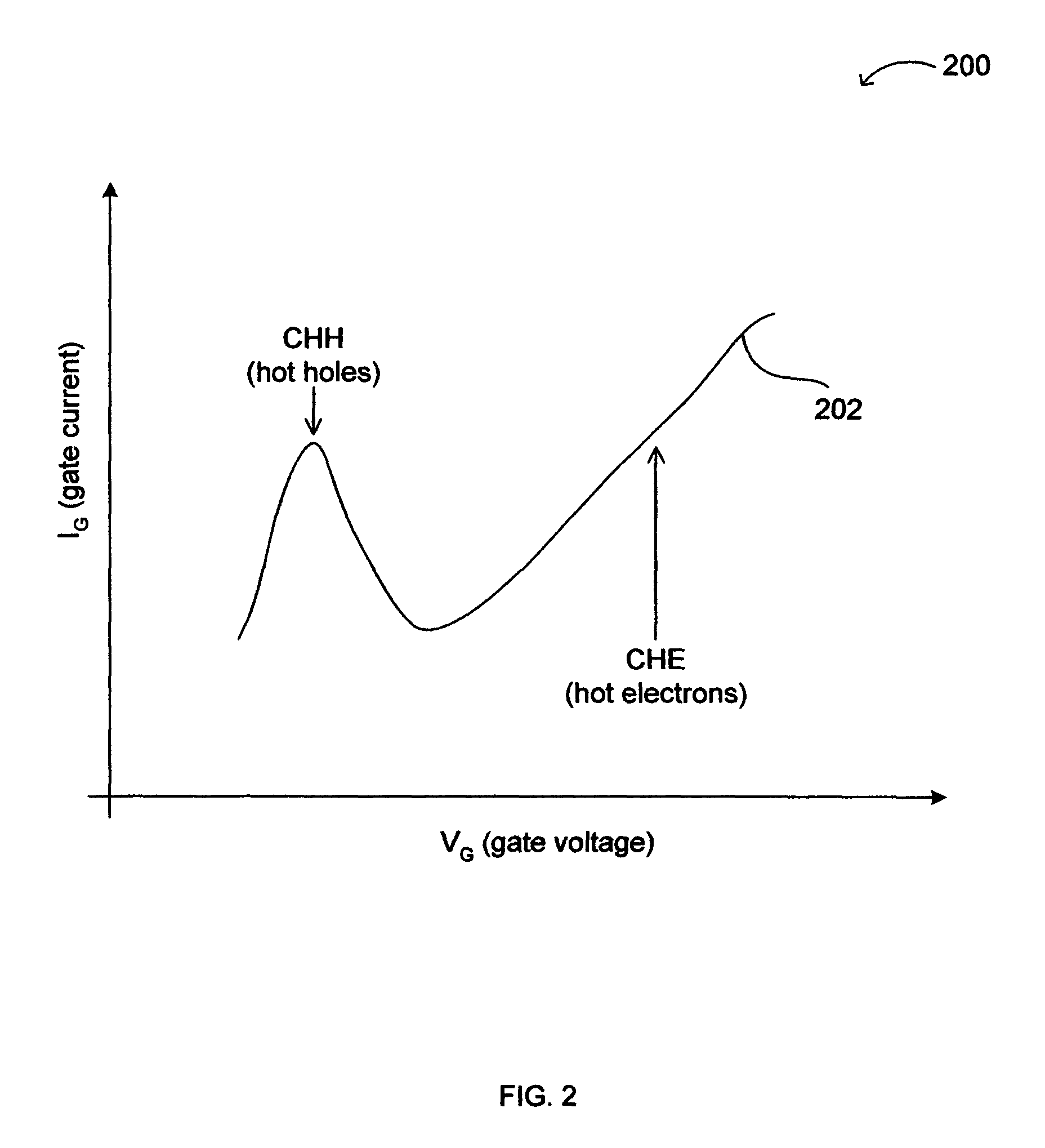

Method, circuit and device for disturb-control of programming nonvolatile memory cells by hot-hole injection (HHI) and by channel hot-electron (CHE) injection

InactiveUS7692961B2Read-only memoriesSemiconductor/solid-state device manufacturingHot holesComputer science

Programming a NVM memory cell such as an NROM cell by using hot hole injection (HHI), followed by channel hot electron (CHE) injection. CHE injection increases the threshold voltage (Vt) of bits of memory cells that were disturbed (unnecessarily programmed) in HHI programming step. Page Write may be performed using a combination of only HHI, followed by CHE without any Erase.

Owner:SAIFUN SEMICON

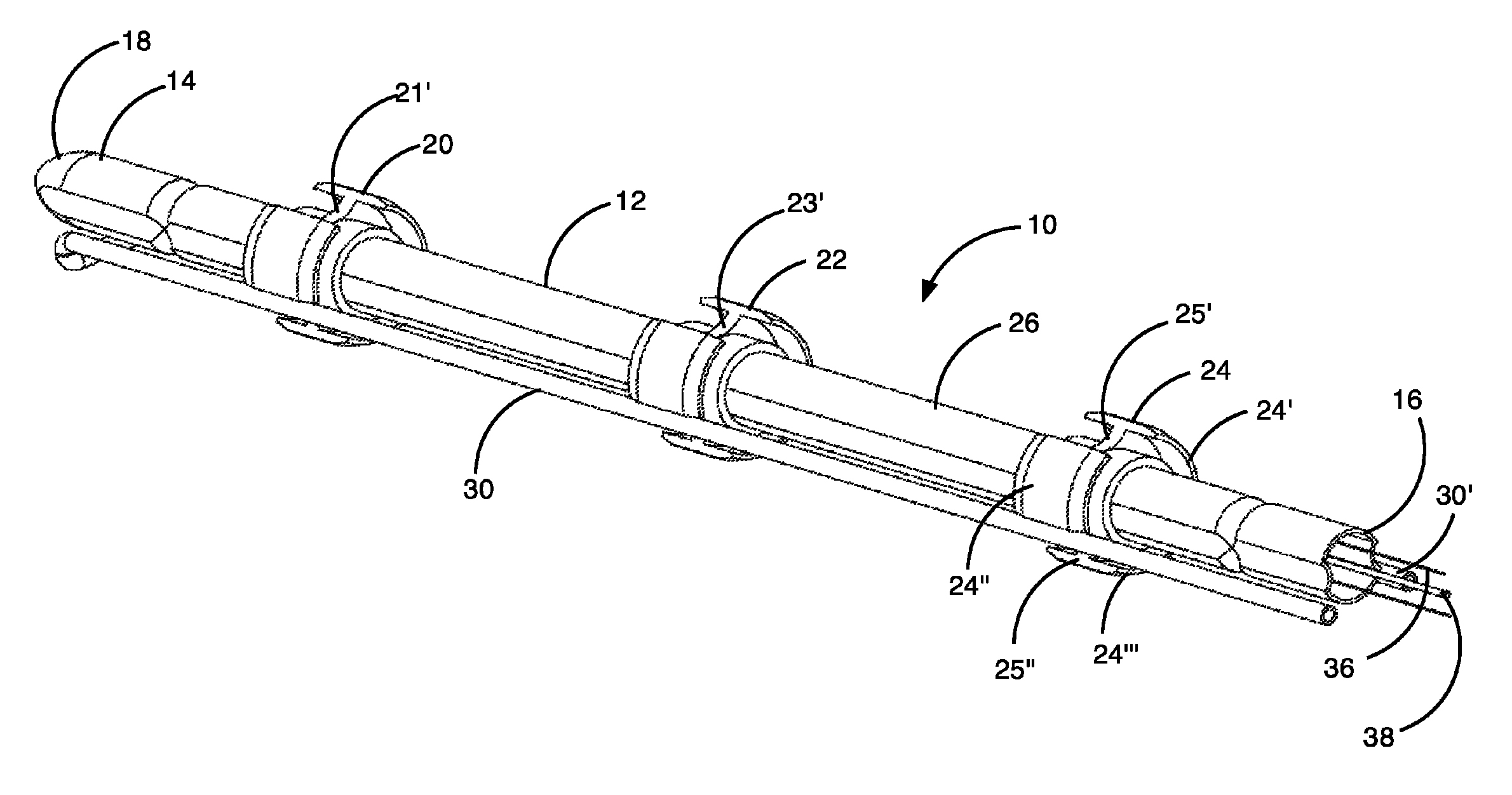

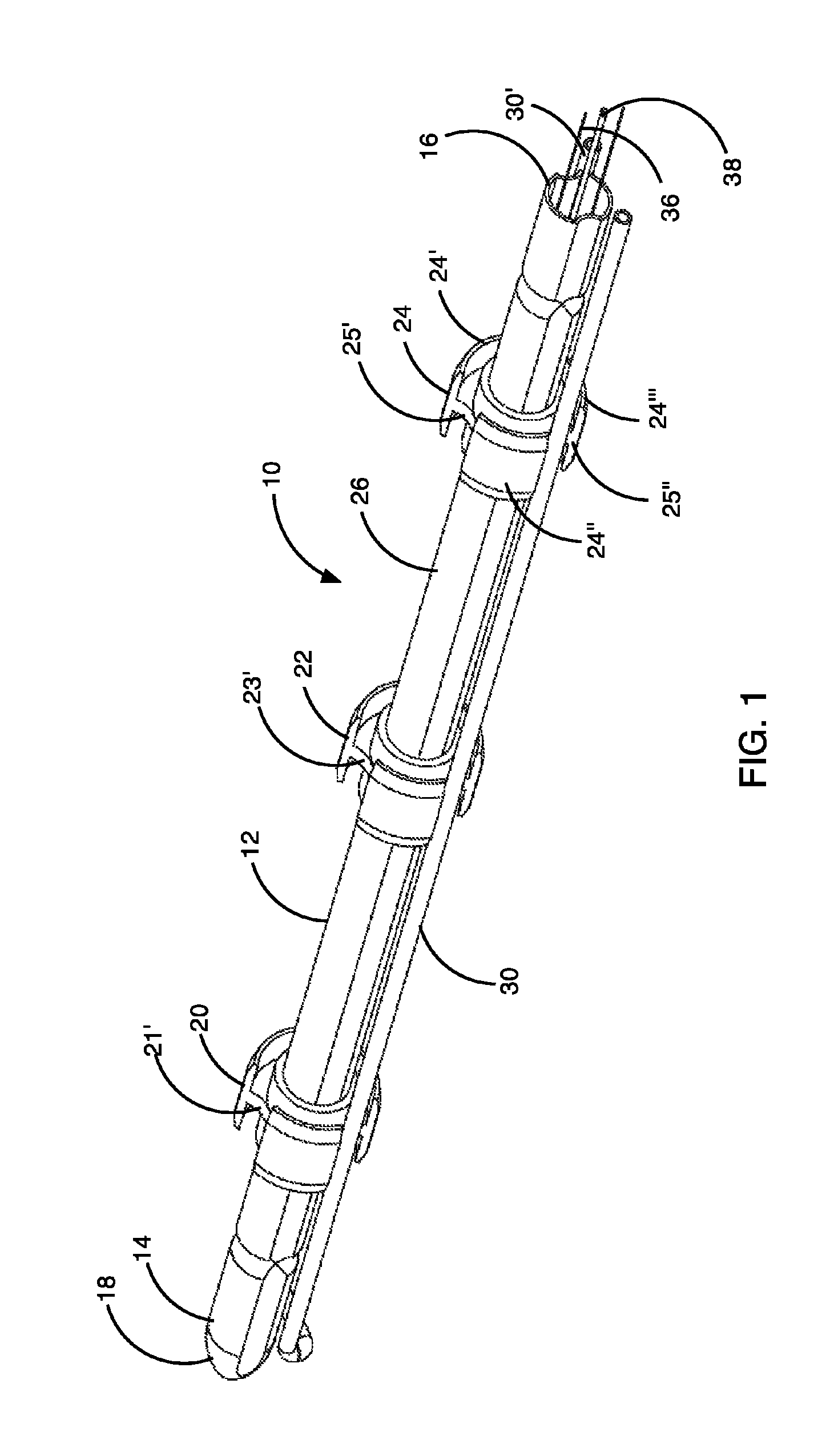

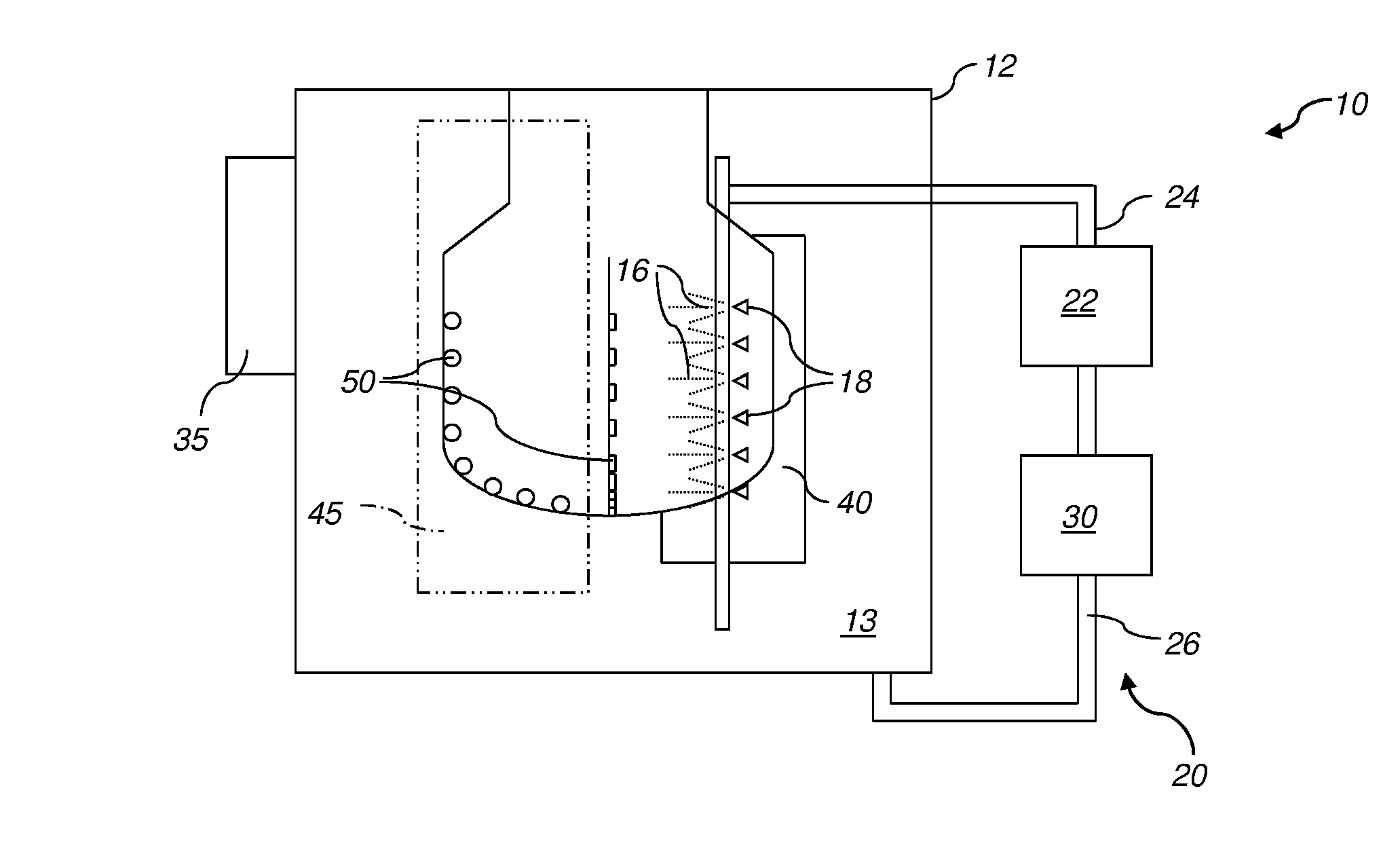

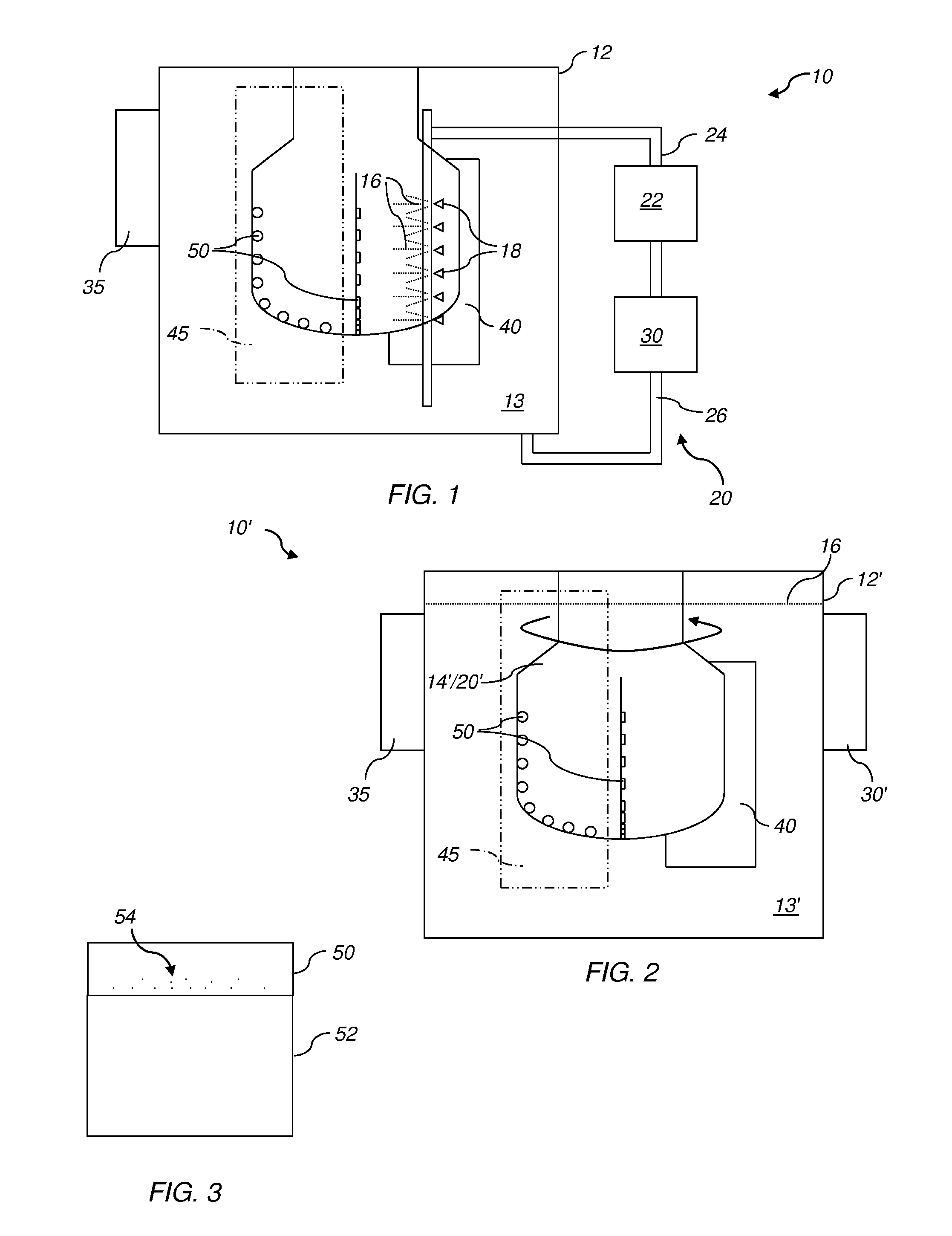

Methods and systems for removing diamond-diamond bonding catalysts from polycrystalline diamond

ActiveUS20130340352A1Pigmenting treatmentOrganic chemistryPolycrystalline diamondCompound (substance)

Methods for removing, or leaching, cobalt or other diamond-diamond bonding catalysts from polycrystalline diamond compacts (PDCs) or other structures formed from polycrystalline diamond include leaching under conditions that simulate use of PDCs in a hot hole drilling environment. A leaching agent may be formulated, when used under appropriate conditions, to remove or substantially remove cobalt or another catalyst from polycrystalline diamond without dissolving, degrading or otherwise attacking a substrate that supports or carries the polycrystalline diamond. The leaching agent may include one or more components that mimick the chemicals or conditions to which a PDC would be exposed in a hot hole drilling environment. Polycrystalline diamond structures from which cobalt or another diamond-diamond bonding catalyst has been removed or substantially removed are also disclosed, as are systems for leaching cobalt or other diamond-diamond bonding catalysts from polycrystalline diamond.

Owner:EVE BIT SALES

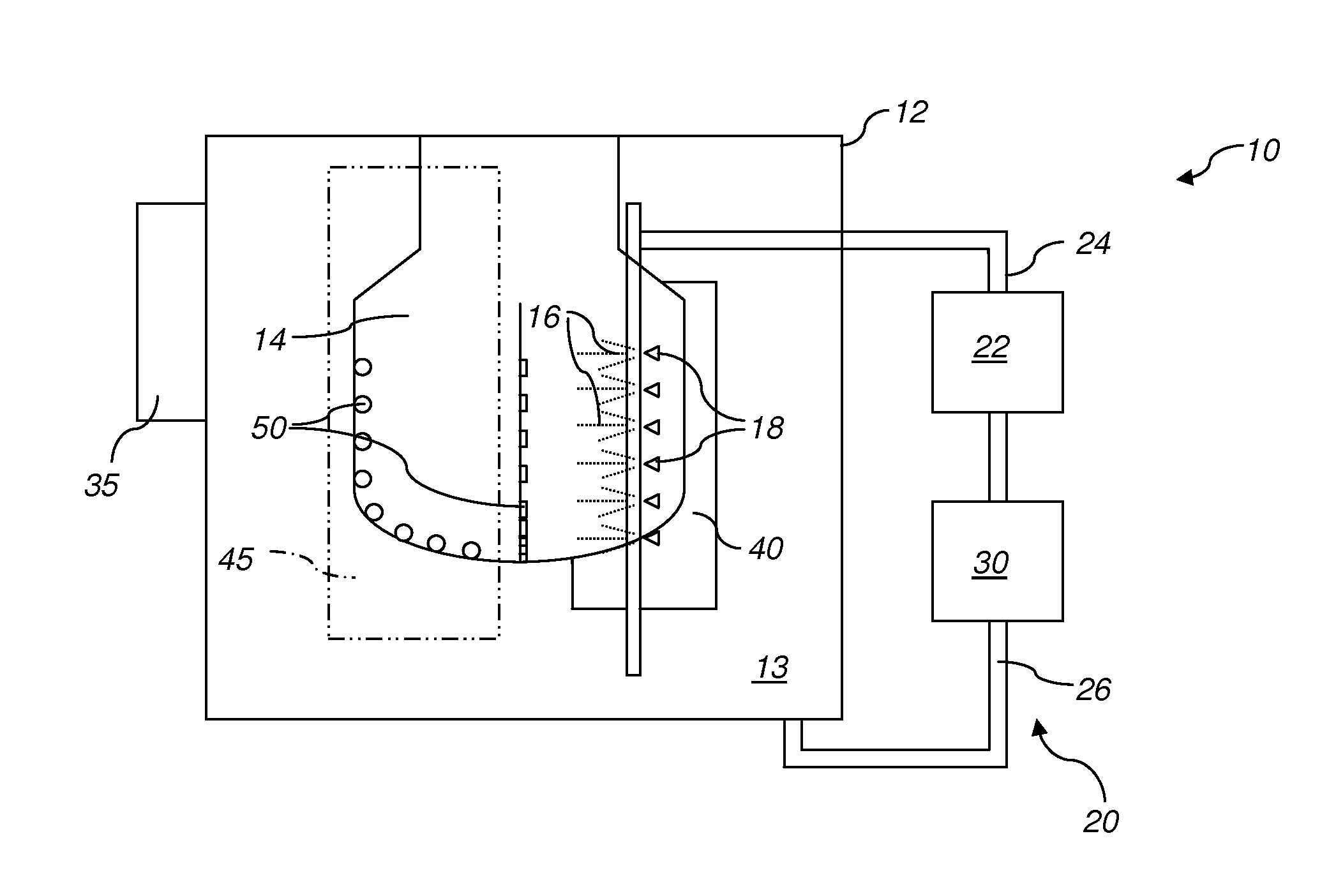

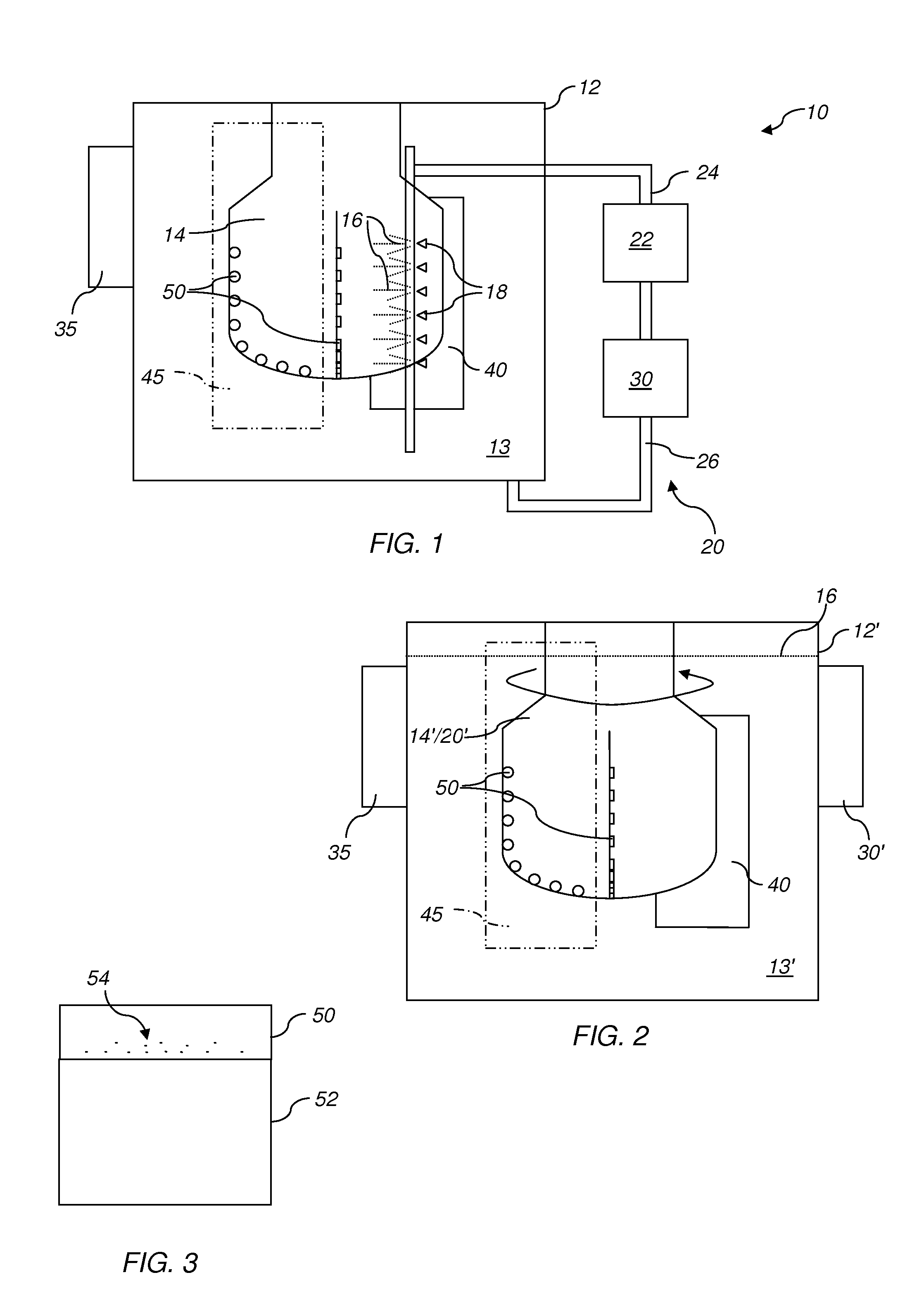

Hot hole charge system

InactiveUS8820242B2Maximize the effectSimple and safe to useDrilling using explosivesThermal insulationDetonatorHot holes

An apparatus, method and insulation medium for inserting and insulating a charge medium within a borehole includes a charge tube comprised of an elongate tube having a length and diameter sufficient for containing a desired quantity of a charge medium. A charge medium in a pumpable form is provided for substantially filling the charge tube. An insulation medium in a pumpable form is provided for substantially encapsulating the charge tube and substantially filling an annular space between the charge tube and the borehole for insulating the charge tube from a downhole environment in which the charge tube is to be inserted. A detonator is inserted within the charge medium proximate a distal end of the charge tube and a charge cable extends from the detonator through the charge tube and exits from the charge tube.

Owner:ALEXANDER BRENT DEE

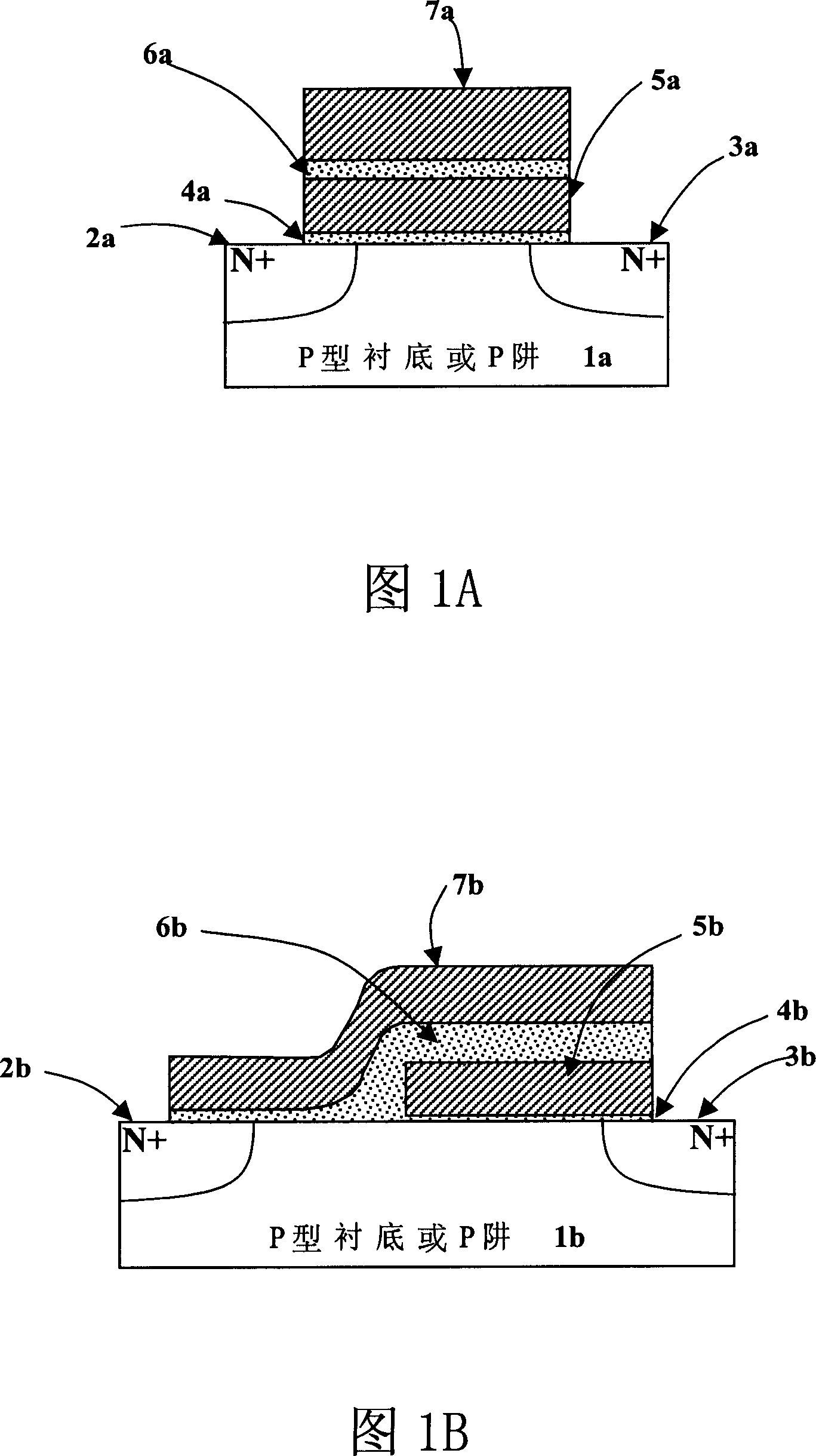

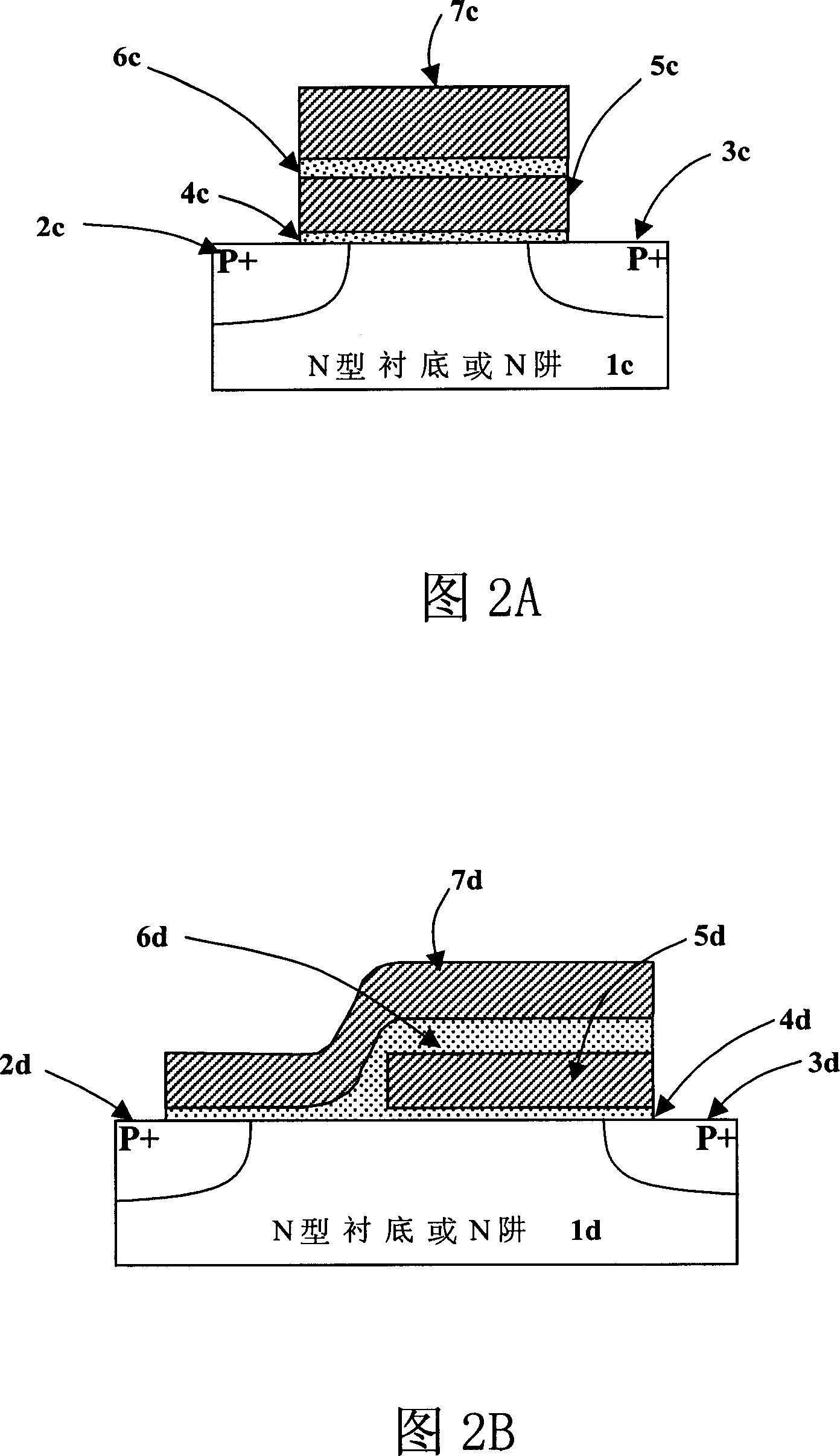

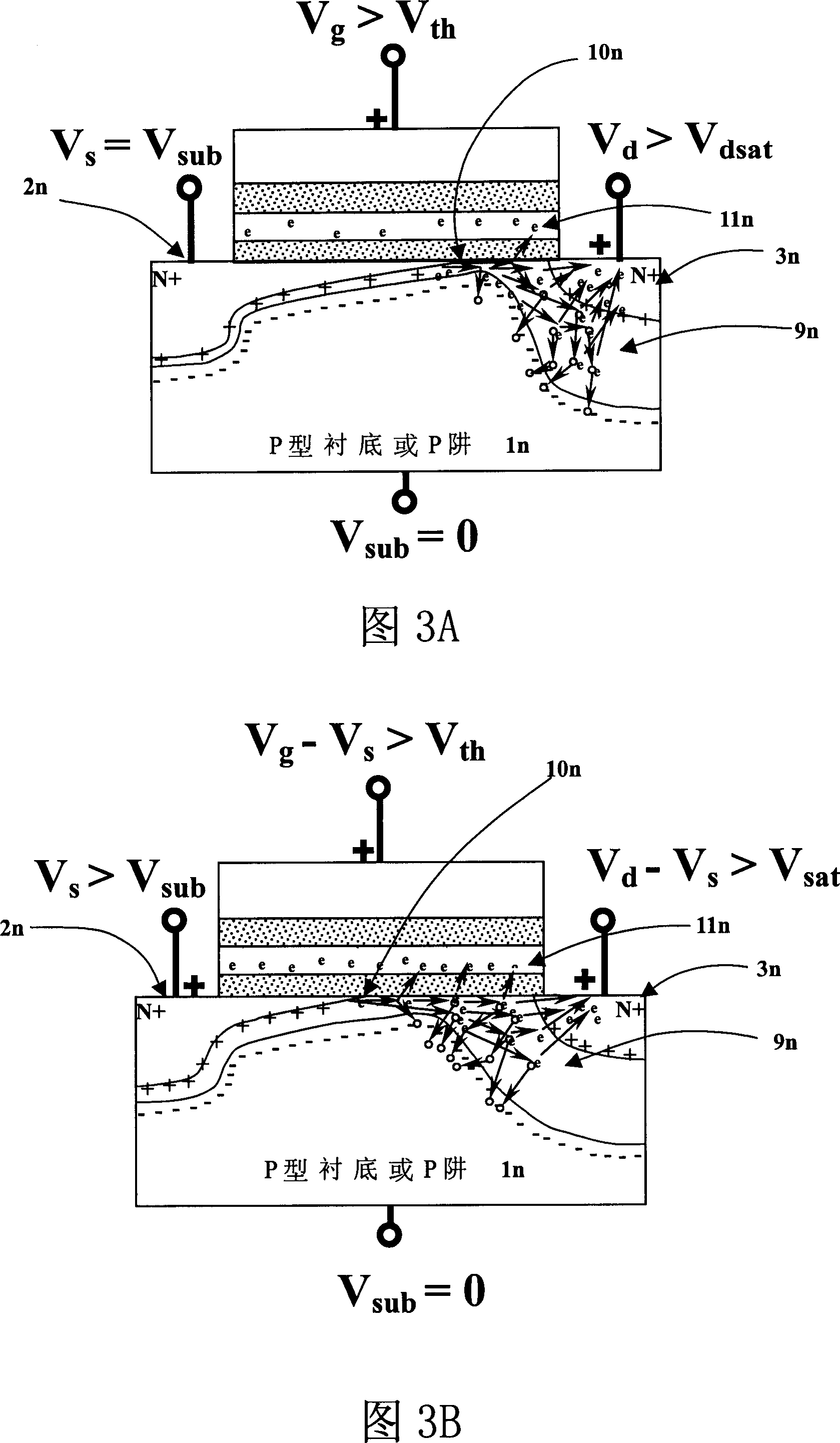

Programming and erasing method for non-volatile memory

InactiveCN101000801AReduce the burden onProgram disturbRead-only memoriesDigital storageElectron injectionLow voltage

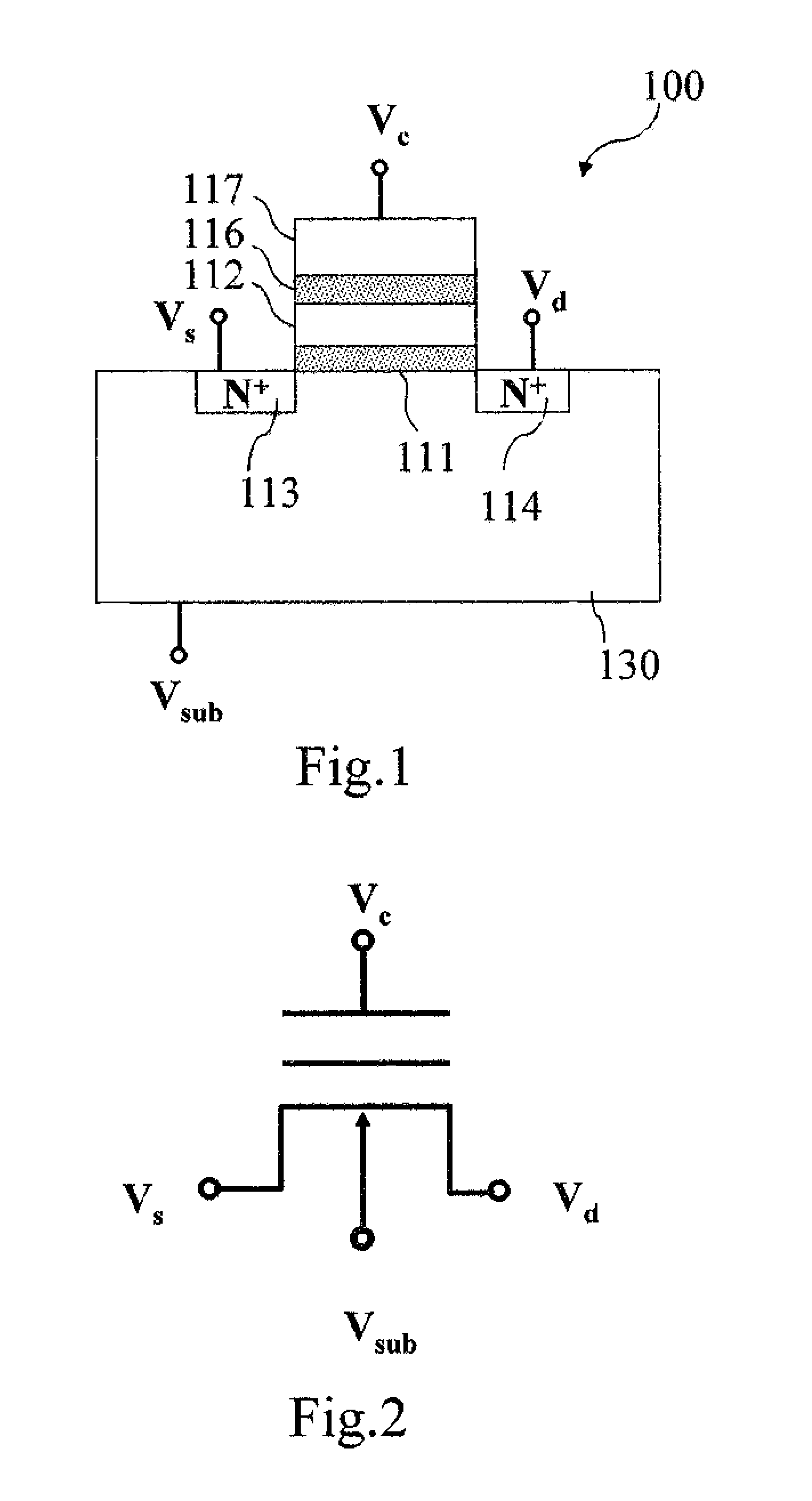

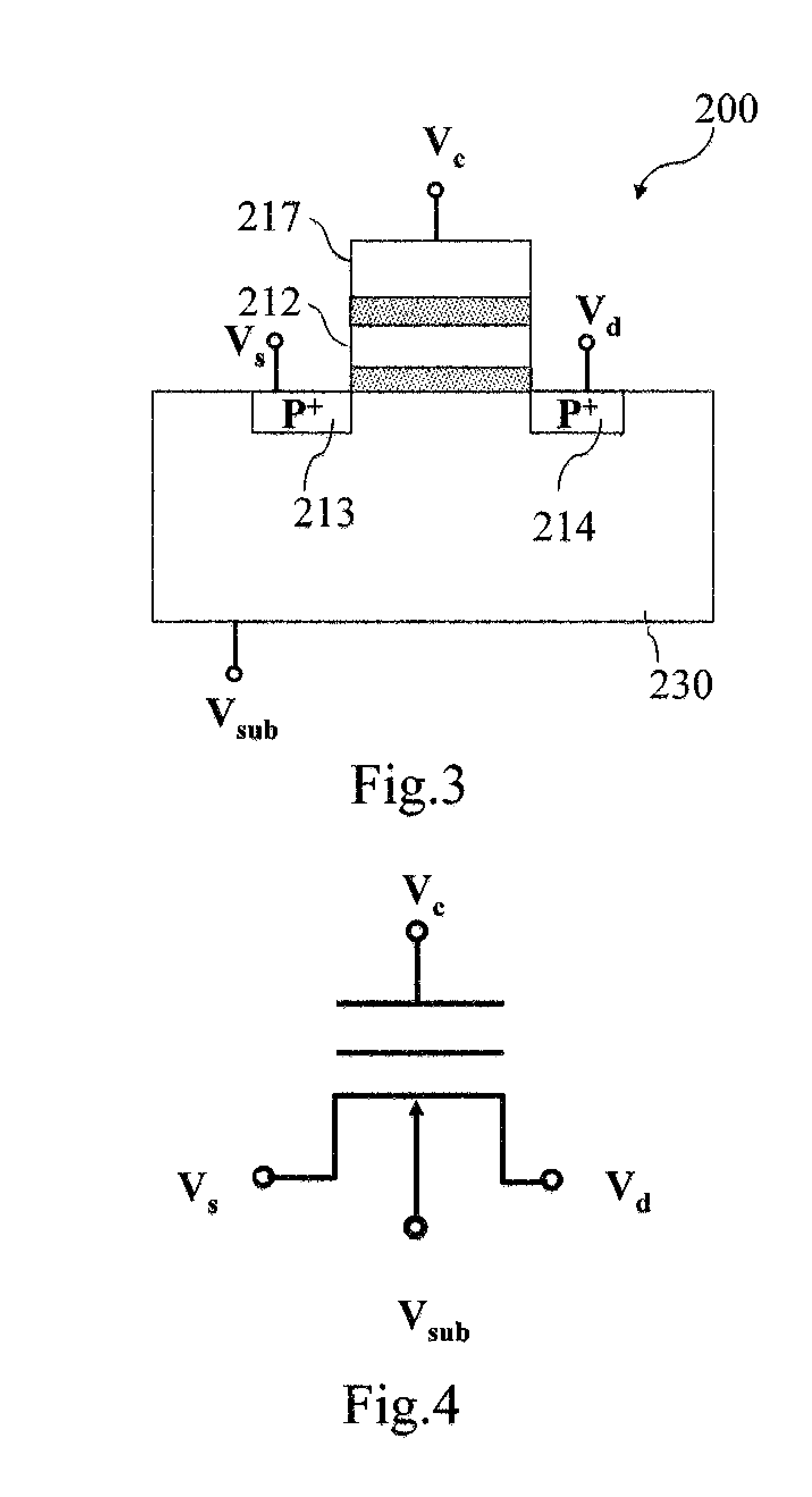

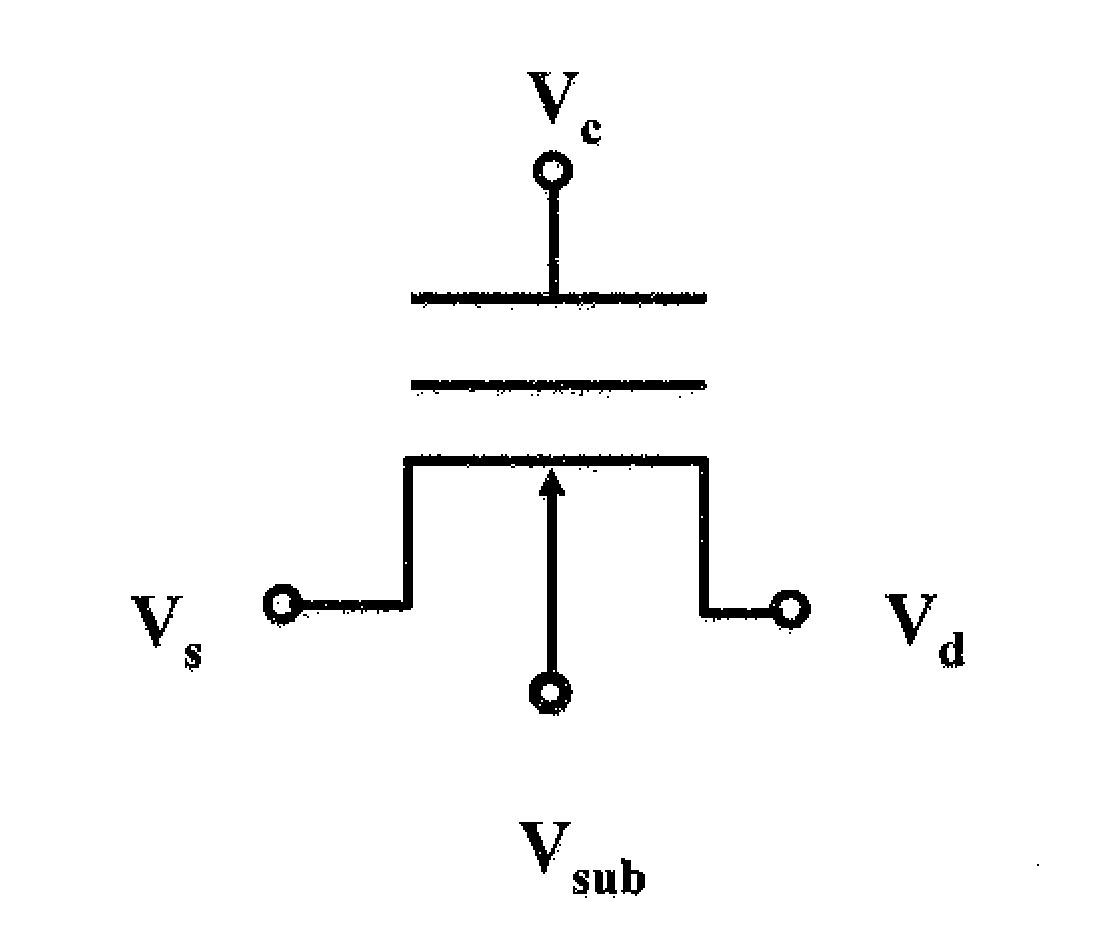

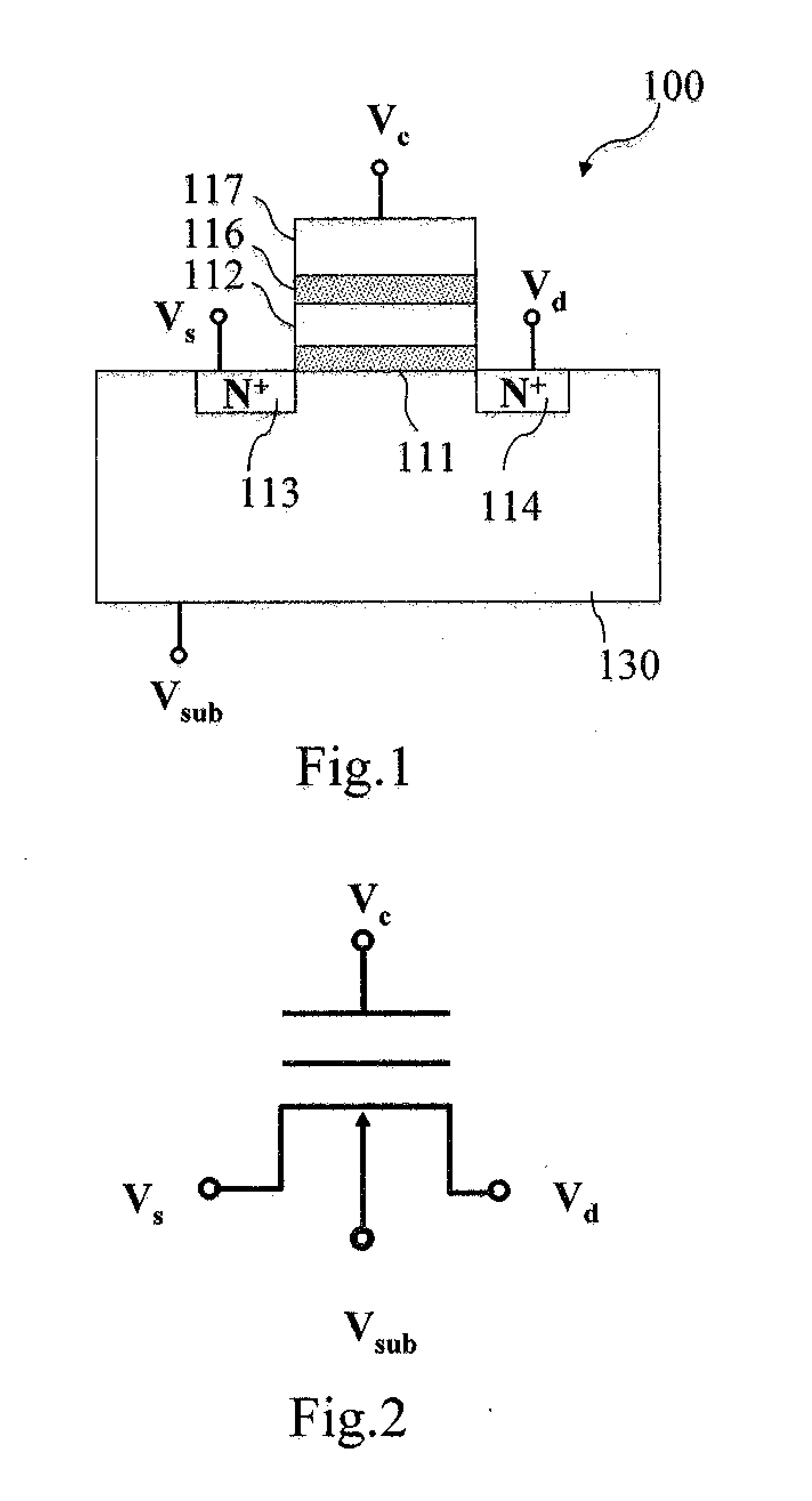

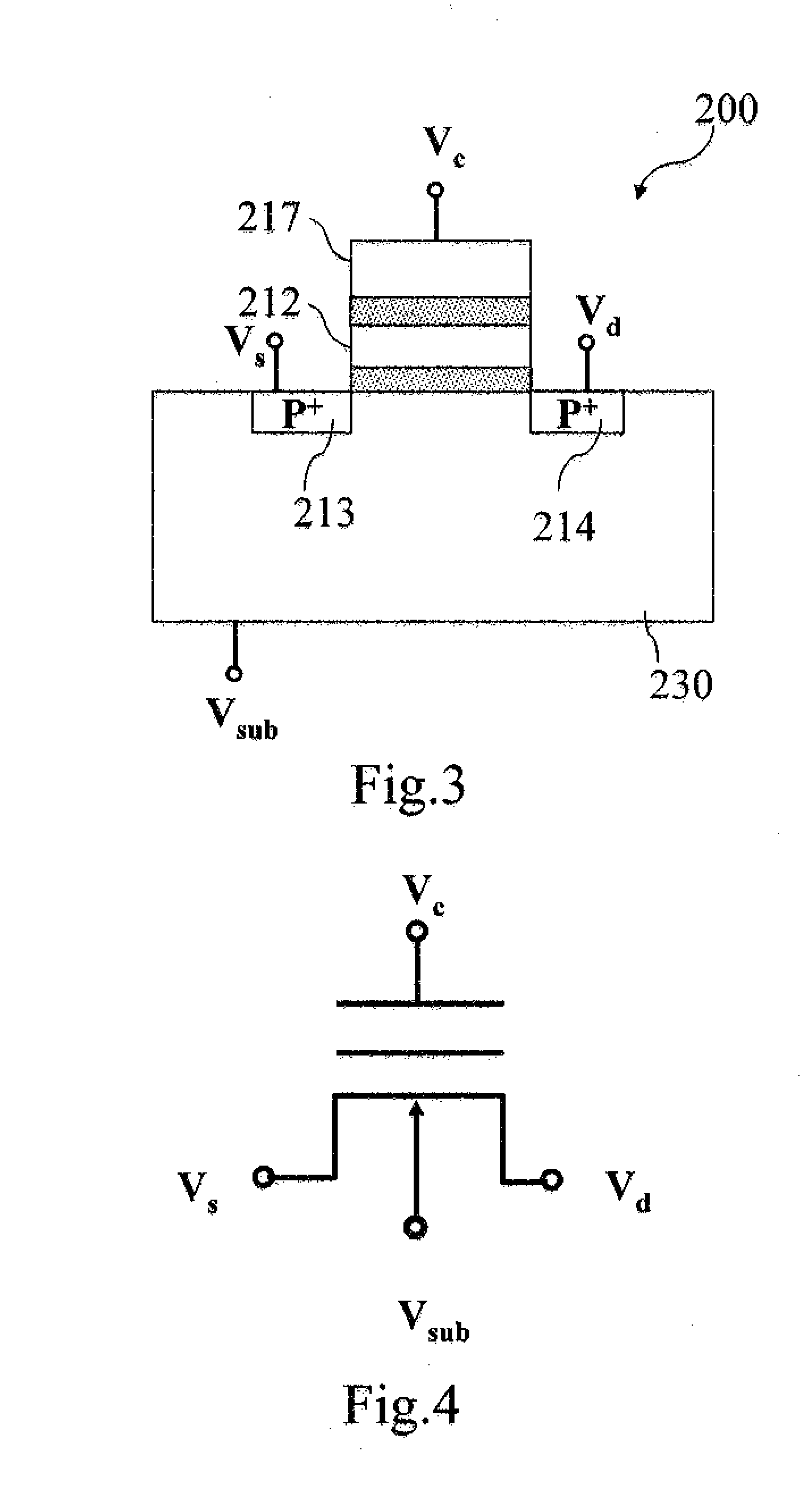

The present invention provides a high-speed low-voltage programming scheme and self-convergent high-speed low-voltage erasing schemes for Electrically Erasable Programmable Read-Only Memories. For the N-type Field Effect Transistor based NVM programming, an elevated source voltage to the substrate can achieve high efficient Drain-Avalanche-Hot-Electron Injection into the floating gate resulting in high-speed and low-voltage operations. The self-convergent and low-voltage erasing can be achieved by applying Drain-Avalanche-Hot Hole Injection with the conditions of restricted maximum drain current and a moderate control gate voltage enough to turn on the NFET. For the p-type FET based EEPROM programming, a negative source voltage relative to the substrate can achieve high efficient Drain-Avalanche-Hot-Hole Injection into the floating gate resulting in high-speed and low voltage operations. The self-convergent and low voltage erasing can be achieved by applying Drain-Avalanche-Hot-Electron Injection with the conditions of restricted maximum magnitude of drain current and a negative moderate control gate voltage enough to turn on the PFET.

Owner:YIELD MICROELECTRONICS CORP

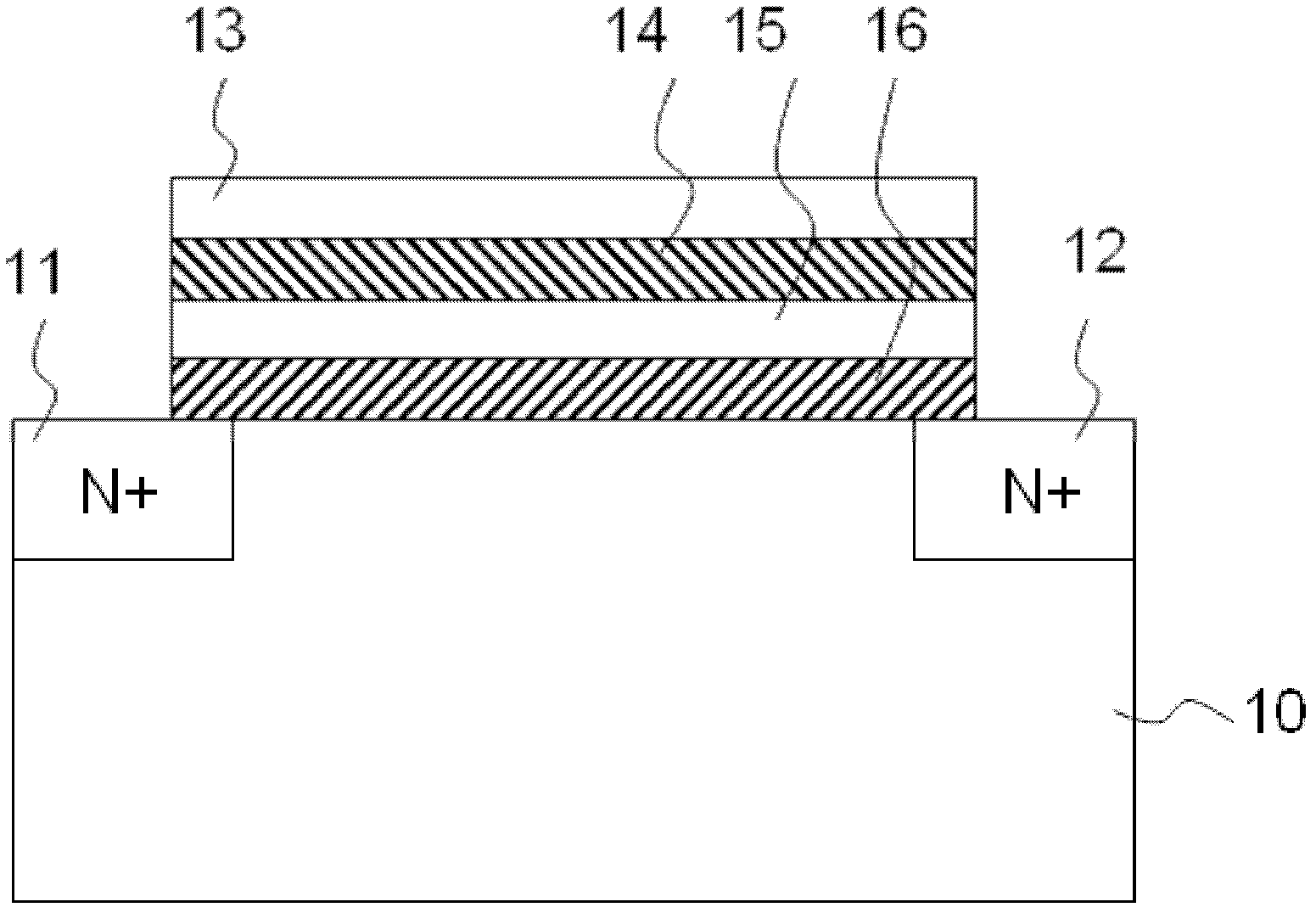

Non-volatile semiconductor memory device

InactiveUS20080258205A1Small currentLower threshold voltageRead-only memoriesSemiconductor/solid-state device manufacturingGate dielectricSilicon oxide

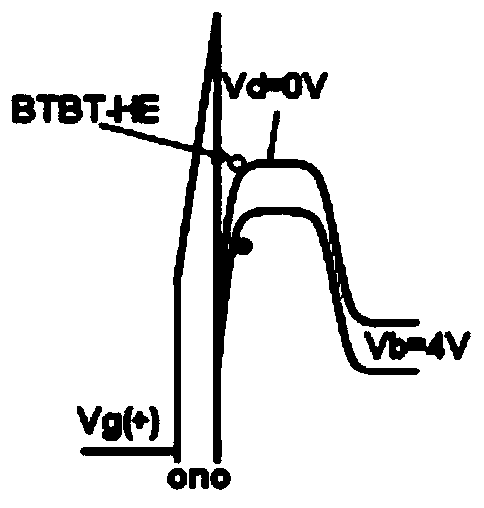

An erase current of a non-volatile semiconductor memory device is decreased. A memory cell of the non-volatile semiconductor memory device comprises a source region and a drain region formed in a semiconductor substrate. Over a portion of the semiconductor substrate between the source region and the drain region, a select gate electrode is formed via a gate dielectric film. On a side wall of the select gate electrode, a memory gate electrode is formed via a bottom silicon oxide film and a charge-trapping silicon oxynitride film. In the memory cell configured as above, erase operation is performed as follows. By applying a positive voltage to the memory gate electrode, holes are injected from the memory gate electrode into the silicon oxynitride film to decrease a threshold voltage in a program state to a certain level. Thereafter, hot holes generated by a band-to-band tunneling phenomenon are injected into the silicon oxynitride film and the erase operation is completed.

Owner:RENESAS ELECTRONICS CORP

Non-volatile memory low voltage and high speed erasure method

ActiveUS8218369B2Ultra-low operation voltageLower average currentTransistorRead-only memoriesLow voltageReverse bias

Owner:YIELD MICROELECTRONICS CORP

Non-volatile memory low voltage and high speed erasure method

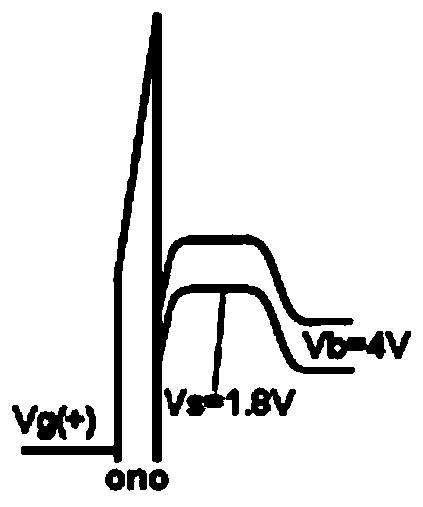

A non-volatile memory low voltage and high speed erasure method, the non-volatile memory is realized through disposing a stacked gate structure having a control gate and a floating gate on a semiconductor substrate or in an isolation well, such that adequate hot holes are generated in proceeding with low voltage and high speed erasure operation through a drain reverse bias and making changes to gate voltage. In addition, through applying positive and negative voltages on a drain, a gate, and a semiconductor substrate or well regions, adequate hot holes are generated, so as to lower the absolute voltage in achieving the objective of reducing voltage of erasing memory.

Owner:YIELD MICROELECTRONICS CORP

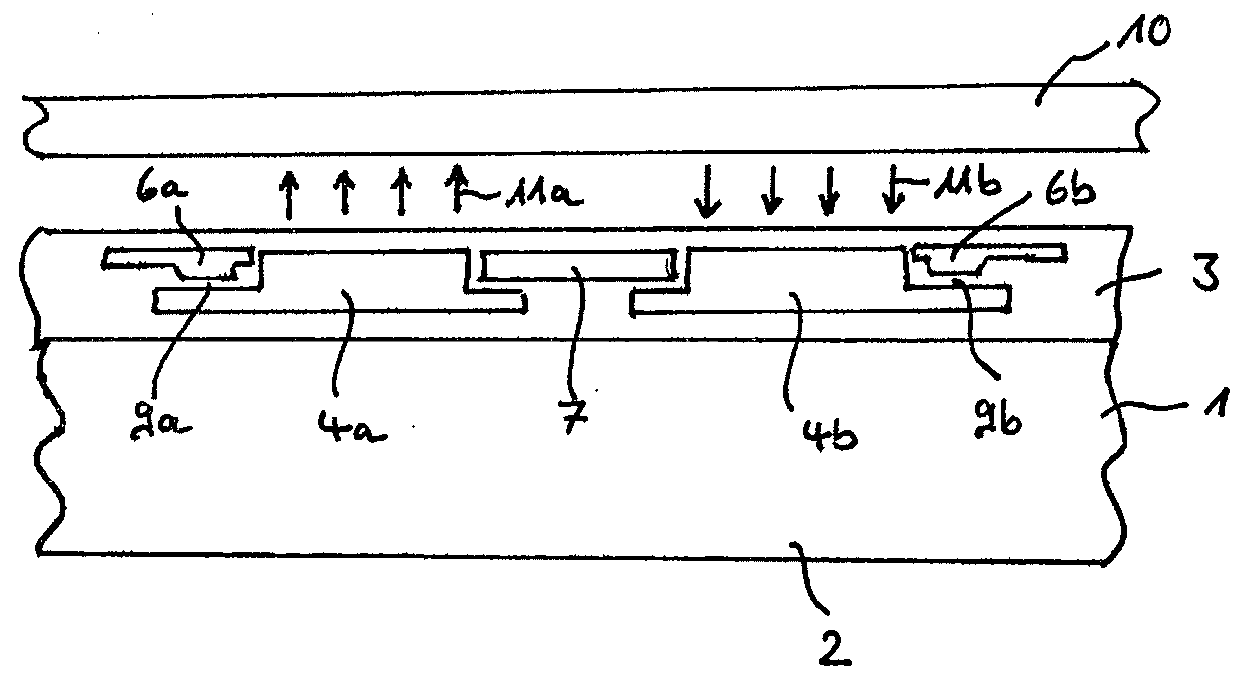

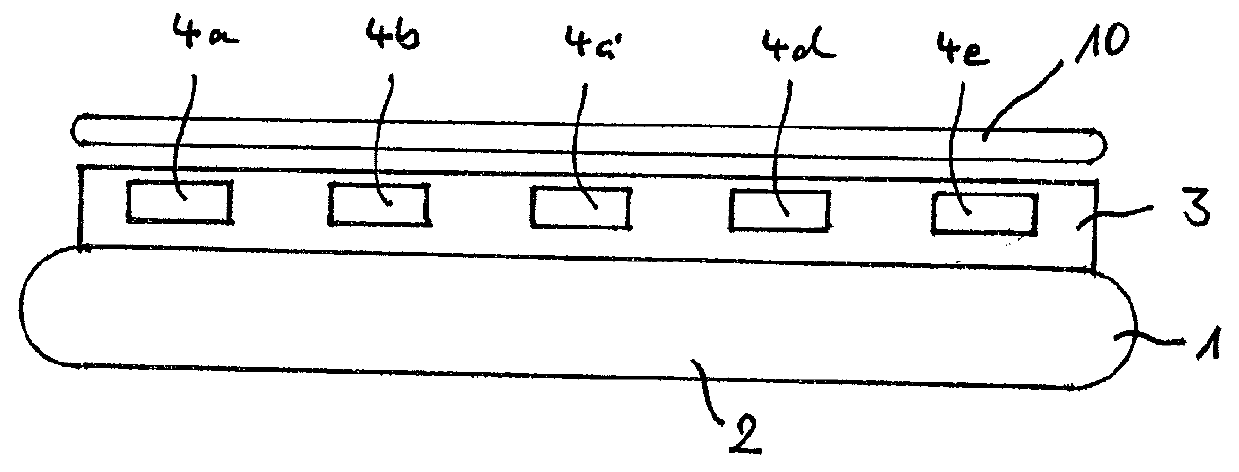

Carrier wafer, method for holding a flexible substrate and method for the manufacture of a carrier wafer

ActiveUS20160035611A1Easy to disassembleAvoid unnecessary repetitionLine/current collector detailsSolid-state devicesCharge carrierFowler nordheim

Carrier wafers are used to hold thin and ultra-thin substrates such as semiconductor components, for example. The carrier wafer of the invention has a plurality of electrodes insulated on all sides (floating electrodes). This plurality of floating electrodes, but at least 50 floating electrodes, are located next to one another with reference to the plane of the first surface of the carrier wafer. Each of these floating electrodes can be charged, for example by means of Fowler-Nordheim tunnels or by the injection of hot charge carriers, in particular of hot electrons or hot holes. Also provided are a method for holding a flexible substrate by means of a carrier wafer of this type and a method for the manufacture of a carrier wafer of this type.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

Paint processing and drying equipment

InactiveCN106813483AUniform and stable heatingSo as not to damageDrying gas arrangementsDrying machines with non-progressive movementsDual actionHot holes

The invention discloses a paint processing and drying equipment, which comprises a machine case, a material inlet is arranged on the top of the machine case, a motor is arranged at the middle position on the left side of the machine case, the inside of the machine case is divided into a drying box and a fan box by a partition, and the drying box is equipped with a There is a rotating roller connected to the motor. The rotating roller is a hollow cavity structure with a through hole. The outer circle of the rotating roller is provided with stirring teeth, and the inner part of the rotating roller is provided with a heating device. The heating device is provided with air-heating holes , the inside of the heating device is provided with a heating pipe, the right end of the heating device is connected to the air supply device through the first pipeline, the air supply device is provided with a fan, and the second pipeline is provided below the air supply device, the coating processing and drying equipment of the present invention The structure is simple, and the paint can be heated and ventilated and dried while stirring, which improves the drying speed and uniformity of the paint, and ensures the drying quality of the paint. The pipeline control realizes that the same fan has the dual functions of accelerating drying and assisting discharge. Resources are saved.

Owner:李威汉

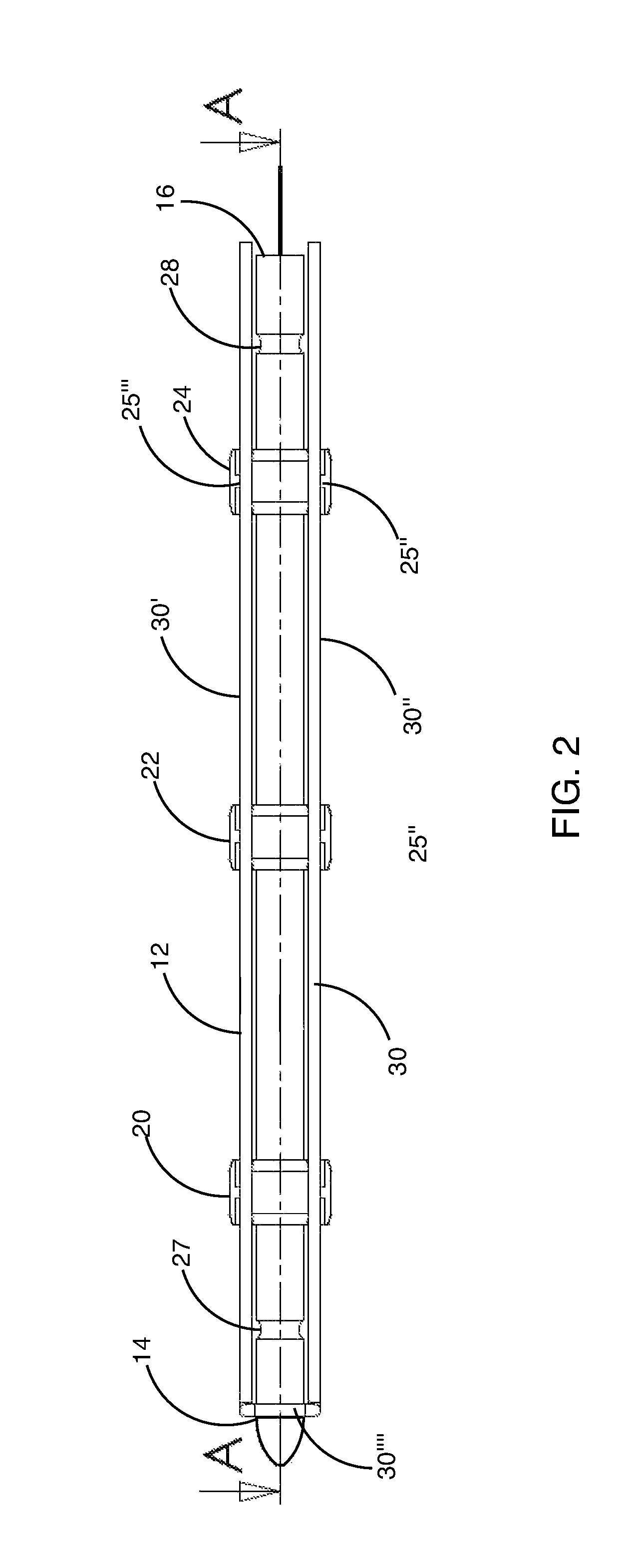

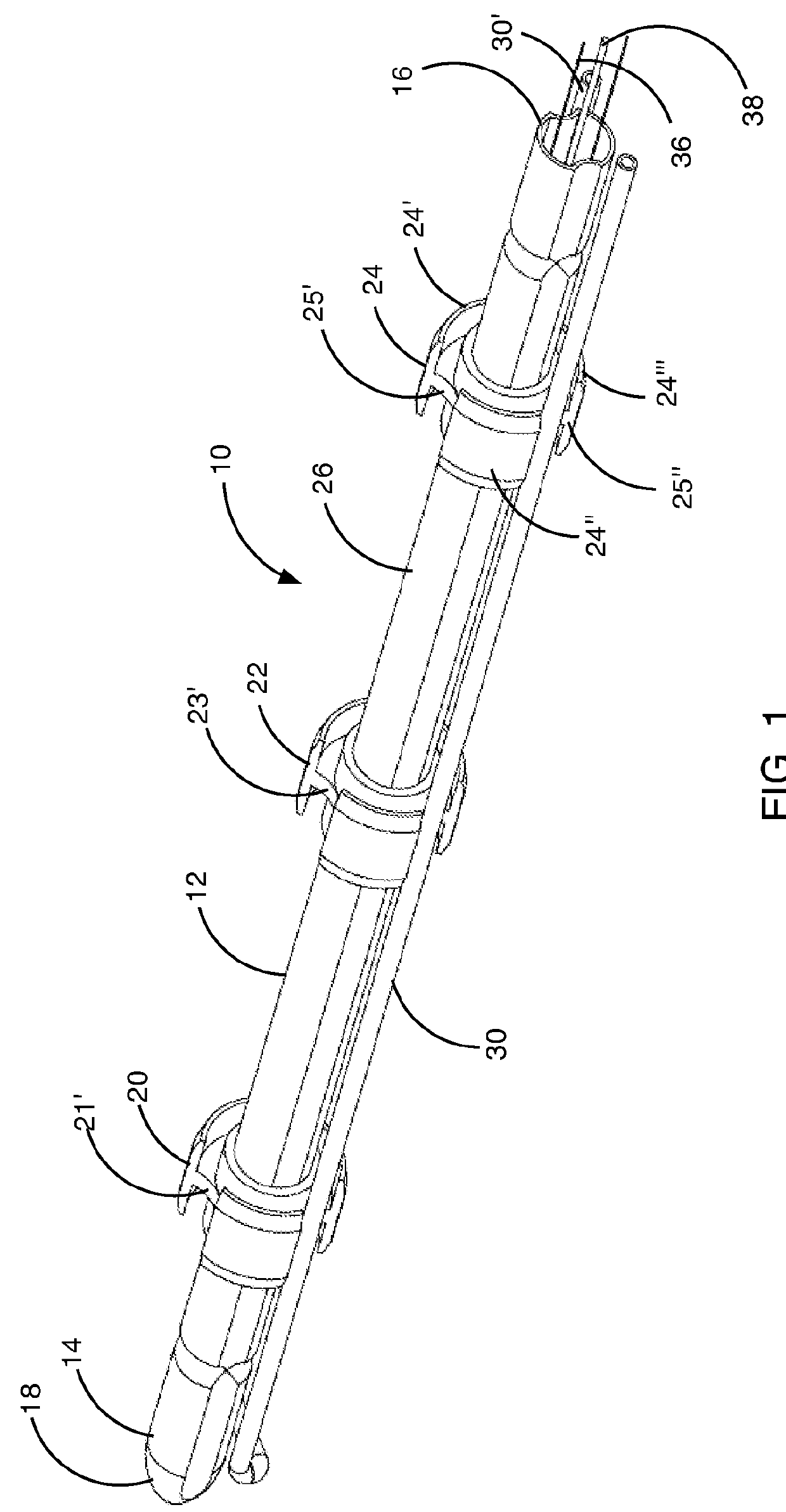

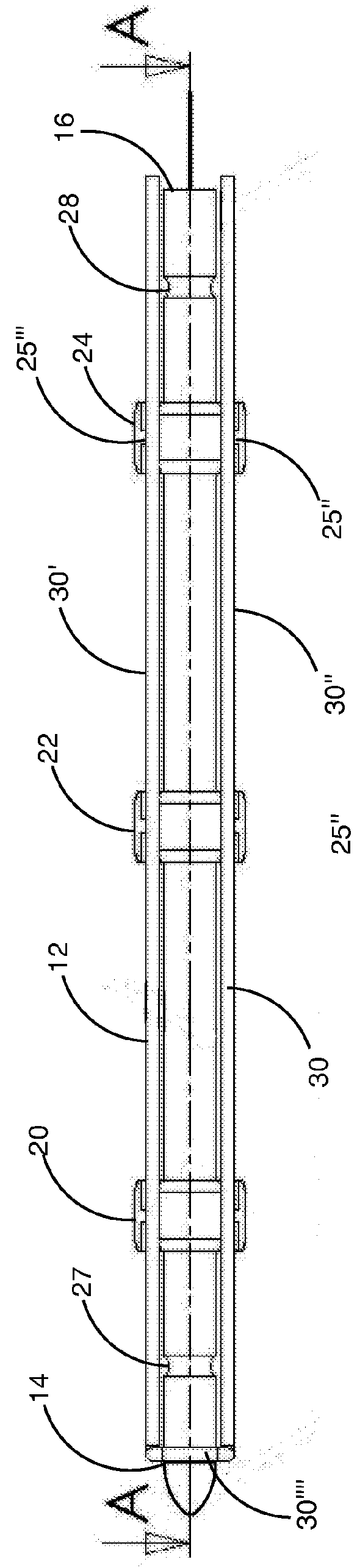

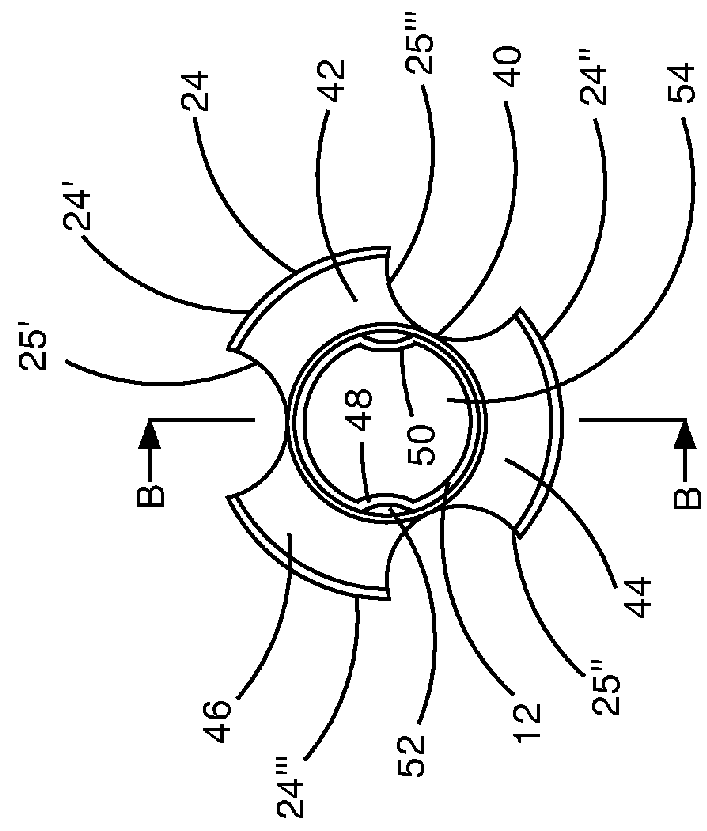

Hot hole charge system and related methods

InactiveUS20160033249A1Maximize the effectSimple and safe to useUnderground miningBlasting cartridgesHot holesEngineering

An apparatus, method and insulation medium for inserting and insulating a charge medium within a borehole includes a charge tube comprised of an elongate tube having a length and diameter sufficient for containing a desired quantity of a charge medium. A charge medium in a pumpable form is provided for substantially filling the charge tube. An insulation medium in a pumpable form is provided for substantially encapsulating the charge tube and substantially filling an annular space between the charge tube and the borehole for insulating the charge tube from a downhole environment in which the charge tube is to be inserted. The apparatus, methods and insulating medium can also be used for the improvement and repair of underground liners and installations and for improved treatment of mining and hazardous waste.

Owner:ALEXANDER BRENT DEE

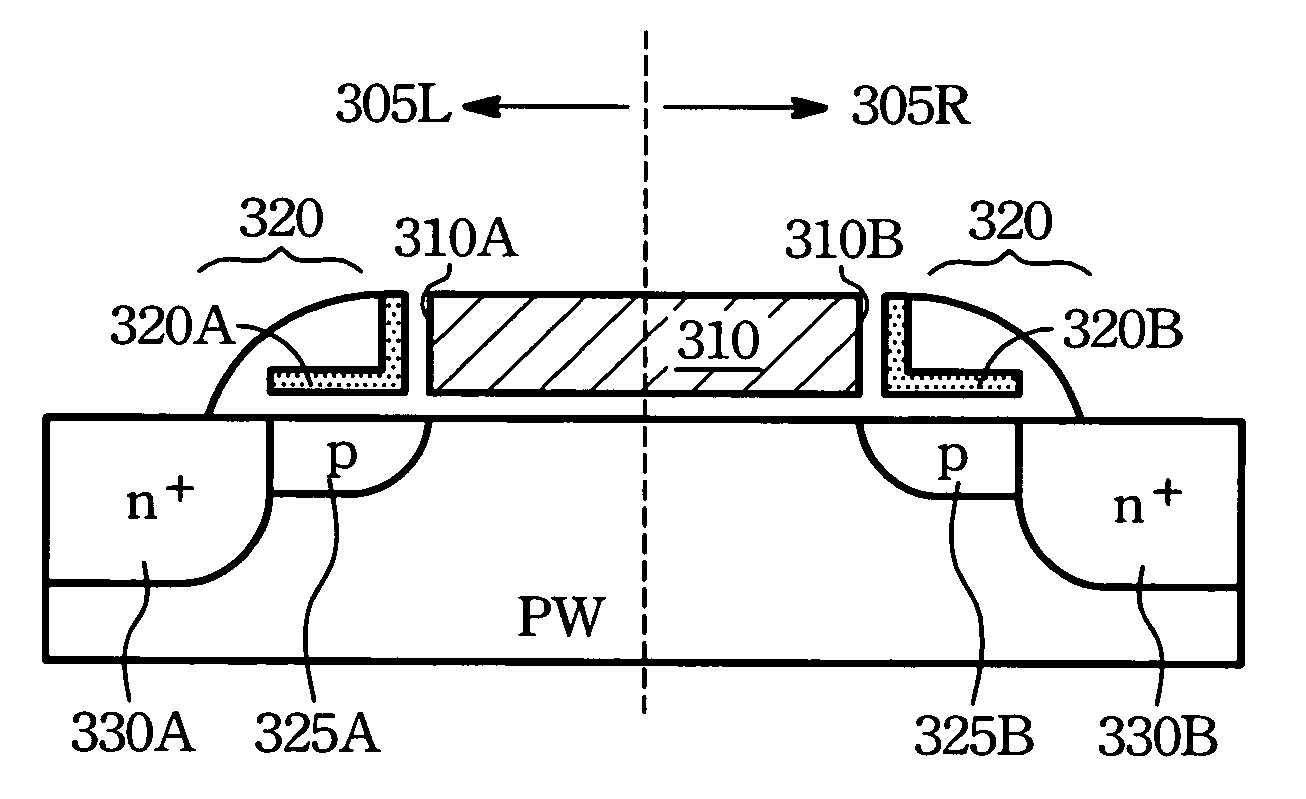

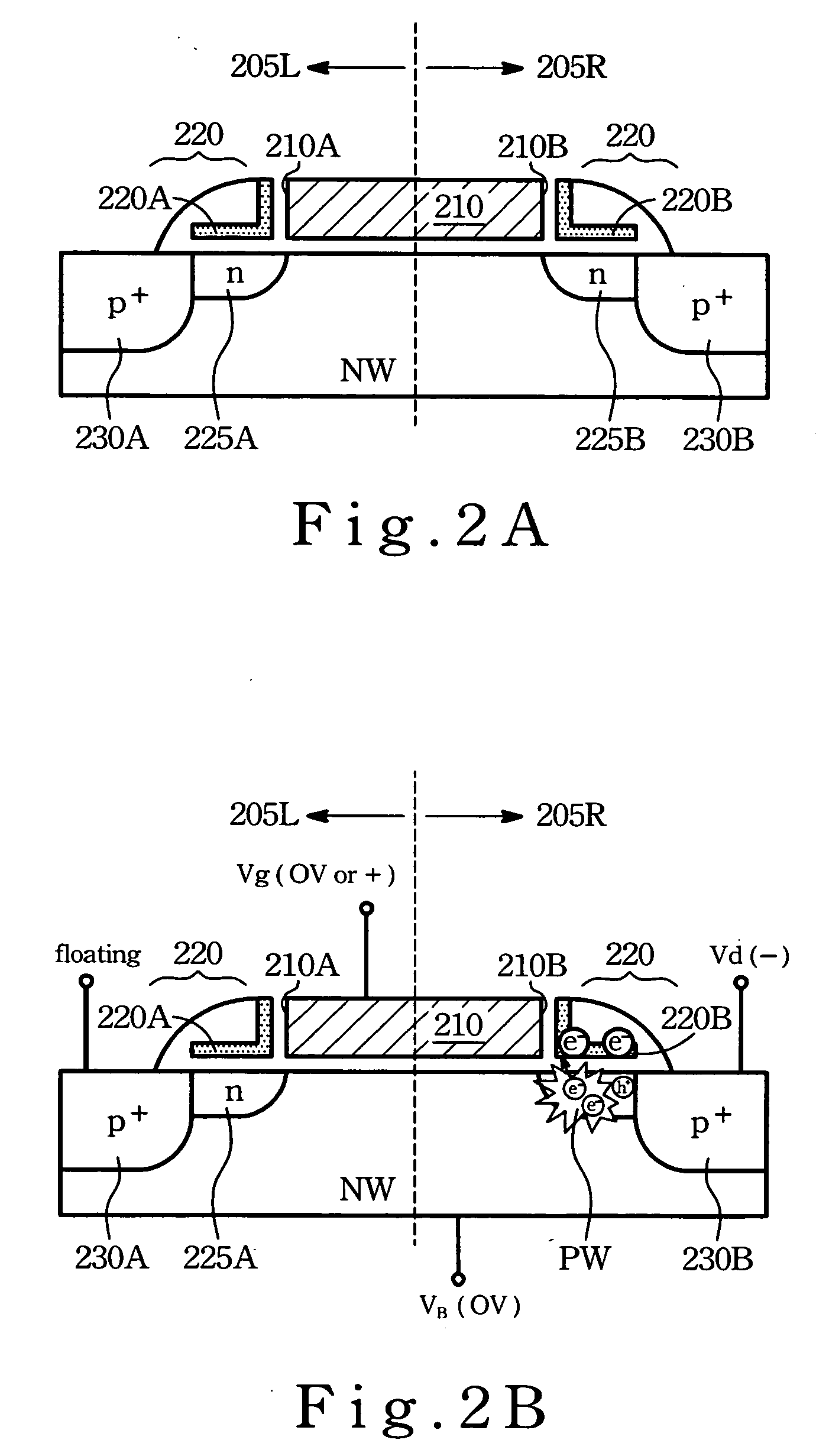

Two bits non volatile memory cells and method of operating the same

A twin non-volatile memory cell on unit device and method of operating the same are disclosed. The device is formed in the n-well and compatible with CMOS processes comprising a selecting gate, two ONO spacers, a p+ source / drain, and n extended source / drain. To program the cells, two strategies can be taken. One is by a band to band hot electron injection can be carried out. The other is by channel hot hole induced hot electron injection. To read the right cell of the twin nonvolatile cells, a reverse read is taken so as to shield the left cell. In the reading process, the biased on the selecting gate and the source electrode have to make sure the tapered main channel beneath selecting gate has its narrower end through the depletion boundary to connect the second channel beneath the extended source. To erase the datum in the selected cell, two approaching can be carried out. One is by FN erase, the other is by band to band induced hot hole injection.

Owner:EMEMORY TECH INC

Non-volatile memory with improved erasing operation

A method for performing an erase operation is disclosed in a non-volatile memory having a plurality of memory cells. At least one memory cell is programmed having a threshold voltage level in a first region before programming, and after programming the memory cell has a threshold voltage level in a second region, wherein the second region is higher in threshold voltage than the fist region. The erasing operation implements a programming of memory bits that can inject negative charge carriers or electrons into a memory cell instead of using the conventional technique of injecting hot holes into the memory cell. This can avoid room temperature drift and charge loss caused by hot hole injection.

Owner:MACRONIX INT CO LTD

Low voltage non-volatile memory with charge trapping layer

ActiveUS7969785B1Reduce power consumptionReadily apparentRead-only memoriesDigital storageTrappingLow voltage

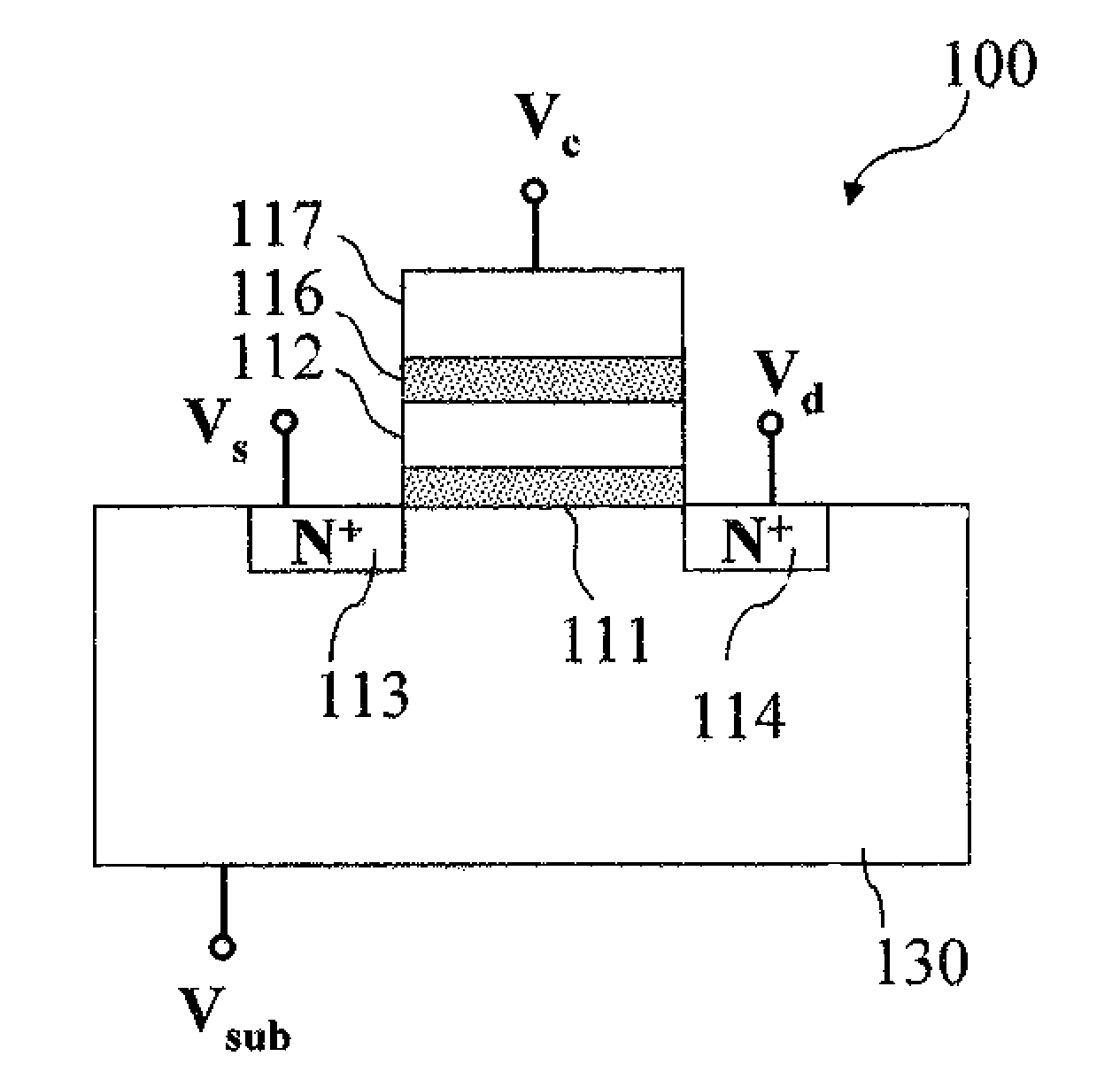

Methods, circuits, processes, devices, and / or arrangements for a non-volatile memory (NVM) cell operable at relatively low voltages are disclosed. In one embodiment, an NVM cell can include: (i) a gate over a charge trapping layer, the charge trapping layer being insulated from the gate by a first insulating layer, the charge trapping layer being insulated from a channel by a second insulating layer; and (ii) source and drain on either side of the channel, the channel being under the second insulating layer, where the NVM cell is configured to be erased by channel-induced hot holes (CHH).

Owner:CHEMTRON RES

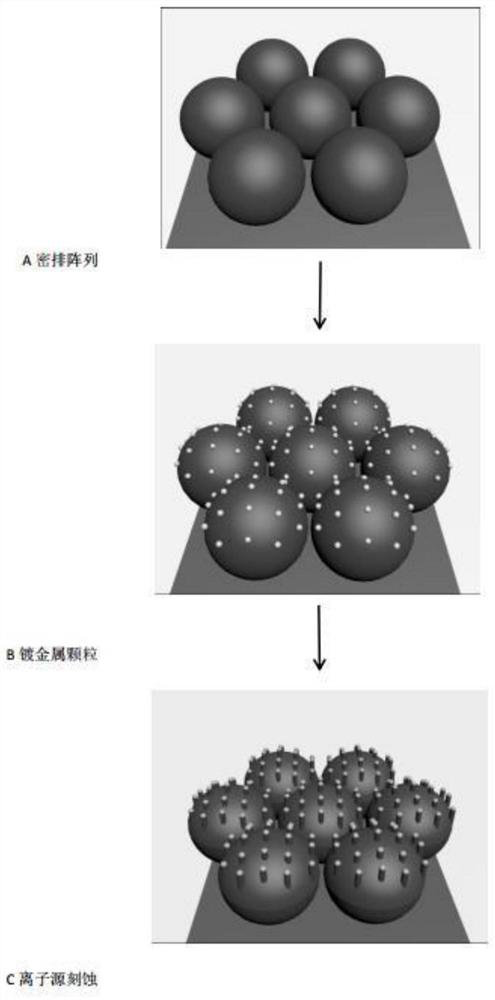

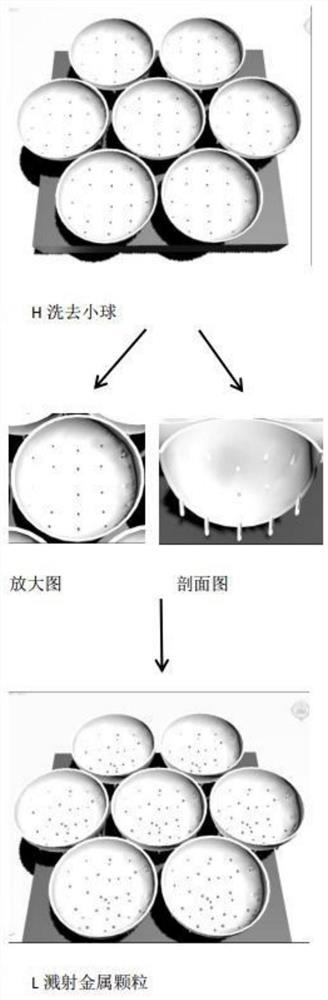

Preparation method of hollow nano bowl-shaped structure, nano material and application

ActiveCN113512708AEasy transferHigh catalytic efficiencyMaterial nanotechnologyVacuum evaporation coatingNano structuringMaterials science

The invention provides a preparation method of a hollow nano bowl-shaped structure, a nano material and application. Firstly, a hollow copper nano bowl-shaped structure is obtained through magnetron sputtering and plasma etching, light is irradiated on the hollow copper nano bowl, the chemical interaction between adsorption molecules and the metal surface can be enhanced, comprising chemical bond enhancement, surface hybridization resonance enhancement, phonon-induced charge transfer enhancement and the like. The composite nano structure grows on a silicon wafer, local surface plasmon polaritons on the composite structure are excited through light irradiated on the composite structure, and transfer of charges in the nano structure is accelerated through hot electrons, hot holes and chemical energy excited by metal local surface plasmon polaritons, so that the catalytic efficiency is improved, and the catalysis of CO2 is enhanced through the surface plasmon polariton effect of gold and copper. The preparation cost is low, the preparation process is simple, and the method can be effectively copied and applied on a large scale.

Owner:HANGZHOU DIANZI UNIV

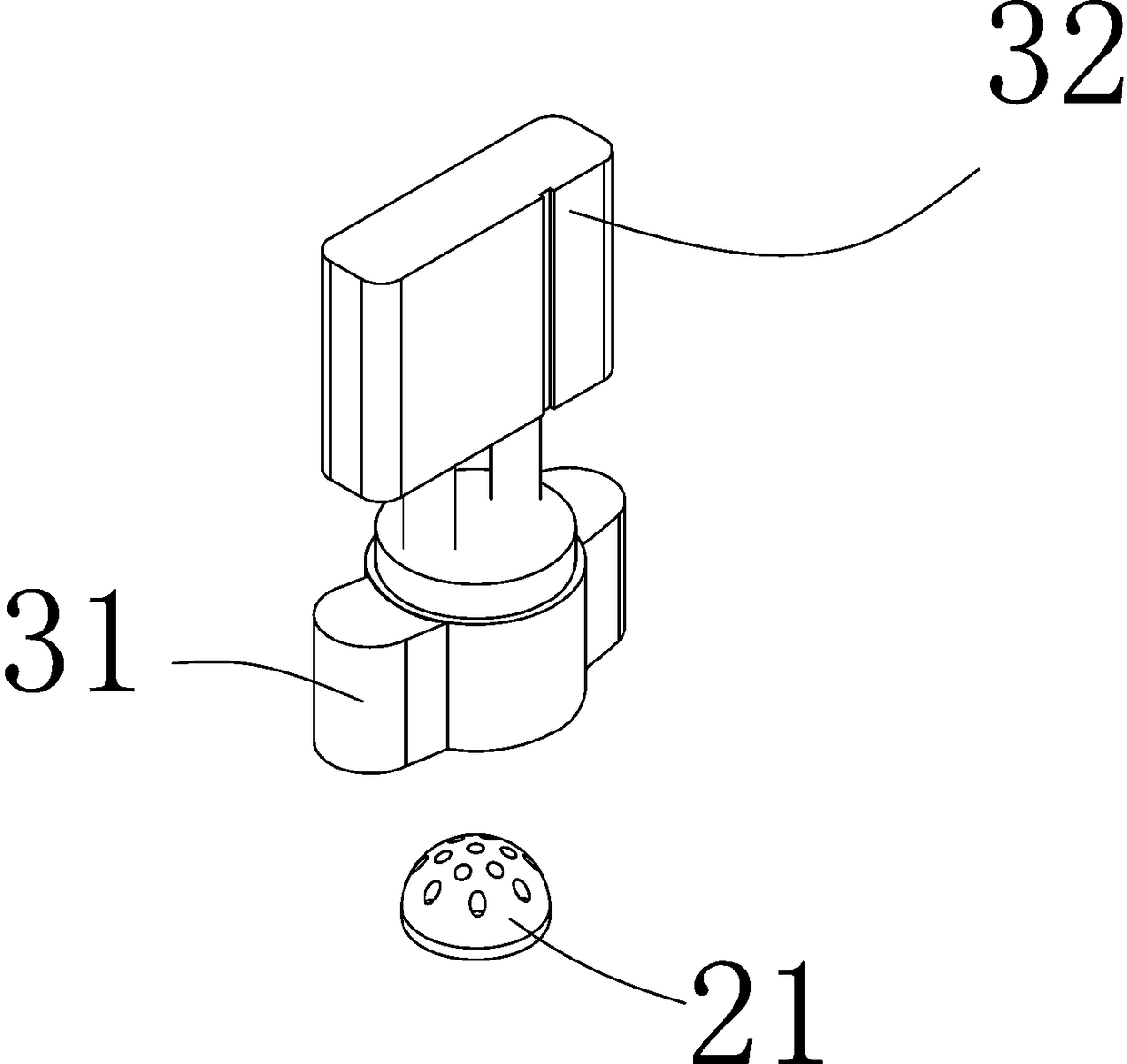

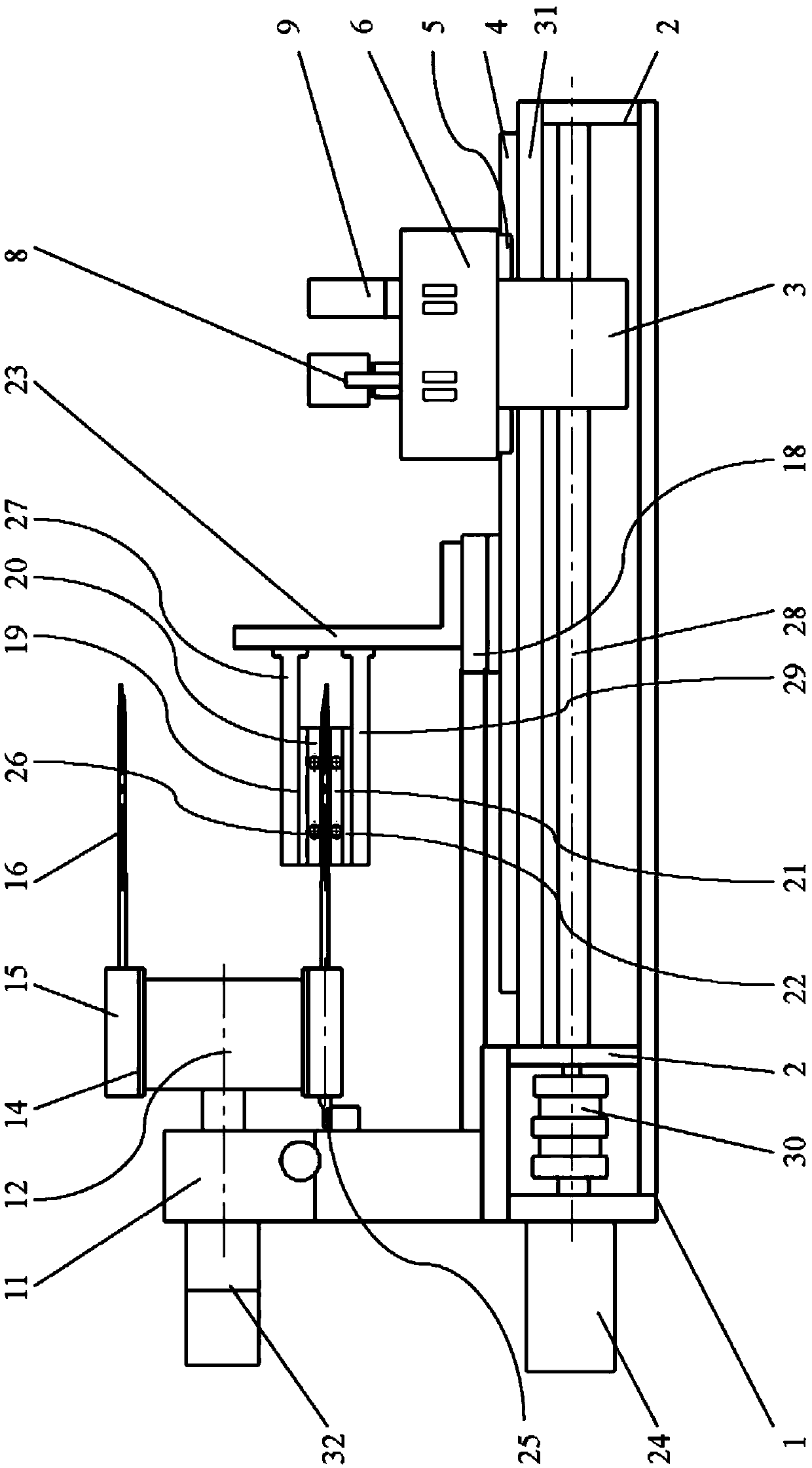

A perforating unit device

The invention discloses a hole ironing unit device which comprises a base. A bottom pit is formed in the base and communicated with an air pump. By changing a mode, forming is firstly implemented, drilling is secondly implemented, drilled holes are ironed in a coil heating manner, the device effectively solves the problems of deformation of the holes and edge layering of the holes, the holes of an interlayer of each mask are kept consistent, and waste of raw materials is reduced.

Owner:SUZHOU XINENG ENVIRONMENTAL SCI & TECH CO LTD

Methods and systems for removing diamond-diamond bonding catalysts from polycrystalline diamond

Methods for removing, or leaching, cobalt or other diamond-diamond bonding catalysts from polycrystalline diamond compacts (PDCs) or other structures formed from polycrystalline diamond include leaching under conditions that simulate use of PDCs in a hot hole drilling environment. A leaching agent may be formulated, when used under appropriate conditions, to remove or substantially remove cobalt or another catalyst from polycrystalline diamond without dissolving, degrading or otherwise attacking a substrate that supports or carries the polycrystalline diamond. The leaching agent may include one or more components that mimick the chemicals or conditions to which a PDC would be exposed in a hot hole drilling environment. Polycrystalline diamond structures from which cobalt or another diamond-diamond bonding catalyst has been removed or substantially removed are also disclosed, as are systems for leaching cobalt or other diamond-diamond bonding catalysts from polycrystalline diamond.

Owner:EVE BIT SALES

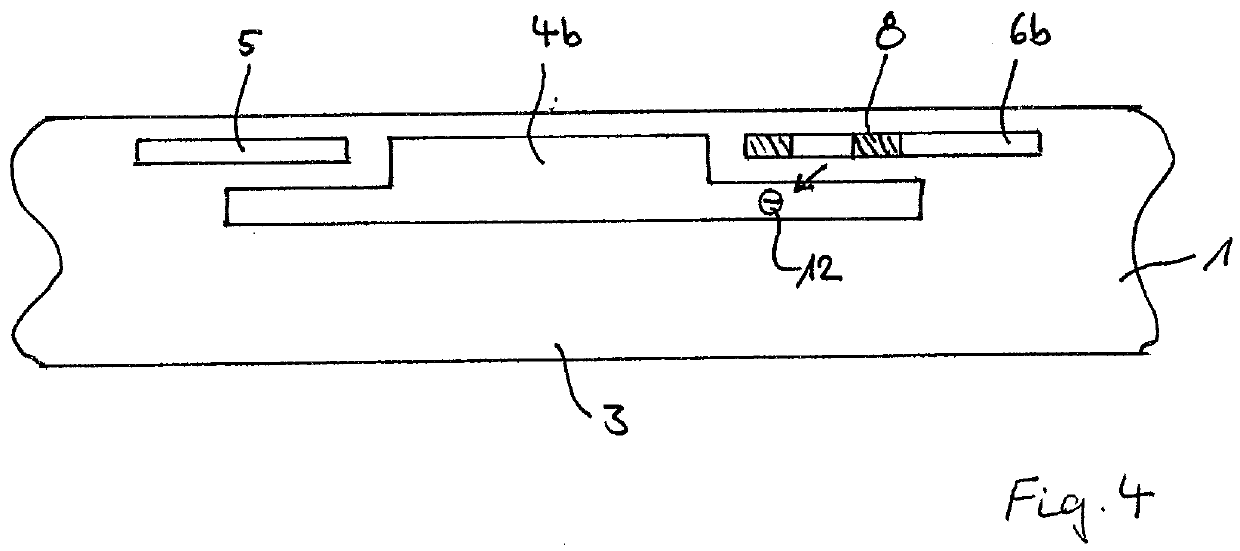

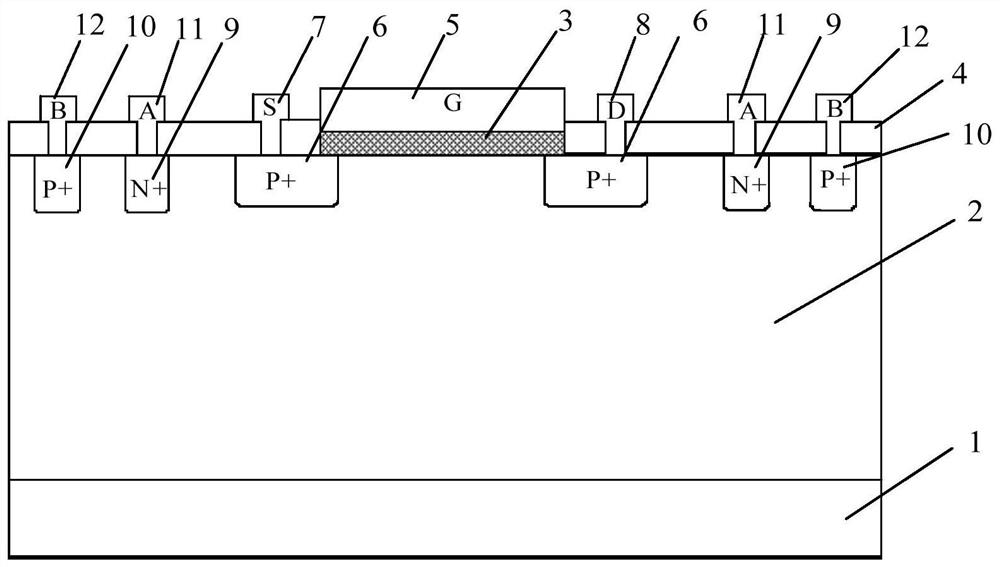

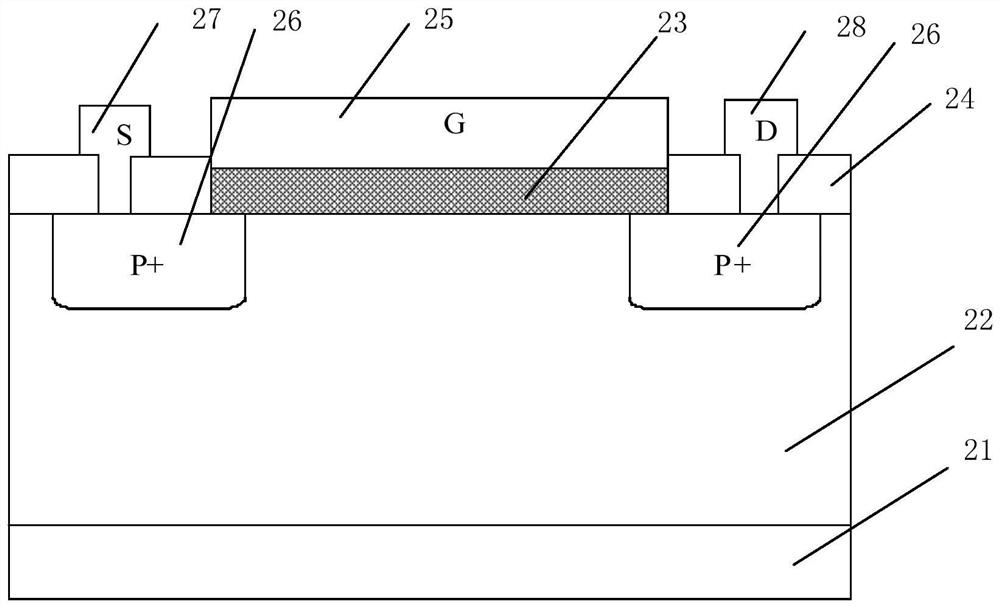

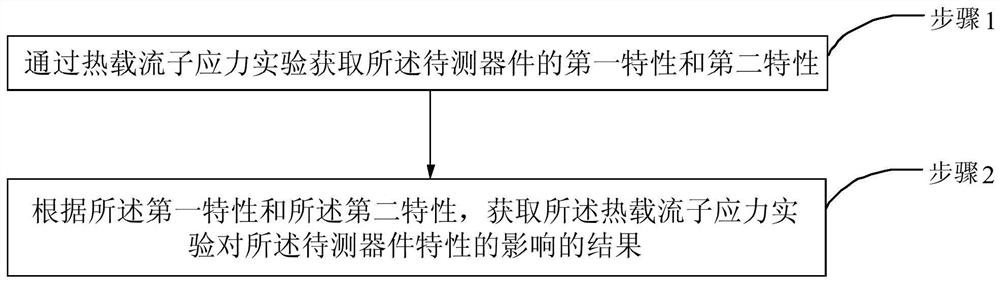

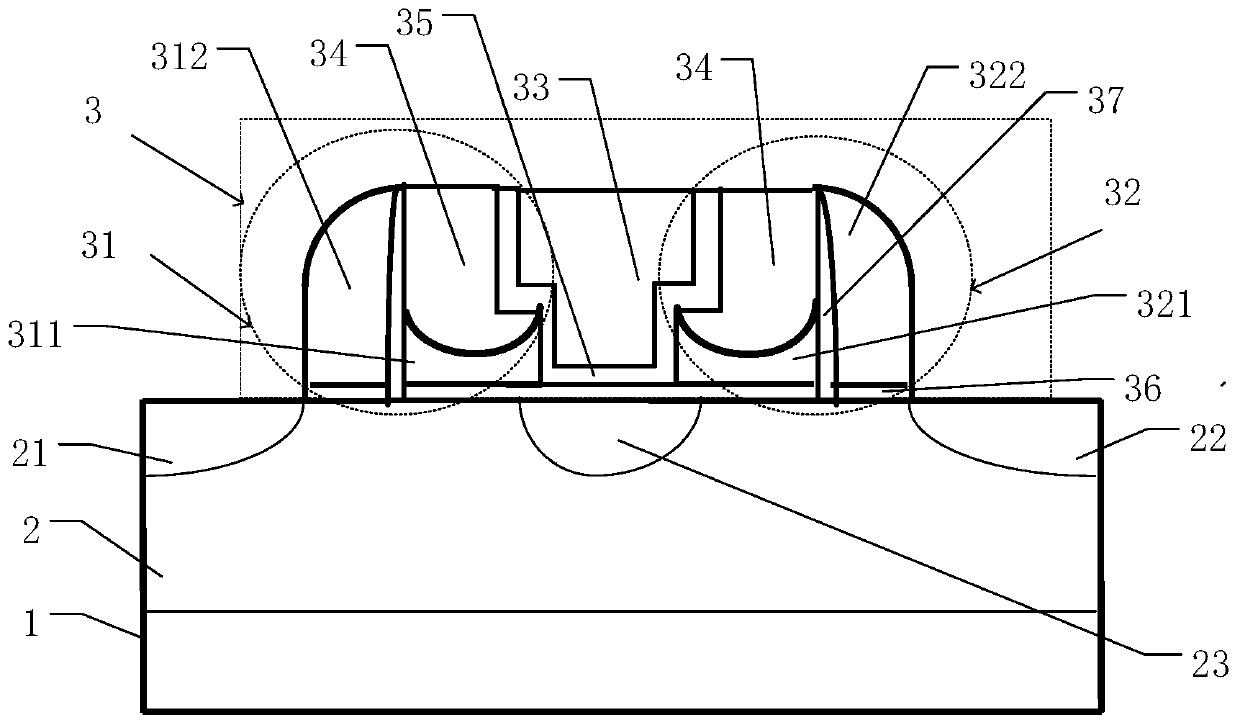

Structure for testing hot hole effect of compound MISFET device, and characterization method thereof

ActiveCN111668126AAdjustable injection quantityAdjustable bias voltage (Vb-Va) to control the amount of injectionSemiconductor/solid-state device testing/measurementHeterojunctionEngineering

The invention relates to a structure for testing the hot hole effect of a compound MISFET device. The structure comprises a substrate (1), an N type epitaxial layer (2), an insulating layer (3), a passivation layer (4), a gate (5), a first P+ doped region (6), a source electrode (7), a drain electrode (8), an N+ doped region (9), a second P+ doped region (10), an electrode A (11) and an electrodeB (12). The embodiment of the invention provides a structure for testing a hot hole effect of a compound MISFET device by a hot hole injection quantity and energy controllable technology, and a characterization method thereof, wherein the injection quantity of hot holes in an insulating layer is controlled by adjusting a voltage Va and a voltage Vb, and the injection energy of the hot holes in theinsulating layer is controlled by adjusting the voltage Va, so that the problems that the injection quantity and the injection energy of the hot holes of the device are uncontrollable, the insulatinglayer is non-uniformly injected and the like are solved, and the deep analysis of the hot hole effect in the heterojunction device is facilitated.

Owner:XIDIAN UNIV

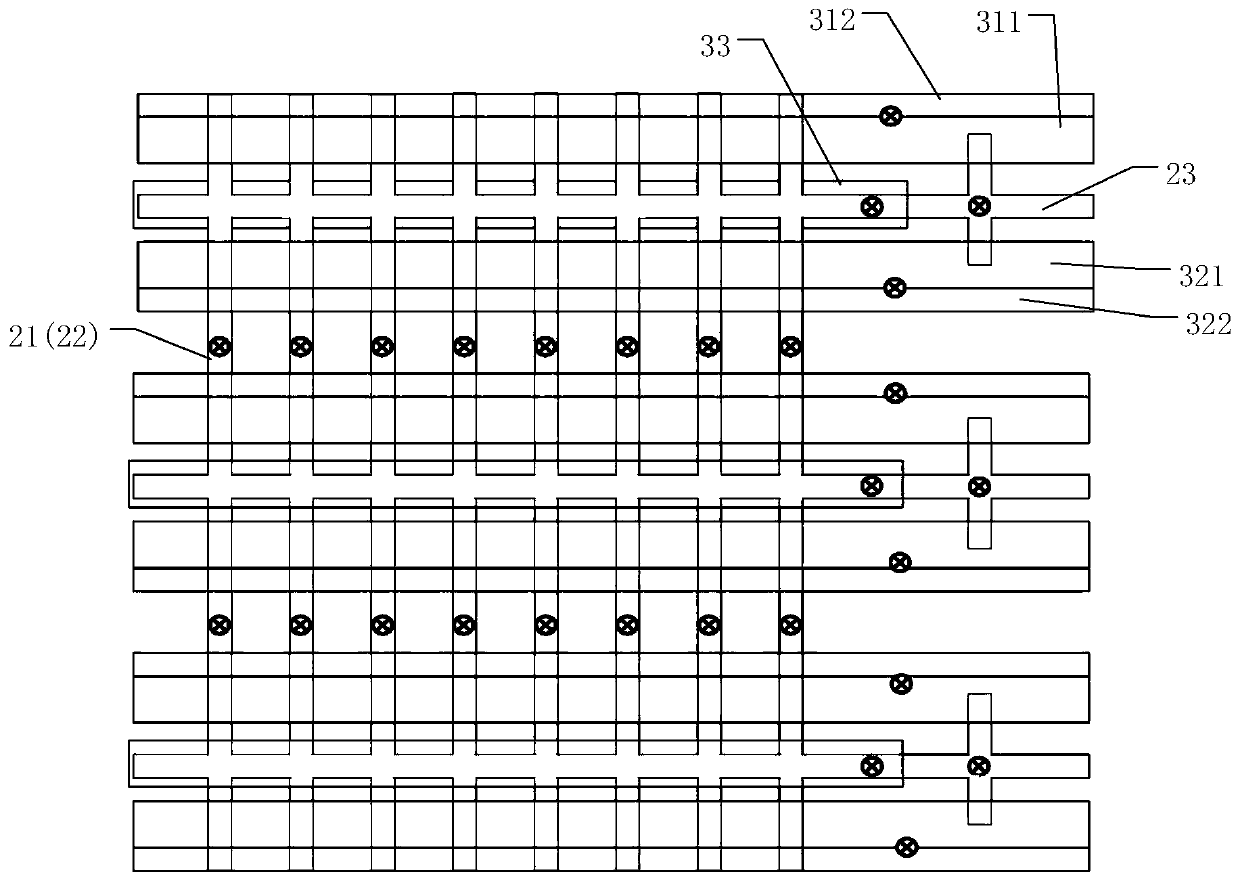

Flash memory cell, flash memory array and method of operation thereof

ActiveCN107658301BReduce areaSimple designSolid-state devicesRead-only memoriesMiniaturizationHemt circuits

The invention provides a flash memory unit, a flash memory array and an operation method thereof, comprising: an N well is formed in a P-type substrate, a P-type doped region is formed in the N well, and the P-type doped region is used as the first A source, a second source, and a drain; the gate structure on the N well is located between the first source and the second source, and the gate structure has a symmetrical shape about the erasing gate Two storage bits, each containing a floating gate and a word line gate. The flash memory unit provided by the present invention is programmed by generating high-energy electrons or even hot electrons through the collision ionization of hot holes at the drain pinch-off point, which is beneficial to the miniaturization of the device and achieves the purpose of reducing the area of the device unit, and the flash memory unit provided by the present invention With a special erasing gate, it can be erased without applying high voltage to the word line gate, so that the second oxide layer under the word line gate can be made very thin, so the read voltage can be very small, which simplifies the design of the read circuit .

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

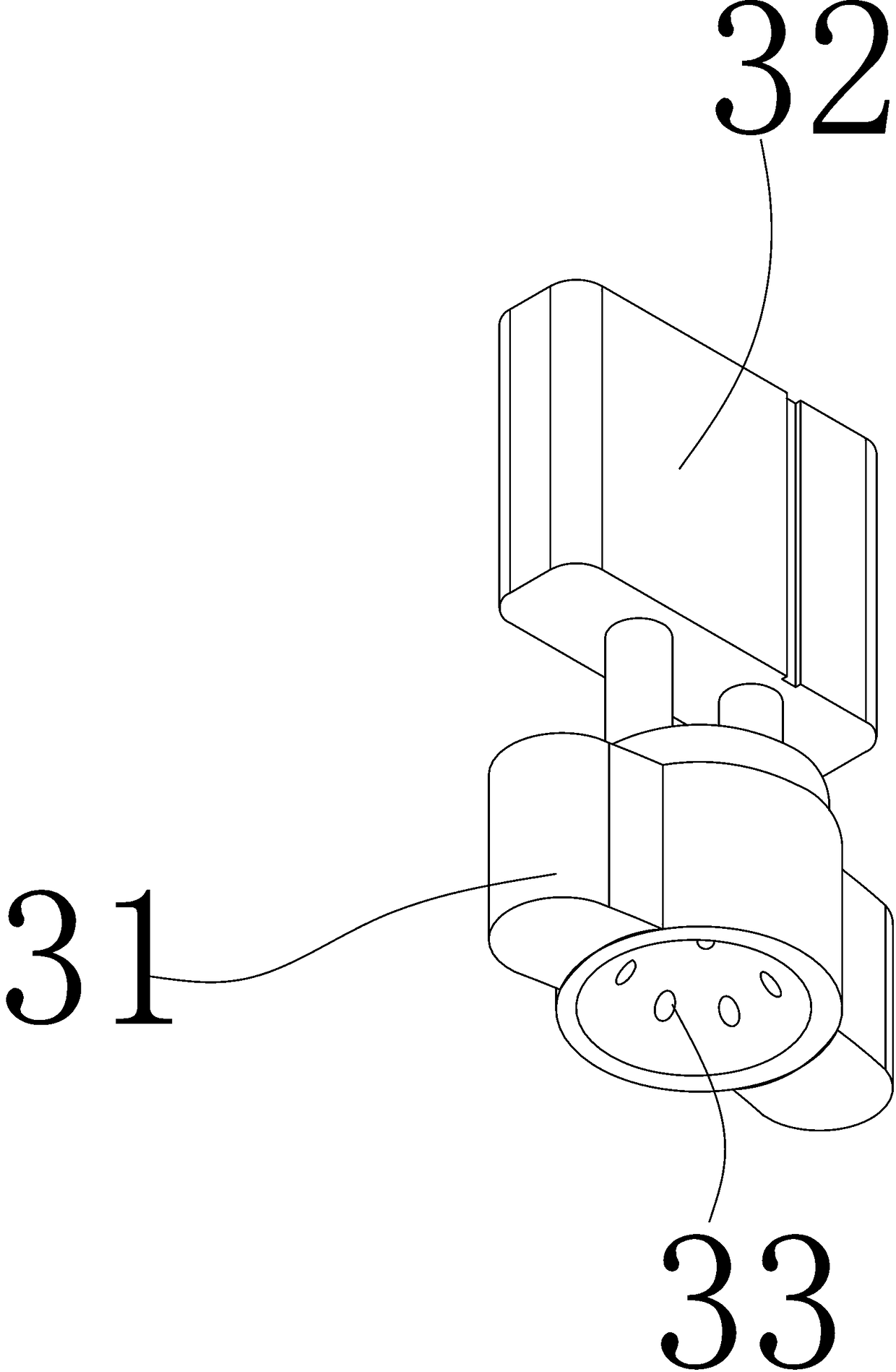

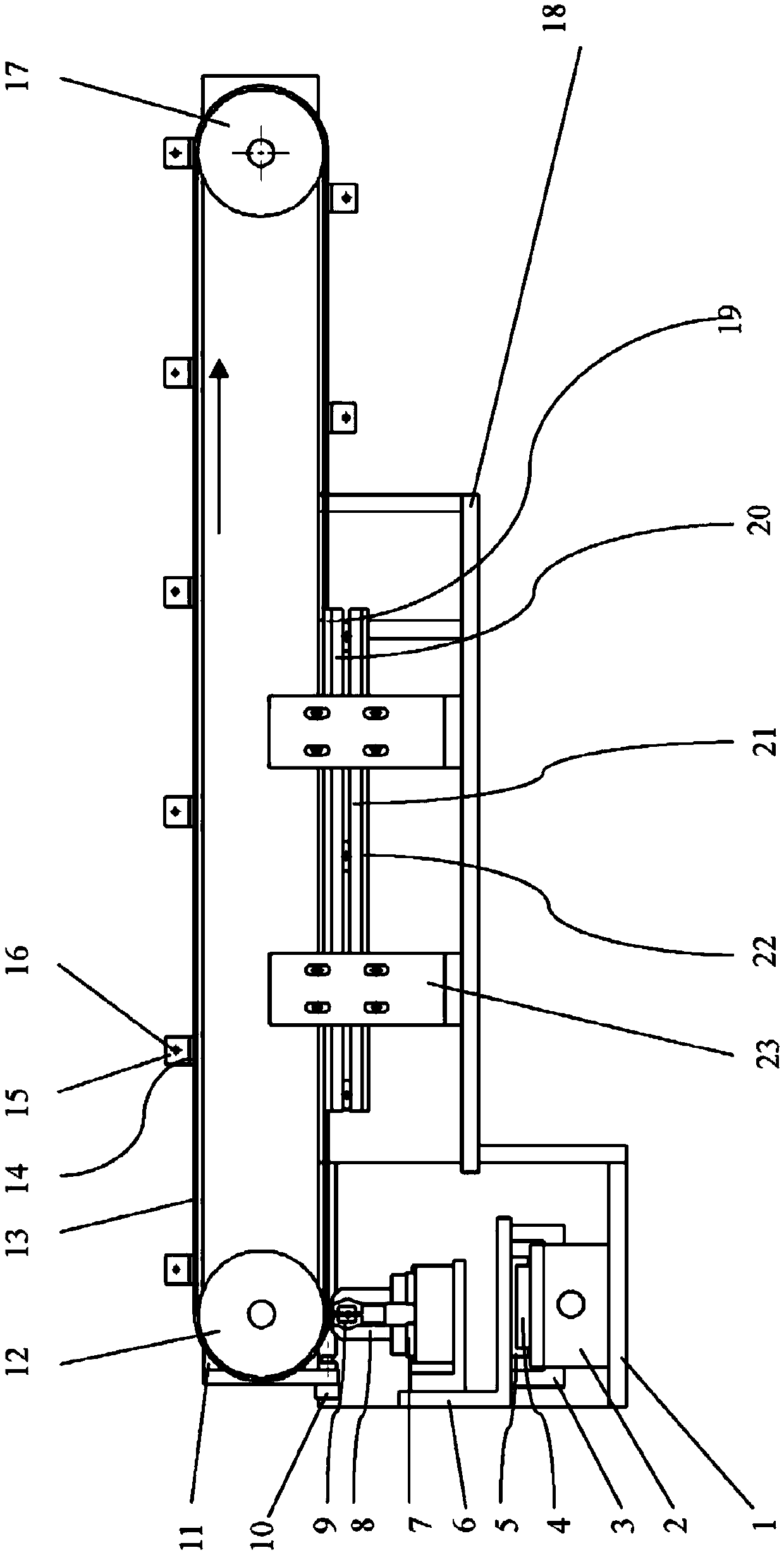

Lithium battery cell hot needle reaming device

ActiveCN106099200BAccurate insertionFull heating timeFinal product manufactureElectrolyte accumulators manufactureGear wheelEngineering

The invention relates to a device for reaming needles for lithium battery cells, which is characterized in that it includes a cell clamping and moving mechanism, a scalding needle transmission mechanism, and a scalding needle heating mechanism; the cell clamping and moving mechanism includes a The cell gripper, the guide gripper of the cell, and the cell moving mechanism that drives the cell gripper and the guide gripper to move to the reaming station, and the guide gripper is provided with a guide hole coaxial with the cell; The needle ironing transmission mechanism includes a driving sprocket, a driven sprocket and a chain wound between the driving sprocket and the driven sprocket, and a plurality of ironing installation plates are fixed on the chain, and the ironing installation plates are installed Go to the needle ironing seat with heat insulation effect, and install the ironing needle on the needle ironing seat. The invention can accurately and quickly complete the ironing hole in the center of the circular battery core, and can avoid damage to the transmission chain caused by the high temperature of the ironing needle.

Owner:WUXI LEAD INTELLIGENT EQUIP CO LTD

An n-channel non-volatile flash memory device and methods for compiling, erasing and reading the same

ActiveCN105097821BSmall gate lengthReduce surplusSolid-state devicesSemiconductor devicesSilicon oxideP type silicon

The invention discloses an N-channel non-volatile flash memory device, which includes: a P-type silicon substrate, with N-type doped source terminals, drain terminals and N-channels in the substrate; The gate structure on the substrate between them includes, from bottom to top, a gate oxide layer, a polysilicon floating gate, a first silicon dioxide layer, a silicon nitride layer, a second silicon dioxide layer and a polysilicon control gate. , the polycrystalline silicon floating gate is used to store charges; the flash memory device proposed by the invention uses a low-power band tunneling hot hole injection compiler and a channel FN electron tunneling and erasing method, which solves the problem of the original channel hot electron Injecting the problem of high power consumption in programming can make the traditional floating-gate transistor structure have a smaller gate length and overcome the erase saturation problem that traditional p-channel B4-Flash cannot solve, making it easier to manufacture.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

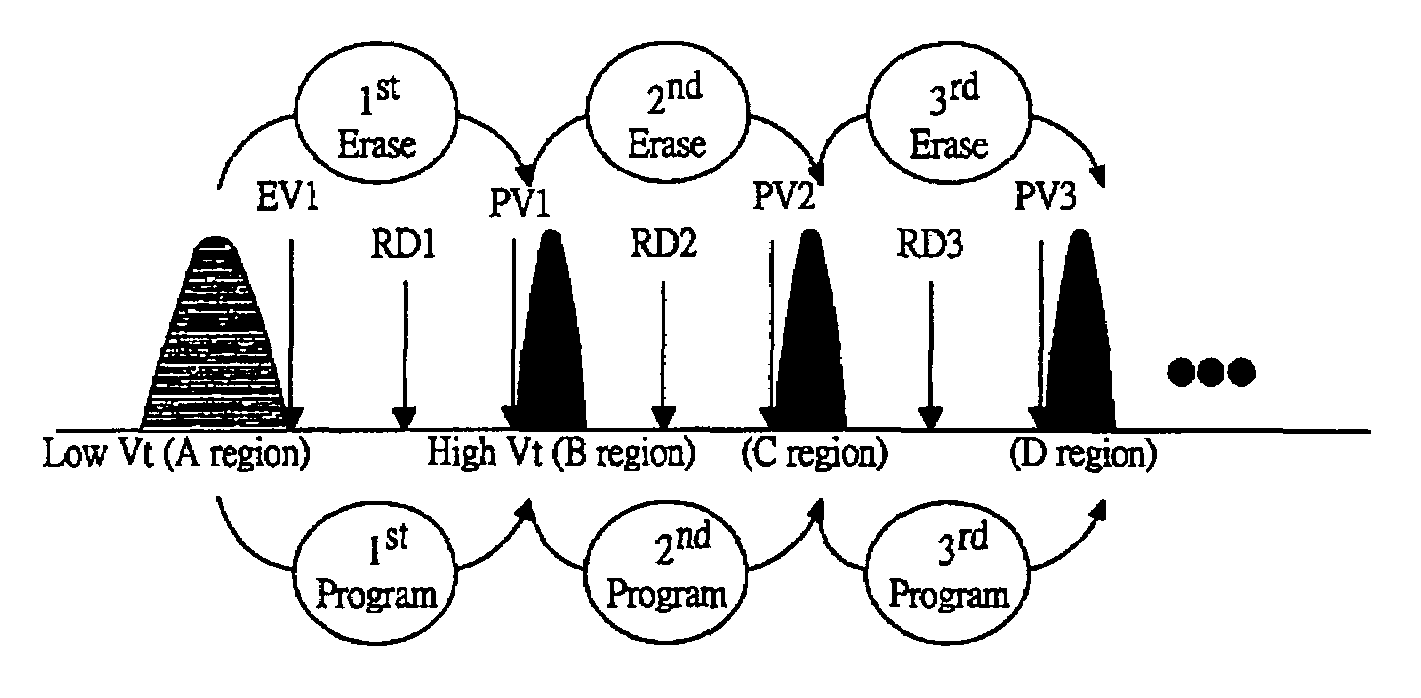

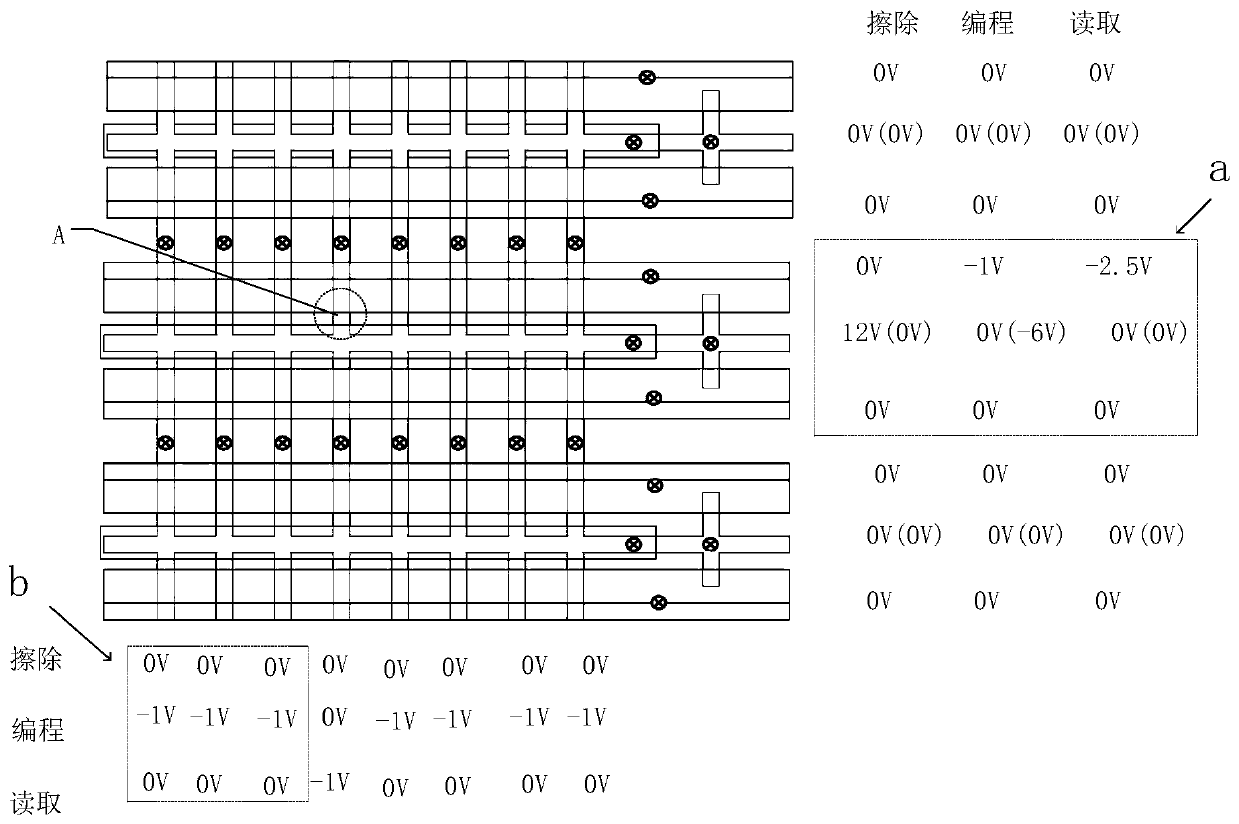

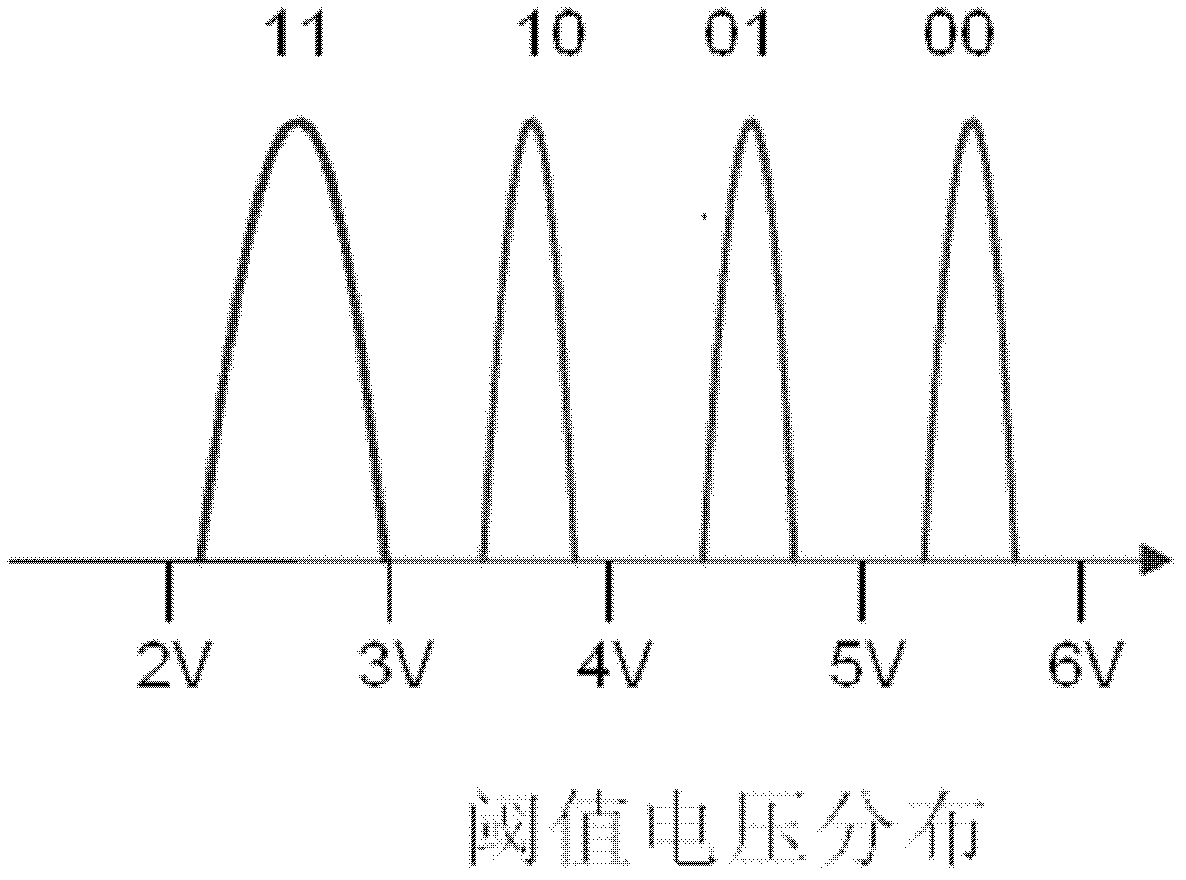

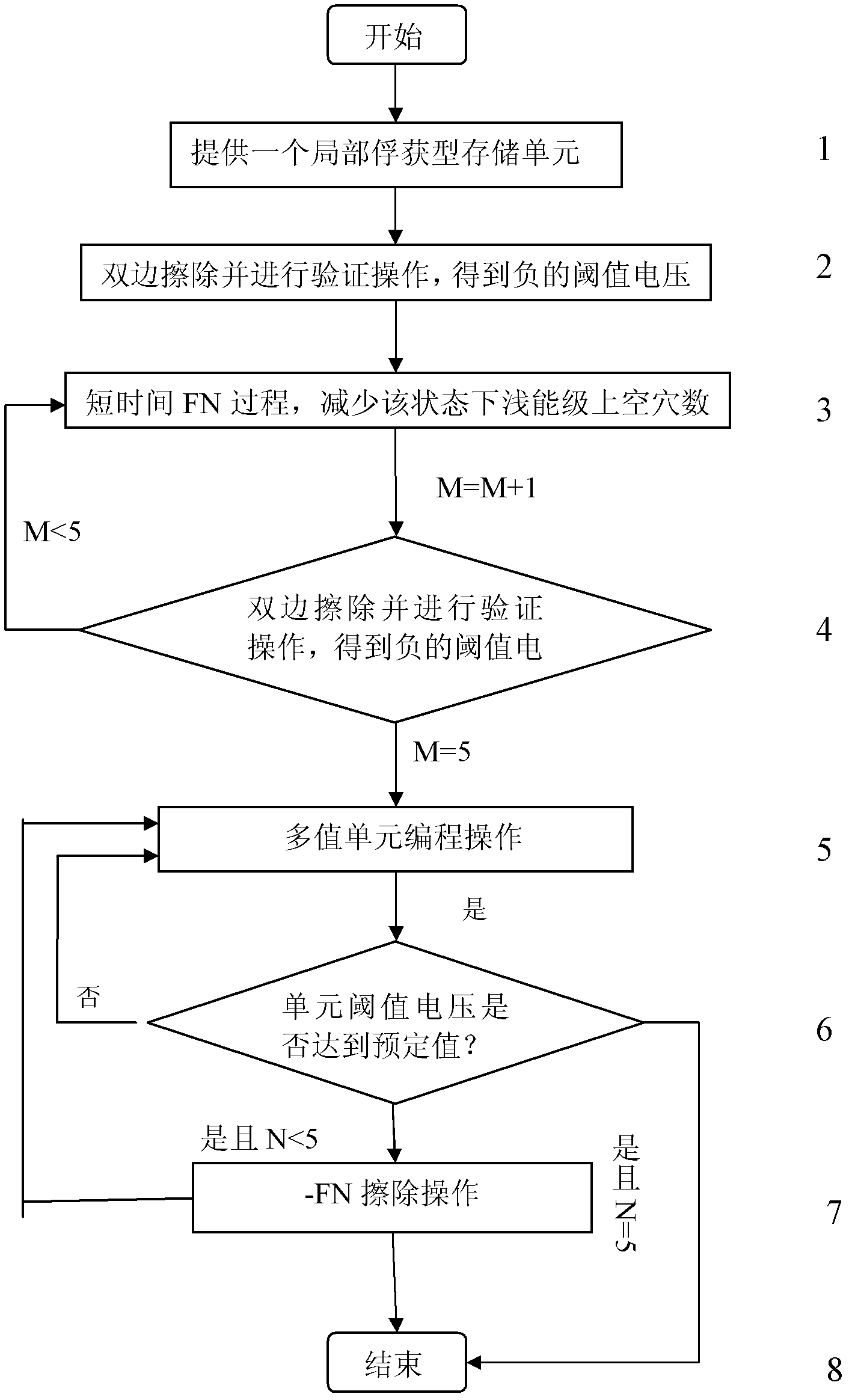

Operation method for increasing high-density storage characteristic of non-volatile flash memory

ActiveCN102509559BIncrease spacingLess likely to overlapRead-only memoriesHigh densityComputer science

An operation method to improve the high-density multi-value storage characteristics of non-volatile flash memory. 1) First adjust the initial state of the local capture type non-volatile flash memory cell to the threshold voltage -2V~-1V: use bilateral band -The erasing method with tunneling hot hole injection (BBHH) is adjusted to the threshold voltage; then a transient FN operation is performed to promote uniform charge distribution in the channel; 2) Step 1) is performed by repeating several times , the bilateral BBHH and FN operation steps adjust the initial state to a threshold voltage of -2V ~ -1V, and finally achieve the same threshold voltage distribution in the channel area; 3) Using the above threshold as the initial state of multi-value storage, for NOR type The local capture memory unit performs the programming operation of the multi-valued unit; 4) After reaching the programming state, a short-time -FN process is performed; the present invention can improve the retention characteristics and tolerance characteristics of the memory device.

Owner:NANJING UNIV

Multifunctional test circuit of integrated circuit stress degradation and test method thereof

The invention belongs to a integrated circuit reliability test technology field and especially relates to a multifunctional test circuit of integrated circuit stress degradation and a test method thereof. A core part of the test circuit takes an annular oscillator as a basis. Several auxiliary transistors, switch transistors and control terminals are added. By using the circuit and the method of the invention, a negative bias temperature instability, a positive bias temperature instability, hot hole injection or hot electron injection stress can be applied to pMOSFETs or nMOSFETs in a ring vibration inverter respectively; a ring oscillator is in a normal oscillation and stress oscillation state; the pMOSFETs or nMOSFETs of the inverter in the ring oscillator is in a measuring state of a charge pump. The degradation of the MOSFETs in the ring vibration inverter can be shown through changes of a ring oscillator oscillation frequency after the stress and can be shown through the changes of a CP current (Icpp or Icpn) of the pMOSFETs or nMOSFETs in the ring oscillator.

Owner:FUDAN UNIV

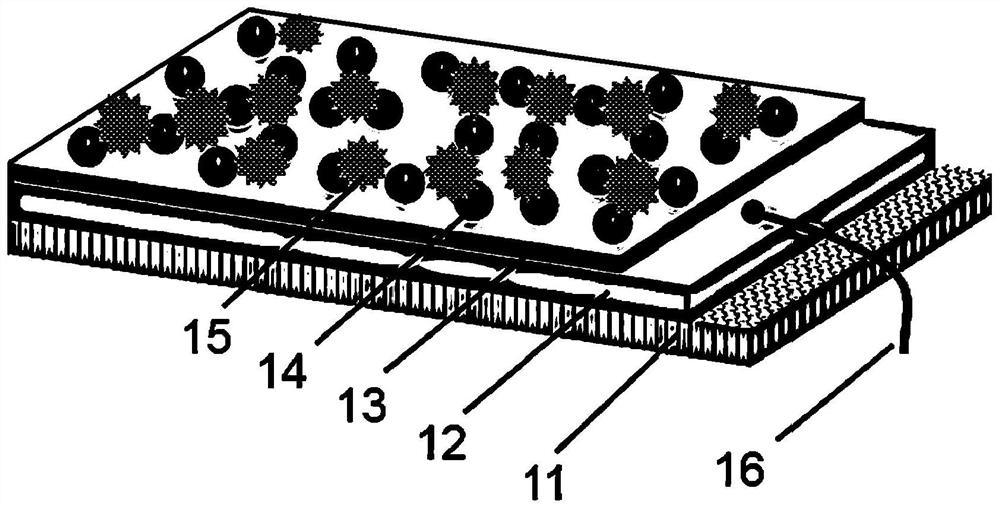

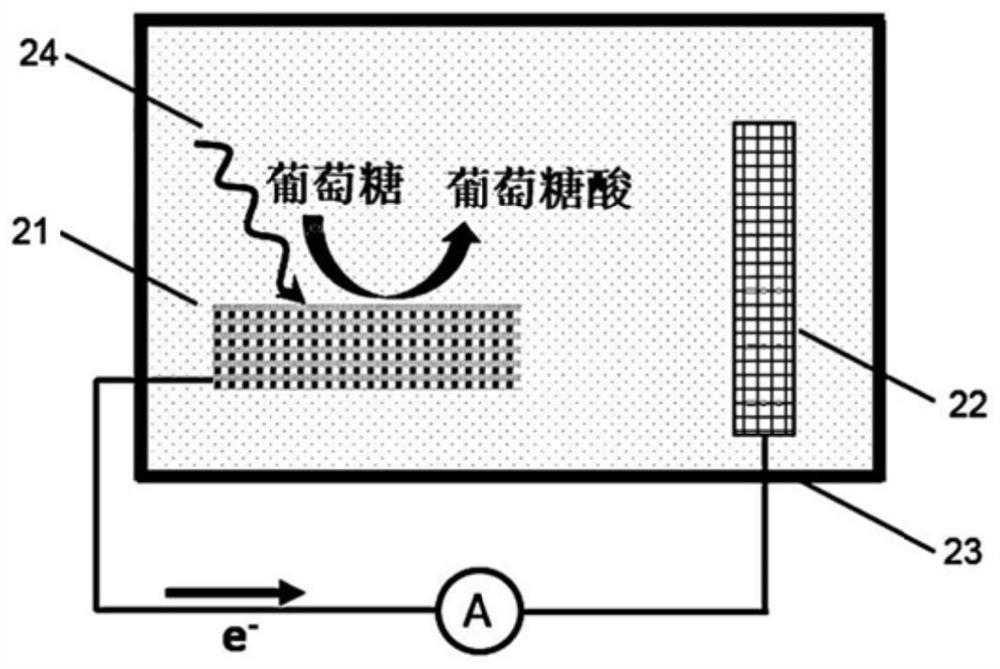

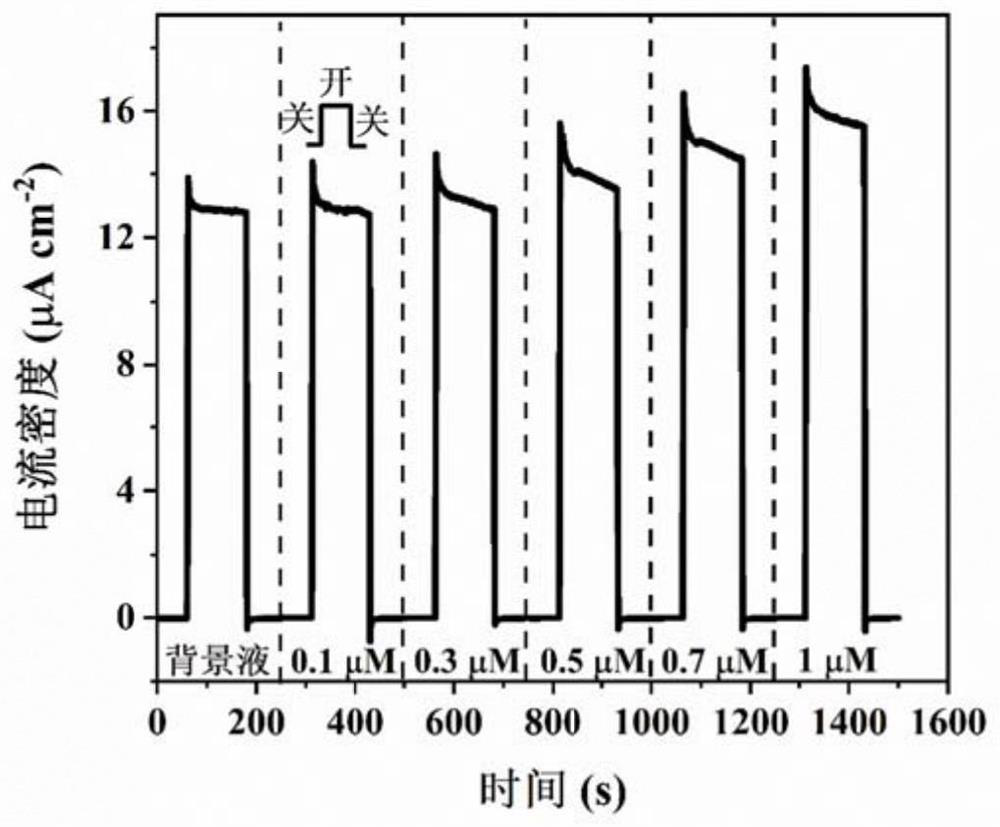

Unbiased enzymatic glucose photoelectrochemical sensing electrode and preparation method thereof

The invention belongs to the field of photoelectrochemistry, and discloses a bias-voltage-free enzymatic glucose photoelectrochemical sensing electrode and a preparation method thereof.The bias-voltage-free enzymatic glucose photoelectrochemical sensing electrode sequentially comprises a glucose oxidase layer, a metal nanoparticle layer, an n-type semiconductor thin film layer, a metal thin film layer and a plane insulation substrate in the light incidence direction; the metal film layer and the n-type semiconductor film layer form ohmic contact; the metal nanoparticle layer and the n-type semiconductor thin film layer form Schottky contact; and an optical resonant cavity is formed among the metal film layer, the n-type semiconductor film layer and the metal nanoparticle layer. When a light source irradiates the sensing electrode, the metal nanoparticle layer and the n-type semiconductor film layer can generate effective light absorption and generate a hot electron hole pair and a photo-induced electron hole pair respectively; under the action of the Schottky junction, the hot holes and the photo-generated holes are transferred to glucose molecules under the catalytic action of glucolase; and the glucose concentration is detected by monitoring the change of the light current.

Owner:SUZHOU UNIV

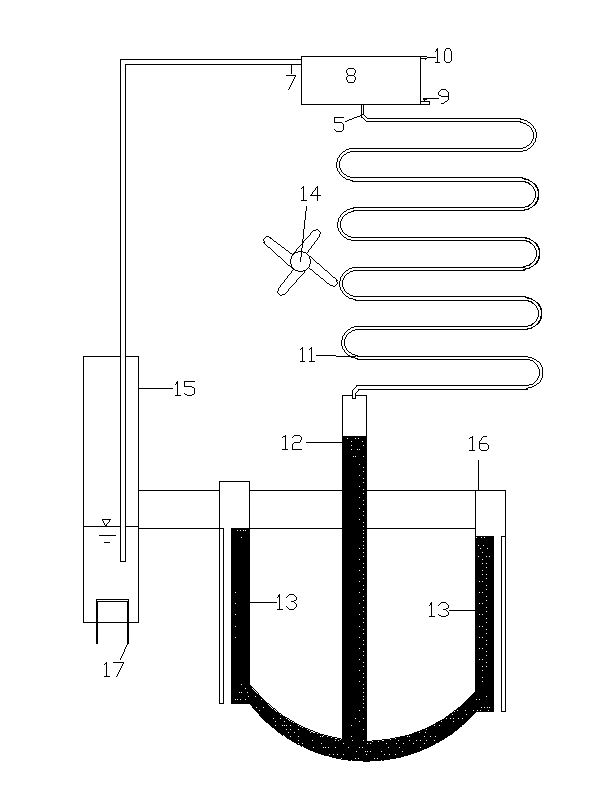

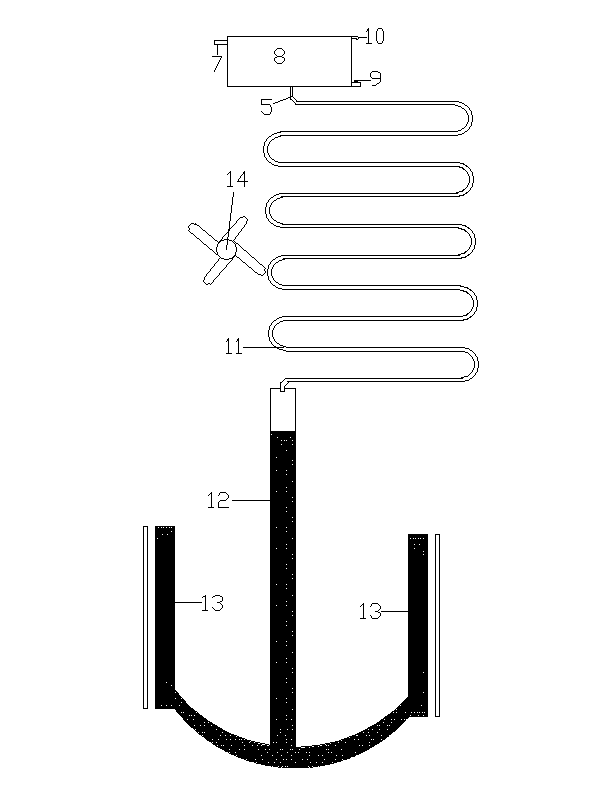

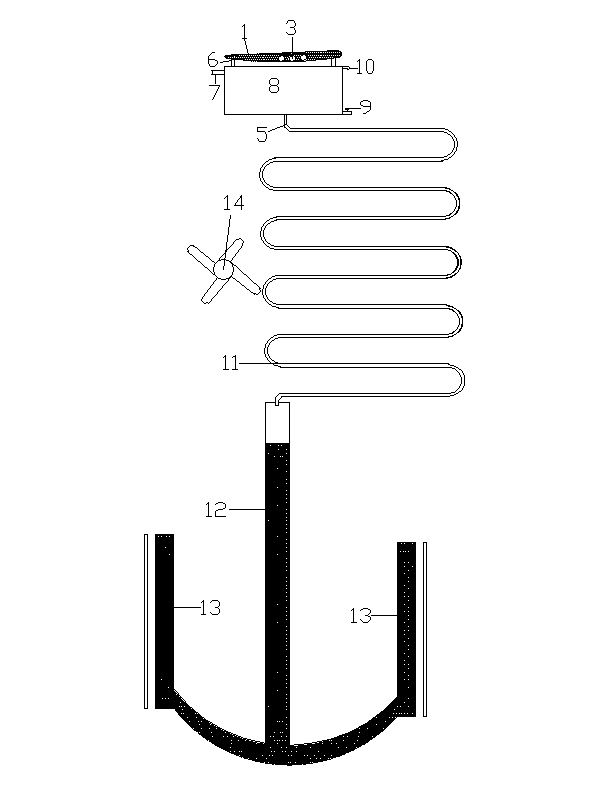

Air conditioning system device based on icy-hot-hole imitated refrigeration mechanism

InactiveCN103512112ARelieve pressureReduce the temperatureLighting and heating apparatusSpace heating and ventilation detailsThermal energyEvaporation

The invention discloses an air conditioning system device based on an icy-hot-hole imitated refrigeration mechanism. The air conditioning system device is mainly composed of a throttle pipe (5), a water tank (8), a refrigeration pipe (11), a negative-pressure capillary tube (12), a solar evaporator (13) and the like. Due to the solar heating effect, water or refrigerating fluid in the solar evaporator (13) is evaporated into gas, and the water or refrigerant in the refrigeration pipe (11) is reduced; due to the fact that the pipe diameter of the throttle pipe (5) is very small, the amount of the supplemented water or refrigerating fluid is smaller than the amount of the gas formed by evaporation of the water or the refrigeration fluid in the solar evaporator (13), the temperature inside the refrigeration pipe (11) is lower and lower, the thermal energy outside the refrigeration pipe (11) is absorbed, and therefore the purpose that the solar energy, wind energy, geothermal energy and the like on buildings are converted into cooling capacity and are reused by the refrigeration air conditioning system is achieved.

Owner:孙善骏

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com