Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

88results about How to "Uniform etch rate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

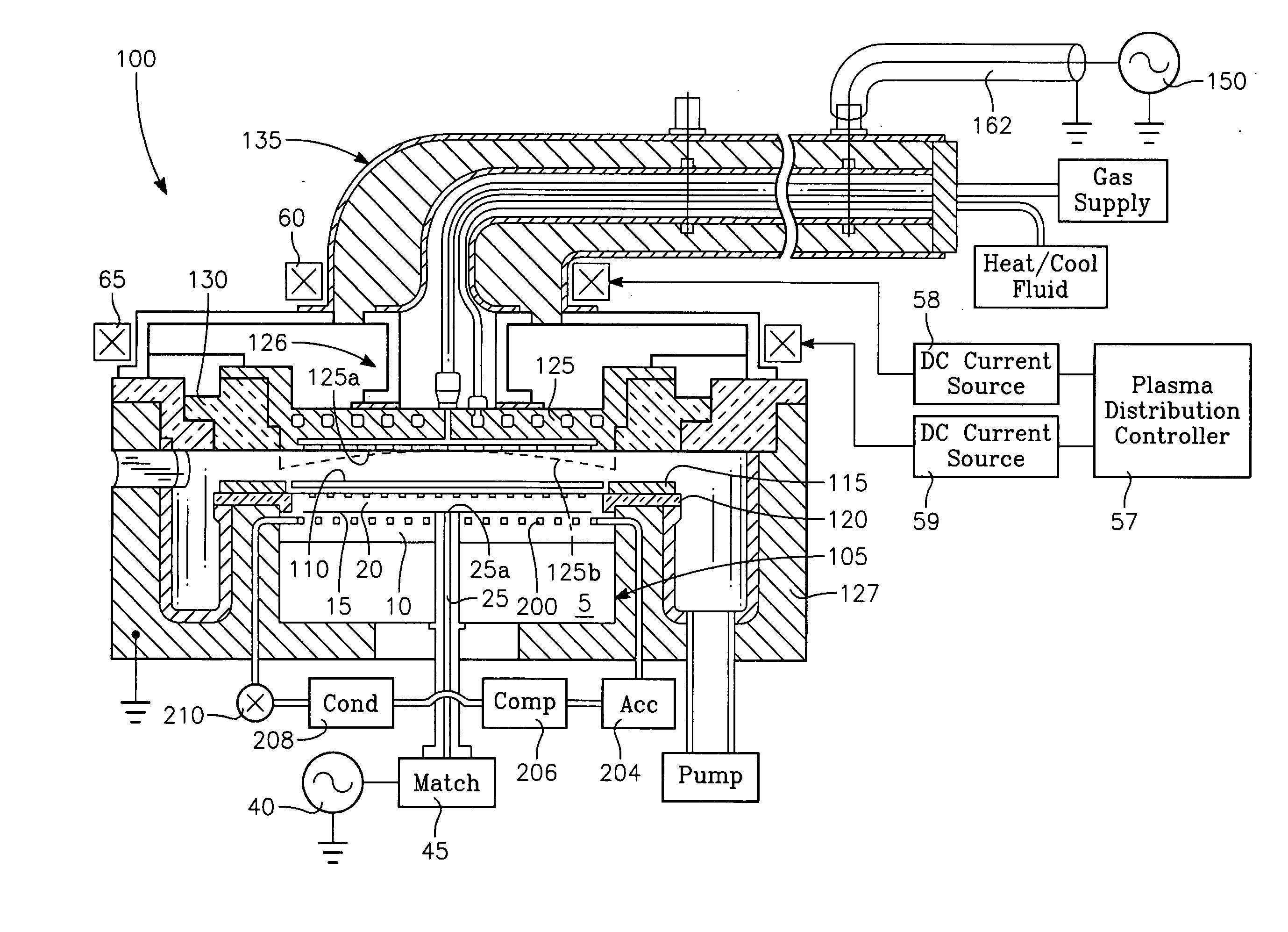

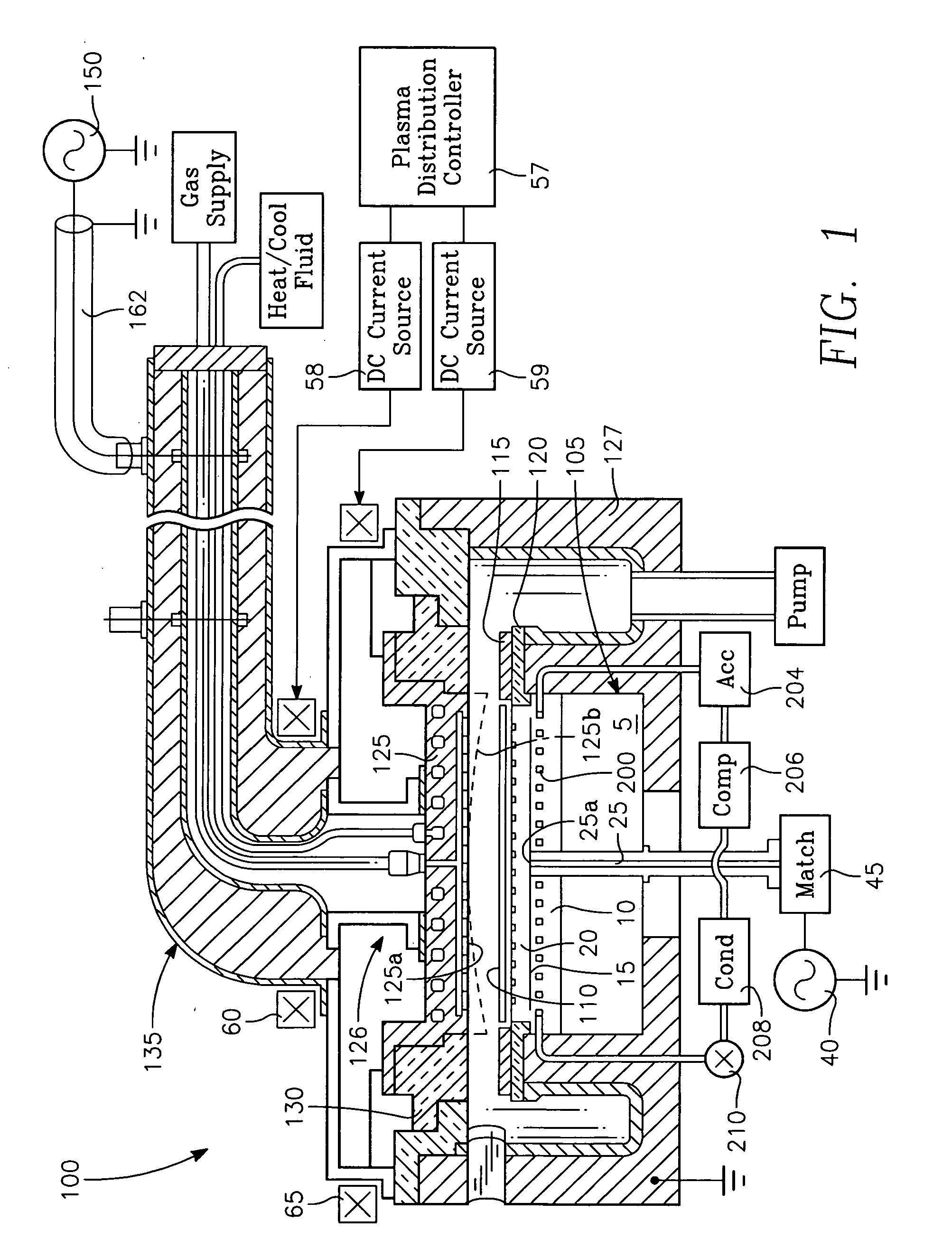

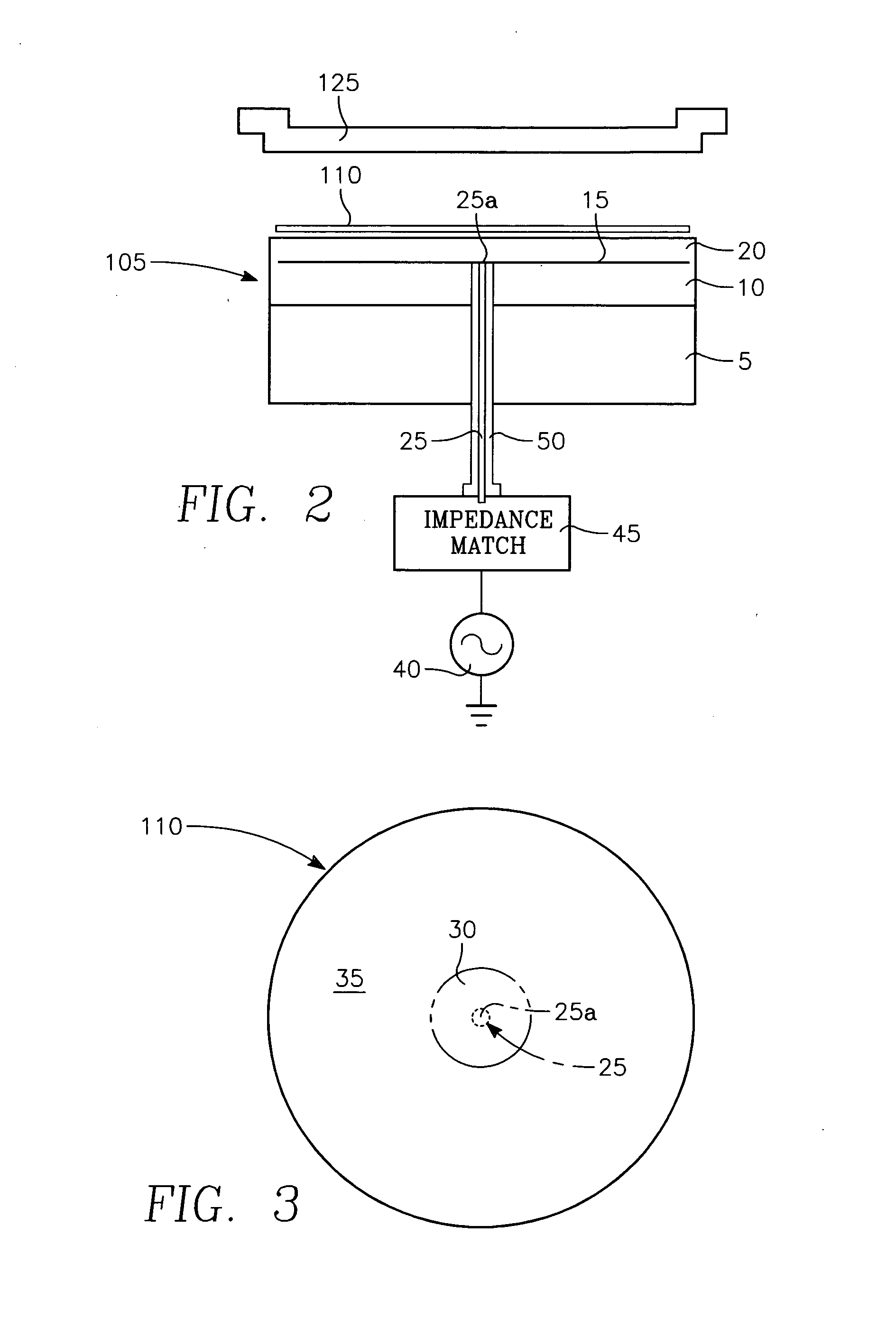

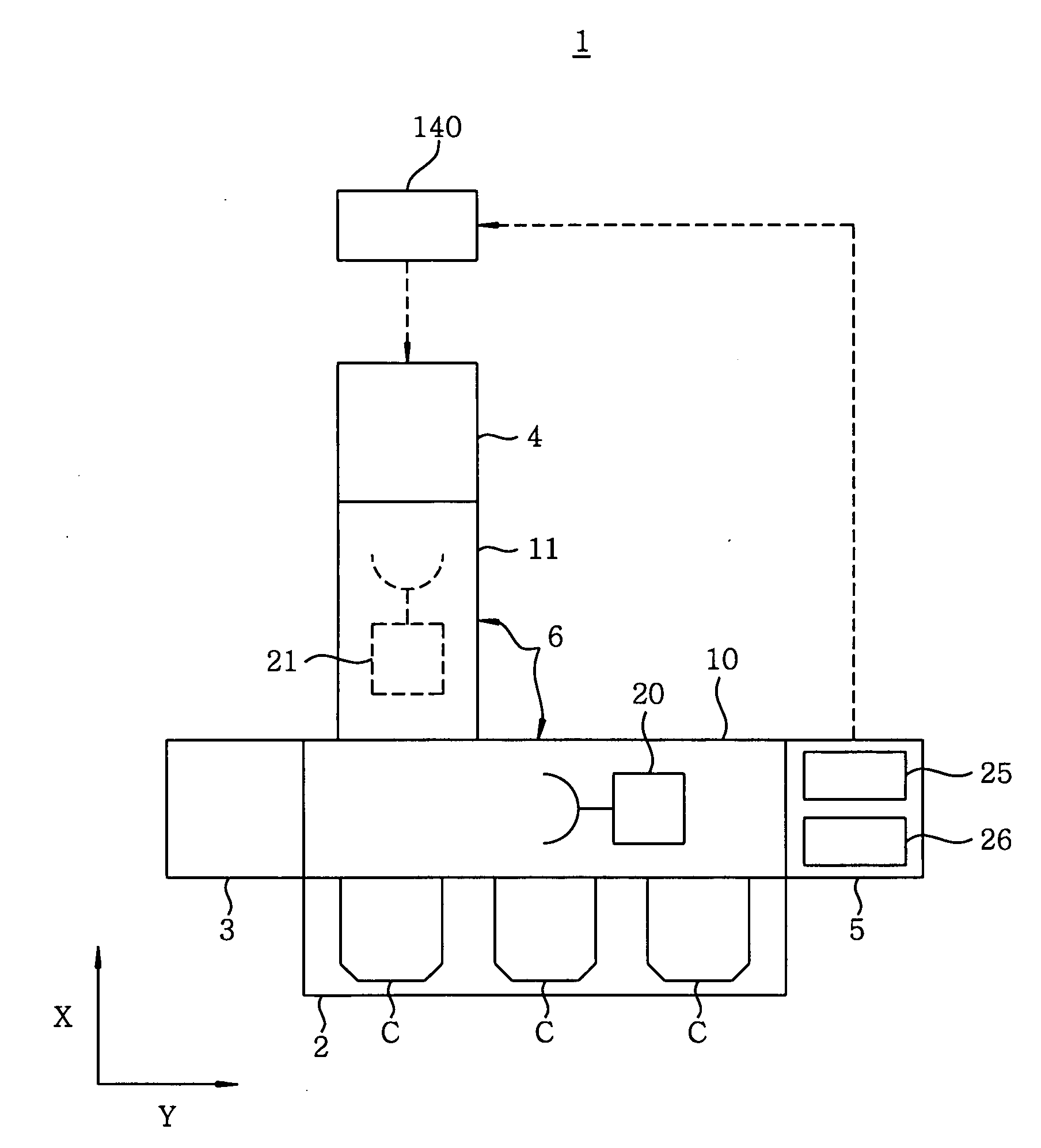

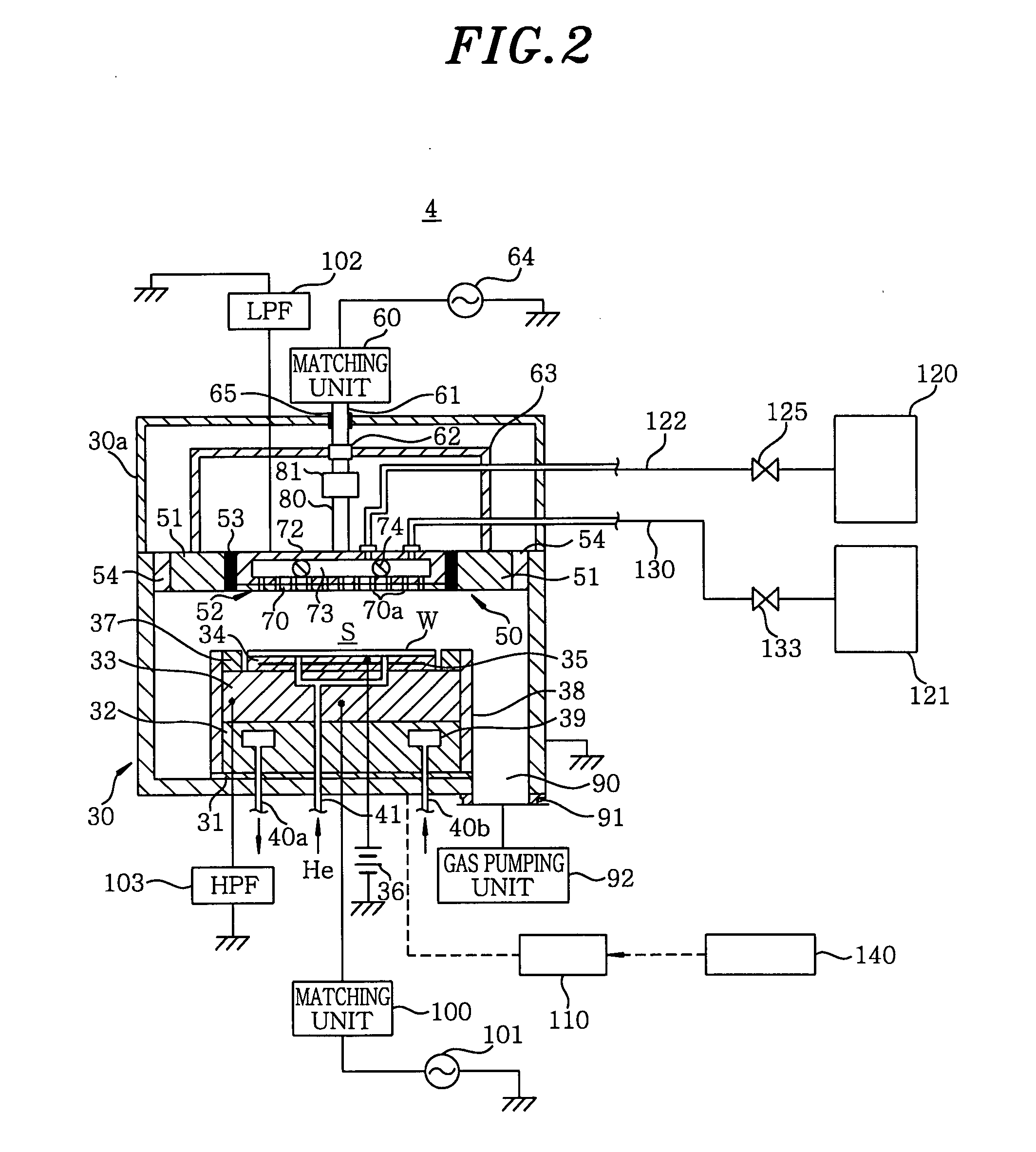

Capacitively coupled plasma reactor having a cooled/heated wafer support with uniform temperature distribution

ActiveUS20070081295A1Improve uniformityWide pressure rangeSemiconductor/solid-state device manufacturingCapacitanceGas phase

A plasma reactor for processing a workpiece includes a reactor chamber, an electrostatic chuck within the chamber for supporting a workpiece, an RF plasma bias power generator coupled to apply RF power to the electrostatic chuck and a refrigeration loop having an evaporator inside the electrostatic chuck with a refrigerant inlet and a refrigerant outlet. Preferably, the evaporator includes a meandering passageway distributed in a plane beneath a top surface of the electrostatic chuck. Preferably, refrigerant within the evaporator is apportioned between a vapor phase and a liquid phase. As a result, heat transfer between the electrostatic chuck and the refrigerant within the evaporator is a constant-temperature process. This feature improves uniformity of temperature distribution across a diameter of the electrostatic chuck.

Owner:BE AEROSPACE INCORPORATED

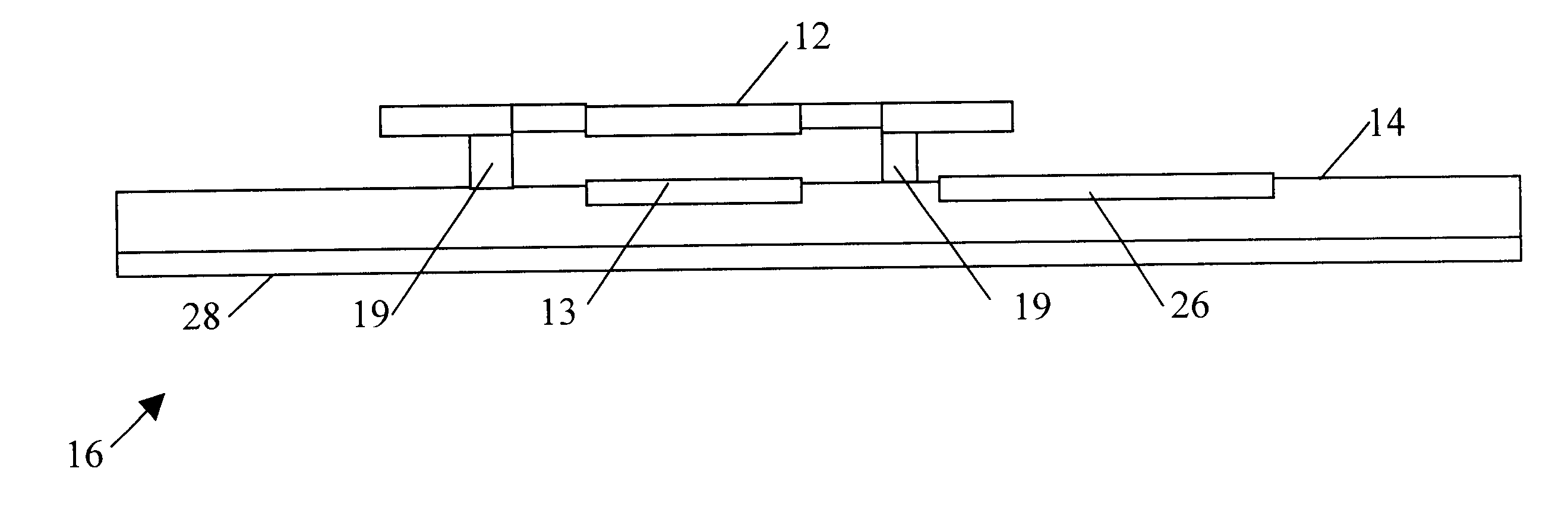

Microelectromechanical device manufacturing process

InactiveUS6337027B1Quantity minimizationEasily terminatedDecorative surface effectsSemiconductor/solid-state device manufacturingDissolutionEngineering

The present invention relates to micro electromechanical systems (MEMS) devices and more specifically to a process for manufacturing MEMS devices having at least one suspended structural element. The present invention seeks to provide an improved method for manufacture of MEMS devices having improved safety and increased yield and throughput compared to conventional EDP immersion process techniques. MEMS devices are made using a modified dissolution process that removes, in a selective etch step, inactive silicon to release an active silicon device from a sacrificial substrate. The present invention uses a selective etchant in conjunction with a commercial spray acid processing tool to provide a dissolution process with improved throughput, improved repeatable and uniform etch rates and reduction in the number of processing steps and chemical containment for improved safety. When the etch process is complete, the solvent spray is turned off and a spray of de-ionized water is directed onto composite structure to remove residual solvent without causing suspended elements to adhere to the support substrate.

Owner:TELEDYNE SCI & IMAGING

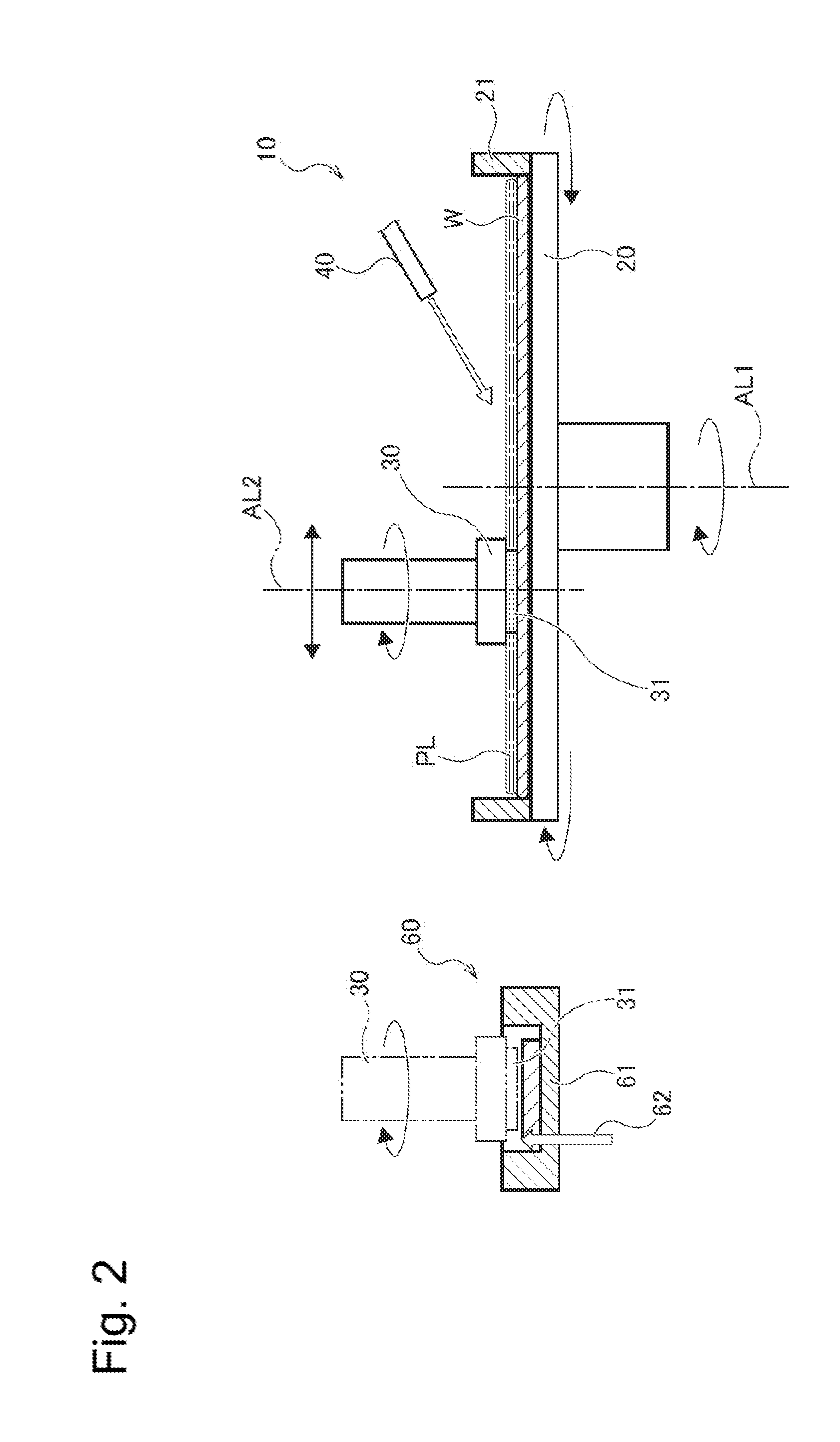

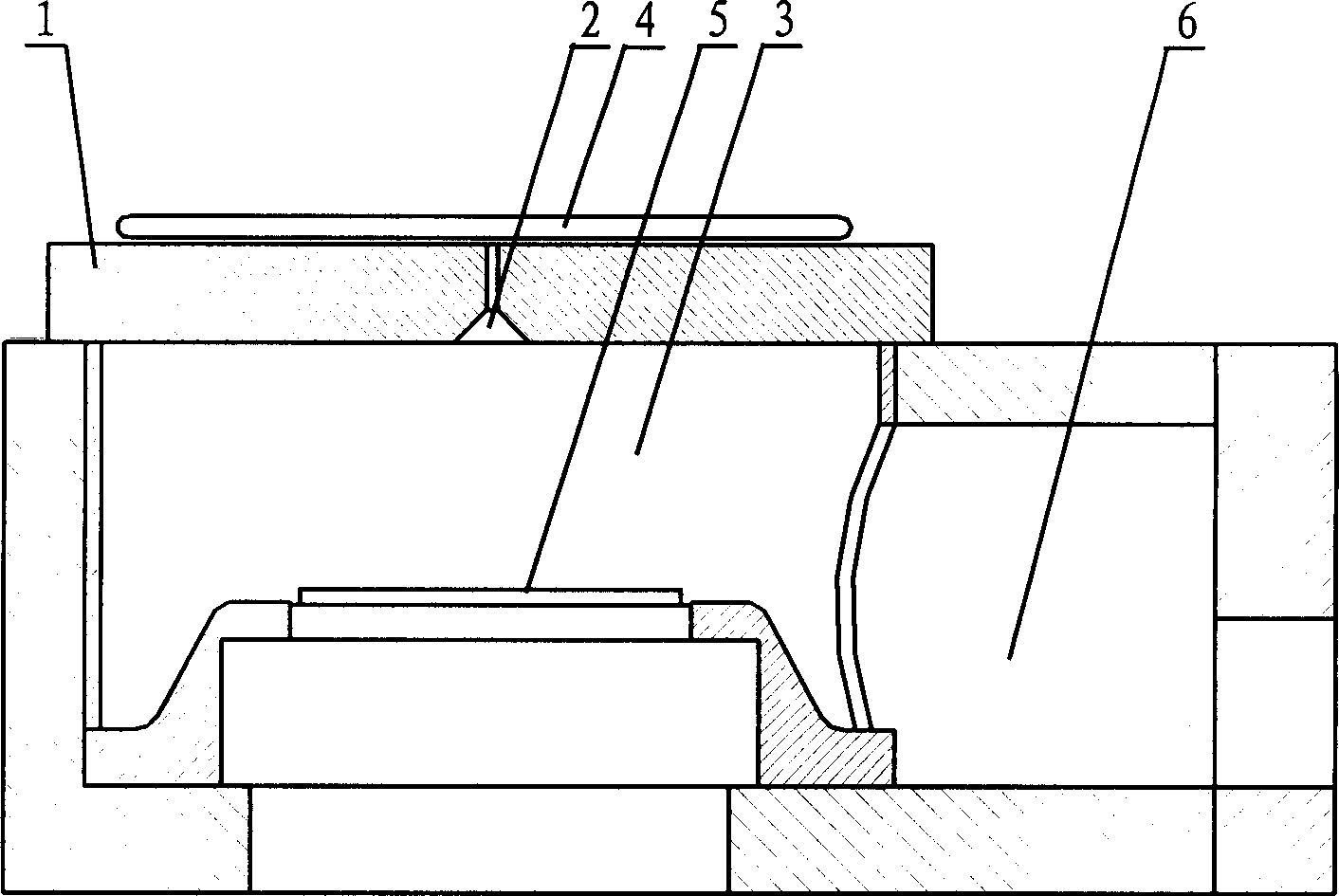

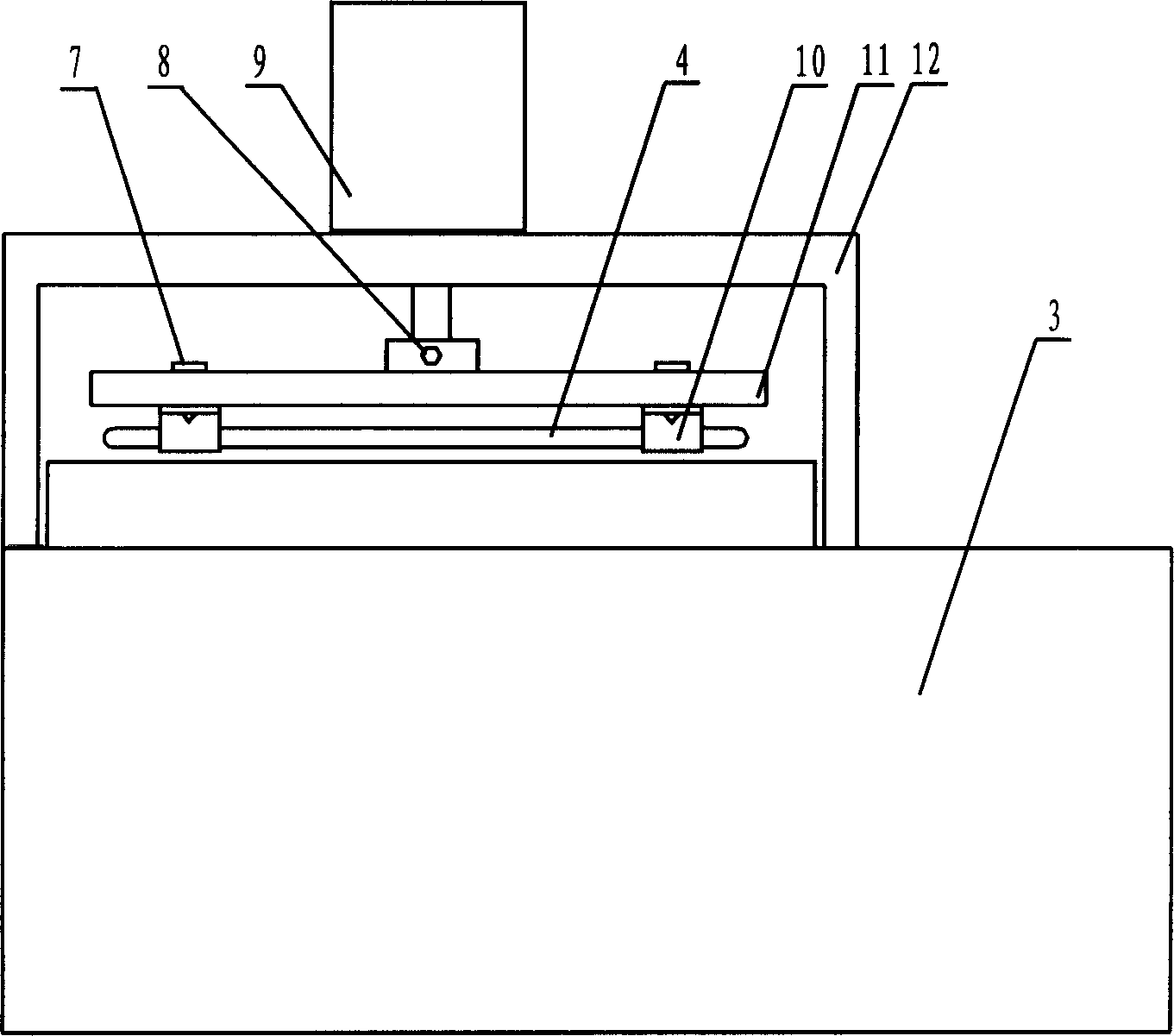

Substrate processing apparatus, substrate processing system. and substrate processing method

ActiveUS20170047237A1Uniform etch rateImprove controllabilitySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingEngineering

An object of the present invention is to improve a substrate processing apparatus using the CARE method.The present invention provides a substrate processing apparatus for polishing a processing target region of a substrate by bringing the substrate and a catalyst into contact with each other in the presence of processing liquid. The substrate processing apparatus includes a substrate holding unit configured to hold the substrate, a catalyst holding unit configured to hold the catalyst, and a driving unit configured to move the substrate holding unit and the catalyst holding unit relative to each other with the processing target region of the substrate and the catalyst kept in contact with each other. The catalyst is smaller than the substrate.

Owner:EBARA CORP

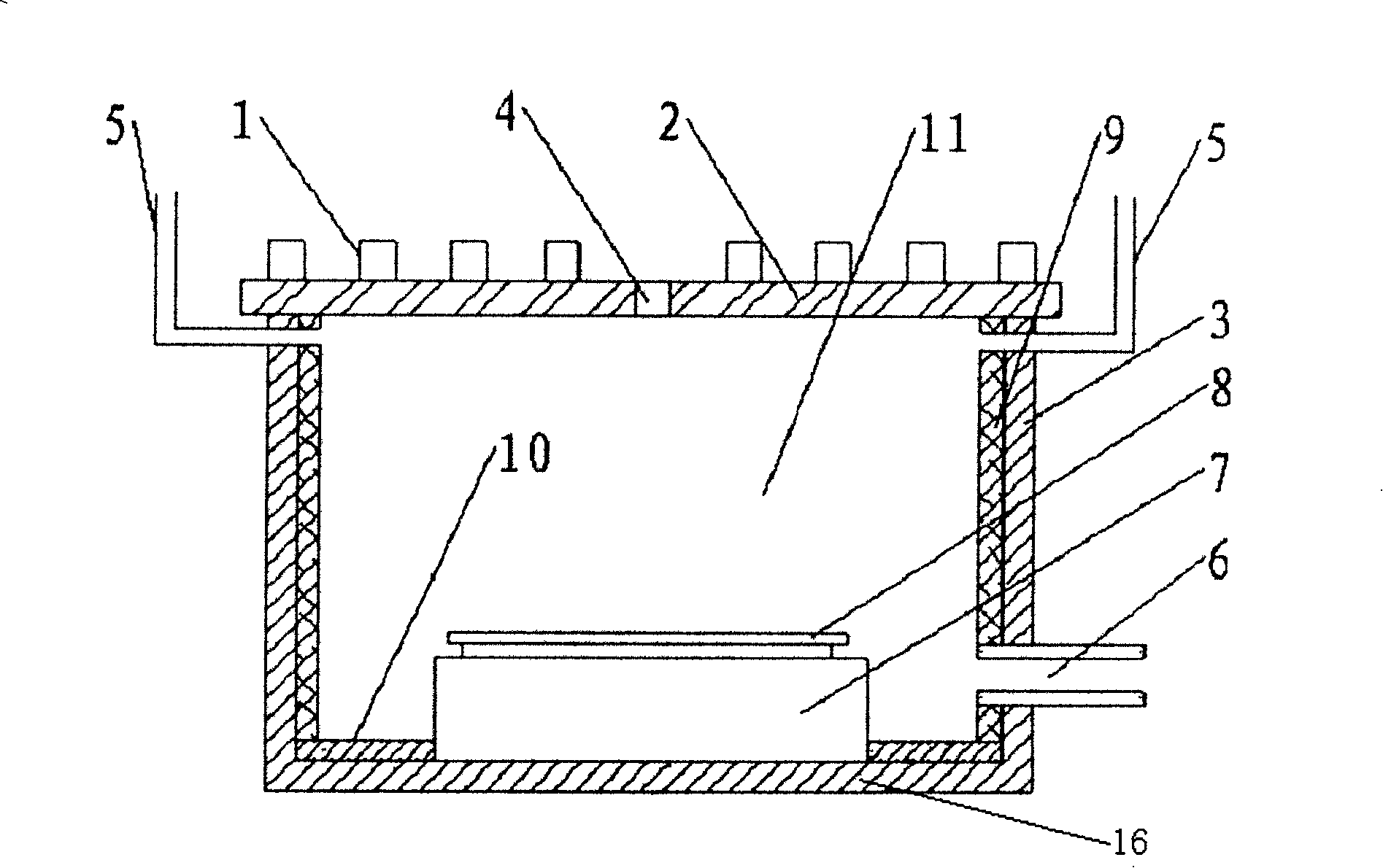

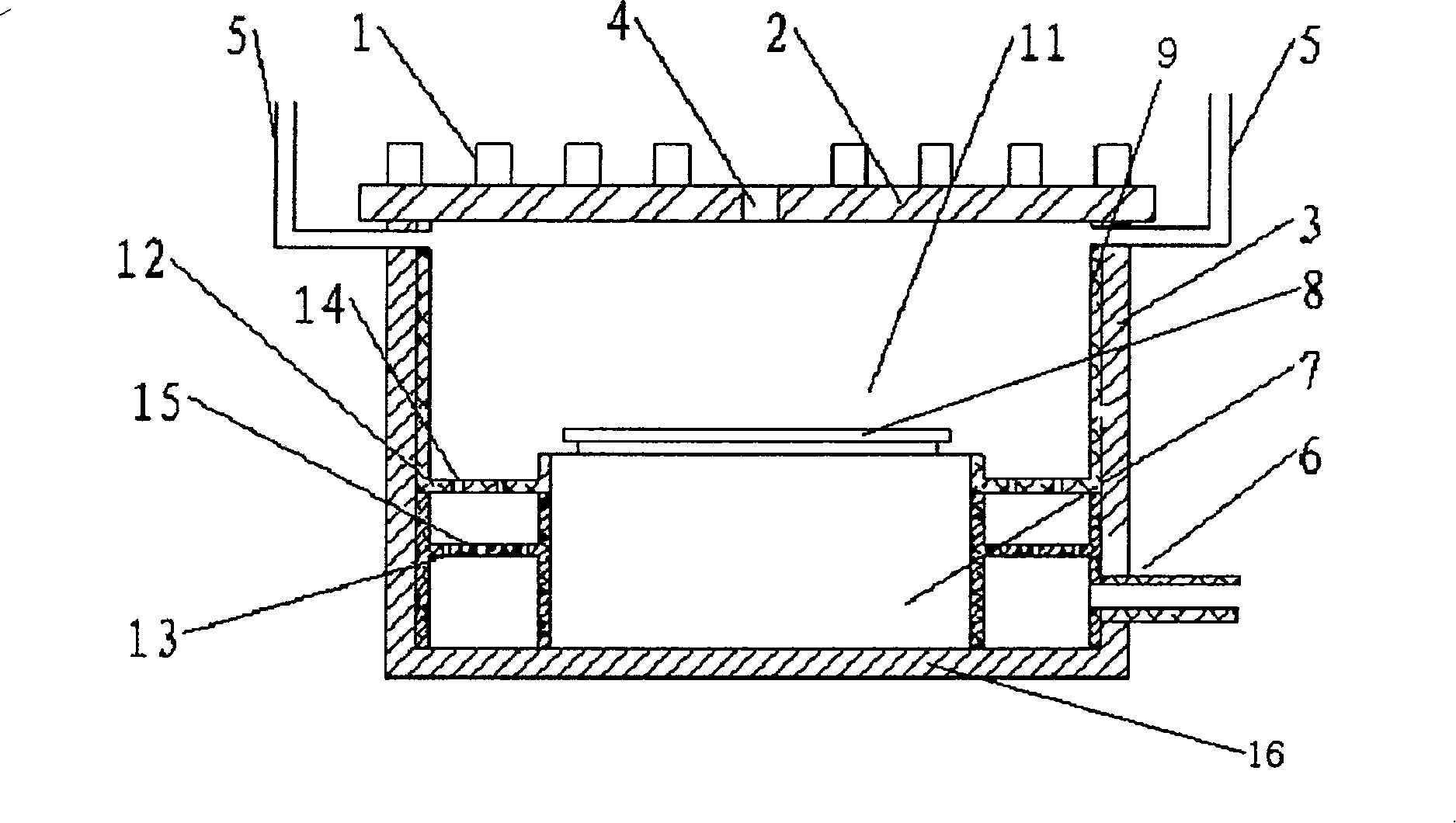

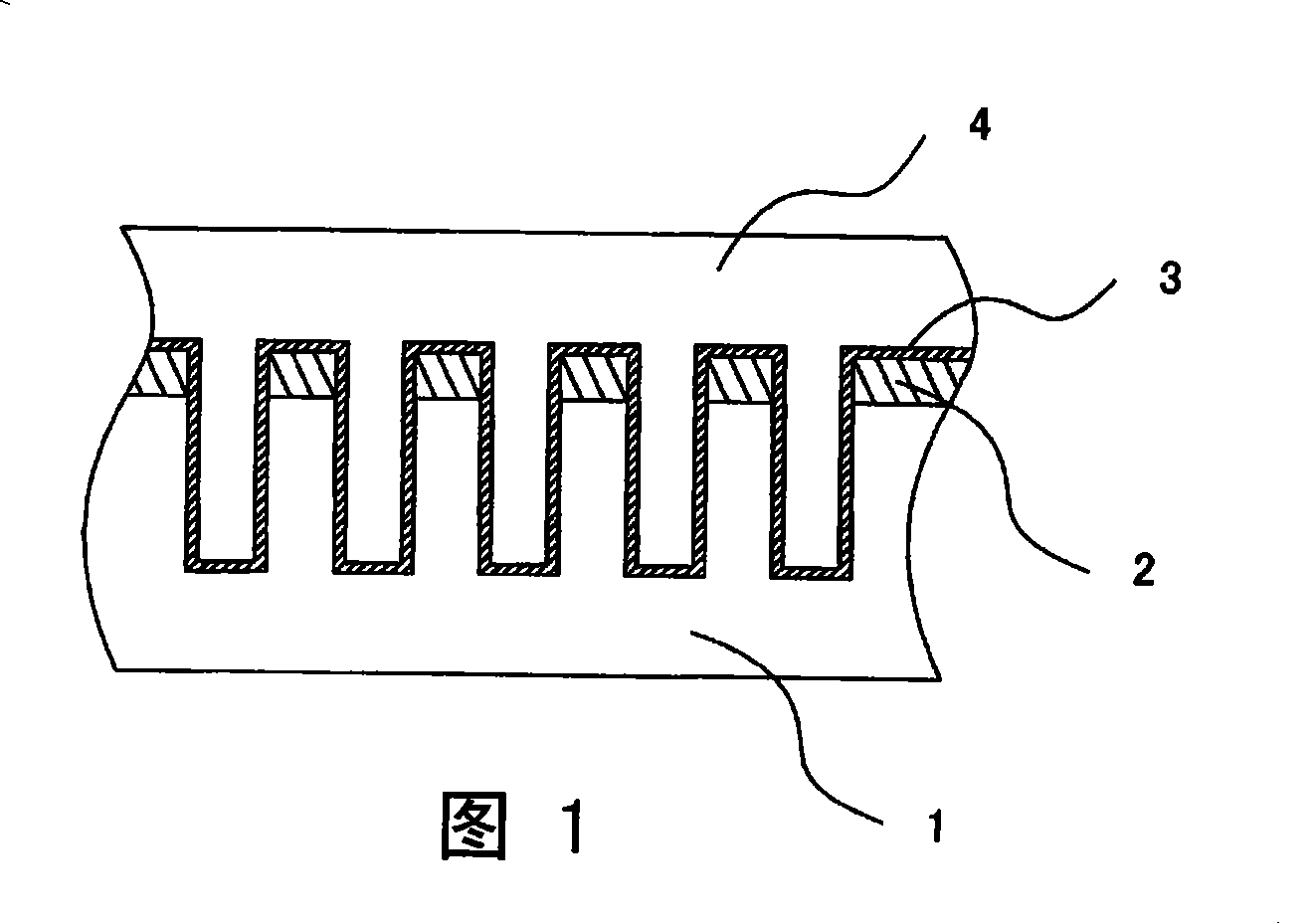

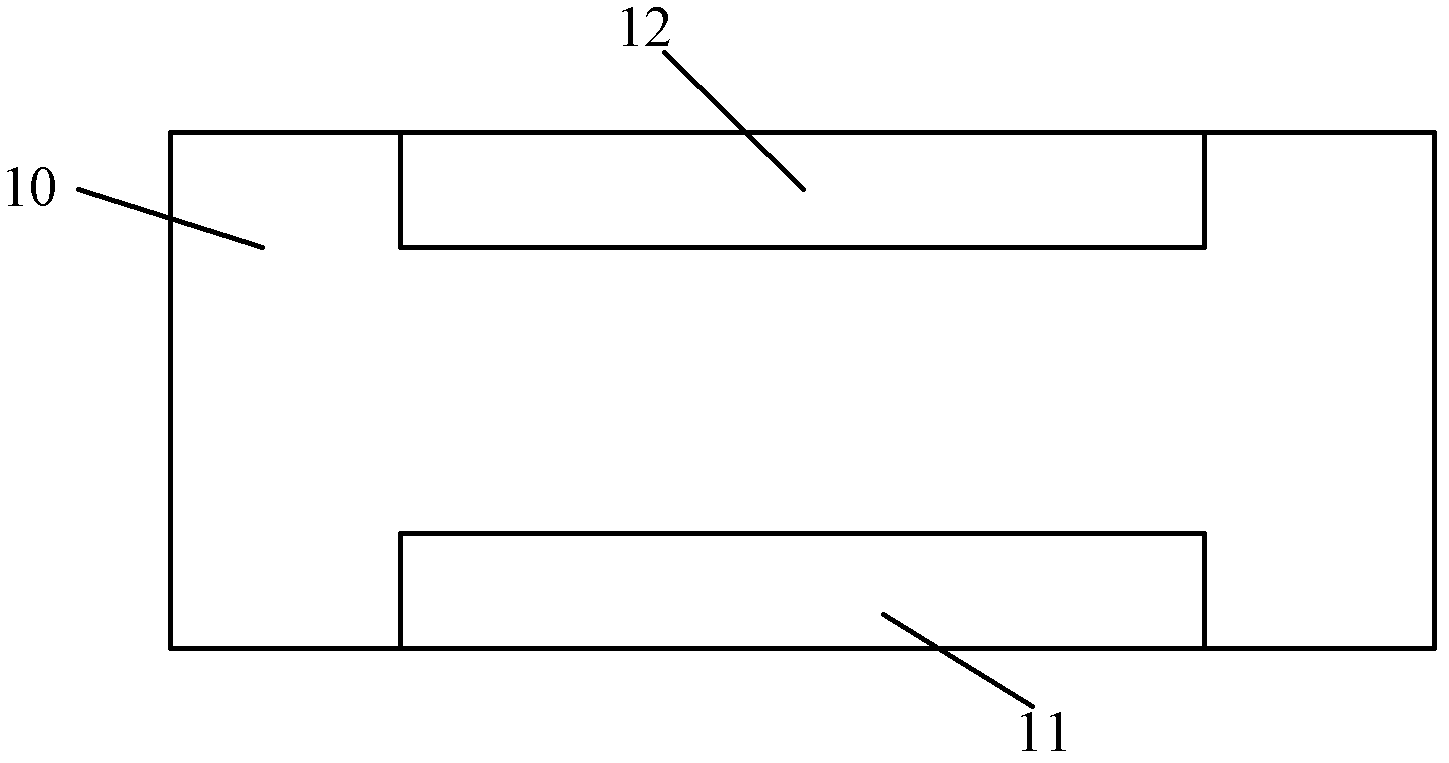

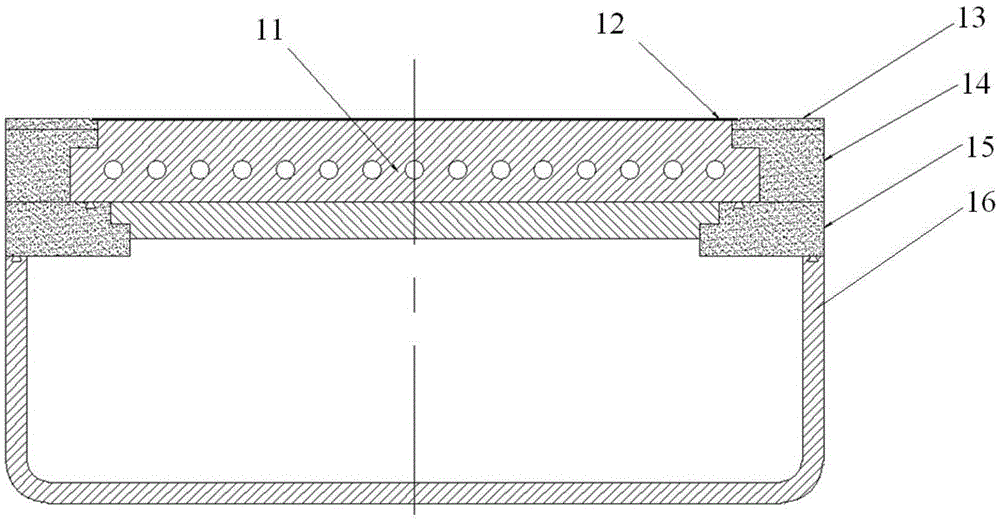

Reaction cavity lining and reaction cavity including the same

ActiveCN101197249AUniform flow rateEvenly distributedElectric discharge tubesSemiconductor/solid-state device manufacturingSemiconductorPhysics

The invention discloses a reaction cavity lining and a reaction cavity including the lining, which comprises a side lining and a bottom lining, wherein, the bottom lining is higher than the lower edge of the side lining and at least one bottom lining is provided. A plurality of lining holes are arranged on the bottom lining. The reaction cavity including the lining is divided into an upper space and a lower space. The upper space is communicated with the lower space through the lining hole. The technics air coming from an air inlet into the reaction cavity can only be pumped from an air outlet by passing the lining hole on the bottom lining. The air flowing speed in the reaction cavity tends to be even, thus protecting the wall of the cavity and allowing uniform distribution of air in the cavity. When the wafer is performed with etching technics in the cavity, the surface of entire wafer can acquire uniform etching speed rate. The invention is mainly applicable to the reaction cavity for the semi-conductor manufacture device, also applicable to other similar cavities.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

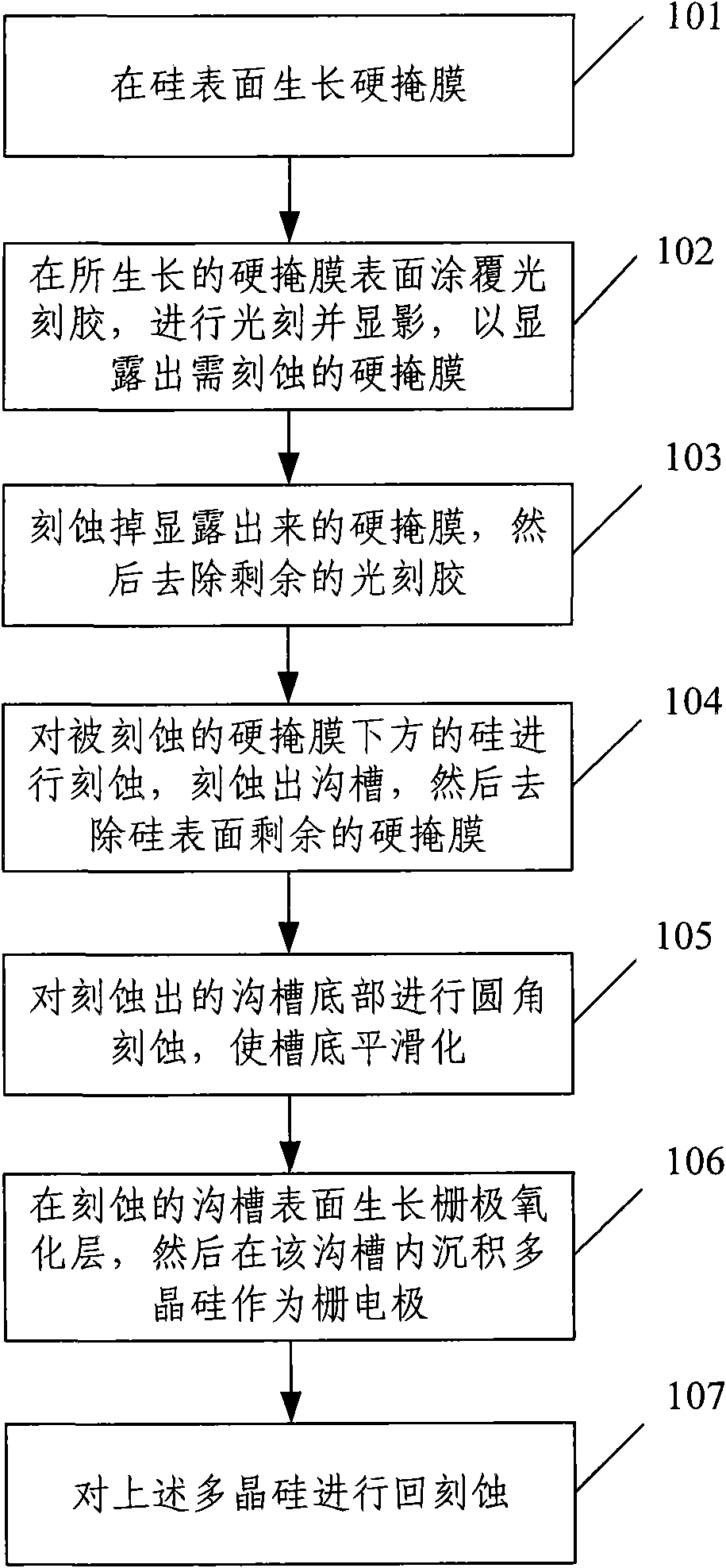

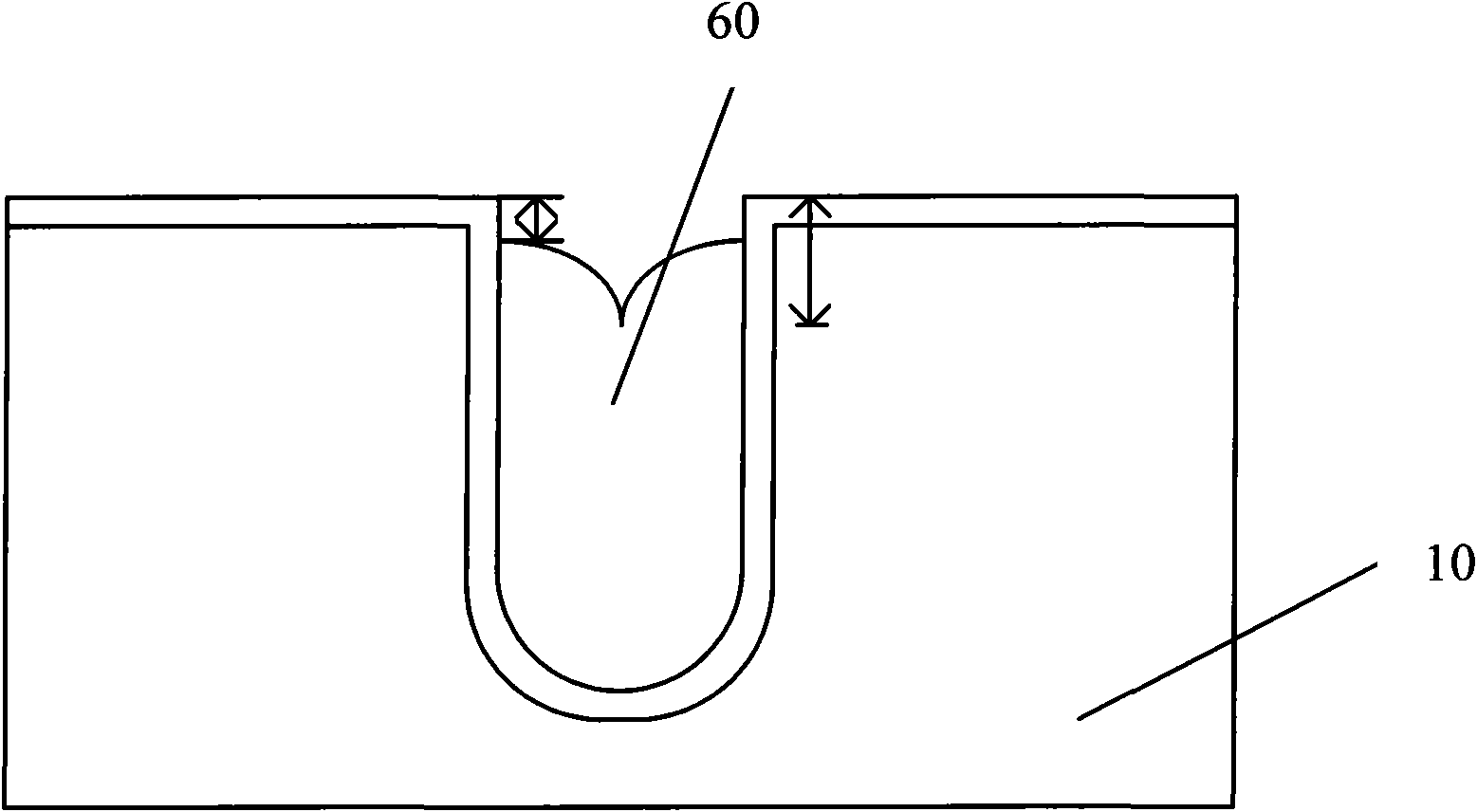

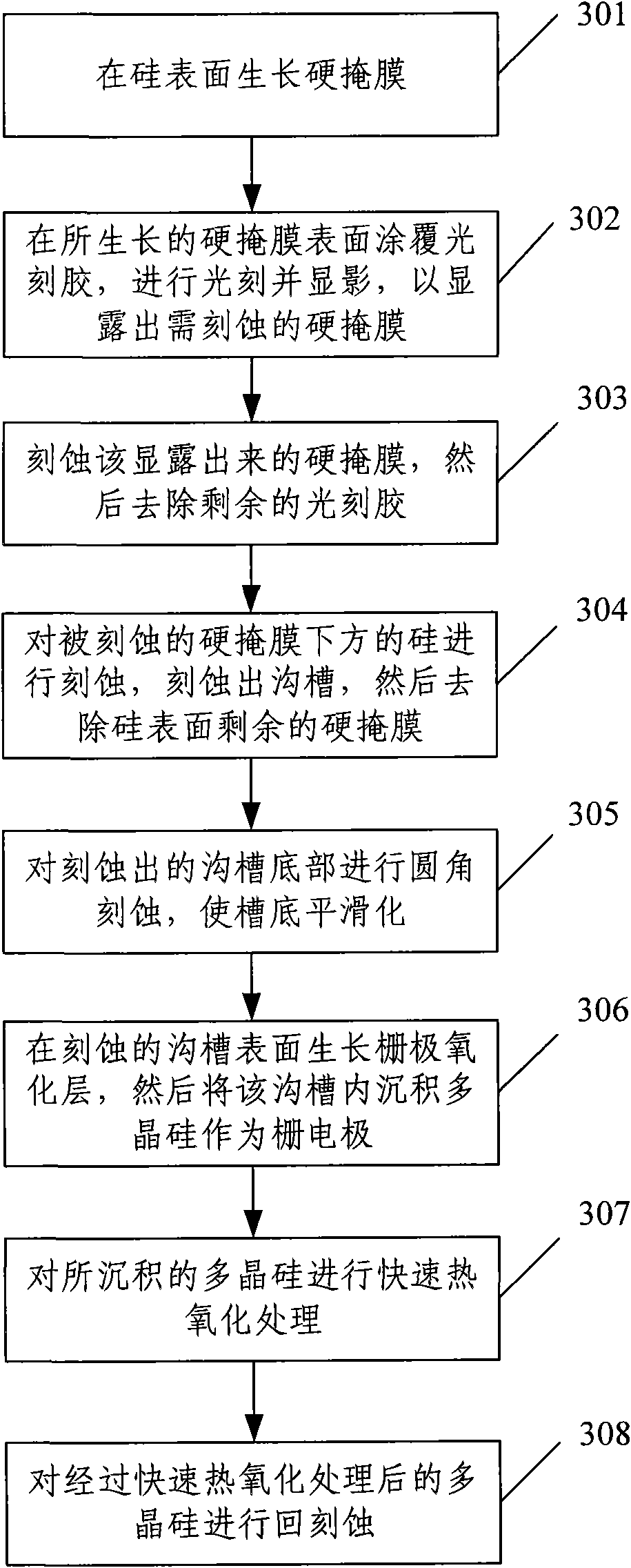

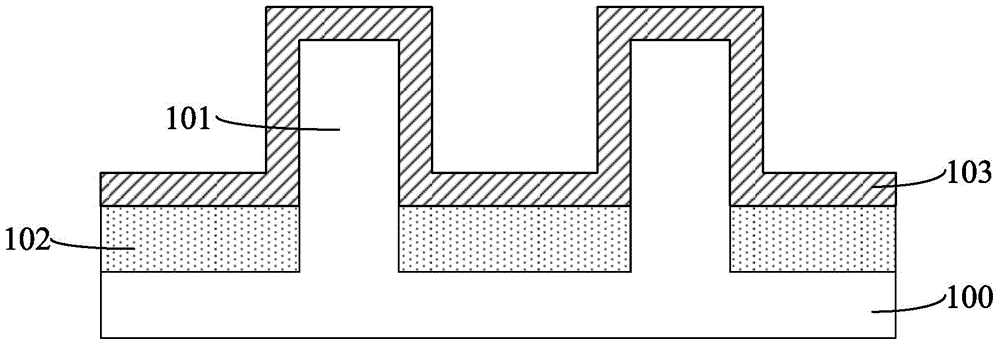

Method for flattening surface of polysilicon

InactiveCN101572229AIncrease thermal oxidation treatmentEvenly distributedSemiconductor/solid-state device manufacturingSemiconductor devicesPhotoresistHard mask

The invention discloses a method for flattening the surface of polysilicon, comprising the following steps: (1) growing a hard masking film on the surface of the polysilicon, coating photoresist on the surface of the hard masking film, where the hard masking film is raised, and carrying out photoetching and developing to expose the hard masking film to be etched; (2) etching the exposed hard masking film, removing left photoresist, etching a groove in the polysilicon below the etched hard masking film, and removing the photoresist left on the surface of the polysilicon; (3) etching the bottom of the etched groove in a filleting way, forming a gate oxidizing layer on the surface of the etched groove, and using the polysilicon settled in the groove as a gate electrode; (4) rapidly and thermally oxidizing the polysilicon settled in the groove; and (5) etching rapidly and thermally oxidized polysilicon once again.

Owner:PEKING UNIV FOUNDER GRP CO LTD +1

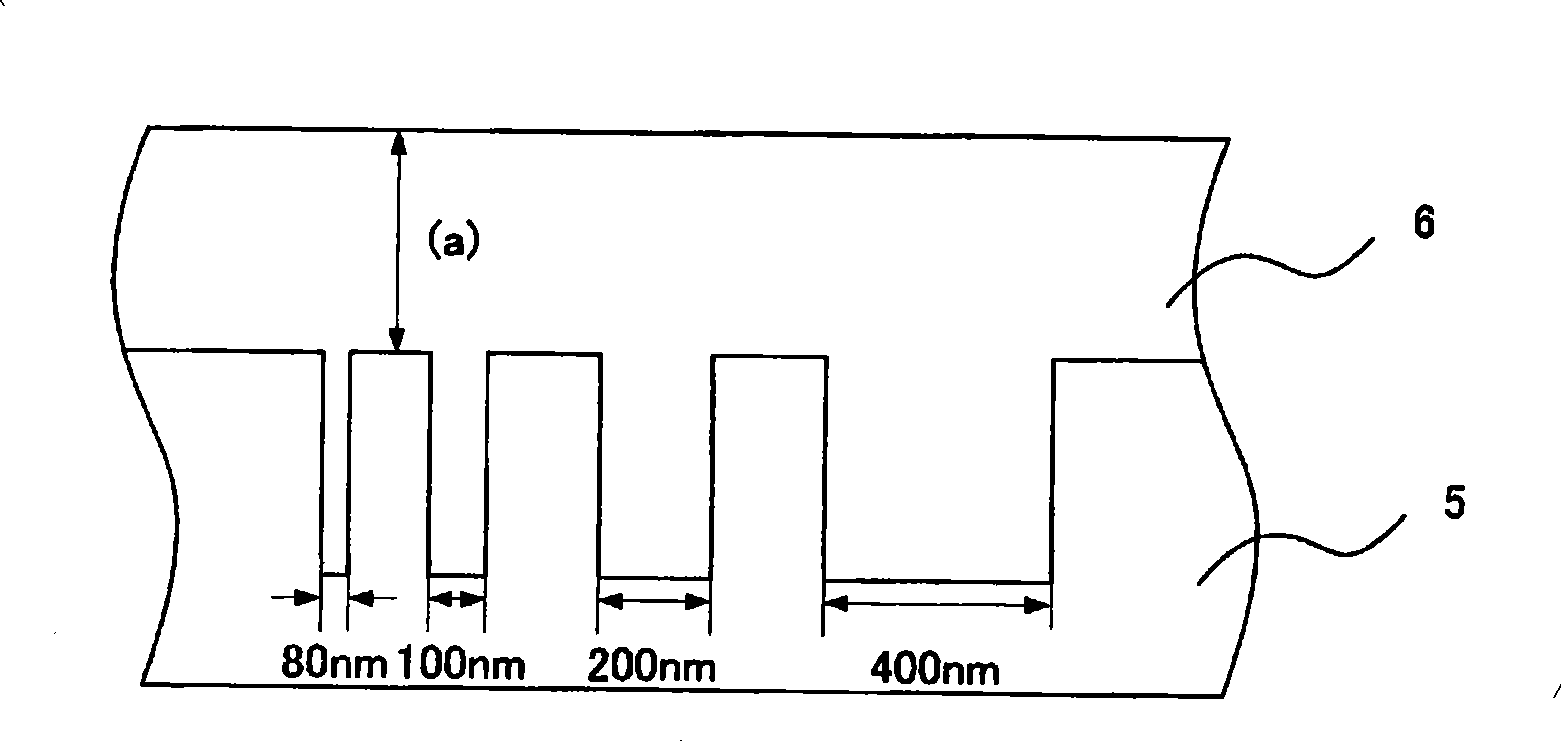

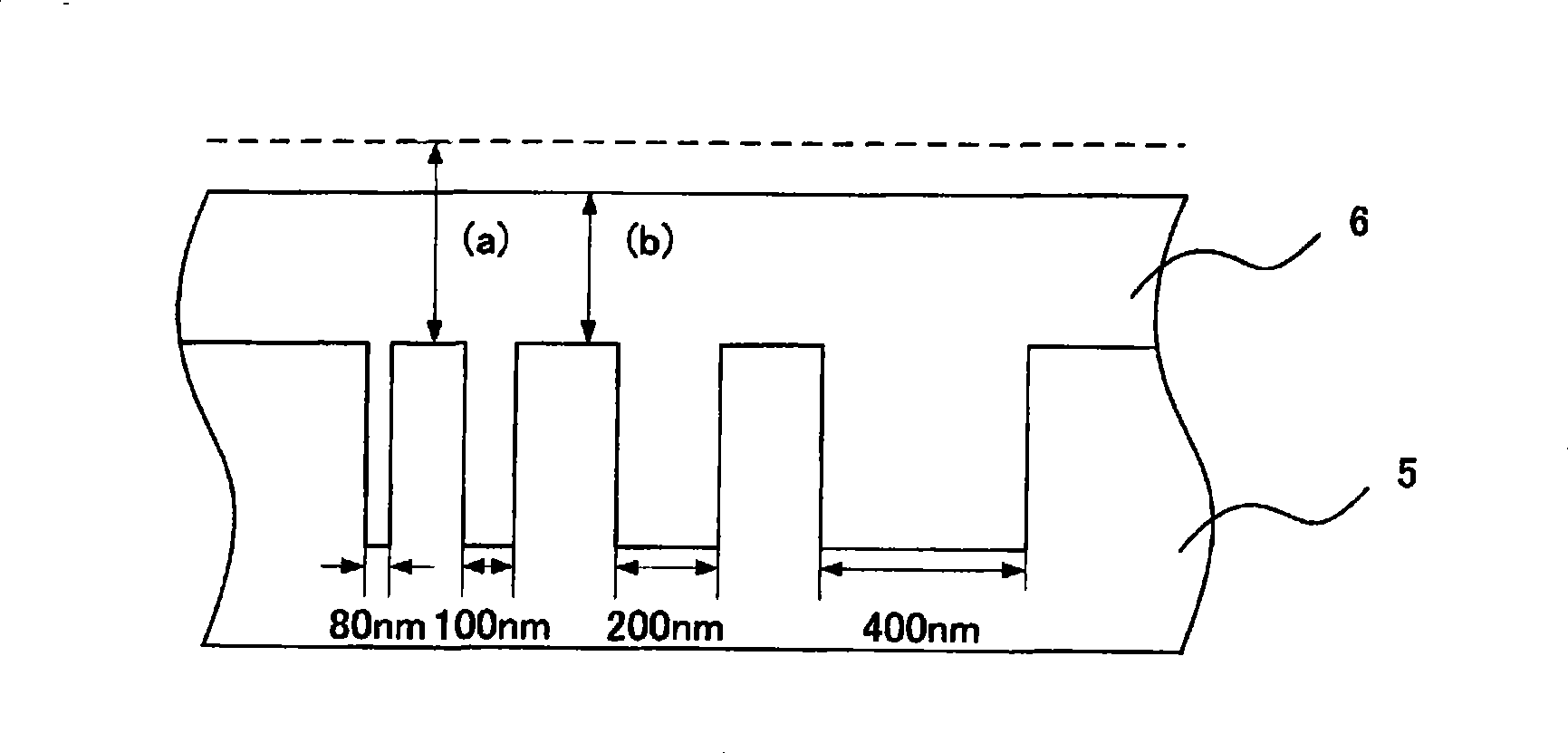

Gas setting method, gas setting apparatus, etching apparatus and substrate processing system

InactiveUS20060157445A1Short timeEffective regulationElectric discharge tubesVacuum gauge using ionisation effectsMixing ratioMaterials science

Mixing ratio and flow rate of a first gaseous mixture supplied to a central portion of the substrate are set. Subsequently, etching is performed by changing a mixing ratio of a second gaseous mixture supplied to an outer peripheral portion of the substrate while a setting of the first gaseous mixture is fixed, thereby, setting the mixing ratio of the second gaseous mixture based on an etching result to make etching selectivities and shapes at the central portion and the outer peripheral portion of the substrate uniform. Then, etching is performed by changing a flow rate of the second gaseous mixture while settings of the first gaseous mixture and the mixing ratio of the second gaseous mixture are fixed, thereby, setting the flow rate of the second gaseous mixture based on etching results to make etching rates at the central portion and the outer peripheral portion of the substrate uniform.

Owner:TOKYO ELECTRON LTD

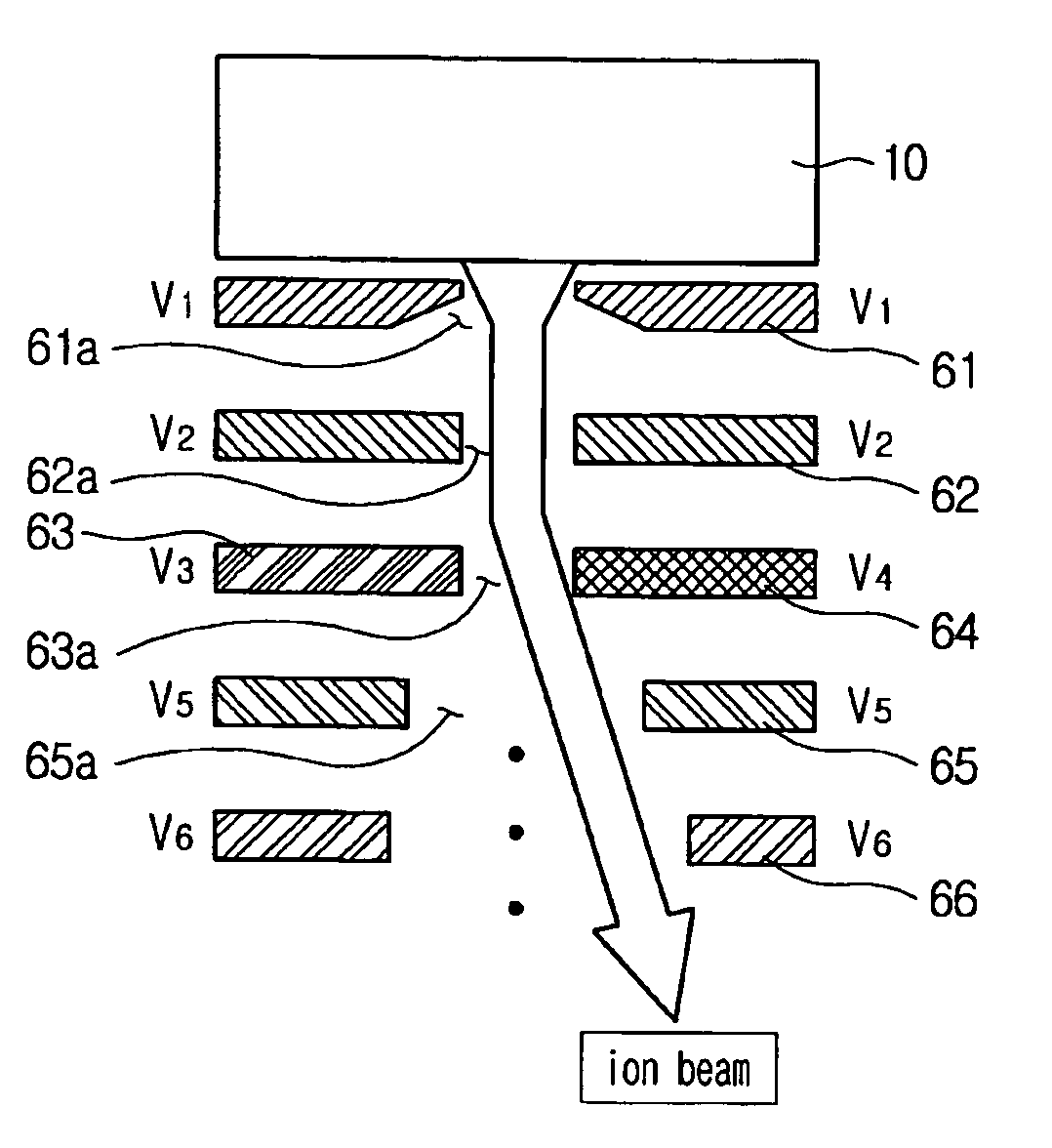

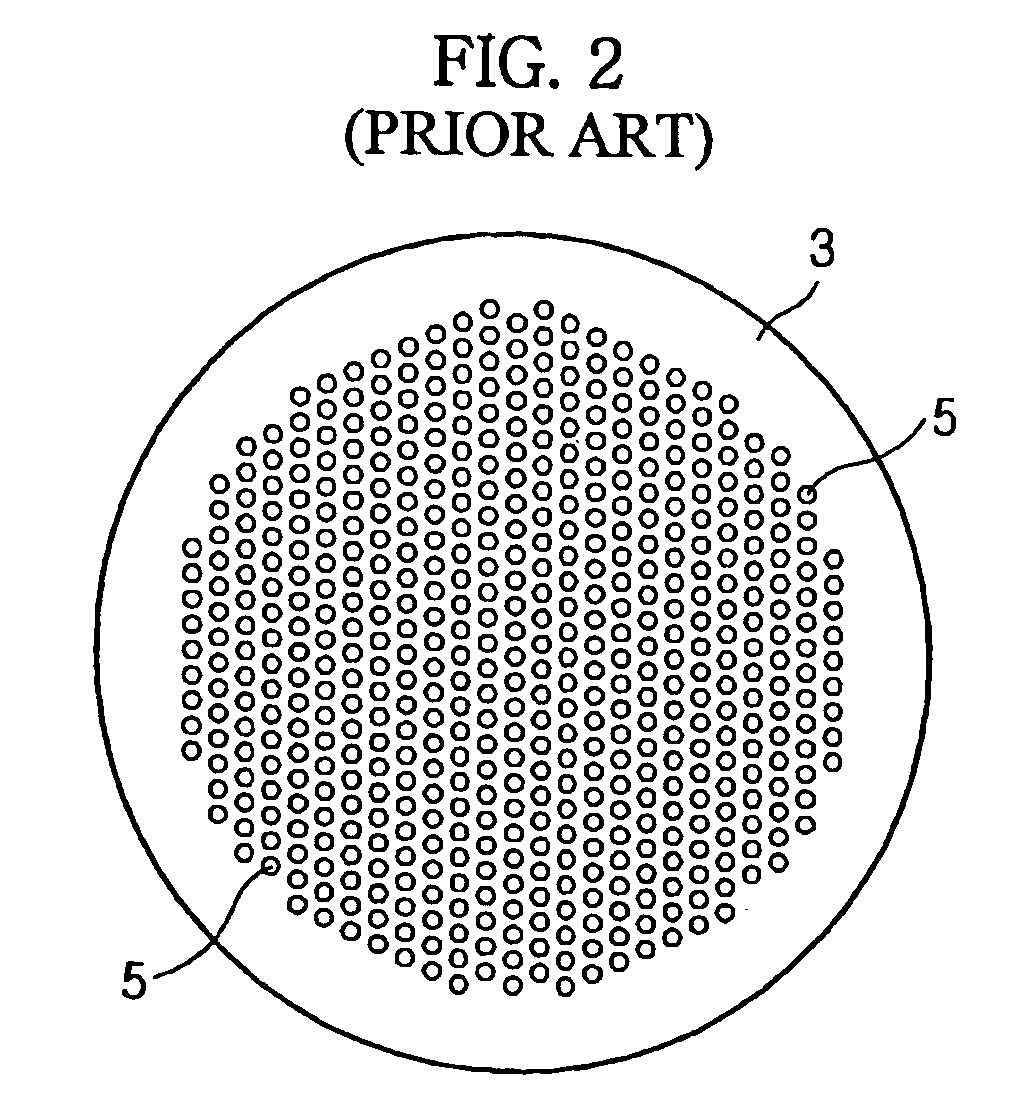

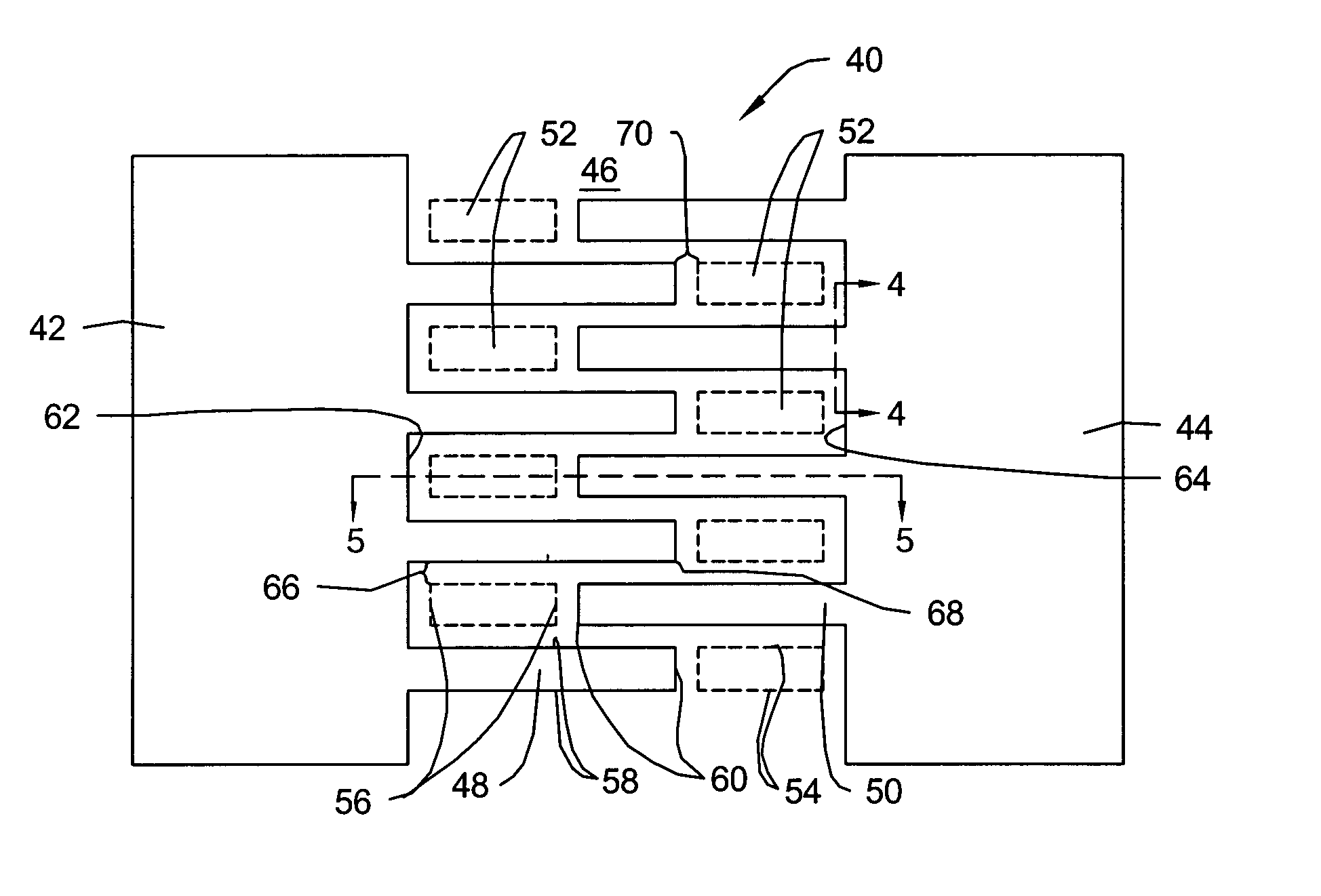

Ion beam extractor

InactiveUS7285788B2Increase the areaHigh ion fluxStability-of-path spectrometersBeam/ray focussing/reflecting arrangementsIon beamSemiconductor

An ion beam extractor controls a direction and an intensity of ion beams by adjusting a voltage applied to a grid having slits formed therein, thereby enhancing uniformity of an etching rate of a wafer, leading to an increase of productivity of semiconductor diodes. The ion beam extractor comprises an ion source to produce an ion beam and at least one grid located at a rear end of the ion source in a progressing path of the ion beam produced by the ion source to adjust a direction of the ion beam by controlling a voltage applied to the at least one grid.

Owner:SAMSUNG ELECTRONICS CO LTD

Ion beam extractor

InactiveUS20060152164A1Increase the areaHigh ion fluxControl electrodesElectric arc lampsIon beamSemiconductor

An ion beam extractor controls a direction and an intensity of ion beams by adjusting a voltage applied to a grid having slits formed therein, thereby enhancing uniformity of an etching rate of a wafer, leading to an increase of productivity of semiconductor diodes. The ion beam extractor comprises an ion source to produce an ion beam and at least one grid located at a rear end of the ion source in a progressing path of the ion beam produced by the ion source to adjust a direction of the ion beam by controlling a voltage applied to the at least one grid.

Owner:SAMSUNG ELECTRONICS CO LTD

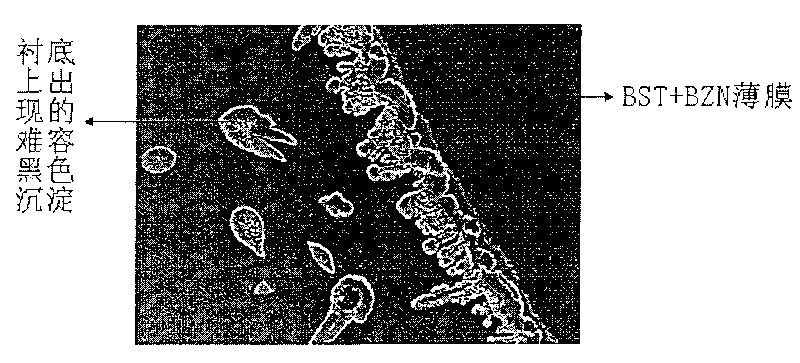

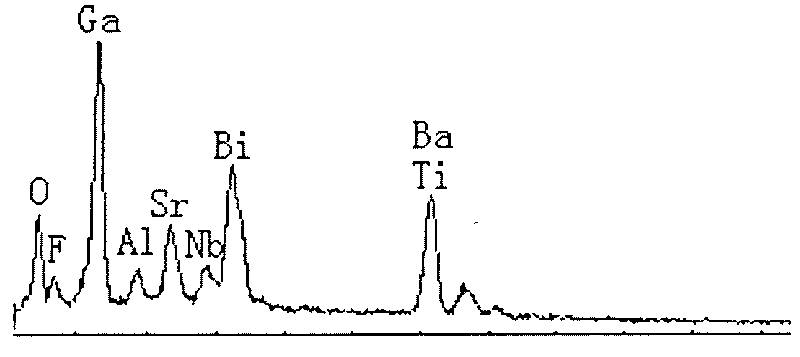

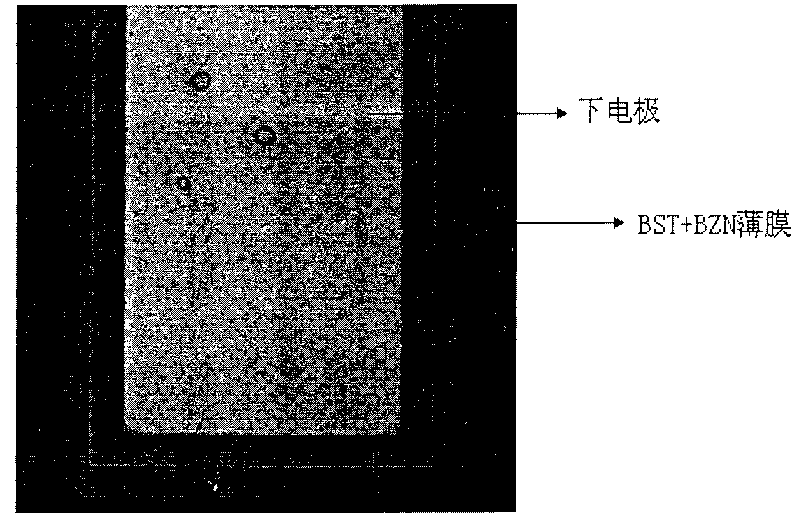

Wet etching method of barium-strontium titanate and bismuth zinc niobate composite films

InactiveCN101694012AUniform etch rateIncrease etch ratePolycrystalline material growthAfter-treatment detailsPolymer scienceComposite film

A processing method of barium-strontium titanate and bismuth zinc niotate composite films is characterized by 1, preparing a photoresist mask graphic on the surface of a BST+BZN composite film sample, 2, preparing etching: A is water solution prepared by nitricacid (HNO3), hydrofluoric acid (HF) and citrate (CA), and B is water prepared by hydrochloric acid (HC1) and hydrofluoric acid (HF), 3, sequentially etching the BST+BZN composite film sample in etching solutions A,B, and determining etching time according to respective thicknesses of BST and BZN, 4, removing a photoresist mask by aid of acetone / alcohol, and preparing the photoresist mask again, 5, performing low-power ultrasonic processing on the BST+BZN composite film sample in the etching A, and 6, utilizing the acetone / alcohol to remove the photoresist mask, cleaning the sample, and drying the sample by nitrogen (N2). Surfaces of positions etched by the processing method do not have residue, and then the processing method is complete in etching and high in graphic transforming precision.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

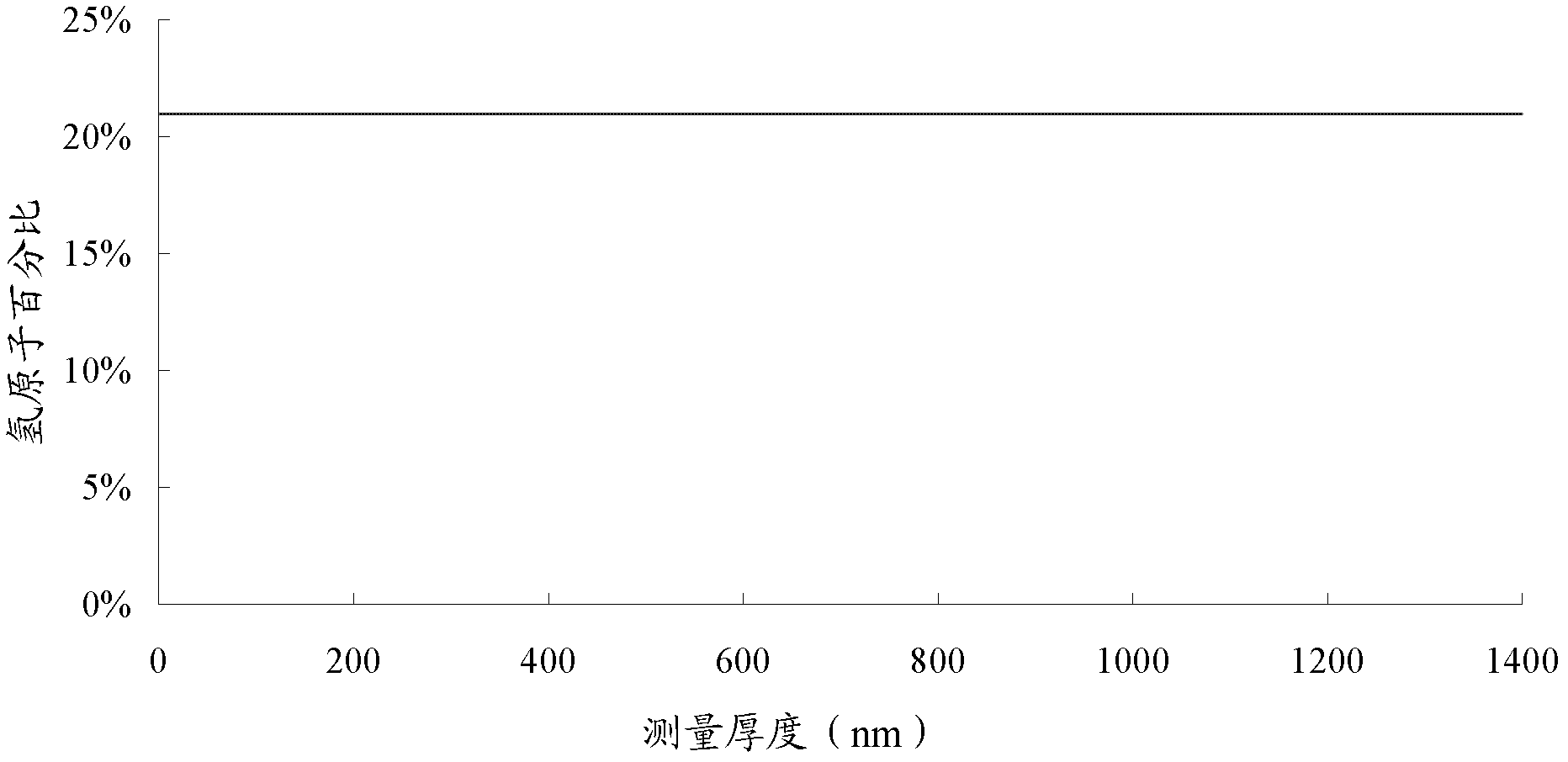

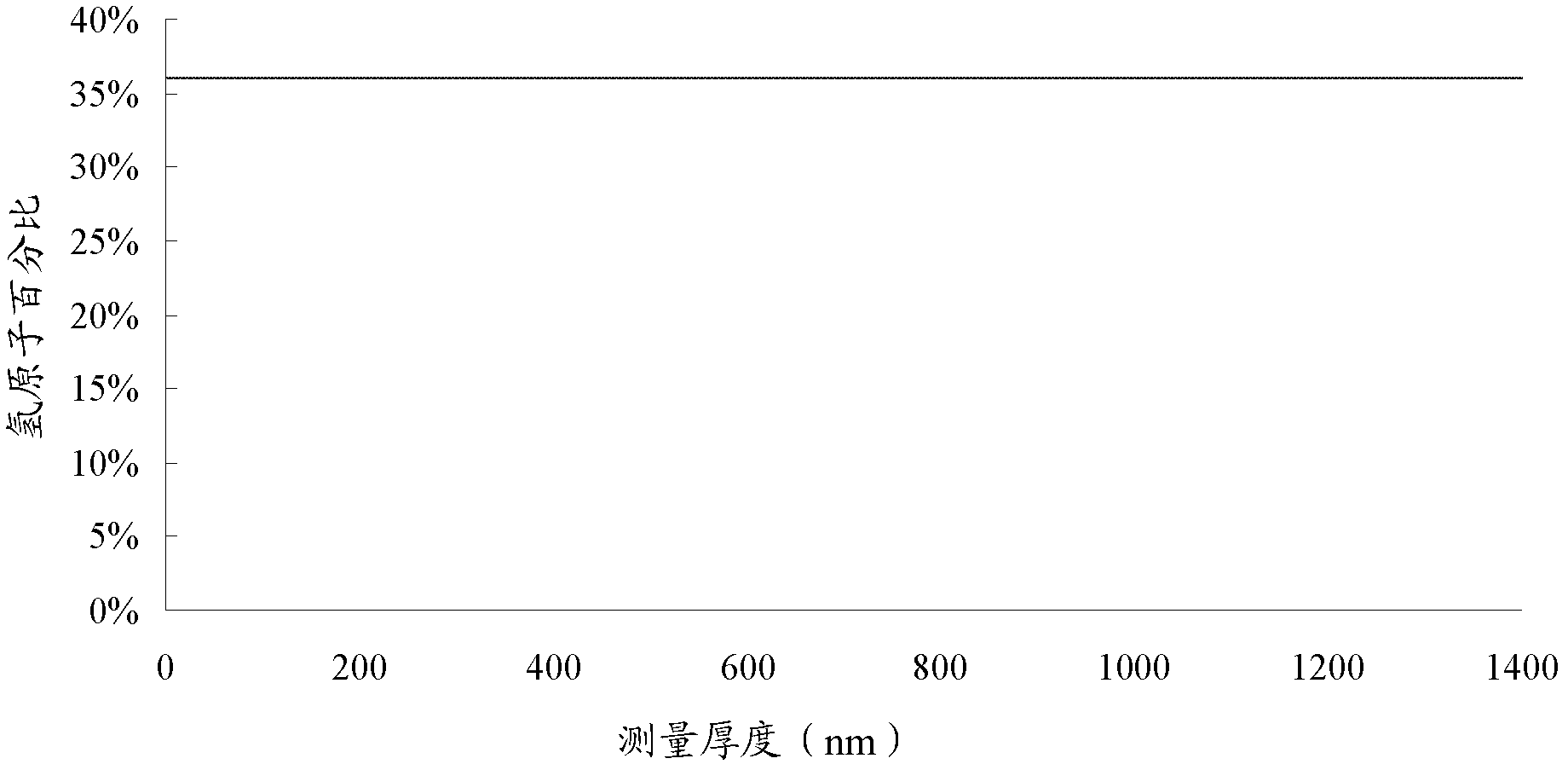

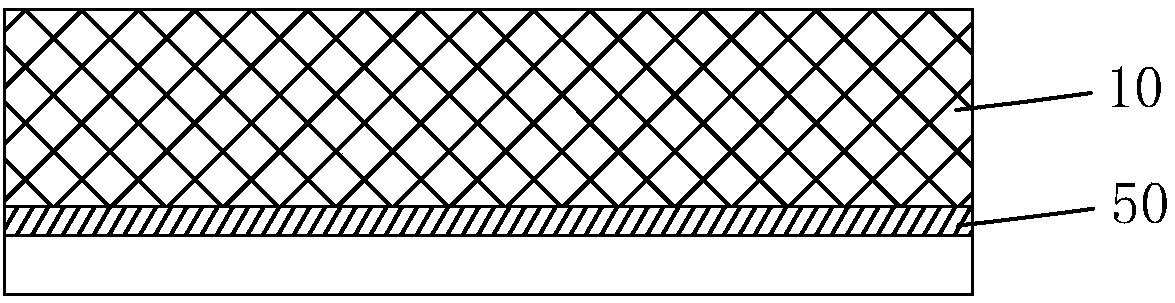

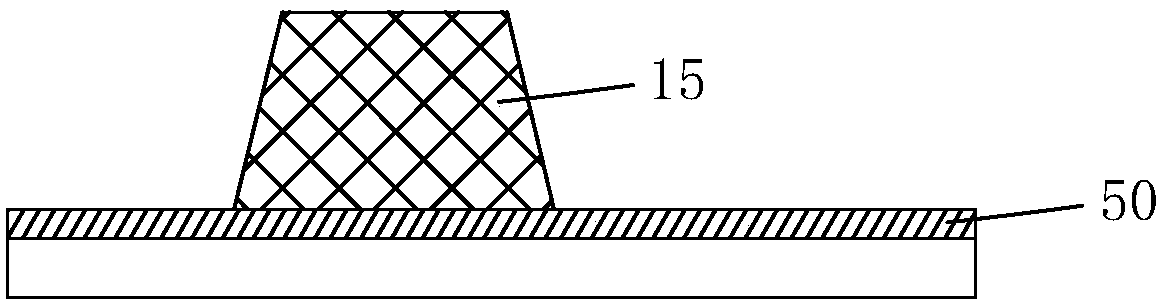

Amorphous carbon film processing method and opening forming method

ActiveCN102915953AUniform etch rateEvenly distributedSemiconductor/solid-state device manufacturingHydrogen atomHydrogen

The invention discloses an amorphous carbon film processing method and an opening forming method. The amorphous carbon film processing method comprises the following steps: a substrate is provided; an amorphous carbon film is formed on the surface of the substrate; the amorphous carbon film is subjected to annealing treatment; and the amorphous carbon film after the annealing treatment is subjected to ultraviolet light treatment. Through the treatment method of amorphous carbon film, provided by the invention, the distribution of hydrogen atoms in the amorphous carbon film is uniform, so that the etching speed of the amorphous carbon film is uniform, a flat and uniform etched surface in the etching process of different regions is favorably formed, and the performance of the semiconductor device is accordingly improved. Correspondingly, the invention also provides a method for forming an opening by etching the treated amorphous carbon film.

Owner:SEMICON MFG INT (SHANGHAI) CORP

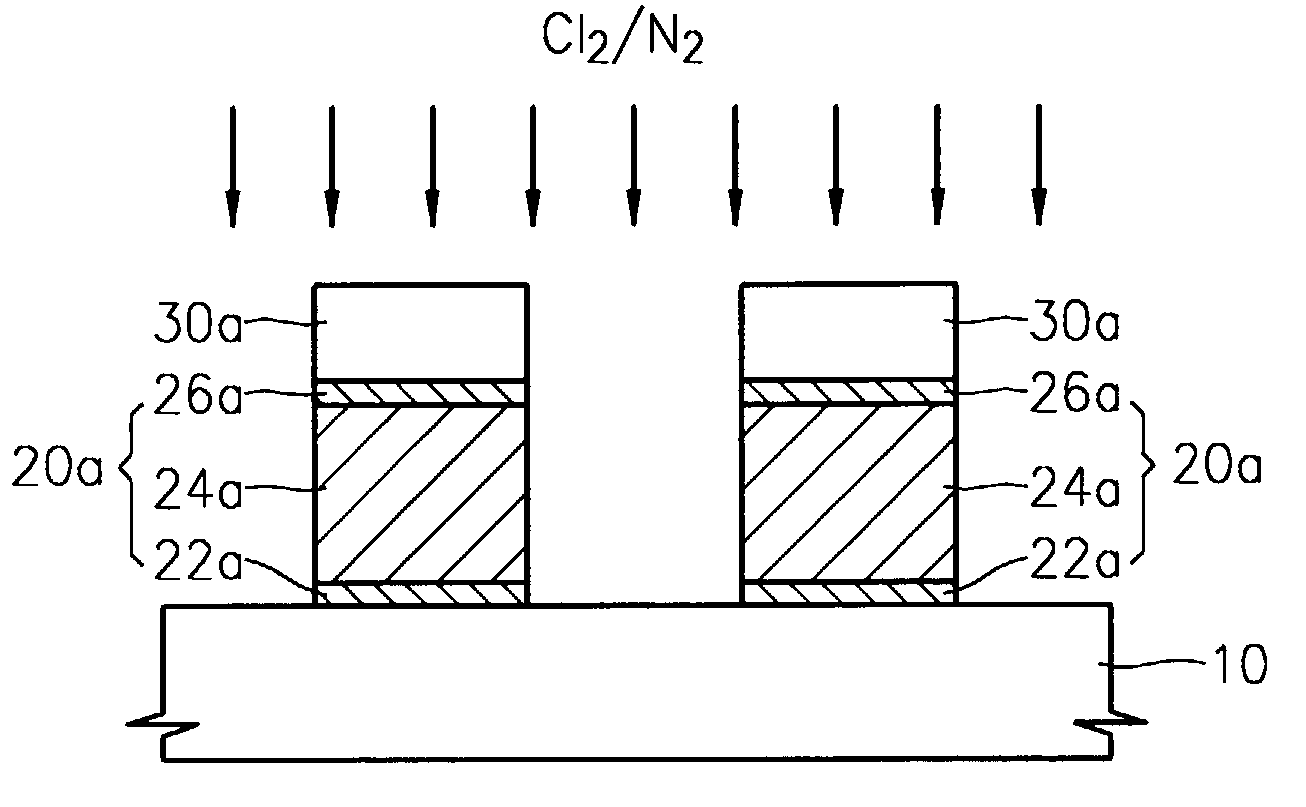

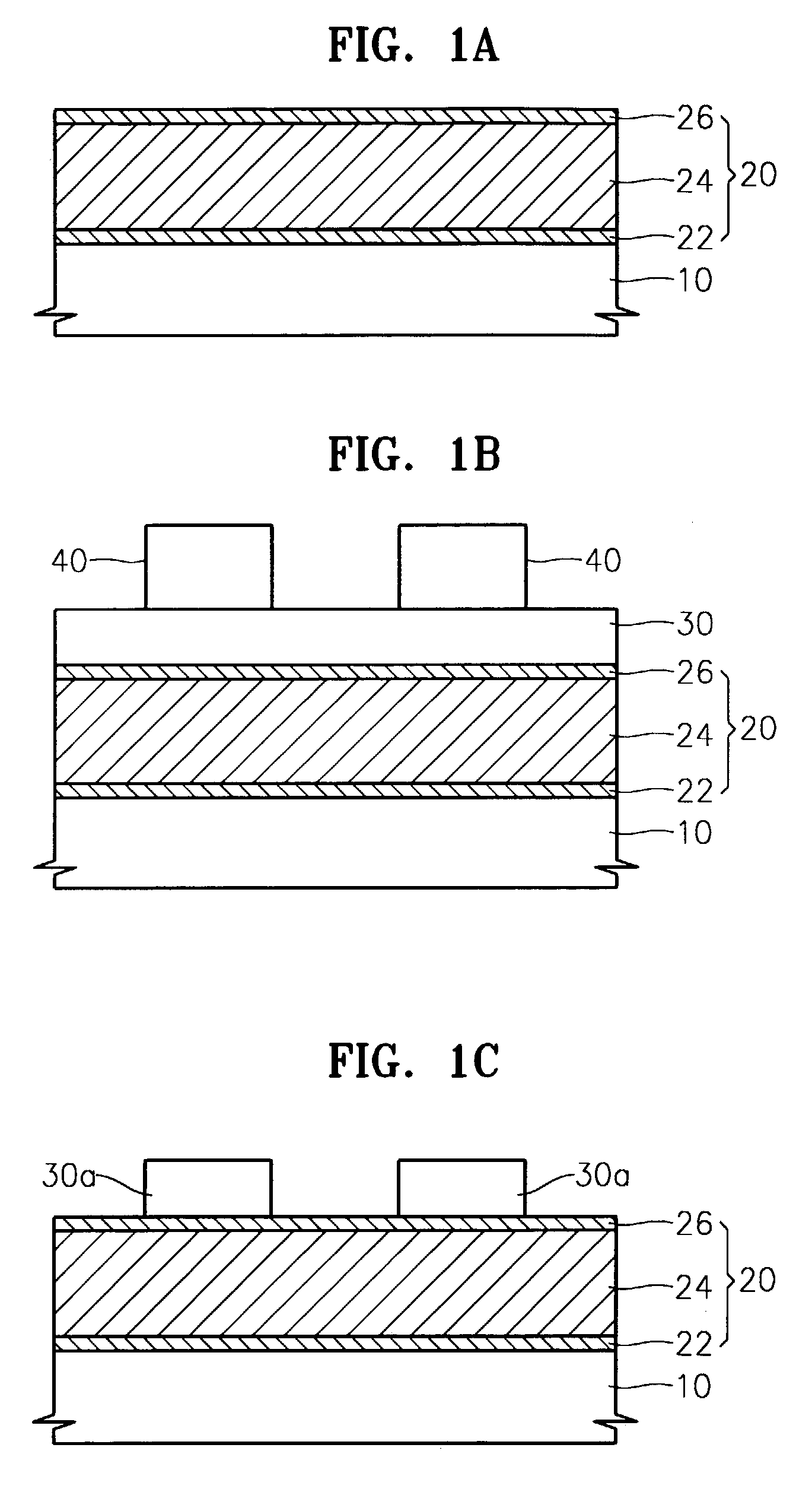

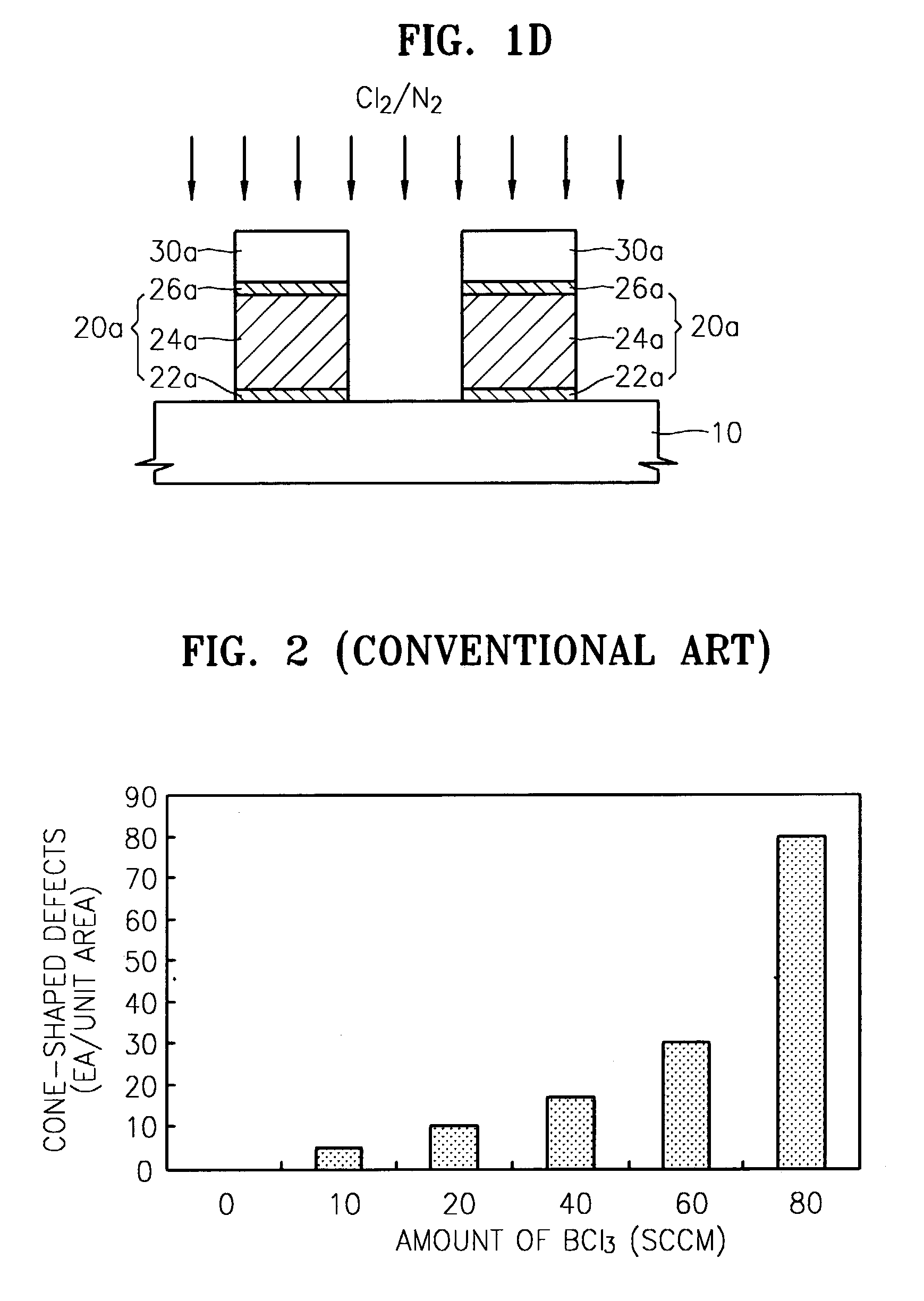

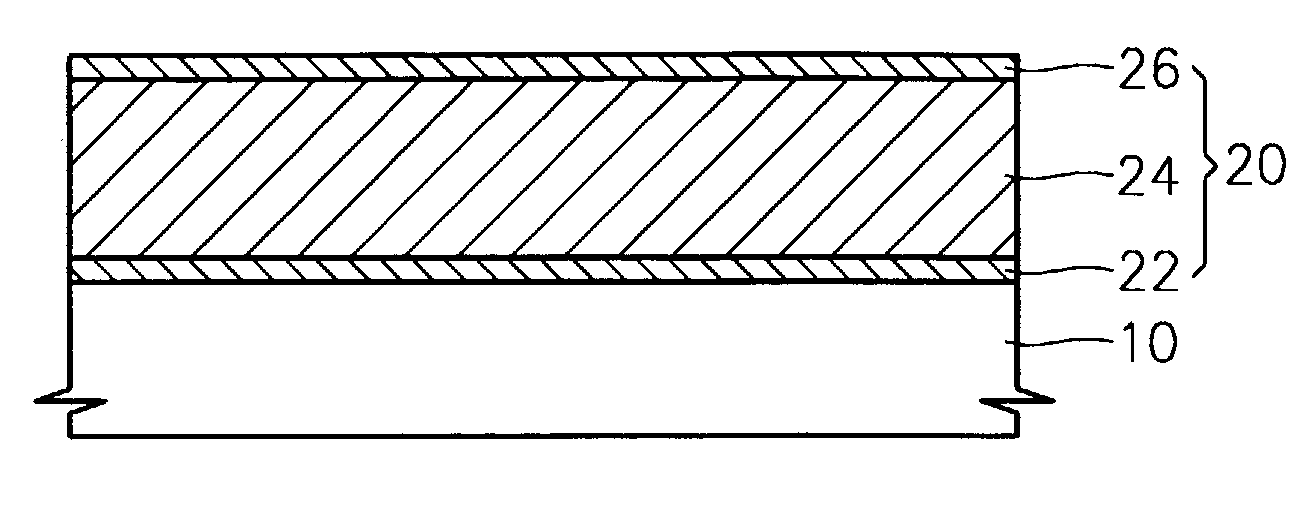

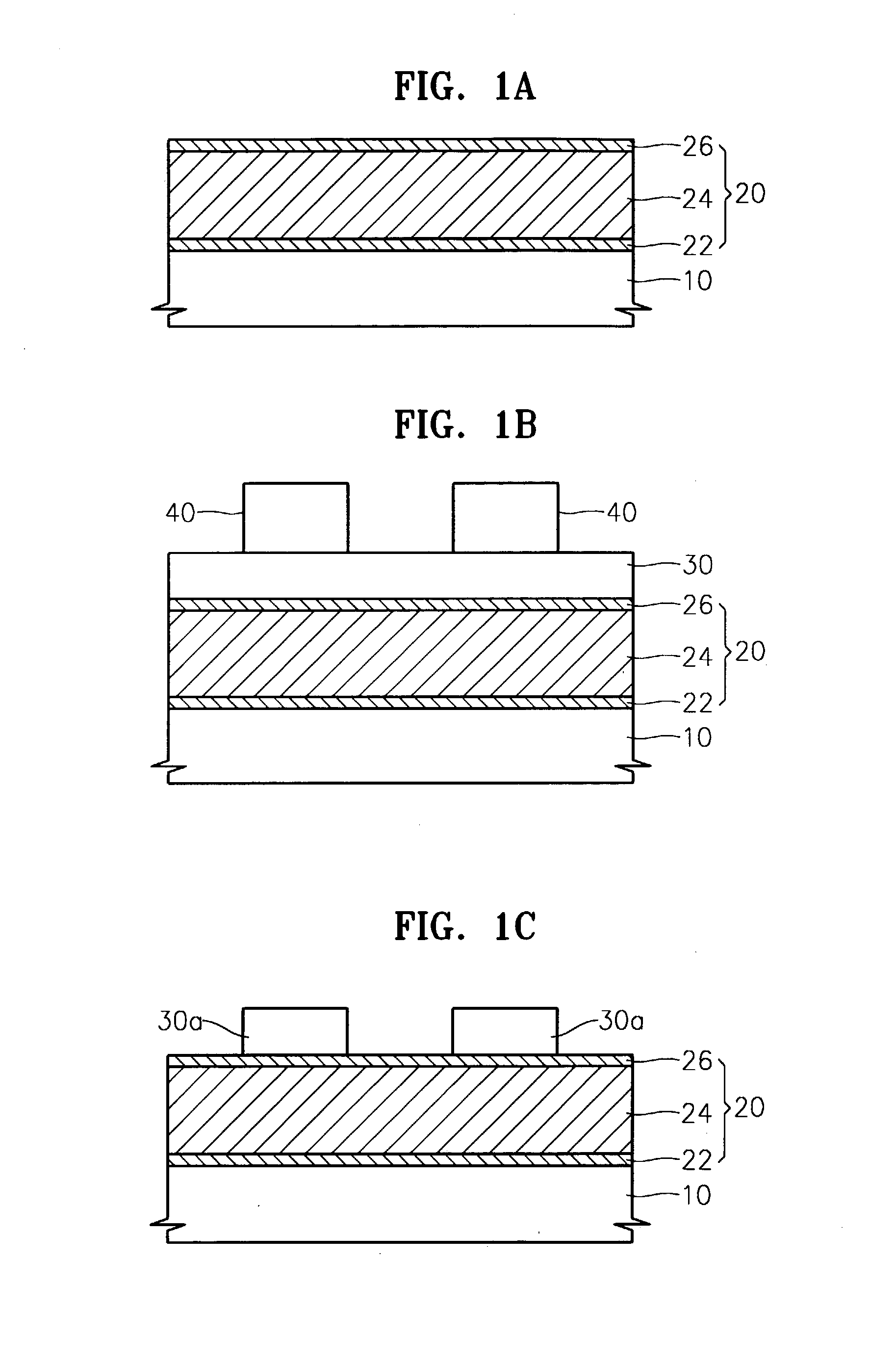

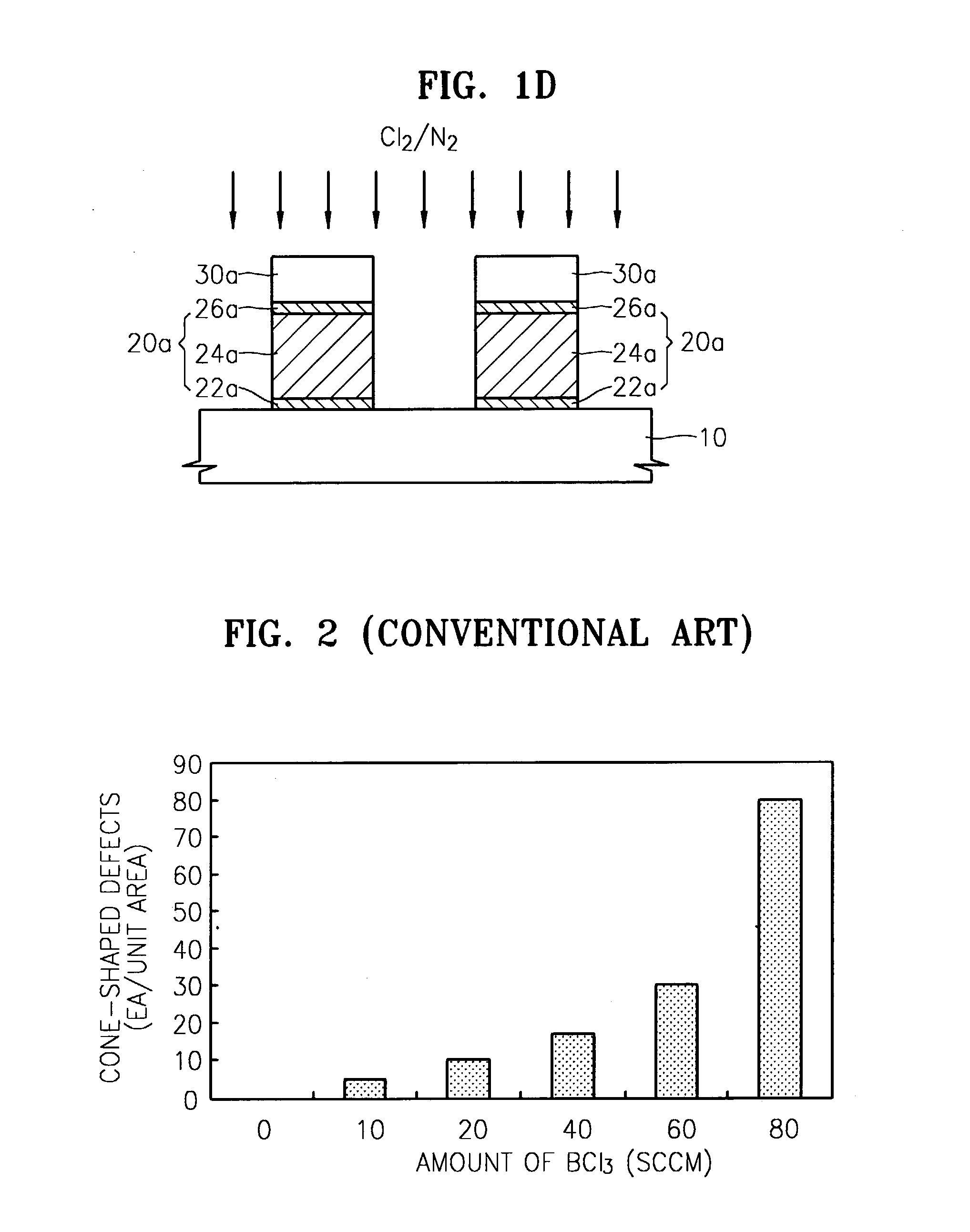

Method of etching a metal layer using a mask, a metallization method for a semiconductor device, a method of etching a metal layer, and an etching gas

InactiveUS7226867B2Micro-loading may be reducedUniform etch rateSemiconductor/solid-state device detailsSolid-state devicesSemiconductorMetal

Methods for etching a metal layer and a metallization method of a semiconductor device using an etching gas that includes Cl2 and N2 are provided. A mask layer is formed on the metal layer, the etching gas is supplied to the metal layer, and the metal layer is etched by the etching gas using the mask layer as an etch mask. The metal layer may be formed of aluminum or an aluminum alloy. Cl2 and N2 may be mixed at a ratio of 1:1 to 1:10. The etching gas may also include additional gases such as inactive gases or gases that include the elements H, O, F, He, or C. In addition, N2 may be supplied at a flow rate of from 45–65% of the total flow rate of the etching gas, which results in a reduction in the occurrence of micro-loading and cone-shaped defects in semiconductor devices.

Owner:SAMSUNG ELECTRONICS CO LTD

Method of etching a metal layer using a mask, a metallization method for a semiconductor device, a method of etching a metal layer, and an etching gas

InactiveUS20040038547A1Micro-loading may be reducedUniform etch rateSemiconductor/solid-state device detailsSolid-state devicesSemiconductorMetal

Methods for etching a metal layer and a metallization method of a semiconductor device using an etching gas that includes Cl2 and N2 are provided. A mask layer is formed on the metal layer, the etching gas is supplied to the metal layer, and the metal layer is etched by the etching gas using the mask layer as an etch mask. The metal layer may be formed of aluminum or an aluminum alloy. Cl2 and N2 may be mixed at a ratio of 1:1 to 1:10. The etching gas may also include additional gases such as inactive gases or gases that include the elements H, O, F, He, or C. In addition, N2 may be supplied at a flow rate of from 45-65% of the total flow rate of the etching gas, which results in a reduction in the occurrence of micro-loading and cone-shaped defects in semiconductor devices.

Owner:SAMSUNG ELECTRONICS CO LTD

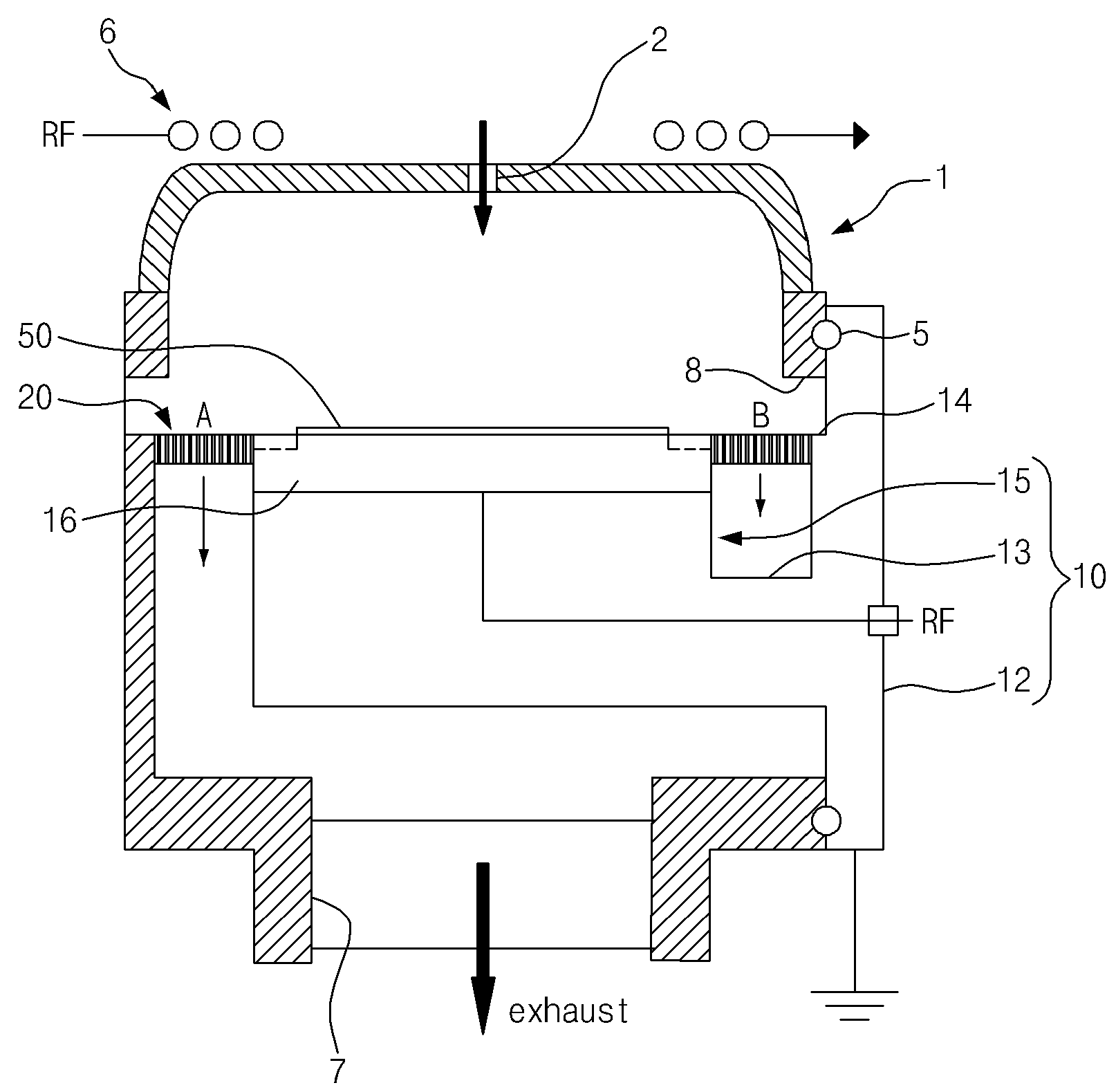

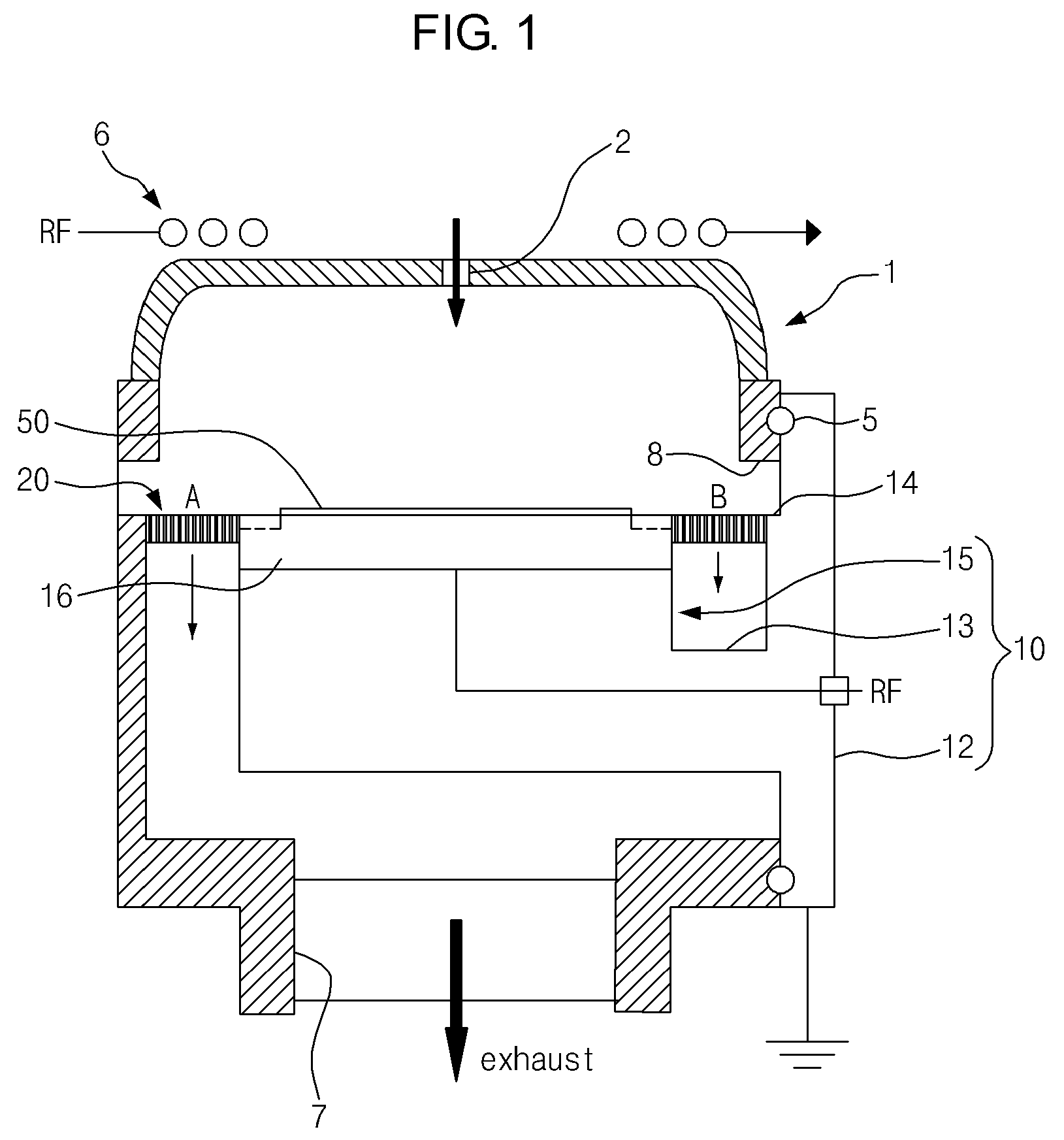

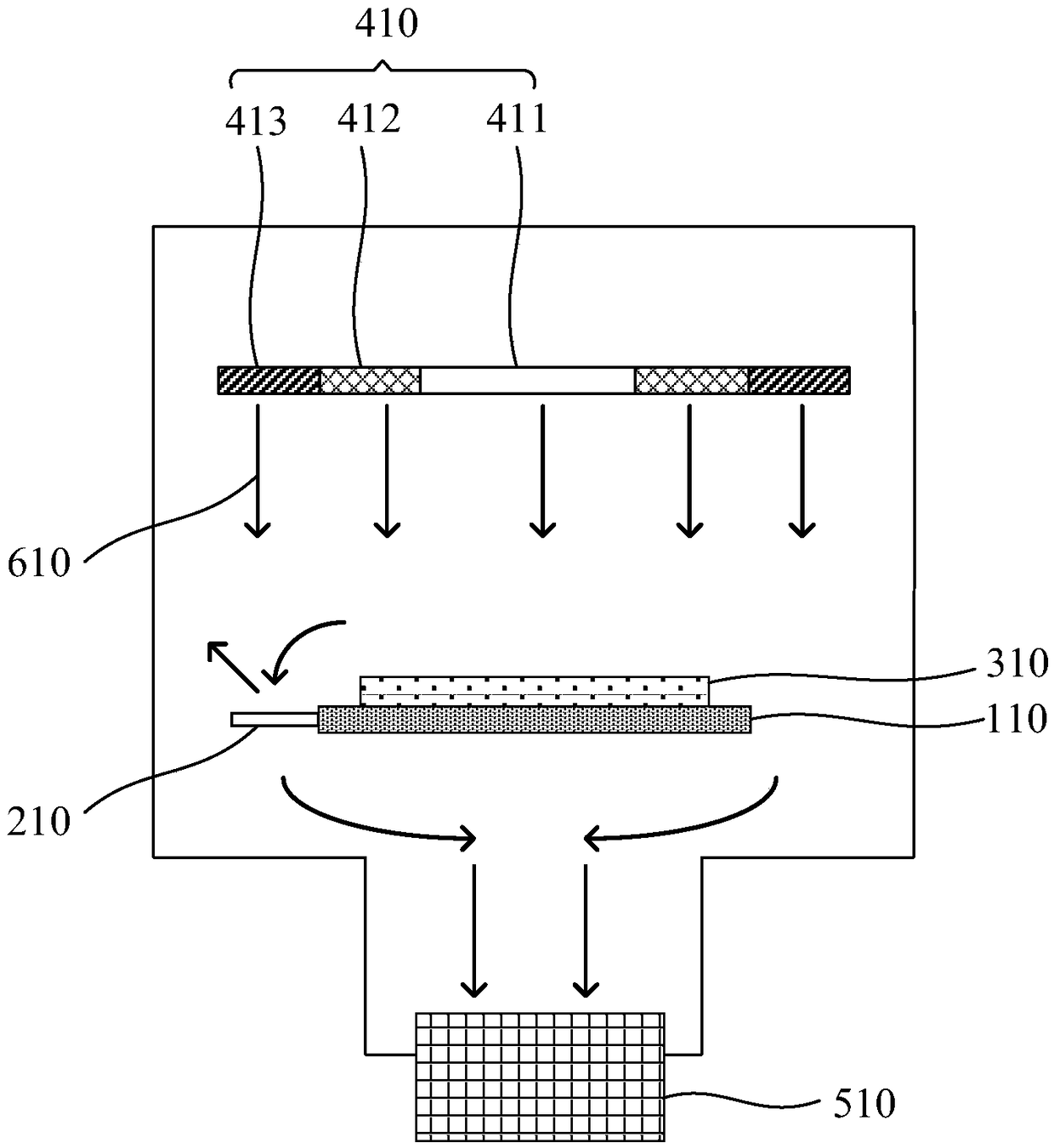

Plasma reactor

ActiveUS20090280040A1Uniform dischargeImprove uniformityElectric discharge tubesSemiconductor/solid-state device manufacturingChemical reactorEngineering

A plasma chemical reactor is provided. The reactor includes a chamber, a cathode assembly, and a baffle plate. The chamber forms a plasma reaction space. The cathode assembly includes a cathode support shaft and a substrate support. The cathode support shaft is coupled at one side to a wall surface of the chamber. The substrate support is coupled to the other side of the cathode support shaft and supports the substrate. The baffle plate is out inserted and coupled to the substrate support, and has a plurality of vents arranged to be spaced apart and through formed such that reaction gas can pass through, and the vents asymmetrically arranged and formed to get a vent area smaller at an opposite side than a top side of the cathode support shaft.

Owner:DMS CO LTD

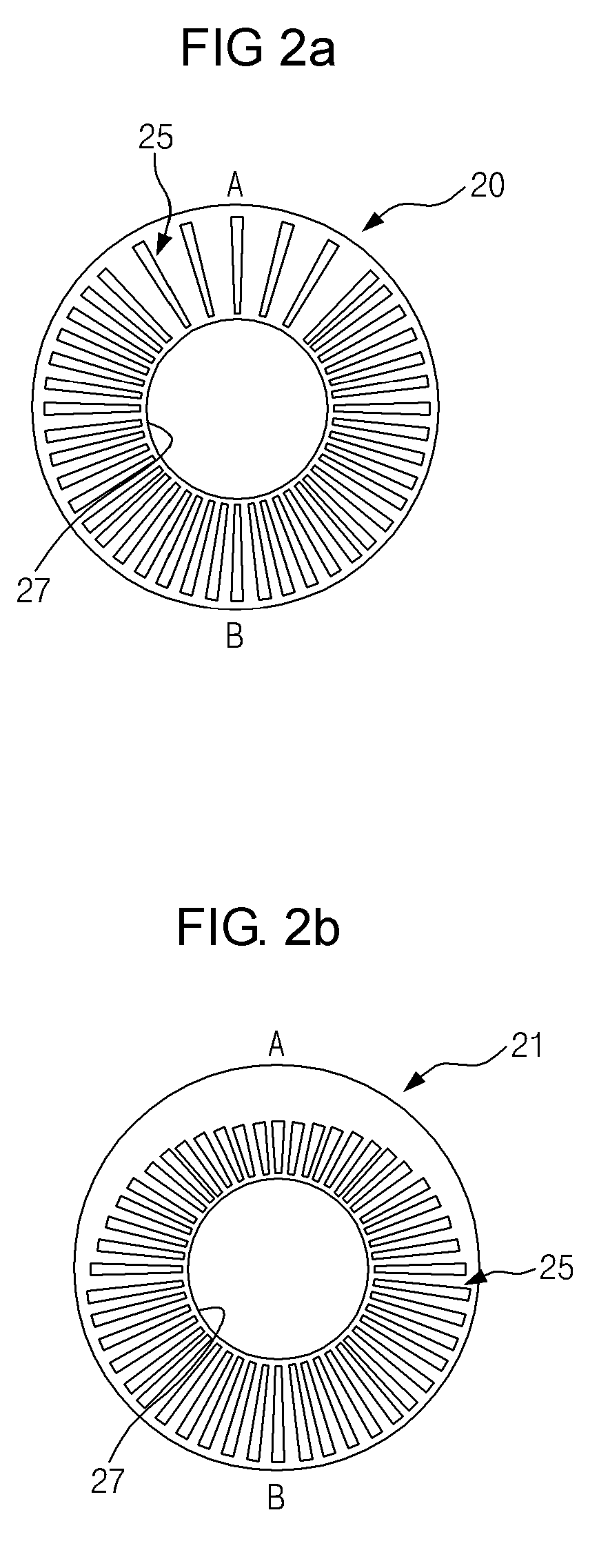

Inductive coupling plasma device

ActiveCN1848385ASmall difference in chemical reaction speedQuality improvementSemiconductor/solid-state device manufacturingPlasma techniqueInductively coupled plasmaSurface chemical reaction

The present invention relates to an inductively-coupled plasma device, including inductively-coupled plasma cavity body, inductively-coupled coil and coil rotating device. The inductively-coupled coil is positioned over the inductively-coupled plasma cavity body, the inductively-coupled coil is mounted on the coil rotating device, the coil rotating device is fixed on the inductively-coupled plasma cavity body, the rotation of said coil rotating device can drive the inductively-coupled coil and make it be rotated, the coil rotating device is formed from motor, fixed plate and support. Said invention can make the plasma produced in reaction cavity chamber be uniformly distributed, so that the wafer processing quality and stability can be greatly raised.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

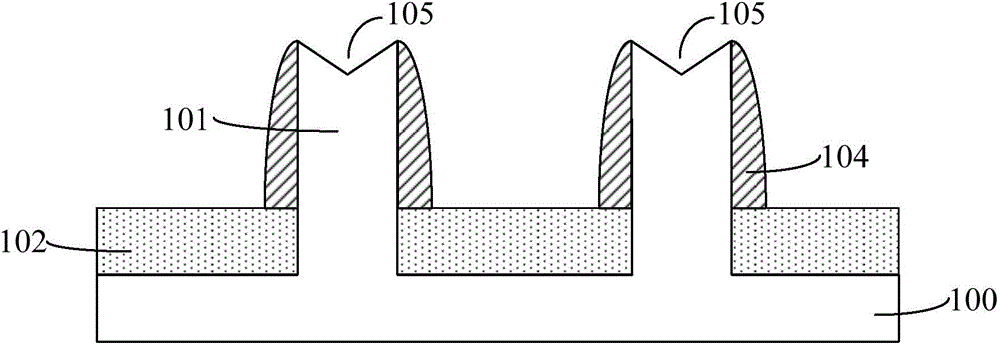

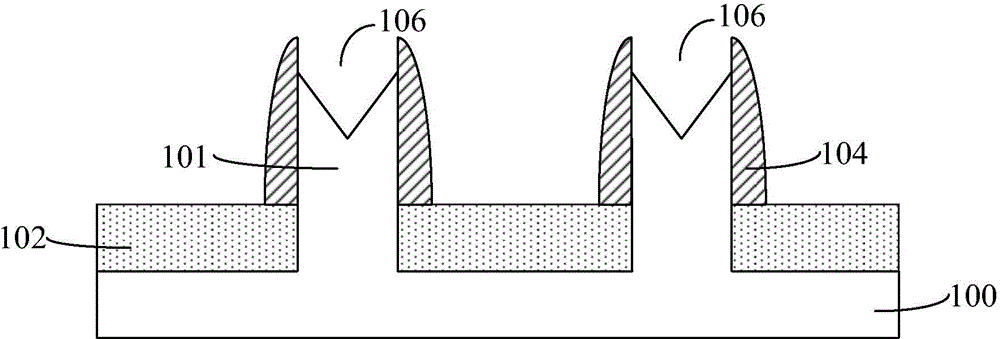

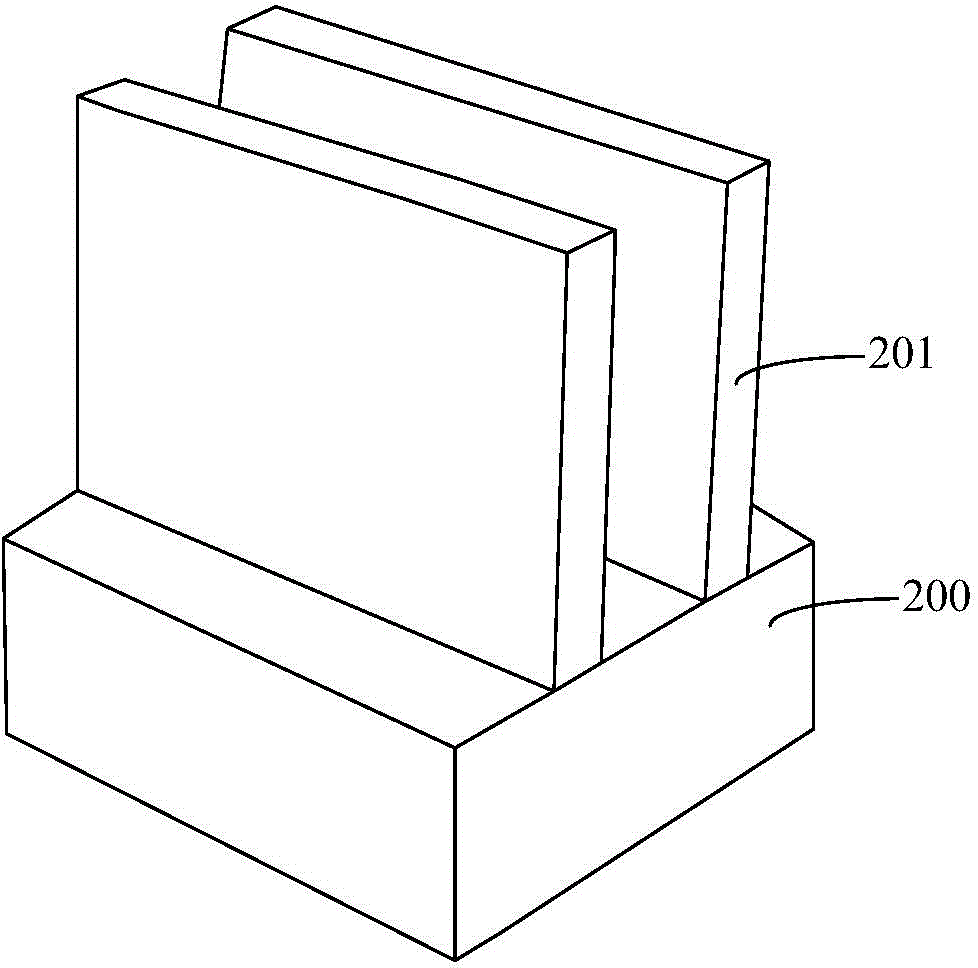

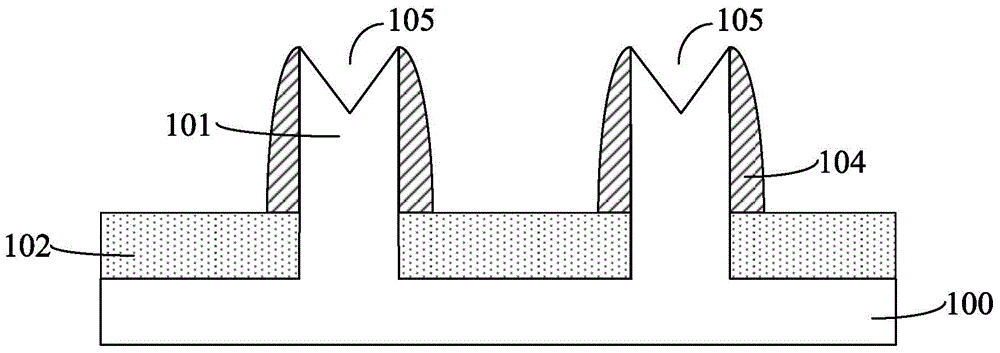

Fin-type field effect transistor forming method

ActiveCN105719969AImprove electrical performanceUniform etch rateSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingElectrical performance

The invention discloses a fin-type field effect transistor forming method, and the method comprises the steps: providing a substrate, wherein the surface is provided with a plurality of separated fin parts; forming a separation layer on the surface of the substrate, wherein the top of the separating layer is lower than the top of the fin parts, and covers the surface of a part of side walls of the fin parts; forming a side wall layer covering the surfaces of the side walls of the fin parts, and exposing the top surfaces of the fin parts; carrying out the selective nitrogen treatment of the tops of the fin parts, and enabling the fin parts at a certain thickness to be converted into a semiconductor nitridation layer; carrying out the etching of the semiconductor nitridation layer through employing a wet etching method, so as to form openings between the adjacent side wall layers and the remaining fin parts; and placing stress layers in the openings. The method improves the flatness of the bottom of the opening, improves the quality of the formed stress layers, and optimizes the electrical performances of a fin-type field effect transistor.

Owner:SEMICON MFG INT (SHANGHAI) CORP

A dry etching apparatus

InactiveCN109065432AEvenly distributedUniform etch rateElectric discharge tubesSemiconductor/solid-state device manufacturingEngineeringGas chamber

A dry etching apparatus includes a gas supply portion located in an upper electrode of the dry etching apparatus and disposed parallel to a wafer, a lower surface area of the gas supply portion beingnot smaller than an upper surface area of the wafer,. The gas supply portion sequentially comprises a central region, an intermediate region surrounding the central region and an edge region surrounding the intermediate region from inside to outside, wherein the edge region is divided into at least two edge region gas chambers, and the edge region gas chambers penetrate the edge region; The waferhas a uniform etching rate by adjusting the reaction gas in each region of the gas supply portion.

Owner:HUAIAN IMAGING DEVICE MFGR CORP

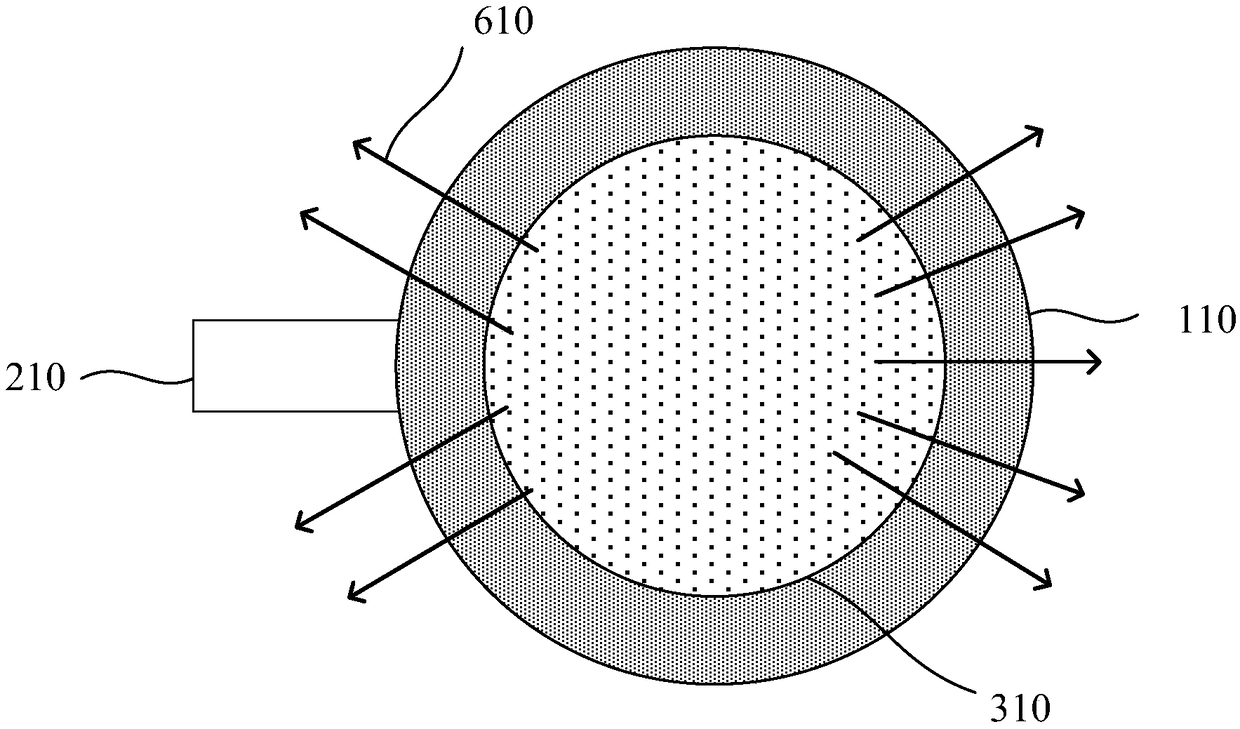

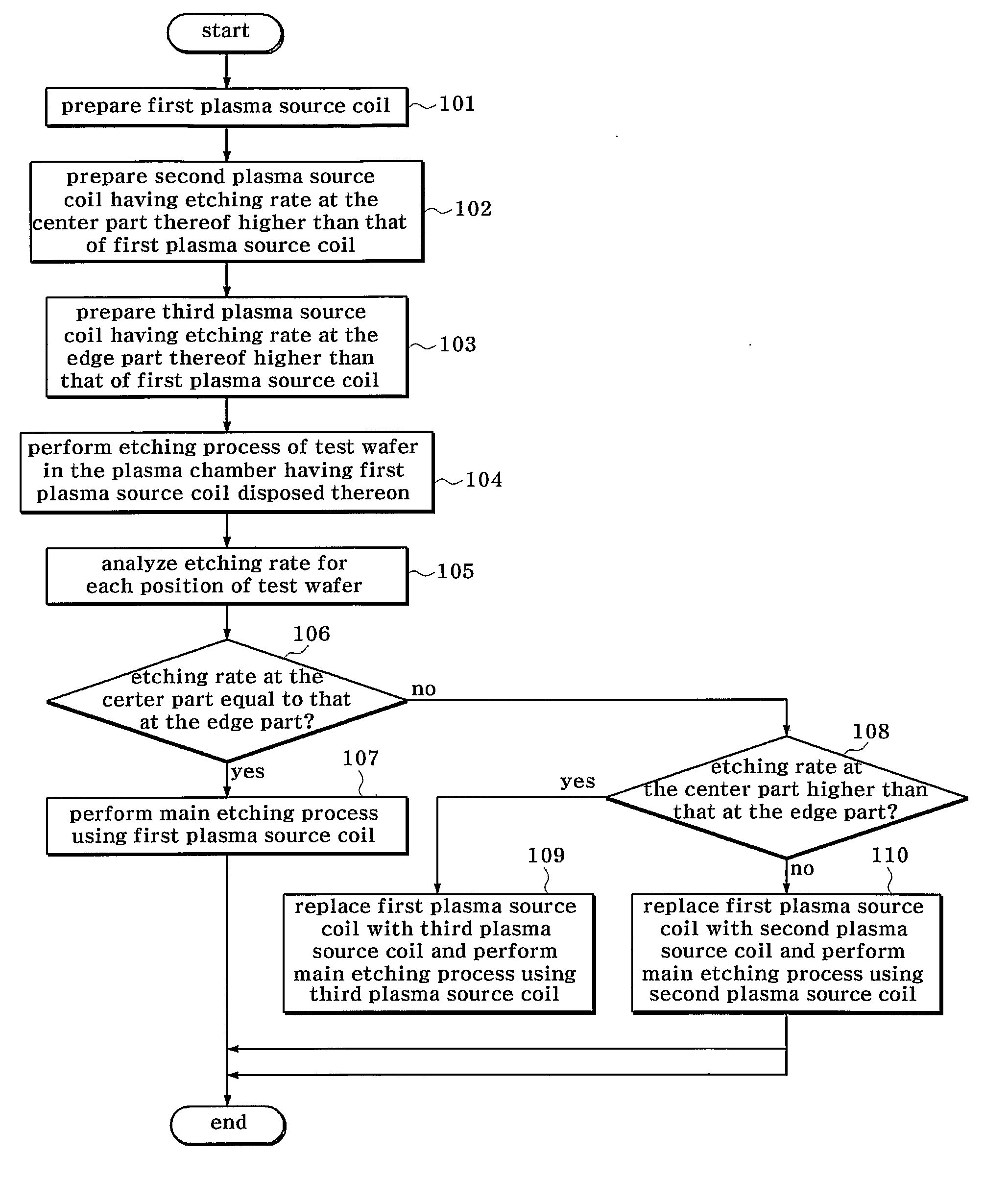

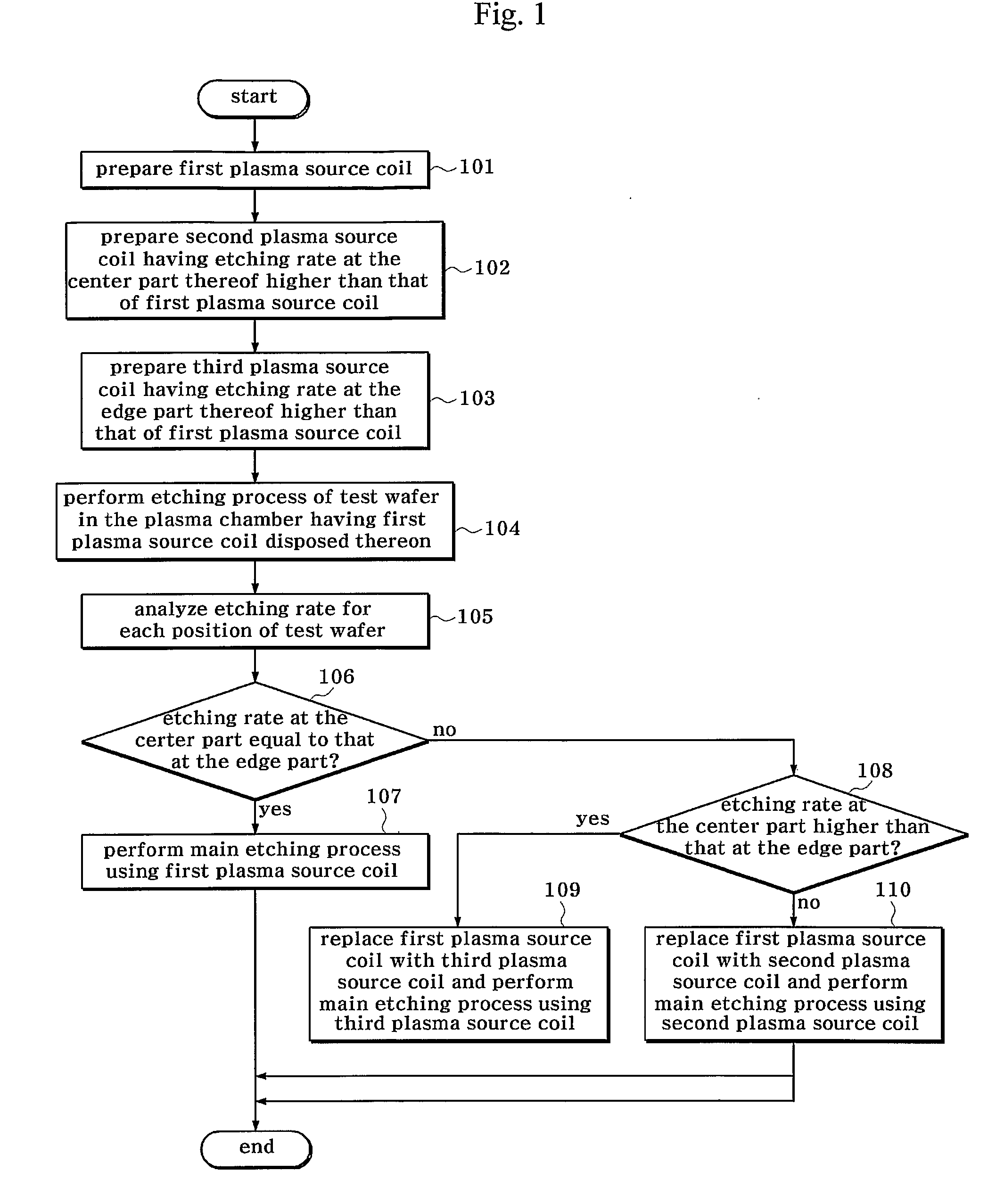

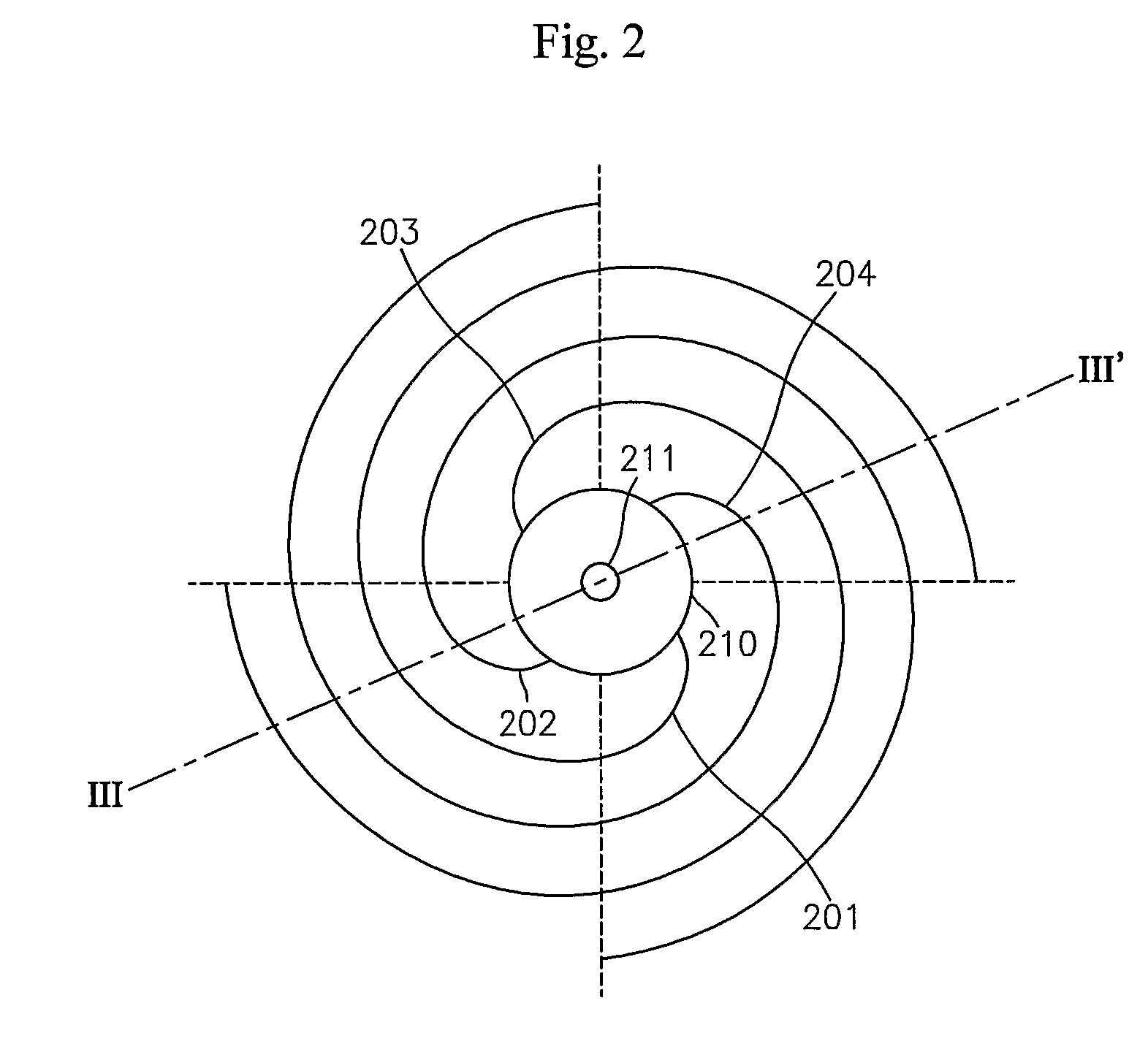

Method for setting plasma chamber having an adaptive plasma source, plasma etching method using the same and manufacturing method for adaptive plasma source

InactiveUS20070151947A1Satisfactory pattern profileLow powerElectric discharge tubesDecorative surface effectsPlasma chamberNuclear physics

Disclosed herein is a plasma chamber setting method for generating plasma in a plasma chamber. A plurality of plasma source coils, including a first plasma source coil, a second plasma source coil having an etching rate at the center part thereof higher than that of the first plasma source coil, and a third plasma source coil having an etching rate at the edge part thereof higher than that of the first plasma source coil, are prepared. The first plasma source coil is disposed on the plasma chamber, and a test wafer is etched. The etching rate for each position of the test wafer is analyzed, and first plasma source coil is replaced with the second plasma source coil or the third plasma source coil based on the analysis results.

Owner:ADAPTIVE PLASMA TECH

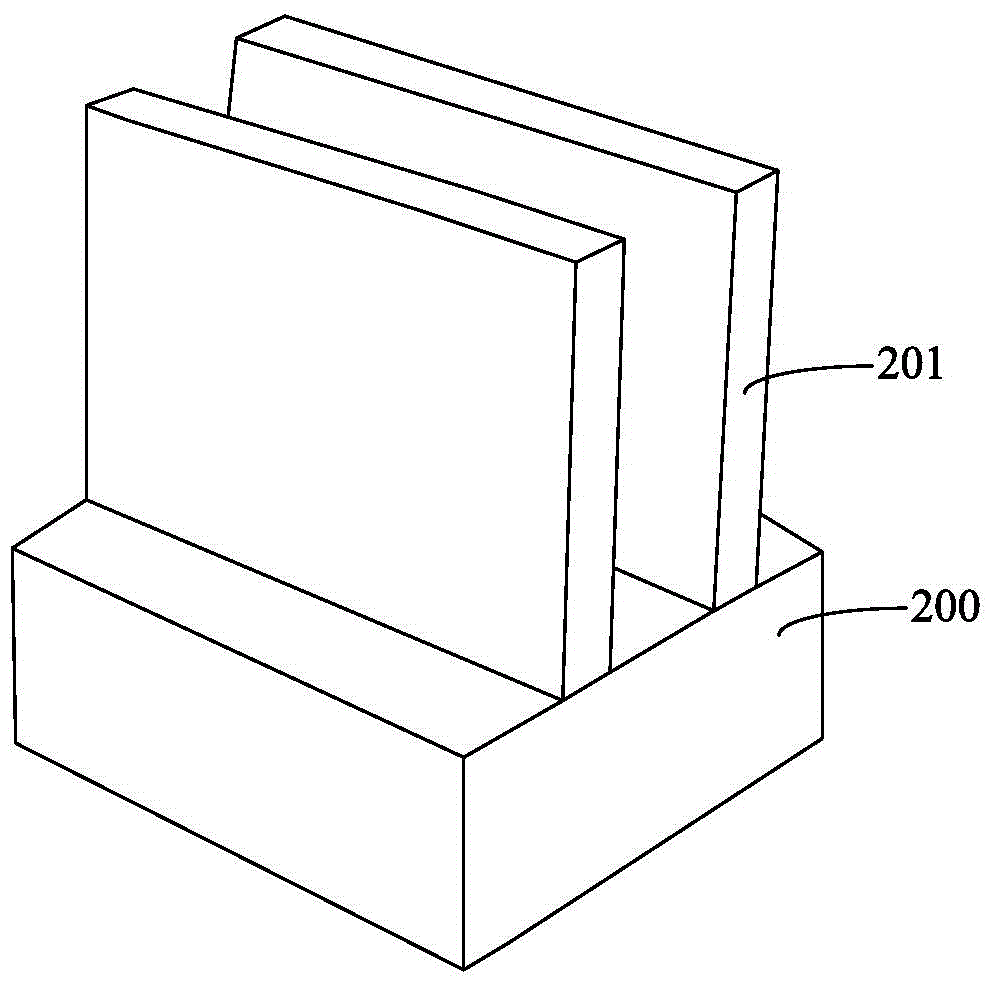

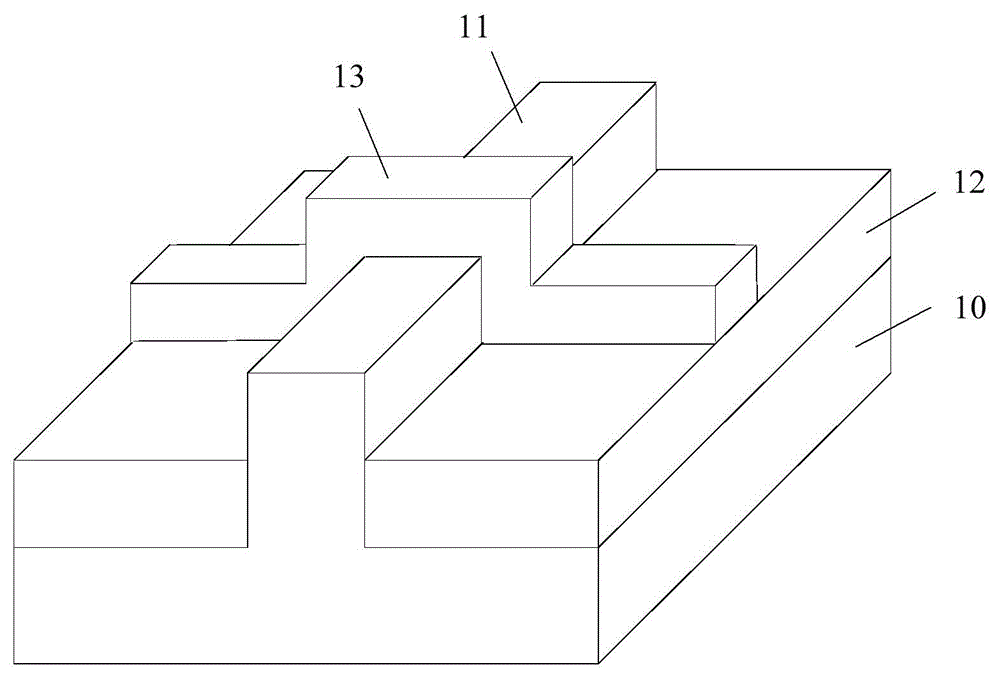

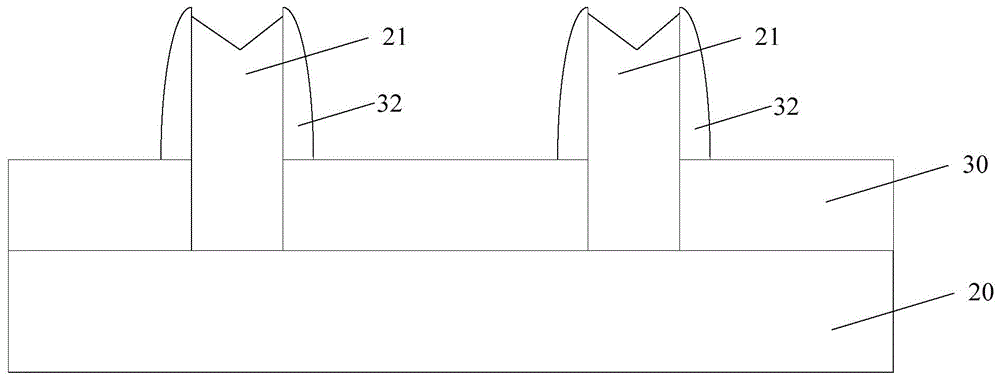

Fin field-effect transistor formation method

ActiveCN105470132AUniform etch rateReduce etch damageSolid-state devicesSemiconductor/solid-state device manufacturingEtchingEngineering

Provided is a fin field-effect transistor formation method which comprises the following steps: providing a substrate, and forming a plurality of independent fin portions on the surface of the substrate; forming an isolating layer on the surface of the substrate, the top surface of the isolating layer being lower than the top surface of each fin portion and the isolating layer covering a part of the surfaces of the side walls of the fin portions; forming a barrier layer covering the surface of the isolating layer and the top and side wall surfaces of the fin portions; converting a part of the barrier layer of a certain thickness into a passivation layer through oxidation treatment; etching back the passivation layer to form passivated side walls covering on the surface of the barrier layer on the side wall surfaces of the fin portions; and with the passivated side walls being as a mask, removing the barrier layer on the top surfaces of the fin portions by utilizing a wet etching process, and retaining the barrier layer on the side wall surfaces of the fin portions as barrier side walls. According to the fin field-effect transistor formation method, the quality of a formed stress layer is improved, and meanwhile, growth of the stress layer on the side wall surfaces of the fin portions can be prevented, and performance of a fin field-effect transistor is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Process for producing siliceous film and substrate with siliceous film produced thereby

ActiveCN101366103AUniform qualityUniform etch rateSemiconductor/solid-state device manufacturingChemical vapor deposition coatingPolysilazaneHydrogen content

A process for producing a siliceous film with quality uniform irrespective of locality or groove interior or exterior wherein in the groove interior there is no void or crack. This substrate with siliceous film can be produced by first forming an insulating film of high hydrogen content on the surface of an uneven silicon substrate, subsequently coating the substrate with a composition containing a polysilazane compound and thereafter heating the coating product to thereby convert the polysilazane compound into a silicon dioxide film.

Owner:MERCK PATENT GMBH

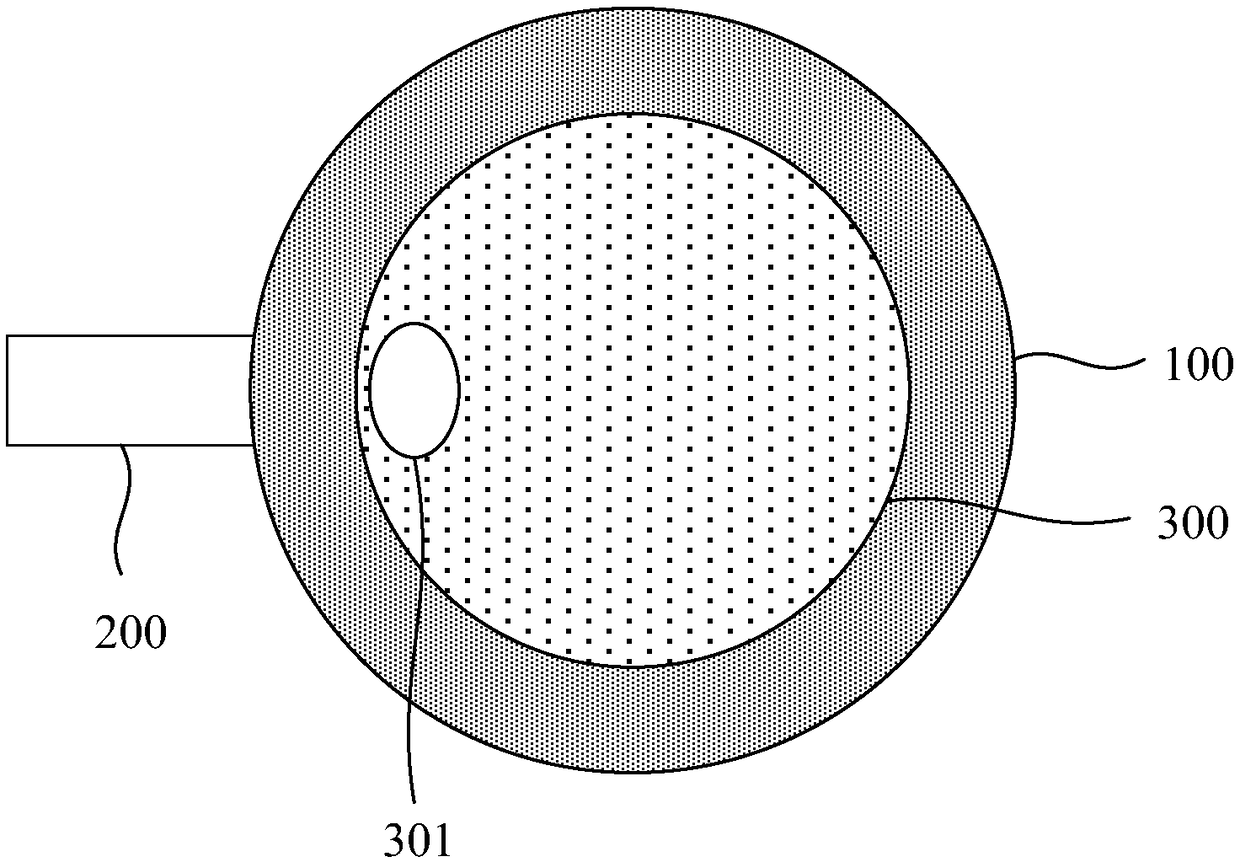

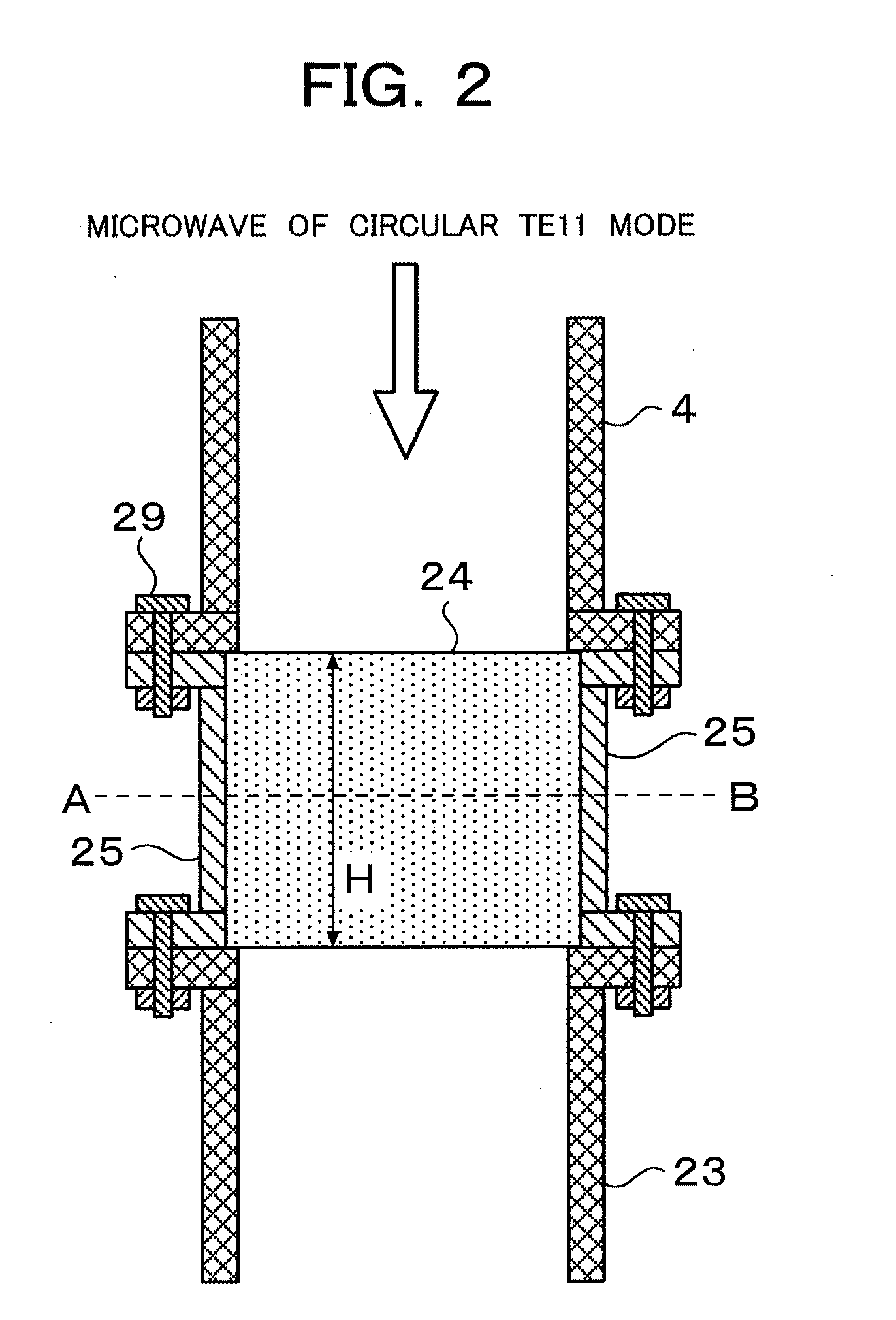

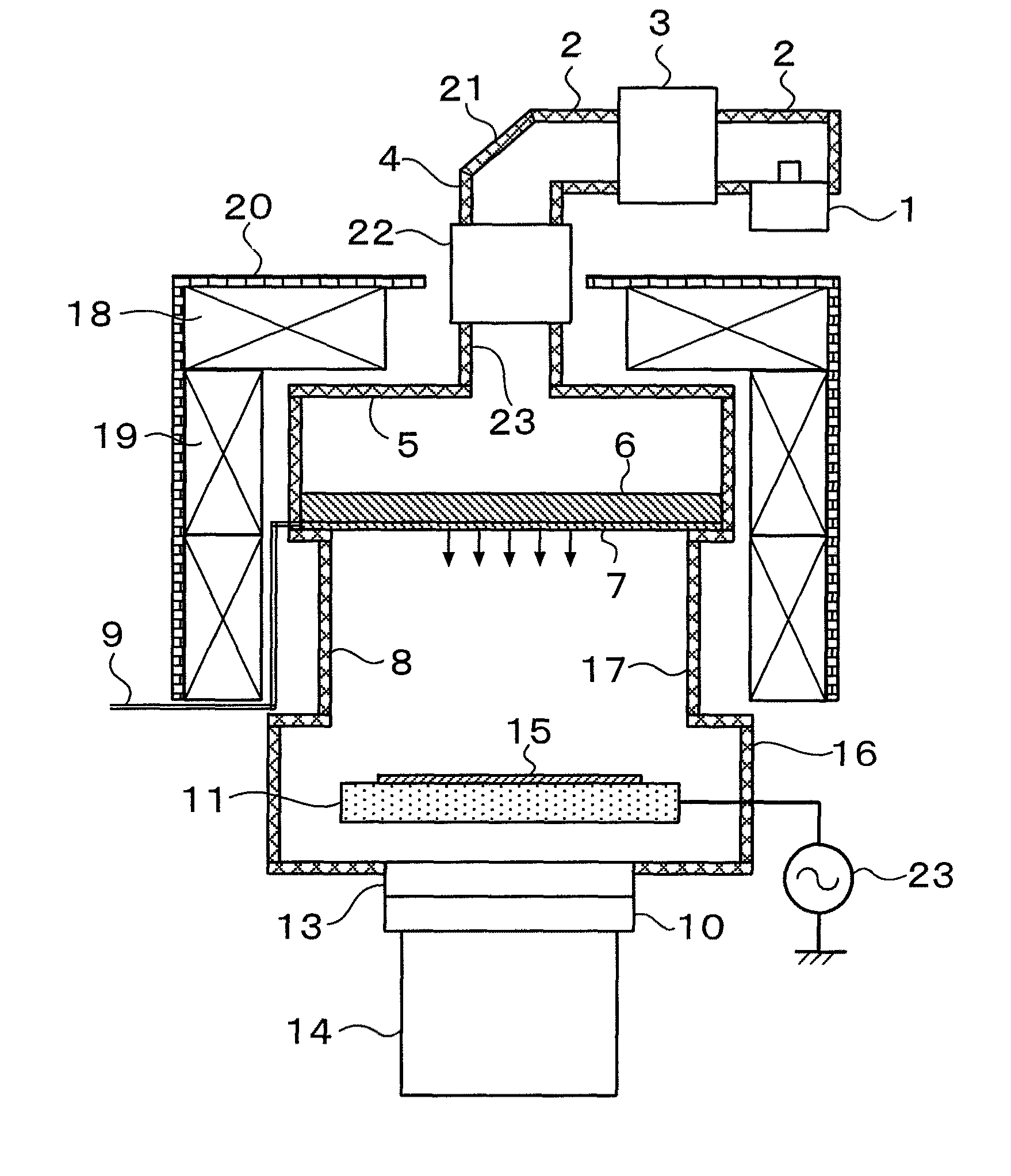

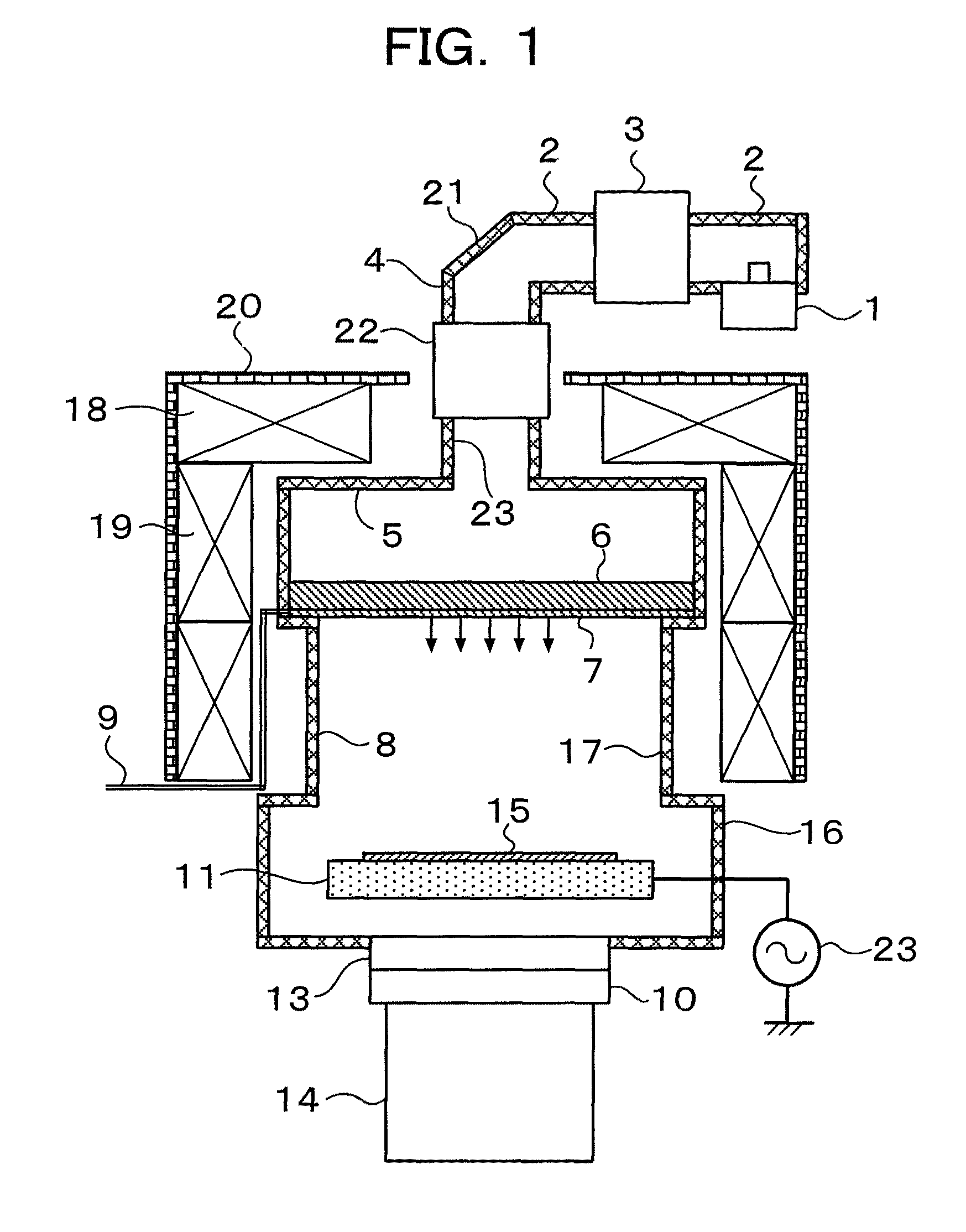

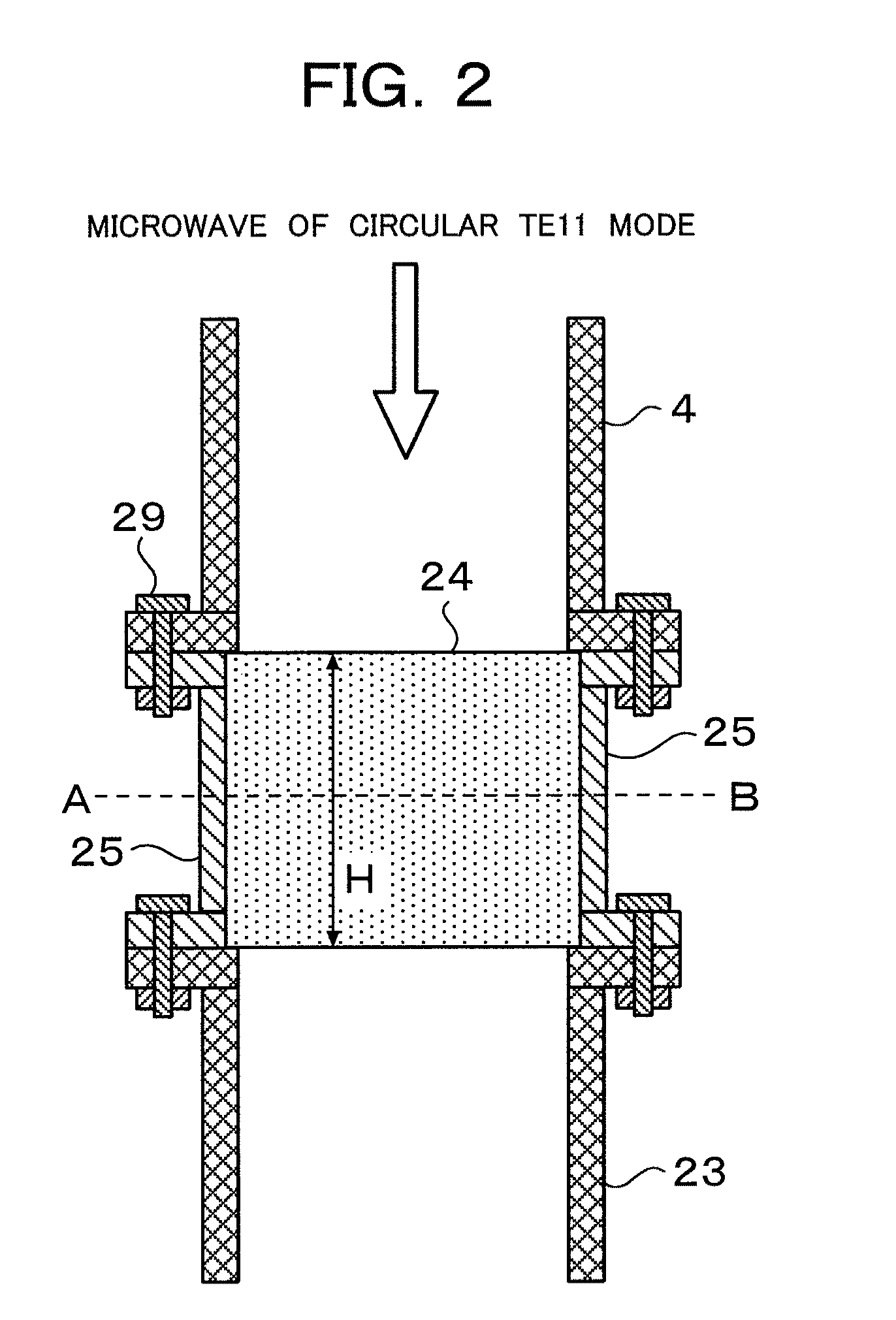

Plasma processing apparatus

ActiveUS20100043976A1Improve uniformityHighly integratedElectric discharge tubesSemiconductor/solid-state device manufacturingMicrowaveDecompression chamber

A plasma processing apparatus includes: a decompression chamber of which the inside is depressed; a gas supply unit that supplies process gas into said chamber; a microwave supply unit that supplies a microwave into the chamber to generate plasma; an object-placing electrode where a processing material, is placed and which holds the processing material in the chamber; and a vacuuming unit that is connected to the chamber to discharge the gas in the chamber, in which the chamber, a part for providing gas into the chamber of the gas supply unit, a part for introducing a microwave into the chamber of the microwave supply unit, the object-placing electrode, and the vacuuming unit are disposed coaxially with the center axis of the chamber, and the part for introducing a microwave includes a microwave rotation generator that rotates a polarization plane of the input microwave and supplies the microwave to the chamber.

Owner:HITACHI HIGH-TECH CORP

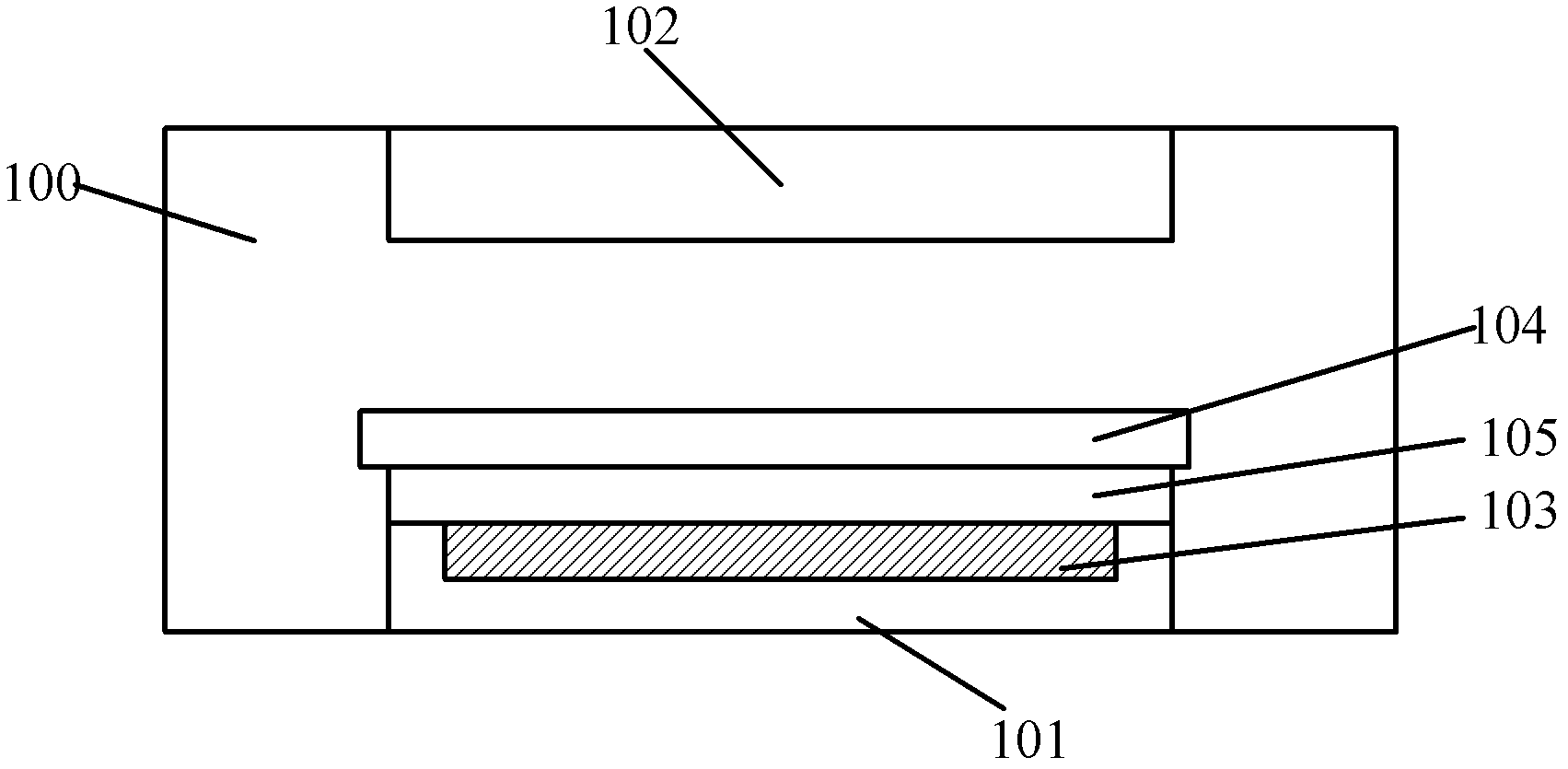

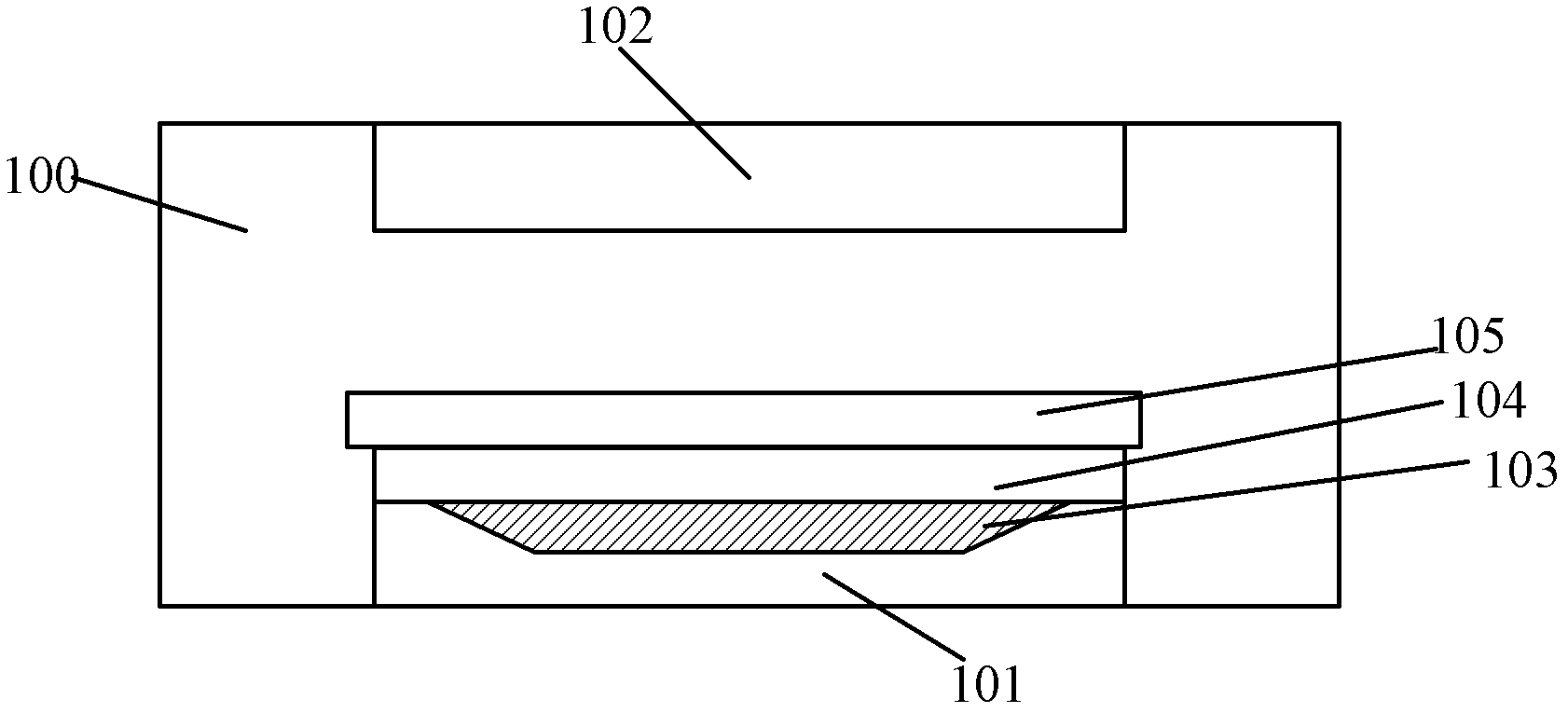

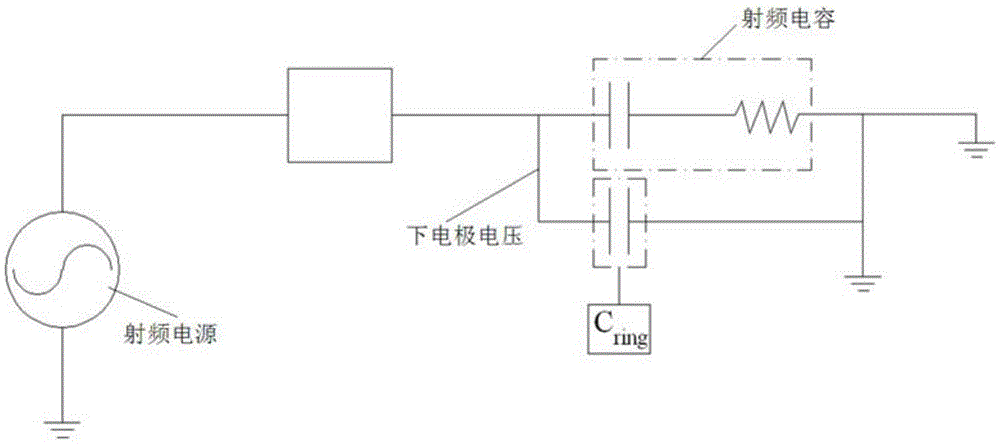

Plasma treatment device

ActiveCN102280342AEven energy distributionUniform densityElectric discharge tubesOptoelectronicsRadio frequency

The embodiment of the invention provides a plasma treatment device. The plasma treatment device comprises a vacuum treatment cavity, a first electrode, and a non-dielectric material layer, wherein the first electrode is positioned in the vacuum treatment cavity; a platform for placing wafers to be treated is arranged above the first electrode; the first electrode is electrically connected with two radio frequency power supplies, and the frequency of a first radio frequency source is 1.5 times higher than that of a second radio frequency source; the non-dielectric material layer is positioned between the first electrode and the platform for placing the wafers to be treated; and the resistivity of the non-dielectric material layer is higher than that of the first electrode. The plasma treatment device provided by the embodiment of the invention improves the distribution uniformity of plasmas in the vacuum treatment cavity and improves the uniformity of the wafers which are treated by the plasma treatment device.

Owner:ADVANCED MICRO FAB EQUIP INC CHINA

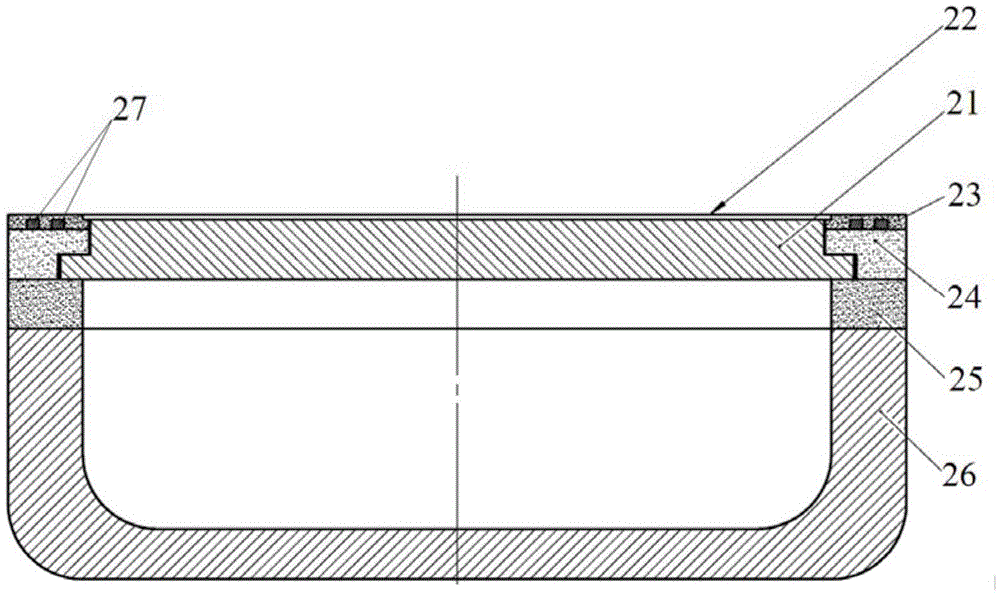

Carrying device and semiconductor processing equipment

ActiveCN106548967AUniform etch rateImprove process uniformitySemiconductor/solid-state device manufacturingSemiconductorPhysics

The invention provides a carrying device and semiconductor processing equipment. The carrying device comprises a chuck and a focusing ring, wherein the upper surface of the chuck is used for carrying a processed workpiece; the focusing ring encircles the periphery of the chuck; and moreover, the dielectric constant values of the focusing ring at different areas in the peripheral direction are different, so that the etching rate of the edge of the processed workpiece everywhere tends to be uniform. According to the carrying device provided by the invention, the etching rate of the edge of the processed workpiece everywhere can tend to be uniform, so that the technological uniformity can be improved.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

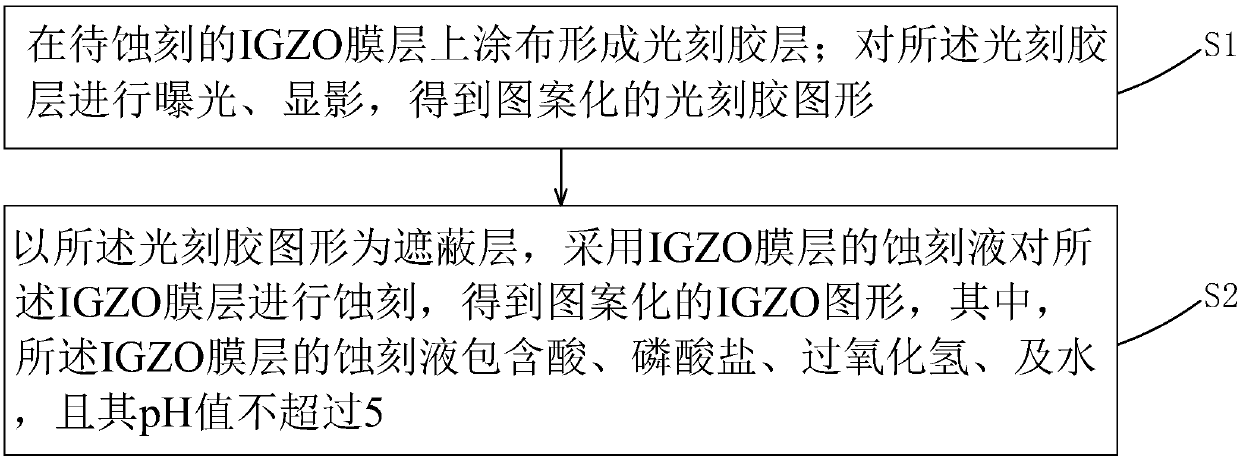

Etching solution for IGZO film and etching method thereof

ActiveCN107564809AEtch stableImprove stabilitySemiconductor/solid-state device manufacturingSurface treatment compositionsPhosphateIndium gallium zinc oxide

The invention provides an etching solution for an IGZO (Indium Gallium Zinc Oxide) film and an etching method thereof. The etching solution for the IGZO film comprises an acid, a phosphate, hydrogen peroxide and water, and the pH value of the etching solution is not more than 5. By adopting the etching solution, the etching rate can be effectively controlled, so that the etching rate is uniform; the IGZO film can be etched stably, and some impuritiesaffecting the electrical properties of the IGZO are not introduced at the same time, so that the stability of an IGZO-TFT (Thin Film Transistor) device can be effectively improved. The etching method for the IGZO film adopts the etching solution for the IGZO film. By adopting the etching method, the etching rate can be effectively controlled, so that the etching rate is uniform; the IGZO film can be etched stably, and some impuritiesaffecting the electrical properties of the IGZO are not introduced at the same time, so that the stability ofan IGZO-TFT device can be effectively improved.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

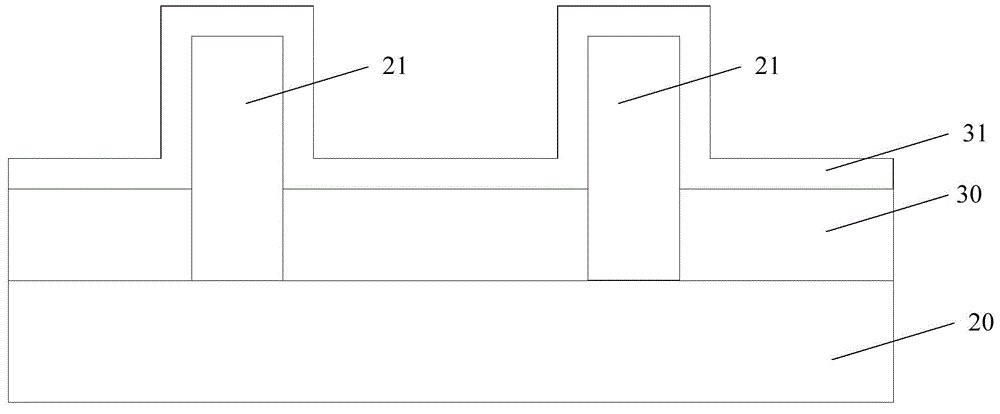

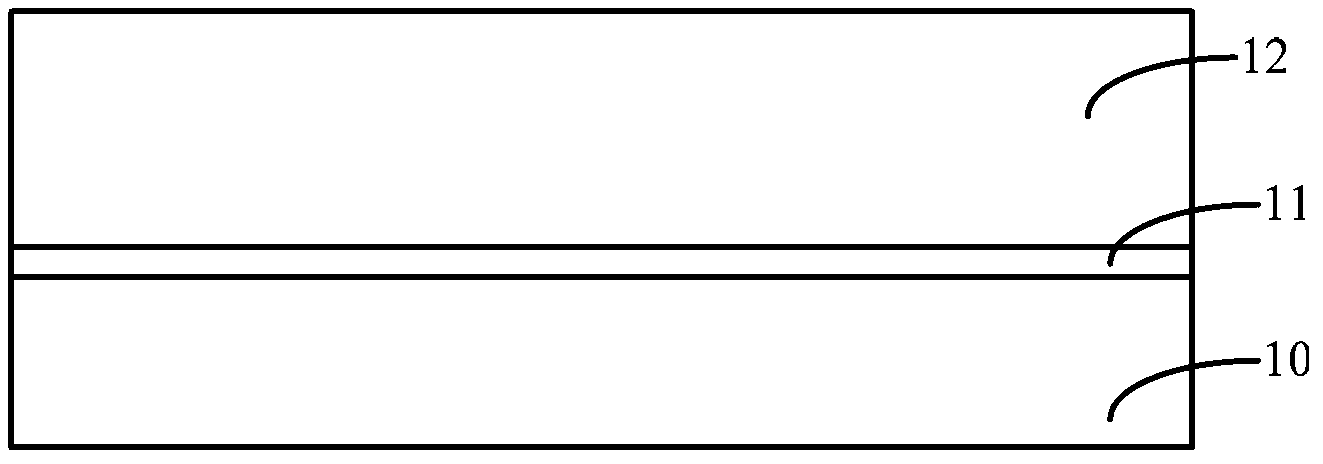

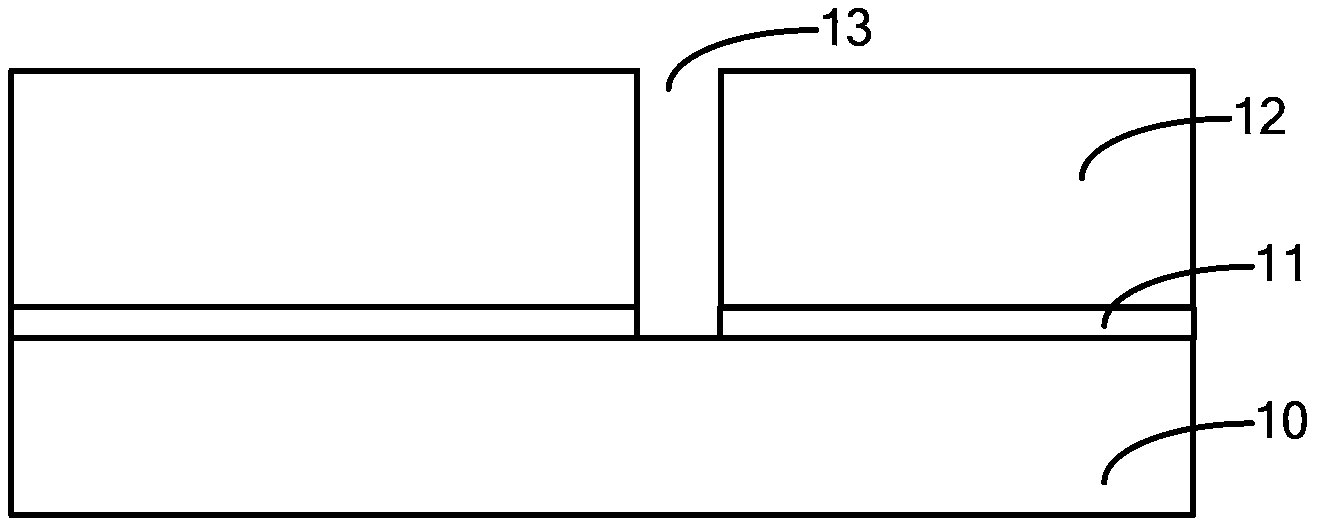

Formation method of semiconductor structure

ActiveCN105336616AUniform etch rateFully contactedSemiconductor/solid-state device manufacturingSemiconductor structureIsolation layer

A formation method of a semiconductor structure comprises the following steps of providing a semiconductor substrate; forming a fin portion on the semiconductor substrate; forming an isolation layer on the semiconductor substrate, wherein a surface of the isolation layer is lower than a top surface of the fin portion and covers a side wall of parts of the fin portion; forming a dielectric layer on a fin portion surface; forming a sidewall of the dielectric layer covering a fin portion sidewall surface; taking the side wall as a mask layer, using a wet etching process to etch the dielectric layer so that the top surface of the fin portion is exposed. By using the method, damages to the fin portion, which is generated through using dry etching, can be reduced, which is good for subsequent epitaxial growth; and performance of the formed semiconductor structure is increased.

Owner:SEMICON MFG SOUTH CHINA CORP

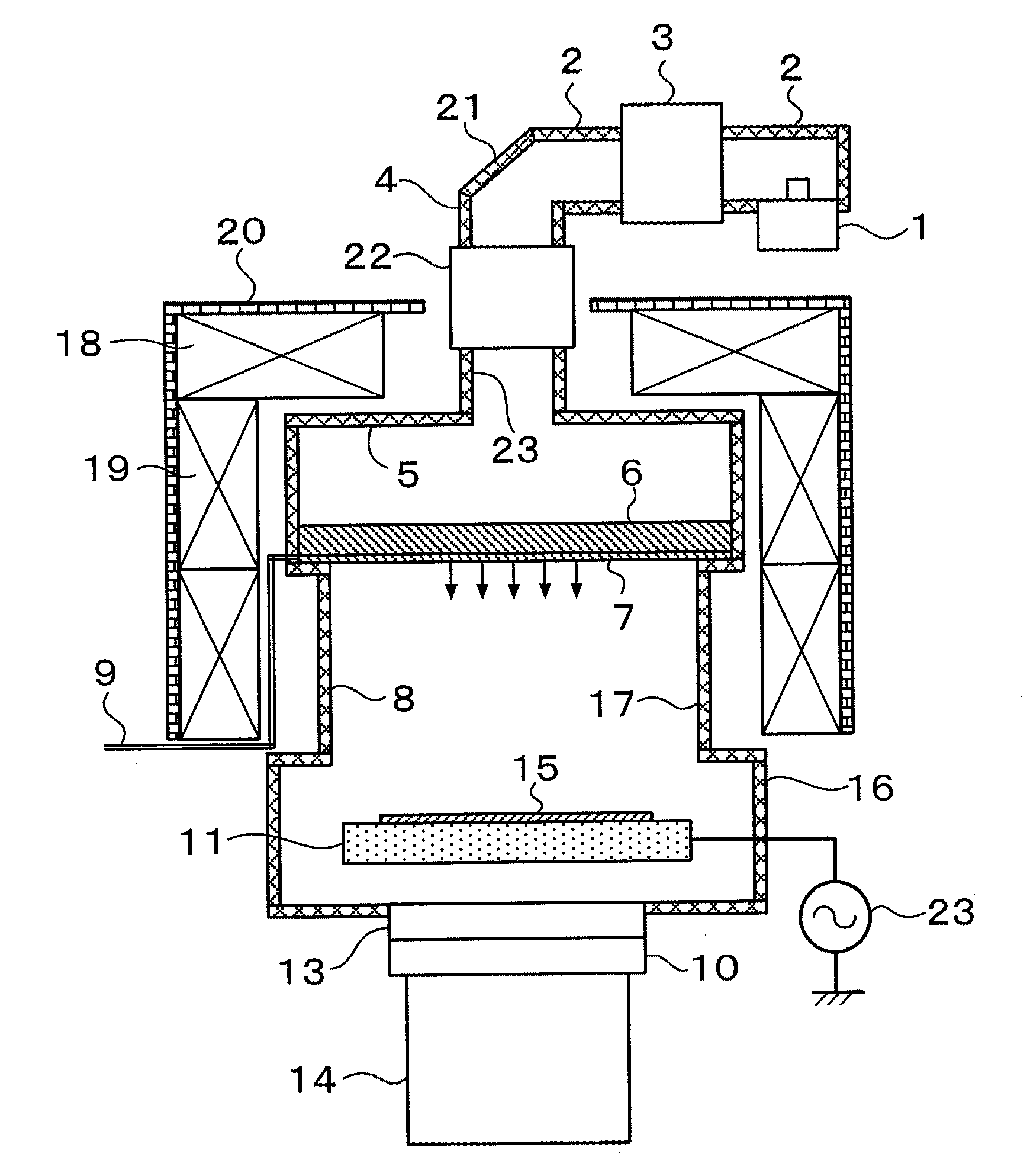

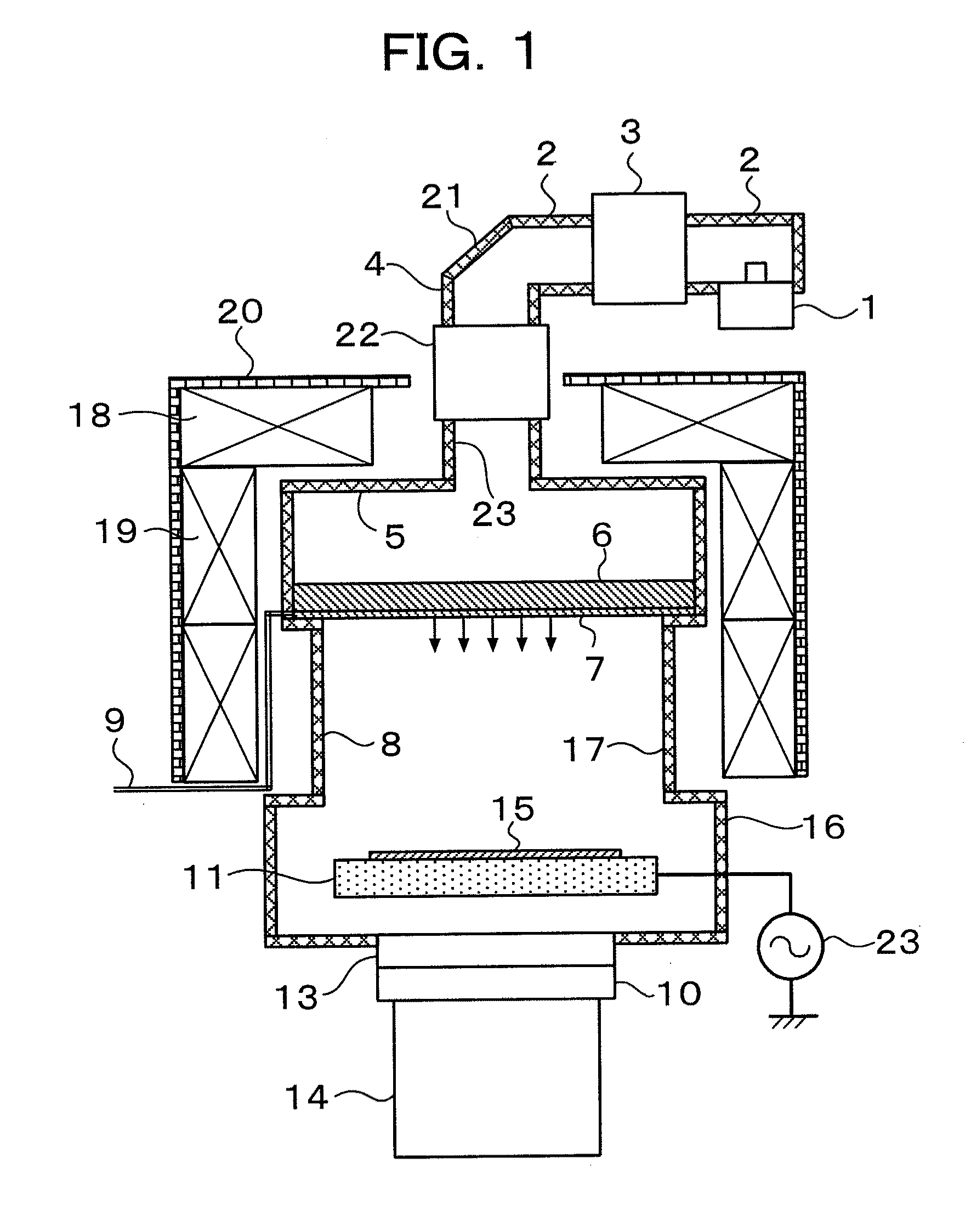

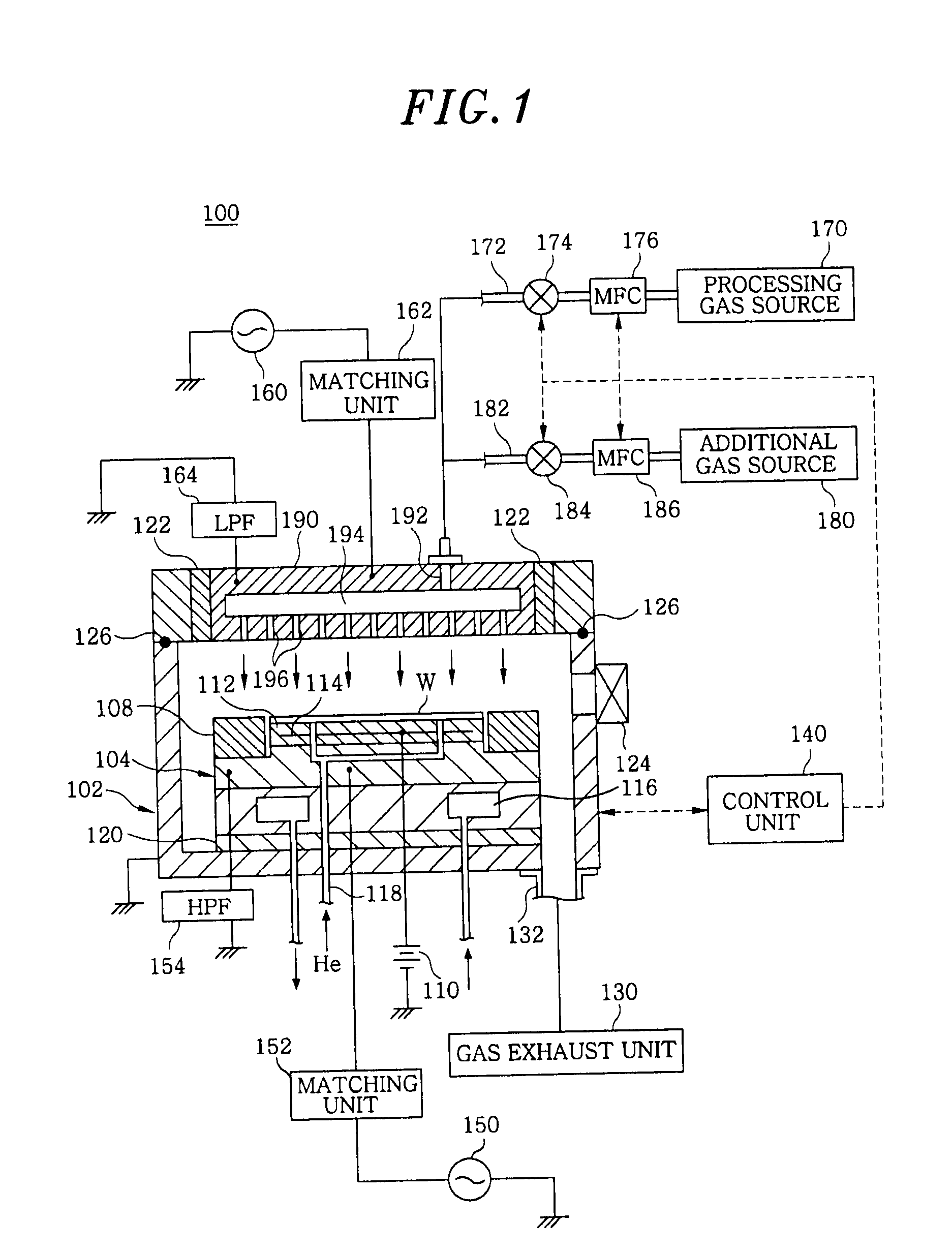

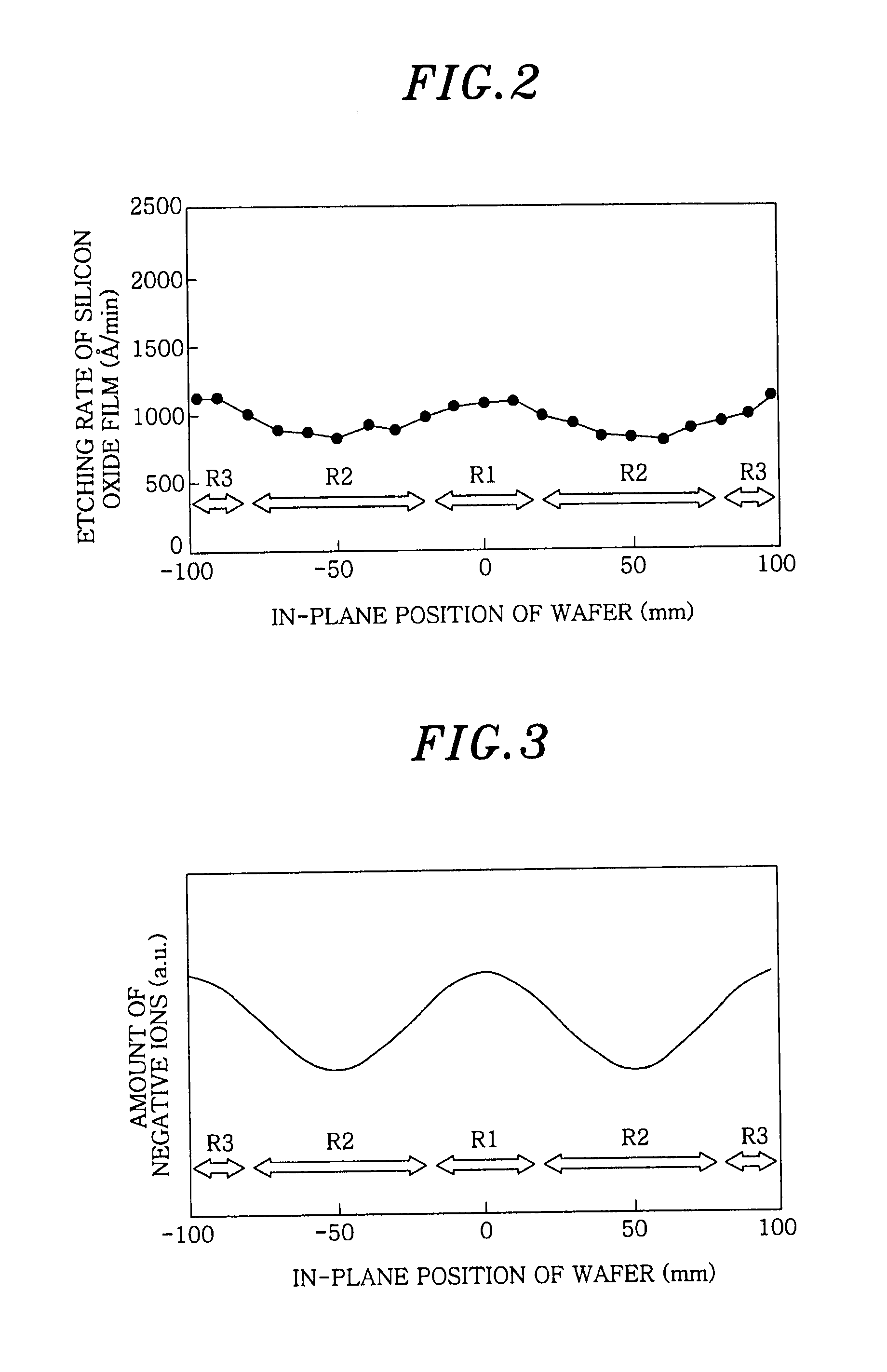

Plasma processing method and apparatus

InactiveUS20100267243A1Uniform etch rateImprove in-plane uniformityElectric discharge tubesSemiconductor/solid-state device manufacturingIn planeIon density

In the plasma processing by an electrically negative gas, the in-plane uniformity of plasma processing is enhanced compared to the conventional case by controlling the ion density in the plasma. Not only is a processing gas being an electrically negative gas introduced from a processing gas source 170 into a processing chamber 102 but also an electrically negative gas having electron attachment coefficient greater than that of the processing gas is introduced as an additional gas from an additional gas source 180 to thereby form a plasma. In the plasma formation, the ion density in the plasma is controlled by regulating the flow rate of the additional gas relative to that of the processing gas.

Owner:TOKYO ELECTRON LTD

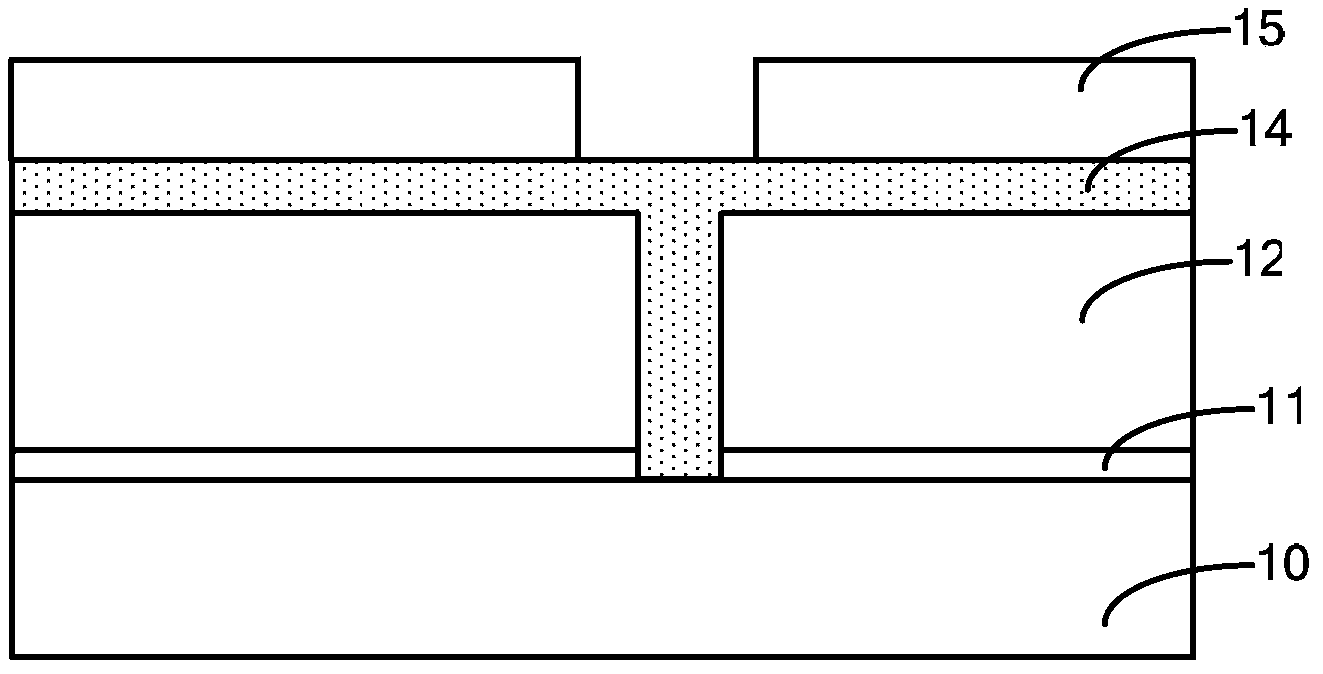

Formation method of dual damascene structure

InactiveCN104124202ATime equalizationAvoid damageSemiconductor/solid-state device manufacturingDielectric layerPhysics

The invention provides a formation method of a dual damascene structure. The formation method of the dual damascene structure comprises the steps of providing a substrate, forming a dielectric layer on the surface of the substrate, forming a through hole in the dielectric layer, forming a bottom antireflection layer in the through hole in such a manner that the through hole is full of the bottom antireflection layer and the surface of the dielectric layer is covered, forming, on the surface of the bottom antireflection layer, a mask layer with an opening which is located above the through hole in position and exposes partial surface of the bottom antireflection layer, removing the partial bottom antireflection layer which is located on the surface of the dielectric layer under the opening and exposing the surface of partial dielectric layer and the surface of the bottom antireflection layer in the through hole, etching the dielectric layer and the bottom antireflection layer in the through hole along the opening to form a first groove, removing the rest bottom antireflection layer in the through hole, and etching the dielectric layer along the first groove to form a second groove. The formation method is capable of improving the flatness of the inner wall of the damascene structure.

Owner:SEMICON MFG INT (SHANGHAI) CORP

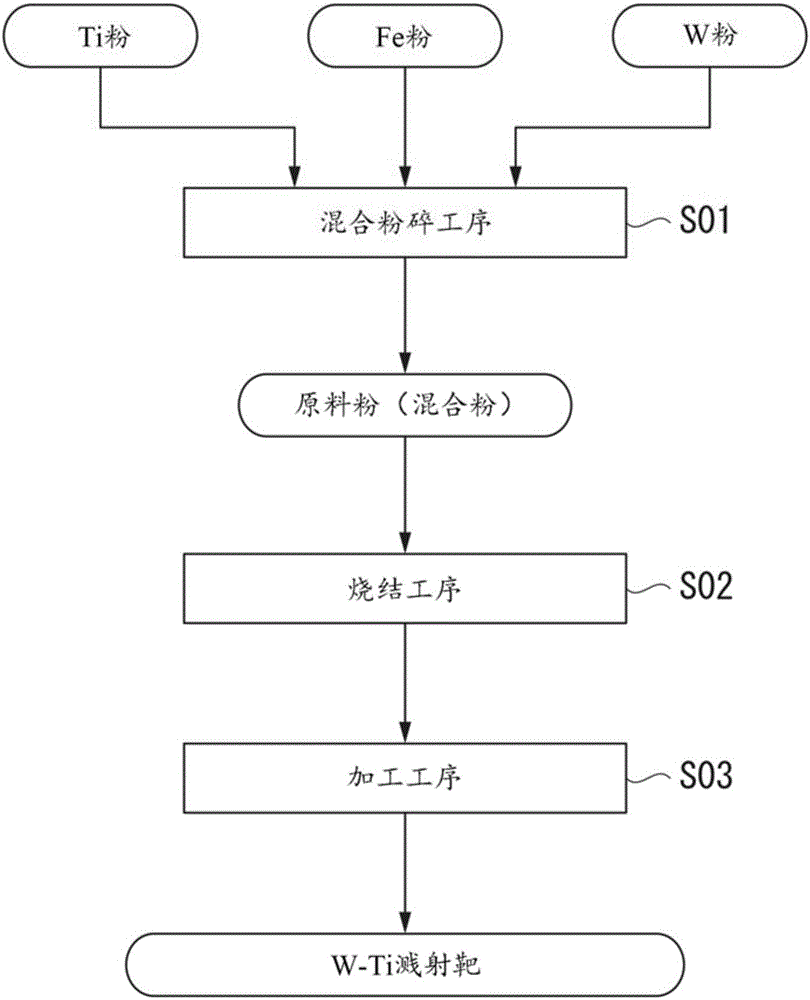

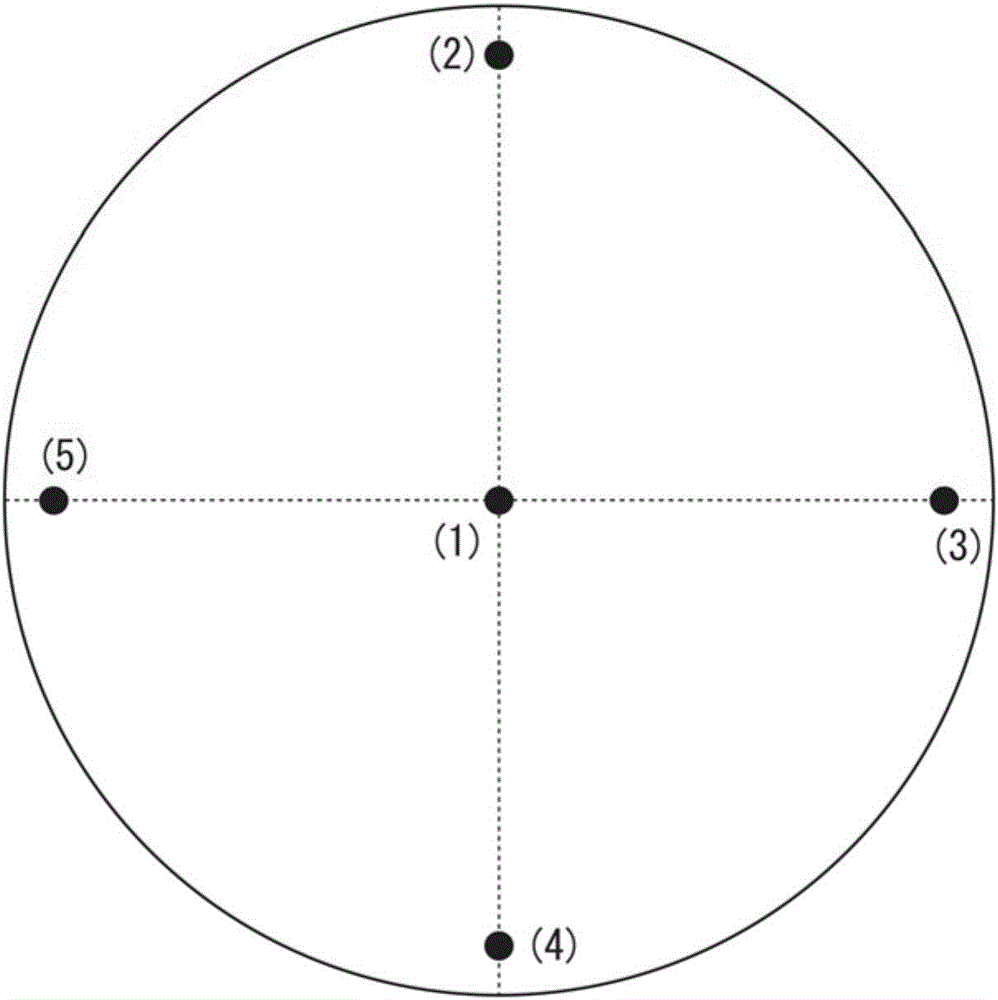

W-ti sputtering target

ActiveCN106460160AFe concentration variation is smallUniform etch rateVacuum evaporation coatingSputtering coatingImpurityMaterials science

This W-Ti sputtering target has a composition containing Ti in a range of 5% by mass to 20% by mass and Fe in a range of 25 ppm by mass to 100 ppm by mass, the remainder comprising W and unavoidable impurities, and satisfies the relational expression (Femax-Femin) / (Femax+Femin) <= 0.25, where Femax is the maximum value of the Fe concentration and Femin is the minimum value of the Fe concentration when the Fe concentration is measured in a plurality of locations in the plane of the target.

Owner:MITSUBISHI MATERIALS CORP

Plasma processing apparatus

ActiveUS8075733B2Highly integratedUniform etch rateElectric discharge tubesSemiconductor/solid-state device manufacturingMicrowaveDecompression chamber

A plasma processing apparatus includes: a decompression chamber of which the inside is depressed; a gas supply unit that supplies process gas into said chamber; a microwave supply unit that supplies a microwave into the chamber to generate plasma; an object-placing electrode where a processing material, is placed and which holds the processing material in the chamber; and a vacuuming unit that is connected to the chamber to discharge the gas in the chamber, in which the chamber, a part for providing gas into the chamber of the gas supply unit, a part for introducing a microwave into the chamber of the microwave supply unit, the object-placing electrode, and the vacuuming unit are disposed coaxially with the center axis of the chamber, and the part for introducing a microwave includes a microwave rotation generator that rotates a polarization plane of the input microwave and supplies the microwave to the chamber.

Owner:HITACHI HIGH-TECH CORP

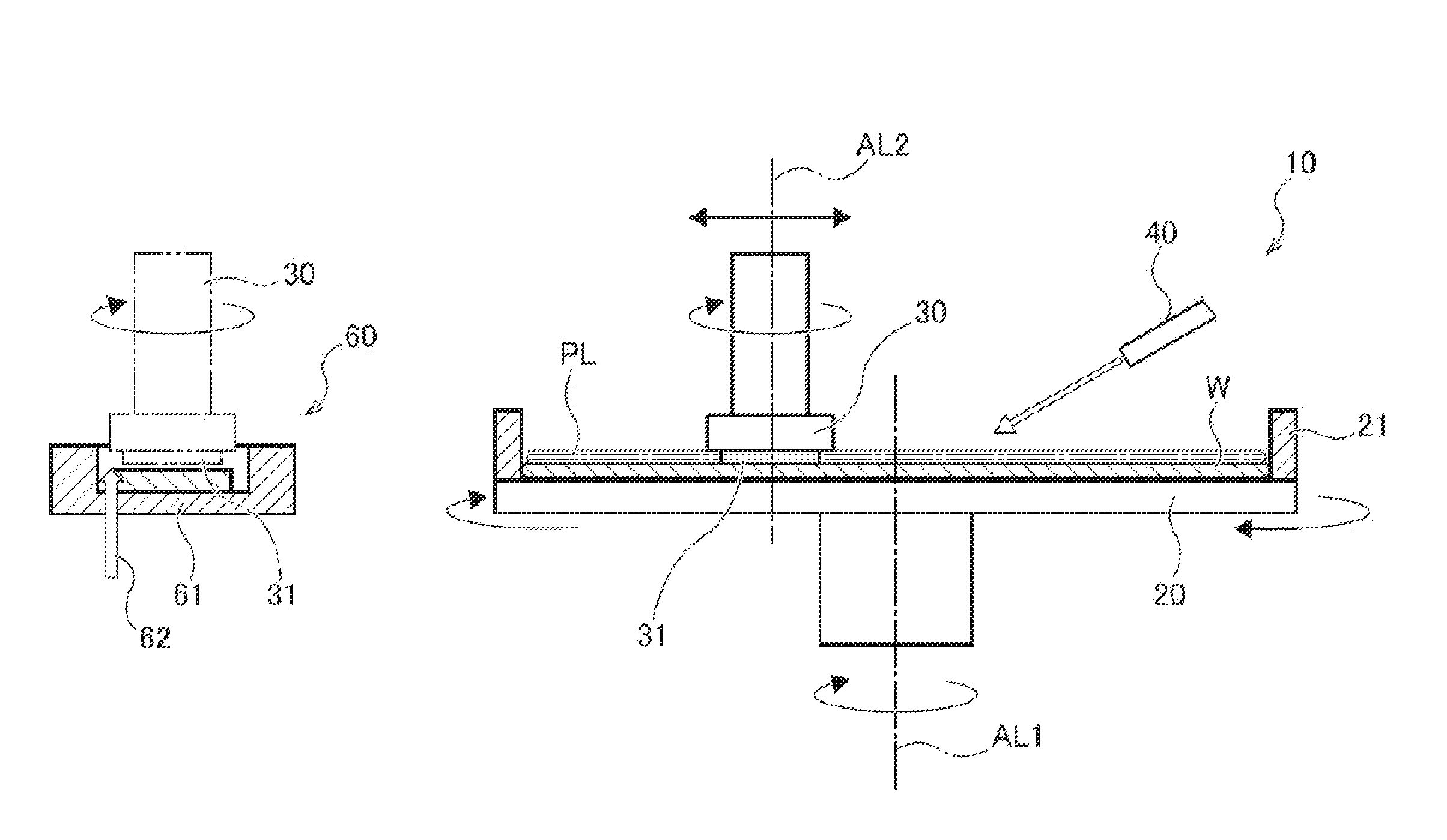

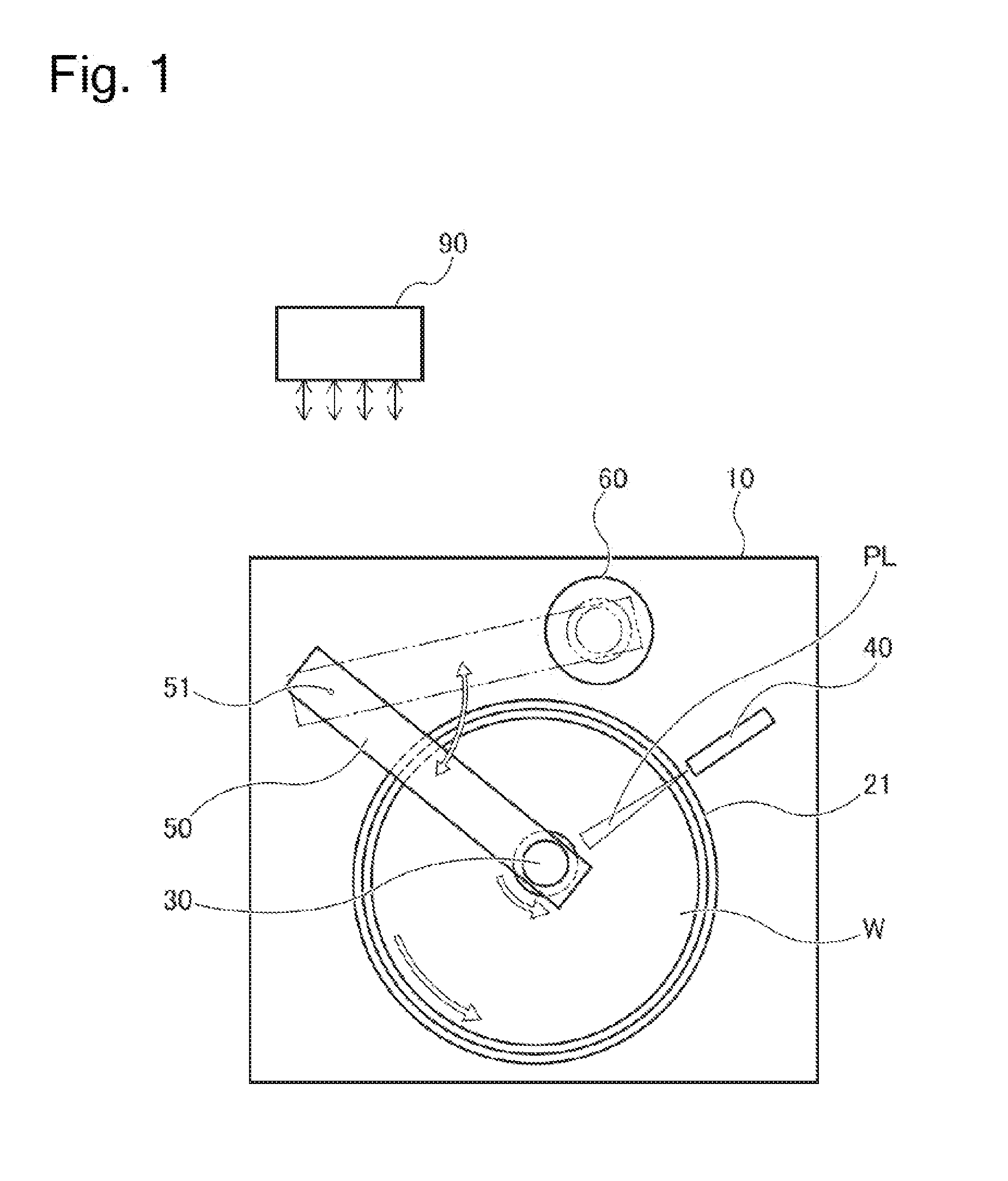

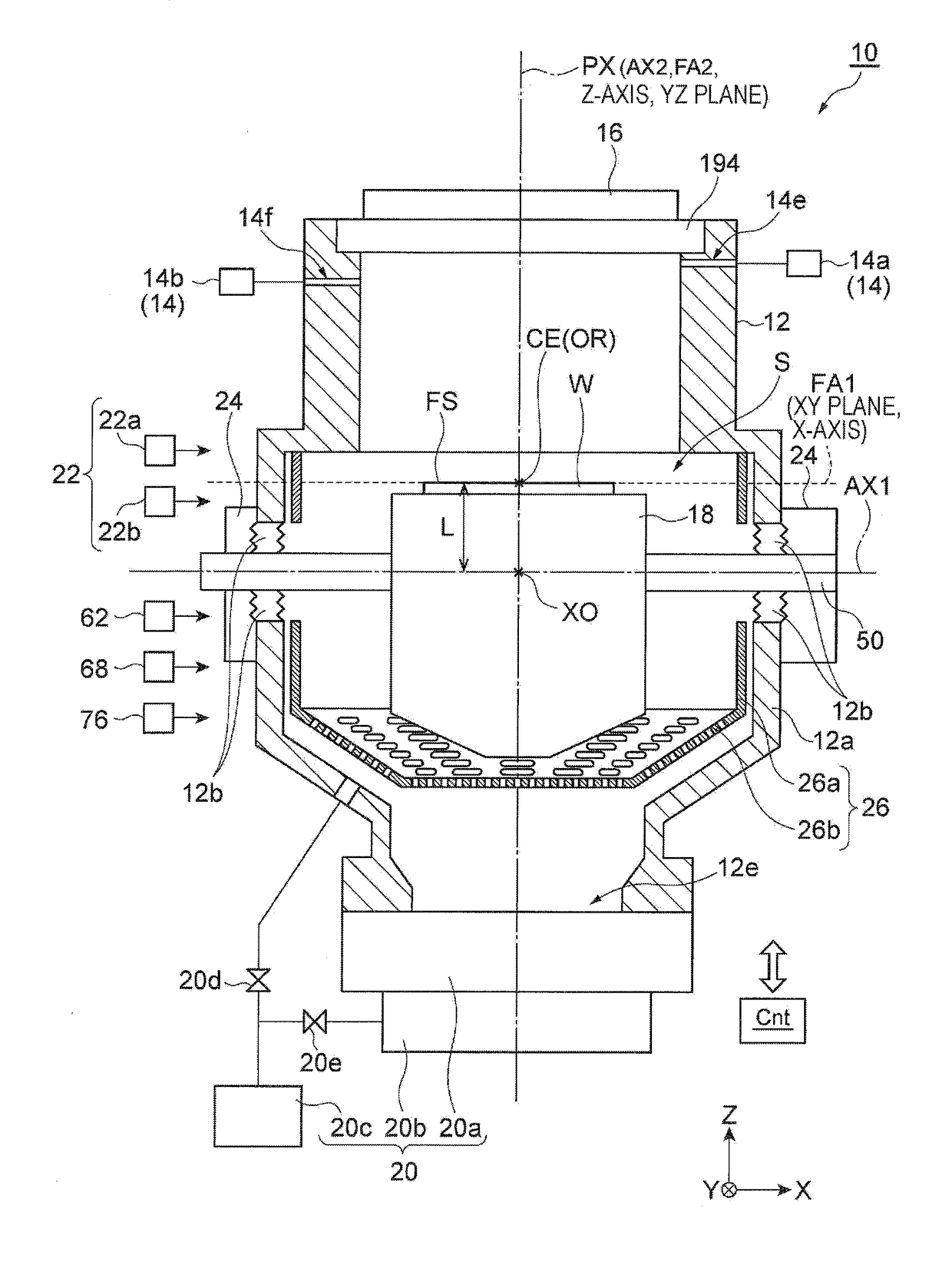

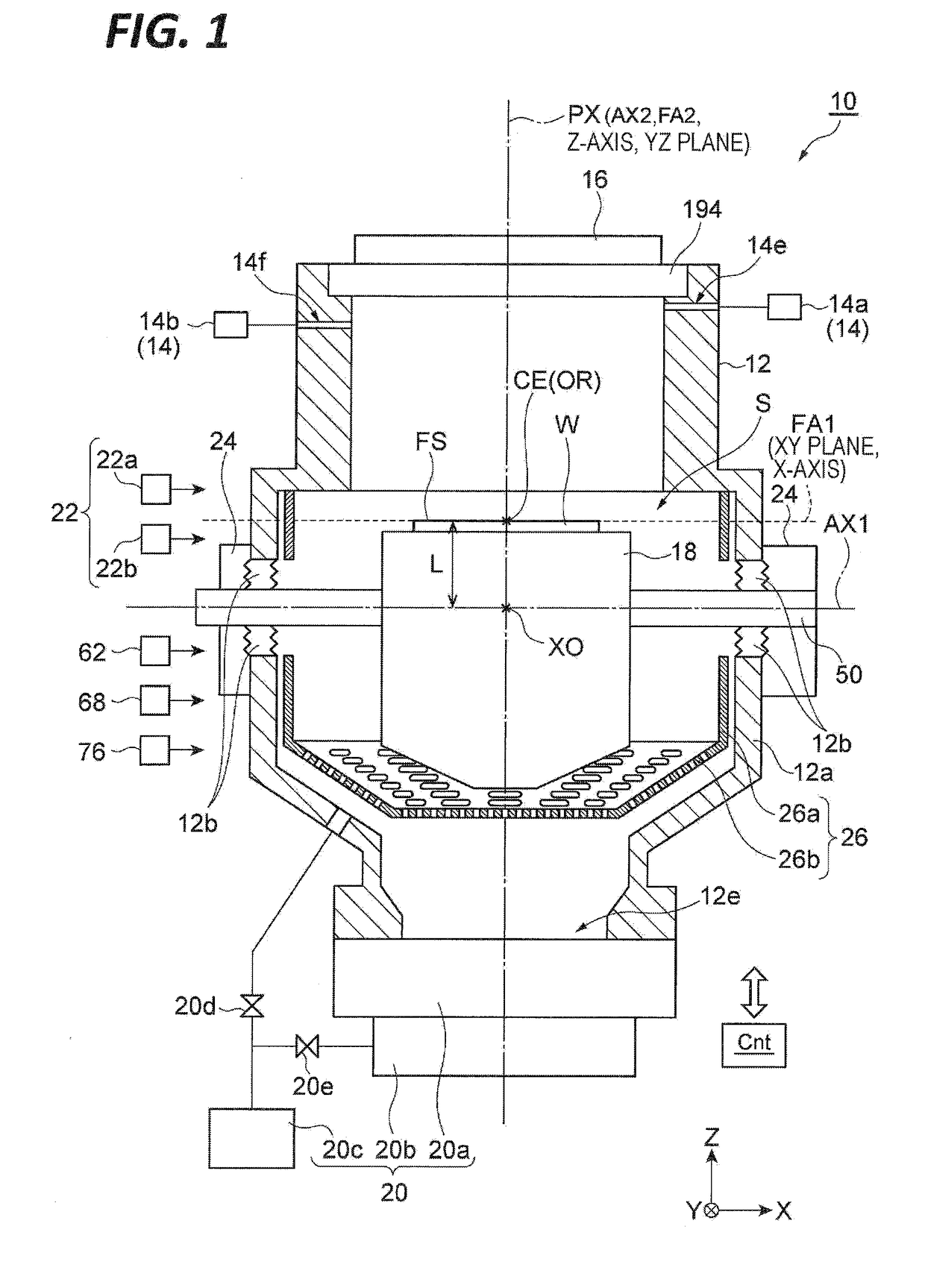

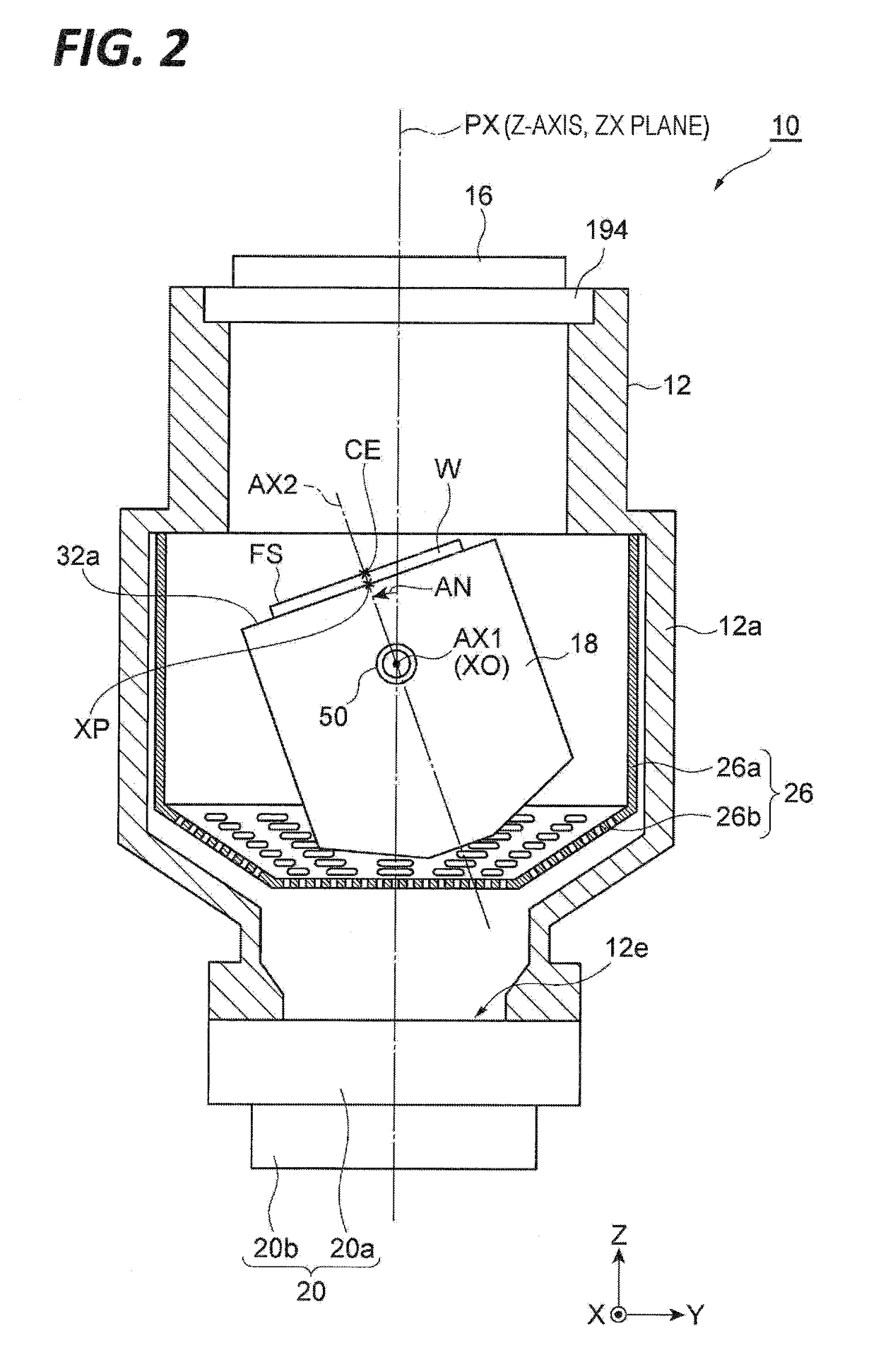

Method of etching object to be processed

ActiveUS20180337025A1Uniform etch rateImprove uniformityElectric discharge tubesSolid-state devicesEtchingProcess time

A method MT includes etching a wafer W using plasma generated in a processing container. The etching includes a process of inclining and rotating a holding structure holding the wafer W during execution of the etching and the process successively creating a plurality of inclined rotation states RT(φ, t) with respect to the holding structure. In the inclined rotation states, the wafer W is rotated about a central axis of the wafer W over a predetermined process time while maintaining a state where the central axis is inclined with respect to a reference axis of the processing container which is in the same plane as the central axis. A combination of a value φ of an inclination angle AN of the central axis with respect to the reference axis and the process time t differs for each of the plurality of inclined rotation states.

Owner:TOKYO ELECTRON LTD

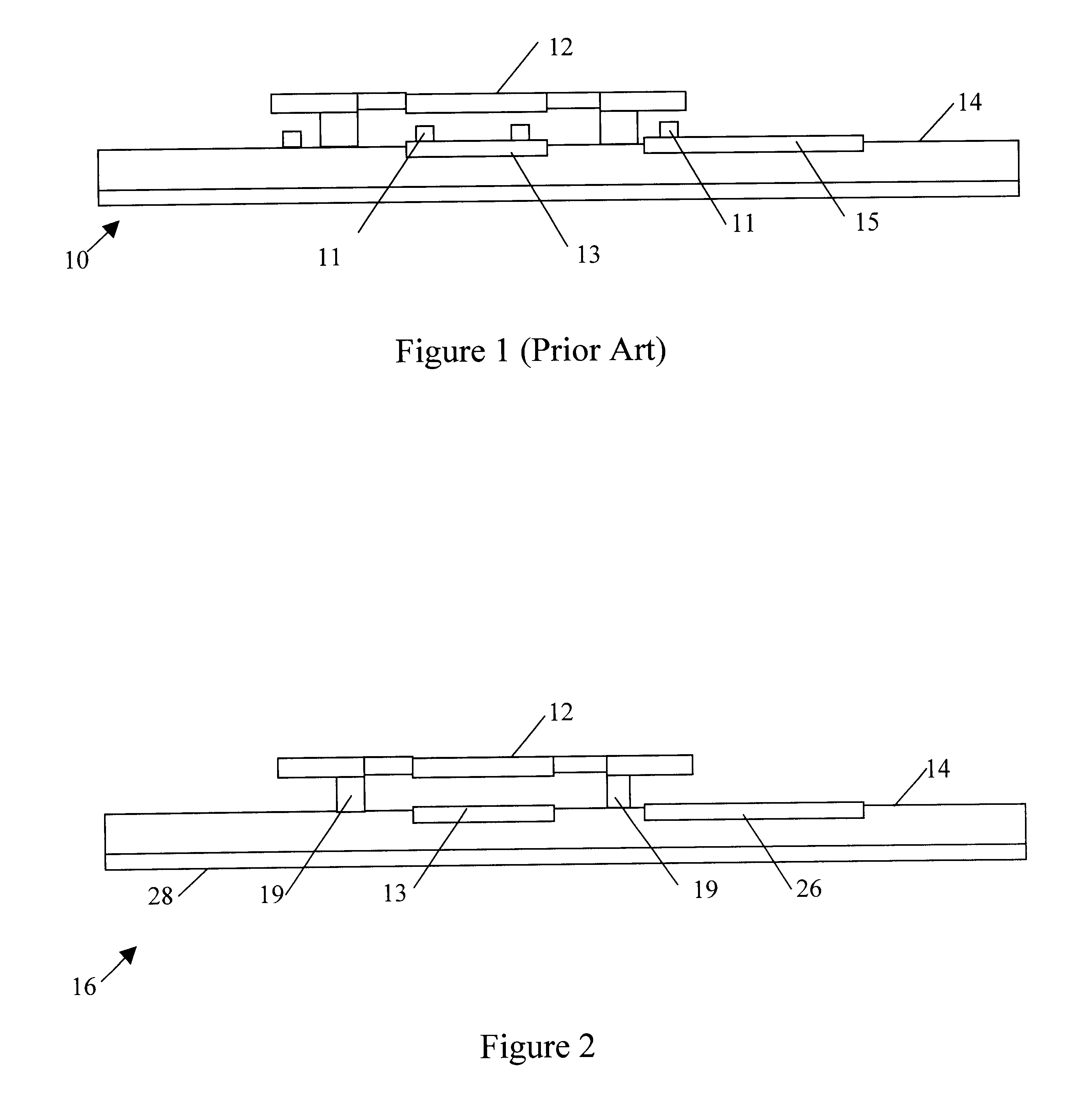

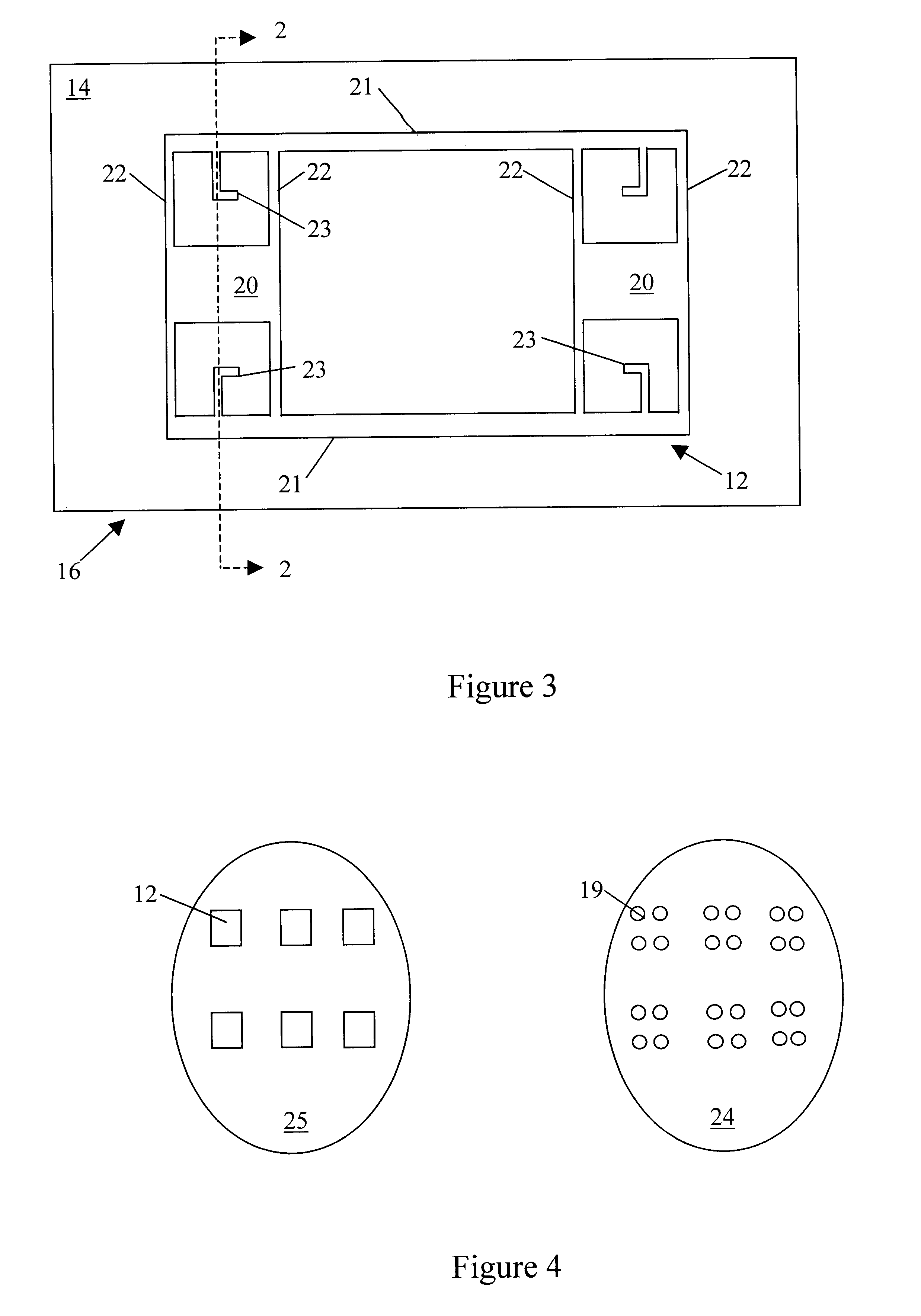

Method for reducing harmonic distortion in comb drive devices

InactiveUS20050136621A1Reduce and eliminate gapUniform etch rateSemiconductor/solid-state device detailsSolid-state devicesHarmonicComb finger

Methods of fabricating comb drive devices utilizing one or more sacrificial etch-buffers are disclosed. An illustrative fabrication method may include the steps of etching a pattern onto a wafer substrate defining one or more comb drive elements and sacrificial etch-buffers, liberating and removing one or more sacrificial etch-buffers prior to wafer bonding, bonding the etched wafer substrate to an underlying support substrate, and etching away the wafer substrate. In some embodiments, the sacrificial etch-buffers are removed after bonding the wafer to the support substrate. The sacrificial etch-buffers can be provided at one or more selective regions to provide greater uniformity in etch rate during etching. A comb drive device in accordance with an illustrative embodiment can include a number of interdigitated comb fingers each having a more uniform profile along their length and / or at their ends, producing less harmonic distortion during operation.

Owner:HONEYWELL INT INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com