Formation method of semiconductor structure

A technology of semiconductor and gate structure, applied in the field of semiconductor structure formation, can solve the problems of poor deposition quality of stress layer, affecting the performance of fin field effect transistor, etc., and achieve the effects of high selectivity, less damage and uniform etching rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] As mentioned in the background art, the deposition quality of the stress layer formed in the prior art is poor, which affects the performance of the formed FinFET.

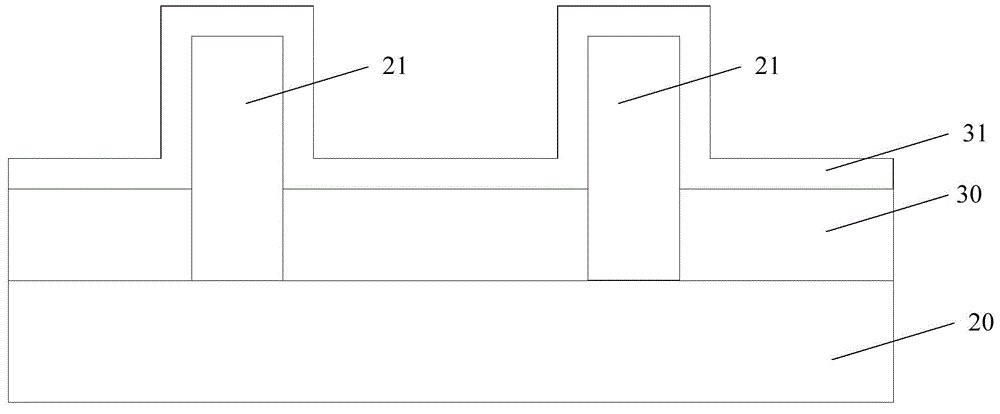

[0034] Please refer to figure 2 , in one embodiment of the present invention, after forming the fin 21 on the semiconductor substrate 20 and the isolation layer 30, a gate structure (not shown) across the fin is formed, and then the isolation layer 30. After the dielectric layer 31 is formed on the surface of the fin 21 and the gate structure, it is a schematic cross-sectional view along the length direction of the fin 21 on both sides of the gate structure.

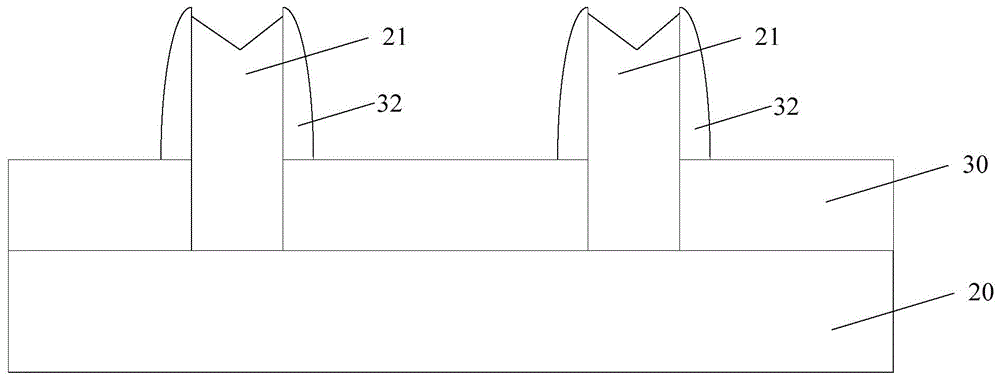

[0035] Please refer to image 3 , using an anisotropic etching process to etch the dielectric layer 31 to expose the top surfaces of the fins 21 on both sides of the gate structure, and form sidewalls 32 covering the sidewall surfaces of the fins 21 .

[0036] In the actual process, the inventors found that after removing the dielectric layer 31 at...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com