Fin-type field effect transistor forming method

一种鳍式场效应管、鳍部的技术,应用在电气元件、半导体/固态器件制造、电路等方向,能够解决应力层质量差、鳍式场效应管电学性能低下等问题,达到刻蚀损伤小、提高电学性能、高选择性的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] It can be seen from the background art that the quality of the stress layer formed in the prior art is poor, which leads to the low performance of the FinFET.

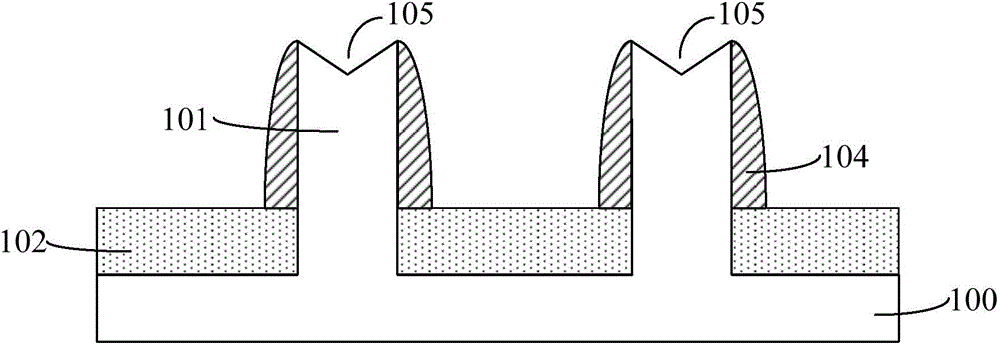

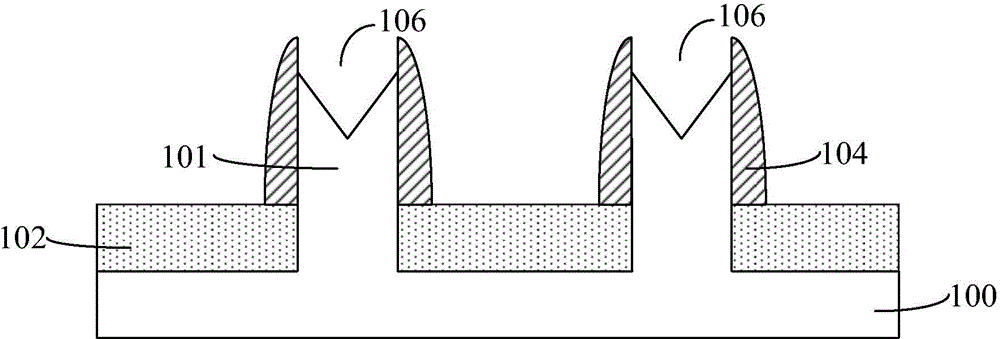

[0038] Please refer to figure 1, in one embodiment, a substrate 100 having fins 101 is provided, an isolation layer 102 is formed on the surface of the substrate 100 between adjacent fins 101, and the isolation layer 102 covers part of the sidewall surface of the fins 101 , and the top surface of the isolation layer 102 is lower than the top surface of the fin 101; a barrier layer covering the surface of the isolation layer 102, the sidewall and the top surface of the fin 101 is formed; a maskless etching process is used to etch and remove the The top surface of the fin portion 101 and the barrier layer on the surface of the isolation layer 102 form a sidewall layer 104 on the sidewall surface of the fin portion 101 , exposing the top surface of the fin portion 101 .

[0039] The function of the sidewall layer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com