Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

116results about How to "Reduce etch damage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

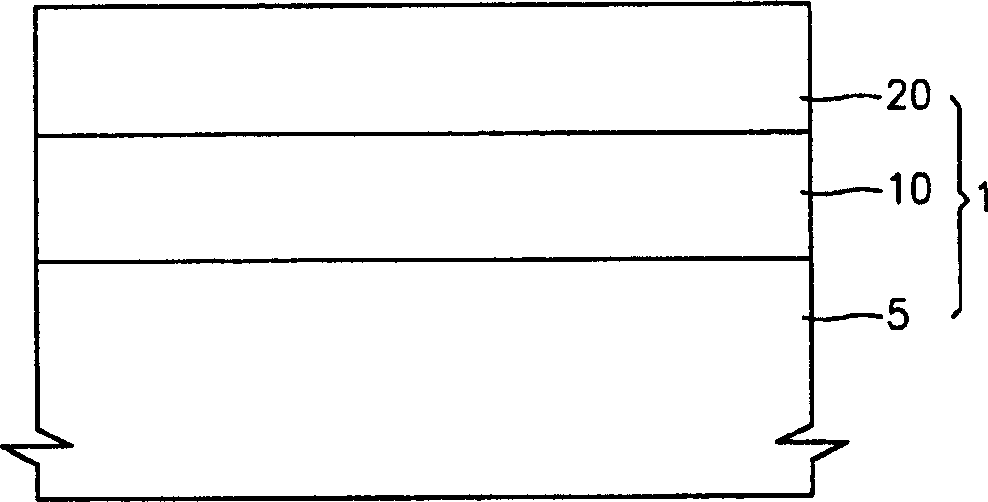

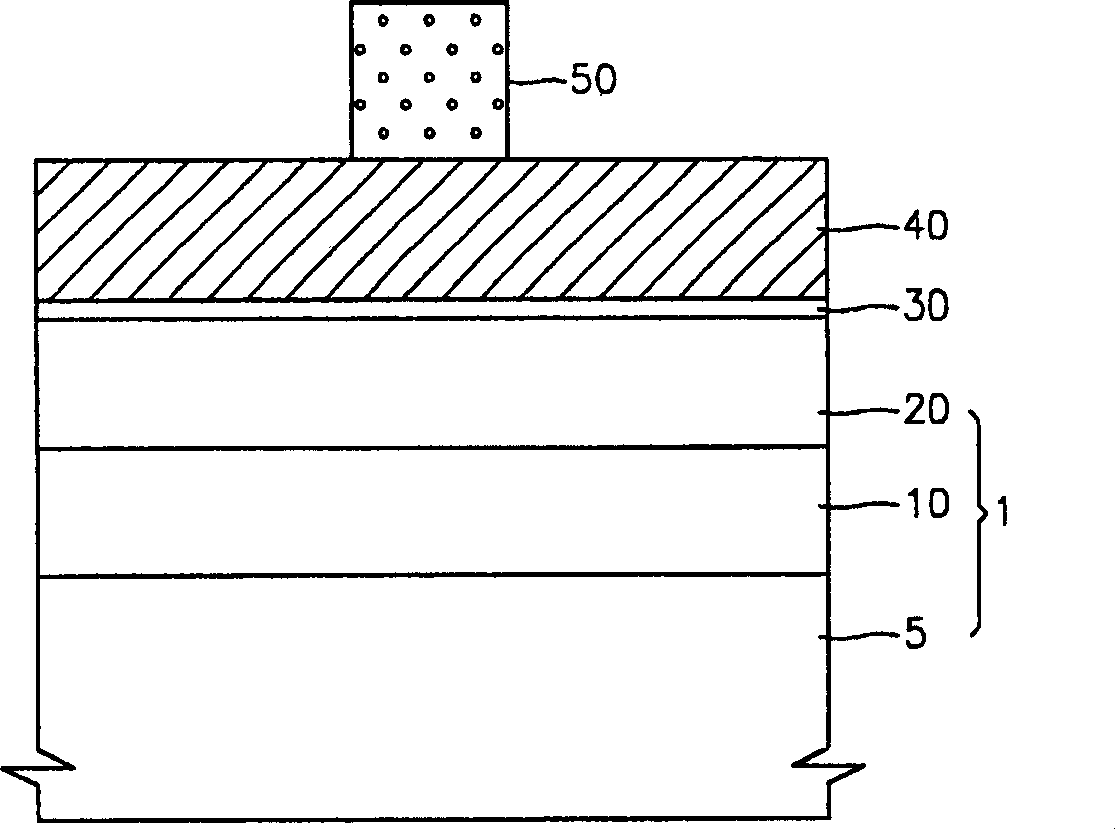

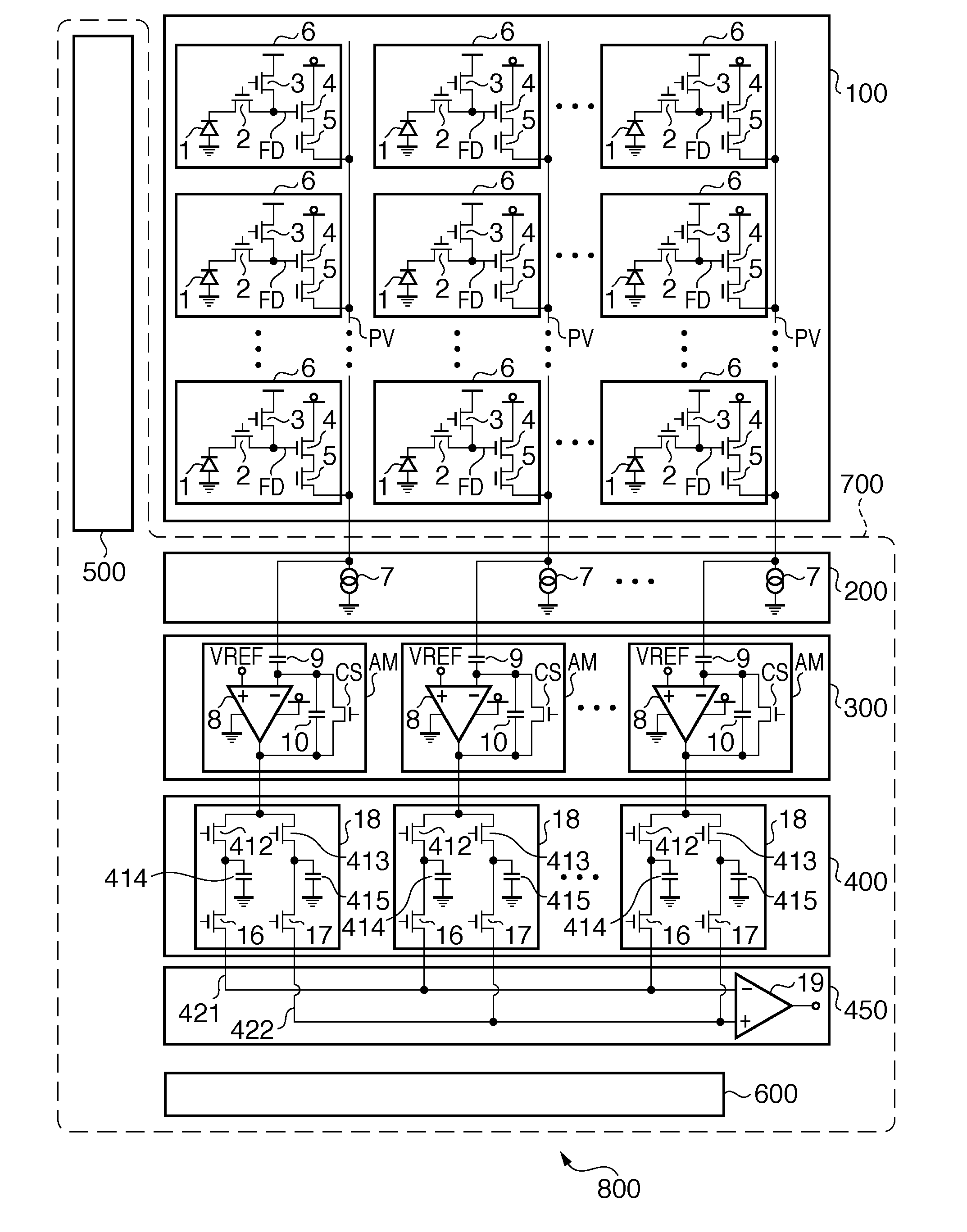

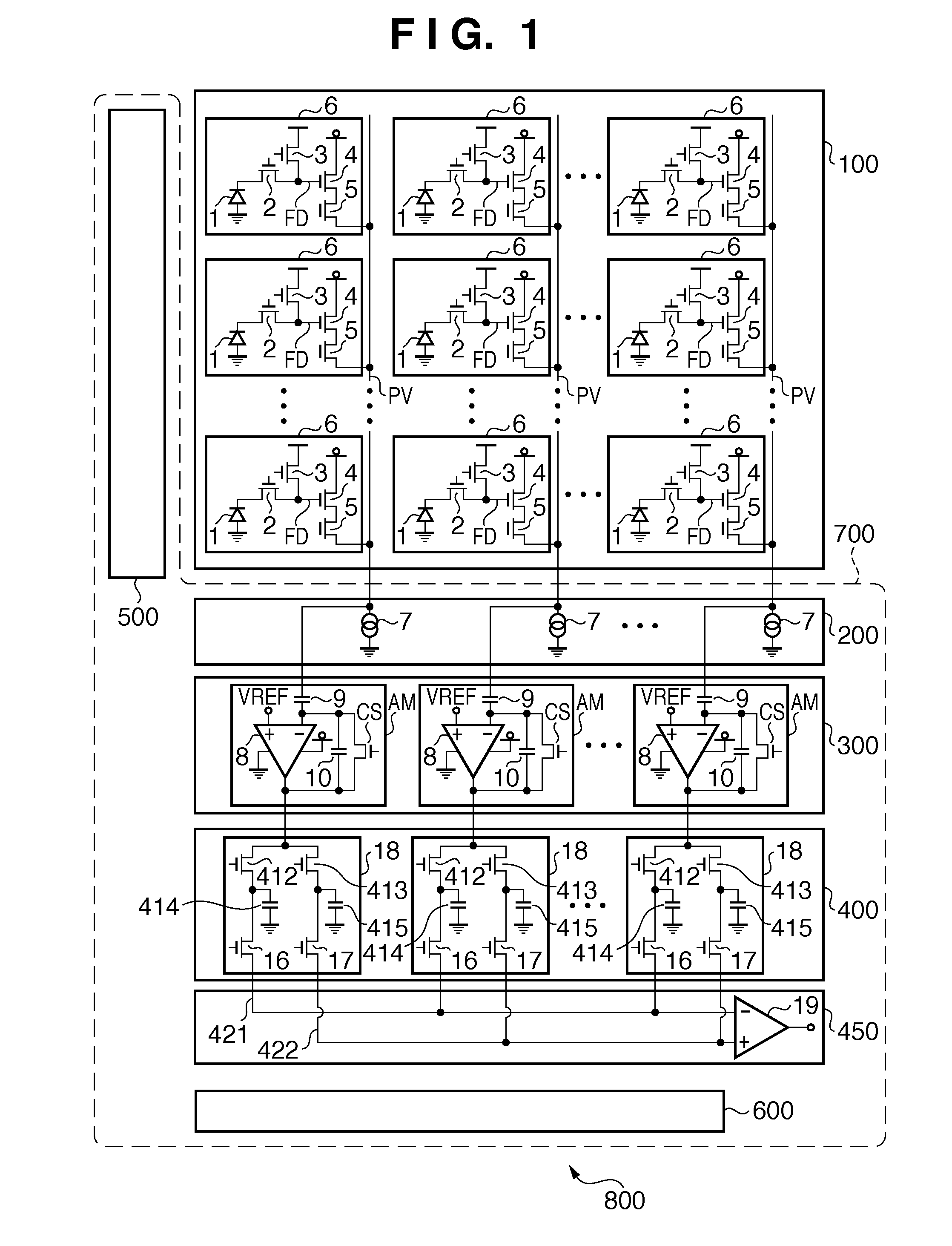

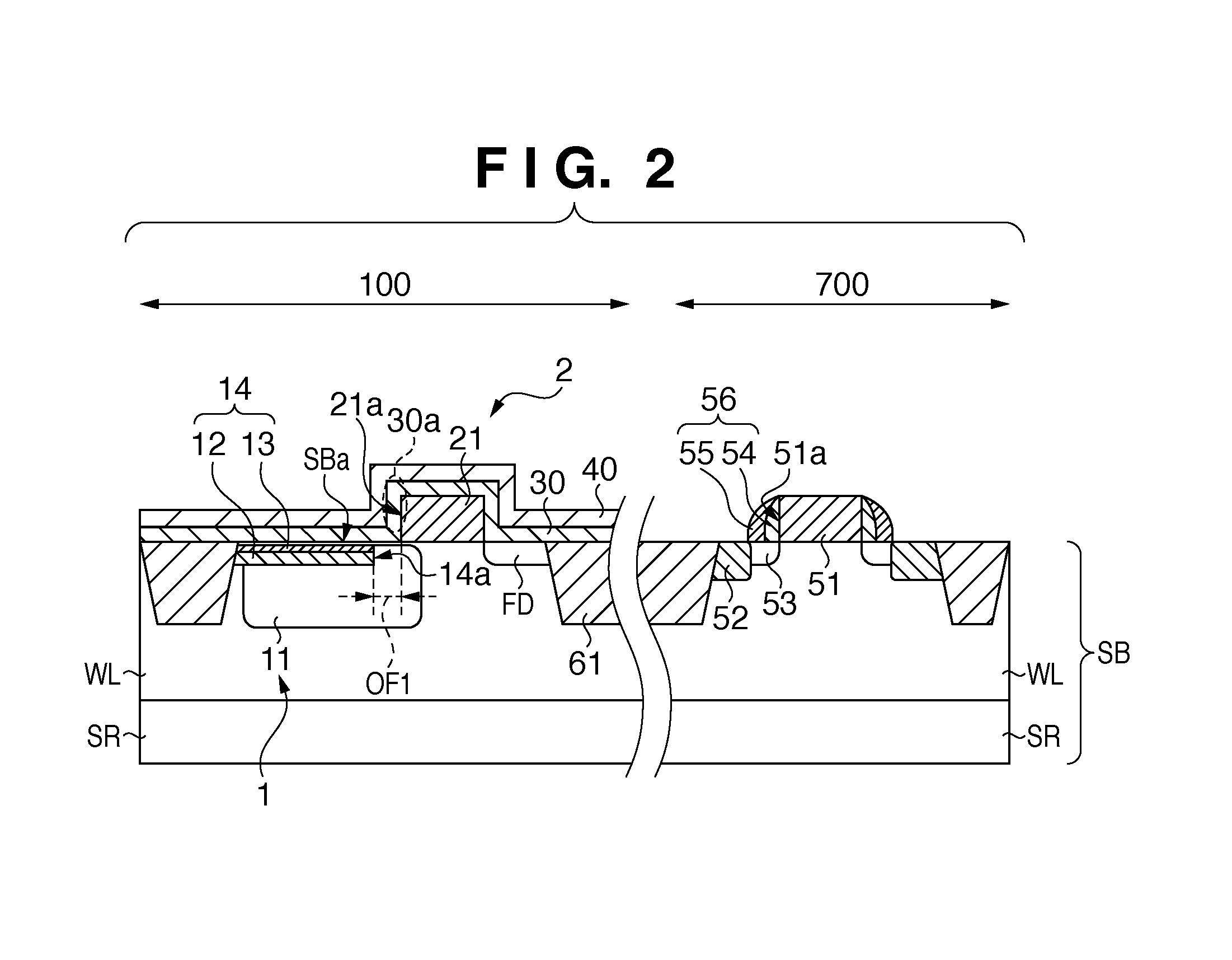

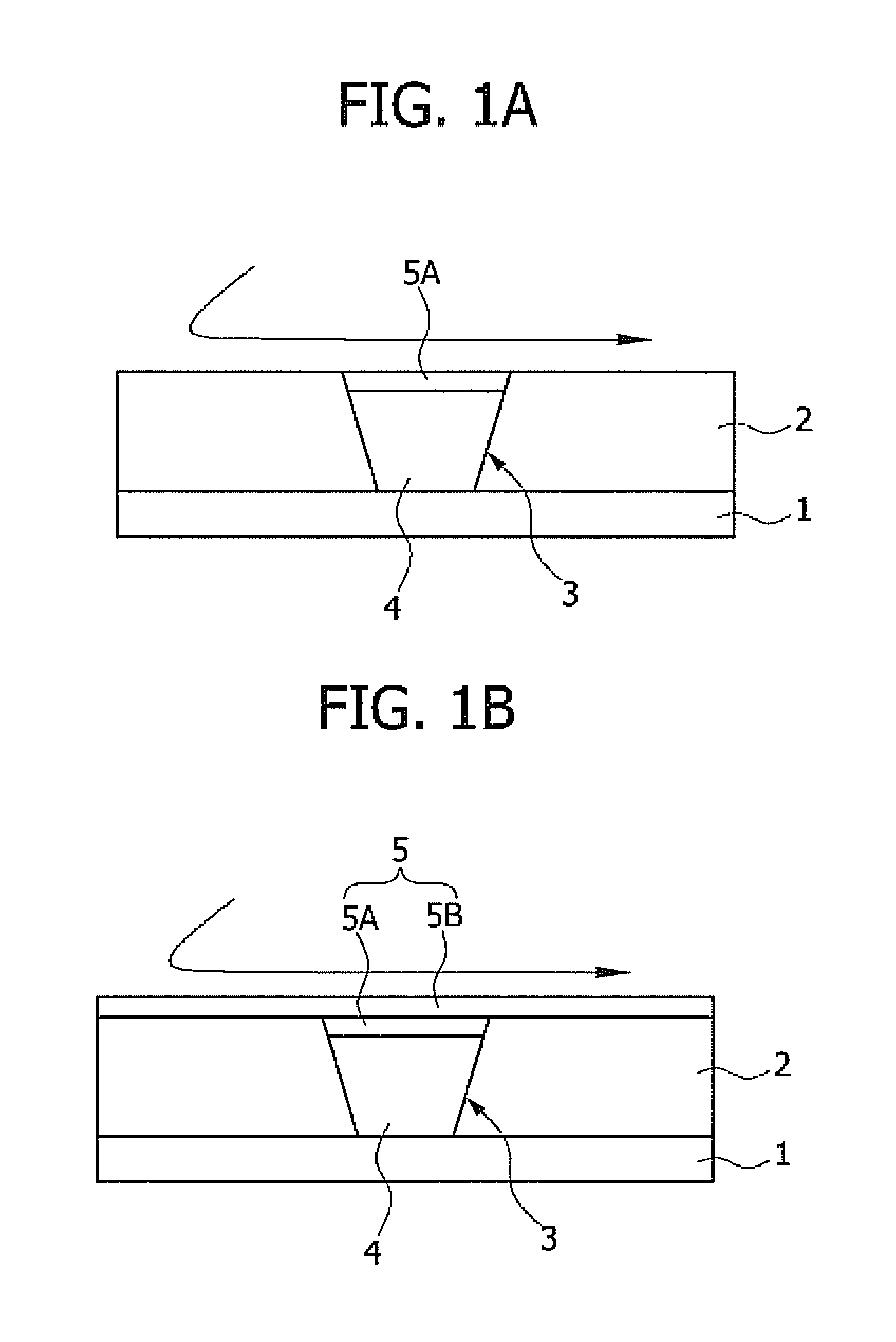

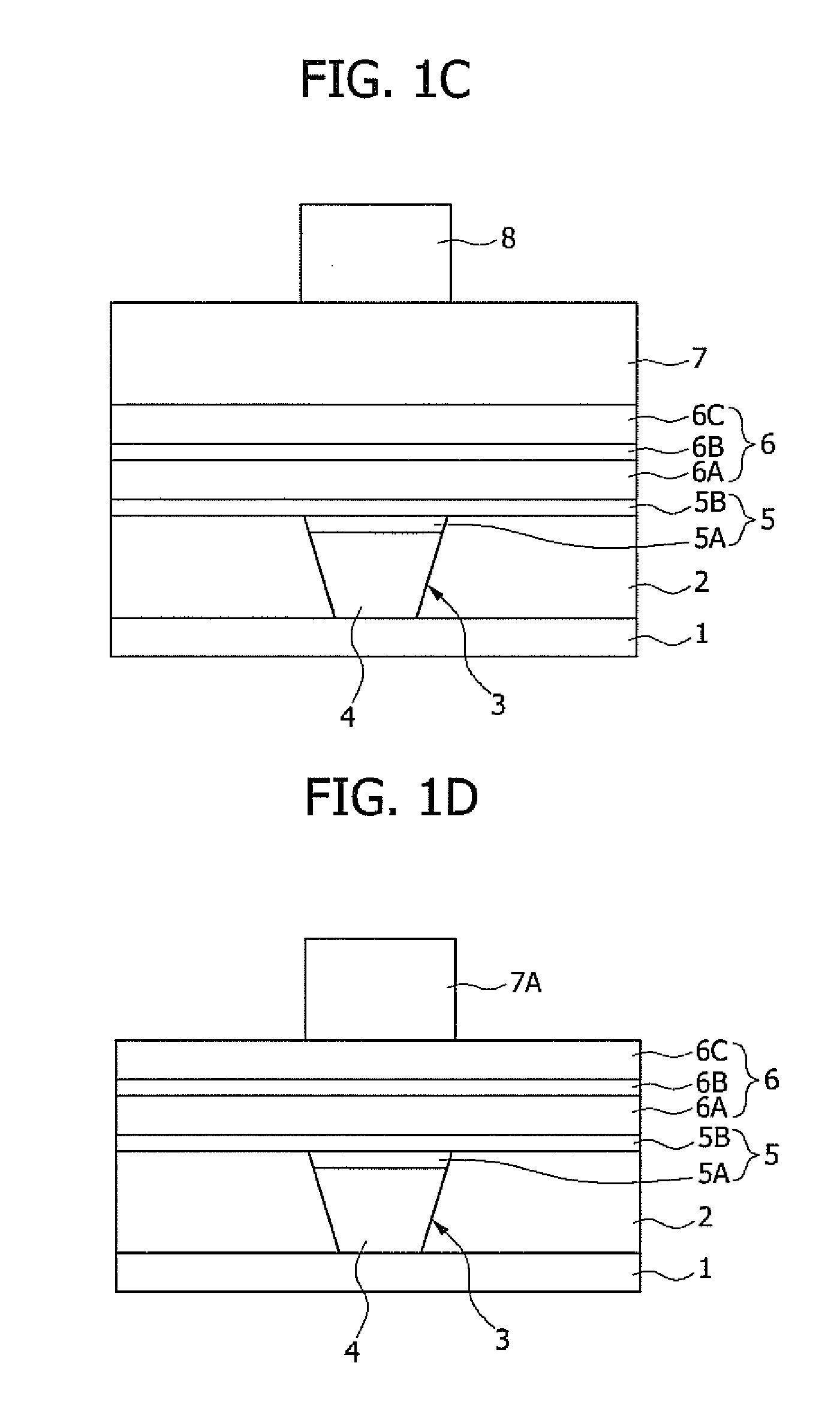

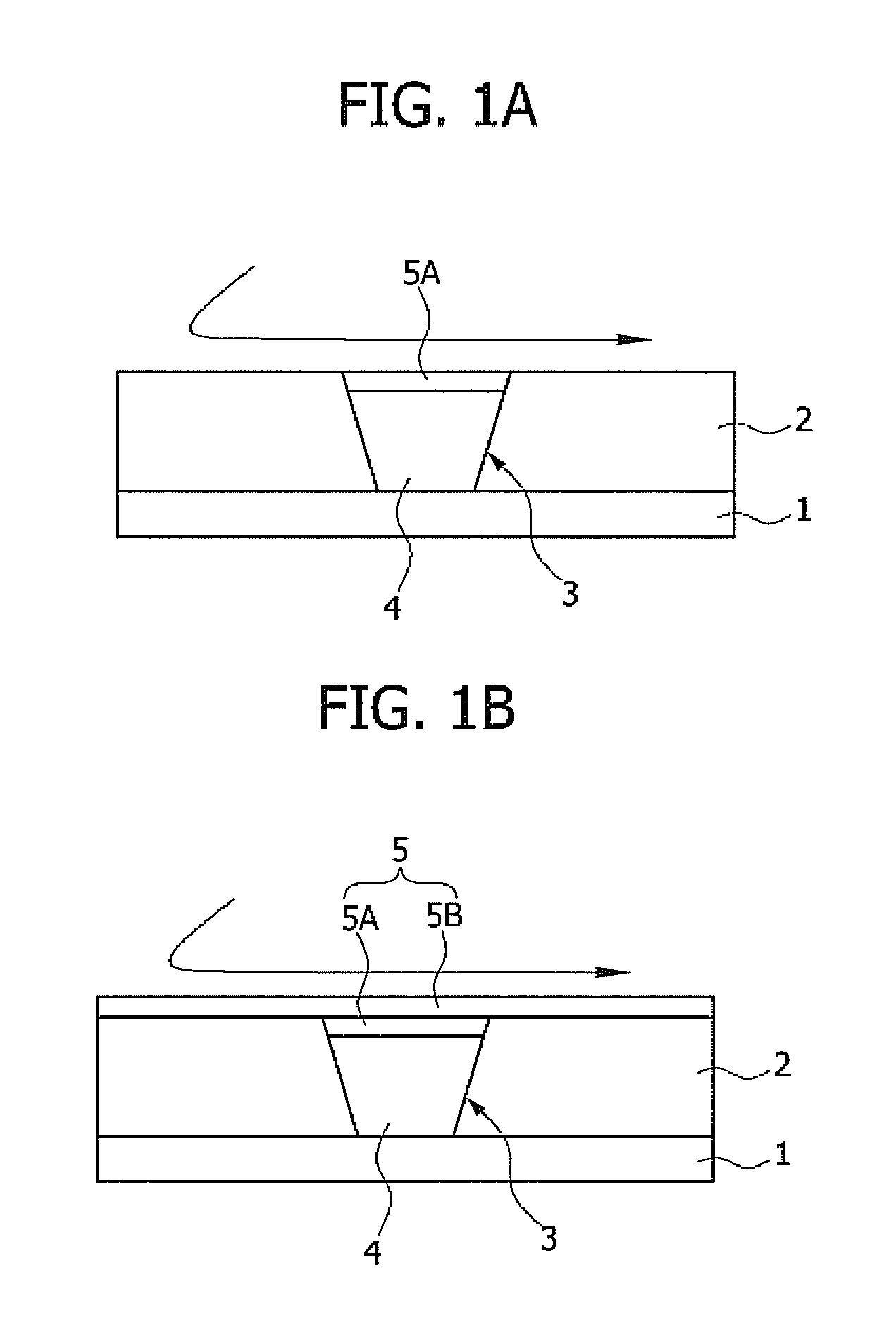

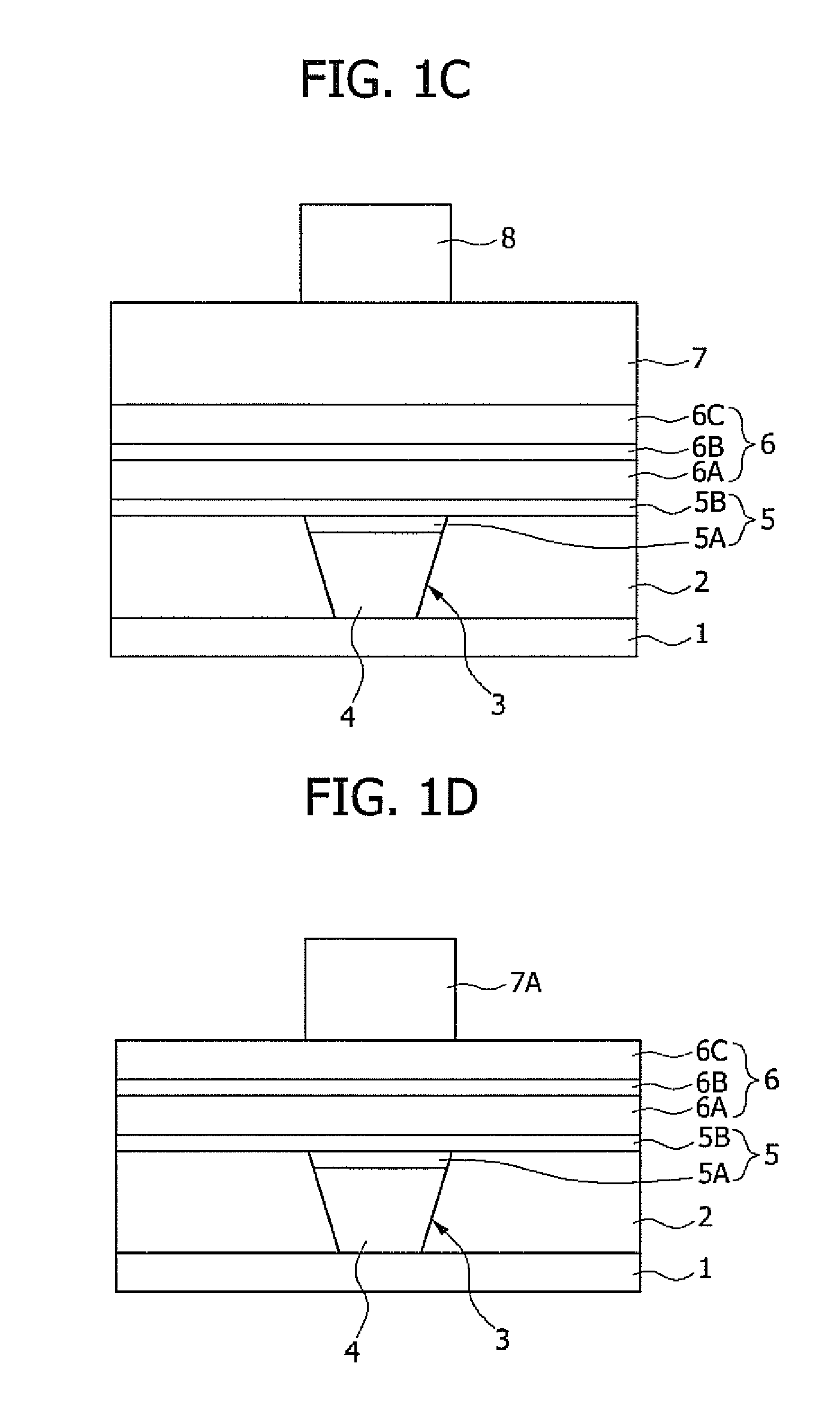

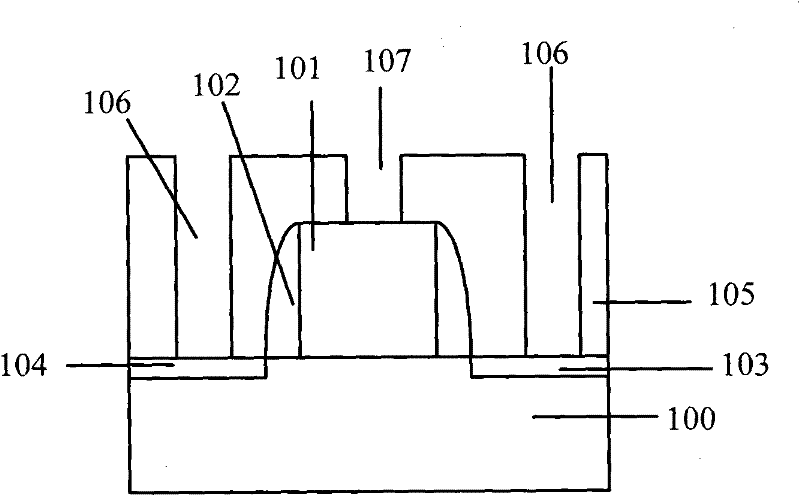

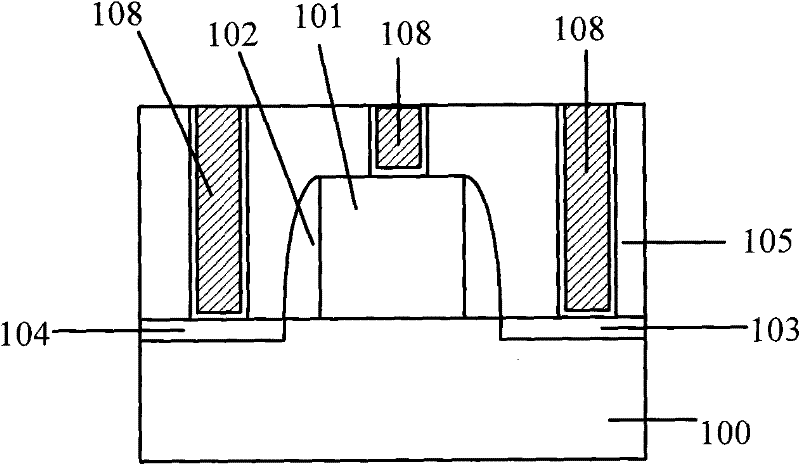

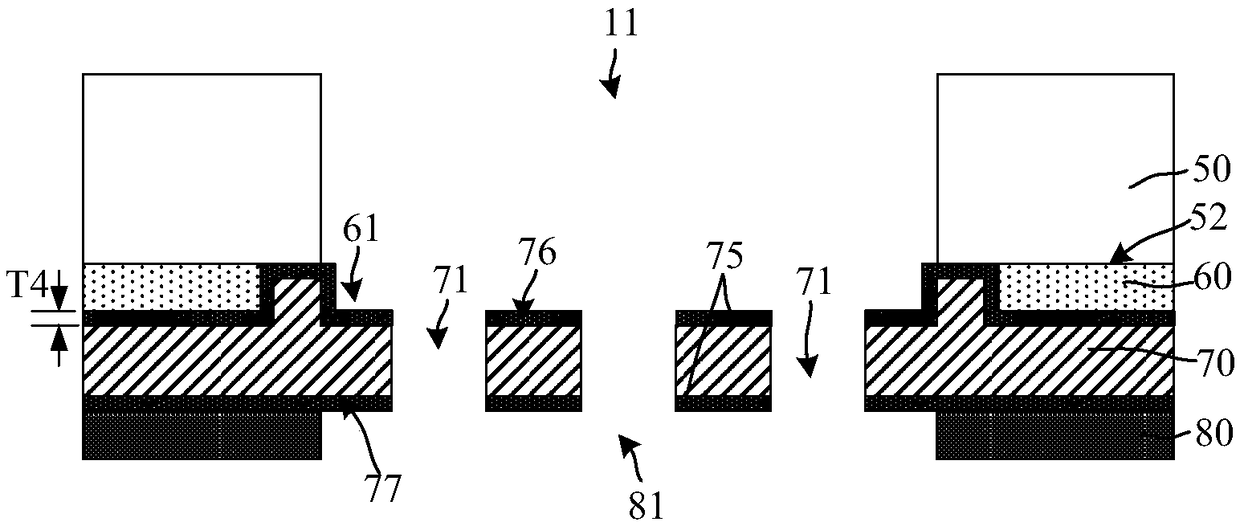

Manufacturing method of a photoelectric conversion device

InactiveUS7935557B2Reduce etch damageHigh control precisionSolid-state devicesSemiconductor/solid-state device manufacturingPhotoelectric conversionEngineering

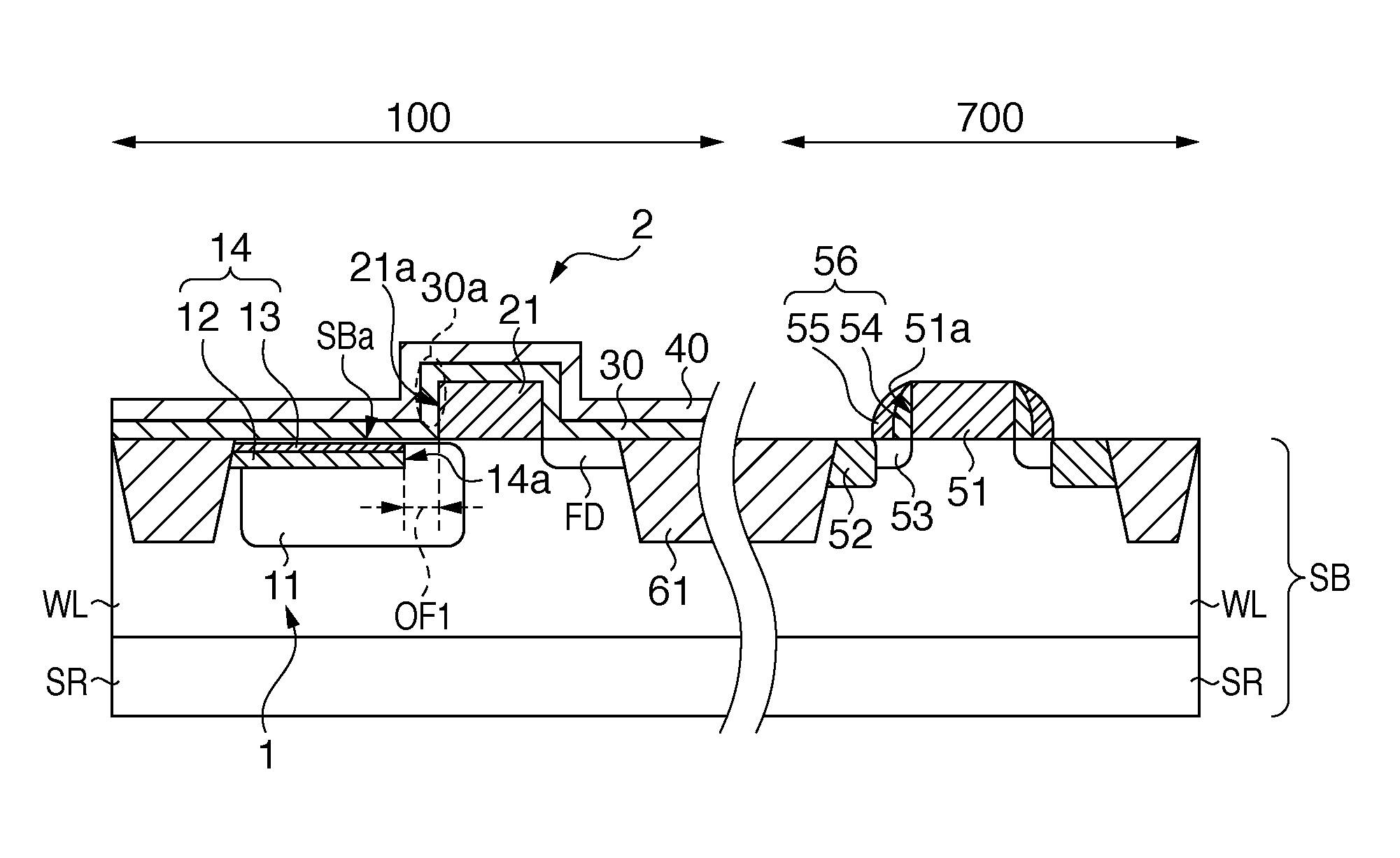

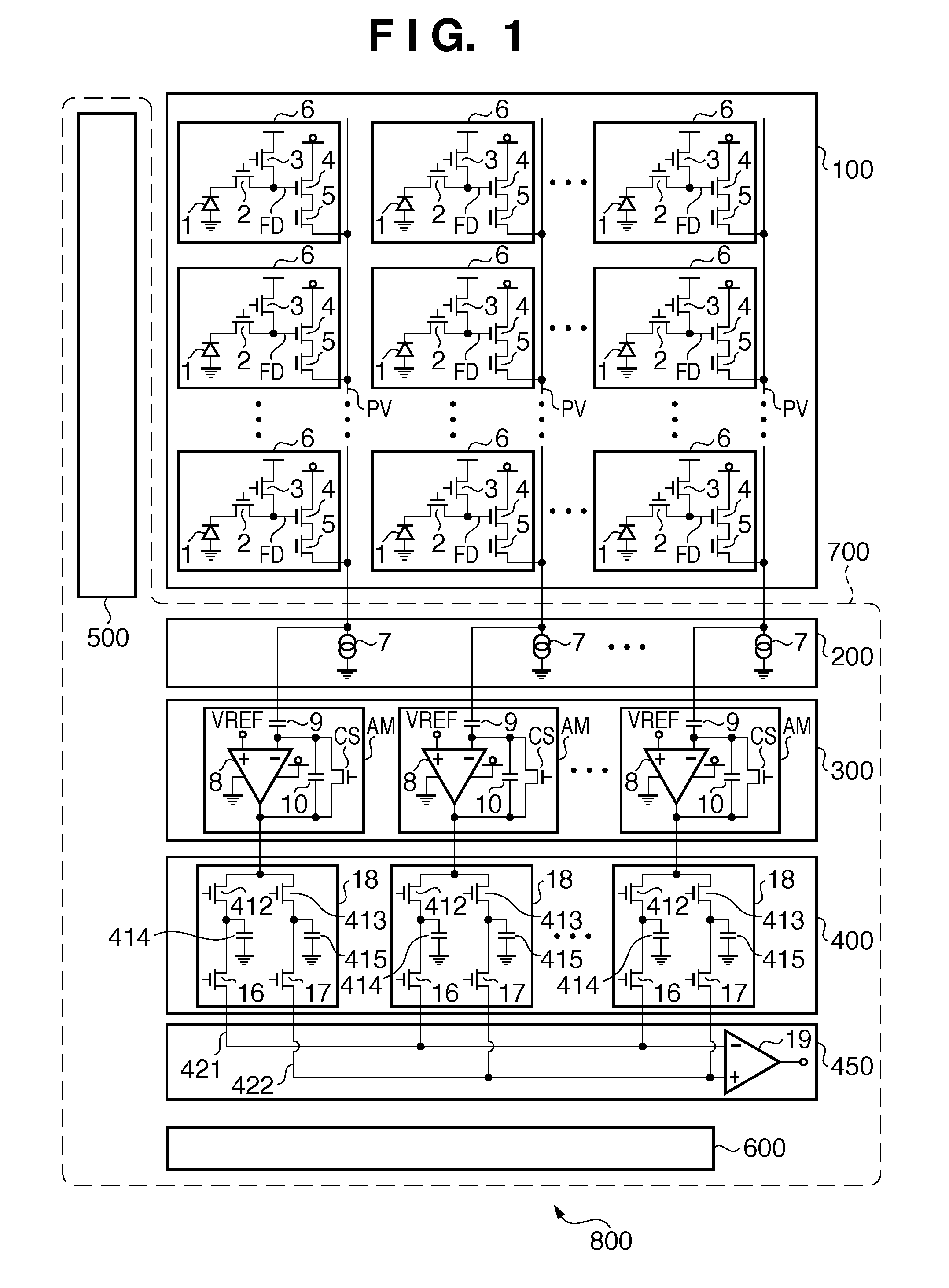

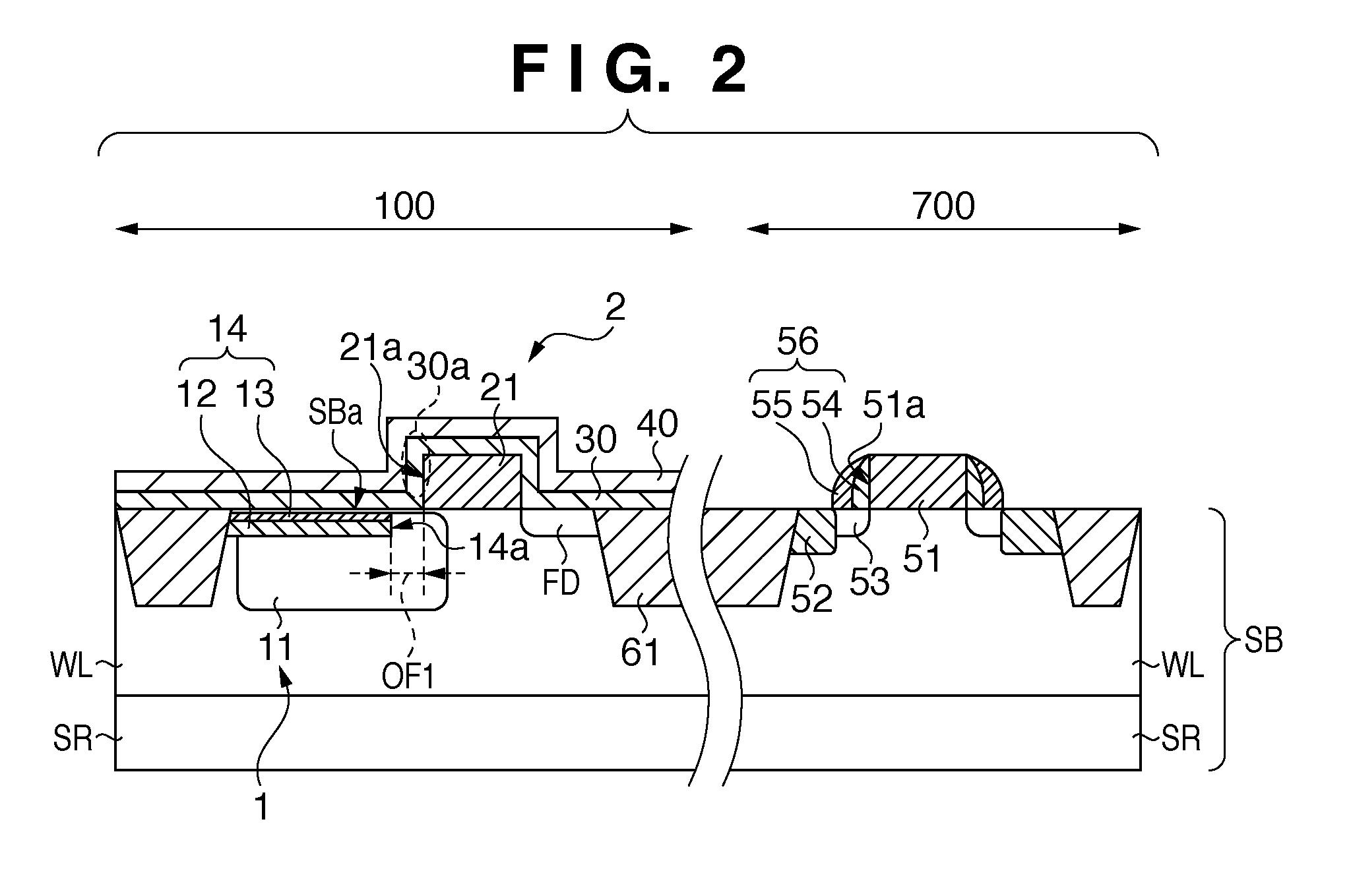

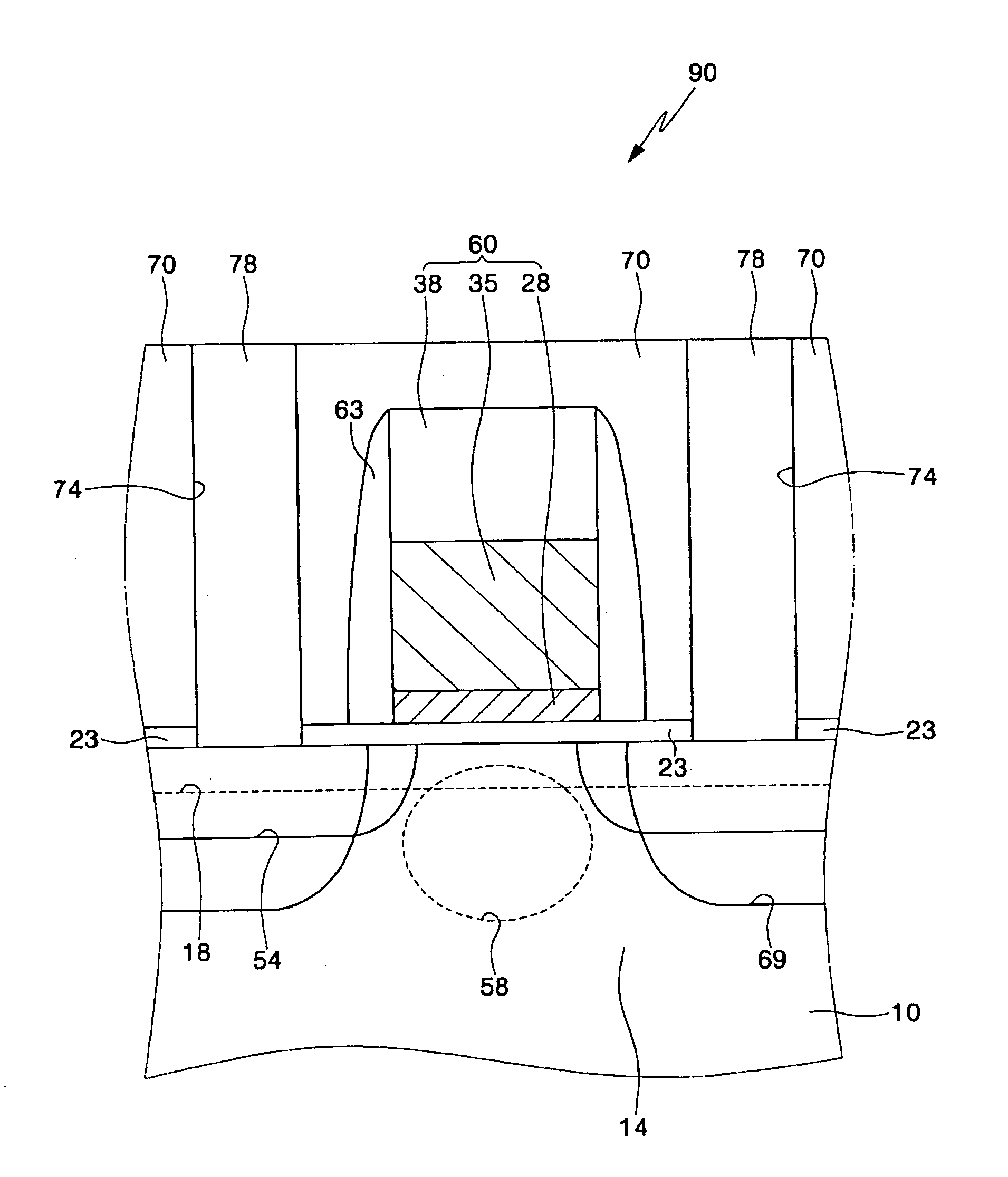

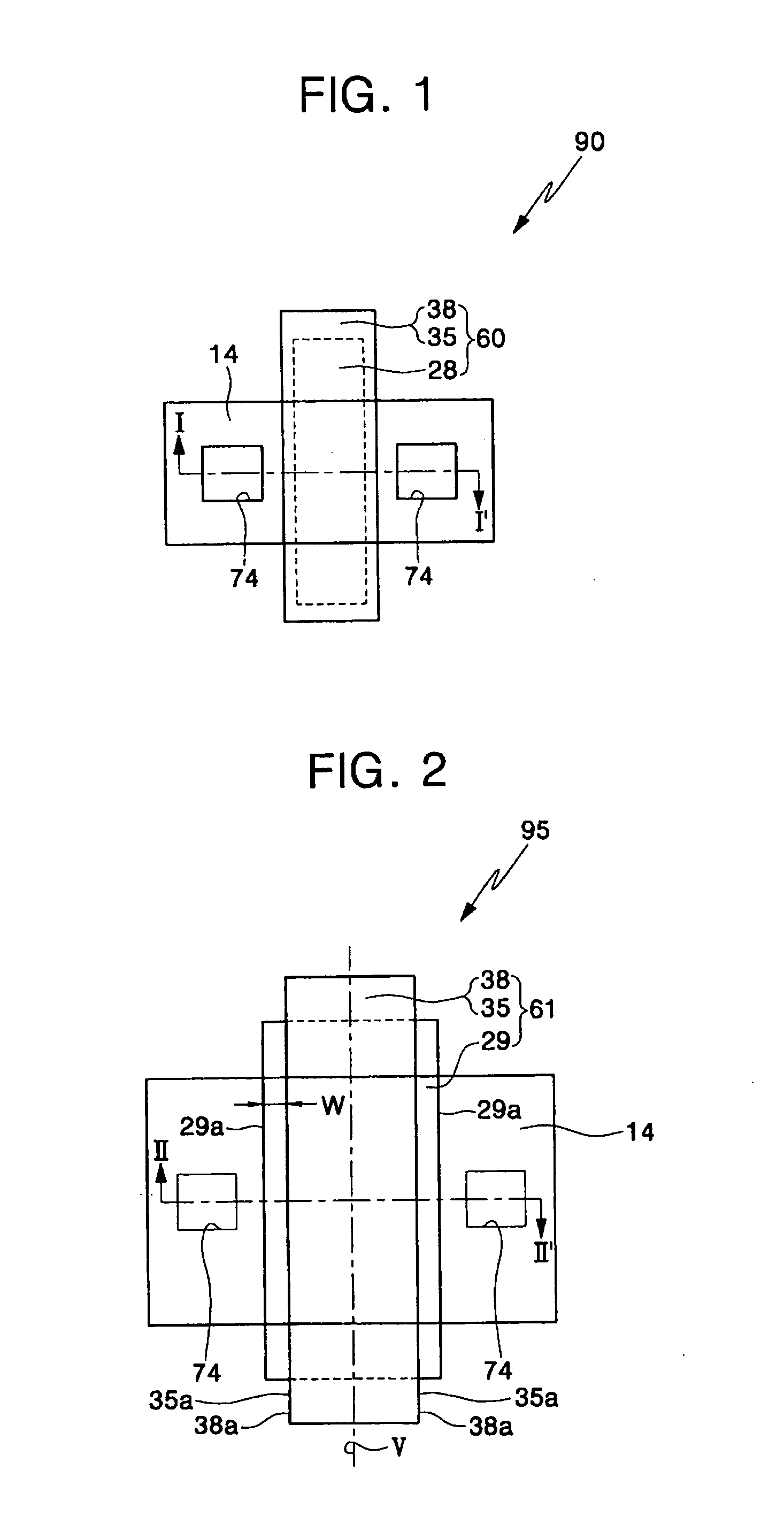

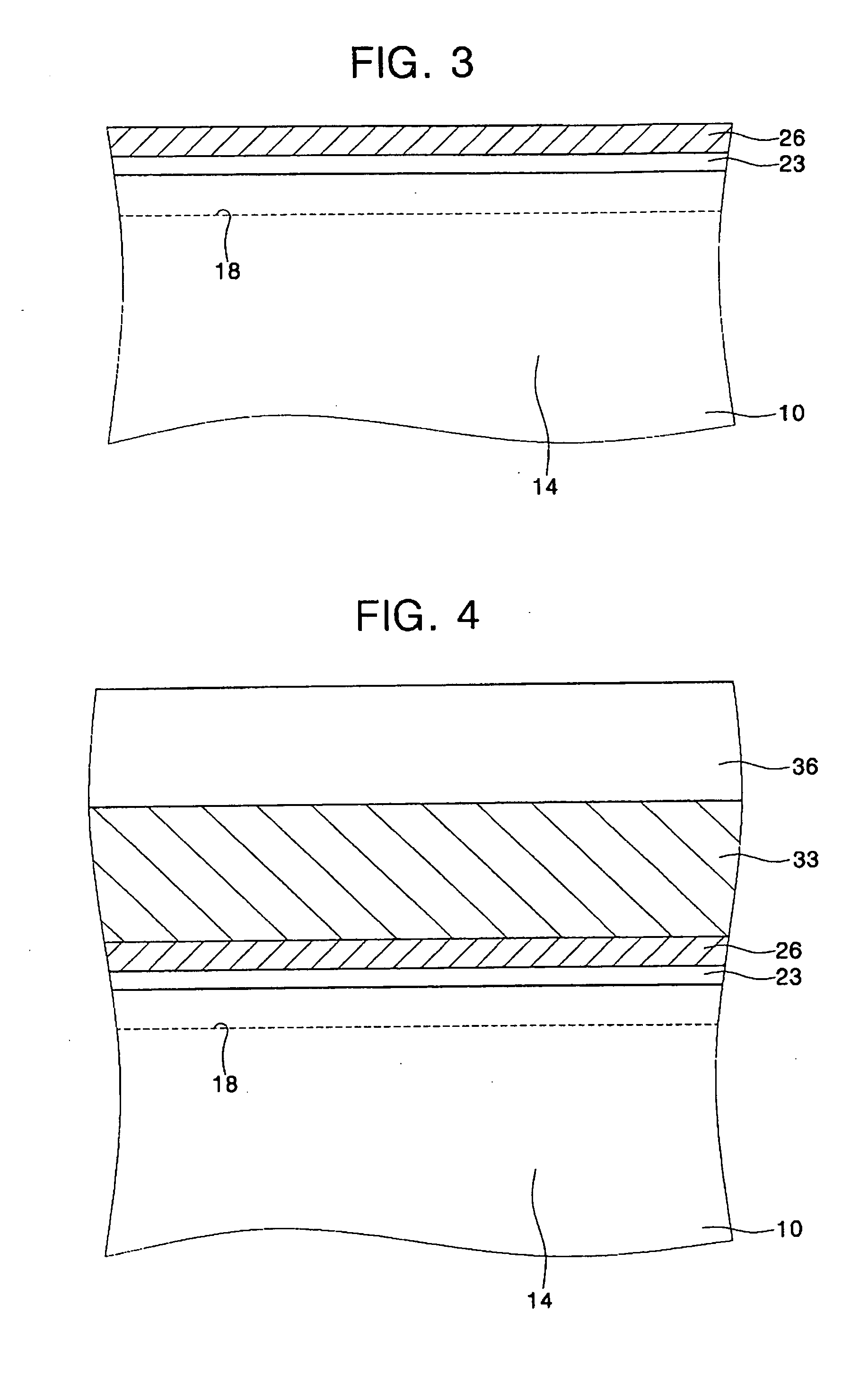

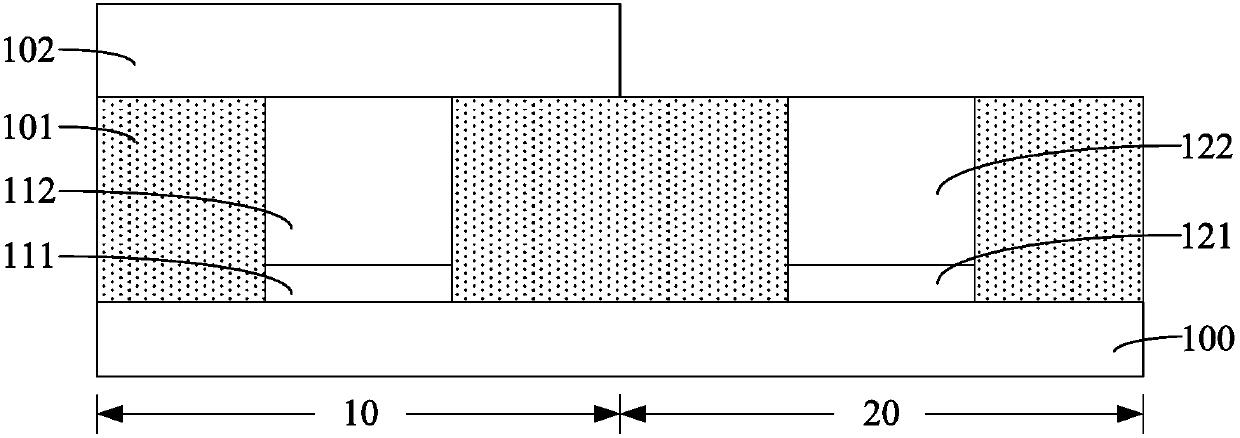

A manufacturing method of a photoelectric conversion device included a first step of forming a gate electrode, a second step of forming a semiconductor region of a first conductivity type, a third step of forming an insulation film, and a fourth step of forming a protection region of a second conductivity type, which is the opposite conductivity type to the first conductivity type, by implanting ions in the semiconductor region using the gate electrode of the transfer transistor and a portion covering a side face of the gate electrode of the transfer transistor of the insulation film as a mask in a state in which the semiconductor substrate and the gate electrode of the transfer transistor are covered by the insulation film, and causing a portion of the semiconductor region of the first conductivity type from which the protection region is removed to be the charge accumulation region.

Owner:CANON KK

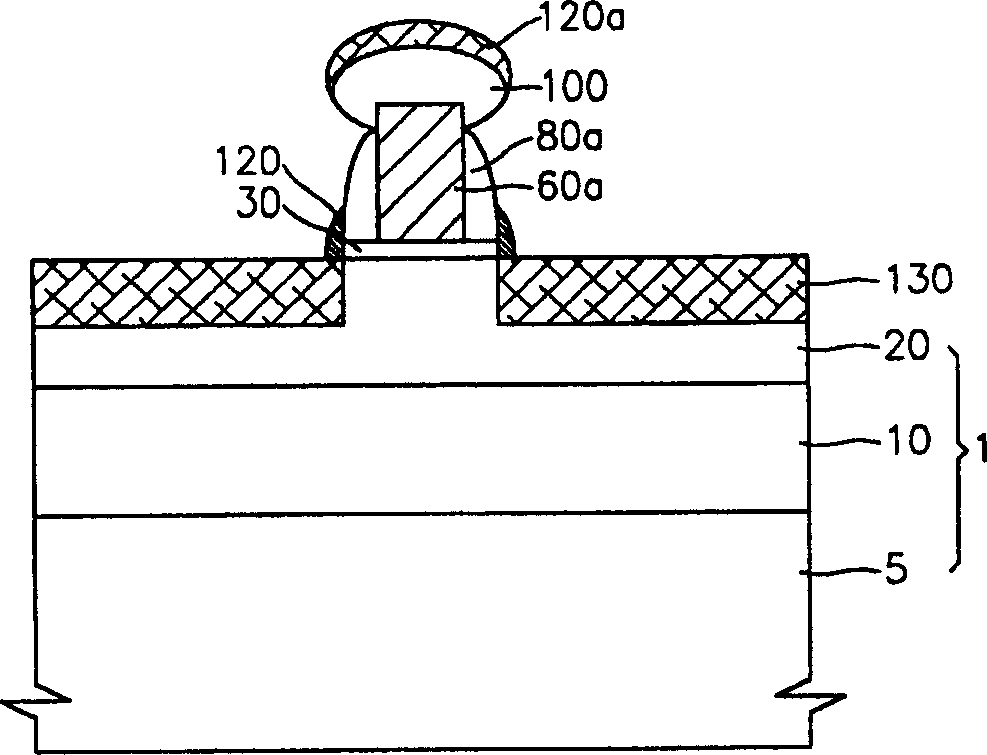

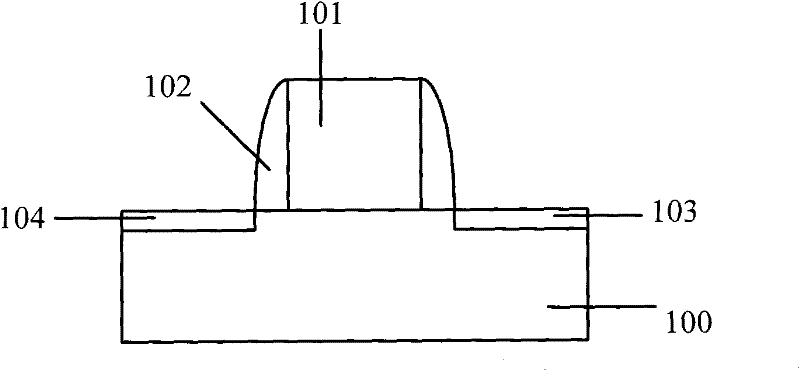

Schotthy barrier transistor and manufacturing method thereof

InactiveCN1538531AReduce etch damageTransistorSemiconductor/solid-state device manufacturingEtchingSchottky barrier

Owner:ELECTRONICS & TELECOMM RES INST

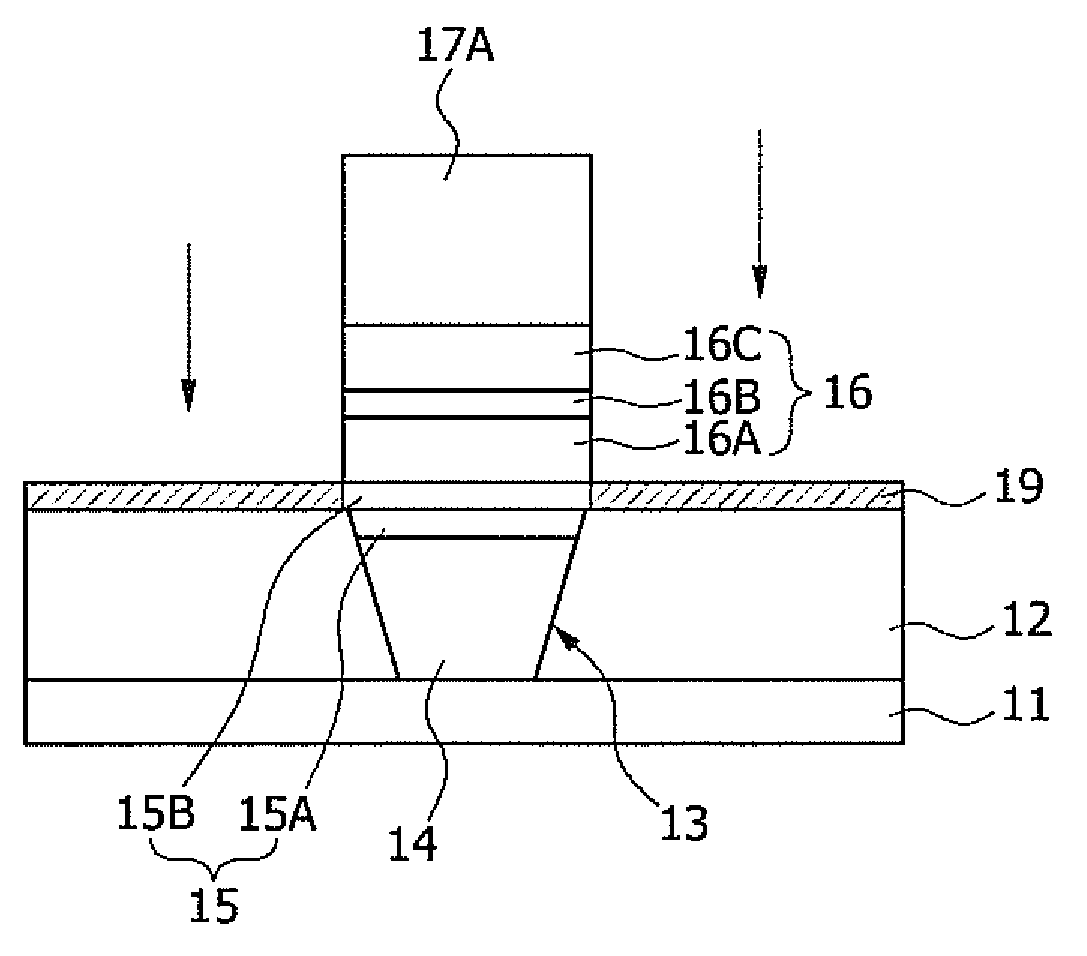

Manufacturing method of a photoelectric conversion device

InactiveUS20100173444A1Reducing amount of etching damageHigh control precisionSolid-state devicesSemiconductor/solid-state device manufacturingPhotoelectric conversionEngineering

A manufacturing method of a photoelectric conversion device comprises a first step of forming a gate electrode, a second step of forming a semiconductor region of a first conductivity type, a third step of forming an insulation film, and a fourth step of forming a protection region of a second conductivity type, which is the opposite conductivity type to the first conductivity type, by implanting ions in the semiconductor region using the gate electrode of the transfer transistor and a portion covering a side face of the gate electrode of the transfer transistor of the insulation film as a mask in a state in which the semiconductor substrate and the gate electrode of the transfer transistor are covered by the insulation film, and causing a portion of the semiconductor region of the first conductivity type from which the protection region is removed to be the charge accumulation region.

Owner:CANON KK

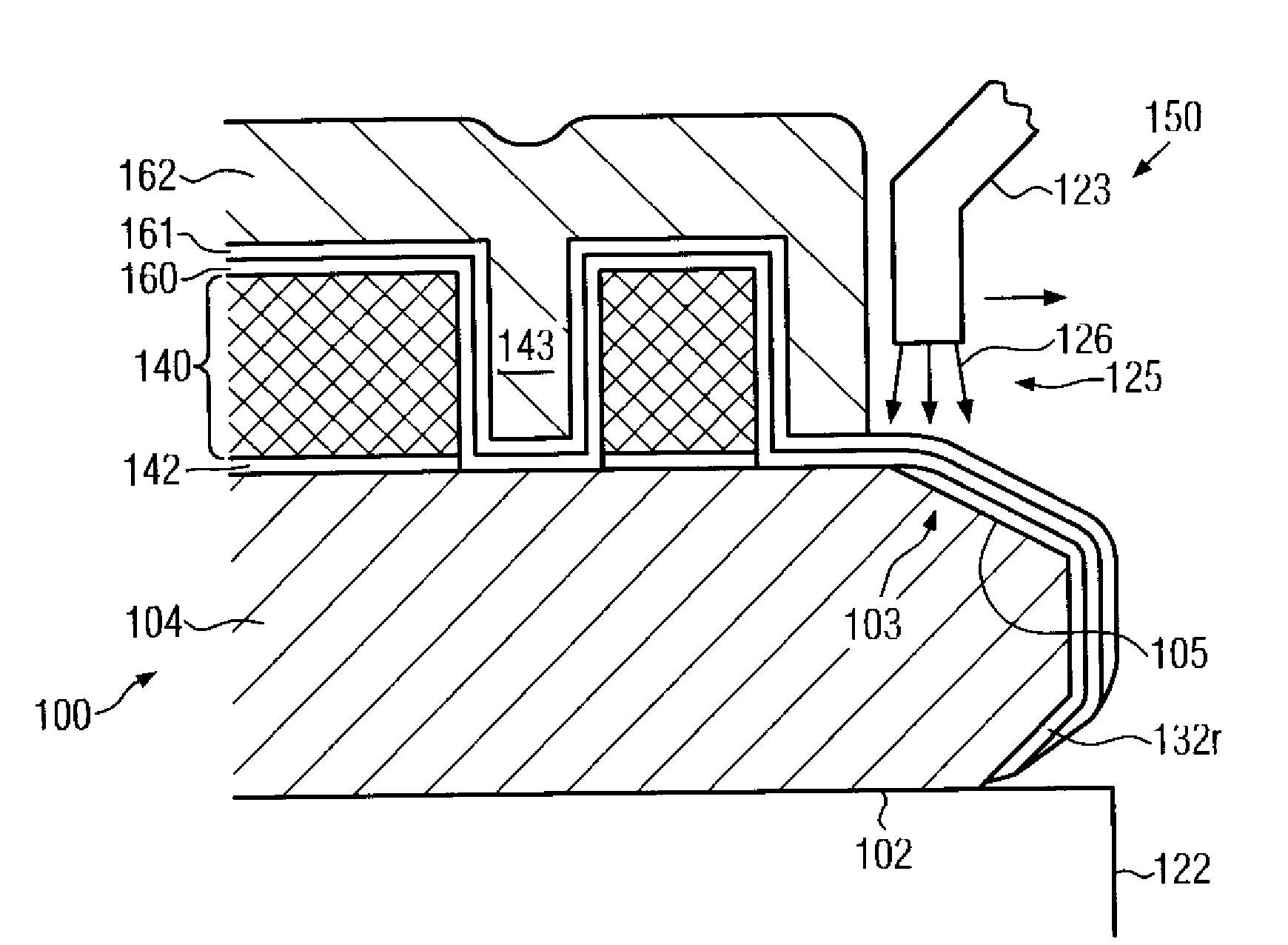

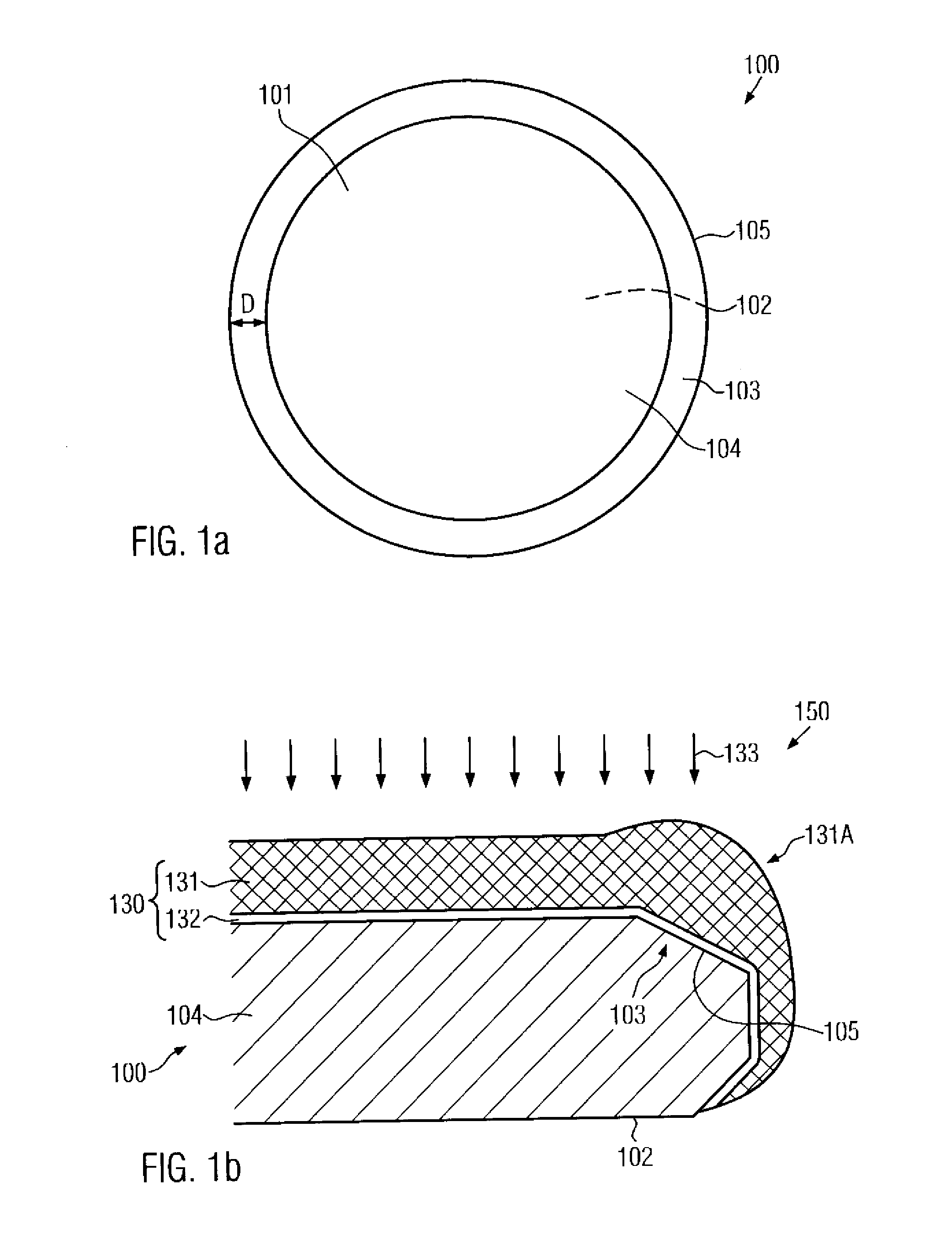

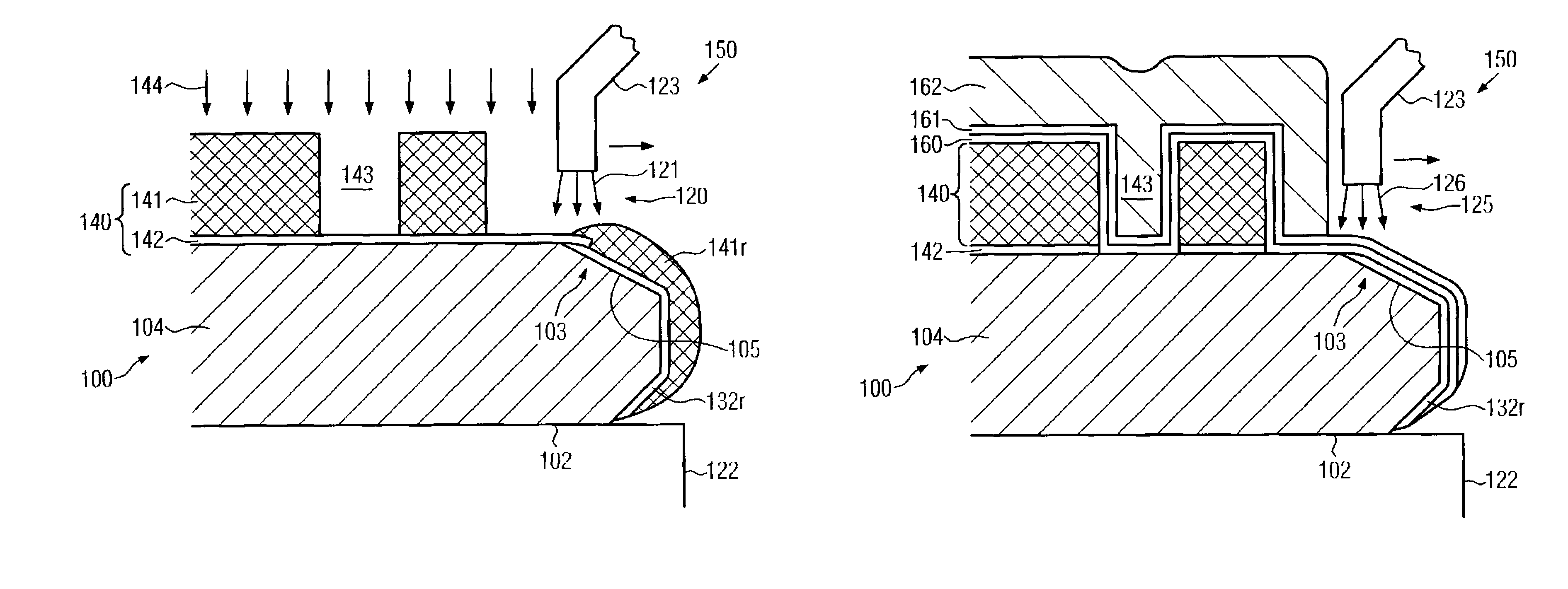

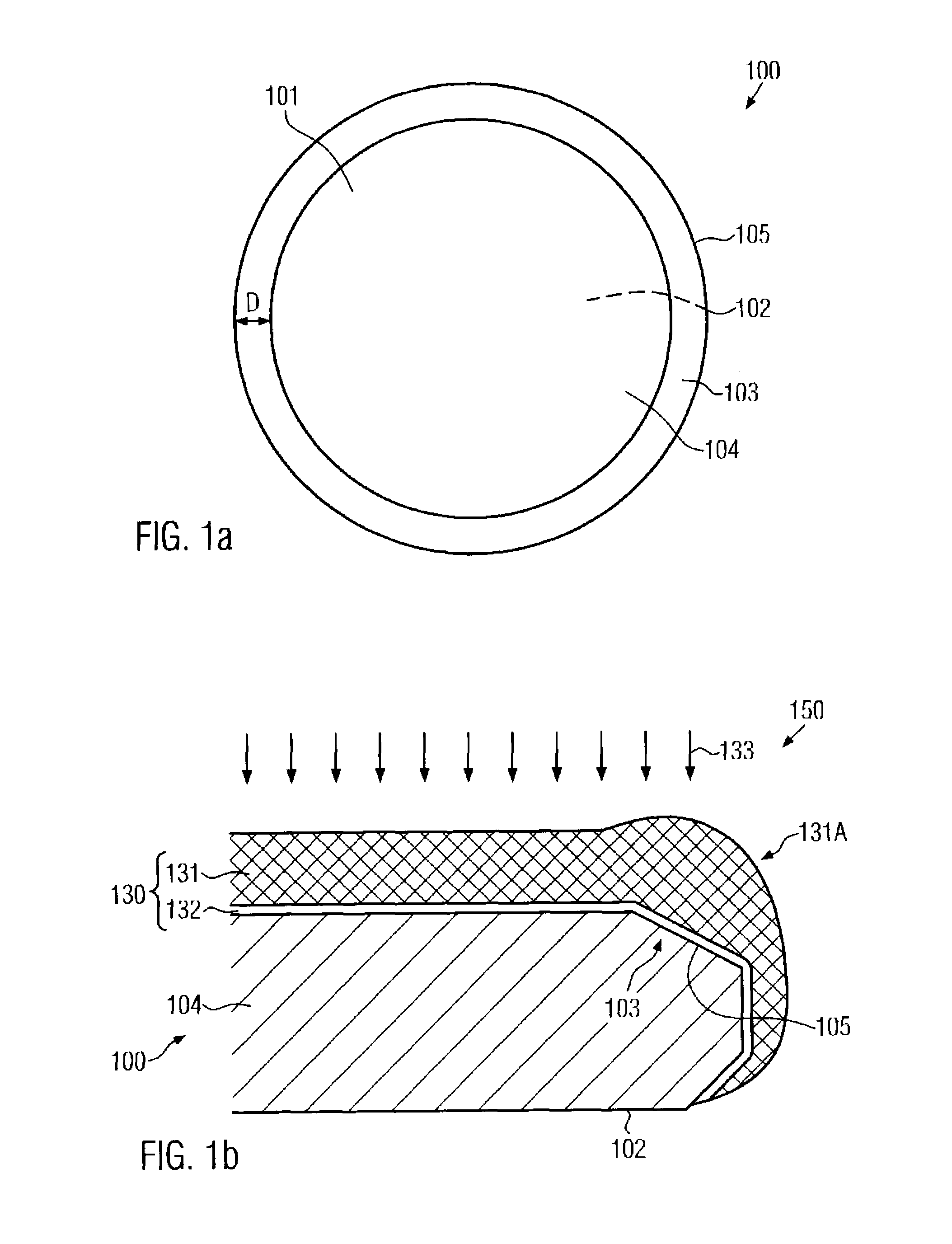

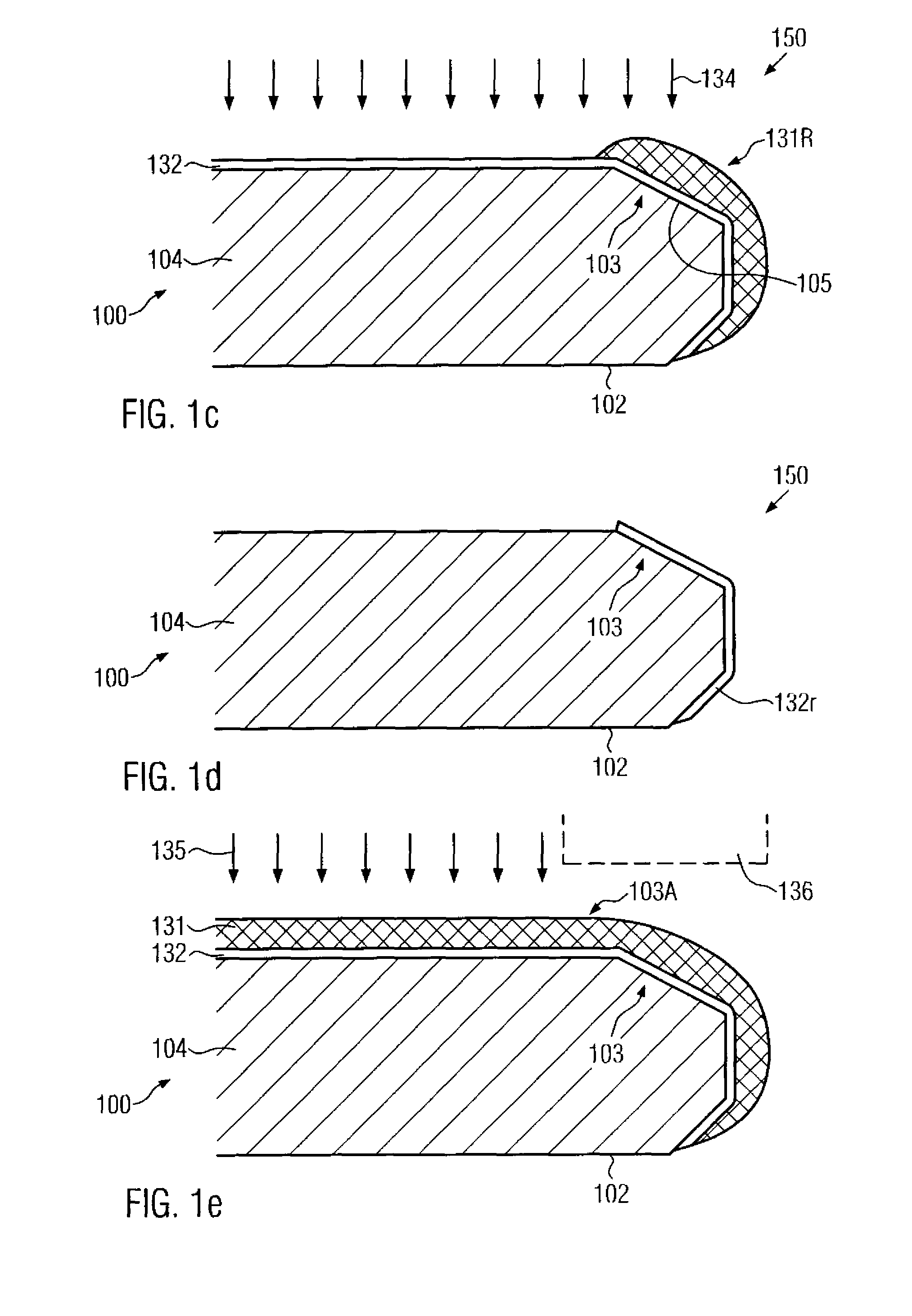

Method of reducing contamination by providing an etch stop layer at the substrate edge

InactiveUS20070155133A1Reduce probabilityEfficient removalSemiconductor/solid-state device manufacturingContaminationMetal

By providing an etch stop layer selectively at the bevel, at least one additional wet chemical bevel etch process may be performed prior to or during the formation of a metallization layer without affecting the substrate material. Hence, the dielectric material, especially the low-k dielectric material, may be reliably removed from the bevel prior to the formation of any barrier and metal layers. The etch stop layer may be formed at an early manufacturing stage so that a bevel etch process may be performed at any desired stage of the formation of circuit elements.

Owner:ALSEPHINA INNOVATIONS INC

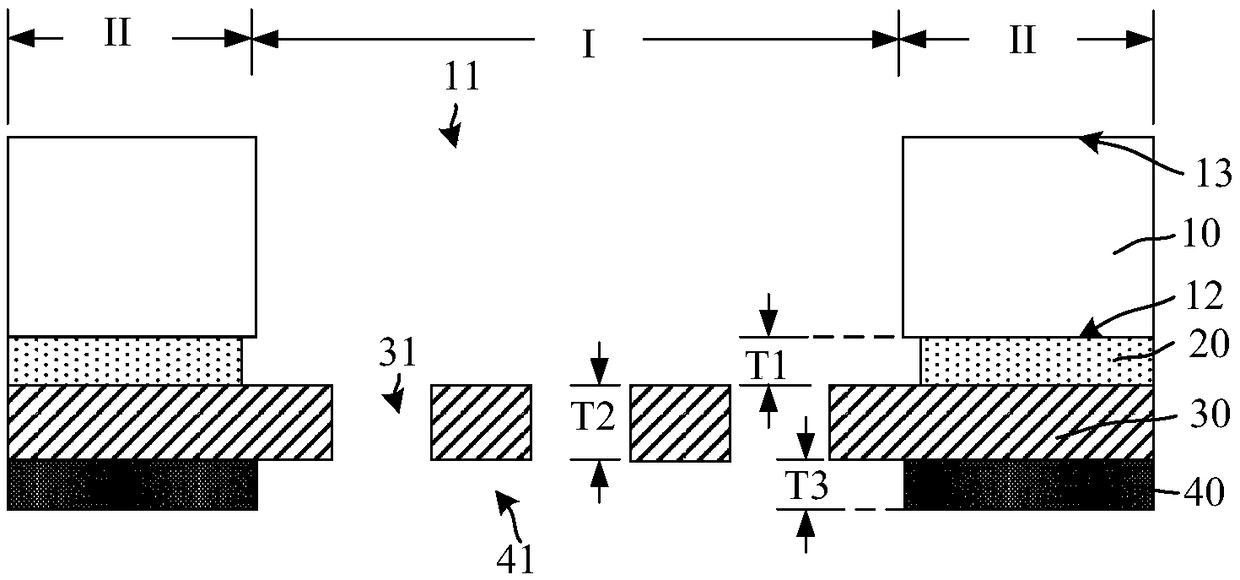

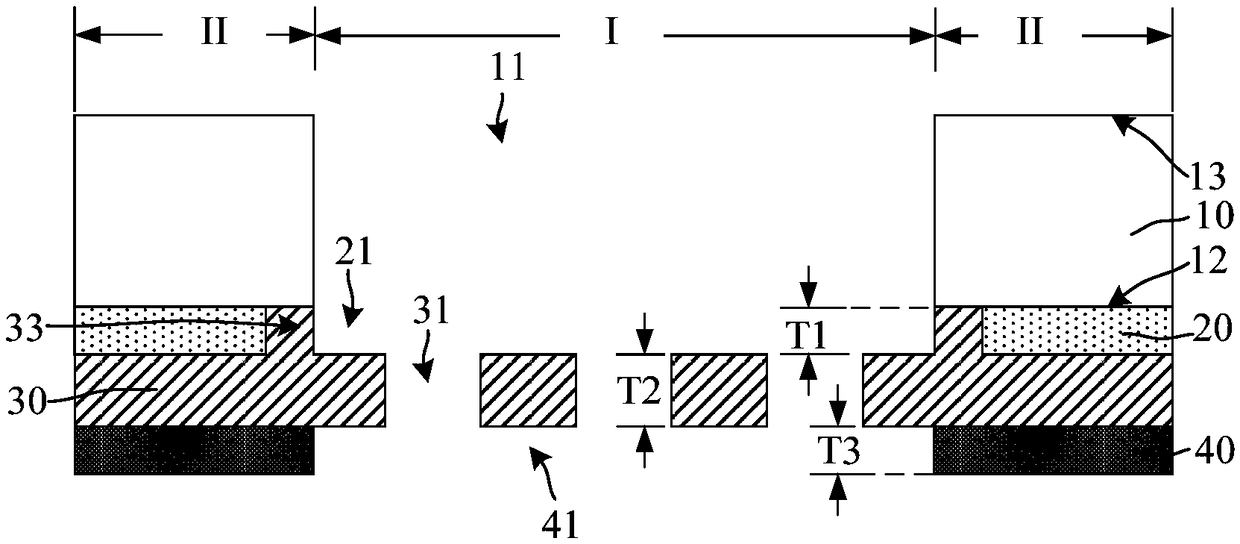

Method for forming semiconductor device

ActiveCN102856257AReduce etch rate and etch damageImprove protectionSemiconductor/solid-state device manufacturingOxide semiconductorN channel

The invention discloses a method for forming a semiconductor device. The method includes that a substrate is provided, the substrate includes a first area and a second area, two gate structures which are located in the first area and the second area respectively are formed on the substrate, a first side wall and a second side wall are formed, the first side wall covers the substrate surface and two sides and surface of the gate structure in the first area, the second side wall covers the substrate surface and two sides and surface of the gate structure in the second area, the second side wall and the substrate are subjected to patterning etching, an opening is formed in the substrate which is located on two sides of the second side wall, an epitaxial layer is formed in the opening, before the epitaxial layer is formed, the first side wall is subjected to an ion implantation or an ion doping process, and thereby the density of the first side wall is improved. According to the method, the density of the first side wall is improved by the ion implantation or the ion doping process, and thereby the process selection ratio of the n-channel metal oxide semiconductor (NMOS) and the p-channel metal oxide semiconductor (PMOS) is improved when the epitaxial layer is formed on the same substrate.

Owner:SEMICON MFG INT (SHANGHAI) CORP

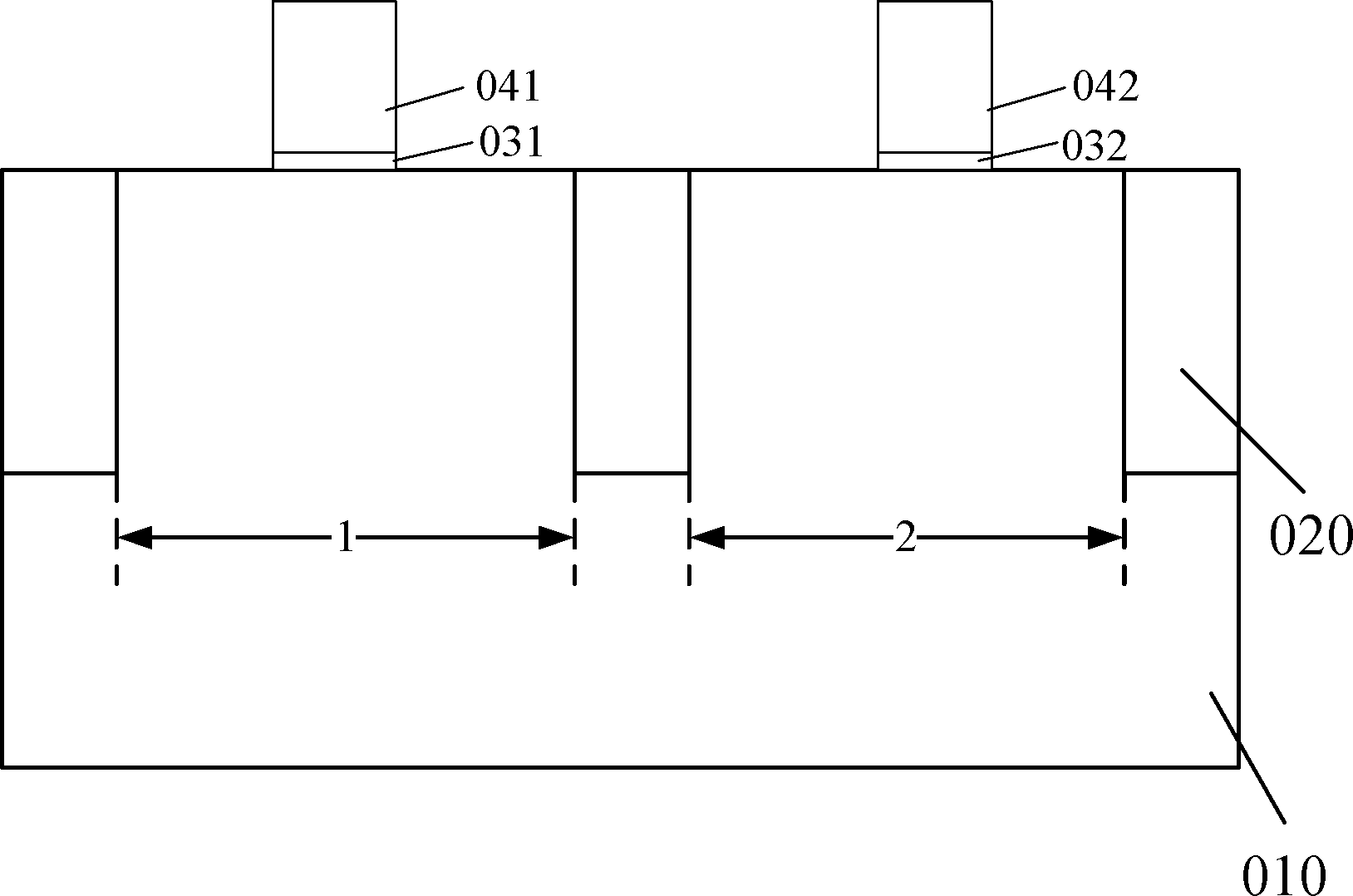

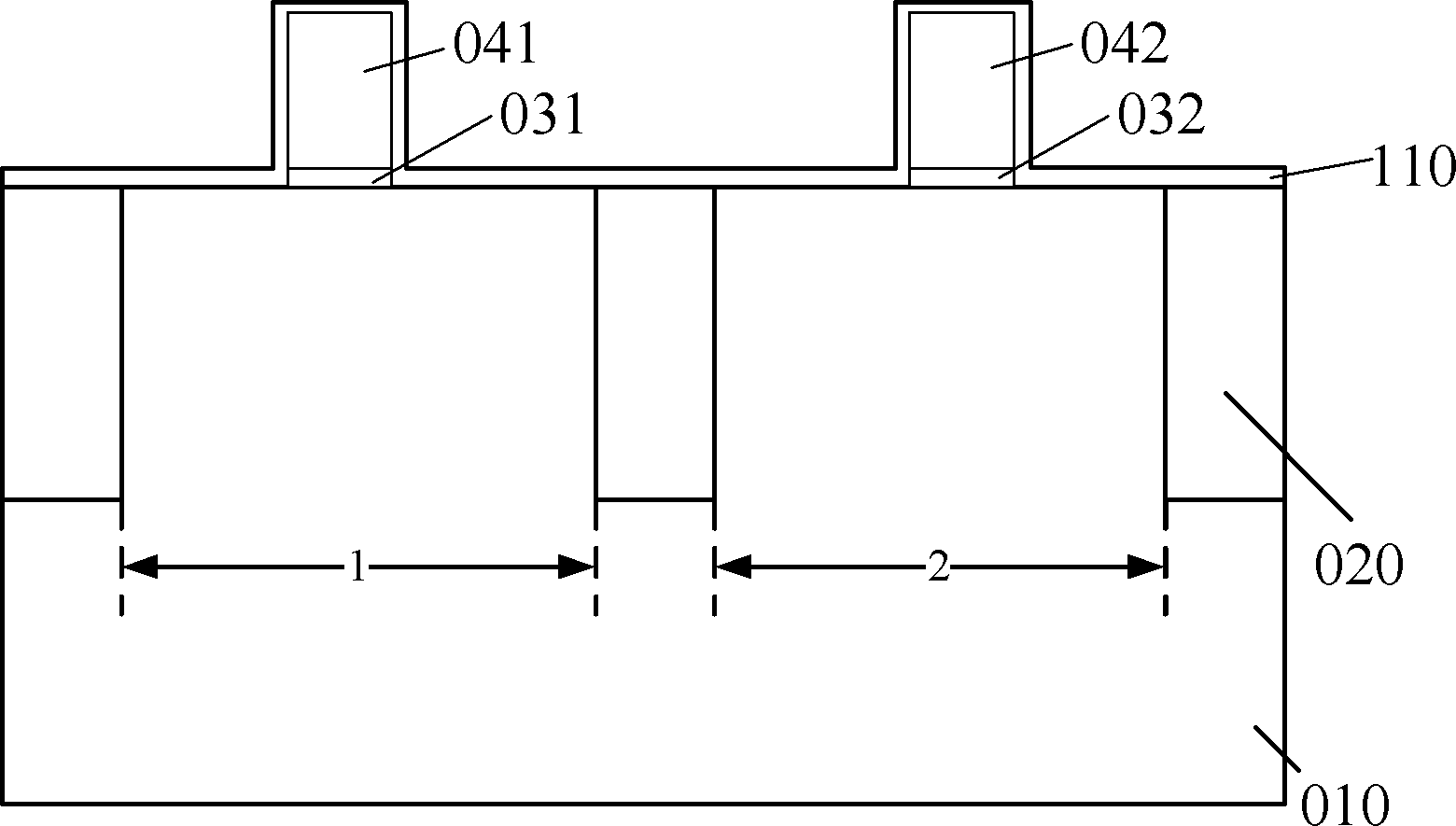

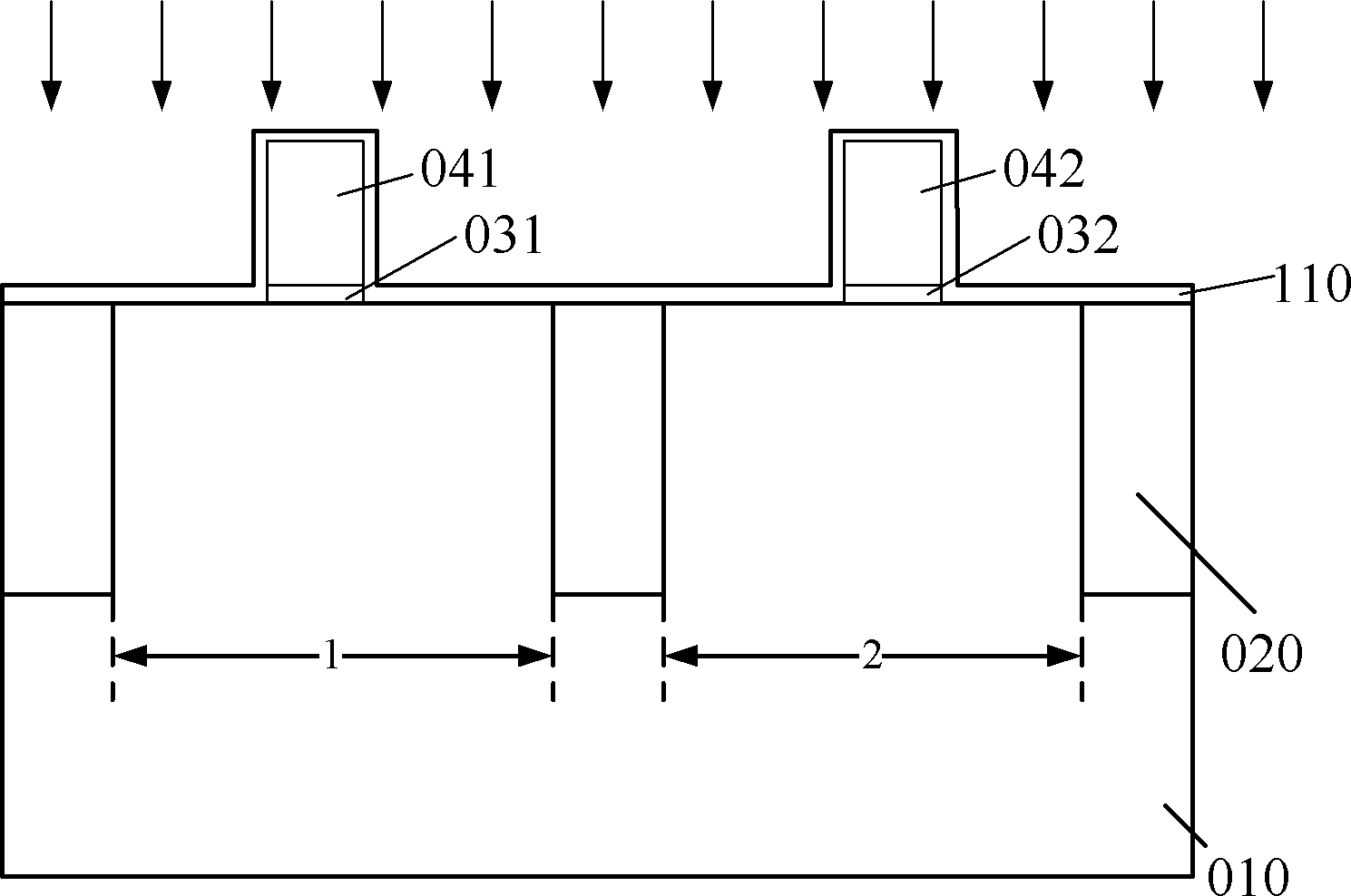

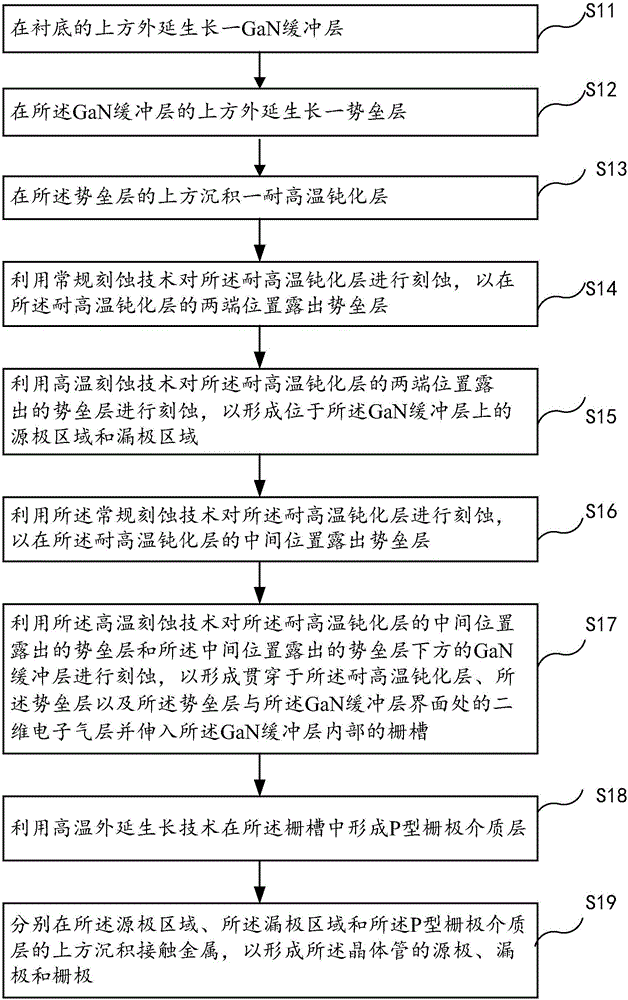

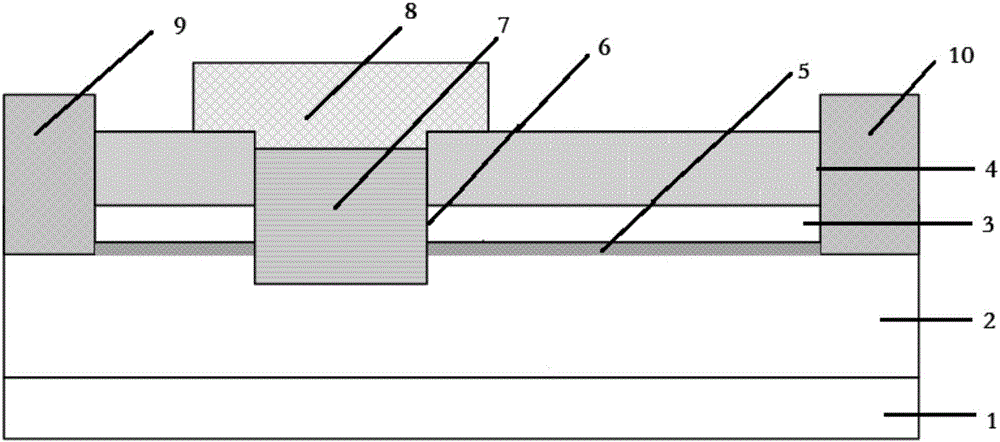

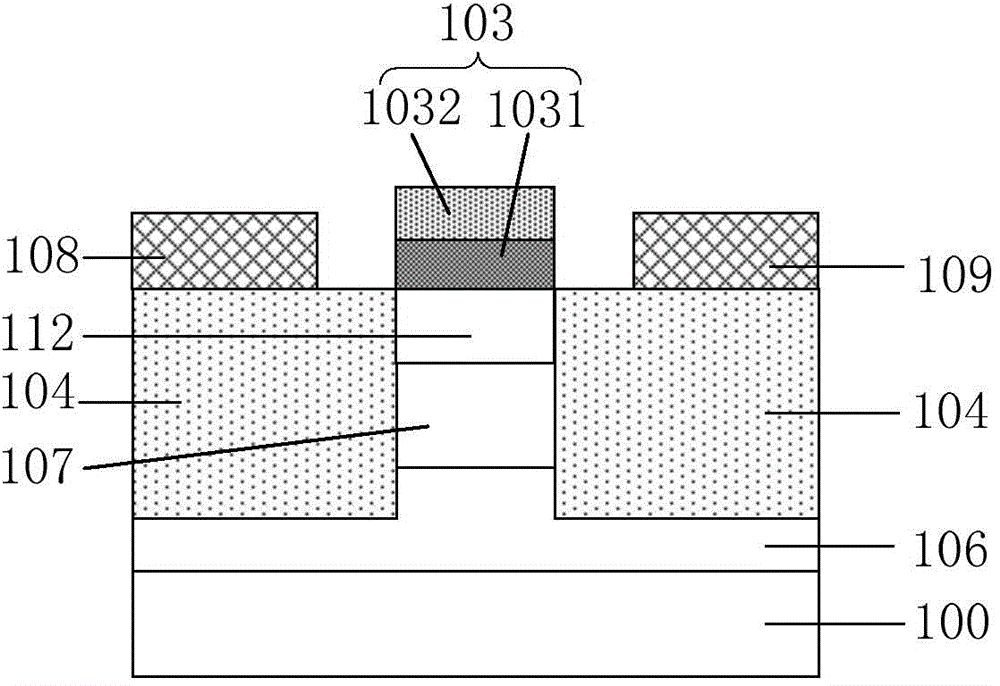

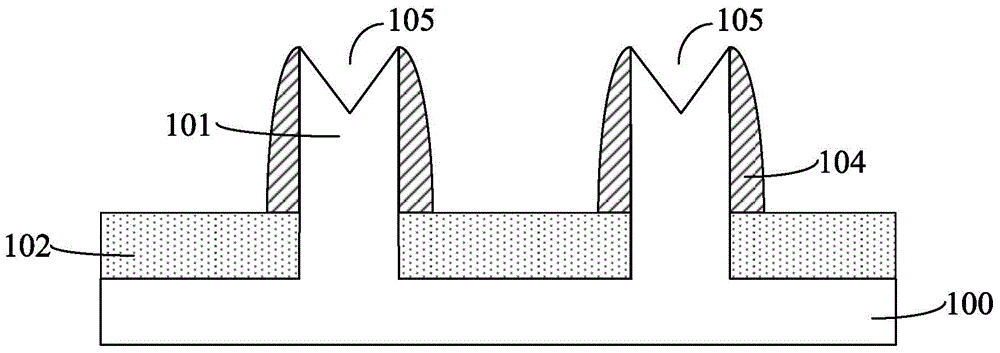

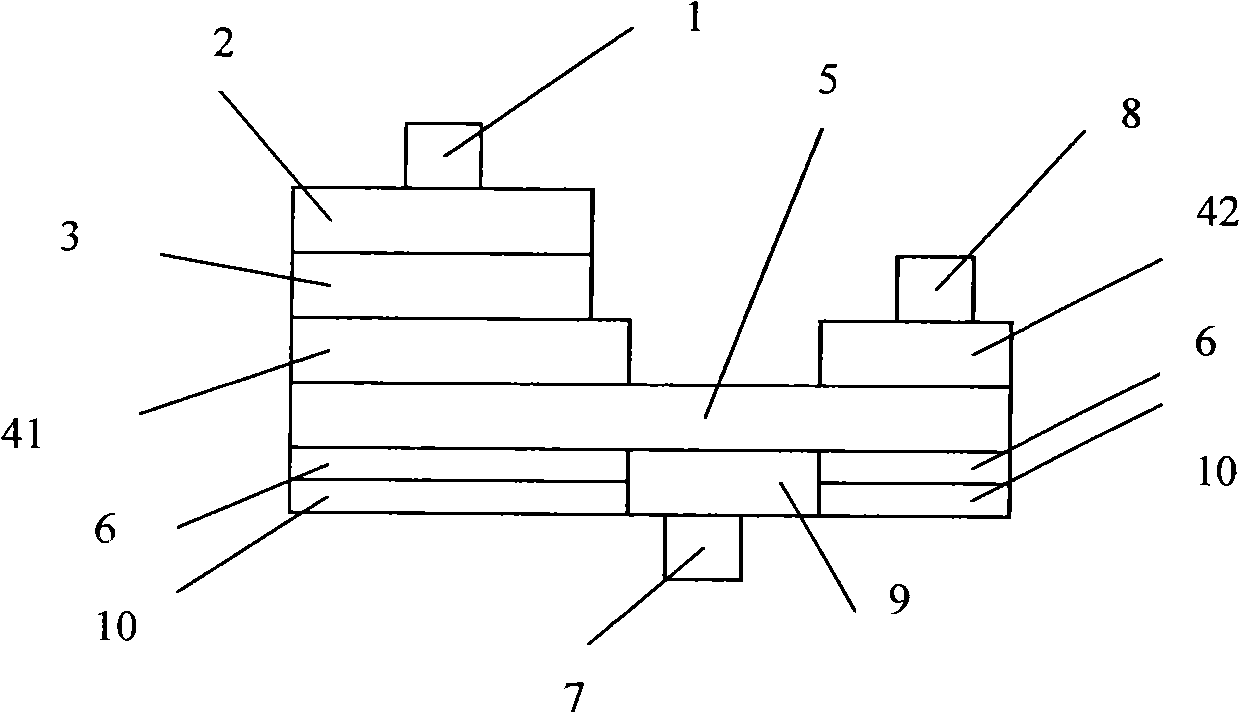

Enhanced GaN-based high electron mobility transistor and preparation method thereof

ActiveCN105845723ARaise the gate threshold voltageOvercoming etch damage is difficult to controlSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricCharge carrier mobility

The invention provides a GaN-based enhanced high electron mobility transistor and a preparation method thereof. The transistor comprises a substrate GaN buffer layer, a barrier layer and a passivation layer from the bottom to the top. The transistor further comprises a gate groove which runs through the high temperature resistance passivation layer, the barrier layer and a two-dimensional electron gas layer on the interface of the barrier layer and the GaN buffer layer and extends into the GaN buffer layer. A P-type gate dielectric layer grows in the gate groove. The gate of the transistor is located above the P-type gate dielectric layer. The source and the drain of the transistor are respectively located on both sides of the GaN buffer layer. According to the invention, higher gate threshold voltage can be acquired; and the defects of difficult control of etching damage and damaged conduction channel carrier mobility caused by over-etching can be overcome.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

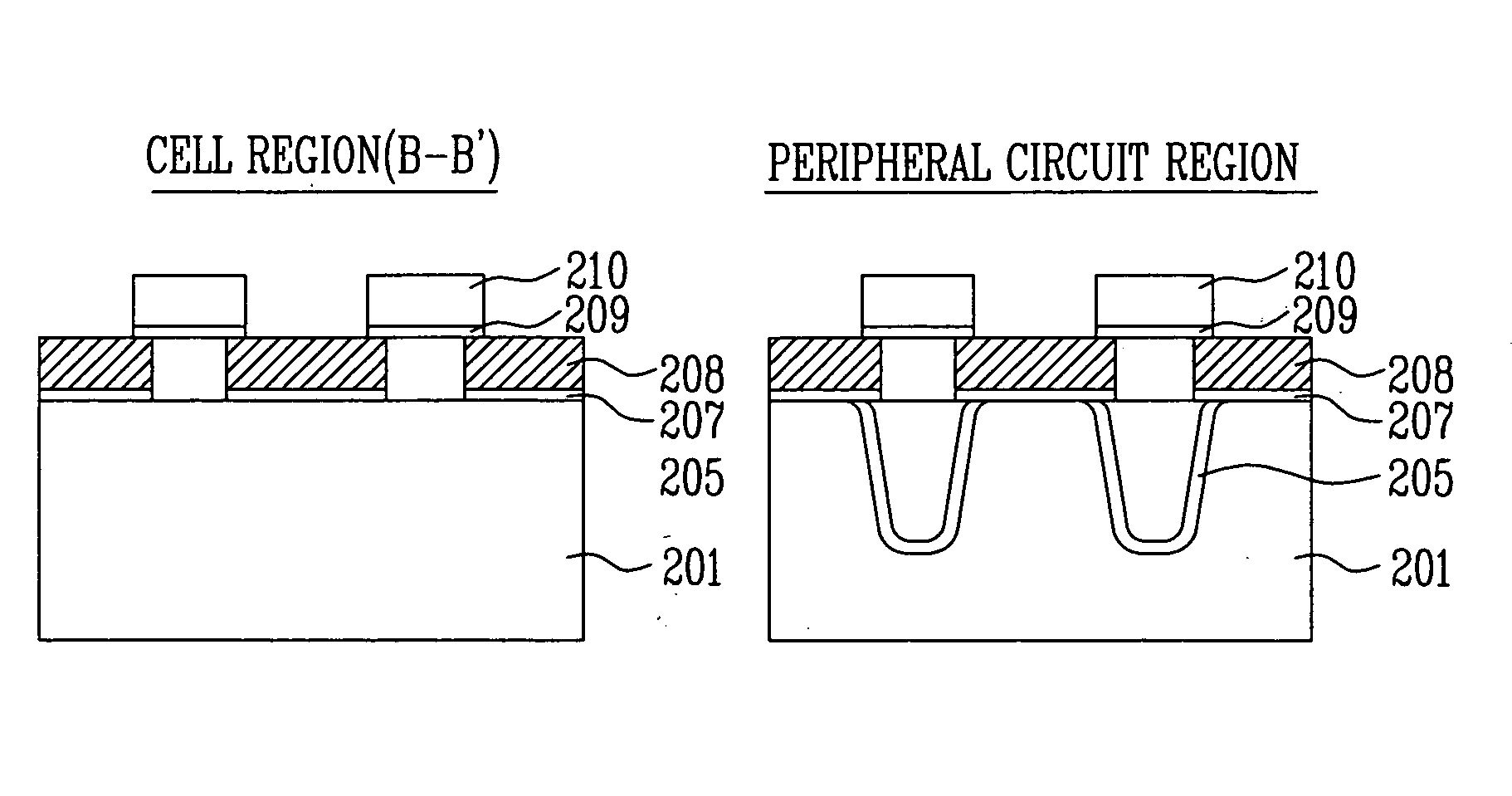

Semiconductor device and method of manufacturing the same

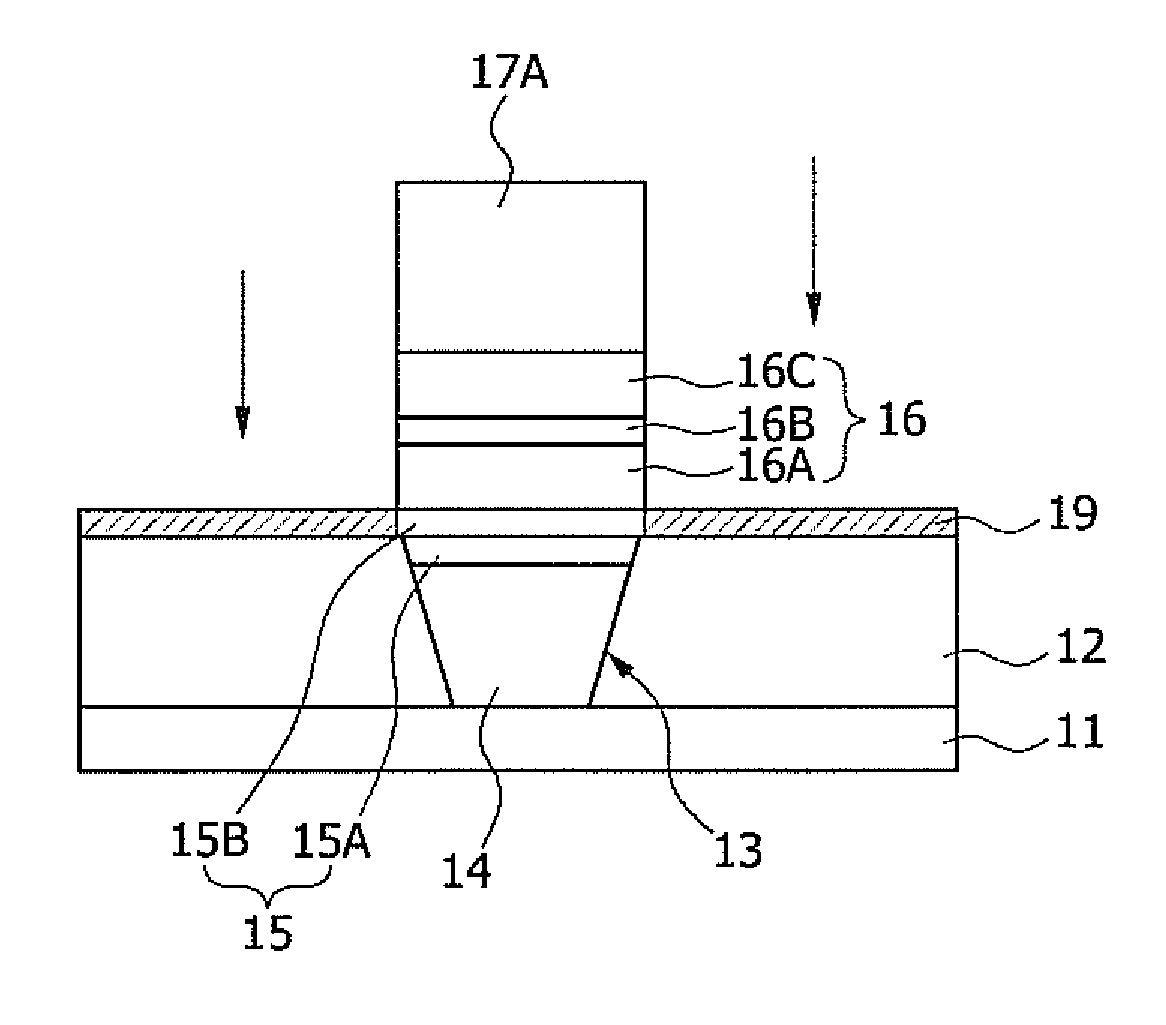

InactiveUS20060081906A1Gate height is minimizedEasy to processSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialCell region

Disclosed herein is a semiconductor device and method of manufacturing the same. A step between a memory cell formed in a cell region and a transistor formed in a peripheral circuit region is minimized, and the height of a gate in the memory cell is minimized. Accordingly, subsequent processes are facilitated and the electrical property of the device is thus improved.

Owner:STMICROELECTRONICS SRL +1

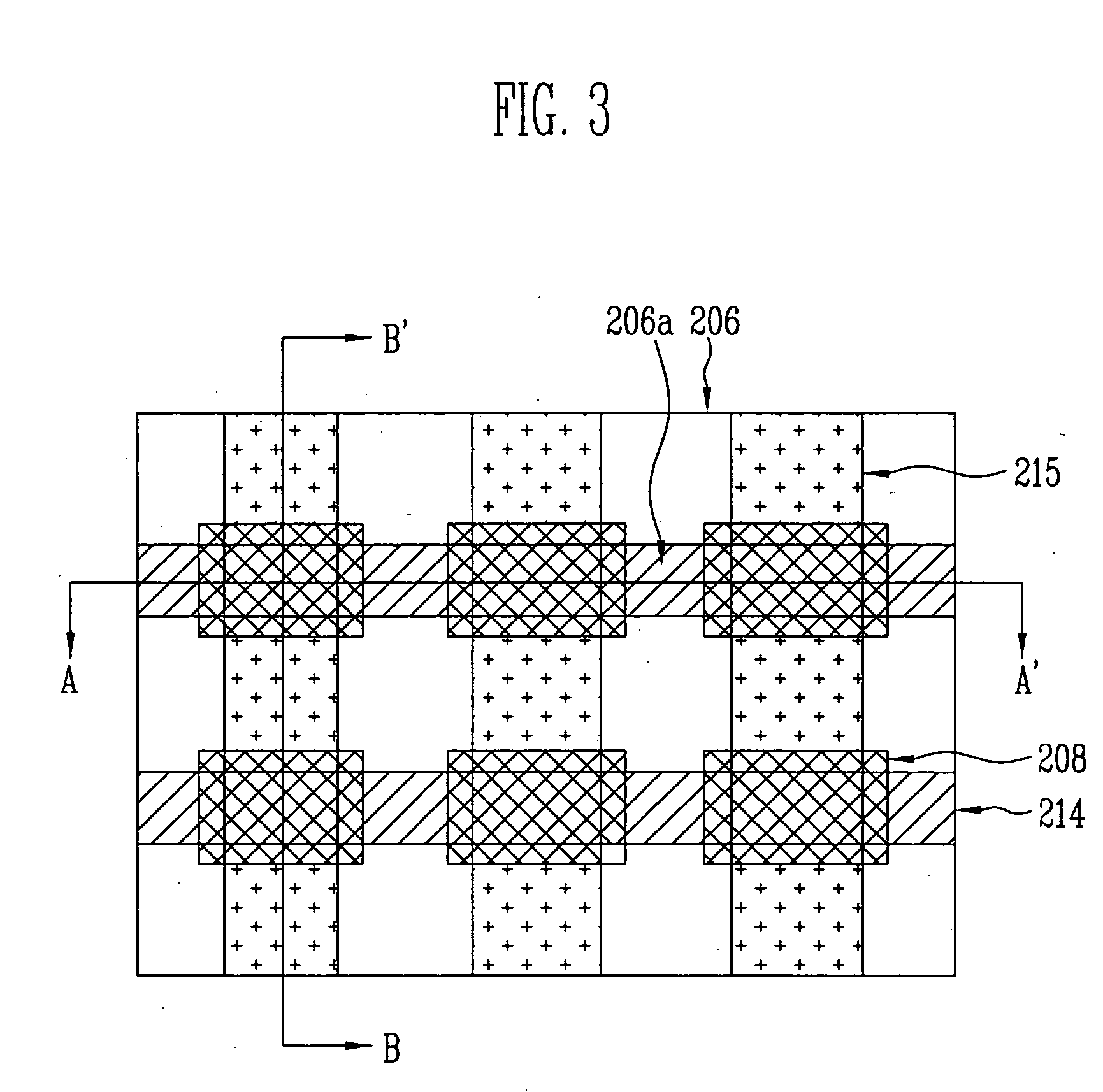

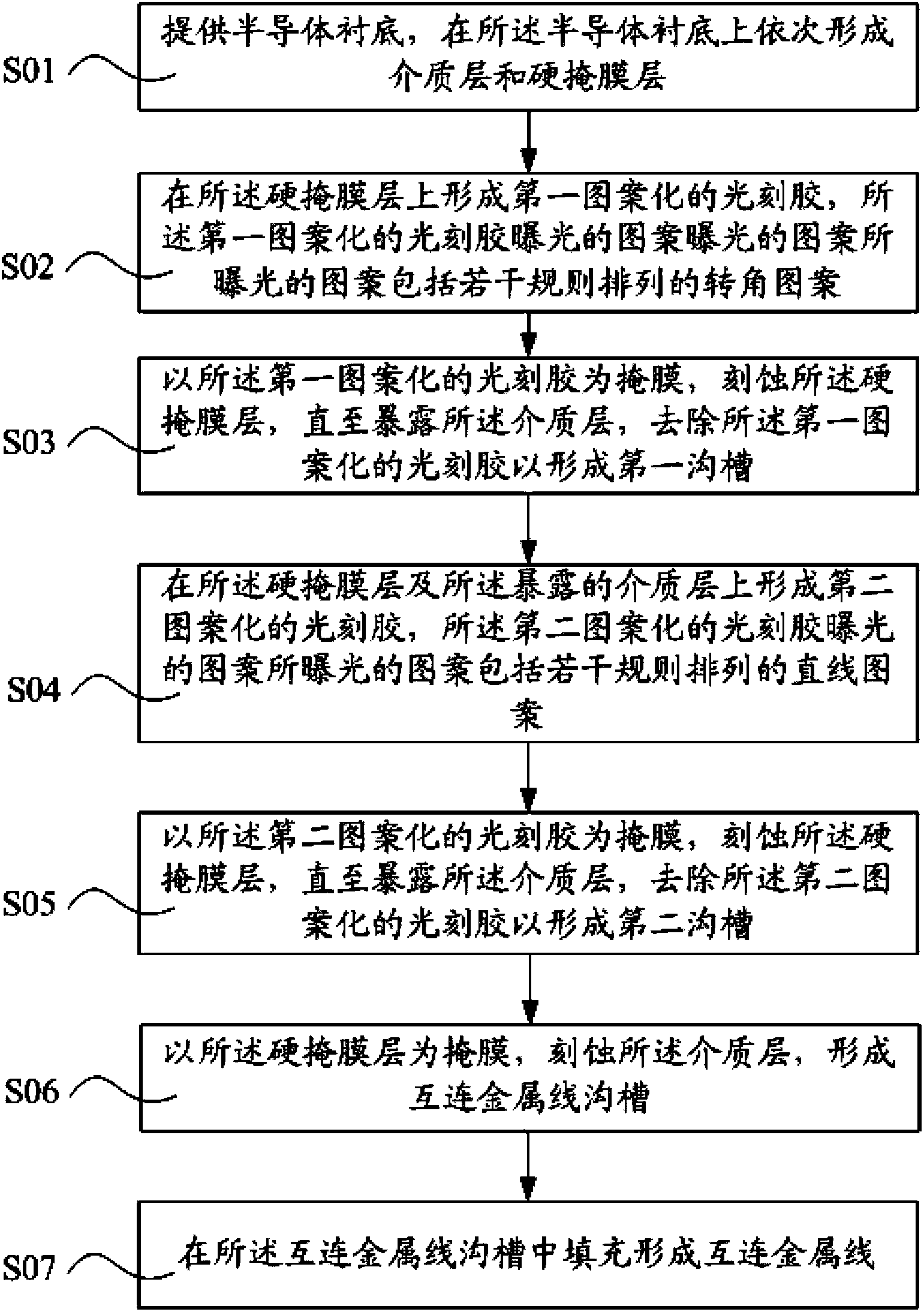

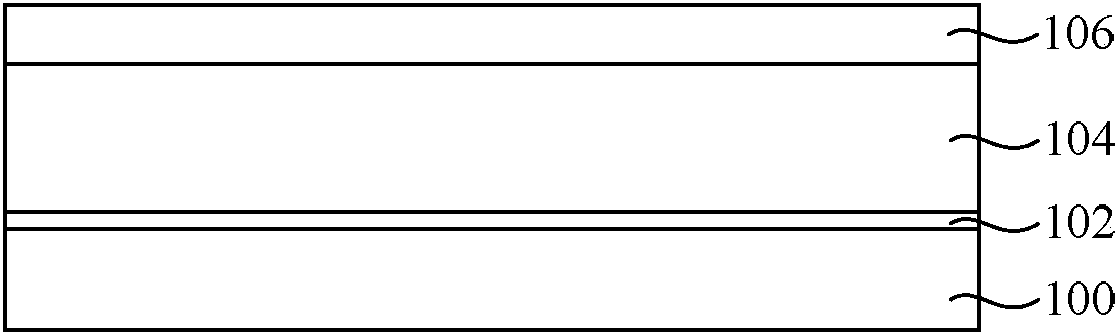

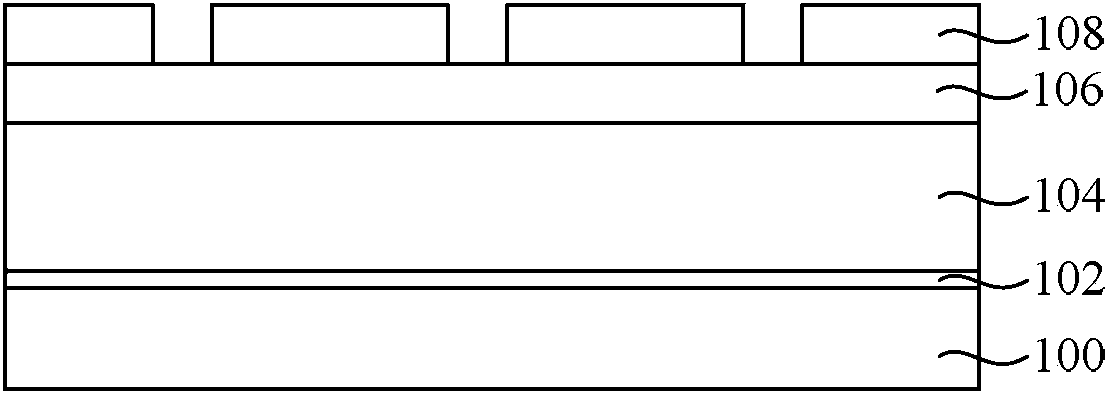

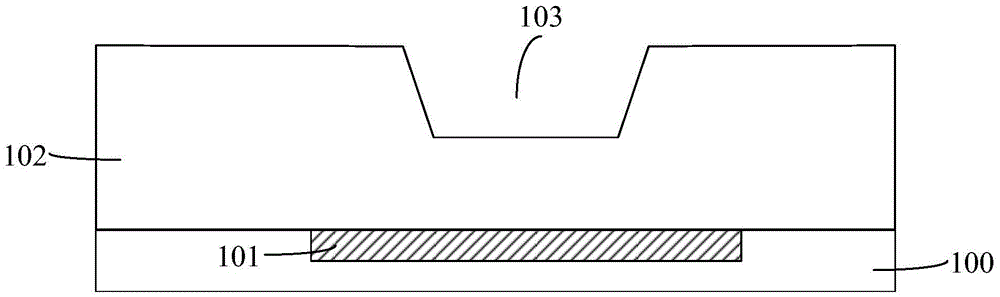

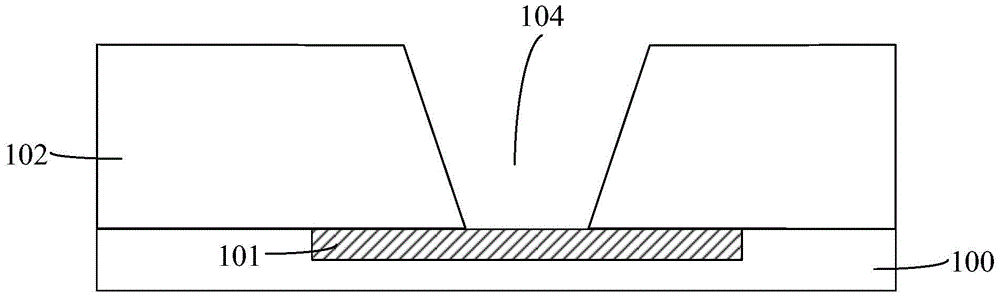

Double patterning method in back-end-of-line

ActiveCN103426810AEasy alignment error sizeImprove alignment accuracySemiconductor/solid-state device manufacturingOriginals for photomechanical treatmentResistOptoelectronics

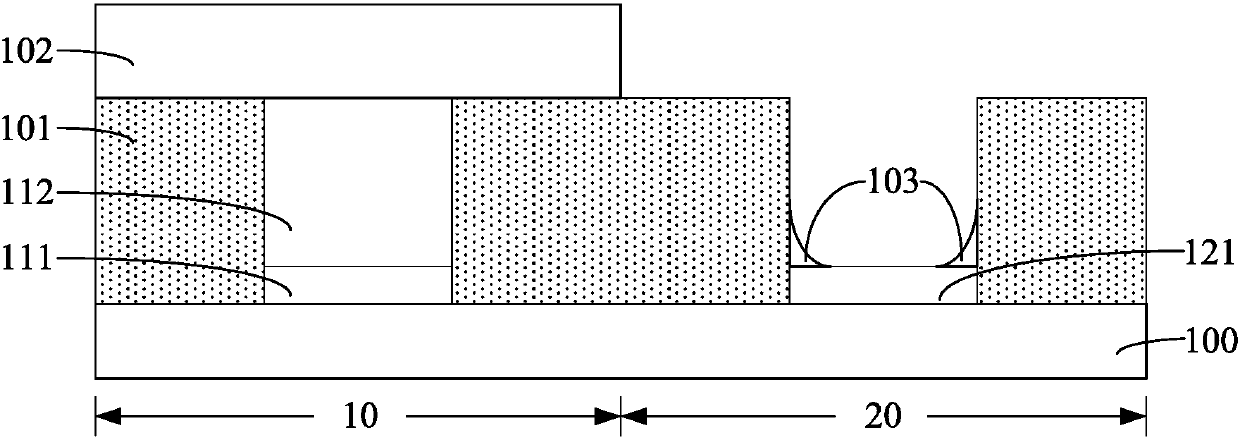

The invention provides a double patterning method in a back-end-of-line. The double patterning method in the back-end-of-line comprises the steps of forming a medium layer and a hard mask layer on a semiconductor substrate in sequence; forming first patterning optical resist, wherein patterns exposed by the first patterning optical resist comprise a plurality of turn angle patterns arranged regularly; etching the hard mask layer to formed a first groove; forming second patterning optical resist, wherein patterns exposed by the second patterning optical resist comprise a plurality of straight line patterns arranged regularly; etching the hard mask layer to form a second groove; etching the medium layer to form interconnected metal wire grooves with the hard mask layer taken as a mask; carrying out stuffing on the interconnected metal wire grooves to form interconnected metal wires. According to the double patterning method in the back-end-of-line, error size alignment can be carried out more easily, and therefore alignment precision in the back-end-of-line with the turn angle patterns can be improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

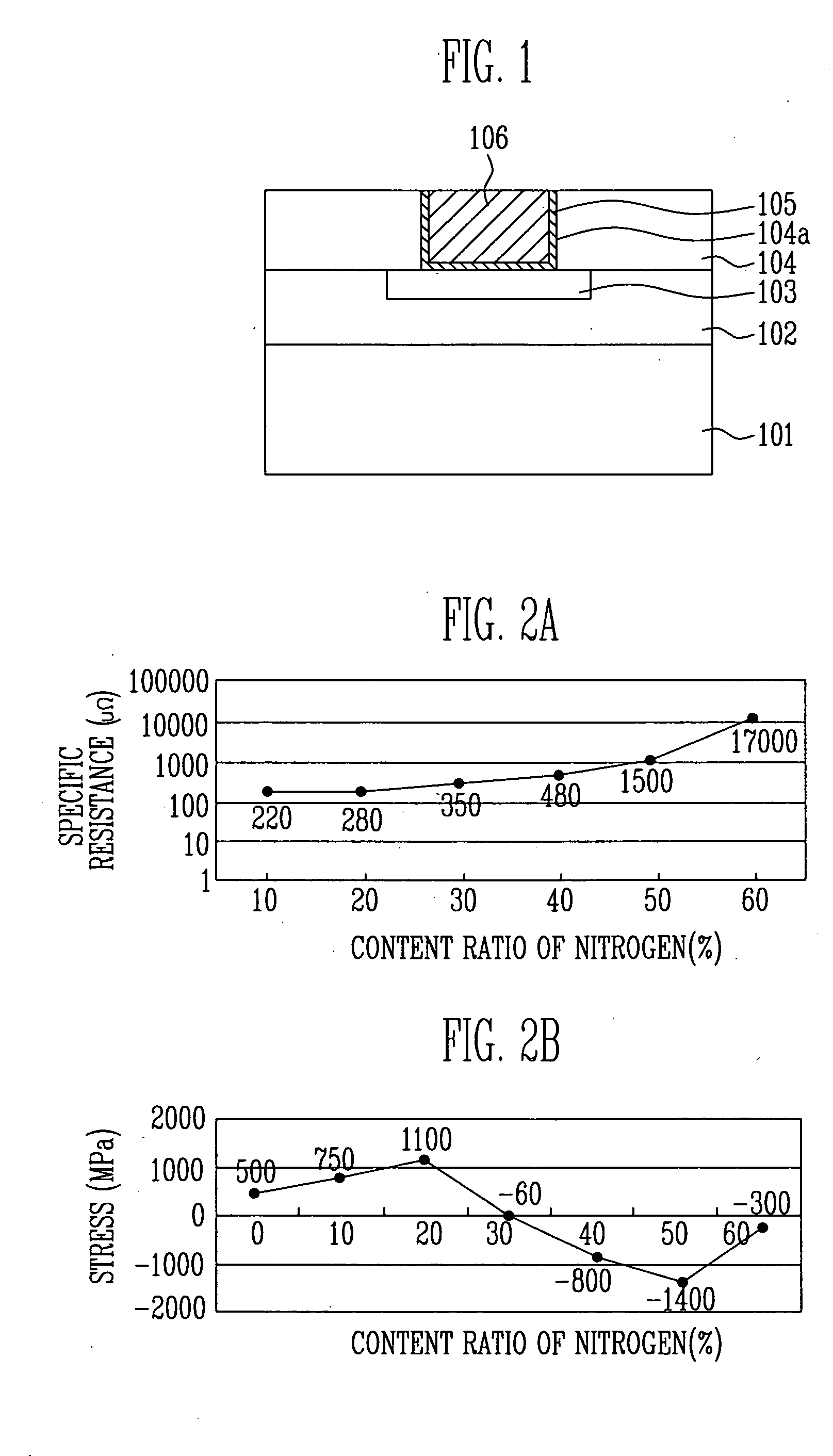

Transistor having a metal nitride layer pattern, etchant and methods of forming the same

ActiveUS20100019292A1Reduce etch damageTransistorSemiconductor/solid-state device manufacturingNitrideOxidizing agent

Owner:SAMSUNG ELECTRONICS CO LTD

Method for fabricating semiconductor device

ActiveUS20130037895A1Reduce etch damageAvoid failureMagnetic-field-controlled resistorsGalvano-magnetic material selectionOxygenSemiconductor

In a method for fabricating a semiconductor device, a conductive layer is formed on a substrate, where the substrate has a bottom layer formed thereon. A magnetic tunnel junction layer is formed on the conductive layer. The magnetic tunnel junction layer is patterned using an etching gas containing oxygen. An insulating layer is formed by oxidizing the conductive layer exposed outside the patterned magnetic tunnel junction layer using the etching gas.

Owner:SK HYNIX INC

Test structures of a semiconductor device and methods of forming the same

InactiveUS20090020756A1Reduce etch damageReduce areaSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsEngineeringSemiconductor

A test structure including a transistor, a conductive pattern and a pad unit is provided. The transistor may be formed on a substrate having circuit patterns. The conductive pattern is electrically connected to the transistor. The conductive pattern may be used in aligning the circuit patterns and / or sensing plasma damage to the semiconductor device. The conductive pattern may be used in reducing etching damage to the circuit patterns and sensing plasma damage to the semiconductor device. The pad unit is electrically connected to the transistor, and provides electrical signals to the transistor. The conductive pattern may serve as an antenna pattern and / or an align / overlay pattern or a dummy pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

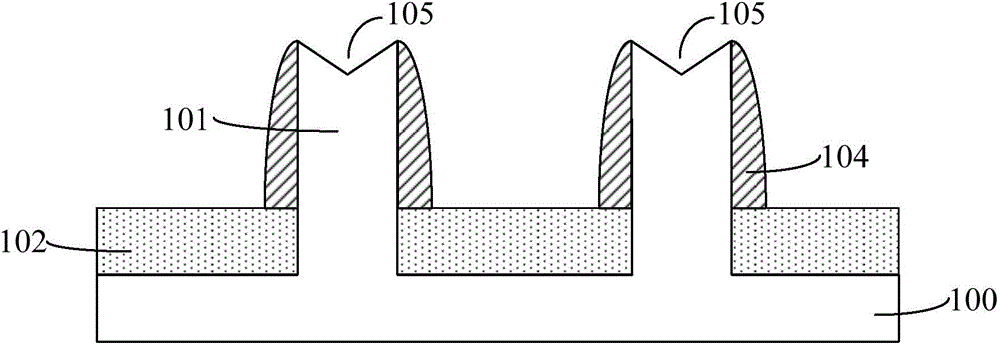

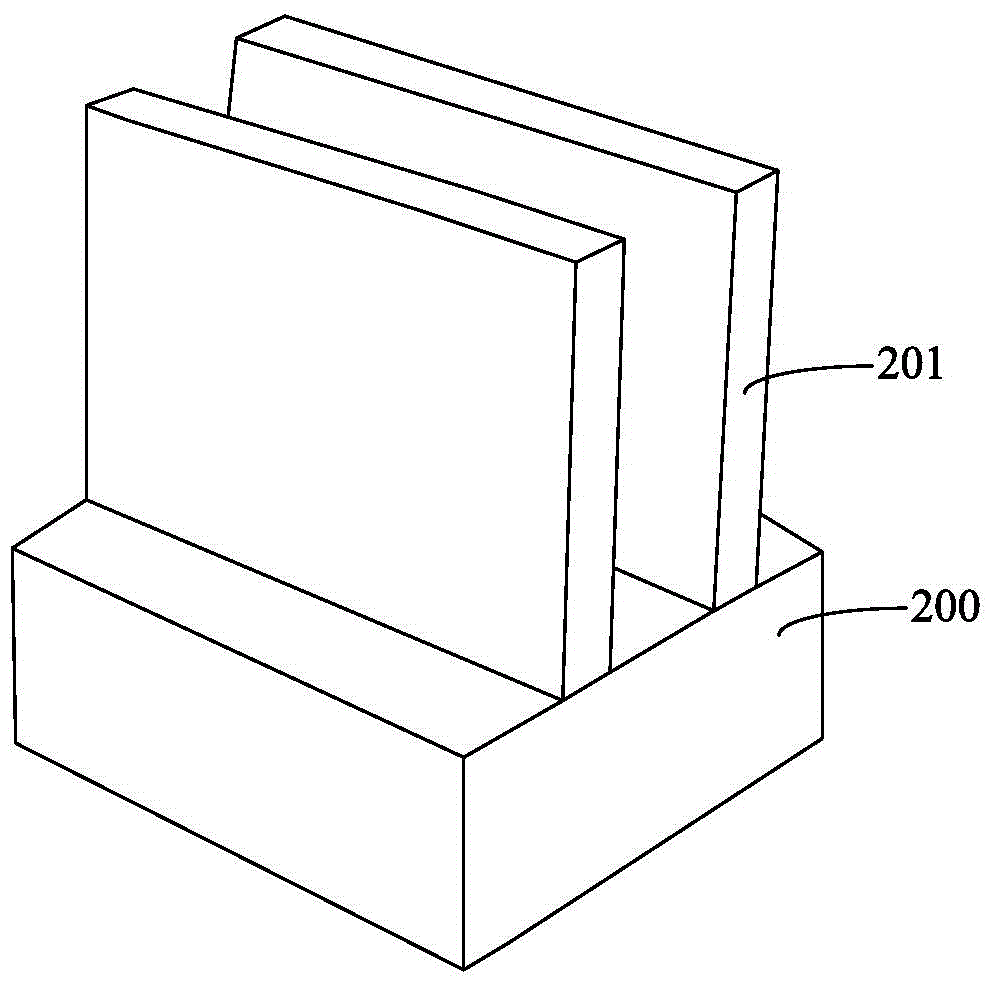

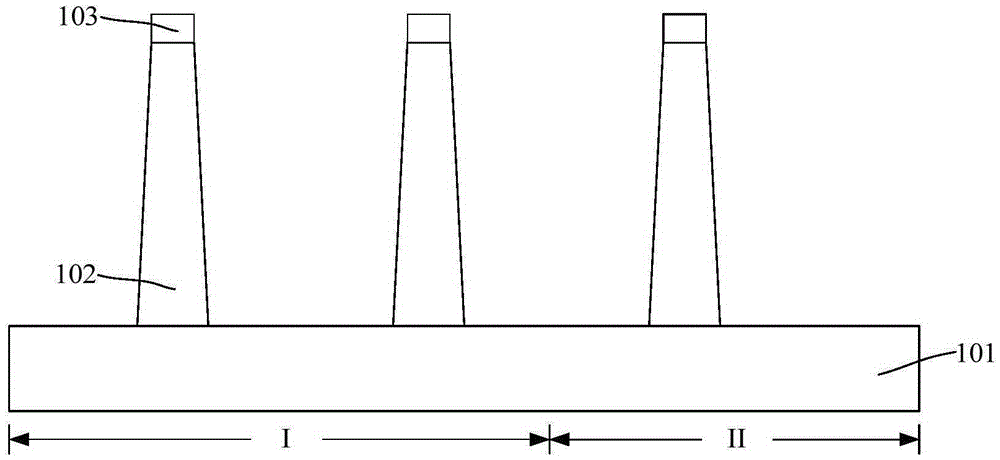

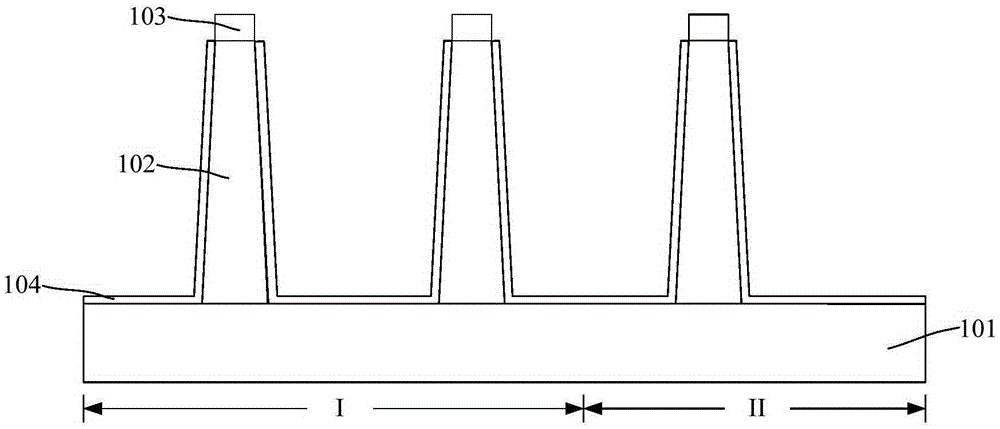

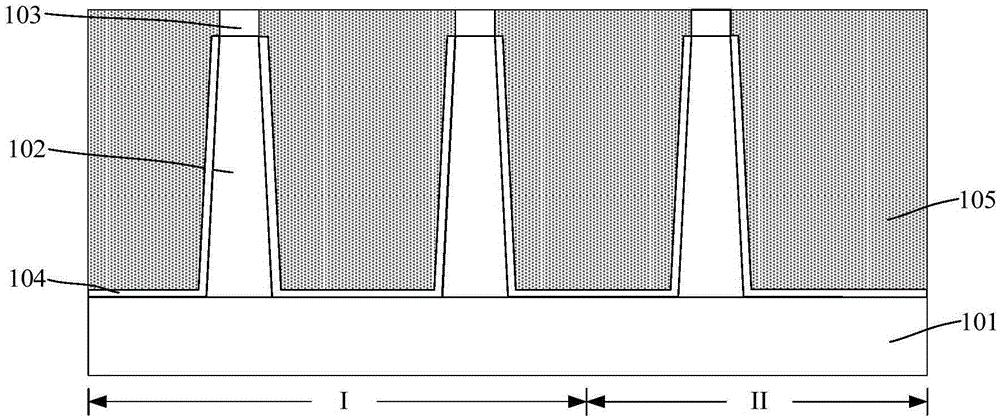

Fin-type field effect transistor forming method

ActiveCN105719969AImprove electrical performanceUniform etch rateSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingElectrical performance

The invention discloses a fin-type field effect transistor forming method, and the method comprises the steps: providing a substrate, wherein the surface is provided with a plurality of separated fin parts; forming a separation layer on the surface of the substrate, wherein the top of the separating layer is lower than the top of the fin parts, and covers the surface of a part of side walls of the fin parts; forming a side wall layer covering the surfaces of the side walls of the fin parts, and exposing the top surfaces of the fin parts; carrying out the selective nitrogen treatment of the tops of the fin parts, and enabling the fin parts at a certain thickness to be converted into a semiconductor nitridation layer; carrying out the etching of the semiconductor nitridation layer through employing a wet etching method, so as to form openings between the adjacent side wall layers and the remaining fin parts; and placing stress layers in the openings. The method improves the flatness of the bottom of the opening, improves the quality of the formed stress layers, and optimizes the electrical performances of a fin-type field effect transistor.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Semiconductor device having insulating layer formed through oxidization of electrode

ActiveUS8941195B2Prevent an etching defectReduce etch damageMagnetic-field-controlled resistorsGalvano-magnetic material selectionOxygenTunnel junction

In a method for fabricating a semiconductor device, a conductive layer is formed on a substrate, where the substrate has a bottom layer formed thereon. A magnetic tunnel junction layer is formed on the conductive layer. The magnetic tunnel junction layer is patterned using an etching gas containing oxygen. An insulating layer is formed by oxidizing the conductive layer exposed outside the patterned magnetic tunnel junction layer using the etching gas.

Owner:SK HYNIX INC

Method for manufacturing contact plug

InactiveCN102347270AAvoid damageQuick responseSemiconductor/solid-state device manufacturingMedia layerSemiconductor

The invention provides a method for manufacturing a contact plug. The method comprises the following steps of: providing a semiconductor substrate on which a grid structure and a first interlamination medium layer are formed, wherein the grid structure is flushed with the first interlamination medium layer, and a source and a drain are formed in the semiconductor substrate on two sides of the grid structure; etching the first interlamination medium layer to form a first contact hole which is used for exposing the source and the drain; filling a first metal layer into the first contact hole; forming a second interlamination medium layer on the first interlamination medium layer; etching the second interlamination medium layer to form a second contact hole, wherein the position of the second contact hole corresponds to the position of the first contact hole; and filling a second metal layer into the second contact hole, wherein the resistivity of the second metal layer is smaller than that of the first metal layer; and the second metal layer in the second contact hole and the first metal layer in the first contact hole form the contact plug together. The contact plug manufactured by using the method has small resistance.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

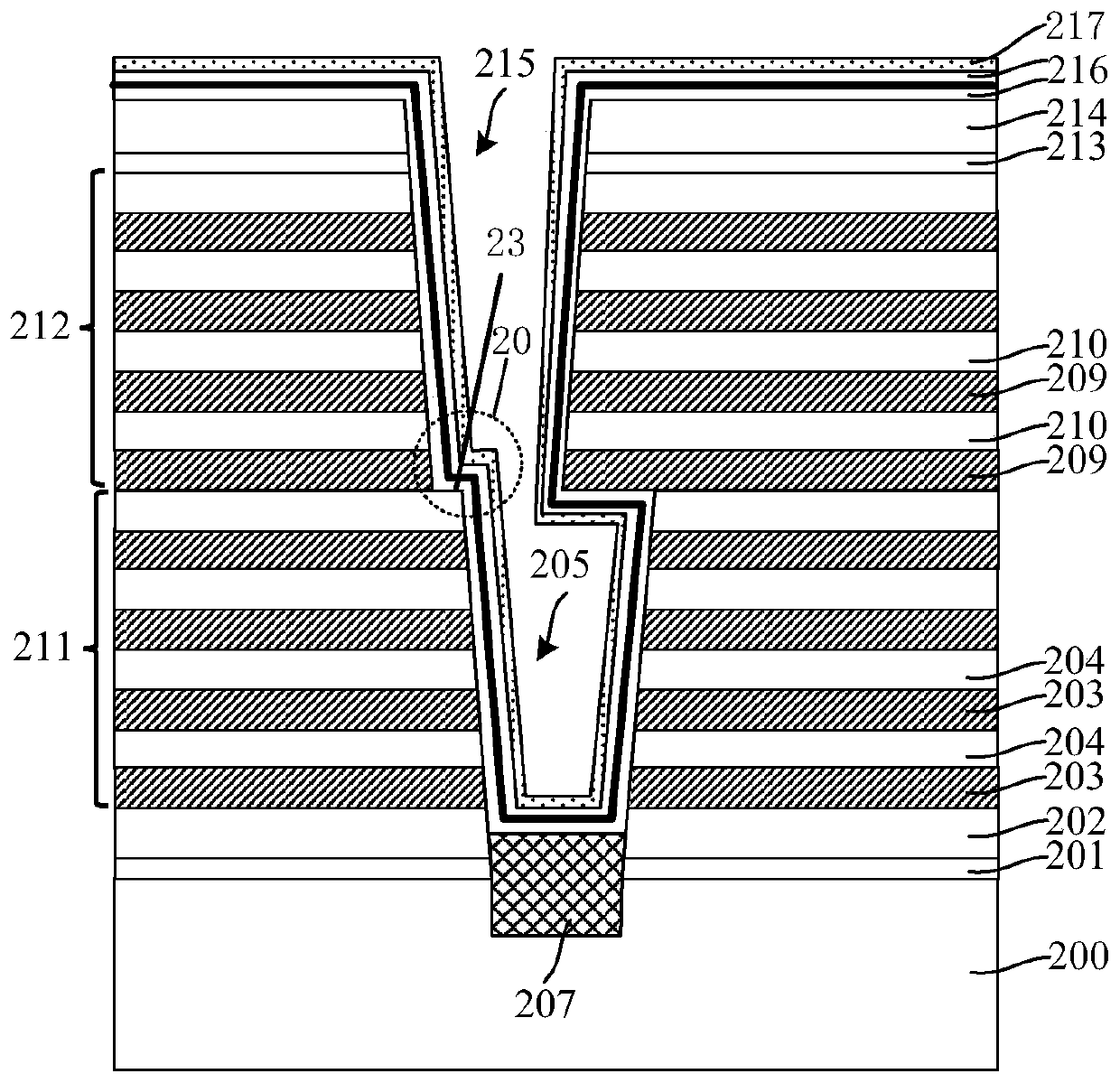

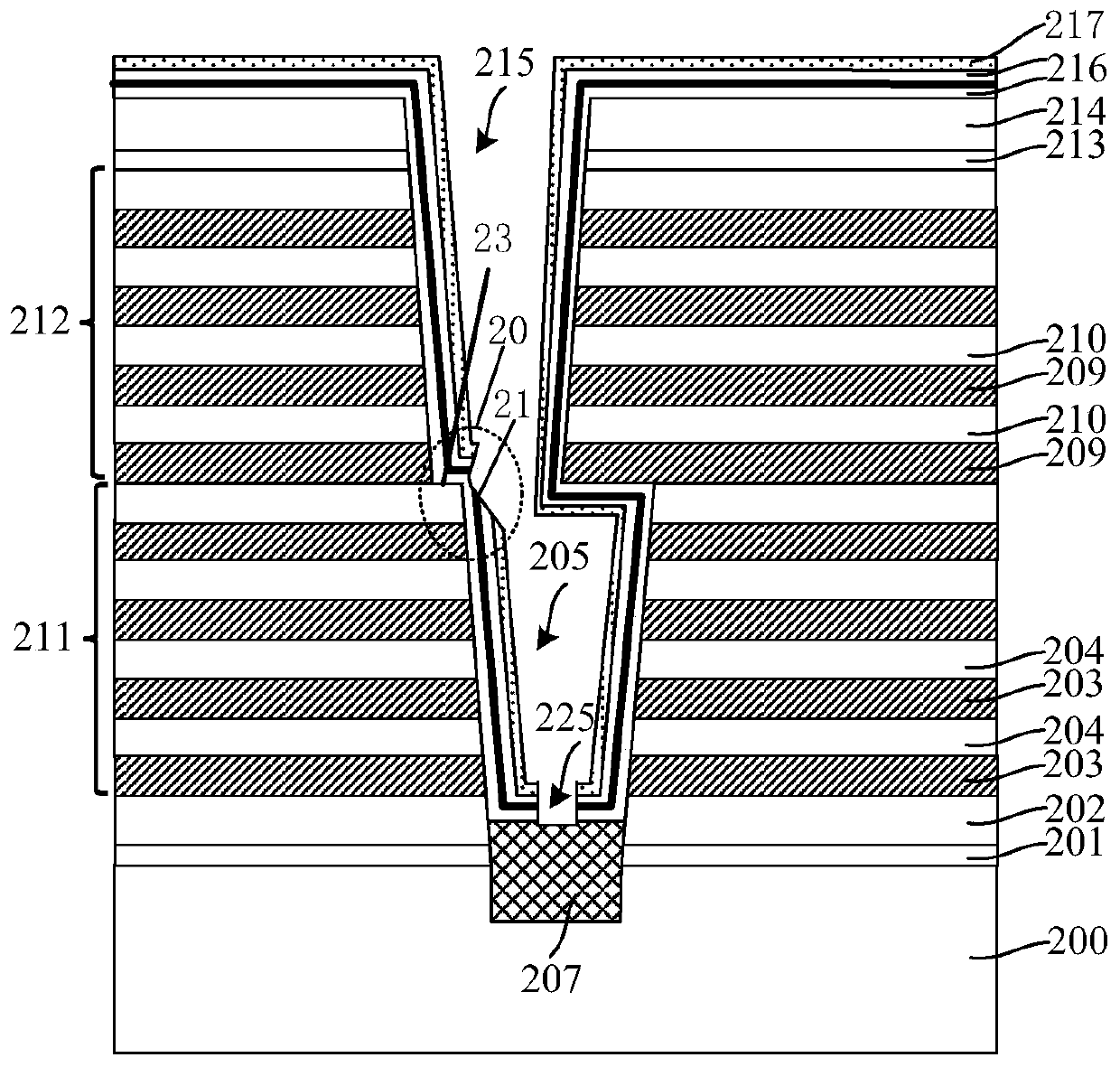

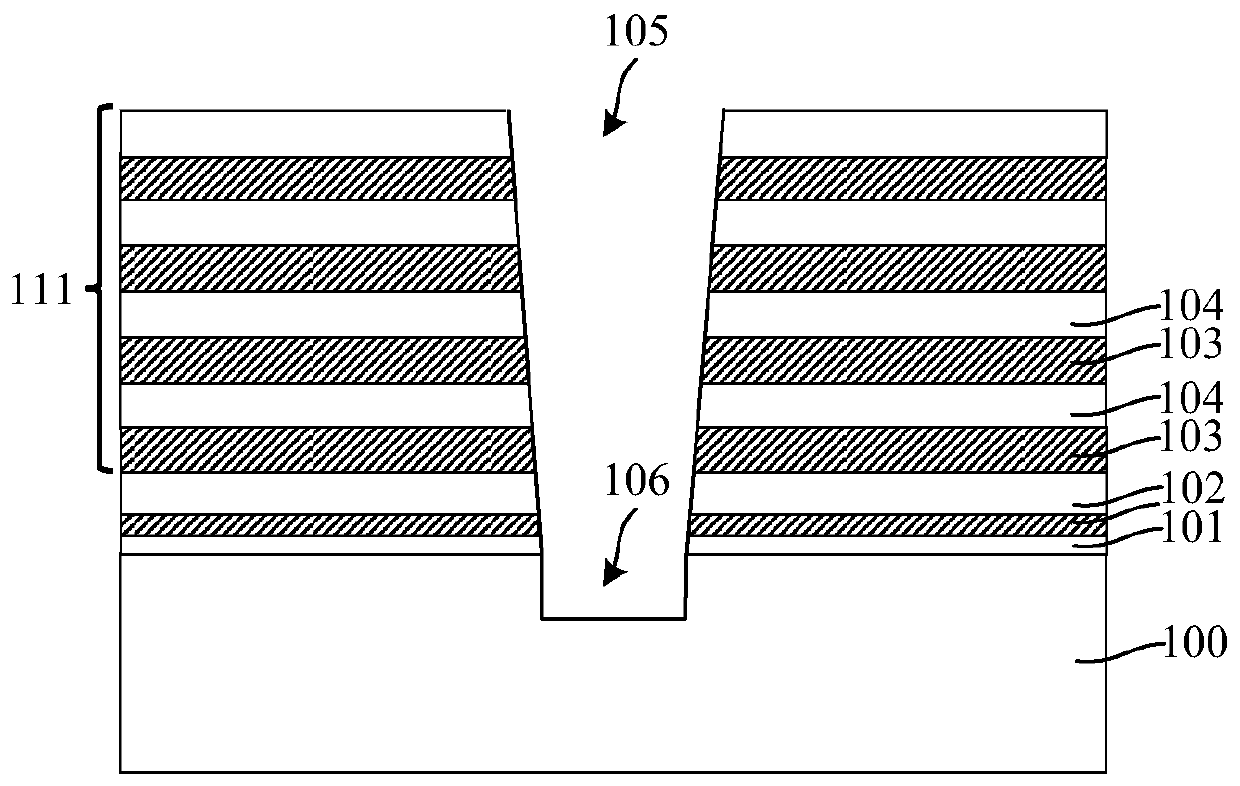

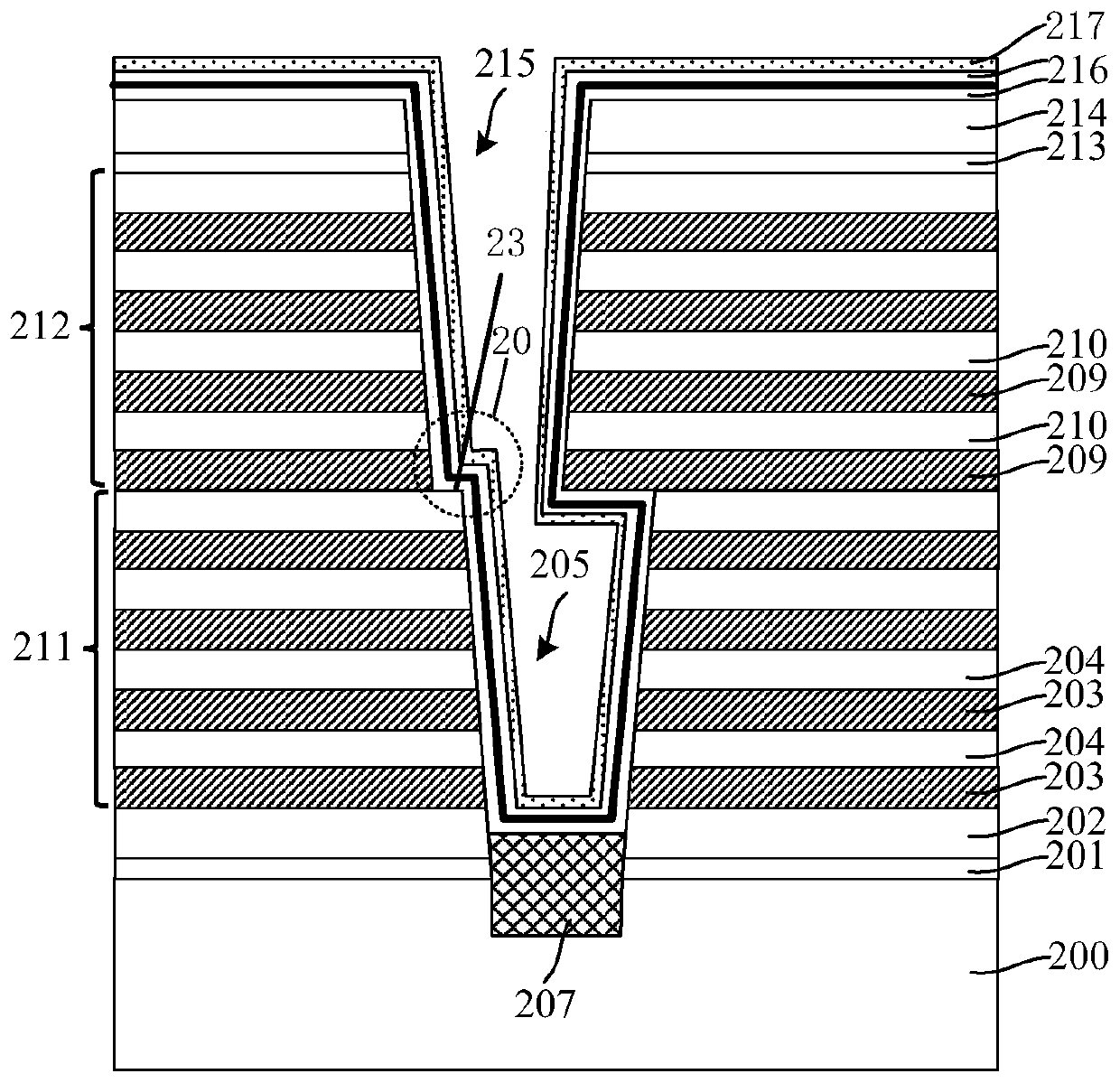

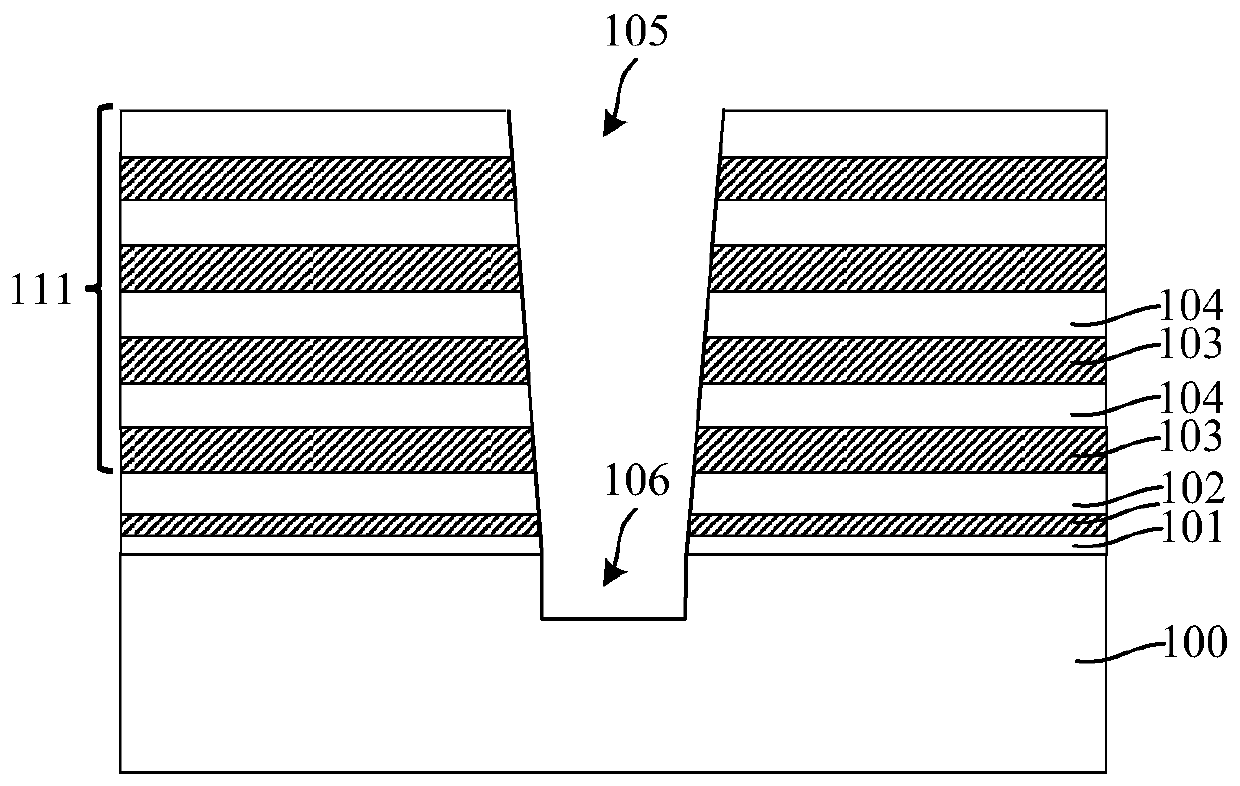

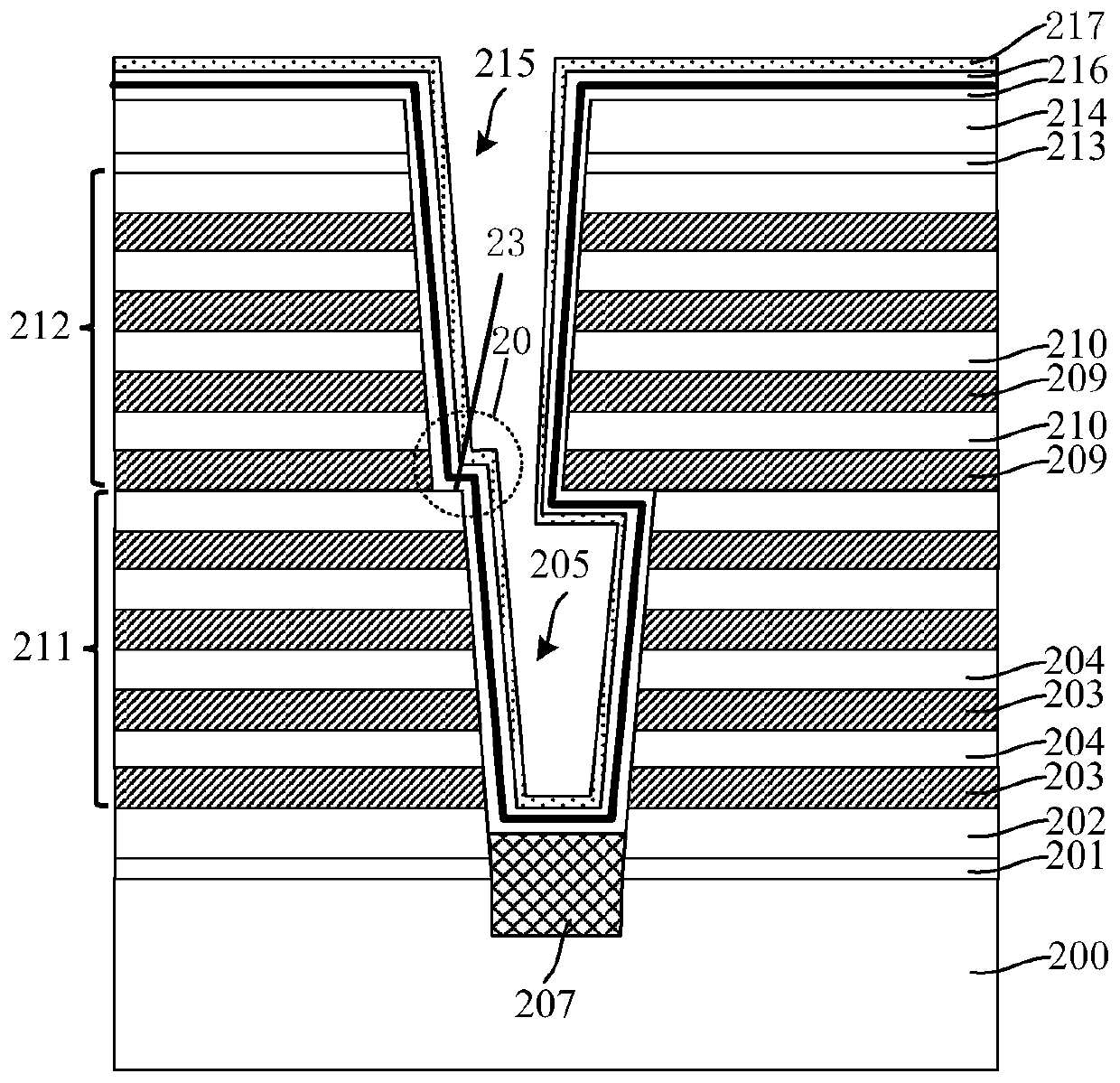

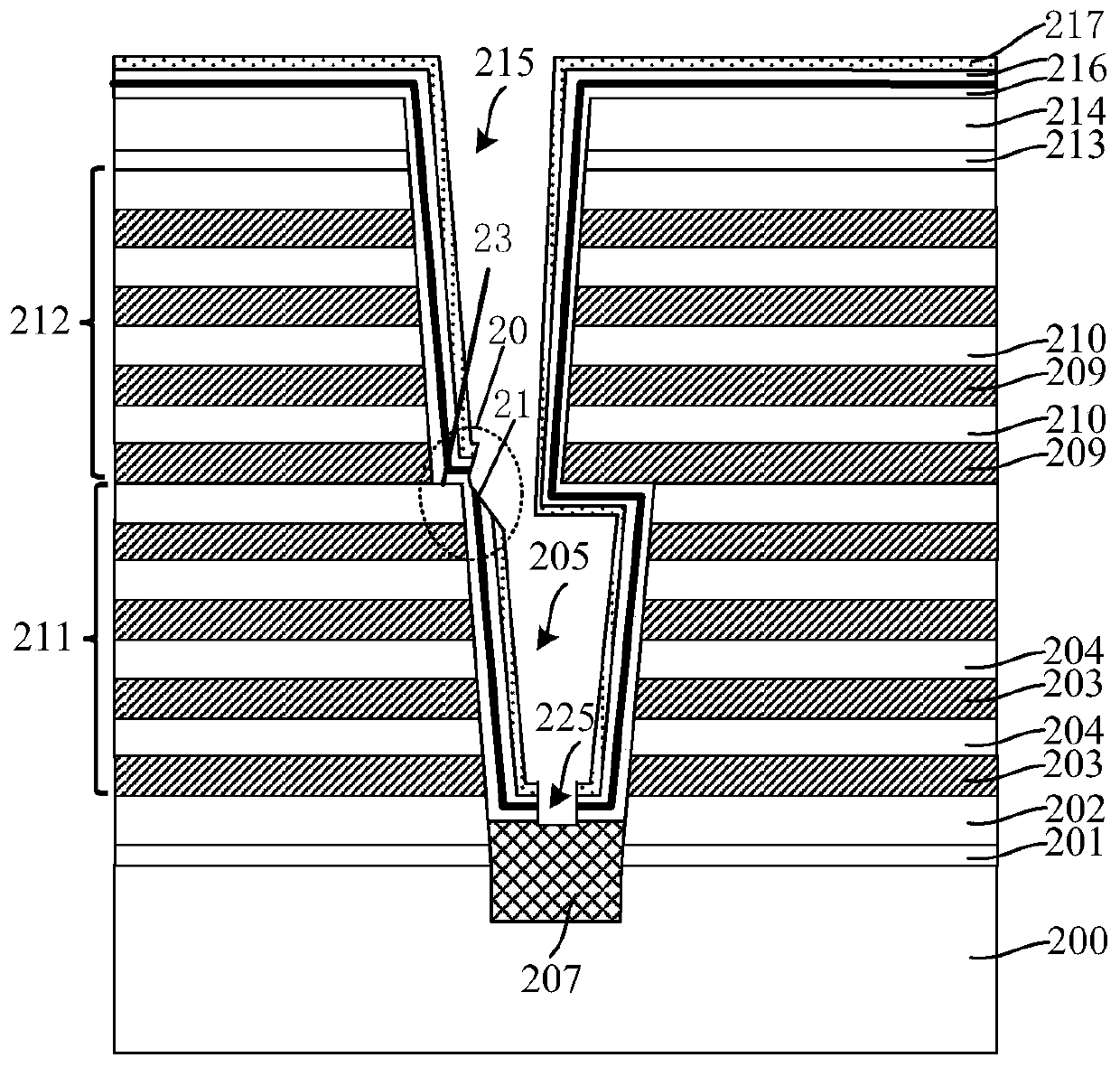

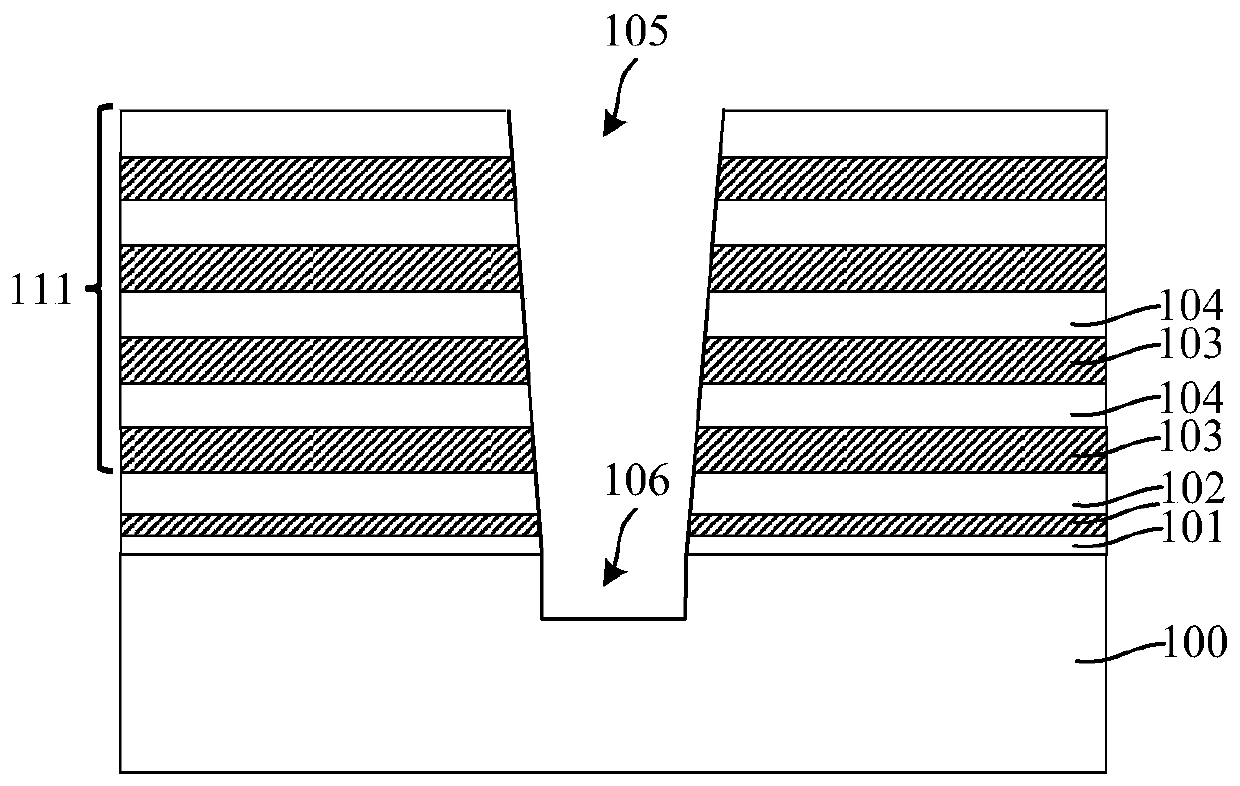

Forming method for 3D NAND memory

ActiveCN109904169AAvoid failureAvoid etch damageSolid-state devicesSemiconductor devicesEtchingComputer science

A forming method for a 3D NAND memory comprises the following steps: providing a semiconductor substrate, wherein stack structures are formed on the semiconductor substrate, each stack structure comprises a plurality of sacrificial layers and a plurality of isolating layers which are alternately stacked, the stack structures are respectively provided with a first channel hole and a second channelhole which are communicated with each other, the second channel hole has an alignment offset relative to the first channel hole, a step is formed at the junction of the first channel hole and the second channel hole, and the first channel hole is filled with a sacrificial material layer; after a side wall is formed, carrying out etching-back to remove the sacrificial material layer with a part ofthe thickness; carrying out etching on the step, so that the gradient of the step is reduced; forming charge storage layers on the side walls and at the bottoms of the first channel hole and the second channel hole; forming channel hole sacrificial layers on the charge storage layers; and sequentially carrying out etching on the channel hole sacrificial layer and the charge storage layer at the bottom of the first channel hole, so that an opening is formed. The method provided by the invention has the advantages that the charge storage layer at the step can be prevented from being broken or damaged during the etching, so that failure of the memory can be avoided.

Owner:YANGTZE MEMORY TECH CO LTD

HEMT device and manufacturing method of HEMT device

ActiveCN104465746AReduce etch damageReducing requirements for overlay accuracySemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringPhotolithography

Owner:DYNAX SEMICON

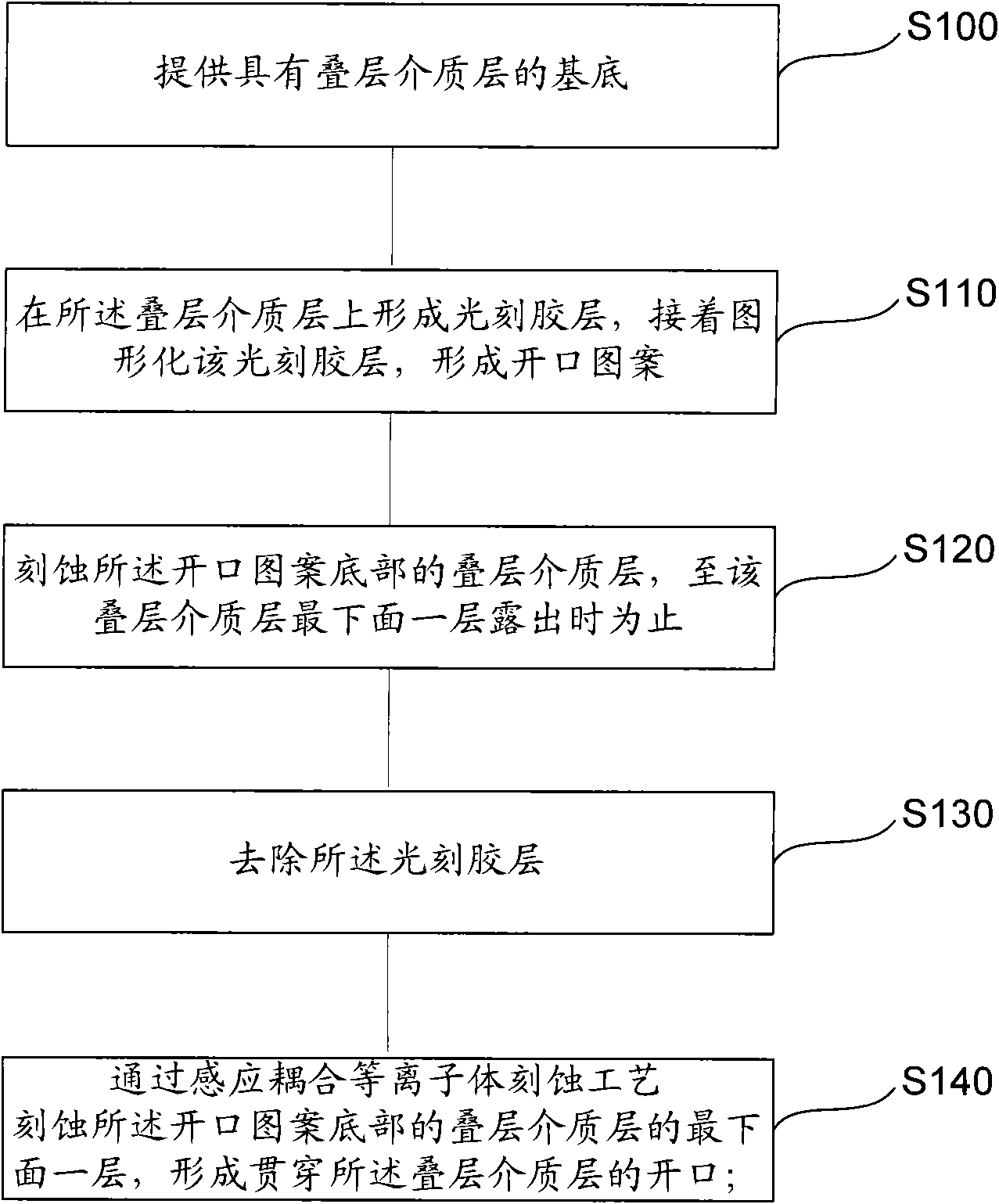

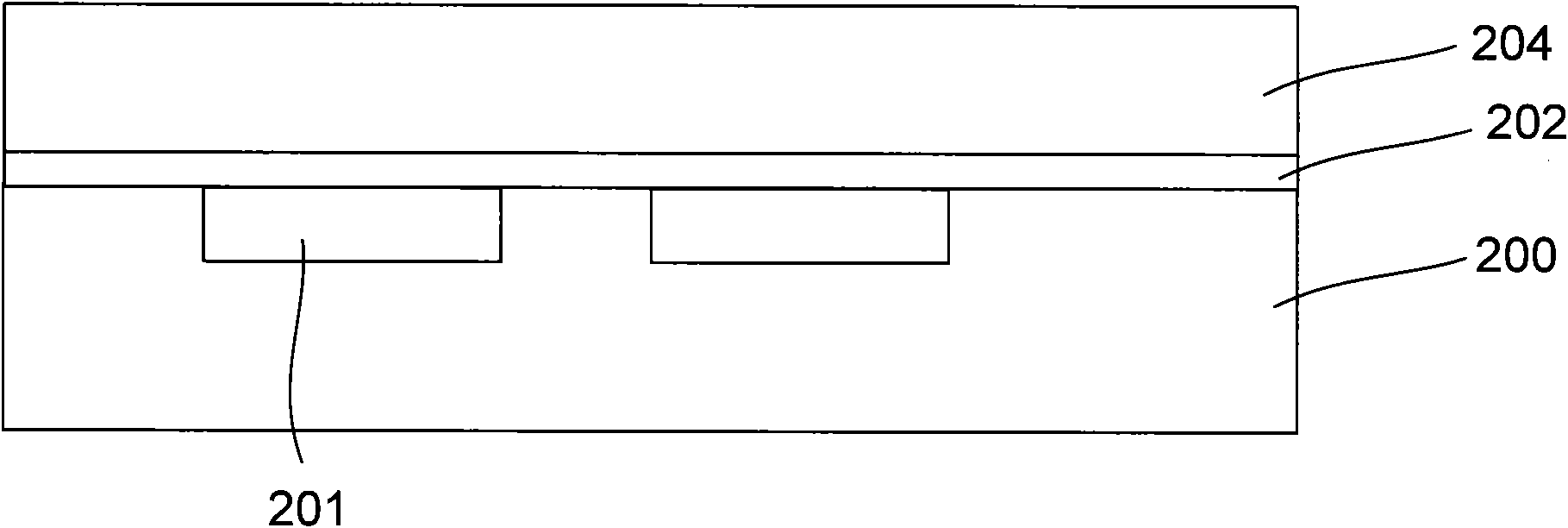

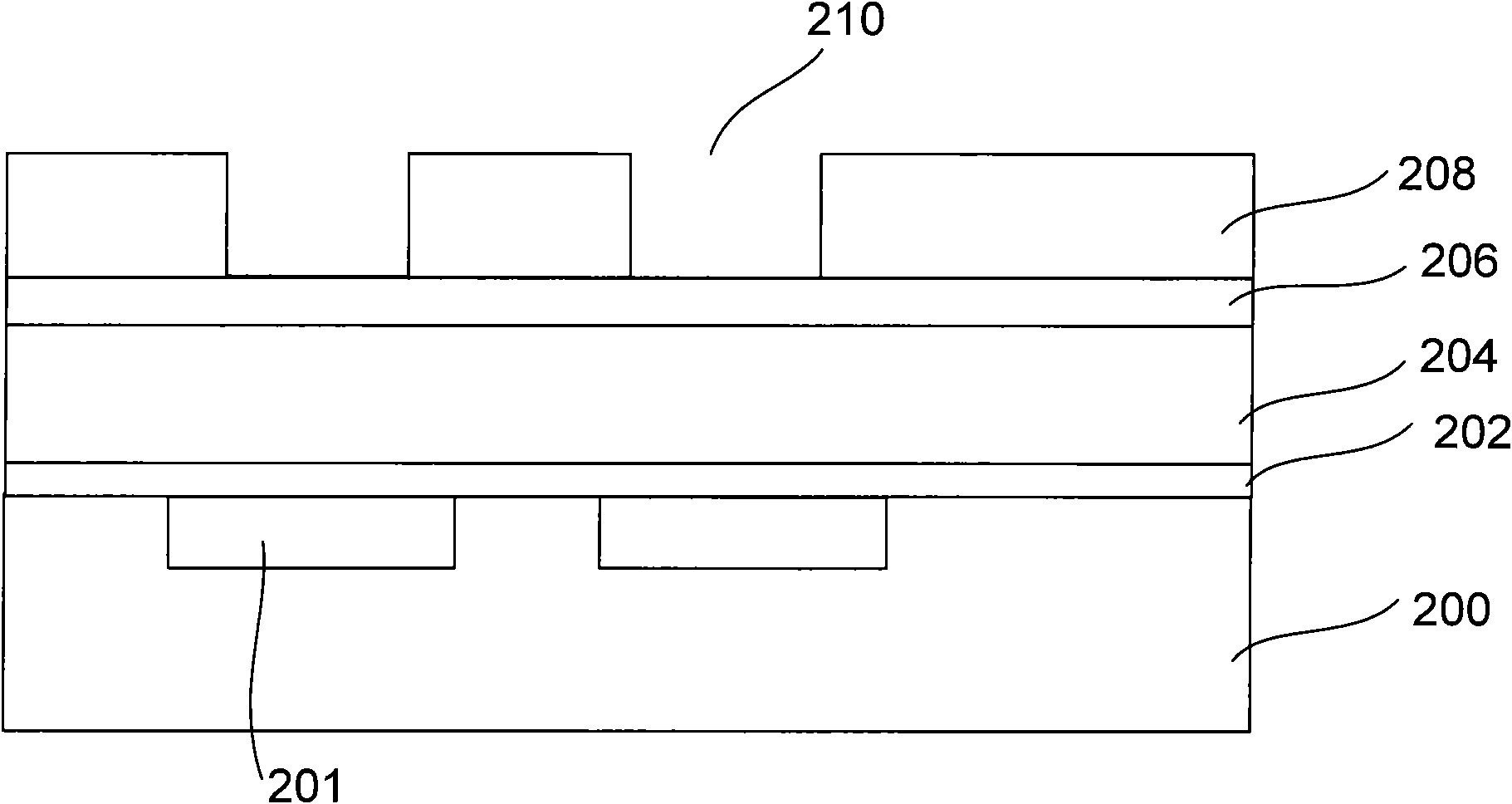

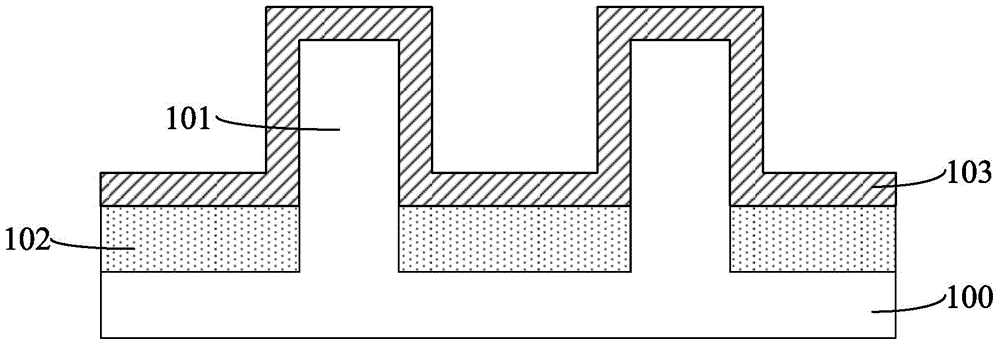

Method for etching opening in laminated dielectric layer

InactiveCN101593721ALow powerReduce etch damageSemiconductor/solid-state device manufacturingInductive couplingDielectric layer

A method for etching an opening in laminated dielectric layers comprises: providing a substrate with laminated dielectric layers; forming a photoetching adhesive layer on the laminated dielectric layers, imaging the photoetching adhesive layer to form an opening pattern; etching the laminate dielectric layers at the bottom of the opening pattern and not stopping until the downmost layer in the laminate dielectric layers is exposed; removing the photoetching adhesive layer; etching the downmost layer in the laminated dielectric layers at the bottom of the opening pattern; forming an opening penetrating through the laminate dielectric layer; wherein, in the step of etching the downmost layer in the laminate dielectric layer at the bottom of the opening pattern, etching is carried out by inductive coupling of plasma body. The invention can reduce the damage on the opening side wall when the opening is etched in the laminated dielectric layer.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

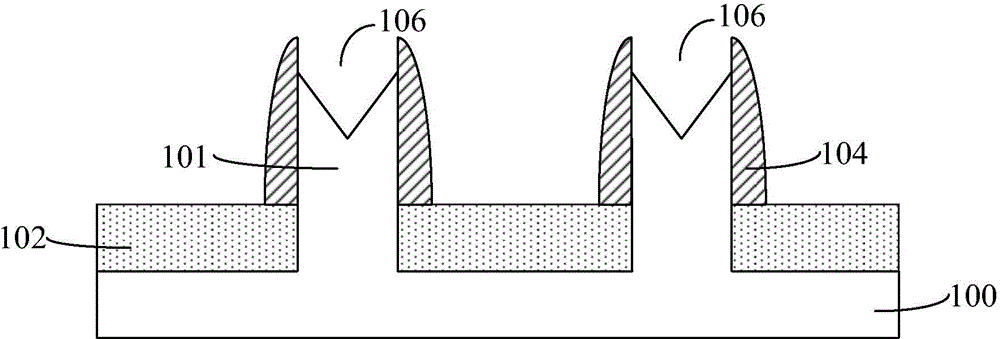

Fin field-effect transistor formation method

ActiveCN105470132AUniform etch rateReduce etch damageSolid-state devicesSemiconductor/solid-state device manufacturingEtchingEngineering

Provided is a fin field-effect transistor formation method which comprises the following steps: providing a substrate, and forming a plurality of independent fin portions on the surface of the substrate; forming an isolating layer on the surface of the substrate, the top surface of the isolating layer being lower than the top surface of each fin portion and the isolating layer covering a part of the surfaces of the side walls of the fin portions; forming a barrier layer covering the surface of the isolating layer and the top and side wall surfaces of the fin portions; converting a part of the barrier layer of a certain thickness into a passivation layer through oxidation treatment; etching back the passivation layer to form passivated side walls covering on the surface of the barrier layer on the side wall surfaces of the fin portions; and with the passivated side walls being as a mask, removing the barrier layer on the top surfaces of the fin portions by utilizing a wet etching process, and retaining the barrier layer on the side wall surfaces of the fin portions as barrier side walls. According to the fin field-effect transistor formation method, the quality of a formed stress layer is improved, and meanwhile, growth of the stress layer on the side wall surfaces of the fin portions can be prevented, and performance of a fin field-effect transistor is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

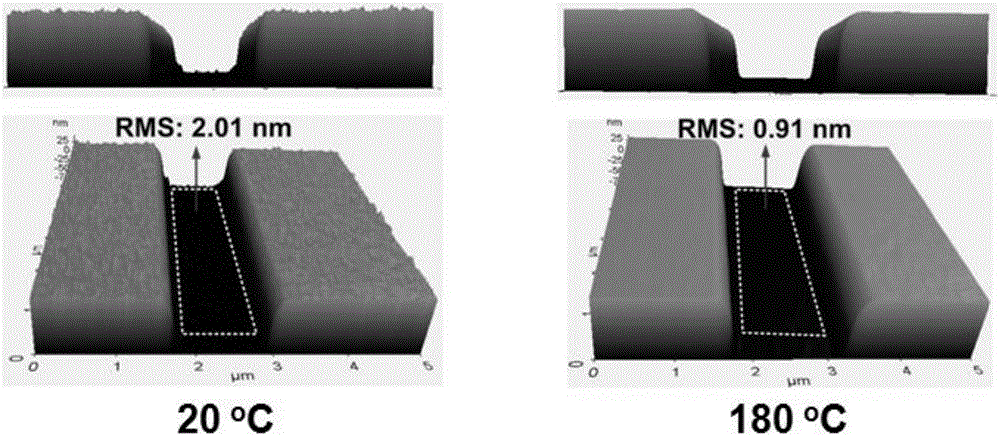

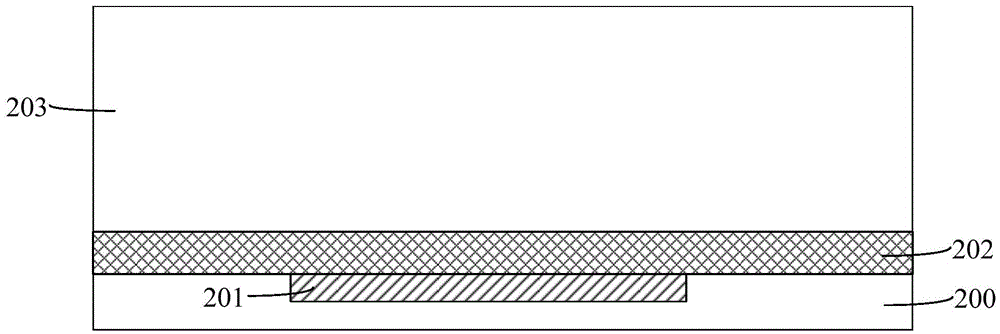

Mask and production method thereof

ActiveCN108624841AReduce thicknessSmall sizeVacuum evaporation coatingSputtering coatingCompound (substance)Engineering

The invention discloses a mask and a production method thereof. The mask comprises a substrate, a mask pattern layer and a sacrificial layer, wherein the substrate comprises a first surface and a second surface opposite to the first surface; a plurality of openings running through the substrate are formed in the substrate; the substrate can be patterned by a semiconductor etching technology; the mask pattern layer is positioned on the first surface; the mask pattern layer comprises adjacent pattern areas and blocked areas; each pattern area is provided with at least one through hole running through the mask pattern layer; the openings expose the pattern areas, and each pattern area corresponds to the corresponding opening; the sacrificial layer is positioned between the substrate and the mask pattern layer. The mask is produced by a semiconductor technology; compared with a metal mask produced in the conventional chemical etching way, the mask produced by the semiconductor technology has the advantages as follows: the quality of the mask and the precision of the through holes can be improved, reduction in the size of the through holes and the thickness of the mask pattern layer isfacilitated, the mask pattern layer and the substrate can be prevented from displacement, and the quality and the precision of the mask are relatively high.

Owner:NINGBO SEMICON INT CORP

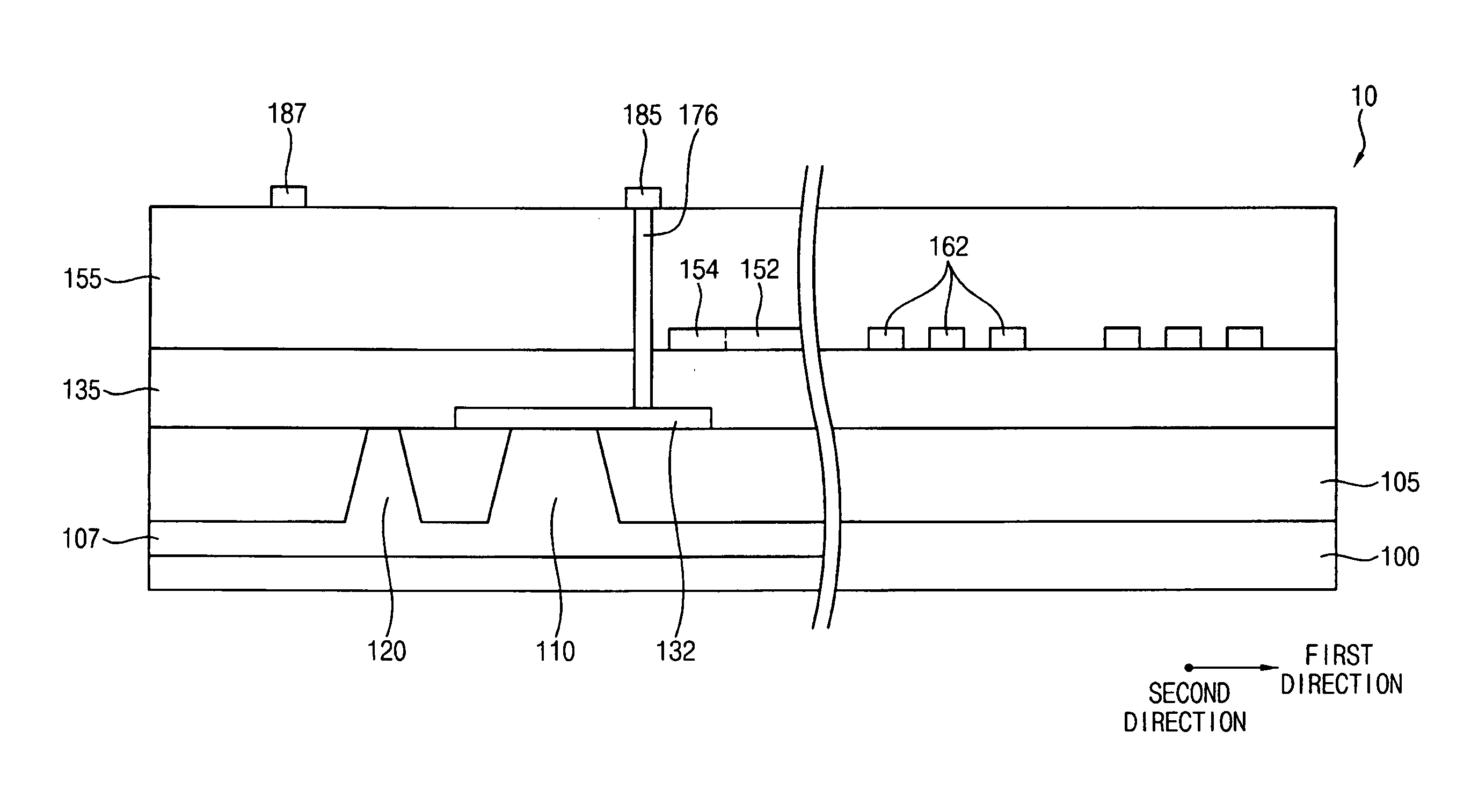

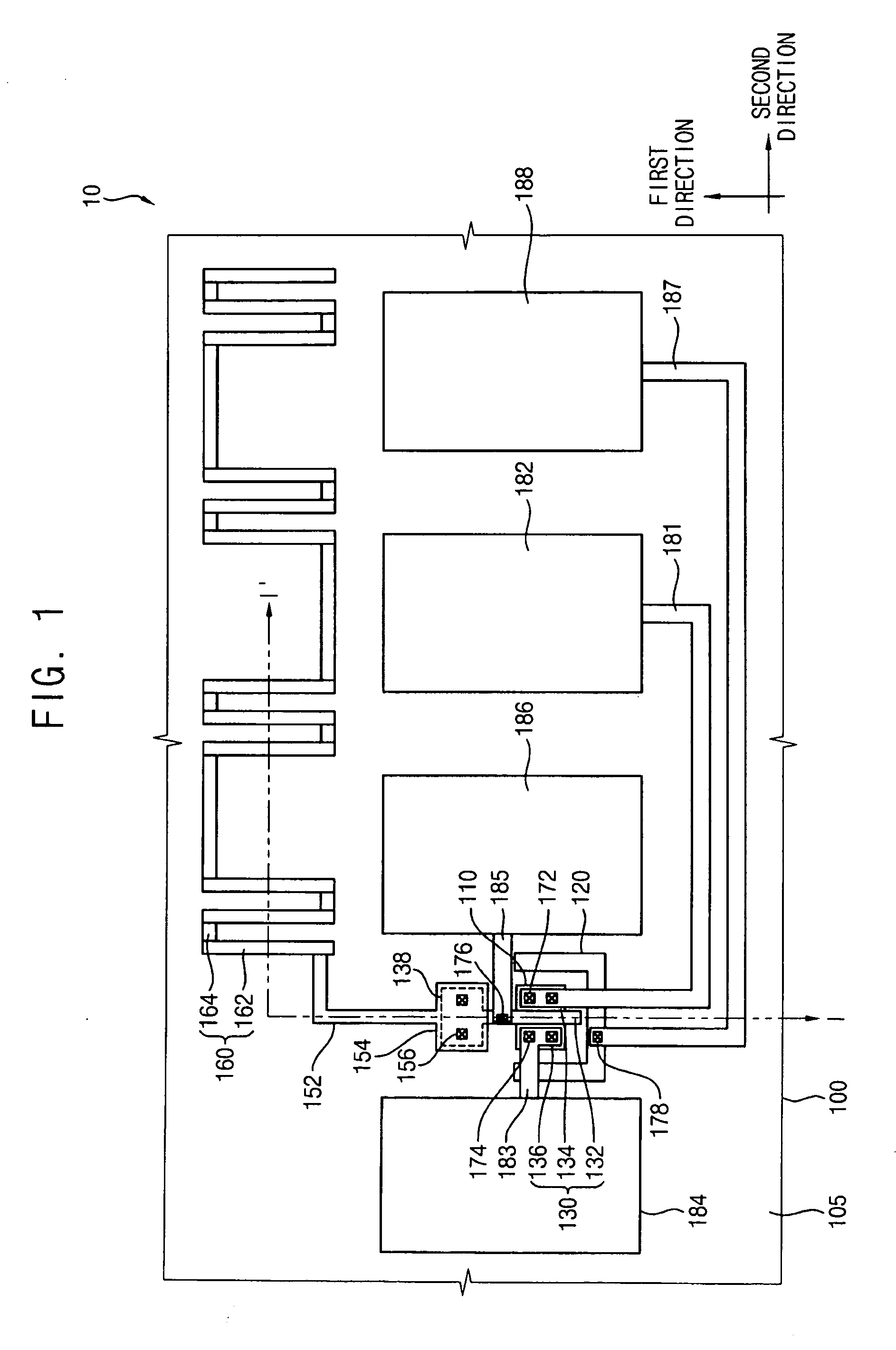

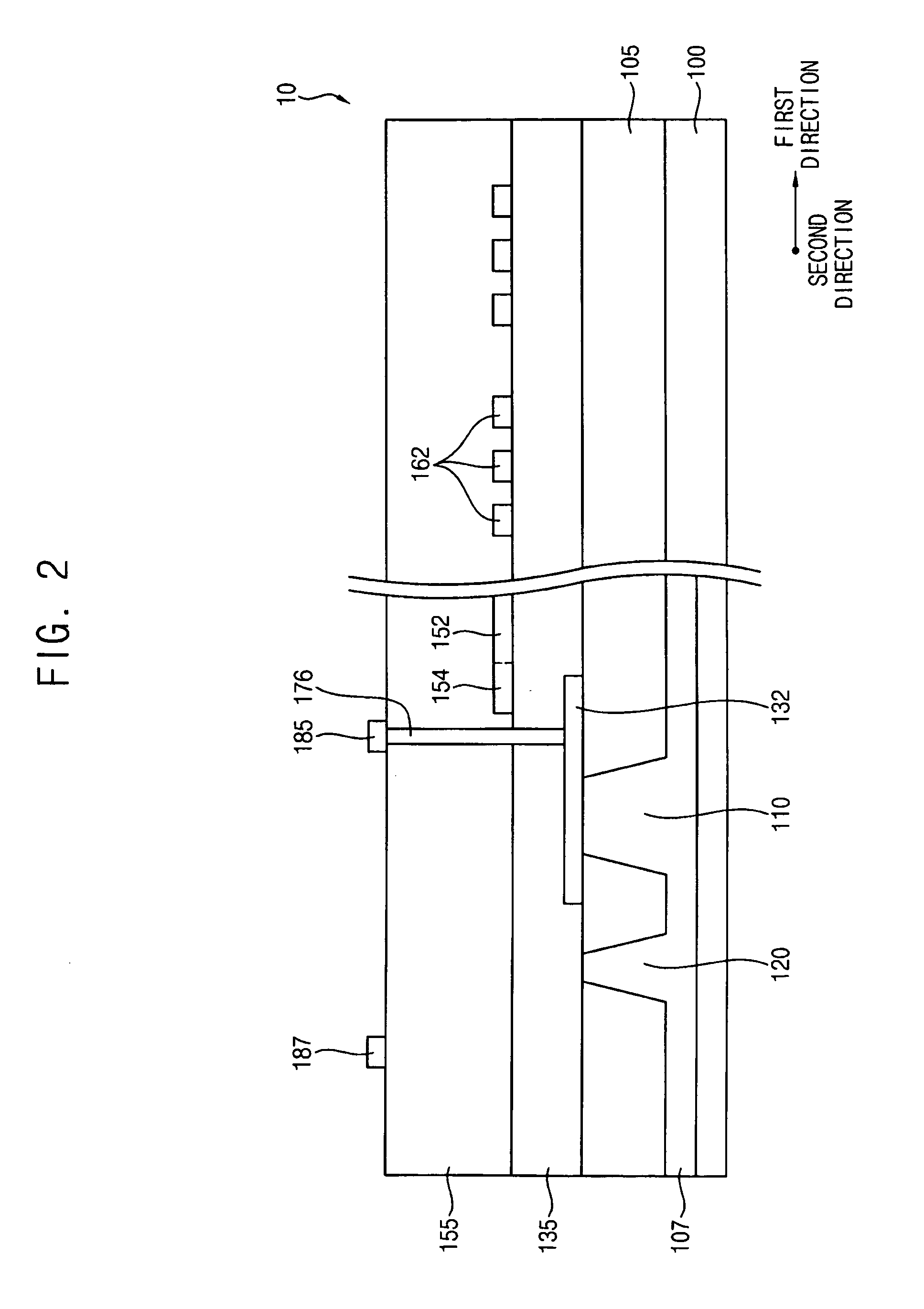

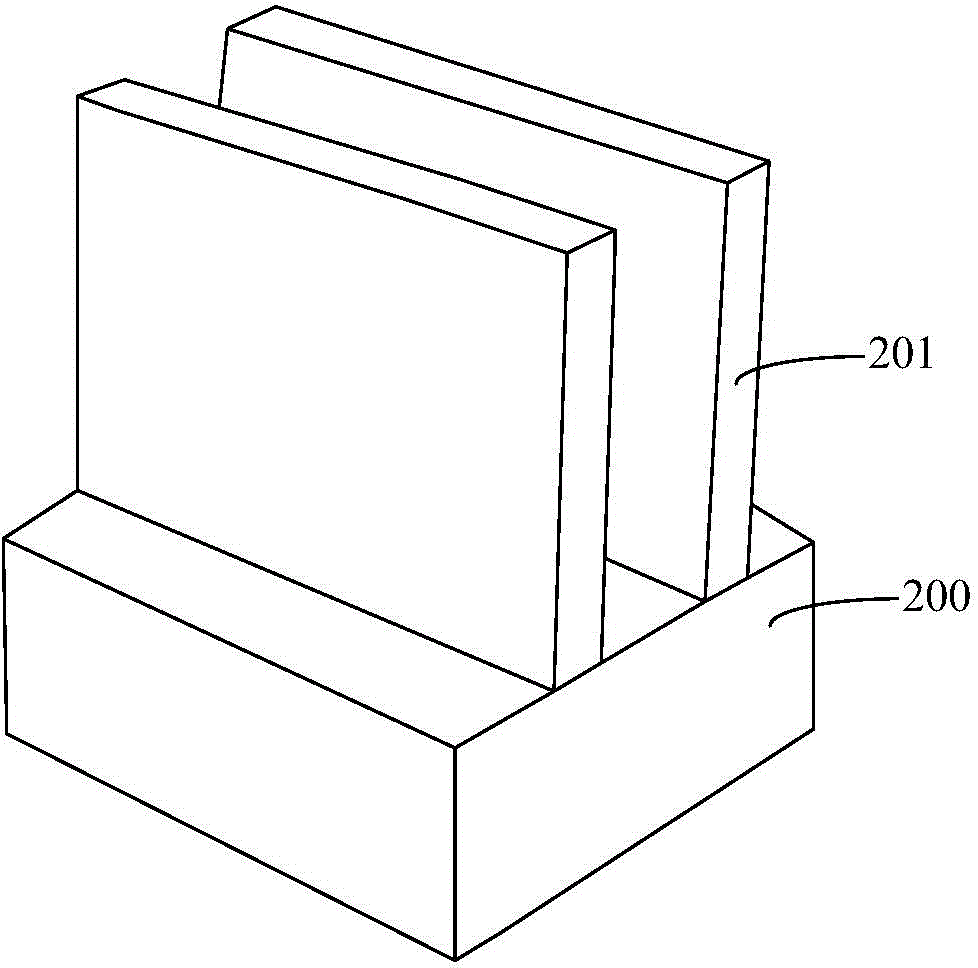

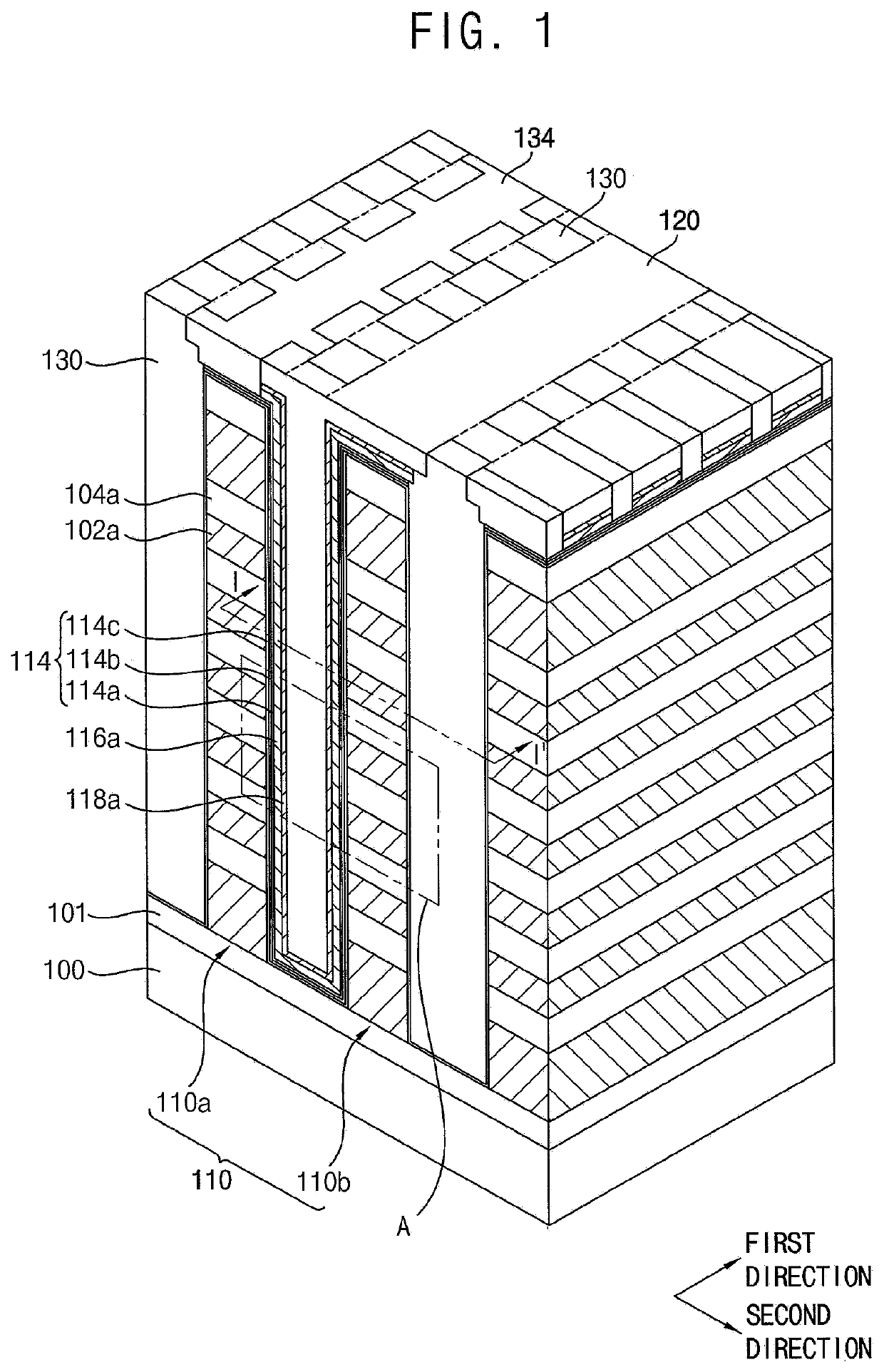

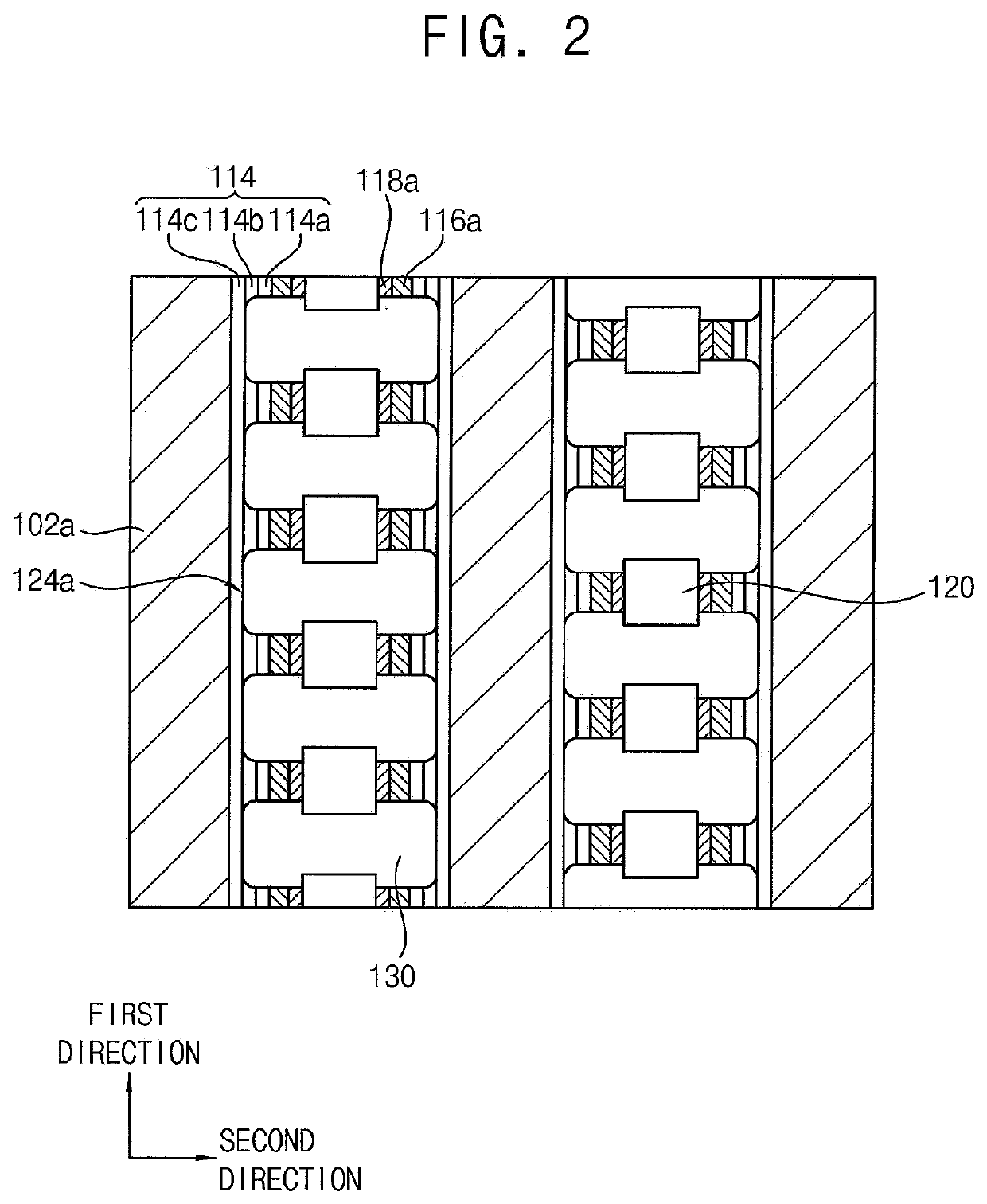

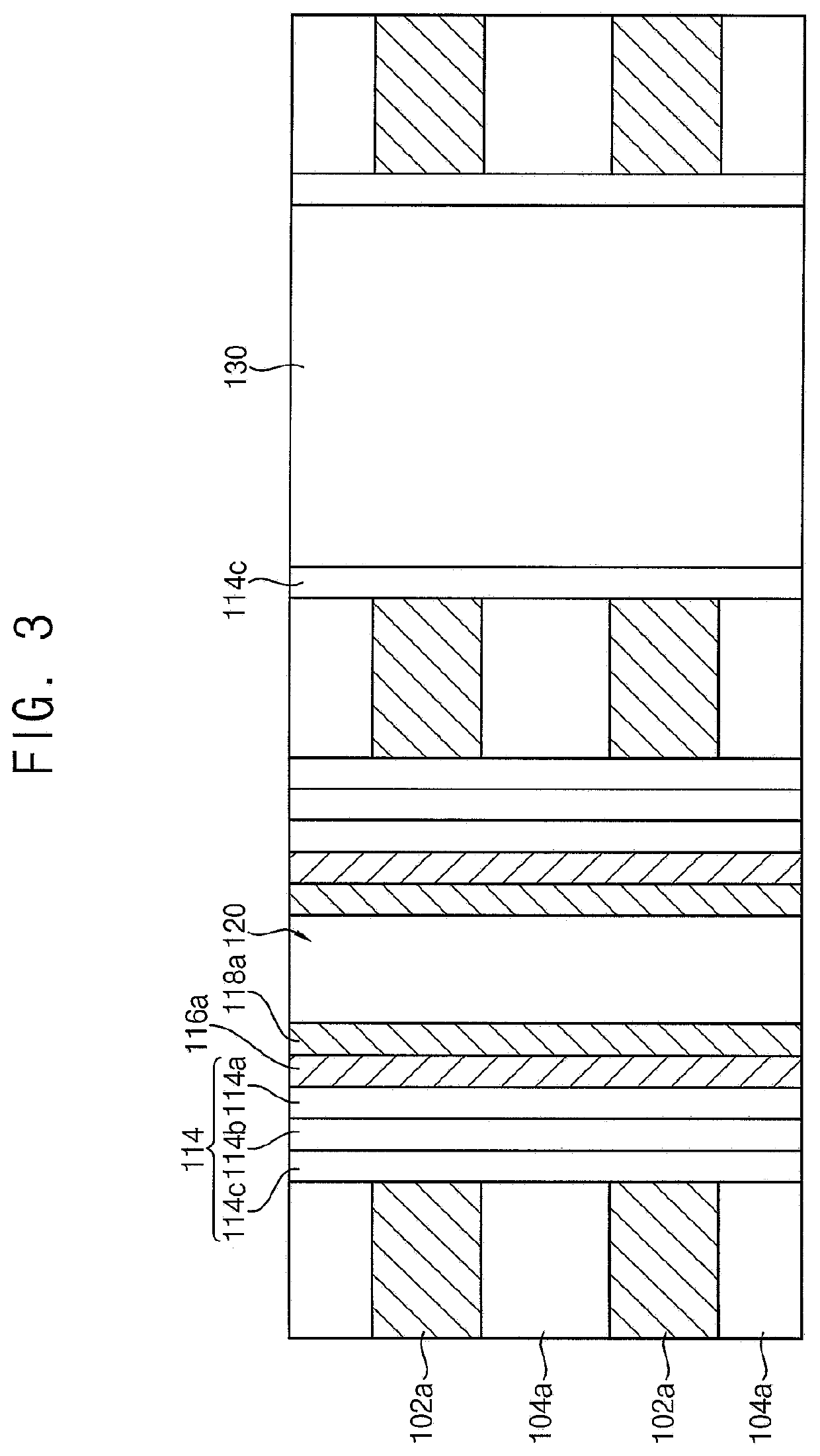

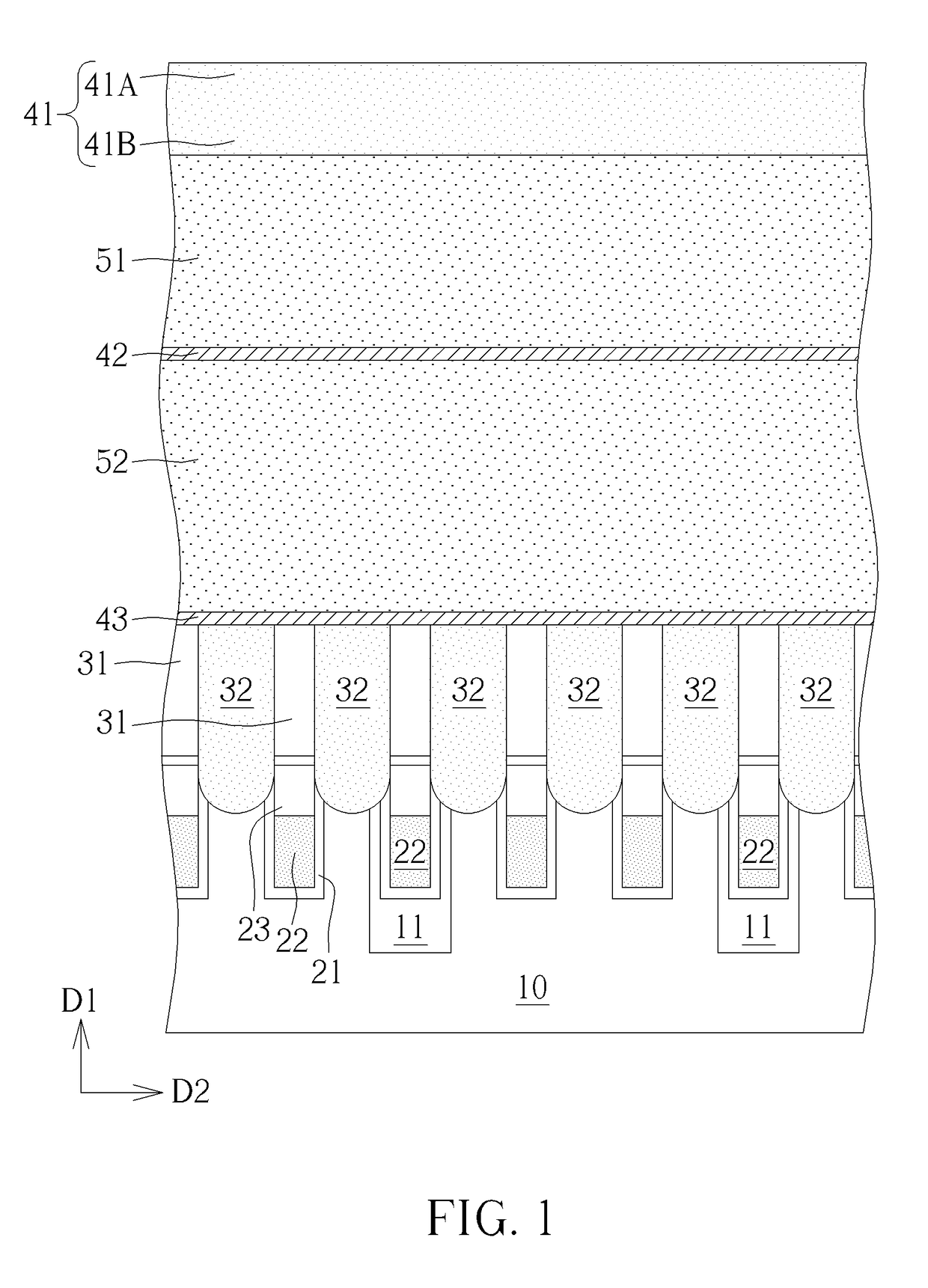

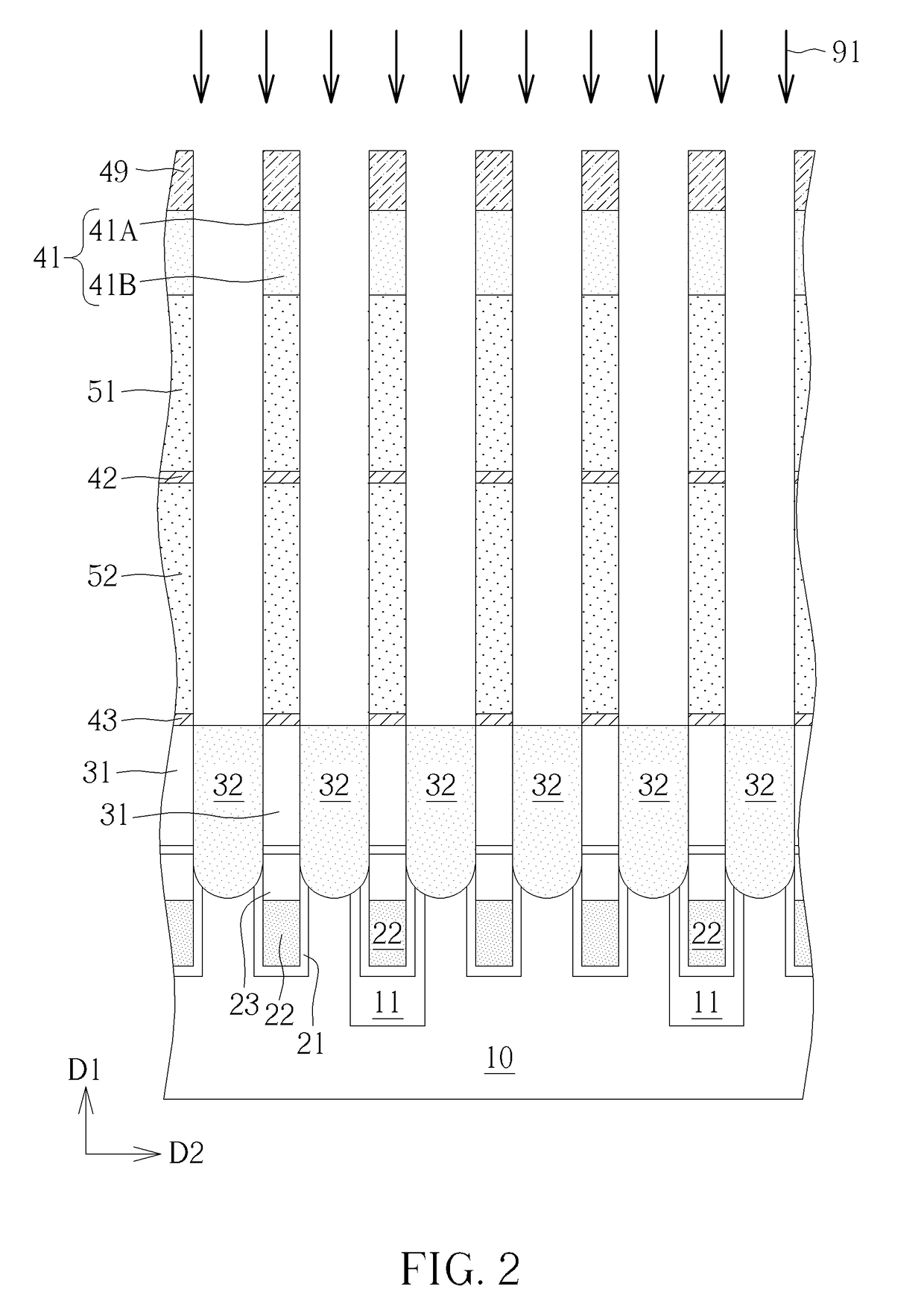

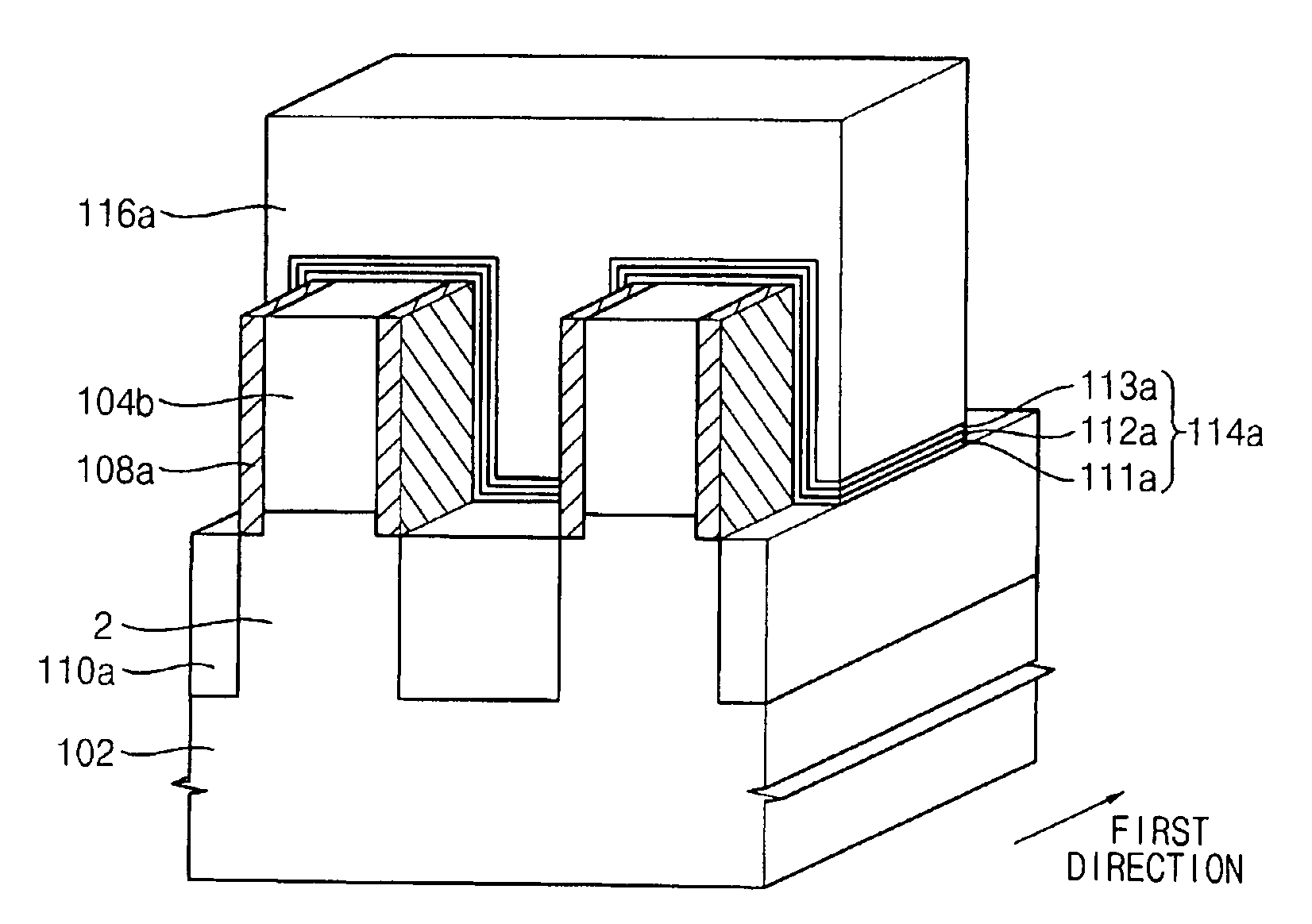

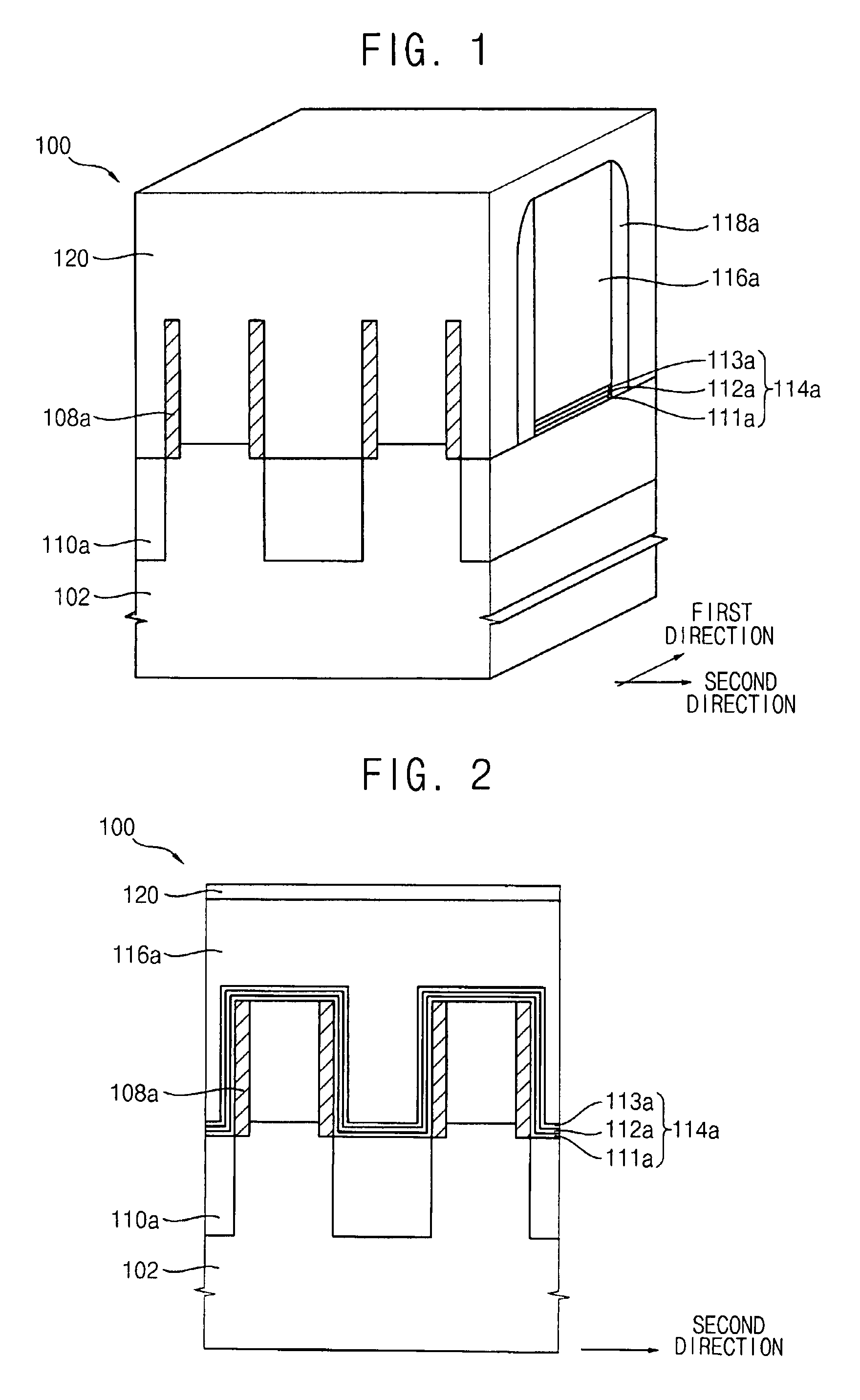

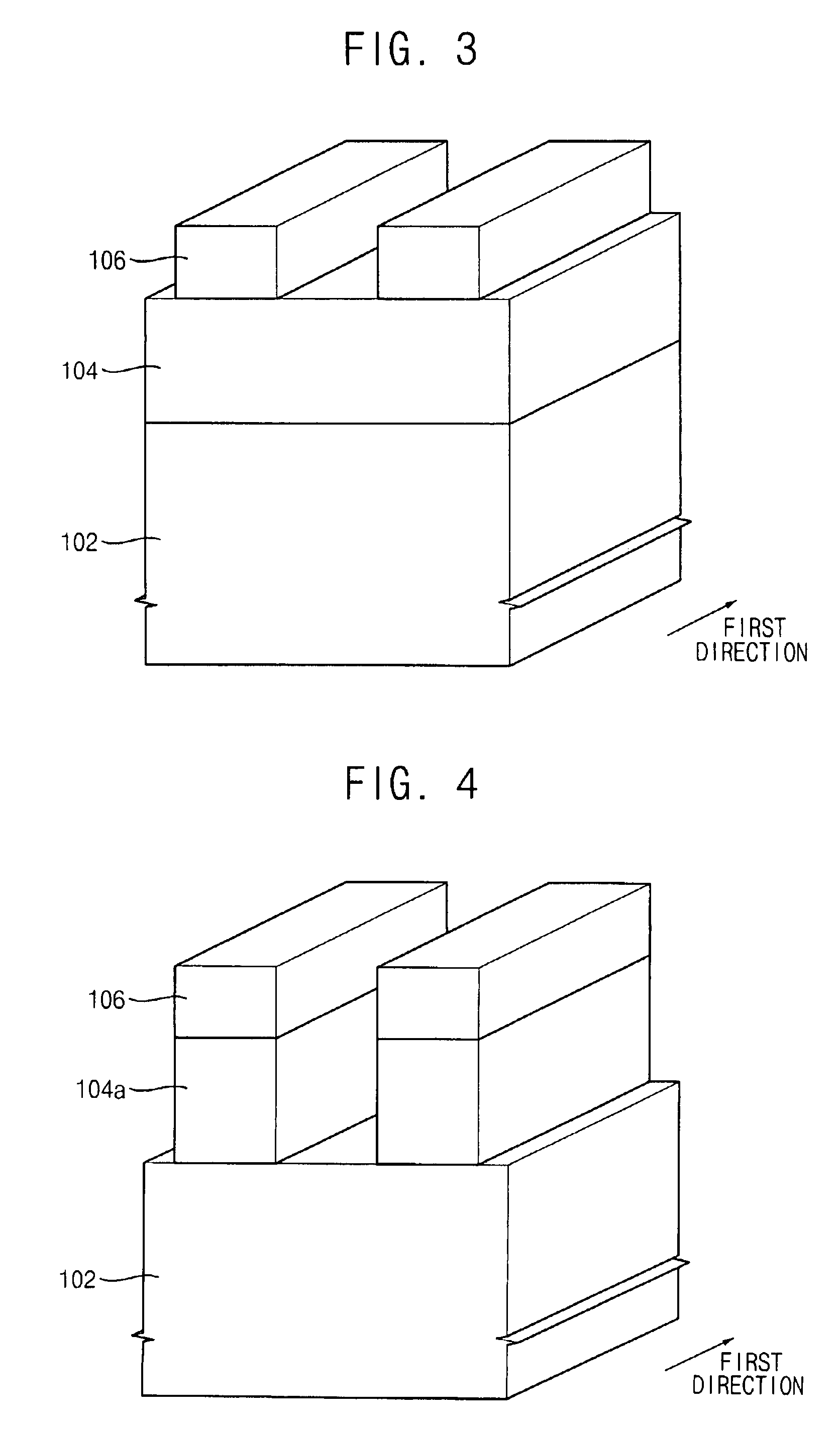

Vertical semiconductor devices

ActiveUS20200194451A1Excellent electrical characteristicReduce damageSolid-state devicesSemiconductor/solid-state device manufacturingPhysicsElectrically conductive

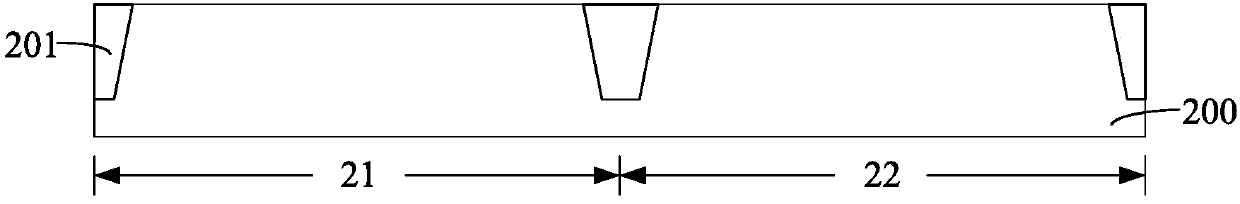

A vertical semiconductor device includes conductive pattern structures extending in a first direction, a trench between two adjacent conductive pattern structures in a second direction crossing the first direction, a memory layer disposed on sidewalls of the trench, first insulation layers disposed in the trench and spaced apart from each other in the first direction, channel patterns disposed on the memory layer and in the trench and spaced apart from each other in the first direction, and etch stop layer patterns disposed in the trench. Each conductive pattern structure includes conductive patterns and insulation layers alternately stacked on an upper surface of the substrate. Each etch stop layer pattern is disposed between a corresponding first insulation layer and the blocking dielectric layer. Etch stop layer patterns are spaced apart from each other in the first direction.

Owner:SAMSUNG ELECTRONICS CO LTD

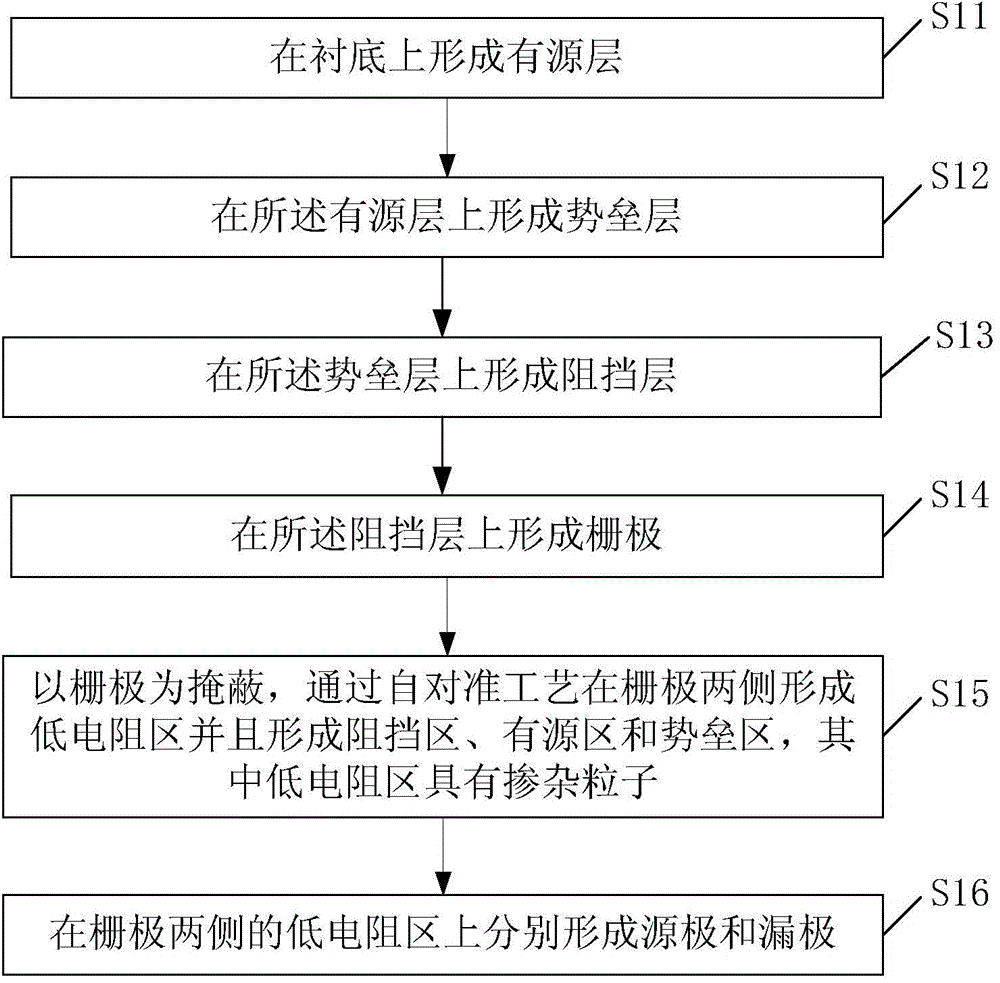

Formation method of transistor

ActiveCN105513964AImprove electrical performanceGood lookingSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical performanceDielectric layer

The invention provides a formation method of a transistor. The formation method of a transistor comprises providing a substrate, wherein a pseudo-grid is arranged on the substrate; forming an interlayer dielectric layer covered on the surface of the substrate and the surface of the side wall of the pseudo-grid, wherein the top of the interlayer dielectric layer flushes with the surface of the top of the pseudo-grid; forming a mask layer on the surface of the interlayer dielectric layer, wherein the mask layer exposes the surface of the top of the pseudo-grid; taking the mask layer to remove the pseudo-grid for mask layer etching, and forming a groove in the interlayer dielectric layer wherein a root defect is formed on the surface of the side wall of the bottom of the groove; and utilizing a dry etching process to remove the root defect. The formation method of a transistor utilizes the dry etching process to remove the root defect after removing the pseudo-grid so as to improve the morphology, of the grid, formed in the groove subsequently and optimize the electrical performance of a formed transistor.

Owner:SEMICON MFG INT (SHANGHAI) CORP

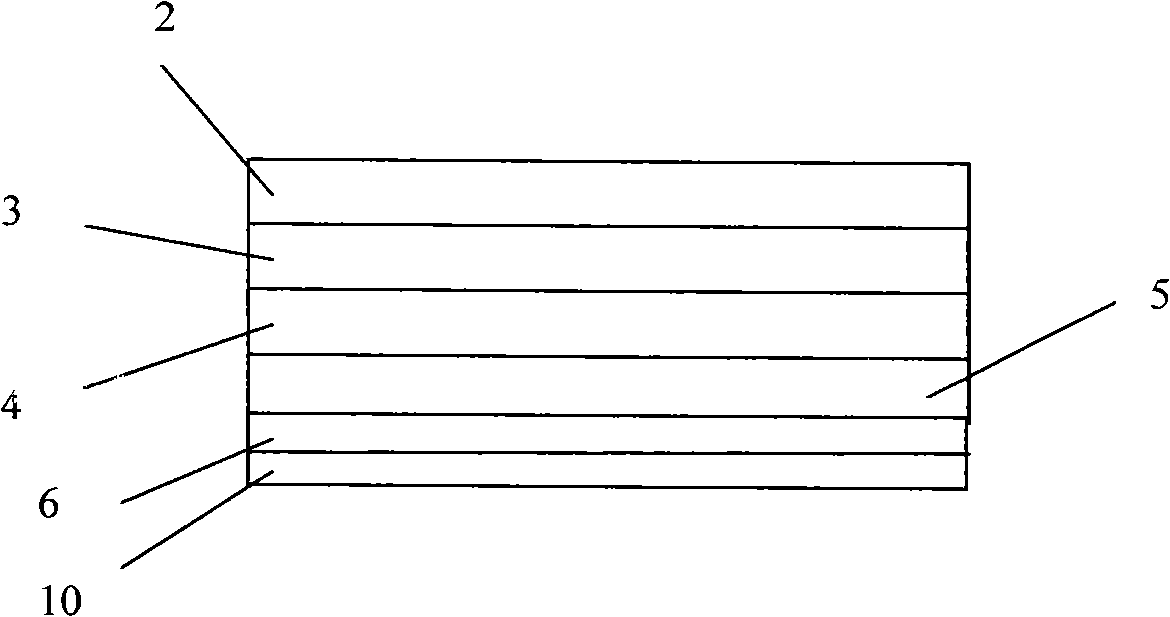

Semiconductor memory device and manufacturing method thereof

ActiveUS20180308923A1Improve manufacturing yieldReduce etch damageTransistorSolid-state devicesDielectric layerNitride

A semiconductor memory device includes a semiconductor substrate, a first support layer, a first electrode, a capacitor dielectric layer, and a second electrode. The first support layer is disposed on the semiconductor substrate. The first electrode is disposed on the semiconductor substrate and penetrates the first support layer. The capacitor dielectric layer is disposed on the first electrode. The second electrode is disposed on the semiconductor substrate, and at least a part of the capacitor dielectric layer is disposed between the first electrode and the second electrode. The first support layer includes a carbon doped nitride layer, and a carbon concentration of a bottom portion of the first support layer is higher than a carbon concentration of a top portion of the first support layer.

Owner:UNITED MICROELECTRONICS CORP +1

Method of reducing contamination by providing an etch stop layer at the substrate edge

InactiveUS8426312B2Reduce probabilityEfficient removalSemiconductor/solid-state device manufacturingContaminationMetal

By providing an etch stop layer selectively at the bevel, at least one additional wet chemical bevel etch process may be performed prior to or during the formation of a metallization layer without affecting the substrate material. Hence, the dielectric material, especially the low-k dielectric material, may be reliably removed from the bevel prior to the formation of any barrier and metal layers. The etch stop layer may be formed at an early manufacturing stage so that a bevel etch process may be performed at any desired stage of the formation of circuit elements.

Owner:ALSEPHINA INNOVATIONS INC

Metal semiconductor field effect light emitting transistor and preparing method thereof

InactiveCN101308895AImprove performanceReduce etch damageSemiconductor devicesQuantum wellOhmic contact

The invention discloses a metal semiconductor field effect transistor and the fabrication method thereof. The metal semiconductor field effect transistor comprises a substrate, a buffer layer which is arranged on the substrate, a first n type heavily doped layer above the buffer layer, a multi-quantum well layer and a p type layer which are sequentially arranged on the n type layer, a second n type heavily doped layer above the buffer layer, a source electrode which is in Ohmic contact with the second n type heavily doped layer, and a drain electrode which is in Ohmic contact with the p type layer. The first n type heavily doped layer is not connected with the second n type heavily doped layer. The metal semiconductor field effect transistor is characterized in that a slightly doped n type layer is arranged between the buffer layer and first and second n type heavily doped layers, and a SiO2 layer connected with the slightly doped n type layer is embedded between the substrate and the buffer layer. The metal semiconductor field effect transistor further comprises a gate electrode which is in Schottky contact with the SiO2 layer. The metal semiconductor field effect transistor reduces etching damages, thus improving the performance of the components.

Owner:SOUTH CHINA NORMAL UNIVERSITY

Formation method of semiconductor structure

ActiveCN106409752AImprove electrical performancePlay a protective effectSemiconductor/solid-state device manufacturingSemiconductor structureProtection layer

A formation method of a semiconductor structure comprises the steps of providing a substrate in which a bottom-layer metal layer is formed; forming an etching barrier layer covering the surfaces of the substrate and the bottom-layer metal layer; forming a dielectric layer covering the surface of the etching barrier layer; forming an opening penetrating the dielectric layer, and exposing the surface of the etching barrier layer out of the bottom of the opening; adopting a dry etching process of an etching gas containing CF3I to etch a part of thickness of etching barrier layer located at the bottom of the opening, and forming a protection layer on the surface of the side wall of the opening while etching the part of thickness of etching barrier layer; after the protection layer is formed, adopting an isotropy dry etching process to etch and remove the residual thickness of etching barrier layer until the top surface of the bottom-layer metal layer is exposed; forming a conductive layer on the surface of the exposed bottom-layer metal layer, wherein the conductive layer fills the opening. According to the present invention, the etching damage to the bottom-layer metal layer is reduced, and the electrical property of the semiconductor structure is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

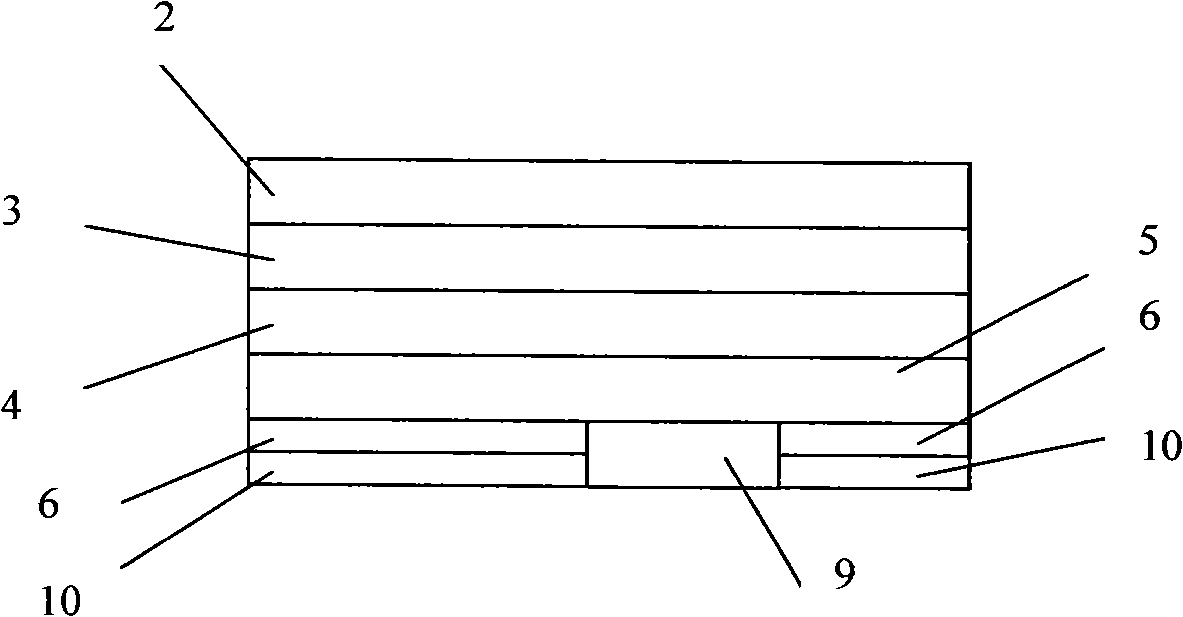

Memory device and method of manufacturing the same

ActiveUS7674661B2Reduce etch damageReduce coupling effectSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSingle crystal

In a memory device and a method of manufacturing the memory device, a pair of channel layers included in the memory device may be formed on a sidewall of the sacrificial single crystalline layer pattern located on a protrusion of a semiconductor substrate. Accordingly, an etch damage may be reduced at the channel layer. The sacrificial single crystalline layer pattern may be removed to generate a void between the pair of the channel layers. As a result, a generation of a coupling effect may be reduced between the channel layers.

Owner:SAMSUNG ELECTRONICS CO LTD

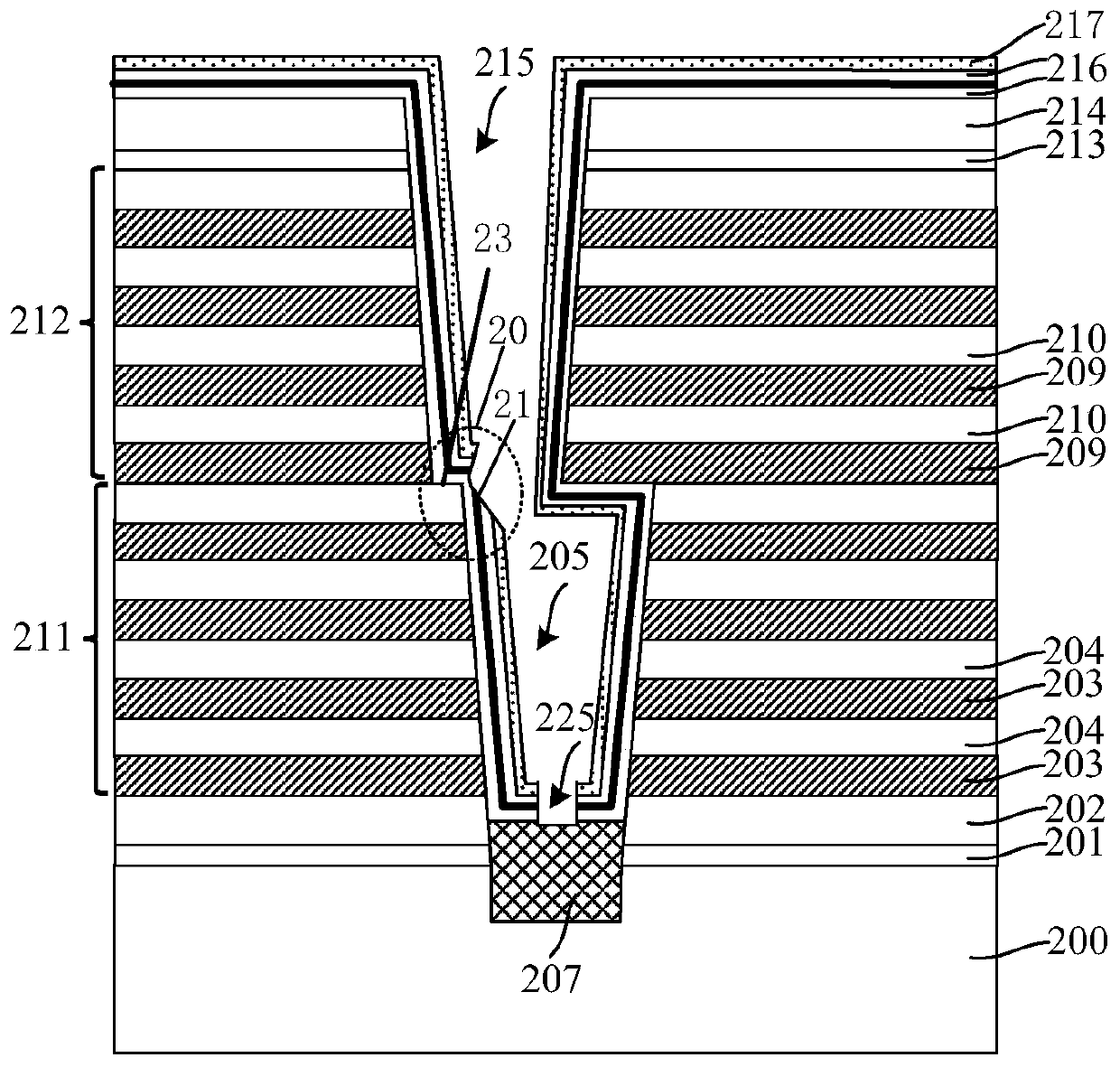

Forming method of 3D NAND memory

ActiveCN109817635AReduce widthAvoid failureSolid-state devicesSemiconductor devicesIsolation layerSemiconductor

The invention discloses a forming method of a 3D NAND memory. The method comprises the steps of providing a semiconductor substrate, wherein a stacking structure is formed on the semiconductor substrate and comprises a plurality of sacrificial layers and isolation layers which are alternately stacked; the stacking structure is provided with a first channel hole and a second channel hole which communicate with each other, the second channel hole is aligned and deviated relative to the first channel hole, a step is formed at the junction of the first channel hole and the second channel hole, andthe first channel hole is filled with a sacrificial material layer; forming a side wall on the side wall of the second channel hole; etching the first channel hole to enable the width of the first channel hole to be widened and enable the width of the step to be reduced; forming charge storage layers on the side walls and the bottoms of the first channel hole and the second channel hole; forminga channel hole sacrificial layer on each charge storage layer; and sequentially etching the channel hole sacrificial layer and the charge storage layer on the bottom of the first channel hole to forman opening. The method provided by the invention prevents the charge storage layer at the step from being etched or damaged, thereby preventing the memory from failing.

Owner:YANGTZE MEMORY TECH CO LTD

Forming method of 3D NAND storage

ActiveCN109887924AGradientPrevent etch through or damageSolid-state devicesSemiconductor devicesEngineeringSemiconductor

The invention relates to a forming method of a 3D NAND storage. The forming method comprises the steps of: providing a semiconductor substrate, wherein a stacked structure comprising a plurality of sacrificial layers and isolation layers, which are alternatively stacked, is formed on the semiconductor substrate, a first channel hole and a second channel hole which are communicated are formed in the stacked structure, the second channel hole has an alignment offset relative to the first channel hole, a step is formed at a junction of the first channel hole and the second channel hole, and the first channel hole is full filled with a sacrificial material layer; forming a side wall on the side wall of the second channel hole; removing a part of the sacrificial material layer; etching the first channel hole to increase a width of the first channel hole and reduce a width of the step; forming charge storage layers on the side walls and at the bottoms of the first channel hole and the secondchannel hole; forming channel hole sacrificial layers on the charge storage layers; and sequentially etching the channel hole sacrificial layer and the charge storage layer at the bottom of the firstchannel hole so as to form an opening. By the method provided by the invention, the charge storage layers at the step are prevented from being etched off or damaged so as to prevent a failure of thestorage.

Owner:YANGTZE MEMORY TECH CO LTD

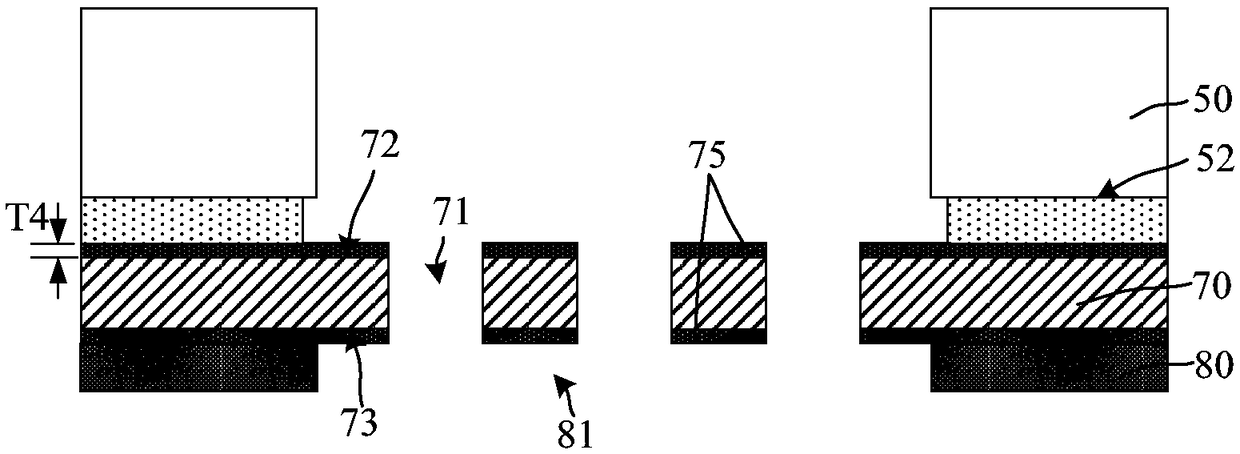

Method for improving performance of core device and input-output device

ActiveCN106653693AReduce in quantityReduce adverse effectsSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringOutput device

The invention provides a method for improving performance of a core device and an input-output device. The method comprises steps of providing a substrate; forming a first oxide layer on the surface of the substrate in a core device region and an input-output device region; forming a cap layer on the surface of the first oxide layer; performing etching to remove the cap layer in the core device region; forming a pseudo grid film on the surface of the cap layer in the input-output device region and the substrate in the core device region; patterning the pseudo grid film to form a pseudo grid layer; forming an interlayer dielectric layer to cover the surface of the side wall of the pseudo grid layer on the substrate after the pseudo grid layer is formed; performing etching to remove the pseudo grid layer; removing the cap layer in the input-output device region; and forming a second oxide layer on the surface of the substrate in the core device region after the cap layer is removed, wherein the thickness of the second oxide layer is smaller than the thickness of the first oxide layer. The method provided by the invention improves integrity of the grid oxide layer of the input-output device and the core device, and the NBTI performance and the PBTI performance.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Mask and fabrication method thereof

ActiveCN108666448ASmall sizeReduce thicknessVacuum evaporation coatingSolid-state devicesEngineeringSemiconductor

The invention relates to a mask and a fabrication method thereof. The mask comprises a substrate, a sacrificial layer and a mask pattern layer, wherein the substrate comprises a first surface and a second surface, the second surface deviates from the first surface, a plurality of openings are formed in the substrate and penetrate through the substrate, the substrate can be used for patterning by asemiconductor etching process, the sacrificial layer is arranged on the first surface, a plurality of holes are formed in the sacrificial layer, the mask pattern layer is arranged on the sacrificiallayer and comprises pattern regions and shielding regions which are adjacent to each other, at least one through hole is formed in the pattern regions and penetrates through the mask pattern layer, the pattern regions are exposed out of the openings and holes, each pattern region is corresponding to the openings and holes, the mask pattern layer is provided with an annular bulge extending to the openings, and the annular bulge is in contact with side walls of the openings. The mask is made by the semiconductor process, the quality of the mask and the through hole accuracy can be improved by the semiconductor process, the through hole size and the thickness of the mark pattern layer are favorably reduced, displacement of the mask pattern layer and the substrate also can be prevented, and the quality and the accuracy of the mask are higher.

Owner:NINGBO SEMICON INT CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com