Method for forming semiconductor device

A semiconductor and device technology, applied in the field of semiconductor device formation, can solve problems such as reducing the reliability of semiconductor devices, achieve the effects of reducing etching rate and etching damage, improving protection, and improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

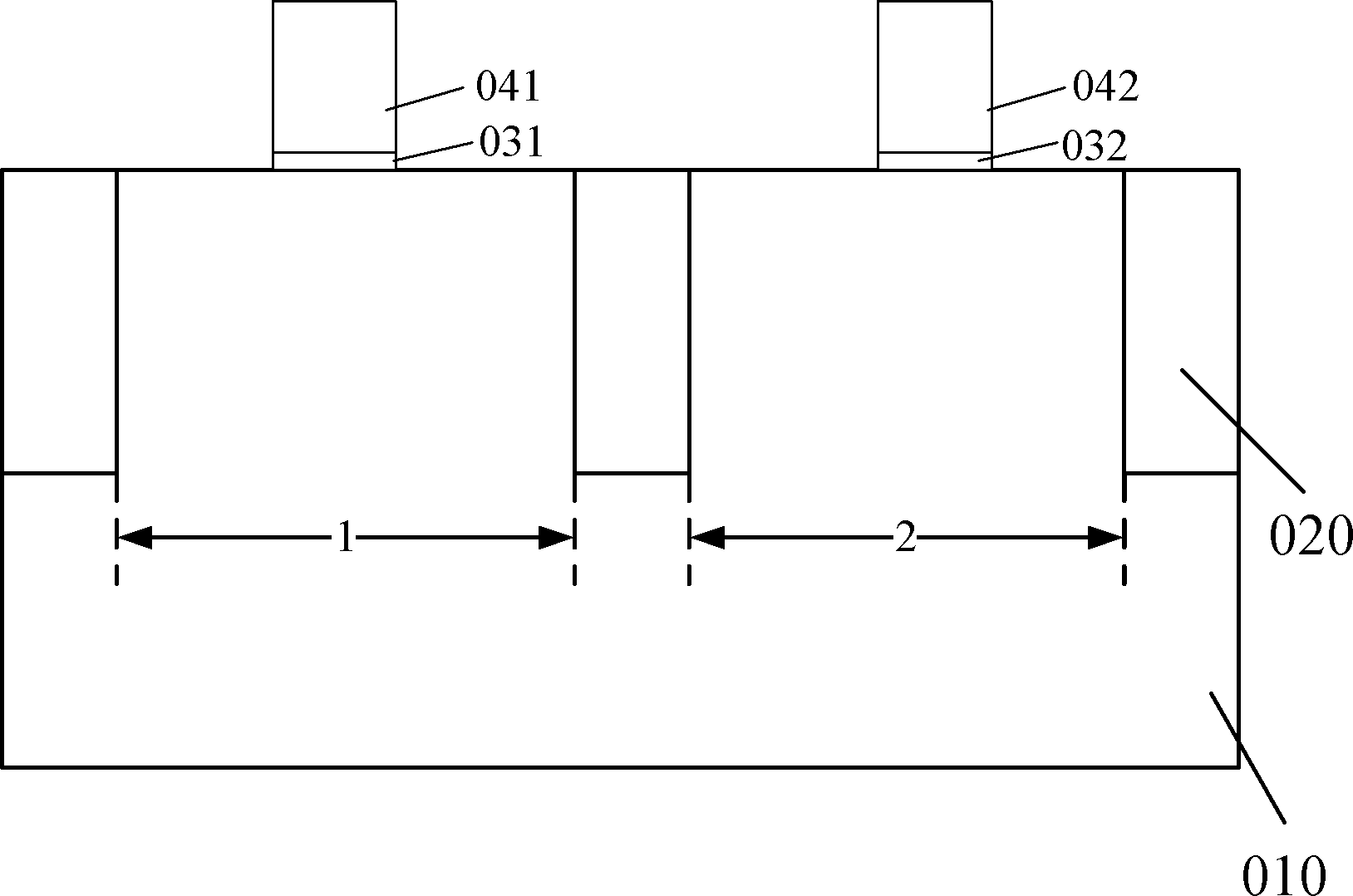

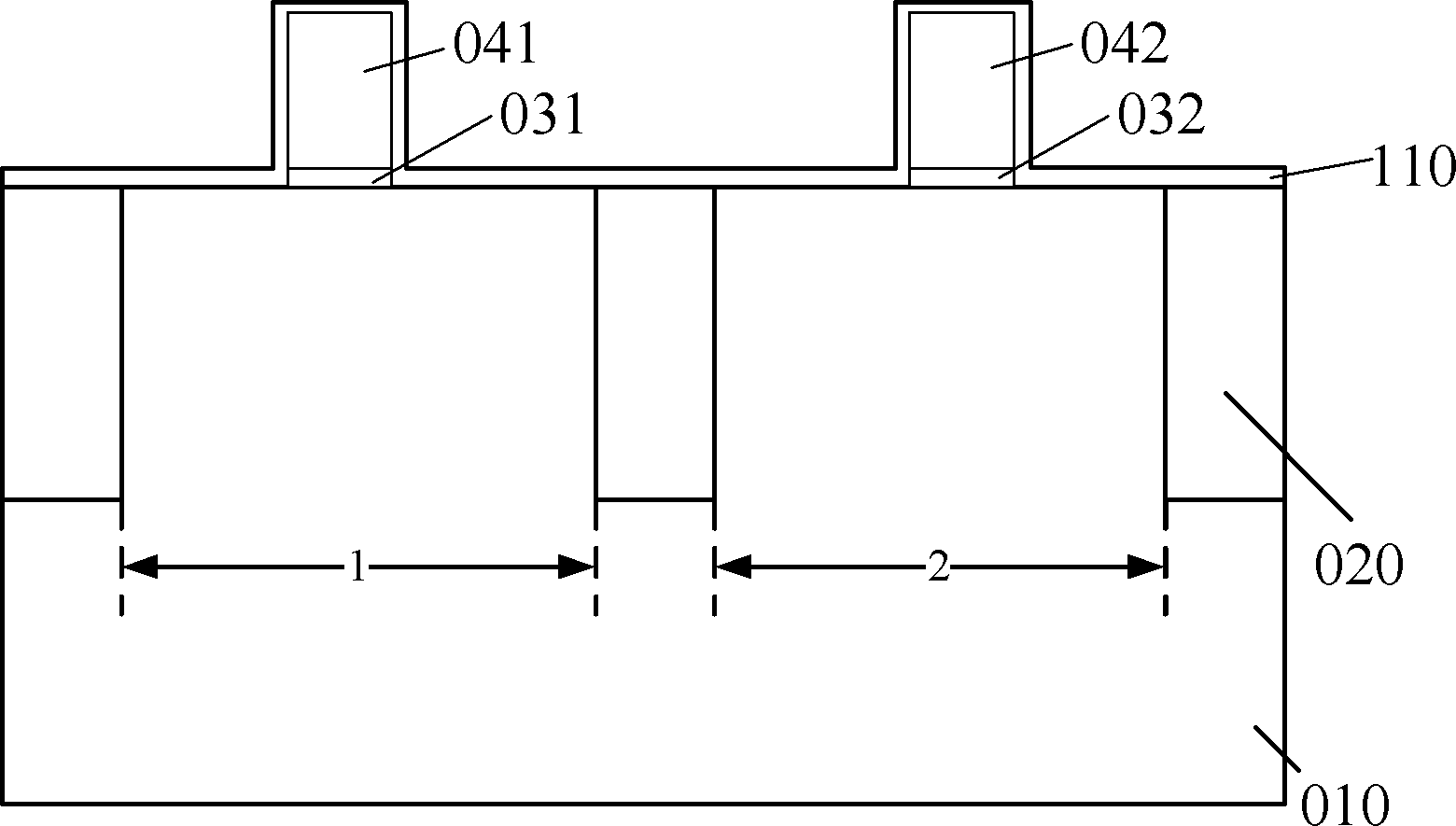

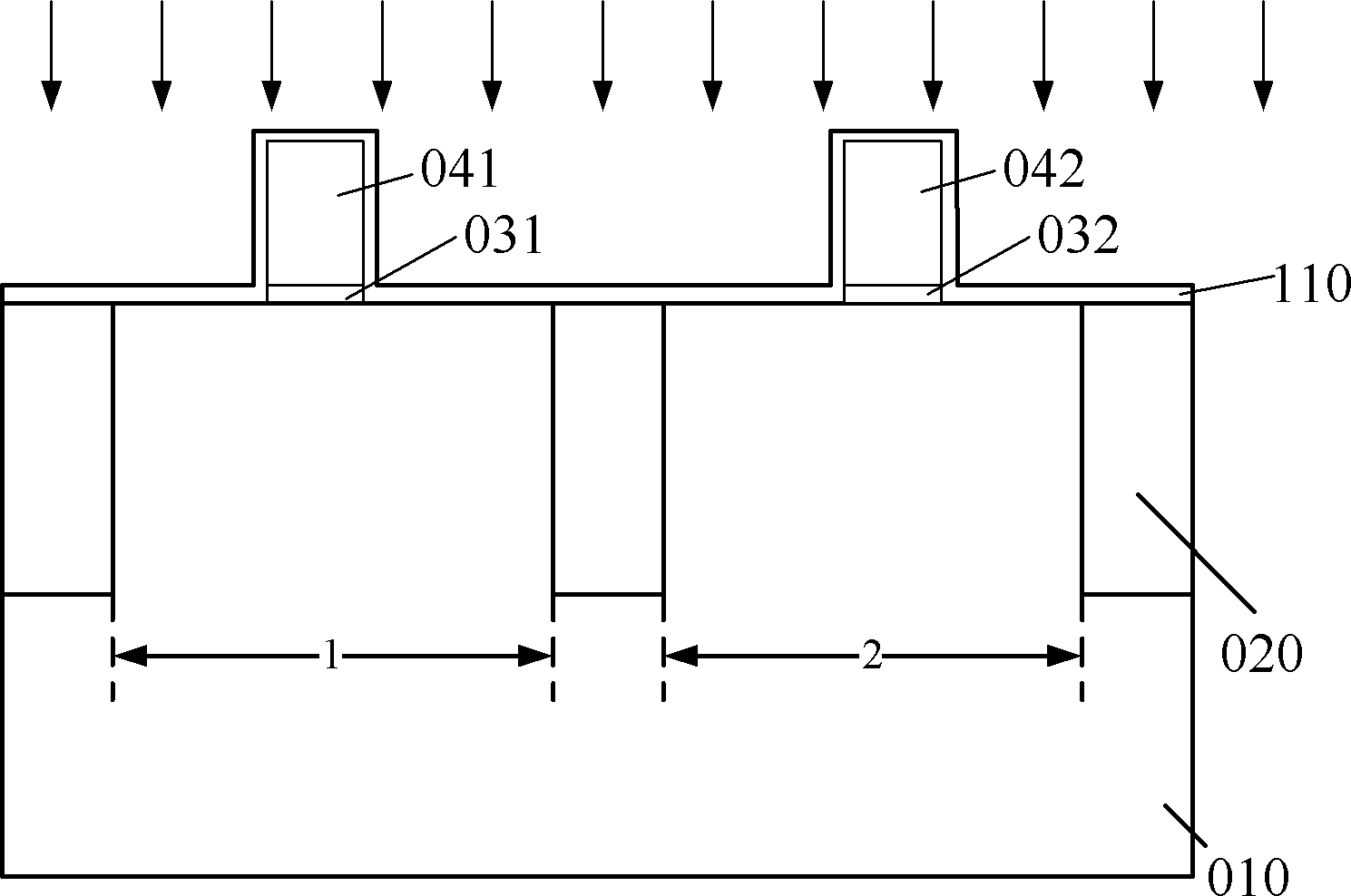

[0029] The inventors found that before forming the epitaxial layer, it is necessary to perform a series of dry etching, wet etching or cleaning processes on the above-mentioned semiconductor device. The above-mentioned processes will damage the sidewalls located in the NMOS region, so that the sidewalls of the NMOS region The walls thinned. The thinned sidewalls will not be able to provide better protection for the gate structure and the substrate, and even cause the NMOS gate structure and substrate to be exposed to the subsequent growth environment of the PMOS epitaxial layer, reducing the reliability of the NMOS device. Similarly, if the NMOS epitaxial layer is formed, the thinned sidewalls will not be able to protect the gate structure and the substrate well, and even cause the PMOS gate structure and substrate to be exposed to the subsequent NMOS epitaxial layer. In the growth environment, the reliability of the PMOS device is reduced.

[0030] In order to solve the abov...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com