Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

30results about How to "Reduced impact ionization" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

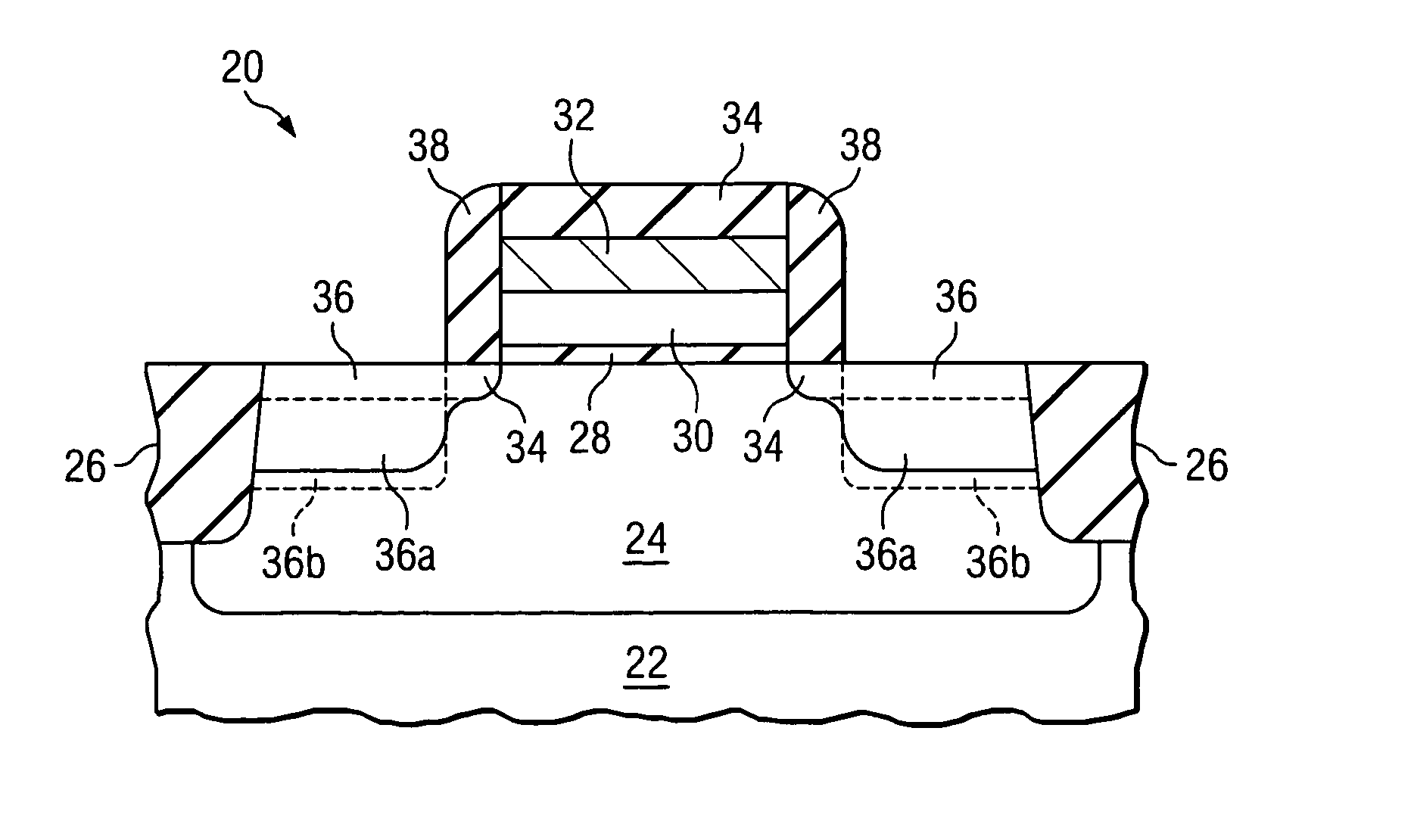

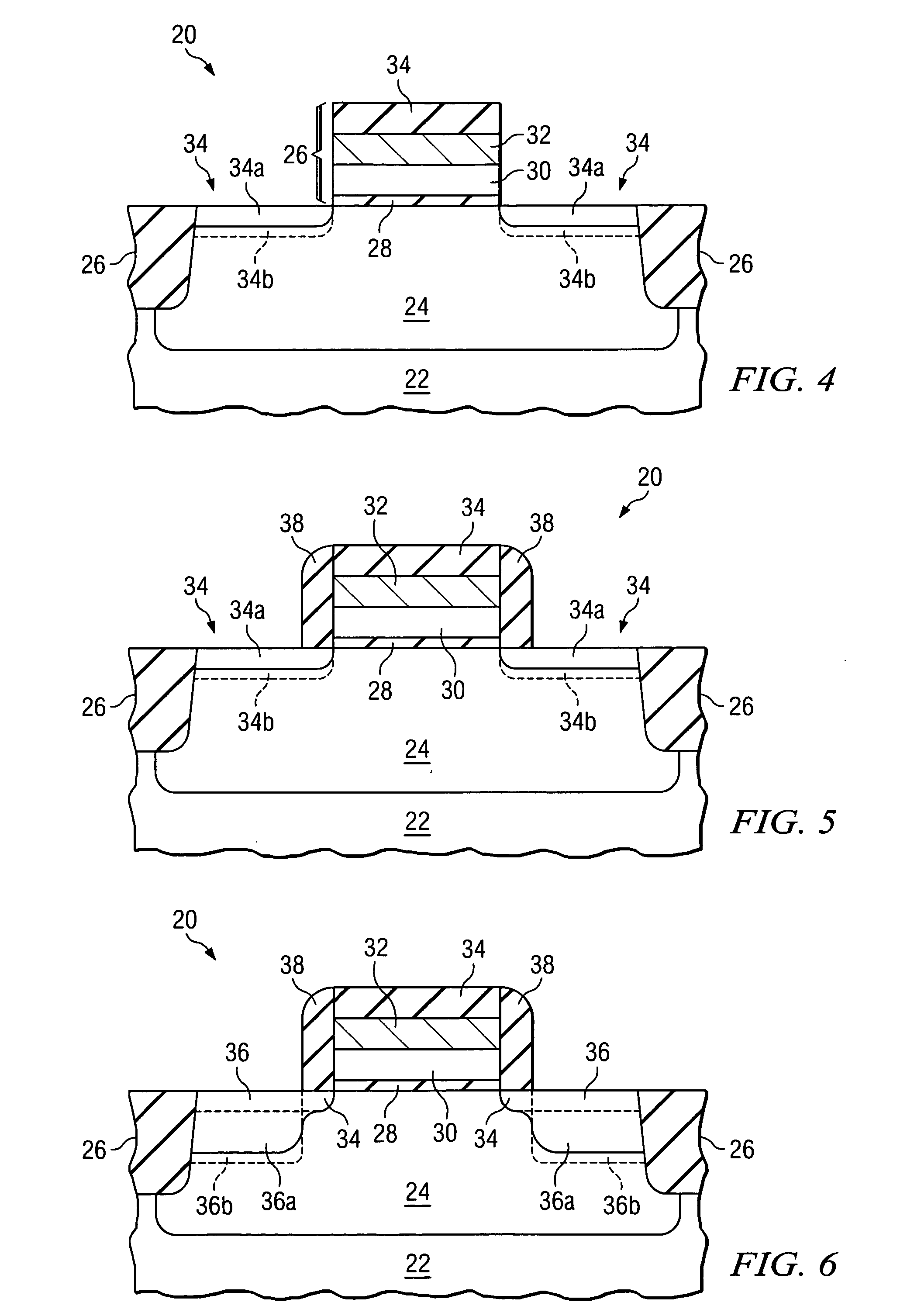

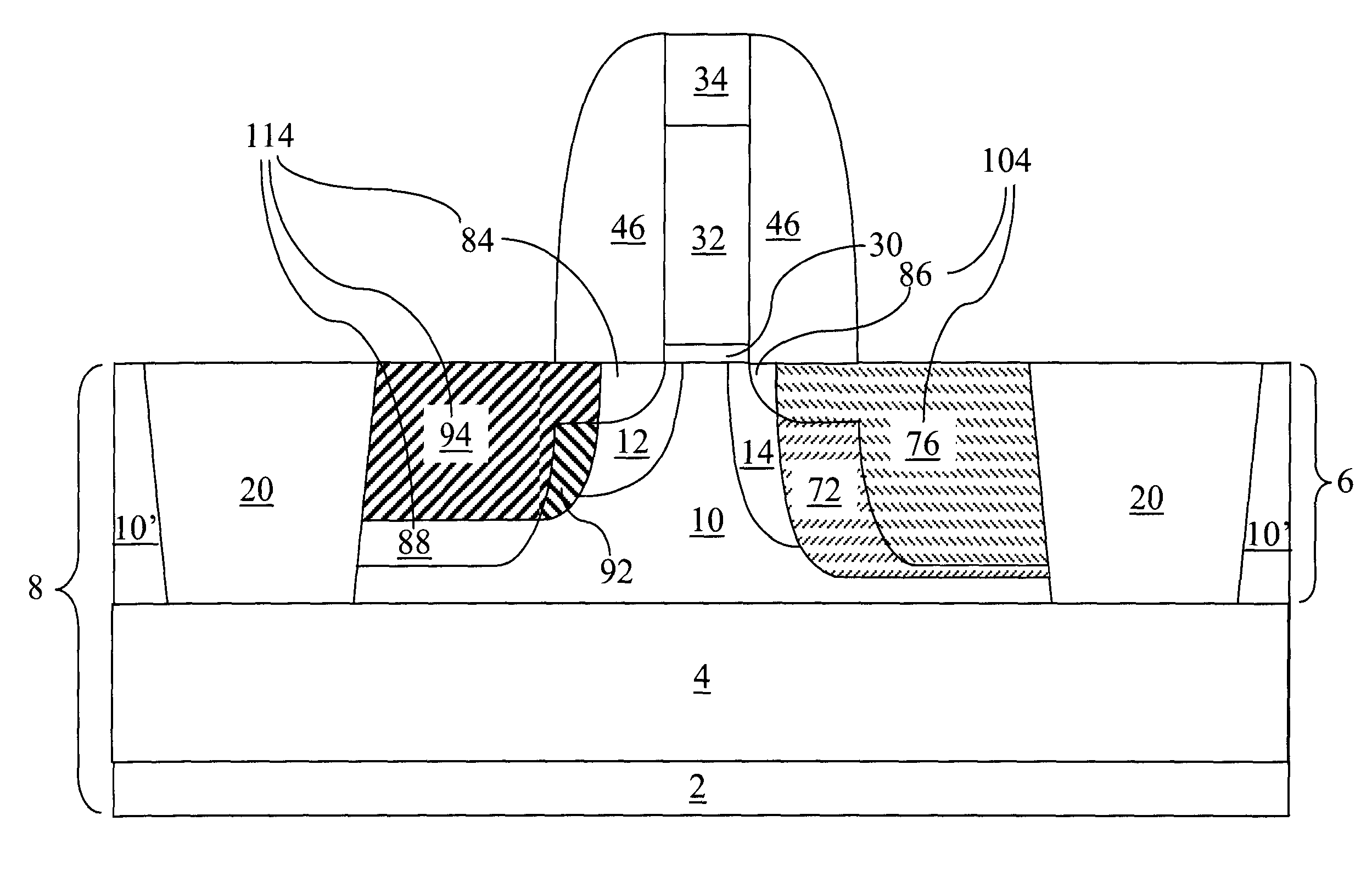

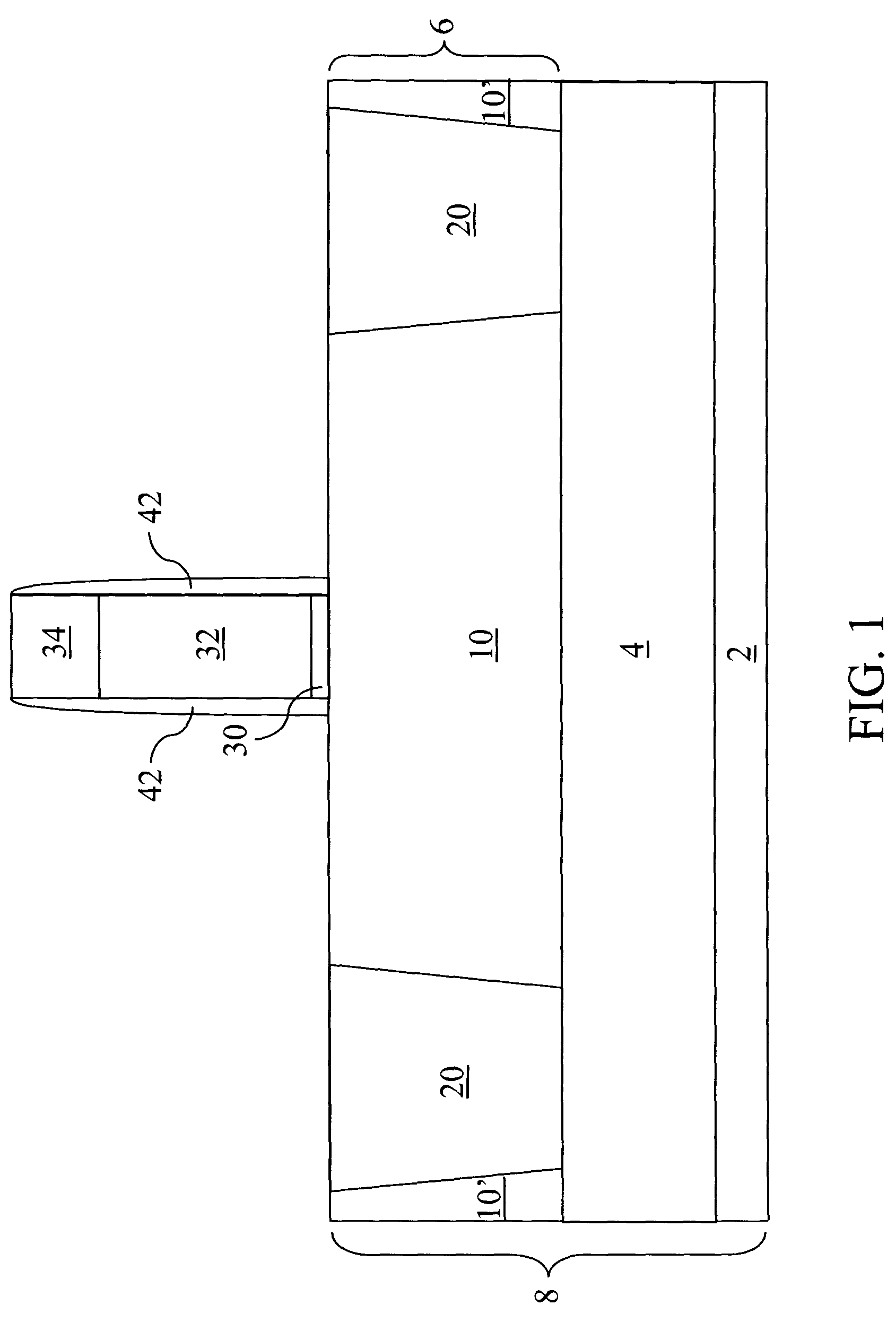

Field effect transistor containing a wide band gap semiconductor material in a drain

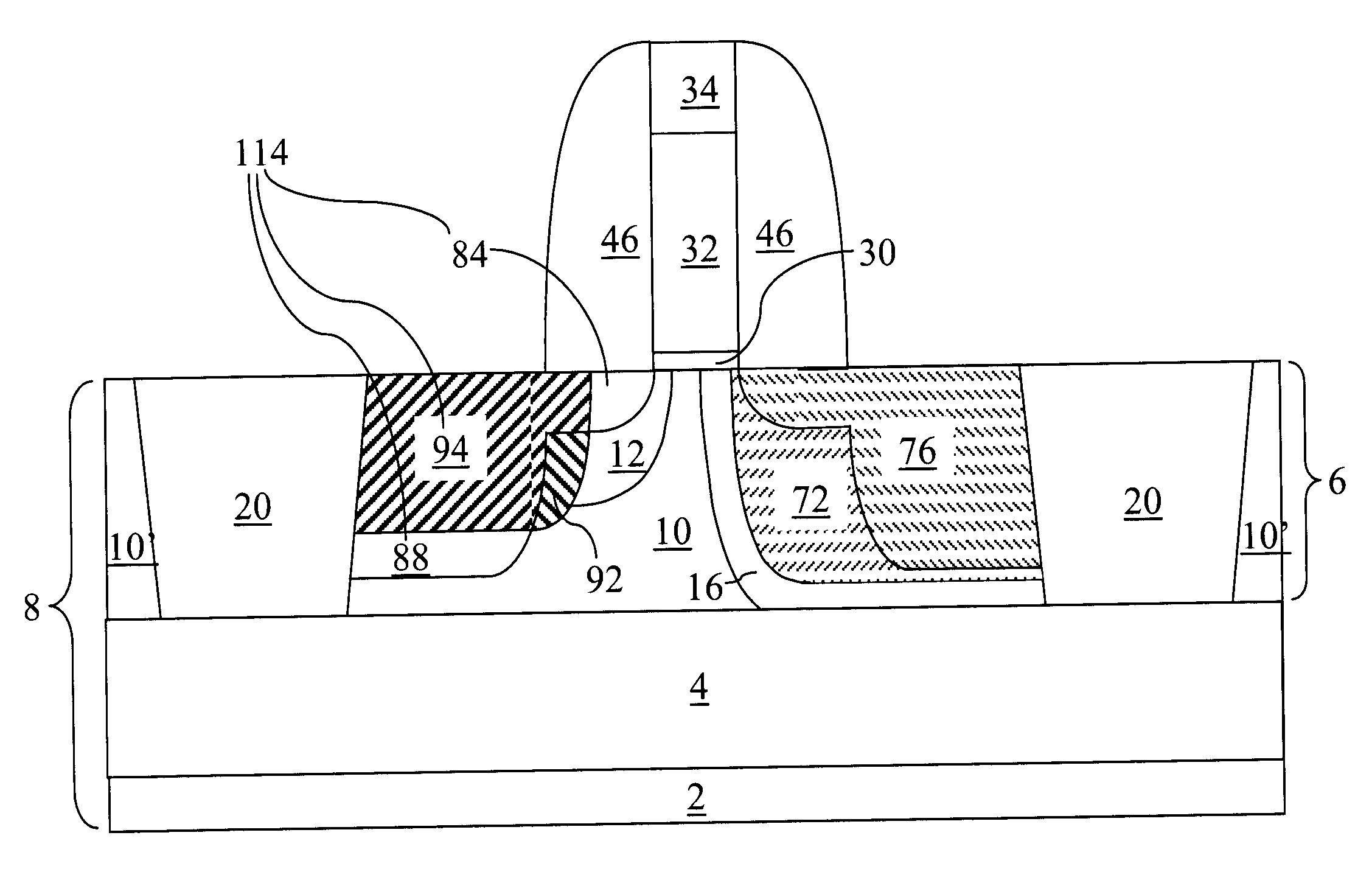

InactiveUS20090121258A1Suppress impact ionizationLarge band gapTransistorSemiconductor/solid-state device manufacturingSemiconductor materialsGate dielectric

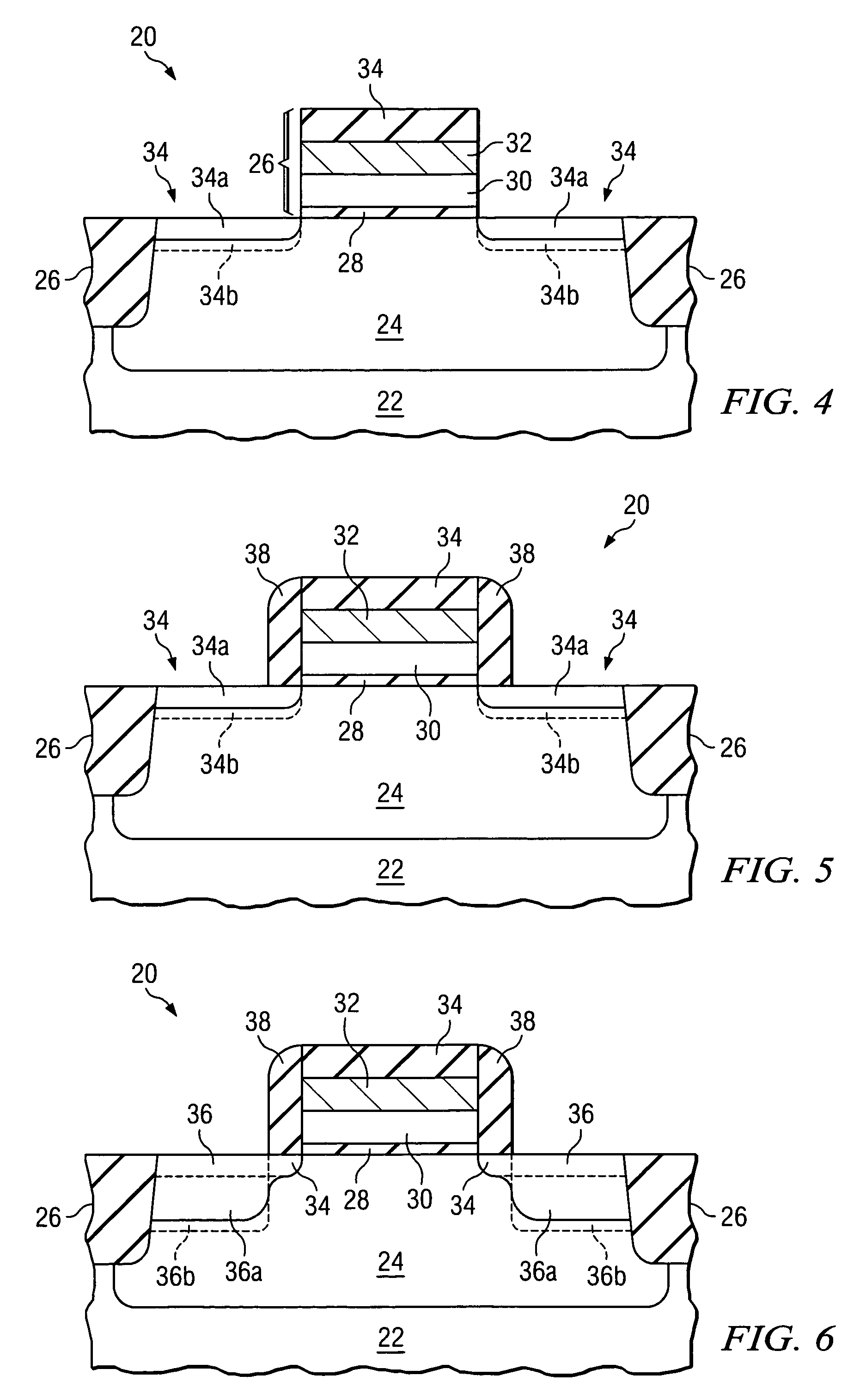

A field effect transistor comprising a silicon containing body is provided. After formation of a gate dielectric, gate electrode, and a first gate spacer, a drain side trench is formed and filled with a wide band gap semiconductor material. Optionally, a source side trench may be formed and filled with a silicon germanium alloy to enhance an on-current of the field effect transistor. Halo implantation and source and drain ion implantation are performed to form various doped regions. Since the wide band gap semiconductor material as a wider band gap than that of silicon, impact ionization is reduced due to the use of the wide band gap semiconductor material in the drain, and consequently, a breakdown voltage of the field effect transistor is increased compared to transistors employing silicon in the drain region.

Owner:GLOBALFOUNDRIES INC

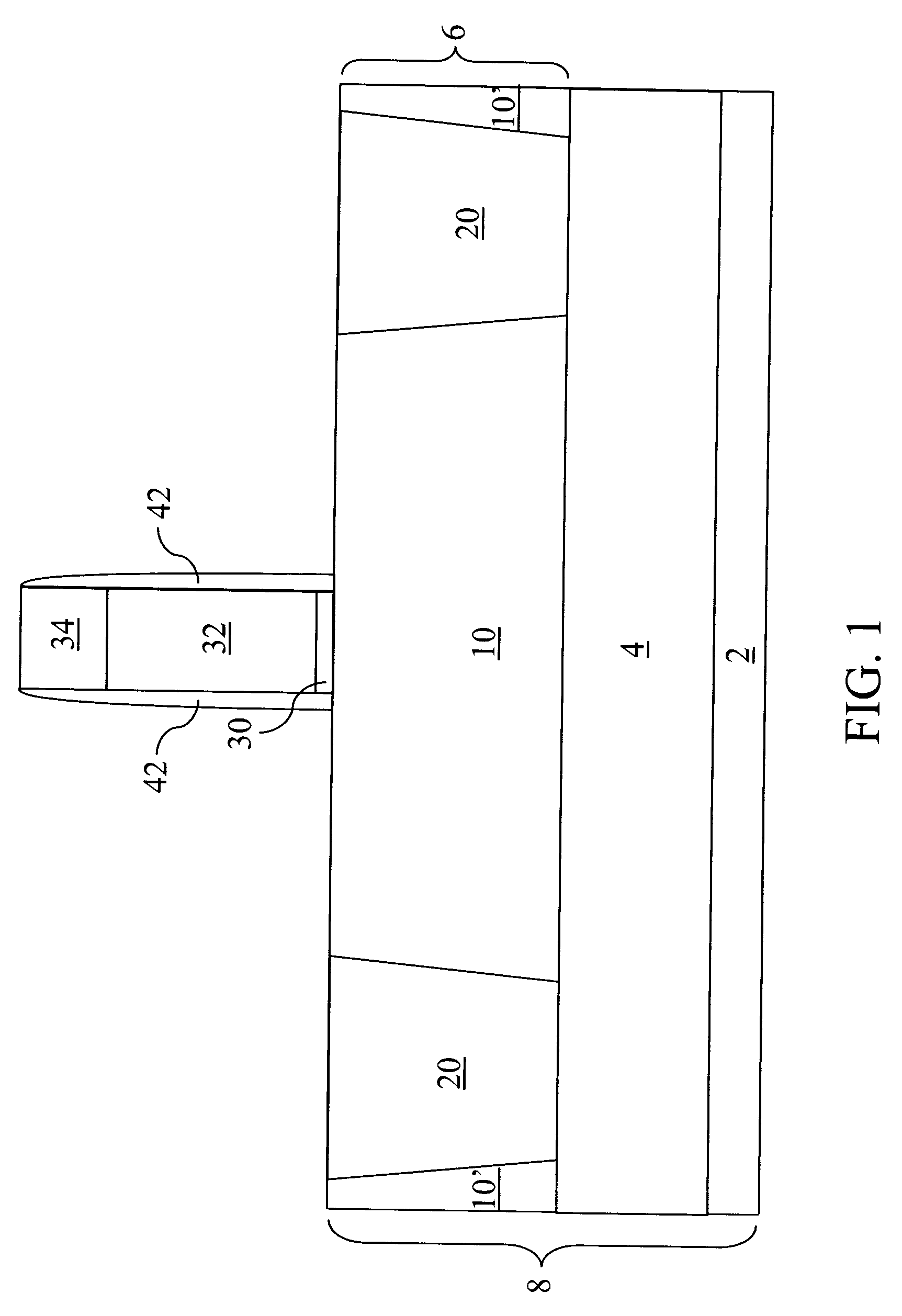

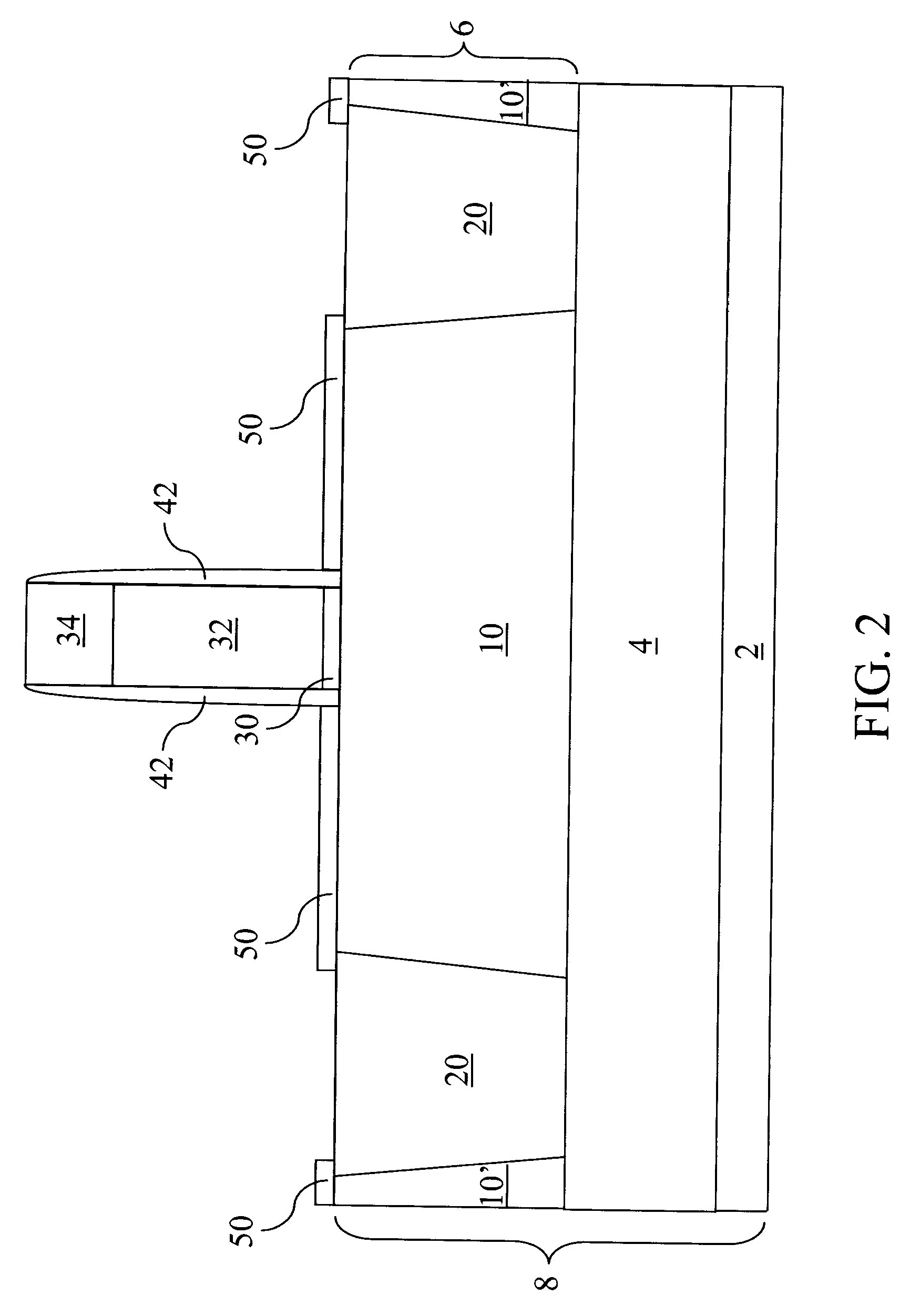

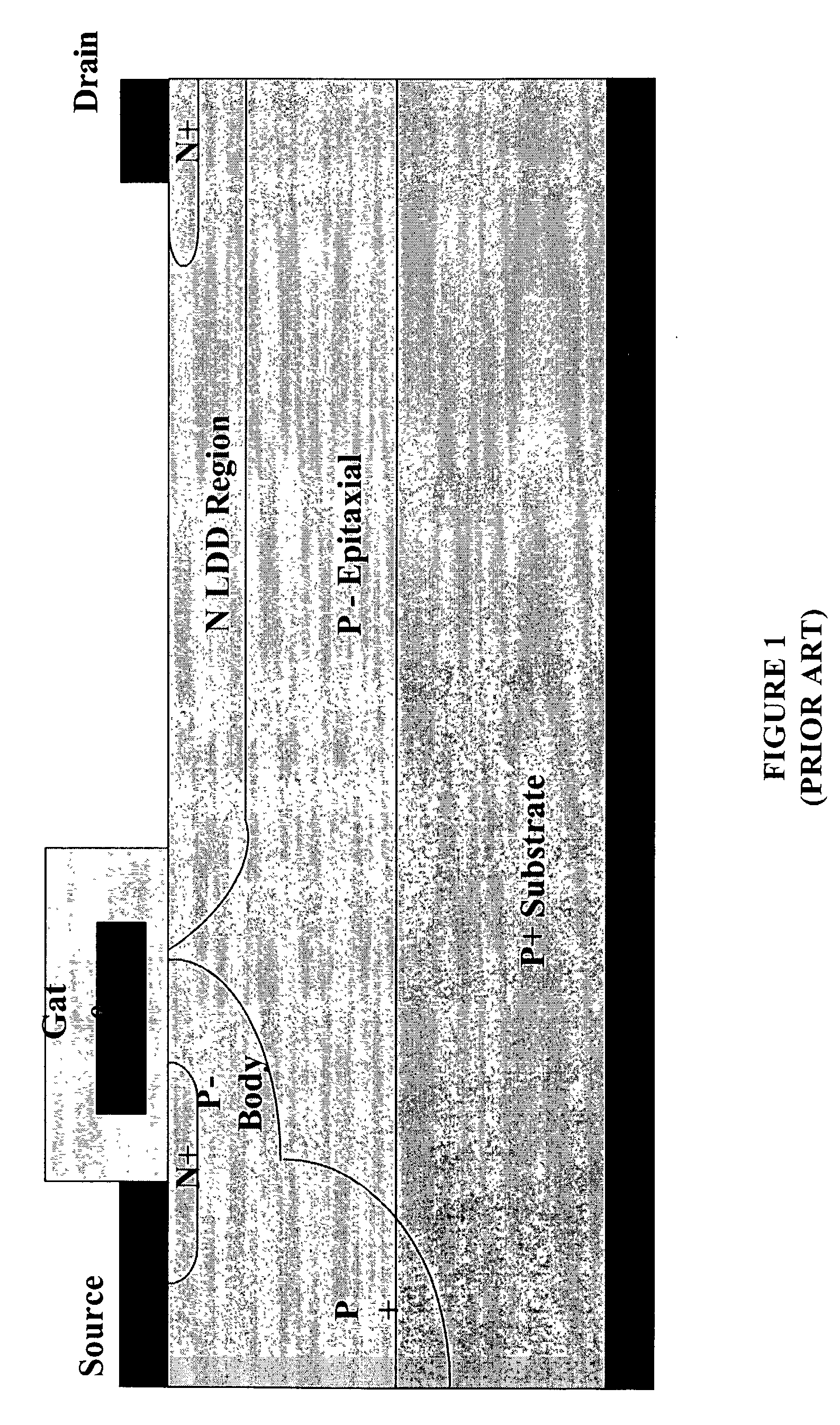

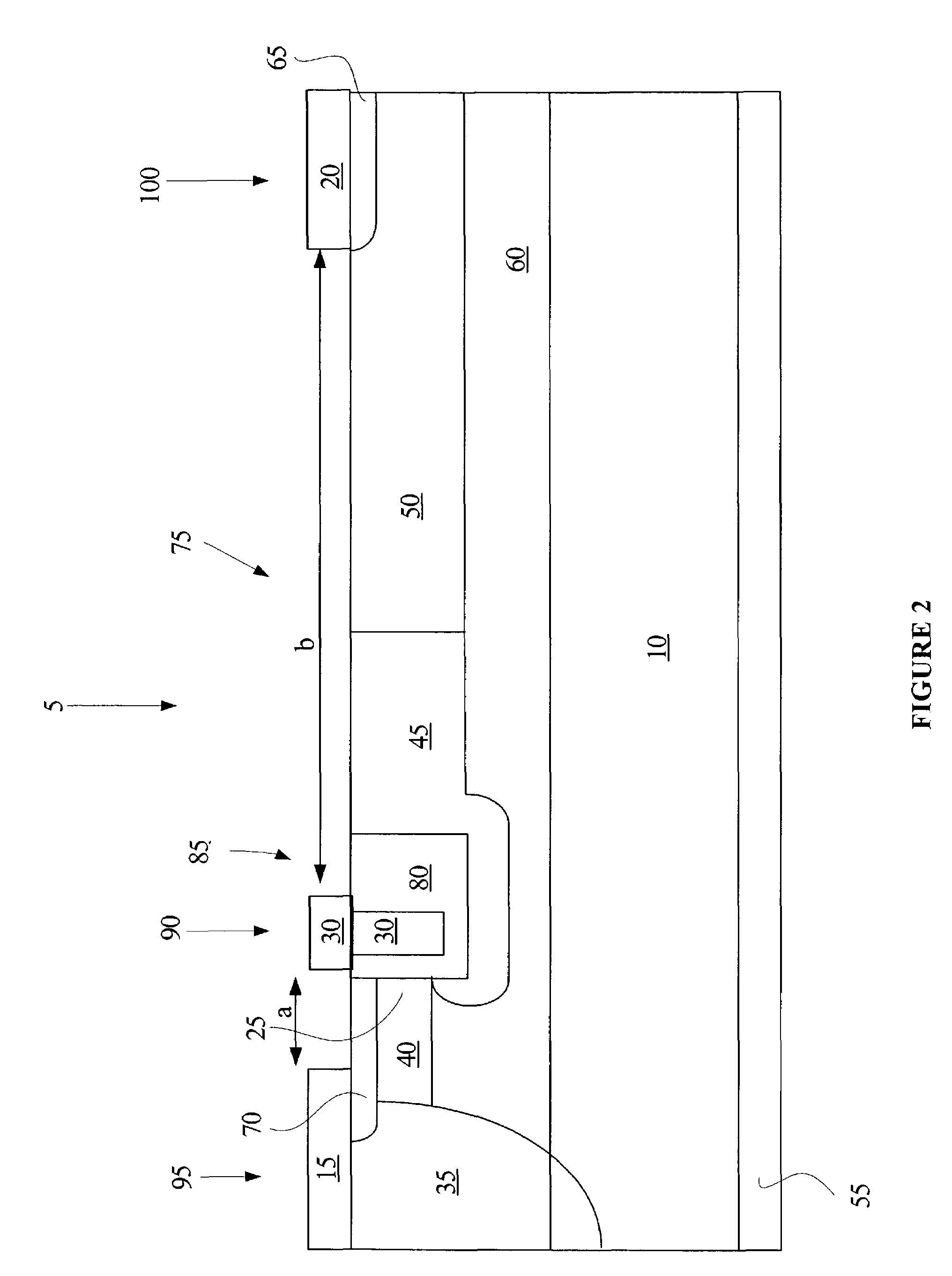

Trench gate laterally diffused MOSFET devices and methods for making such devices

InactiveUS7033891B2Well breakdown capabilityLow gate-drain capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesHot carrier effectElectric field

A MOSFET device for RF applications that uses a trench gate in place of the lateral gate used in lateral MOSFET devices is described. The trench gate in the devices of the invention is provided with a single, short channel for high frequency gain. The device of the invention is also provided with an asymmetric oxide in the trench gate, as well as LDD regions that lower the gate-drain capacitance for improved RF performance. Such features allow these devices to maintain the advantages of the LDMOS structure (better linearity), thereby increasing the RF power gain. The trench gate LDMOS of the invention also reduces the hot carrier effects when compared to regular LDMOS devices by reducing the peak electric field and impact ionization. Thus, the devices of the invention will have a better breakdown capability.

Owner:SEMICON COMPONENTS IND LLC

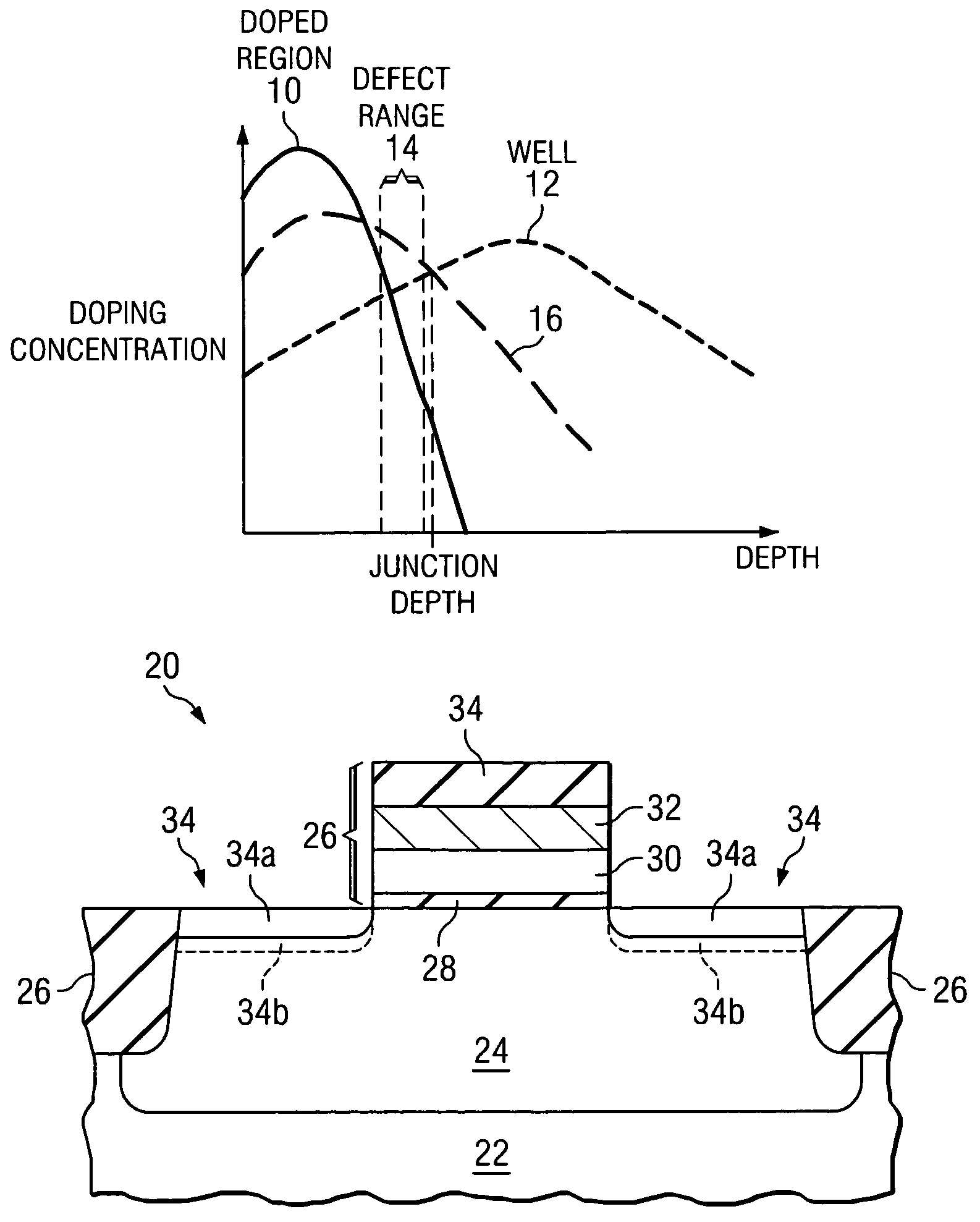

Implantation process in semiconductor fabrication

ActiveUS20060252239A1Smoothens junctionReduces band-to-band tunnelingTransistorSemiconductor/solid-state device manufacturingDopantOptoelectronics

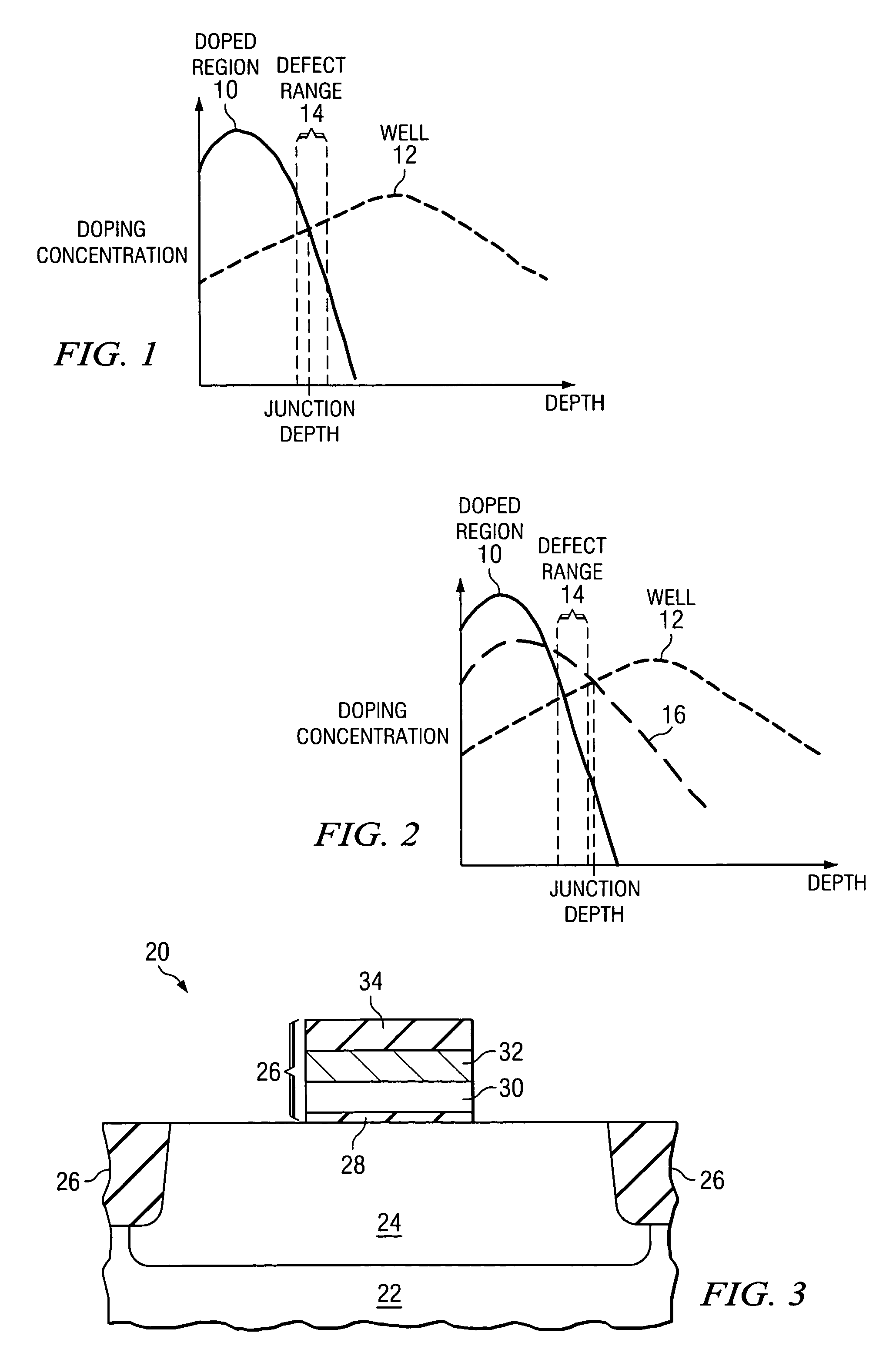

A semiconductor device is formed by performing an amorphizing ion implantation to implant dopants of a first conductivity type into a semiconductor body. The first ion implantation causes a defect area (e.g., end-of-range defects) within the semiconductor body at a depth. A non-amorphizing implantation implants dopants of the same conductivity type into the semiconductor body. This ion implantation step implants dopants throughout the defect area. The dopants can then be activated by heating the semiconductor body for less than 10 ms, e.g., using a flash anneal or a laser anneal.

Owner:INFINEON TECH AG

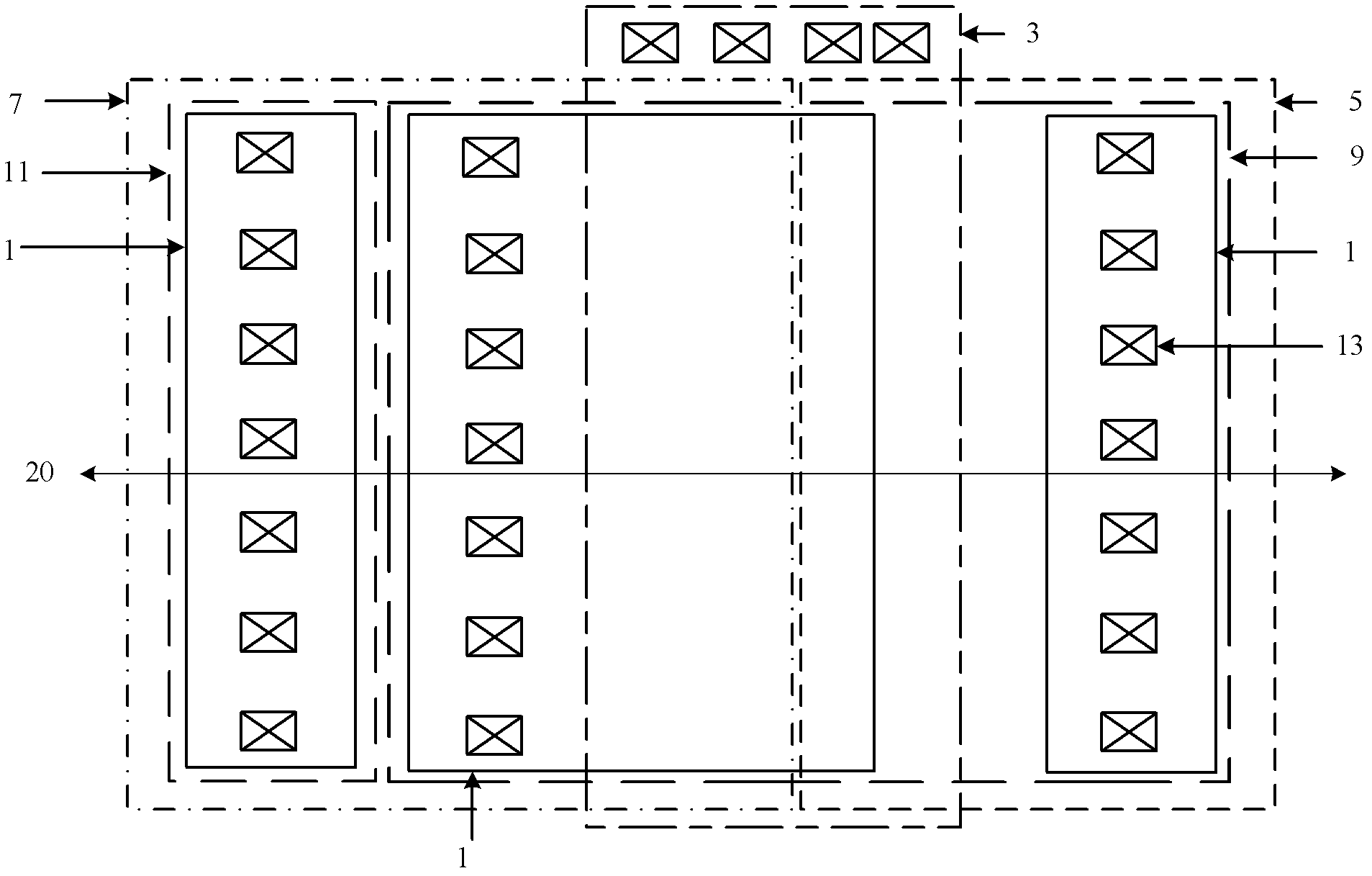

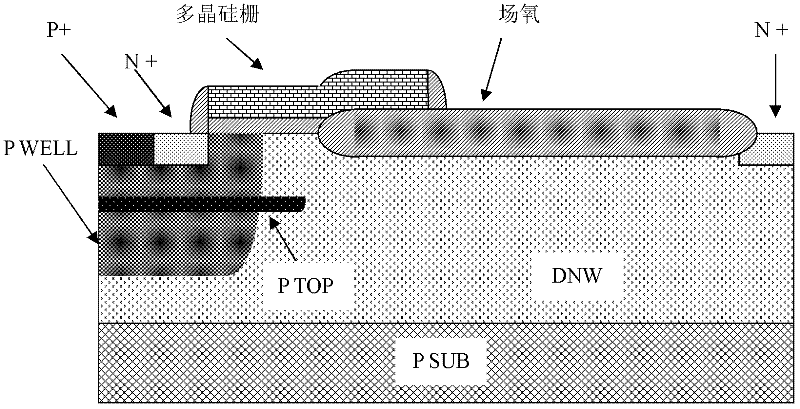

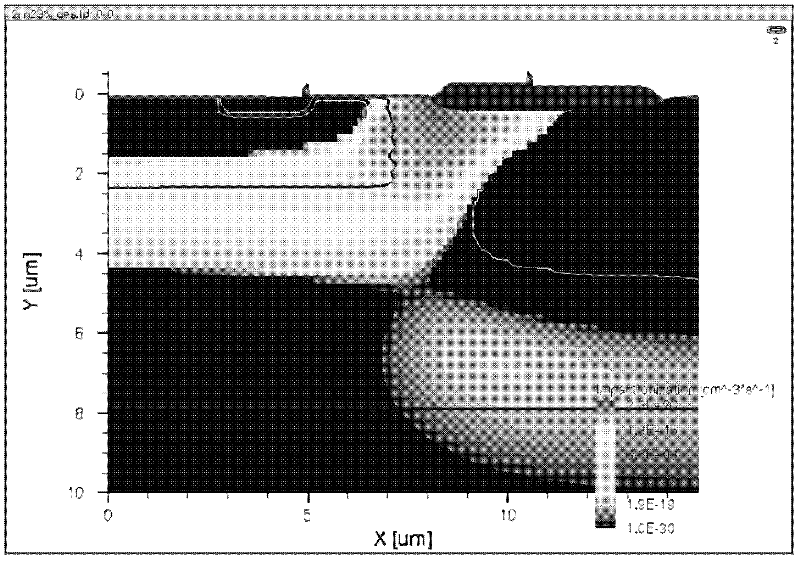

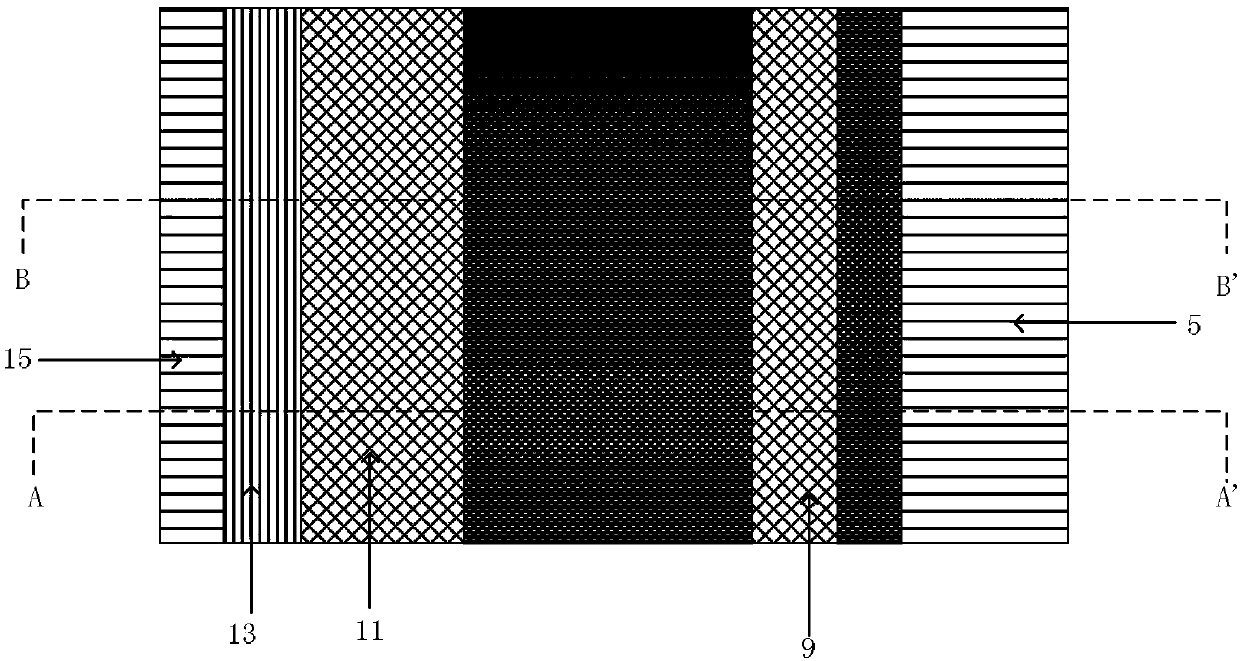

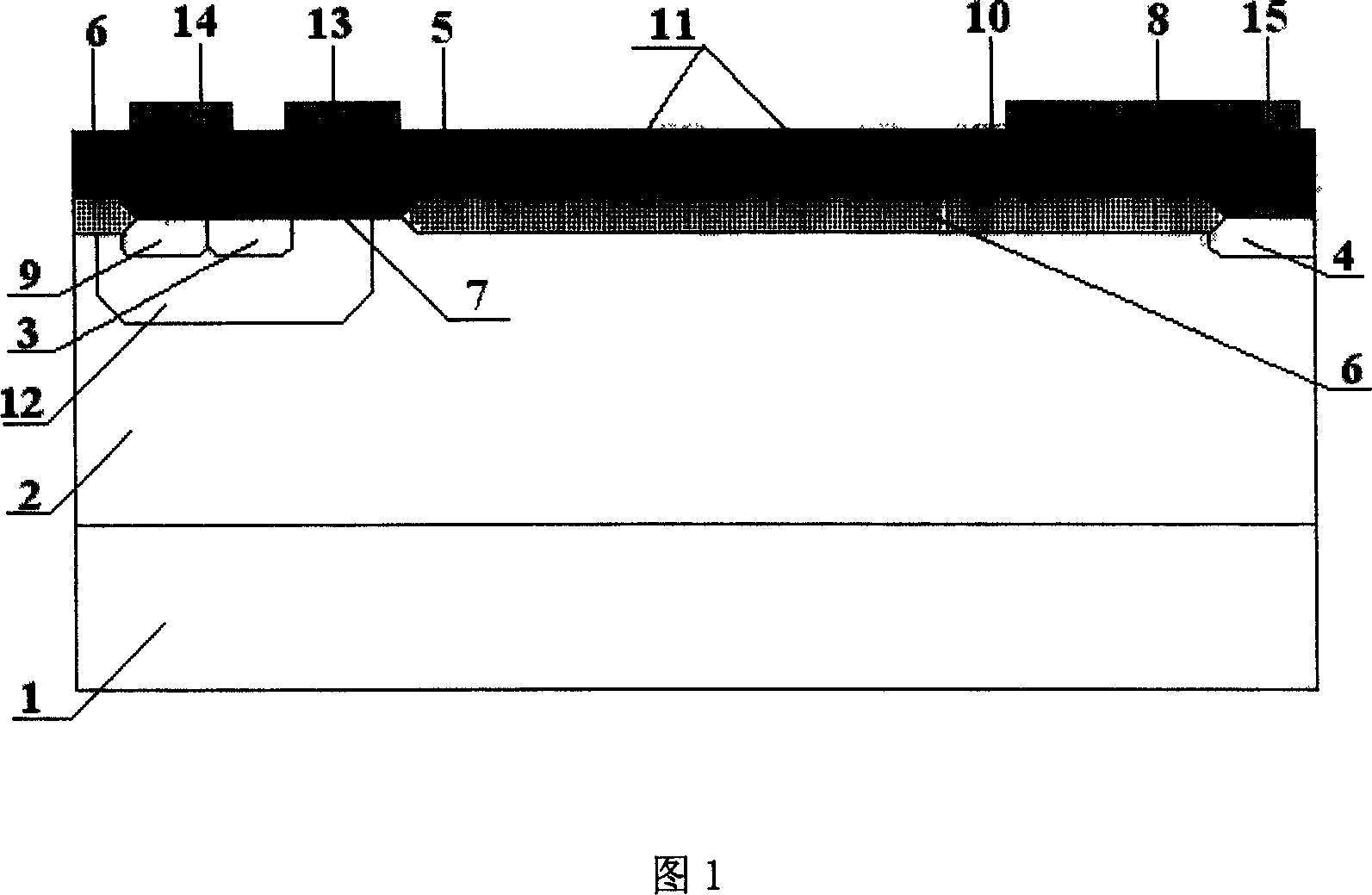

Preparation method of LDMOS (Laterally Diffused Metal Oxide Semiconductor) for efficiently collecting substrate current

InactiveCN102222620AAvoid burnsEfficient collectionSemiconductor/solid-state device manufacturingLDMOSBody region

The invention discloses an LDMOS (Laterally Diffused Metal Oxide Semiconductor) preparation method for efficiently collecting substrate current, wherein the method comprises the following steps: adopting standard preparation technology of LDMOS, and realizing the LSMOS capable of efficiently collecting the substrate current just through the following layout design, namely, using an active region, an N-type drift region and a P-type body region to form the drain region, the source region and the body leading-out region of an LDMOS device; defining a channel region by using polycrystalline; and realizing the drain electrode, the source electrode and the body leading-out electrode by using N+ injection and P+ injection. The regions used for source electrode leading-out N+ injection and the regions used for body leading-out P+ injection are arranged alternatively in the source region. In the invention, the body leading-out position is closer to the channel region formed by a hot carrier and the corresponding substrate current; therefore, the substrate current can be more efficiently collected, parasitical NPN (Negative-Positive-Negative) bipolar transistor is prevented from being turned on due to overlarge substrate current, the device is prevented from entering Snapback state for burning, and the purpose of enlarging safe work area of the LDMOS is achieved.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

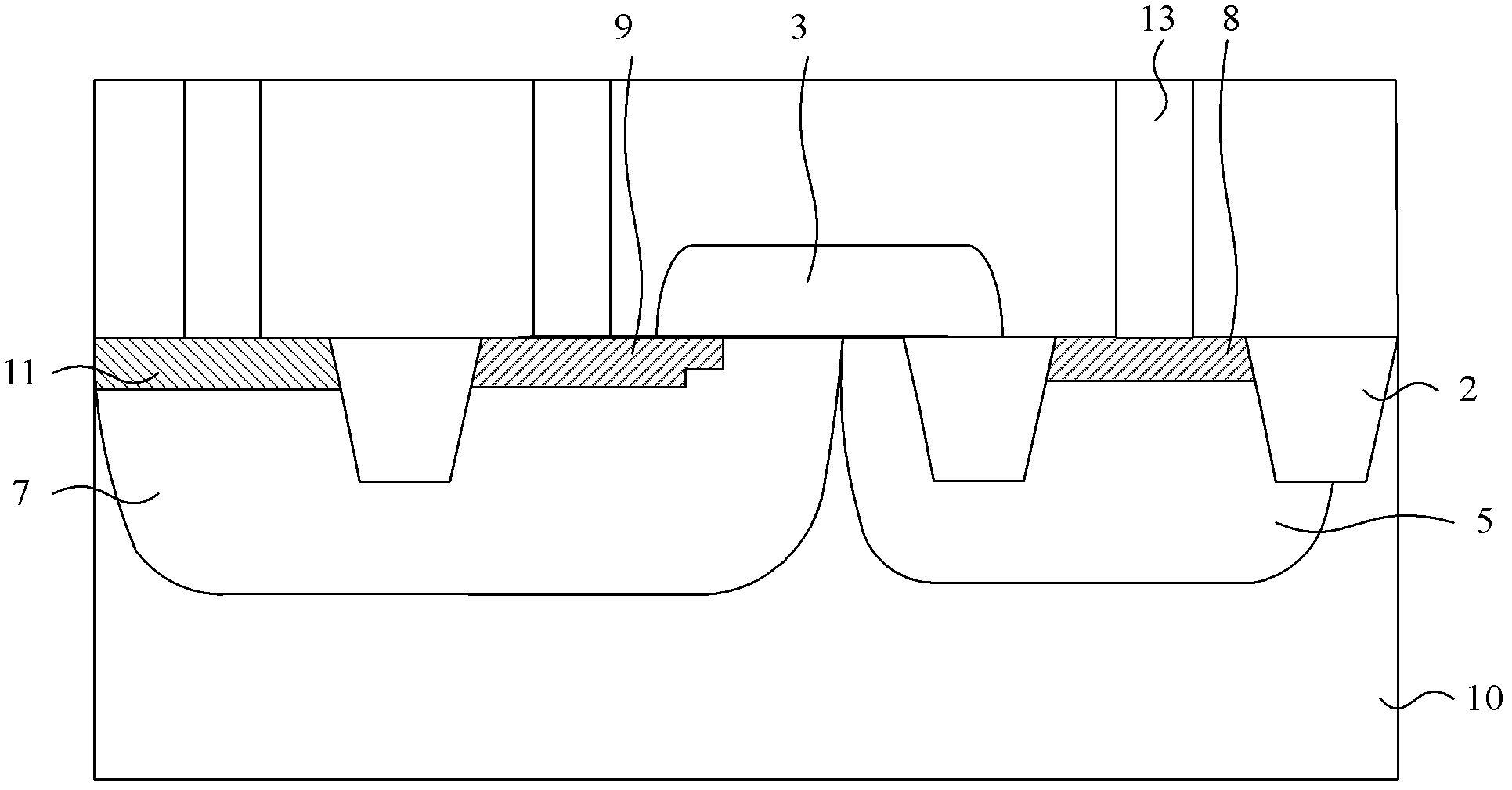

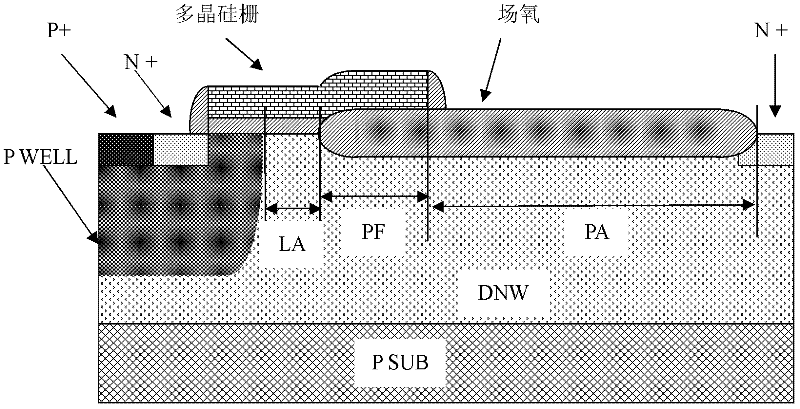

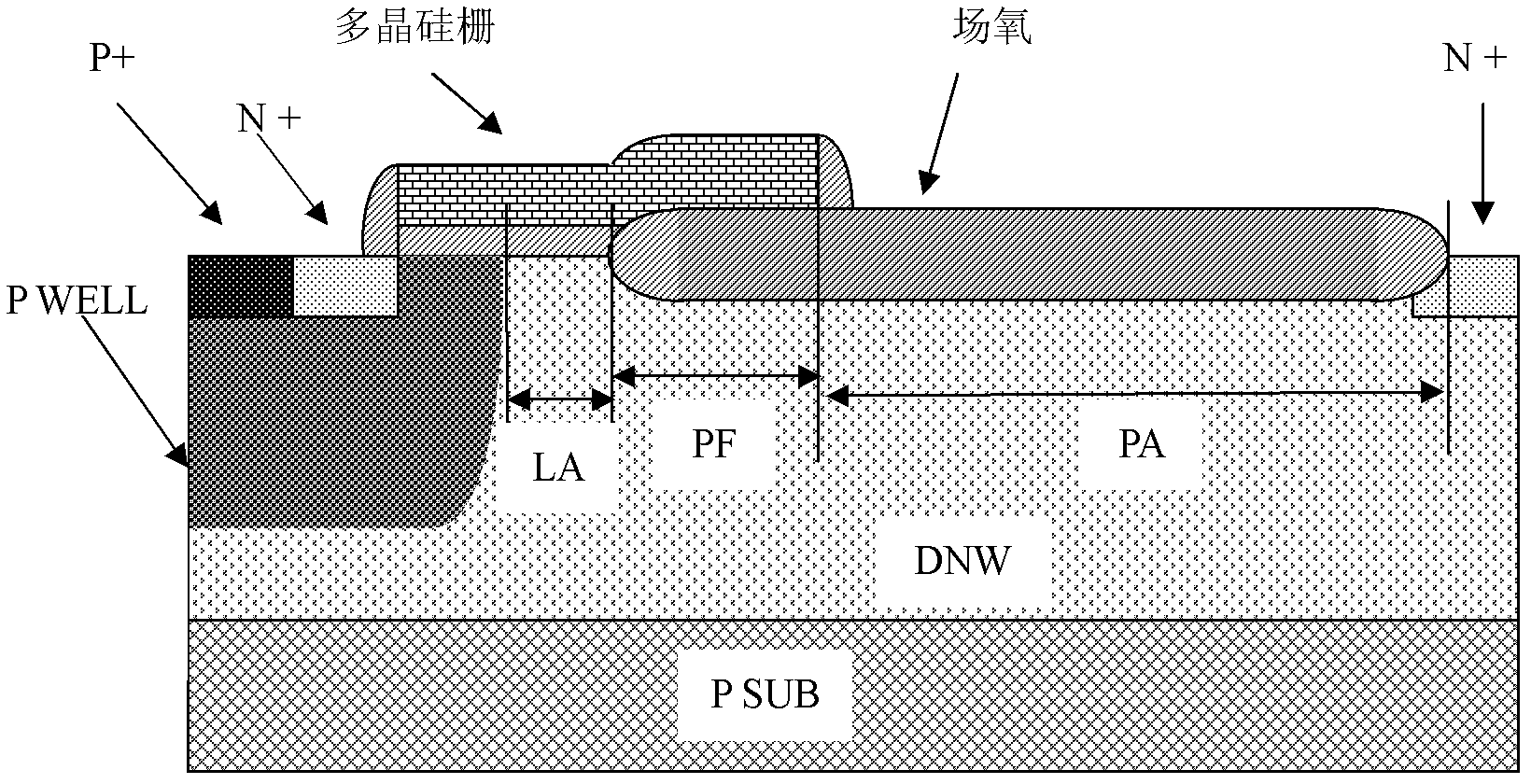

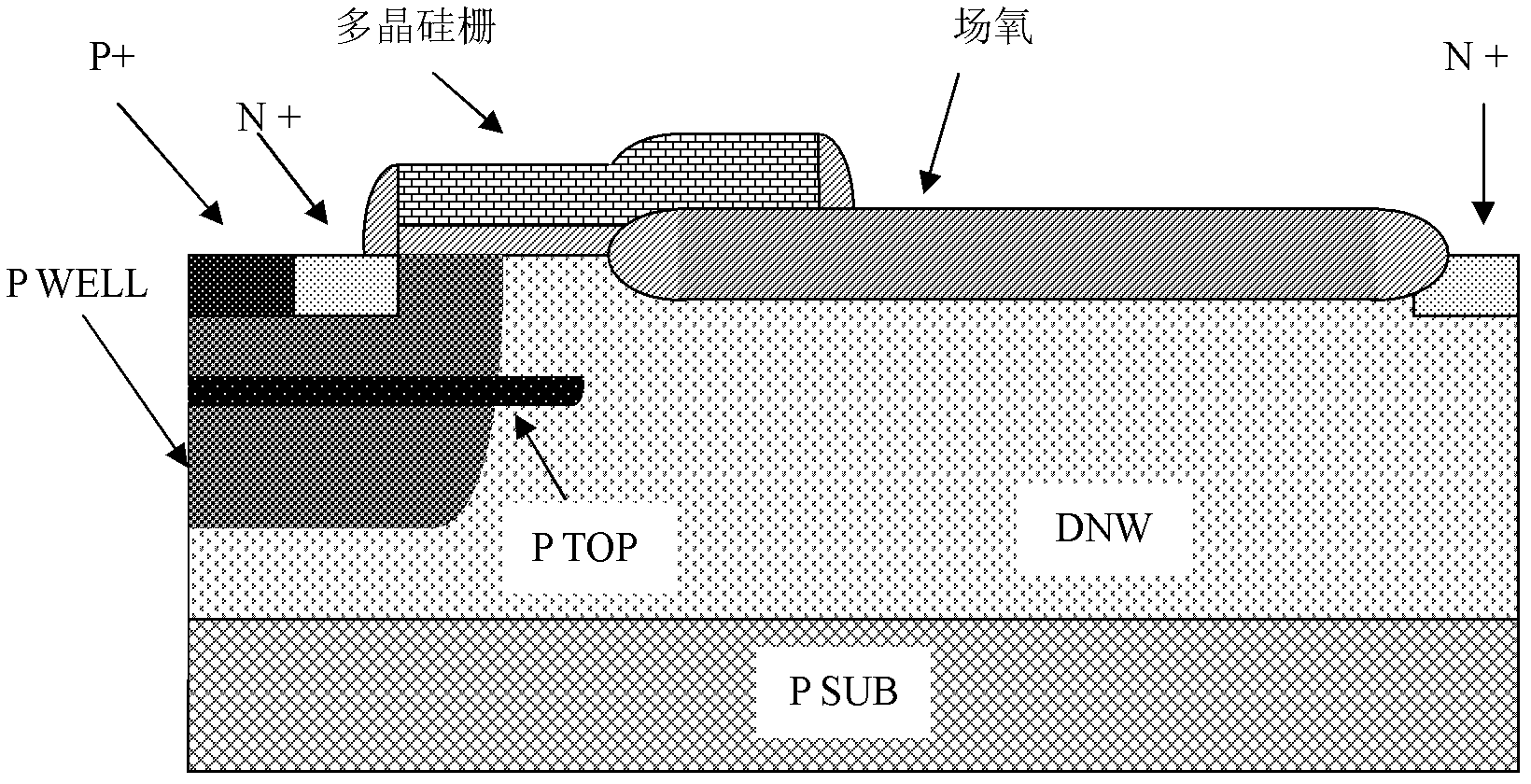

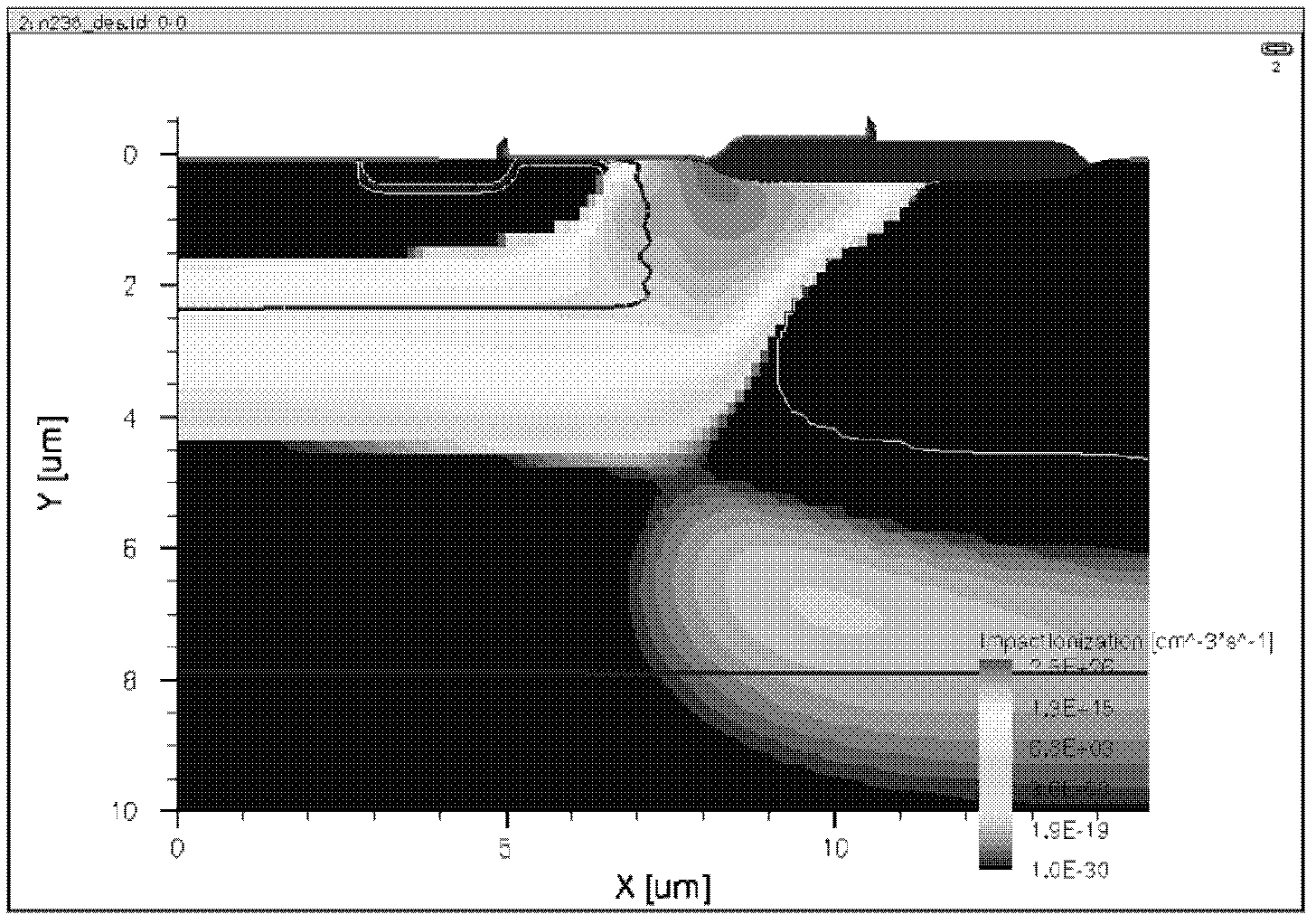

Method for improving breakdown voltage of N-groove laterally diffused metal oxide semiconductor (LDMOS)

ActiveCN102412162AReduced impact ionizationImprove pressure resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSEngineering

The invention discloses a method for improving breakdown voltage of an N-groove laterally diffused metal oxide semiconductor (LDMOS). The method comprises the following steps of:1, manufacturing a deep N well (DNW), implanting phosphorus into a P-type substrate (P SUB), and performing high-temperature drive-in and forming; 2, performing thermal growth to form field oxide, manufacturing a P well, and implanting boron impurities once or for multiple times; 3, manufacturing a PTOP, implanting boron impurities and forming after well implantation is finished and before gate oxide is grown; 4, manufacturing a polycrystalline silicon gate and a polycrystalline silicon field plate; after gate oxide is grown, depositing a layer of polycrystalline silicon, and defining the positions of the polycrystalline silicon gate and the field plate by etching; and manufacturing a source and a drain, after the polycrystalline silicon gate is formed, implanting phosphorus or arsenic into a device region once or for multiple times by using the polycrystalline silicon gate and the field oxide as hard masks, and implanting boron once or for multiple times to form P+ which is required by the P well. The impact ionization of the thinnest position of the device can be reduced, so that voltage resistance of the device can be improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Field effect transistor containing a wide band gap semiconductor material in a drain

InactiveUS7936042B2Increase the on-currentGreat band gapSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsGate dielectric

A field effect transistor comprising a silicon containing body is provided. After formation of a gate dielectric, gate electrode, and a first gate spacer, a drain side trench is formed and filled with a wide band gap semiconductor material. Optionally, a source side trench may be formed and filled with a silicon germanium alloy to enhance an on-current of the field effect transistor. Halo implantation and source and drain ion implantation are performed to form various doped regions. Since the wide band gap semiconductor material as a wider band gap than that of silicon, impact ionization is reduced due to the use of the wide band gap semiconductor material in the drain, and consequently, a breakdown voltage of the field effect transistor is increased compared to transistors employing silicon in the drain region.

Owner:GLOBALFOUNDRIES INC

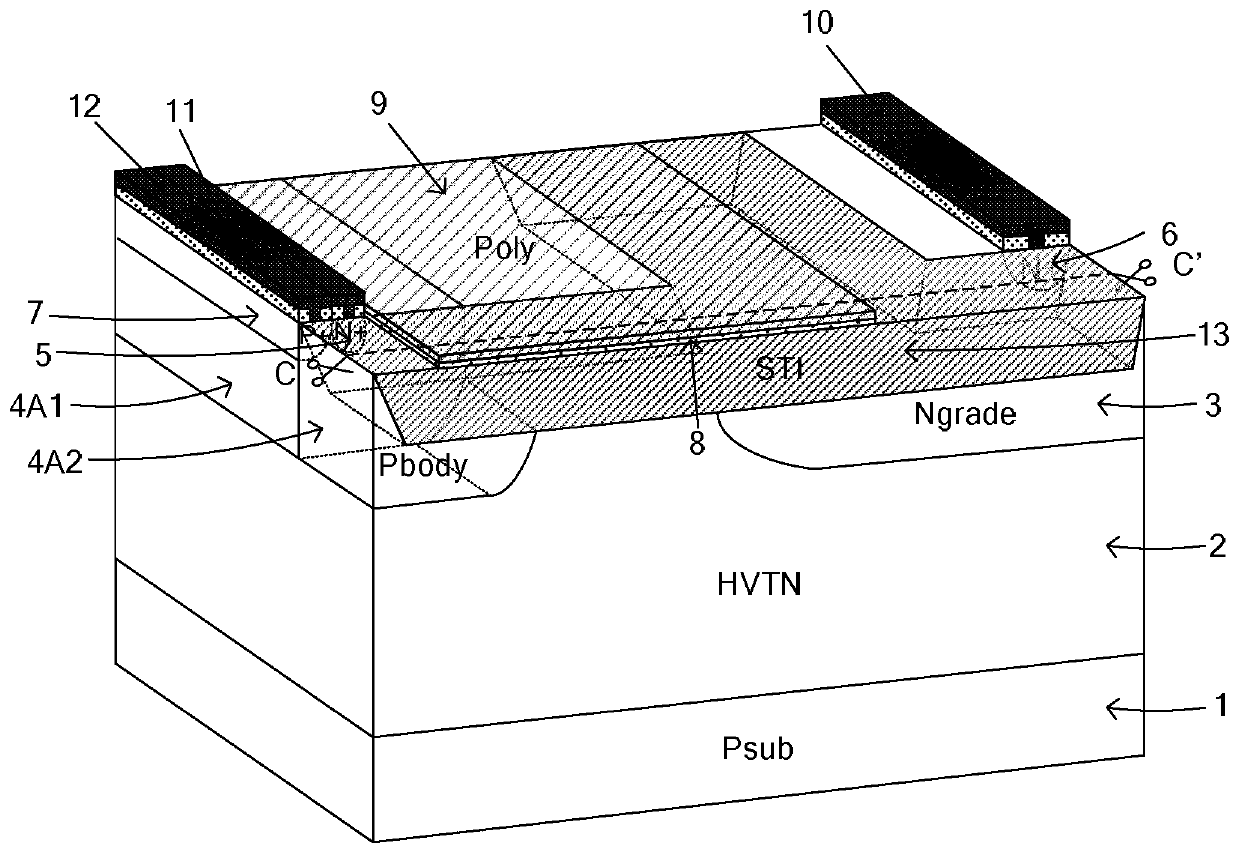

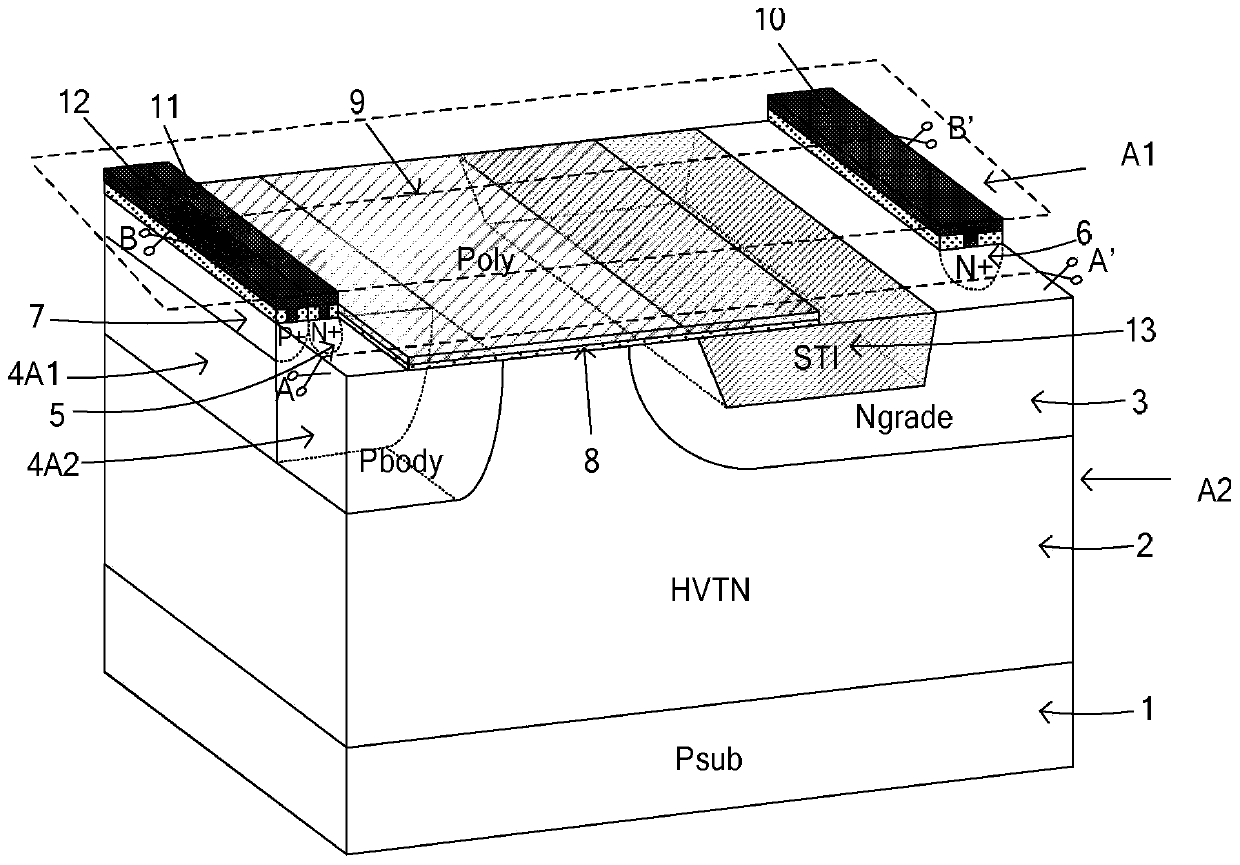

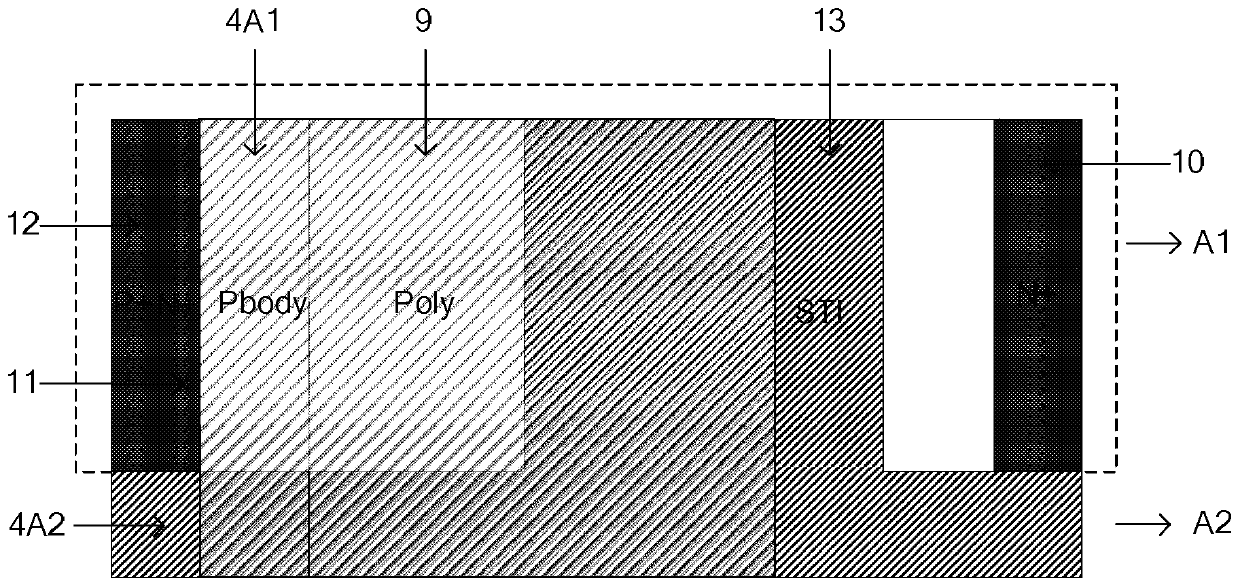

Lateral double-diffused metal oxide semiconductor device

ActiveCN107342325AImprove breakdown voltageLarge off-state breakdown voltageSemiconductor devicesHigh pressurePolysilicon gate

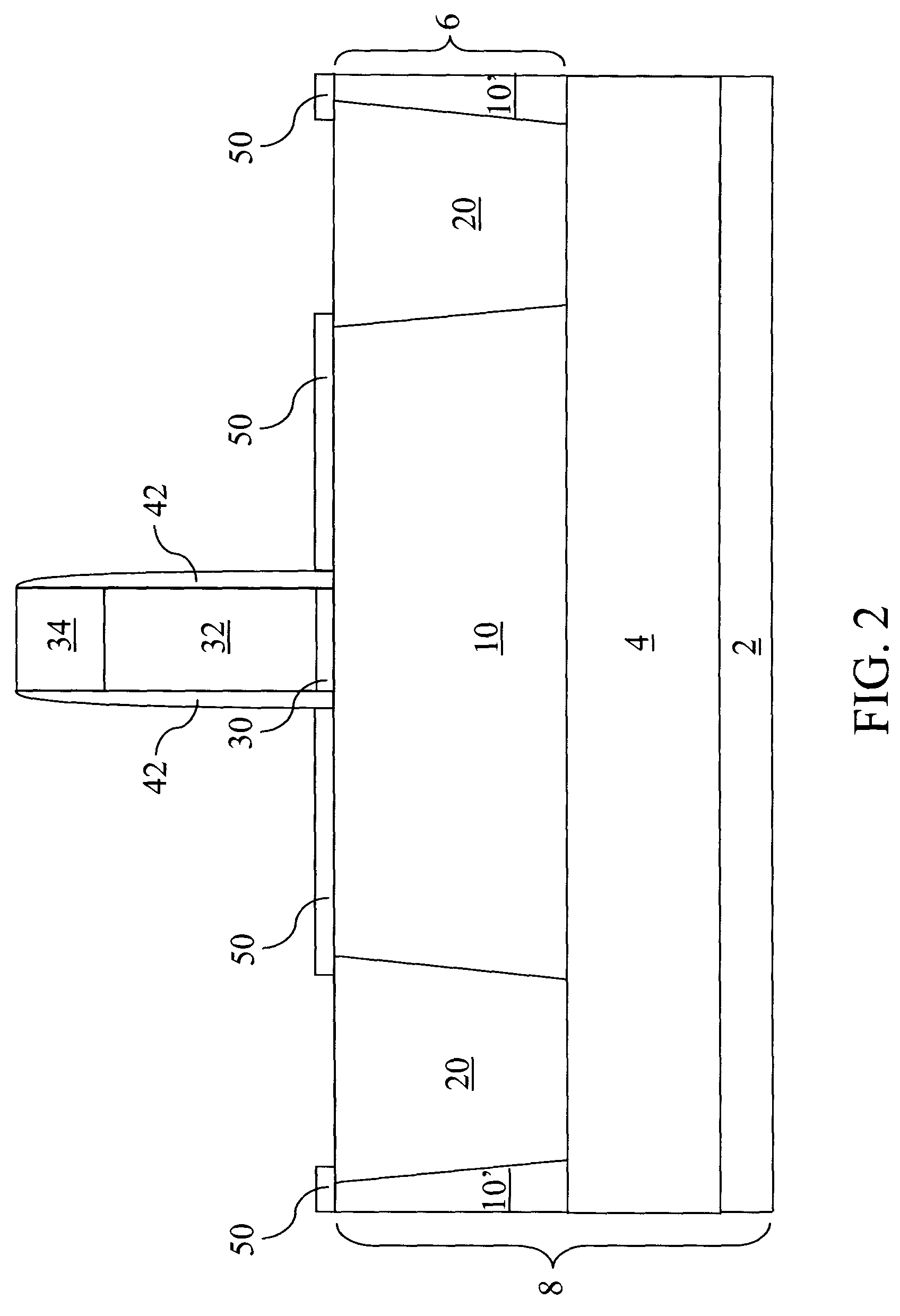

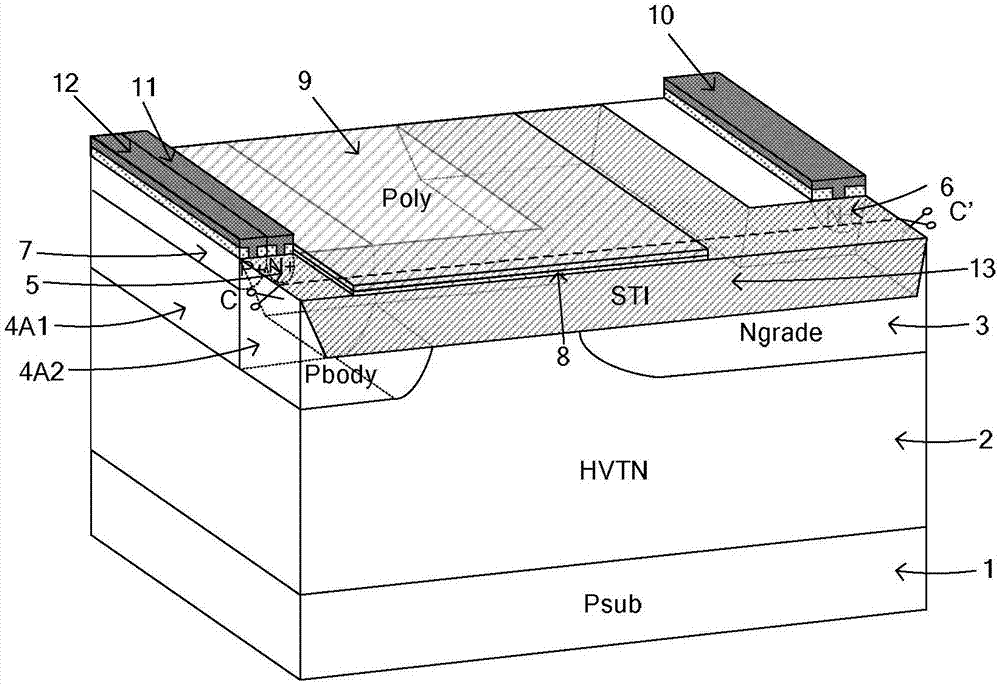

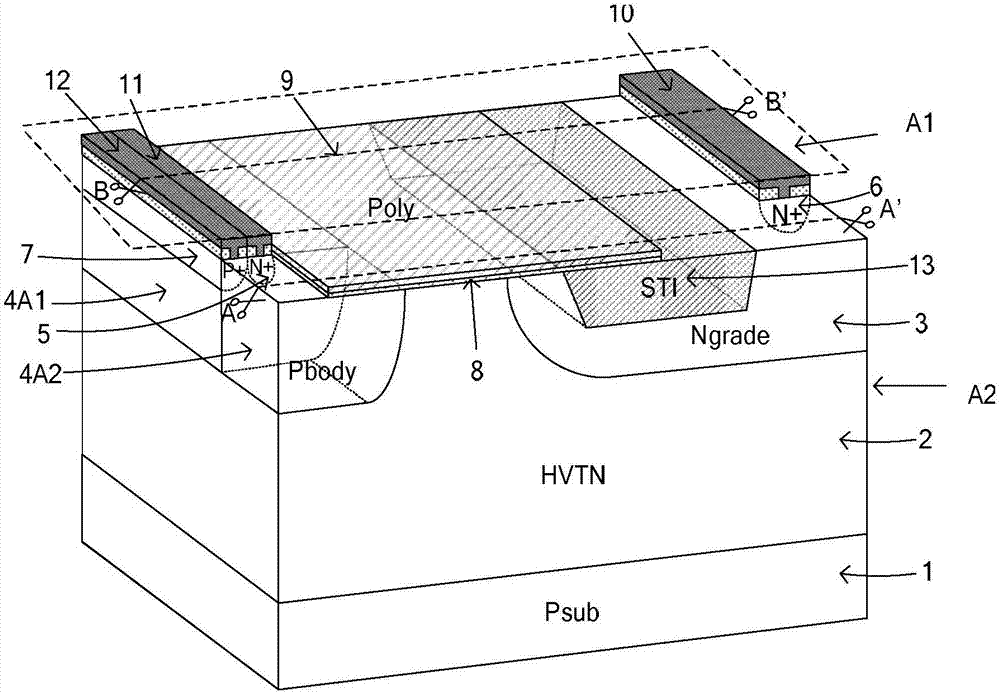

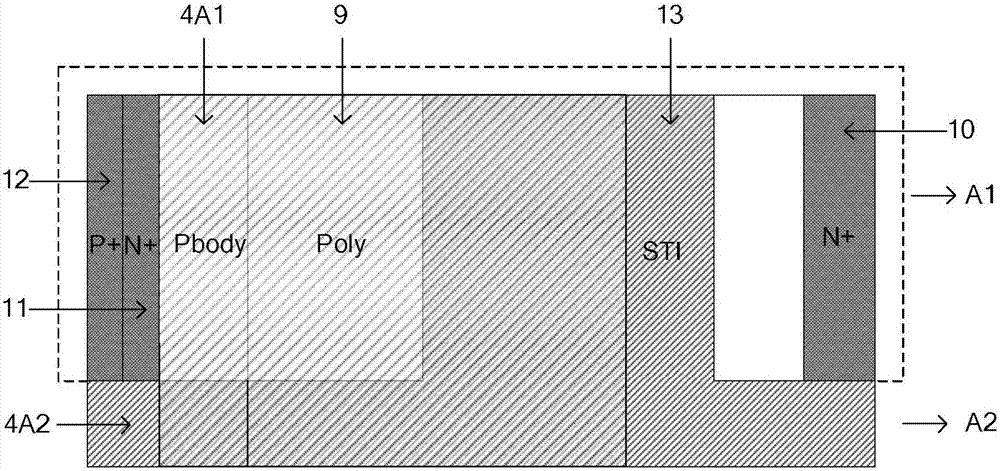

The invention relates to a lateral double-diffused metal oxide semiconductor device. The lateral double-diffused metal oxide semiconductor device comprises a device part, a terminal part and a P type substrate; a high-voltage N type region, an N type drift region, a P type body region 4A1 and a P type body region 4A2 are arranged over the P type substrate; the P type body region 4A1 is positioned in the device part; the P type body region 4A2 is positioned in the terminal part, and formed by diffusion of the P type body region 4A1 in the device part; a gate oxidization layer and a polycrystalline silicon gate field plate are also arranged over the high-voltage N type region; the device part further comprises an N type drain region, an N type source region, a P type region and a metal contact, wherein a shallow trench isolation region is arranged in the N type drift region; the shallow trench isolation region is shaped as a straight bar; the shallow trench isolation region extends to the terminal part from the device part; namely, the width of the shallow trench isolation region is the same as that of the N type drift region; and furthermore, the N type drain region, the N type source region, the P type region and the metal contact are not arranged over the P type body region 4A2 and the N type drift region of the terminal part. By means of the lateral double-diffused metal oxide semiconductor device disclosed by the invention, the breakdown voltage is improved when various performance parameters of an LDMOS device are kept same.

Owner:SOUTHEAST UNIV

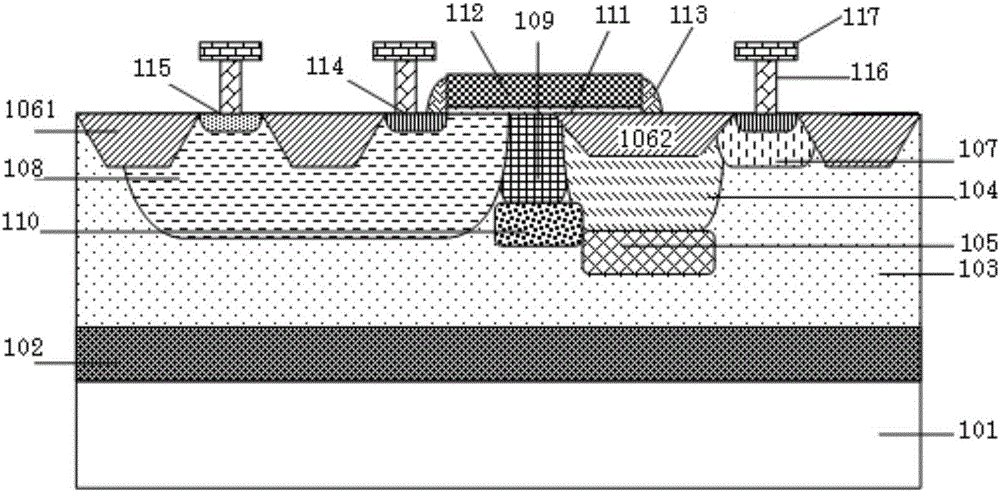

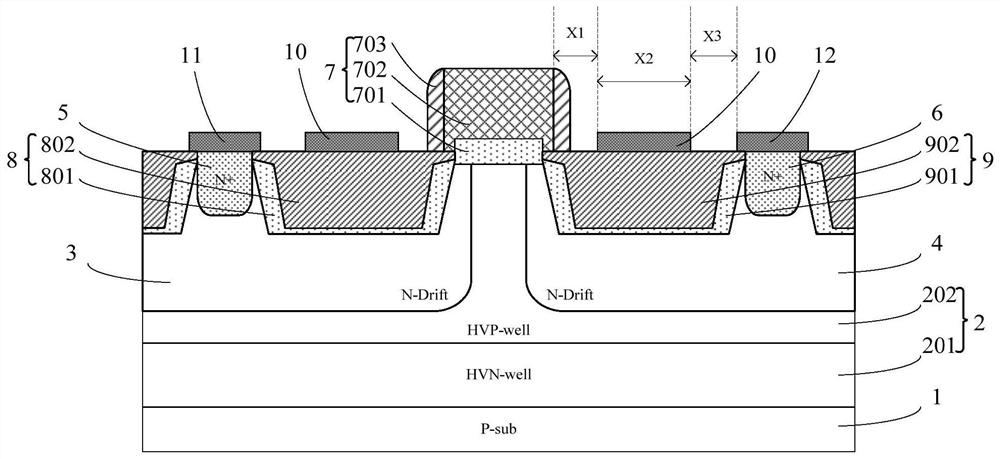

LDMOS device and manufacturing method thereof

ActiveCN106298935AReduced impact ionizationLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSGate oxide

The invention discloses an LDMOS device which comprises a P-type epitaxial layer, an N-well, a P-well, a first N-type drift region, a first P-type layer, a second N-type drift region, a second P-type layer, a gate oxide layer and gate polysilicon. The P-well, the second N-type drift region, the first N-type drift region and the N-well are sequentially contiguous from left to right at the upper part of the P-type epitaxial layer. The second N-type drift region is shallower than the first N-type drift region. The second P-type layer is adjacent to the lower part of the second N-type drift region. The first P-type layer is adjacent to the lower part of the first N-type drift region. The second P-type layer is shallower than the first P-type layer. The second P-type layer has a higher doping concentration than the first P-type layer. The invention further discloses a manufacturing method for the LDMOS device. According to the invention, the LDMOS device has lower on-resistance, and can satisfy off-state breakdown voltage and on-state breakdown voltage at the same time.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Implantation process in semiconductor fabrication

ActiveUS7172954B2Small diffusionSmoothens junctionTransistorSemiconductor/solid-state device manufacturingDopantIon implantation

A semiconductor device is formed by performing an amorphizing ion implantation to implant dopants of a first conductivity type into a semiconductor body. The first ion implantation causes a defect area (e.g., end-of-range defects) within the semiconductor body at a depth. A non-amorphizing implantation implants dopants of the same conductivity type into the semiconductor body. This ion implantation step implants dopants throughout the defect area. The dopants can then be activated by heating the semiconductor body for less than 10 ms, e.g., using a flash anneal or a laser anneal.

Owner:INFINEON TECH AG

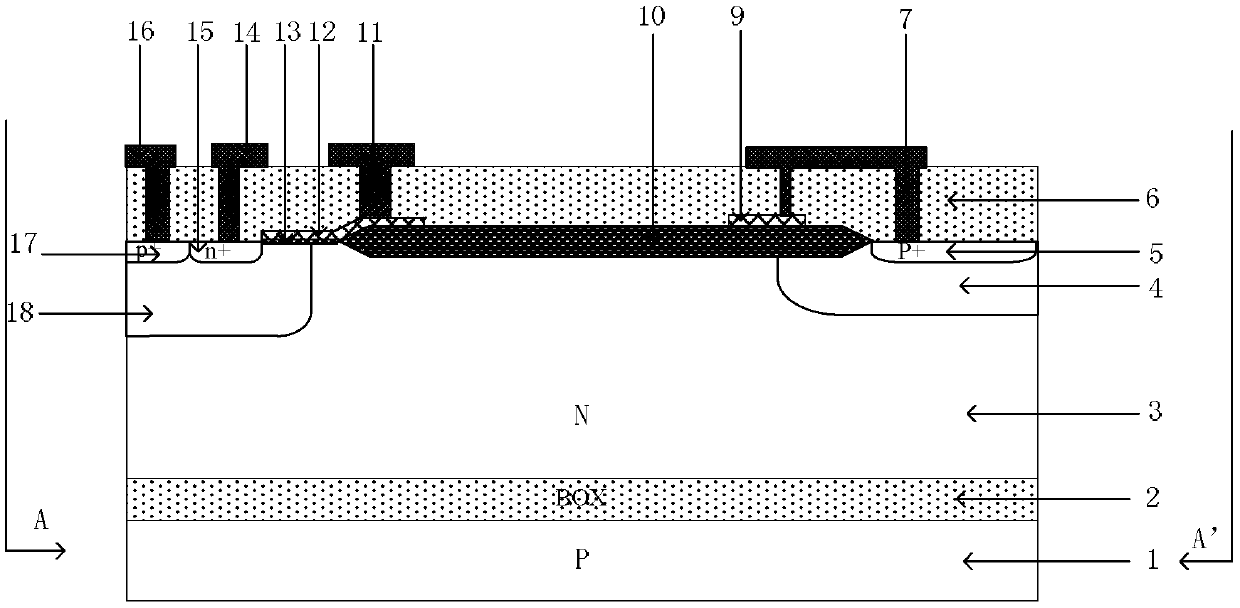

Method of manufacturing a semiconductor integrated circuit and semiconductor integrated circuit

InactiveUS20070254426A1Reduce generationReduce concentrationTransistorSolid-state devicesHigh densityLOCOS

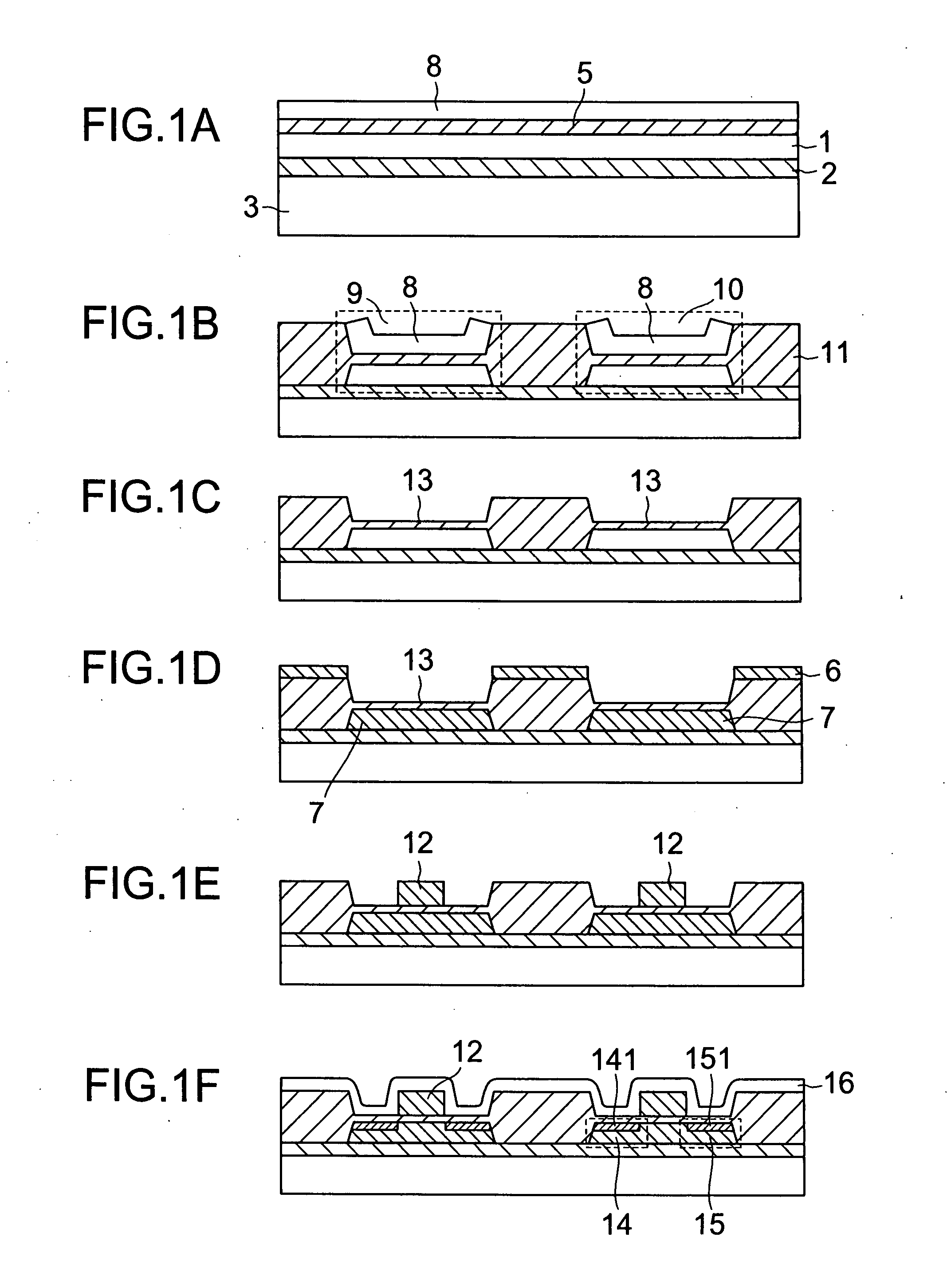

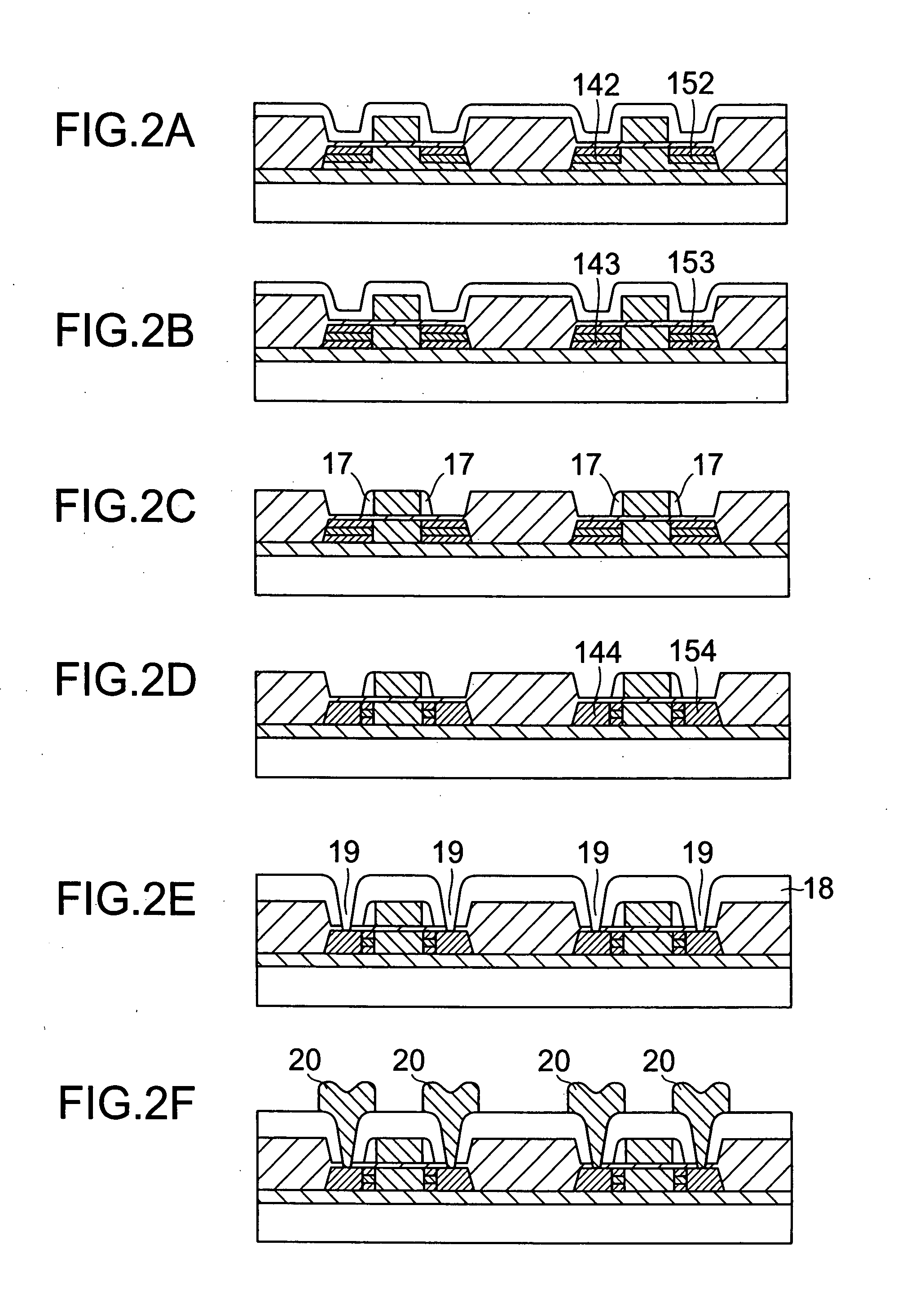

Conventionally, when an electric potential of a supporting substrate is fixed, there arises a problem in that impact ions are generated even in the vicinity of embedded insulating film in the proximity of a drain due to generation of a parasitic transistor using the supporting substrate as a gate so as to be likely to cause a parasitic bipolar operation. A method of the present invention includes the steps of: forming and patterning a LOCOS reaching an embedded insulating film, a gate oxide film, a well and a polysilicon film serving as a gate electrode; forming a second conductivity type high-density impurity region in an ultra-shallow portion of each of a source region and a drain region, a second conductivity type impurity region having a low density under the second conductivity type high-density impurity region of the ultra-shallow portion, and a second conductivity type impurity region having a high density under the second conductivity type impurity region having a low density and above the embedded insulating film; forming a sidewall around the gate electrode; forming a second conductivity type impurity region in each of the source region and the drain region; forming an interlayer insulating film and forming contact holes in the source region, the drain region and the gate electrode; and forming a wiring on the interlayer insulating film.

Owner:ABLIC INC

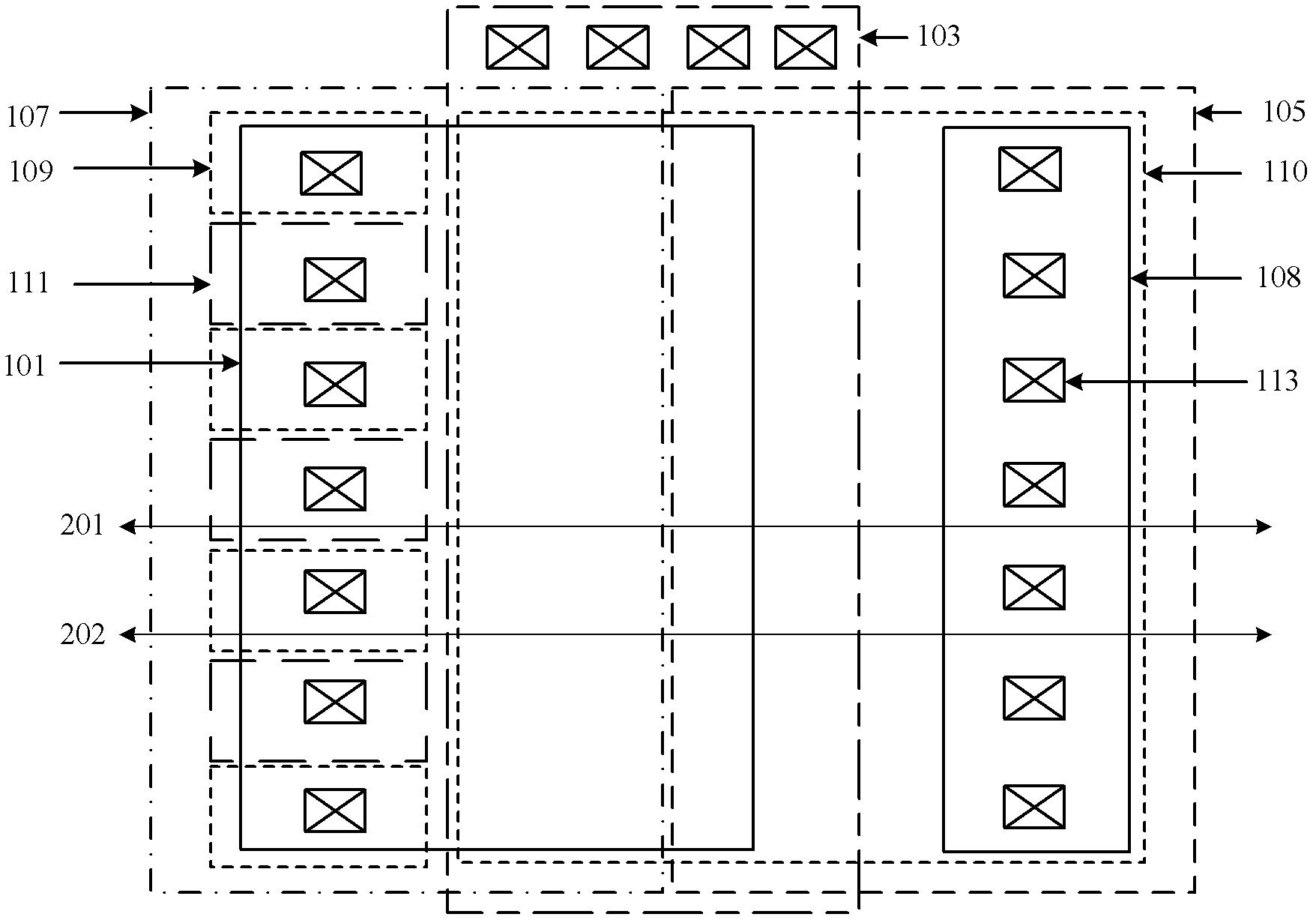

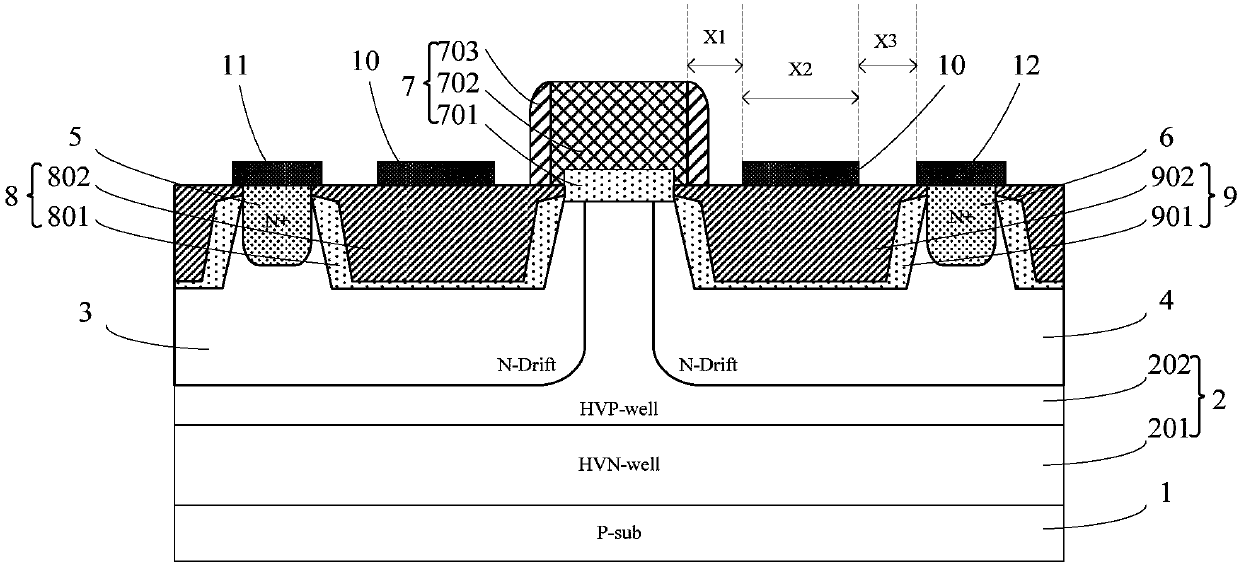

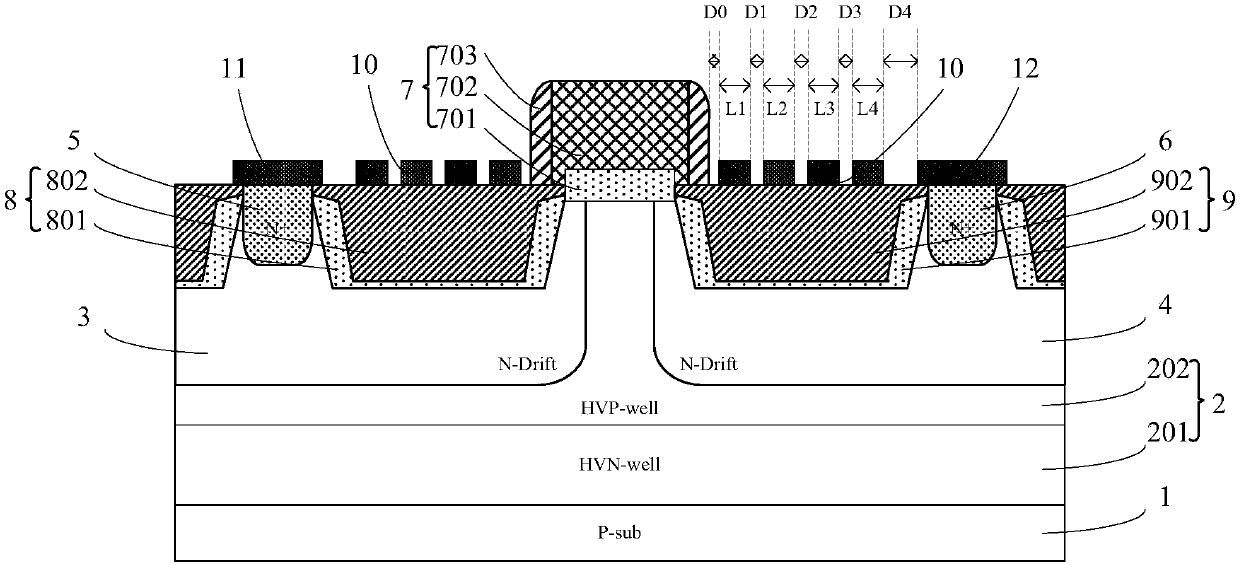

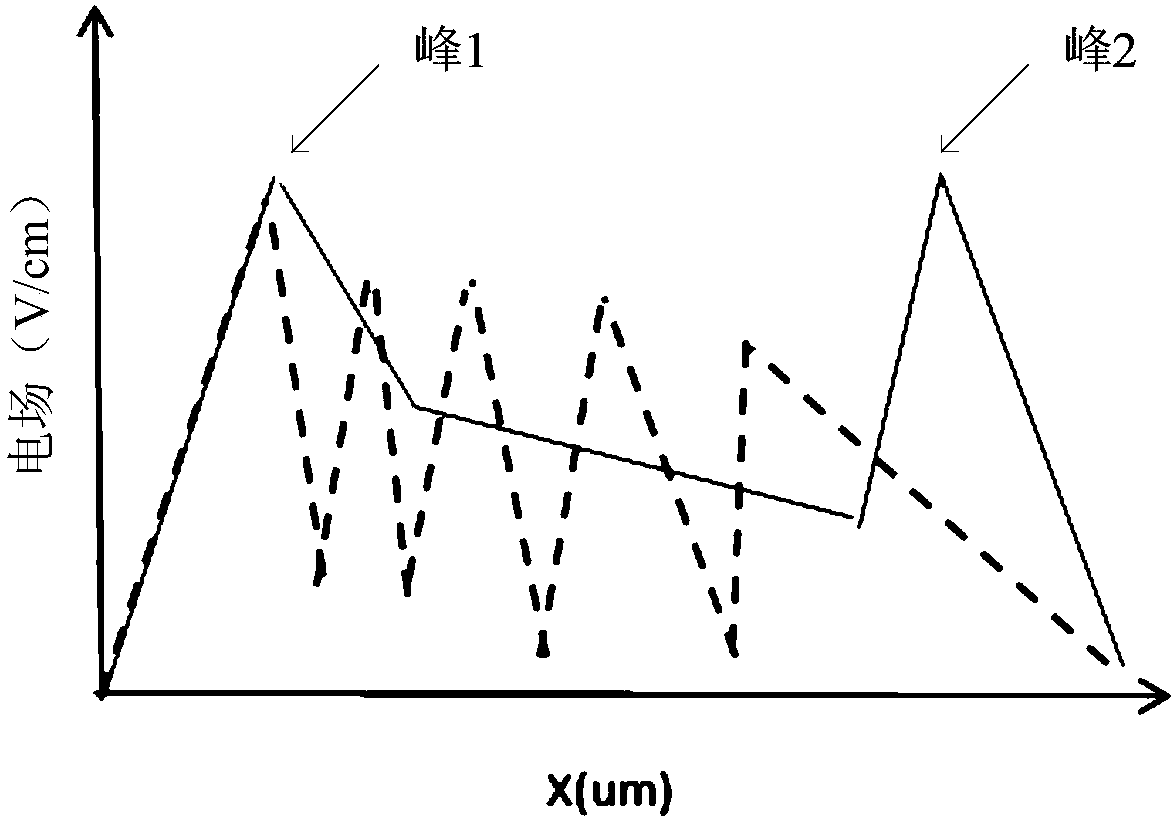

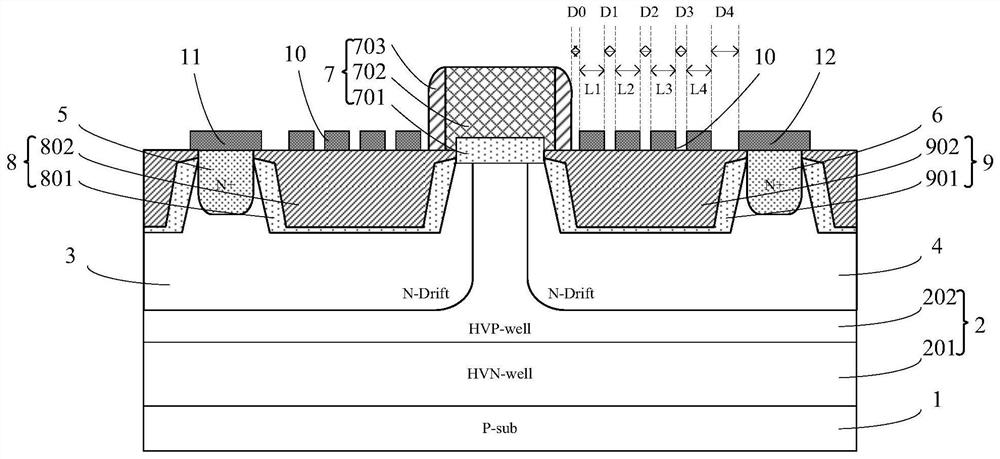

LDMOS (Lateral Diffusion MOS) structure

ActiveCN107785423AWill not increase the quantityIncrease the area of the depleted regionSemiconductor devicesLDMOSGate source capacitance

The invention provides a LDMOS (Lateral Diffusion MOS) structure. The LDMOS structure comprises a semiconductor substrate, a first drift area and a second drift area which are located in the semiconductor substrate and are arranged separately, a source which is located in the first drift area, a drain which is located in the second drift area, a gate structure which is located on the semiconductorsubstrate and whose two sides are contacted with the first drift area and the second drift area respectively, a first isolation structure which is located in the first drift area and isolates the source and the gate structure, and a second isolation structure which is located in the second drift area and isolates the drain and the gate structure, wherein both the first isolation structure and thesecond isolation structure are provided with floating field plates. One or more floating field plates is arranged on the isolation structures between the source-gate and the drain-gate, the area of adepleted area can be increased, collision ionization can be reduced, higher breakdown voltage and saturation leakage current Idsat can thus be acquired, and the gate-drain capacitance Cgd and the gate-source capacitance Cgs of the device are not deteriorated.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

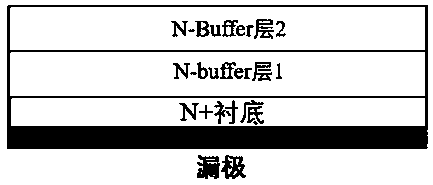

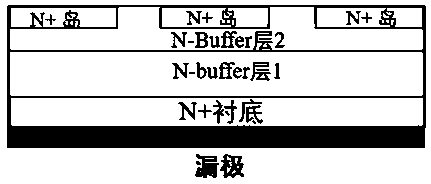

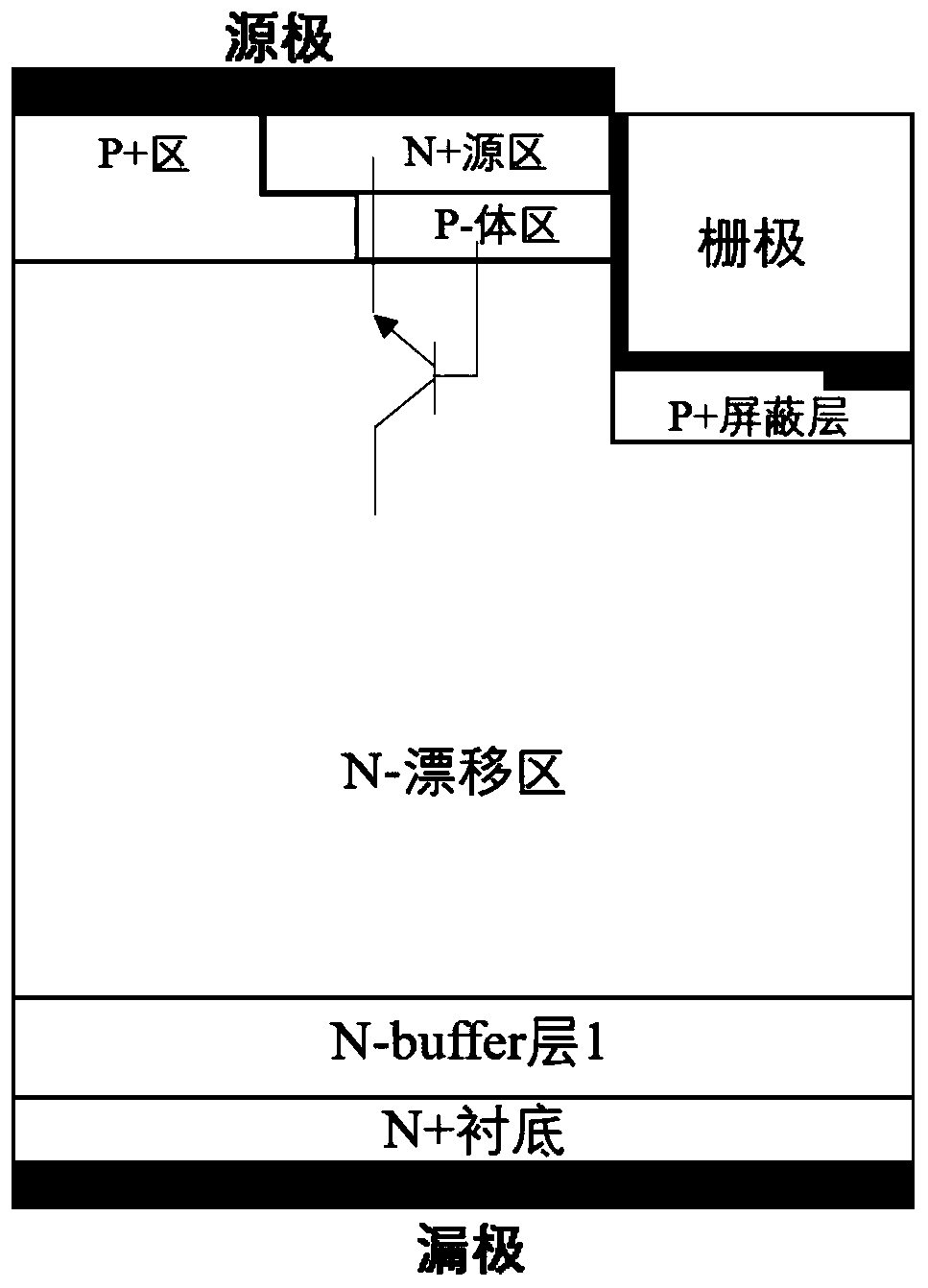

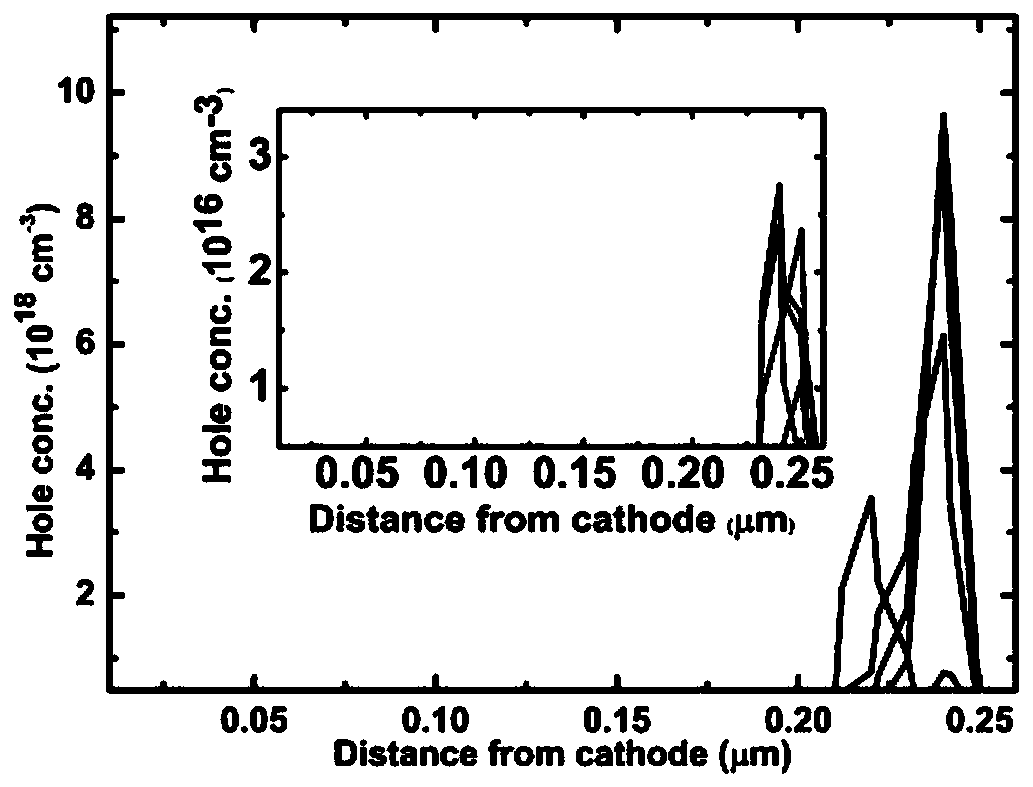

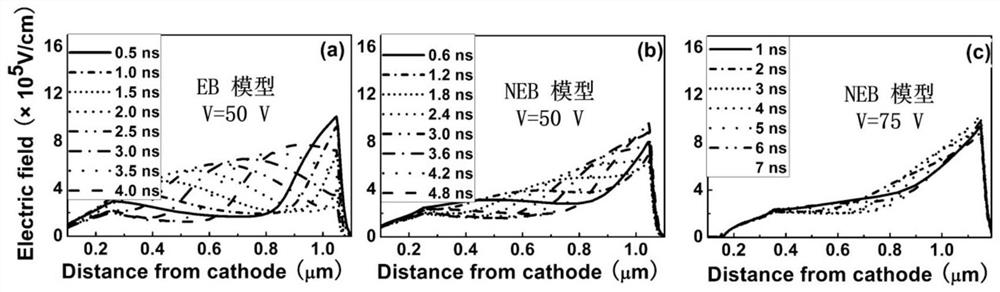

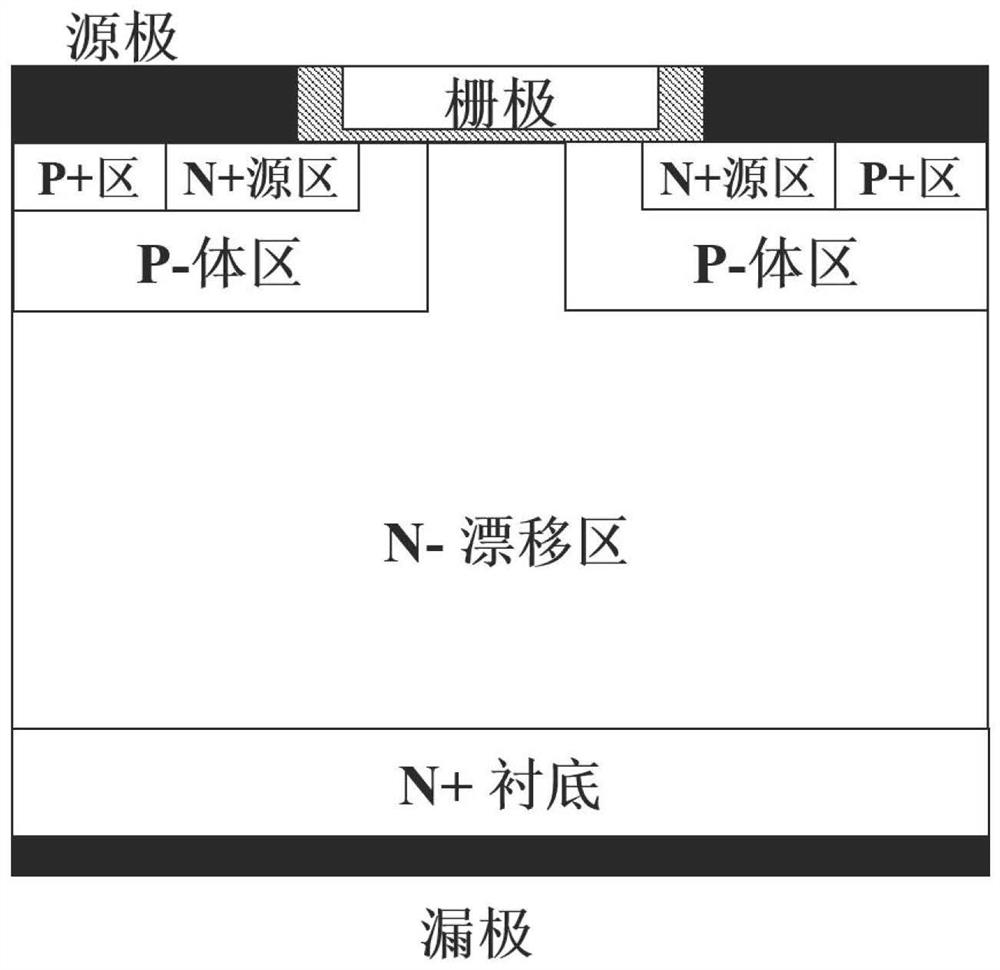

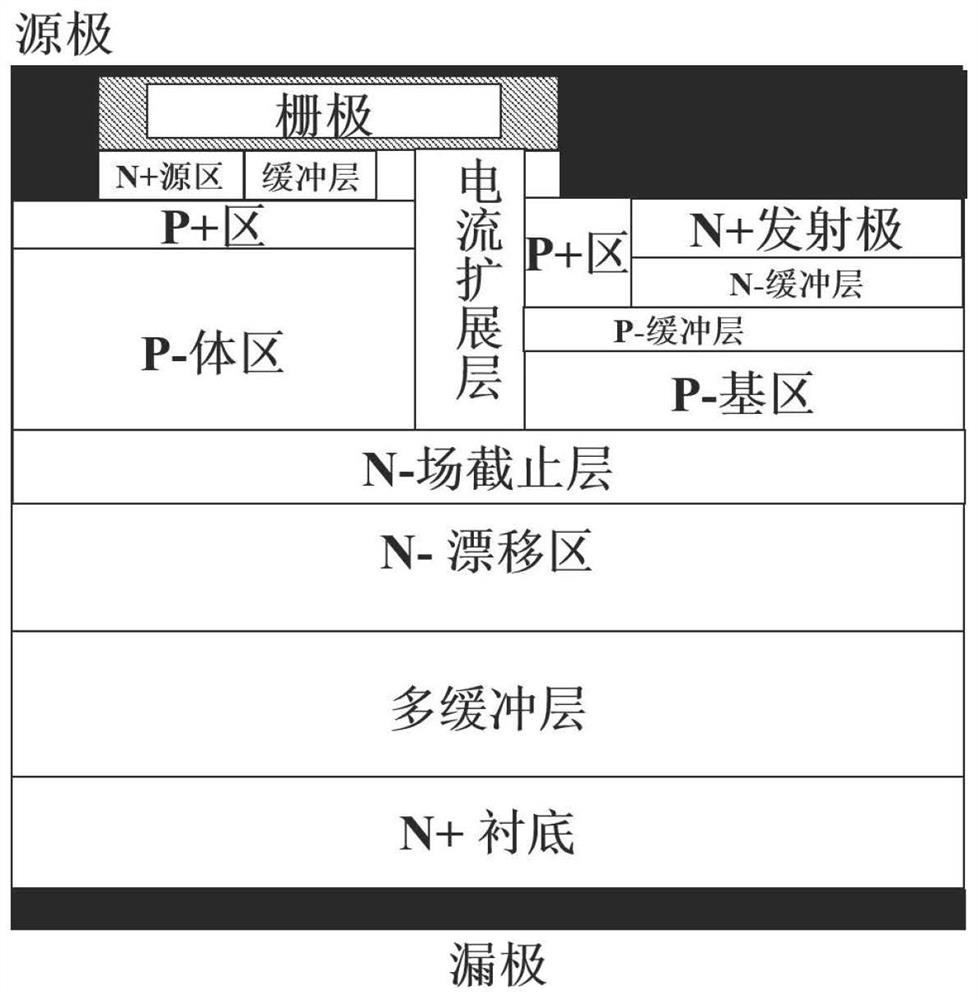

Half-cell structure of gate power MOSFET anti-single-particle-burnout device

InactiveCN110610995AImprove anti-SEB performanceReduce in quantitySemiconductor devicesCharge carrierParasitic bipolar transistor

The invention proposes a half-cell structure of a gate power MOSFET anti-single-particle-burnout device. According to the structure, an N-type buffer layer with an N-type local doped region is manufactured in the drain (cathode) electrode region of a semiconductor power device, which can significantly reduce the electric field peak and impact ionization degree of a semiconductor power device driftregion and high and low junctions of a substrate. The number of carriers generated by avalanche multiplication caused by impact ionization can be reduced. The transient current acting on a parasiticbipolar transistor is greatly reduced, so that the parasitic bipolar transistor is difficultly turned on. The device's ability to resist single particle burnout can be improved without sacrificing basic electrical characteristics.

Owner:HANGZHOU DIANZI UNIV

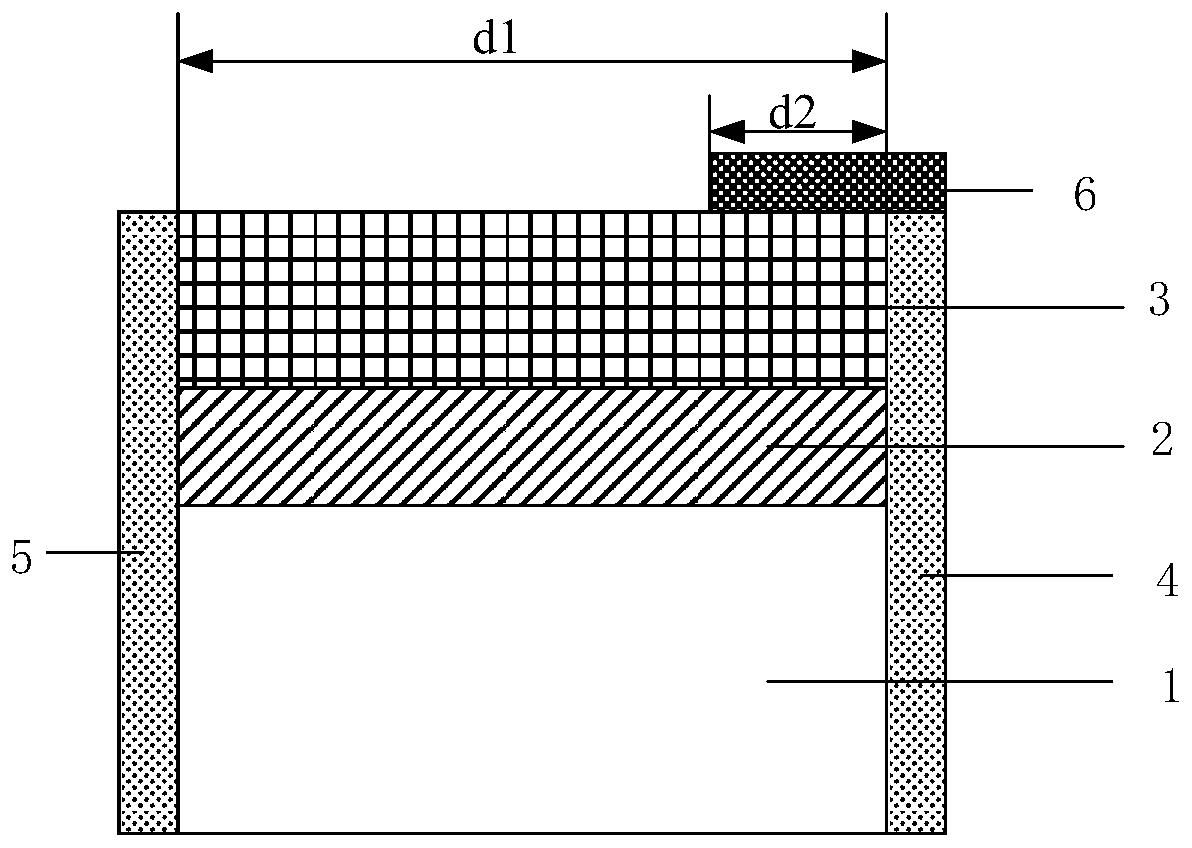

Hybrid PIN Schottky diode and preparation method thereof

InactiveCN105810756APrevent degradationImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky diodeDislocation

The invention belongs to the technical field of semiconductor devices, and in particular relates to a hybrid PIN Schottky diode and a preparation method thereof. The hybrid PIN Schottky diode disclosed by the invention comprises a GaN substrate, a GaN epitaxial layer, a rectangular-ambulatory-plane GaN structure array, a double-edge terminal structure and a first metal structure, wherein the GaN epitaxial layer is formed on the GaN substrate; the rectangular-ambulatory-plane GaN structure array comprises a plurality of rectangular-ambulatory-plane GaN structures adjacent to each other and is formed on the GaN epitaxial layer; each rectangular-ambulatory-plane GaN structure comprises a GaN peripheral region and a GaN central region; the double-edge terminal structure is positioned on the periphery of the rectangular-ambulatory-plane GaN structure array and comprises a whole edge terminal compensation layer and a partial edge terminal compensation layer, wherein the whole edge terminal compensation layer is positioned on the partial edge terminal compensation layer; and the first metal structure is positioned on the rectangular-ambulatory-plane GaN structure array and is in Schottky contact with the GaN peripheral region. The relatively high reverse breakdown voltage can be obtained in the event that the area of a chip cannot be lost; simultaneously, the problem that the device performance is degraded due to the dislocation problem can be avoided; and thus, the hybrid PIN Schottky diode and the preparation method thereof disclosed by the invention can be well applied in the field of power electronics.

Owner:FUDAN UNIV +1

LDMOS device and manufacturing method thereof

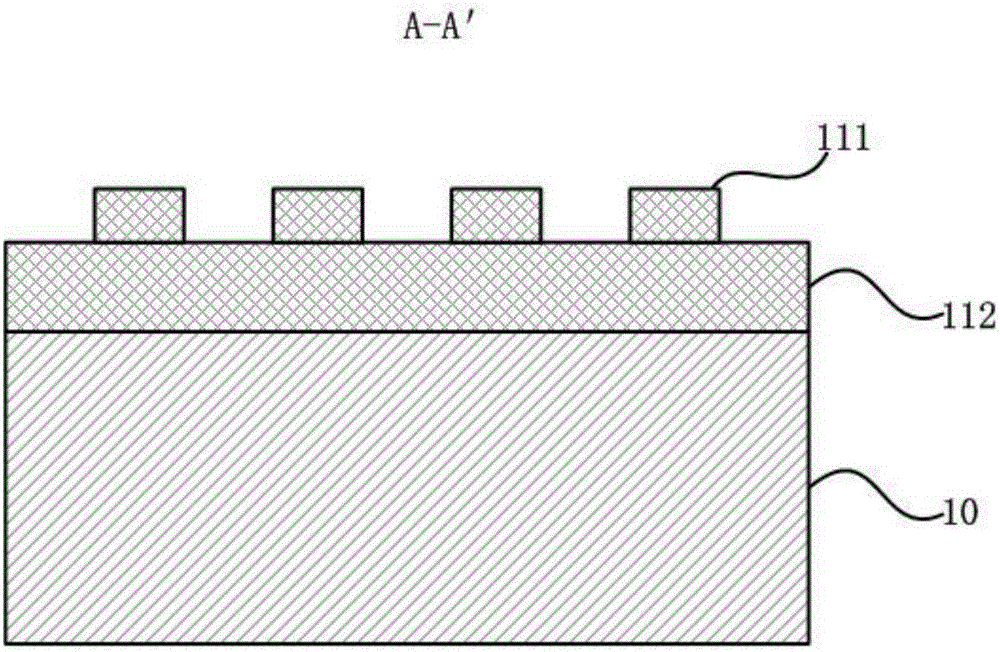

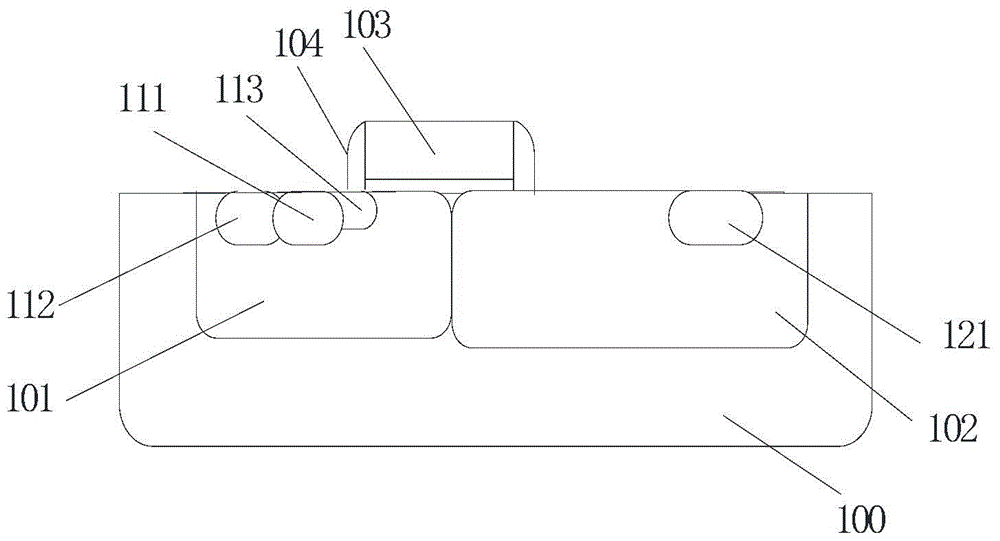

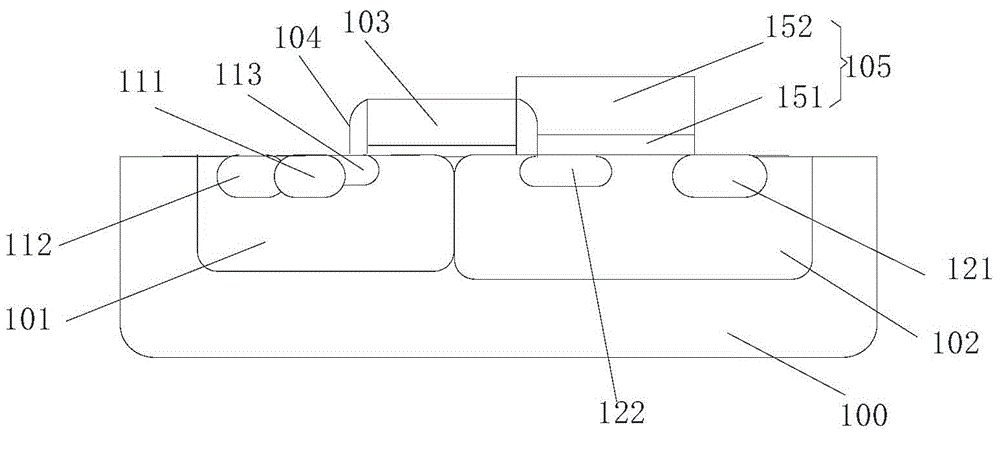

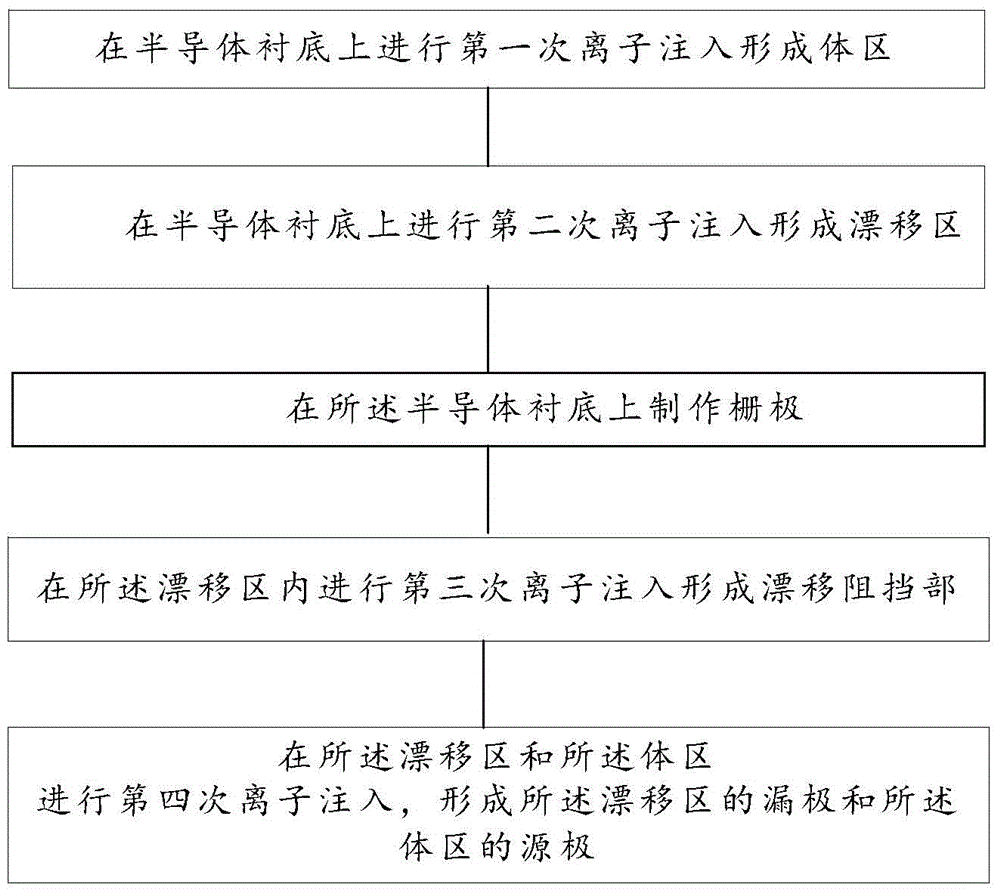

InactiveCN104867974AImprove breakdown voltageReduced impact ionizationSemiconductor/solid-state device manufacturingSemiconductor devicesBody regionElectric field

This invention provides an LDMOS device and a manufacturing method thereof. The LDMOS device comprises a semiconductor substrate, a body region and a drift region arranged in the semiconductor substrate, a gate arranged on the semiconductor substrate and a drain electrode arranged in the drift region, and the drift region also comprises a drift blocking part which blocks drift region hot carrier drift. According to the LDMOS device and the manufacturing method, the drift of a hot carrier to a gate direction can be blocked by the drift blocking part arranged at the drift region, the electric field intensity under the gate can be reduced, the position of strongest electric field generation moves downward to be far from the gate oxide layer of the gate. The electric field intensity is reduced, the breakdown voltage of the drift region is raised, and the generation of impact ionization is reduced, which means that the number of hot carrier generation is reduced. Since the position of the strongest electric field moves downward, the distance to the gate oxide layer is increased, the number of the hot carriers which act on the gate oxide layer actually is reduced, thus the effect of blocking the hot carriers is realized finally, and the reliability of the device is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

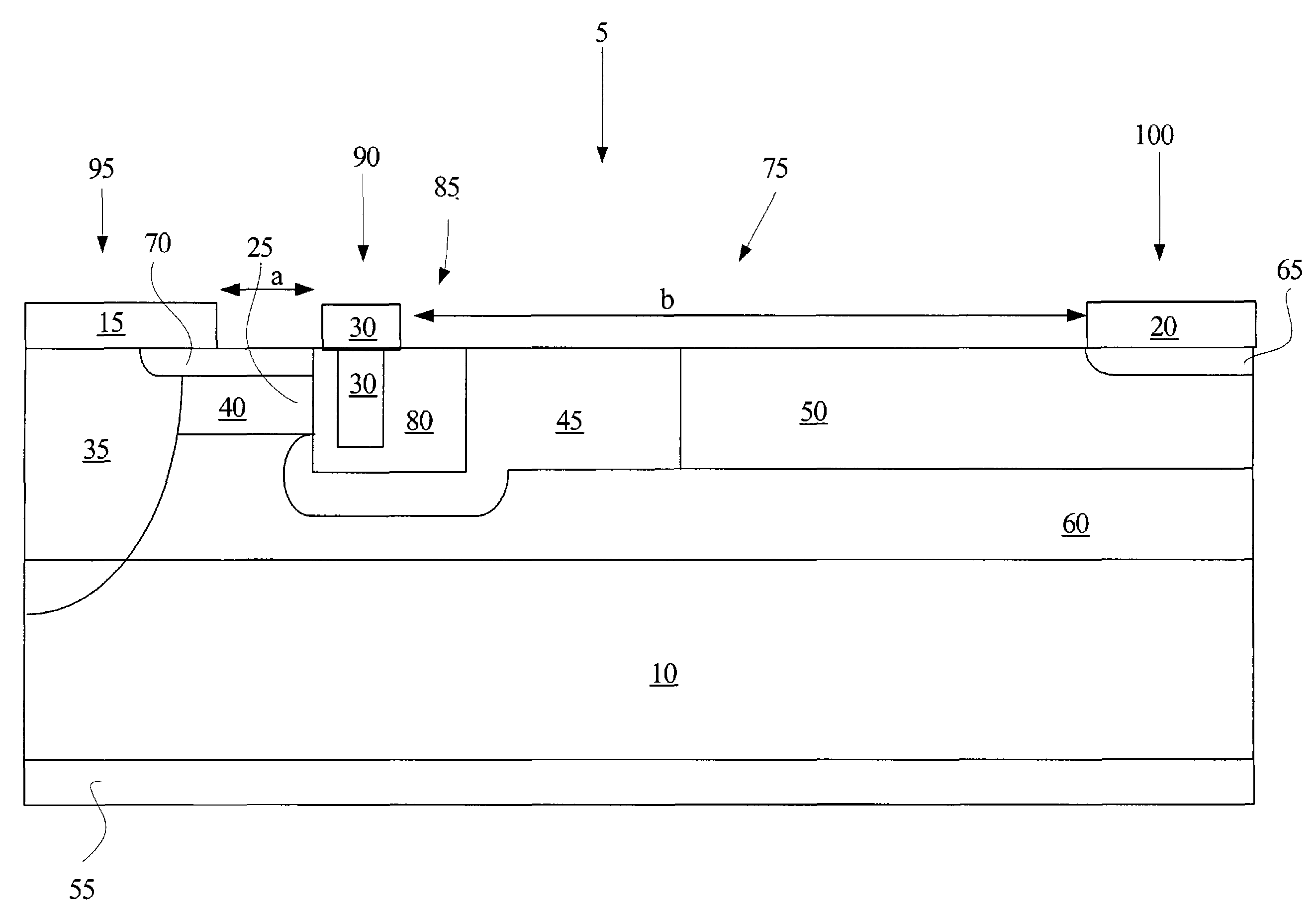

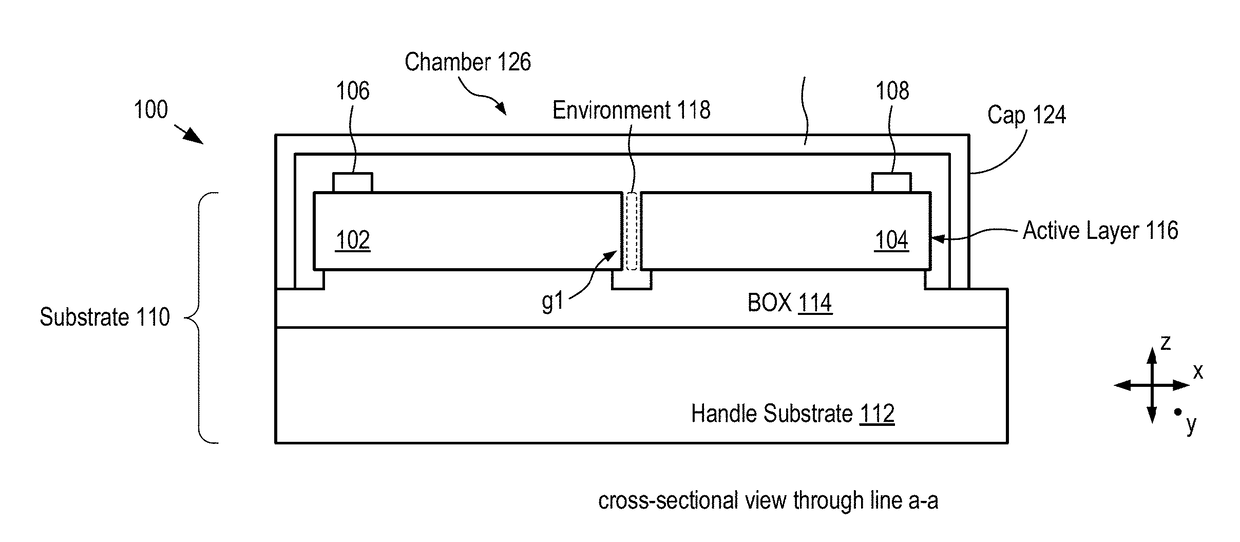

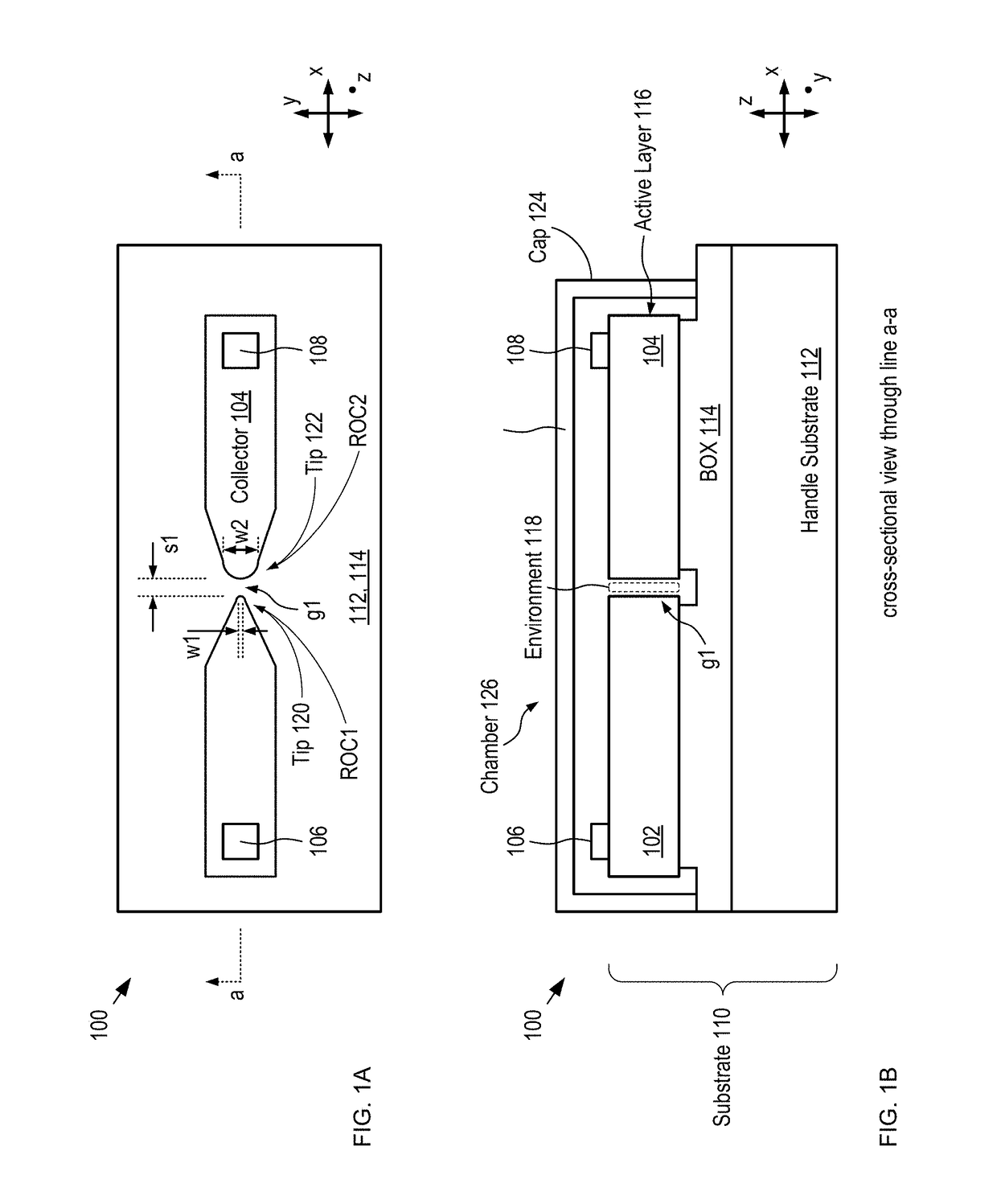

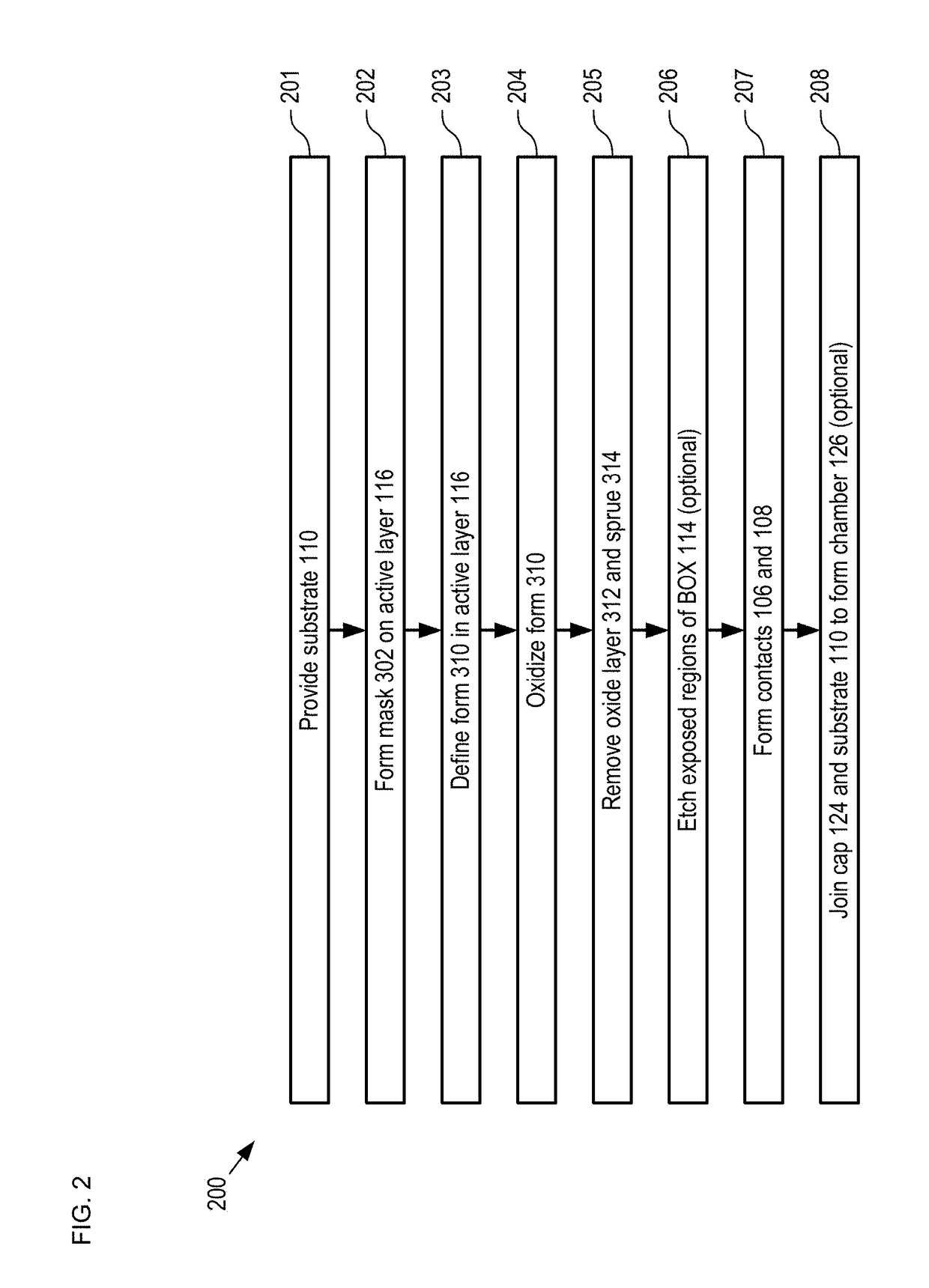

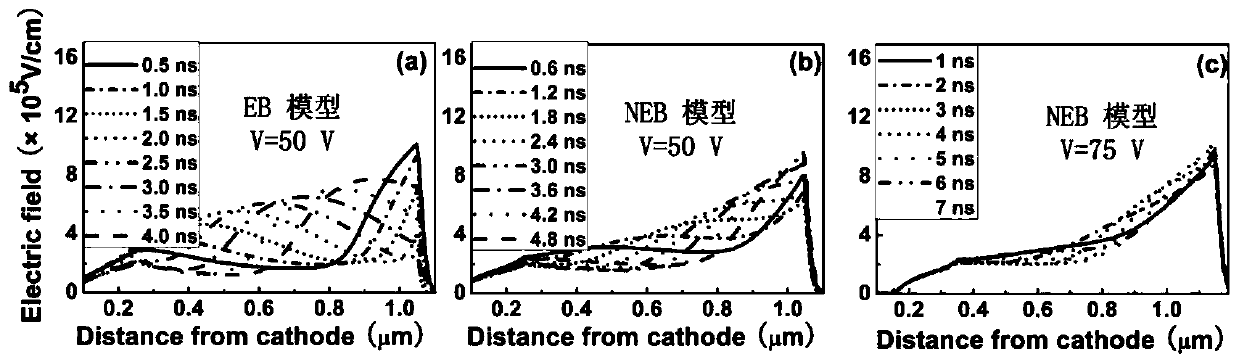

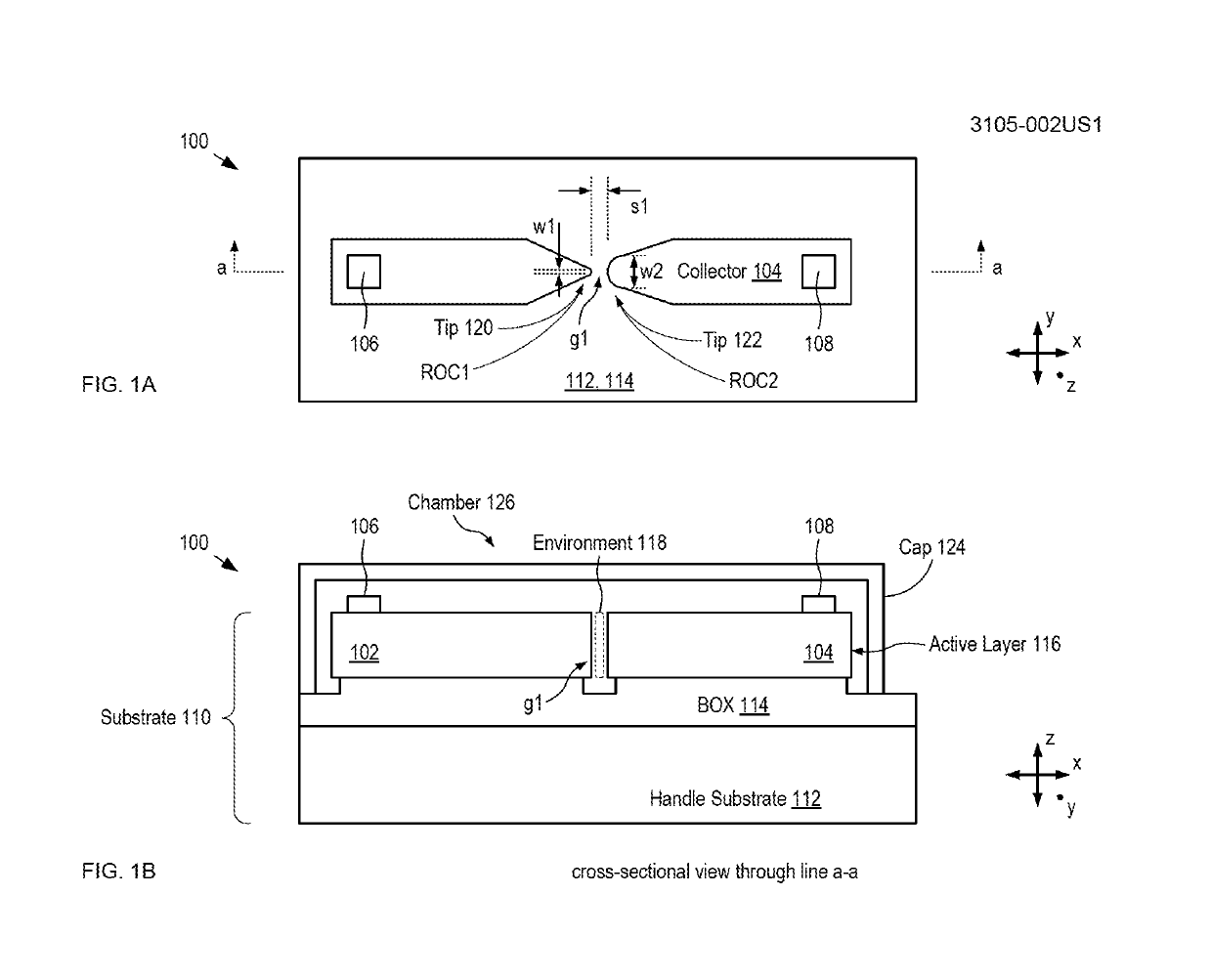

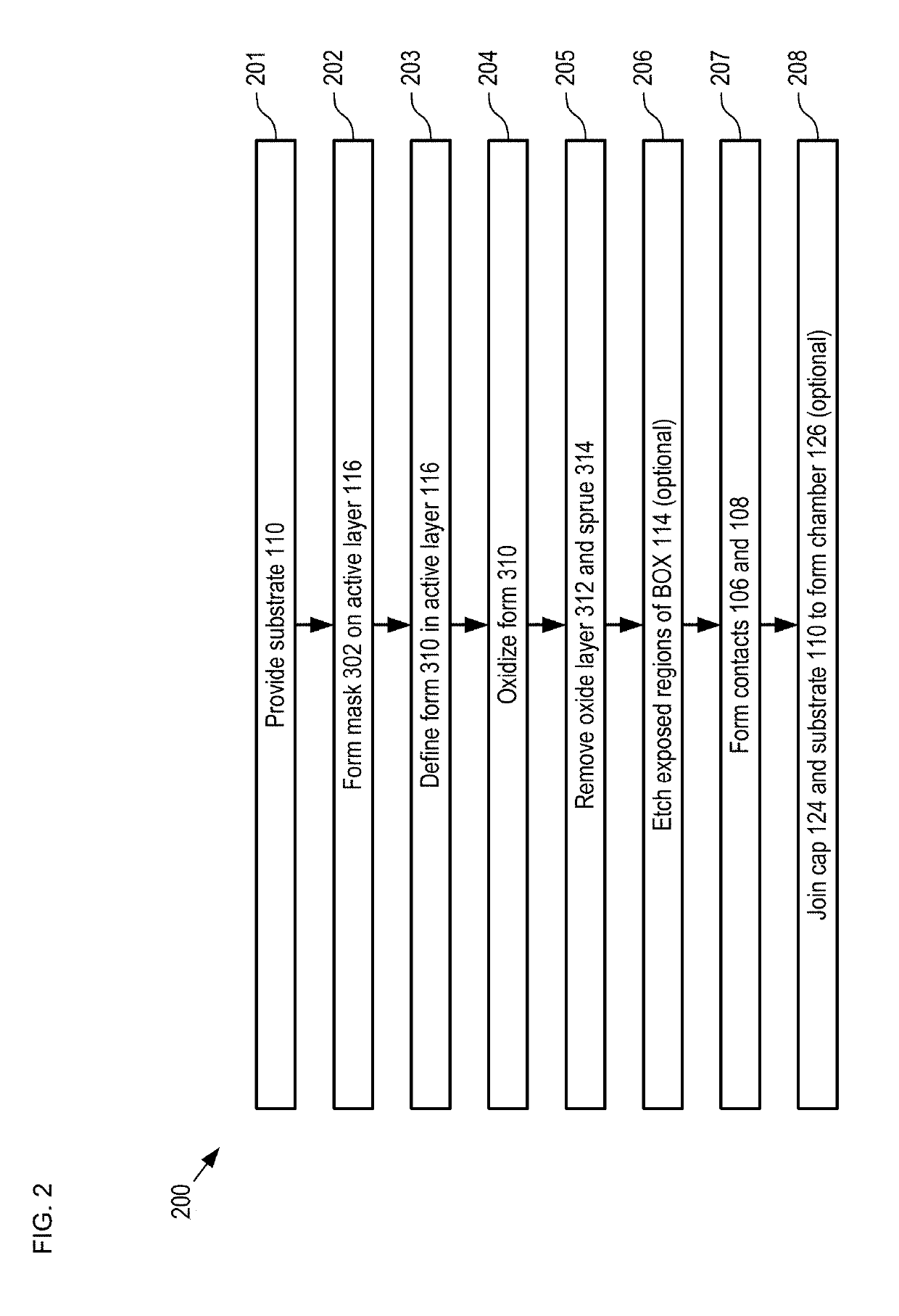

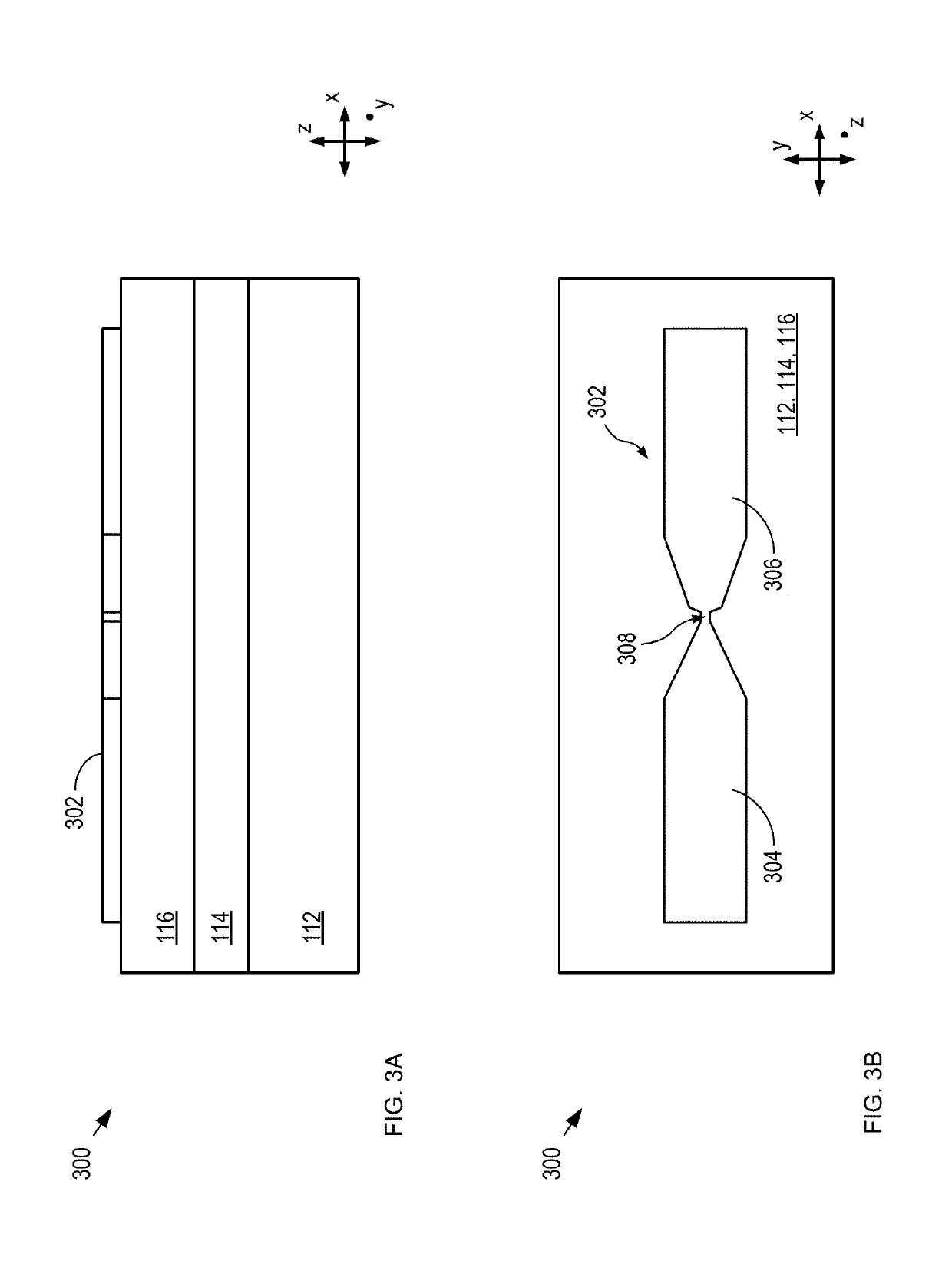

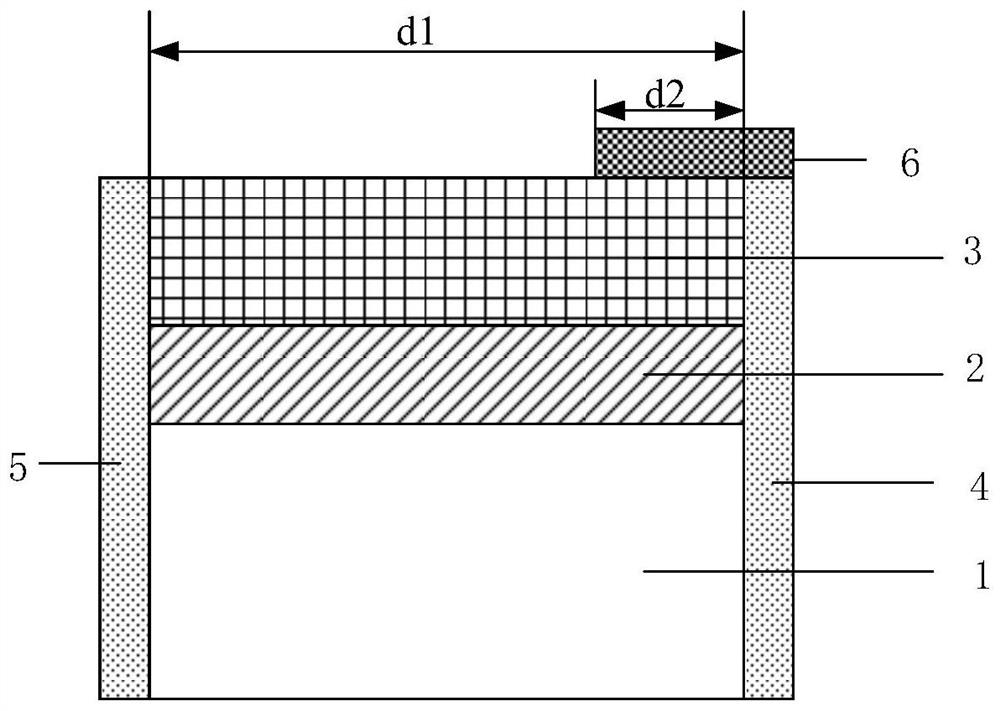

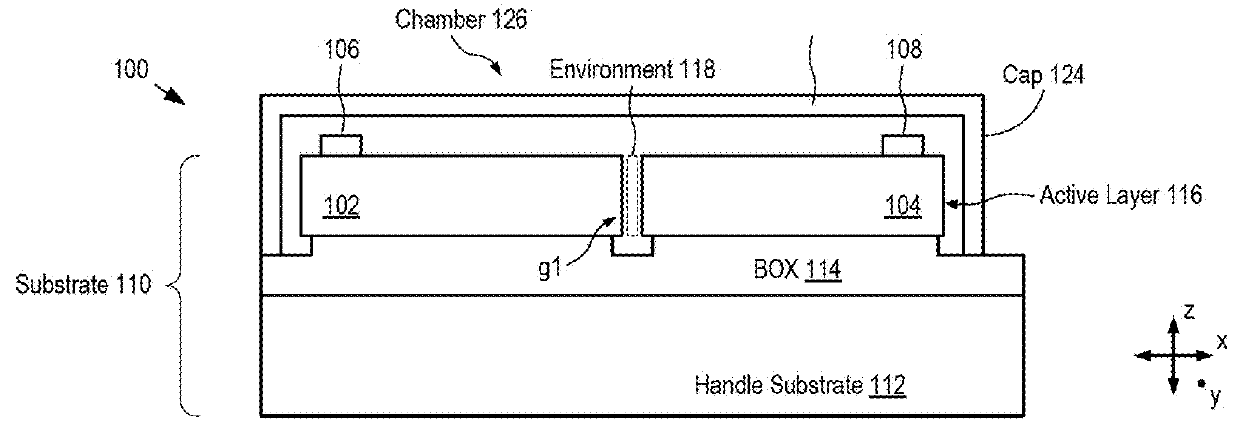

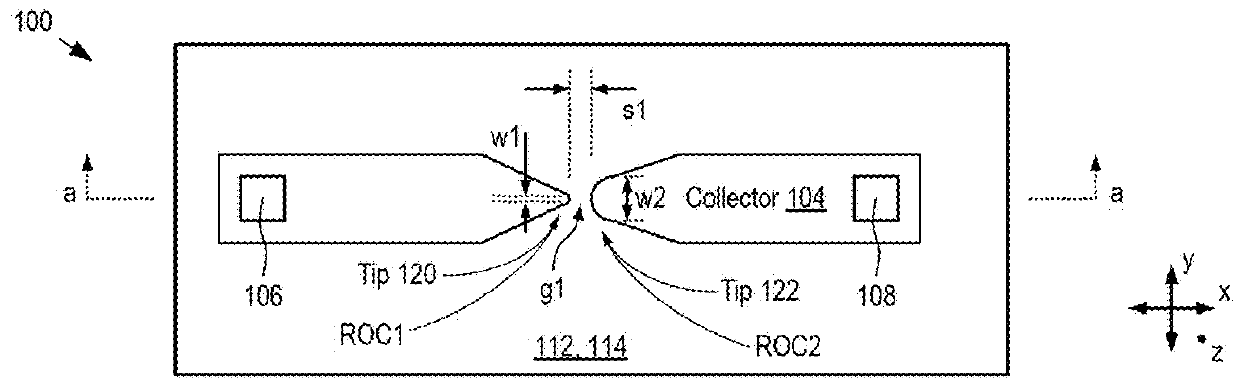

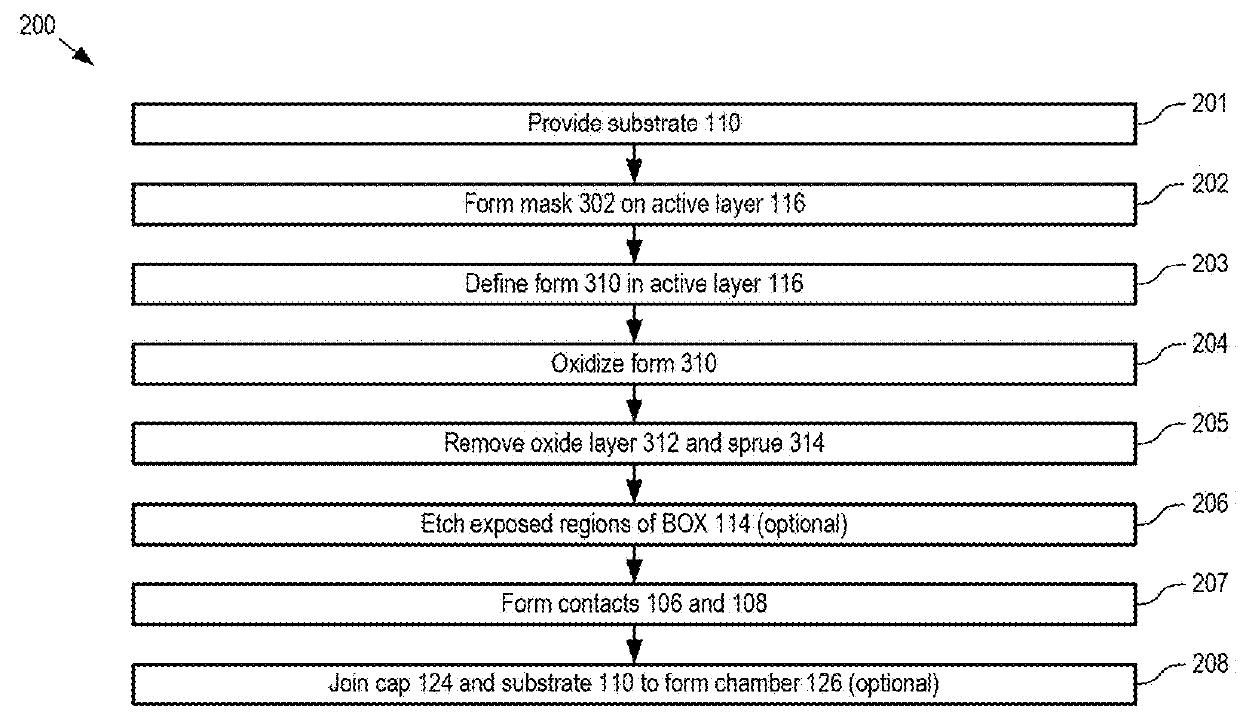

Nanoscale Field-Emission Device and Method of Fabrication

ActiveUS20170250048A1Reduced impact ionizationAvoid excessive degradationCold cathodesSingle discharge path tubesField emission deviceMean free path

Nanoscale field-emission devices are presented, wherein the devices include at least a pair of electrodes separated by a gap through which field emission of electrons from one electrode to the other occurs. The gap is dimensioned such that only a low voltage is required to induce field emission. As a result, the emitted electrons energy that is below the ionization potential of the gas or gasses that reside within the gap. In some embodiments, the gap is small enough that the distance between the electrodes is shorter than the mean-free path of electrons in air at atmospheric pressure. As a result, the field-emission devices do not require a vacuum environment for operation.

Owner:CALIFORNIA INST OF TECH

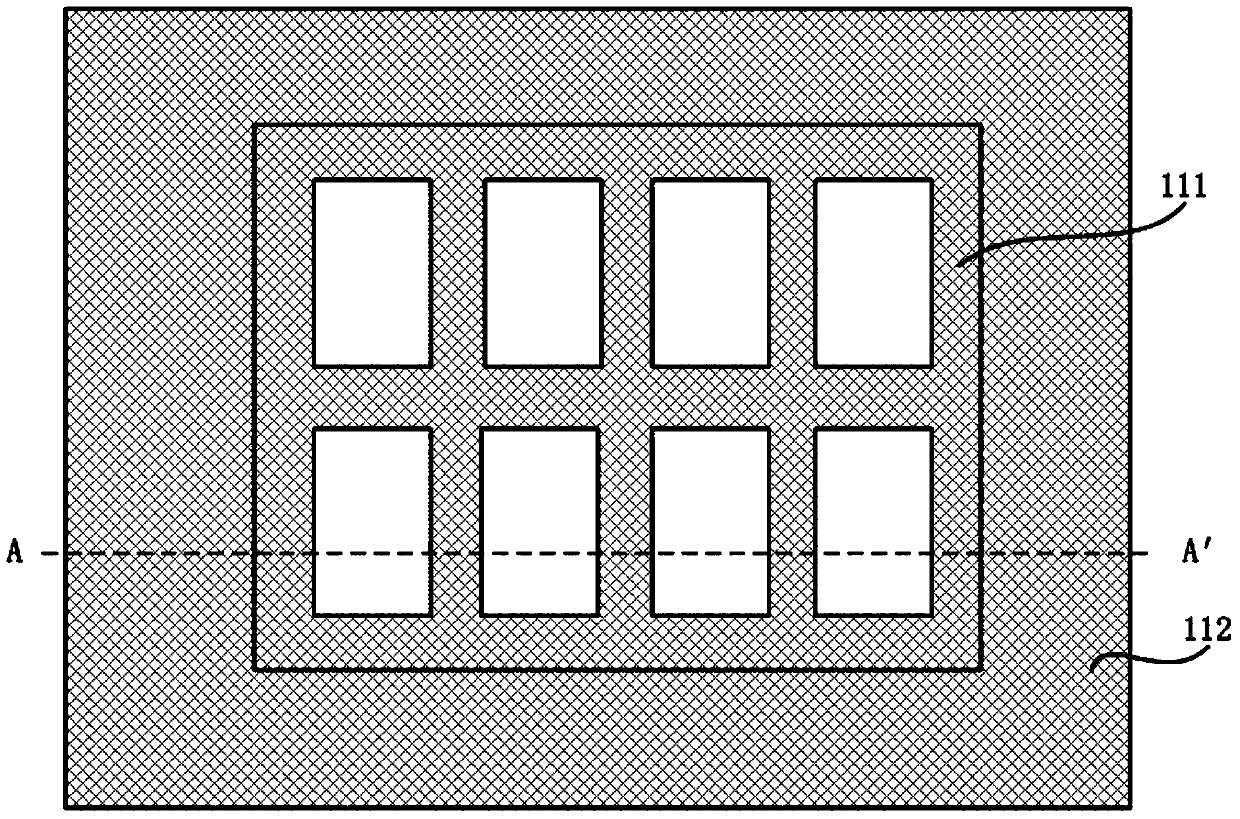

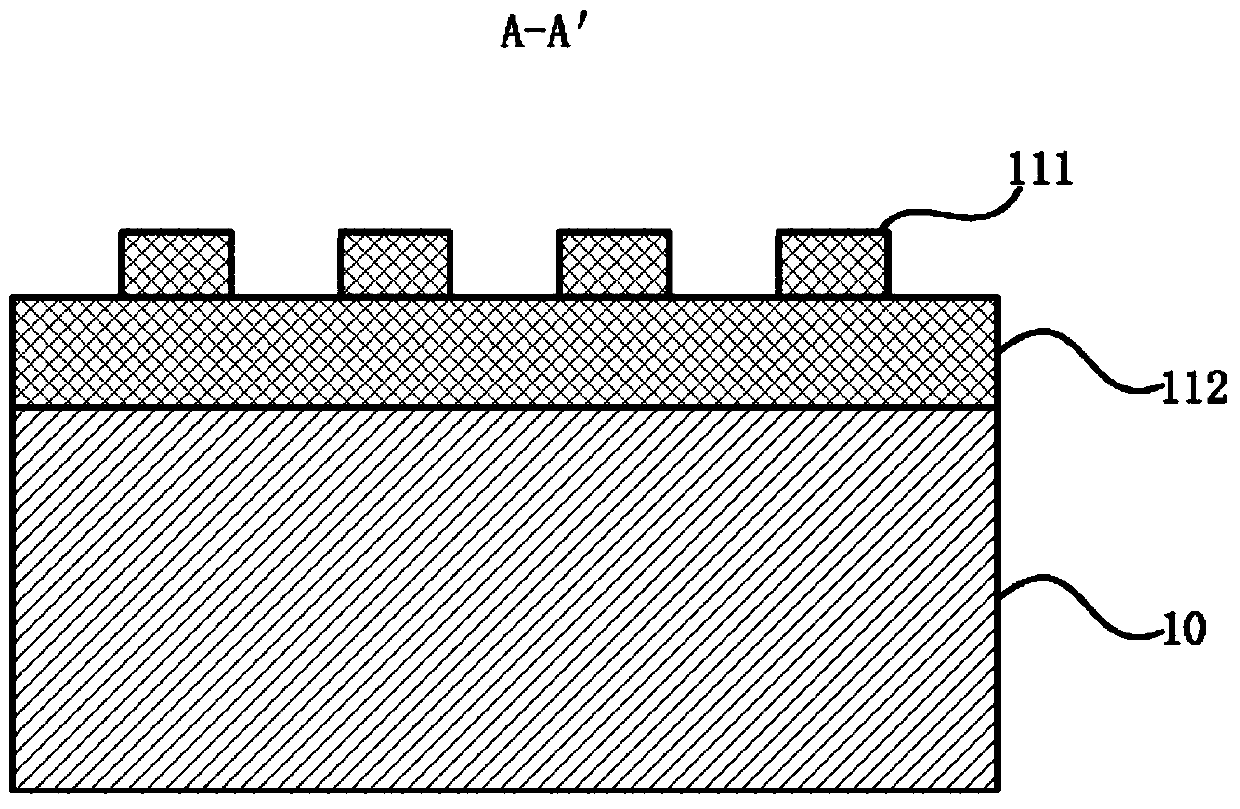

Switching power-semiconductor device and manufacturing method thereof

PendingCN106684118AReduce functionImprove safe work areaSemiconductor/solid-state device manufacturingSemiconductor devicesEdge cellSwitching power

The invention relates to the technical filed of a power semiconductor device, in particular to a switching power semiconductor and a manufacturing method thereof. The device comprises a silicon layer and a metal layer connected with the silicon layer, wherein the silicon lay comprises a relative first surface and a second surface on the opposite side, and the first surface comprises an active area and a junction termination area, and the active area is surrounded by the junction termination area. The second surface comprises a first ion doping region according to the junction termination area and a second ion doping region according to the junction termination area which ion doping concentration is lower than the first ion doping region, the second ion doping region is surrounded by the first ion doping region. The switching power semiconductor and a manufacturing method thereof has the advantages that the free carrier concentration and current density in the device junction termination area is reduced, the collision ionization and dynamic avalanche breakdown is cut down, the edge cell latch-up damage due to the concentration of the current is decreased and the integral safety area of the device is expanded.

Owner:CR TECH PINGTAN CO LTD

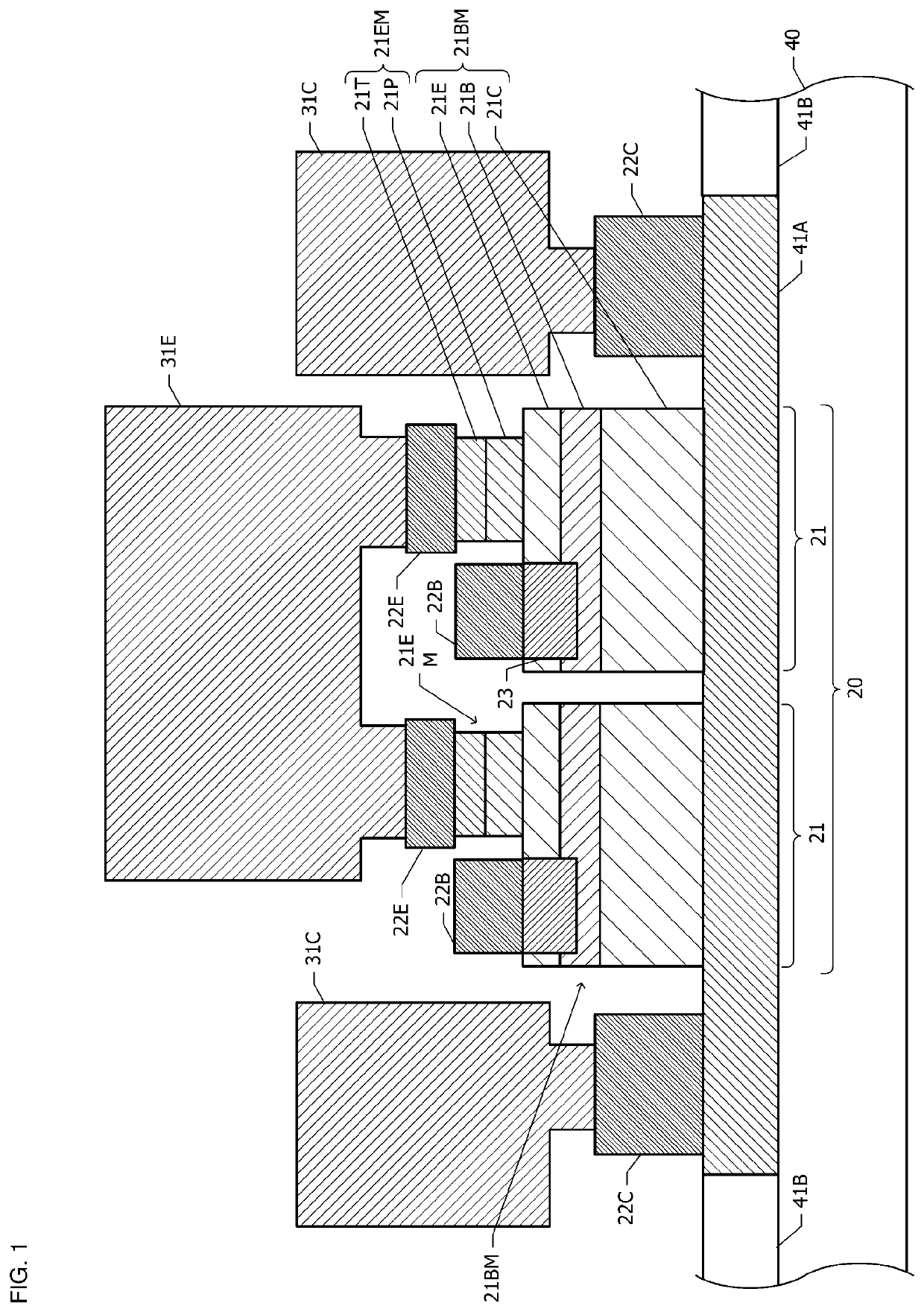

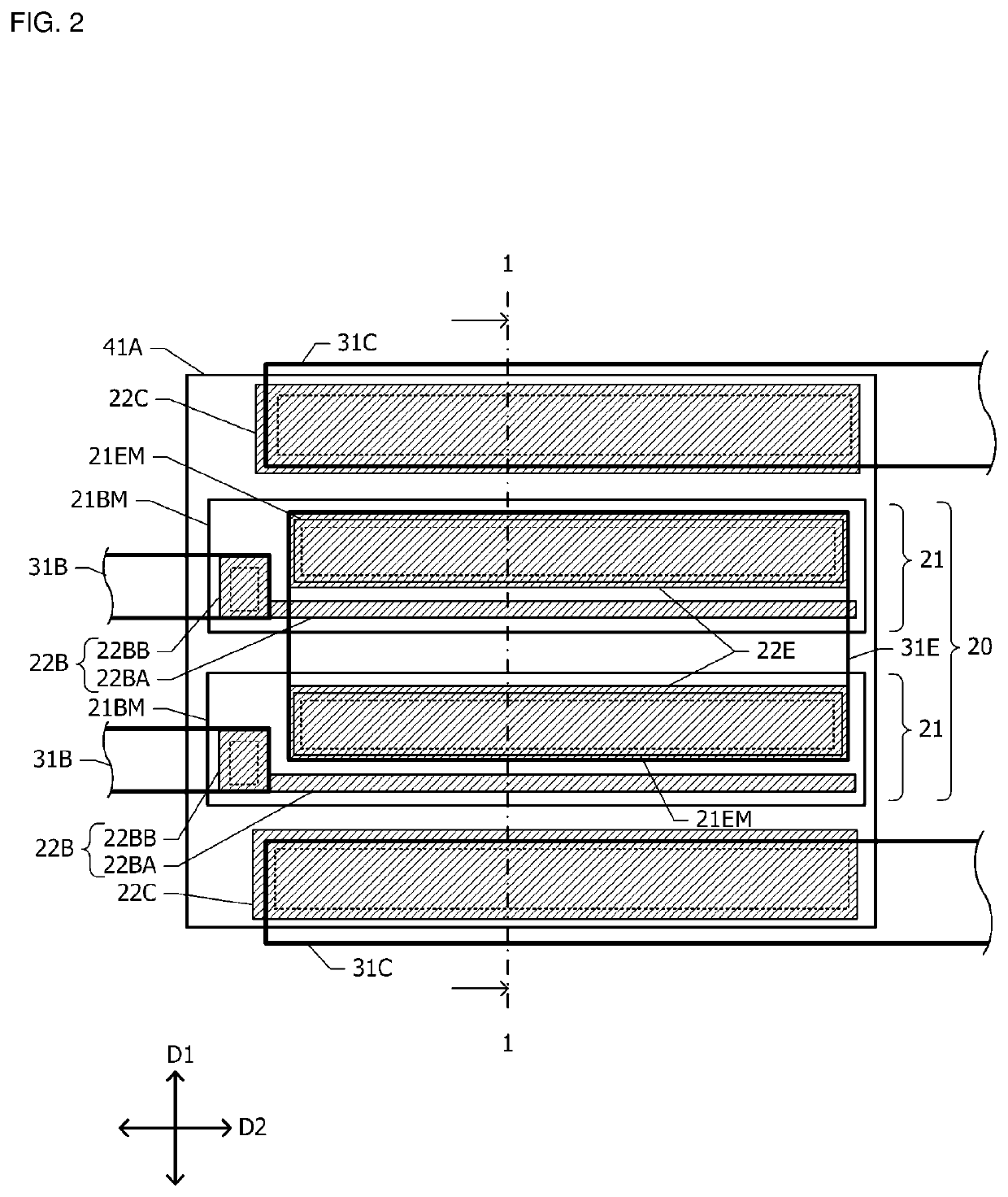

Semiconductor device

PendingUS20220059527A1Improve thermal stabilityBreakdown tolerance can be improvedTransistorHigh frequency amplifiersDevice materialEngineering

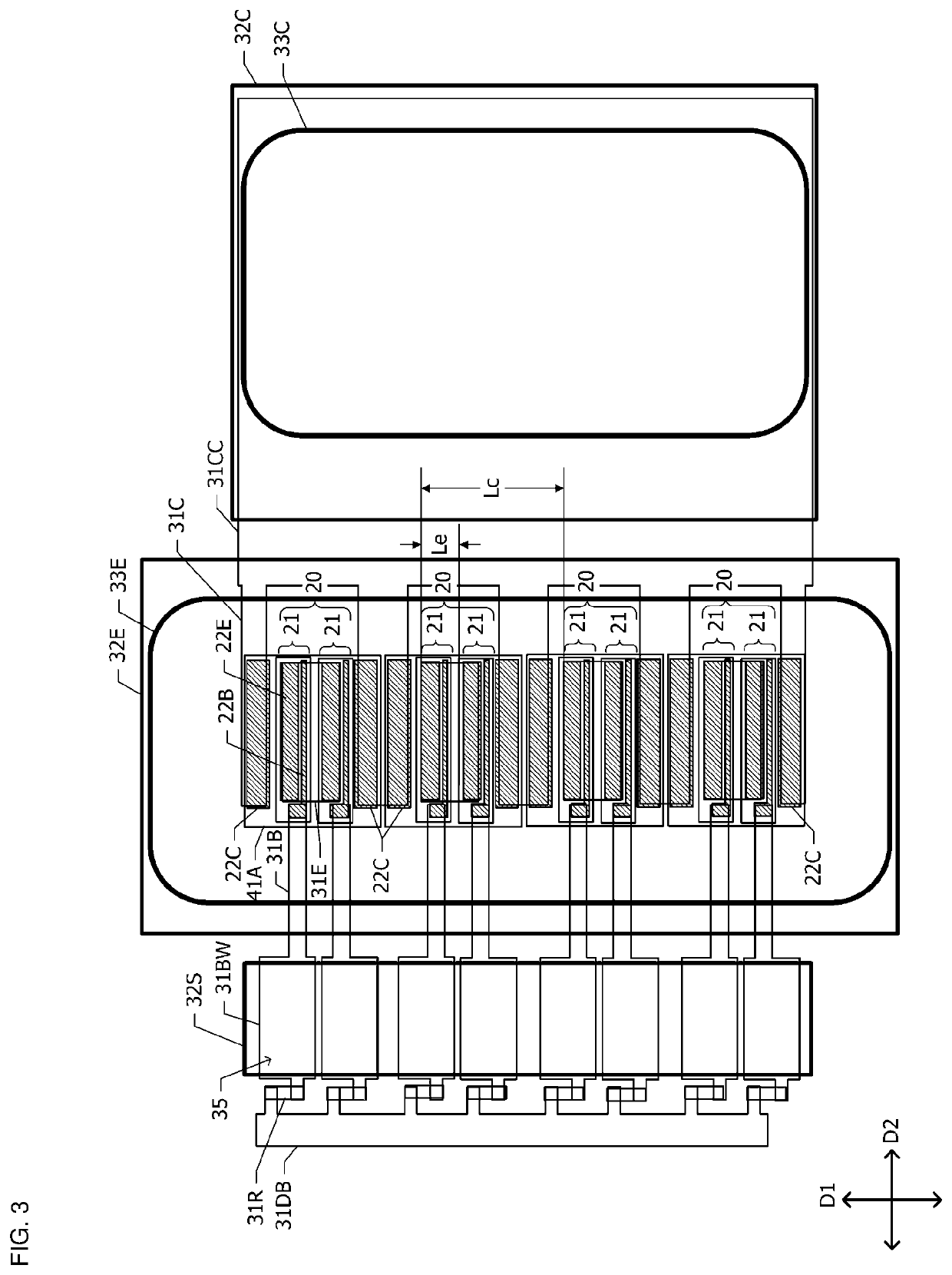

Each of cells arranged on a substrate surface along a first direction includes at least one unit transistor. Collector electrodes are arranged between two adjacent cells. A first cell, which is at least one of the cells, includes unit transistors arranged along the first direction. The unit transistors are connected in parallel to each another. In the first cell, the base electrode and the emitter electrode in each unit transistor are arranged along the first direction, and the order of arrangement of the base electrode and the emitter electrode is the same among the unit transistors. When looking at one first cell, a maximum value of distances in the first direction between the emitter electrodes of two adjacent unit transistors in the first cell being looked at is shorter than ½ of a shorter one of distances between the first cell being looked at and adjacent cells.

Owner:MURATA MFG CO LTD

Composite cooling positive electrode-based GaN planar gunn diode and fabrication method thereof

InactiveCN110350084AReduce intensityDisperse energyMaterial nanotechnologySemiconductor/solid-state device detailsOhmic contactHigh energy

The invention relates to a composite cooling positive electrode-based GaN planar gunn diode and a fabrication method thereof. The planar gunn diode comprises an AlGaN back barrier layer, a GaN channellayer, an AlGaN barrier layer, an ohmic contact positive electrode, an ohmic contact negative electrode and a Schottky extension layer, wherein the GaN channel layer is arranged on the AlGaN back barrier layer, the AlGaN barrier layer is arranged on the GaN channel layer, the ohmic contact positive electrode and the ohmic contact negative electrode are respectively arranged at two ends of the AlGaN back barrier layer, the GaN channel layer and the AlGaN barrier layer, and the Schottky extension layer is arranged on the AlGaN barrier layer and covers the ohmic contact positive electrode. The Schottky extension layer of the planar gunn diode forms a depletion layer in a channel of the planar gunn diode, the strength of high-energy dipole domain is reduced, so that the energy of electronic domain is dispersed, the collision ionization of a positive electrode end of the planar gunn diode is reduced, heat generation is buffered, the self-heating effect of a device is further effectively prevented, and the negative resistance effect, the power and the frequency of the device are improved.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

Method for improving breakdown voltage of N-groove laterally diffused metal oxide semiconductor (LDMOS)

ActiveCN102412162BReduced impact ionizationImprove pressure resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSEngineering

The invention discloses a method for improving breakdown voltage of an N-groove laterally diffused metal oxide semiconductor (LDMOS). The method comprises the following steps of:1, manufacturing a deep N well (DNW), implanting phosphorus into a P-type substrate (P SUB), and performing high-temperature drive-in and forming; 2, performing thermal growth to form field oxide, manufacturing a P well, and implanting boron impurities once or for multiple times; 3, manufacturing a PTOP, implanting boron impurities and forming after well implantation is finished and before gate oxide is grown; 4, manufacturing a polycrystalline silicon gate and a polycrystalline silicon field plate; after gate oxide is grown, depositing a layer of polycrystalline silicon, and defining the positions of the polycrystalline silicon gate and the field plate by etching; and manufacturing a source and a drain, after the polycrystalline silicon gate is formed, implanting phosphorus or arsenic into a device region once or for multiple times by using the polycrystalline silicon gate and the field oxide as hard masks, and implanting boron once or for multiple times to form P+ which is required by the P well. The impact ionization of the thinnest position of the device can be reduced, so that voltage resistance of the device can be improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

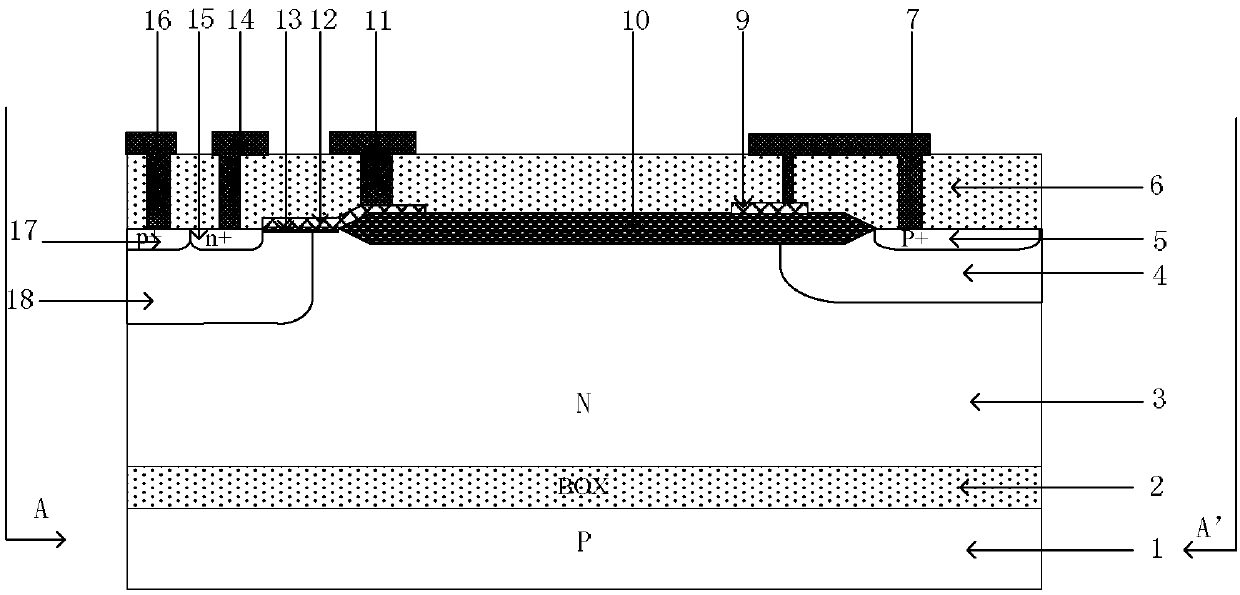

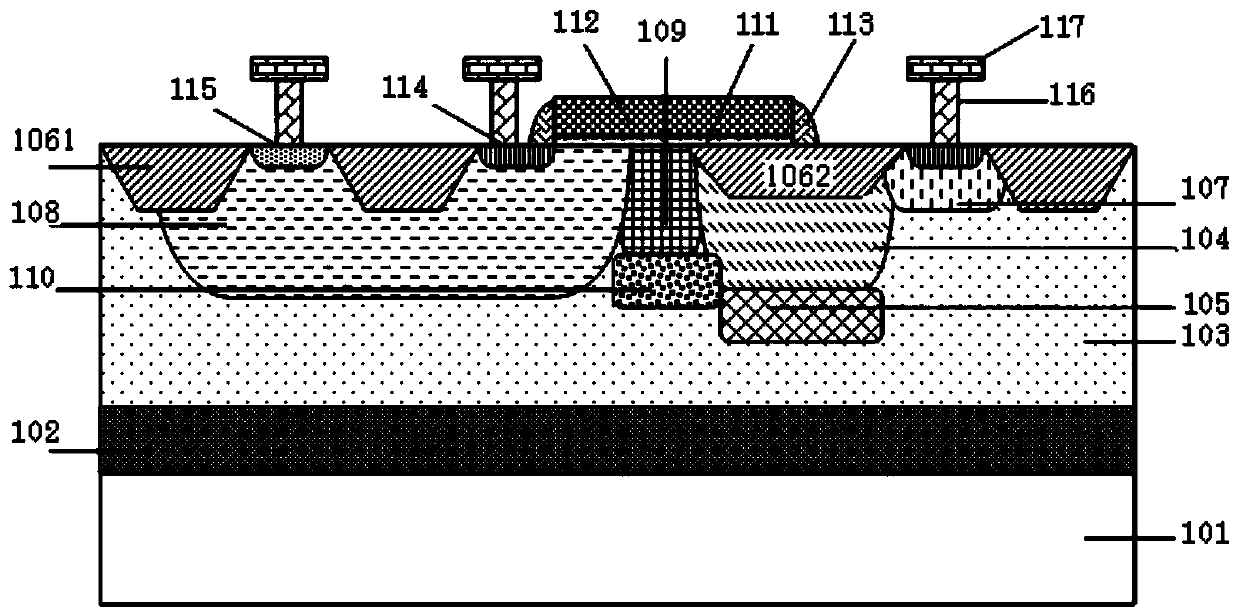

A Lateral Insulated Gate Bipolar Transistor with High Hot Carrier Reliability

ActiveCN106298901BReduce emission efficiencyAvoid damageSemiconductor devicesBody contactEmission efficiency

The invention provides a transverse insulated gate bipolar transistor with high thermal carrier reliability, which comprises a P-type substrate with a buried oxide layer. An N-type epitaxial layer is provided on the buried oxide layer. In the N-type epitaxial layer, an N-type buffer well and a P-type body region are provided. In the N-type buffer well, a P-type positive region is provided. In the P-type body region, an N-type negative region and a P-type body contact region are provided. The surface of the N-type epitaxial layer is provided with a gate oxide layer and a field oxide layer. A polysilicon gate is provided on the surface of the gate oxide layer, and polysilicon is arranged on the right upper surface of the field oxide layer. The P-type positive region consists of block shaped N-type regions arranged in rows; in the N-type buffer region, a floating hollow N-type contact region is provided. The P-type positive region is arranged in the floating hollow N-type contact region, and each of the block shaped N-type regions is surrounded by the floating hollow N-type contact region on three sides. And the other end of the field oxide layer extends toward the P-type positive region and ends at the floating hollow N-type contact region. According to the invention, it is possible to reduce the emission efficiency of a parasitic PNP transistor, reduce the hot carrier damage in the on-state and the switching state, and improve the reliability of devices.

Owner:SOUTHEAST UNIV

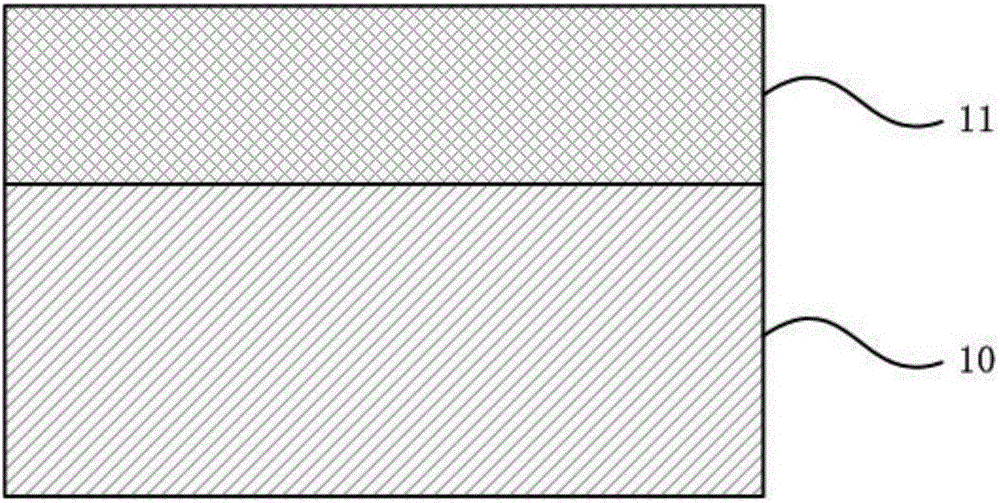

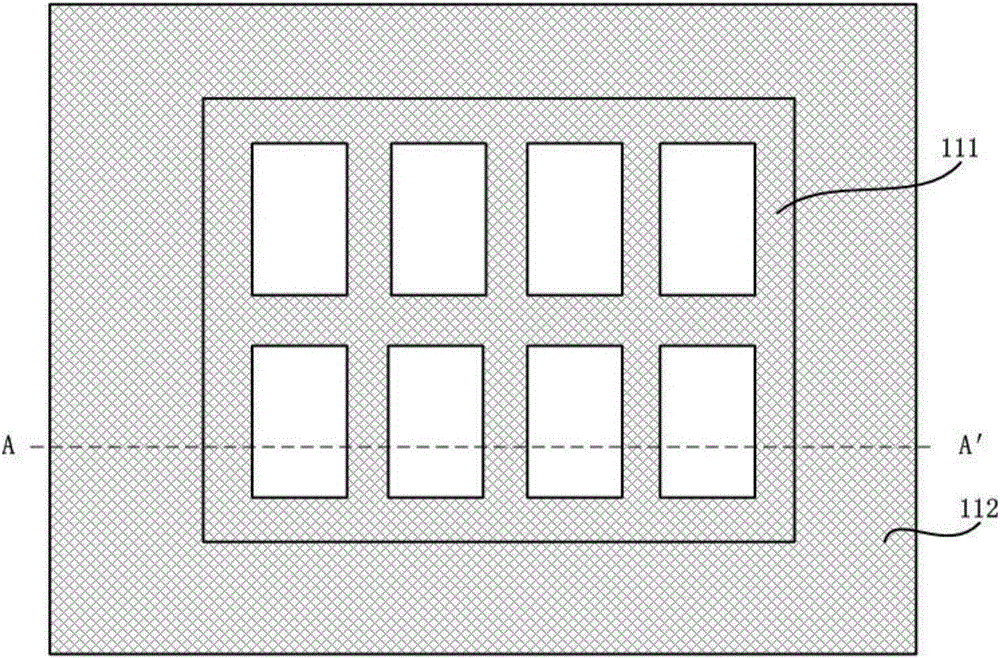

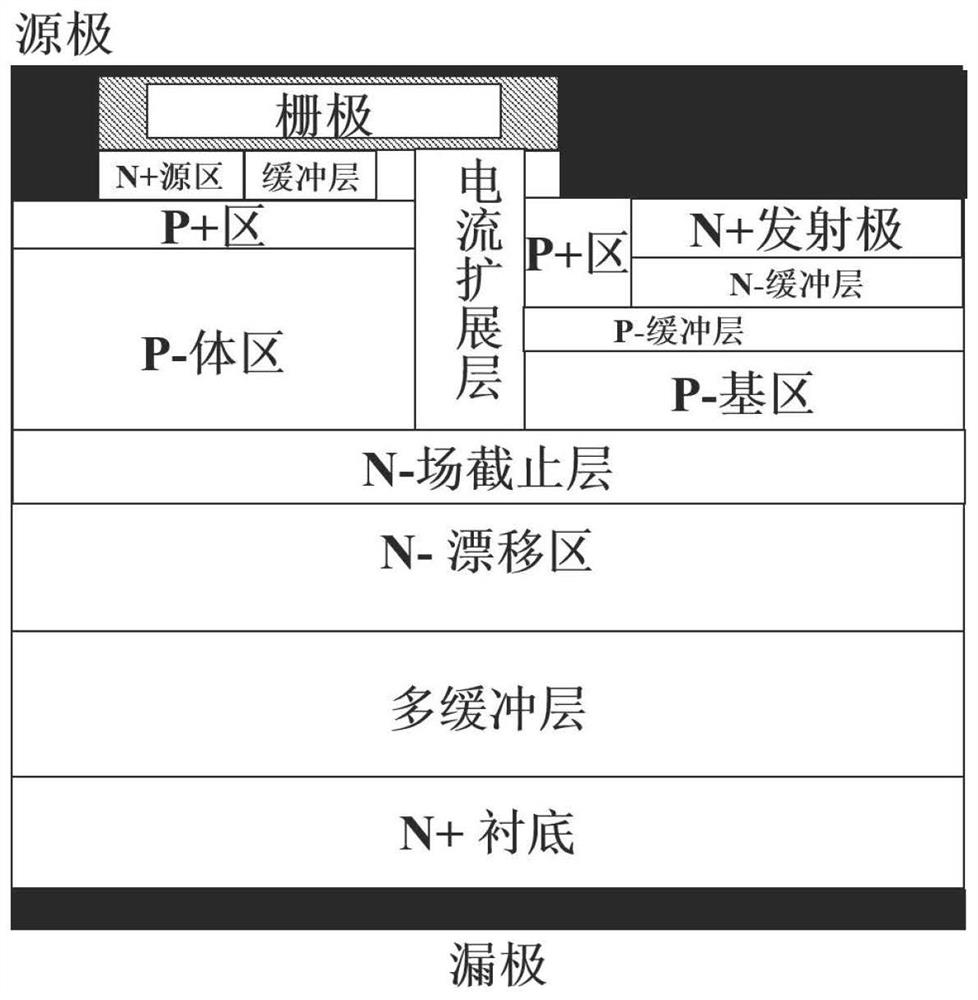

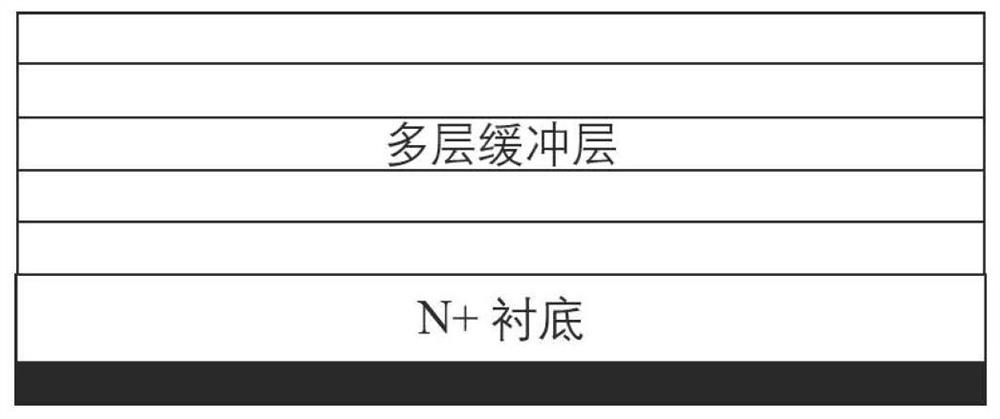

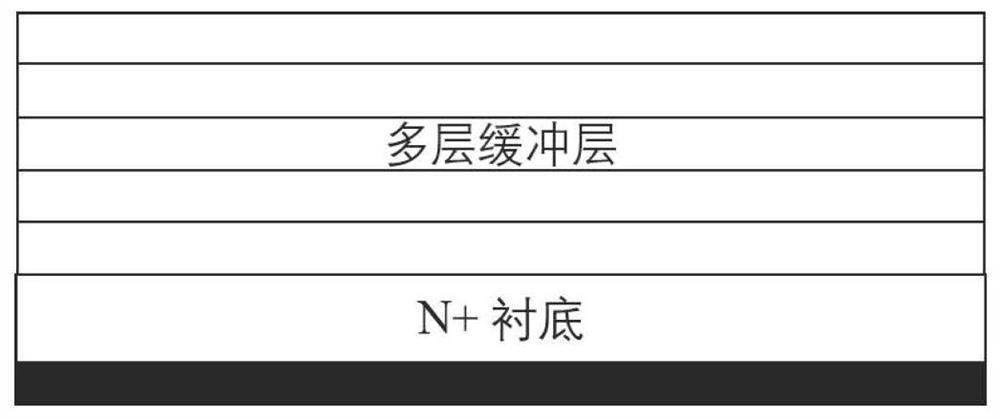

A kind of power device anti-single particle burnout reinforcement structure and preparation method

ActiveCN112951915BImprove anti-SEB performanceReduce in quantityEfficient power electronics conversionSemiconductor/solid-state device manufacturingMetallic electrodeEngineering

The invention discloses a power device anti-single event burning reinforced structure electrode and a preparation method thereof. An N-type multi-buffer layer structure is arranged in the drain electrode region of a semiconductor power device; a groove is formed at the source electrode and the neck region electrode and A metal electrode is formed; an integrated transistor is arranged under the neck region; an N-type field stop layer is arranged between the P-type body region and the drift region. Adopting the technical scheme of the present invention can greatly reduce the electric field peak value and impact ionization at the drift region of the semiconductor power device and the substrate homojunction, and reduce the number of carriers generated by the avalanche multiplication caused by the impact ionization; The current density is greatly reduced, thereby reducing the heat generated by the thermal effect of the current, and the SEB safe working voltage of the device is significantly improved.

Owner:HANGZHOU DIANZI UNIV +1

Nanoscale field-emission device and method of fabrication

ActiveUS10366856B2Reduced impact ionizationAvoid excessive degradationCold cathodesSingle discharge path tubesField emission deviceMean free path

Nanoscale field-emission devices are presented, wherein the devices include at least a pair of electrodes separated by a gap through which field emission of electrons from one electrode to the other occurs. The gap is dimensioned such that only a low voltage is required to induce field emission. As a result, the emitted electrons energy that is below the ionization potential of the gas or gasses that reside within the gap. In some embodiments, the gap is small enough that the distance between the electrodes is shorter than the mean-free path of electrons in air at atmospheric pressure. As a result, the field-emission devices do not require a vacuum environment for operation.

Owner:CALIFORNIA INST OF TECH

An ldmos transistor structure

ActiveCN107785423BWill not increase the quantityIncrease the area of the depleted regionSemiconductor devicesLDMOSGate source capacitance

The present invention provides an LDMOS transistor structure, comprising: a semiconductor substrate; a first drift region and a second drift region disposed separately in the semiconductor substrate; a source electrode located in the first drift region and a source electrode located in the semiconductor substrate. The drain in the second drift region; the gate structure located on the semiconductor substrate and in contact with the first drift region and the second drift region on both sides; located in the first drift region and a first isolation structure isolating the source from the gate structure; a second isolation structure located in the second drift region and isolating the drain from the gate structure; wherein: the first isolation Both the structure and the second isolation structure are provided with floating field plates. In the present invention, one or more floating field plates are arranged on the isolation structure between source-gate and drain-gate, which can increase the area of depletion region and reduce impact ionization, thereby obtaining higher breakdown voltage and saturated drain Current I dsat , and will not deteriorate the gate-to-drain capacitance C of the device gd and gate-source capacitance C gs .

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

A kind of Gan planar Gunn diode based on compound heat dissipation anode and its preparation method

InactiveCN110350084BReduce intensityDisperse energyMaterial nanotechnologySemiconductor/solid-state device detailsParticle physicsImpact ionization

The invention relates to a GaN planar Gunn diode based on a composite heat dissipation anode and a preparation method thereof. The planar Gunn diode comprises: an AlGaN back barrier layer; a GaN channel layer located on the AlGaN back barrier layer; an AlGaN barrier layer, located on the GaN channel layer; ohmic contact anode and ohmic contact cathode, respectively located at the two ends of the AlGaN back barrier layer, the GaN channel layer and the AlGaN barrier layer; and Schottky The extension layer is located on the AlGaN barrier layer and covers the ohmic contact anode. The planar Gunn diode Schottky extension forms a depletion layer in the channel of the planar Gunn diode, which weakens the strength of the high-energy dipole domains, thereby dissipating the energy of the electronic domains and lowering the anode terminal of the planar Gunn diode. The impact ionization buffers the generation of heat, thereby effectively suppressing the self-heating effect of the device, and improving the negative resistance effect, power and frequency of the device.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

A kind of mixed pin schottky diode and preparation method thereof

InactiveCN105810756BPrevent degradationImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsSchottky diode

Owner:FUDAN UNIV +1

Power device single particle burnout resistant reinforced structure and preparation method thereof

ActiveCN112951915AImprove anti-SEB performanceReduce in quantityEfficient power electronics conversionSemiconductor/solid-state device manufacturingMetallic electrodeImpact ionization

The invention discloses a power device single particle burnout resistant reinforced structure and a preparation method thereof. The method comprises the steps of arranging an N-type multi-buffer layer region structure in a drain electrode region of a semiconductor power device; forming a groove at a source electrode and a neck region electrode and forming a metal electrode; arranging an integrated transistor below the neck region; and arranging an N-type field stop layer between a P-type body region and a drift region. By adopting the technical scheme of the invention, the electric field peak value and collision ionization at the homojunction of a drift region and a substrate of the semiconductor power device can be greatly reduced, the number of carriers generated by avalanche multiplication caused by collision ionization is reduced, and meanwhile, the current density in the device is greatly reduced, so that the heat generated by a current heat effect is reduced, and the SEB safe working voltage of the device is remarkably improved.

Owner:HANGZHOU DIANZI UNIV +1

ldmos device and its manufacturing method

ActiveCN106298935BReduced impact ionizationLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSGate oxide

The invention discloses an LDMOS device which comprises a P-type epitaxial layer, an N-well, a P-well, a first N-type drift region, a first P-type layer, a second N-type drift region, a second P-type layer, a gate oxide layer and gate polysilicon. The P-well, the second N-type drift region, the first N-type drift region and the N-well are sequentially contiguous from left to right at the upper part of the P-type epitaxial layer. The second N-type drift region is shallower than the first N-type drift region. The second P-type layer is adjacent to the lower part of the second N-type drift region. The first P-type layer is adjacent to the lower part of the first N-type drift region. The second P-type layer is shallower than the first P-type layer. The second P-type layer has a higher doping concentration than the first P-type layer. The invention further discloses a manufacturing method for the LDMOS device. According to the invention, the LDMOS device has lower on-resistance, and can satisfy off-state breakdown voltage and on-state breakdown voltage at the same time.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Nanoscale Field-Emission Device and Method of Fabrication

ActiveUS20180277329A1Reduced impact ionizationAvoid excessive degradationCold cathodesSingle discharge path tubesField emission deviceMean free path

Owner:CALIFORNIA INST OF TECH

A lateral double diffused metal oxide semiconductor device

ActiveCN107342325BImprove breakdown voltageLarge off-state breakdown voltageSemiconductor devicesLDMOSPhysical chemistry

The invention relates to a lateral double-diffused metal oxide semiconductor device. The lateral double-diffused metal oxide semiconductor device comprises a device part, a terminal part and a P type substrate; a high-voltage N type region, an N type drift region, a P type body region 4A1 and a P type body region 4A2 are arranged over the P type substrate; the P type body region 4A1 is positioned in the device part; the P type body region 4A2 is positioned in the terminal part, and formed by diffusion of the P type body region 4A1 in the device part; a gate oxidization layer and a polycrystalline silicon gate field plate are also arranged over the high-voltage N type region; the device part further comprises an N type drain region, an N type source region, a P type region and a metal contact, wherein a shallow trench isolation region is arranged in the N type drift region; the shallow trench isolation region is shaped as a straight bar; the shallow trench isolation region extends to the terminal part from the device part; namely, the width of the shallow trench isolation region is the same as that of the N type drift region; and furthermore, the N type drain region, the N type source region, the P type region and the metal contact are not arranged over the P type body region 4A2 and the N type drift region of the terminal part. By means of the lateral double-diffused metal oxide semiconductor device disclosed by the invention, the breakdown voltage is improved when various performance parameters of an LDMOS device are kept same.

Owner:SOUTHEAST UNIV

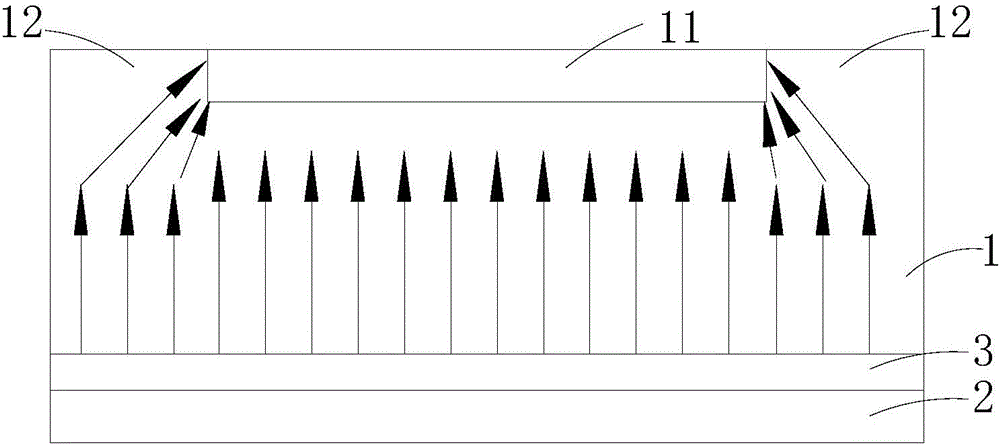

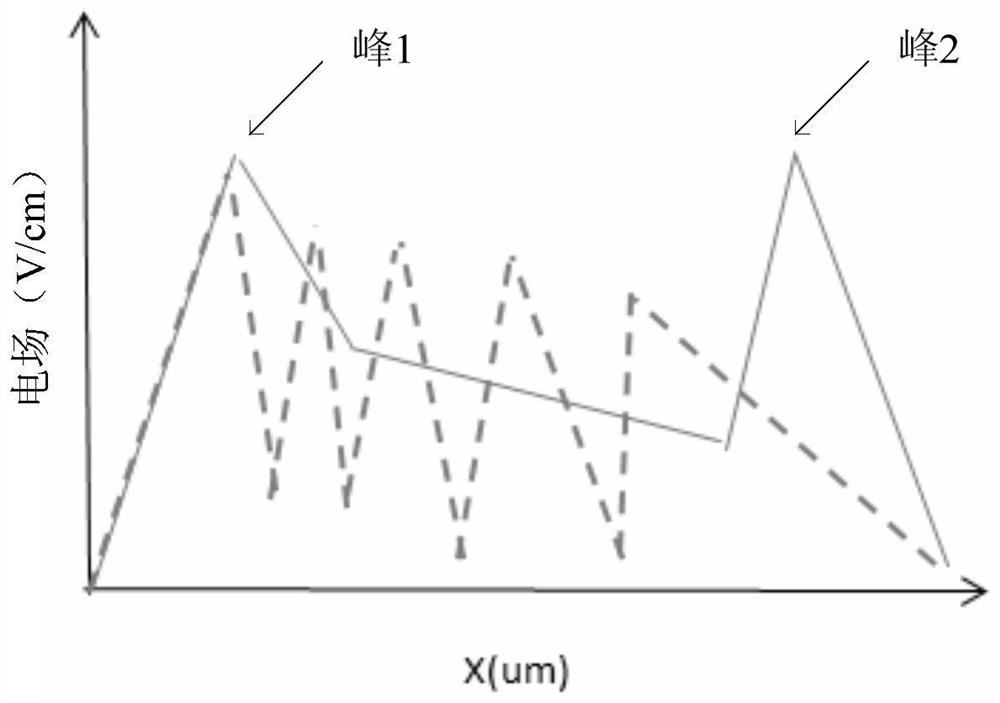

Multi electric potential field plate lateral high voltage N type MOS transistor

InactiveCN1324717CReduce peak electric fieldReduced impact ionizationSemiconductor devicesPeak valueHigh pressure

Disclosed relates to multi electric potential field electrode plate high-pressured N-typed metal oxide semiconductor of high-voltaged component, comprising N-typed substrate, P-typed epitaxial layer, source and drain, multi- silicon polycrystal, field oxide layer and oxide layer, silicon polycrystal field electrode plate above field oxide layer and between drain and silicon polycrystal gate , which is connected to drain. The invention brings in silicon polycrystal field electrode plate with the same electric potential of drain end, which makes the surface of floating area deviation area below silicon polycrystal field electrode plate in accumulation condition of current carrier, greatly reducing peak electric field between drain end and silicon polycrystal field electrode plate when in operation work condition and impact ionization of current carrier on drain end, so Kirk effect(the effect of breakdown voltage reduction caused by electric field accumulating under large current ) is notably decreased, breakdown voltage and area of safe operation are increased.

Owner:SOUTHEAST UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com