A Lateral Insulated Gate Bipolar Transistor with High Hot Carrier Reliability

A bipolar transistor and carrier technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of reduced withstand voltage and increased on-resistance of devices, and achieve reduced area and impact ionization rate. , the effect of reducing the transverse electric field

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

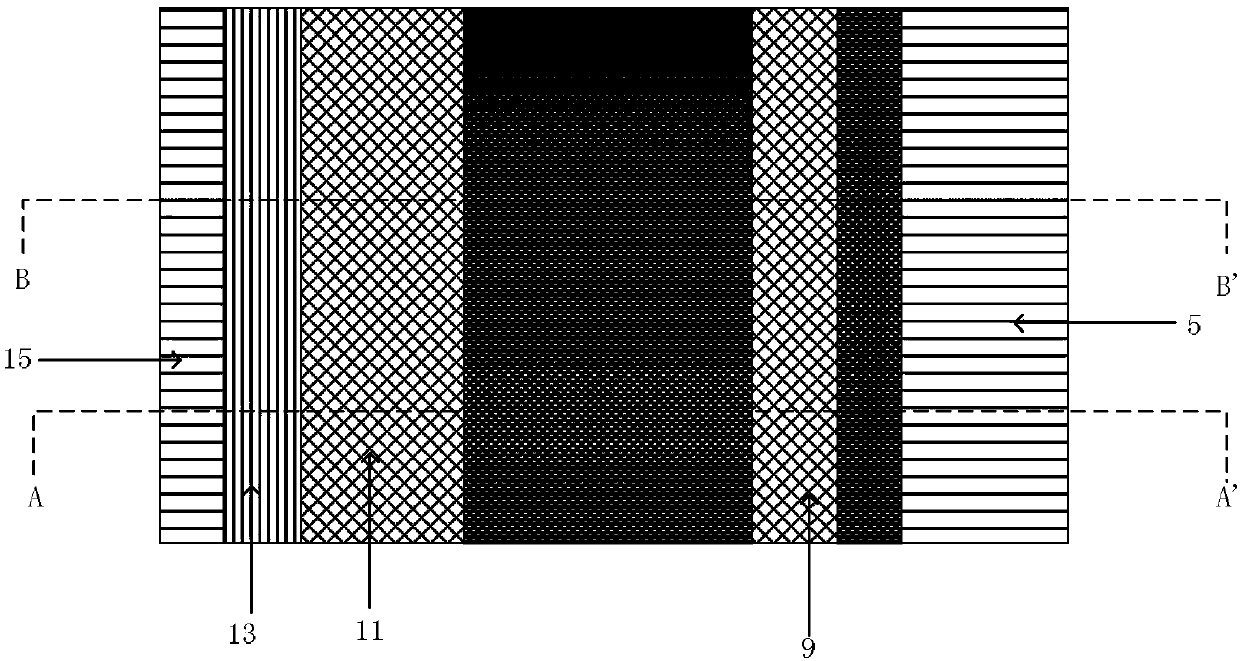

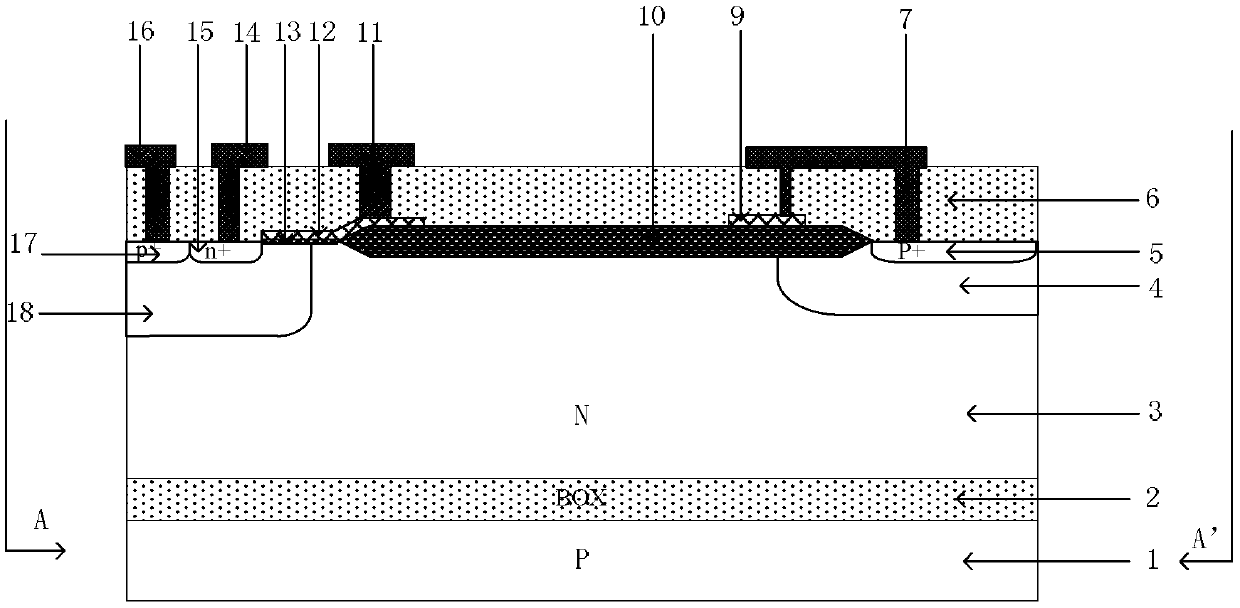

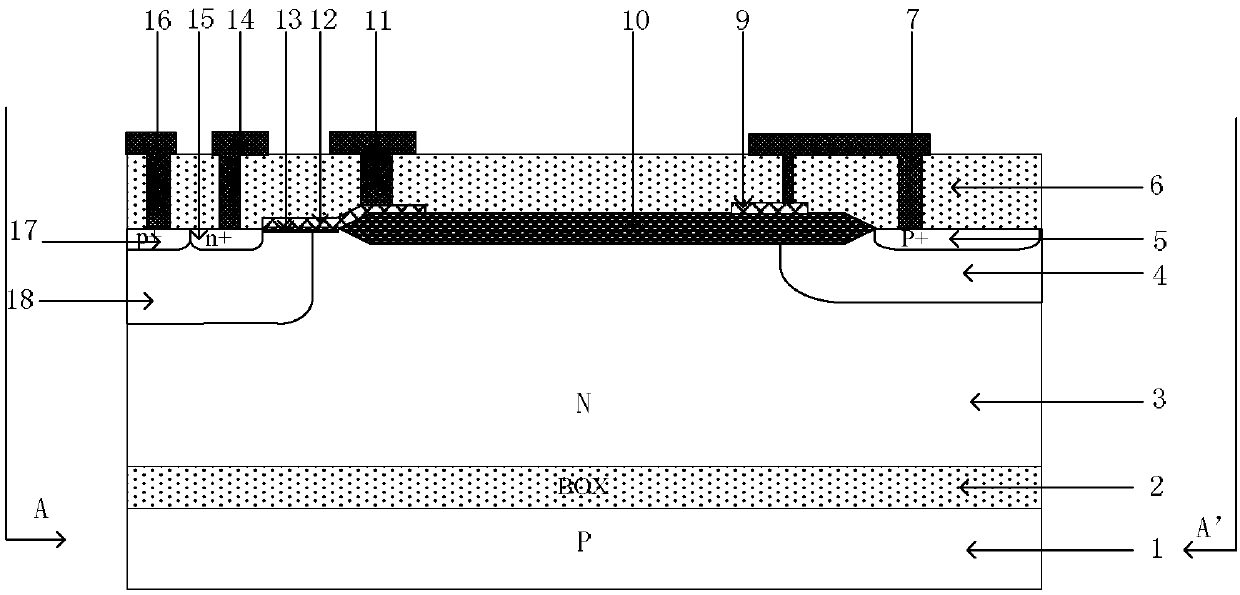

[0026] Attached below Figure 5 , the present invention is described in detail, a lateral insulated gate bipolar transistor with high hot carrier reliability, comprising: a P-type substrate 1, a buried oxide layer 2 is arranged on the P-type substrate 1, and a buried oxide layer 2 is provided with an N-type epitaxial layer 3, an N-type buffer well 4 and a P-type body region 18 are arranged inside the N-type epitaxial layer 3, and a P-type anode region 5 and an N-type floating region 18 are arranged in the N-type buffer well 4. The empty contact region 8 is provided with an N-type negative region 15 and a P-type body contact region 17 in the P-type body region 18, and a gate oxide layer 13 and a field oxide layer 10 are arranged on the surface of the N-type epitaxial layer 3, and the gate oxide layer 13 and one end of the field oxide layer 10, the other end of the gate oxide layer 13 extends to the N-type negative region 15 and ends at the boundary of the N-type negative region...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com