Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

110results about How to "Raise the bias" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

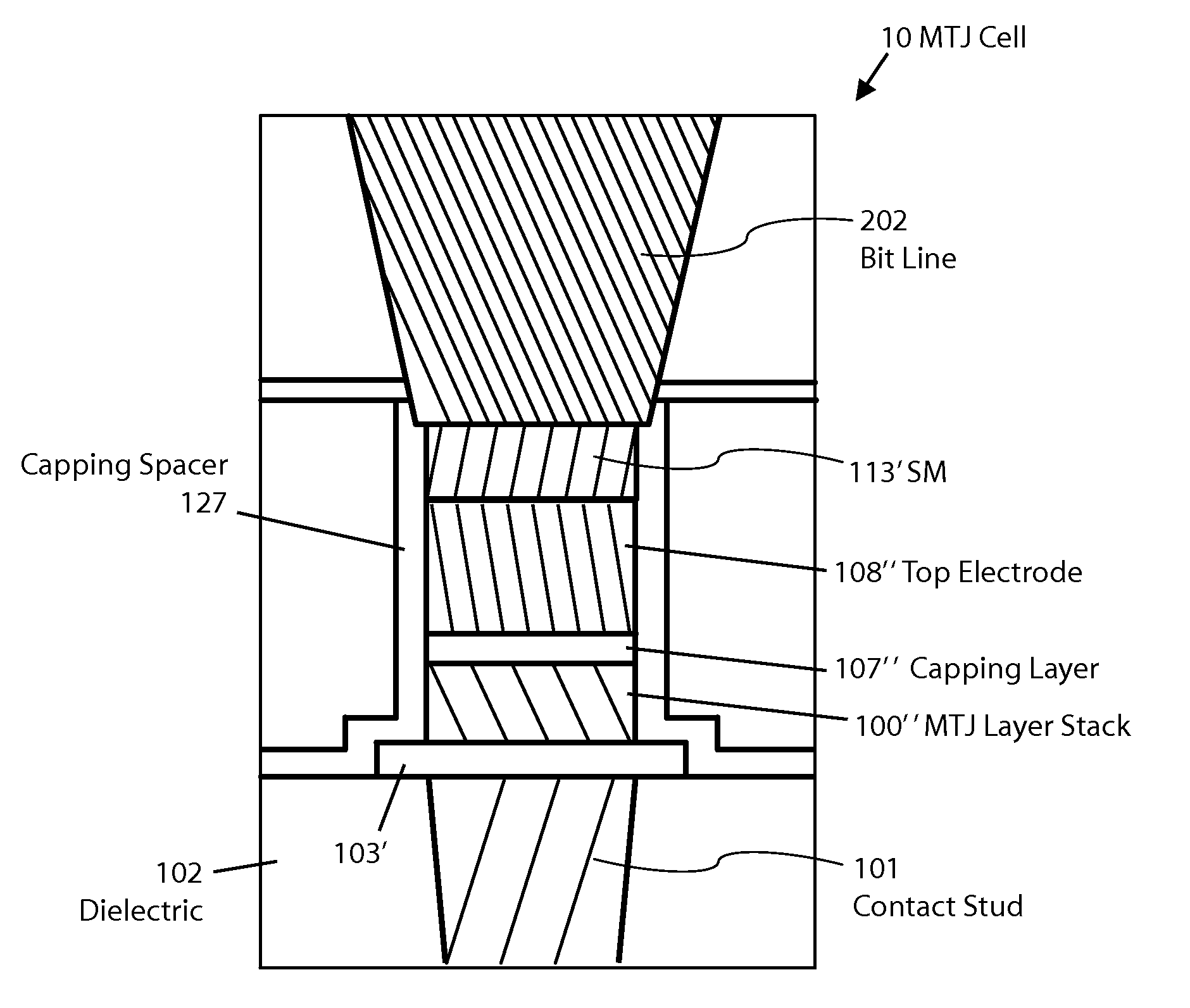

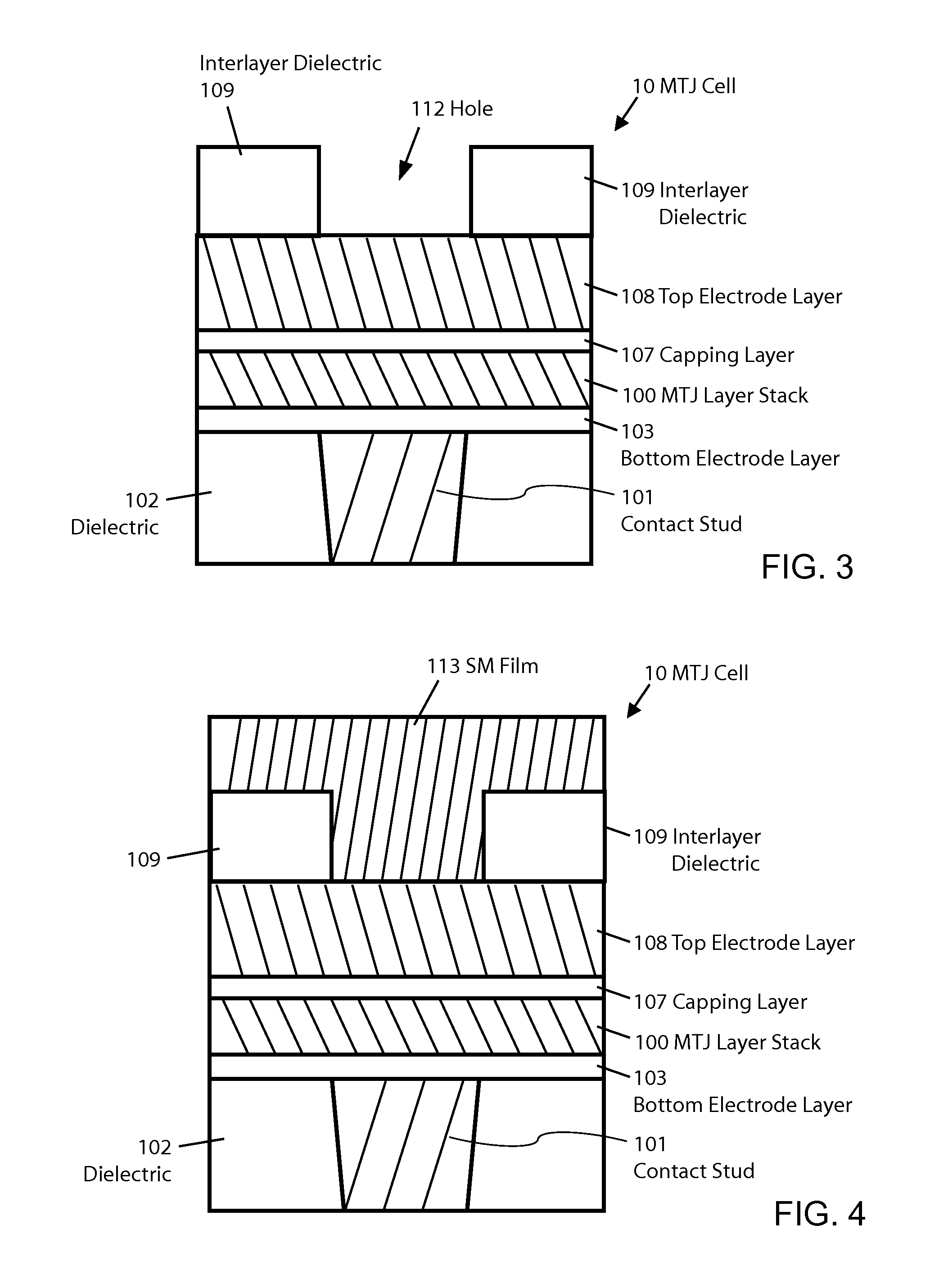

MTJ MRAM with stud patterning

ActiveUS8772888B2Reduce widthImprove errorMagnetic-field-controlled resistorsSolid-state devicesEtchingConductive materials

Owner:AVALANCHE TECH

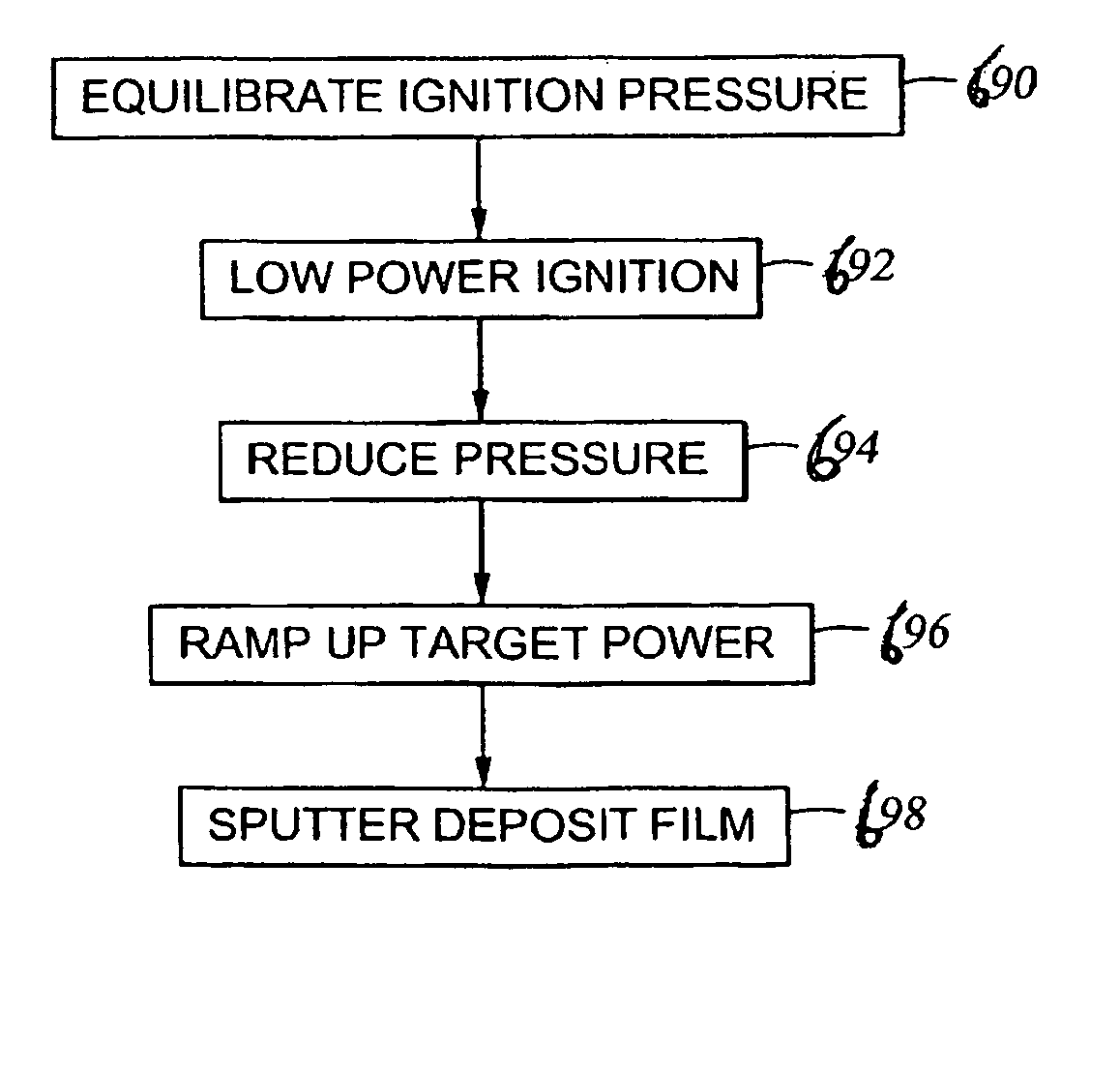

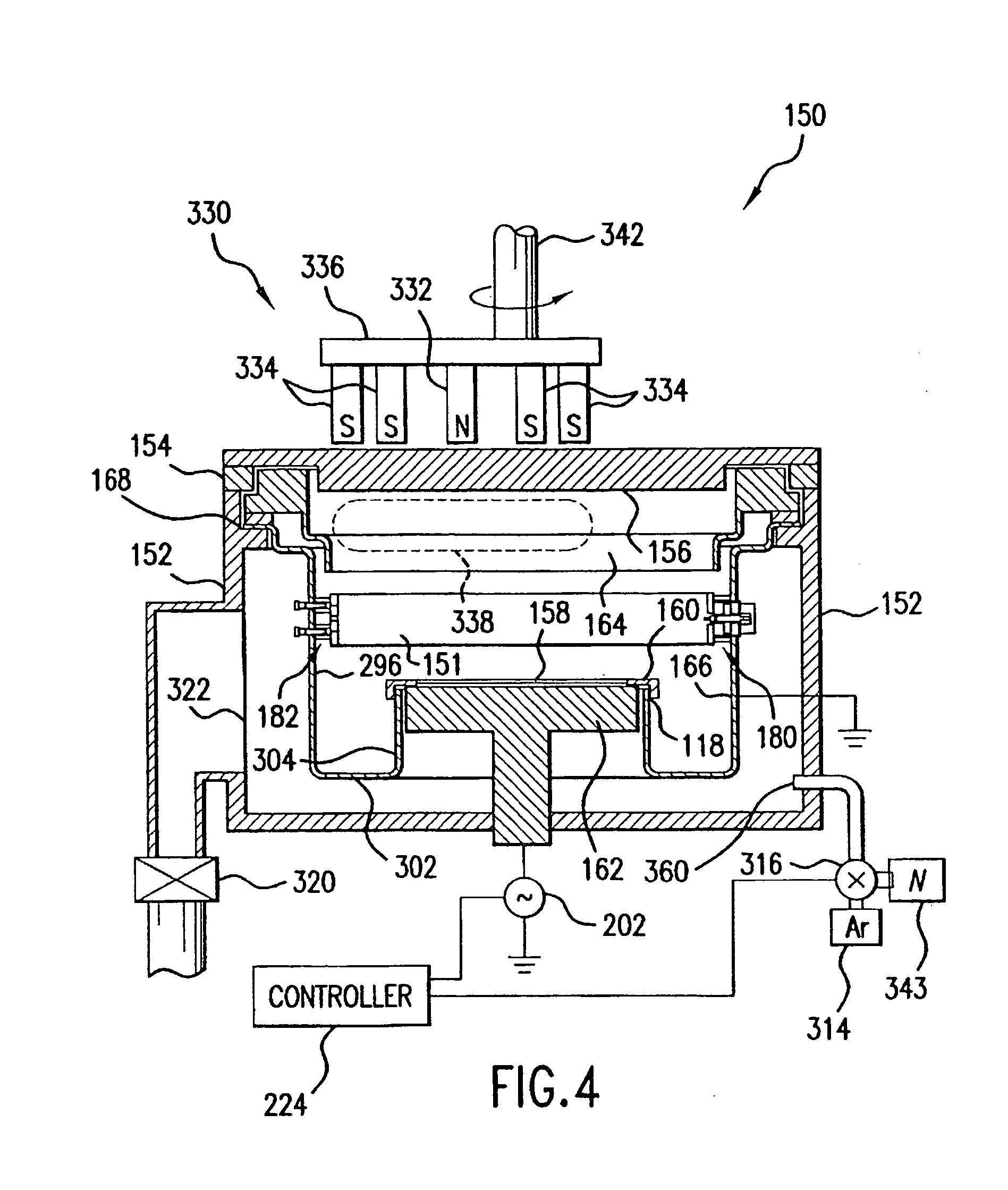

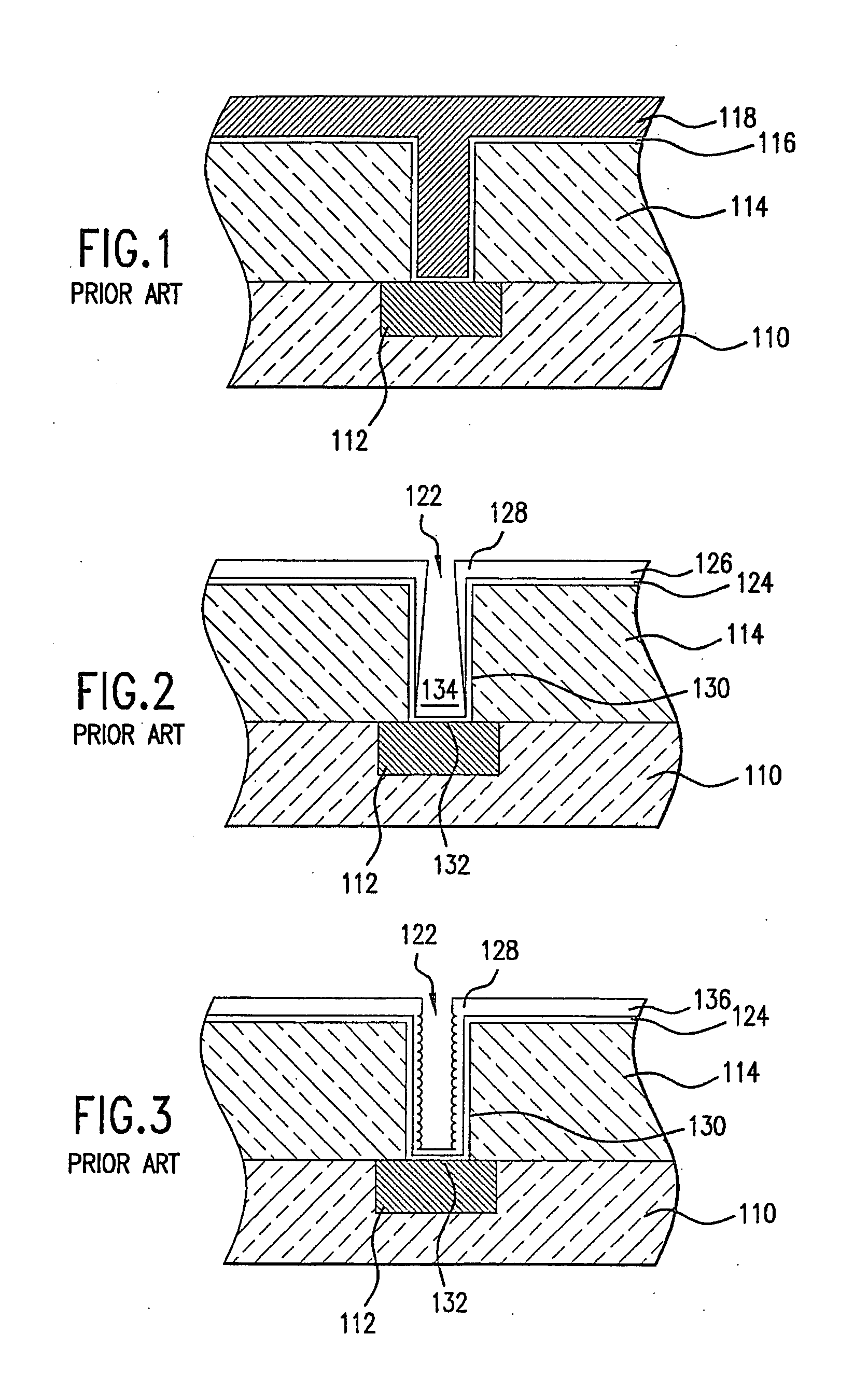

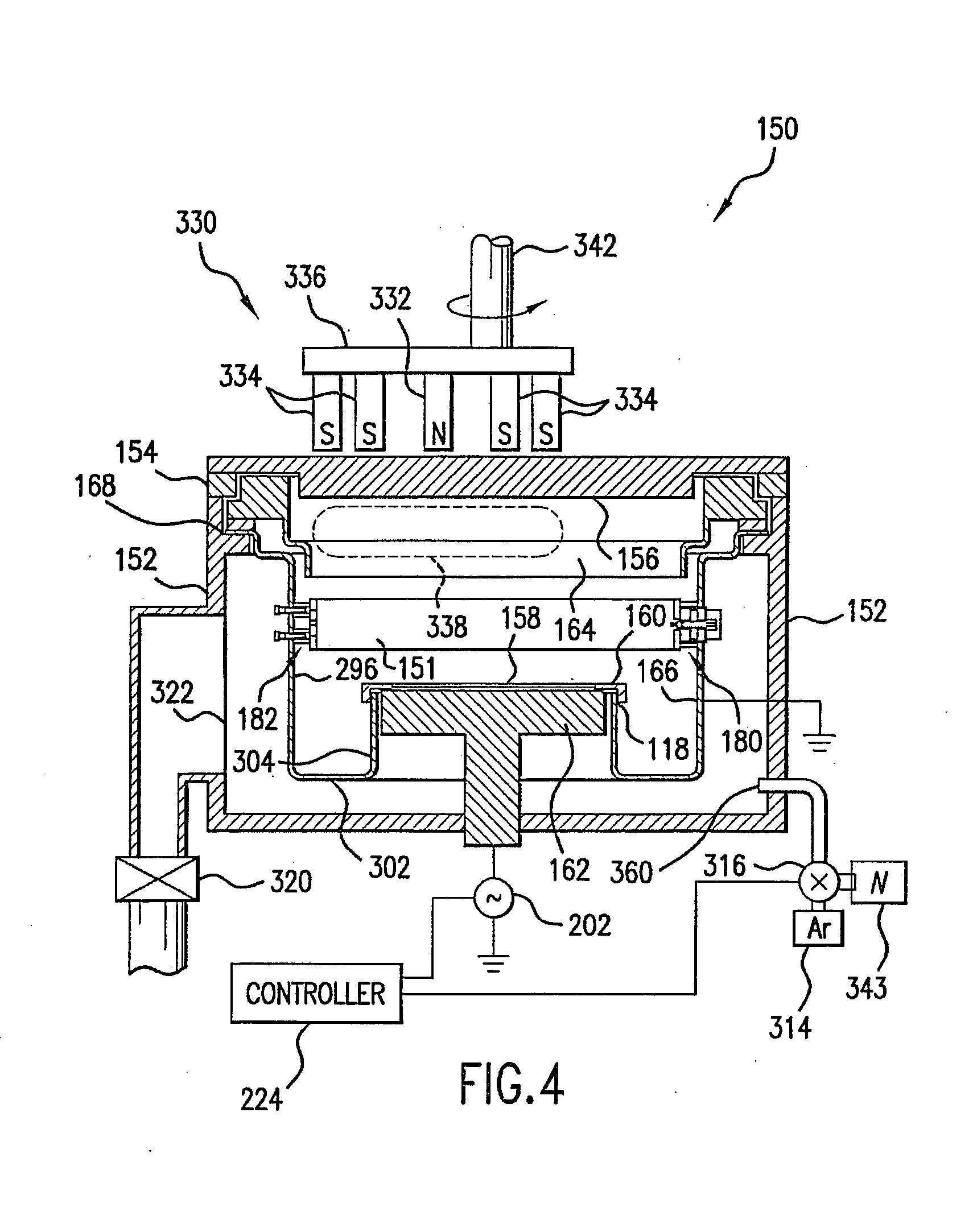

Self-ionized and inductively-coupled plasma for sputtering and resputtering

InactiveUS20050006222A1Raise the ratioReduce layer thicknessCellsElectric discharge tubesSputteringInductively coupled plasma

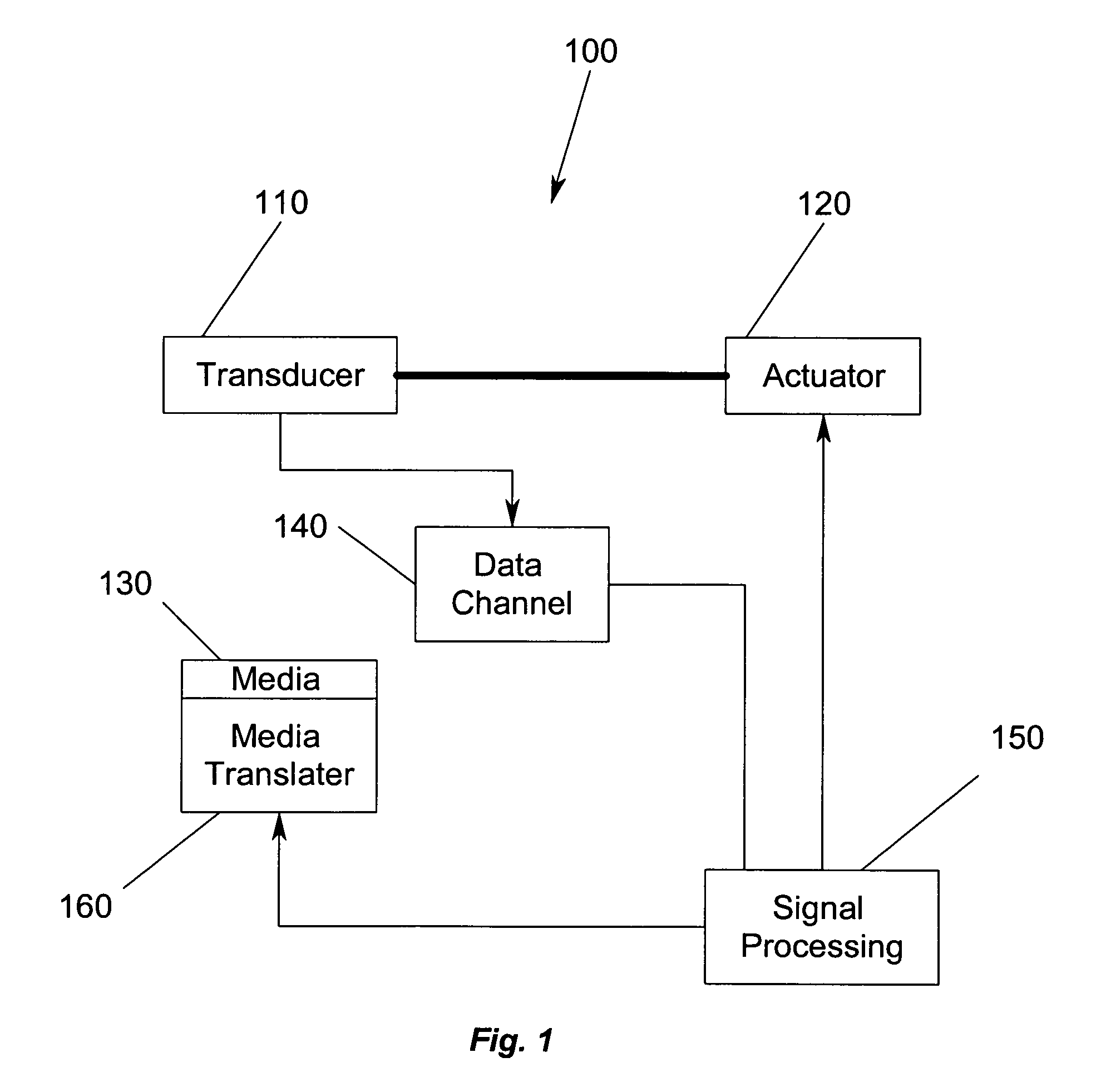

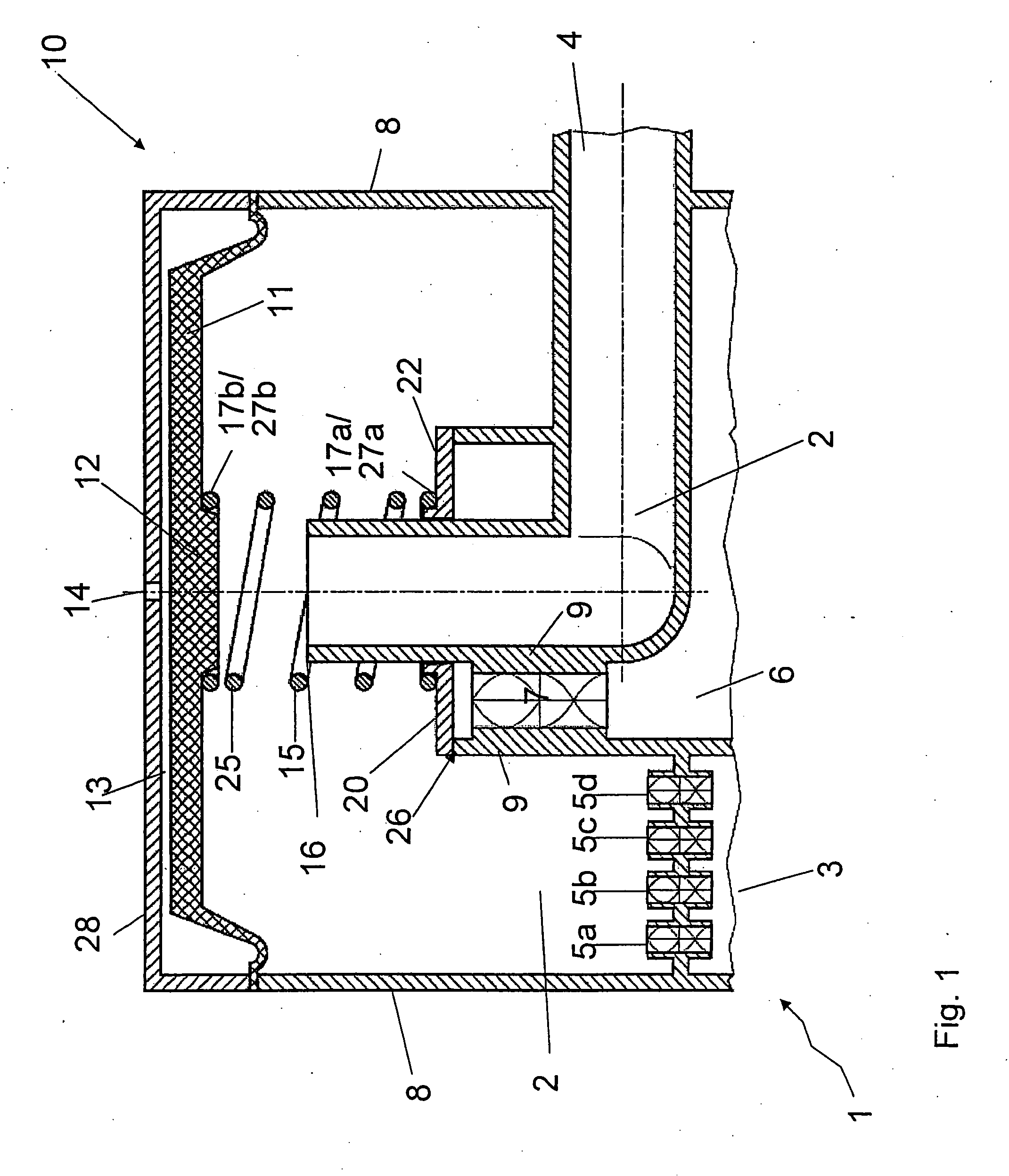

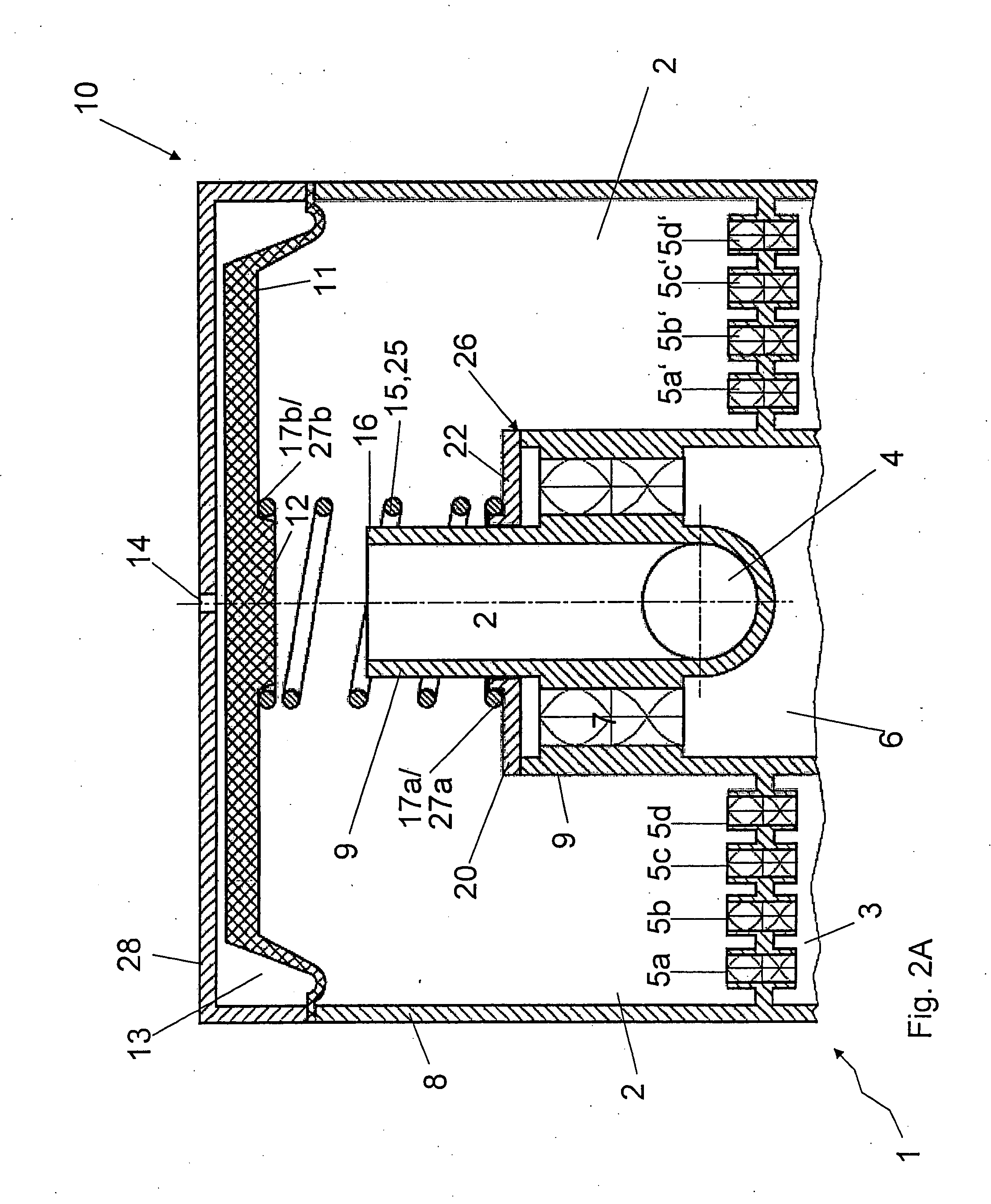

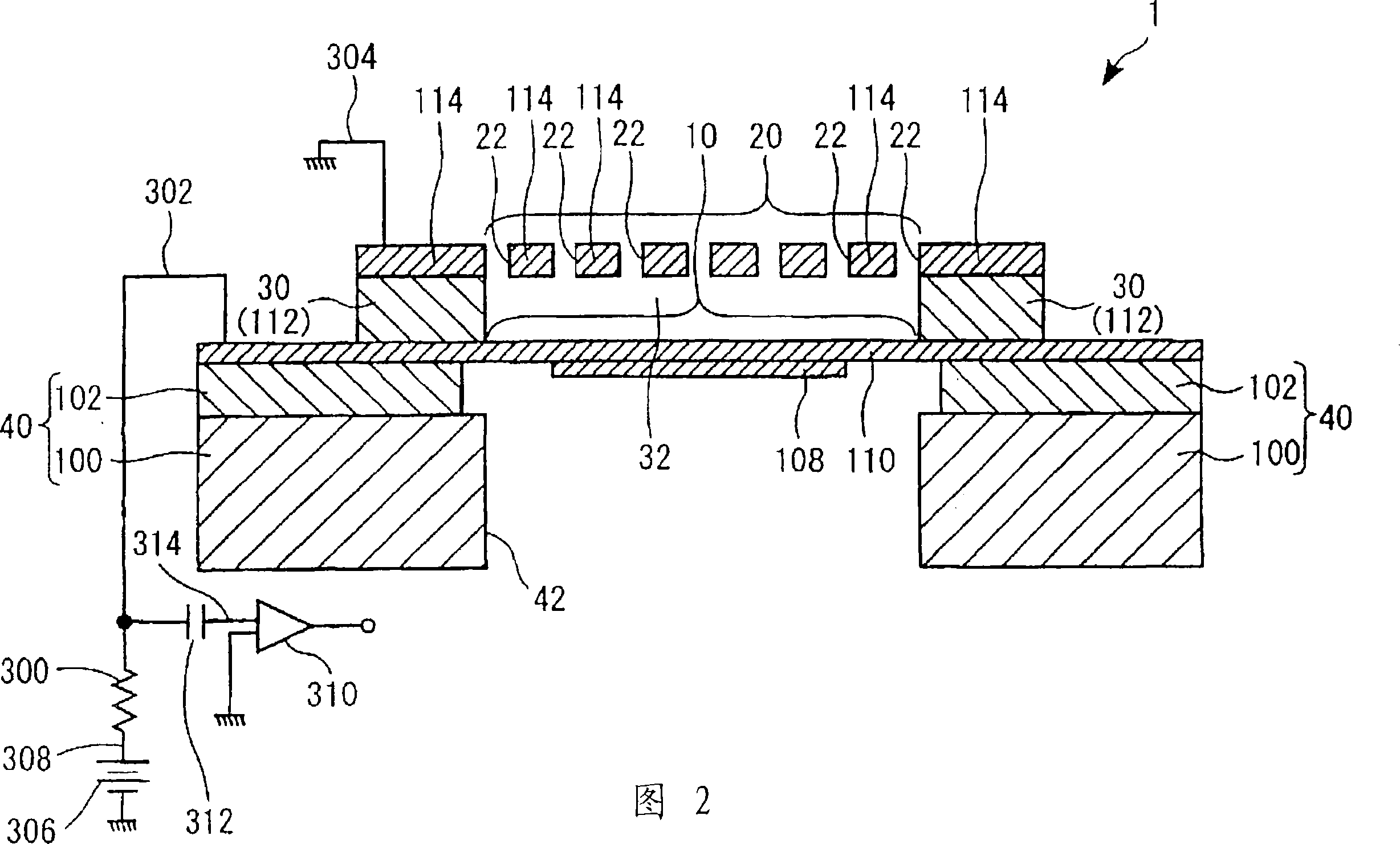

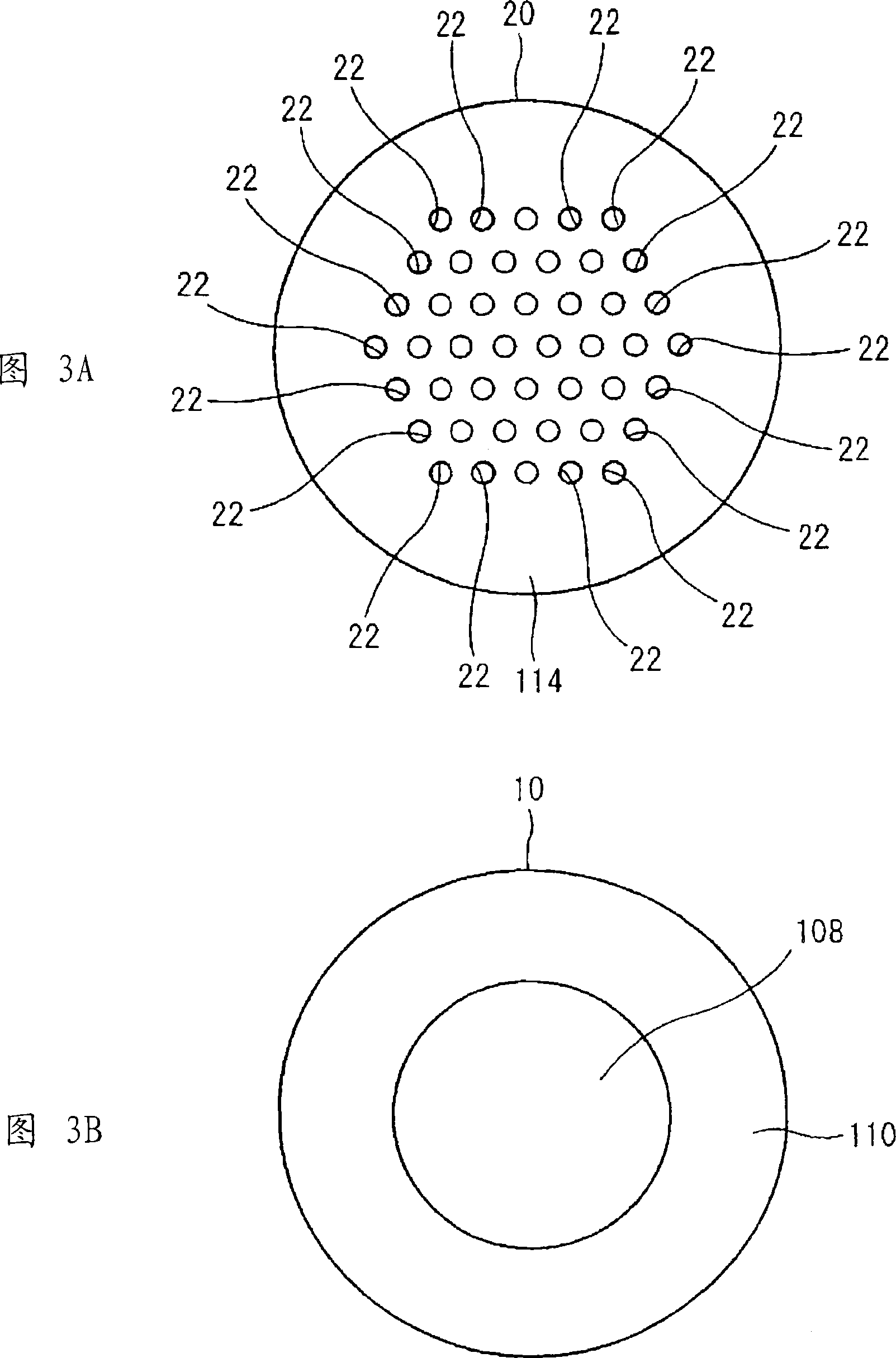

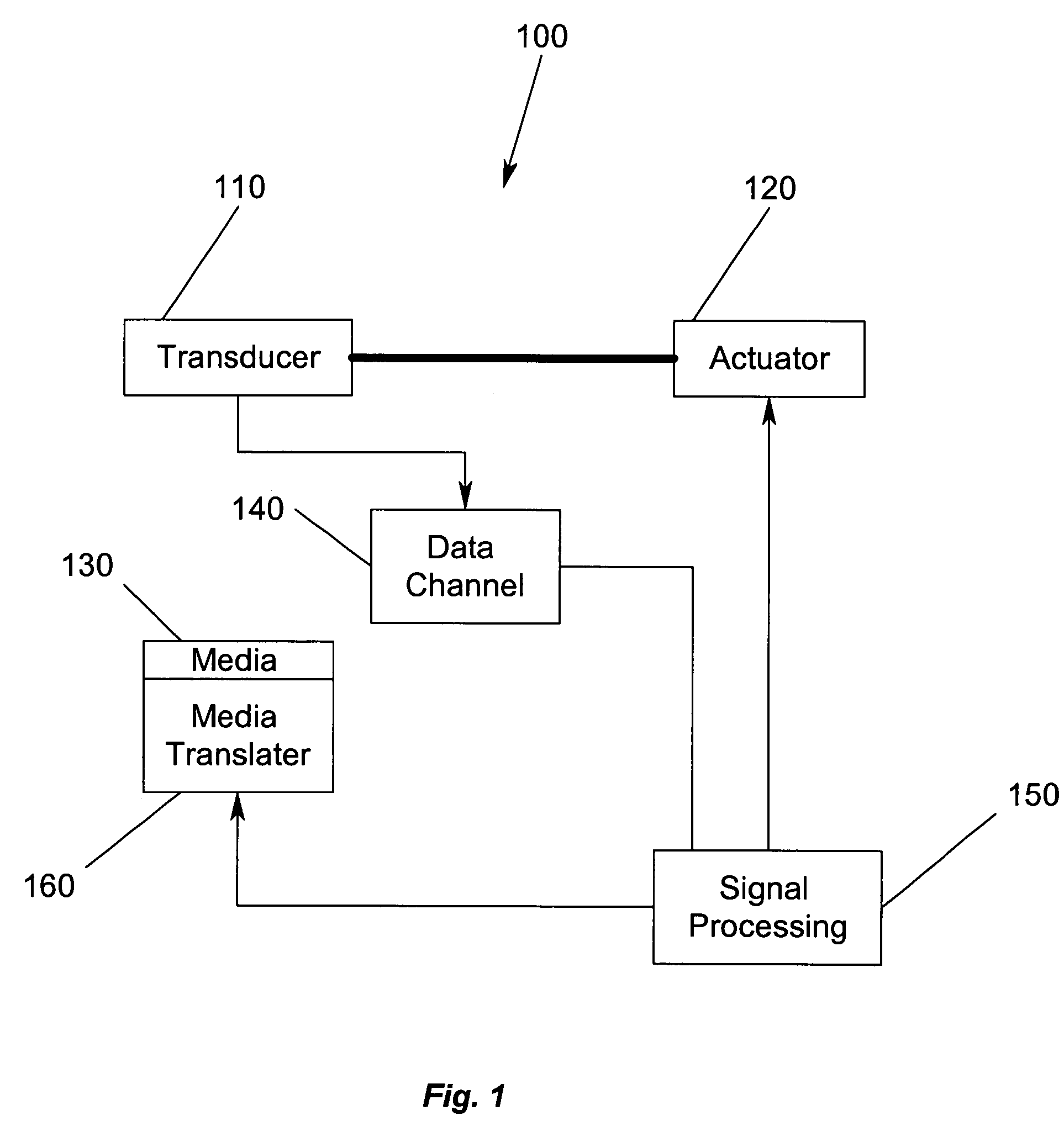

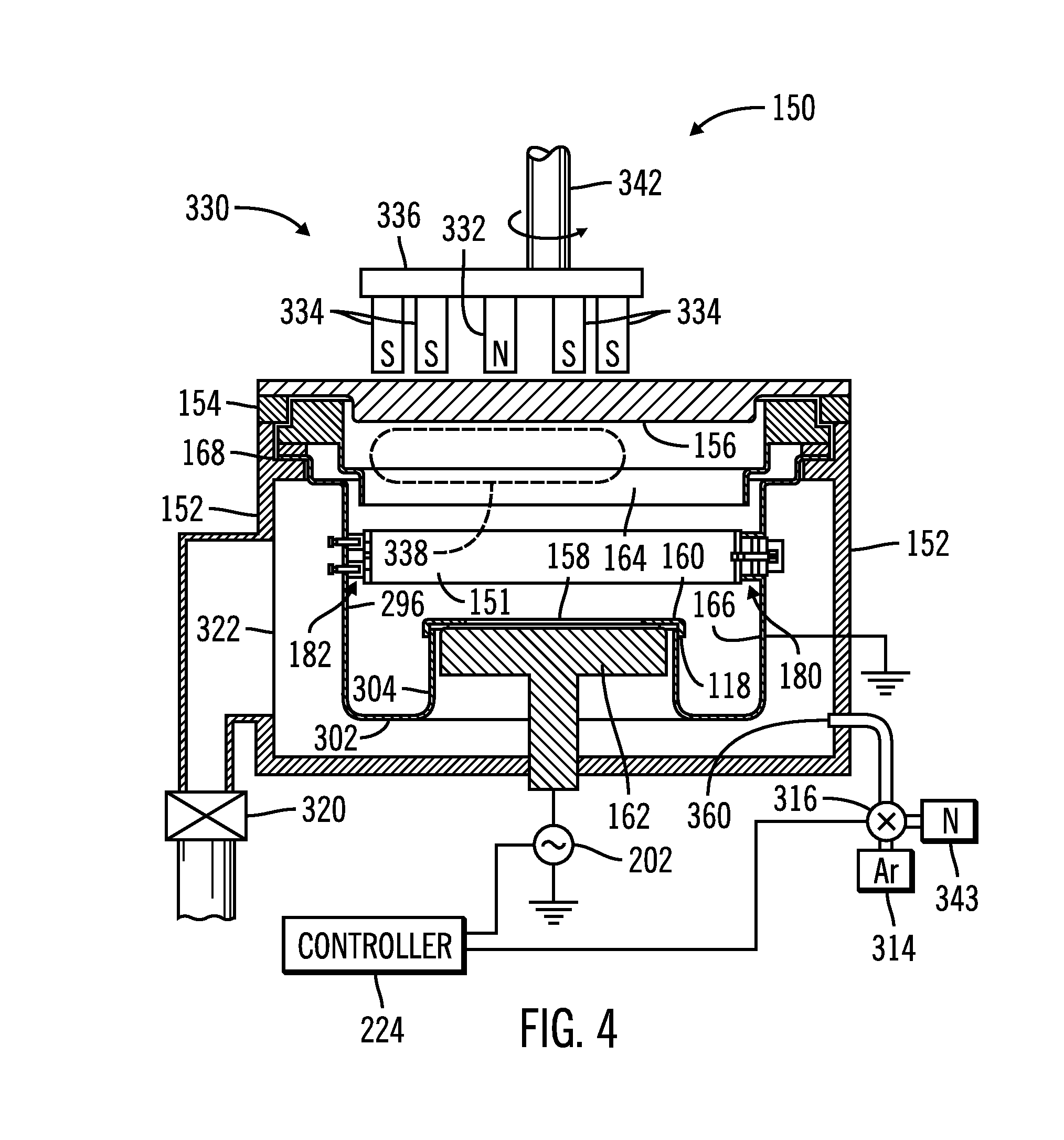

A magnetron sputter reactor (410) and its method of use, in which SIP sputtering and ICP sputtering are promoted is disclosed. In another chamber (412) an array of auxiliary magnets positioned along sidewalls (414) of a magnetron sputter reactor on a side towards the wafer from the target is disclosed. The magnetron (436) preferably is a small one having a stronger outer pole (442) of a first polarity surrounding a weaker inner pole (440) of a second polarity all on a yoke (444) and rotates about the axis (438) of the chamber using rotation means (446, 448, 450). The auxiliary magnets (462) preferably have the first polarity to draw the unbalanced magnetic field (460) towards the wafer (424), which is on a pedestal (422) supplied with power (454). Argon (426) is supplied through a valve (428). The target (416) is supplied with power (434).

Owner:APPLIED MATERIALS INC

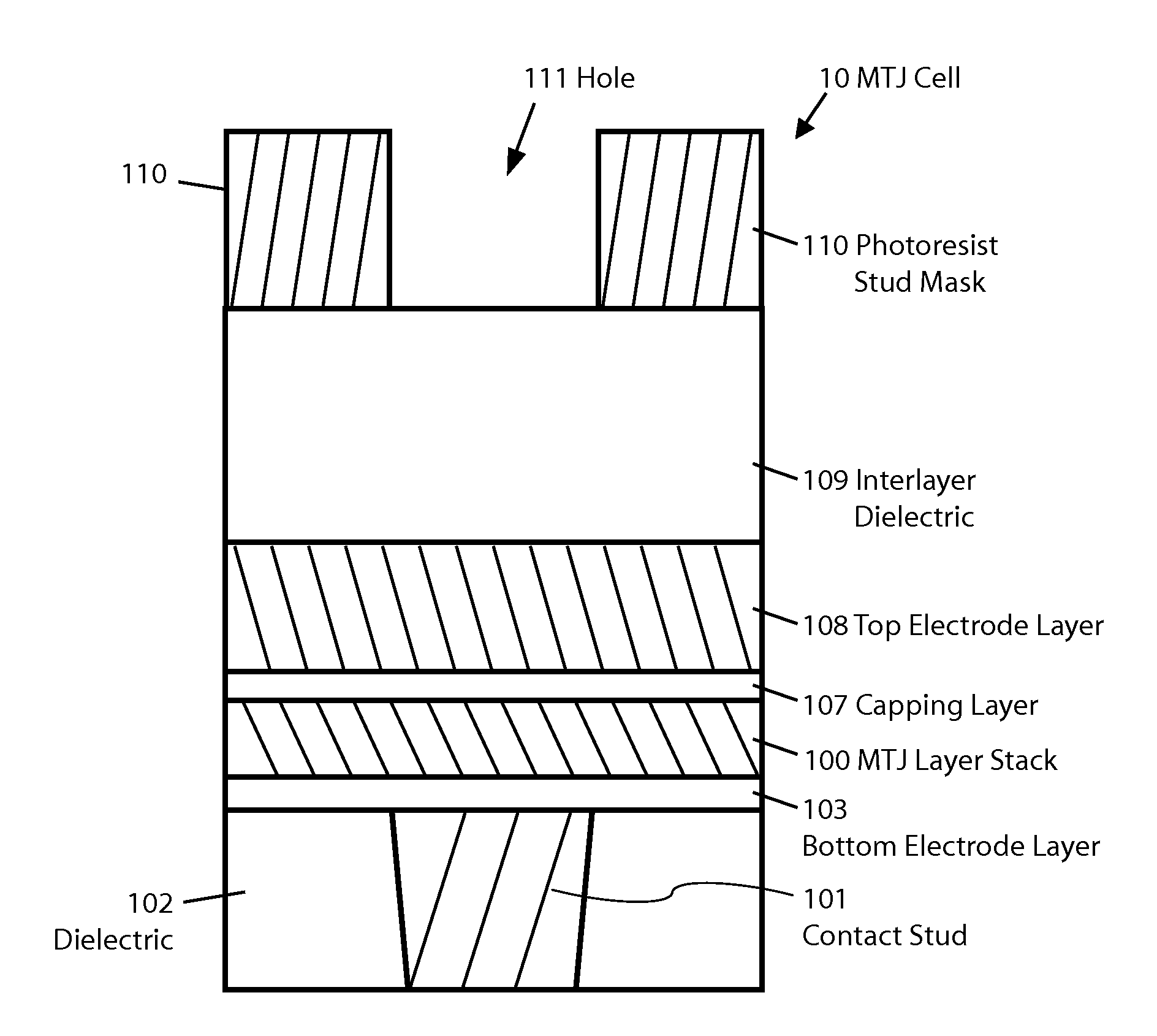

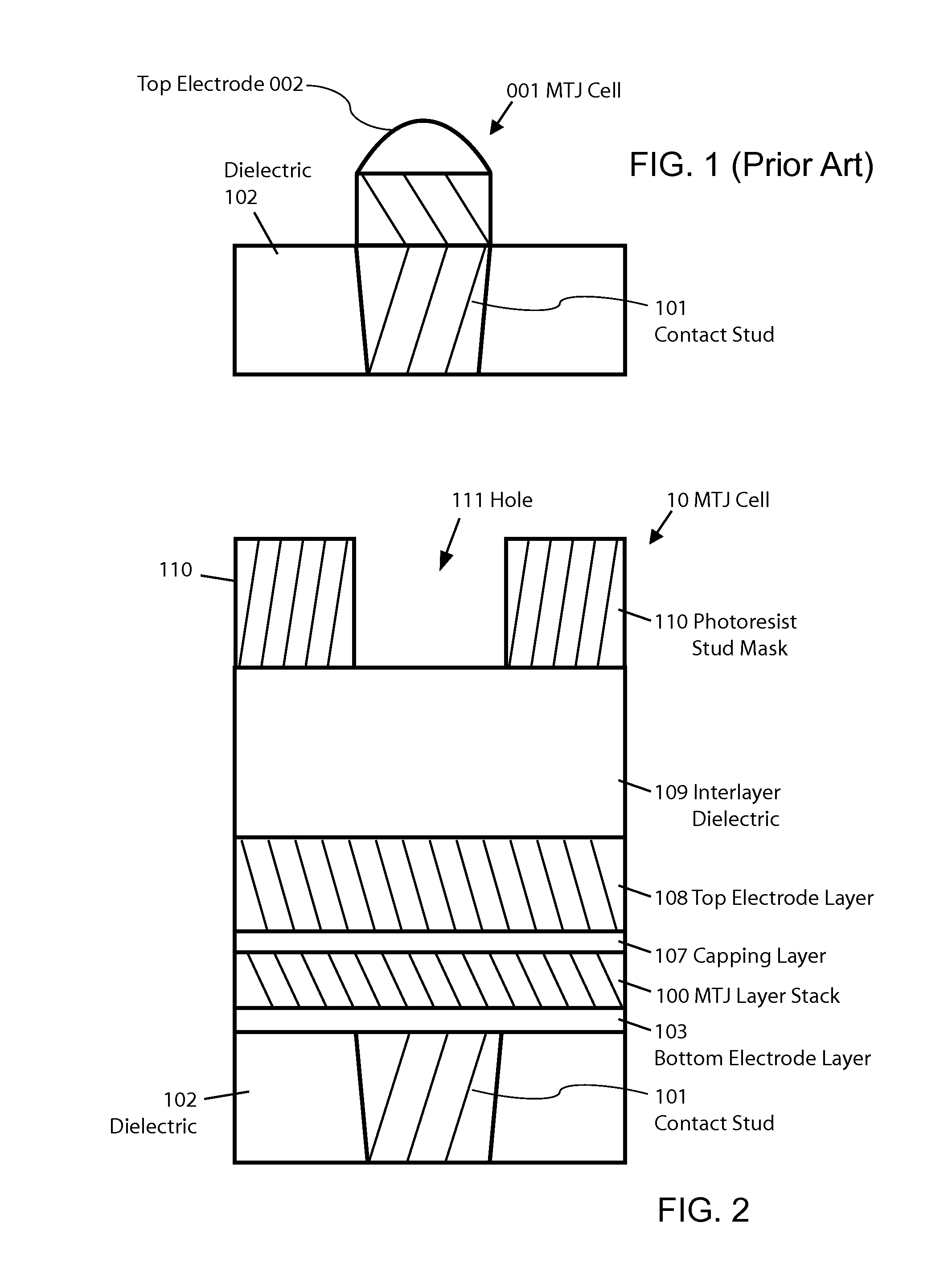

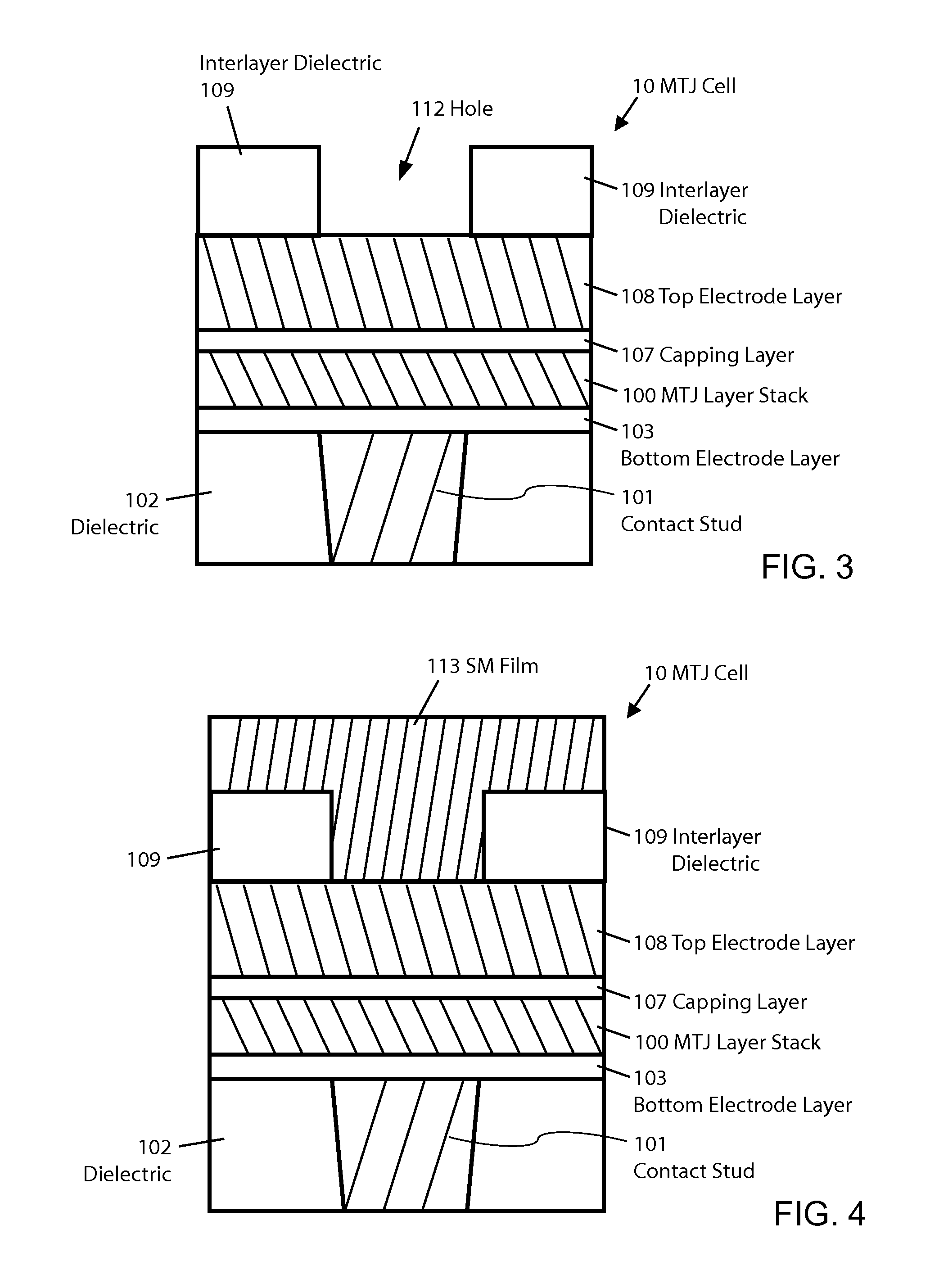

Mtj MRAM with stud patterning

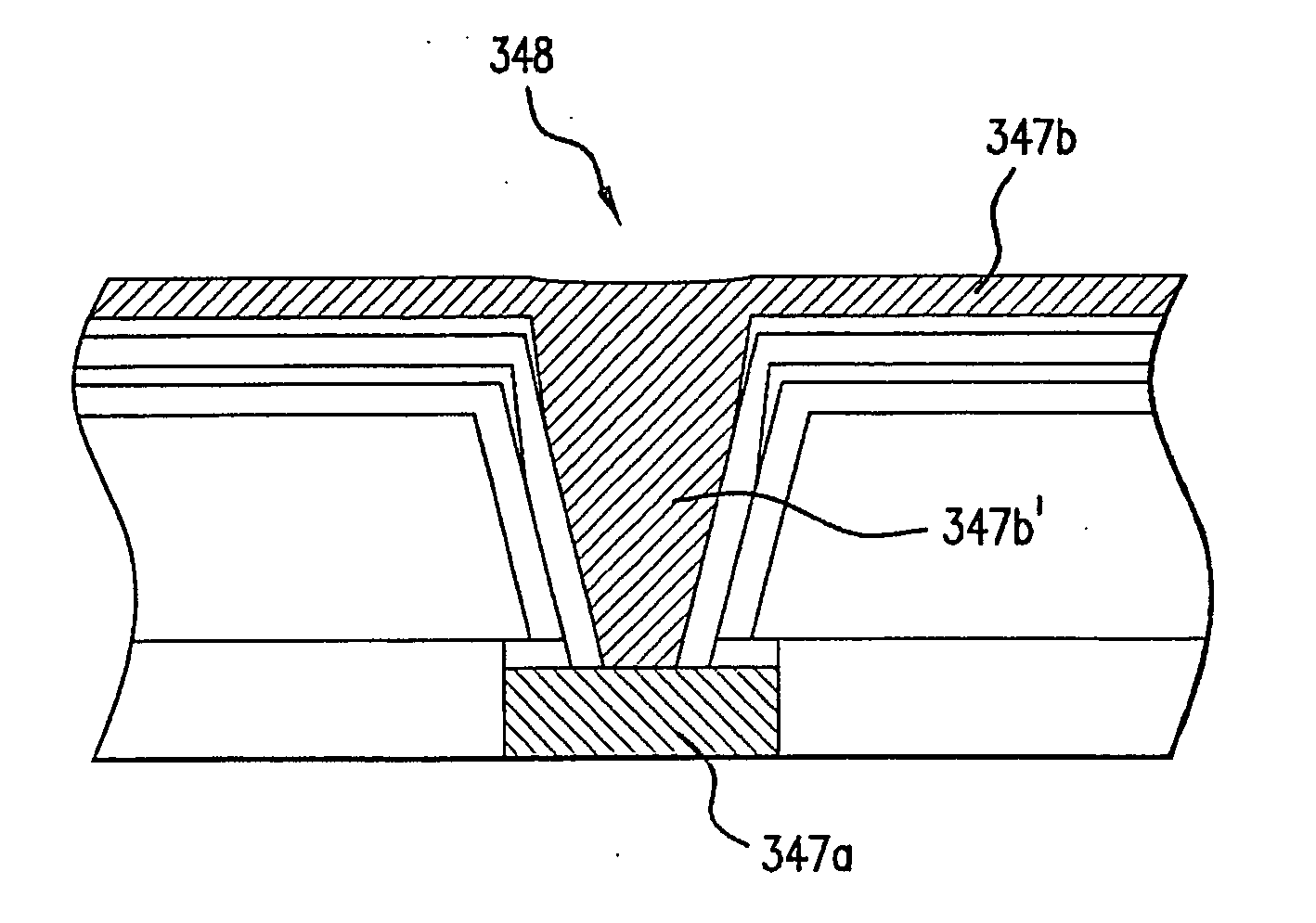

ActiveUS20140042567A1Raise the biasReduce widthSemiconductor/solid-state device manufacturingGalvano-magnetic device detailsEtchingConductive materials

Use of a multilayer etching mask that includes a stud mask and a removable spacer sleeve for MTJ etching to form a bottom electrode that is wider than the rest of the MTJ pillar is described. The first embodiment of the invention described includes a top electrode and a stud mask. In the second and third embodiments the stud mask is a conductive material and also serves as the top electrode. In embodiments after the stud mask is formed a spacer sleeve is formed around it to initially increase the masking width for a phase of etching. The spacer is removed for further etching, to create step structures that are progressively transferred down into the layers forming the MTJ pillar. In one embodiment the spacer sleeve is formed by net polymer deposition during an etching phase.

Owner:AVALANCHE TECH

Self-ionized and inductively-coupled plasma for sputtering and resputtering

InactiveUS20050255691A1Raise the ratioReduce layer thicknessElectric discharge tubesSolid-state devicesRadio frequency energyMagnetic poles

Owner:APPLIED MATERIALS INC

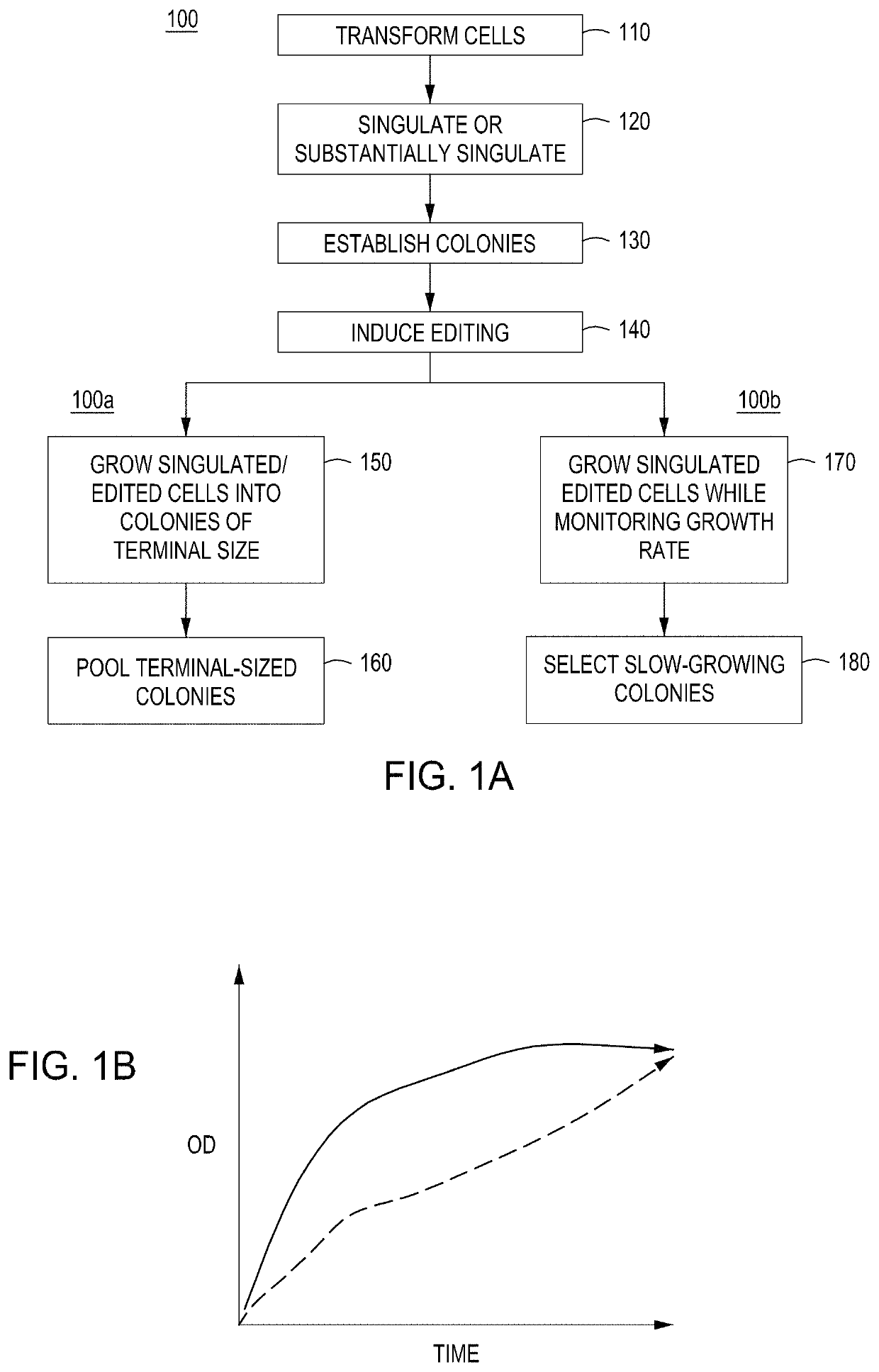

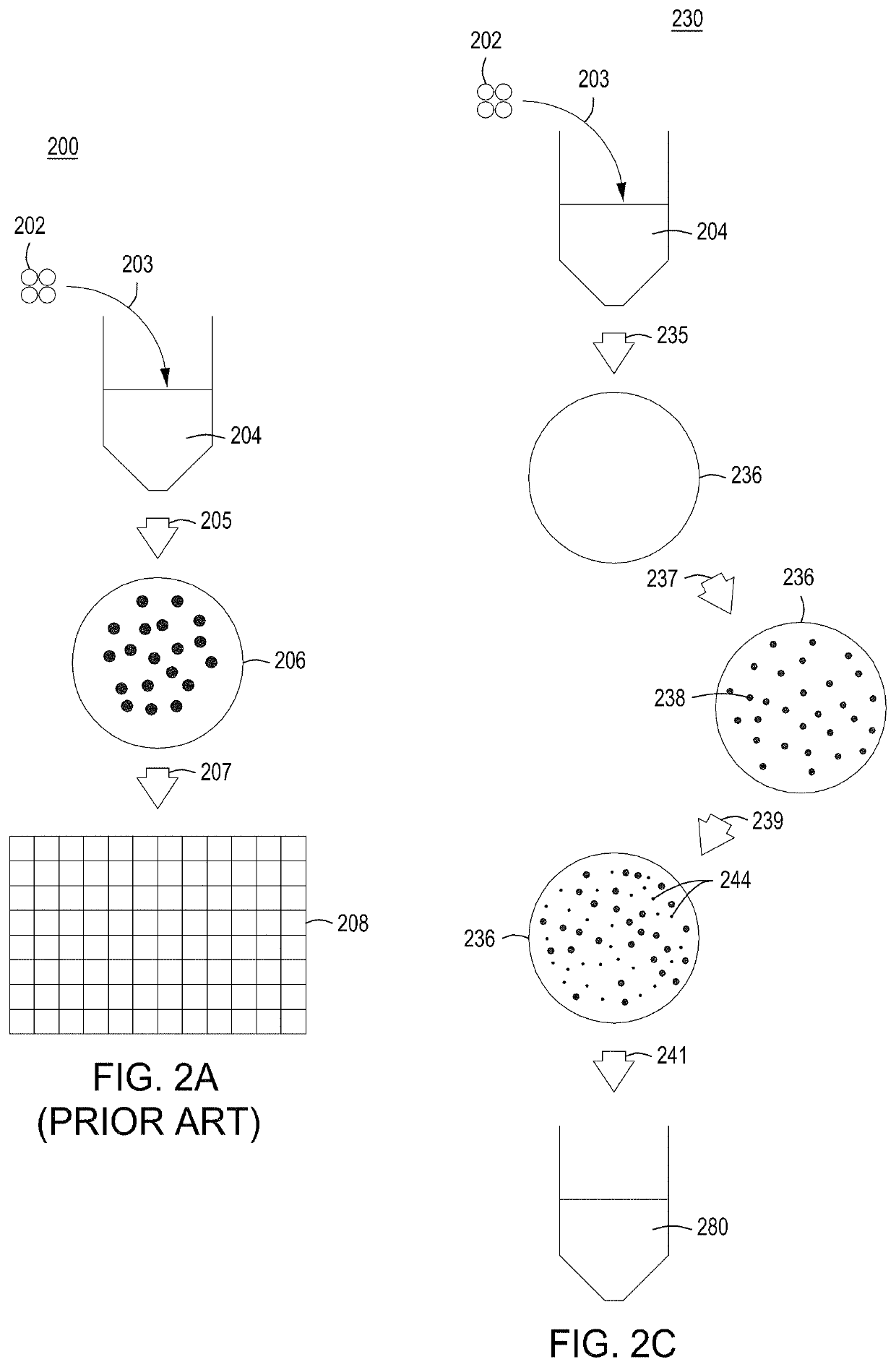

Instruments, modules, and methods for improved detection of edited sequences in live cells

ActiveUS10533152B1Increase efficiencyImprove efficiencyBioreactor/fermenter combinationsBiological substance pretreatmentsNucleaseMolecular biology

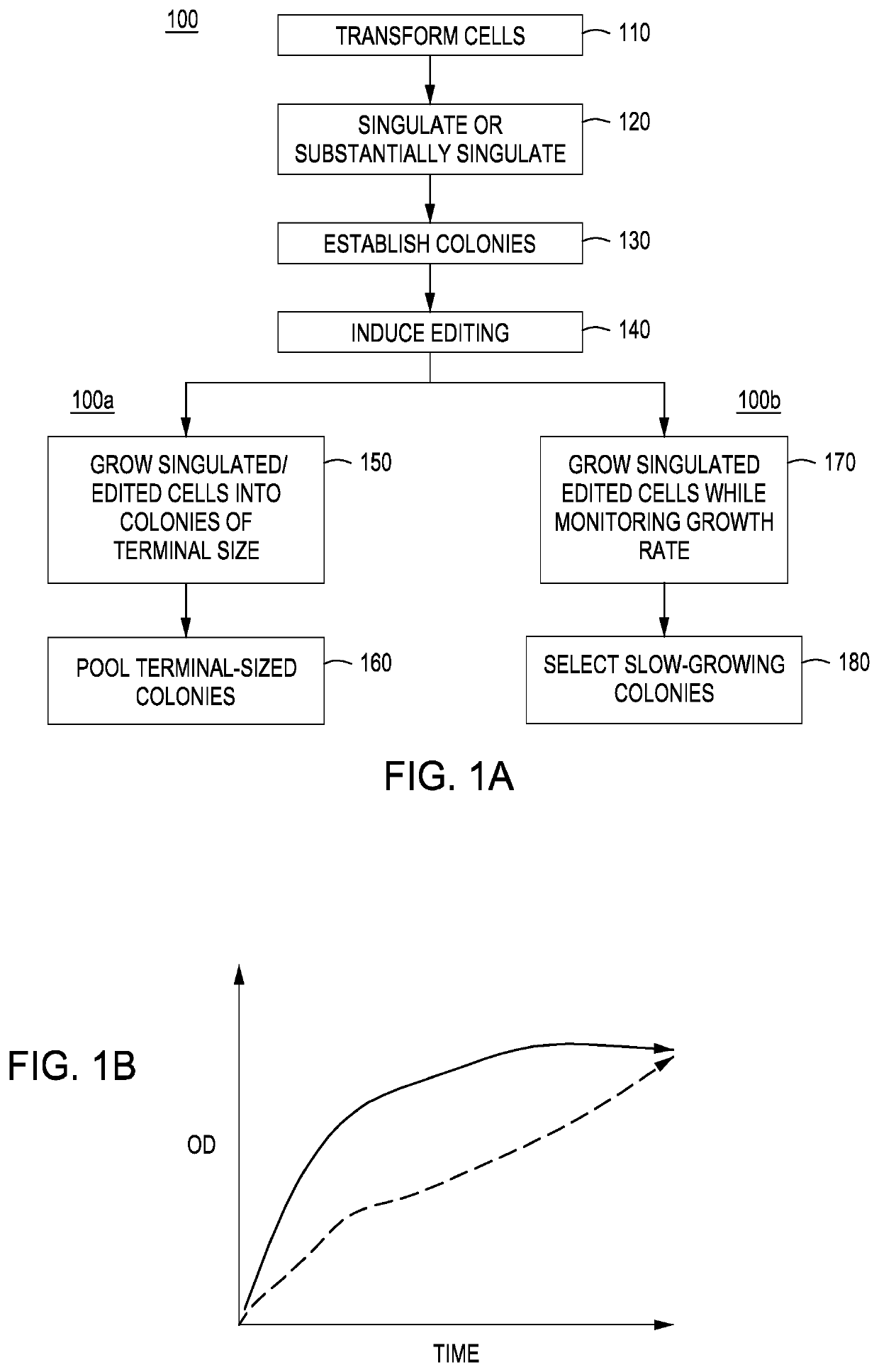

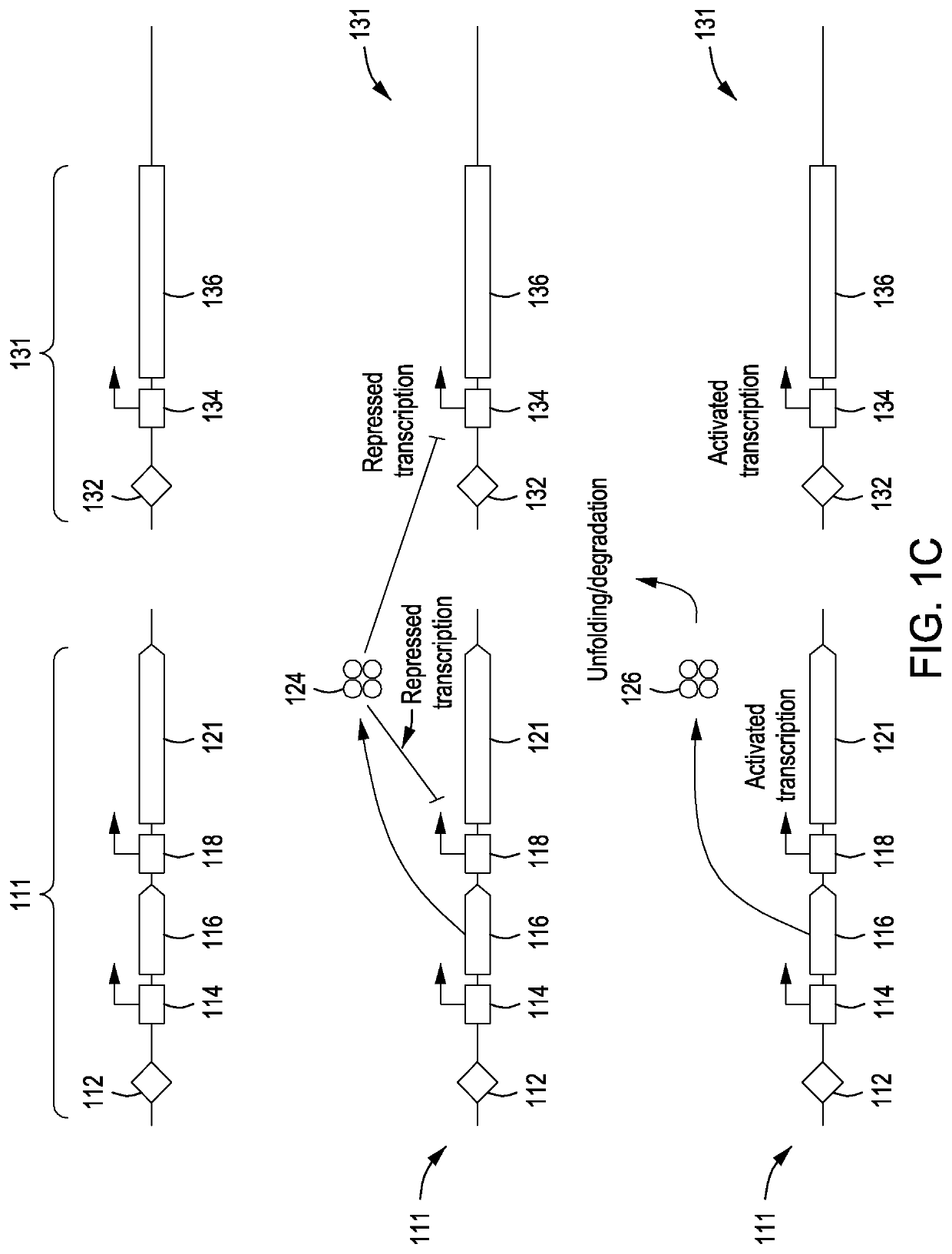

The present disclosure provides instruments, modules and methods for improved detection of edited cells following nucleic acid-guided nuclease genome editing. The disclosure provides improved automated instruments that perform methods—including high throughput methods—for screening cells that have been subjected to editing and identifying cells that have been properly edited.

Owner:INSCRIPTA INC

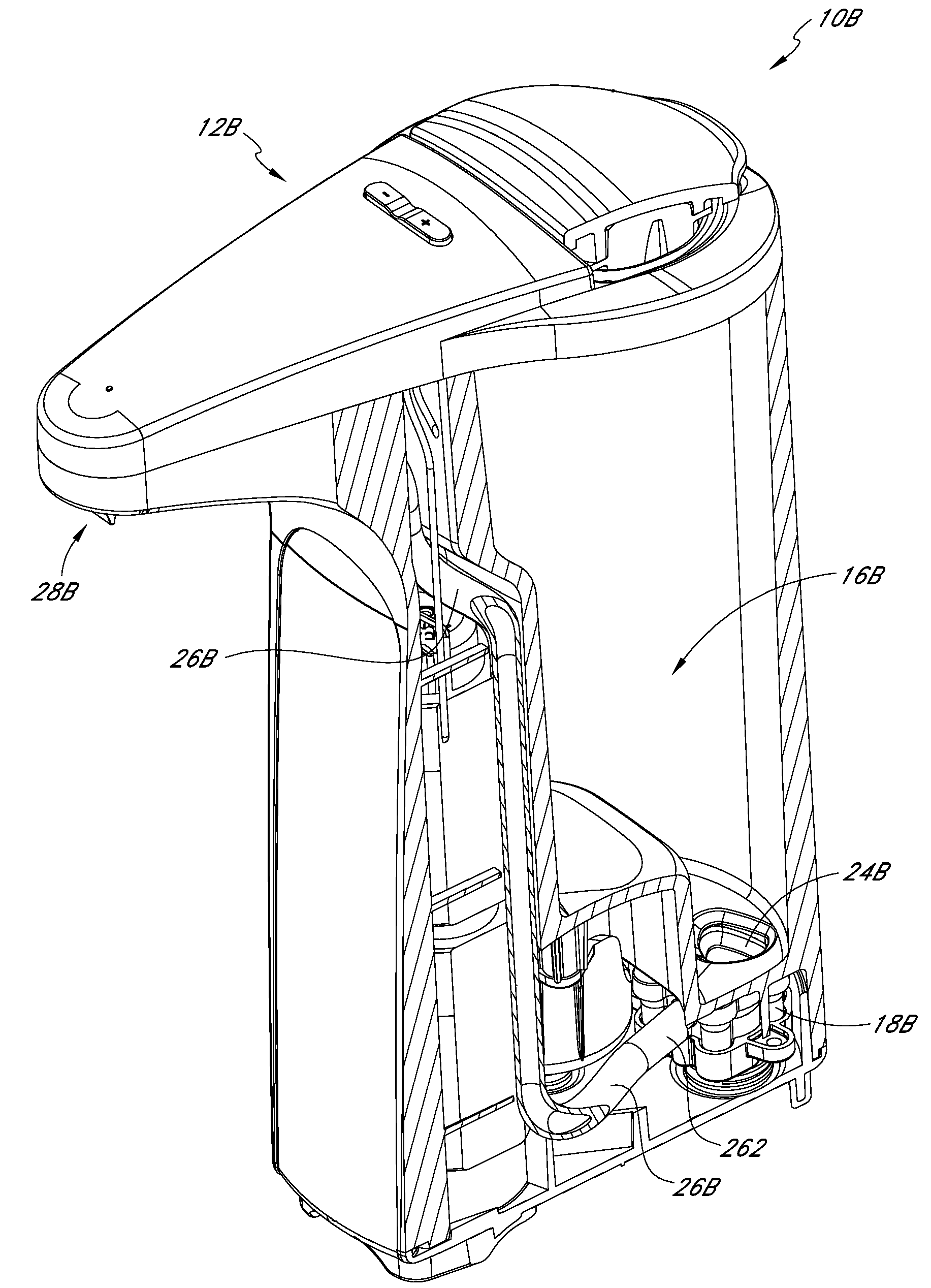

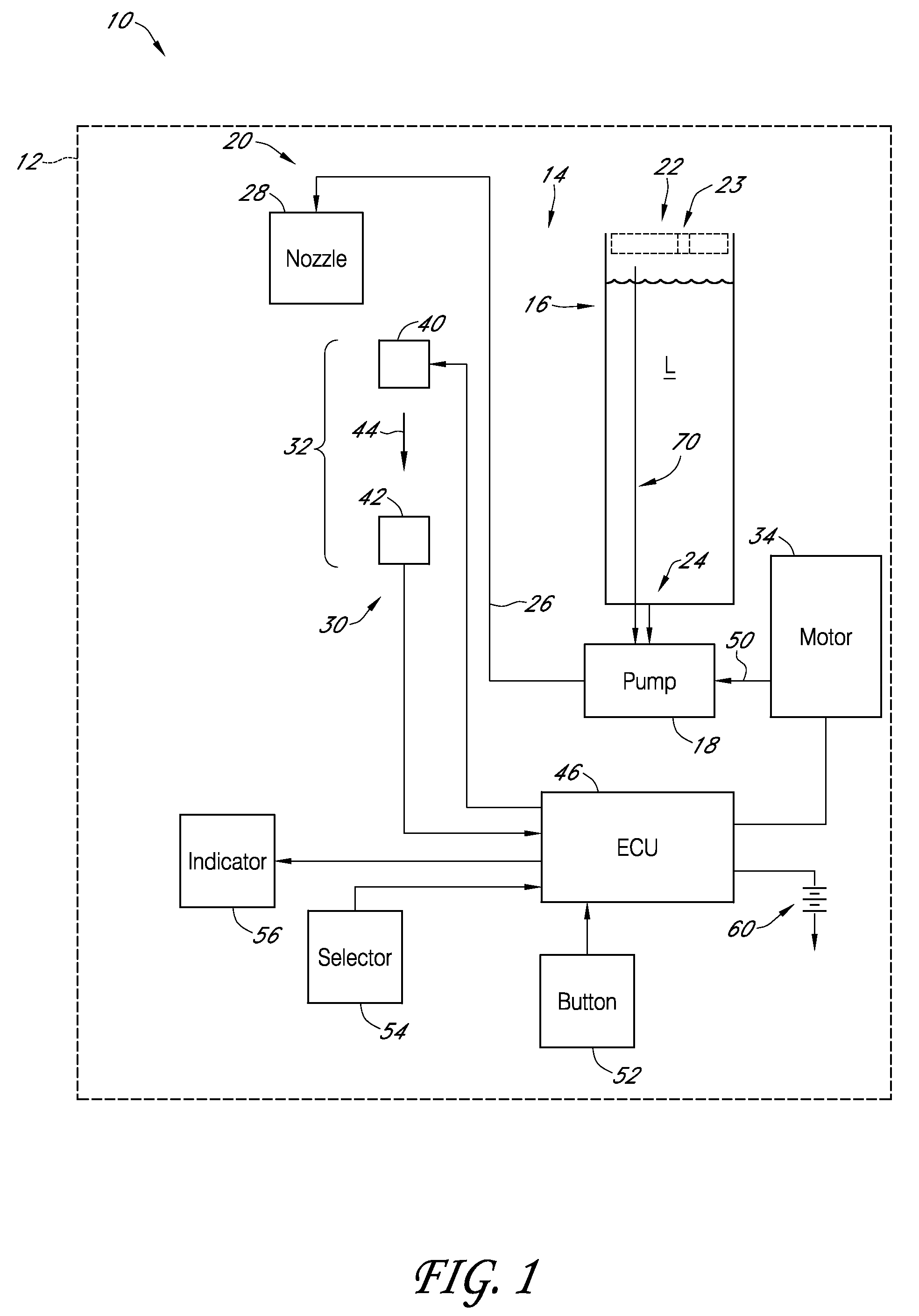

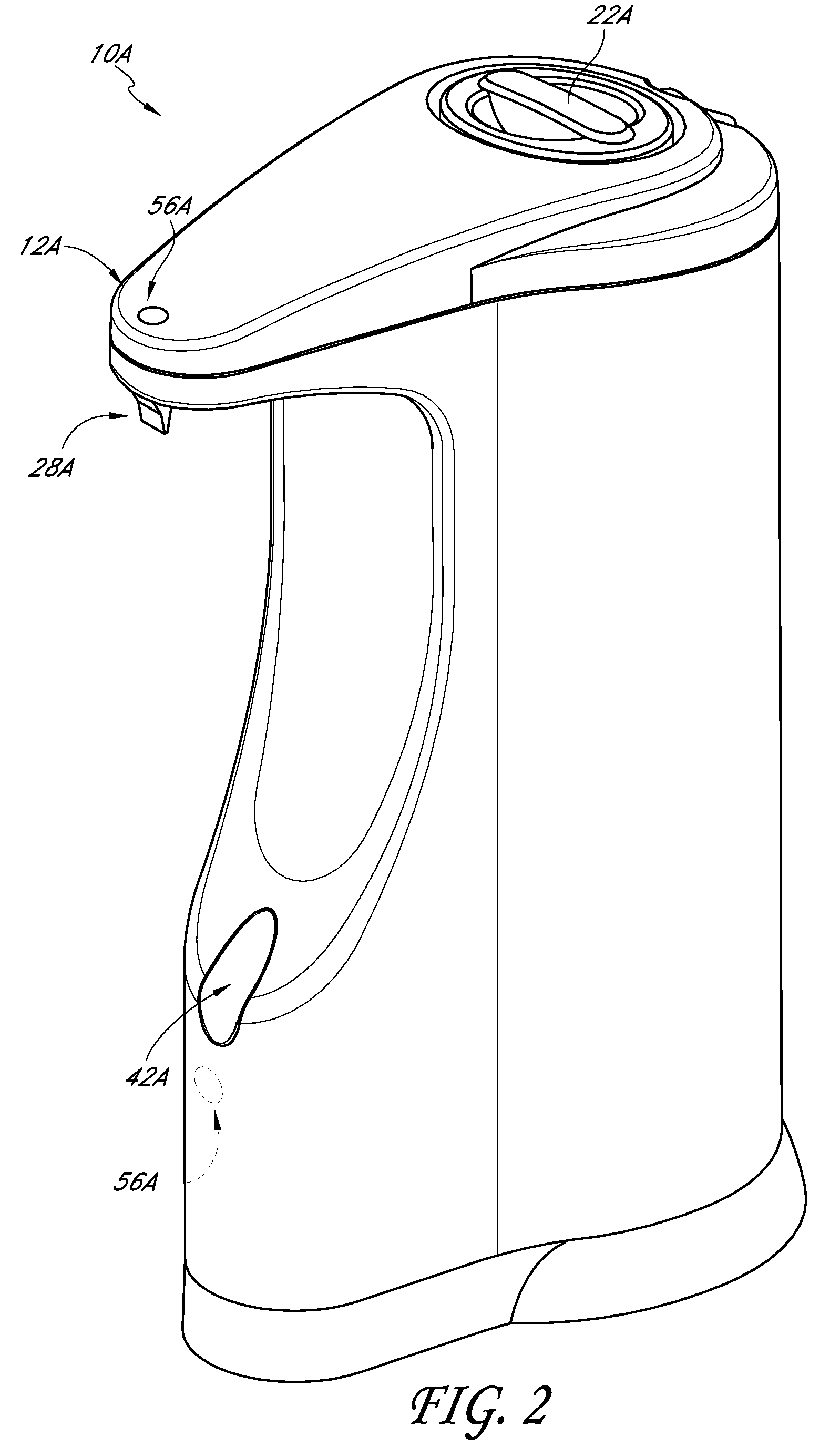

Soap dispensing units with anti-drip valve

ActiveUS8678244B2Enhanced anti-drip and primability benefitAvoid accidentsLiquid flow controllersLarge containersEngineeringSoap dispenser

A soap dispenser can be configured to dispense an amount of liquid soap, for example, upon detecting the presence of an object. Certain embodiments of the dispenser include a housing, reservoir, pump, and nozzle. In some embodiments, the dispenser includes a bypass passage, which can facilitate priming of the pump. In certain embodiments, the dispenser is configured to inhibit or avoid the formation of an air bubble that could obstruct the liquid soap from entering the pump. In some embodiments, the pump includes engaging gears, which can include a plurality of teeth with substantially pointed tips. In certain embodiments, the nozzle comprises a one-way valve, such as a duckbill valve. Some embodiments of the one-way valve are shaped or otherwise configured to provide certain biases to the valve, which can, for example, facilitate rapid opening and closing of the valve.

Owner:SIMPLEHUMAN

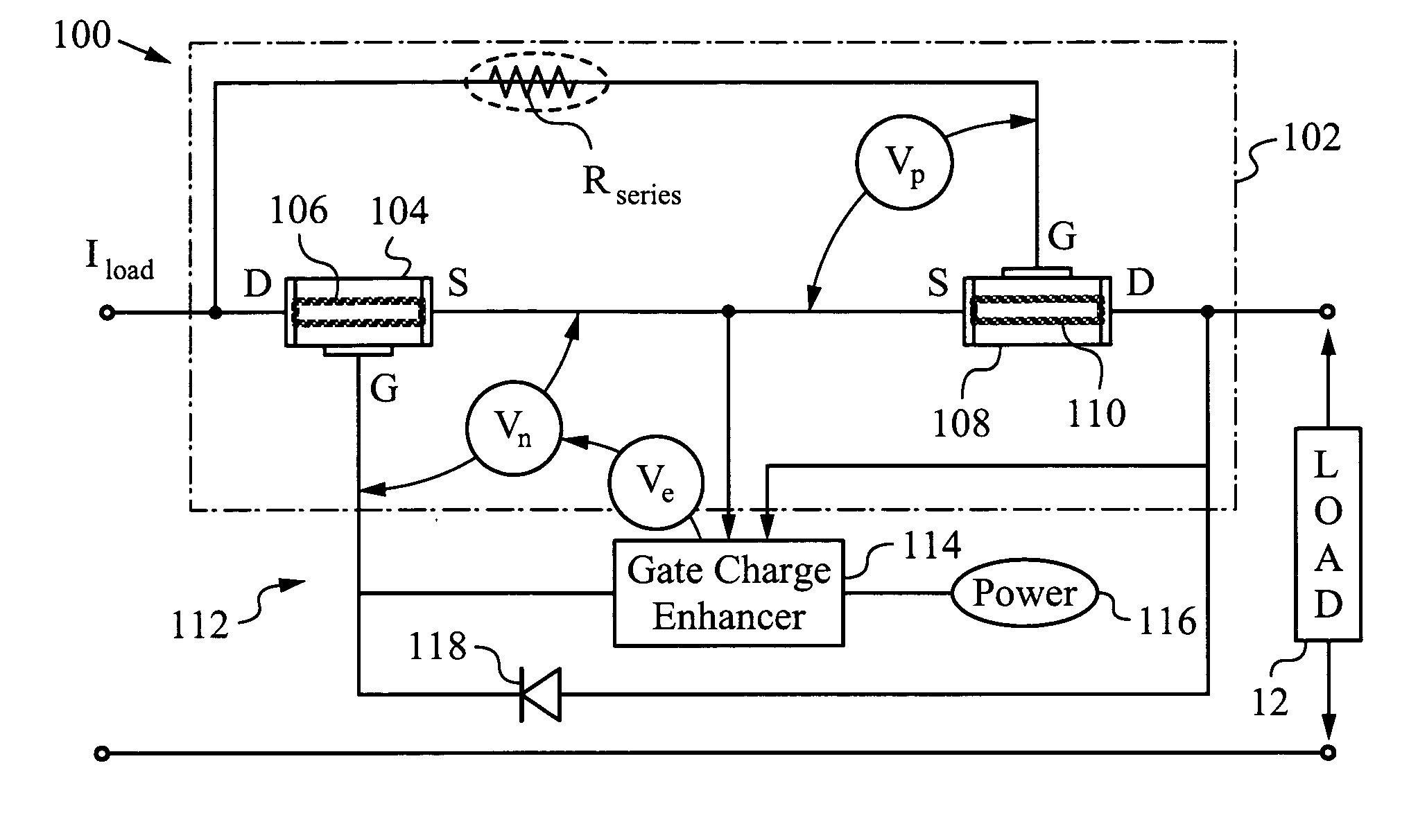

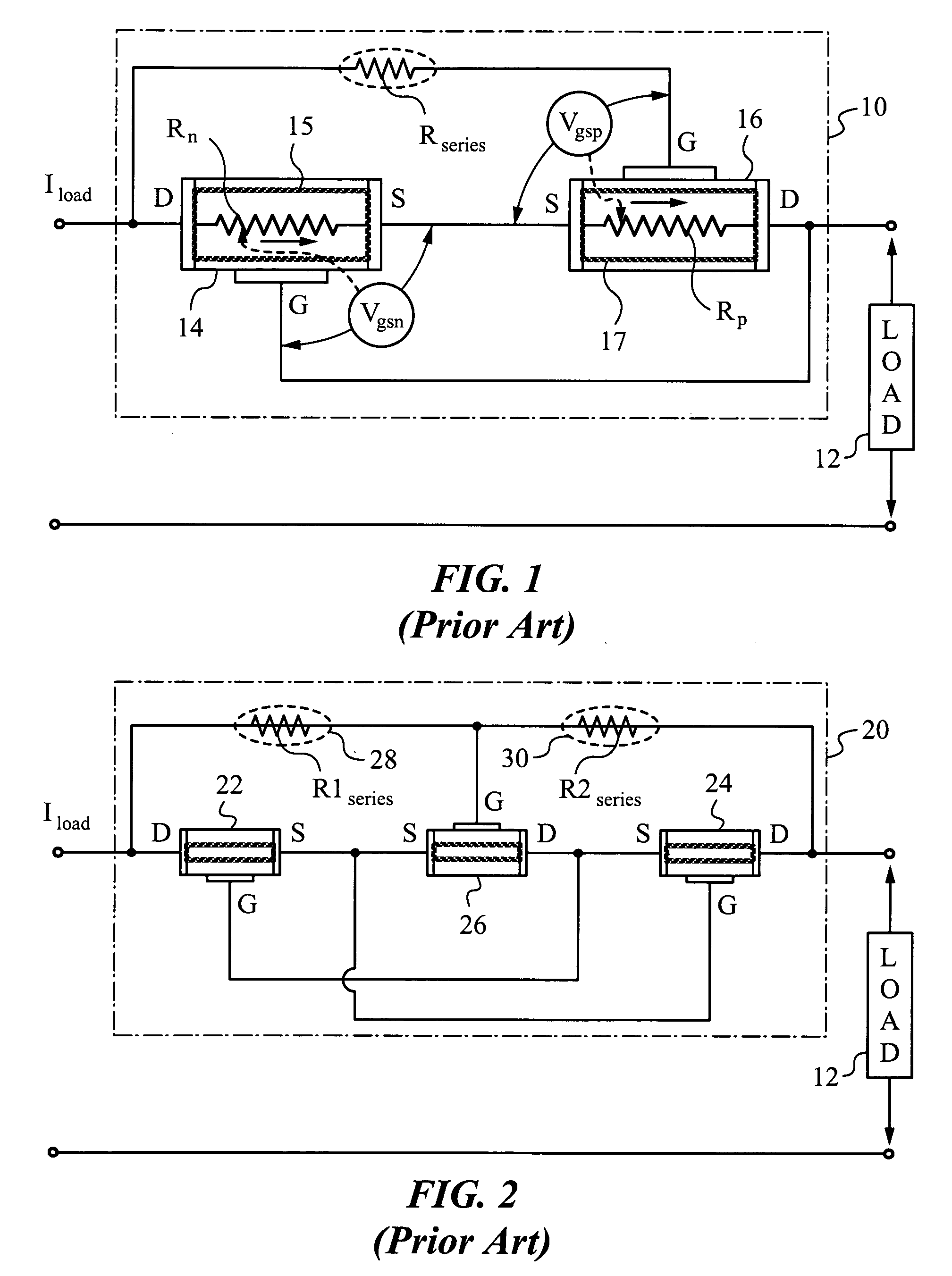

Apparatus and method for enhanced transient blocking

ActiveUS20060098364A1Reduce power lossImprove system efficiencyTransistorElectronic switchingInterconnectionP channel

An apparatus and method for enhanced transient blocking employing a transient blocking unit (TBU) that uses at least one depletion mode n-channel device interconnected with at least one depletion mode p-channel device. The interconnection is performed such that a transient alters a bias voltage Vp of the p-channel device and a bias voltage Vn of the n-channel device such that the p- and n-channel devices mutually switch off to block the transient. The apparatus has an enhancer circuit for applying an enhancement bias to a gate terminal of at least one of the depletion mode n-channel devices of the TBU to reduce a total resistance Rtot of the apparatus. Alternatively, the apparatus has an enhancement mode NMOS transistor and a TBU connected thereto to help provide an enhancement bias to a gate terminal of the enhancement mode NMOS.

Owner:BOURNS INC

Kalman filtering image reconstruction method in PET imaging

ActiveCN101499173AQuality improvementRaise the bias2D-image generationComputerised tomographsFractographyImaging quality

The invention provides a method for rebuilding Kallman filtering image in PET imaging. The method includes steps as follows: obtaining a sinusoidal chart of an original projective line through PET positron emission faultage scanner, establishing a state space system, getting radioactivity activity distribution through the Kallman filtering method based on the state space and rebuilding image. The method rebuild PET image by using the Kallman filtering method based on the state space system which can increase the rebuild image quality efficiently; compared with the prior rebuild method, declination and dispersion of the rebuild result are increased greatly.

Owner:刘华锋

Restraint

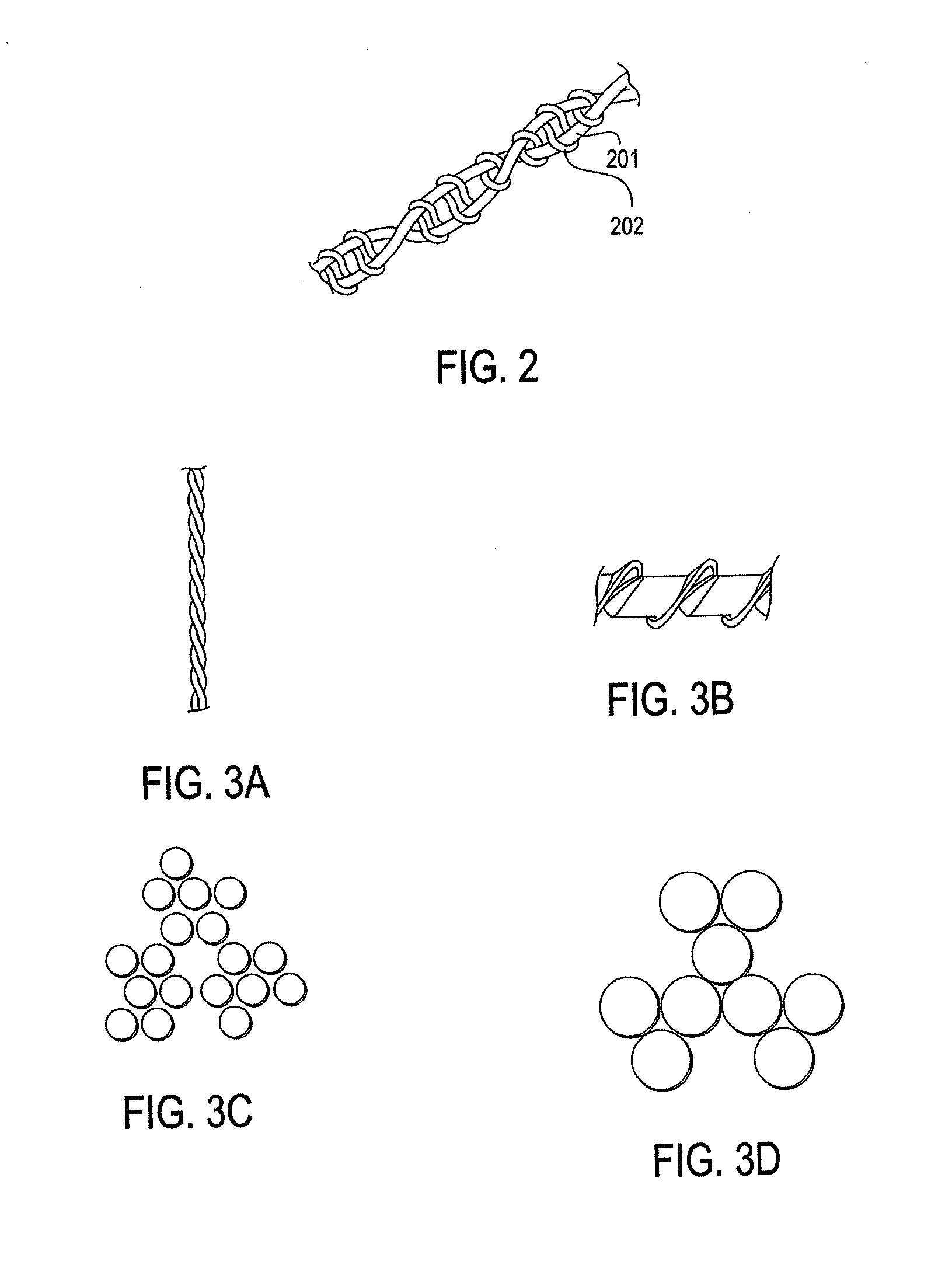

InactiveUS6971316B2Reduce the minimum diameterIncreasing minimum projected diameter of apertureSnap fastenersFasteningsEngineering

A restraint for retaining a person within a seat. The restraint has a lap bar and a shoulder bar which can be independently adjusted. The lap bar can be rotated either to retain a person or to permit a person to enter or exit. Also, the lap bar can be pulled farther away or pushed closer to a person. When extended completely, the lap bar will remain locked in such position until the lap bar is rotated toward the position a person will occupy. When pushed toward a person, the lap bar cannot be pushed farther away until a rod to which the lap bar is attached is released from a lock. The shoulder retainer is attached to a similar rod which is locked in this same fashion.

Owner:S&S WORLDWIDE

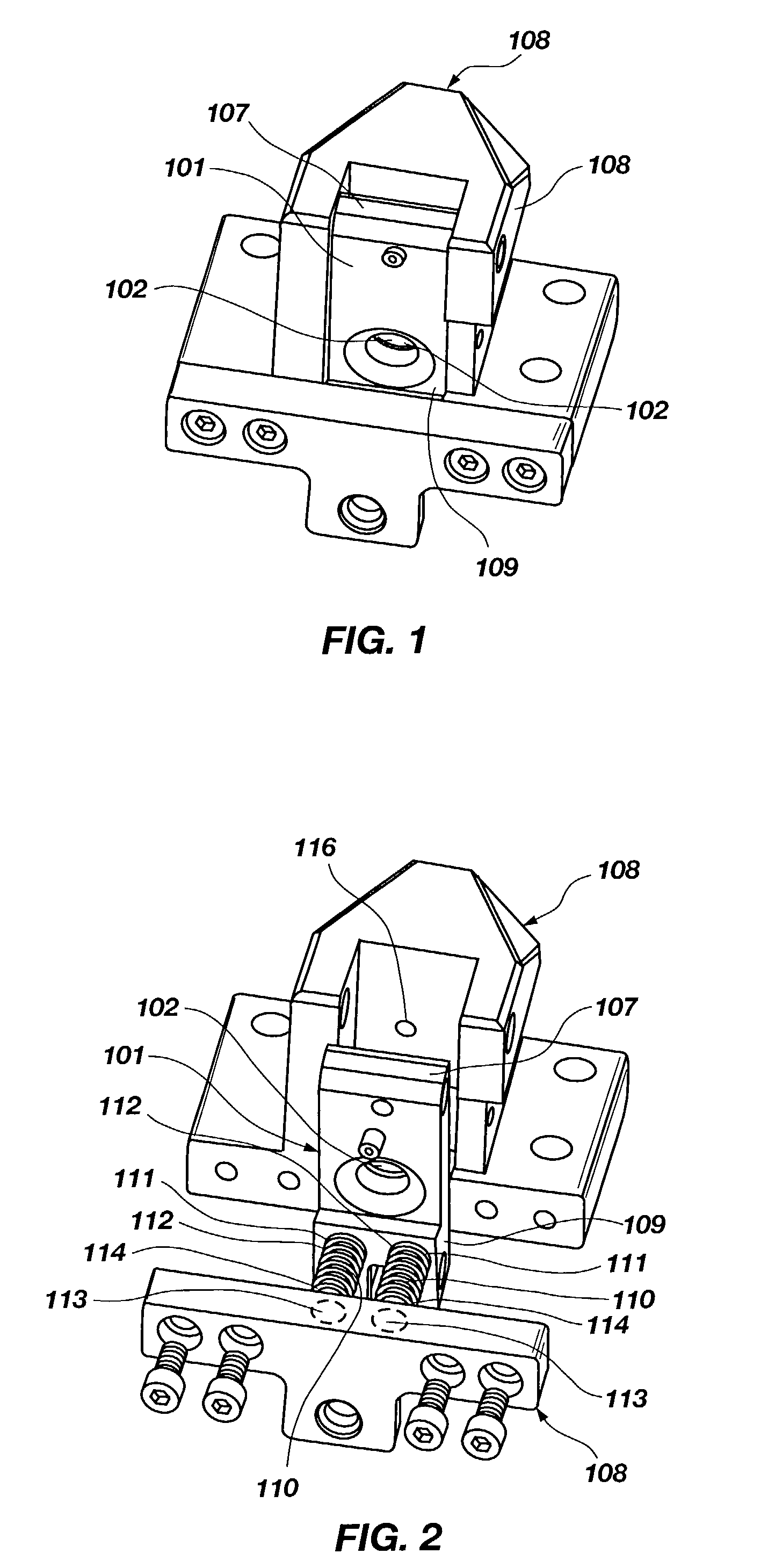

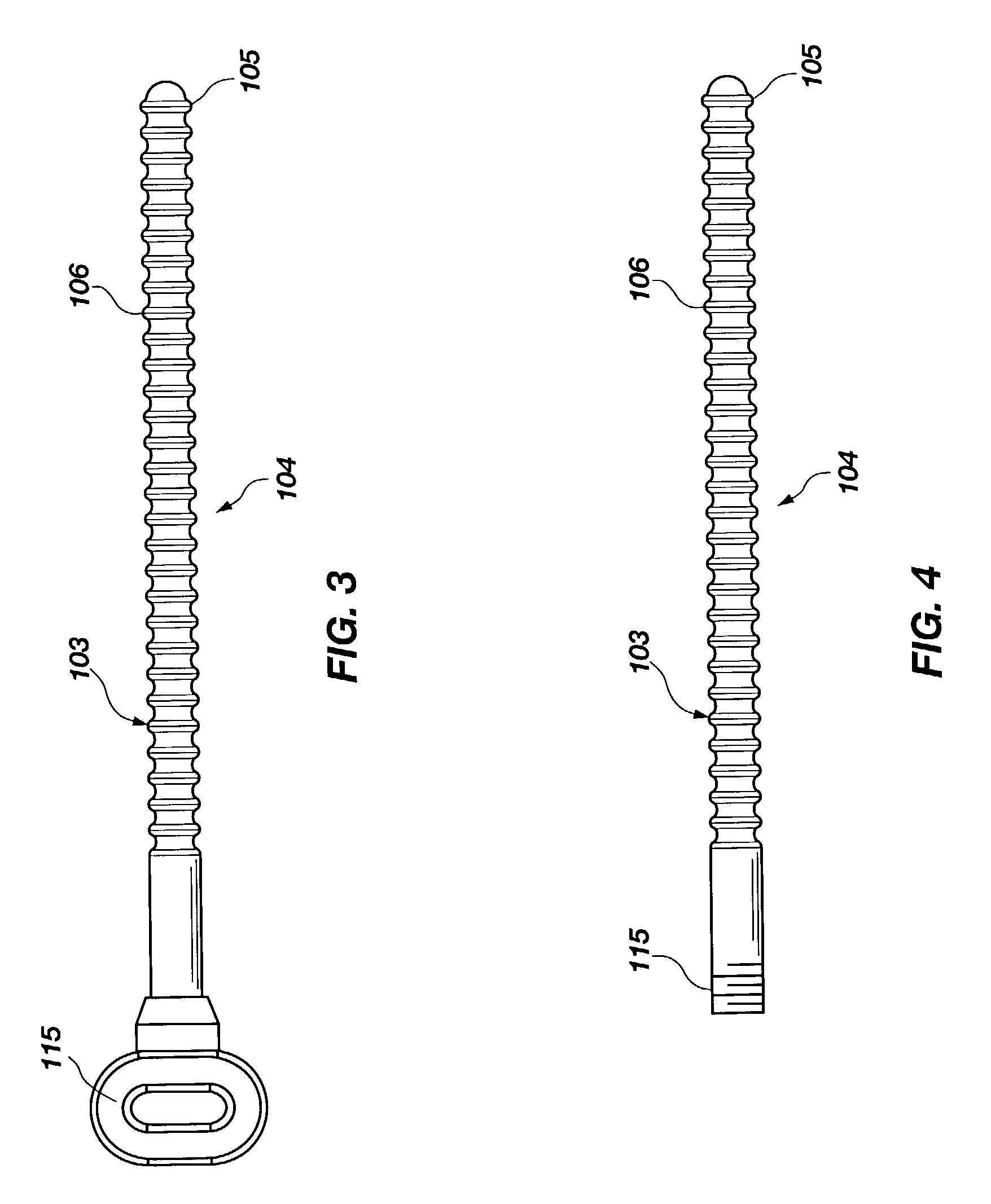

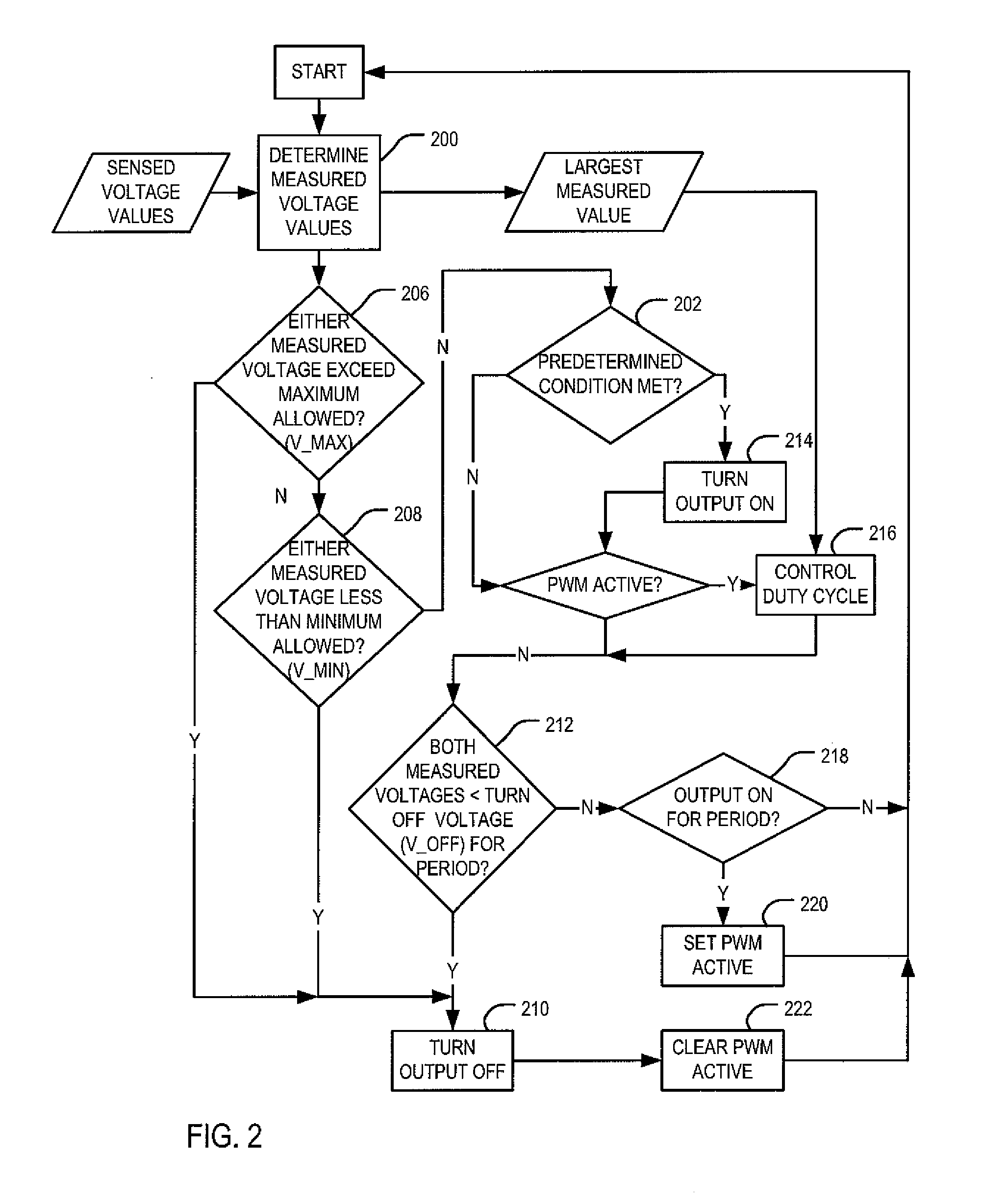

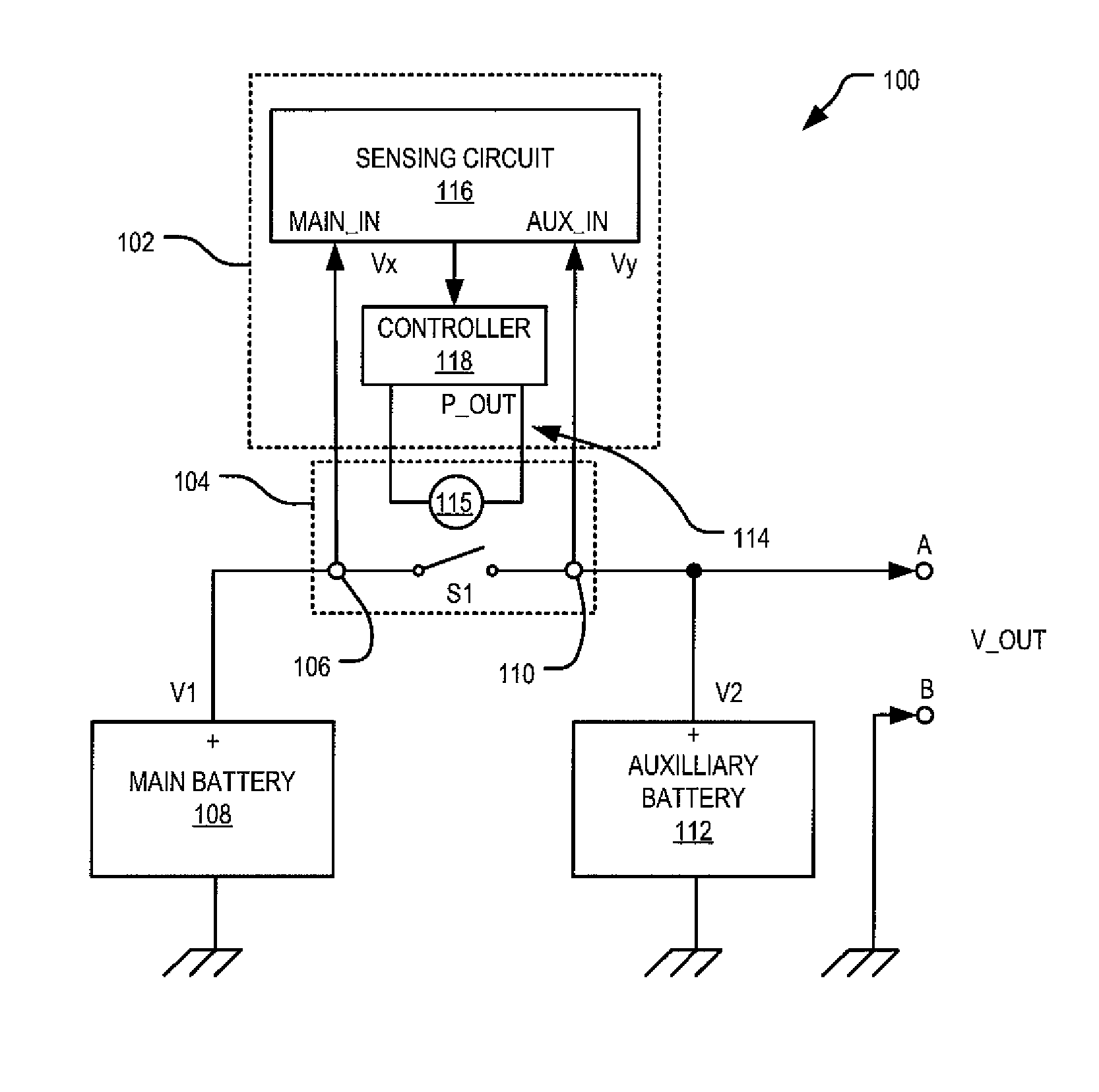

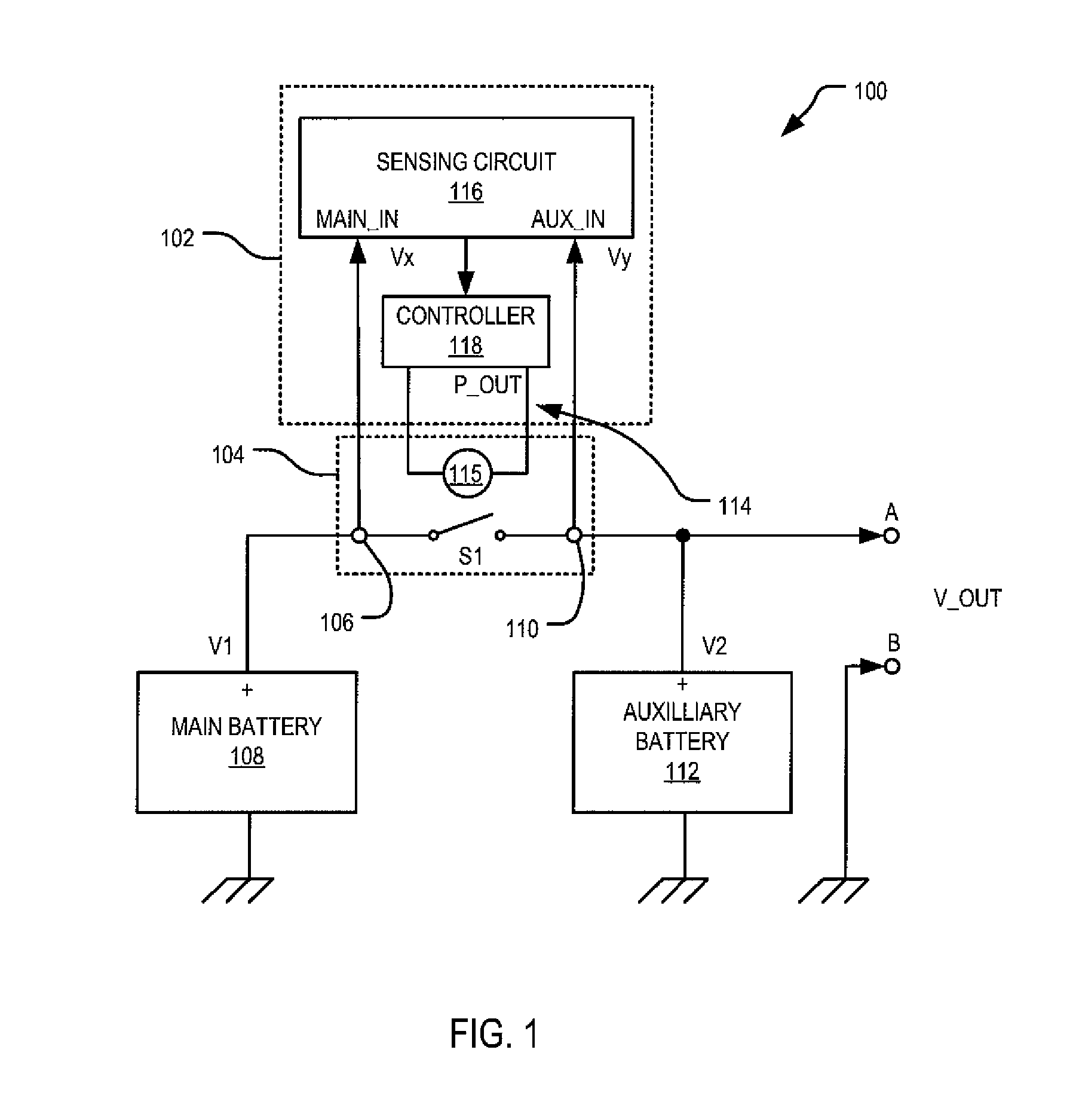

Battery Isolator Unit

ActiveUS20110127830A1Reducing duty cycleRaise the biasBatteries circuit arrangementsElectric devicesControl signalTerminal voltage

A battery isolator unit is disclosed for controlling a switching means having a first contact for connection to a terminal of a first battery, a second contact for connection to a corresponding terminal of a second battery, and an actuating input for biasing a switch element of the switching means switch in a closed position. The battery isolator unit includes a sensing circuit and a switch controller. The sensing circuit periodically determines a first and second value attributable to terminal voltage values of the first battery and the second battery respectively. The switch controller is responsive to detecting a predetermined condition of the first battery and / or the second battery to provide to the actuating input a control signal having a characteristic for biasing the switch element to the closed position. The switch controller periodically determines a difference between the first and second values when the switch element is in the closed position to obtain a obtain a sequence of difference values, and controls the characteristic of the control signal according to a comparison of a present difference value with a previous difference value to modify the bias of the switch element.

Owner:REDARC TECH

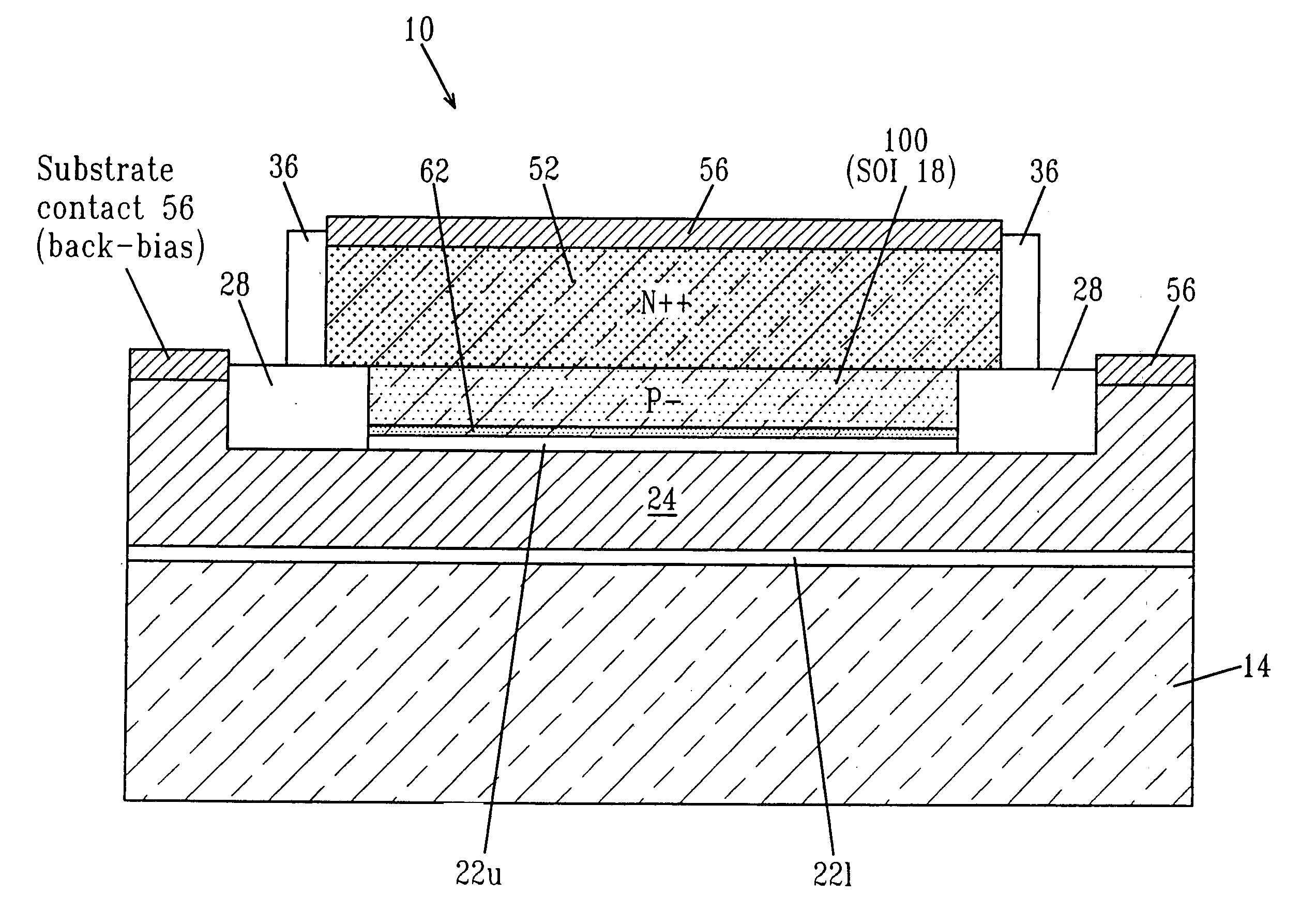

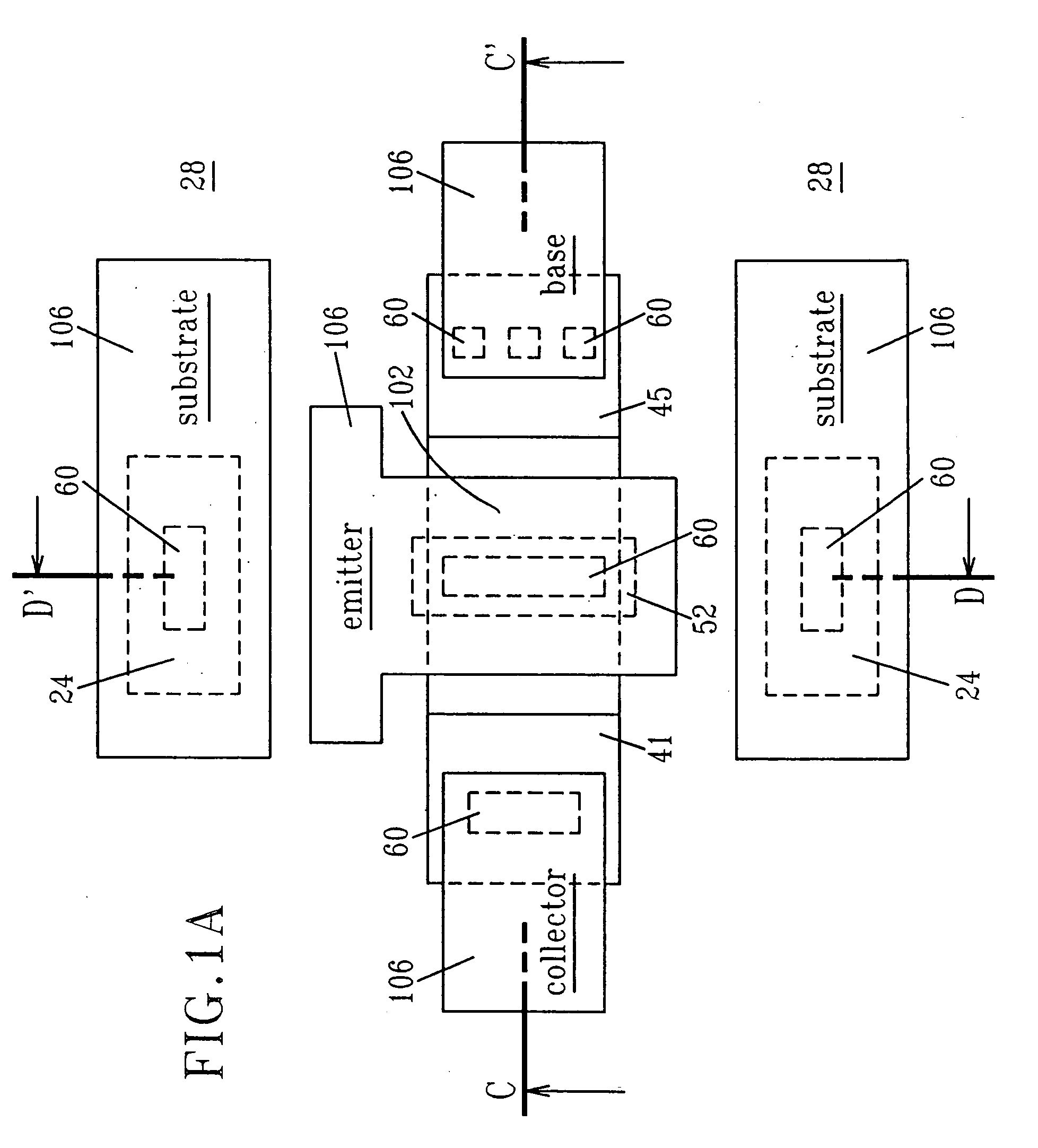

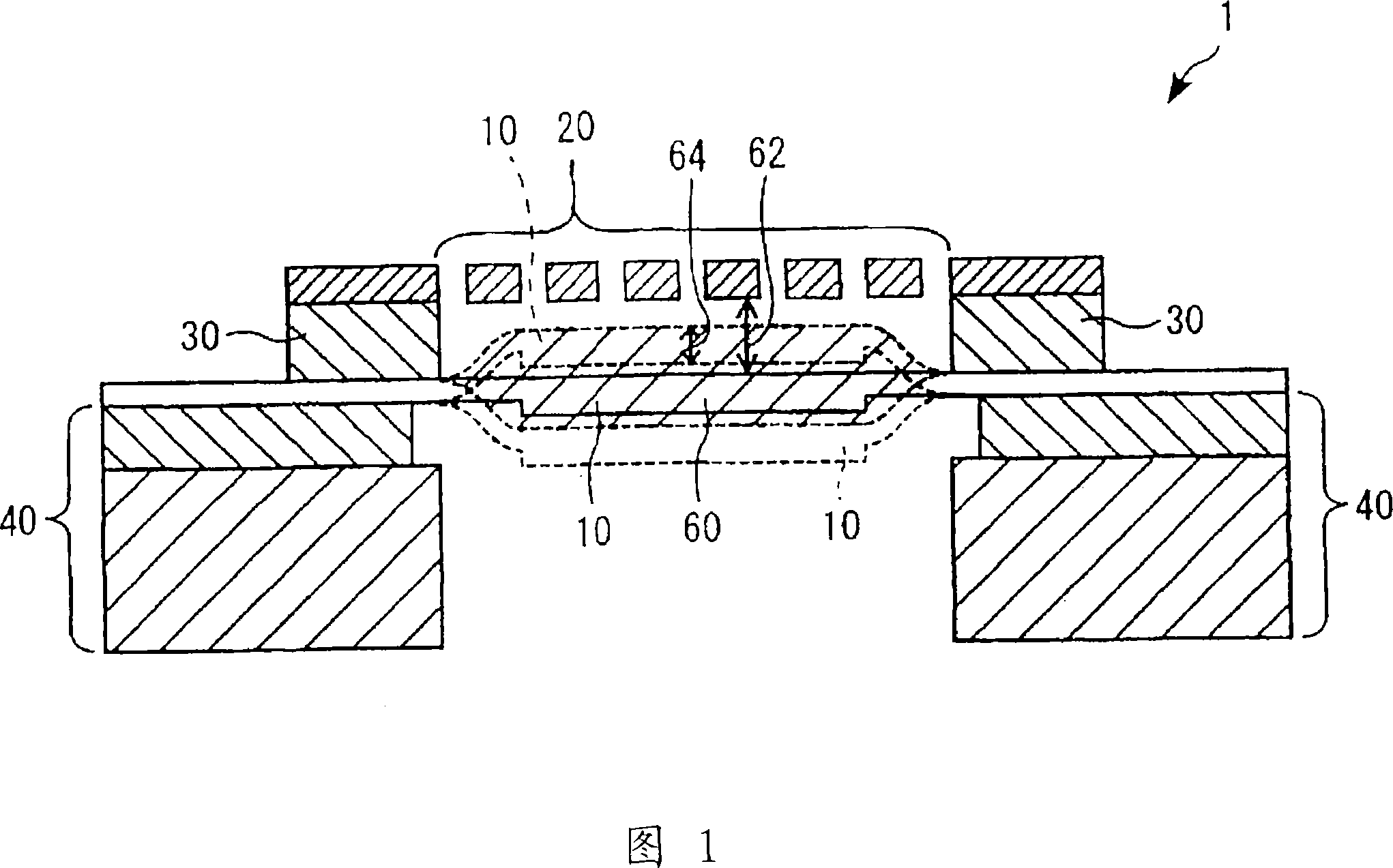

Ultra-thin SOI vertical bipolar transistors with an inversion collector on thin-buried oxide (BOX) for low substrate-bias operation and methods thereof

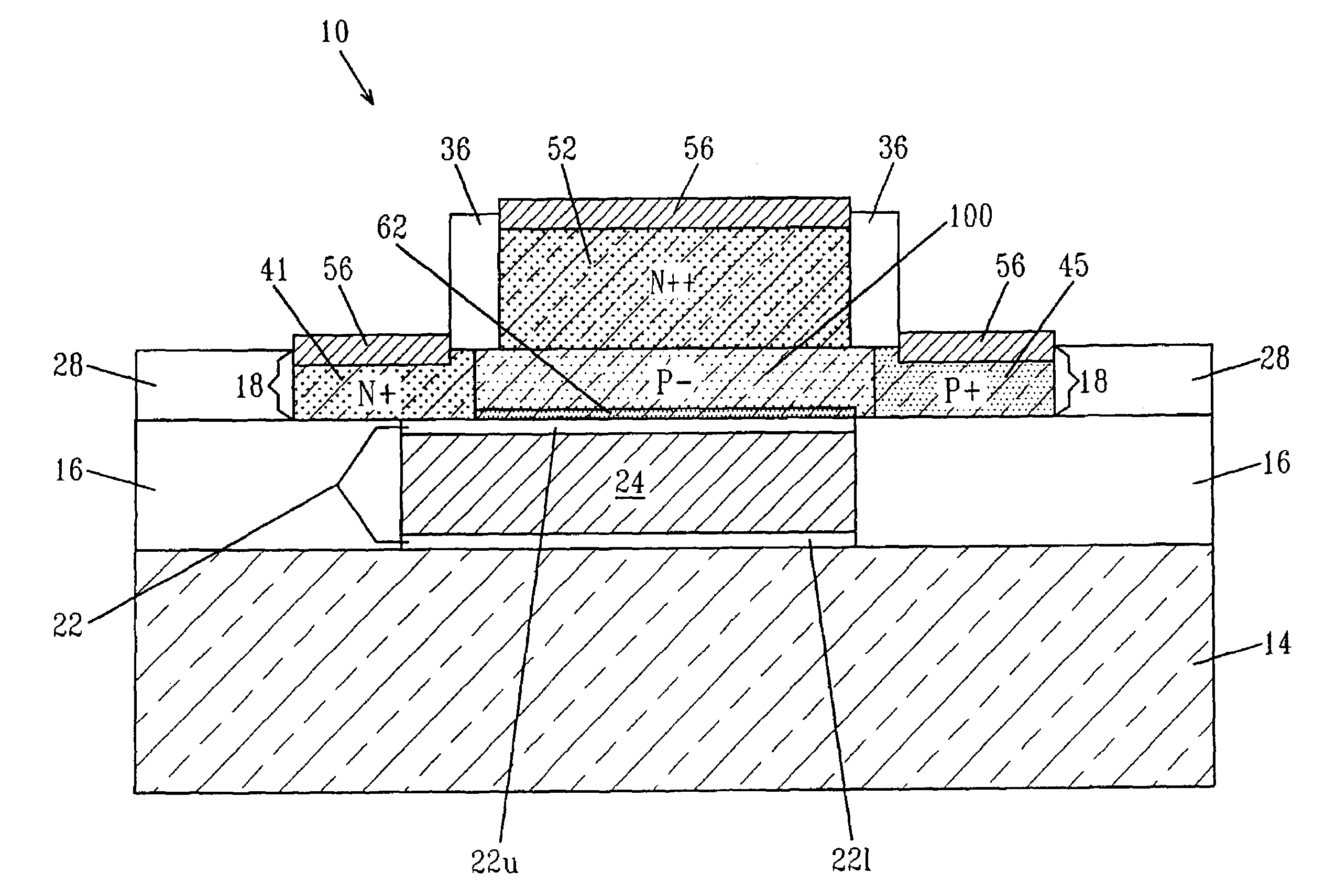

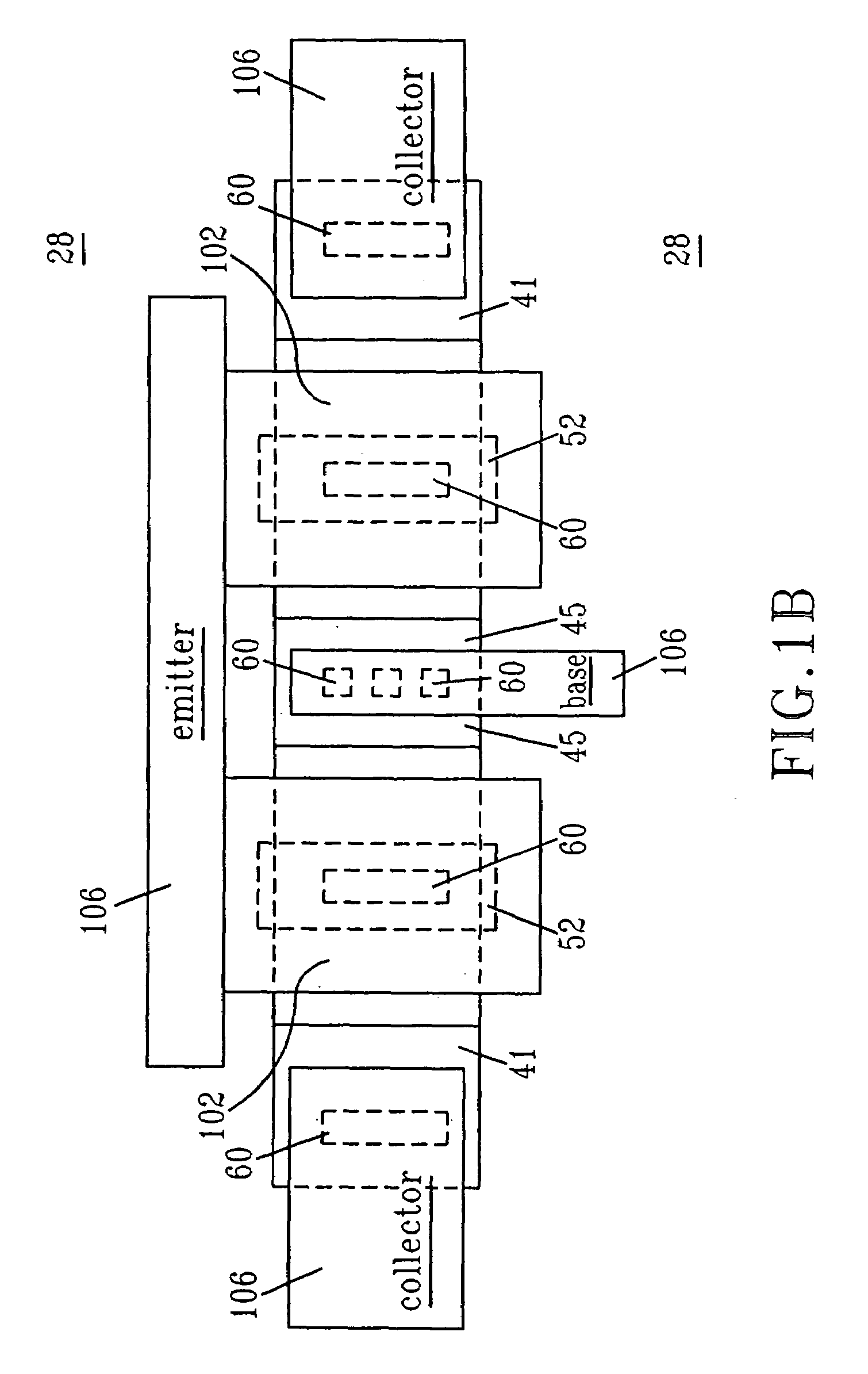

ActiveUS20050184360A1Easy to integrateReduce manufacturing costTransistorSolid-state devicesManufacturing cost reductionCMOS

The present invention provides a “collector-less” silicon-on-insulator (SOI) bipolar junction transistor (BJT) that has no impurity-doped collector. Instead, the inventive vertical SOI BJT uses a back gate-induced, minority carrier inversion layer as the intrinsic collector when it operates. In accordance with the present invention, the SOI substrate is biased such that an inversion layer is formed at the bottom of the base region serving as the collector. The advantage of such a device is its CMOS-like process. Therefore, the integration scheme can be simplified and the manufacturing cost can be significantly reduced. The present invention also provides a method of fabricating BJTs on selected areas of a very thin BOX using a conventional SOI starting wafer with a thick BOX. The reduced BOX thickness underneath the bipolar devices allows for a significantly reduced substrate bias compatible with the CMOS to be applied while maintaining the advantages of a thick BOX underneath the CMOS.

Owner:GLOBALFOUNDRIES US INC

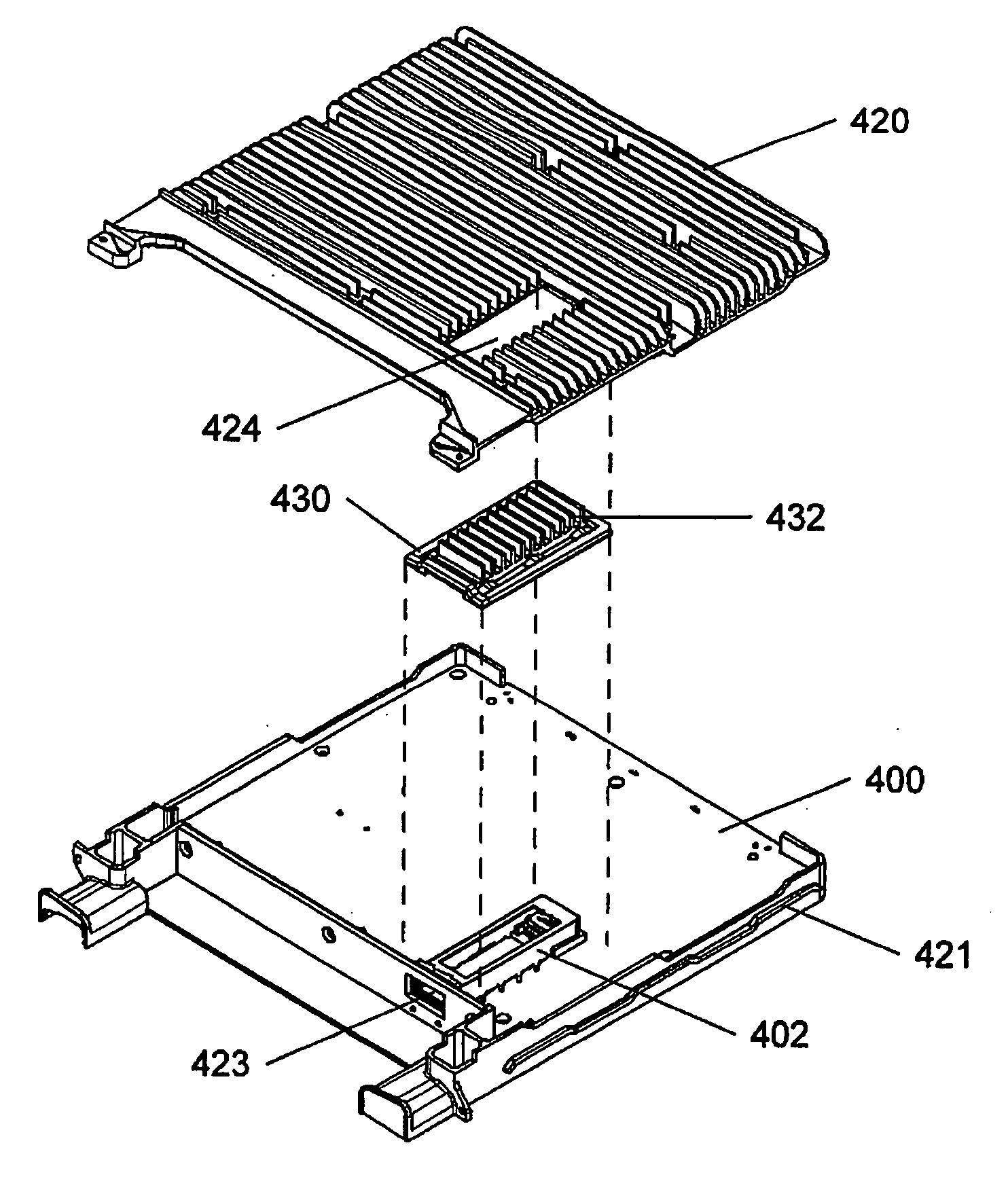

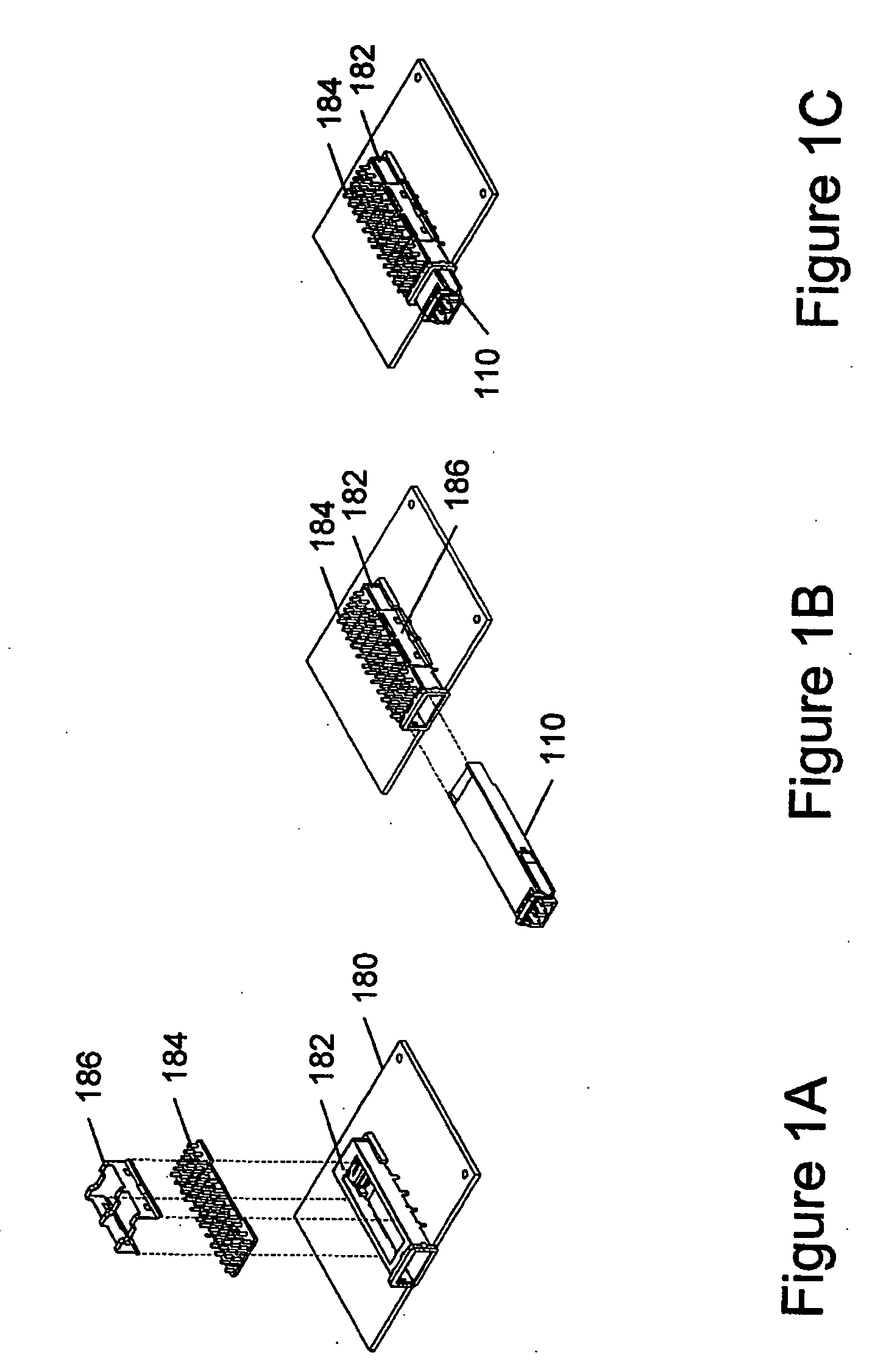

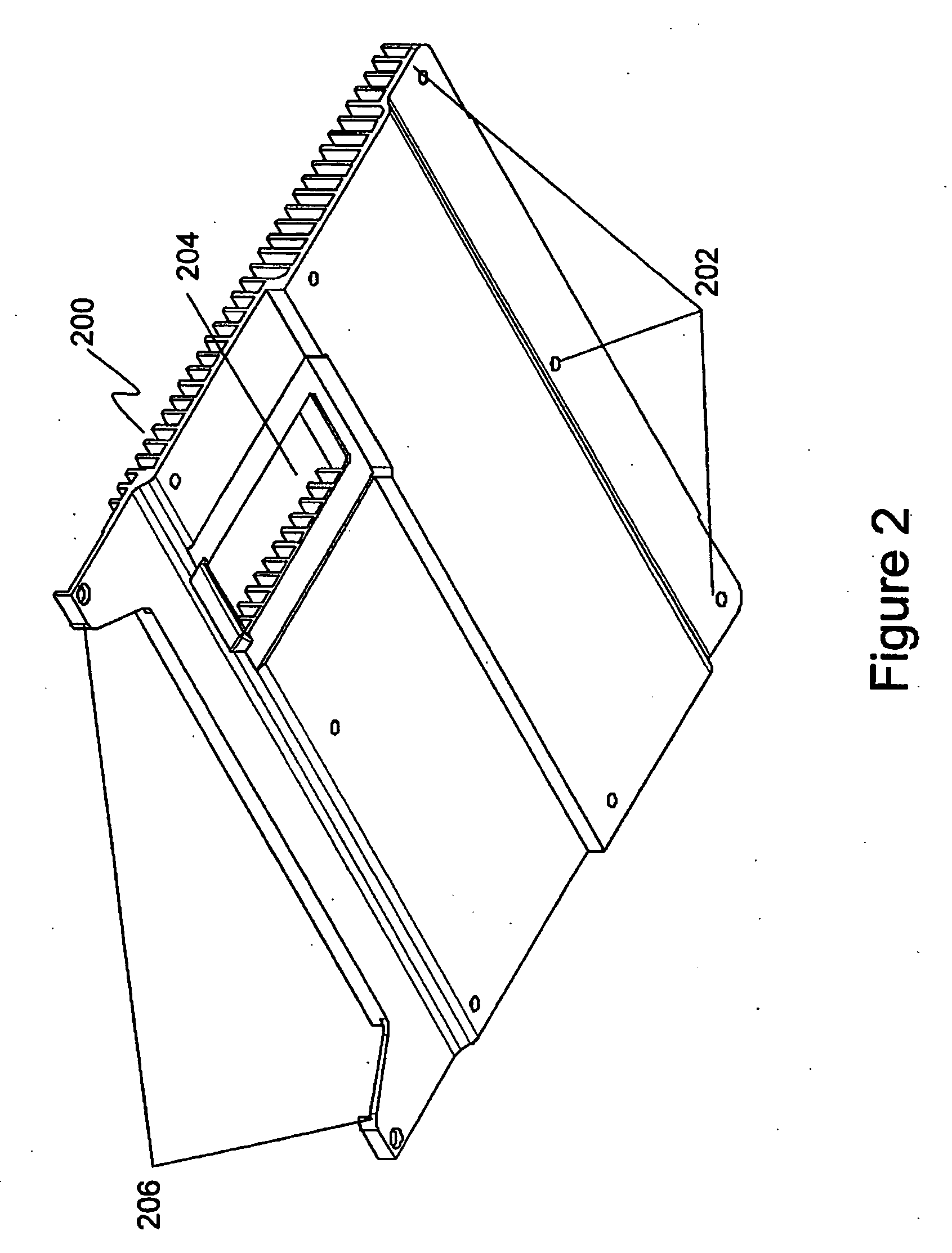

Floating heatsink for removable components

ActiveUS20060176666A1Raise the biasEasy to controlIncorrect coupling preventionDigital data processing detailsEngineeringHeat spreader

A floating heatsink is disclosed for components mounted within an electromagnetic enclosure. The floating heatsink includes an aperture within the enclosure wall against which a floating heatsink is disposed on the interior of the enclosure. The floating heatsink is dimensioned to overlap the enclosure around the aperture. A resilient bias member is disposed along the overlap between the floating heatsink and the enclosure. The resilient bias member acts as an electromagnetic gasket while urging the floating heatsink against the component. In certain embodiments the component is replaceable via a second aperture in the enclosure. The floating heatsink is particularly useful for overcoming the need for thermal compounds of heatsinks using the enclosure known in the art.

Owner:CIENA

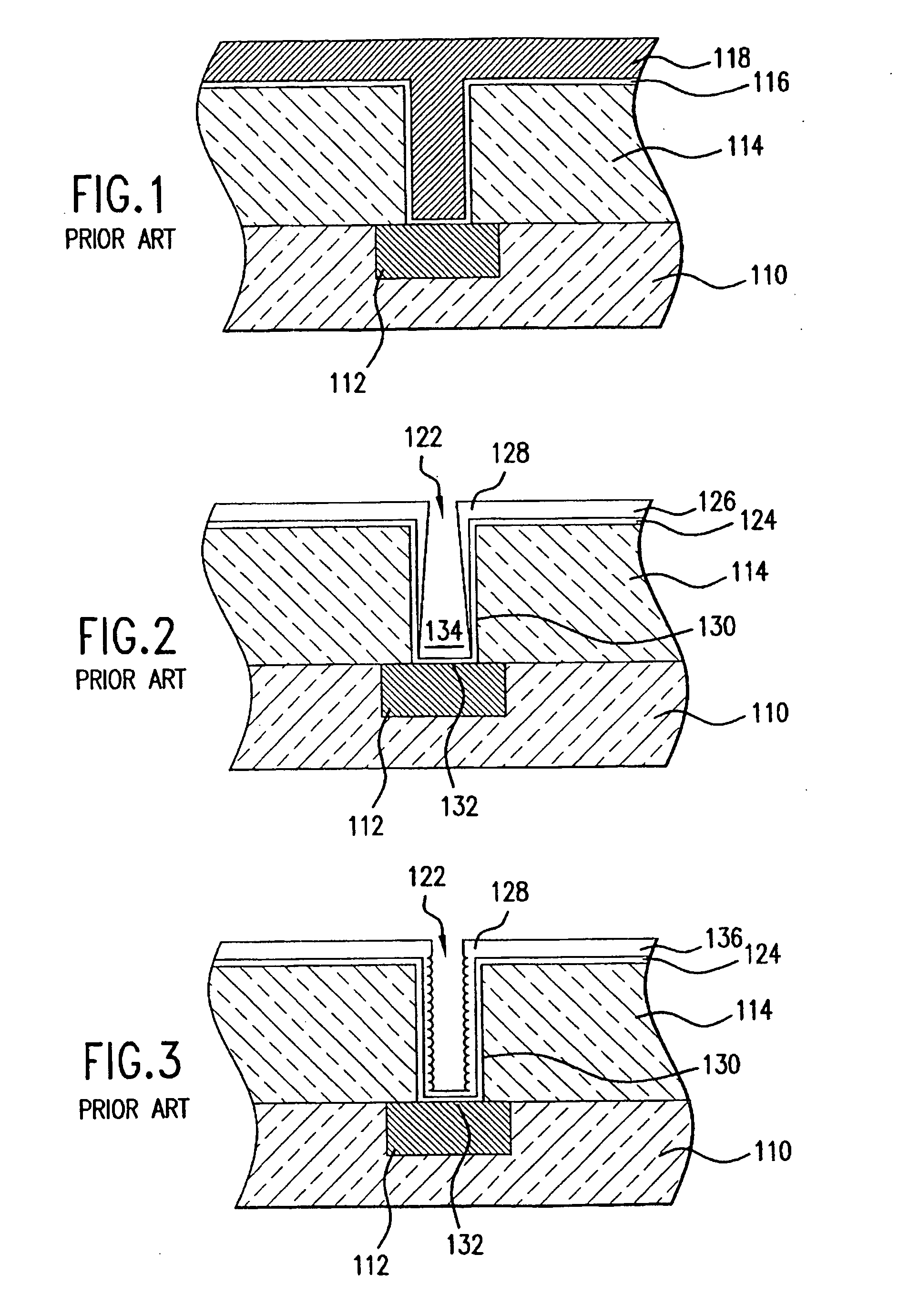

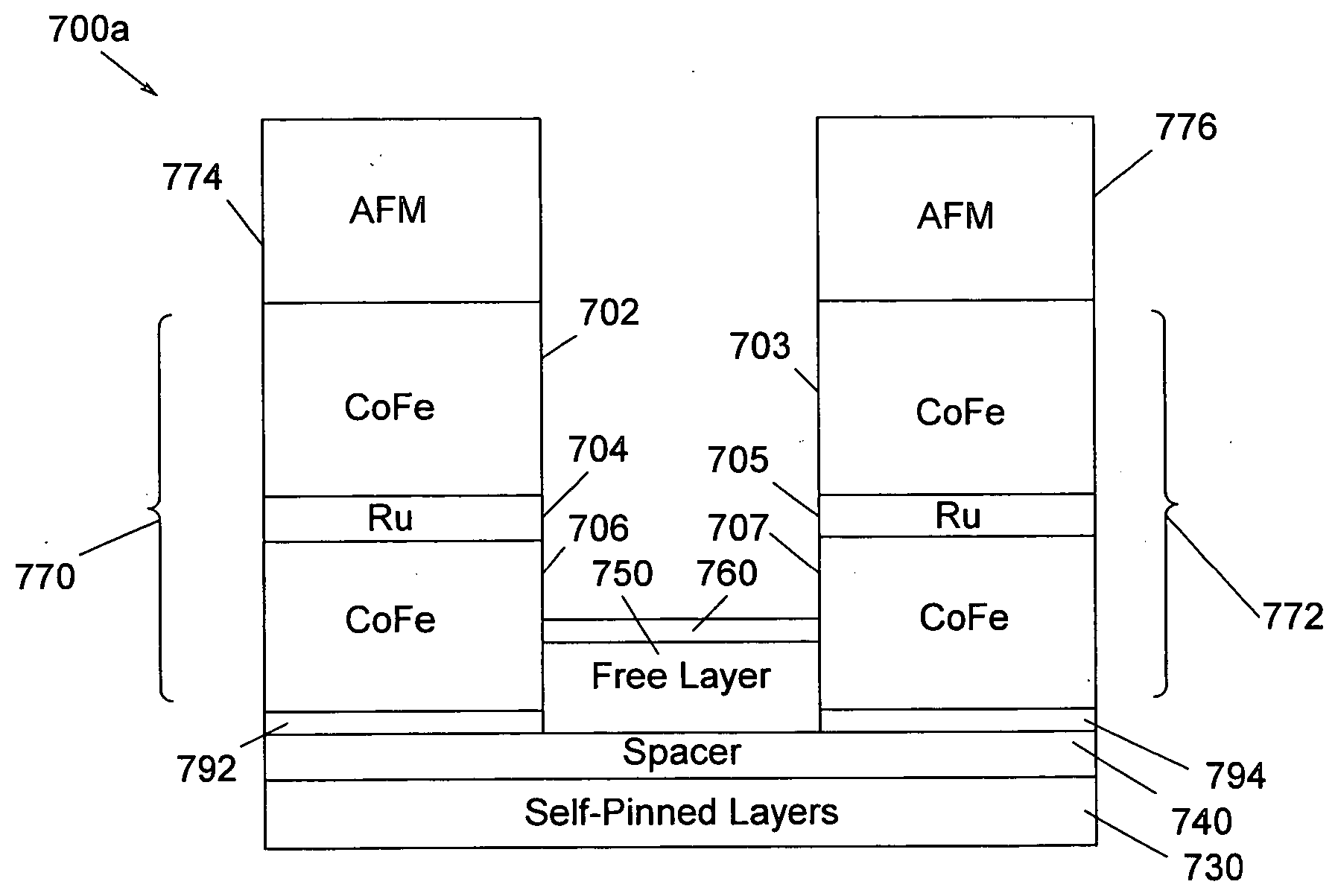

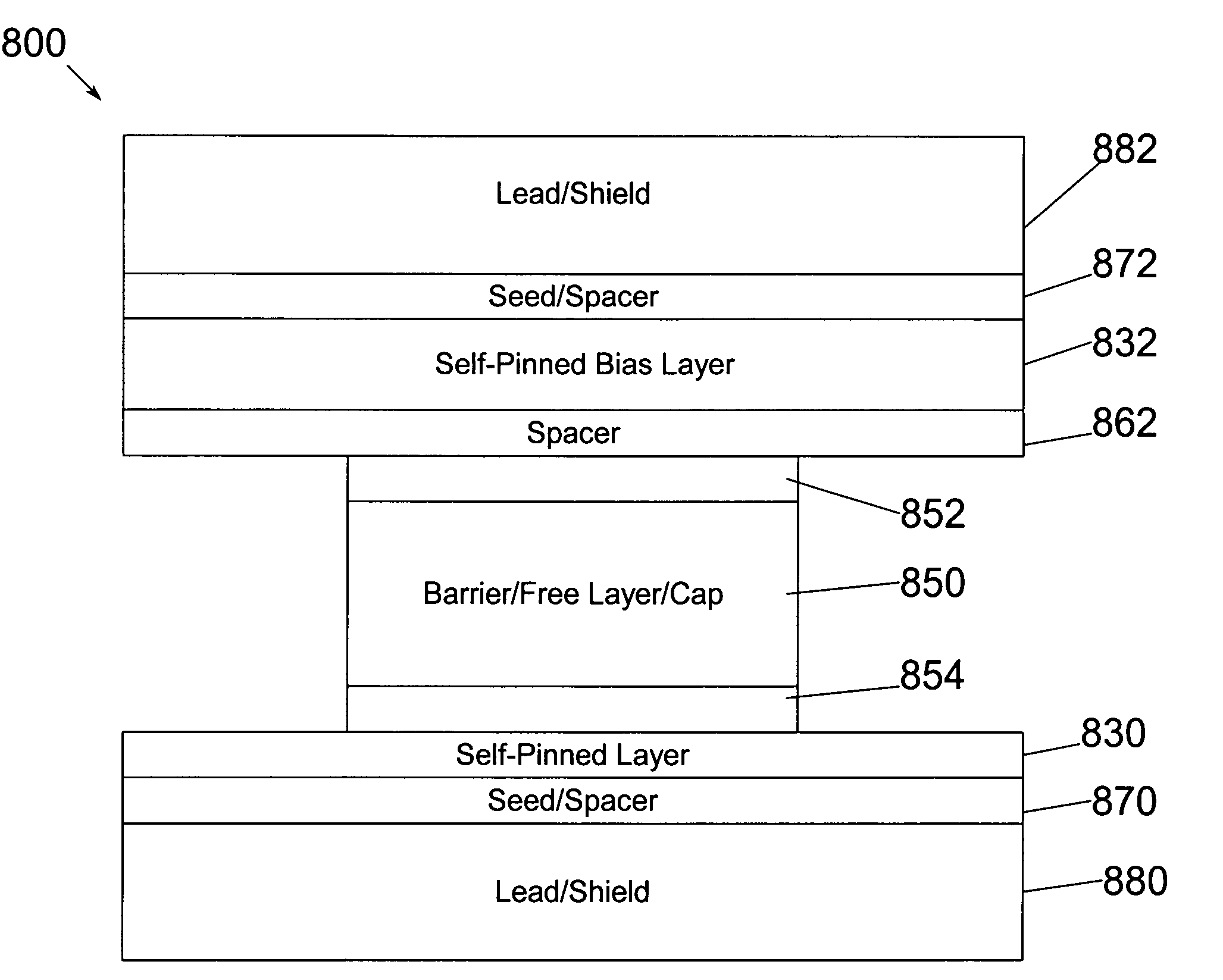

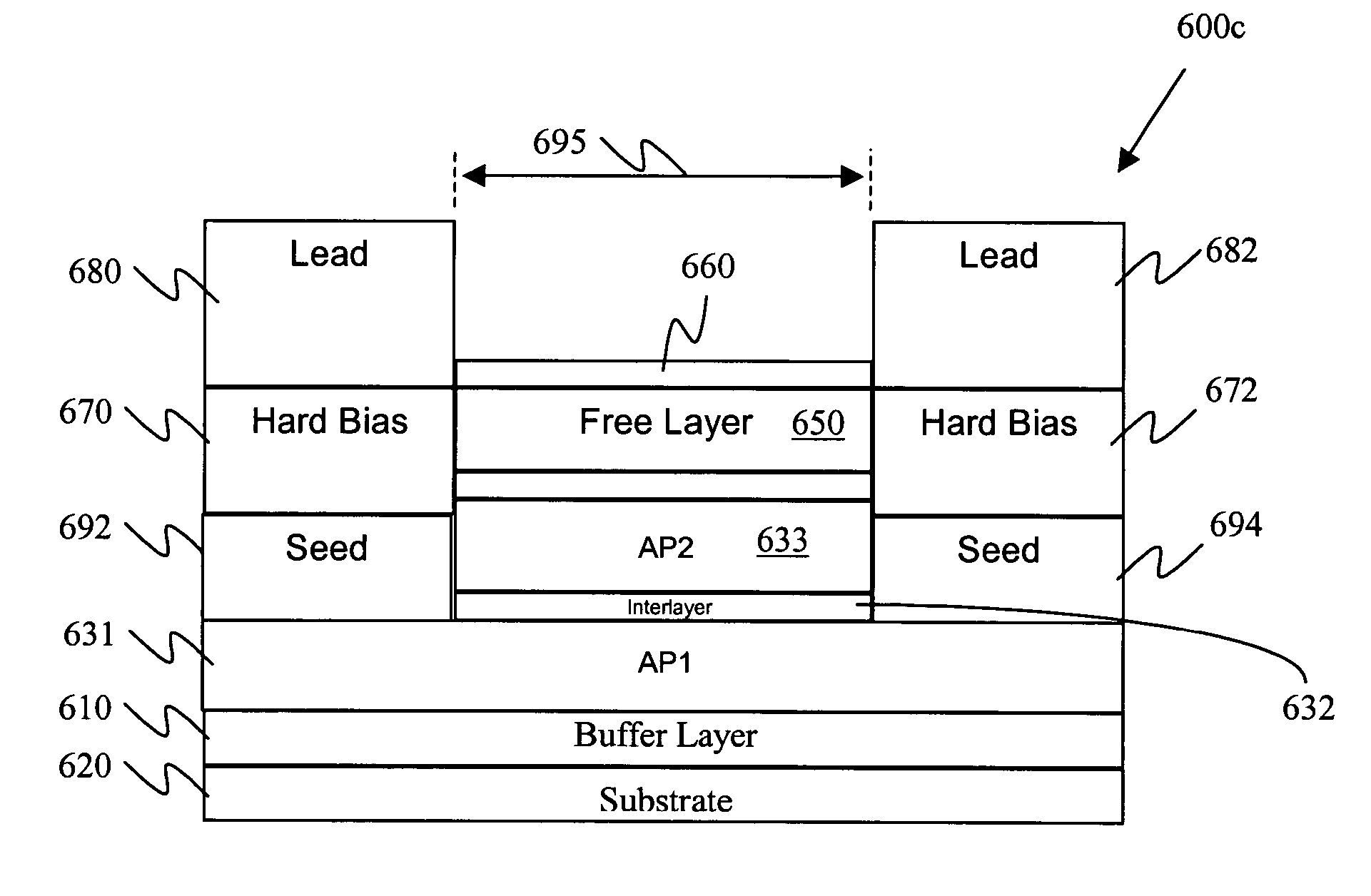

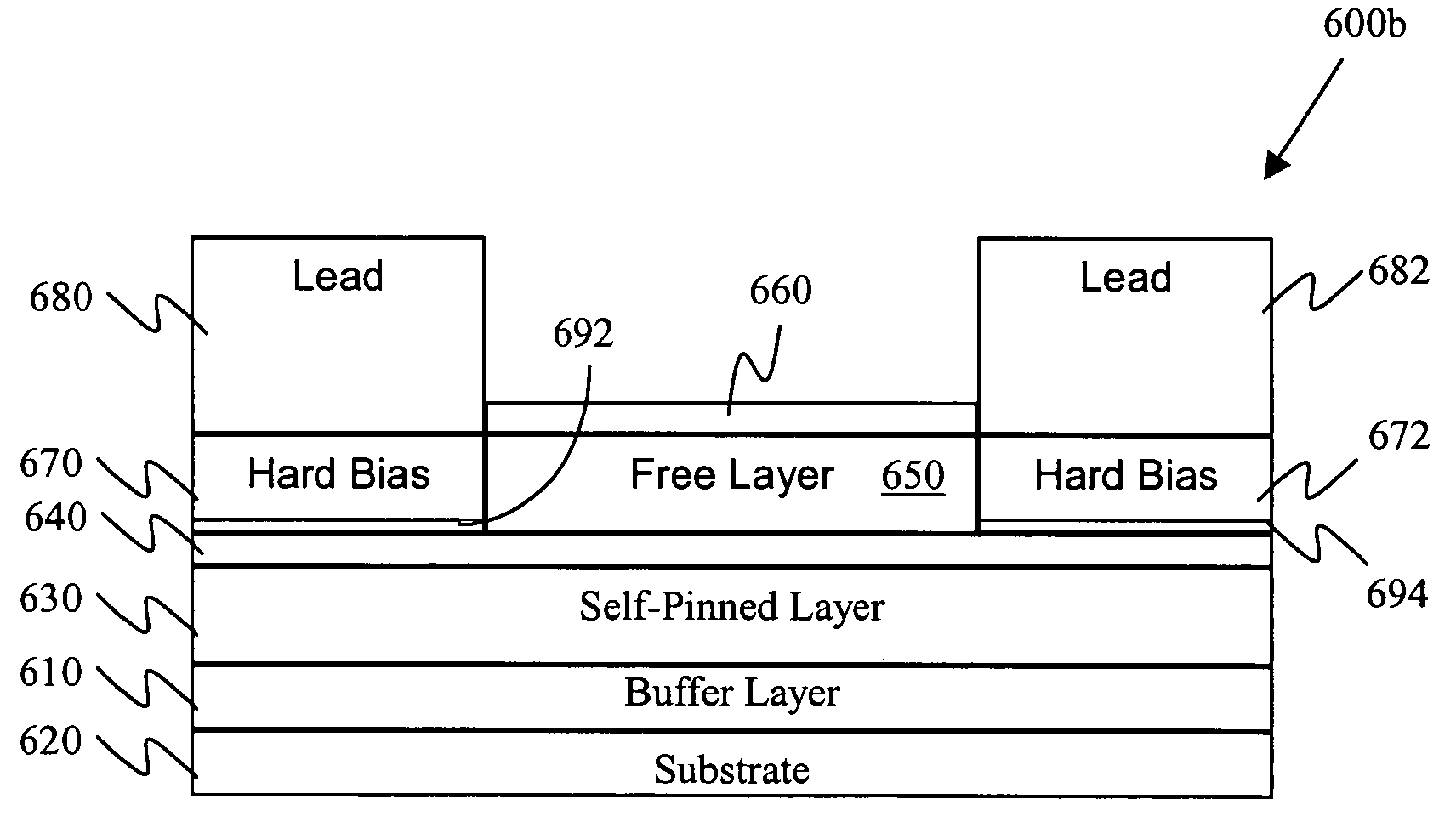

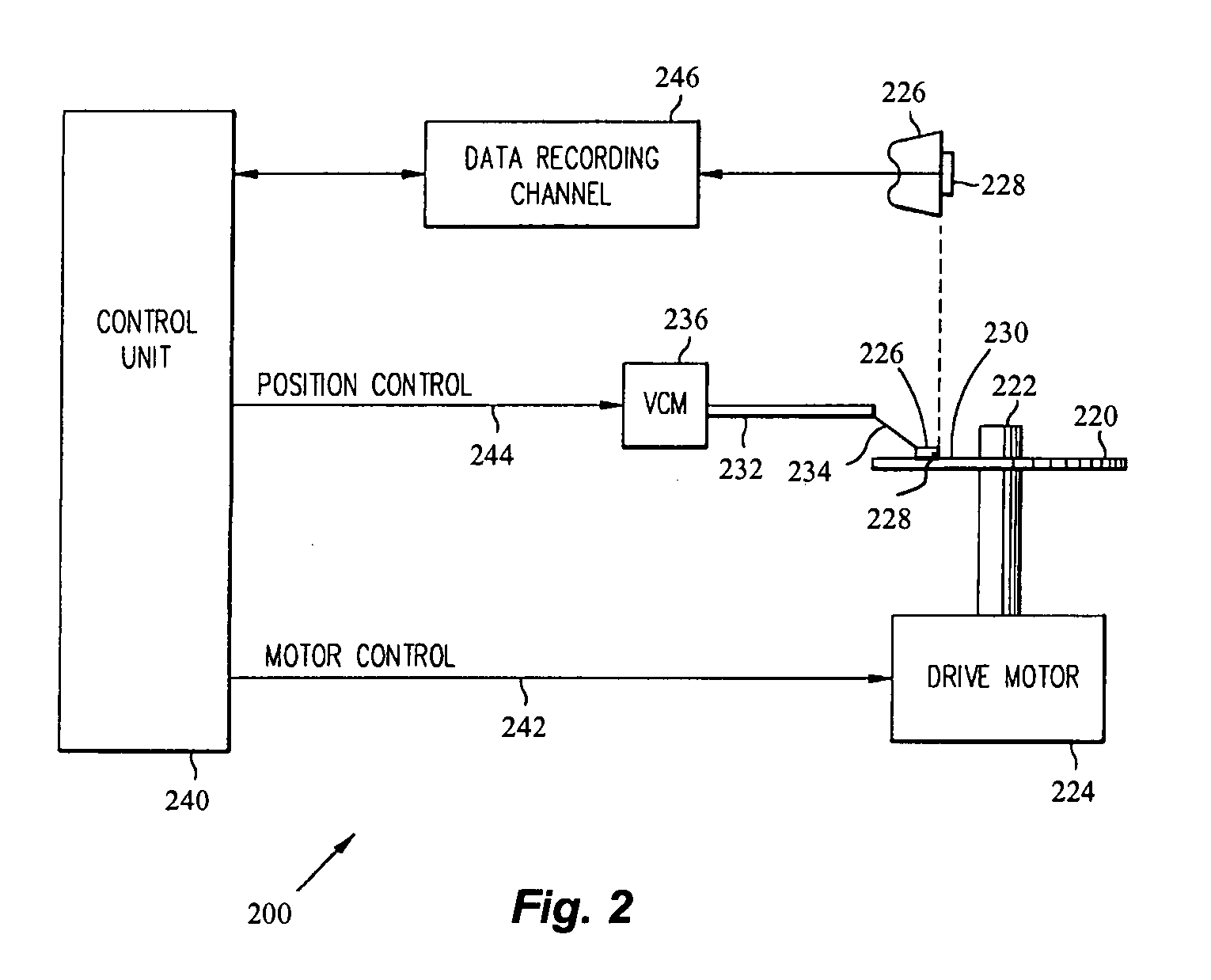

Method and apparatus for enhancing thermal stability, improving biasing and reducing damage from electrostatic discharge in self-pinned abutted junction heads having a first self-pinned layer extending under the hard bias layers

InactiveUS20050024786A1Reduce harmImprove thermal stabilityNanostructure applicationNanomagnetismEngineeringThermal stability

A method and apparatus for enhancing thermal stability, improving biasing and reducing damage from electrical surges in self-pinned abutted junction heads. A first self-pinned layer having a first magnetic orientation is provided, wherein the first self-pinned layer has a first end, a second end and central portion. A second self-pinned layer is formed over only the central portion of the first self-pinned layer and an interlayer is disposed between the first and second self-pinned layers. A free layer is formed in a central region over the second self-pinned layer. First and second hard bias layers are formed over the first and second ends of the first self-pinned layer respectively, the first and second hard bias layer abutting the free layer, the first and second end of the first self-pinned layer extending under the hard bias layers at the first and second ends.

Owner:HITACHI GLOBAL STORAGE TECH NETHERLANDS BV

Method and apparatus for providing a self-pinned bias layer that extends beyond the ends of the free layer

InactiveUS7072154B2Reduce harmImprove thermal stabilityRecord information storageManufacture of flux-sensitive headsThermal stabilityElectrical and Electronics engineering

A method and apparatus for enhancing thermal stability, improving biasing and reducing damage from electrical surges in self-pinned abutted junction heads. The head includes a free layer having a first end and a second end defining a width selected to form a desired trackwidth and an extended self-pinned bias layer extending beyond the ends of the free layer, the self-pinned bias layer extending beyond the free layer increasing the volume of the extended self-pinned bias layer to provide greater thermal stability and stronger pinning of the free layer.

Owner:WESTERN DIGITAL TECH INC

Ultra-thin SOI vertical bipolar transistors with an inversion collector on thin-buried oxide (BOX) for low substrate-bias operation and methods thereof

ActiveUS7375410B2Easy to integrateReduce manufacturing costTransistorSolid-state devicesCMOSManufacturing cost reduction

The present invention provides a “collector-less” silicon-on-insulator (SOI) bipolar junction transistor (BJT) that has no impurity-doped collector. Instead, the inventive vertical SOI BJT uses a back gate-induced, minority carrier inversion layer as the intrinsic collector when it operates. In accordance with the present invention, the SOI substrate is biased such that an inversion layer is formed at the bottom of the base region serving as the collector. The advantage of such a device is its CMOS-like process. Therefore, the integration scheme can be simplified and the manufacturing cost can be significantly reduced. The present invention also provides a method of fabricating BJTs on selected areas of a very thin BOX using a conventional SOI starting wafer with a thick BOX. The reduced BOX thickness underneath the bipolar devices allows for a significantly reduced substrate bias compatible with the CMOS to be applied while maintaining the advantages of a thick BOX underneath the CMOS.

Owner:GLOBALFOUNDRIES U S INC

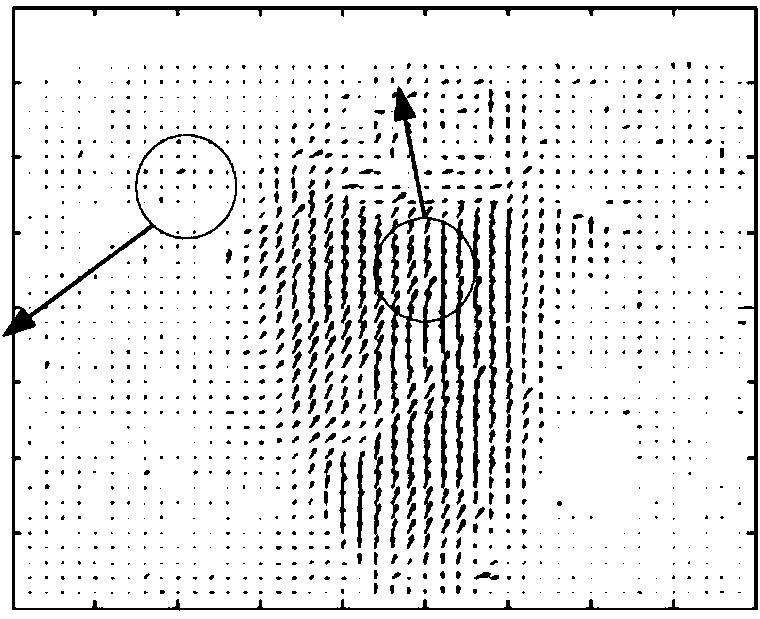

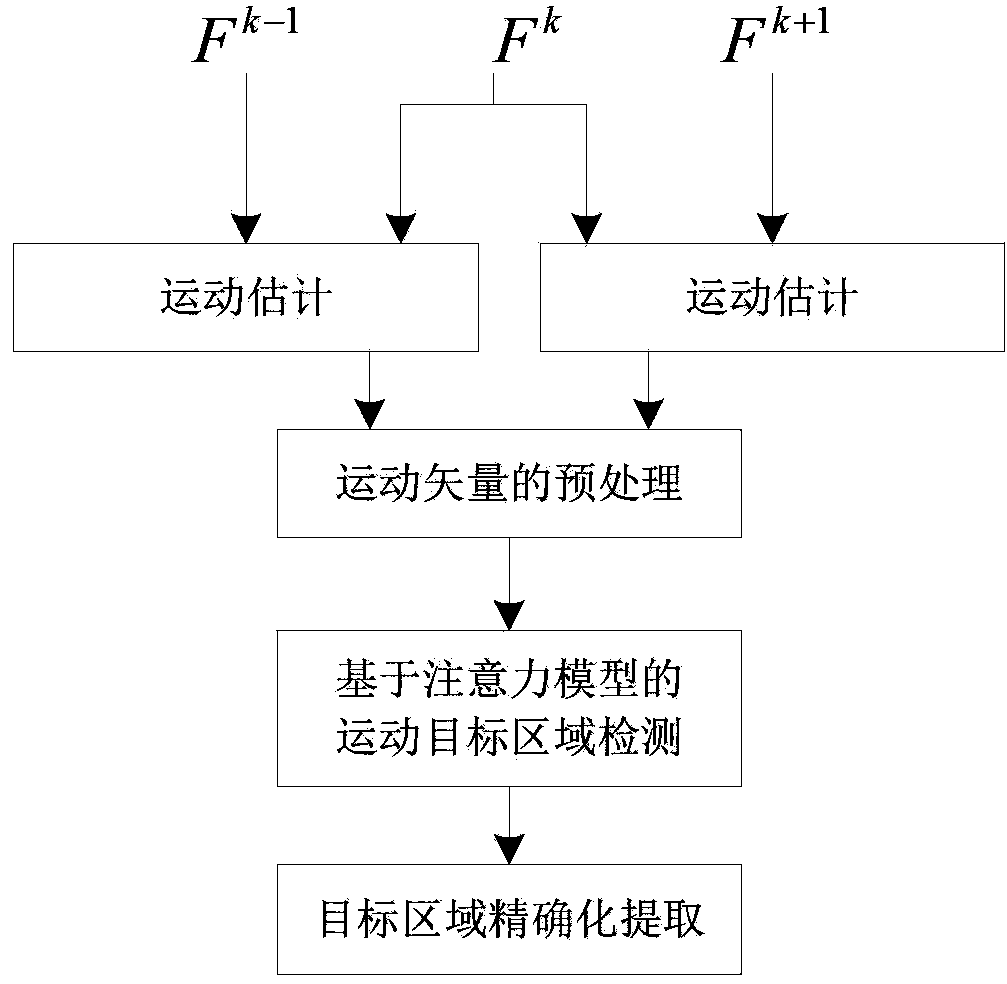

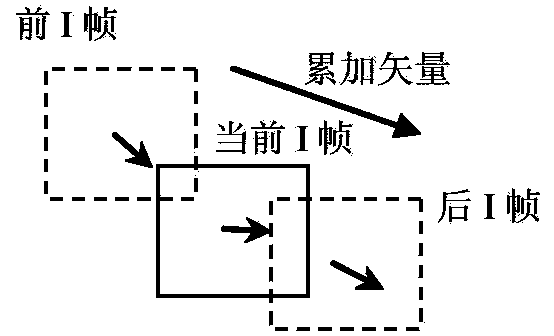

Movement target detection and extraction method based on movement attention fusion model

The invention relates to a movement target detection and extraction method based on a movement attention fusion model. The movement target detection and extraction method is characterized in that the movement attention fusion model is constructed through change characteristics of motion vectors in time and space according to movement contrasts of target movement in the time and the space, and accurate extraction on a movement target under an overall movement scene is achieved by combining noise removal, median filtering and edge detection. In order to remove limitations of target detection and extraction under the overall movement scene at present, the time-space movement attention fusion model, the noise removal technology, the image filtering technology and the edge tracking and detection technology are adopted. Testing results of multiple overall movement video scenes display that compared with other algorithms, the algorithm has the advantages that the accuracy is high, the complexity is low, the operation amount is small, and the instantaneity is high.

Owner:XIAN UNIV OF TECH

Adaptive oil separator

InactiveUS20080105494A1Improve control characteristicsEasy to separateCombustion enginesCrankcase ventillationEngineeringPressure difference

An oil mist separator has a pressure regulator valve which is located in the blow-by line downstream of the oil mist separator element in the flow direction of the gas. The pressure regulator valve has a bias so that it opens above a specified pressure difference between the blow-by line and a neighboring chamber. Located around the oil mist separator element is a bypass line which has a bypass valve. The bypass valve has a bias that causes the bypass valve to close below a specified pressure difference between the suction side and the pressure side of the oil mist separation element. The pressure regulator valve and the bypass valve are connected with each other so that the pressure regulator valve, as it closes, increases the bias of the bypass valve.

Owner:DANA AUTOMOTIVE SYST GRP LLC

Apparatus for enhancing thermal stability, improving biasing and reducing damage from electrostatic discharge in self-pinned abutted junction heads having a first self-pinned layer extending under the hard bias layers

InactiveUS7092220B2Reduce harmImprove thermal stabilityNanostructure applicationNanomagnetismHeat stabilityEngineering

A method and apparatus for enhancing thermal stability, improving biasing and reducing damage from electrical surges in self-pinned abutted junction heads. A first self-pinned layer having a first magnetic orientation is provided, wherein the first self-pinned layer has a first end, a second end and central portion. A second self-pinned layer is formed over only the central portion of the first self-pinned layer and an interlayer is disposed between the first and second self-pinned layers. A free layer is formed in a central region over the second self-pinned layer. First and second hard bias layers are formed over the first and second ends of the first self-pinned layer respectively, the first and second hard bias layer abutting the free layer, the first and second end of the first self-pinned layer extending under the hard bias layers at the first and second ends.

Owner:HITACHI GLOBAL STORAGE TECH NETHERLANDS BV

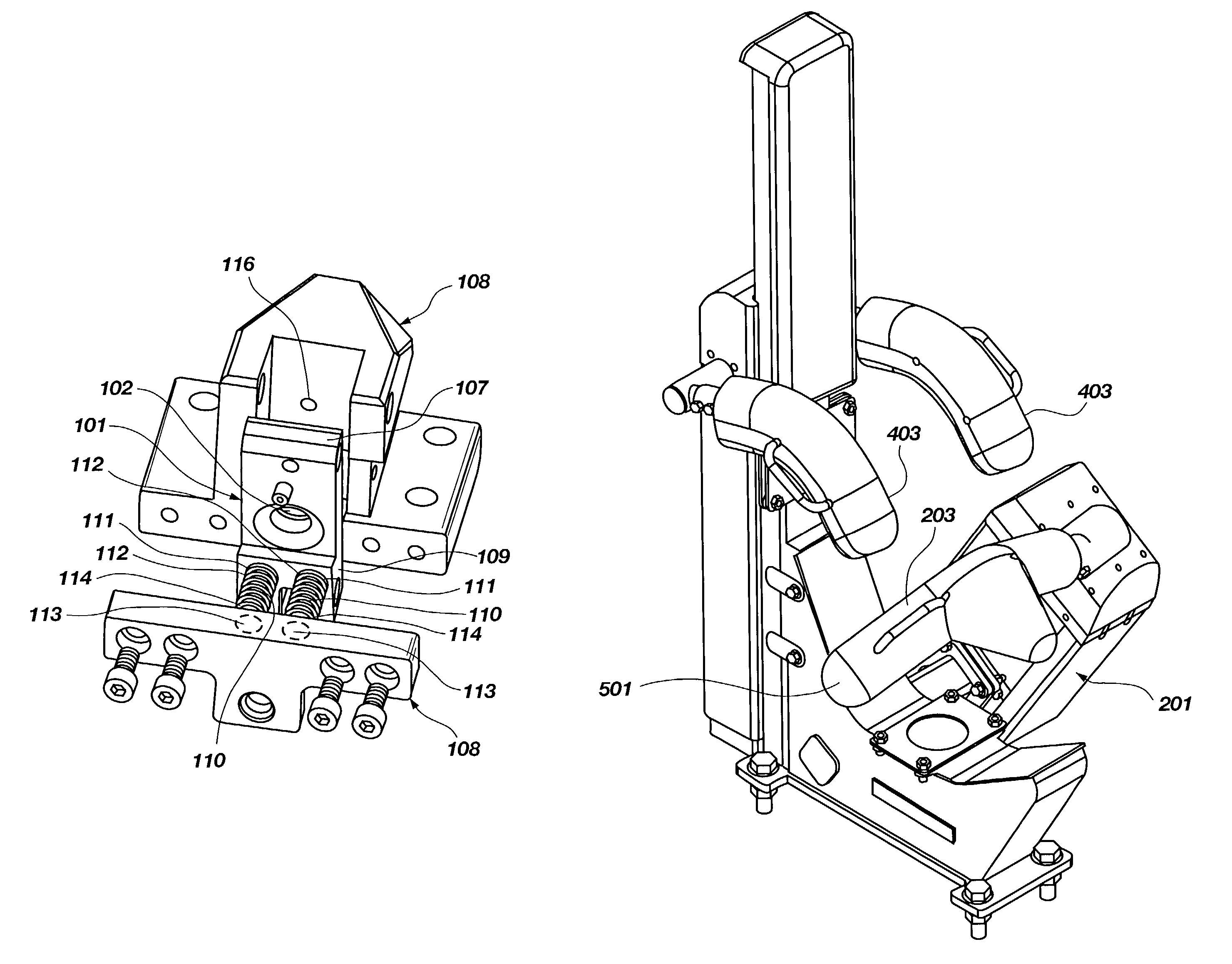

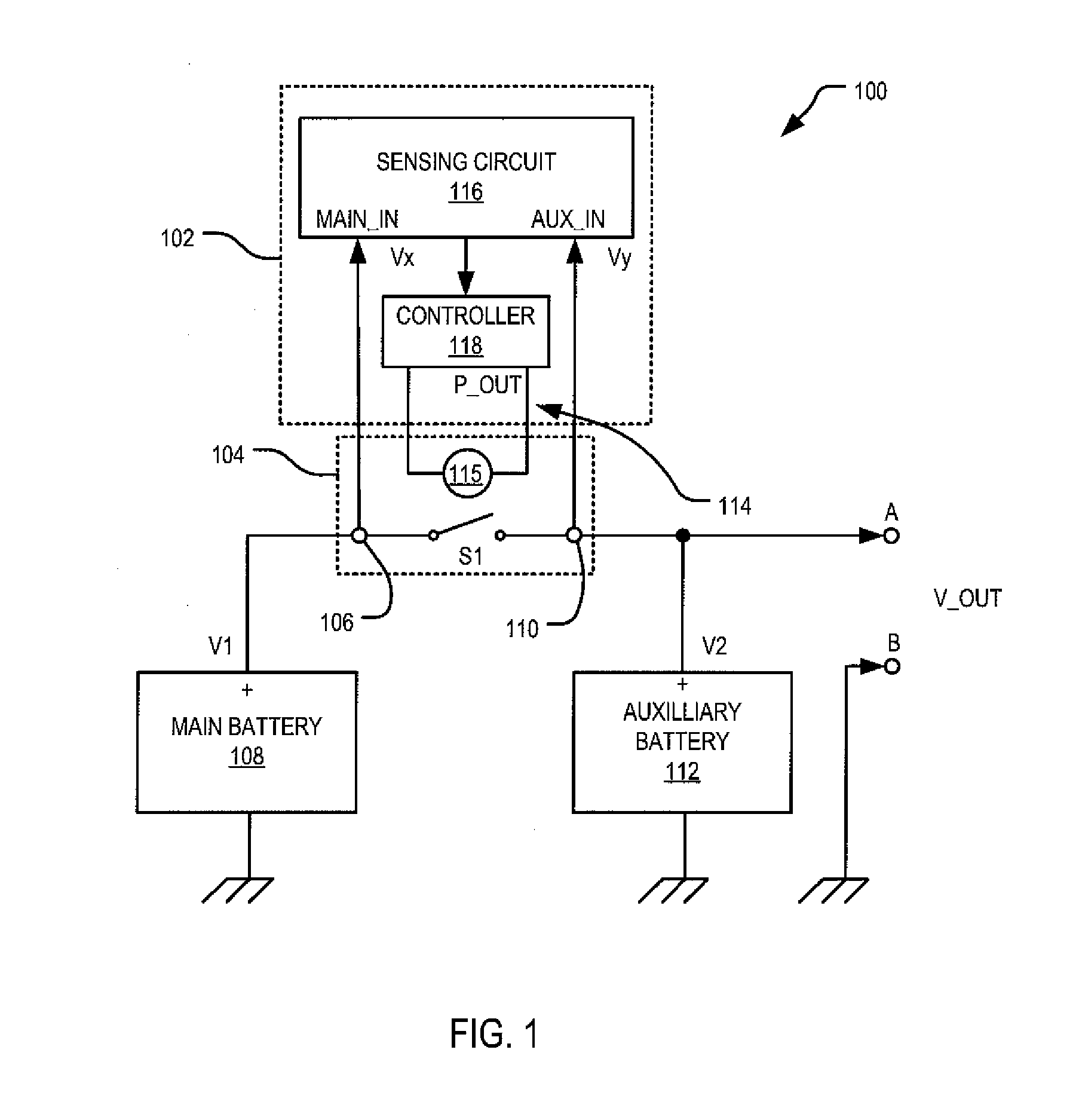

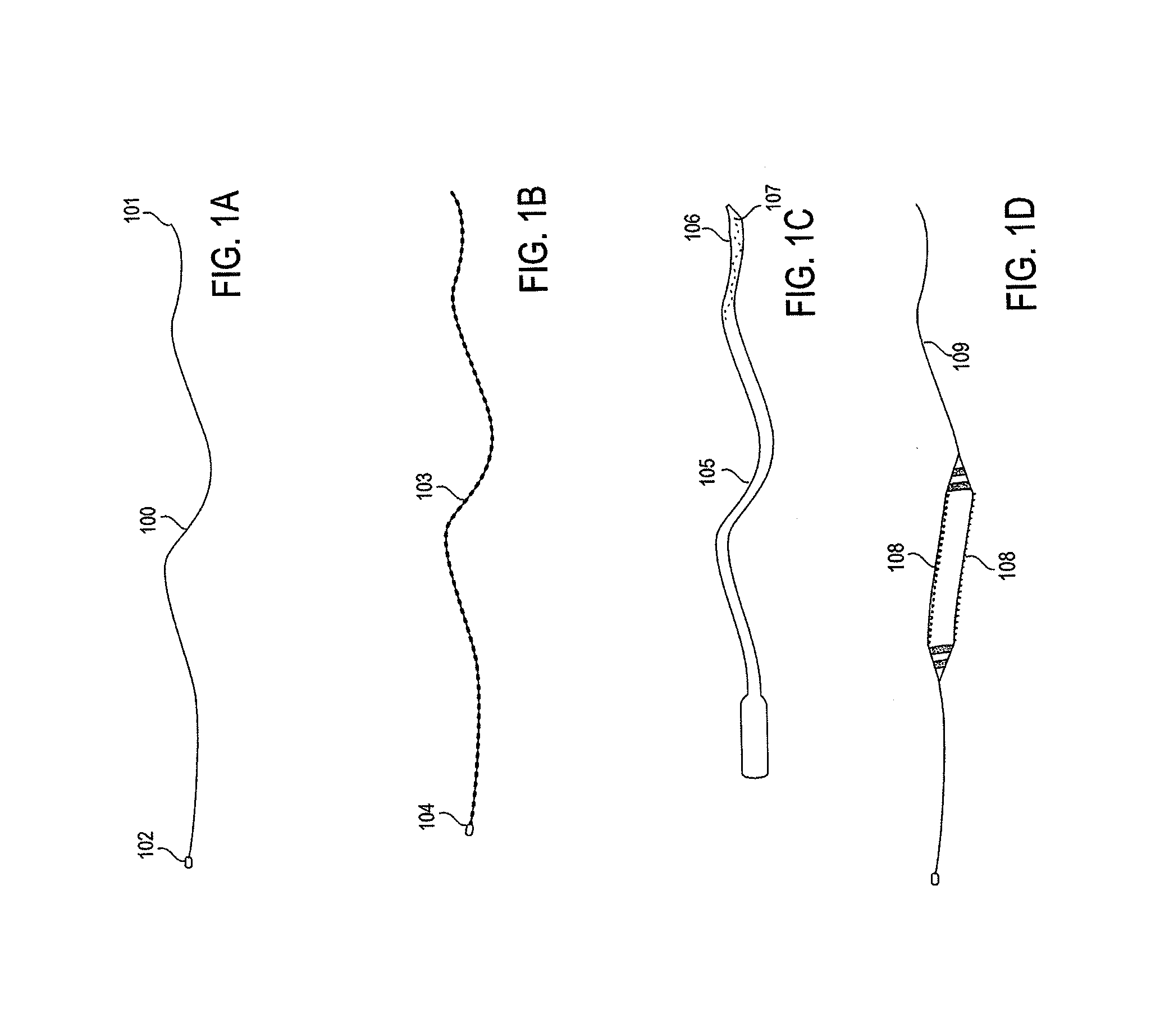

Tissue modification devices

Owner:SPINAL ELEMENTS INC

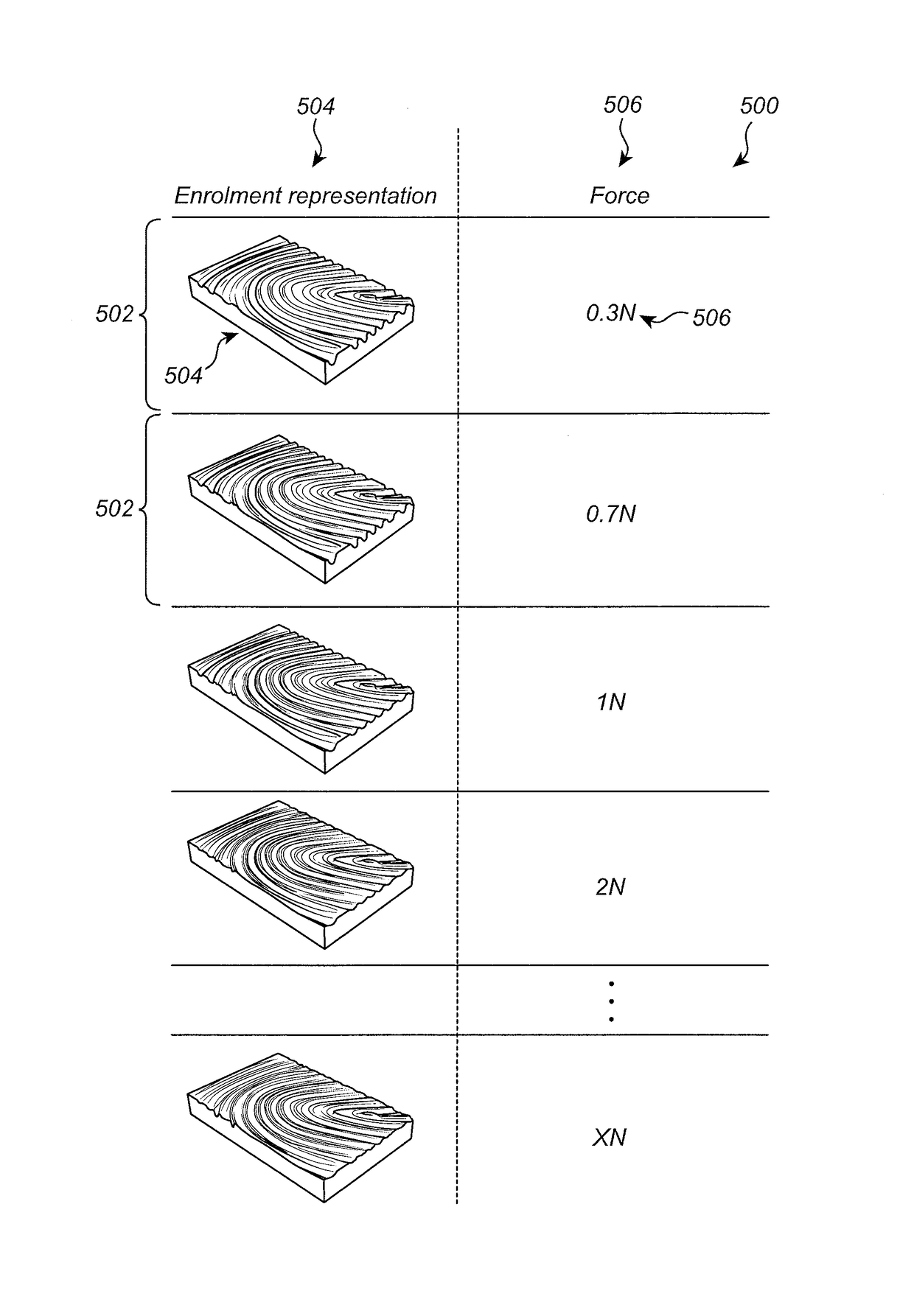

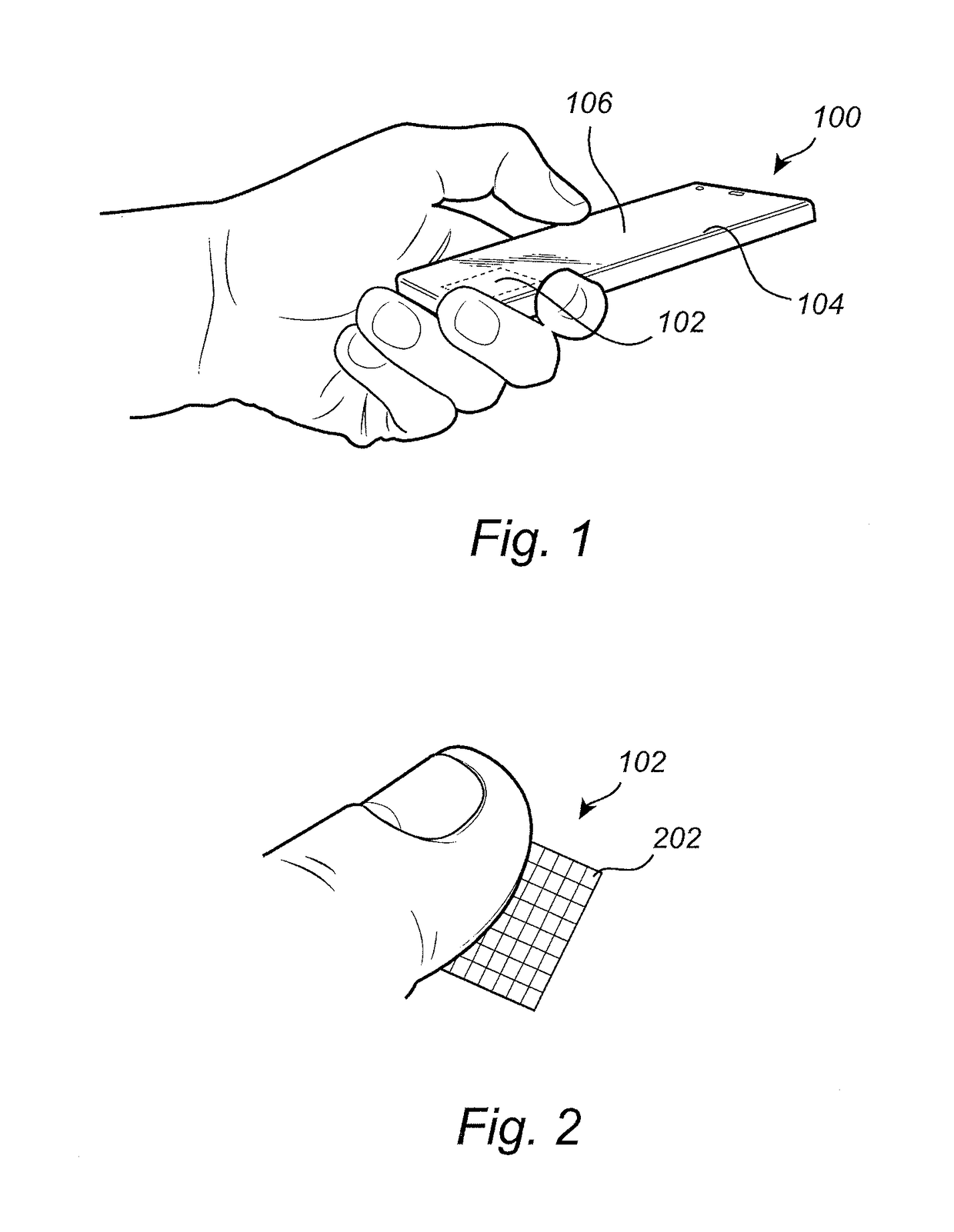

Fingerprint sensor with force sensor

ActiveUS20170344782A1Improve authentication securityImproved authentication securityDigital data authenticationPrint image acquisitionFingerprintComputer hardware

The present invention generally relates to a method for authenticating a user of an electronic device comprising a fingerprint sensor and a force sensor, the method comprising: retrieving a stored plurality of fingerprint enrolment templates comprising an enrolment representation of at least part of a user's finger and a corresponding enrolment force parameter, acquiring a first verification image of an object and determining a first verification representation, determining a first verification force parameter, performing a fingerprint authentication procedure based on the first verification template and the plurality of fingerprint enrolment templates, wherein when the first verification representation and the first verification force parameter comprised in the first verification template matches each of the enrolment representation and the enrolment force parameter comprised in the same fingerprint enrolment template providing a signal indicating successful authentication of the user. The invention also relates to a fingerprint sensing system and an electronic device.

Owner:FINGERPRINT CARDS ANACATUM IP AB

Capacitor microphone

InactiveCN101189910ASmooth vibration without disturbanceSmooth vibrationElectrostatic transducer microphonesEngineeringSound wave

A capacitor microphone is constituted by a plate having a fixed electrode, a diaphragm including a center portion and at least one near-end portion that is fixed to the outer periphery, in which the center portion having a vibrating electrode, which is positioned relative to the fixed electrode and which vibrates in response to sound waves, is increased in rigidity in comparison with the near-end portion; and a spacer that is fixed to the plate and the near-end portion of the diaphragm and that has an air gap formed between the plate and the diaphragm. Alternatively, a diaphragm electrode is horizontally supported by extension arms extended from a circular plate thereof and is vertically held in a hanging state being apart from a fixed electrode with a controlled distance therebetween.

Owner:YAMAHA CORP

Apparatus having a self-pinned abutted junction magnetic read sensor with hard bias layers formed over ends of a self-pinned layer and extending under a hard bias layer

InactiveUS7050277B2Reduce harmImprove thermal stabilityHeads using thin filmsRecord information storageEngineeringThermal stability

A method and apparatus for enhancing thermal stability, improving biasing and reducing damage from electrical surges in self-pinned abutted junction heads. The head includes a self-pinned layer, the self-pinned layer having a first end, a second end and central portion, a free layer disposed over the central portion of the self-pinned layer in a central region and a first and second hard bias layers formed over the first and second ends of the self-pinned layer respectively, the first and second hard bias layer abutting the free layer, the first and second end of the self-pinned layer extending under the hard bias layers at the first and second ends.

Owner:HITACHI GLOBAL STORAGE TECH NETHERLANDS BV

Insulated gate type source-leakage composite field plate transistor with high electron mobility and preparing method thereof

InactiveCN101414627AImprove breakdown voltageLarge drain-source voltageSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionSource field

The invention discloses an insulated gate type source-drain composite field plate transistor with high electron mobility and a fabrication method thereof. The transistor comprises a substrate, a transition layer, a barrier layer, a source electrode, a drain electrode, an insulated gate electrode, a passivation layer, a source field plate, a drain field plate and a protection layer from bottom to top,; the source field plate is electrically connected with the source electrode, the drain field plate is electrically connected with the drain electrode, wherein, an insulation medium layer is deposited on the upper part of the source electrode, the upper part of the drain electrode as well as the upper part of the barrier layer between the source electrode and the drain electrode; and n floating field plates are deposited on the passivation layer arranged between the source field plate and the drain field plate. All the floating field plates have the same size and are mutually independent in floating state, and the floating field plates are equidistantly distributed between the source field plate and the drain field plate. The n floating plates, the source field plate and the drain plate are completed on the passivation layer by one-time process. The transistor has the advantages of simple process, strong reliability and high breakdown voltage, and the transistor and the fabrication method can be used for fabricating high power devices based on a wide band gap compound semiconductor material heterojunction.

Owner:XIDIAN UNIV

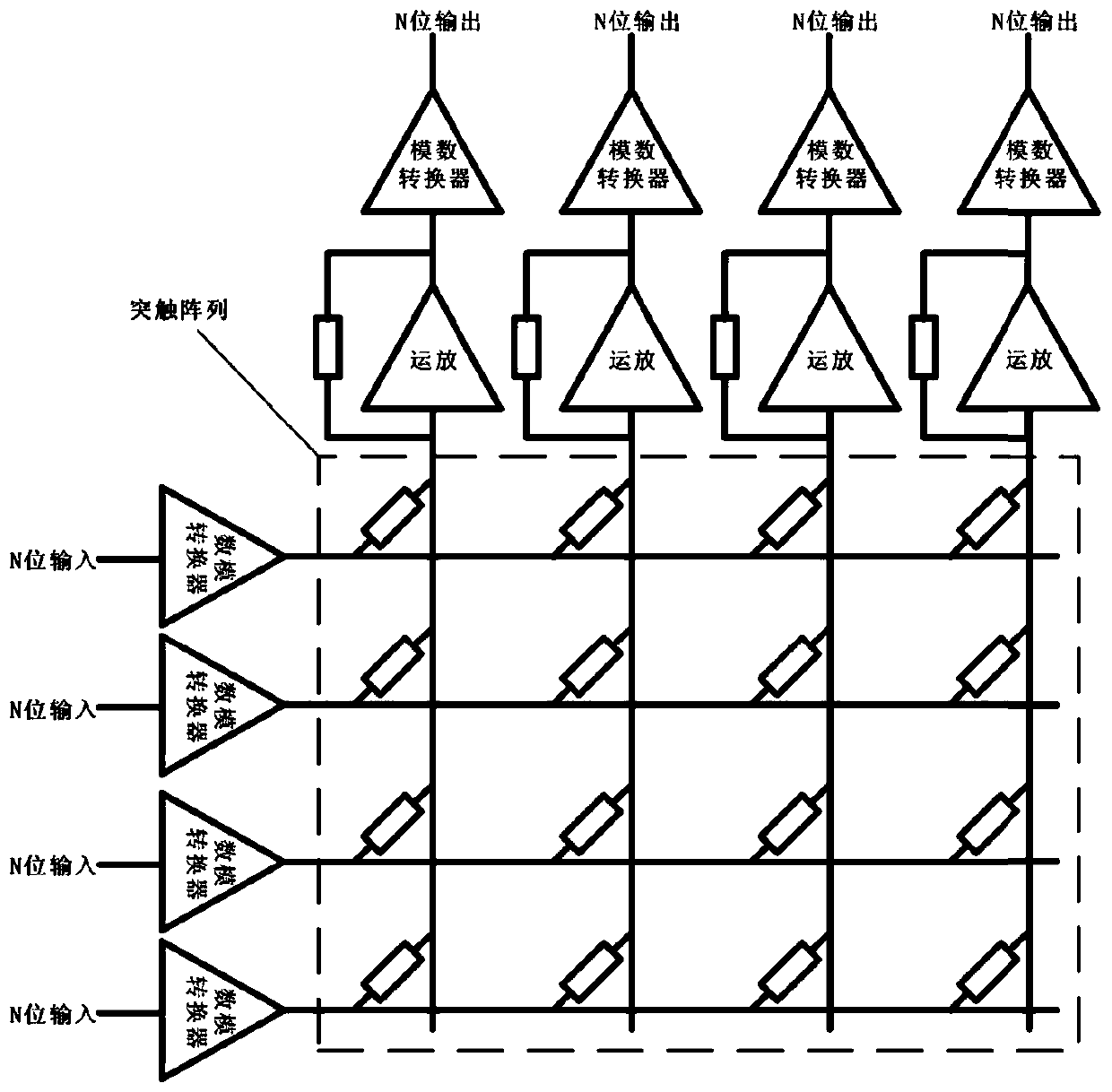

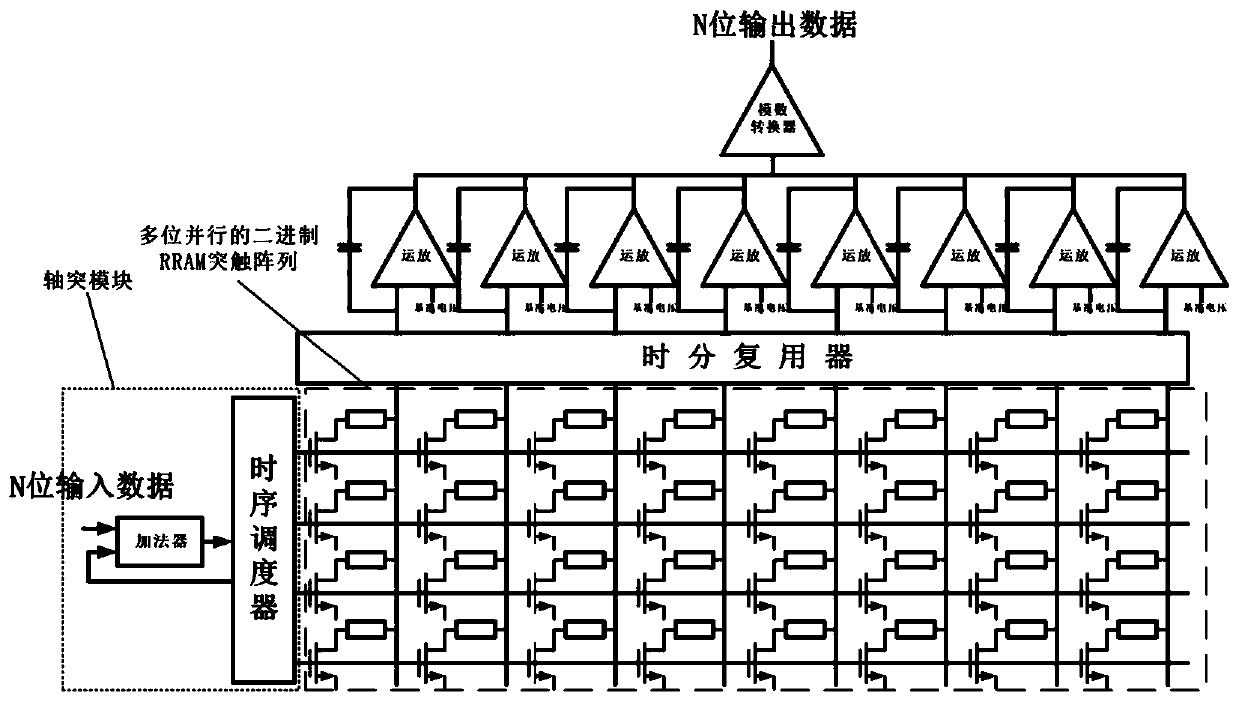

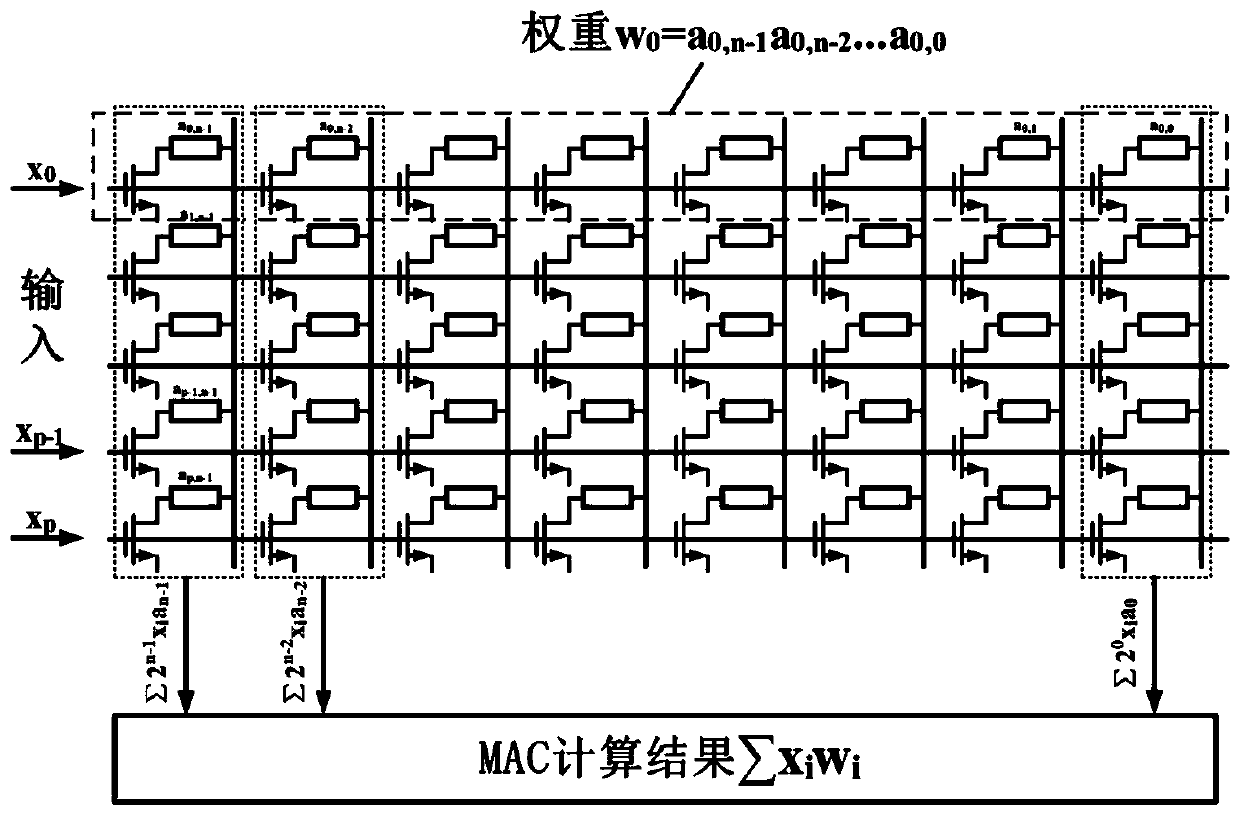

Neuromorphic calculation circuit based on multi-bit parallel binary synaptic array

ActiveCN110378475ASave area and powerReduce biasAnalogue/digital conversionElectric signal transmission systemsDeep neural networksPower consumption

The invention discloses a neuromorphic calculation circuit based on a multi-bit parallel binary synapse array. The neuromorphic calculation circuit comprises a neural axon module, the multi-bit parallel binary RRAM synapse array, a time division multiplexer, a plurality of integrators and a shared successive approximation analog-to-digital converter, wherein the neural axon module comprises two basic units, namely a time sequence scheduler and an adder, and the time sequence scheduler is used for arranging the time sequence of signals, so that input signals are sequentially input into a multi-bit parallel binary RRAM synapse array by adopting a dendritic priority strategy; the adder is used for expanding the array scale, and when the configured neural network input layer is greater than the input of one RRAM array, the adder is used for adding the calculation results of the plurality of arrays to obtain the output of the network layer. Compared with the current system, the method has the advantages of high precision and low power consumption, can be configured into most deep neural network applications, and is particularly suitable for being deployed in edge computing equipment with high energy consumption requirements.

Owner:ZHEJIANG UNIV

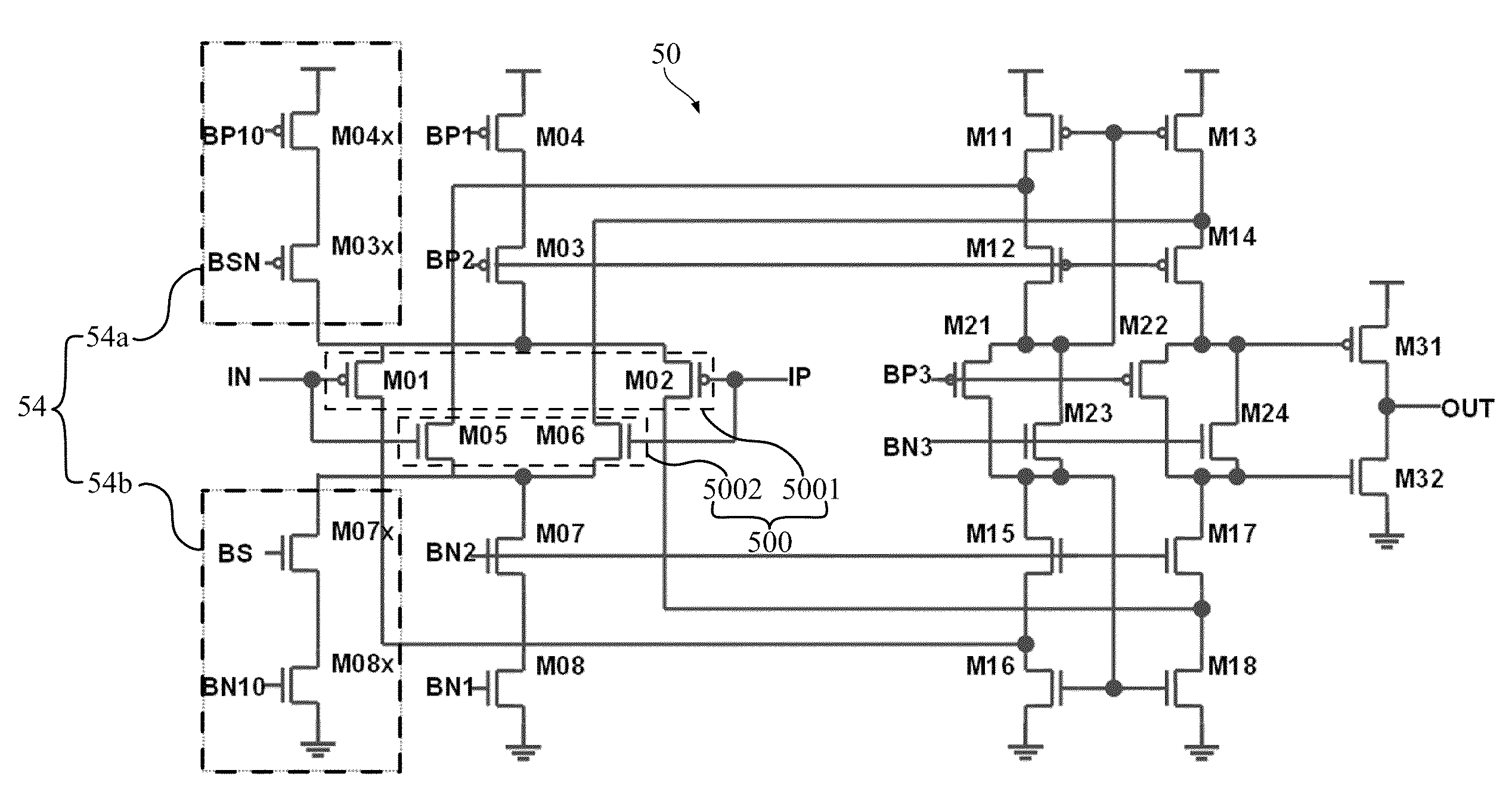

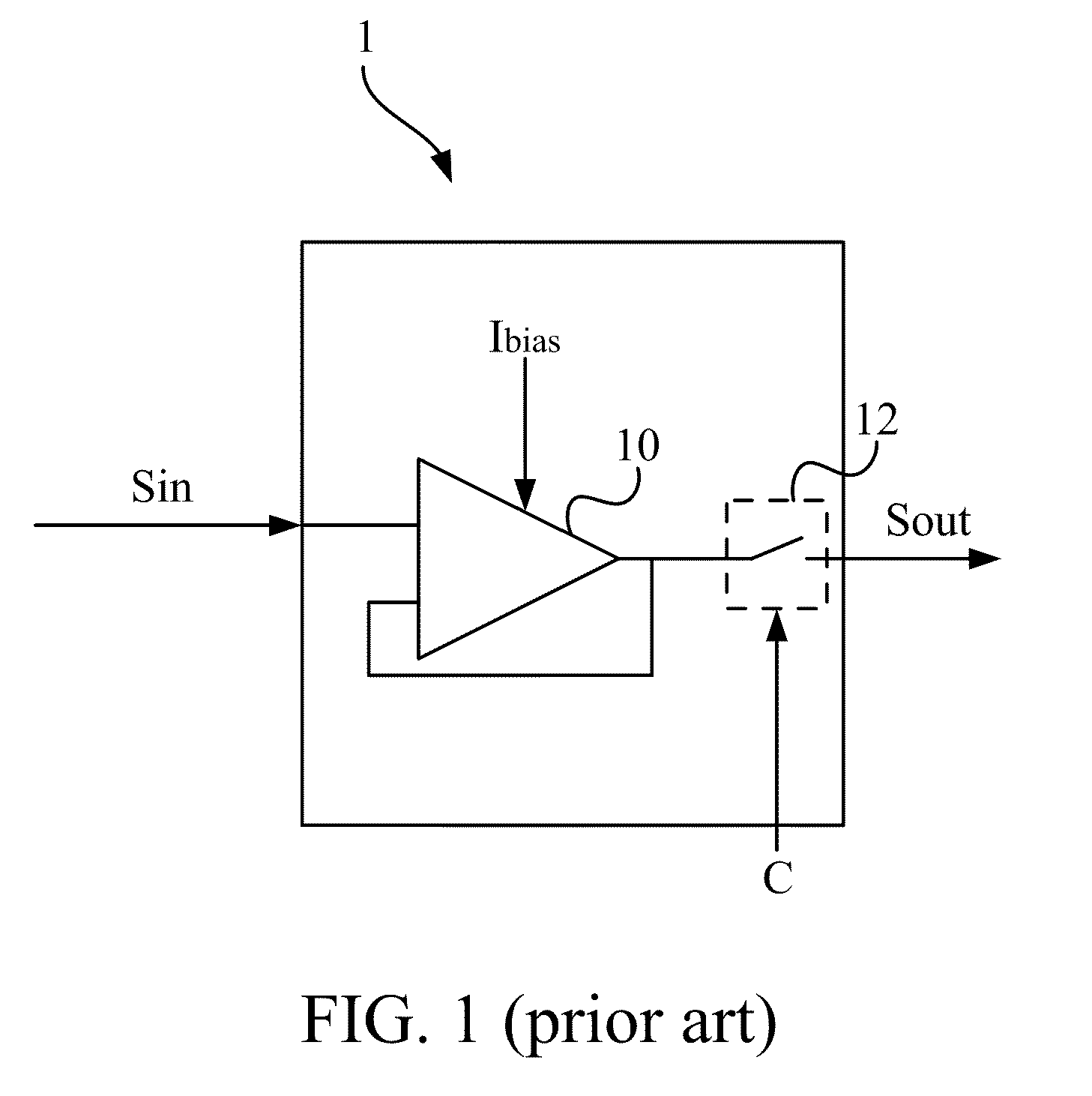

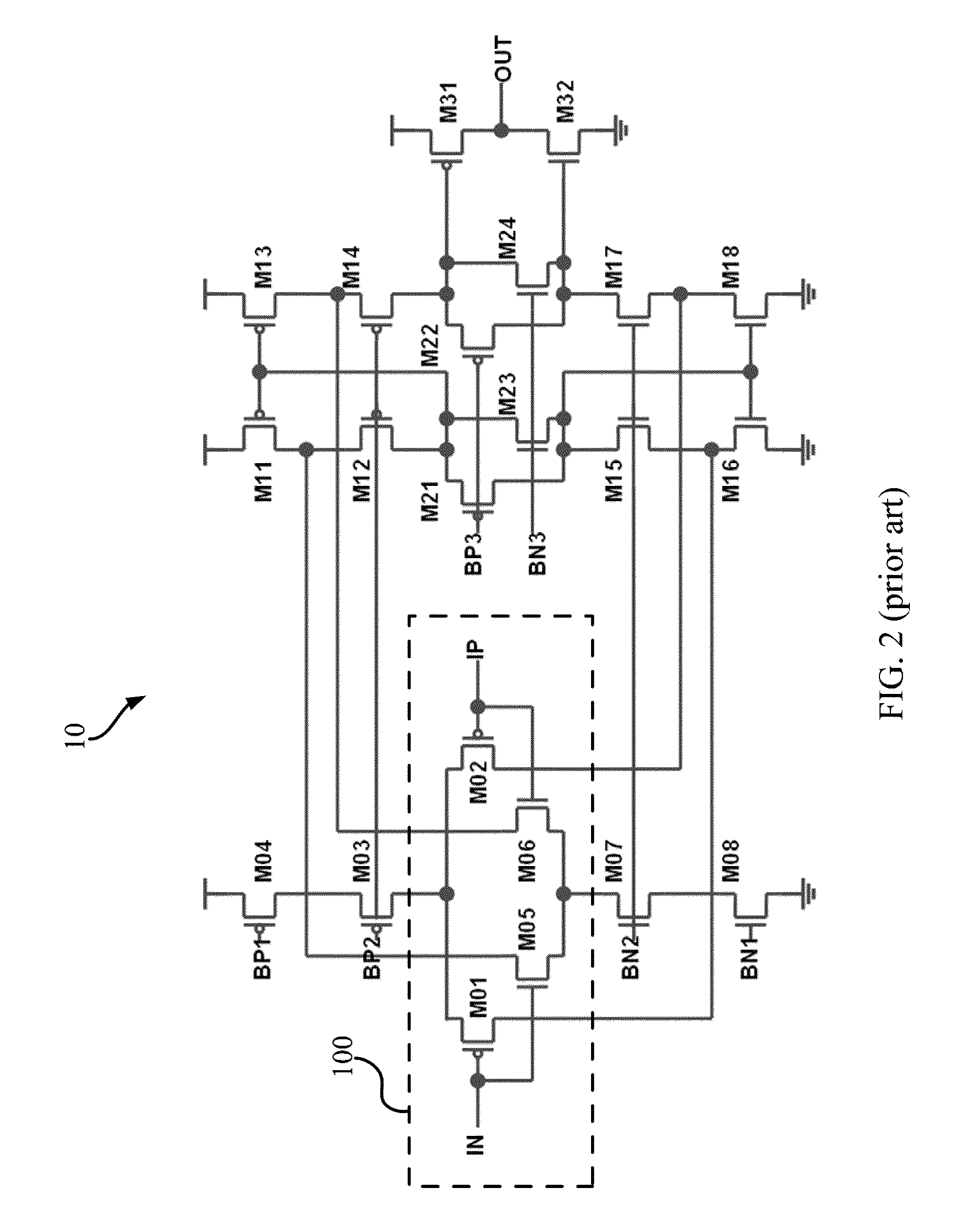

Driving circuit system and method of elevating slew rate of operational amplifier

ActiveUS20100097142A1Avoid negative effectsShort response timeAmplififers with field-effect devicesDifferential amplifiersAudio power amplifierControl signal

The invention discloses a driving circuit system and a method of elevating a slew rate of an operational amplifier. The driving circuit system comprises an operational amplifier, a judging module and a bias enhancing module. The operational amplifier has an input stage driven by a bias current. The bias enhancing module is electrically connected to the judging module and the input stage of the operational amplifier respectively. The judging module is used to generate a bias enhancing signal according to an edge-trigger of a control signal. When the bias enhancing module receives the bias enhancing signal, the bias enhancing module provides an additional current, which cooperates with the bias current, for driving the input stage of the operational amplifier, so as to elevating a slew rate of the operational amplifier.

Owner:RAYDIUM SEMICON

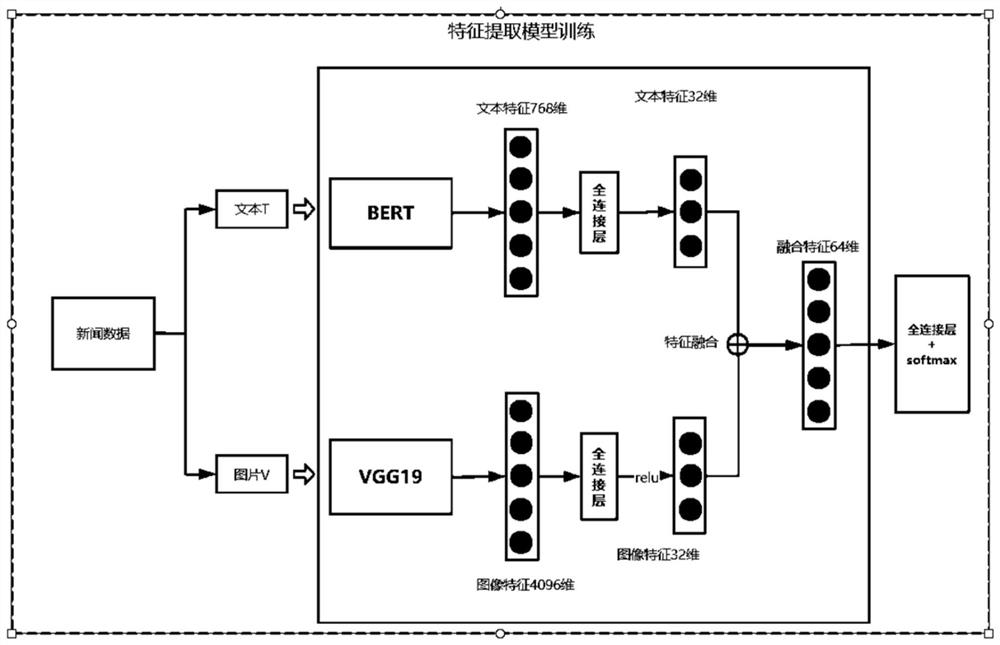

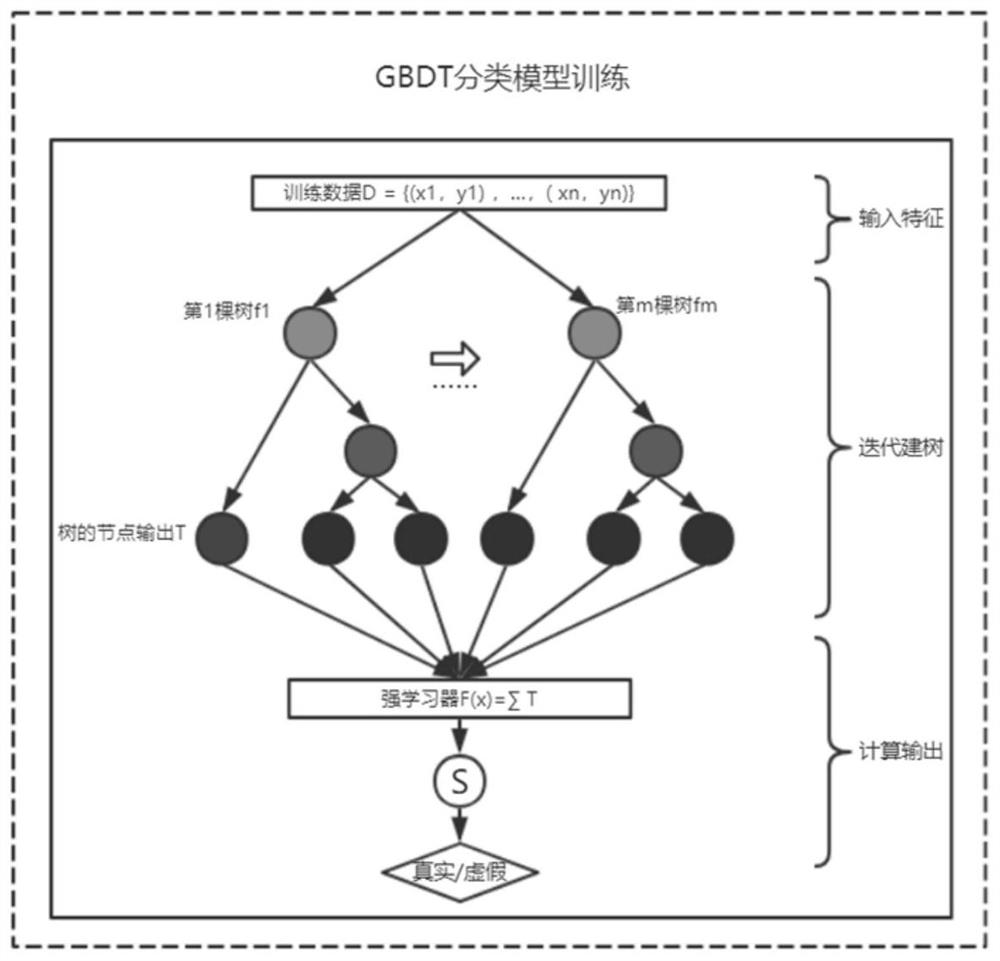

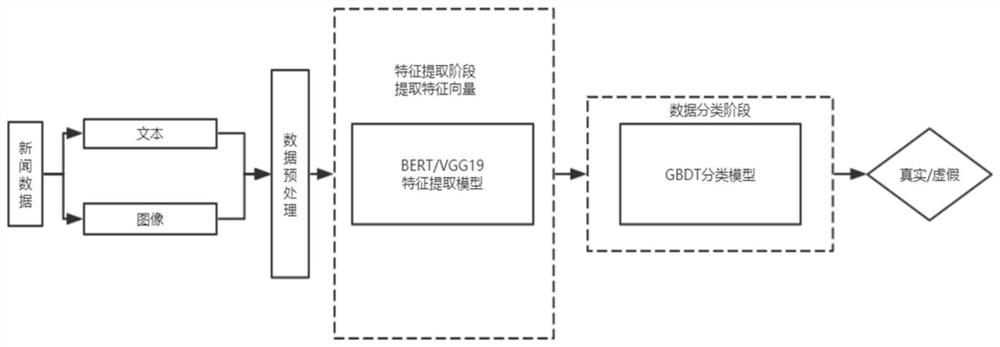

False news detection method based on multi-modal fusion

PendingCN112131347AImprove detection accuracyImprove classification performanceSemantic analysisCharacter and pattern recognitionData setFeature set

The invention discloses a false news detection method based on multi-modal fusion. The false news detection method comprises the following steps of: (1) preprocessing news text data and news picture data of news; (2) extracting features of news data, specifically, using a news data feature extraction model composed of a pre-training model BERT model and a VGG19 model to perform feature extractionon the preprocessed news text and news picture data, and performing optimization training to obtain a trained news data feature extraction model; (3) performing data feature classification, specifically, inputting a training data set into the news data feature extraction model to obtain a news feature set, inputting the news feature set into a classifier as training data to perform training of a classification model, and completing model training based on the false news detection method.

Owner:TIANJIN UNIV

Battery isolator unit

ActiveUS8390145B2Reducing duty cycleRaise the biasBatteries circuit arrangementsElectric devicesControl signalTerminal voltage

Owner:REDARC TECH

Self-ionized and inductively-coupled plasma for sputtering and resputtering

InactiveUS20140305802A1Raise the ratioReduce layer thicknessCellsElectric discharge tubesTantalum nitrideInductively coupled plasma

A magnetron sputter reactor for sputtering deposition materials such as tantalum, tantalum nitride and copper, for example, and its method of use, in which self-ionized plasma (SIP) sputtering and inductively coupled plasma (ICP) sputtering are promoted, either together or alternately, in the same or different chambers. Also, bottom coverage may be thinned or eliminated by ICP resputtering in one chamber and SIP in another. SIP is promoted by a small magnetron having poles of unequal magnetic strength and a high power applied to the target during sputtering. ICP is provided by one or more RF coils which inductively couple RF energy into a plasma. The combined SIP-ICP layers can act as a liner or barrier or seed or nucleation layer for hole. In addition, an RF coil may be sputtered to provide protective material during ICP resputtering. In another chamber an array of auxiliary magnets positioned along sidewalls of a magnetron sputter reactor on a side towards the wafer from the target. The magnetron preferably is a small, strong one having a stronger outer pole of a first magnetic polarity surrounding a weaker outer pole of a second magnetic polarity and rotates about the central axis of the chamber. The auxiliary magnets preferably have the first magnetic polarity to draw the unbalanced magnetic field component toward the wafer. The auxiliary magnets may be either permanent magnets or electromagnets.

Owner:APPLIED MATERIALS INC

Instruments, modules, and methods for improved detection of edited sequences in live cells

ActiveUS10550363B1Facilitate “ cherry picking ”Raise the biasBioreactor/fermenter combinationsBiological substance pretreatmentsGenome editingNuclease

The present disclosure provides instruments, modules and methods for improved detection of edited cells following nucleic acid-guided nuclease genome editing. The disclosure provides improved automated instruments that perform methods—including high throughput methods—for screening cells that have been subjected to editing and identifying cells that have been properly edited.

Owner:INSCRIPTA INC

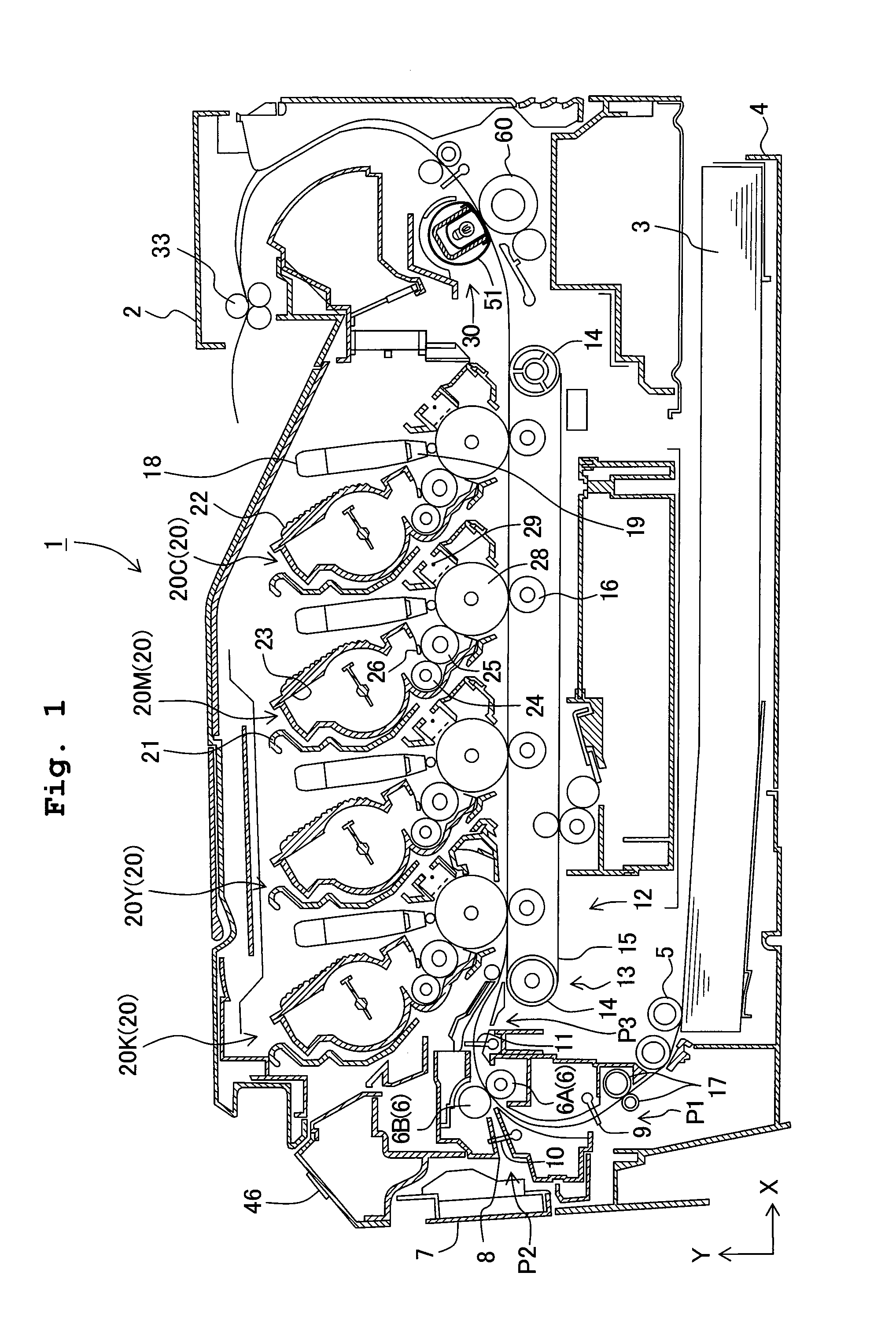

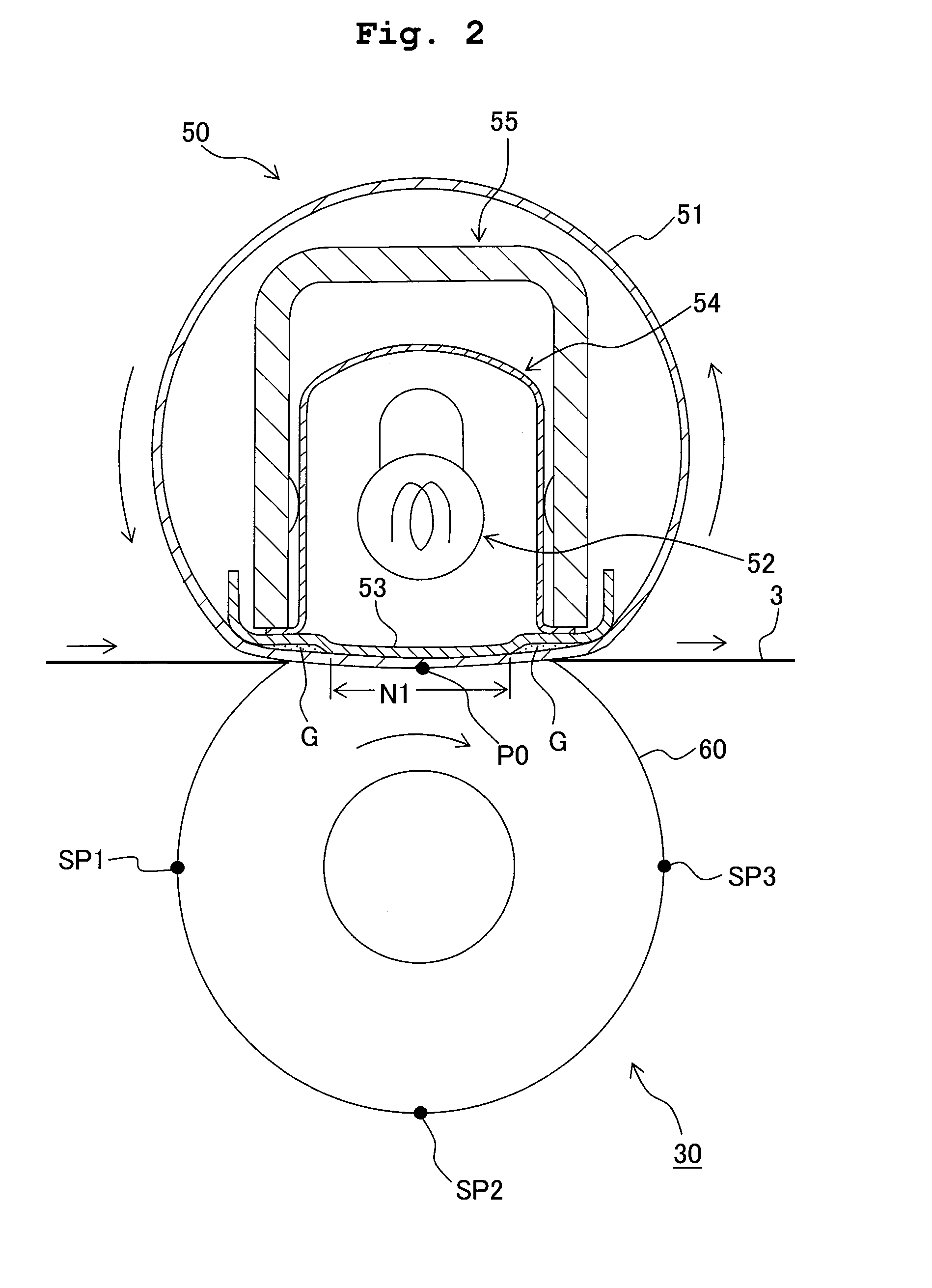

Image forming apparatus and heating method for fixation section of the same

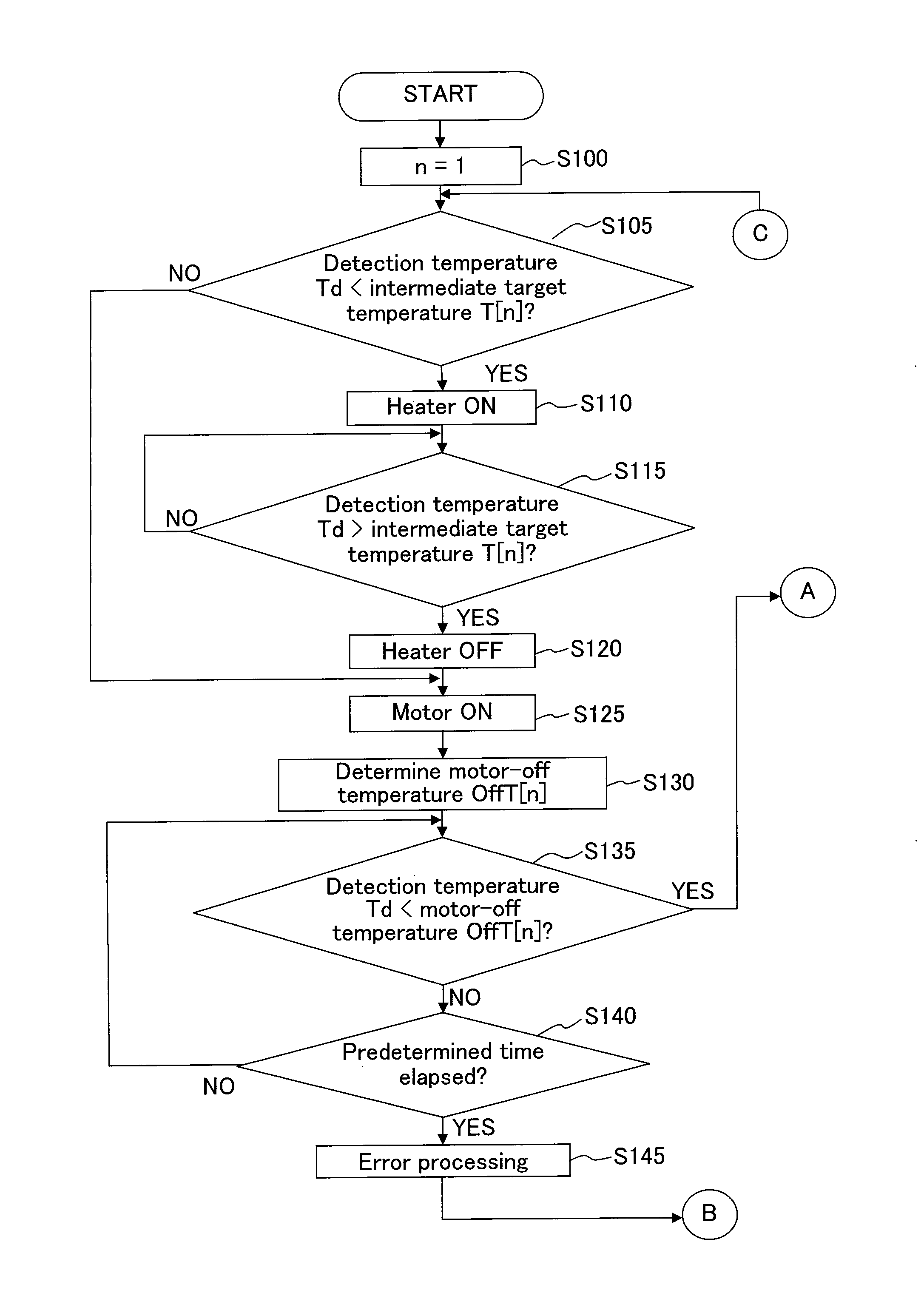

ActiveUS20120163848A1Reduce maximum power consumptionHigh power consumptionElectrographic process apparatusImage formationBiomedical engineering

An image forming apparatus includes: an image forming section; a fixation section having a heating mechanism and a roller arranged to face the heating mechanism; a temperature detector for detecting temperature of the fixation section; and a controller for performing a first heating-control in a first heating mode to raise the temperature of the fixation section at a first changing rate, and a second heating-control in a second heating mode to change the temperature of the fixation section at a second changing rate lower than the first changing rate upon rotating the roller when the temperature of the fixation section has reached an intermediate target temperature. The controller performs the first and second heating-controls, respectively, at the time of startup of the fixation section at least once until the temperature of the fixation section reaches a final target temperature.

Owner:BROTHER KOGYO KK

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com