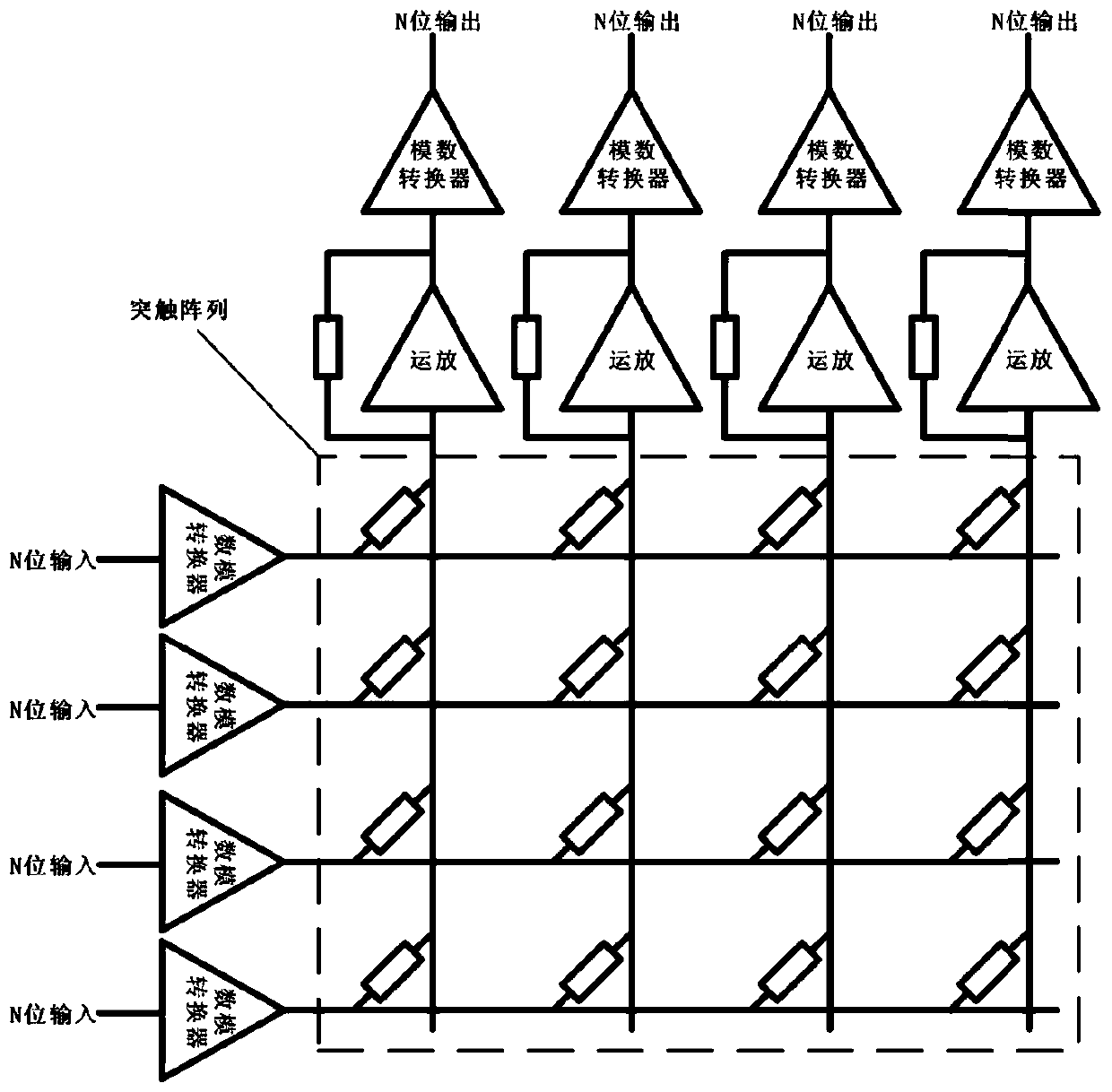

Neuromorphic calculation circuit based on multi-bit parallel binary synaptic array

A computing circuit and binary technology, applied in biological neural network models, electrical components, electrical signal transmission systems, etc., can solve the problems of low weight quantization accuracy and activation value quantization accuracy, deep neural network performance loss, unfavorable edge computing equipment applications, etc. problem, to achieve the effect of reducing power consumption and area, high precision and power consumption, and low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings.

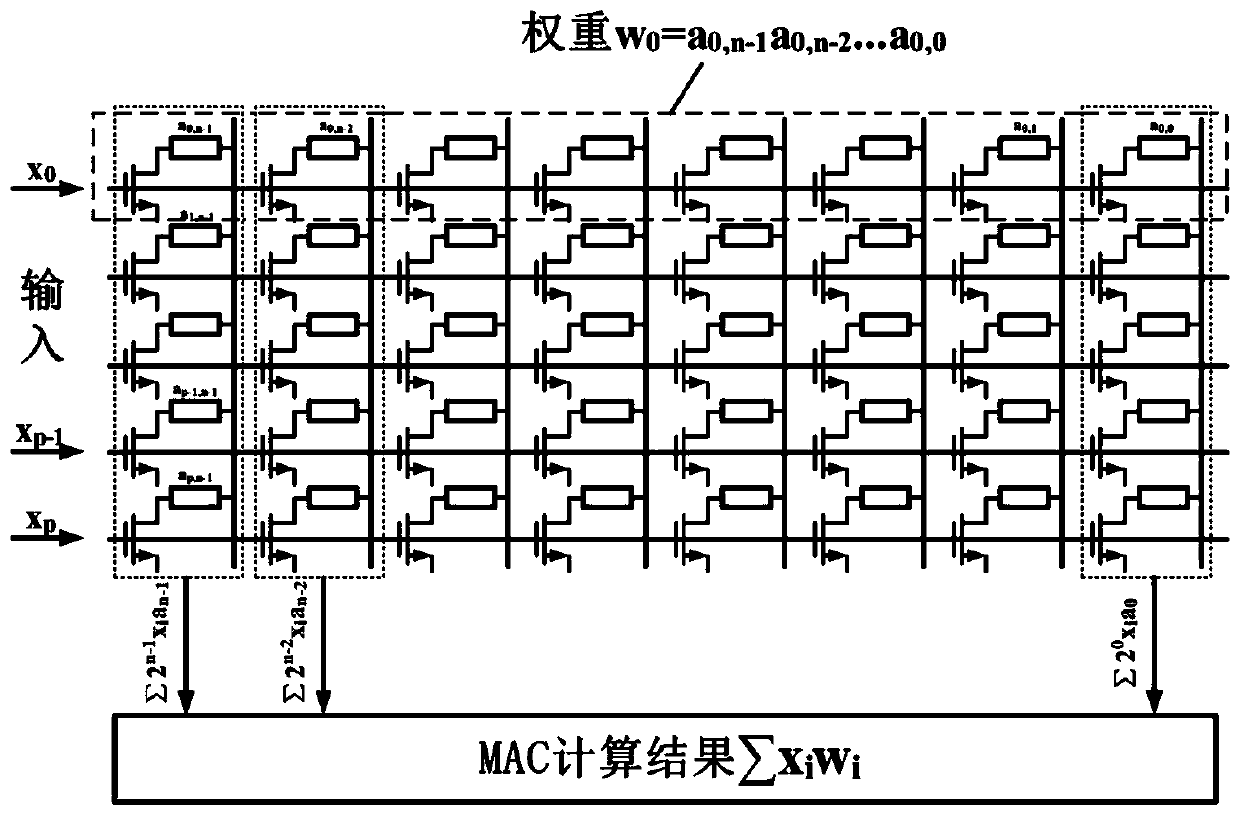

[0020] image 3 It is the neural synapse array structure adopted by the present invention. N binary RRAMs are used to simulate a synapse, so an N-bit fixed-point weight can be expressed as w=a n-1 a n-2 …a 0 , further the dendrite output can be expressed as:

[0021] y=∑x i w i =∑2 n-1 a i,n-1 x i +…+∑2 1 a i,1 x i +∑2 0 a i,0 x i (1)

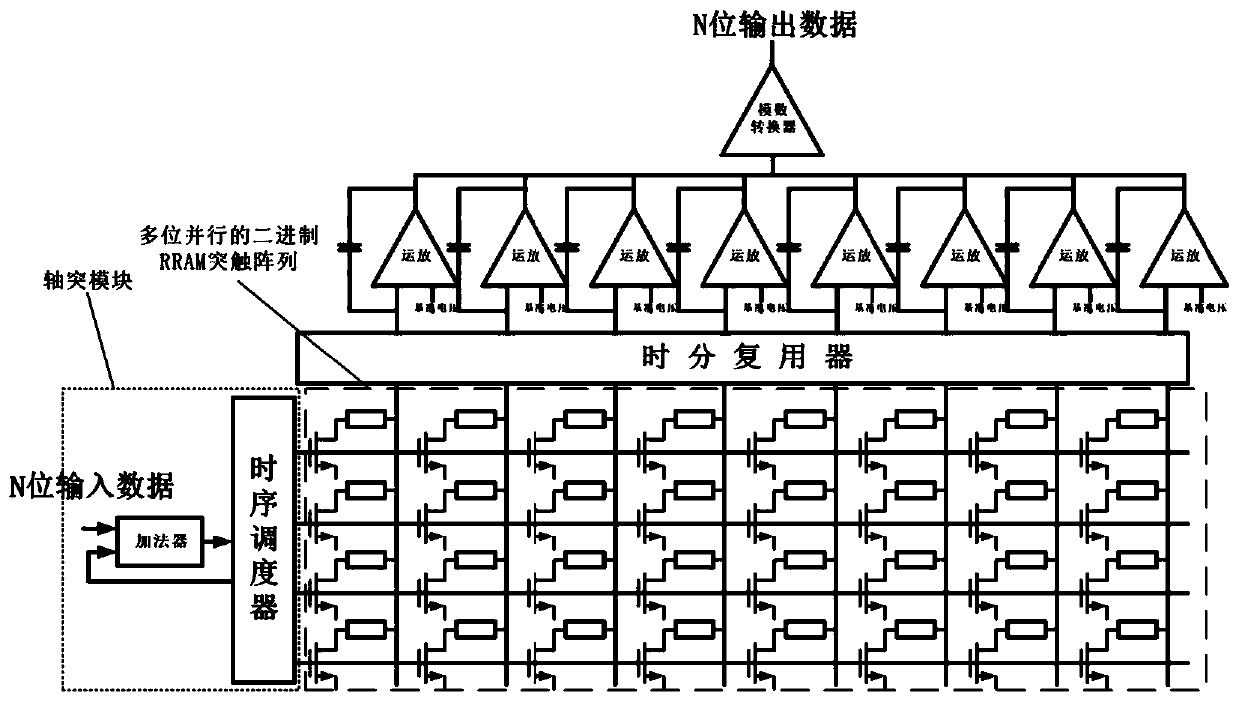

[0022] Figure 5 and Figure 6 It is the specific calculation circuit integration principle and integration system. Each integrator consists of an integrating op amp, C n Capacitance, C f -C n Capacitor and S1, S2, S3, S4 switches, the specific connection relationship is shown in the figure. Using 256 parallel inputs, each input data is quantized into N-bit fixed points, and enters the integration circuit sequentially from low to high, in other words, A 0,0 A 1,0 …...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com