Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

72 results about "Signal-flow graph" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A signal-flow graph or signal-flowgraph (SFG), invented by Claude Shannon, but often called a Mason graph after Samuel Jefferson Mason who coined the term, is a specialized flow graph, a directed graph in which nodes represent system variables, and branches (edges, arcs, or arrows) represent functional connections between pairs of nodes. Thus, signal-flow graph theory builds on that of directed graphs (also called digraphs), which includes as well that of oriented graphs. This mathematical theory of digraphs exists, of course, quite apart from its applications.

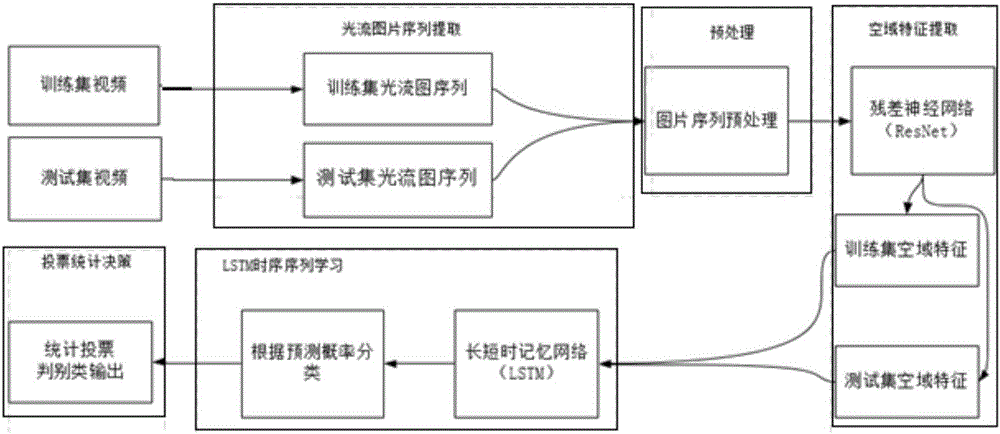

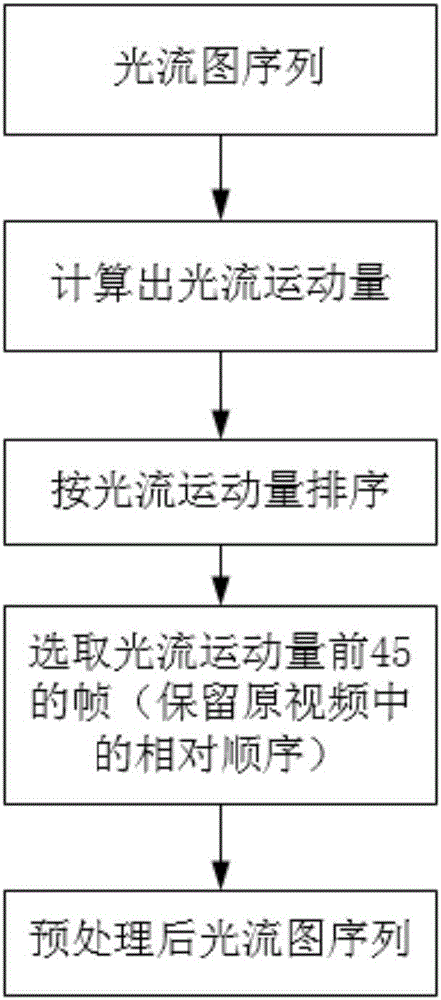

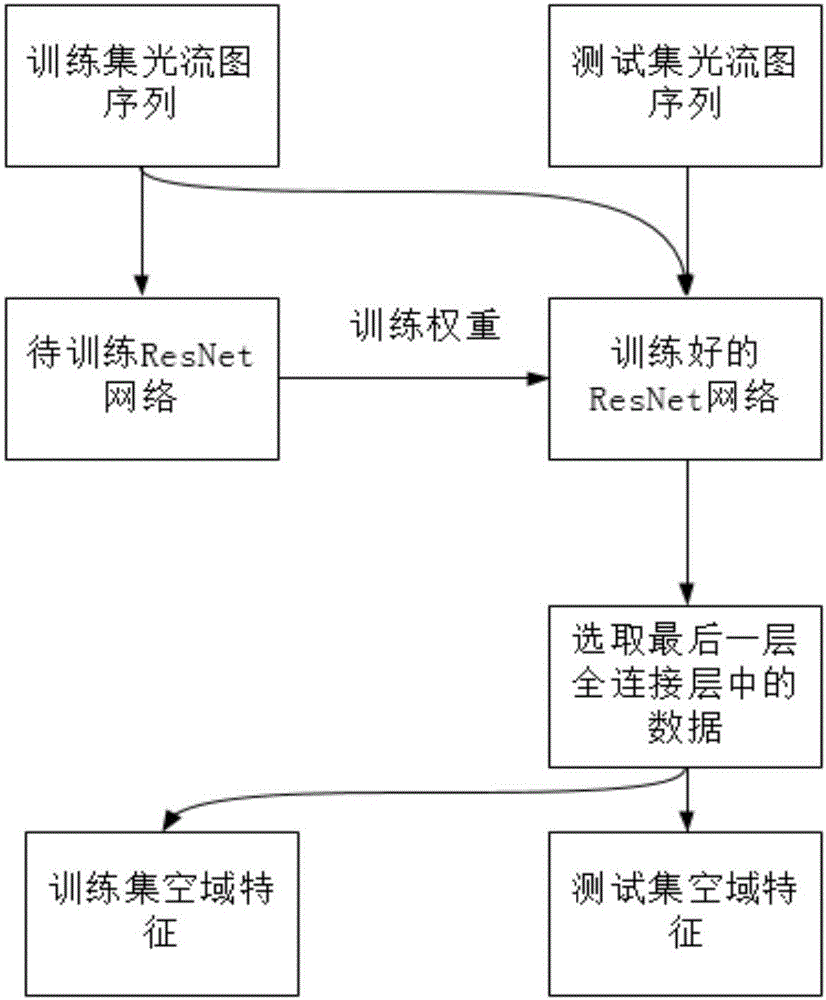

Video human body interaction motion identification method based on optical flow graph depth learning model

ActiveCN106407889AImprove recognition accuracyCharacter and pattern recognitionHuman bodyNerve network

The invention discloses a video human body interaction motion identification method based on an optical flow graph depth learning model. The method mainly comprises steps that step 1, deframing of a test set video and a training set video is carried out, an optical flow sequence graph is calculated through utilizing two adjacent frames; step 2, the optical flow sequence graph is pre-processed, and optical flow graphs with relatively few information quantity are deleted; step 3, a residual error neural network is trained through utilizing the training set optical flow sequence acquired in the step 2, the test set and training set optical flow graph sequences are taken as input, and spatial domain characteristics are acquired; step 4, a long and short memory model is trained through utilizing training set characteristics, test set characteristics are inputted to acquire each type of probability output; and step 5, a classification result is acquired through employing voting model statistics. The method is advantaged in that relevant patent blanks are filled through utilizing the depth learning model to carry out human body motion identification, identification accuracy is high, and the method is applicable to multiple occasions.

Owner:SHANGHAI JIAO TONG UNIV

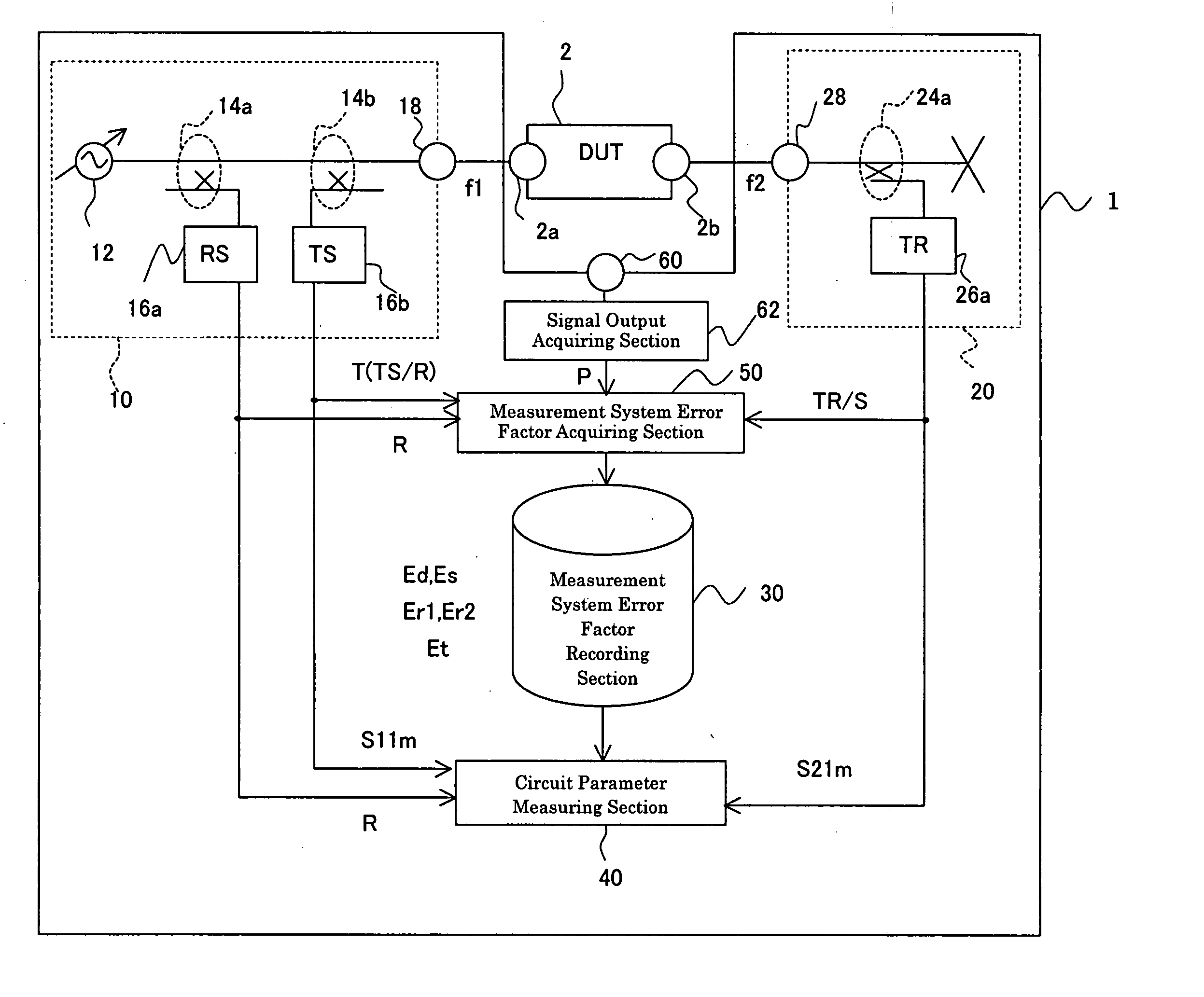

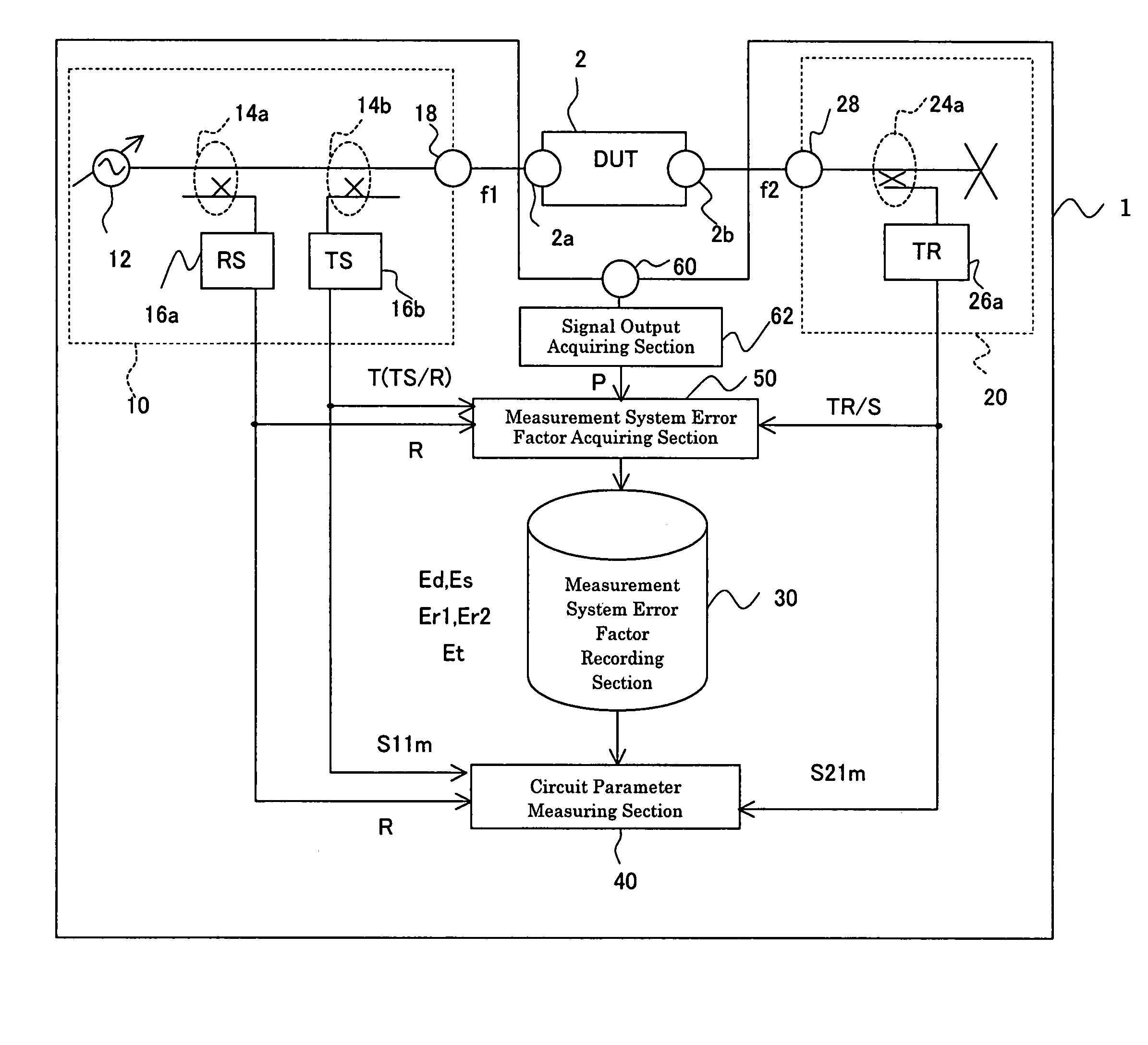

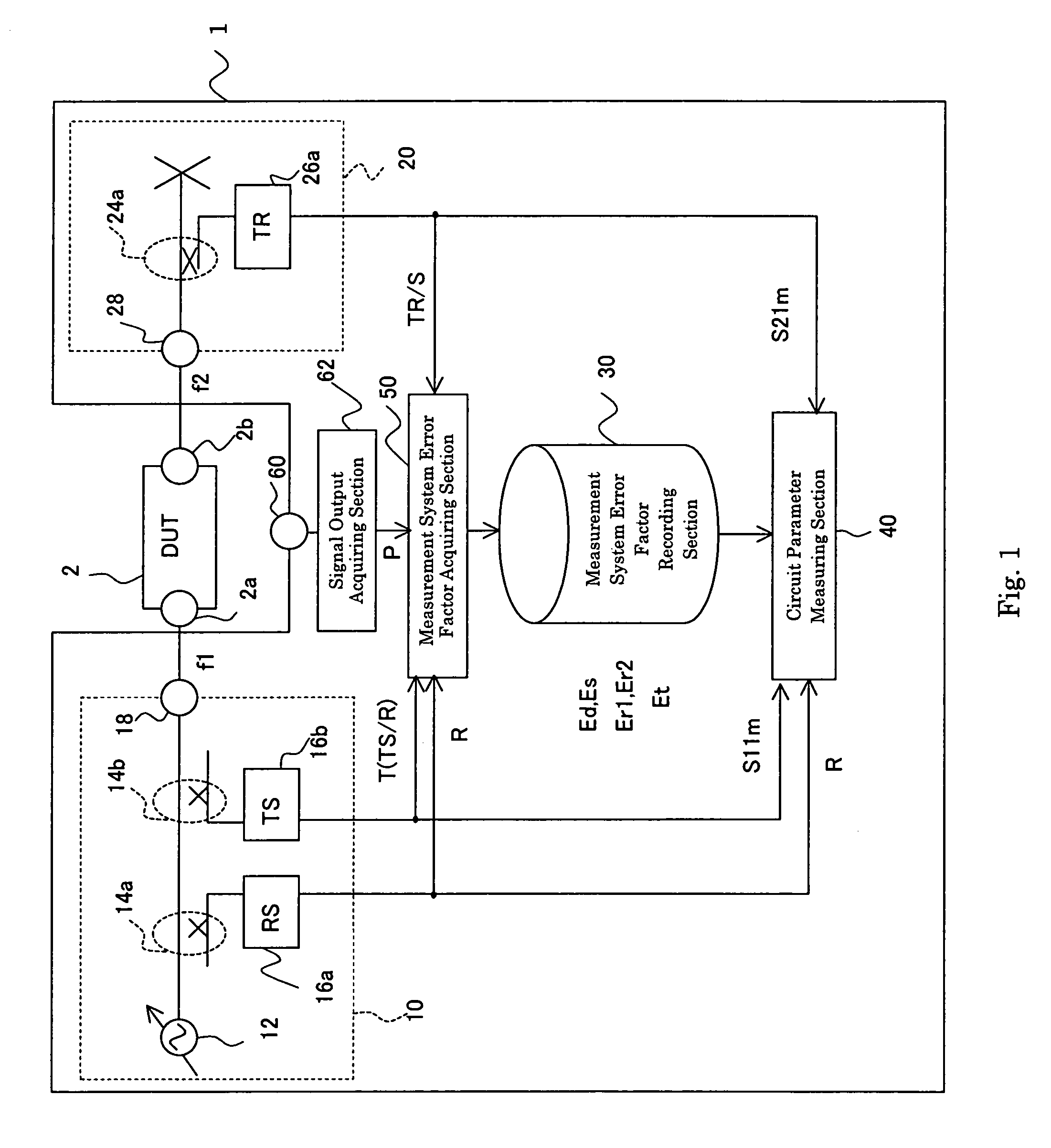

Network analyzer, network analyzing method, automatic corrector, correcting method, program, and recording medium

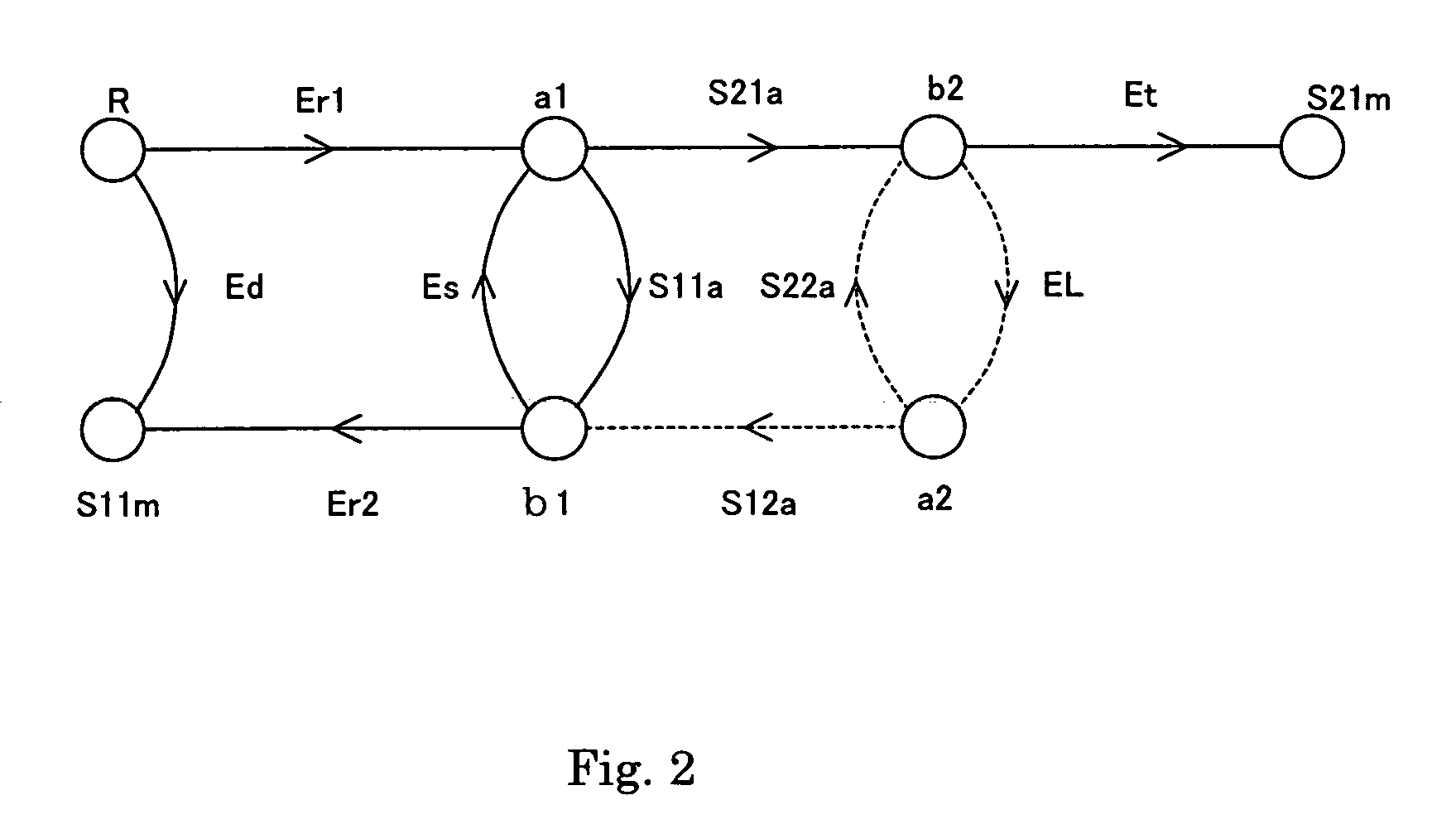

InactiveUS20060005065A1Measuring system is not accurateCorrect measurement system errorResistance/reactance/impedenceError detection/correctionEquipment under testWattmeter

The error of a measurement system can be corrected even if the frequency of an input signal of a device under test is different from that of the output signal. A signal output acquiring section acquires the power of the input signal by means of a power meter not shown in the drawing. Thus, errors due to frequency tracking can be separated depending on the direction in a signal flow graph. Since a receiver measures the parameter concerning the received signal when a signal source is directly connected to receiving means, the measurement system error factor of the receiving means can be acquired. The parameter of a device under test can be measured while the error is corrected when the results of measurement, concerning the device under test of receivers are combined.

Owner:ADVANTEST CORP

Reliability analysis method for embedded safety-critical system

InactiveCN102033789AAssessment reliabilityError detection/correctionEmbedded securityFuzzy probability

The invention relates to a reliability analysis method for an embedded safety-critical system, and belongs to the technical field of information safety. The method comprises the following steps of: constructing a software and hardware fault representation set; classifying faults in the fault representation set to acquire a software and hardware fault mode set and constructing a subsequent fault mode set by combining a fault-associated probability table; constructing a static fault tree associated with a software and hardware fault on the basis of the subsequent fault mode set; and analyzing the static fault tree to acquire a fault analysis result. In the method, software and hardware basic units of the embedded safety-critical system are subdivided, a subsequent fault mode is constructed through a fuzzy probability multi-signal flow graph model by combining association of faults of each basic unit, a static fault tree model is constructed by using time sequence logic relation between the faults reflected by the subsequent fault mode set, and the reliability of the system can be more accurately and effectively evaluated by using the model.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

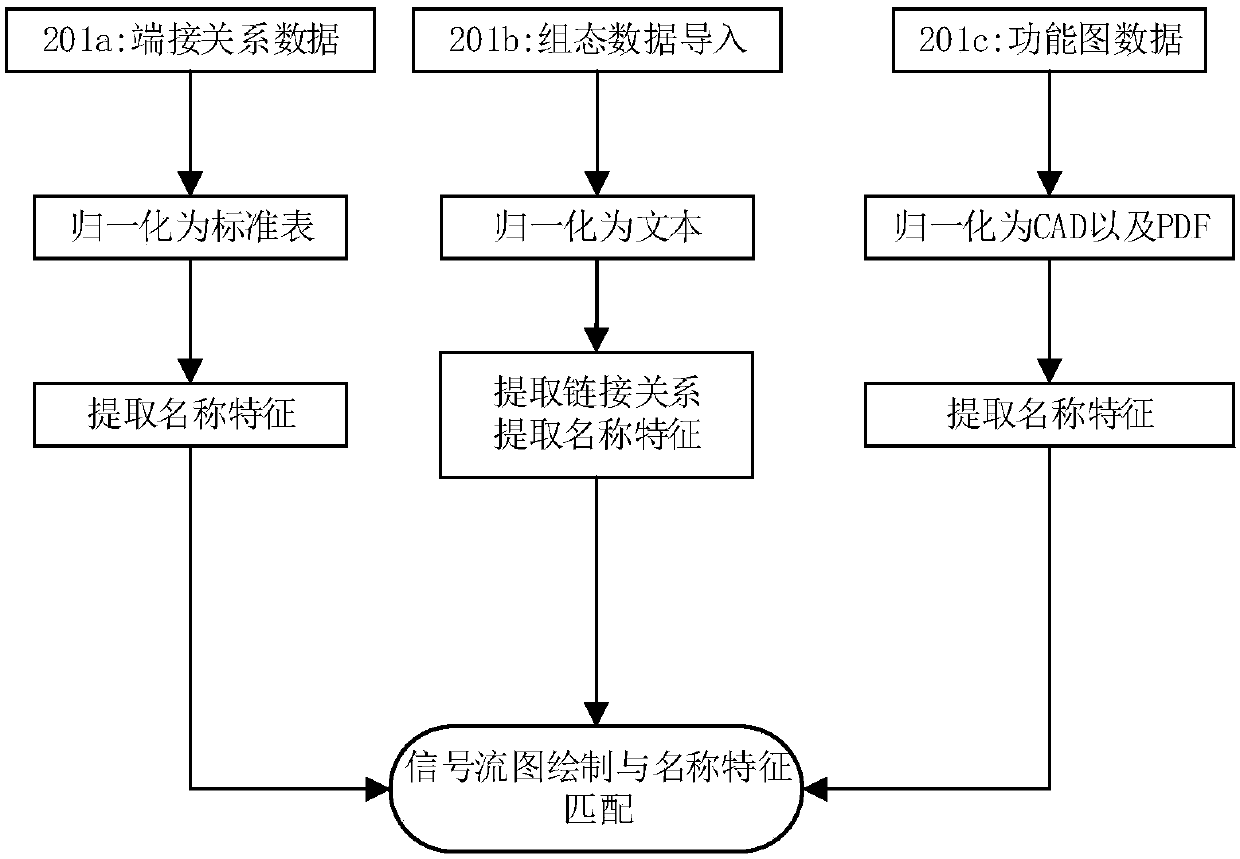

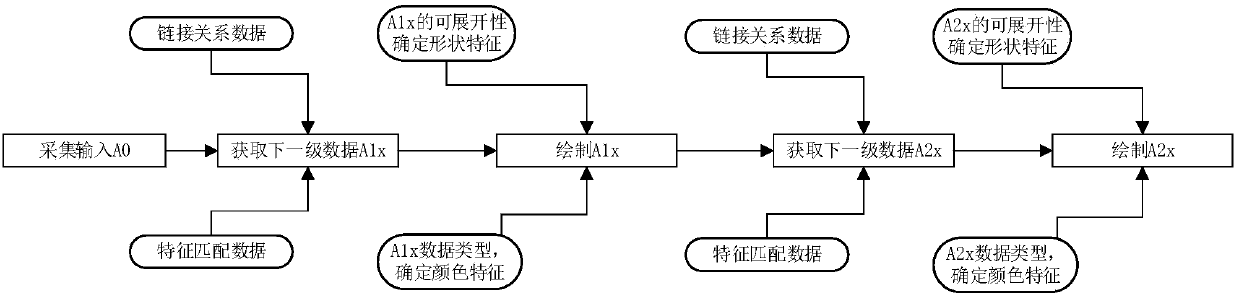

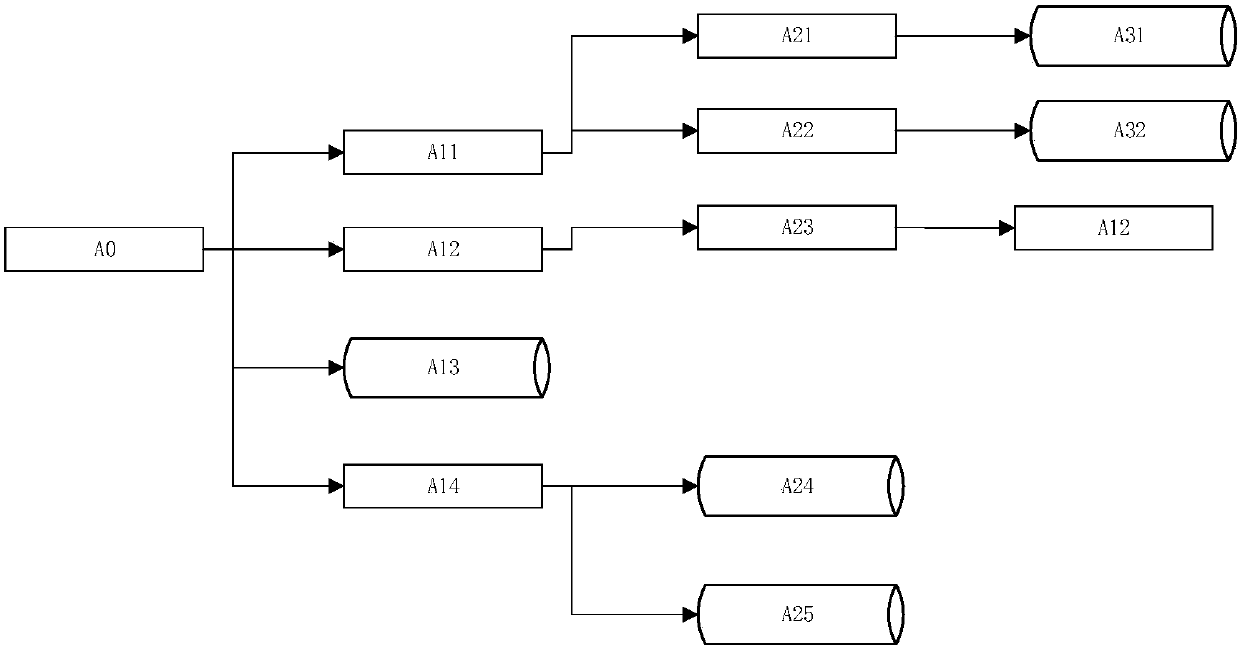

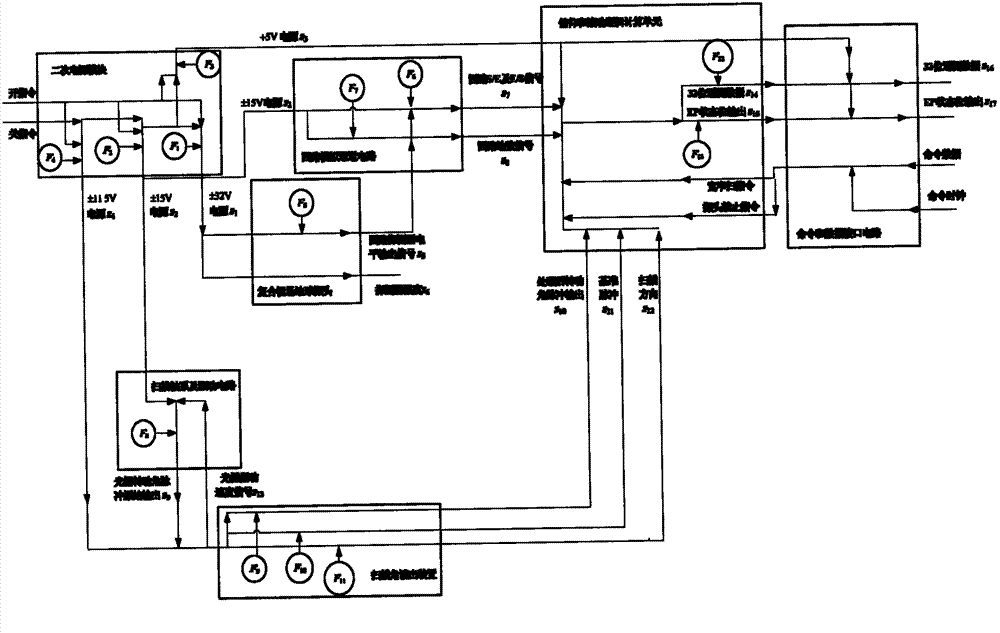

Reverse self-organization signal flow chart generation method for control system of nuclear power plant

ActiveCN107590206AAvoid human errorReduce misuseData processing applicationsSpecial data processing applicationsControl systemNuclear power

The invention belongs to the technical field of DCS control of nuclear power plants, and particularly relates to a reverse self-organization signal flow chart generation method for a control system ofa nuclear power plant. The method comprises the following steps of (1) establishing a framework of a system; (2) collecting and processing data; (3) drawing a signal flow chart; and (4) connecting adesktop or mobile query service terminal with a network server, inputting a query signal, analyzing a request of the terminal by the server, returning a query result image or form, and performing display in the form of an overview chart and a detail chart in the terminal. The invention relates to integration analysis, relationship reconstruction and graphic display of DCS configuration data; the purposes of freely querying a signal flow topology relationship by a user, friendly displaying the topology relationship and performing state marking on a key link in the topology relationship are achieved; and especially for a functional drawing problem, when an important logic relationship is missing or omitted, remediation can be performed in time to avoid human errors.

Owner:CNNC FUJIAN FUQING NUCLEAR POWER

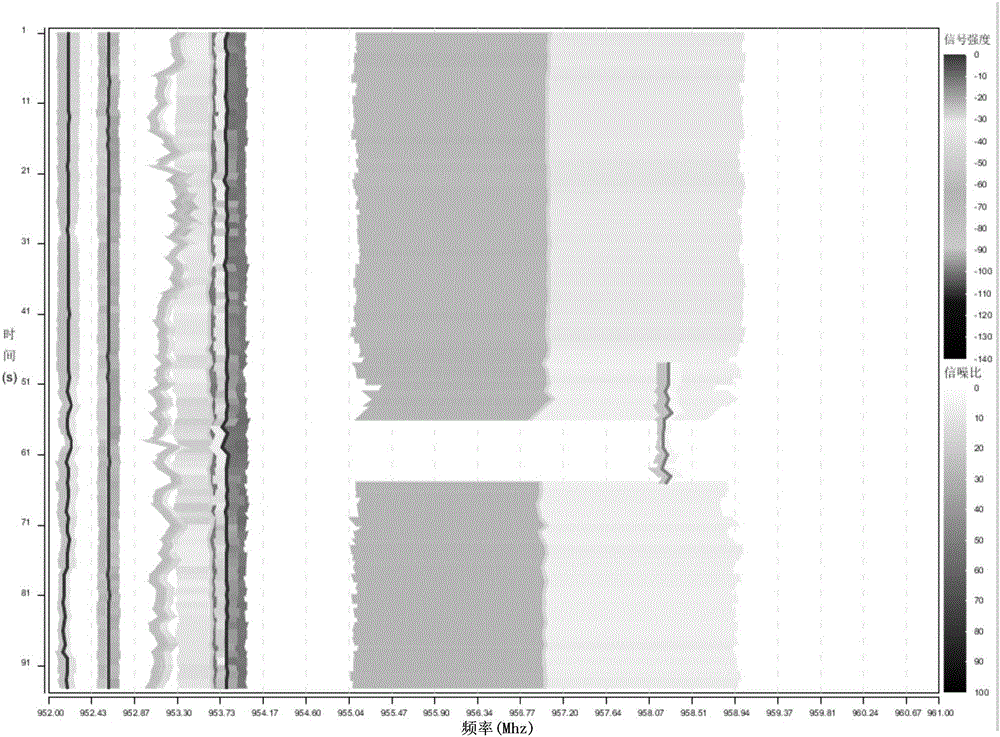

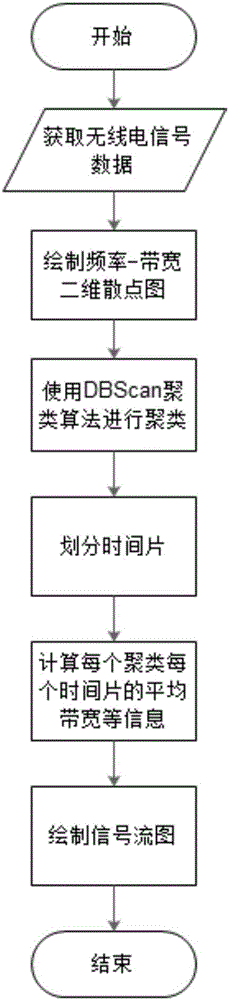

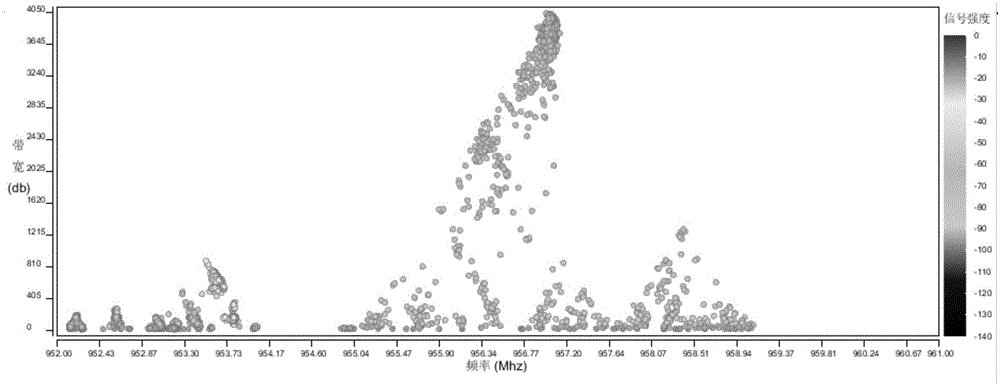

Visualization method of radio signal data

ActiveCN105897488AEasy to observeEasy to compareTransmission monitoringData switching networksCluster algorithmSignal-to-noise ratio (imaging)

The invention provides a visualization method of radio signal data. The visualization method of the radio signal data comprises a first step of obtaining the radio signal data extracted from frequency spectrum data and original electric level sampling data; a second step of drawing a frequency-bandwidth scatter diagram; a third step of clustering the radio signal data by using a clustering algorithm; a fourth step of dividing time slices; a fifth step of calculating an average center frequency, an average bandwidth, an average signal-to-noise ratio and an average signal intensity of each time slice for each cluster; and a sixth step of drawing a signal flow diagram. Multiple characteristics of radio signals are coded efficiently by utilizing the signal flow diagram, multiple types of important characteristics of relatively scattered signal data at a time frequency are shown smoothly, a multi-characteristic time-varying mode of the radio signal is shown in a better manner, and a macroscopic perceiving efficiency of an analyzer for the radio signal time-varying mode is speeded up.

Owner:CENT SOUTH UNIV

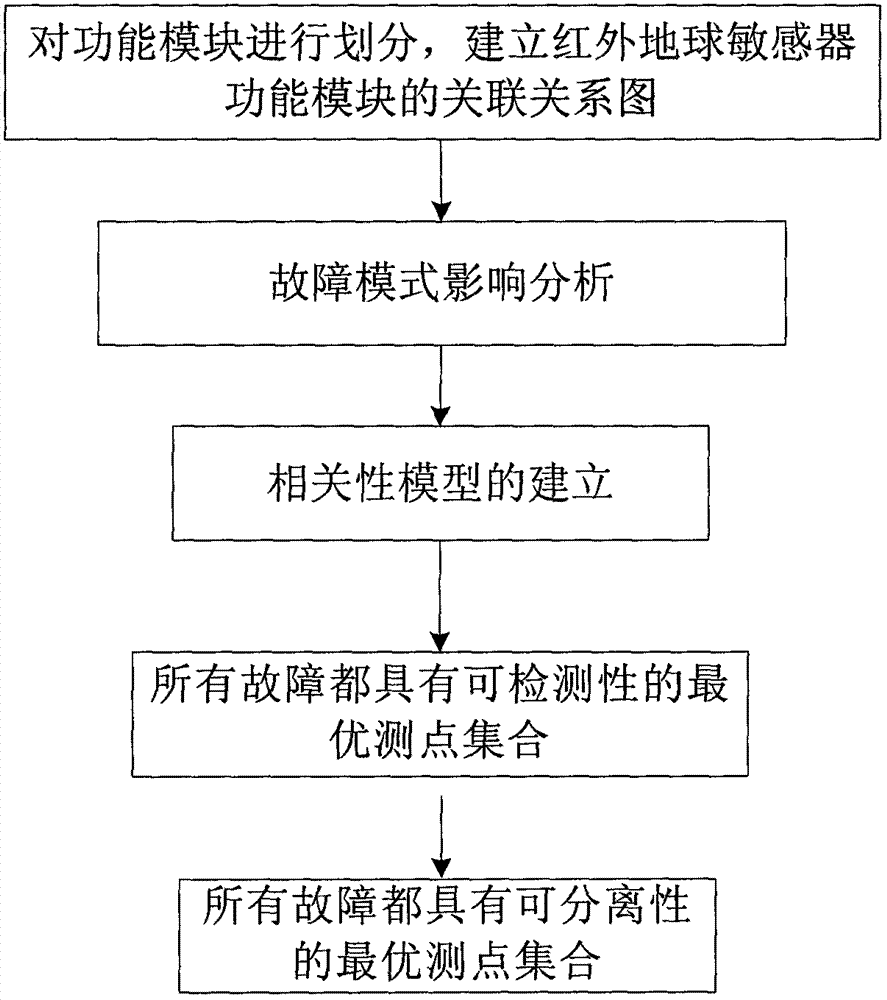

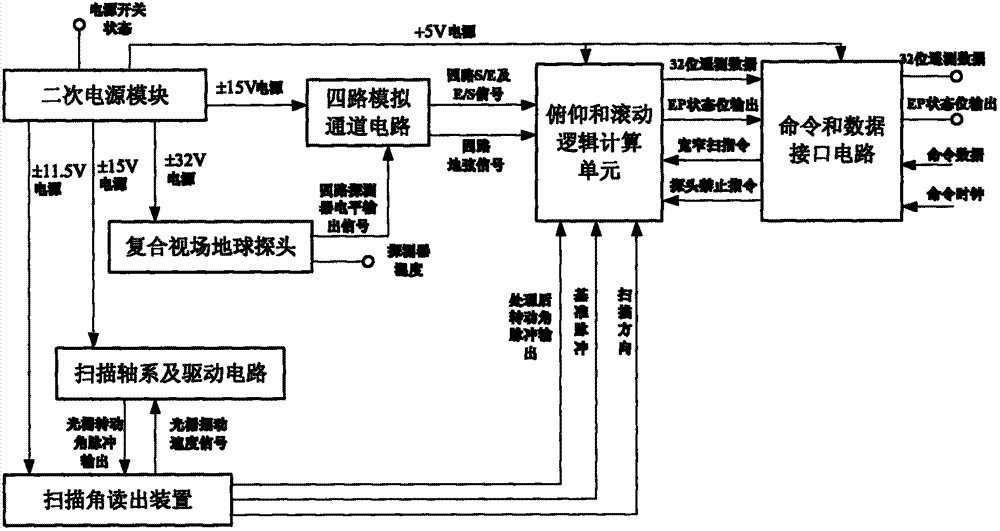

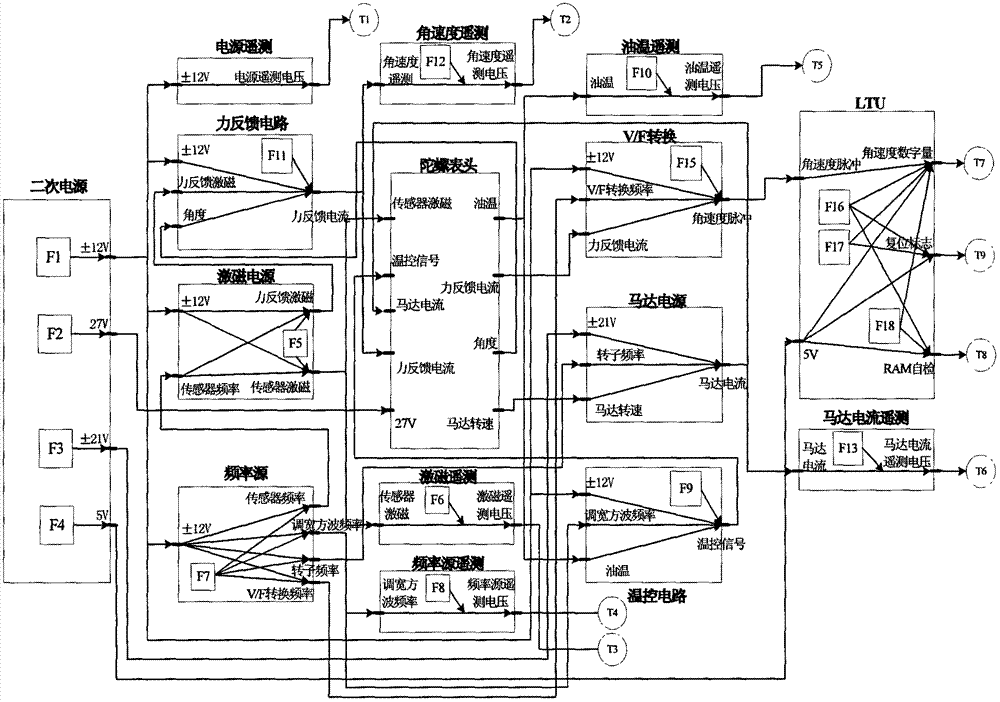

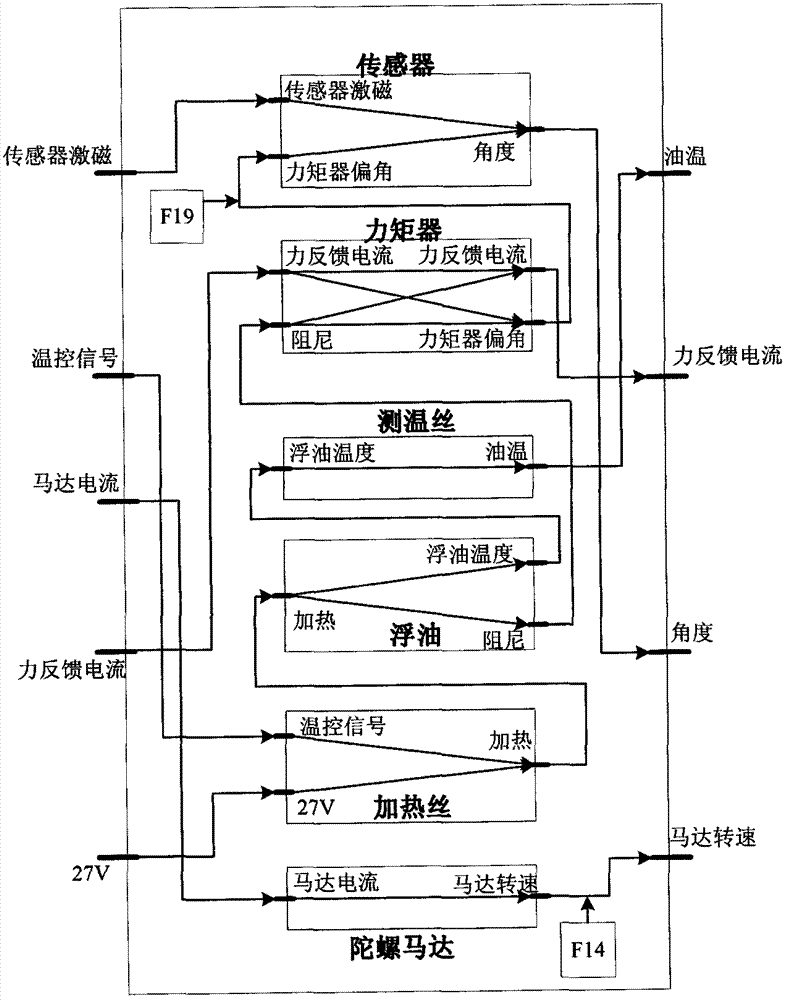

Relevance model based infrared earth sensor measuring point optimal configuration method

ActiveCN102735238AEasy to detectEasy to separateInstruments for comonautical navigationControl systemS function

The invention discloses a relevance model based infrared earth sensor measuring point optimal configuration method. Firstly, an association graph of an infrared earth sensor's function modules is built. Then, aiming at various kinds of faults happened during on-orbit and test stages of the infrared earth sensor, its fault pattern set is determined. Based on the association graph of each function module, a multi-signal flow graph of the infrared earth sensor is acquired. Based on the multi-signal flow graph, a fault and state information incidence matrix of the infrared earth sensor is established. And based on the established fault and state information incidence matrix, an optimal measuring point set which endows all the faults with detectability and an optimal measuring point set which makes all the faults separable are acquired. According to the invention, based on the case that it is ensured that resource constraint is satisfied, many faults are detected and separated, and a basis for diagnosable design of a satellite control system is provided.

Owner:BEIJING INST OF CONTROL ENG

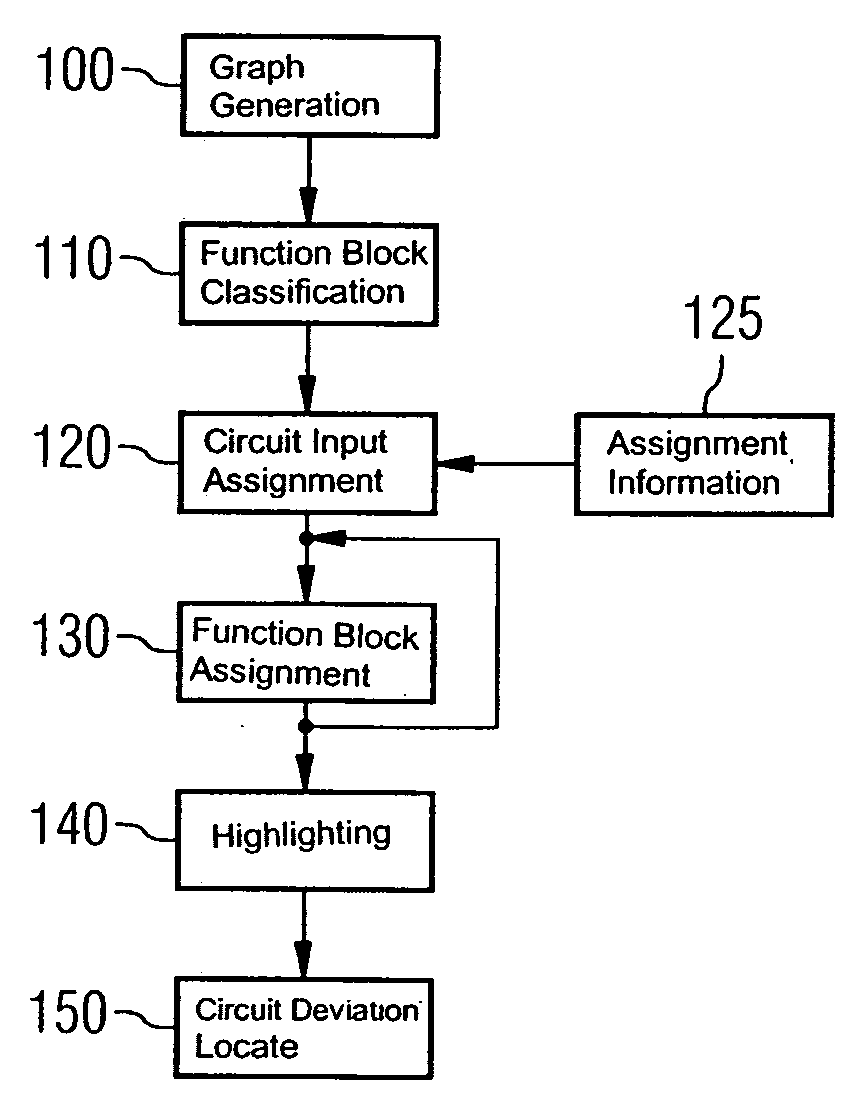

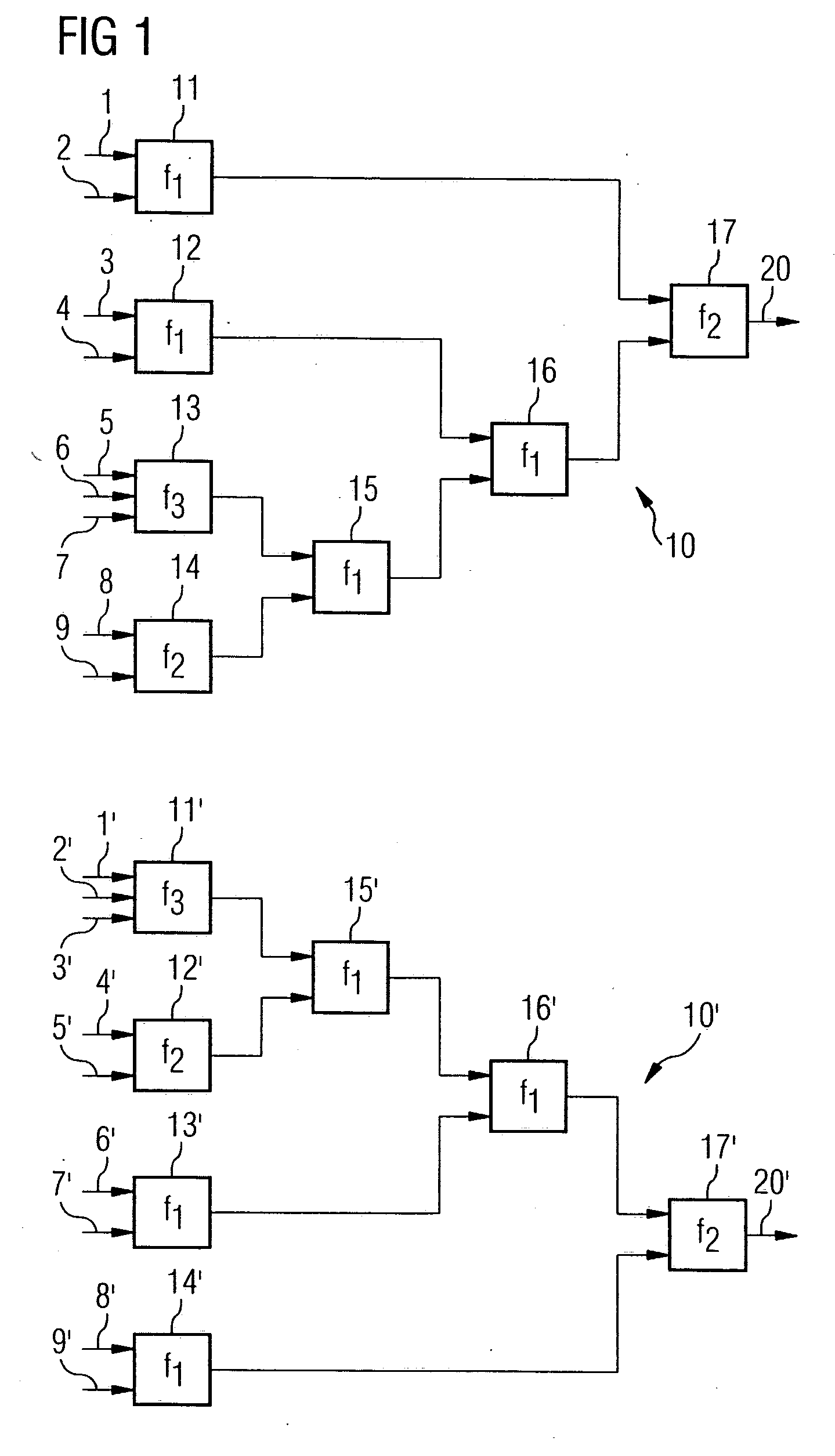

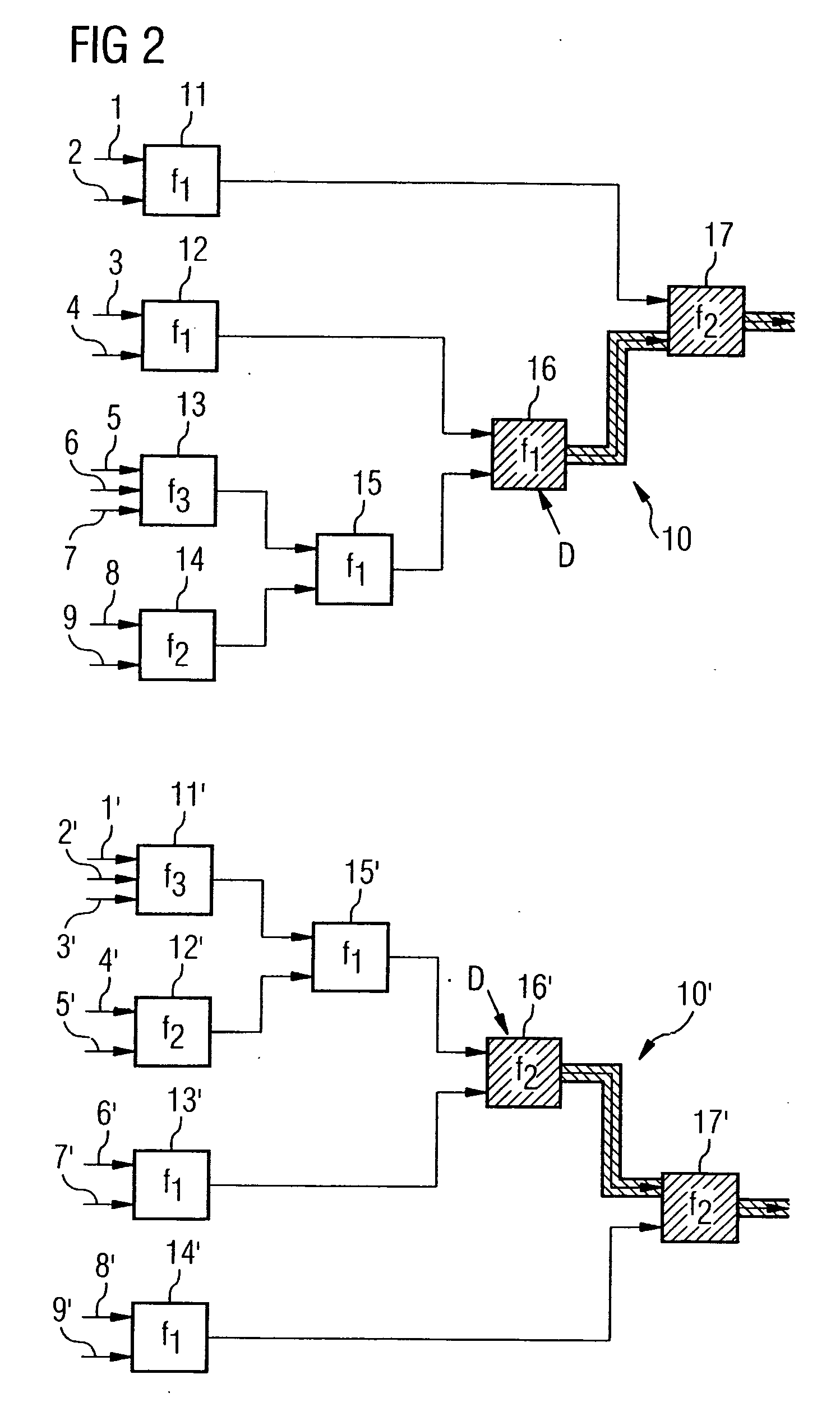

Method and apparatus for locating circuit deviations

ActiveUS20060064655A1High precisionSmall amount of effortElectronic circuit testingCAD circuit designReference circuitComputer science

A system and method for locating circuit deviations or circuit faults in a circuit in respect of a reference circuit. The circuit and the reference circuit are respectively describable by signal-flow graphs, the signal-flow graphs being composed of a multiplicity of interconnected function blocks. The function blocks of the circuit are first assigned to corresponding function blocks of the reference circuit. There are then ascertained those function blocks of the circuit and of the reference circuit for which assignment has not been possible, and which have disposed upstream in the signal flow at least one function block for which assignment has been possible. The result is a boundary between an assigned and a non-assigned region of the circuit and the reference circuit, respectively. A representation of the circuit and reference circuit is preferably produced in which the regions corresponding to the non-assigned function blocks are highlighted.

Owner:SIEMENS ELECTRONIC DESIGN AUTOMATION GMBH

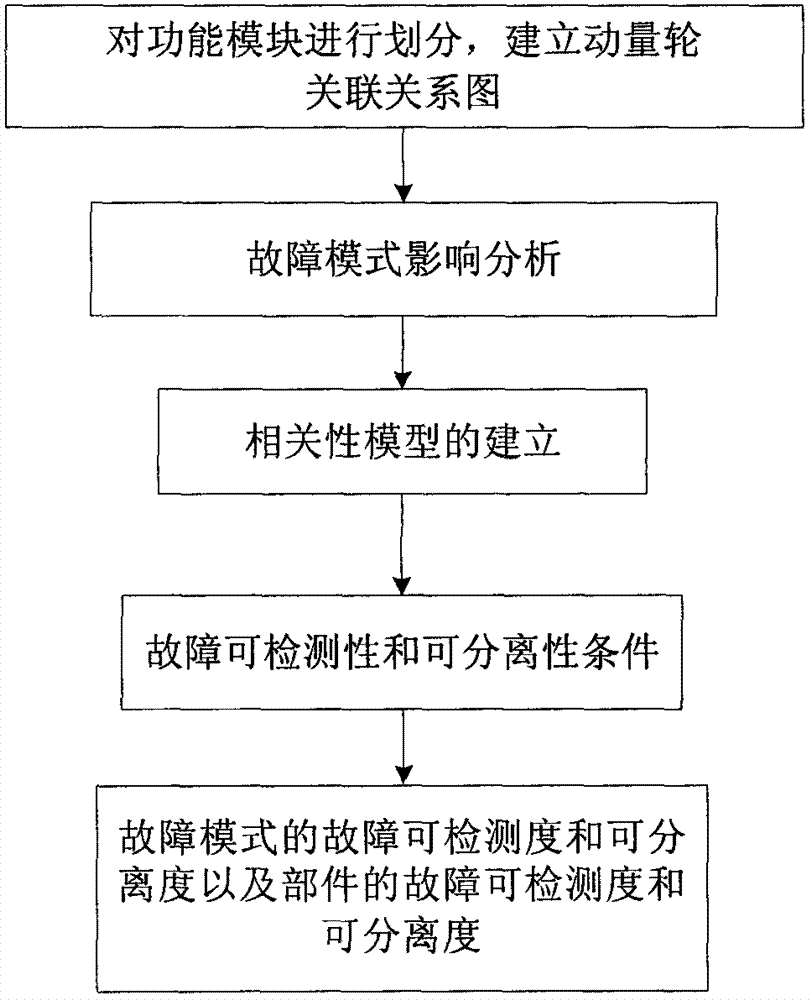

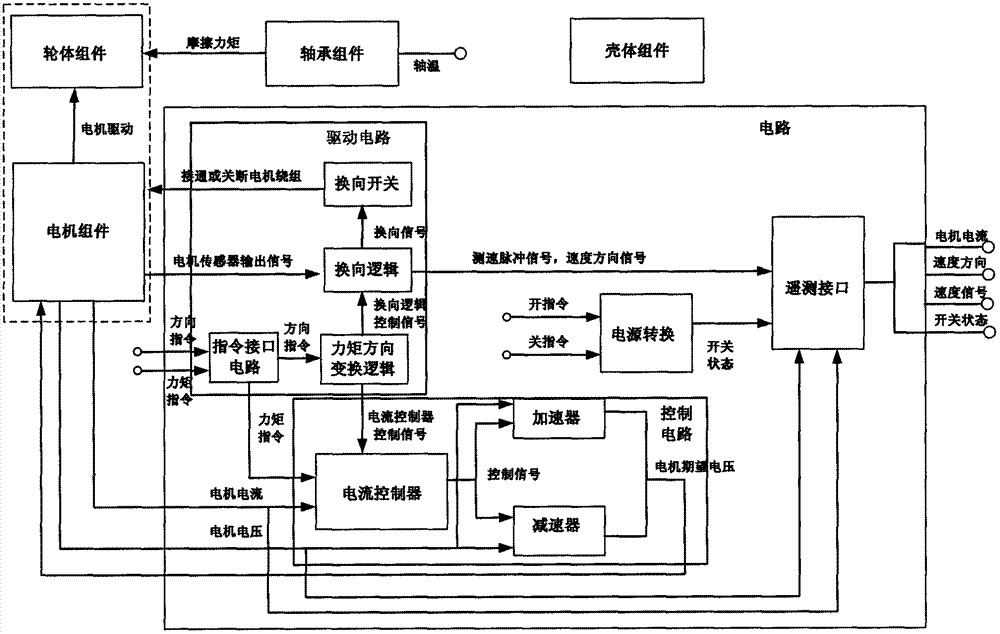

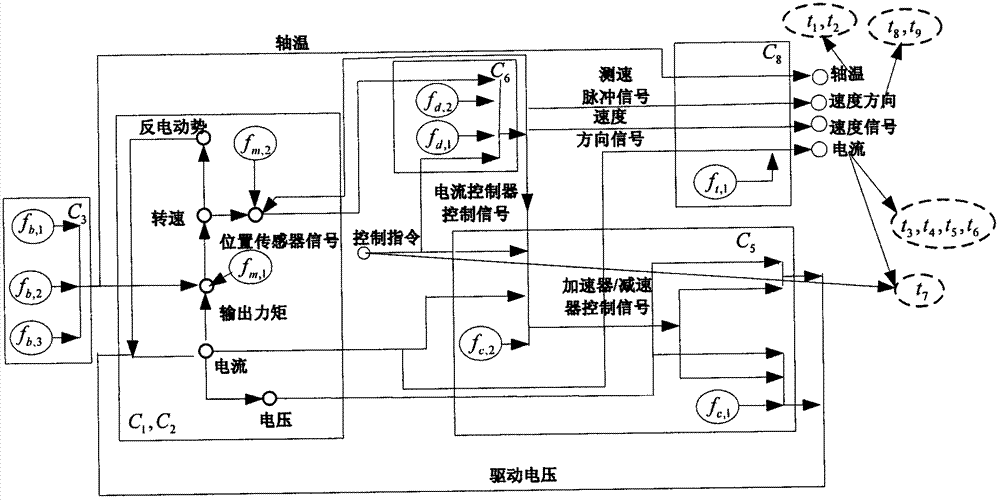

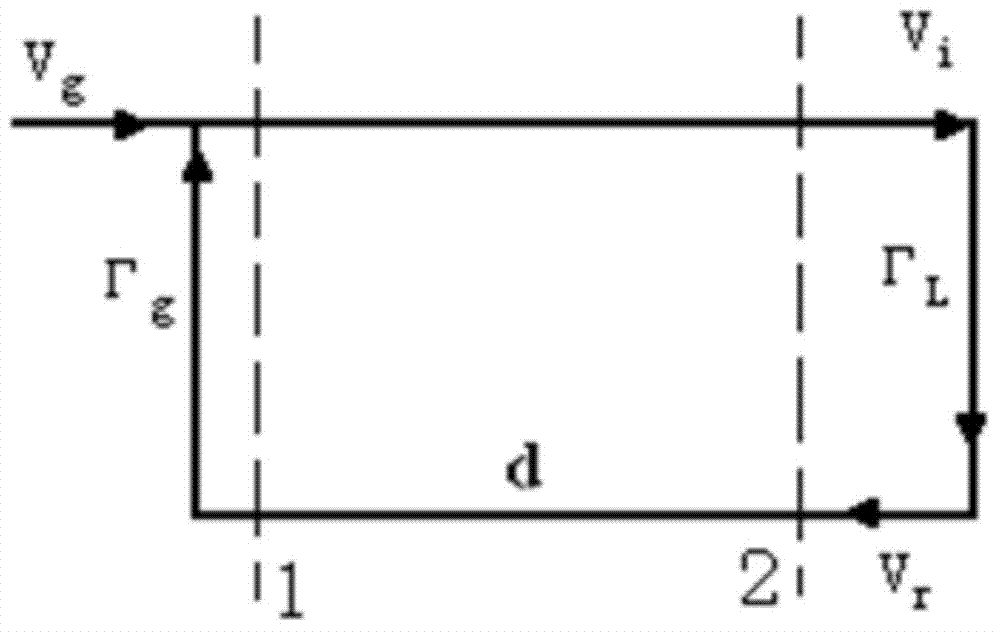

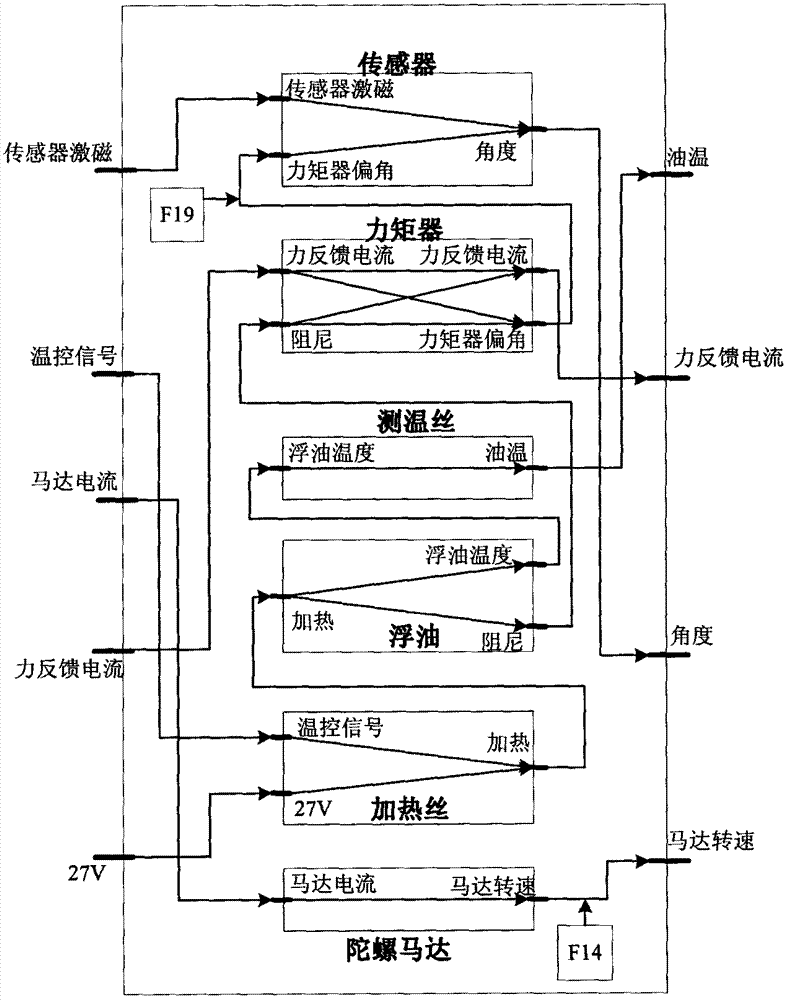

Method for determining fault diagnosability of momentum wheel based on relevance model

ActiveCN102735435AComprehensive considerationDeeper level of analysisMachine part testingMomentumEngineering

The invention discloses a method for determining the fault diagnosability of a momentum wheel based on a relevance model. The method comprises the following steps of: establishing an association relation diagram of functional modules of the momentum wheel; determining a momentum wheel fault mode set; obtaining a multi-signal flow diagram of the momentum wheel, and establishing a fault and test association matrix of the momentum wheel based on the multi-signal flow diagram; giving detectability and separability conditions corresponding to various faults of the momentum wheel based on the relevance model; and obtaining the fault detectability and separability of momentum wheel fault modes and parts by a diagnosability measurement calculation method. By the method, the detectability and separability of the momentum wheel fault modes are distinguished, and the diagnosability of the momentum wheel is measured.

Owner:BEIJING INST OF CONTROL ENG

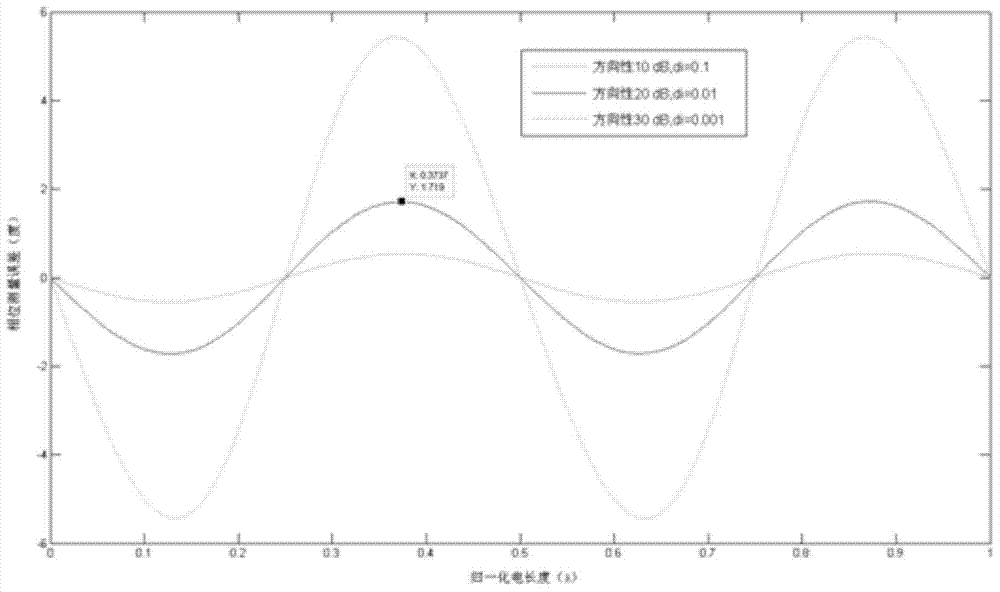

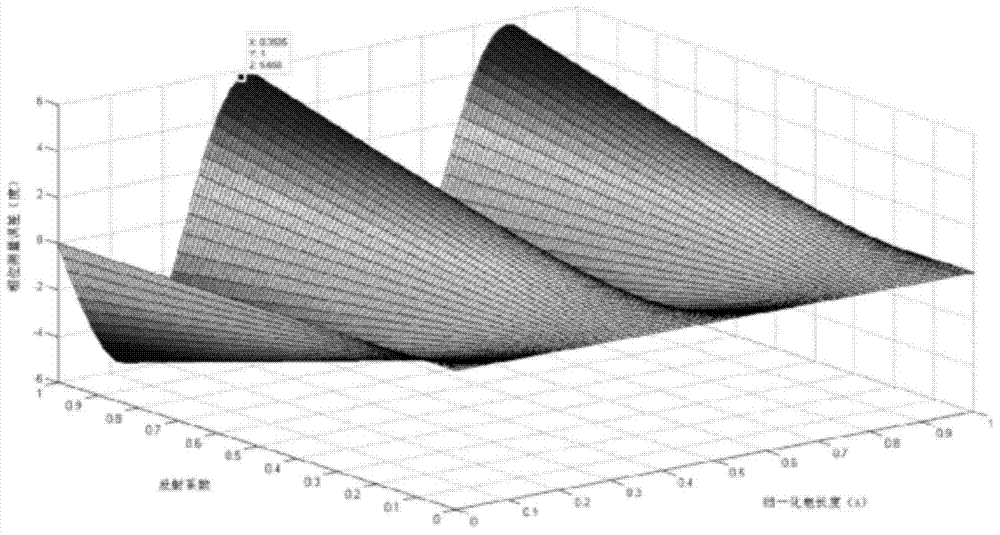

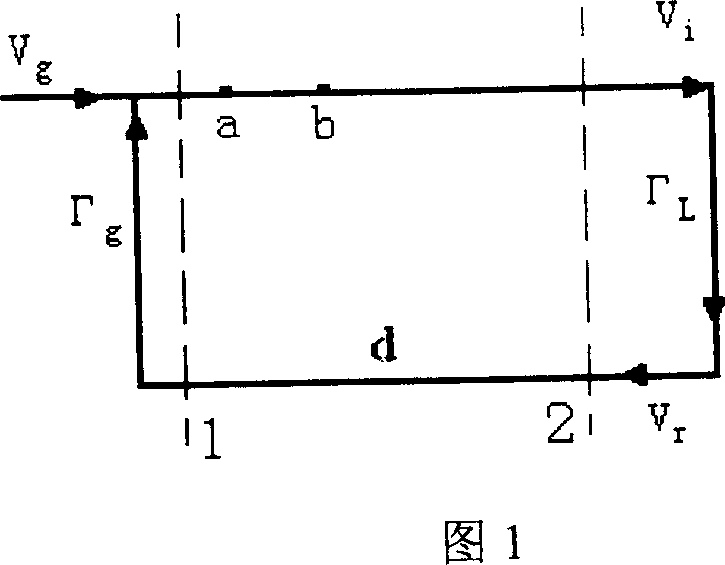

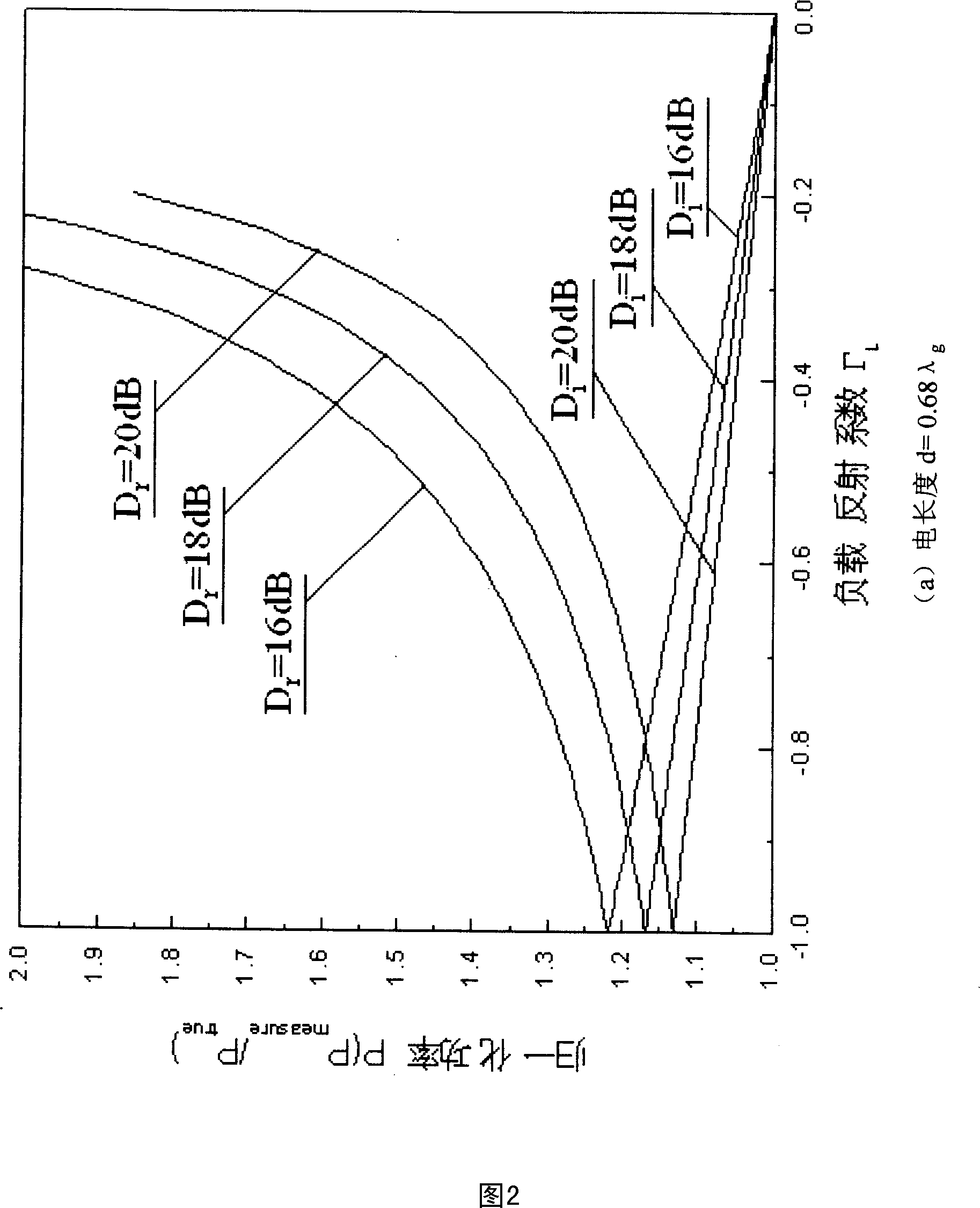

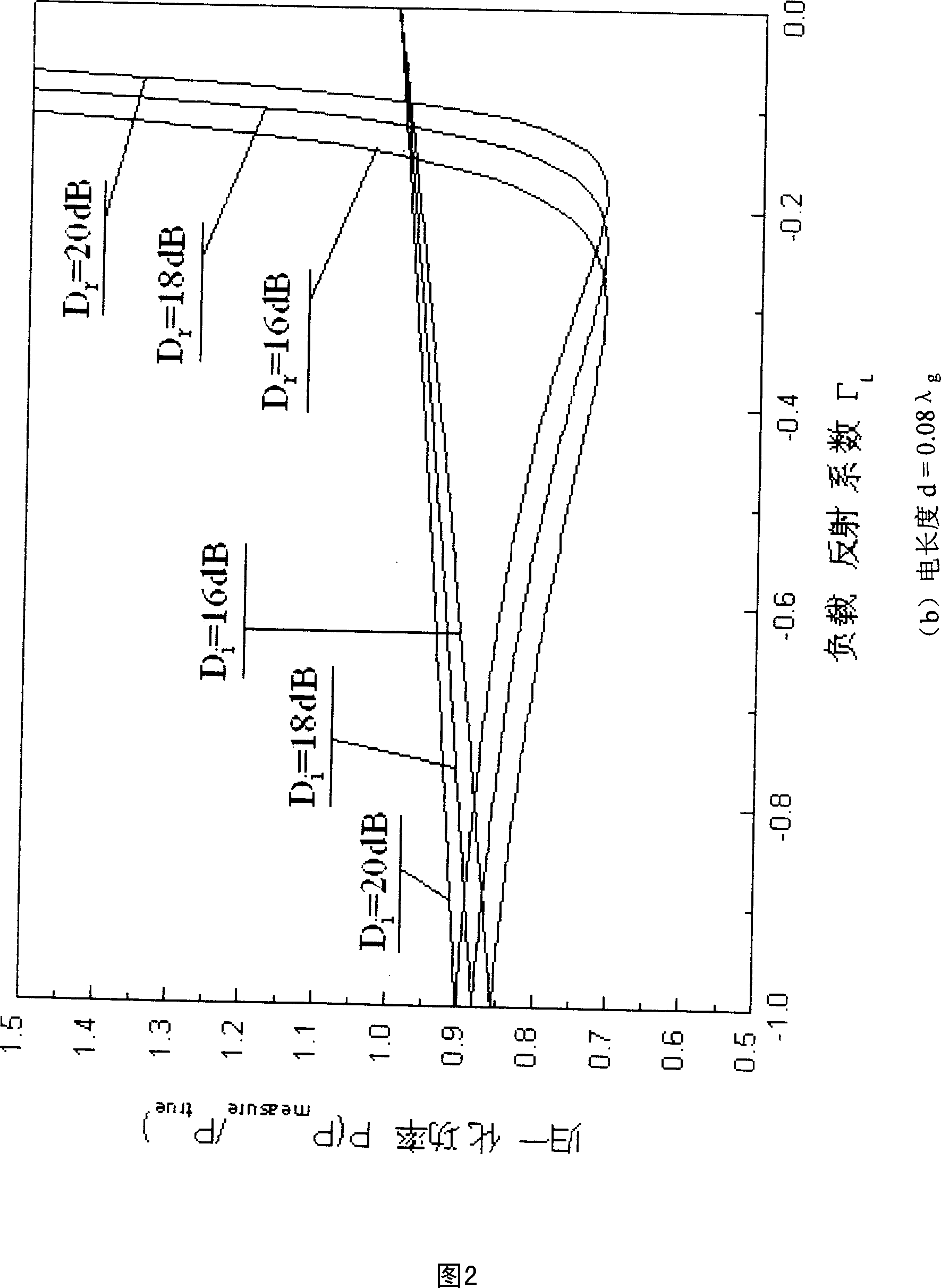

Error analysis method for measuring high-power microwave phase position through directional coupler

The invention discloses an error analysis method for measuring a high-power microwave phase position through a directional coupler. The method includes the first step of obtaining a relational expression between a measured phase position and an actual phase position through analysis of a simplified signal flow diagram according to the microwave transmission line theory, the second step of carrying out analytical calculation by means of programming according to the relational expression obtained in the first step to obtain a quantized phase error, and the third step of carrying out optimization on a hardware system through the direction of error analysis so as to reduce the error to the maximum degree. Through the method, the phase measurement error of a high-power microwave system of a TOKMAK device is analyzed to obtain factors influencing the phase measurement error; on the basis of analysis of the simplified signal flow diagram, the expression of the high-power microwave phase measurement error is obtained, the measurement error is analyzed through a calculation program according to the relational expression, and finally the relation between the phase measurement error and a directivity factor and the relation between the electrical length and a reflection coefficient are obtained.

Owner:INST OF PLASMA PHYSICS CHINESE ACAD OF SCI

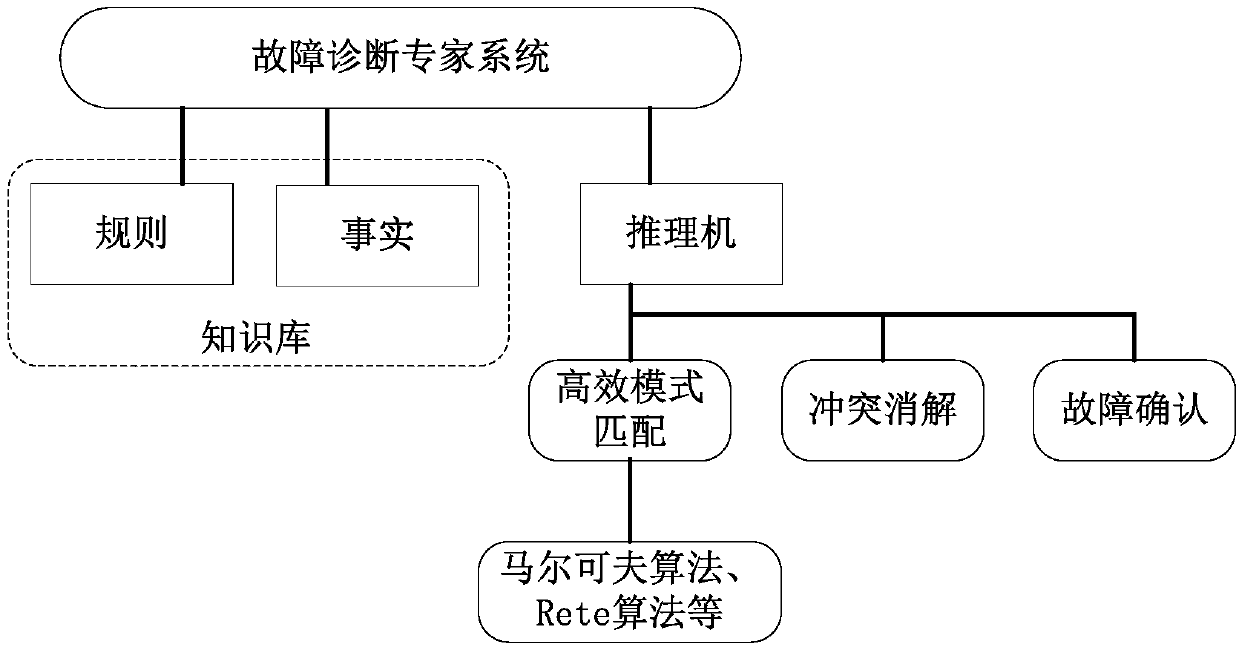

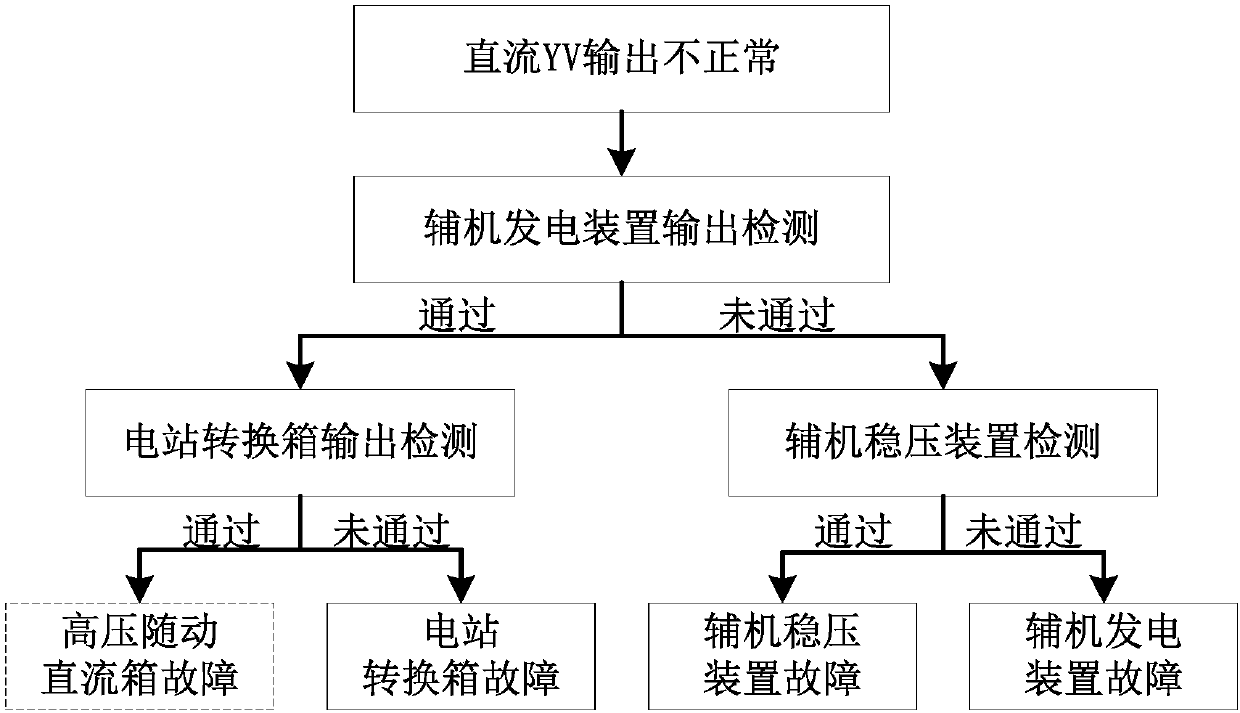

System fault inference method

The invention relates to a system fault inference method, and relates to the technical field of aviation fault testing. The method is based on a fault diagnosis expert system and a multi-signal flow graph testability module. The method specifically comprises the steps: carrying out the fault judgment of a diagnosed system under a single state parameter, identifying a judgment result through a double-attribute value, and finally forming a state matrix of the diagnosed system; carrying out the testability modeling of the diagnosed system, and obtaining a correlation matrix of the fault mode of the diagnosed system and the state of the diagnosed system; carrying out the calculation of the state matrix of the diagnosed system and the correlation matrix, and obtaining a diagnosis result of thediagnosed system. According to the invention, the method is high in speed and precision when the method is used in a fault inference process.

Owner:SHENYANG AIRCRAFT DESIGN INST AVIATION IND CORP OF CHINA

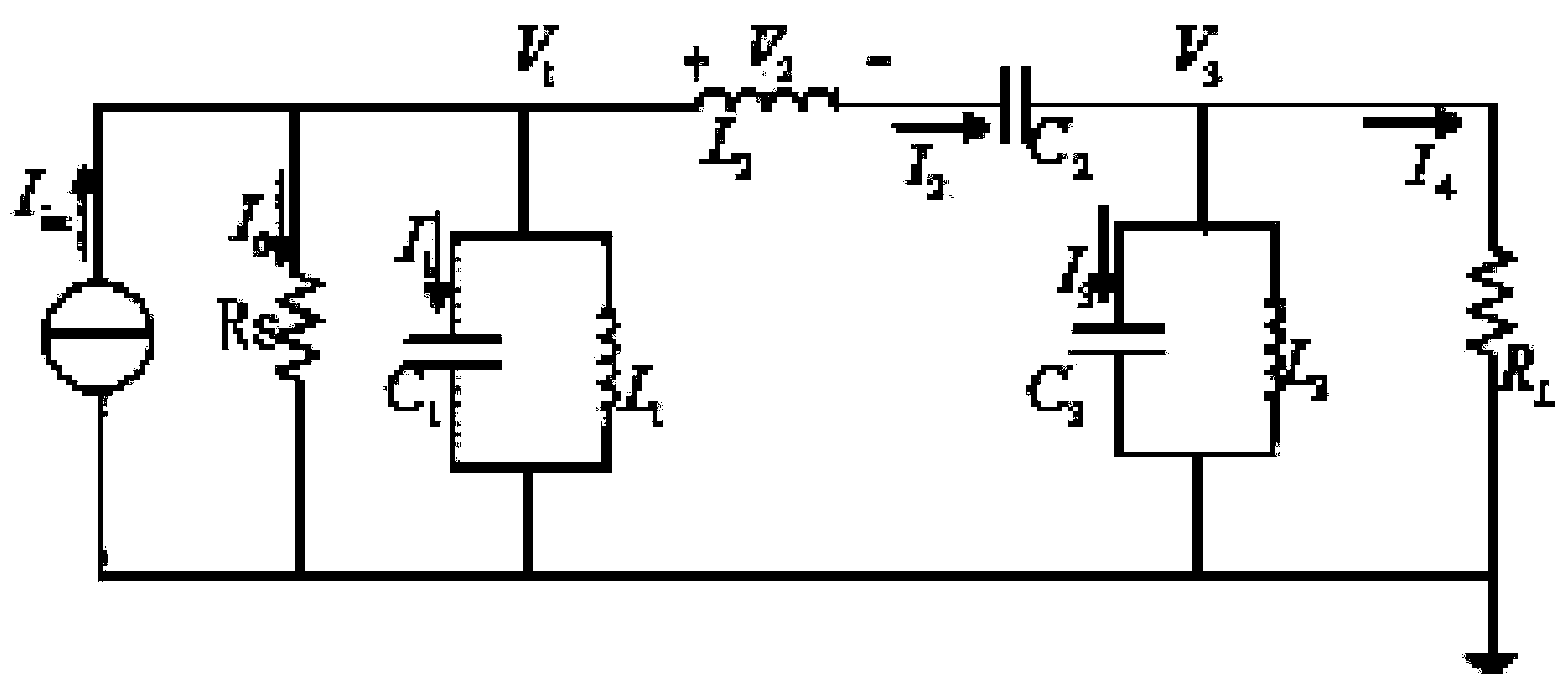

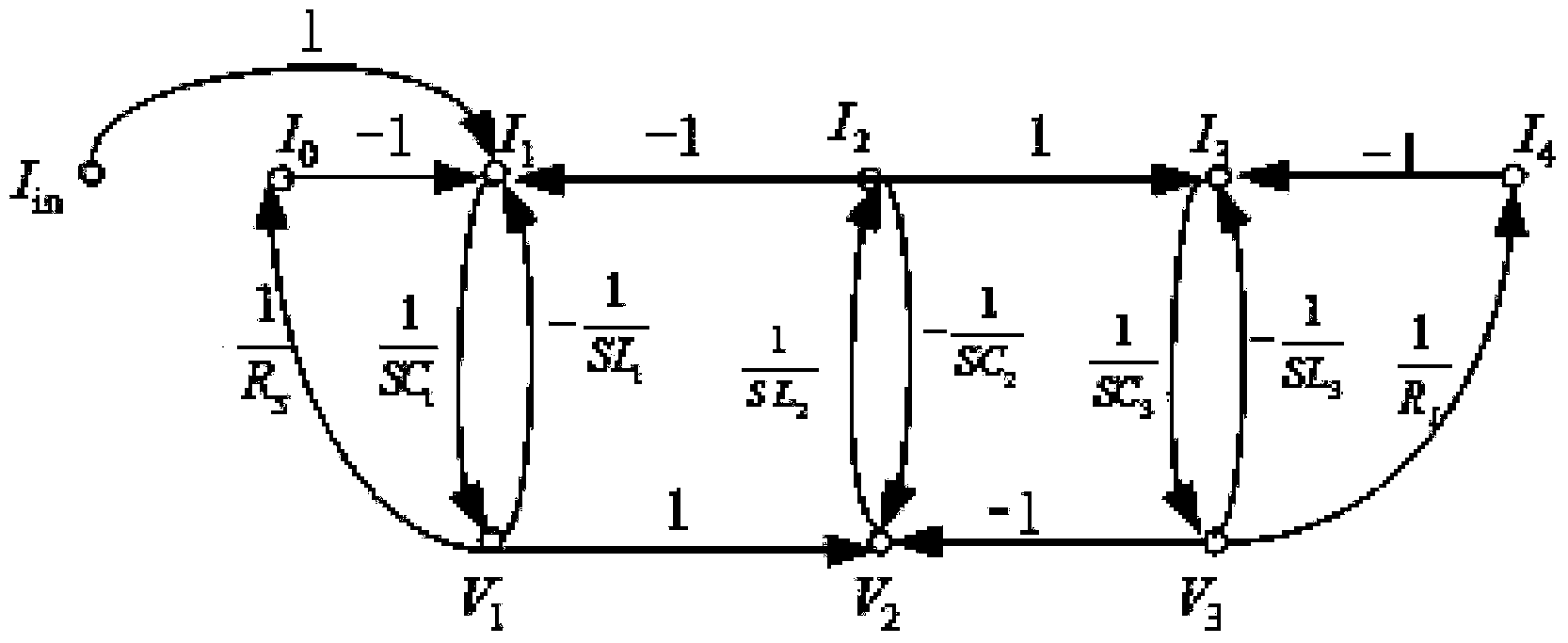

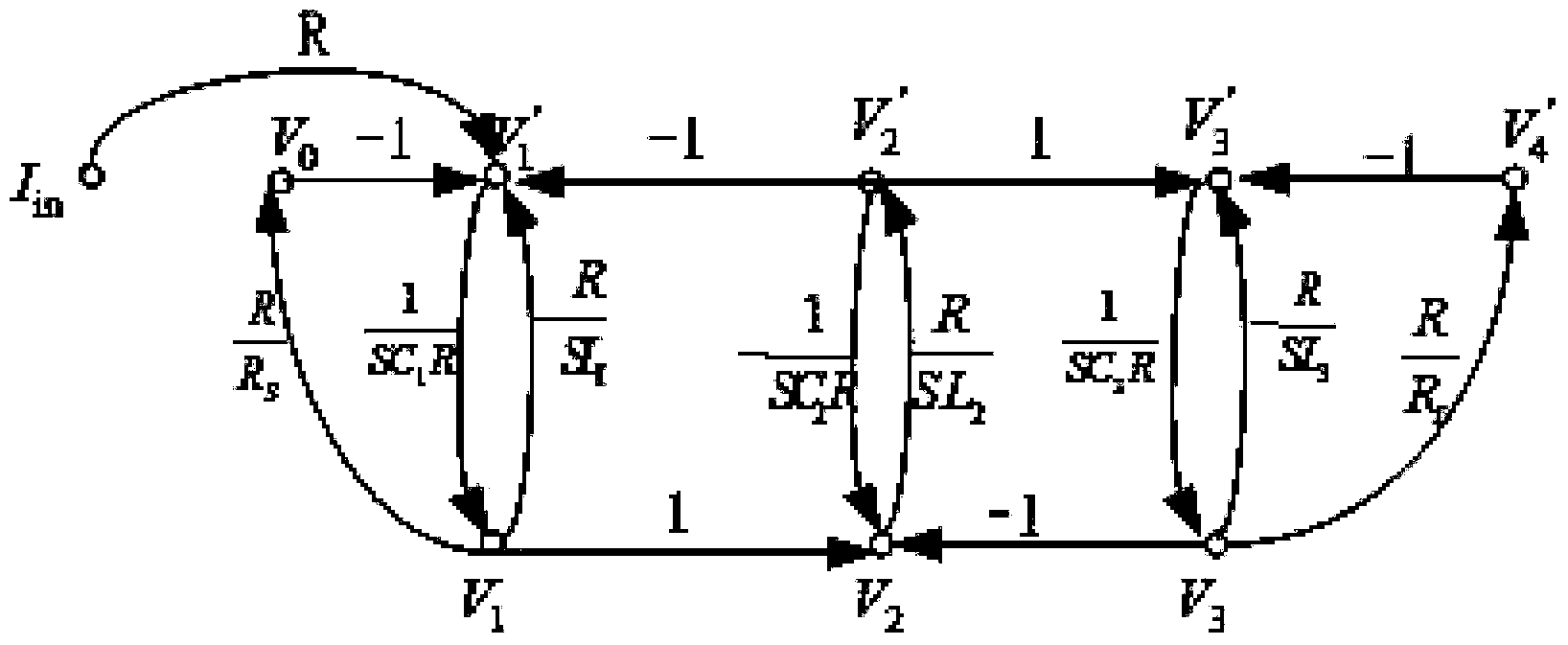

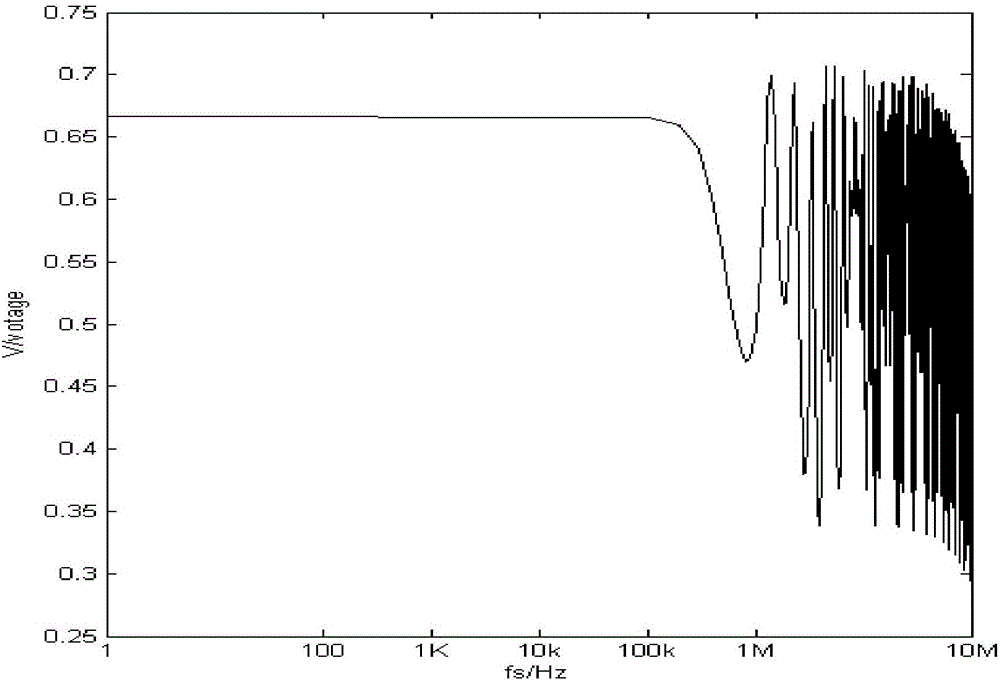

Transimpedance type integrated band-pass filter design method

InactiveCN103973254AReduce sensitivityStable currentMultiple-port networksBandpass filteringConverters

A transimpedance type integrated band-pass filter design method includes the steps: (1) using a signal flow graph method to derivate a transimpedance type passive LC band-pass filter to obtain a signal flow graph of an LC filter; (2) using an invert integrator to realize the signal flow graph to obtain an all-pole transimpedance band-pass filter based on the invert integrator; (3) further replacing the invert integrator with an all-differential integrator to obtain a transimpedance type all-differential active RC band-pass filter circuit. The transimpedance filter designed according to the method can be directly connected with devices such as transducers, D / A (digital / analog) converters and the like directly outputting current, so that current-voltage conversion is avoided.

Owner:TIANJIN UNIVERSITY OF TECHNOLOGY

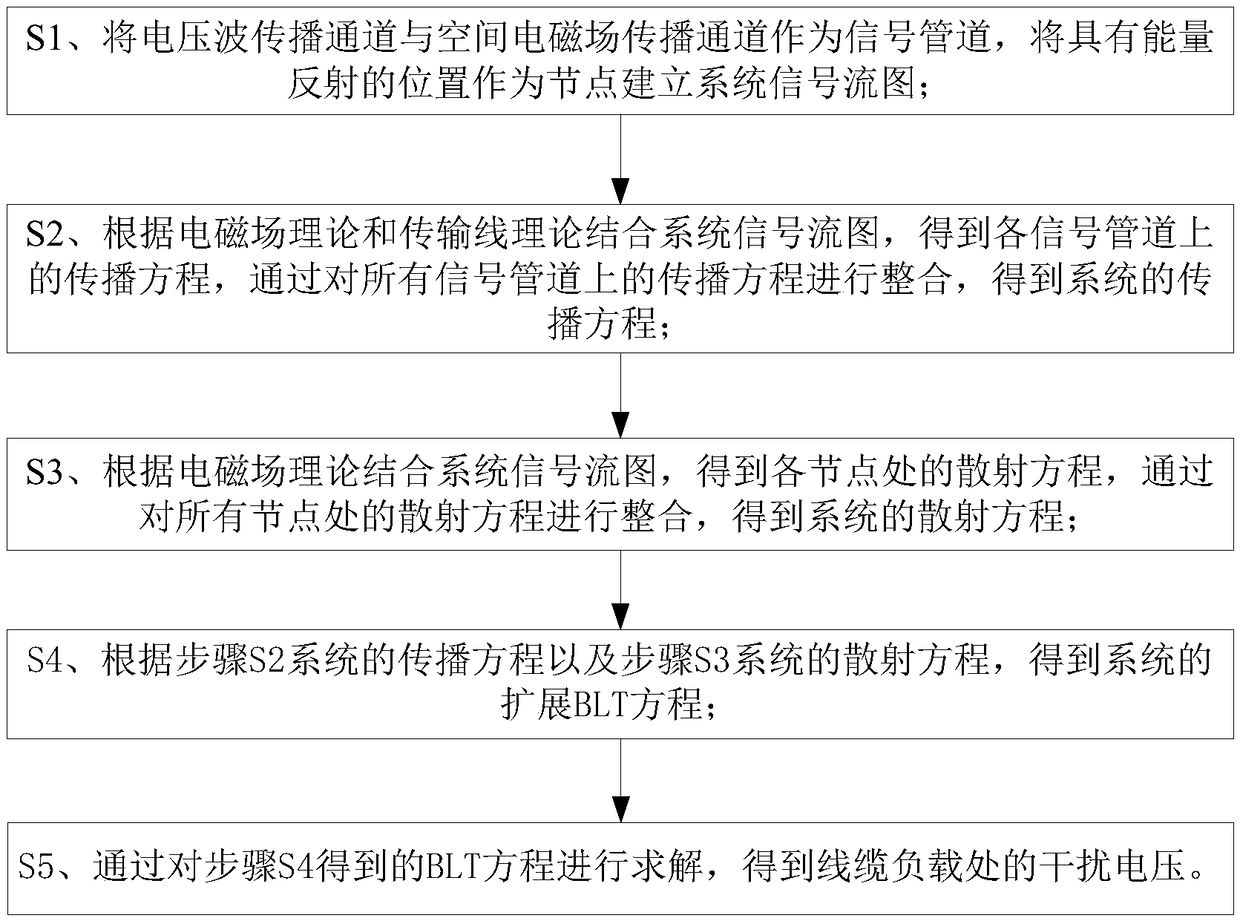

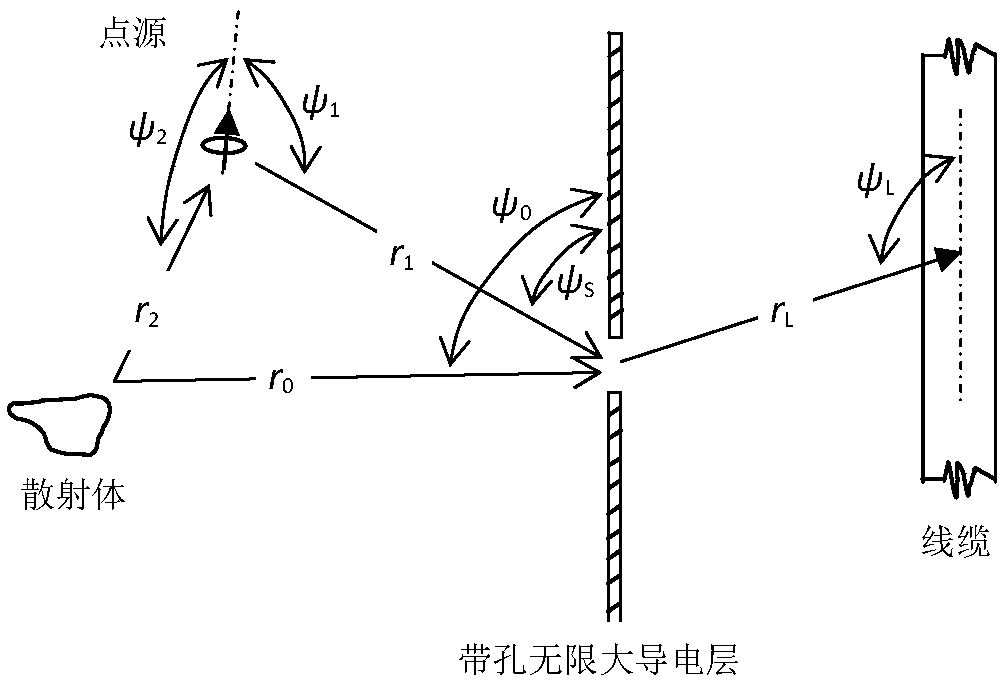

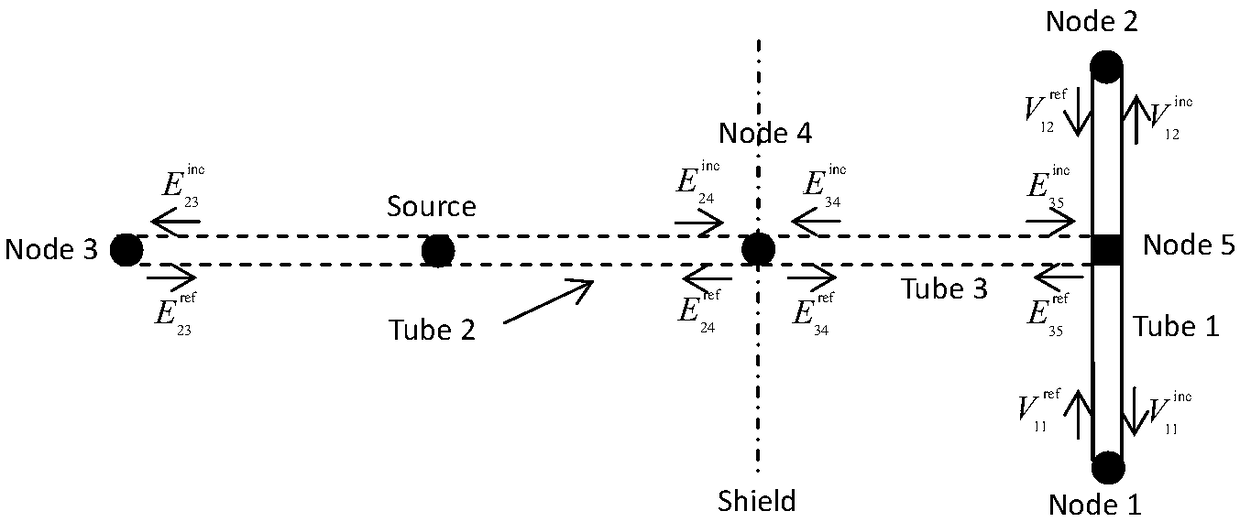

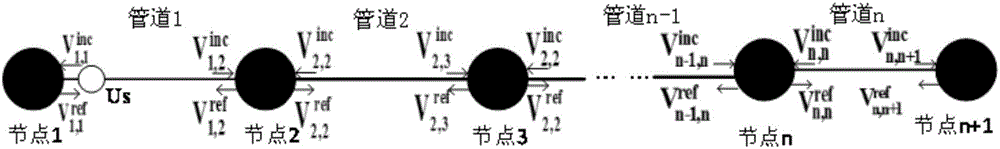

Method for calculating cable interference in infinite shielding layer with holes in point source radiation field

InactiveCN108663589AAccurate calculationThe result is accurateMeasuring interference from external sourcesElectromagnetic fieldRadiation field

The invention discloses a method for calculating cable interference in an infinite shielding layer with holes in a point source radiation field, is applied to the field of electromagnetic interference, and has the advantages of simple algorithm, accurate result, high efficiency and the like. In that method, the aisle of the voltage wave on the cable and the propagation aisle of the space electromagnetic field are represented by signal pipelines, the position with the energy reflection is represented by nodes, a signal flow graph reflecting the electromagnetic energy flow of the system is established, the propagation equation of the whole system signal pipeline and the scattering equation on all the nodes are established by using the magnetic flow element radiation instead of the small holetransmission, the extended BLT (Baum-Liu-Tesche) equation of the system electromagnetic interference is obtained, and the interference intensity on the cable is obtained by solving the extended BLT equation. The method realizes the accurate calculation of the electromagnetic interference of the point source radiation field in the infinite shielding layer with holes and is coupled to the transmission line, and the method effectively reduces the dependence on the computing resources and improves the efficiency.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

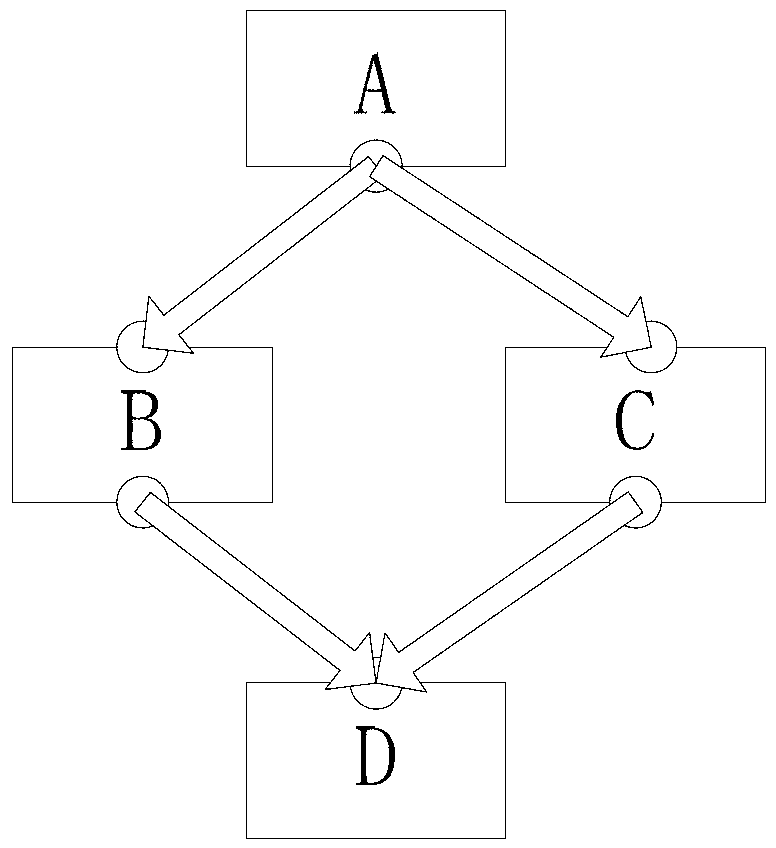

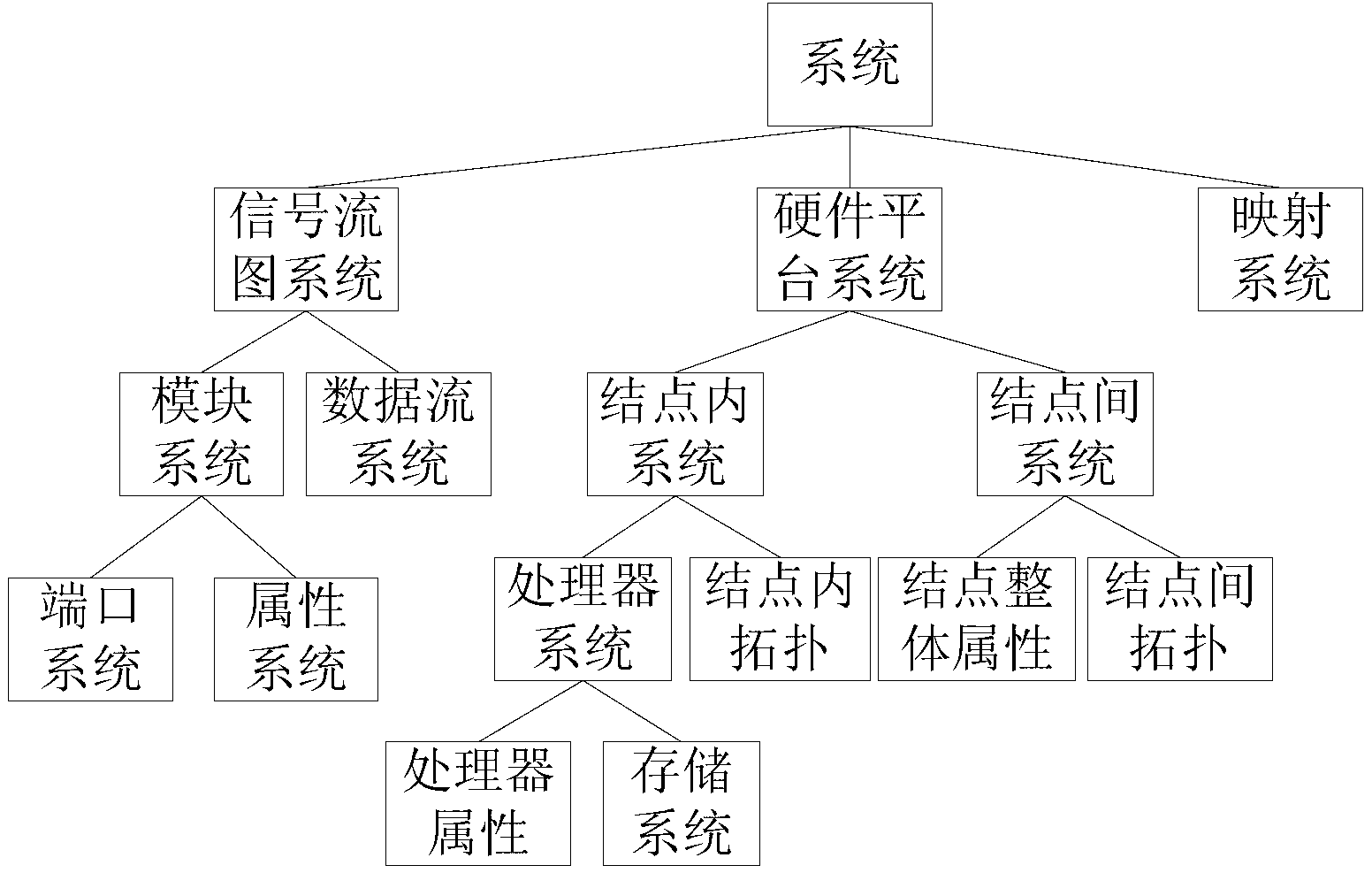

Modular signal processing flow graph and multiprocessor hardware platform modeling method

ActiveCN103019743ARealize automatic generationRealize the modeling taskSpecific program execution arrangementsNODALData stream

A modular signal processing flow graph and multiprocessor hardware platform modeling method is characterized by being a modeling method of mapping modular signal processing flow graphs to a multiprocessor hardware platform. The method comprises three parts of a signal flow graph system, a hardware platform system and a mapping system. Firstly, the modular signal processing flow graphs are modeled, that is, a module system and a data stream system are modeled respectively, the former is used for modeling all functional modules in the flow graphs, and the latter is used for modeling data communication relations among all modules in the flow graphs. Secondly, the multiprocessor hardware platform is modeled, that is, an internal-node system and an among-node system are modeled respectively, the former is used for modeling a processor system of single node and interconnection topology among processors in the nodes, and the latter is used for modeling overall attribute of single node and topology structures among the nodes. And finally, the mapping system is modeled to achieve mapping relations between the modules in the flow graphs and cores of the processors.

Owner:TSINGHUA UNIV

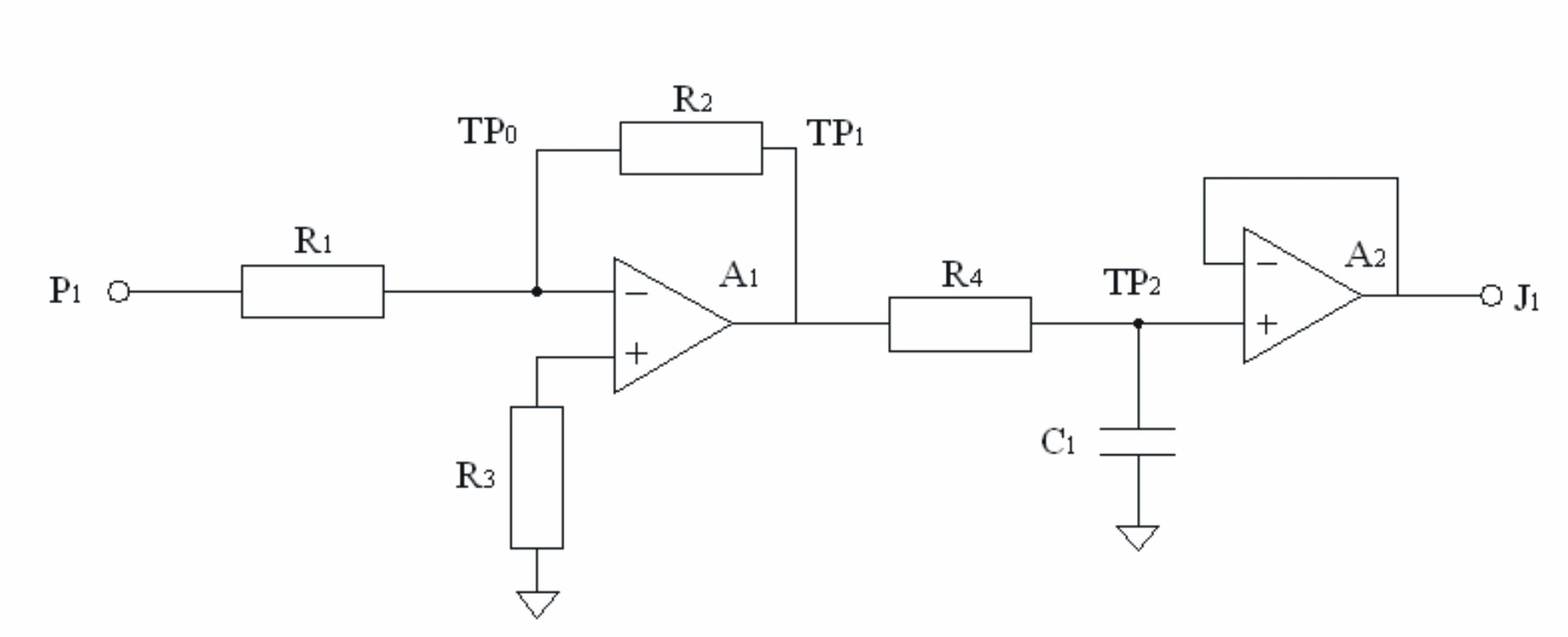

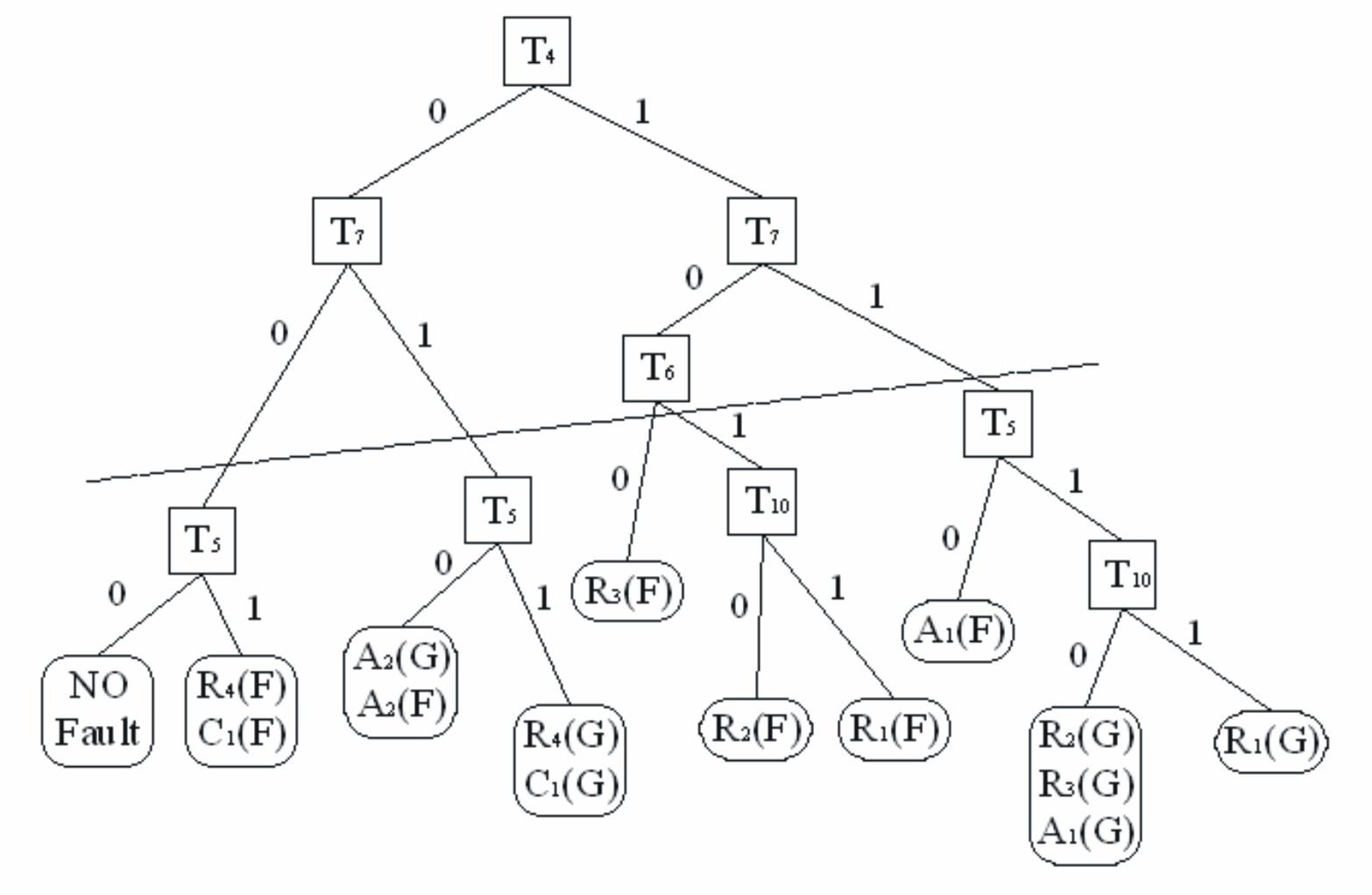

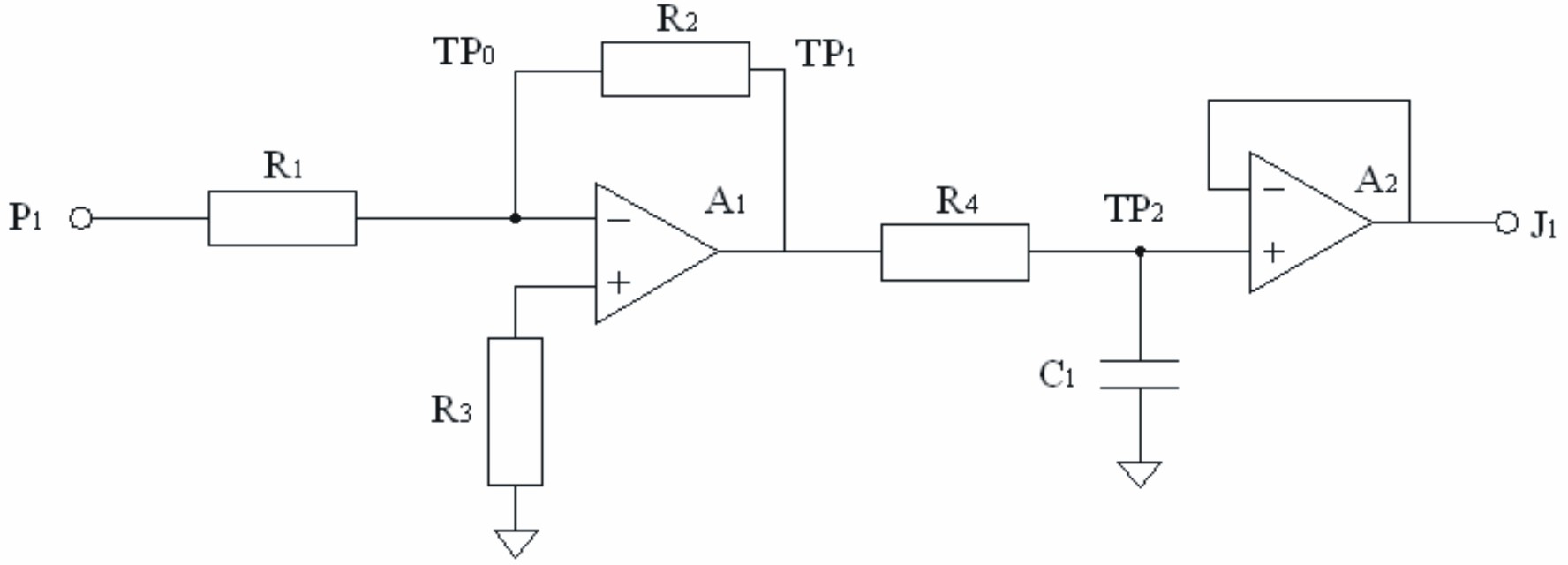

Fault removal method for multi-signal flow graph

The invention provides a fault removal method for a multi-signal flow graph. In a multi-signal flow graph model, tests for detecting the same attribute or with the same excitation can be simultaneously performed and are grouped accordingly, and in a fault removal process, a testing sequence is determined according to the probability of fault occurrences capable of being detected in each group, therefore the fault removal method based on test partition is developed. According to the method, the testing time is reduced to the largest extent; and the probability of fault occurrences and the lowest cost are both considered.

Owner:CHENGDU QIANGFENG TECH

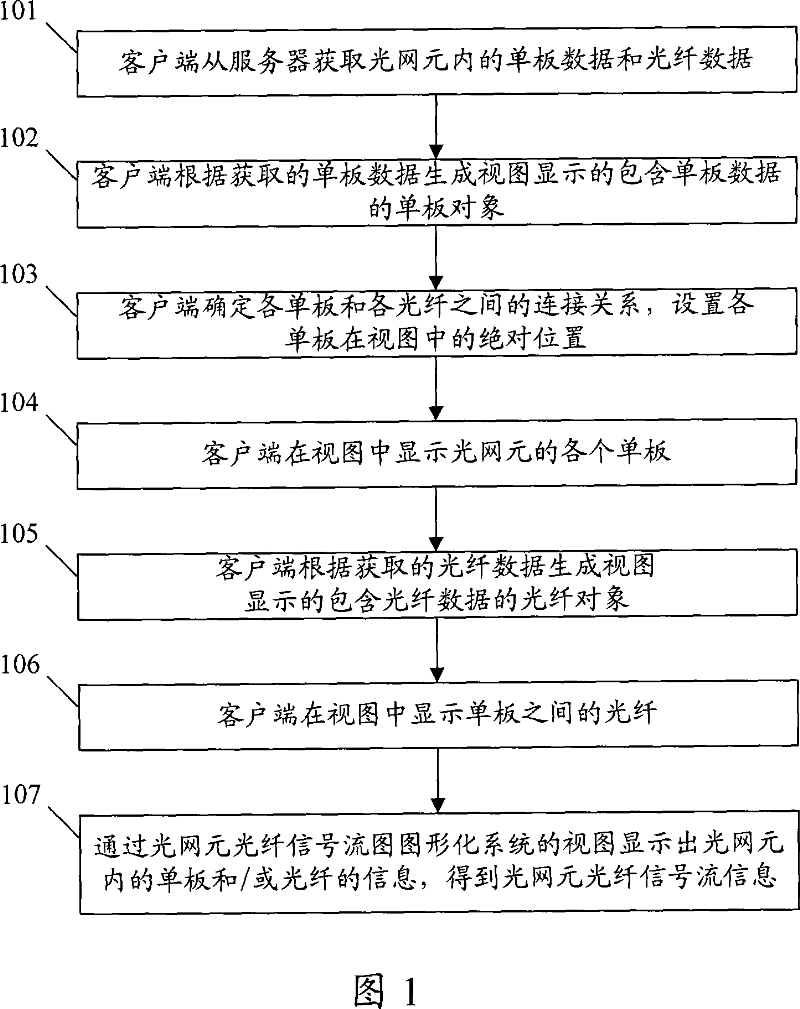

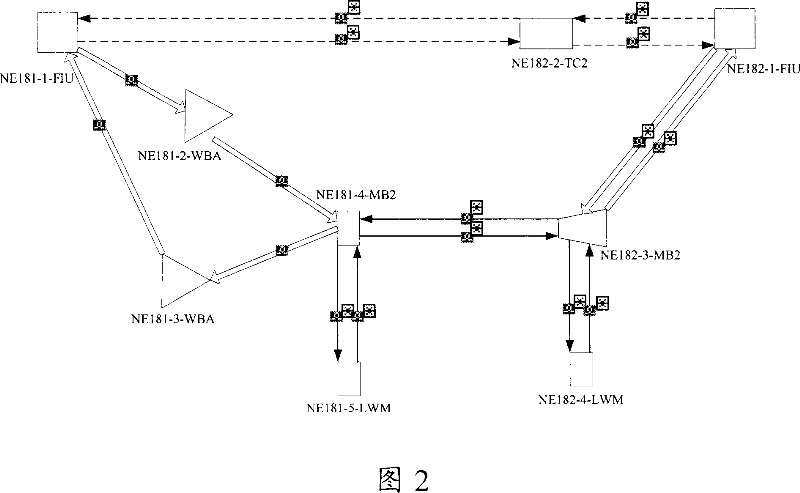

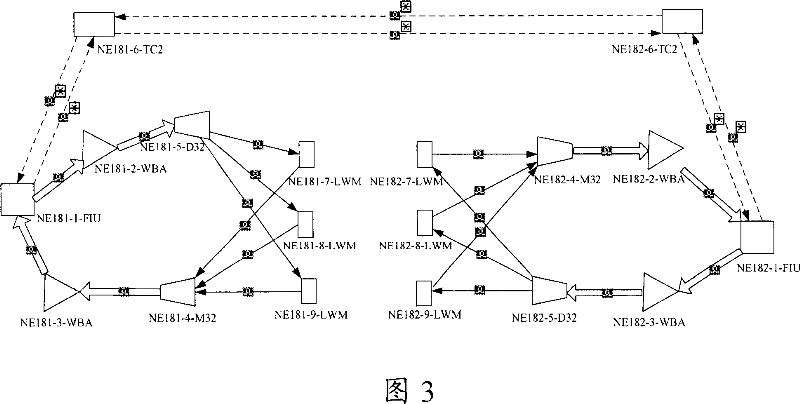

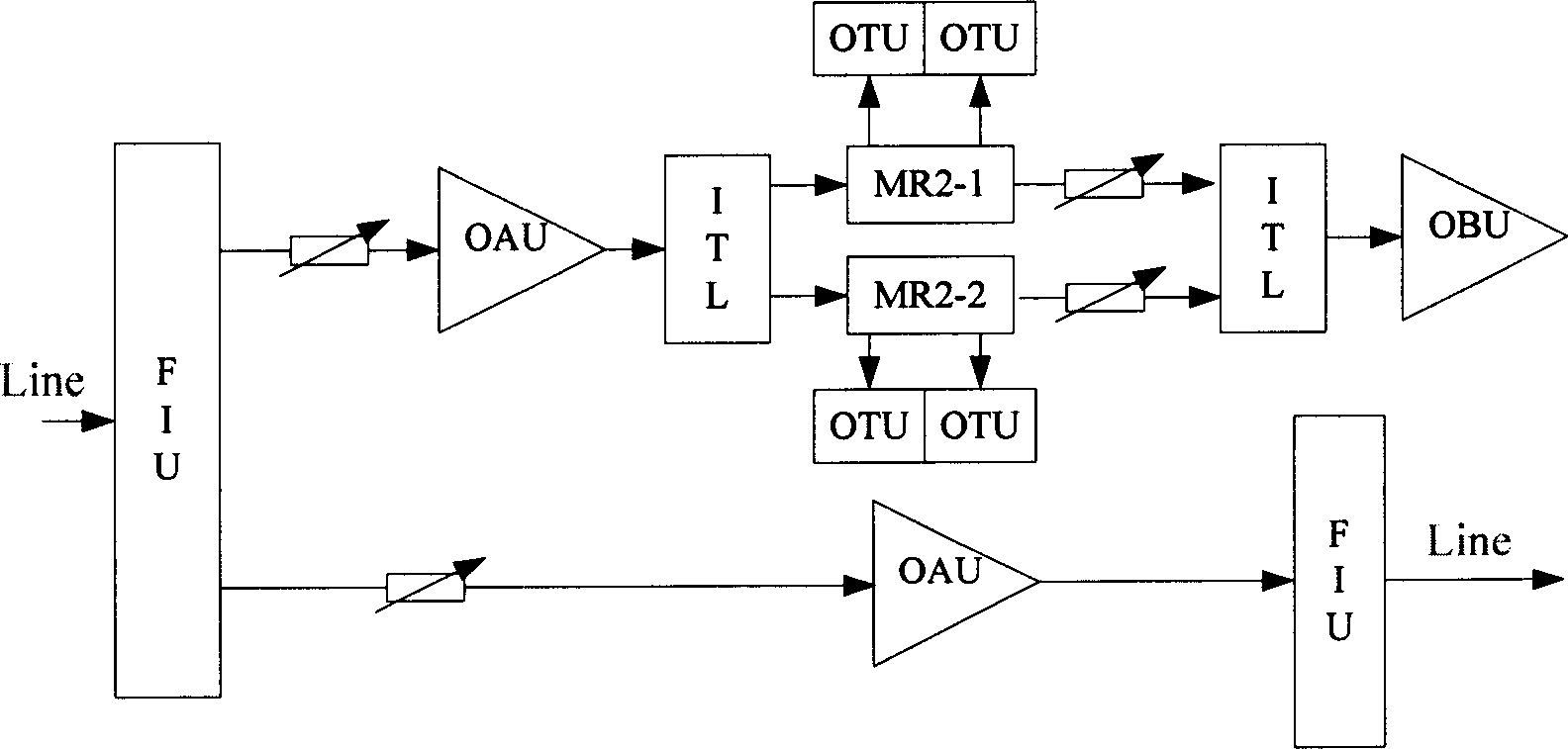

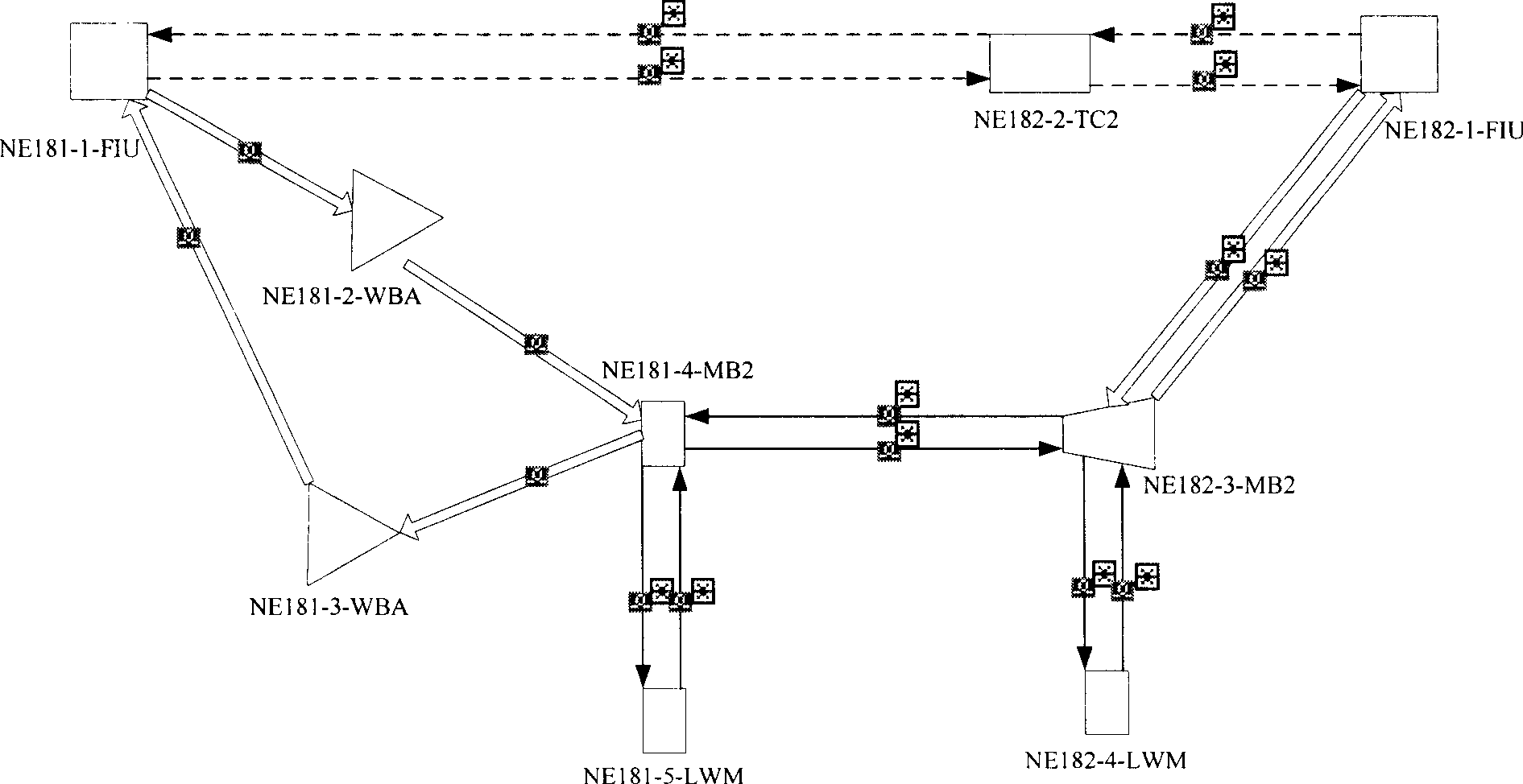

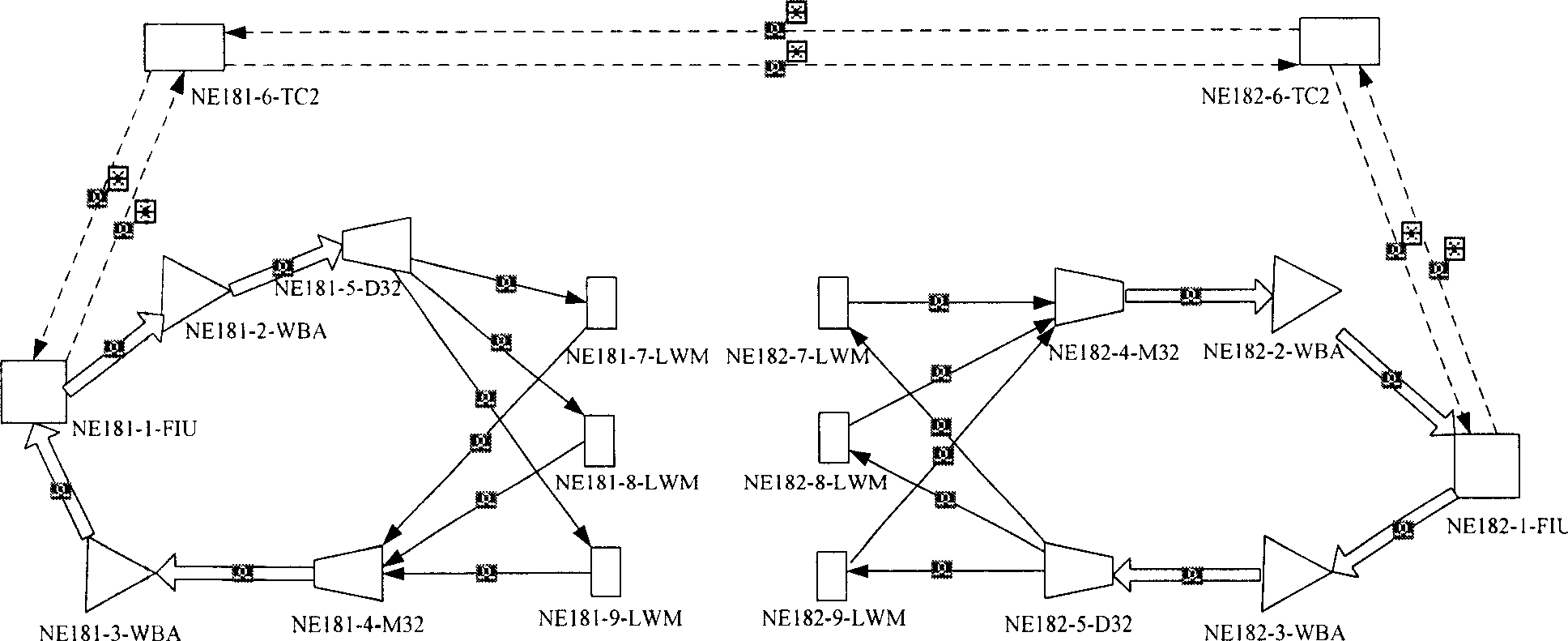

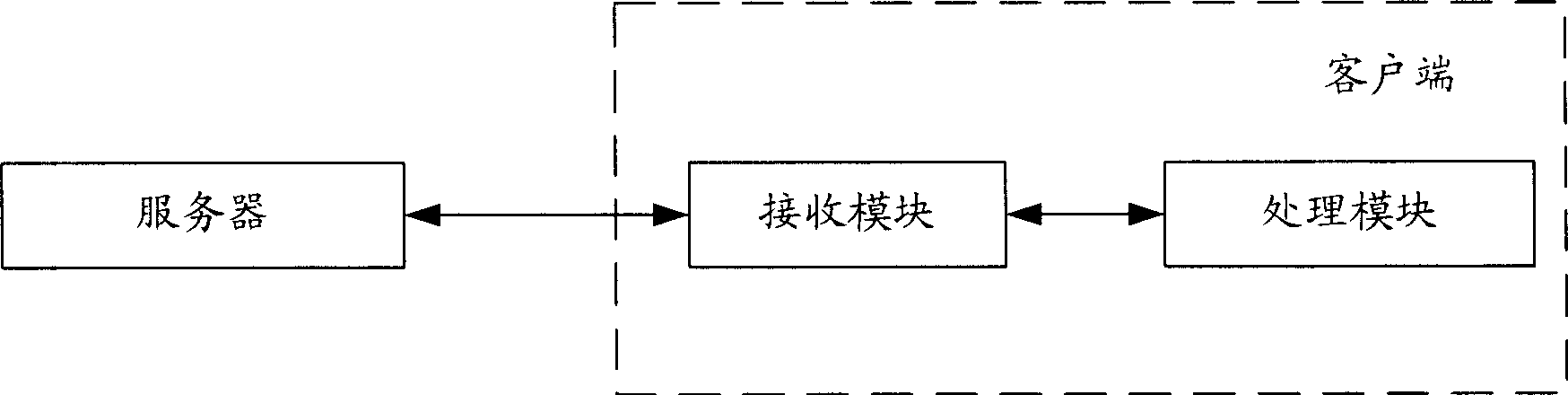

Method, system and client equipment for obtaining optical fiber signal flow information of optical network

InactiveCN101039151AImprove maintenance efficiencyEasy to manageWavelength-division multiplex systemsFibre transmissionFiberOptical network unit

The invention discloses a method for obtaining optical network element fiber signal flow information, comprises as follow: the veneer data and fiber data in optical network element which is transmitted by a server are received; veneer object and fiber object are generated according to the veneer data and fiber data, and then the optical network element fiber signal flow graph graphical system is obtained; the information of the veneer or fiber in the optical network element is displayed via the optical network element fiber signal flow graph graphical system and the optical network element fiber signal flow is obtained. The invention also discloses a method for maintaining the optical network element fiber signal flow and a system and client device for obtaining optical network element fiber signal flow information. The invention can conveniently and rapidly manage the optical network element and improve the maintenance efficiency of the optical network element.

Owner:HUAWEI TECH CO LTD

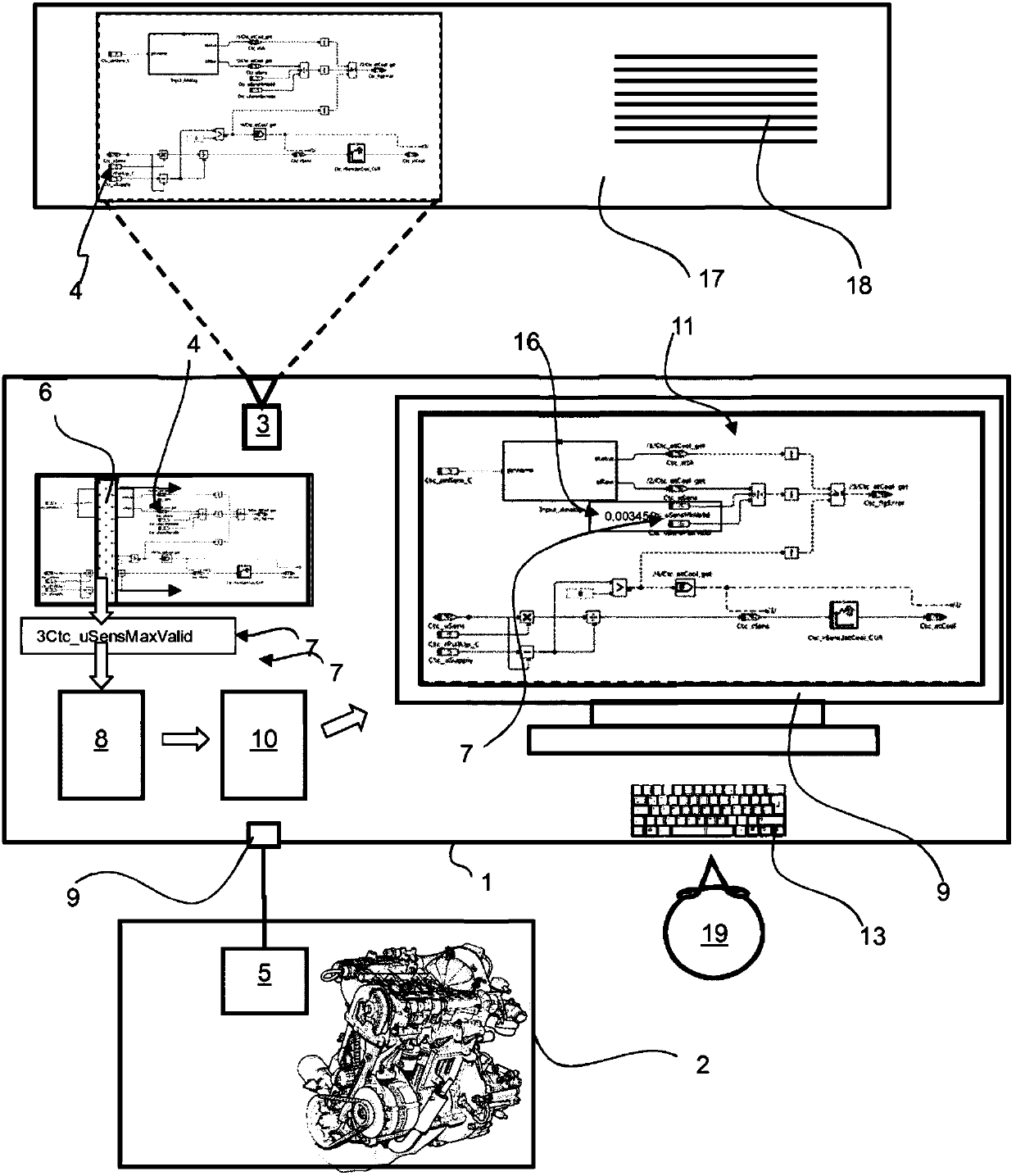

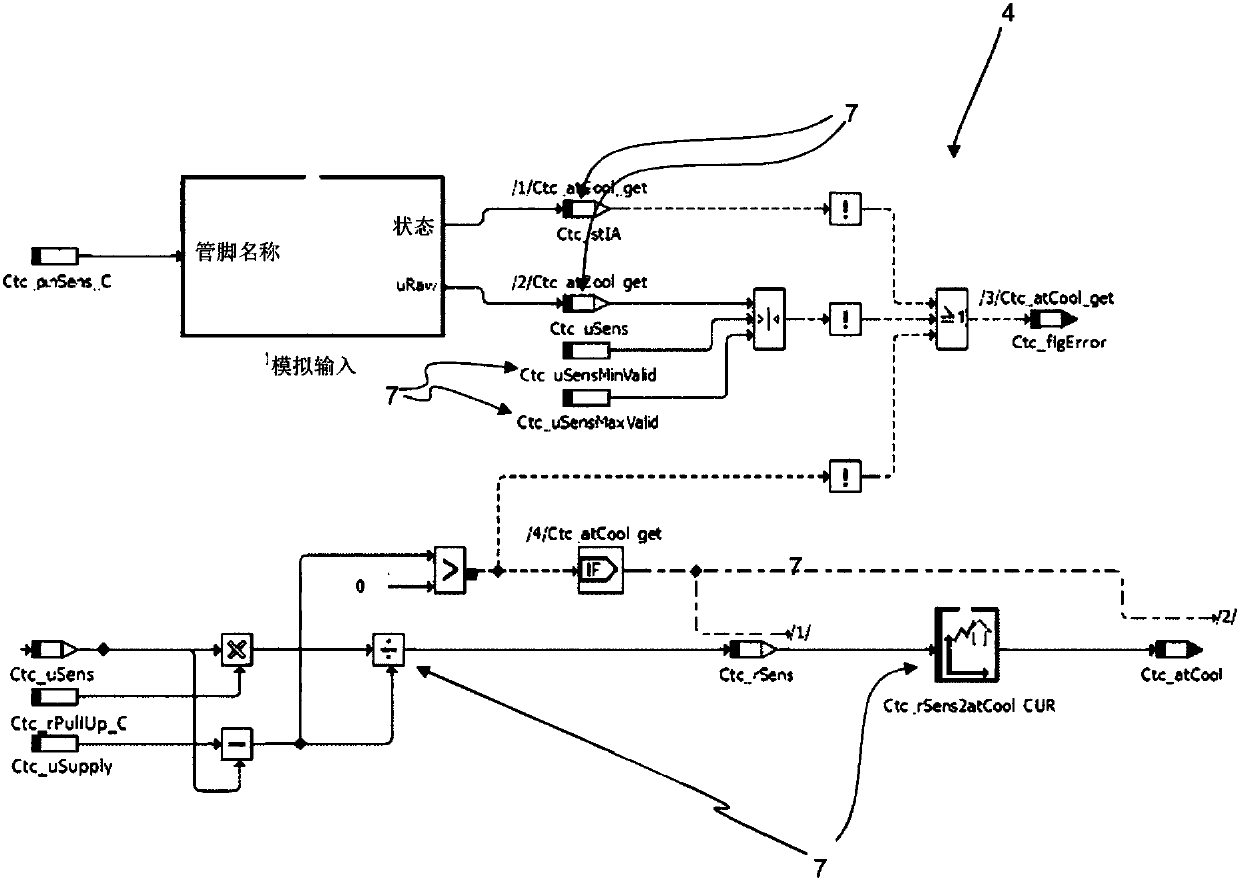

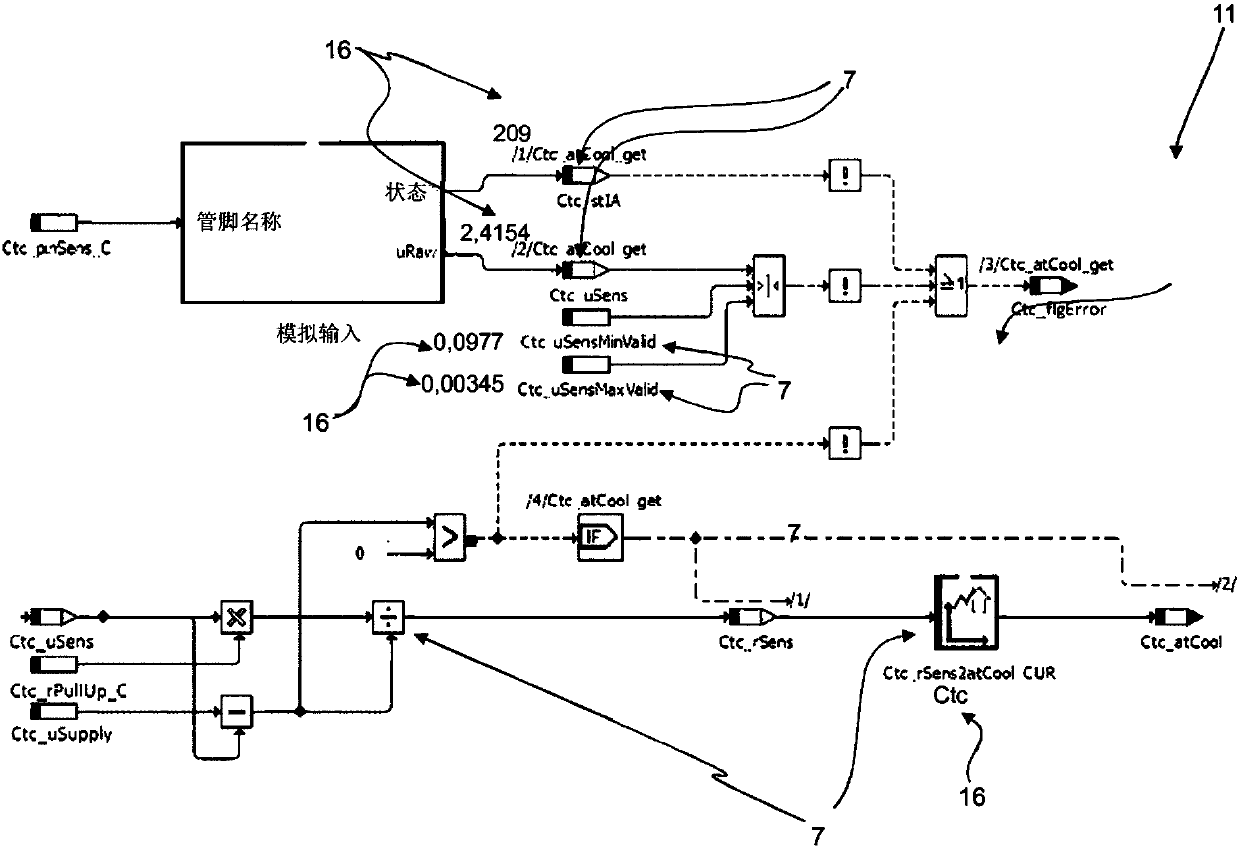

System for monitoring technical device

ActiveCN108027597AReduce multiple meaningsEasy to operateVehicle testingMachine gearing/transmission testingMedicineEngineering

The invention relates to a system for monitoring a technical device, in particular a drive apparatus, which system has a capturing means, in particular an image storage means, for reading in a first visual representation, in particular a signal flow diagram, wherein the first visual representation contains information regarding at least one setting parameter and / or at least one measurement parameter of a controller, which is designed to control the device. Furthermore, the at least one setting parameter and / or the at least one measurement parameter is suitable for characterizing a state of thedevice. The system preferably also has a scanning means for detecting at least one symbol, in particular lettering, in the visual representation, in particular by means of optical character recognition. Furthermore, the system preferably has a database for associating at least one setting parameter and / or at least one measurement parameter with the at least one detected symbol. An interface to the controller preferably exists in the system in order to capture a value of the at least one setting parameter and / or of the at least one measurement parameter of the controller. Furthermore, the system preferably has an image generation means for generating a second visual representation, wherein the image generation means is coupled to the controller preferably in such a way that information ofat least one setting parameter and / or of the at least one measurement parameter is displayed with at least part of the first visual representation. Finally, the system preferably has an image displaymeans, in particular a screen, for presenting the generated second visual representation for the monitoring of the technical device.

Owner:AVL LIST GMBH

Method for measuring error with high power microwave under mismatched load eliminated condition

InactiveCN101082673AGuaranteed safe operationEliminate errorsNuclear energy generationRadiation intensity measurementObservational errorMicrowave

The invention discloses an error measuring method of high-power microwave in the mismatch load eliminating condition, which is characterized by the following: analyzing through simplified signal flowchart according to microwave transmitting line theory; obtaining the relationship formula between measured power and real power; analyzing and calculating through writing and compiling program according to the relationship formula; obtaining the quantized error; controlling and protecting the control program according to real power; ensuring safe operation of huge TOKAMAK system; providing reliable safe guard for power measurement and protection under high-power mismatch load.

Owner:INST OF PLASMA PHYSICS CHINESE ACAD OF SCI

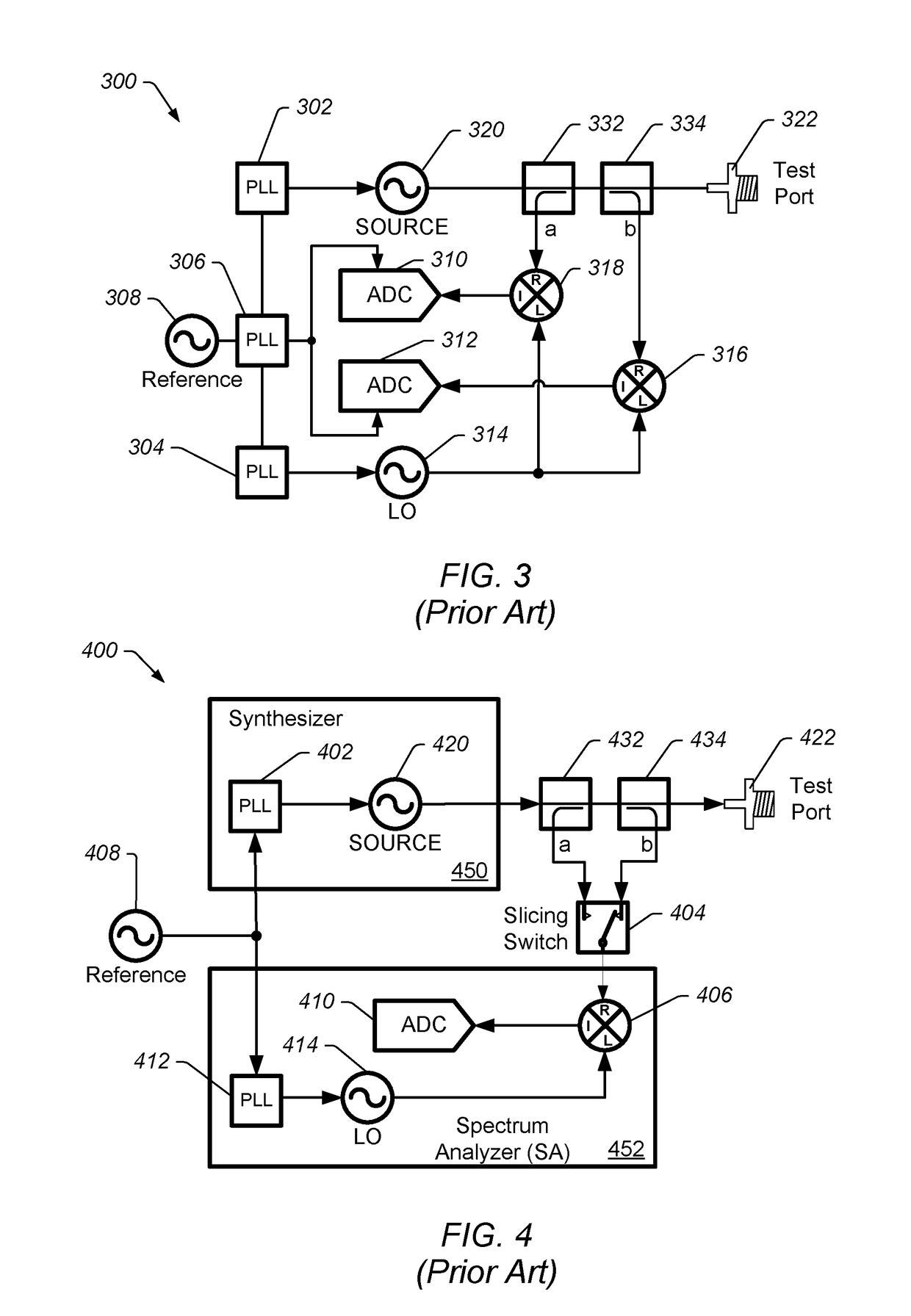

Cold Source Based Noise Figure Measurement Using S-Parameters and a Vector Signal Transceiver/Vector Signal Analyzer/Spectrum Analyzer

ActiveUS20180188306A1Accurate measurementNoise figure or signal-to-noise ratio measurementResistance/reactance/impedenceTransceiverMeasuring instrument

The noise figure for a radio frequency device may be obtained through power measurements. A signal flow graph based upon the S-parameter information of the entire RF system may be constructed. The S-parameter information may be representative of the microwave termination, the device, the measurement instrument and any losses due to additional components such as connecting cables / attenuators / switches, etc. The signal flow graph includes proper placement and values of the source nodes corresponding to each RF sub-system enumerated above. Noise figure measurements may include a calibration step and a measurement step. During the calibration step the noise figure and the noise temperature of the measurement instrument used for the measurement may be obtained. During the measurement step, the noise figure and the noise temperature of the device may be obtained based at least on the noise figure and noise temperature of the measurement instrument obtained during the calibration step.

Owner:NATIONAL INSTRUMENTS

Optimization method for measuring point of measuring sensor for satellite angular rate based on correlation matrix

ActiveCN102735877AEasy to detectGuaranteed separation effectTesting/calibration of speed/acceleration/shock measurement devicesPoint correlationControl system

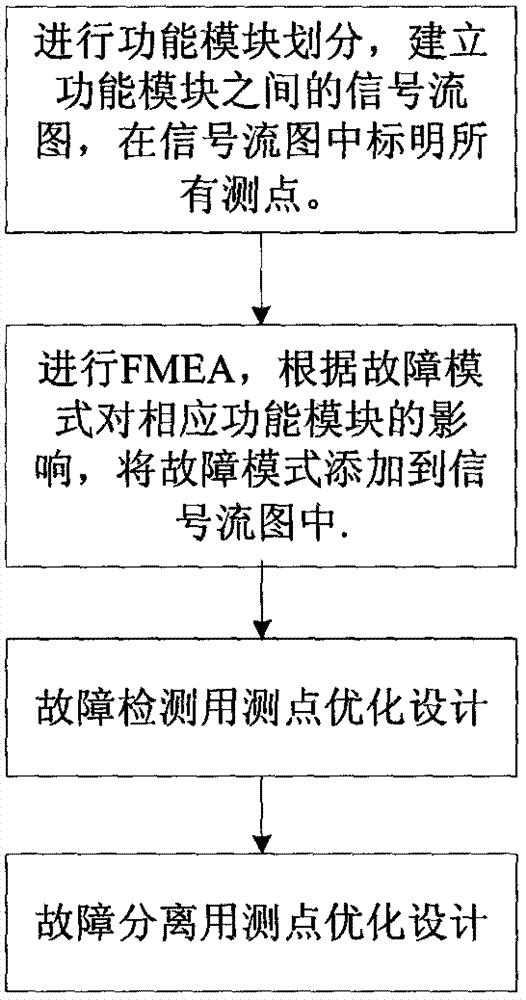

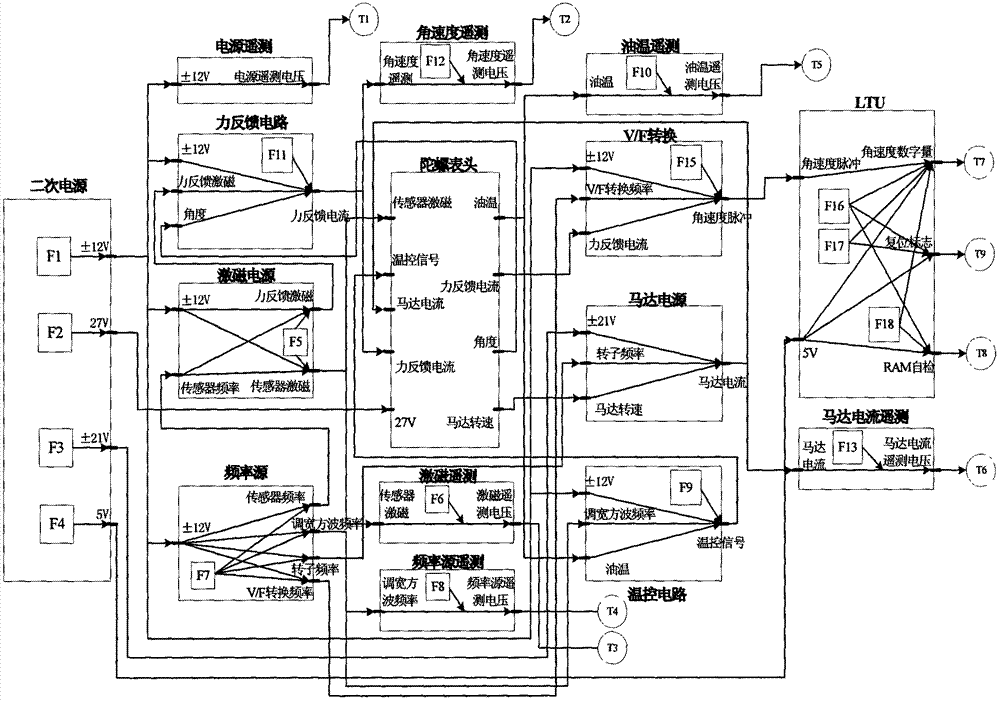

The invention relates to an optimization method for a measuring point of a measuring sensor for a satellite angular rate based on a correlation matrix. The optimization method comprises the following steps: (1) dividing function modules for the measuring sensor for the angular rate, establishing a signal flow graph for each of the function modules, and marking all the measuring points in the signal flow graph; (2) performing FMEA (Failure Mode and Effects Analysis) on the measuring sensor for the angular rate, confirming failure mode and failure effects of the measuring sensor for the angular rate, and adding the failure mode to the signal flow graph according to the failure effects; (3) establishing a fault-measuring point correlation matrix; (4) performing assignment on the correlation matrix according to the signal flow graph; and (5) performing fault testability analysis on the measuring sensor for the angular rate according to the fault-measuring point correlation matrix D established in the step (4). According to the optimization method provided by the invention, the defects of the prior art are overcome, the faults can be detected and separated as much as possible under the condition of meeting resource restraint, and a basis is supplied for diagnostic design of a satellite control system.

Owner:BEIJING INST OF CONTROL ENG

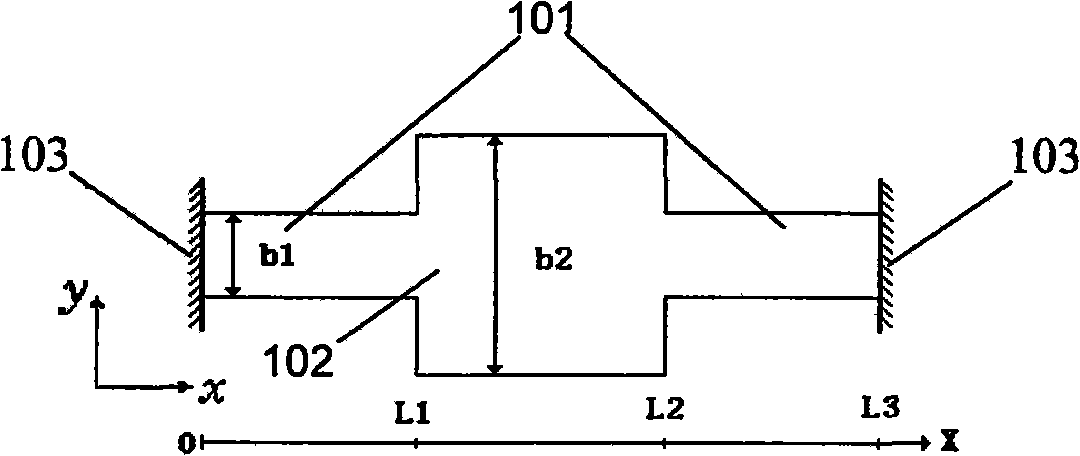

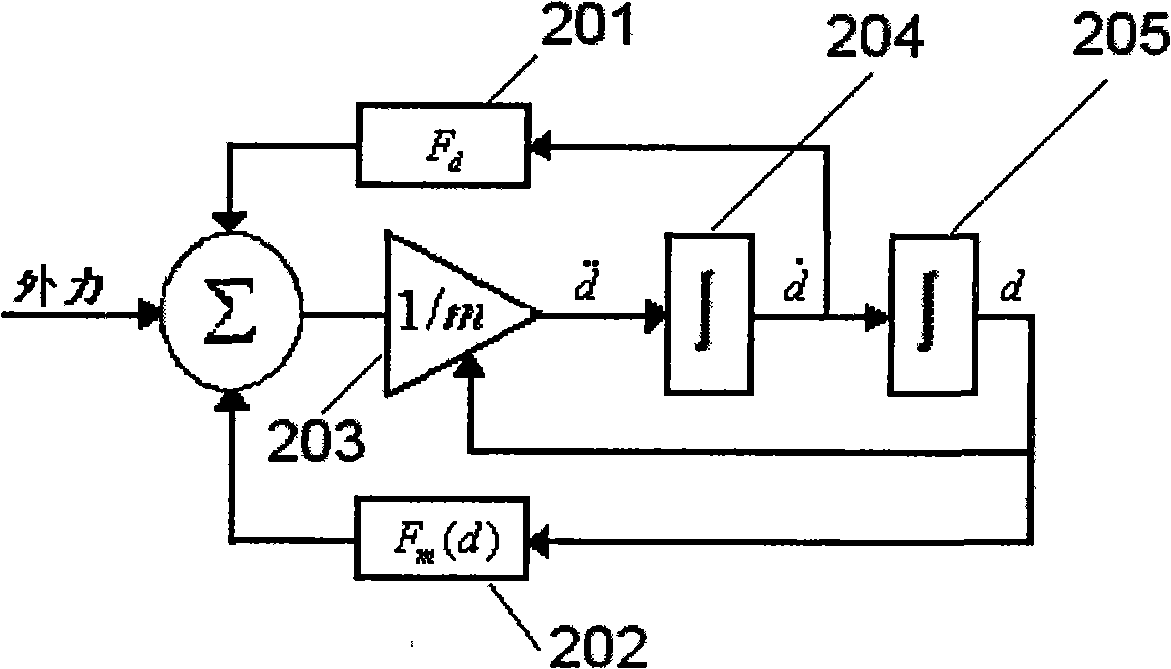

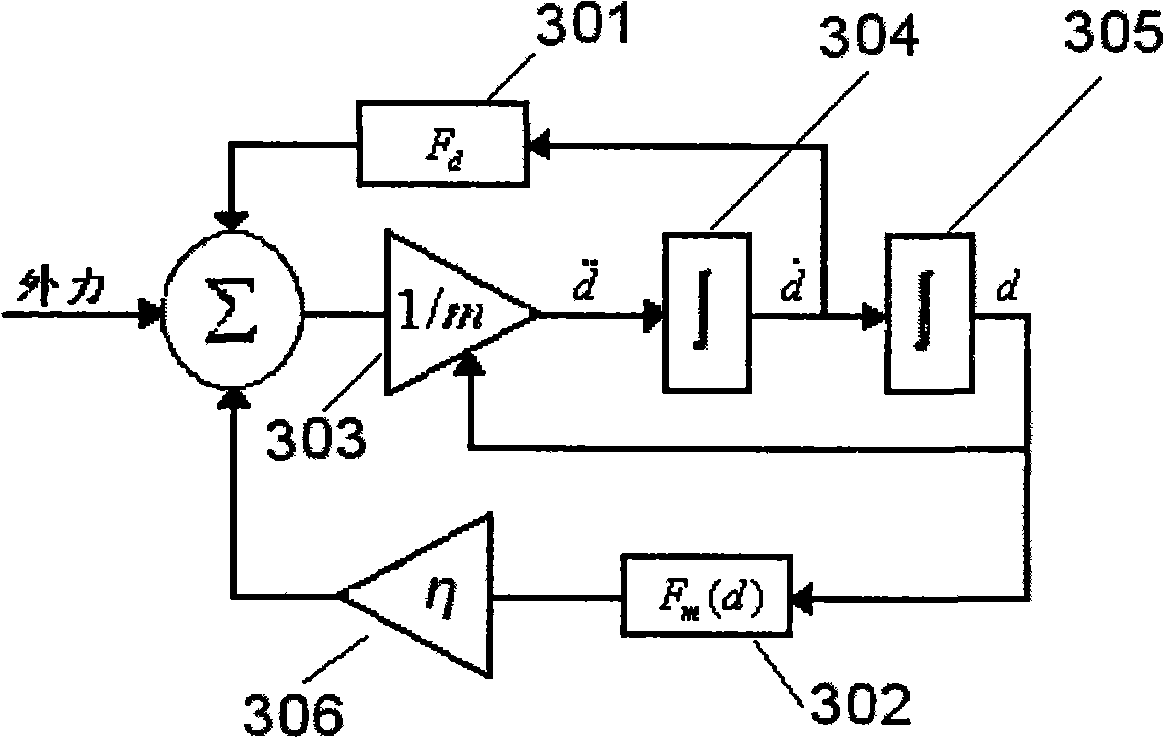

Method for establishing micro-electromechanical variable cross-section clamped beam system-level macro model

InactiveCN101320398ASimple structureMeet the precision requirementsSemi-permeable membranesPiezoelectric/electrostrictive/magnetostrictive devicesSystem-level simulationEngineering

The present invention provides a changing cross section clamped beam system-level macro model building method of a micro-electromechanical system, and relates to a system-level modeling method of the micro-electromechanical system (MEMS) device. The elastic reverting force correction term are introduced into the one-dimensional signal flow model of the changing cross section clamped beam, so as to transform the two-dimensional effects generated by the bending of the wide part of the beam into the one-dimensional model correction; then the accuracy of the model is higher than the model of the one-dimensional signal flow diagram; thus the model and the method can conveniently achieve the system-level simulation of the changing cross section beam with two ends of different sizes, and analyze the static and dynamic behaviors of the changing cross section beam.

Owner:JIANGSU JIANGHAI MACHINE TOOLS GROUP +1

Network analyzer, network analyzing method, automatic corrector, correcting method, program, and recording medium

InactiveUS7652482B2Solving precise measurementsResistance/reactance/impedenceError detection/correctionEngineeringSignal source

The error of a measurement system can be corrected even if the frequency of an input signal of a device under test is different from that of the output signal. A signal output acquiring section acquires the power of the input signal by a power meter not shown in the drawing. Thus, errors due to frequency tracking can be separated depending on the direction in a signal flow graph. Since a receiver measures the parameter concerning the received signal when a signal source is directly connected to a receiver, the measurement system error factor of the receiver can be acquired. The parameter of a device under test can be measured while the error is corrected when the results of measurement, concerning the device under test of receivers are combined.

Owner:ADVANTEST CORP

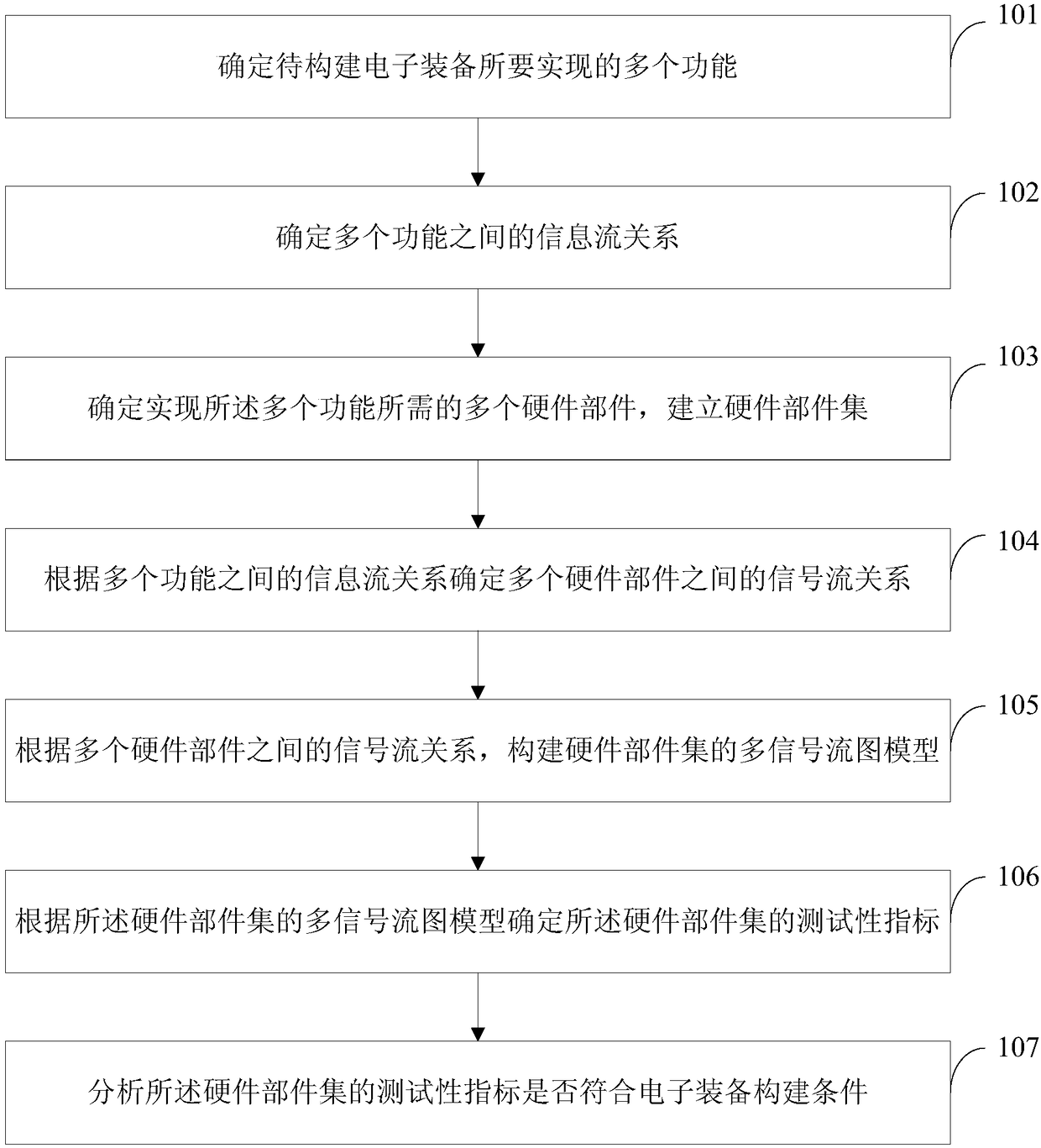

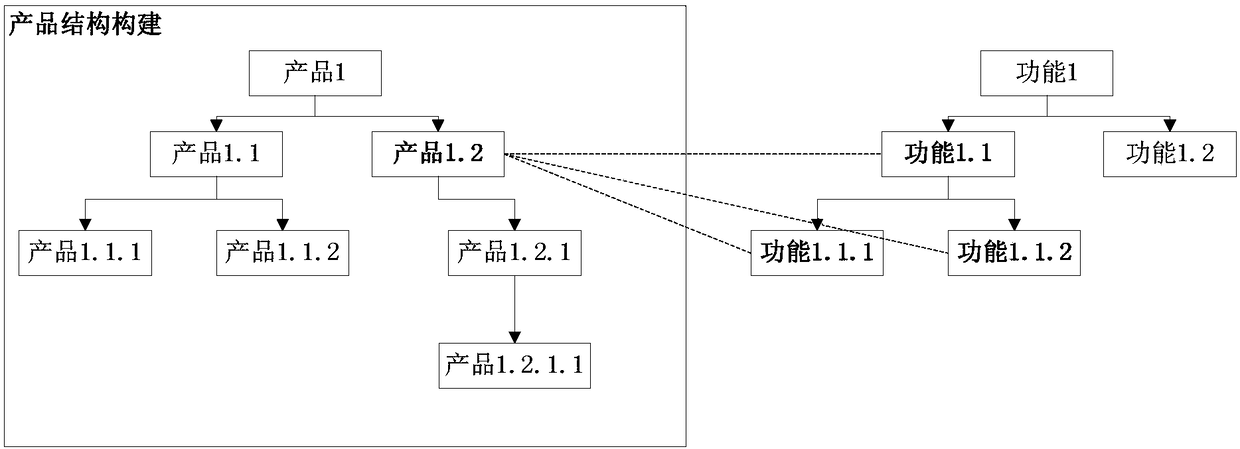

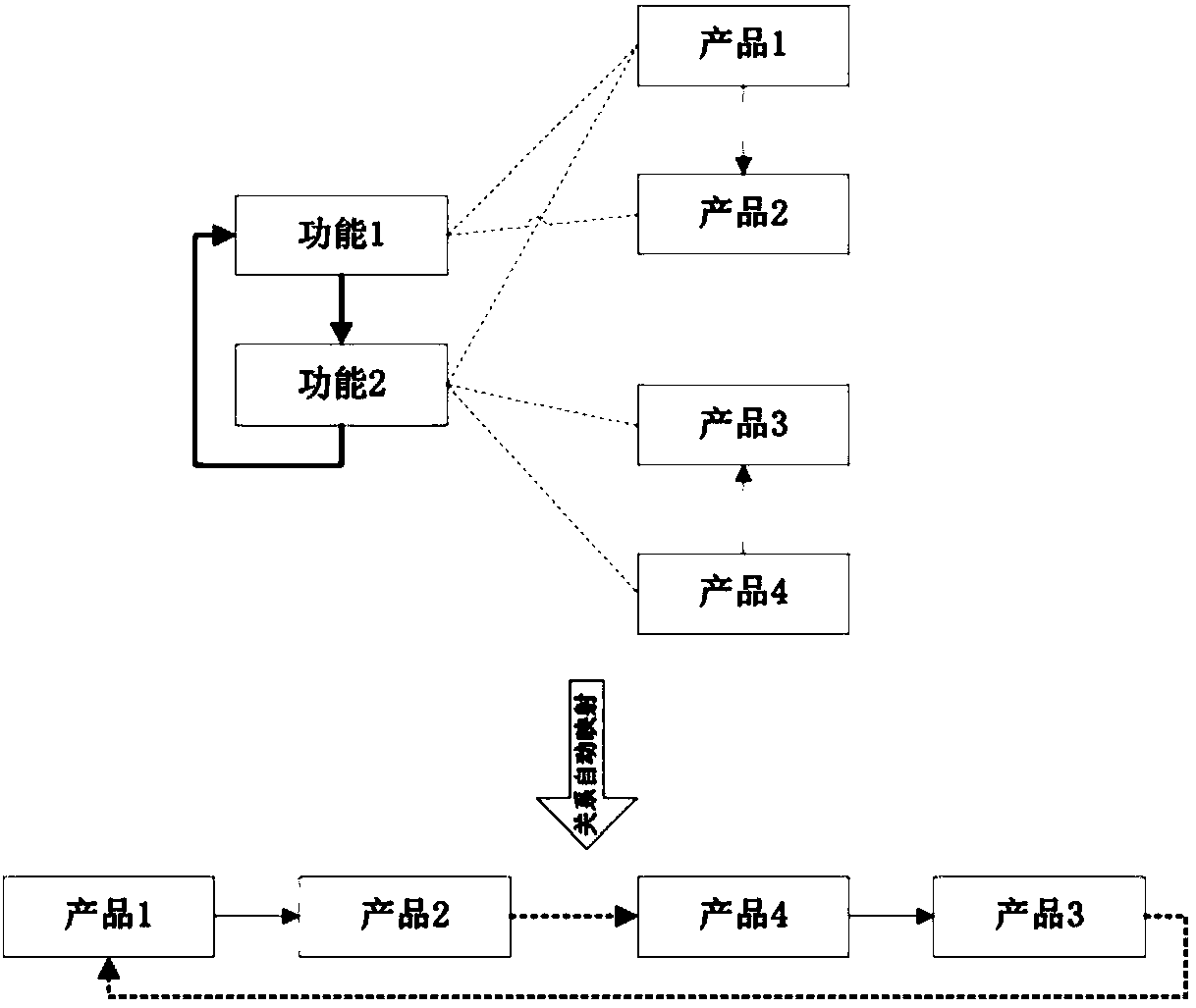

Testability analysis method and device for electronic equipment

ActiveCN108427778AReduce buildReduce difficultyDesign optimisation/simulationSpecial data processing applicationsTestability analysisComputer science

The invention provides a testability analysis method and device for electronic equipment. The method includes determining multiple functions to be achieved by to-be-built electronic equipment; determining information flow relations between the multiple functions; determining multiple hardware parts required to achieve the multiple functions and building a hardware part set; determining the information flow relations between the multiple hardware parts according to the information flow relations between the multiple functions; building a multi-signal flow graph model of the hardware part set according to the information flow relations between the multiple hardware parts; determining the testability index of the hardware part set according to the multi-signal flow graph model of the hardwarepart set; and analyzing whether the testability index of the hardware part set accords with electronic equipment building conditions. Through the information flow analysis on functional levels, the establishment of the testability information flow model at hardware levels can be reduced. The state of testability can be known in the functional level and assistance is provided for system staff in consideration on testability, the difficulty of testability works can be reduced, and popularization can be achieved easily.

Owner:北京国基科技股份有限公司

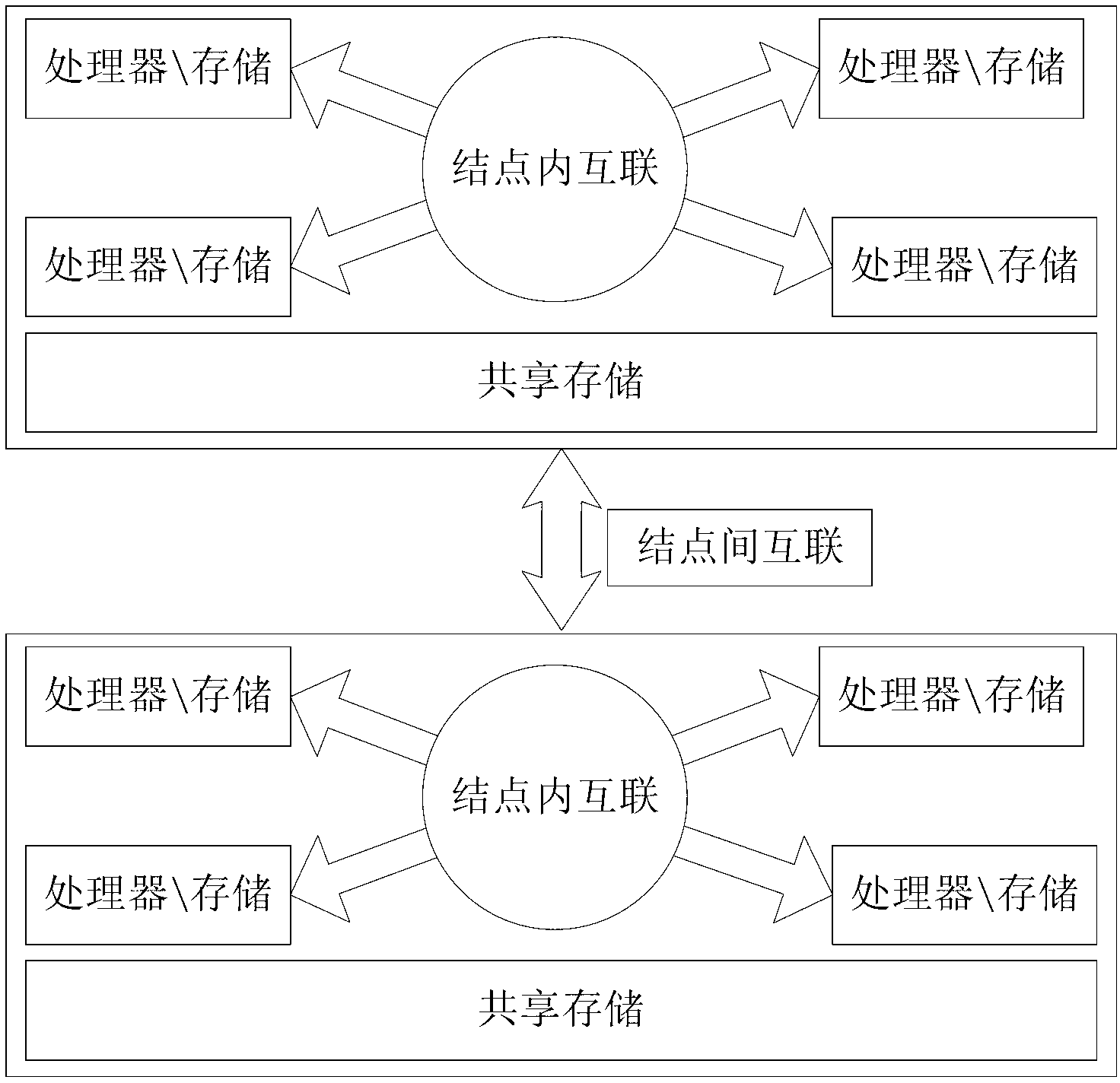

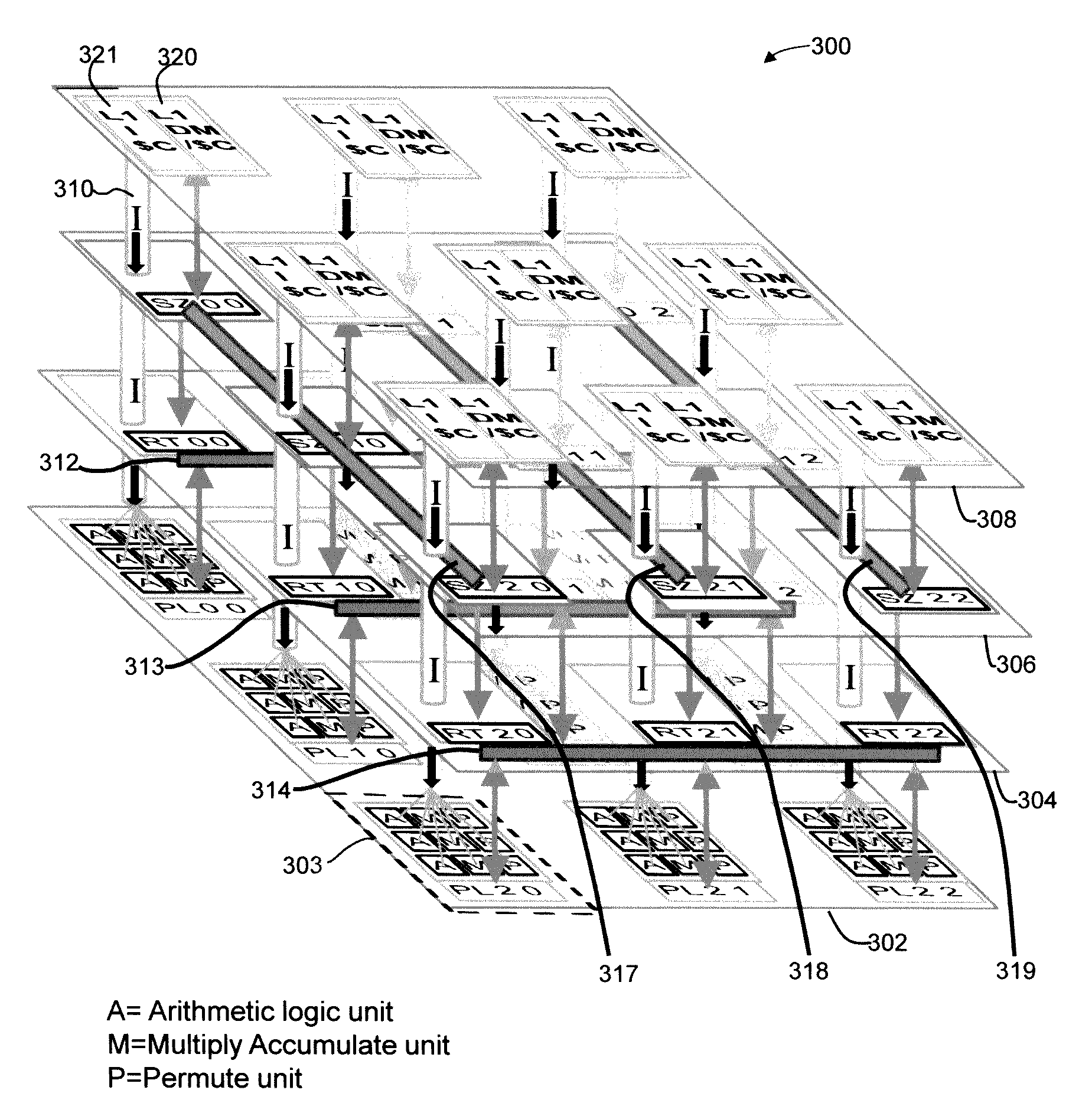

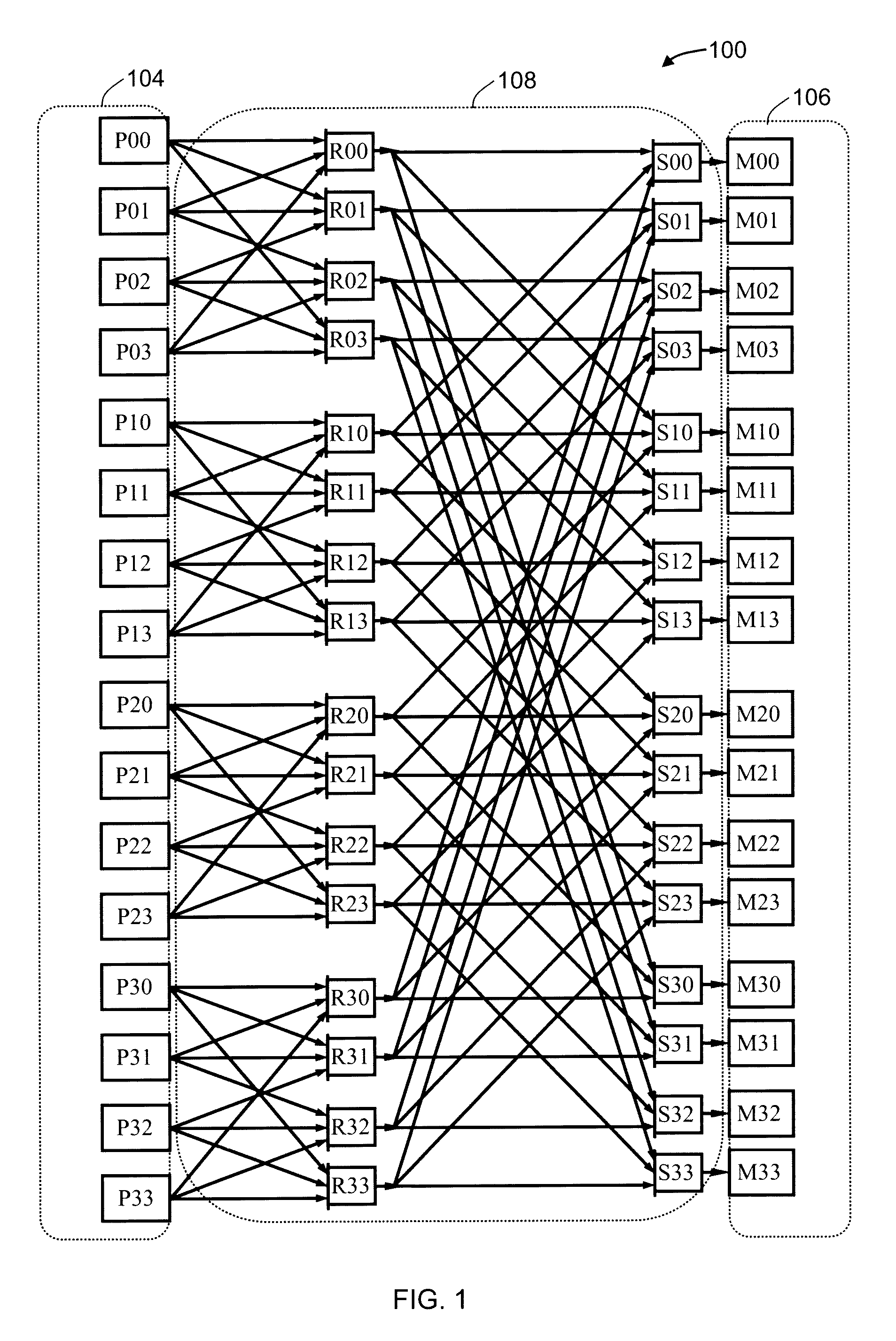

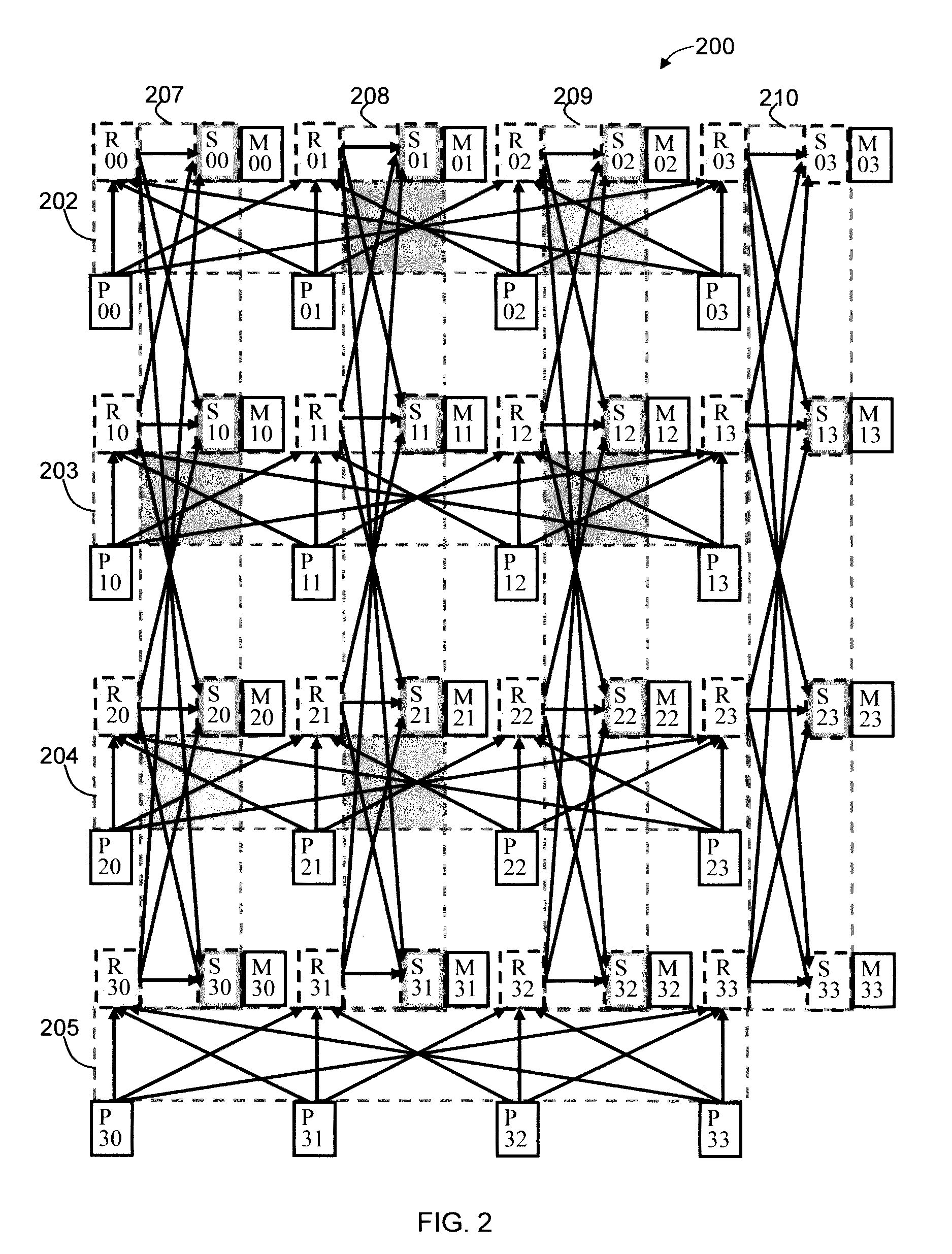

Methods and apparatus for signal flow graph pipelining that reduce storage of temporary variables

InactiveUS9507603B2Digital computer detailsConcurrent instruction executionGraphicsTemporary variable

A system for pipelining signal flow graphs by a plurality of shared memory processors organized in a 3D physical arrangement with the memory overlaid on the processor nodes that reduces storage of temporary variables. A group function formed by two or more instructions to specify two or more parts of the group function. A first instruction specifies a first part and specifies control information for a second instruction adjacent to the first instruction or at a pre-specified location relative to the first instruction. The first instruction when executed transfers the control information to a pending register and produces a result which is transferred to an operand input associated with the second instruction. The second instruction specifies a second part of the group function and when executed transfers the control information from the pending register to a second execution unit to adjust the second execution unit's operation on the received operand.

Owner:PECHANEK GERALD GEORGE

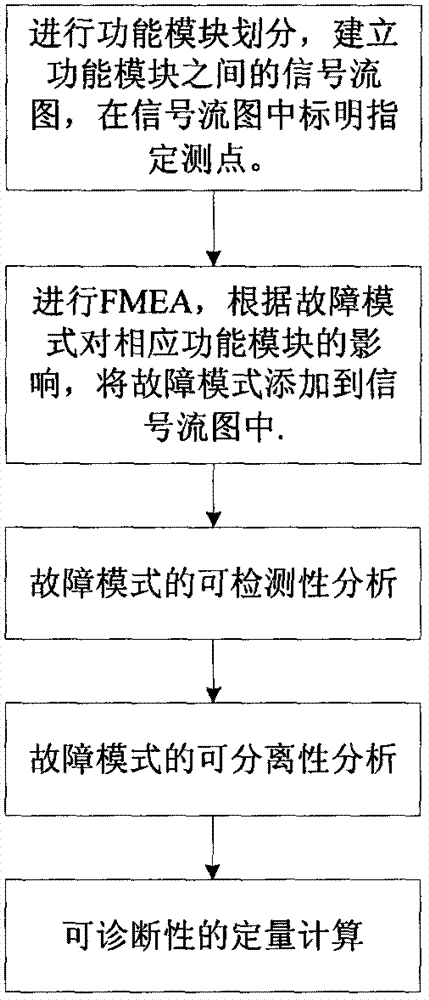

Method for determining diagnosability of angular rate measuring sensor of satellite based on correlation matrix

ActiveCN102735875AIncreased measuring pointsIncreased severityTesting/calibration of speed/acceleration/shock measurement devicesPoint correlationIsolation rate

The invention discloses a method for determining the diagnosability of an angular rate measuring sensor of a satellite based on a correlation matrix. The method comprises the following steps of: (1) dividing functional modules of the angular rate measuring sensor, establishing a signal flow diagram of each module, and marking specified measuring points in the signal flow diagram; (2) performing failure mode and effect analysis (FMEA) on the angular rate measuring sensor, determining the failure mode, failure occurrence probability, failure severity and failure effects of the angular rate measuring sensor, and according to the failure effects, adding the failure mode into the signal flow diagram; (3) establishing a failure-measuring point correlation matrix; (4) assigning the failure-measuring point correlation matrix; (5) according to the failure-measuring point correlation matrix D which is established in the step (4), performing failure detectability analysis on the angular rate measuring sensor; (6) according to the failure-measuring point correlation matrix D which is established in the step (4), performing failure isolability analysis on the angular rate measuring sensor; and(7) determining the diagnosability of the angular rate measuring sensor, and measuring the diagnosability according to failure detection rate RD and failure isolation rate RI.

Owner:BEIJING INST OF CONTROL ENG

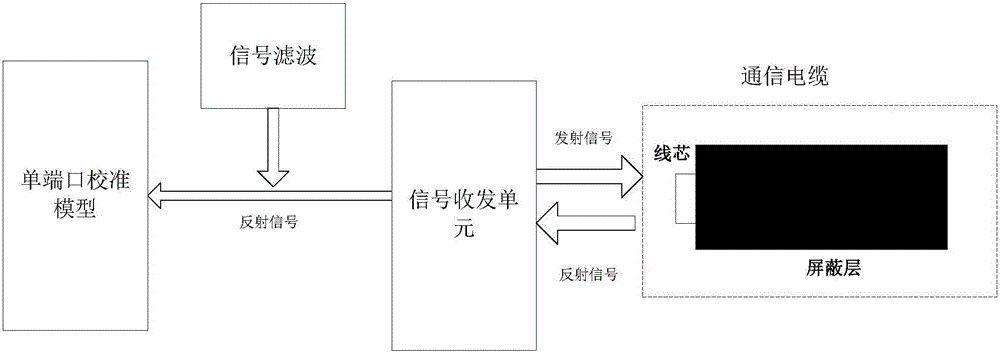

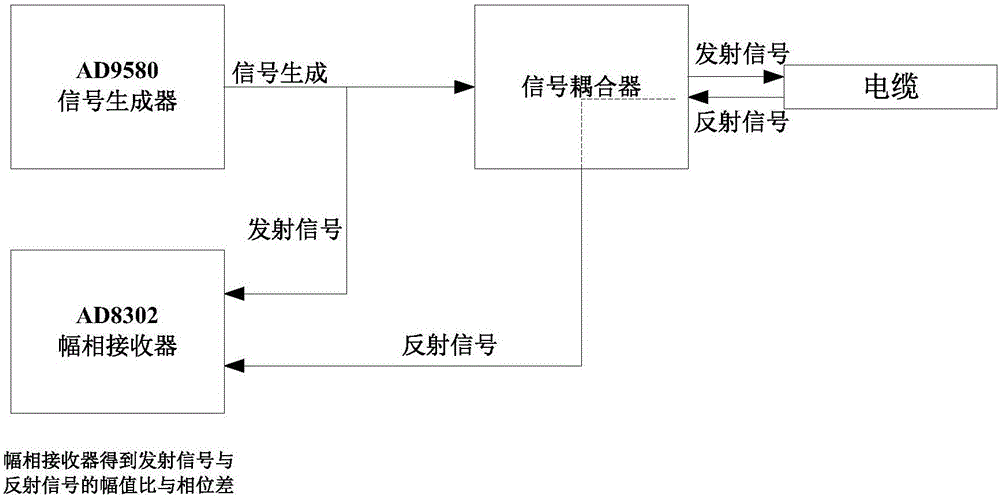

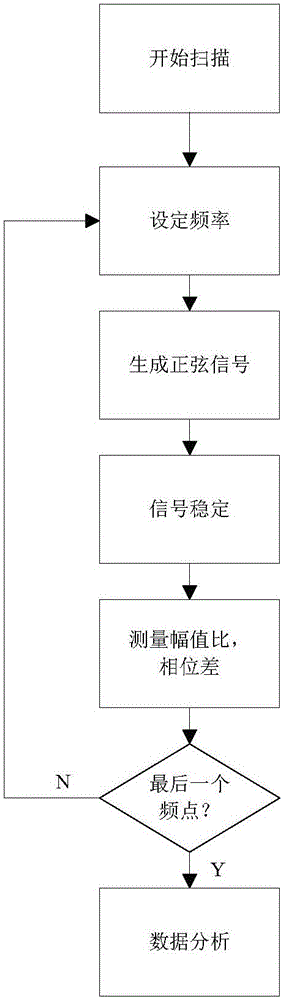

Single port measurement calibration model based cable sweep frequency positioning analyzing system and method

InactiveCN106405323AEnabling Integrity Data AnalysisGuaranteed uptimeFault location by conductor typesPhase differenceVIT signals

The invention relates to a single port measurement calibration model based cable sweep frequency positioning analyzing system and method wherein the system comprises a signal receiving and sending unit and a single port calibration model. The signal receiving and sending unit is provided with a signal emitter, a signal coupler and a signal receiver. The signal emitter generates a signal with certain frequency and sends it to the signal coupler. The signal coupler acts the emitted signal onto a to-be-detected cable hung at its end and receives the reflection signal from the cable. The signal coupler is used to separate the emitted signal and the reflection signal. The signal receiver is used to receive the reflection signal and the emitted signal and outputs the amplitude ratio of the two and their phase difference as measurement data. The single port calibration model is connected with the signal receiver. According to the application of the signal flow graph theory on the expression of the single port calibration model, the measurement data is analyzed; the position with damage or breakage is located; therefore, complete cable data analysis can be realized.

Owner:康威通信技术股份有限公司

Method for generating signal flow graph

InactiveCN1885958AIntegrity guaranteedWon't impactElectromagnetic network arrangementsSelection arrangementsRegular distributionAlgorithm

The related method for signal flow graph comprises: taking regular distribution firstly, then adjusting according to inner cable information. This invention combines the advantages of rule and longest path distributions, eliminates effect from new added unit to original graph, and can ensure the graph integrality.

Owner:HUAWEI TECH CO LTD

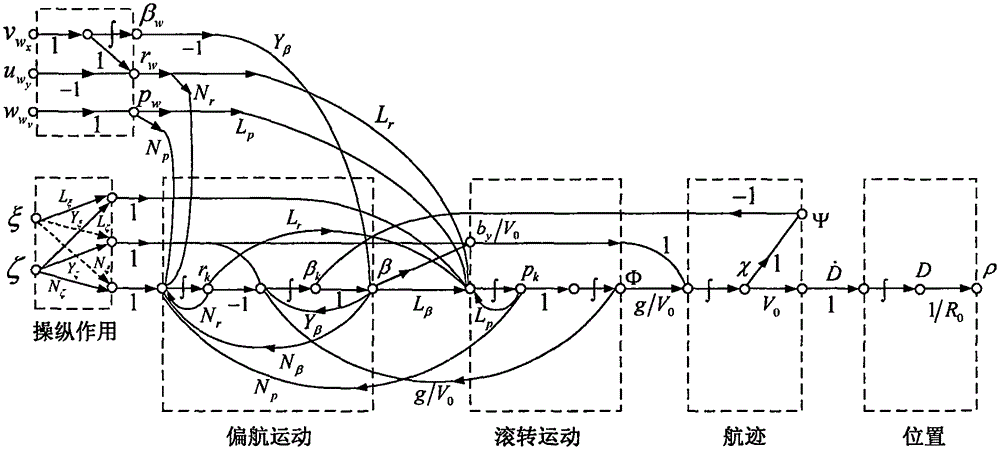

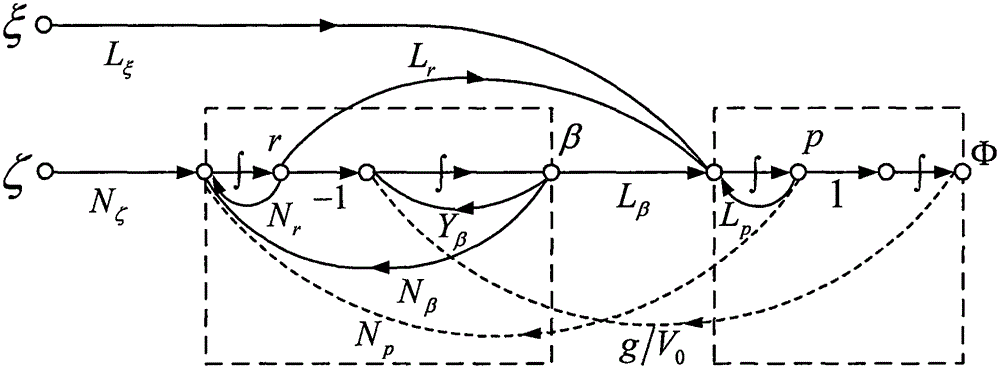

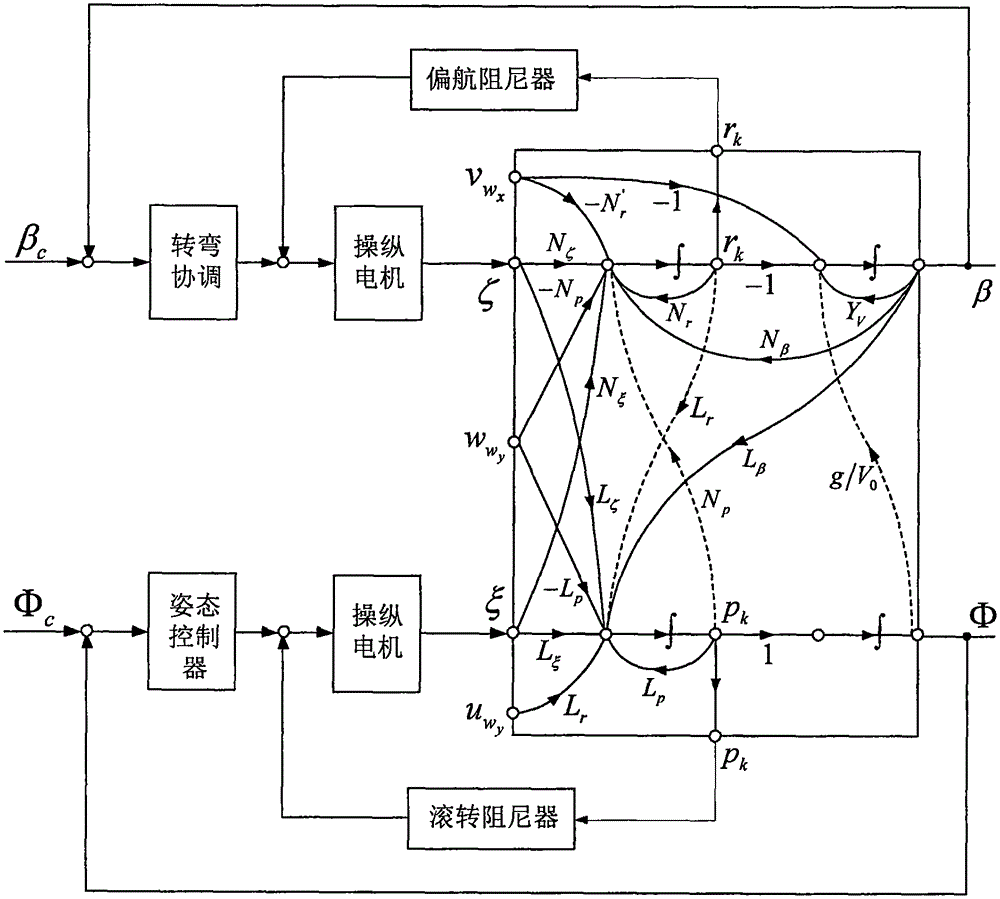

Method for designing aircraft automatic flight control system rolling attitude control structure based on signal flow graphs

The invention discloses a method for designing an aircraft automatic flight control system rolling attitude control structure based on signal flow graphs. The method comprises the steps of firstly approximately separating local signal flow graphs of a Dutch roll motion mode and a rolling motion mode from a general signal flow graph of aircraft lateral motions; secondly, selecting a forward channel with the minimum number of integrators to act as a control transmission channel of each mode, and determining an optimal feedback loop so as to improve damping and natural frequency characteristics; and finally, configuring the determined feedback control loop to the general signal flow graph of the lateral motions, and determining a lateral rolling attitude control structure. The method disclosed by the invention overcomes a defect that an automatic flight control system rolling attitude optimal control structure cannot be determined because a feedback control loop is selected according to design experience in the prior art.

Owner:AIR FORCE UNIV PLA

Logic expression extraction and switch level design method of CMOS transmission gate logic circuit

ActiveCN110263354AReduce the numberReduce areaDesign optimisation/simulationCAD circuit designCMOSTransmission gate

The invention discloses a logic expression extraction and switch level design method for a CMOS transmission gate logic circuit, and the method comprises the steps: carrying out the expansion of a Boolean algebra system, and obtaining an expanded Boolean algebra system; a CMOS transmission gate logic circuit establishing a corresponding switch level signal flow graph model; extracting the equivalent signal flow graph model of the circuit output function by the model, and obtaining the switch-level function expression of the circuit by combining the switch-level signal flow graph model with an extended Boolean algebra system, so that the CMOS transmission gate logic circuit is obtained. According to the CMOS transmission gate logic circuit designed through the method, the number of required MOS tubes is small, the number of required connection wires is small, power consumption can be reduced, and the chip area can be saved; and the designed switch level CMOS transmission gate logic circuit is full in swing amplitude, and is suitable for the design of a low-power consumption CMOS circuit.

Owner:HUAIBEI NORMAL UNIVERSITY

Method, system and client equipment for obtaining optical fiber signal flow information of optical network

InactiveCN101039151BImprove maintenance efficiencyEasy to manageWavelength-division multiplex systemsFibre transmissionFiberComputer science

The invention discloses a method for obtaining optical network element fiber signal flow information, comprises as follow: the veneer data and fiber data in optical network element which is transmitted by a server are received; veneer object and fiber object are generated according to the veneer data and fiber data, and then the optical network element fiber signal flow graph graphical system is obtained; the information of the veneer or fiber in the optical network element is displayed via the optical network element fiber signal flow graph graphical system and the optical network element fiber signal flow is obtained. The invention also discloses a method for maintaining the optical network element fiber signal flow and a system and client device for obtaining optical network element fiber signal flow information. The invention can conveniently and rapidly manage the optical network element and improve the maintenance efficiency of the optical network element.

Owner:HUAWEI TECH CO LTD

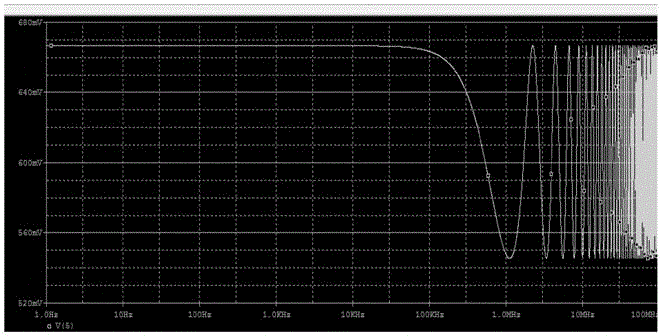

Solution for frequency domain response of impedance discontinuity transmission line

InactiveCN106326548ASave resourcesExact frequency domain solutionDesign optimisation/simulationSpecial data processing applicationsReflected wavesSimultaneous equations

The invention discloses a solution for frequency domain response of an impedance discontinuity transmission line. The solution is realized by the following steps: firstly, dividing an impedance discontinuity line into n impedance uniform segments, and establishing a signal flow graph according to a traveling-wave theory; secondly, solving a scattering coefficient of each node according to an electromagnetic topology theory, and then establishing a transmission relationship equation of waves according to a transmission theory of the waves; establishing a scattering equation of the waves according to the relationship between incident waves and reflected waves; finally, solving the frequency domain response of each node by the two simultaneous equations. Simulation verification of test software shows that the technical scheme is effective and reasonable for solving the frequency domain response of the impedance discontinuity transmission line.

Owner:TIANJIN UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com