Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

83results about How to "Realize a small area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

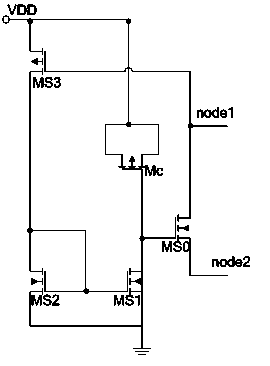

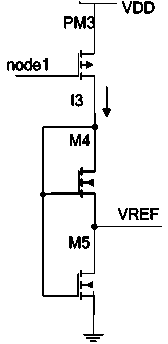

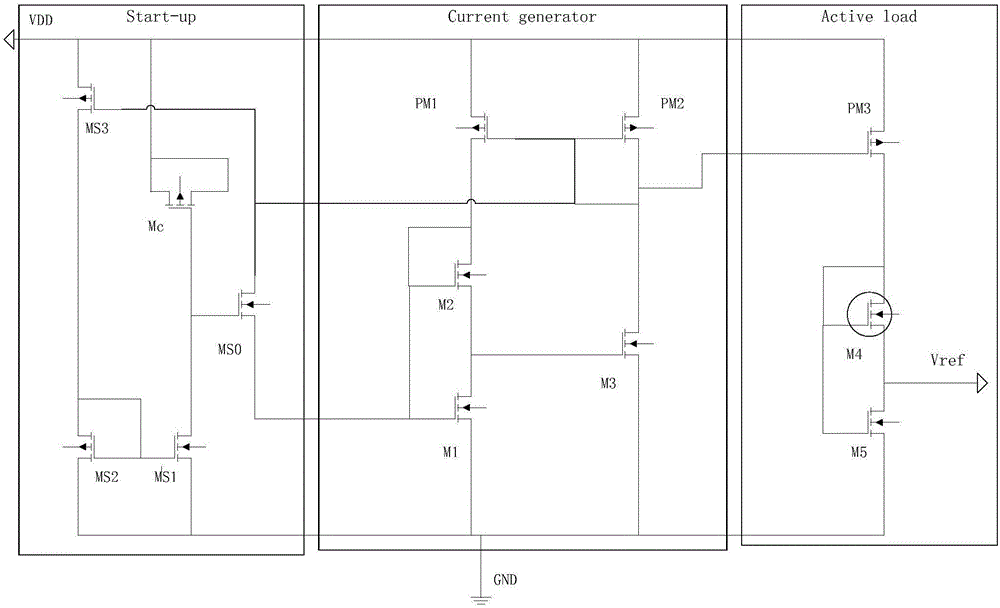

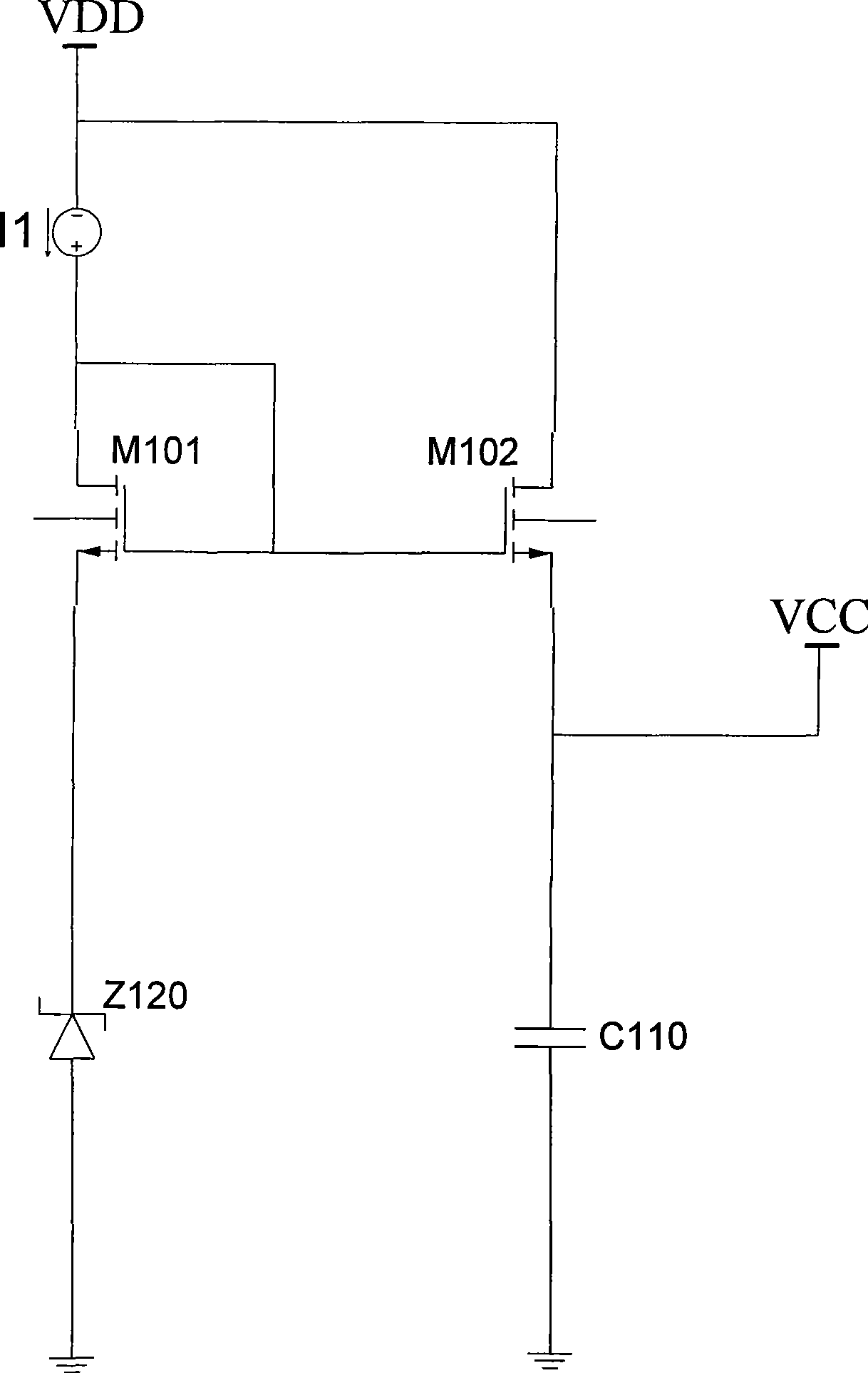

Lower-power-consumption reference source circuit

ActiveCN103513689ASimple structureRealize a small areaElectric variable regulationLoad circuitEngineering

The invention discloses a lower-power-consumption reference source circuit. The lower-power-consumption reference source circuit comprises a starting circuit unit, a current generation circuit unit and an output load circuit unit, wherein the starting circuit unit, the current generation circuit unit and the output load circuit unit are connected in sequence, the starting circuit unit is used for providing starting voltage, and preventing operation in a zero state area, the current generation circuit unit is used for generating microcurrent for the output load circuit unit, and reducing power consumption of the lower-power-consumption reference source circuit, and the output load circuit unit is used for achieving output of a zero-temperature coefficient and low-output voltage. The lower-power-consumption reference source circuit has the advantages of being low in power consumption, low in temperature coefficient, large in range of operating voltage and small in area.

Owner:SUN YAT SEN UNIV +1

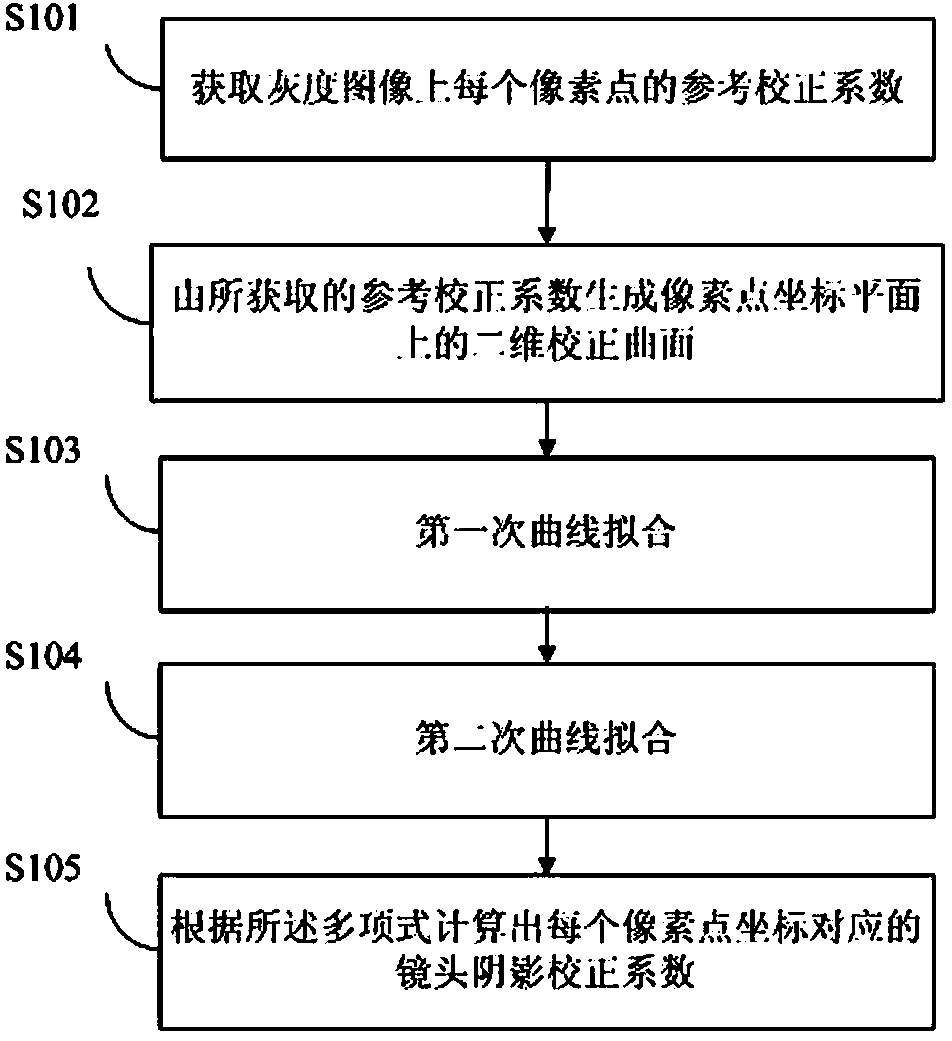

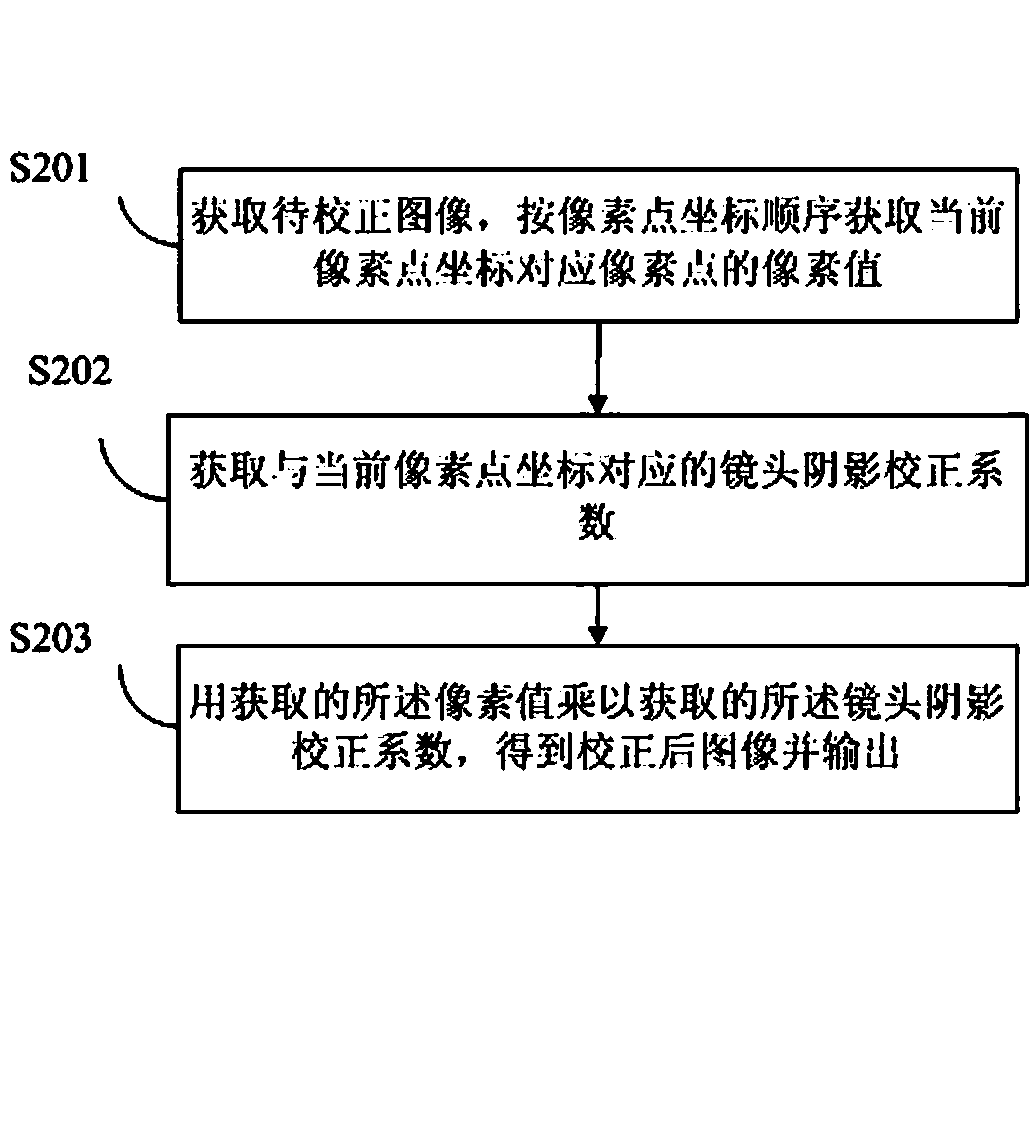

Camera lens shadow correction coefficient determination method and device, and camera lens shadow correction method and device

ActiveCN103377474ARealize a small areaImprove the correction effectImage analysisPicture signal generatorsCamera lensCurve fitting

The invention discloses a camera lens shadow correction coefficient determination method and device, and a camera lens shadow correction method and device. The camera lens shadow correction coefficient determination method includes the steps of obtaining the reference correction coefficient of each pixel on a gray level image, generating a two-dimension correction curved surface, conducting primary curve fitting, conducting secondary curve fitting, and calculating the camera lens shadow correction coefficient corresponding to each pixel coordinate. The invention further discloses the camera lens shadow correction coefficient determination device. The camera lens shadow correction method includes the steps of obtaining an image to be corrected, obtaining a camera lens shadow correction coefficient, and obtaining the corrected image by the way that a pixel value is multiplied by the camera lens shadow correction coefficient. The invention further discloses the camera lens shadow correction device. The camera lens shadow correction coefficient determination method and device, and the camera lens shadow correction method and device are suitable for conducting camera lens shadow correction on images shot by various camera lenses, the correction effect is good, the implementation method is simple, and hardware implementation area is small.

Owner:BYD SEMICON CO LTD

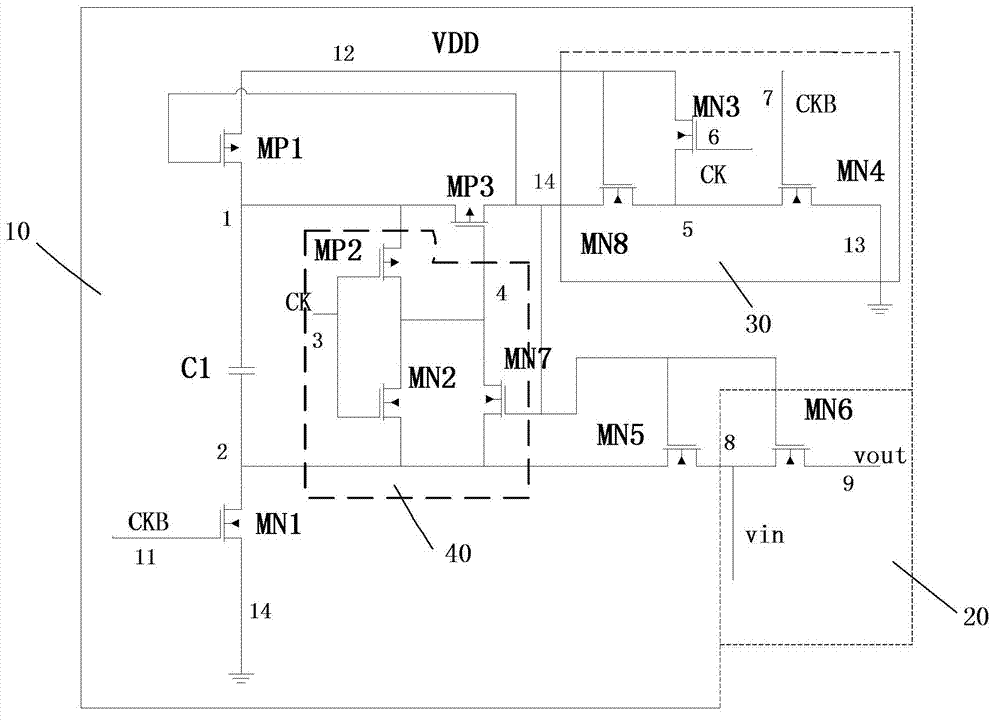

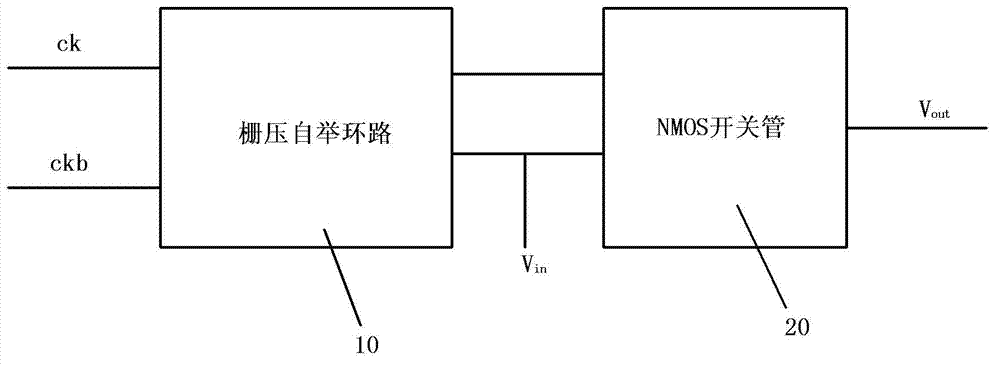

Grid voltage bootstrapped switch circuit

The invention provides a grid voltage bootstrapped switch circuit. The grid voltage bootstrapped switch circuit comprises a grid voltage bootstrapped loop circuit (10) and an NMOS (N-Metal Oxide Semiconductor) switching tube (MN6), wherein the grid voltage bootstrapped loop circuit (10) is used for generating grid control voltage under the control of a clock signal, and the grid control voltage can be influenced by an input analog signal; and a grid end of the NMOS switching tube (MN6) is connected with the grid voltage bootstrapped circuit (10), a leakage end of the NMOS switching tube (MN6) is connected to an analog signal input end, a source end of the NMOS switching tube (MN6) is connected to a discrete signal output end, and the NMOS switching tube (MN6) is used for keeping the grid source voltage difference unchanged under the control of the grid control voltage, sampling the analog signal input by the analog signal input end into a discrete signal and outputting the discrete signal from the discrete signal output end. According to the grid voltage bootstrapped switch circuit provided by the invention, the nonlinearity of switching on a resistor by a switch is removed to the maximum, the signal distortion is reduced, and the circuit accuracy is increased.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

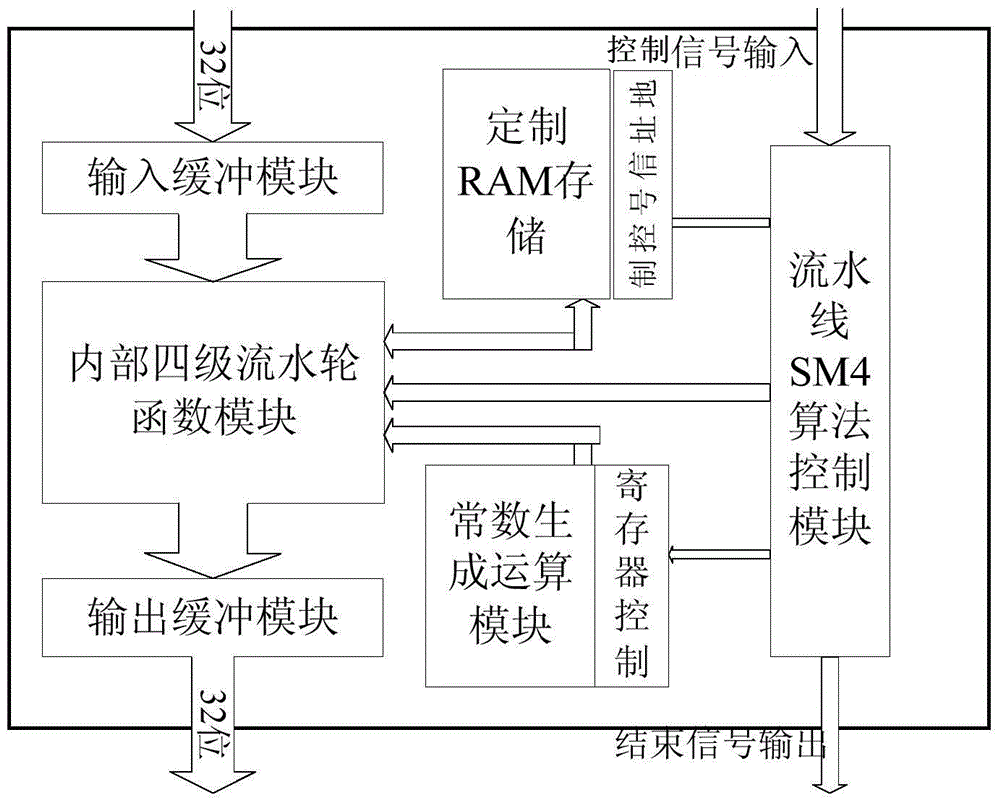

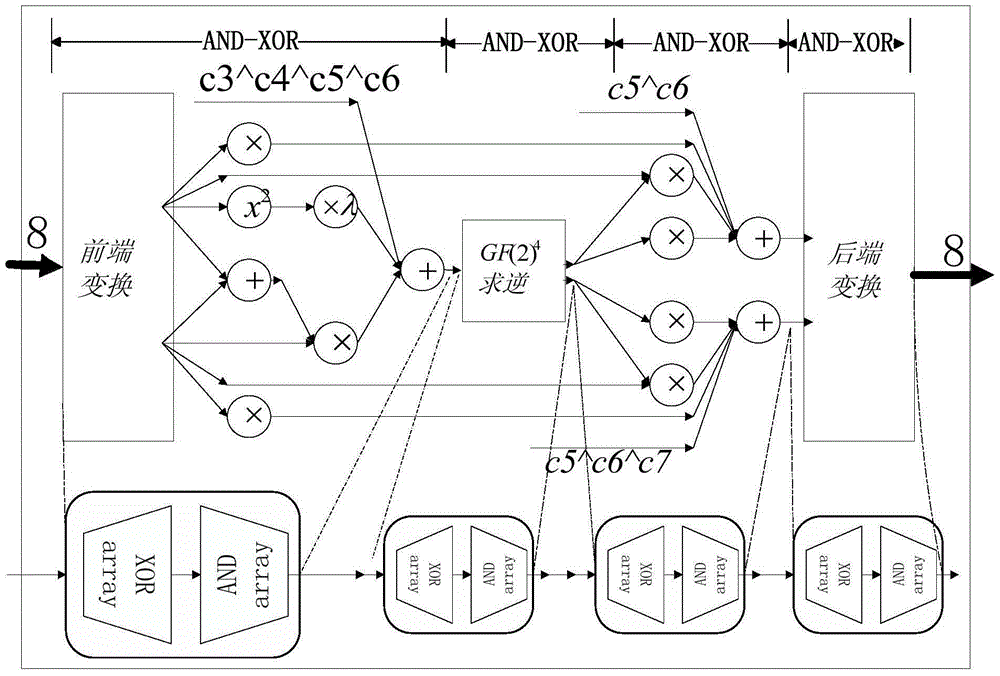

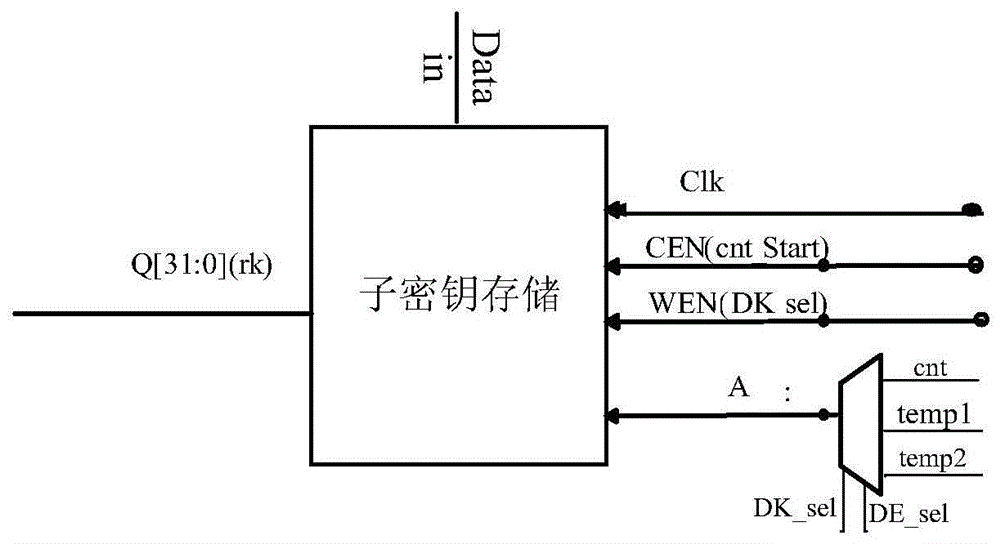

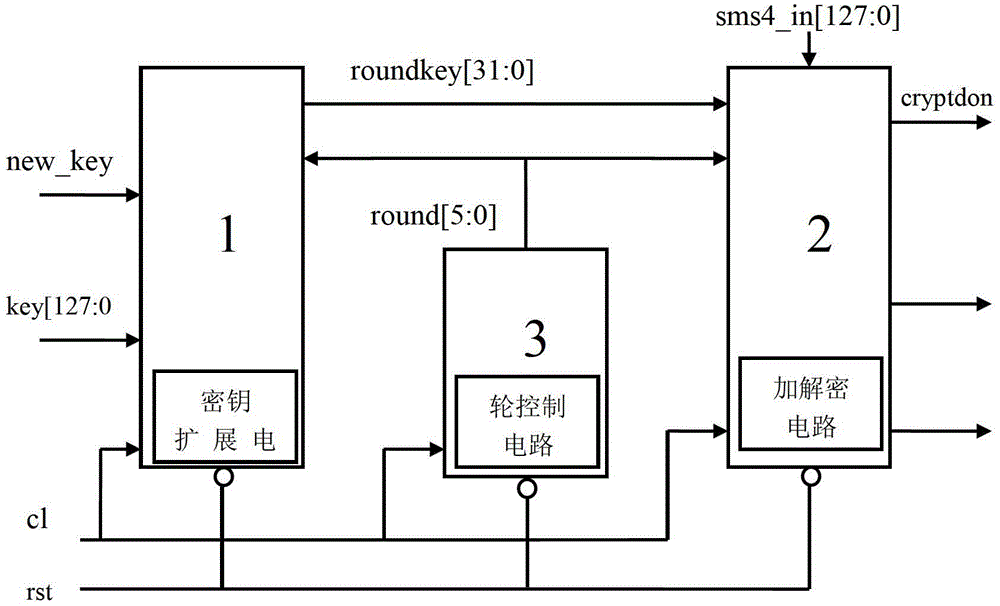

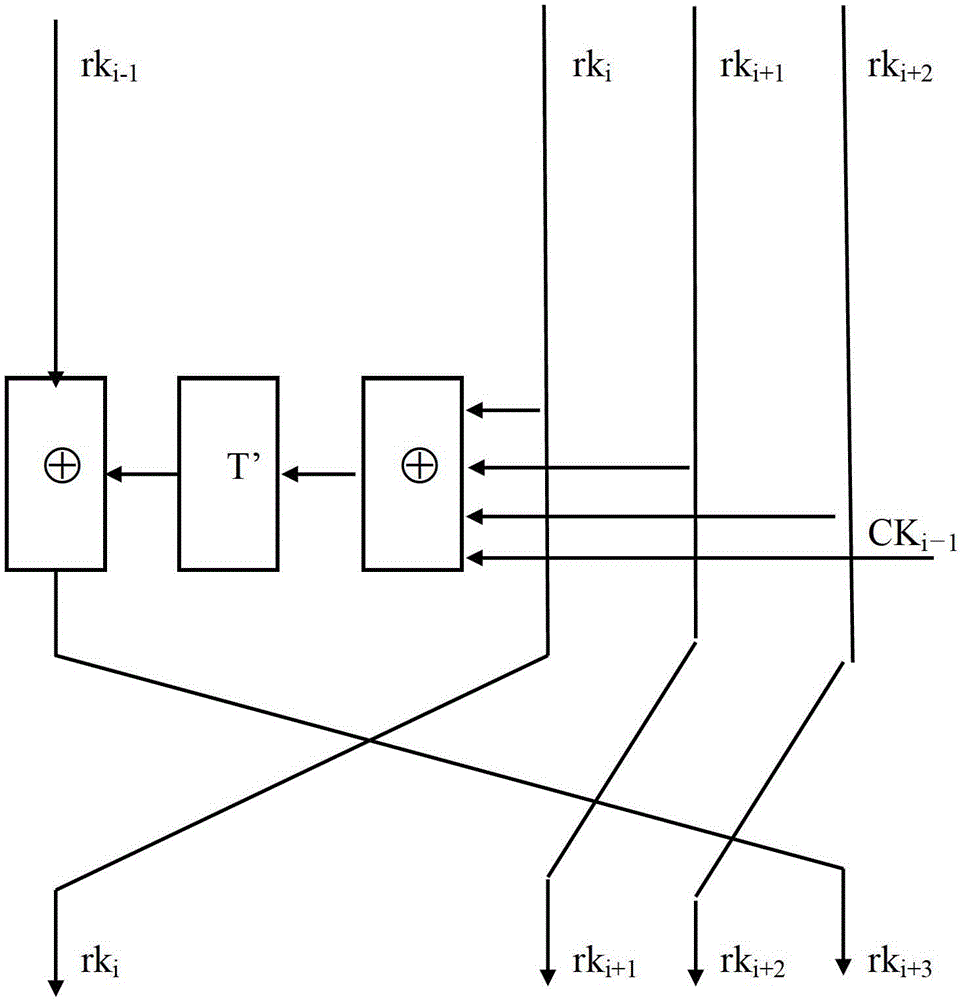

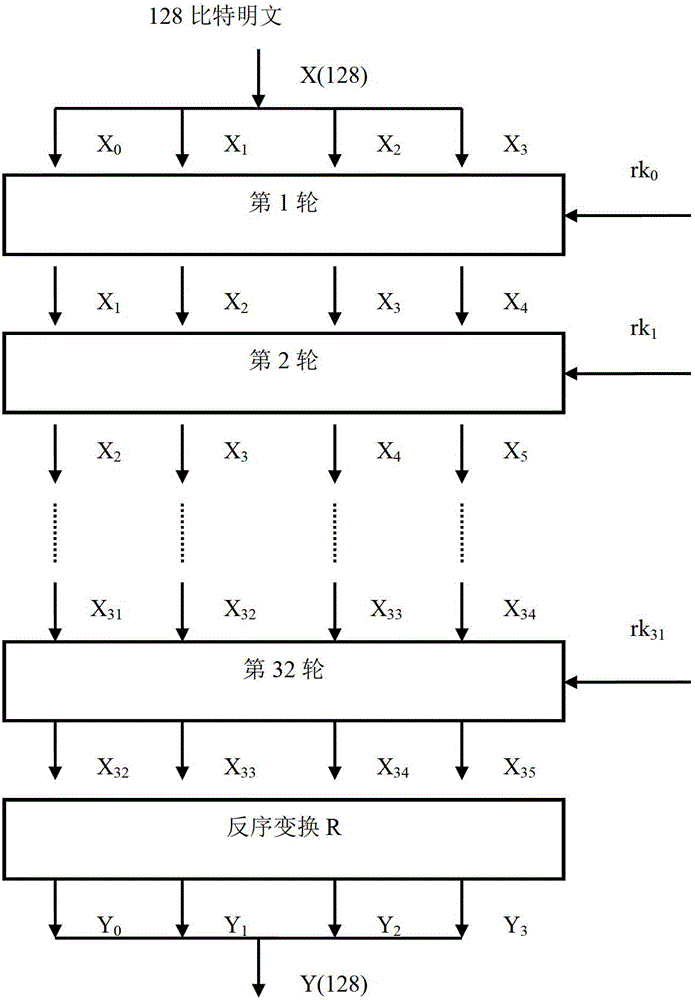

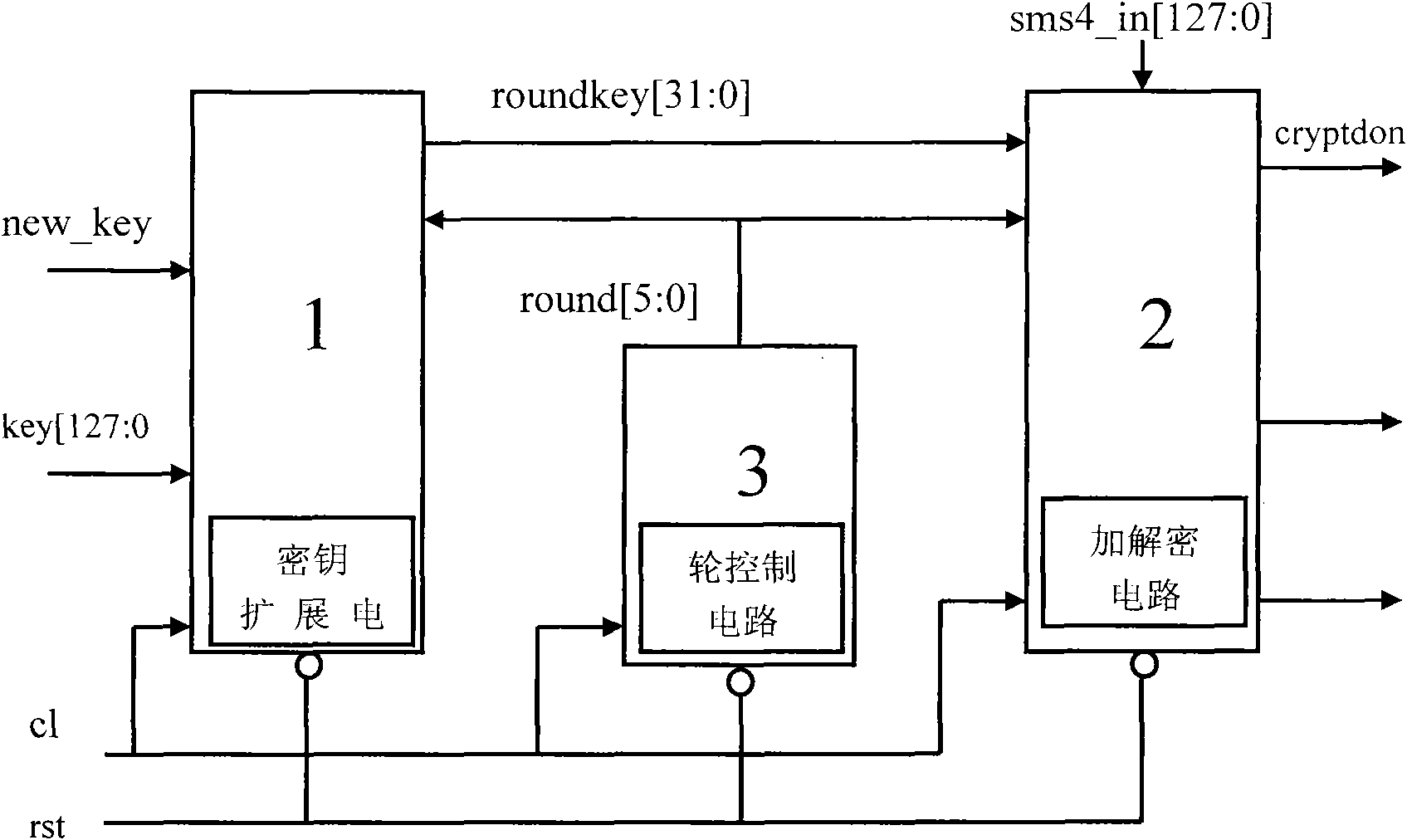

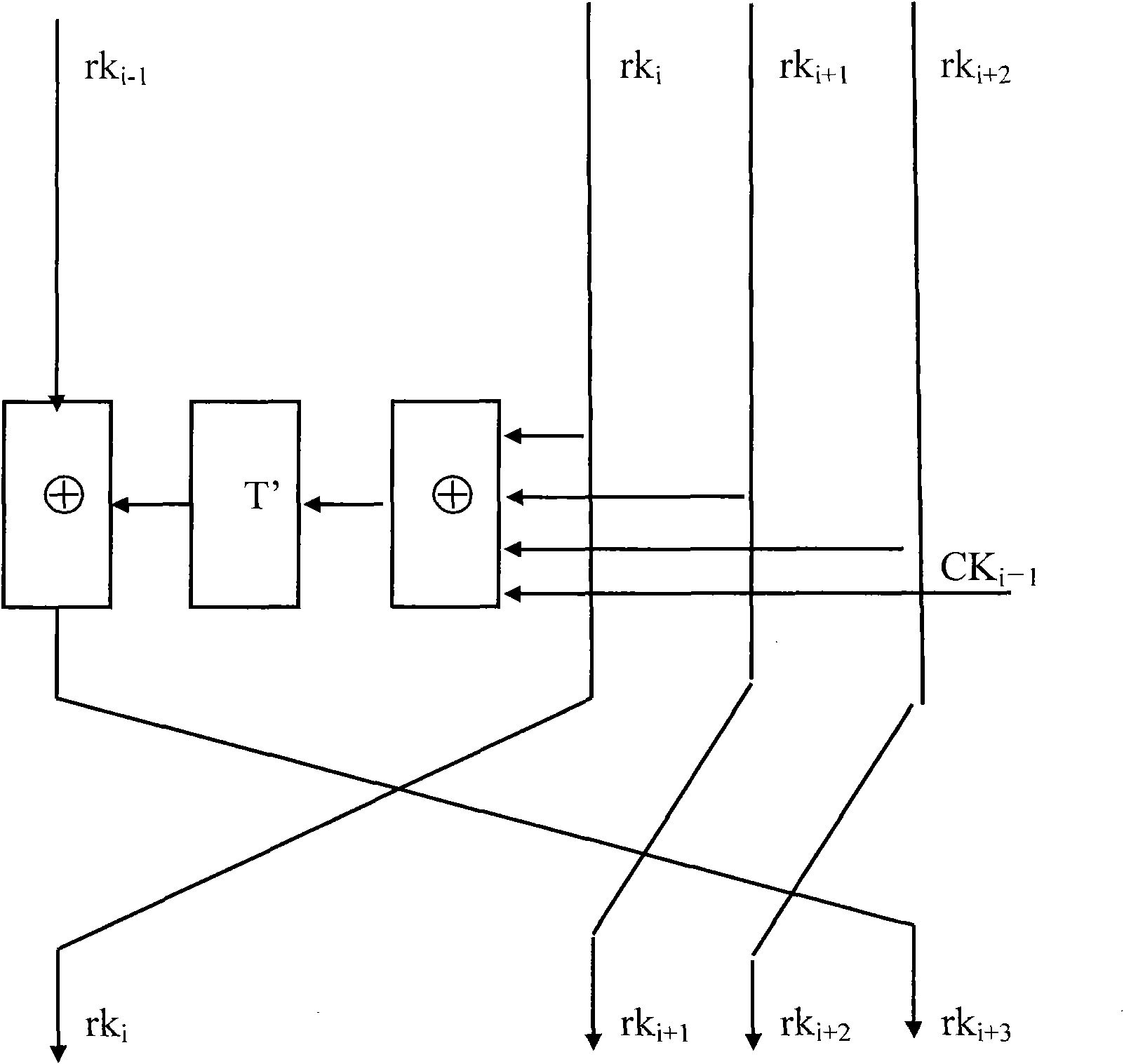

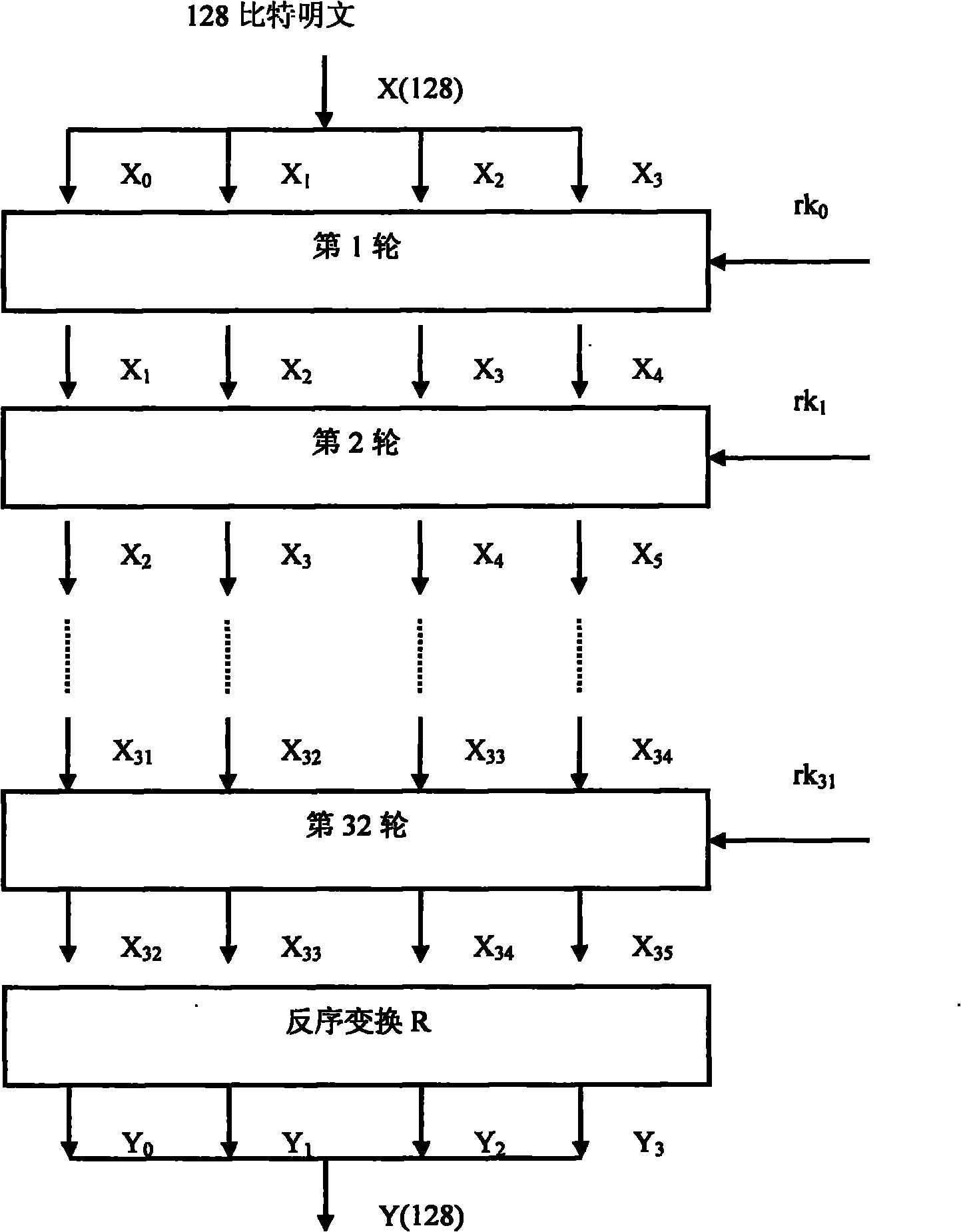

SM4 algorithm realization system of pipeline structure

ActiveCN105049194ALower latencyReduce areaKey distribution for secure communicationEncryption apparatus with shift registers/memoriesWater turbineMode control

The invention relates to an SM4 algorithm realization system of a pipeline structure. An input buffer module, an internal four-level water turbine function module, an output buffer module, a storage module, a constant generating operation module and a control module are included. An enable signal is received, a mode control signal is obtained and parsed, key expansion operation, encryption operation and decryption operation are completed according to the mode control signal, and encryption result data and decryption result data are obtained and output. The realization system employs a non-linear S box for displacement operation, the non-linear S box uses random mask and addition mask technology of PPRM structure and a single-wheel iteration internal four-level pipeline structure, and compared with the prior art, the realization area is small, the safety level is high, resistance to zero-value attack is high, the operation speed is higher, the power consumption of operation is lower, and the application prospect is better.

Owner:BEIJING MXTRONICS CORP +1

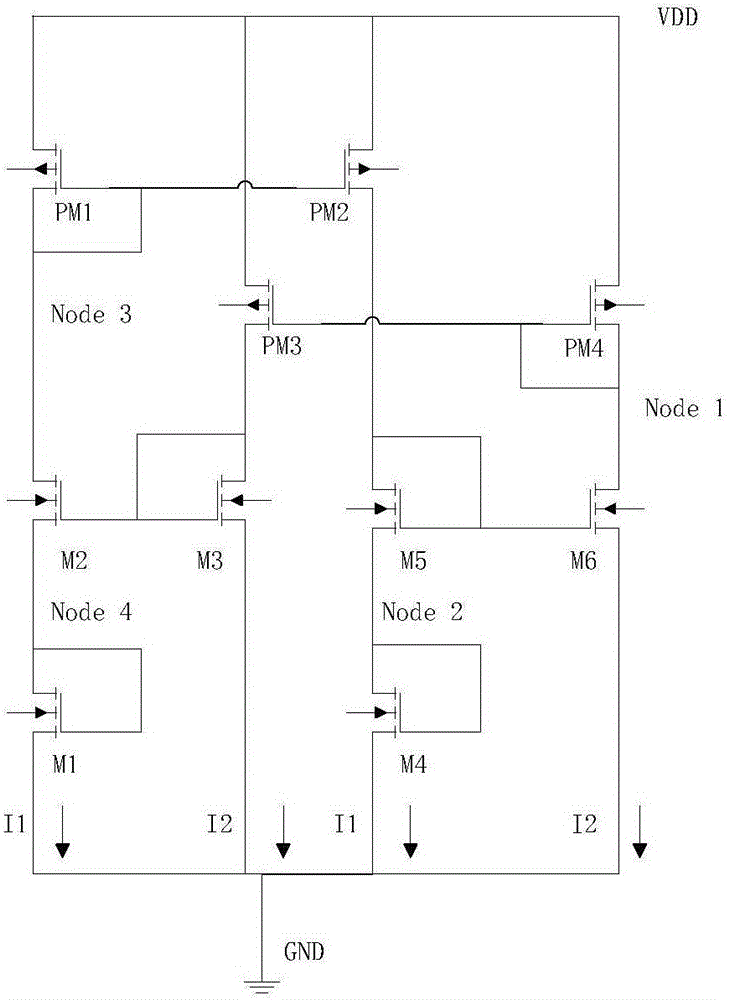

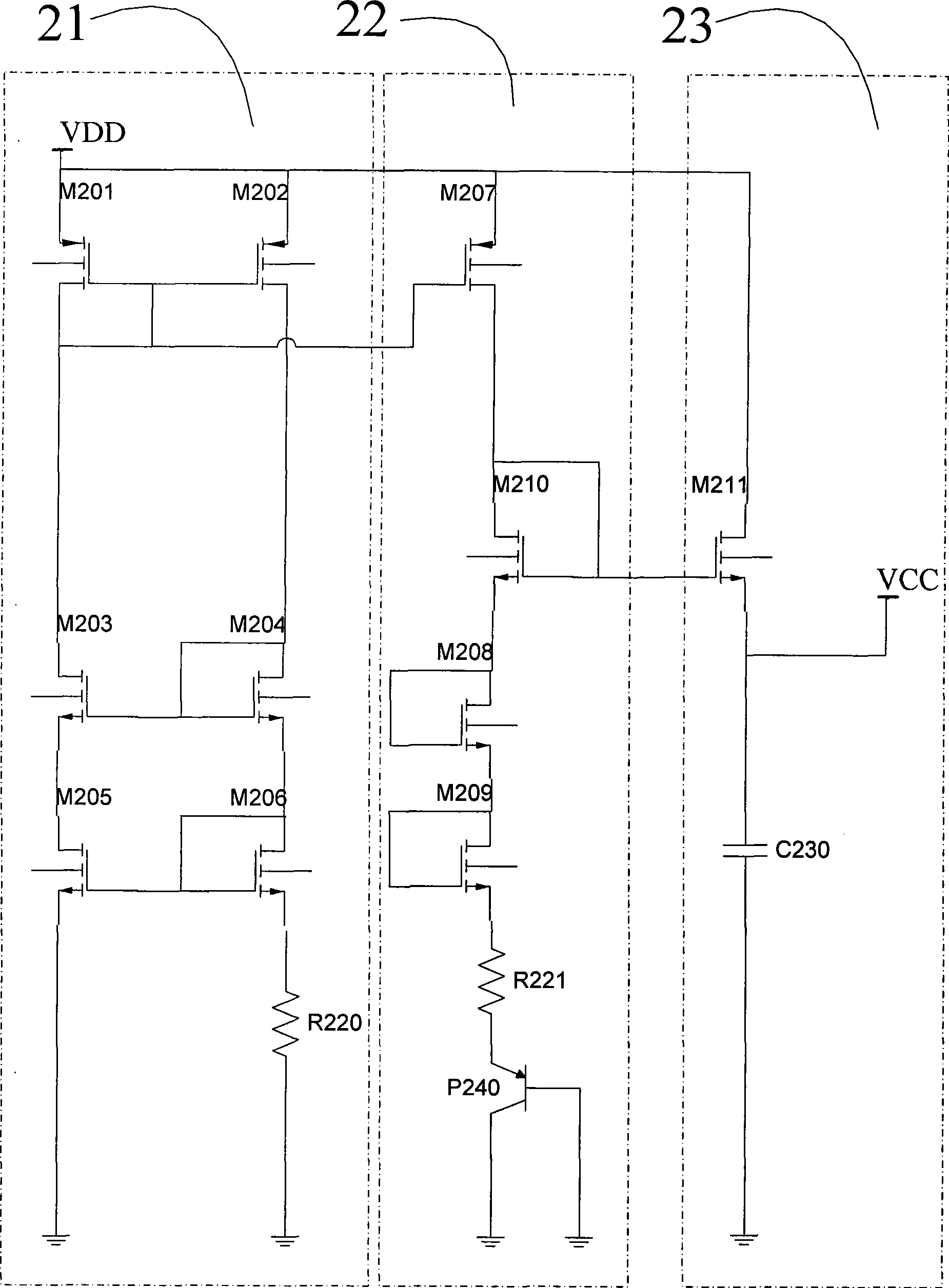

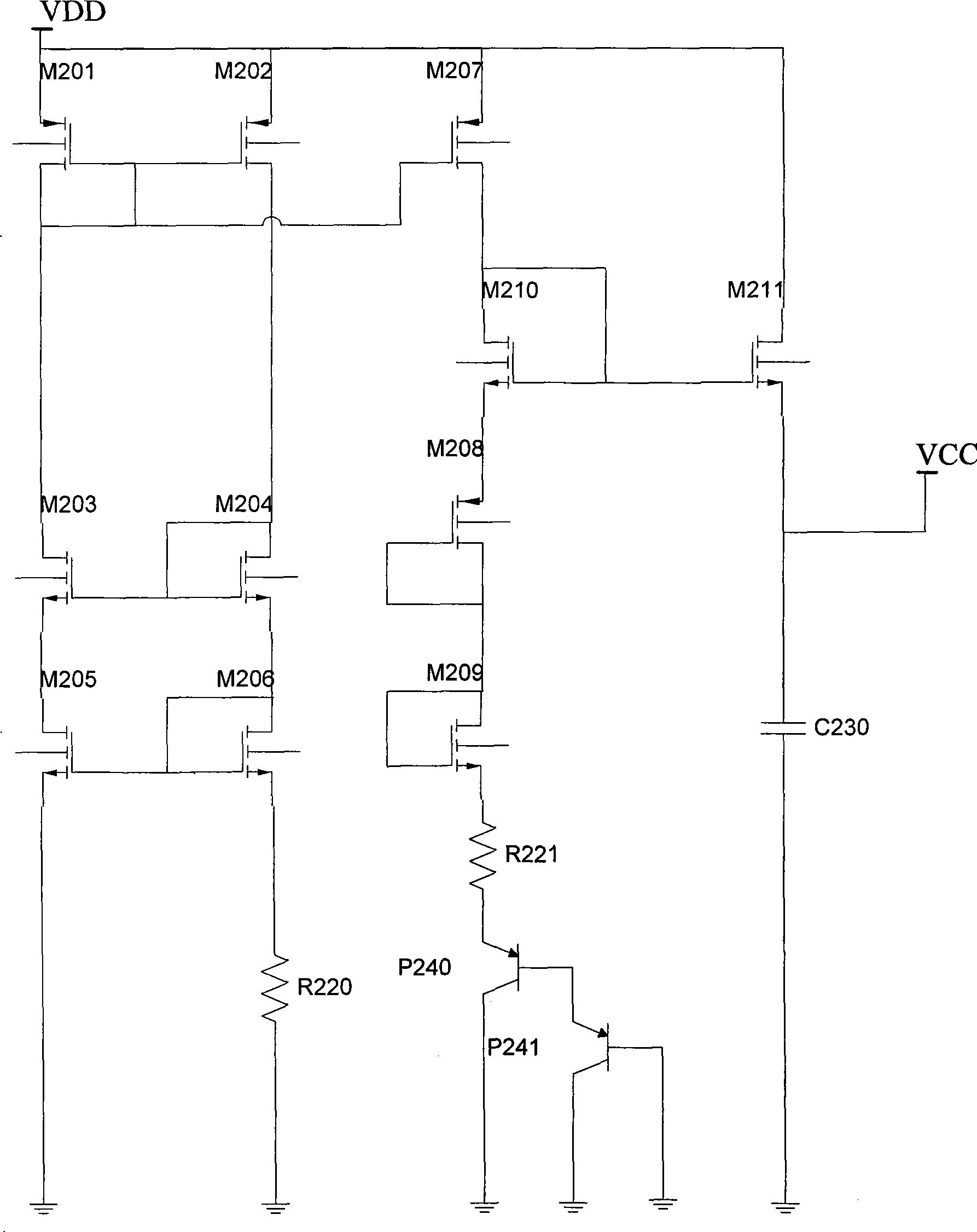

Low-power-consumption full-CMOS reference source circuit based on subthreshold value

The invention discloses a low-power-consumption full-CMOS reference source circuit based on a subthreshold value. The low-power-consumption full-CMOS reference source circuit based on the subthreshold value comprises a start circuit unit, a current generating circuit unit and an active load circuit unit. The start circuit unit is used for providing a start current to enable the current to get into a normal work state. The current generating circuit unit is used for generating a current irrelevant to input power voltages. Due to the fact that part of MOS transistors work in a subthreshold state, the work current is low, and the power consumption of the circuit can be reduced. The output active load circuit unit outputs a zero temperature coefficient and low output voltages through the body polarization technology. The circuit has the advantages of being low in power consumption, low in temperature coefficient, wide in work voltage range, small in area and the like.

Owner:SUN YAT SEN UNIV +2

KLEIN encryption implementation method based on area and performance balanced optimization

ActiveCN103684749AImprove parallelismFast encryptionEncryption apparatus with shift registers/memoriesS-boxByte

The invention discloses a KLEIN encryption implementation method based on area and performance balanced optimization. The method includes: optimizing an S box, allowing two modules to share the S box, building a Tab box for fast table look-up, allowing key expansion round constant i to be in a self-adding manner, encapsulating and integrating round key adding, byte substitution, row shifting, line mixing, and key expansion sub-modules into one module, using continuous assignment statement to realize algorithm assignment, updating a clock signal control counter, using Verilog HDL (hardware description language) parallel execution features and the manner integrating the sub-modules into one module, using global synchronization clock pulse triggering, and fully utilizing the device trigger and wiring resources. By the method, the area resource occupation required by implementing the KLEIN encryption algorithm can be saved effectively, encryption speed is increased, and the KLEIN encryption algorithm can be implemented with low hardware area and keep high performance.

Owner:HENGYANG NORMAL UNIV

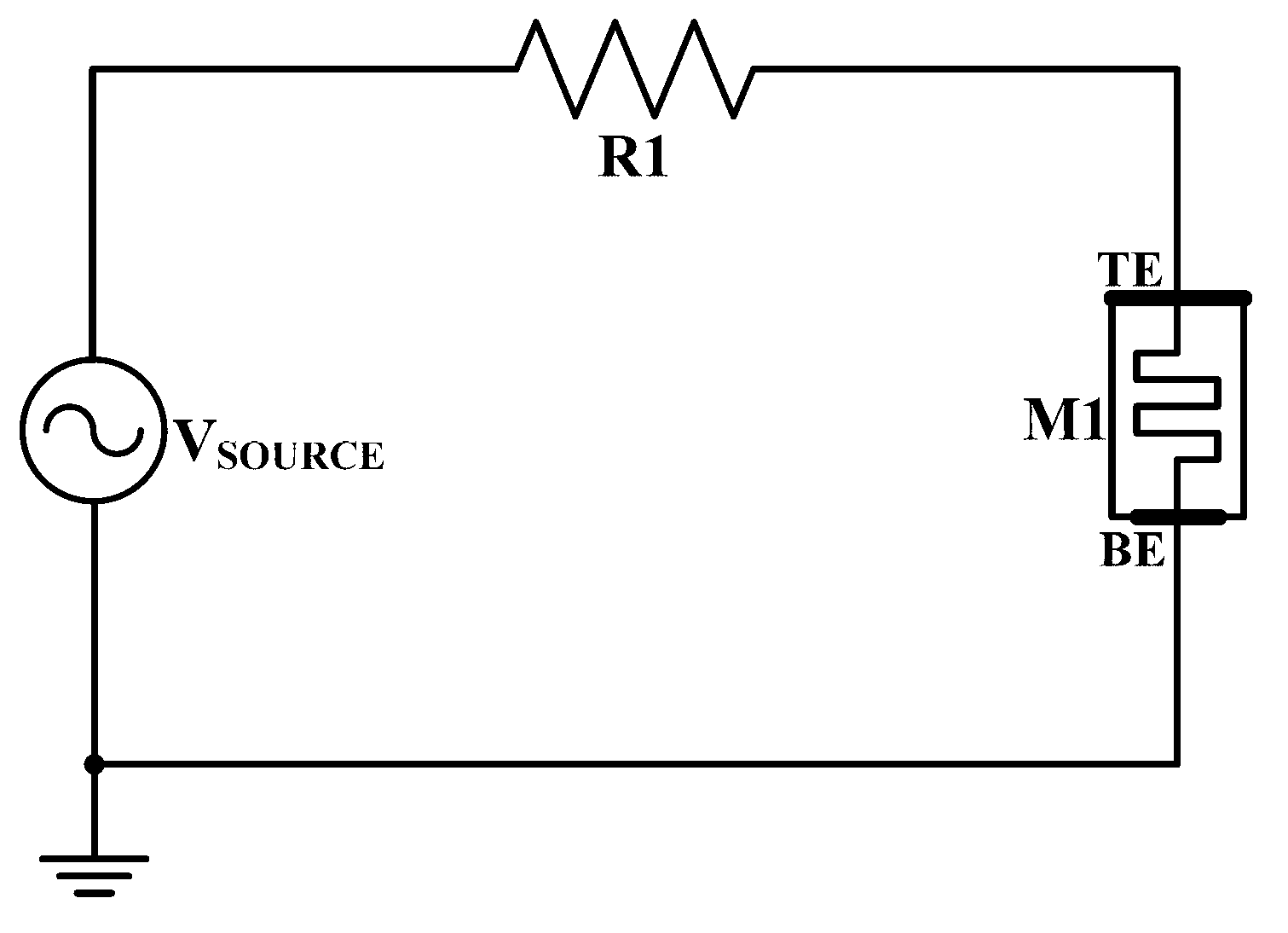

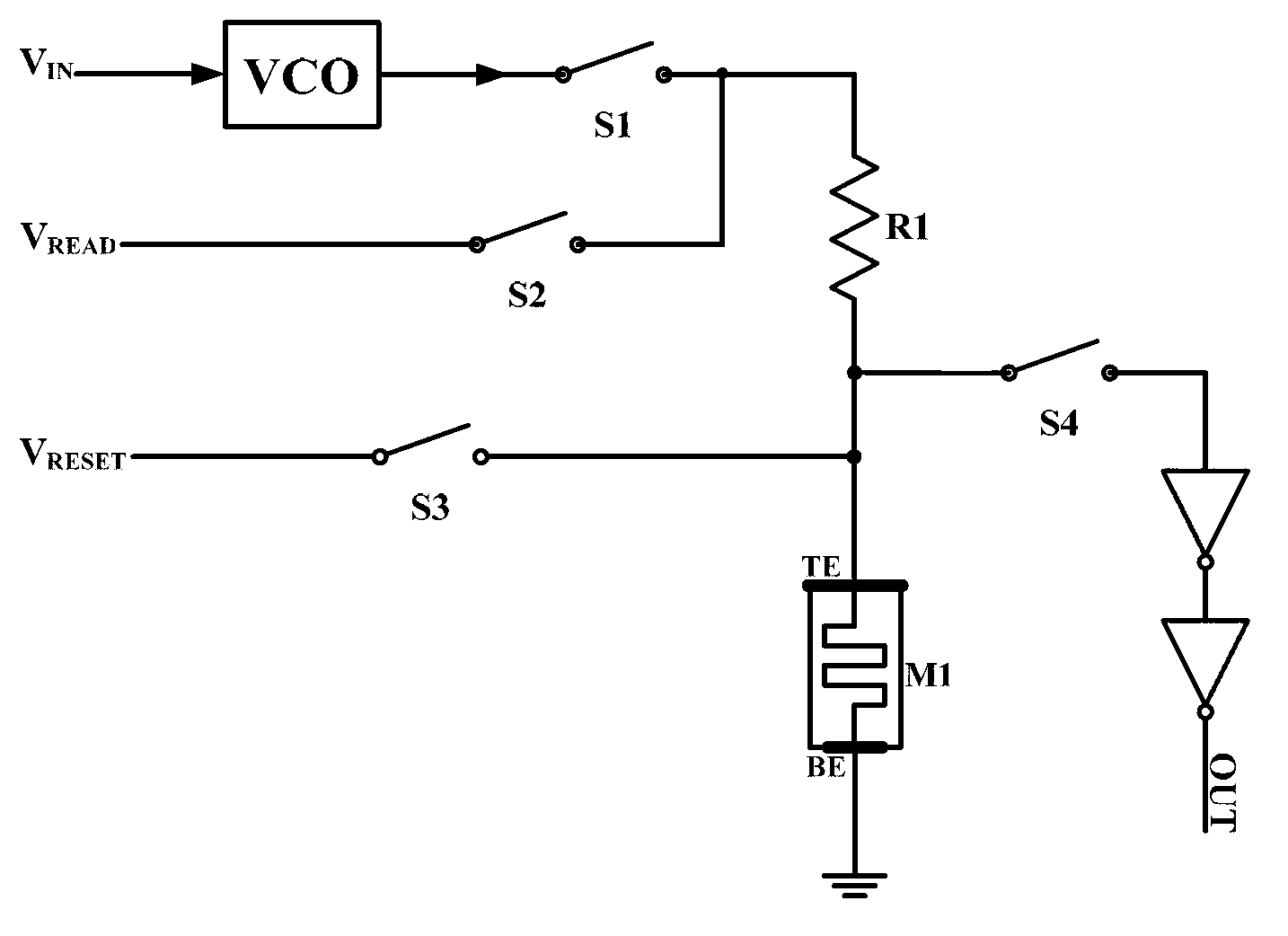

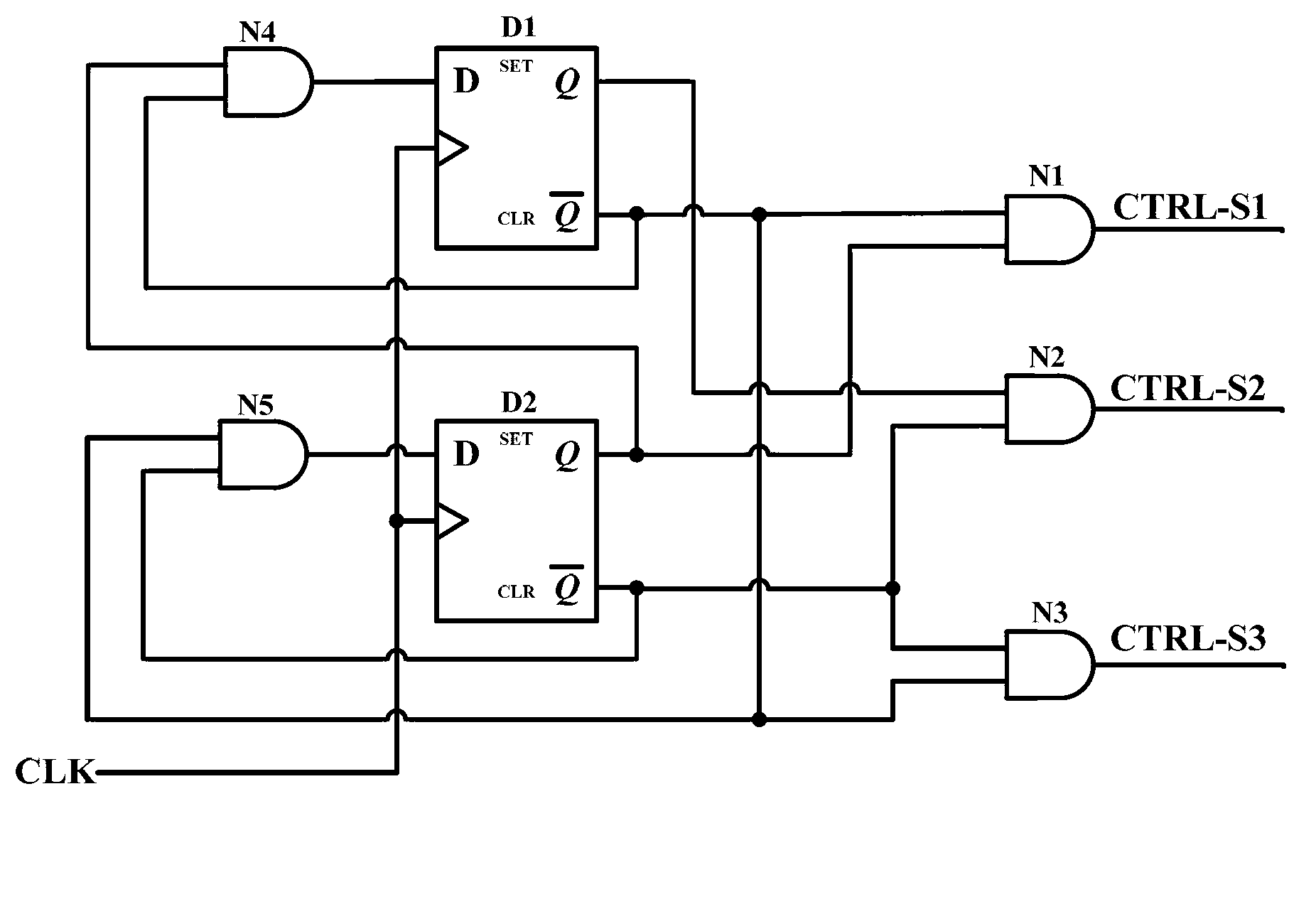

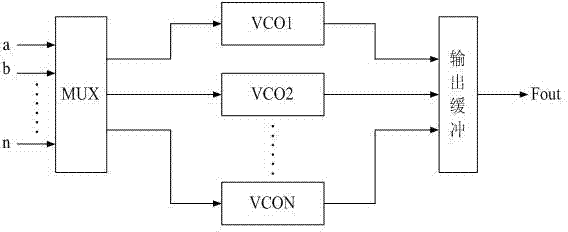

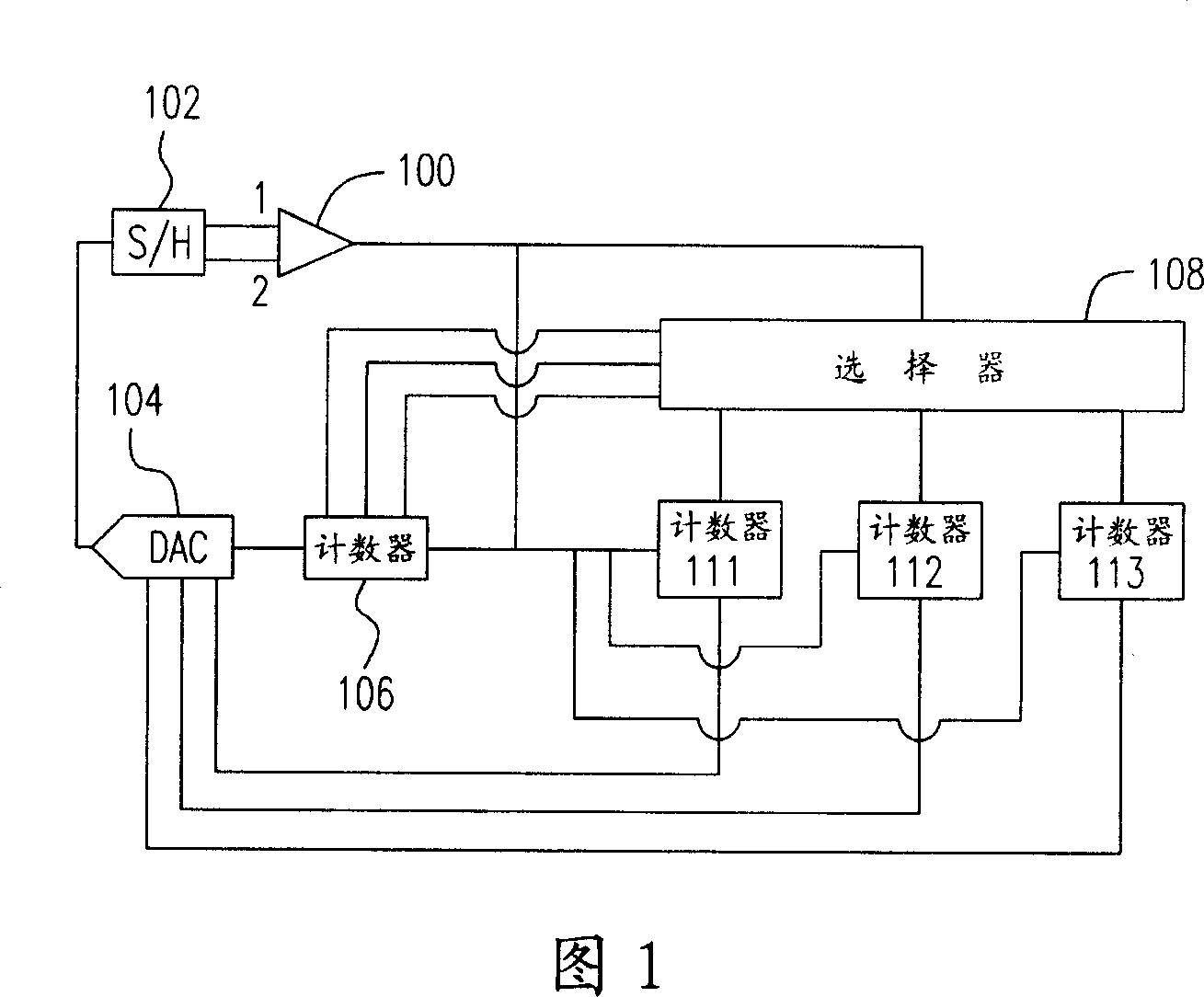

Analog-digital conversion circuit based on memristor

ActiveCN103281082ARealize a small areaLow costAnalogue-digital convertersEngineeringAlternating current

The invention relates to the field of semiconductor integrated circuits, and discloses a novel analog-digital conversion circuit based on a memristor. The analog-digital conversion circuit based on the memristor is high in precision, low in power consumption and small in chip area occupation. The analog-digital conversion circuit based on the memristor comprises a voltage-controlled oscillator, a state control circuit, a frequency comparison circuit and an output circuit. The voltage-controlled oscillator is used for conversing input analog voltage into periodic alternative current signal frequency to indicate an electric signal, and the electric signal is used for programming the frequency comparison circuit. The state control circuit is used for controlling programming, state reading and the reset operation of the frequency comparison circuit according to a control time sequence. The frequency comparison circuit is used for converting the frequency of the periodic alternative current signal output by the voltage-controlled oscillator into a resistance value of the memristor to indicate a digital signal. The output circuit is used for outputting the digital signal which is converted by the frequency comparison circuit under the control of the state control circuit. The analog-digital conversion circuit based on the memristor is suitable for being used for converting analog signals to digital signals.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

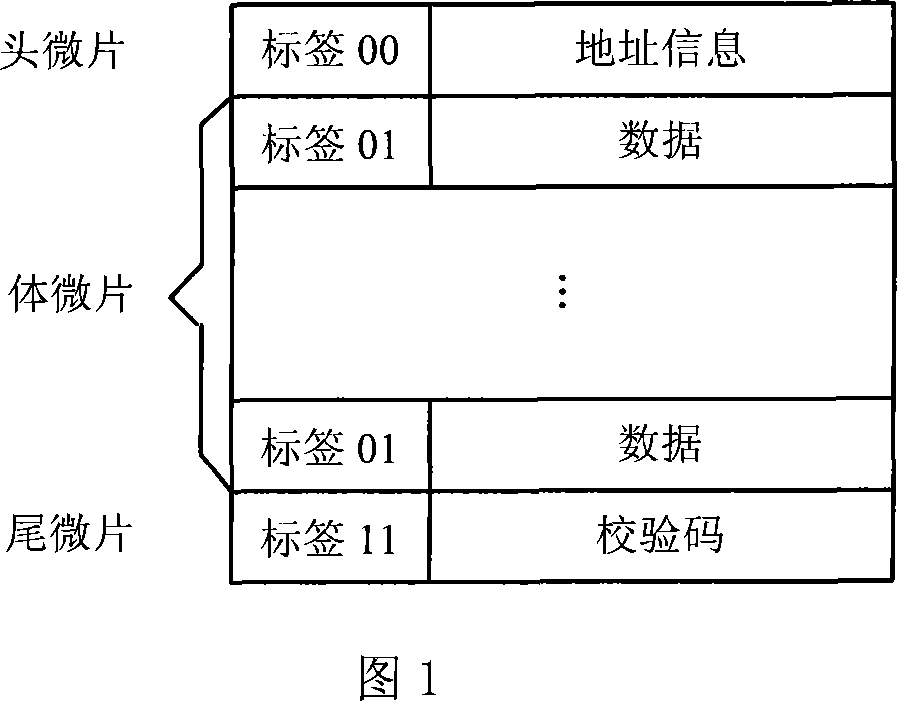

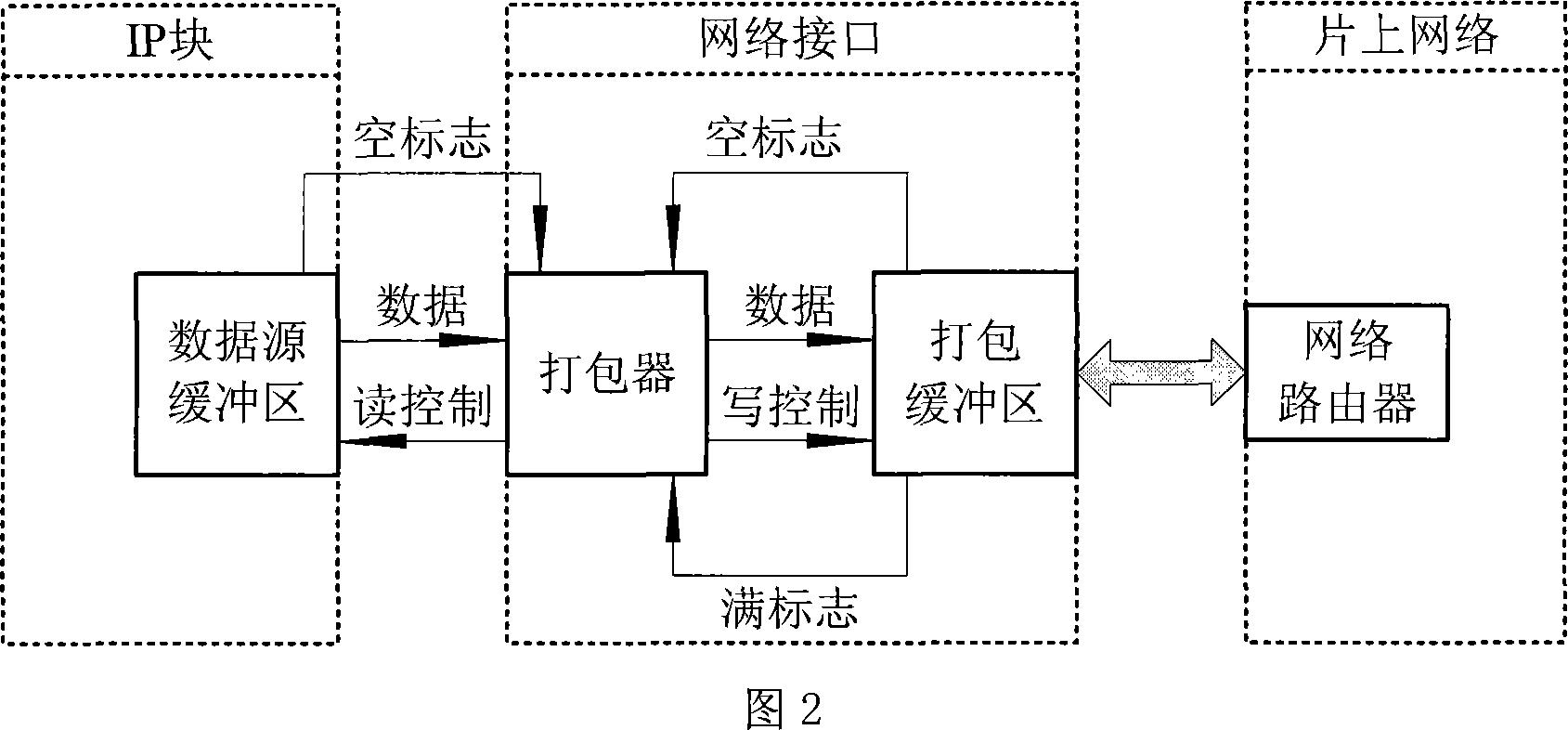

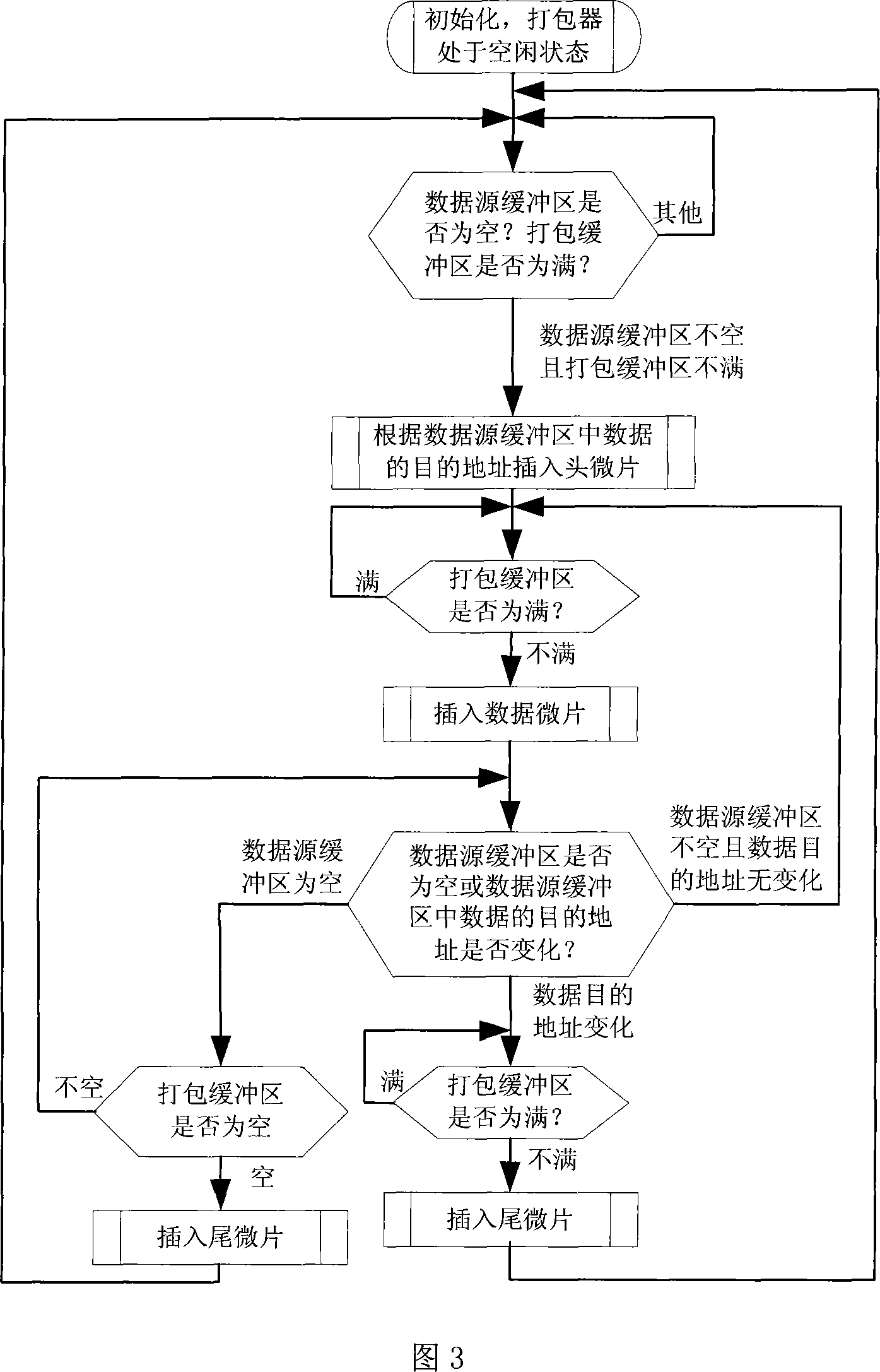

Self-adaptable package for designing on-chip network

InactiveCN101075961AImprove throughputLower latencyData switching networksData sourceNetwork on chip design

The method feature the following: setting up a data source buffer area at IP block; setting up a packager and a packaging buffer area at the network interface; after system initiation, the packager is at a idle state; when the data source buffer area is not empty and the packaging buffer area is not full, the packager inserts header and tailor and body micro plate, and enters into the busy state; if the data source buffer area is not empty and the packaging buffer area is not full, and the destination address of the data is not changed, the packager inserts the body micro plate; if the destination address in the data buffer source area is changed or the data source buffered area and the packaging buffer area both are empty, the packager inserts the body micro plate and enters into idle state.

Owner:TSINGHUA UNIV

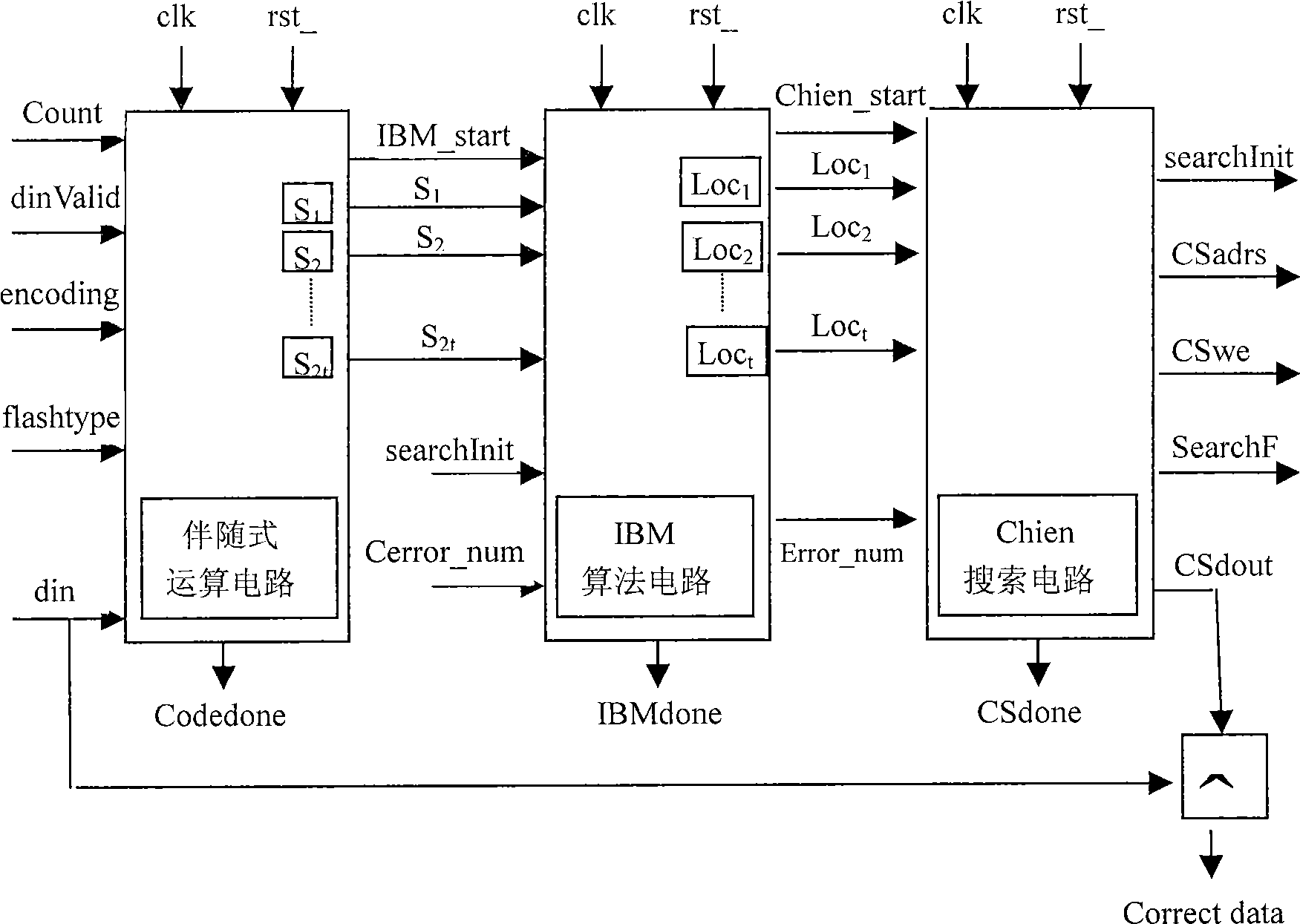

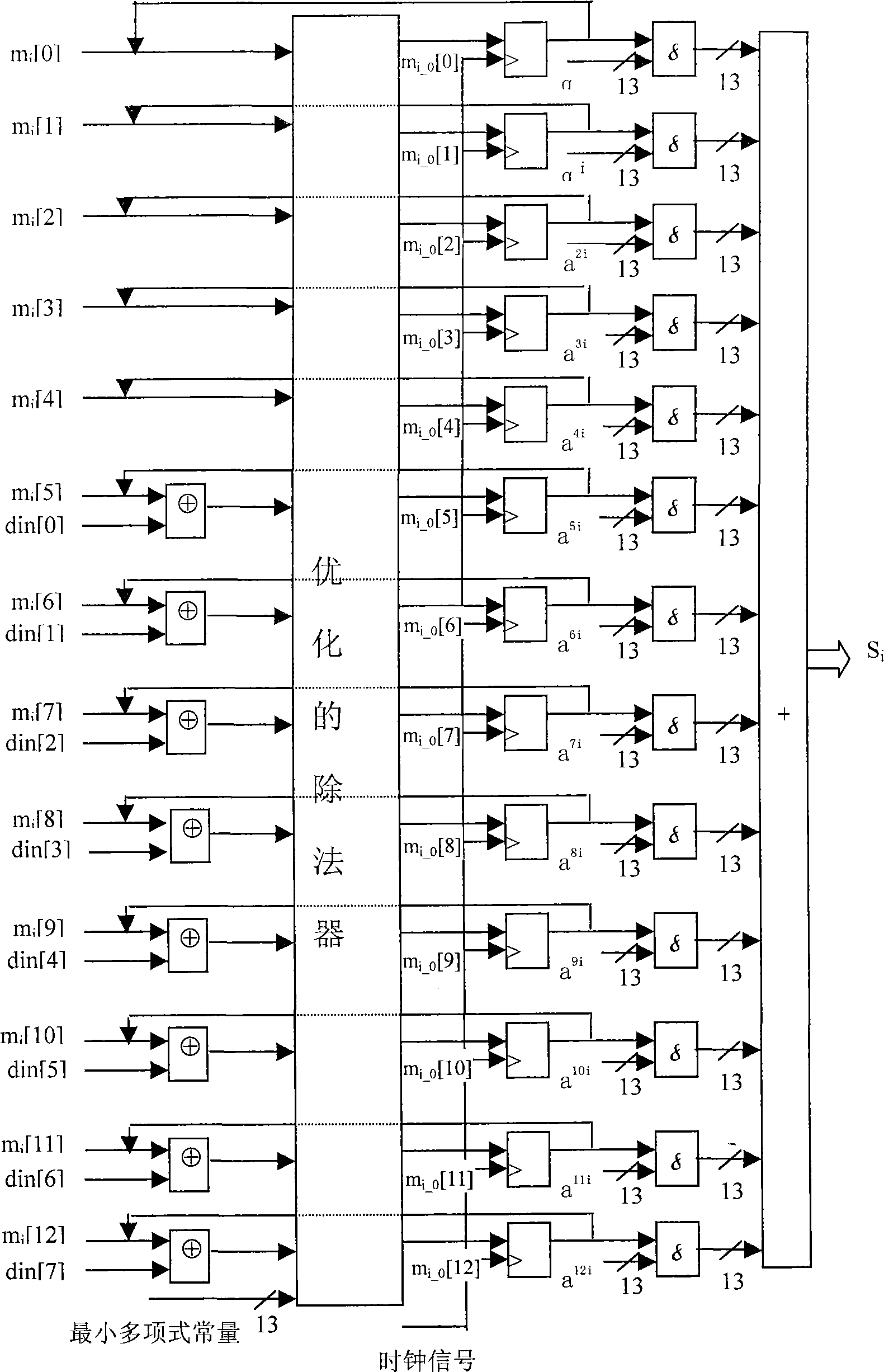

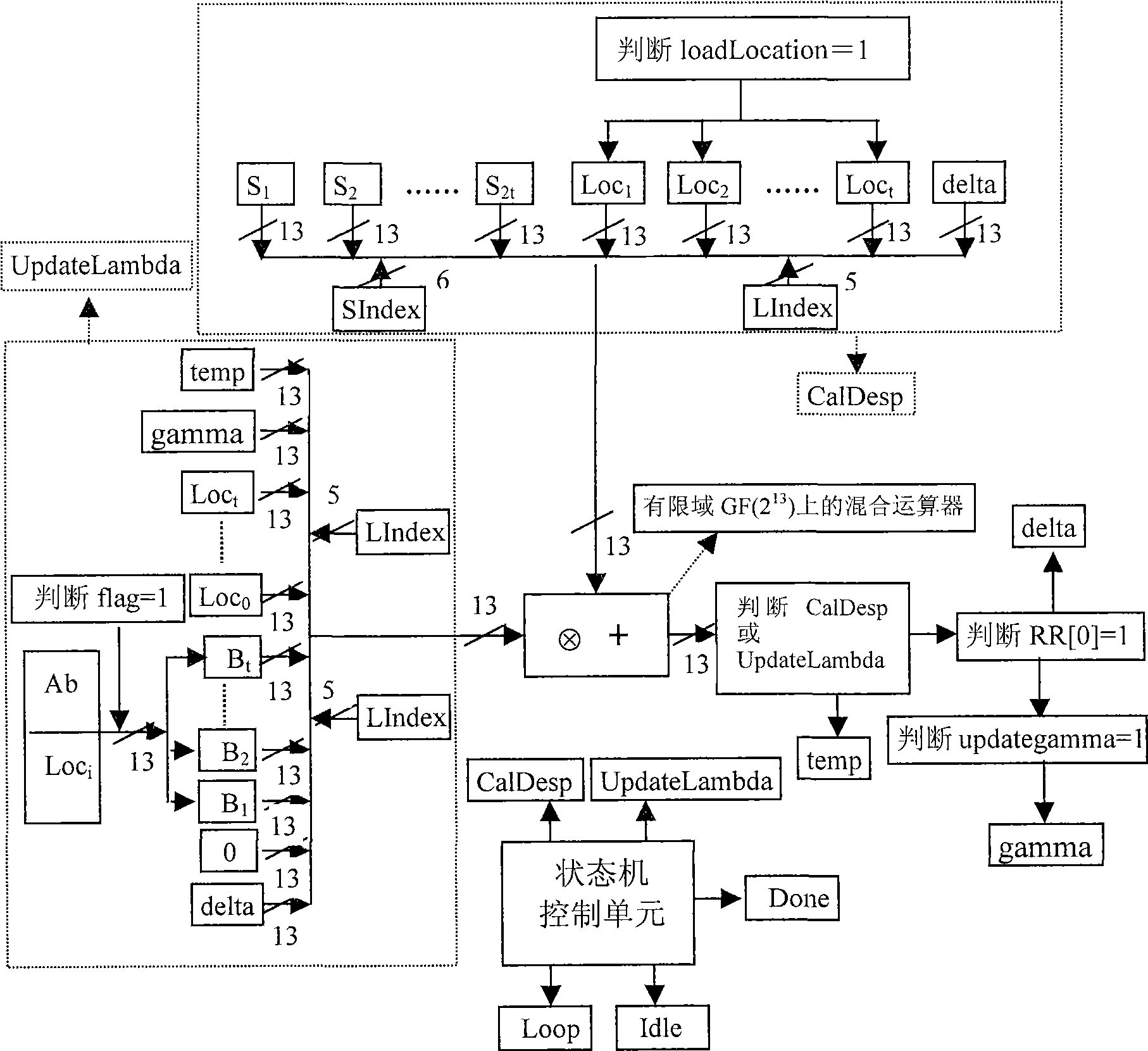

Area compact and fast BCH parallel decoding method

ActiveCN101488762ARealize a small areaFlexible configuration of error correction capabilitiesCyclic codesError locationReusability

The invention relates to a quick BCH parallel decoding method with compact area in a control chip of a NandFlash type storage device, and is characterized in that a hybrid arithmetic unit of a finite field GF(2) is multiplexed by the combination of the configuration logic of a control unit of a state machine and the state machine in the multinomial process of iterative operation of wrong position by using one-time multiple-beating manner, and the hybrid arithmetic unit consists of a two-input multiplier and a two-input adder of the finite field GF(2); if the iterative number of rounds is an even number 2k, the hybrid arithmetic unit needs to be multiplexed by 2k+1 times in the round; if the iterative number of rounds is an odd number 2k-1, the hybrid arithmetic unit needs to be multiplexed by 3k+3 times in the round; wherein, k is an integer greater than or equal to 1. In the invention, efficient optimization is carried out by controlling area in a multinomial circuit of error position so that the availability ratio of the hybrid arithmetic unit is maximized, but the reusability is minimized. The method causes better balance of the circuit between area and arithmetic speed, thereby being capable of meeting the requirements of different applied environments.

Owner:苏州国芯科技股份有限公司

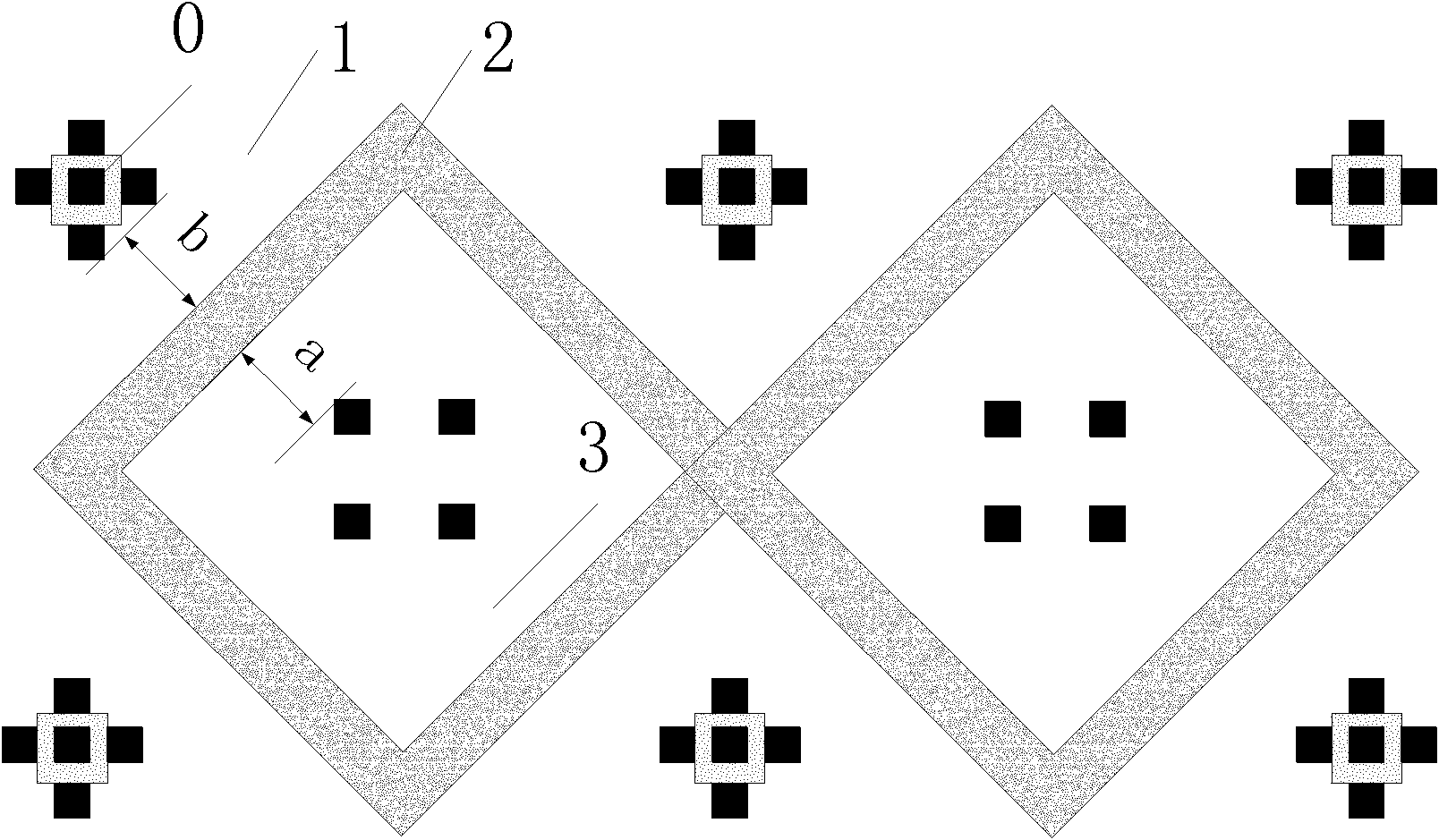

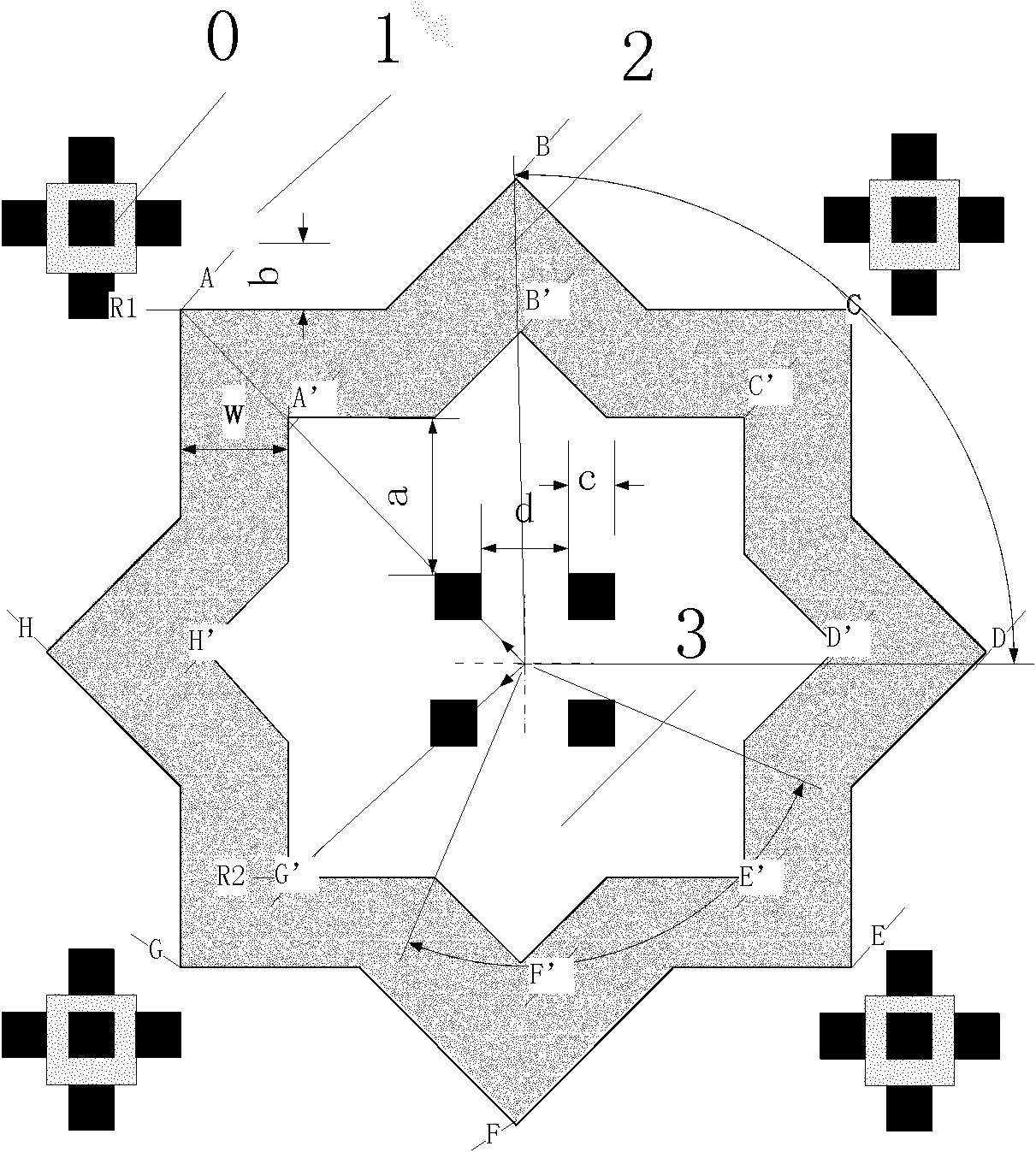

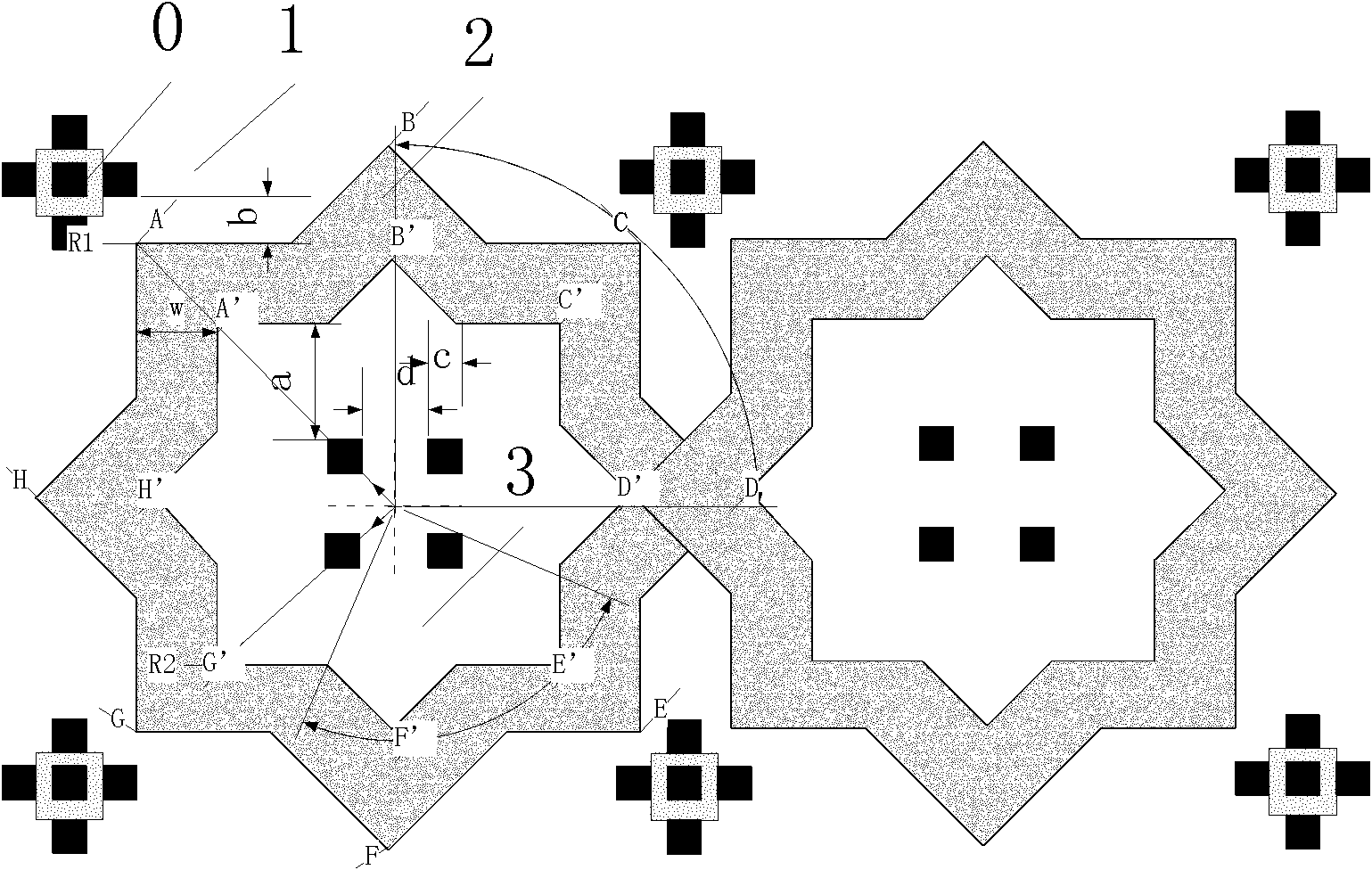

Power MOS transistor of asymmetric structure and array thereof

The invention provides a power metal oxide semiconductor (MOS) transistor, and belongs to the field of semiconductor devices. The power MOS transistor comprises a source, a drain and a grid structure, wherein the grid structure is specifically designed as: a circle is drawn by using the geometric center of the layout as a circle center, and two sixteen-edge octagonal graphs are made respectively; the edges of the two sixteen-edge octagonal graphs are mutually parallel, a gap between the edges form an octagonal bent belt, and the bent belt is the graph of the grid structure. On the premise of ensuring that the distance between a contact hole of the drain and the grid structure is not changed, the distance between the source and the grid structure is shortened, and smaller layout realization area and lower source connecting metal voltage drop are obtained.

Owner:PEKING UNIV

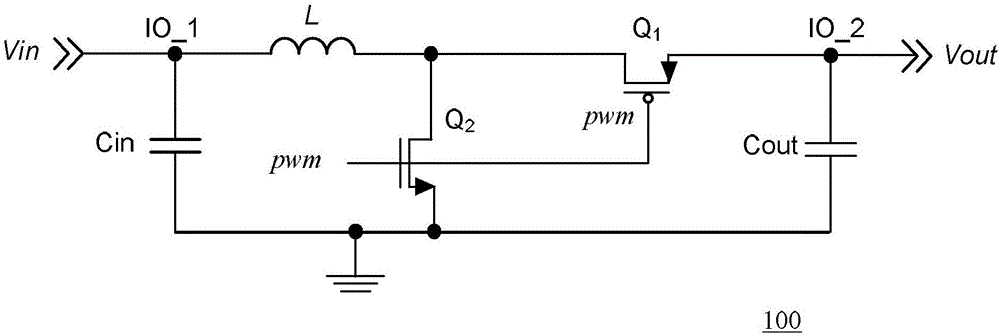

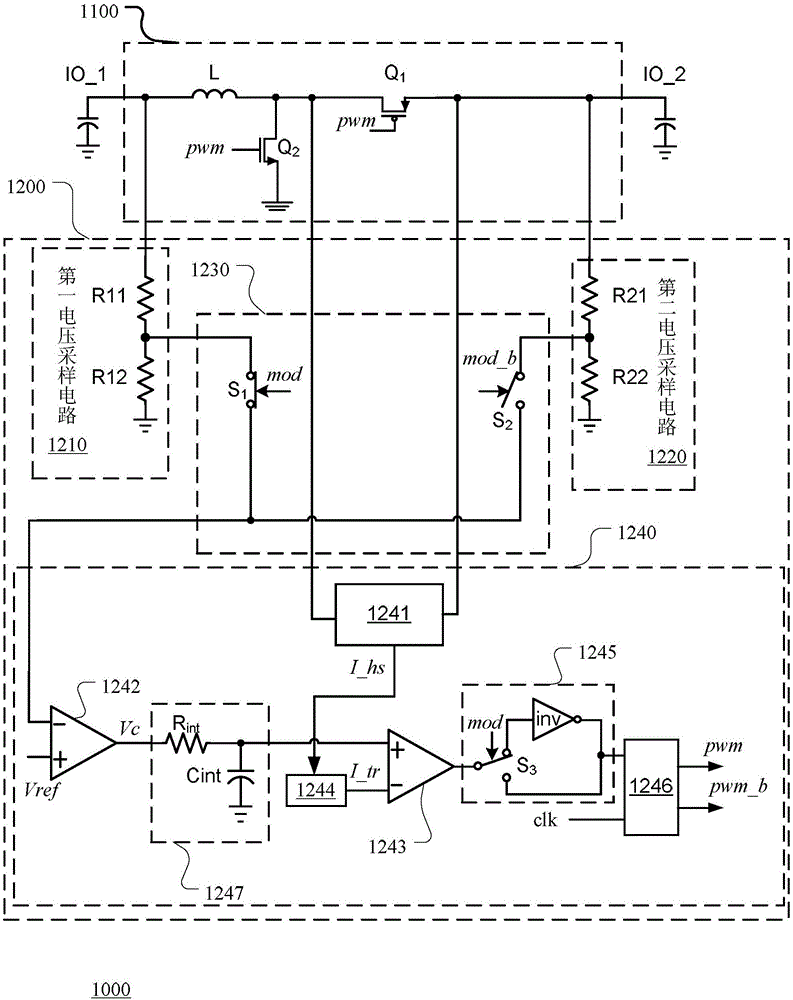

Buck-boost conversion device

PendingCN106602878ARealize a small areaEasy to convertDc-dc conversionElectric variable regulationPulse controlControl signal

The invention provides a buck-boost conversion device. The device comprises a main circuit and a control circuit, wherein the main circuit possesses a first port and a second port; the main circuit is used for converting an input voltage received by one of the first port and the second port according to a pulse control signal into an output voltage and the output voltage is output by another one of the first port and the second port; the control circuit is used for providing the pulse control signal; the control circuit generates an adjusting signal according to a feedback signal of the output voltage; under a boost mode, according to the adjusting signal, the pulse control signal is generated; and under a buck mode, according to an anti-phase signal of the adjusting signal, the pulse control signal is generated. By using the buck-boost conversion device in an embodiment, based on a condition of guaranteeing performance and a function, a uniform circuit are used to control boost and buck modes of a main circuit in the buck-boost conversion device; and a designer can conveniently carry out boost and buck function conversion on the circuit so that operation difficulty, and a circuit area and cost are reduced.

Owner:CHIPONE TECH BEIJINGCO LTD

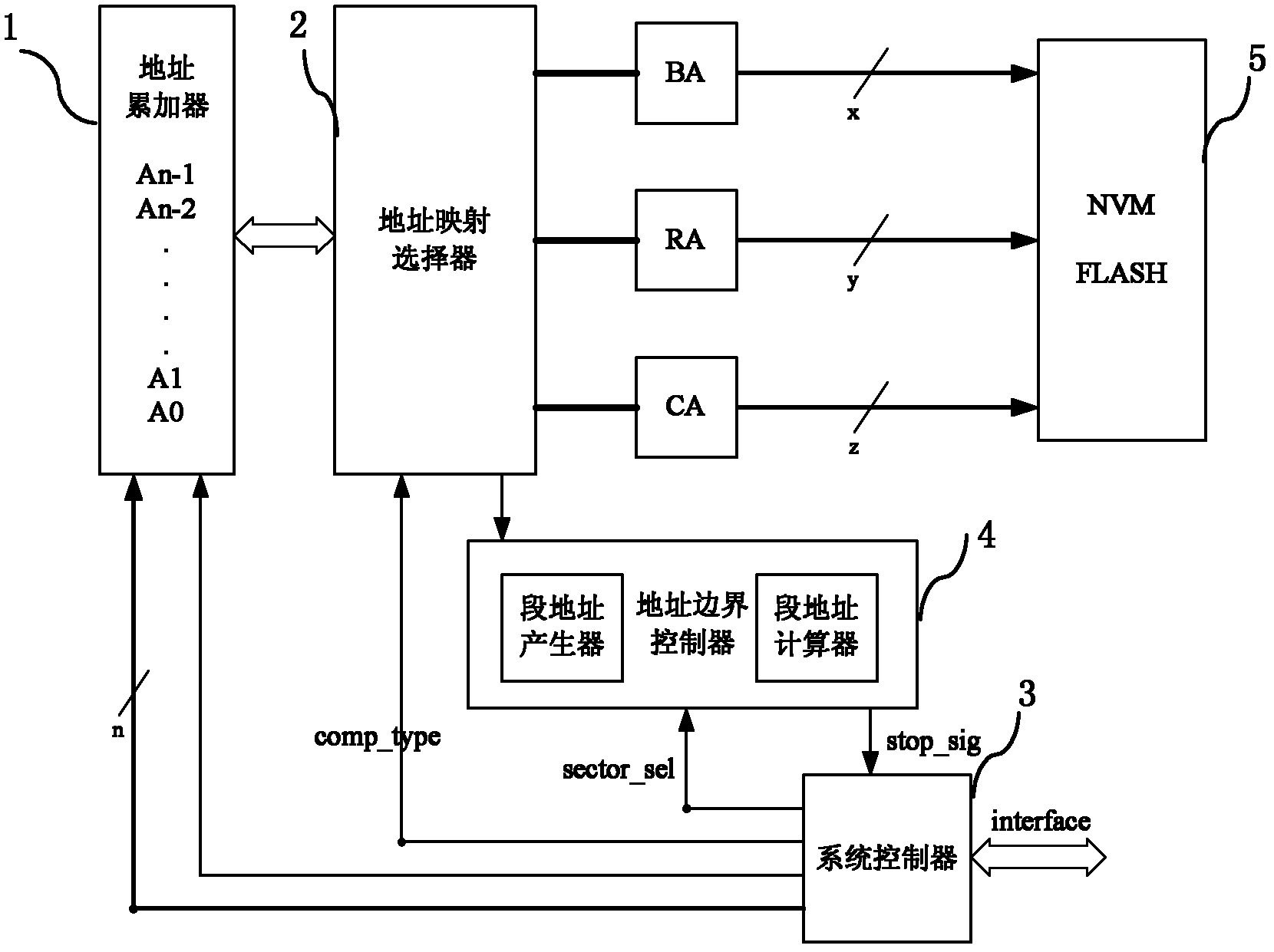

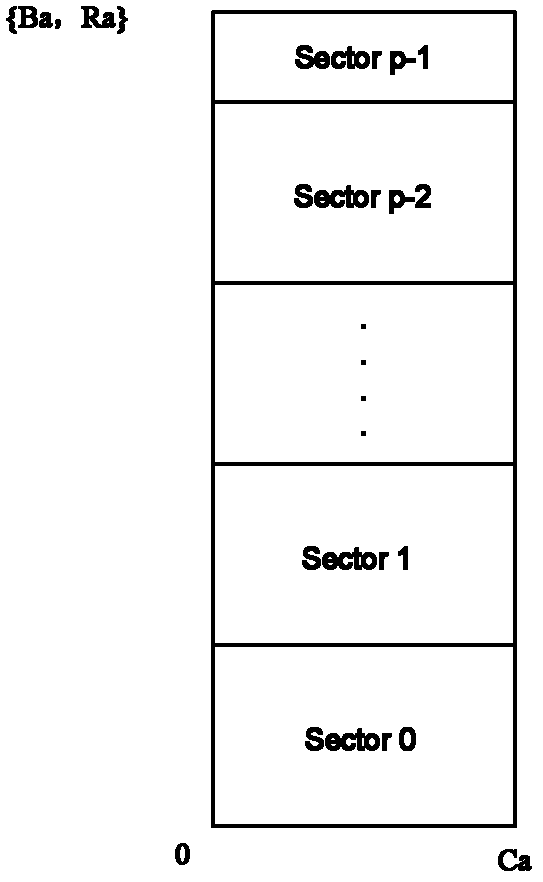

Data automatically-comparing test circuit of non-volatile memory

ActiveCN103325423ARealize unified and continuous operationRealize a small areaStatic storageData segmentComputer module

The invention discloses a data automatically-comparing test circuit of a non-volatile memory, comprises an address accumulator, an address mapping selector, a system controller and an address boundary controller. The address accumulator is used for completing addition and subtraction of the test circuit. The address mapping selector is used for implementing mapping between a test circuit address and a non-volatile memory address, and for generating the non-volatile memory address. The address boundary controller is composed of a segment address generation module and a segment address calculation module, and is used for dividing the non-volatile memory into a plurality of data segments, calculating address boundary of each data segment, and generating a stop condition of segment comparison. The data automatically-comparing test circuit of a non-volatile memory can reduce usage of addition, can reduce a circuit area, can flexibly and effectively implement the segment comparison of the address, and can implement flexible comparison data with different bits.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

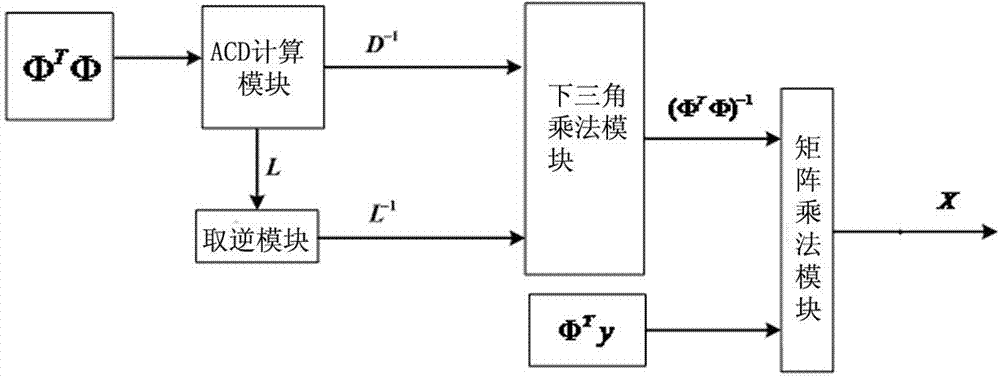

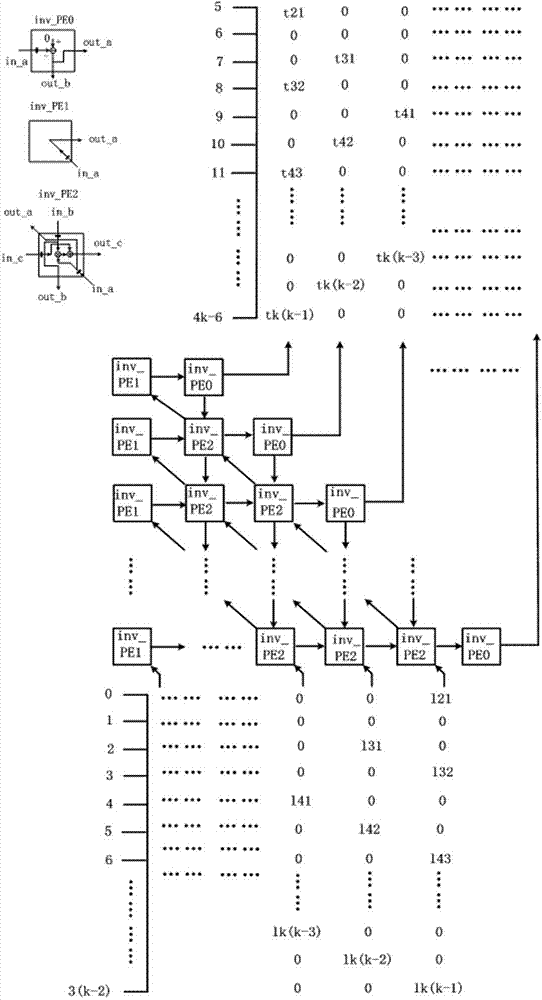

Circuit structure for conducting least square equation solving according to positive definite symmetric matrices

ActiveCN103902762AIncrease usageRealize a small areaSpecial data processing applicationsInverse operationLeast squares

The invention belongs to the technical field of integrated circuit design, and particularly relates to a circuit structure for conducting least square equation solving according to positive definite symmetric matrices. The circuit structure is composed of an ACD computation module, an inversing module, a triangle multiplication module and a matrix multiplication module, wherein the ACD computation module is used for matrix decomposition, the inversing module is used for solving lower triangular matrix inverse matrices, and the triangle multiplication module and the matrix multiplication module are used for calculation of matrix multiplication. According to the circuit structure, the ACD decomposition algorithm is adopted for matrix decomposition, square root operation and repeated inversing operation are avoided, operation is simple, and the implementation area is small. Meanwhile, in an implementation process, the systolic array architecture is fully used and the multiplexing technique of the circuit structure is adopted, so that it is guaranteed that functions are correct, the utilization rate of hardware structures is increased, and the implementation area is reduced further. The circuit structure can be well used for solving least square equations.

Owner:FUDAN UNIV

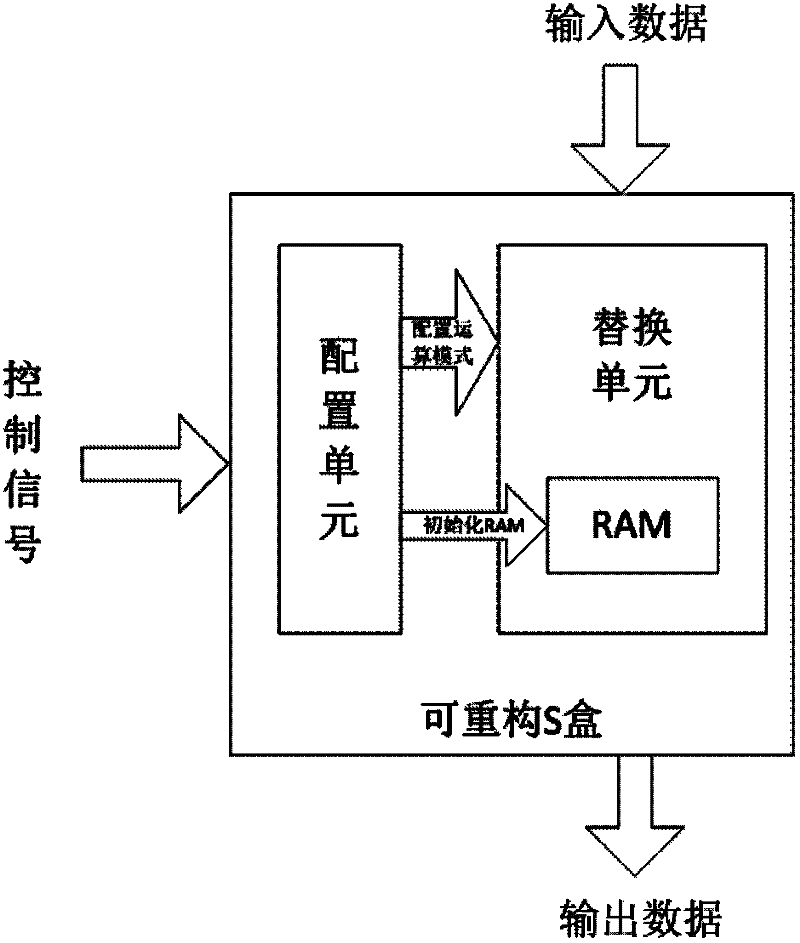

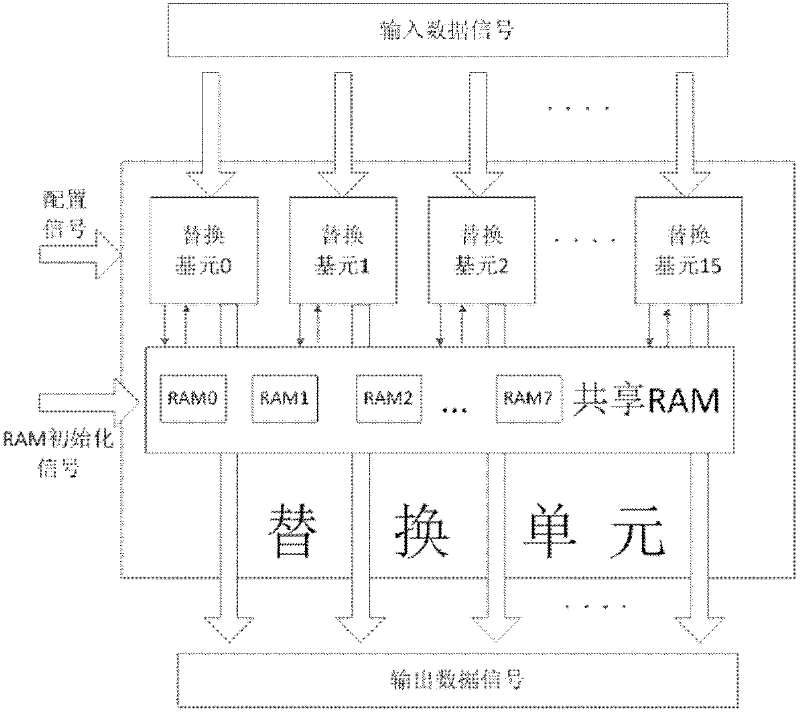

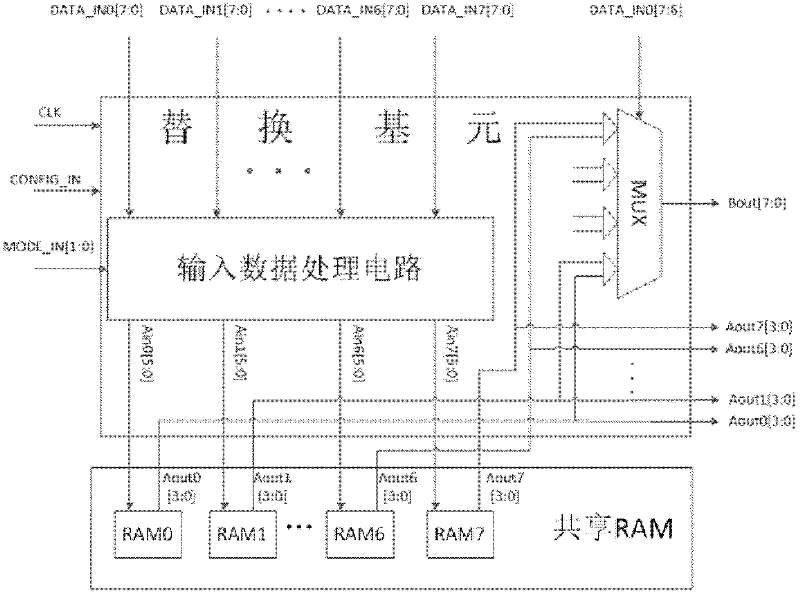

Reconfigurable S box circuit structure based on RAM (Radom Access Memory) sharing technology

InactiveCN102347833ARealize a small areaFast operationEncryption apparatus with shift registers/memoriesS-boxControl signal

The invention discloses a reconfigurable S box circuit structure based on a RAM (Radom Access Memory) sharing technology, which can realize S box substitution operation in various block cipher algorithms and is suitable for various block cipher processors. The S box circuit structure consists of a configuration unit circuit and a substitution unit circuit, wherein the configuration unit is used for receiving and storing input control signals and configurating and controlling the operation state of the substitution unit; the substitution unit comprises n substitution elements and a RAM, and all substitution elements work in parallel and share one RAM. The invention has the advantages of high operation speed, flexible configuration, capability of processing data in parallel, small memory unit occupation and small circuit realization area.

Owner:SOUTHEAST UNIV

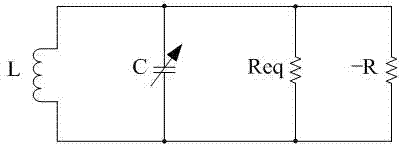

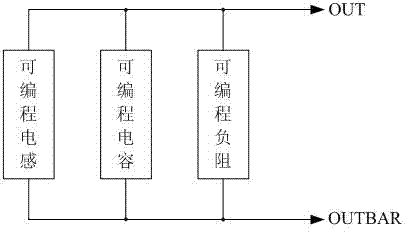

Frequency channel programmable LC_digitally controlled oscillator (DCO) circuit structure

ActiveCN102931918AAchieve oscillationReduce the difficulty of implementationOscillations generatorsCapacitanceEngineering

The invention discloses a frequency channel programmable LC_digitally controlled oscillator (DCO) circuit structure. An LC_DCO circuit comprises a cross-coupling tailless current source complementary programmable negative resistance module, a programmable inductor module and switched capacitor arrays. Firstly, inductors with different inductance values are selected to form a resonant cavity with a natural capacitor; then, current of a left branch circuit and a right branch circuit of a negative resistance circuit is modulated to generate negative resistance required for starting oscillation so as to achieve oscillation of an LC_DCO; and finally, effective capacitance values which are switched in the resonant cavity by the two different switched capacitor arrays are controlled, so that modulation of operating frequency ranges and tuning accuracy is achieved. The circuit structure has the characteristics of being programmable in output frequency channel and adjustable in tuning accuracy and the advantages of being small in achievement area, high in integration level and high in deign flexibility.

Owner:CHANGSHA JINGJIA MICROELECTRONICS

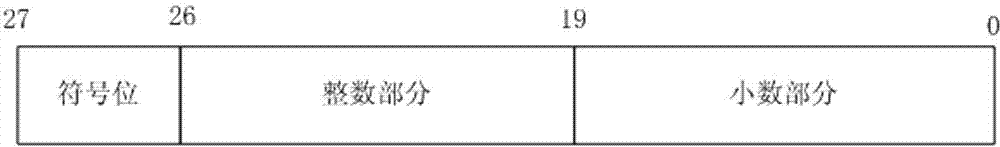

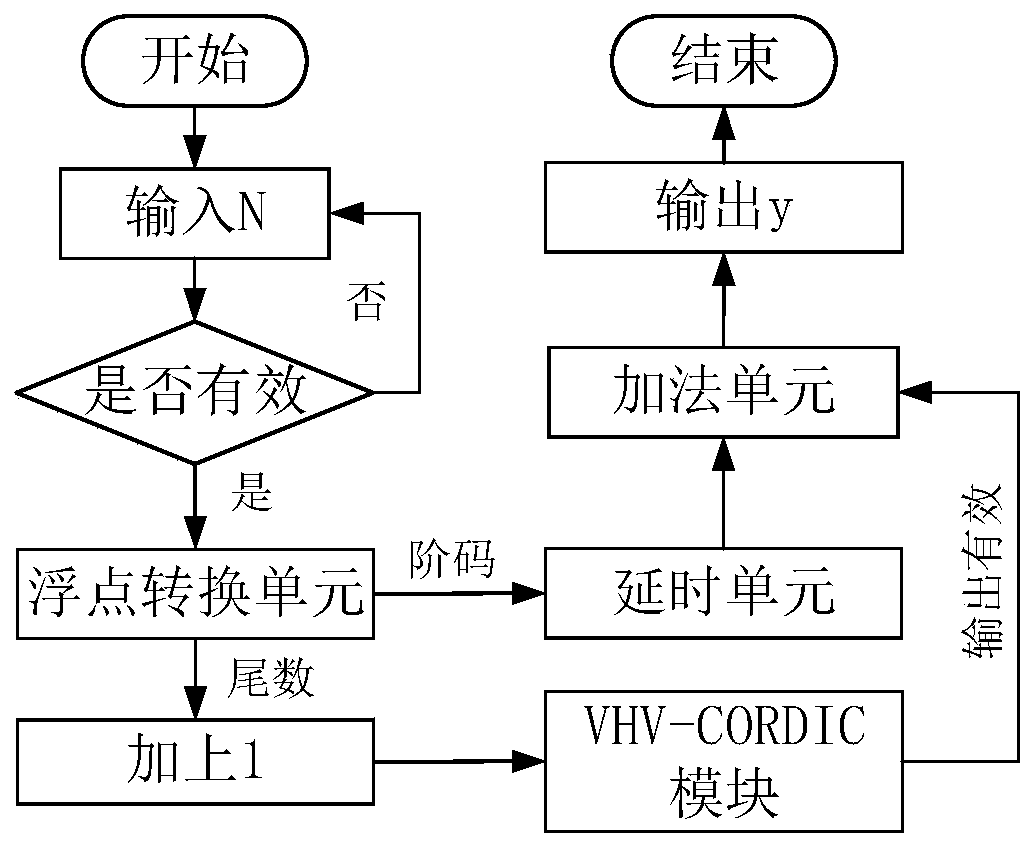

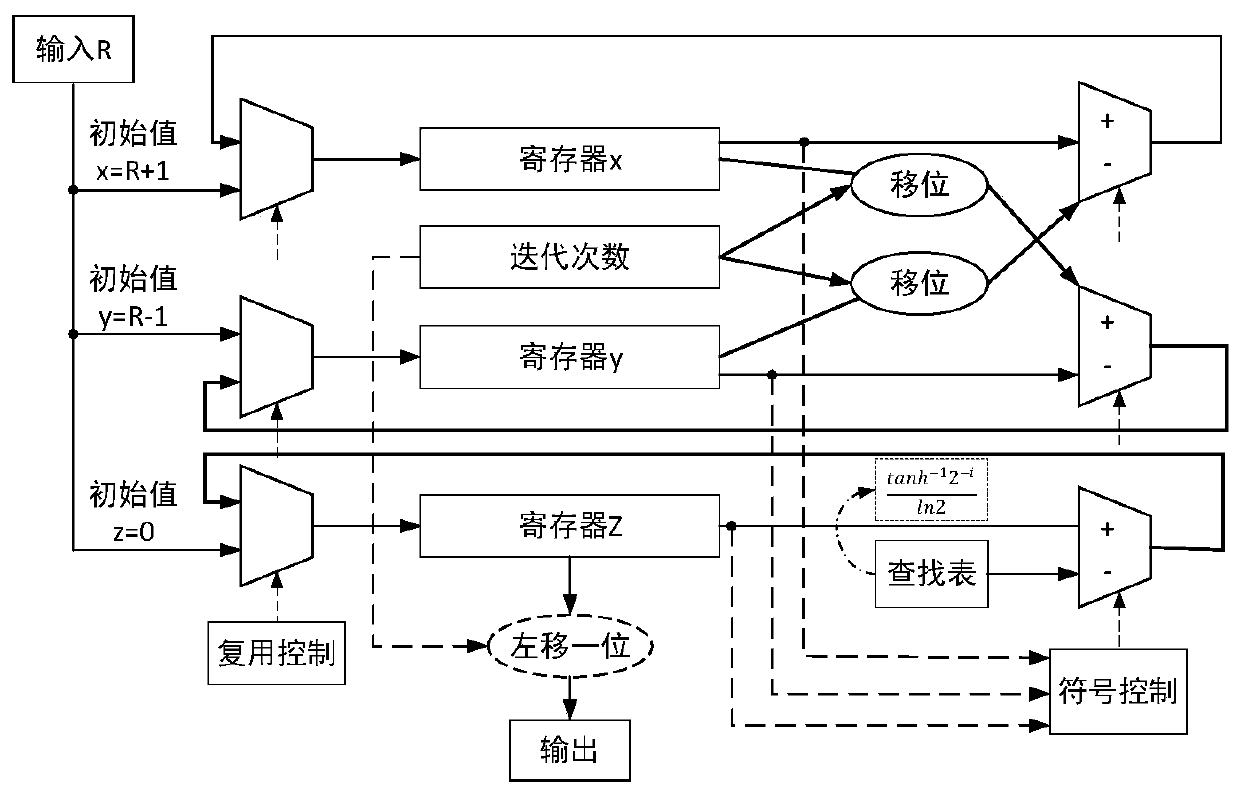

Hyperbolic CORDIC-based logarithmic function calculation system and method

ActiveCN110222305ARealize a small areaImprove applicabilityEnergy efficient computingComplex mathematical operationsFloating pointCORDIC

The invention discloses a hyperbolic CORDIC-based logarithmic function calculation system and method, and belongs to the field of function calculation. The system comprises a control module, a varianthyperbolic vector mode CORDIC module and a basic operation module, the control module and the variant hyperbolic vector mode CORDIC module are respectively connected with the basic operation module,and the variant hyperbolic vector mode CORDIC module is connected with the control module. According to the method disclosed by the invention, the control module, the variant hyperbolic vector mode CORDIC module and the basic operation module are matched for calculation, so that logarithmic function calculation taking 2 as the bottom can be carried out on any floating point type true number. The system aims to overcome the defects that in the prior art, the hardware area needed by logarithmic function calculation is large, and the calculation precision is low, logarithmic function calculationwith 2 as the bottom can be conducted on any floating point type true number, the hardware resource cost is low, the calculation precision is high, and the application requirements of different precisions can be met.

Owner:南京宁麒智能计算芯片研究院有限公司

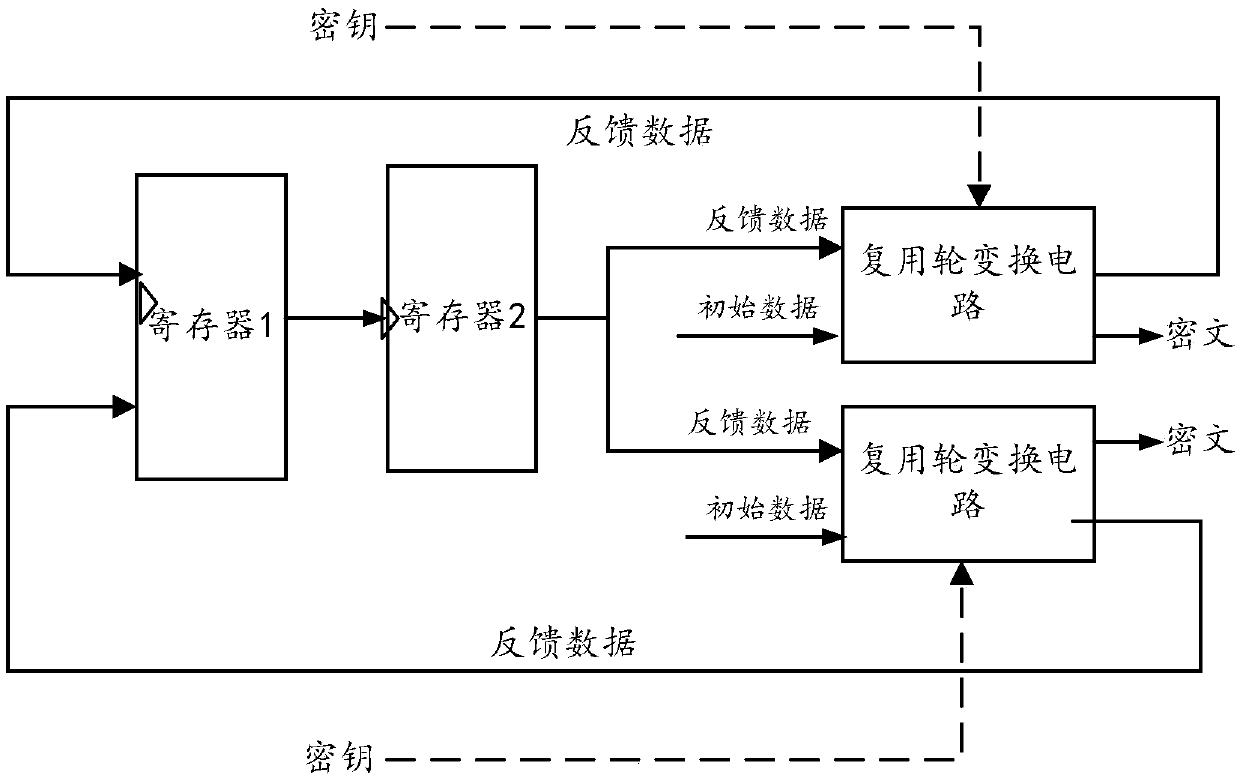

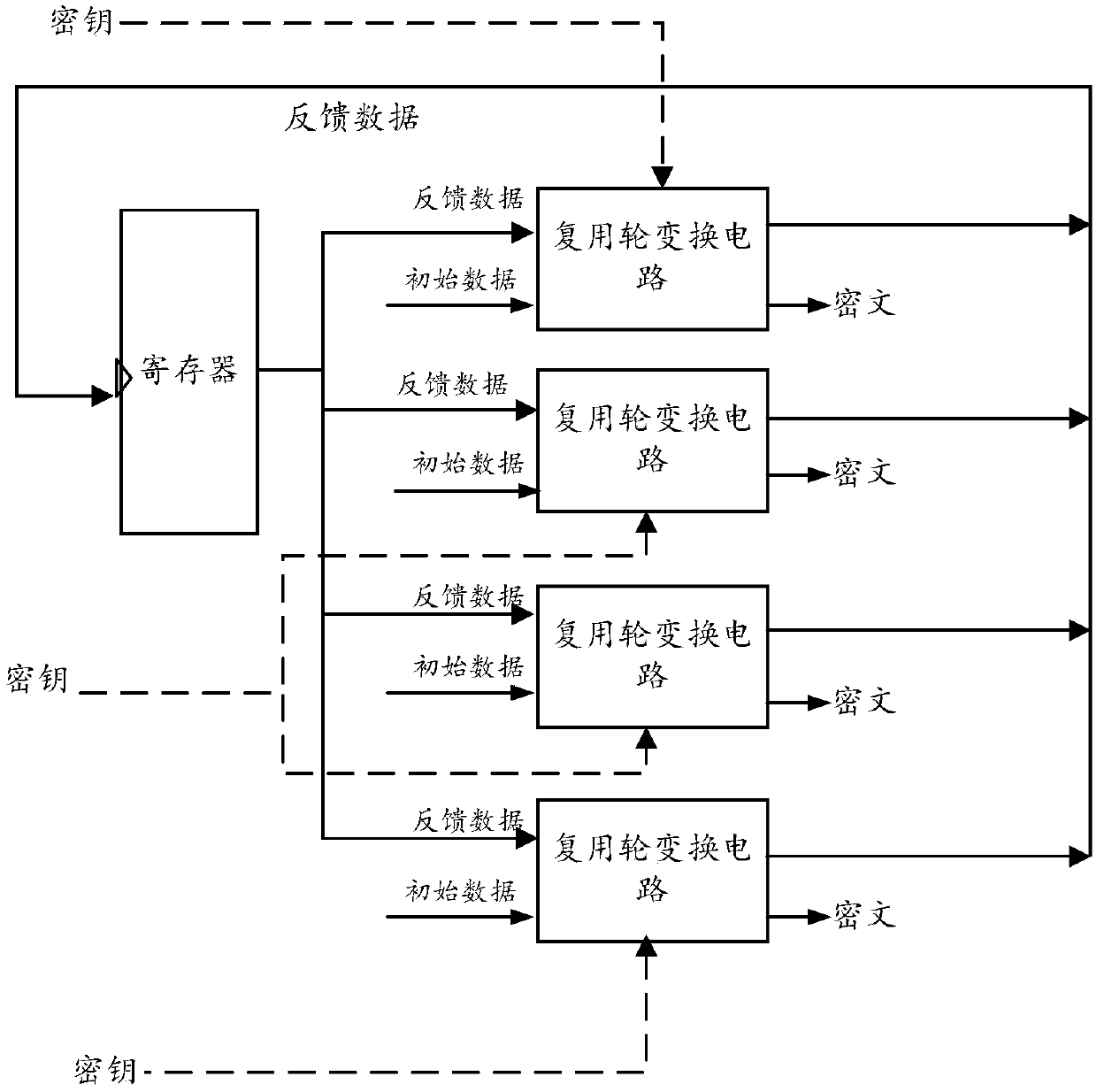

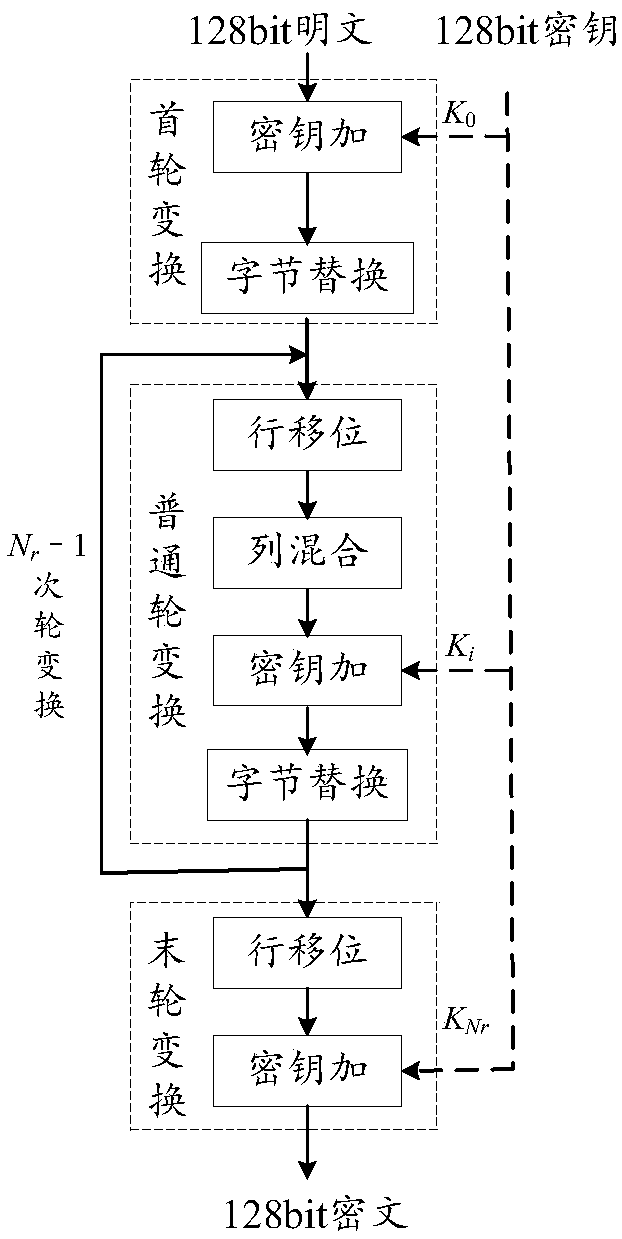

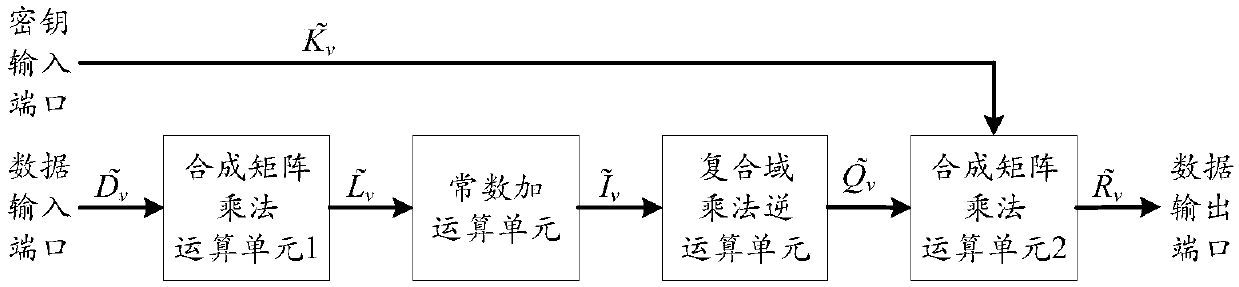

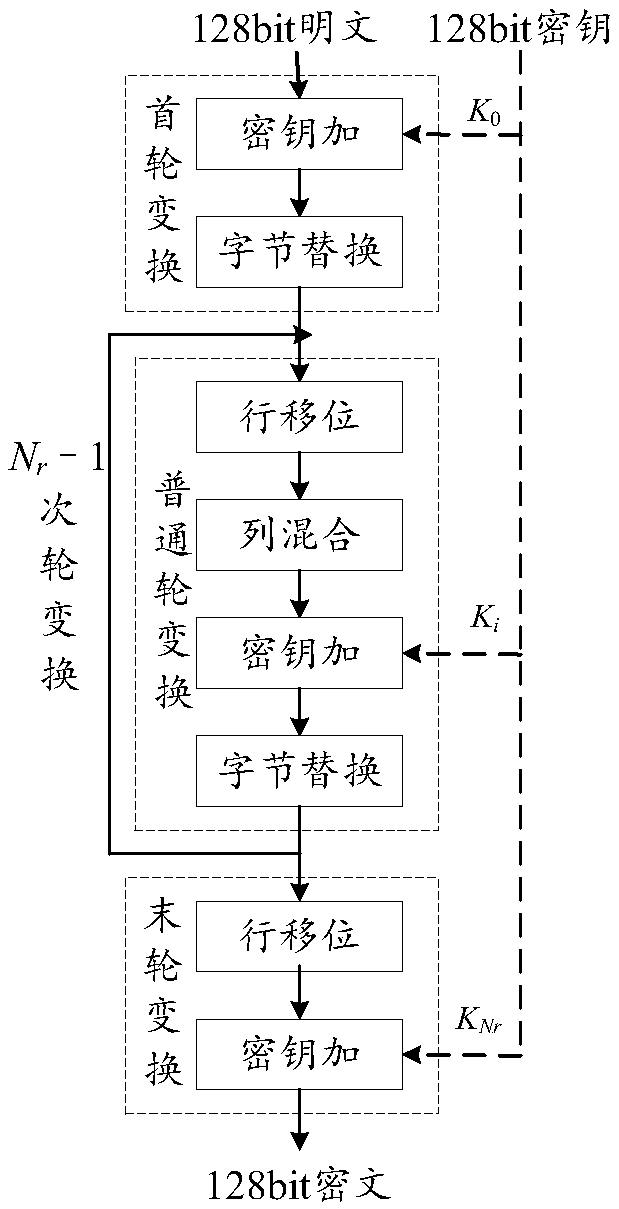

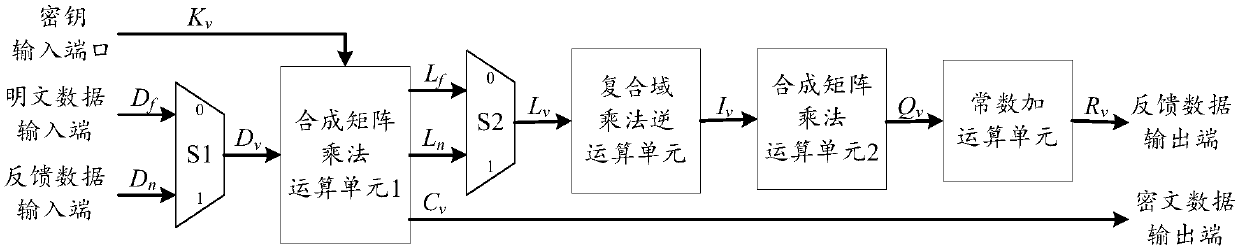

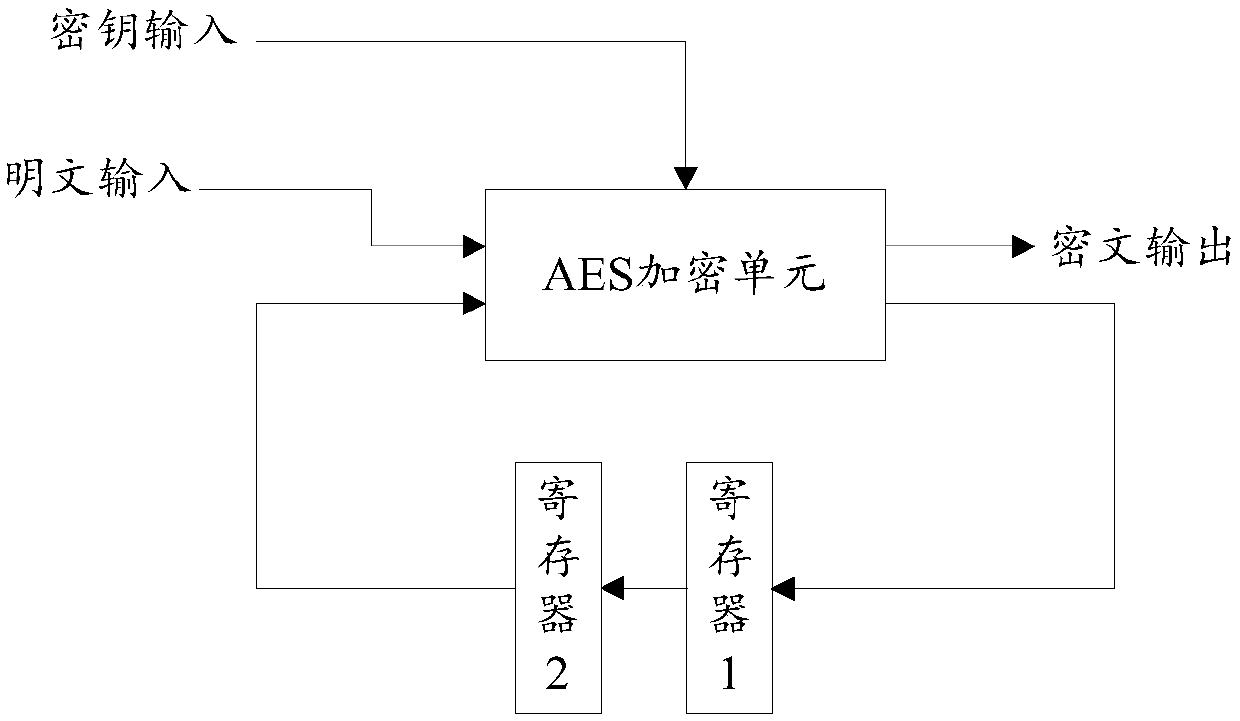

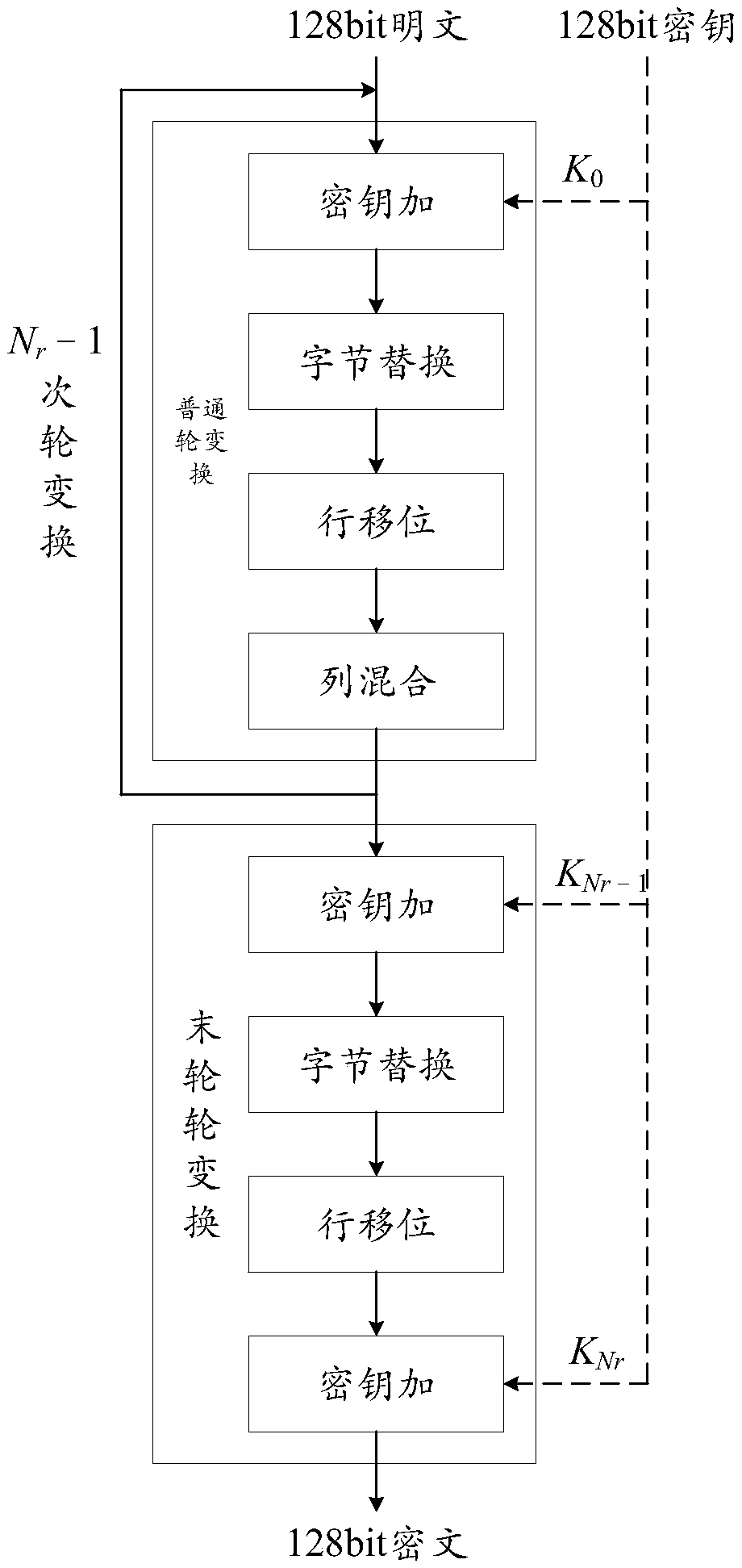

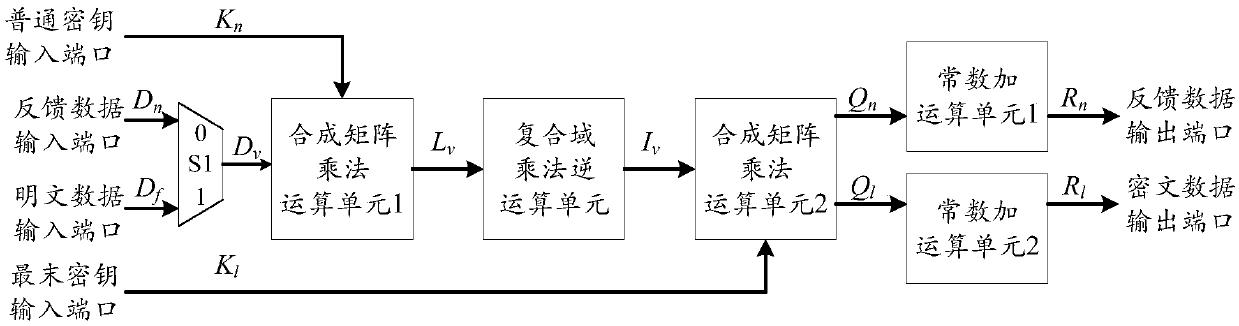

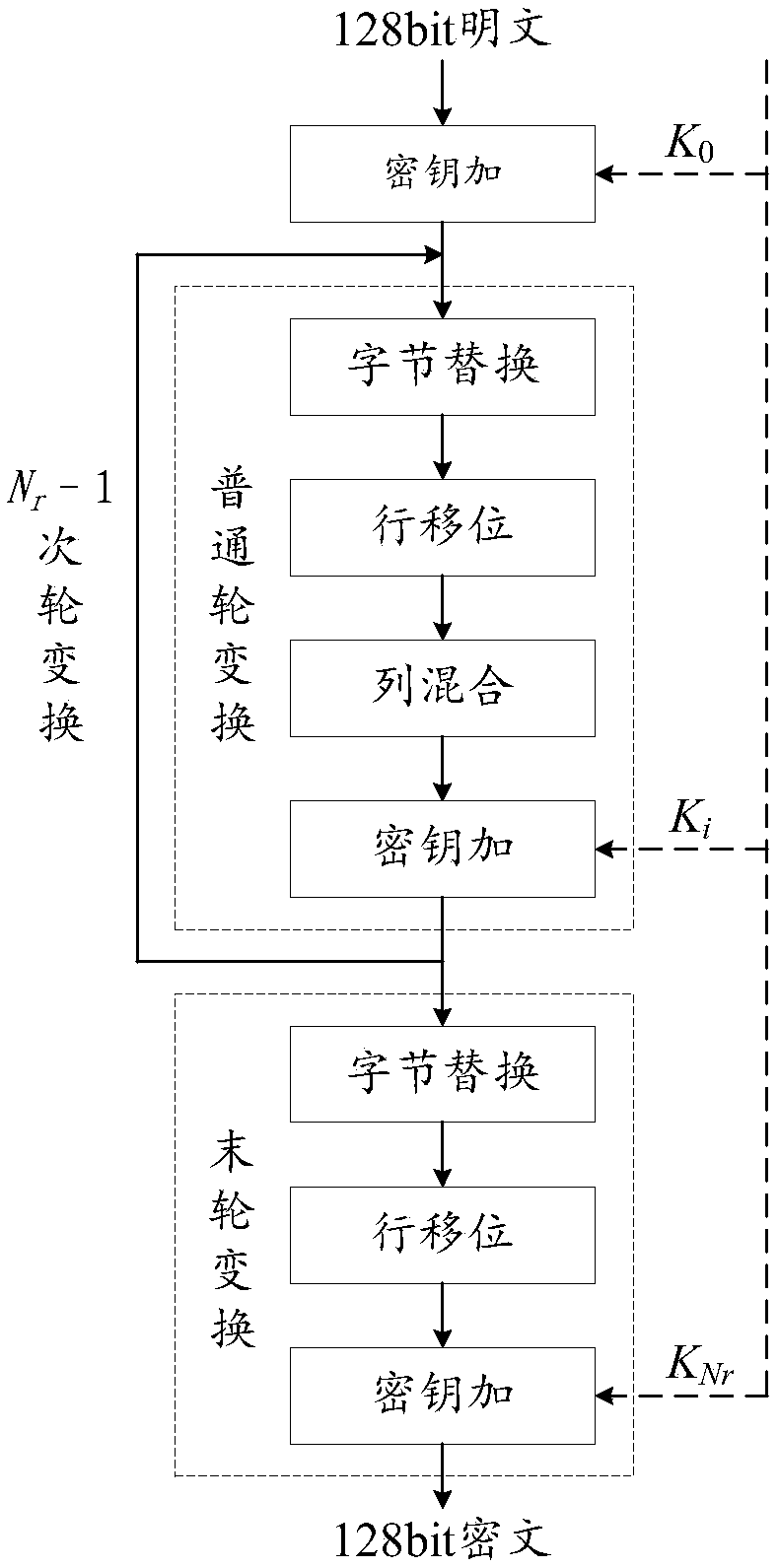

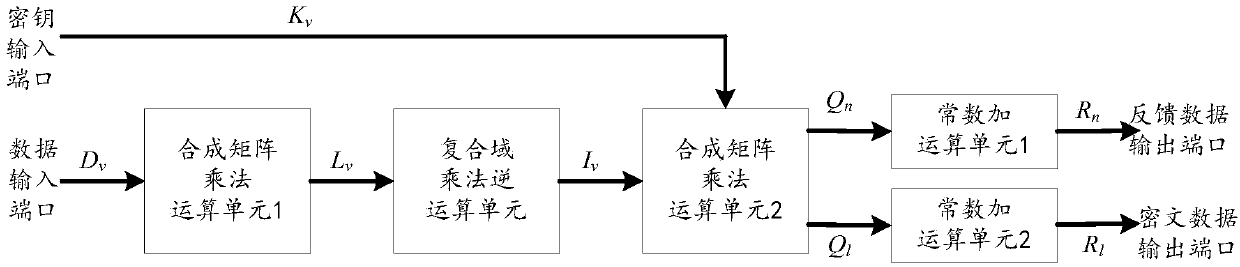

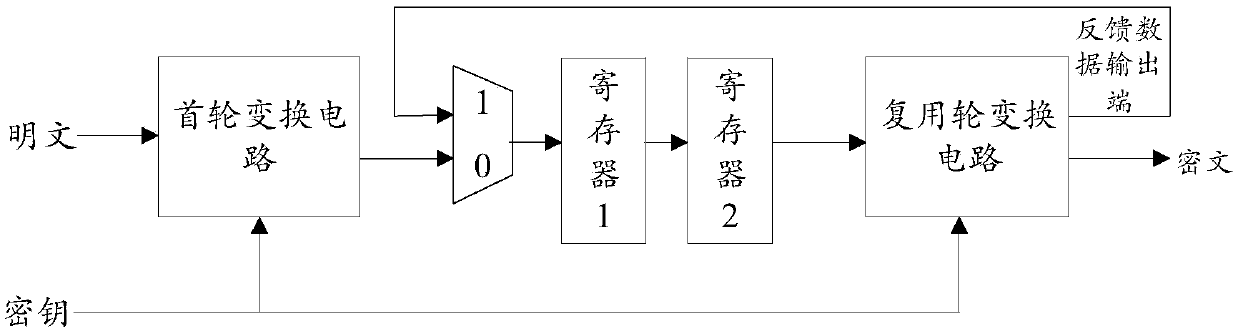

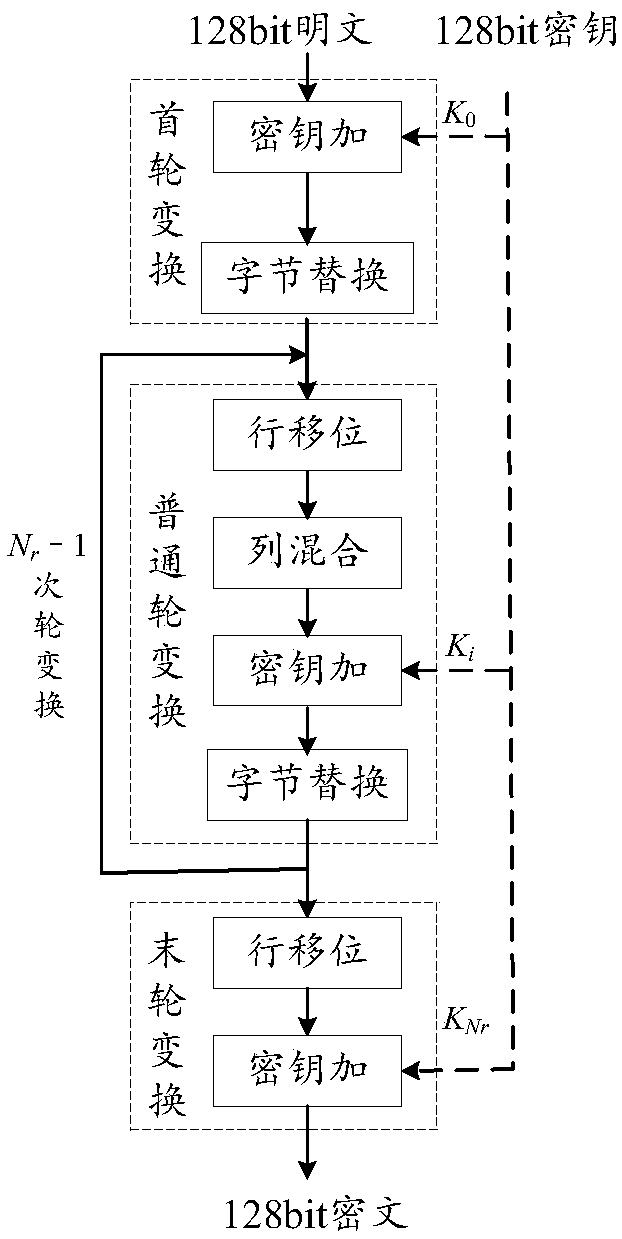

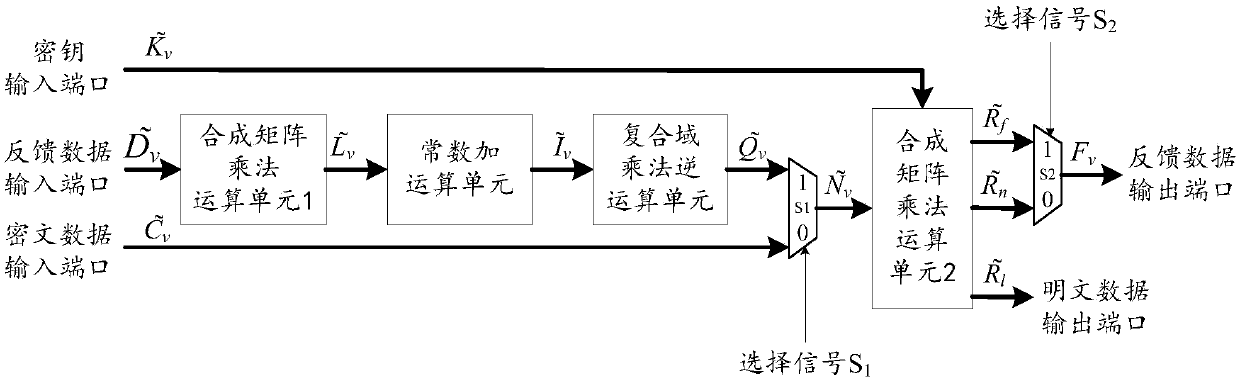

Multiplex wheel conversion circuit, AES encryption circuit and encryption method

ActiveCN109039583ARealize a small areaSave resourcesEncryption apparatus with shift registers/memoriesComputer hardwareMultiplexing

The invention is applicable to the field of encryption technology, provides a multiplex wheel conversion circuit, an AES encryption circuit and an encryption method. The AES encryption wheel transformation multiplexing circuit of the invention combines and synthesizes constant matrices, all the linear transformation operations in AES cryptographic algorithm are combined into two composite matrices, namely the composite matrix delta and the composite matrix lambda, so as to shorten the critical path of the AES encryption wheel conversion circuit, reduce the circuit realization area, and realizethe common wheel conversion and the last round conversion by multiplexing the composite matrix multiplication unit 1, the composite field multiplication inverse operation unit and the composite matrix multiplication operation unit 2, thereby saving a large amount of circuit resources.

Owner:ANHUI UNIVERSITY OF TECHNOLOGY AND SCIENCE

High and low voltage changeover circuit

ActiveCN101458541ALow costRealize a small areaElectric variable regulationCapacitanceElectrical resistance and conductance

The invention discloses a high-low pressure converting circuit which belongs to the integrated circuit technique field. The high-low voltage converting circuit includes a basic current generating circuit, a low pressure generating circuit and an output voltage regulator circuit; wherein, the basic current generating circuit provides current for the low pressure generating circuit; the low pressure generating circuit includes an autoeciousness PNP, a compensating resistor and a low pressure MOS pipe, an autoeciousness PNP, the autoeciousness PNP, the compensating resistor and the low pressure MOS pipe provide stable driving voltage for the output voltage regulator circuit; the driving voltage outputs stable low voltage on the output voltage regulator circuit through a stabilized voltage capacitance through a first current mirror. The high-low voltage converting circuit uses standard apparatus such as MOS pipe, audion, resistor and capacitance without Zener diode, and needs not extra cost, reduces chip cost and modulation cost.

Owner:SHENZHEN SUNMOON MICROELECTRONICS

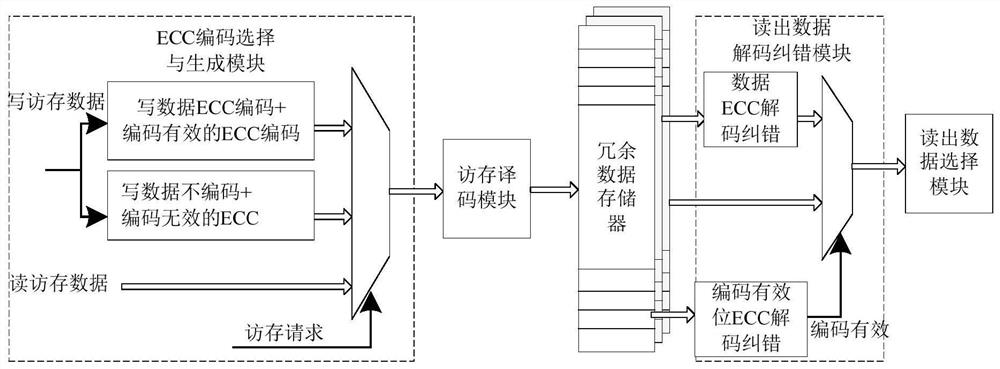

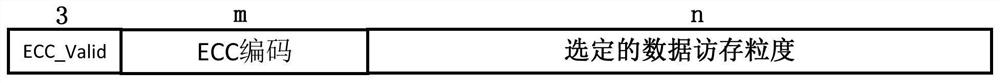

High-energy-efficiency on-chip memory error detection and correction circuit and implementation method

ActiveCN113076219AReduce areaReduce in quantityStatic storageRedundant data error correctionData selectionData memory

The invention discloses a high-energy-efficiency on-chip memory error detection and correction circuit and an implementation method. The circuit comprises an ECC code selection and generation module which is used for determining whether to carry out ECC coding or not according to the information in a memory access request sent by a memory access operation, carrying out ECC coding on memory access data ECC coding effective bits, and sending the memory access information and related ECC coding results to a subsequent memory access decoding module; a memory access decoding module and a redundant data memory, wherein the memory access decoding module is used for performing memory access decoding and generating a memory access port signal of the redundant data memory; a read-out data decoding error correction module, which is used for carrying out error detection and error correction on the ECC codes; and a read data selection module used for selecting read data according to the memory access address and the memory access granularity information sent along with the memory access pipeline. The implementation method is used for implementing the circuit. The method has the advantages that the area of an on-chip memory and the implementation area of an ECC circuit can be remarkably reduced, and the overall power consumption of the microprocessor is effectively reduced.

Owner:NAT UNIV OF DEFENSE TECH

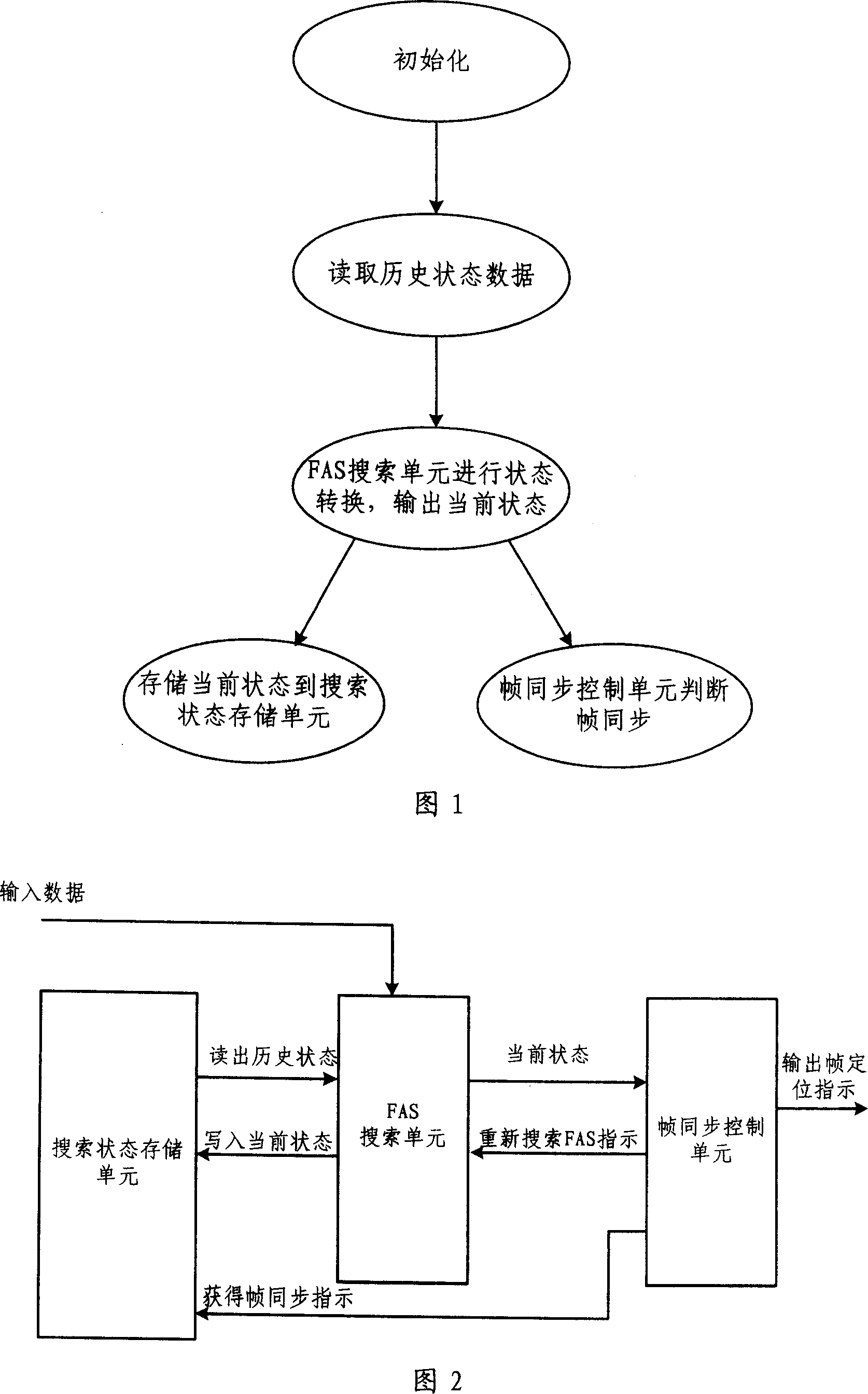

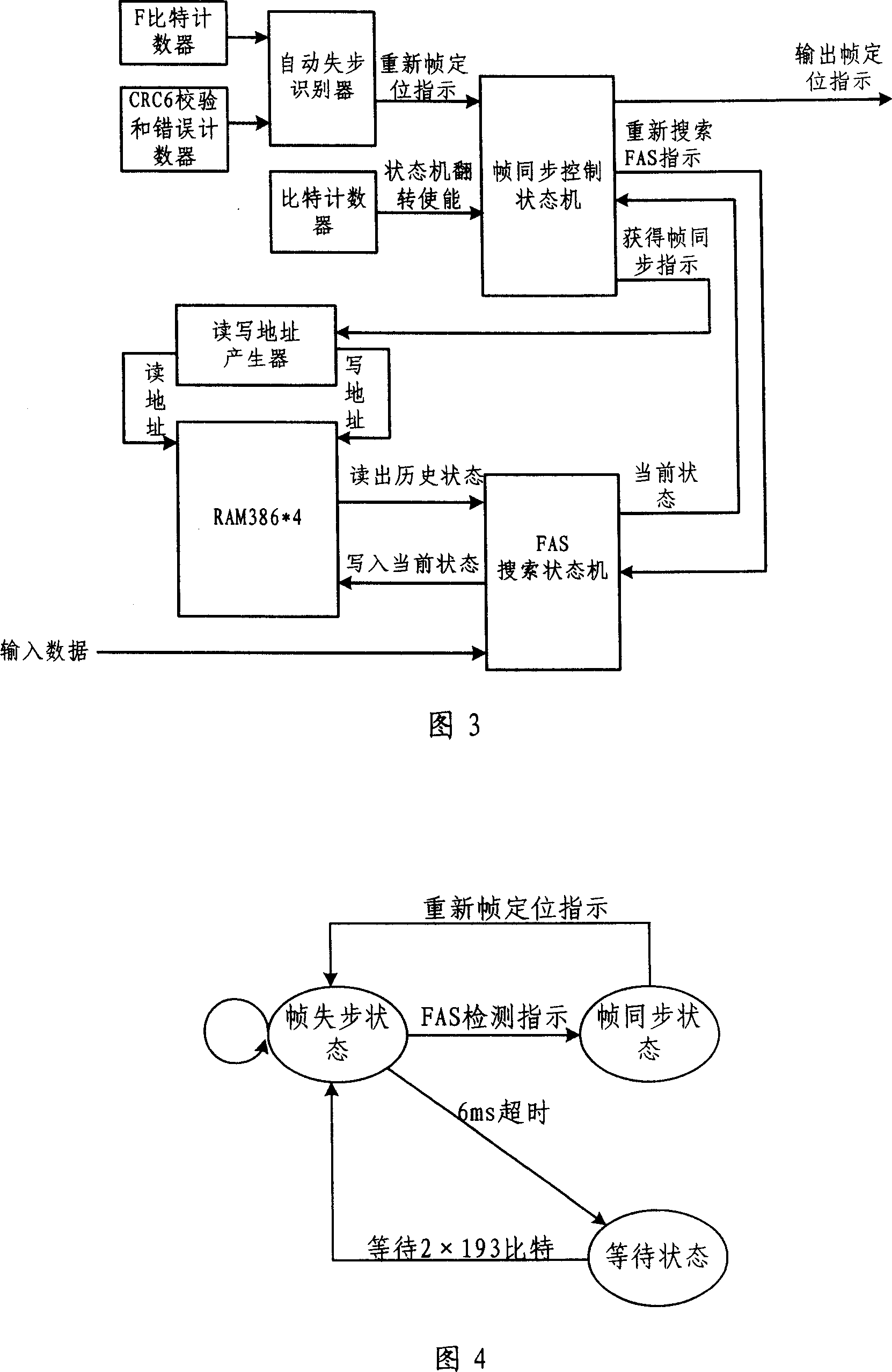

Method and device for extended super frame synchronization for T1 system

ActiveCN101072090AUse small memoryRealize a small areaSynchronising arrangementMemory addressComputer hardware

The method includes steps: initializing the memory unit of search mode (MUSM), the search unit of frame alignment pattern (FAP), and frame synchronous control unit; reading out data of history state from MUSM according reading addresses corresponding to sequence number of the serial input data; based on inputted serial data of expanded supreframe, data of history state, and re-searched FAP indicator signal, the method carries out state transition for the search unit of FAP, and outputs current state; storing data of current state to MUSM at memory address identical to addresses for reading data of history state; based on the search unit of frame alignment pattern, the frame synchronous control unit outputs out current data of state, converts state, and determines whether frame Synch of the expanded supreframe is reached, and outputs the frame alignment indicator. Features are: using few memories, small area of the implementing device, and quick frame Synch.

Owner:SANECHIPS TECH CO LTD

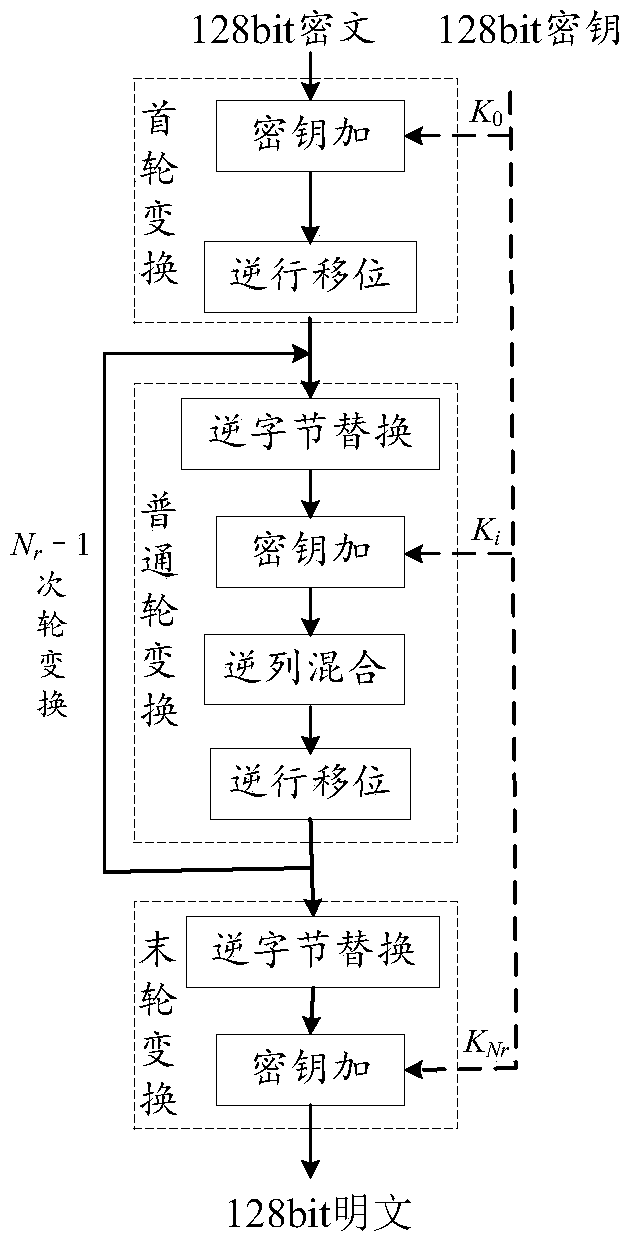

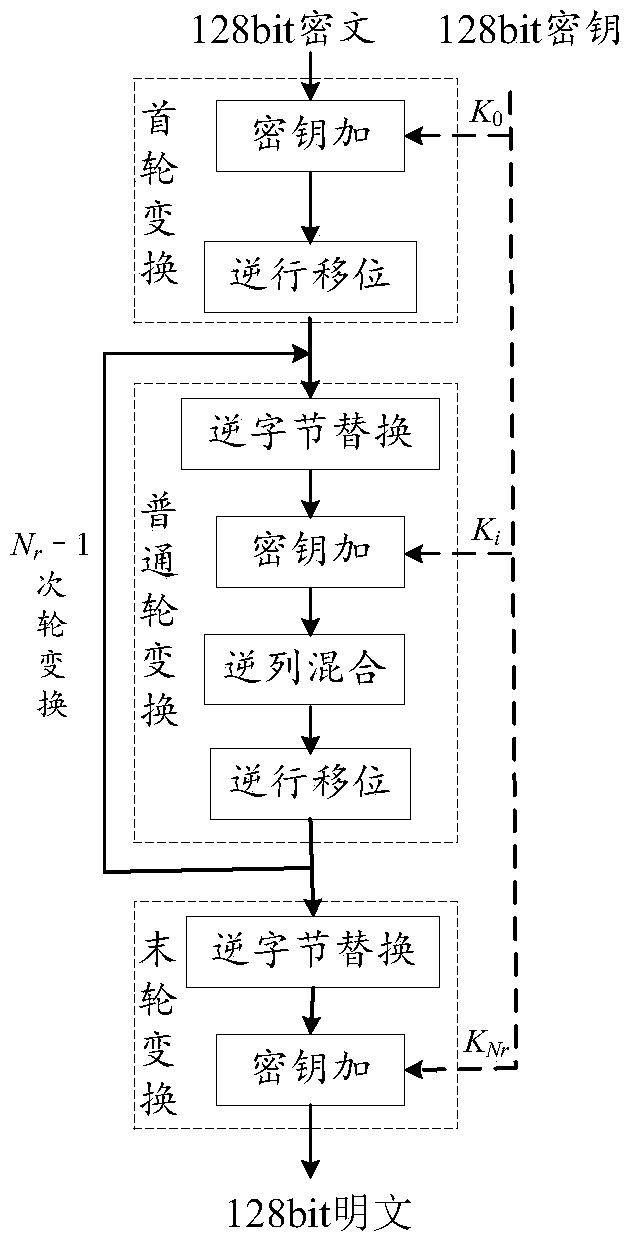

Common round transformation operation unit, common round transformation circuit and AES decryption circuit

ActiveCN108933652AShorten the critical pathRealize a small areaEncryption apparatus with shift registers/memoriesComputer hardwareTransformation unit

The invention relates to the technical field of cryptographic circuits, in particular to a common round transformation operation unit, a common round transformation circuit and an AES (Advanced Encryption Standard) decryption circuit. In the common round transformation unit used for AES decryption, all linear transformation operations in common round transformation in an AES decryption algorithm are combined into two composite matrixes through combination of constant matrixes and compositional operation, and the composite matrixes are shown in the description. A circuit critical path can be shortened and the circuit implementation area can be reduced.

Owner:ANHUI POLYTECHNIC UNIV

Algorithm hardware realizing method for improving network safety

InactiveCN103338449ASimple designIncrease profitNetwork topologiesSecurity arrangementExclusive orComputer science

The invention relates to an algorithm hardware realizing method for improving network safety. The method comprises the following steps: dividing plaintext codes into 4 coded words by taking a word as a unit and dividing key codes into 4 key words by taking a word as a unit; after performing operation on the first key word to the third key word and a constant, performing exclusive-or operation on the zeroth key word to generate a first turn of key with one word length, forwards moving the position of from the first key word to the third key word to the position of from the zeroth key word and the second key word, and moving the first turn of key to the position of the third key word; after performing operation on the first turn of key and the first coded word to the third coded word, performing exclusive-or operation on the zeroth key word to generate a first turn of ciphertext word, forwards moving the position of from the first coded word to the third coded word to the position of from the zeroth coded word to the second coded word, and moving the first turn of ciphertext word to the position of the third coded word. By the method, the area for realizing algorithm hardware is compact, and the circuit area for realizing the algorithm hardware is greatly reduced on the premise of guaranteeing the algorithm realizing efficiency.

Owner:苏州国芯科技股份有限公司

AES encryption unit based on composite matrix, AES encryption circuit and encryption method thereof

ActiveCN109033893AShorten the critical pathRealize a small areaInternal/peripheral component protectionComputations using residue arithmeticByteEncryption

The invention is applicable to the field of encryption technology and provides an AES encryption unit based on a composite matrix is provided, an AES encryption circuit and an encryption method. The AES encryption unit is used to realize 4 bytes AES encryption. By combining and synthesizing the constant matrix, all the linear transformation operations in the round transformation are combined intotwo composite matrices, the composite matrix delta and the composite matrix lambda, so as to shorten the critical path of the AES encryption circuit and reduce the area of the AES encryption circuit.

Owner:ANHUI UNIVERSITY OF TECHNOLOGY AND SCIENCE

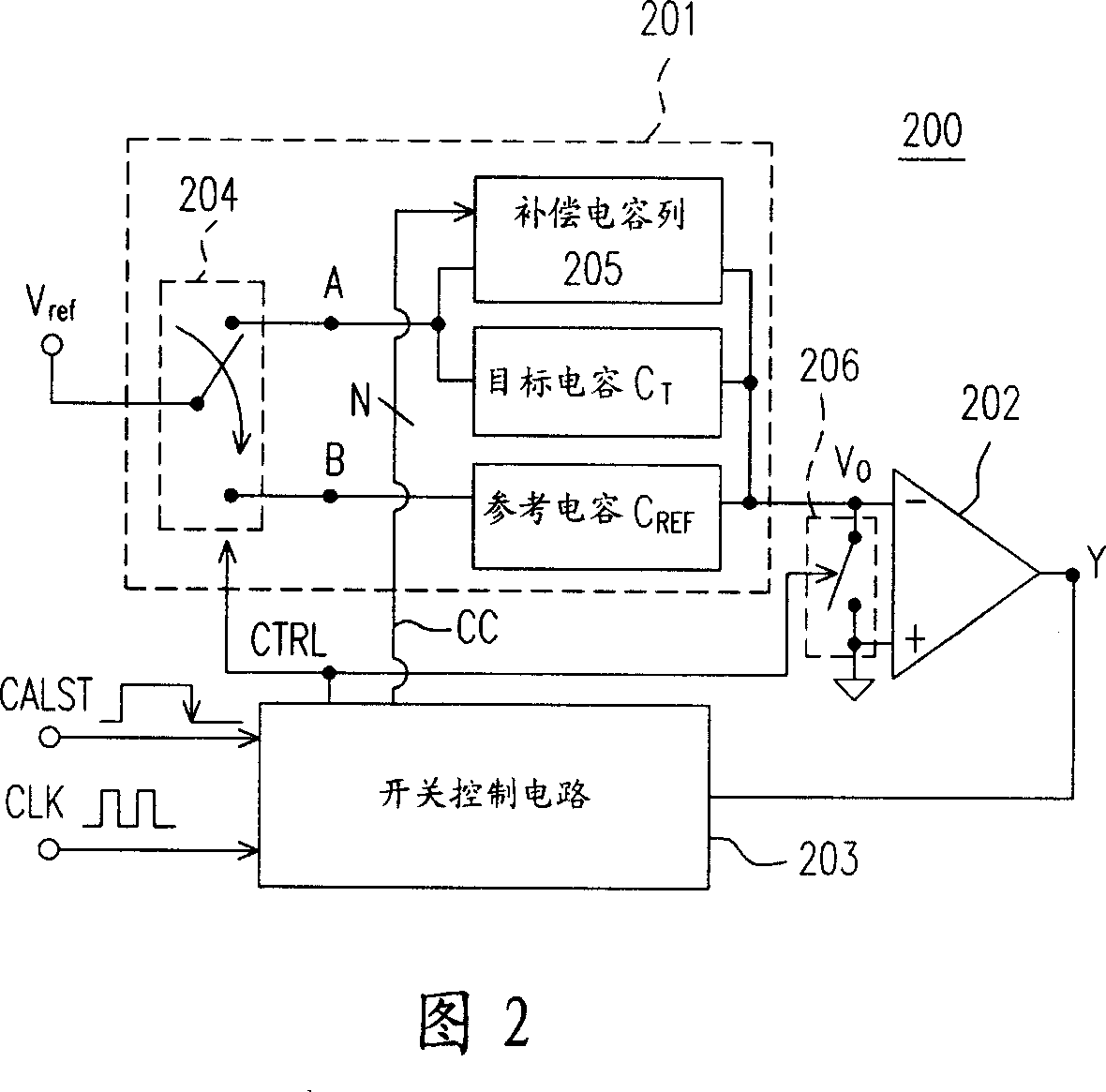

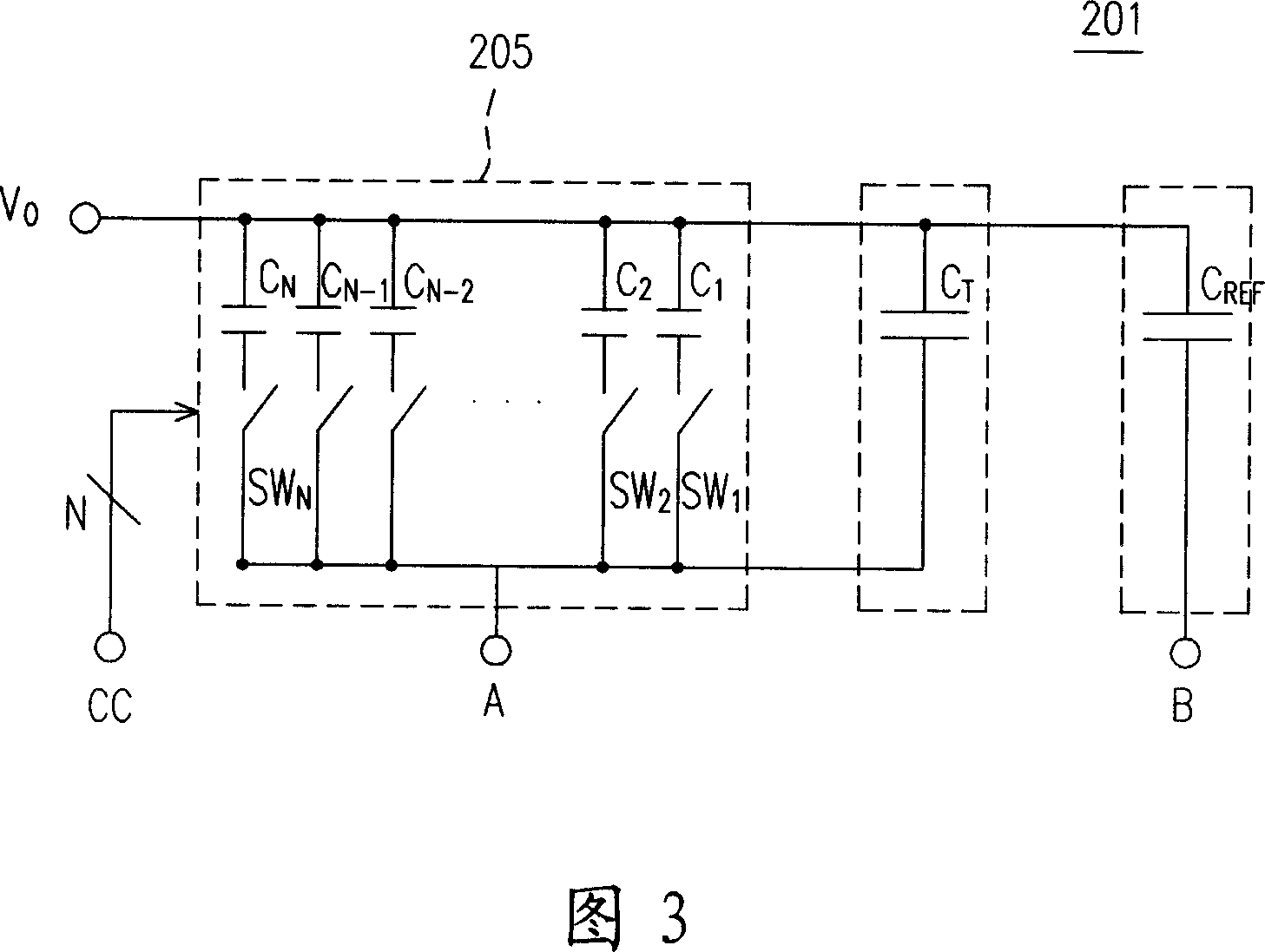

Self-correcting circuit for mismatch capacity

InactiveCN1967840ASimplify Design ComplexityRealize a small areaActive element networkSolid-state devicesCapacitanceControl circuit

The invention relates to a capacity unmatched automatic correct circuit, which comprises sampling hold circuit, comparer, and switch control circuit, wherein the sampling hold circuit comprises compensating capacitor array, target capacity, and reference capacity, to provide output voltage; said output voltage is the calculation result of equivalent capacitor, target capacitor, and reference capacitor; the comparer via the output voltage of sampling hold circuit provides compare signal; the switch control circuit provides compensating control signal to the compensating capacitor array ton control the equivalent capacitor of said array, and in each period of time pulse signal, based on the compare signal, adjusts the compensating control signal, adds target capacitor on the equivalent capacitor, to reach reference capacitor along the time pulse signal.

Owner:PROLIFIC TECH INC

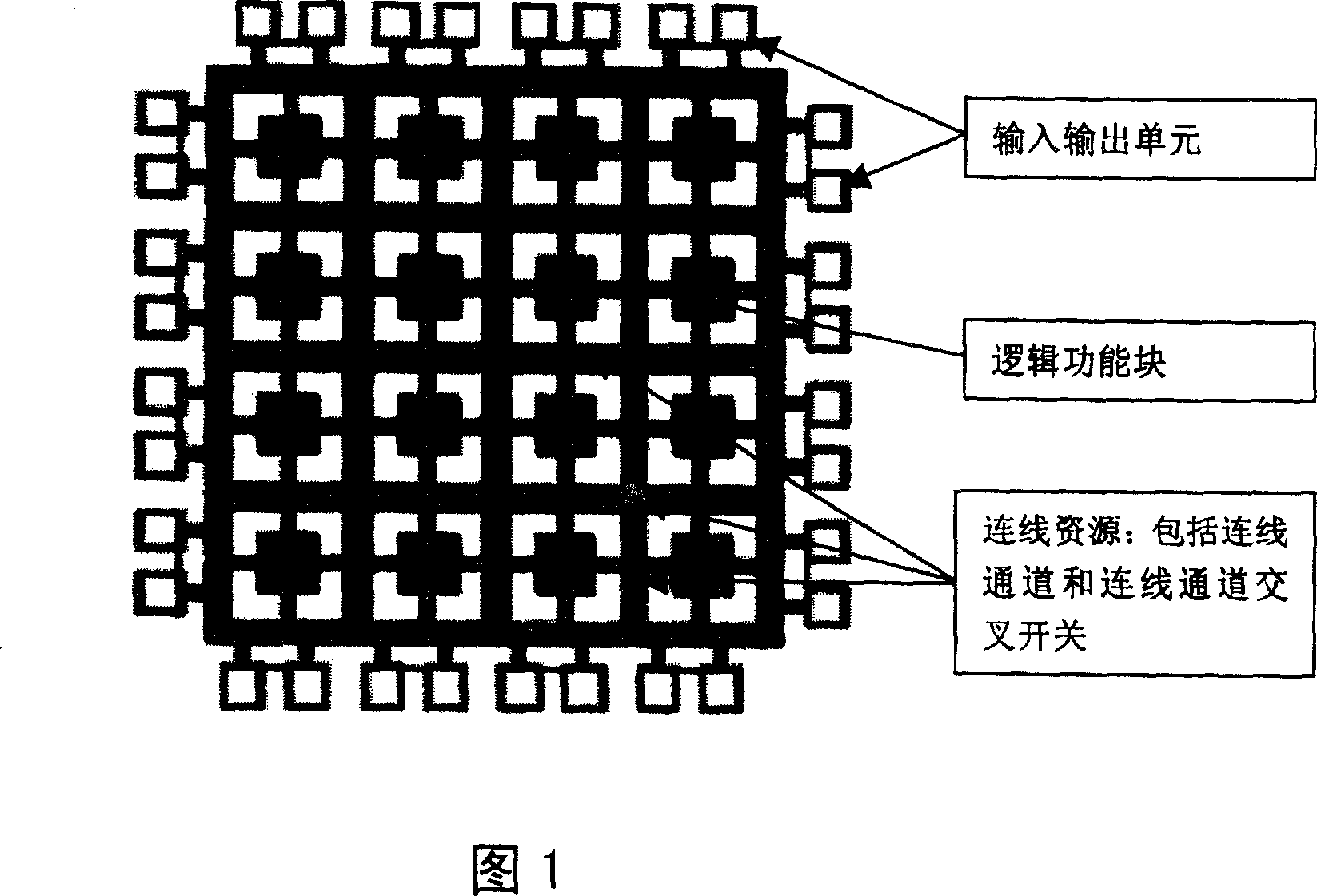

Symmetric connect passage of programmable logic device

ActiveCN1967833ALower latencyImprove featuresSemiconductor/solid-state device detailsSolid-state devicesCrossbar switchProgrammable logic device

The invention relates to a programmable logic element, especially the connecting channel and channel cross switch, as compensate cross switch, wherein the connecting line in the horizontal connecting channel is equally divided into upper and lower parts which are symmetry with the central line of connecting channel; the line of vertical connecting channel is same as the line in horizontal connecting channel; the line in horizontal connecting channel is rotated 90degree anti-clockwise, then turned over based on the central line, to obtain the vertical connecting channel. The invention can reduce time delay of connecting channel, and reduce area of cross switch, to improve property.

Owner:INST OF ELECTRONICS CHINESE ACAD OF SCI

AES encryption arithmetic unit, AES encryption circuit and encryption method thereof

ActiveCN109033847AShorten the critical pathRealize a small areaDigital data protectionComputer hardwareCritical path method

The invention is applicable to the field of encryption technology and provides an AES encryption arithmetic unit, an AES encryption circuit and an encryption method thereof. The AES encryption operation unit combines all the linear transformation operations in the wheel transformation into two composite matrices, the composite matrix delta and the composite matrix lambda through the combination and synthesis operation of the constant matrices, thereby shortening the critical path of the AES encryption circuit and simultaneously reducing the realization area of the AES encryption circuit.

Owner:ANHUI UNIVERSITY OF TECHNOLOGY AND SCIENCE

Multiplexing round conversion circuit, AES encryption circuit and encryption method thereof

ActiveCN108566271ASave resourcesShorten the critical pathEncryption apparatus with shift registers/memoriesMultiplexingComputer hardware

The invention is applicable to the technical field of encryption and provides a round conversion multiplexing circuit, an AES encryption circuit and an encryption method. The multiplexing round conversion circuit proposed by the invention combines all linear conversion operations in an AES cryptographic algorithm into two composite matrices of a composite matrix delta and a composite matrix lambdaby merging and compositional operation of constant matrices; thereby shortening the critical path of the AES encryption circuit formed by the multiplexing round conversion circuit, reducing the implementation area of the AES encryption circuit, and realizing ordinary round conversion and final multiplexing round conversion through a multiplexing composite matrix multiplication unit 1 and a composite domain inverse-of-multiplication unit, so as to save large amounts of circuit resources.

Owner:ANHUI UNIVERSITY OF TECHNOLOGY AND SCIENCE

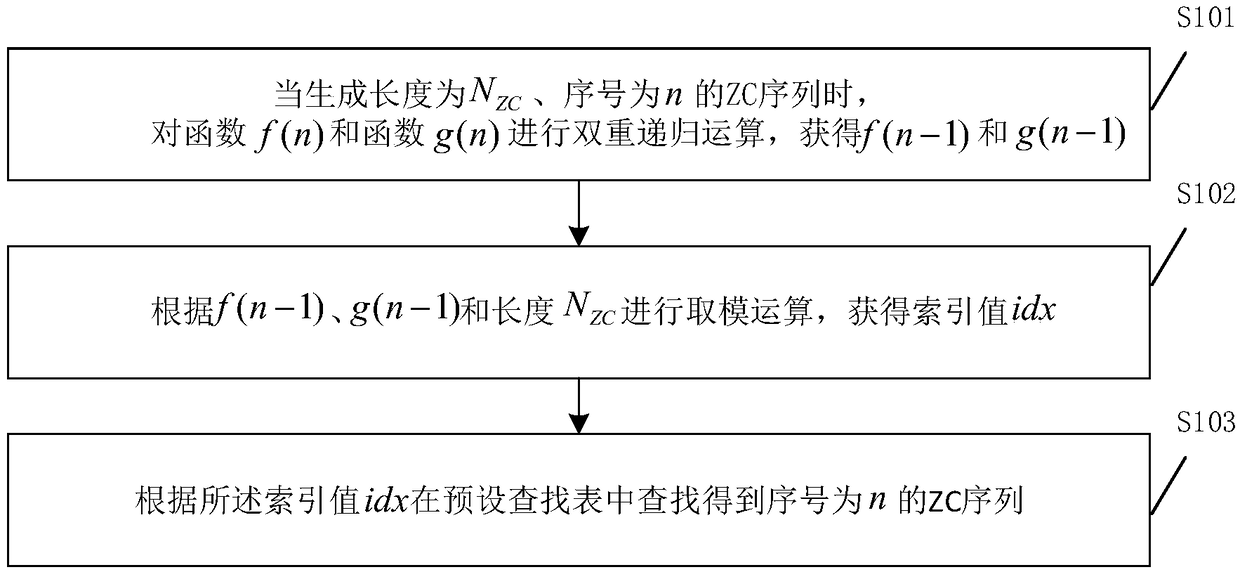

ZC sequence generation method and apparatus

ActiveCN108400829AReduce processing latencyReduce power consumptionMultiplex code generationBinary multiplierLookup table

The invention relates to a ZC sequence generation method and apparatus, and relates to the technical field of communication. The method comprises the following steps: when a ZC sequence with a lengthof NZC and a sequence number of n is generated, performing double recursive operation on a function f(n) and a function g(n) to obtain f(n-1) and g(n-1); performing modulo operation according to the f(n-1), the g(n-1) and the length NZC to obtain an index value idx; and searching a preset lookup table according to the index value idx to obtain the ZC sequence with the sequence number of n. In thisway, a multiplier or a divider required in the modulo process in the prior art is avoided, and only an adder and a comparator are used in the whole process of generating the ZC sequence, thereby reducing the complexity of implementing the general ZC sequence by hardware, shortening the hardware processing delay, reducing the hardware implementation area, and reducing the hardware implementation power consumption, in addition, the method is not limited to the generation of the ZC sequence when k=0, and is also universal to the generation of ZC sequences in other scenes.

Owner:BEIJING XIAOMI PINECONE ELECTRONICS CO LTD

Round transformation multiplexing circuit and AES (Advanced Encryption Standard) decryption circuit

ActiveCN108809627ARealize a small areaImprove optimization efficiencyEncryption apparatus with shift registers/memoriesComputer hardwareMultiplexing

The invention relates to the technical field of a password circuit and provides a round transformation multiplexing circuit and an AES (Advanced Encryption Standard) decryption circuit. According to the round transformation multiplexing circuit provided by the invention, through combination and composite calculations of a constant matrix, all linear transformation calculations in an AES decryptionalgorithm are combined into two composite matrixes: a composite matrix delta(-tilde) and a composite matrix inverse-V(-tilde). A key path of the AES decryption circuit is reduced, and moreover, an AES decryption realization area is reduced.

Owner:ANHUI UNIVERSITY OF TECHNOLOGY AND SCIENCE

Implementation method of area-compact arithmetic hardware for wireless local area network

ActiveCN101945383ASimple designIncrease profitNetwork topologiesSecurity arrangementComputer hardwareCiphertext

The invention relates to an implementation method of area-compact arithmetic hardware for a wireless local area network. The method comprises the following steps of: dividing a plaintext code into four coded words by taking words as units, and dividing a secret key code into four secret key words by taking words as units; operating the secret key words from a first bit to a third bit and a constant; performing WXOR operation on the secret key word of a zeroth bit to generate a first round secret key with one word length; shifting the secret key words from the first bit to the third bit to thepositions of the secret key words from the zeroth bit to the second bit forwards; shifting the first round secret key to the position of the secret key word of the third bit; operating the first round secret key and the coded words from the first bit to the third bit, and performing the WXOR operation on the coded word of the zeroth bit to generate a first round ciphertext word with one word length; shifting the coded words from the first bit to the third bit to the positions of the coded words from the zeroth bit to the second bit forwards; and shifting the first round ciphertext word to theposition of the coded word of the third bit. The method of the arithmetic hardware is implemented with a compact area and greatly reduces circuit areas for realizing the arithmetic hardware on the premise of ensuring algorithm implementation efficiency.

Owner:苏州国芯科技股份有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com