Self-adaptable package for designing on-chip network

An on-chip network and self-adaptive technology, applied in the direction of data exchange network, digital transmission system, electrical components, etc., can solve the problems of wasting network capacity and increasing the power consumption of on-chip network

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

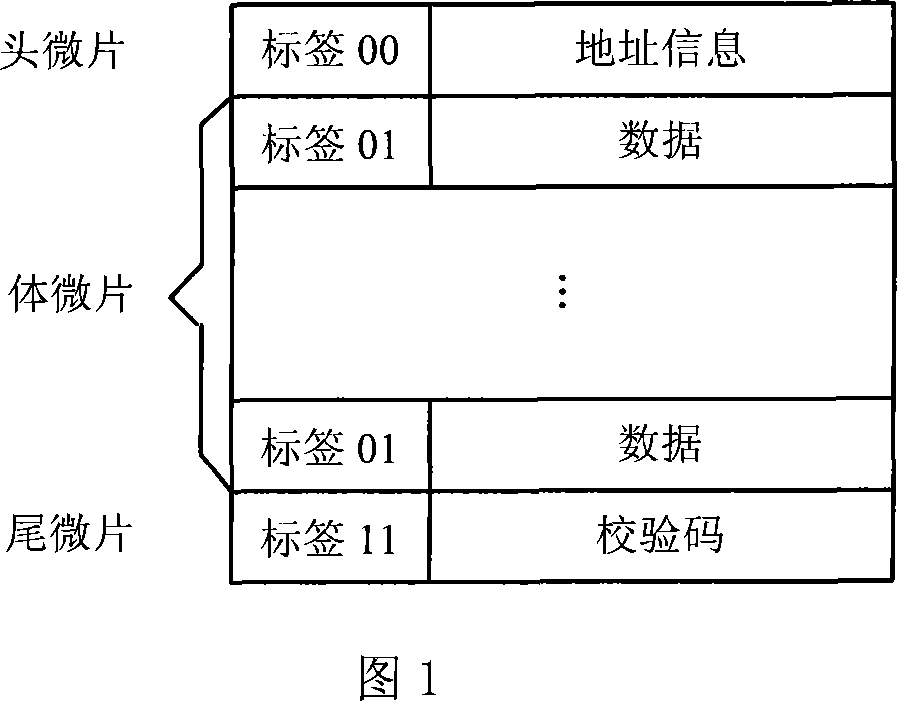

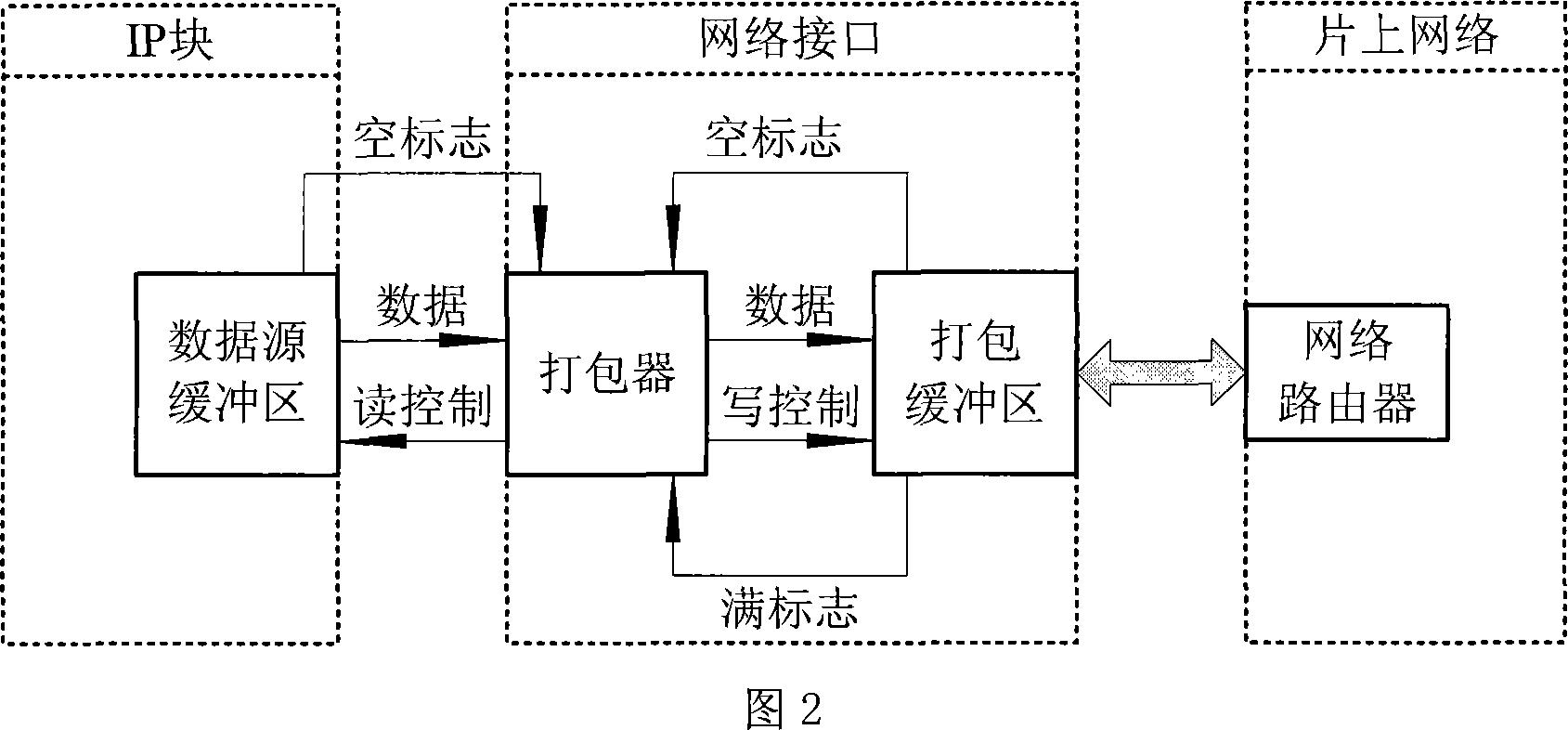

Method used

Image

Examples

Embodiment approach

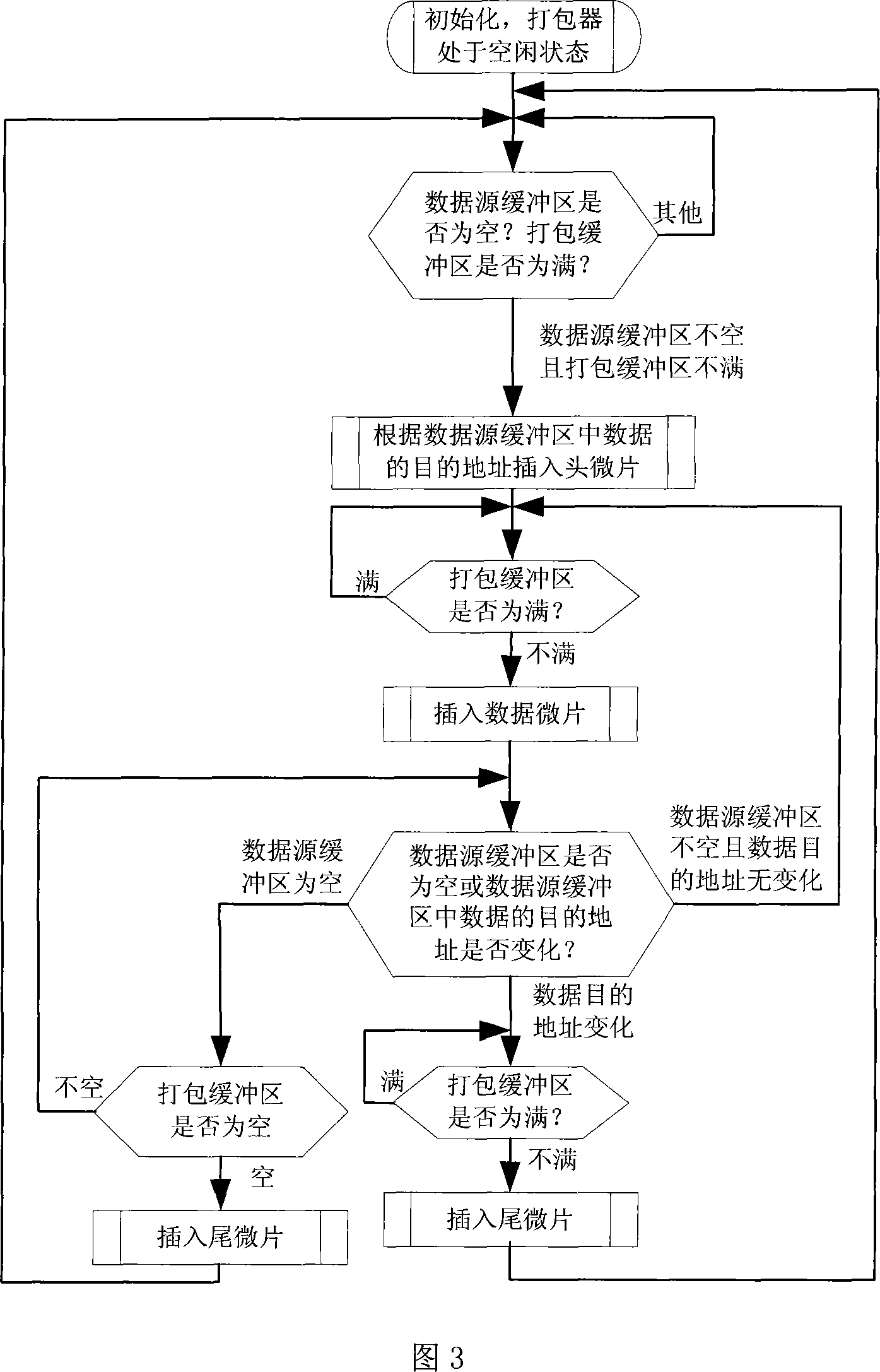

[0025] Embodiment: Figure 3 is a flow chart of the packaging process of the packager. After the packer is initialized, the packer is idle. In the idle state, in each clock cycle, the packer detects the empty flag signal of the data source buffer and the full flag signal of the packed buffer. If the data source buffer is not empty and the packed buffer is not full, the packer buffers according to the data source The destination address of the data in the area is inserted into the head microchip, and the body microchip containing the data is inserted in the next clock cycle when the packing buffer is not full, and the packer enters a busy state. In the busy state, if the data source buffer is not empty, the packing buffer is not full, and the destination address of the data in the data source buffer remains unchanged, the packer will continue to insert volume flakes; if the destination address of the data source data changes, then When the packaging buffer is not full, insert t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com