Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

175results about How to "Prevent characteristic deterioration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

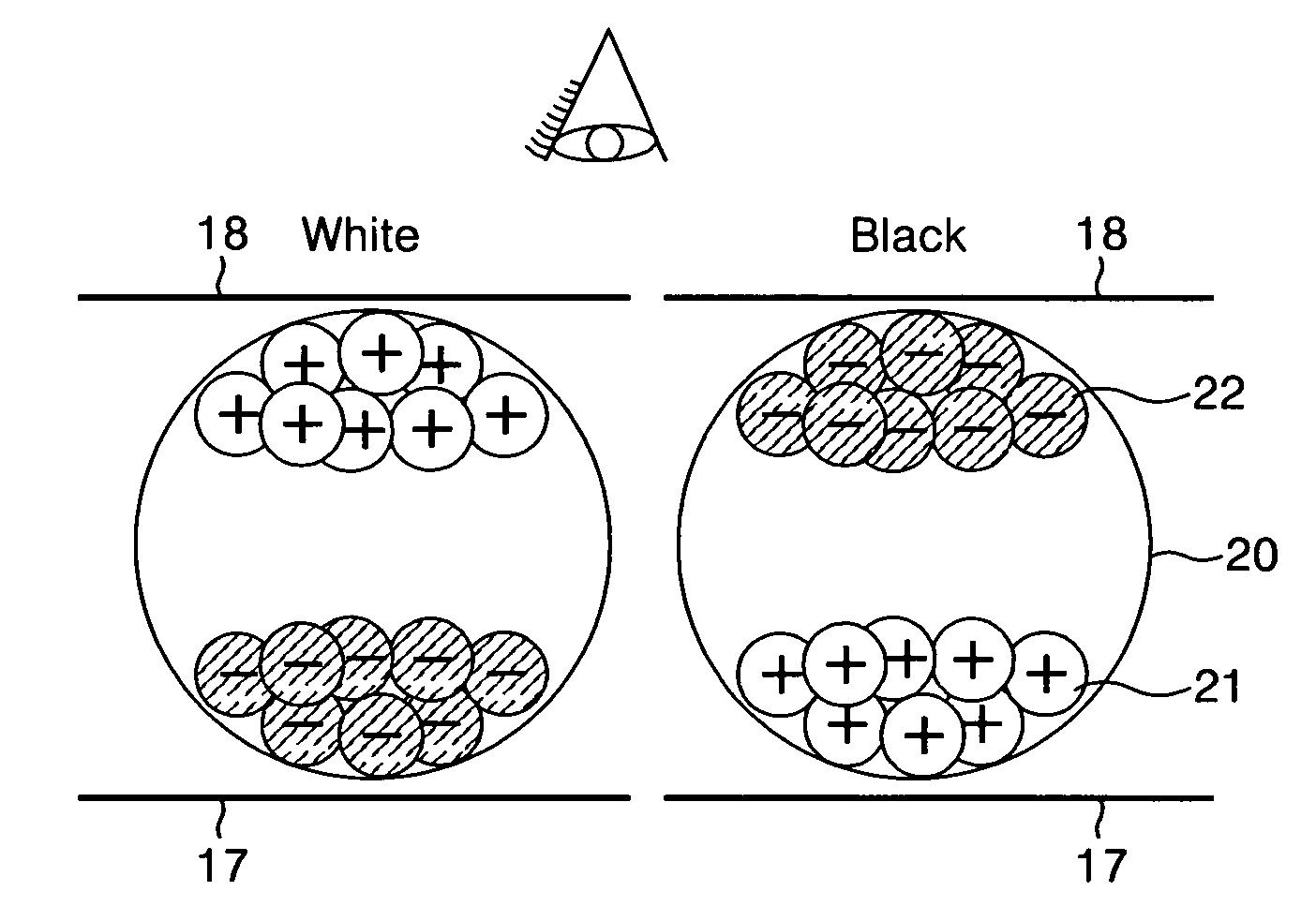

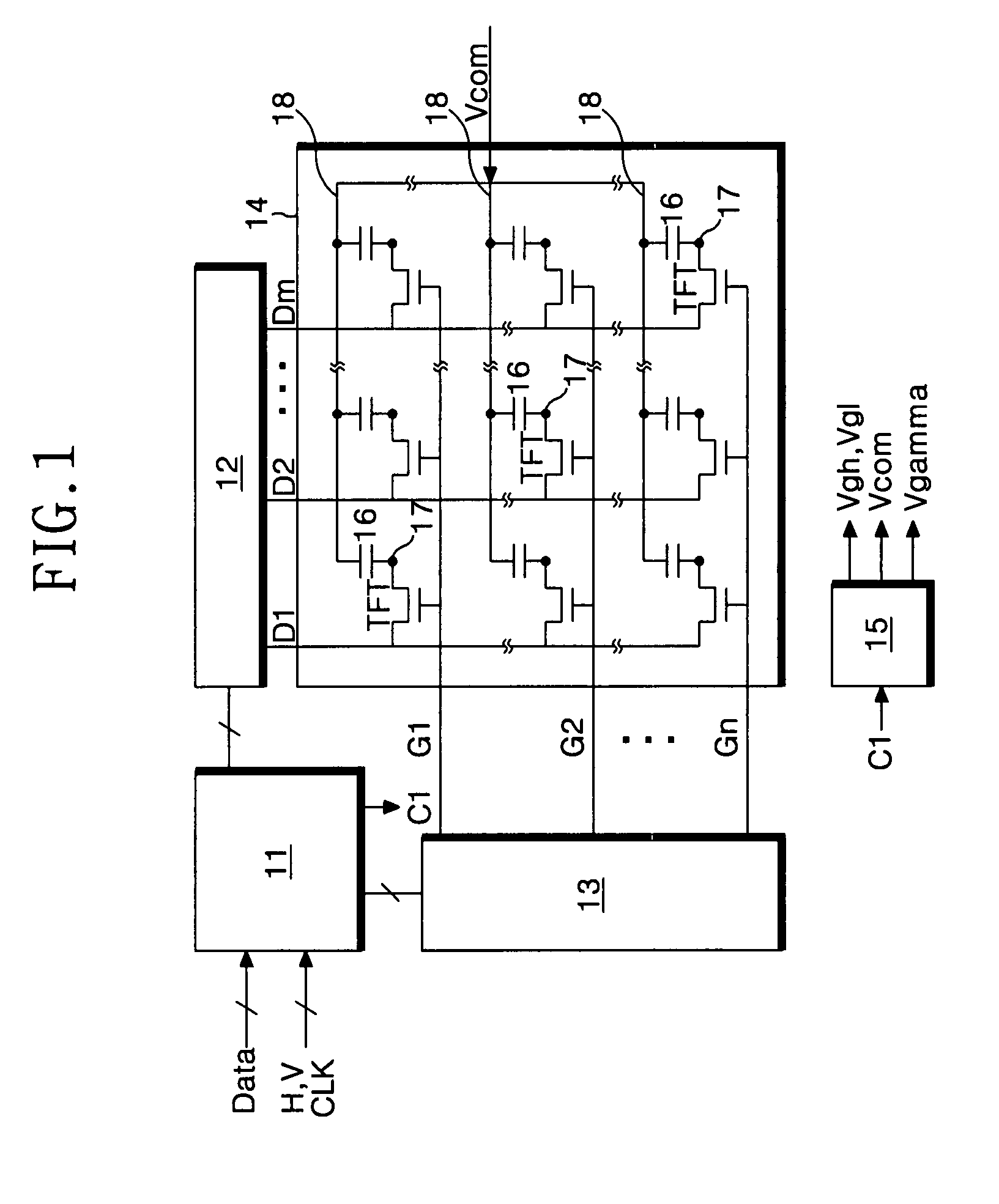

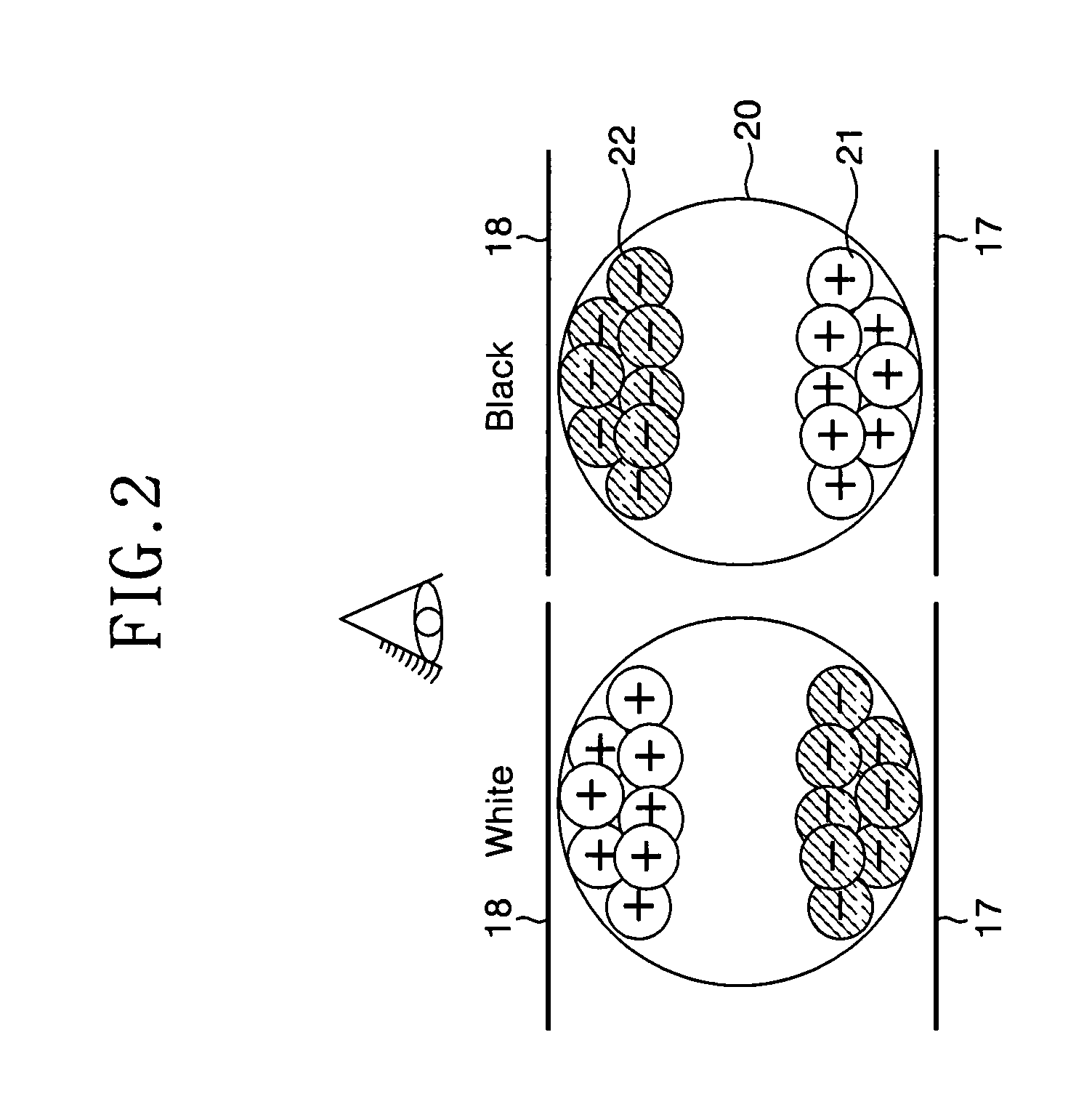

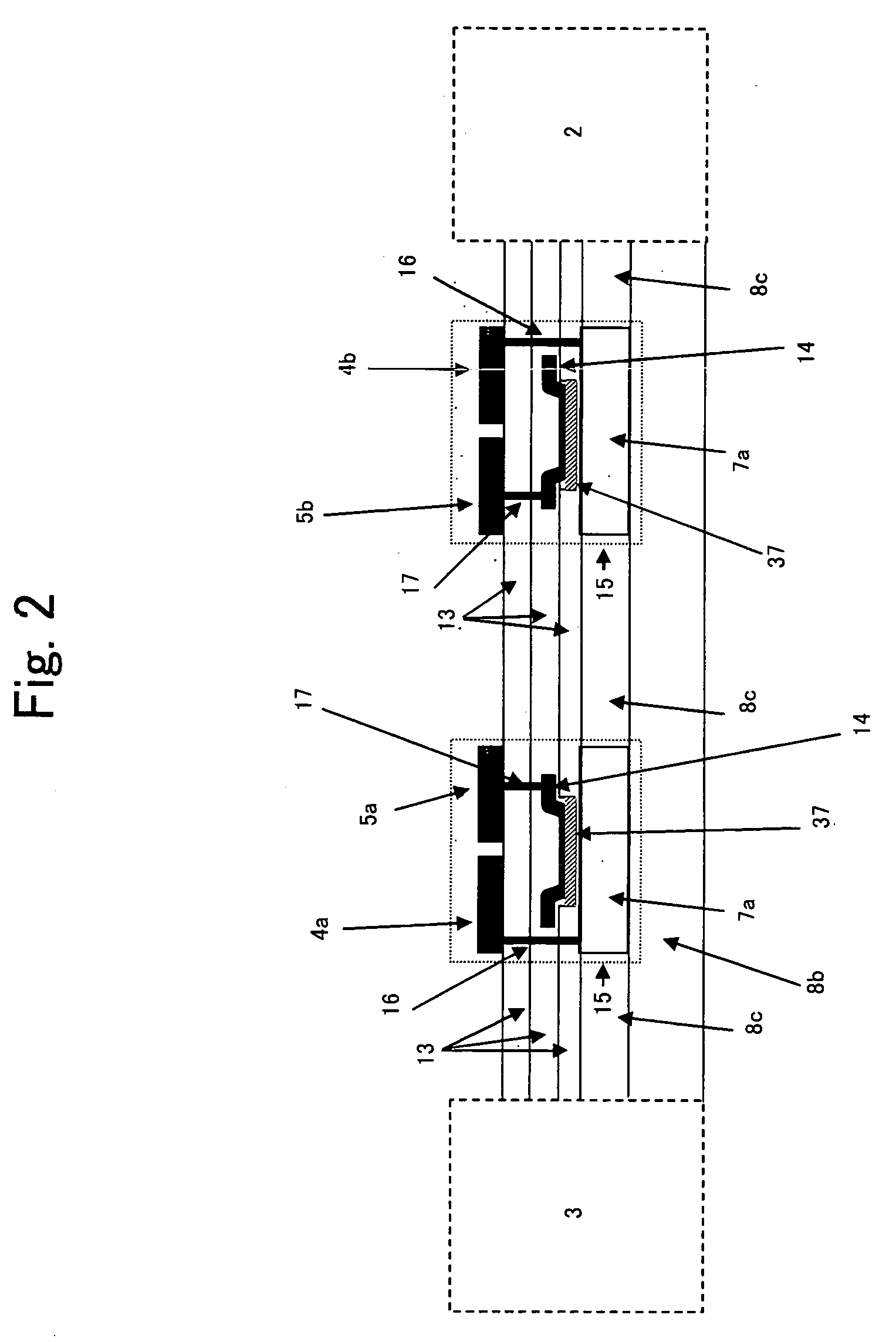

Electrophoretic display and driving method thereof

ActiveUS20080150887A1Prevent degradationRelieve pressureCathode-ray tube indicatorsNon-linear opticsElectrophoresisDisplay device

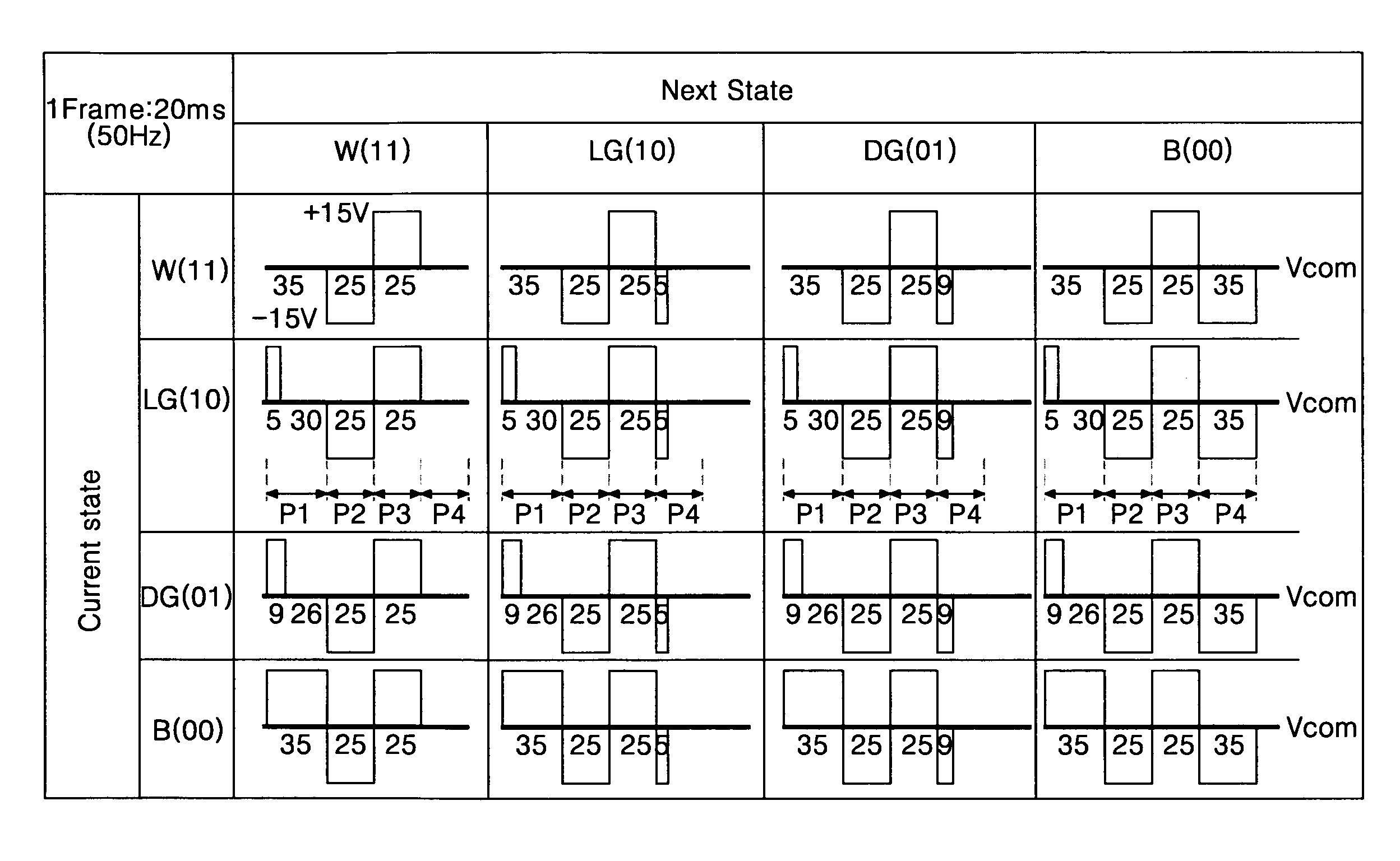

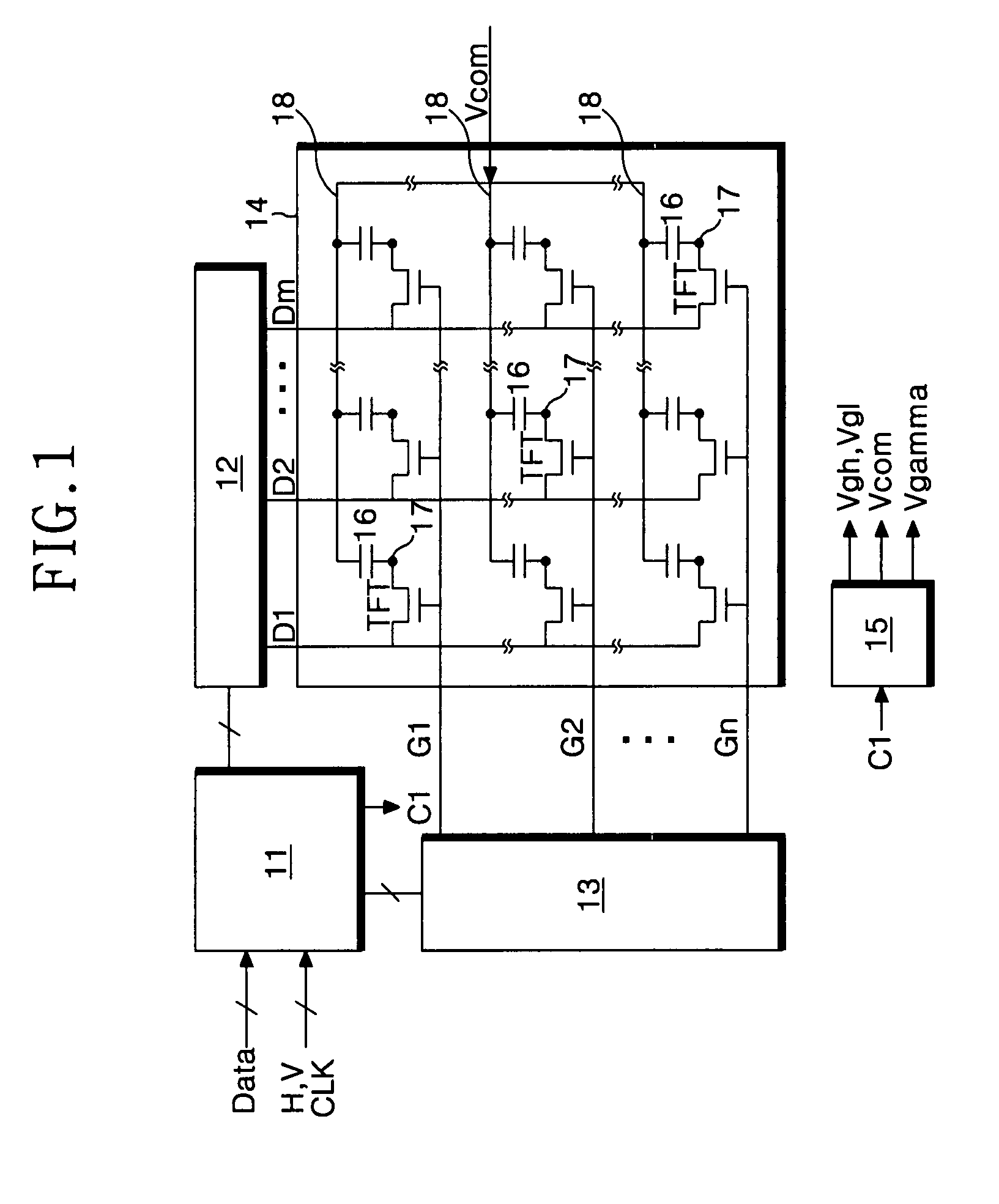

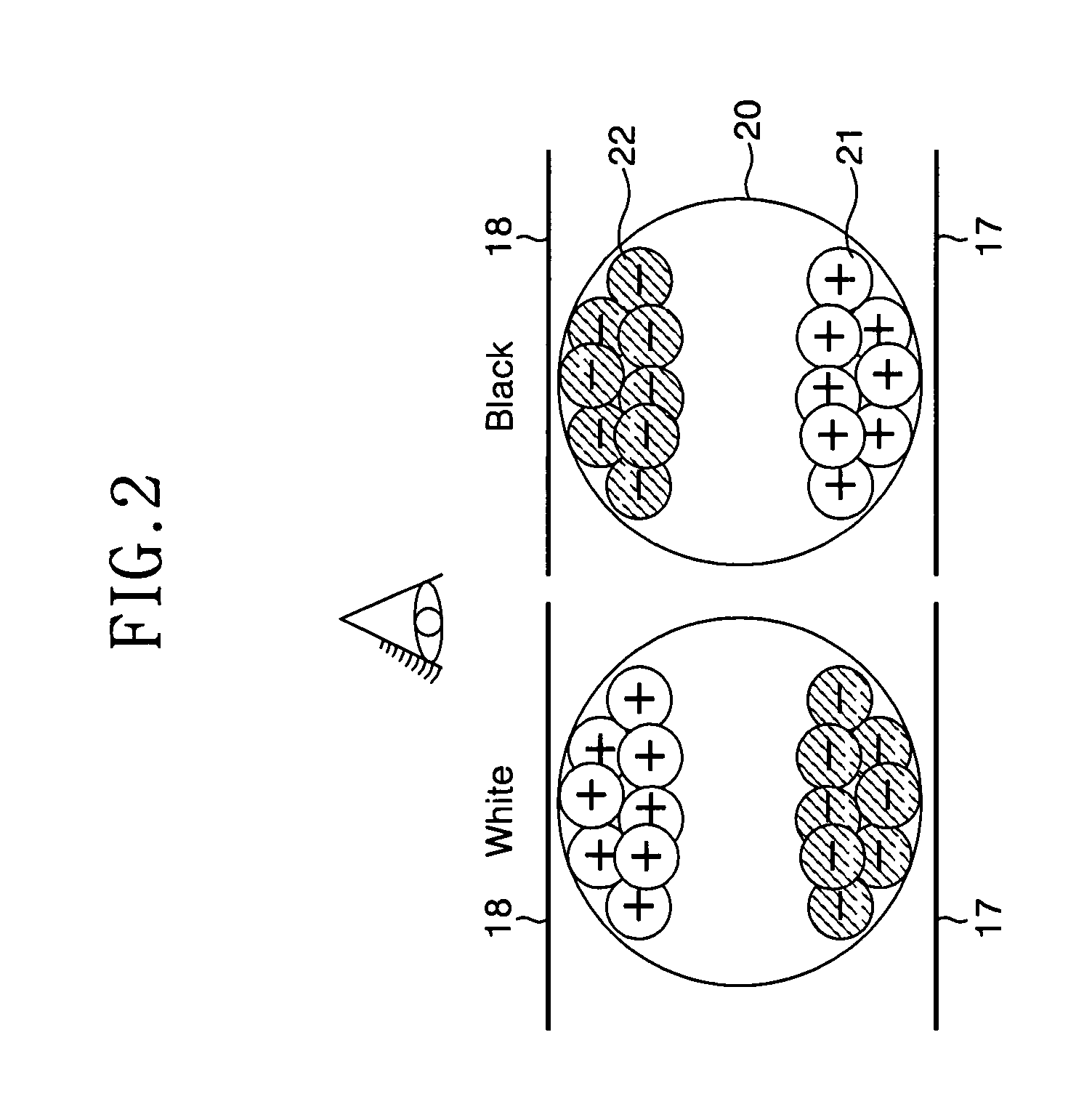

An electrophoretic display device sequentially driven during a data updating period when a data is updated and a sleep-mode period when a data is maintained includes an electrophoretic display panel including a plurality of data lines crossing a plurality of gate lines to form a plurality of cells, a plurality of pixel electrodes, a common electrode for driving each of the plurality of cells, and a TFT at a crossing of one of the data lines and one of the gate lines to supply a data voltage from the one of the data lines to a corresponding one of the pixel electrodes; a data driving circuit supplying the data voltage to the data lines during the data updating period; a gate driving circuit supplying a scanning pulse to the gate lines during the data updating period; and a controller sequentially raising an impedance of each of the data lines, the common electrode, and the gate lines during the sleep-mode period.

Owner:E INK CORPORATION

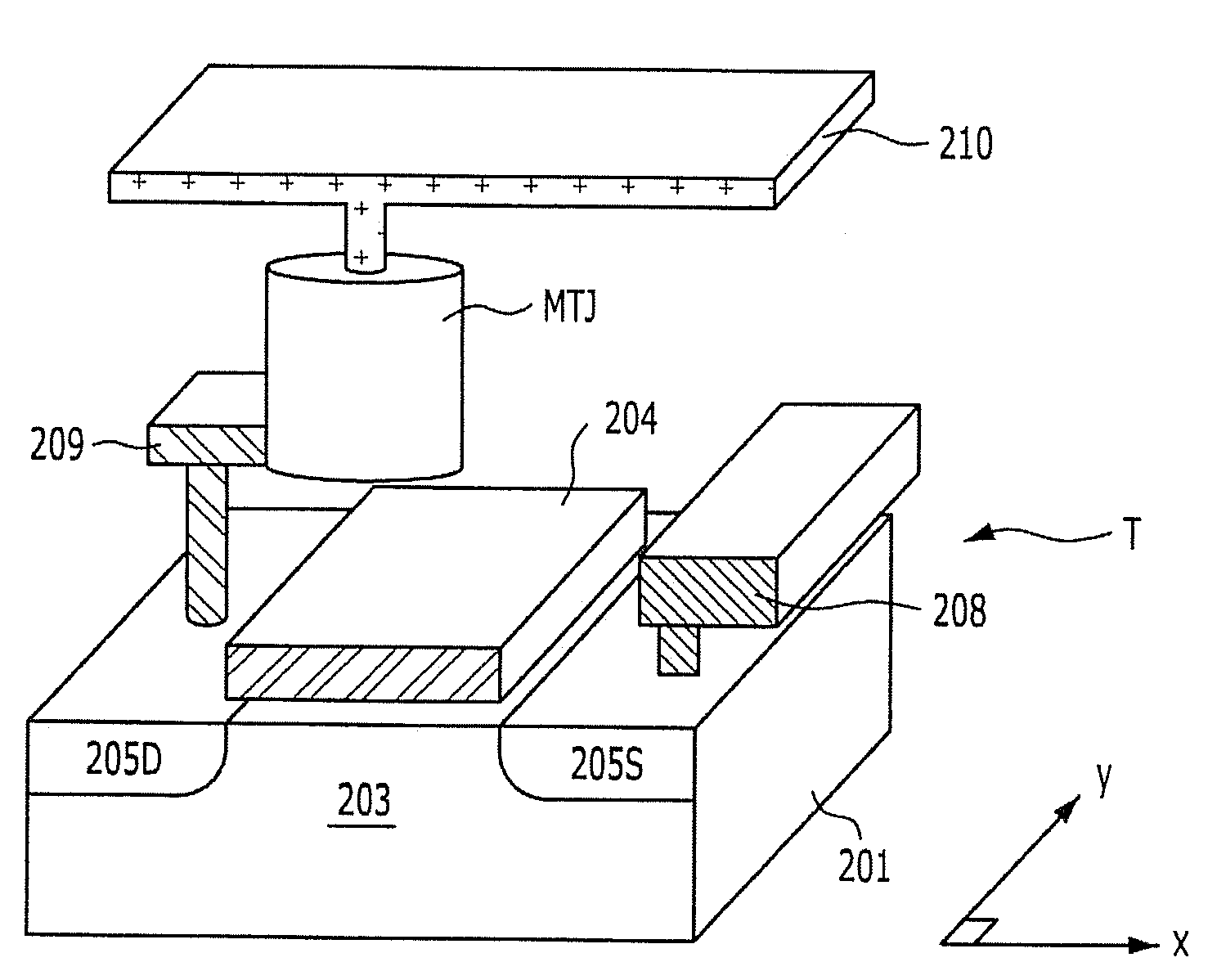

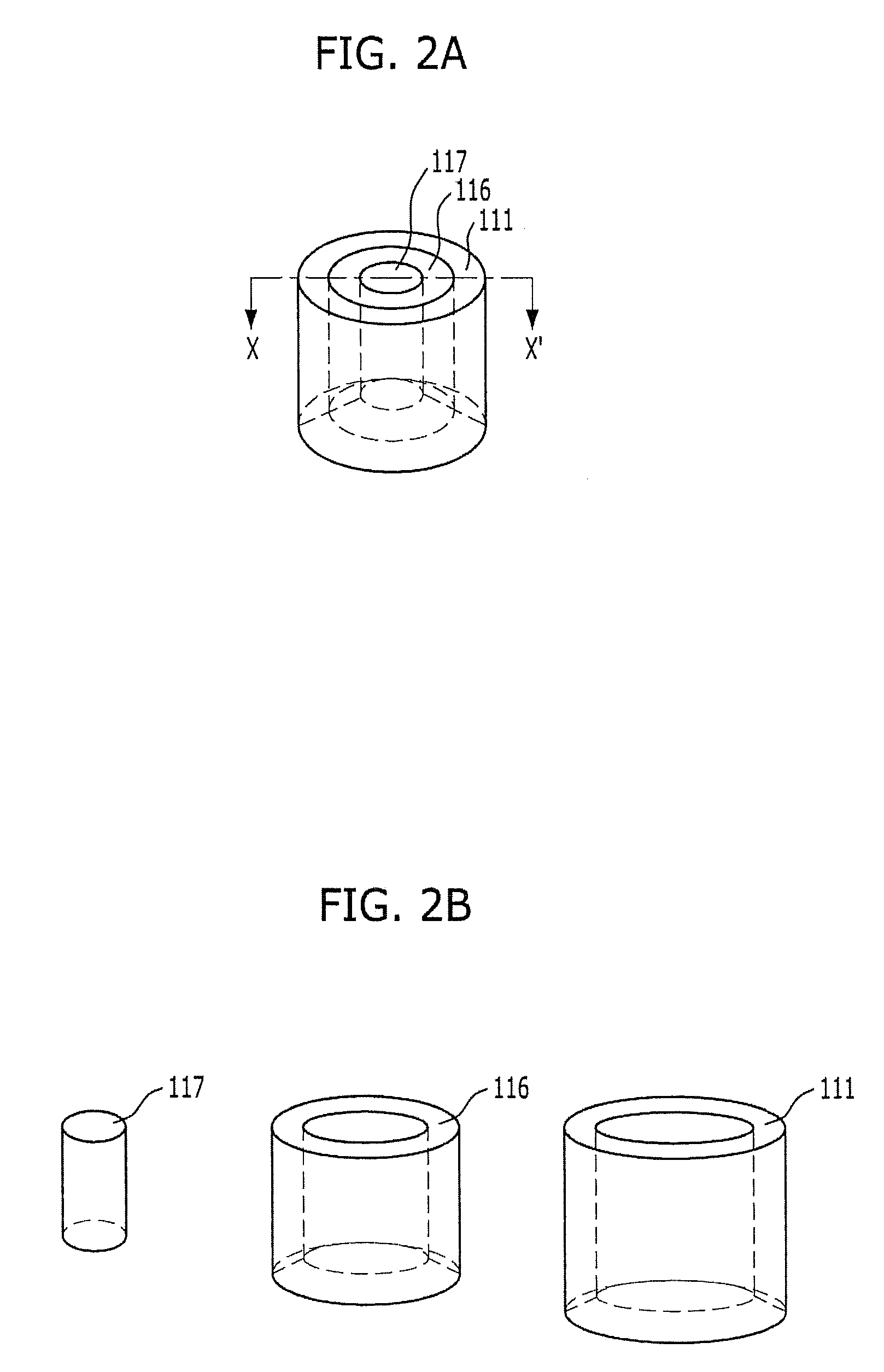

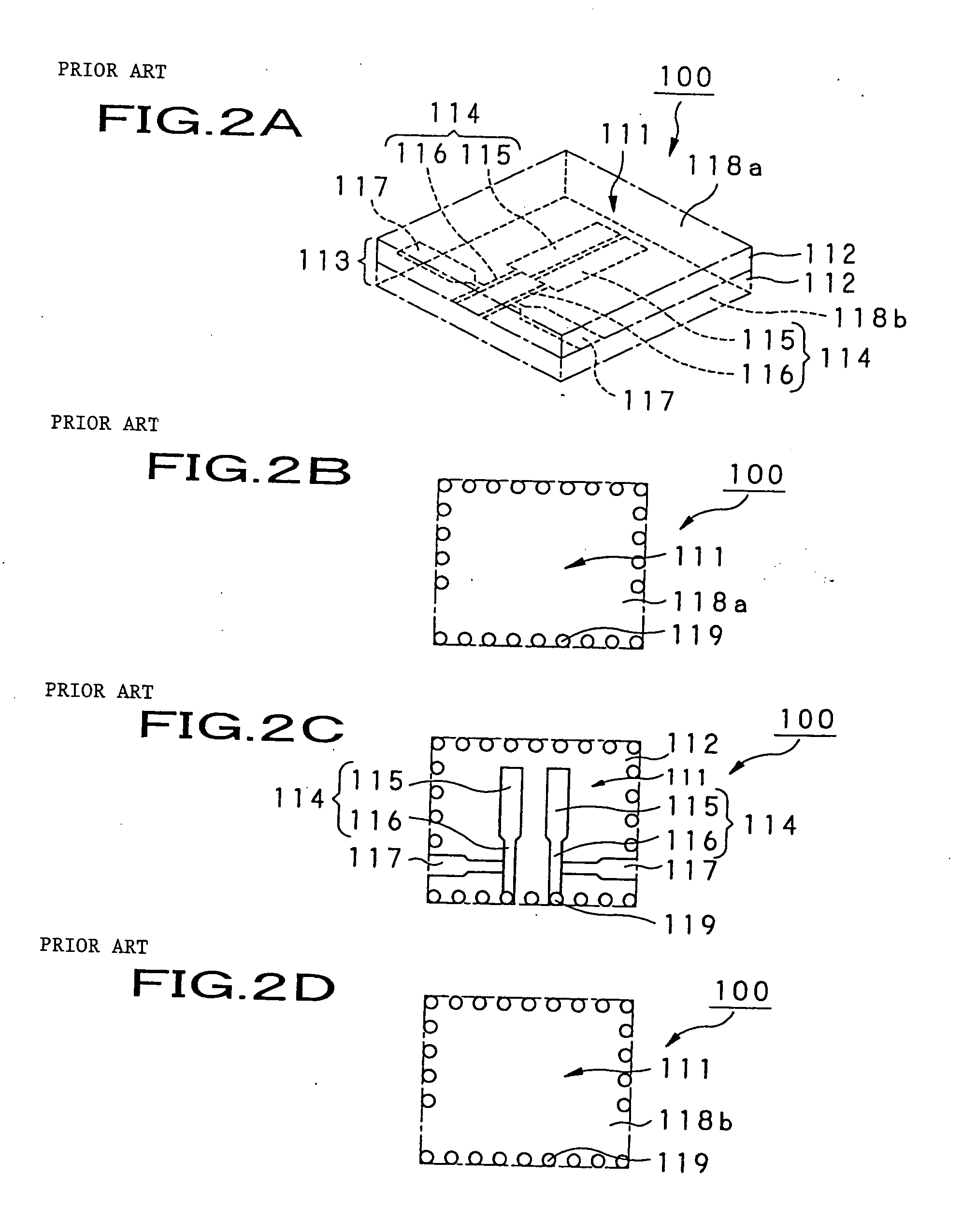

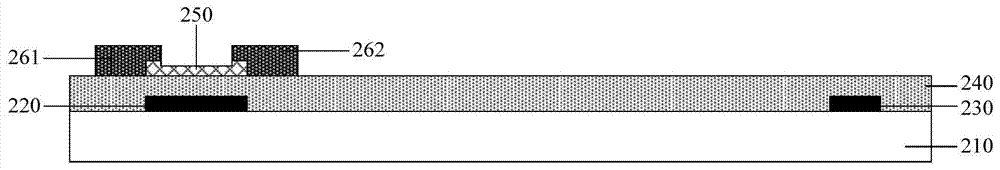

Magnetic tunnel junction device, memory cell having the same, and method for fabricating the same

InactiveUS20100003767A1Prevent characteristic deteriorationMagnetic-field-controlled resistorsSolid-state devicesInsulation layerEngineering

A method for fabricating a magnetic tunnel junction device includes forming an insulation layer having a plurality of openings, forming a first electrode over the bottom and the sidewall of an opening of the plurality of openings, forming a magnetic tunnel junction layer over the first electrode, and forming a second electrode over the magnetic tunnel junction layer to fill the remaining openings.

Owner:SK HYNIX INC

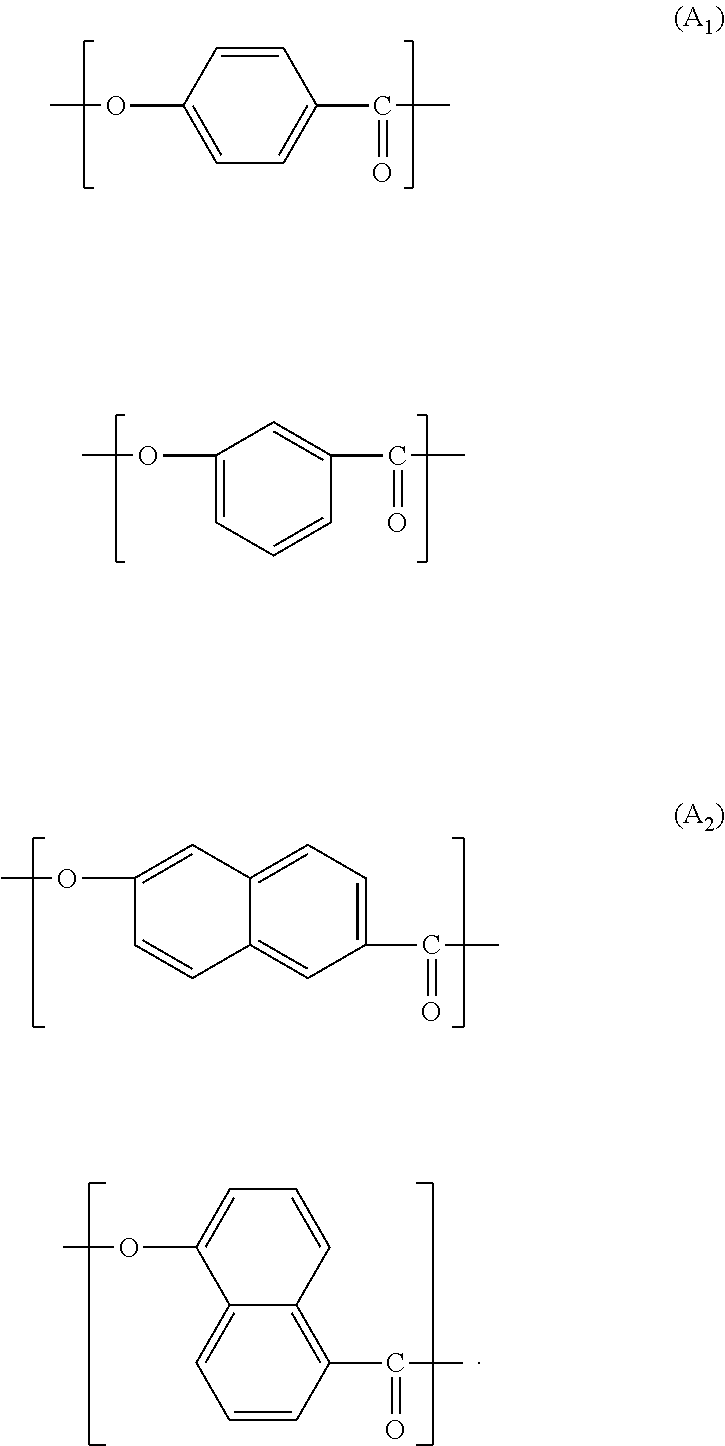

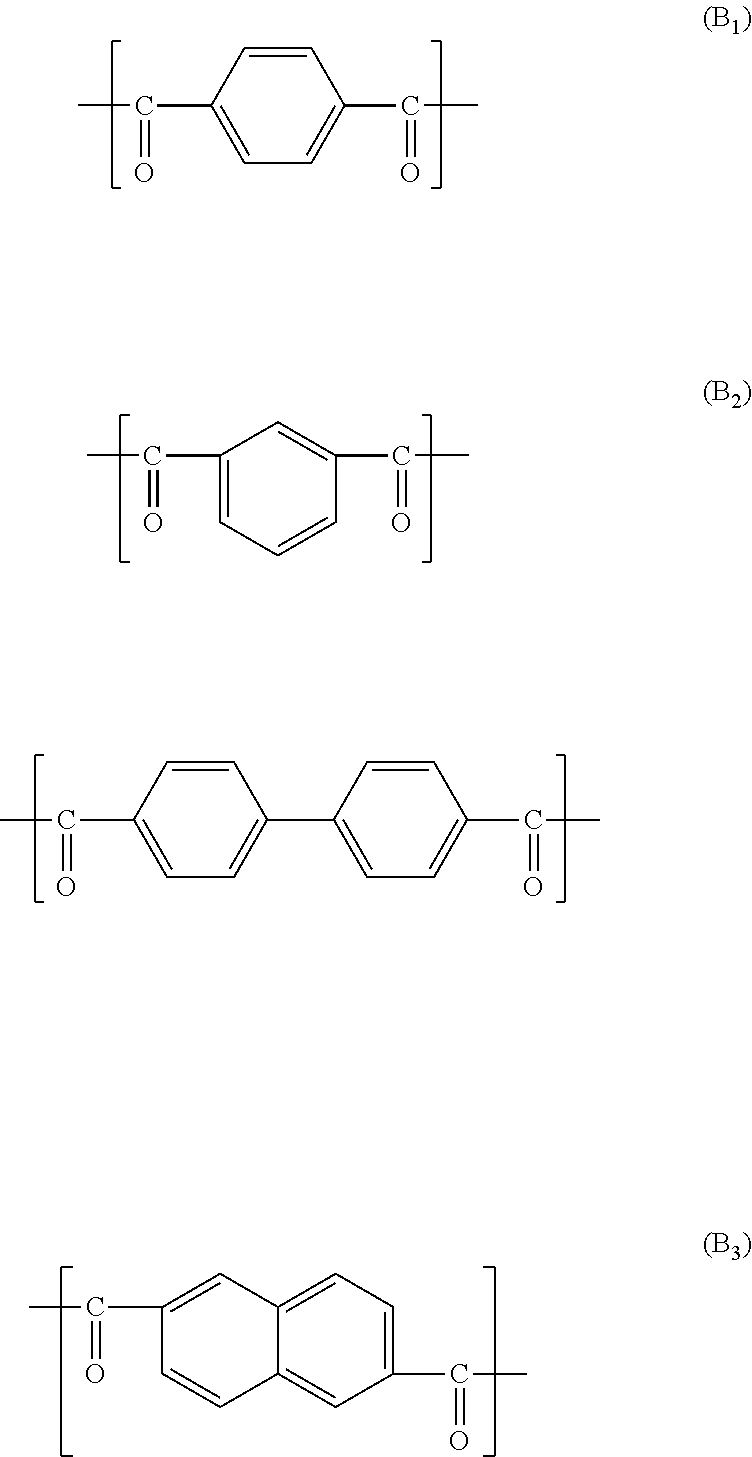

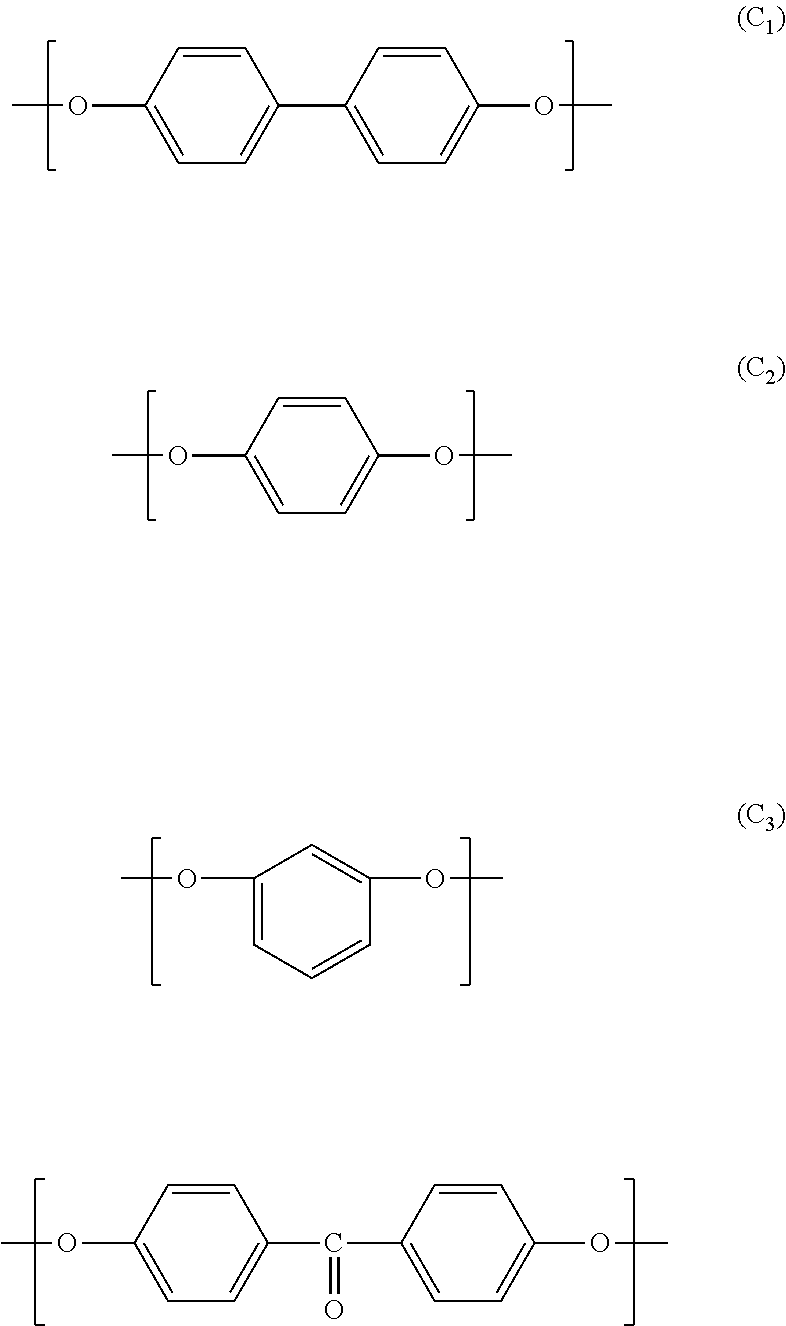

Liquid crystalline polyester composition, method for producing the same, and connector

InactiveUS20110189454A1InhibitionHigh mechanical strengthSynthetic resin layered productsSpecial tyresCrystallographyLiquid crystalline

The present invention provides a composition comprising a liquid crystalline polyester, a plate-like filler and a carbon black having a number average particle size of more than 20 nm and 45 nm or less. The composition is less likely to cause blister even at a high temperature.

Owner:SUMITOMO CHEM CO LTD

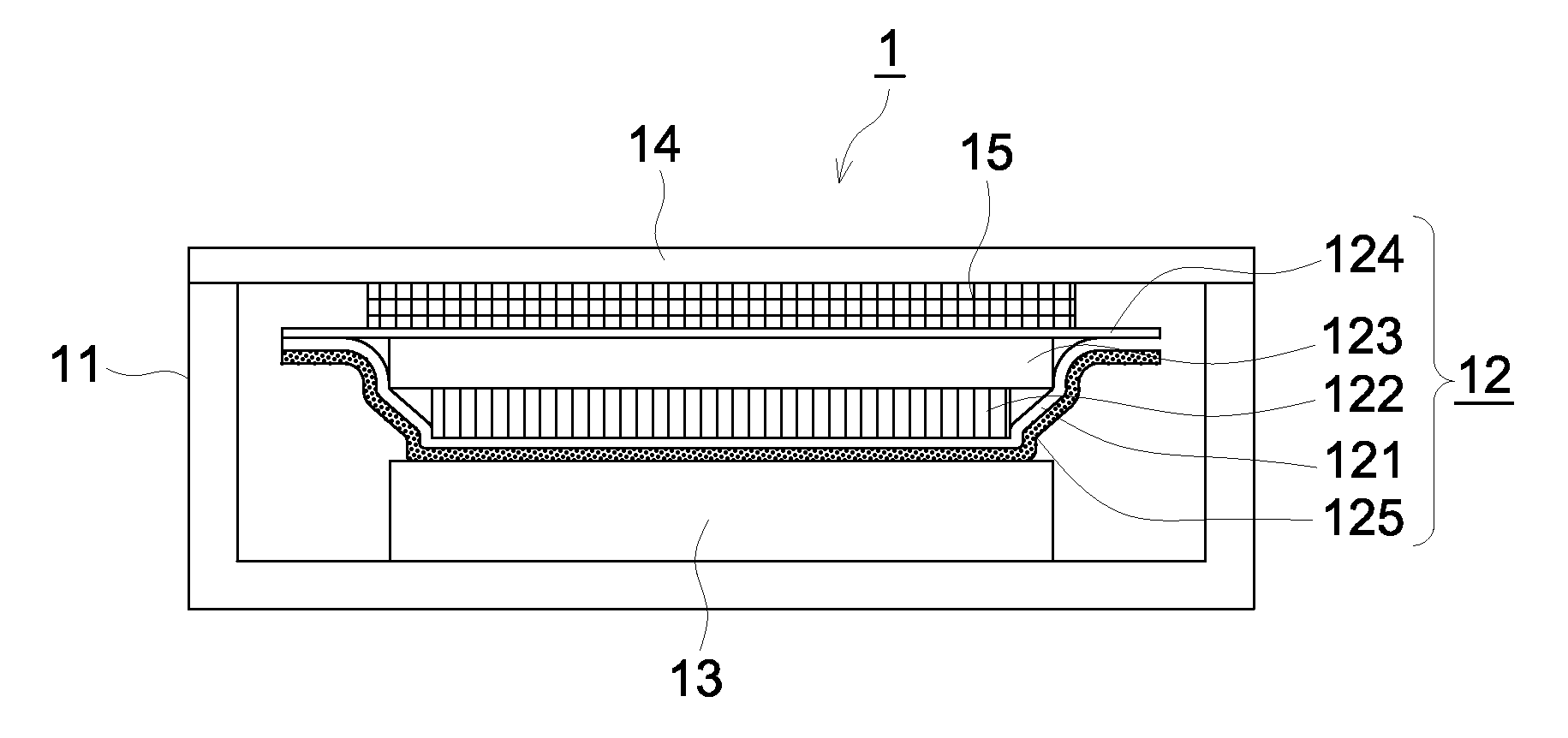

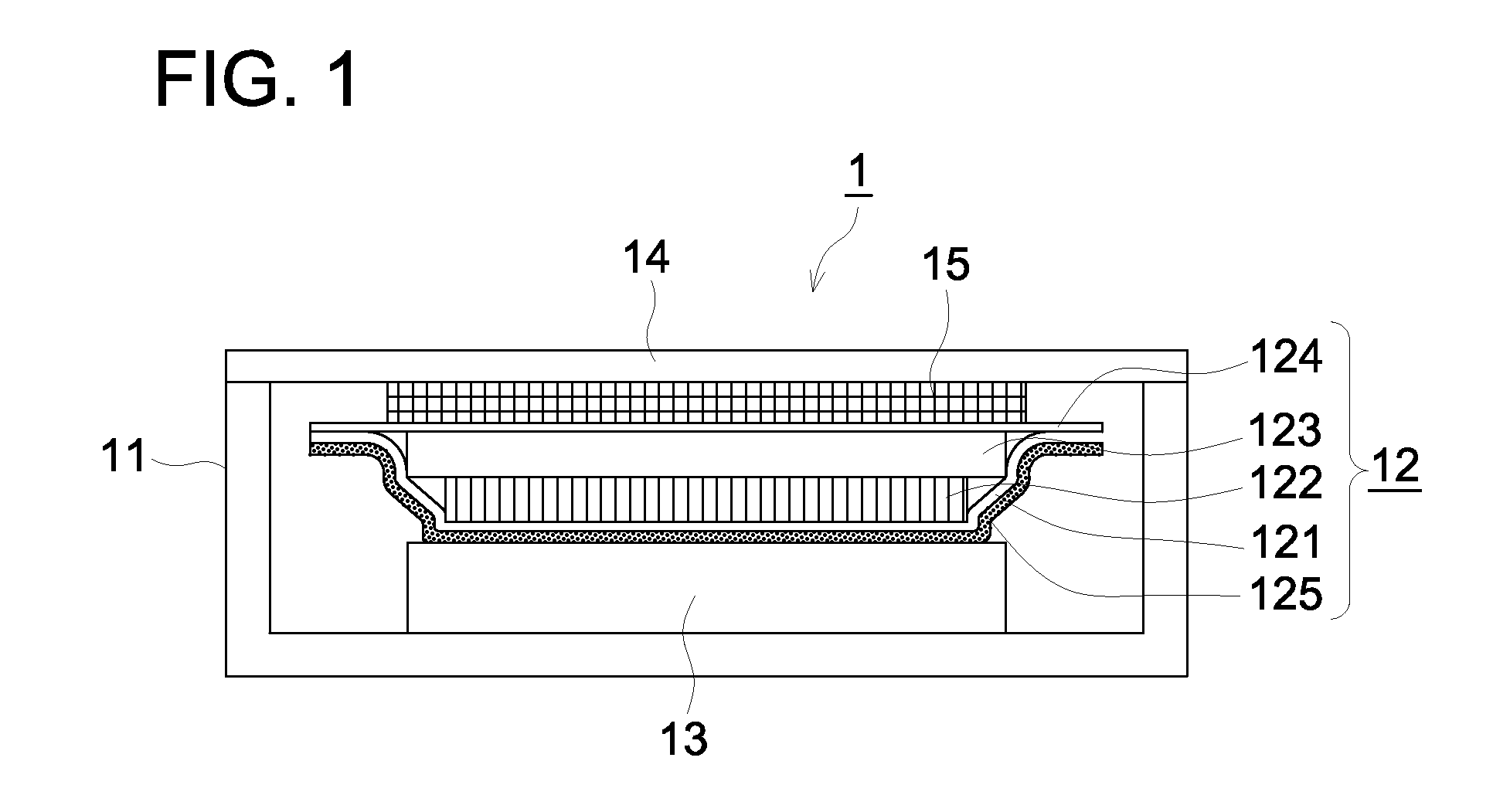

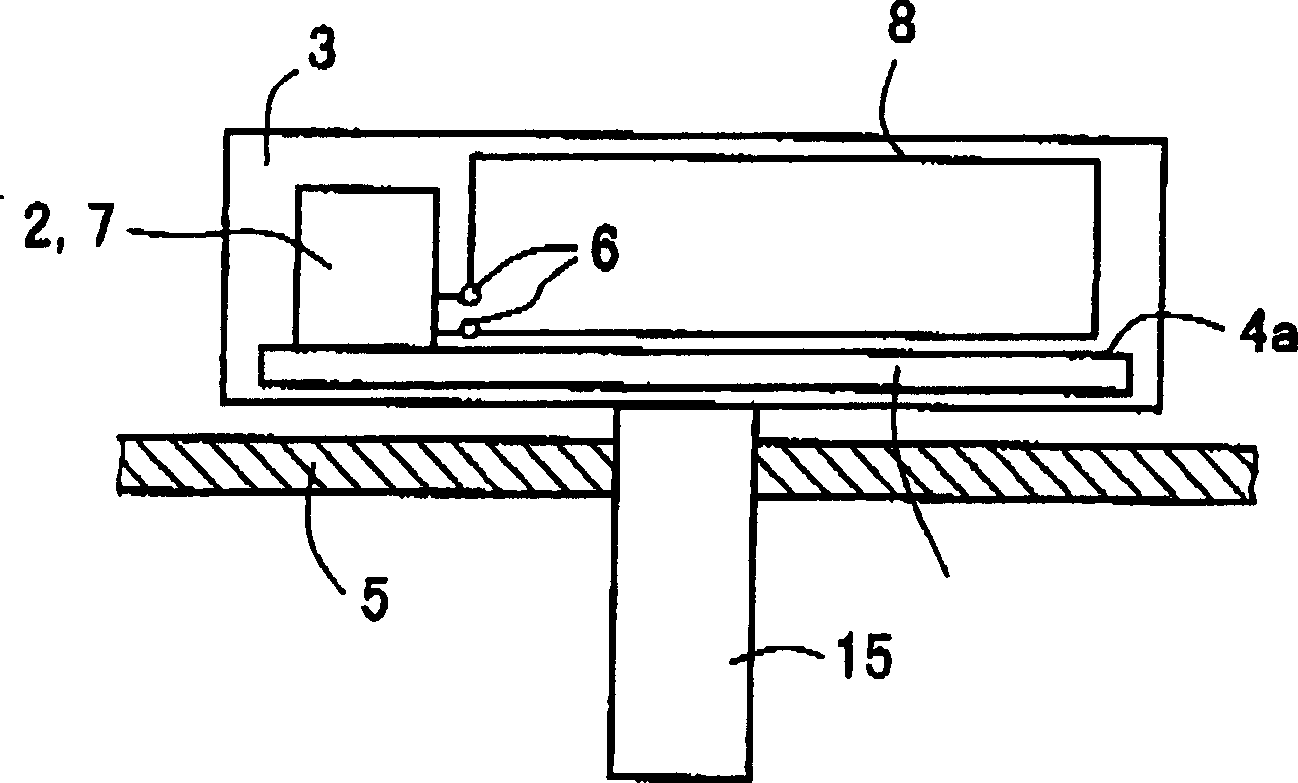

Flat Panel Detector

ActiveUS20100243908A1Prevent characteristic deteriorationGlass dosimetersSolid-state devicesFlat panel detectorFluorescence

Provided is a flat panel detector which prevents aging deterioration of characteristics of a phosphor layer, protects the phosphor layer from chemical alteration or physical impact, and maintains a stable contact state between a scintillator panel and a flat light receiving element. Disclosed is a flat panel detector comprising a scintillator panel comprising a scintillator provided with a phosphor layer on a substrate and a protective layer covering the phosphor surface of the scintillator, and the scintillator panel being placed on the surface of a flat light receiving element comprising plural picture elements which are two-dimensionally arranged, wherein a re-releasable adhesive layer is provided on the protective layer surface.

Owner:KONICA MINOLTA MEDICAL & GRAPHICS INC

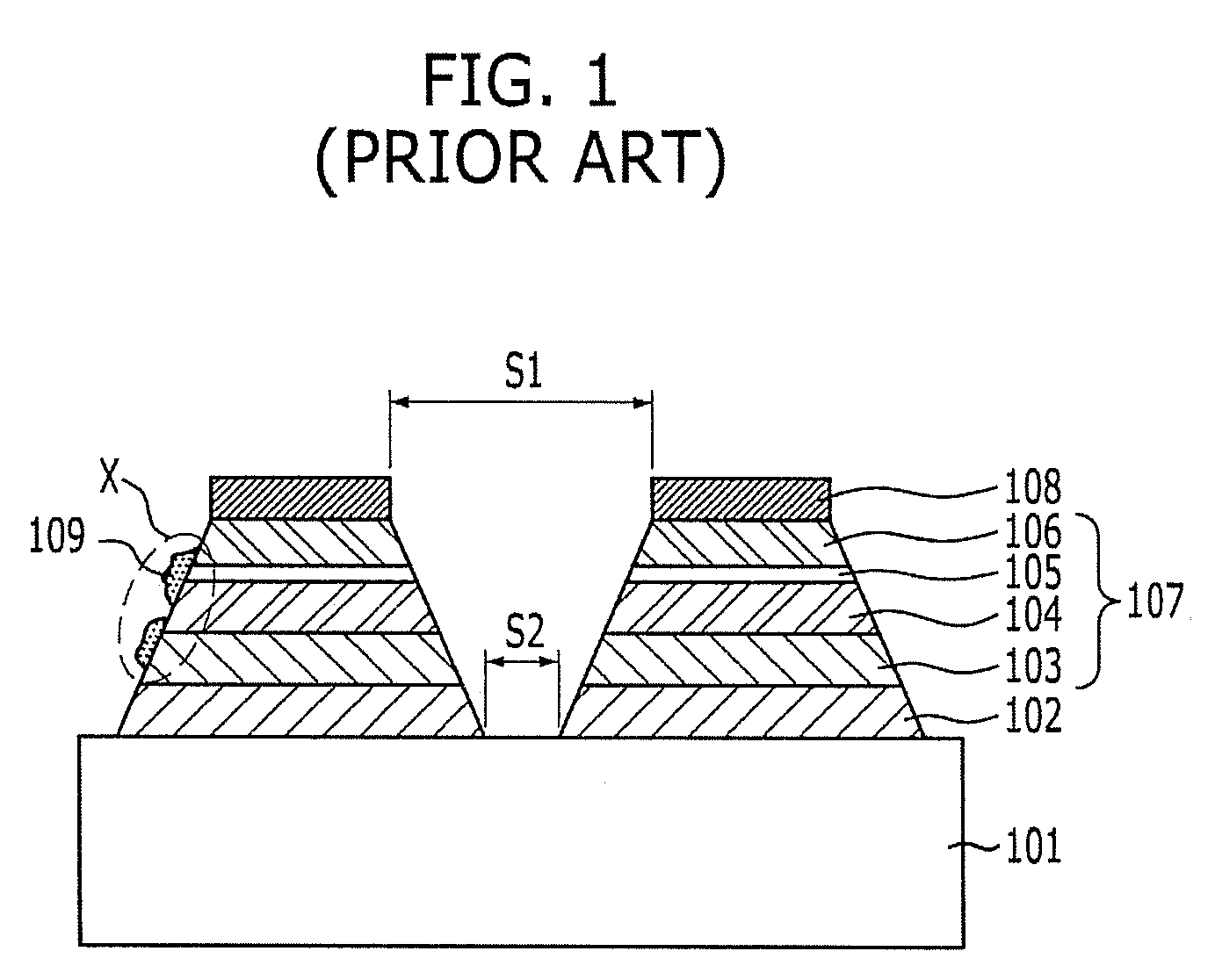

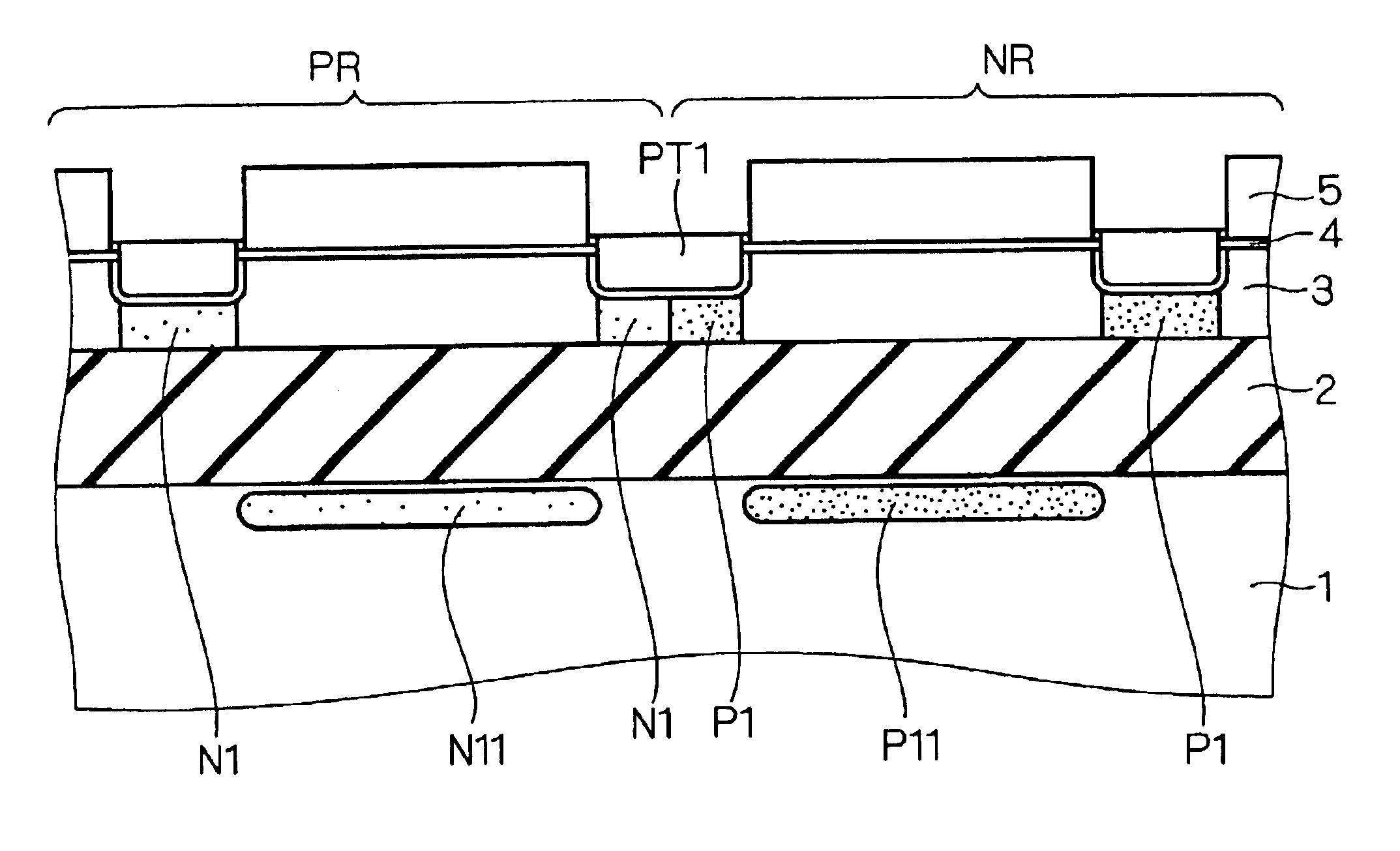

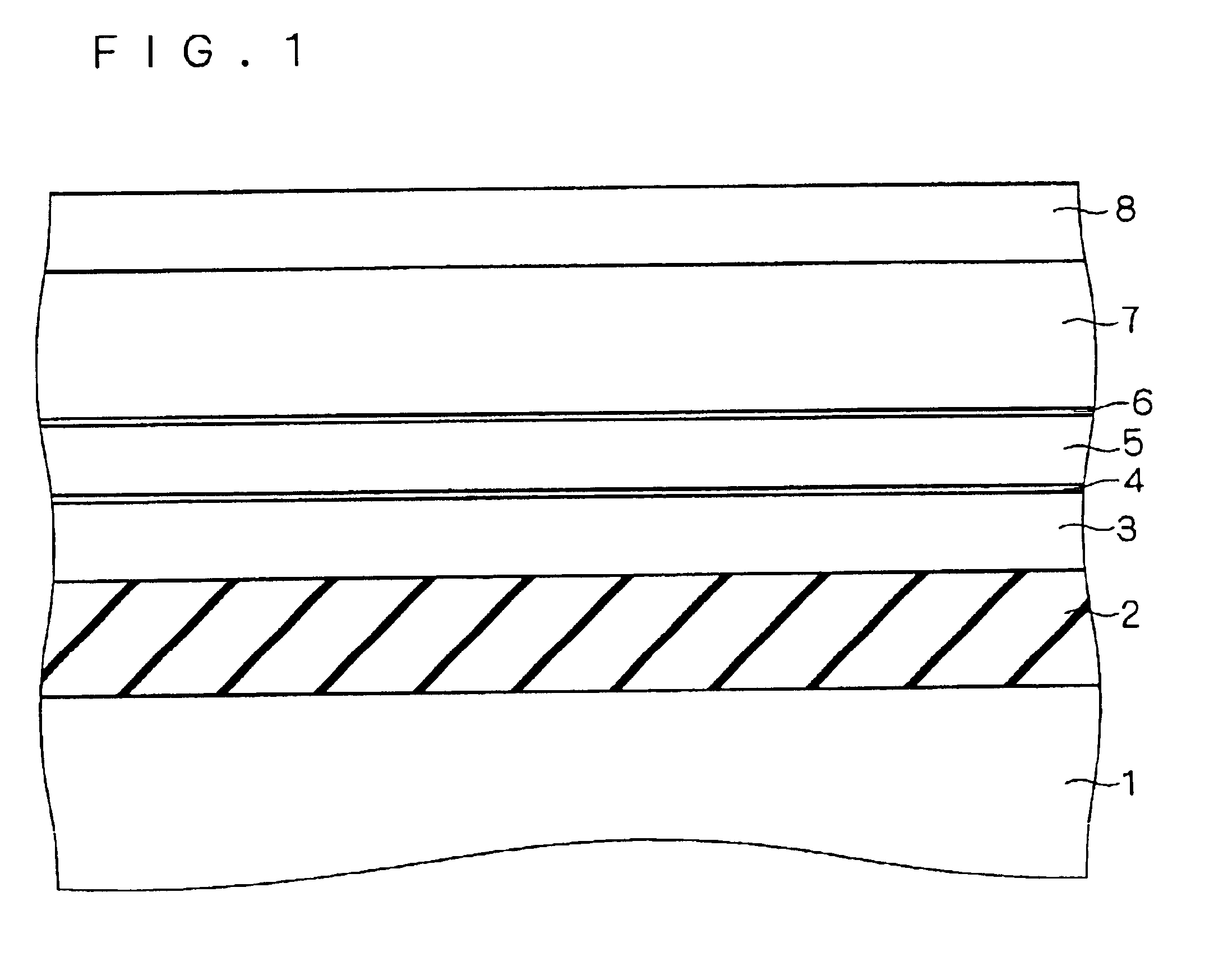

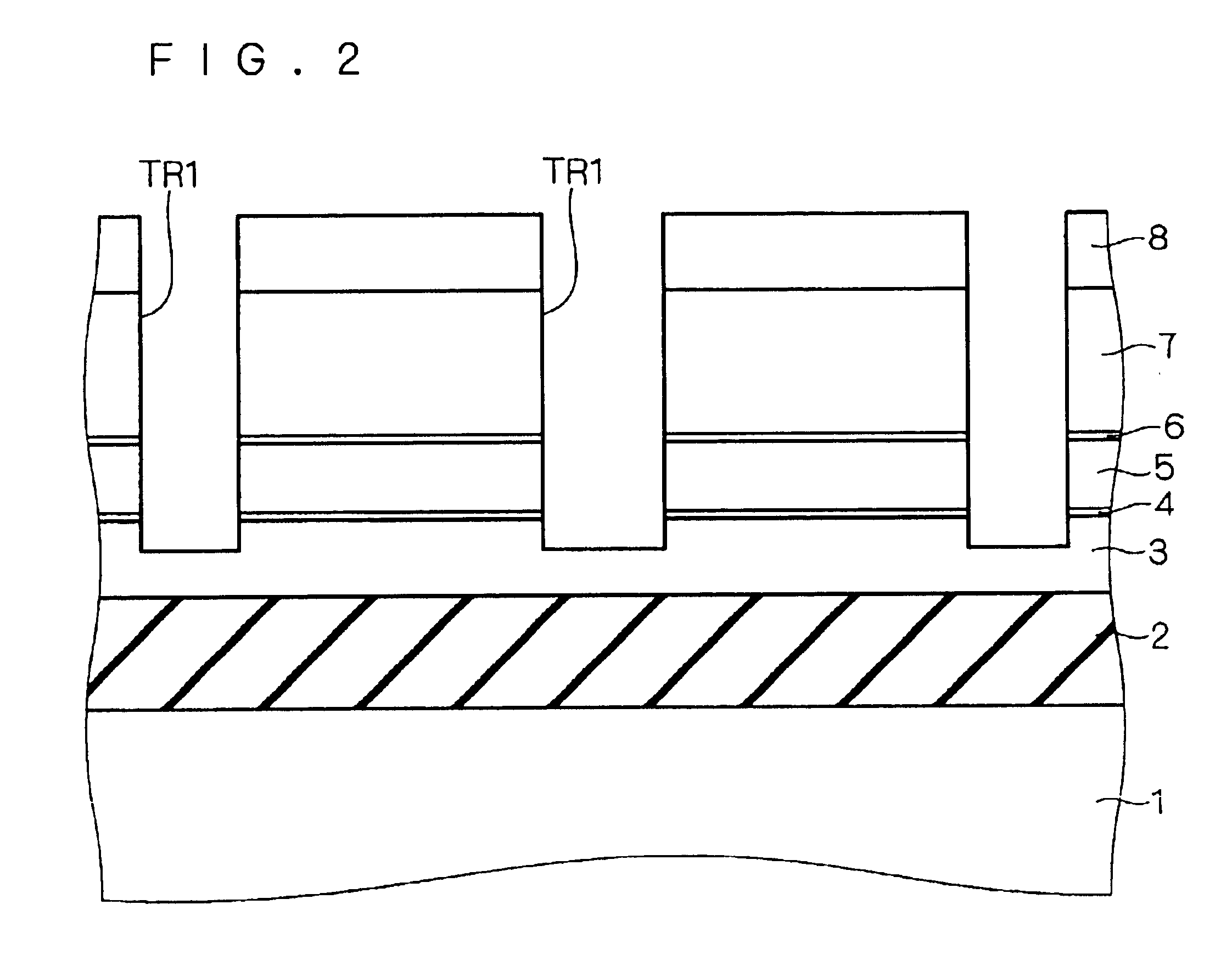

Semiconductor device having a trench isolation and method of fabricating the same

InactiveUS6875663B2Prevent characteristic deteriorationInhibit deteriorationTransistorSolid-state devicesResistPeak value

The present invention provides a method of fabricating a semiconductor device in which deterioration in a transistor characteristic is prevented by preventing a channel stop implantation layer from being formed in an active region. A resist mask is formed so as to have an opening over a region in which a PMOS transistor is formed. Channel stop implantation is performed with energy by which ions pass through a partial isolation oxide film and a peak of an impurity profile is generated in an SOI layer, thereby forming a channel stop layer in the SOI layer under the partial isolation oxide film, that is, an isolation region. An impurity to be implanted here is an N-type impurity. In the case of using phosphorus, its implantation energy is set to, for example, 60 to 120 keV, and the density of the channel stop layer is set to 1×1017 to 1×1019 / cm3. At this time, the impurity of channel stop implantation is not stopped in the SOI layer corresponding to the active region.

Owner:RENESAS ELECTRONICS CORP

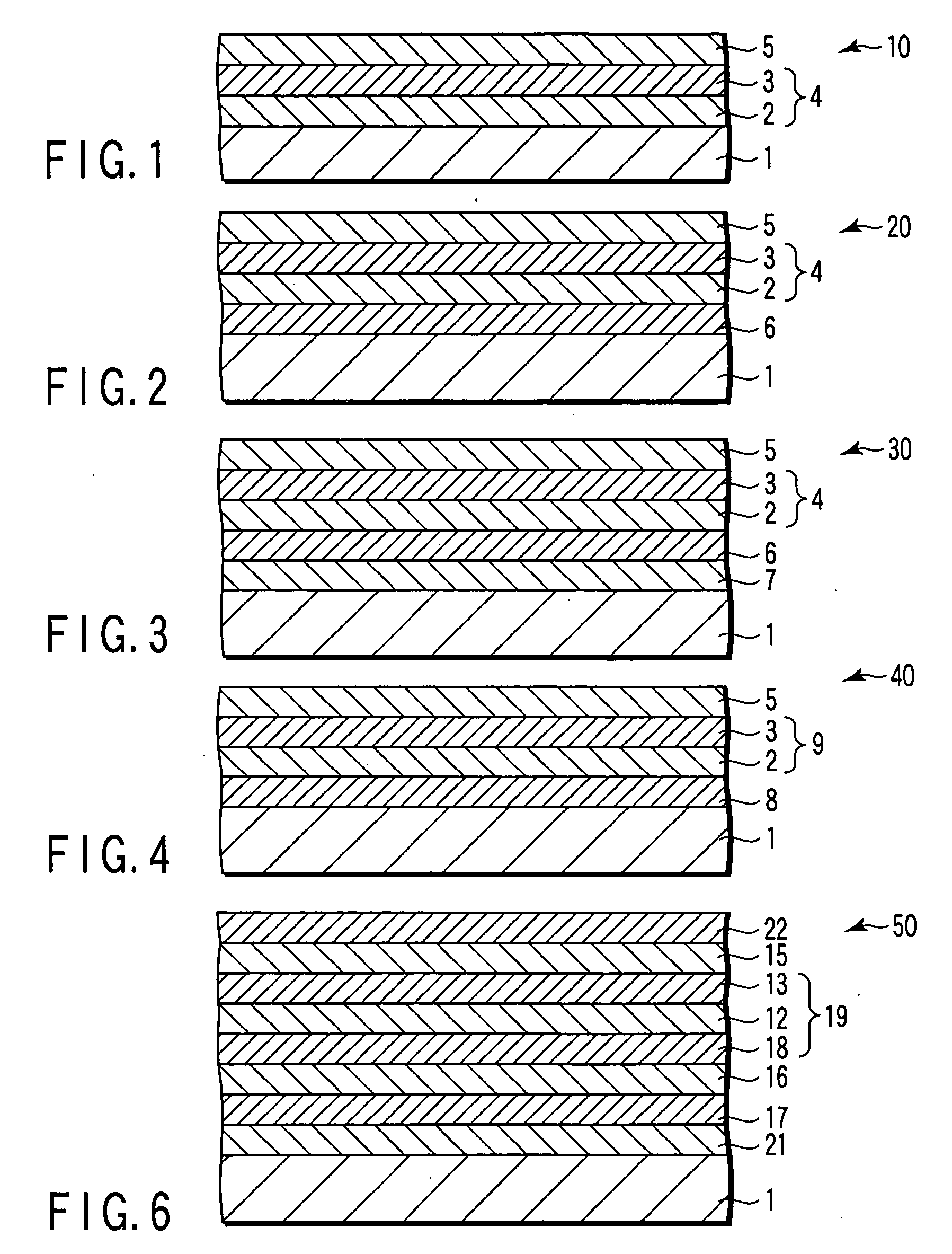

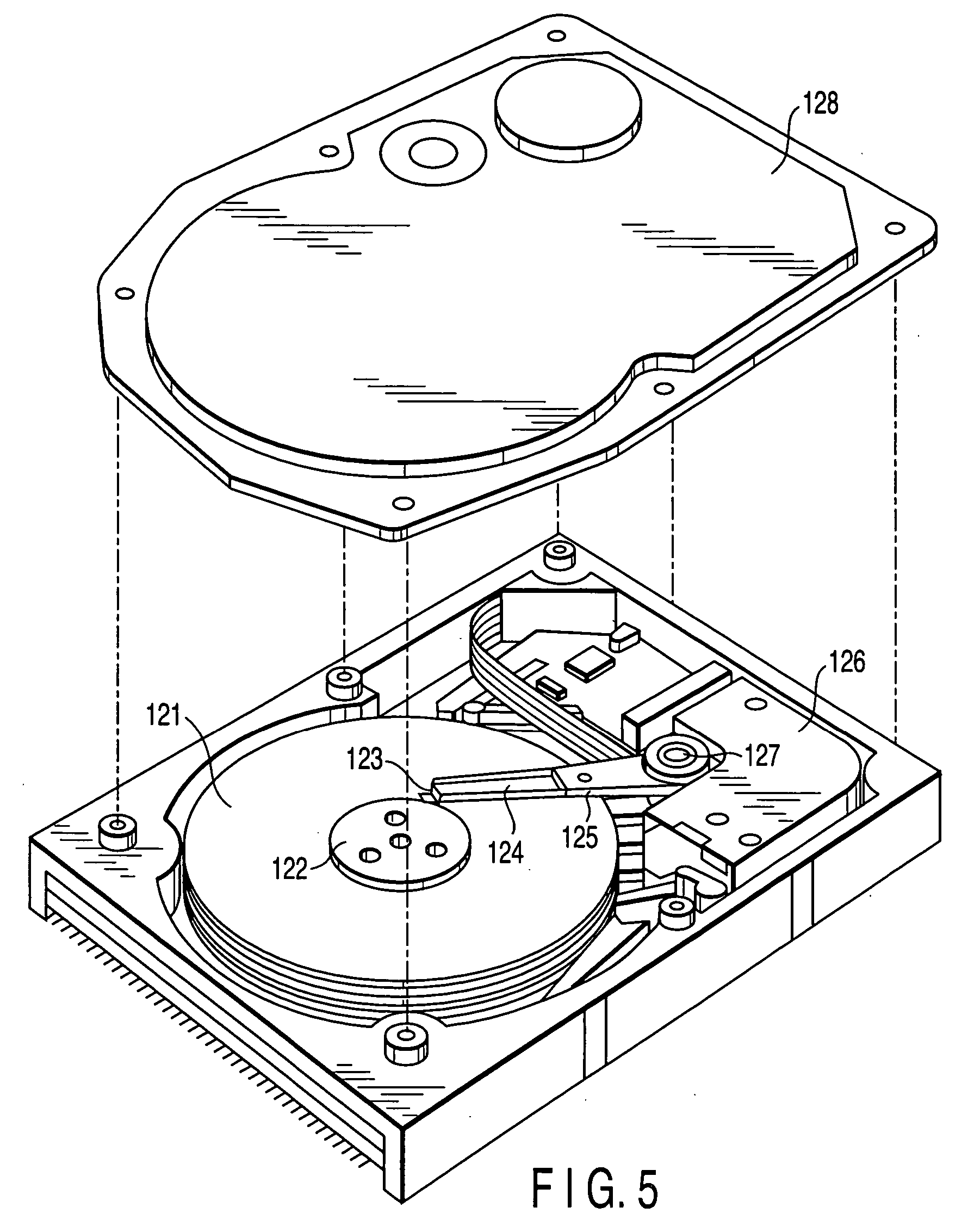

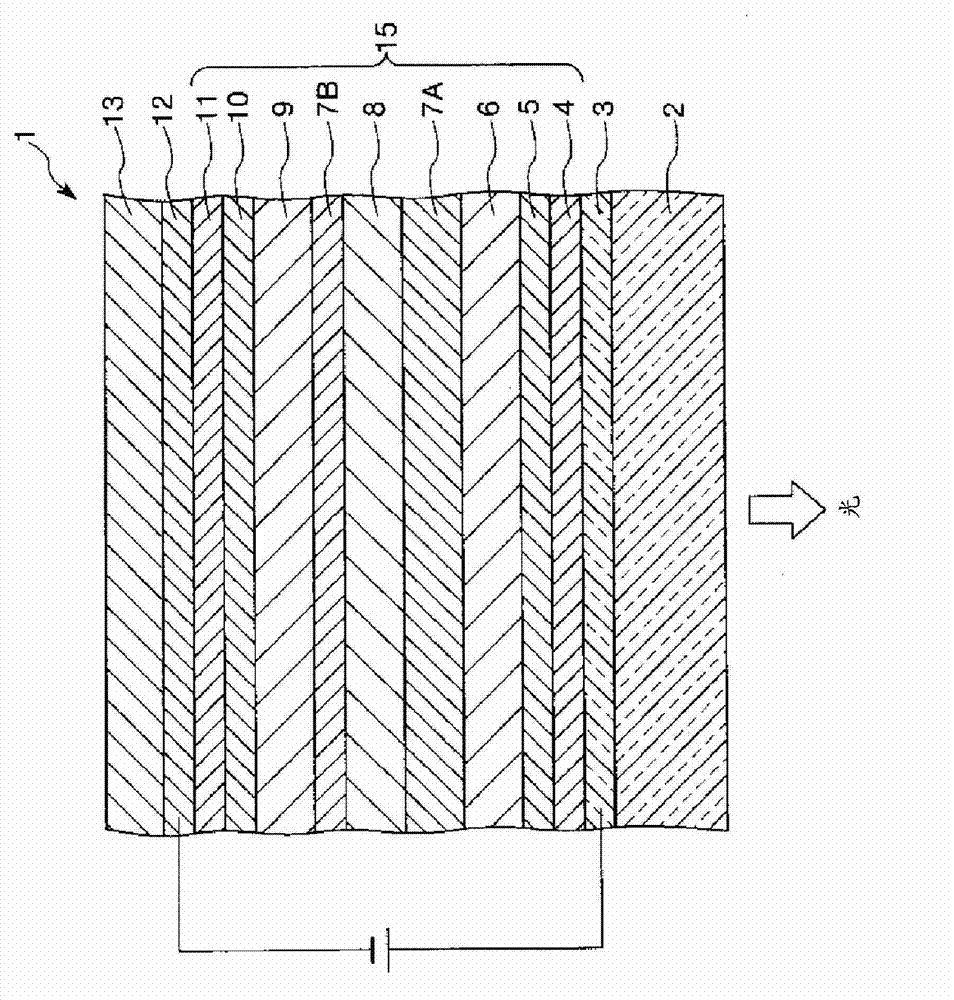

Perpendicular magnetic recording medium and magnetic recording/reproducing apparatus

InactiveUS20040219329A1Prevent characteristic deteriorationReduce noiseBase layers for recording layersLayered productsMagnetizationRecording layer

Disclosed is a perpendicular magnetic recording medium including a nonmagnetic substrate, a multilayered underlayer which includes a ferromagnetic underlayer having a perpendicular coercive force of 39.5 kA / m or less and a weakly magnetic underlayer having a saturation magnetization Ms of 50 to 150 emu / cc, and a perpendicular magnetic recording layer.

Owner:KK TOSHIBA +1

Film-forming ink, film-forming method, method of manufacturing light emitting element, light emitting element, light emitting device, and electronic apparatus

ActiveCN103173060APrevent characteristic deteriorationReduce aggressionElectroluminescent light sourcesSolid-state devicesLiquid mediumEther

A film-forming ink according to an embodiment of the invention includes a film-forming material; and a liquid medium which dissolves or disperses the film-forming material, in which the liquid medium contains an ether compound represented by Formula (I).

Owner:SEIKO EPSON CORP

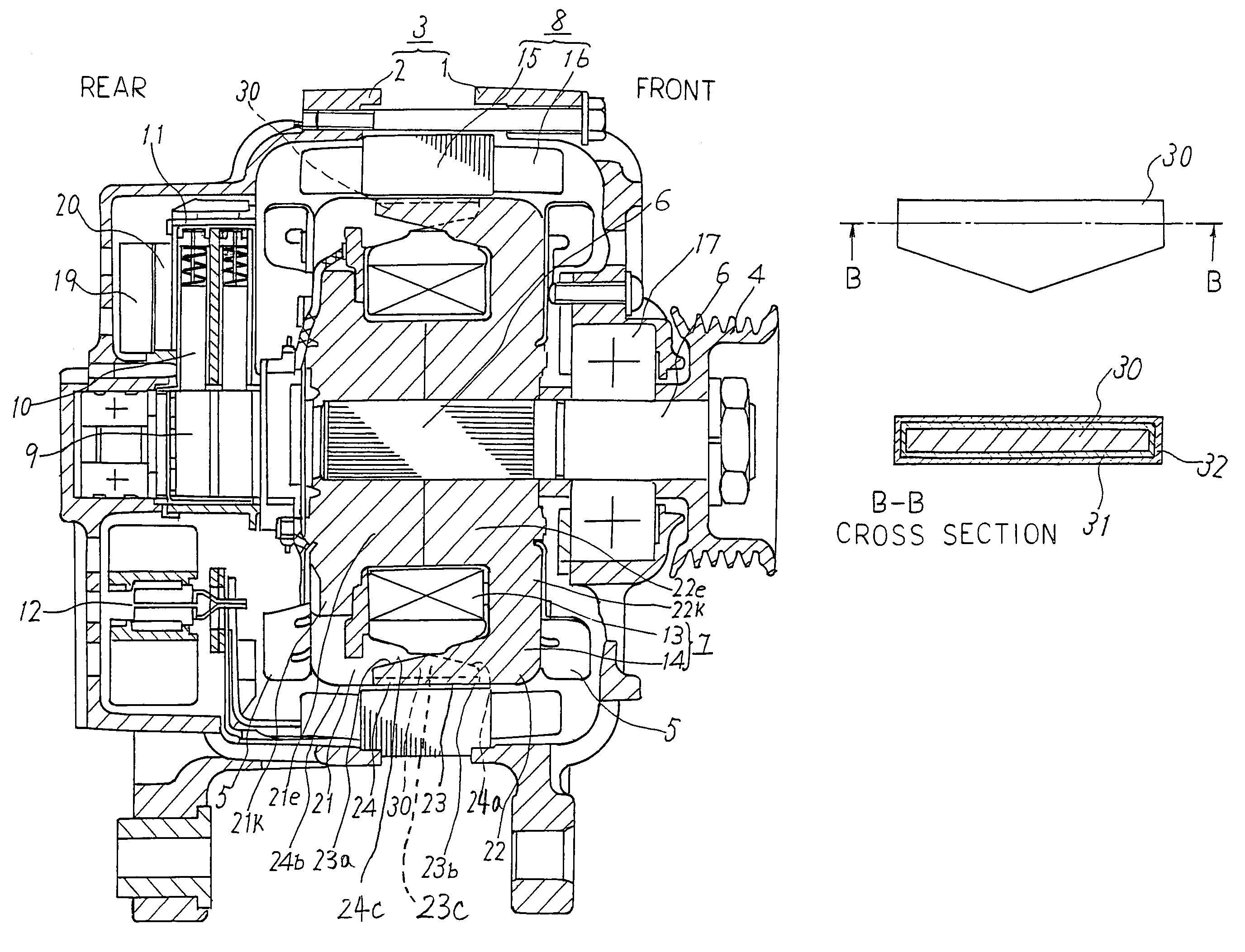

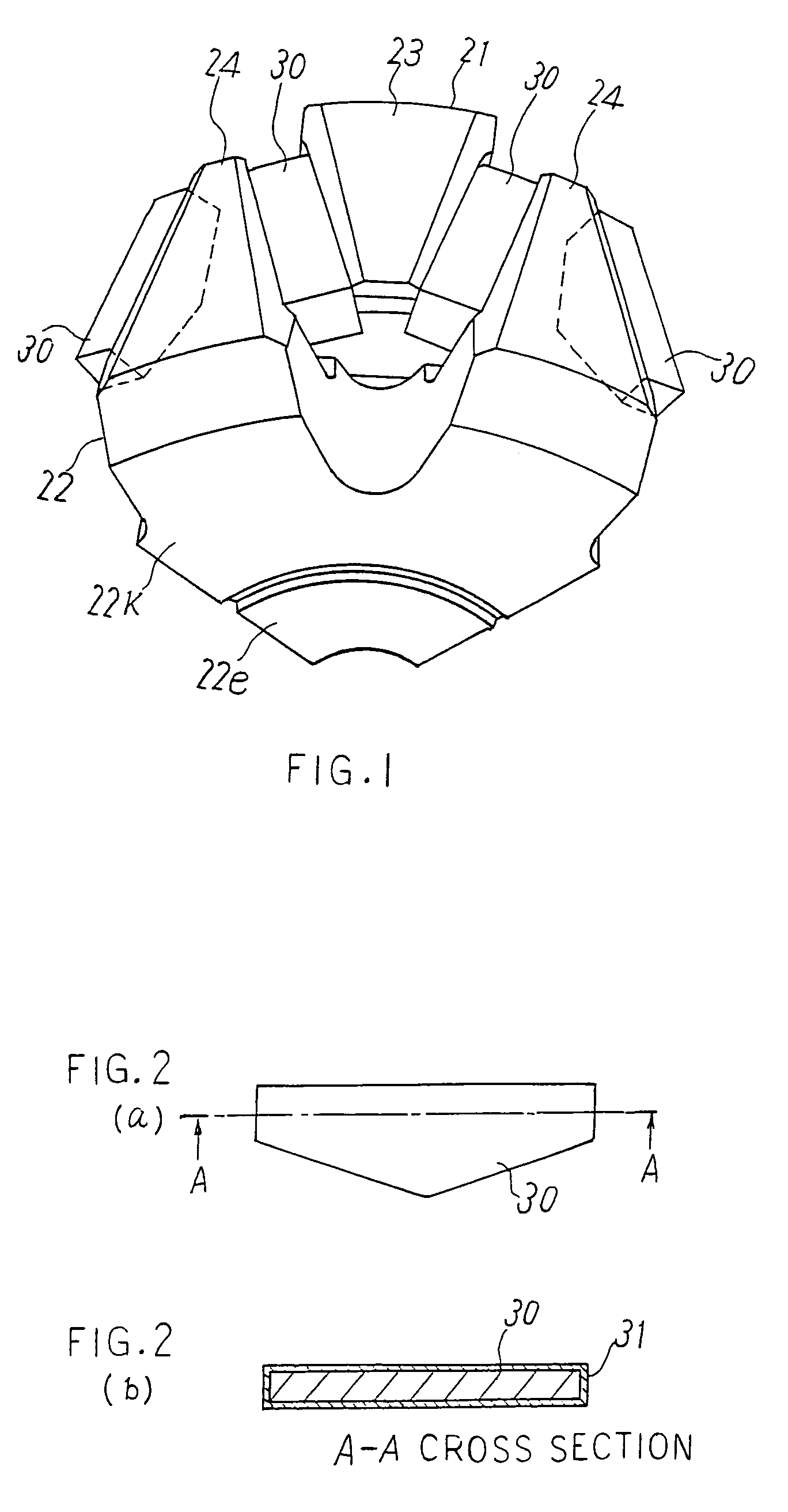

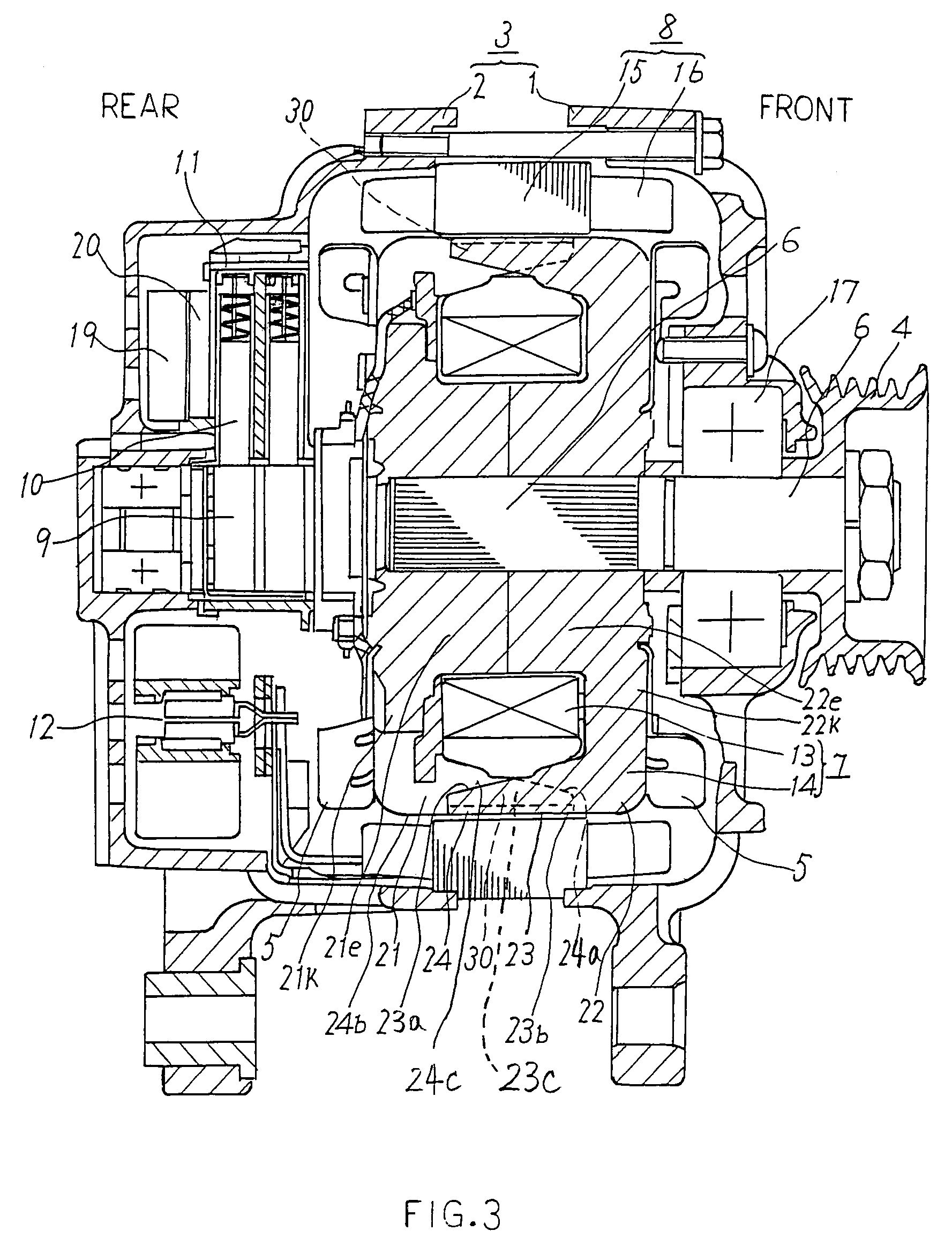

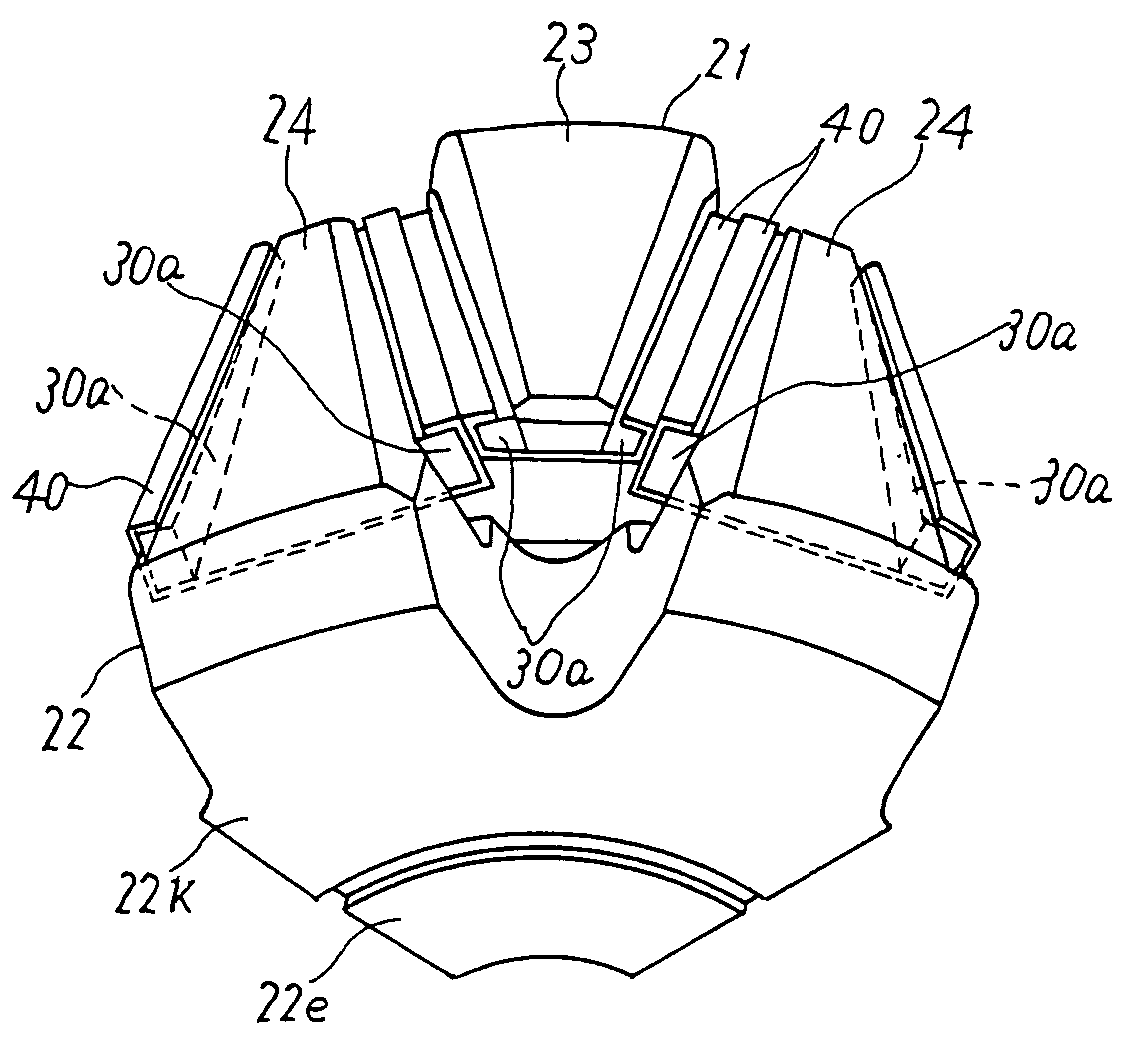

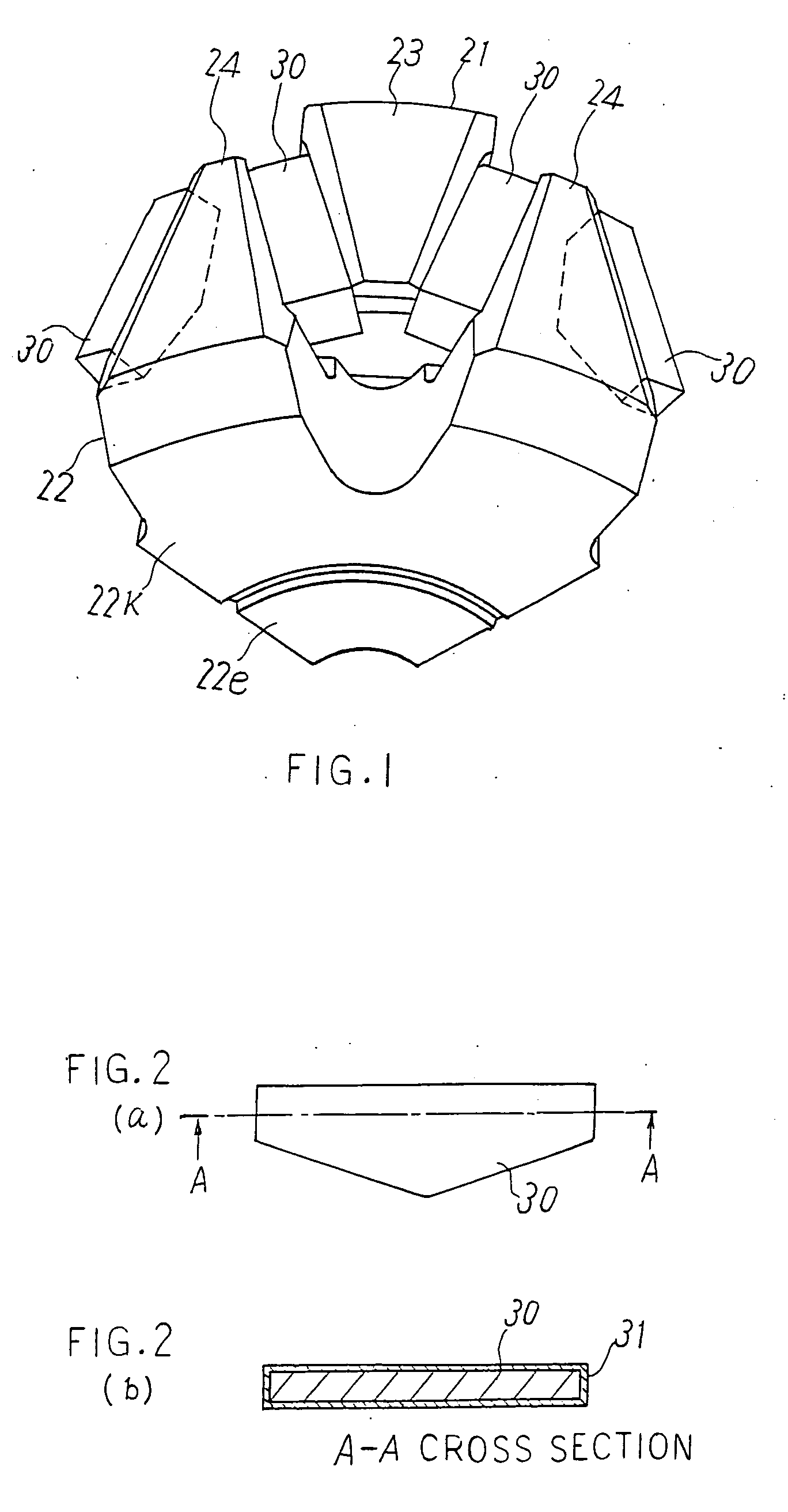

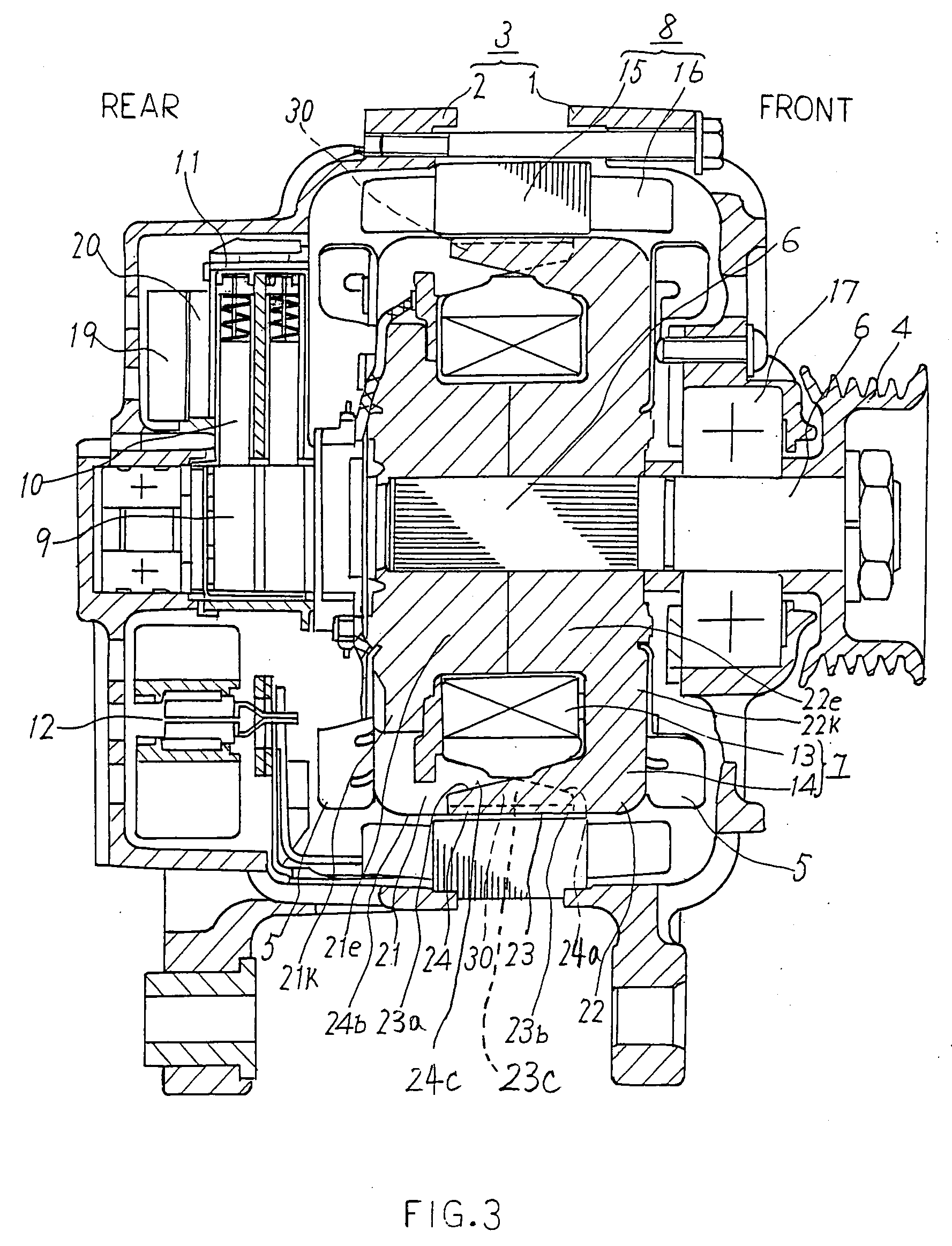

Electric rotating machine

ActiveUS7208856B2Prevent characteristic deteriorationImprove featuresSynchronous generatorsMagnetic circuit rotating partsMagnetic polesIonization

Claw-shaped magnetic poles are alternately disposed along the rotation plane of a rotor of an electric rotating machine, and a permanent magnet is disposed between the claw-shaped magnetic poles. Surface of the permanent magnet is coated with a coating layer. The coating layer is composed of a anticorrosive material performing sacrificial anticorrosion (metal flake in a coating film rusts prior to a matrix resulting in protection of the matrix) such as inorganic material containing zinc and a film of the anticorrosive material is formed by spraying. Ionization tendency of zinc is larger than that of iron composing the permanent magnet, and the permanent magnet is difficult to be rusted owing to the sacrificial anticorrosion. Consequently, anticorrosion of the permanent magnet disposed between the claw-shaped magnetic poles is improved.

Owner:MITSUBISHI ELECTRIC CORP

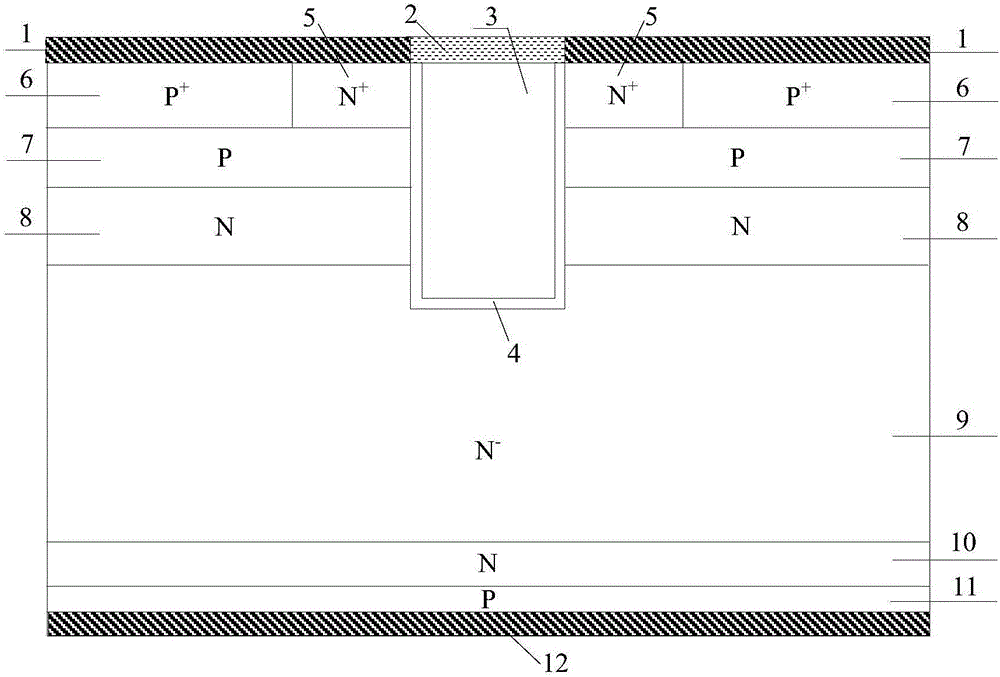

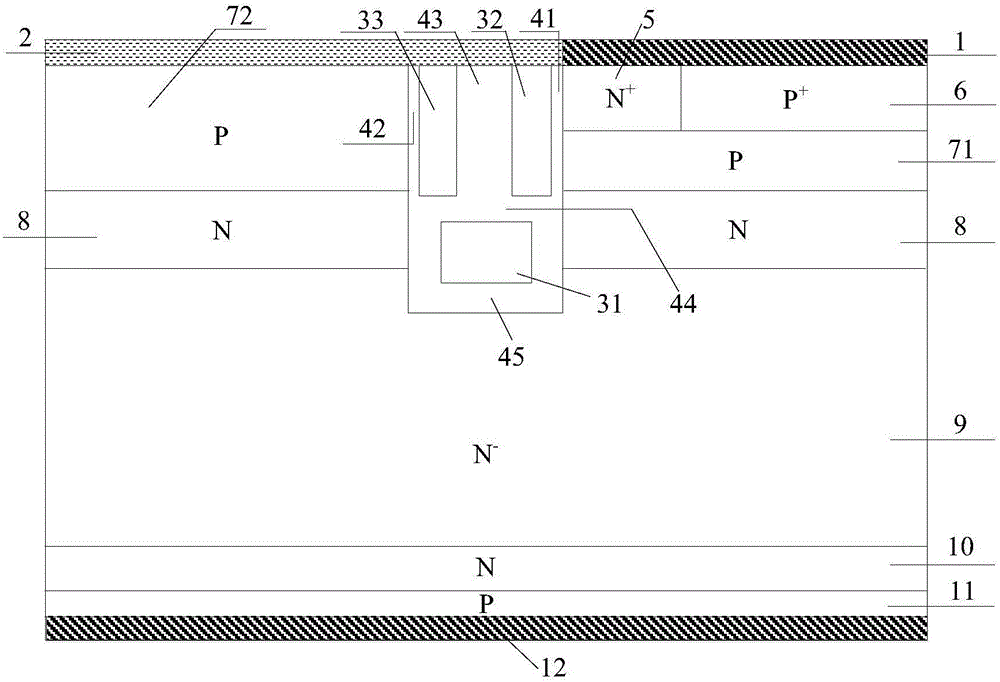

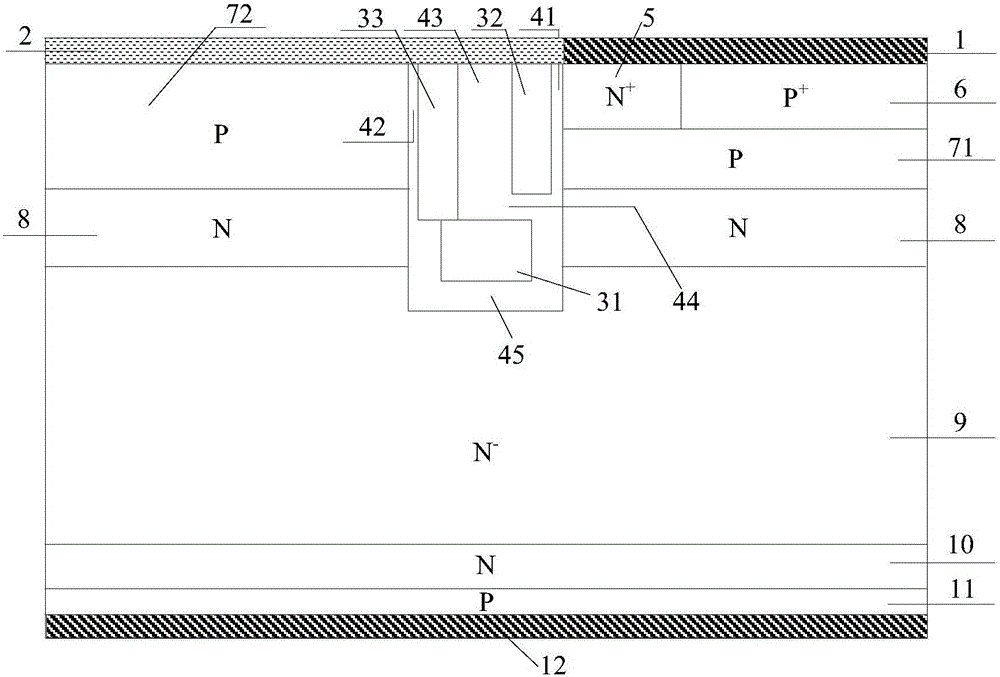

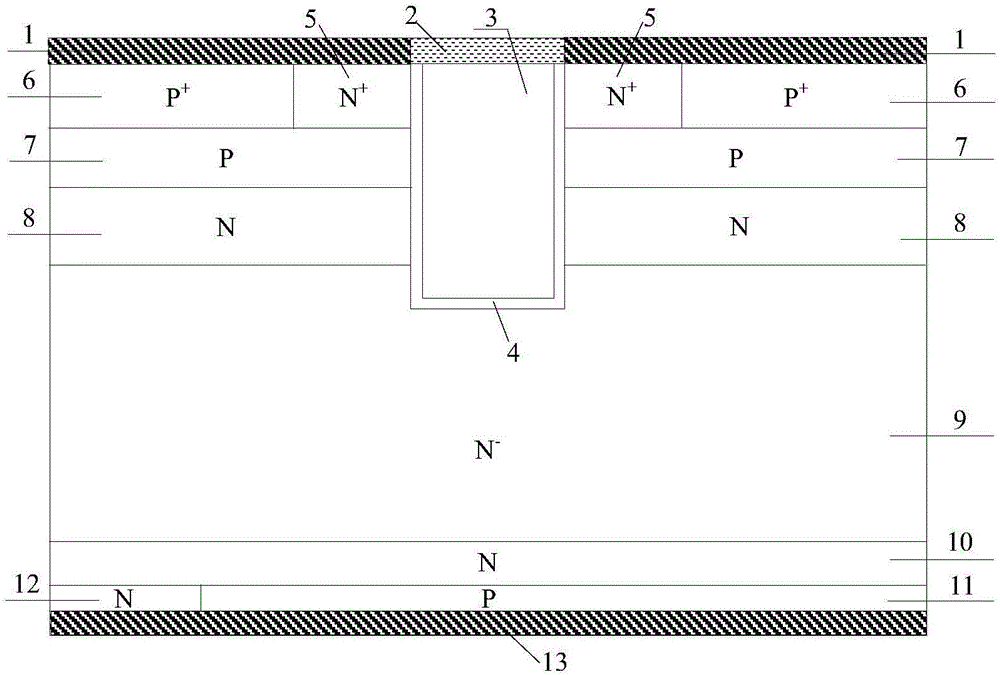

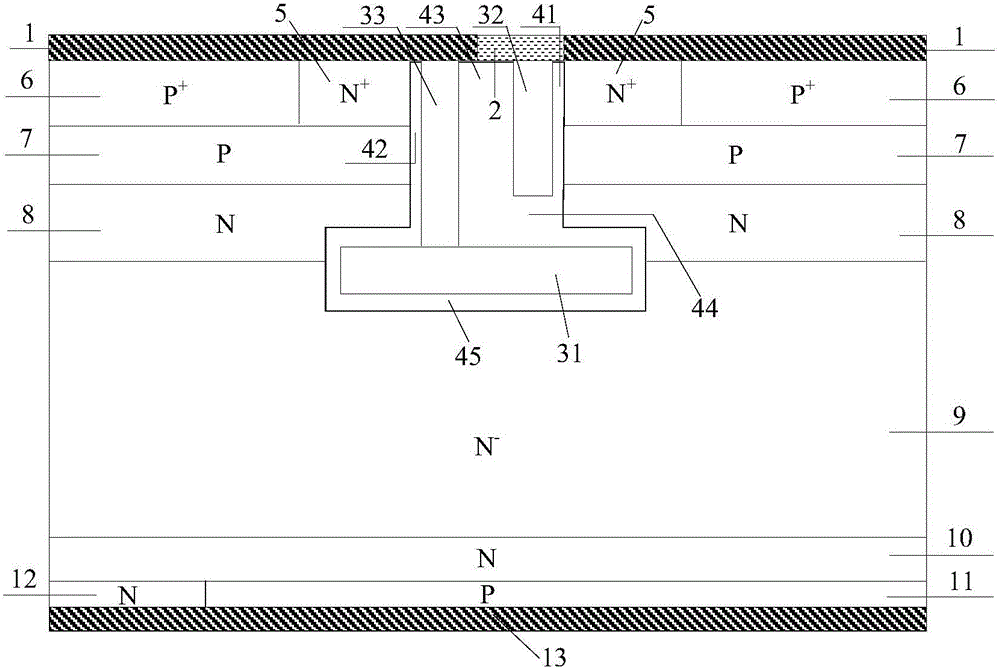

Double-split groove gate charge storage type IGBT and manufacturing method thereof

ActiveCN105932042AFast switching speedImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitancePower semiconductor device

The invention belongs to the technical field of a power semiconductor device and specifically relates to a groove gate charge storage type IGBT (insulated gate bipolar transistor). The bottom and side surfaces of a gate electrode in a groove of the device are provided with a double-split electrode equipotential with an emitter and a dielectric layer between the double-split electrode and the gate electrode, so that under the condition of not influencing threshold voltage and turning on of the IGBT device, grid capacitance is reduced, switching speed of the device is improved, and switching loss of the device is reduced; and meanwhile, the side-surface split electrode and a floating p-type base region at one side of the side-surface split electrode improve short circuit safety operation area of the device and carrier concentration distribution of the whole N drifting region, thereby improving performance and reliability of the device. The double-split groove gate charge storage type IGBT manufacturing method does not need extra processing steps, and is compatible with a conventional CSTB manufacturing method.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

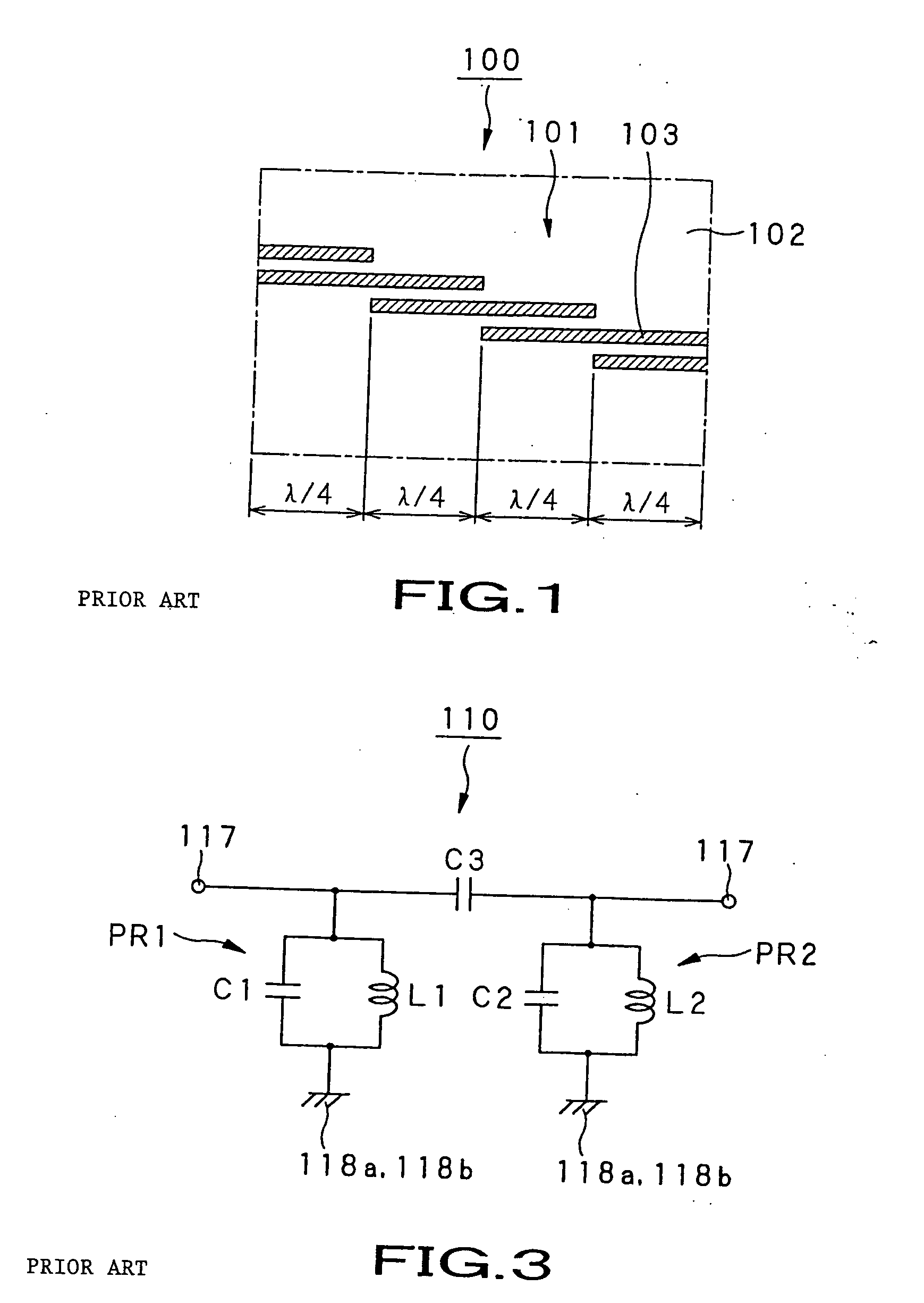

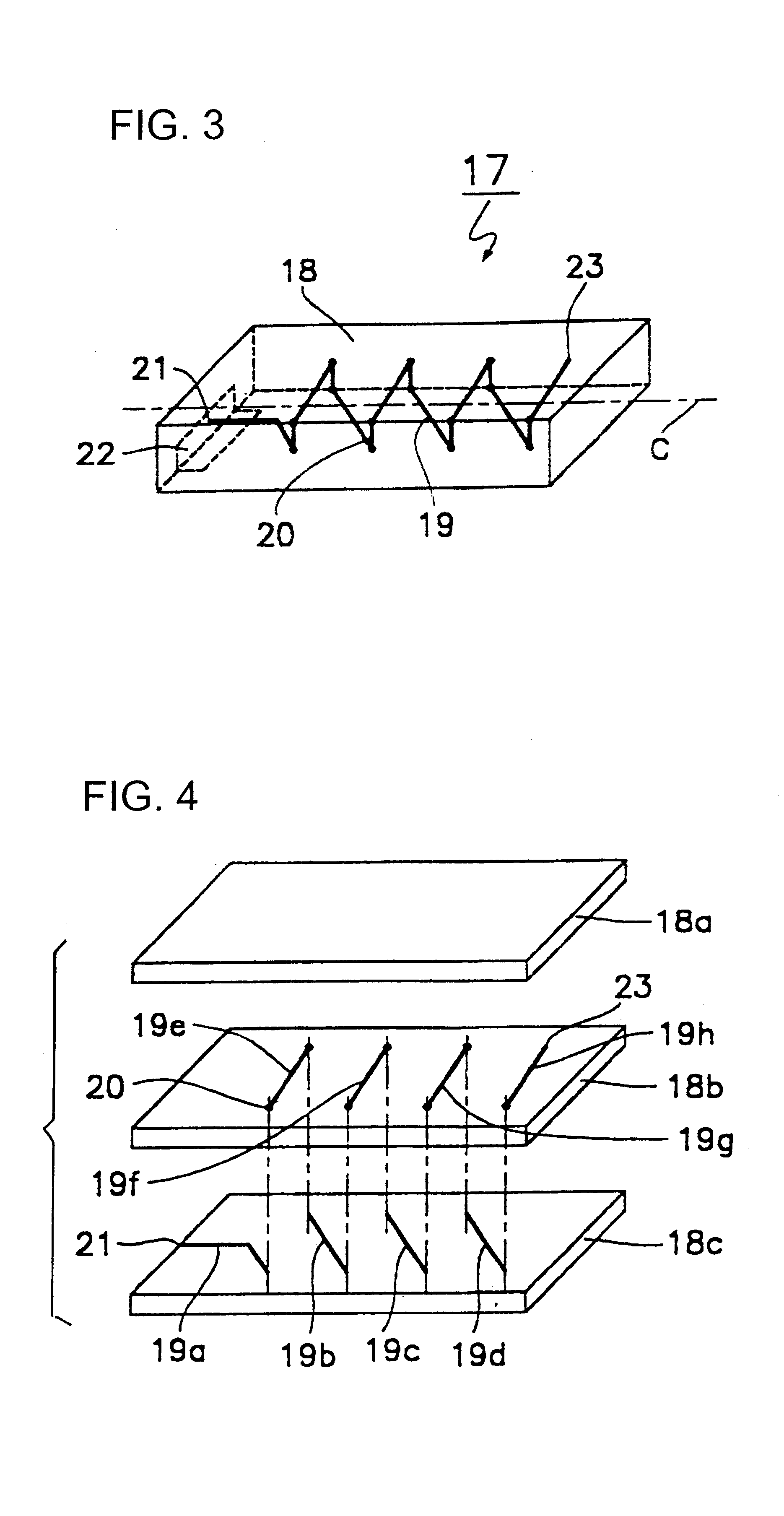

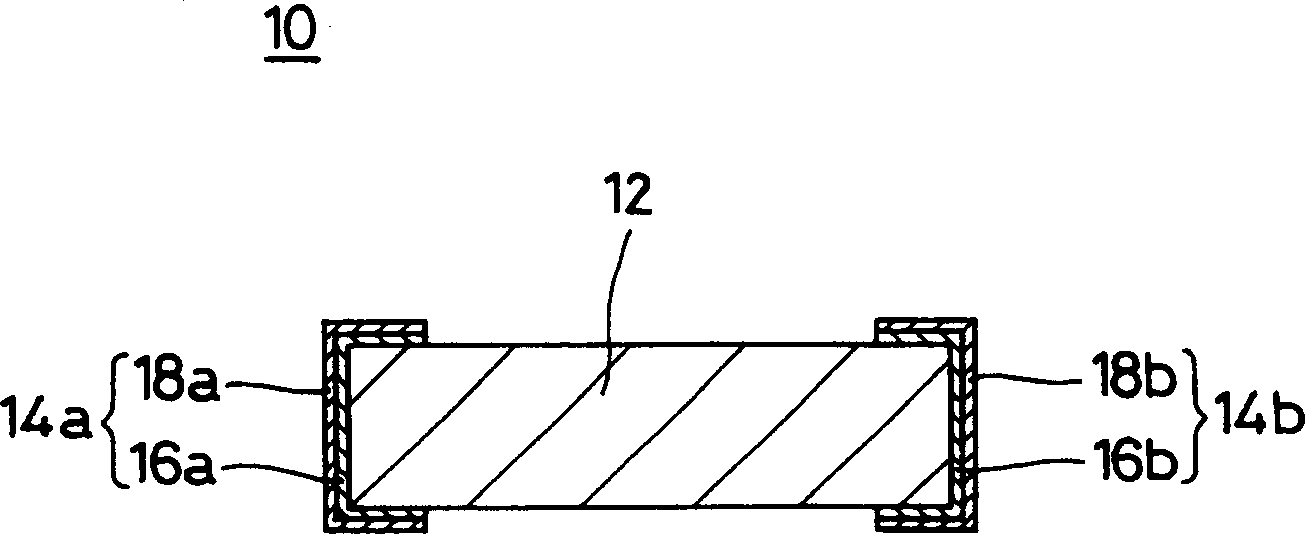

Filter circuit device and method of manufacturing the same

InactiveUS20050190017A1Prevent characteristic deteriorationInhibit deteriorationPrinted electric component incorporationPrinted circuit aspectsMiniaturizationEngineering

This invention is a filter circuit having a filter element. A filter element (4) is a parallel resonator circuit including a pair of first resonator lines (19a) (19b) formed by a thick film forming technique and a pair of second resonator lines (20a) (20b). As the thickness of the pair of second resonator lines (20a) (20b) is significantly reduced, the impedance ratio between the pair of second resonator lines (20a) (20b) and the pair of first resonator lines (19a) (19b) is increased. Therefore, the length of these pairs of resonator lines (19a) (19b) (20a) (20b) is reduced and miniaturization of the filter element is realized.

Owner:SONY CORP

Electric rotating machine

ActiveUS20050156480A1Prevent characteristic deteriorationImprove featuresSynchronous generatorsSynchronous machine detailsElectric machineMagnetic poles

Claw-shaped magnetic poles are alternately disposed along the rotation plane of a rotor of an electric rotating machine, and a permanent magnet is disposed between the claw-shaped magnetic poles. Surface of the permanent magnet is coated with a coating layer. The coating layer is composed of a anticorrosive material performing sacrificial anticorrosion (metal flake in a coating film rusts prior to a matrix resulting in protection of the matrix) such as inorganic material containing zinc and a film of the anticorrosive material is formed by spraying. Ionization tendency of zinc is larger than that of iron composing the permanent magnet, and the permanent magnet is difficult to be rusted owing to the sacrificial anticorrosion. Consequently, anticorrosion of the permanent magnet disposed between the claw-shaped magnetic poles is improved.

Owner:MITSUBISHI ELECTRIC CORP

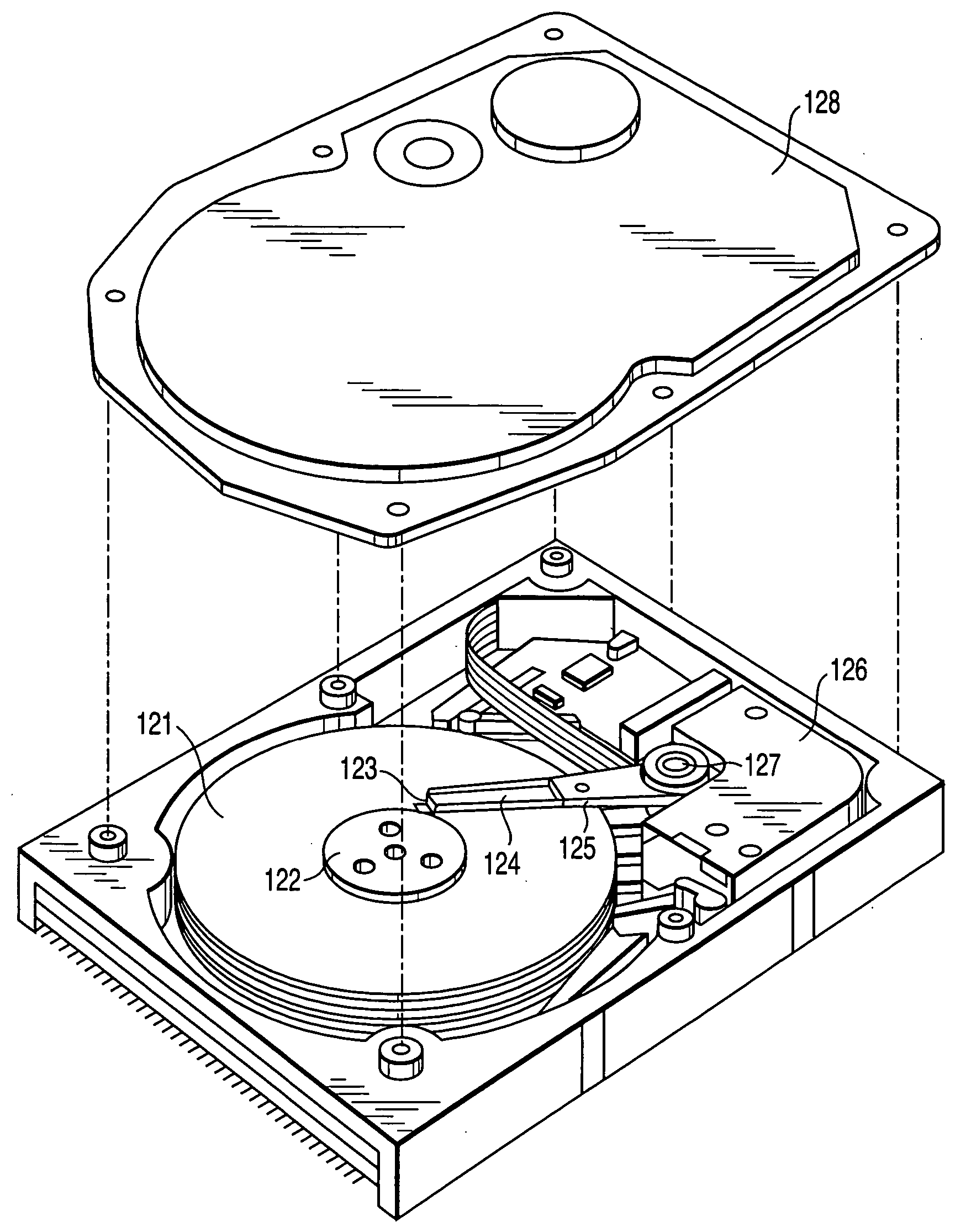

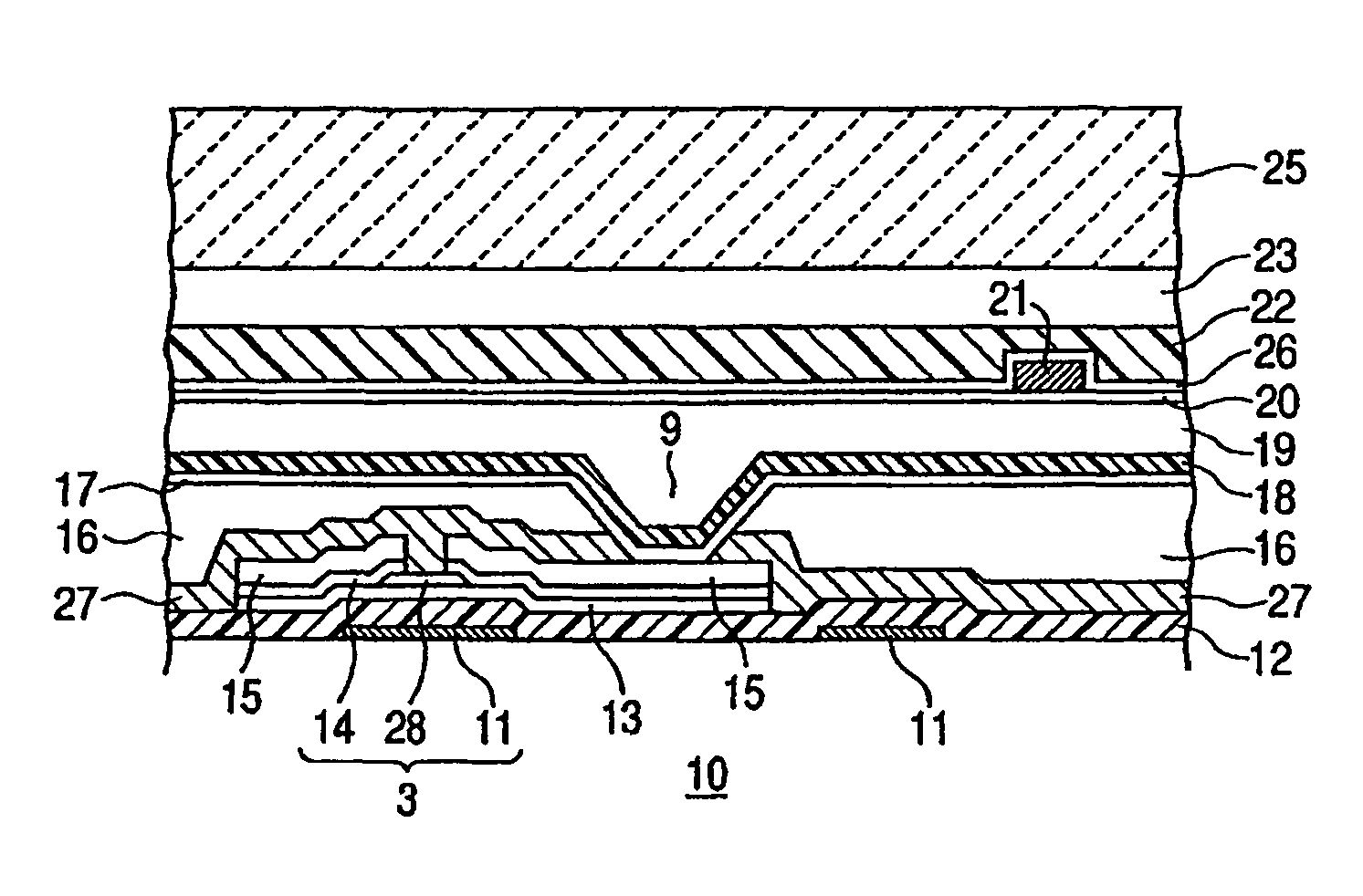

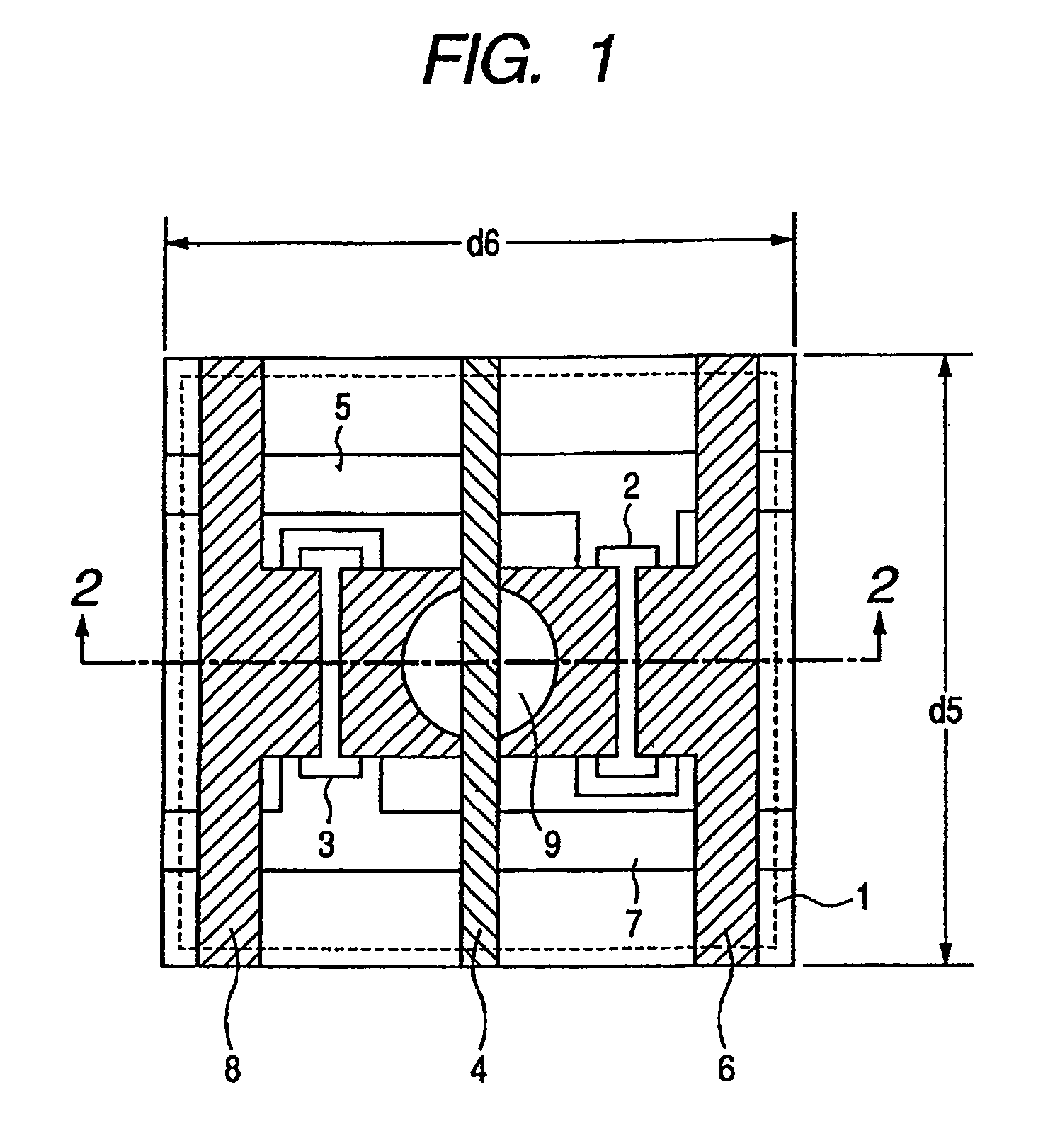

Imaging apparatus and radiation imaging apparatus

InactiveUS8067743B2Prevent characteristic deteriorationEasy to identifySolid-state devicesMaterial analysis by optical meansRadiation imagingEngineering

Pixels including a photoelectric conversion element 1, a signal transfer TFT (thin film transistor) 2 electrically connected to the photoelectric conversion element, and a reset TFT 3 electrically connected to the photoelectric conversion element and for applying a bias to the photoelectric conversion element are two-dimensionally disposed on the insulating substrate, and the photoelectric conversion element 1, signal transfer TFT 2, and reset TFT 3 are electrically connected through a common contact hole 9. A source or drain electrode of the signal transfer TFT 2 and the source or drain electrode of the reset TFT 3 are formed from a common electroconductive layer.

Owner:CANON KK

Semiconductor device

InactiveUS20050156277A1Inhibit deteriorationPrevent characteristic deteriorationTransistorSemiconductor/solid-state device detailsCapacitanceDevice material

There is provided a semiconductor device, wherein a digital circuit region and an analog circuit region are located independently. A power supply wiring and a ground wiring are placed on the periphery of each circuit region and are connected to elements in each circuit region. A MOS capacitor is formed under the power supply wiring and the ground wiring. The terminals of the MOS capacity are connected to the power supply wiring and the ground wiring. Pads are placed in each circuit region surrounded by the power supply wiring, the ground wiring, and the MOS capacitor and are connected to the elements of each circuit region.

Owner:PANASONIC CORP

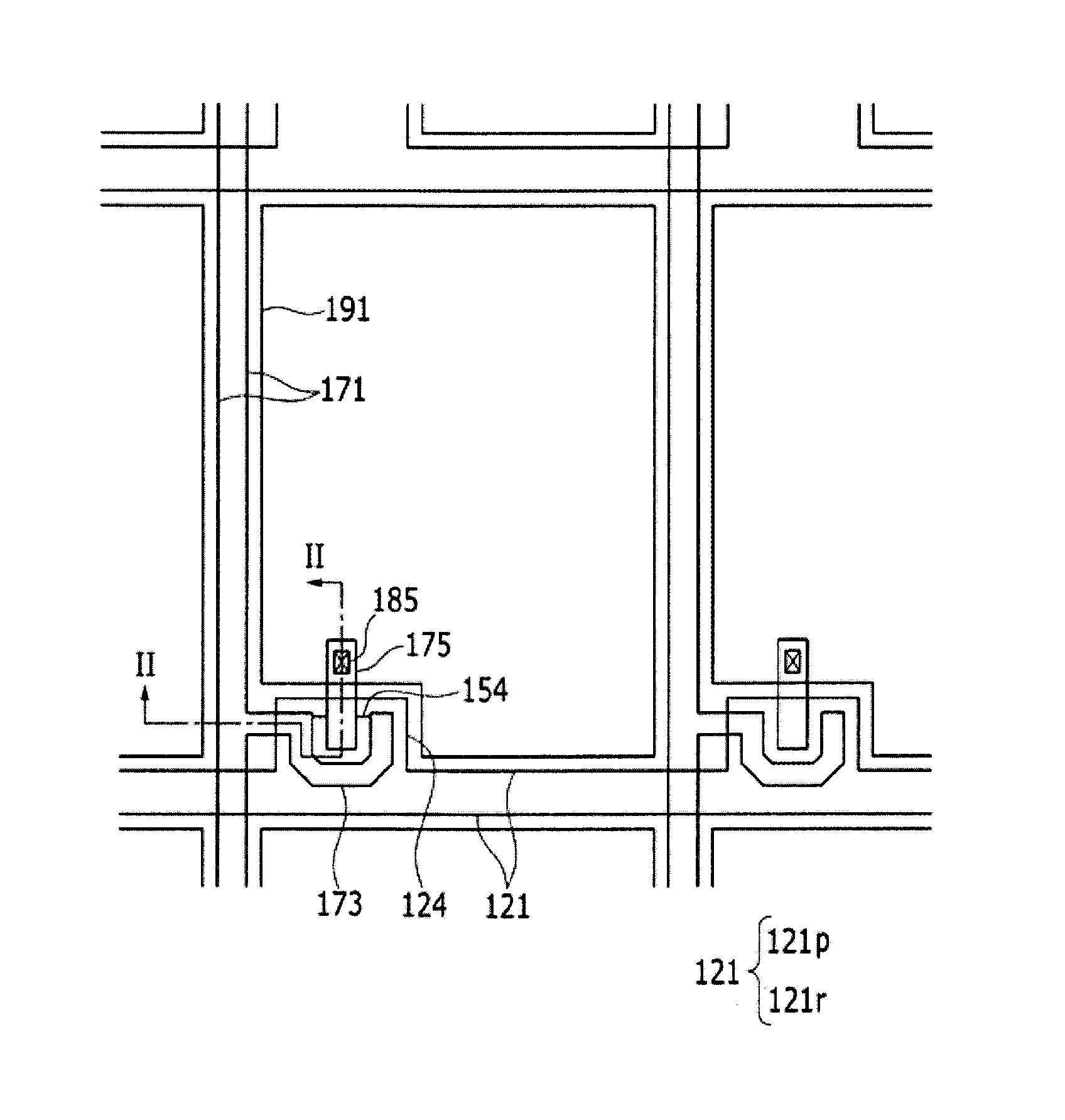

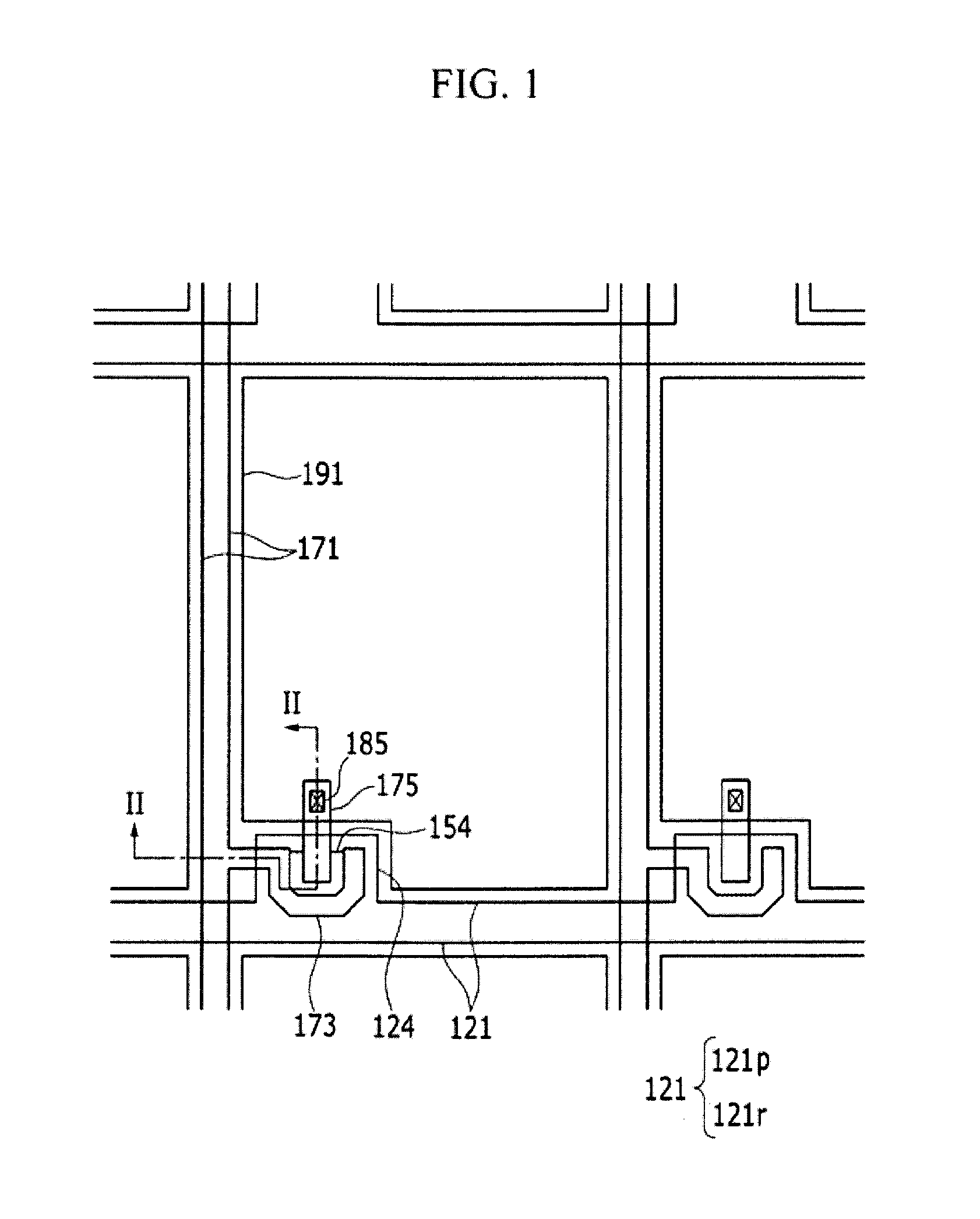

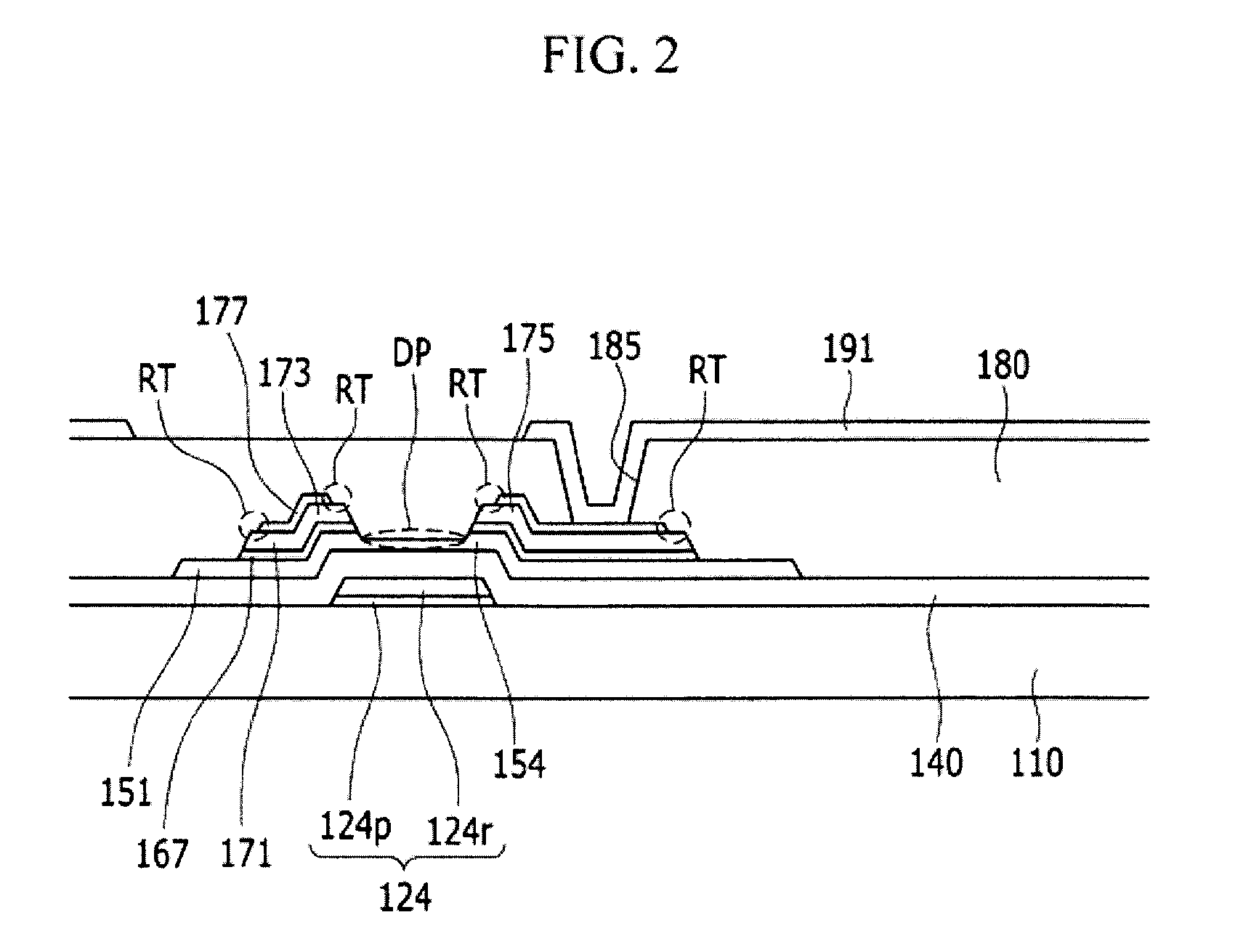

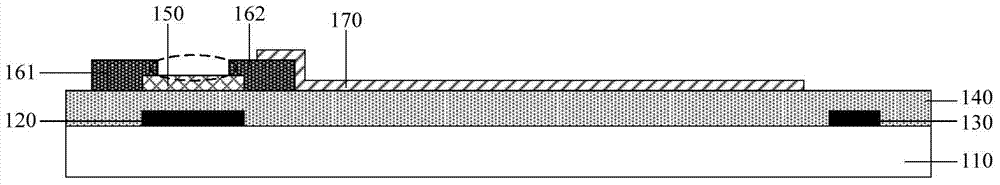

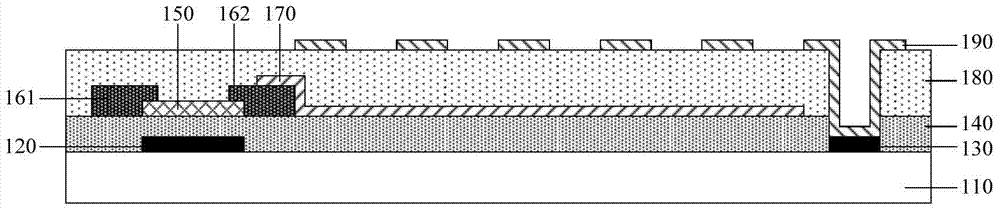

Thin film transistor array panel and method of manufacturing the same

ActiveUS20140175424A1Avoid damagePrevent characteristic deteriorationSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A thin film transistor array panel includes: a substrate, a gate line positioned on the substrate and including a gate electrode, a semiconductor layer positioned on the substrate and including an oxide semiconductor, a data wire layer positioned on the substrate and including a data line crossing the gate line, a source electrode connected to the data line, and a drain electrode facing the source electrode, and a capping layer covering the data wire layer, in which an end of the capping layer is inwardly recessed as compared to an end of the data wire layer.

Owner:SAMSUNG DISPLAY CO LTD

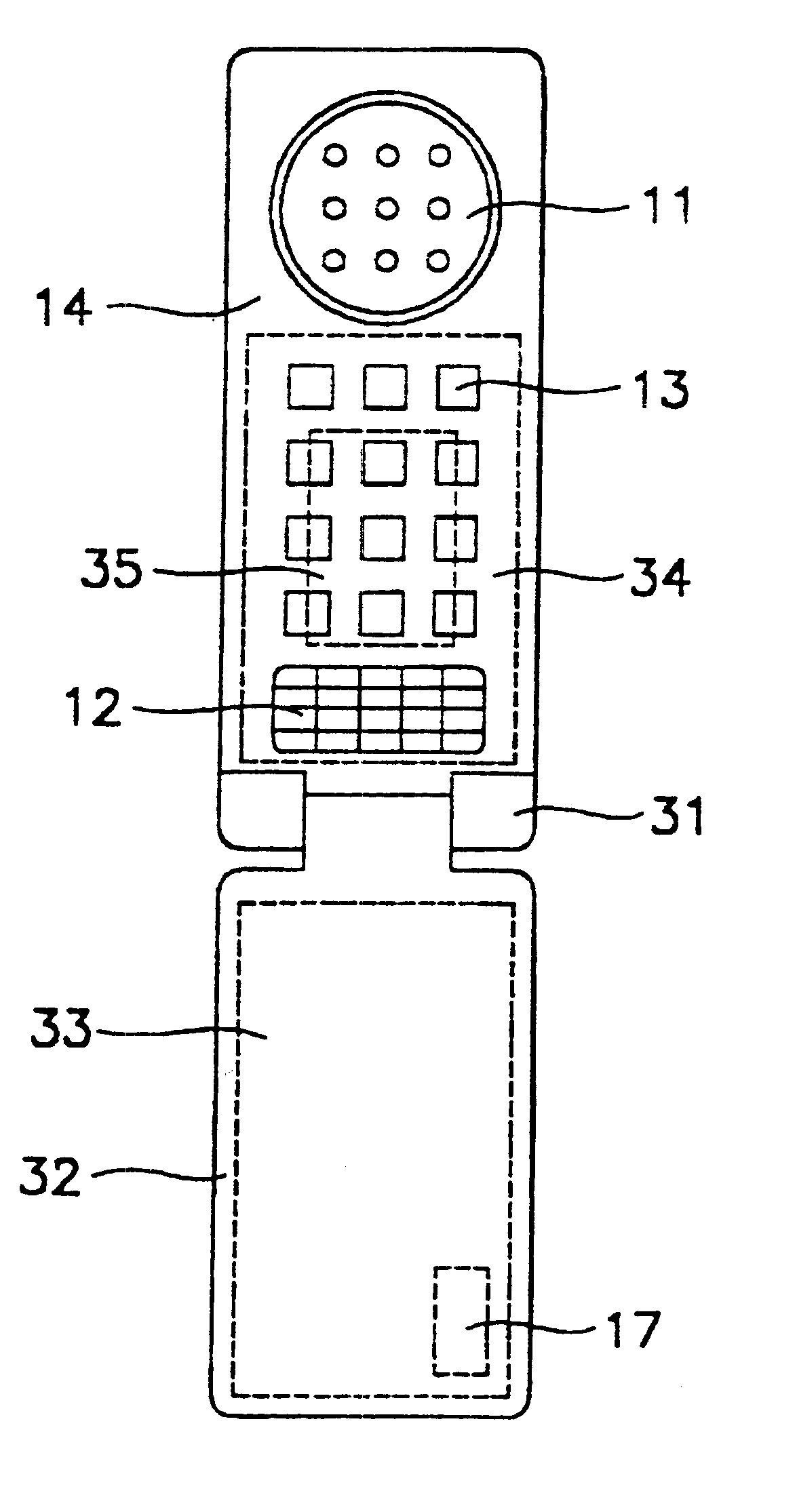

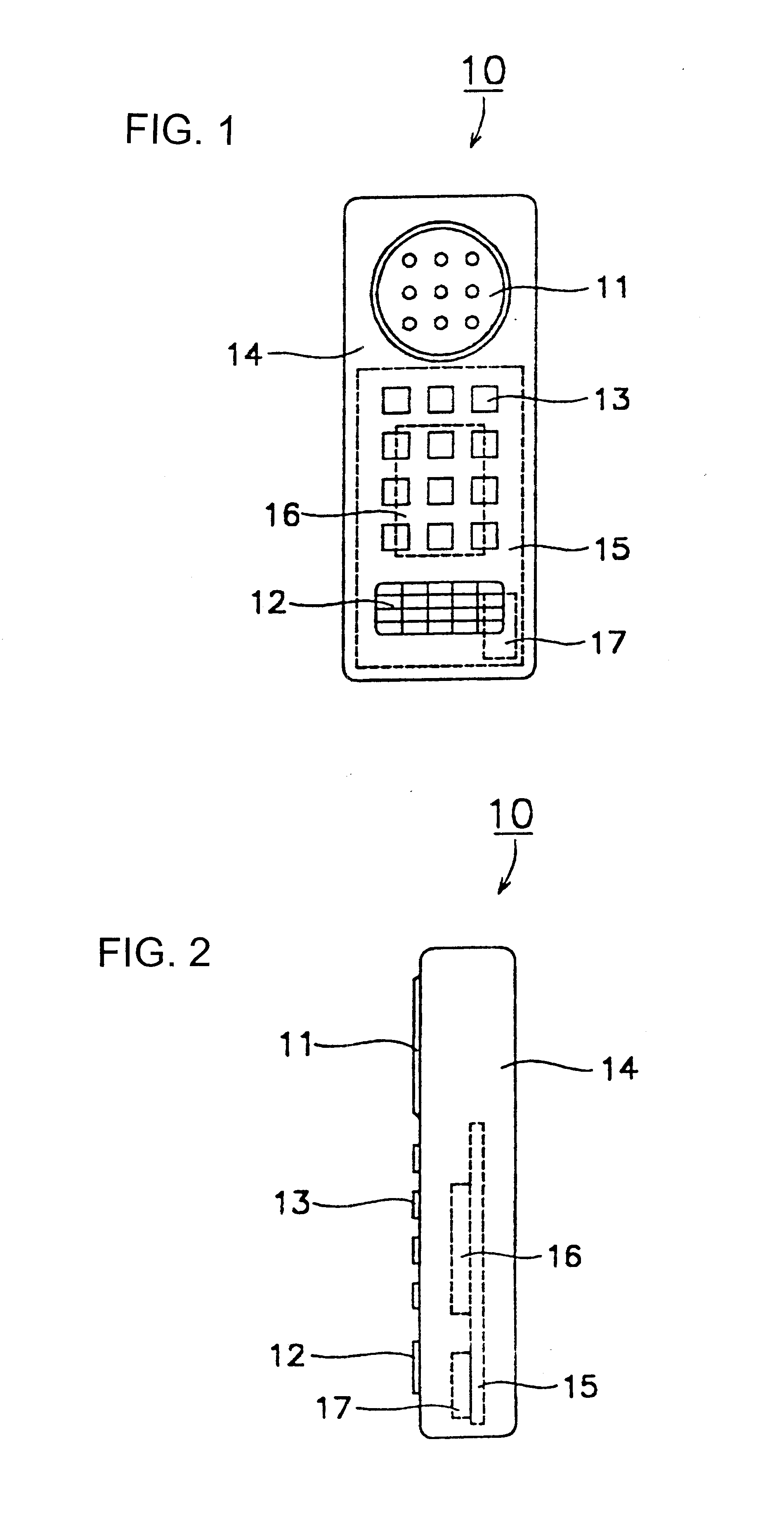

Mobile communication apparatus

InactiveUS6442399B1Prevent characteristic deteriorationAntenna supports/mountingsRadiating elements structural formsEngineeringCommunication device

A portable telephone includes a portable telephone body made from plastic having a receiver, a transmitter, and dial keys, and a chip antenna which is mounted on a circuit board secured at the inside of the portable telephone body and which is electrically connected to an RF section provided on the circuit board in the portable telephone. The chip antenna is disposed near the transmitter at a location where a transmitted electromagnetic signal is unlikely to be affected by the body of a person who is holding the portable telephone.

Owner:MURATA MFG CO LTD

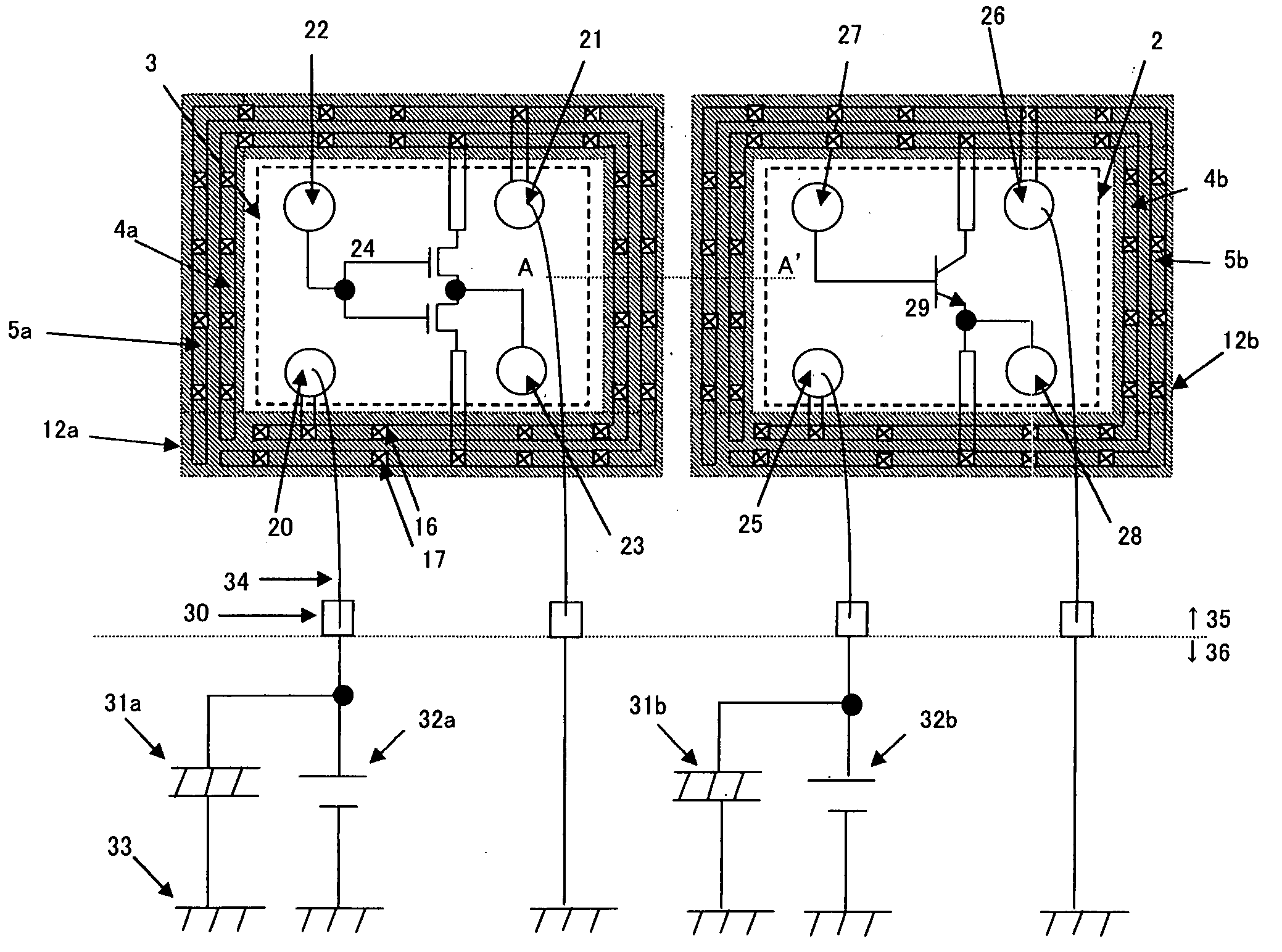

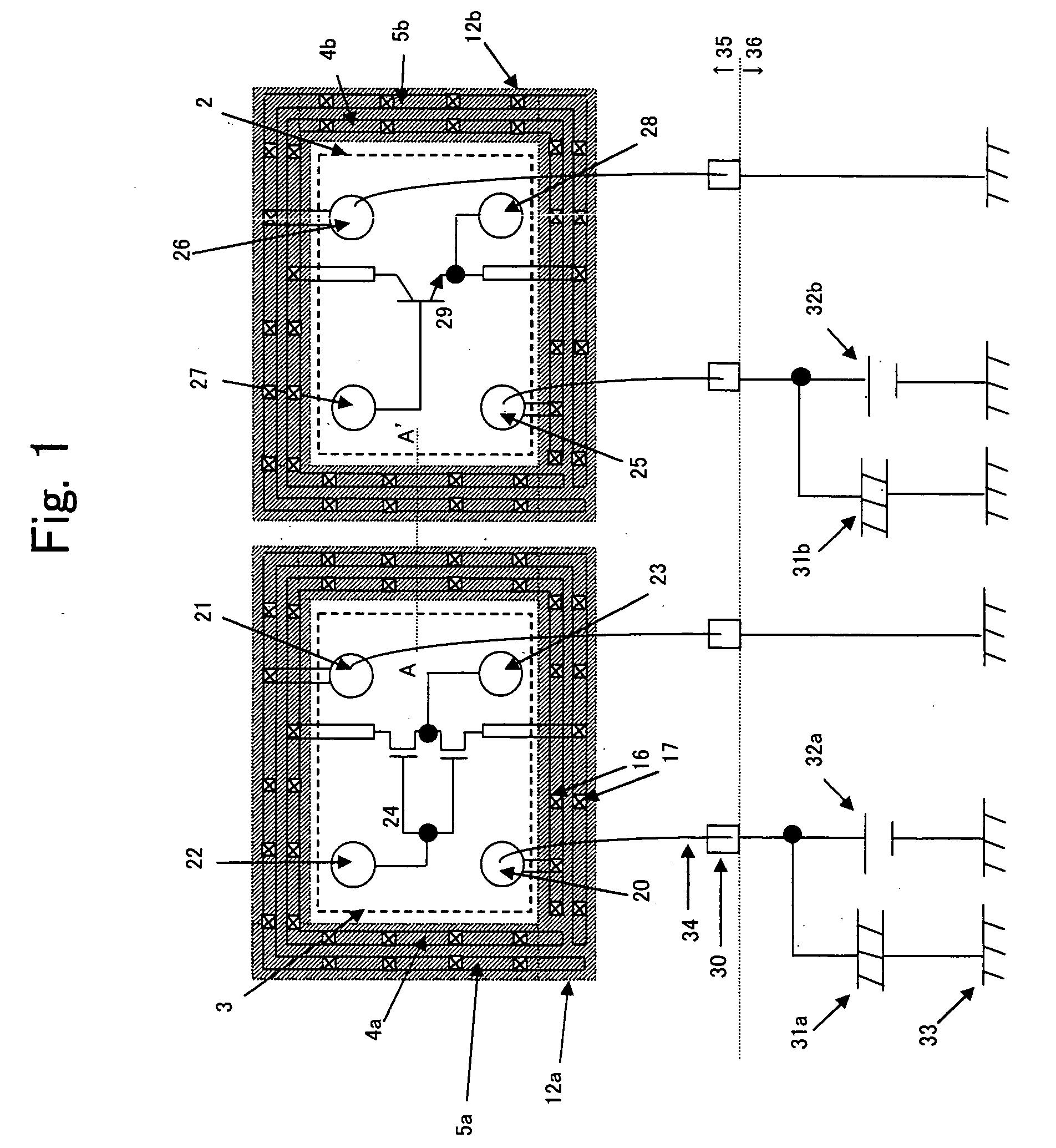

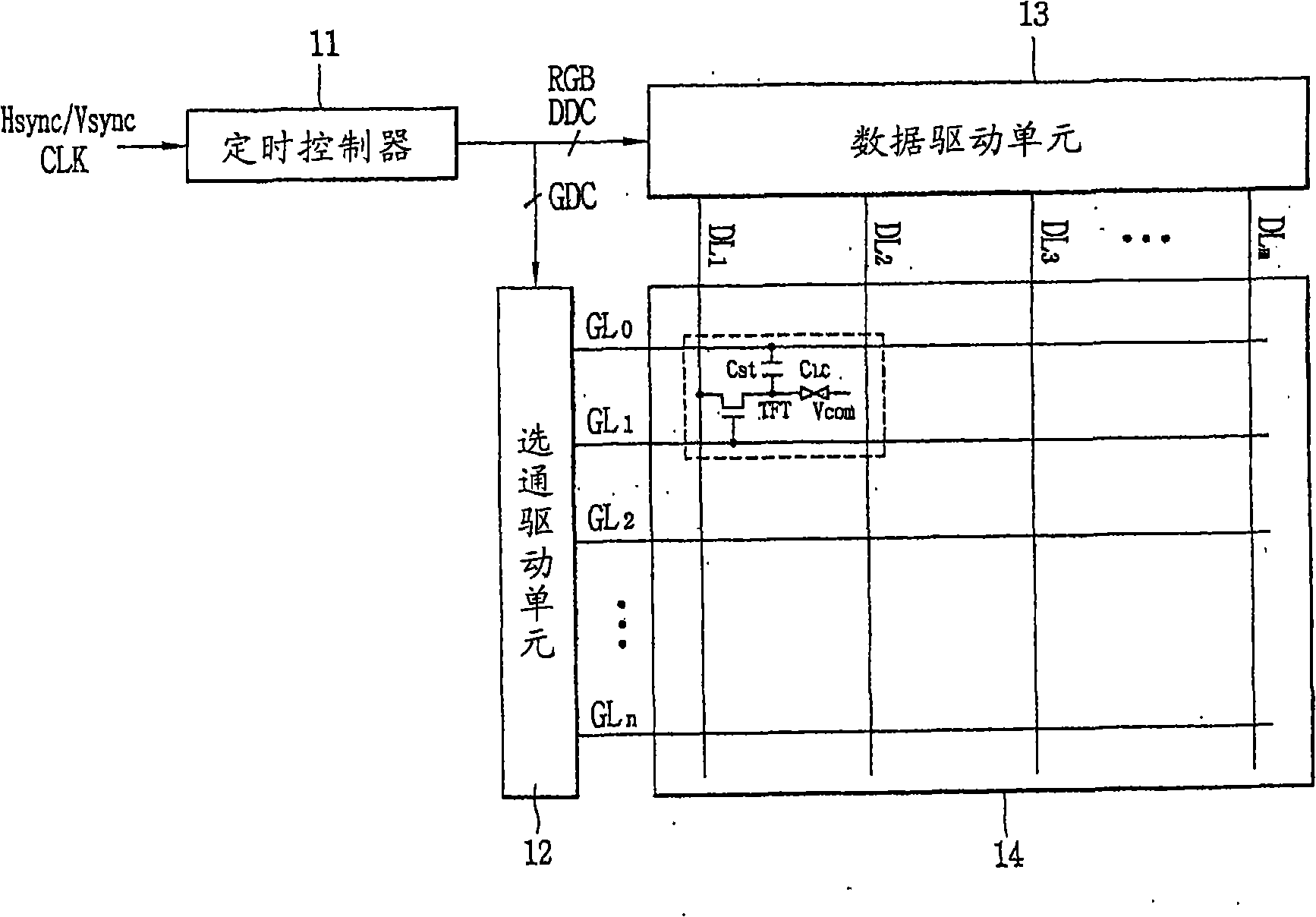

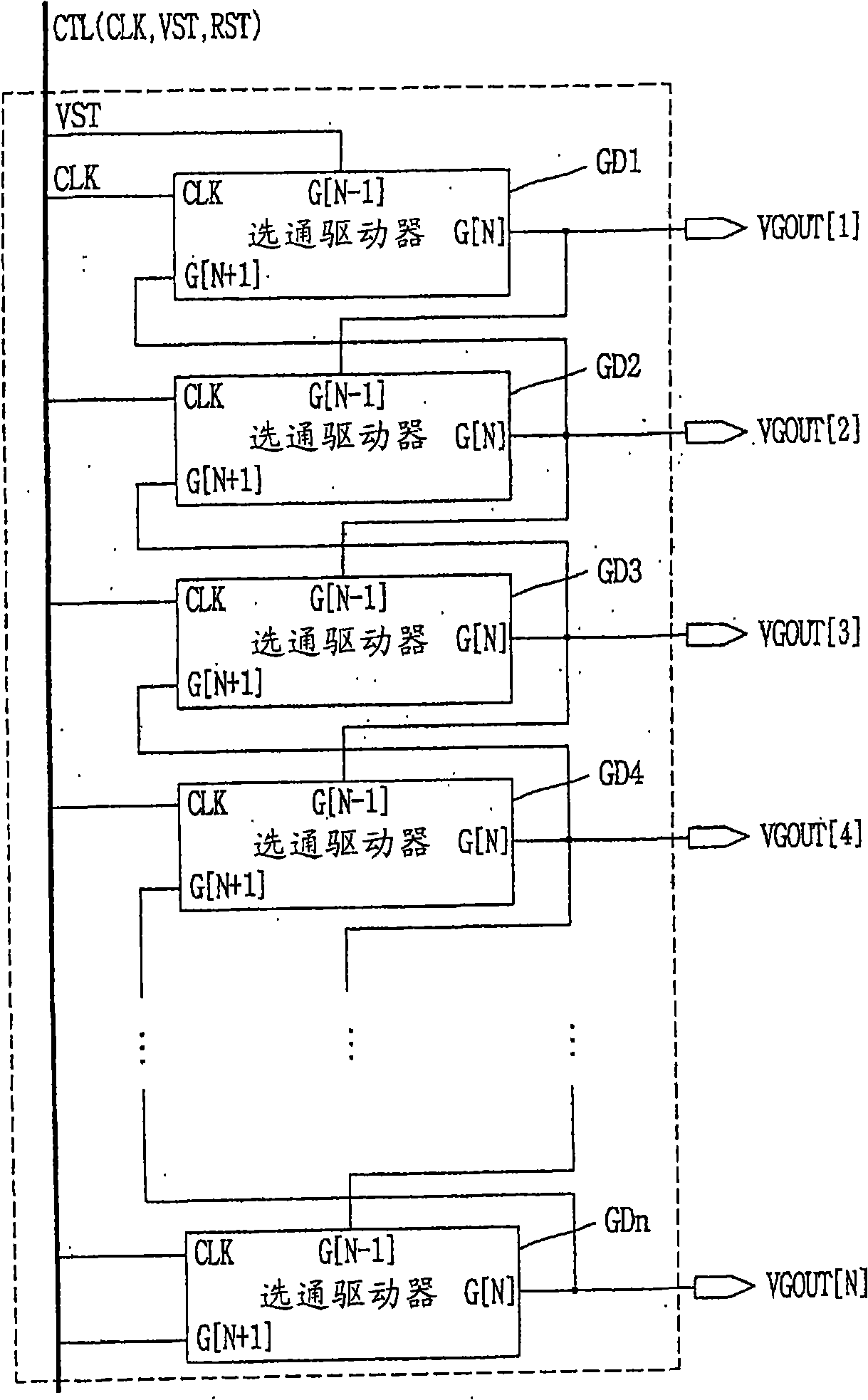

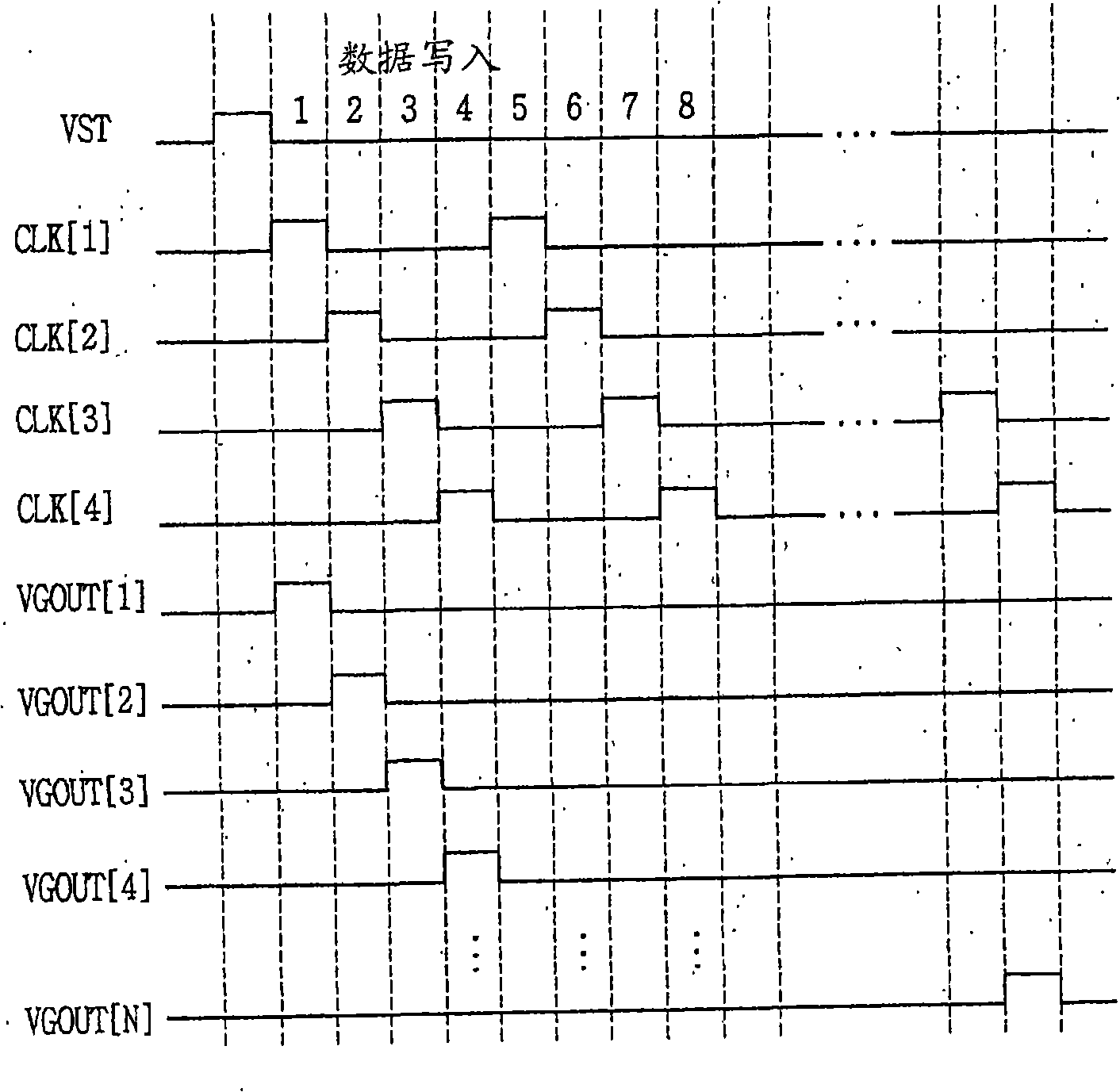

Driving circuit of liquid crystal display

ActiveCN101567172APrevent characteristic deteriorationLogic circuits characterised by logic functionStatic indicating devicesDigital videoData control

A driving circuit of a liquid crystal display includes: a timing controller to output a gate control signal and a data control signal to control driving of a gate driving unit and a data driving unit and to output digital video data; a pair of gate driving units to be alternately driven by using at least one frame as a period to supply gate signals to gate lines of a liquid crystal panel in-response to the gate control signal; and a data driving unit to supply pixel signals to data lines of the liquid crystal panel in response to the data control signal. Degradation of characteristics of transistors constituting each gate driver can be prevented.

Owner:LG DISPLAY CO LTD

Mimo/diversity antenna with high isolation

InactiveCN102969568APrevent characteristic deteriorationImprove isolationRadiating elements structural formsIndividually energised antenna arraysPower flowEngineering

Disclosed is a MIMO / diversity antenna high isolation including a printed circuit board, a plurality of antenna elements, a current conversion element connected with a common ground of the printed circuit board apart from the antenna elements at a predetermined distance, wherein the current conversion element is coupled with the antenna elements to induce an electric current from the antenna elements into the antenna elements again via the common ground.

Owner:LS MTRON LTD

Electrophoretic display and driving method thereof

ActiveUS8264454B2Prevent characteristic deteriorationRelieve pressureCathode-ray tube indicatorsNon-linear opticsElectrophoresisDisplay device

An electrophoretic display device sequentially driven during a data updating period when a data is updated and a sleep-mode period when a data is maintained includes an electrophoretic display panel including a plurality of data lines crossing a plurality of gate lines to form a plurality of cells, a plurality of pixel electrodes, a common electrode for driving each of the plurality of cells, and a TFT at a crossing of one of the data lines and one of the gate lines to supply a data voltage from the one of the data lines to a corresponding one of the pixel electrodes; a data driving circuit supplying the data voltage to the data lines during the data updating period; a gate driving circuit supplying a scanning pulse to the gate lines during the data updating period; and a controller sequentially raising an impedance of each of the data lines, the common electrode, and the gate lines during the sleep-mode period.

Owner:E INK CORPORATION

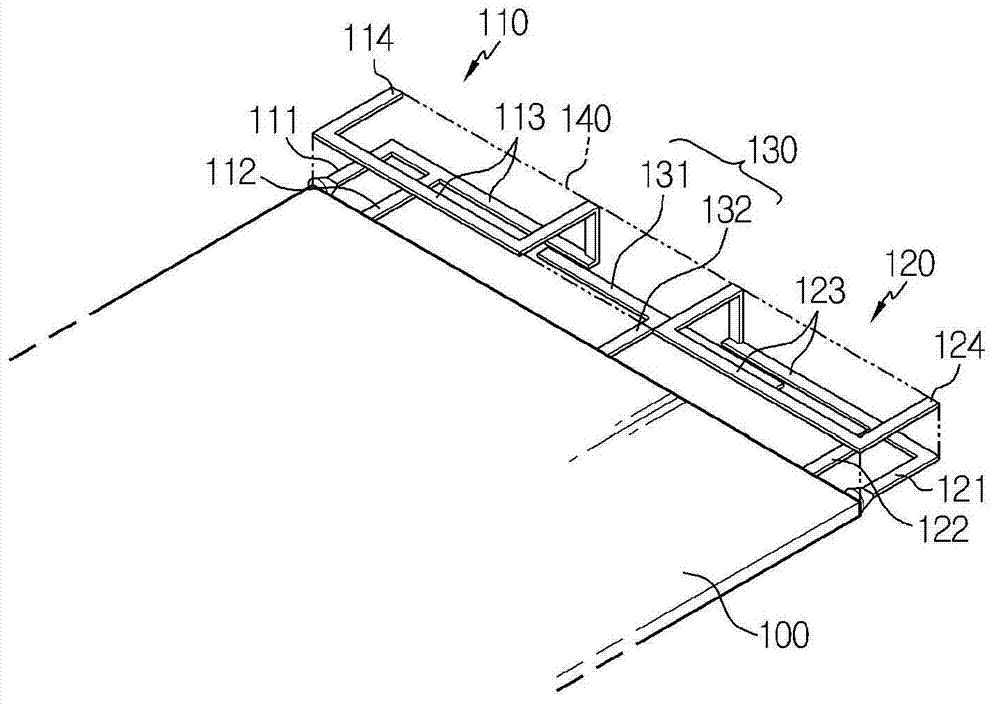

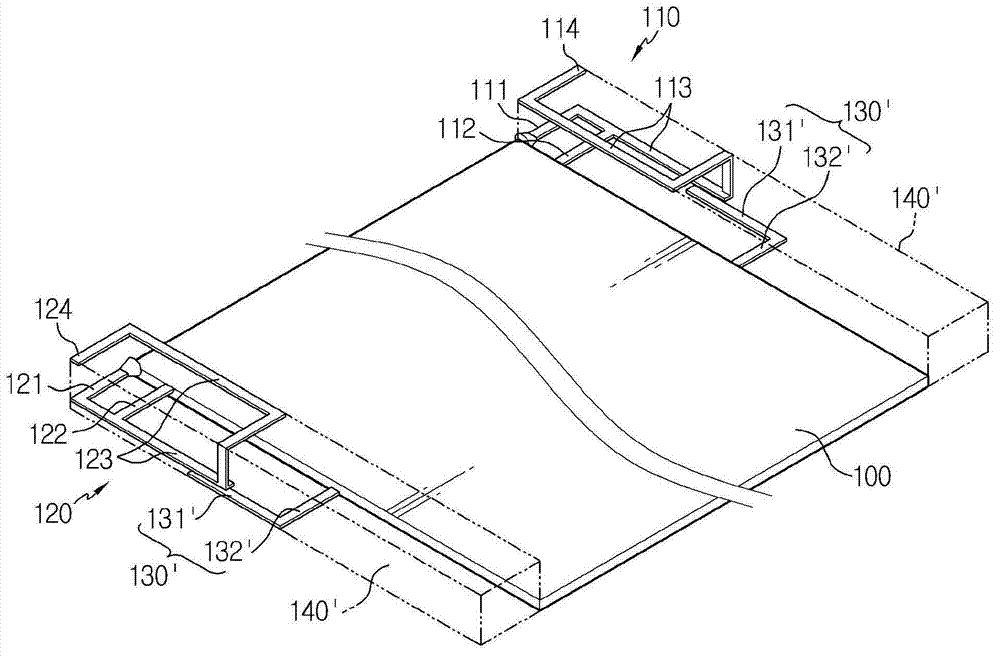

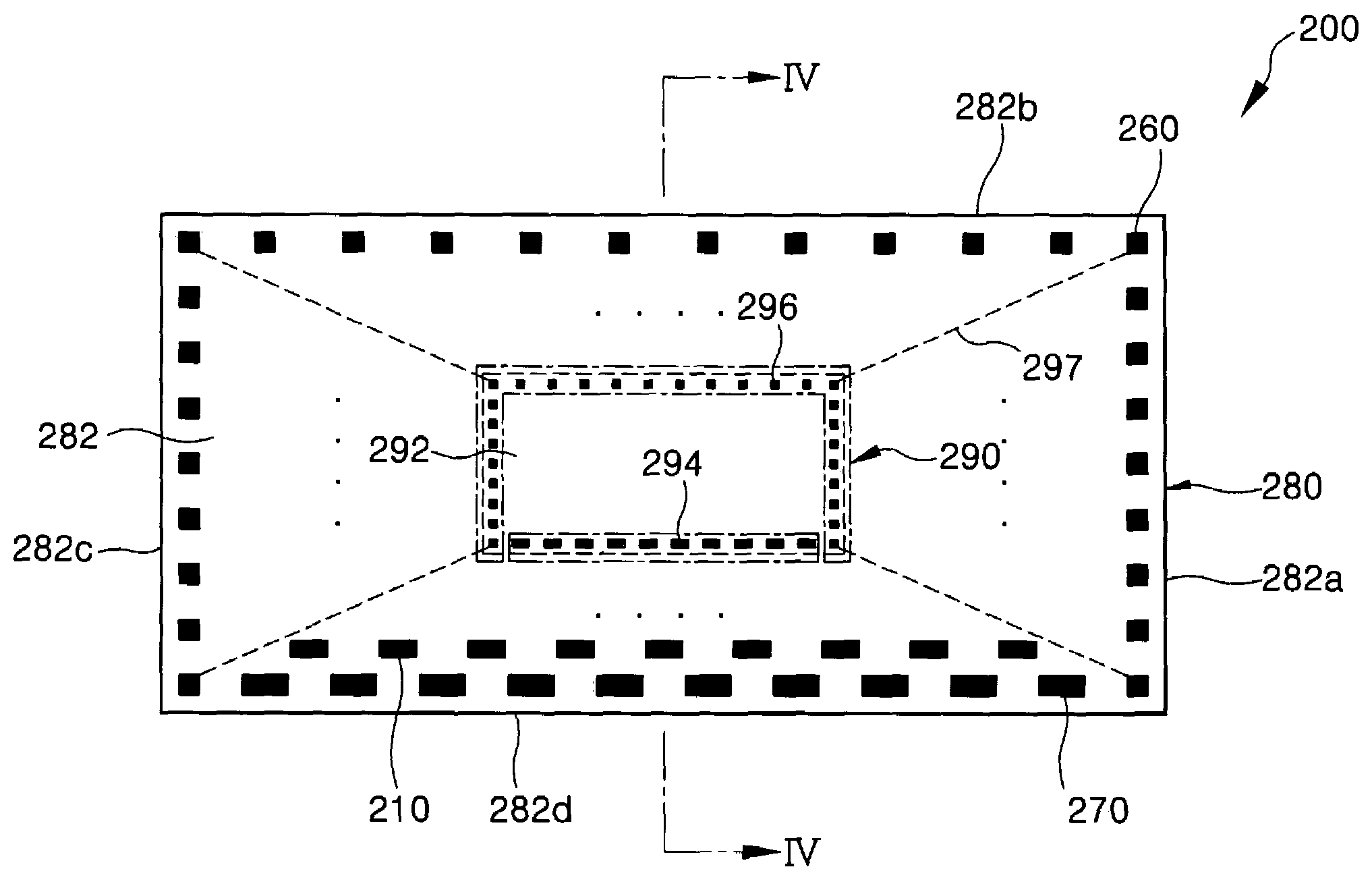

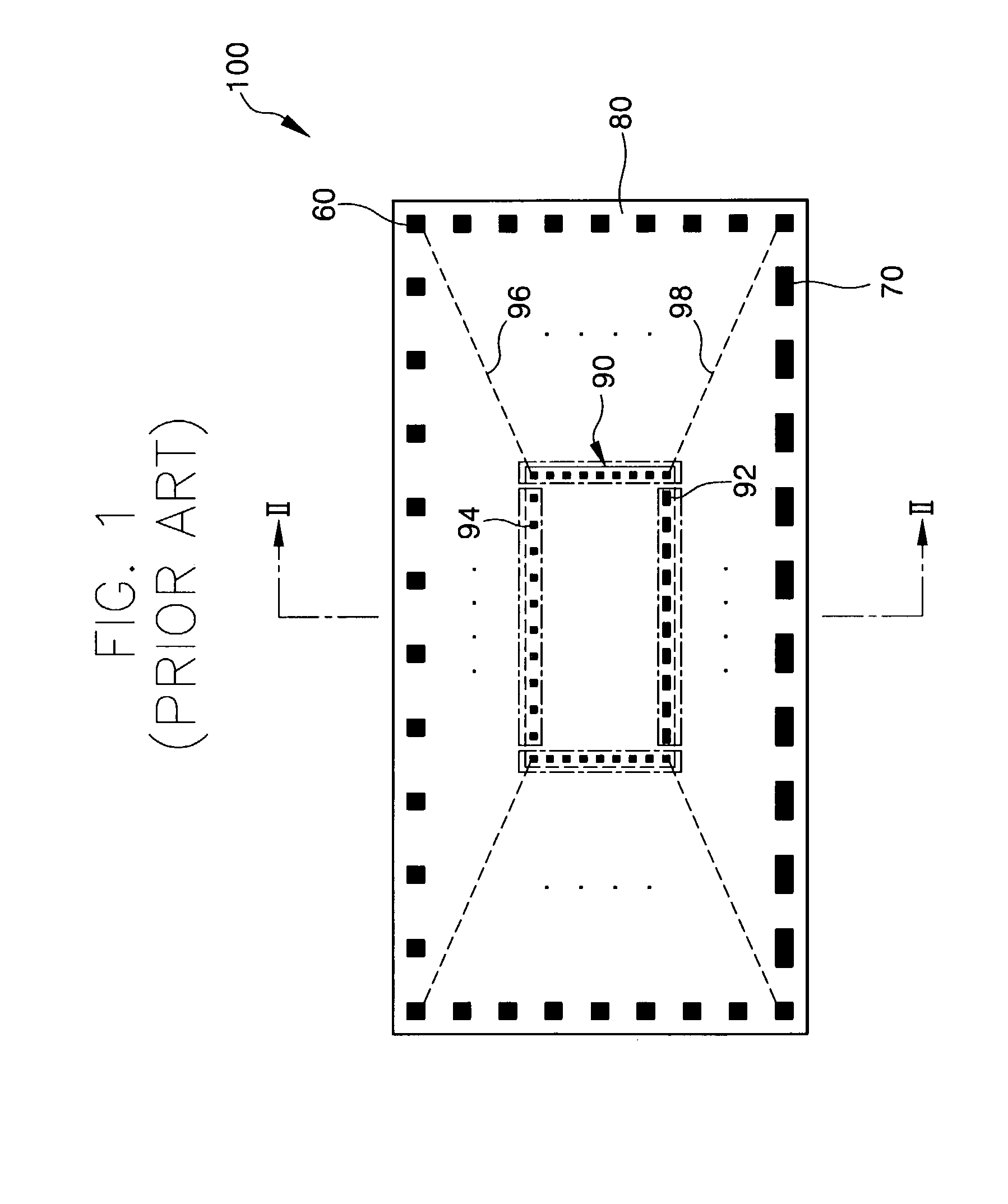

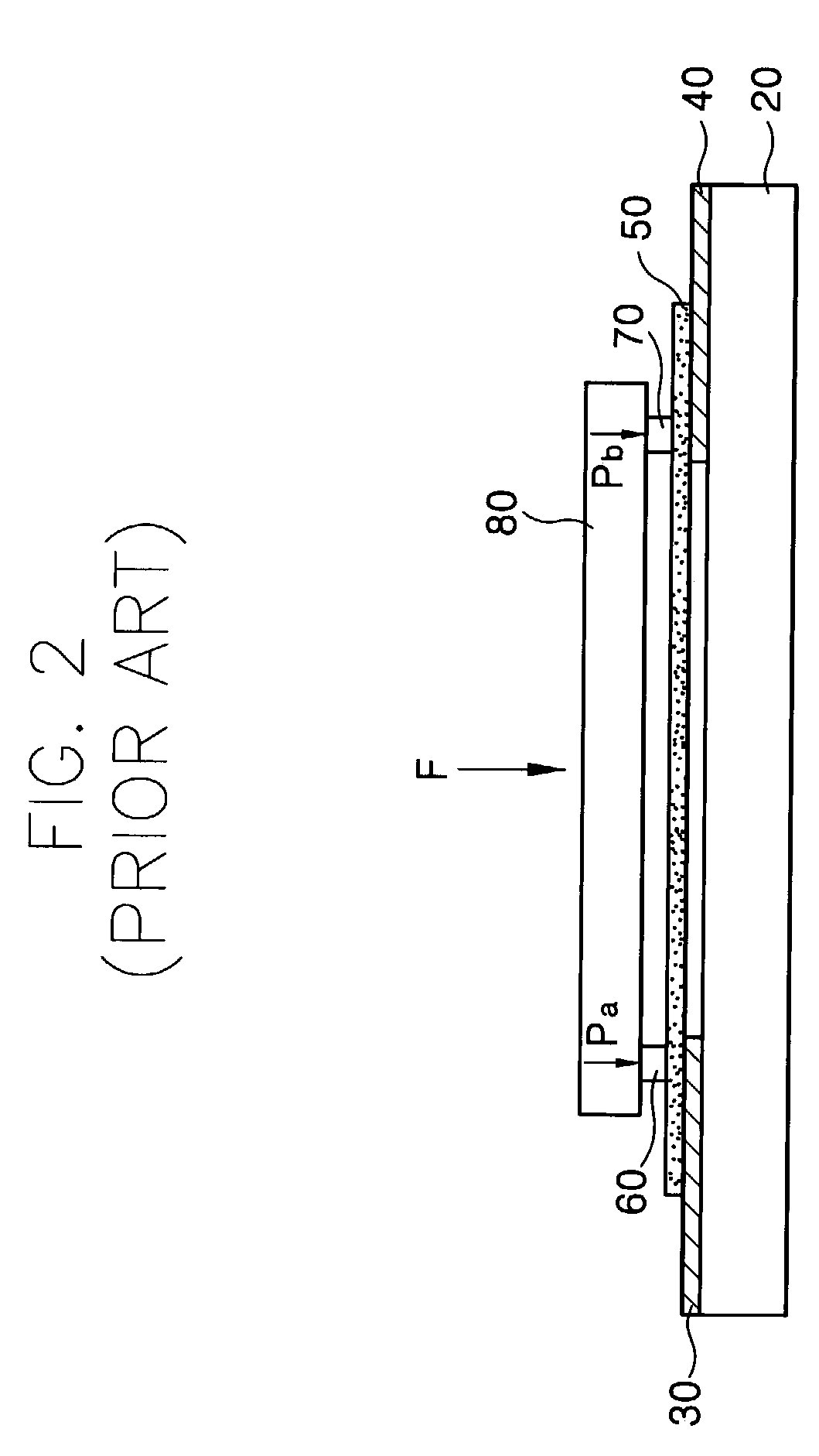

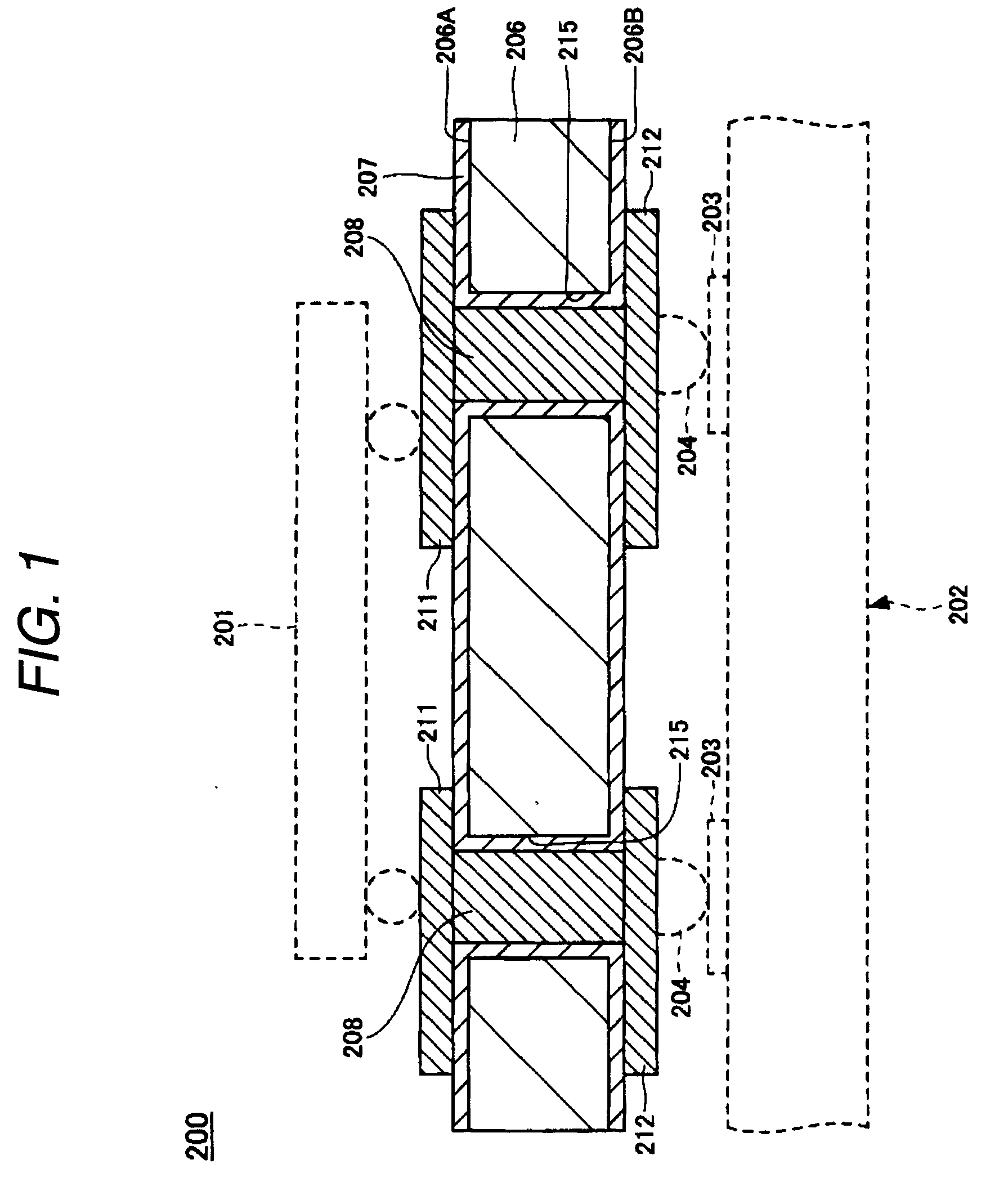

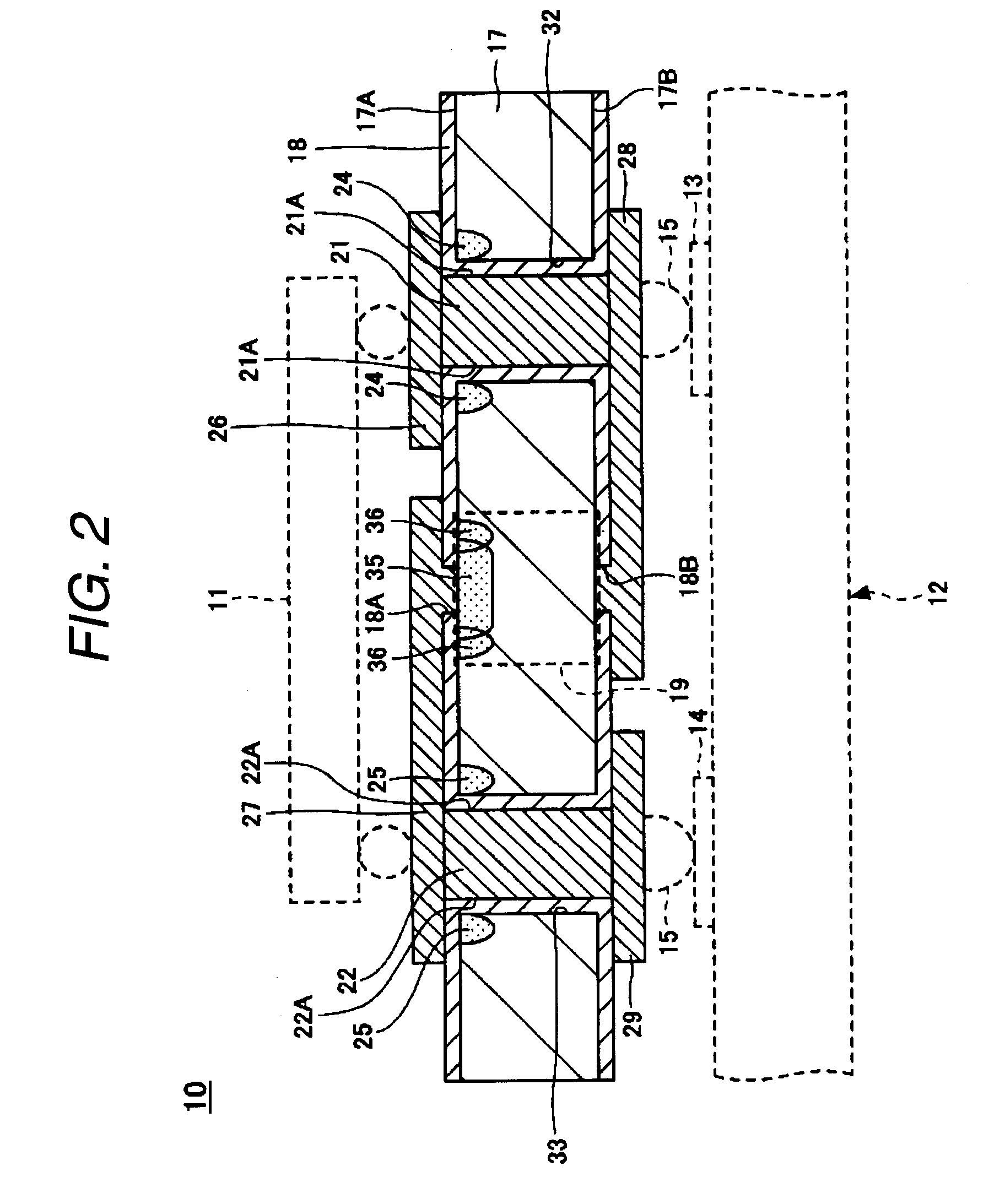

Liquid crystal display driver integrated circuit package

InactiveUS7002809B2Reduce the differenceQuality improvementSemiconductor/solid-state device detailsSolid-state devicesDevice failurePressure controlled ventilation

Disclosed is an LCD driver integrated circuit package and a chip on glass type LCD device using the package. The LCD driver integrated circuit package includes a mold that has signal output bumps and signal input bumps formed thereon, wherein the signal output bumps and the signal input bumps have different surface areas that contact the mold and an adjacent conductive film. Due to the different contact surface areas, different amounts of pressure are applied to different parts on the conductive film when a force is applied to the mold. One or more bump pressure control patterns are formed on the mold compensate for the difference in pressure caused by this difference between the total contact areas. Accordingly, the LCD driver integrated circuit package can be mounted on a chip on glass type LCD panel without causing device failure.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

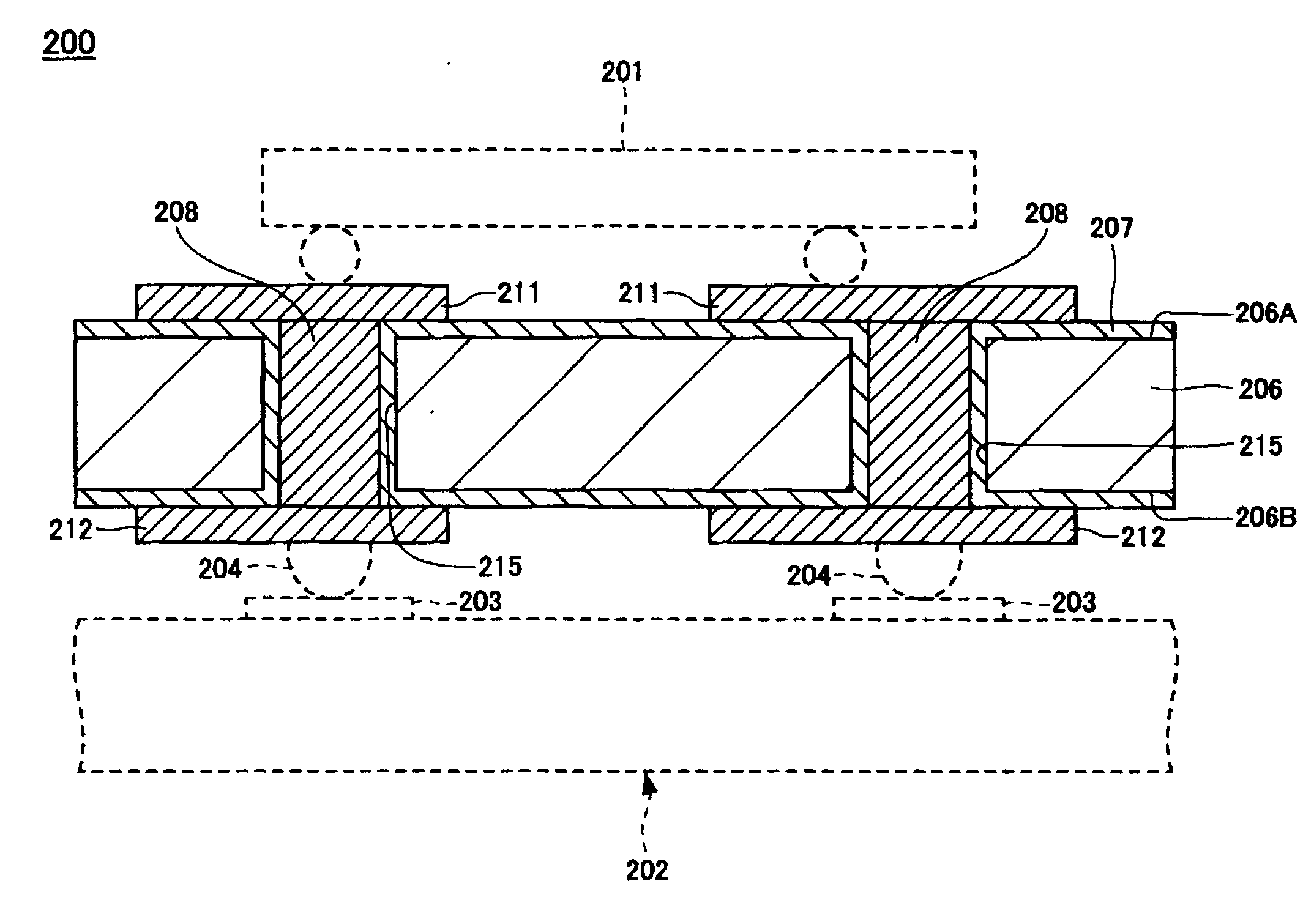

Wiring board

ActiveUS20090085164A1Improve leakage currentGeneration of layerSemiconductor/solid-state device detailsSolid-state devicesImpurity diffusionEngineering

There is provided a wiring board. The wiring board includes: a semiconductor substrate having a through hole and covered with an insulating film; a through electrode formed in the through hole; a first wiring connected to one end of the through electrode; and a second wiring connected to the other end of the through electrode. The semiconductor substrate includes: a semiconductor element and a first guard ring formed to surround the through hole. The semiconductor element includes a first conductivity-type impurity diffusion layer having a different conductivity-type from that of the semiconductor substrate and is electrically connected to the first wiring and the second wiring.

Owner:SHINKO ELECTRIC IND CO LTD

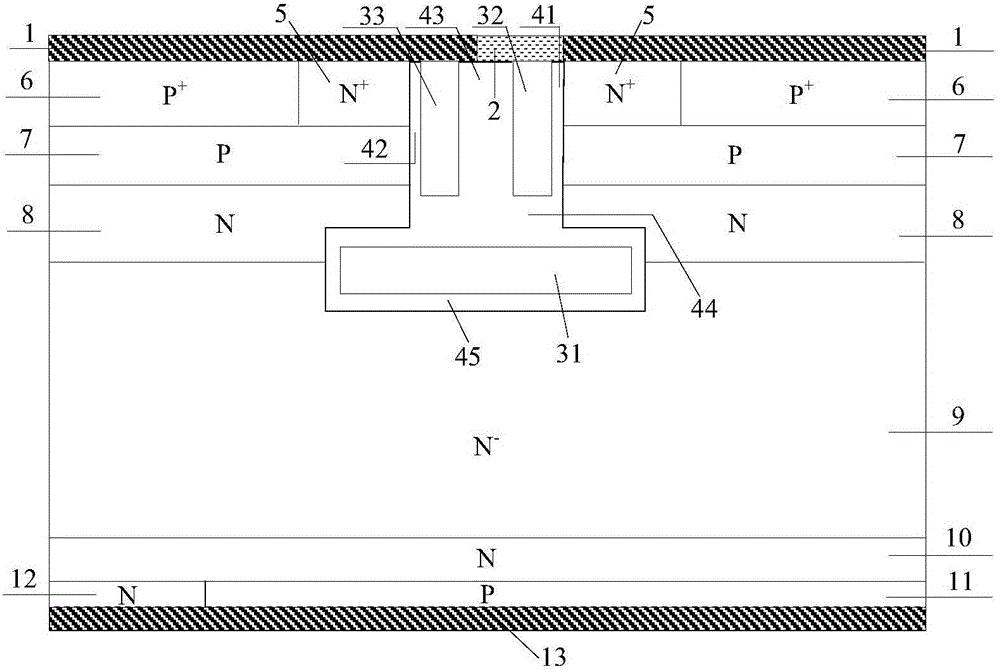

Double split trench gate charge storage-type RC-IGBT and manufacturing method thereof

ActiveCN105742346AReduced carrier concentration distributionReduced short-circuit safe operating areaSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringFlyback diode

The invention belongs to the technical field of power semiconductor devices, and particularly relates to a reverse trench gate charge storage-type insulated gate bipolar transistor. Double split electrodes which are equal to an emitter in potential and dielectric layers between the double split electrodes and a gate electrode are introduced into the bottom part and the side surface of the gate electrode in a trench of an RC-IGBT device, so that the switching speed of the device in the IGBT working mode is improved; the carrier concentration distribution of the whole N-type drift region is improved; the switching loss of the device is reduced; the saturated current density of the device is reduced; the short-circuit safe operation area of the device is improved; the reliability is improved; a reverse free-wheeling diode has a low diode conduction voltage drop in a reverse free-wheeling diode working mode; the reverse recovery characteristics of the free-wheeling diode are improved; and meanwhile, the manufacturing method of the double split trench gate charge storage-type IGBT does not need to increase an extra processing step and is compatible with a traditional RC-IGBT manufacturing method.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

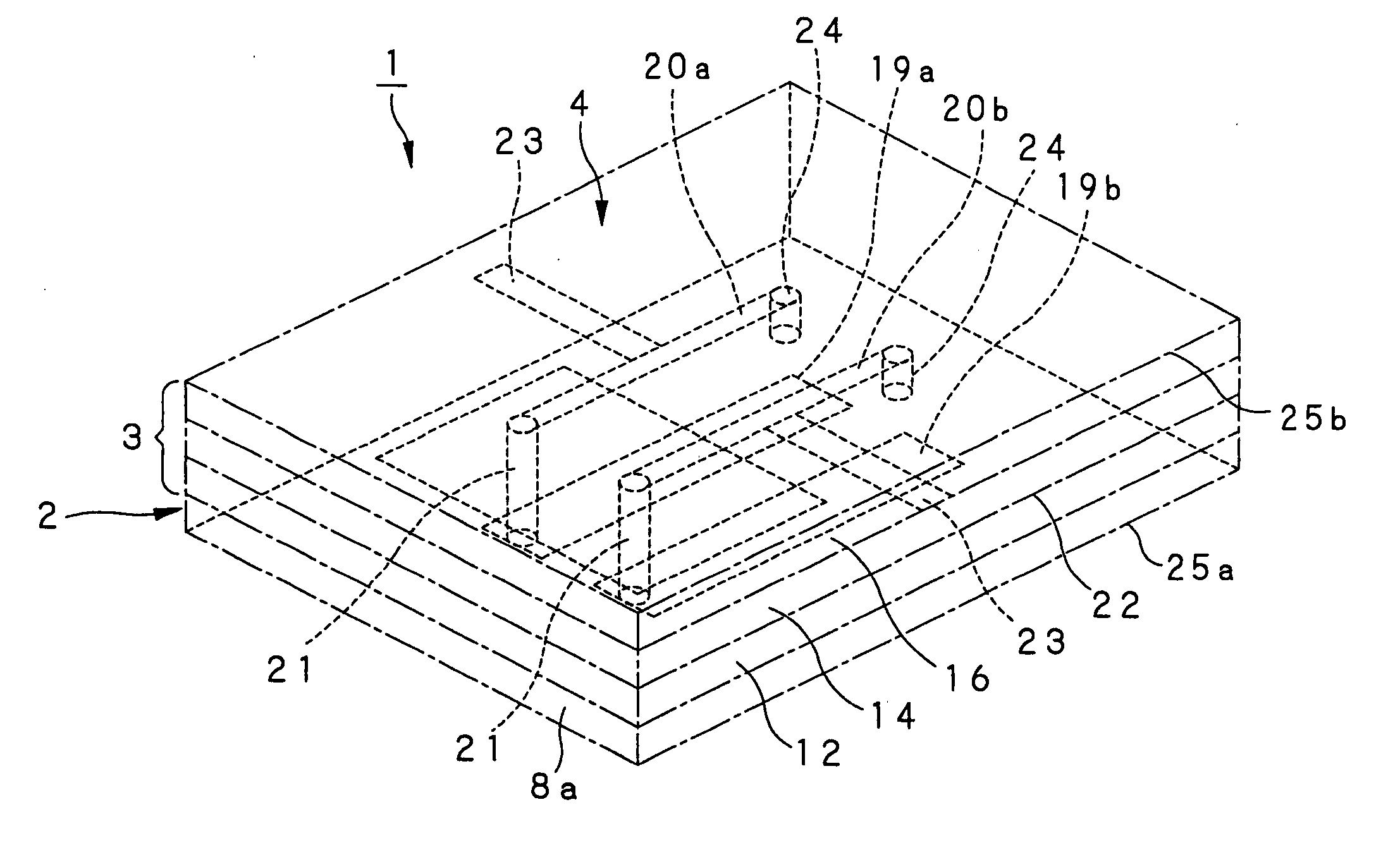

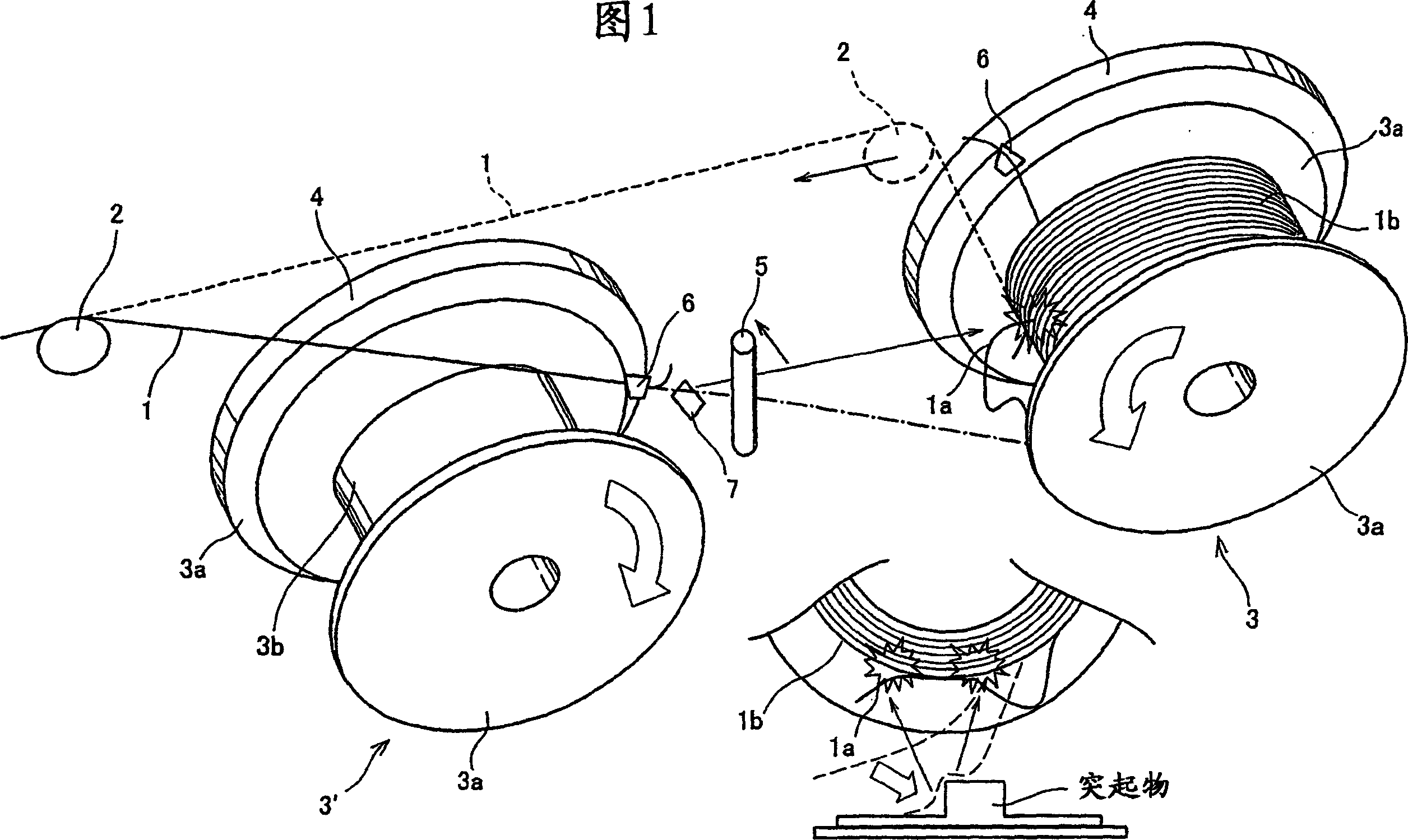

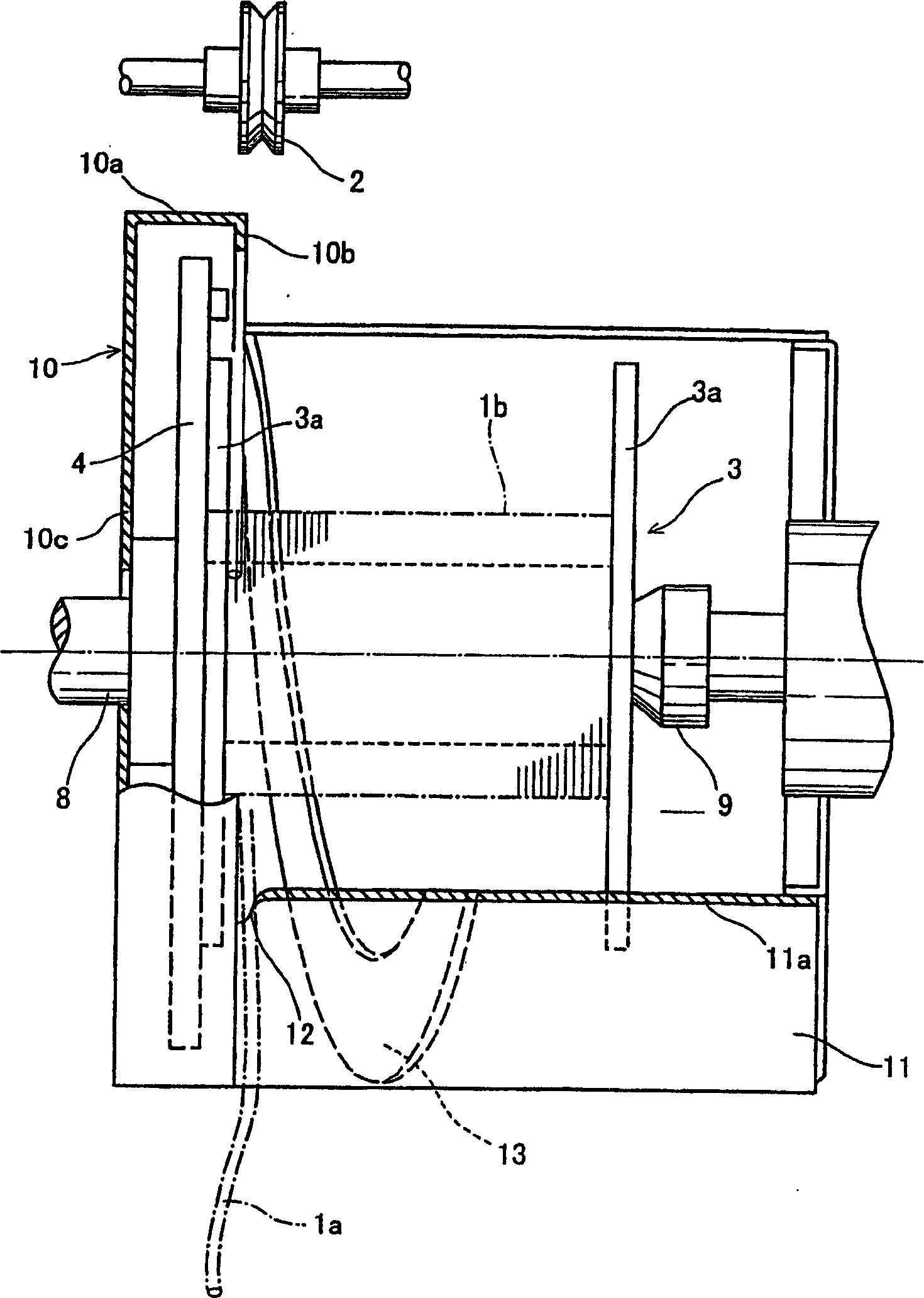

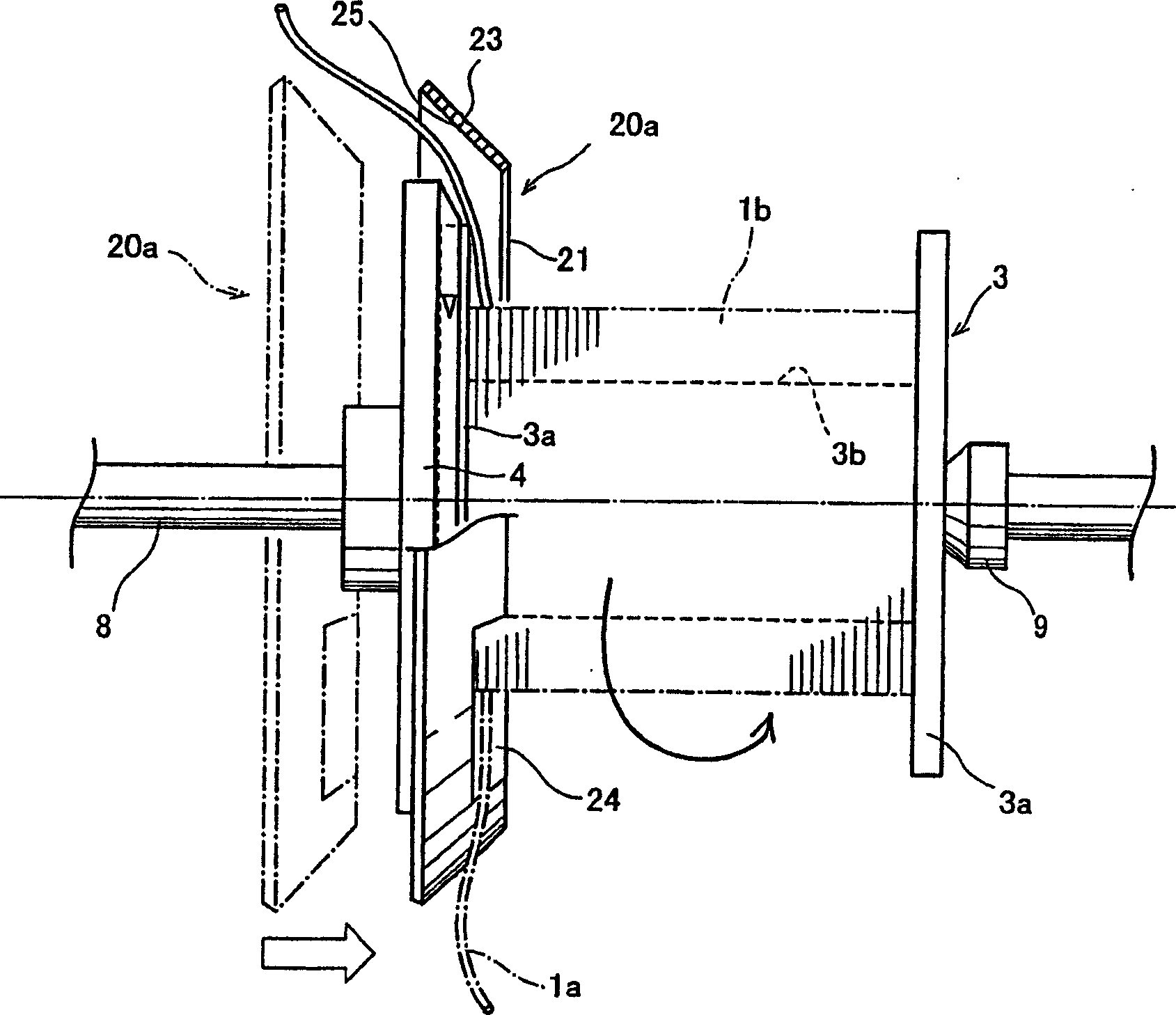

Winder and winding method of filament body

ActiveCN1759057APrevent characteristic deteriorationAvoid knockingFilament handlingBobbinEngineering

A winding device of a wire body having a simple arrangement and a winding method wherein the cut end wire at the end of winding is contained in an annular guide arranged movably on one end part side and does not project from the annular guide. The annular guide (20b) is arranged such that it can cover one flange part of the wire body winding bobbin (3) and provided with a cut (24) for guiding the wire body, wherein the diameter of the inner circumferential surface (25) is enlarged sequentially toward the direction away from the bobbin. The annular guide (20b) may be shaped to have a stop part (26) for preventing the wire body from projecting to the outside of the bobbin. The annular guide (20b) is arranged on the flange part (3a) movably in the axial direction of the bobbin or the annular guide (20b) is constituted of a plurality of parts which are moved to be arranged annularly on the flange part (3a).

Owner:SUMITOMO ELECTRIC IND LTD

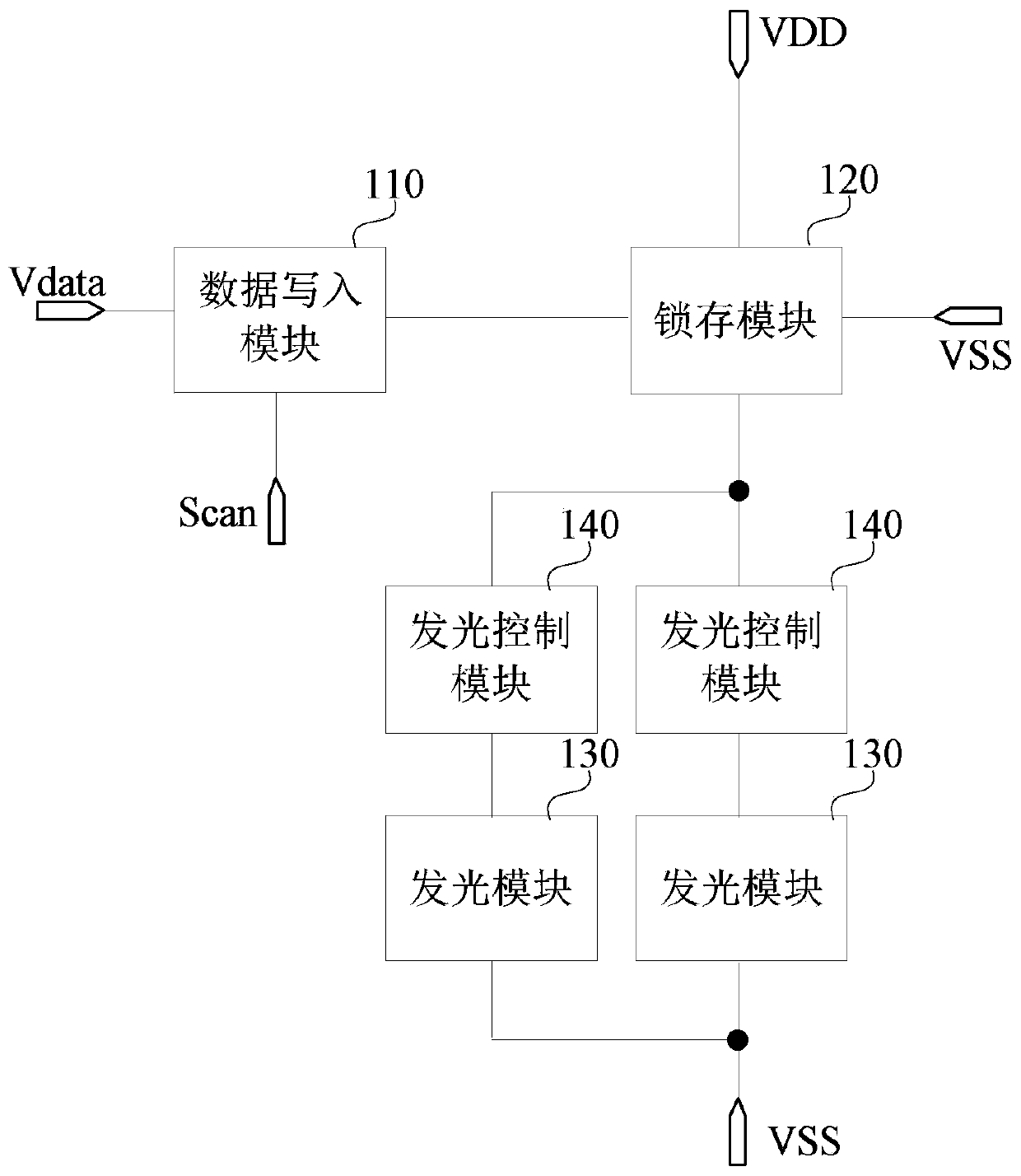

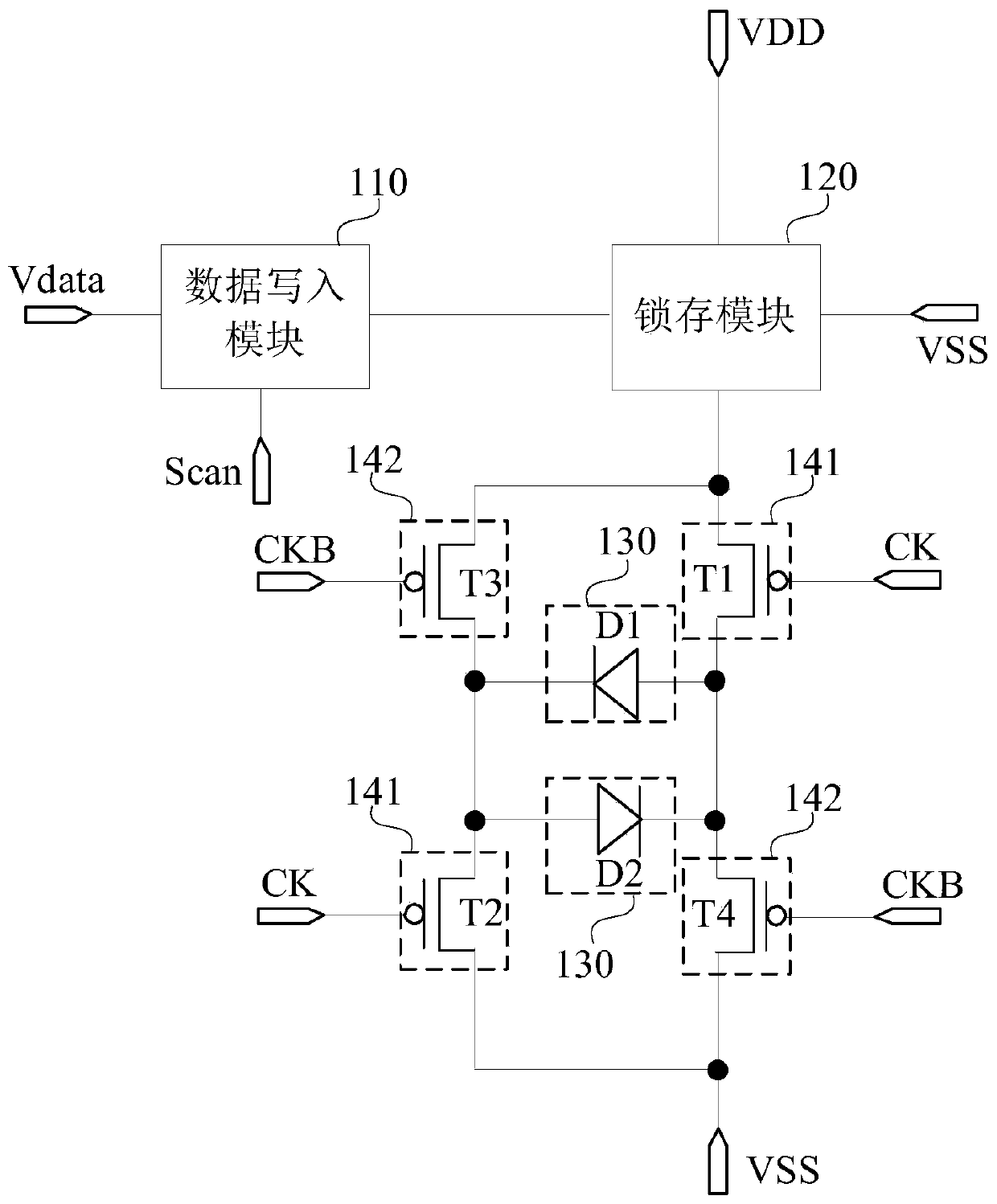

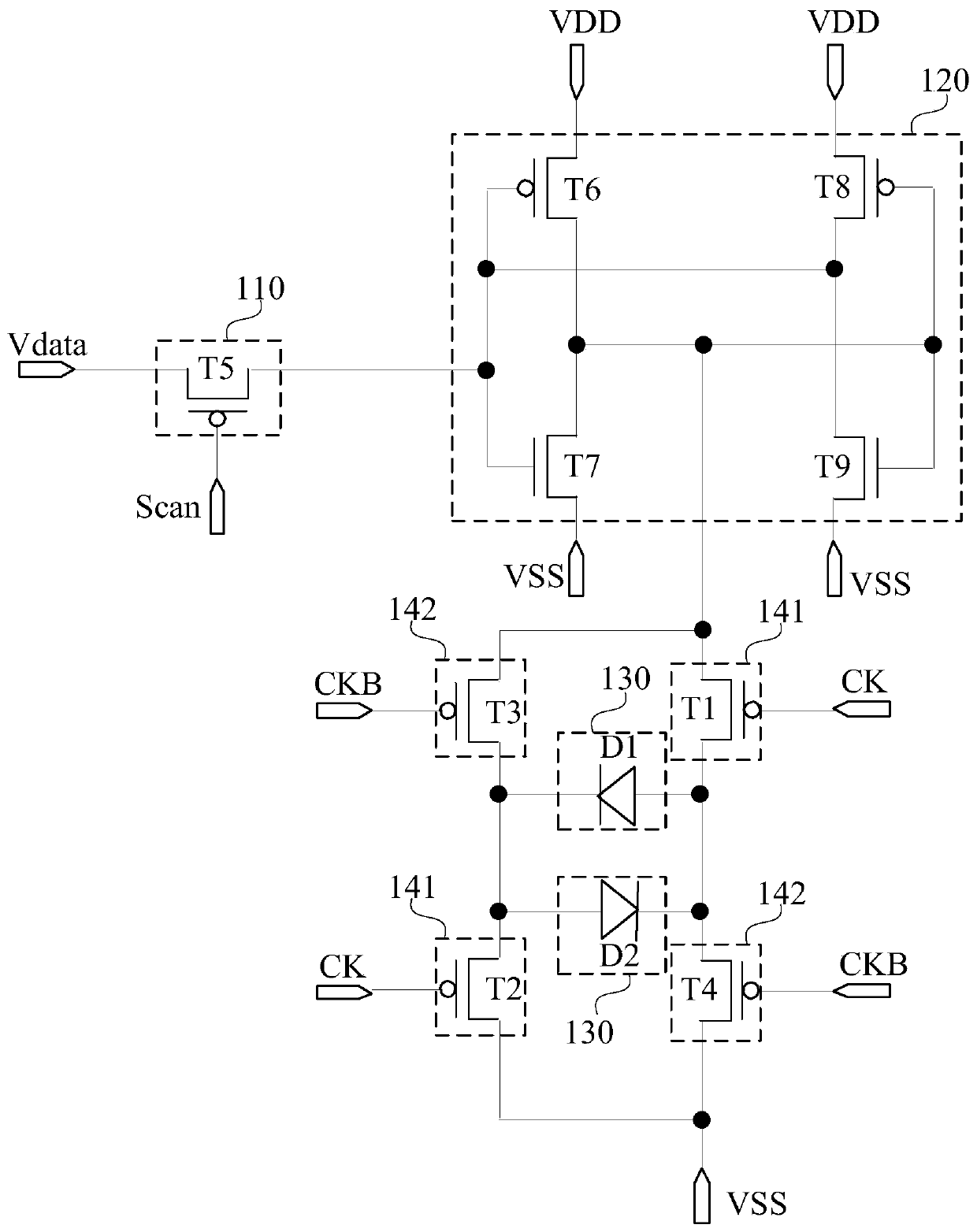

Digital driving pixel circuit, driving method thereof and display panel

InactiveCN110459169AImprove the display effectPrevent characteristic deteriorationStatic indicating devicesEngineeringDriving circuit

The embodiment of the invention discloses a digital driving pixel circuit, a driving method thereof and a display panel. The digital driving pixel circuit comprises a data writing module, a latch module, at least two light-emitting modules and light-emitting control modules in one-to-one correspondence with the light-emitting modules, the data writing module is used for controlling writing of datavoltage into the latch module; the latch module is used for latching data voltage; the light-emitting control module is used for alternate conduction; the at least two light-emitting modules are controlled to emit light alternately; further, the characteristic deterioration caused by long-time continuous work of the light-emitting module can be avoided; according to the digital drive circuit, theproblems of failure of the light-emitting modules and the like in the prior art are solved, so that each light-emitting module can release heat and be cooled after emitting light for a period of timeand when not emitting light, the temperature of each light-emitting module is not too high, good characteristics of the light-emitting modules are guaranteed, and the display effect of the display panel comprising the digital drive circuit is improved.

Owner:CHENGDU VISTAR OPTEOLECTRONICS CO LTD

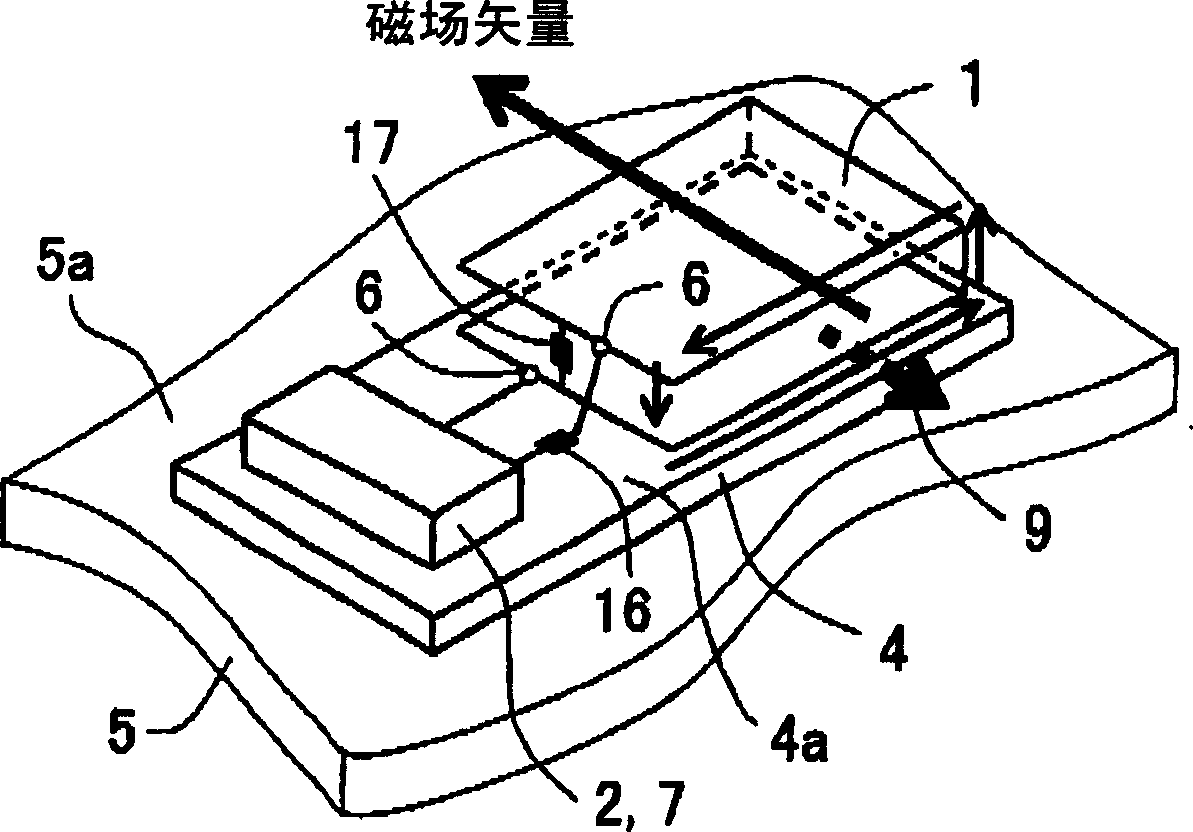

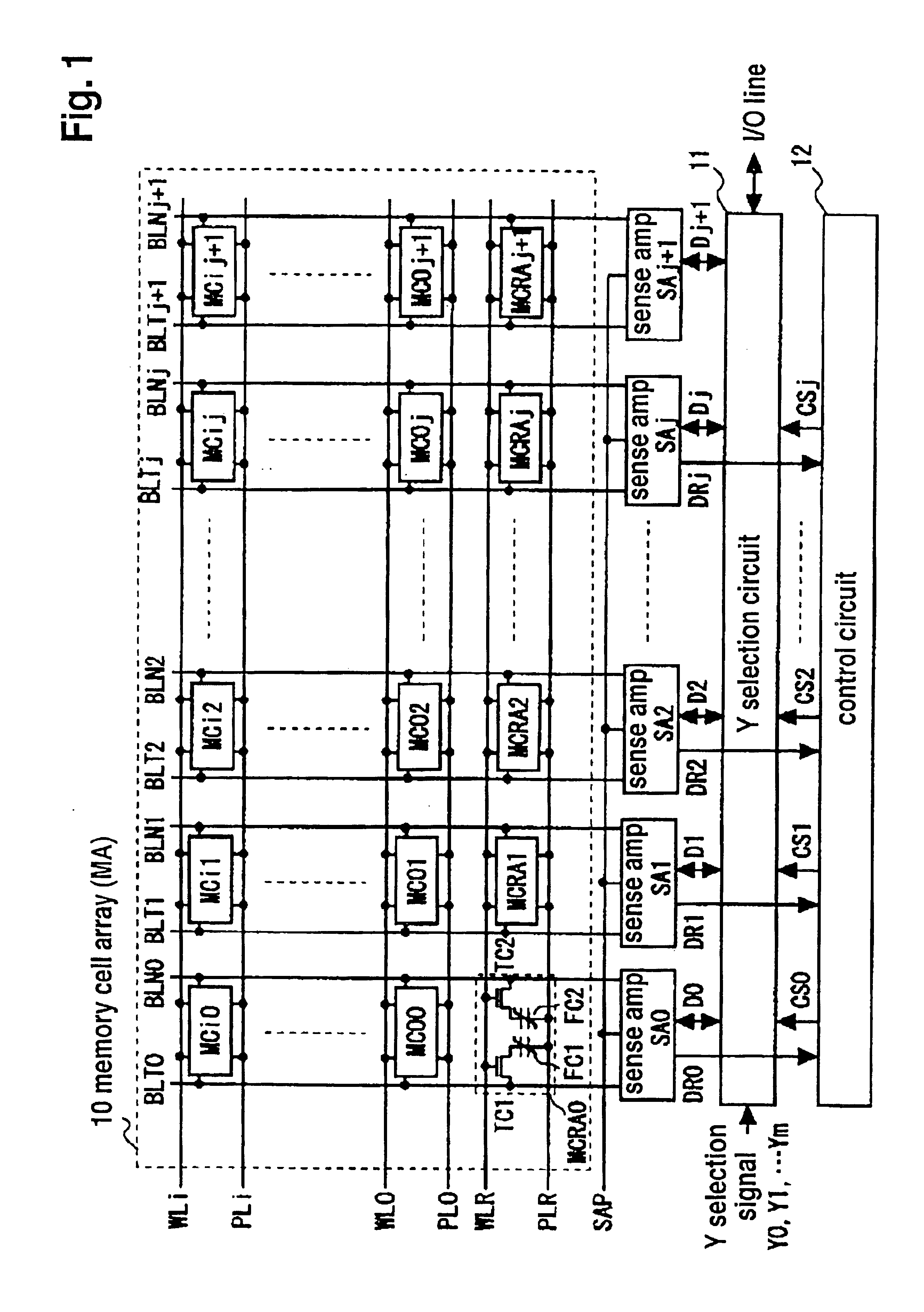

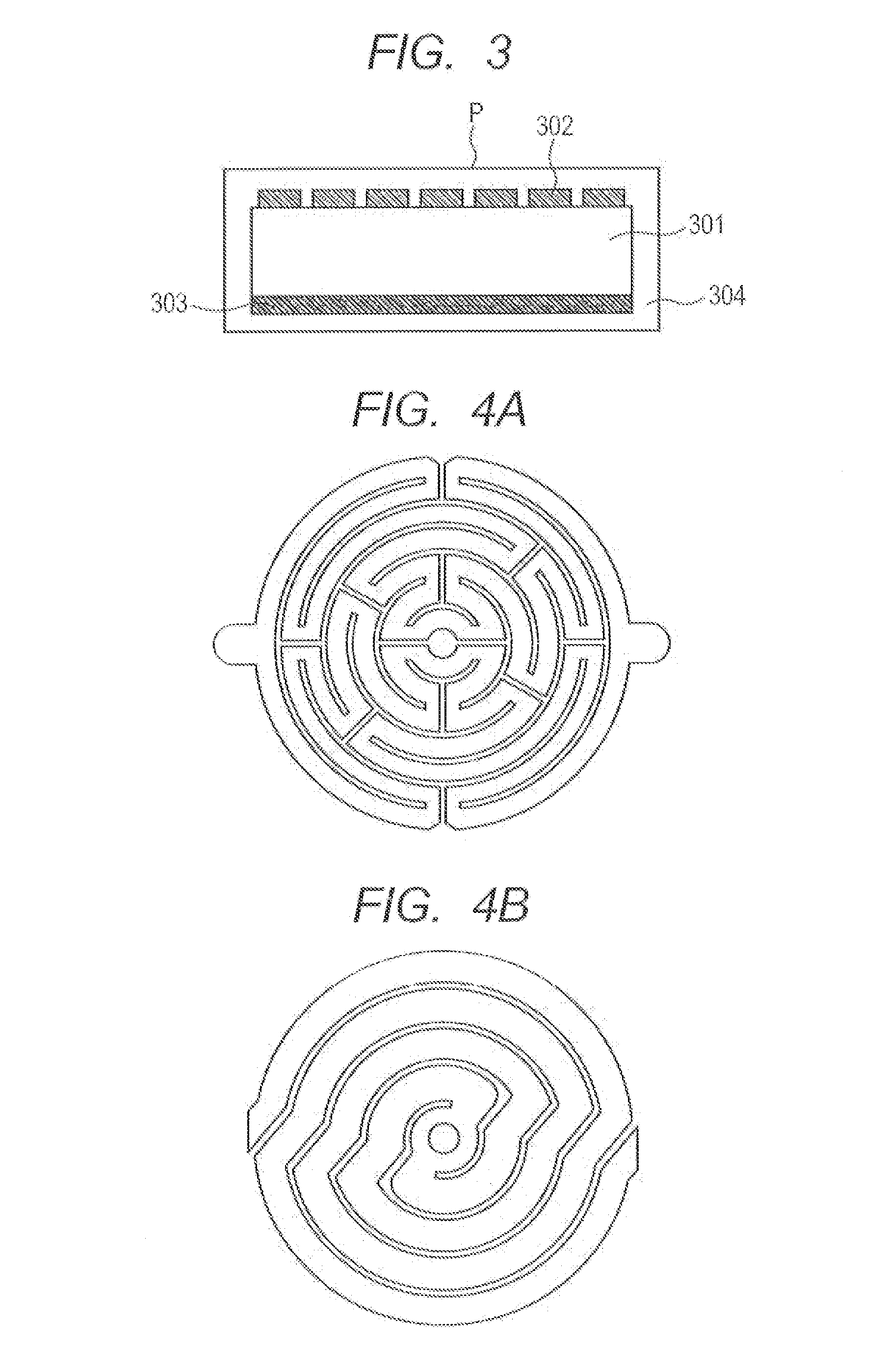

Antenna for tire pressure information sending apparatus and tire pressure information sending apparatus using the same

InactiveCN1658429APrevent characteristic deteriorationImprove emission efficiencyInflated body pressure measurementTransmission systemsMirror reflectionAtmospheric pressure

The antenna 1 for the tire air pressure information transmitting device comprises a circuit board 4 provided with feeding electrodes 6, and a radiation electrode 8 for transmitting tire air pressure information as electric waves and having a loop plane 9 nearly perpendicular to a main surface 4a on the main surface 4a of the circuit board 4, thereby a magnetic field vector is generated to be in parallel with the main surface 4a of the circuit board 4 and also in parallel with the wheel rim 5, when being provided as a device on the wheel rim 5. Since the magnetic field vector caused by a mirror reflection effect to the wheel rim 5 becomes nearly the same direction as a magnetic field vector of the antenna 1, deterioration in the antenna characteristics can be effectively prevented.

Owner:KYOCERA CORP

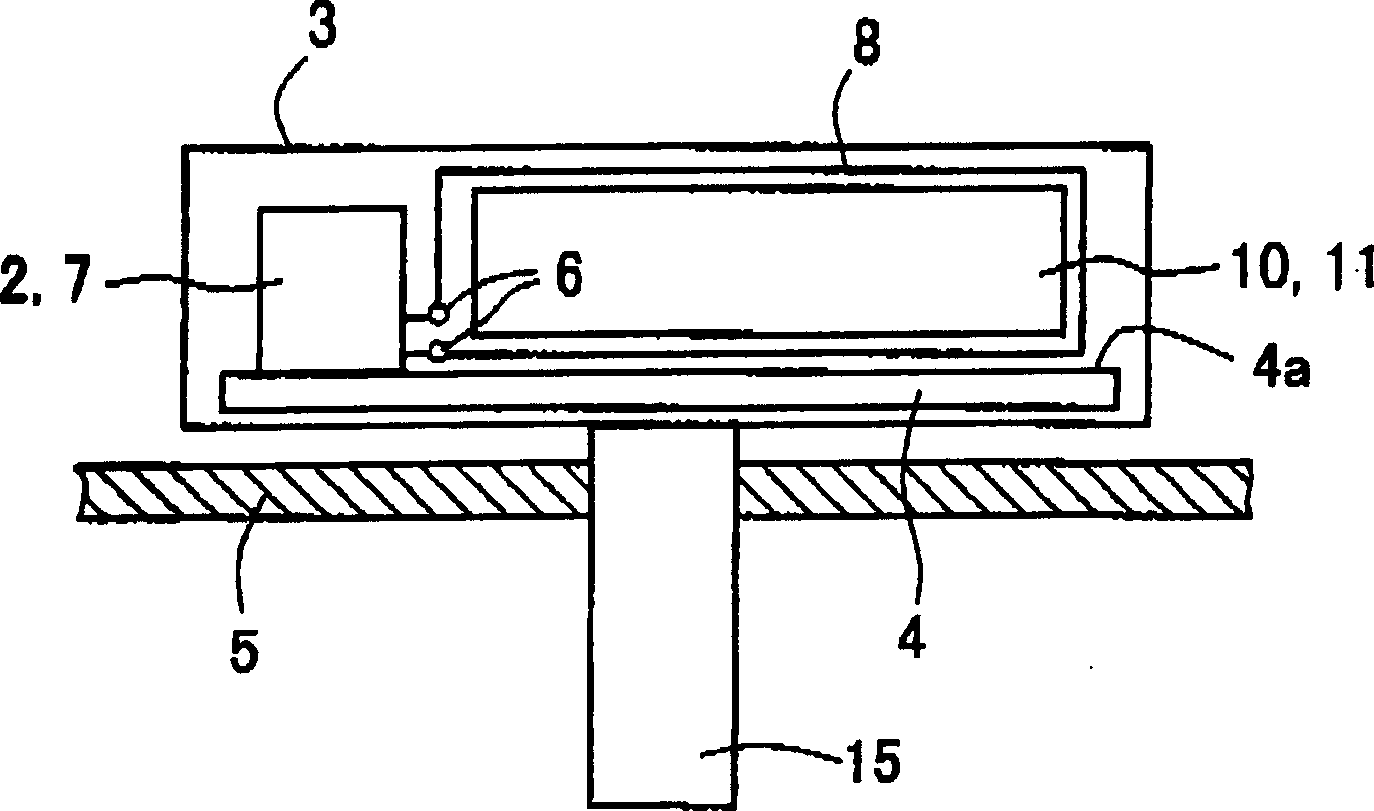

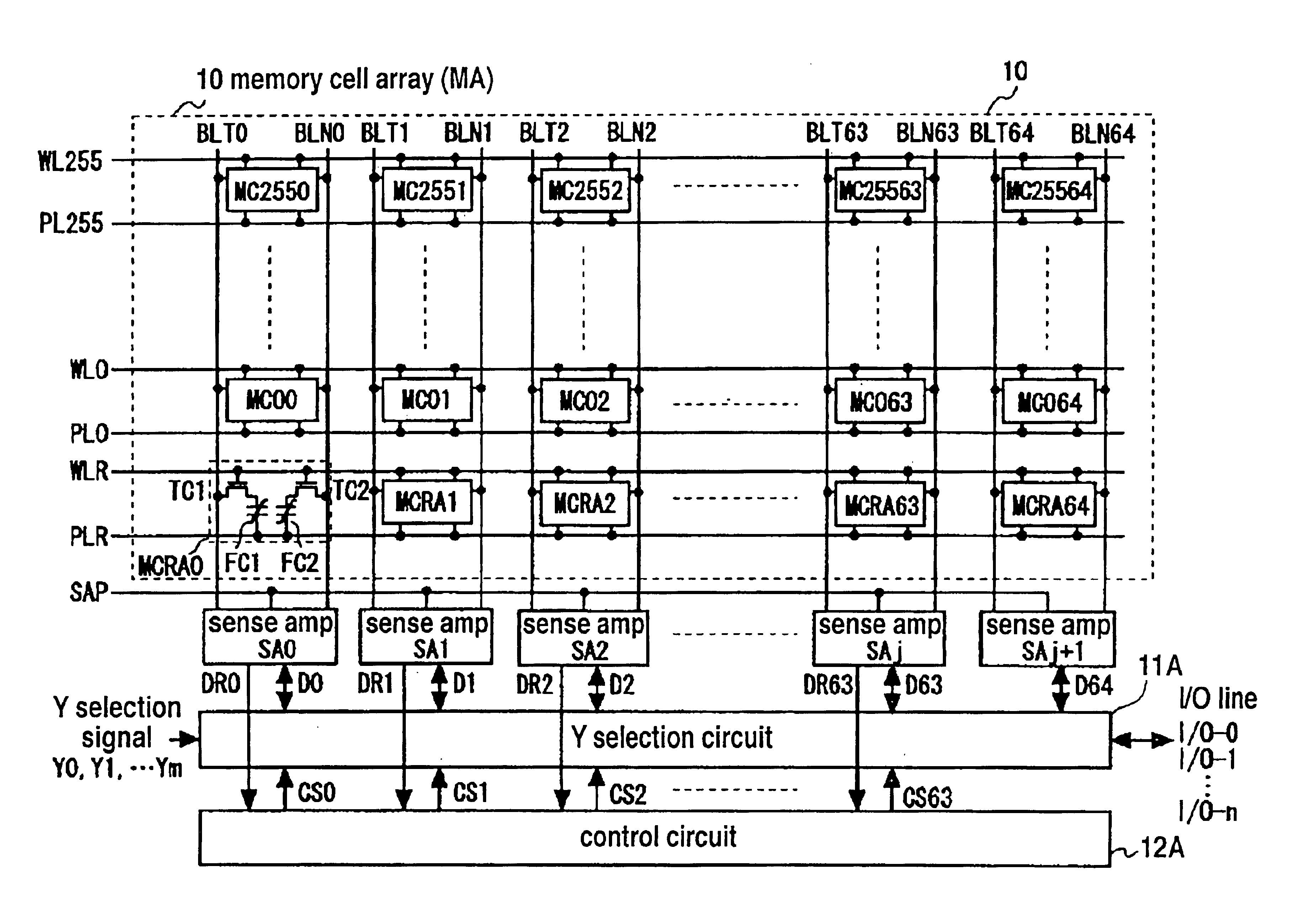

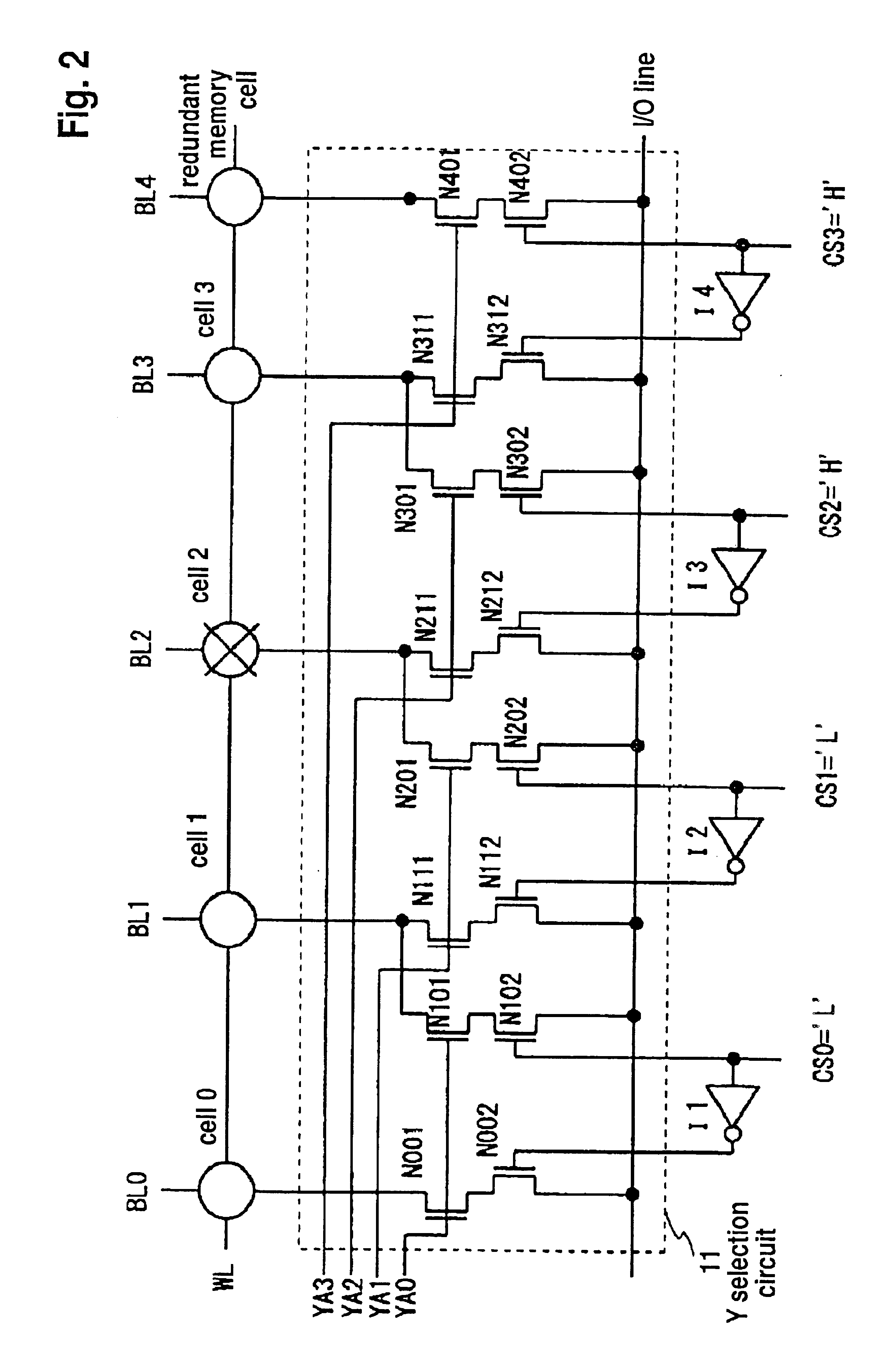

Semiconductor memory having a defective memory cell relieving circuit

InactiveUS6879529B2Minimized area overhead and access time overheadImprove chip yieldDigital storageComputer architectureAccess time

In a semiconductor memory incorporating therein a circuit for relieving a defective memory cell, a memory cell array constituted of a number of main memory cells MC00 to MCij is added with one column of redundant memory cells MC0j+1 to MCij+1 and one word line of substitution information storing memory cells MCRA0 to MCRAj+1. In only a first cycle after the power supply is turned on, the substitution information DR0 to DRj is read out from the substitution information storing memory cells by use of a writing / reading circuit associated with the main memory cells, and is transferred to and held in a control circuit. In a second and succeeding cycles, the control circuit generates Y selection circuit control signals CS0 to CSj on the basis of the substitution information held in the control circuit, and a Y selection circuit is controlled by the control signals CS0 to CSj so as to selectively connect the columns other than a defective column to an input / output line. Thus, a chip area overhead attributable to the installation of the defective memory cell relief circuit is minimized. In addition, an address comparing circuit for a defective memory cell substitution is no longer necessary, and an access time overhead attributable to the address substitution operation does not occur.

Owner:NEC CORP

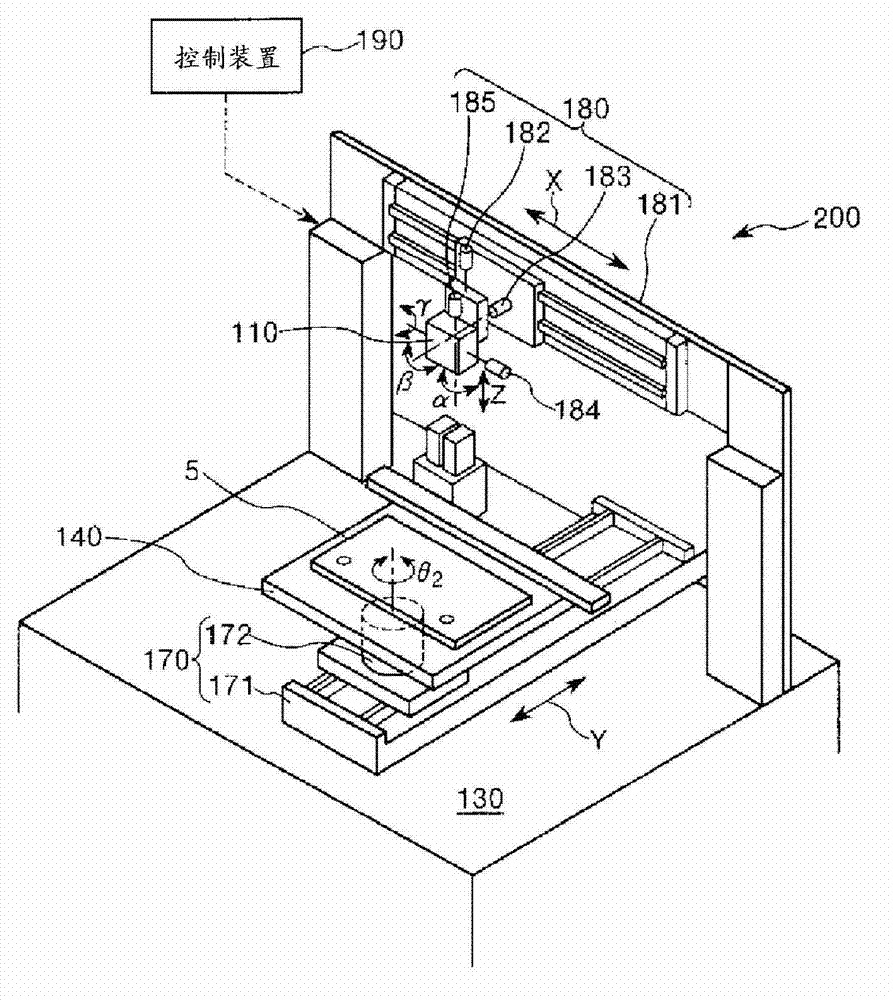

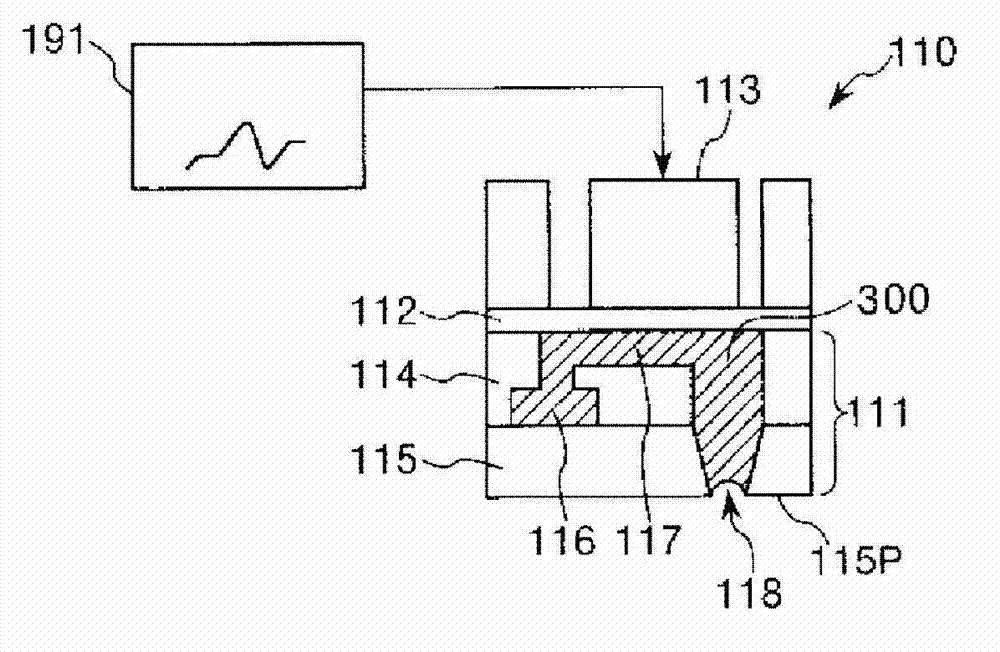

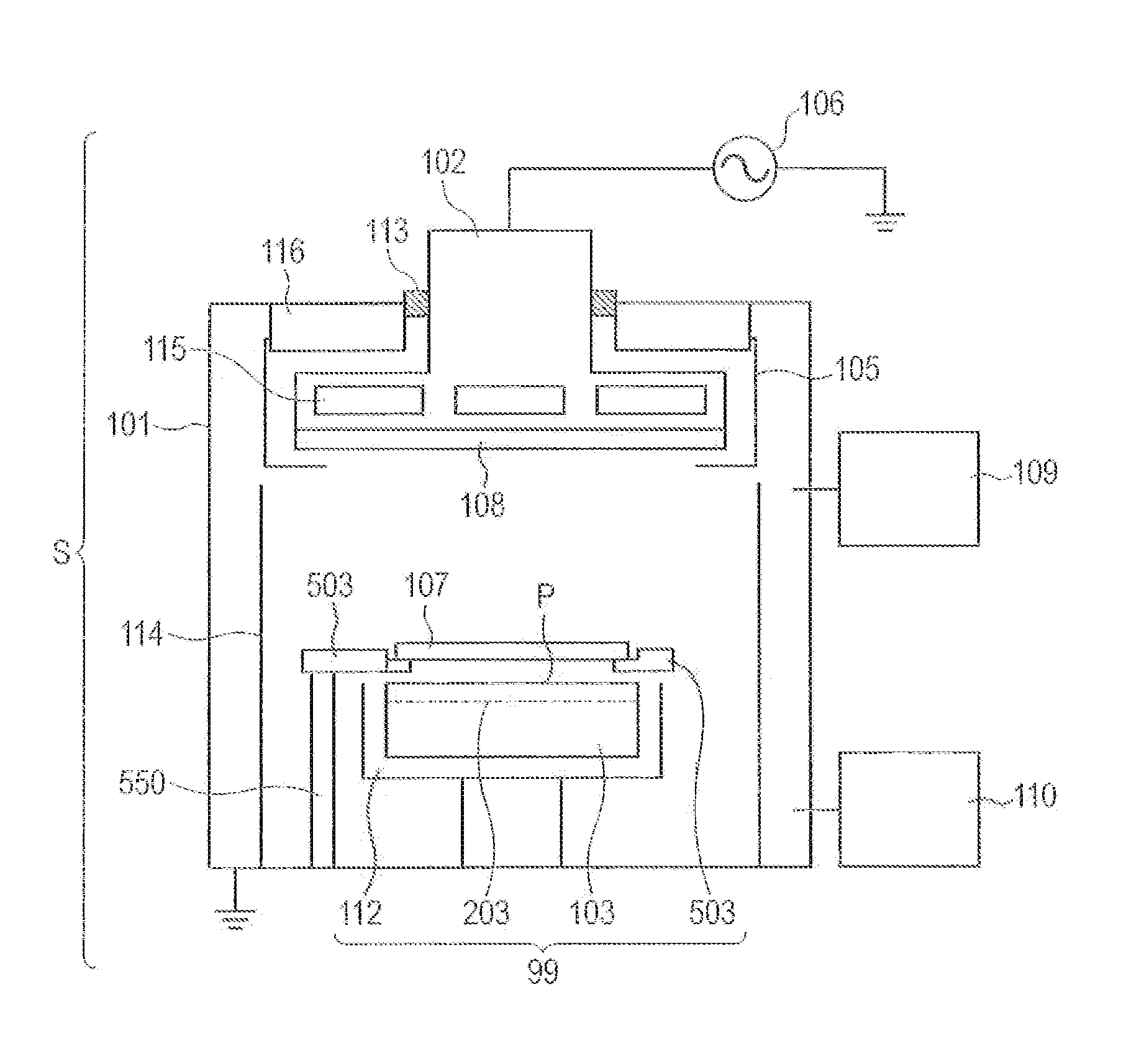

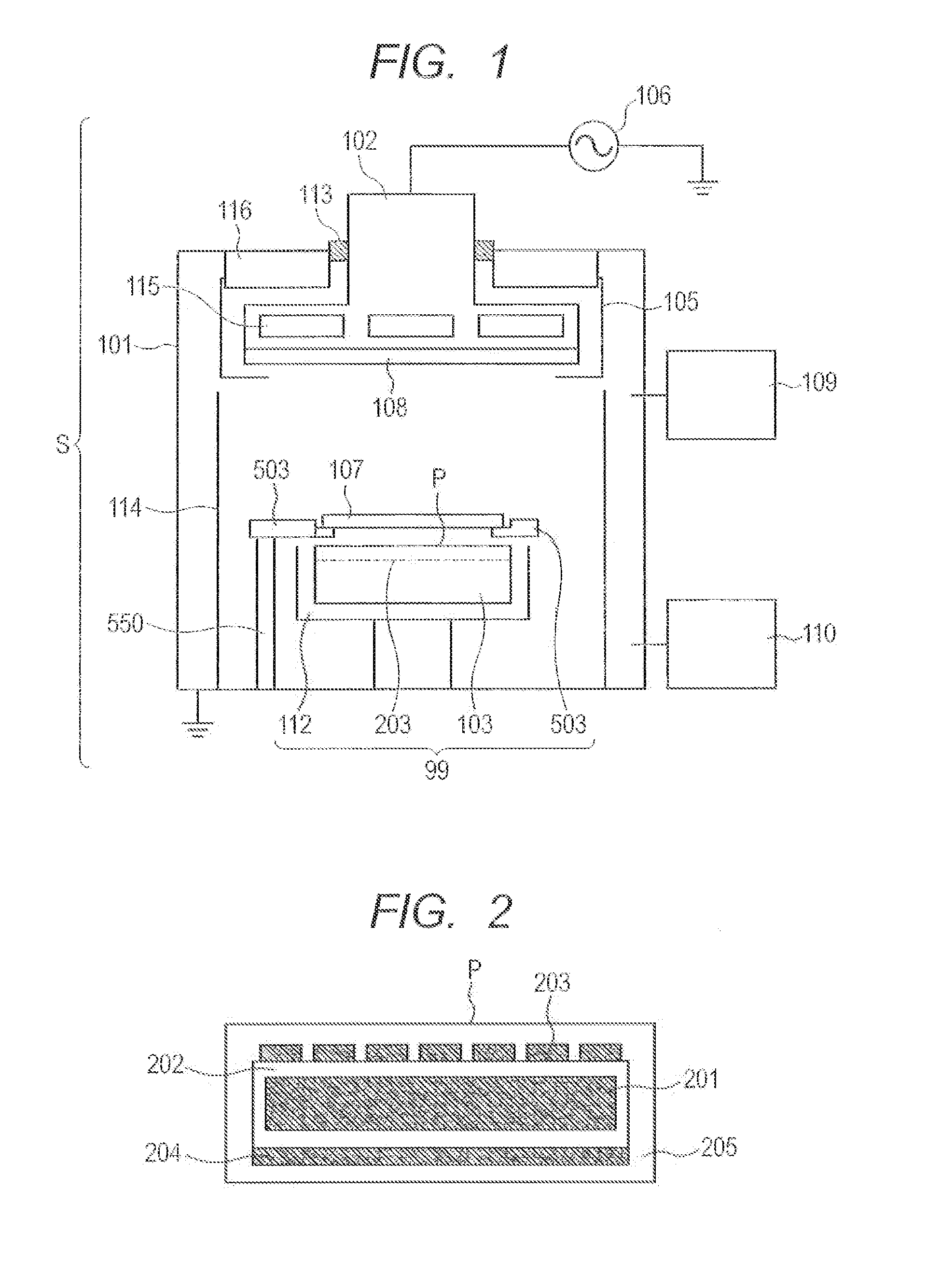

Film forming method, vacuum processing apparatus, semiconductor light emitting element manufacturing method, semiconductor light emitting element, and illuminating device

ActiveUS20140225154A1Small tiltConvenient lightingCellsPolycrystalline material growthSemiconductorMaterials science

In one embodiment of the present invention, a film forming method of epitaxially growing a semiconductor film having a wurtzite structure by sputtering on a substrate for epitaxial growth heated to a desired temperature by using a heater, comprises the following steps. First, the substrate is disposed on a substrate holder including the heater in such a way that the substrate is disposed away from the heater by a predetermined distance. Then, the epitaxial film of the semiconductor film having the wurtzite structure is formed on the substrate in the state where the substrate is disposed away from the heater by the predetermined distance.

Owner:CANON ANELVA CORP

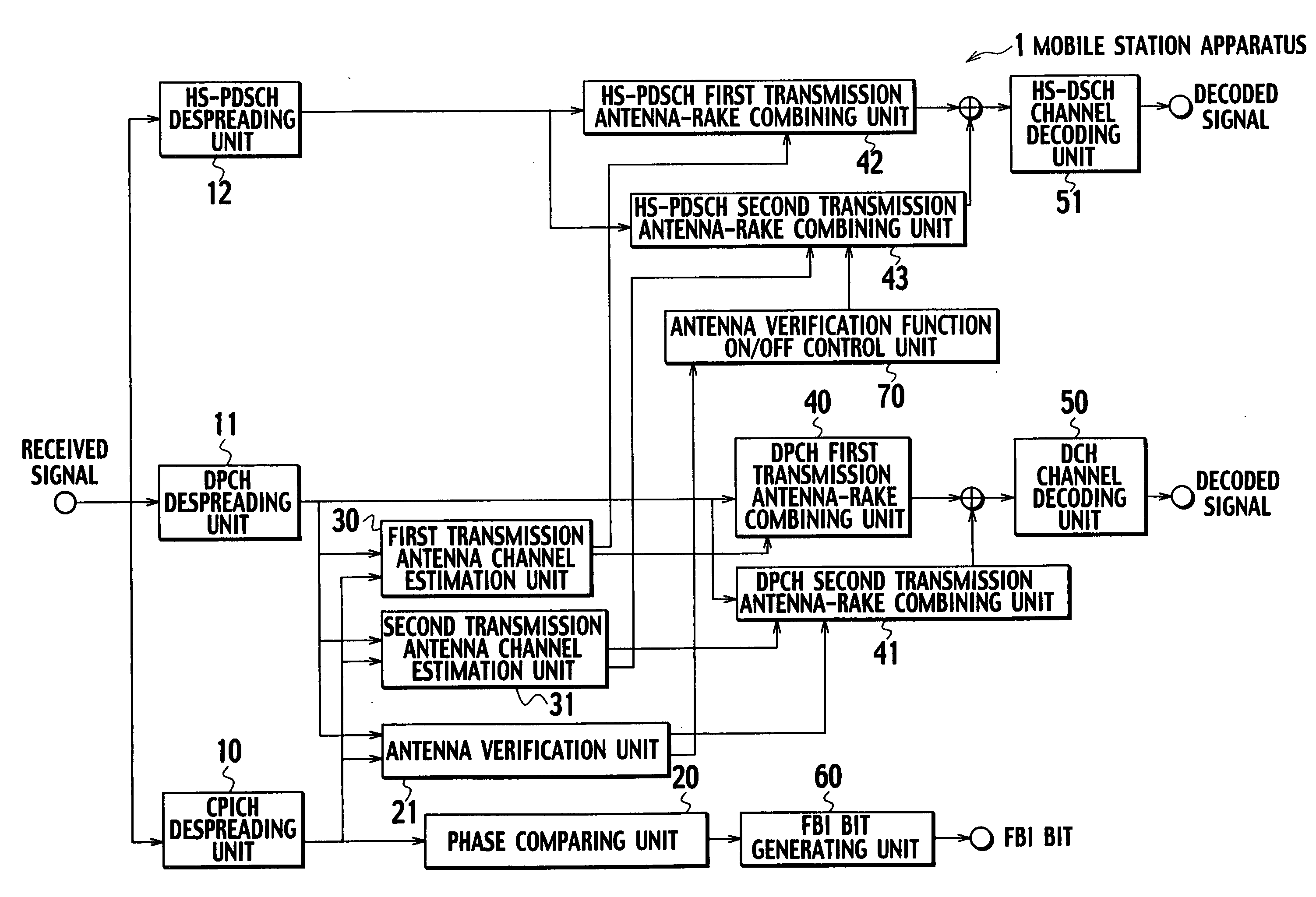

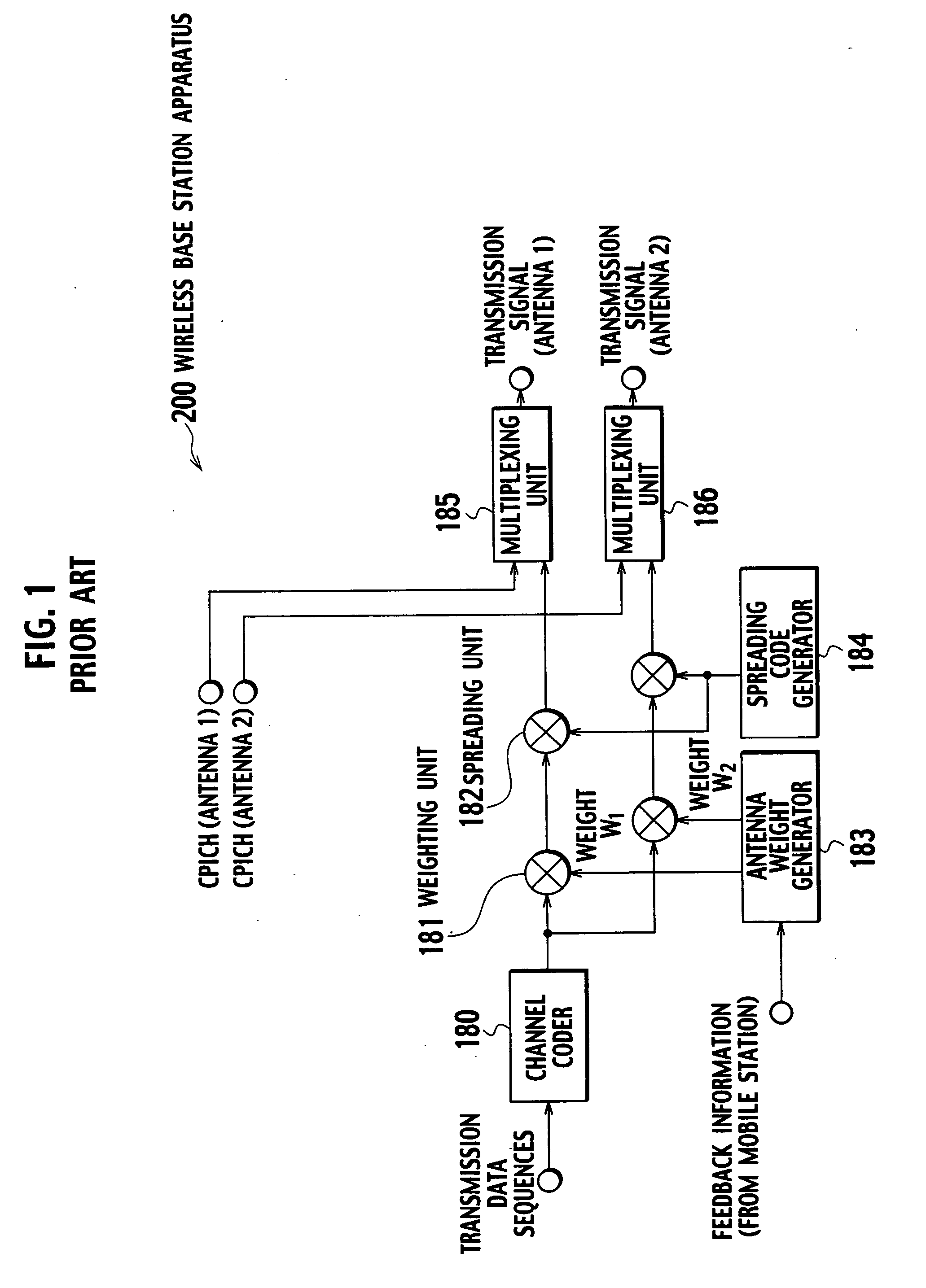

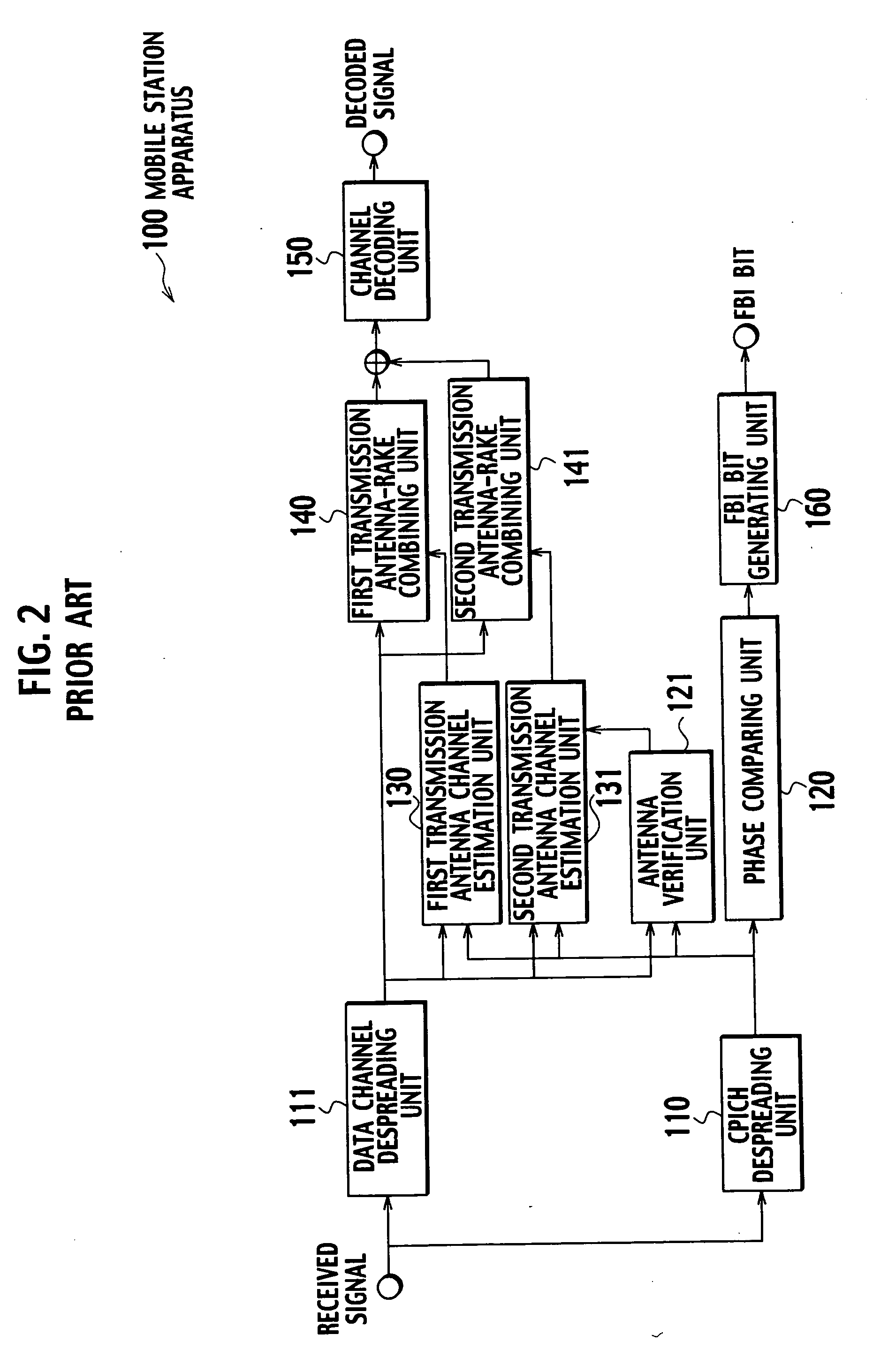

Mobile station apparatus and control method for the mobile station apparatus

InactiveUS20060176858A1Prevent characteristic deteriorationSpatial transmit diversityCode division multiplexClosed loopMobile station

A mobile station apparatus communicates with a wireless base station apparatus to which closed-loop transmission diversity control is applied, the closed-loop transmission diversity control controlling phases of signals transmitted from two antennas based upon feedback information notified by the mobile station apparatus and transmitting the signals. The mobile station apparatus includes a control unit which determines whether to reflect an estimated phase result of the signals transmitted from the two antennas or not, depending on a channel type of signals transmitted from the wireless base station apparatus.

Owner:NTT DOCOMO INC

Ceramic electronic parts and its making method

InactiveCN1379421APrevent immersionPrevent intrusionFixed capacitor electrodesResistor terminals/electrodesElectronic componentElectroplating

Owner:MURATA MFG CO LTD

Array substrate, manufacturing method thereof and display device

InactiveCN103928400AAvoid pollutionAvoid deterioration of TFT characteristicsSolid-state devicesSemiconductor/solid-state device manufacturingOptoelectronicsData lines

The invention relates to the technical field of displaying, and discloses a manufacturing method of an array substrate. The manufacturing method comprises the steps that a pattern comprising a grid electrode, a grid line, a common electrode line and a grid insulating layer is formed on a substrate body; a pattern comprising a data line, a source electrode, a drain electrode and an active layer is formed; a pattern comprising an insulating spacer layer is formed on the pattern comprising the source electrode, the drain electrode and the active layer; a pattern comprising a first transparent electrode is formed on the insulating spacer layer; a pattern comprising a passivation layer is formed on the first transparent electrode; a pattern comprising a second transparent electrode is formed on the passivation layer. The invention further discloses the array substrate and a display device. The pollution to a TFT channel due to the ITO technology can be effectively avoided.

Owner:BOE TECH GRP CO LTD +1

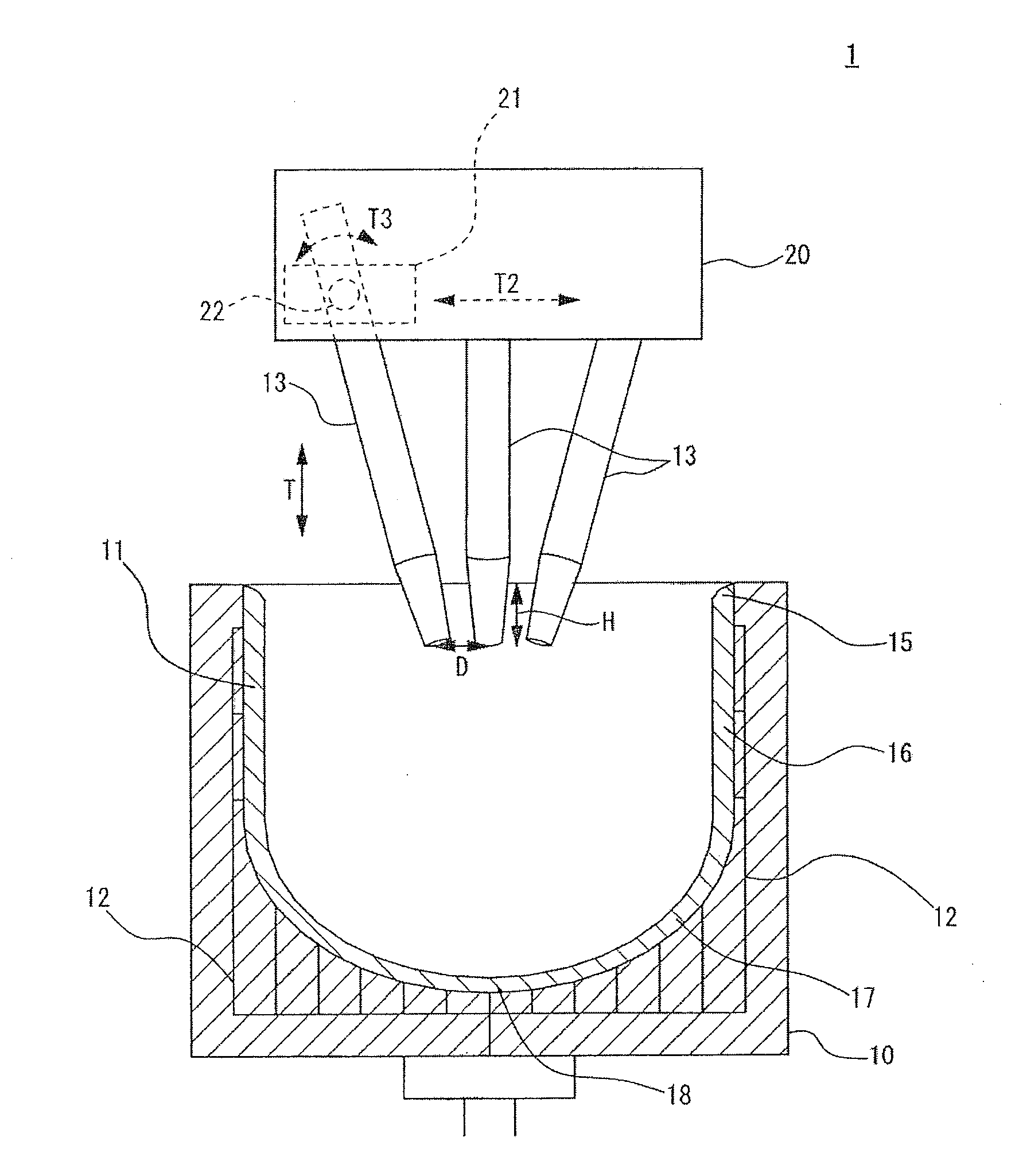

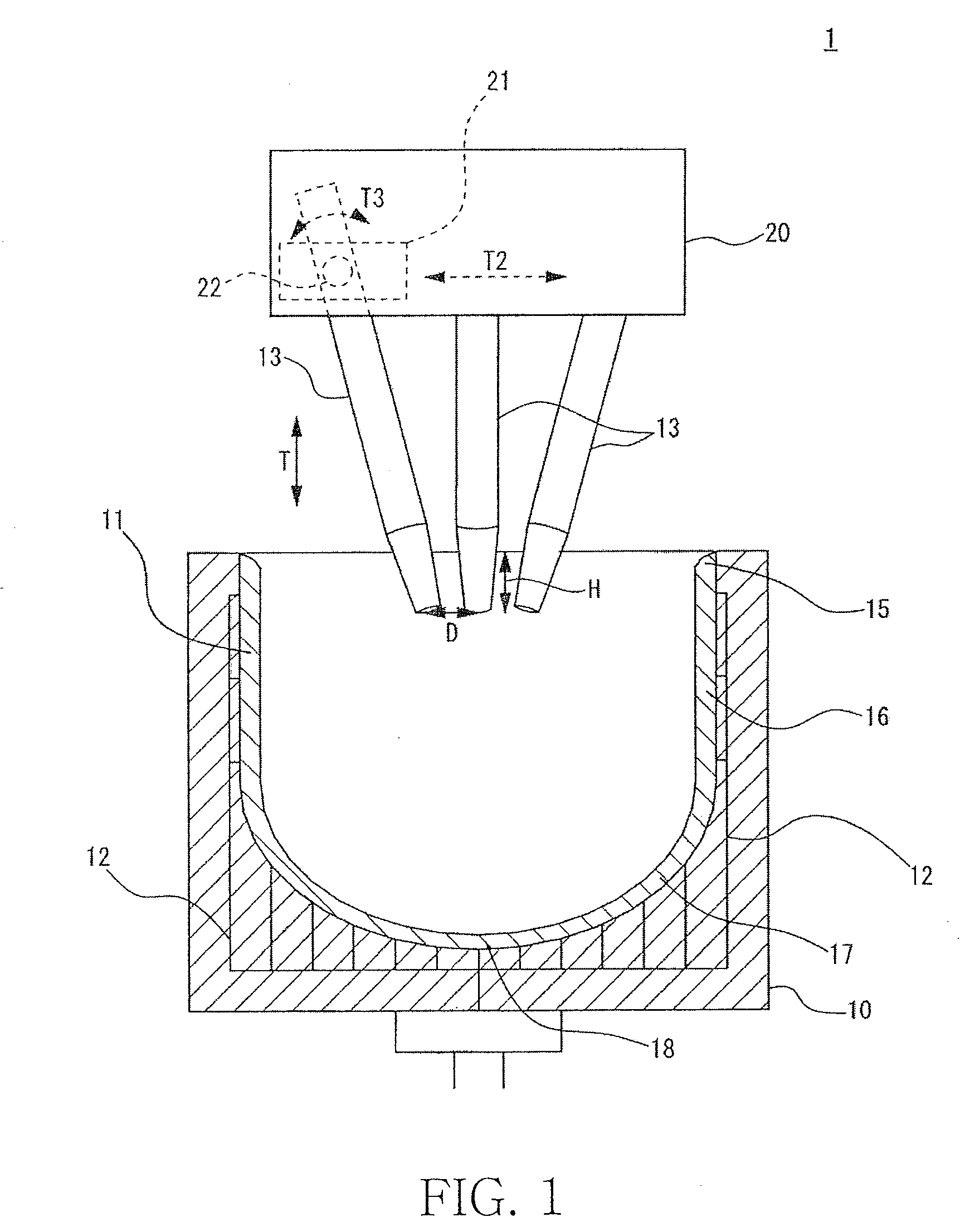

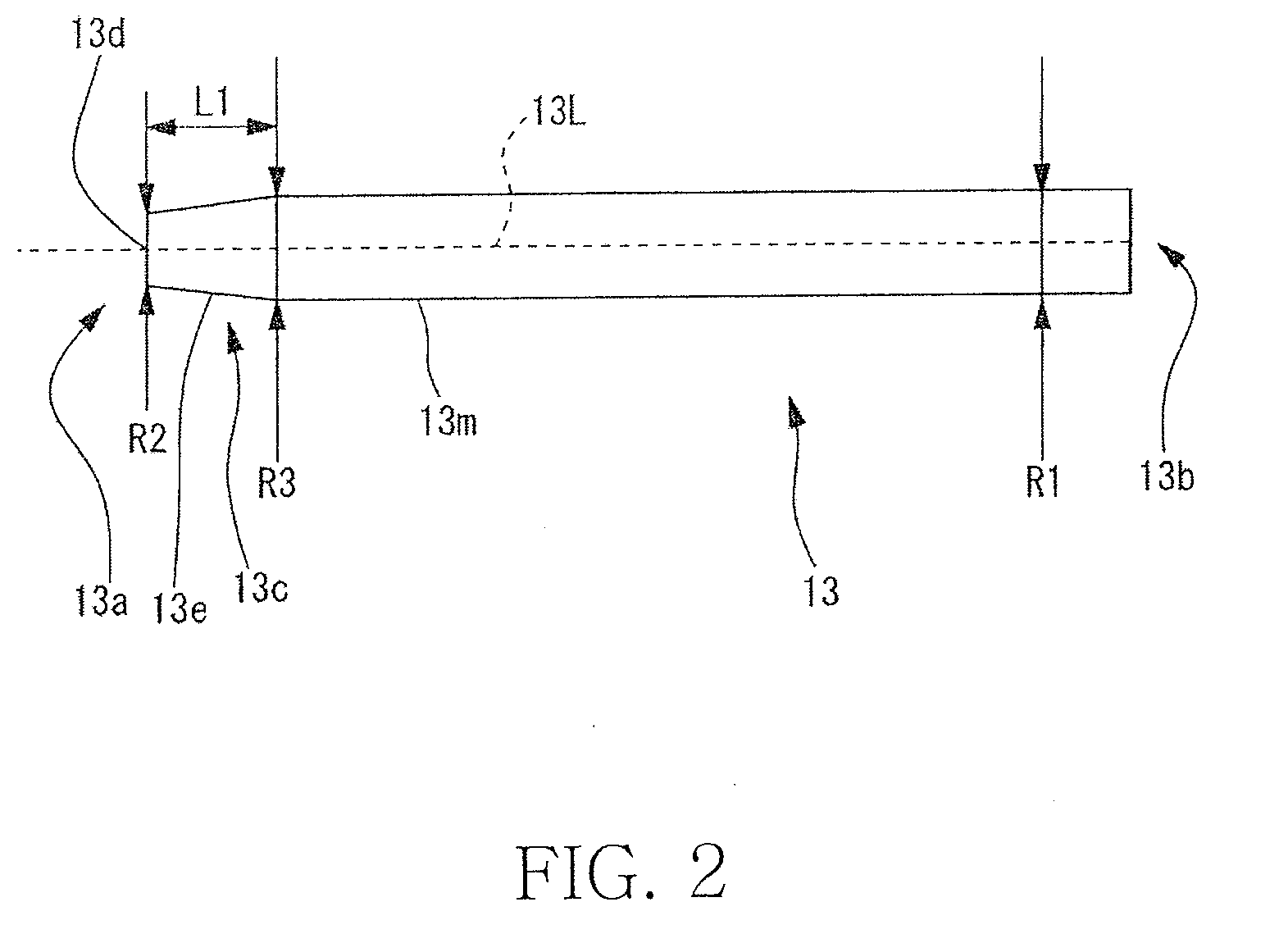

Vitreous silica crucible manufacturing apparatus

ActiveUS20100170298A1PreventFacilitate arc generationElectric discharge heatingArc welding apparatusCrucibleRaw material

A vitreous silica crucible manufacturing apparatus includes a plurality of carbon electrodes configured to heat and melt raw material powder by arc discharge, and a value of a ratio R2 / R1 of a diameter R2 of a front end of each of the carbon electrodes to a diameter R1 of a base end is set in a range of 0.6 to 0.8. Each carbon electrode has a diameter reduction portion formed at a front end position and reduced in diameter from a diameter R3 of a base end side to the diameter R2 of the front end. When a length of the diameter reduction portion is L1, the diameter of the front end is R2, the diameter of the base end is R1, an angle between the axis lines of the carbon electrodes is θ1, and X=(R1−R2) / 2, a value of L1−(X / tan(θ1 / 2)) is set in a range of 50 to 150 mm.

Owner:SUMCO CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com