Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

51results about How to "High speed action" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

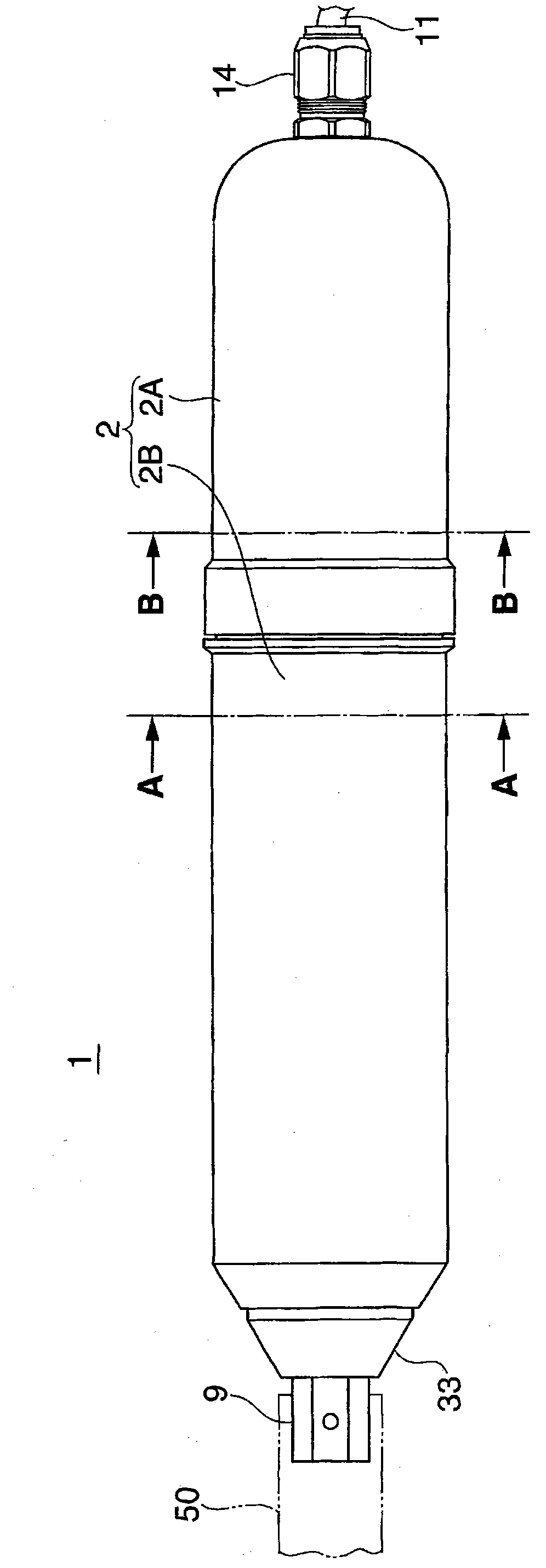

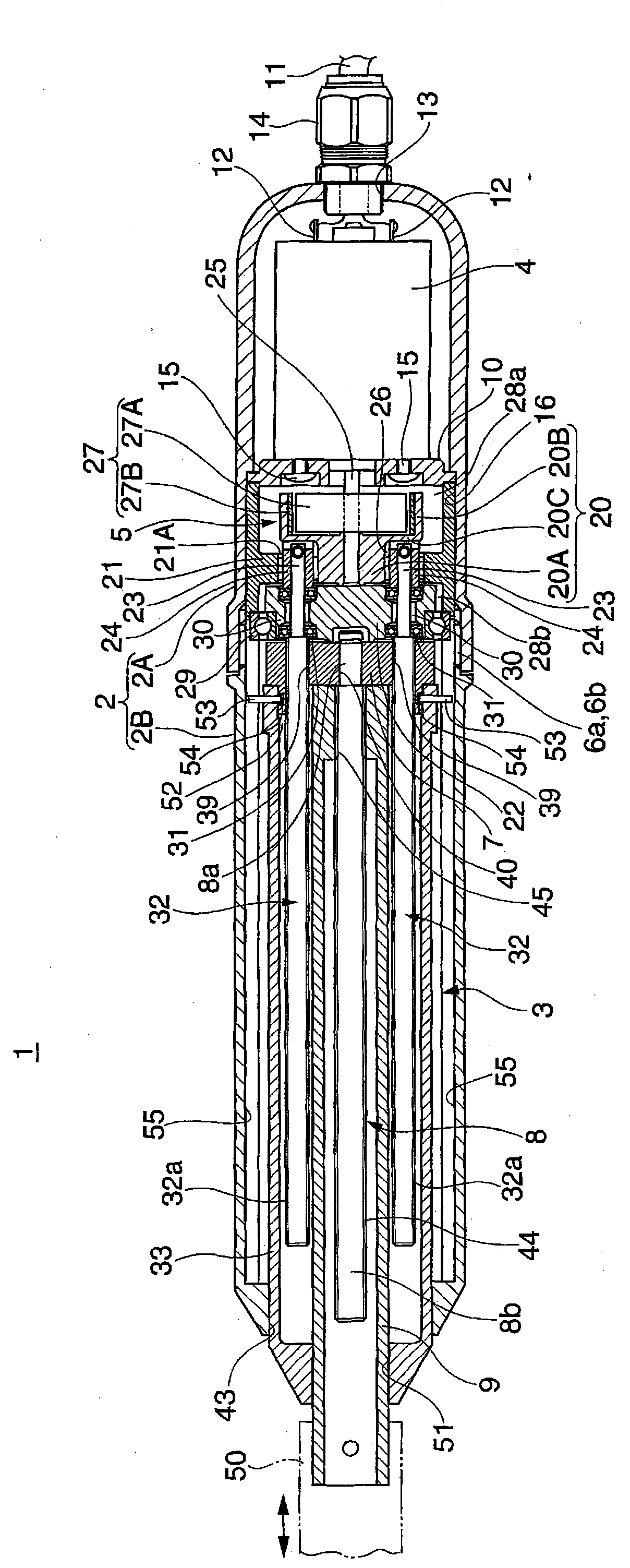

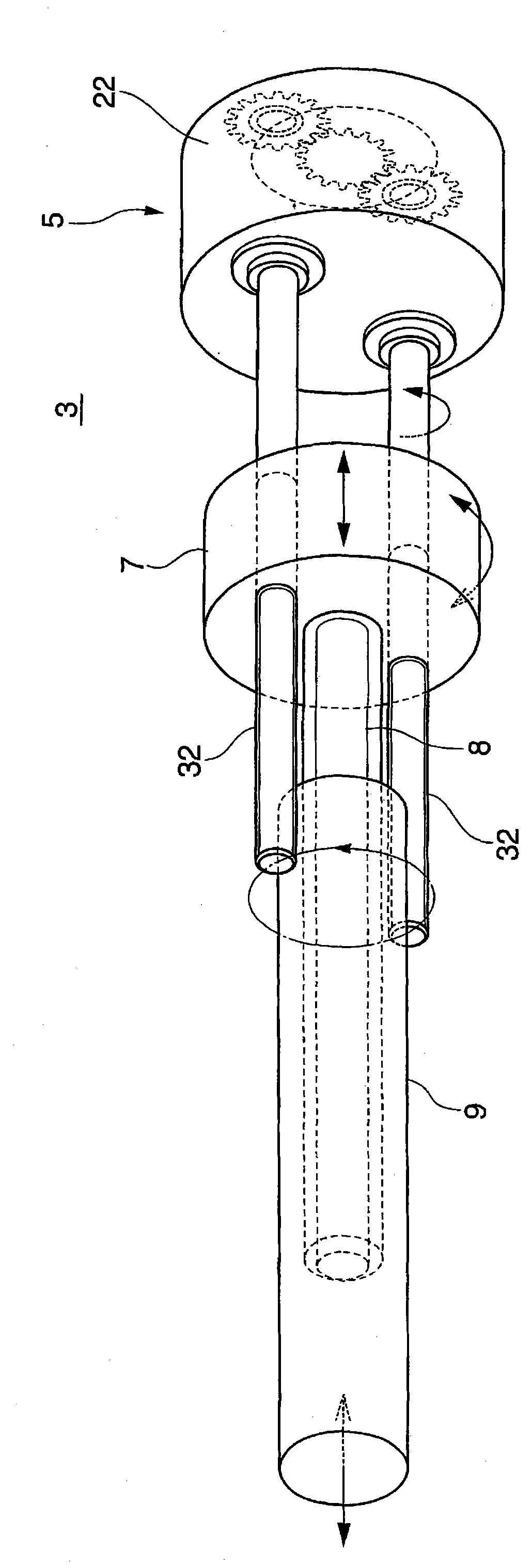

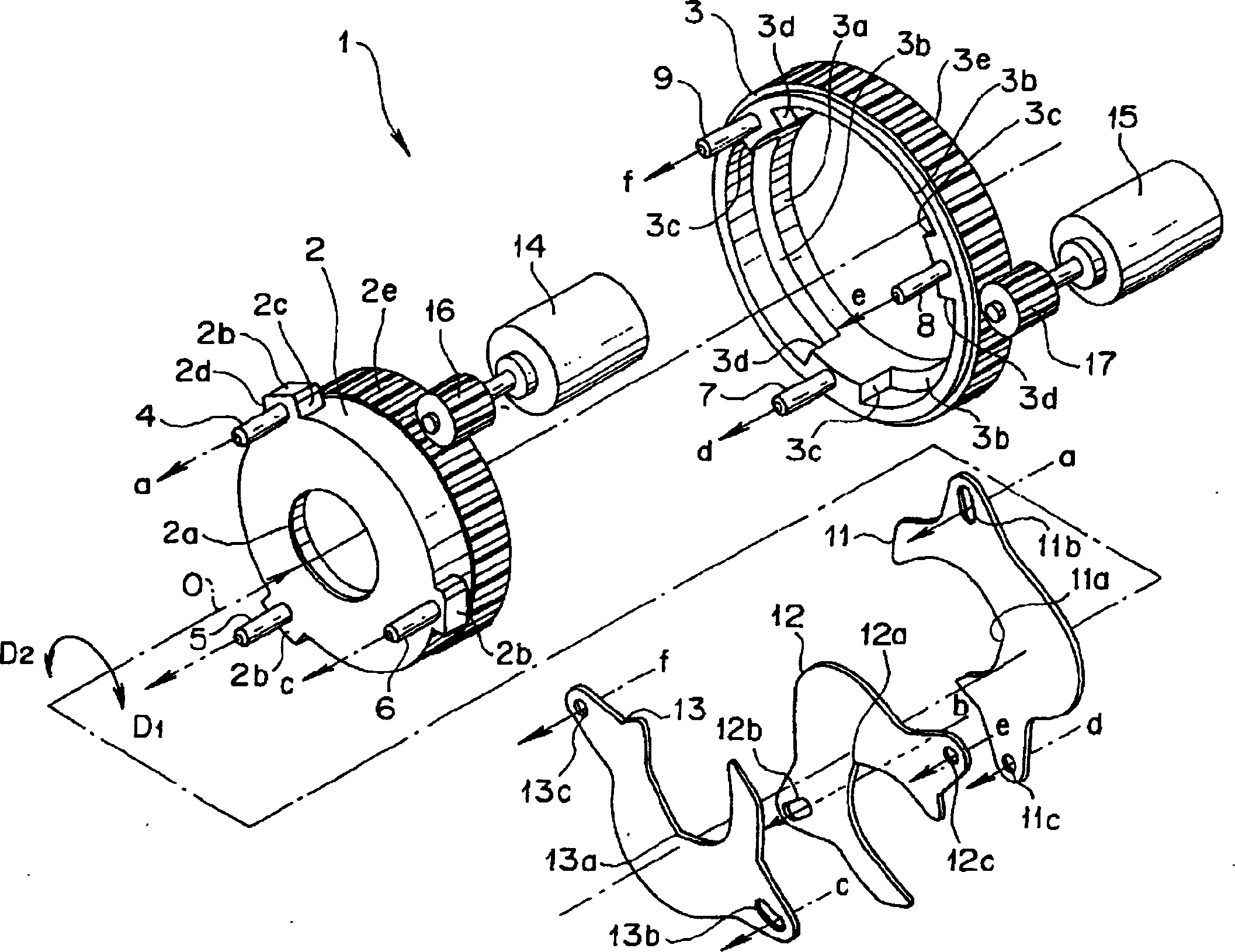

Rotary-linear movement change mechanism and actuator

The invention provides a rotary-linear movement change mechanism and an actuator, capable of simultaneously accomplishing two contradictious technical objects of minaturization and large action amount. The rotary-linear movement change mechanism (3) comprises a planet gear mechanism (5), first, second screw shafts (8,32), a transmission unit (7), a main shaft (9) and a sleeve (33). The planet gear mechanism (5) drives a sun gear (20) by an electric machine (4) to make a planet gear (24) rotate and revolve. The first screw shaft (8) is integrated with the transmission unit (7), thus the main shaft (9) linearly moves. The second screw shaft (32) is integrated with a planet gear shaft (23). The transmission unit (7) rotates together with the revolution of the planet gear (24) and linearly moves along the second screw shaft (32). A cover (2B) makes the sleeve not rotate and freely integrated with the transmission unit (7) to perform the linear movement.

Owner:YAMATAKE HONEYWELL CO LTD

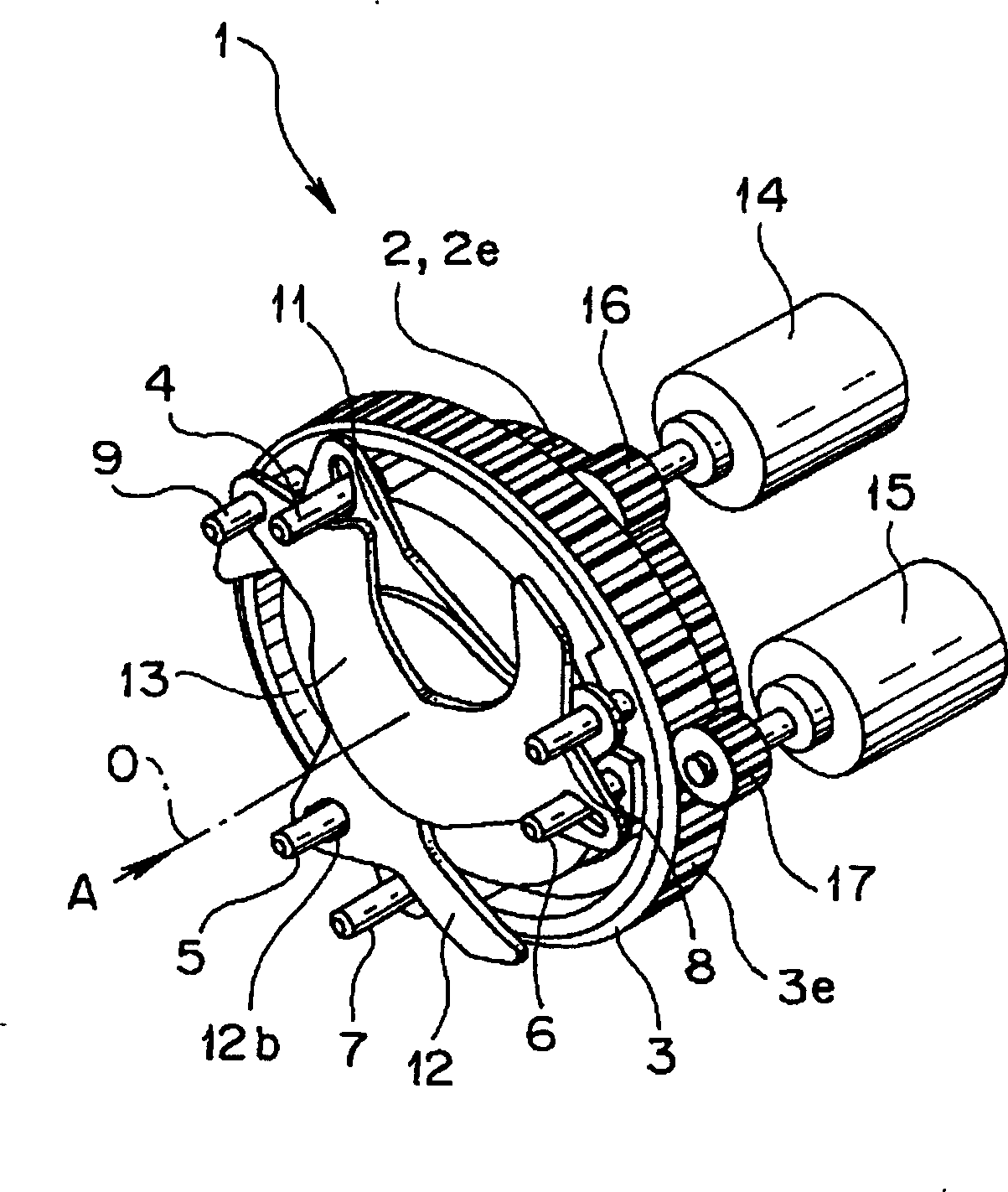

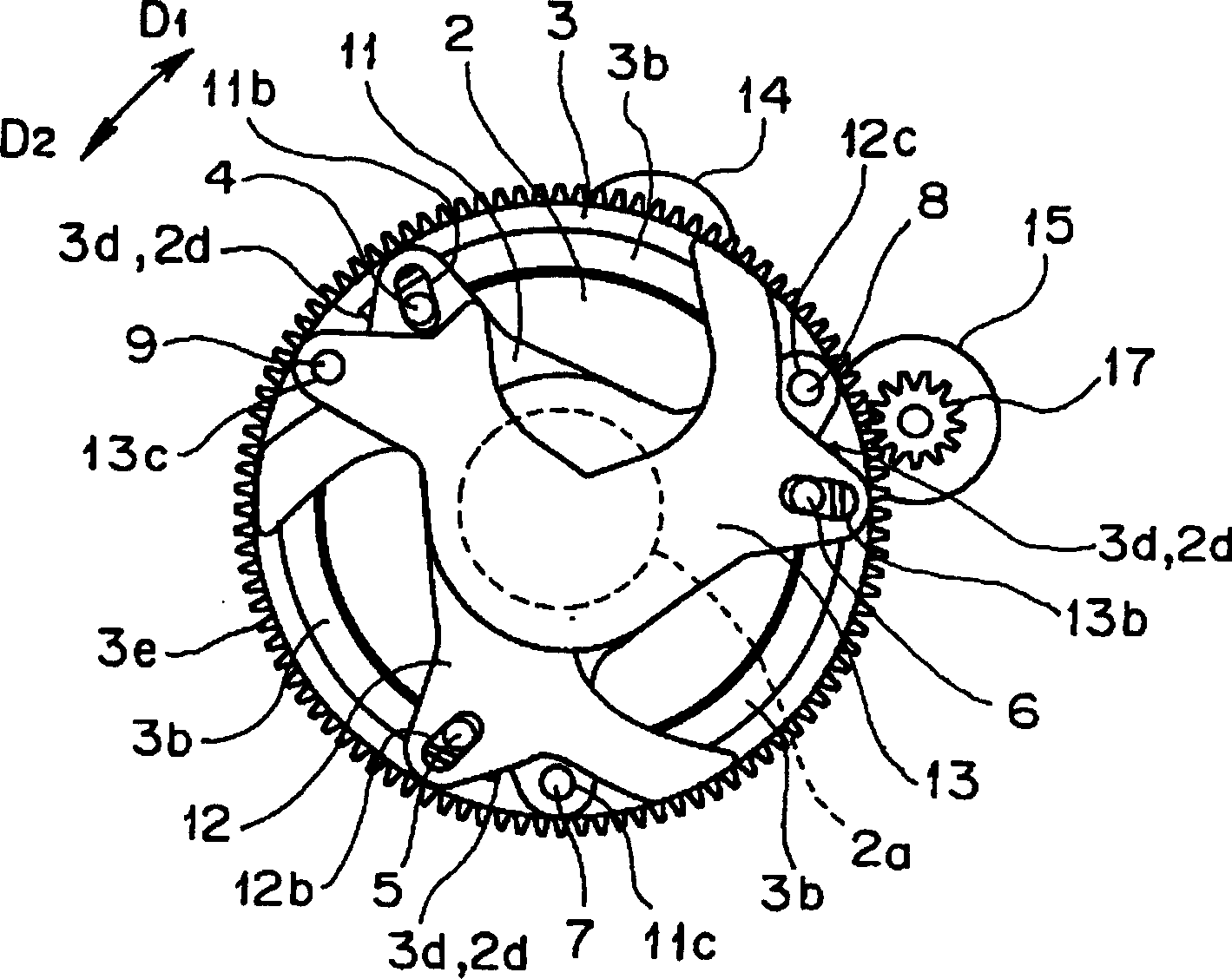

Lens optical shutter means

A lens shutter system has an inner drive ring which is rotated by a drive motor and an outer drive ring which is rotated by the drive motor. A plurality of shutter blades of the lens shutter system are driven through drive pins of the inner drive ring and drive pins of the outer drive ring so as to be opened and closed or are rotatably supported by the respective pins of the rings. Upon shutter opening, only the inner drive ring is driven clockwise to open the shutter blades. Upon shutter closing, only the outer drive ring is similarly driven clockwise to close the shutter blades. As mentioned above, upon switching between shutter opening mode and shutter closing mode, the direction of rotation of the inner and outer drive rings is not changed. Thus, the shutter operation can be performed at high speed.

Owner:OLYMPUS CORP

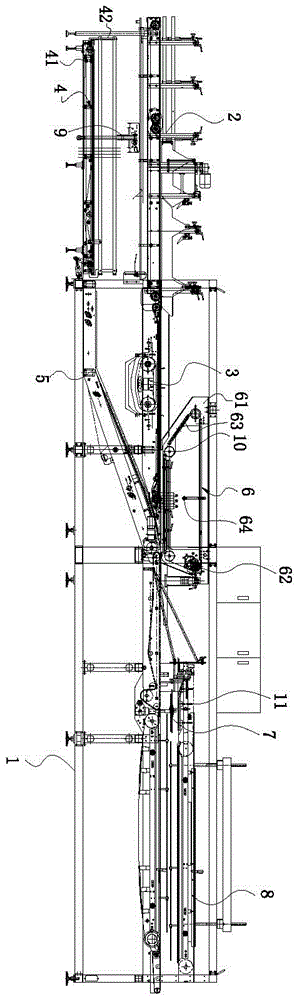

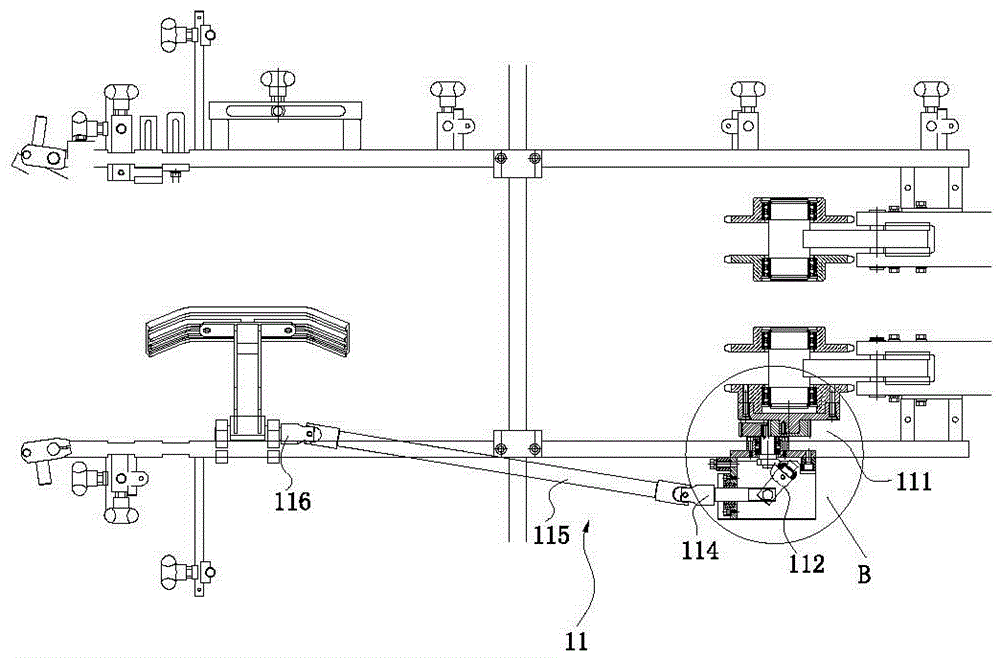

Paper packaging machine

The invention discloses a paper packaging machine comprising a rack, wherein a bottle conveying device, a bottle allocating device, a paperboard bin, a paper feeding device, a bottle driving device, a side face folding device and a press box forming device are arranged on the rack; a pneumatic constant pressure paper pushing device is installed at the paperboard bin, the pneumatic constant pressure paper pushing device comprises a paper pushing upright column, a paper pushing frame, a paper pushing transmission mechanism, a paper pushing slide block, a stop lever and a locking cylinder component; a bottle clamping prevention device is arranged on a bottle moving frame, and the bottle clamping prevention device comprises a cylinder, a sliding seat, a slide rail and a chain guide block; a mechanical page taking device is arranged between the bottle driving device and the press box forming device; and the mechanical page taking device comprises a transmission mechanism, a connecting plate, a driving shaft, a front connecting rod, a connecting rod, a back connecting rod, a page taking frame and a page taking plate. By adoption of the structure of the paper packaging machine disclosed by the invention, constant thrust can be provided for the paperboard in the paperboard bin so as to ensure the paper feeding device to stably convey the paperboard. Bottle explosion or overload damage of parts caused by bottle clamping in a bottle moving process can be avoided. High-speed page taking action can be realized.

Owner:广州市万世德智能装备科技有限公司

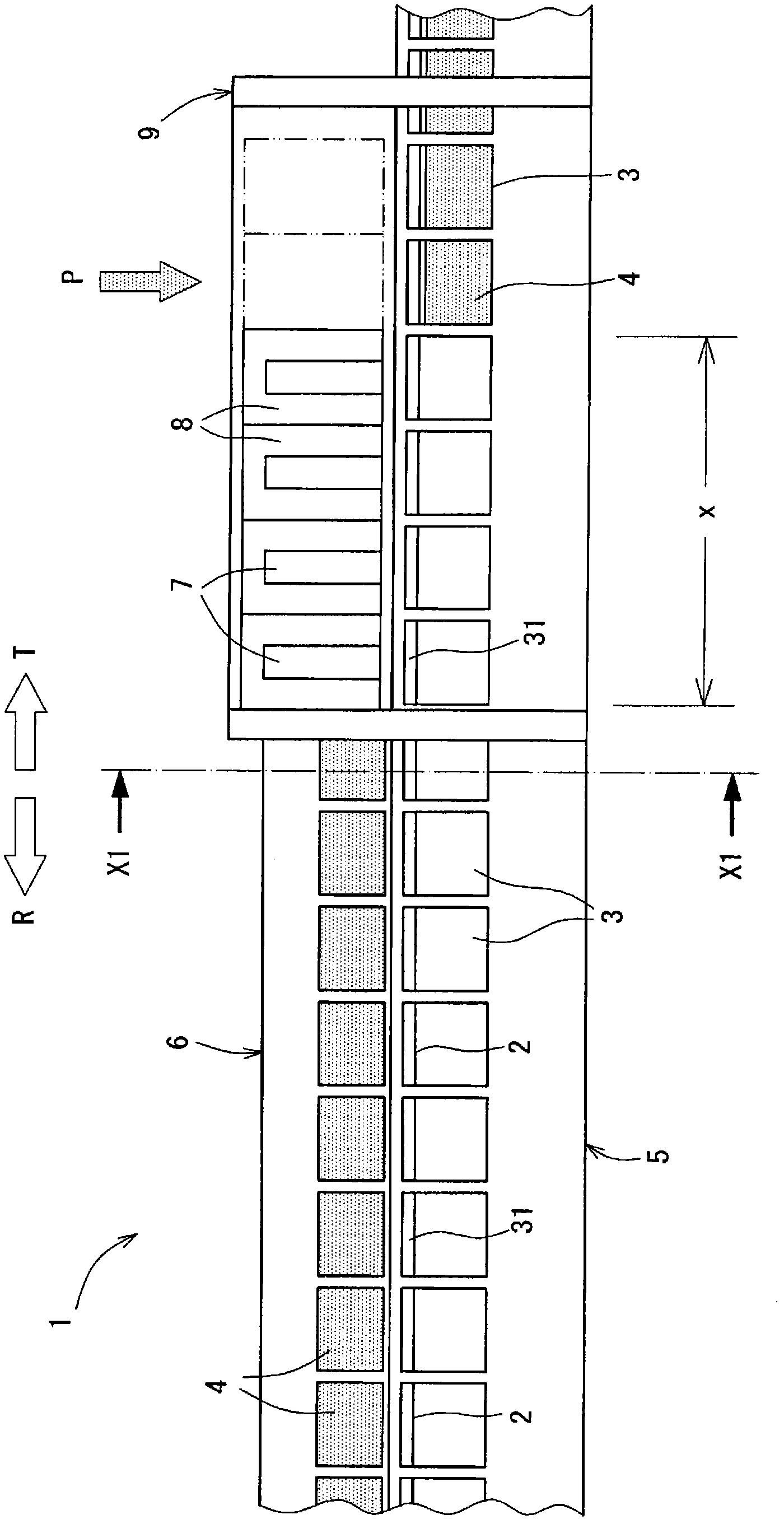

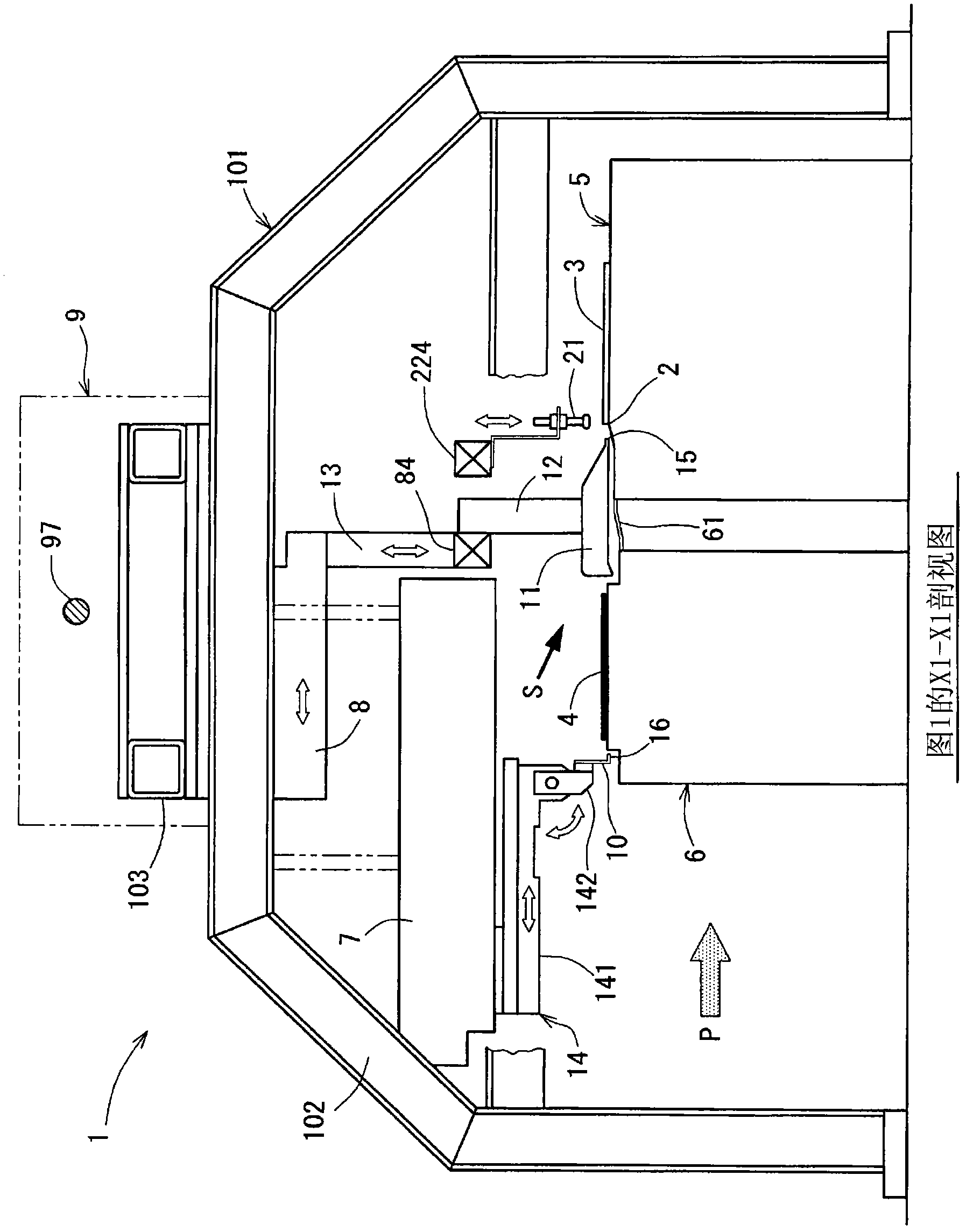

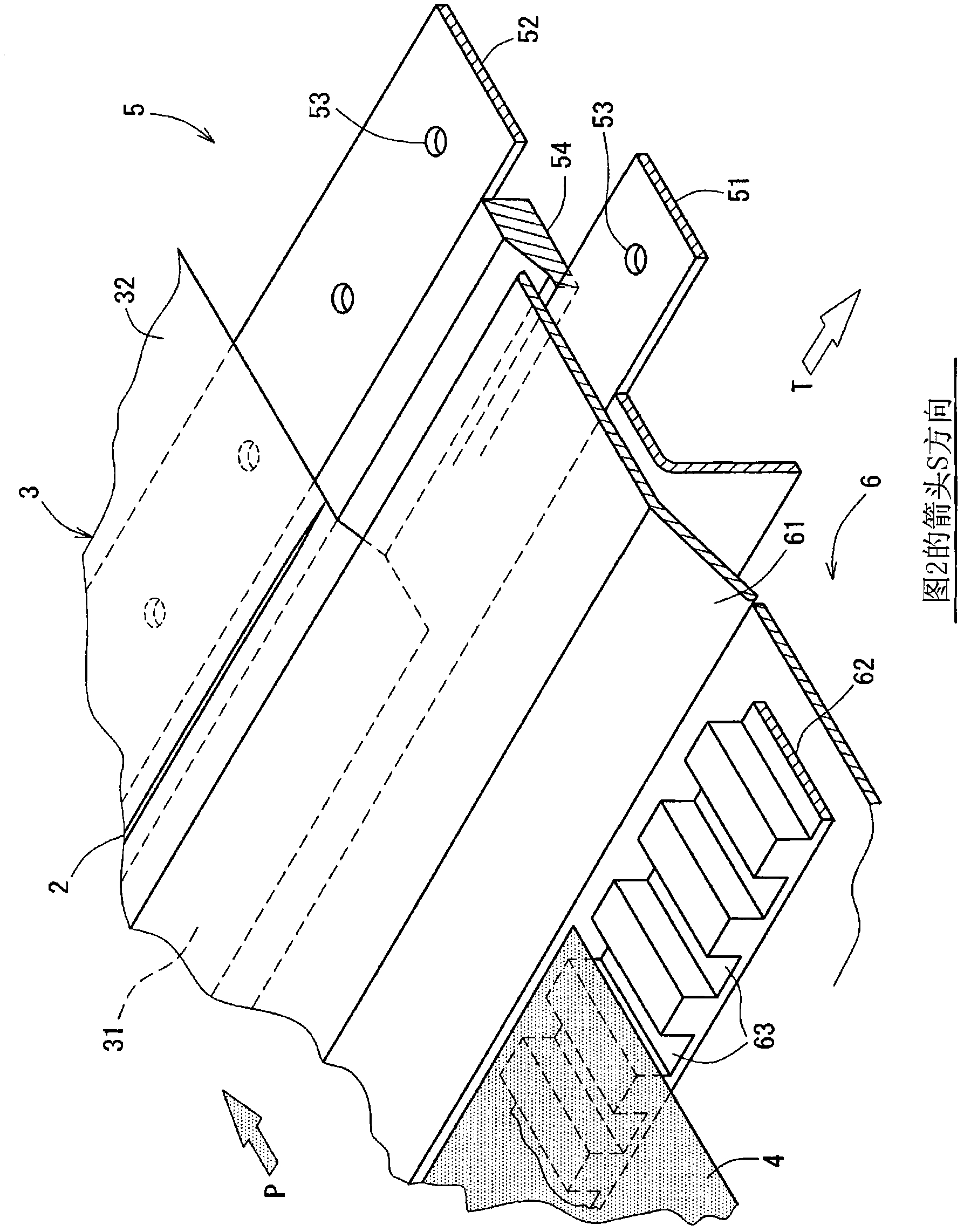

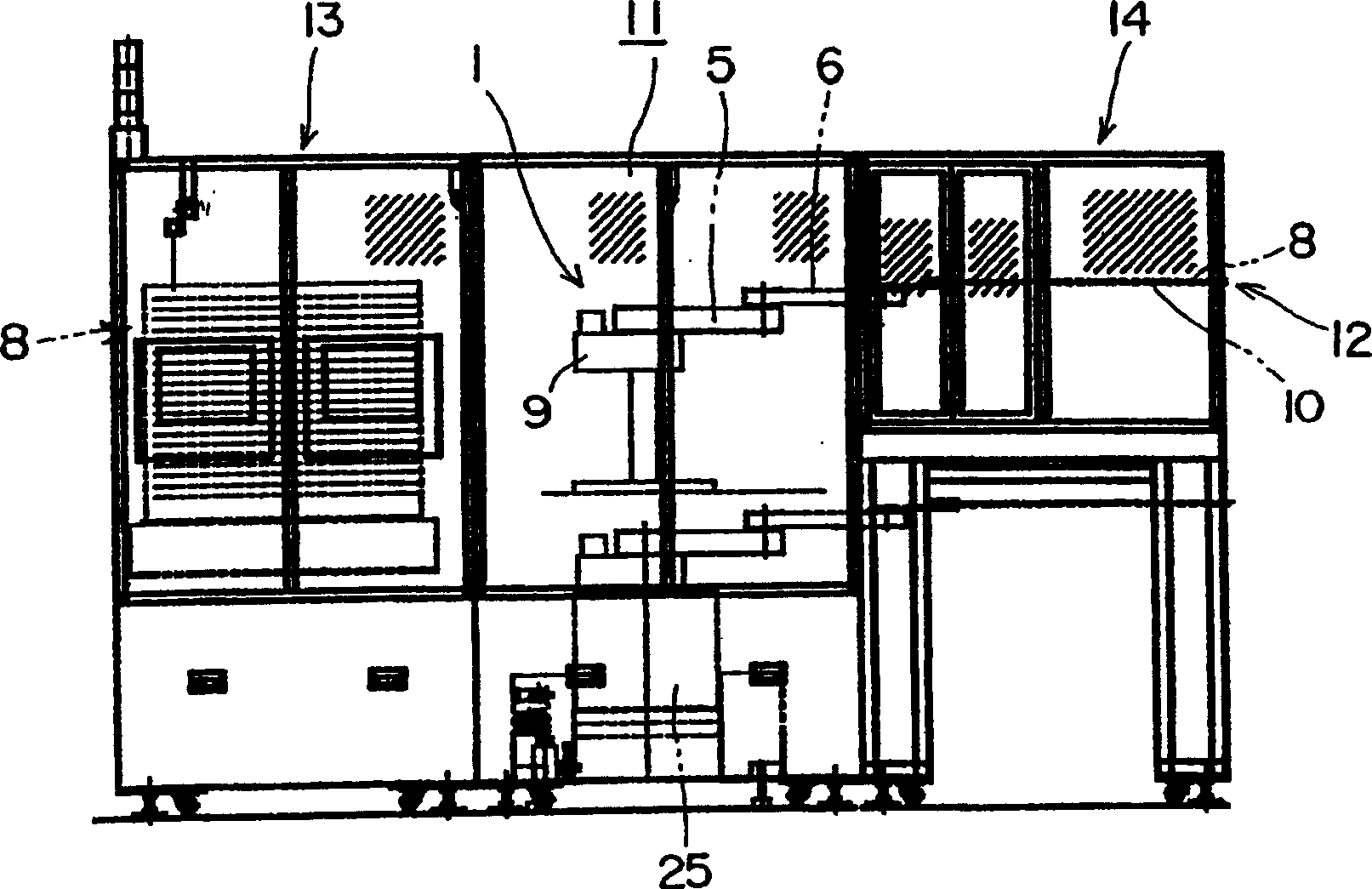

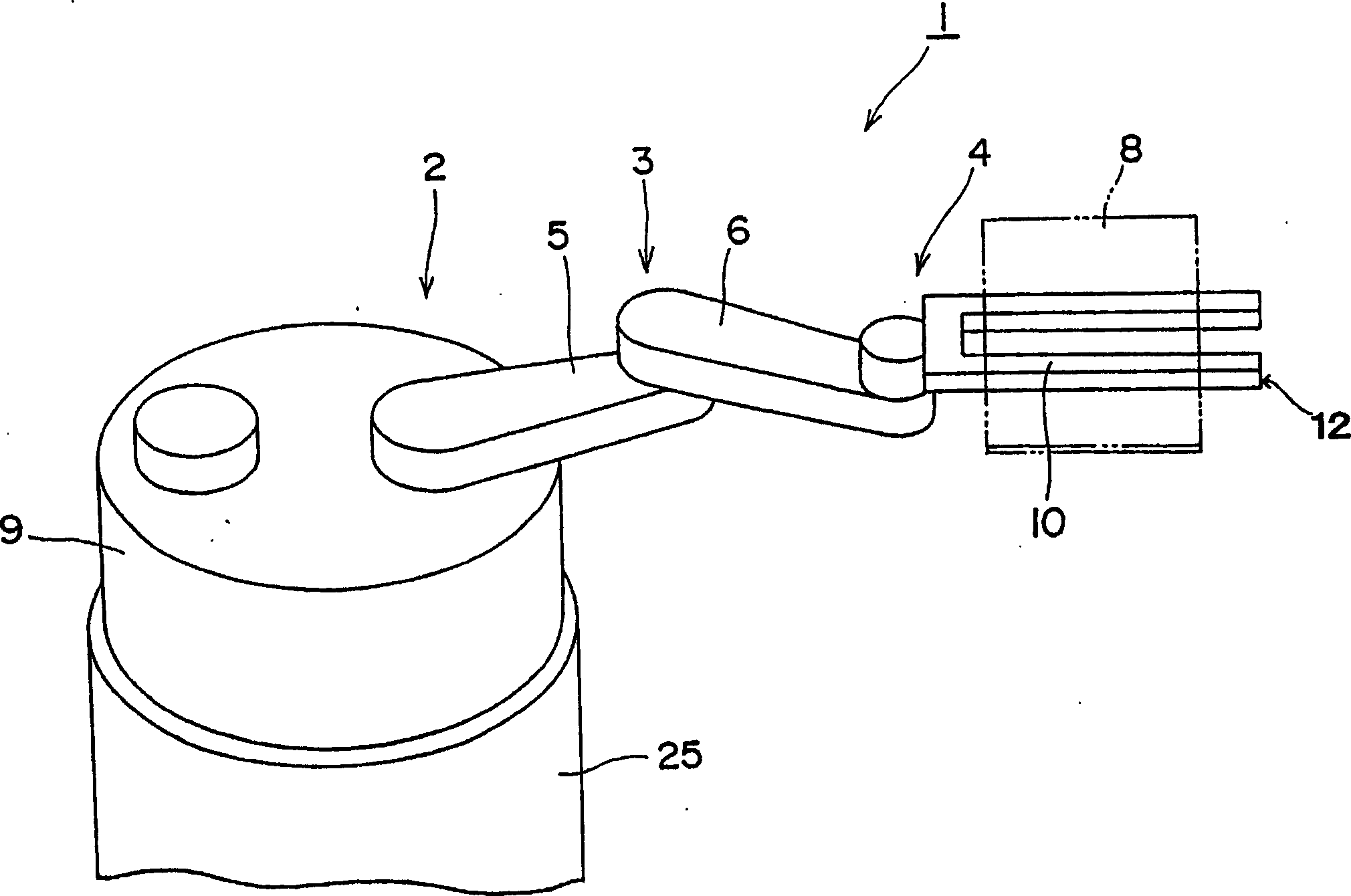

Reciprocating insertion device

InactiveCN102083692AInsert smoothlyIncrease the number ofPaper article packagingIndividual articlesEngineeringSynchronism

The present invention provides a reciprocating insertion device capable of inserting contents into a large number of bag bodies in a reduced time. The reciprocating insertion device (1), in a process in which bag bodies (3) having openings (2) are conveyed in a conveying direction (T), inserts contents (4) into the openings (2). The reciprocating insertion device (1) is provided with a moving means (6) for moving, in synchronism with the speed at which the bag bodies (3) are conveyed, the contents (4) in an attitude in which the contents (4) face the bag bodies (3), an in-and-out means (8) for advancing and retracting guide horns relative to the bag bodies (3), the guide horns guiding the contents (4) to the openings (2) of the bag bodies (3), an advancing and retracting means (7) for advancing and retracting pushers relative to the bag bodies (3), the pushers pushing out the contents (4) from the moving means (6) to the openings (2) of the bag bodies (3), and a reciprocating means (9) for moving forward or in the opposite direction the in-and-out means (8) and the advancing and retracting means (7) in the conveying direction (T) at the conveying speed. In the process in which the reciprocating means (9) moves forward the in-and-out means (8) and the advancing and retracting means (7), the in-and-out means (8) and the advancing and retracting means (7) perform the following operations. That is, the operations by the in-and-out means (8) are an operation in which the in-and-out means (8) advances the guide horns until the guide horns enter the openings (2) of the bag bodies (3) and an operation in which the in-and-out means (8) retracts the guide horns from the bag bodies (3).

Owner:GUNZE LTD

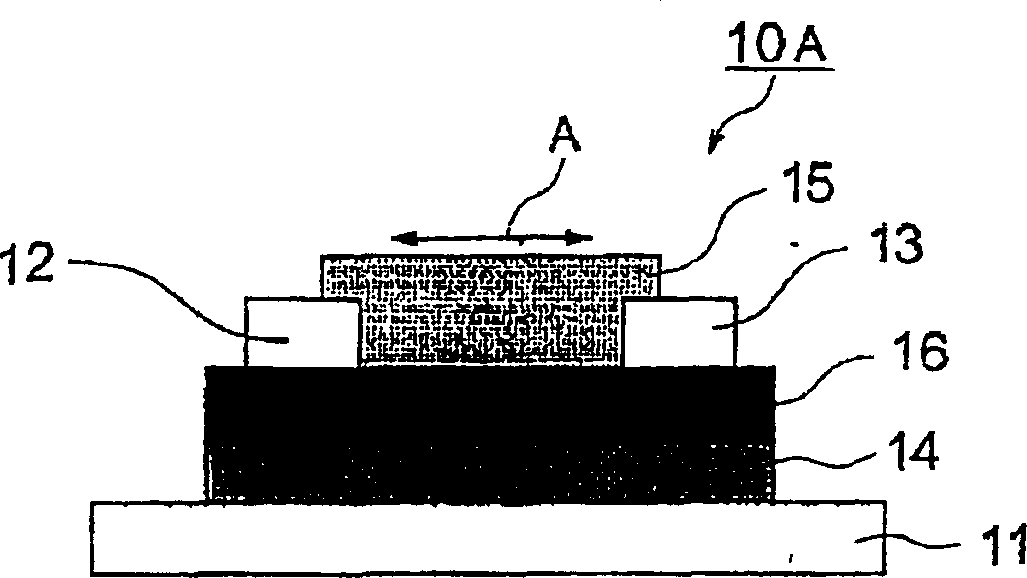

Organic thin film transistor

InactiveCN1412864AHigh on/off ratioHigh speed actionTransistorSolid-state devicesAromatic hydrocarbonCarbon atom

An organic thin film transistor includes: an organic thin film which includes a compound represented by the following general formula [A]:where each of Ar<1 >and Ar<2 >is selected independently from unsubstituted or substituted aromatic hydrocarbon groups having 6 to 20 carbon atoms and from unsubstituted or substituted aromatic heterocyclic groups having 6 to 20 carbon atoms; and X is selected from unsubstituted or substituted condensed aromatic hydrocarbon groups having 6 to 34 carbon atoms, and the condensed aromatic hydrocarbon groups are monovalent, divalent, trivalent or tetravalent groups; and n is the natural number in the range of 1-4.

Owner:NEC CORP

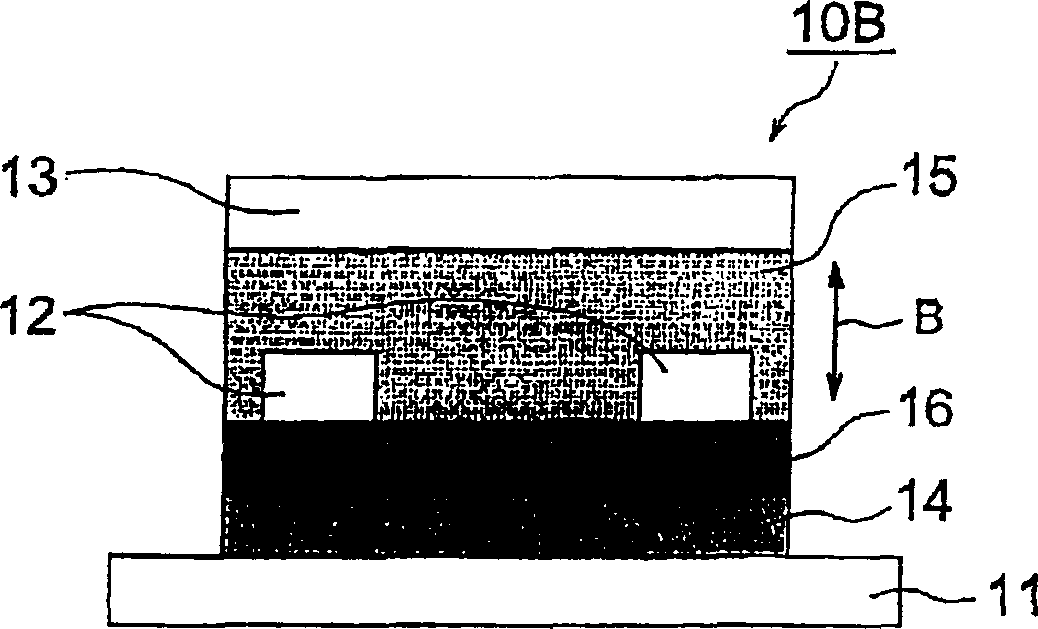

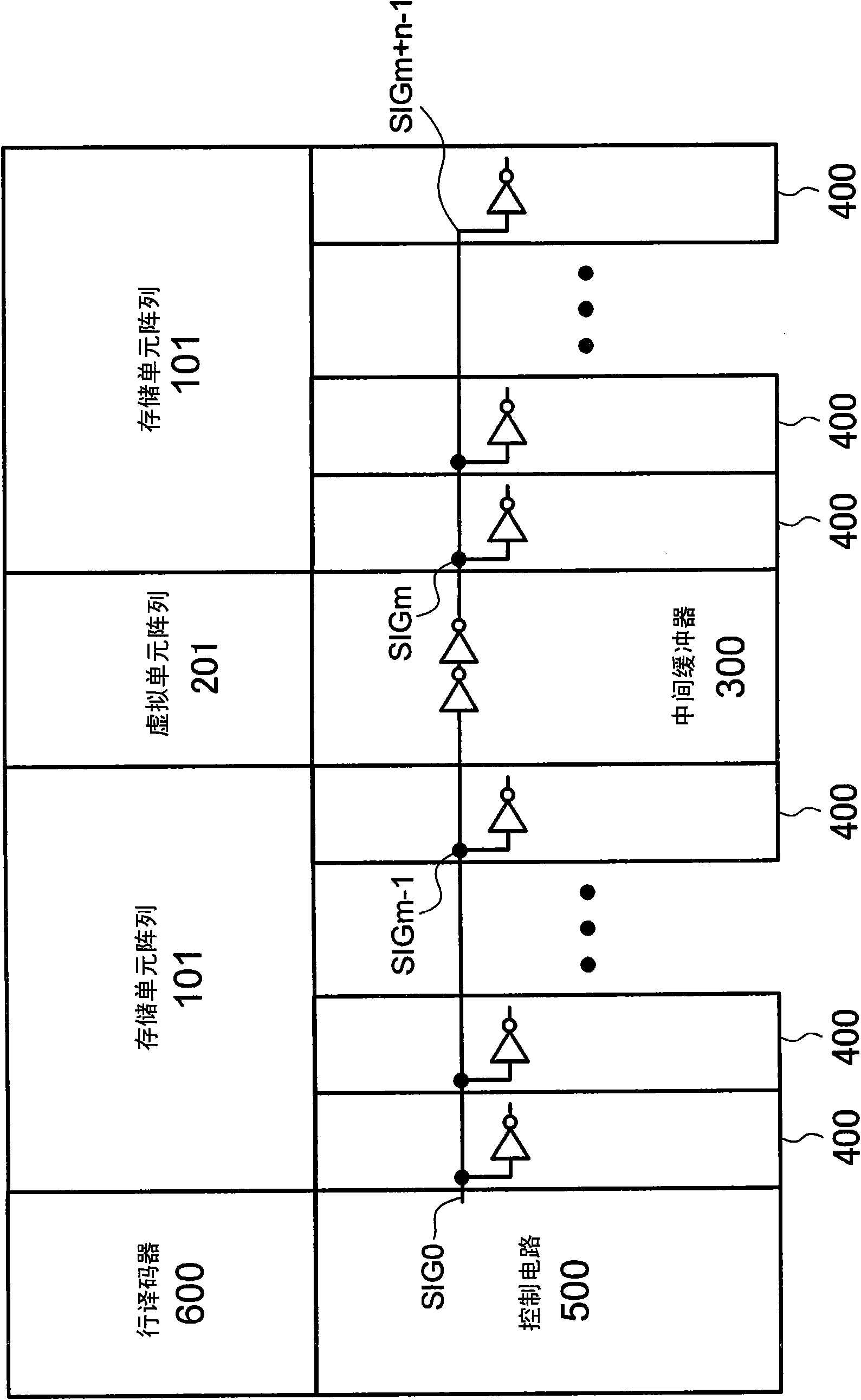

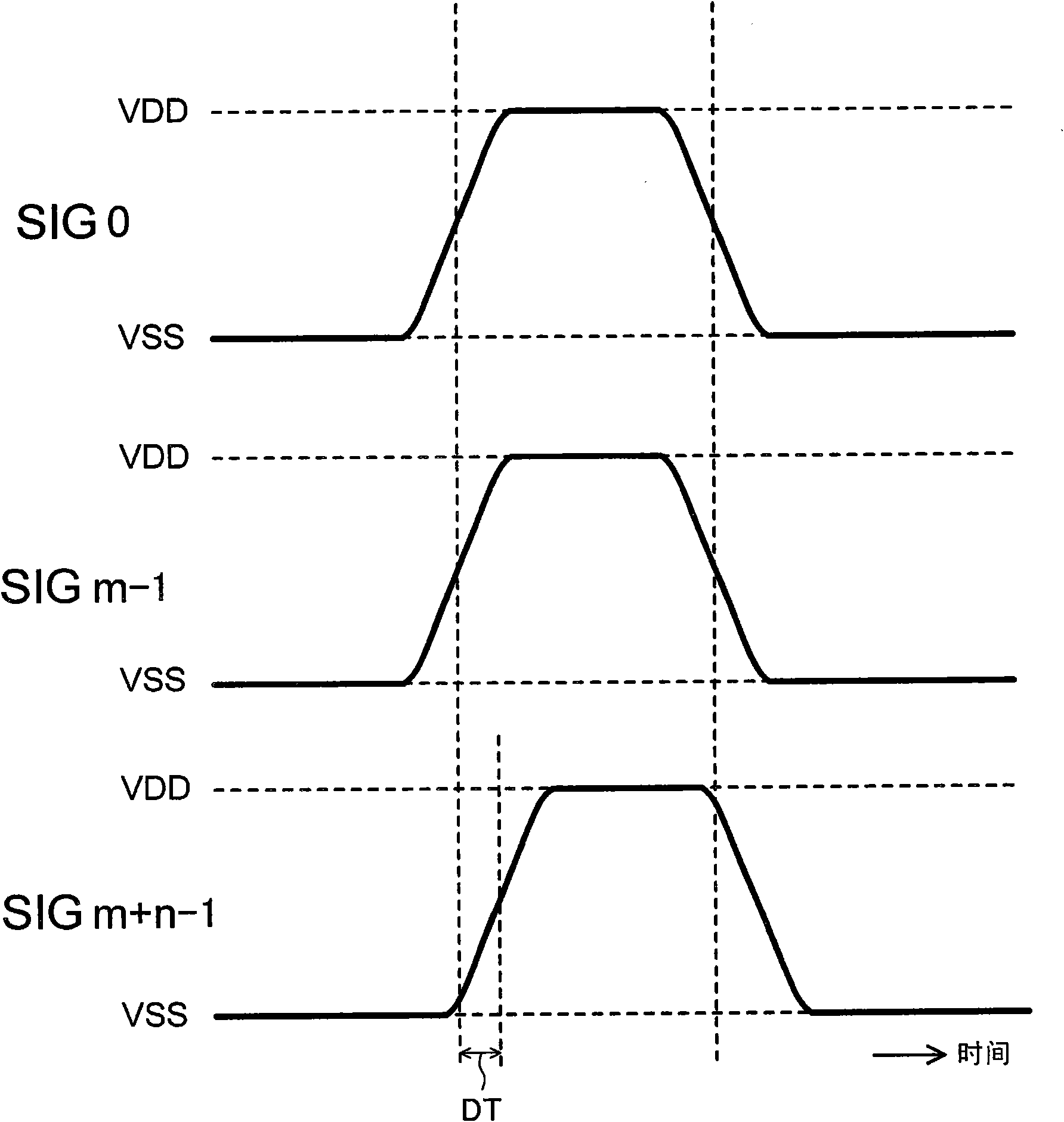

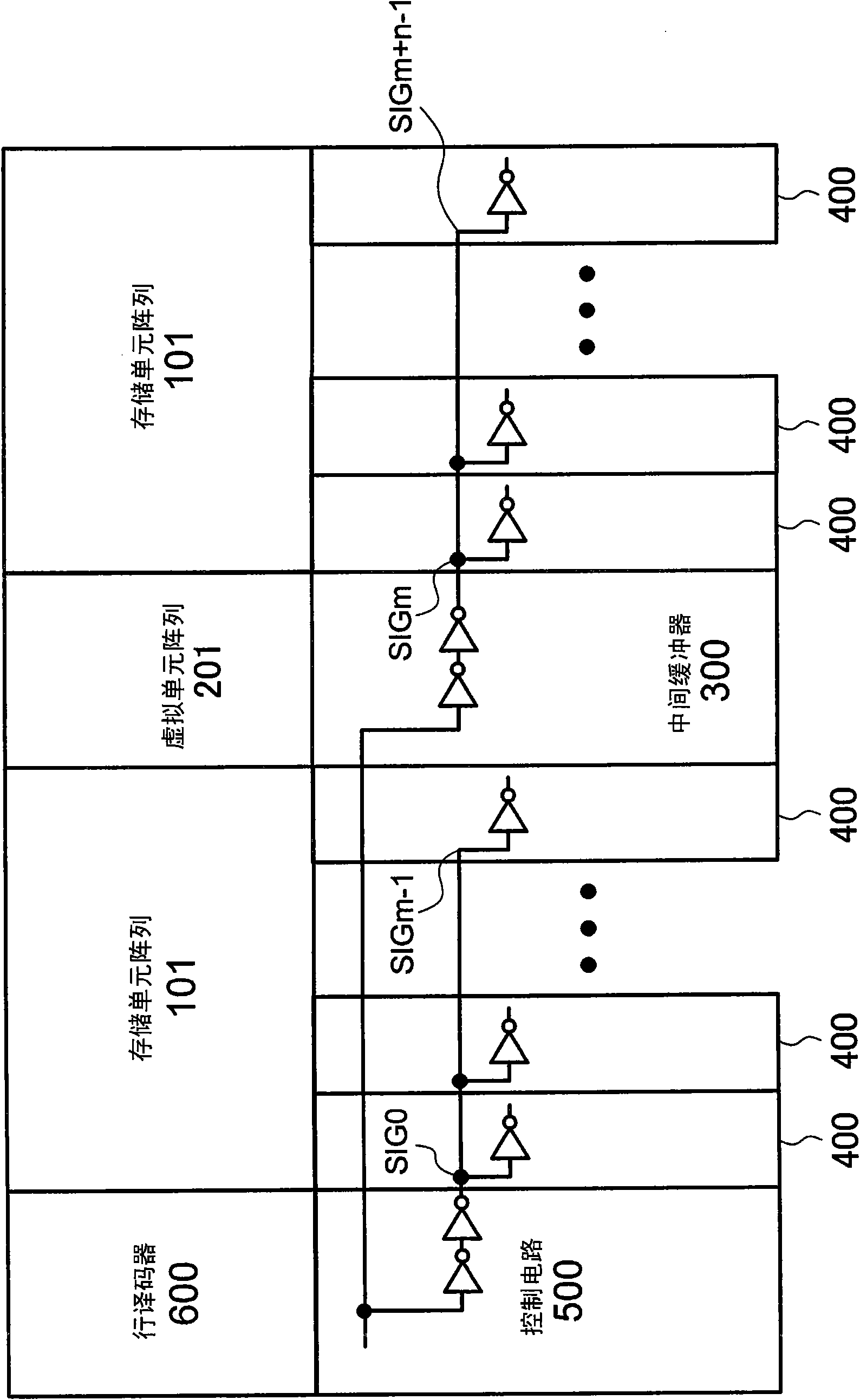

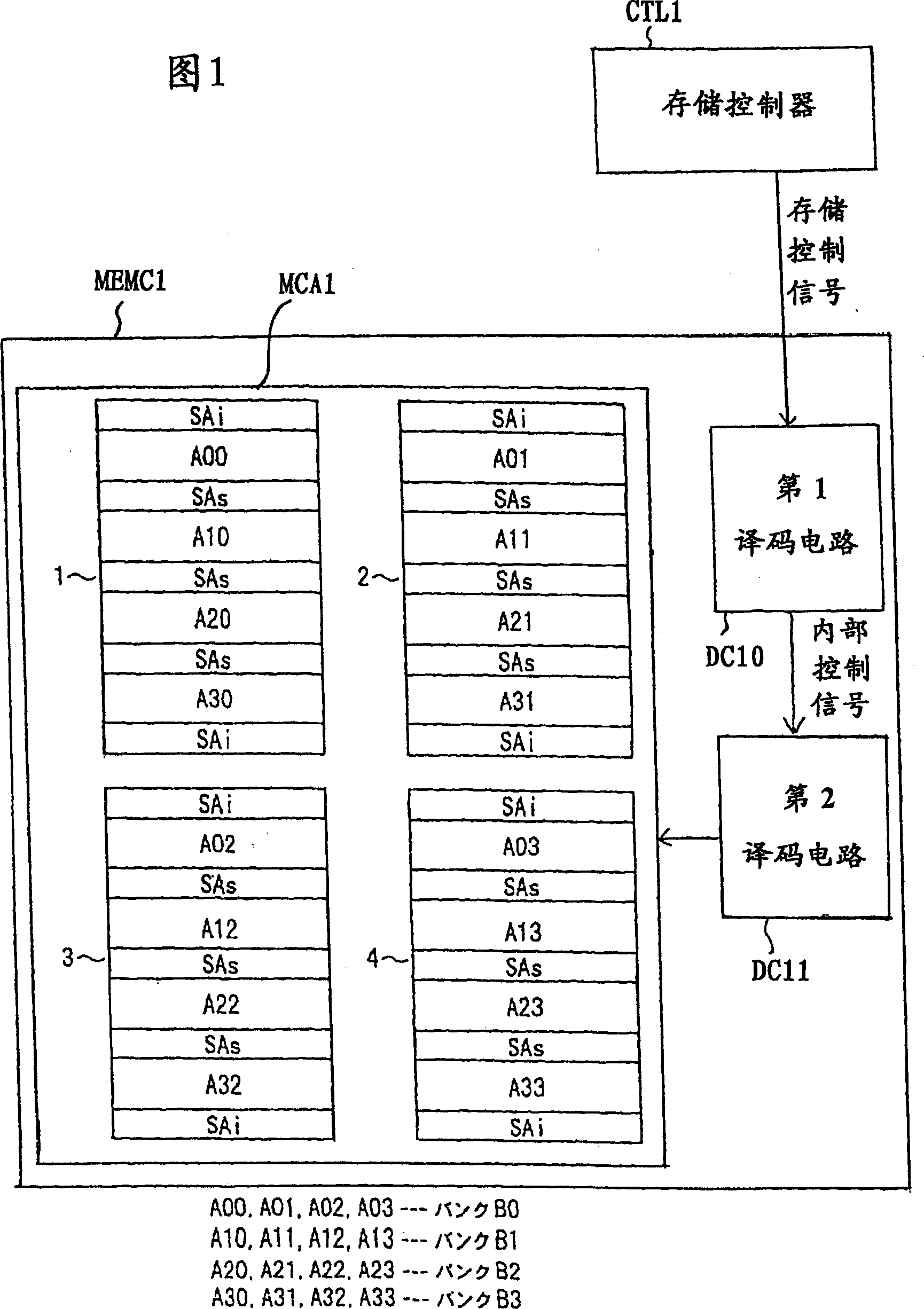

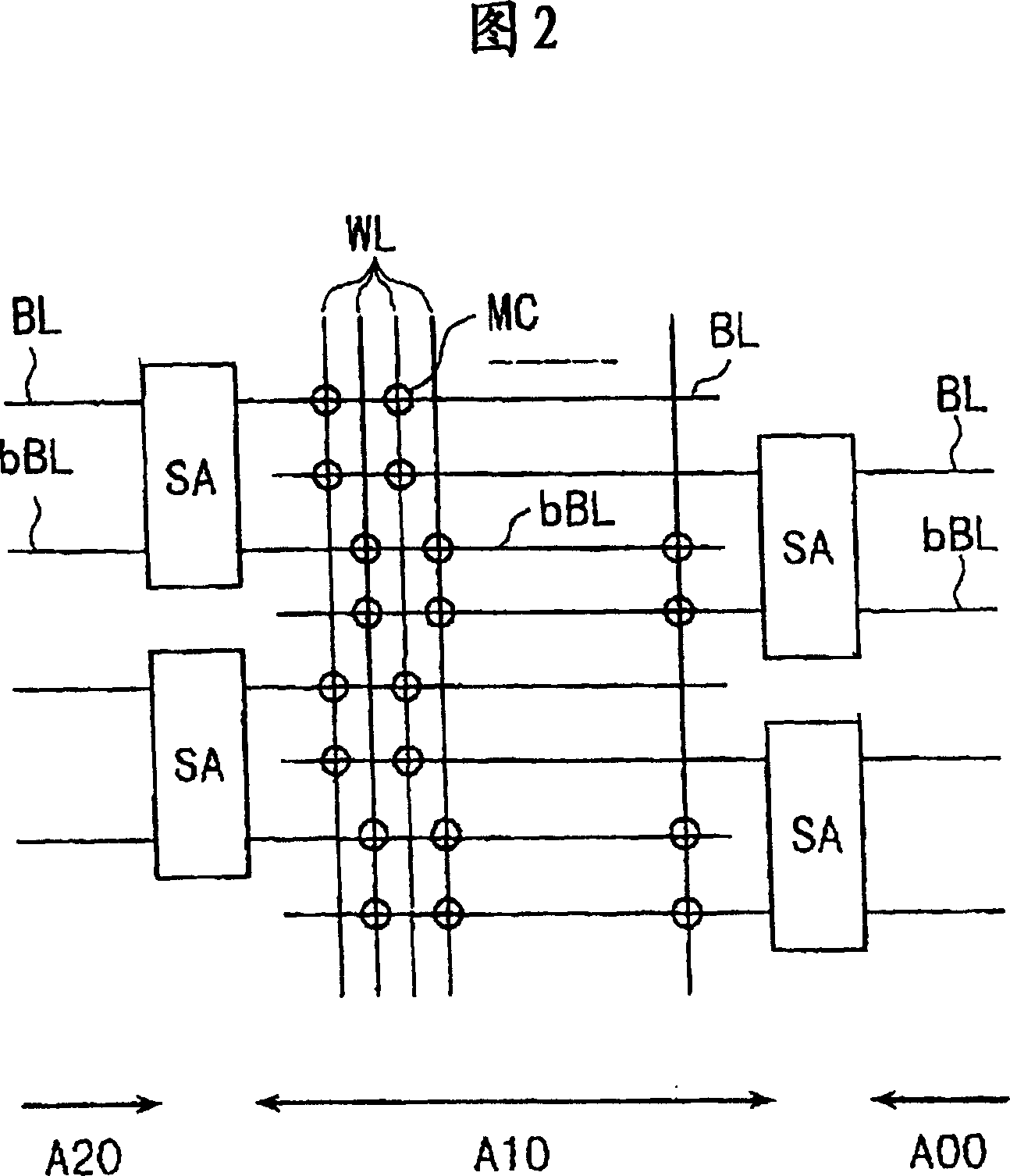

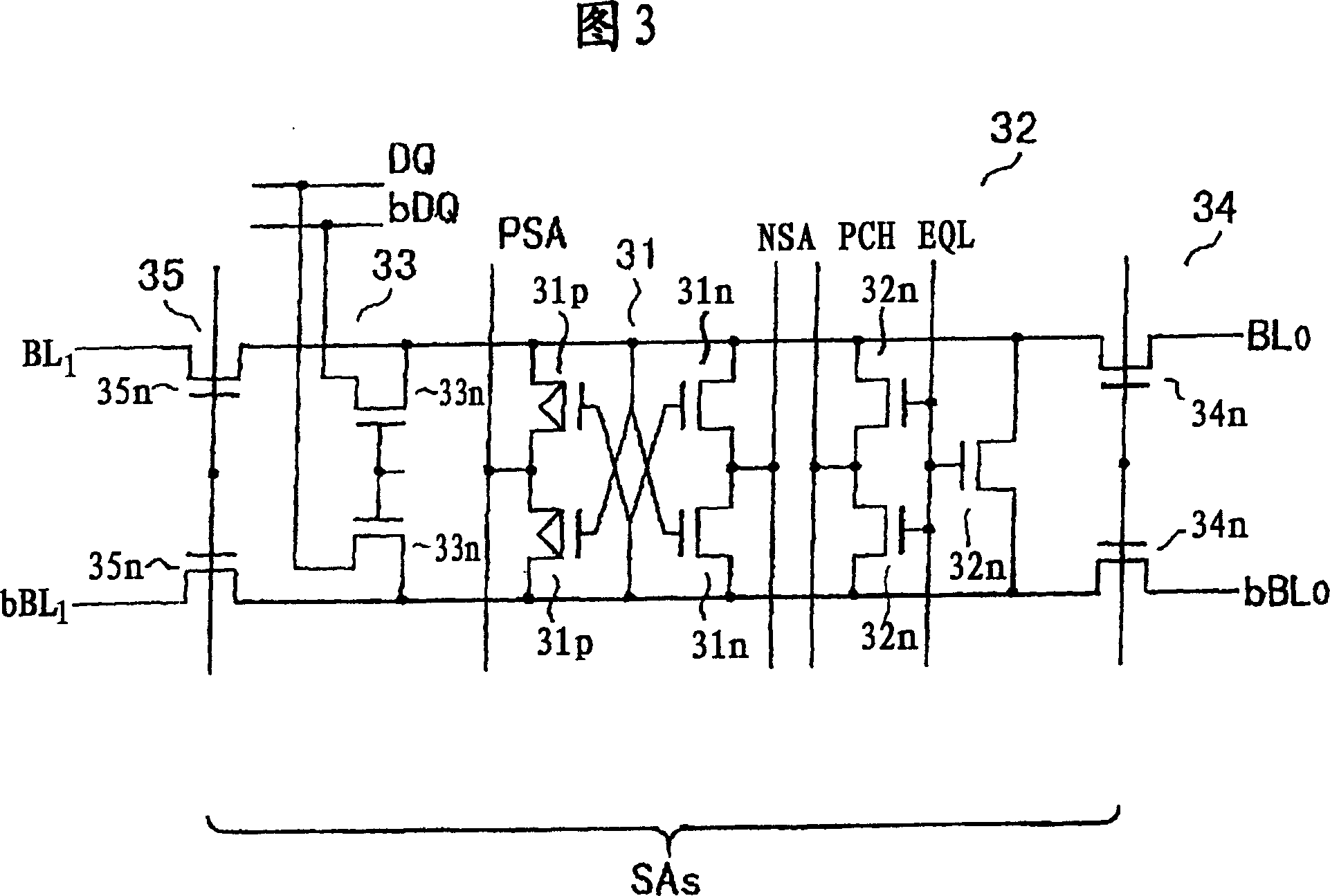

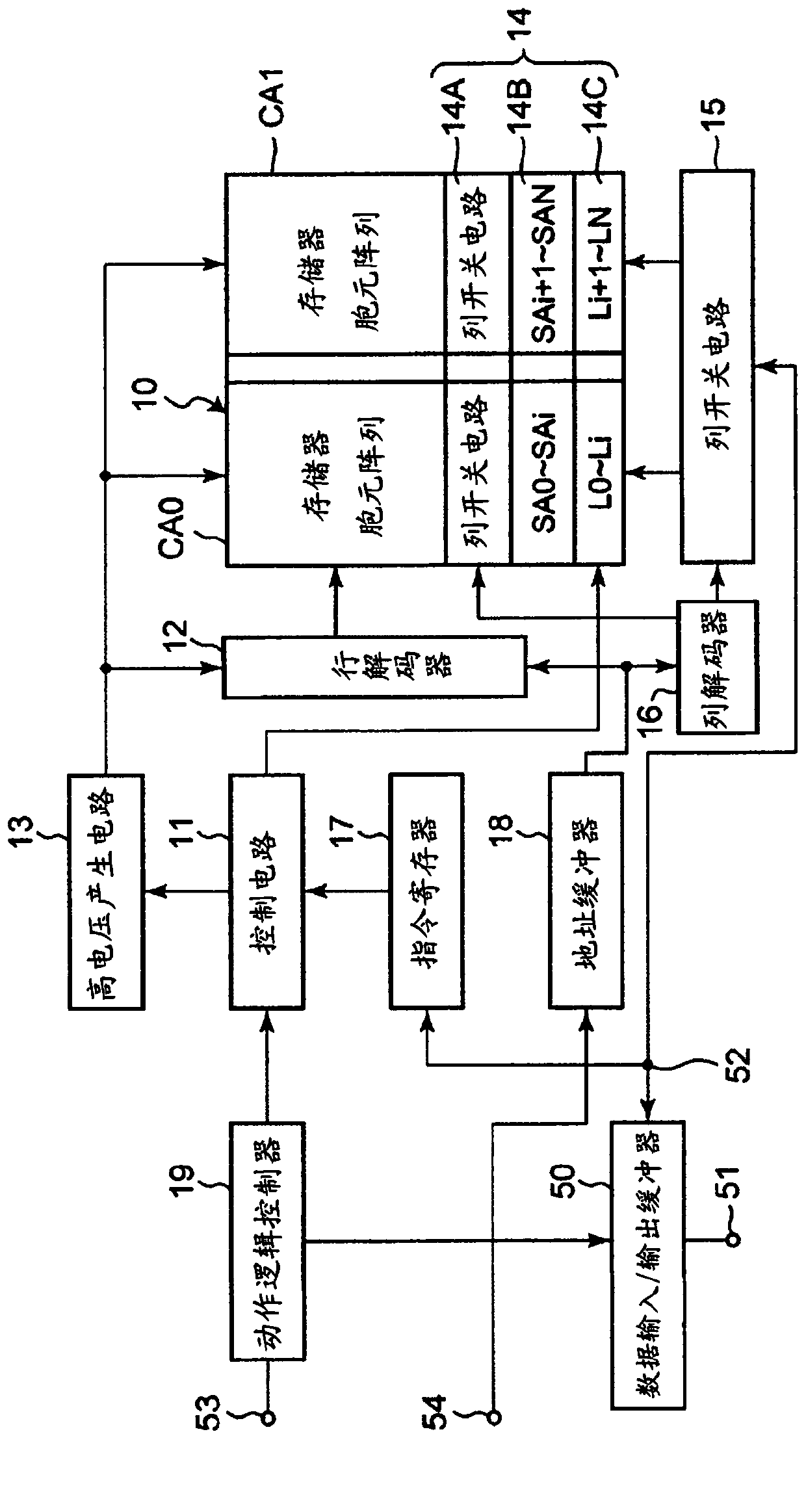

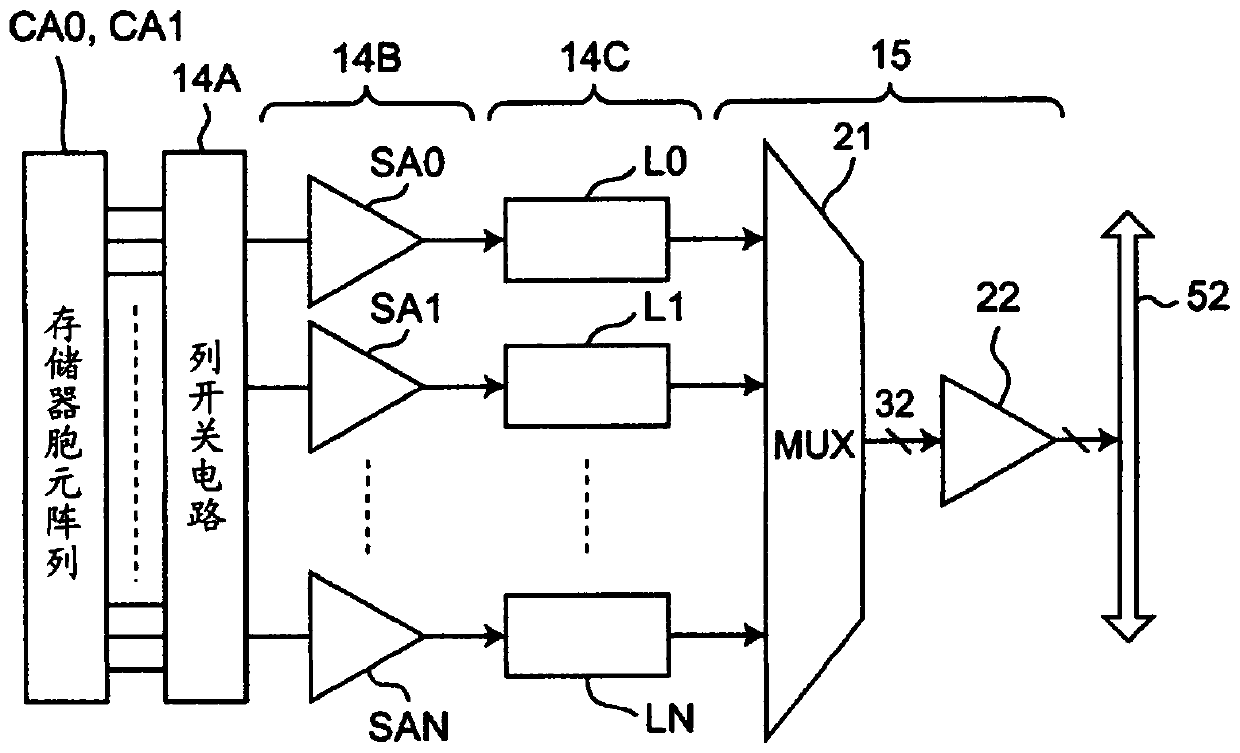

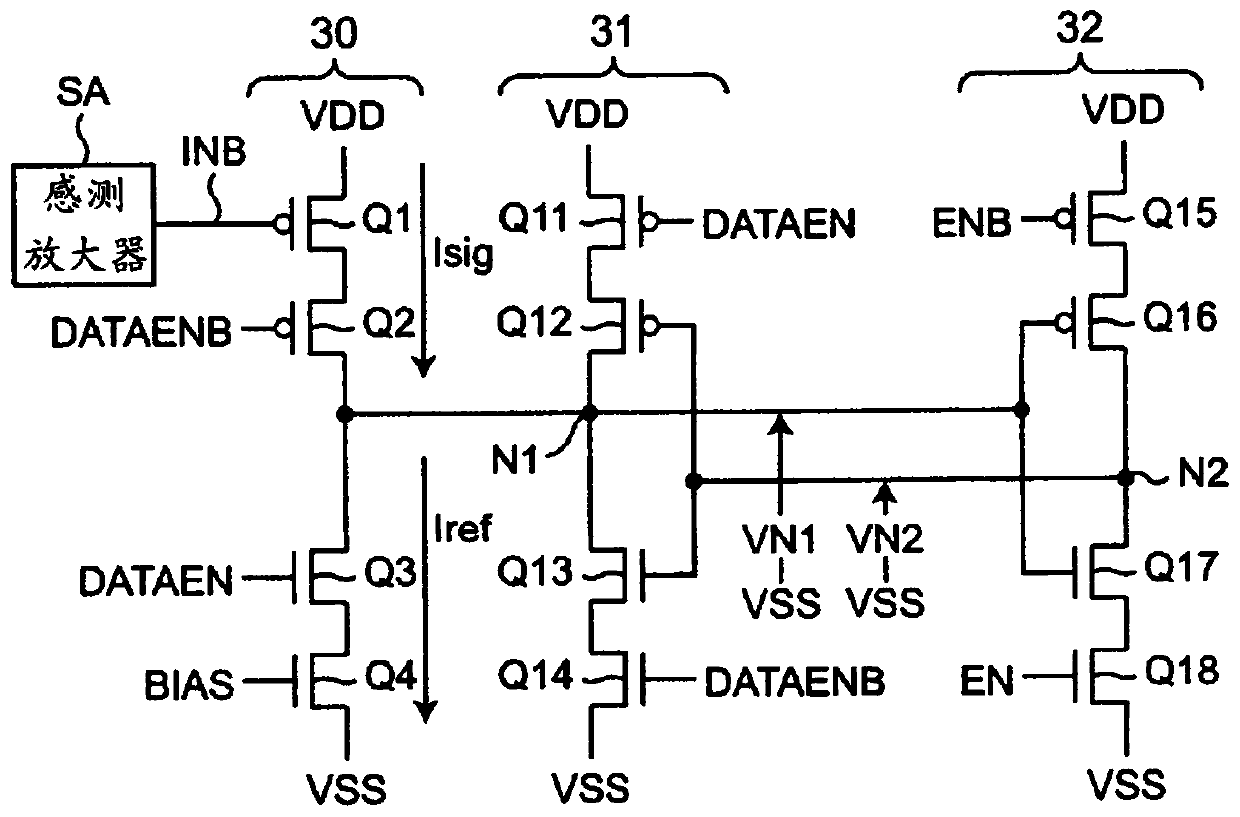

Semiconductor storage device

InactiveCN102105940AHigh speed actionIncrease the areaDigital storageControl signalSemiconductor storage devices

By arranging a dummy cell array (201) in a memory array (101), and an intermediate buffer (300) between input / output circuits (400), control signals of the input / output circuits (400) can be operated at a high speed and a high frequency, while minimizing increase in circuit size even for memory having a wide bit-width.

Owner:PANASONIC CORP

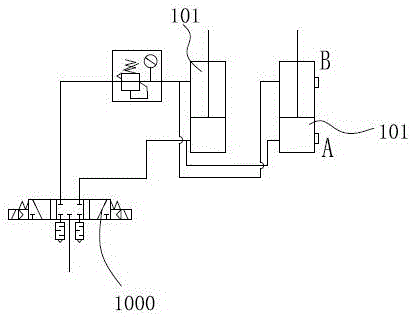

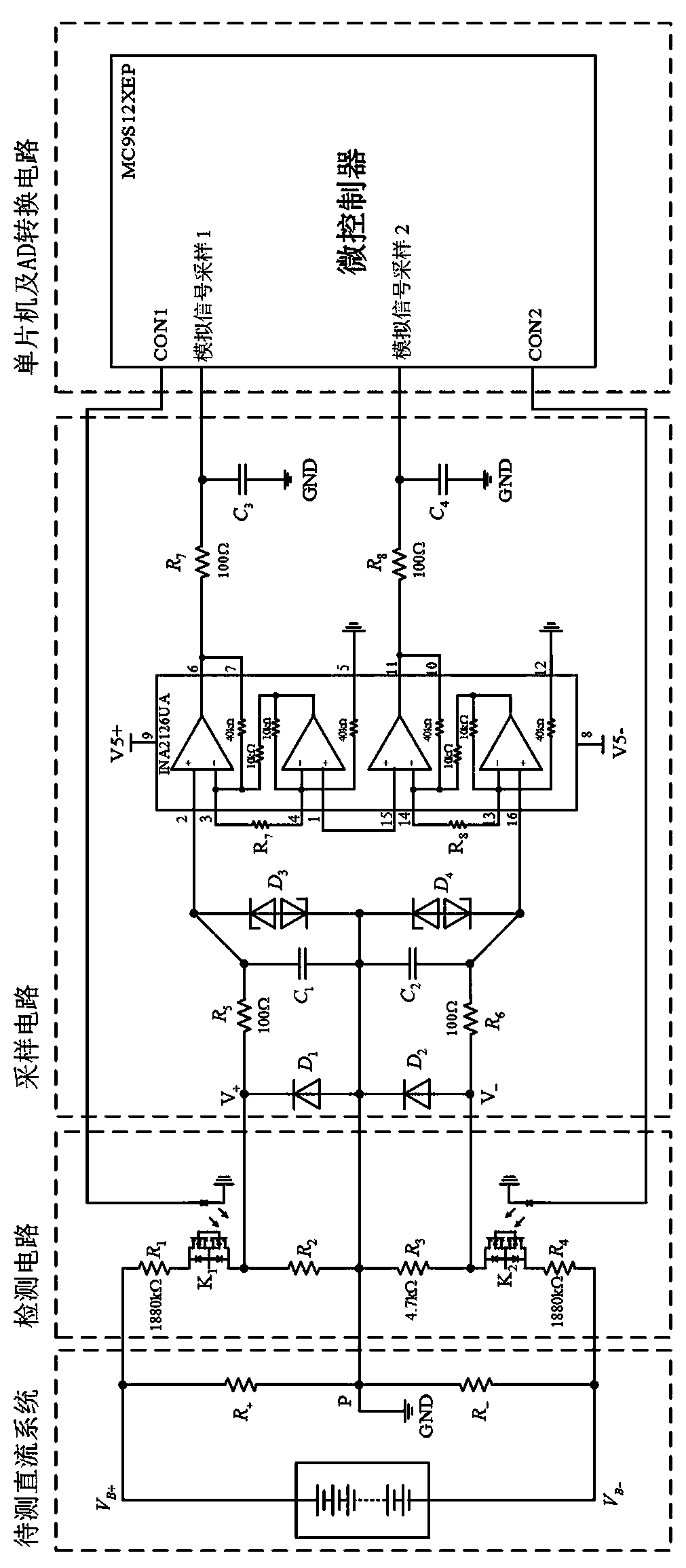

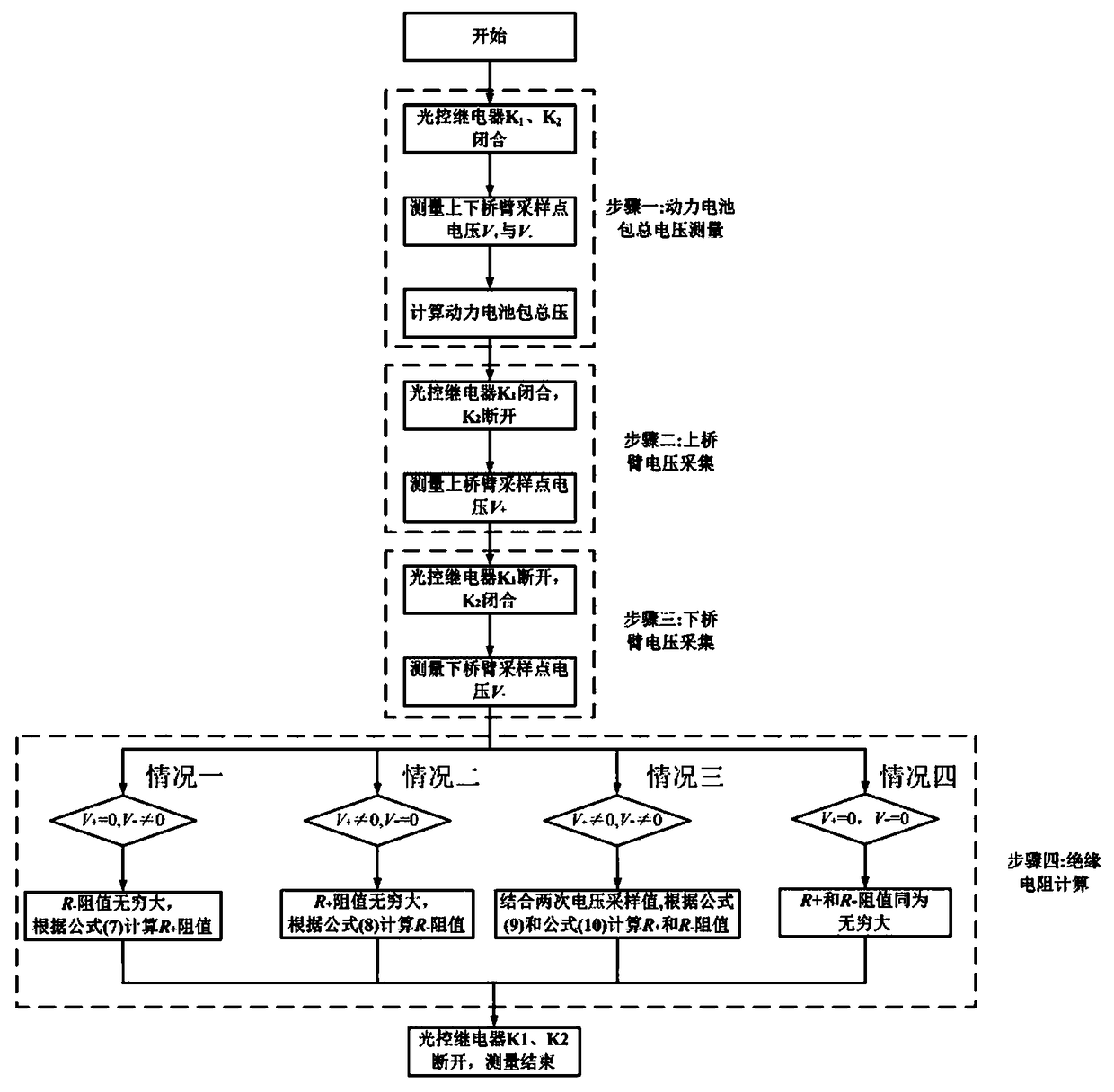

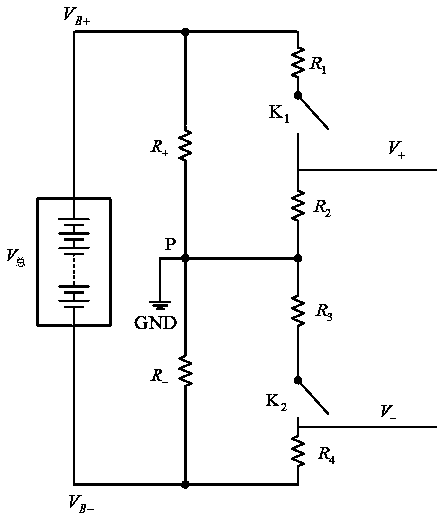

Insulation resistance detecting control circuit and detecting method of electric vehicle

InactiveCN108614158AReduce the impactLower Offset VoltageResistance/reactance/impedenceElectrical resistance and conductanceInstrumentation amplifier

The invention discloses an insulation resistance detecting control circuit and detecting method of an electric vehicle. The circuit is based on a balanced bridge; a light-control type relay is used for controlling opening or closing of corresponding bridge arms of the bridge; a high-precision instrumentation amplifier is used for amplifying a weak voltage signal and realizing voltage polarity conversion. On the basis of the basic characteristics of the above circuit, a four-step insulation resistance calculation method is designed. The insulation resistance detecting control circuit and the detecting method, the insulation resistance of the positive and negative terminals can be measured simultaneously; online detection is realized; and the precision and reliability are high.

Owner:ZHENGZHOU UNIVERSITY OF LIGHT INDUSTRY

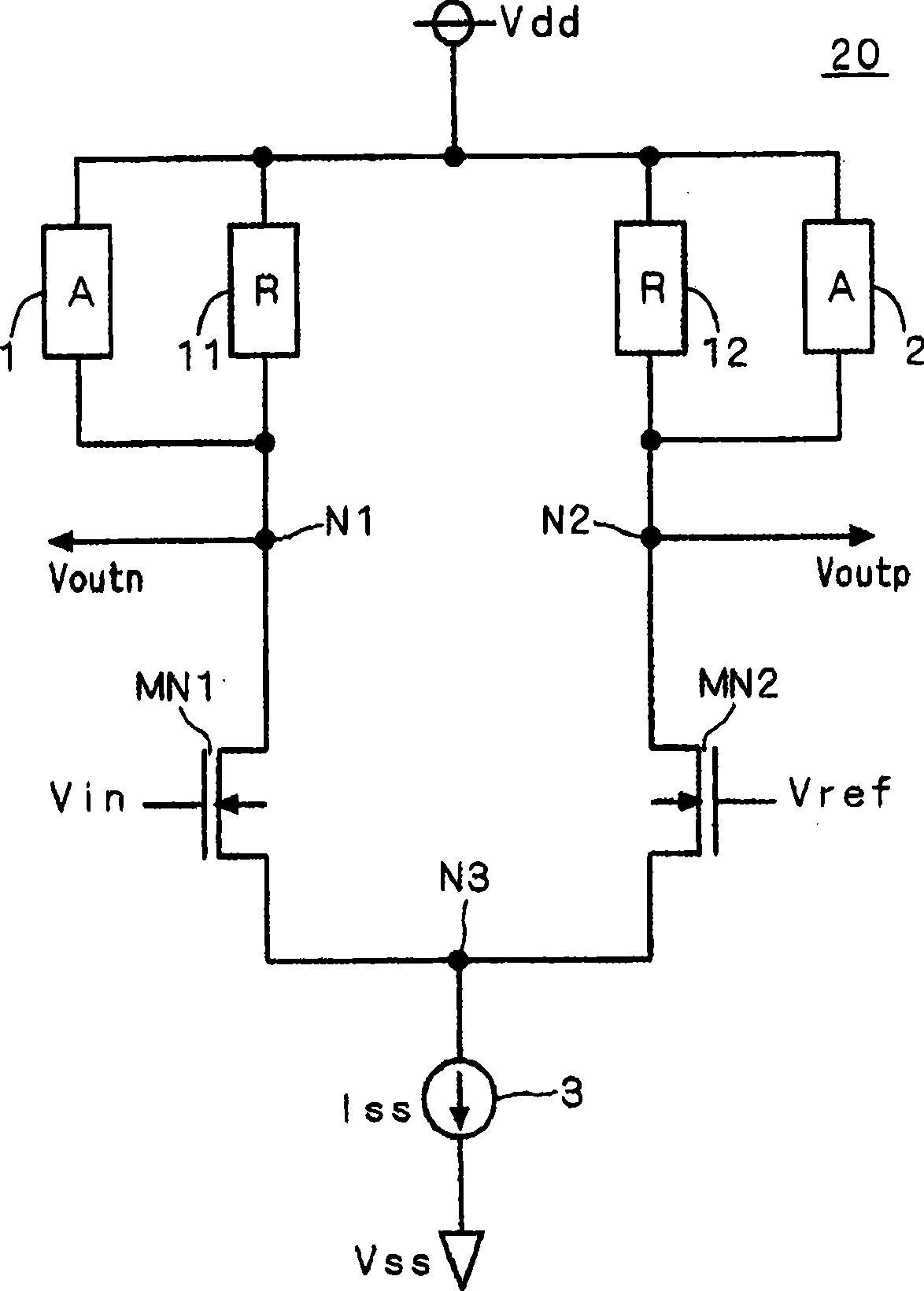

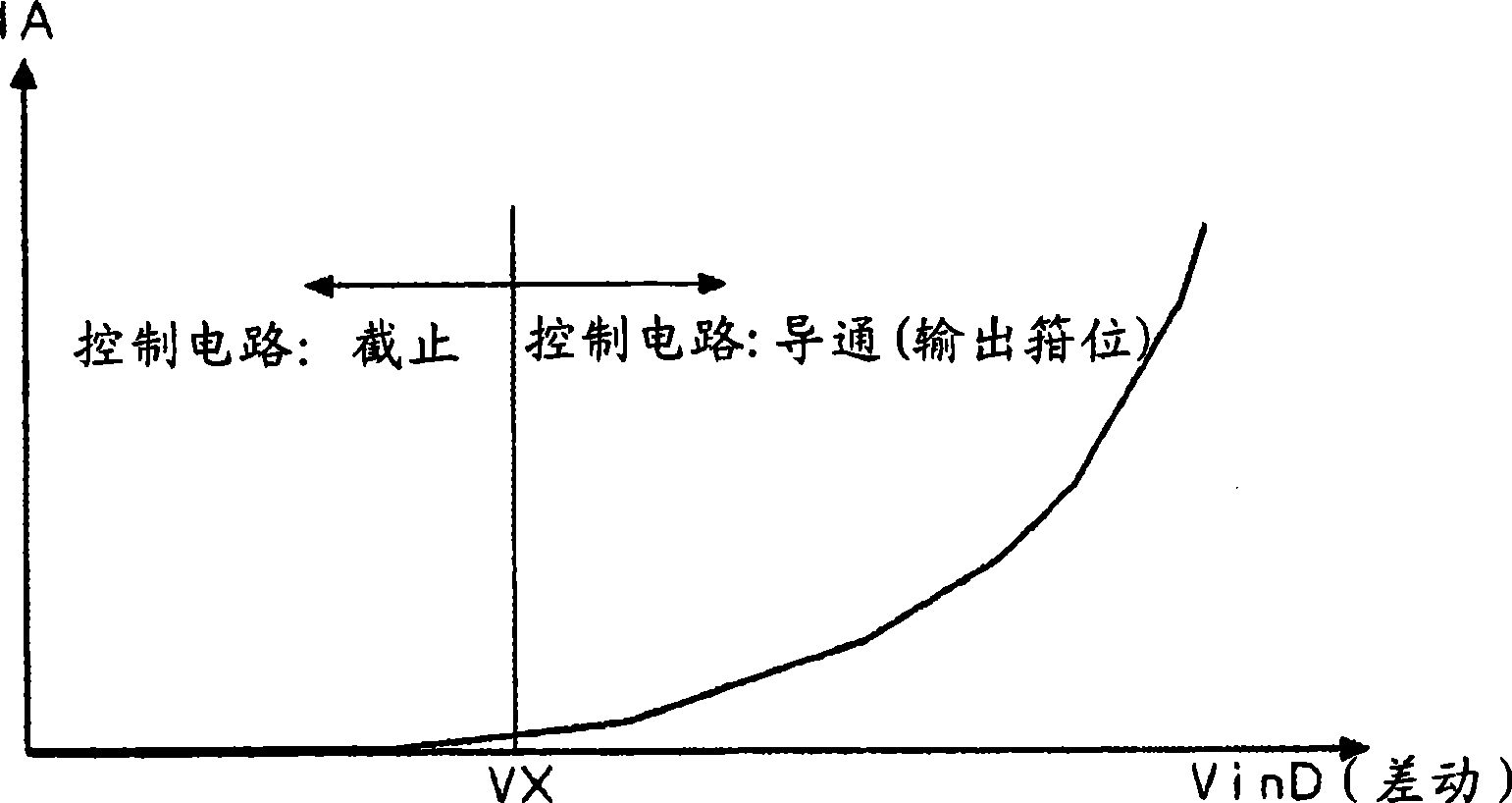

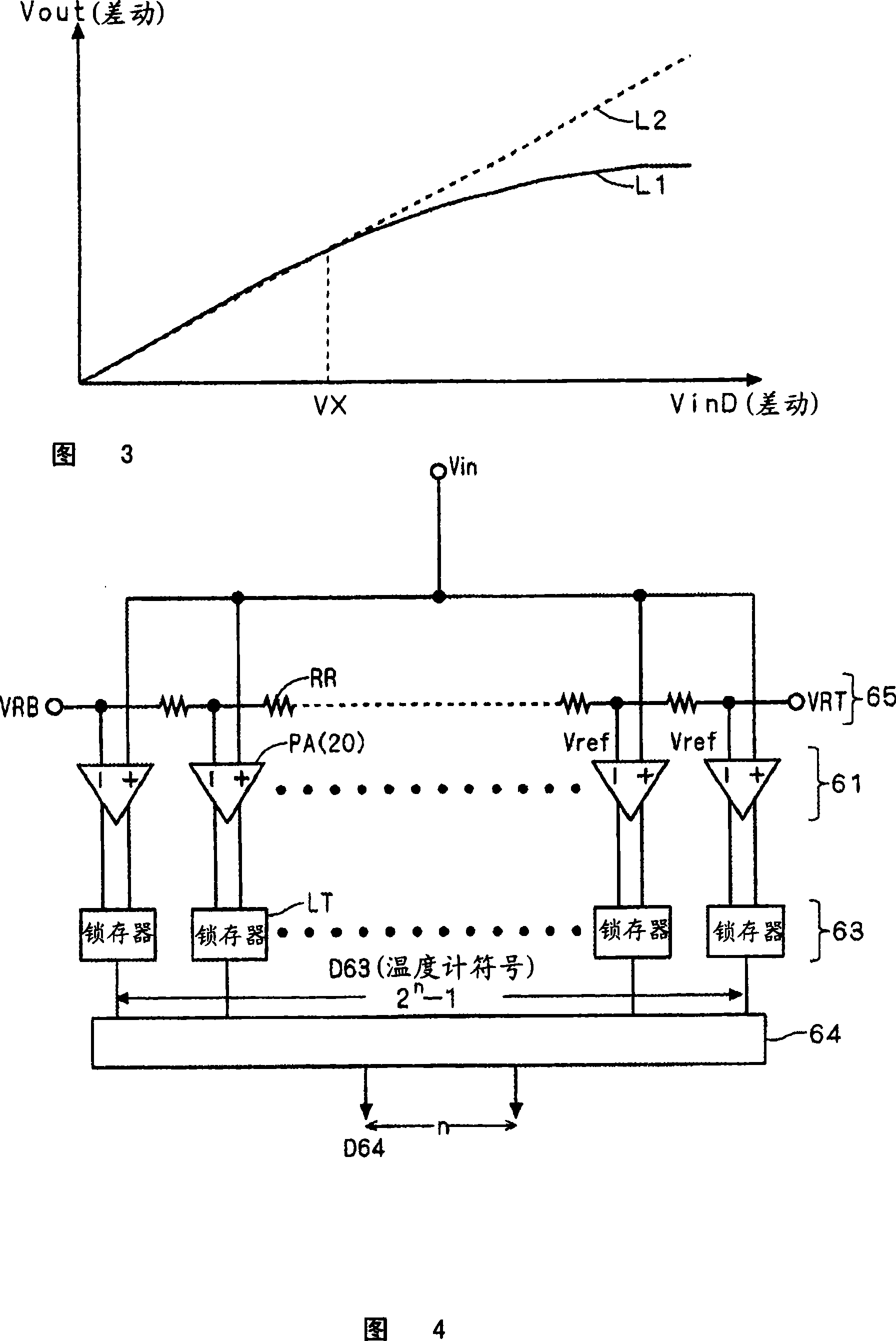

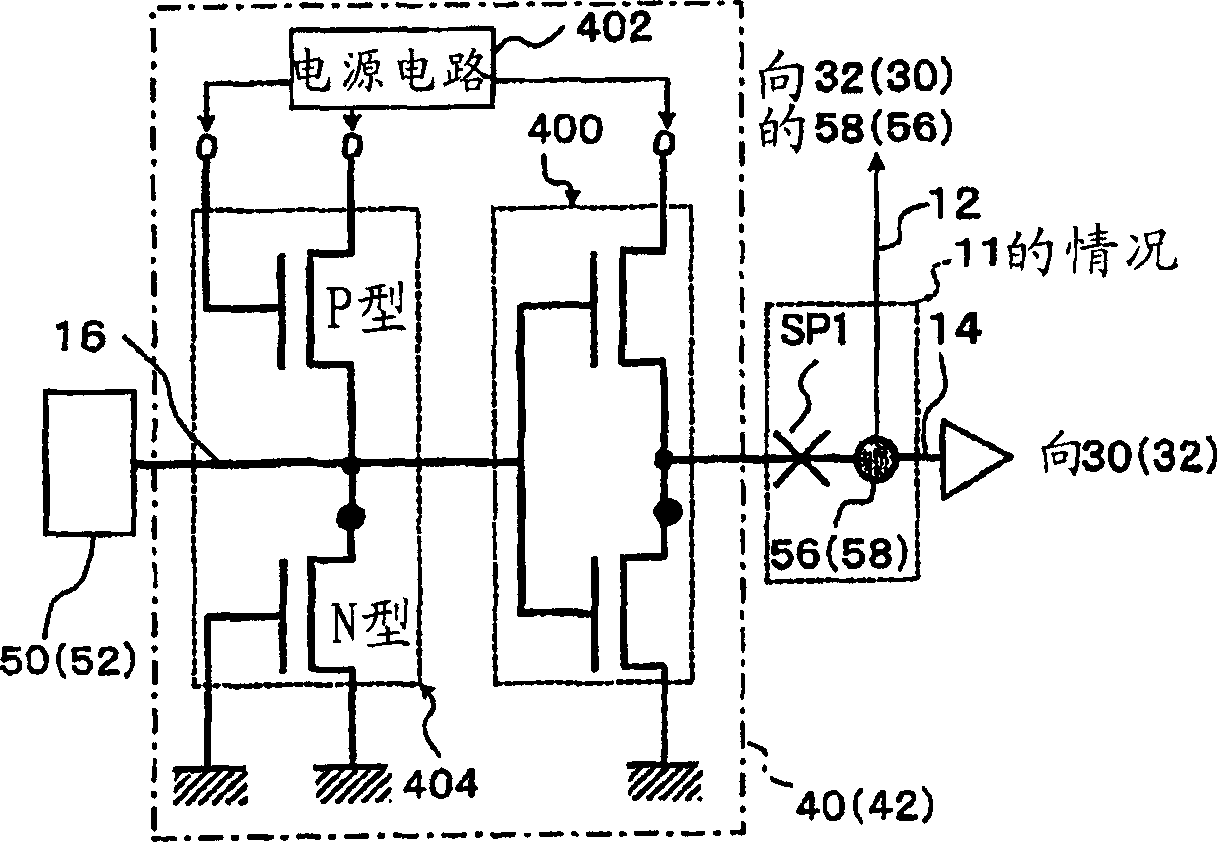

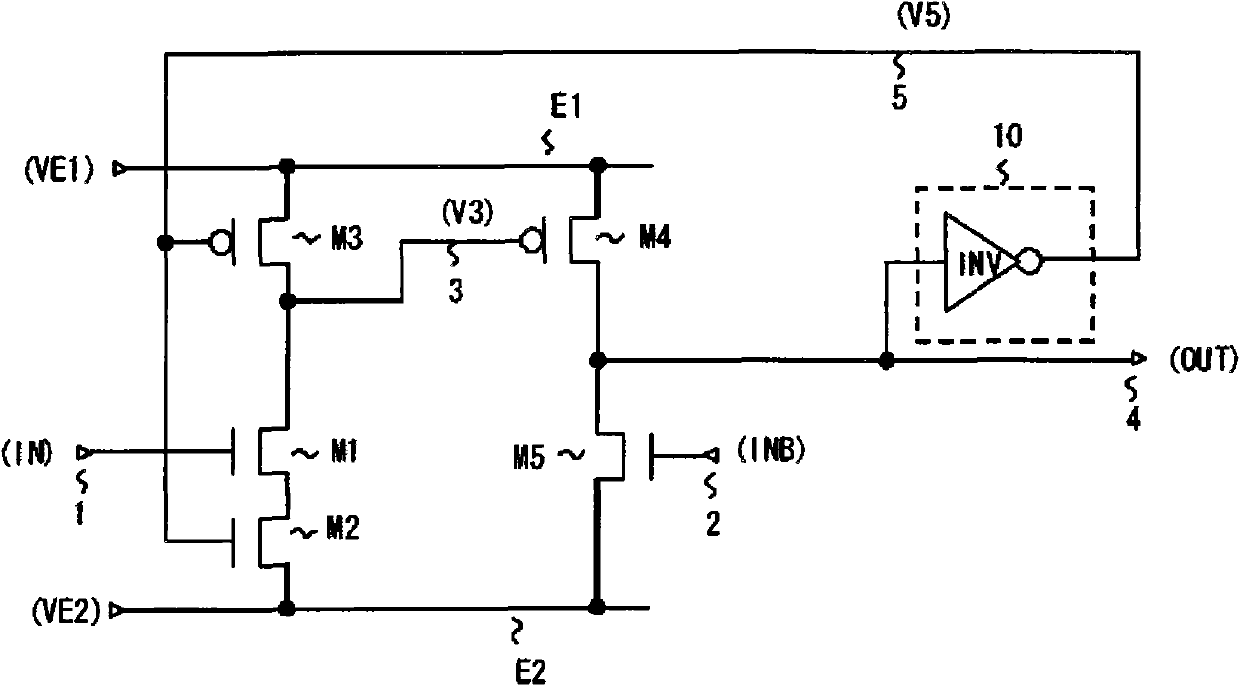

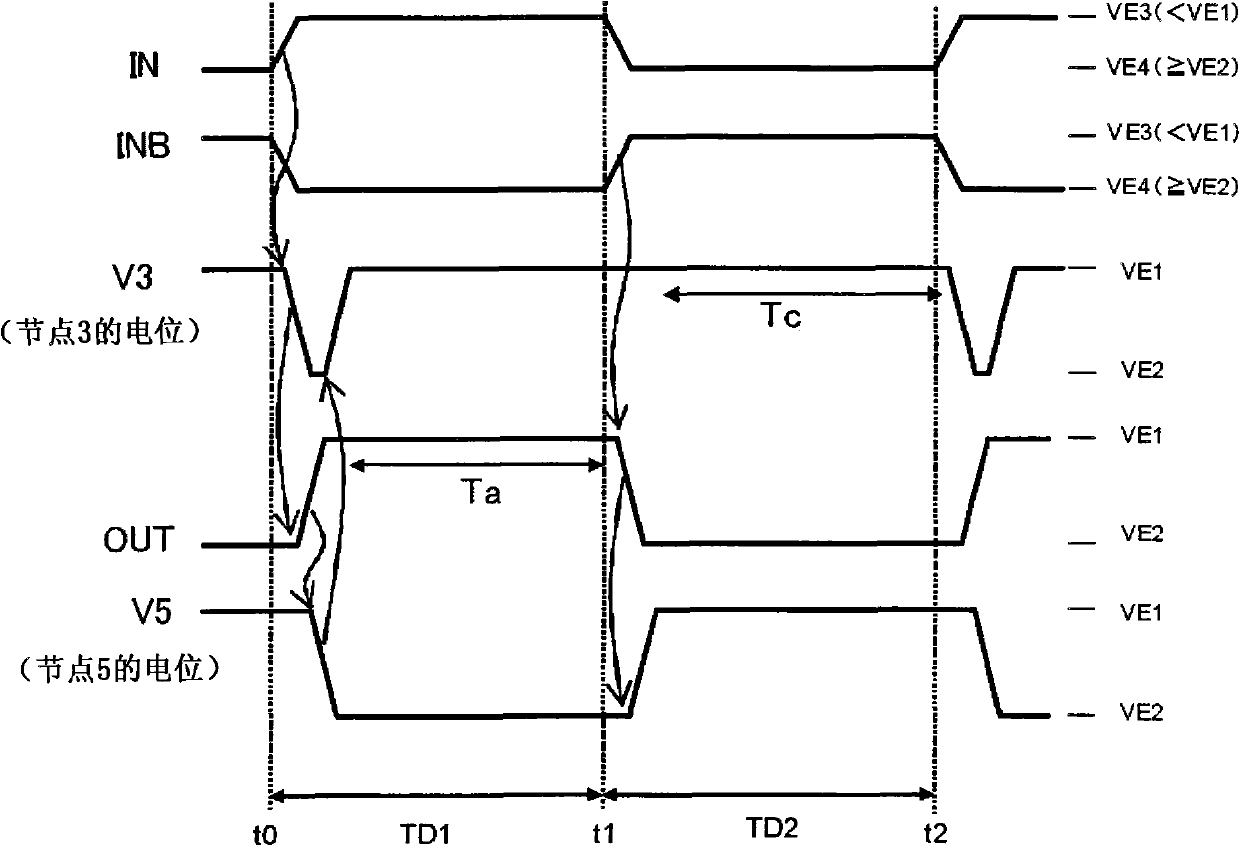

Differential amplifier circuit and A/D converter

InactiveCN101373955AHigh magnificationHigh speed actionAnalogue/digital conversionElectric signal transmission systemsBuck converterPotential difference

The present invention aims to provide a differential amplifier circuit that prevents degradation of performance and that can be overdrive recovered even if a power supply voltage is relatively small. PMOS transistors are interposed parallel to each other between a node, which is a first output part, and a power supply; and PMOS transistors are interposed in parallel to each other between a node, which is a second output part, and the power supply. Output voltages in time of a balanced state in which an input potential difference between an input voltage and a reference voltage is '0' are bothset to a reference output common voltage by a replica circuit and a comparator. The reference output common voltage of the replica circuit is set so that the potential difference between the power supply voltage and the output common voltage becomes a value lower than a threshold voltage of the diode connected PMOS transistors.

Owner:RENESAS ELECTRONICS CORP

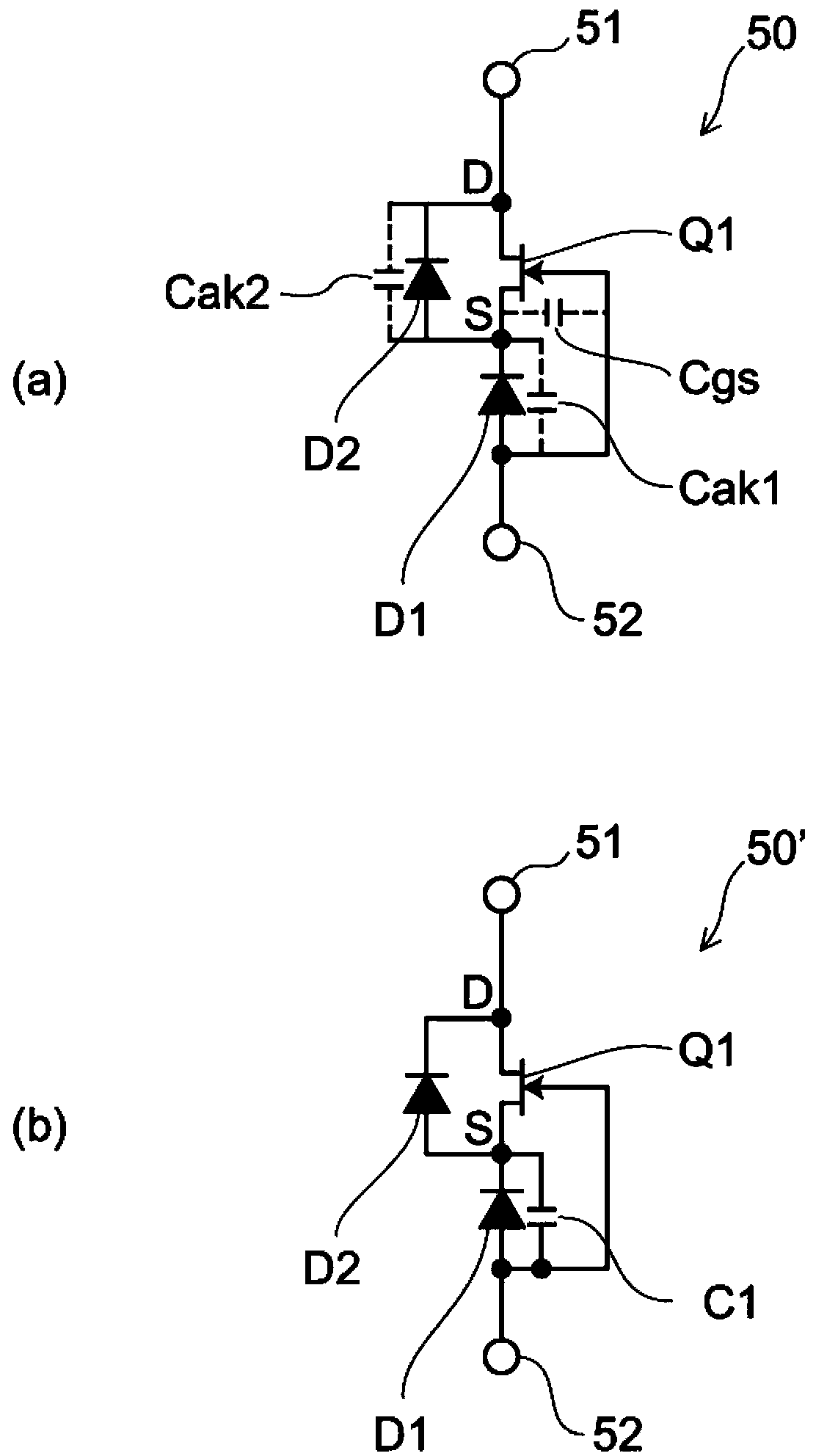

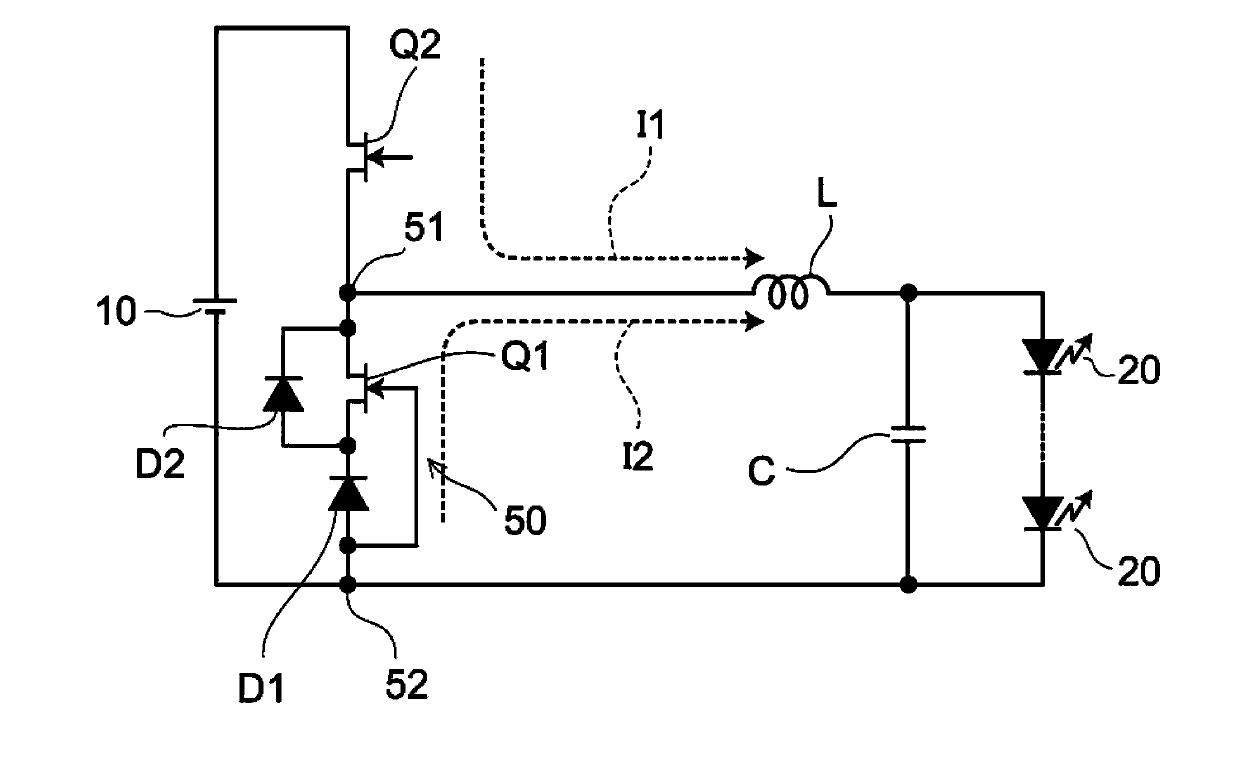

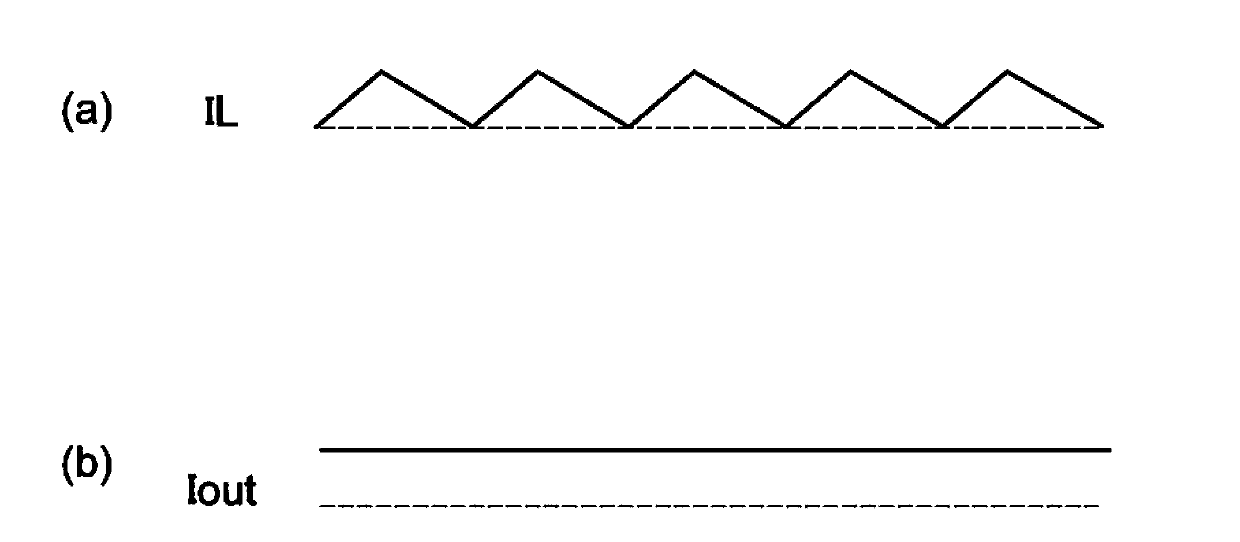

Rectifier circuit and power source circuit

InactiveCN103997193AHigh speed actionThyristorAc-dc conversion without reversalPower circuitsRectifier

According to an embodiment, a rectifier circuit includes a first diode, a switching element, and a second diode. The first diode is connected between a first terminal and a second terminal so that a direction toward the first terminal from the second terminal is in a forward direction. The switching element has a first main electrode connected to the first terminal, a second main electrode connected to a cathode of the first diode, and a gate electrode connected to an anode of the first diode. The second diode is connected in parallel with respect to the switching element so that a direction toward the first terminal from the cathode of the first diode is in a forward direction, between the first main electrode and the second main electrode of the switching element.

Owner:TOSHIBA LIGHTING & TECH CORP

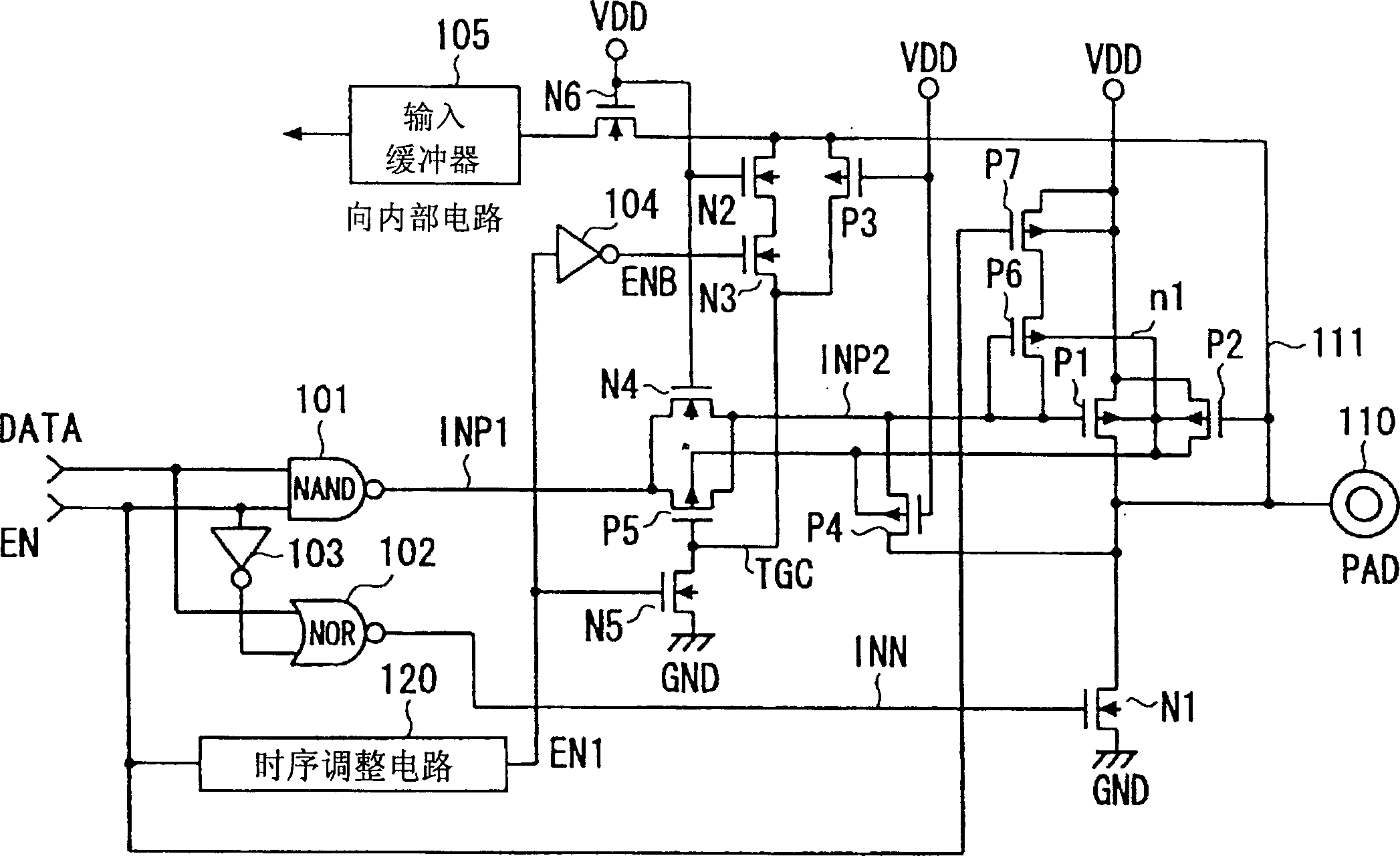

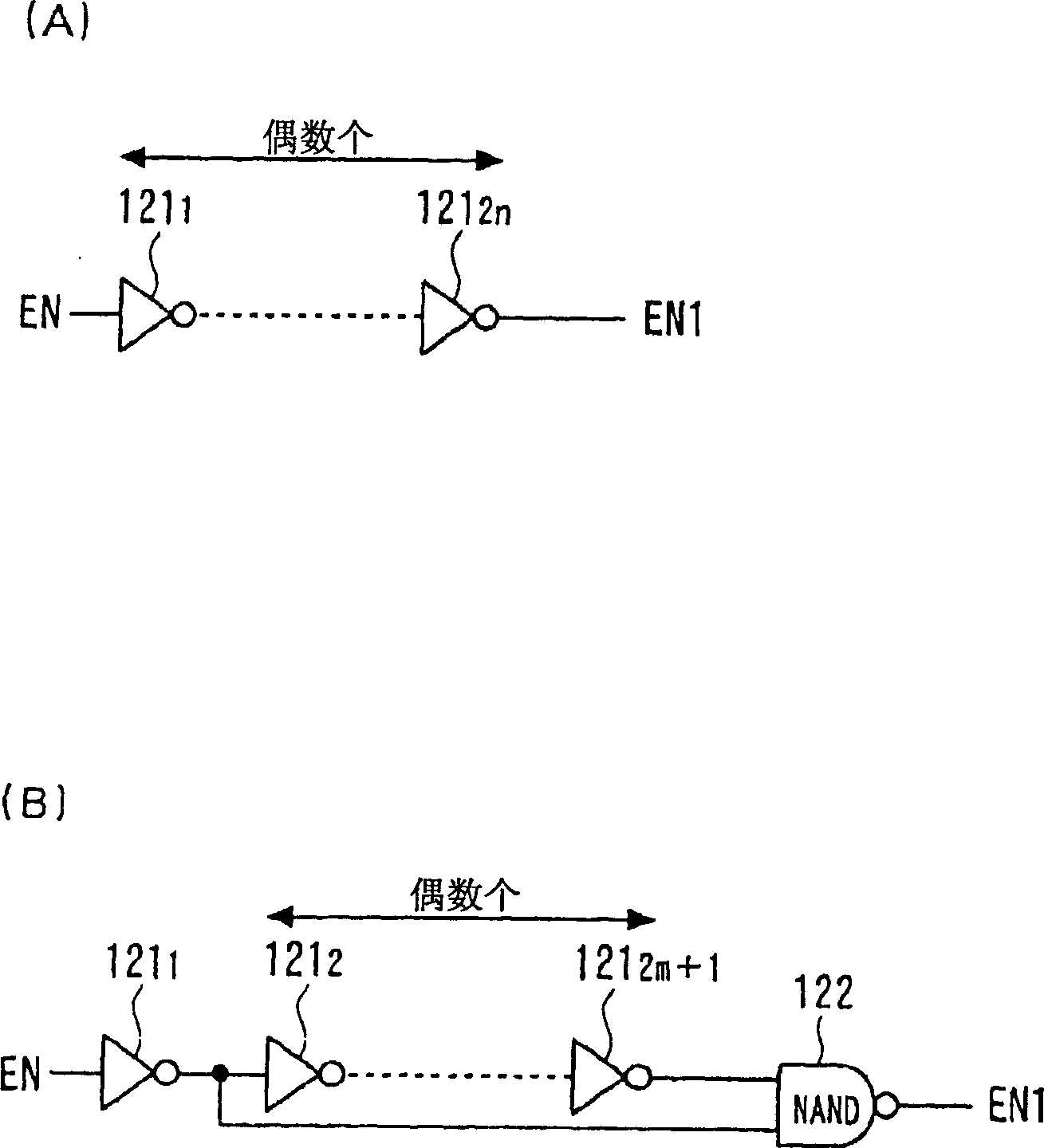

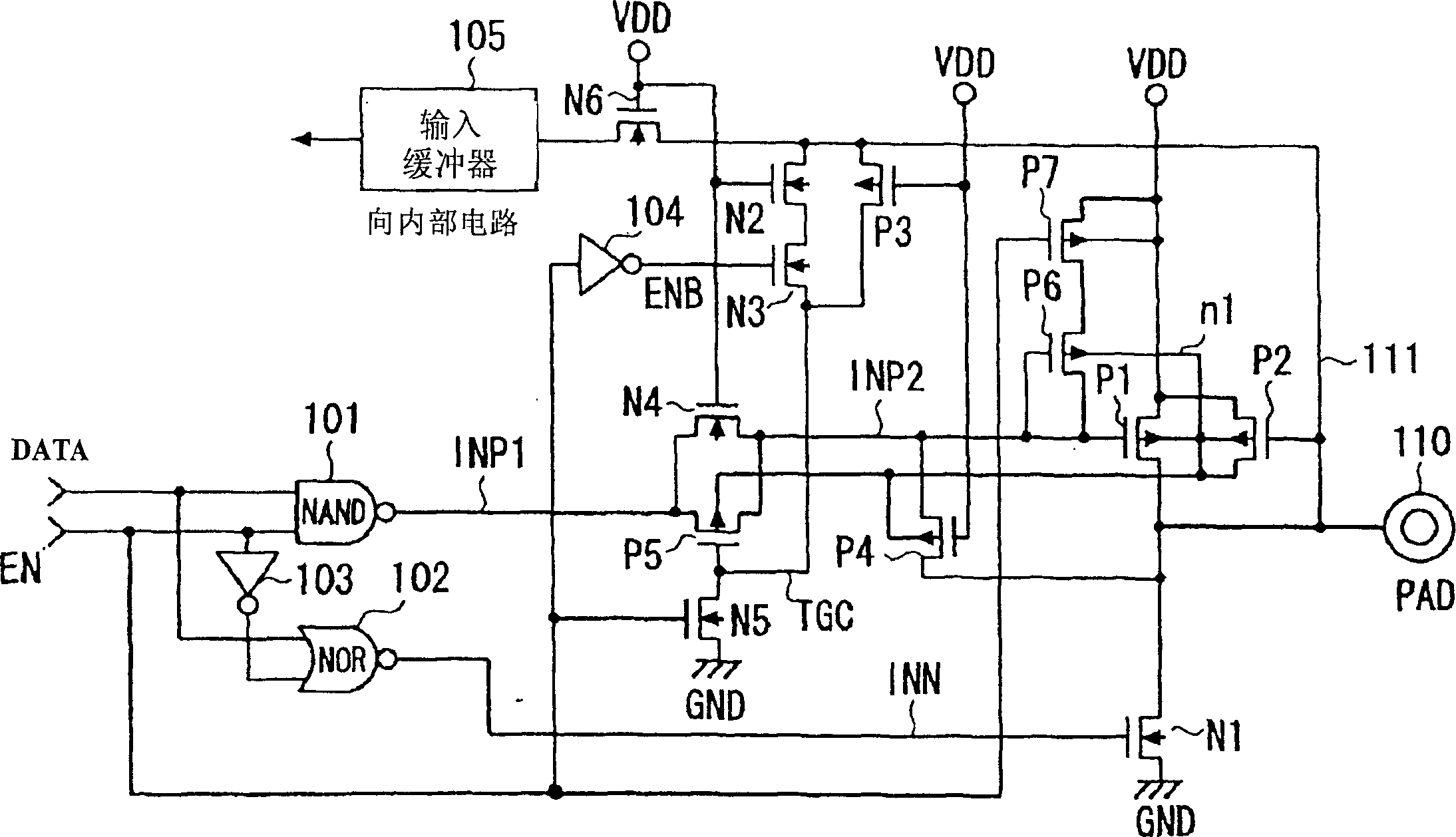

Semiconductor device4

InactiveCN1540864AShorten the timeHigh speed actionSwitching accelaration modificationsReliability increase in field effect transistorsControl signalData signal

A semiconductor device including a tristate buffer circuit, which includes, on an output stage, at least a first transistor (P1) for pull-up driving and a second transistor (N1) for pull-down driving, in which, when a control signal (EN) is of a value indicating an enable state, an output is set to a high level or to a low level, depending on a data signal, and in which, when the control signal is of a value indicating a disable state, the first and second transistors are turned off to set a high impedance state of the output. The semiconductor device further includes a control unit (120, P6, P7) for performing control for speeding up the transition from the on-state to the off-state of the first transistor (P1) at the time of switching the control signal (EN) from the enable state to the disable state.

Owner:RENESAS ELECTRONICS CORP

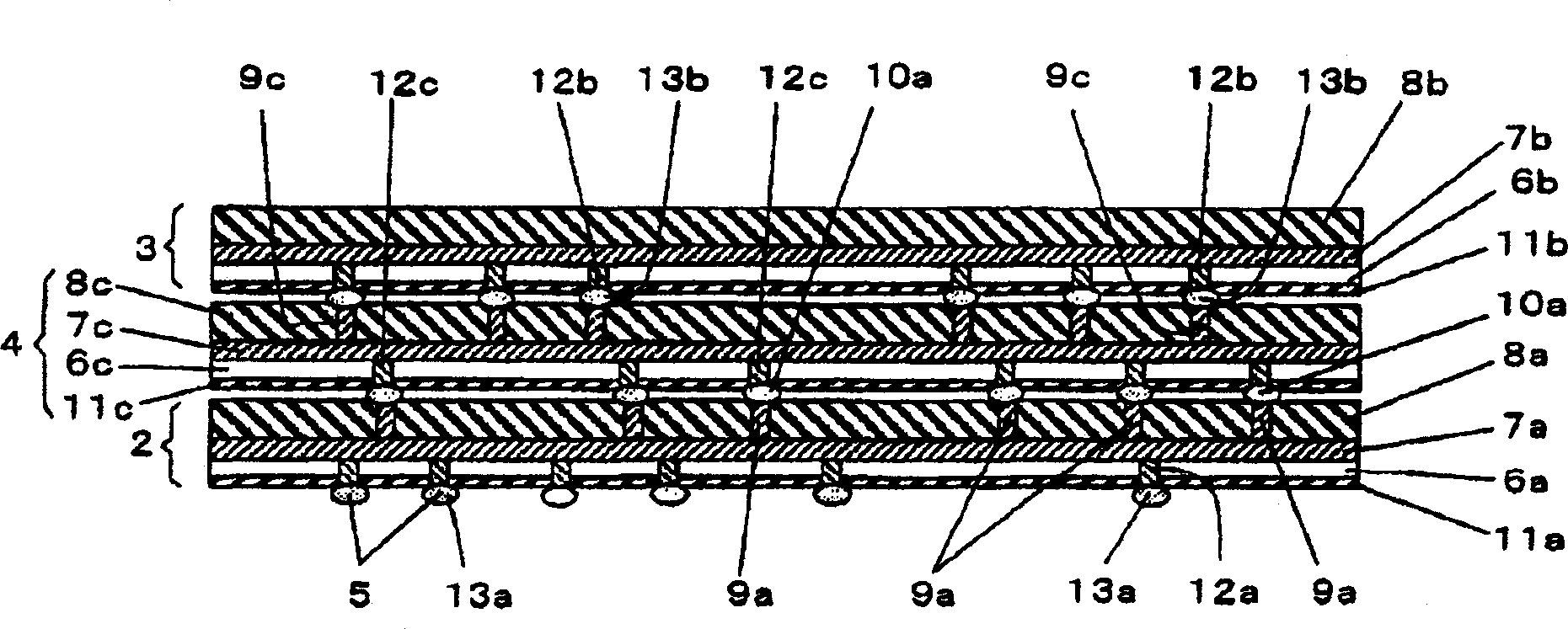

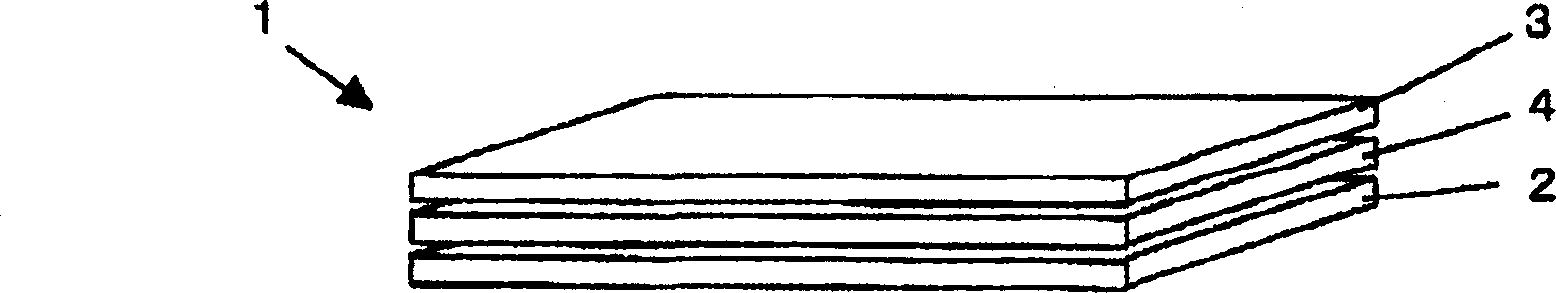

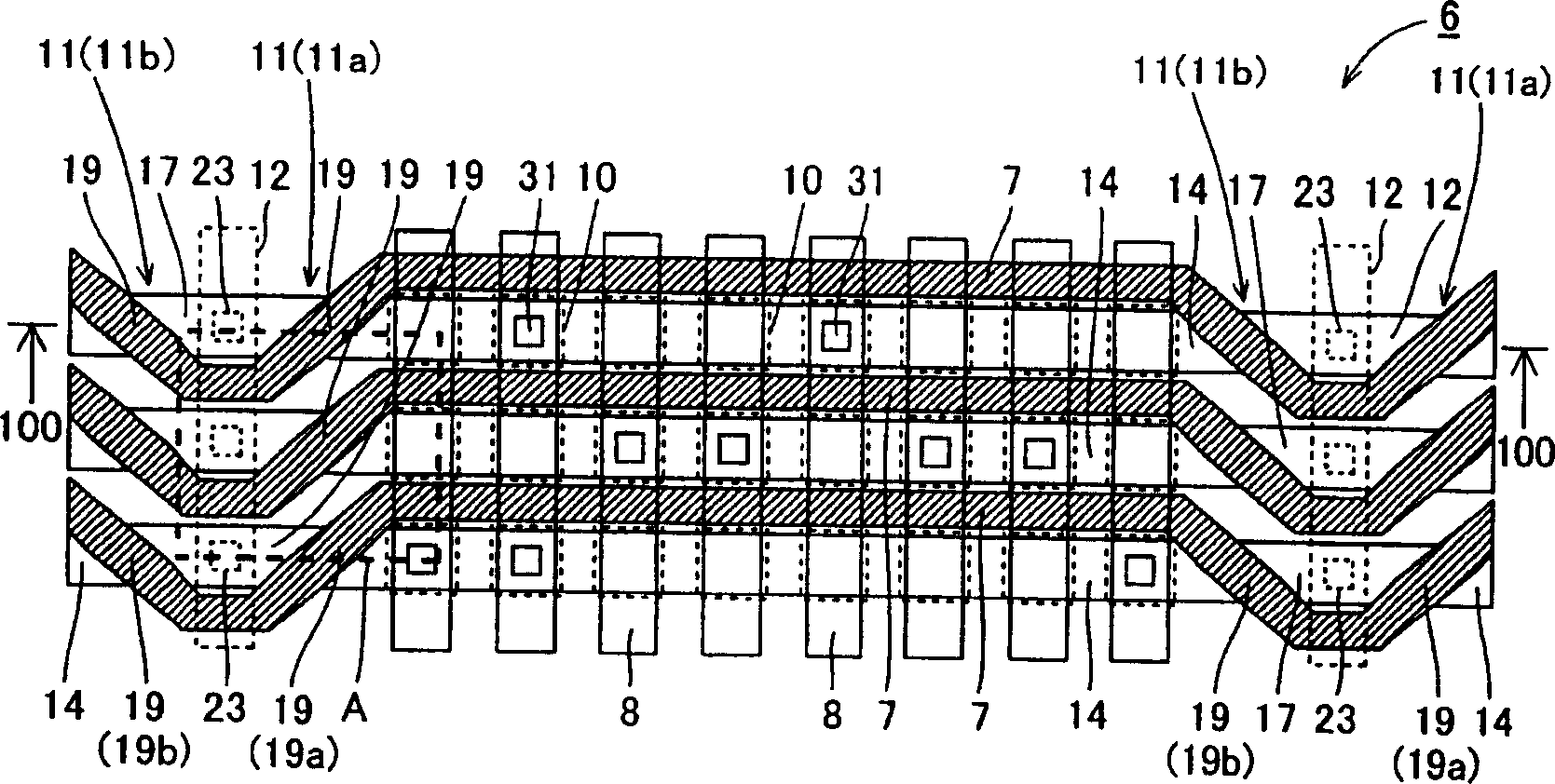

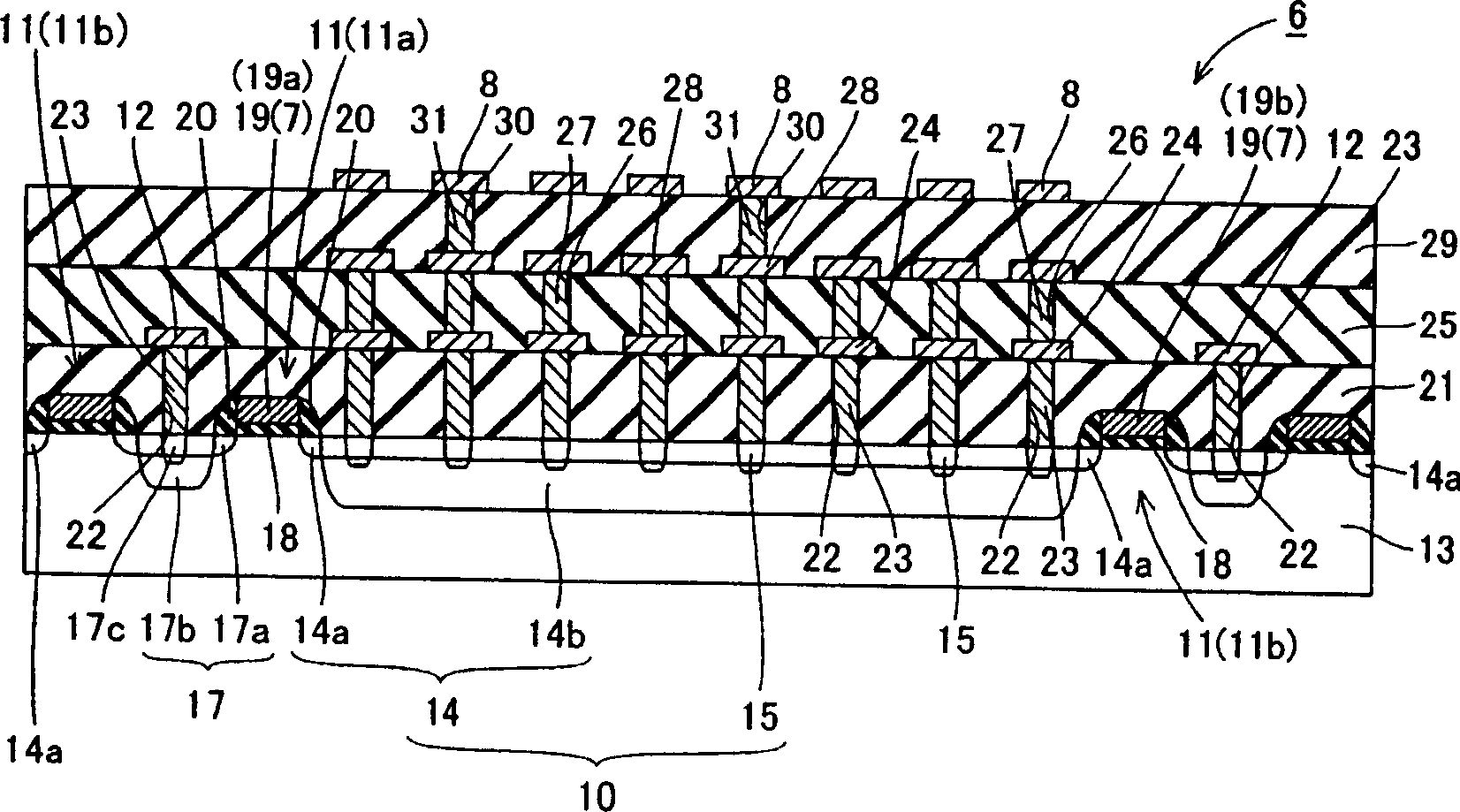

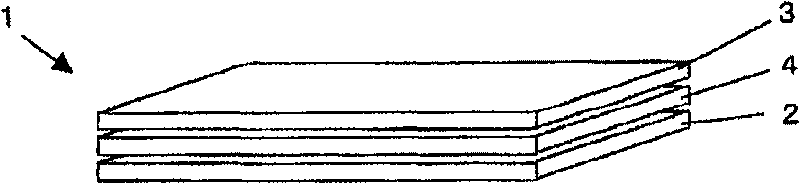

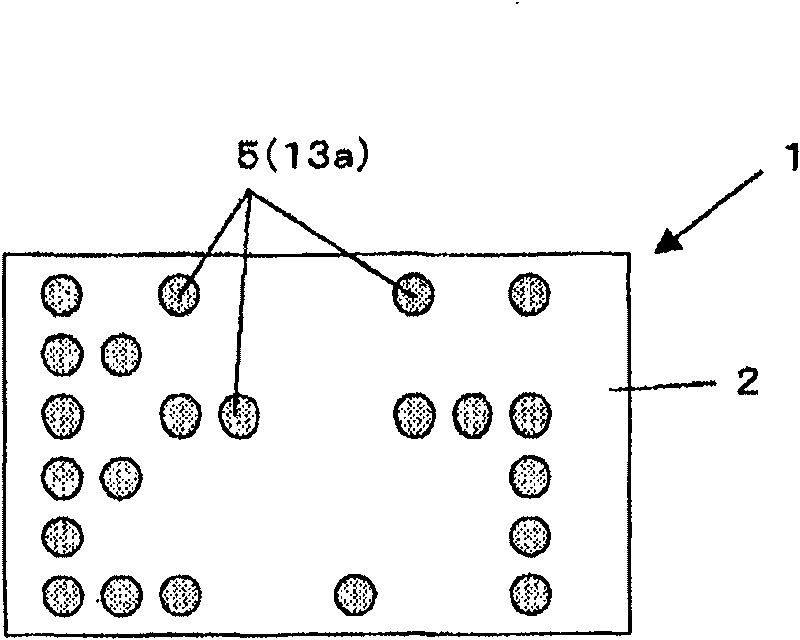

Semiconductor device and process for fabricating the same

ActiveCN1875481AAchieve thinningExcellent electrical propertiesSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

A thin stacked semiconductor device suitable for high speed operation. A plurality of specified circuits are formed on one surface of a semiconductor substrate while being arranged, and wiring and insulating layers being connected electrically with the circuits are laminated and formed sequentially in a specified pattern to form a multilayer wiring part. At the stage for forming the multilayer wiring part, a filling electrode is formed on the semiconductor substrate such that the surface is covered with an insulating film, a post electrode is formed on specified wiring at the multilayer wiring part, a first insulating layer is formed on one surface of the semiconductor substrate, the surface of the first insulating layer is removed by a specified thickness to expose the post electrode, the other surface of the semiconductor substrate is ground to expose the filling electrode and to form a through-type electrode, forward end of the through-type electrode is projected by etching one surface of the semiconductor substrate, a second insulating layer is formed on one surface of the semiconductor substrate while exposing the forward end of the through-type electrode, bump electrodes are formed on both electrodes and then the semiconductor substrate is divided to form a semiconductor device. A plurality of semiconductor devices thus obtained are stacked and secured at the bump electrodes thus manufacturing a stacked semiconductor device.

Owner:阿奇里斯科技公司

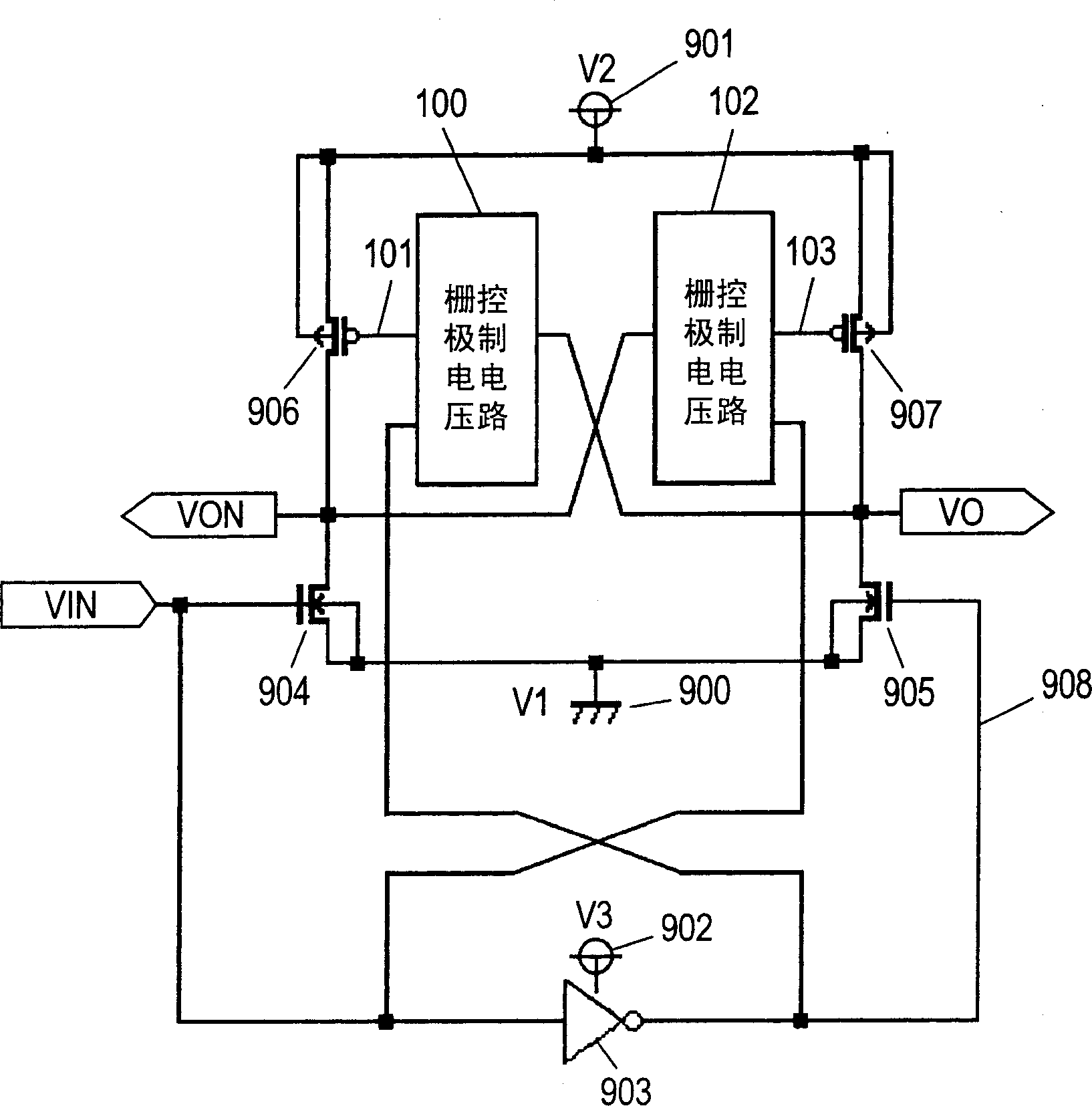

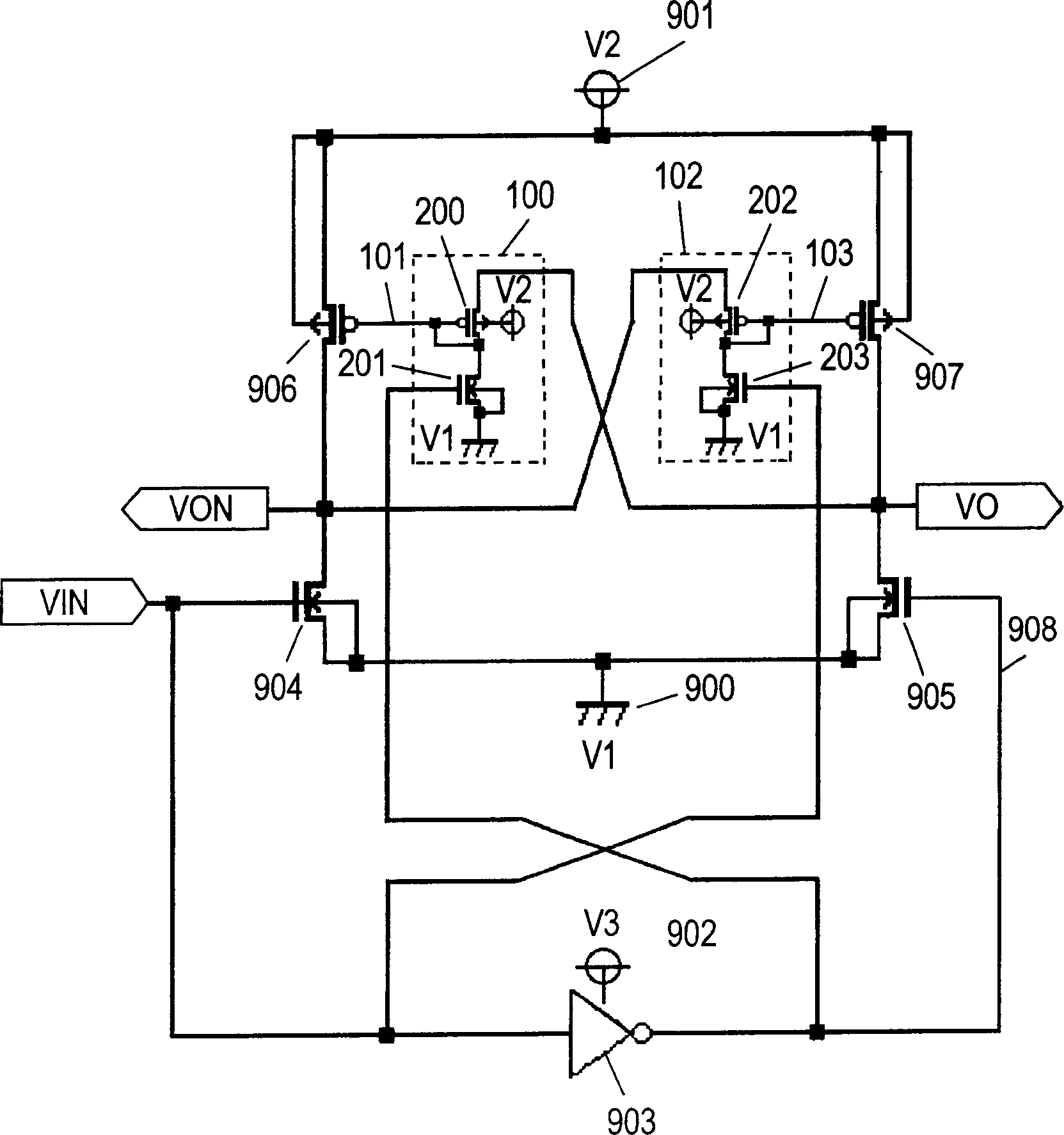

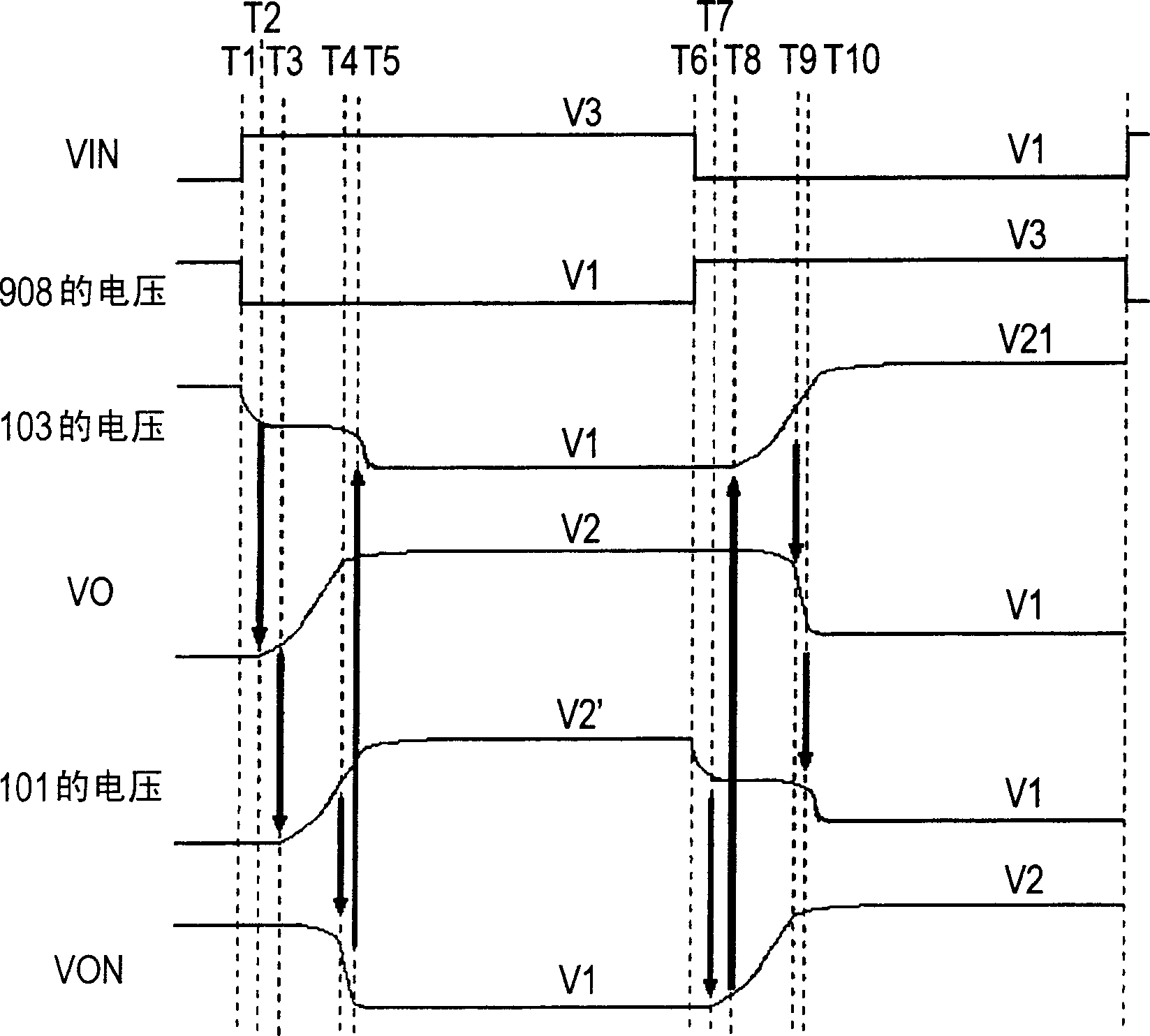

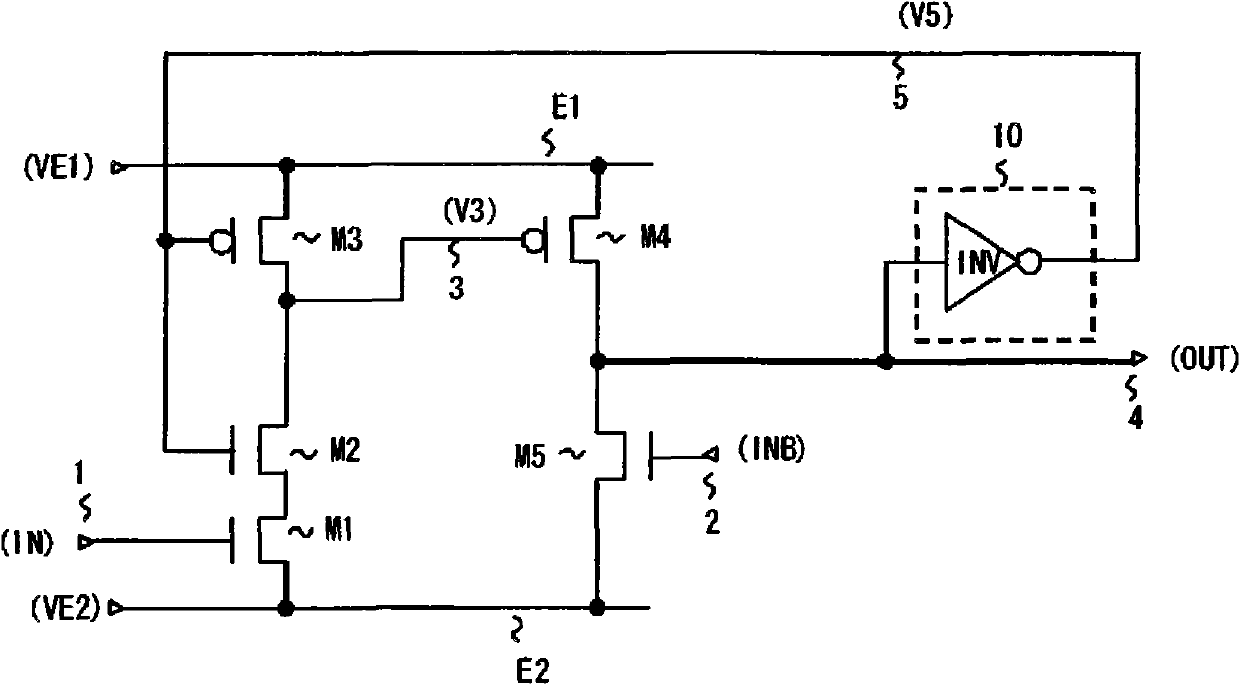

Level chagning circuit

InactiveCN1499724AIncrease the areaHigh speed actionPulse automatic controlLogic circuits coupling/interface using field-effect transistorsEngineeringGate voltage

A level shift circuit which realizes a high-speed and power-saved operation particularly when the input voltage is at a low level is provided. The level shift circuit of the present invention comprises a first gate voltage control circuit controlled by a inverted signal of an input signal, which is inserted between a gate of a third transistor and a second output terminal; a second gate voltage control circuit controlled by the input signal, which is inserted between a gate of a fourth transistor and a first output terminal; a first transistor; and a second transistor. When the input signal shifts from 'H' to 'L', the first transistor turns OFF, the third transistor is turned ON by the first gate voltage control circuit, and then a voltage of the first output terminal rises. The second transistor turns ON, the fourth transistor is turned OFF by the second gate voltage control circuit, and then the voltage of the second output terminal goes down.

Owner:CETUS TECH INC

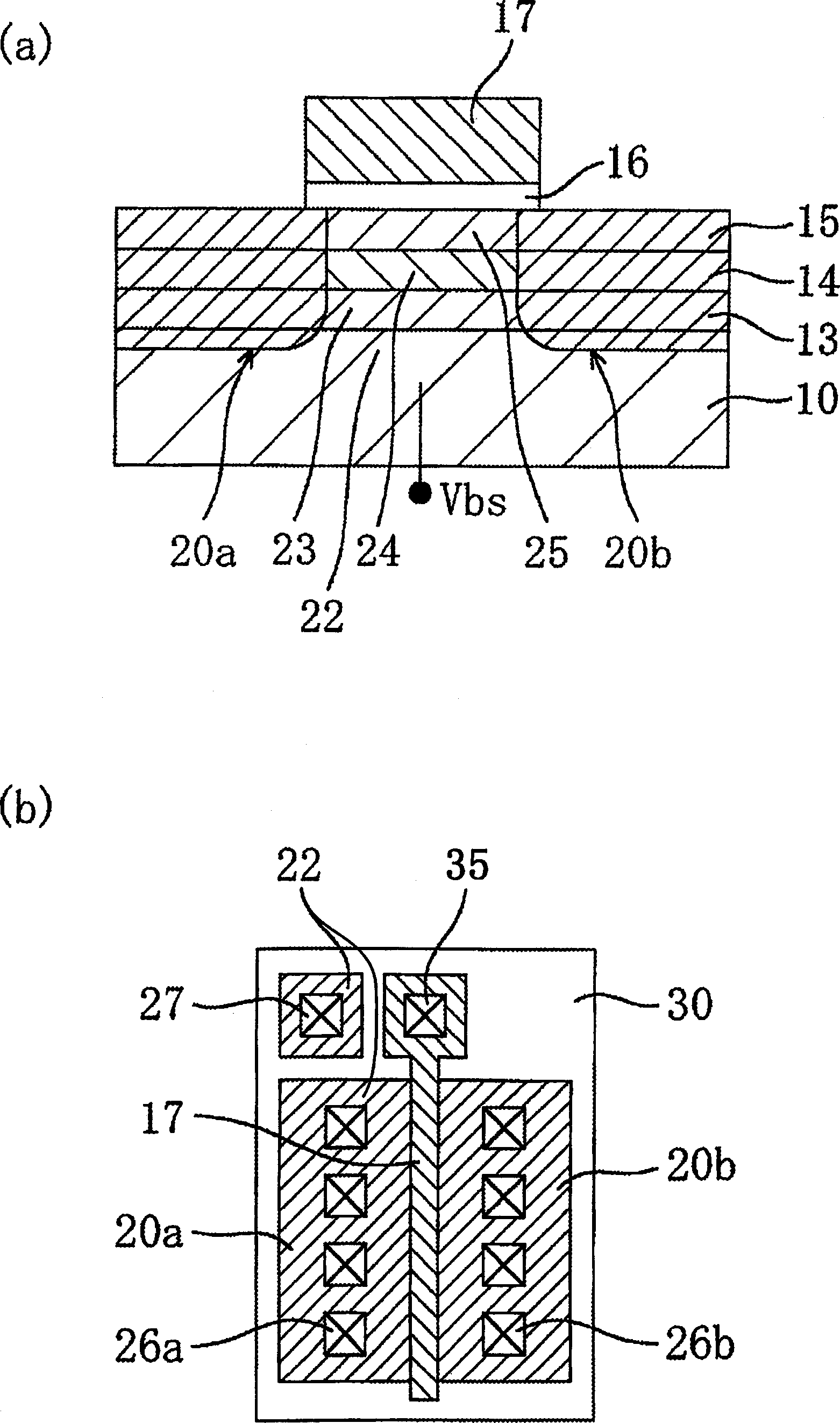

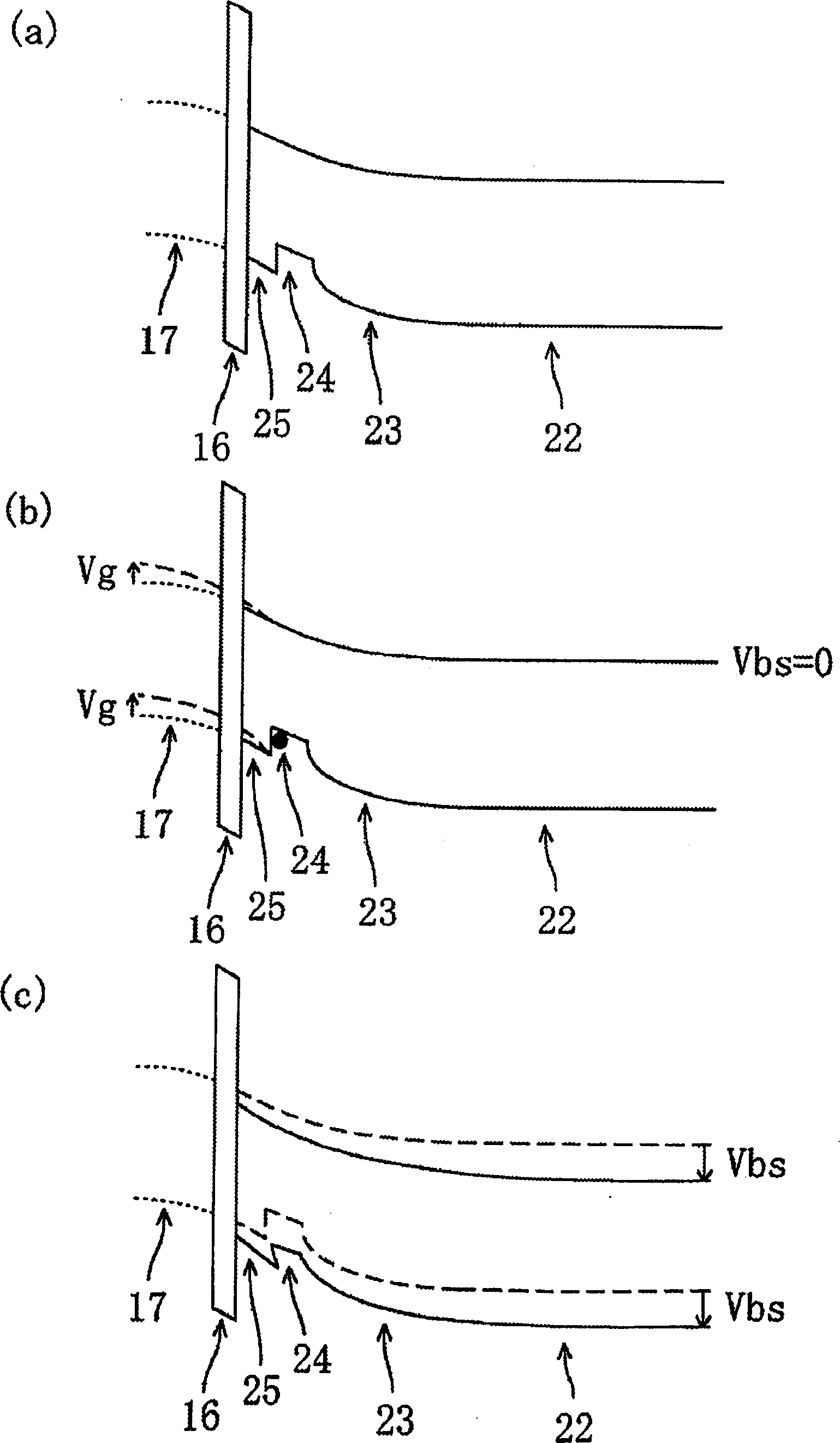

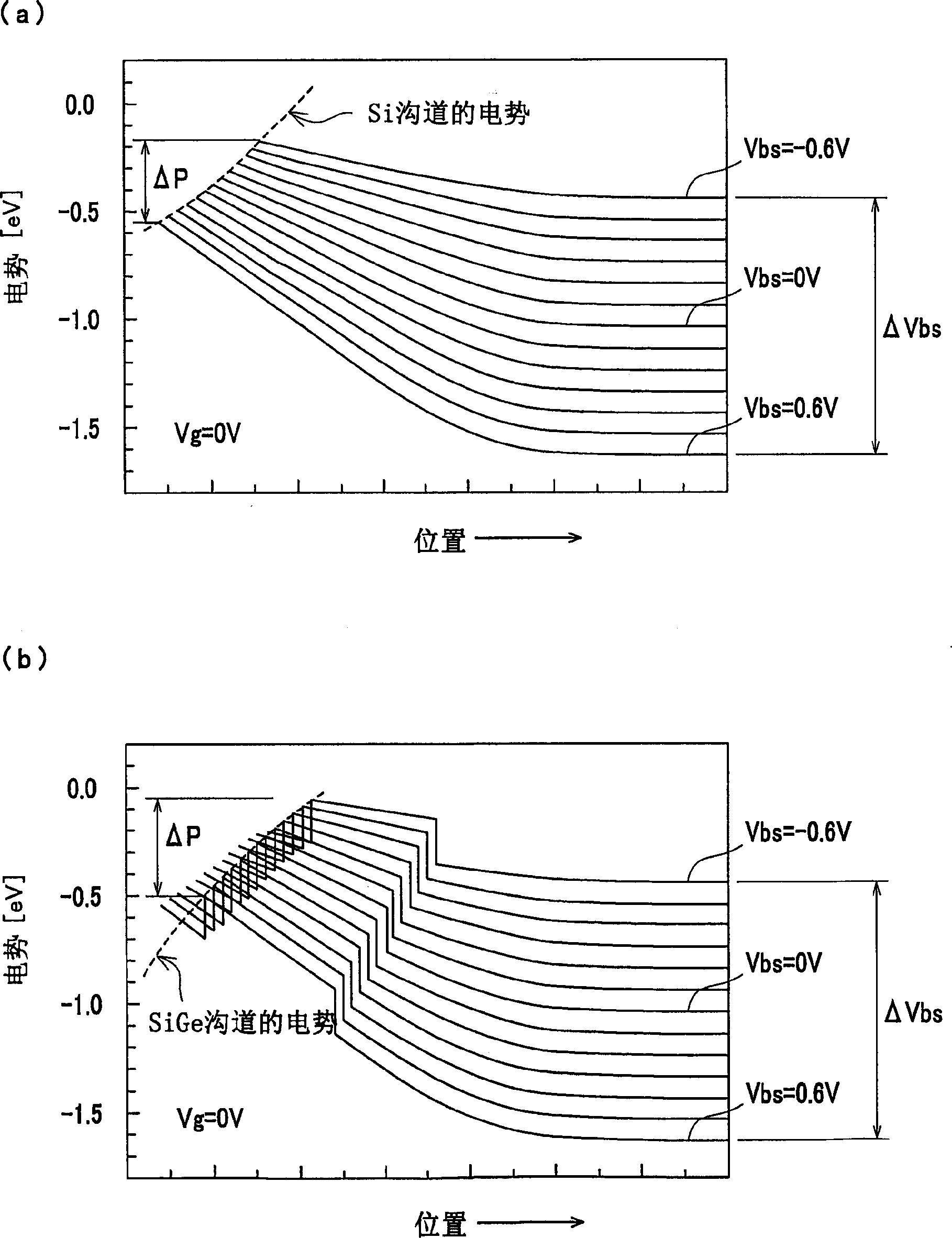

Semiconductor device

InactiveCN1620728ALower threshold voltageHigh speed actionTransistorSolid-state devicesSemiconductor packageSemiconductor device

The semiconductor device of the present invention includes a semiconductor layer (10-15), a gate insulating film (16) provided on the semiconductor layer, a gate electrode (17) provided on the gate insulating film, and in the semiconductor layer A source region (20a) and a drain region (20b) of the first conductivity type provided on both sides of the gate electrode are viewed from a plan view, and between the source region and the drain region in the semiconductor layer, The gap layer (25), the channel region (24) and the region below the channel (23, 22) of the second conductivity type arranged in sequence downward from the interface with the above-mentioned gate insulating film, and the application to the above-mentioned channel below the region A bias electrode part (Vbs) for voltage, wherein the channel region is composed of a first semiconductor, and the gap layer and the region below the channel are respectively composed of a second semiconductor and a third semiconductor having a band gap larger than that of the first semiconductor, The above-mentioned bias electrode member is provided independently of the above-mentioned gate electrode and capable of applying a voltage.

Owner:PANASONIC CORP

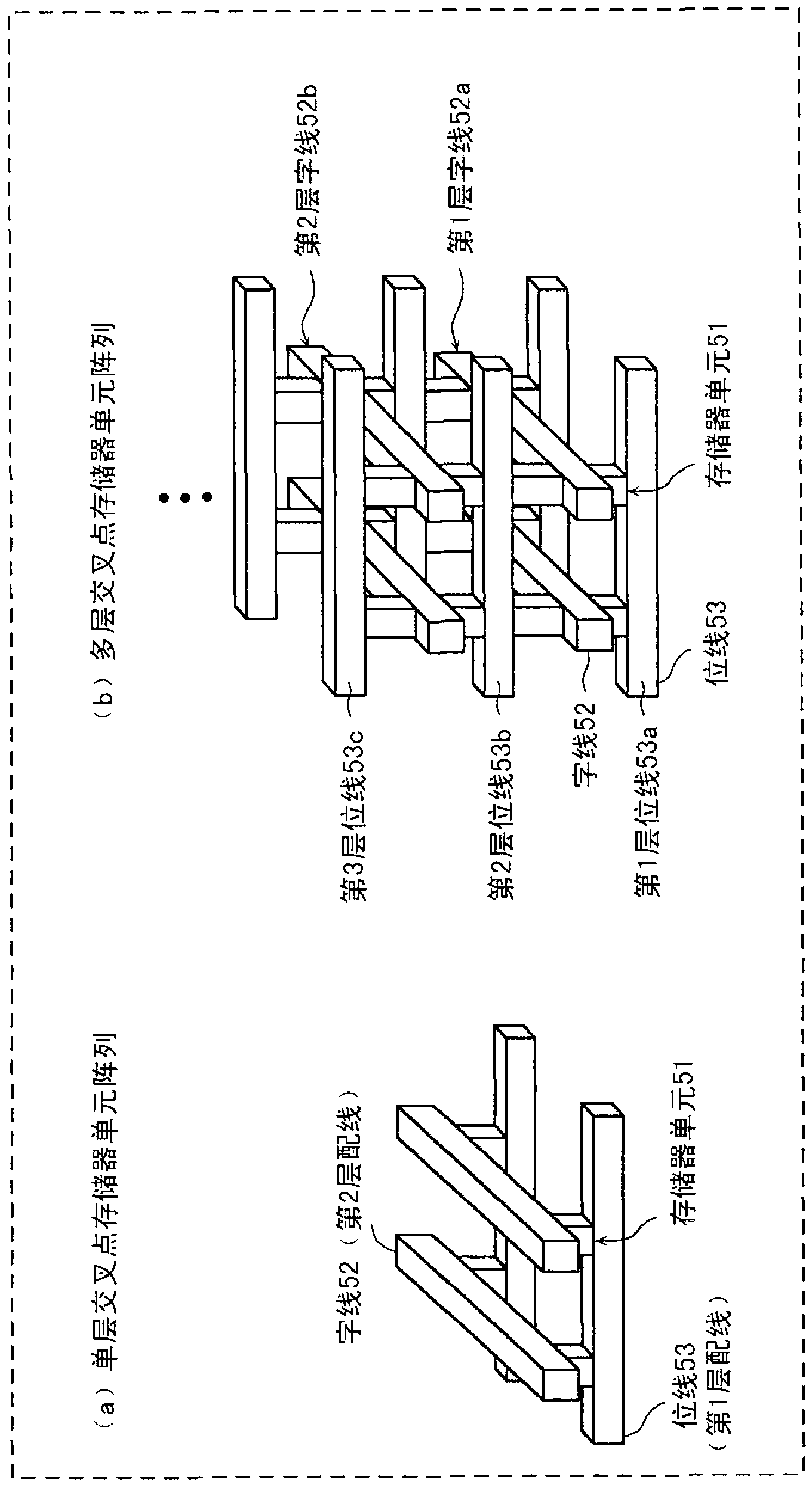

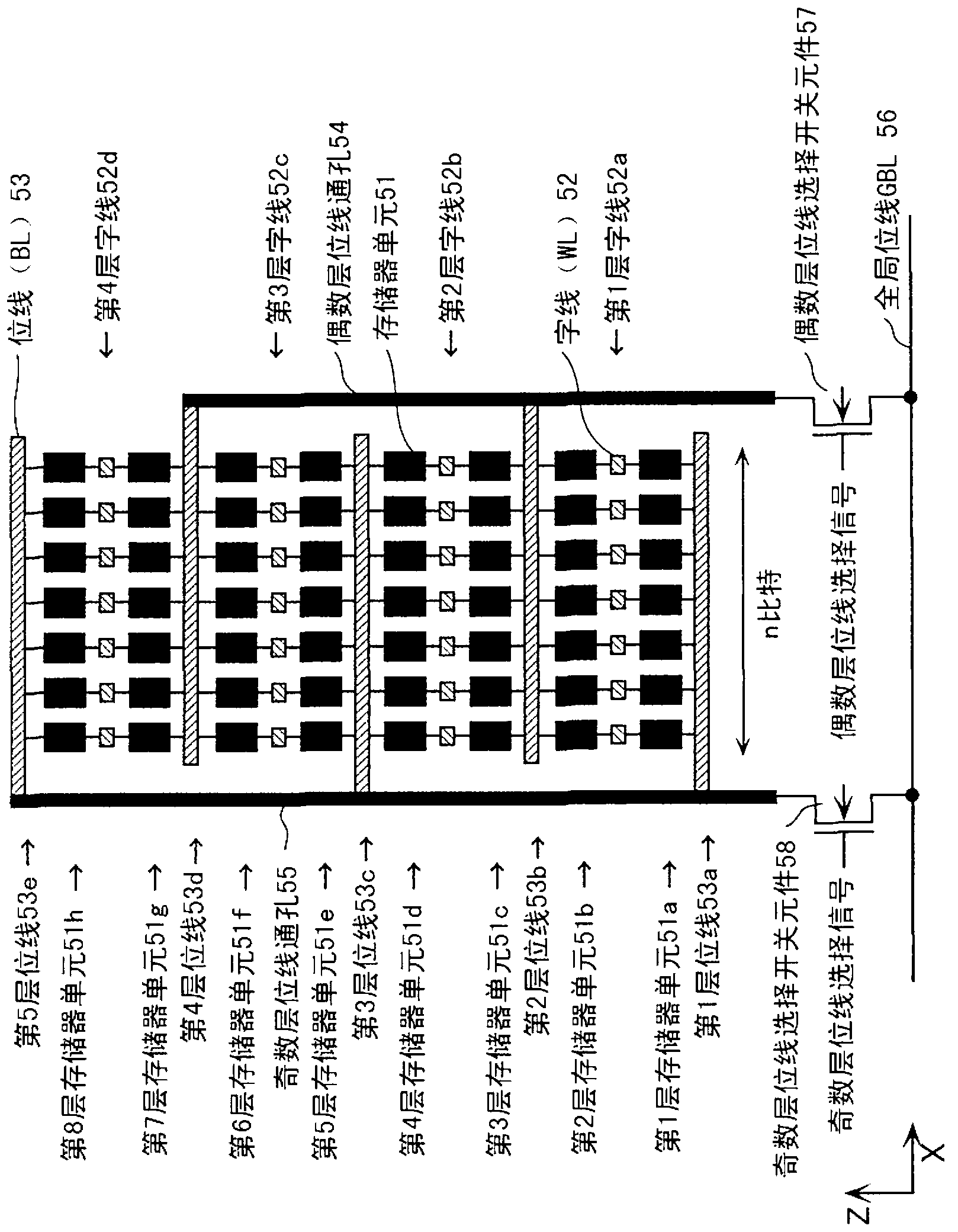

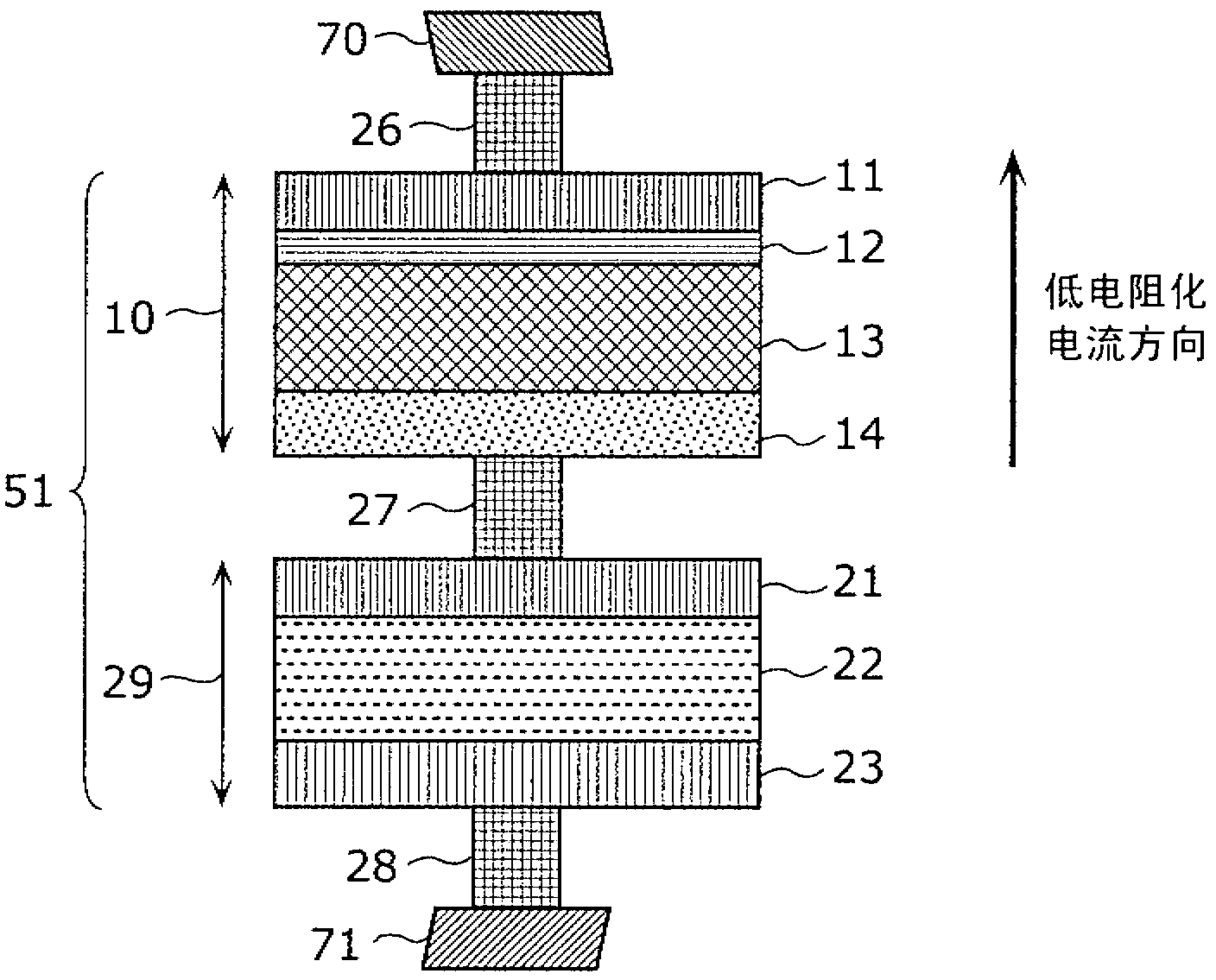

Crosspoint-type variable-esistance non-volatile storage device

ActiveCN103238214AEasy to manufactureWrite operation is stableSolid-state devicesDigital storageElectrical resistance and conductancePower flow

Memory cells (51) are formed at each intersection between X-axis bit lines (53a and 53b) and Y-axis word lines (52a) formed in a plurality of layers. In a multi-layer crosspoint structure in which there is a plurality of vertical array surfaces sharing a word line arranged on the Y axis for every group of bit lines aligned with the Z axis, the even-numbered layer bit lines (53b) sharing a connection are connected and disconnected from a global bit line (56) by an even-numbered layer bit line-selecting switching element (1002), and the odd-numbered layer bit lines (53a) sharing a connection are connected and disconnected from the global bit line (56) by an odd-numbered layer bit line-selecting switching element (1001). The even-numbered layer bit line-selecting switching element (1002) and the odd-numbered layer bit line-selecting switching element (1001) have a bit line-selecting function and, during low-resistance writing, a current-limiting function.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

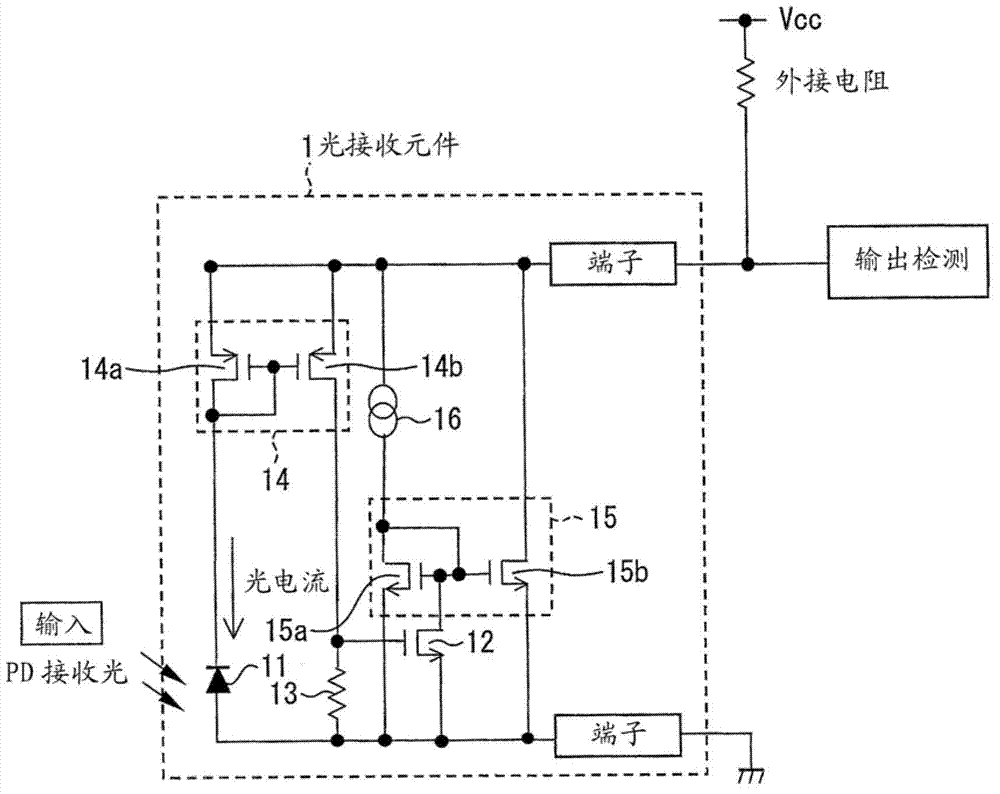

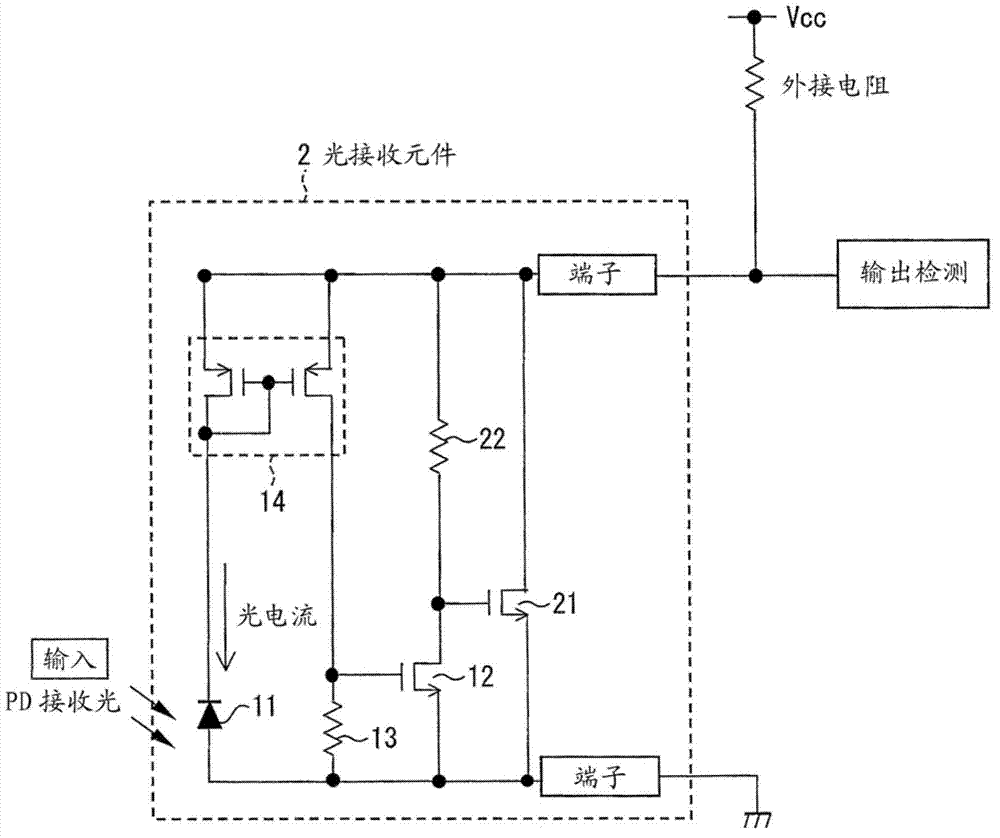

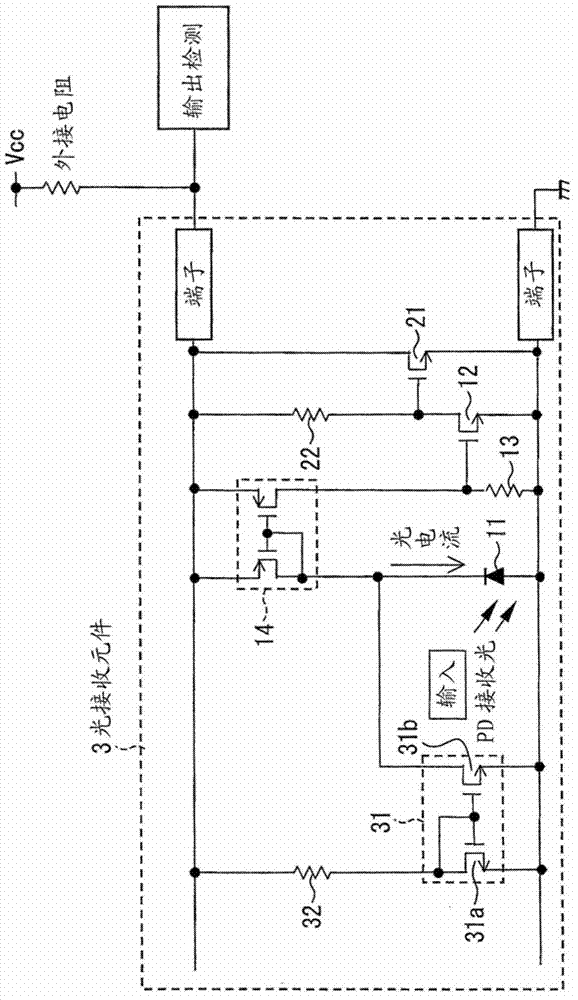

Optical sensor and electronic device

ActiveCN103017898AHigh speed actionAmplifiers controlled by lightPhotometry electrical circuitsPotential differencePhotodiode

The invention relates to an optical sensor and an electronic device. When no light enters a photodiode, a second current mirror circuit operates. Consequently, a current that decreases a potential difference between two terminals of a light-receiving element flows into a transistor of the second current mirror circuit and an output of an optical sensor becomes low. Meanwhile, when light enters the photodiode, a transistor of the light-receiving element is turned on and the second current mirror circuit stops operating. Consequently, the current that decreases the potential difference between the two terminals of the light-receiving element is stopped in the transistor of the second current mirror circuit and the output of the optical sensor becomes high. This makes it possible to provide an optical sensor that has a circuit in which an output of a light-receiving element does not depend on a photocurrent and that is capable of operating at a high speed.

Owner:SHARP KK

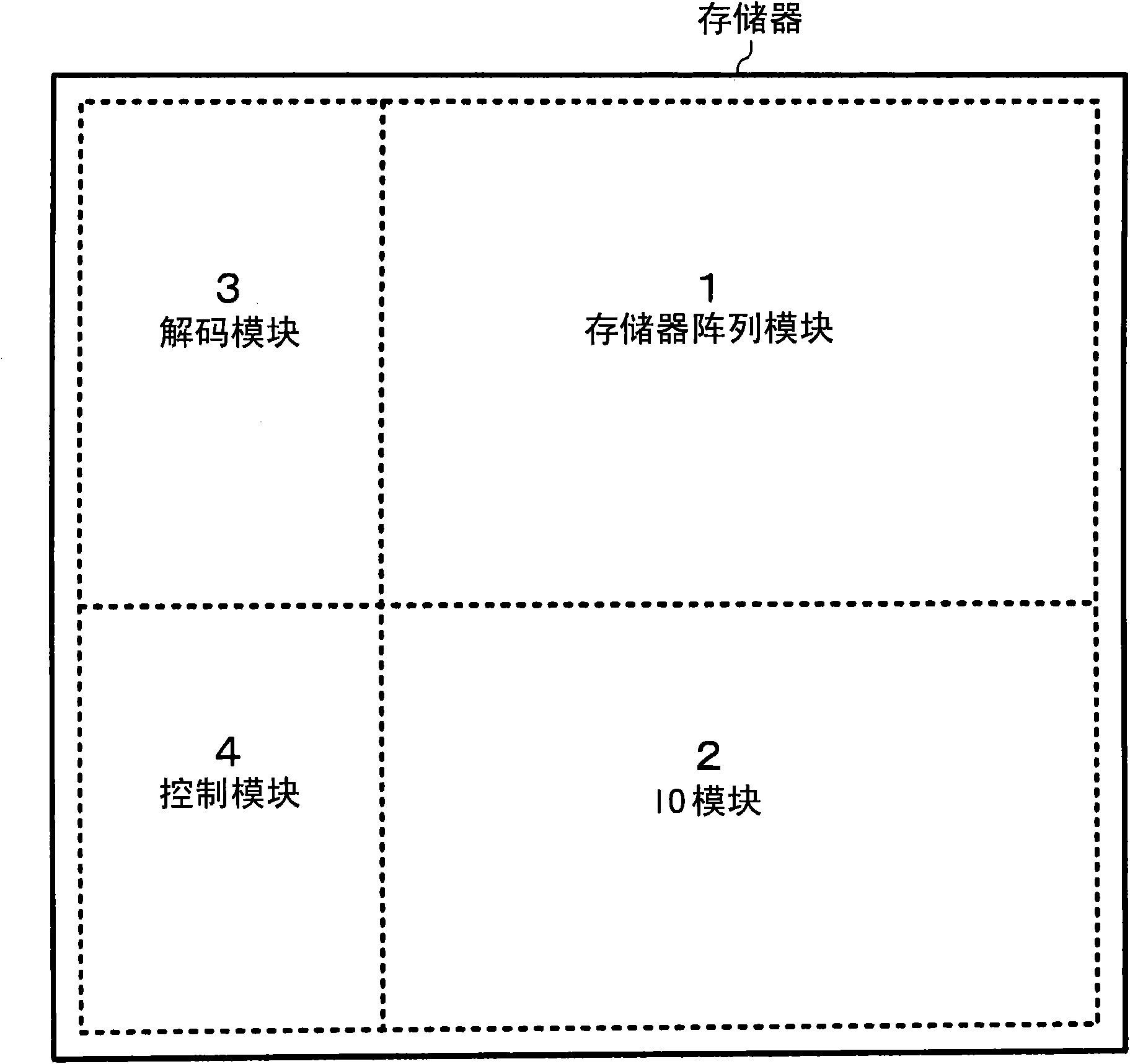

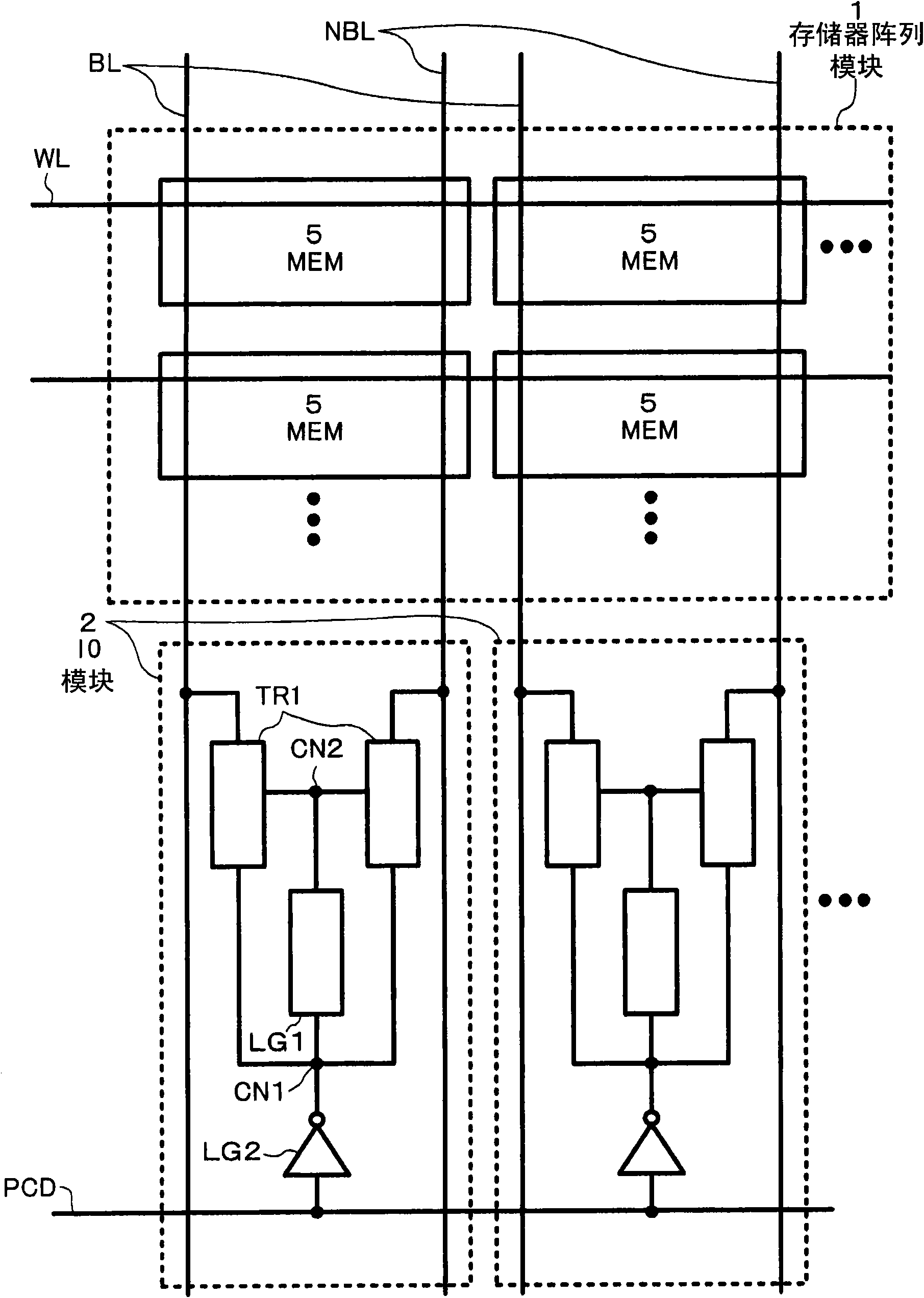

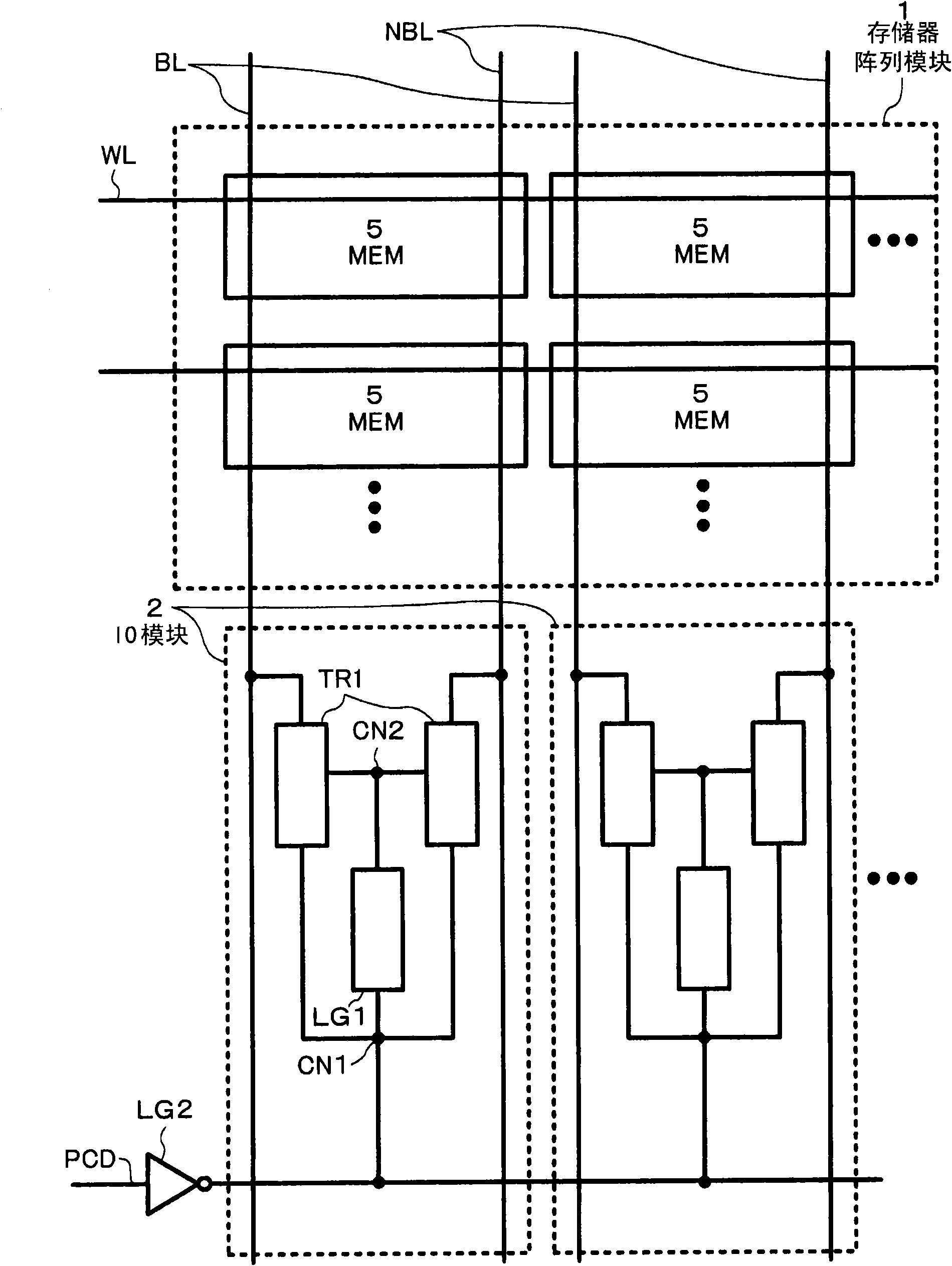

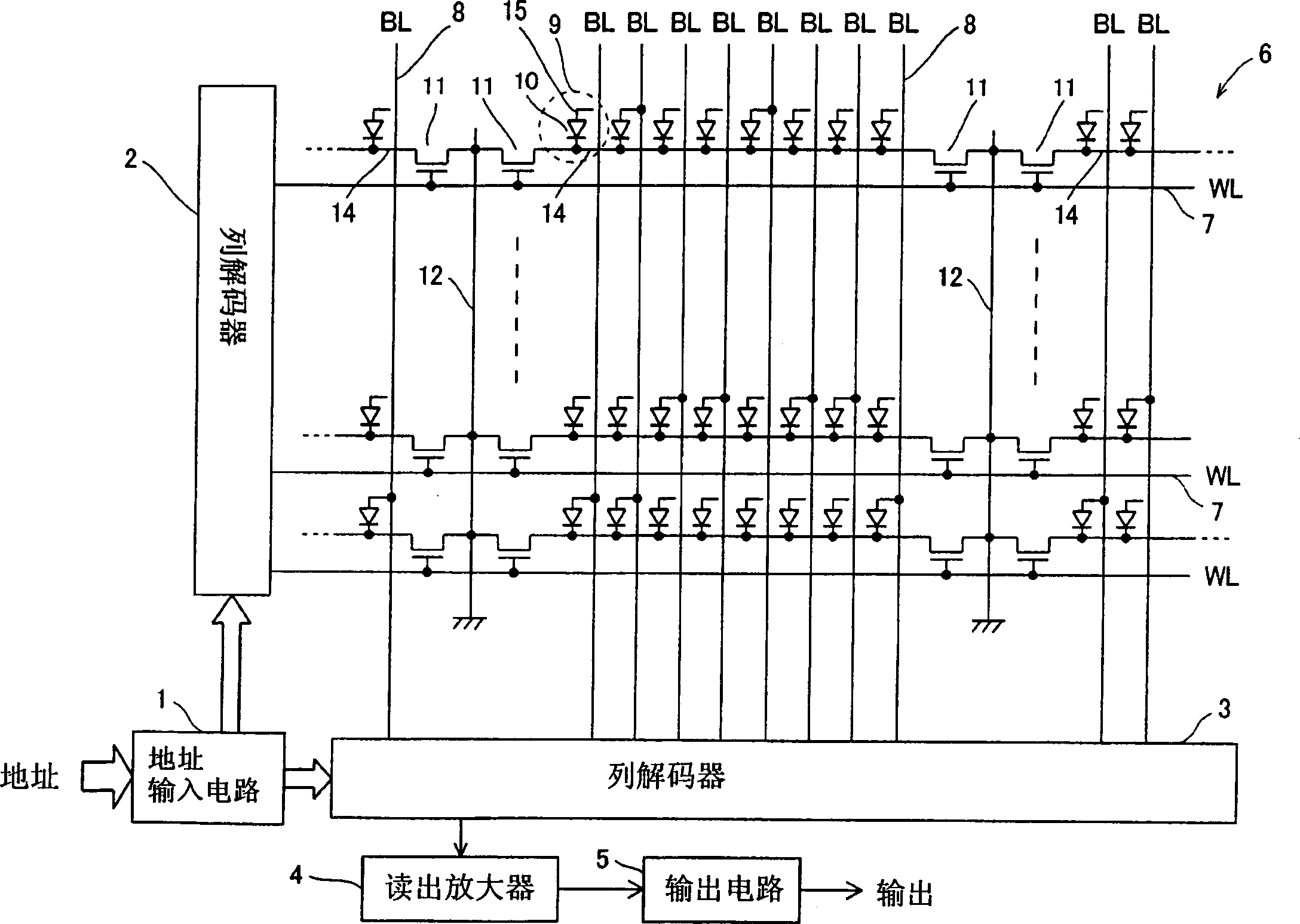

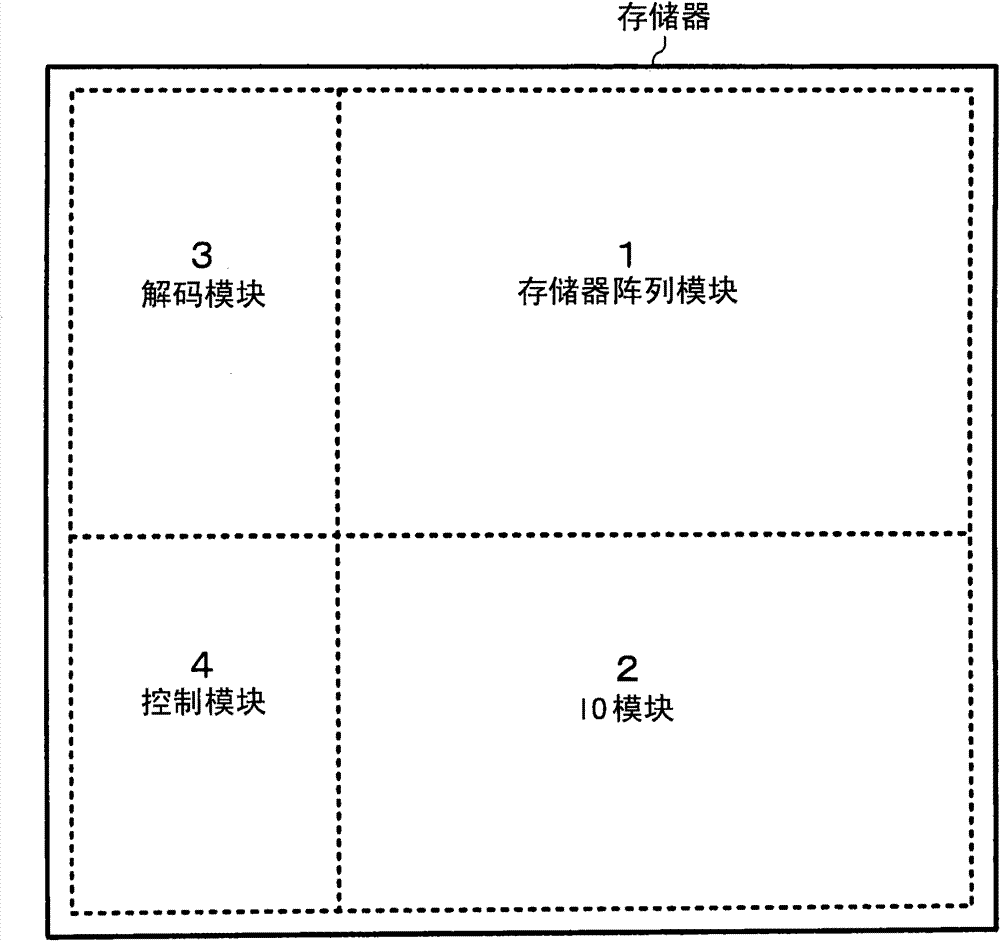

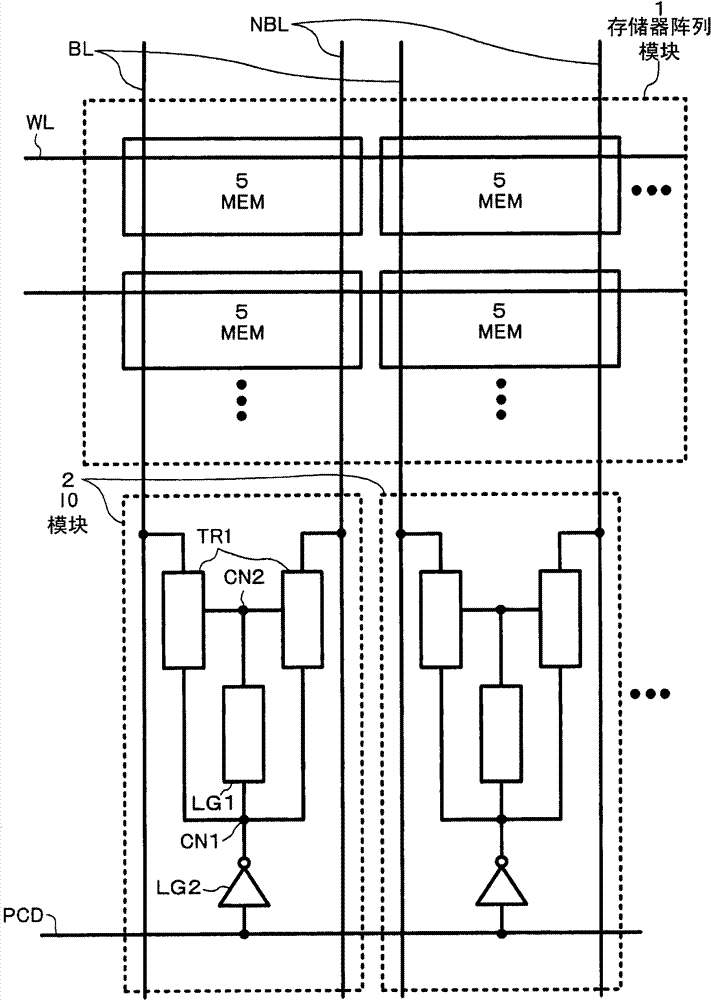

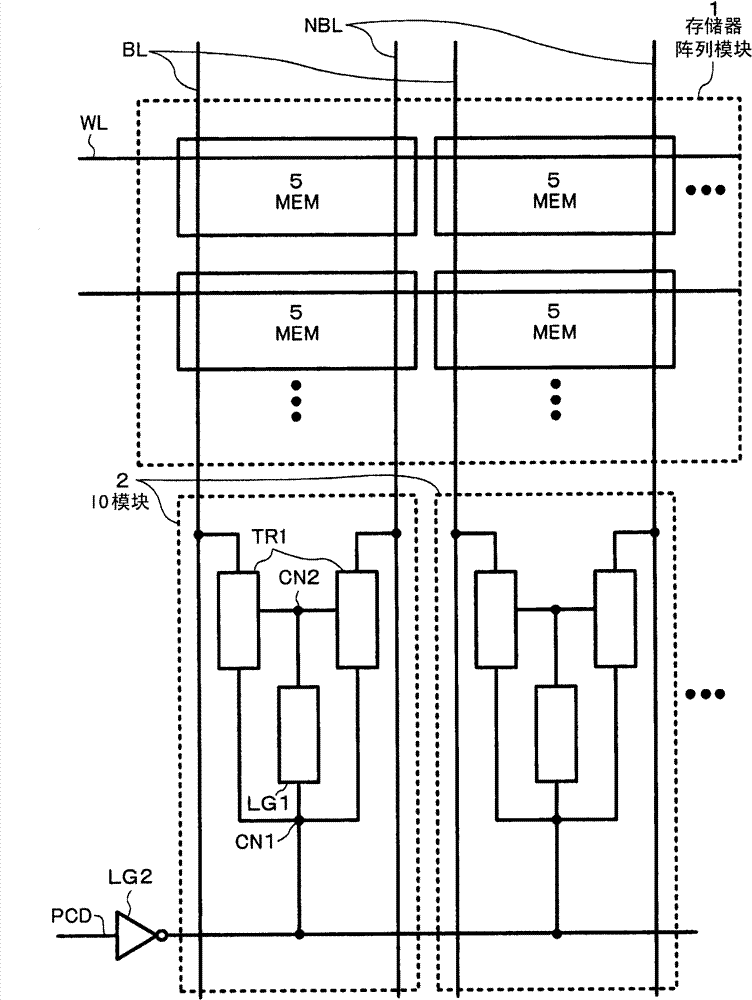

Semiconductor memory device

ActiveCN101981626APrevent accidental writingSNM improvementDigital storageComputer architectureComputer module

The invention provides a semiconductor memory device. With respect to memory that applies bit line step-down technology, an IO block (2) is provided with: a first transistor (TR1) that controls the potential of a first bit line (BL / NBL) provided for a memory cell line; and a first logic gate (LG1) that controls the first transistor (TR1). The drain or the source of the first transistor (TR1) and the input of the first logic gate (LG1) are connected, the gate of the first transistor (TR1) and the output of the first logic gate (LG1) are connected, and the first transistor (TR1) is pulse-driven. In addition, a data readout circuit (11) is provided only on one of the bit lines (BL).

Owner:SOCIONEXT INC

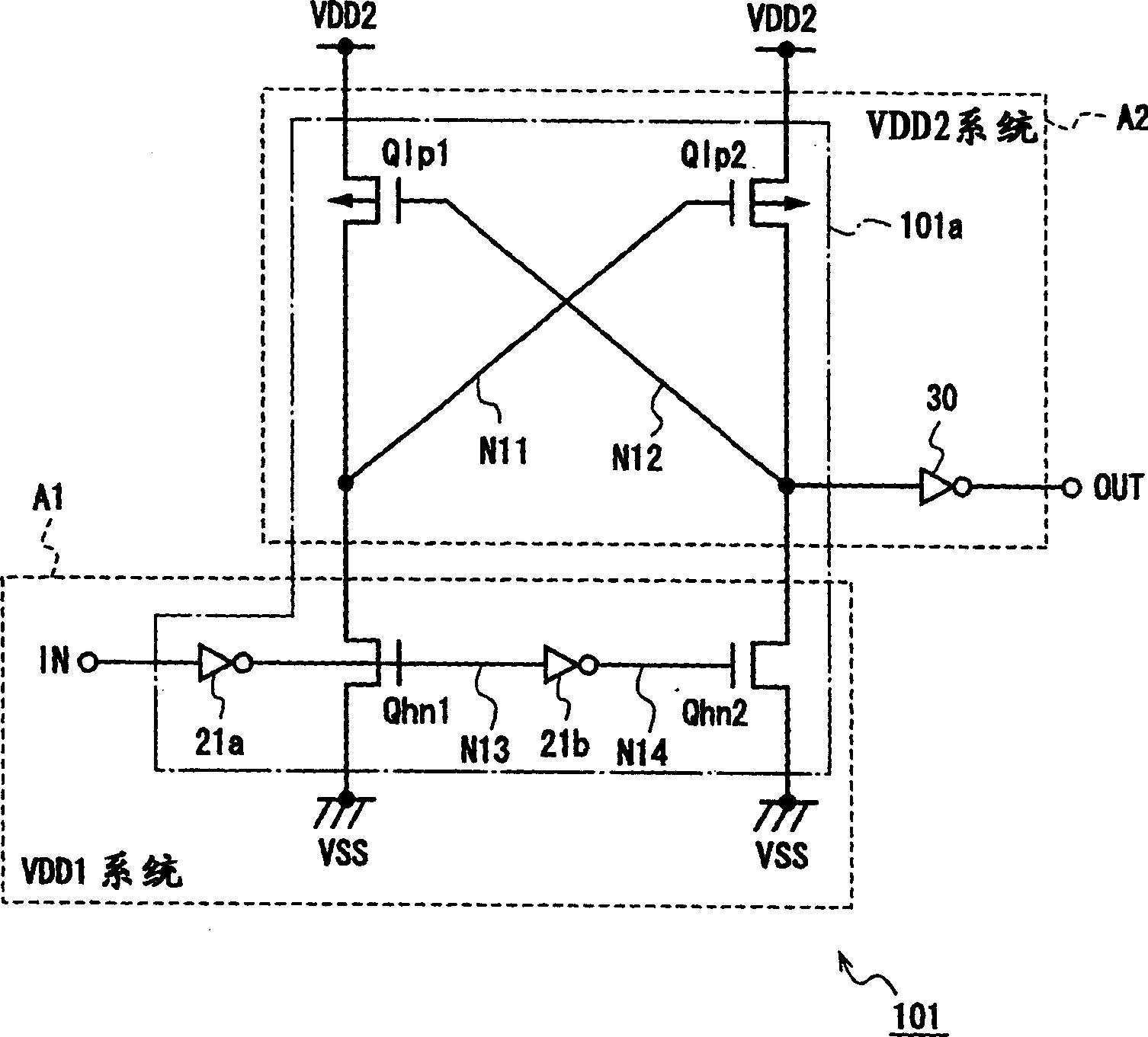

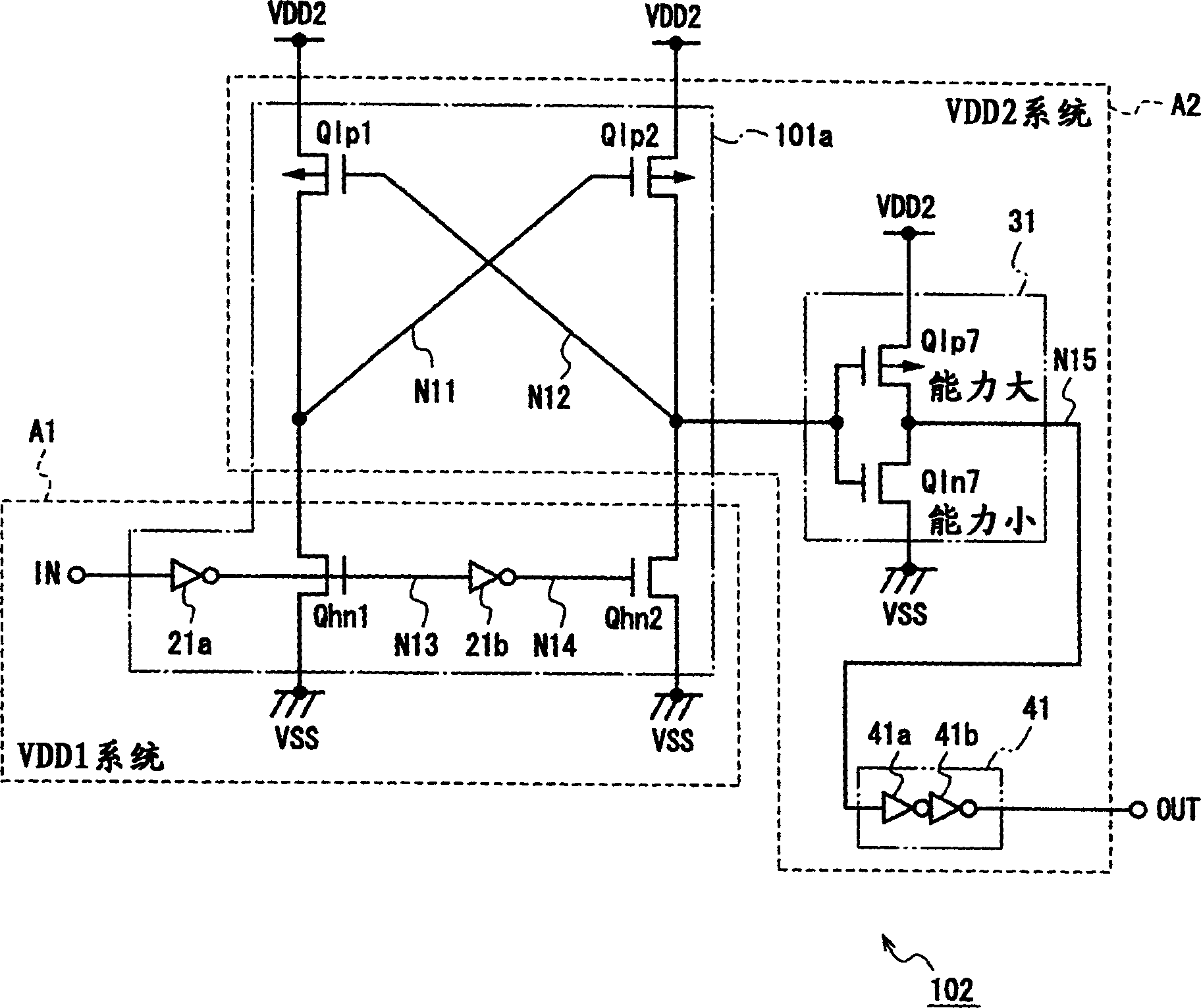

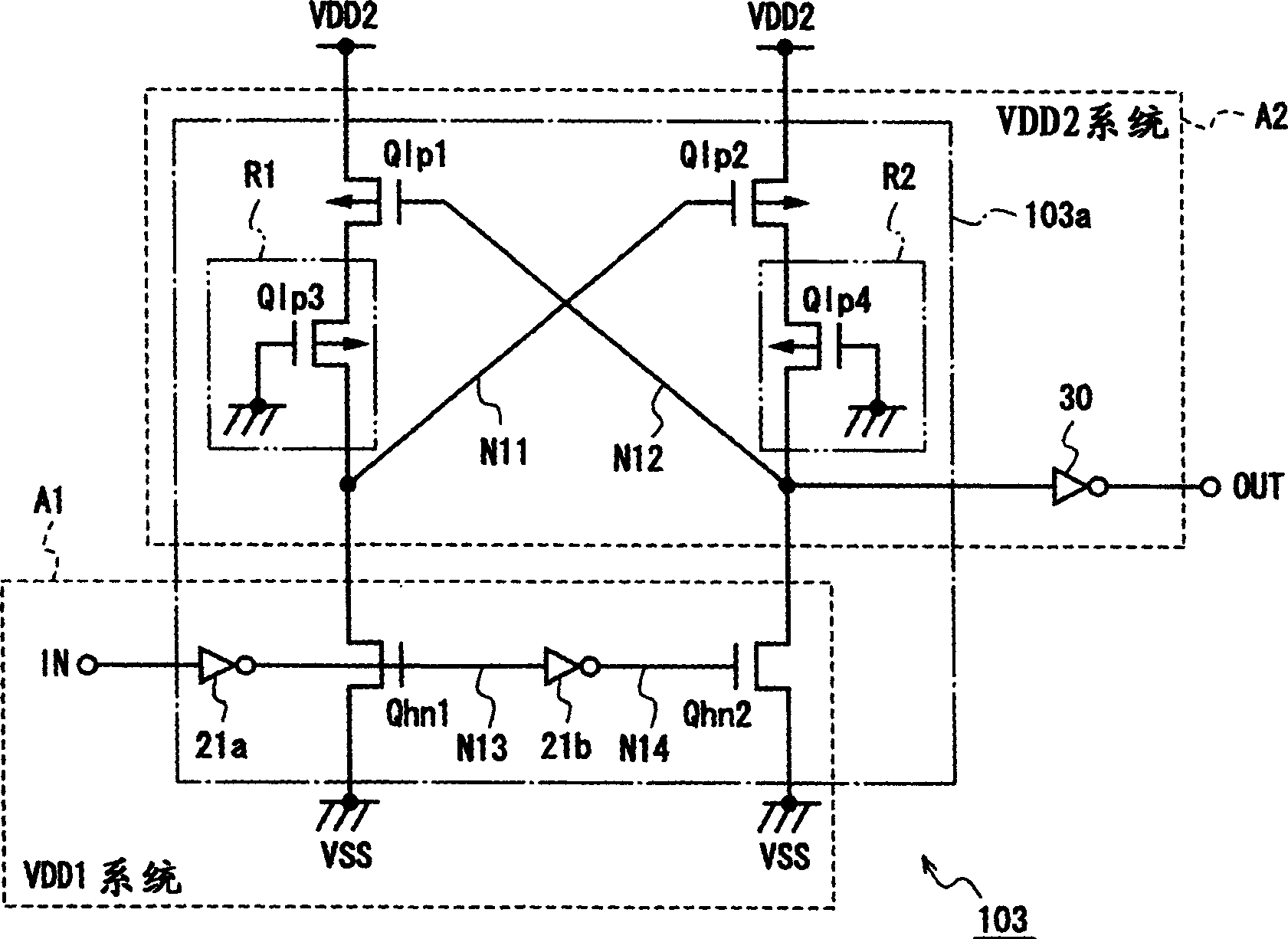

Voltage level conversion circuit

InactiveCN1700600AReduced driving abilityAchieve high speedPulse automatic controlLogic circuits coupling/interface using field-effect transistorsHigh voltage transistorsSource level

To make a voltage level converting circuit, which converts an input signal having a logical voltage level corresponding to a high power supply voltage VDD1 into a signal having a logical voltage level corresponding to a low supply voltage VDD2 and outputs it, operable at the lower low supply voltage VDD2. A power source level converting circuit comprises a level converting portion for converting an input signal of a VDD1 system to a signal of a VDD2 system and a NOT circuit 30 for reversing the level converted input signal and outputting it. Outputs of NOT circuits and of the VDD1 system constituting the level converting portion 101a are inputted only into high breakdown voltage transistors Qhn1 and Qhp2 in the level converting portion . A signal having a logical voltage level corresponding to the low supply voltage VDD2 is inputted in low breakdown voltage transistors Qln1 and Qlp2 in the level converting portion . Furthermore, only the level converted input signal from the level converting portion is inputted into the NOT circuit at post-stage of the level converting portion .

Owner:PANASONIC CORP

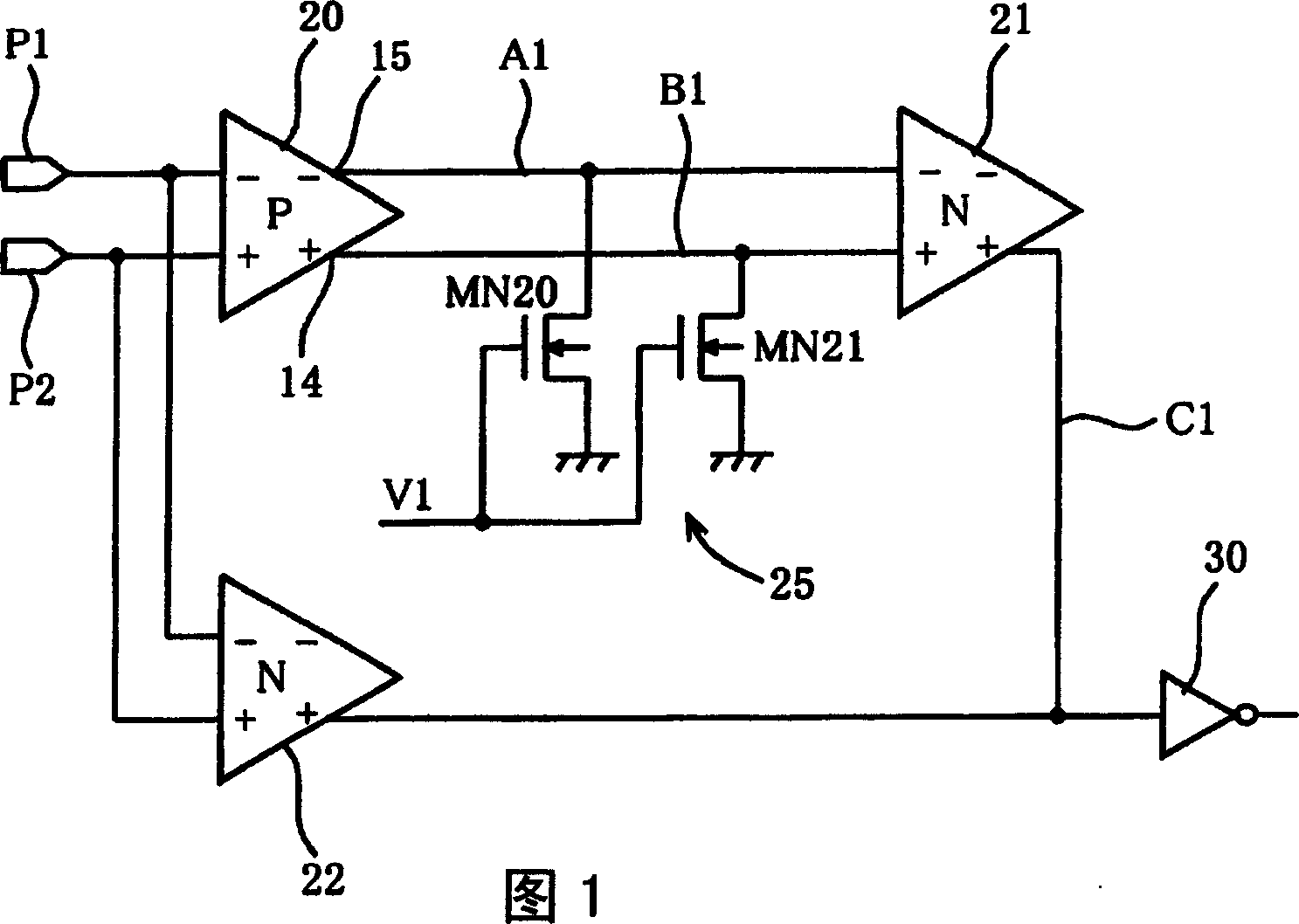

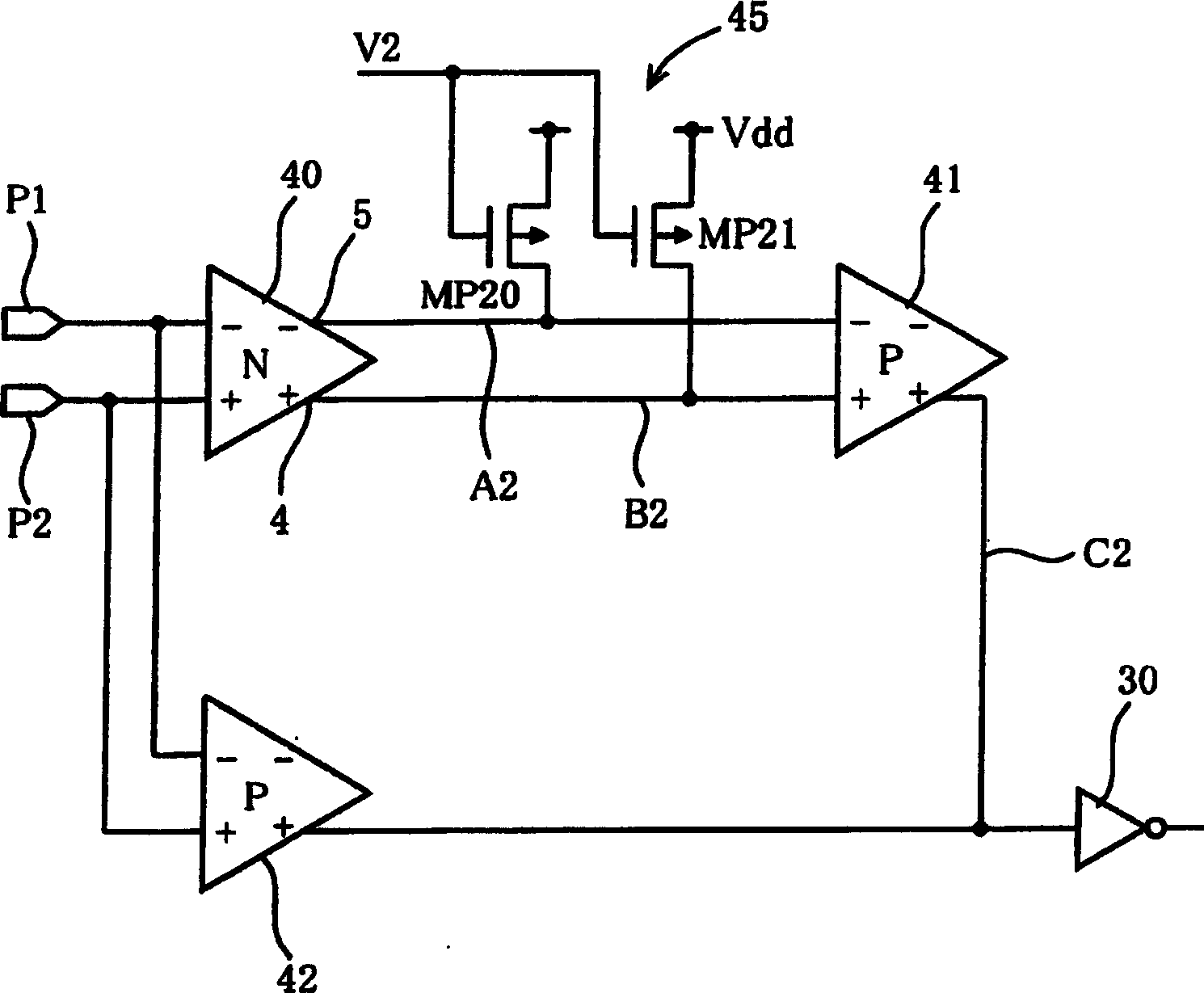

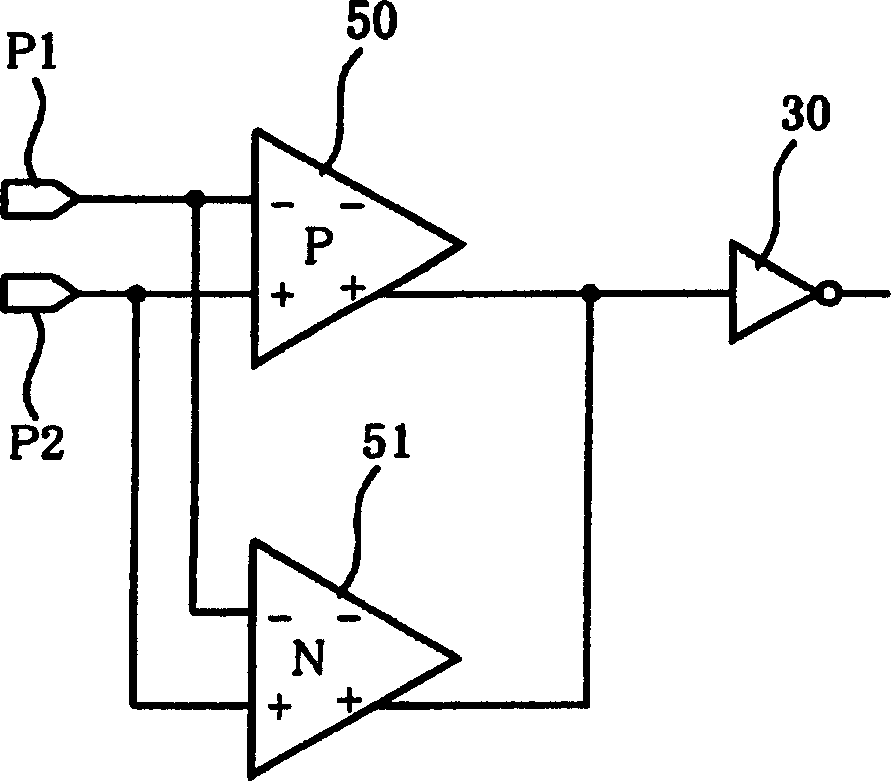

Comparator circuit

InactiveCN1674437AReduce component countHigh speed actionMultiple input and output pulse circuitsLogic circuits characterised by logic functionComparators circuitsVoltage range

The present invention provided a comparator circuit operating normally over a wide input voltage range of Vss to Vdd. The comparator circuit comprises a first comparator 20 receiving a pair of differential input signals from input terminals P1 and P2, a second comparator 21 receiving a pair of differential outputs from the first comparator 20, a current source 25 for feeding a very small current from a pair of differential output terminals of the first comparator 20 to the ground voltage Vss, and a third comparator 22 receiving a pair of differential input signals from the input terminals P1 and P2 wherein the differential outputs from the second comparator 21 and the third comparator 22 are synthesized to produce an output signal. The output signal is received by an inverter 30 on the next stage. The first comparator 20 is a P type comparator and the second and third comparators 21 and 22 are N type comparators.

Owner:SANYO ELECTRIC CO LTD

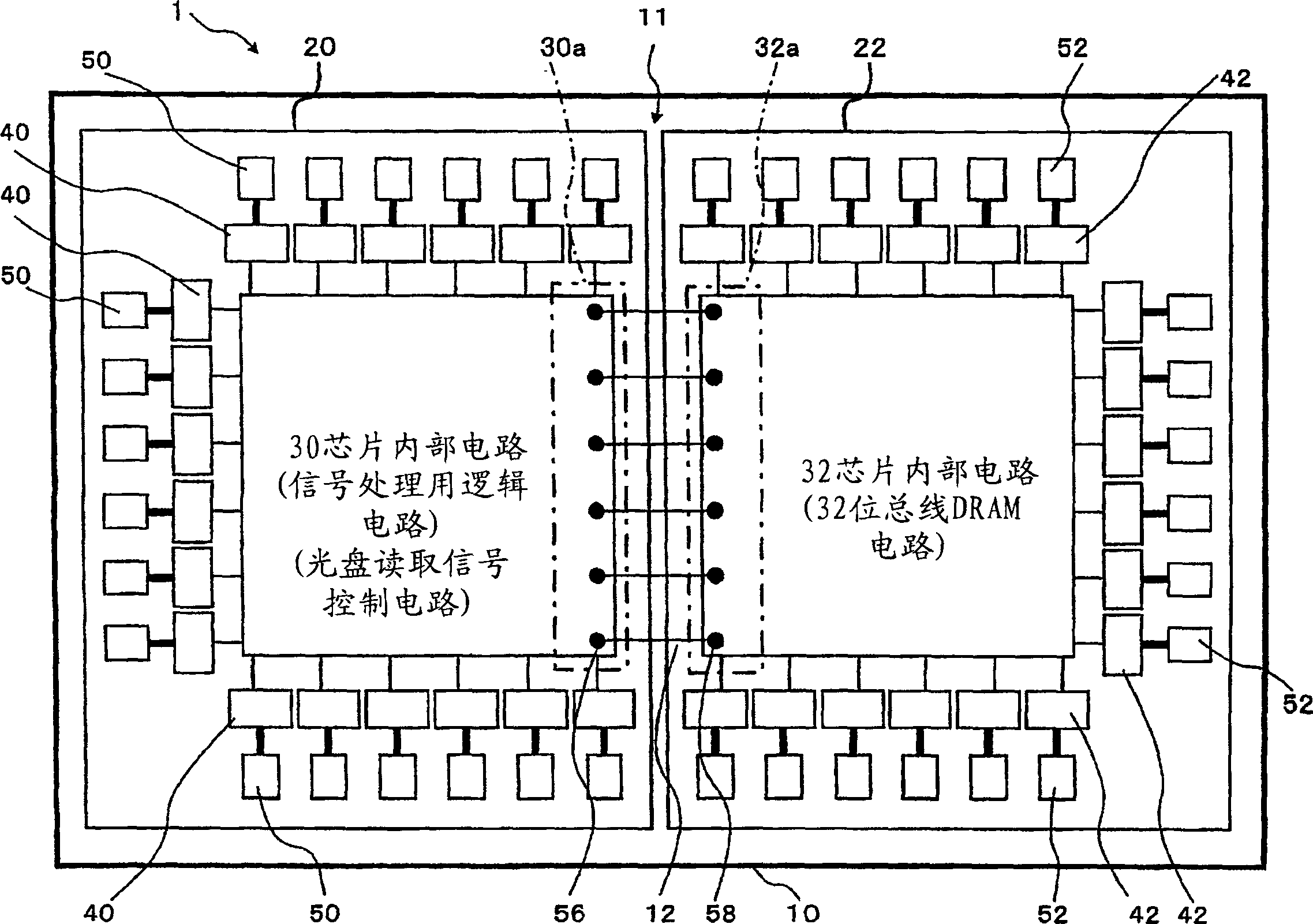

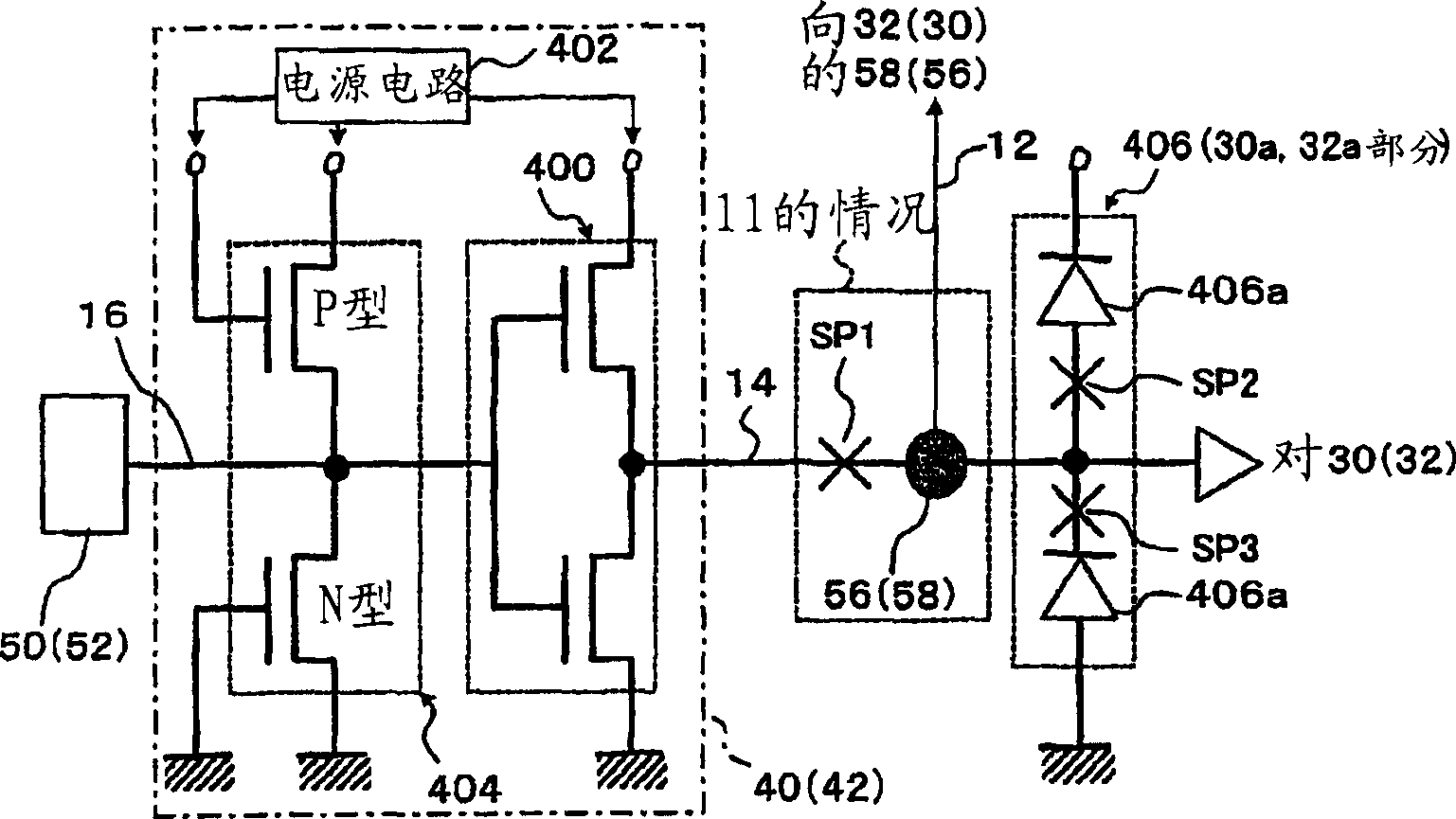

Semiconductor device and method for making the same

InactiveCN1836326AAvoid power consumptionImprove actionSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipInterconnection

An MCM-type semiconductor device allowing high-speed operation and reduction in power consumption, and is also capable of preventing reliability and yield rate of MCM from degrading. The reduction in power consumption and increase in operation speed are attained by connecting signal lines between in-chip circuits (30), (32) in an electrically direct manner. On the signal line, a protection circuit (406) for electrostatic damage protection is provided. In device fabrication, connection using interconnections (12) between the in-chip circuits (30), (32) is carried out while keeping a protection circuit (406) connected to the signal lines (internal draw-out lines (12a), internal interconnections (14)), by which circuit components can be protected from static electricity even if electric charge accumulated on the semiconductor chips (20), (22) should flow into the signal lines, because the protection circuit (406) can absorb the charge. After the connection is completed, the protection circuit (406) can be disconnected from the signal lines, so as to avoid the protection circuit (406) to function as a load on the in-chip circuits (30), (32) during normal operation, and to thereby prevent the operation speed from decreasing.

Owner:SONY CORP

Memory

InactiveCN1877840ASmall sizeReduce load capacitySolid-state devicesSemiconductor devicesEngineeringComputer memory

The invention provides the computer memory which can reduce the memory cell. In the computer memory, the first gate electrode of the first selection transistor, the second gate electrode of the second selection transistor and the word line are integrally installed, on the forming area of memory cell, and they is cross-configured with the first impurity area on the first selection transistor and the forming area of second selection transistor, when they extend along the tilted direction of the first impurity extending on the forming area of memory cell.

Owner:SANYO ELECTRIC CO LTD

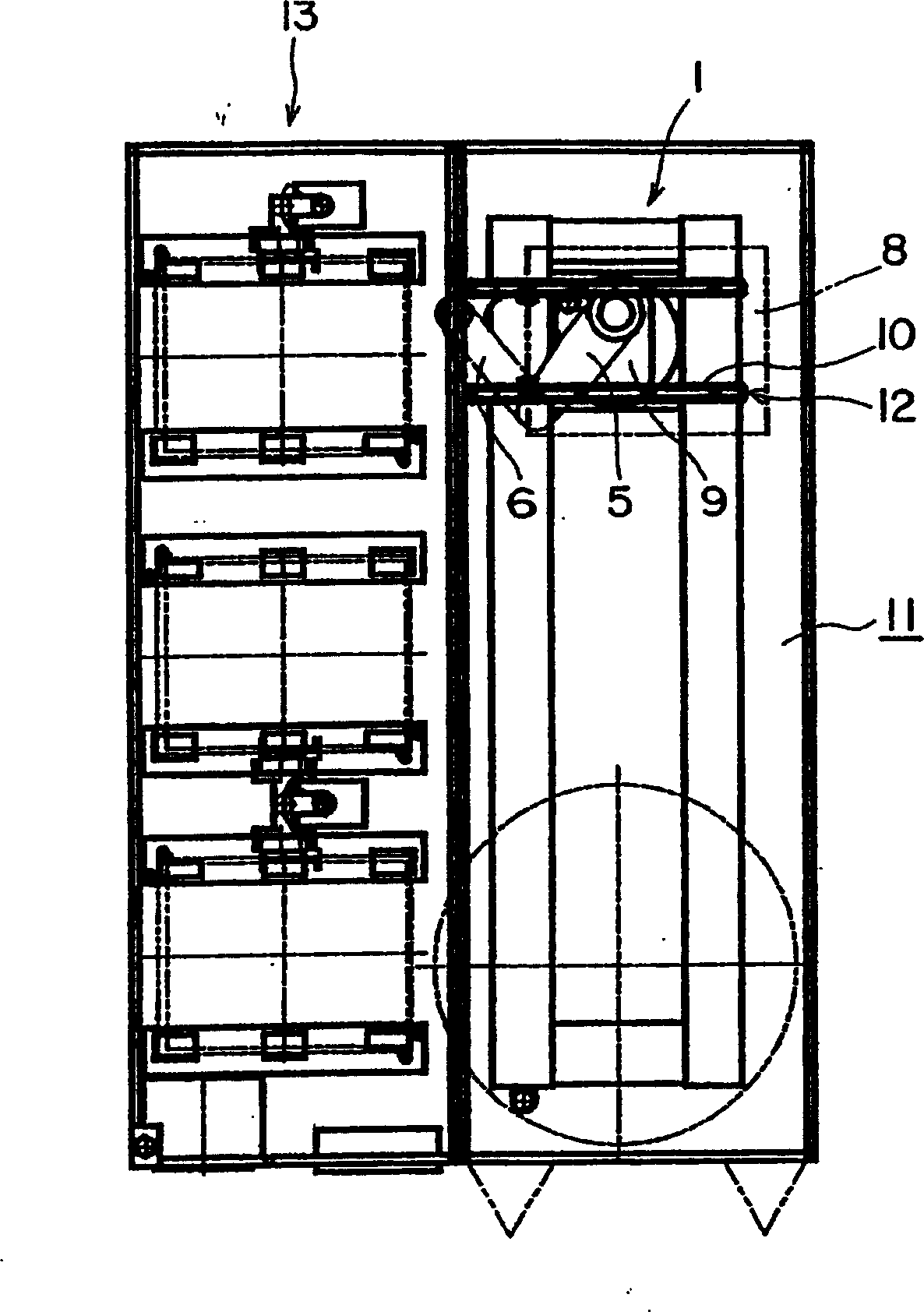

An industrial robot

InactiveCN1861334ARaise the resonance frequencyFast actionGripping headsSemiconductor/solid-state device manufacturingEngineeringHollow shape

An industrial robot, the hand (2) of which is set on the side of the transport robot that takes out the transported object (3) from the storage device for storing the transported object (3) or puts the transported object (3) into the storage device The fork (4) constituting the hand (2) at the front end of the arm is made of a hollow shape, and at the same time, the thickness of the fork (4) becomes thinner toward the front end of the fork (4). The present invention can obtain high rigidity while suppressing weight.

Owner:NIDEC SANKYO CORP

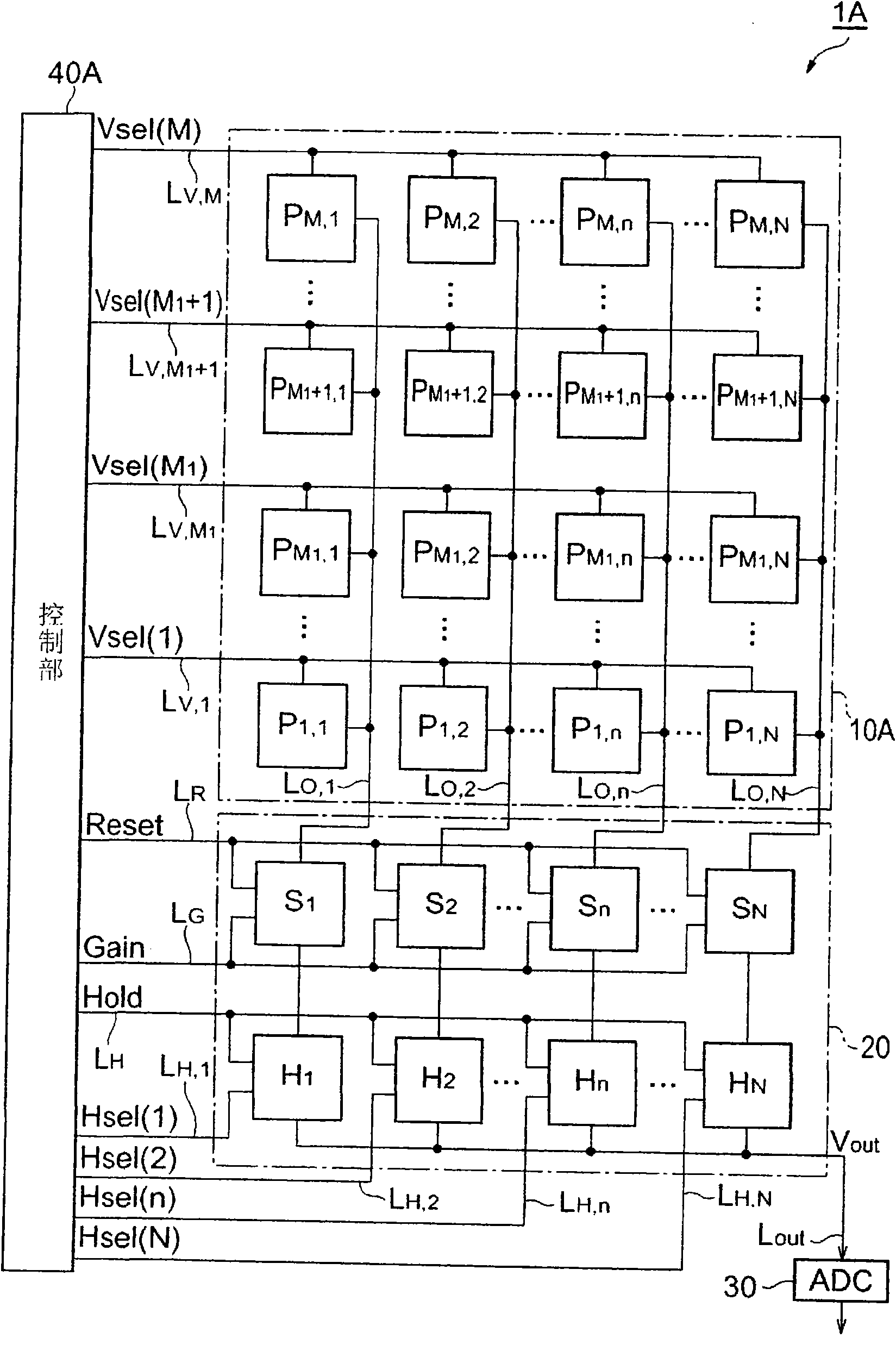

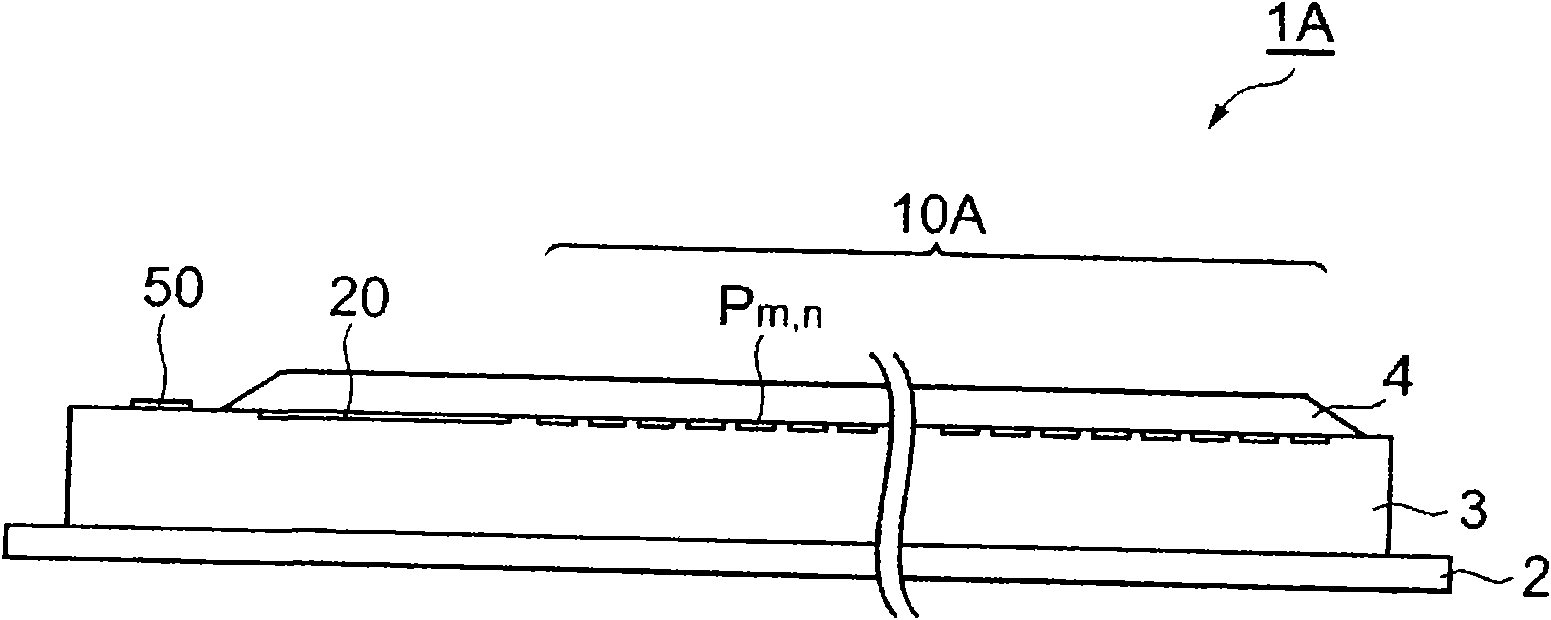

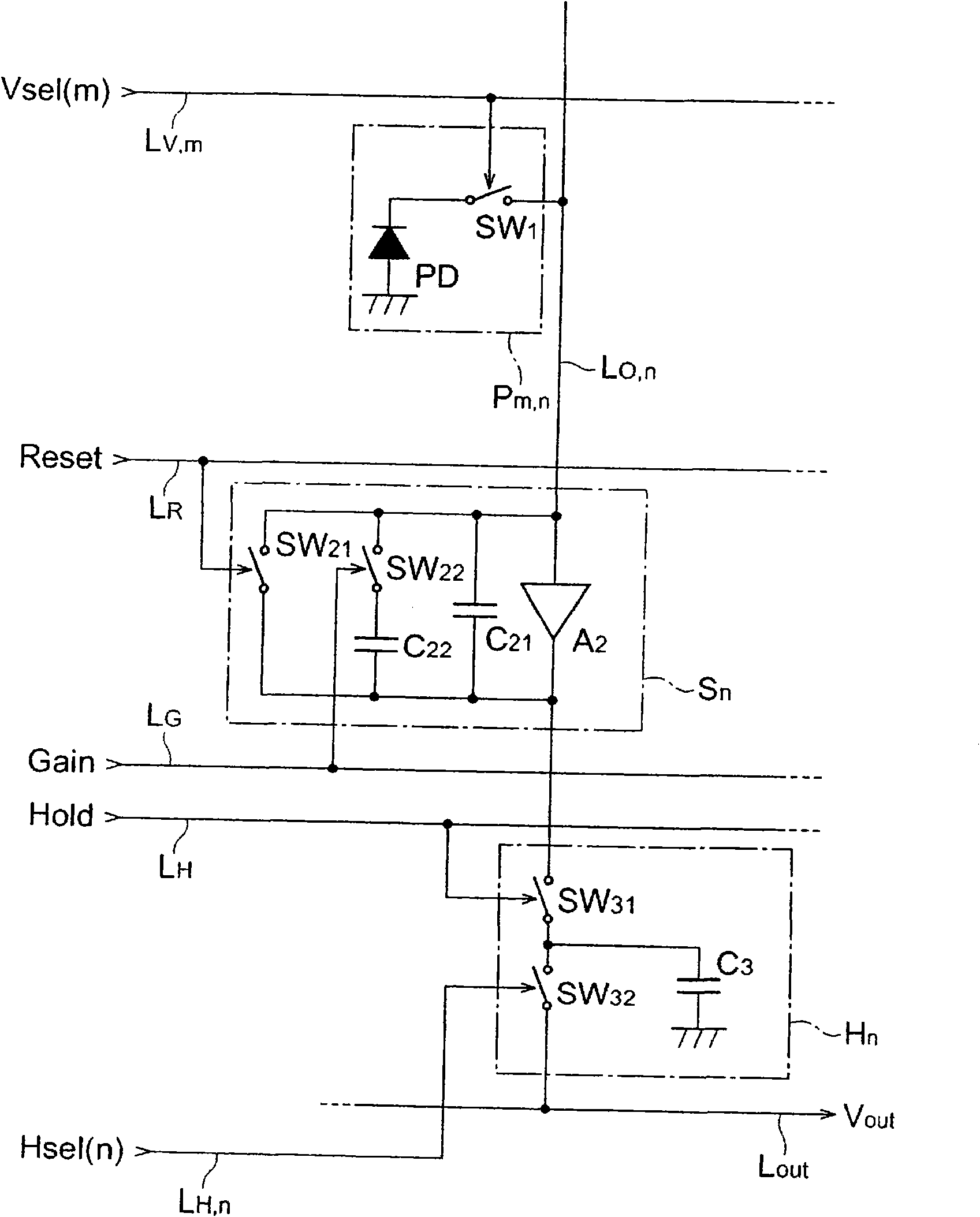

Solid-state image pickup apparatus and X-ray inspection system

A solid-state image pickup apparatus 1A includes a photodetecting section 10A, a signal readout section 20, and a controlling section 40A. In the photodetecting section 10A, M×N pixel units P 1,1 to P M,N each including a photodiode and a readout switch are arrayed in M rows and N columns. Charges generated in each pixel unit P m,n are input to an integrating circuit S n through a readout wiring L O,n , and a voltage value output from the integrating circuit S n in response to the charge amount is output through a holding circuits H n . When in a first imaging mode, a voltage value according to an amount of charges generated in the photodiode PD of each of the M×N pixel units P 1,1 to P M,N in the photodetecting section 10A is output from the signal readout section 20. When in a second imaging mode, a voltage value according to an amount of charges generated in the photodiode PD of each pixel unit P m,n included in consecutive M 1 rows in the photodetecting section 10A is output from the signal readout section 20.

Owner:HAMAMATSU PHOTONICS KK

Level shift circuit, and driver and display device using the same

InactiveCN102006053AHigh speed conversionSuppression of Duty Cycle DeteriorationStatic indicating devicesLogic circuits coupling/interface using field-effect transistorsDisplay deviceEngineering

The invention provides a level shift circuit, and a driver and a display device using the same. The level shift circuit includes a first circuit connected between a first power supply terminal (PST) and an output terminal (OT) of the level shift circuit to set OT to a first voltage (V1) when conducting, a second circuit connected between a second PST and OT to set OT to the second voltage (V2) when conducting, and a third circuit that receives an input signal and a feedback signal from OT so that, when OT=V2 and input=a third voltage (V3), the first circuit conducts, and when OT=V1, the first circuit is made nonconductive irrespective of the value of the input signal. The second circuit is made conductive and nonconductive when the reverse-phase signal of the input signal is equal to V3 and the reverse-phase signal of the input signal is equal to a fourth voltage (V4), wherein V2<=V4<V3<V1.

Owner:RENESAS ELECTRONICS CORP

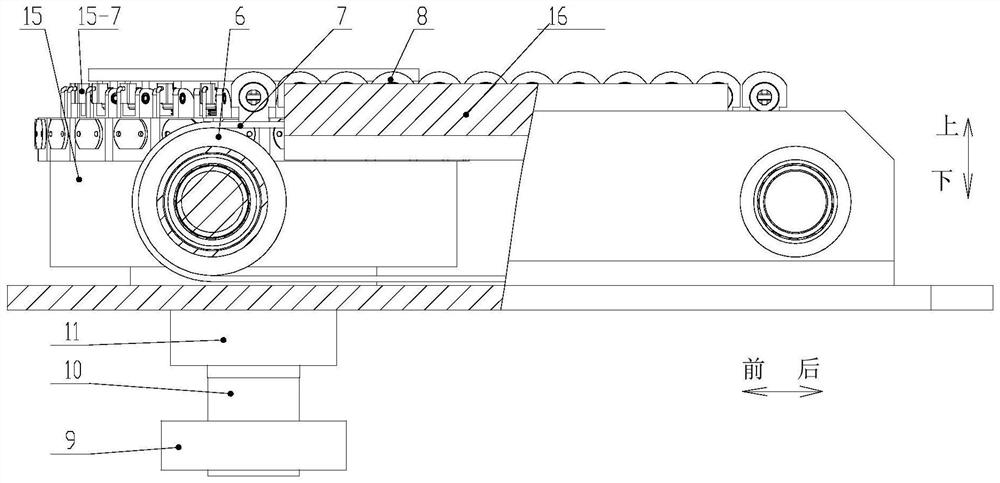

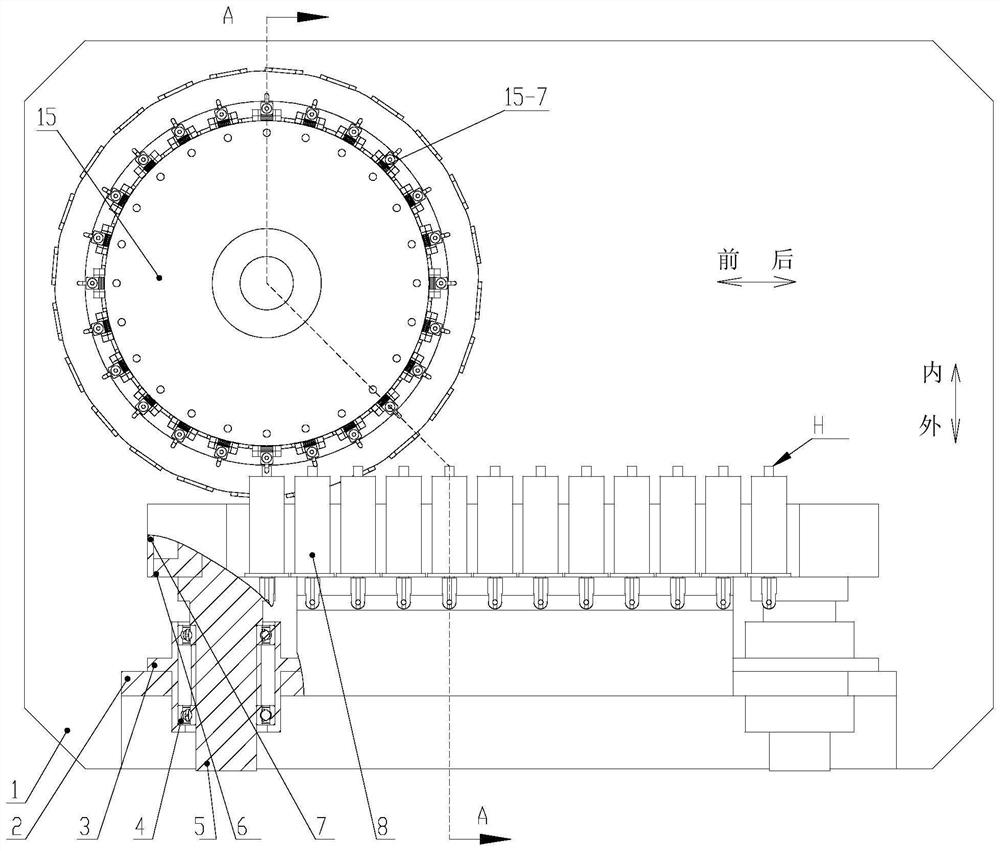

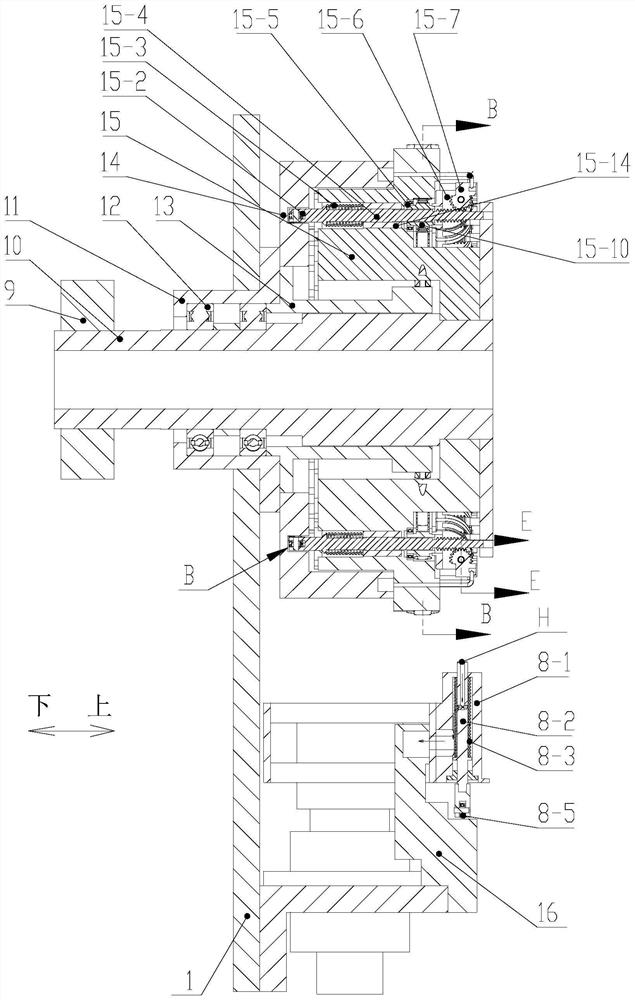

Handover and turnover device and method for tubular container end face sealing paper sheets

InactiveCN114193826AEasy to implementSimple structurePaper-makingBox making operationsEngineeringPaper sheet

The invention discloses a tubular container end face sealing paper sheet transferring and overturning device which comprises a paper receiving mechanism and a paper sheet conveying mechanism, a plurality of overturning gears and suction cups are distributed on a paper receiving wheel of the paper receiving mechanism in the circumferential direction, and paper suction discs of the overturning gears and the suction cups can suck sealing paper sheets; a paper sheet conveying mechanism is arranged on the outer side of the paper receiving mechanism, and a plurality of paper suction assemblies are arranged on the paper sheet conveying mechanism; when the overturning gear, the suction cup and the paper suction assembly move to the paper sheet connecting area at the same time, the paper suction assembly delivers the sucked sealing paper sheets to the overturning gear and the suction cup. The overturning gear and the paper suction disc of the suction cup receive the sealing paper sheets delivered by the paper suction assembly, and the sealing paper sheets in the vertical state are overturned to be in the horizontal state. Through the same paper receiving mechanism, not only can the handover action of paper sheets be completed, but also the overturning of the paper sheets can be realized, and the equipment integration degree is high. The invention further discloses a connecting and overturning method of the tubular container end face sealing paper piece.

Owner:杜国锋

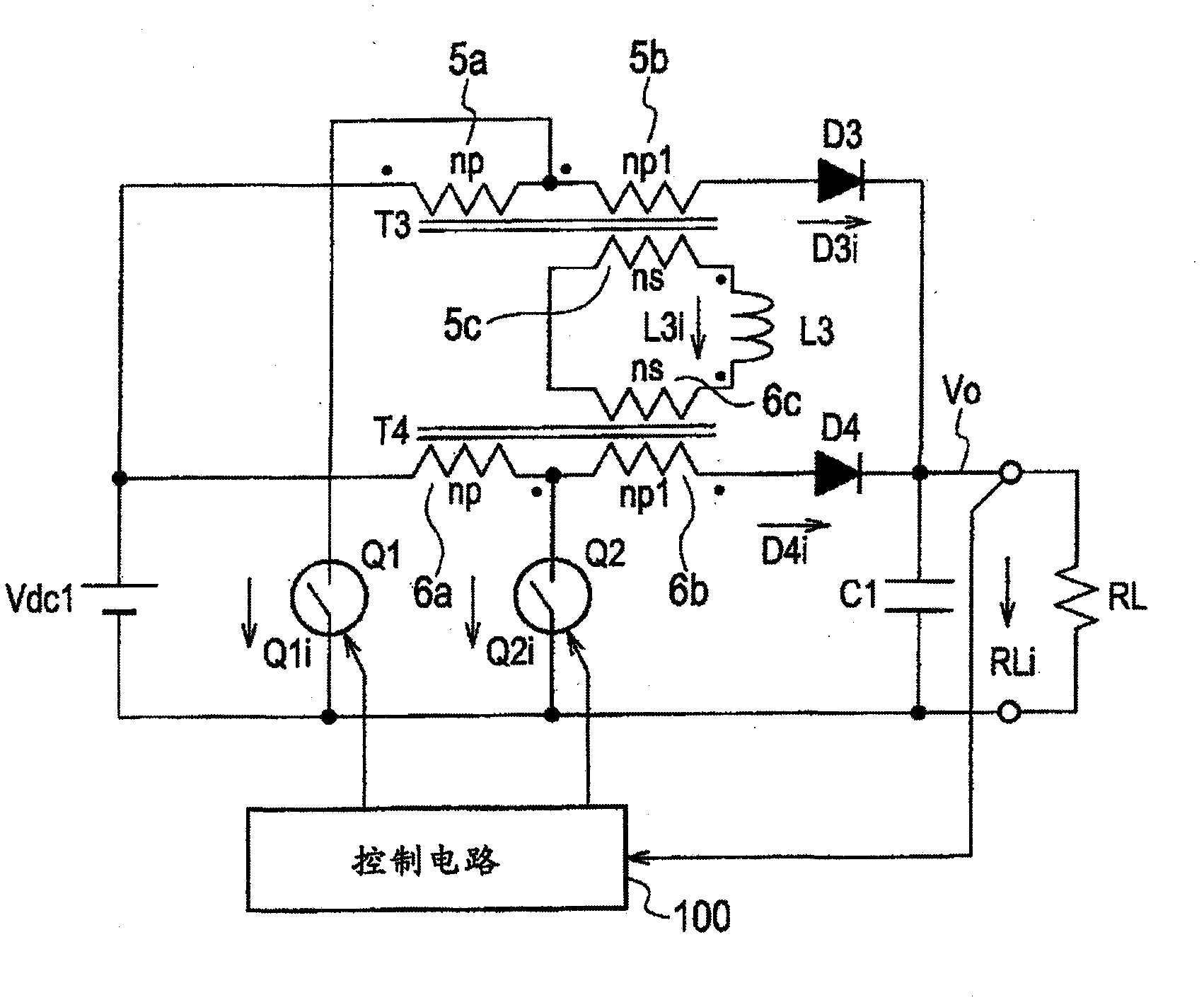

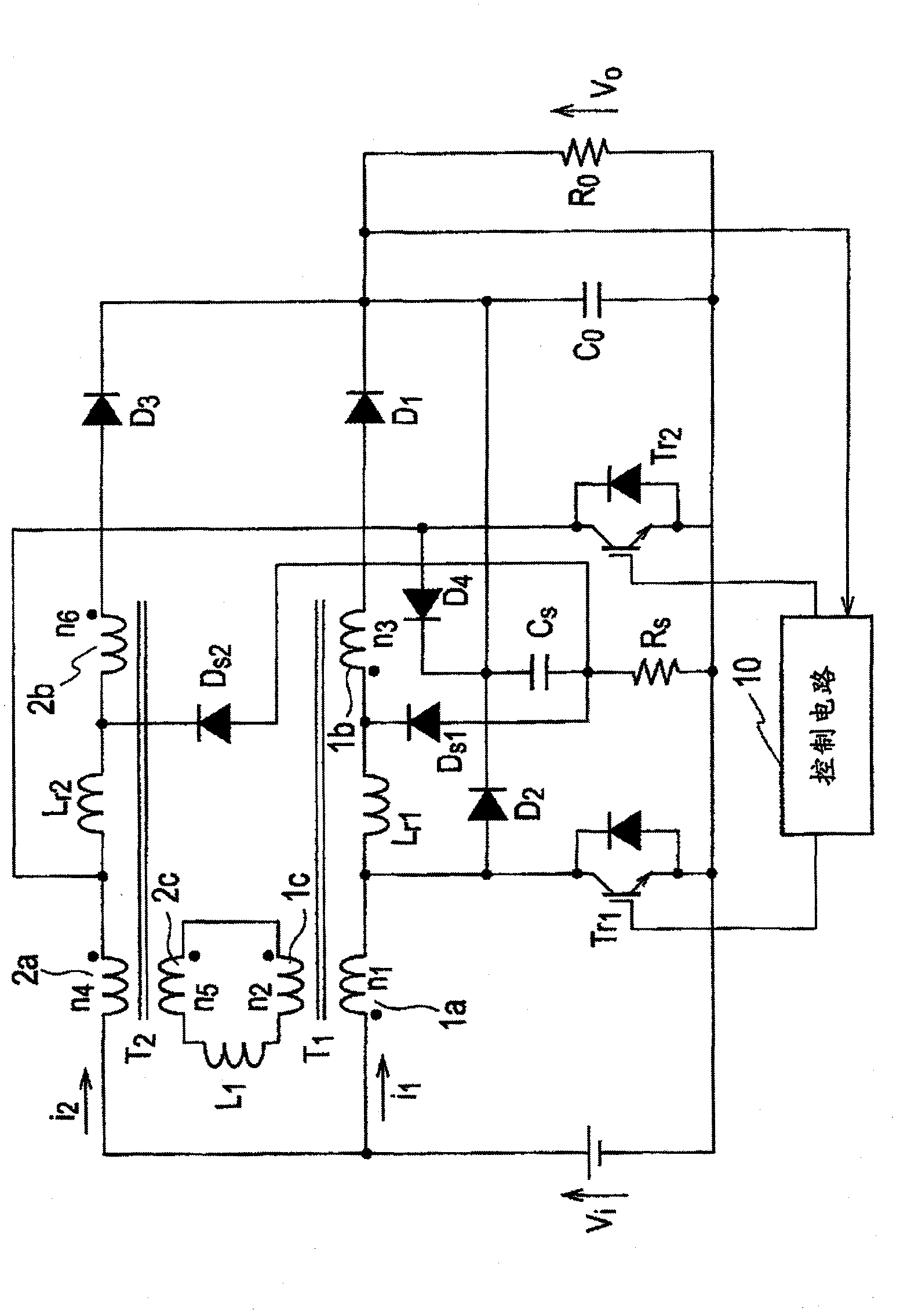

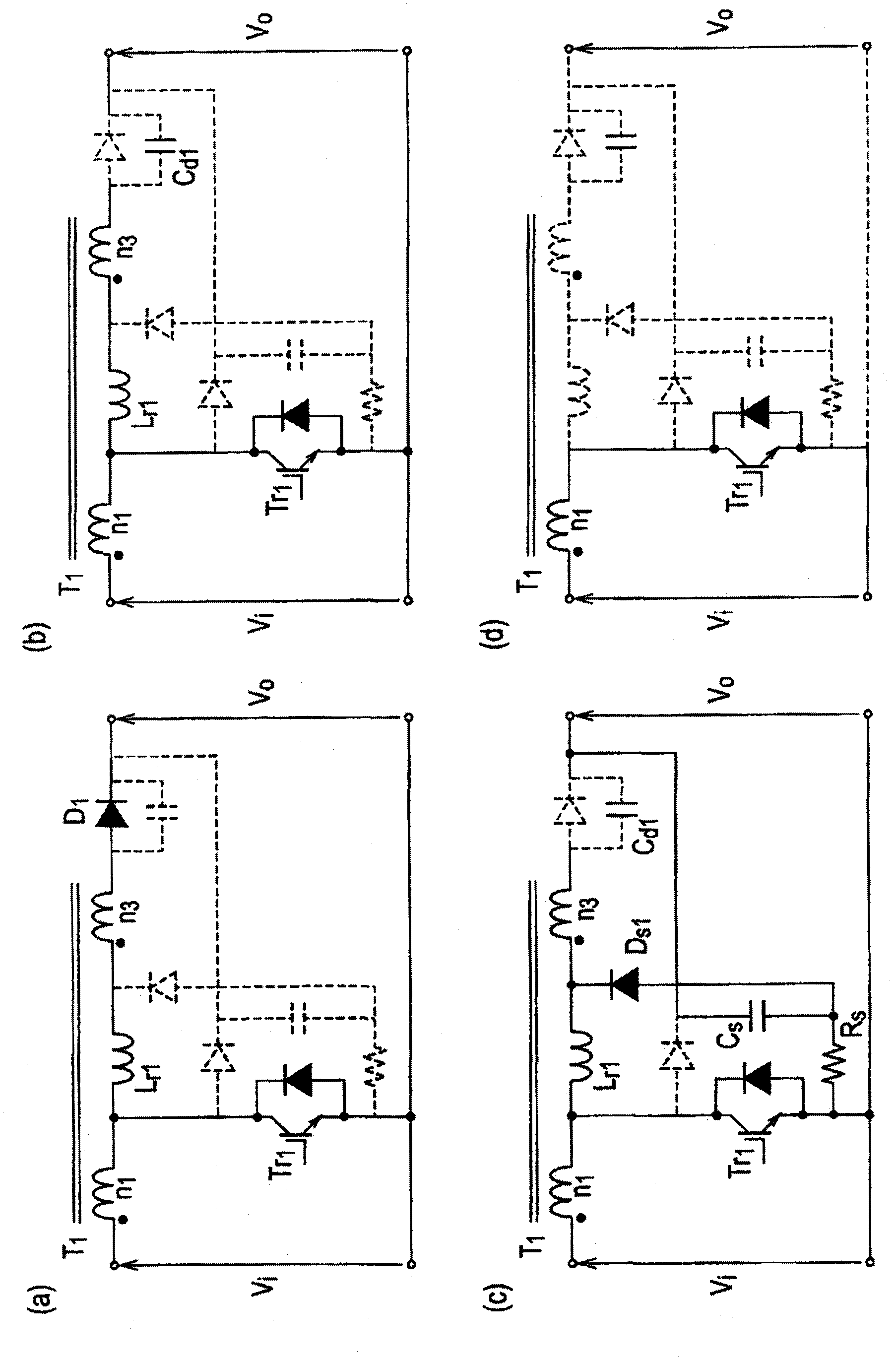

DC-DC converter with snubber circuit

InactiveCN102067425BSuppress recovery lossAvoid destructionEfficient power electronics conversionDc-dc conversionNoise generationSnubber capacitor

In order to achieve an object to reduce a surge voltage and suppress noise generation, the present invention provides a DC-DC converter with a snubber circuit, which boosts a voltage Vi of a DC power supply. The snubber circuit includes: a series circuit connected to both ends of a smoothing capacitor Co and including a snubber capacitor Cs and a snubber resistor Rs; a snubber diode Ds1 connected to a node at which the snubber capacitor Cs and the snubber resistor Rs are connected, and to a node at which a reactor Lr1 and an additional winding 1b of a transformer T1 are connected; and a snubber diode Ds2 connected to the node at which the snubber capacitor Cs and the snubber resistor Rs are connected, and to a node at which a reactor Lr2 and an additional winding 2b of a transformer T2 are connected.

Owner:SANKEN ELECTRIC CO LTD +1

Dynamic semiconductor memory and semiconductor IC device

InactiveCN1322513CReduce loadImprove performanceTransistorDigital storageComputer scienceSemiconductor

A DRAM, including a plurality of banks each having a plurality of sub-arrays, and sense amplifier circuits commonly shared by sub-arrays in different banks, has a row access mode for activating a sub-array selected from each bank for reading or writing data, and a refresh mode for activating a plurality of sub-arrays in each bank and refreshing memory cell data therein at substantially the same timing. Sub-arrays in each bank activated at substantially the same timing in the refresh mode are more than sub-arrays in each bank activated in the row access model. Thereby, occurrence of operation constrains is minimized to ensure high-speed operation and improve the system performance of DRAMs employing the non-independent bank system.

Owner:KK TOSHIBA

Semiconductor device and process for fabricating the same

ActiveCN1875481BAchieve thinningExcellent electrical propertiesSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

A thin stacked semiconductor device suitable for high speed operation. A plurality of specified circuits are formed on one surface of a semiconductor substrate while being arranged, and wiring and insulating layers being connected electrically with the circuits are laminated and formed sequentially in a specified pattern to form a multilayer wiring part. At the stage for forming the multilayer wiring part, a filling electrode is formed on the semiconductor substrate such that the surface is covered with an insulating film, a post electrode is formed on specified wiring at the multilayer wiringpart, a first insulating layer is formed on one surface of the semiconductor substrate, the surface of the first insulating layer is removed by a specified thickness to expose the post electrode, theother surface of the semiconductor substrate is ground to expose the filling electrode and to form a through-type electrode, forward end of the through-type electrode is projected by etching one surface of the semiconductor substrate, a second insulating layer is formed on one surface of the semiconductor substrate while exposing the forward end of the through-type electrode, bump electrodes areformed on both electrodes and then the semiconductor substrate is divided to form a semiconductor device. A plurality of semiconductor devices thus obtained are stacked and secured at the bump electrodesthus manufacturing a stacked semiconductor device.

Owner:TAIWAN SEMICON MFG CO LTD

Latch circuit and semiconductor memory device

latch circuits and semiconductor memory devices. The latch circuit includes an input circuit including an input PMOS transistor that causes a signal current corresponding to the sensed voltage to flow; a first inverter including a first PMOS transistor, a first NMOS transistor, and a first node. The first PMOS transistor and the first NMOS transistor are connected and connected to the input circuit; and the second inverter includes a second PMOS transistor, a second NMOS transistor and a second node, the second node connects the second PMOS transistor and the second NMOS transistor. The first inverter and the second inverter are connected in cascade.

Owner:POWERCHIP SEMICON MFG CORP

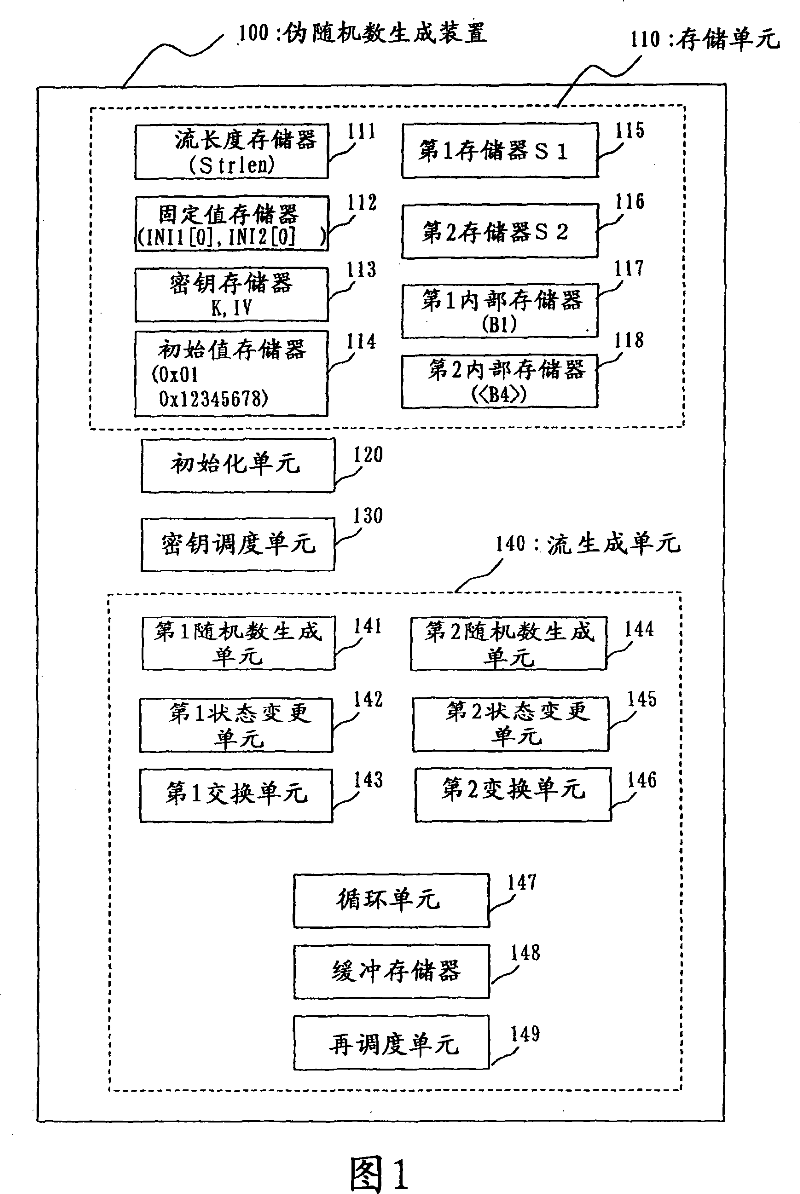

Pseudo random number generation device

InactiveCN101040306AImprove securityHigh speed actionRandom number generatorsCoding/ciphering apparatusInternal memoryTheoretical computer science

A pseudo random number generation device (100) generates a pseudo random number as follows. In C.2, S1[B41] is decided from B41 set in a second internal memory, and S2[B40] is decided from B40. R[J] is generated from S1[I], S1[B41], and S2[B40]. In C.3, S1[I] is newly generated according to S1[B41] and S2[B40]. In C.4, B4 is updated from S2(I). In the aforementioned process, the association of R[J] with S2(I) is cut off and it is difficult to estimate S2(I) from R[J], which increases the safety. Moreover, the S1[I], S1[B41], S2[B40], and the like are four-byte codes and processing speed can be increased.

Owner:MITSUBISHI ELECTRIC CORP

Semiconductor memory device

ActiveCN101981626BPrevent accidental writingSNM improvementDigital storageBit lineComputer architecture

A memory to which a bit line potential step-down technique is applied is provided. The memory includes an IO block including first transistors which control potentials of first bit lines provided with respect to columns of memory cells, and first logic gates which control the first transistors. The drain or source of each first transistor is connected to an input of the corresponding first logic gate, and the gate of each first transistor is connected to an output of the corresponding first logic gate. The first transistors are driven by pulses.

Owner:SOCIONEXT INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com