Level shift circuit, and driver and display device using the same

A level shifting circuit and circuit technology, which is applied in the direction of logic circuit connection/interface layout, logic circuit, logic circuit coupling/interface using field effect transistors, etc., which can solve the difficulty of saving area, complex circuit, large number of components, etc. problem, to achieve the effects of suppressing through current, suppressing duty cycle deterioration, and low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

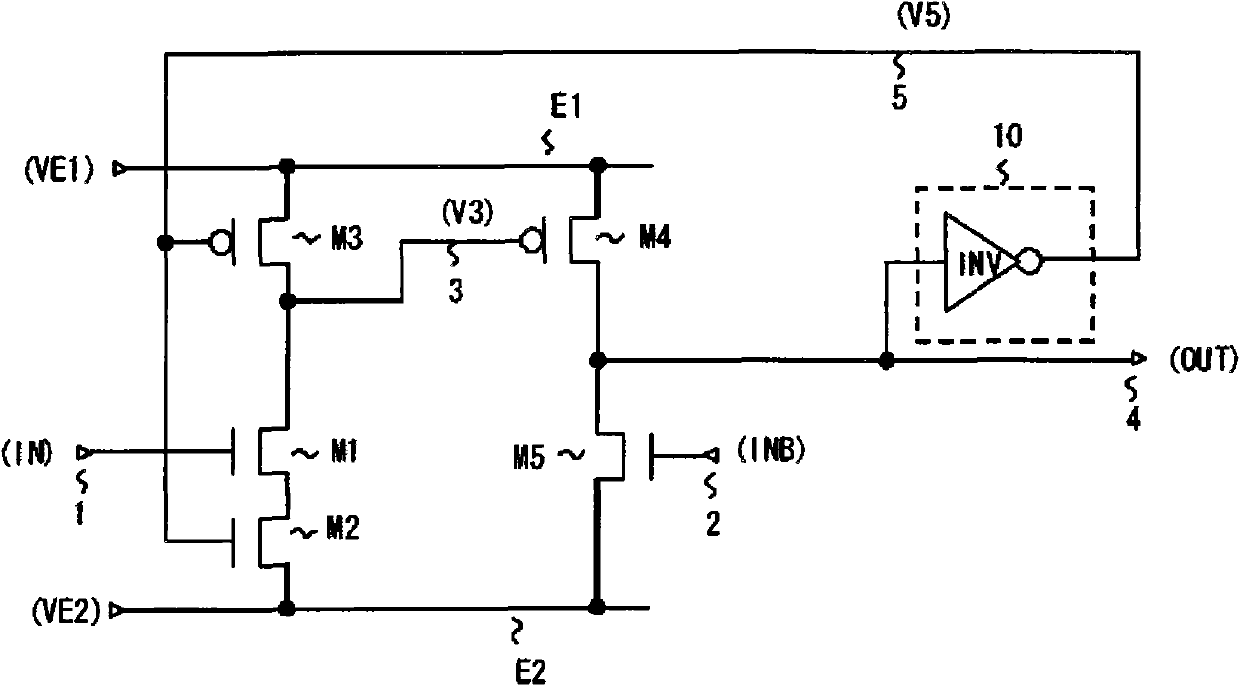

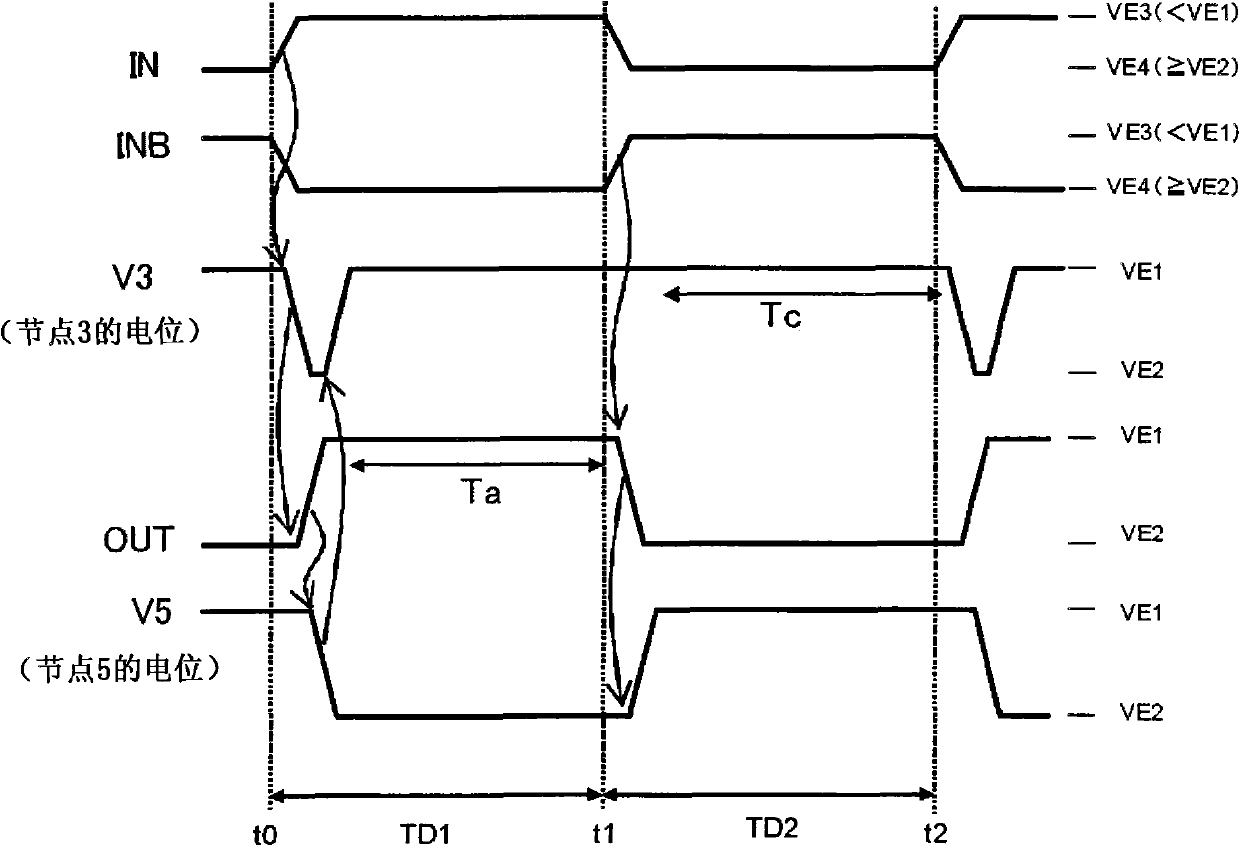

[0036] figure 1 is a diagram showing the structure of the first embodiment of the present invention. exist figure 1 Among them, IN and INB are complementary low-amplitude input signals having the amplitudes of the third and fourth voltage levels (VE3 and VE4). OUT is a high-amplitude output signal having amplitudes of the first and second voltage levels (VE1 and VE2). VE1 and VE2 are the first and second power supply voltages on the high potential and low potential sides. exist figure 1 Among them, the potential relationship of VE1, VE2, VE3, and VE4 is VE2≤VE4<VE3<VE1.

[0037] refer to figure 1 , the level shift circuit of the first embodiment of the present invention has: a pMOS transistor M3 whose source is connected to the first power supply terminal (E1) supplying a first voltage level (VE1); an nMOS transistor M1 whose drain is connected to The drain of the pMOS transistor M3, the gate of which receives a low-amplitude input signal (IN); the nMOS transistor M2...

Embodiment 2

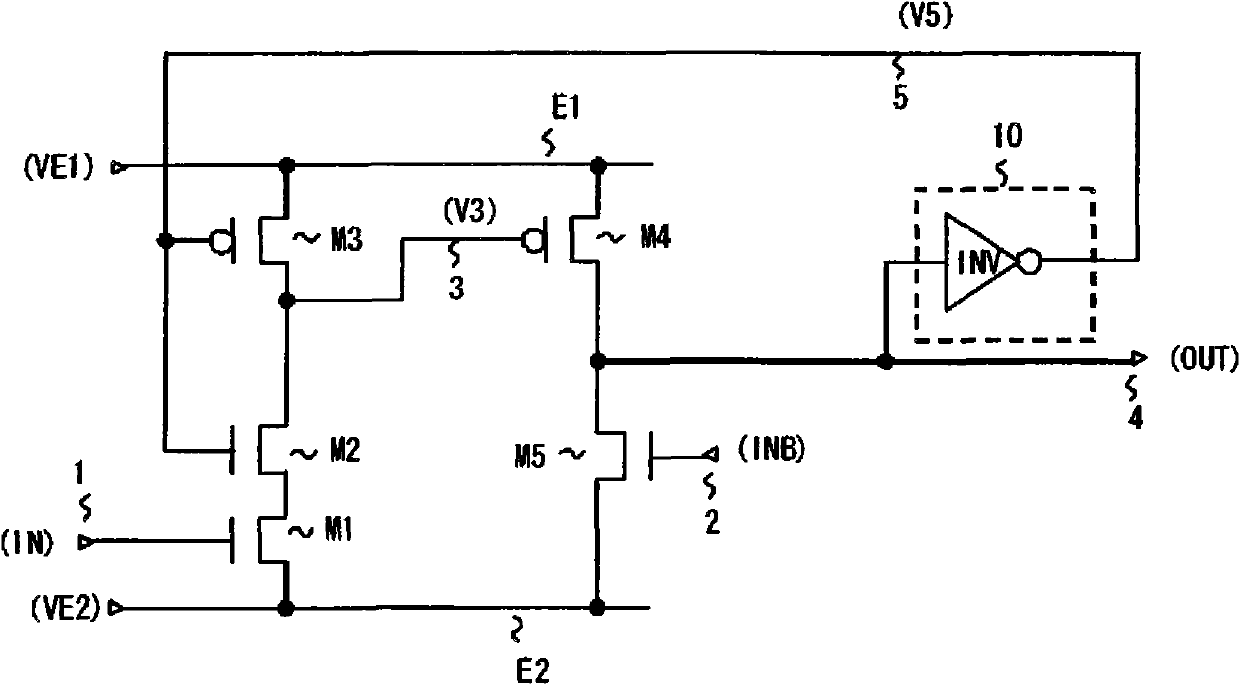

[0053] The second embodiment of the present invention will be described below. image 3 is a diagram showing the structure of the second embodiment of the present invention. refer to image 3 , in this example, swapping the figure 1 Connection of nMOS transistors M1, M2 in the shown structure. That is, the source of the nMOS transistor M1 whose gate receives the input signal IN is connected to the second power supply terminal (E2), and the nMOS transistor M2 whose gate receives the output 5 of the first delay circuit 10 is connected to the node 3 and the drain of the nMOS transistor M1 between poles. Also in this configuration, the same operation as that of the first embodiment described above is performed.

Embodiment 3

[0055] Next, a third embodiment of the present invention will be described. Figure 4 is a diagram showing the structure of a third embodiment of the present invention. refer to Figure 4 , in the third embodiment of the present invention has an nMOS transistor M5 and an nMOS transistor M6 connected in series between the second power supply terminal E2 and the output terminal 4 . and figure 1 Same as the first embodiment, the drain of the nMOS transistor M5 is connected to the output terminal 4, and the gate receives the input signal INB. The drain of the nMOS transistor M6 is connected to the source of the nMOS transistor M5, the source is connected to the second power supply terminal E2, and the gate receives a delayed signal in phase with the output signal OUT. In addition, as in the first and second embodiments, the connection order of the nMOS transistors M1 and M2 may be switched in this embodiment as well.

[0056] In addition, this embodiment also shows as a prefe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com