Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

90results about How to "Reduced driving ability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

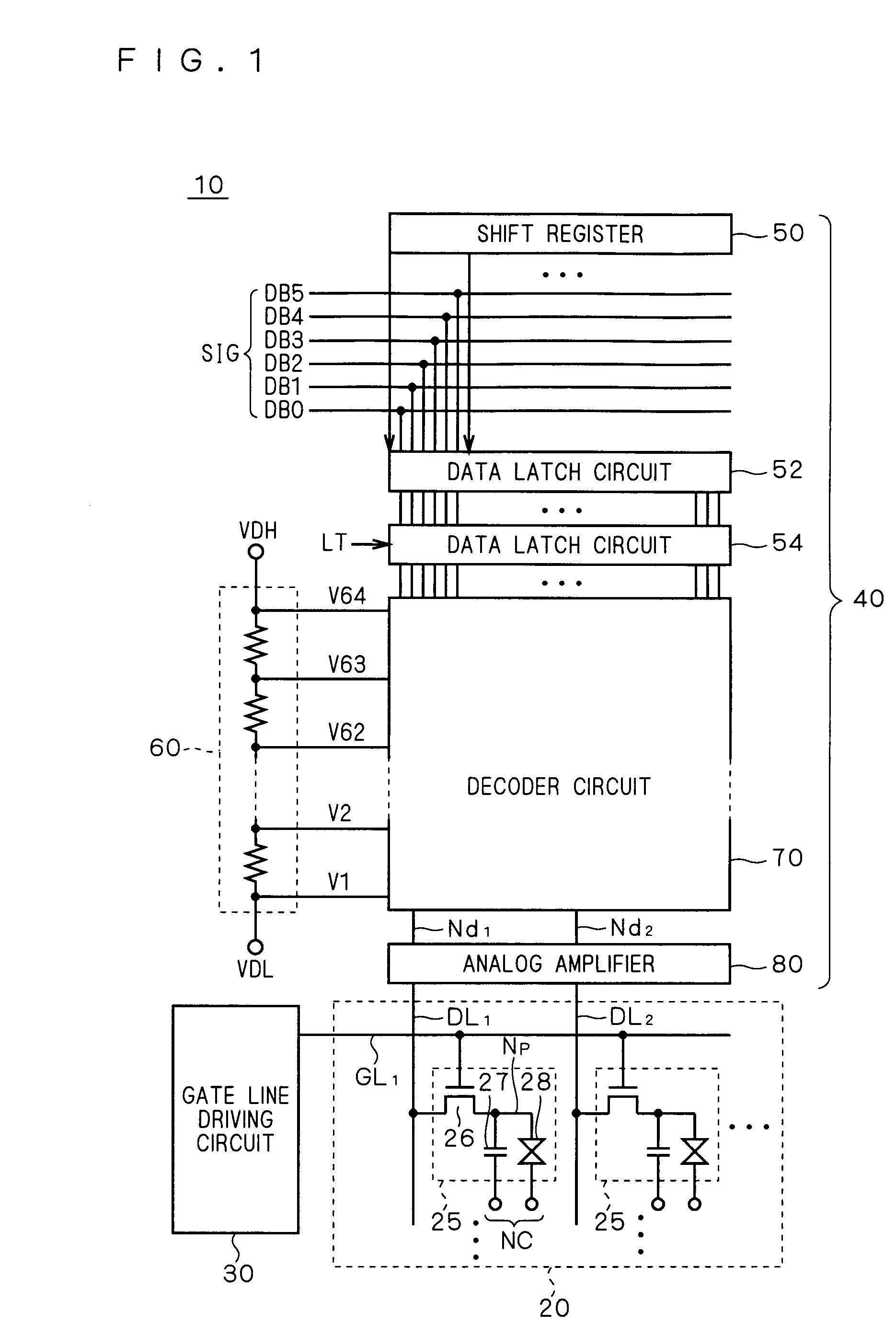

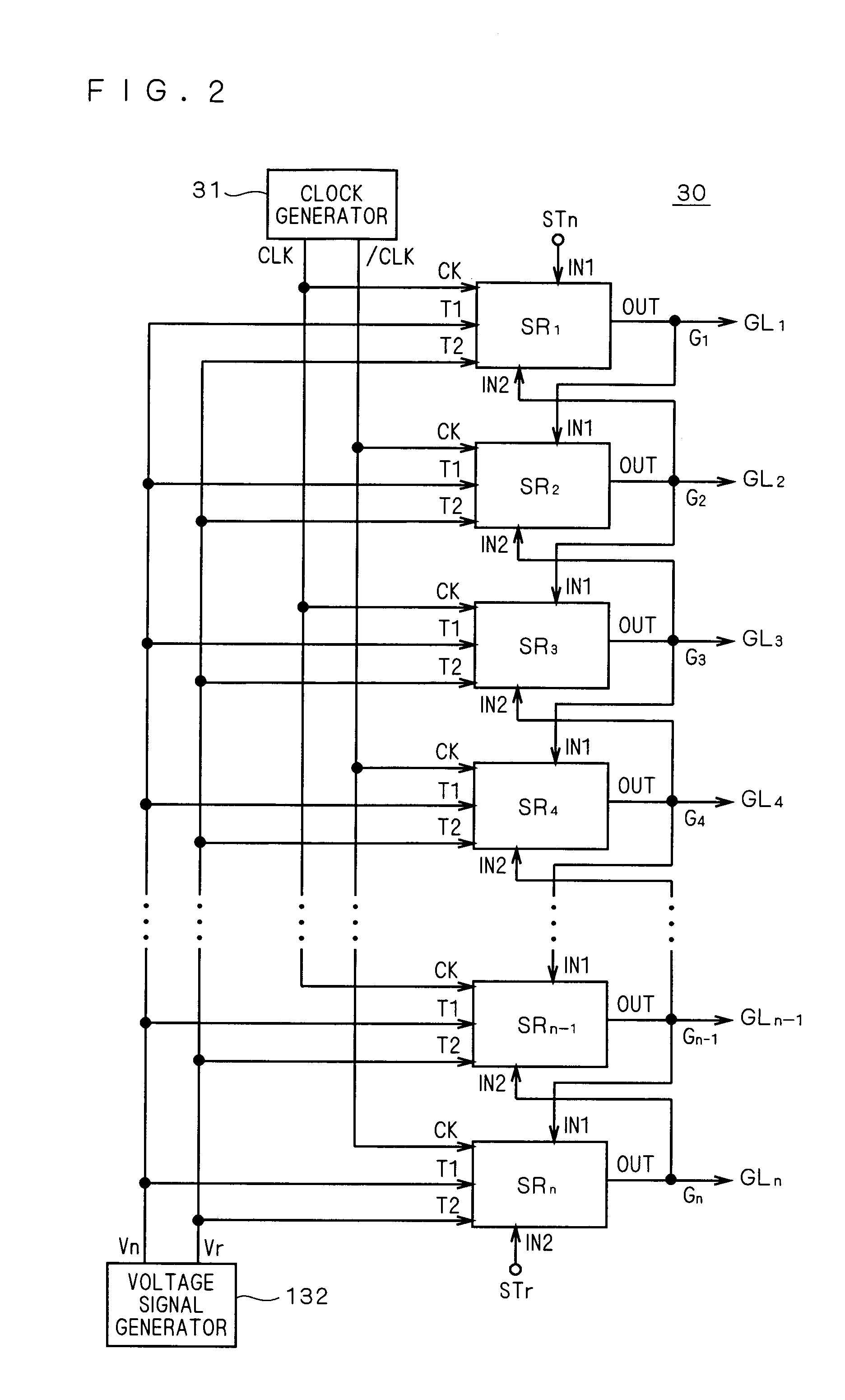

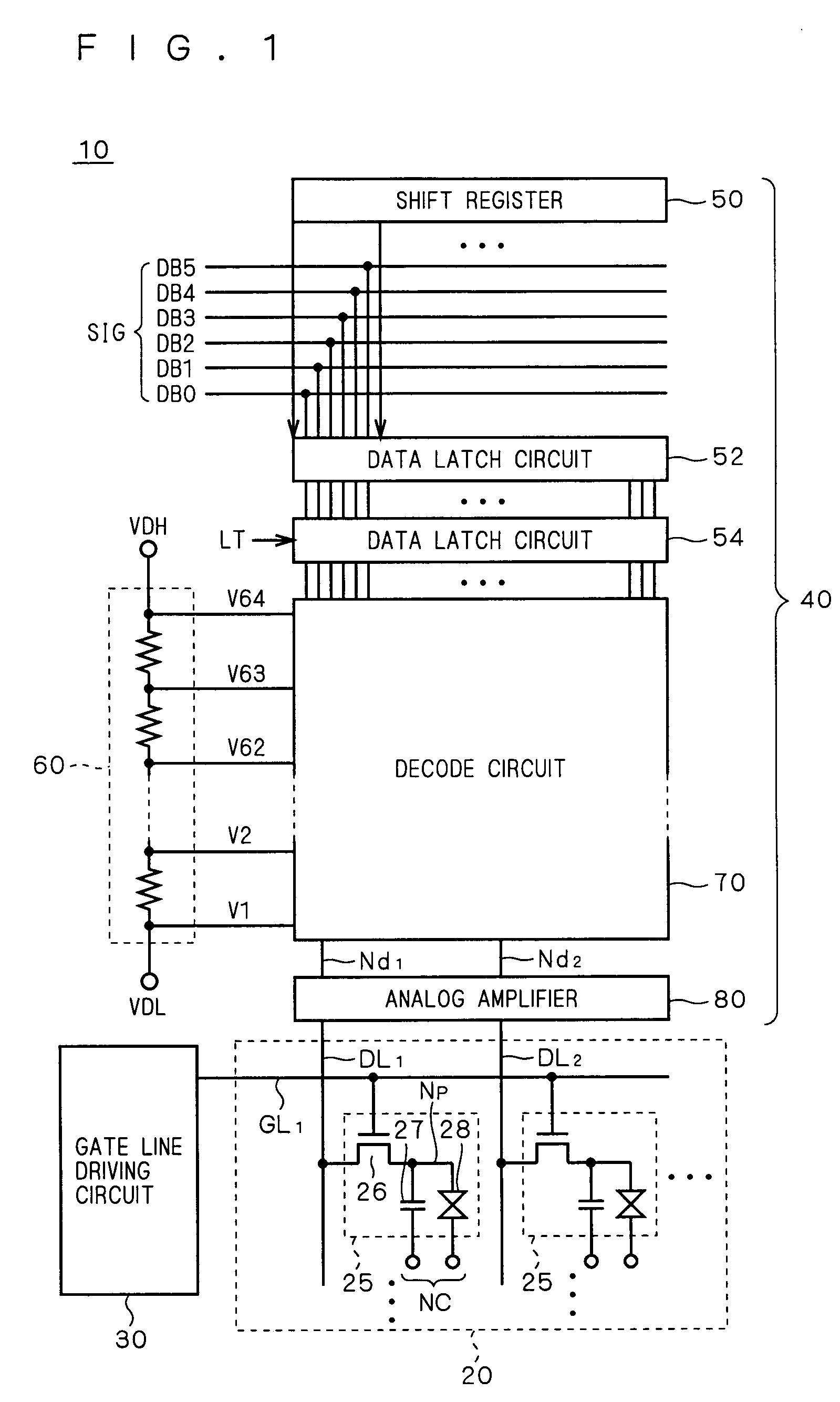

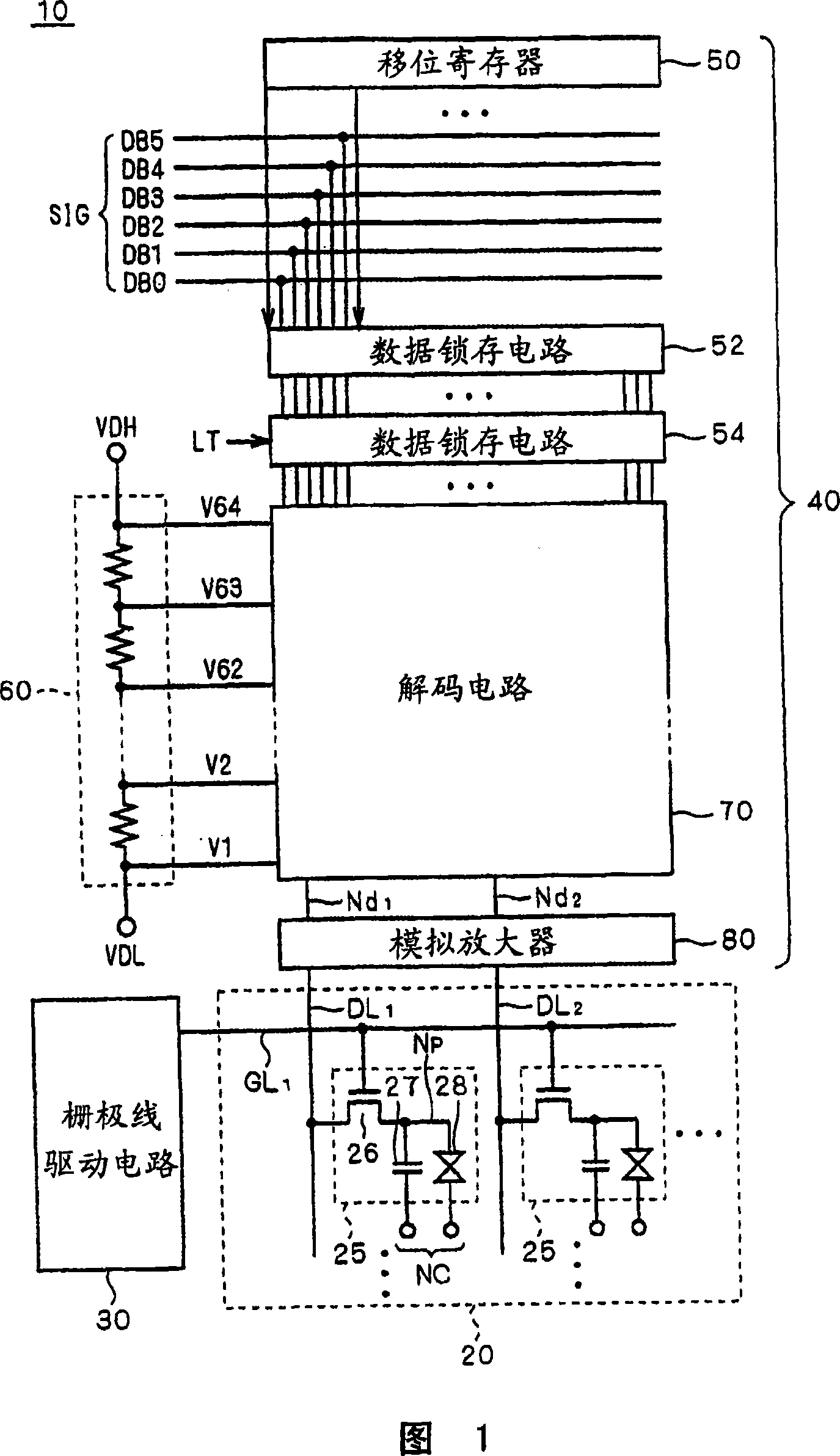

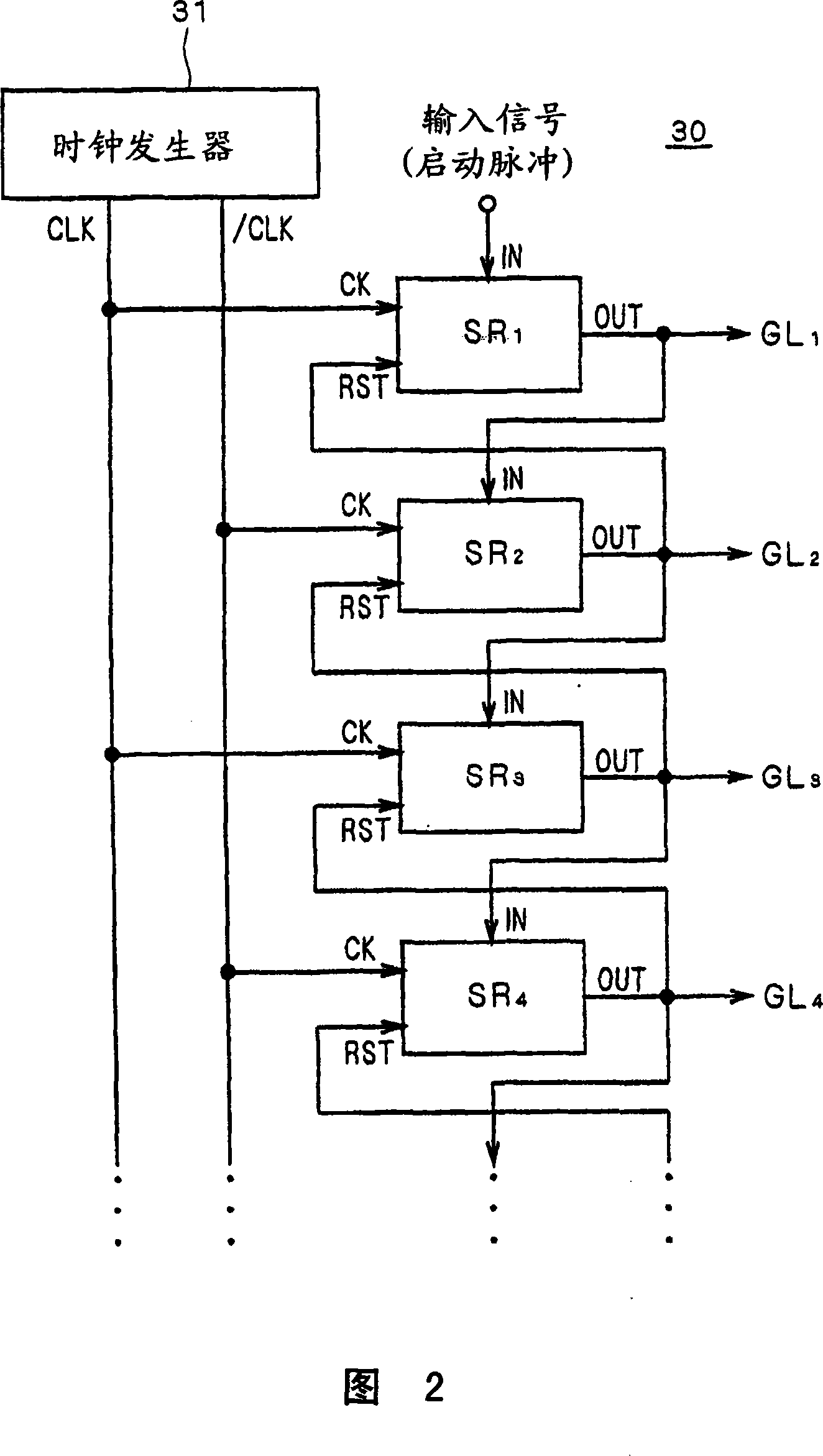

Shift register circuit and image display apparatus containing the same

InactiveUS20080219401A1Avoid failureReduced driving abilityStatic indicating devicesDigital storageShift registerProcessor register

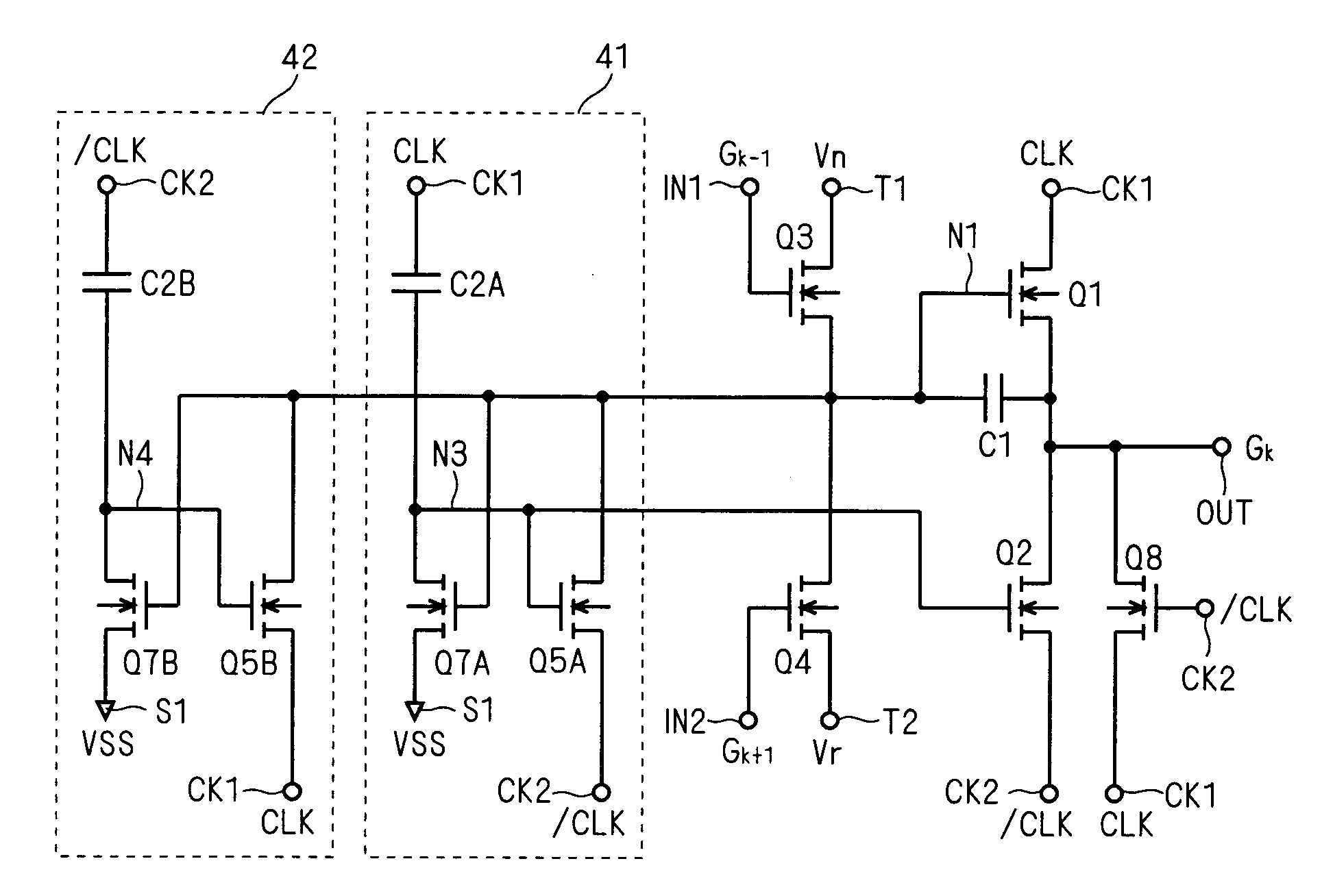

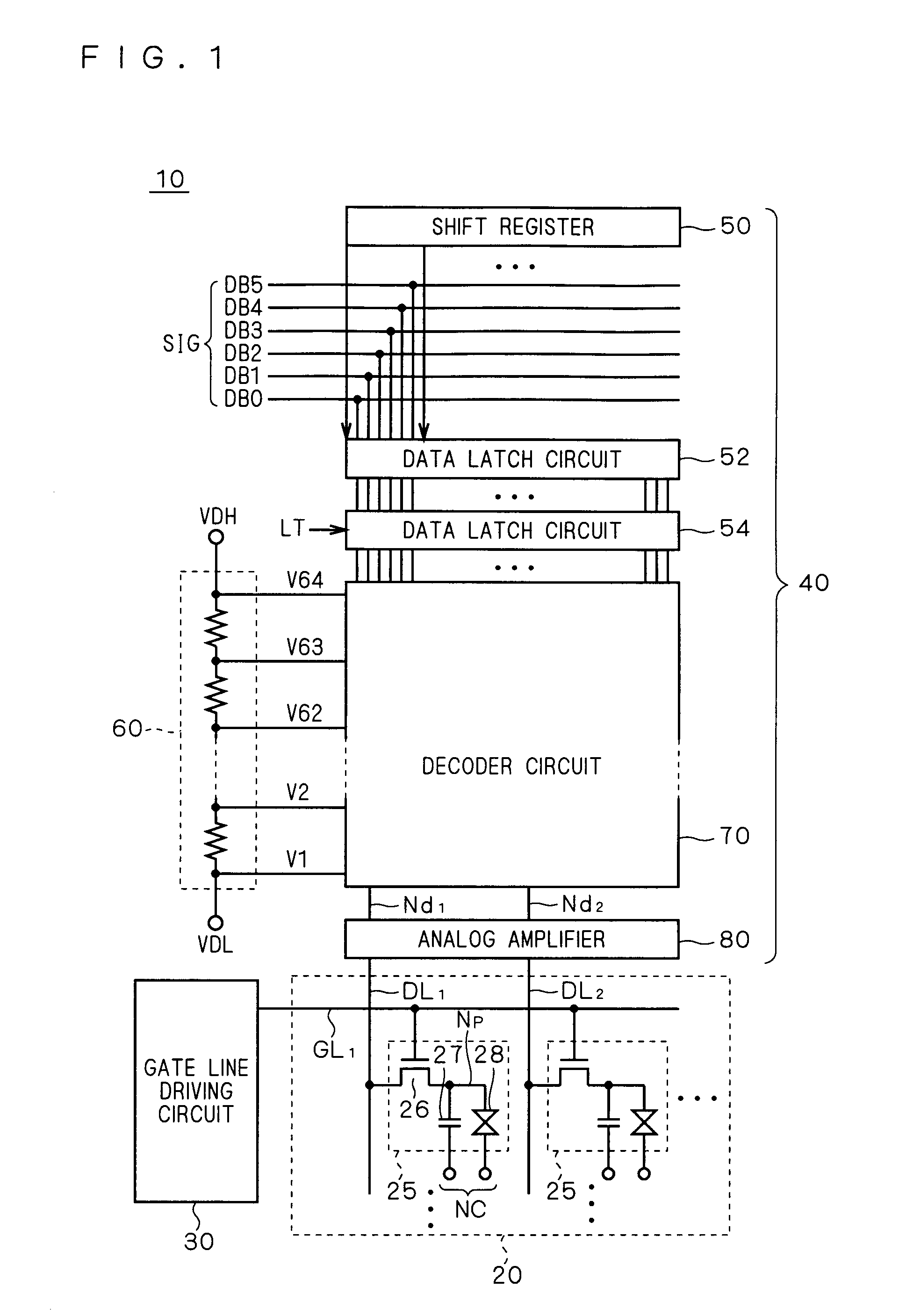

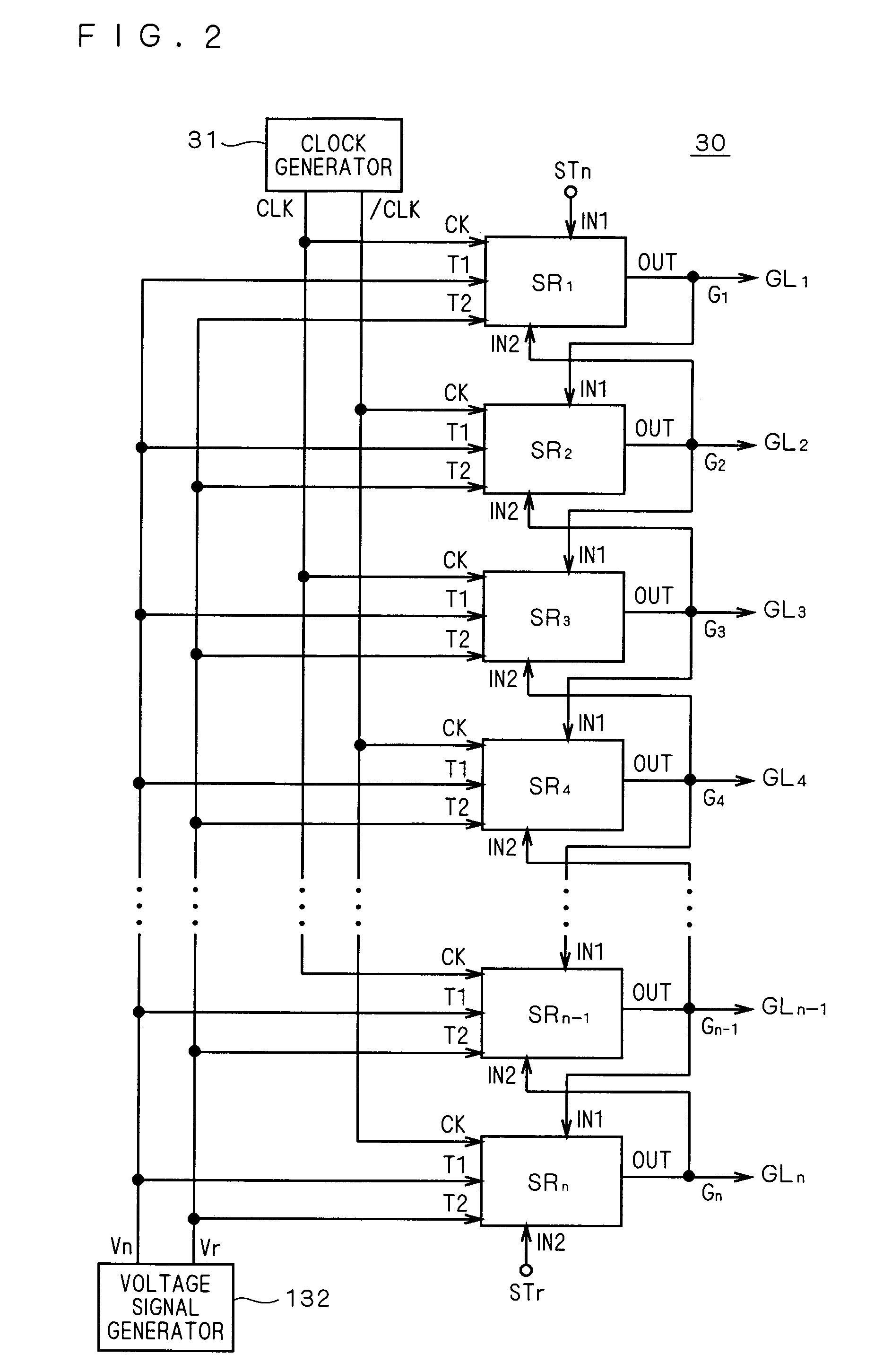

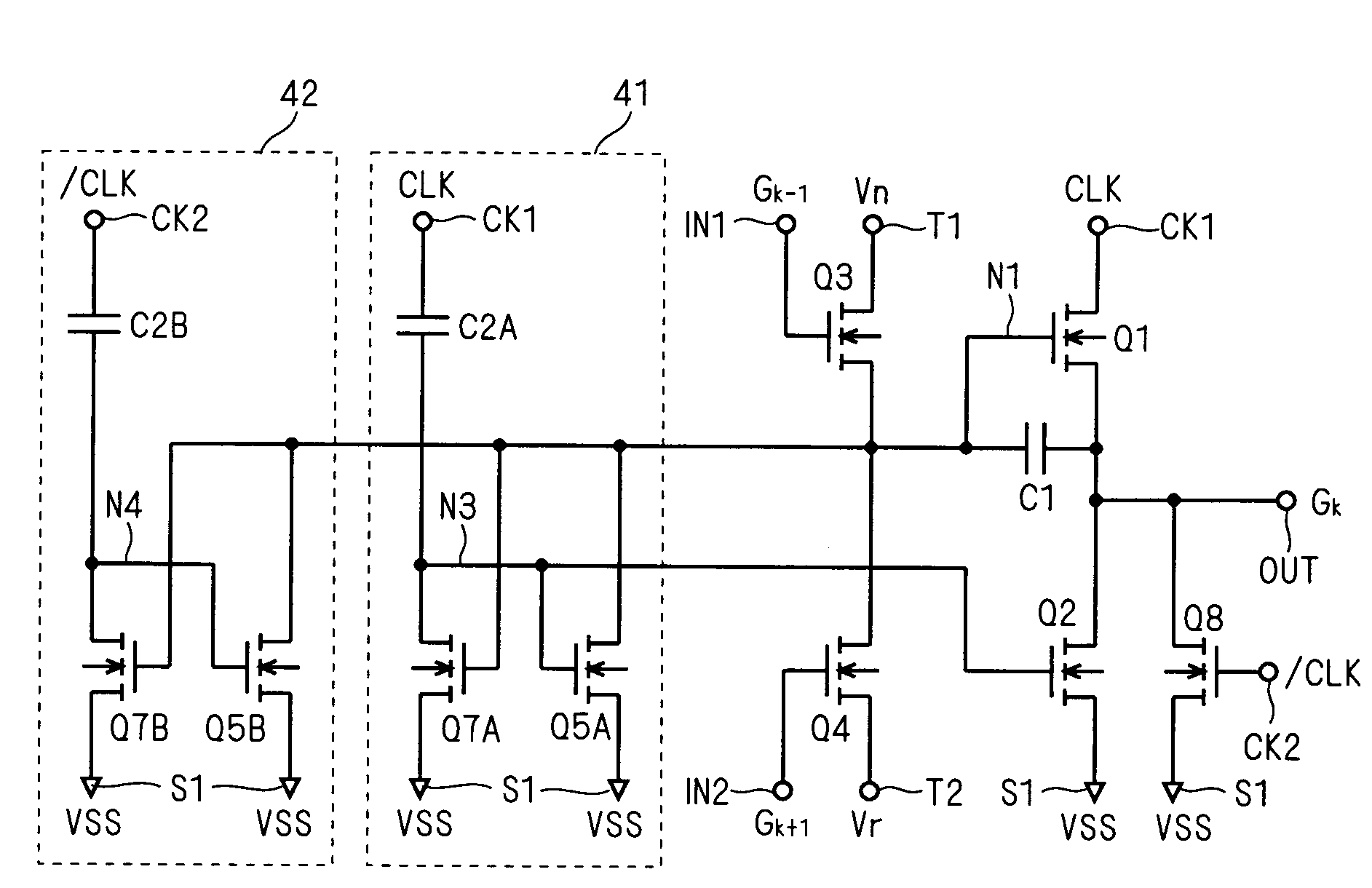

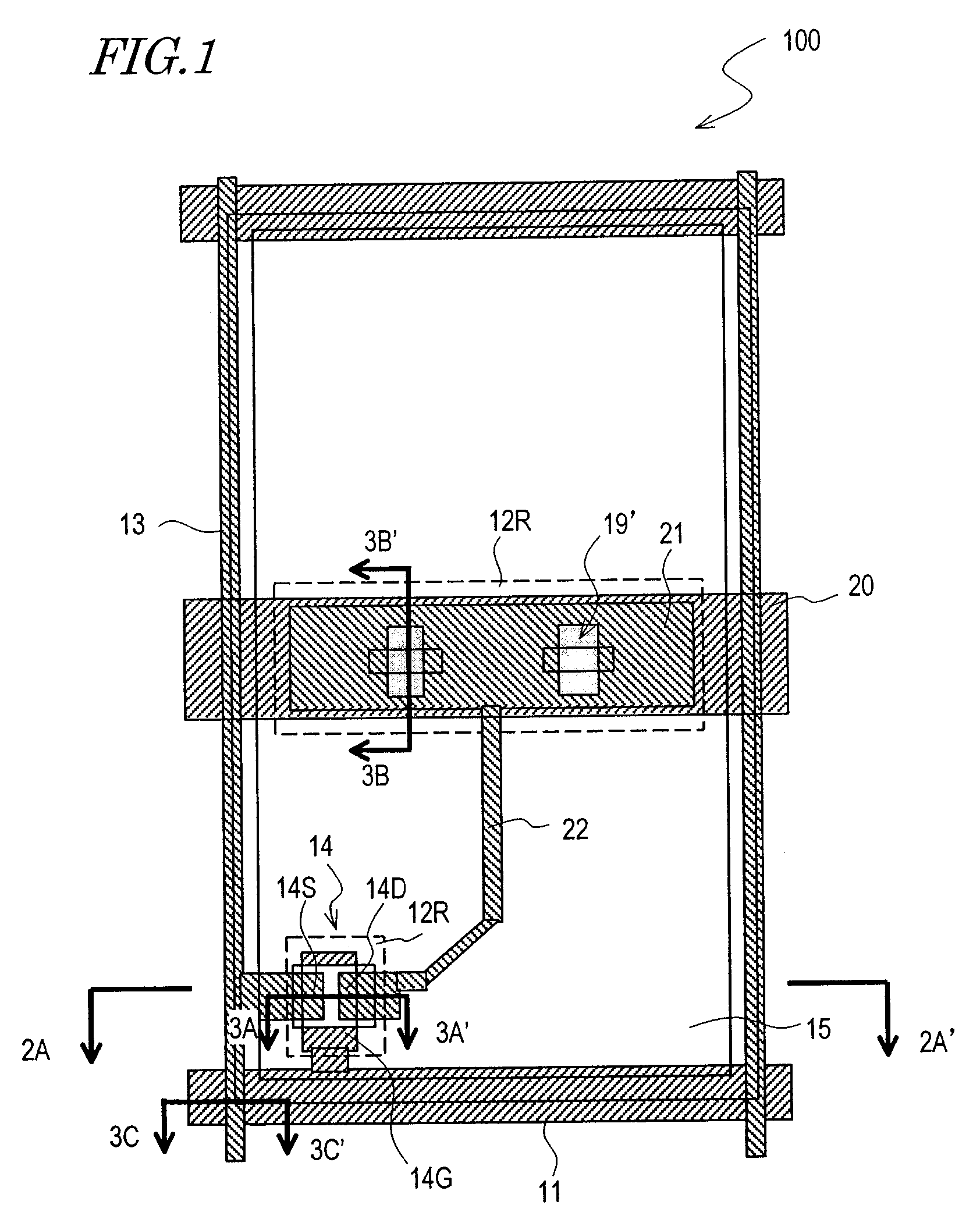

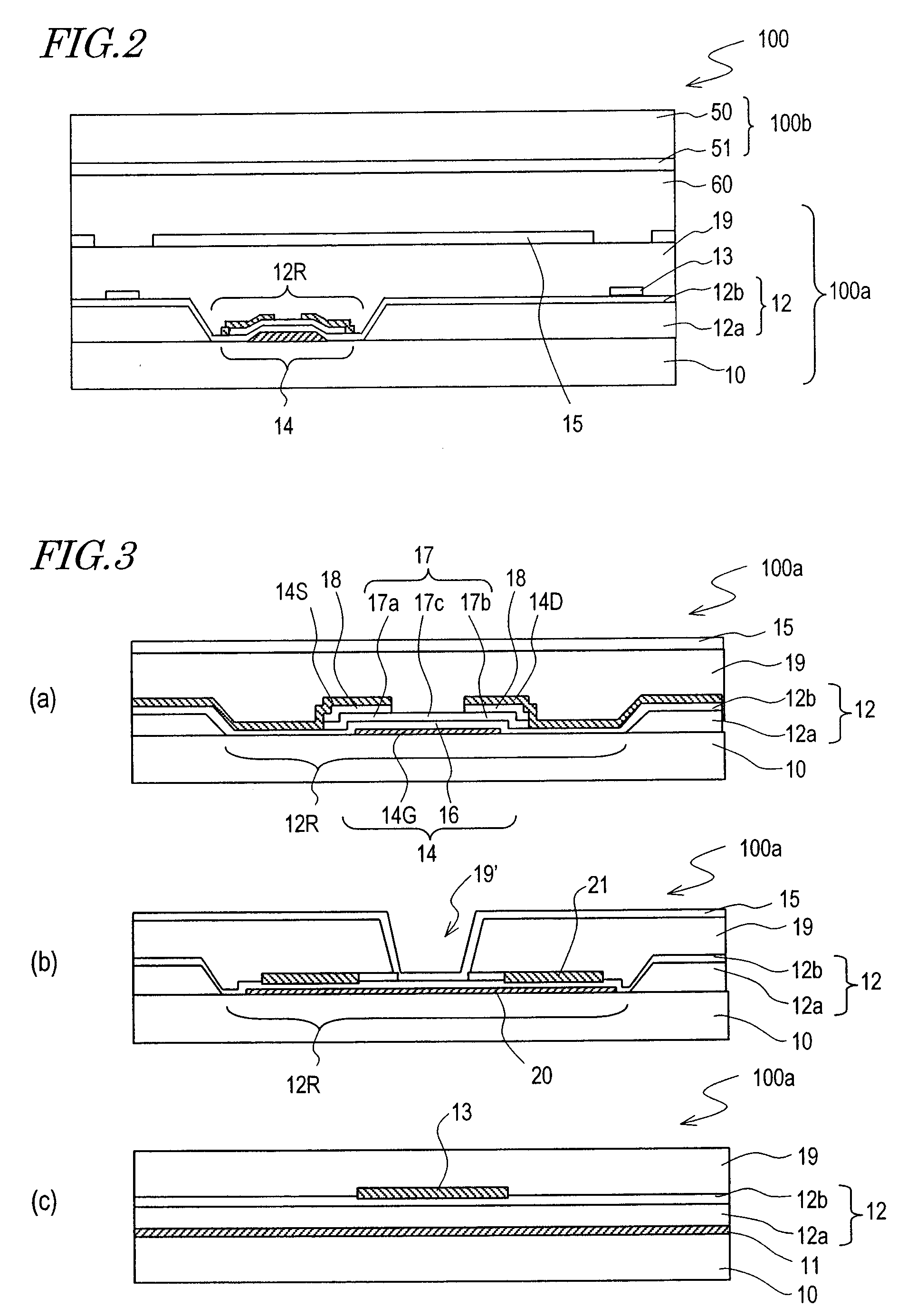

Threshold voltage shifts of transistors which are constituents of a bidirectional shift register are reduced to prevent a malfunction in the shift register. A bidirectional unit shift register includes first and second pull-down circuits (41, 42) connected to the gate of a first transistor (Q1) that supplies a first clock signal (CLK) to an output terminal (OUT). The first pull-down circuit (41) includes a first inverter that uses the gate of the first transistor (Q1) as the input node and that is activated by the first clock signal (CLK), and a second transistor (Q5A) that discharges the gate of the first transistor (Q1) according to the output of the first inverter. The second pull-down circuit (42) includes a second inverter that uses the gate of the first transistor (Q1) as the input node and that is activated by a second clock signal ( / CLK) having a different phase from the first clock signal (CLK), and a third transistor (Q5A) that discharges the gate of the first transistor according to the output of the second inverter.

Owner:TRIVALE TECH LLC

Shift register circuit and image display apparatus containing the same

InactiveUS7436923B2Avoid failureReduced driving abilityStatic indicating devicesDigital storageShift registerProcessor register

Threshold voltage shifts of transistors which are constituents of a bidirectional shift register are reduced to prevent a malfunction in the shift register. A bidirectional unit shift register includes first and second pull-down circuits (41, 42) connected to the gate of a first transistor (Q1) that supplies a first clock signal (CLK) to an output terminal (OUT). The first pull-down circuit (41) includes a first inverter that uses the gate of the first transistor (Q1) as the input node and that is activated by the first clock signal (CLK), and a second transistor (Q5A) that discharges the gate of the first transistor (Q1) according to the output of the first inverter. The second pull-down circuit (42) includes a second inverter that uses the gate of the first transistor (Q1) as the input node and that is activated by a second clock signal ( / CLK) having a different phase from the first clock signal (CLK), and a third transistor (Q5A) that discharges the gate of the first transistor according to the output of the second inverter.

Owner:TRIVALE TECH LLC

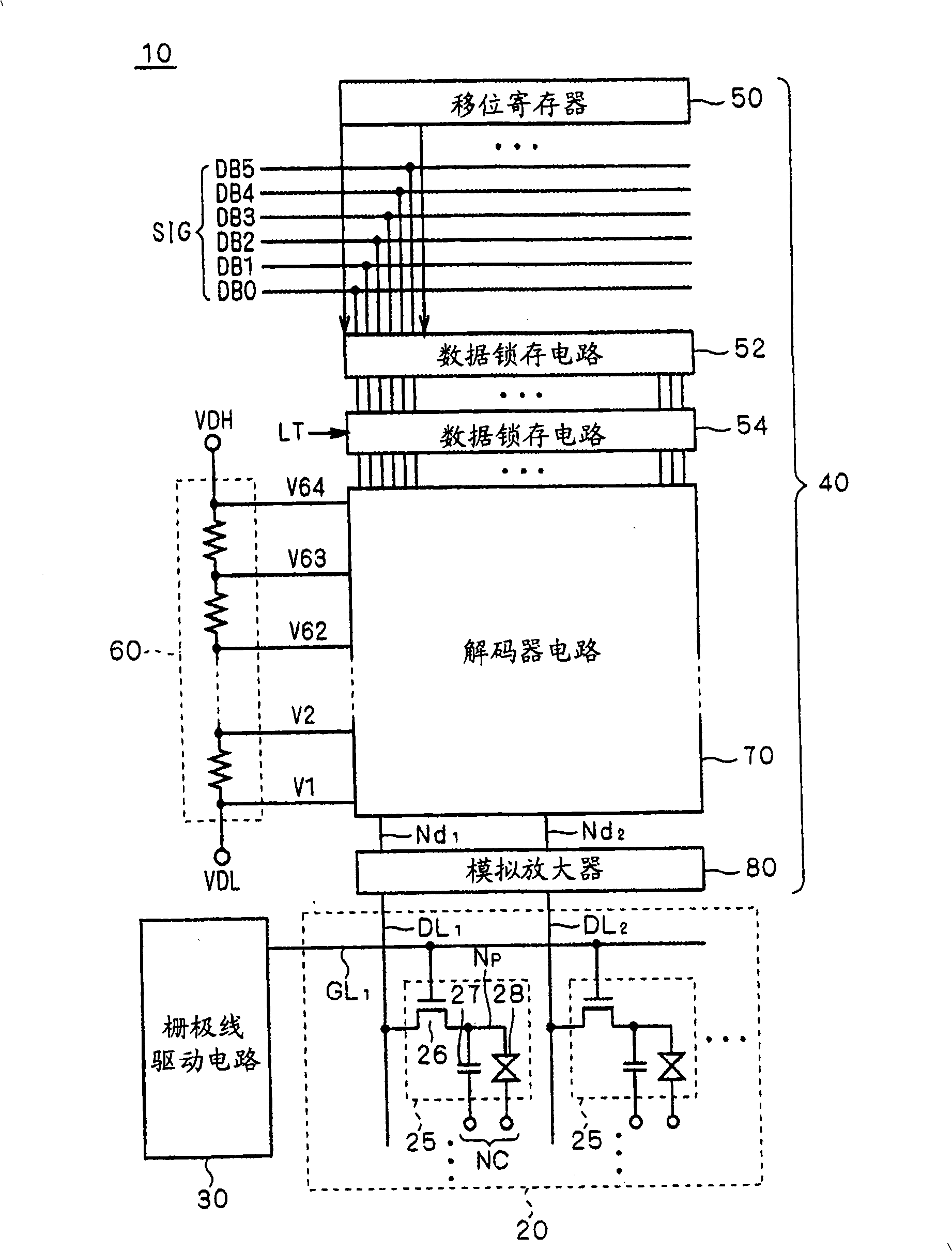

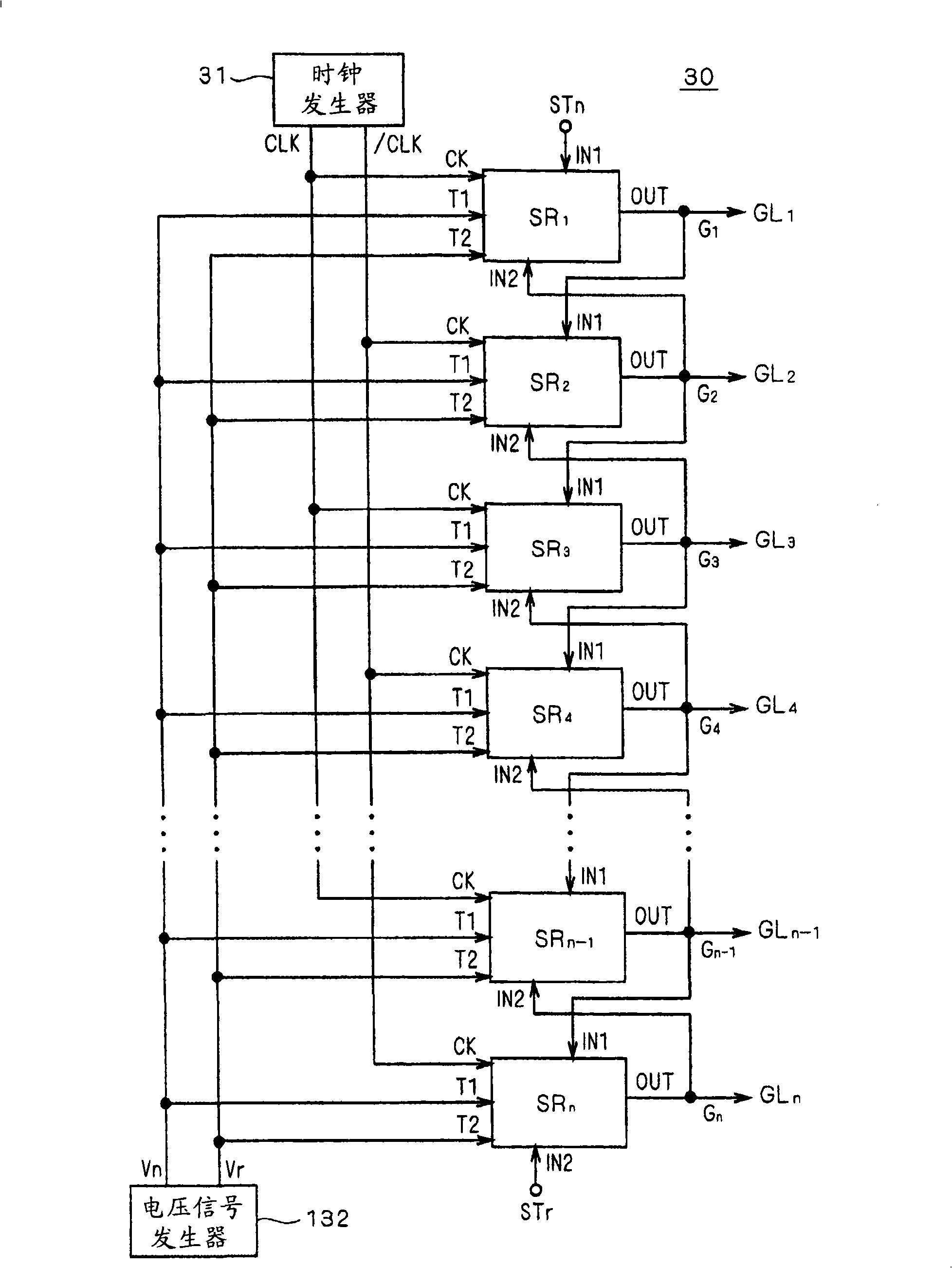

Shift register circuit and image display apparatus containing the same

InactiveCN101261881AReduced driving abilityAvoid misuseStatic indicating devicesDigital storageShift registerProcessor register

Threshold voltage shifts of transistors which are constituents of a bidirectional shift register are reduced to prevent a malfunction in the shift register. A bidirectional unit shift register includes first and second pull-down circuits (41, 42) connected to the gate of a first transistor (Q1) that supplies a first clock signal (CLK) to an output terminal (OUT). The first pull-down circuit (41) includes a first inverter that uses the gate of the first transistor (Q1) as the input node and that is activated by the first clock signal (CLK), and a second transistor (Q5A) that discharges the gate of the first transistor (Q1) according to the output of the first inverter. The second pull-down circuit (42) includes a second inverter that uses the gate of the first transistor (Q1) as the input node and that is activated by a second clock signal ( / CLK) having a different phase from the first clock signal (CLK), and a third transistor (Q5A) that discharges the gate of the first transistor according to the output of the second inverter.

Owner:MITSUBISHI ELECTRIC CORP

Shift register circuit and image display apparatus equipped with the same

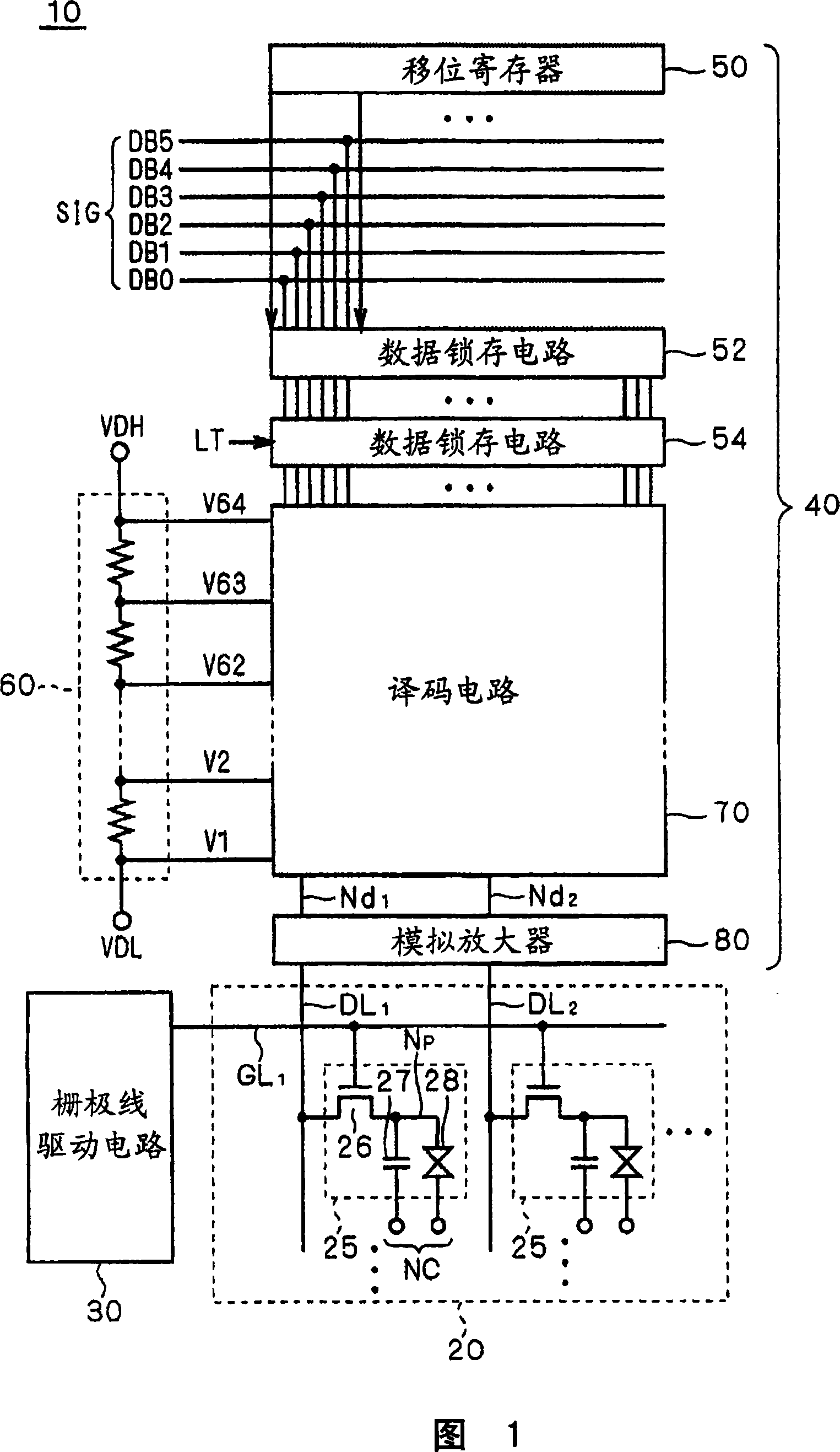

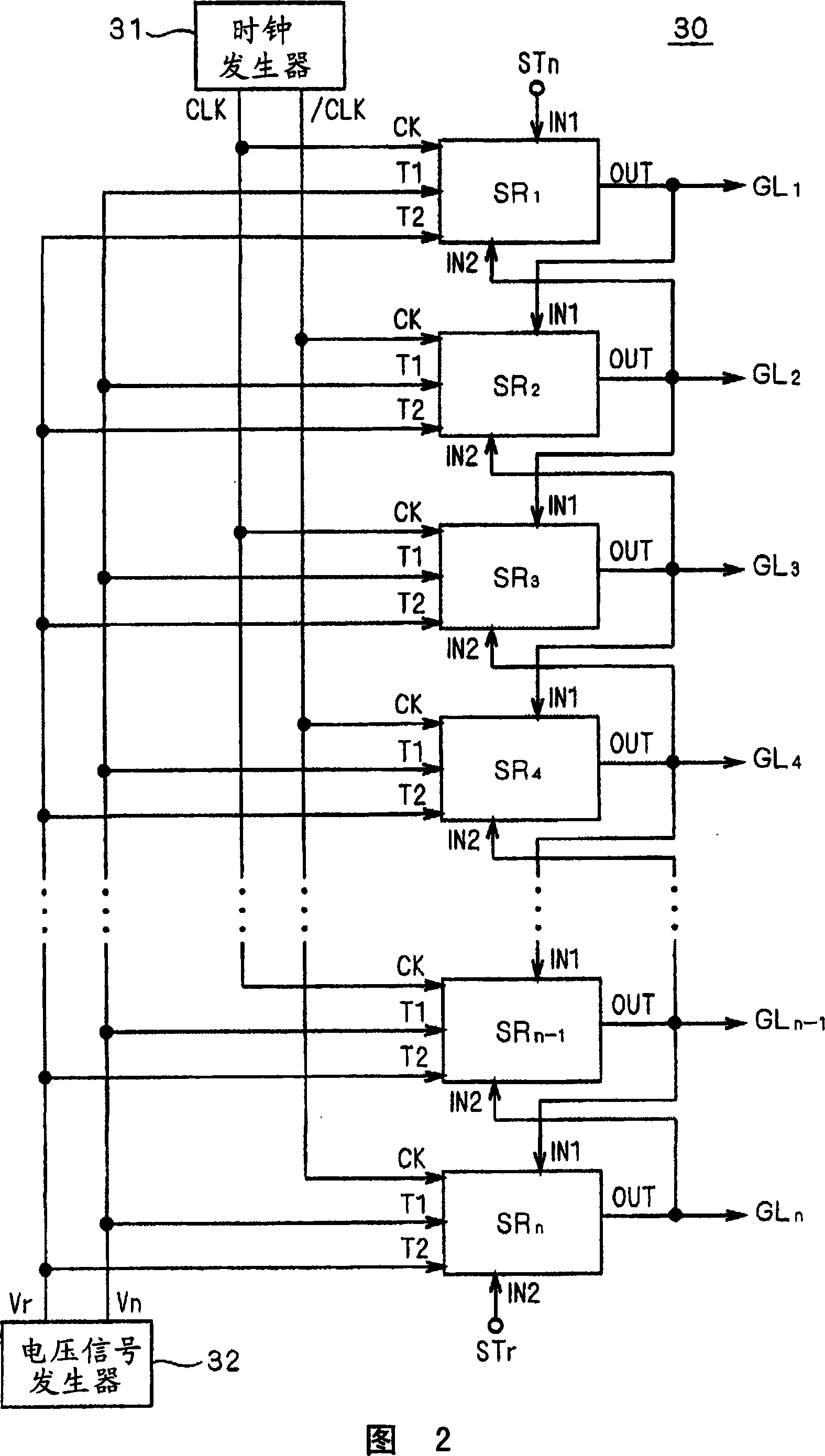

InactiveCN101079243AImprove driving abilityReduced driving abilityStatic indicating devicesDigital storageElectricityShift register

Owner:MITSUBISHI ELECTRIC CORP

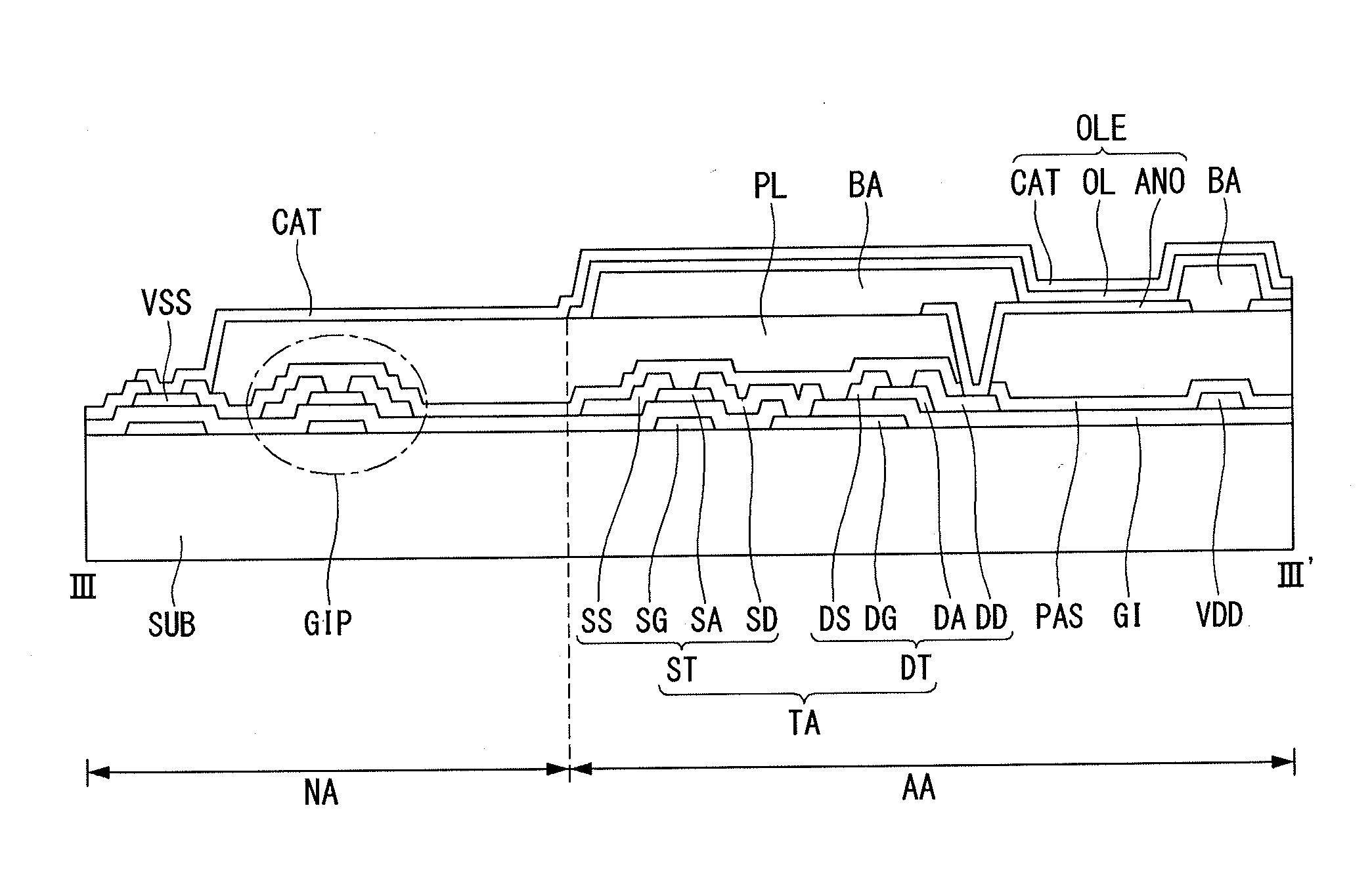

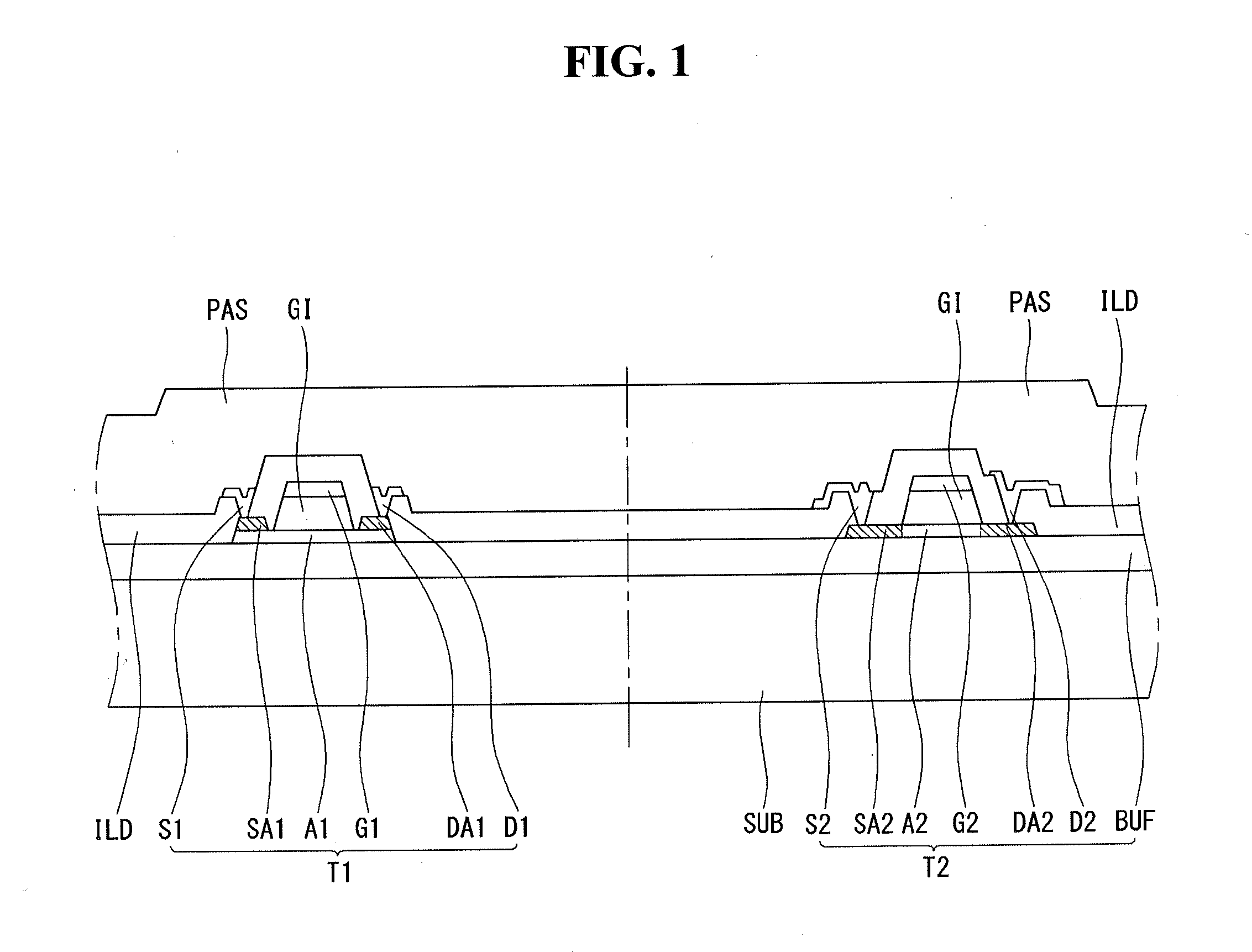

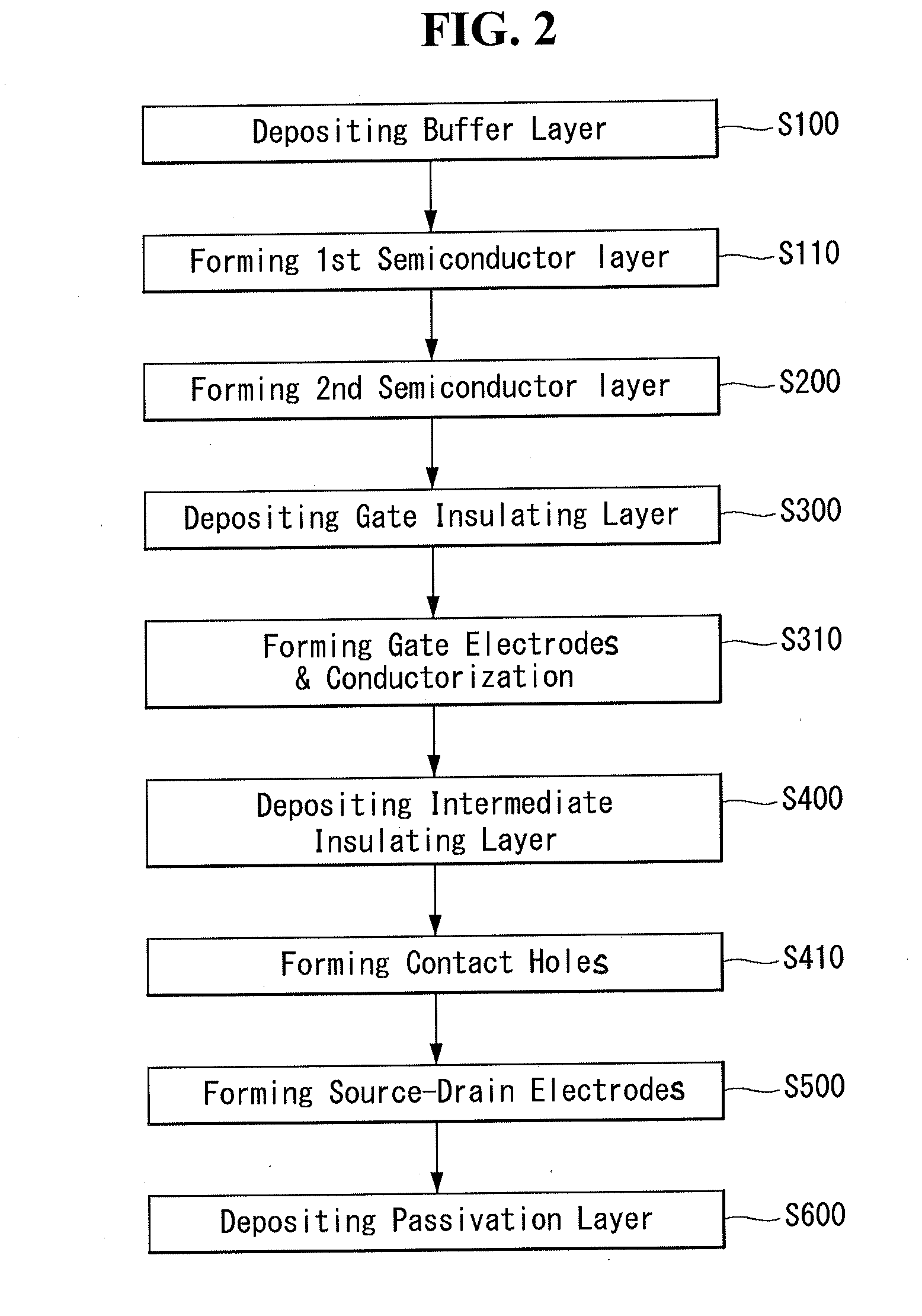

Thin film transistor substrate and display using the same

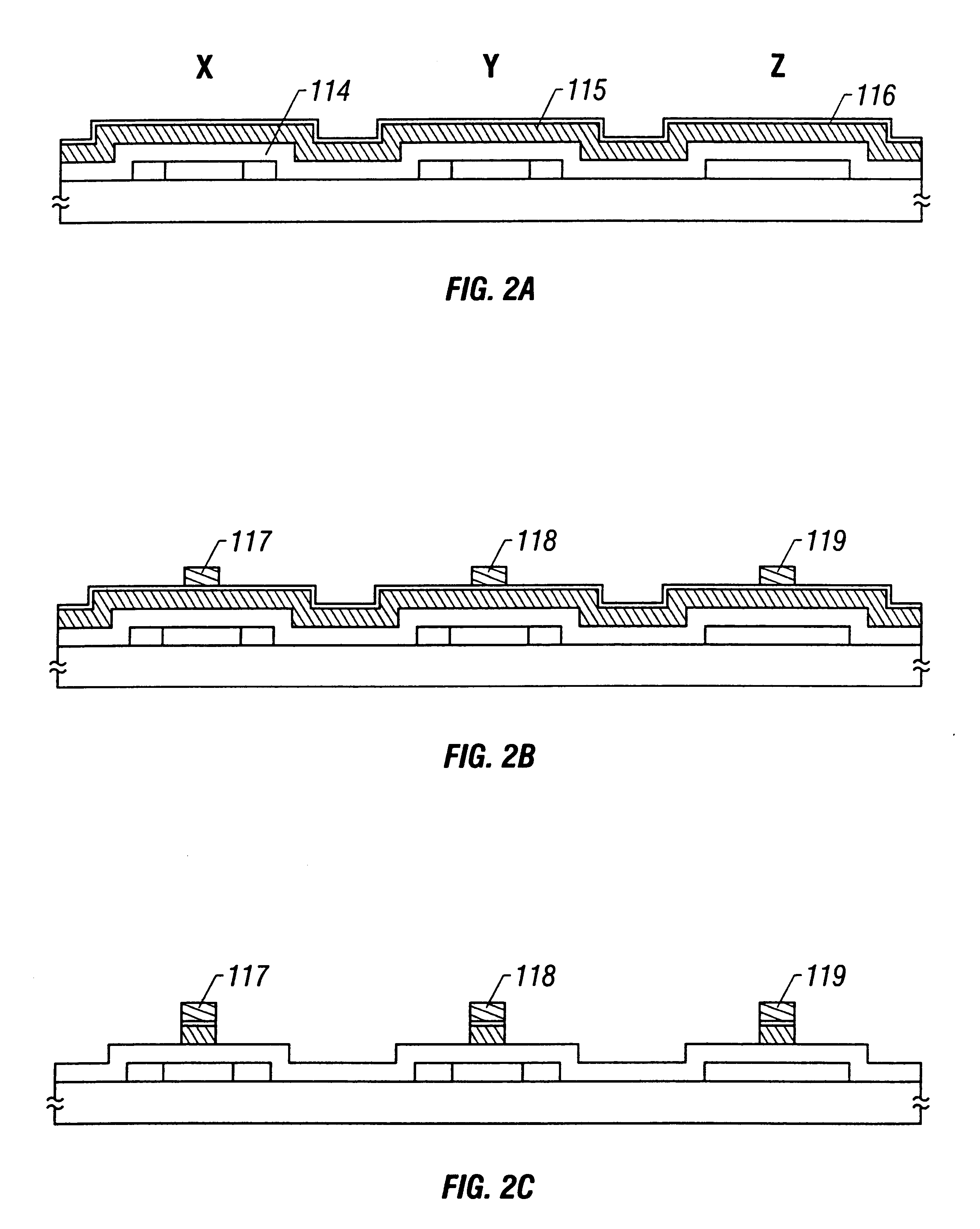

ActiveUS20160064465A1Simple preparation processReduce in quantityTransistorSolid-state devicesSemiconductor materialsDisplay device

The present invention relates to a thin film transistor substrate having two different types of semiconductor materials on the same substrate, and a display using the same. A disclosed display may include a substrate, a first thin film transistor having a polycrystalline semiconductor material on the substrate and a second thin film transistor having an oxide semiconductor material on the substrate.

Owner:LG DISPLAY CO LTD

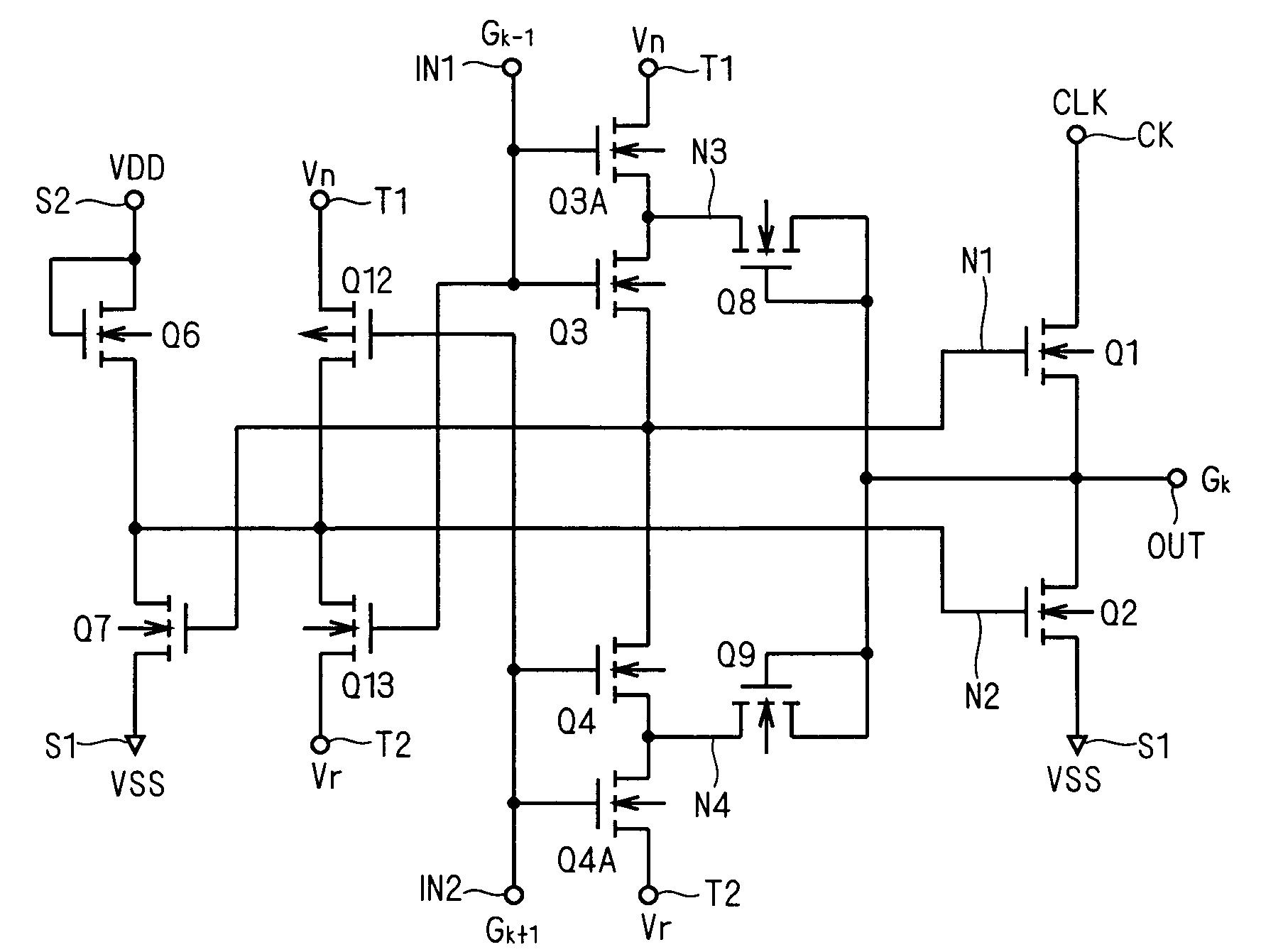

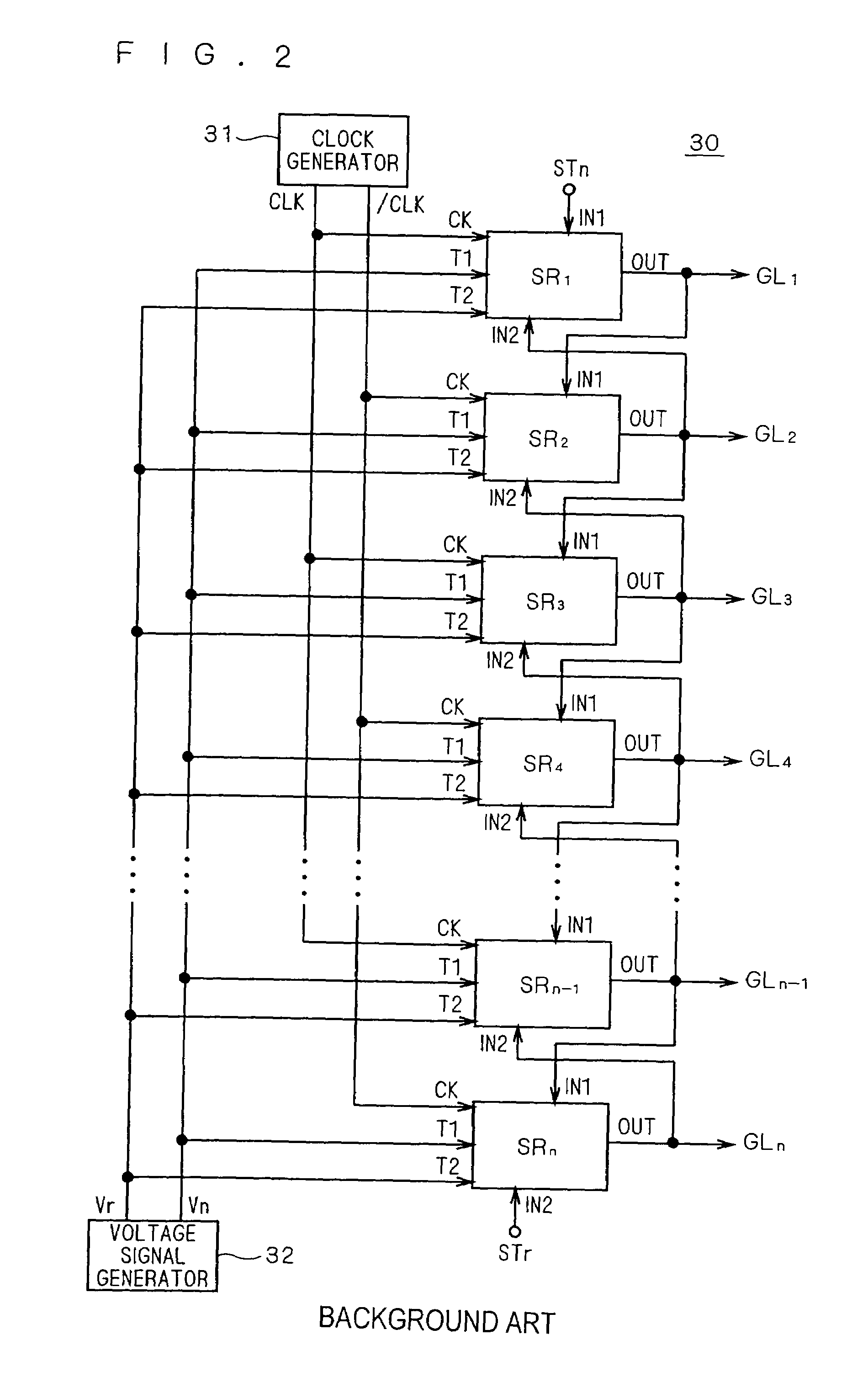

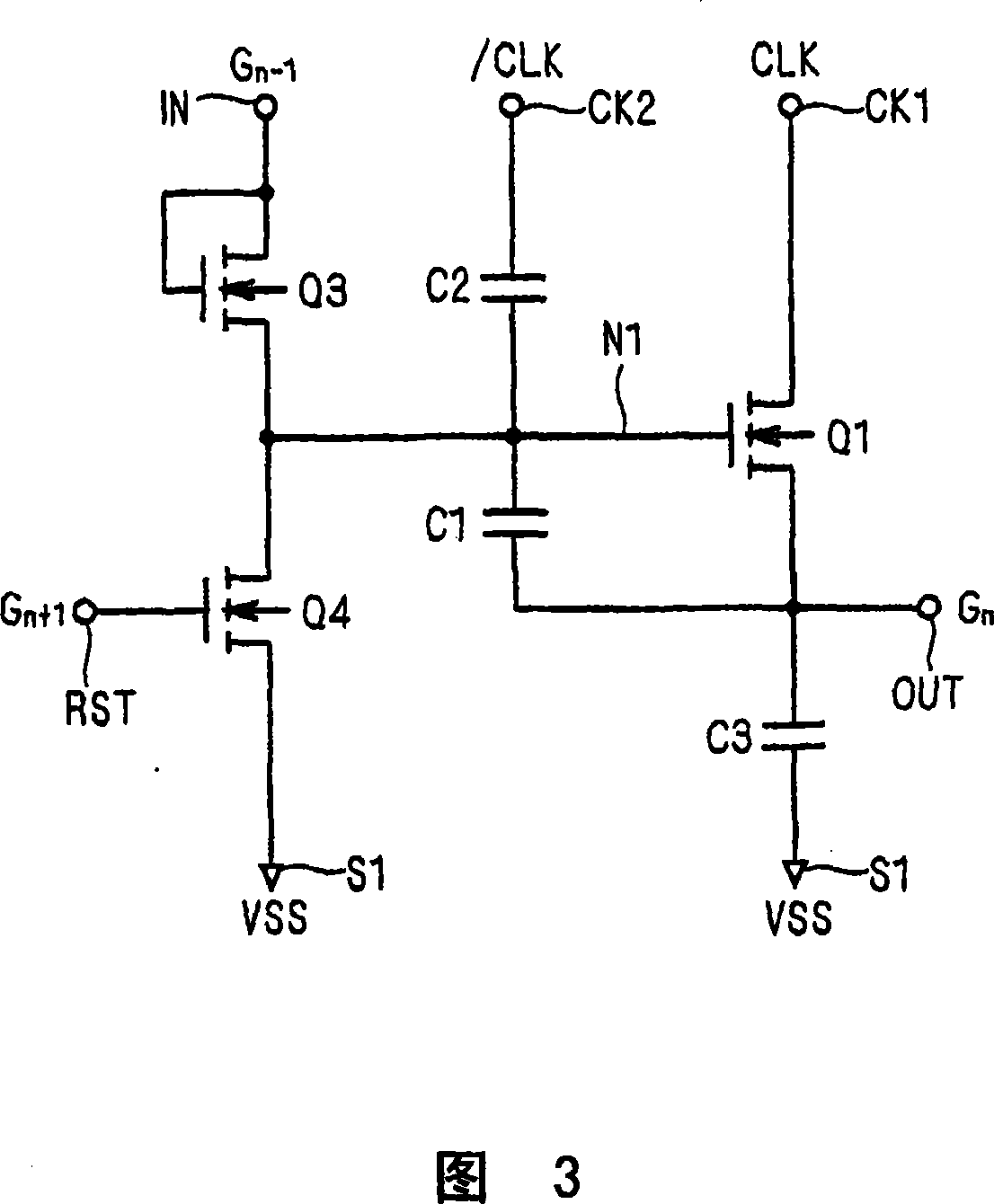

Shift register circuit and image display apparatus equipped with the same

ActiveUS7636412B2Reduce impactSuppress failureStatic indicating devicesDigital storageShift registerProcessor register

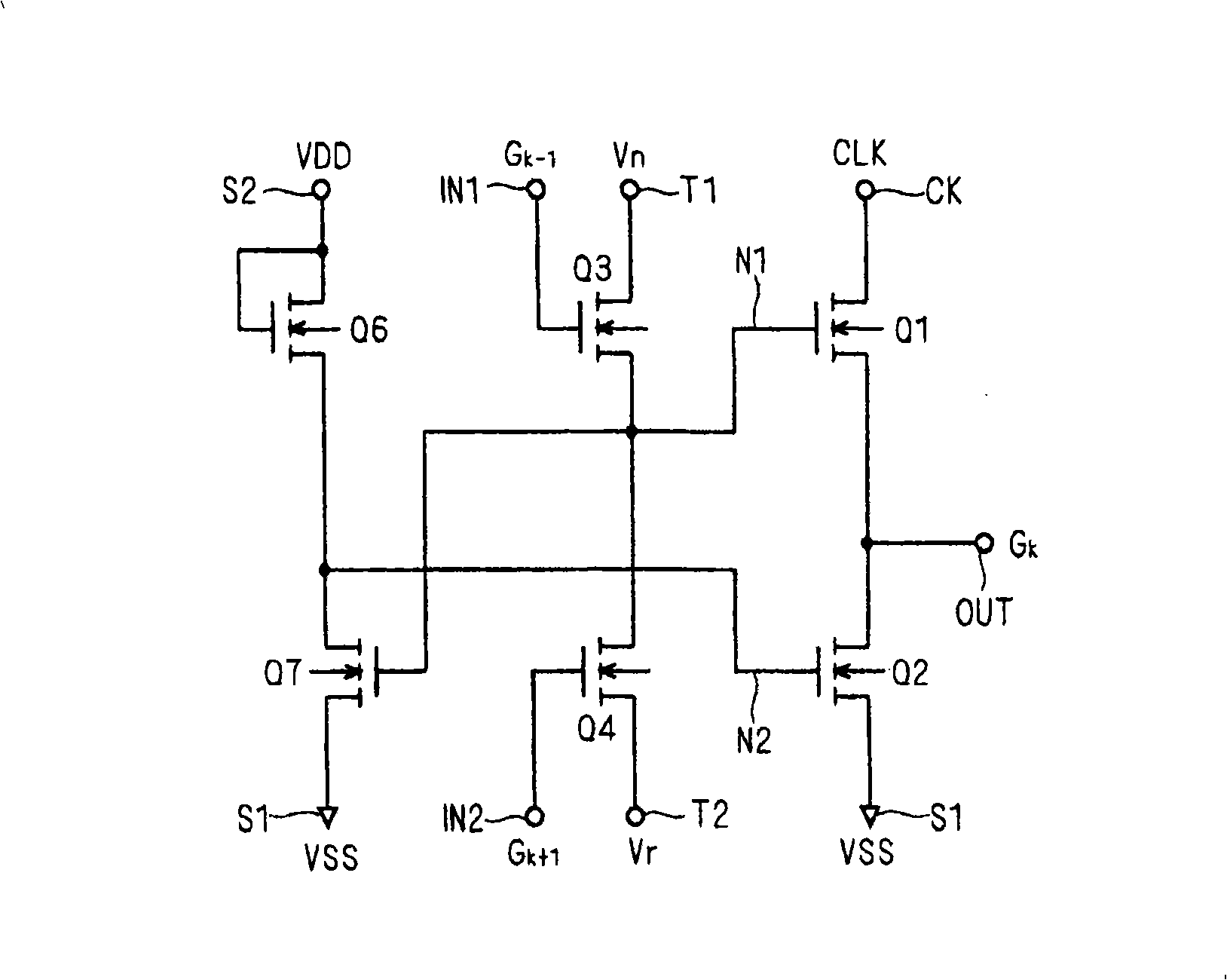

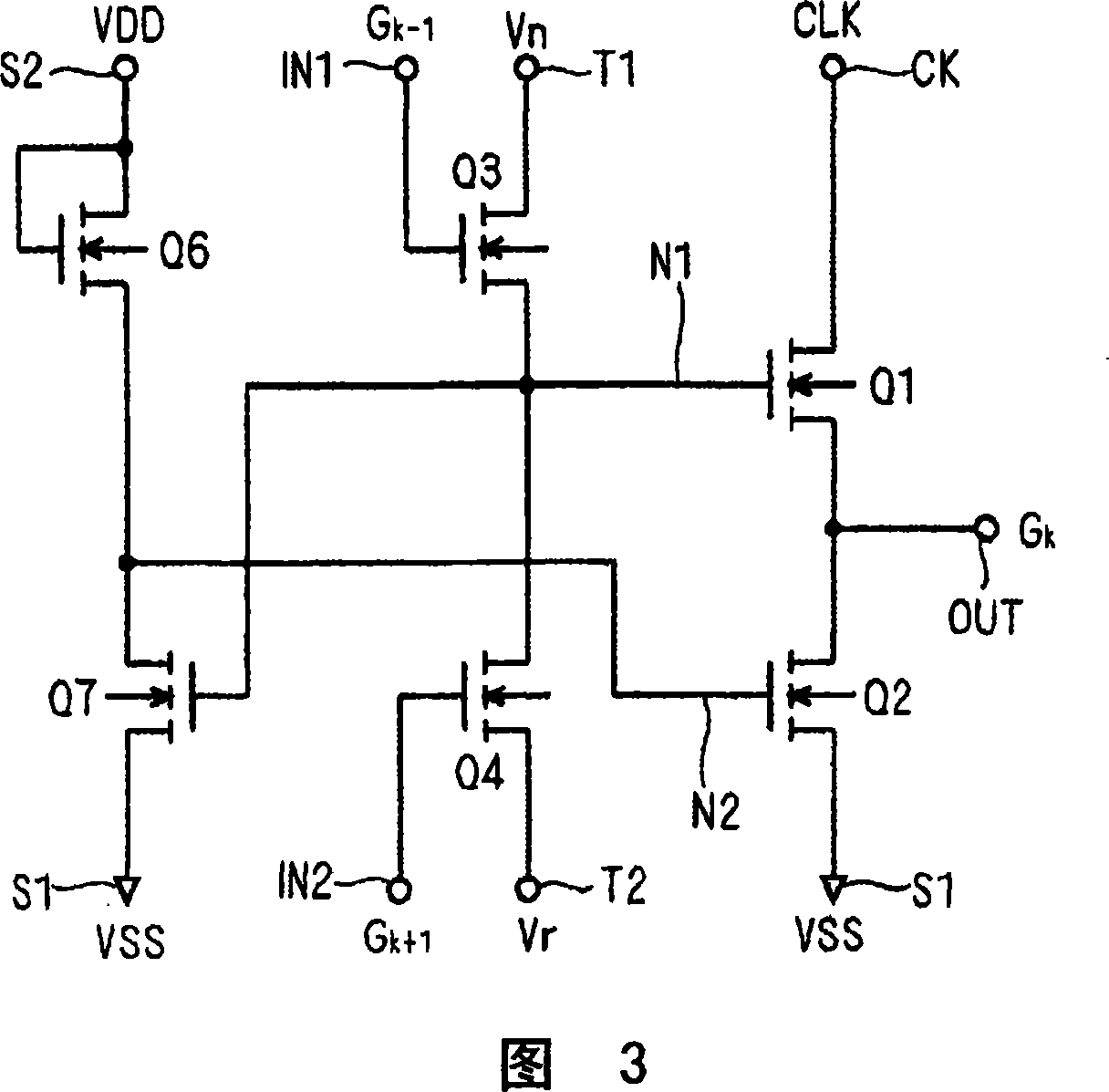

Malfunction caused by leakage current of the transistor is prevented in the shift register in which the signal can be shifted bi-directionally. The bi-directional unit shift register includes a transistor Q1 between a clock terminal CK and an output terminal OUT, a transistor Q2 for discharging the output terminal OUT, and transistors Q3, Q4 for providing first and second voltage signals Vn, Vr, which are complementary to each other, to the first node or a gate node of the transistor Q1. Furthermore, a transistor Q5, having a gate connected to a second node or a gate node of the transistor Q2, for discharging the first node is arranged.

Owner:TRIVALE TECH

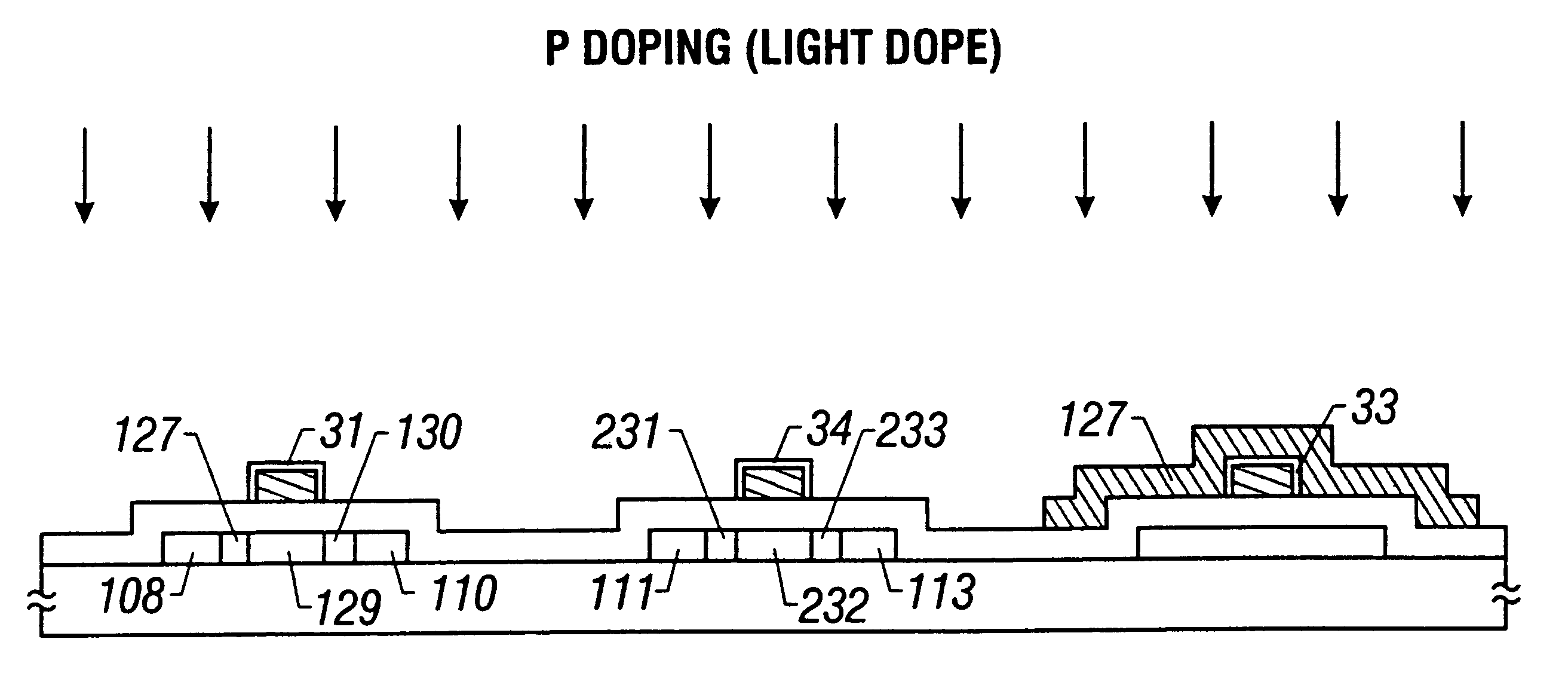

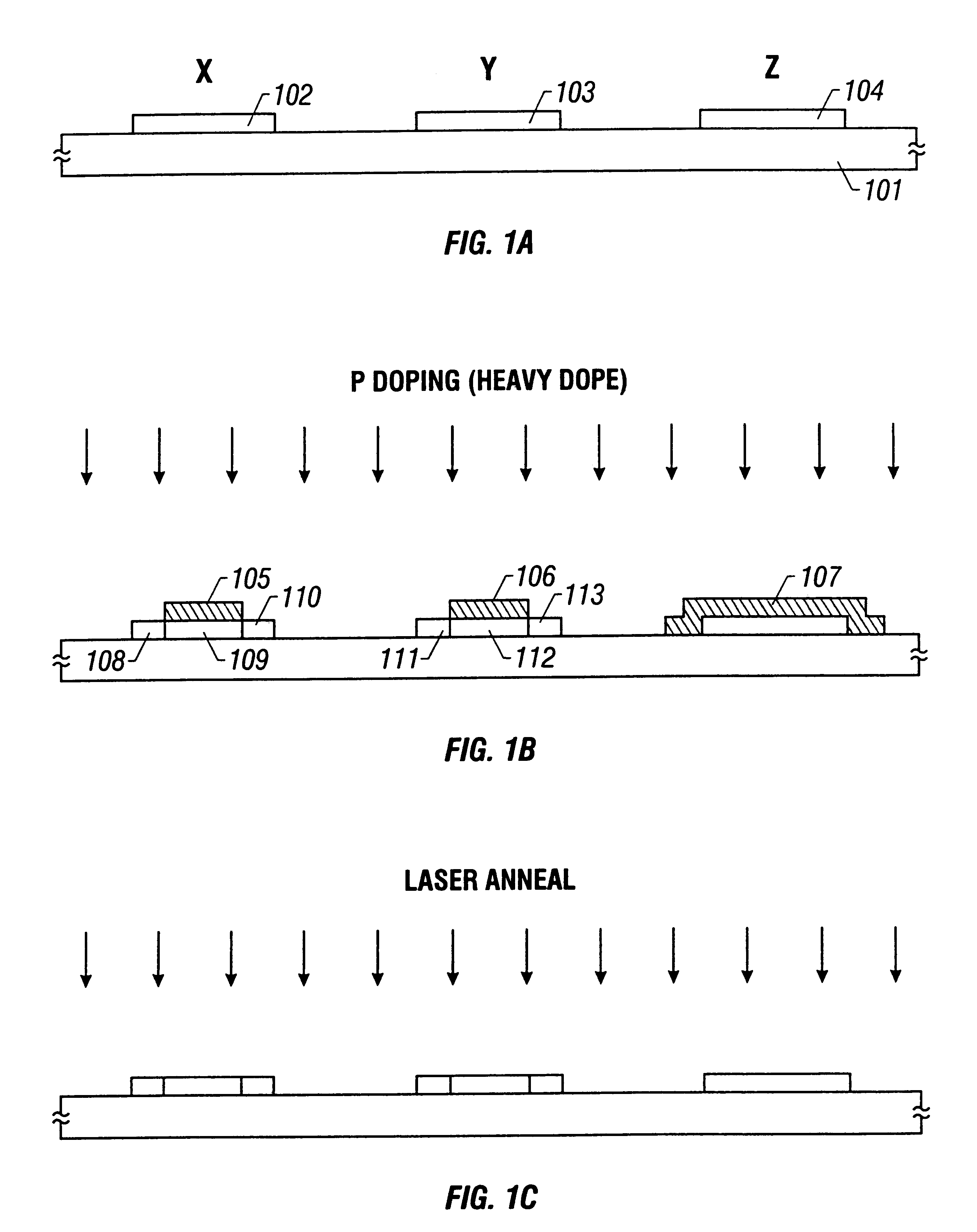

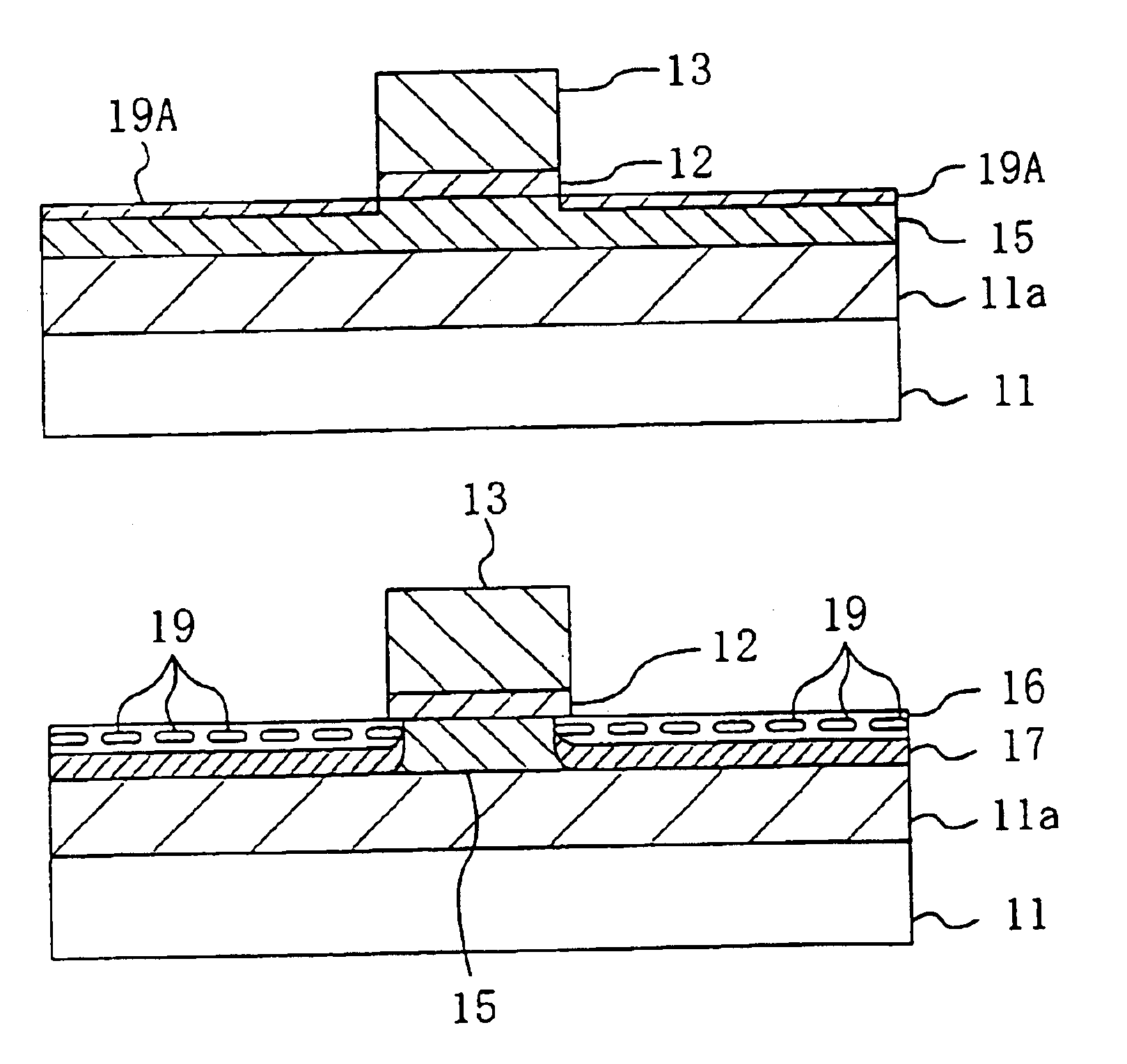

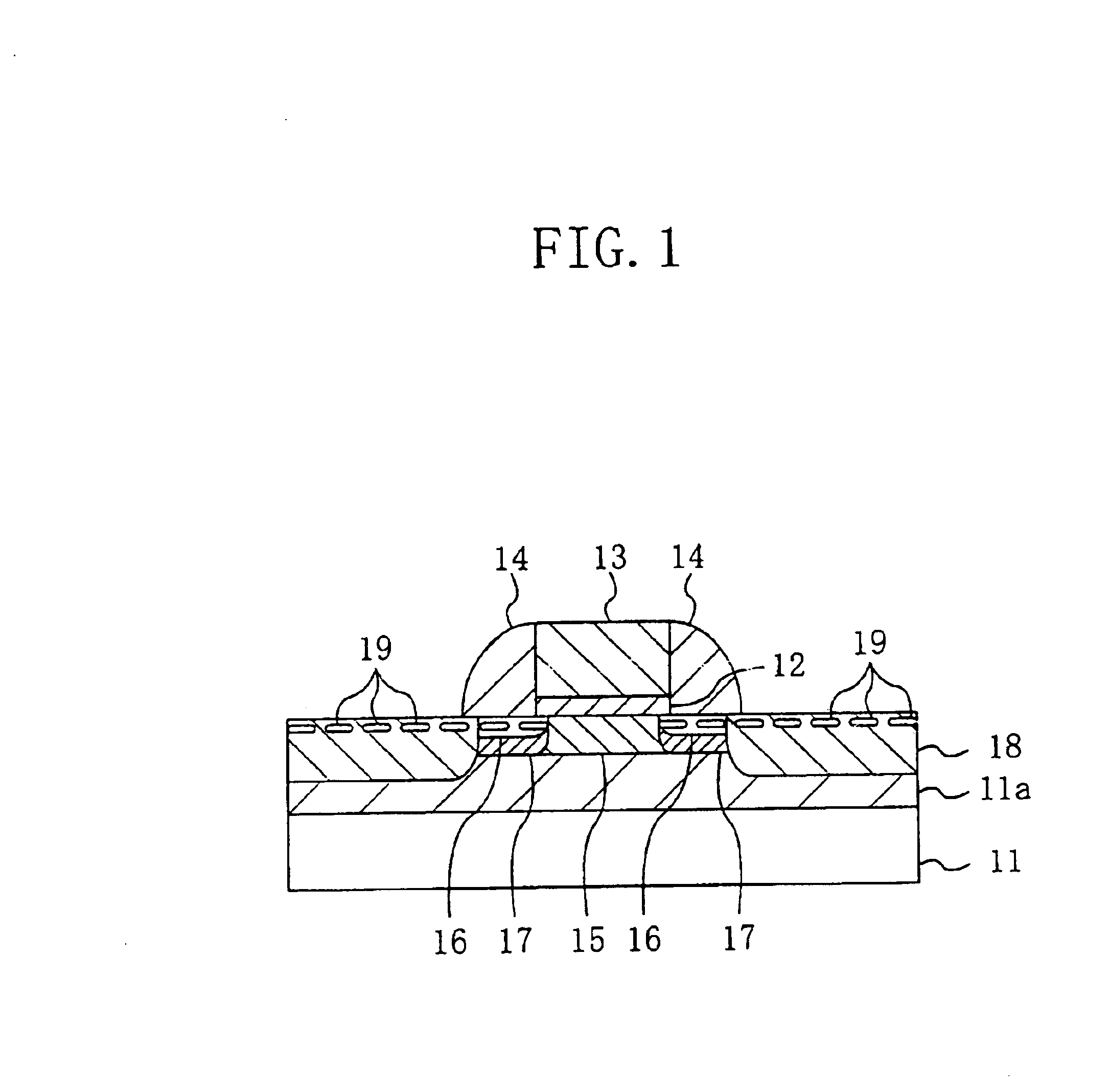

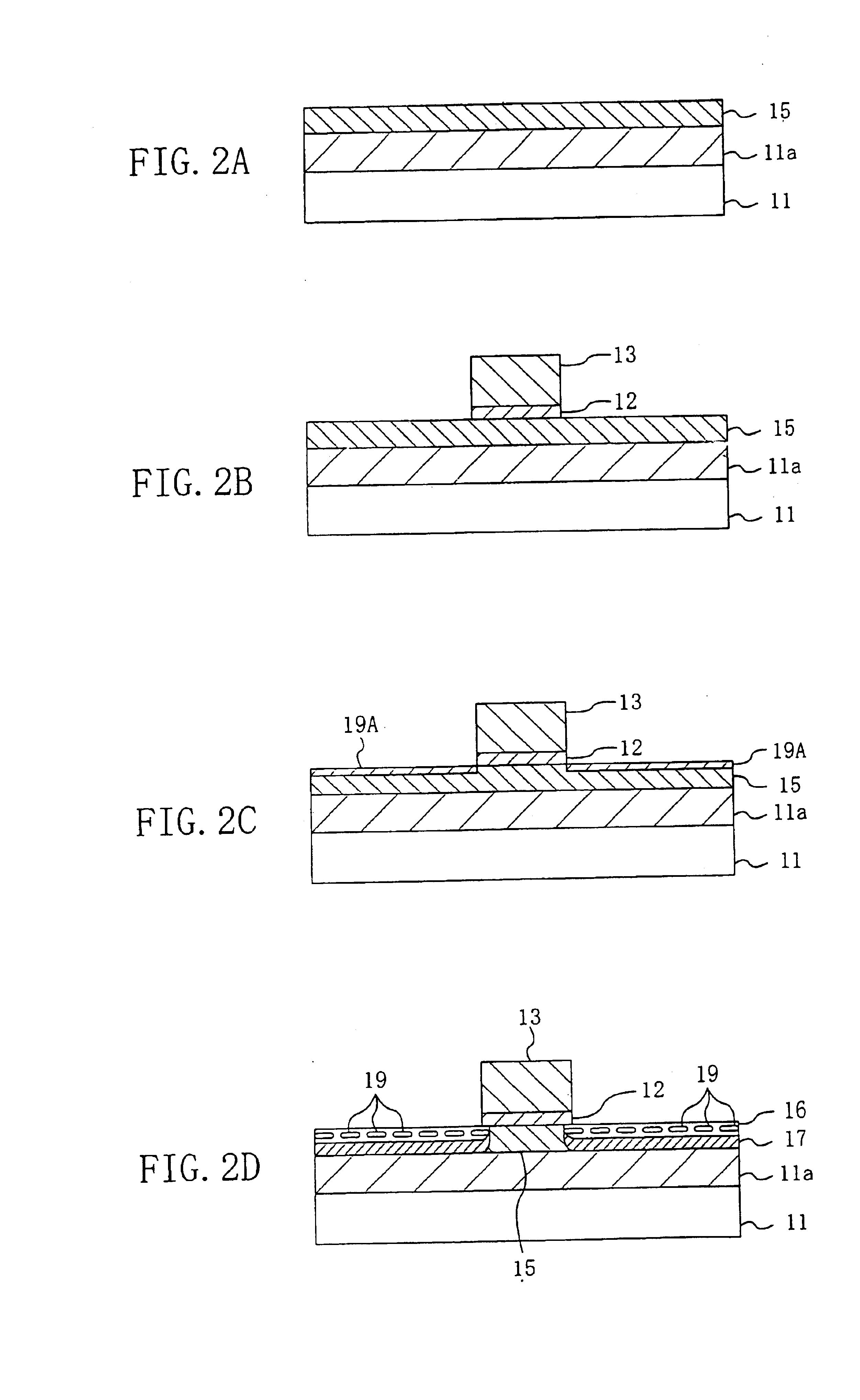

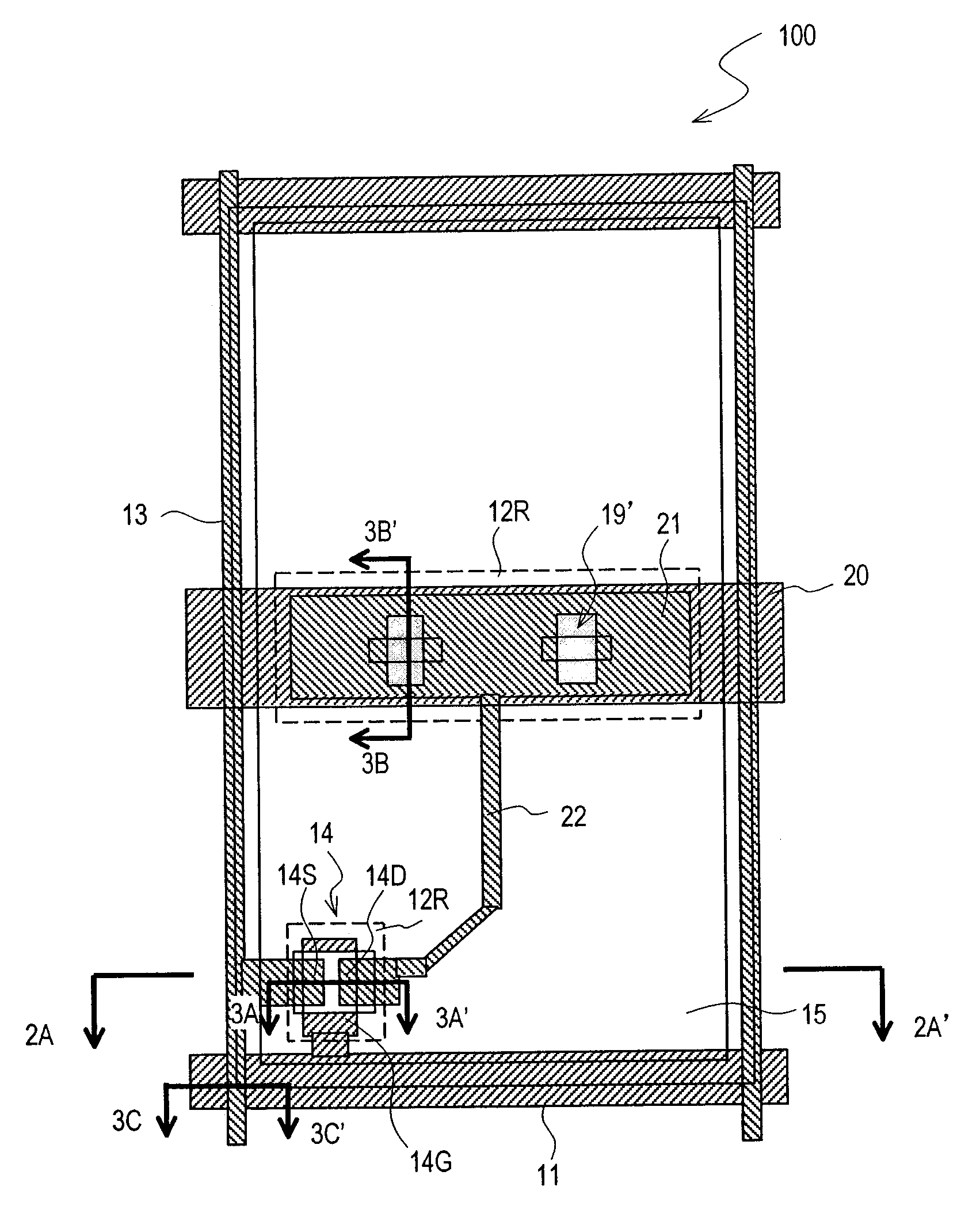

Active matrix type display device and fabrication method of the same

InactiveUS6172671B1Improve reliabilityReduced driving abilityTransistorSolid-state devicesActive matrixDisplay device

There is provided an active matrix type display in which thin film transistors having required characteristics are provided selectively in a pixel matrix portion and a peripheral driving circuit portion. In a structure having the pixel matrix portion and the peripheral driving circuit portion on the same substrate, N-channel type thin film transistors having source and drain regions formed through a non-self-alignment process and low concentrate impurity regions formed through a self-alignment process are formed in the pixel matrix portion and in an N-channel driver portion of the peripheral driving circuit portion. A P-channel type thin film transistor in which no low concentrate impurity region is formed and source and drain regions are formed only through the self-alignment process is formed in a P-channel driver portion of the peripheral driving circuit portion.

Owner:SEMICON ENERGY LAB CO LTD +1

Shift register circuit and image display device provided with the same

InactiveCN101064085AIncrease ascent speedIncrease the speed of descentStatic indicating devicesElectricityShift register

In a shift register circuit, a defective operation while an output signal is not outputted and a drive capability lowering while the output signal is outputted are prevented. A unit shift register comprises a first transistor for supplying a clock signal inputted to a first clock terminal to an output terminal, and the first transistor is driven by a drive circuit. A second transistor is connected between the gate of the first transistor and the output terminal and has a gate connected to the first clock terminal. The second transistor connects the gate of the first transistor to the output terminal based on the clock signal when the gate of the first transistor is at L (Low) level.

Owner:MITSUBISHI ELECTRIC CORP

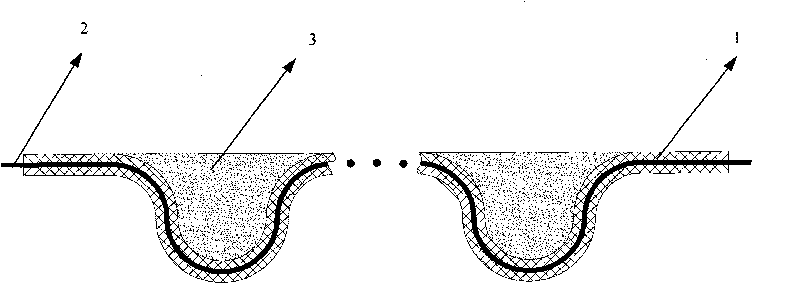

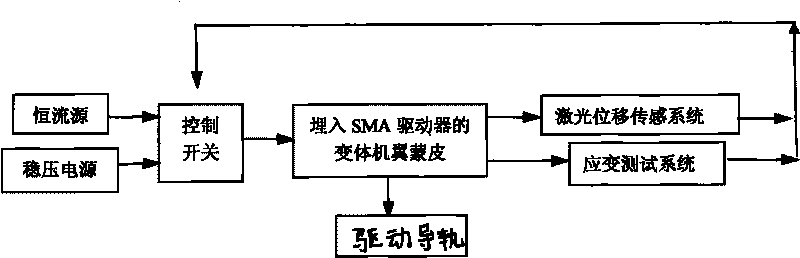

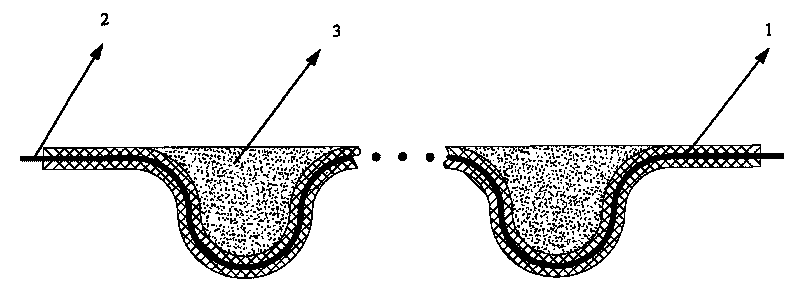

Skin of morphing wing and drive method thereof

InactiveCN101708772AImprove flexibilityLarge amount of deformationWingsMorphing wingRoom temperature

The invention provides a skin of a morphing wing, which is made from fiber-reinforced composite material (1). The skin is characterized in that: a shape memory alloy driver (2) is arranged between the two layers of the fiber-reinforced composite material (1); the wave trough of the upper layer fiber-reinforced composite material is internally filled with silica-based rubber (3) for meeting the requirements of smoothness, continuity and whole gas tightness on the surface of the wing; the fiber-reinforced composite material (1) and the shape memory alloy driver (2) are jointly pressed into to a corrugated structure under room temperature; the shape memory alloy driver (2) is in the shape of a high-temperature memory straight line; and the silica-based rubber (3) can be solidified under normal temperature. The invention also provides a drive method of the skin of the morphing wing. The skin of the morphing wing has the corrugated structure, thereby having high flexibility, large morphing amount and fast morphing response speed on the morphing direction, having high carrying capability on the perpendicular morphing direction, and having simple structure, light weight and reliable performance.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

Semiconductor device and method for manufacturing the same

InactiveUS6852610B2Loss of dosingLocated reliablyTransistorSemiconductor/solid-state device manufacturingHigh concentrationDislocation

A semiconductor device includes a gate electrode formed on a semiconductor region via a gate insulative film and an extension high concentration diffusion layer of a first conductivity type formed in the semiconductor region beside the gate electrode. A dislocation loop defect layer is formed in a region of the semiconductor region beside the gate electrode and at a position shallower than an implantation projected range of the extension high concentration diffusion layer.

Owner:TAIWAN SEMICON MFG CO LTD

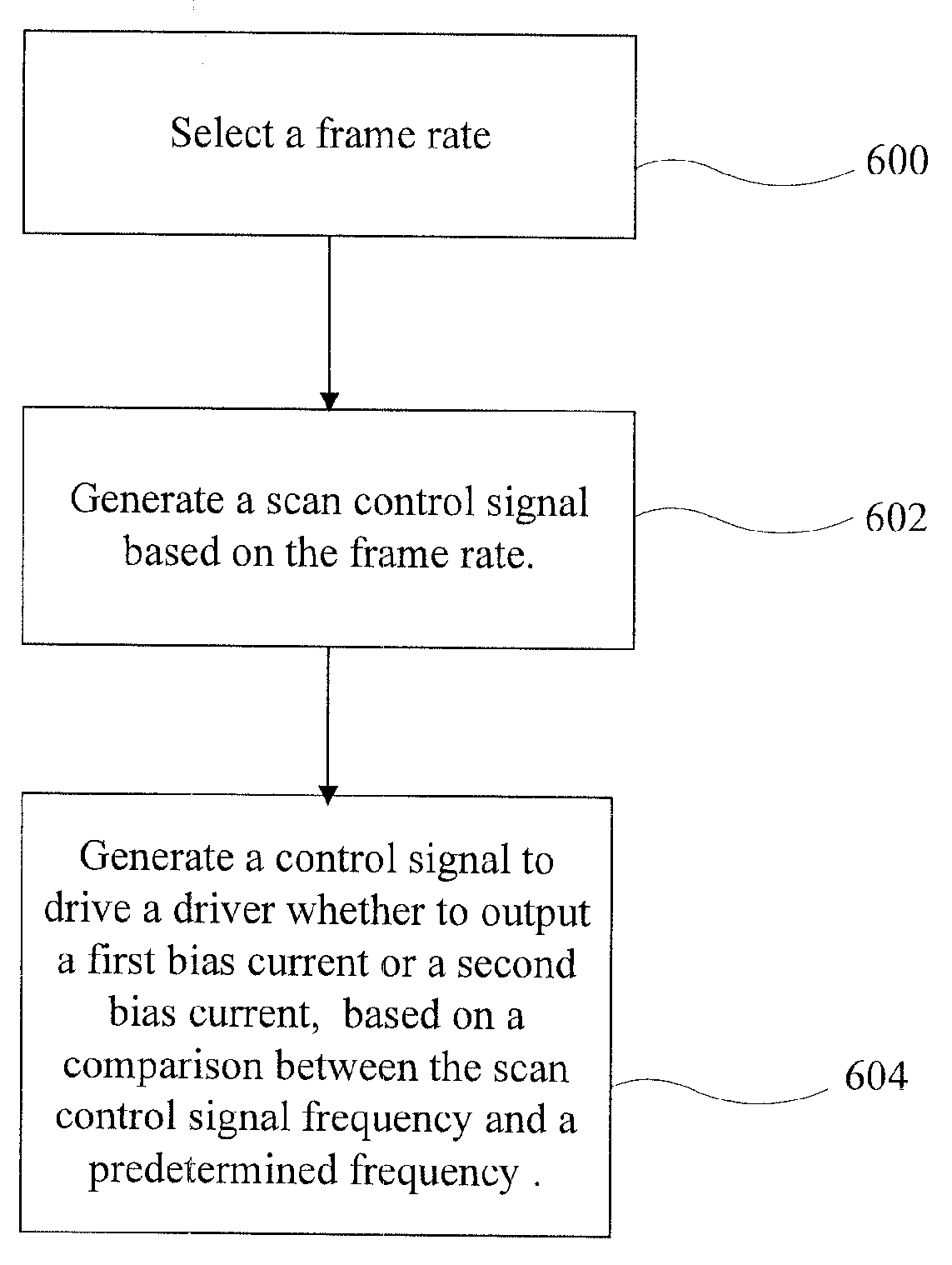

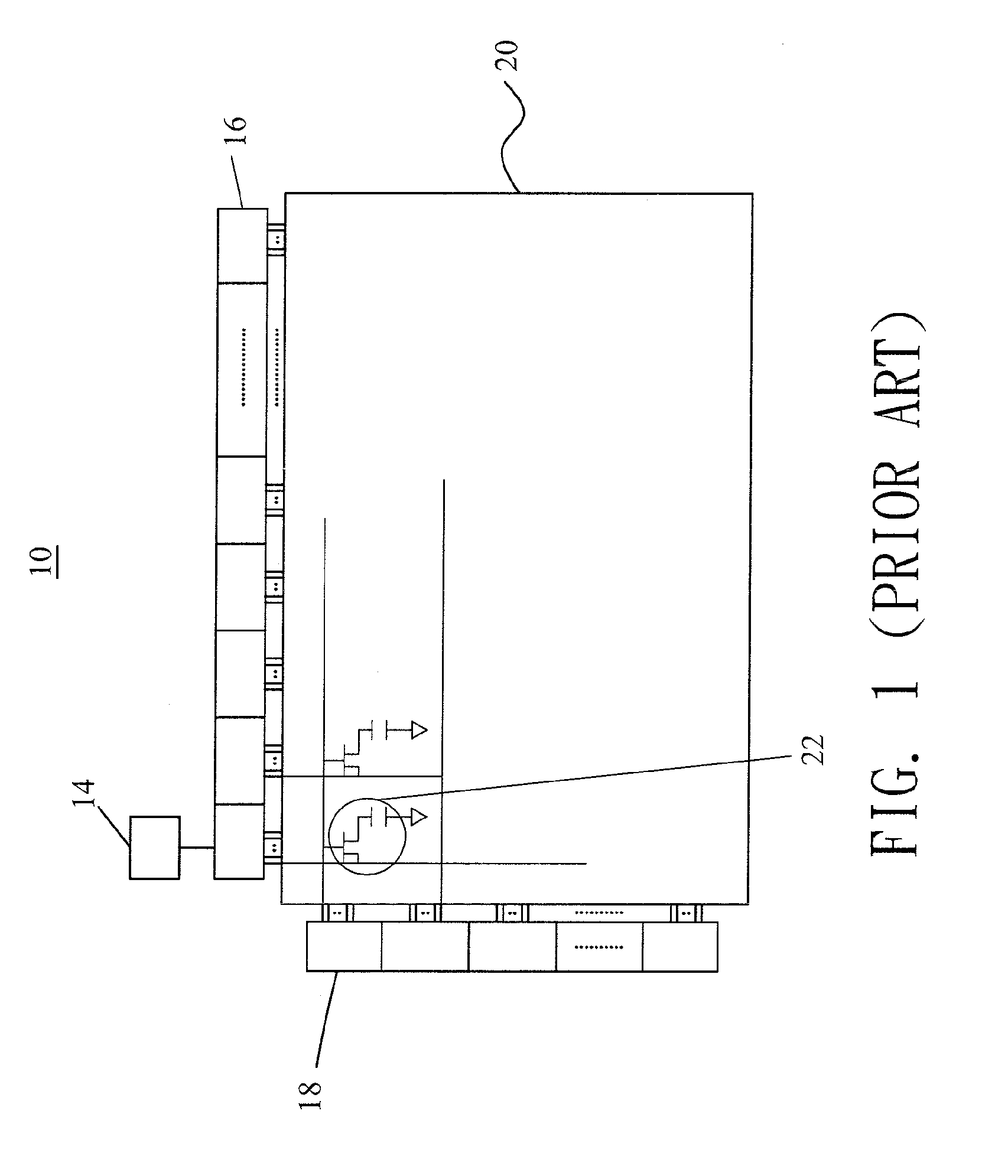

Liquid crystal display device with dynamically switching driving method to reduce power consumption

ActiveUS20090128540A1Reduce power consumptionLower frame rateCathode-ray tube indicatorsInput/output processes for data processingElectricityLiquid-crystal display

A liquid crystal display device of reducing power consumption includes a liquid crystal panel having a plurality of liquid crystal capacitors for displaying an image, an input interface for generating a scan control signal, an oscillator for generating a predetermined frequency, a control unit electrically coupled to the oscillator for outputting a current control signal when a frequency of the scan control signal is lower than the predetermined frequency, and a driving circuit electrically coupled to the controller for generating a first bias current to charge the plurality of liquid crystal capacitors of the liquid crystal panel.

Owner:AU OPTRONICS CORP

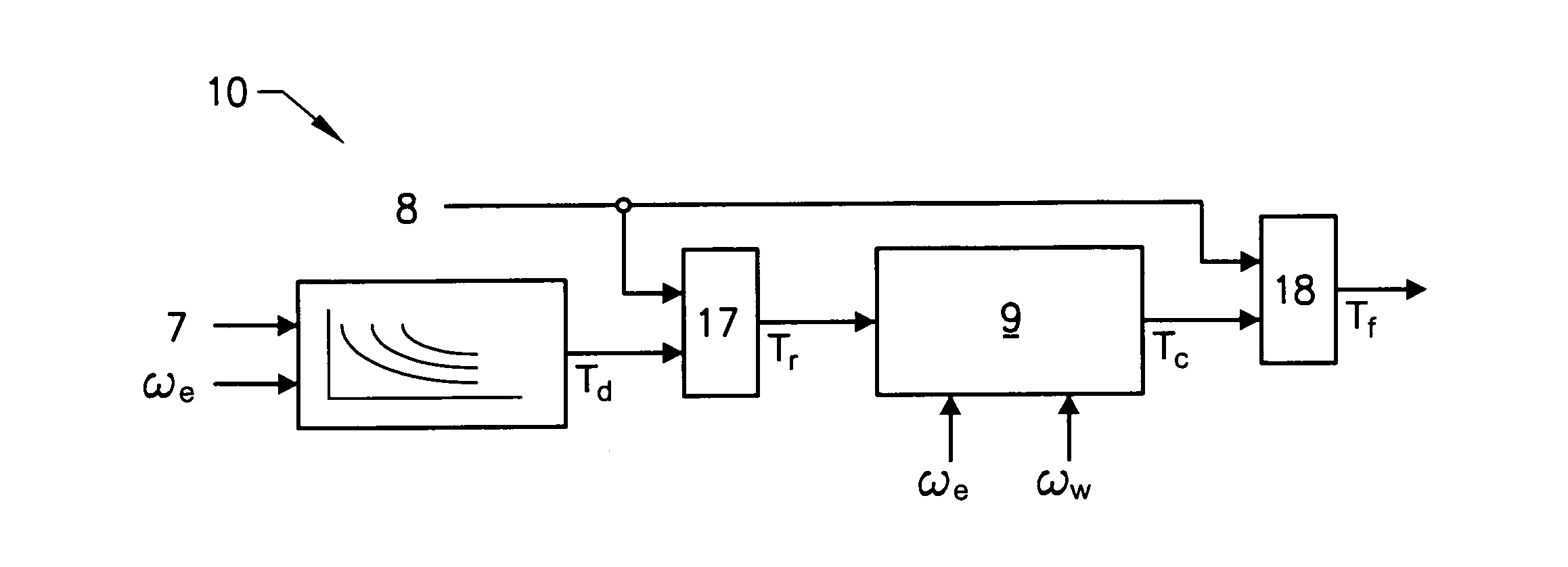

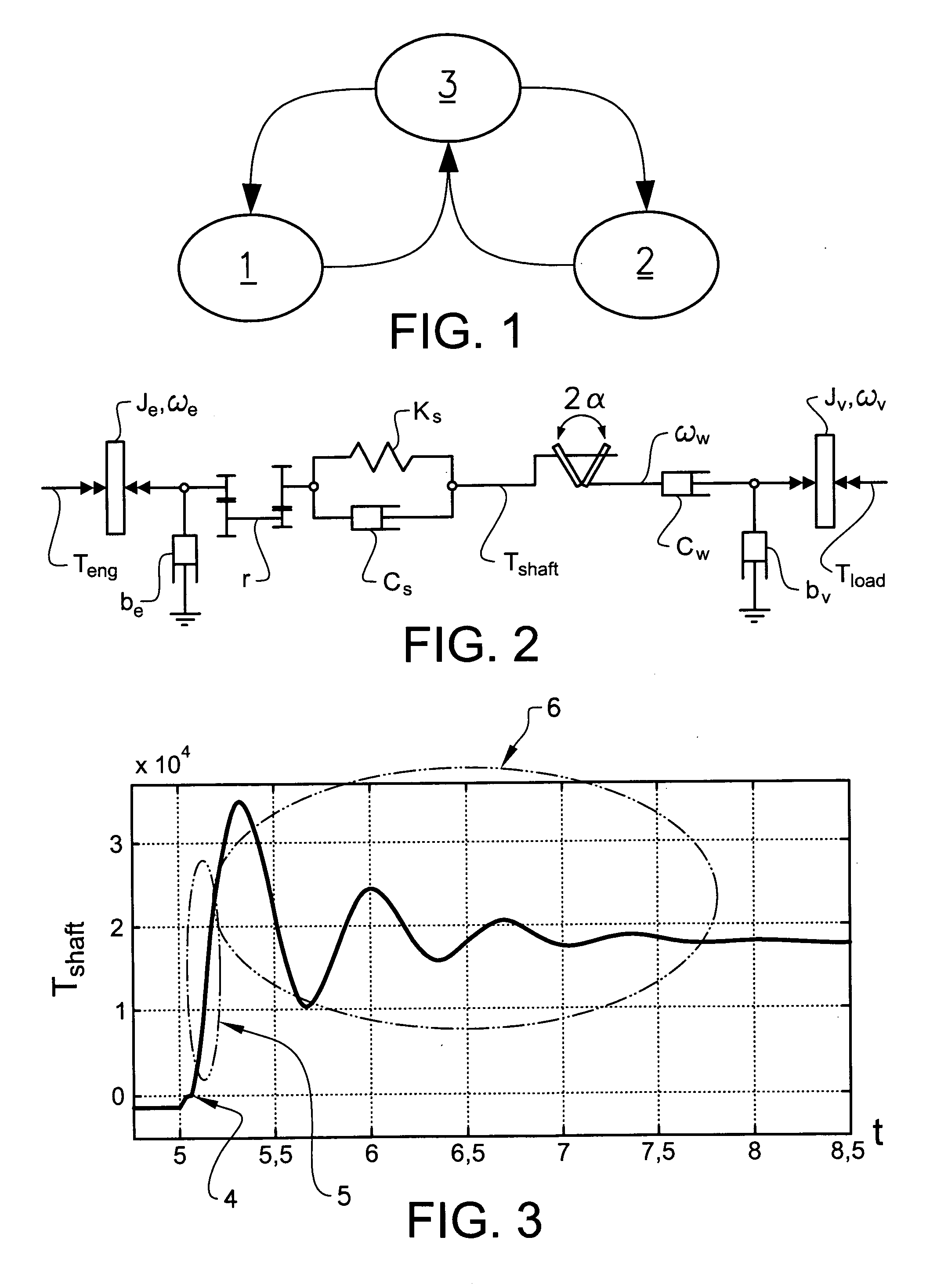

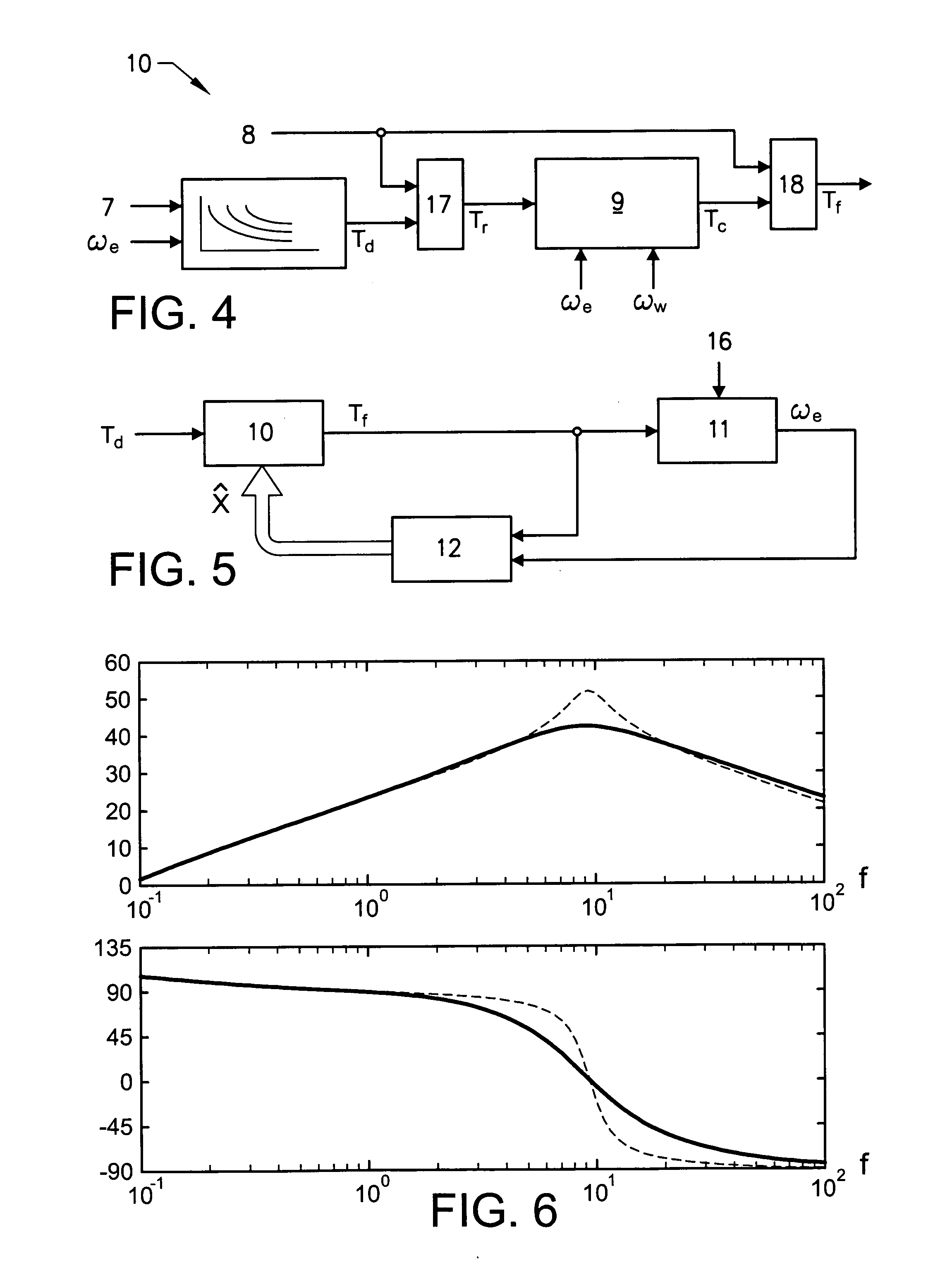

Method and controller for controlling output torque of a propulsion unit

ActiveUS20120101705A1Eliminate disadvantagesMinimize driveline oscillationAnalogue computers for vehiclesSpecial data processing applicationsLinear-quadratic regulatorPowertrain

Method for controlling output torque (Teng) of a propulsion unit in a vehicle powertrain including driven wheels drivingly connected to the propulsion unit via a mechanical transmission with a drive shaft, wherein the method including the steps of registering driver torque demand (Td) for vehicle propulsion, registering propulsion unit rotational speed (ωe), and controlling the output torque (Teng) of the propulsion unit to asymptotically follow the driver torque demand (Td) using a closed-loop linear-quadratic regulator (LQR) based controller (9) having the driver torque demand (Td) and the propulsion unit rotational speed (ωe) as input data, in order to minimize driveline oscillations.

Owner:VOLVO LASTVAGNAR AB

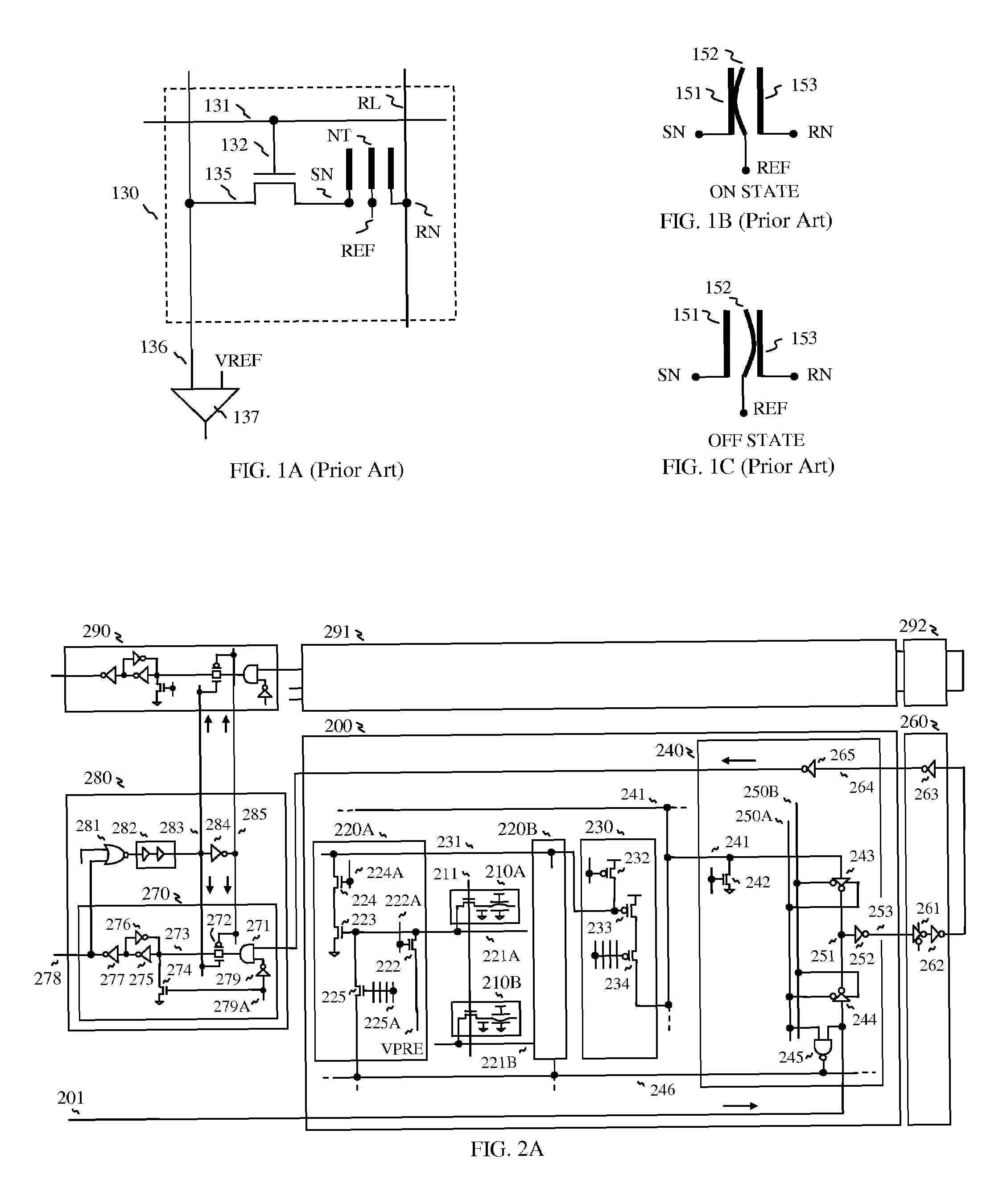

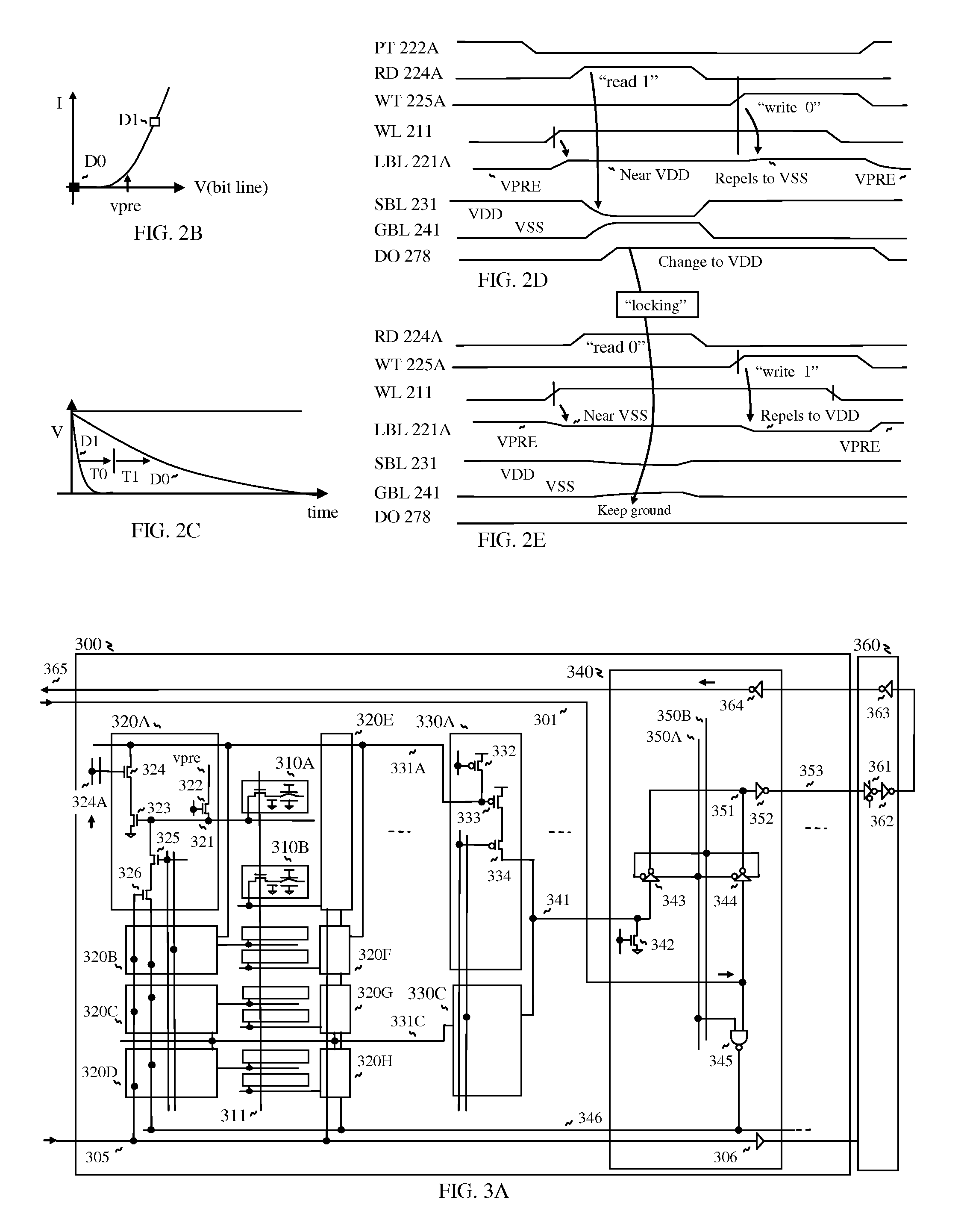

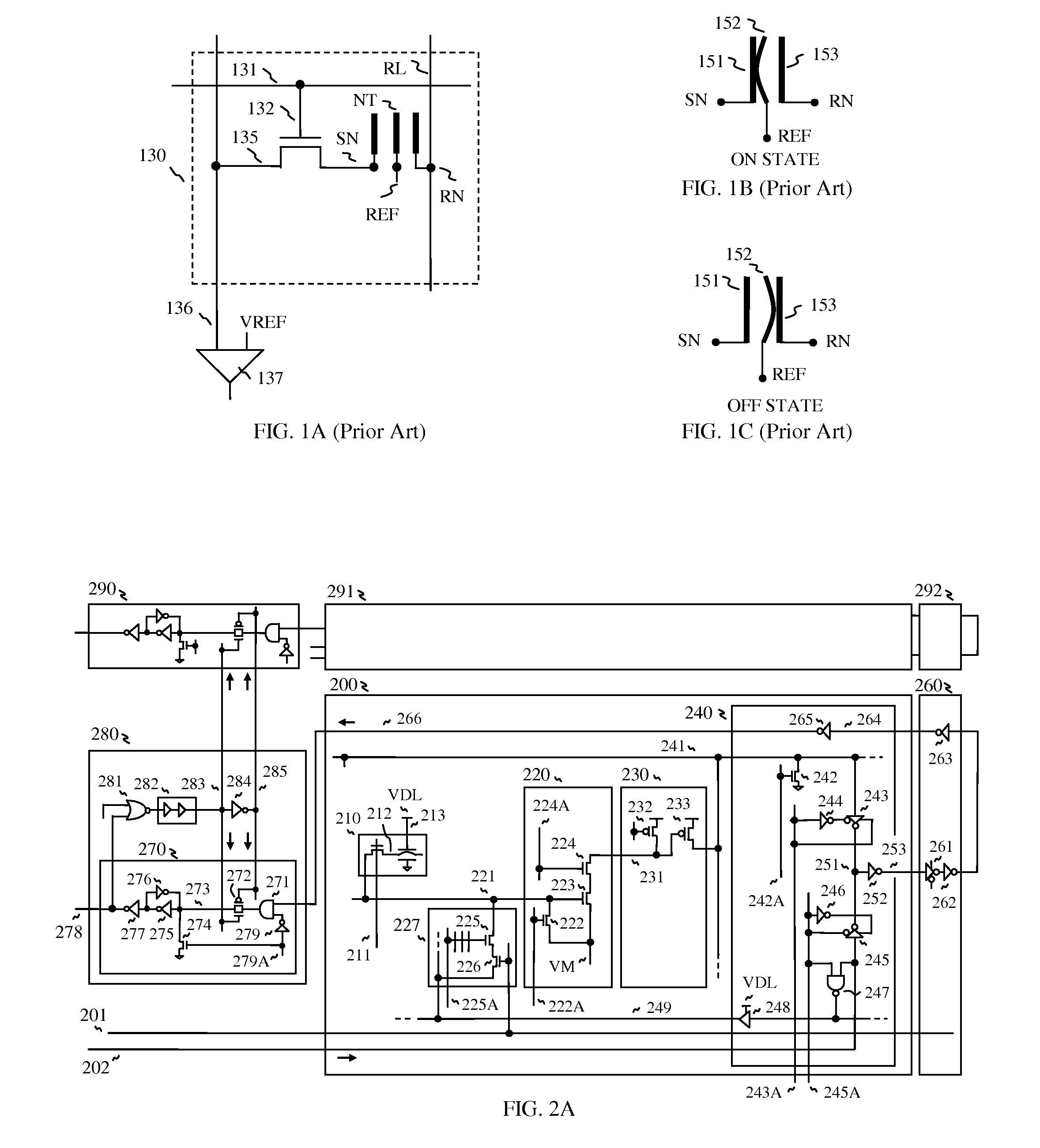

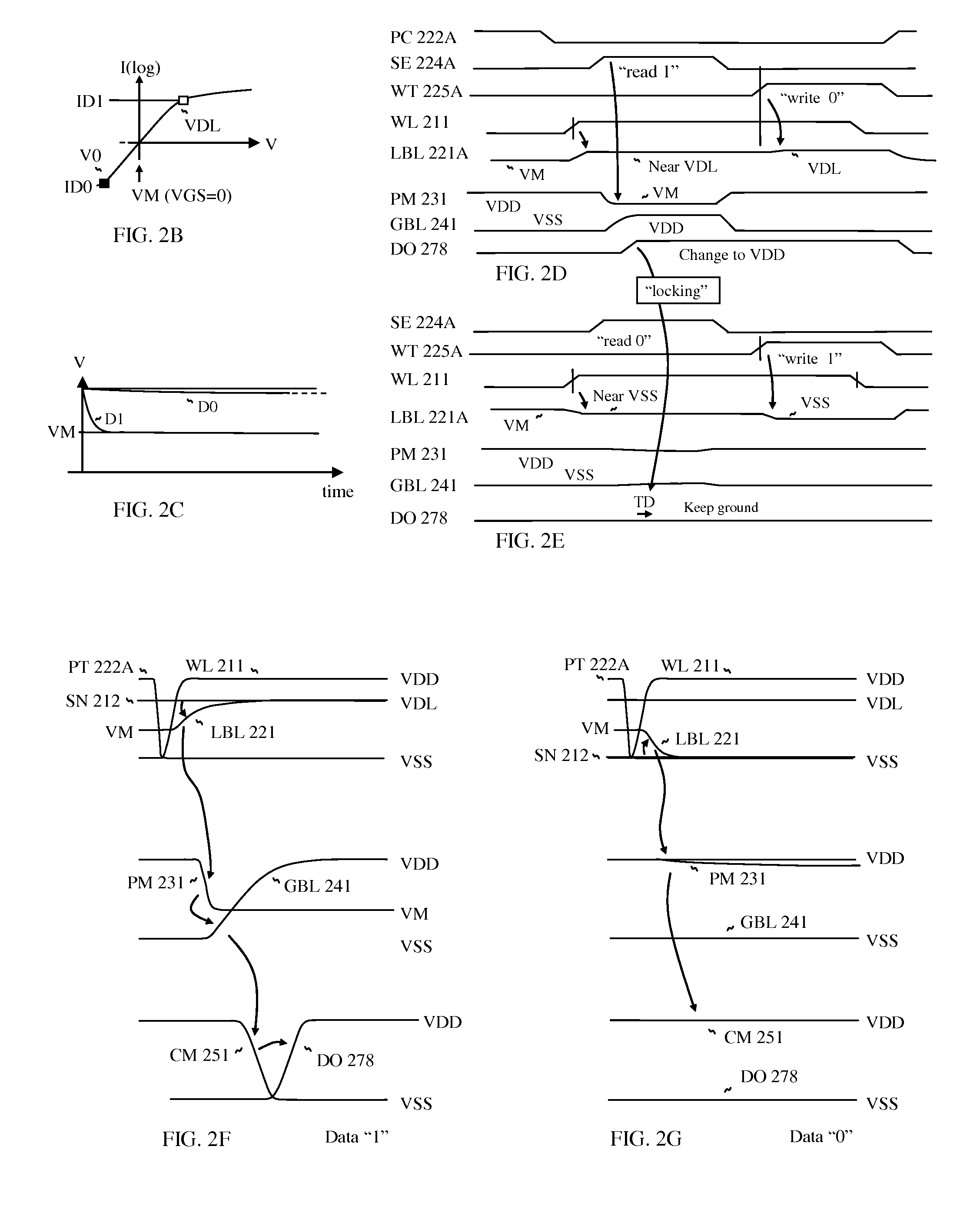

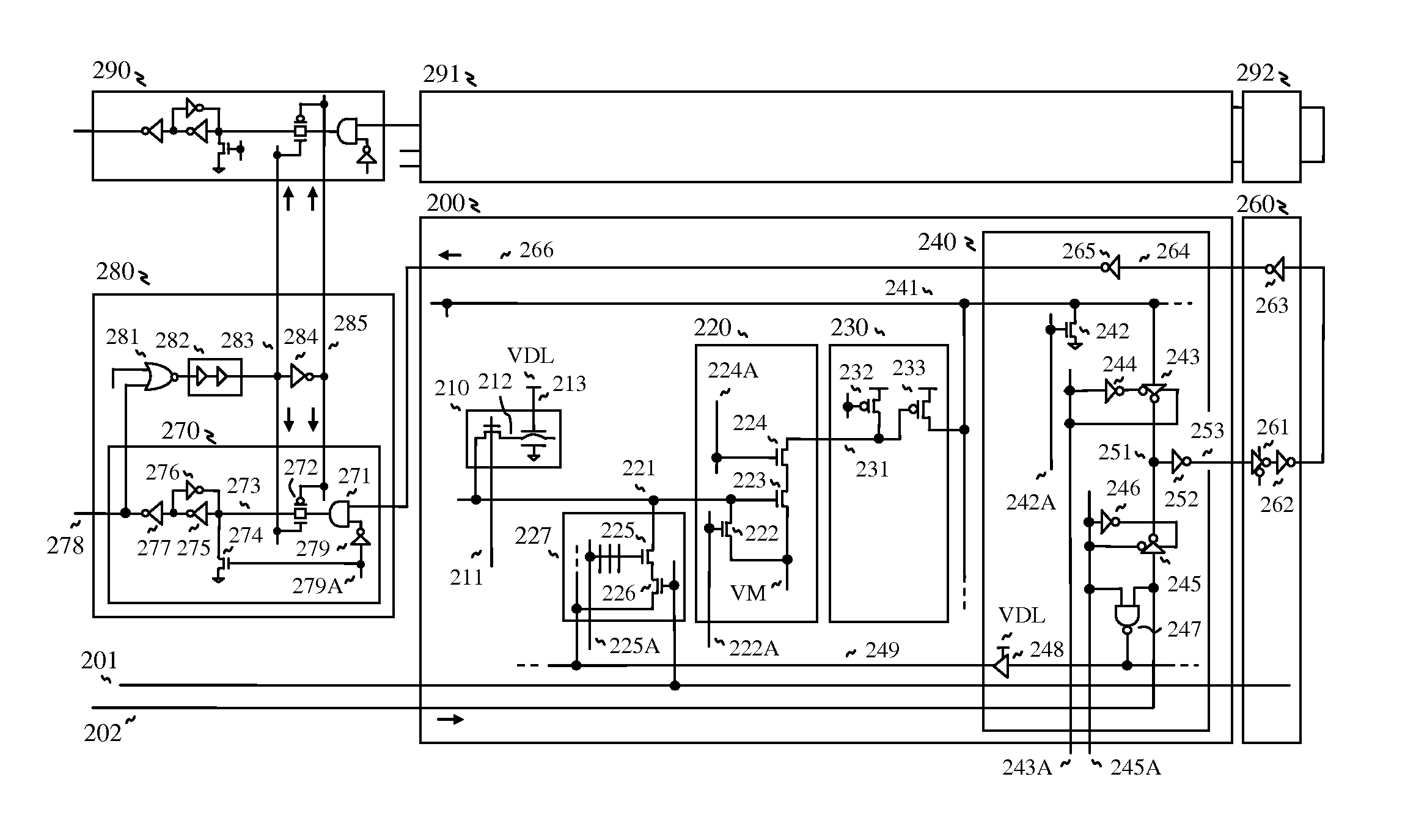

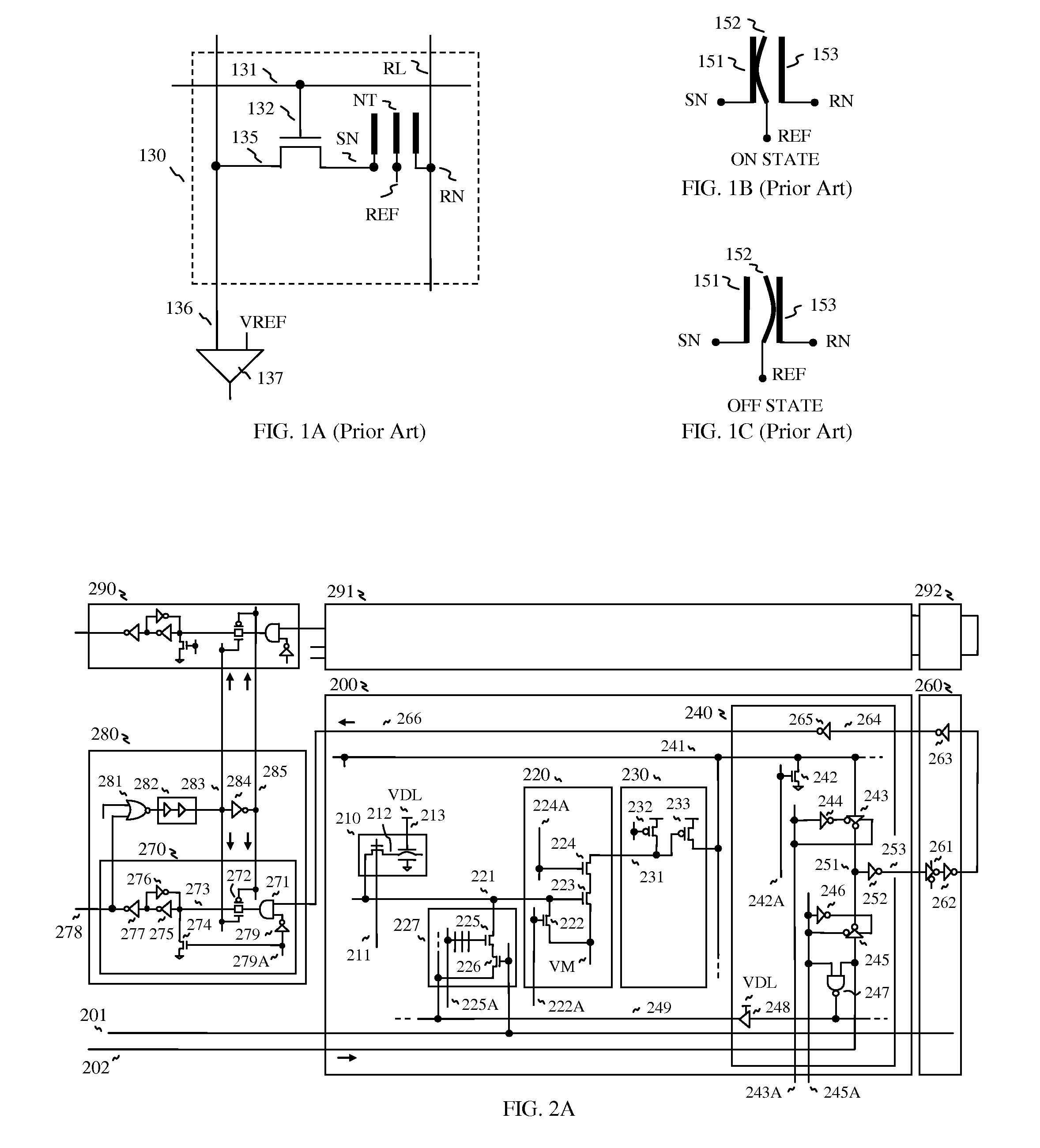

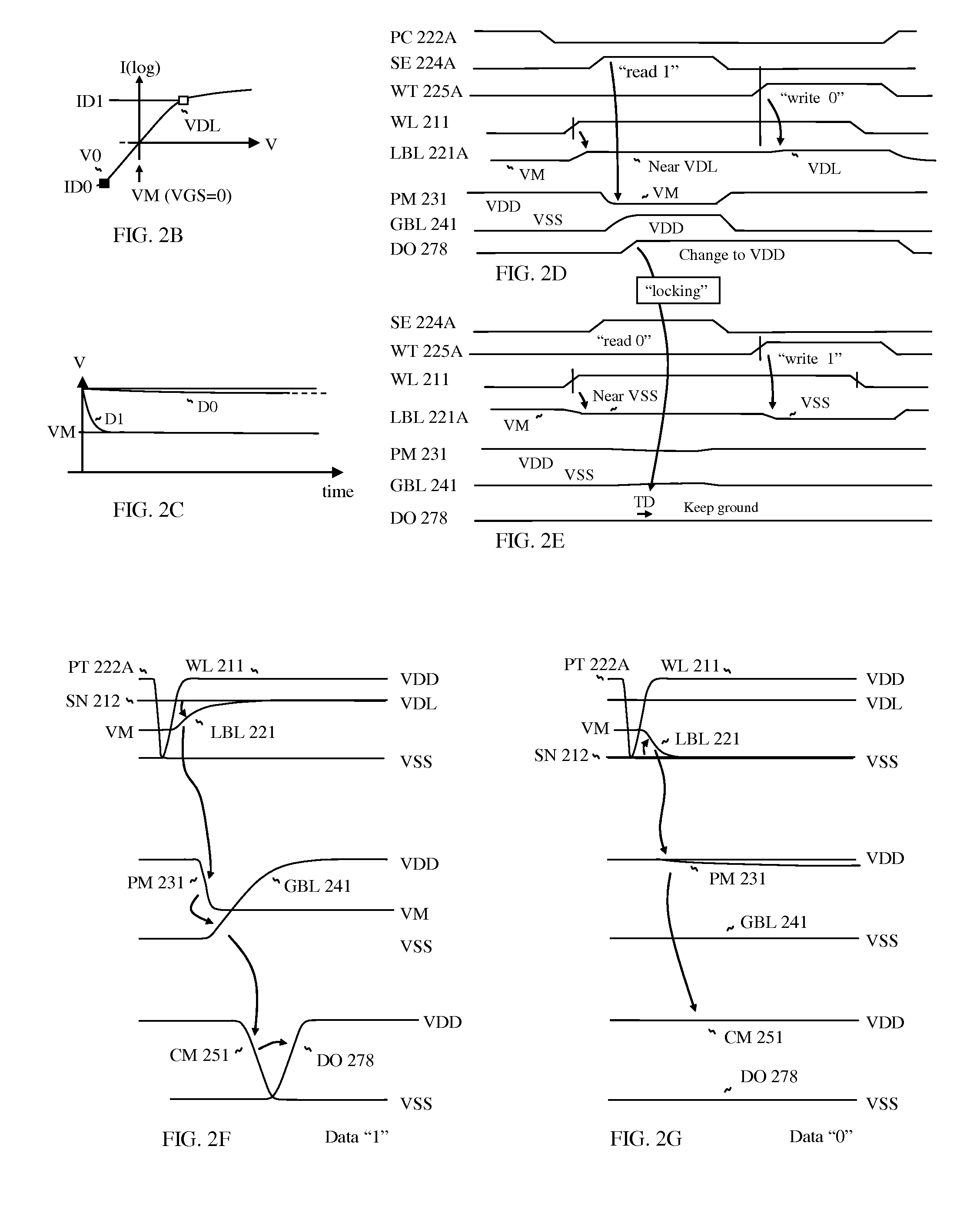

Low power carbon nanotube memory

InactiveUS7675768B1Reduce operating powerTotal current dropNanoinformaticsDigital storageBit lineAudio power amplifier

Low power carbon nanotube memory is realized such that a first dynamic circuit serves as a local sense amp for reading a memory cell through a lightly loaded local bit line, a second dynamic circuit serves as a segment sense amp for reading the local sense amp, a first tri-state inverter serves as an inverting amplifier of a global sense amp, and a second tri-state inverter serves as a bypass circuit for bypassing output from previous memory block. When reading, a voltage difference in the local bit line is converted to a time difference for differentiating high data and low data by the sense amps for realizing low power with dynamic operation. In particular, amplify transistor of the sense amps is composed of relatively long channel transistor for reducing turn-off current. And buffered data path is used for achieving fast data transfer. Additionally, alternative circuits and memory cell structures are described.

Owner:FRONTEON

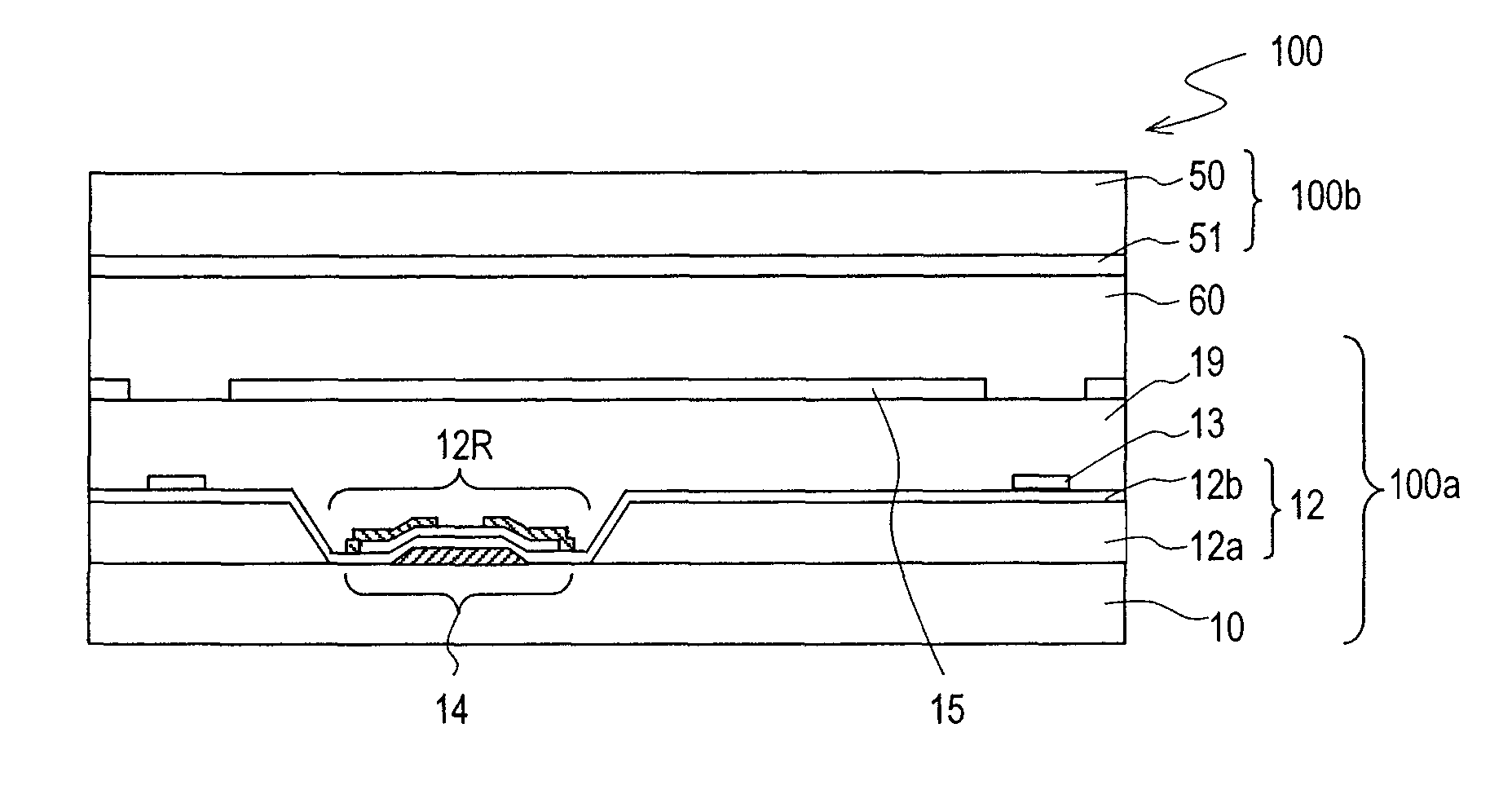

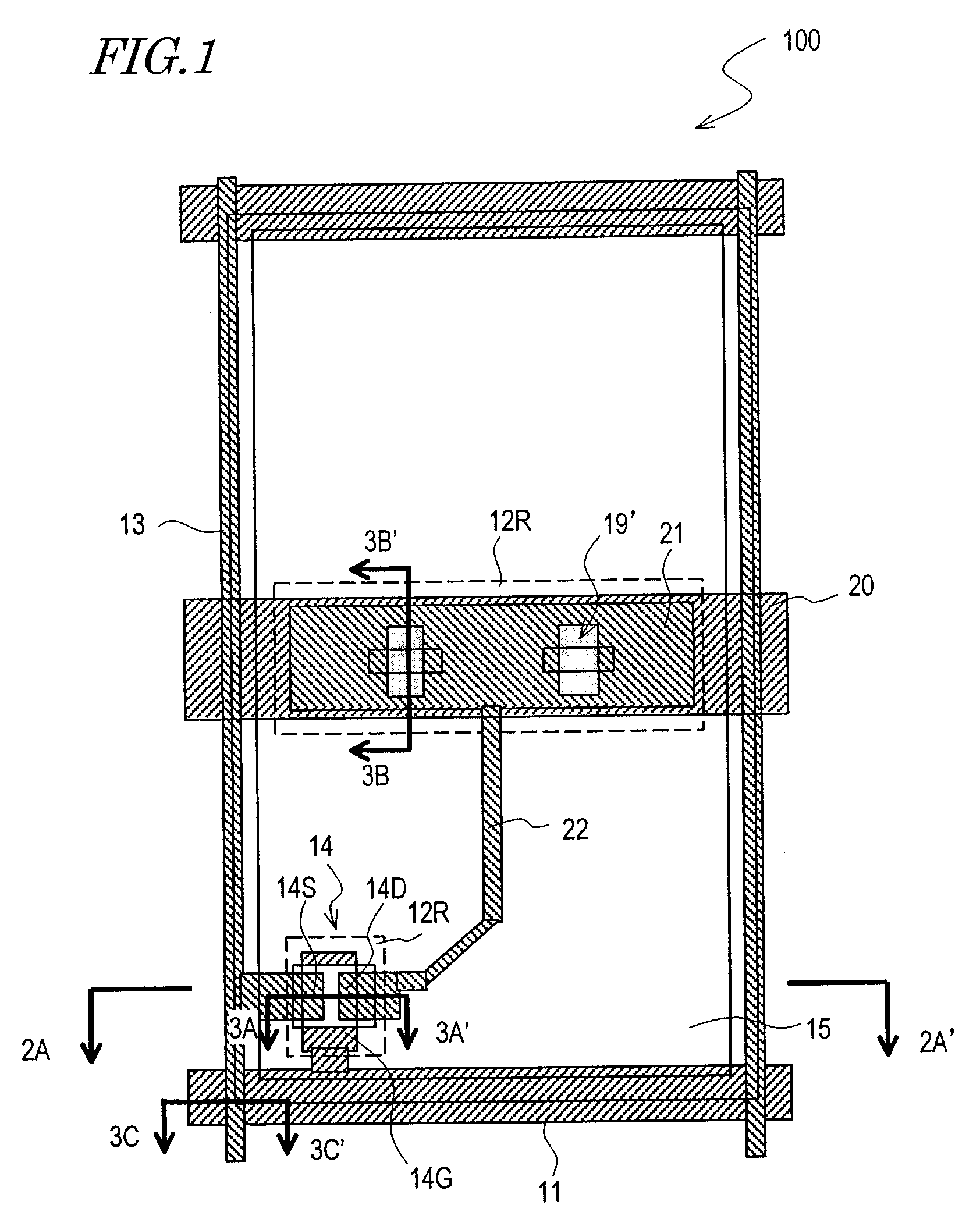

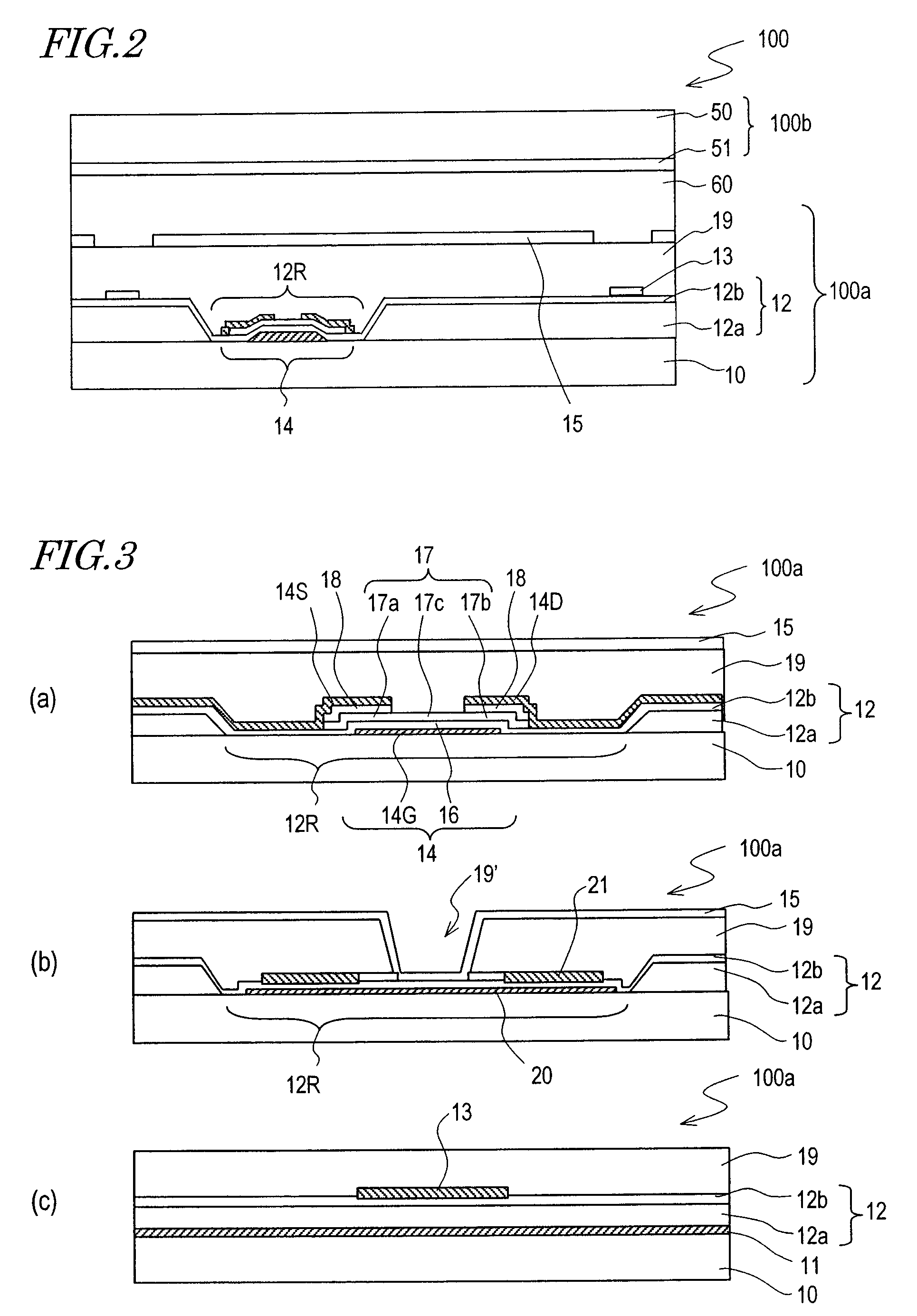

Active Matrix Substrate and Display Unit Provided with It

ActiveUS20070268438A1Reduce capacitanceDriving ability is not degradedNon-linear opticsCapacitanceEngineering

An active matrix substrate includes a substrate; scanning lines formed on the substrate; an insulating film covering the scanning lines; signal lines intersecting the scanning lines via the insulating film; switching elements formed on the substrate, each operating in response to a signal which is applied to the corresponding scanning line; and pixel electrodes each capable of being electrically connected to the corresponding signal line via the switching elements. The insulating film is a multilayer insulating film including a first insulating layer and a second insulating layer. The first insulating layer is formed of an insulating material containing an organic component, and the multilayer insulating film has a low-stack region in at least a portion of a region overlapping each switching element, the first insulating layer not being formed in the low-stack region. The active matrix substrate reduces the capacitance formed at each intersection between a scanning line and a signal line, without causing an increase in the wiring resistance or a degradation of the driving ability of switching elements.

Owner:MERCK PATENT GMBH

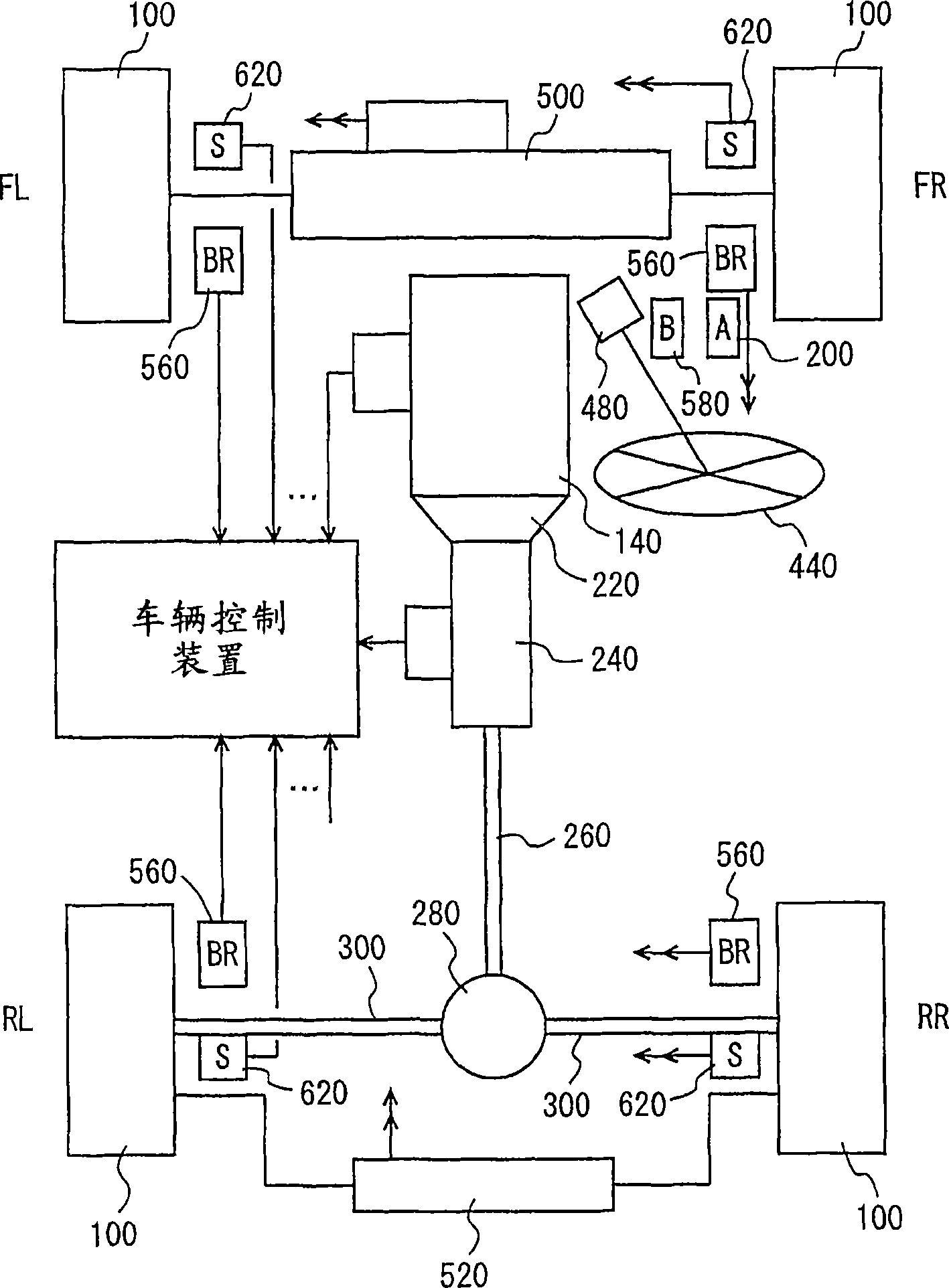

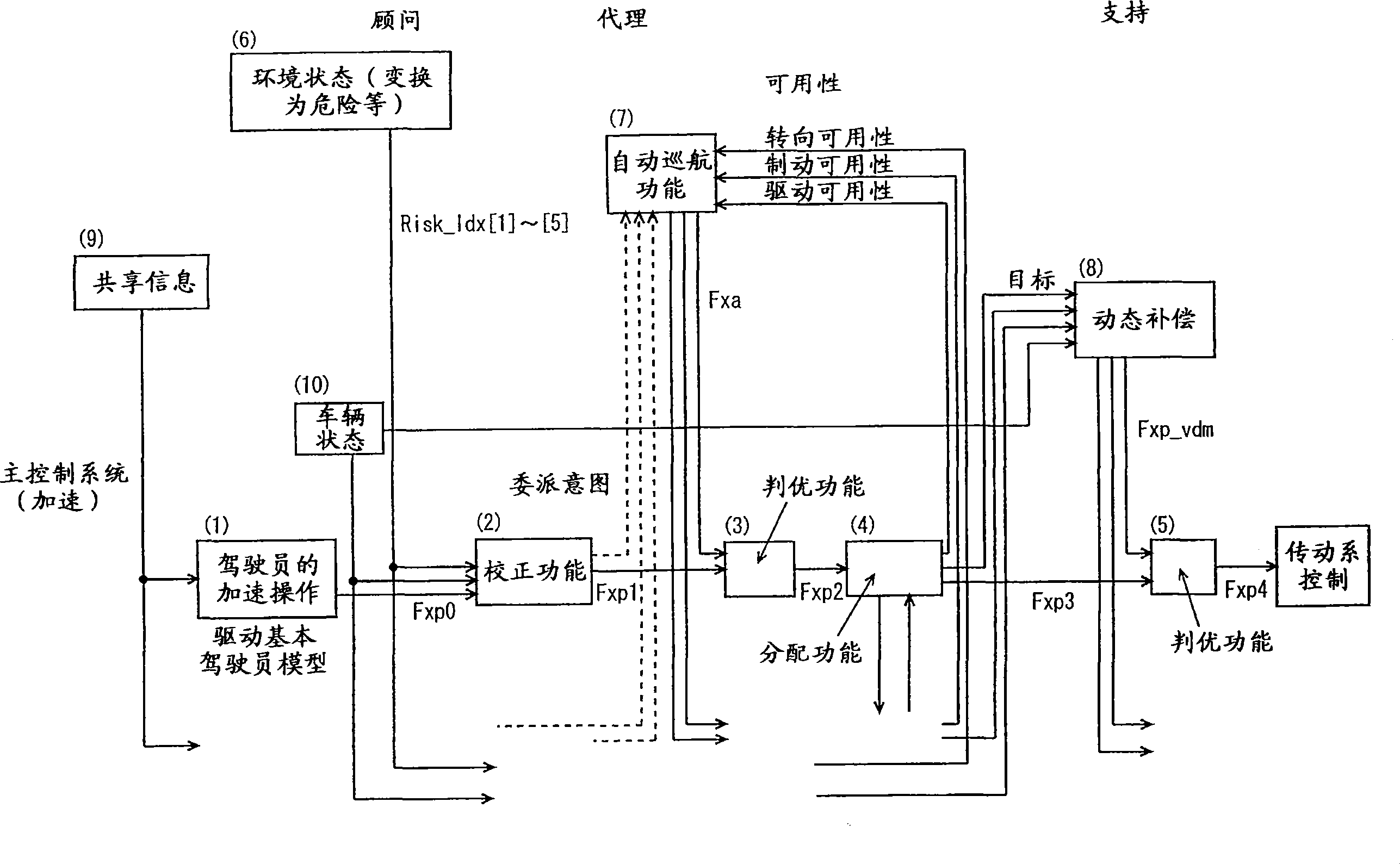

Vehicle integrated control system

InactiveCN1898115ASmall braking forceHigh torqueAnti-collision systemsEngine controllersControl systemBraking system

An integrated control system includes a main control system (accelerator) controlling a driving system, a main control system (brake) controlling a brake system, and a main control system (steering) controlling a steering system, based on manipulation by a driver, as well as an adviser unit generating and providing information to be used at each main control system based on environmental information around a vehicle or information related to a driver. The advisor unit executes a program including the steps of: sensing a vehicle state, driver's manipulation, and environmental information (S 1000, S 1100 and S 1200); operating an expected value by the driver with regard to a driving force (S 1300); performing distribution processing of a braking / driving torque (S 1500); and operating a distribution ratio (S 1600) so as to carry out distribution (S 1700).

Owner:TOYOTA JIDOSHA KK

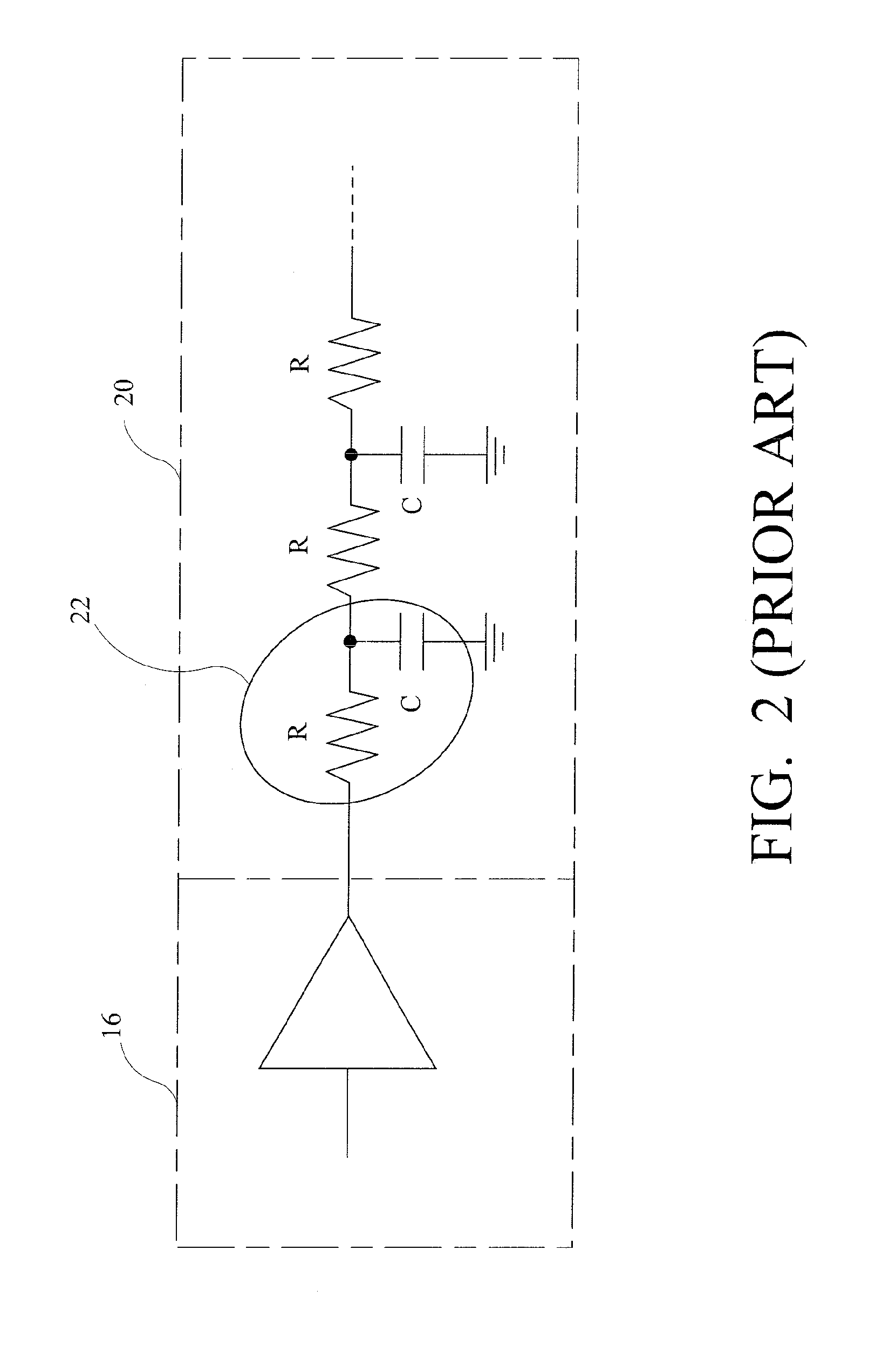

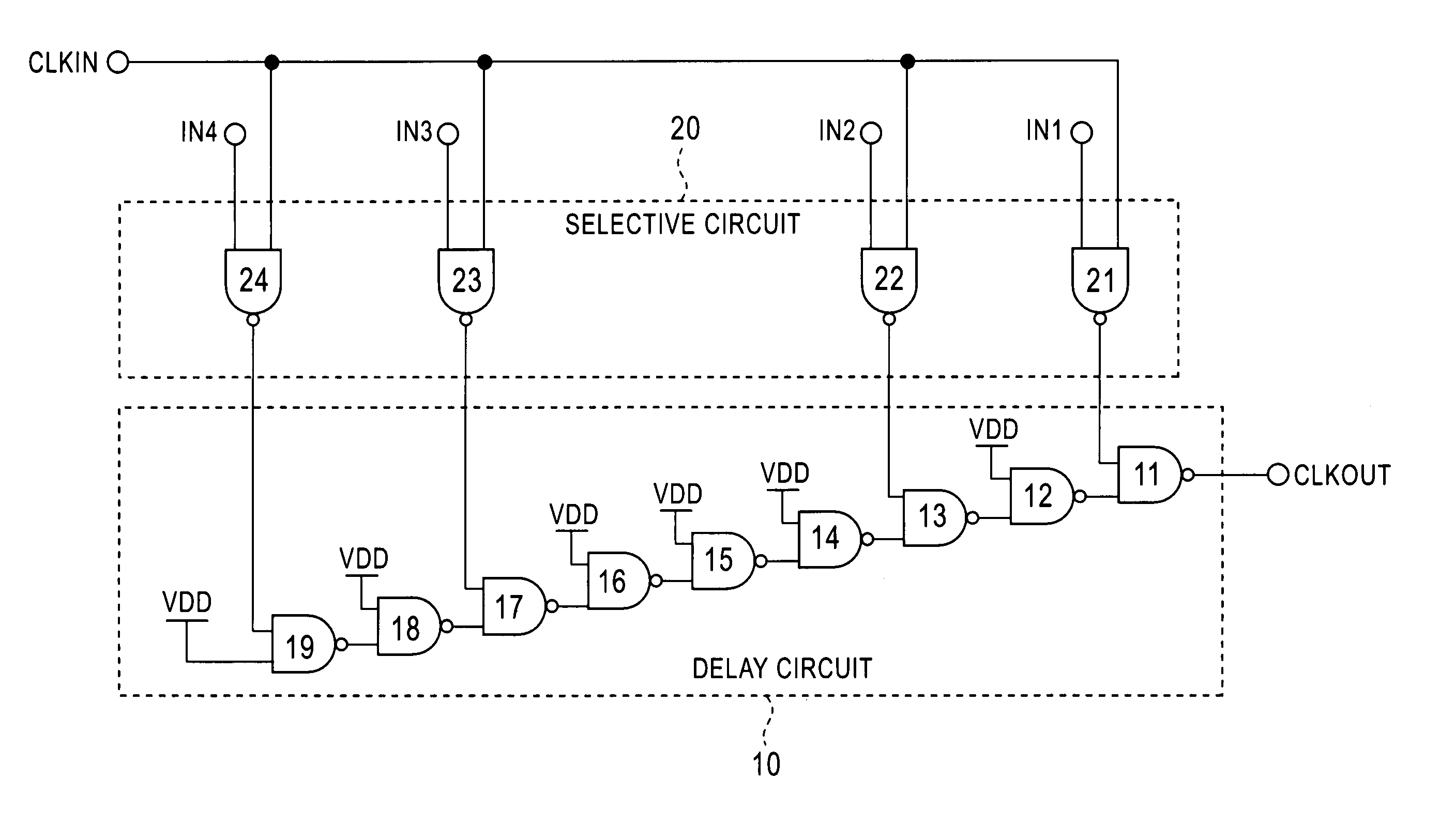

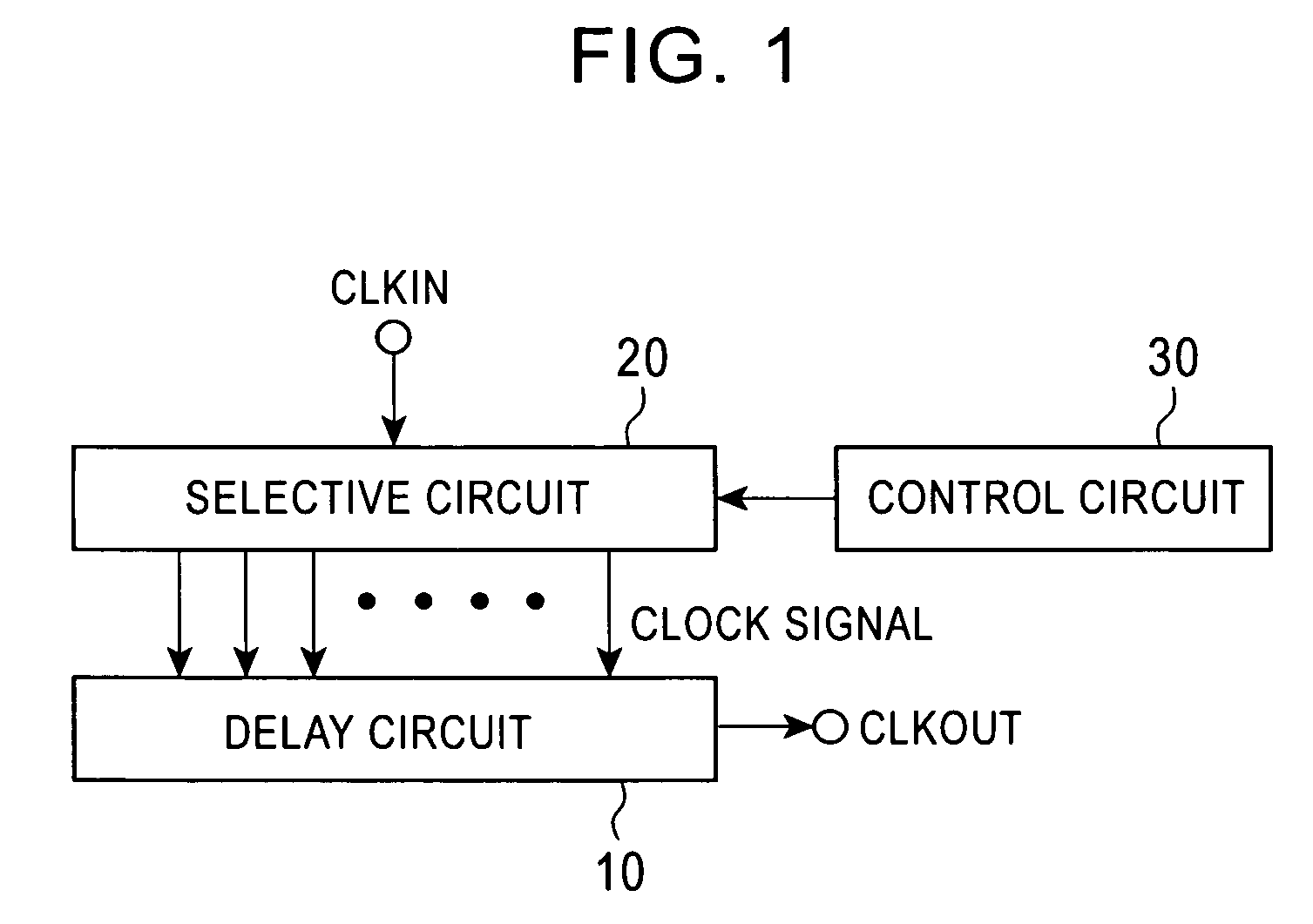

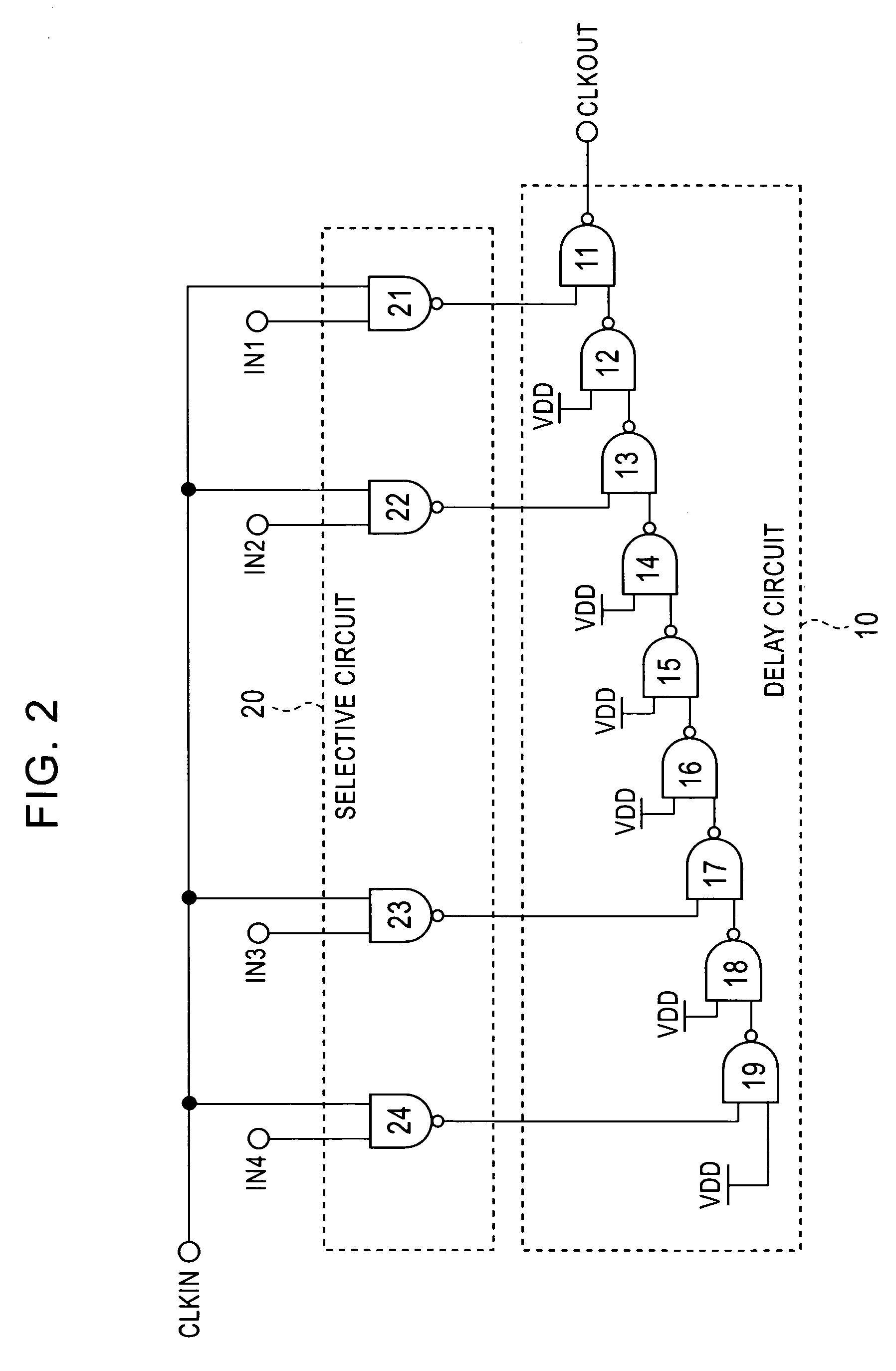

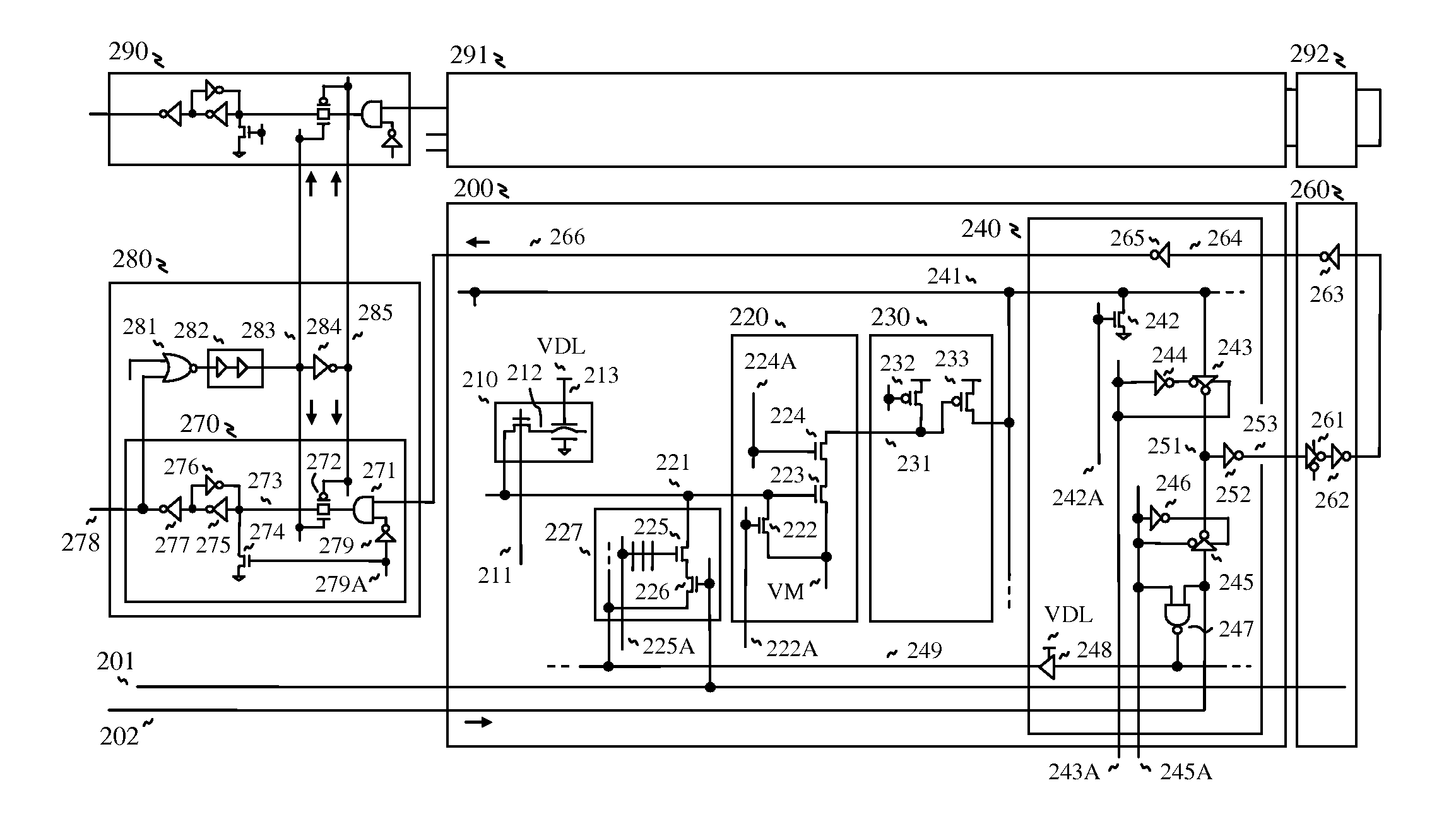

Spread spectrum clock generating circuit

ActiveUS7061293B2Small driving abilityReduce circuit areaDelay line applicationsPulse automatic controlControl circuitSignal delay

A clock generating circuit includes a delay circuit which has input terminals and which delays a signal input from each of the input terminals by a different delay time, and outputs the delayed signal from at least one output terminal, a selective circuit which receives an input clock signal and selectively outputs the clock signal to one of the input terminals of the delay circuit, and a control circuit which switches selective operations of the selective circuit. A modulated clock signal in which the period of the clock signal is increased or decreased is output from the at least one output terminal of the delay circuit such that the control circuit sequentially switches the selective operations of the selective circuit.

Owner:RENESAS ELECTRONICS CORP

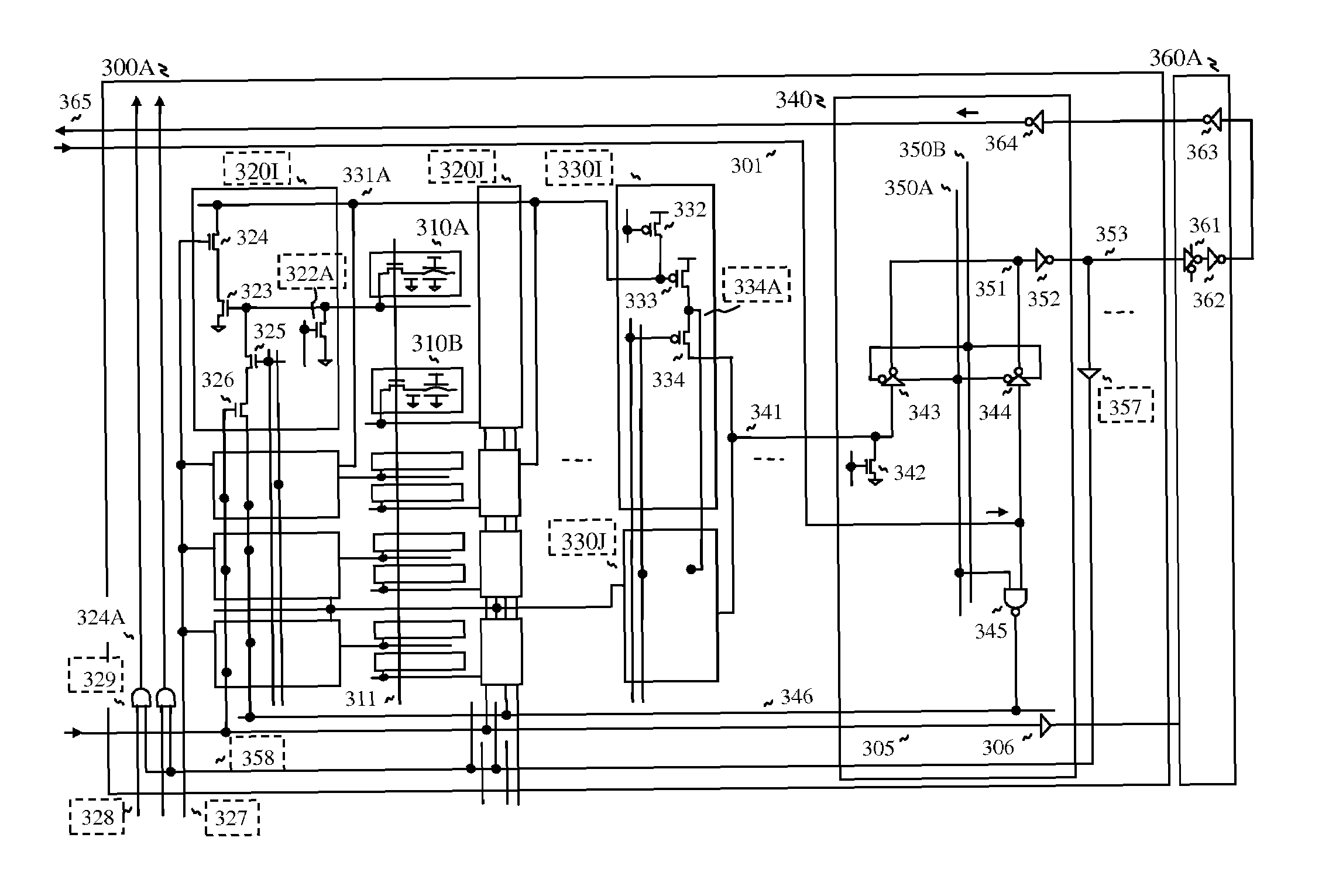

High speed carbon nanotube memory

InactiveUS7933160B2Reduce parasitic capacitanceEasy to operateNanoinformaticsDigital storageTime domainAudio power amplifier

In order to realize high speed carbon nanotube memory, bit line is multi-divided into short lines for reducing parasitic capacitance. For reading, a small local sense amp is composed of a local pre amplifier and a local main amplifier with high gain, and a simple global sense amp is composed of an inverter as amplifying circuit for receiving an output of the local sense amp through a global bit line. By the sense amps, time domain sensing scheme is realized such that a voltage difference in the bit line is converted to a time difference as an output of the global sense amp, for differentiating high data and low data. In this manner, fast read operation is realized with fast sensing circuit. And alternative circuits are described. Particularly, field-effect alignment process is realized for aligning the carbon nanotubes on exact location of the memory cell, when forming the memory cell.

Owner:KIM JUHAN

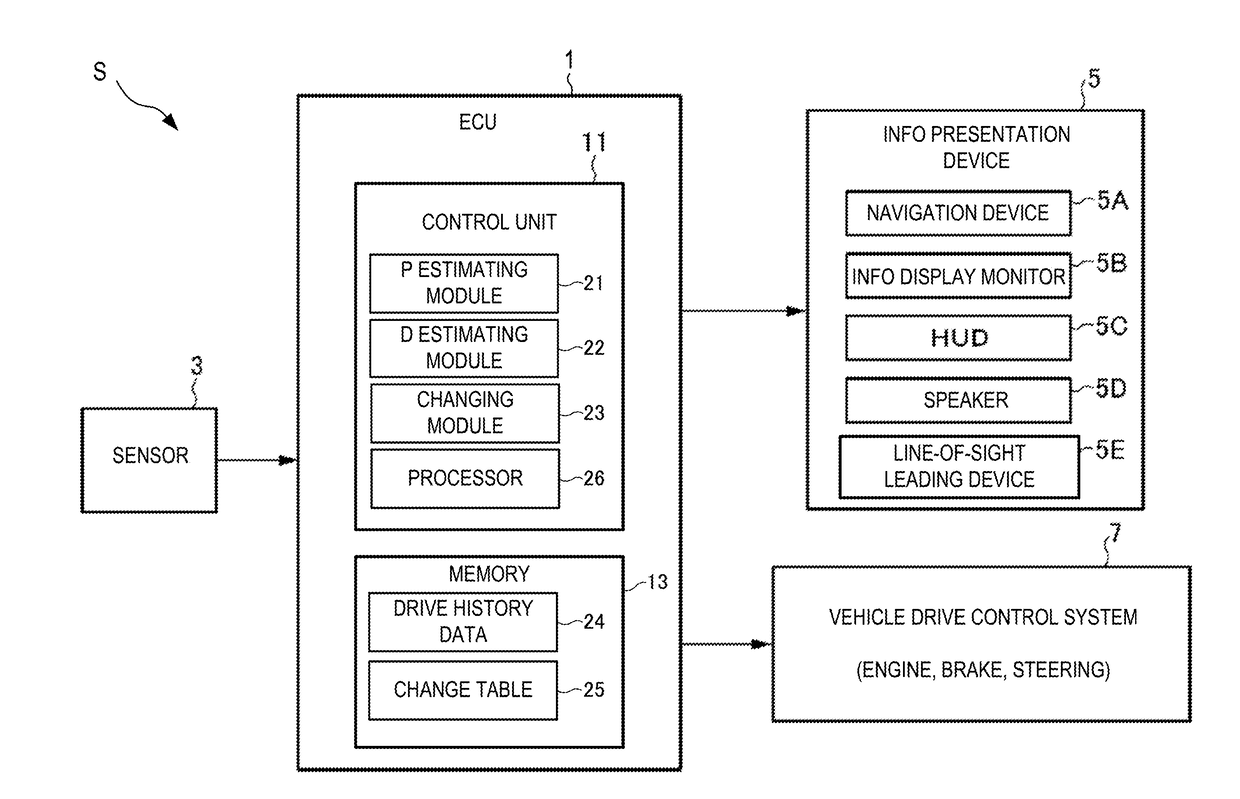

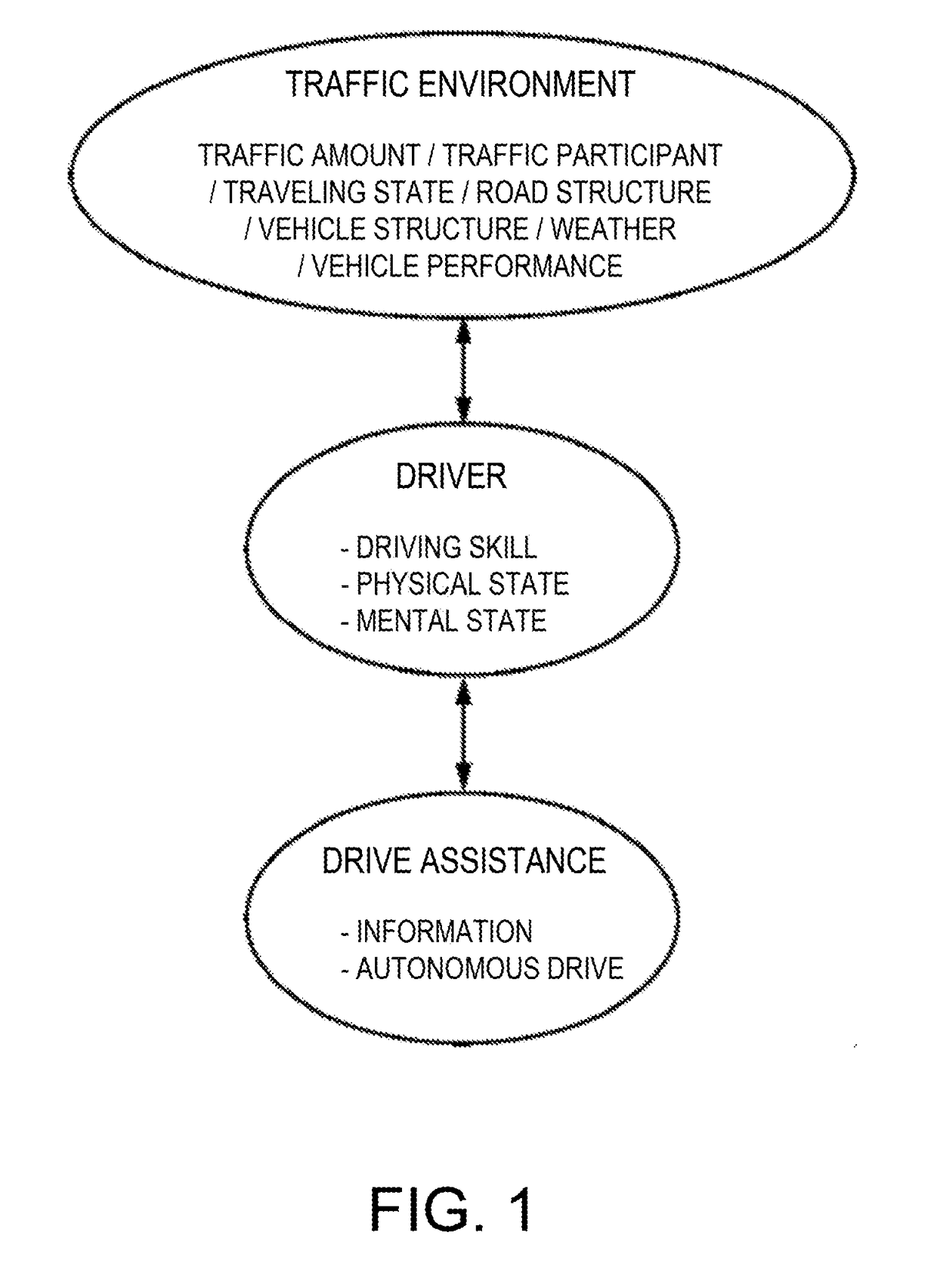

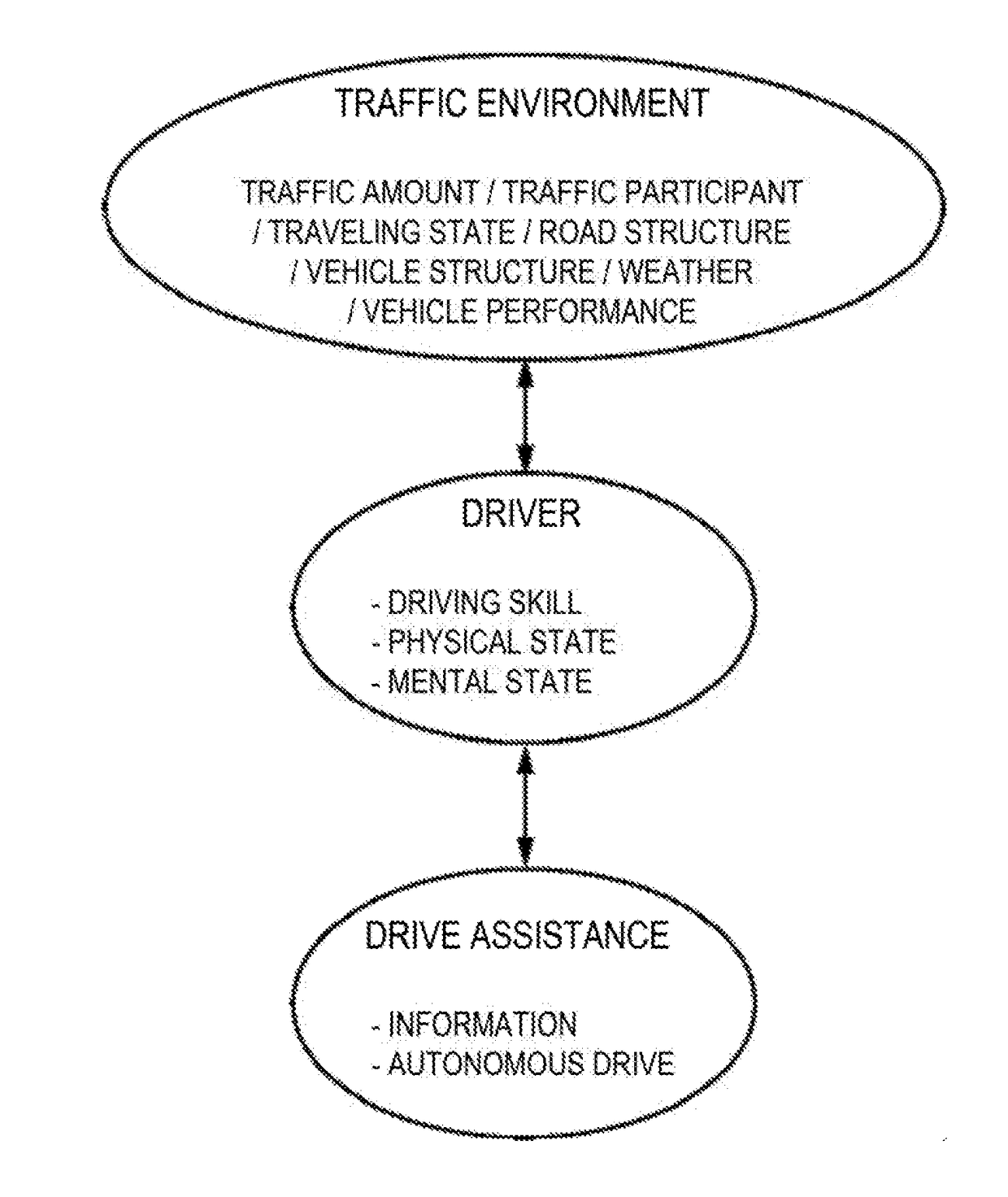

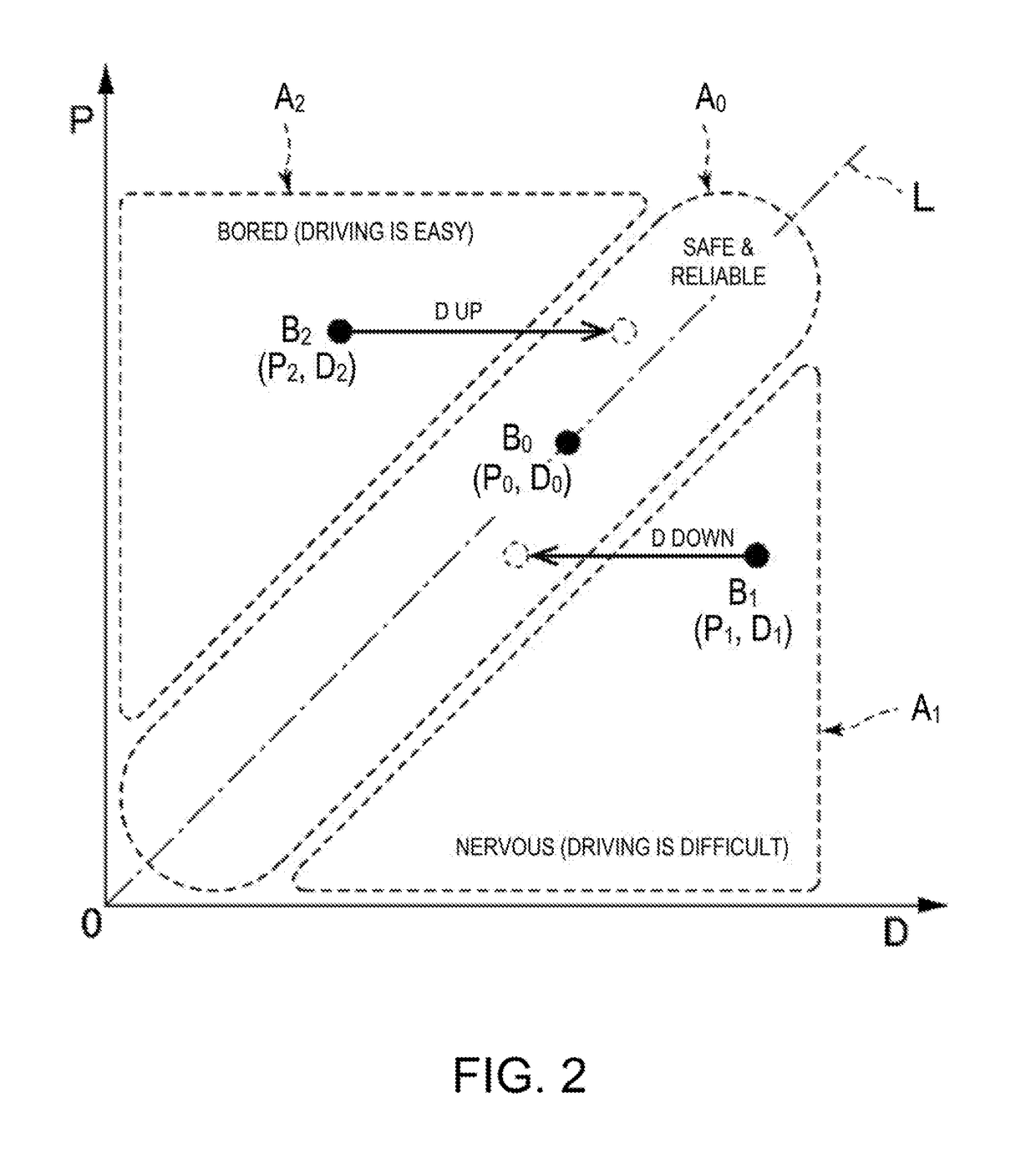

Vehicle drive assistance system

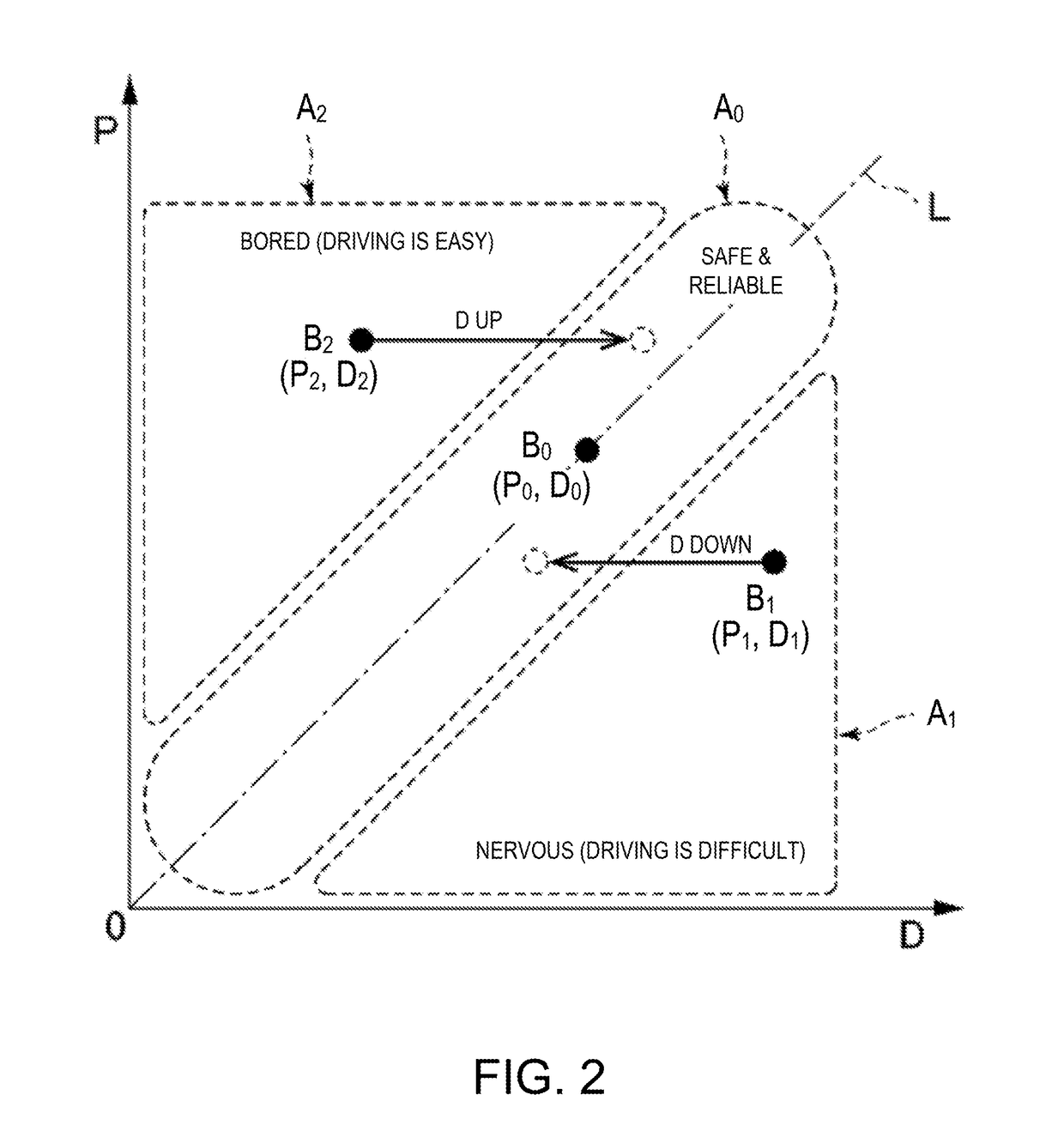

ActiveUS20180284766A1Enhances a driving skill of a vehicle driverReduced driving abilityAutonomous decision making processExternal condition input parametersDriver/operatorEngineering

A vehicle drive assistance system is provided, which includes a processor configured to execute a required driving ability estimating module to estimate a driver's driving ability required for driving a vehicle based on a traffic environment around the vehicle and drive assistance provided to the driver by the vehicle, a current driving ability estimating module to estimate a driver's current driving ability, and a changing module to reduce the required driving ability by performing reduction processing in which comprehension of the traffic environment by the driver is facilitated when the current driving ability is lower than the required driving ability.

Owner:MAZDA MOTOR CORP

High speed carbon nanotube memory

In order to realize high speed carbon nanotube memory, bit line is multi-divided into short lines for reducing parasitic capacitance. For reading, a small local sense amp is composed of a local pre amplifier and a local main amplifier with high gain, and a simple global sense amp is composed of an inverter as amplifying circuit for receiving an output of the local sense amp through a global bit line. By the sense amps, time domain sensing scheme is realized such that a voltage difference in the bit line is converted to a time difference as an output of the global sense amp, for differentiating high data and low data. In this manner, fast read operation is realized with fast sensing circuit. And alternative circuits are described. Particularly, field-effect alignment process is realized for aligning the carbon nanotubes on exact location of the memory cell, when forming the memory cell.

Owner:KIM JUHAN

Active matrix substrate and display unit provided with it

ActiveUS7864281B2Increase in wiring resistanceReduced form requirementsNon-linear opticsCapacitanceElectricity

An active matrix substrate includes a substrate; scanning lines formed on the substrate; an insulating film covering the scanning lines; signal lines intersecting the scanning lines via the insulating film; switching elements formed on the substrate, each operating in response to a signal which is applied to the corresponding scanning line; and pixel electrodes each capable of being electrically connected to the corresponding signal line via the switching elements. The insulating film is a multilayer insulating film including a first insulating layer and a second insulating layer. The first insulating layer is formed of an insulating material containing an organic component, and the multilayer insulating film has a low-stack region in at least a portion of a region overlapping each switching element, the first insulating layer not being formed in the low-stack region. The active matrix substrate reduces the capacitance formed at each intersection between a scanning line and a signal line, without causing an increase in the wiring resistance or a degradation of the driving ability of switching elements.

Owner:MERCK PATENT GMBH

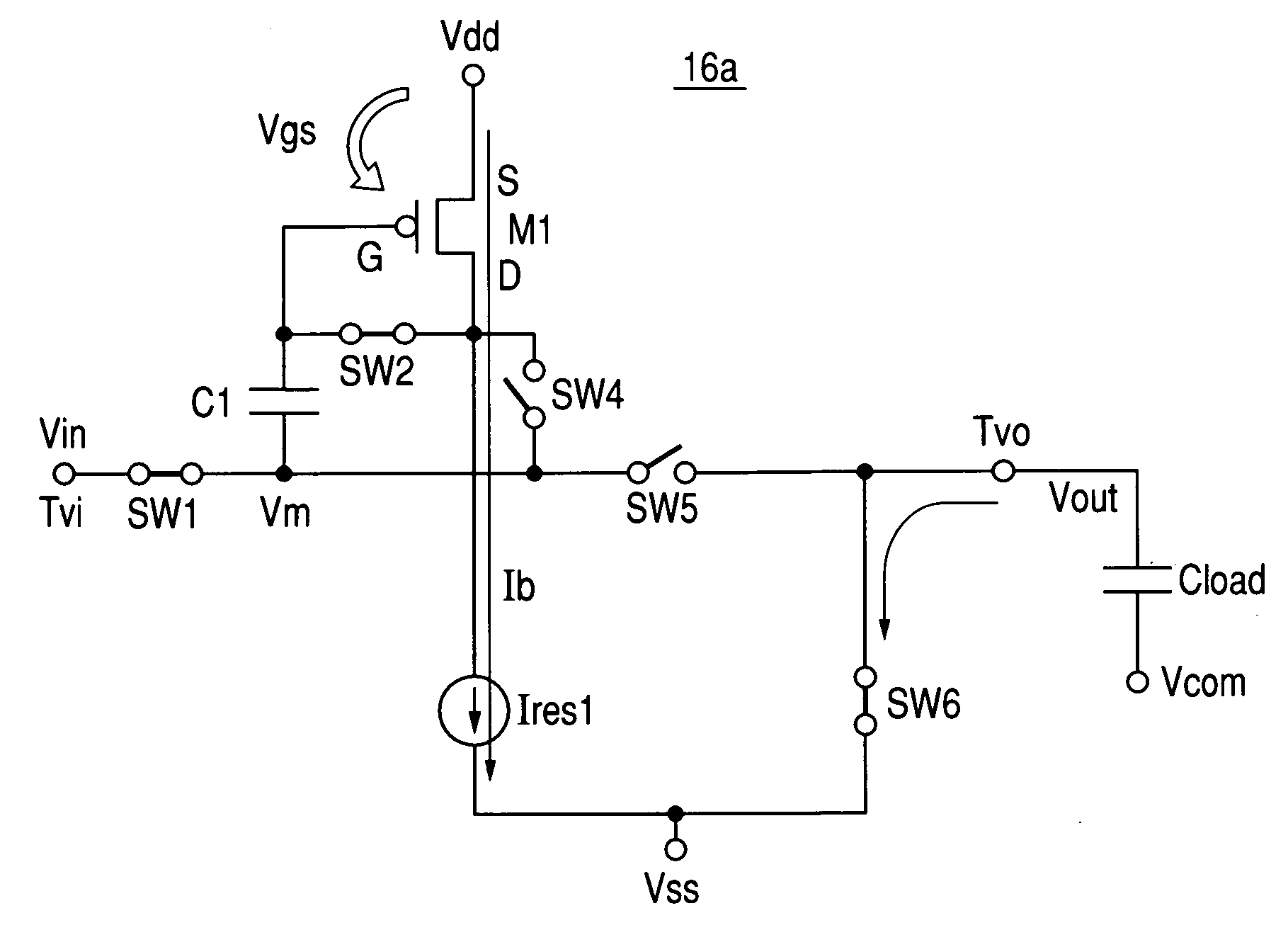

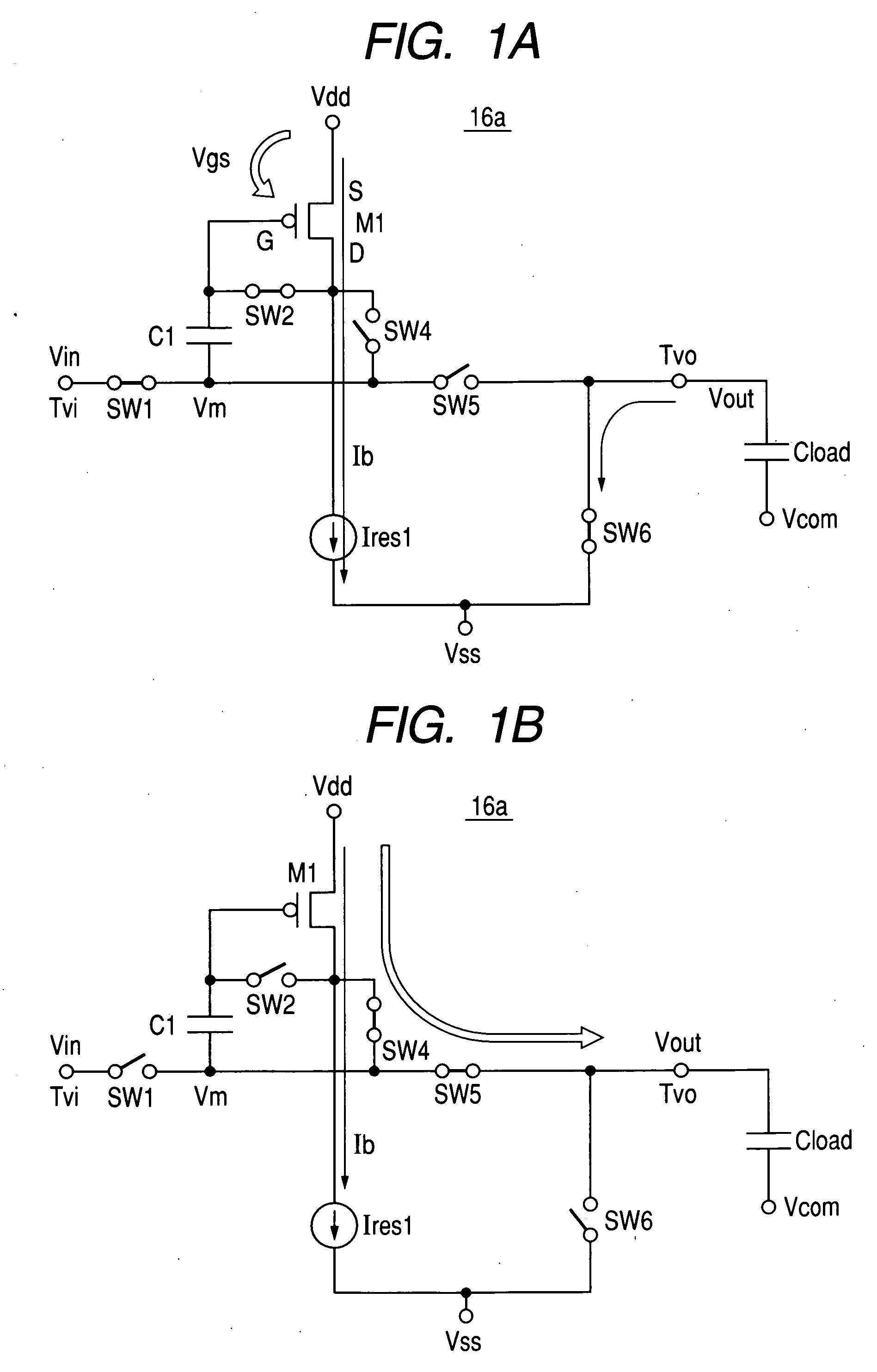

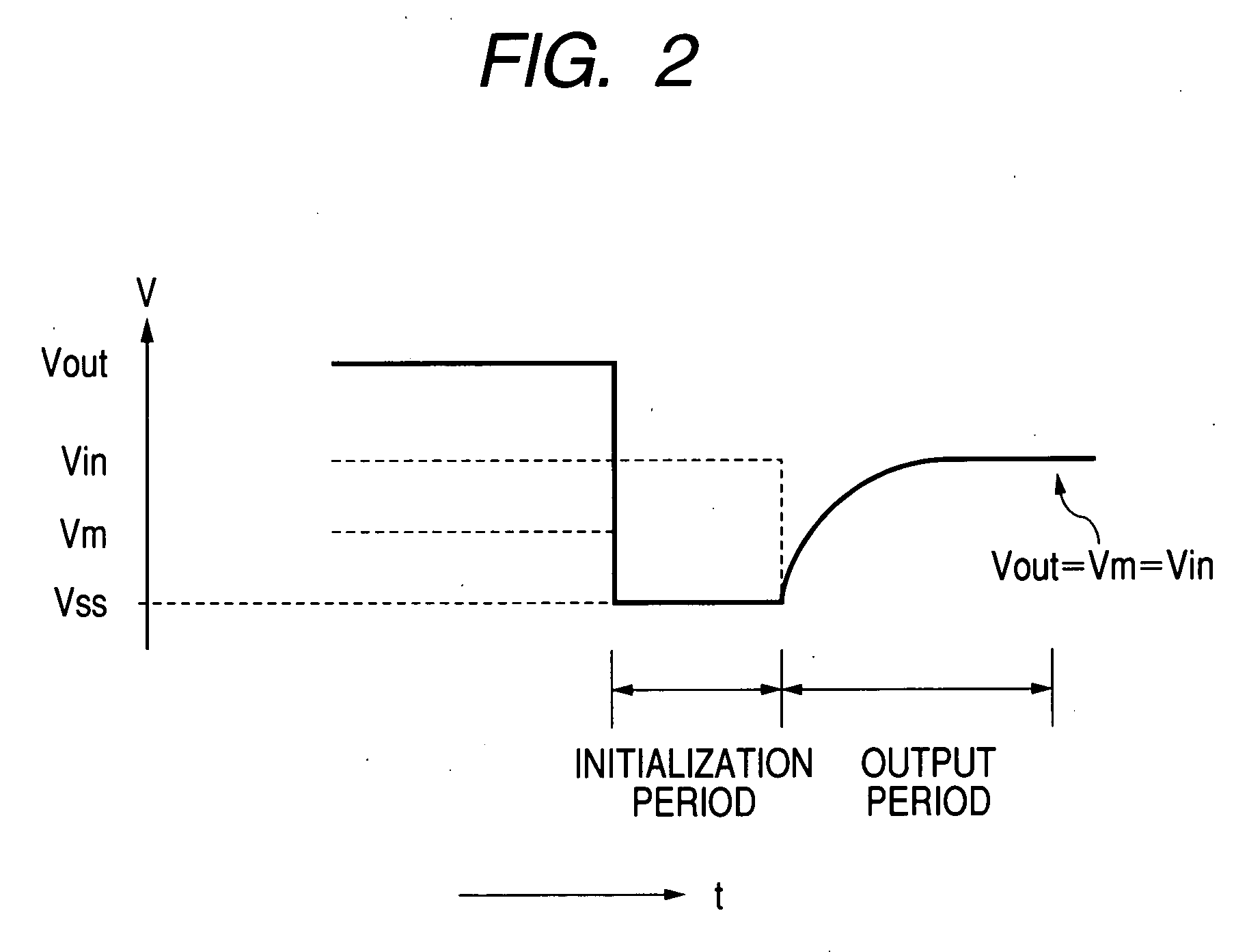

Load capacity driving circuit and liquid crystal driving circuit

InactiveUS20050190139A1Reduce power consumptionDrivability be suppressedStatic indicating devicesLighting elementsEngineeringLoad capacity

The present invention provides a load capacity driving circuit capable of implementing low power consumption. Switches become closed in an initialization period, and a constant current source allows a bias current to flow through a drain of a MOS transistor, which causes a voltage determined by the current to be generated between a source and a gate thereof. A differential voltage between the potential of the gate of the MOS transistor and an input voltage is stored in a capacitor, and a load capacitor is connected to Vss to be discharged. In a subsequent output period, the switches become open, and switches become closed. Then, the capacitor is connected to the load capacitor, and the MOS transistor is turned on due to a decrease in the potential of the gate, so that the load capacitor is charged until the potential of the gate is restored.

Owner:ALPS ALPINE CO LTD

Vehicle drive assistance system

ActiveUS20180281807A1Reduced driving abilityEasy to understandCharacter and pattern recognitionExternal condition input parametersDriver/operatorComputer module

A vehicle drive assistance system is provided, which includes a processor configured to execute a required driving ability estimating module to estimate a driver's driving ability required for driving a vehicle based on a traffic environment around the vehicle and drive assistance provided to the driver by the vehicle, a current driving ability estimating module to estimate a driver's current driving ability, and a changing module to perform reduction processing in which the required driving ability is reduced when the current driving ability is lower than the required driving ability, the required driving ability being reduced less in a case where the current driving ability is lower than a given threshold compared to a case where the current driving ability is equal to or higher than the given threshold, even when a difference between the required driving ability and the current driving ability is constant.

Owner:MAZDA MOTOR CORP

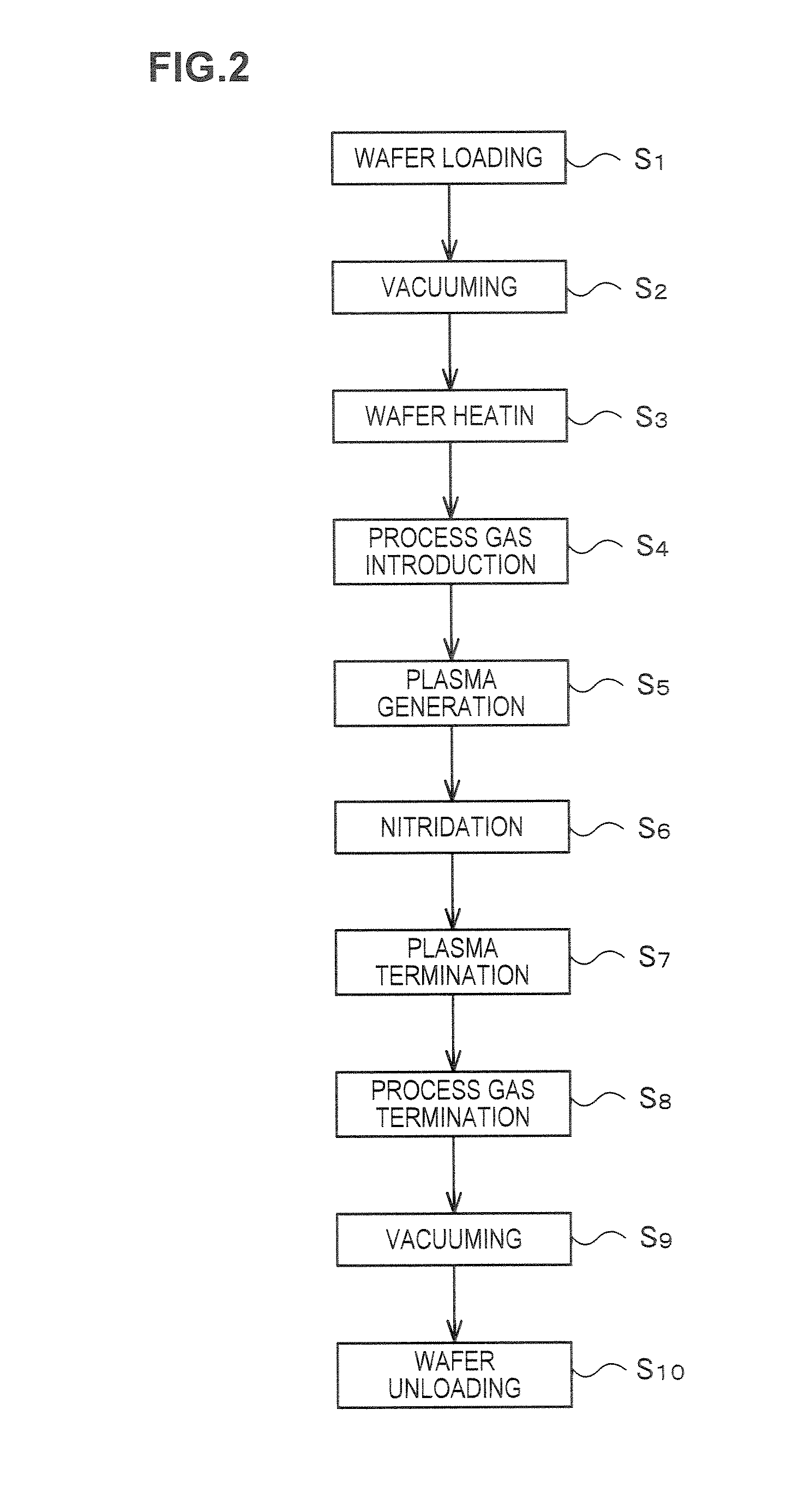

Method of forming gate insulating film, semiconductor device and computer recording medium

InactiveUS7674722B2Deteriorating capability of deviceReduced driving abilitySolid-state devicesSemiconductor/solid-state device manufacturingMicrowaveNitrogen

In the present invention, when a gate insulation film in a DRAM is formed, an oxide film constituting a base of the gate insulation film is plasma-nitrided. The plasma nitridation is performed with microwave plasma generated by using a plane antenna having a large number of through holes. Nitrogen concentration in the gate insulation film formed by the plasma nitridation is 5 to 20% in atomic percentage. Even without subsequent annealing, it is possible to effectively prevent a boron penetration phenomenon in the DRAM and to reduce traps in the film causing deterioration in driving capability of the device.

Owner:TOKYO ELECTRON LTD

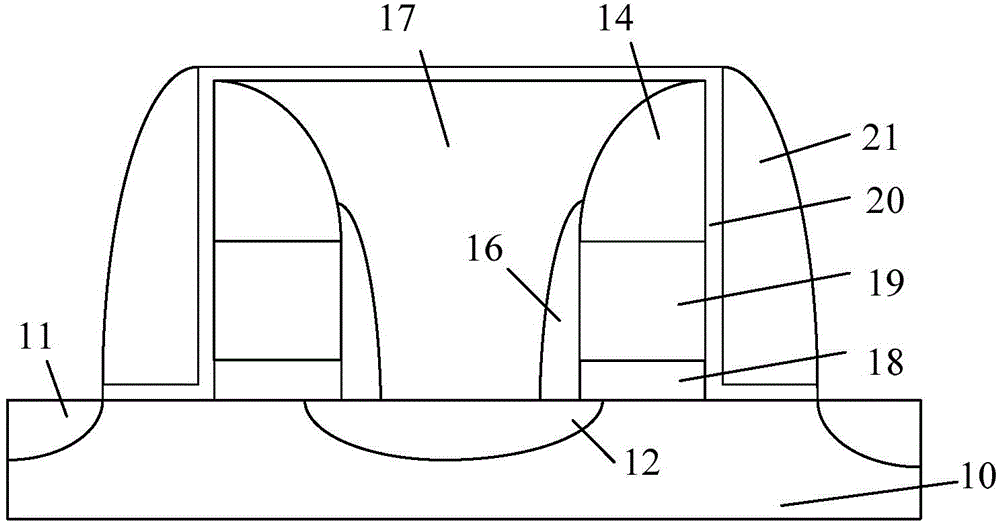

Storage cell, formation method of storage cell and reading method of storage cell

ActiveCN104091802AHighly integratedLow costSolid-state devicesRead-only memoriesGate dielectricDielectric layer

The invention discloses a storage cell, a formation method of the storage cell and a reading method of the storage cell. The formation method of the storage cell comprises the steps that a semiconductor substrate is provided, wherein the semiconductor substrate comprises a first bit area and a second bit area, and a first dielectric layer, a floating gate material layer and a second dielectric layer are formed on the surface of the semiconductor substrate; a first doping area is formed in the first bit area; a second doping area is formed in the second bit area, wherein the dosage concentration of the second doping area is smaller than that of the first doping area; the second dielectric layer is etched to form an opening; a side wall is formed on the surface of the side wall of the opening; the floating gate material layer and the first dielectric layer are etched with the side wall as a mask to the surface of the semiconductor substrate; a source line is formed in the opening; the second dielectric layer and the floating gate material layer and the first dielectric layer below the second dielectric layer are removed, and a floating gate and a floating gate dielectric layer below the side wall are formed; a tunneling dielectric layer is formed; a word line located on the surface of the tunneling dielectric layer is formed; a first drain area and a second drain area are formed. The formation method of the storage cell can lower the cost of a storage.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

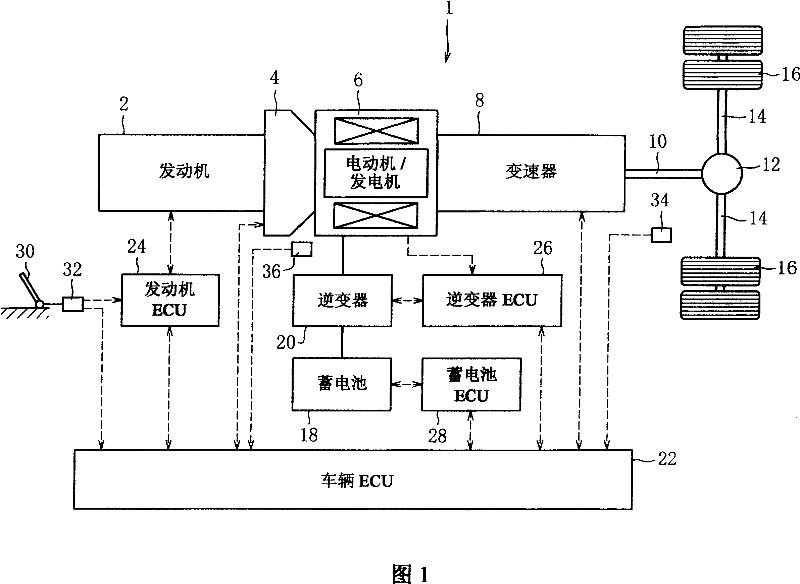

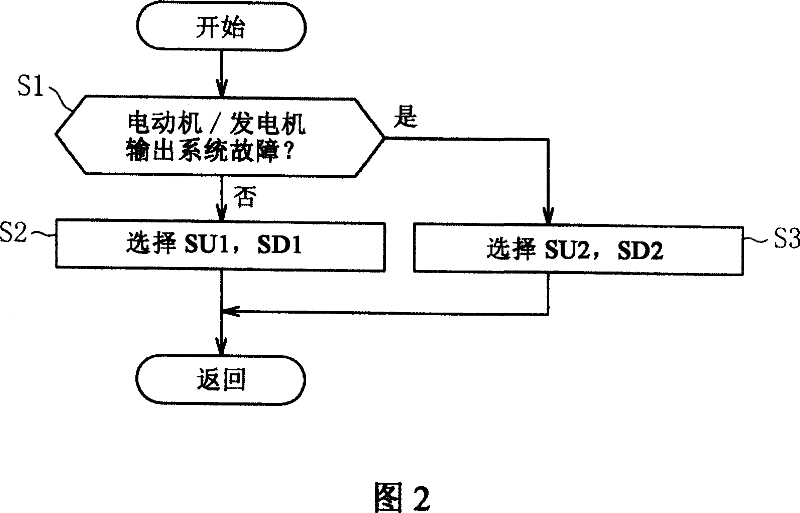

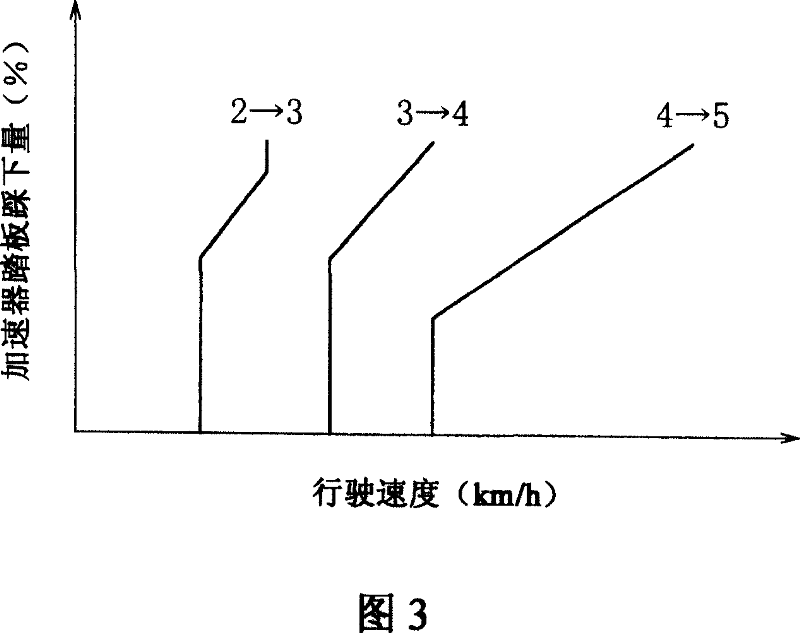

Control device for a hybrid electric vehicle

InactiveCN101038031ASmooth startSmooth accelerationSpeed controllerElectric devicesDrive wheelLow speed

A hybrid electric vehicle is equipped with an engine output system that makes the engine generate a driving force and outputs the driving force of the engine and a motor output system that makes an electric motor generate a driving force and outputs the driving force of the electric motor, and is capable of transmitting to driving wheels the driving forces outputted from the respective systems. If a failure of the motor output system is not detected, a vehicle ECU sets the gear of an automatic transmission for start-up of the vehicle to a first gear. If the failure is detected, the vehicle ECU sets the gear of the automatic transmission for start-up the vehicle to a second gear that is lower than the first gear.

Owner:MITSUBISHI FUSO TRUCK AND BUS CORPORATION

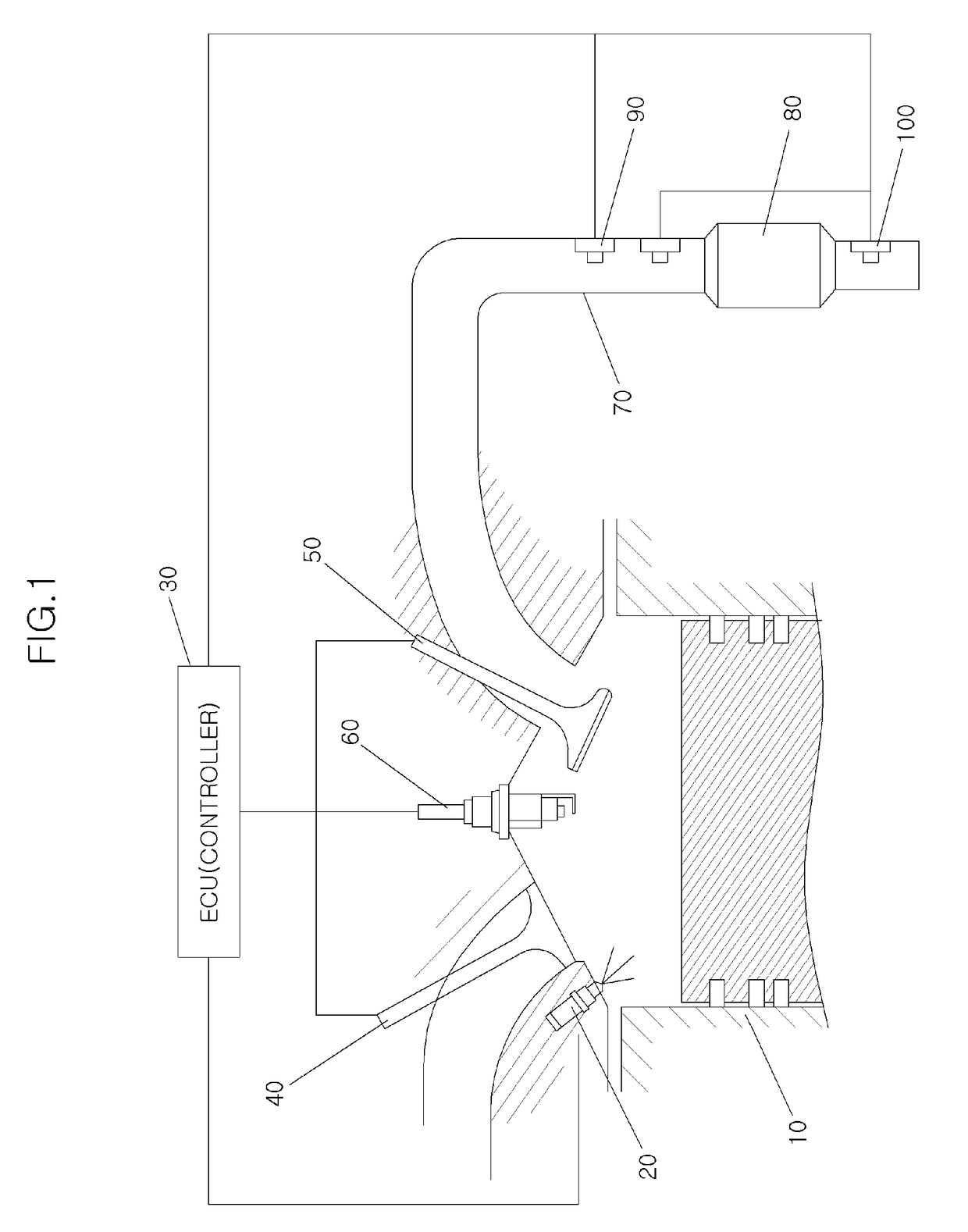

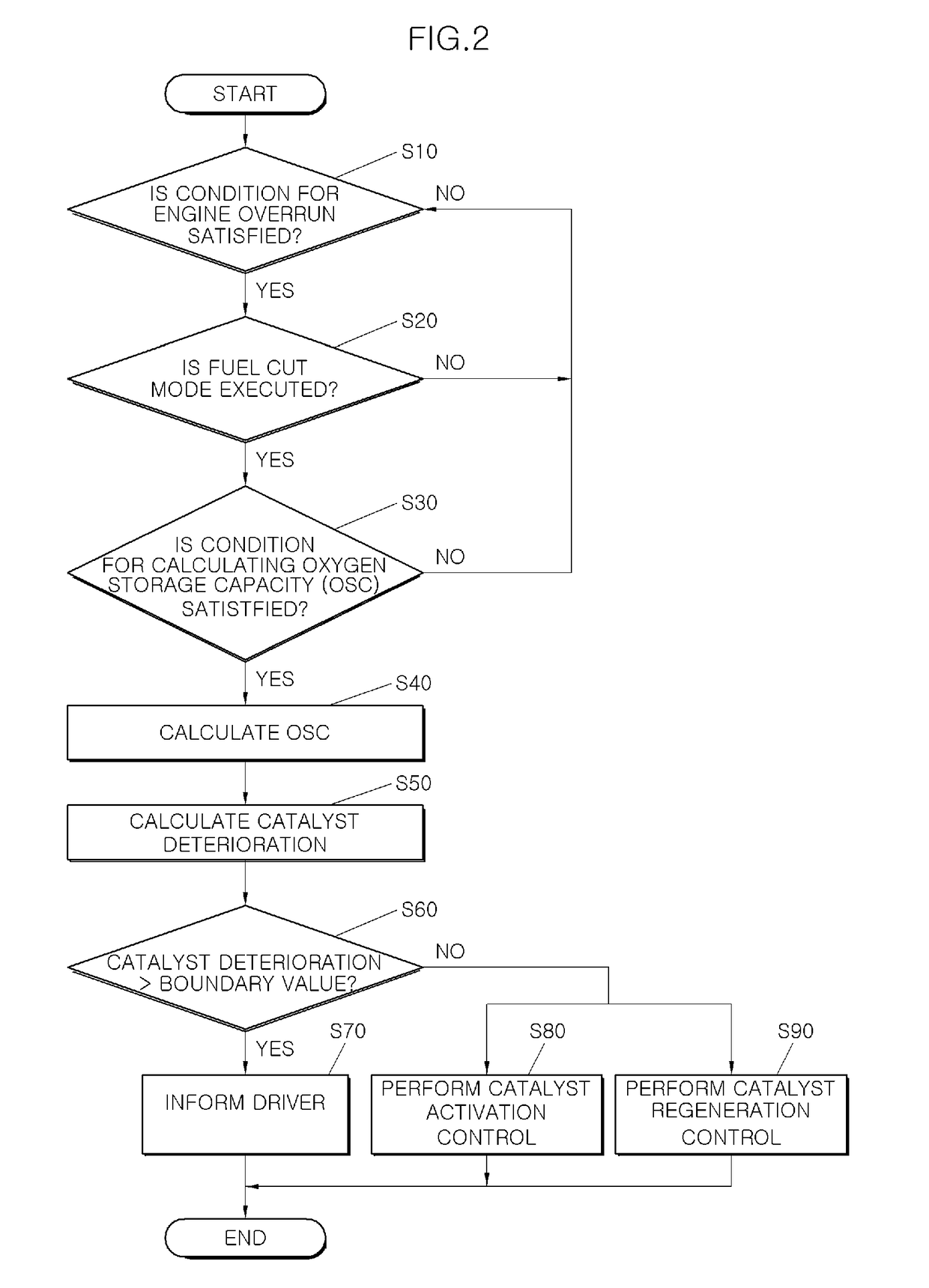

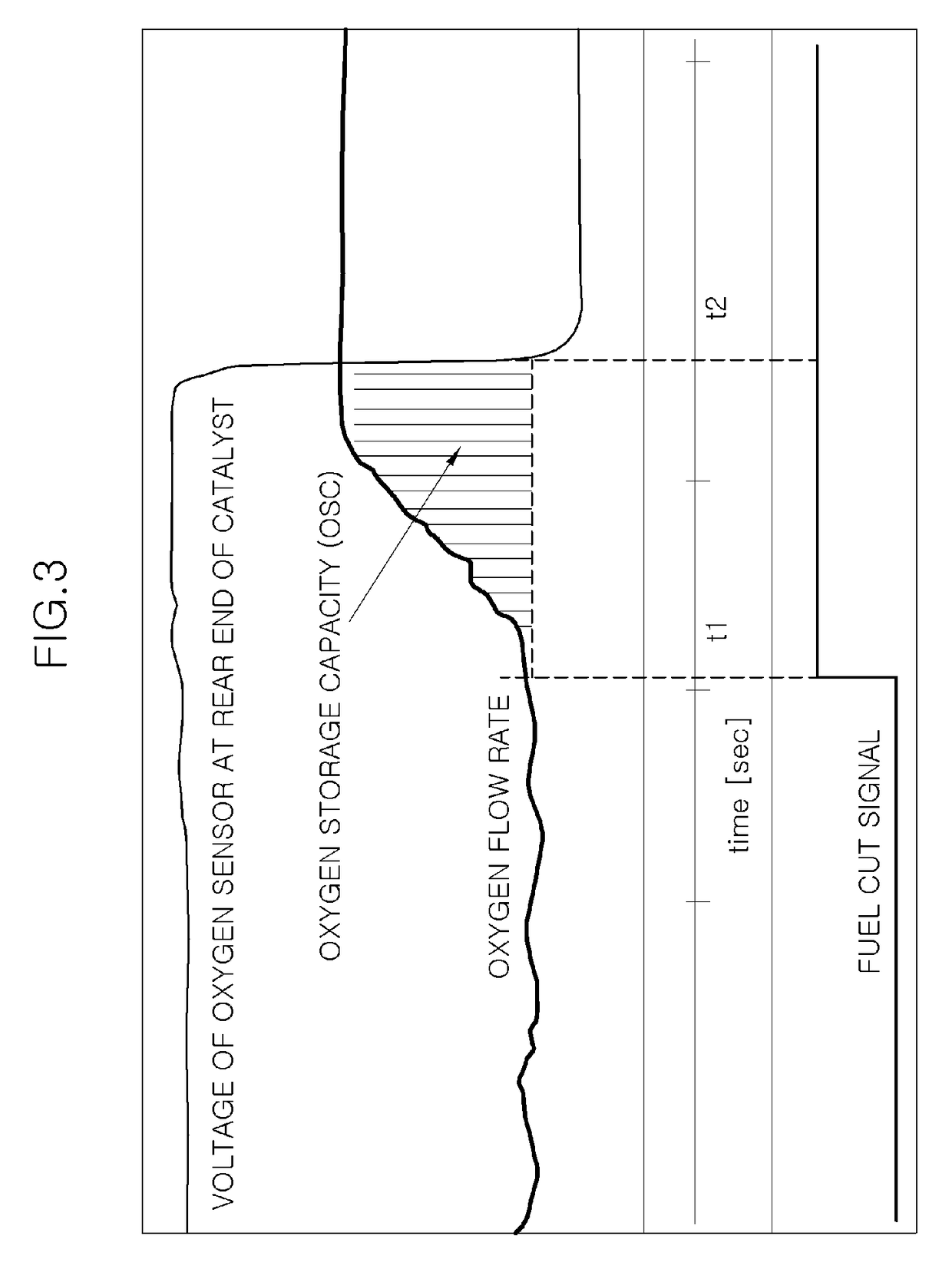

Method for detecting catalyst deterioration of vehicle

ActiveUS20190078490A1Reduced driving abilityImprove drivabilityElectrical controlInternal combustion piston enginesOxygen sensorEngineering

A method for detecting catalyst deterioration in a vehicle includes executing a fuel-cut mode of an engine of the vehicle according to a operating state of the vehicle; calculating an oxygen storage capacity (OSC) of a catalyst using an oxygen sensor during the executing of the fuel-cut mode of the engine; and calculating catalyst deterioration based on the calculated OSC.

Owner:HYUNDAI MOTOR CO LTD +1

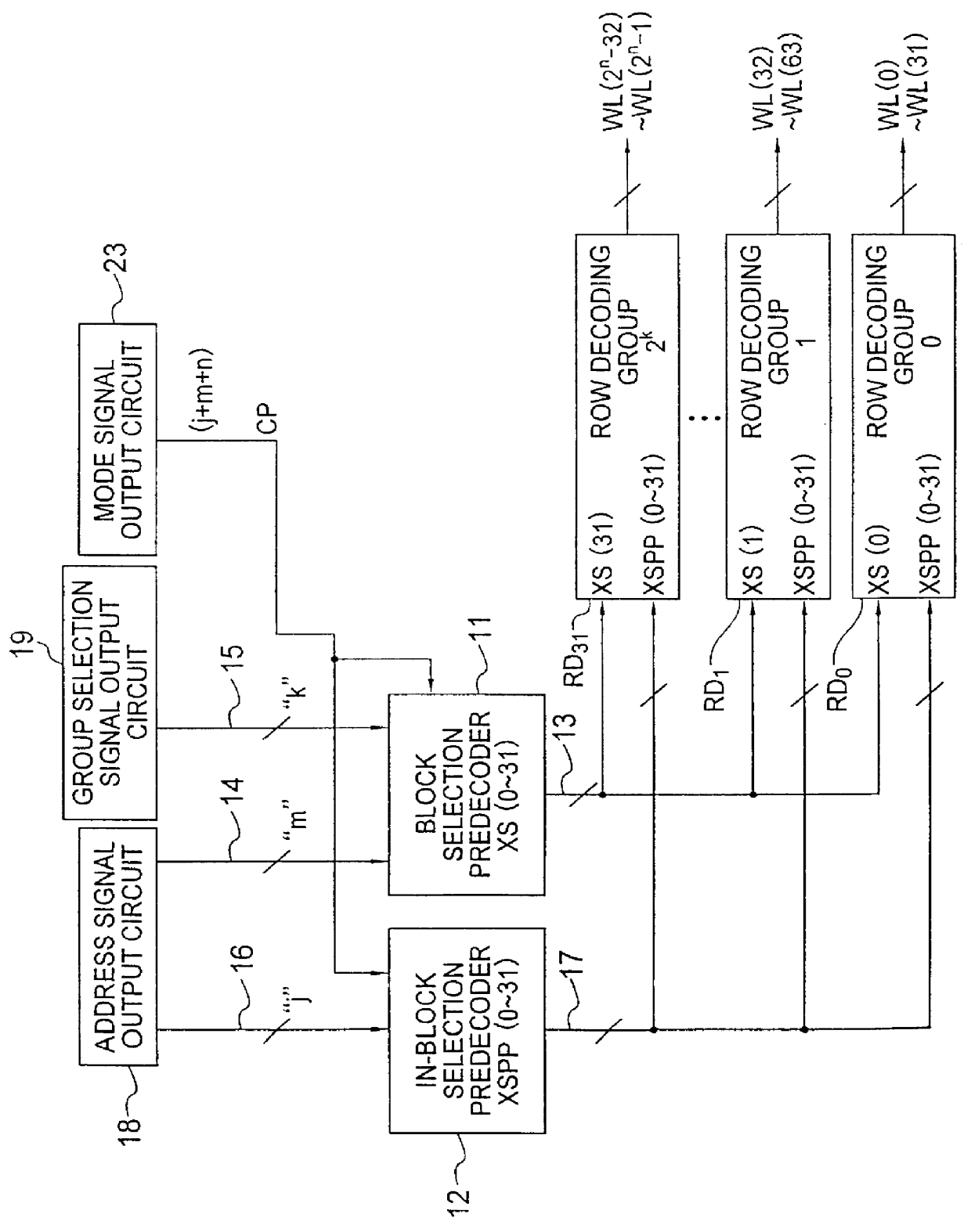

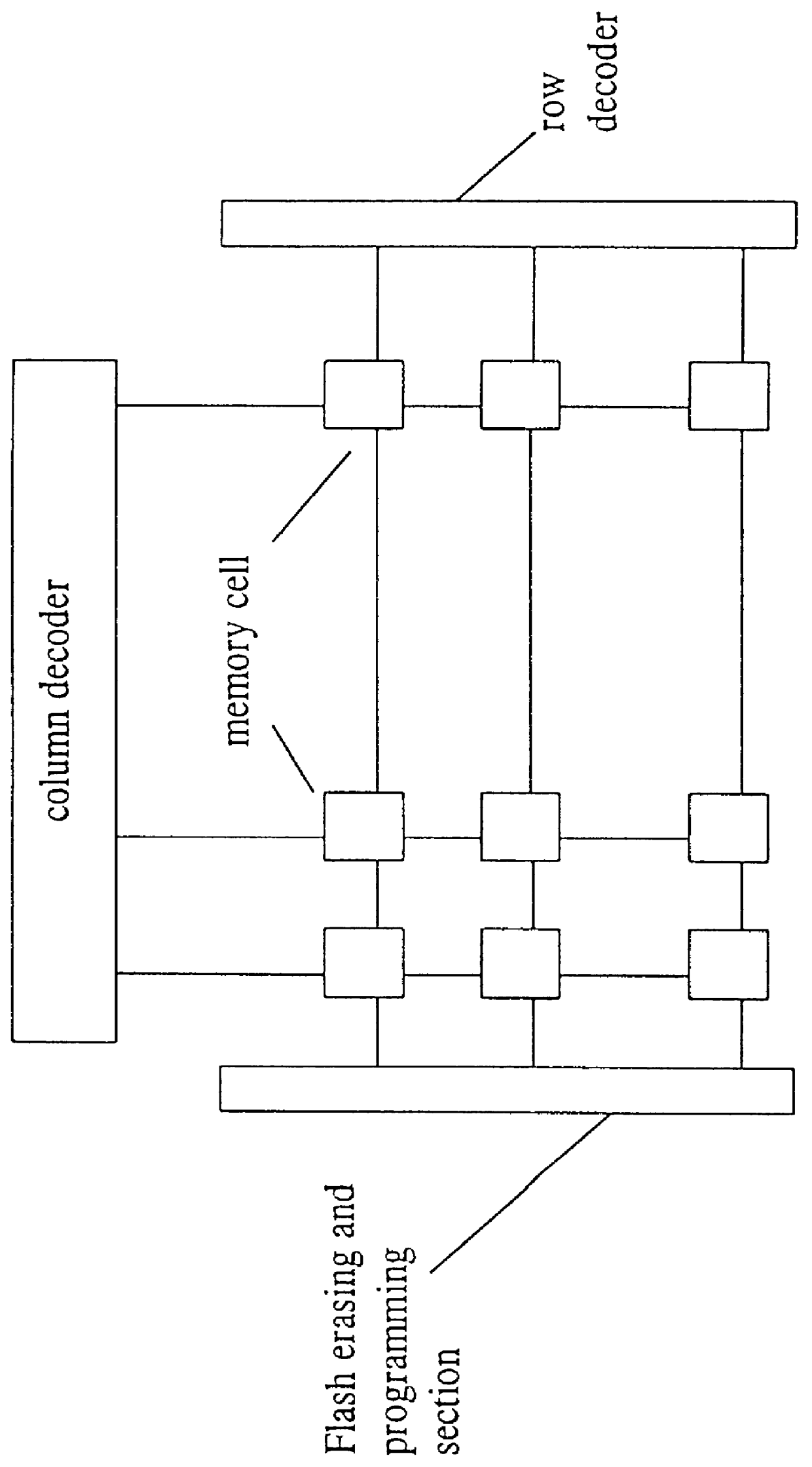

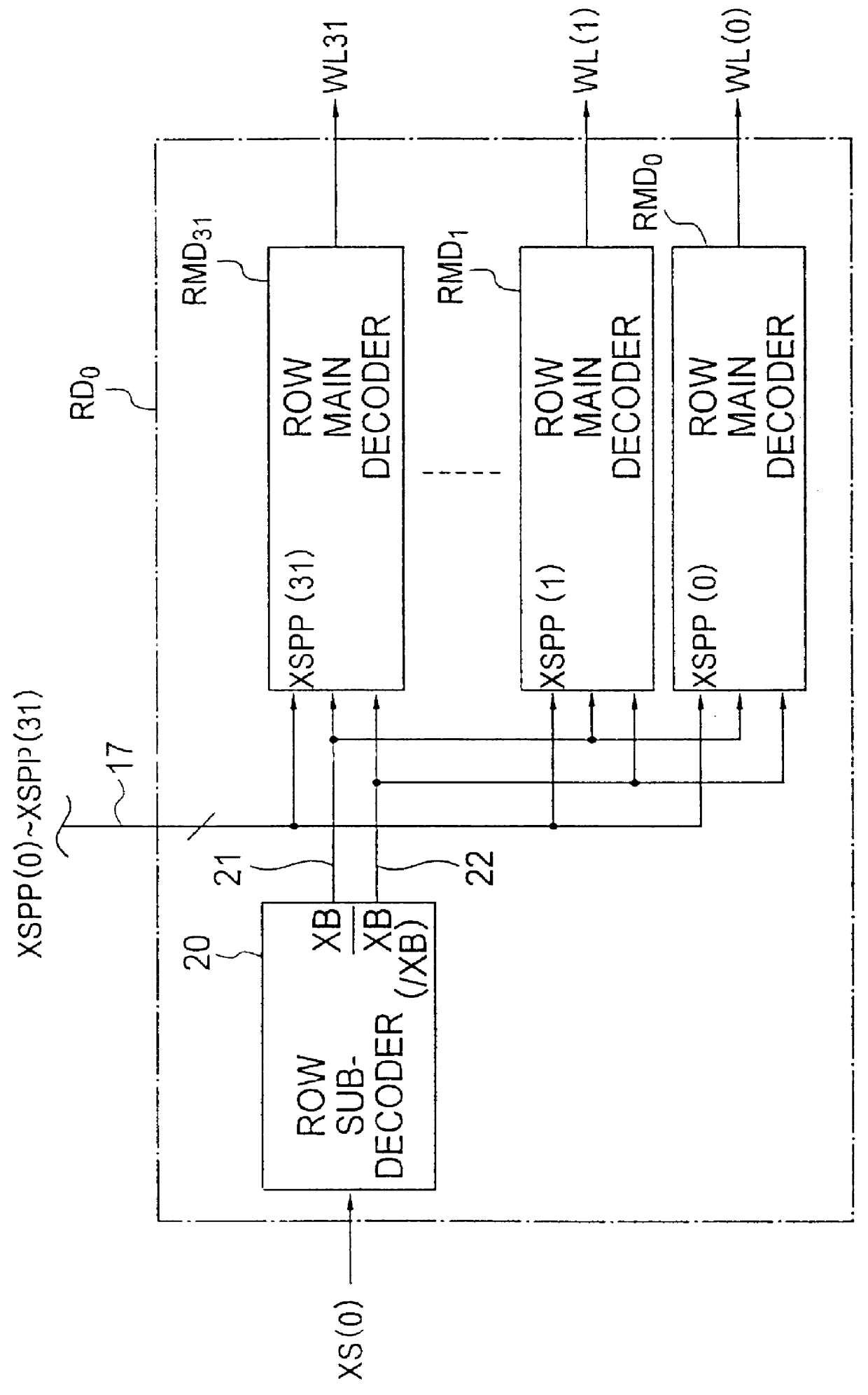

Non-volatile semiconductor memory device for selective cell flash erasing/programming

InactiveUS6111792AShorten the length of timeReduce chip areaRead-only memoriesDigital storageGroup controlComputer science

Disclosed herein is a non-volatile semiconductor memory device comprising a mode signal output means for outputting a mode signal for conducting flash programming or flash erasing, a group selection signal output means for outputting a group selection signal for selecting a row decoding group, a first selection means for selecting the row decoding group controlling the word line in accordance with 10 the group selection signal, and a second selection means selecting the word line corresponding to the memory cell from a plurality of the word lines controlled by the row decoding group selected by the first selection means. In the present inventions the time required for the flash programming and the flash erasing can be reduced without the addition of a further element and the chip areas can be reduced.

Owner:RENESAS ELECTRONICS CORP

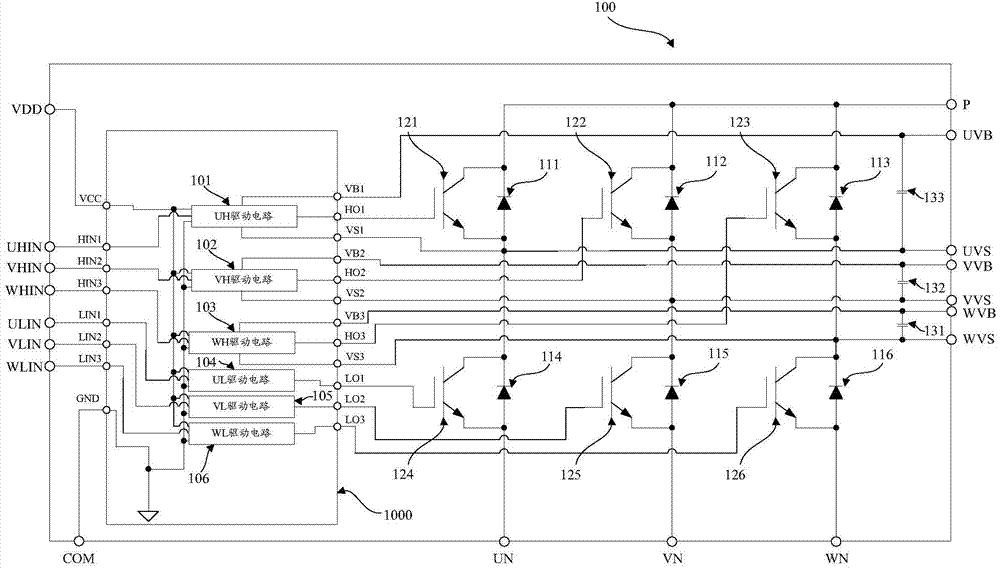

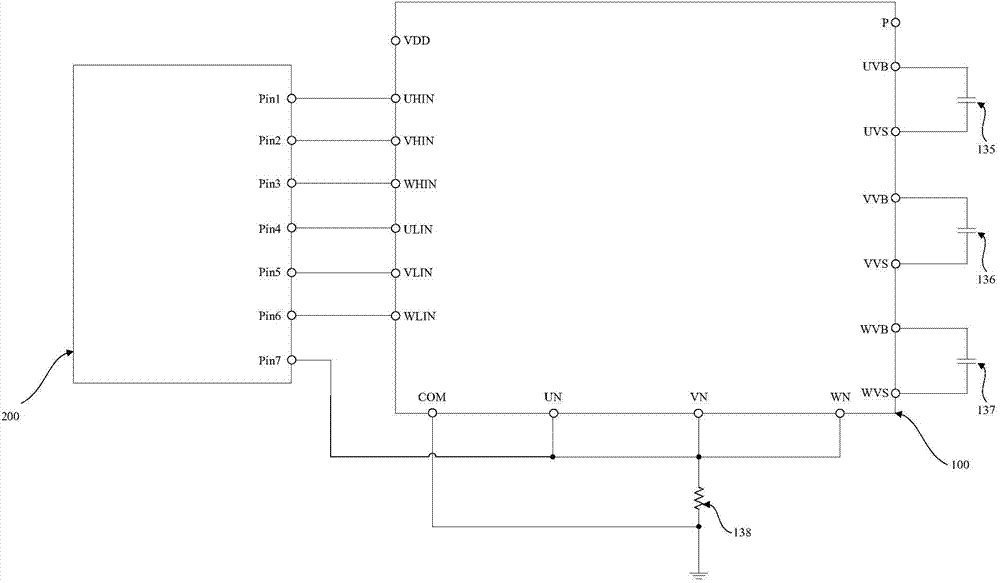

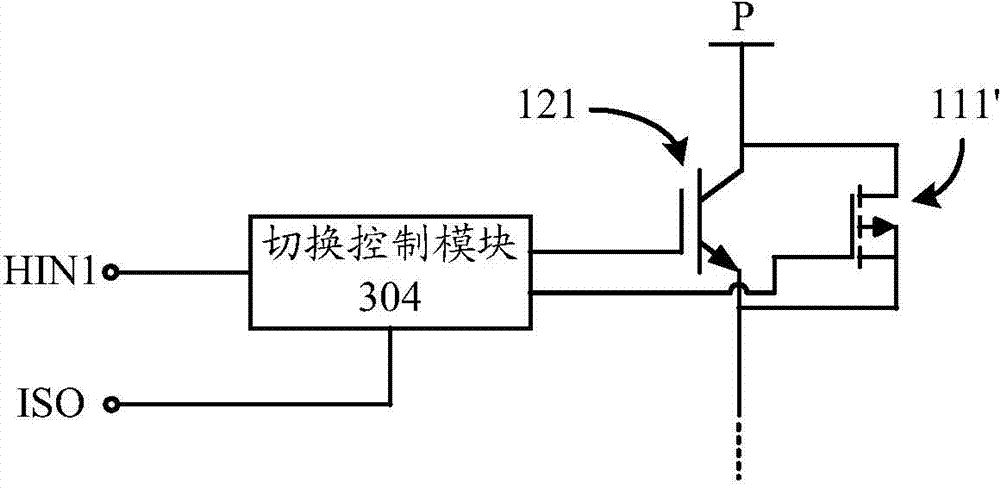

Power consumption control circuit, intelligent power module and frequency variable household appliance

ActiveCN103795248AEnsure safetyAvoid overcurrent breakdownDc-dc conversionElectric variable regulationOvercurrentComputer module

The invention provides a power consumption control circuit which comprises a low-power-consumption switch element and a switching control module. The low-power-consumption switch element is connected to any IGBT in an intelligent power module in parallel to form a switch assembly, and the switching control module is connected to a control chip corresponding to the intelligent power module, used for only enabling any IGBT or simultaneously enabling any IGBT and the low-power-consumption switch element to be in the working state under the condition that a high-frequency working signal coming from a control chip is received, and used for only enabling the low-power-consumption switch element to be in the working state under the condition that a low-frequency working signal coming from the control chip is received. The invention further provides the intelligent power module and a frequency variable home appliance. According to the technical scheme, different on-off parts can be adopted at the different working frequencies, the power consumption of the intelligent power module is easily reduced accordingly, and the risk that the on-off parts are broken down by an overcurrent can be avoided.

Owner:GD MIDEA AIR-CONDITIONING EQUIP CO LTD

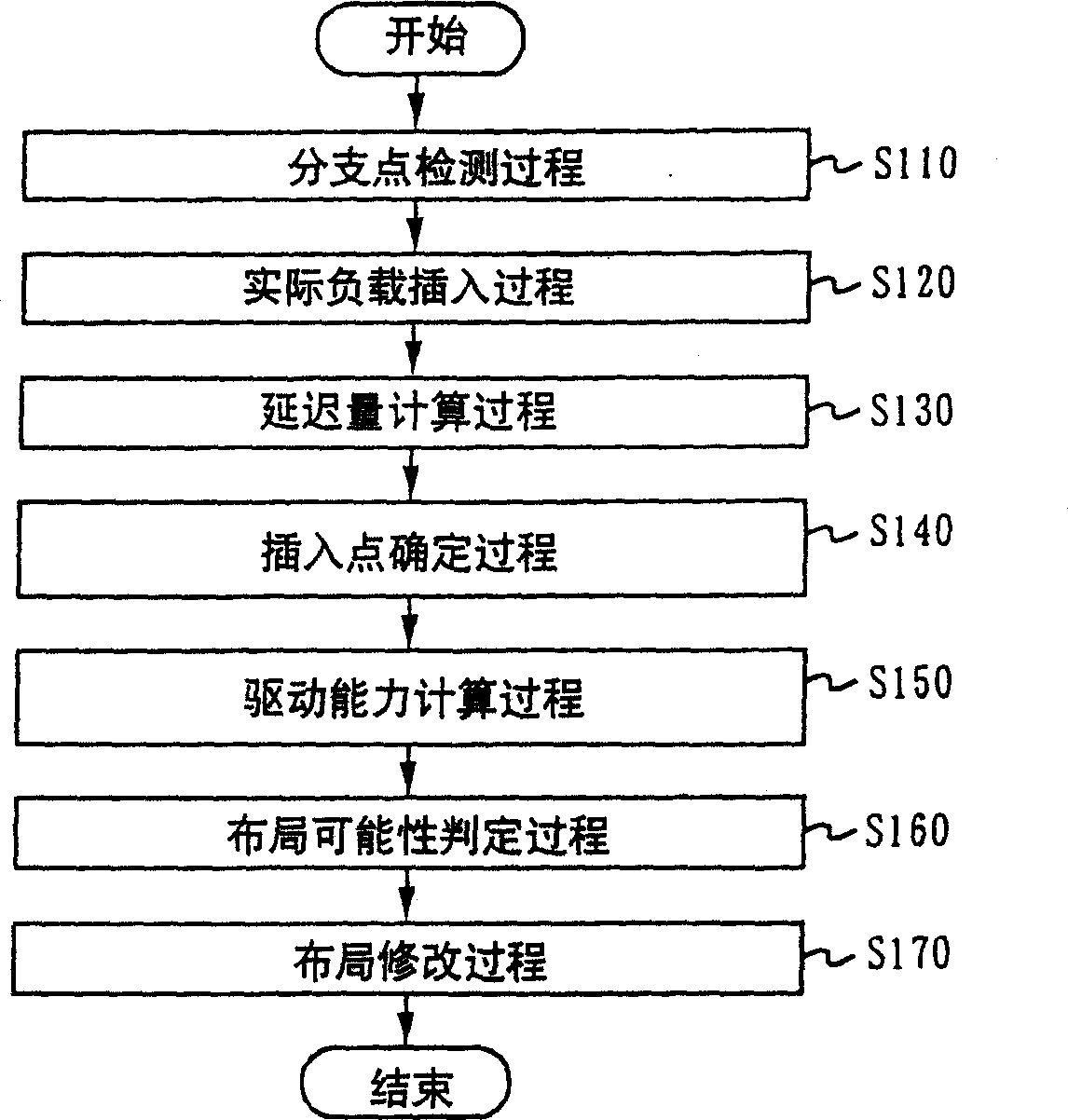

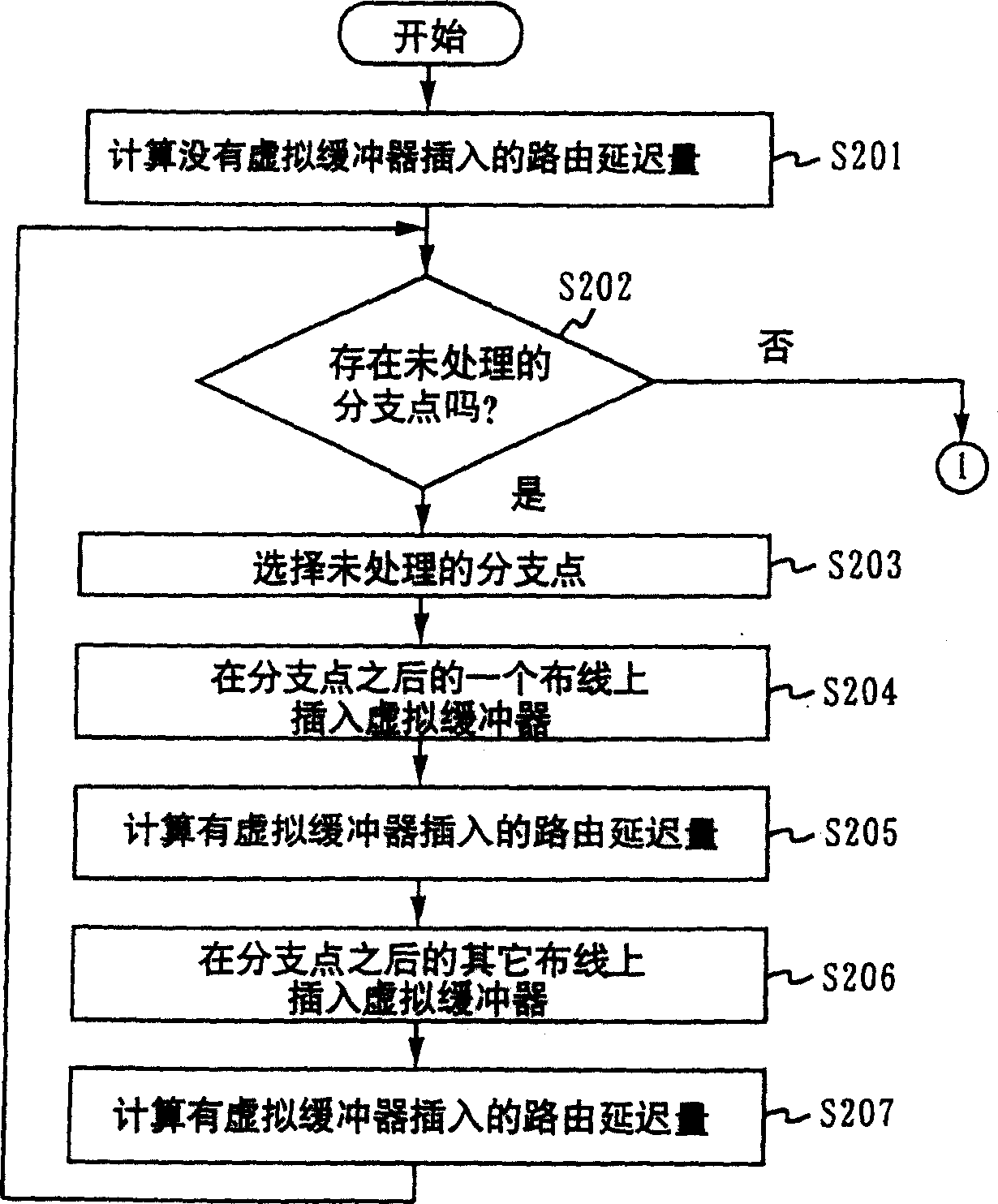

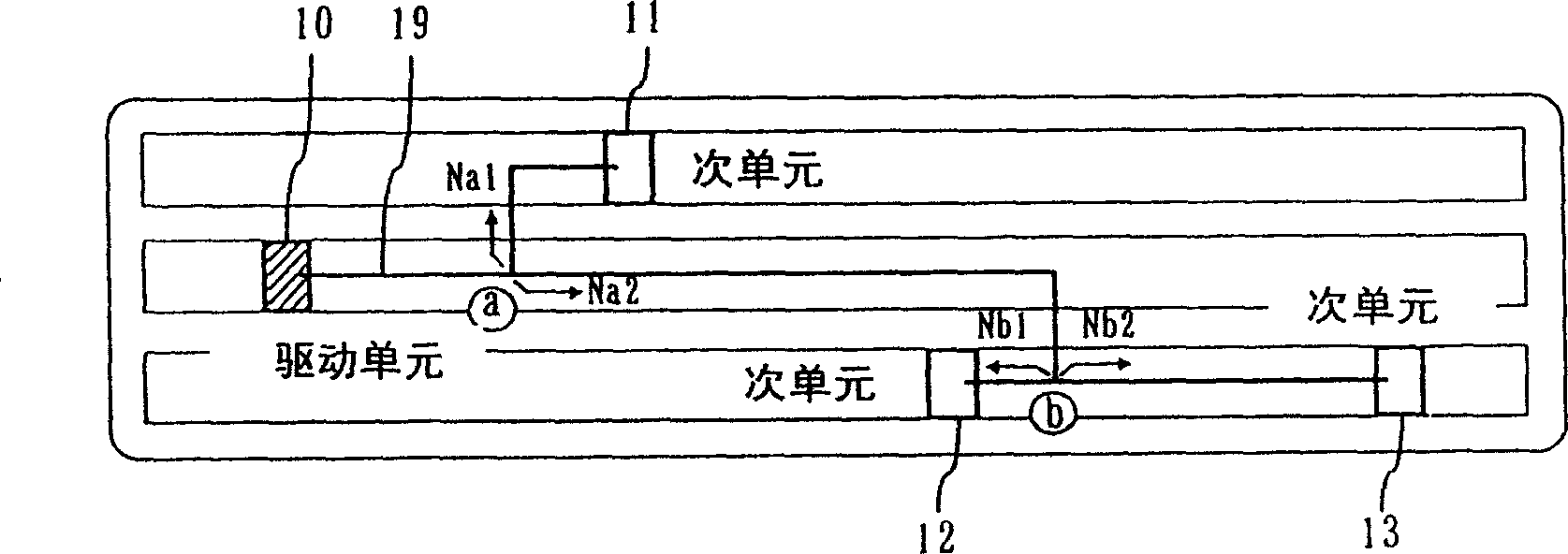

Method of designing low power consumption semiconductor integrated circuit

InactiveCN1540745AReduce Excess Design MarginReduced driving abilitySemiconductor/solid-state device manufacturingCAD circuit designInsertion pointLow power dissipation

A branching point on a wire is detected in the layout results S101. A delay amount of a route with a dummy buffer being inserted on a wire subsequent to the branching point S102 and that of the route without a dummy buffer being inserted are then calculated S103. Based on the delay amounts, an insertion point at which a load-dividing buffer is to be inserted is determined S104. On condition that a load-dividing buffer is to be inserted at the insertion point, the drive capability of a driving cell preceding the insertion point is calculated so that timing constraints are satisfied S105. Then, after it is confirmed that a load-dividing buffer is insertable at the determined insertion point S106, processes of placing a load-dividing buffer, changing the drive capability of the driving cell, and changing wiring information are performed on the layout results S107.

Owner:PANASONIC CORP

Method of Forming Gate Insulating Film, Semiconductor Device and Computer Recording Medium

InactiveUS20070290247A1Deteriorating capability of deviceReduced driving abilityTransistorSolid-state devicesMicrowaveDevice material

In the present invention, when a gate insulation film in a DRAM is formed, an oxide film constituting a base of the gate insulation film is plasma-nitrided. The plasma nitridation is performed with microwave plasma generated by using a plane antenna having a large number of through holes. Nitrogen concentration in the gate insulation film formed by the plasma nitridation is 5 to 20% in atomic percentage. Even without subsequent annealing, it is possible to effectively prevent a boron penetration phenomenon in the DRAM and to reduce traps in the film causing deterioration in driving capability of the device.

Owner:TOKYO ELECTRON LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com