Method of designing low power consumption semiconductor integrated circuit

A technology of integrated circuits and design methods, applied in semiconductor/solid-state device manufacturing, circuits, computer-aided design, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

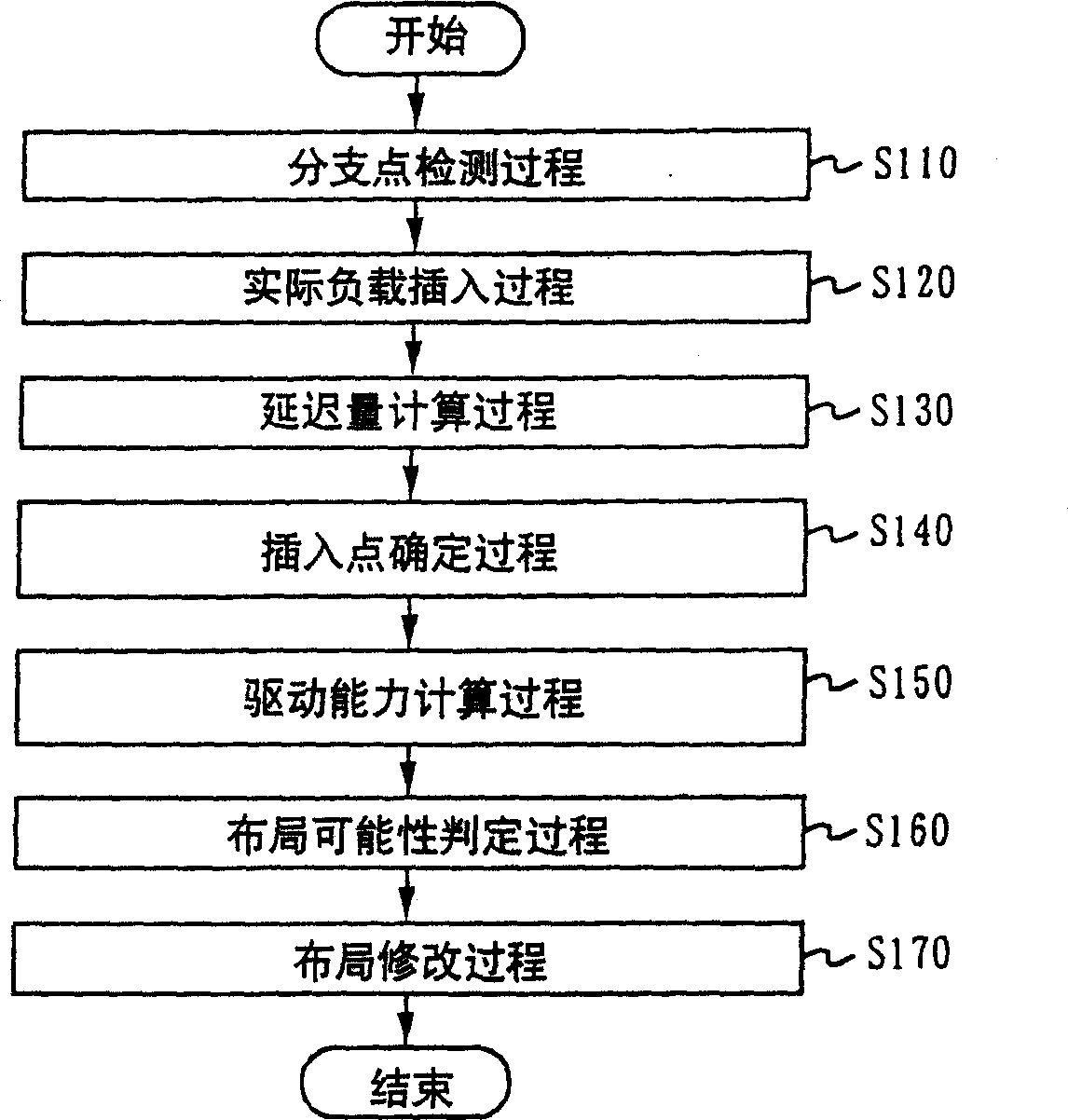

[0049] refer to figure 1 Through 8, the design method according to the first embodiment of the present invention is described. figure 1 is a process flowchart of the design method according to the first embodiment of the present invention. The design method includes a branch point detection process S110, an actual load insertion process S120, a delay amount calculation process S130, an insertion point determination process S140, a driving capability calculation process S150, a layout possibility determination process S160, and a layout modification process S170.

[0050] In the branch point detection process S110, the design tool detects branch points of wiring in the layout results to be processed. Next, in the actual load insertion process S120, for each branch point detected in the branch point detection process S110, the design tool actually inserts a load having a predetermined amount (the load is hereinafter referred to as a virtual buffer) one at a time in the actual...

no. 2 example

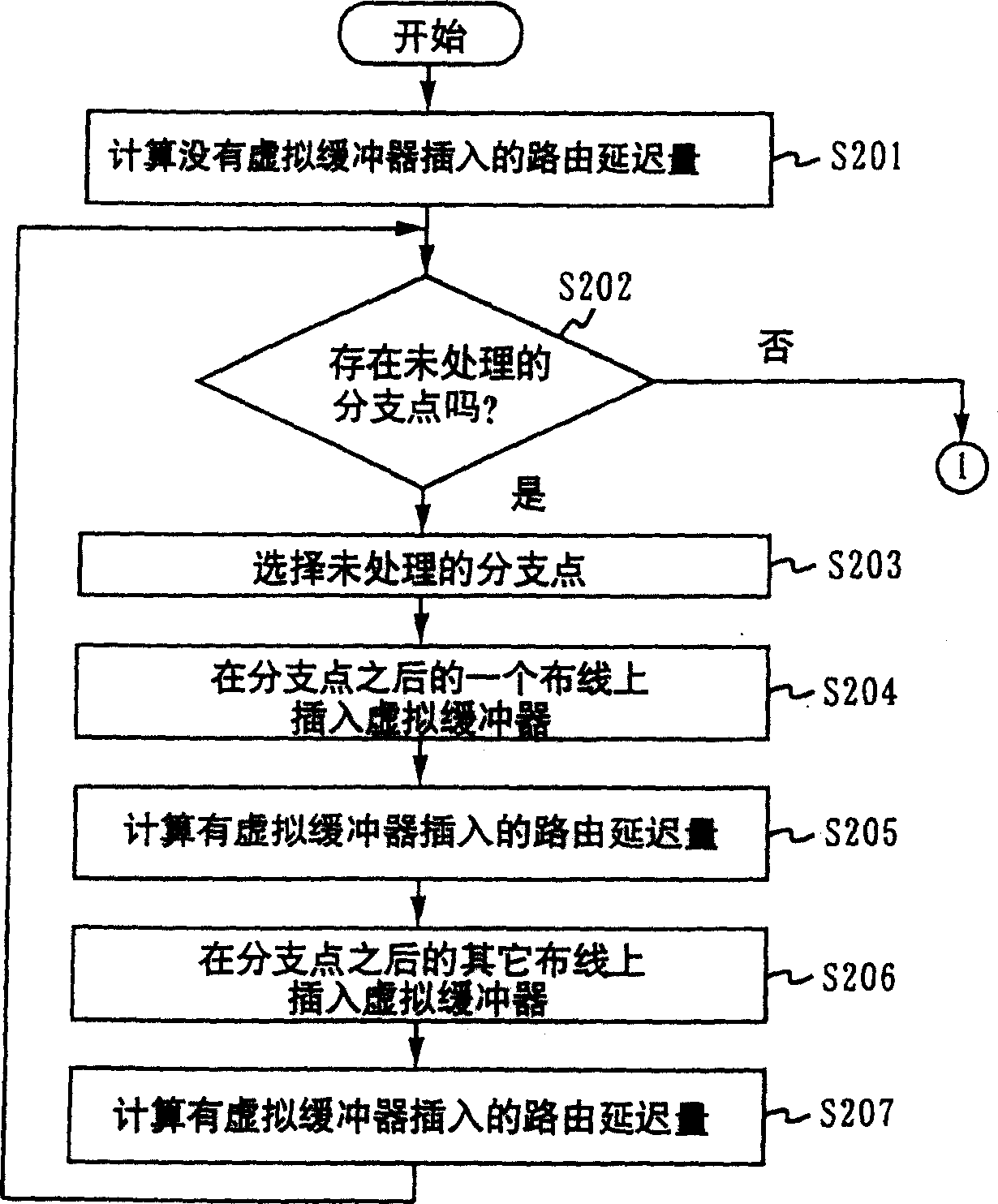

[0098] refer to Figure 9 and 10 , the second embodiment of the present invention will be described below. Figure 9 is a process flowchart of the design method according to the second embodiment of the present invention. By replacing the design method ( figure 1 ) in the actual load insertion process S120 to obtain the design method. exist Figure 9 in the process shown, with figure 1 The same processes as those shown in are given the same reference numerals and are not described again here.

[0099] In the actual load insertion process S121, the design tool determines whether a dummy buffer is required according to a predetermined standard, and then inserts the dummy buffer into the wiring after the branch point detected in the branch point detection process S110 according to the determination that the dummy buffer is required. at the predetermined point above. The actual load insertion process S121 according to the present embodiment includes a total post-branching...

no. 3 example

[0106] refer to Figure 10 and 11 , the third embodiment of the present invention will be described below. Figure 11 is a process flowchart of the design method according to the third embodiment of the present invention. By replacing the design method ( figure 1 ) in the actual load insertion process S120 to obtain the design method. exist Figure 11 in the process shown, with figure 1 The same processes as those shown in are given the same reference numerals and are not described again here.

[0107] Like the actual load insertion process S121 according to the second embodiment, in the actual load insertion process S122, the design tool determines whether a dummy buffer is required according to a predetermined standard, and then inserts the dummy buffer in the At a predetermined point on the wiring after the branch point detected in the branch point detection process S110. The actual load insertion process S122 according to the present embodiment includes a branch-b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com