Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

144results about How to "Improve memory efficiency" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Selective lossless, lossy, or no compression of data based on address range, data type, and/or requesting agent

InactiveUS7190284B1Increase performanceIncrease system bandwidthMemory architecture accessing/allocationEnergy efficient ICTMemory controllerData transmission

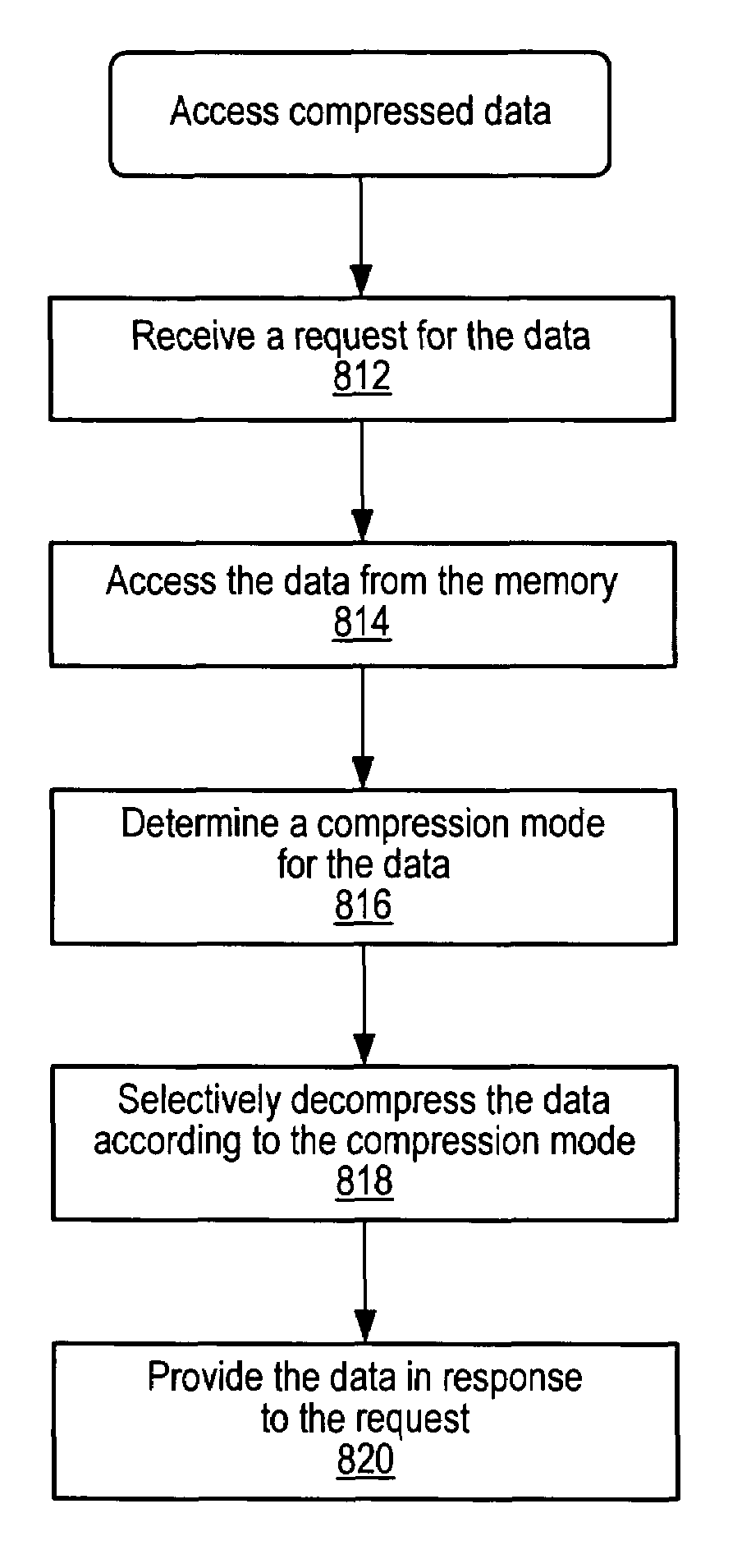

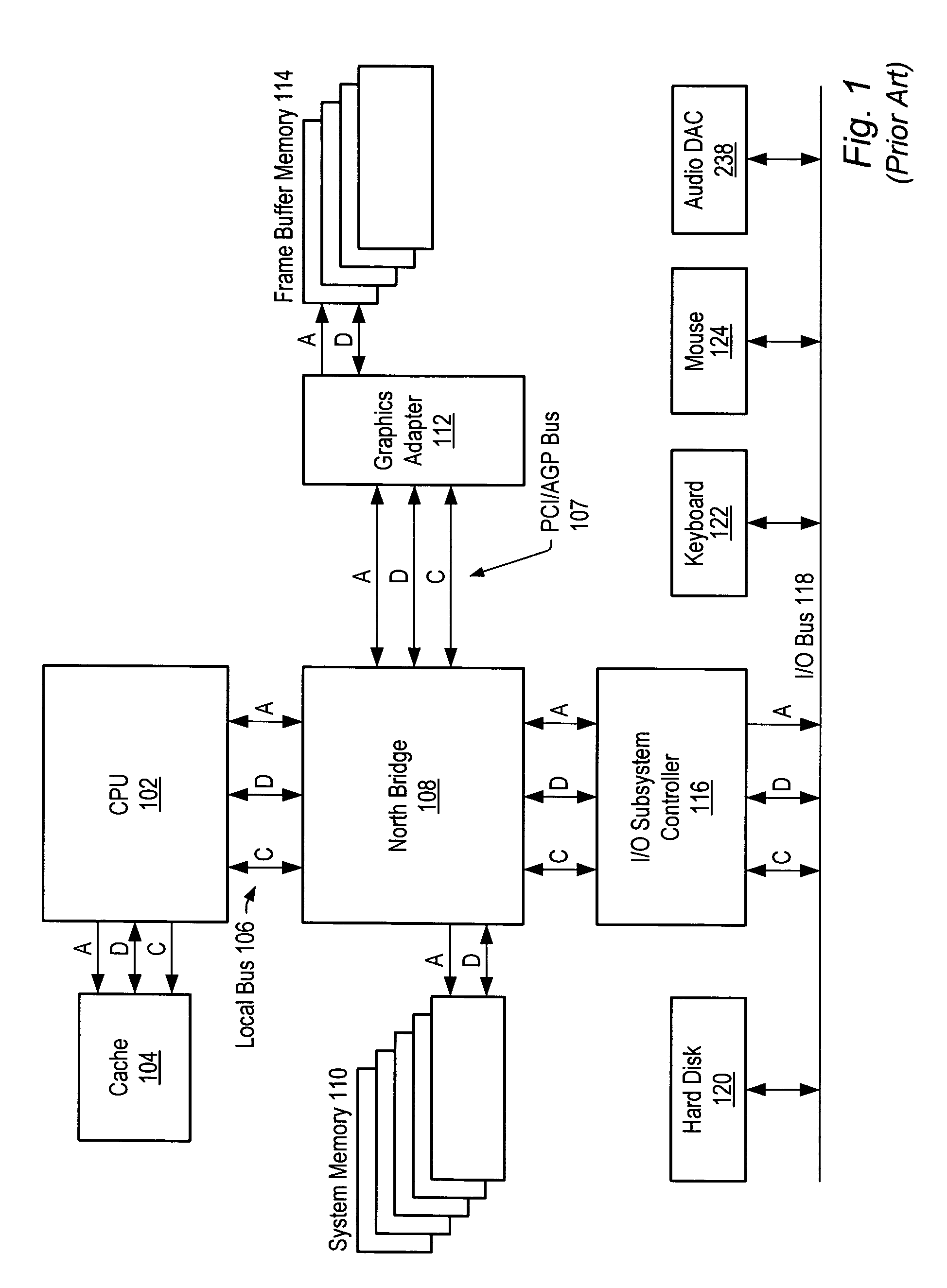

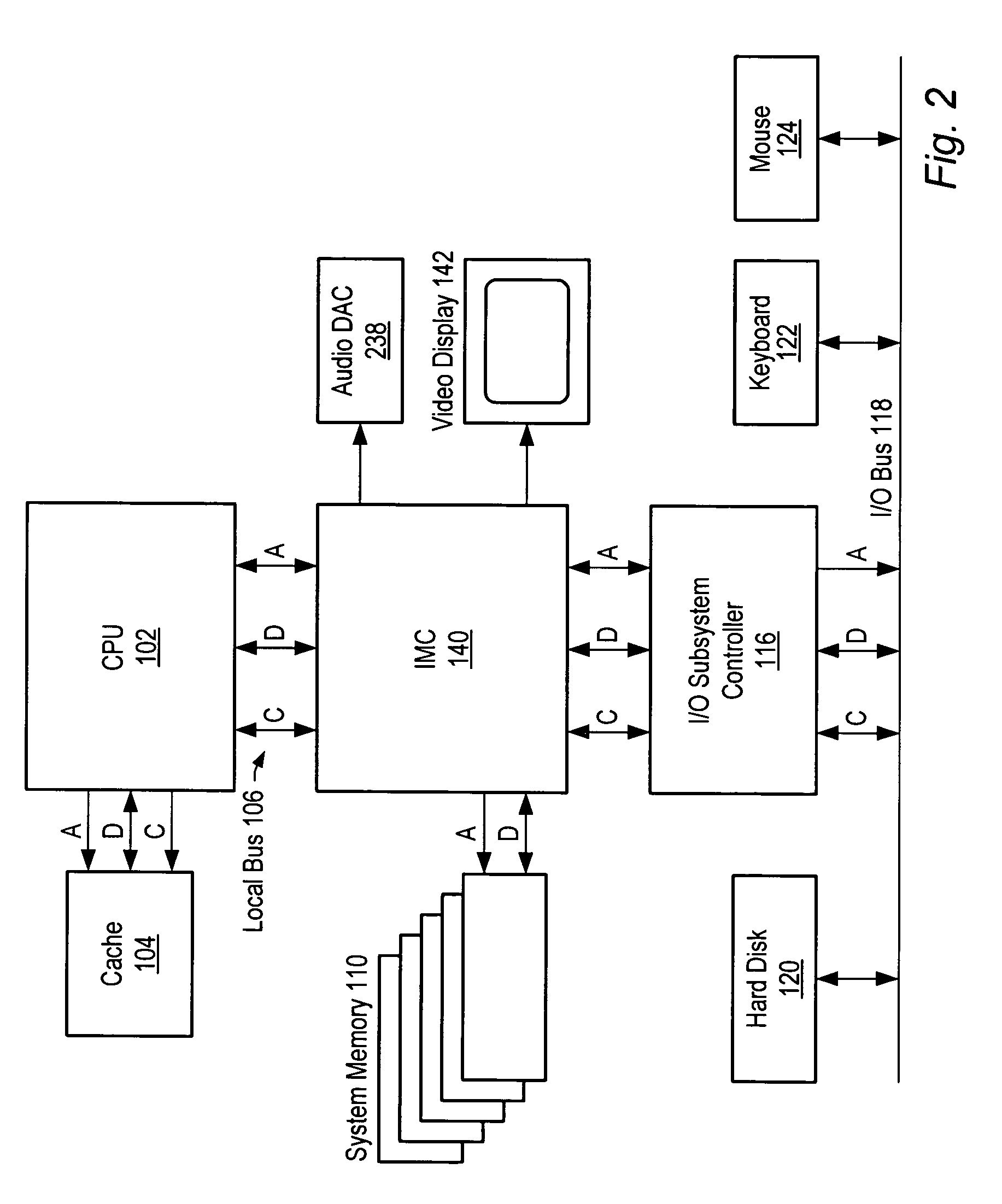

An integrated memory controller (IMC) including MemoryF / X Technology which includes data compression and decompression engines for improved performance. The memory controller (IMC) of the present invention preferably selectively uses a combination of lossless, lossy, and no compression modes. Data transfers to and from the integrated memory controller of the present invention can thus be in a plurality of formats, these being compressed or normal (non-compressed), compressed lossy or lossless, or compressed with a combination of lossy and lossless. The invention also indicates preferred methods for specific compression and decompression of particular data formats such as digital video, 3D textures and image data using a combination of novel lossy and lossless compression algorithms in block or span addressable formats. To improve latency and reduce performance degradations normally associated with compression and decompression techniques, the MemoryF / X Technology encompasses multiple novel techniques such as: 1) parallel lossless compression / decompression; 2) selectable compression modes such as lossless, lossy or no compression; 3) priority compression mode; 4) data cache techniques; 5) variable compression block sizes; 6) compression reordering; and 7) unique address translation, attribute, and address caches. The parallel compression and decompression algorithm allows high-speed parallel compression and high speed parallel decompression operation. The IMC also preferably uses a special memory allocation and directory technique for reduction of table size and low latency operation. The integrated data compression and decompression capabilities of the IMC remove system bottle-necks and increase performance. This allows lower cost systems due to smaller data storage, reduced bandwidth requirements, reduced power and noise.

Owner:INTELLECTUAL VENTURES I LLC

Scratch pad block

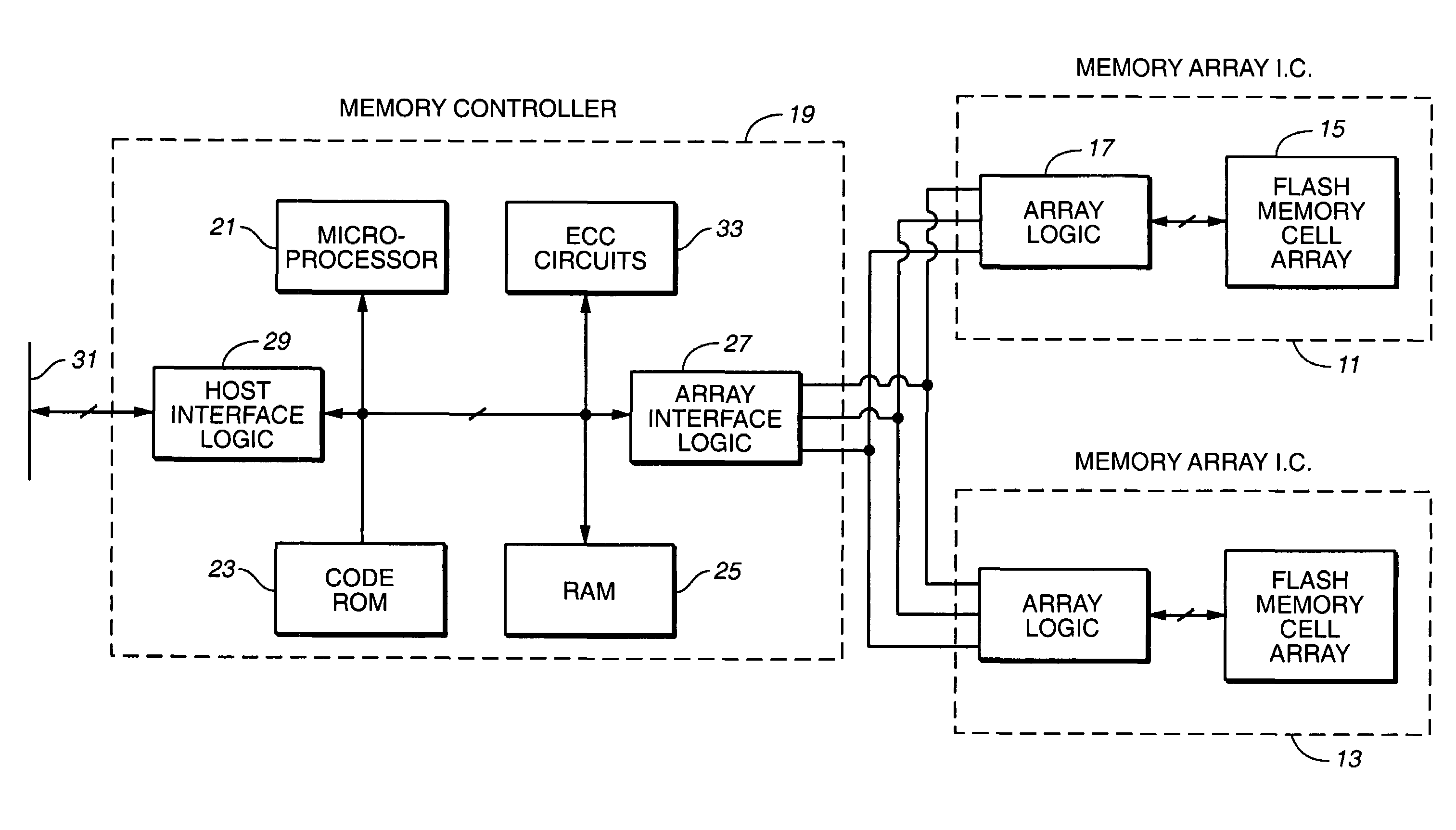

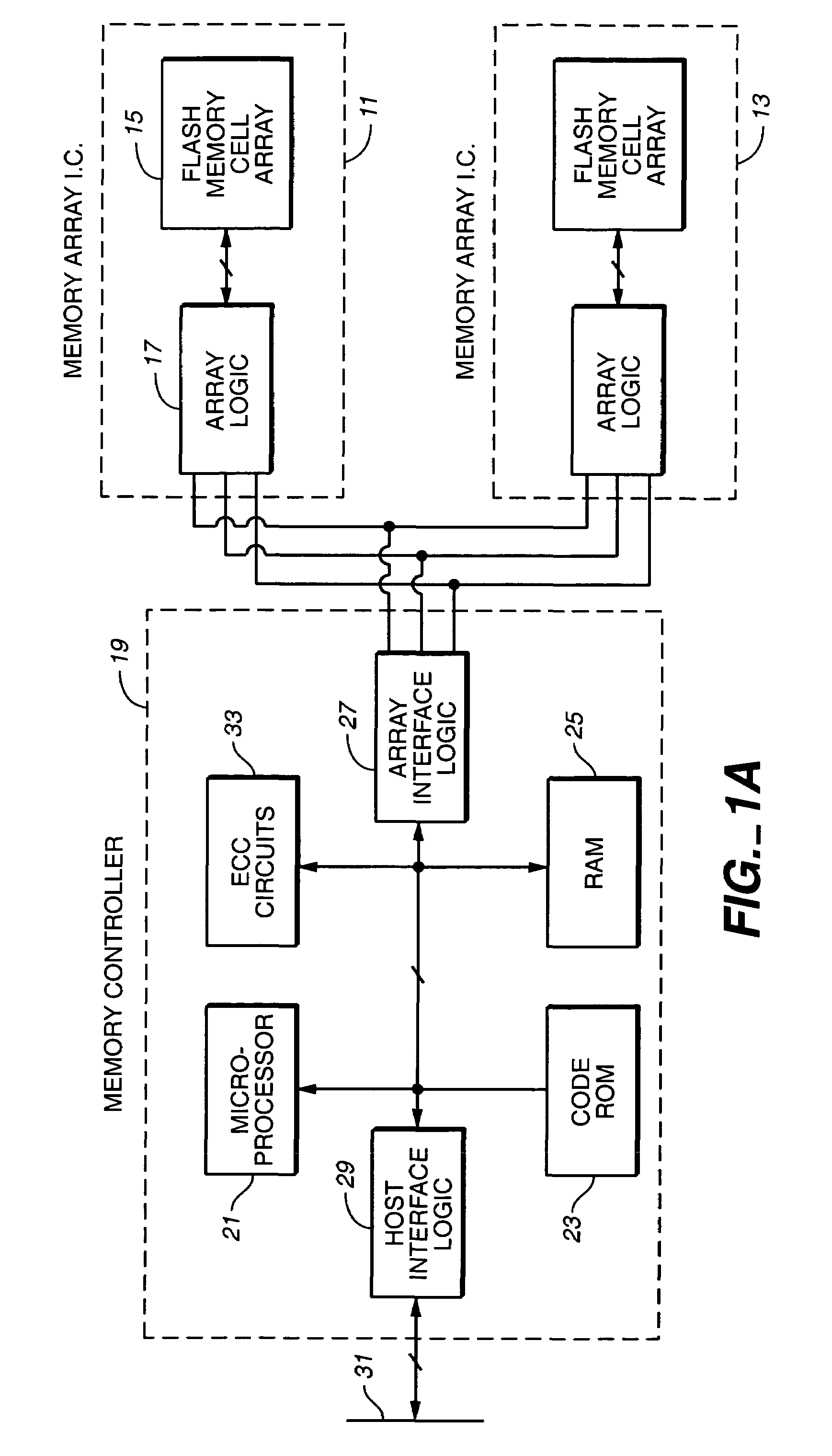

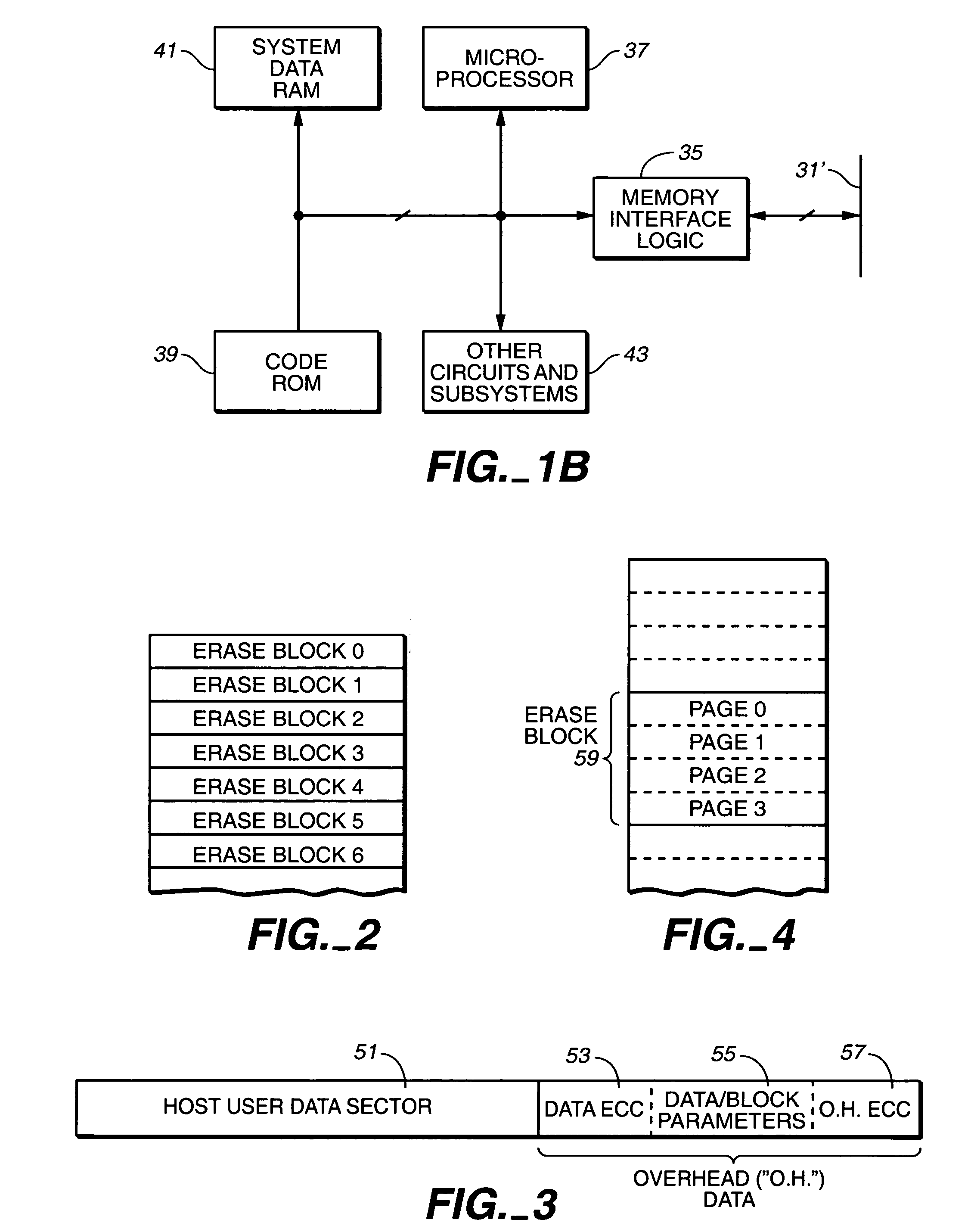

ActiveUS7315916B2Improve performanceWrite efficientlyMemory architecture accessing/allocationRead-only memoriesHigh densityHigh velocity

In a memory array having a minimum unit of erase of a block, a scratch pad block is used to store data that is later written to another block. The data may be written to the scratch pad block with a low degree of parallelism and later written to another location with a high degree of parallelism so that it is stored with high density. Data may be temporarily stored in the scratch pad block until it can be more efficiently stored elsewhere. This may be when some other data is received. Unrelated data may be stored in the same page of a scratch pad block.

Owner:SANDISK TECH LLC

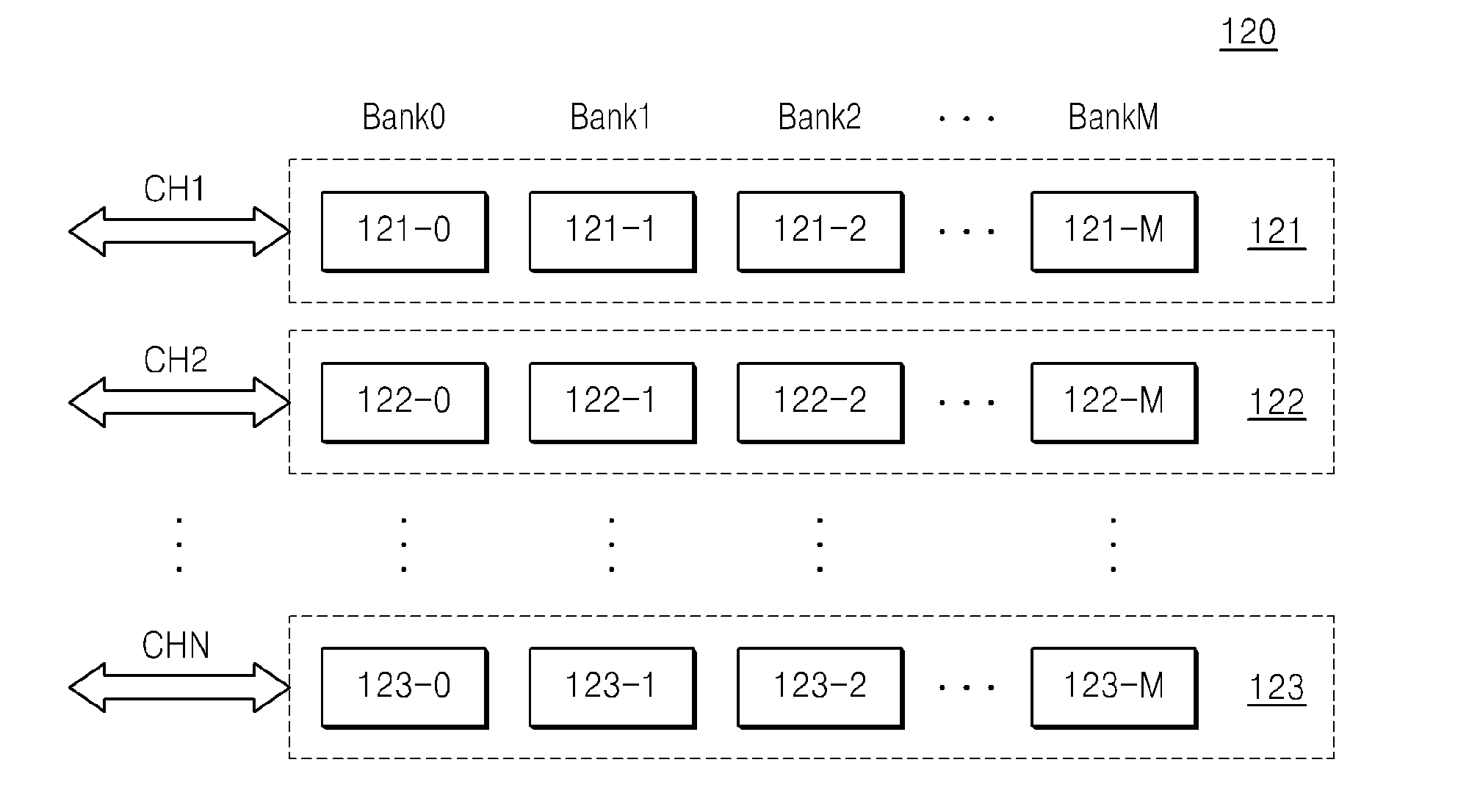

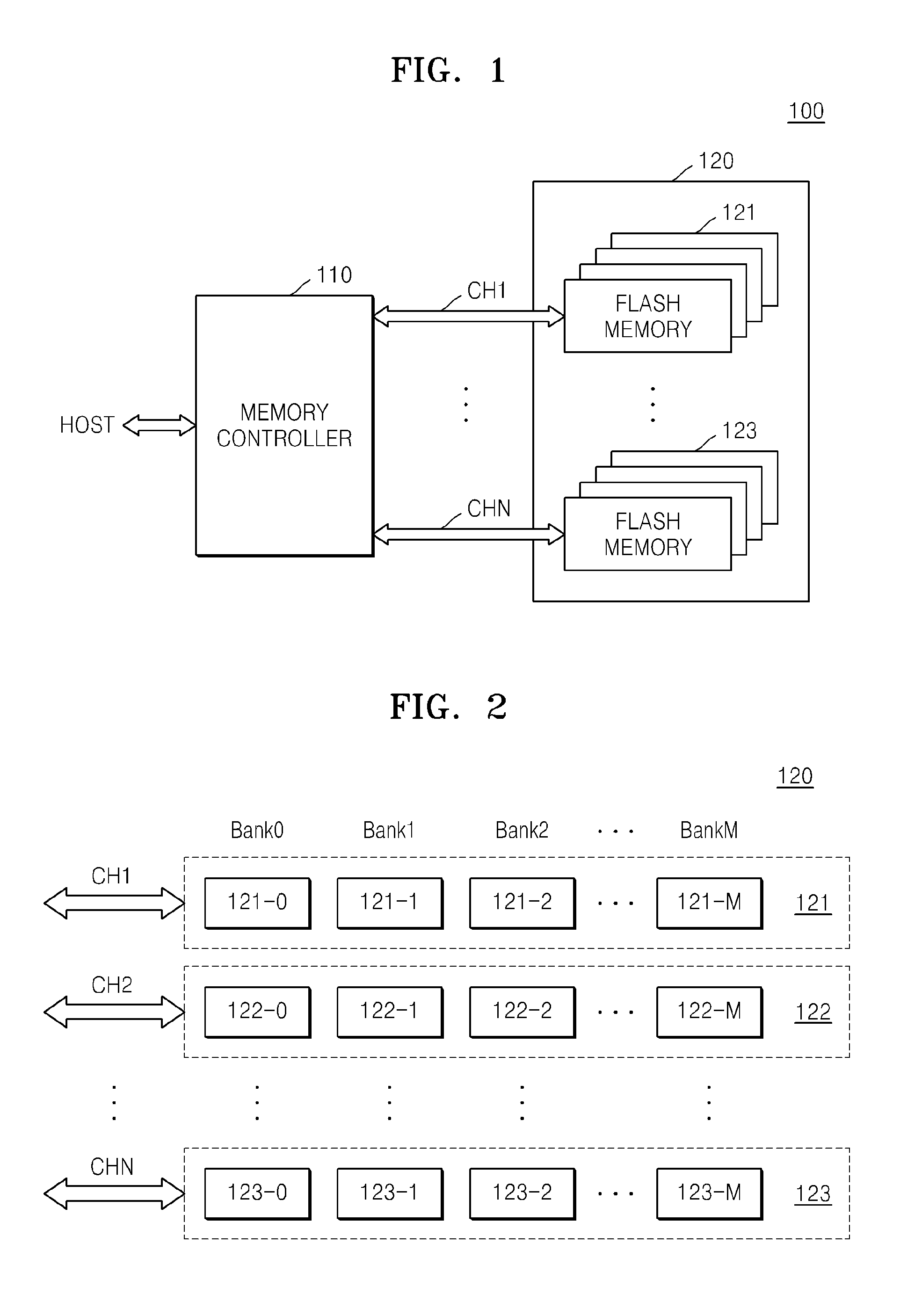

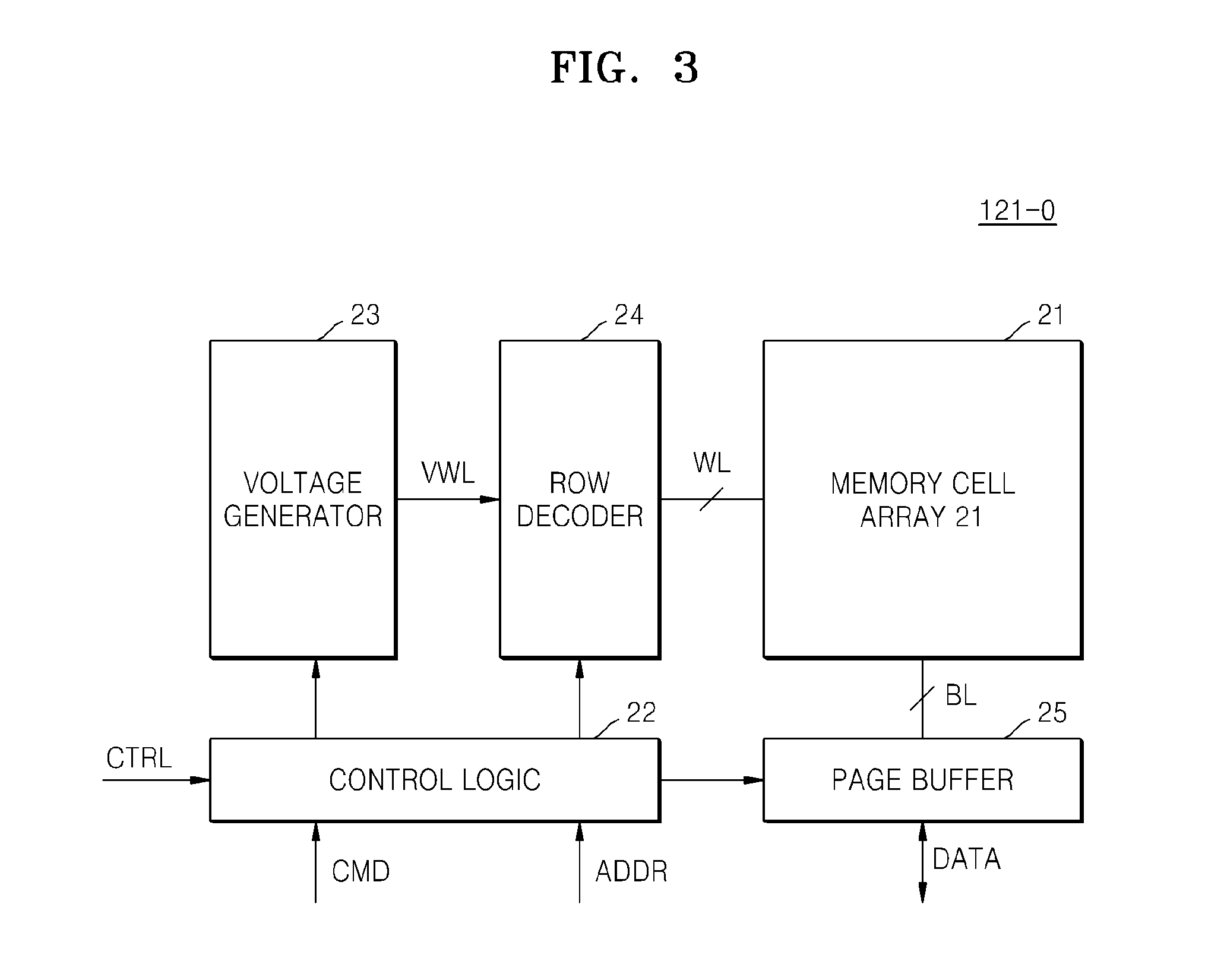

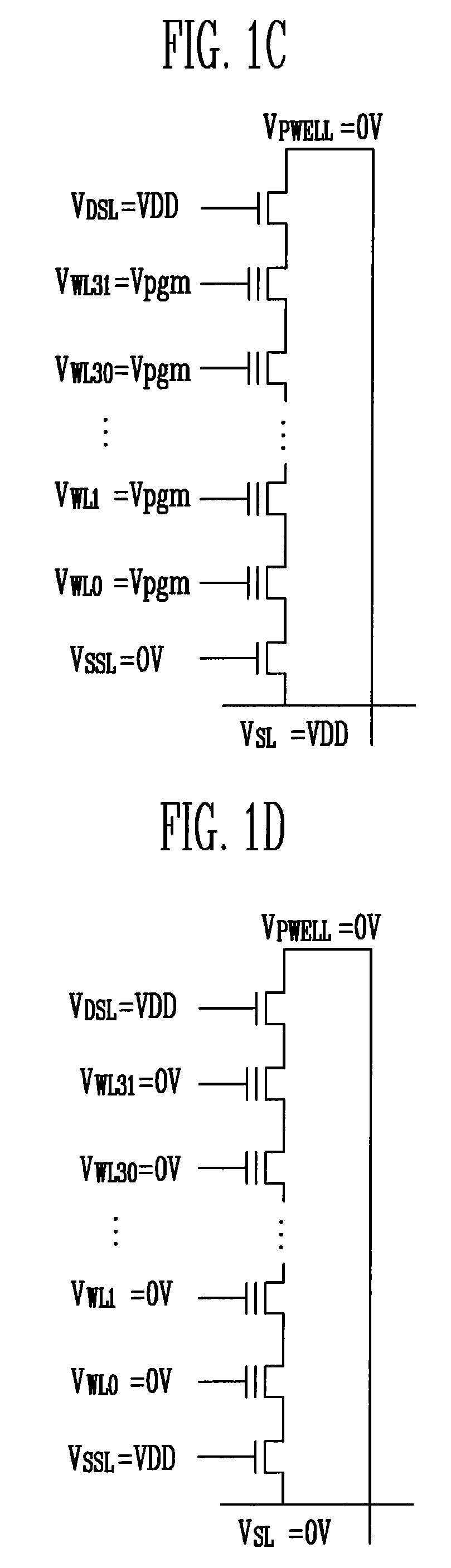

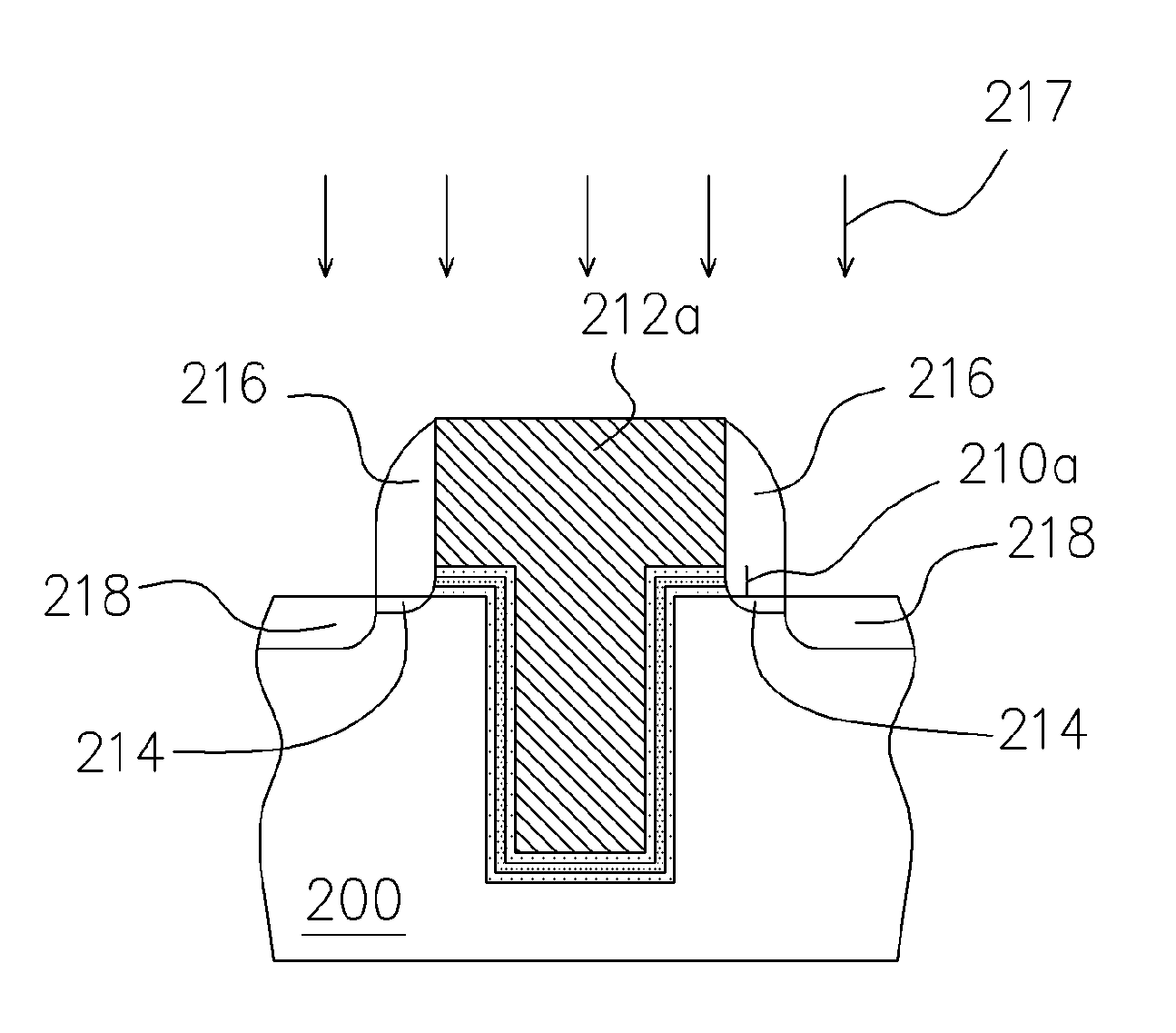

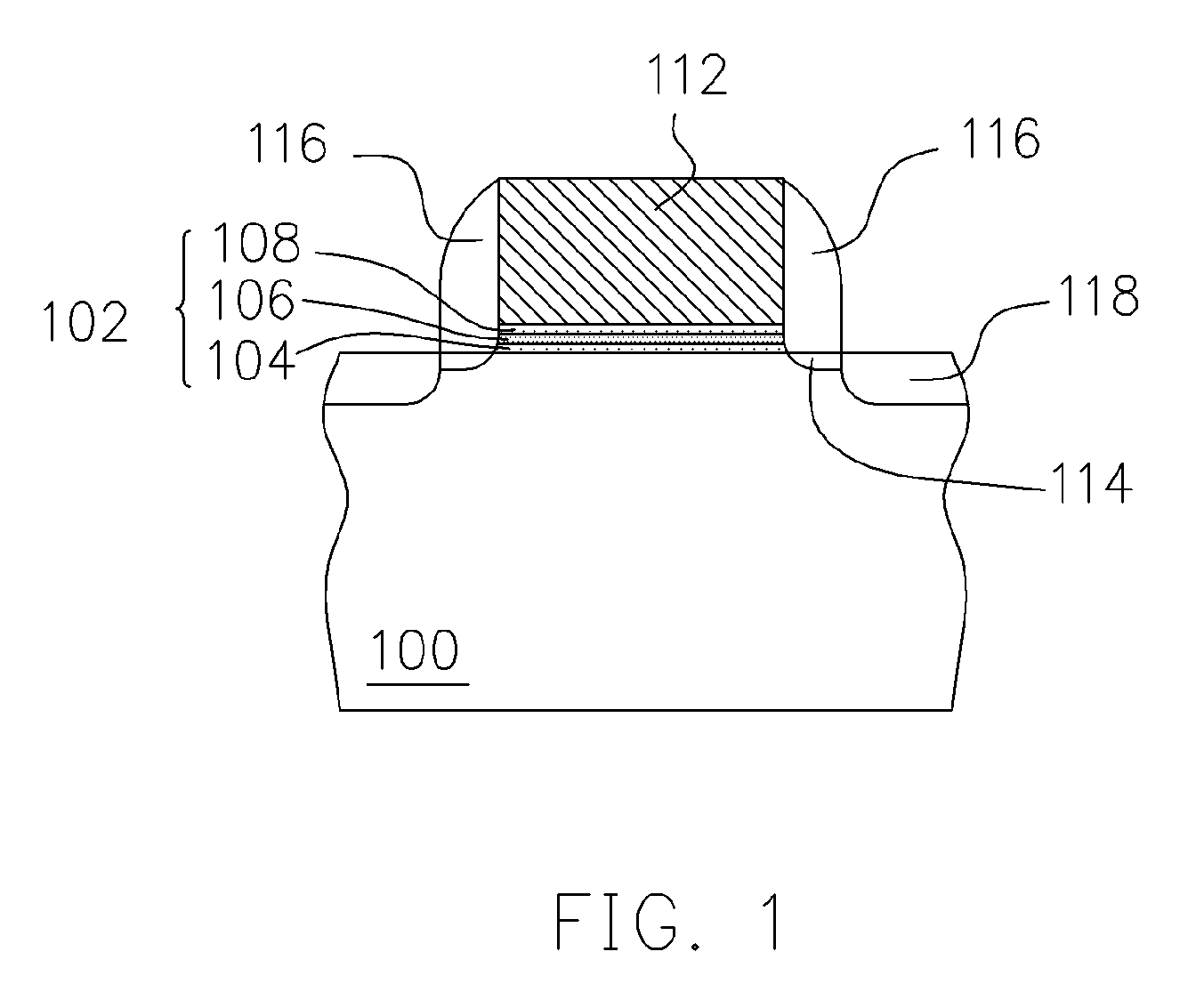

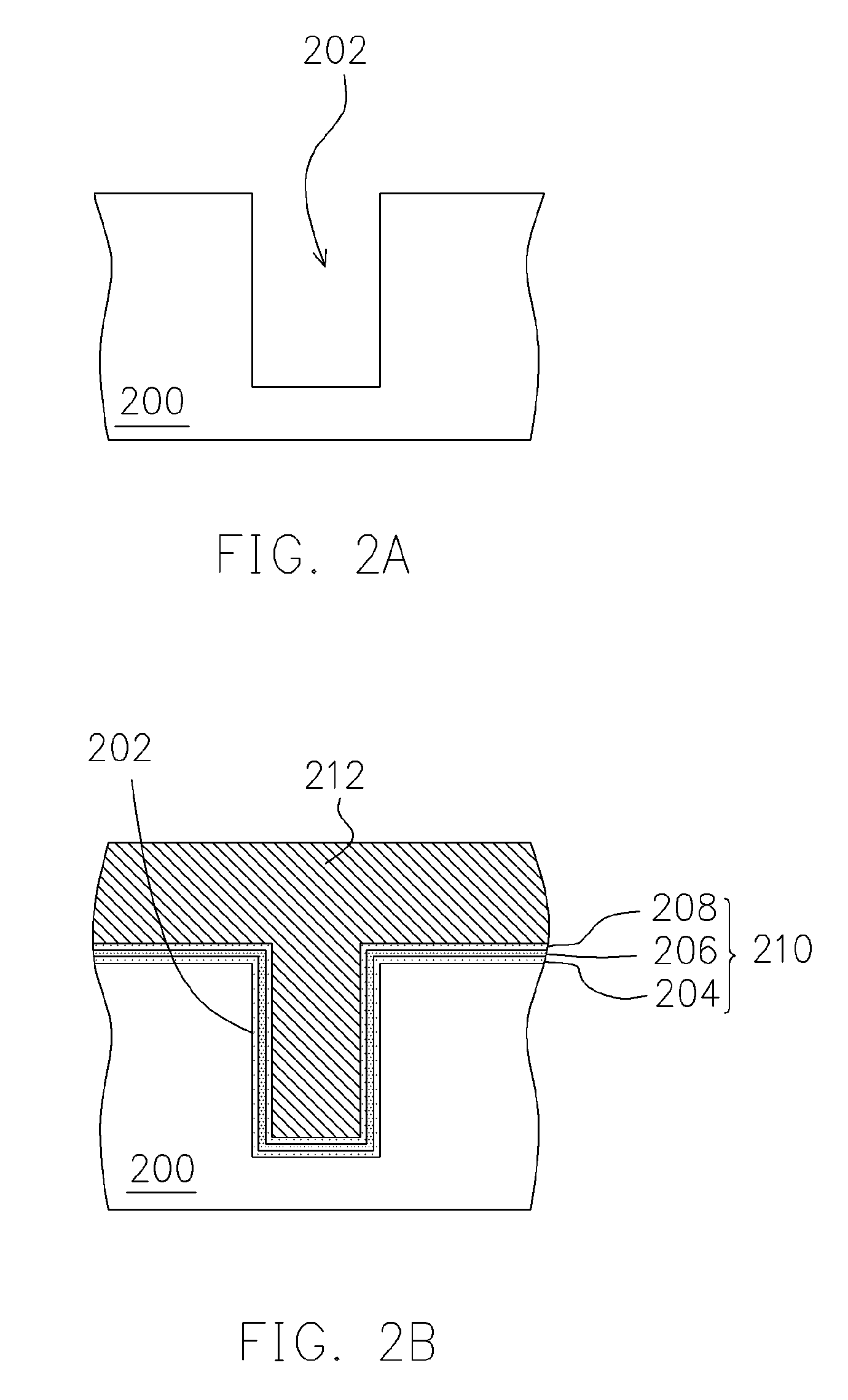

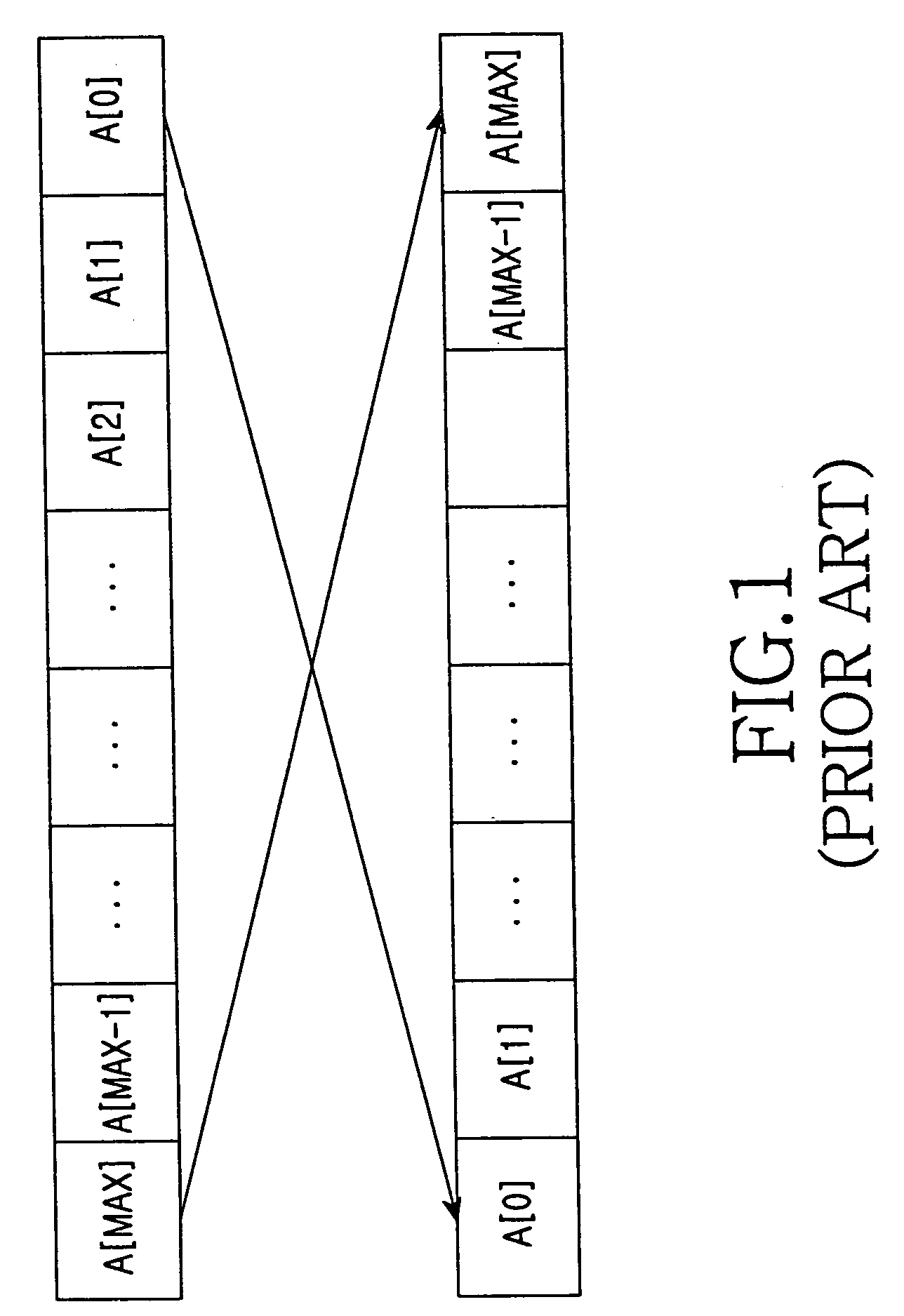

[NAND flash memory cell row, NAND flash memory cell array, operation and fabrication method thereof]

InactiveUS20050087892A1Simplify the manufacturing processIncrease speedTransistorSolid-state devicesBit lineComputer architecture

A NAND flash memory cell array including a plurality of memory cell row is provided. Each of memory cell row includes a plurality of memory cells disposed between first selecting transistor and second selecting transistor connected in series. Each memory cell has a tunneling dielectric layer, a floating gate, an inter-gate dielectric, a control gate and source / drain regions. An erase gate is disposed between two adjacent memory cells. A plurality of word lines serve to connect the memory cells in rows. A source line serves to connect the source region of the first transistor in a row, whereas a plurality of bit lines serve to connect the drain region of second transistor in a row. A first selecting gate line and a second selecting gate line serve to connect the gate of the first transistor in a row and the gate of second transistor in a row respectively. A plurality of erase gate lines is connected to the erase gates in a row.

Owner:POWERCHIP SEMICON CORP

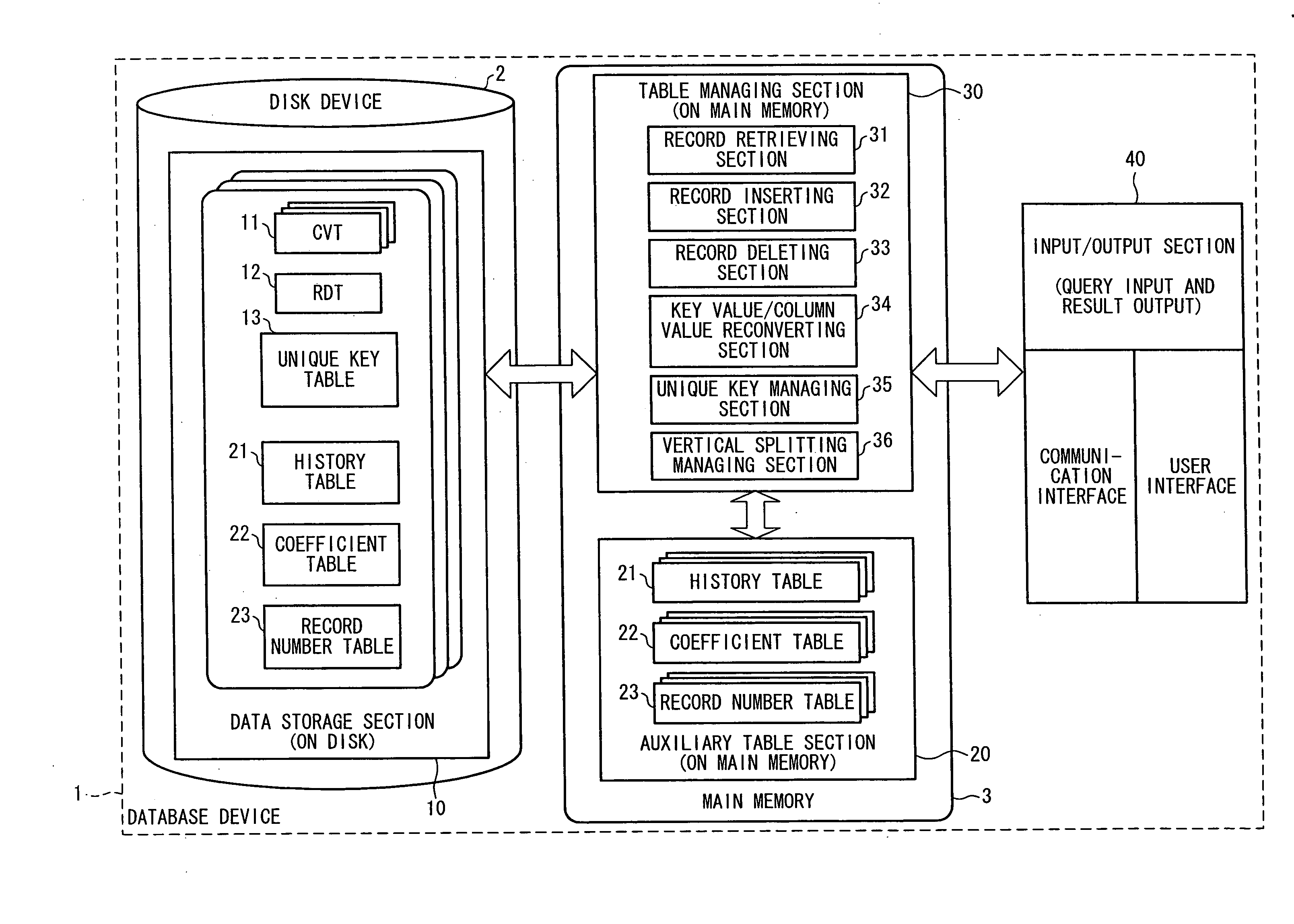

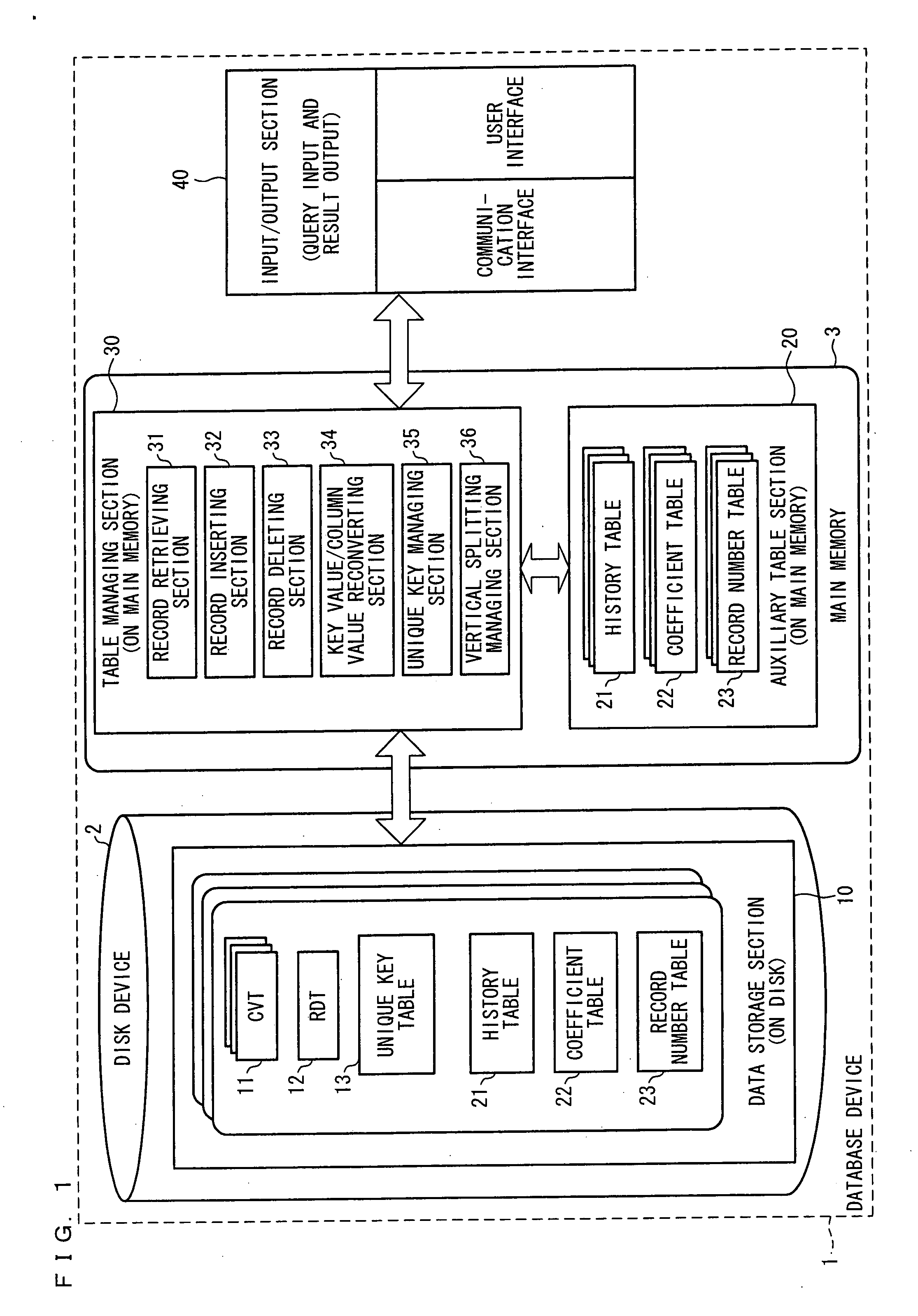

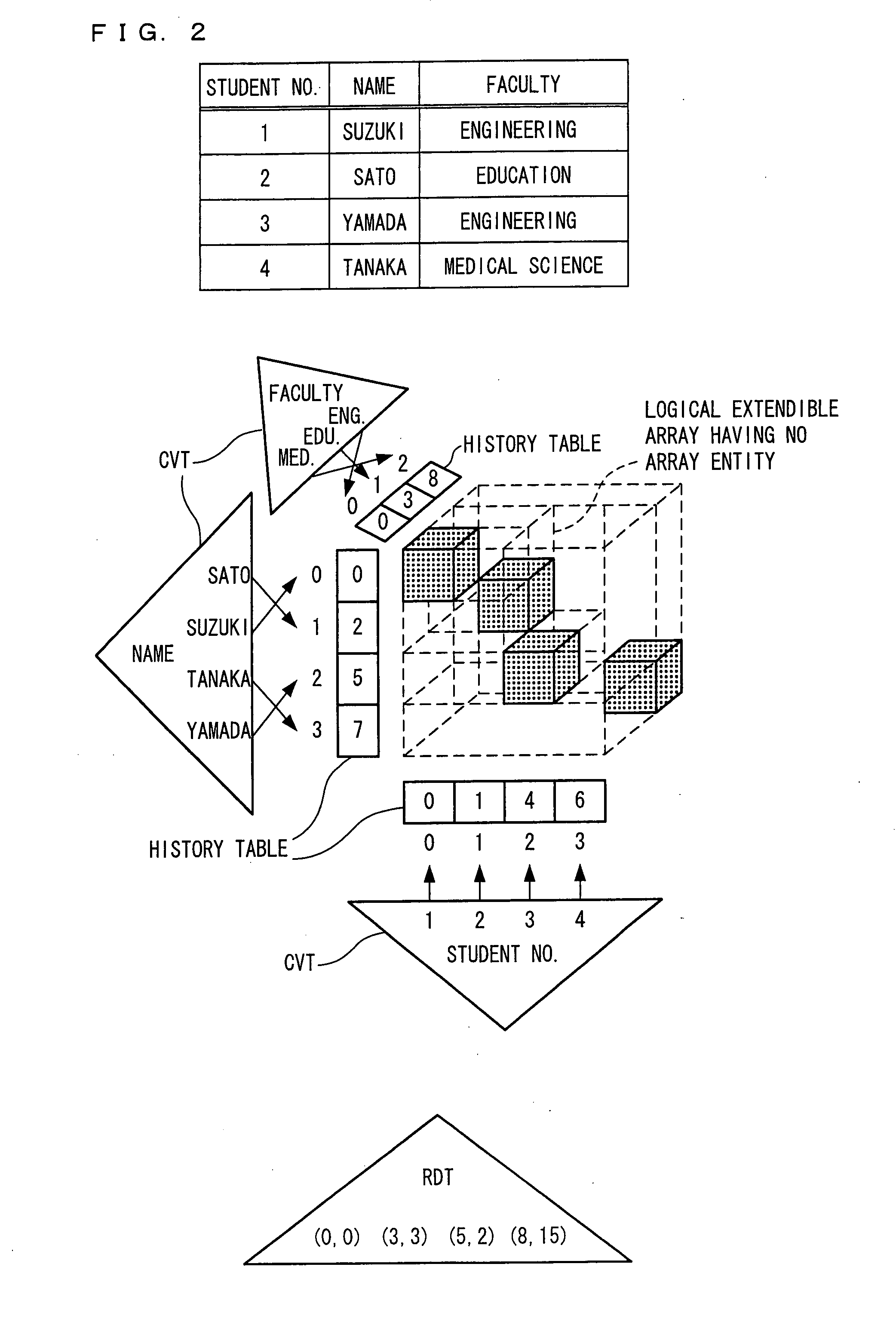

Datebase Device, Database Management Method, Data Structure Of Database, Database Management Program, And Computer-Readable Storage Medium Storing Same Program

InactiveUS20080091691A1Improve memory efficiencyQuick searchRelational databasesSpecial data processing applicationsRelational databaseData structure

When a record inserting section inserts a record having a new column value, the record inserting section registers the column value in a CVT such that an extendible array is extended; registers, in a history table, a history value indicating a chronological sequence of array extension; registers, in a coefficient table, coefficients of a linear function for calculating an offset of an element in an subarray; registers an initial value in a record number table; and inserts as a key value a 2-tuple expression of the history value and the offset of the element of the extendible array into RDT. This makes it possible to dynamically add, upon operation, a record having a new column value and to register only an existing record, thereby realizing a relational database allowing for fast record retrieval.

Owner:FUKUI UNIV OF

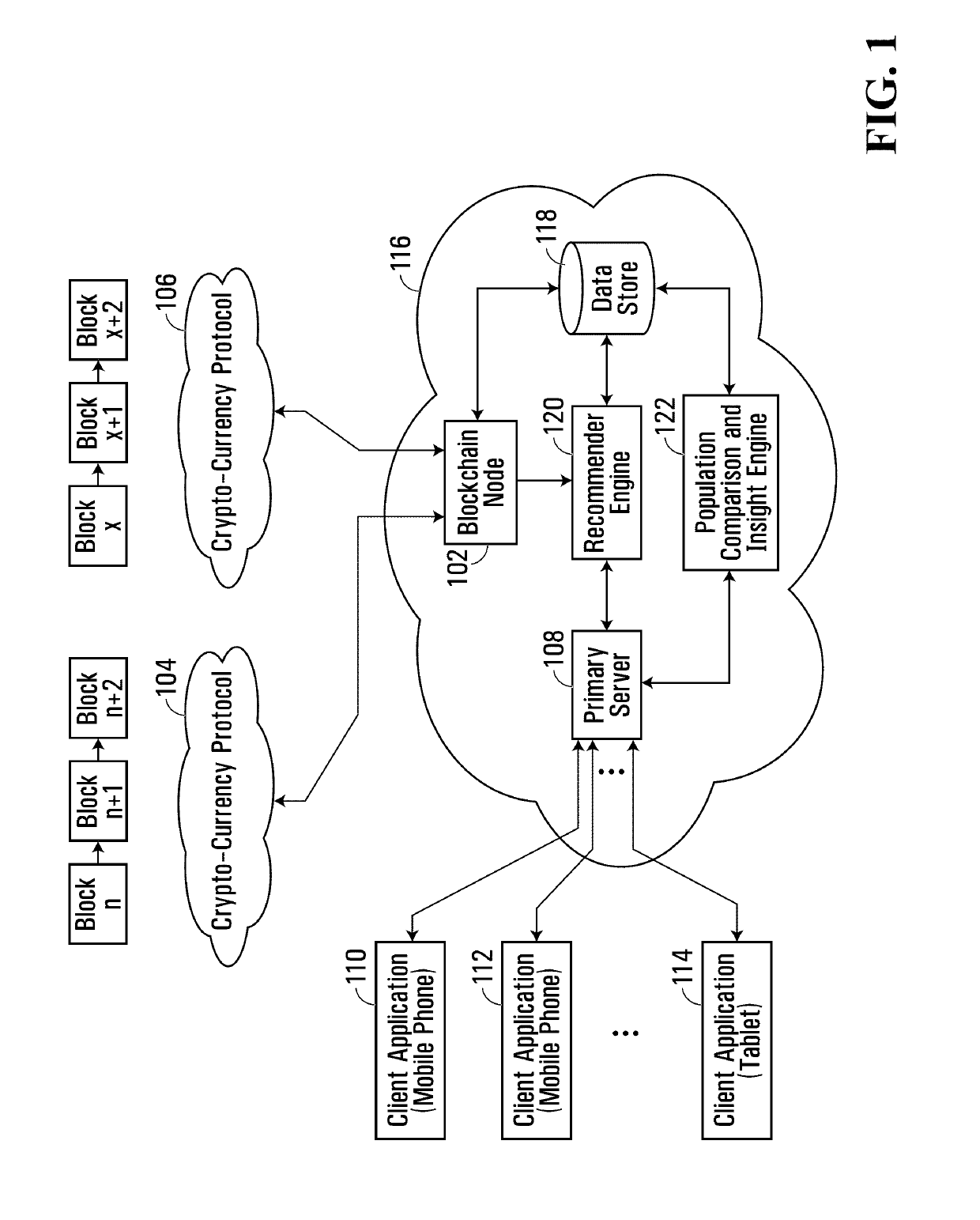

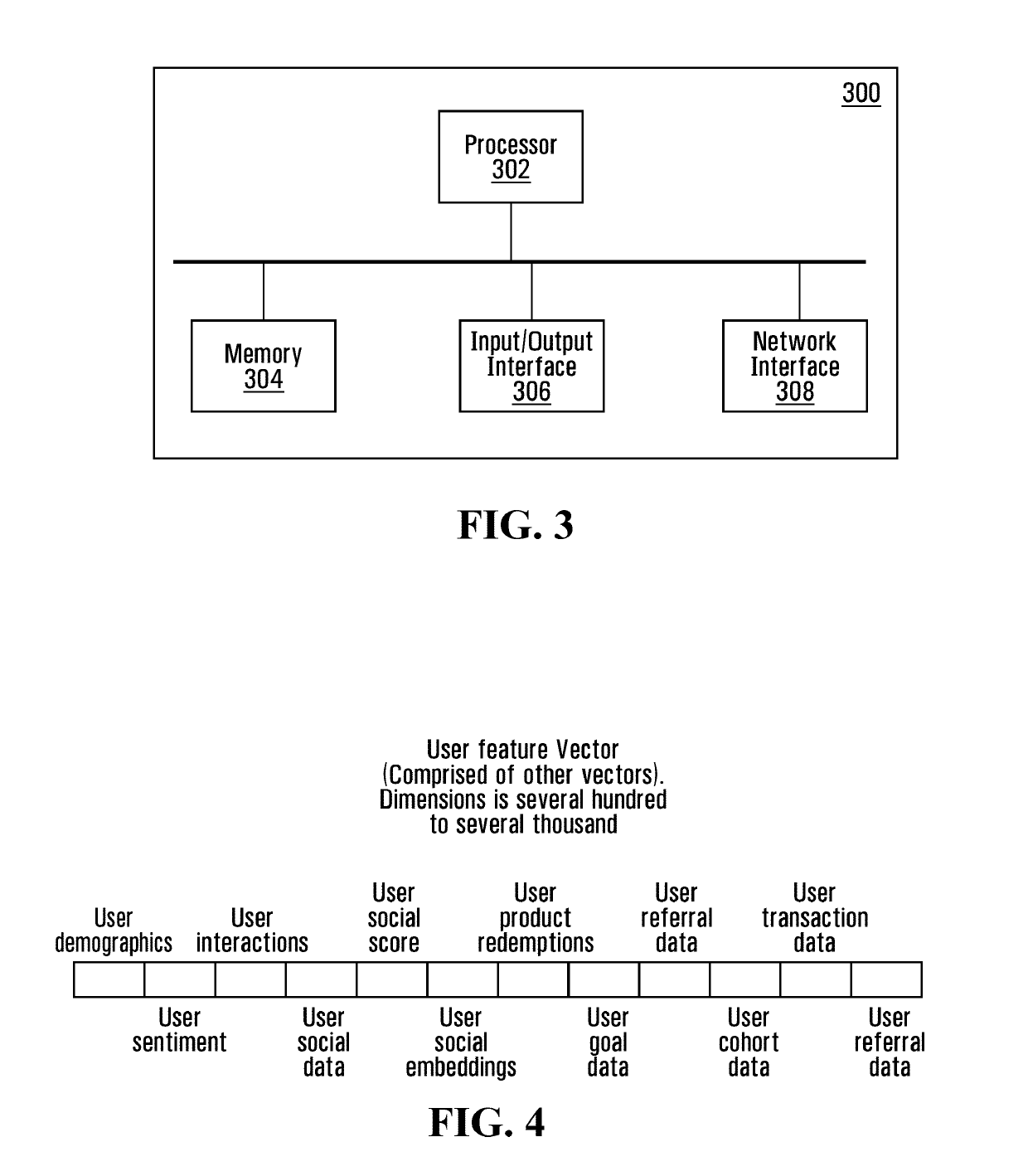

Digital banking platform and architecture

ActiveUS20190295114A1More efficientImprove memory efficiencyFinanceCharacter and pattern recognitionData setApplication software

A computer implemented device is described that is adapted for improving memory efficiency for conducting machine learning on multi-dimensional vectors stored as specially configured data structures. The device includes network interfaces adapted for receiving data sets and communicating with data harvesting applications, as well as data storage and memory for storing the configured data structures. The multi-dimensional vectors and the system provide a data architecture that processes disparate data sets to programmatically extract features transformed from raw information, the extracted features stored in the form of data values suitable for conducting data approximations and neural network processing.

Owner:STACK FINTECH INC

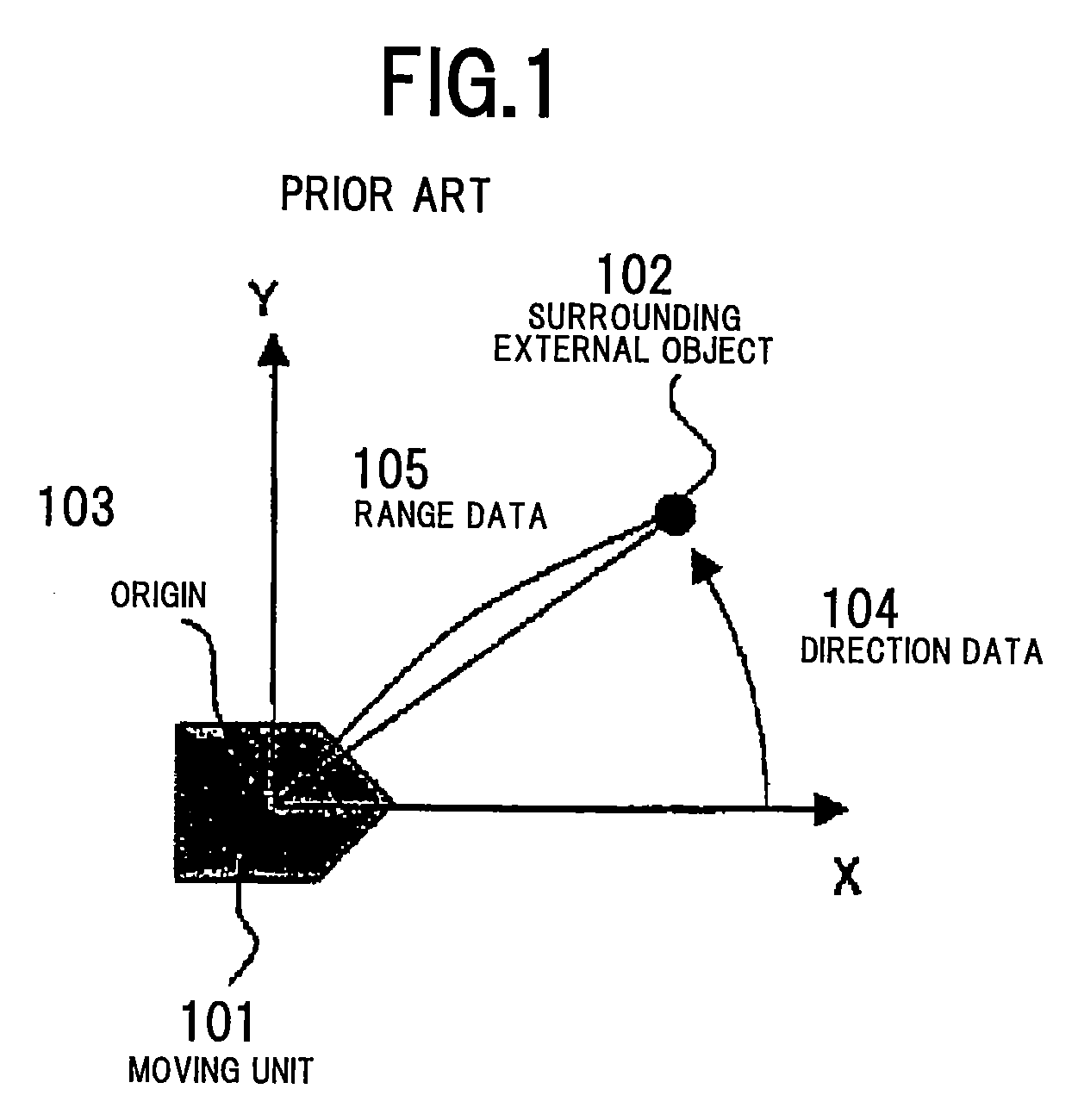

Self-position identifying method and device, and three-dimensional shape measuring method and device

InactiveUS20090167761A1Improve memory efficiencyExact matchImage enhancementImage analysisVoxelAlgorithm

The invention includes a step S1 for inputting into a computer coordinate values on a three-dimensional shape; a step S4 for structuring an environment model that partitions a spatial region, in which a three-dimensional shape exists, into a plurality of voxels of rectangular solids, and stores each position; and a step S5 for setting and recording a representative point and an error distribution thereof, within the voxel corresponding to the coordinate value. If there is no data in a previous measurement position, position matching is performed in a fine position matching step S7 so as to minimize an evaluation value regarding the distances between adjacent error distributions by rotating and translating a new measurement data and error distribution for the environment model for a previous measuring position, or rotating and translating an environment model for a new measuring position, relative to an environment model for a previous measuring position.

Owner:IHI CORP

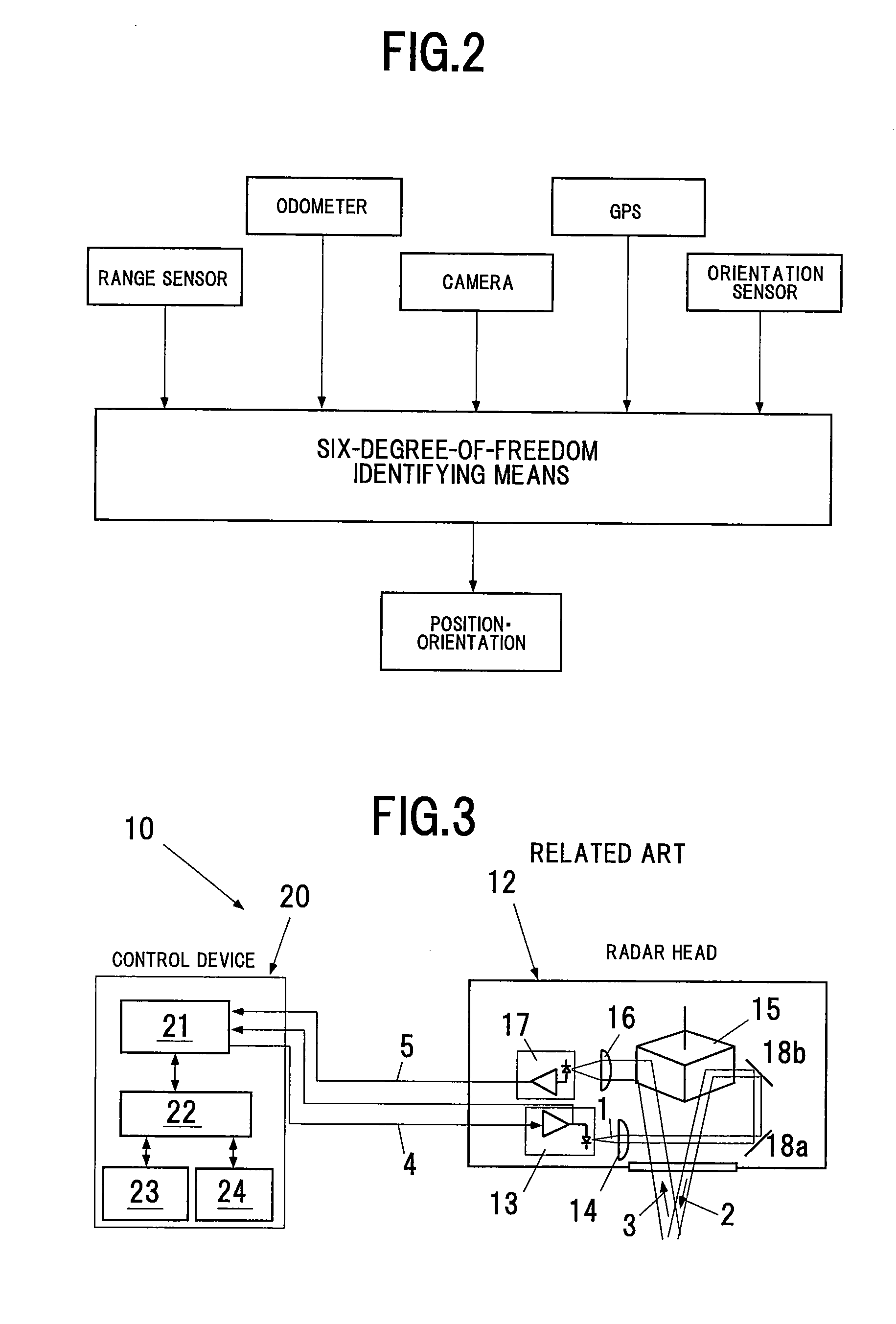

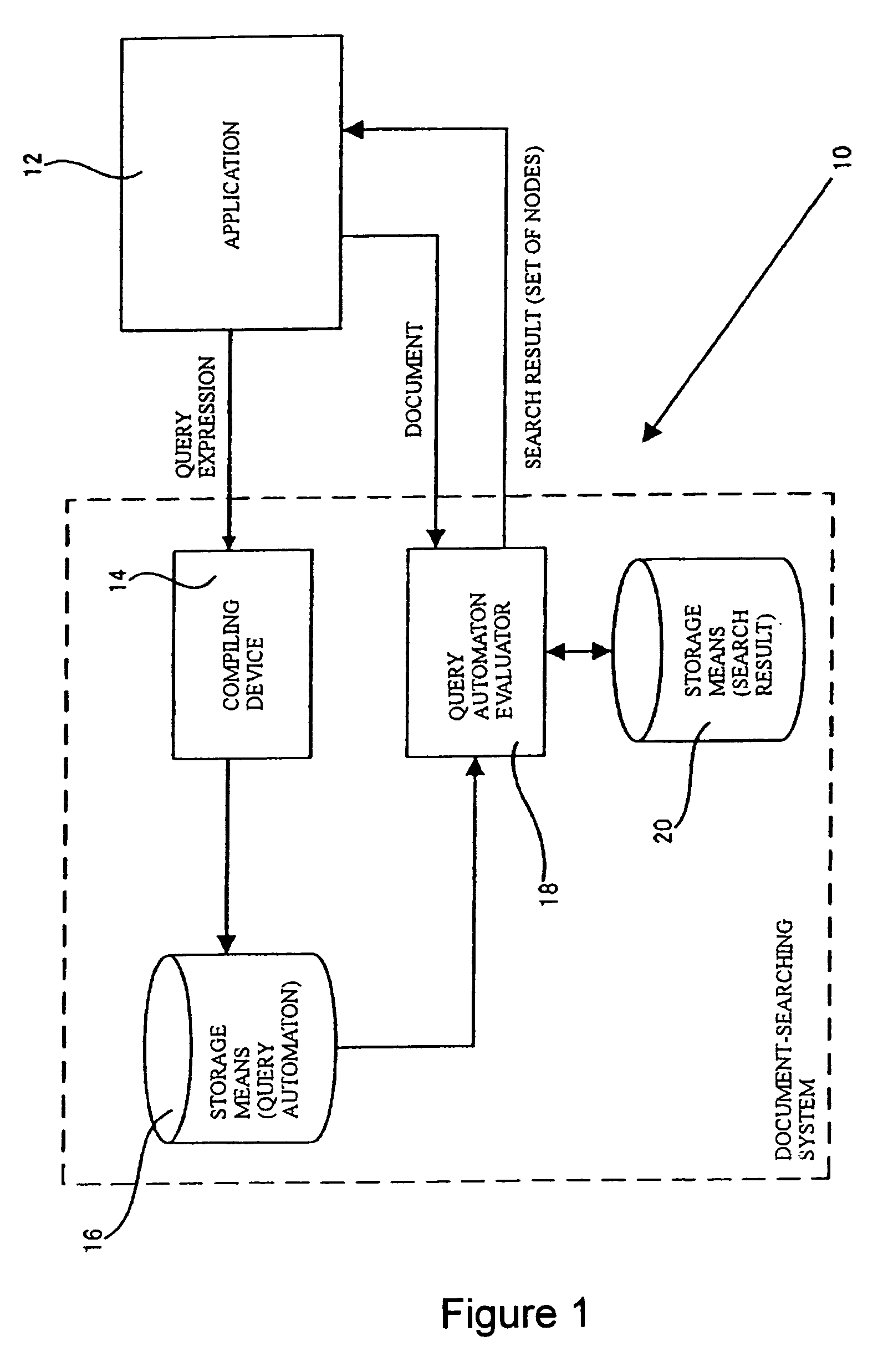

Method for document-searching

InactiveUS7509305B2Improve versatilityImprove efficiencyDigital data processing detailsSemi-structured data retrievalState switchingAutomaton

Document-searching using a compiling device for generating a two-state input automaton for enabling a state transition by storing an input query expression, performing parsing, and reading at least two states from different types of nodes in an element identifier, and a storage device for storing the two-state input automaton. Also included is an automaton-evaluating device for enabling three state transitions by reading out a two-state input automaton from the storage device and storing the automaton, while reading in a document and identifying the input two states.

Owner:IBM CORP

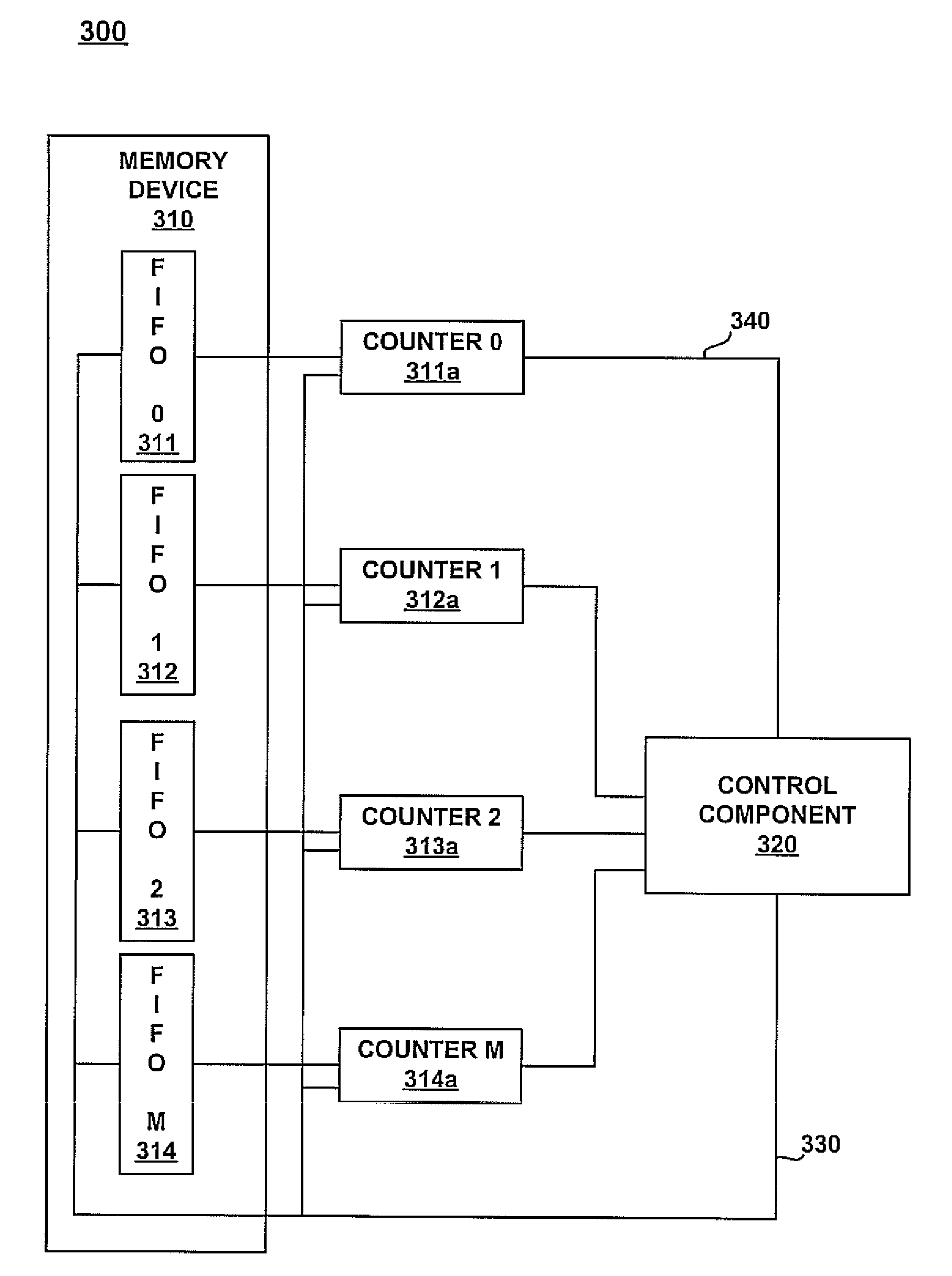

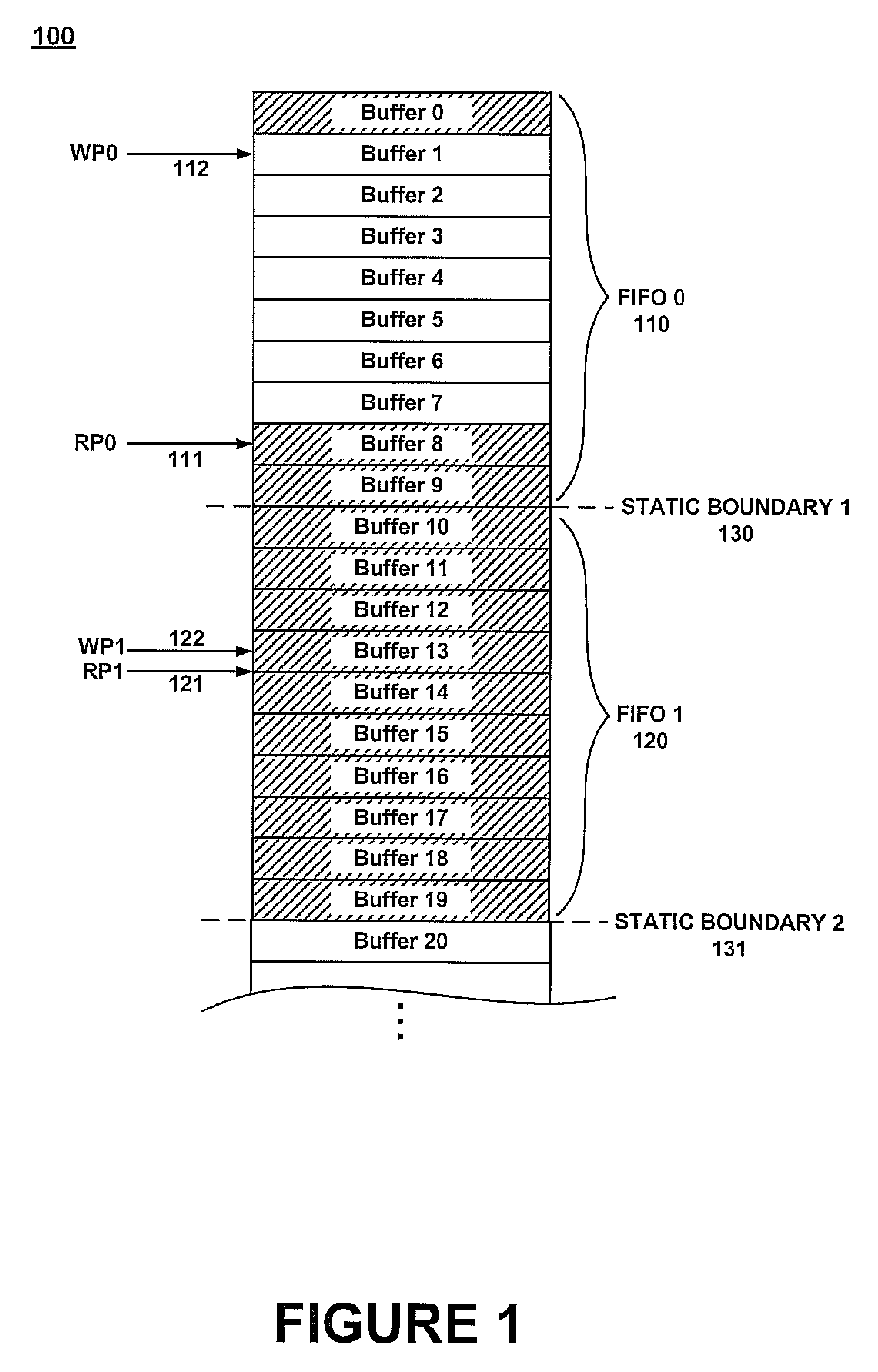

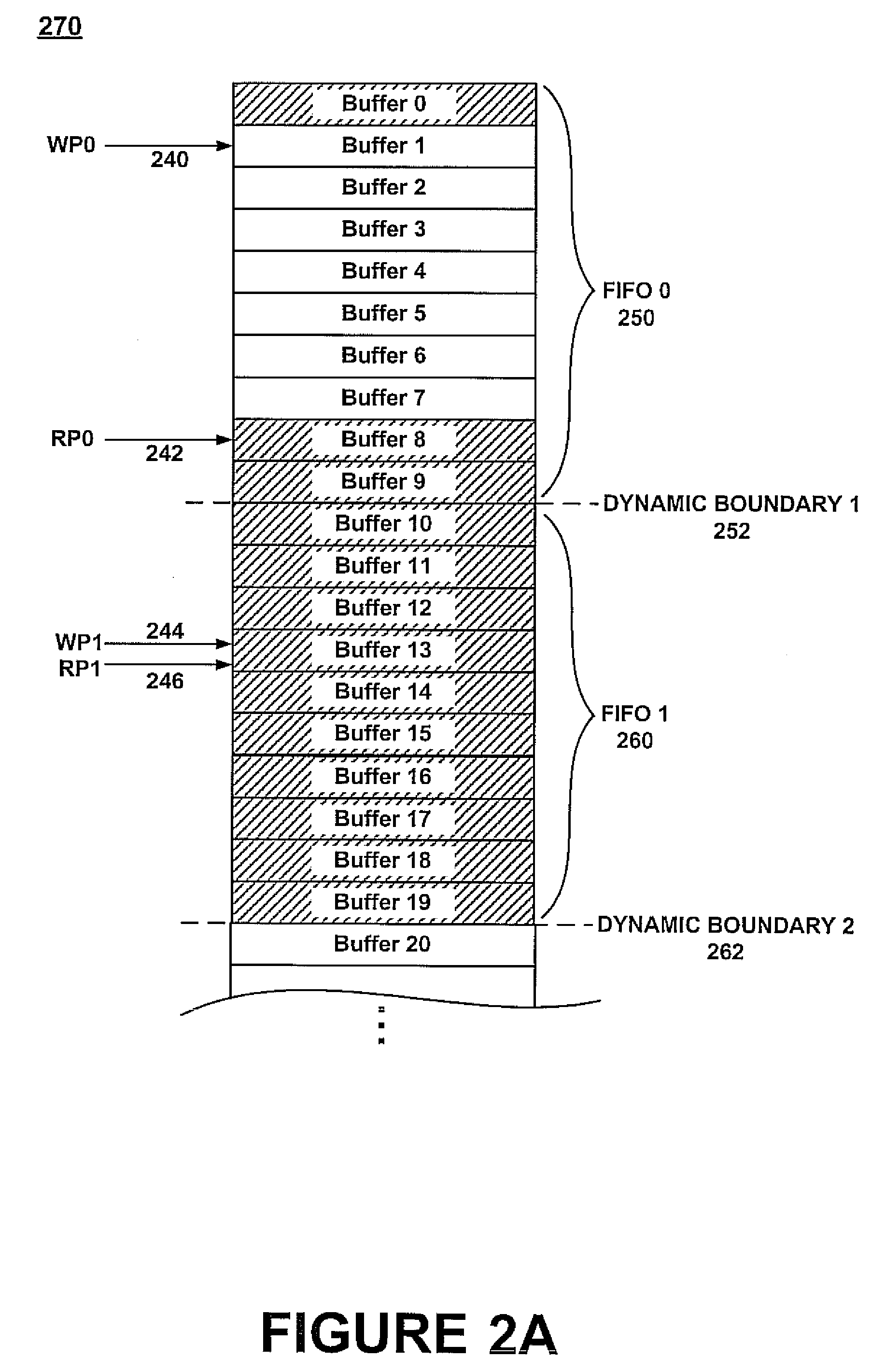

Automatic resource sharing between FIFOs

ActiveUS7444491B1Reduce in quantityExact numberMemory systemsData conversionParallel computingFifo queue

Embodiments of the present invention recite a method and system for allocating memory resources. In one embodiment, a control component coupled with a memory device determines that a data buffer adjacent to a boundary of a first FIFO queue does not contain current data. The control component also determines that a second data buffer of a second FIFO queue adjacent to the boundary does not contain current data. The control component then automatically shifts the boundary to include the second data buffer in the first FIFO queue.

Owner:NVIDIA CORP

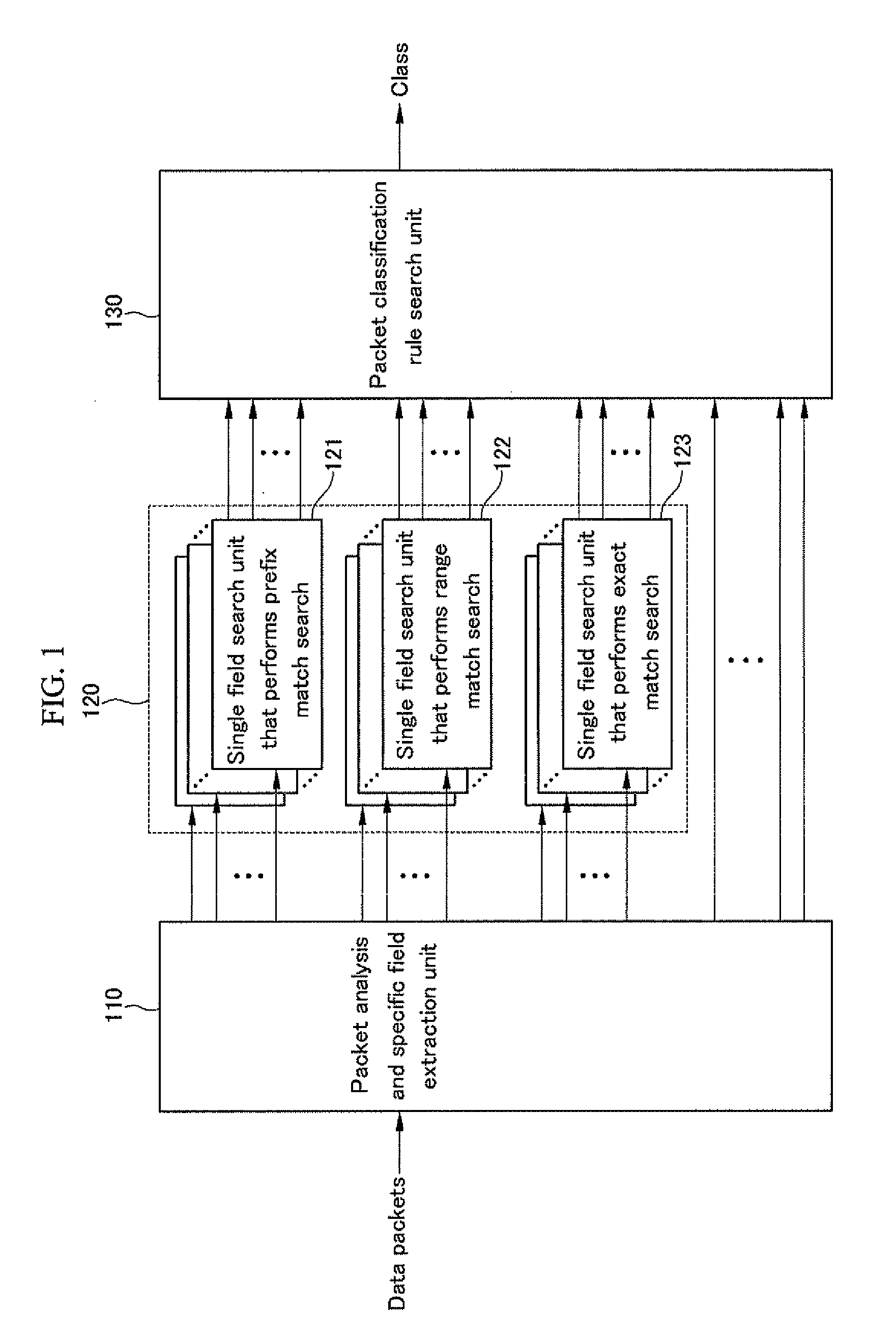

Apparatus and method of classifying packets

InactiveUS20090135826A1Improve memory efficiencyEasy to integrateData switching by path configurationQuality of serviceNetworked system

The present invention relates to an apparatus and method of classifying packets that can support a quality of service (QoS) in a network system. An apparatus for classifying packets according to an exemplary embodiment of the present invention includes, a first unit that analyzes input data packets, extracts pluralities of specific fields from the data packets using an analyzed result, and outputs the pluralities of specific fields; pluralities of second units that compare data of a first portion of the pluralities of extracted specific fields with data in a table, determine whether items that satisfy a predetermined condition exist in the table, and output hit signals and pointers indicating positions of the items that satisfy the predetermined condition when the items that satisfy the predetermined condition exist in the table; and a third unit that compares data of a second portion of the pluralities of extracted specific fields and key data including the pointers input from the pluralities of second units and rule data in a is rule table and outputs classes corresponding to the items when the key data and the rule data are matched.

Owner:ELECTRONICS & TELECOMM RES INST

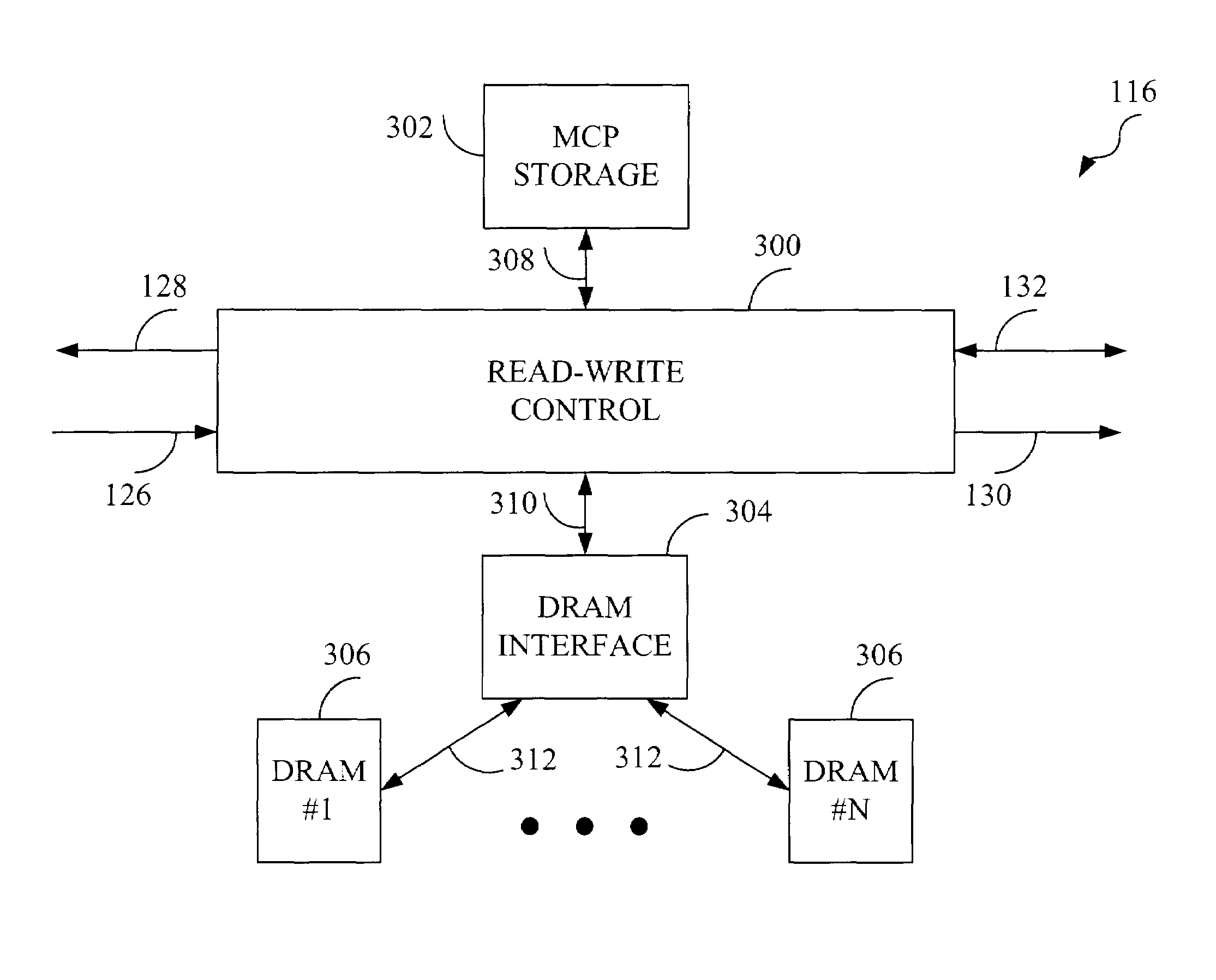

High-speed memory having a modular structure

InactiveUS7352766B2Improve performanceCost reductionMultiplex system selection arrangementsMemory adressing/allocation/relocationModularityModular structure

A high-speed memory is provided, the memory having a write port and a read port and comprised of the following: a plurality of N memory modules for storing fixed size cells, which are segments of a variable size packet divided into X cells, the X cells being grouped into ┌X / N┐ groups of cells; a read-write control block receiving cells from the write port and storing each cell, which belongs to the same group, in a selected different one of the N memory modules at the same memory address (the group address); a multi-cell pointer (MCP) storage for storing an MCP for the group of cells (an associated MCP) at an MCP address, the MCP having N memory module identifiers to record the order in which cells of the group of cells are stored in the N memory modules; the MCP address being the same as the group address.

Owner:ALCATEL LUCENT CANADA

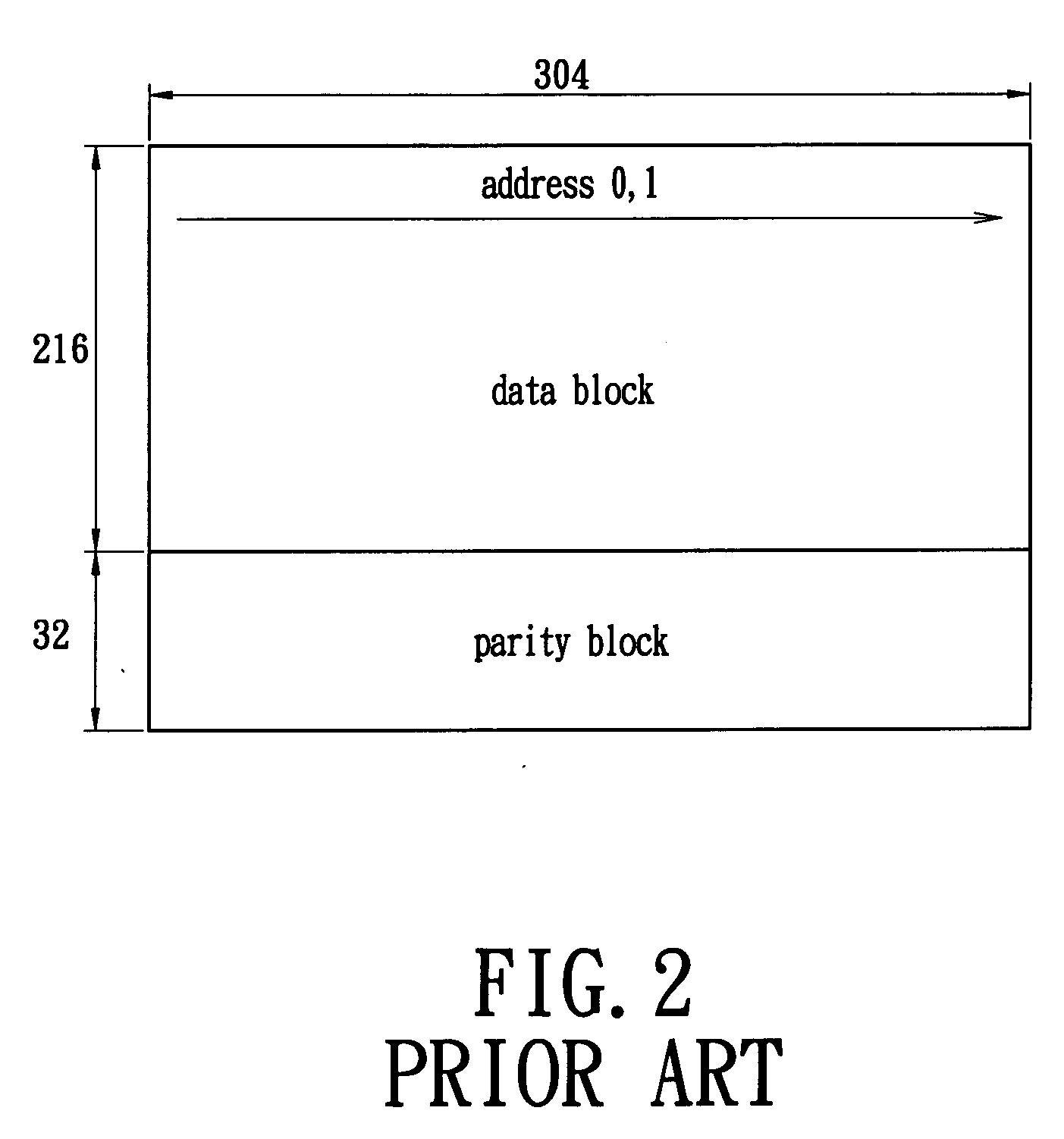

Apparatus for accessing and transferring optical data

ActiveUS20050229081A1Improve access efficiencyImprove memory efficiencyData representation error detection/correctionOptical discsComputer hardwareOptical storage

An apparatus for accessing and transferring optical data has a memory supporting the page-mode function, an accessing device used to access an error correction block from the optical storage medium and store it into the memory to make the portion of data in the same column of the error correction block stored in a particular locality greater than the portion of data in the same row of the error correction block stored in the particular locality, and an error correction decoder used to access the data of the error correction block to perform the error correction process. The apparatus uses the feature of the DRAM, such as page-mode function, and the data arrangement of the memory to improve the access efficiency of the memory. The apparatus can thus increase the access speed of the error correction decoder and improve the accessing efficiency.

Owner:XUESHAN TECH INC

Method of updating mapping information and memory system and apparatus employing the same

InactiveUS20140281188A1Improve performanceImprove memory efficiencyProgram control using stored programsMemory adressing/allocation/relocationOperating systemMemory systems

A method of updating mapping information for a memory system comprises generating write transaction information based on multiple write requests issued by a host, performing program operations in the memory system based on the write transaction information, and following completion of the program operations, updating mapping information based on an order in which the write requests were issued by the host.

Owner:SAMSUNG ELECTRONICS CO LTD +1

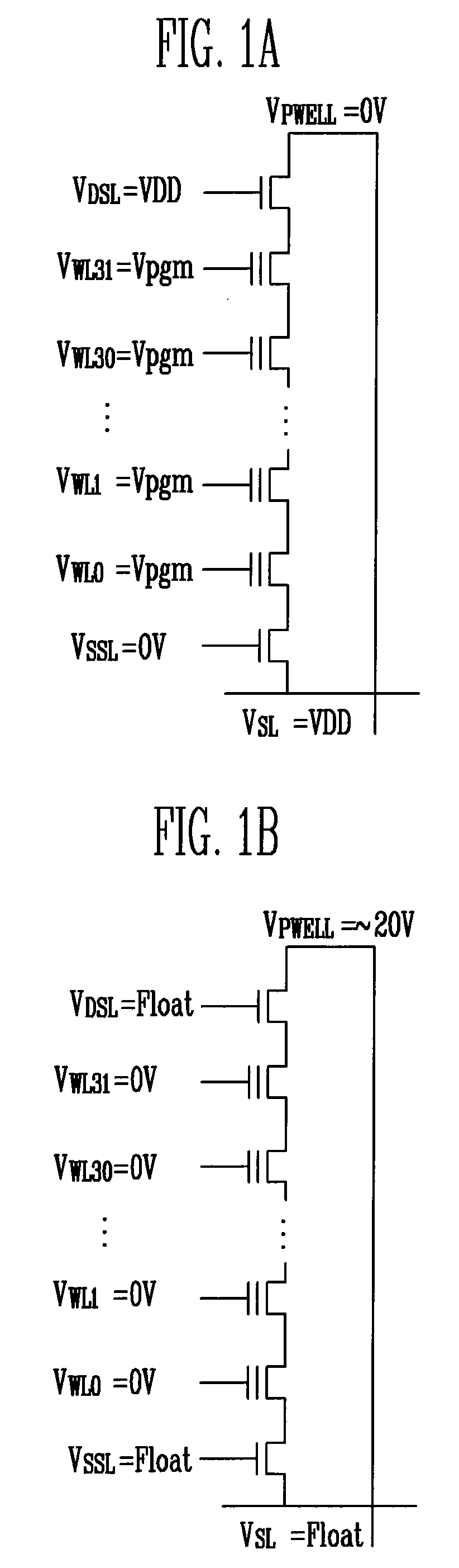

Method of performing an erase operation in a non-volatile memory device

ActiveUS20080175069A1Reduce distractionsImprove memory efficiencyRead-only memoriesDigital storageStorage cellVoltage

An erase method having a memory cell array which includes at least one blocks having MLC is disclosed. The erase method includes shifting every threshold voltage distribution into a threshold voltage distribution having highest level by pre-programming every cell in a block selected for erase, performing an erase operation on the pre-programmed memory block, performing a soft program and a verifying operation on the memory block, dividing the memory block into a first group and a second group in case that the memory block is passed, performing a verifying operation on the first group, and performing a soft program and a verifying operation on the first group in case that the first group is not passed, and performing a verifying operation on the second group in case that the first group is passed, and performing a soft program and a verifying operation on the second group in case that the second group is not passed.

Owner:SK HYNIX INC

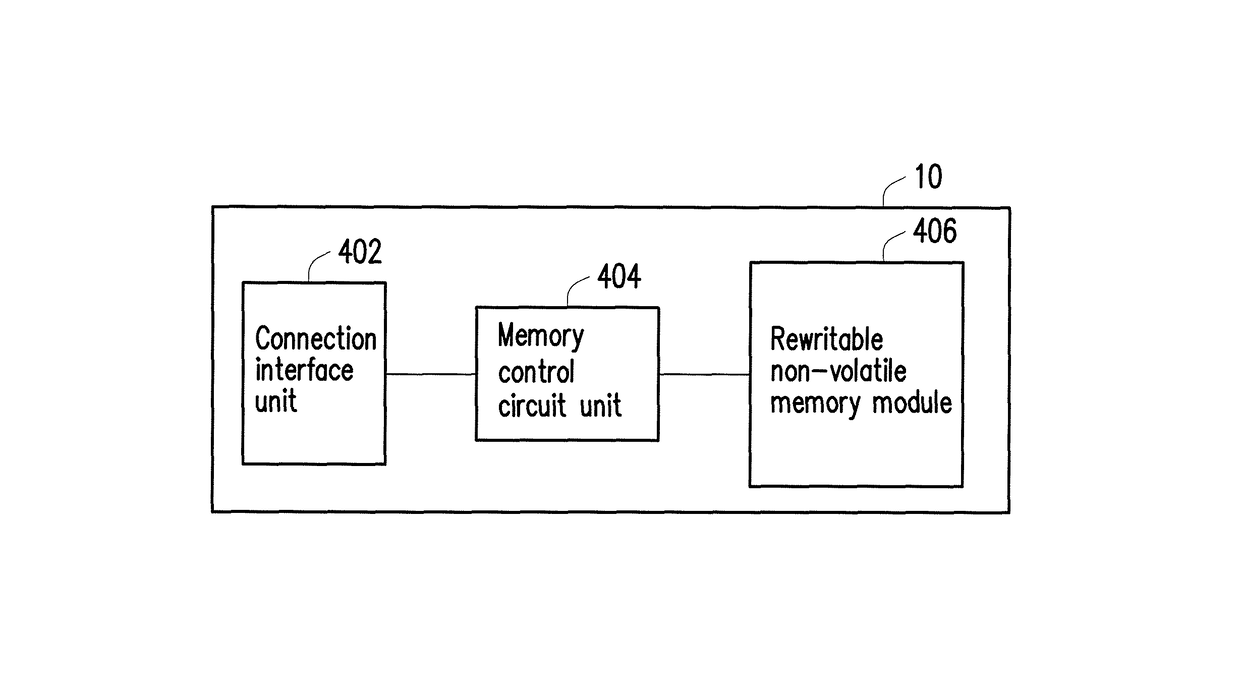

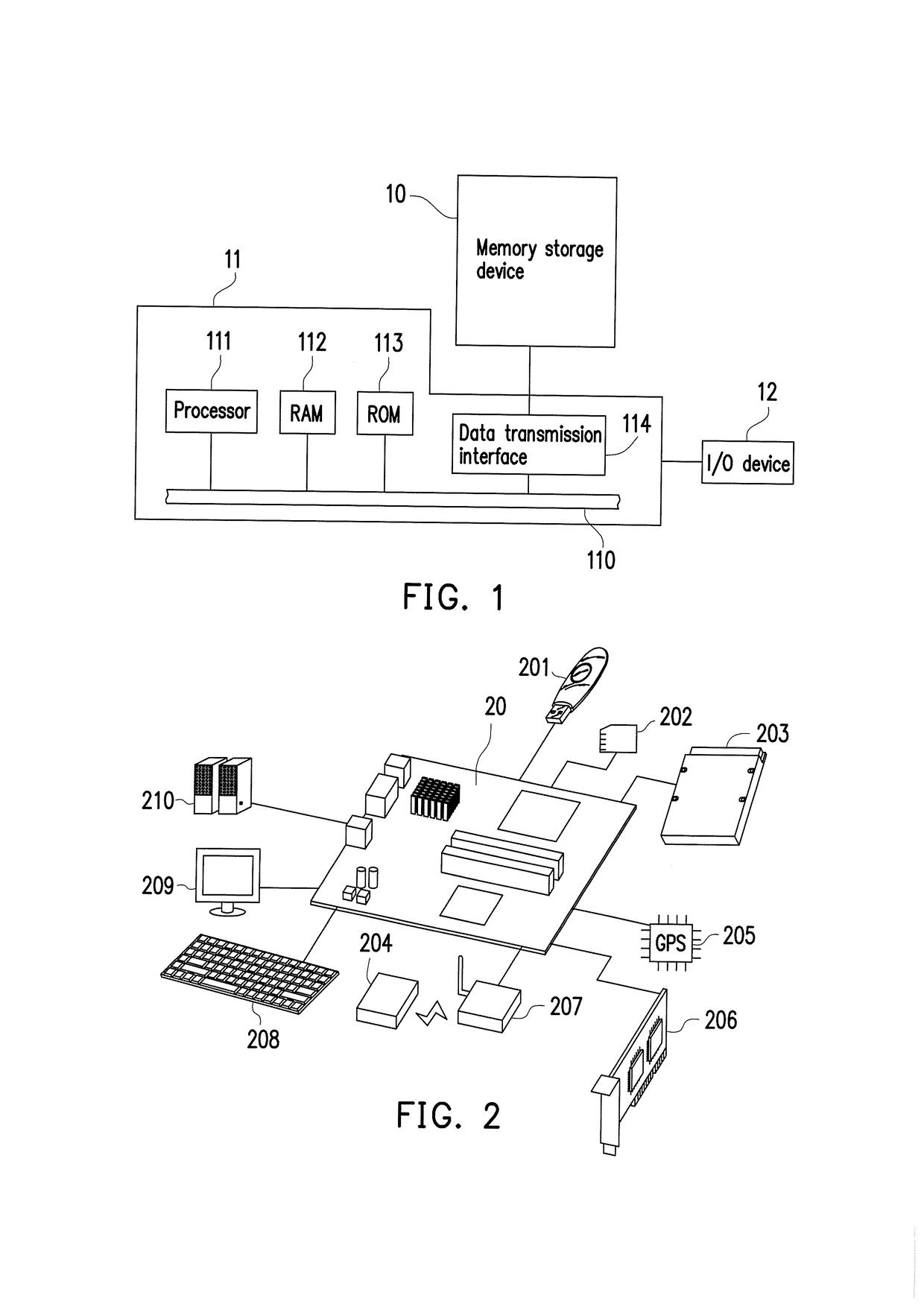

Decoding method, memory storage device and memory control circuit unit

ActiveUS9715429B1Improve decoding efficiencyQuick fixInput/output to record carriersRead-only memoriesVoltageControl circuit

A decoding method, a memory storage device and a memory control circuit unit are provided. The decoding method includes: reading first data from a plurality of first memory cells of a rewritable non-volatile memory module based on a first read voltage level and performing a first decoding operation; estimating a channel status of the rewritable non-volatile memory module and obtaining a second read voltage level according to the channel status if the first decoding operation fails, and the second read voltage level is different from the first read voltage level, and the second read voltage level is different from an optimal read voltage level; and reading second data from the plurality of first memory cells based on the second read voltage level and performing a second decoding operation. Therefore, an encoding efficiency can be improved.

Owner:PHISON ELECTRONICS

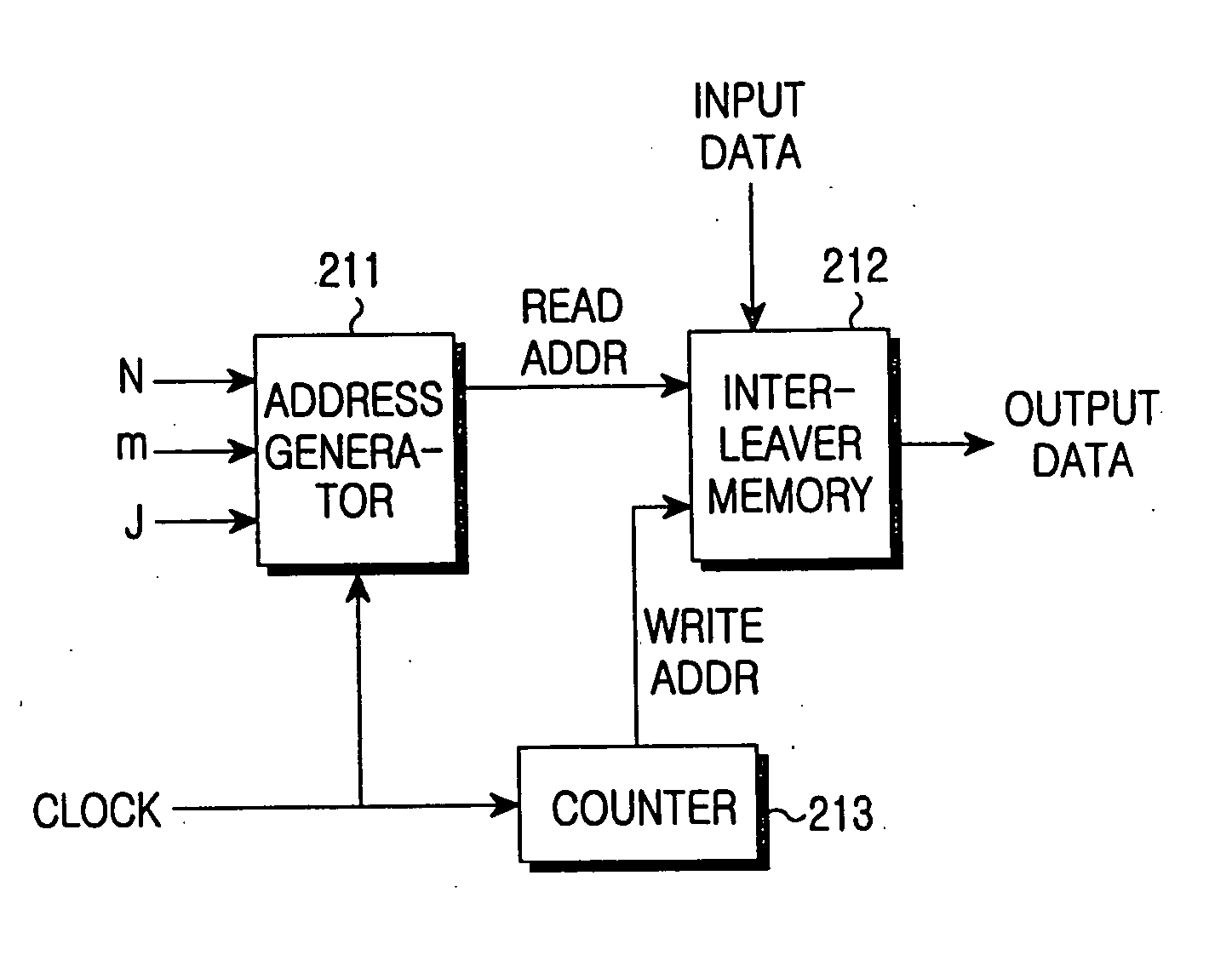

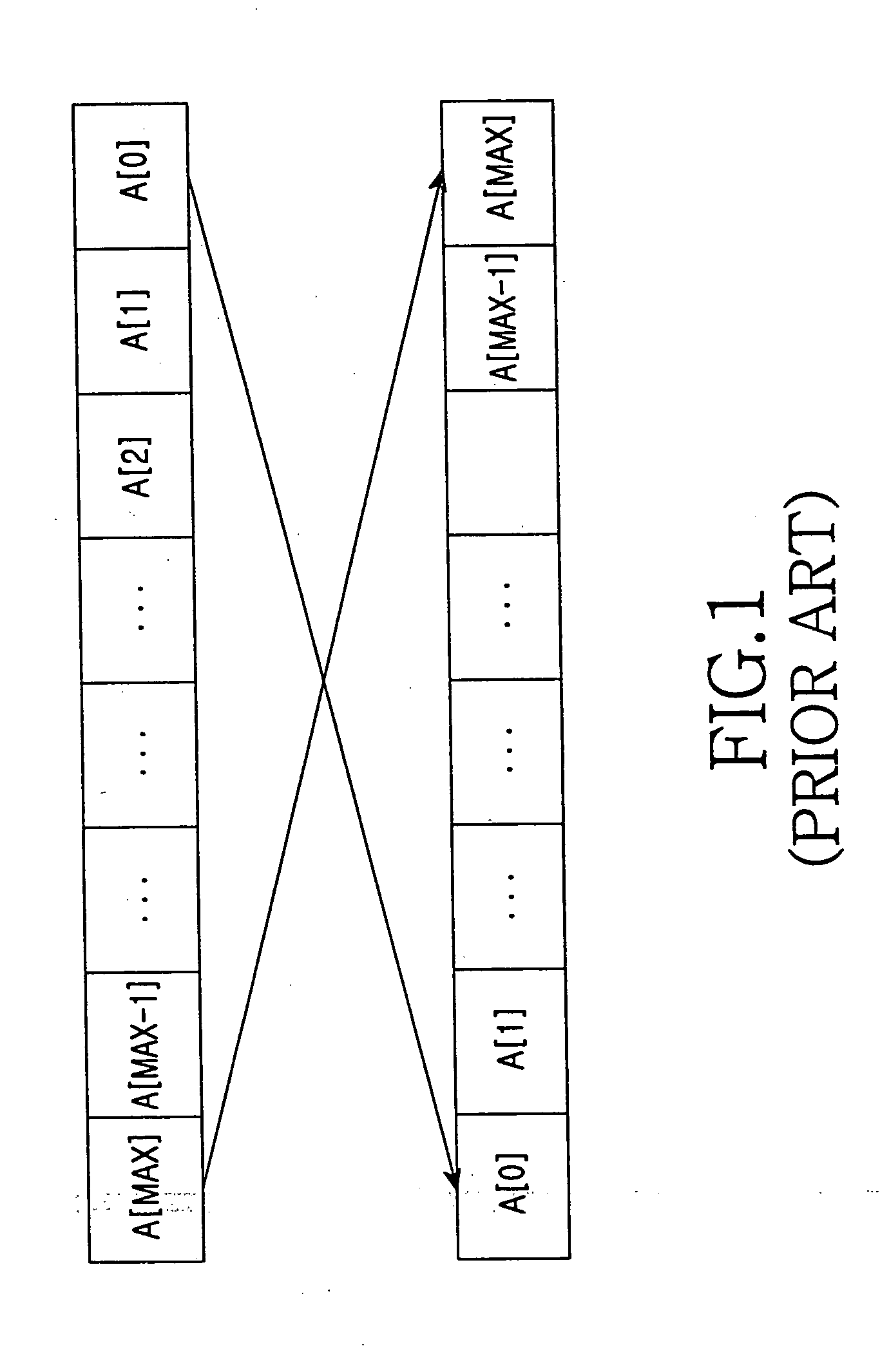

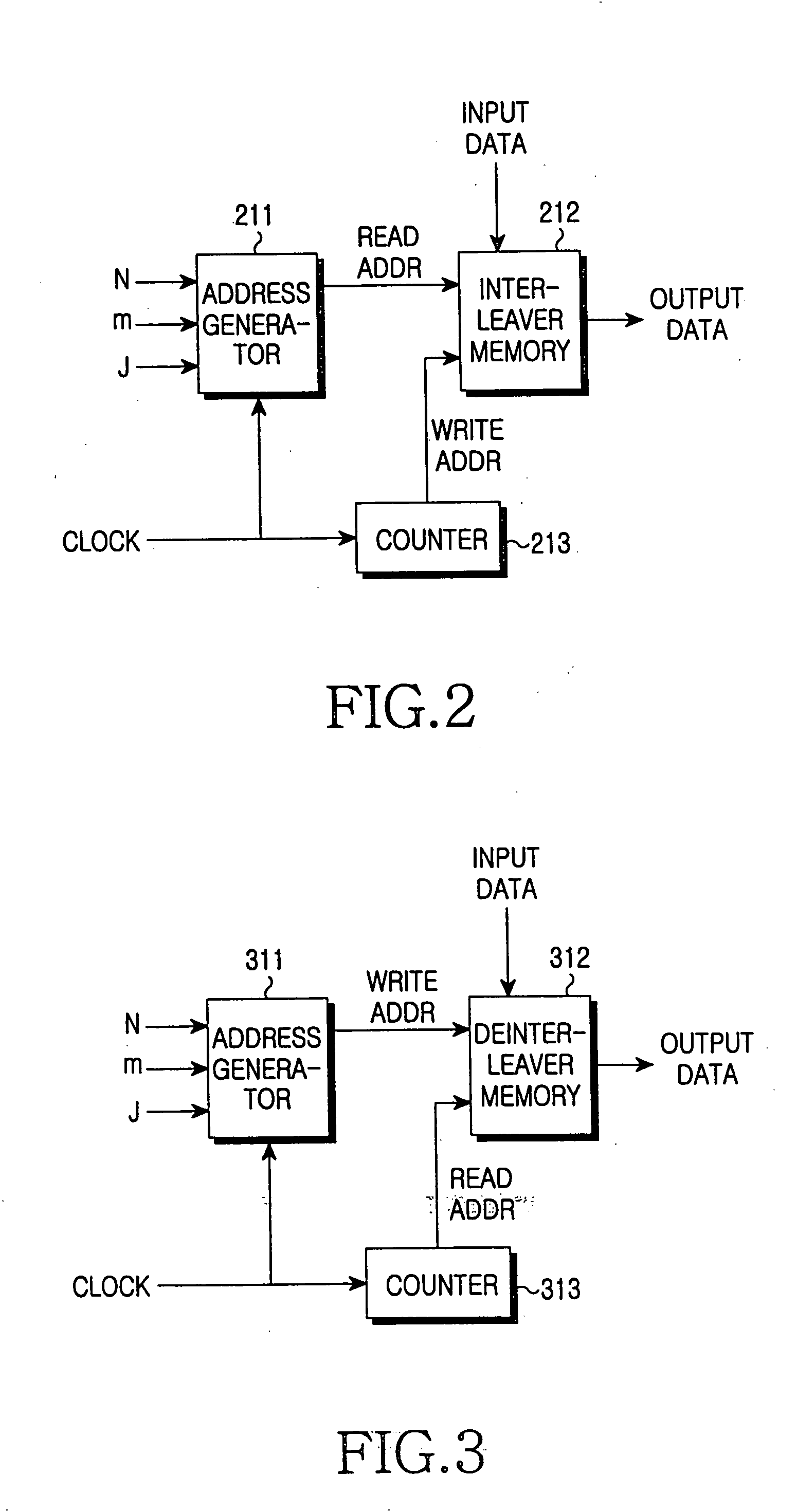

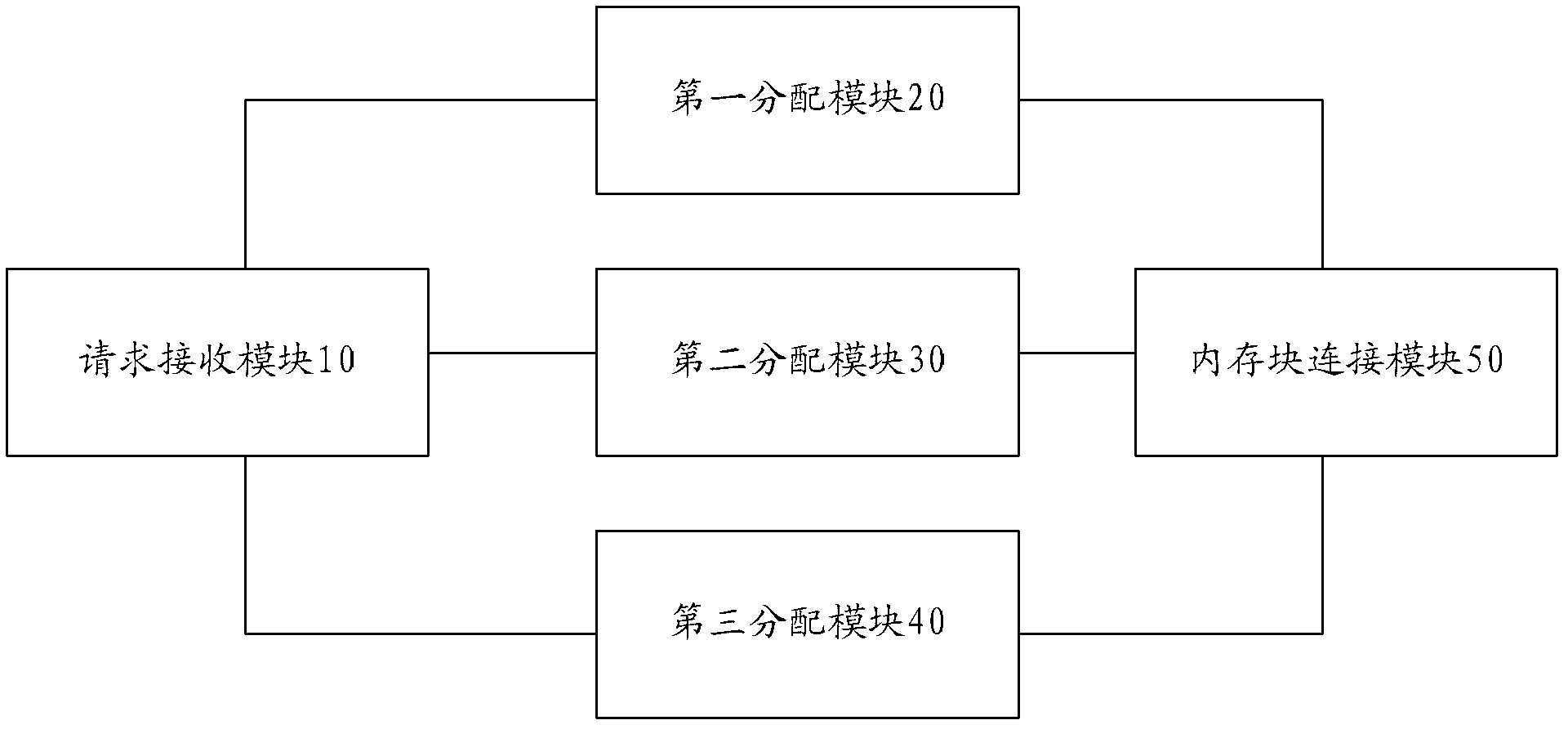

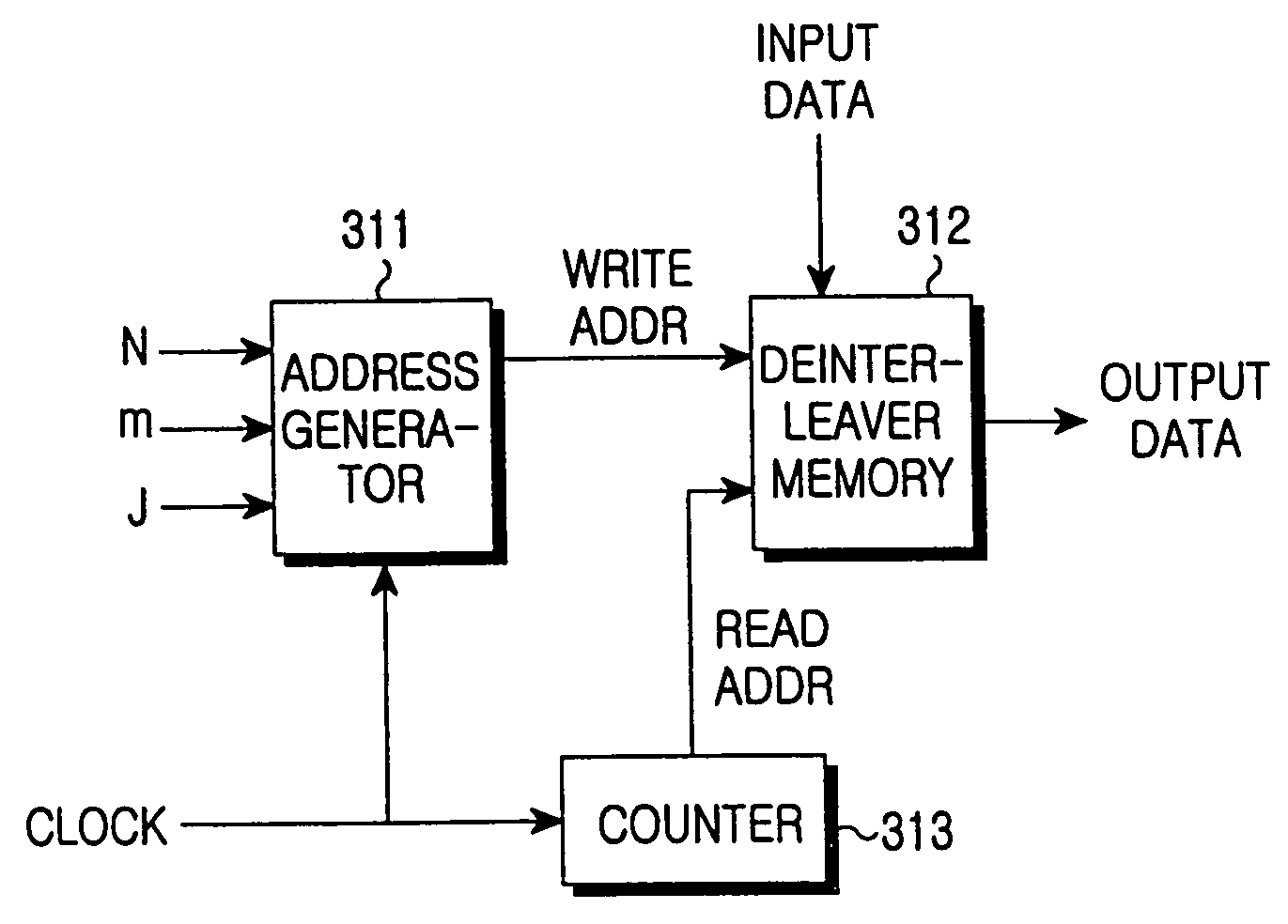

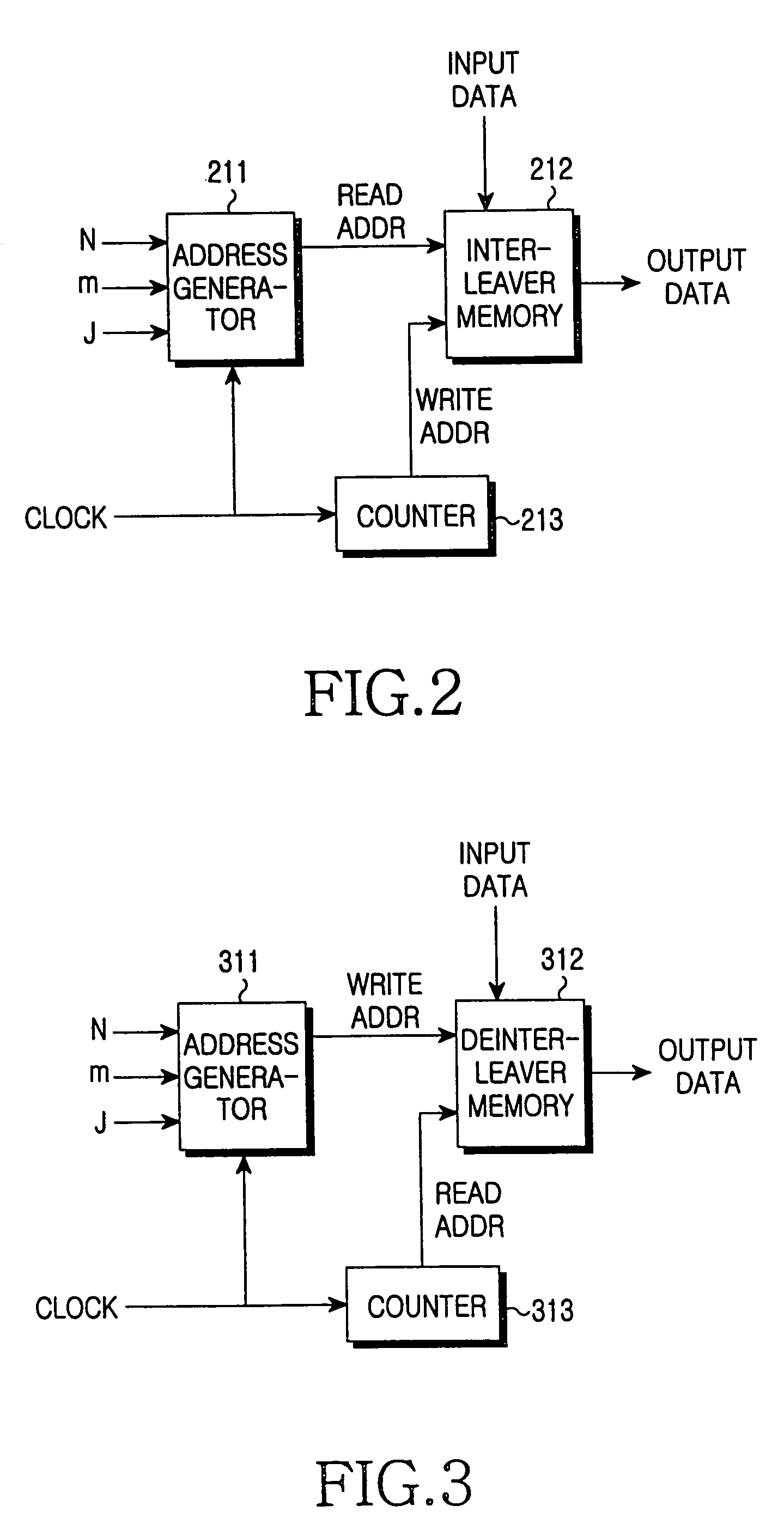

Interleaving.deinterleaving device and method for communication system

InactiveUS20050071729A1Low efficiencySave memory capacityError preventionMemory adressing/allocation/relocationCommunications systemTheoretical computer science

A device for sequentially storing input bit symbols of a given interleaver size N in a memory at an address from 0 to N-1 and reading the stored bit symbols from the memory. The device comprises a look-up table for providing a first variable m and a second variable J satisfying the equation N=2m×J; and an address generator for generating a read address depending on the first and second variables m and J provided from the look-up table. The read address is determined by 2m(K mod J)+BROm(K / J), where K (0≦K≦(N-1)) denotes a reading sequence, BROm(y) is the bit-reversed m-bit value of y and / is a function in which a quotient of K divided by d is obtained, the quotient being an integer.

Owner:SAMSUNG ELECTRONICS CO LTD

Method of editing audio data and recording medium thereof and digital audio player

InactiveUS20020133246A1Improve memory efficiencySpeech analysisSpecial data processing applicationsData rateData file

An audio data editing method, recording medium employing the same, and a digital audio player. The digital audio player extracts an audio data, which is received through a key input portion having an editing key for adjusting an extraction data rate and also through an input portion, according to the extraction data rate selected through the key input portion. The digital audio player includes a controller for storing the extracted audio data in a memory portion. According to the audio data editing method, recording medium, and digital audio player, the audio data file can be edited at any scale, and accordingly, the memory capacity of portable digital audio device can be utilized more efficiently.

Owner:BLUETEK

Fast channel switching method and apparatus for digital broadcast receiver

InactiveUS20080072259A1Reducing channel switching delayQuick switchTelevision system detailsSpecific information broadcast systemsDigital broadcastingAdjacent channel

A fast channel switching method and apparatus for a digital broadcast receiver that can reduce a channel switching delay caused by limitations in real time broadcasting systems is provided. A fast channel switching method of the present invention includes simultaneously receiving broadcast signals of a first service channel and a second service channel; presenting the broadcast signal of the first service channel through a player; and circular-buffering the broadcast signal of the second service channel. A digital broadcast receiver using a fast channel switching technique of the present invention can buffer an adjacent service channel while serving the current service channel such that the buffered broadcast signal is output when the adjacent channel is selected, thereby reducing a channel switching delay.

Owner:SAMSUNG ELECTRONICS CO LTD

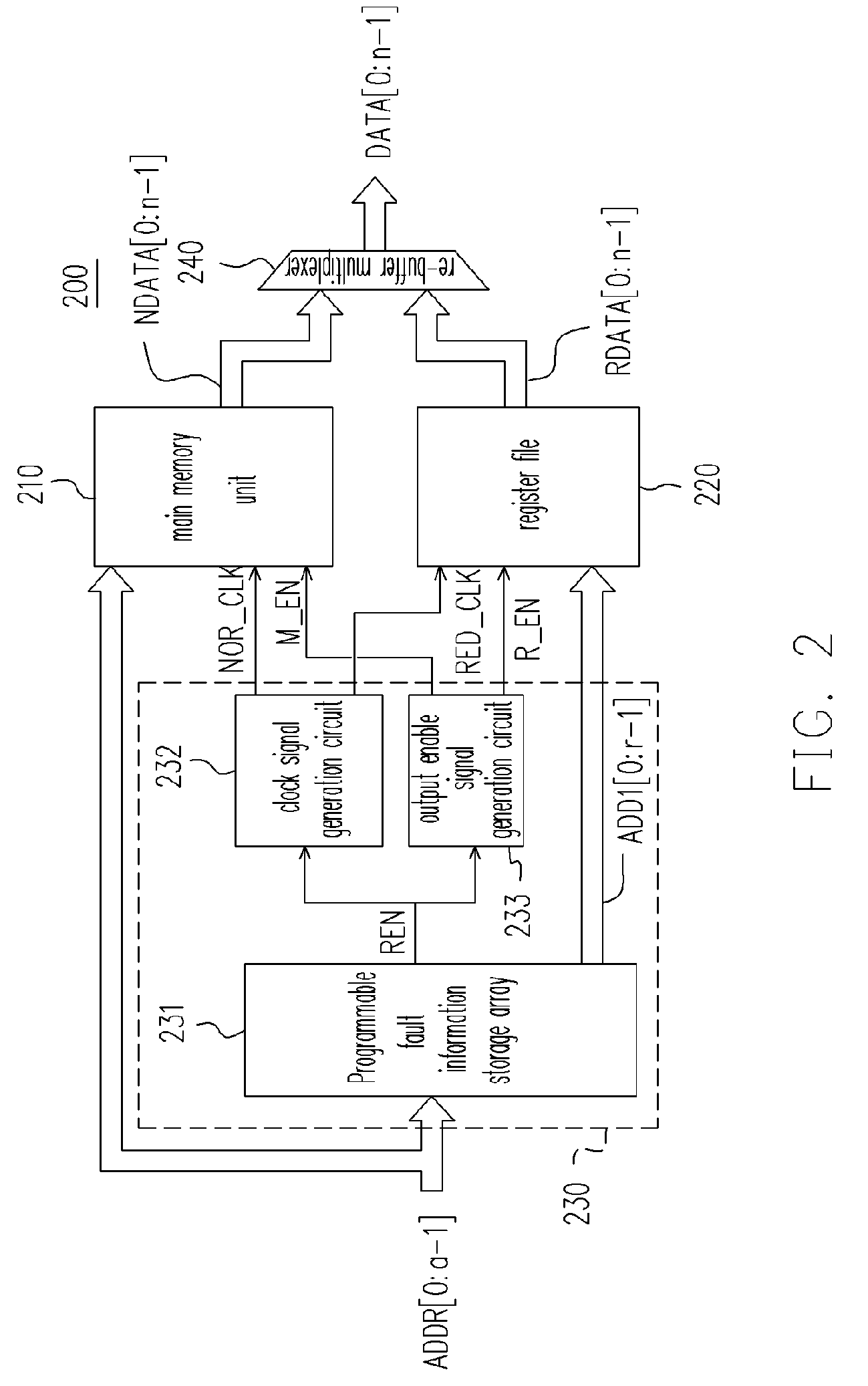

Method and device for data storage

InactiveCN102446139AEfficient insertionEfficient searchMemory adressing/allocation/relocationPagingMemory block

The invention provides a method and a device for data storage so as to solve the problem of low memory utilization rate. The method includes that if requested data can be stored in a paging allocation memory block, an idle memory block is selected to store the requested data; and if data size is larger than the paging allocation memory block, a part of data of the requested data is stored in the idle memory block, the other part of surplus data is stored in one or a plurality of available memory blocks, and all the memory blocks storing the requested data are connected through indicating needles. The available memory blocks are scattered memory blocks, the size of the scattered memory blocks is not necessarily to be the same as that of the paging allocation memory block, and accordingly memory waste can be avoided to the greatest extent, and memory utilization rate can be improved to the maximum limit.

Owner:BEIJING QIHOO TECH CO LTD +1

Memory structure with repairing function and repairing method thereof

InactiveUS7221604B2Improve memory efficiencyImprove access efficiencyDigital storageProcessor registerModularity

A memory structure with a repair function and a repairing method thereof are provided. The memory structure has an independent main memory unit and register file design. It also incorporates a record control unit for storing the fault information of the main memory unit. Upon receiving an access command, the memory structure determines if the main memory space pointed by the access command is faulty according to the stored fault information. When the main memory space pointed by the access command is faulty, a backup memory space is selected from the register file to replace the faulty main memory space. Therefore, the present invention can provide the convenience of a modularized design and reduce the space occupation of the register file, and also improve the access efficiency of the memory.

Owner:AMIC TECH TAIWAN

Non-volatile memory device and method of manufacturing the same

ActiveUS7091550B2Small dimensionImprove the coupling ratioTransistorSemiconductor/solid-state device manufacturingTrappingCoupling ratio

A non-volatile memory device and method of manufacturing the same is provided. A substrate is provided and then a trench is formed in the substrate. Thereafter, a bottom oxide layer, a charge-trapping layer and a top oxide layer are sequentially formed over the substrate and the surface of the trench. A conductive layer is formed over the top oxide layer filling the trench. The conductive layer is patterned to form a gate over the trench. The top oxide layer, the charge-trapping layer and the bottom oxide layer outside the gate are removed. A source / drain doping process is carried out. Because the non-volatile memory device is manufactured within the trench, storage efficiency of the device is improved through an increase in the coupling ratio. Furthermore, more charges can be stored by increasing the depth of the trench.

Owner:POWERCHIP SEMICON MFG CORP

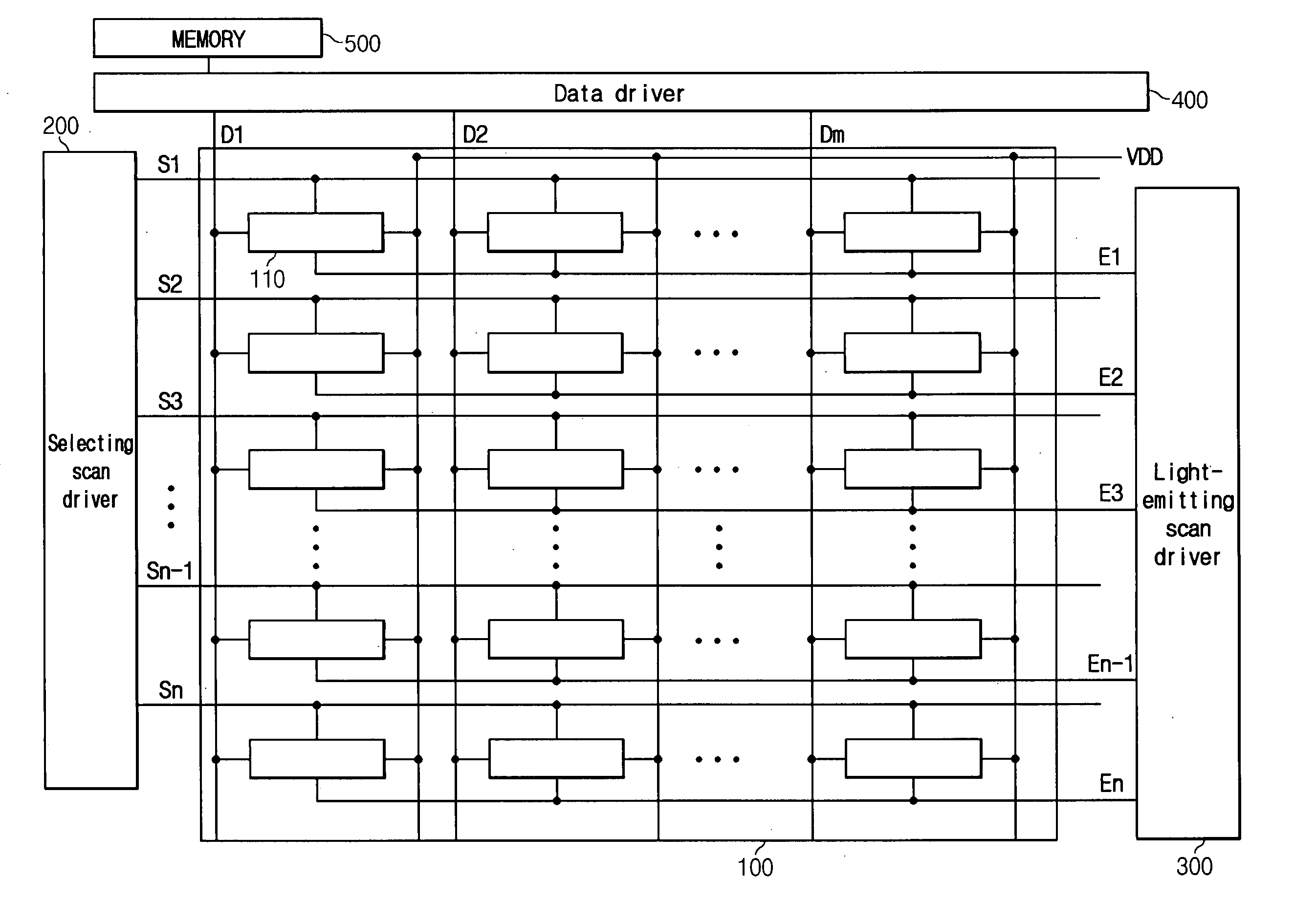

Method for managing display memory data of light emitting display

ActiveUS20060038757A1Easy to readShorten the timeElectrical apparatusElectroluminescent light sourcesComputer graphics (images)Scan line

A memory managing method for display data of a light emitting display device, which uses field light-emitting of organic materials. A plurality of pixels are each provided with at least two sub-pixels to emit different color lights, wherein one field has at least first and second subfields divided and driven independently. At least two data signals corresponding to substantially the same color are time-divided and applied to a data line during the one field, and selecting signals are sequentially applied to a plurality of scan lines at the first and second subfields. The method includes a) dividing input data corresponding to a display image into data for the first and second subfields, b) arranging the data for the first and second subfields according to a sequence of light-emitting driving, and c) storing the arranged data as pixel-based data.

Owner:SAMSUNG DISPLAY CO LTD

Decoding method, memory storage device and memory control circuit unit

InactiveUS20170294217A1Improve memory efficiencyImprove decoding efficiencyDigital storageRedundant data error correctionDecoding methodsControl circuit

A decoding method, a memory storage device and a memory control circuit unit are provided. The method includes: reading data from a plurality of first memory cells of a rewritable non-volatile memory module; estimating an error bit occurrence rate of the data before performing a first decoding process on the data; and performing the first decoding process on the data by using a first decoding parameter according to the estimated error bit occurrence rate, wherein the first decoding parameter corresponds to a strict level for locating an error bit in the first decoding process. As a result, a decoding efficiency of the memory storage device can be improved.

Owner:PHISON ELECTRONICS

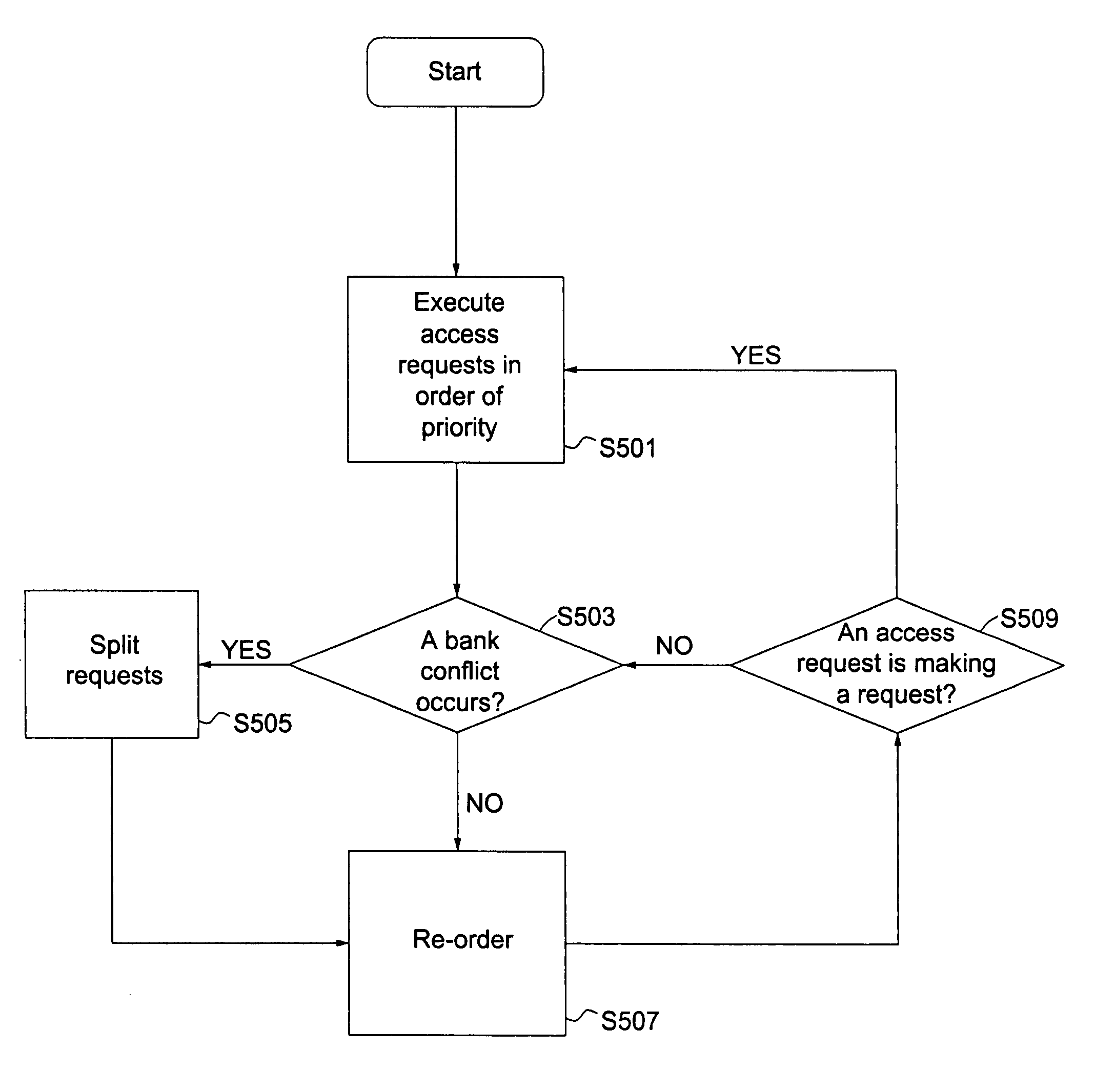

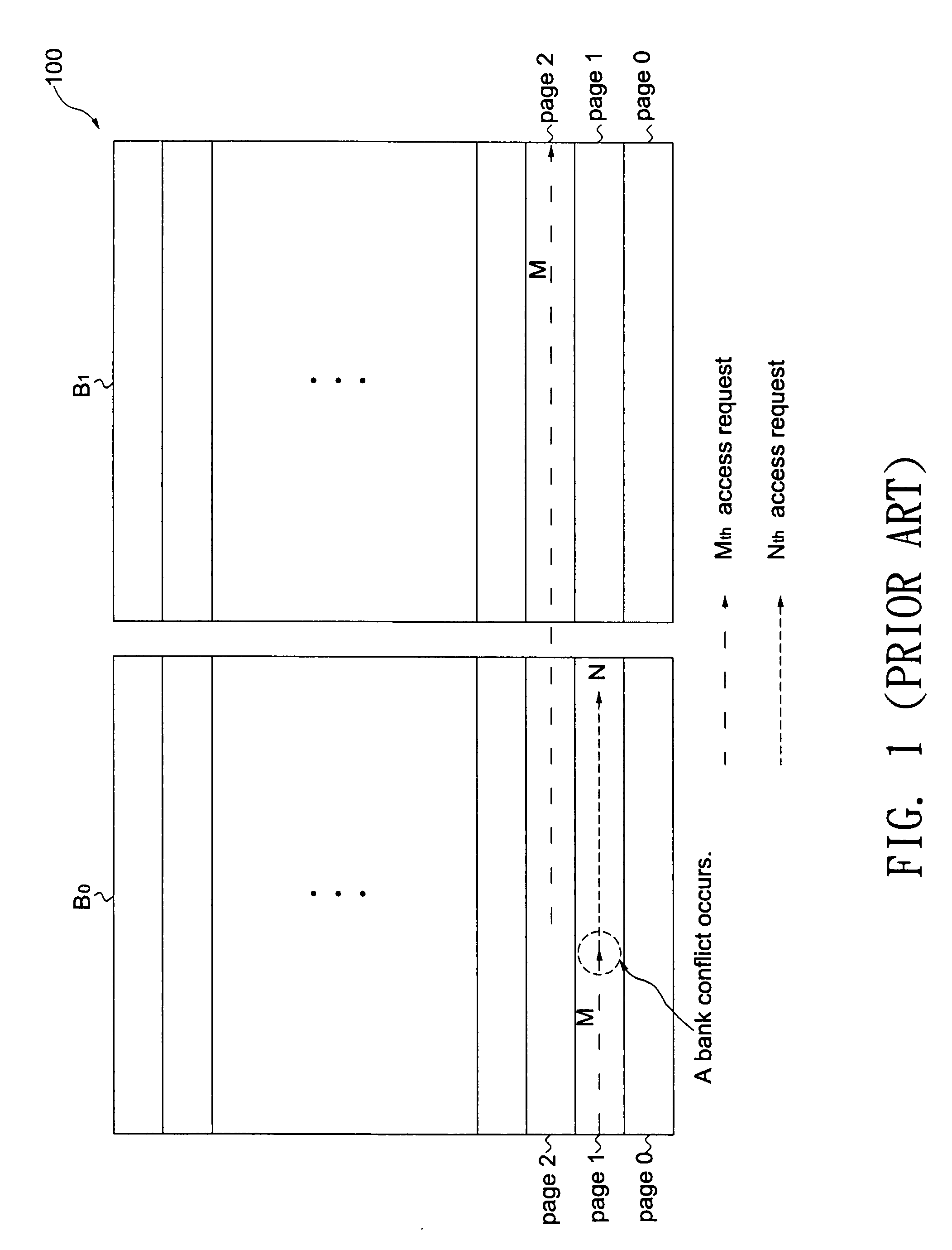

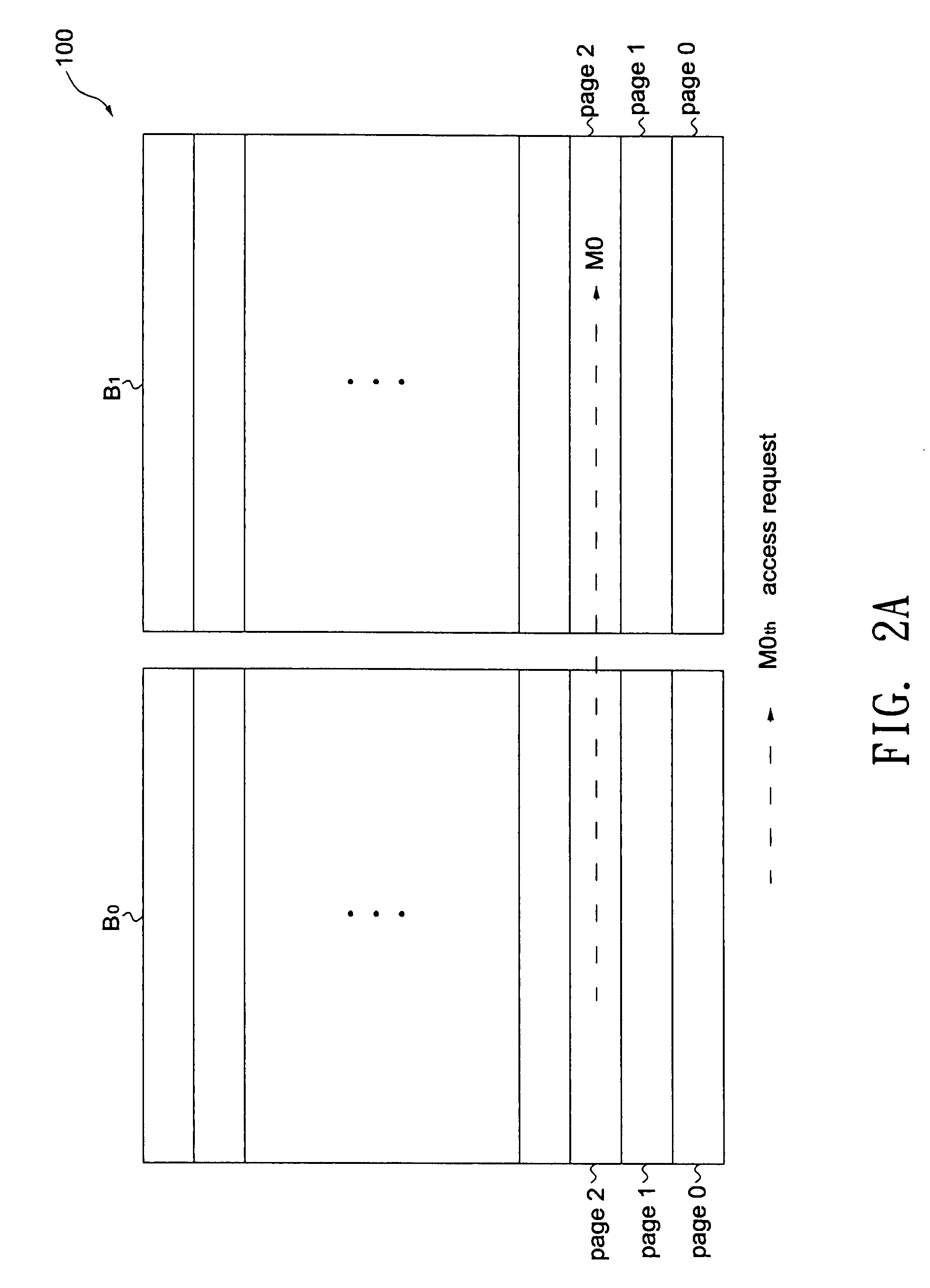

Method of memory management

ActiveUS20080104340A1Maximizes bank diversityMinimize bank conflictMemory systemsMicro-instruction address formationParallel computingTerm memory

A method of memory management is disclosed. The invention increases bank diversity by splitting requests and is also integrated with re-ordering and priority arbitration mechanisms. Therefore, the probabilities of both bank conflicts and write-to-read turnaround conflicts are reduced significantly, so as to increase memory efficiency.

Owner:REALTEK SEMICON CORP

Interleaving.deinterleaving device and method for communication system

InactiveUS7302620B2Low efficiencySave memory capacityError preventionMemory adressing/allocation/relocationCommunications systemTheoretical computer science

A device for sequentially storing input bit symbols of a given interleaver size N in a memory at an address from 0 to N−1 and reading the stored bit symbols from the memory. The device comprises a look-up table for providing a first variable m and a second variable J satisfying the equation N=2m×J; and an address generator for generating a read address depending on the first and second variables m and J provided from the look-up table. The read address is determined by 2m(K mod J)+BROm(K / J), where K (0≦K≦(N−1)) denotes a reading sequence, BROm(y) is the bit-reversed m-bit value of y and / is a function in which a quotient of K divided by d is obtained, the quotient being an integer.

Owner:SAMSUNG ELECTRONICS CO LTD

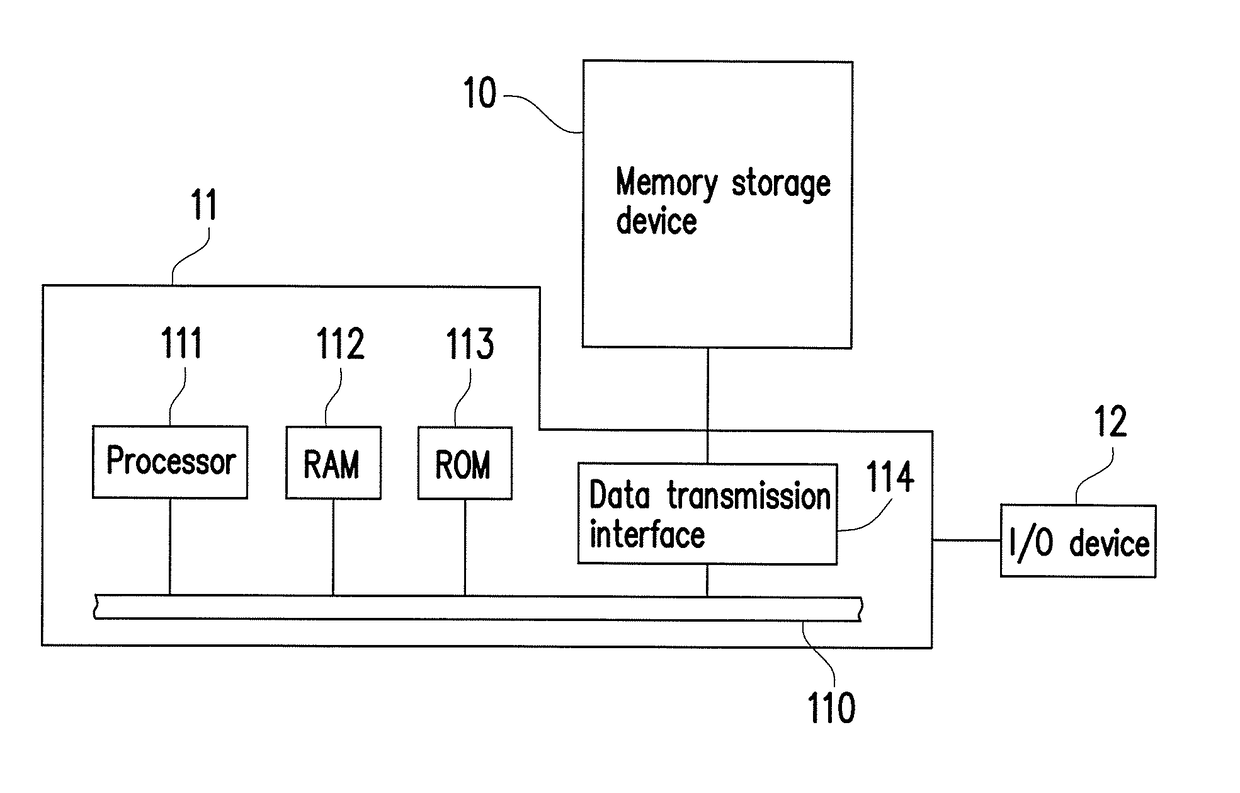

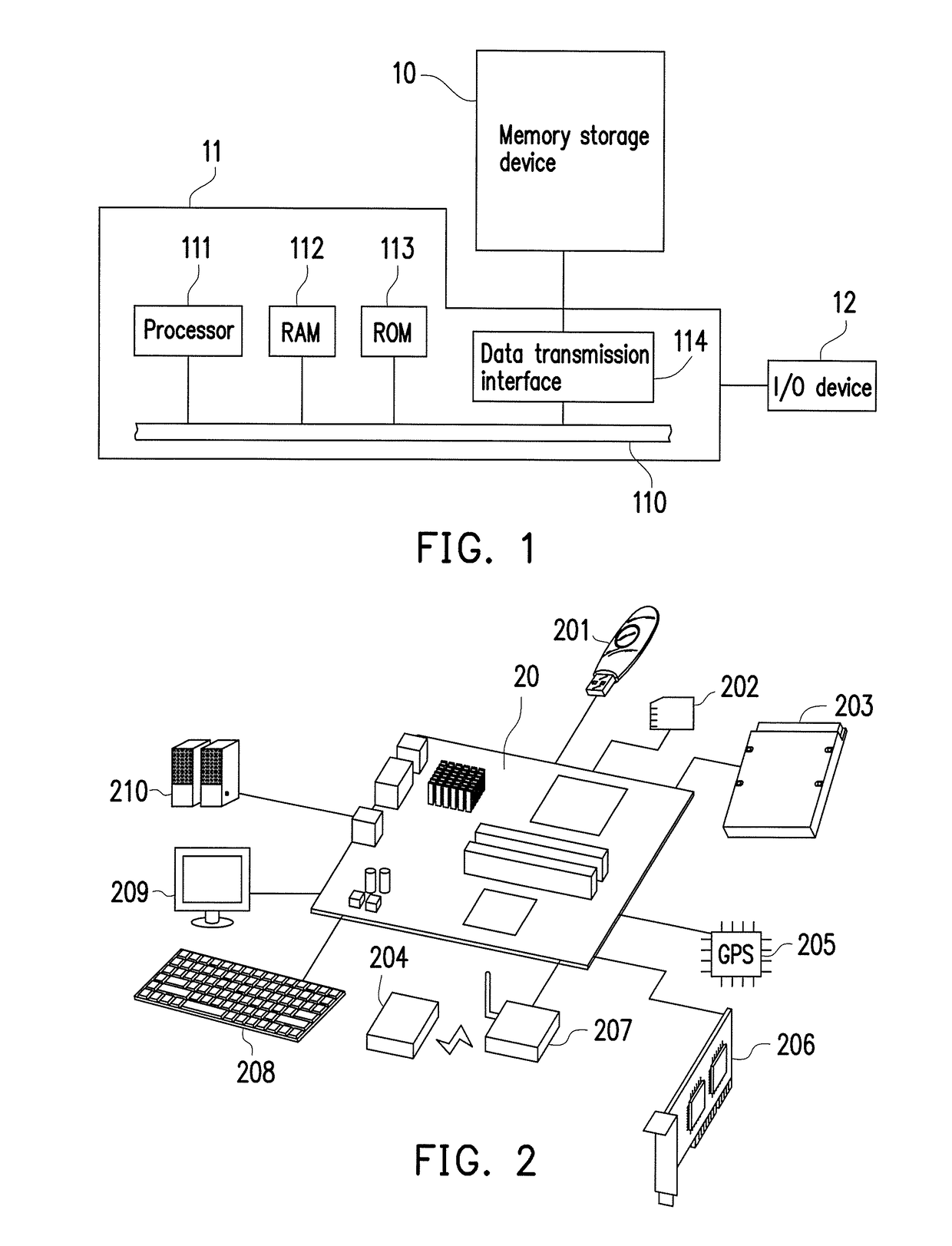

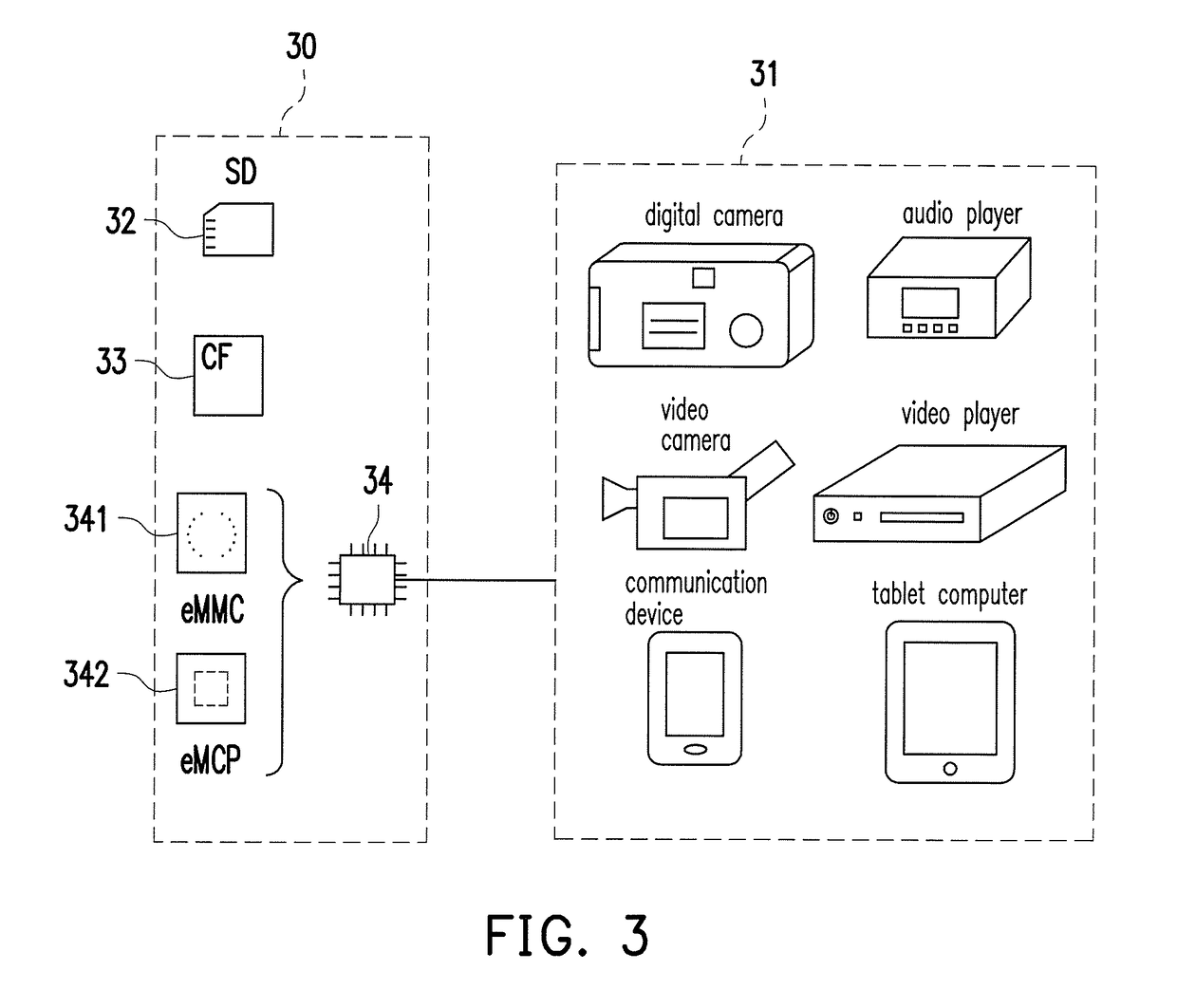

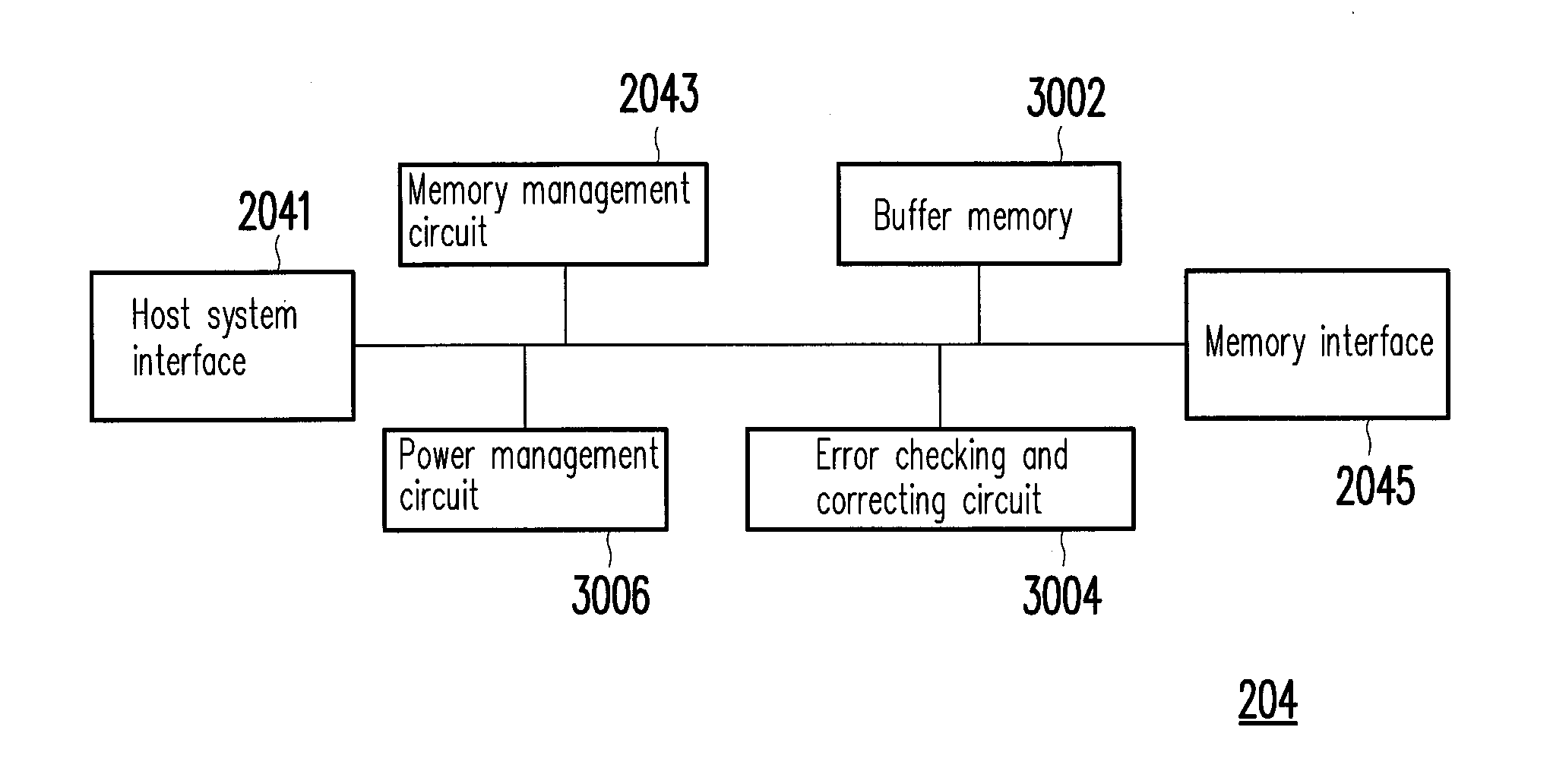

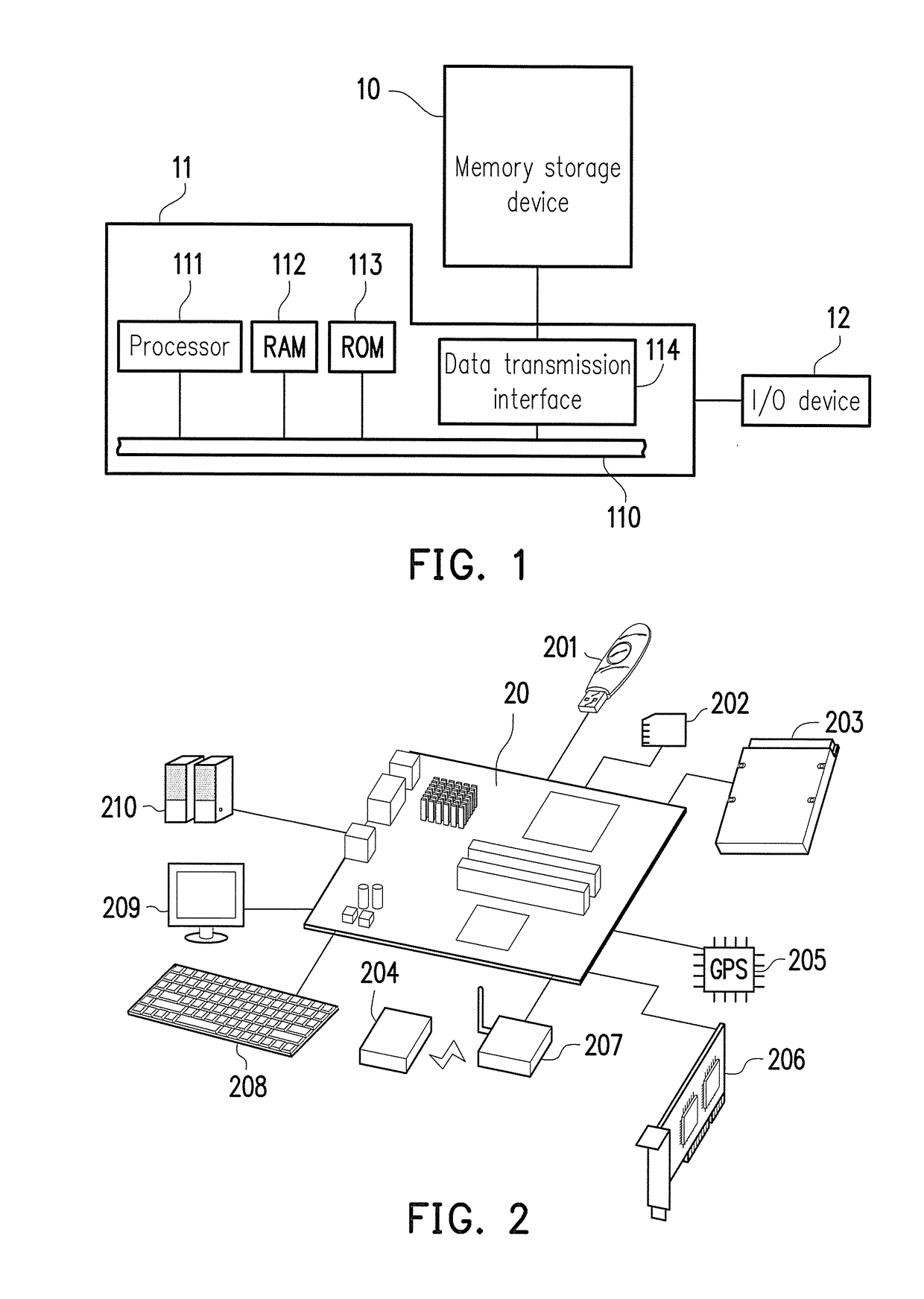

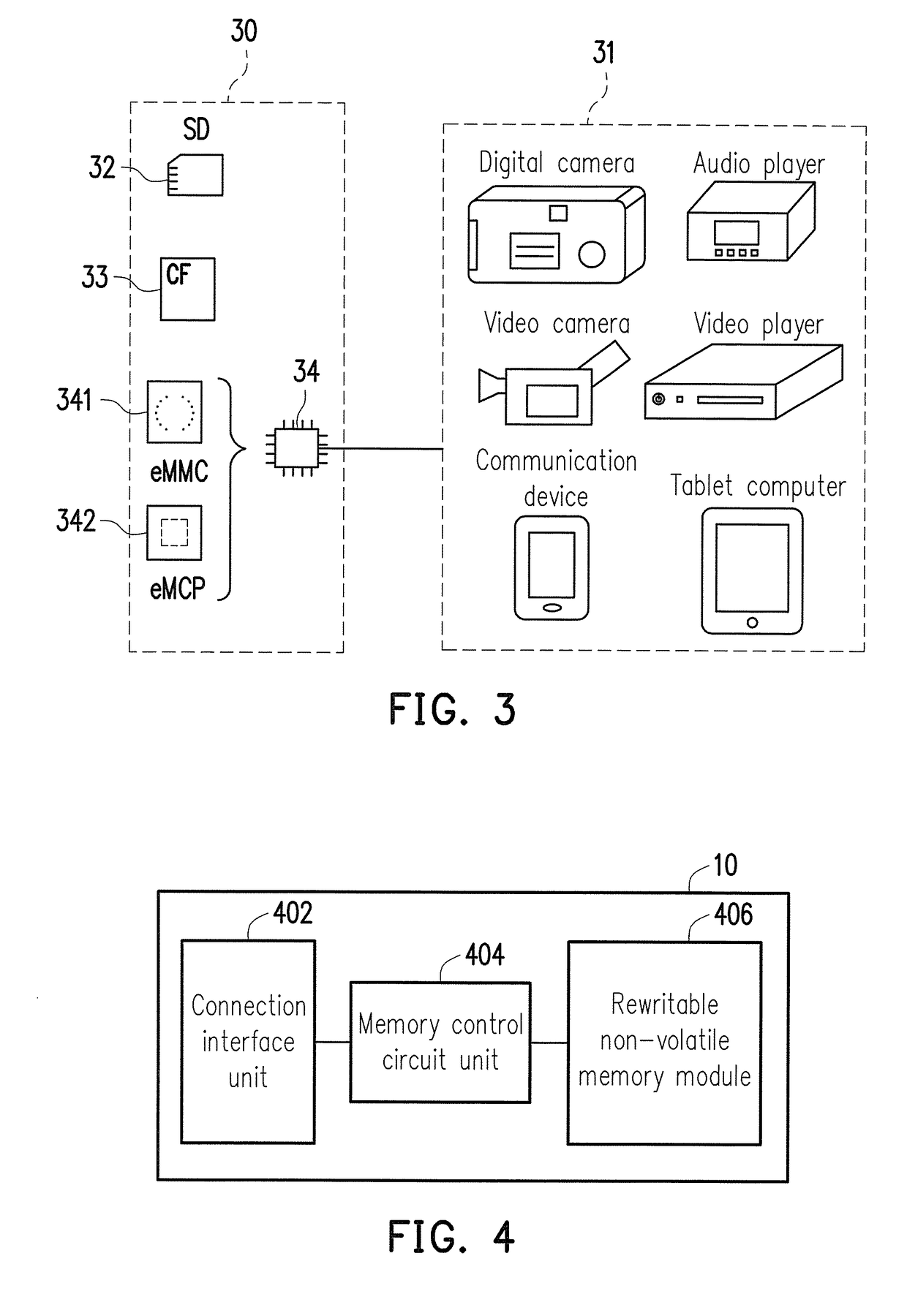

Memory storage device, memory controller thereof, and data transmission method thereof

ActiveUS20130111287A1Increase speedData transfer speed is fastError preventionTransmission systemsMemory controllerData transmission

A memory storage device, a memory controller thereof and a data transmission method thereof are provided. The memory storage device includes a rewritable non-volatile memory module having a first and a second memory dies, and the first and the second memory dies are coupled to the memory controller through the same data input / output bus. The method includes transmitting a read command to the first memory die and then transmitting a write command to the second memory die by the memory controller. The method further includes controlling the first and the second memory dies to respectively read out and put data onto the data input / output bus in accordance with the read command and write the data from the data input / output bus into the second memory die in accordance with the write command at the same time by the memory controller.

Owner:PHISON ELECTRONICS

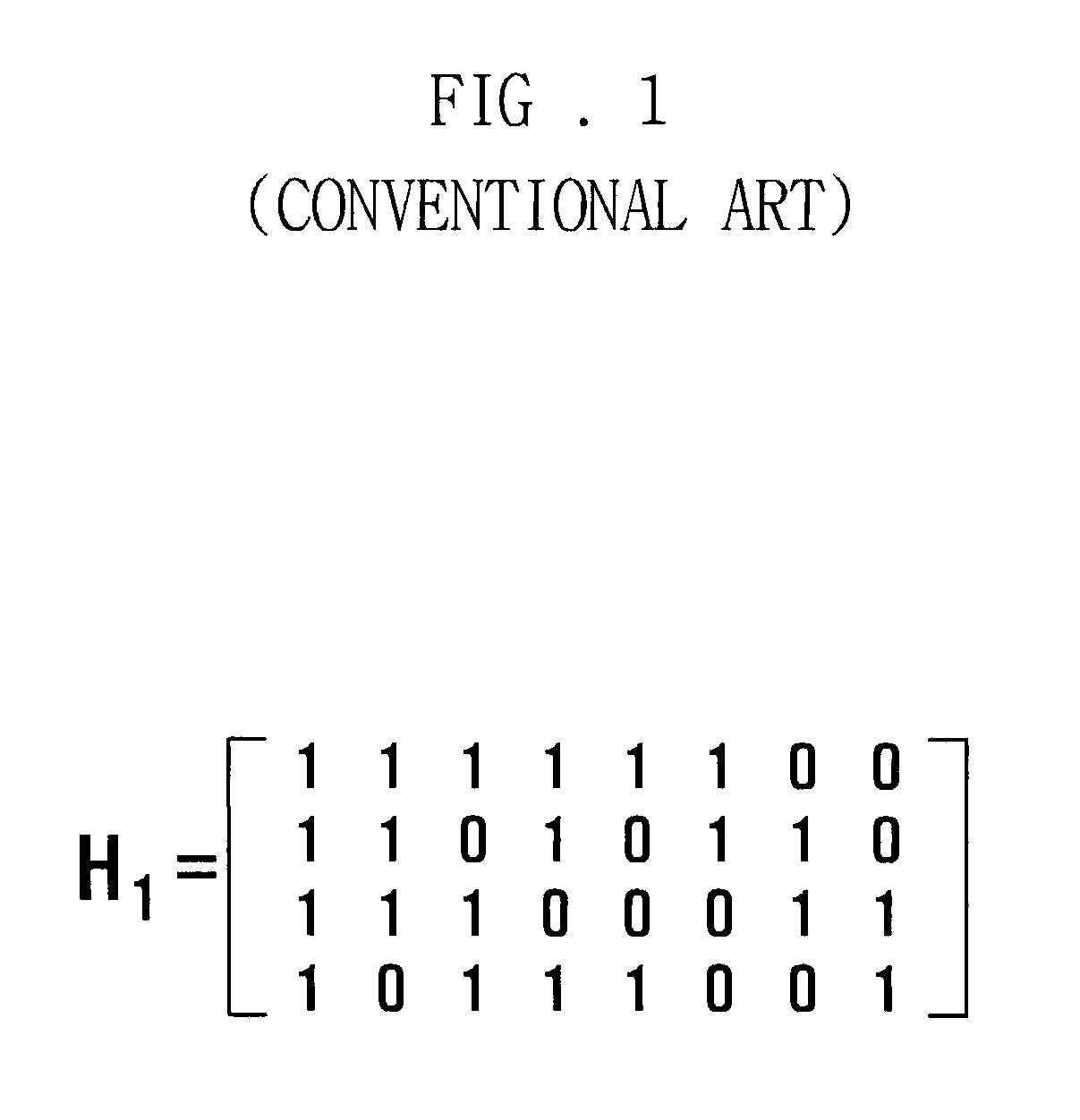

Channel-encoding/decoding apparatus and method using low-density parity-check codes

ActiveUS8495459B2Efficient designImprove memory efficiencyError correction/detection using multiple parity bitsCode conversionParity-check matrixTheoretical computer science

Owner:SAMSUNG ELECTRONICS CO LTD

Decoding method, memory storage device and memory control circuit unit

ActiveUS20170308432A1Easy to read dataImprove memory efficiencyRead-only memoriesRedundant data error correctionDecoding methodsControl circuit

A decoding method, a memory storage device and a memory control circuit unit are provided. The decoding method includes: reading a target physical unit based on a first read voltage level; performing a first decoding operation; reading an authentication physical unit based on a first candidate voltage level to obtain first assistance data and reading the authentication physical unit based on a second candidate voltage level to obtain second assistance data if the first decoding operation fails; obtaining a first estimation parameter according to the first assistance data and authentication data and obtaining a second estimation parameter according to the second assistance data and the authentication data; determining a second read voltage level according to the first estimation parameter and the second estimation parameter; and reading the target physical unit again based on the second read voltage level. Accordingly, the decoding efficiency may be improved.

Owner:SHENZHEN EPOSTAR ELECTRONICS LTD

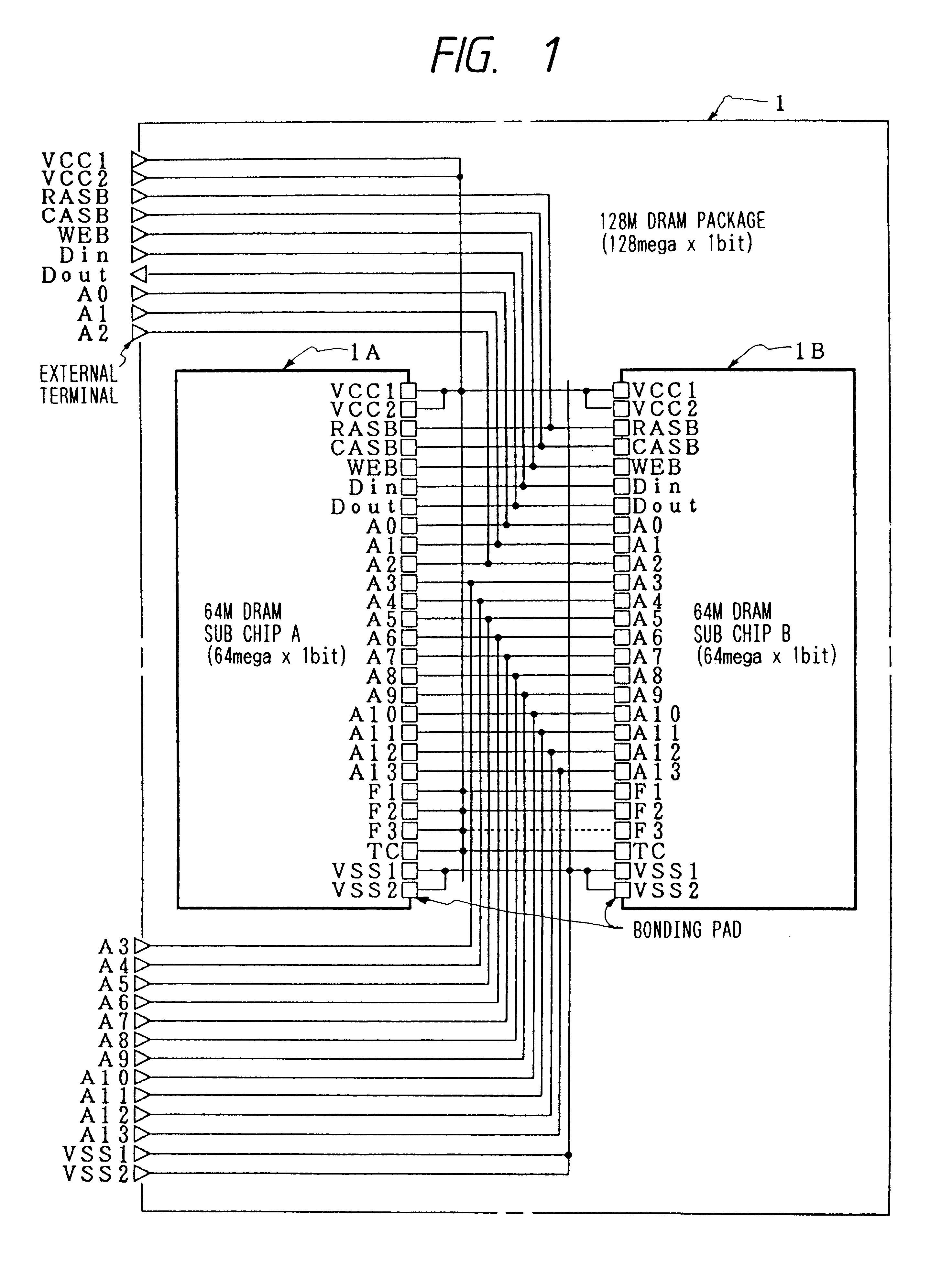

Sealed stacked arrangement of semiconductor devices

InactiveUSRE37539E1Without sacrificing heat radiation characteristicLarge memory capacitySemiconductor/solid-state device detailsSolid-state devicesEngineeringLead frame

A pair of DRAM chips 1A and 1B are mounted opposedly to each other with wiring means such as lead frames put therebetween, the lead frames being substantially integral with external terminals 3B. Then, these DRAM chips and lead frames are connected together by the conventional wire bonding method. Plural pairs of the thus-connected DRAM chips and lead frames are stacked and corresponding leads of the lead frames are connected in common to form a laminate. The plural DRAM chips thus mounted are activated selectively in accordance with a predetermined chip selection signal. Additionally, partial DRAM chips capable of partially functioning normally are combined together by utilizing the above chip mounting method to constitute a single DRAM package.

Owner:ELPIDA MEMORY INC

Method and device for processing data in retransmission processes

InactiveUS20090199061A1Improve efficiencyImprove memory efficiencyError prevention/detection by using return channelTransmission systemsCommunication deviceData buffer

A retransmission process control method is provided that increases the efficiency of memory usage in retransmission processes. A method for processing data in multiple retransmission processes, used in a receiving-side communication device, includes; determining whether or not a received signal can be stored in a reception buffer for retransmission processes; when the received signal cannot be stored in the reception buffer, discarding from the reception buffer at least part of existing received signals corresponding to retransmission processes in progress; and storing the received signal into the reception buffer.

Owner:NEC CORP

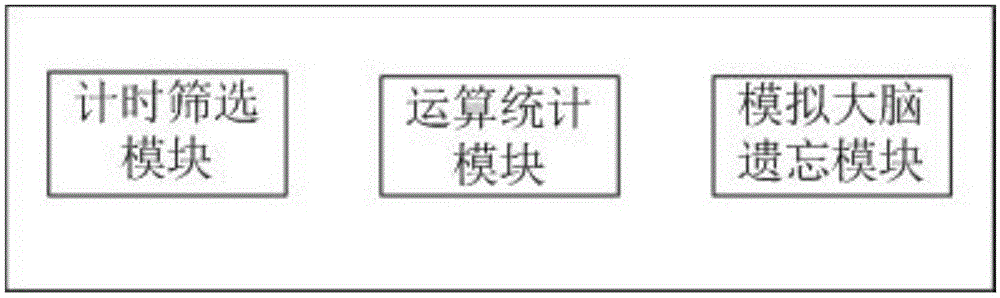

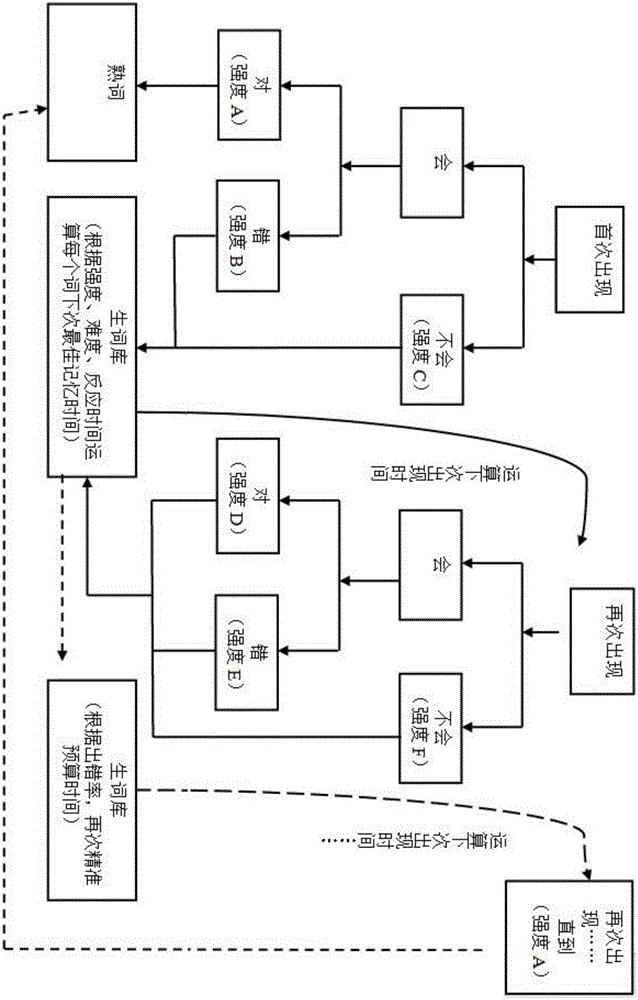

Memory engine system

InactiveCN106846980AEnhance memoryReduce memory loadTeaching apparatusPhysical medicine and rehabilitationMemory difficulties

The invention discloses a memory engine system, which includes a timing screening module, an operation statistics module, and a simulated brain forgetting module; If the students can tell the meaning of the word, they click on the green smiley face, if they can’t say it, they click on the red sad face, if they click on the green smiley face, it means that it is not a new word, and the system will filter it out, so there is no need to review it for the time being; the calculation and statistics module is used for statisticians Response time to learning content or each word and sentence, number of right and wrong times, forgetting interval, frequency of mistakes, memory strength, memory difficulty; the simulated brain forgetting module is used to automatically arrange review of new words according to the law of forgetting. The memory engine of the present invention realizes human brain learning, computer management, and fully automatic learning.

Owner:山东顺势教育科技集团有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com

![[NAND flash memory cell row, NAND flash memory cell array, operation and fabrication method thereof] [NAND flash memory cell row, NAND flash memory cell array, operation and fabrication method thereof]](https://images-eureka-patsnap-com.libproxy1.nus.edu.sg/patent_img/fd24ad20-241c-499a-ae01-18d1c3524bcb/US20050087892A1-20050428-D00000.png)

![[NAND flash memory cell row, NAND flash memory cell array, operation and fabrication method thereof] [NAND flash memory cell row, NAND flash memory cell array, operation and fabrication method thereof]](https://images-eureka-patsnap-com.libproxy1.nus.edu.sg/patent_img/fd24ad20-241c-499a-ae01-18d1c3524bcb/US20050087892A1-20050428-D00001.png)

![[NAND flash memory cell row, NAND flash memory cell array, operation and fabrication method thereof] [NAND flash memory cell row, NAND flash memory cell array, operation and fabrication method thereof]](https://images-eureka-patsnap-com.libproxy1.nus.edu.sg/patent_img/fd24ad20-241c-499a-ae01-18d1c3524bcb/US20050087892A1-20050428-D00002.png)