Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

130results about How to "Large memory capacity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

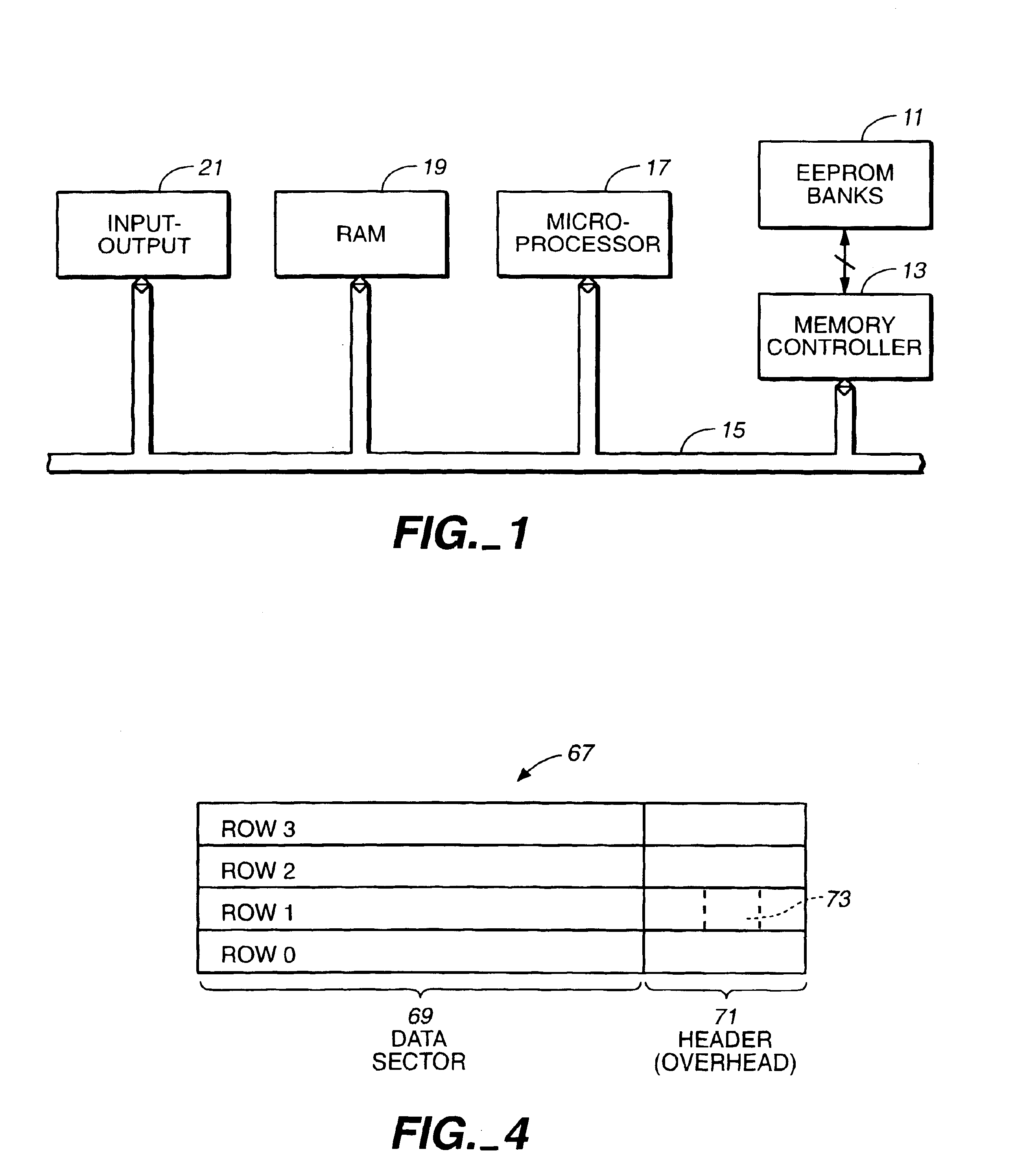

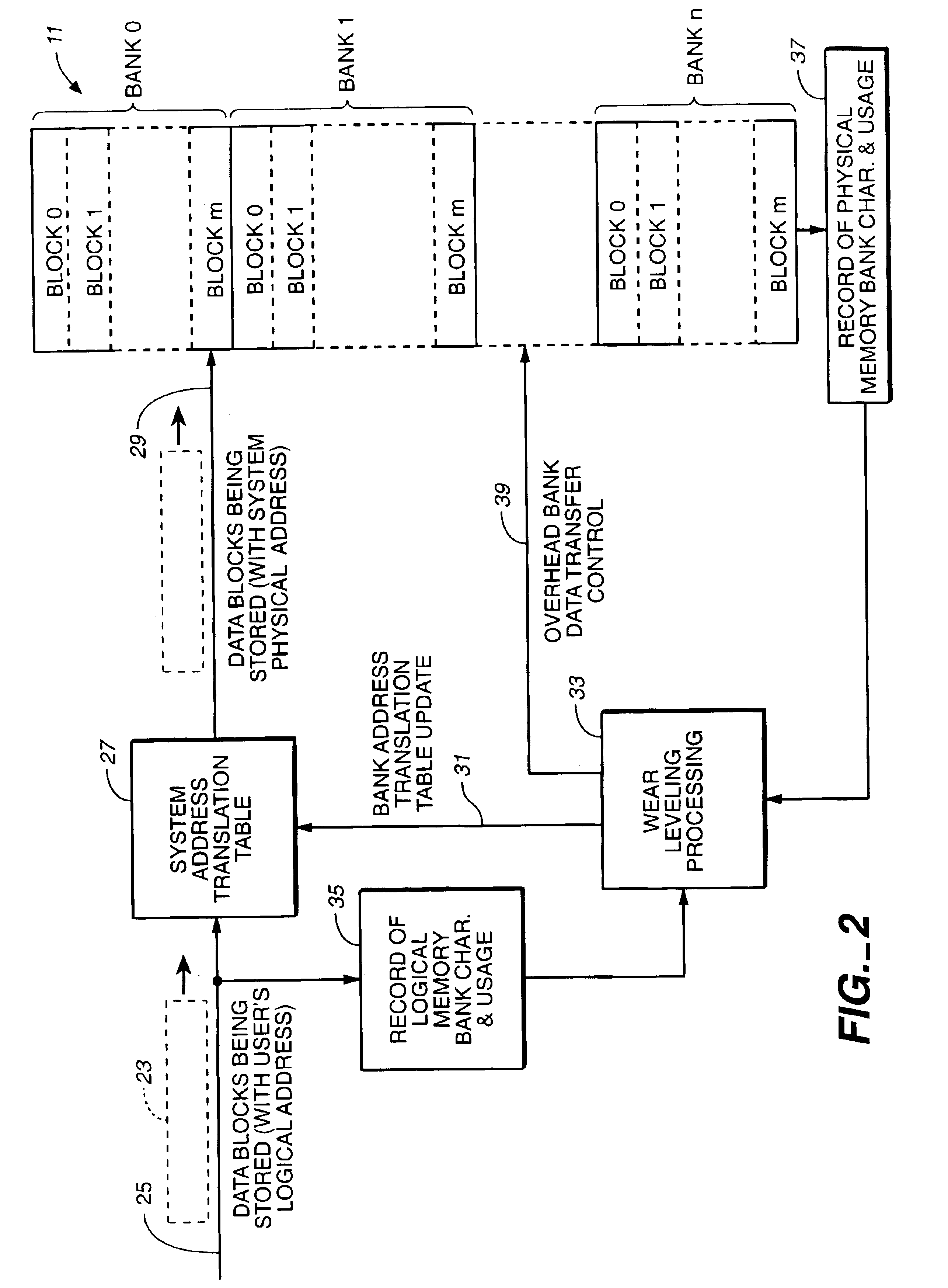

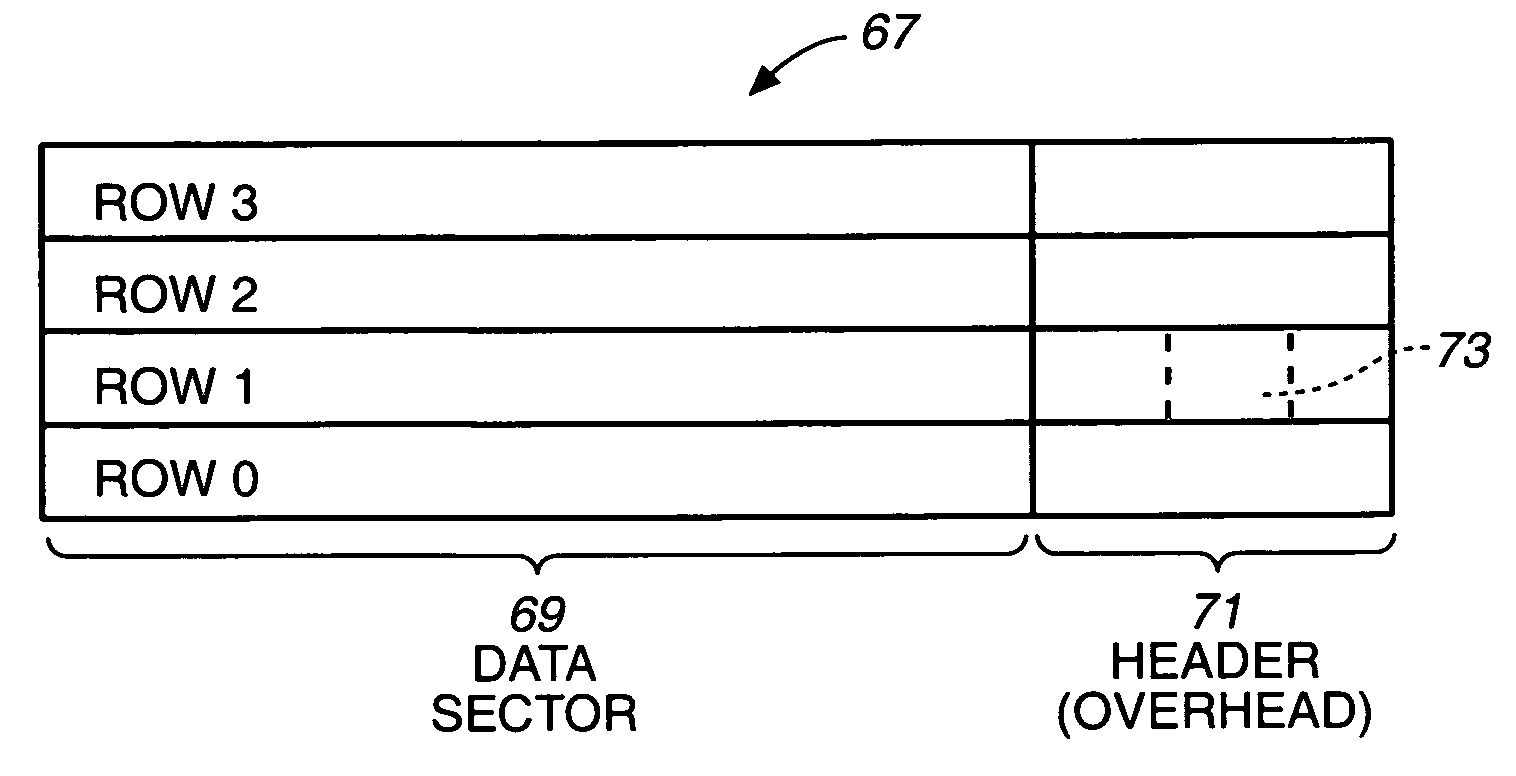

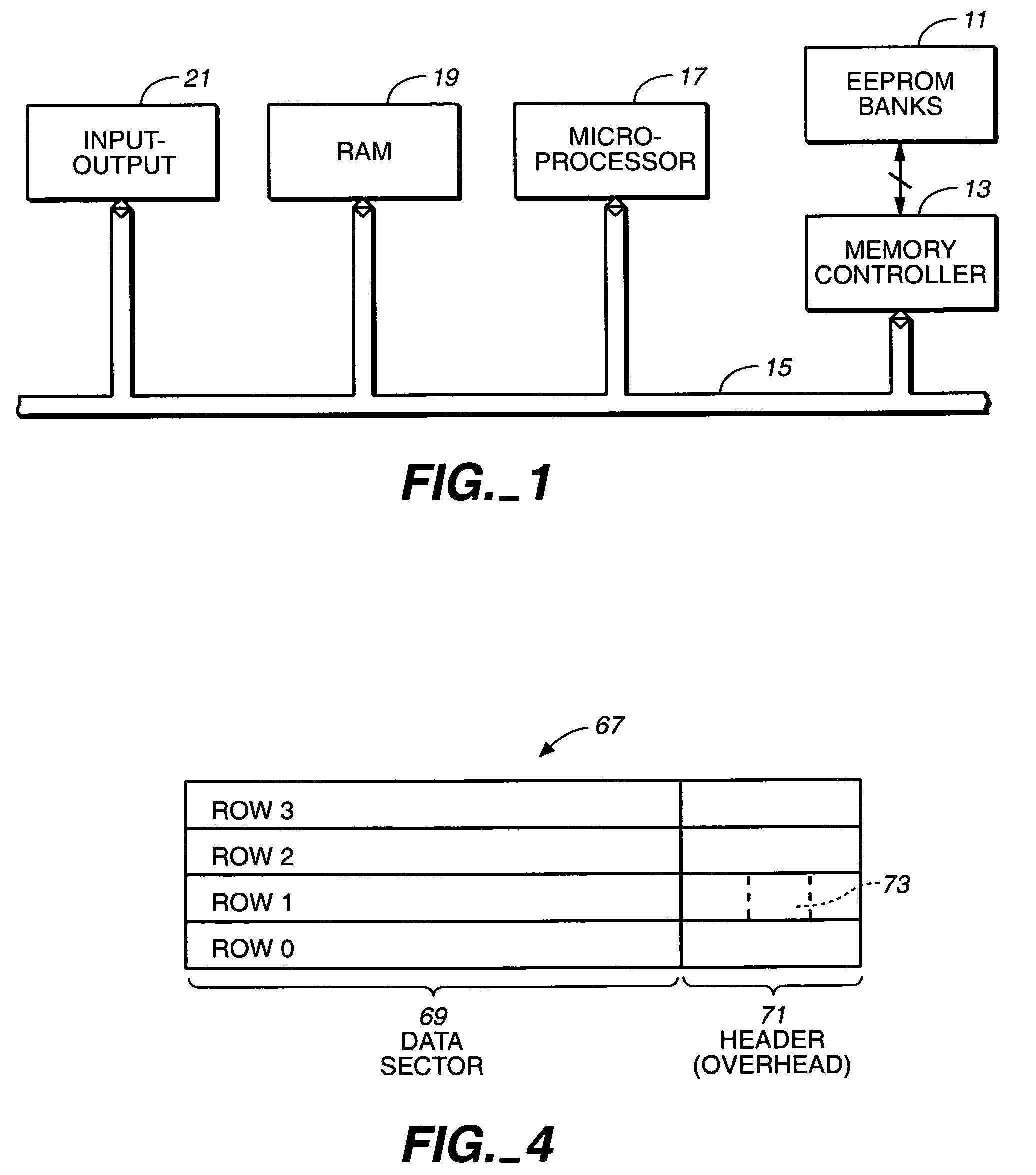

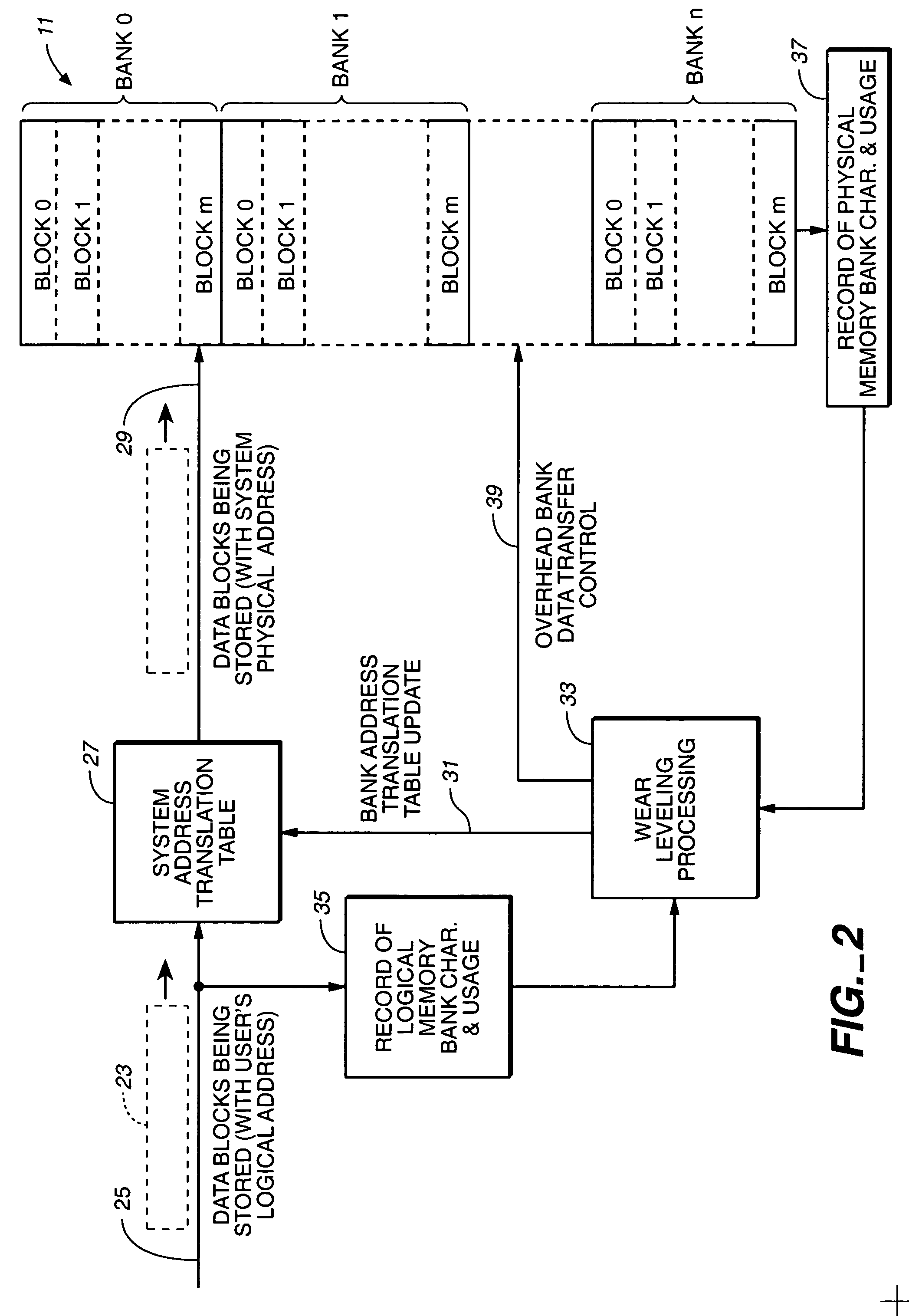

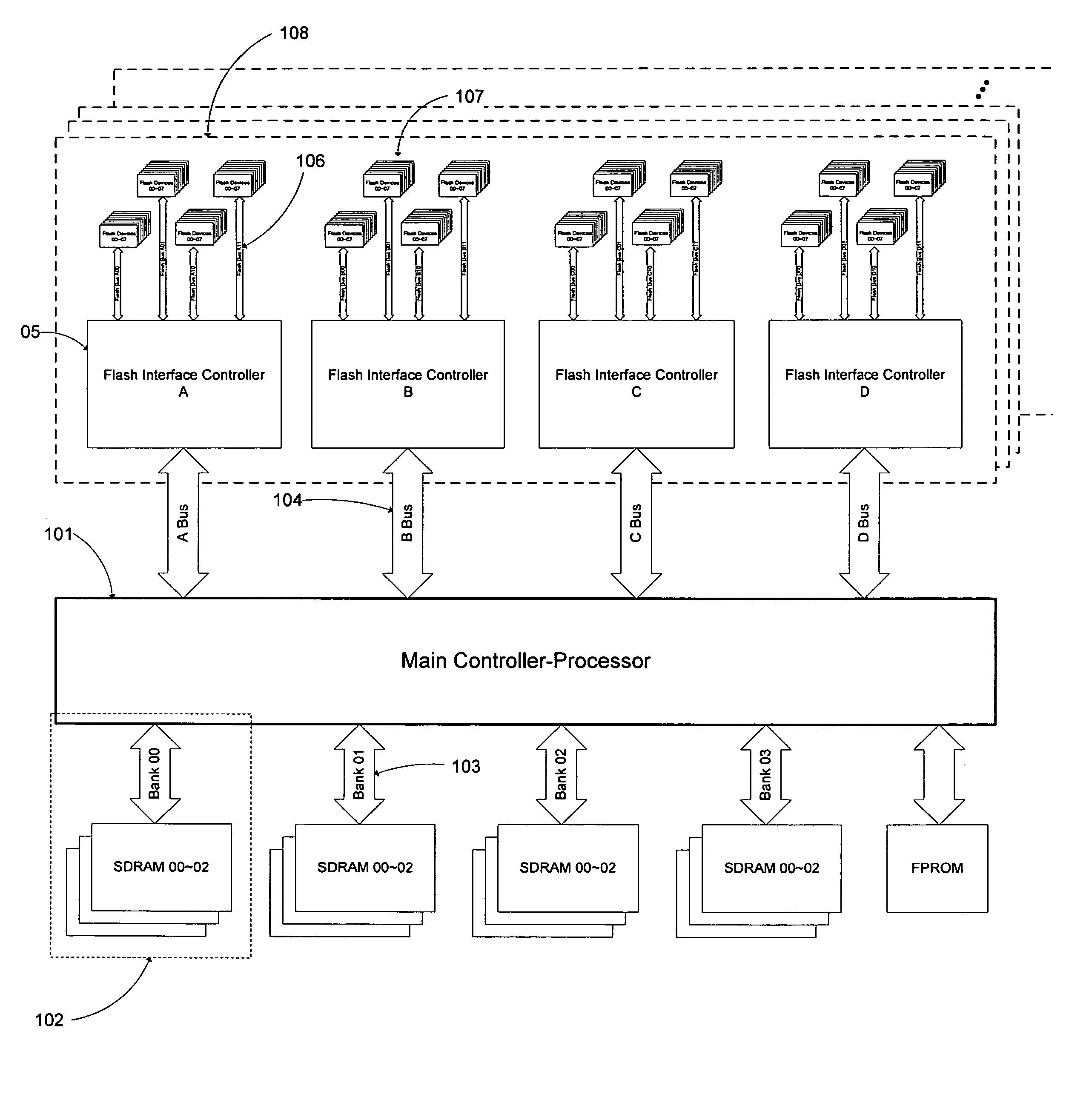

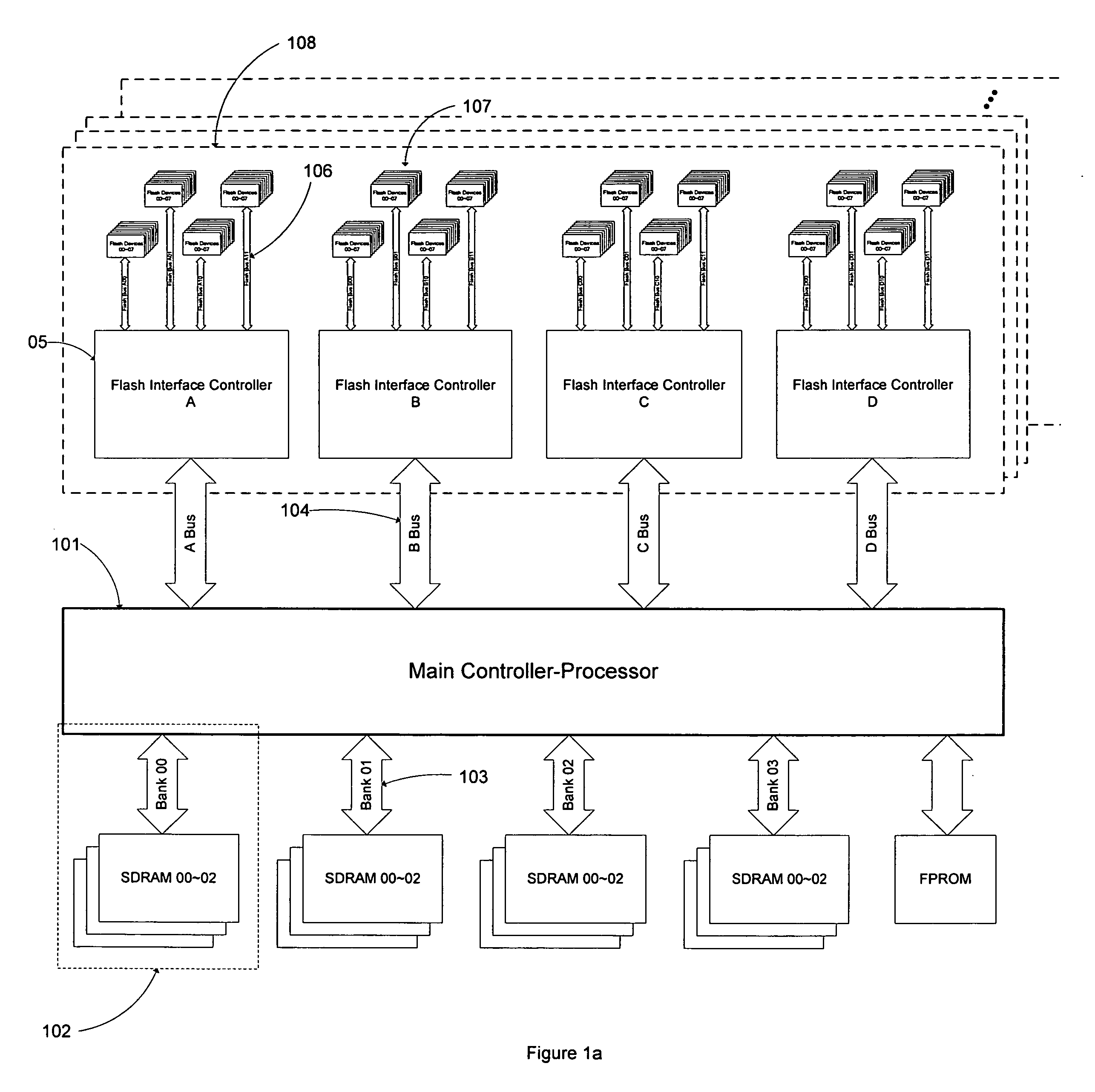

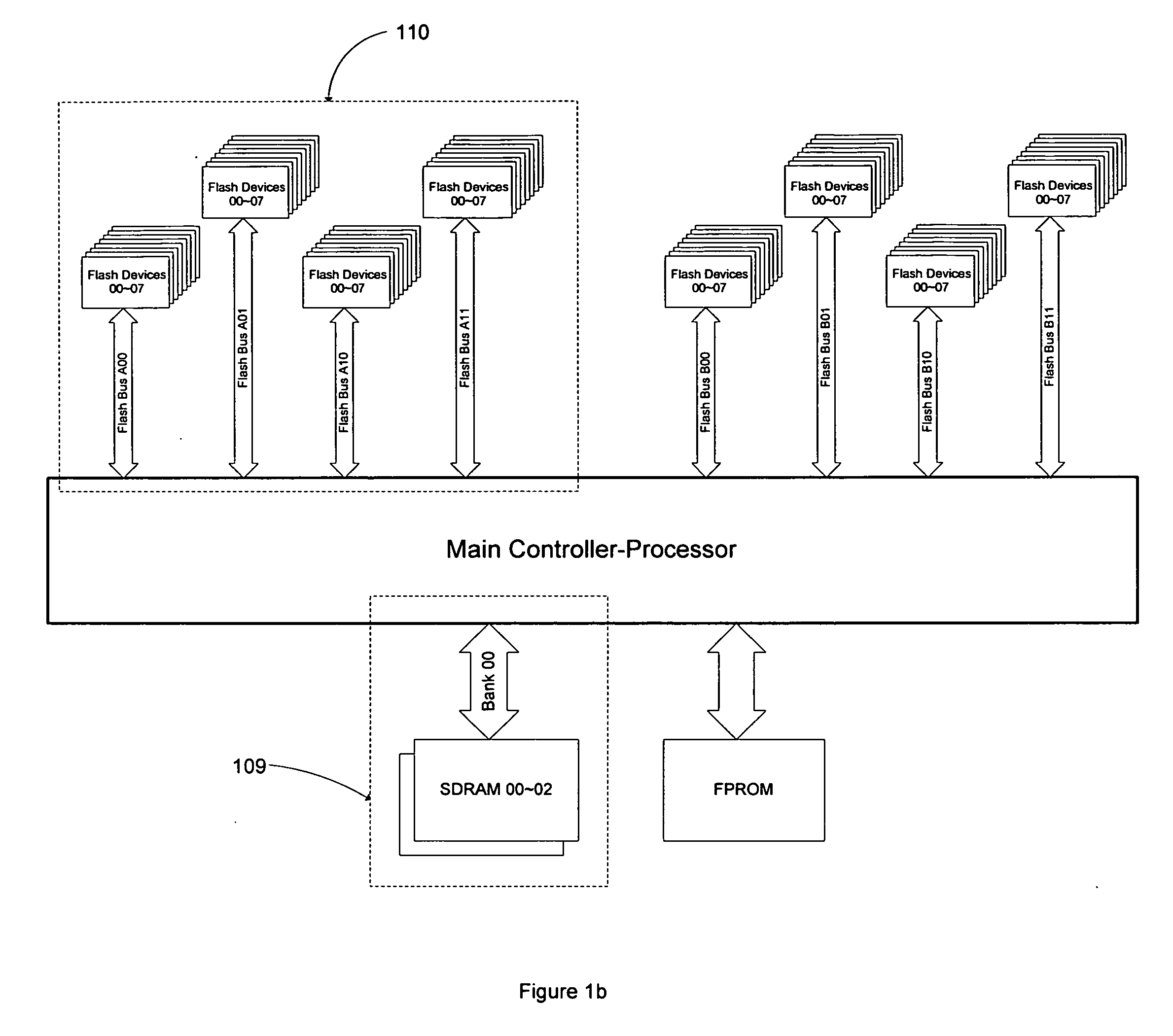

Wear leveling techniques for flash EEPROM systems

InactiveUS6850443B2Avoid uneven wearExtended service lifeMemory architecture accessing/allocationRead-only memoriesElectricityProgrammable read-only memory

A mass storage system made of flash electrically erasable and programmable read only memory (“EEPROM”) cells organized into blocks, the blocks in turn being grouped into memory banks, is managed to even out the numbers of erase and rewrite cycles experienced by the memory banks in order to extend the service lifetime of the memory system. Since this type of memory cell becomes unusable after a finite number of erase and rewrite cycles, although in the tens of thousands of cycles, uneven use of the memory banks is avoided so that the entire memory does not become inoperative because one of its banks has reached its end of life while others of the banks are little used. Relative use of the memory banks is monitored and, in response to detection of uneven use, have their physical addresses periodically swapped for each other in order to even out their use over the lifetime of the memory.

Owner:SANDISK TECH LLC

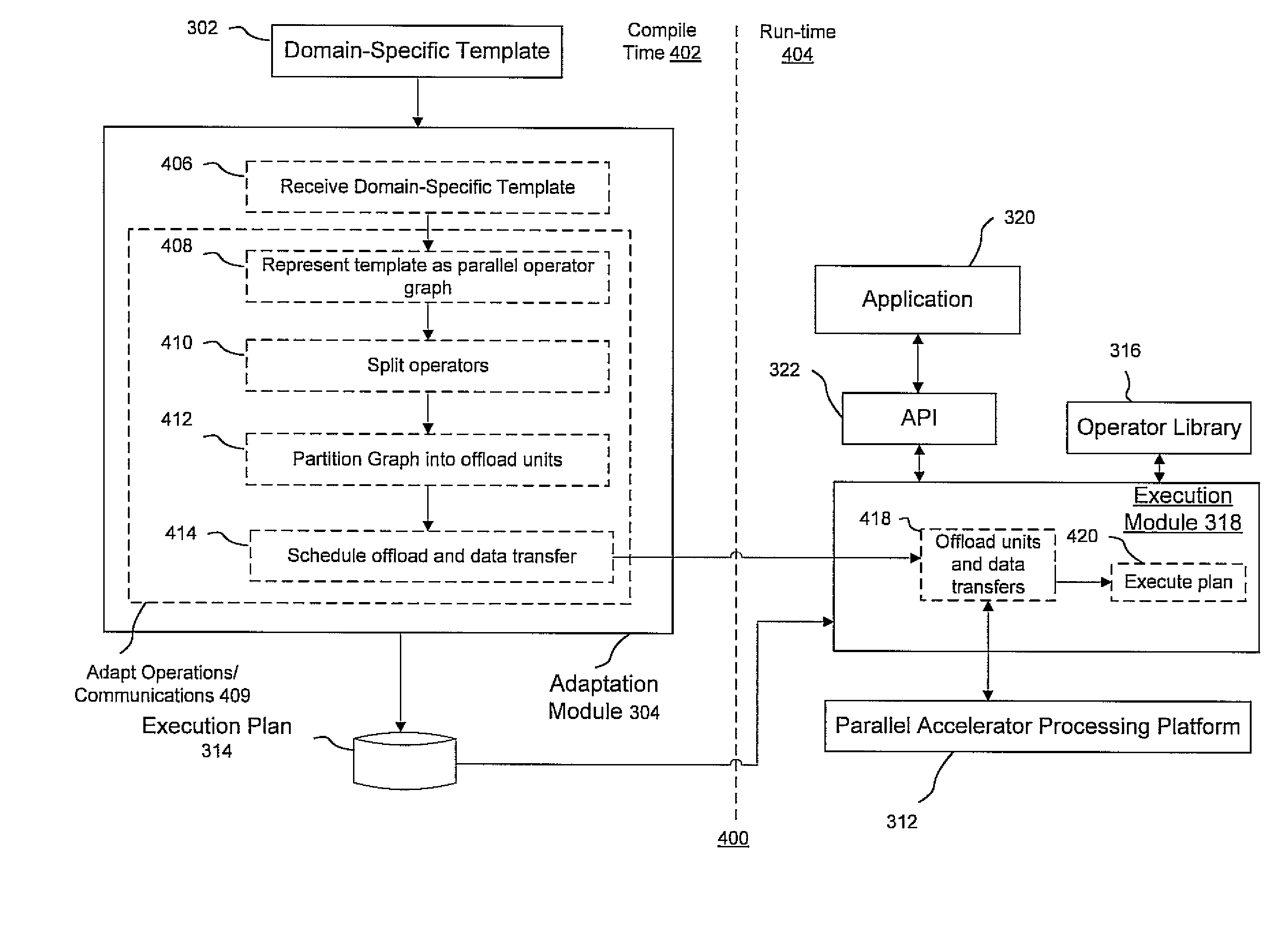

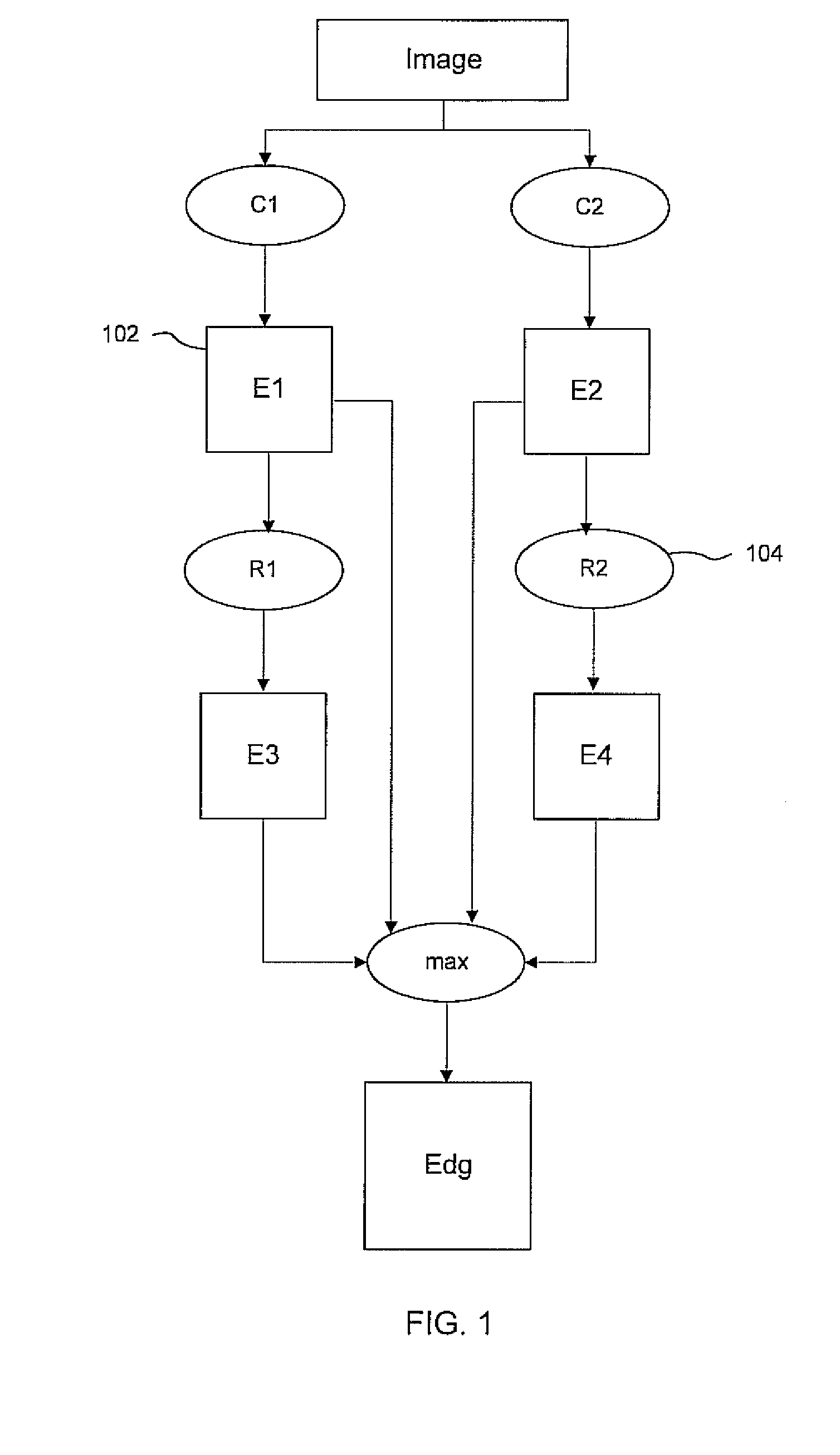

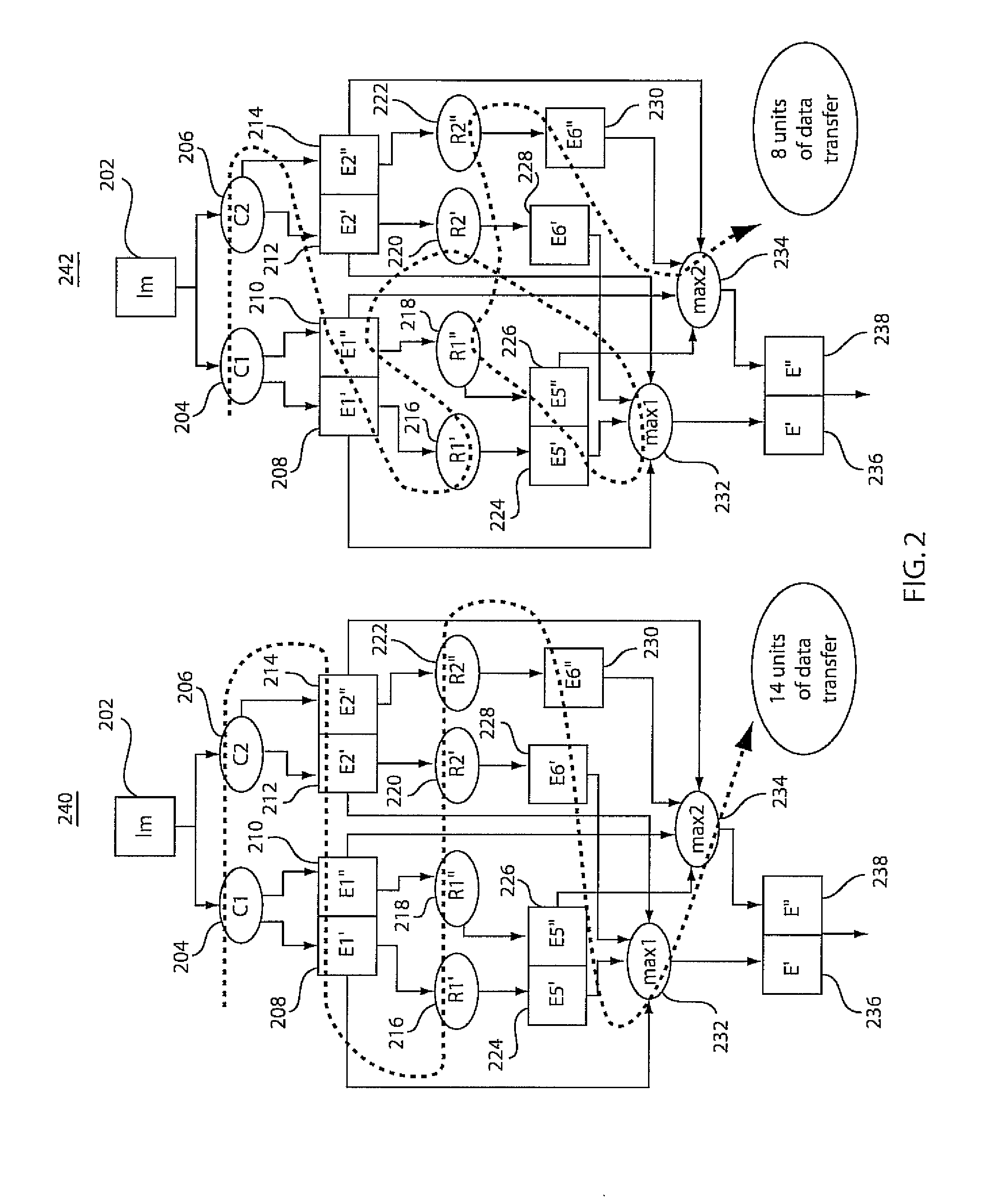

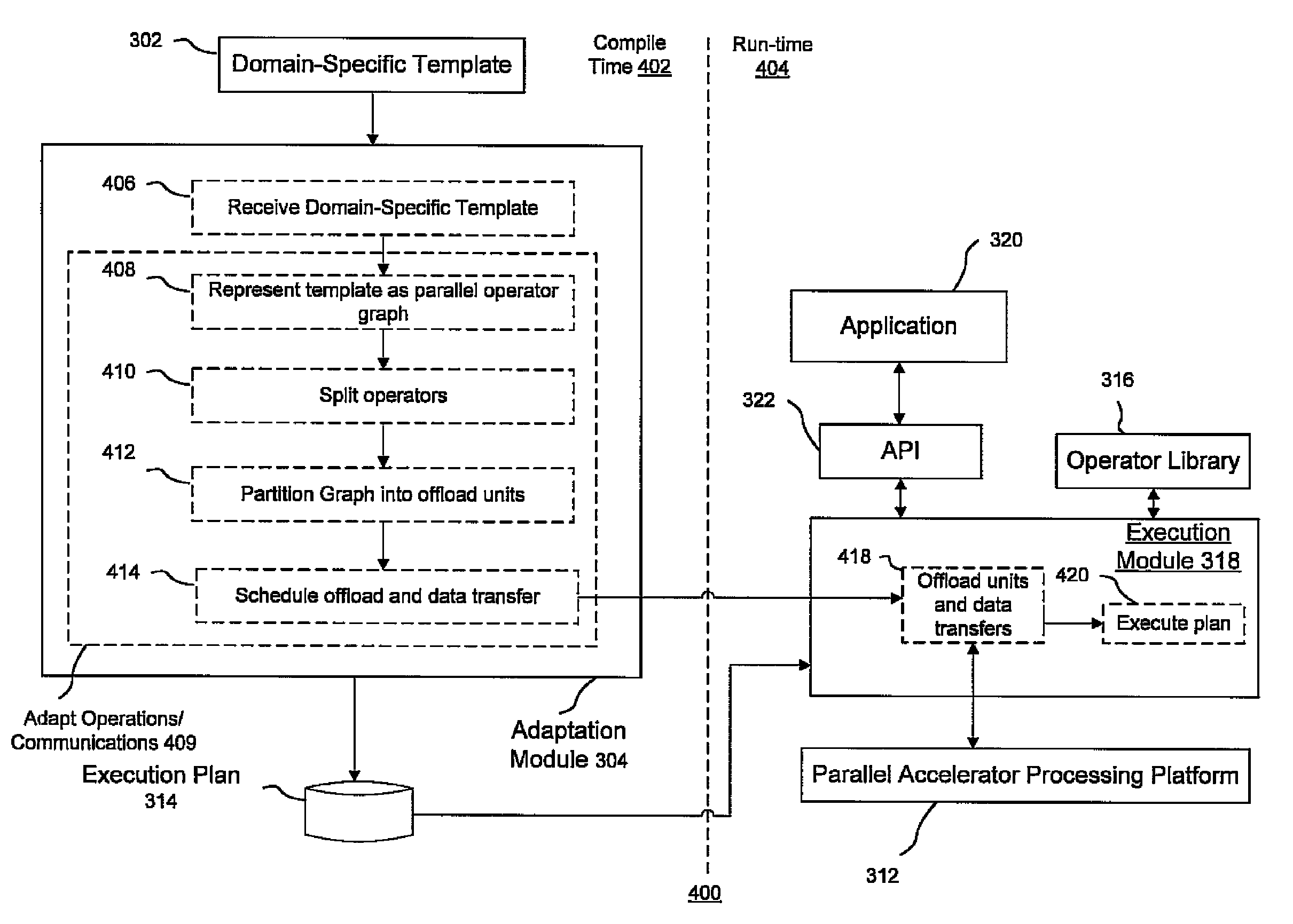

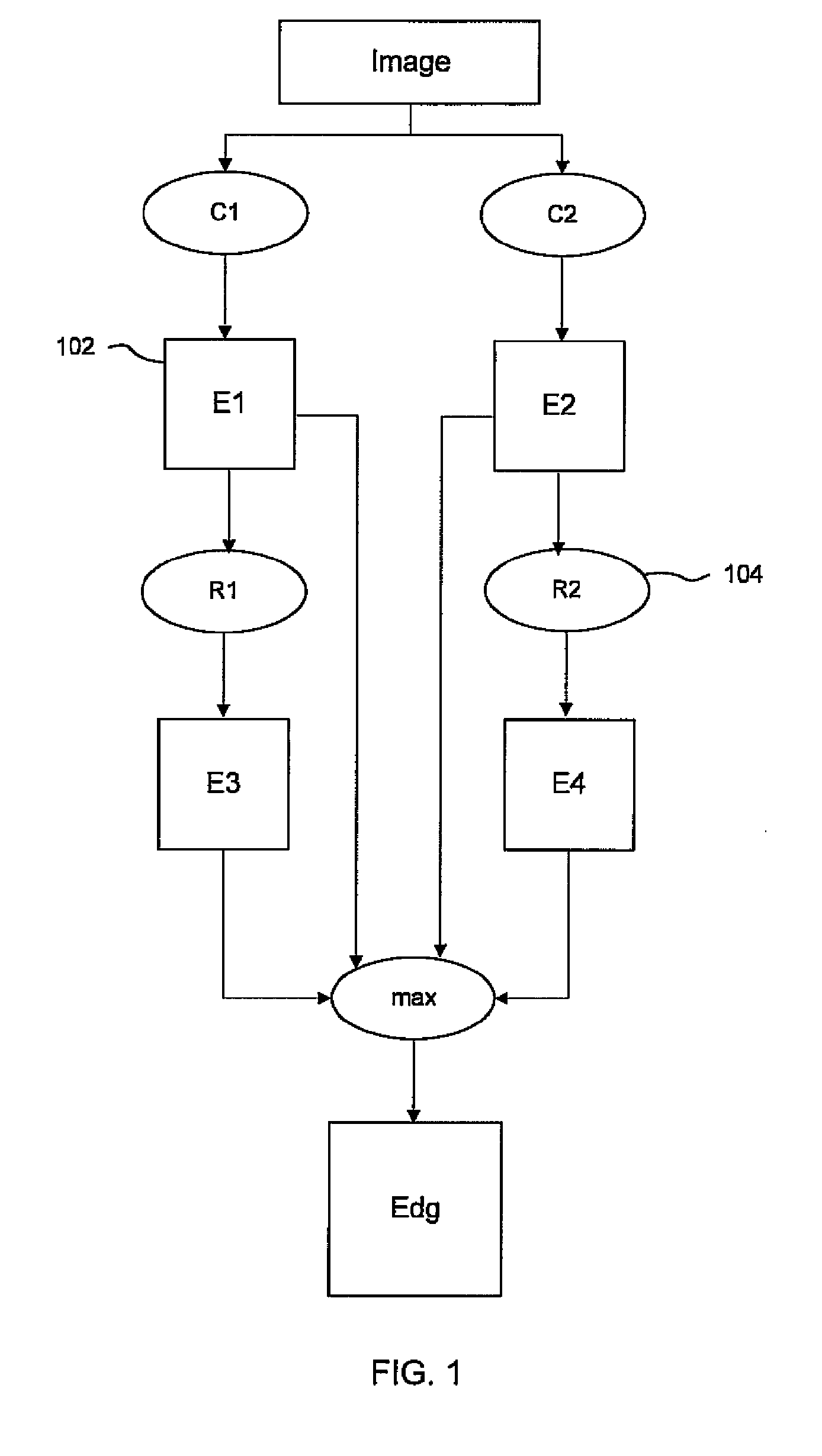

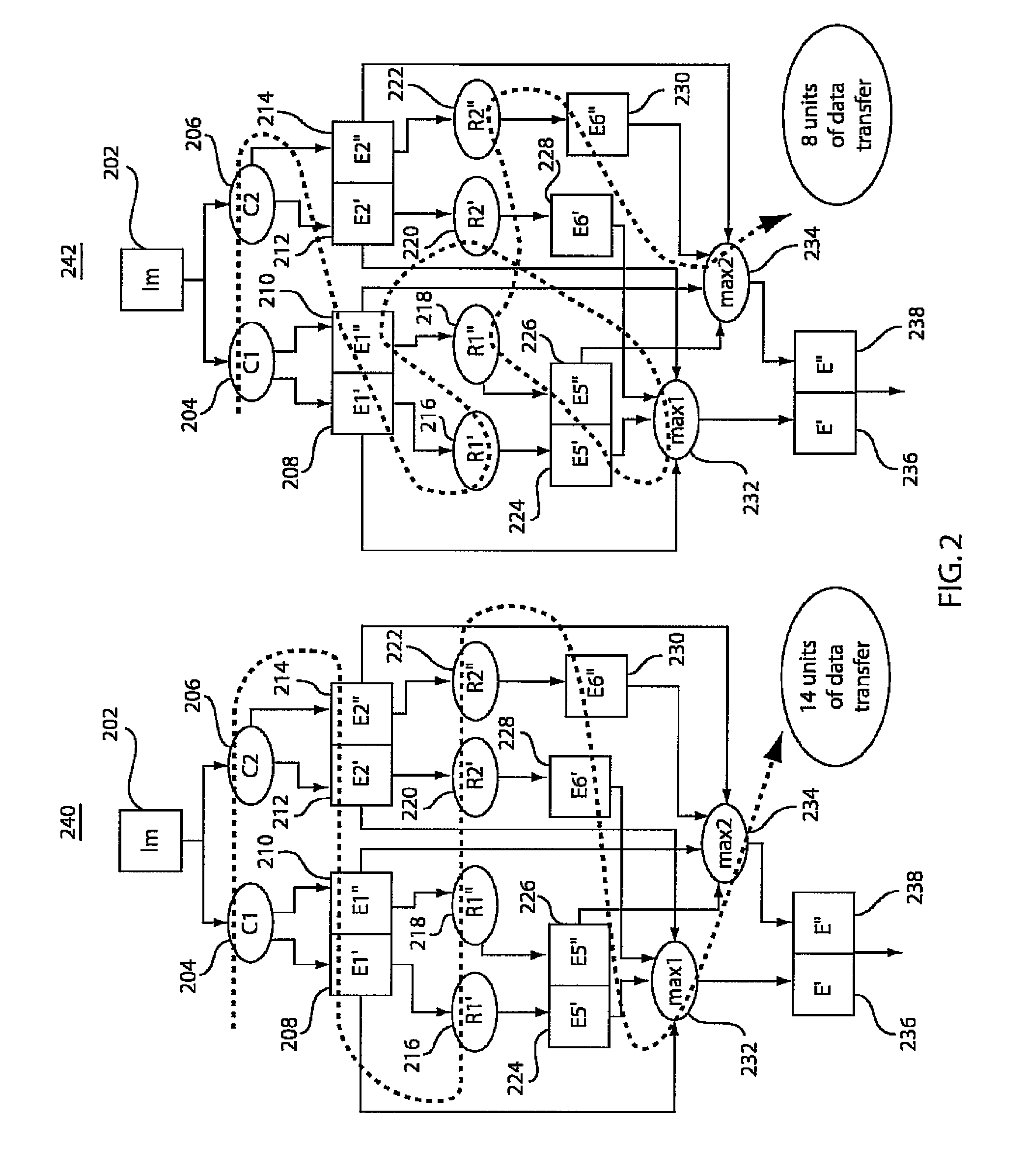

Methods and systems for managing computations on a hybrid computing platform including a parallel accelerator

ActiveUS20100088490A1Improve convenienceEfficient data transferProgram control using stored programsGeneral purpose stored program computerParallel computingData transmission

In accordance with exemplary implementations, application computation operations and communications between operations on a host processing platform may be adapted to conform to the memory capacity of a parallel accelerator. Computation operations may be split and scheduled such that the computation operations fit within the memory capacity of the accelerator. Further, the operations may be automatically adapted without any modification to the code of an application. In addition, data transfers between a host processing platform and the parallel accelerator may be minimized in accordance with exemplary aspects of the present principles to improve processing performance.

Owner:NEC CORP

Wear leveling techniques for flash EEPROM systems

InactiveUS20050114589A1Avoid uneven wearExtended service lifeMemory architecture accessing/allocationRead-only memoriesElectricityProgrammable read-only memory

A mass storage system made of flash electrically erasable and programmable read only memory (“EEPROM”) cells organized into blocks, the blocks in turn being grouped into memory banks, is managed to even out the numbers of erase and rewrite cycles experienced by the memory banks in order to extend the service lifetime of the memory system. Since this type of memory cell becomes unusable after a finite number of erase and rewrite cycles, although in the tens of thousands of cycles, uneven use of the memory banks is avoided so that the entire memory does not become inoperative because one of its banks has reached its end of life while others of the banks are little used. Relative use of the memory banks is monitored and, in response to detection of uneven use, have their physical addresses periodically swapped for each other in order to even out their use over the lifetime of the memory.

Owner:SANDISK TECH LLC

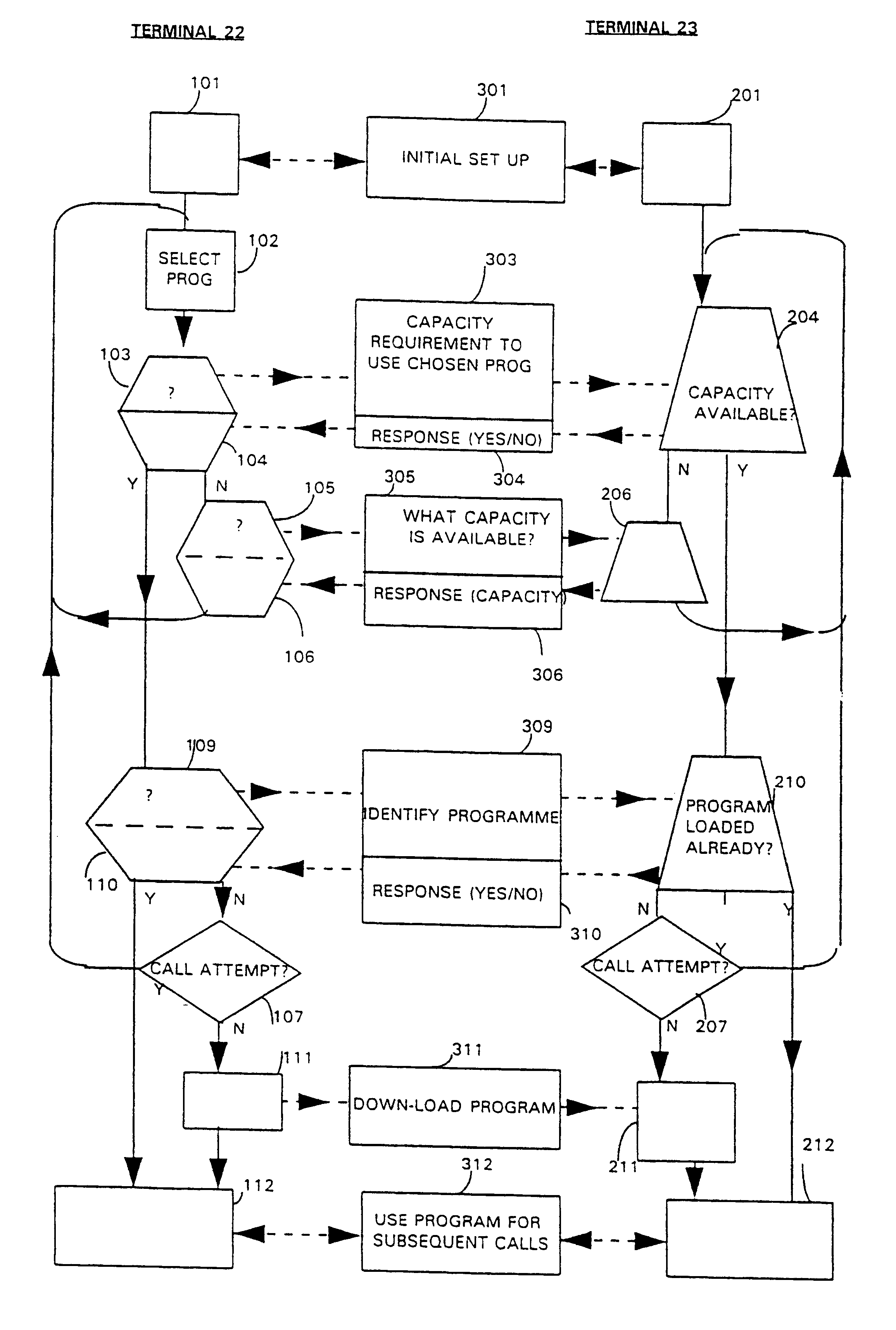

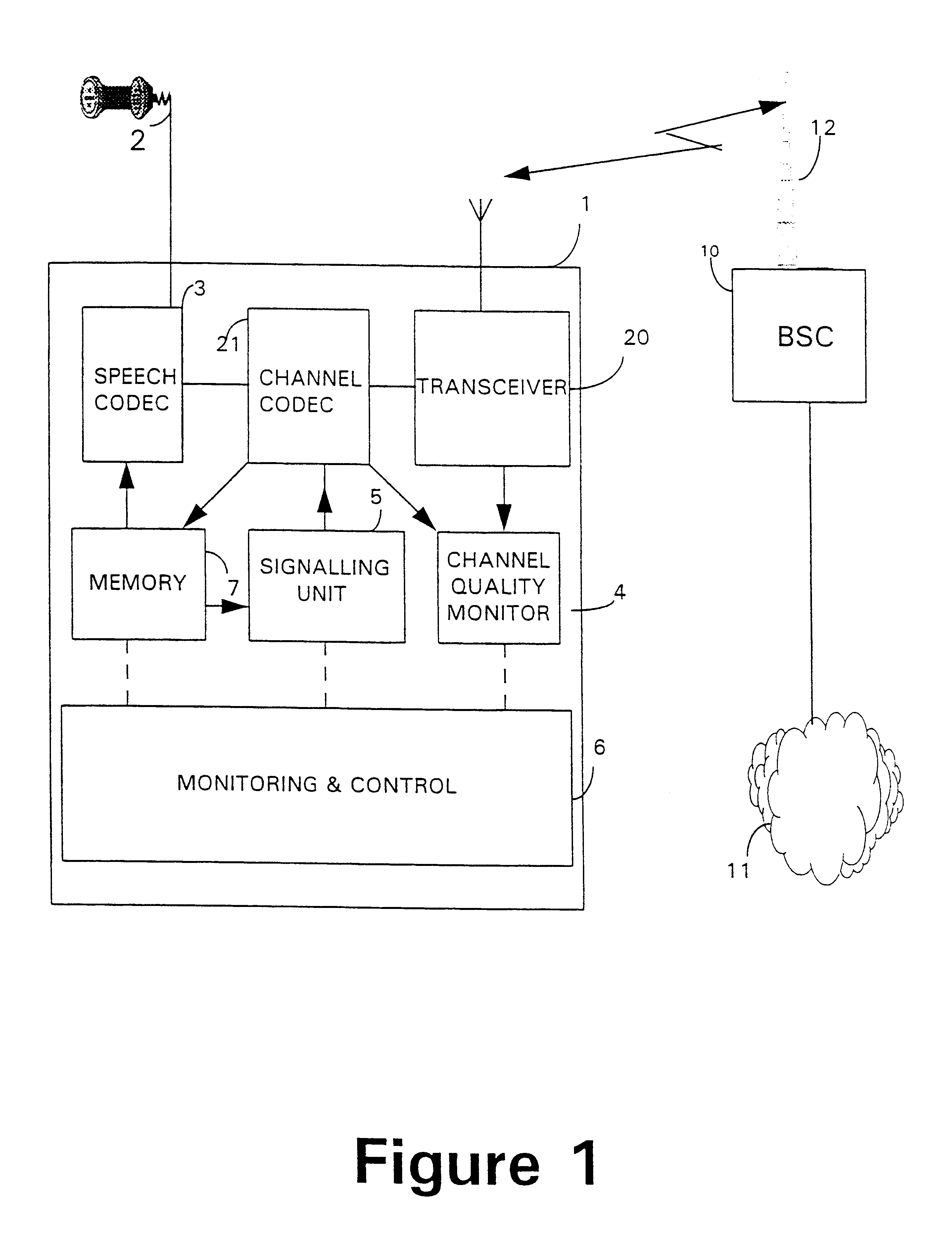

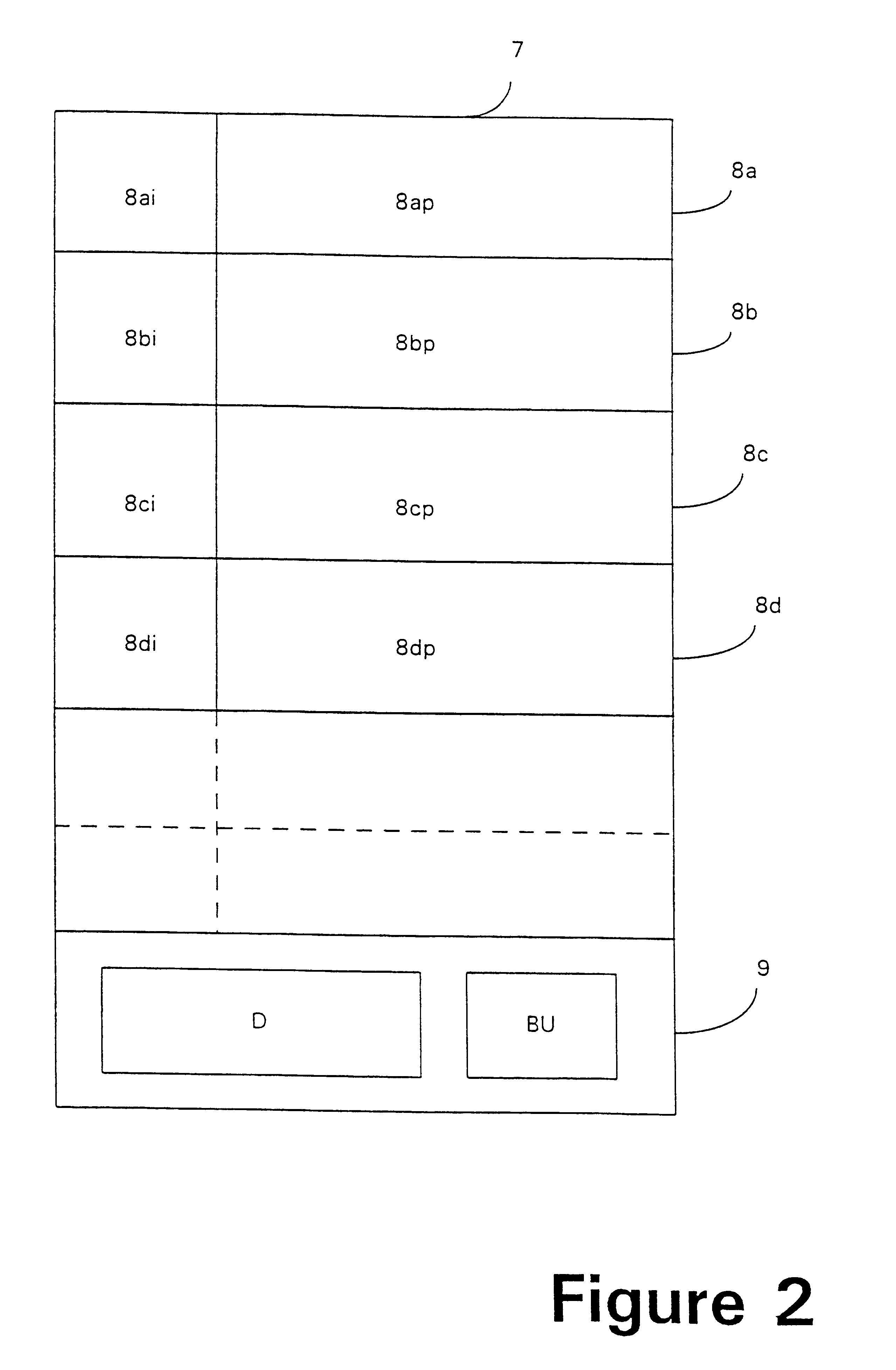

Provision of telecommunications control program data pursuant to preliminary data exchange between system elements

InactiveUS6349204B1Large memory capacityIdentify the optimum program more quicklyConnection managementSource coding adaptationMode controlOperation mode

During connection set up between a mobile telephone and a base station, program data is acquired from the network for controlling its mode of operation. The mobile telephone and base station each have a memory for storing program data relating to one or more modes of operation. The base station transmits a signal indicative of a preferred mode of operation and the mobile responds with a signal indicative of whether its memory already contains program data for this mode of operation. If not, then the base station transmits the required program data. The base station and mobile telephone then operate in this preferred mode. If the mobile is not so capable (for example because it has insufficient memory), the process is repeated with different mode control programs until the most appropriate mutually compatible program is identified. If a call attempt is initiated before this process is complete, the process is curtailed, such that the base station and mobile telephone identify programs already stored in the memory, but make no attempt to load a new program, as this could delay call set-up.

Owner:BRITISH TELECOMM PLC

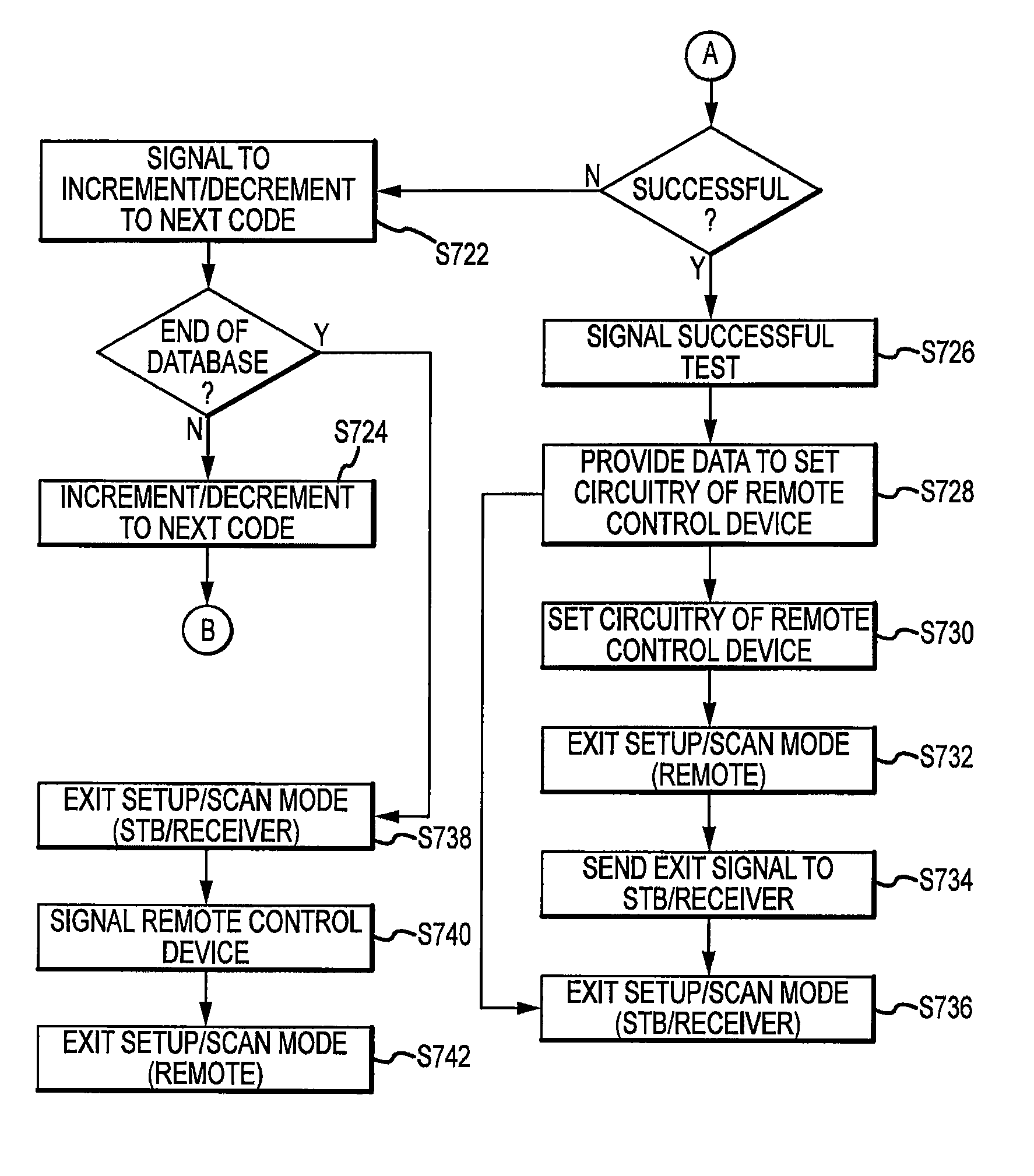

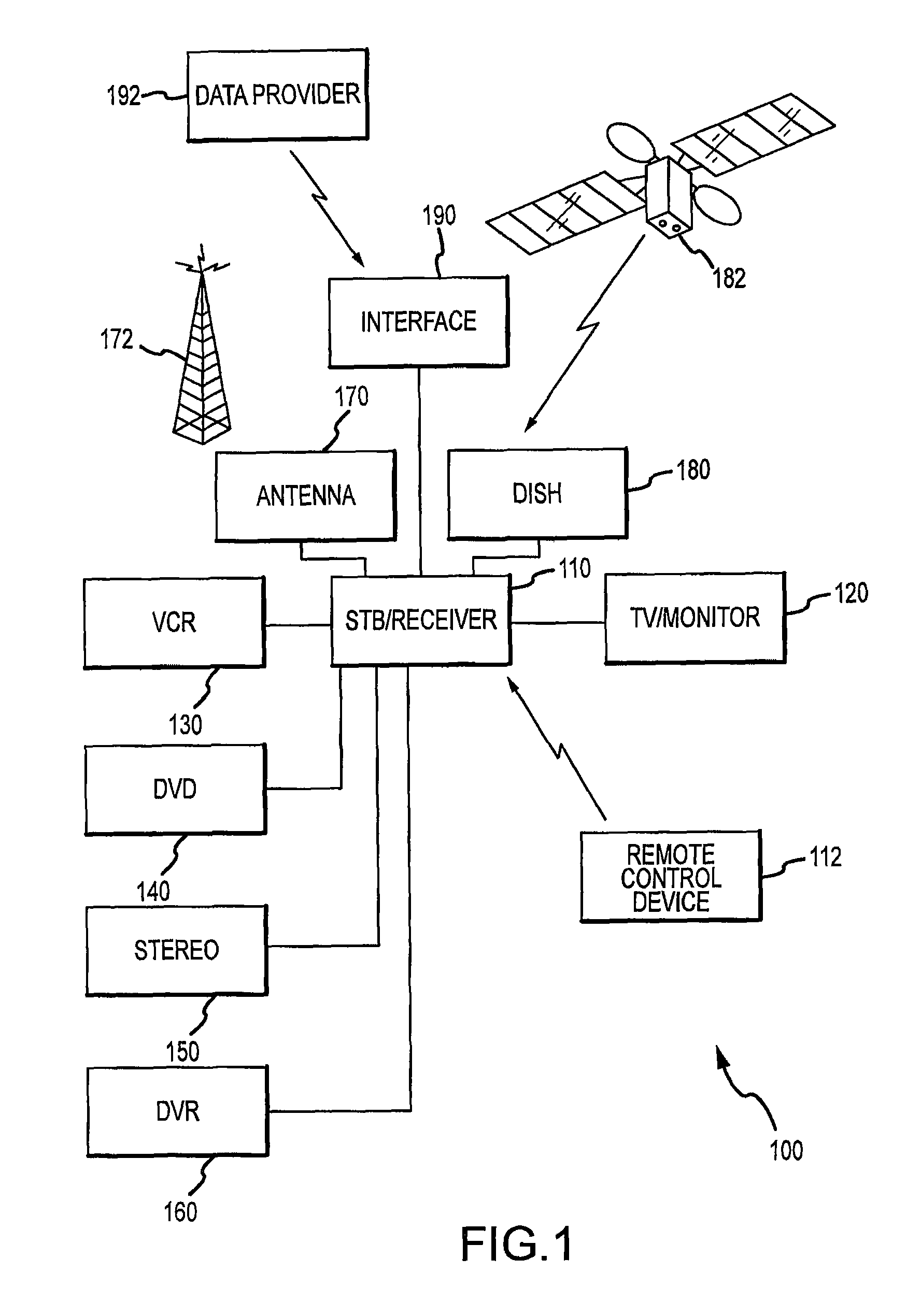

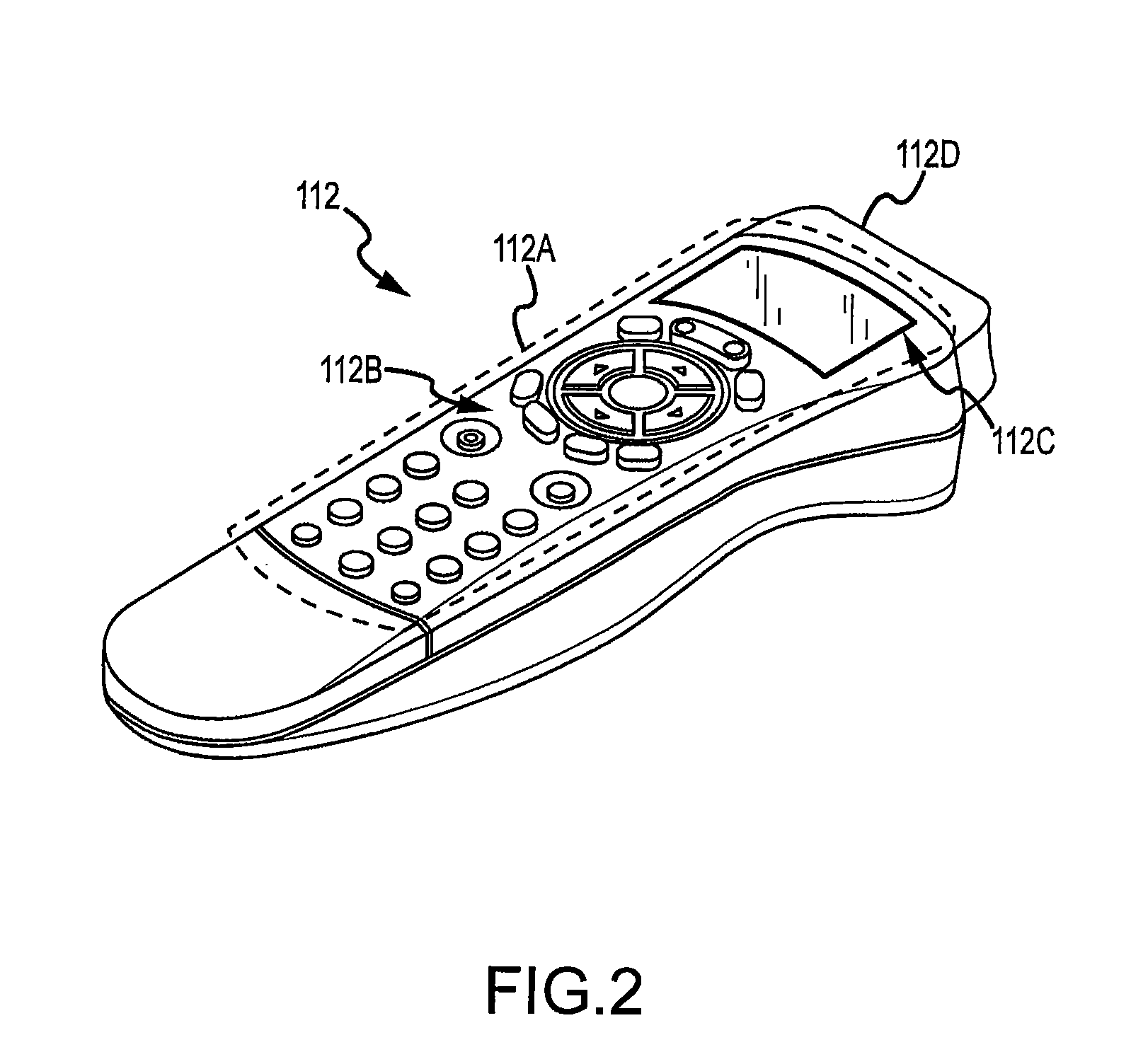

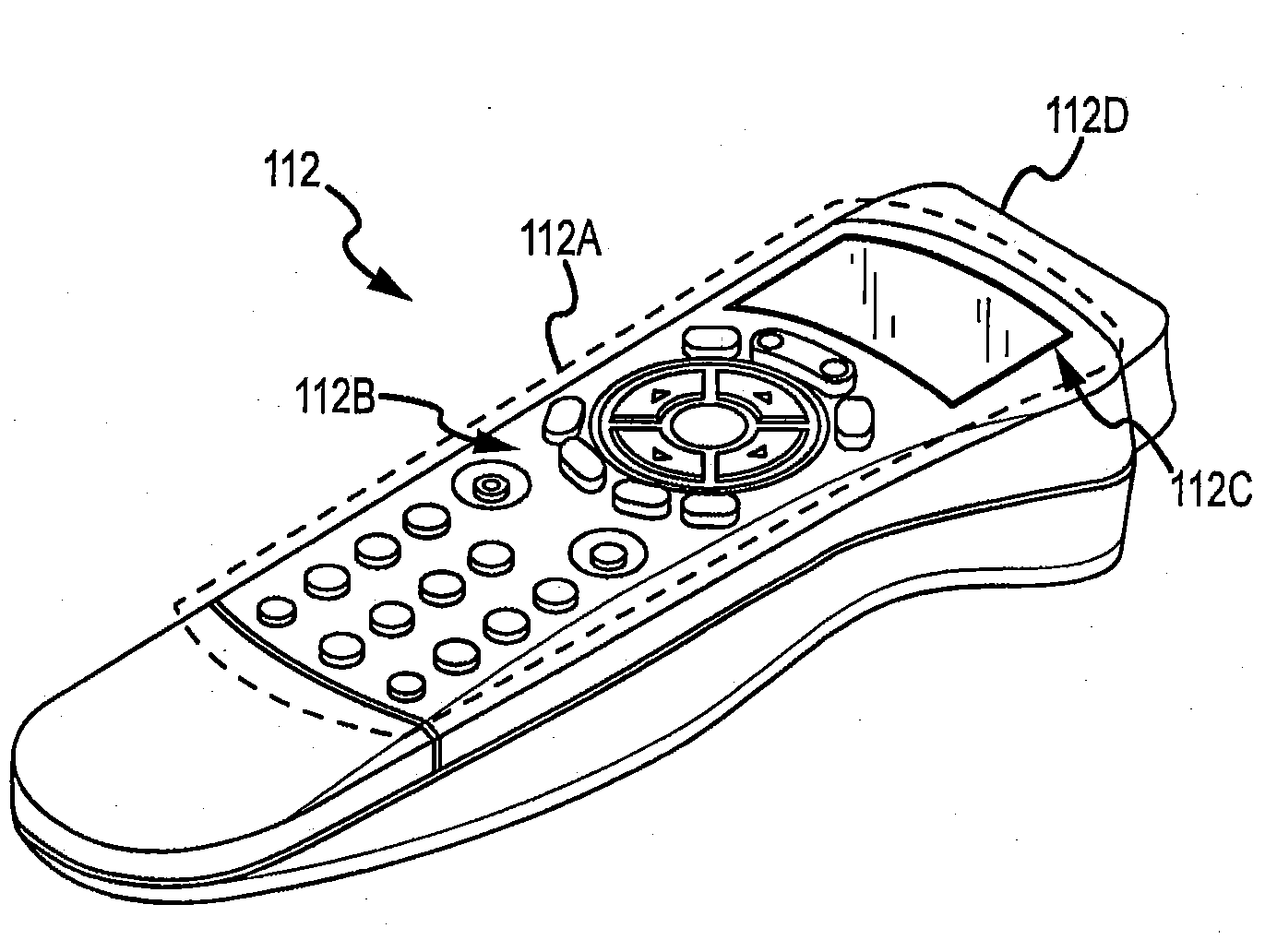

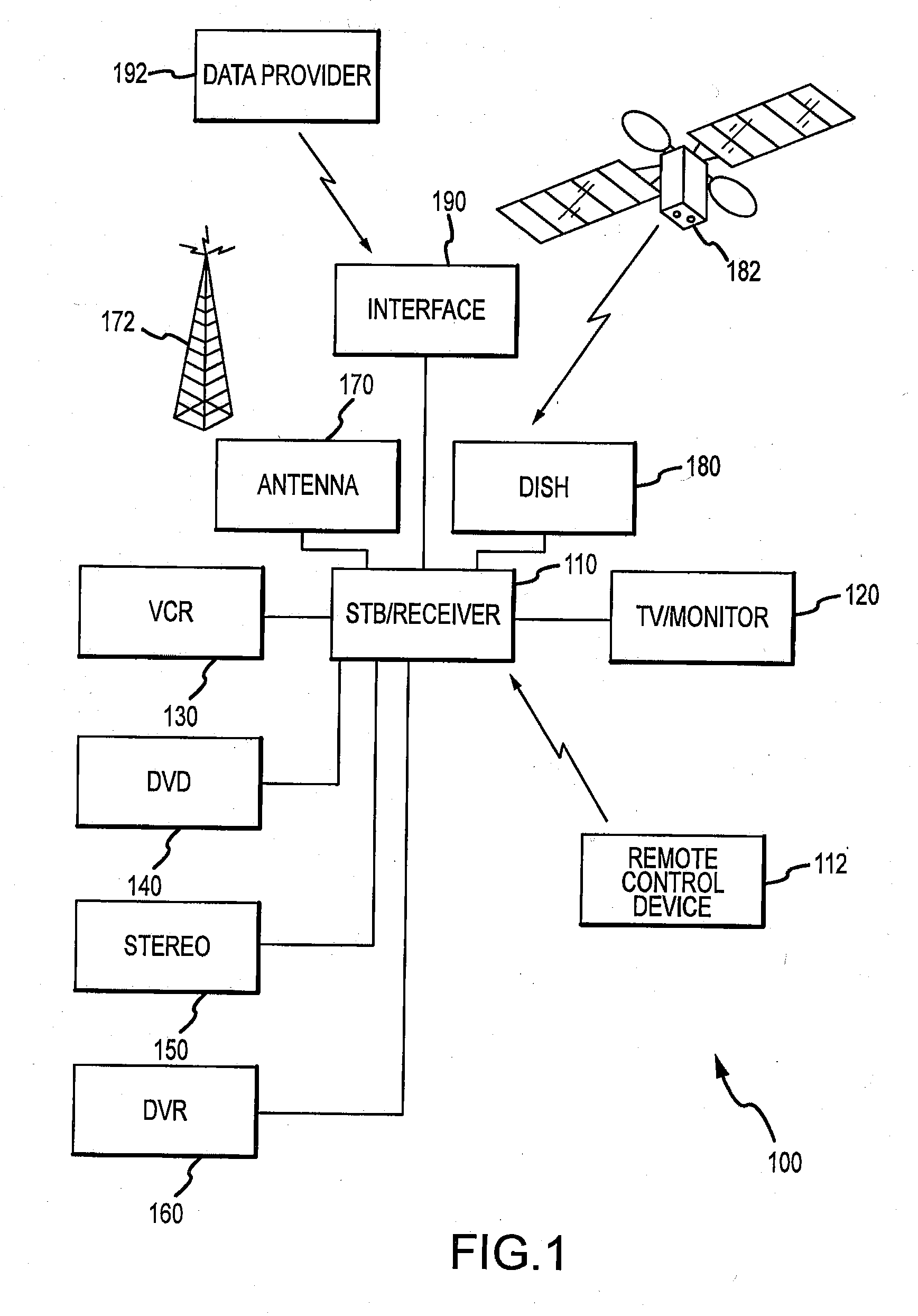

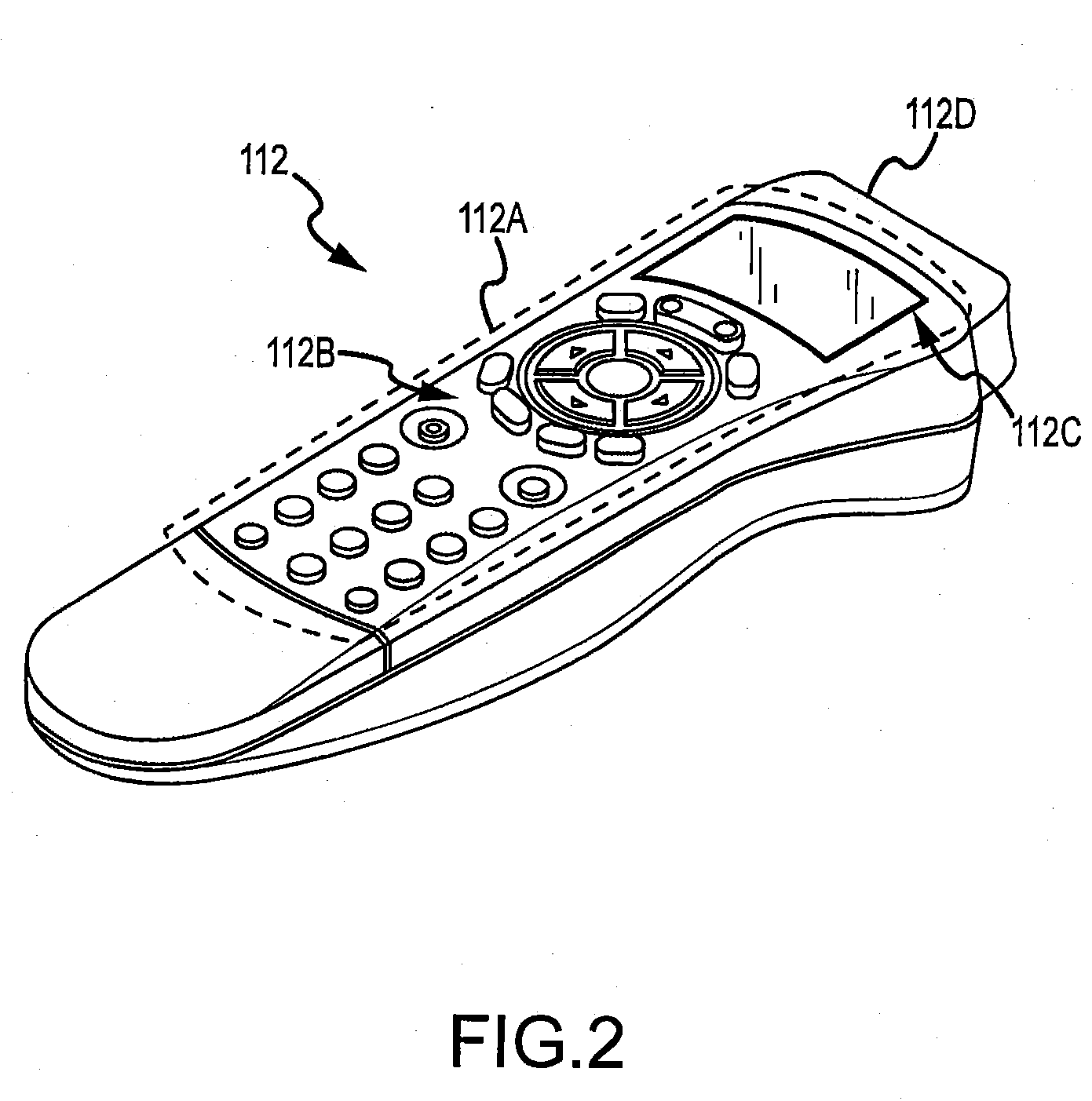

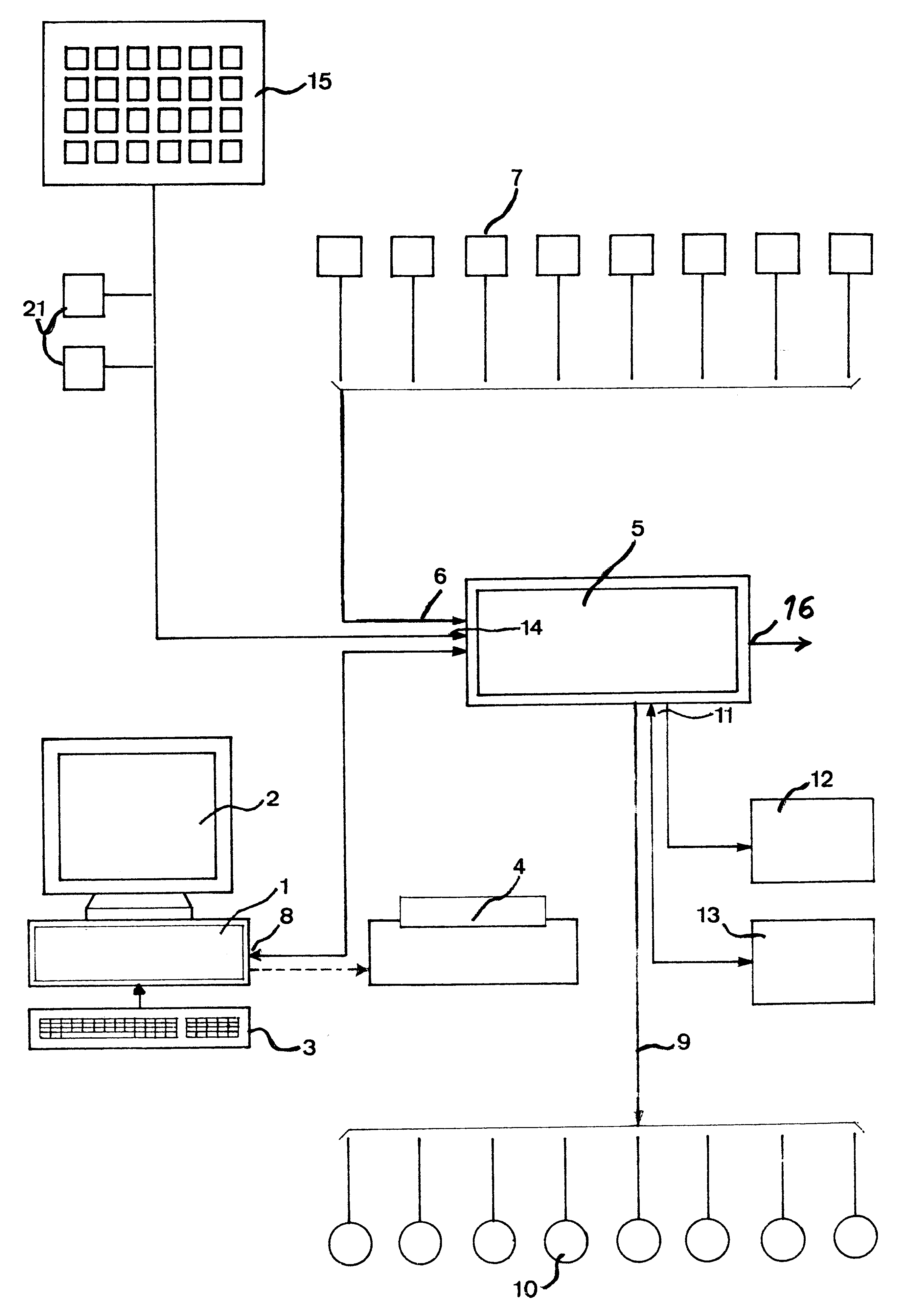

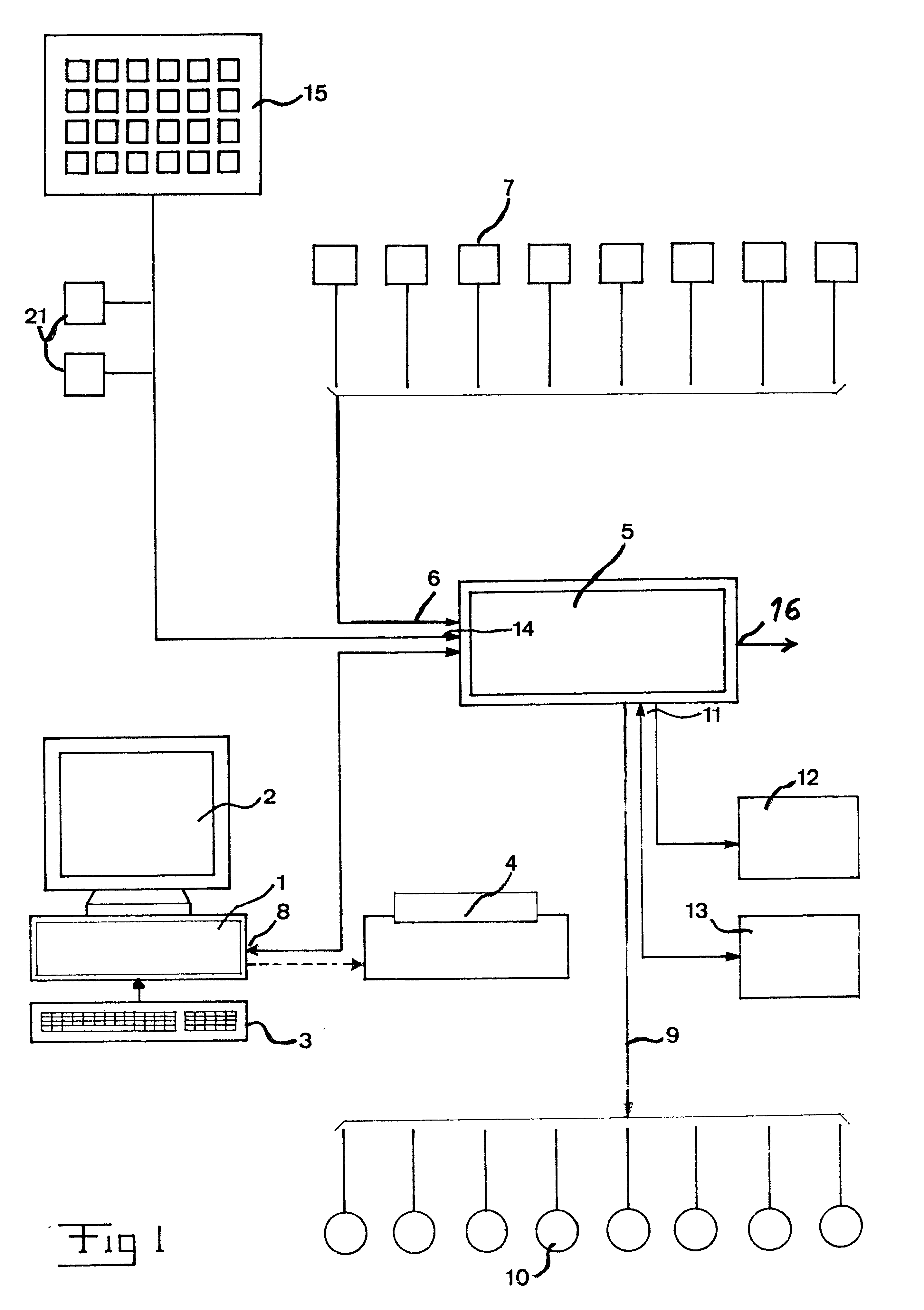

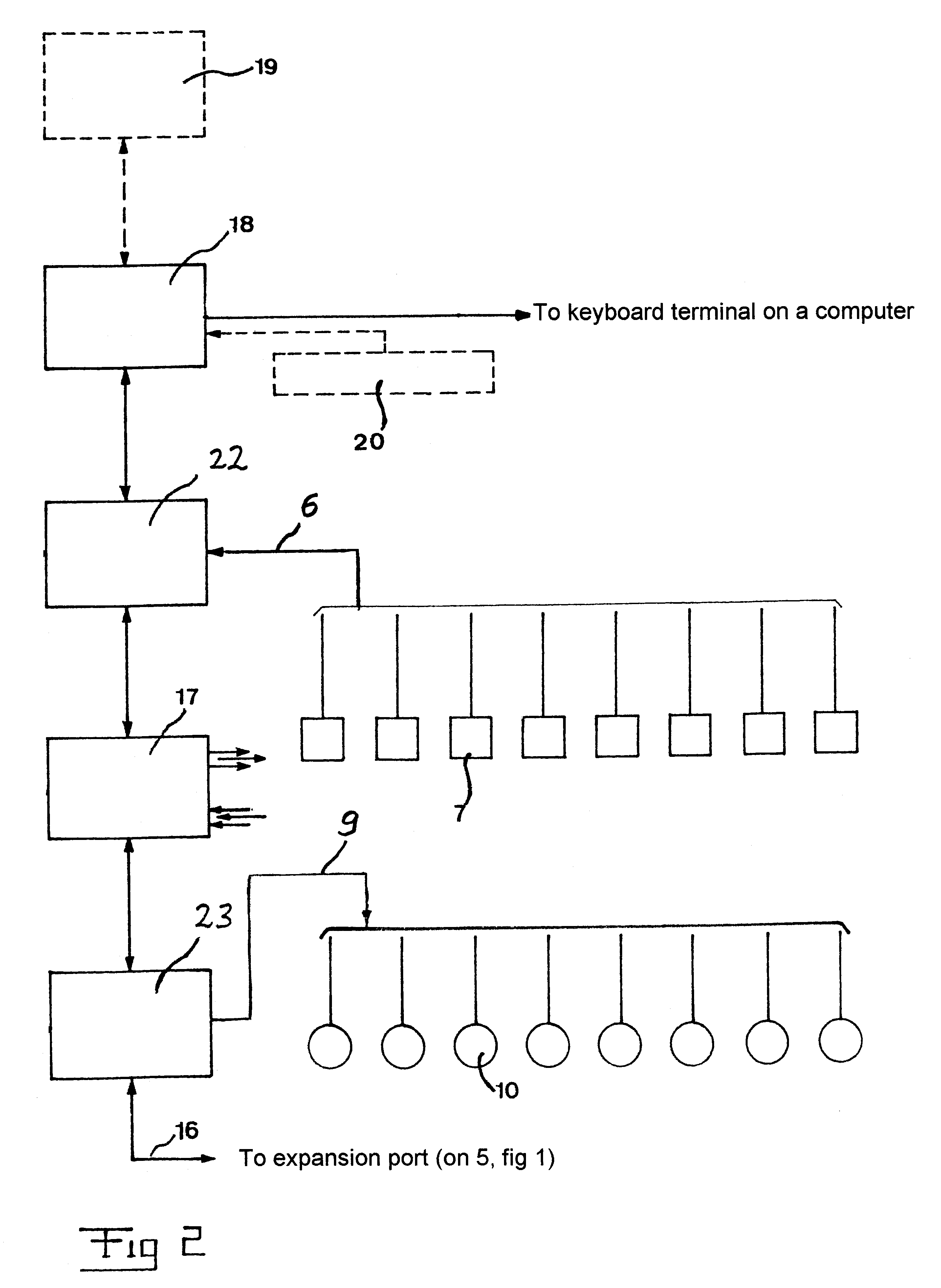

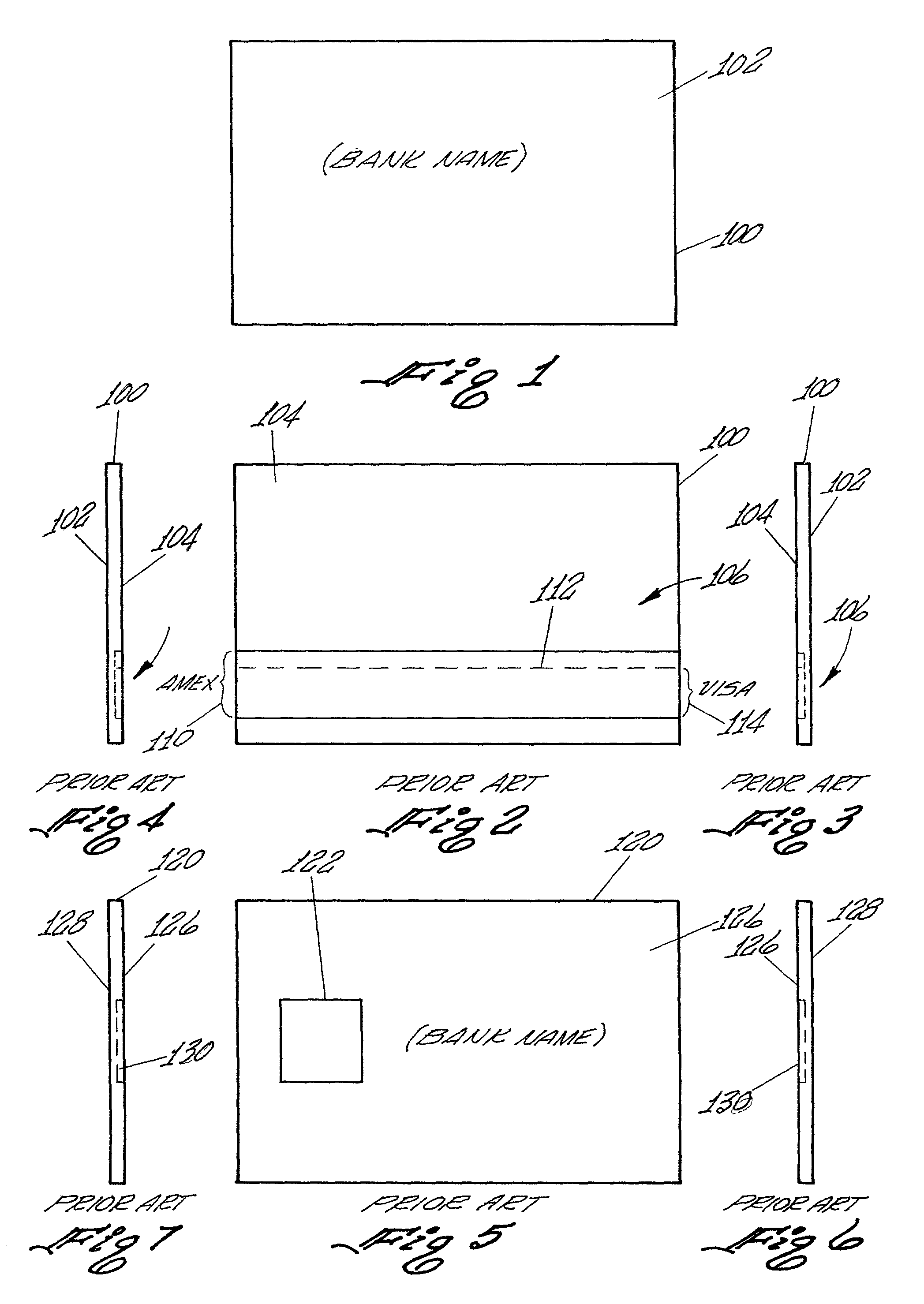

Systems and methods for remote control setup

ActiveUS9202372B2Increase the number ofGreat storage and memory capacityElectric signal transmission systemsEqual length code transmitterRemote controlOutput device

A remote control device may include: first circuitry to control a function of a first electronic device; second circuitry to be set to control a function of a second electronic device; and a setup controller to set the second circuitry to control a function of a target electronic device based on a code received from a separate device. An electronic device to be controlled by a remote control device may include: an input device to receive a signal from the remote control device; an output device to send a signal to the remote control device; and a processor coupled to the input and output devices, and configured to access a database of codes and to selectively provide codes from the database to the remote control device, the codes configured to set circuitry of the remote control device to control a function of the electronic device and / or an auxiliary electronic device.

Owner:DISH TECH L L C

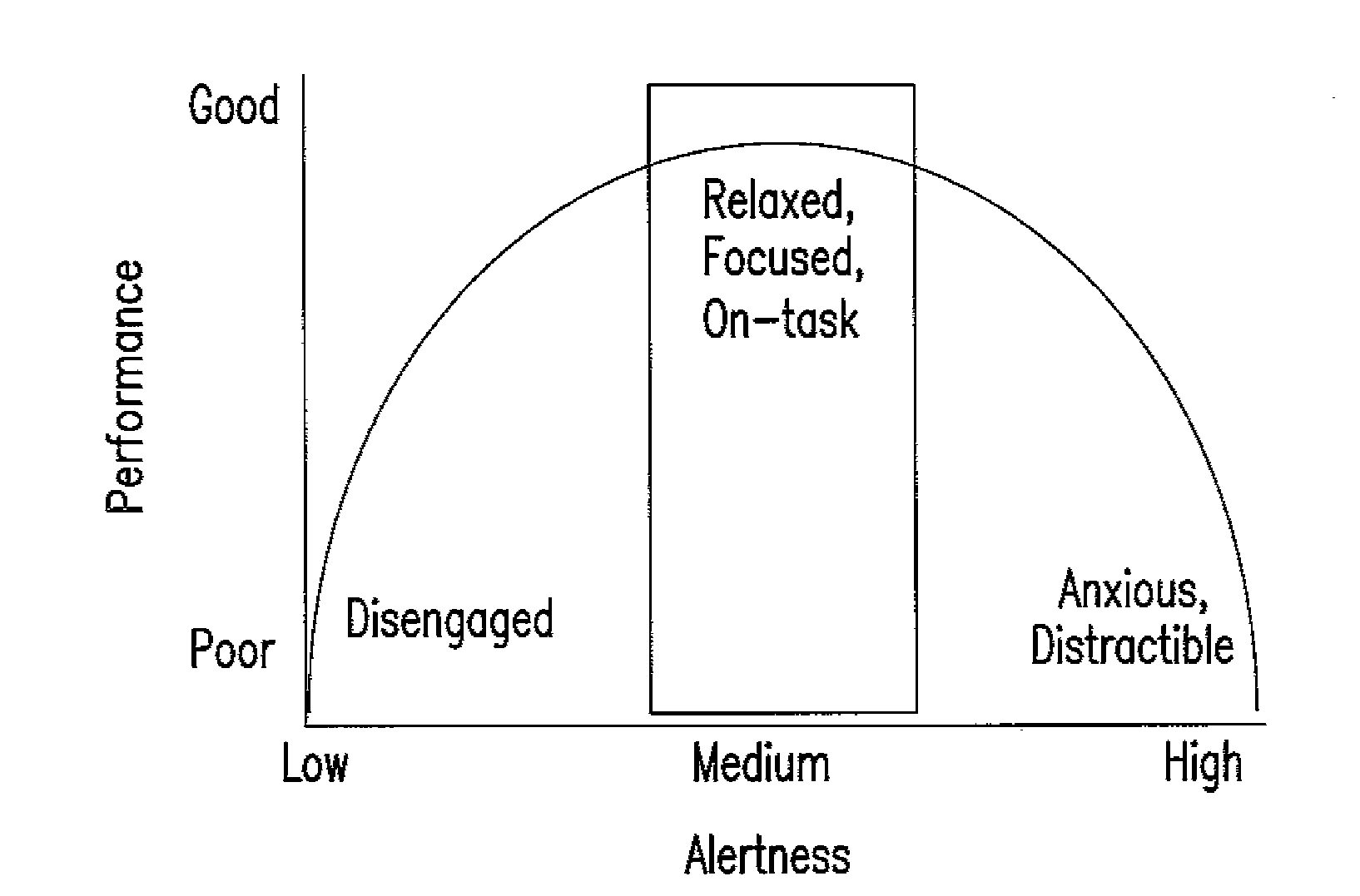

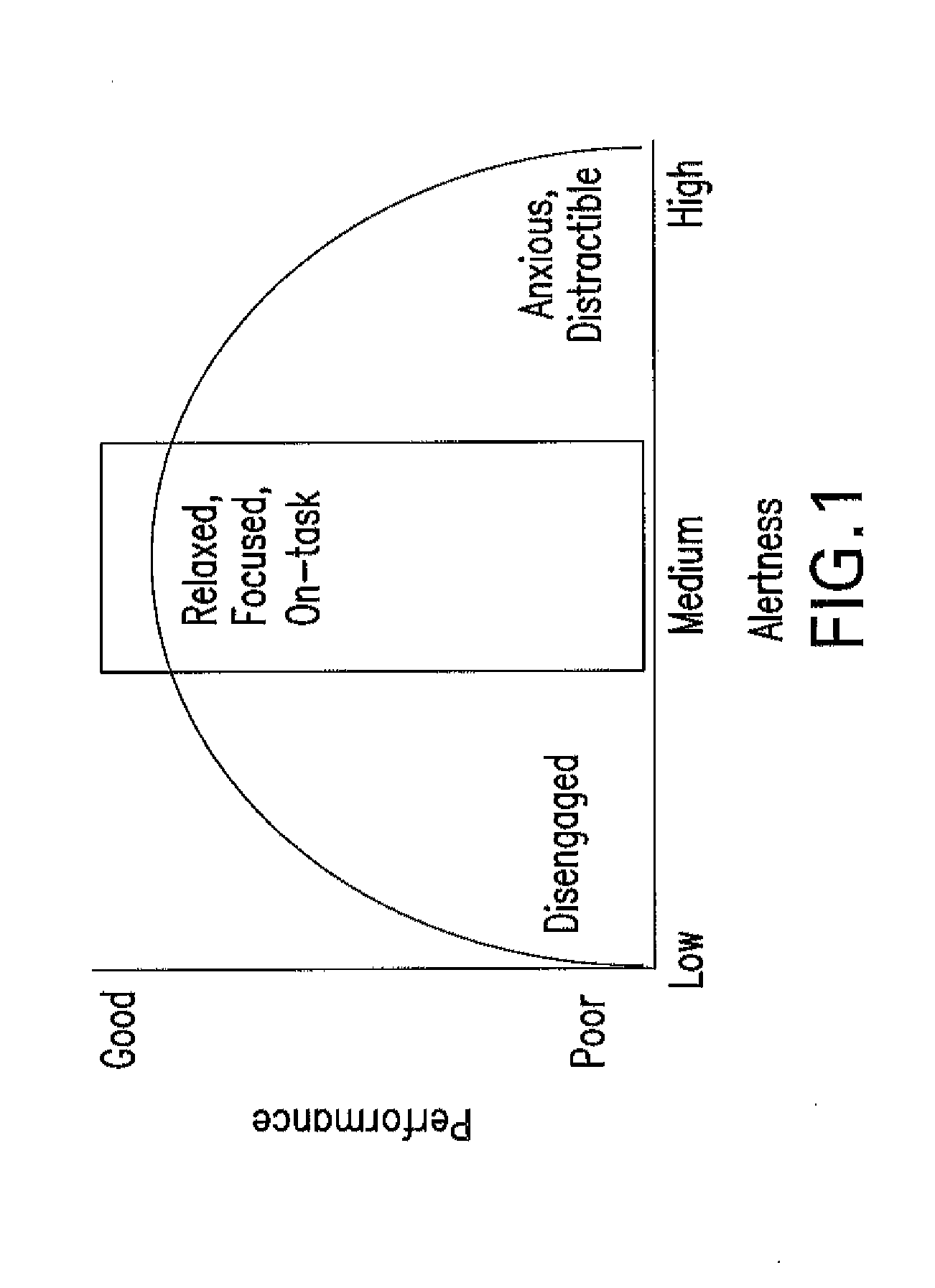

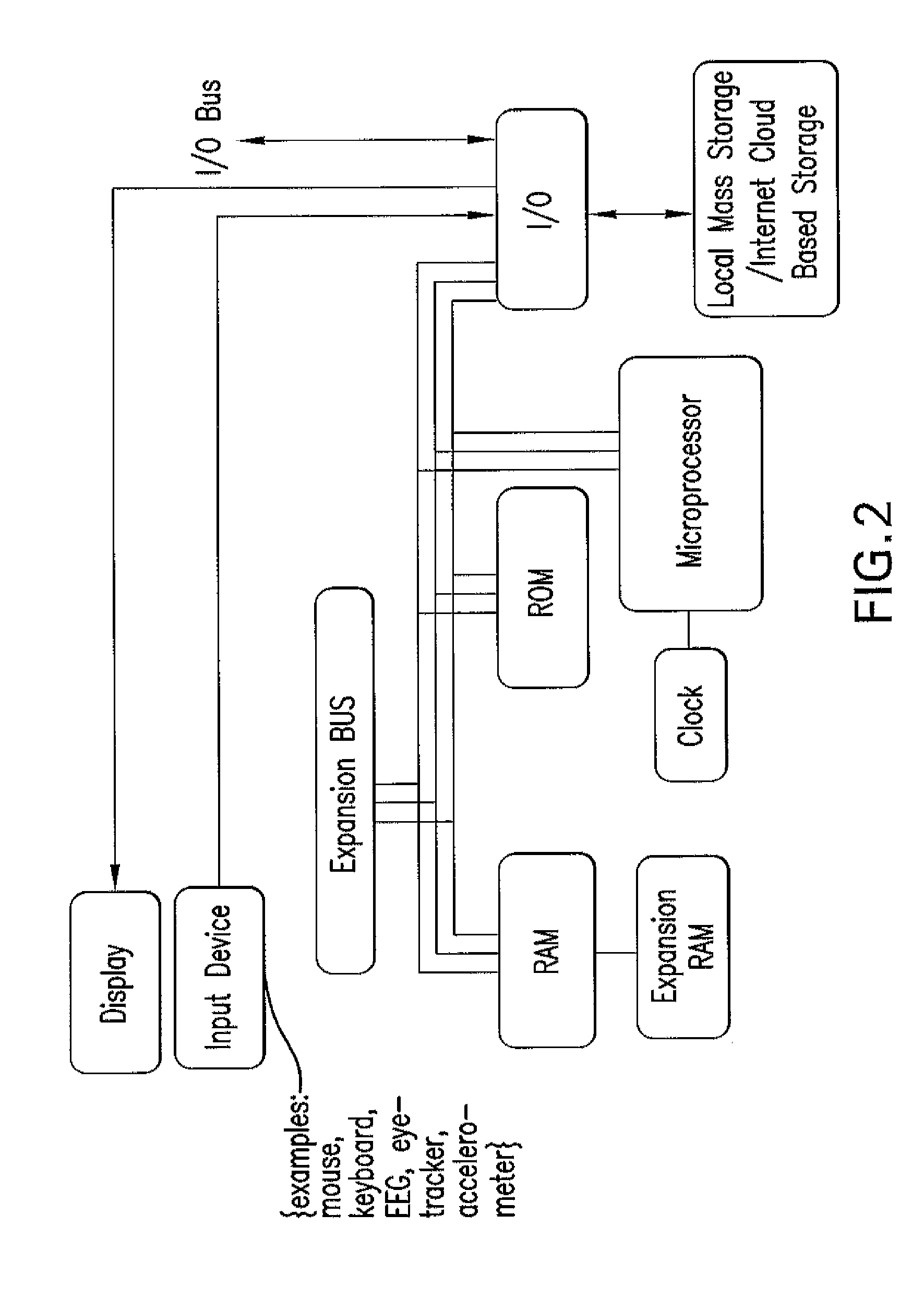

Computer-implemented interactive behavioral training technique for the optimization of attention or remediation of disorders of attention

InactiveUS20120077160A1Enhancing attentional stateGood conditionElectrical appliancesTeaching apparatusTraining courseVisual perception

Owner:THE GOVERNMENT OF THE UNITED STATES OF AMERICA AS REPRESENTED BY THE DEPT OF VETERANS AFFAIRS

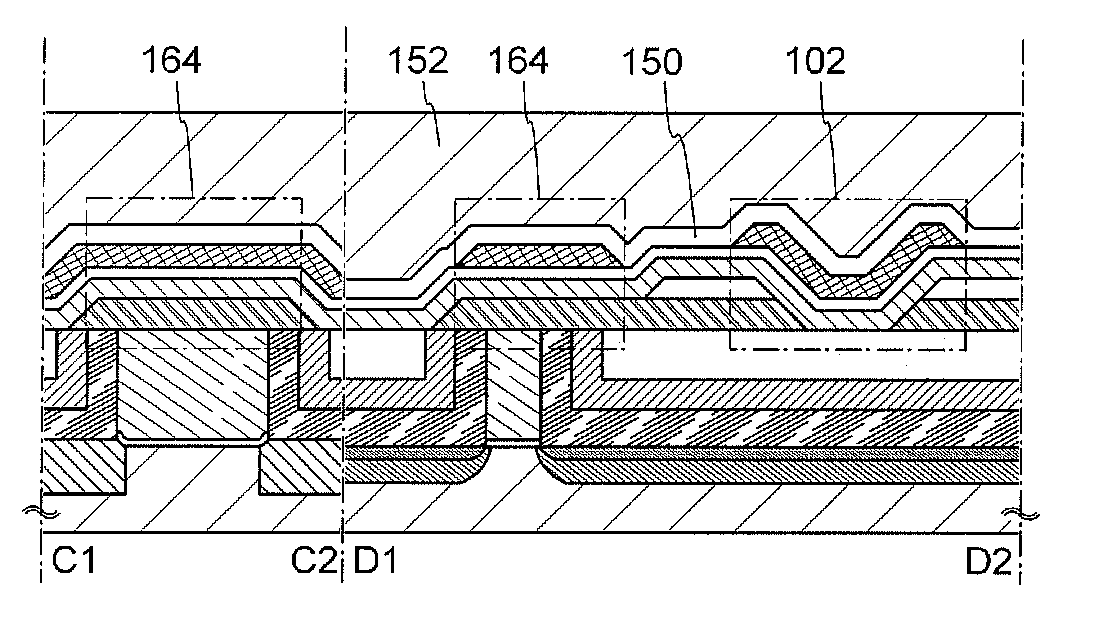

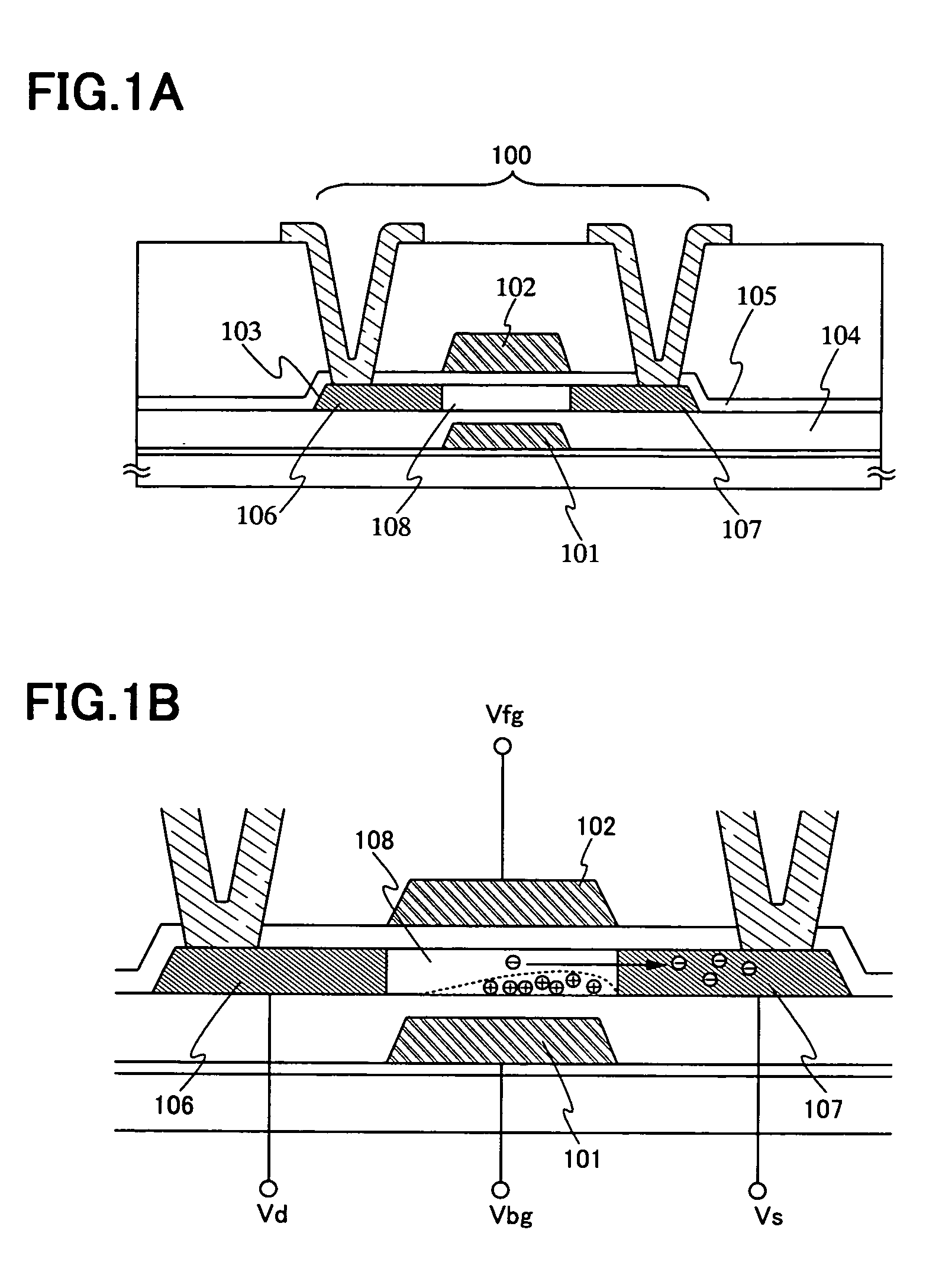

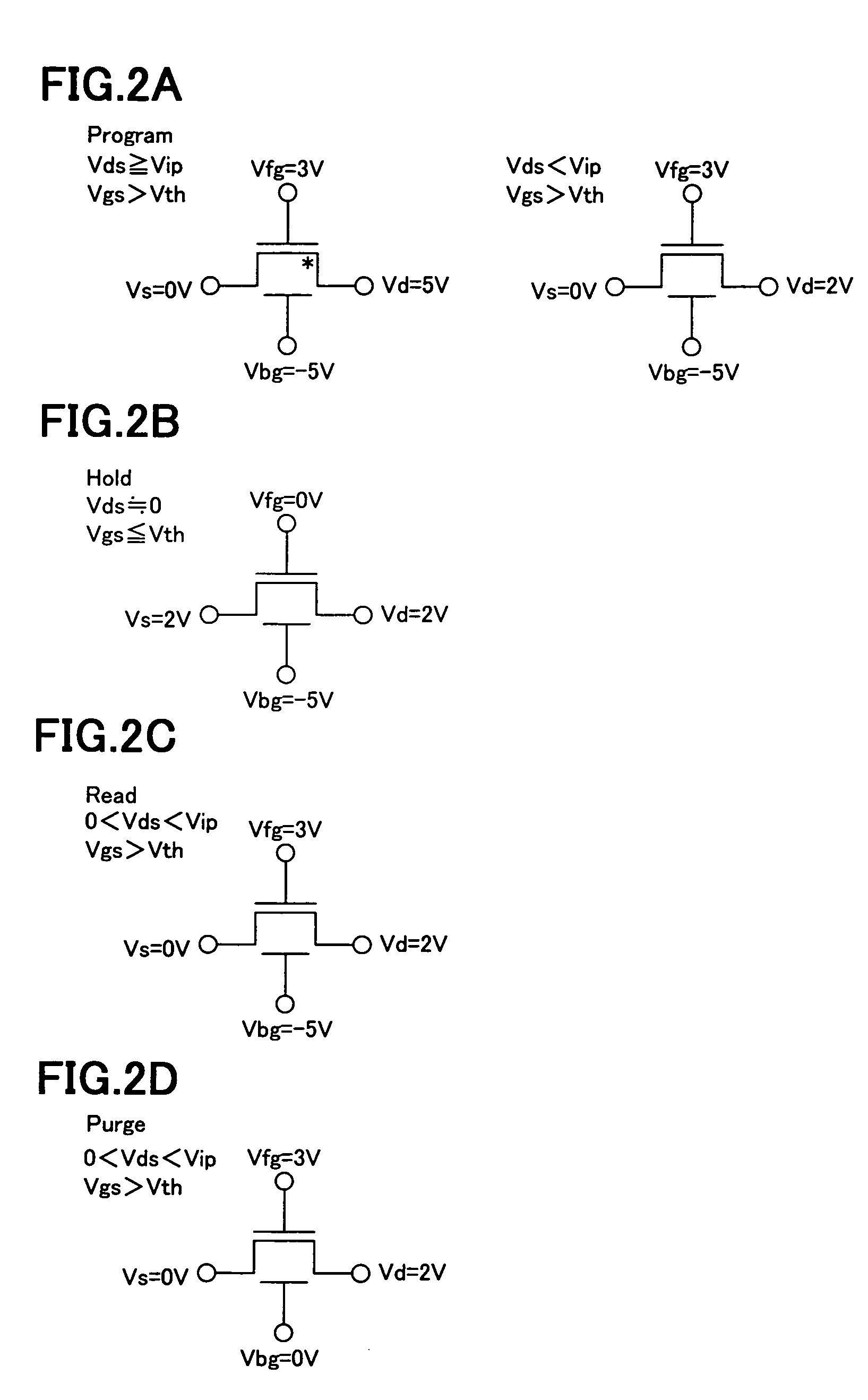

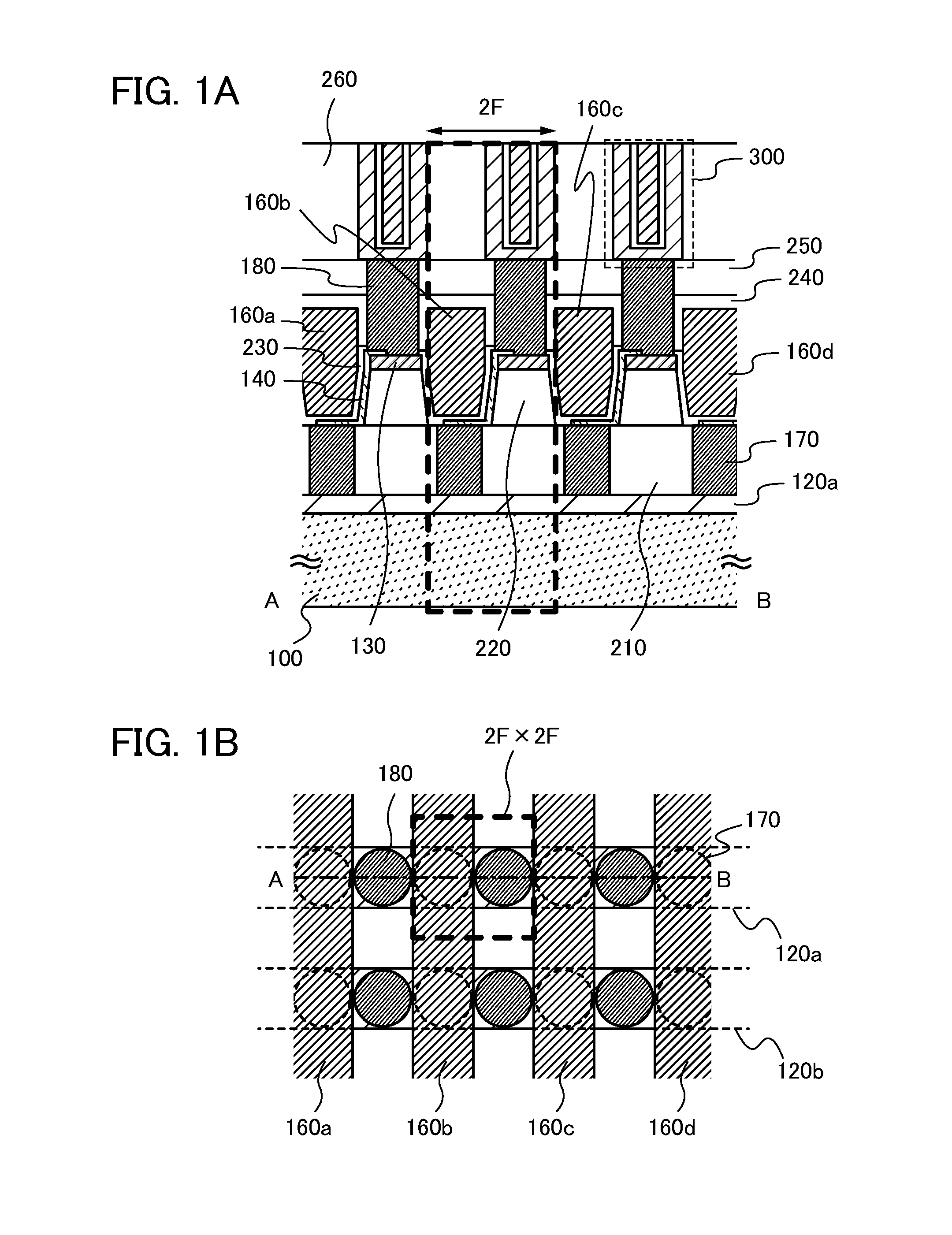

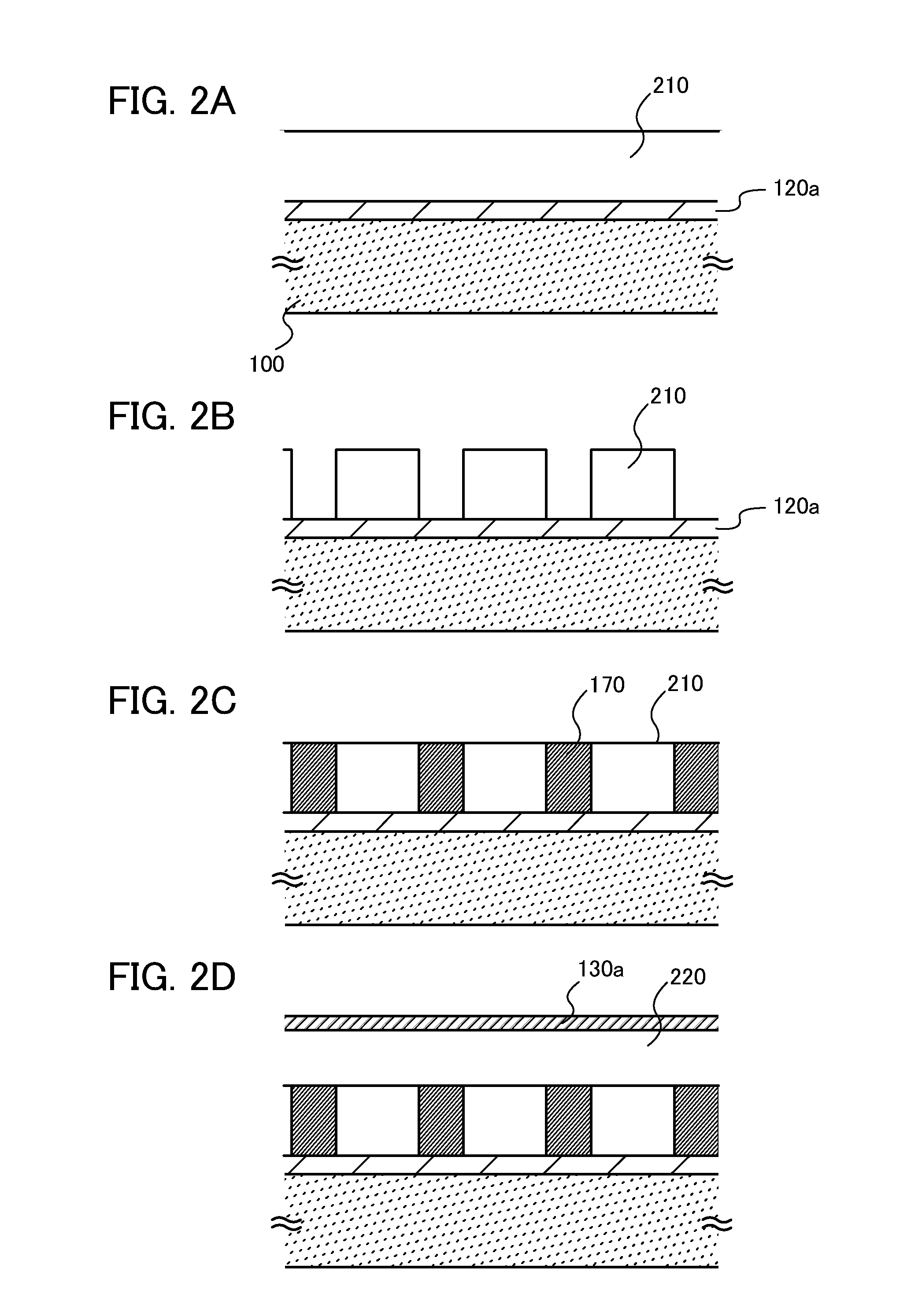

Semiconductor device and method of driving semiconductor device

InactiveUS20110194331A1Easy to integrateLarge memory capacityTransistorSolid-state devicesElectricityPower semiconductor device

The number of wirings per unit memory cell is reduced by sharing a bit line by a writing transistor and a reading transistor. Data is written by turning on the writing transistor so that a potential of the bit line is supplied to a node where one of a source and drain electrodes of the writing transistor and a gate electrode of the reading transistor are electrically connected, and then turning off the writing transistor so that a predetermined amount of charge is held in the node. Data is read by using a signal line connected to a capacitor as a reading signal line or a signal line connected to one of a source and drain electrodes of the reading transistor as a reading signal line so that a reading potential is supplied to the reading signal line, and then detecting a potential of the bit line.

Owner:SEMICON ENERGY LAB CO LTD

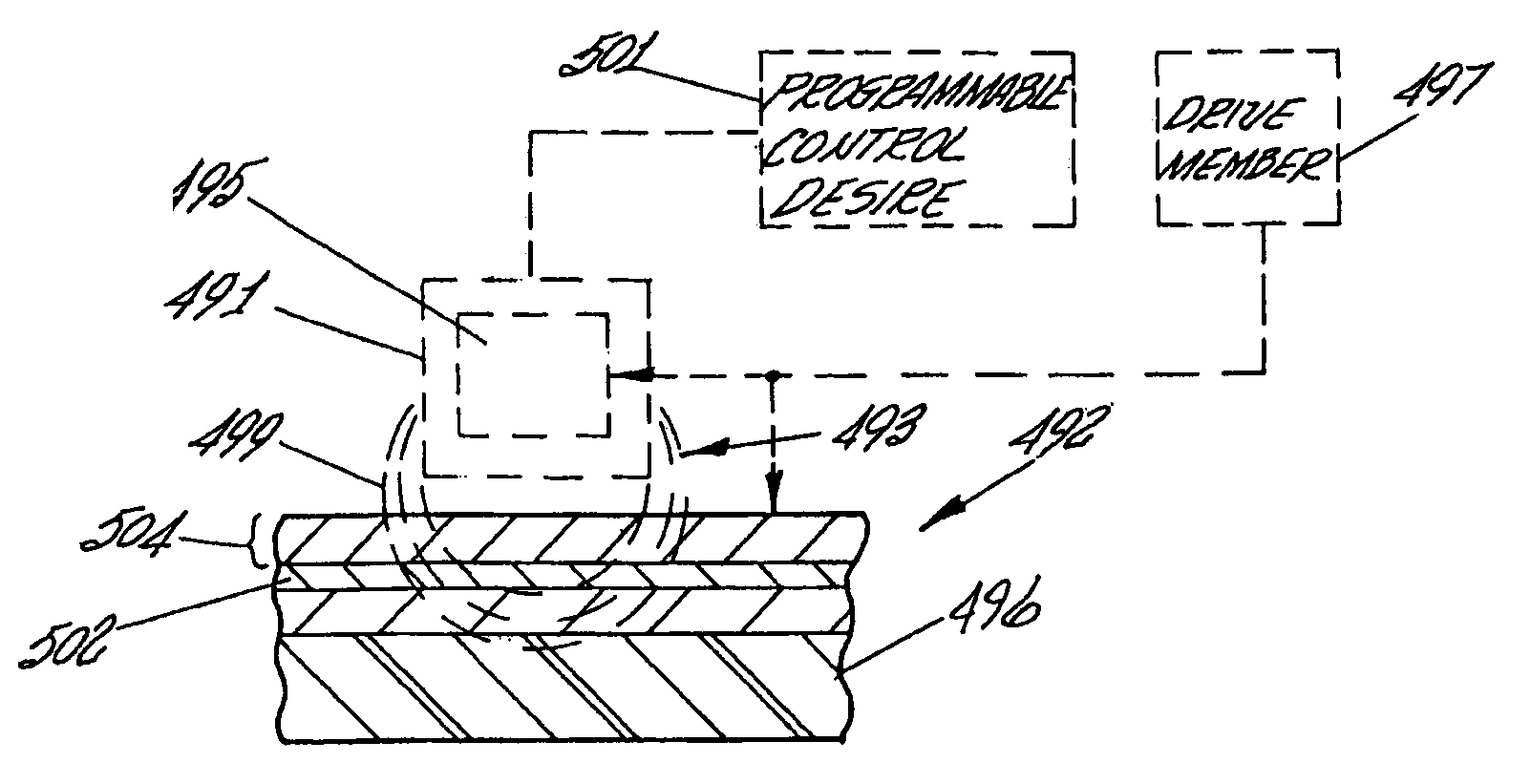

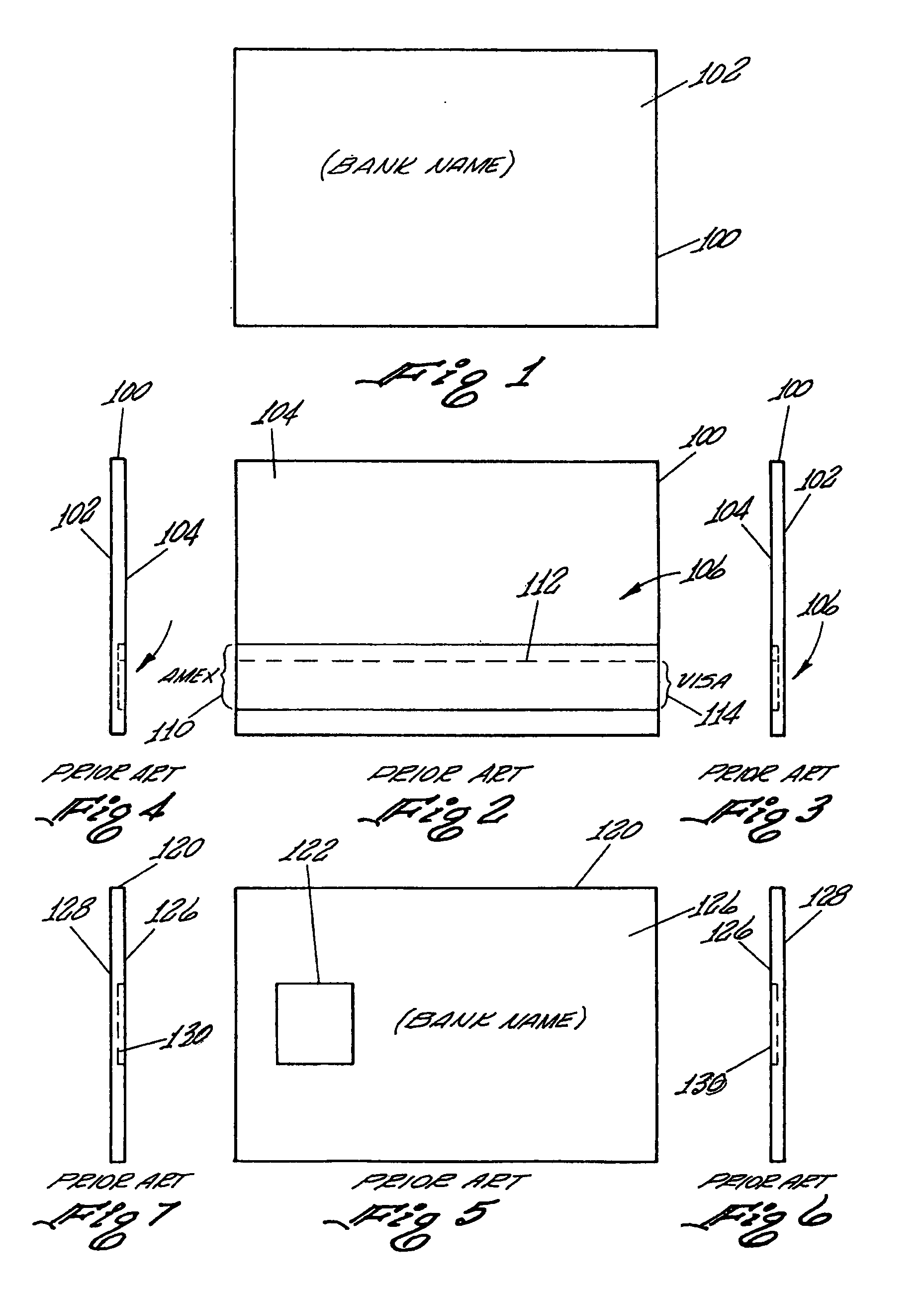

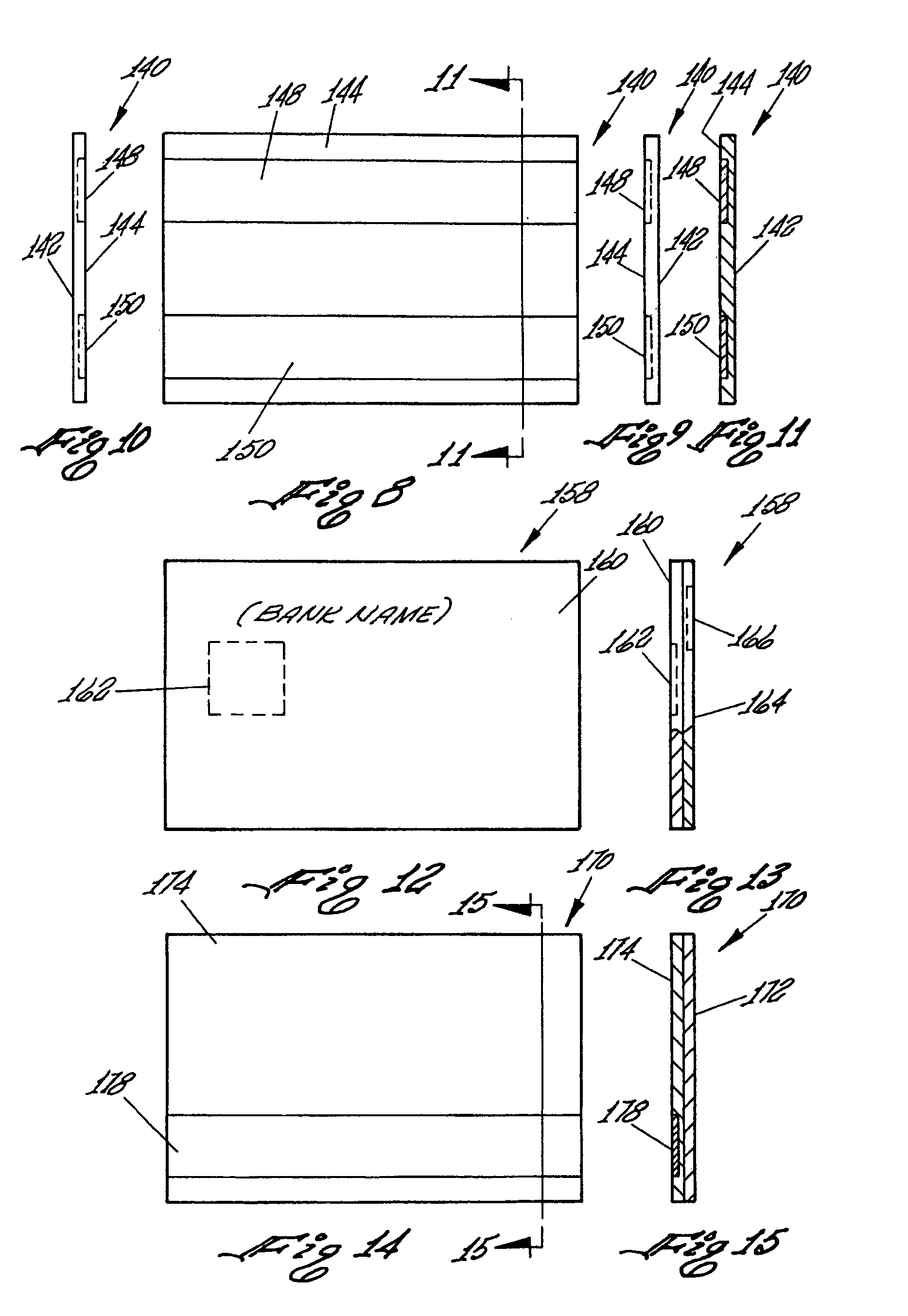

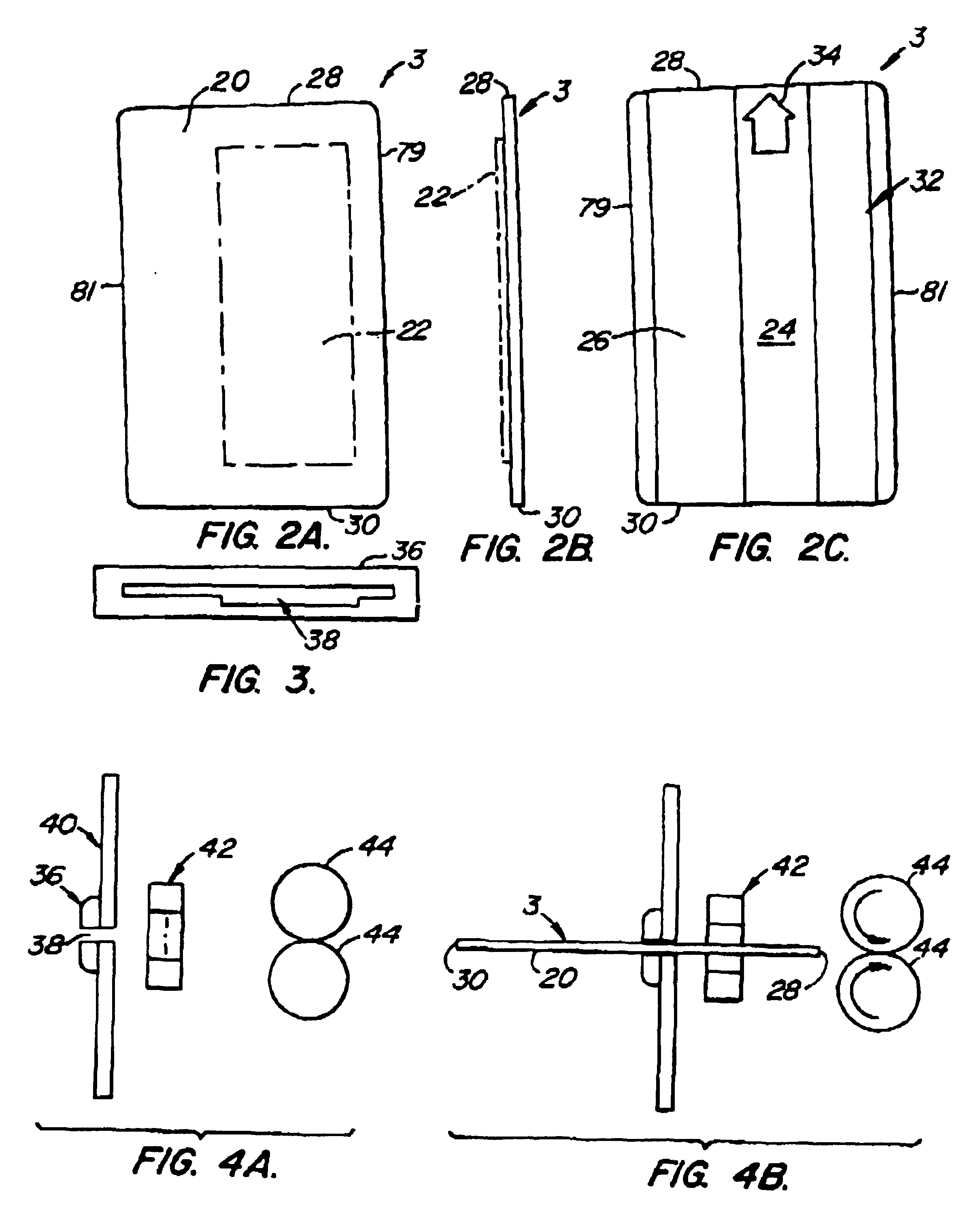

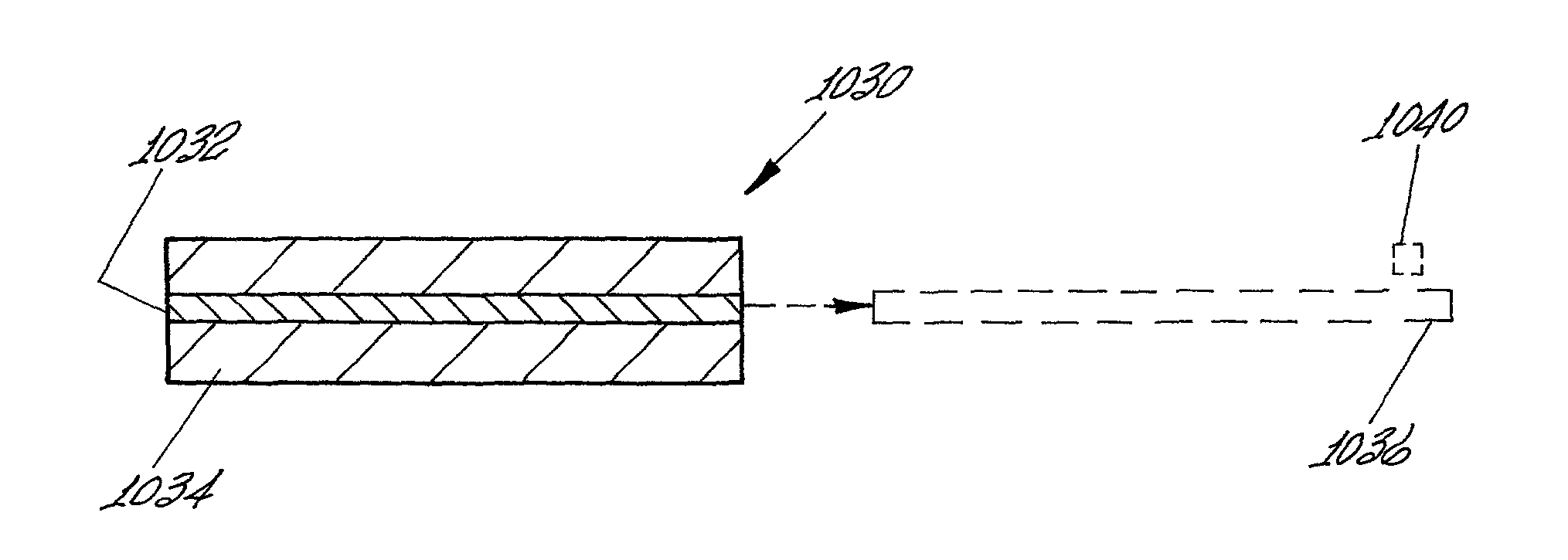

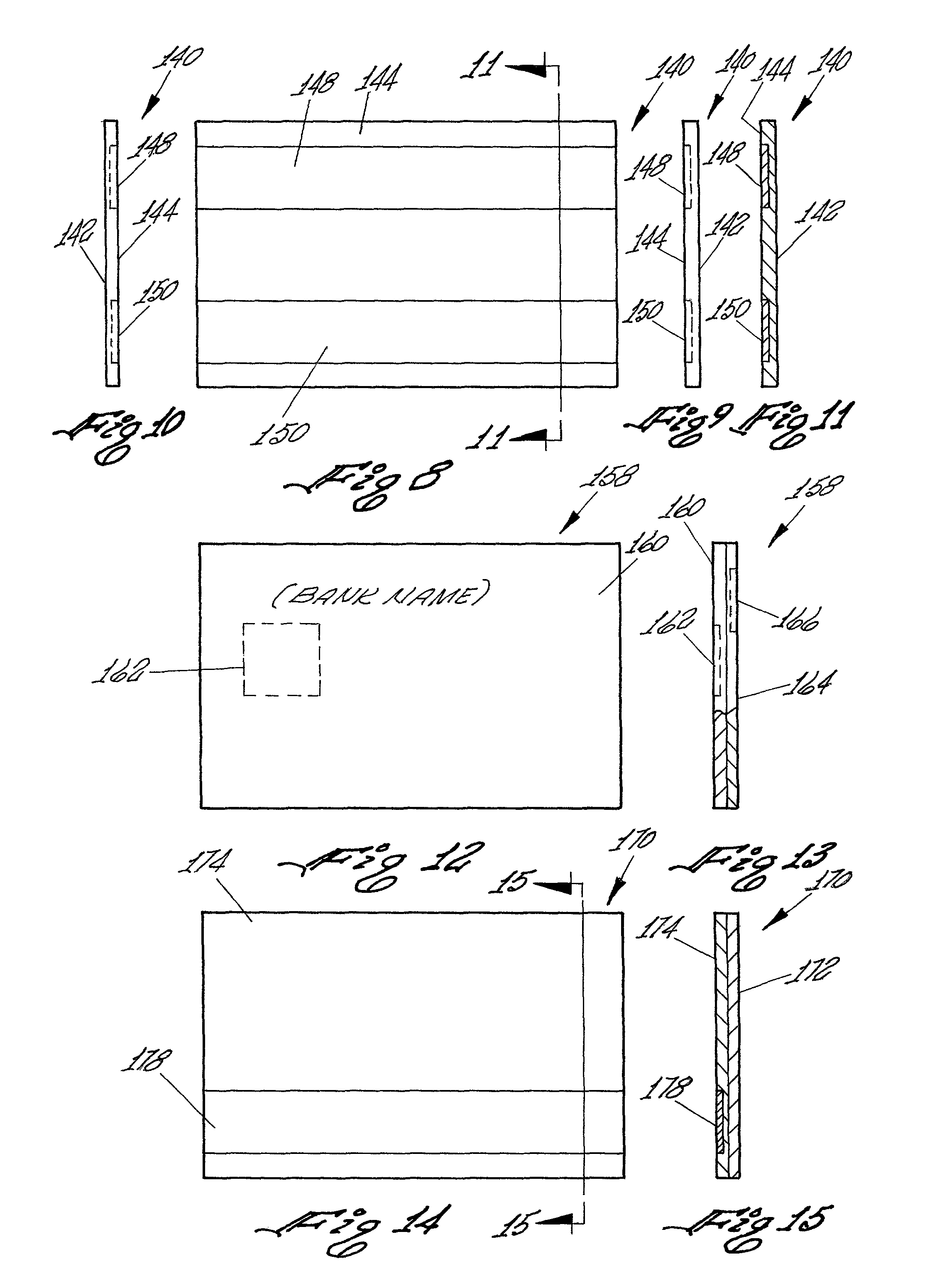

Data storage device apparatus and method for using same

InactiveUS7036739B1Large memory capacityOther printing matterProtective coatings for layersHigh densityTransducer

Owner:ULTRACARD

Systems and Methods for Remote Control Setup

ActiveUS20090322583A1Increase the number ofEasy to storeElectric signal transmission systemsEqual length code transmitterRemote controlControl objective

A remote control device may include: first circuitry to control a function of a first electronic device; second circuitry to be set to control a function of a second electronic device; and a setup controller to set the second circuitry to control a function of a target electronic device based on a code received from a separate device. An electronic device to be controlled by a remote control device may include: an input device to receive a signal from the remote control device; an output device to send a signal to the remote control device; and a processor coupled to the input and output devices, and configured to access a database of codes and to selectively provide codes from the database to the remote control device, the codes configured to set circuitry of the remote control device to control a function of the electronic device and / or an auxiliary electronic device.

Owner:DISH TECH L L C

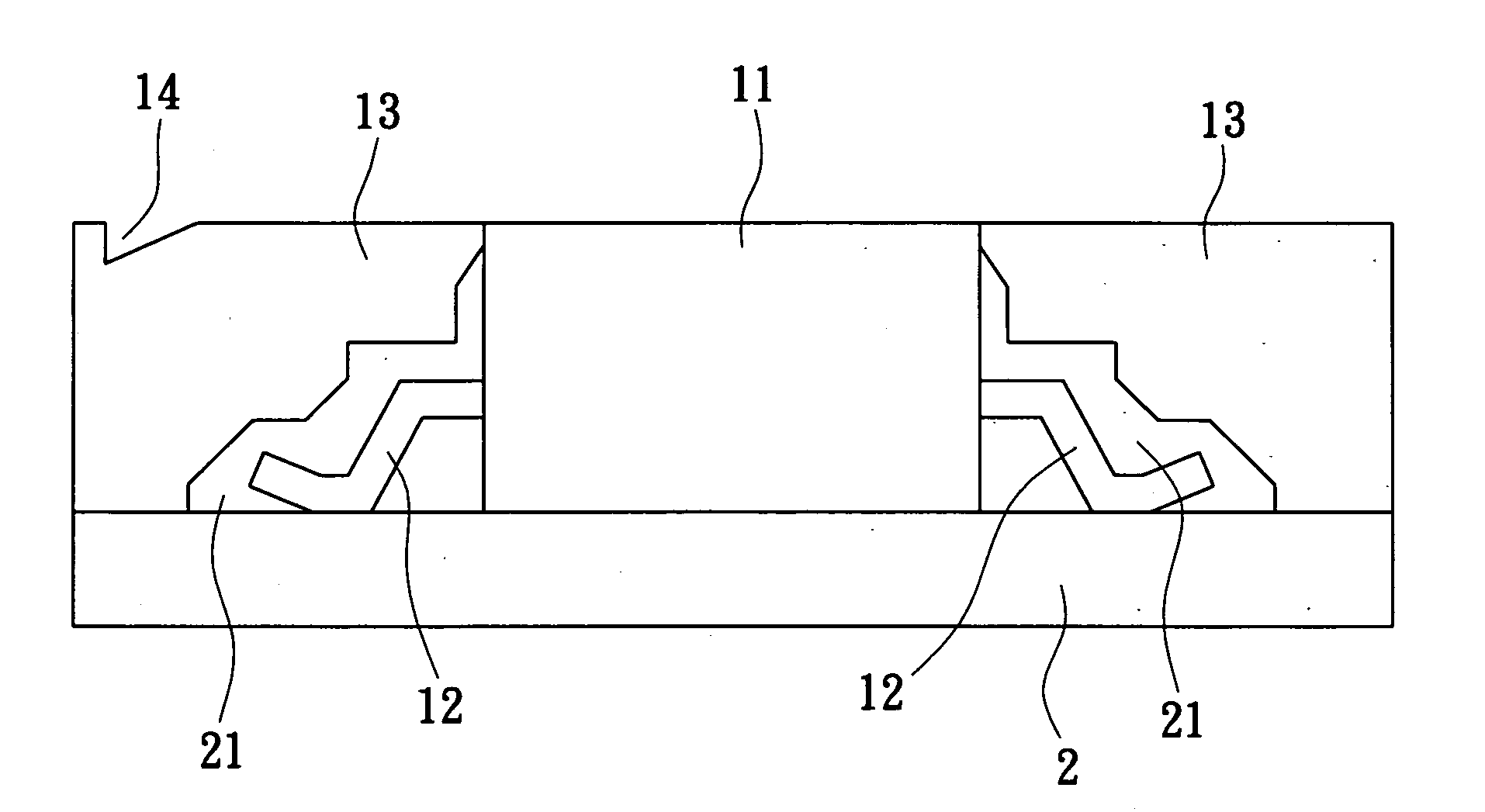

Multiple chip module and package stacking method for storage devices

ActiveUS20070158808A1Increase capacityFunction increaseSemiconductor/solid-state device detailsSolid-state devicesSignal routingSpecific function

Stacking techniques are illustrated in example embodiments of the present invention wherein semiconductor dies are mounted in a module to become a MCM which serves as the basic building block. Combination of these modules and dies in a substrate creates a package with specific function or a range of memory capacity. Several example system configurations are provided using BGA and PGA to illustrate the stacking technique. Several pin assignment and signal routing techniques are illustrated wherein internal and external signals are routed from main board to various stacked modules. Expansion can be done both on the vertical and horizontal orientations.

Owner:BITMICRO LLC

Memory extending system and memory extending method

ActiveCN103488436ALarge memory capacityAvoid the problem of redundant processing powerInput/output to record carriersComputer architectureQuick path interconnect

An embodiment of the invention discloses a memory extending system and a memory extending method. The system comprises processors, extended memories, extended chips and multiple processor installation positions, and a memory installation position is arranged at each process installation position; the processor installation positions are connected mutually through QPI (quick path interconnect) interfaces, at least one processor installation position is provided with a processor, and at least one of the rest installation positions serves as extended installation position; the extended chips are installed in the extended installation position; the extended memories are installed to the memory installation positions connected with the extended chips. The memory extending system has the advantages that the extended chips are mounted at other processor installation positions to replace the processors, and the existing processors are enabled to be capable of accessing the extended memories carried by the extended chips through the extended chips, so that memory capacity of the existing processors is increased on the condition that processing capacity is not improved, and the problem of processing capacity redundancy caused by the fact that memories are extended by adding processors in the prior art is solved.

Owner:XFUSION DIGITAL TECH CO LTD

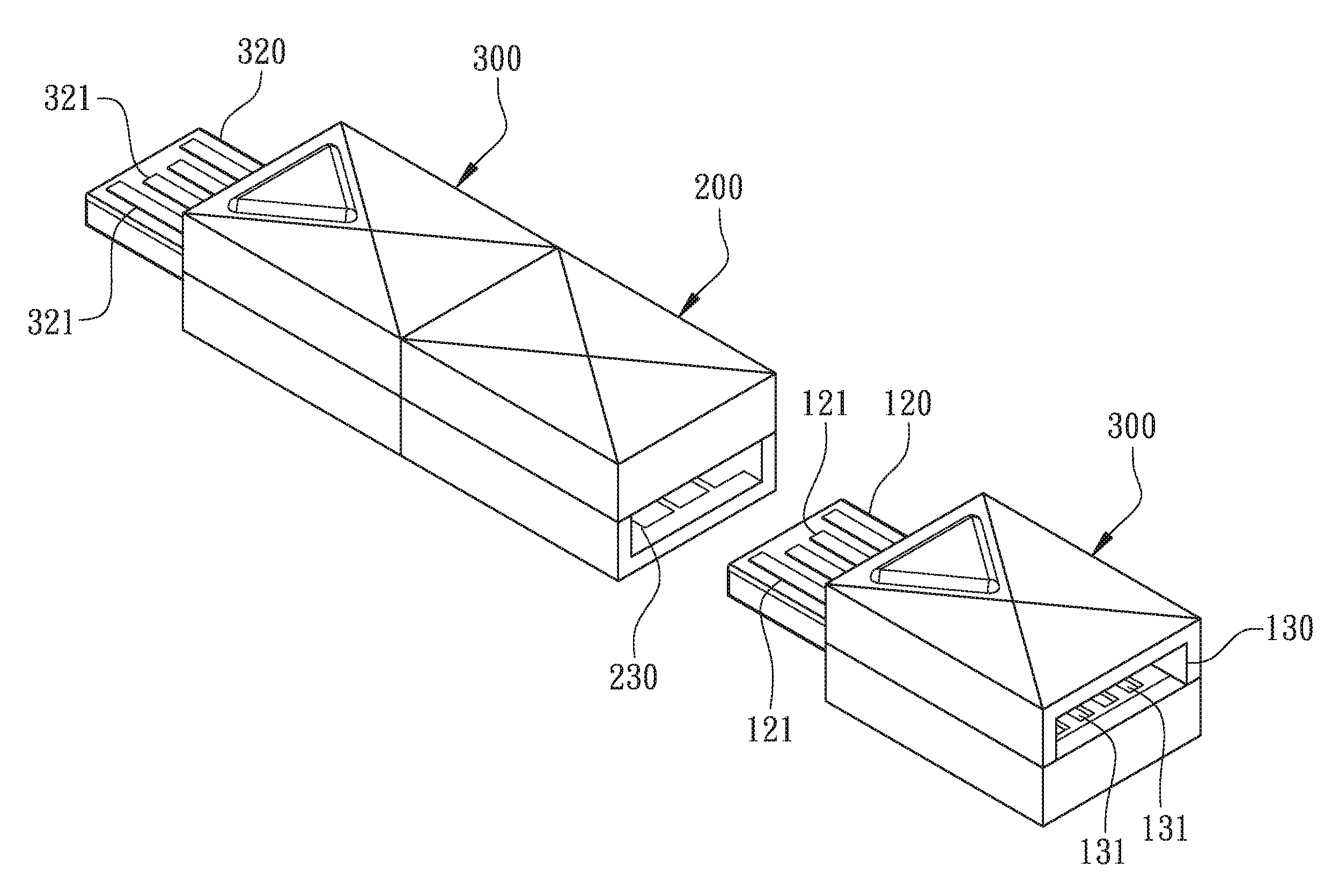

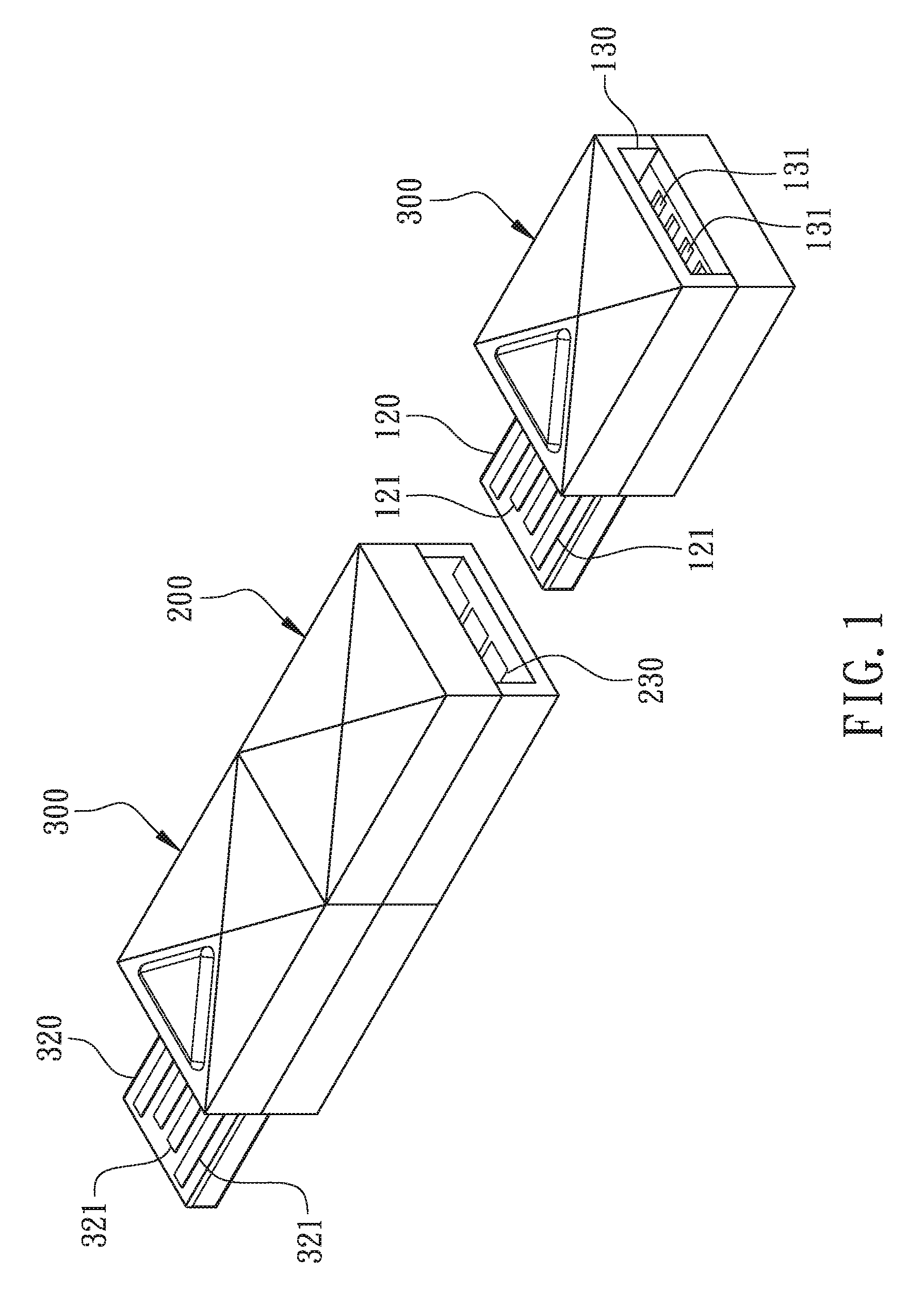

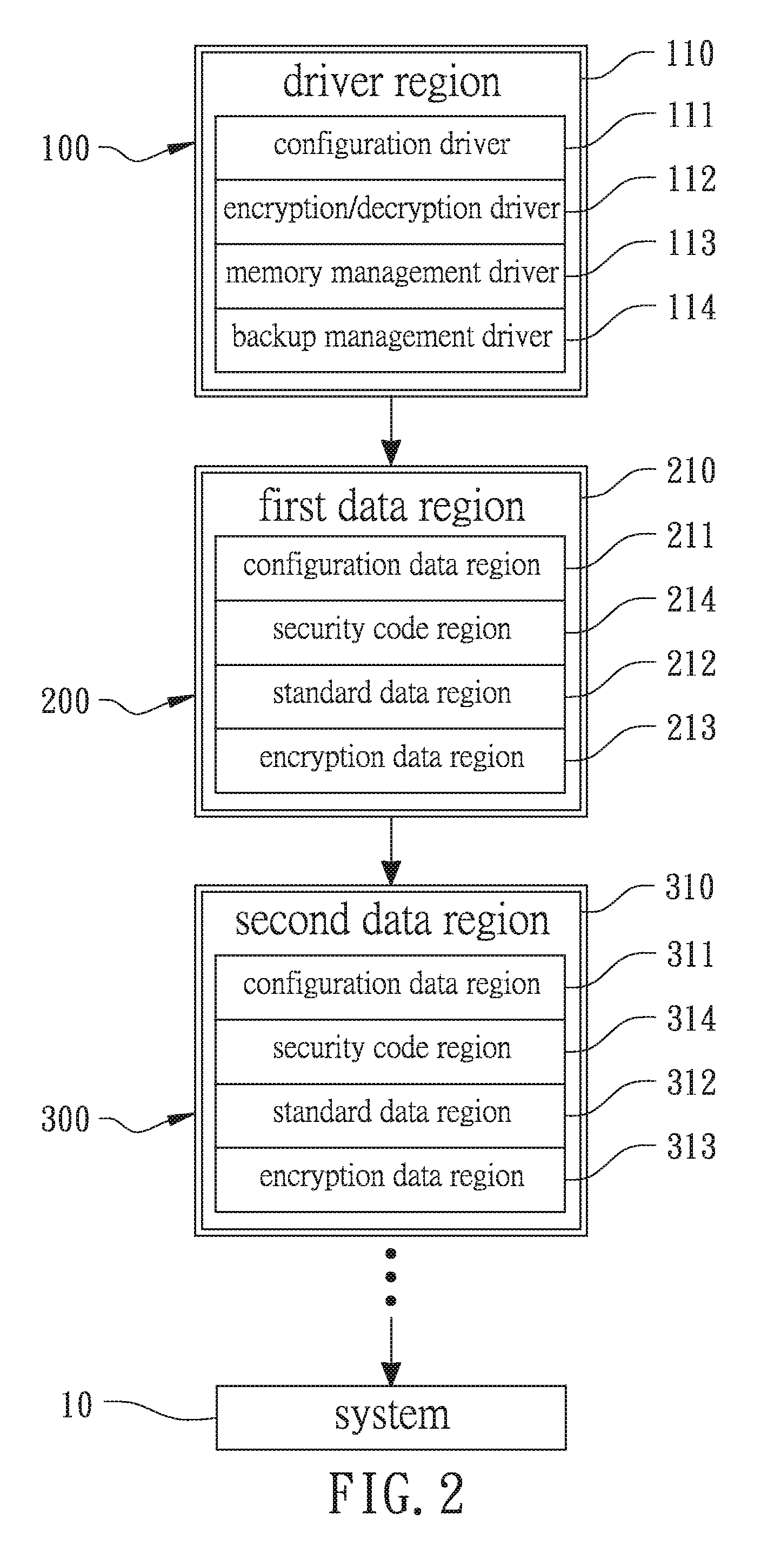

Method for employing USB record carriers and a related module

InactiveUS20100077229A1Achieve protectionLarge memory capacityUnauthorized memory use protectionHardware monitoringUSBData storing

A method of utilizing USB record carriers is disclosed. A USB security drive is serially connected with at least a USB drive to encrypt / decrypt stored data in the USB drive and to integrate a plurality of data regions or even a plurality of encrypted data regions to provide multi-level security protections. In a more specific embodiment, the USB security drive further enables the automatic backup of data stored in the USB drive. A related assembled module by the implementation is also disclosed.

Owner:WALTON ADVANCED ENG INC

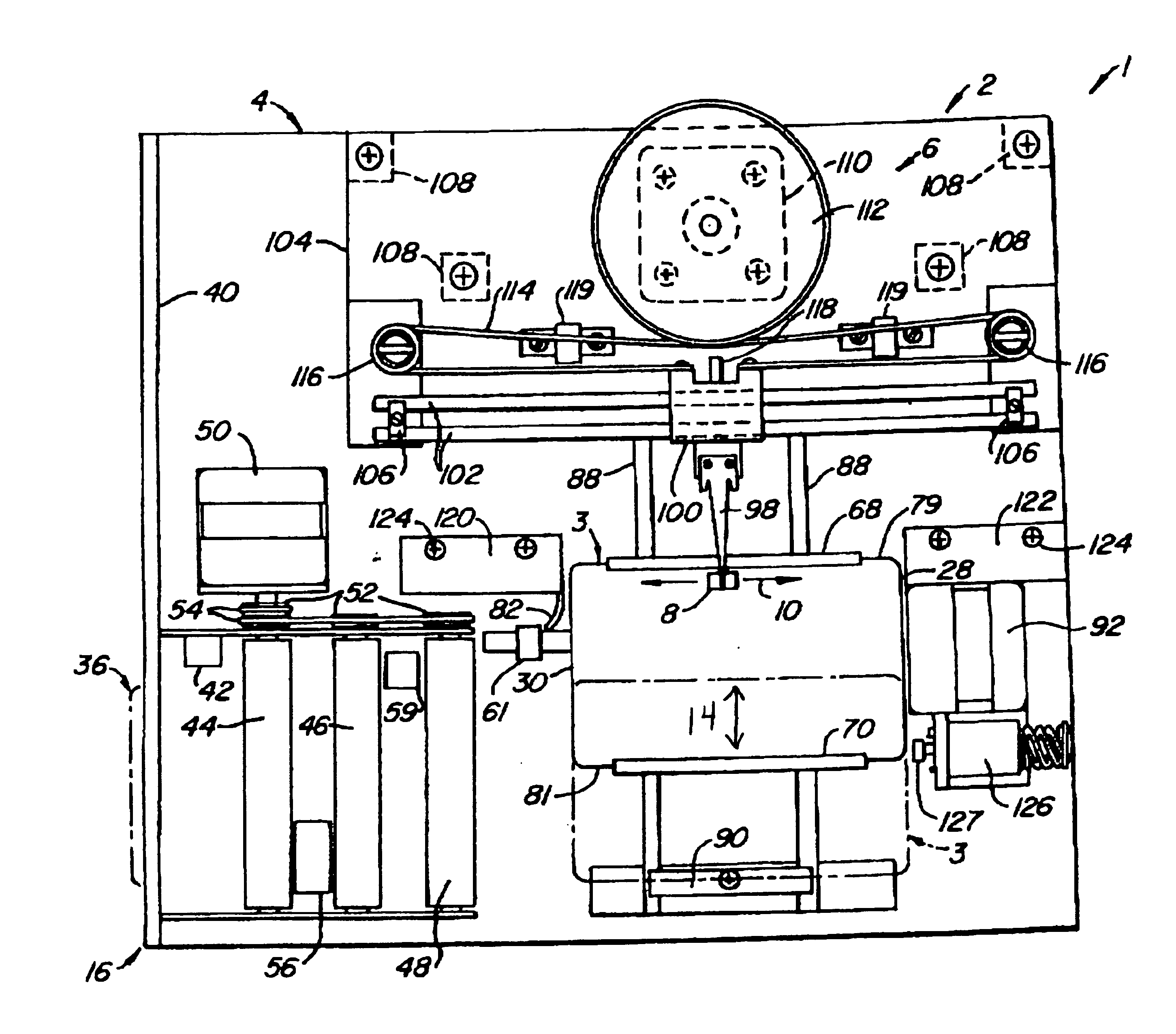

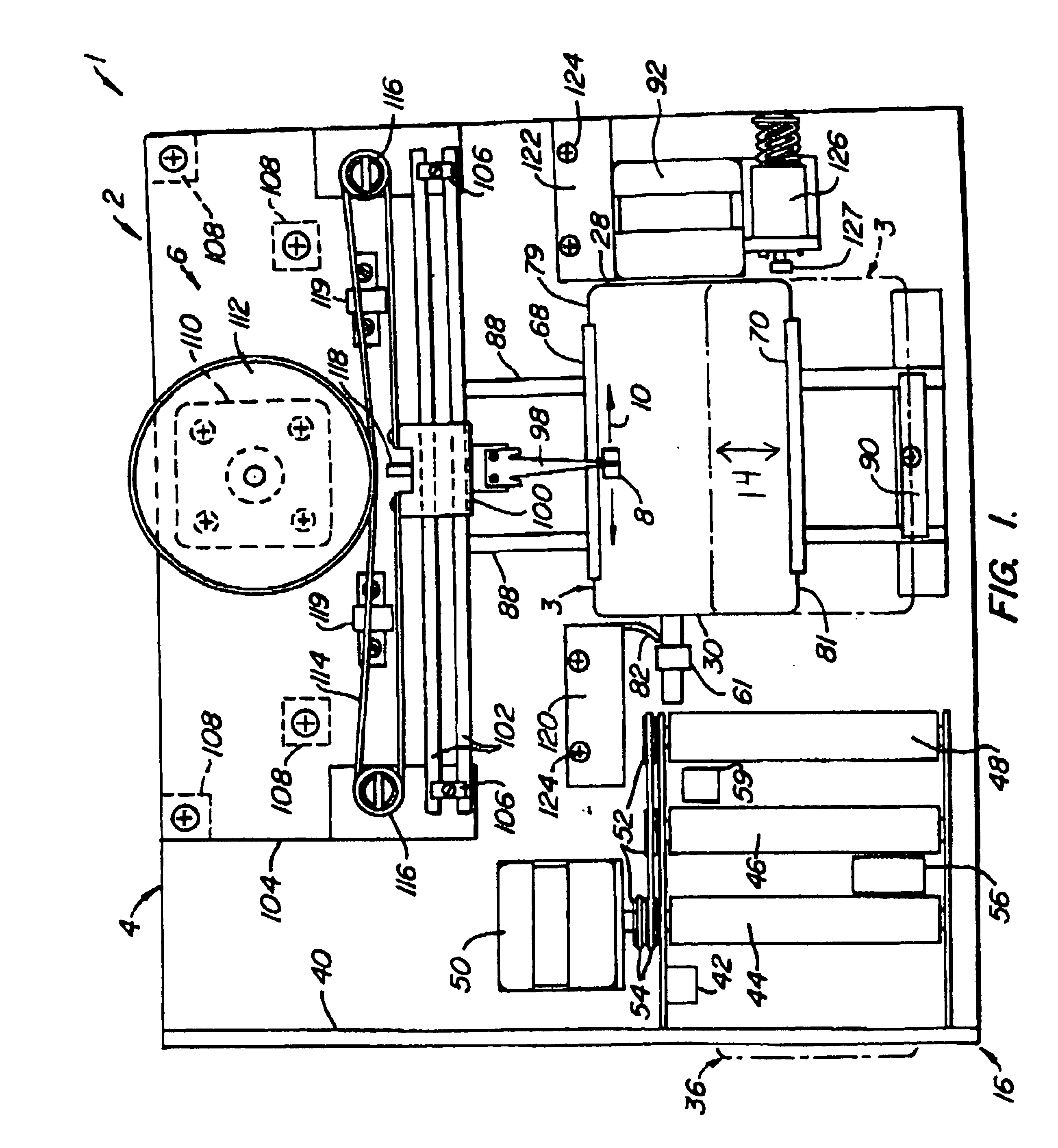

Data storage card having a non-magnetic substrate and data surface region and method for using same

InactiveUS6857569B1Memory capacityFreely handledDisposition/mounting of recording headsDriving/moving recording headsHigh densityMagnetic storage

A data storage card includes a glass substrate having first and second edges. A data storage surface region is located on the glass substrate between the first and second edges. The data surface region includes a magnetic storage medium having at least one layer of high density, high coercivity magnetic material for storing magnetic signals. The data storage card may include a relatively hard, abradeable protective coating formed on the magnetic material layer. The protective coating has a thickness between a maximum thickness which would materially attenuate magnetic signals passing between the magnetic material layer and a transducer of a read device, and a minimum thickness enabling said protective coating to be abraded by usage in an ambient natural atmosphere operating environment for removing therefrom a known quantity of the protective coating.

Owner:ULTRACARD

Apparatus and a method for controlling functions in an environment

InactiveUS6772016B1Facilitate communicationLarge memory capacityComputer controlSimulator controlControl engineeringHuman–computer interaction

Owner:TENTACULUS INDEPENDENT LIVING

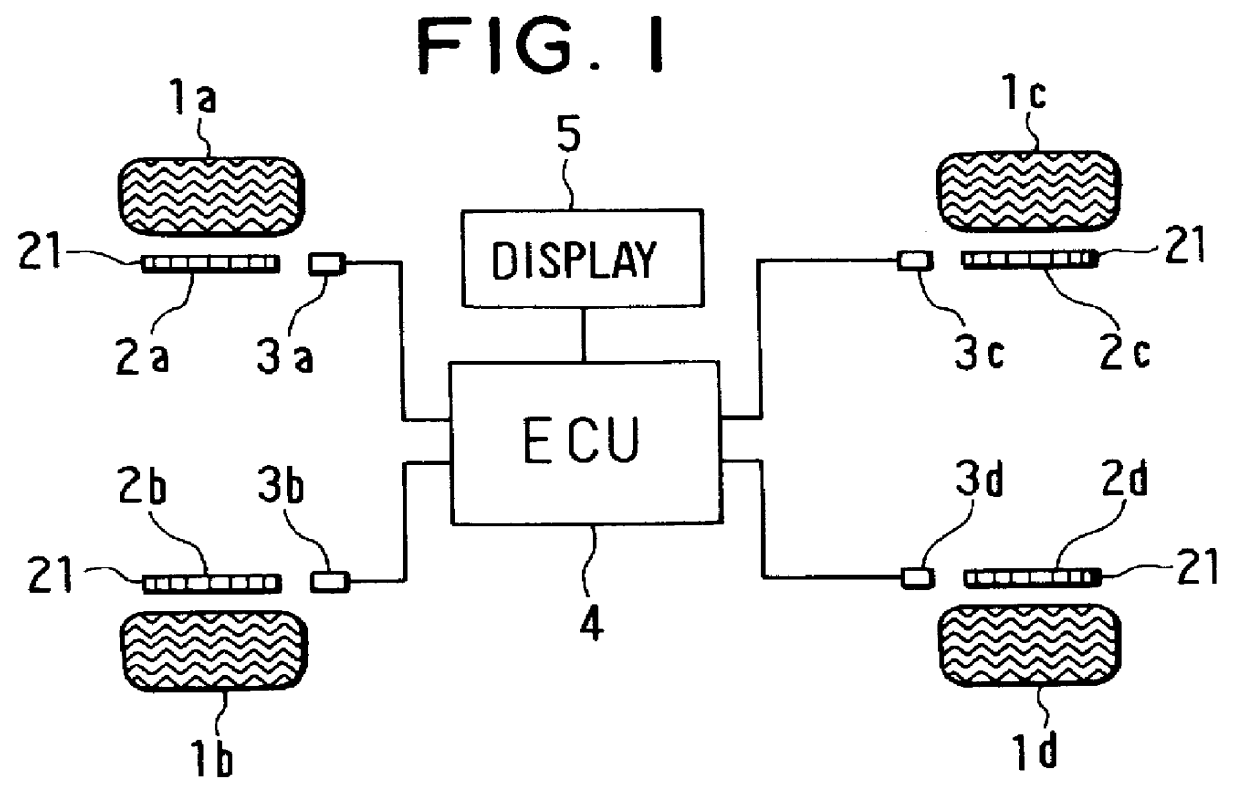

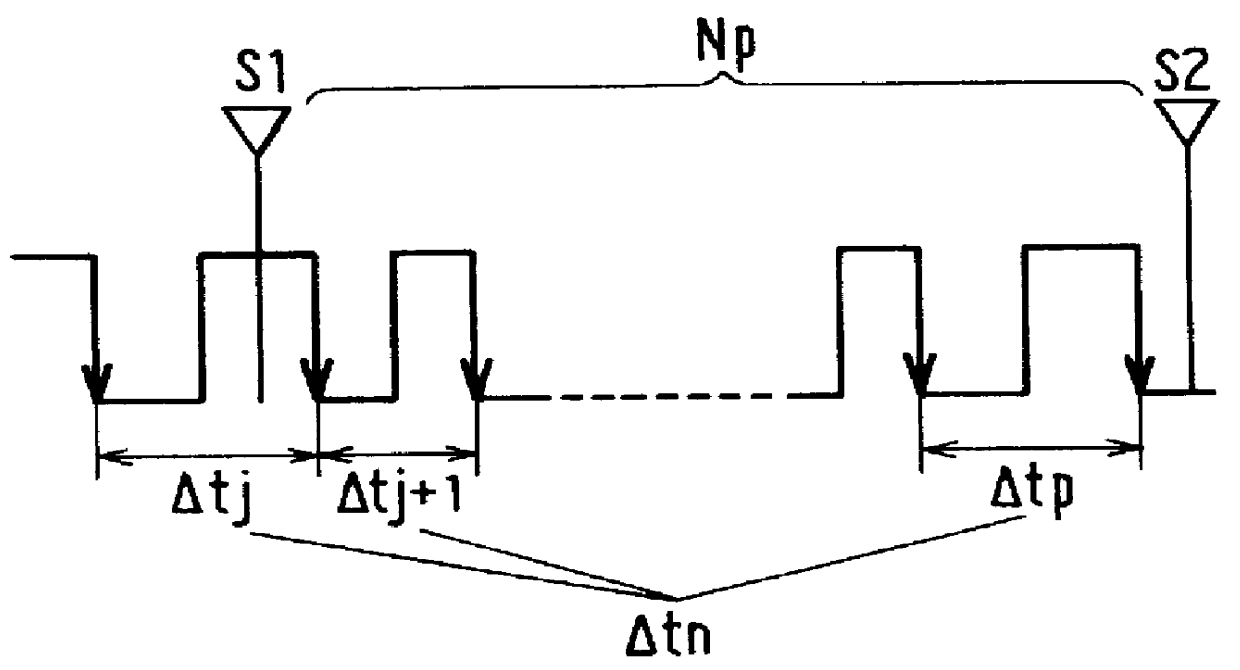

Tire abnormality sensor

InactiveUS6014599AHigh sensing precisionLarge memory capacityVehicle testingRegistering/indicating working of vehiclesEngineeringElectrical and Electronics engineering

To achieve both accuracy in correcting sensing error caused by nonstandard factors of a pulse signal generated by rotation of a rotor to be measured and reduction in cost of an apparatus for doing the same, each passage of rotor sensors which rotate integrally with vehicle tires are sensed to produce pulse signals. The pulse signal periods are sequentially integrated every pulse signal train consisting of multiple pulse signals. When all of the pulse signal periods of the pulse signal train are integrated, the integrated value is stored in memory. The memory always stores the integrated values of the newest one rotation of the rotor to be measured. The pulse signal periods are averaged from the sum of the integrated values. With such a construction, the average of the pulse signal periods can be obtained as a learning reference value in the correction without storing all of the pulse signal periods of one rotation, thereby realizing both correction accuracy and cost reduction.

Owner:DENSO CORP

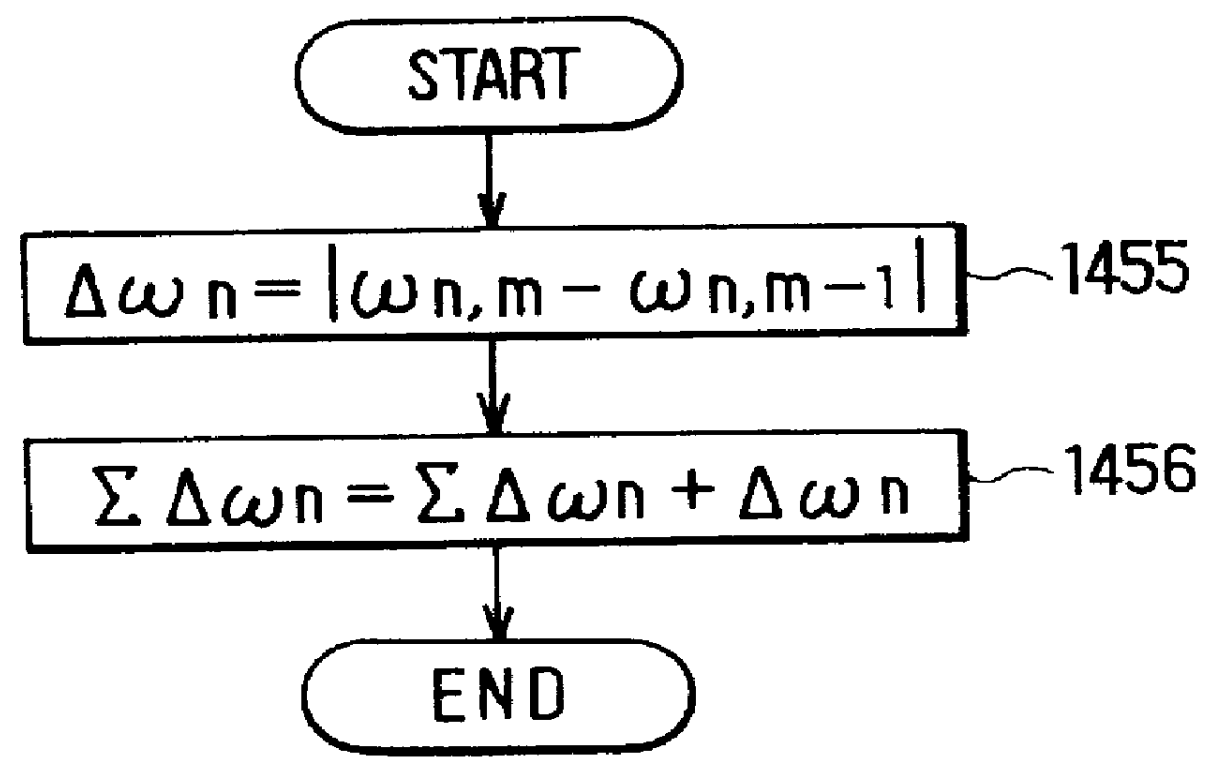

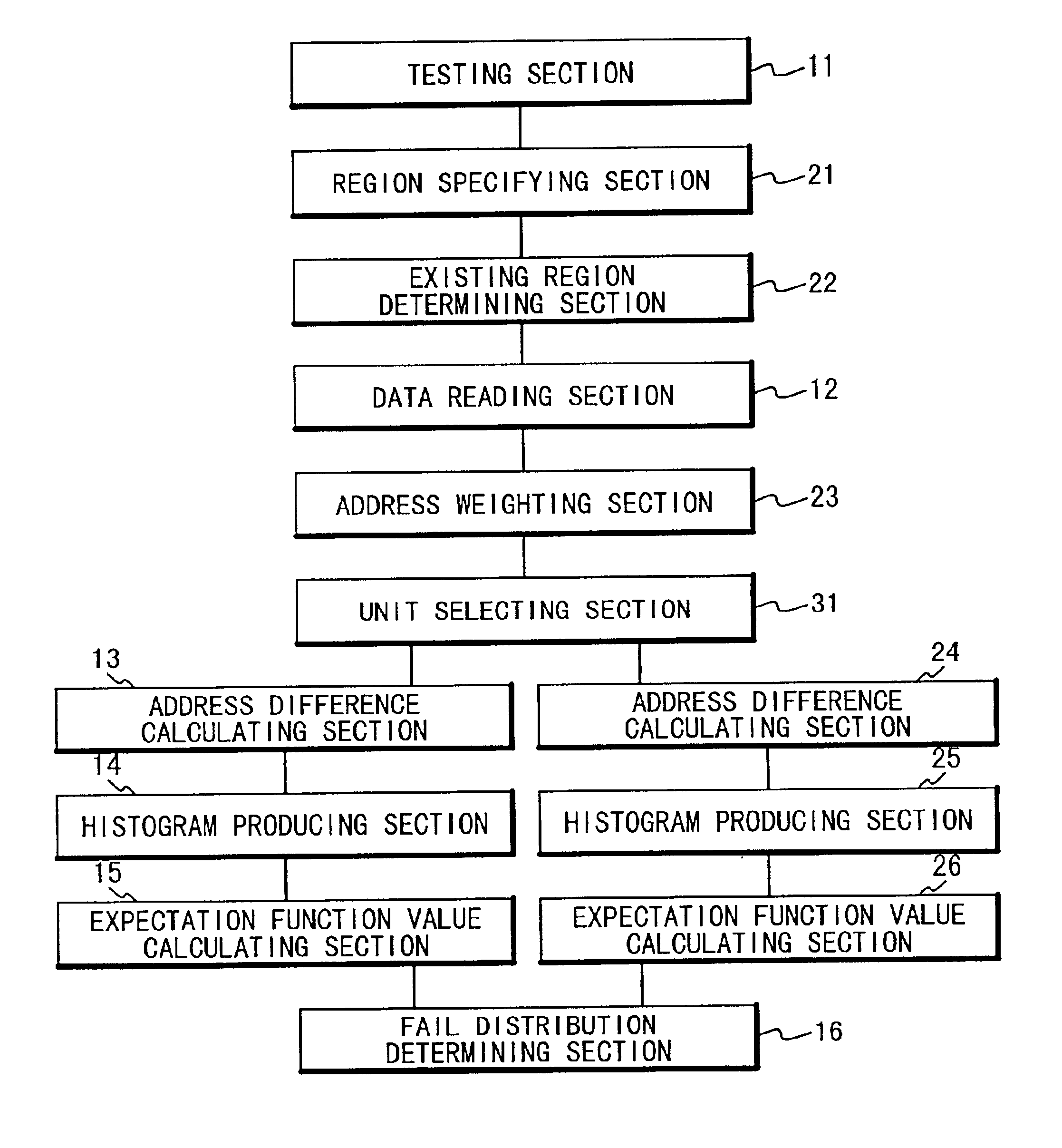

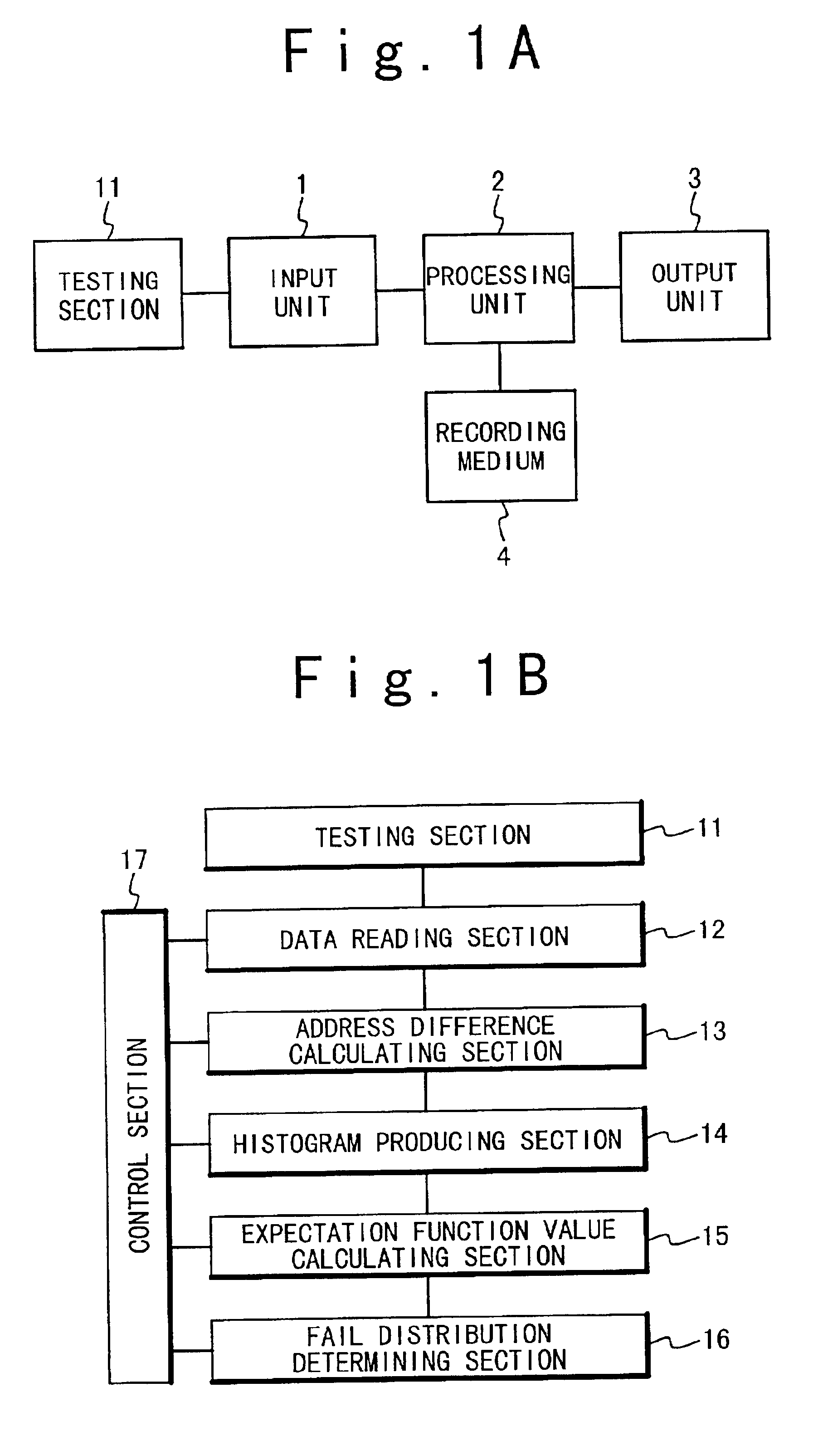

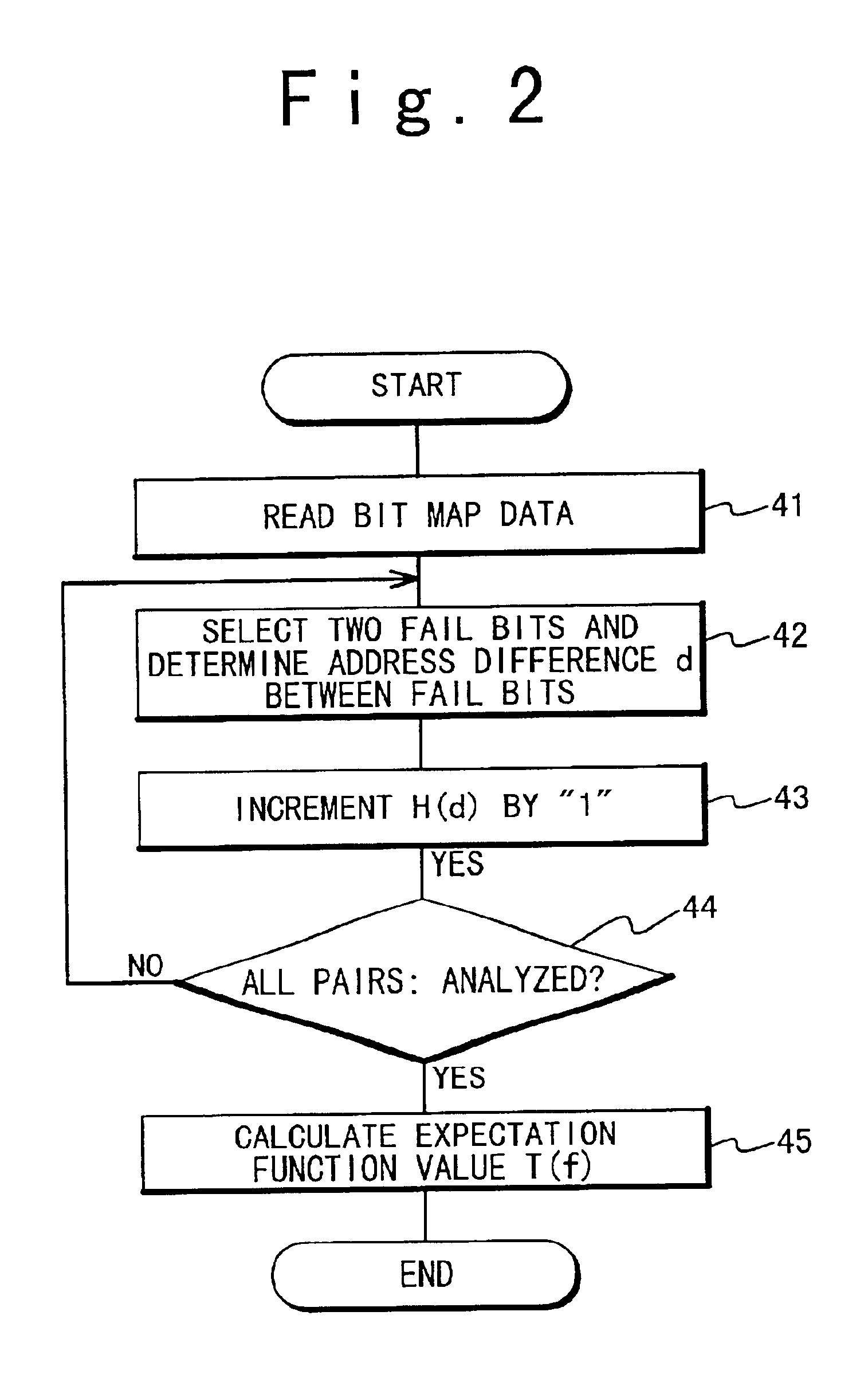

Failure analysis system of semiconductor memory device

InactiveUS6871168B1Reduce processing timeShorten the timeSemiconductor/solid-state device testing/measurementElectronic circuit testingHistogramSemiconductor memory

In failure analysis method of a semiconductor memory device, an absolute value of a position difference between two fail bits of a two-dimensional bit map is calculated while a histogram corresponding to the absolute value of the position difference is updated. The bit map indicates a map of fail bits and each fail bit corresponds to a fail memory cell. The above calculation is repeated to all combinations of two of the fail bits in the bit map. Then, an expectation function value is calculated for each of values from the histograms and the number of the fail bits. Finally, whether the fail bits has regularity or irregularity for each value is determined based on the calculated expectation function value for the value.

Owner:RENESAS ELECTRONICS CORP

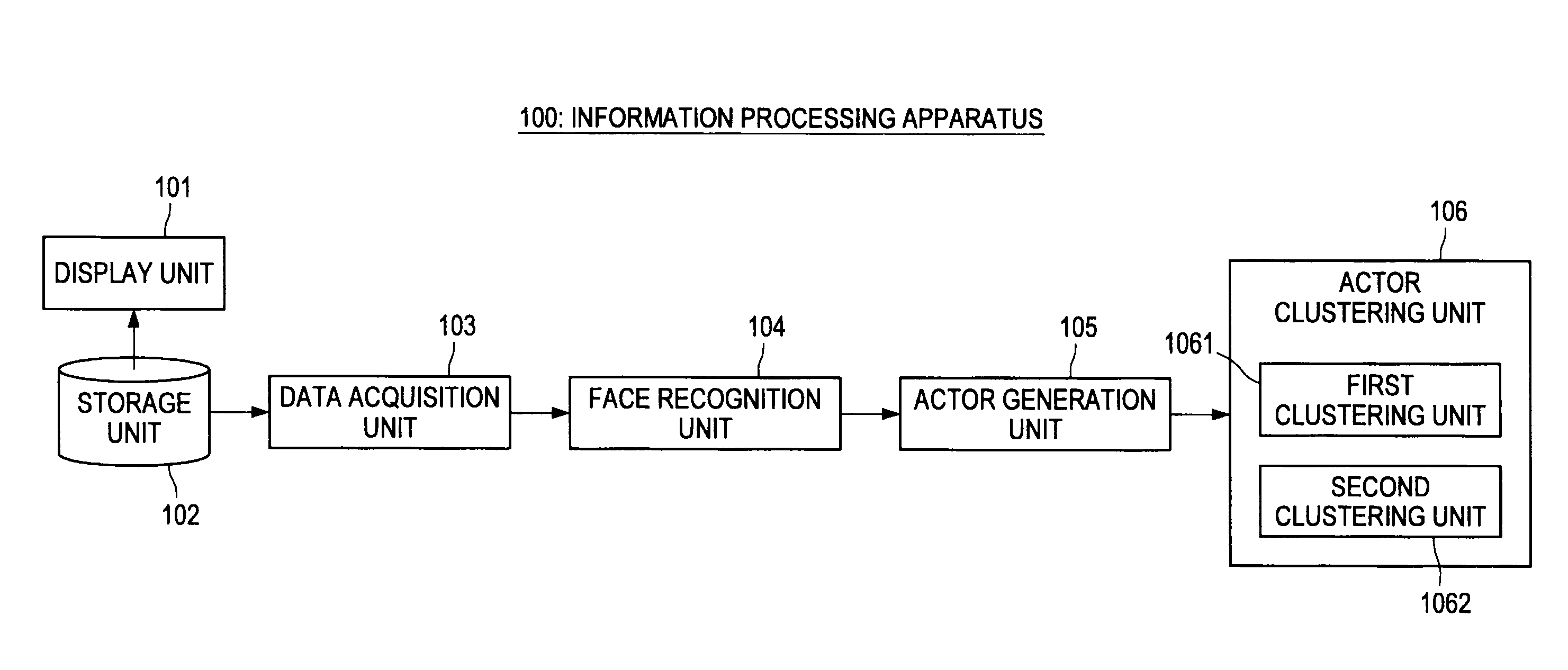

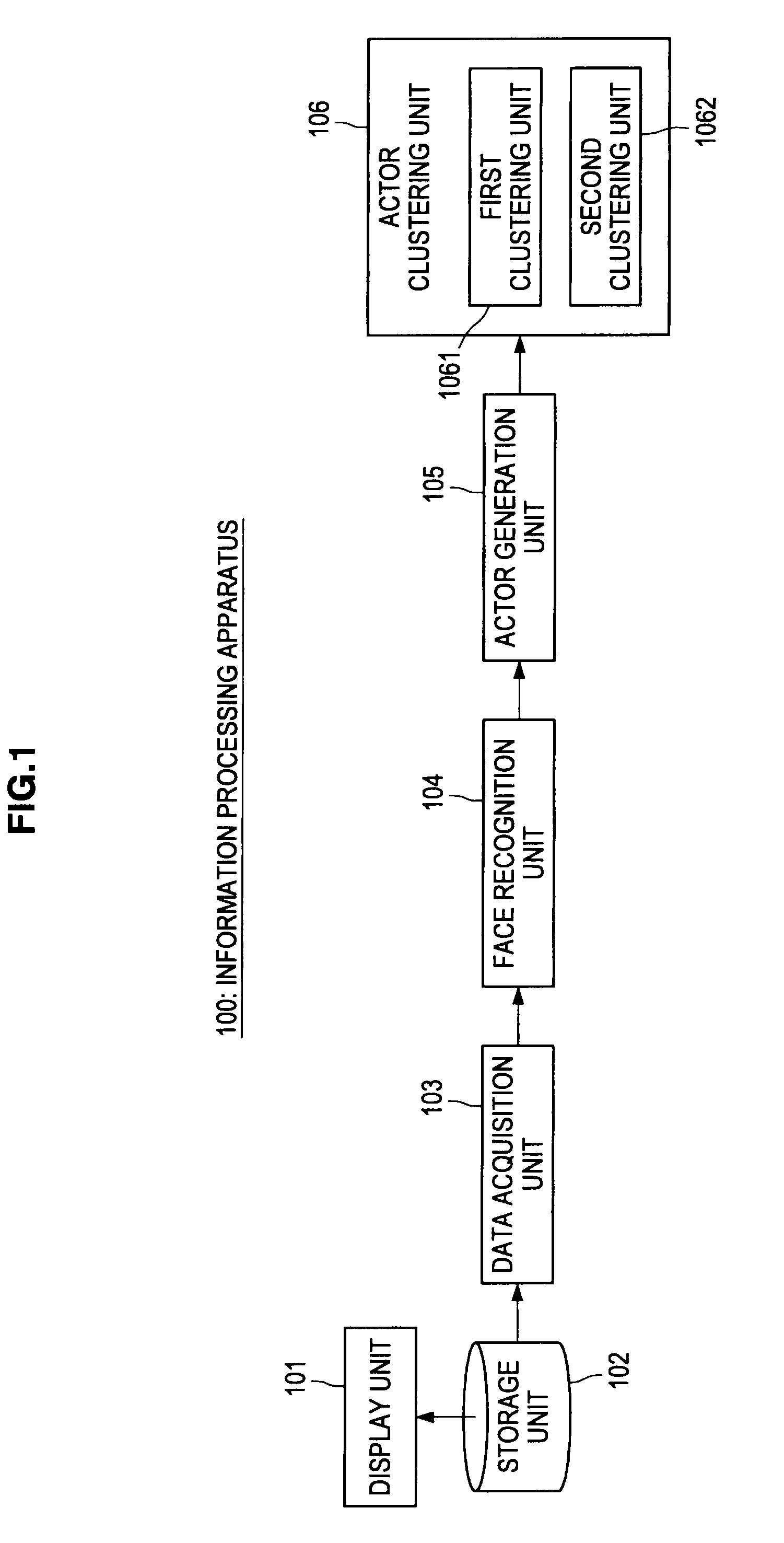

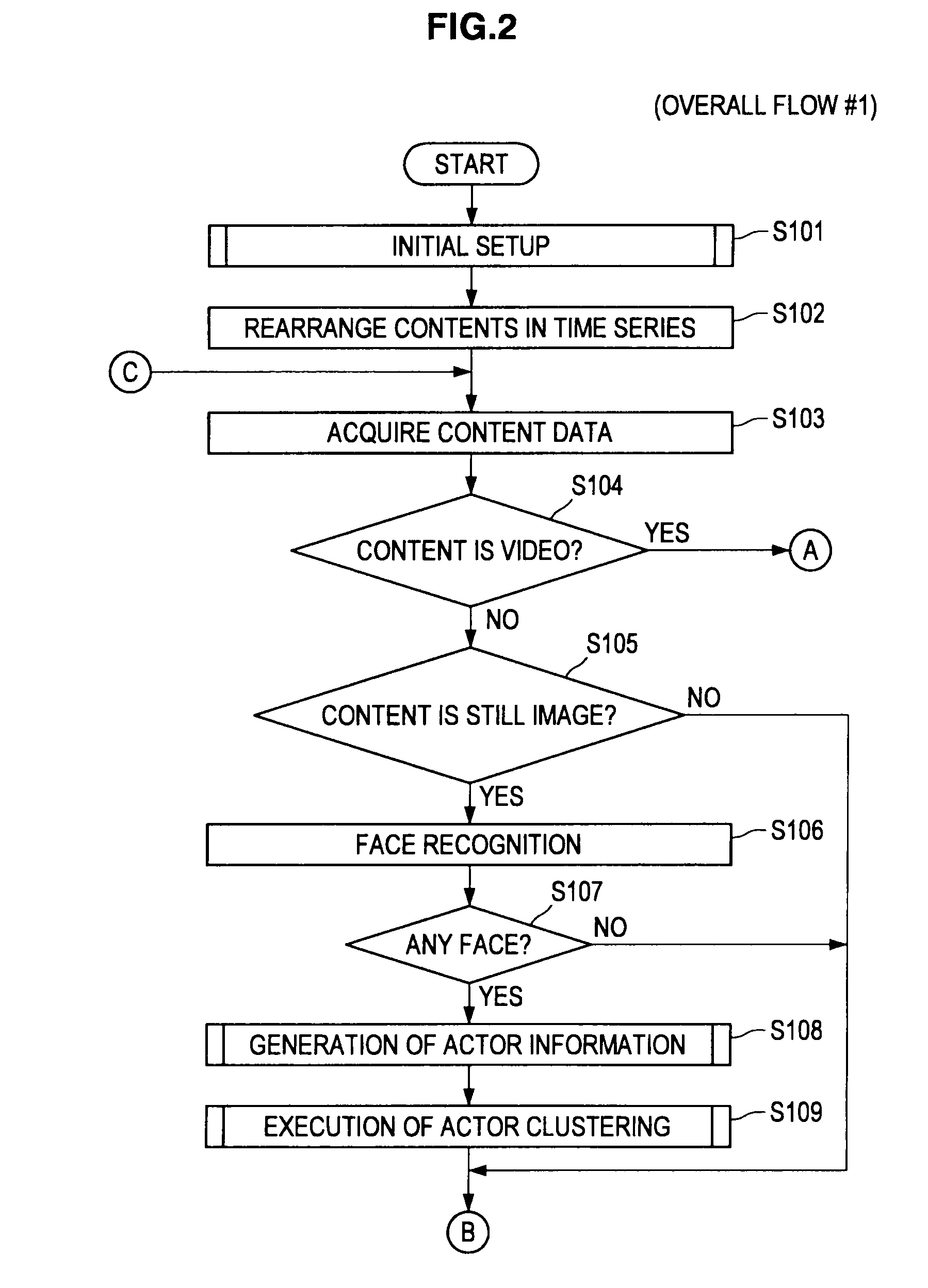

Face clustering device, face clustering method, and program

ActiveUS20110249904A1More efficiencyHigh accuracyCharacter and pattern recognitionCluster basedFace orientation

Provided is a face clustering device that detects a face included in an image, detects a direction of the detected face, detects, taking into account the detected direction of the face, a face with a similar feature and forms a collection of pieces of face information showing a feature of this face, narrows down, for each collection of pieces of face information which has been formed, the number of pieces of face information to a number set in advance for each face direction and sets each collection of pieces of face information for which the number has been narrowed down as a unit group, and performs, with the set unit group as a unit, clustering based on pieces of face information included in each unit group.

Owner:SONY CORP

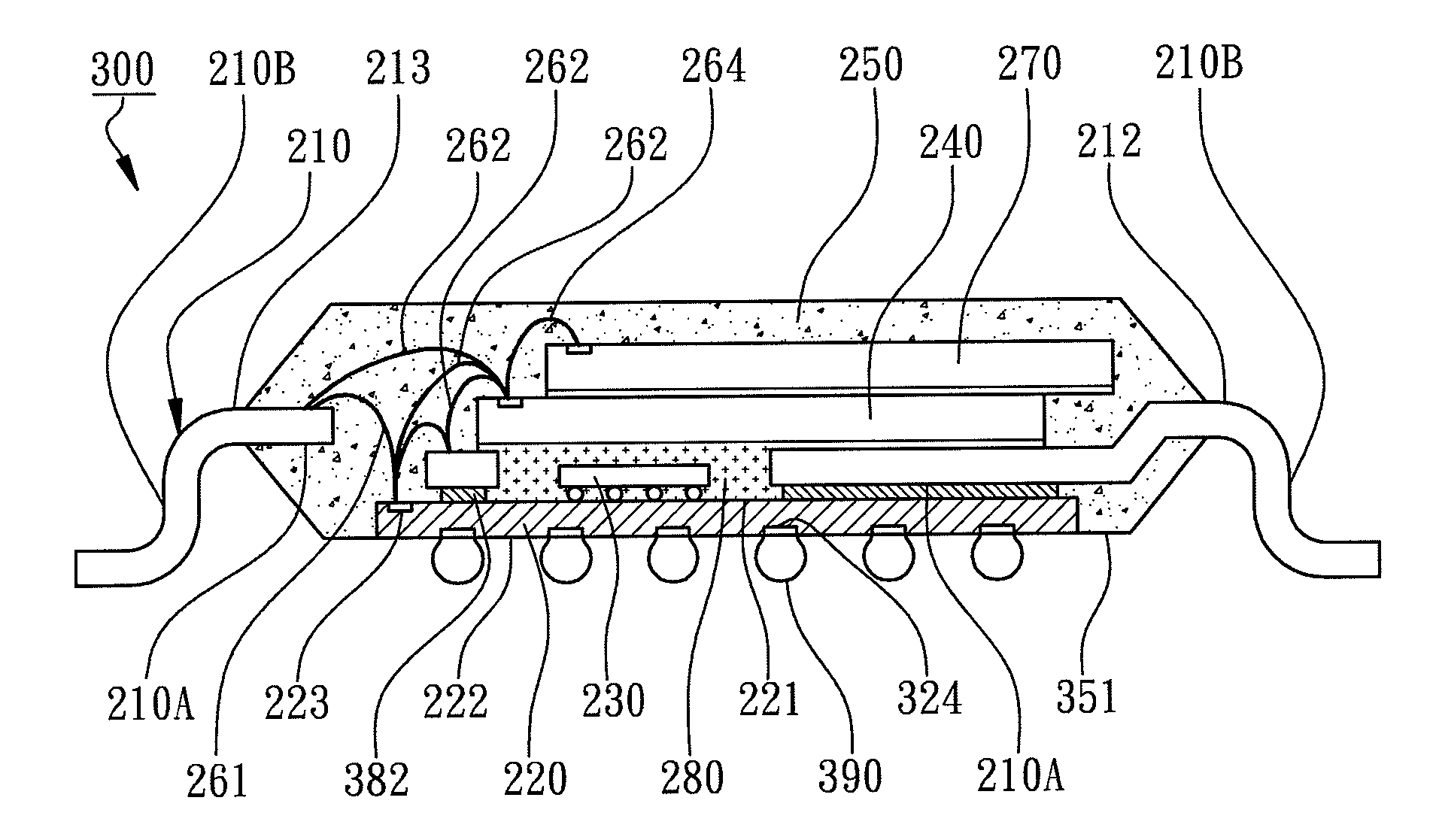

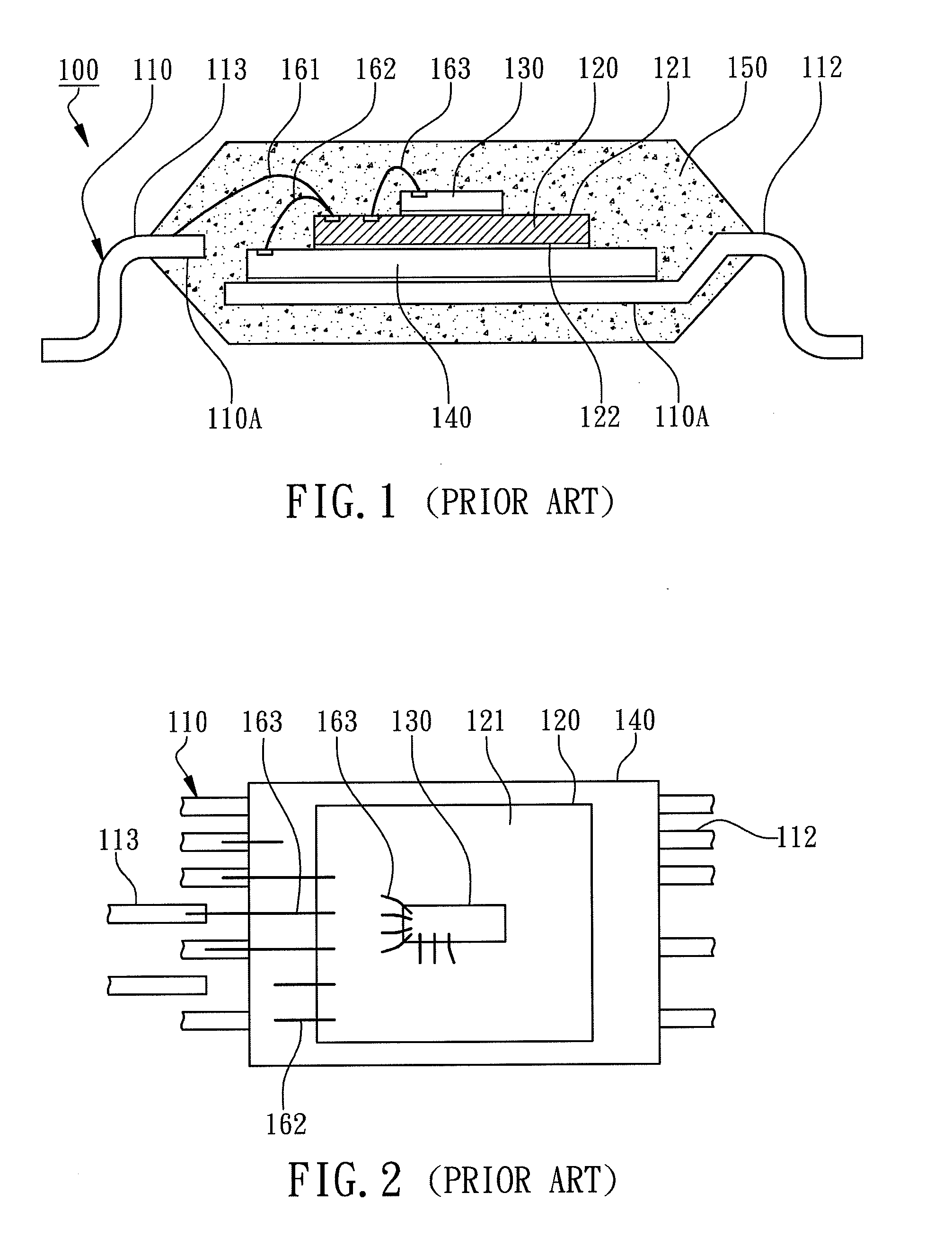

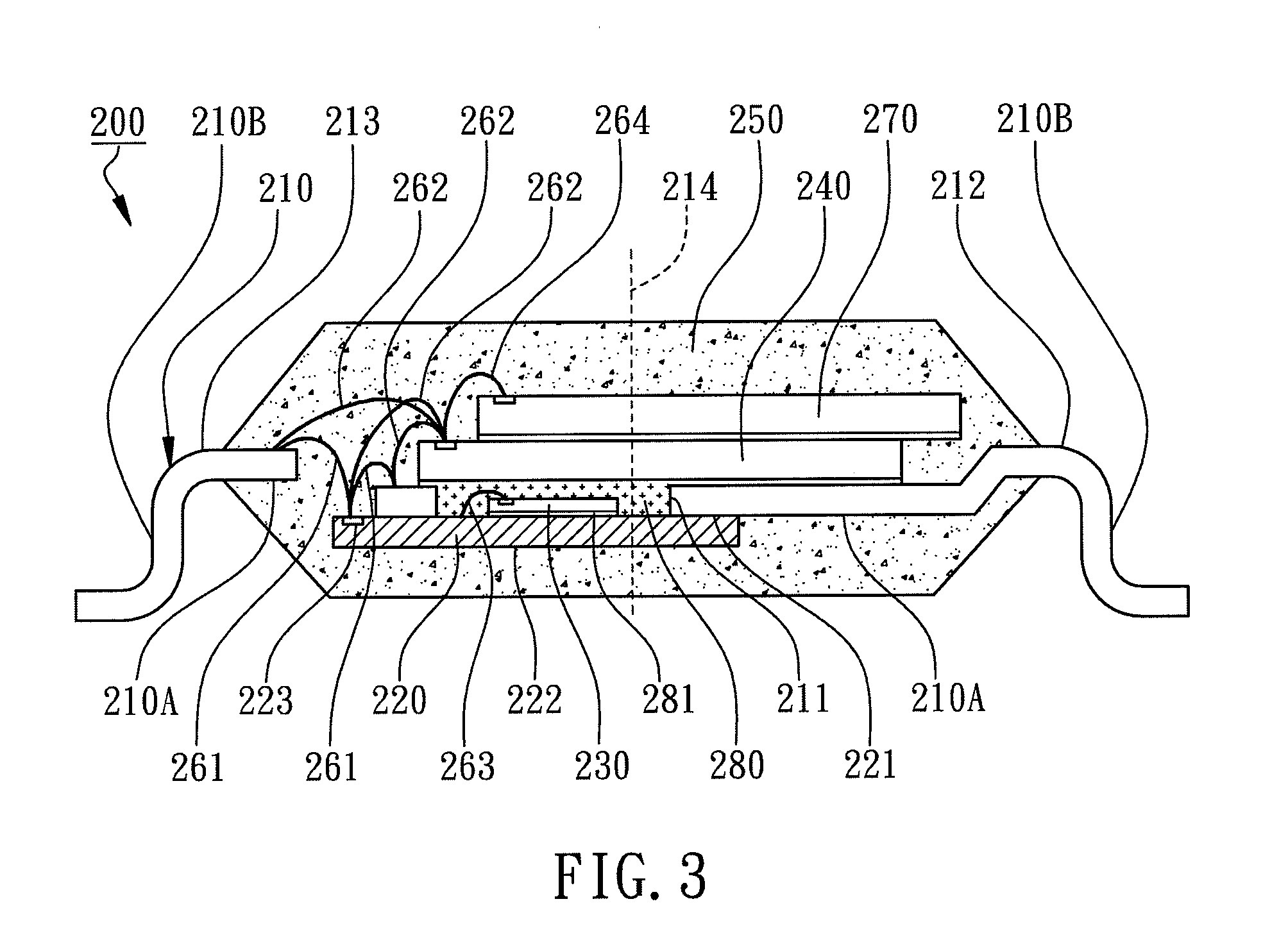

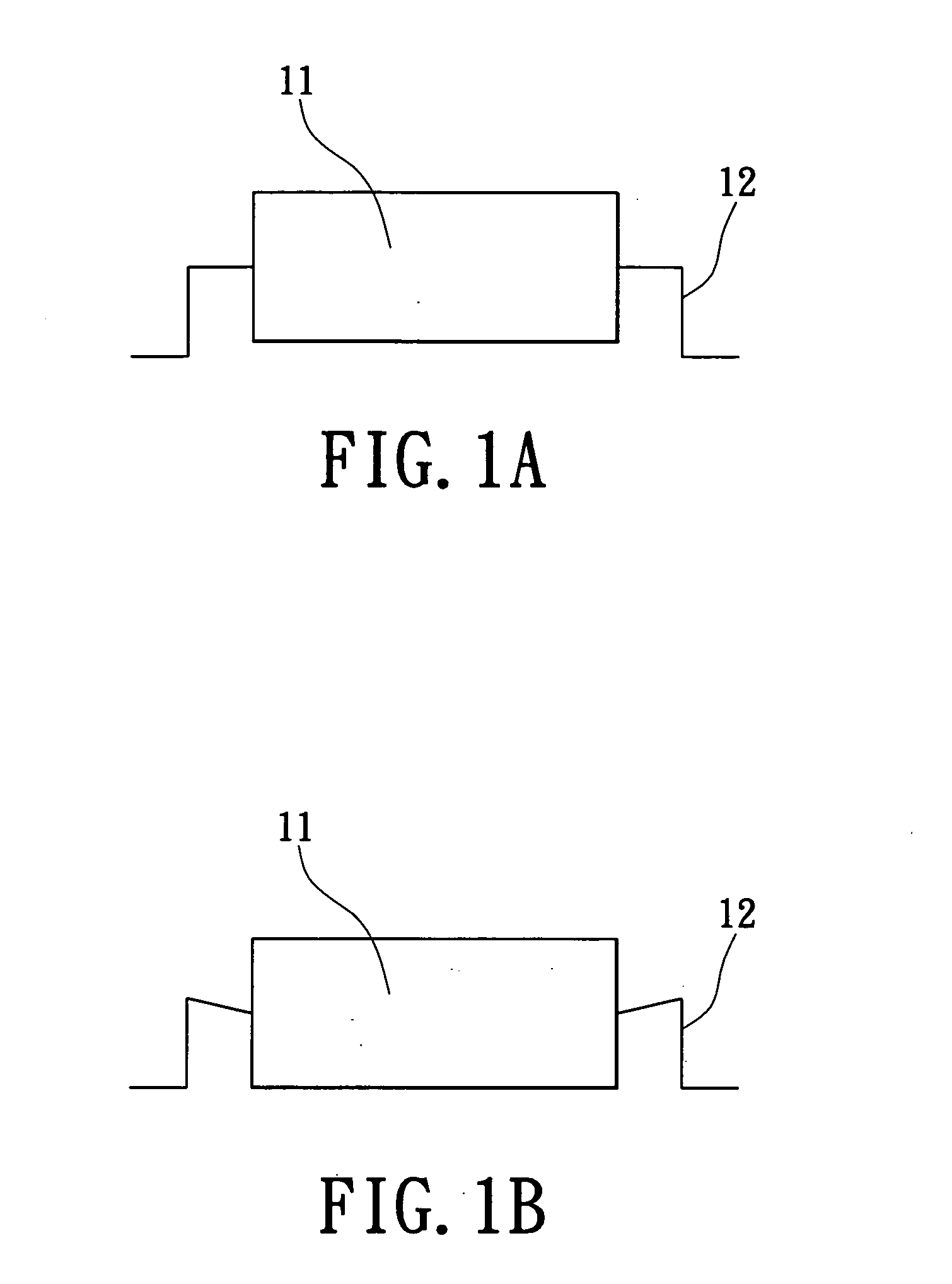

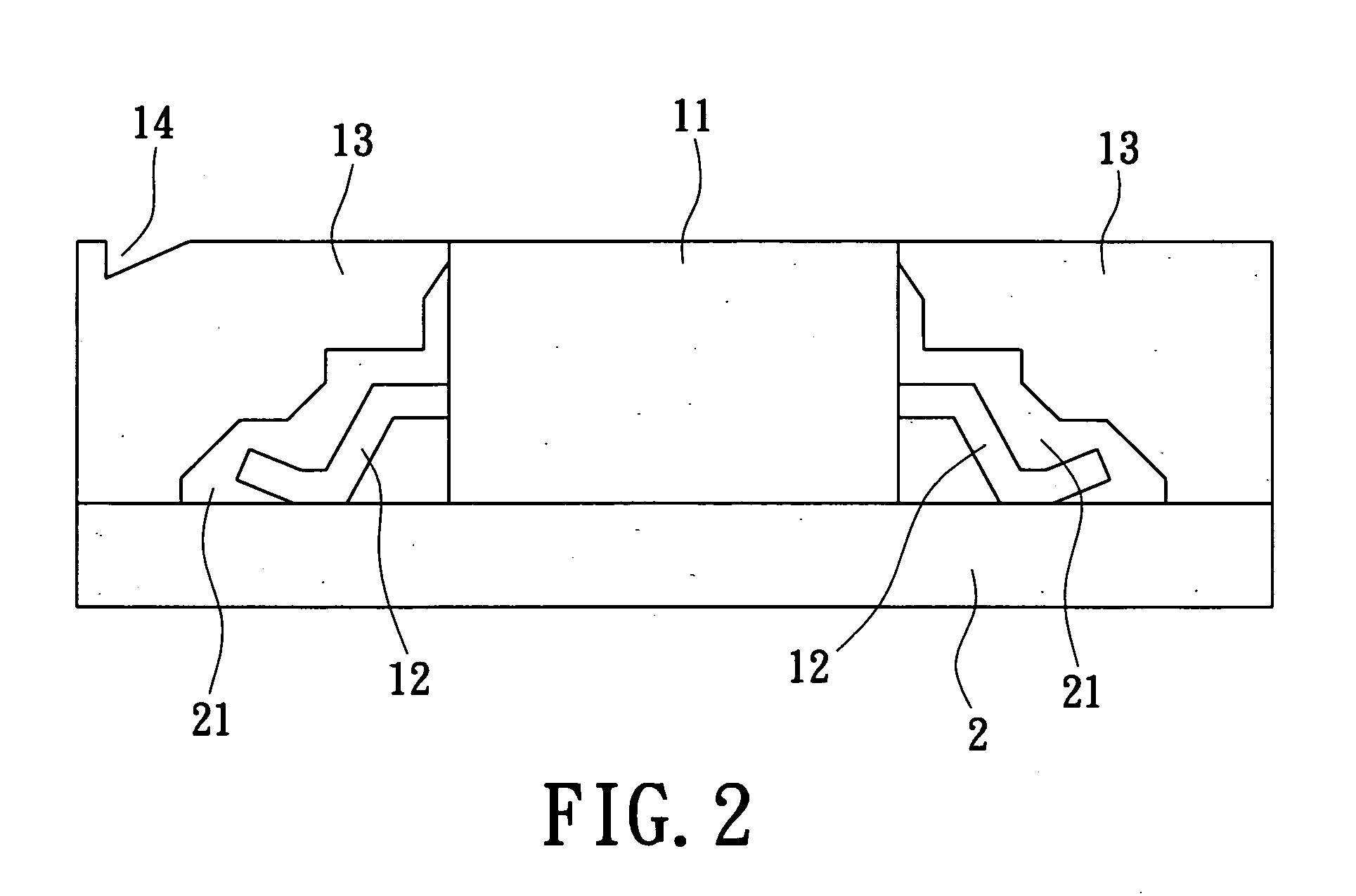

Col package having small chip hidden between leads

ActiveUS20110215454A1Increase the number ofLarge memory capacitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageEngineering

A Chip-On-Lead (COL) type semiconductor package having small chip hidden between leads is revealed. The lower surfaces of the leadframe's leads are attached to a wiring substrate and the leads are horizontally bent to form a die-holding cavity. A smaller chip is disposed on the wiring substrate by passing through the die-holding cavity to be on the same disposing level with the leads. At least a larger chip is disposed on the leads to overlap the smaller chip so that the small chip does not extrude from the leads. The encapsulant encapsulates a plurality of internal parts of the leads, the wiring substrate, and the larger chip. Therefore, the conventional unbalance issue of mold flow above and below the leads leading to cause excessive warpage can be avoided and numbers of stacked larger chips can be increased to have larger memory capacities.

Owner:POWERTECH TECHNOLOGY

Intelligent warehouse goods management method based on RFID technology

InactiveCN102426682AObvious advantagesImprove work efficiencyCo-operative working arrangementsLogisticsDatabase serverData memory

The invention provides an intelligent warehouse goods management method based on a RFID (Radio Frequency Identification) technology. The method is characterized by comprising the following steps of: firstly, respectively implanting a RFID tag for each goods, registering different ID for each RFID tag, and allocating storage space for each ID in a database server; then, reading the RFID tag on each goods through a mobile RFID reader while registering the goods for storage, storing the goods, registering the goods for delivery and packing the goods; obtaining the ID of the RFID tag, inputting related information of the goods; and transmitting the data to the database server through a management system for storage. The method has the advantages of: (1) quick scanning; (2) excellent penetrability and barrier-free reading; (3) strong contamination resistance and durability; (4) large data memory capacity; (5) miniaturized volume and diversified shape; (6) excellent reusable property; (7) high security.

Owner:SHANGHAI GAOCHENG CREATIVE TECH GRP

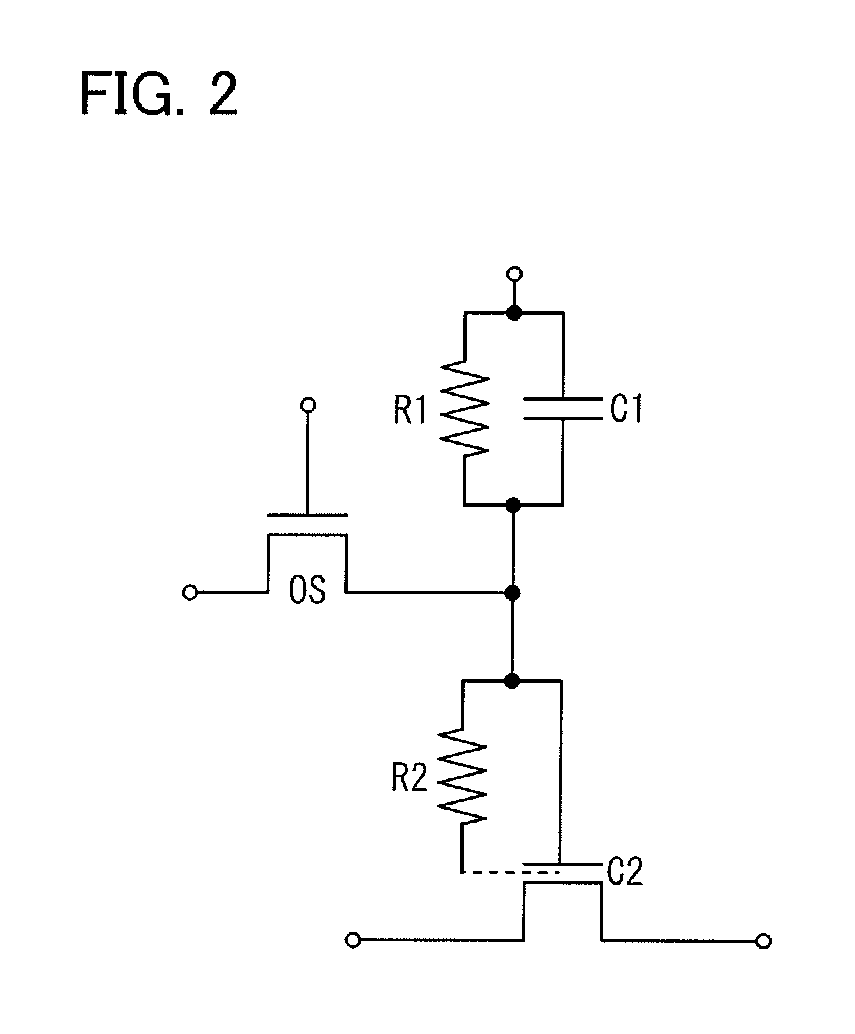

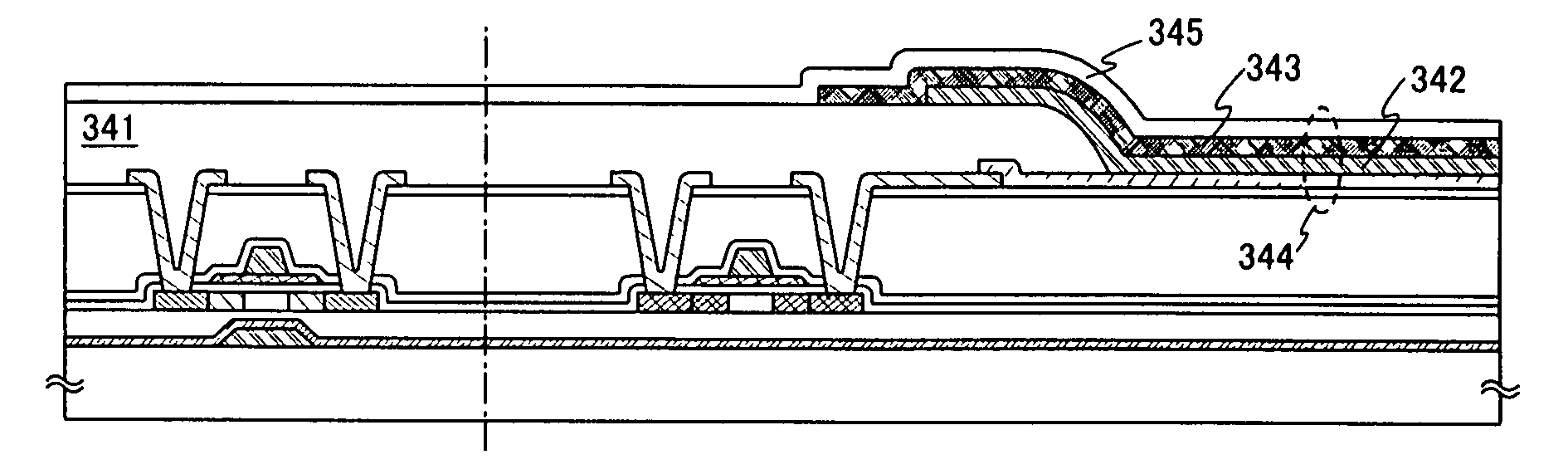

Integrated circuit, semiconductor device comprising the same, electronic device having the same, and driving method of the same

InactiveUS7541614B2Large memory capacityReduce the refresh rateTransistorSolid-state devicesData controlActive layer

An integrated circuit mounting a DRAM which can realize high integration without complicated manufacturing steps. The integrated circuit according to the invention comprises a DRAM in which a plurality of memory cells each having a thin film transistor are disposed. The thin film transistor comprises an active layer including a channel forming region, and first and second electrodes overlapping with each other with the channel forming region interposed therebetween. By controlling a drain voltage of the thin film transistor according to data, it is determined whether to accumulate holes in the channel forming region or not, and data is read out by confirming whether or not holes are accumulated.

Owner:SEMICON ENERGY LAB CO LTD

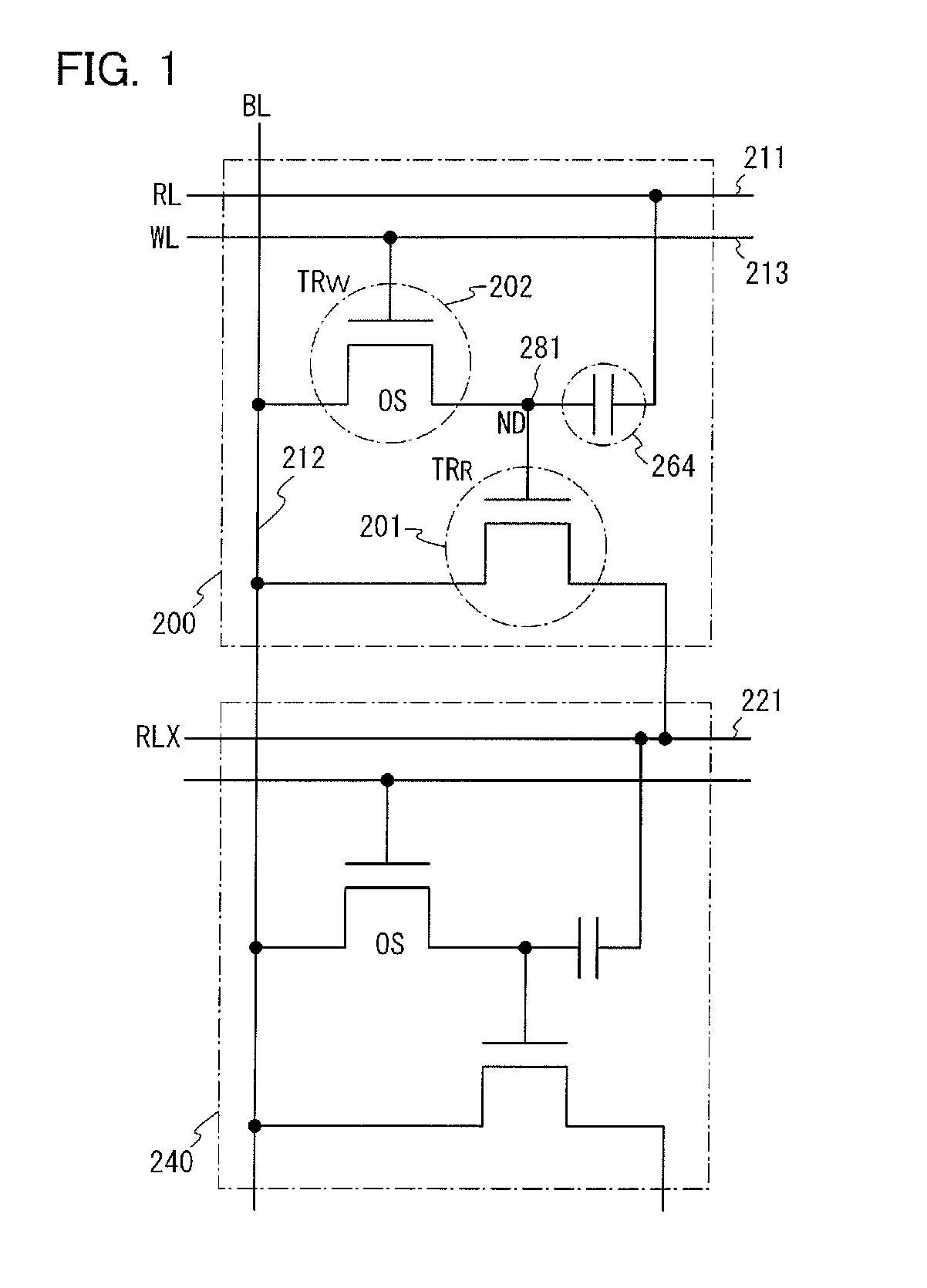

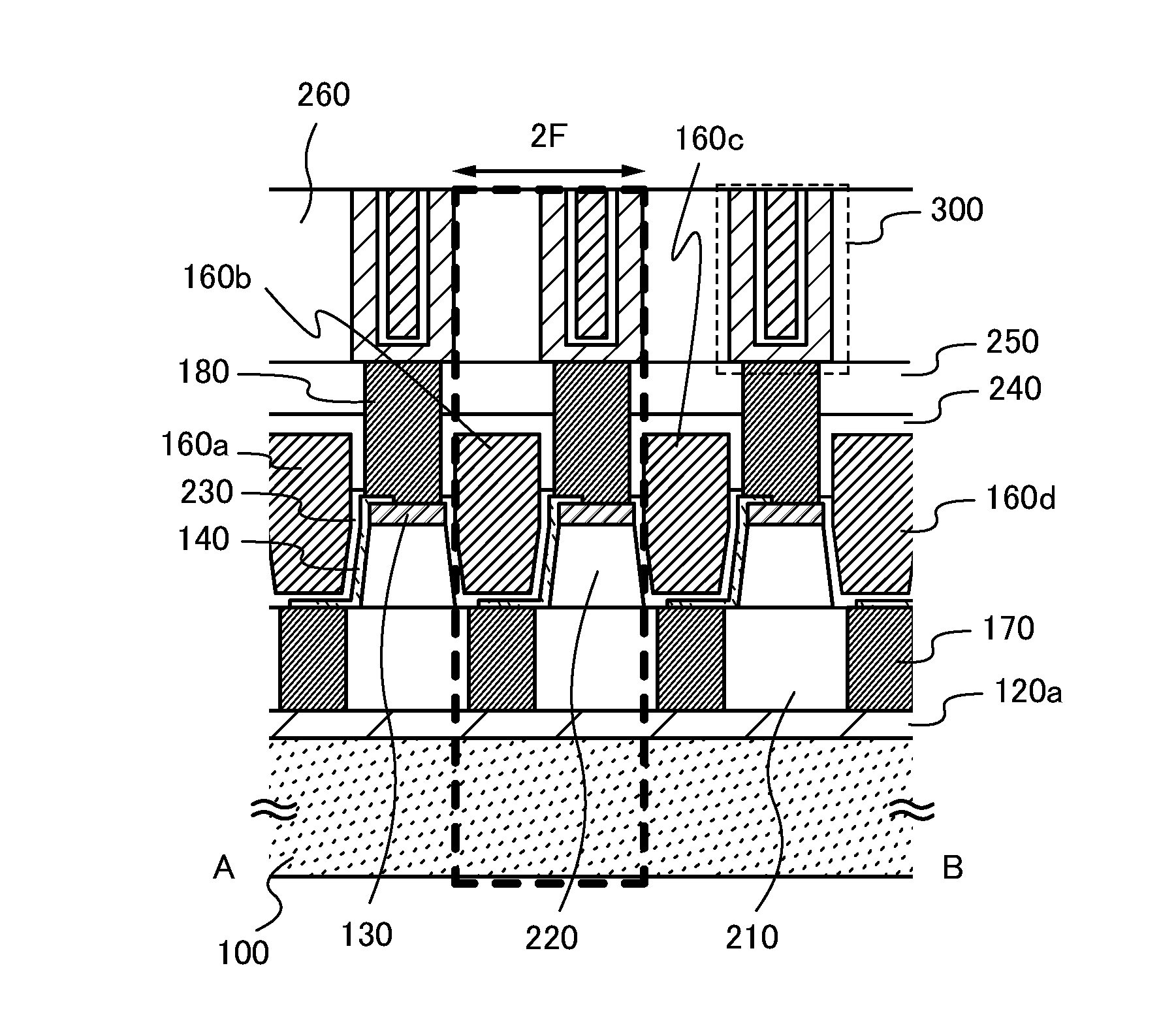

Memory device

InactiveUS8686486B2Reduced footprintLarge memory capacityTransistorSemiconductor/solid-state device detailsBit lineEngineering

It is an object to provide a memory device where an area occupied by a memory cell is small, and moreover, a memory device where an area occupied by a memory cell is small and a data holding period is long. A memory device includes a bit line, a capacitor, a first insulating layer provided over the bit line and including a groove portion, a semiconductor layer, a second insulating layer in contact with the semiconductor layer, and a word line in contact with the second insulating layer. Part of the semiconductor layer is electrically connected to the bit line in a bottom portion of the groove portion, and another part of the semiconductor layer is electrically connected to one electrode of the capacitor in a top surface of the first insulating layer.

Owner:SEMICON ENERGY LAB CO LTD

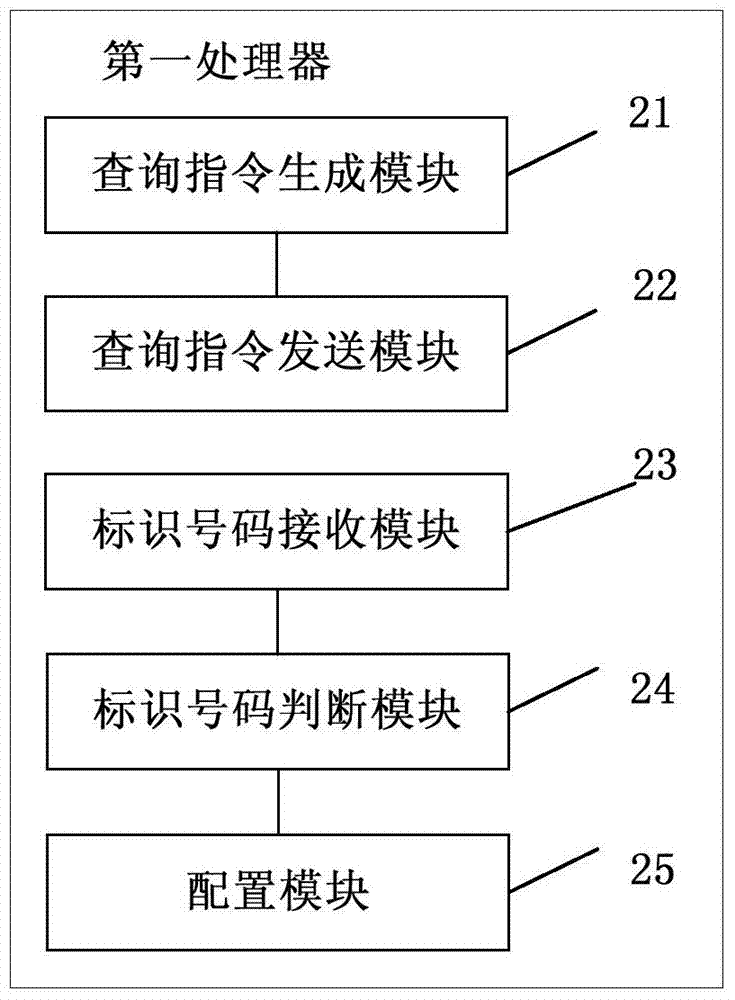

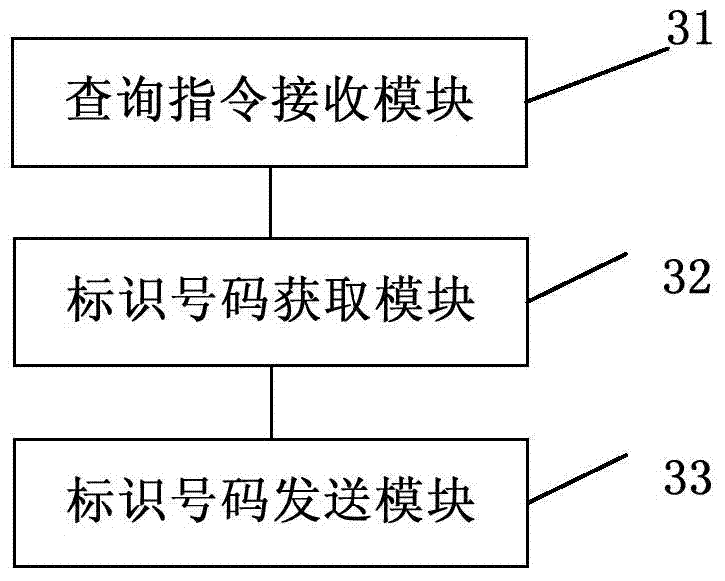

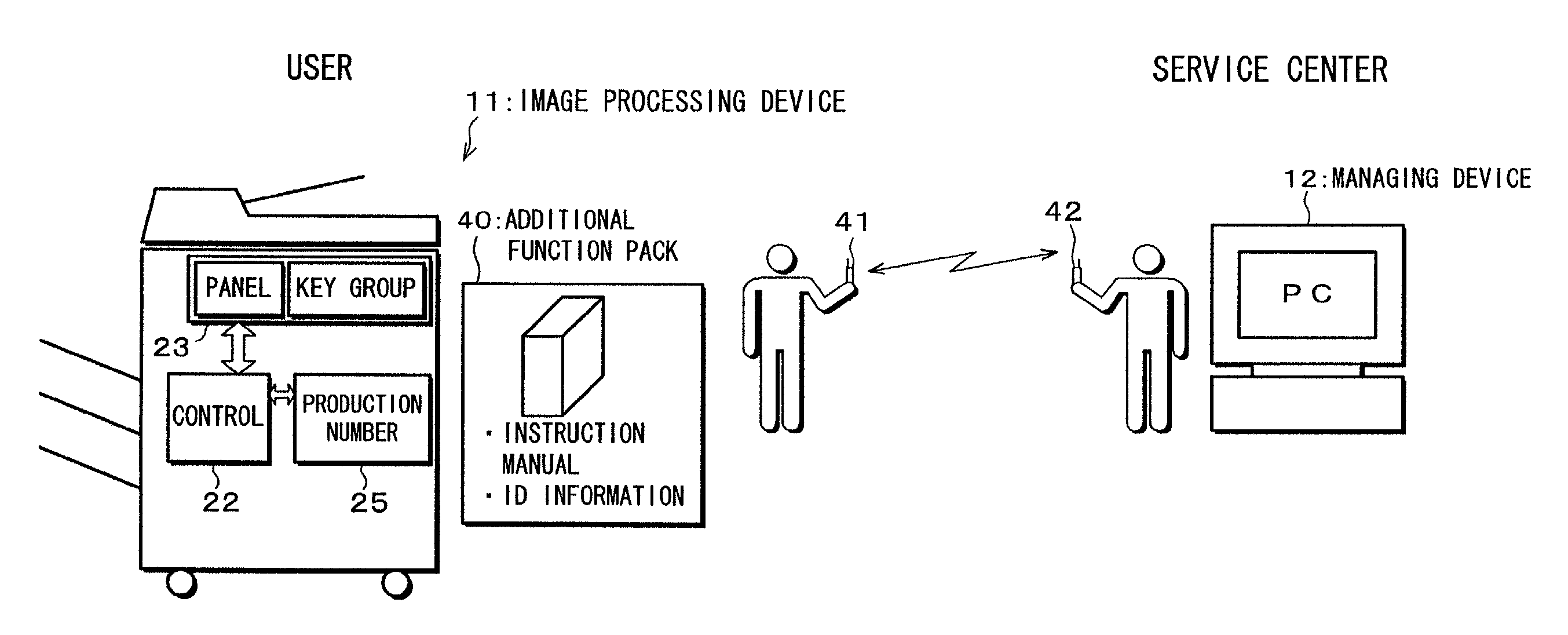

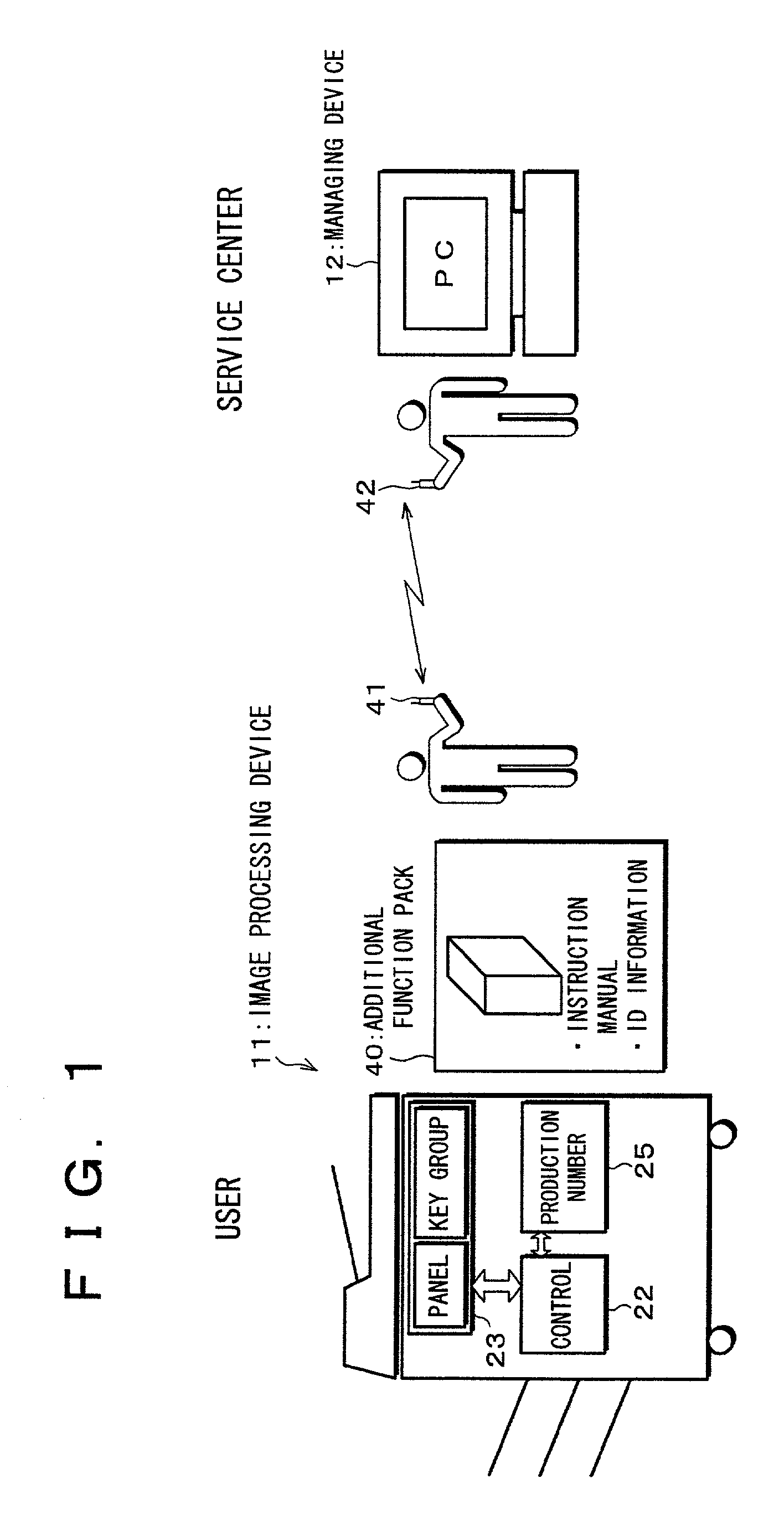

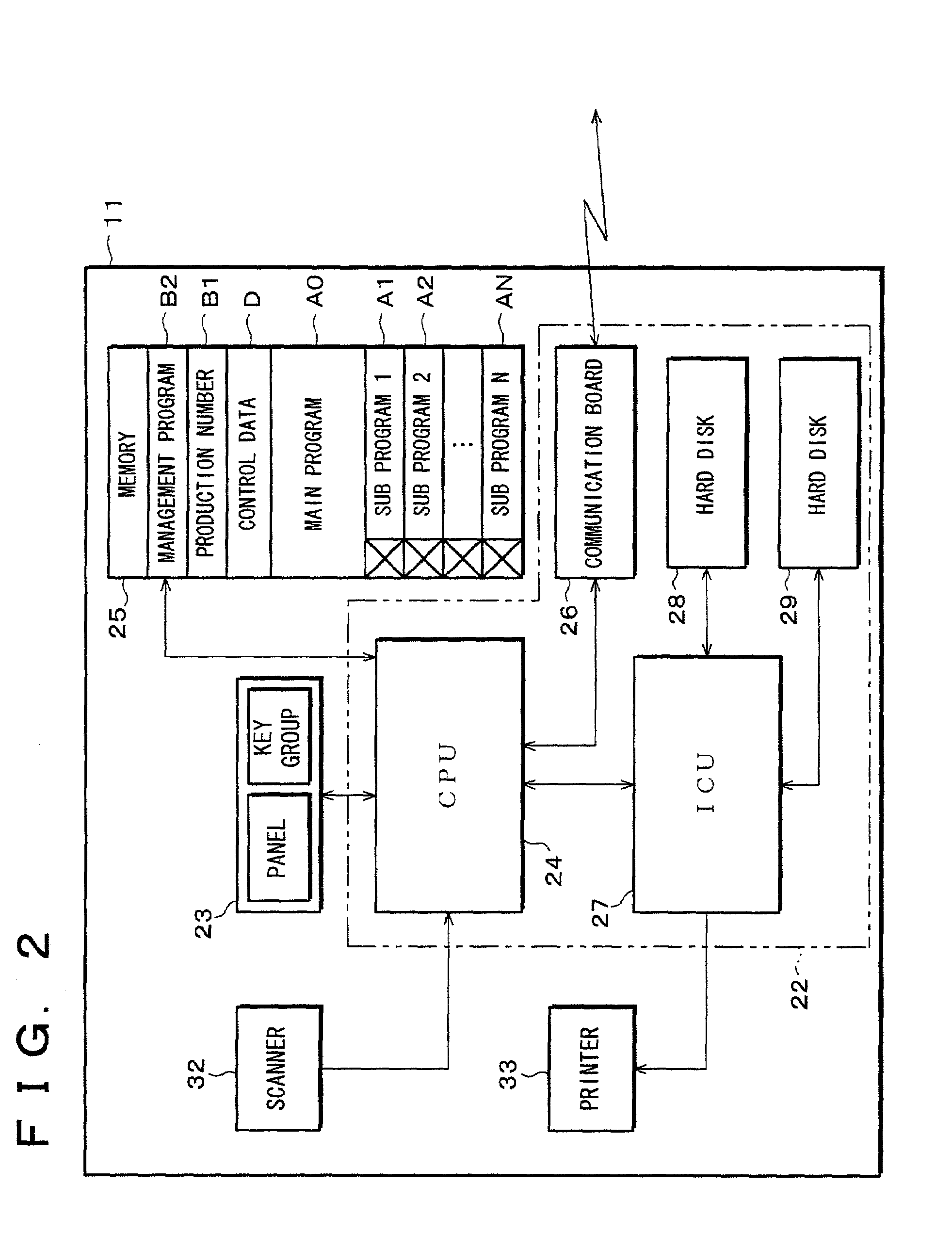

Electronic apparatus and management system of the same

InactiveUS7155413B2Guarantee smooth implementationLow costData processing applicationsDigital computer detailsImaging processingComputer science

An image processing device stores a main program that controls basic operations that the device conducts as a copying machine, a printer, a facsimile machine, etc., as well as a sub program that controls additional operations that the device conducts as a net work scanner. When a user purchases an additional function pack and sends a production number of the image processing device and ID information of the pack to a managing device, the managing device returns a releasing key produced by encoding the production number. A control section of the device decodes the releasing key, and permits the foregoing access if the production number obtained by the decoding matches that stored in the memory section. Therefore, even after shipment, extension of functions can be smoothly implemented at lower costs without replacement of boards or memories. Thus, an image processing device realized with a digital complex machine is arranged so that extension of functions after shipment can be smoothly implemented at lower costs.

Owner:SHARP KK

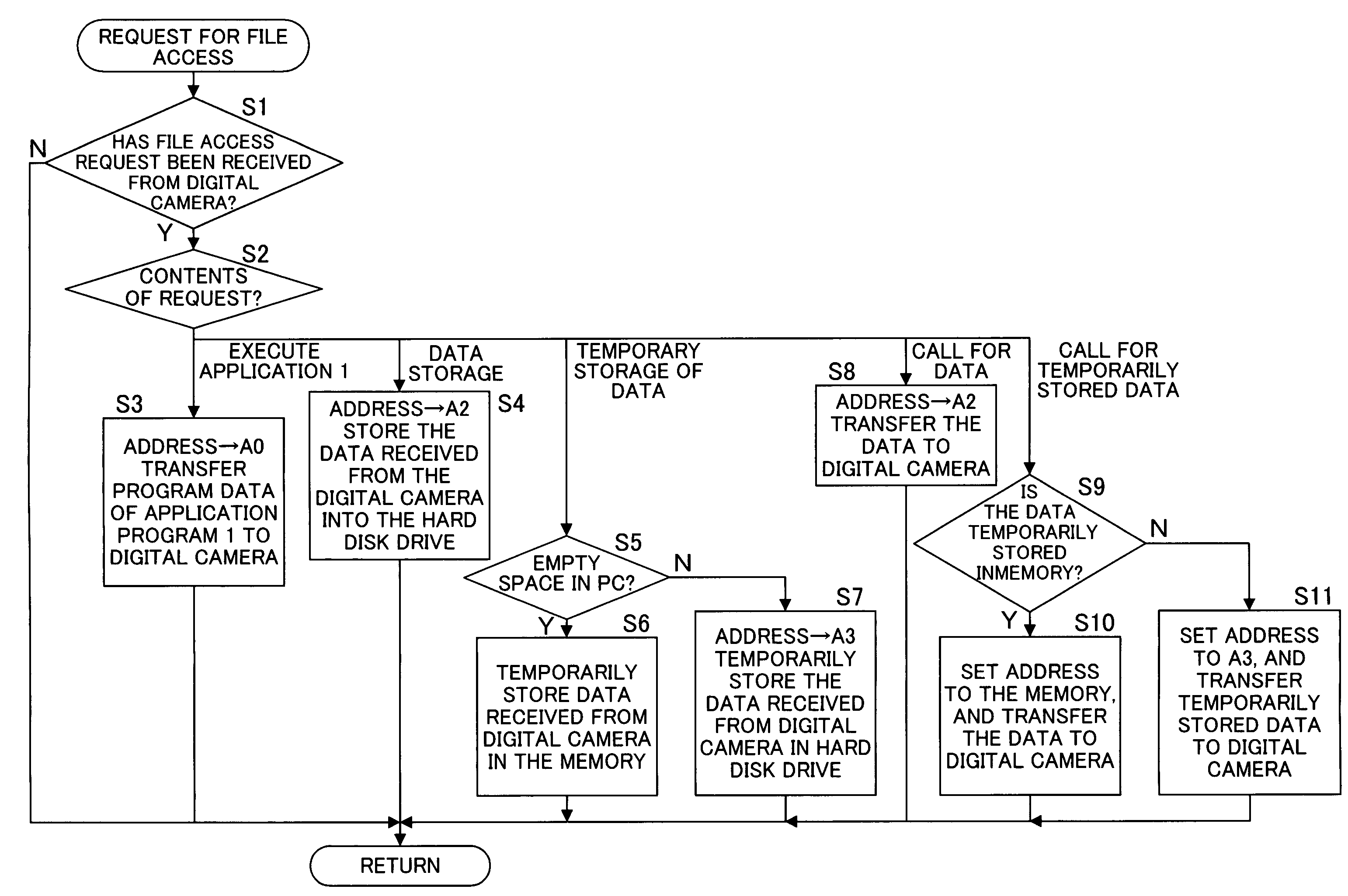

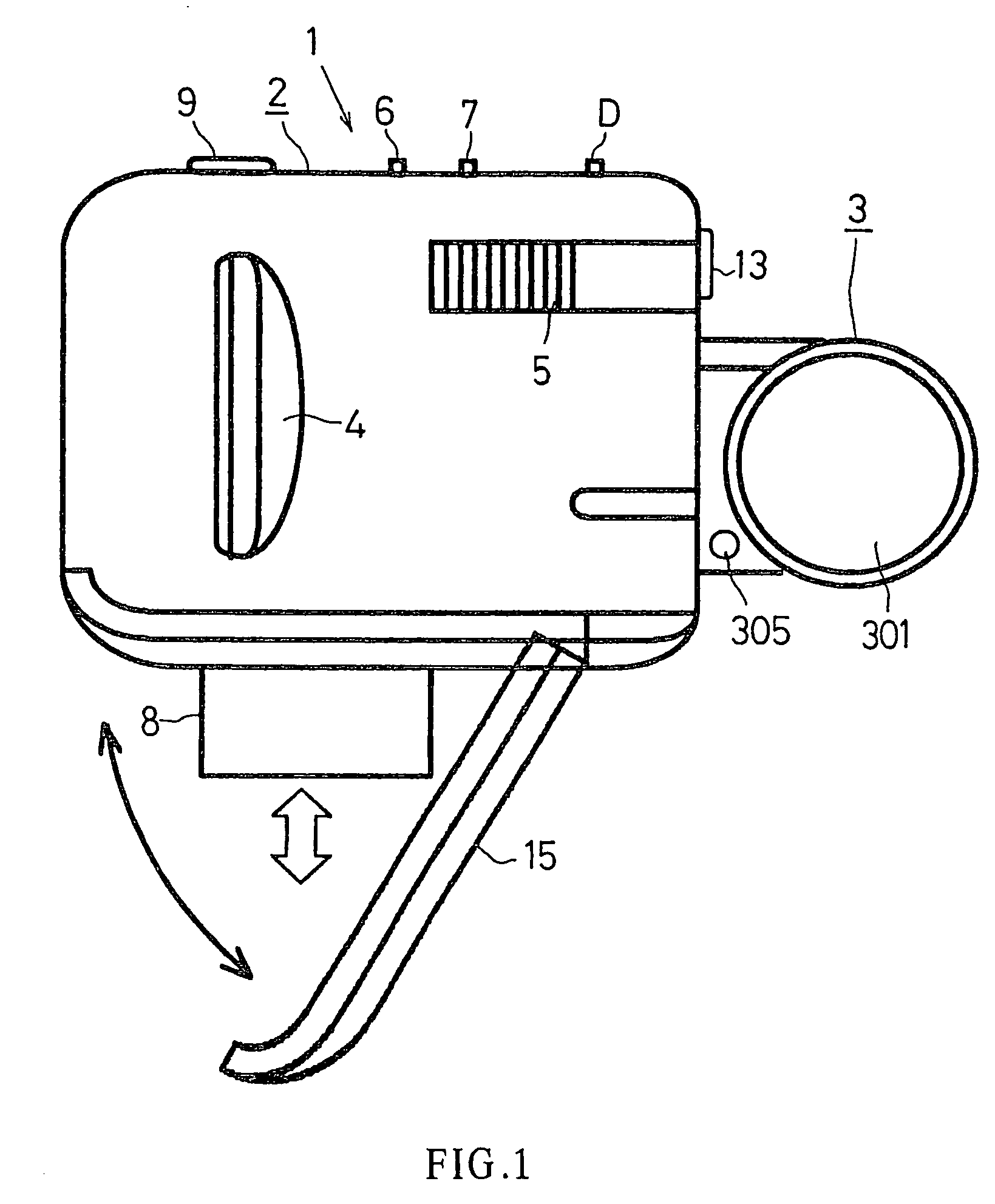

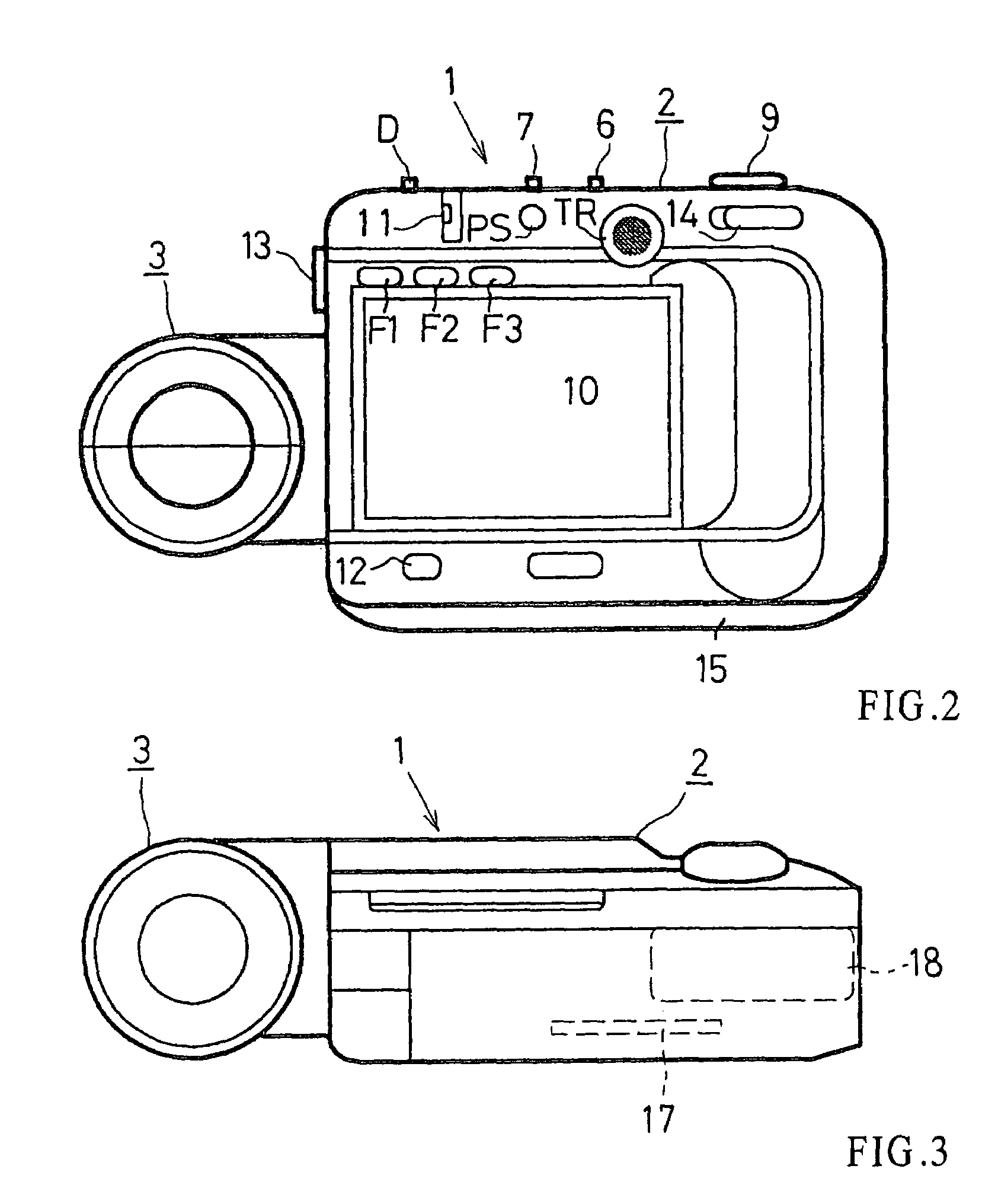

Image processing system, method for formatting recording medium, and program product

InactiveUS7046280B1Large memory capacityInput/output for user-computer interactionTelevision system detailsImaging processingComputer graphics (images)

An image processing system includes a photographing apparatus, and an image processing apparatus to which the photographing apparatus and a recording medium can be connected. The photographing apparatus includes a controller for executing a program recorded in the recording medium. The image processing apparatus includes a processor for creating a region accessible from the photographing apparatus, and a controller for causing the program to be stored in the region.

Owner:MINOLTA CO LTD

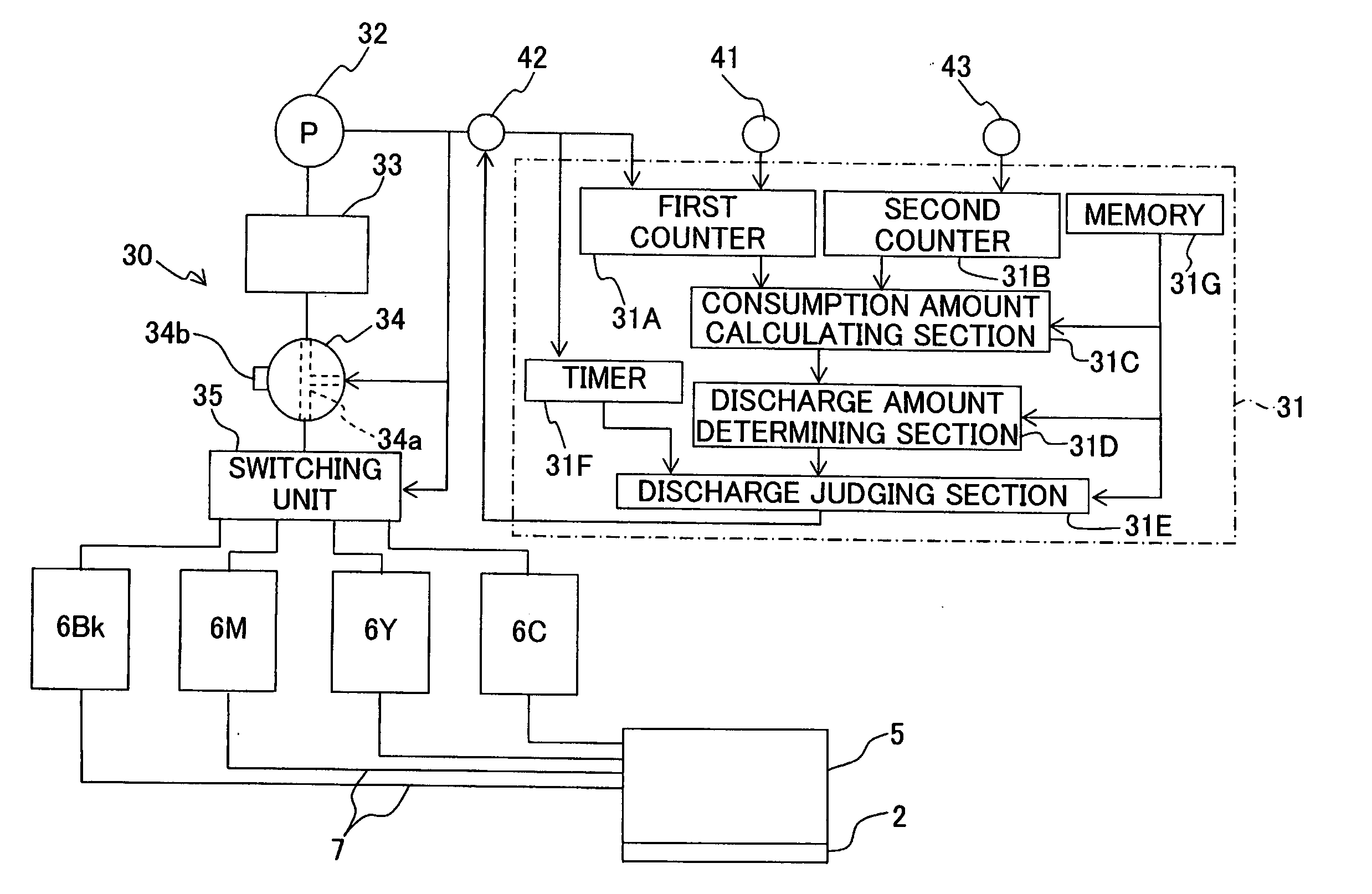

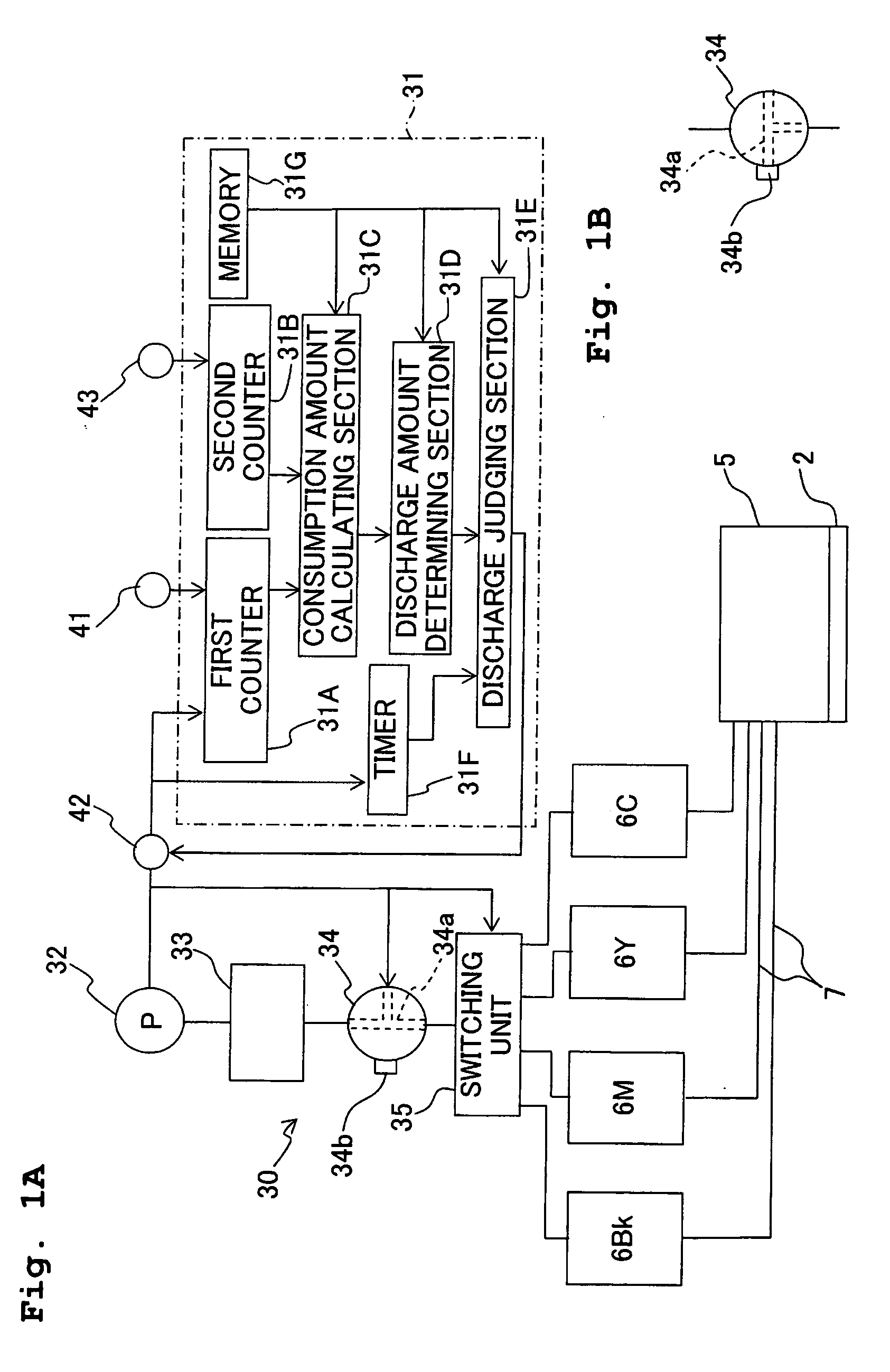

Ink-jet printer and maintenance method for ink-jet printer

InactiveUS20080143764A1Excellent stateLarge memory capacityOther printing apparatusElectrical and Electronics engineeringRecording head

Ink consumption amount is calculated based on an ink amount which is used for recording and periodic preparatory jetting in a predetermined time period after a previous discharge operation. An ink of an ink amount obtained by subtracting a consumption amount for the predetermined time, from an ink capacity of an ink supply system which supplies the ink from an ink cartridge to a recording head, is discharged by a discharge mechanism. Accordingly, it is possible to maintain a favorable state of ink by replacing periodically the ink in the ink supply system without a wasteful consumption. Moreover, when the amount of ink consumed in the predetermined time period is same as or more than the ink capacity of the ink supply system, the discharge operation is not carried out. Therefore, it is possible to suppress the consumption of ink due to the discharge operation.

Owner:BROTHER KOGYO KK

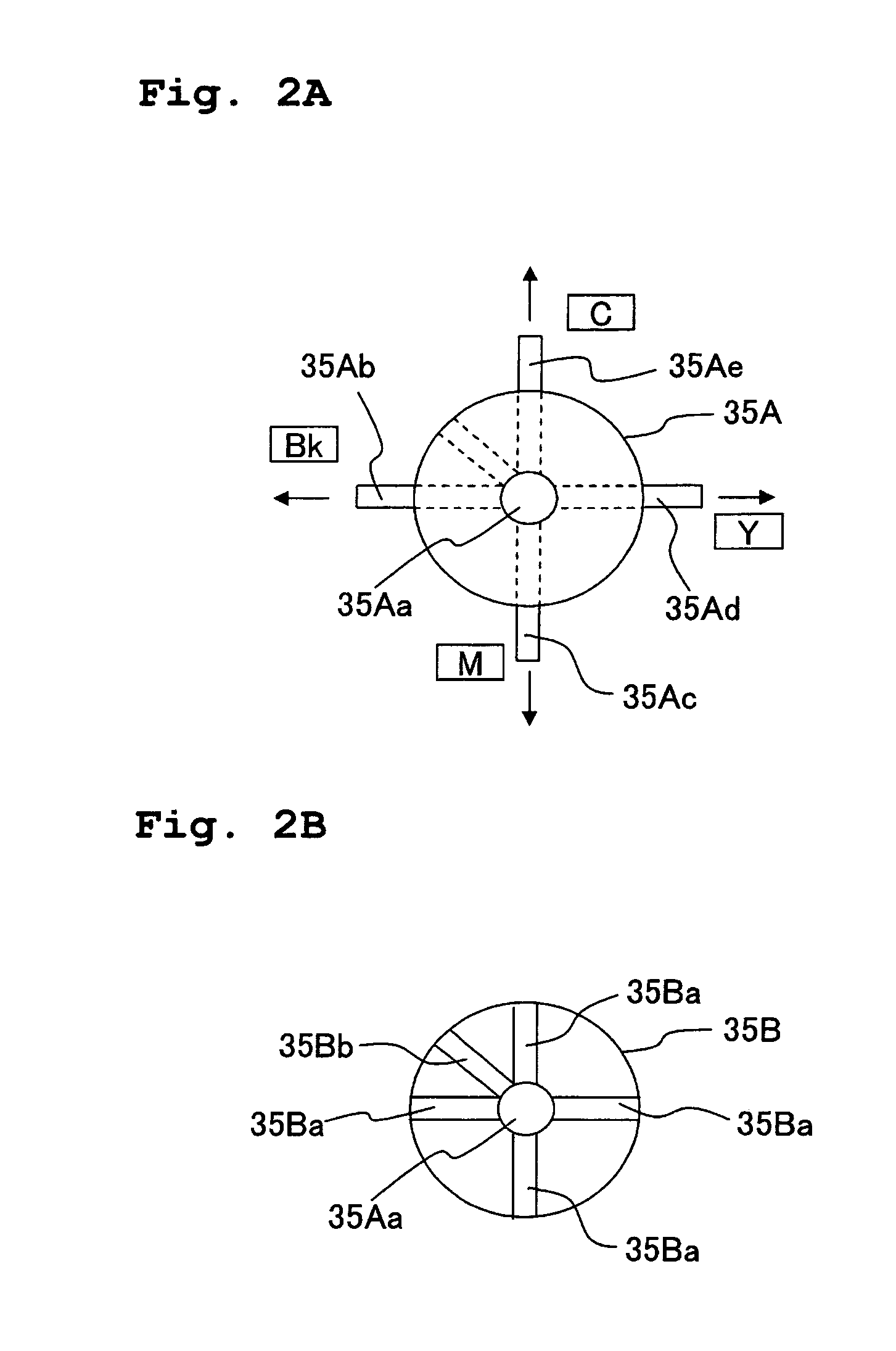

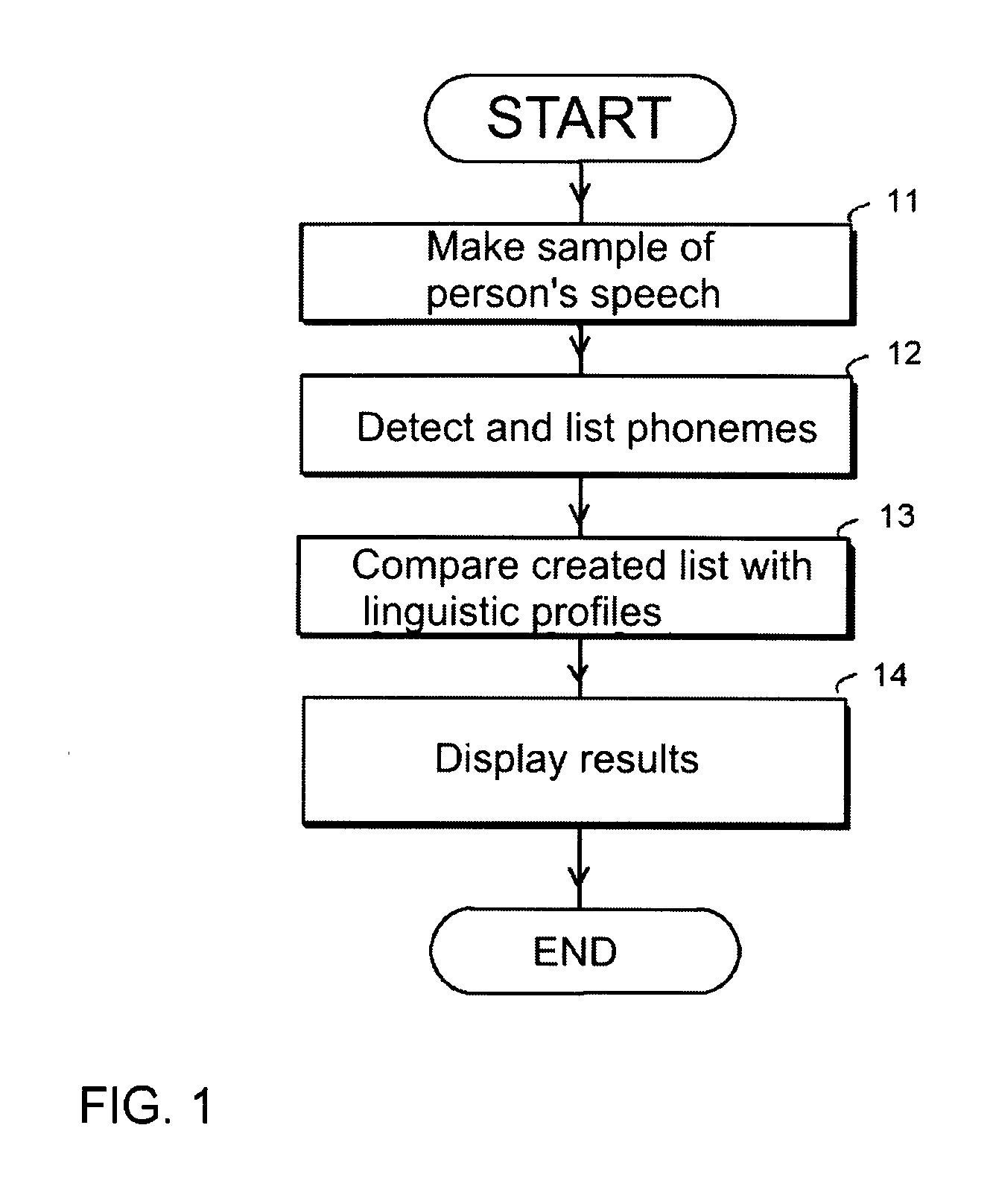

Method of linguistic profiling

InactiveUS20130189652A1Learning speedEasy to learnSpeech analysisElectrical appliancesLanguage speechSpeech sound

In order to define or measure the language proficiency of a person, particularly the degree of flawlessness in the pronunciation, and / or to find out the linguistic background and identity of a person, the person's speech is compared with a selected reference language. This is achieved by applying autocorrelation and / or pattern recognition and / or signal processing and / or other corresponding methods for identifying and registering such sound elements and features that are typical of the reference language and occur repeatedly in the reference language speech sample. On the basis of the obtained linguistic profile of the reference language, corresponding sound elements and features are searched in the speech of the person, and there is calculated how many of the sound elements and features of the reference language linguistic profile the person substitutes with such sound elements or features that deviate from the reference language, and the substitute sound elements and features are defined.

Owner:PRONOUNCER EURO

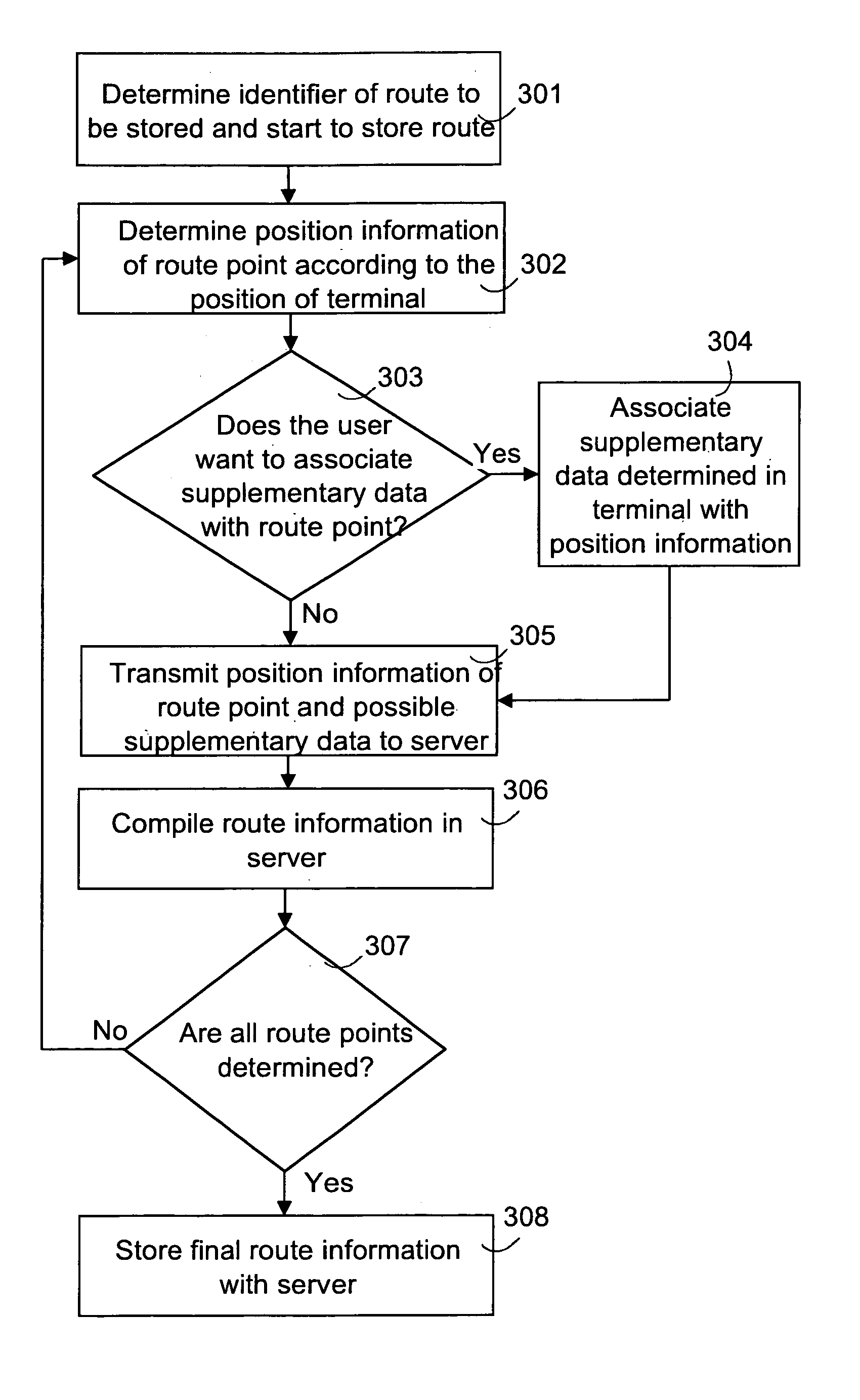

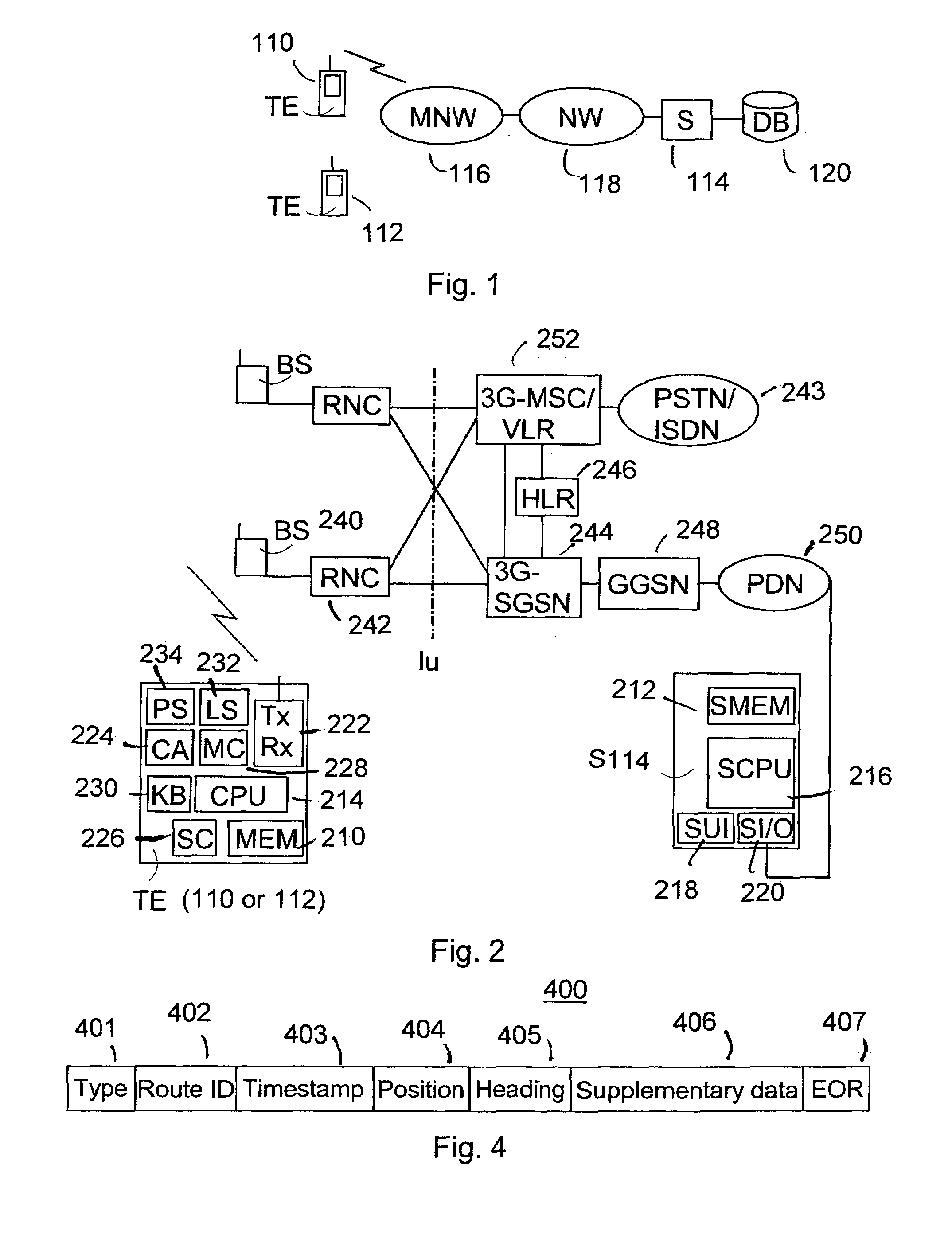

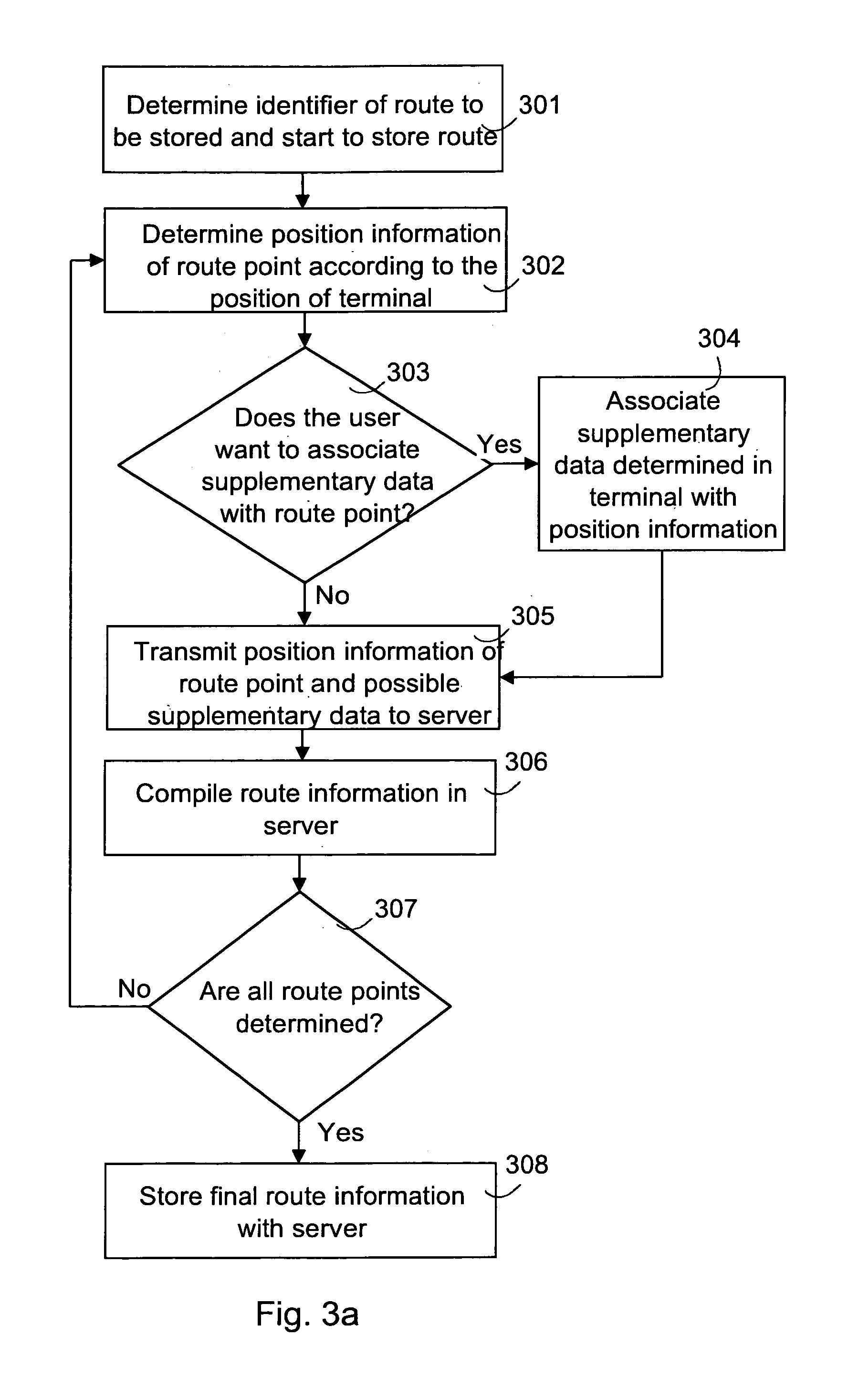

Providing guiding service by means of a wireless terminal

InactiveUS7155338B2Clear instructionsLarge memory capacityInstruments for road network navigationRoad vehicles traffic controlComputer terminalSupplementary data

The invention relates to a guiding system for wireless terminals. In the system, position-specific information of route points of the route on which a first wireless terminal travels is determined and it is sent to a guiding server. Supplementary data used for guiding the route are stored in the first terminal in response to a request of the user. The supplementary data are associated with the position information, and the guiding server compiles and stores route information comprising position information and supplementary data. The route information is transmitted from the guiding server to at least one wireless terminal in response to the route request. The position of the terminal is determined and the received route information is presented in the terminal so that said supplementary data are presented when the terminal is in places with which the supplementary data are associated.

Owner:NOKIA TECHNOLOGLES OY

Intelligent warehouse cargo management method adopting RFID technology

InactiveCN103761631AObvious advantagesImprove work efficiencyCo-operative working arrangementsLogisticsDatabase serverReusability

The invention provides an intelligent warehouse cargo management method adopting an RFID technology. The method is characterized in that steps are: firstly, implanting an RFID label for each cargo respectively, registering a different ID for each RFID label and distributing a storage space for each ID in a database server; then both after the cargos undergo warehousing registration and warehousing, and when the cargos are undergoing ex-warehouse registration and cargo packing, adopting a mobile RFID reader-writer to read the RFID label on each cargo and obtaining the IDs of the RFIDs and inputting related information of the cargos and sending the data to the database server for storage through a management system. The advantages of the intelligent warehouse cargo management method adopting the RFID technology are: (1): rapid scanning; (2) penetrability and no-screen reading; (3) anti-pollution capability and durability; (4) large memory capacity of the data; (5) volume miniaturization and shape diversification; (6) reusability; (7) security.

Owner:TIANJIN CHUANSHI TECH

Memory packaging structure of mini SD card

InactiveUS20070158803A1Reduce componentsLow production costSemiconductor/solid-state device detailsSolid-state devicesEngineeringDirect exposure

A memory packaging structure of mini SD card, the main implementation technology thereof comprises: to perform the pin adjustment to the: memory originally employing TSOP (Thin Small Out-Line Package) packaging structure, eliminating the gap of 0.1 mm to 0.2 mm between the memory and the circuit board, thus completely attached to the circuit board; to leave the top end of the mini SD card open to directly expose the top end of the memory on the surface of the mini SD card, reducing the thickness of a layer of coverage; to cover the pins on the both sides of the memory to hind them, wherein applying glue joint between the auxiliary lateral body and memory pins to enhance the attachment.

Owner:ADATA +1

Methods and systems for managing computations on a hybrid computing platform including a parallel accelerator

ActiveUS8225074B2Efficient managementImprove convenienceGeneral purpose stored program computerPhysical realisationParallel computingData transmission

In accordance with exemplary implementations, application computation operations and communications between operations on a host processing platform may be adapted to conform to the memory capacity of a parallel accelerator. Computation operations may be split and scheduled such that the computation operations fit within the memory capacity of the accelerator. Further, the operations may be automatically adapted without any modification to the code of an application. In addition, data transfers between a host processing platform and the parallel accelerator may be minimized in accordance with exemplary aspects of the present principles to improve processing performance.

Owner:NEC CORP

Data storage device, apparatus and method for using same

InactiveUS8397998B1Large memory capacityFreely handledApparatus for flat record carriersFilamentary/web record carriersCredit cardHigh density

A data storage device for use as a portable card, magnetically encodeable card, magnetic credit card or the like is shown. The data storage device includes a substrate having at least one surface. A high density, magnetically coercive material layer is disposed on or is deposited on the substrate for storing magnetic signals. The magnetically coercive material may have an axis of magnetization that is oriented in a predetermined direction relative to the at least one surface of the substrate. A layer of non-magnetically material is disposed on the substrate for defining an exchange break layer. A relatively hard, abradeable protective coating is formed on said magnetic material layer and is selected to have a thickness between a maximum thickness which would materially attenuate magnetic signals passing between the magnetic material layer and a transducer and a minimum thickness enabling said protective coating to be abraded by usage in an ambient natural atmosphere operating environment for removing therefrom a known quantity of the protective coating. The protective coating may comprise one, two or more layers of materials.

Owner:ULTRACARD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com