Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

63 results about "Thermal nitridation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

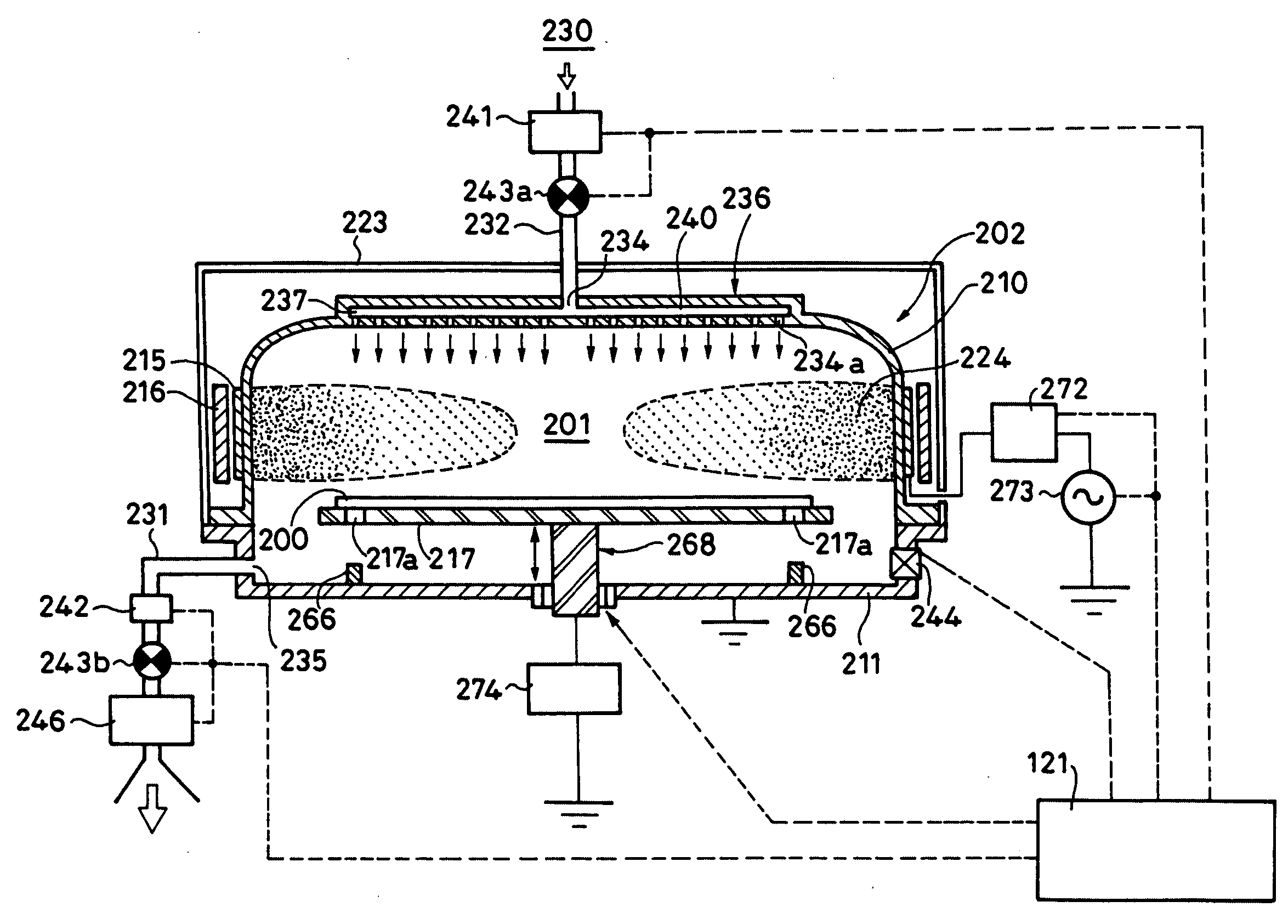

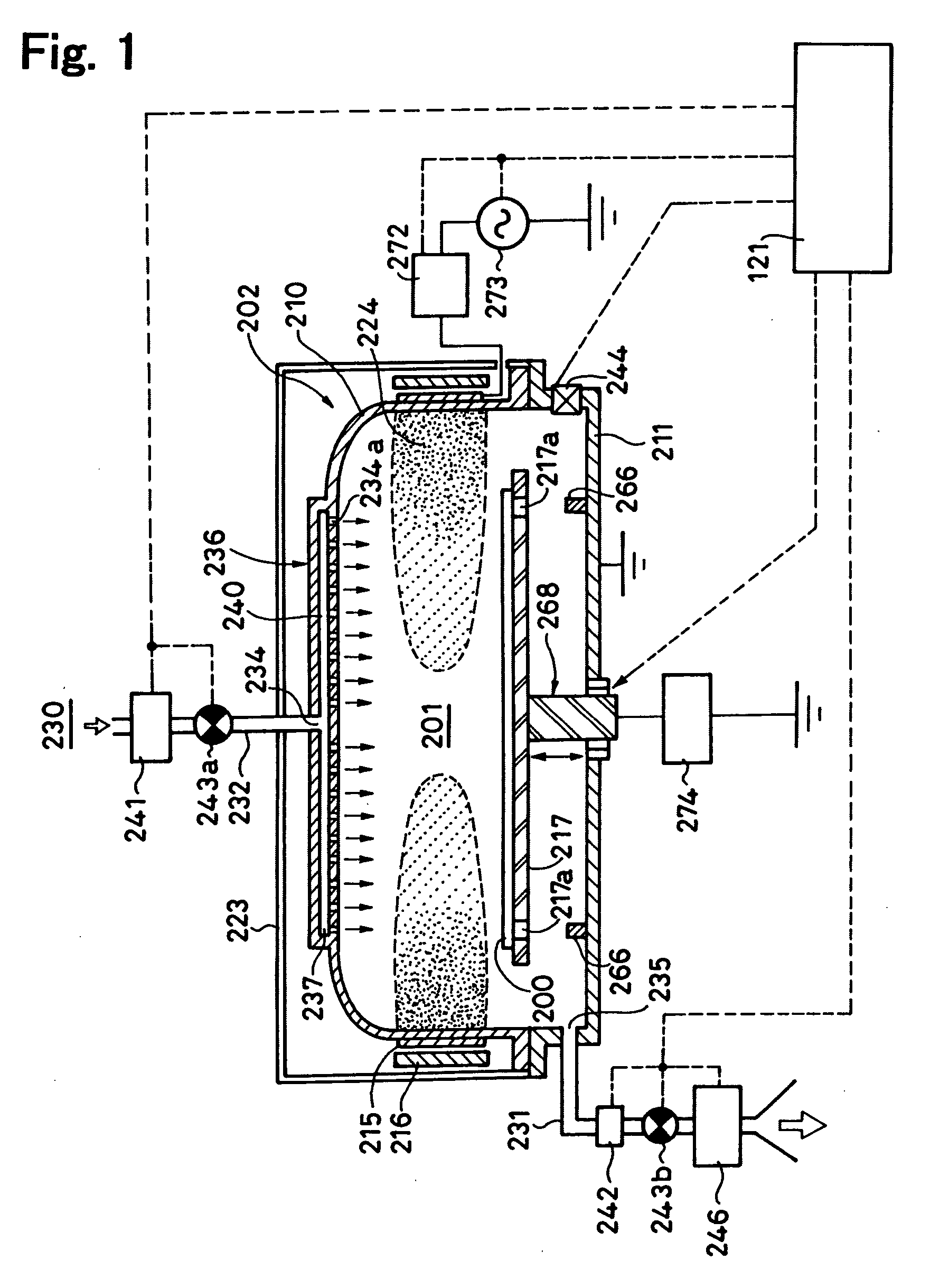

Remote plasma activated nitridation

ActiveUS20060110943A1Semiconductor/solid-state device manufacturingChemical vapor deposition coatingRemote plasmaMicrowave

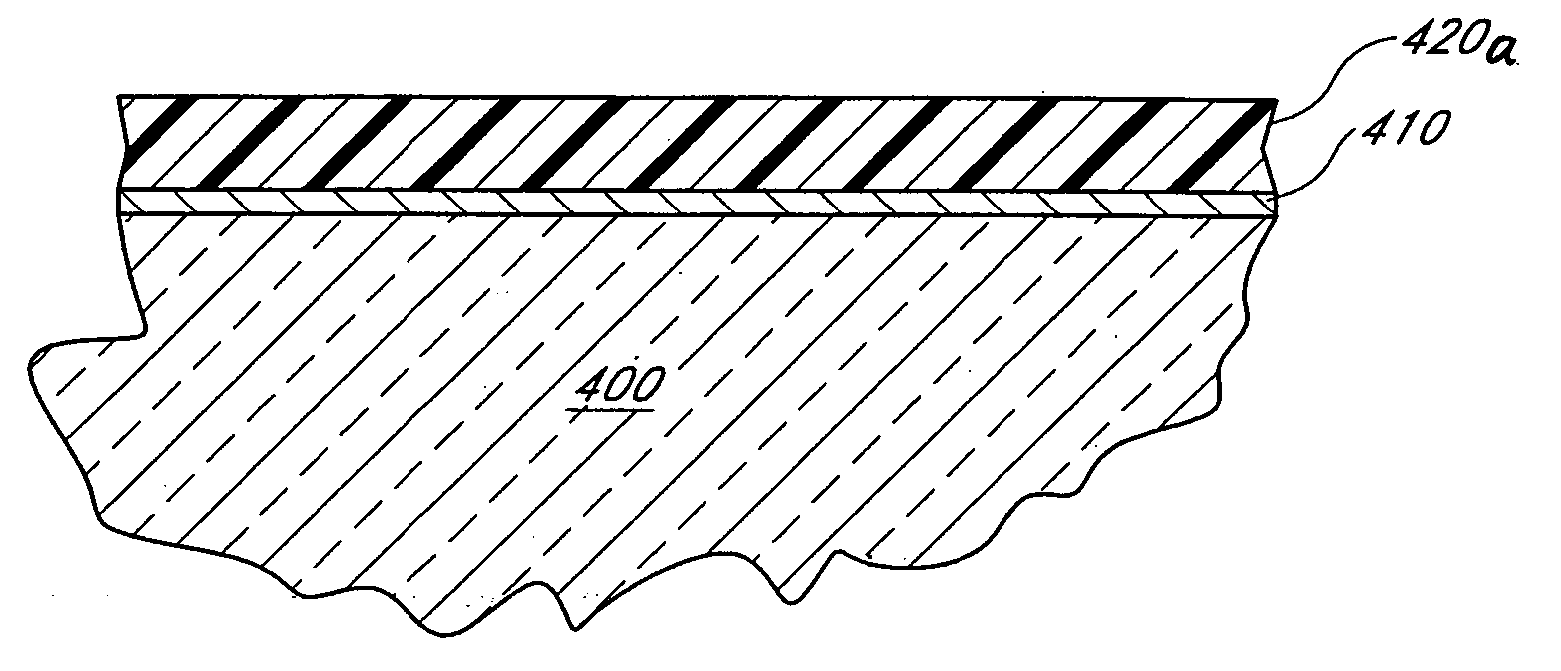

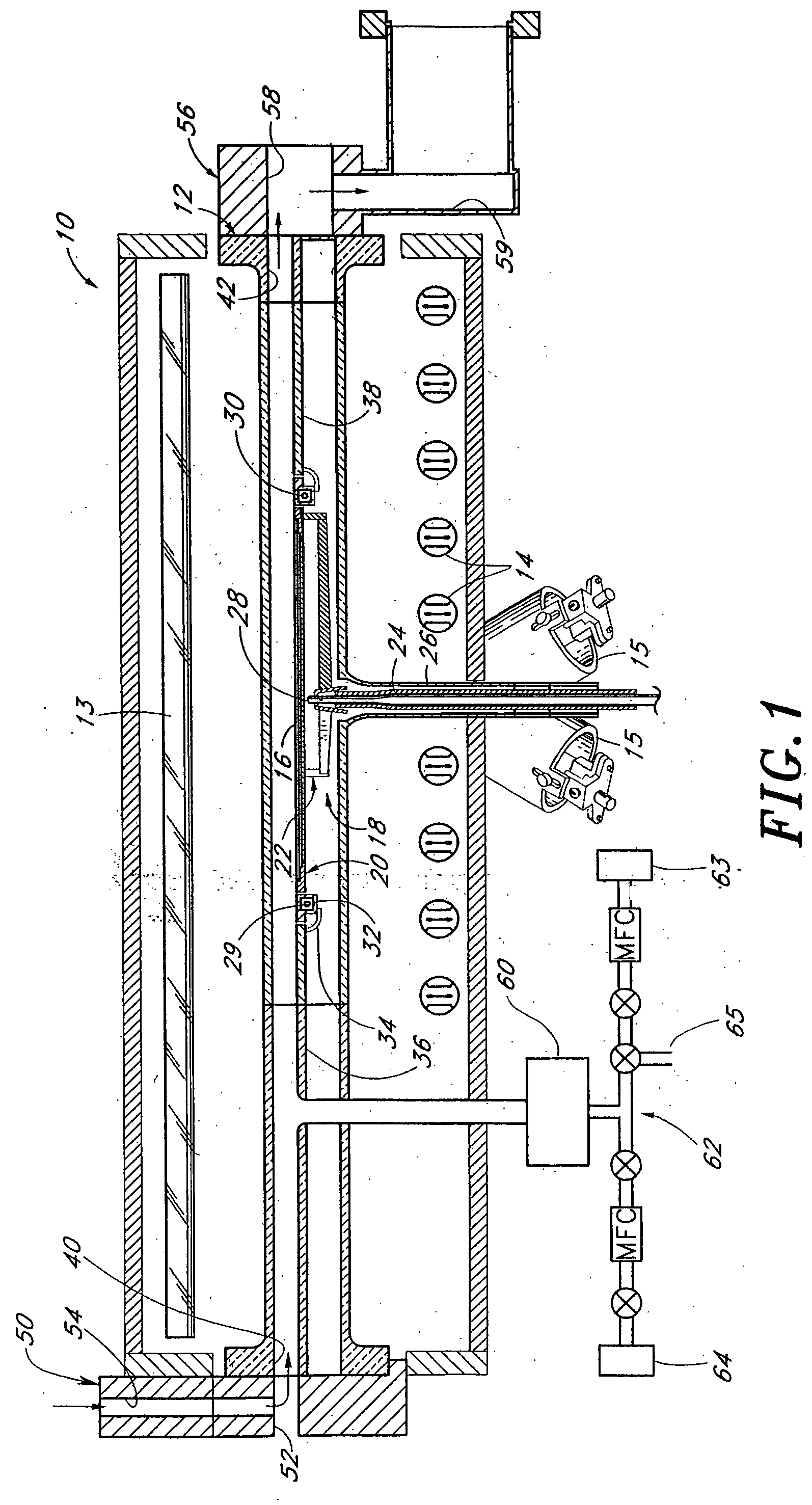

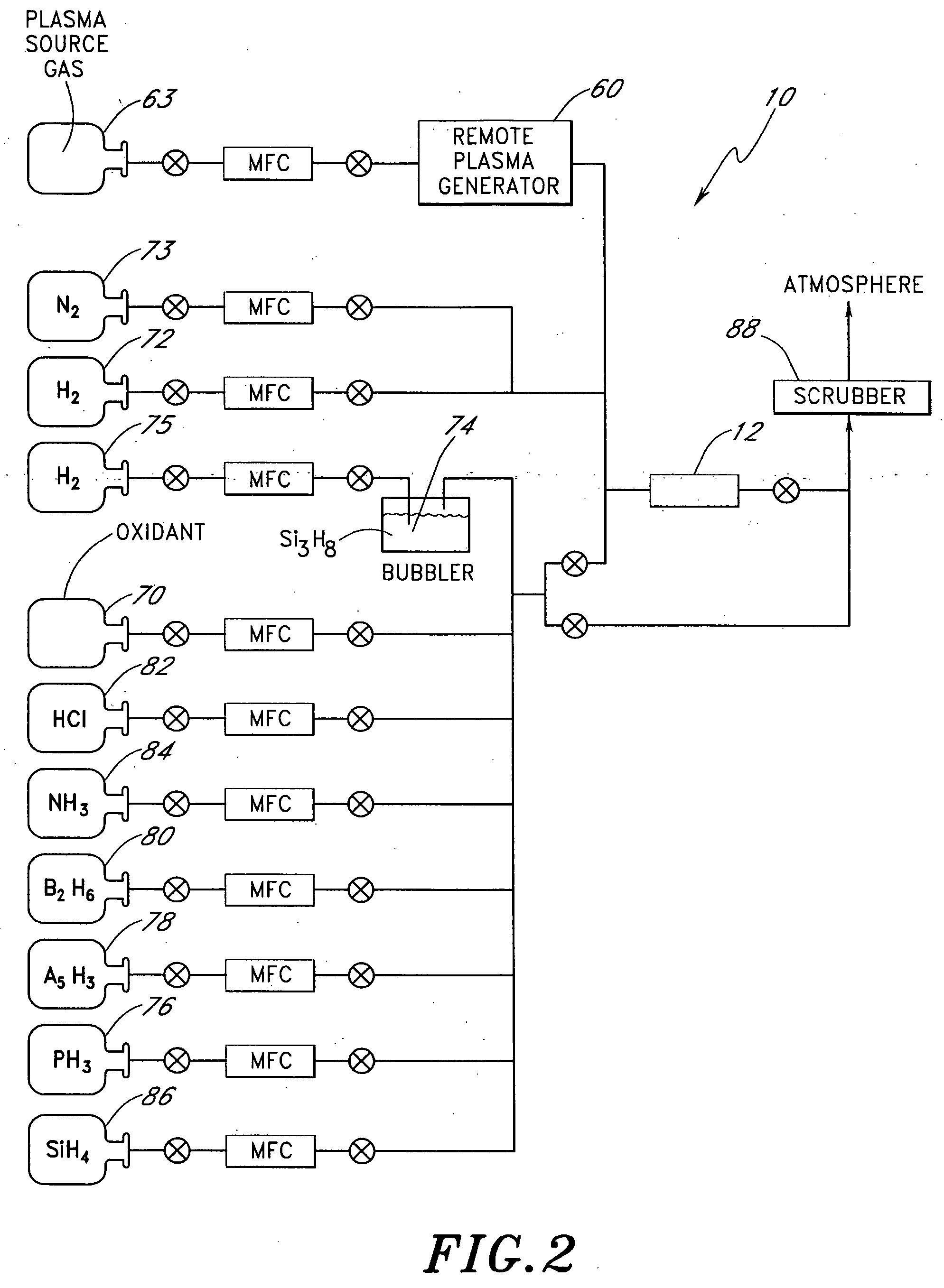

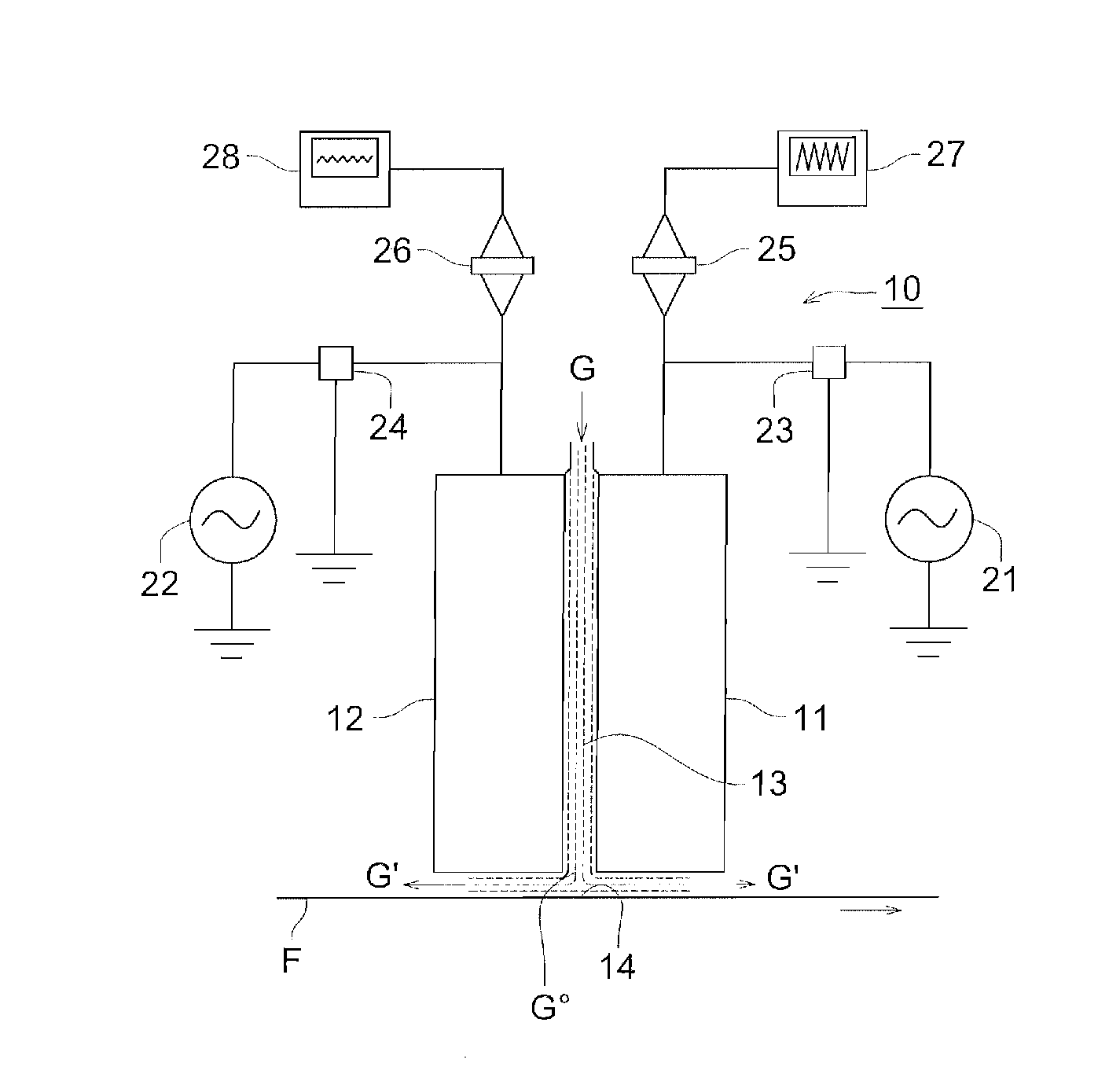

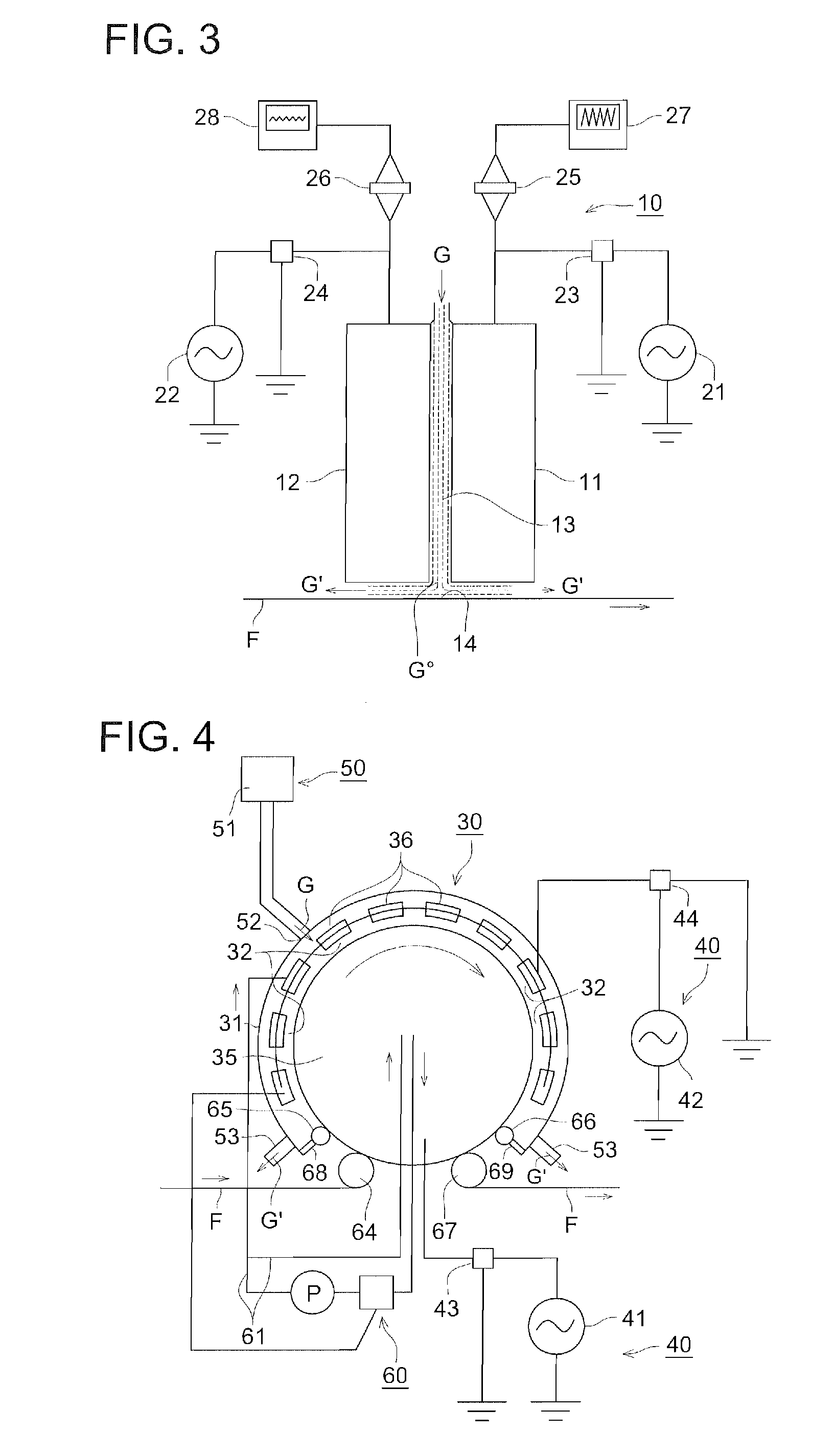

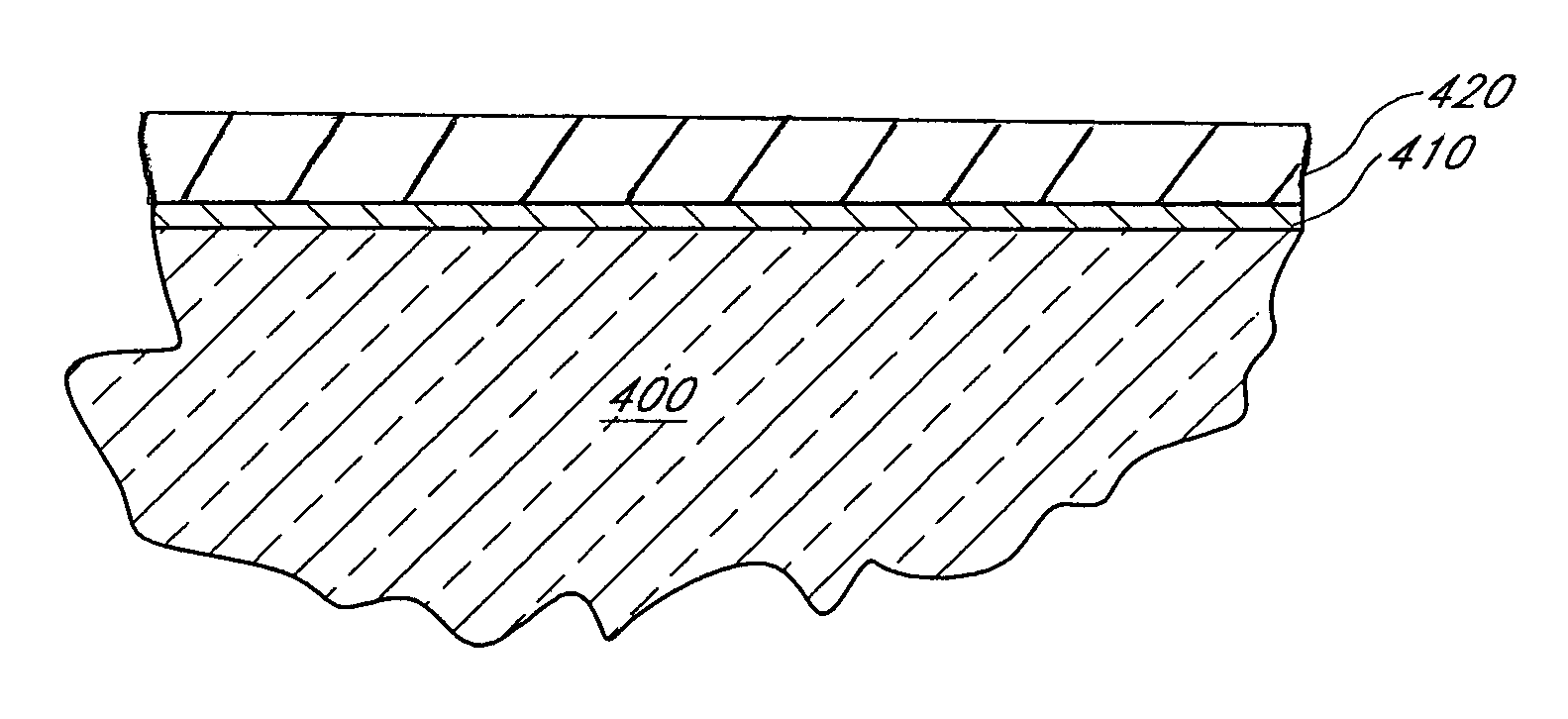

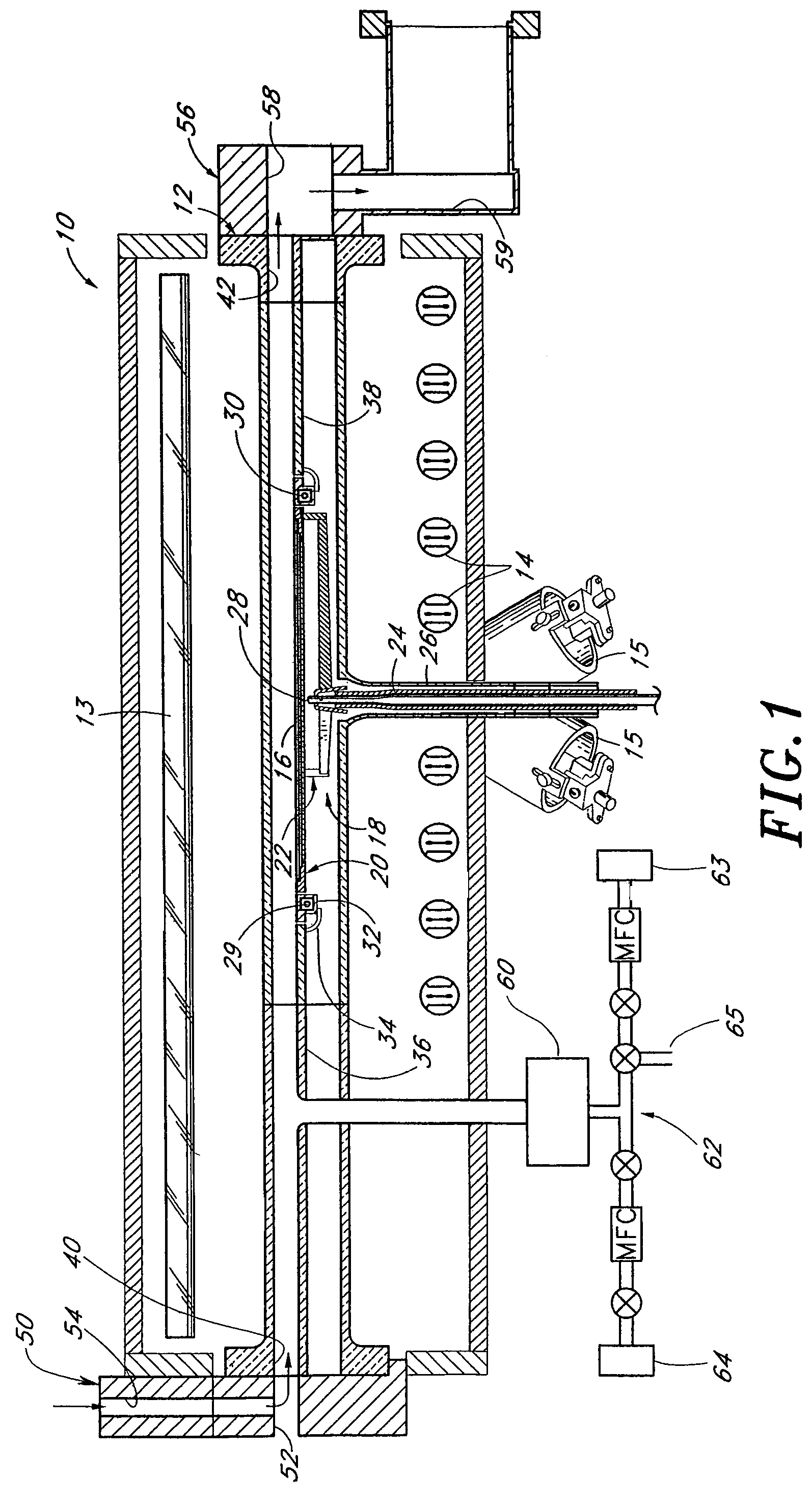

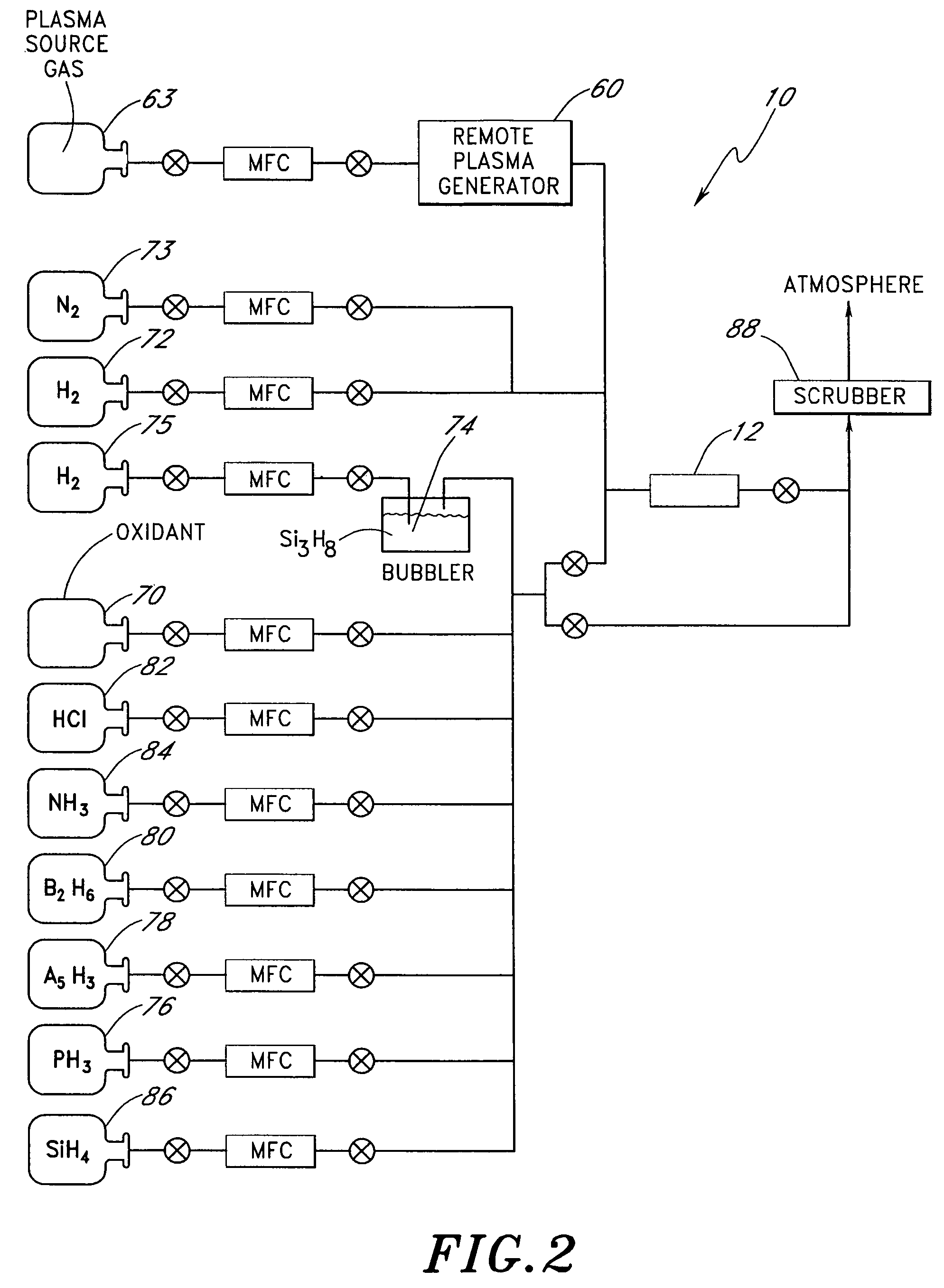

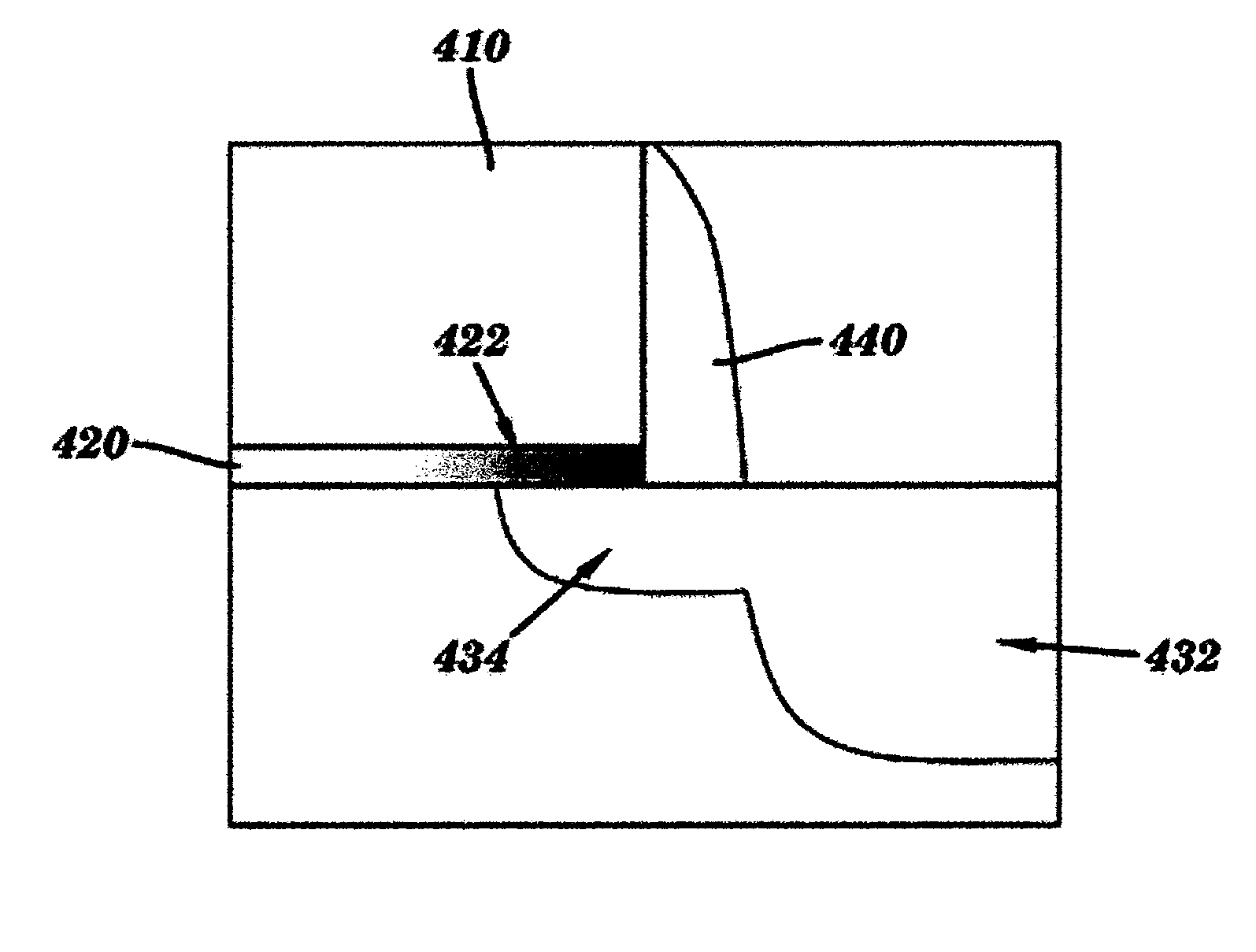

A nitrogen precursor that has been activated by exposure to a remotely excited species is used as a reactant to form nitrogen-containing layers. The remotely excited species can be, e.g., N2, Ar, and / or He, which has been excited in a microwave radical generator. Downstream of the microwave radical generator and upstream of the substrate, the flow of excited species is mixed with a flow of NH3. The excited species activates the NH3. The substrate is exposed to both the activated NH3 and the excited species. The substrate can also be exposed to a precursor of another species to form a compound layer in a chemical vapor deposition. In addition, already-deposited layers can be nitrided by exposure to the activated NH3 and to the excited species, which results in higher levels of nitrogen incorporation than plasma nitridation using excited N2 alone, or thermal nitridation using NH3 alone, with the same process temperatures and nitridation durations.

Owner:ASM IP HLDG BV

Manufacturing method of semiconductor device

ActiveUS20080311718A1Improve operating rateReduce contact resistanceTransistorSolid-state devicesTitanium nitrideNickel silicide

The present invention is to possible to avoid an inconvenience at a coupling portion between a barrier metal film obtained by depositing a titanium nitride film on a titanium film and thus having a film stack structure and a metal film filled, via the barrier metal film, in a connecting hole opened in an insulating film. The manufacturing method of a semiconductor device includes the steps of: forming a contact hole and exposing a nickel silicide layer from the bottom of the contact hole; forming a thermal reaction Ti film by a thermal reaction using a TiCl4 gas, forming a plasma reaction Ti film by a plasma reaction using a TiCl4 gas, carrying out plasma treatment with an H2 gas to decrease the chlorine concentration of the plasma reaction Ti film and at the same time to reduce an oxide film on the surface of the nickel silicide layer; forming a nitrogen-rich TiN film over the surface of the plasma reaction Ti film and at the same time reducing the oxide film on the surface of the nickel silicide layer by thermal nitridation treatment with an NH3 gas and plasma treatment with an NH3 gas.

Owner:RENESAS ELECTRONICS CORP

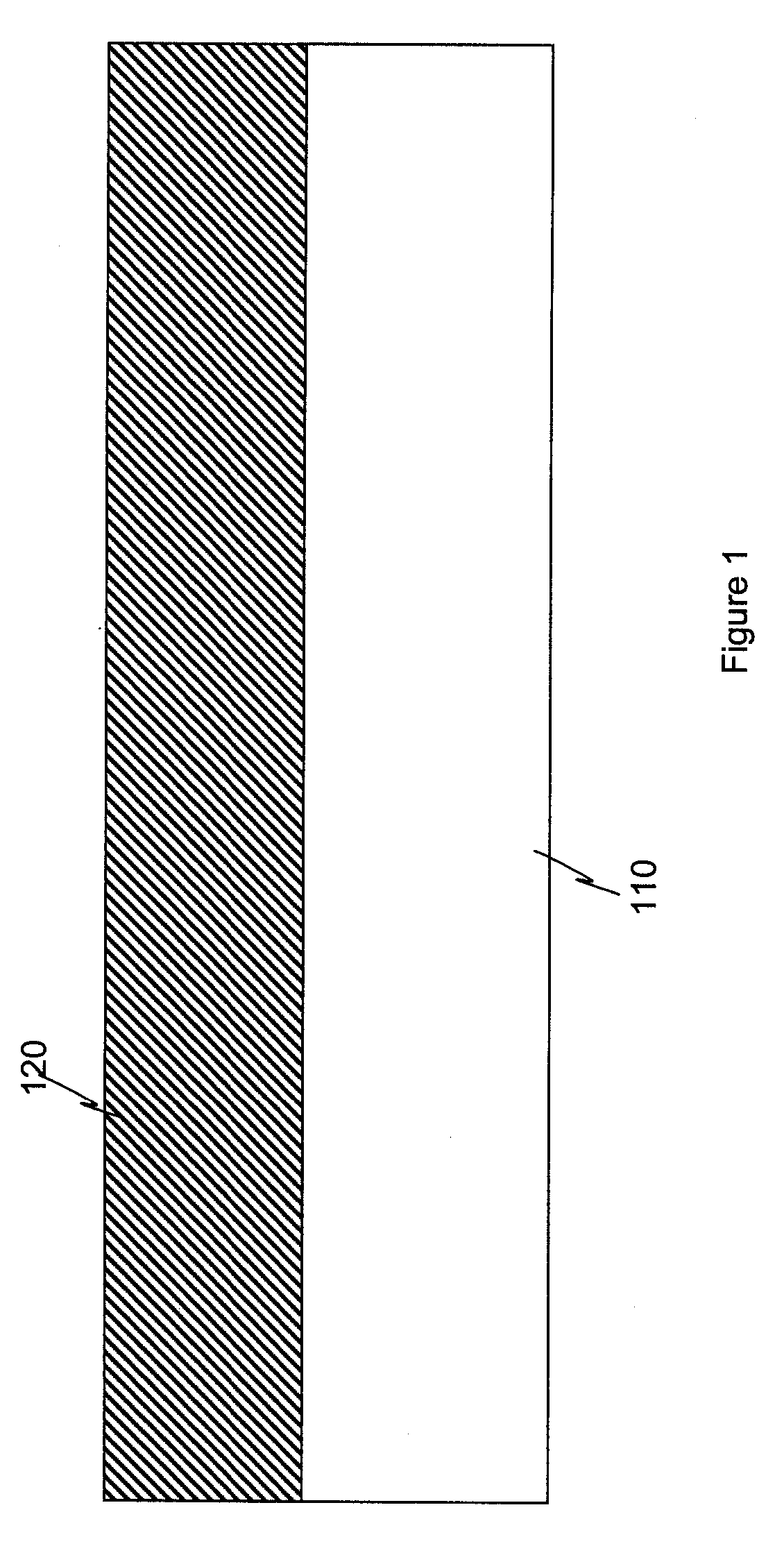

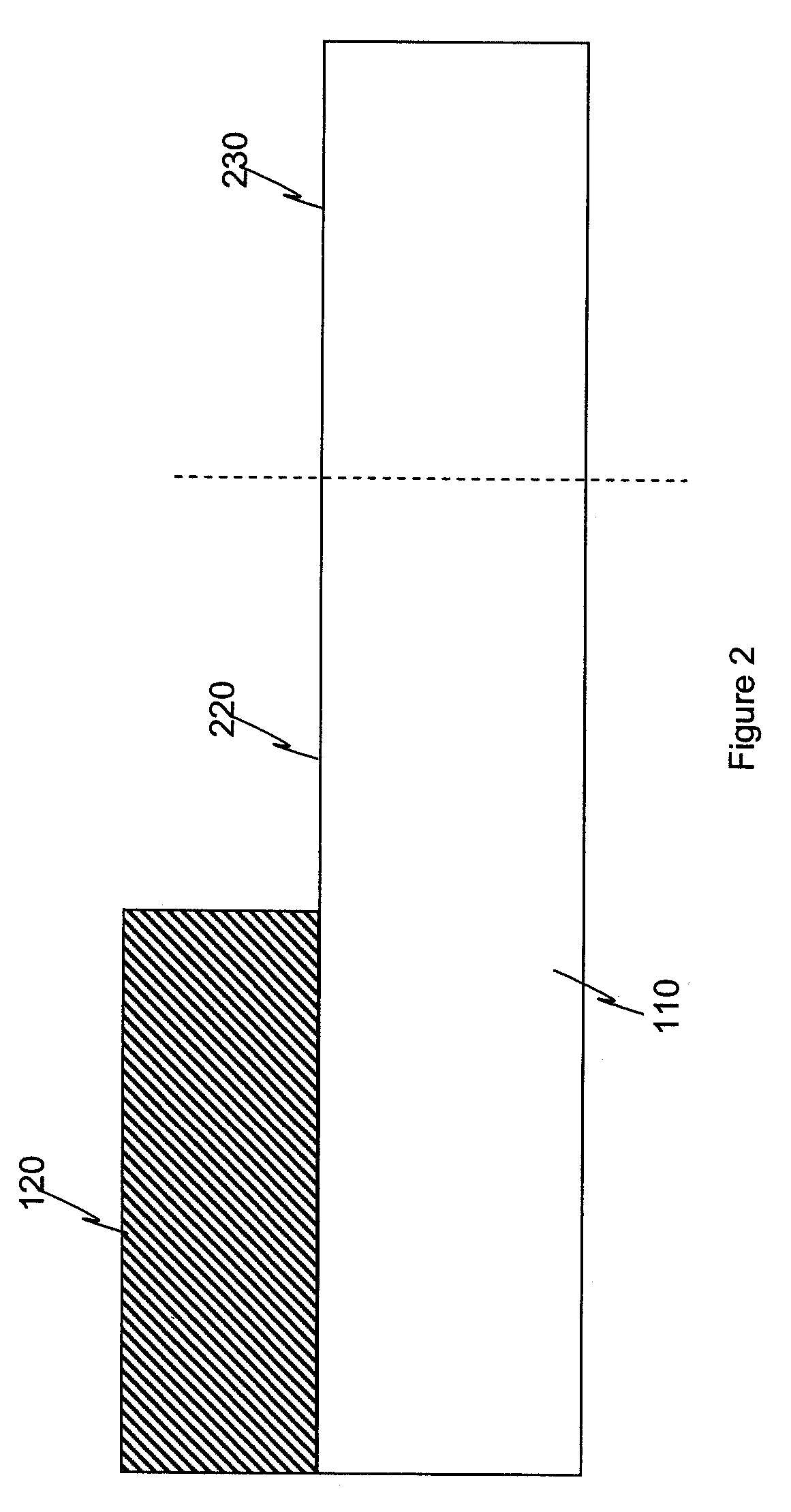

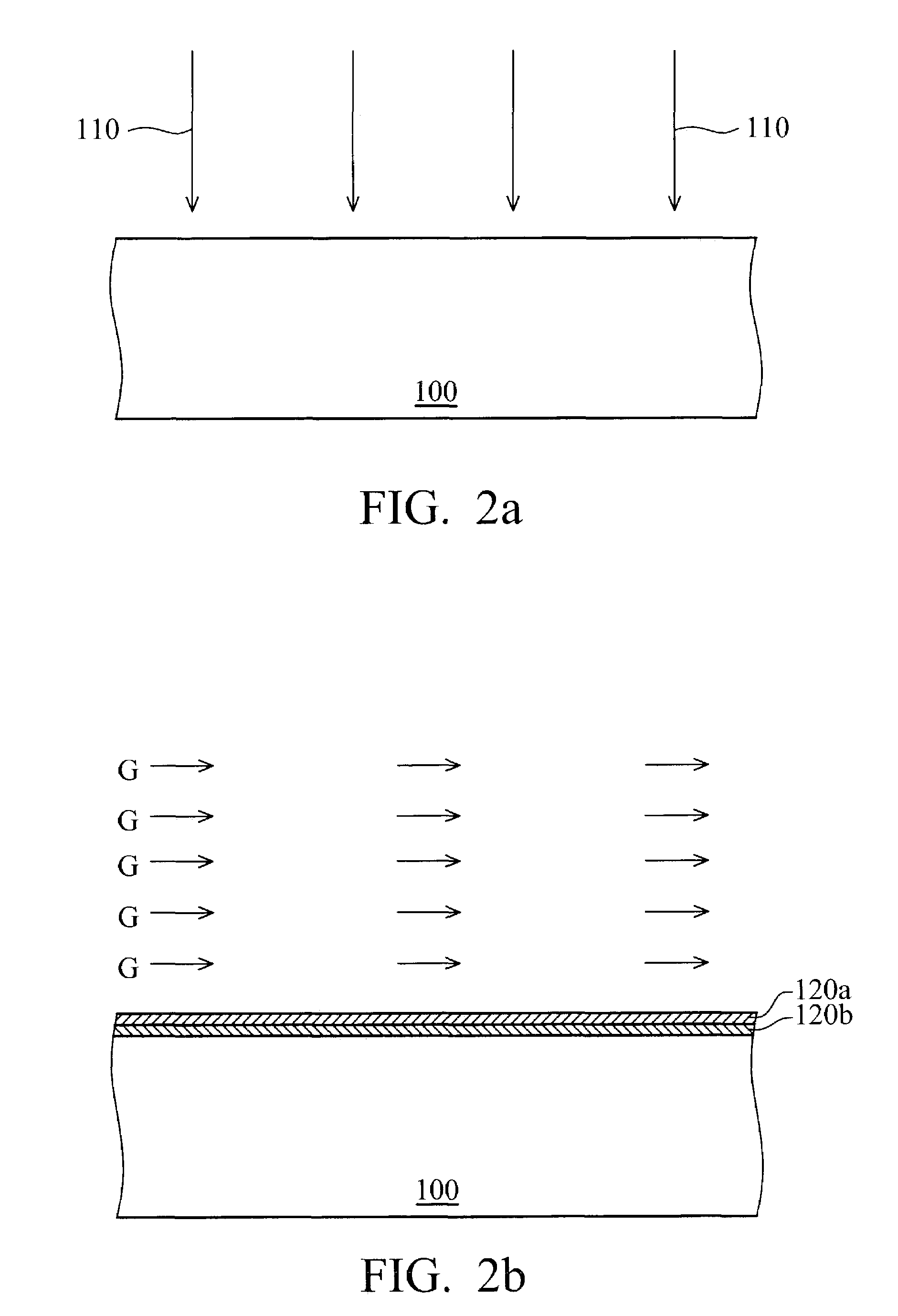

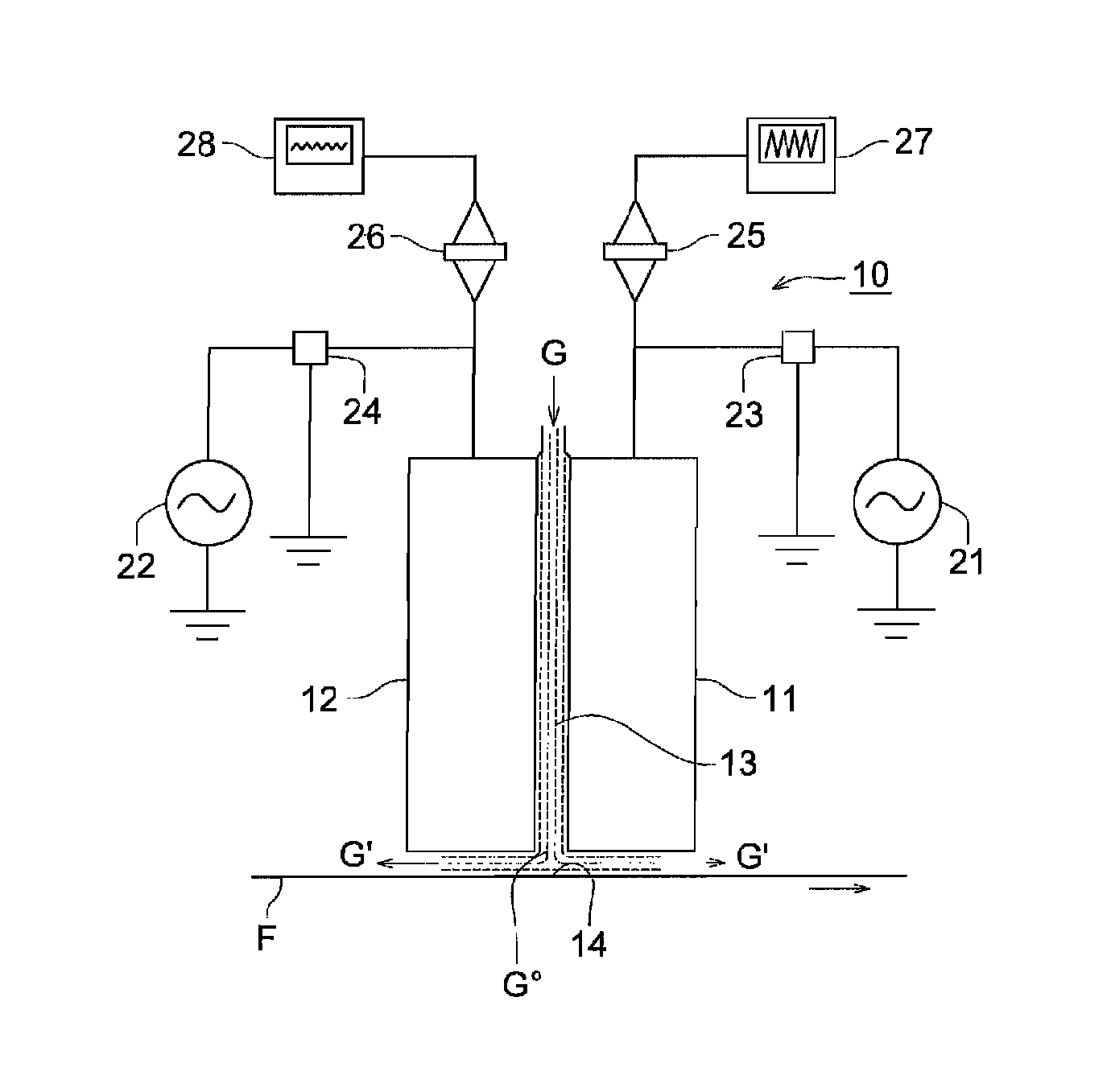

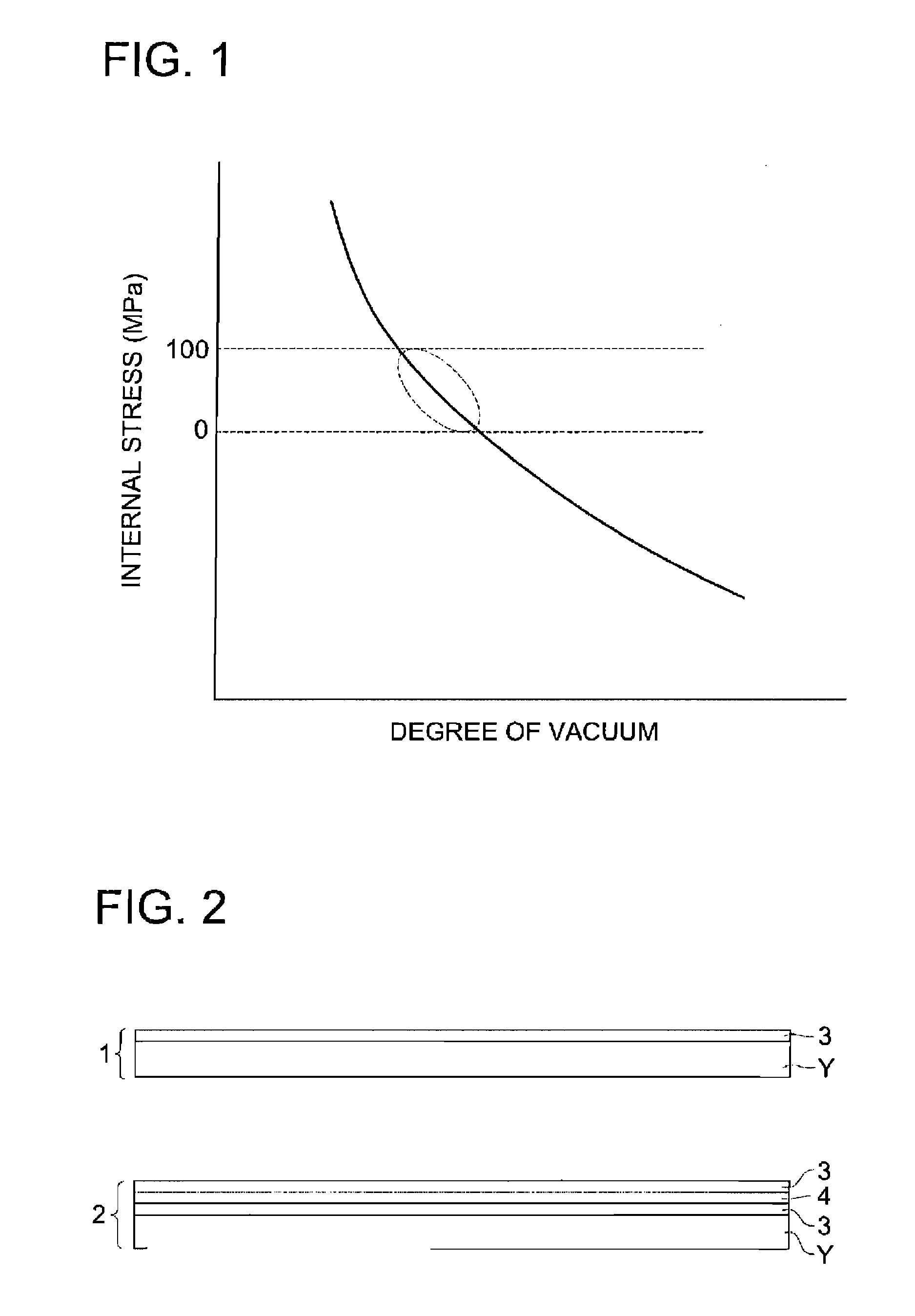

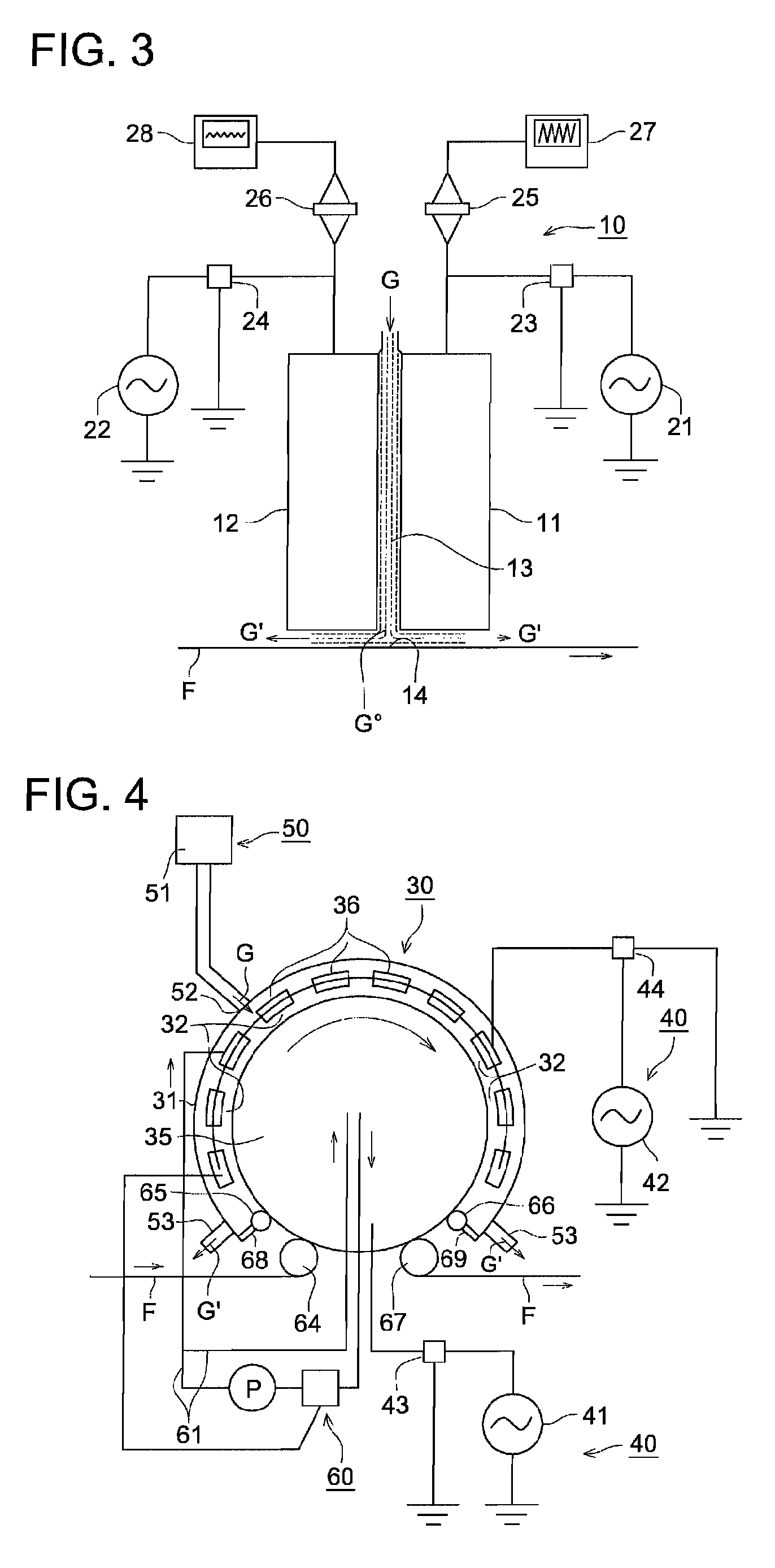

Gas barrier film, gas barrier film manufacturing method, resin substrate for organic electroluminescent device using the aforesaid gas barrier film, and organic electroluminescent device using the aforementioned gas barrier film

ActiveUS20090051272A1Superb adhesionIncreased durabilityVacuum evaporation coatingSolid-state devicesDensity ratioOrganic electroluminescence

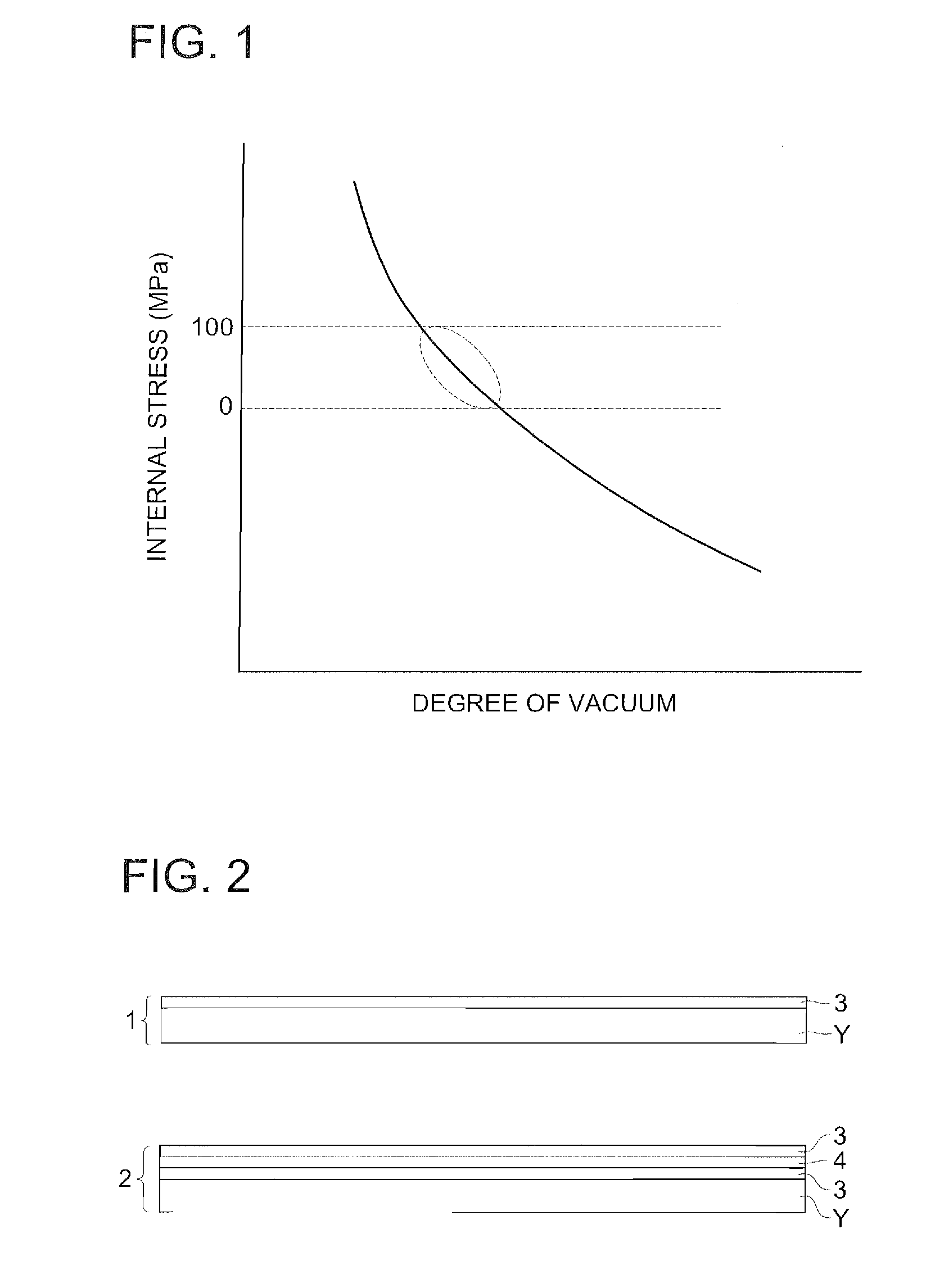

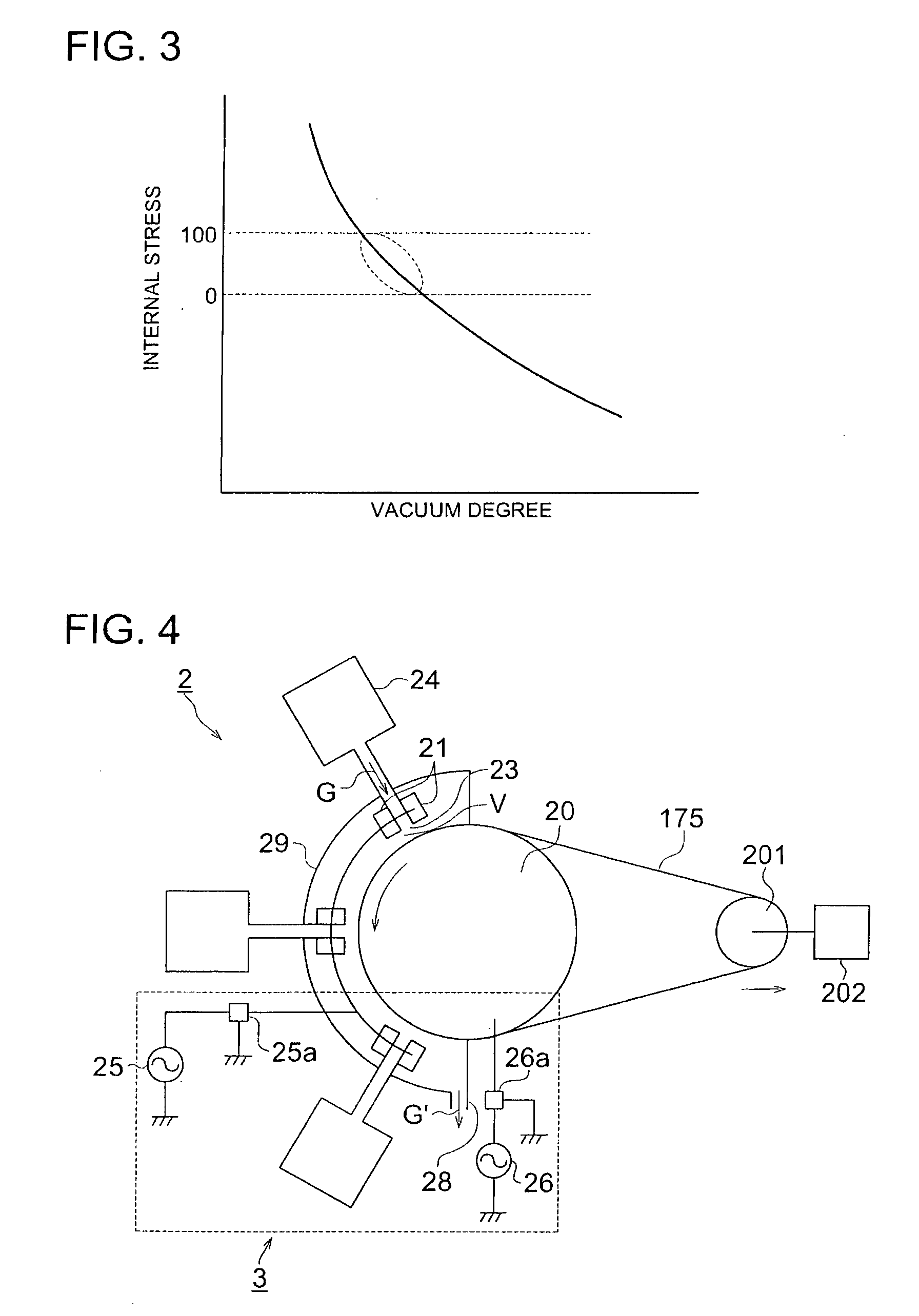

A gas barrier film comprising a resin substrate provided thereon at least one layer of a ceramic film, wherein the density ratio Y (=ρf / ρb) satisfies 1≧Y≧0.95 and the ceramic film has a residual stress being a compression stress of 0.01 MPa or more and 100 Mpa or less, wherein ρf is the density of the ceramic film and ρb is the density of a comparative ceramic film being formed by thermal oxidation or thermal nitridation of a metal as a mother material of the ceramic film so as to being the same composition ratio of the ceramic film.

Owner:KONICA MINOLTA INC

Gas barrier film, gas barrier film manufacturing method, resin substrate for organic electroluminescent device using the aforesaid gas barrier film, and organic electroluminescent device using the aforementioned gas barrier film

ActiveUS20110300770A1Superb adhesionIncreased durabilitySolid-state devicesCeramic layered productsPolymer scienceOrganic electroluminescence

A gas barrier film comprising a resin substrate provided thereon at least one layer of a ceramic film, wherein the density ratio Y (=ρf / ρb) satisfies 1≧Y≧0.95 and the ceramic film has a residual stress being a compression stress of 0.01 MPa or more and 100 Mpa or less, wherein ρf is the density of the ceramic film and ρb is the density of a comparative ceramic film being formed by thermal oxidation or thermal nitridation of a metal as a mother material of the ceramic film so as to being the same composition ratio of the ceramic film.

Owner:KONICA MINOLTA INC

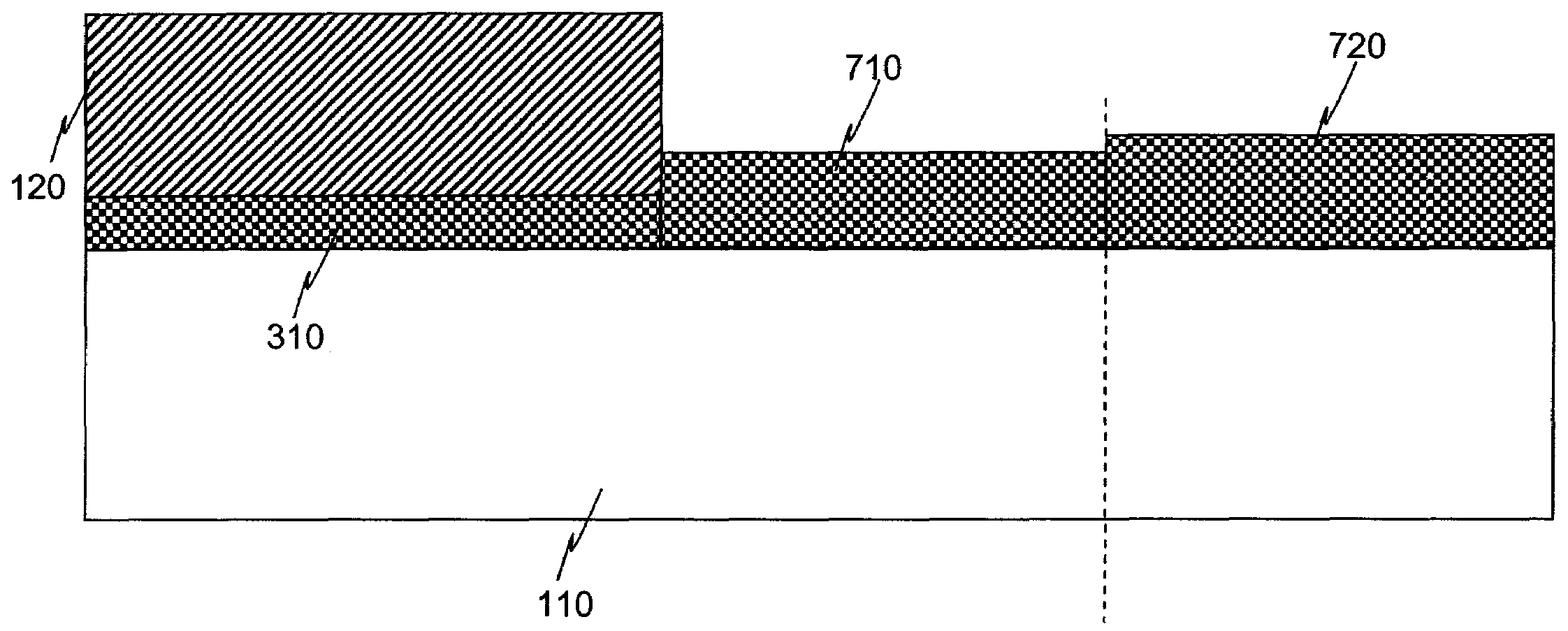

Selective nitridation of gate oxides

ActiveUS7138691B2Reduce diffuseInvention improvedTransistorSemiconductor/solid-state device manufacturingDopantRemote plasma

Owner:GLOBALFOUNDRIES U S INC +1

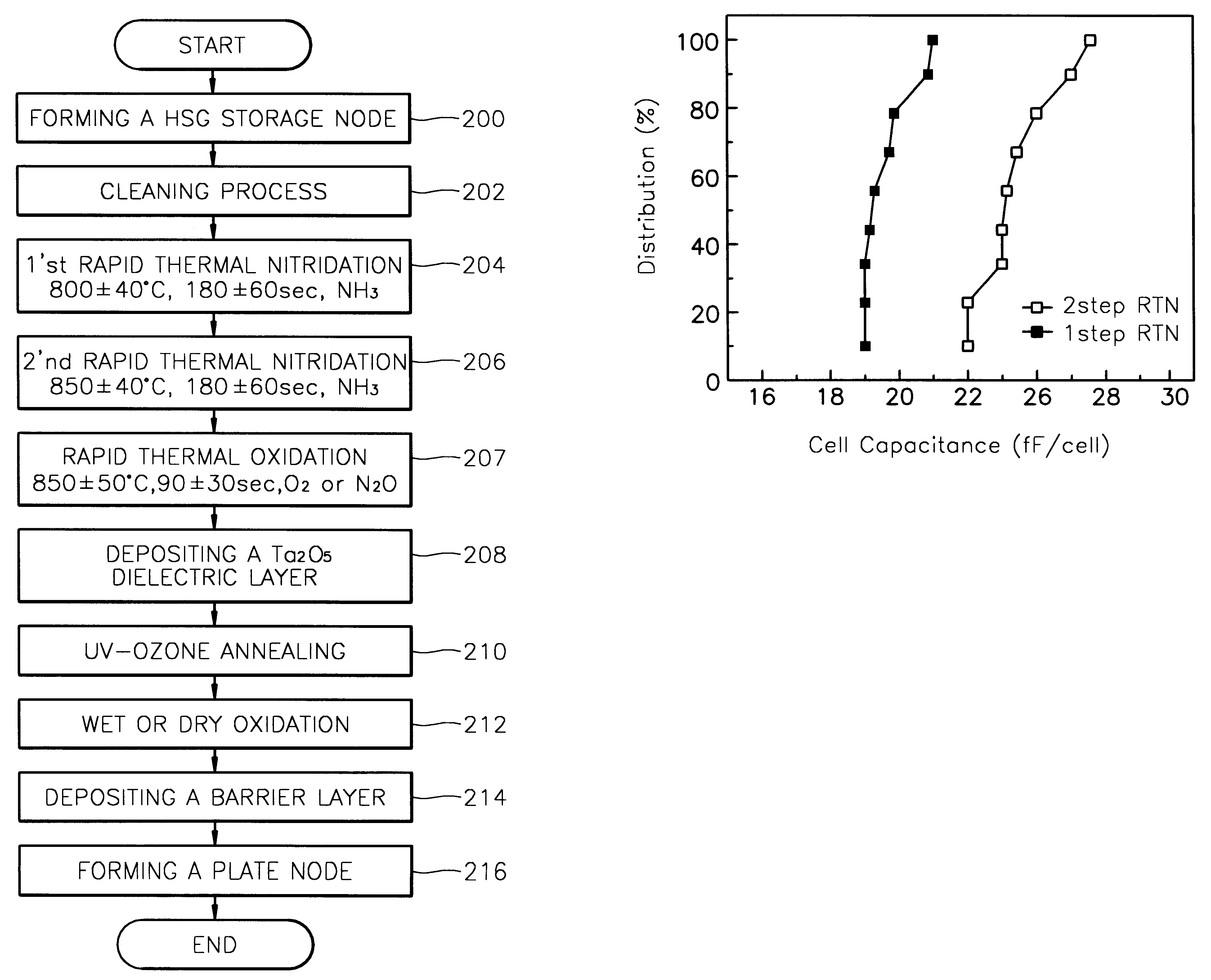

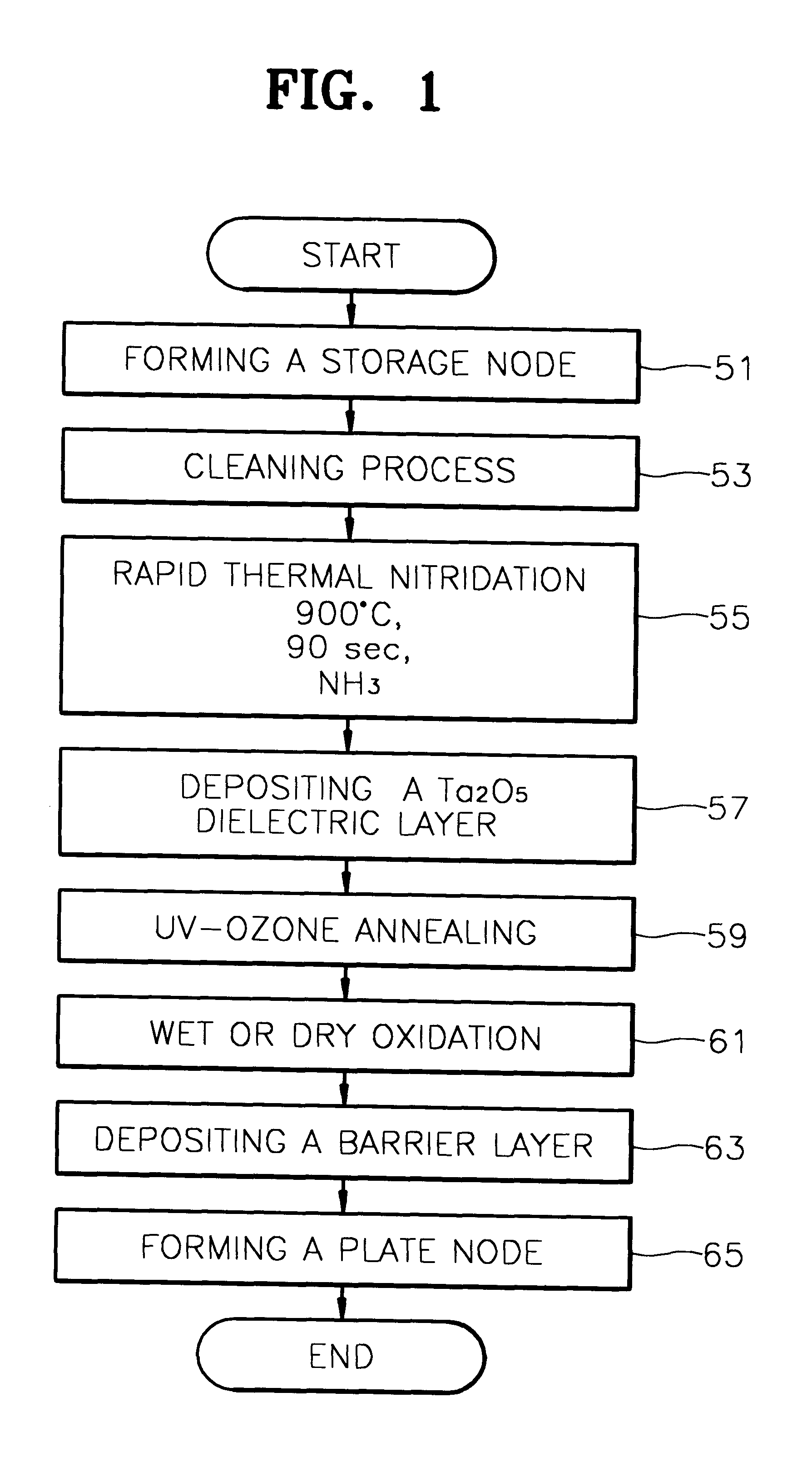

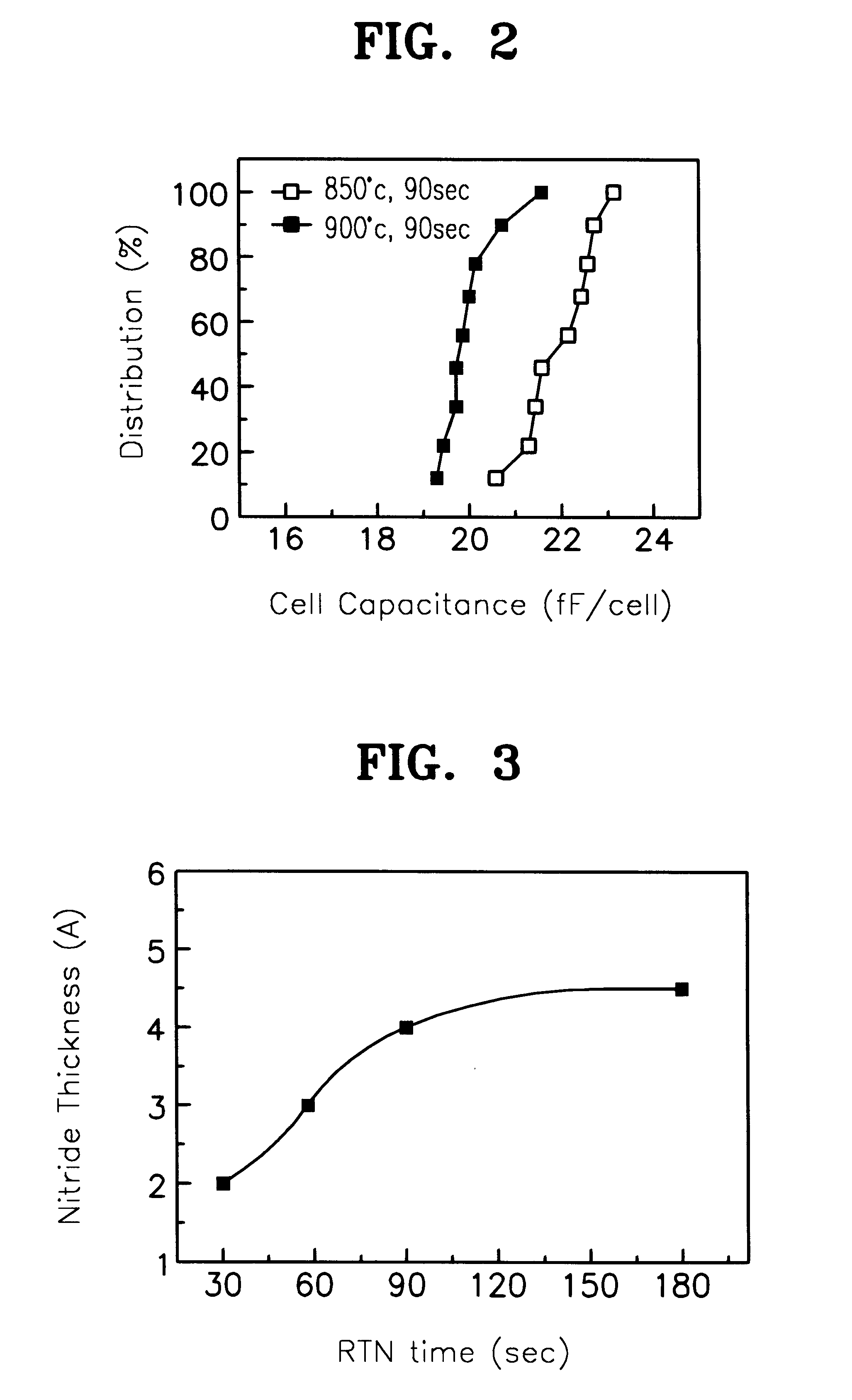

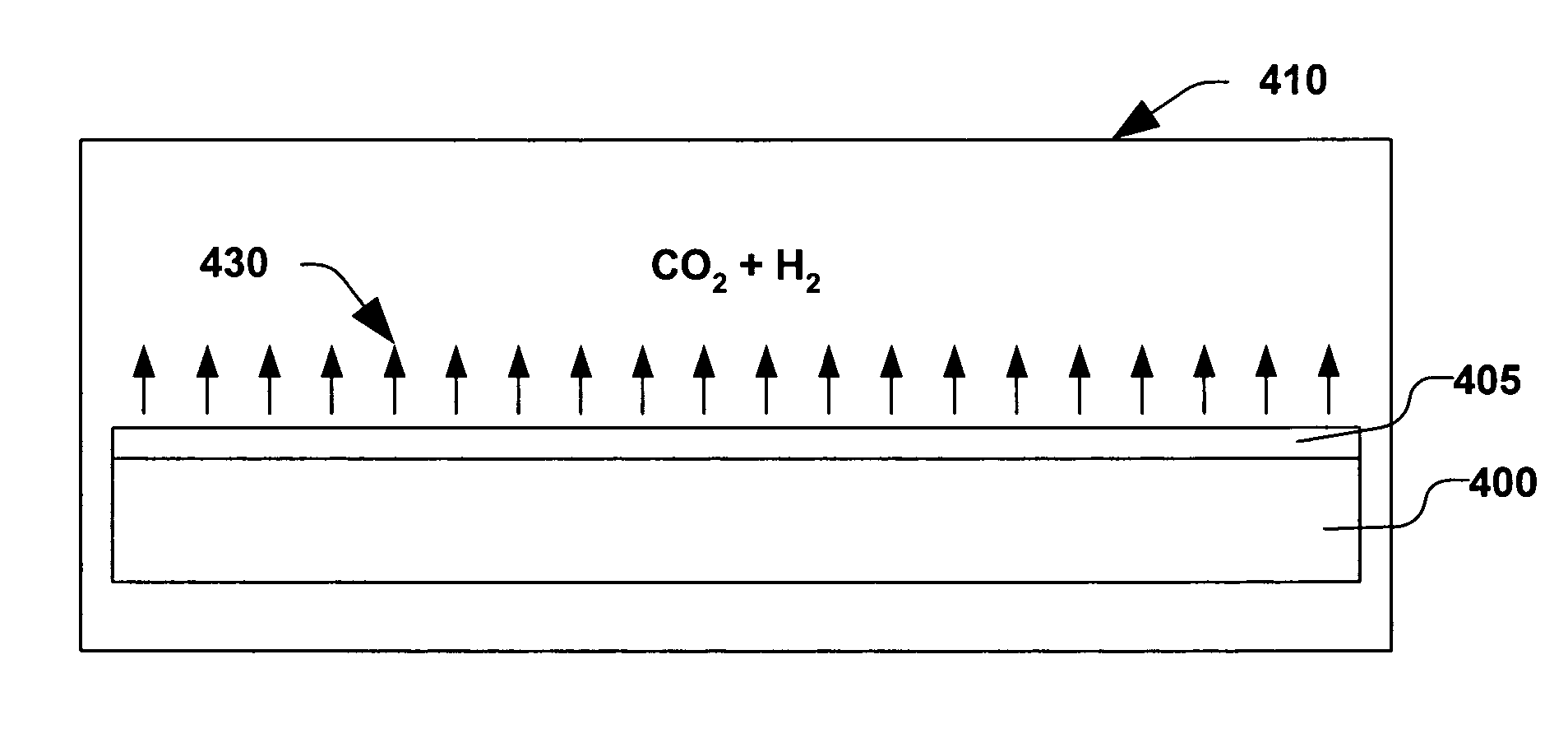

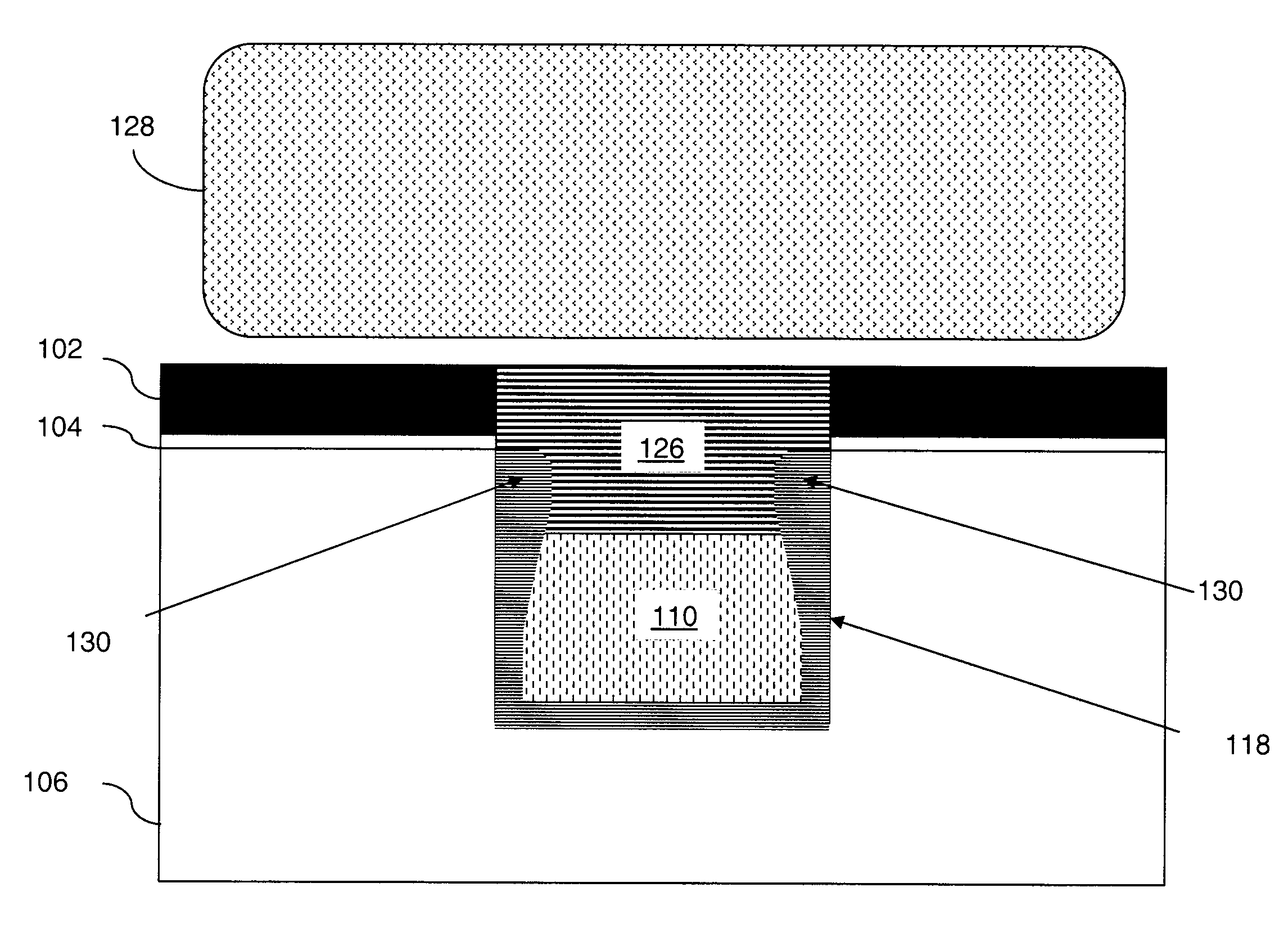

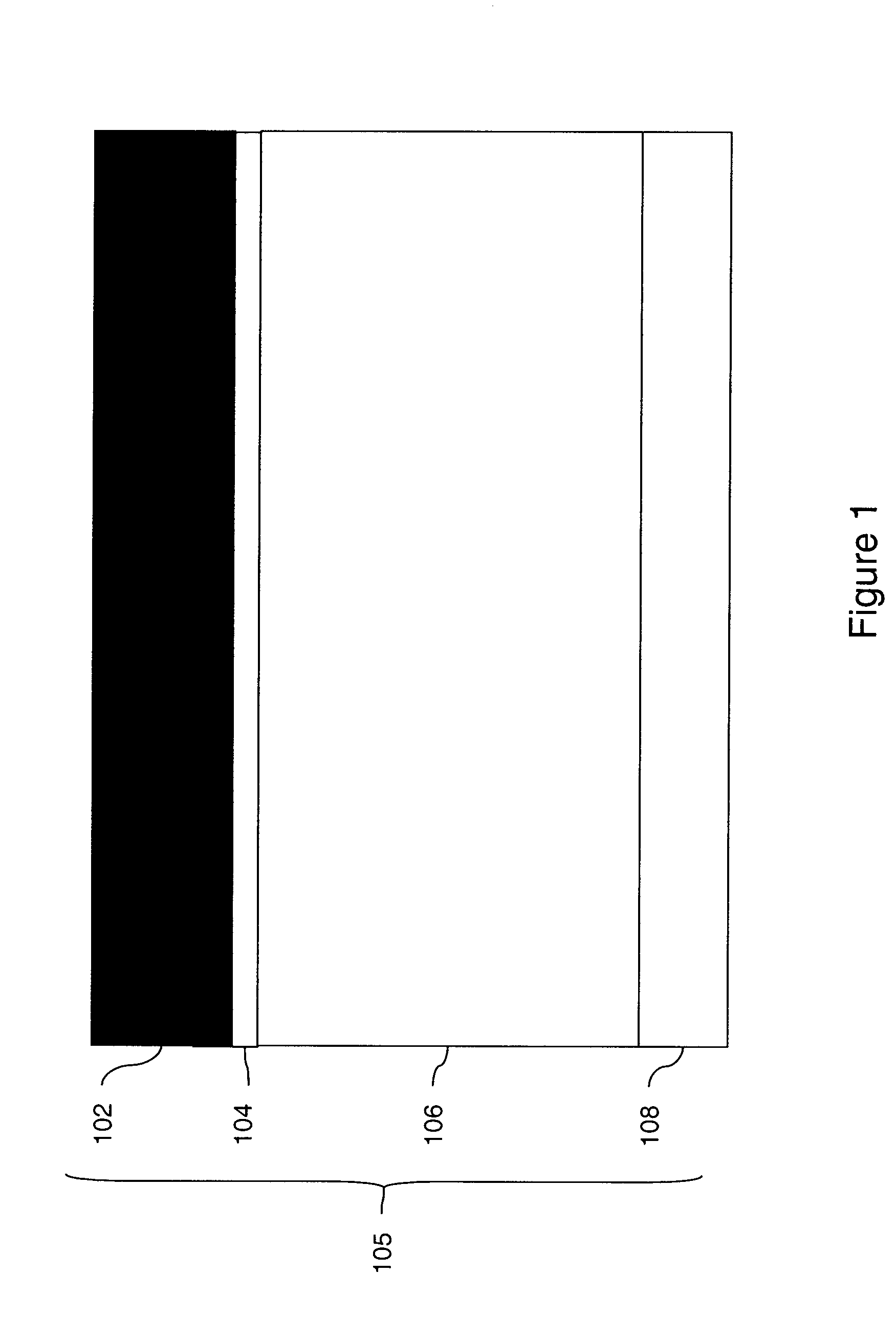

Method for forming a tantalum oxide capacitor using two-step rapid thermal nitridation

A method for forming a Ta2O5 capacitor on a semiconductor device reduces leakage current and increases cell capacitance by utilizing a two-step rapid thermal nitridation (RTN) process to form a nitride layer on a hemi-spherical grain (HSG) storage node. The first RTN process is performed in a NH3 atmosphere at 800±40° C. for 180±60 seconds, thereby forming a nitride layer having a thickness of about 4 Å. The second RTN process is performed in a NH3 atmosphere at 850±40° C. for 180±60 seconds, thereby increasing the thickness of the nitride layer to at least about 7 Å. Therefore, a nitride layer that is thick enough to act as an oxidation barrier is achieved, but agglomeration of the HSGs on the storage node due to high process temperatures is prevented. To make the structure more readily adaptable to process for manufacturing DRAMs with Ta2O5 dielectric layers, a rapid thermal oxidation (RTO) process can then be performed in an O2 or N2O atmosphere at 850±50° C. for 90±30 seconds to thereby form a combined layer comprising a nitride layer and an oxide layer.

Owner:SAMSUNG ELECTRONICS CO LTD

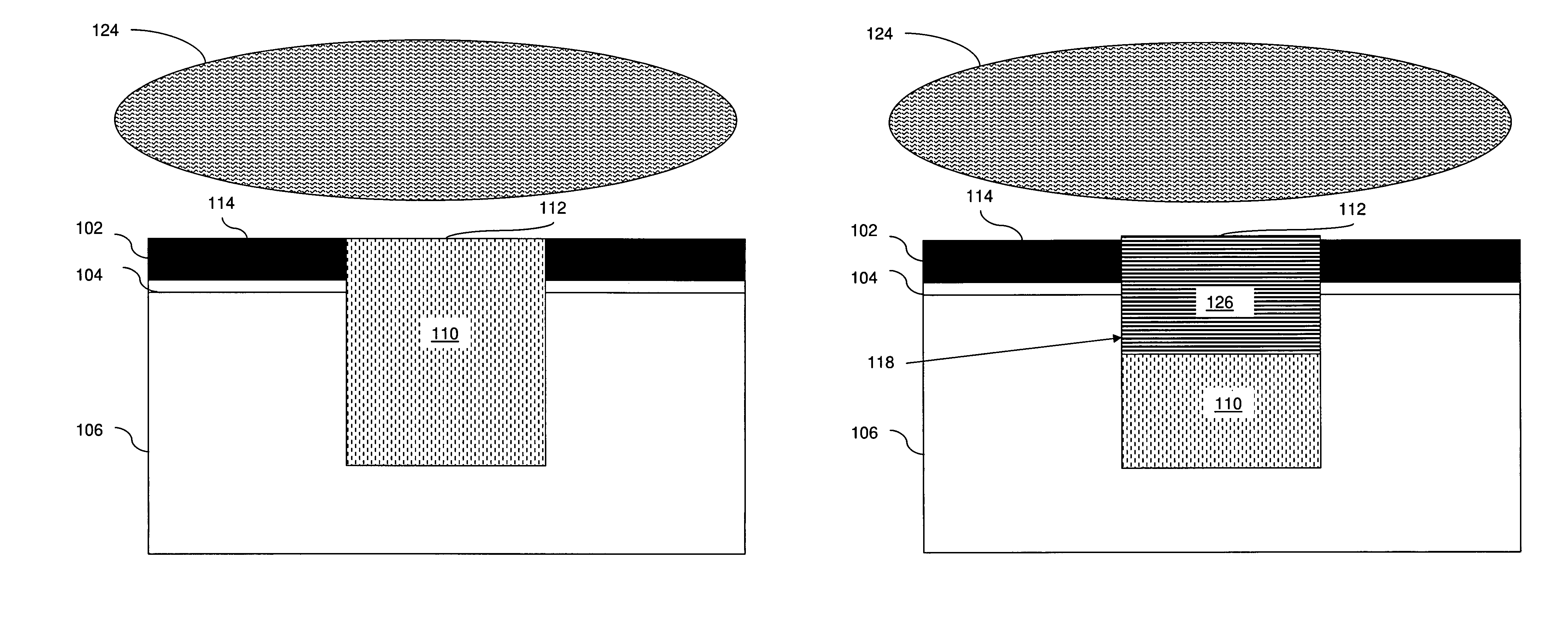

Method for removal of hydrocarbon contamination on gate oxide prior to non-thermal nitridation using "spike" radical oxidation

ActiveUS20050079723A1Avoid layeringPrevent oxidationSemiconductor/solid-state device manufacturingSemiconductor devicesHydrocarbon contaminationNitrogen source

The present invention is generally directed towards a method for removing hydrocarbon contamination from a substrate prior to a nitridation step, therein providing for a generally uniform nitridation of the substrate. The method comprises placing the substrate in a process chamber and flowing an oxygen-source gas into the process chamber. A first plasma is formed in the process chamber for a first predetermined amount of time, wherein the hydrocarbons combine with one or more species of the oxygen-source gas in radical form to form product gases. The gases are removed from the process chamber and a nitrogen-source gas is flowed into the process chamber. A second plasma is then formed in the process chamber for a second predetermined amount of time, therein nitriding the substrate in a significantly uniform manner.

Owner:TEXAS INSTR INC

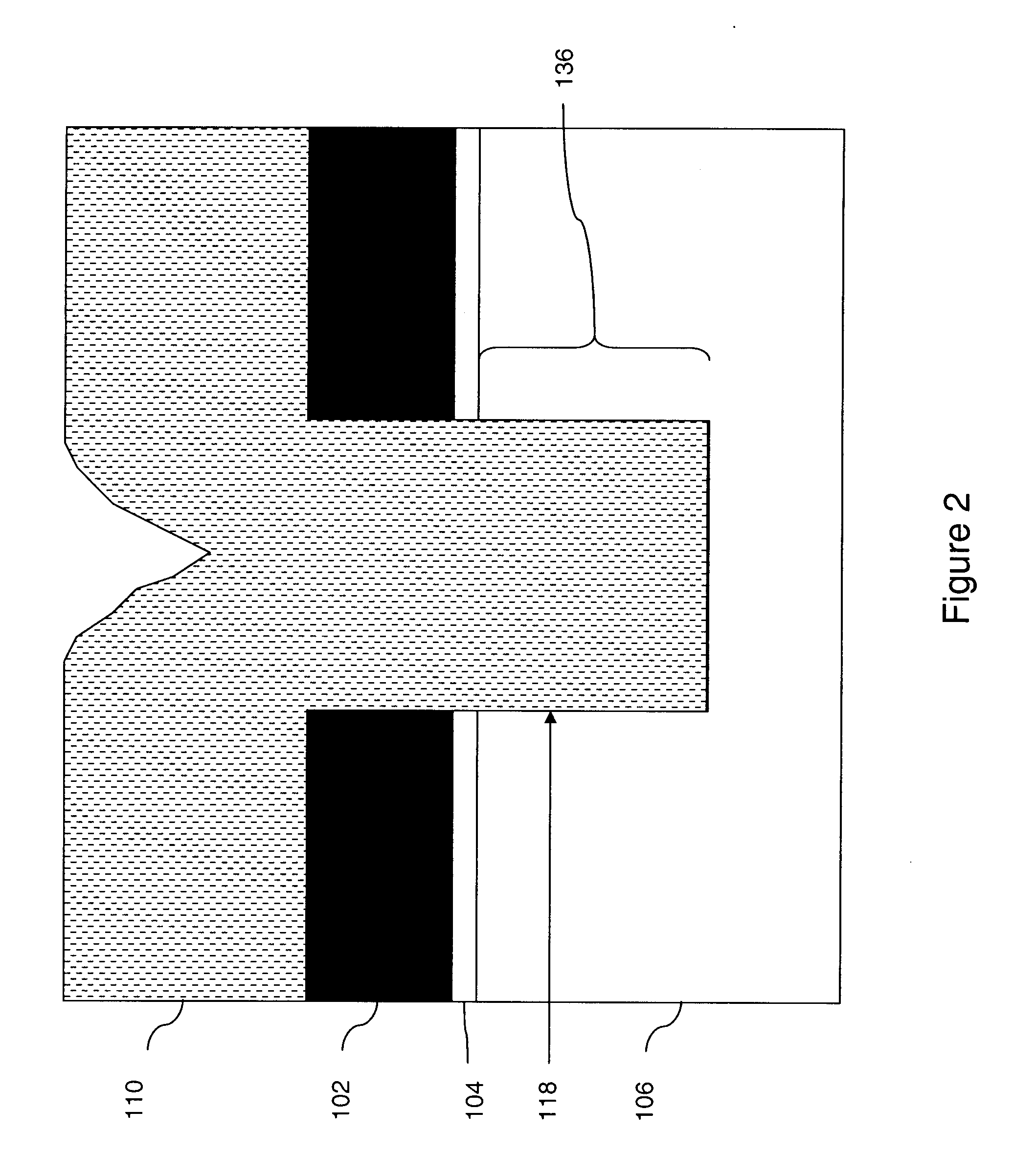

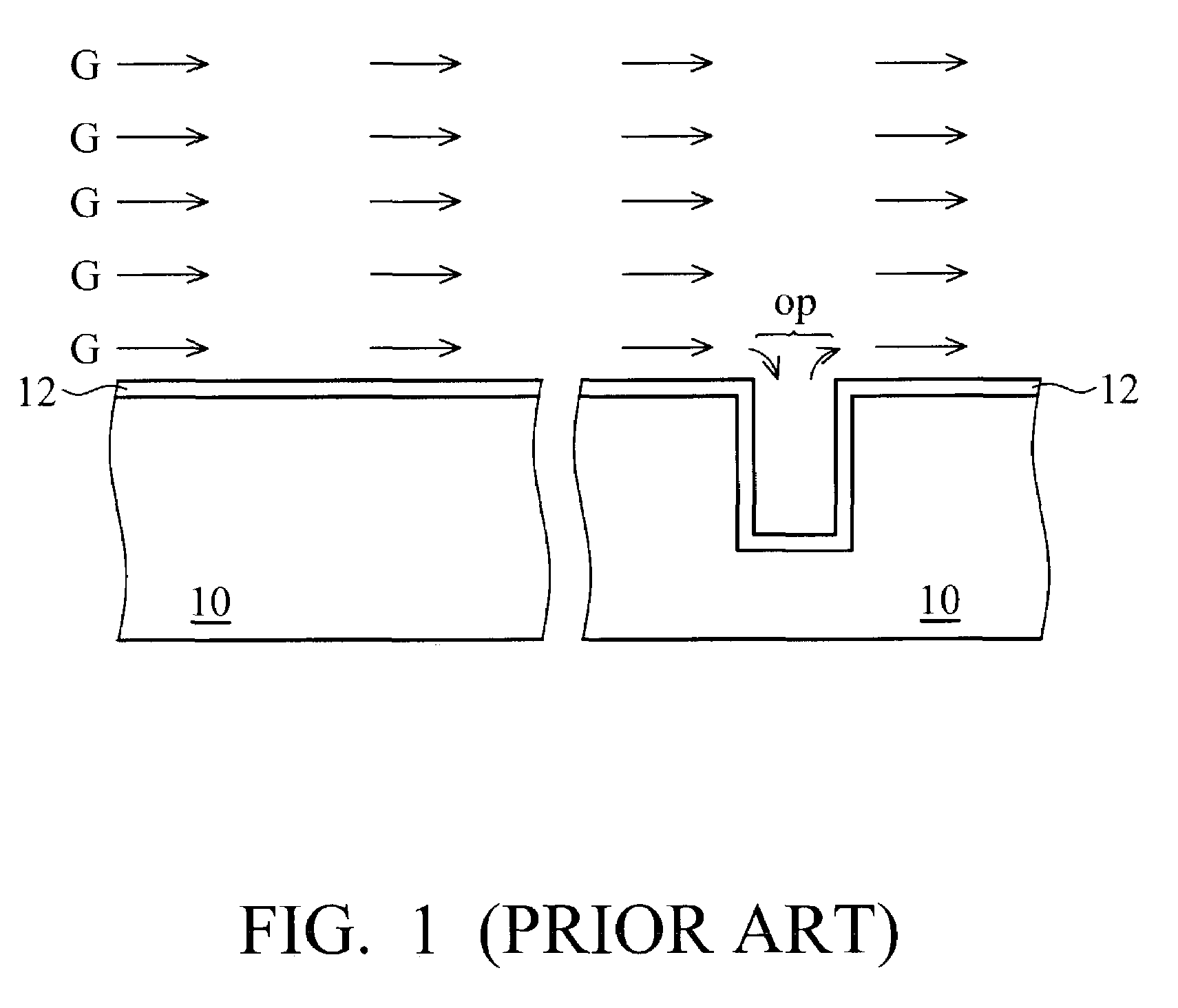

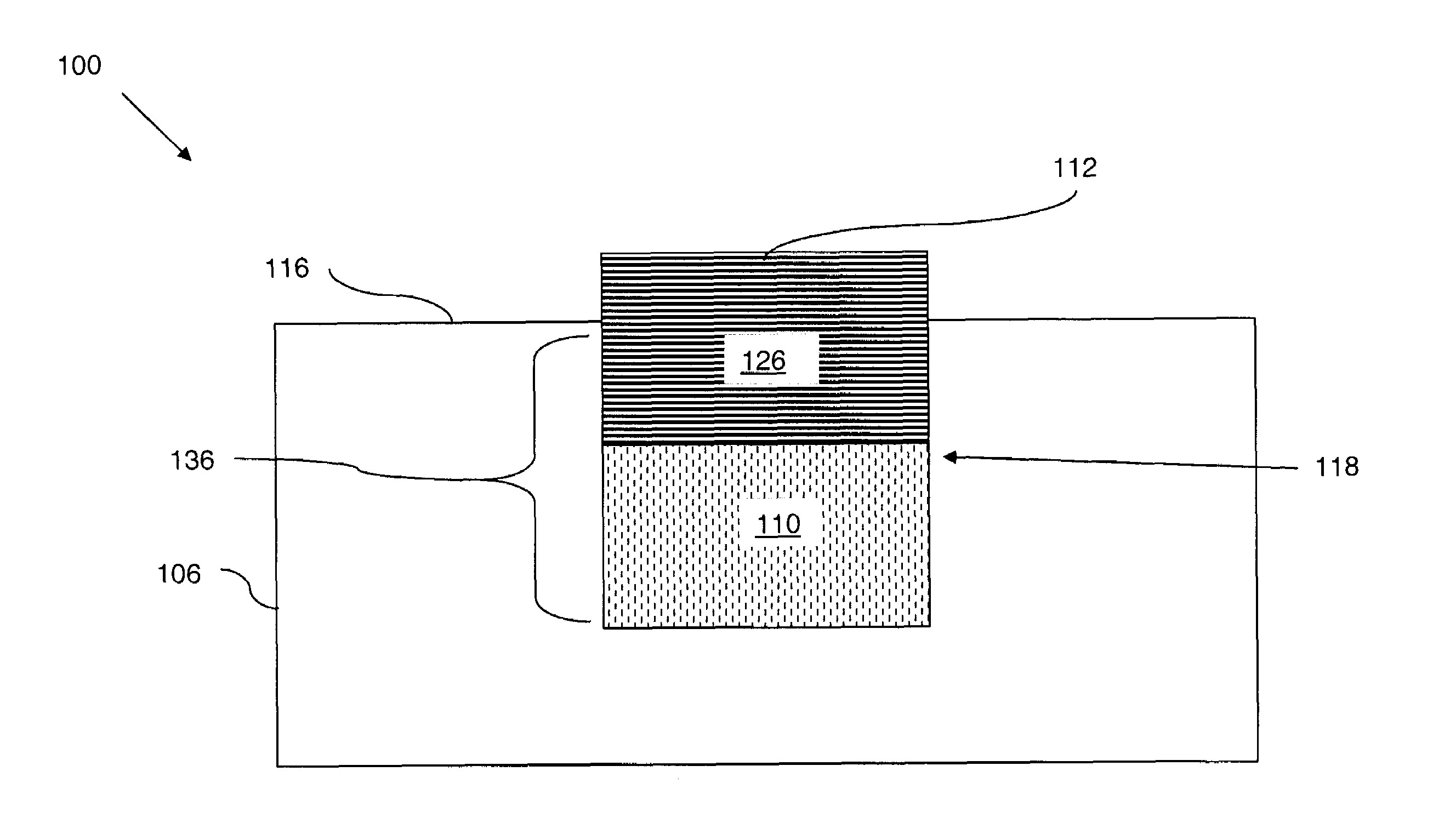

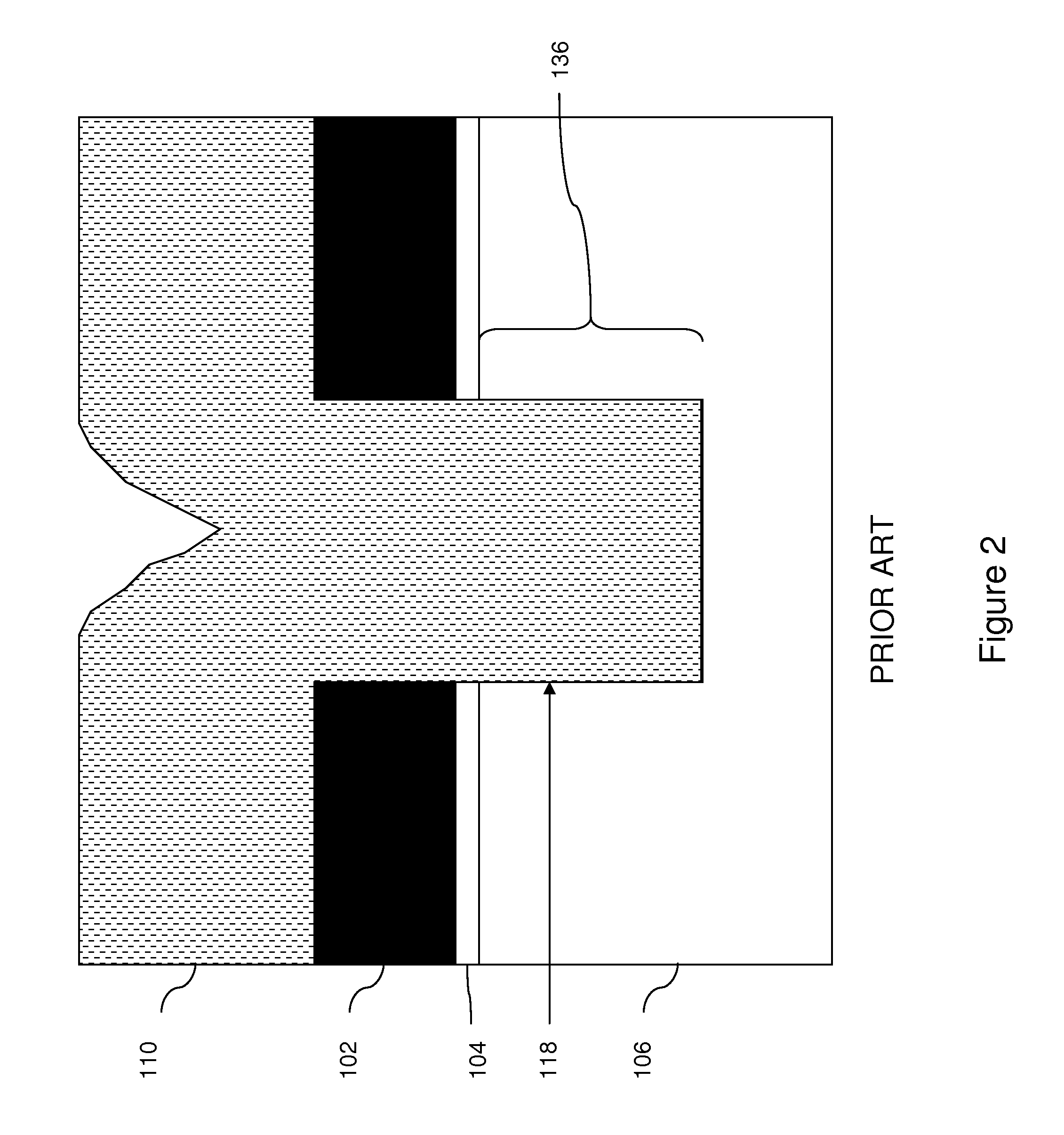

Nitridation of STI fill oxide to prevent the loss of STI fill oxide during manufacturing process

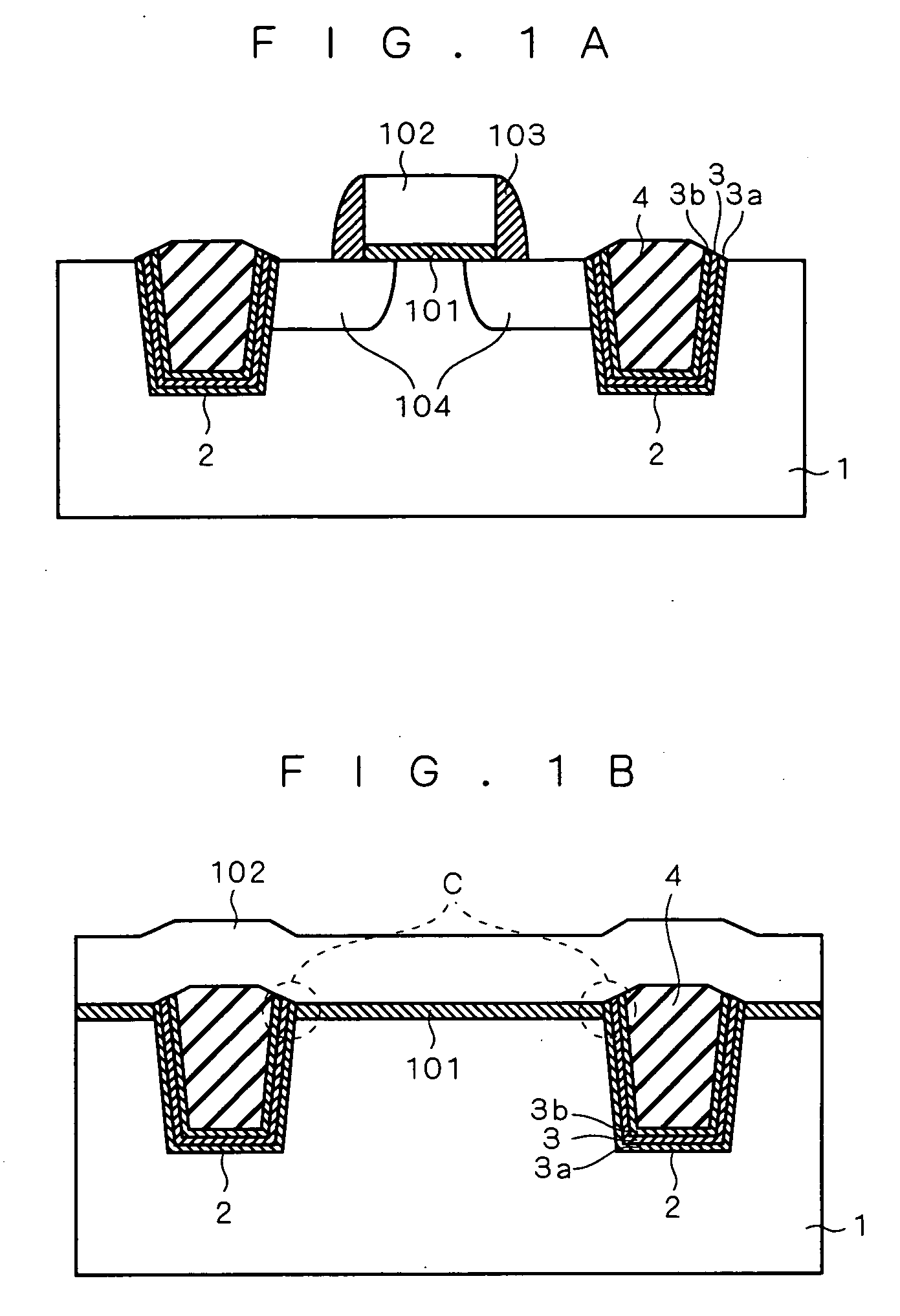

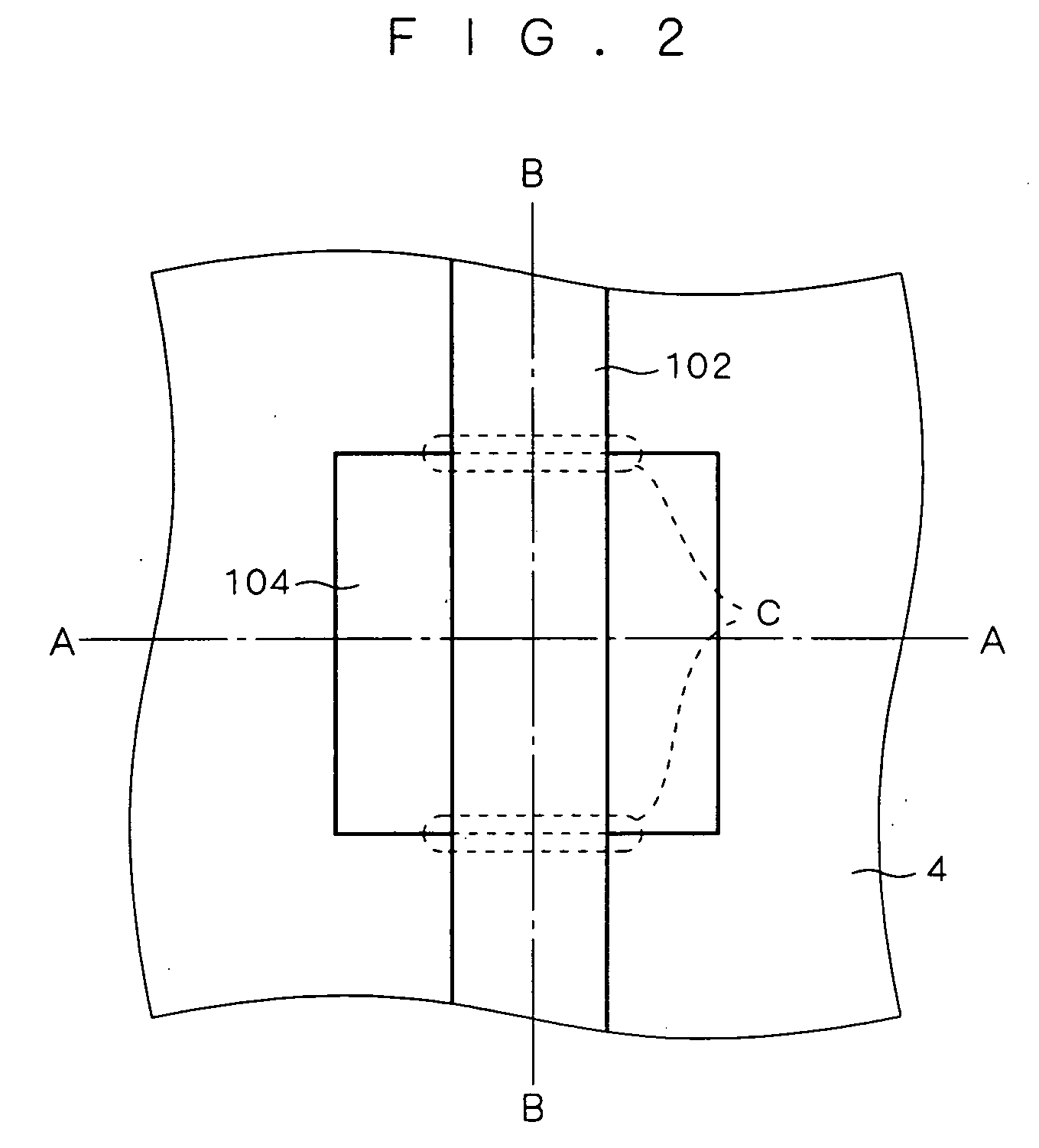

InactiveUS20060160322A1Reduce erosionReduce formationTransistorSemiconductor/solid-state device manufacturingHigh concentrationEtching

A method and structure for an improved shallow trench isolation (STI) structure for a semiconductor device. The STI structure incorporates an oxynitride top layer of the STI fill. Optionally, the STI structure incorporates an oxynitride margin of the STI fill adjacent the silicon trench walls. A region of the oxynitride margin near the upper edges of the silicon trench walls includes oxynitride corners that are relatively thicker and contain a higher concentration of nitrogen as compared to the other regions of the oxynitride margin. The oxynitride features limit the STI fill height loss and also reduce the formation of divots in the STI fill below the level of the silicon substrate cause by hydrofluoric acid etching and other fabrication processes. Limiting STI fill height loss and the formation of divots improves the functions of the STI structure. The method of forming the STI structure is particularly compatible with standard semiconductor device fabrication processes, including chemical mechanical polishing (CMP), because the method incorporates the use of a pure silicon dioxide STI fill and plasma and thermal nitridation processes to form the oxynitride top layer and oxynitride margin, including the oxynitride corners, of the STI fill.

Owner:IBM CORP

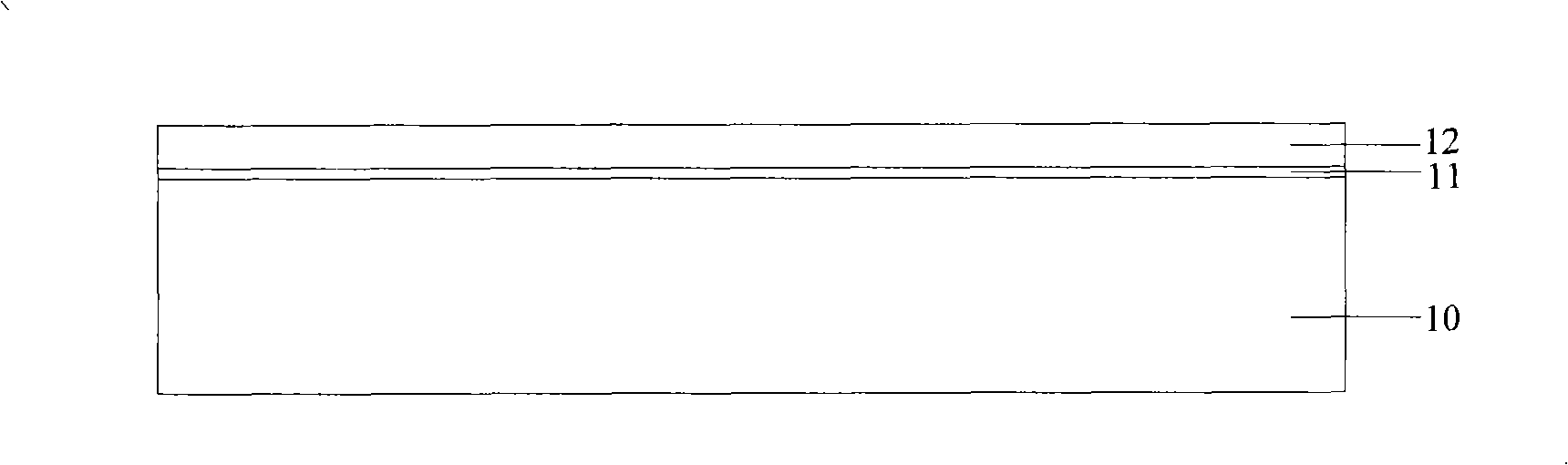

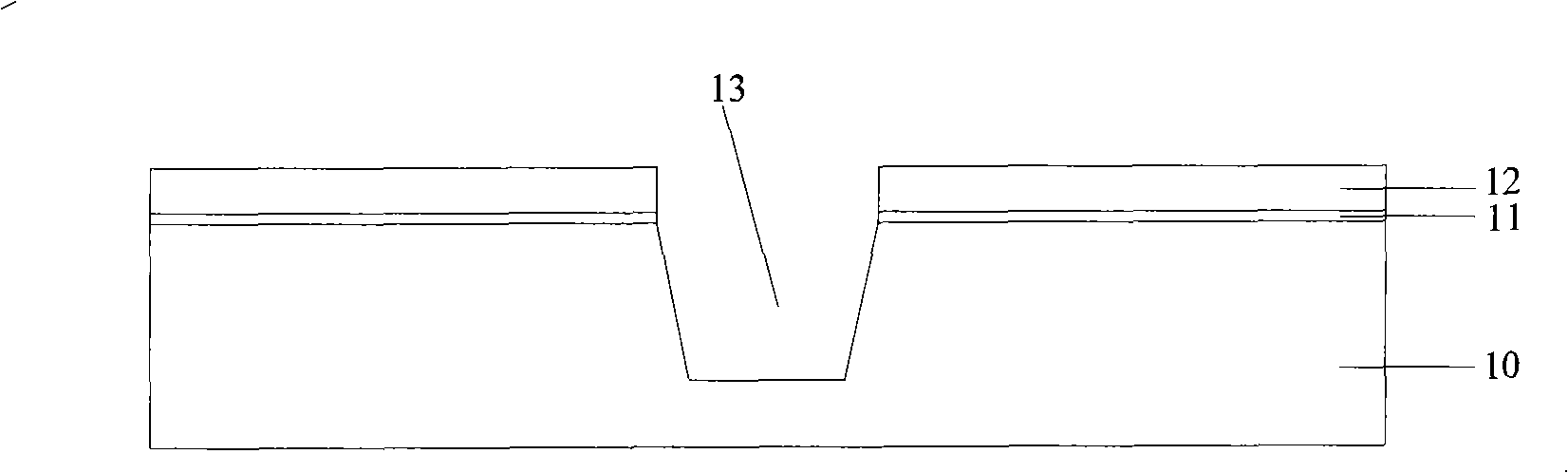

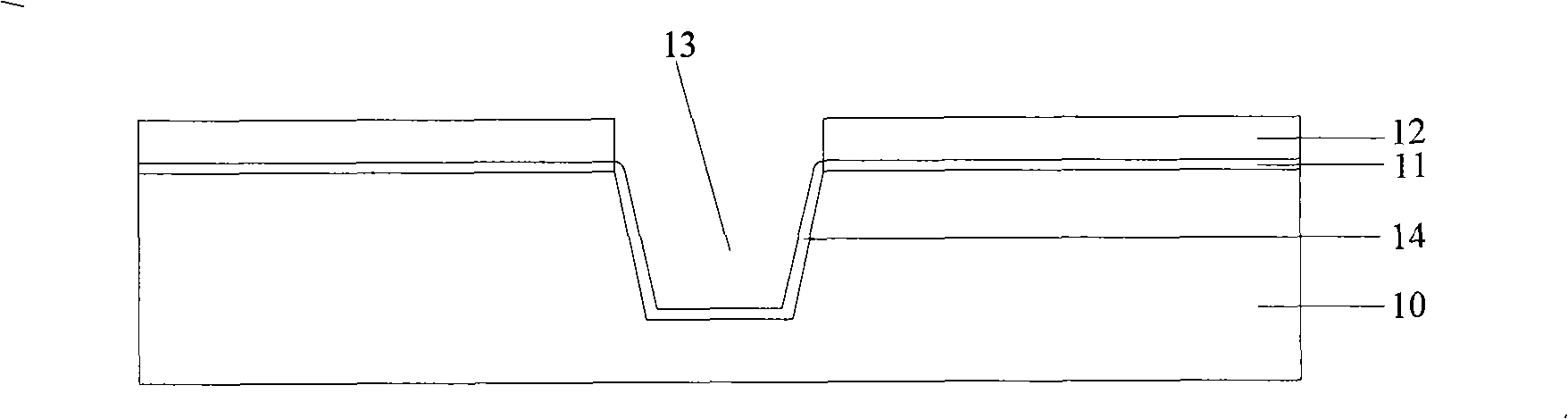

Isolation structure of shallow plough groove and manufacturing method thereof

InactiveCN101295664AImprove grinding endpoint consistencyThickness is precisely controlledSolid-state devicesSemiconductor/solid-state device manufacturingRubbingSilicon nitride

The invention discloses a shallow trench isolating structure and a manufacture method thereof. After the trench is etched, a silicon nitride layer is removed; the silicon nitride layer with a very uniform thickness is formed on an underlay and the surface of the trench by utilizing a furnace thermal nitridation technique to be a rubbing stopping layer. As the thickness of the silicon nitride layer is very uniform, the consistency of the rubbing terminals of the rubbing technique of a chemical machine is greatly improved and the thickness of an oxide filled in the trench after rubbing can be more preciously controlled.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

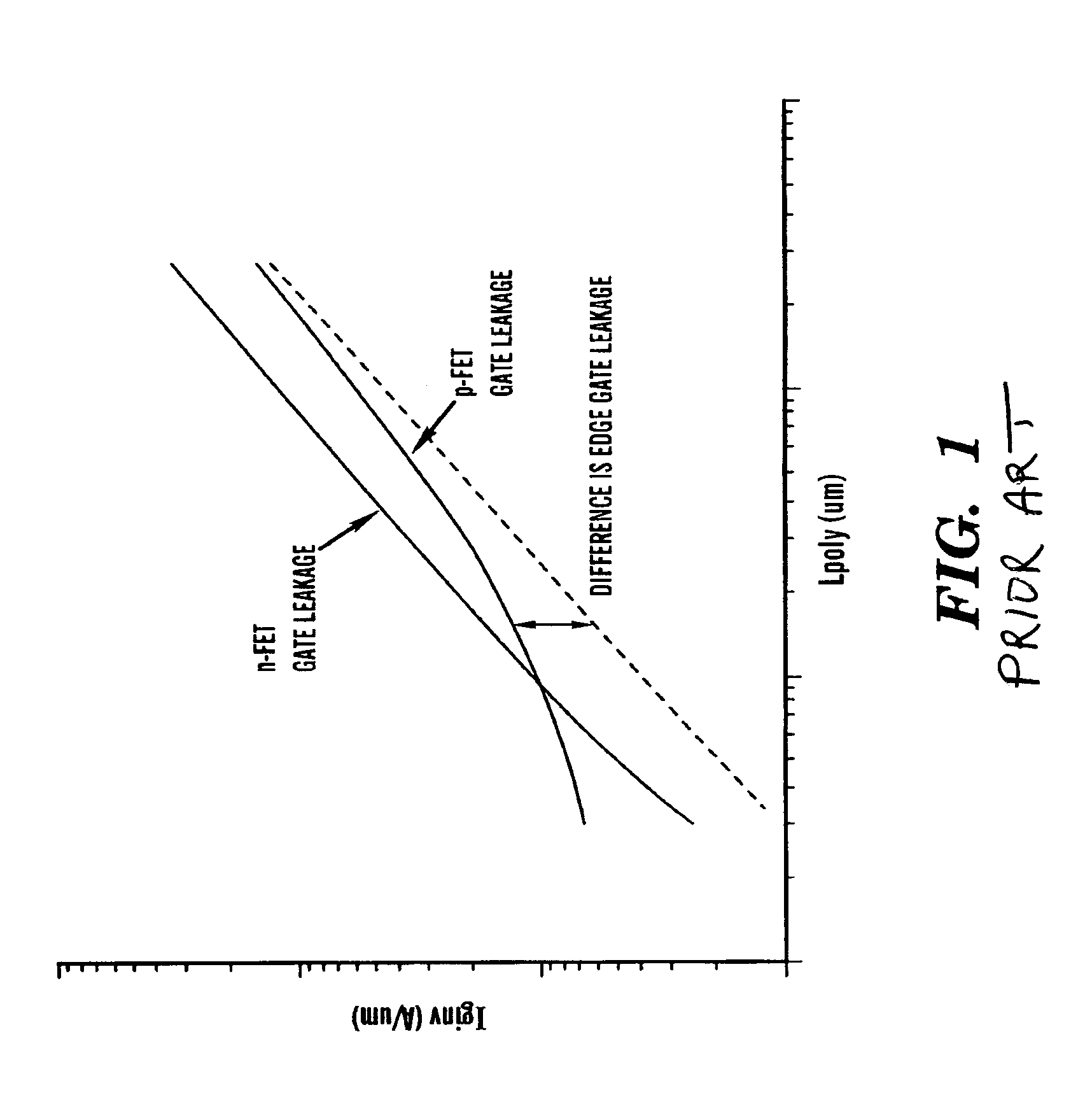

Selective nitridation of gate oxides

ActiveUS20050164444A1Reduce diffuseInvention improvedTransistorSemiconductor/solid-state device manufacturingDopantGate dielectric

A semiconductor structure includes thin gate dielectrics that have been selectively nitrogen enriched. The amount of nitrogen introduced is sufficient to reduce or prevent gate leakage and dopant penetration, without appreciably degrading device performance. A lower concentration of nitrogen is introduced into pFET gate dielectrics than into nFET gate dielectrics. Nitridation may be accomplished selectively by various techniques, including rapid thermal nitridation (RTN), furnace nitridation, remote plasma nitridation (RPN), decoupled plasma nitridation (DPN), well implantation and / or polysilicon implantation.

Owner:GLOBALFOUNDRIES US INC +1

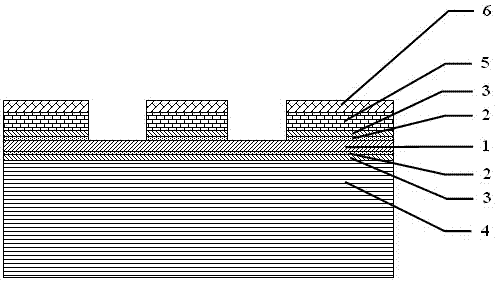

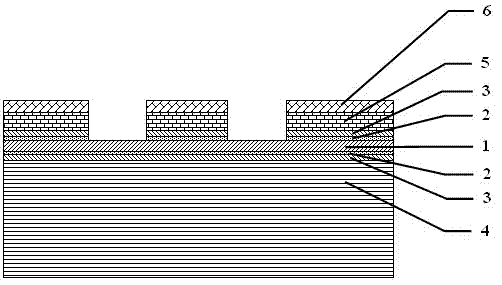

A heat-conducting aluminum nitride insulating metal substrate and its preparation method

InactiveCN102291928ARaw materials are easy to obtainStable production processPrinted circuit manufactureCircuit susbtrate materialsElectrochemistryProtection layer

The invention discloses a heat-conducting aluminum nitride insulating metal substrate and a preparation method thereof. The metal substrate uses an aluminum nitride ceramic plate as a heat-conducting insulating layer, the upper and lower sides of the insulating layer are coated with a buffer layer, and the outer surfaces of the two buffer layers are coated with Putting on the first conductive layer; wherein, the surface of the lower first conductive layer is plated with a metal base layer, the surface of the upper first conductive layer is plated with a second conductive layer, and the second conductive layer is coated with a protective layer. The preparation method uses an aluminum nitride ceramic plate as a thermally conductive insulating layer, and a buffer layer and a first conductive layer are plated by a physical deposition method. One side of the first conductive layer is coated with a metal base layer by electrochemical deposition, and the other side of the conductive layer is coated with an electrochemically high-conductivity layer. The second conductive layer and protective layer. The aluminum nitride insulating metal substrate with high thermal conductivity of the present invention has the advantages of high heat dissipation efficiency, long service life, etc., high reliability, and can meet the packaging requirements of various components.

Owner:SUN YAT SEN UNIV

Gas barrier film, gas barrier film manufacturing method, resin substrate for organic electroluminescent device using the aforesaid gas barrier film, and organic electroluminescent device using the aforementioned gas barrier film

ActiveUS8486487B2Superb adhesionIncreased durabilityLiquid surface applicatorsSolid-state devicesDensity ratioOrganic electroluminescence

Owner:KONICA MINOLTA INC

Remote plasma activated nitridation

ActiveUS7629270B2Semiconductor/solid-state device manufacturingChemical vapor deposition coatingRemote plasmaMicrowave

Owner:ASM IP HLDG BV

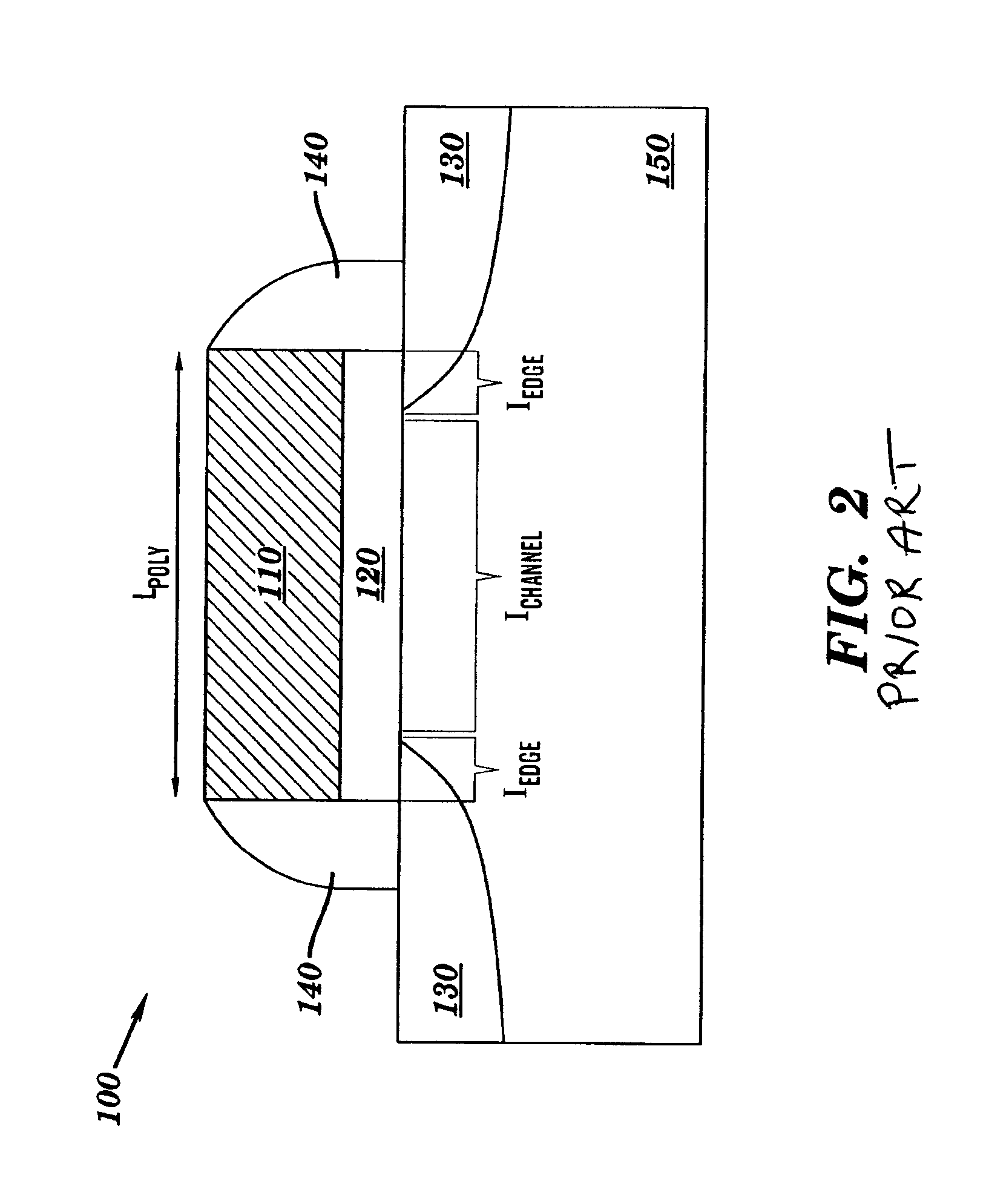

Method for forming semiconductor devices having reduced gate edge leakage current

ActiveUS7456115B2Semiconductor/solid-state device manufacturingSemiconductor devicesEngineeringDrain current

The present invention provides methods for forming semiconductor FET devices having reduced gate edge leakage current by using plasma or thermal nitridation and low-temperature plasma re-oxidation processes post gate etch.

Owner:TAIWAN SEMICON MFG CO LTD

Manufacturing method of semiconductor device including filling a connecting hole with metal film

The present invention is to possible to avoid an inconvenience at a coupling portion between a barrier metal film obtained by depositing a titanium nitride film on a titanium film and thus having a film stack structure and a metal film filled, via the barrier metal film, in a connecting hole opened in an insulating film. The manufacturing method of a semiconductor device includes the steps of: forming a contact hole and exposing a nickel silicide layer from the bottom of the contact hole; forming a thermal reaction Ti film by a thermal reaction using a TiCl4 gas, forming a plasma reaction Ti film by a plasma reaction using a TiCl4 gas, carrying out plasma treatment with an H2 gas to decrease the chlorine concentration of the plasma reaction Ti film and at the same time to reduce an oxide film on the surface of the nickel silicide layer; forming a nitrogen-rich TiN film over the surface of the plasma reaction Ti film and at the same time reducing the oxide film on the surface of the nickel silicide layer by thermal nitridation treatment with an NH3 gas and plasma treatment with an NH3 gas.

Owner:RENESAS ELECTRONICS CORP

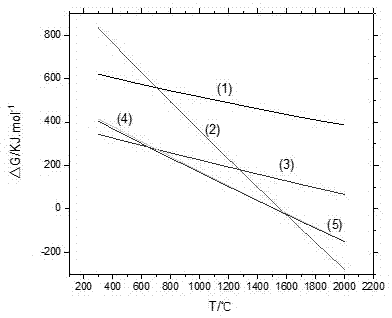

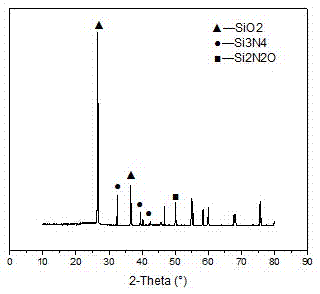

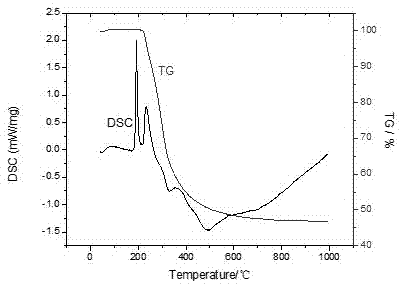

Technology for preparing zirconium nitride ceramic microspheres and zirconium nitride ceramic microspheres

The invention discloses a technology for preparing zirconium nitride ceramic microspheres and the zirconium nitride ceramic microspheres, wherein the technology comprises the following steps: mixing ZrO(NO3)2*xH2O, hexamethylenetetramine, urea, concentrated HNO3 with carbon black to obtain a glue solution; dispersing the glue solution into hot silicone oil dropwise, solidifying droplets in the silicone oil to obtain gel microspheres; aging the gel microspheres in the hot silicone oil to react the gel microspheres completely; washing the gel microspheres to remove the silicone oil on the surface of the microspheres and residual unreacted materials; drying the washed gel microspheres to obtain dried gel microspheres; subjecting the dried gel microspheres to carbon thermal nitridation treatment, and sintering and densifying simultaneously to obtain the zirconium nitride ceramic microspheres. According the technology, the zirconium nitride ceramic microspheres are produced by combining aninternal gel method with a carbon thermal nitridation method, the obtained zirconium nitride ceramic microspheres are pure phase zirconium nitride, and the microspheres have good sphericity, uniform size, complete structure without cracks, and good mechanical properties.

Owner:TSINGHUA UNIV

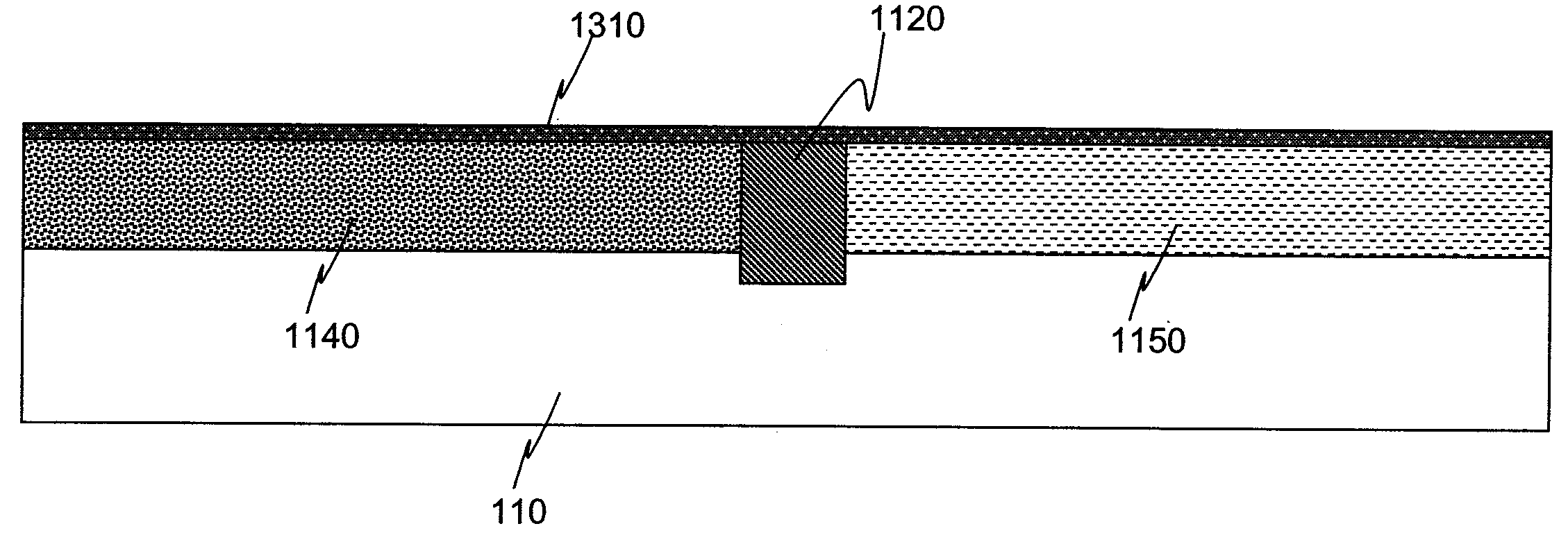

Nitridation of STI Fill Oxide to Prevent the Loss of STI Fill Oxide During Manufacturing Process

InactiveUS20080090379A1Reduce erosionReduce formationSemiconductor/solid-state device manufacturingHigh concentrationEtching

A method and structure for an improved shallow trench isolation (STI) structure for a semiconductor device. The STI structure incorporates an oxynitride top layer of the STI fill. Optionally, the STI structure incorporates an oxynitride margin of the STI fill adjacent the silicon trench walls. A region of the oxynitride margin near the upper edges of the silicon trench walls includes oxynitride corners that are relatively thicker and contain a higher concentration of nitrogen as compared to the other regions of the oxynitride margin. The oxynitride features limit the STI fill height loss and also reduce the formation of divots in the STI fill below the level of the silicon substrate cause by hydrofluoric acid etching and other fabrication processes. Limiting STI fill height loss and the formation of divots improves the functions of the STI structure. The method of forming the STI structure is particularly compatible with standard semiconductor device fabrication processes, including chemical mechanical polishing (CMP), because the method incorporates the use of a pure silicon dioxide STI fill and plasma and thermal nitridation processes to form the oxynitride top layer and oxynitride margin, including the oxynitride corners, of the STI fill.

Owner:INT BUSINESS MASCH CORP

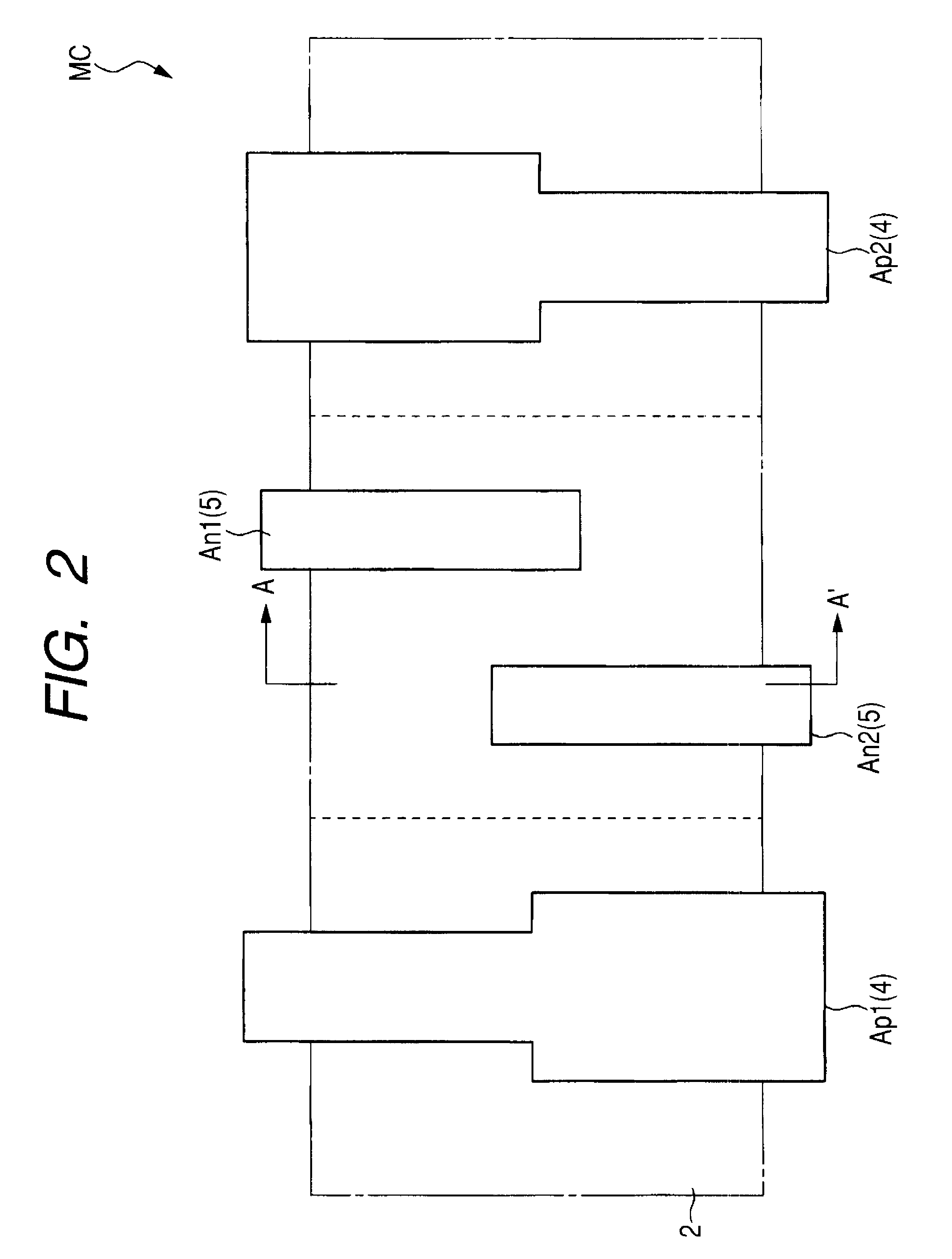

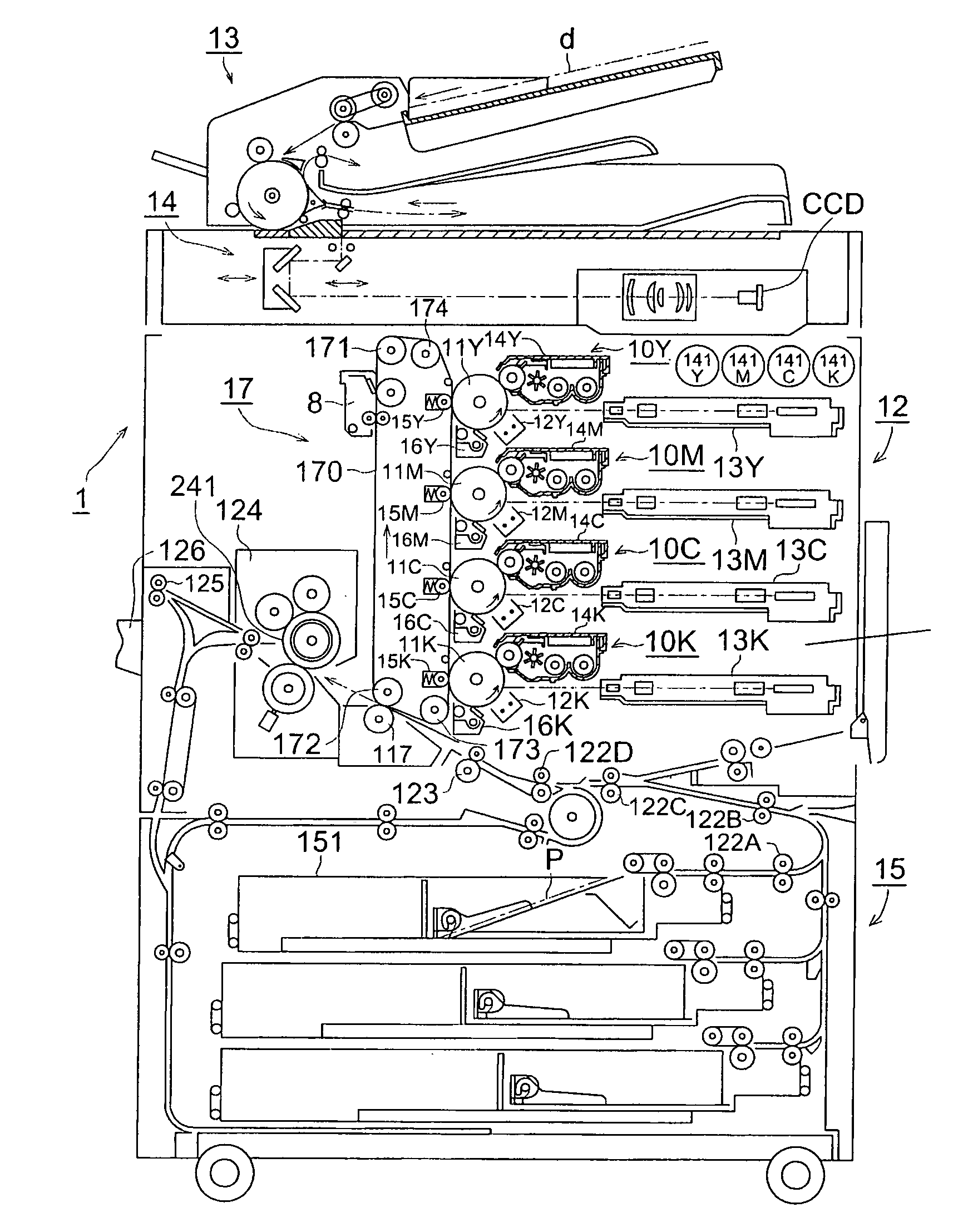

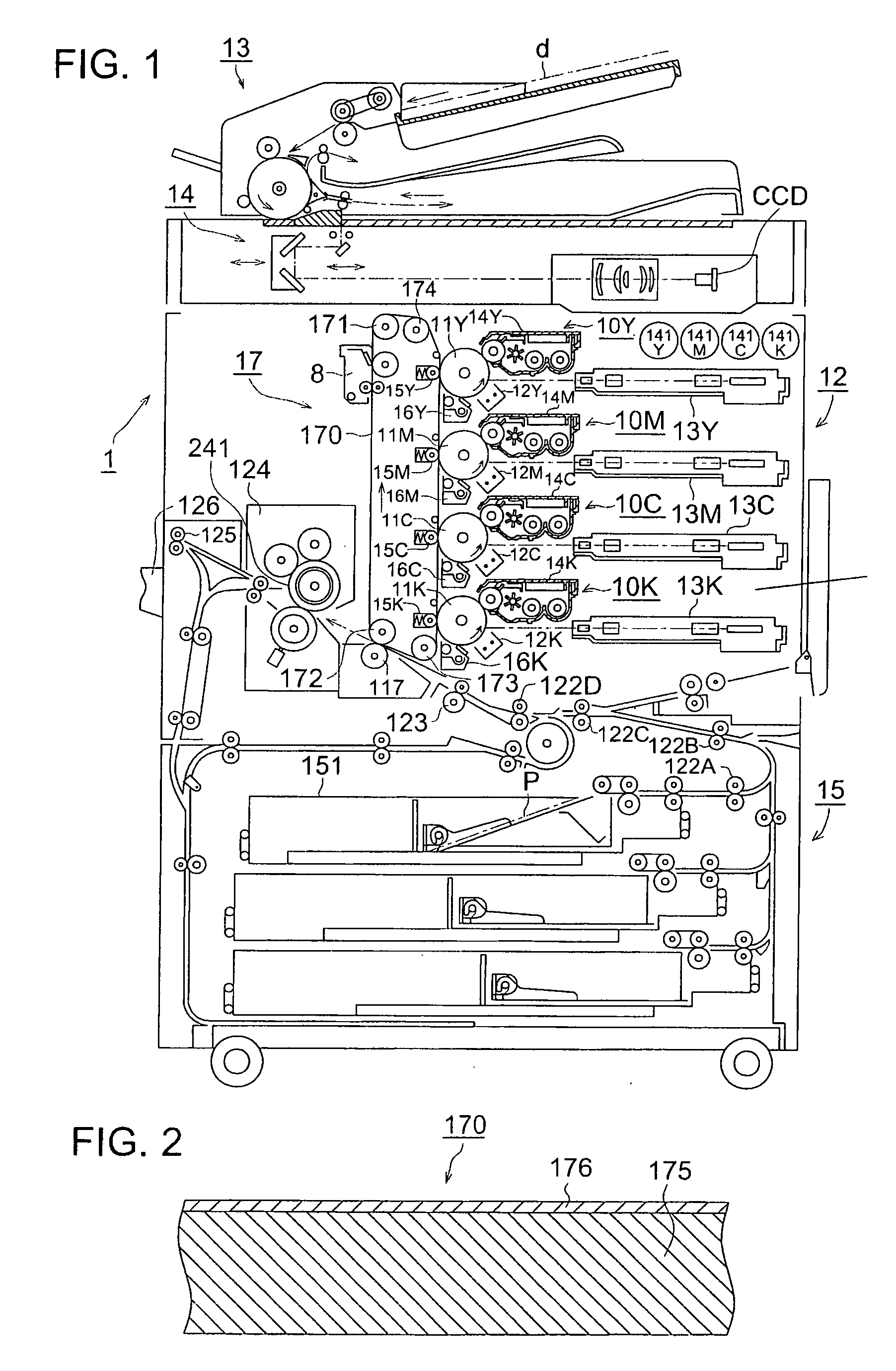

Intermediate Transfer Member, Method of Manufacturing Intermediate Transfer Member, and Image Forming Apparatus

InactiveUS20080267675A1Improve adhesionHigh cleaning propertyCeramic layered productsElectrographic process apparatusEngineeringElectrical and Electronics engineering

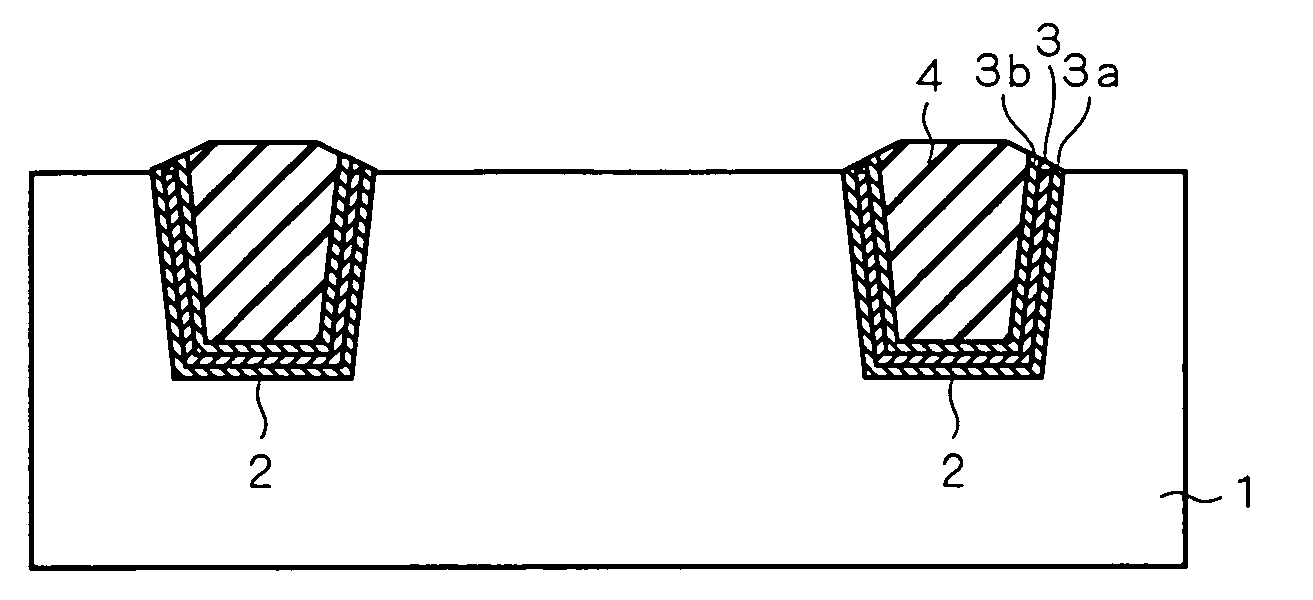

An objective is to provide an intermediate transfer member exhibiting higher transferability together with higher cleaning ability and durability, a manufacturing apparatus of an intermediate transfer member in which no large-scale equipment such as a vacuum evaporator or the like is managed to be installed, and an image forming apparatus fitted with the intermediate transfer member. Also disclosed is intermediate transfer member 170 possessing ceramic film 176 provided on substrate 175, wherein ceramic film 176 has a density of ρf, satisfying the following formula: 0.8<ρf / ρb≦1, provided that another ceramic film having the same composition ratio as that of ceramic film 176 has a density of ρb when the another ceramic film is formed via thermal oxidation or thermal nitridation of a base material.

Owner:KONICA MINOLTA BUSINESS TECH INC

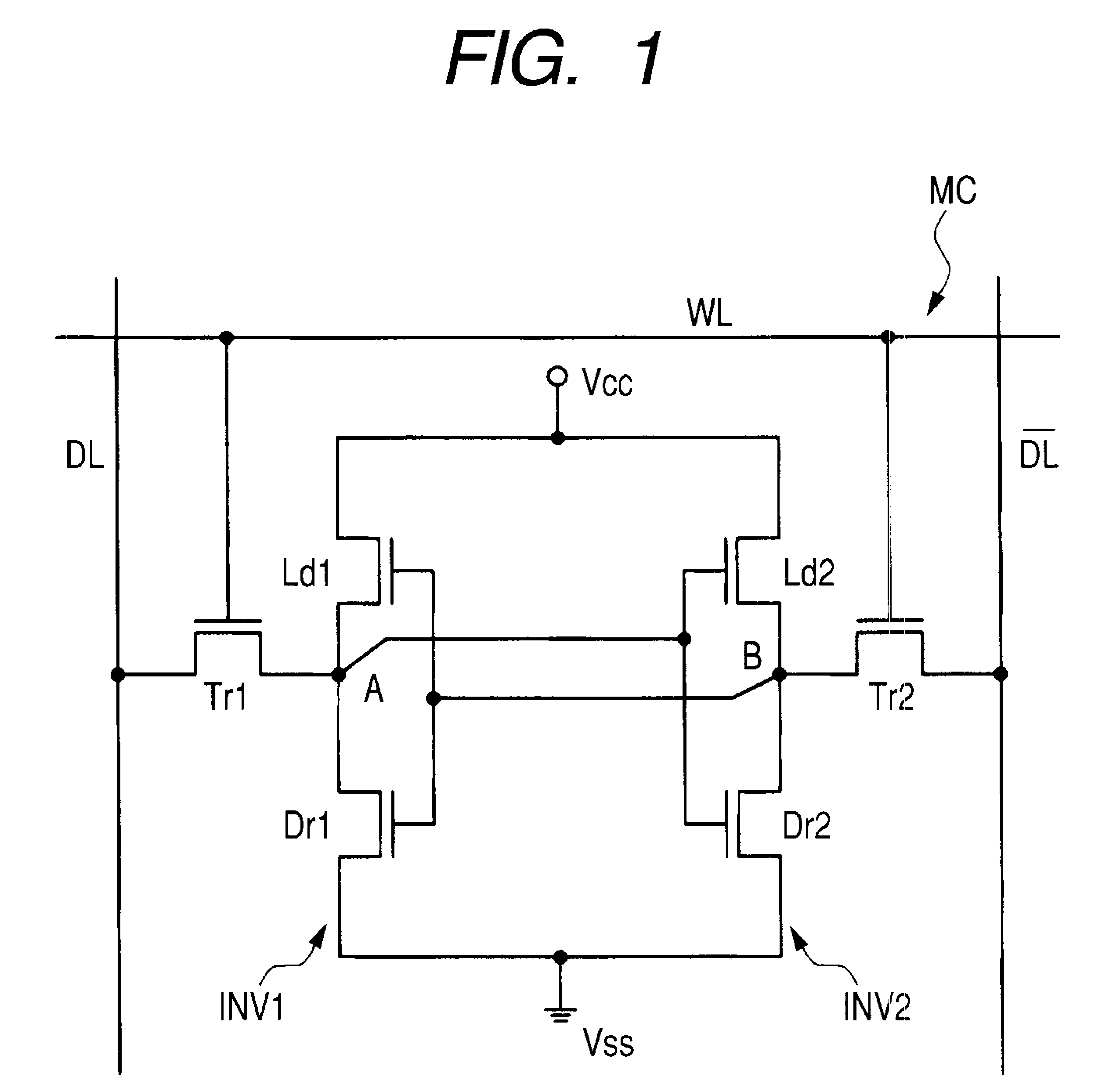

Semiconductor device and method of manufacturing the same

InactiveUS20050269602A1Low reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingDevice materialNitrogen

Owner:RENESAS TECH CORP

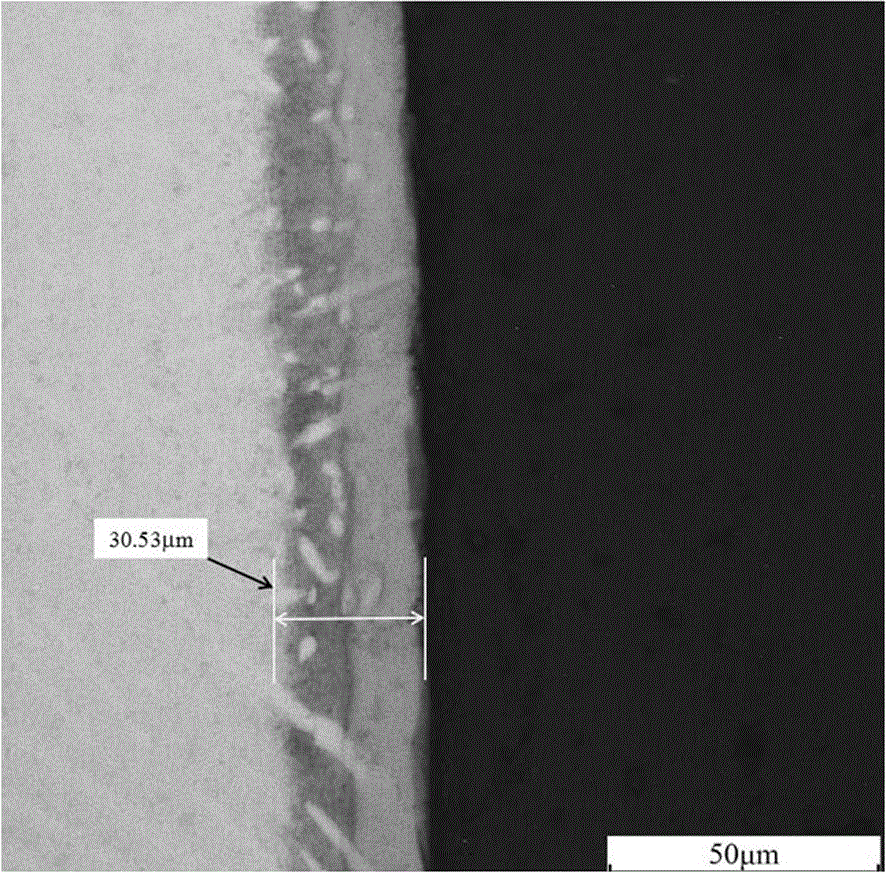

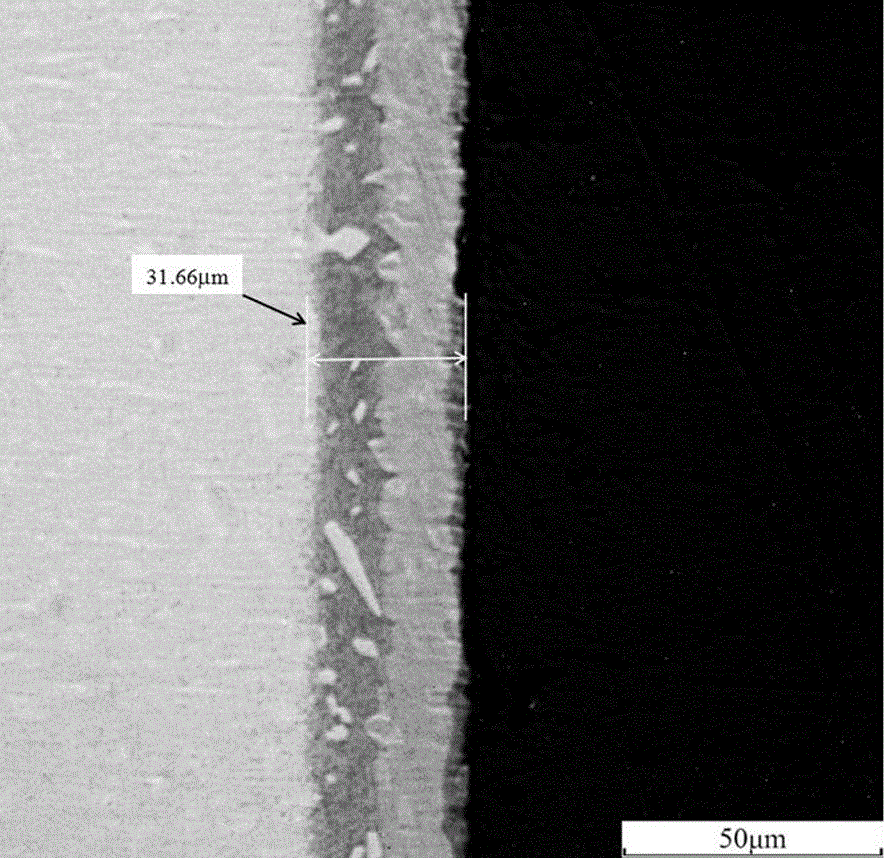

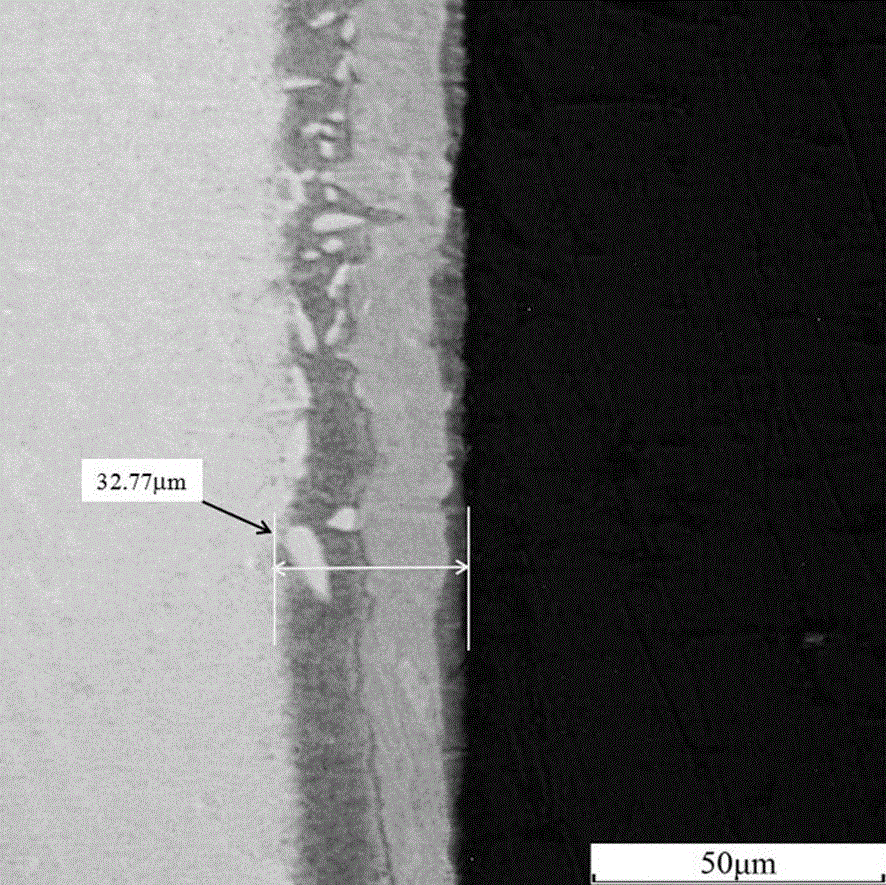

QPQ technology for increasing thickness of infiltrated layer on surface of cast duplex stainless steel

InactiveCN106399921AIncreasing the thicknessImprove wear resistanceSolid state diffusion coatingEconomic benefitsHardness

The invention discloses a QPQ technology used for increasing thickness of an infiltrated layer on the surface of cast duplex stainless steel, wherein the QPQ technology for increasing the thickness of the infiltrated layer comprises the following processes of: cleaning, preheating, nitriding, oxidizing, cleaning and desalting, drying and polishing, wherein the main processes are the salt-bath nitriding process and the salt-bath oxidizing process. Compared with the original QPQ technology, the QPQ technology disclosed by the invention has the advantages of increasing the thickness of the infiltrated layer, and being capable of effectively shortening nitriding time and improving production efficiency under the same conditions. The QPQ technology can form a high-quality infiltrated layer with enough depth and certain hardness on the material surface within relatively short time, can remarkably improve wear resistance and corrosion resistance of the material, can reduce the risk that the material loses efficacy due to wear, expands the application range, in various fields, of stainless steel, and has remarkable economic benefits.

Owner:FUZHOU UNIV

Method for forming a silicon nitride layer

ActiveUS6992021B2Increase capacityIncreased process windowVacuum evaporation coatingSputtering coatingNitrogenIon implantation

A method of forming a silicon nitride layer. The method comprises providing a substrate having a silicon surface thereon, performing an ion implant process on the silicon surface, implanting nitrogen atoms into the silicon surface, and performing a thermal nitridation process and forming a silicon nitride layer on the substrate, wherein the silicon nitride layer comprises the silicon nitride formed on the silicon surface by reaction of the silicon surface with the nitrogen atoms contained therein.

Owner:NAN YA TECH

Producing Method of Semiconductor Device

Disclosed is a producing method of a semiconductor device comprising a step of forming a tunnel insulating film of a flash device comprising a first nitridation step of forming a first silicon oxynitride film by nitriding a silicon oxide film formed on a semiconductor silicon base by one of plasma nitridation and thermal nitridation, the plasma nitridation carrying out nitridation process by using a gas activated by plasma discharging a first gas including a first compound which has at least a nitrogen atom in a chemical formula thereof, and the thermal nitridation carrying out nitridation process using heat by using a second gas including a second compound which has at least a nitrogen atom in a chemical formula thereof, and a second nitridation step of forming a second silicon oxynitride film by nitriding the first silicon oxynitride film by the other of the plasma nitridation and the thermal nitridation.

Owner:KOKUSA ELECTRIC CO LTD

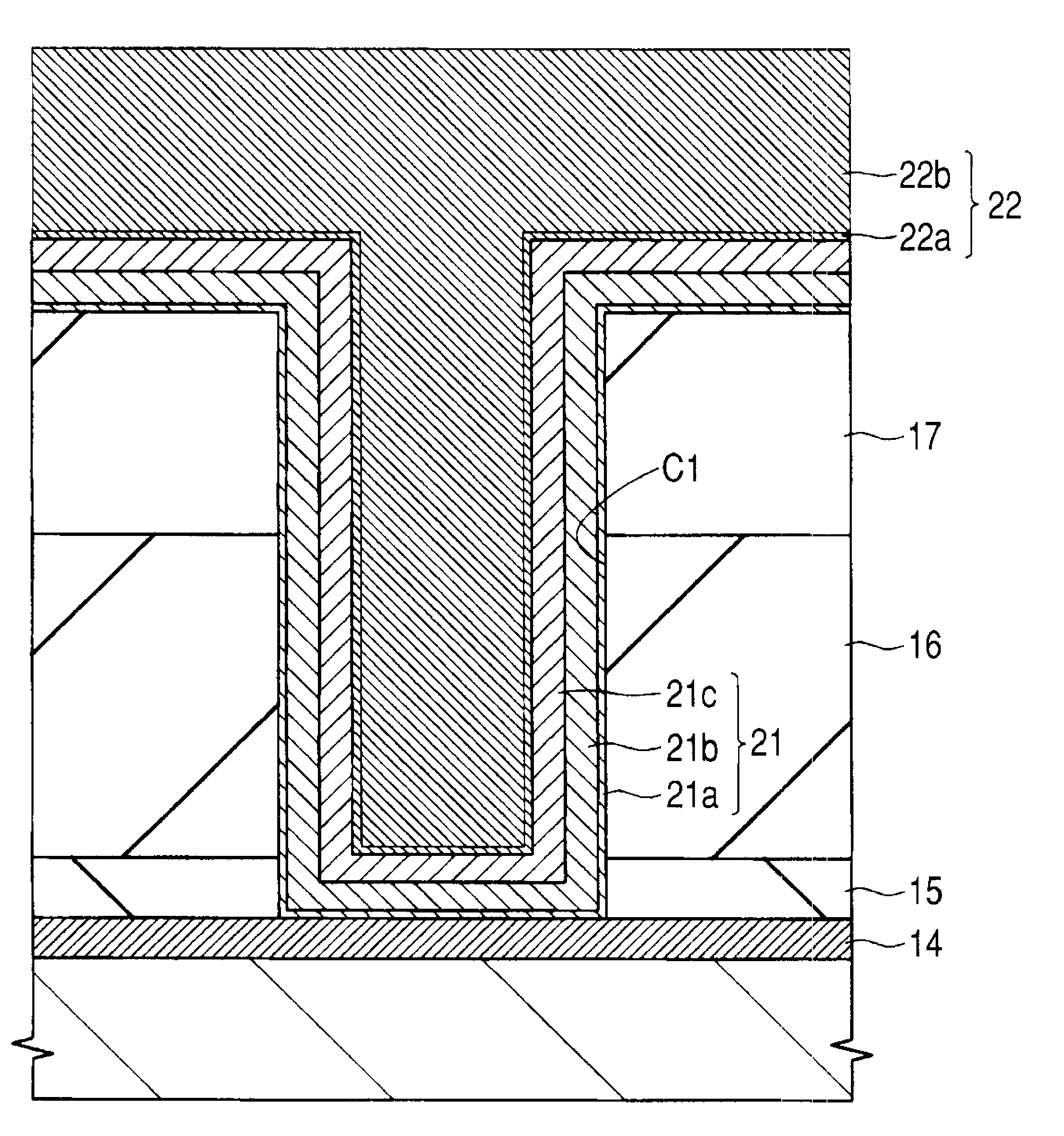

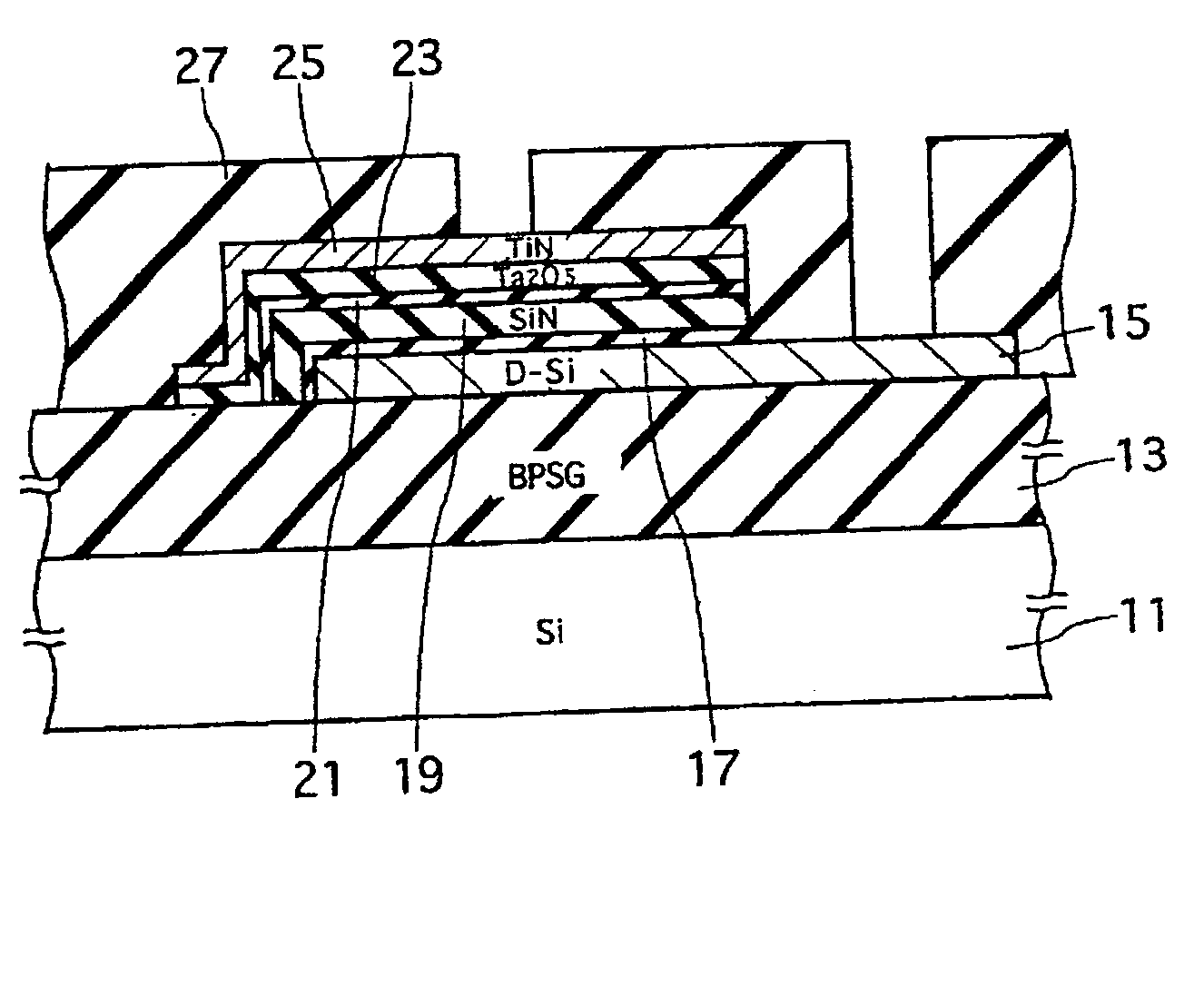

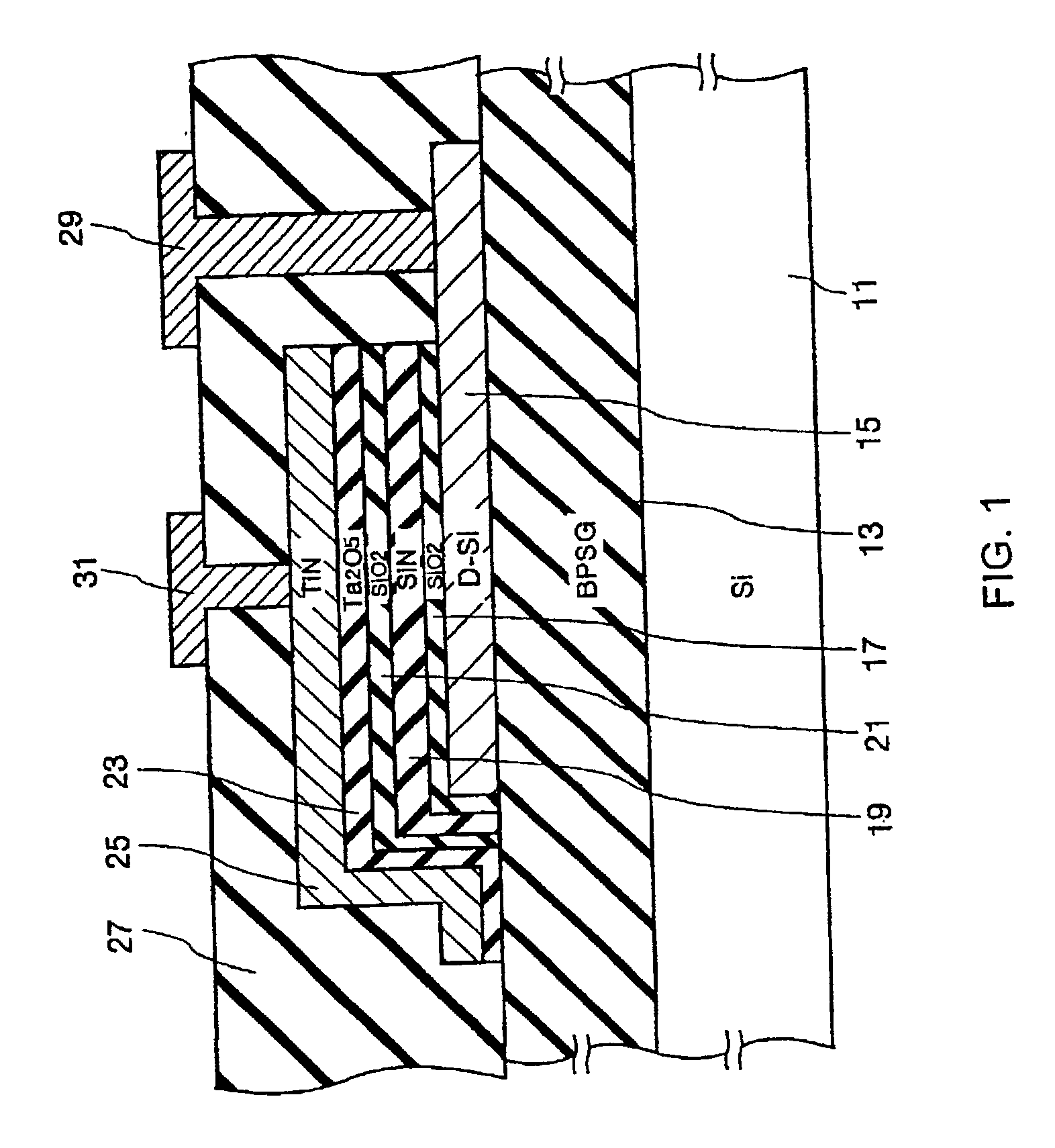

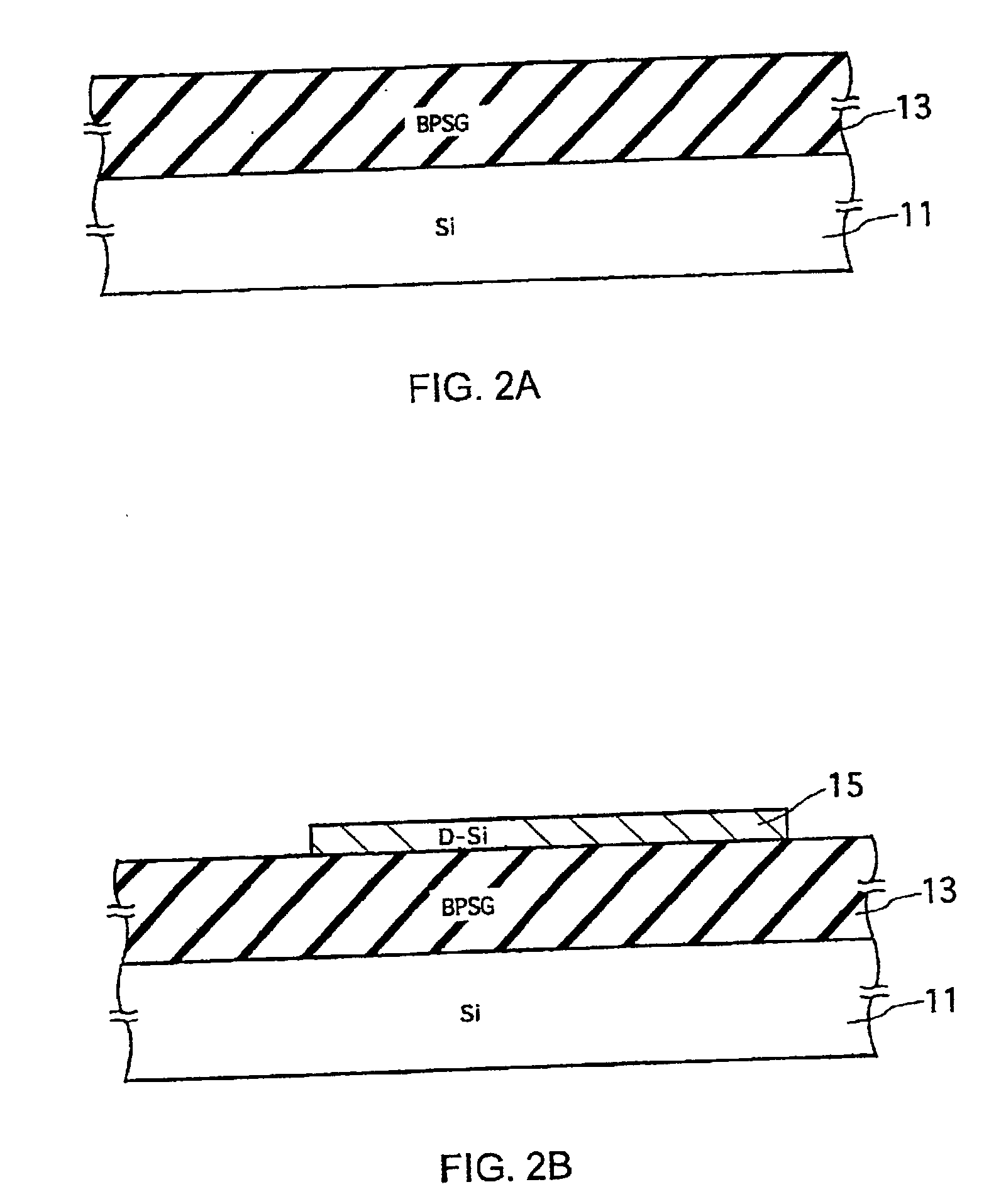

Capacitor for analog circuit, and manufacturing method thereof

InactiveUS20020160577A1Large capacitanceImprove high pressure resistanceTransistorSolid-state devicesDielectricNitrogen

Rapid thermal nitridation is carried out to form a nitride film (19) on a lower electrode (15) which is made of silicon, and a tantalum oxide dielectric film (23) is further formed thereon. Then, wet oxidization is carried out to oxidize the lower electrode through the dielectric film (23) and the nitride film (19), thus an oxide film (17) is formed between the lower electrode (15) and the nitride film (19). Further, silicon which is not bonded to nitrogen in the nitride film (19) is oxidized, thus an oxide film (21) whose effective thickness is equal to or greater than 2 nm. The oxidization also recrystallizes the dielectric film (23). Finally, an upper electrode (25) is formed, and the capacitor is completed.

Owner:TOKYO ELECTRON LTD

Nitridation of STI fill oxide to prevent the loss of STI fill oxide during manufacturing process

InactiveUS7491964B2Reduce erosionReduce formationTransistorSemiconductor/solid-state device manufacturingHigh concentrationEtching

A method and structure for an improved shallow trench isolation (STI) structure for a semiconductor device. The STI structure incorporates an oxynitride top layer of the STI fill. Optionally, the STI structure incorporates an oxynitride margin of the STI fill adjacent the silicon trench walls. A region of the oxynitride margin near the upper edges of the silicon trench walls includes oxynitride corners that are relatively thicker and contain a higher concentration of nitrogen as compared to the other regions of the oxynitride margin. The oxynitride features limit the STI fill height loss and also reduce the formation of divots in the STI fill below the level of the silicon substrate cause by hydrofluoric acid etching and other fabrication processes. Limiting STI fill height loss and the formation of divots improves the functions of the STI structure. The method of forming the STI structure is particularly compatible with standard semiconductor device fabrication processes, including chemical mechanical polishing (CMP), because the method incorporates the use of a pure silicon dioxide STI fill and plasma and thermal nitridation processes to form the oxynitride top layer and oxynitride margin, including the oxynitride corners, of the STI fill.

Owner:INT BUSINESS MASCH CORP

Preparation method of functionalized fused quartz powder for preparing quartz ceramics and functionalized fused quartz powder

The invention discloses a preparation method of functionalized fused quartz powder for preparing quartz ceramics and the functionalized fused quartz powder. According to the preparation method of the functionalized fused quartz powder for preparing the quartz ceramics, products obtained after thermal decomposition of sucrose are used as carbon sources, in the atmosphere of nitrogen, through carbothermal nitridation reduction reaction, a sintering additive is formed through in-situ synthesis on the surface of fused quartz powder, the obtained functionalized fused quartz powder is used for the preparation and shaping of fused ceramics, and compared with mechanical addition of the sintering additive, the obtained functionalized fused quartz powder can be distributed more evenly in a matrix; meanwhile, because a trace amount of oxygen in the fused powder can be consumed in the process of functionalized treatment, and a crystallization phenomenon is inhibited to a certain degree; the volume density of the obtained fused quartz ceramics prepared from the obtained functionalized fused quartz powder is 1.96 g / cm<3>, and the fracture resistance reaches 43.5 MPa. The preparation method is simple and stable to operate, low in energy consumption and economical and environmentally friendly, and the used raw materials are cheap and easy to get, and the preparation method is suitable for industrial production.

Owner:HUNAN UNIV OF TECH

Gas barrier film, gas barrier film manufacturing method, resin substrate for organic electroluminescent device using the aforesaid gas barrier film, and organic electroluminescent device using the aforementioned gas barrier film

ActiveUS8062707B2Superb adhesionIncreased durabilityLiquid surface applicatorsSolid-state devicesDensity ratioVolumetric Mass Density

A gas barrier film comprising a resin substrate provided thereon at least one layer of a ceramic film, wherein the density ratio Y (=ρf / ρb) satisfies 1≧Y≧0.95 and the ceramic film has a residual stress being a compression stress of 0.01 MPa or more and 100 Mpa or less, wherein ρf is the density of the ceramic film and ρb is the density of a comparative ceramic film being formed by thermal oxidation or thermal nitridation of a metal as a mother material of the ceramic film so as to being the same composition ratio of the ceramic film.

Owner:KONICA MINOLTA INC

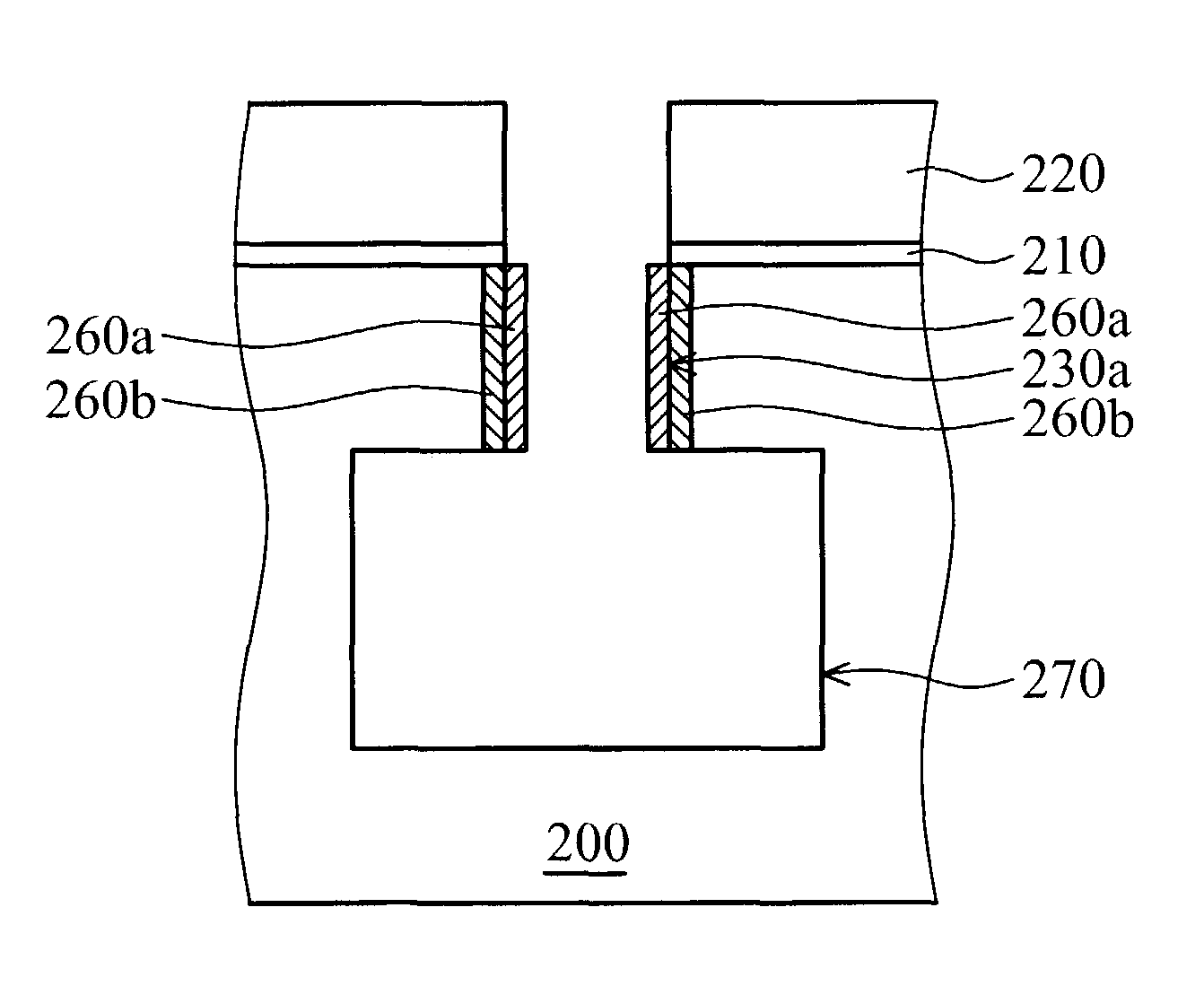

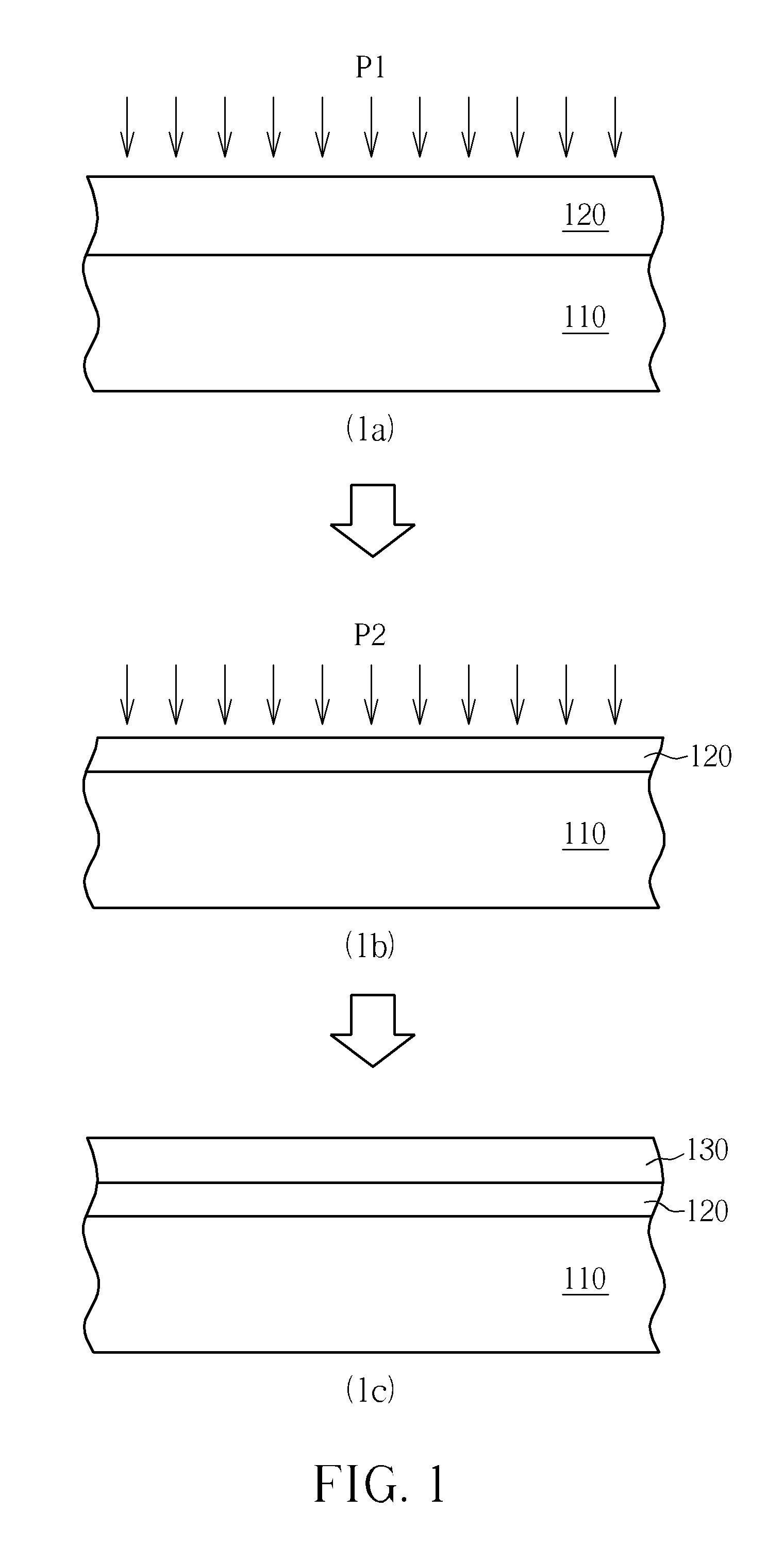

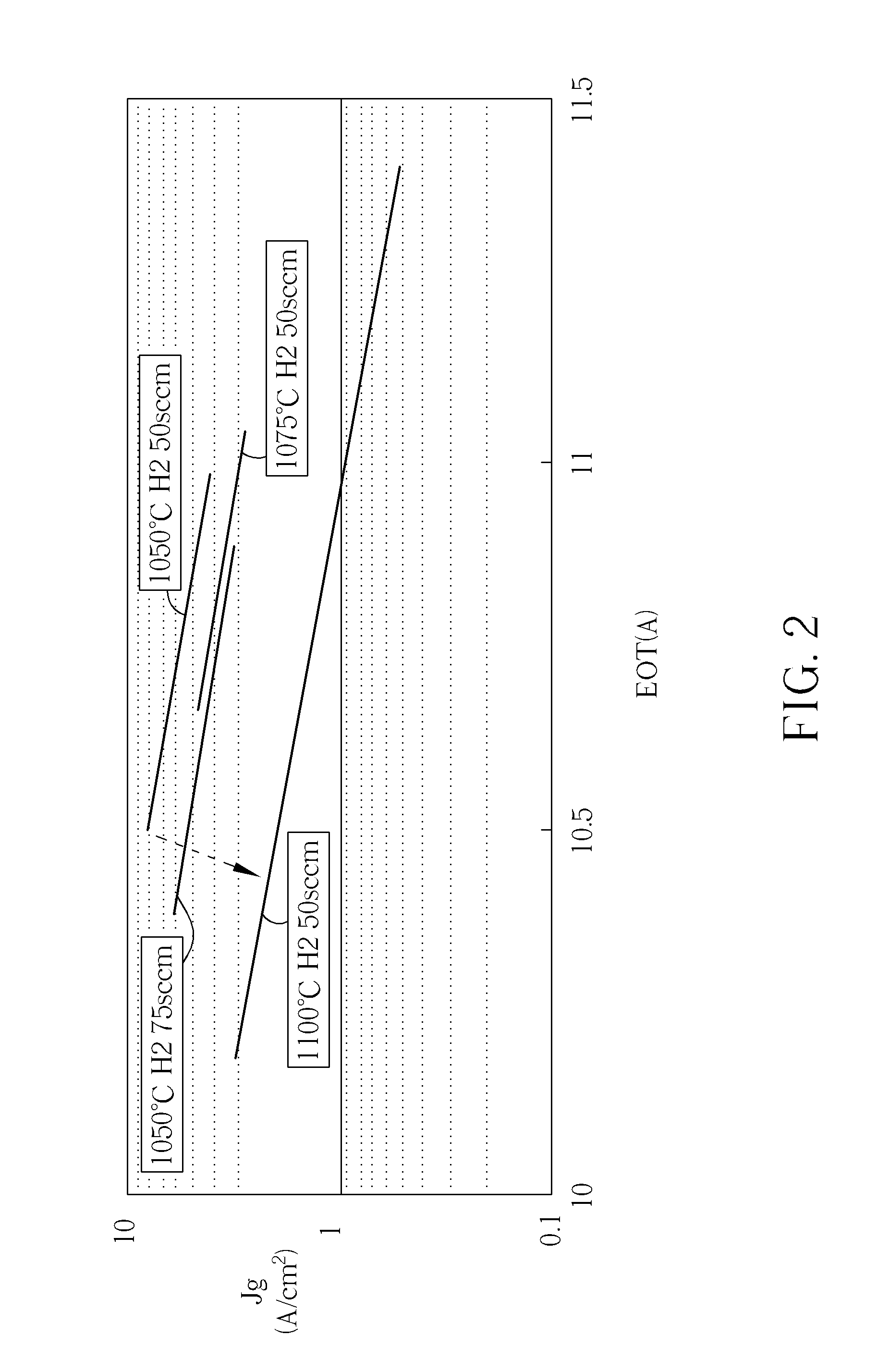

Semiconductor process and structure thereof

InactiveUS20120306028A1Good semiconductor performanceHigh densitySemiconductor/solid-state device manufacturingSemiconductor devicesCooking & bakingSemiconductor structure

A semiconductor process is provided, including: a substrate is provided, a buffer layer is formed, and a dielectric layer having a high dielectric constant is formed, wherein the methods of forming the buffer layer include: (1) an oxidation process is performed; and a baking process is performed; Alternatively, (2) an oxidation process is performed; a thermal nitridation process is performed; and a plasma nitridation process is performed; Or, (3) a decoupled plasma oxidation process is performed. Furthermore, a semiconductor structure fabricated by the last process is also provided.

Owner:UNITED MICROELECTRONICS CORP

Nitridation of STI fill oxide to prevent the loss of STI fill oxide during manufacturing process

InactiveUS7491563B2Reduce erosionReduce formationSemiconductor/solid-state device manufacturingHigh concentrationEtching

Owner:INT BUSINESS MASCH CORP

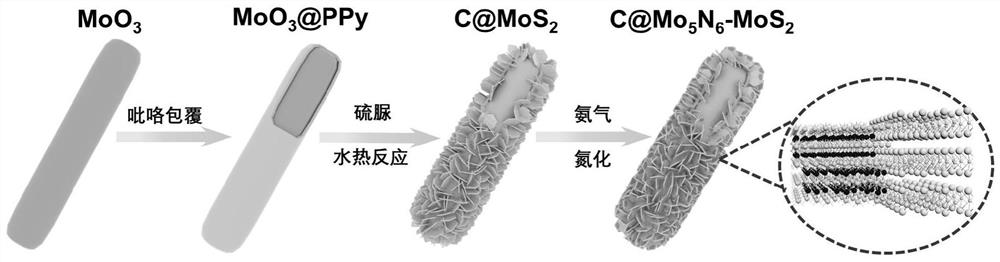

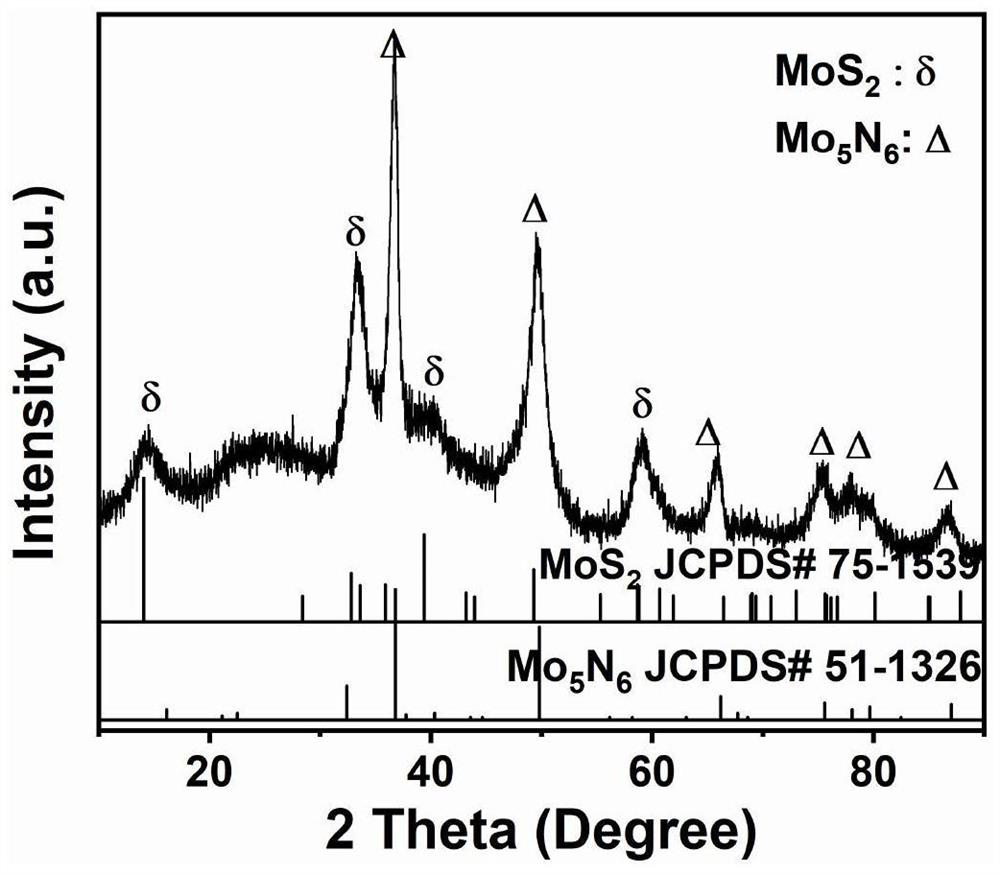

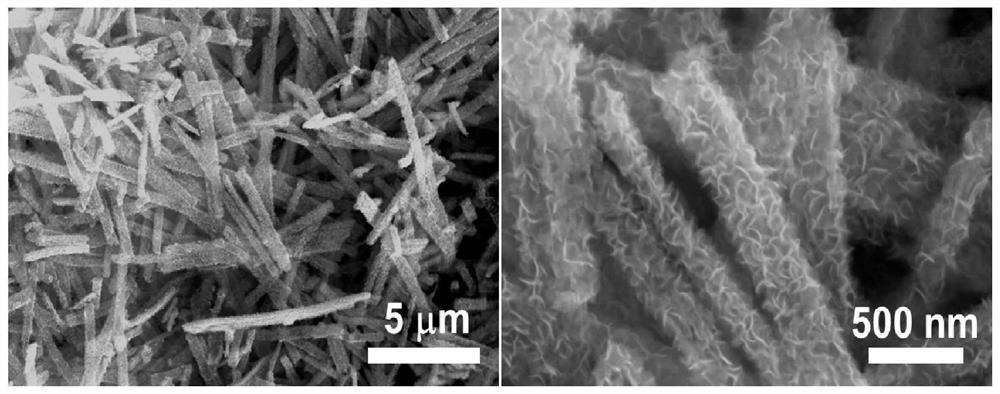

Carbon/molybdenum disulfide-nitrogen-rich molybdenum nitride composite material, preparation and electro-catalytic hydrogen evolution application thereof

ActiveCN113846347AEasy accessImprove electrochemical performanceEnergy inputElectrodesHeterojunctionNanowire

The invention discloses a preparation method of a carbon / molybdenum disulfide-nitrogen-rich molybdenum nitride composite electrochemical catalyst material. The method comprises the following steps: introducing a MoO3 nanowire in a polymerization process of a pyrrole monomer, and preparing MoO3 nanowire with the surface coated with polypyrrole; under a solvothermal reaction condition, promoting the inner core MoO3 nanowire to be dissolved, and reacting with thiourea to vertically grow a molybdenum disulfide nanosheet vertically on the surface of the hollow polypyrrole nanotube; and then carrying out thermal nitridation, wherein the hollow polypyrrole nanotube is converted into a hollow carbon nanotube, and the MoS2 nanosheet is converted into MoS2-Mo5N6, so that the Mott-Schottky heterojunction composite material growing on the surface of the hollow carbon nano tube in situ is obtained. According to the invention, the composite electrochemical catalyst material obtained by the invention can effectively promote the electronic interaction between interfaces, improve the kinetic rate of catalytic hydrogen evolution reaction and effectively improve the catalytic activity of a MoS2-based plane; and the preparation method is simple, convenient to operate and suitable for popularization and application.

Owner:WUHAN UNIV OF SCI & TECH

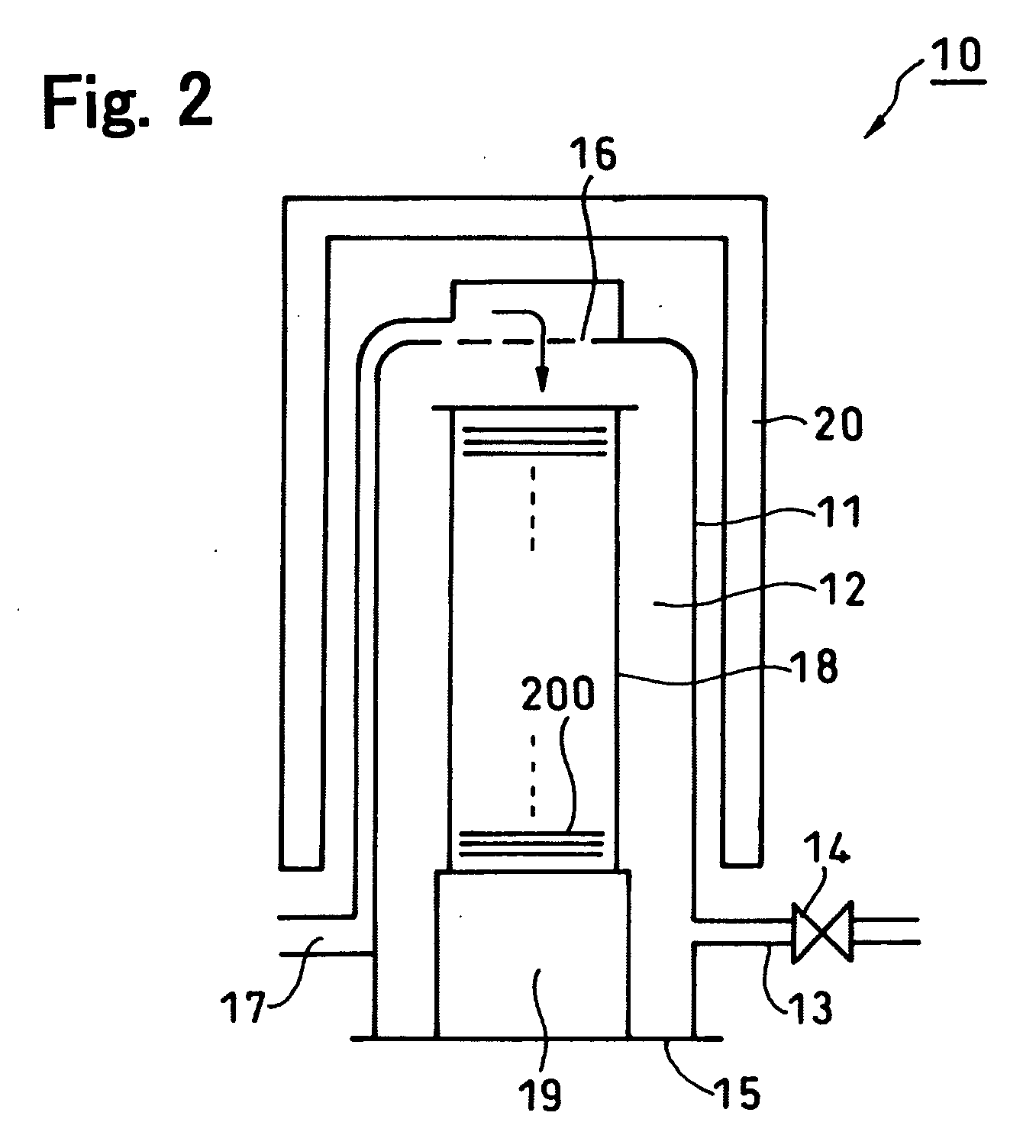

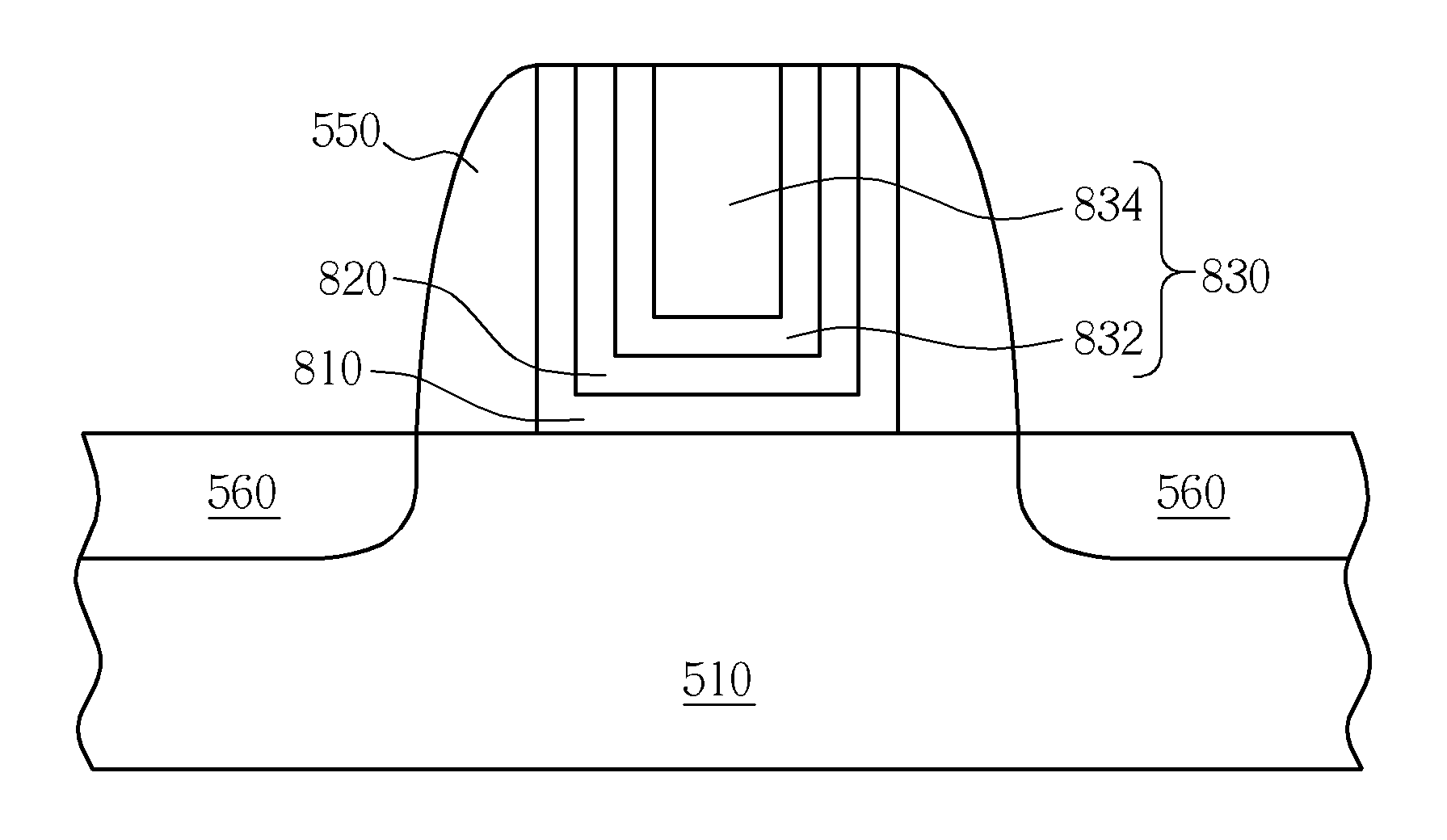

Trench capacitor structure and process for applying a covering layer and a mask for trench etching processes in semiconductor substrates

InactiveUS20050118777A1Minimal restrictionAvoid undercutTransistorSolid-state devicesSingle crystalStress relief

A stress relief layer between a single-crystal semiconductor substrate and a deposited silicon nitride layer or pad nitride is formed from thermally produced silicon nitride. The stress relief layer made from thermally produced silicon nitride replaces a silicon dioxide layer or pad oxide which is customary at this location for example in connection with mask layers. After patterning of a mask, which includes a protective layer portion formed from deposited silicon nitride, the material which is provided according to the invention for the stress relief layer reduces the restrictions imposed for subsequent process steps, such as for example wet-etching steps, acting both on the semiconductor substrate or structures in the semiconductor substrate and also on the stress relief layer. The thermal nitriding is advantageously incorporated into a preanneal step for expelling oxygen from the semiconductor substrate, so that the semiconductor substrate is protected from the etching action of the expelled oxygen by the stress relief layer which is formed, there is no need for an additional temporary etching protection layer for the semiconductor substrate and the overall processing is streamlined.

Owner:POLARIS INNOVATIONS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com