Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

74results about How to "Short operation cycle" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Ultrasonic flux detection system and detection method

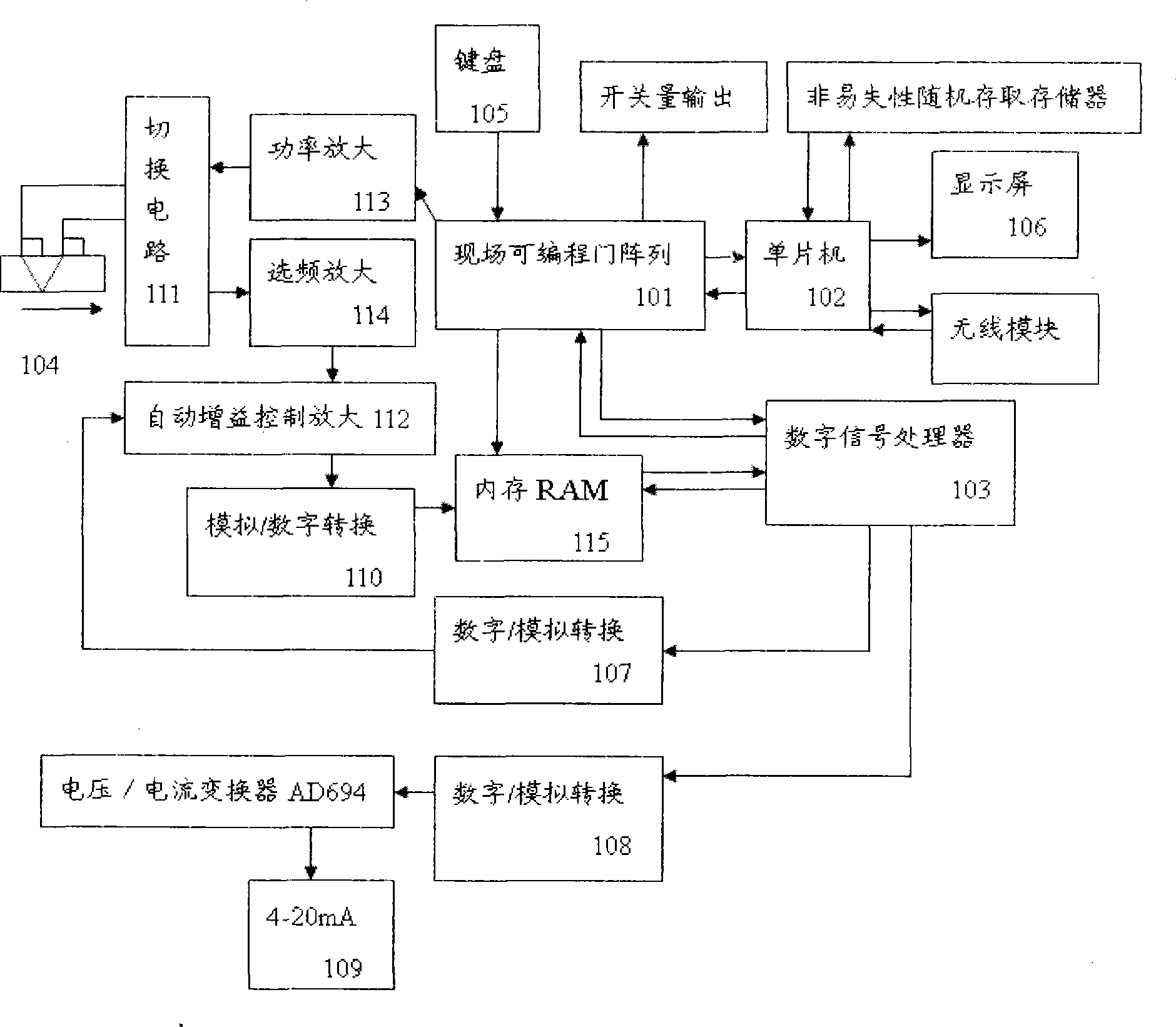

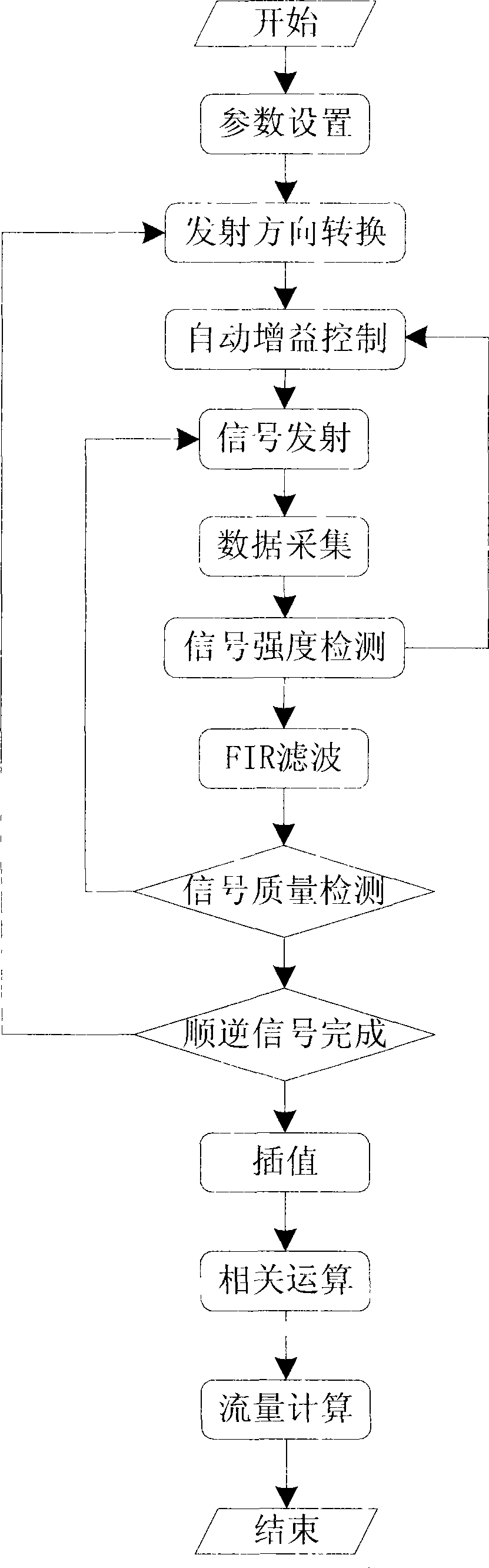

InactiveCN101464171AHigh precisionImprove accuracyVolume/mass flow measurementCorrelation coefficientImage resolution

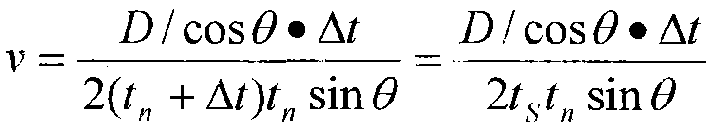

The invention belongs to the detection field, and relates to an ultrasonic wave flow rate detecting system and a detecting method, in particular to a high-precision fluid flow rate ultrasonic wave detecting system and a detecting method. The ultrasonic wave flow rate detecting system includes a system control part, a circuit part and an auxiliary device. The ultrasonic wave flow rate detecting method is characterized in that an improved time difference method is adopted for calculating the speed of a fluid; the delay window reception technique is adopted, and the influence of noise on the detection precision during detection is reduced through pulse width detection; and as the resolution of measuring time for the system is further improved through the adoption of the interpolation correlation method and the correlation coefficient judgment method, and reaches 1.25ns, the accuracy and the precision of the ultrasonic flow-meter are remarkably improved. The detecting system provided by the invention has the characteristics of small size, low power consumption, stable and reliable measurement and the like; the precision reaches 0.5; the sensitivity attains 0.3mm / s; and the system is suitable for measuring the flow rates and the flow velocities of various liquids in plastic or metal pipes with diameters being 25mm-8m.

Owner:SHENZHEN POLYTECHNIC

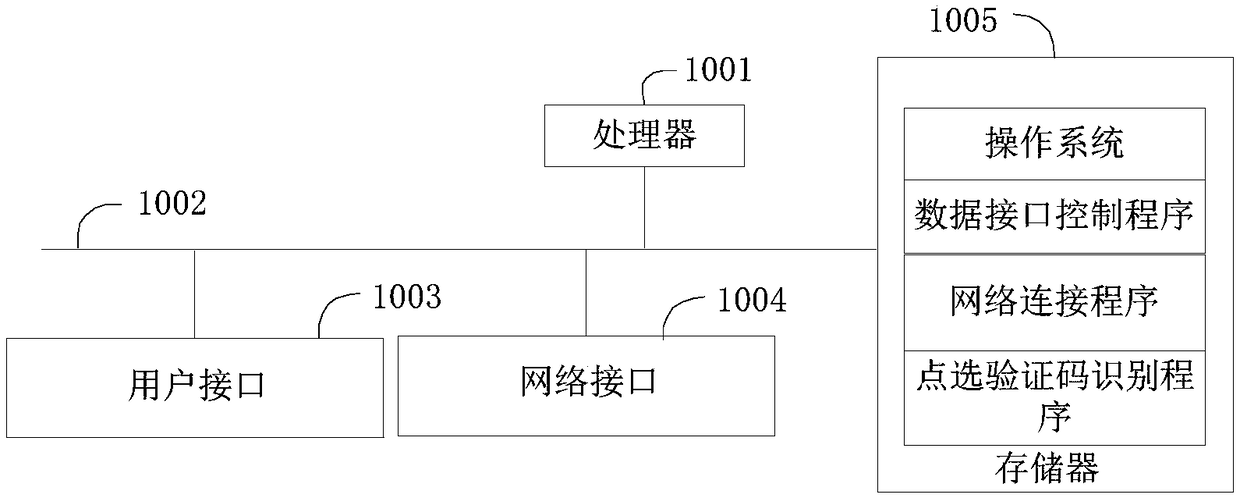

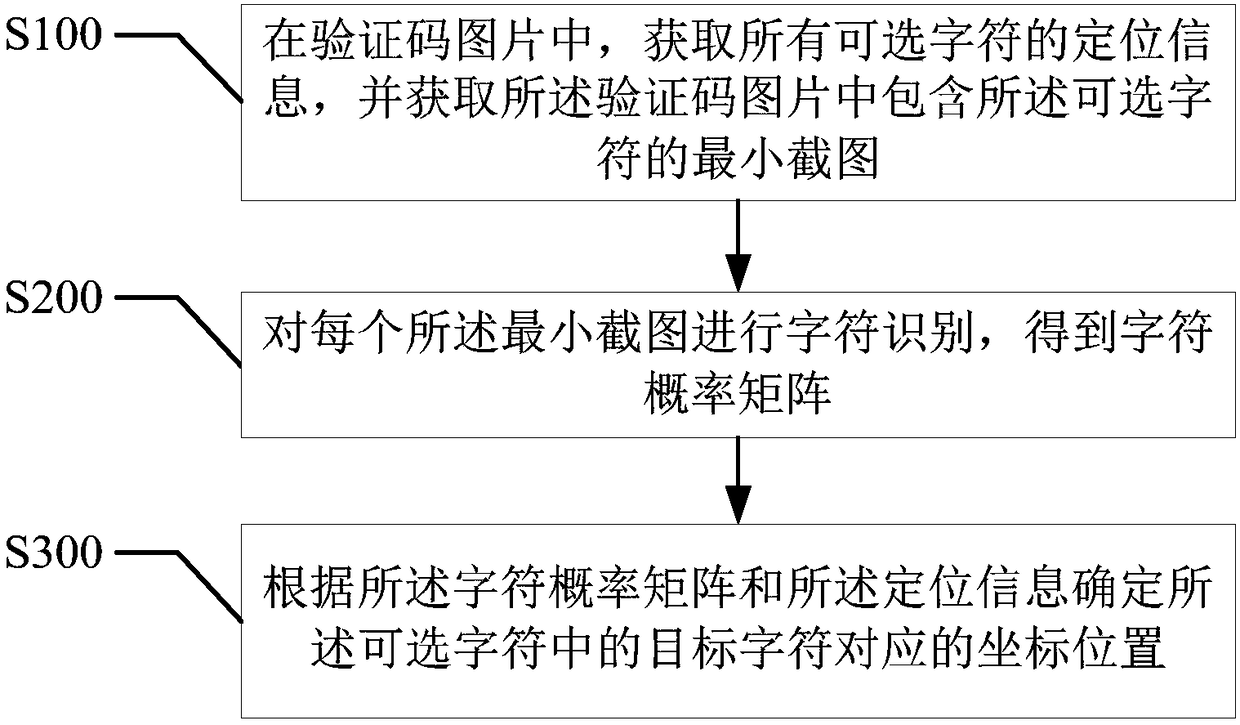

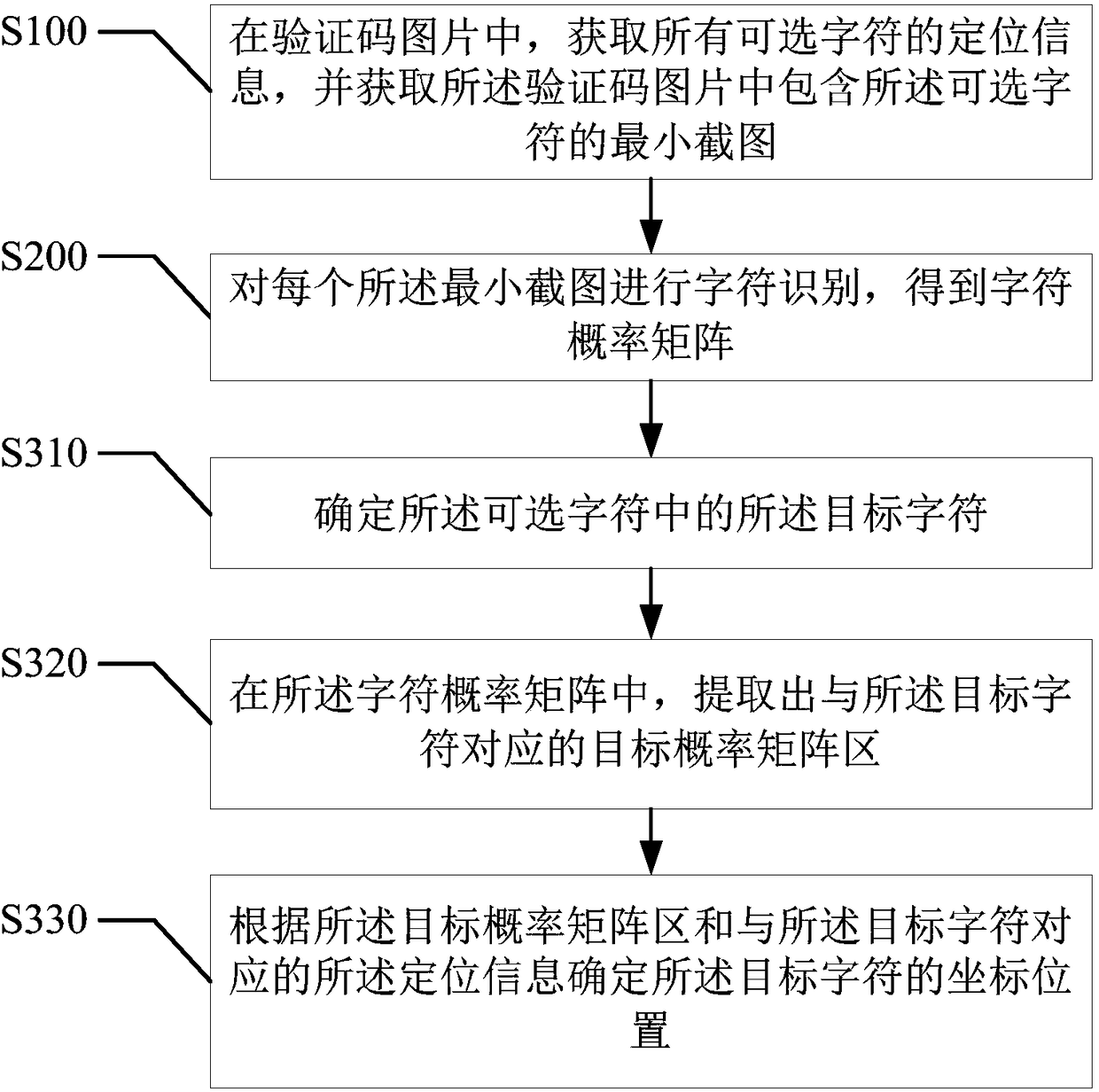

Click verification code identification method and device, and user terminal

ActiveCN108182437ASimple algorithmShort operation cycleCharacter and pattern recognitionTest engineerComputer engineering

The invention provides a click verification code identification method and a device, and a user terminal. The method comprises the following steps of in a verification code picture, acquiring the positioning information of all optional characters and acquiring a minimum screenshot containing the optional character in the verification code picture; carrying out character identification on each minimum screenshot and acquiring a character probability matrix; and according to the character probability matrix and the positioning information, determining a coordinate position corresponding to a target character in the optional characters. By using the click verification code identification method, an algorithm is simple, an operation period is short, identification efficiency is high, verification code identification accuracy is greatly increased, the method is convenient and practical, and great convenience is brought for a test engineer to test the safety of a website click verification mode.

Owner:BEIJING JINTI TECH CO LTD

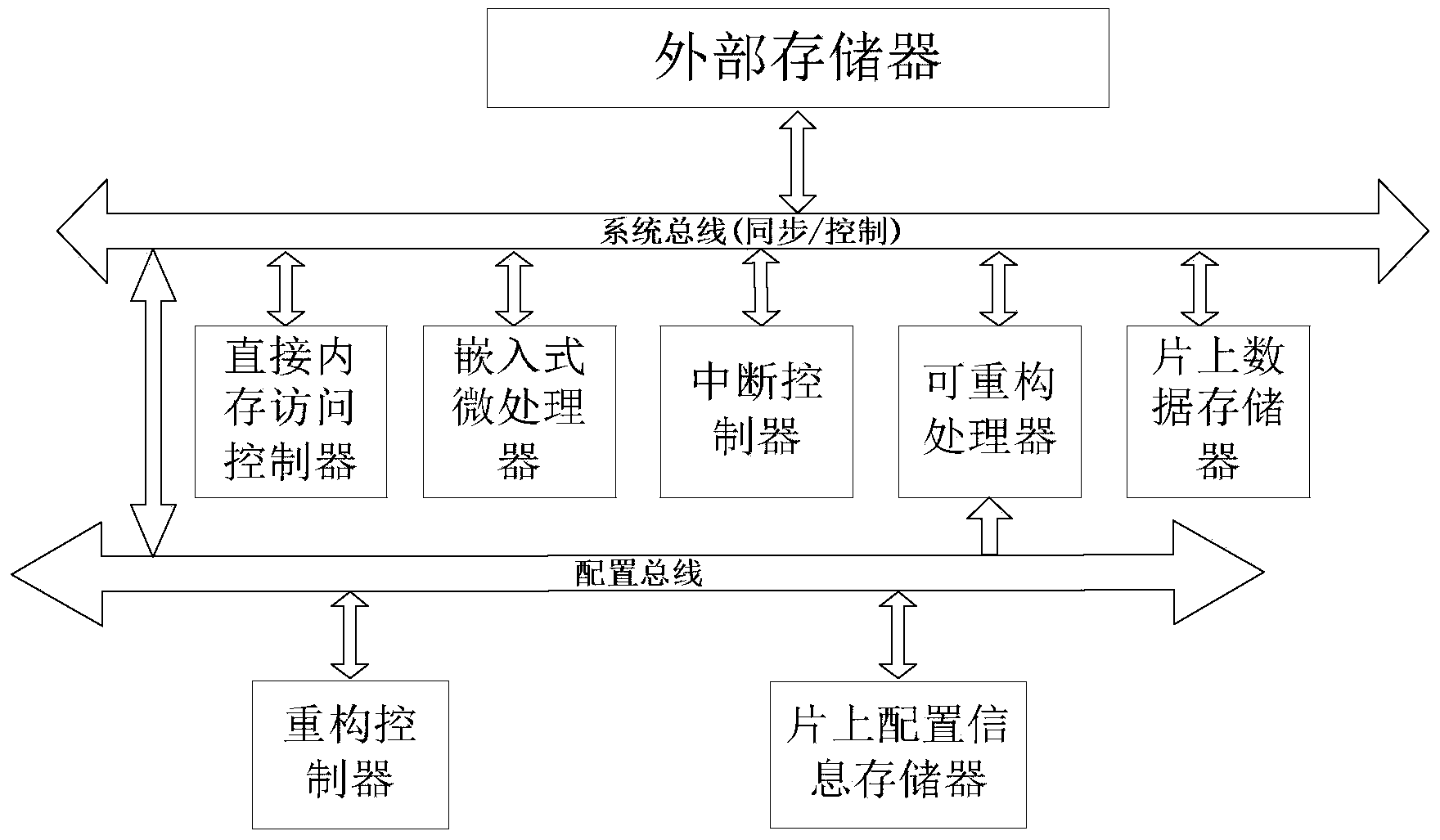

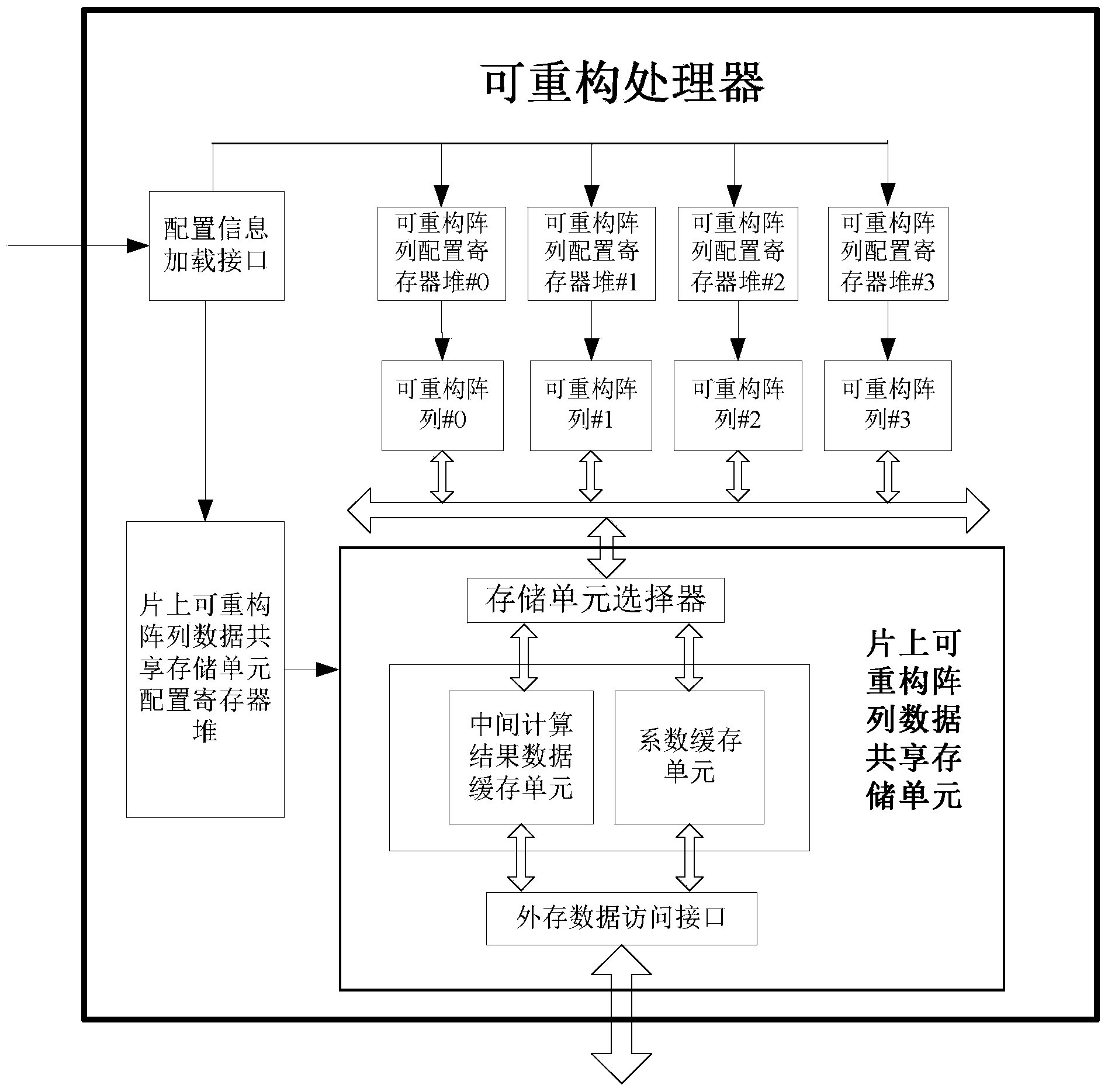

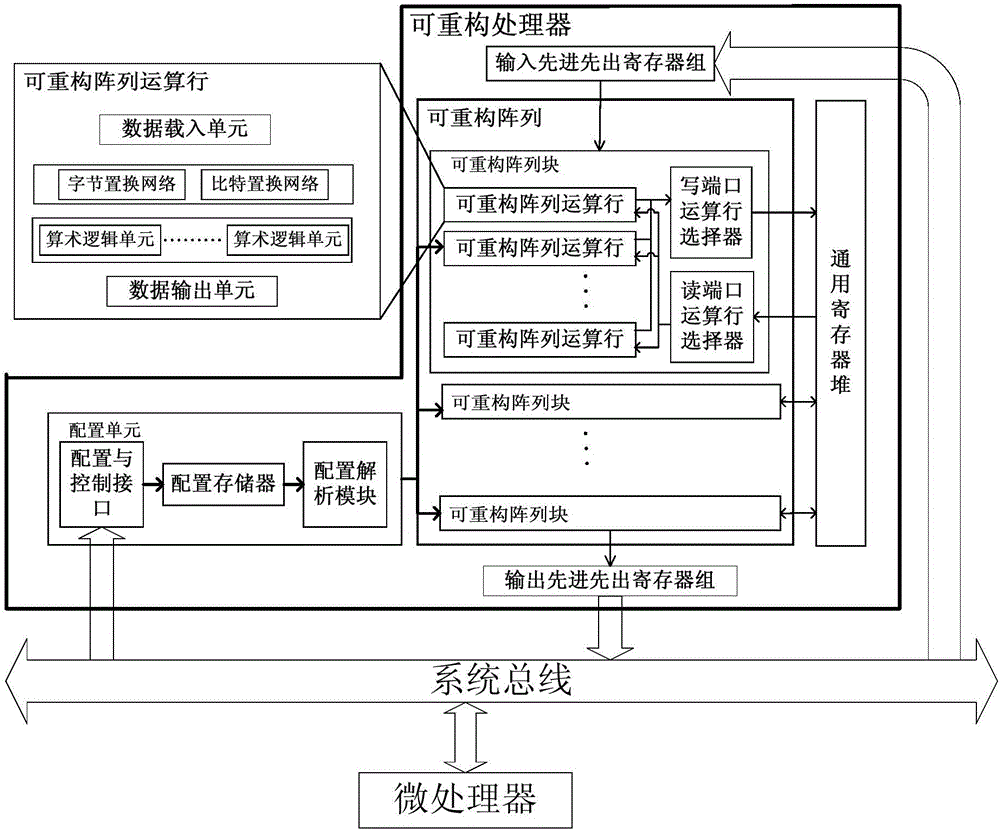

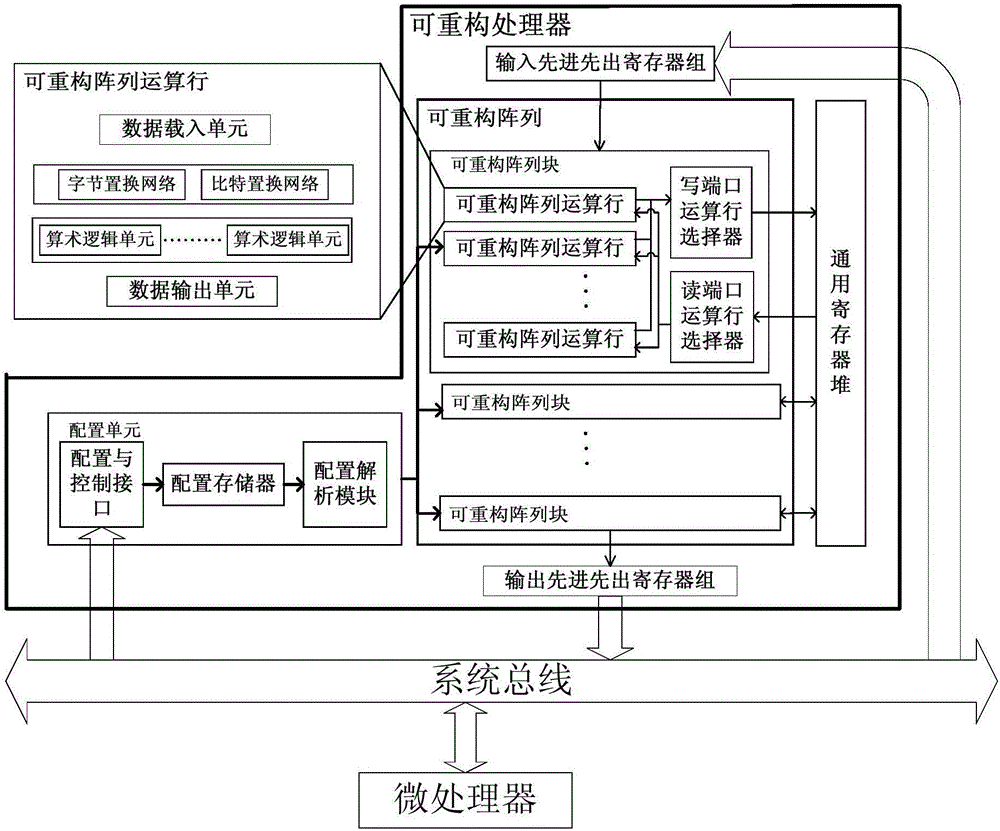

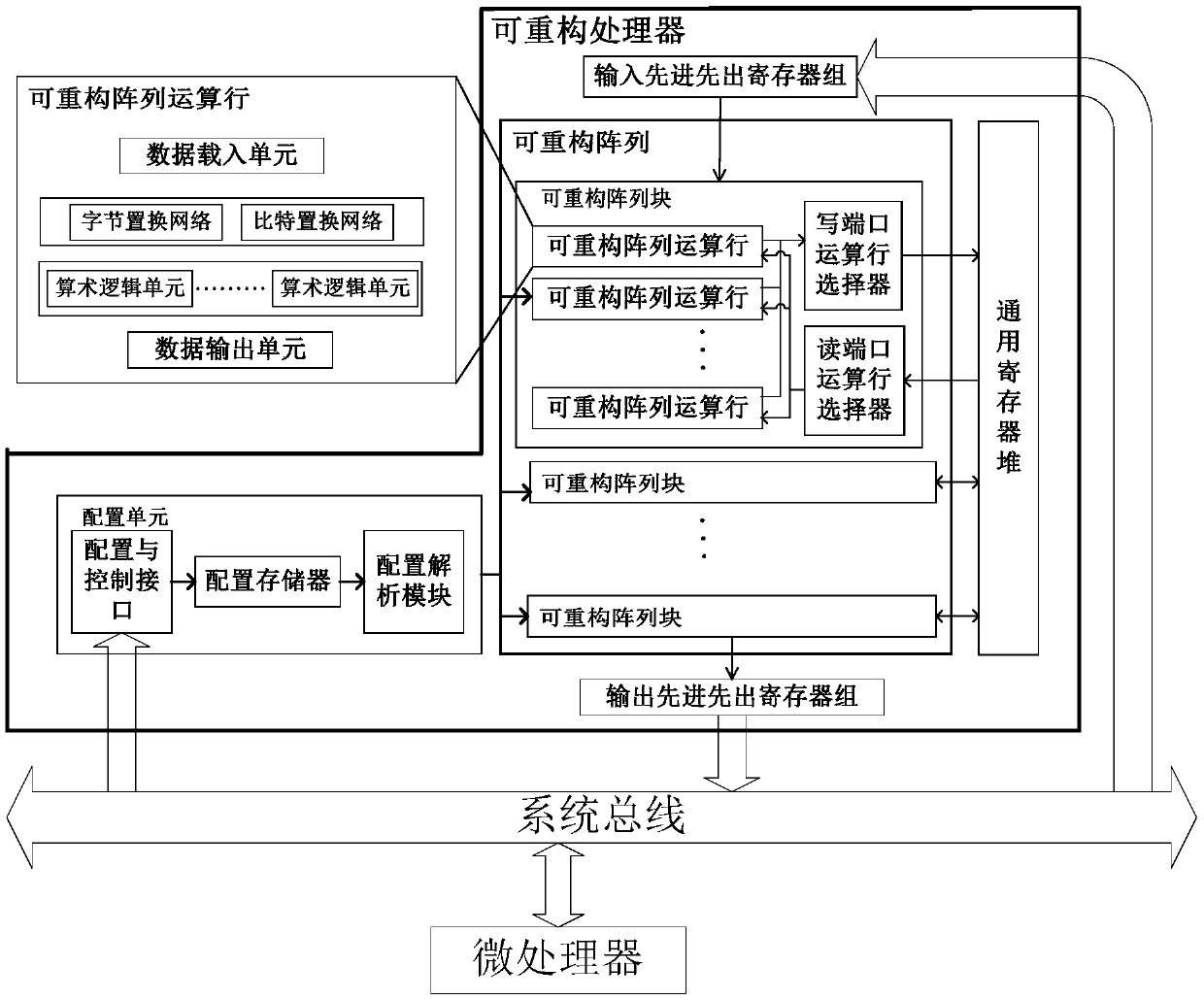

Embedded reconfigurable system based on large-scale coarseness and processing method thereof

ActiveCN103984560AImprove implementation efficiencyIncrease flexibilitySpecific program execution arrangementsSpecial data processing applicationsDirect memory accessExternal storage

The invention discloses an embedded reconfigurable system based on large-scale coarseness and a processing method of the embedded reconfigurable system. The embedded reconfigurable system comprises a system bus, a configuration bus, an embedded microprocessor, an external storage device, an interrupt controller, a direct memory access controller, an on-chip data storage device, an on-chip configuration information storage device, a reconfigurable processor and a reconfiguration controller. The method aims at an N-order FIR filter, the convolution is directly carried out on an input sequence and a filter coefficient sequence of the N-order FIR filter to obtain an output sequence, and on the basis of a direct type structure, the reconfigurable processor is used for optimization and acceleration.

Owner:SOUTHEAST UNIV

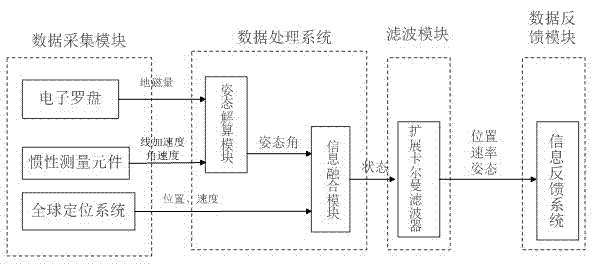

Navigation method and device based on extended Kalman filter

InactiveCN102519463AImprove portabilityWide applicabilityNavigational calculation instrumentsTransfer modelState model

The invention discloses a navigation method and device based on extended Kalman filter. By building a model, including a state model, a state transition model and an observation model, for an actual navigation system, the filtering process in the navigation method is subjected to stagewise optimization and matrix operation is improved. Relationship and independency among eleventh order parameters are analyzed, matrix operation is studied and the system is split, so as to achieve short operation period, reduce calculation amount, save memory space, improve efficiency and lower requirements for hardware.

Owner:SOUTH CHINA UNIV OF TECH

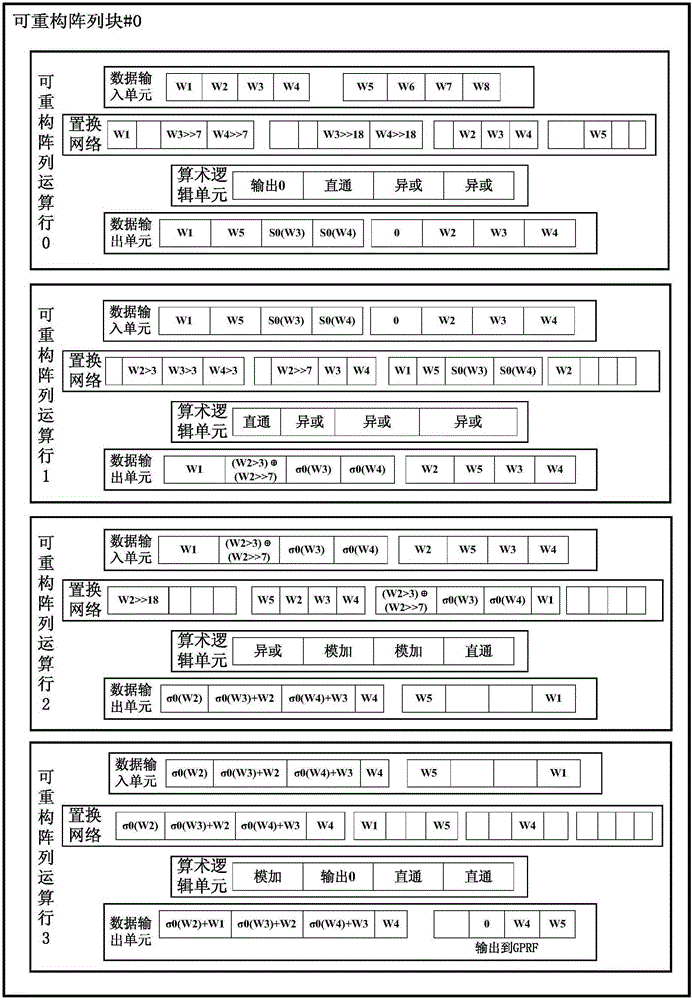

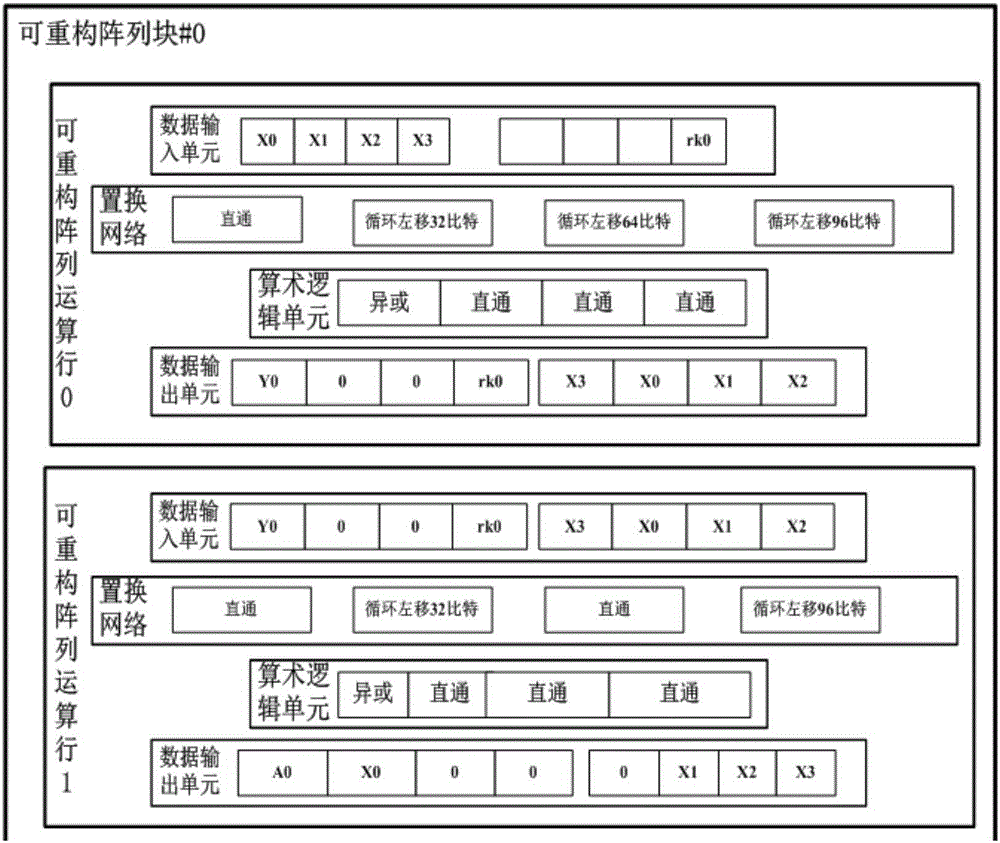

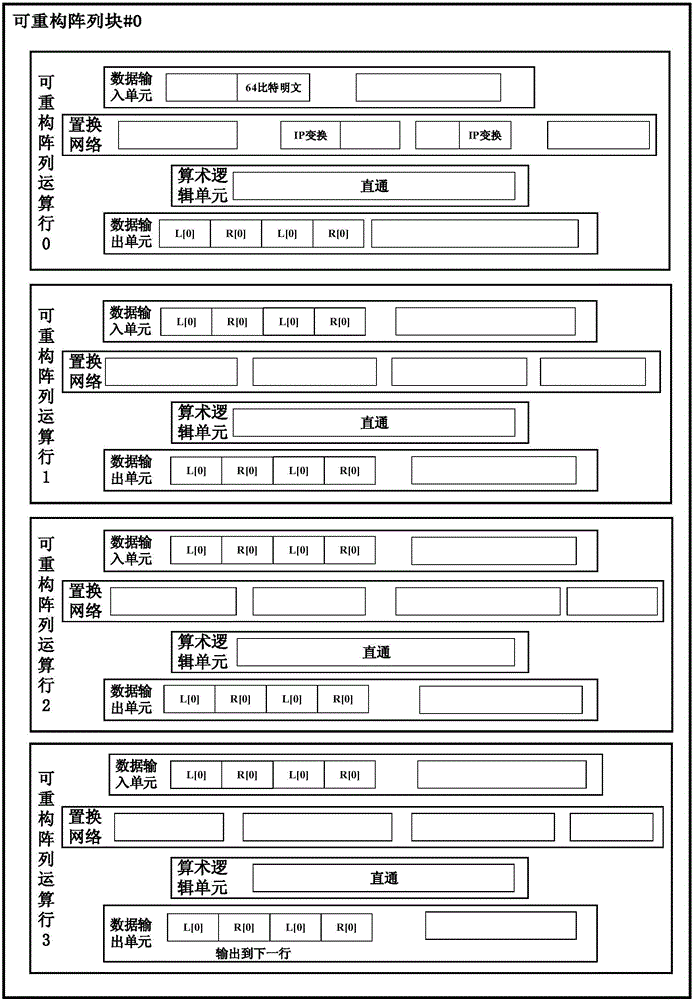

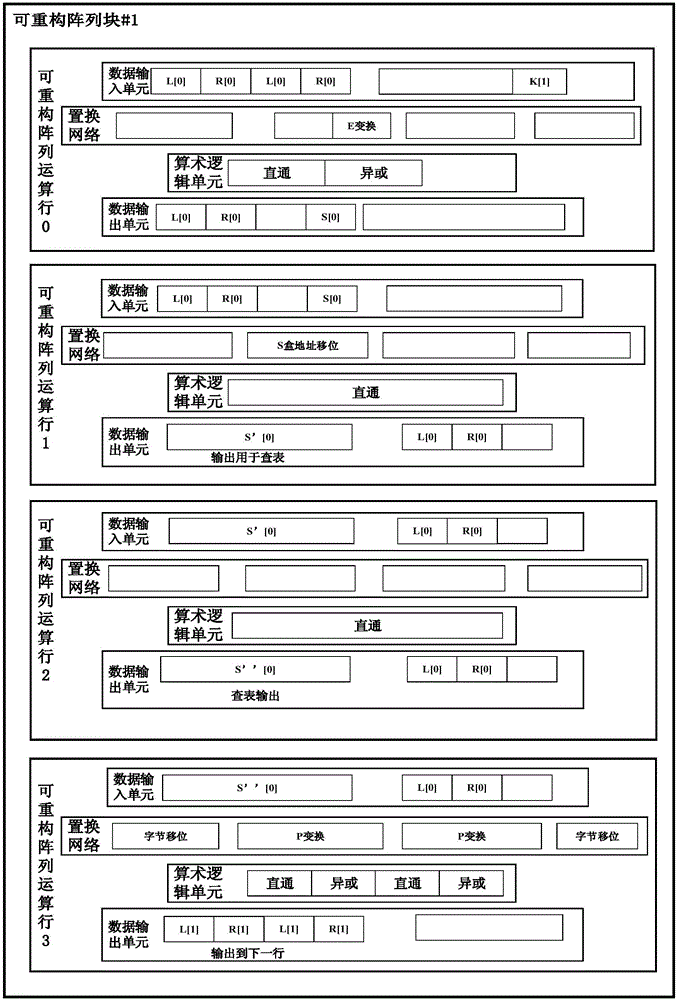

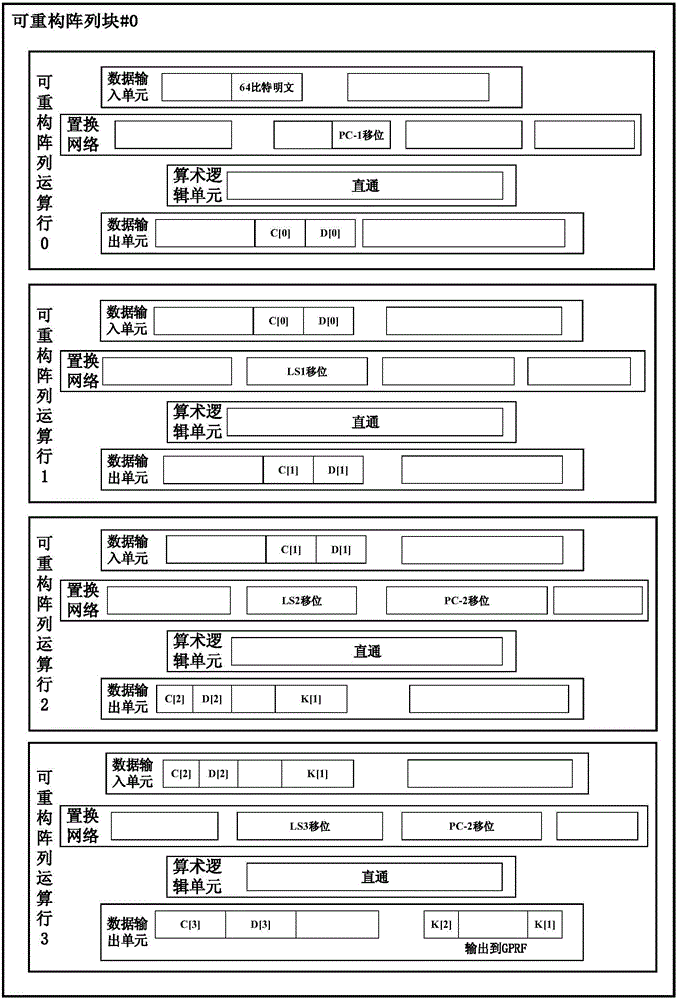

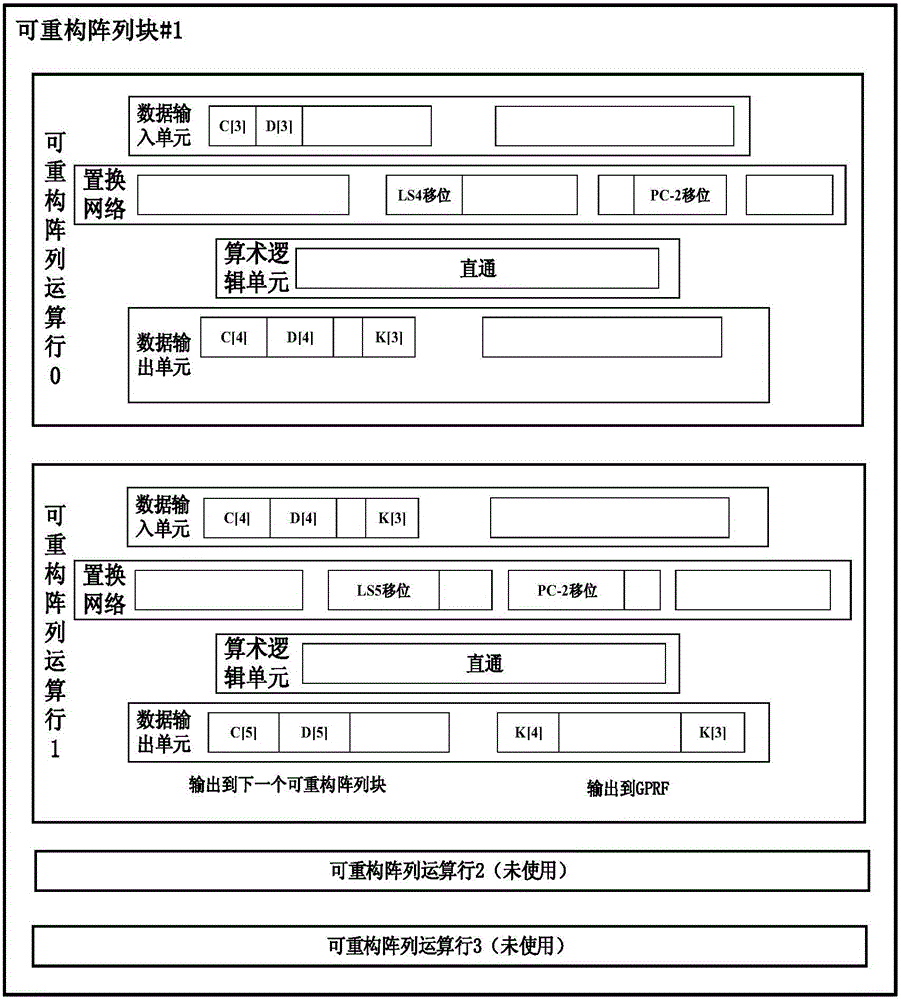

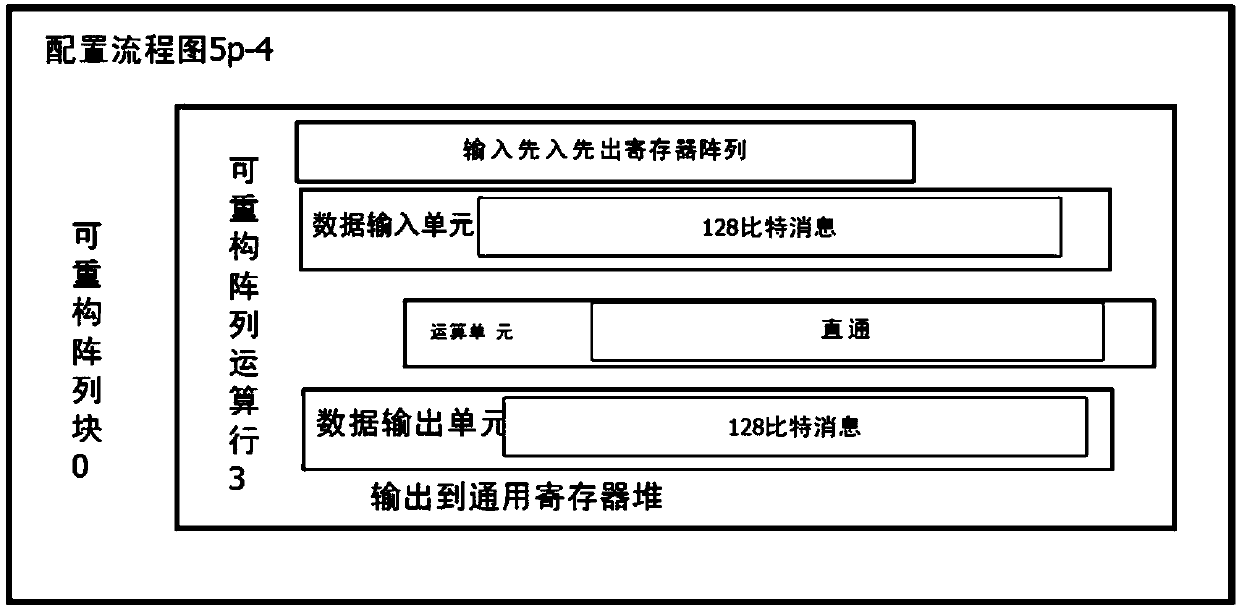

SHA256 realizing method and system based on large-scale coarse-grain reconfigurable processor

ActiveCN105335331AImprove computing parallelismImprove computing efficiencyArchitecture with single central processing unitElectric digital data processingArithmetic logic unitByte

The invention discloses an SHA256 realizing method and system based on a large-scale coarse-grain reconfigurable processor. The system comprises a first-in first-out register set, a general register file, an arithmetic logic unit, a bit permutation network, a byte permutation network, a data loading unit and a data output unit. Aiming at an SHA256 method, by means of multiple times of iteration, optimization and acceleration are carried out in the reconfigurable processor in a partial expansion and middle result data caching mode.

Owner:SOUTHEAST UNIV

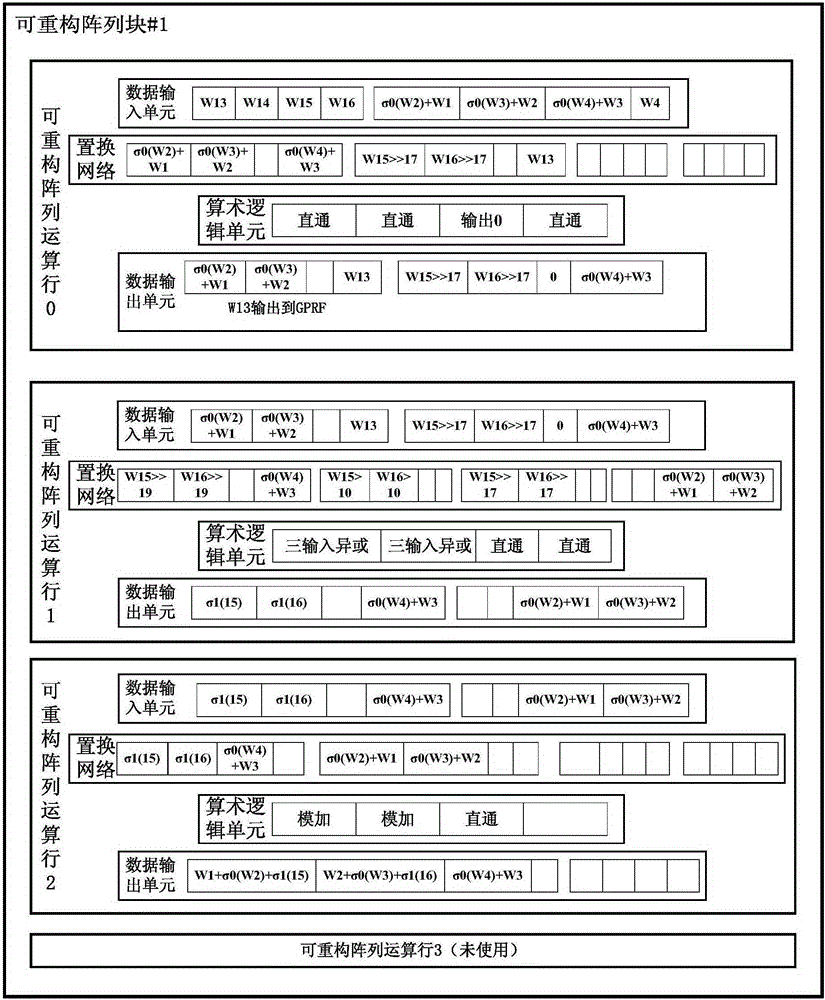

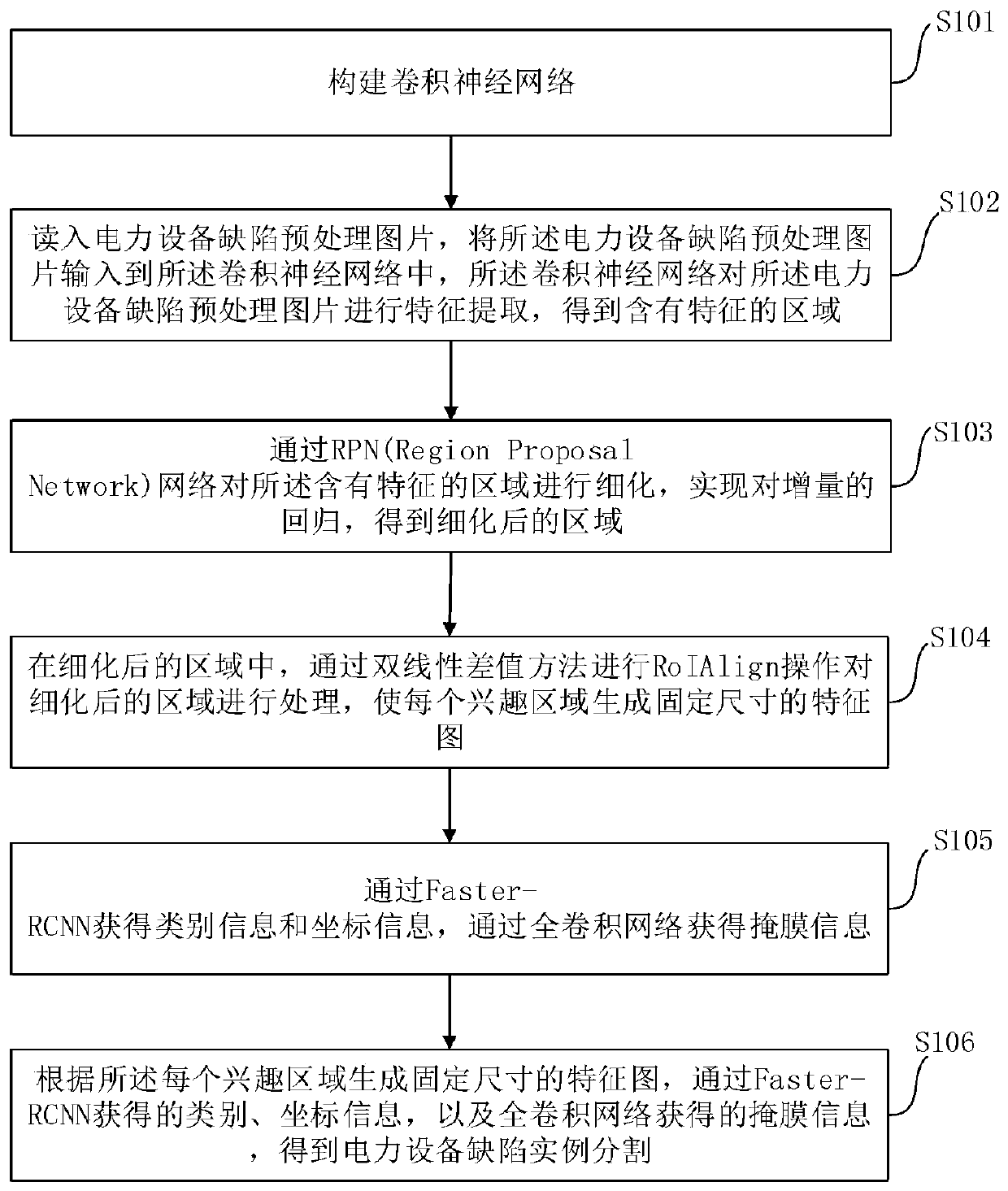

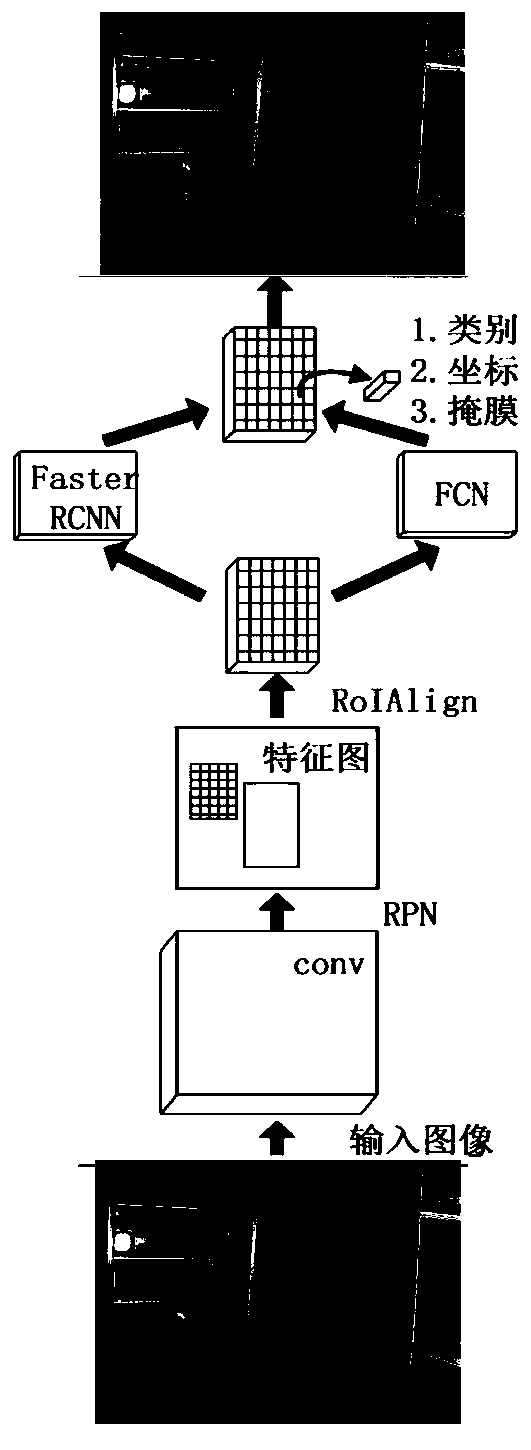

An improved Mask R-CNN image instance segmentation method for identifying defects of power equipment

InactiveCN109816669ASpeed up the ROIAlign processAchieve regressionImage analysisNeural architecturesFeature extractionEquipment Defects

The invention discloses an improved Mask R-CNN image instance segmentation method for identifying defects of power equipment. The method comprises the steps of constructing a convolutional neural network; reading the power equipment defect pre-processed picture, inputting the power equipment defect pre-processed picture into a convolutional neural network, and performing feature extraction on thepower equipment defect pre-processed picture by the convolutional neural network to obtain a feature-containing region; refining the region containing the characteristics through an RPN network; and in the refined region, carrying out RoIAgign operation through a bilinear difference method to process the refined region, generating a feature map of a fixed size for each region of interest, and obtaining power equipment defect instance segmentation through the category, the coordinate information and the mask information. By improving the Mask R-CNN image instance segmentation method, the basiceffect of Mask R-CNN segmentation is reserved, the bilinear interpolation speed in the RoIAgign process is increased, meanwhile, the mapping process fully and uniformly utilizes power equipment defects to preprocess all pixels of an image, and the segmentation effect is more obvious.

Owner:YUNNAN POWER GRID CO LTD ELECTRIC POWER RES INST +1

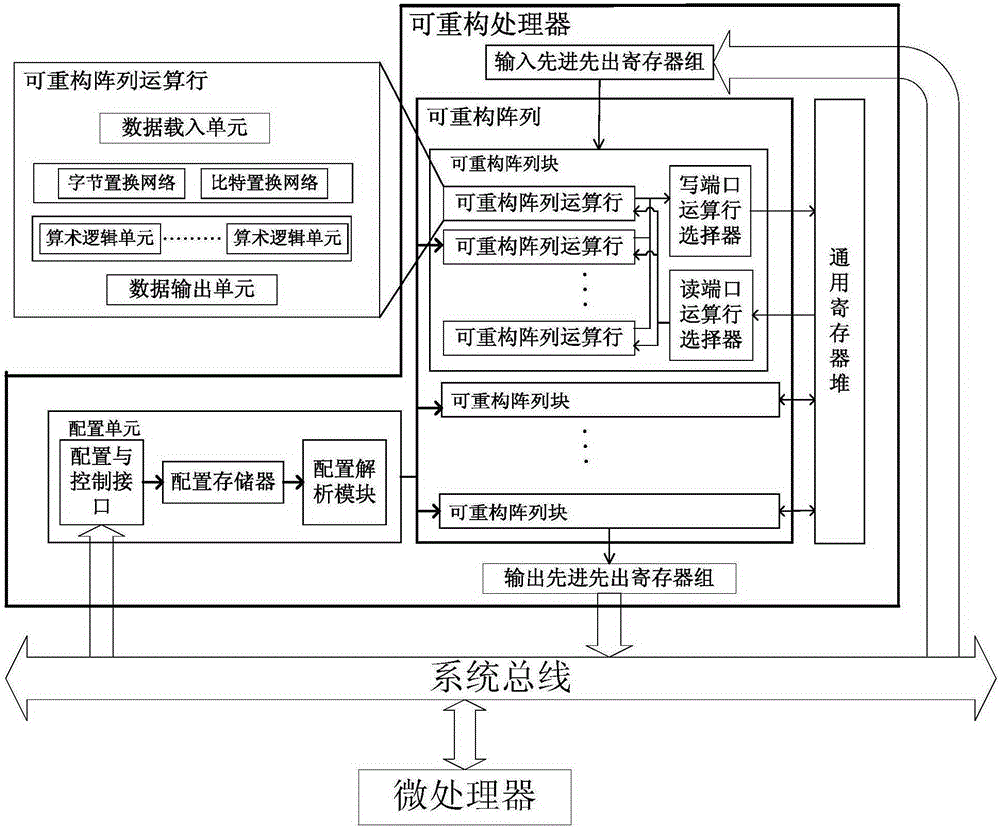

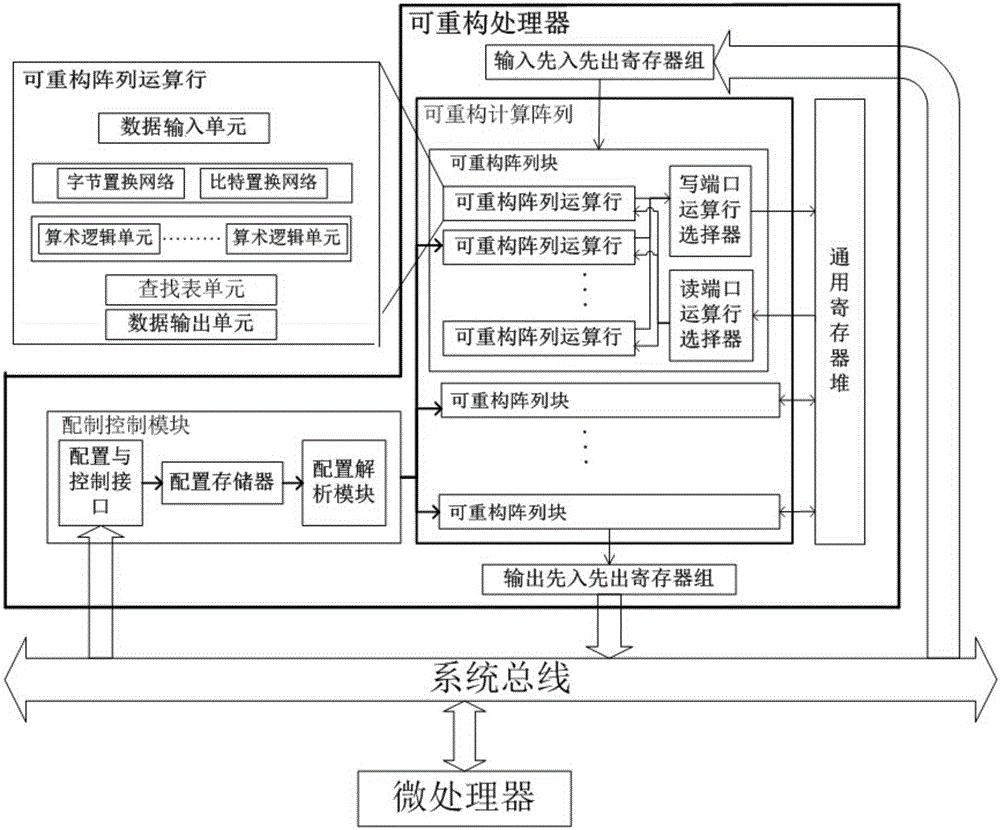

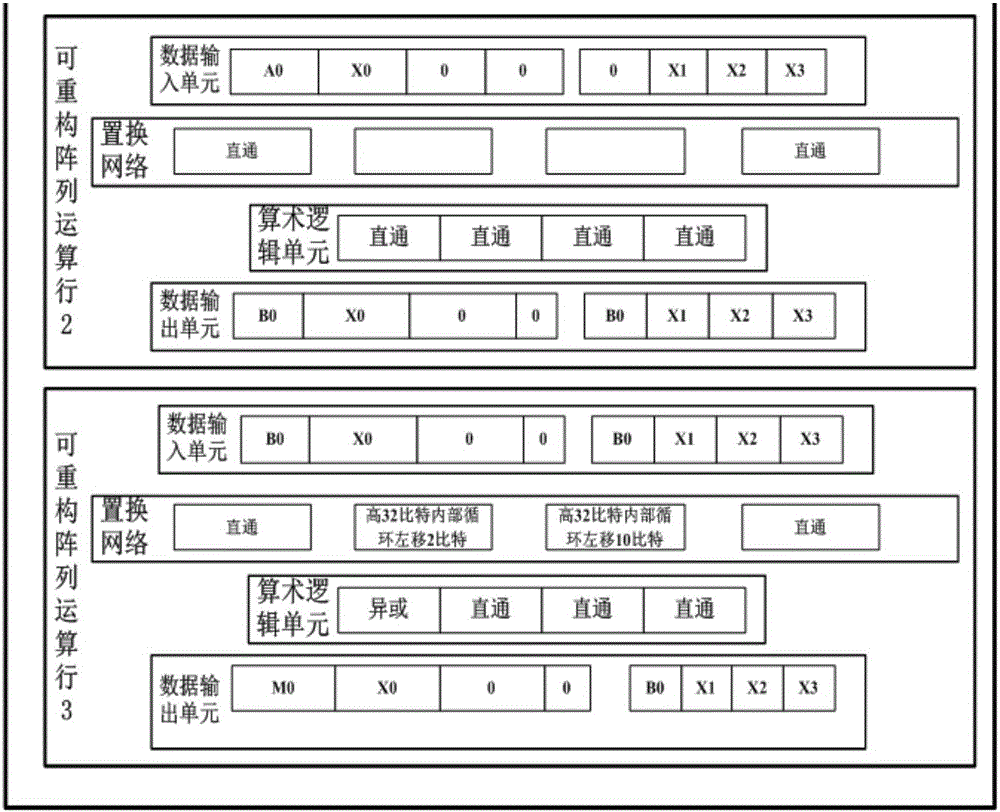

SM4-128 encryption algorithm implementation method and system based on large-scale coarseness reconfigurable processor

ActiveCN105912501AImprove computing parallelismImprove computing efficiencyInternal/peripheral component protectionArchitecture with single central processing unitProcessor registerComputer module

The invention discloses an SM4-128 encryption algorithm implementation method and system based on a large-scale coarseness reconfigurable processor. The system comprises the reconfigurable processor, a microprocessor and a system bus, wherein a reconfigurable computing array comprises a reconfigurable computing array block; the reconfigurable computing array block comprises a reconfigurable array operation line, a write port operation line selector and a read port operation line selector; the microprocessor is independently connected with the configuration and control interface of a configuration control module and the input first-in first-out register group of the reconfigurable processor through a system bus; the input first-in first-out register group is connected with the reconfigurable computing array; the reconfigurable computing array is connected with an output end connection reconfigurable processor; and the output end connection reconfigurable processor is connected with the microprocessor through the system bus. The system and the method aim at the SM4-128 encryption algorithm, and carry out optimization and acceleration in a way that multi-turn iteration is partially unfolded in the reconfigurable processor and intermediate result data is cached.

Owner:SOUTHEAST UNIV WUXI INST OF TECH INTEGRATED CIRCUITS

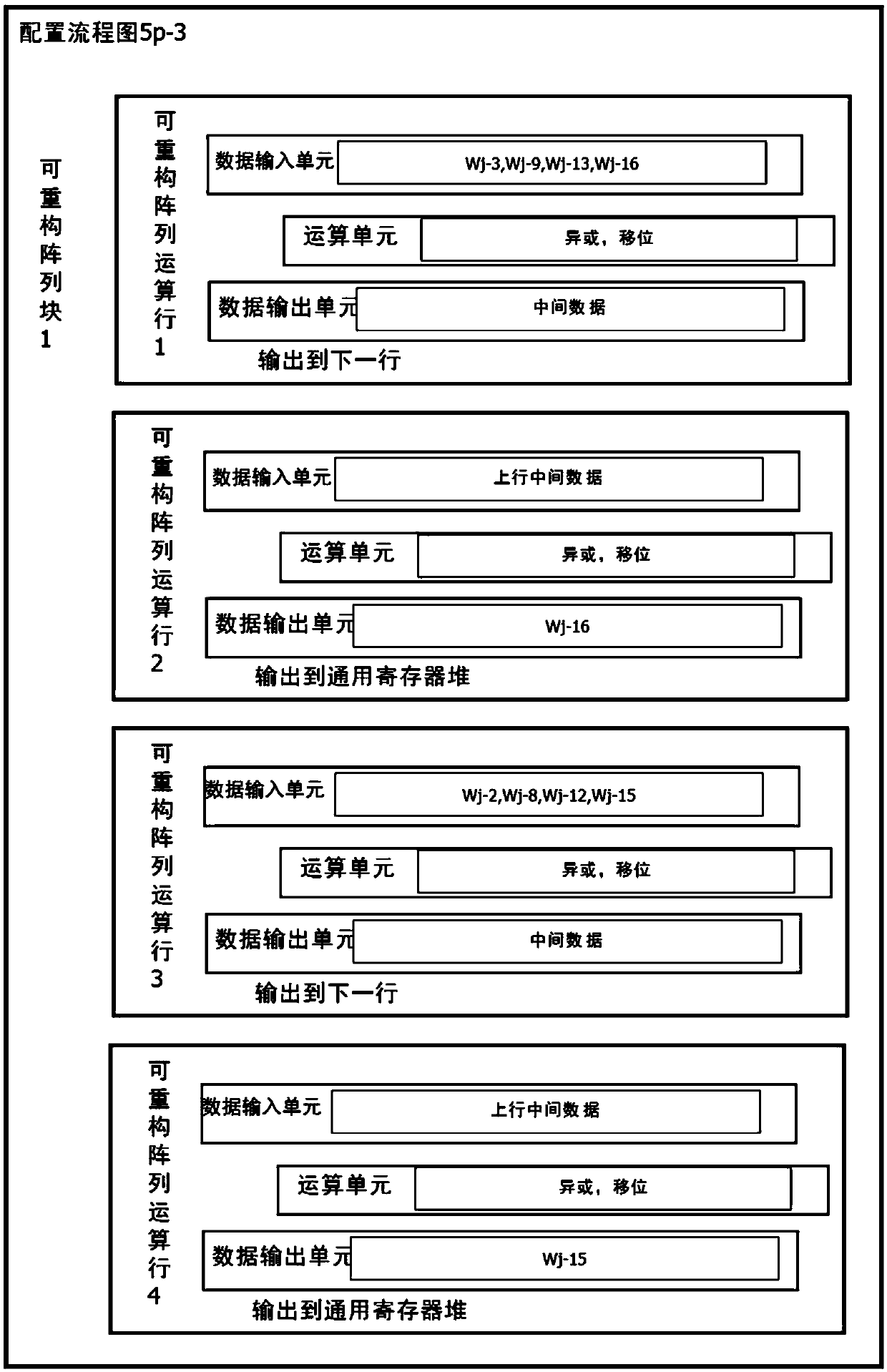

DES algorithm round iteration system and method based on coarse-grained reconfigurable architecture

ActiveCN105975251AImprove computing parallelismImprove computing efficiencyProgram controlMemory systemsAssembly lineLookup table

The invention discloses a DES algorithm round iteration system and method based on a coarse-grained reconfigurable architecture. The system comprises a system bus, a reconfigurable processor and a microprocessor. The reconfigurable processor comprises a configuration unit, an input first-in first-out register bank, an output first-in first-out register bank, a general register file, M reconfigurable array blocks and a lookup table. The advantages of parallel processing of the reconfigurable technology and independent configurability of a calculation module are utilized, and efficient calculation of a DES algorithm is performed through methods for improving the parallelism of the DES algorithm and optimizing an assembly line while the certain flexibility is supported.

Owner:SOUTHEAST UNIV WUXI INST OF TECH INTEGRATED CIRCUITS

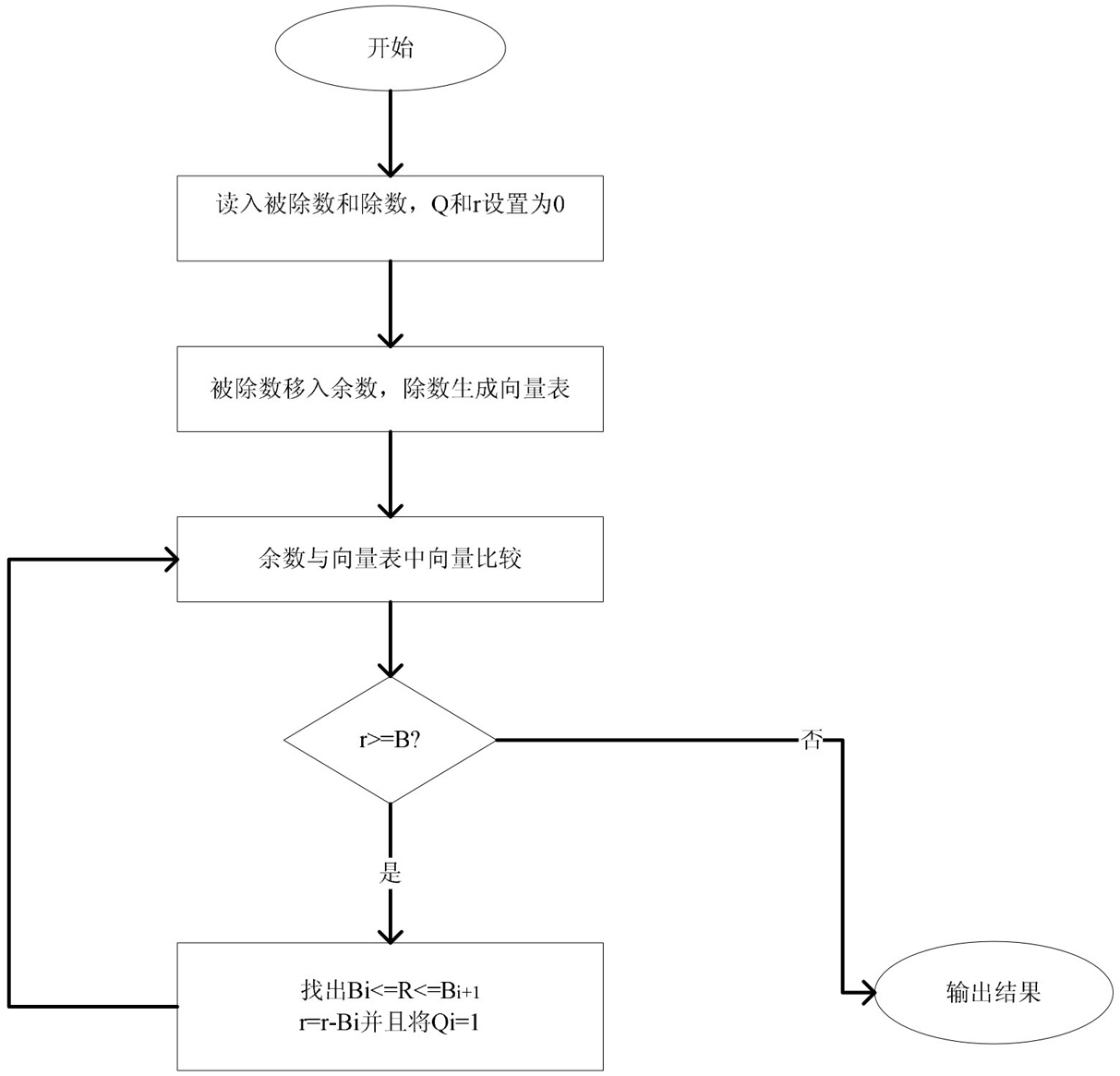

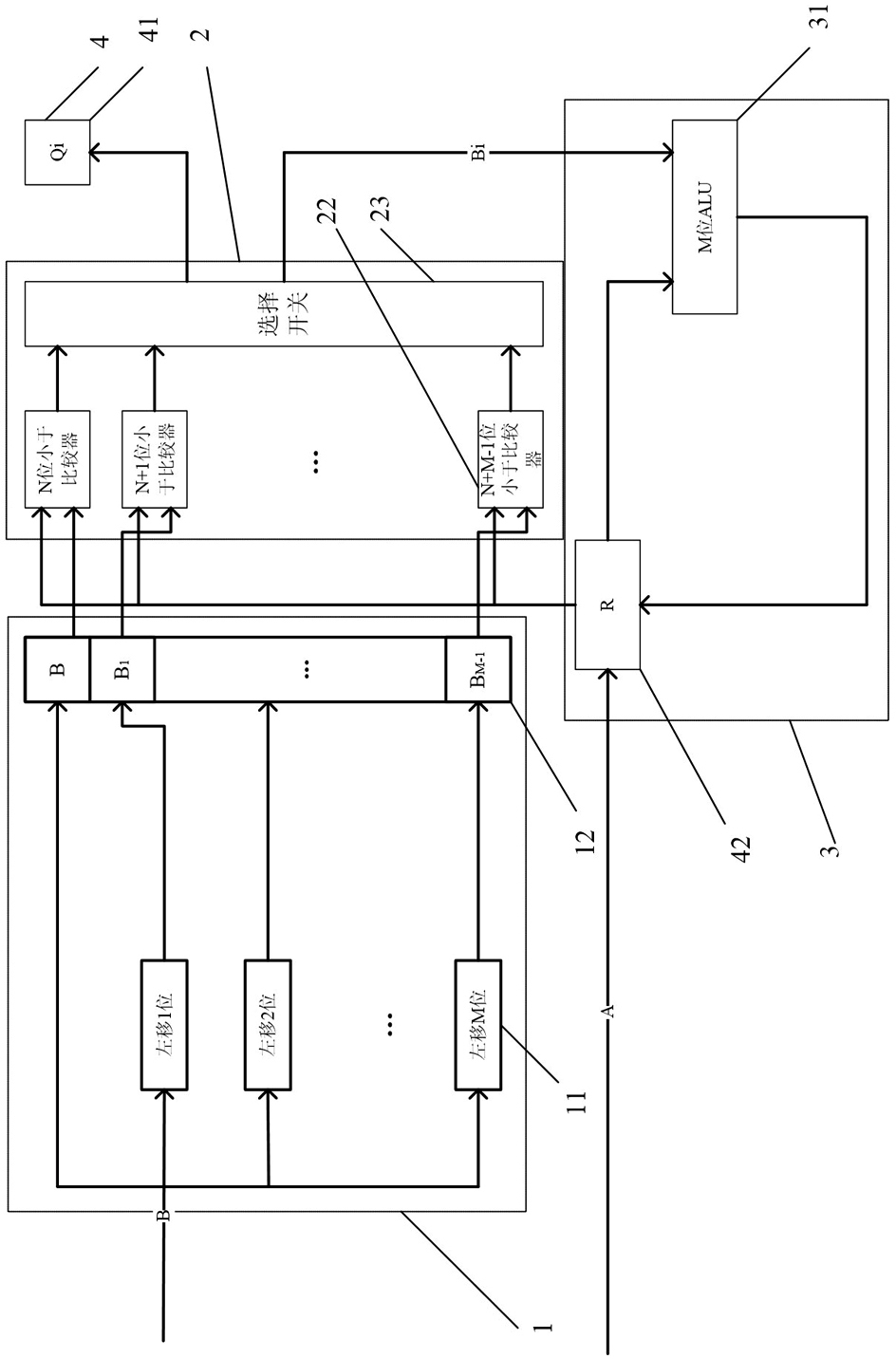

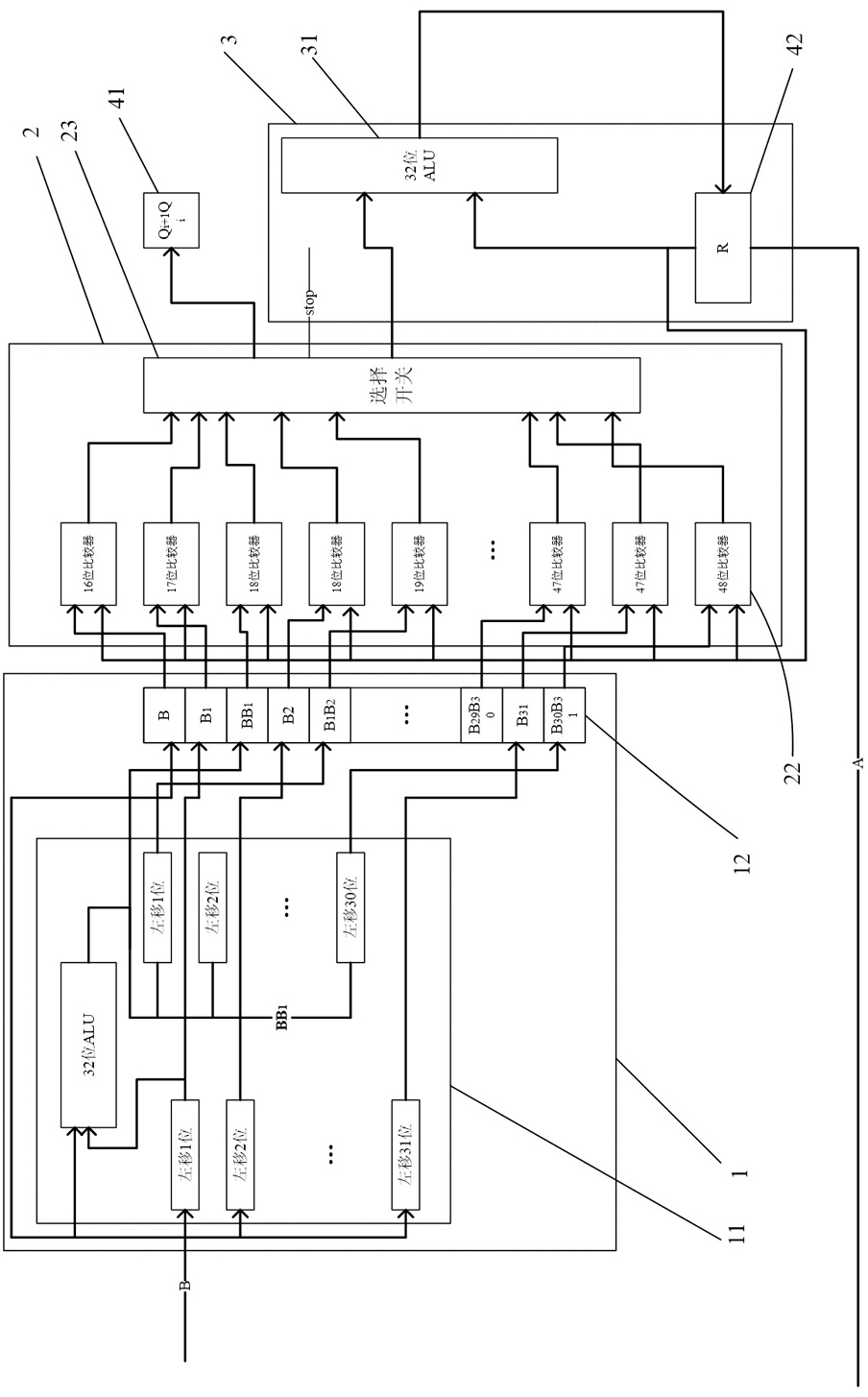

Sign-free fixed point division and sign-free fixed point divider

ActiveCN101986259AShort operation cycleReduce power consumptionComputation using non-contact making devicesHardware structureEngineering

The invention discloses a sign-free fixed point division, comprising the following steps: processing a divisor by a preprocessing unit; inputting the processed divisor and a dividend into a positioning selection unit for positioning selection; performing iterative subtraction operation on the selection result by an iterative operation unit; returning the operation result to the positioning selection unit; and finally outputting a quotient and a remainder. The invention also discloses a sign-free fixed point divider, comprising the preprocessing unit, the positioning selection unit and the iterative operation unit which are successively connected, wherein the input end of the positioning selection unit is respectively connected with the output end of the preprocessing unit and the output end of the iterative operation unit, and the output end of the positioning selection unit is connected with the input end of the iterative operation unit. The invention has the advantages of simple hardware structure, less operation steps, short execution cycle, low hardware realization cost, low energy consumption and the like.

Owner:NAT UNIV OF DEFENSE TECH

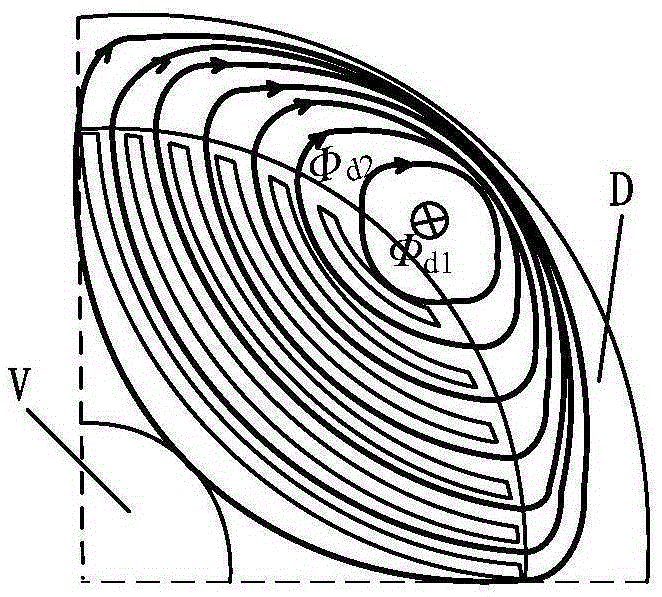

Electric spark micro hole processing control method

InactiveCN101362235AImprove accuracyReduce computationElectric circuitsAdaptive controlCurrent analysisControl system

The invention discloses a processing control method of small holes of an electric spark, belongs to the field of electric spark processing and relates to a processing control method of small holes of an electric spark based on the fuzzy logic algorithm. The method comprises the following steps of: establishing a closed loop control system of small holes of the electric spark firstly, taking the spark / arc rates and short circuit rates in any analytical period as the input variable of a processing control system of the small holes of the electric spark, using a processing fuzzy discrimination algorithm of the small holes of the electric spark to determine a fuzzy set of the spark / arc rates and short circuit rates, adopting a servo feed strategy in the analytical period obtained by the processing control rules of the small holes of the electric spark based on the fuzzy logic as the output of the control system, and finally setting the output variables by using the processing impact factor to determine the processing control method of the small holes of the electric spark in the current analytical period. The method realizes the high accuracy of the processing control of the small holes of the electric spark. The processing efficiency is improved significantly; the calculating amount is small, the operation cycle is short and the control strategy is simple and practical, thus ensuring the timeliness of the processing control.

Owner:DALIAN UNIV OF TECH

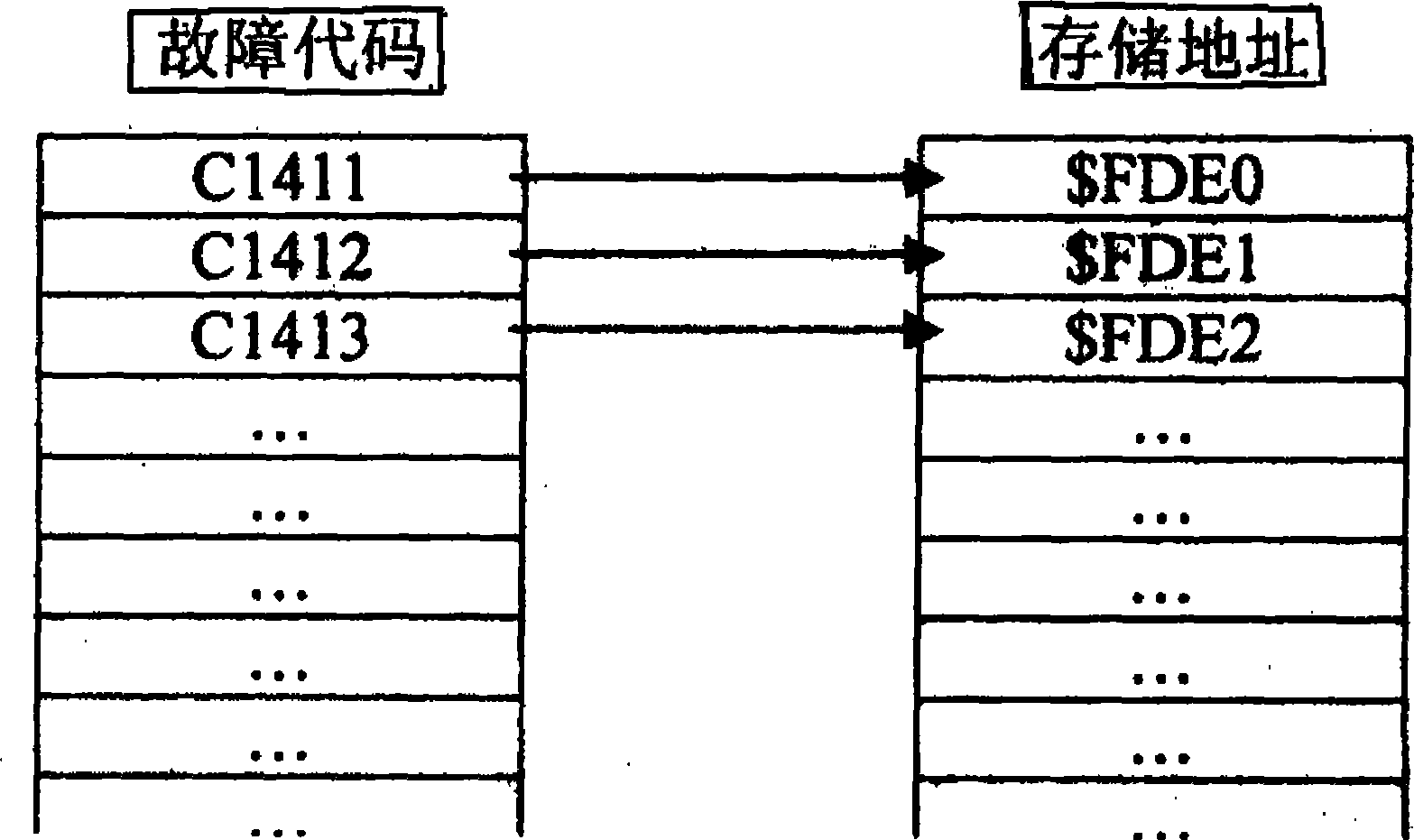

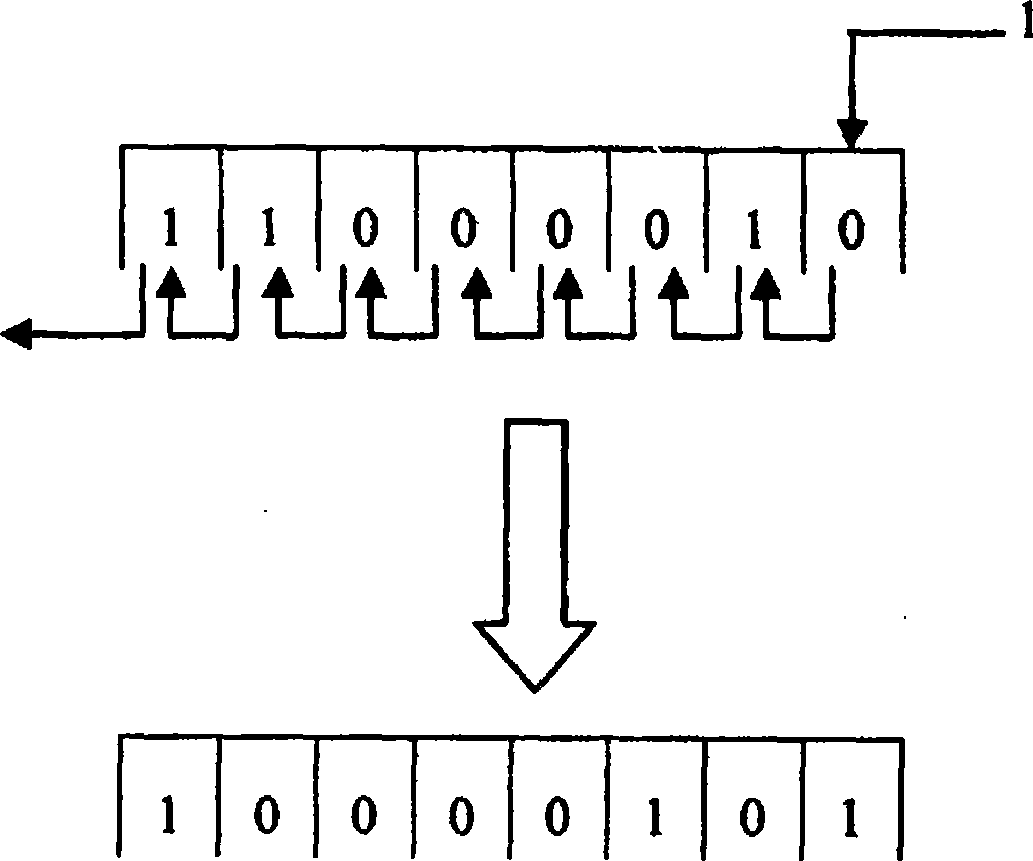

Fault code storage management method for automobile active stabilization control system

InactiveCN101510095AImprove reliabilityImprove efficiencyElectric testing/monitoringSafety management systemsControl system

The invention belongs to a method for storing and managing the fault codes by an automotive active stability control system in the field of vehicle driving safety management system. The automotive active stability control system uses an automotive electronic stability program (ESP) for storing and managing the fault codes; the automotive ESP fault code storage and management is a way that an ESP fault diagnosis system defines, stores and reads the fault codes; firstly the ESP defines the fault codes according to the fault type, leads each fault code to be corresponding to each byte address in a designated storage unit one by one; the storage of the fault codes is carried out in a mode of changing the mark bit of a corresponding storage byte thereof; the fault diagnosis results are stored in chronological sequence from the high bit to the low bit of the corresponding bytes in sequence, thereby ensuring the characteristics of non-volatility, historicity, simple algorithm, high efficiency, and short operating cycle for the fault diagnosis result data storage of the system, guaranteeing the vehicle driving stability and greatly improving the driving safety of the vehicle.

Owner:CHINA AGRI UNIV

Aggregated data analysis method and device, storage medium and electronic device

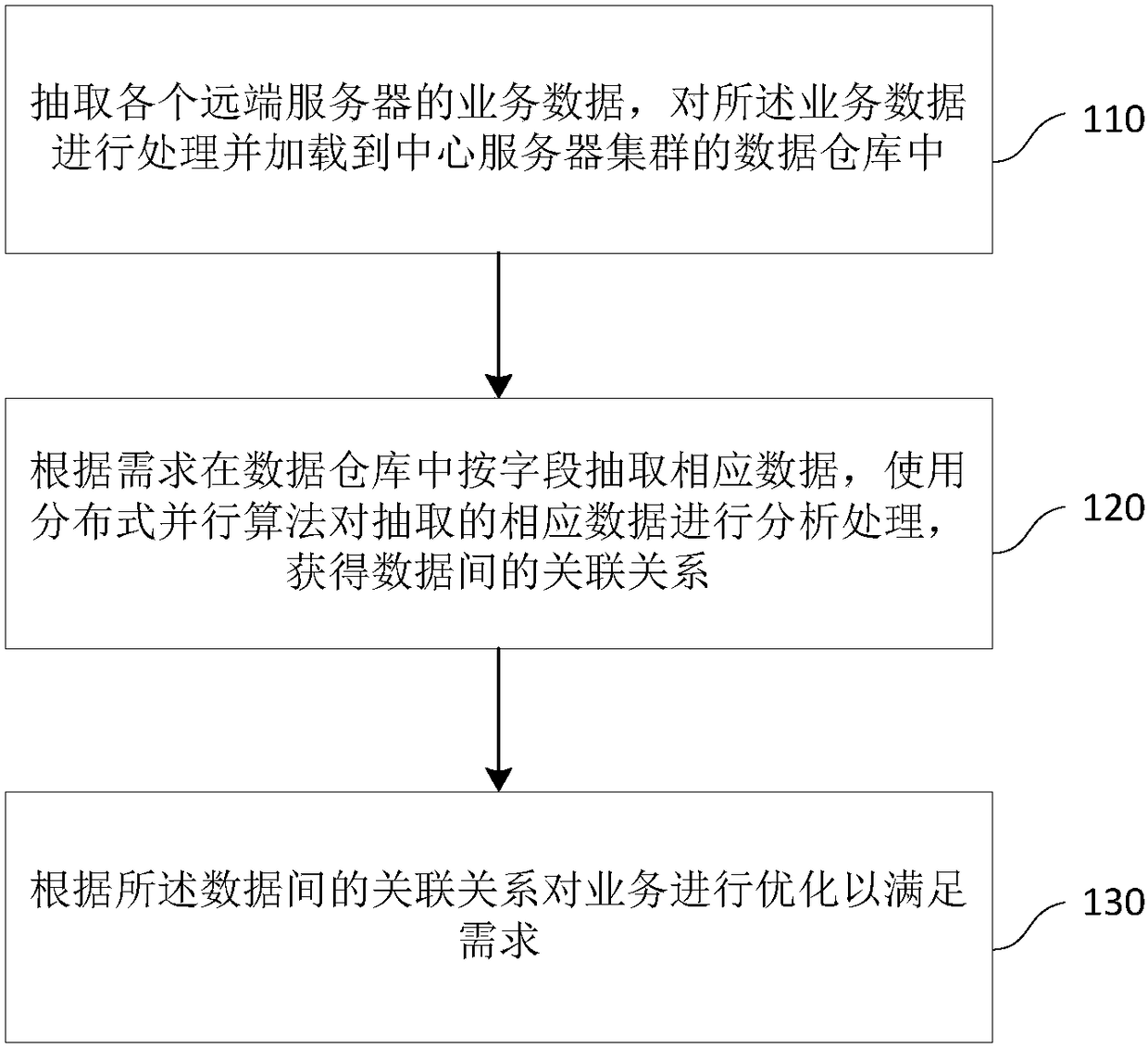

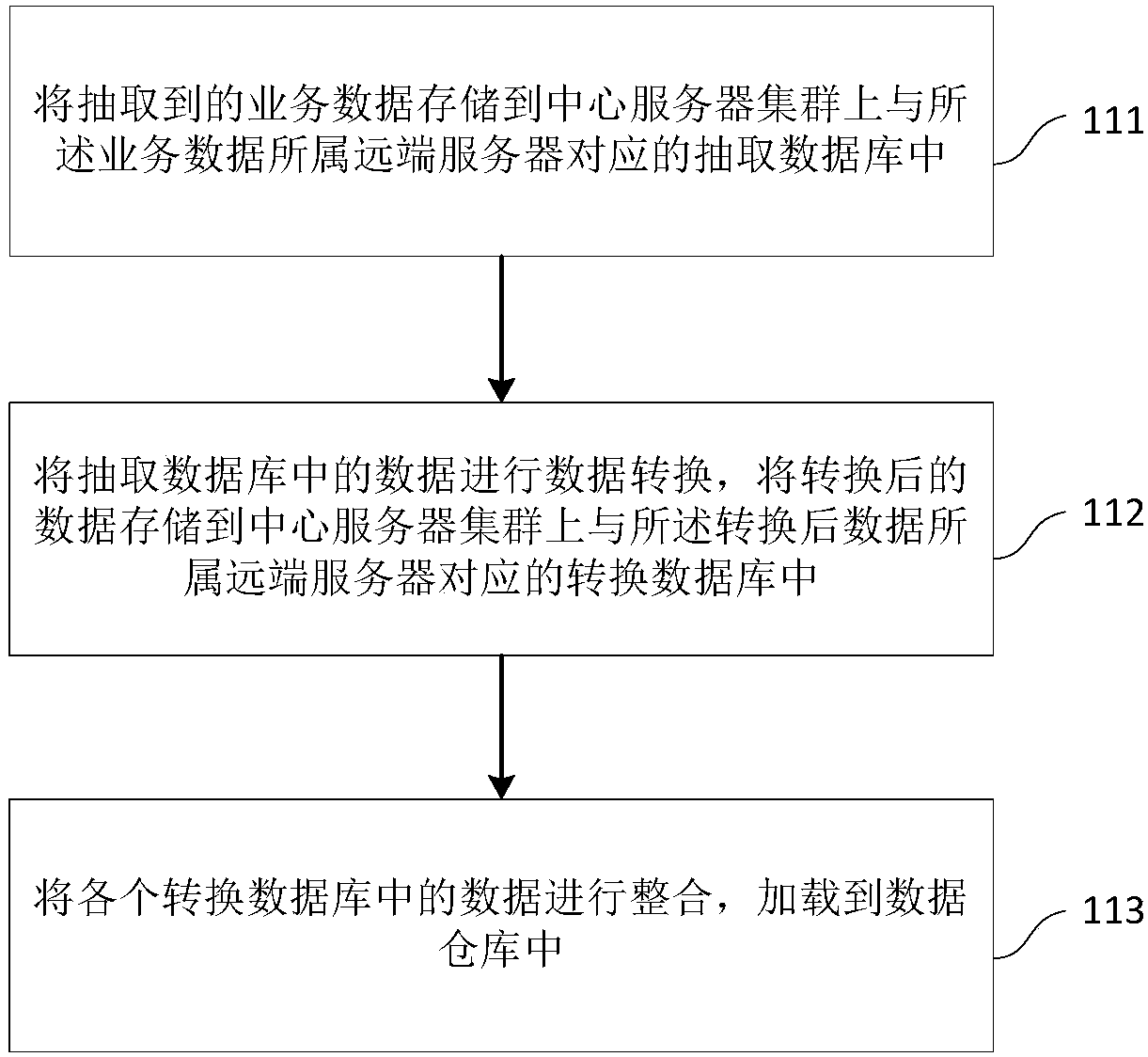

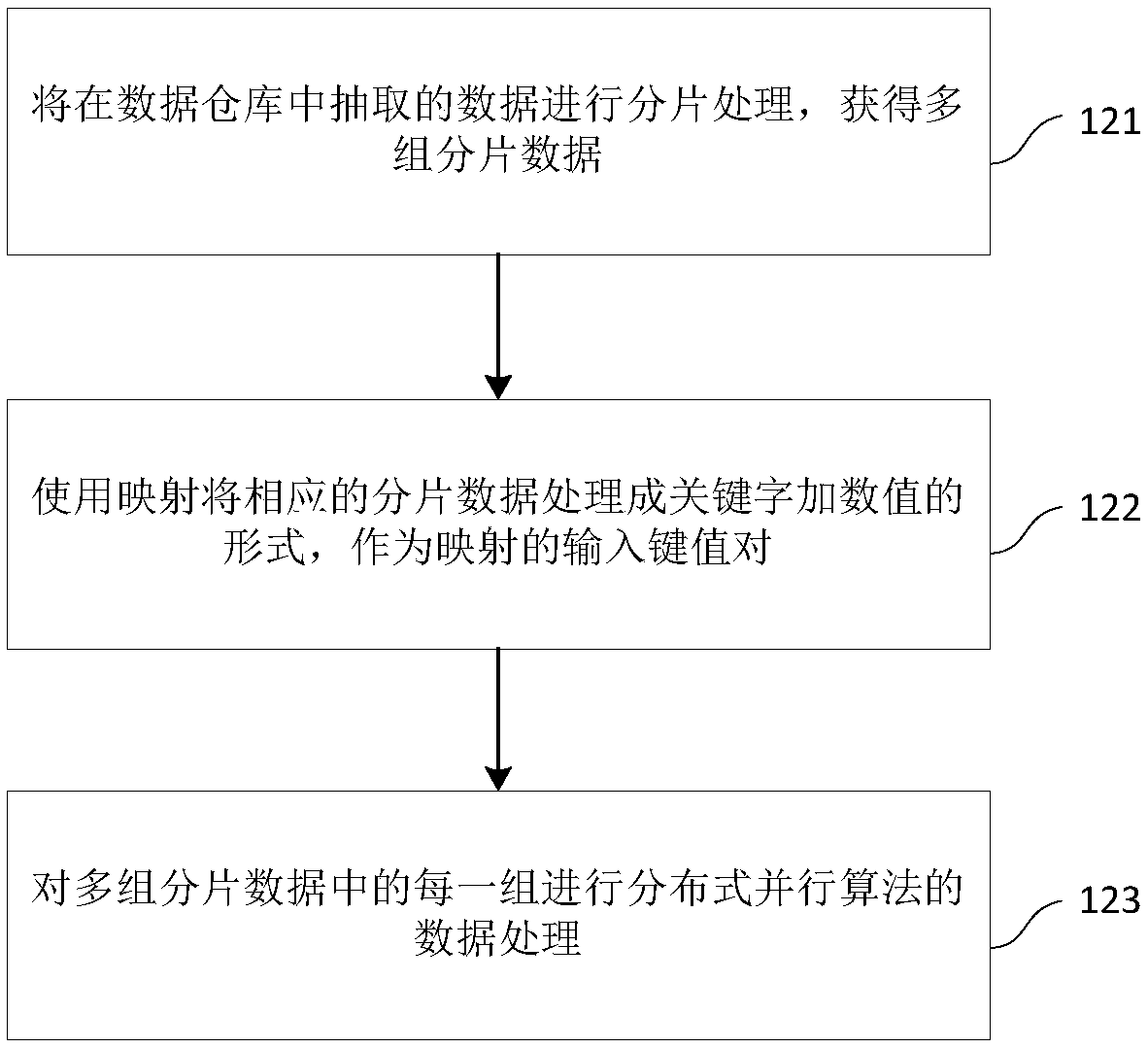

ActiveCN108334557AIncrease profitShort operation cycleMulti-dimensional databasesSpecial data processing applicationsData warehouseAnalysis data

The invention discloses an aggregated data analysis method and device. The method includes the steps: extracting business data of remote servers, processing the business data and loading the processedbusiness data into data warehouses in a central server cluster; extracting corresponding data according to fields and requirements in the data warehouses, and analyzing the extracted corresponding data by the aid of a distributed parallel algorithm to obtain association relationships between the data; optimizing businesses according to the association relationships between the data to meet the requirements. According to the method and device, data with different storage structures and logic structures stored on the remote servers are converted, so that the data can be deployed and used by thecentral server cluster according to target data structures, slicing processing and parallel computing of data to be analyzed are performed by the aid of the distributed parallel algorithm, computingefficiency is improved, association relationships between the data to be analyzed are acquired according to the algorithm, and strong data support is provided for further optimization of the businesses.

Owner:NEUSOFT GRP SHANGHAI CO LTD

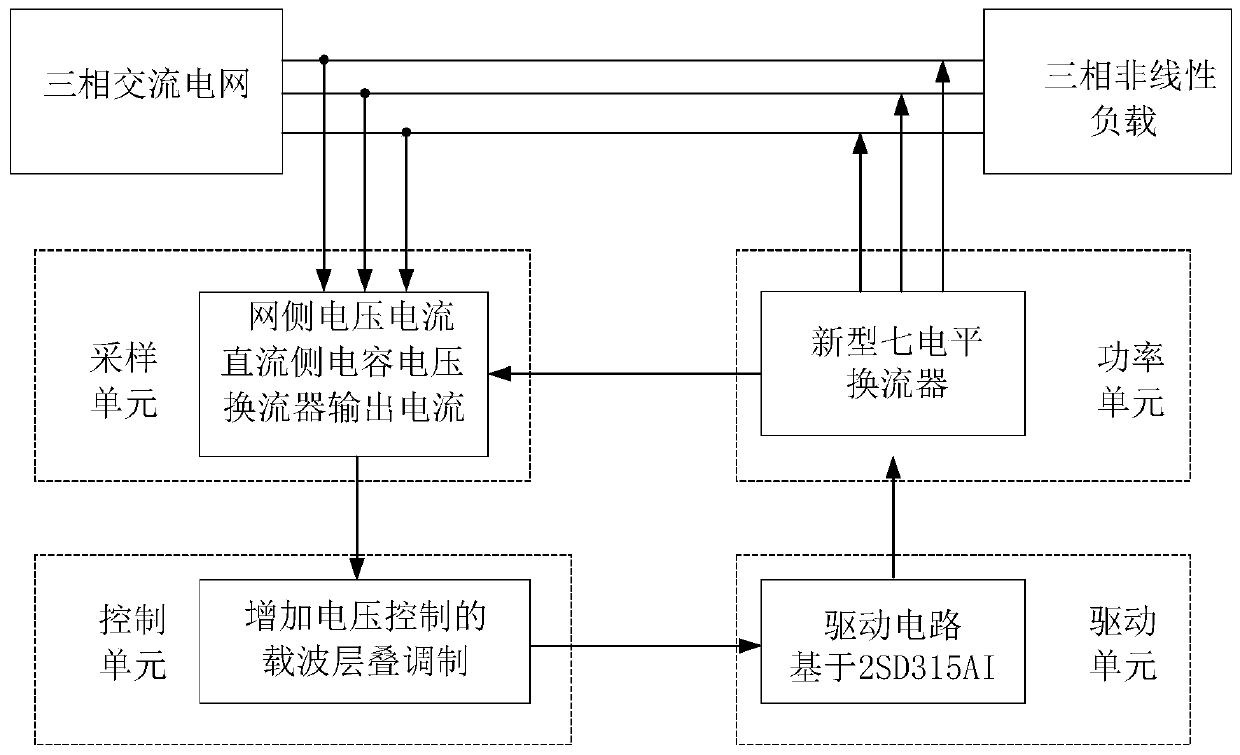

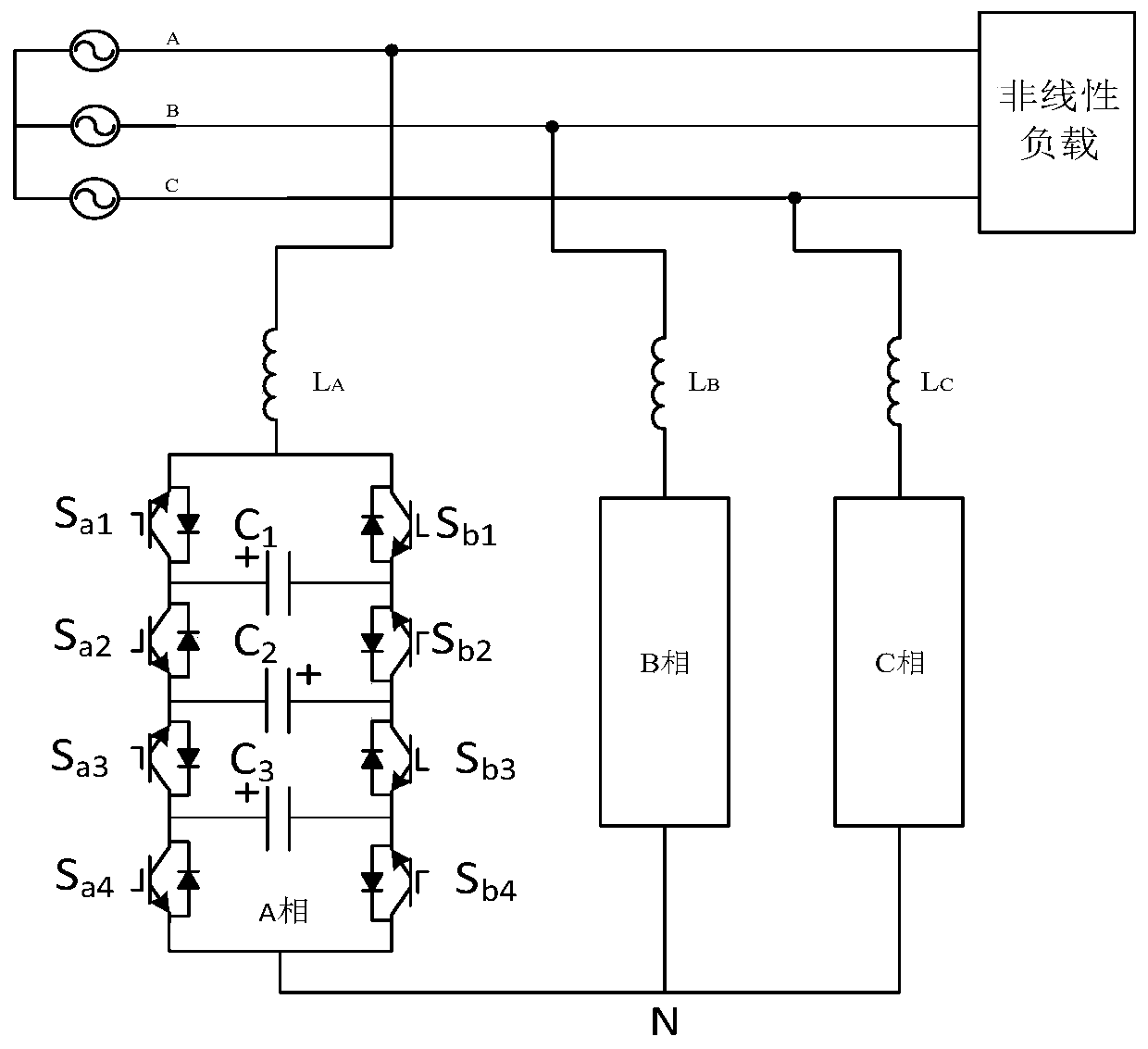

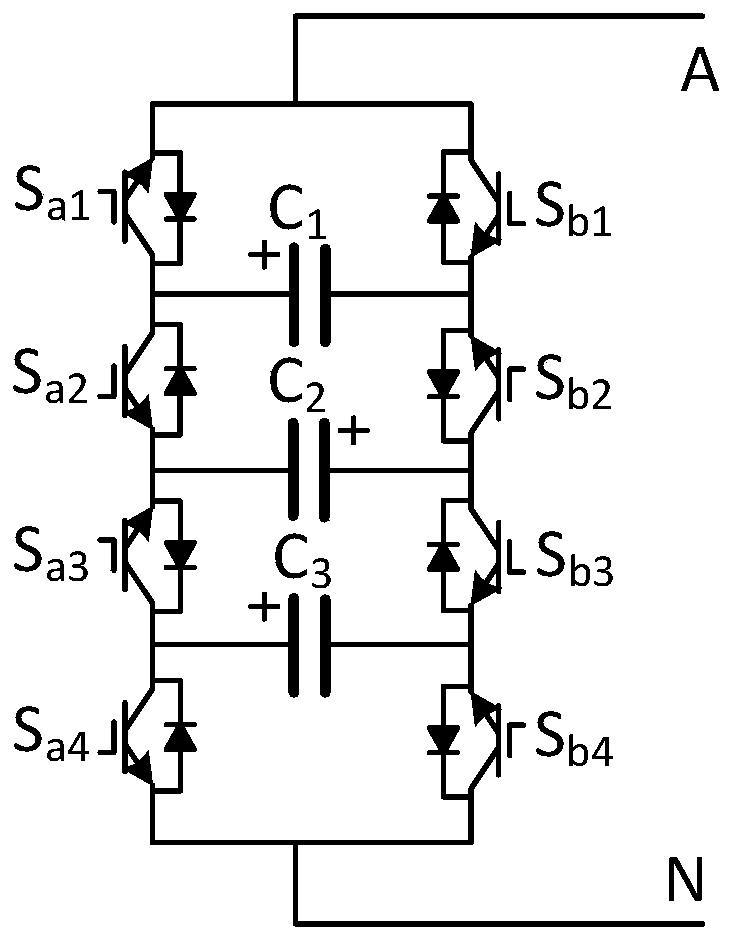

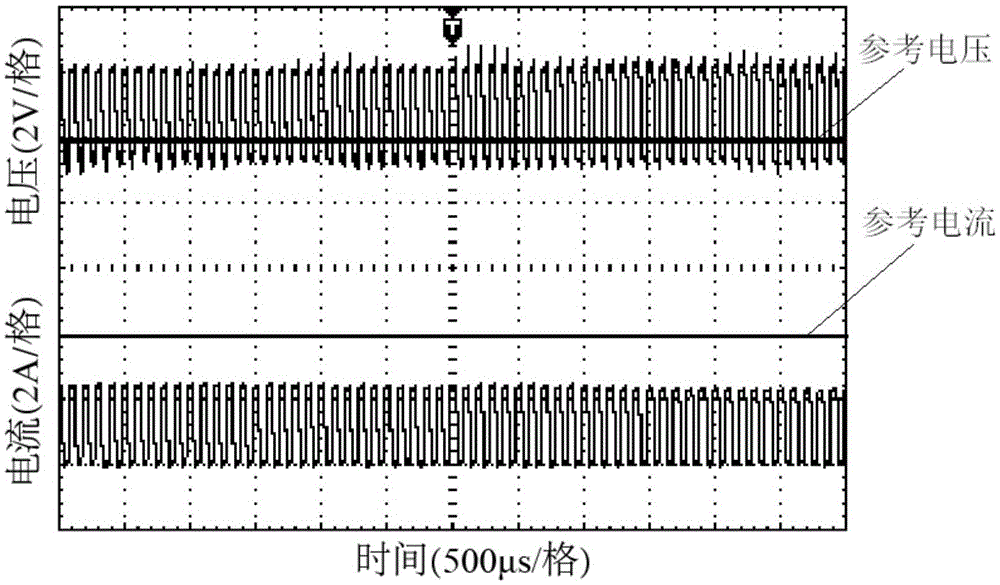

Active power filtering system based on seven-level converter and compensation method thereof

InactiveCN110350534AReduce switching lossesReduce voltage stressActive power filteringAc-dc conversionCapacitanceElectromagnetic interference

The invention discloses an active power filtering system based on a seven-level converter and a compensation method thereof, belongs to the field of power quality control, and solves the problems thatin the prior art, the filter structure is huge and the harmonic content is high because a multi-level active power filtering system uses too many switching tubes. The seven-level current converter comprises an A-phase current converter, a B-phase current converter and a C-phase current converter which have the same structure, wherein the A-phase current converter comprises three direct-current capacitors, a first bridge arm formed by four power switch tubes and a second bridge arm formed by the other four power switch tubes. The system has the advantages of small switching loss, small voltagestress, low electromagnetic interference, large system capacity and the like, and outputs multi-level voltage waveform with small harmonic content, thereby reducing the volume of the filter device.

Owner:HARBIN UNIV OF SCI & TECH

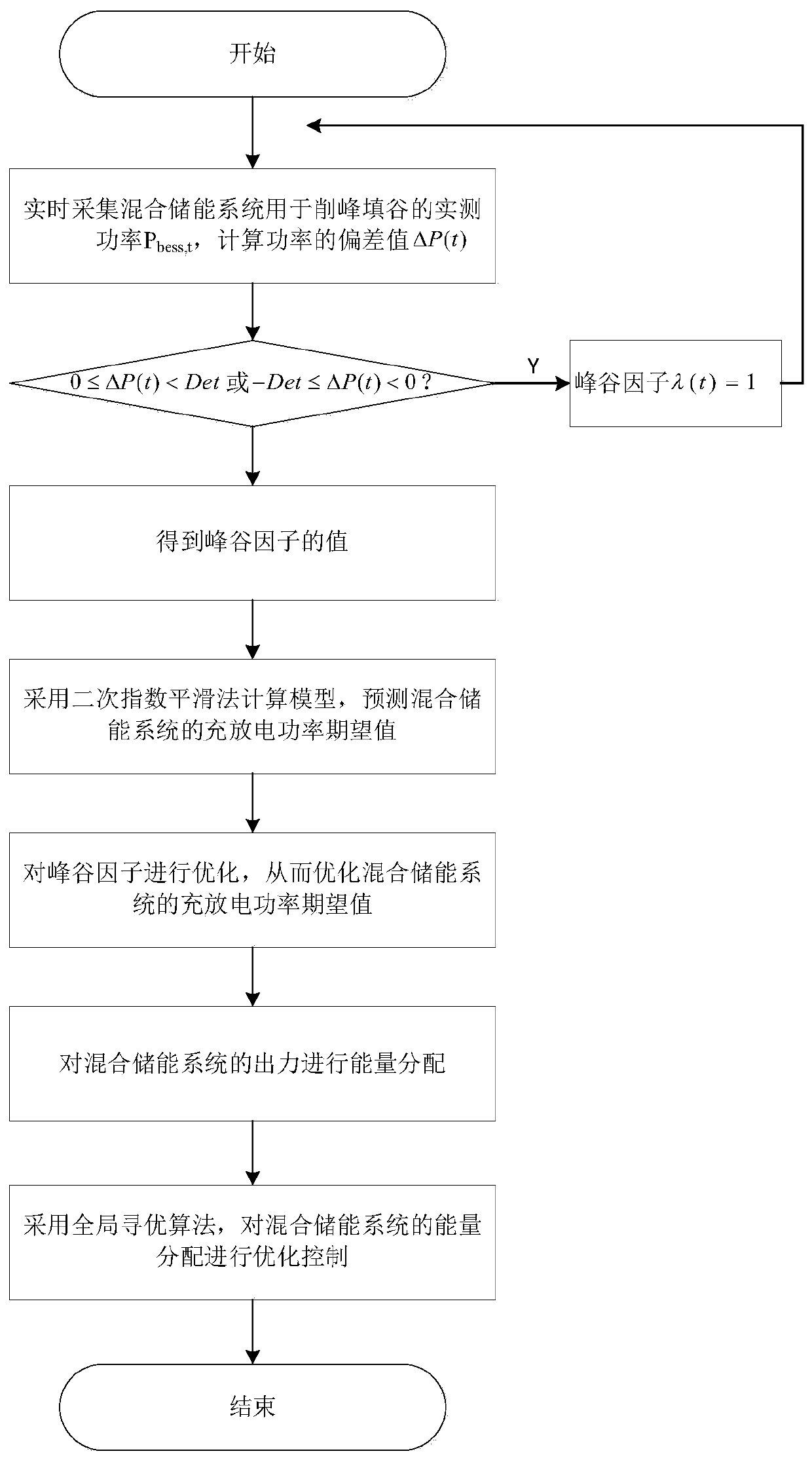

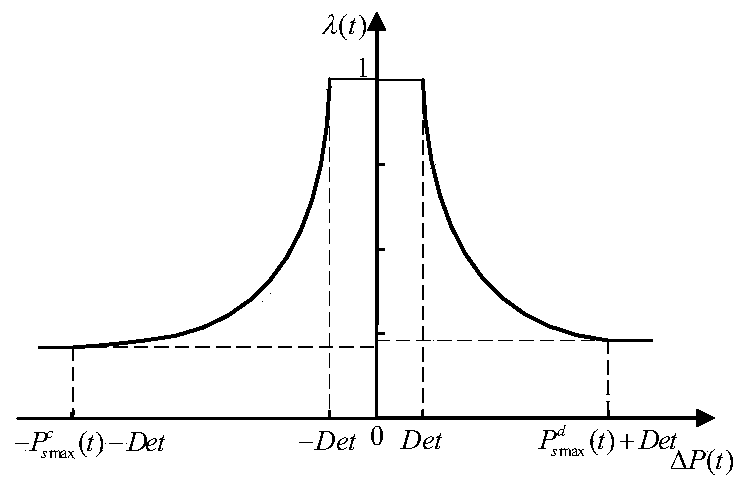

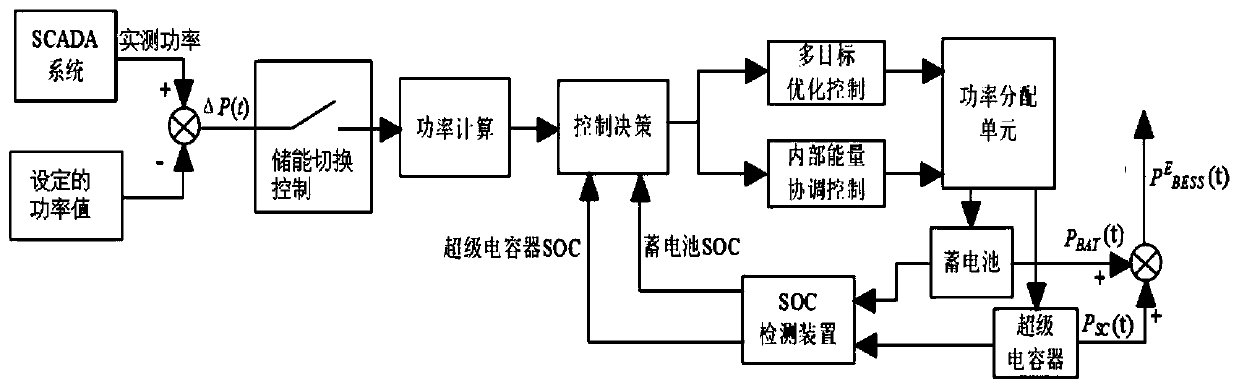

Hybrid energy storage output control method and system for stabilizing peak-valley difference of power grid

ActiveCN110460075AReduce randomnessStable output powerElectrical storage systemBatteries circuit arrangementsCapacity provisioningPower grid

The application relates to a hybrid energy storage output control method and system for stabilizing the peak-valley difference of a power grid, and aims at the problem that the expected value of charge and discharge power of a hybrid energy storage system does not consider the peak and valley of load. The method includes the following steps: first, the measured power of a hybrid energy storage system for peak load shifting is detected and collected in real time, and the expected value of charge and discharge power of the hybrid energy storage system is calculated by adopting a quadratic exponential smoothing algorithm and considering a peak-valley factor; and then, the output of a super capacitor and a lithium battery is determined according to the change of the expected value of charge and discharge power of the hybrid energy storage system, and is optimized by a global parallel optimization algorithm. The method of the invention combines the peak-valley factor, a variable-coefficientexponential peak load shifting method, a non-linear state observation method and the global parallel optimization algorithm, and provides effective reference for the capacity configuration of the energy storage system.

Owner:STATE GRID HENAN ELECTRIC POWER ELECTRIC POWER SCI RES INST +2

DES (Data Encryption Standard) algorithm key expansion system and method based on coarse-grained reconfigurable framework

ActiveCN106155979AImprove computing parallelismImprove computing efficiencyArchitecture with single central processing unitElectric digital data processingExtension methodRegister file

The invention discloses a DES (Data Encryption Standard) algorithm key expansion system and method based on a coarse-grained reconfigurable framework. The DES algorithm key expansion system comprises a system bus, a reconfigurable processor and a microprocessor, wherein the reconfigurable processor comprises a configuration unit, an input first-in and first-out register set, an output first-in and first-out register set, a general register file, M reconfigurable array blocks and a lookup table. Aiming at DES algorithm key expansion, a parallel displacement replacement manner of multi-turn iteration in the reconfigurable processor is optimized and accelerated.

Owner:SOUTHEAST UNIV WUXI INST OF TECH INTEGRATED CIRCUITS

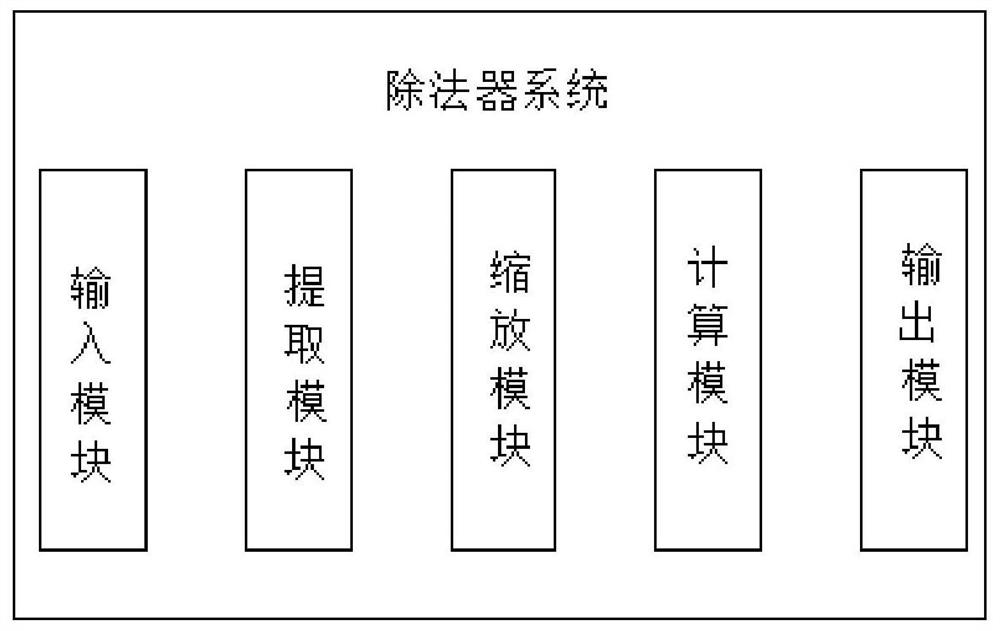

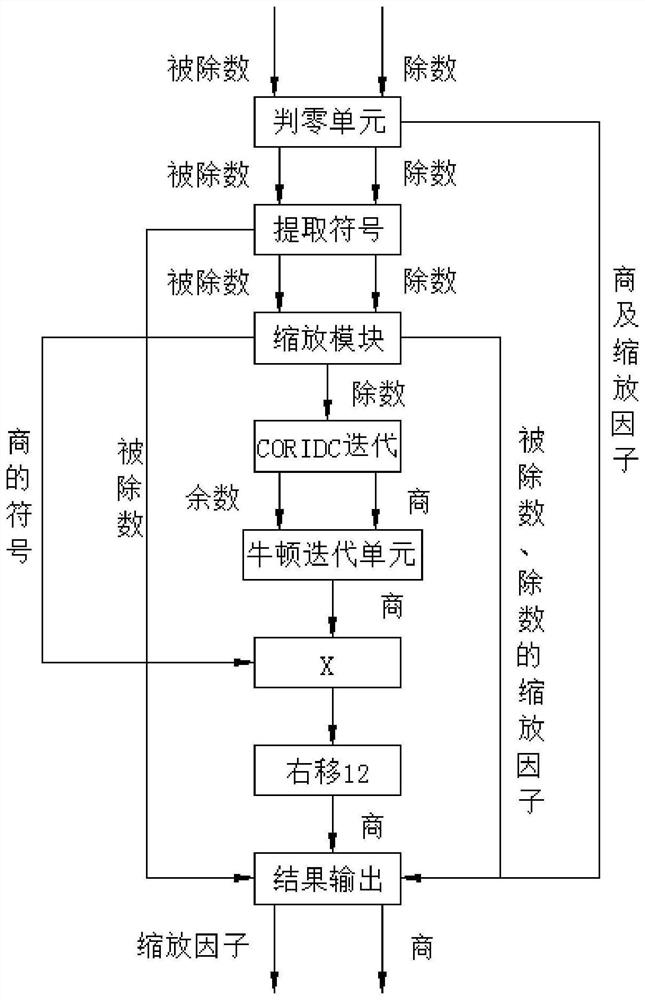

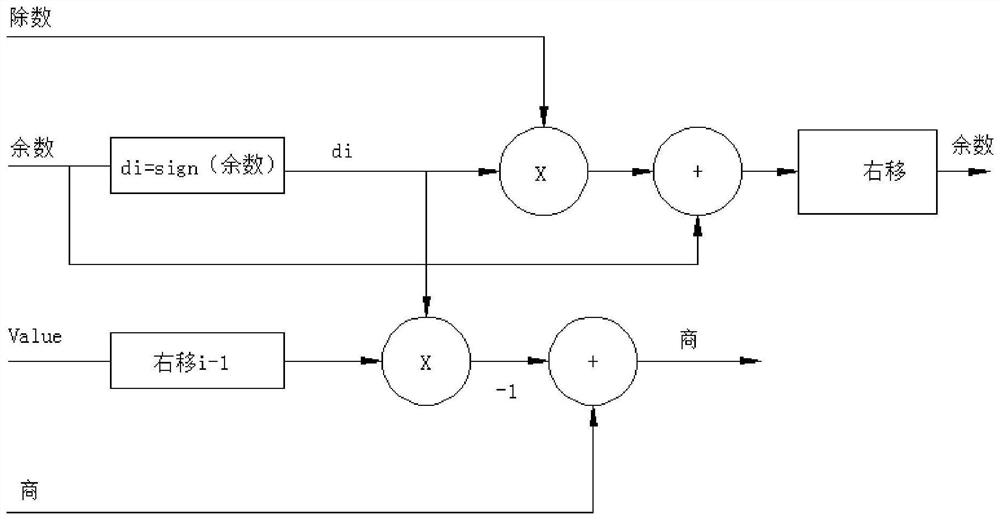

Method and device for realizing 32-bit integer division with high precision and low time delay

ActiveCN111813372AEasy to implementReduce resource consumptionDigital data processing detailsComplex mathematical operationsAlgorithmTime delays

The invention provides a method and a device for realizing 32-bit integer division with high precision and low time delay. The method comprises the following steps: S1, if the dividend, the divisor and the input zero judgment unit are 0, directly outputting 0 and a zoom factor of 0 by a quotient; and S2, inputting the dividend and the divisor output by the step 1 into a symbol extraction module, and outputting the symbol of the quotient and the modulus values of the dividend and the divisor. In the present invention, an initial value of Newton iteration is realized by using a CORDIC with a relatively small number of iterations; addition-only and shift-only operations, resource consumption reduction, facilitating hardware implementation, scaling module, scaling the dividend divisor to the same amplitude position; the calculation bit width is reduced, the requirement for the number of iterations is reduced, the operation period is shortened, Newton iteration is added once, the operationprecision is improved at the cost of a small number of arithmetic units and time delay, the precision of the quotient is effectively guaranteed in the mode that the output result uses the quotient andthe scaling factor, the output bit width is small, and follow-up use is facilitated. Error less than one thousandth.

Owner:上海擎昆信息科技有限公司

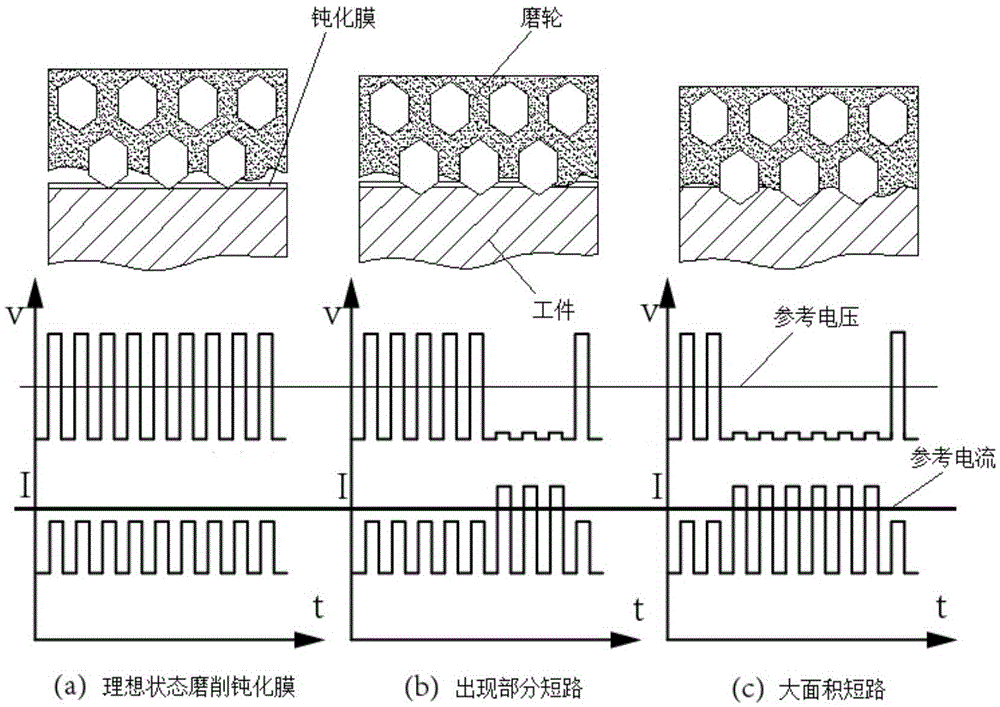

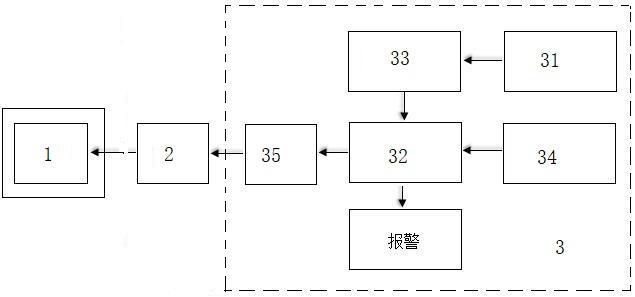

Electrolytic and mechanical combined machining servo control method and system based on short circuit rate

ActiveCN105583479AShort operation cycleThe principle is simpleElectrical-based auxillary apparatusElectrolysisControl theory

The invention discloses an electrolytic and mechanical combined machining servo control method and a system based on a short circuit rate, and belongs to the technical field of electrolytic machining. In the electrolytic and mechanical combined machining servo control method and system based on the short circuit rate, the servo control method uses the short circuit rate, calculated by the servo control system, as judgment data to compare with a preset short circuit rate standard value to judge if relative feeding is needed according to the comparison result; and the servo control system comprises a current sampling circuit, a voltage sampling circuit, a comparison circuit, a counter, or an arithmetical unit and a CPU. The servo control method and system can control feeding and retreating of a grinding wheel in real time to prevent under-cutting and over-cutting phenomenon to accurately remove a passive film on the surface of a workpiece, so that the machining efficiency and the surface quality of the machined workpiece are improved, and the machining stability and the machining precision are improved; and the servo control method and system are simple, effective, convenient for actuation, wide in application range, high in timeliness and accuracy and high in economy and practicability.

Owner:CHANGZHOU INST OF TECH

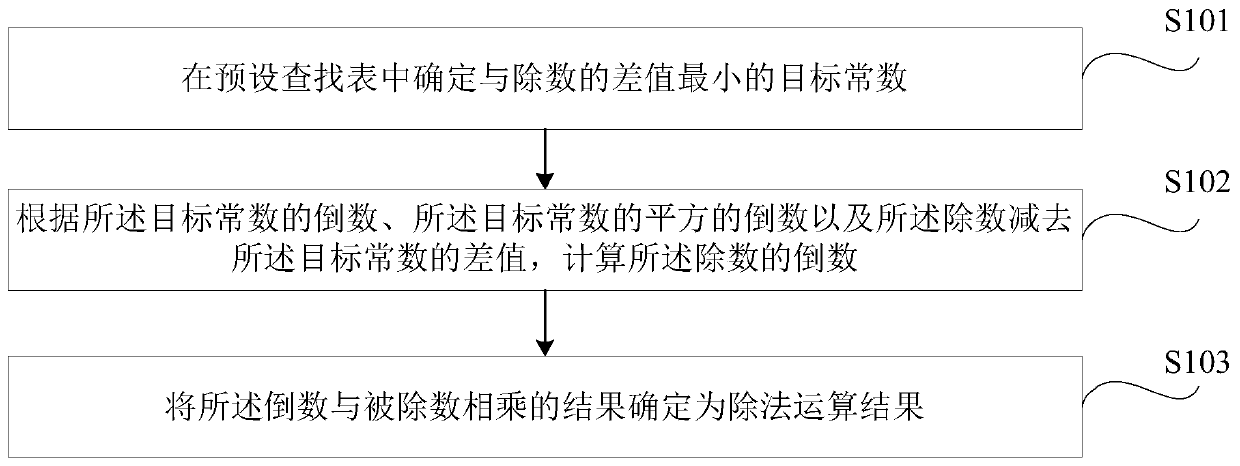

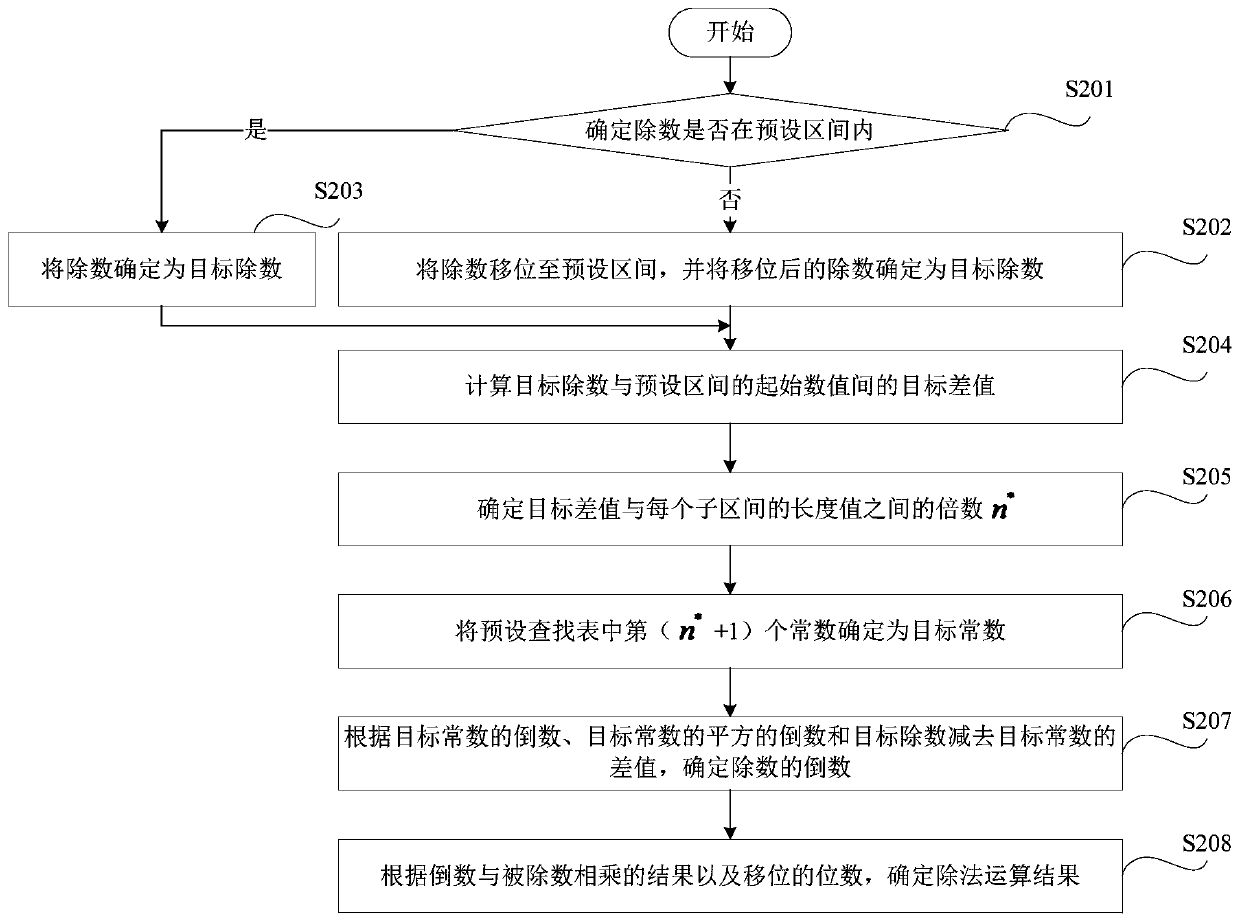

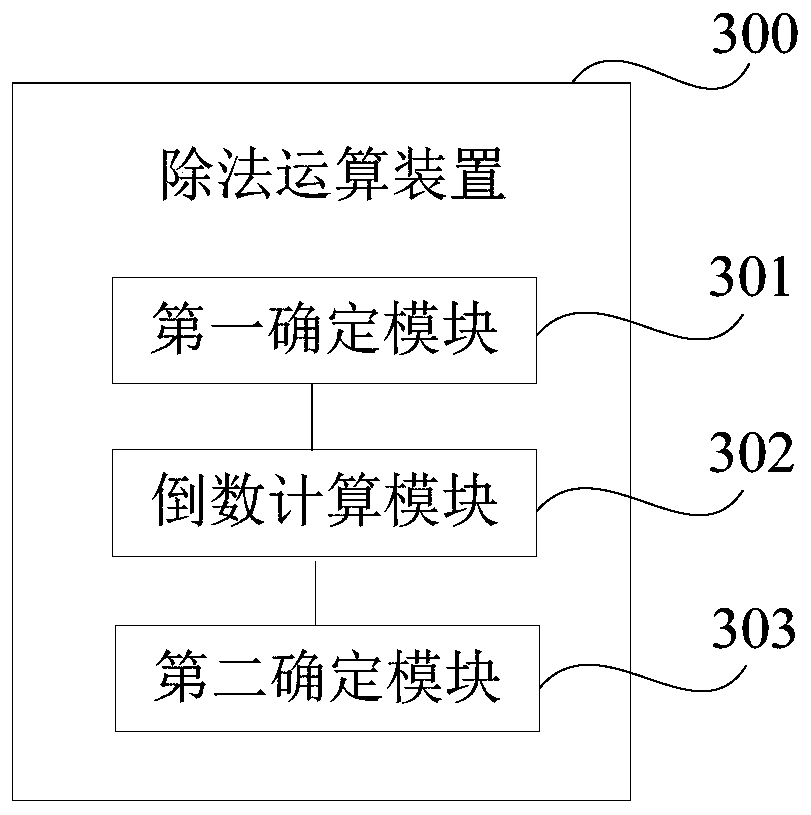

Division operation method and device, storage medium and electronic equipment

ActiveCN111399803AImprove computing efficiencyReduce consumptionDigital data processing detailsLookup tableMechanical engineering

The invention relates to a division operation method and device, a storage medium and electronic equipment, and aims to reduce calculation resources of division operation. The division operation method comprises the steps: determining a target constant with the smallest difference value with the divisor in a preset lookup table, wherein the preset lookup table stores (N+1) constants obtained by dividing a preset section into N sub- sections, reciprocals corresponding to the (N+1) constants respectively, and reciprocals of squares corresponding to the (N+1) constants respectively, and N is a positive integer greater than 1; calculating the reciprocal of the divisor according to the reciprocal of the target constant, the reciprocal of the square of the target constant and the difference obtained by subtracting the target constant from the divisor; and determining a result of multiplying the reciprocal by the dividend as a division operation result.

Owner:BEIJING XIAOMI PINECONE ELECTRONICS CO LTD

SM3 algorithm iteration system and method based on coarse granularity reconfigurable architecture

ActiveCN109672524AImprove computing parallelismImprove computing efficiencyKey distribution for secure communicationEncryption apparatus with shift registers/memoriesProduction lineComputer architecture

The invention discloses a SM3 algorithm iteration system and method based on a coarse granularity reconfigurable architecture. The iteration system comprises a system bus, a reconfigurable processor and a micro-processor, wherein the reconfigurable processor comprises a configuration unit, an input first-in first-out register group, an output first-in first-out register group, a general register pile and four reconfigurable array blocks; a line inlet of the configuration unit is connected with the micro-processor through a system bus; a line outlet of the configuration unit is connected with each reconfigurable array block; the input first-in first-out register group is connected with the micro-processor through the system bus; the four reconfigurable array blocks are connected with the input / output first-in first-out register group and the general register pile respectively; data are stored, read and transmitted among the four reconfigurable array blocks through the general register pile; and the output first-in first-out register group is connected with the micro-processor through the system bus. According to the technical scheme, certain flexibility is supported, and efficient operation of a SM3 algorithm is realized through improvement on the parallel degree of the DES algorithm and optimization of the production line.

Owner:SOUTHEAST UNIV +1

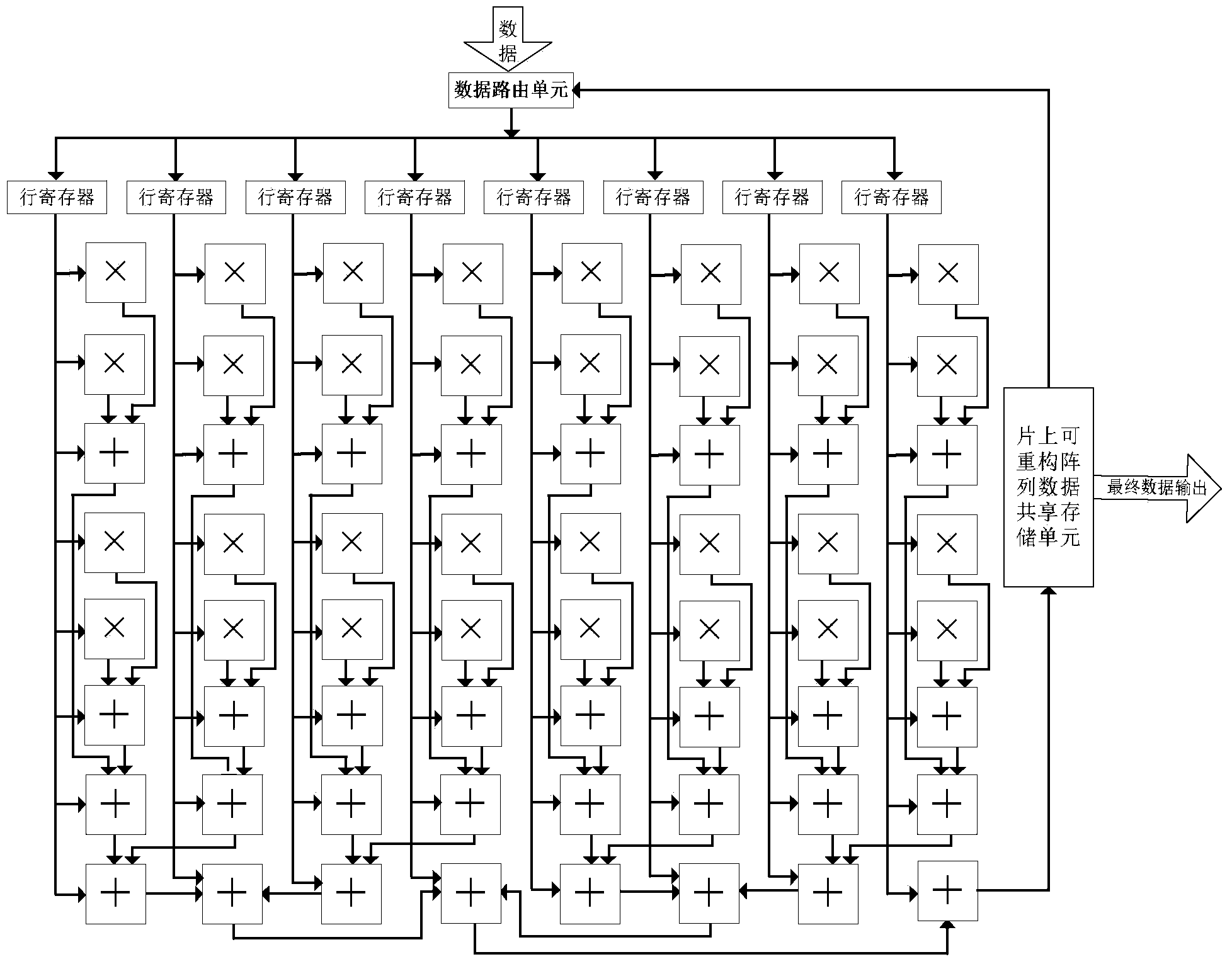

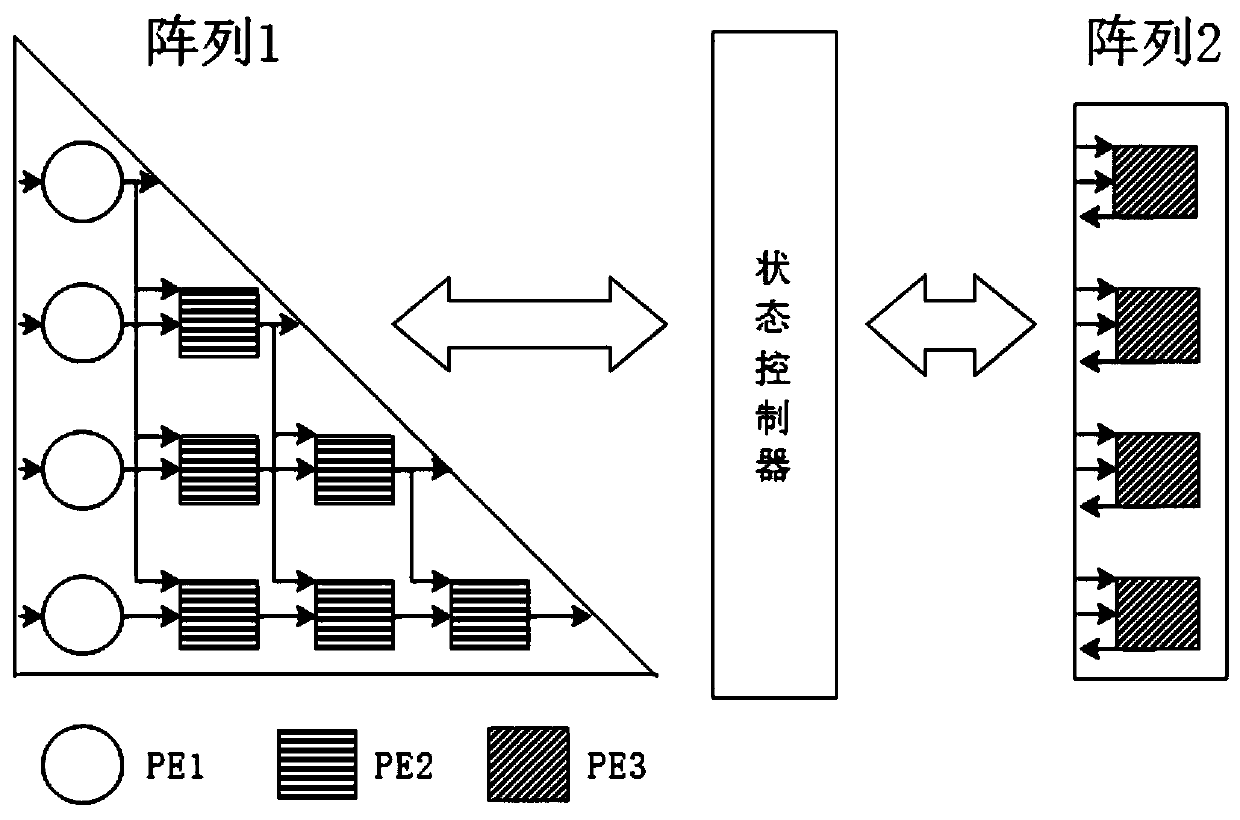

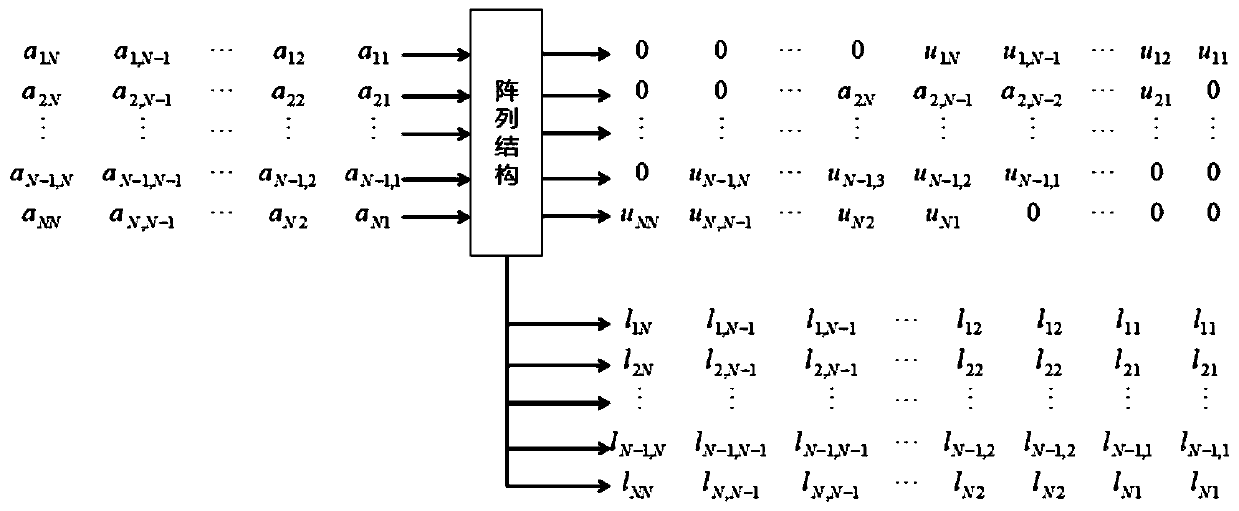

Implementation method of systolic array structure for LU decomposition

ActiveCN110457648AHigh outputReduce usageComplex mathematical operationsDecomposition problemResource utilization

The invention discloses an implementation method of a systolic array structure for LU decomposition. The systolic array structure comprises an arithmetic unit array for calculating an upper triangularmatrix, an arithmetic unit array for calculating a lower triangular matrix, and a state controller module for controlling data input. Compared with an existing operation structure, the implementationmethod has the following innovations that (1) matrix data is input in parallel according to lines, and an input sequence does not need to be planned; (2) the dividers are independently extracted fromthe array processing unit, so that the number of the dividers is reduced, and the resource utilization rate is improved; (3) the pulsation array is partially parallelized, and the number of clock cycles required by operation is reduced while maintaining high pipelining; and (4) the high-dimensional systolic array structure designed by the invention can be compatible with lower-dimensional matrixLU decomposition, so that the same structure can be shared by matrixes with different dimensions, and the redesign of the structure is avoided. The implementation method can be applied to hardware implementation of matrix decomposition problems in the fields of signal processing, numerical analysis, artificial intelligence and the like.

Owner:JINAN UNIVERSITY

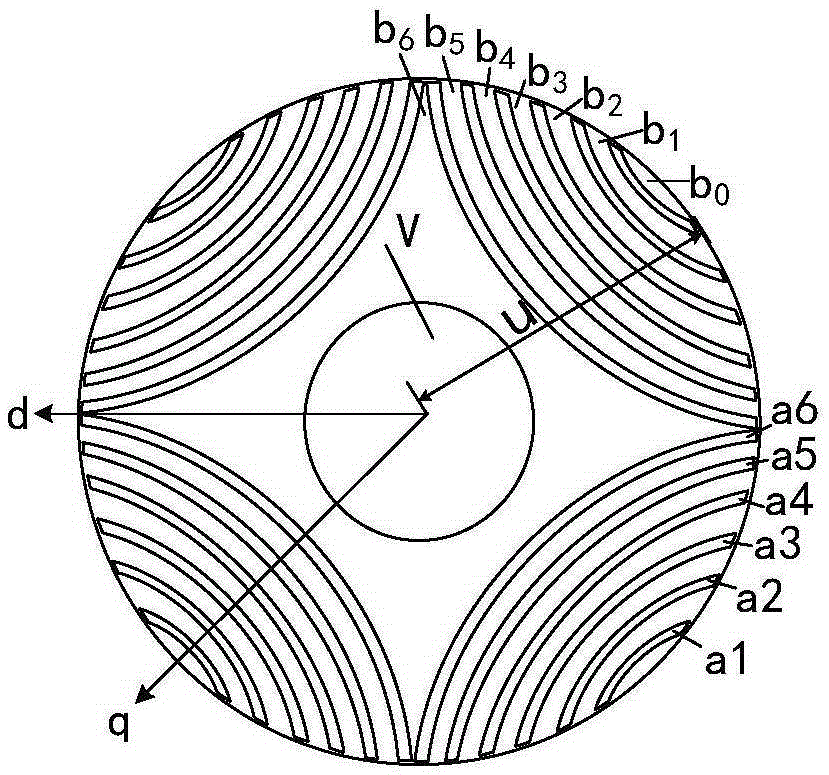

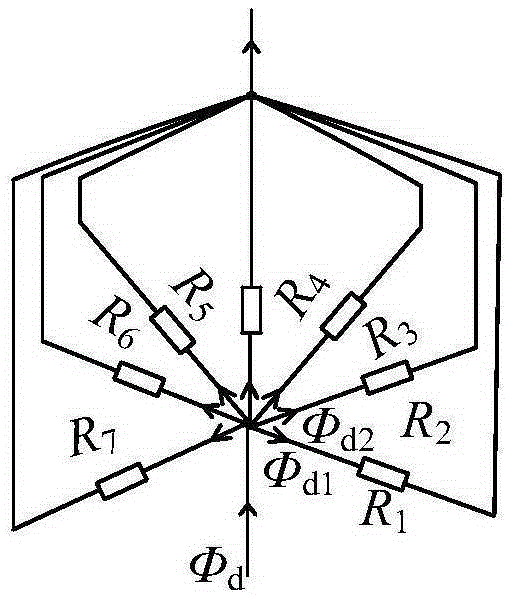

Method for improving saliency ratio of synchronous reluctance machine

ActiveCN105356804AReduce occupancyRaise the saliency ratioElectronic commutation motor controlVector control systemsSynchronous reluctance motorFinite element method

The invention relates to a method for improving the saliency ratio of a synchronous reluctance machine (SynRM). The method is based on the inherent stator and rotor structure parameters of SynRM, a saliency ratio calculation formula is obtained directly according to the equivalent d-axis and q-axis magnetic circuits of SynRM, the relational expression between the saliency ratio and a structure parameter to be optimized of the SynRM is obtained according to the saliency ratio calculation formula, and a higher saliency ratio is obtained by adjusting the value range of the structure parameter. Compared with a finite element method, by adopting the method of the invention, the computer memory resource occupied can be greatly reduced, the difficulty in mathematical operation is lowered, the saliency ratio of SynRM is improved significantly, and the inherent structure parameters of SynRM can be optimized.

Owner:HEBEI UNIV OF TECH

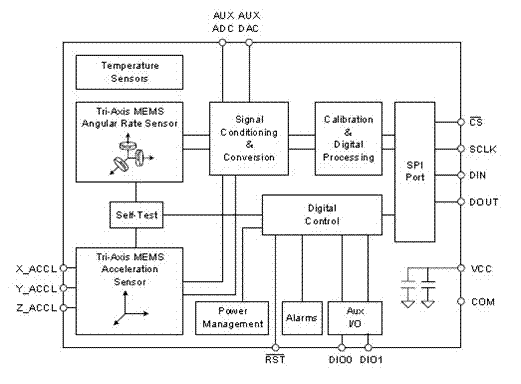

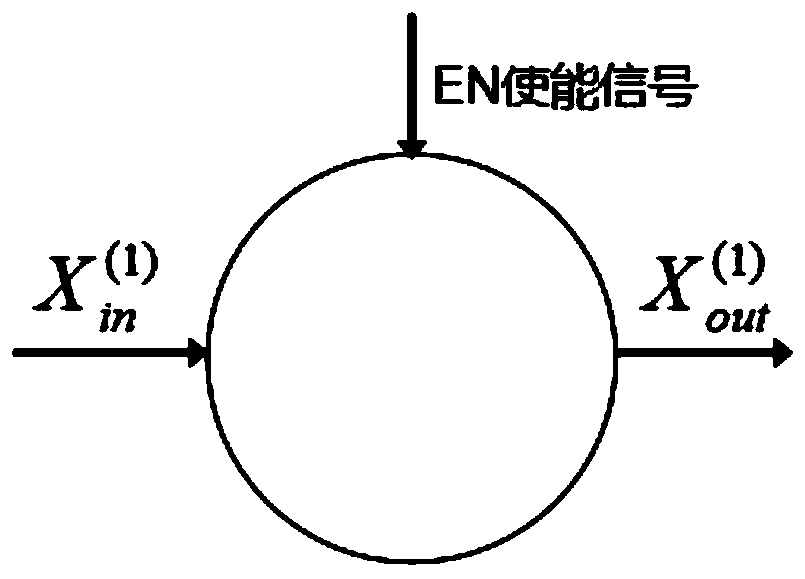

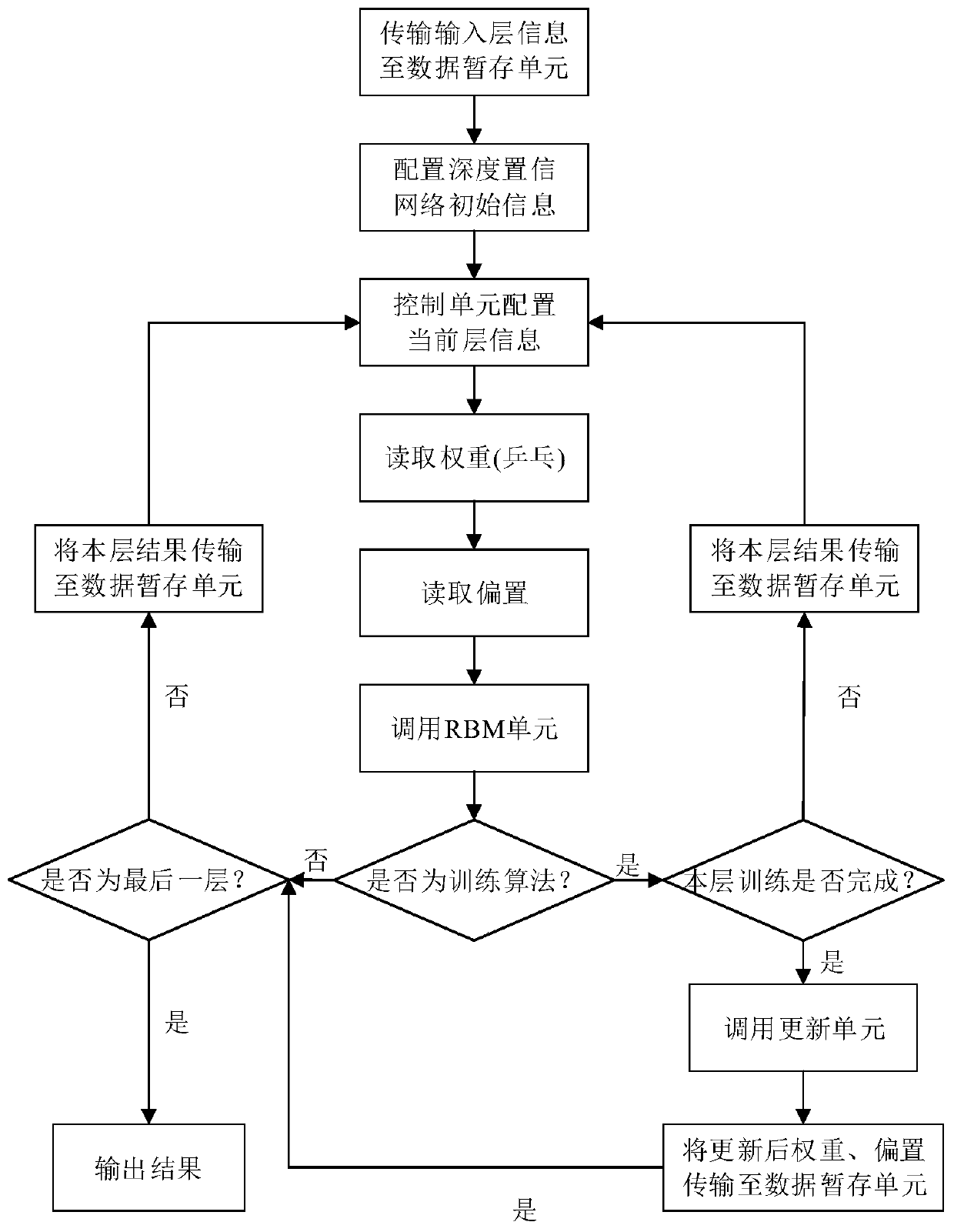

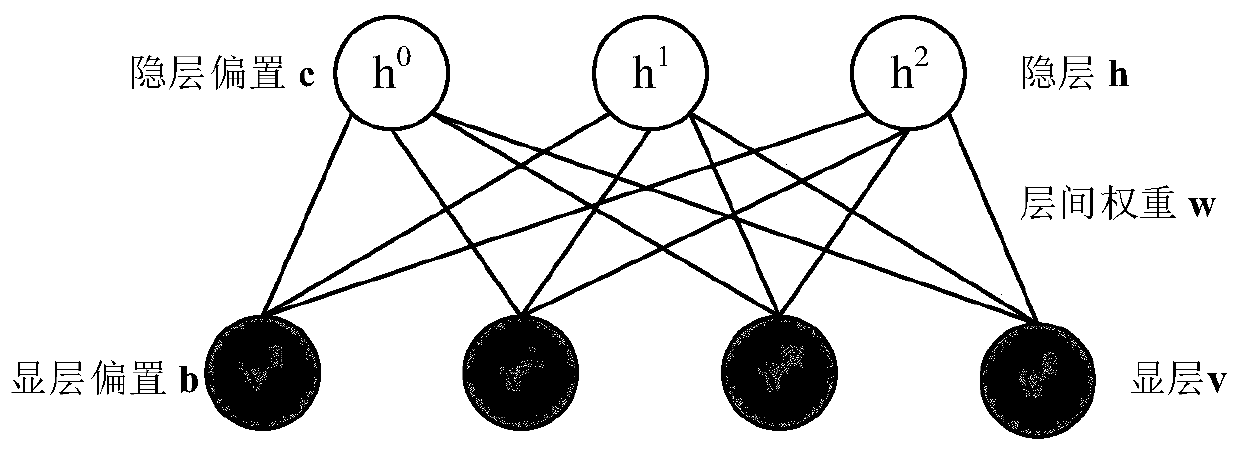

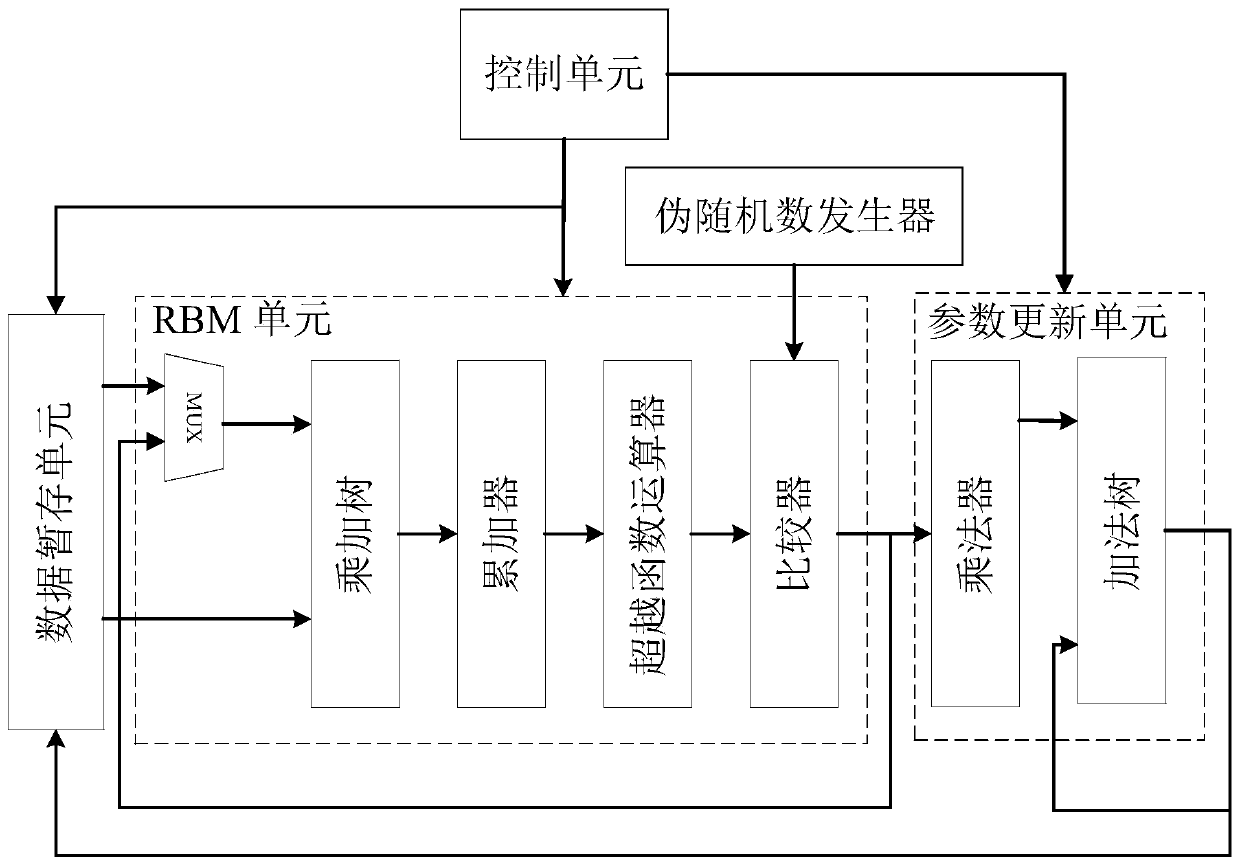

A reconfigurable deep belief network implementation system

ActiveCN109711543AApplicable to various application scenariosShort operation cyclePhysical realisationEnergy efficient computingDeep belief networkRestricted Boltzmann machine

The invention discloses a reconfigurable deep belief network implementation system. The system comprises a control unit used for controlling the operation process of a deep belief network algorithm; the data temporary storage unit is used for storing and calculating required input layer information, weights, offsets and output layer results; the restricted Boltzmann machine is used for calculatingthe activation probability of each layer of nodes in the deep belief network so as to determine the activation state; and the parameter updating unit is used for updating the weight and bias of eachlayer of nodes in the deep belief network, and is only activated in the training algorithm. The implementation system has the beneficial effects that two algorithms of training and reasoning can be supported by multiplexing the restricted Boltzmann machine and controlling the state jump of the algorithm, the hardware resource cost of the algorithm is reduced, the performance of the algorithm is ensured, and the implementation system is suitable for various artificial intelligence scenes.

Owner:NANJING UNIV

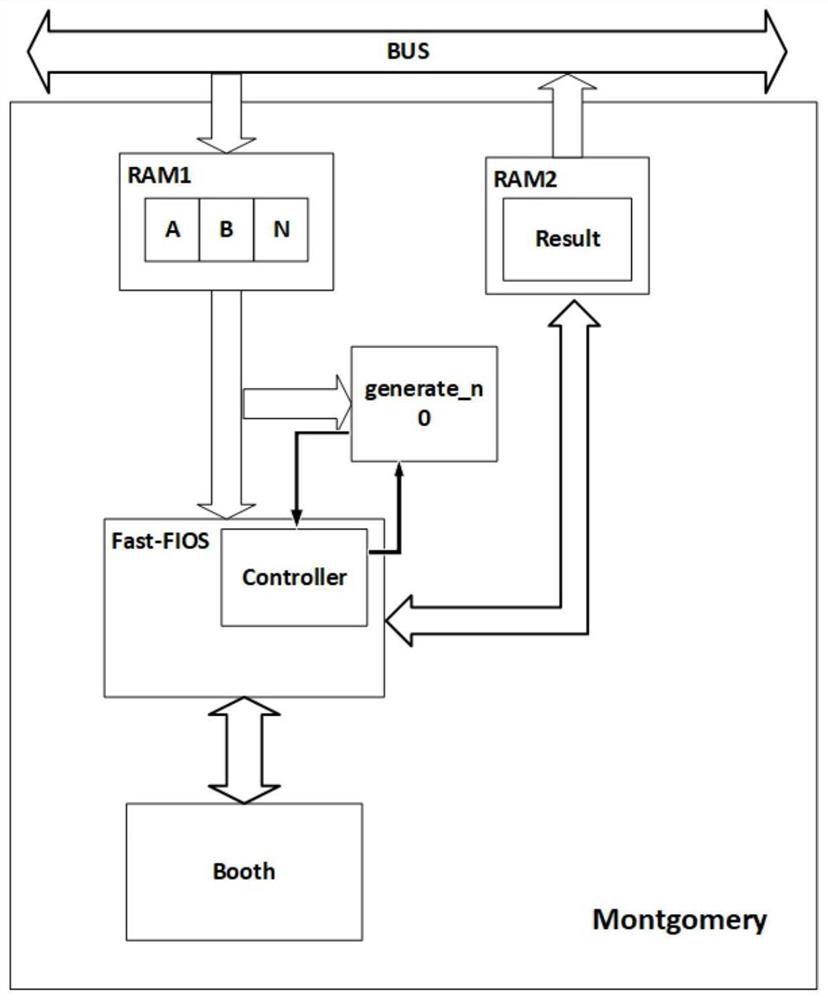

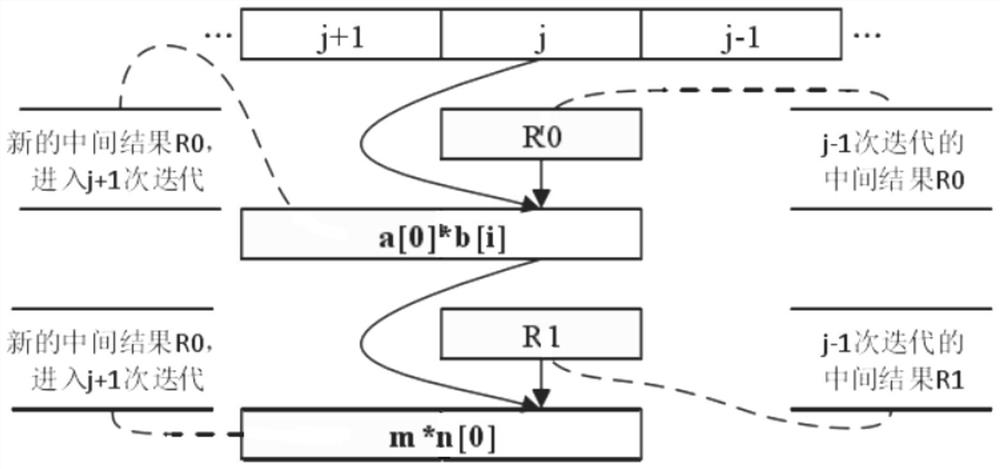

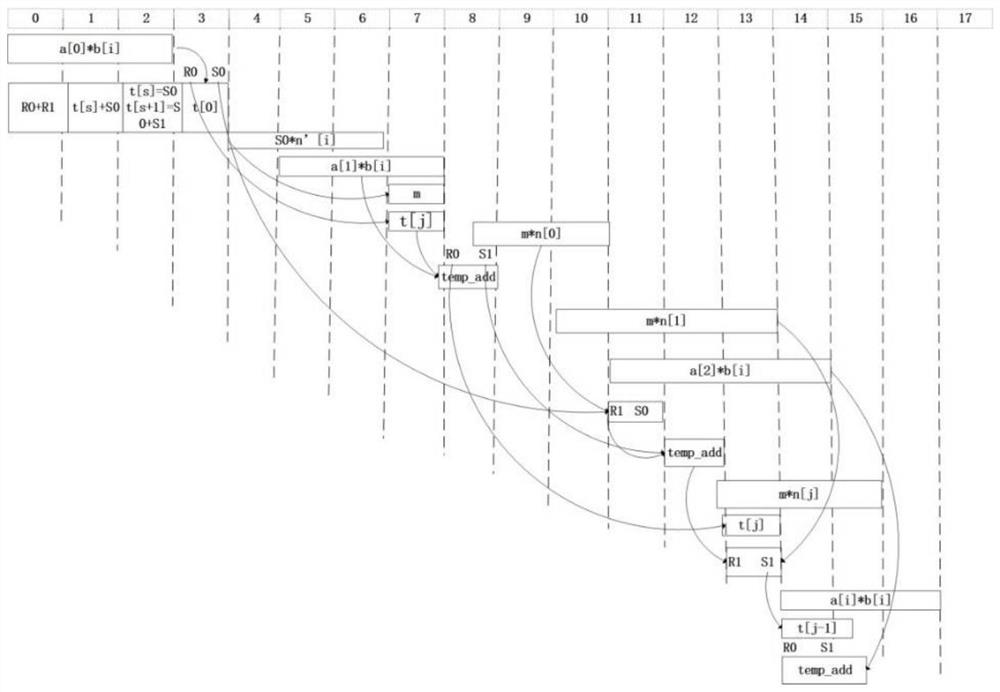

Hardware system for realizing improved FIOS modular multiplication algorithm

ActiveCN112486457AShorten the lengthReduce consumptionComputations using residue arithmeticMultiplexingBinary multiplier

The invention discloses a hardware system for realizing an improved FIOS modular multiplication algorithm. A modular multiplication circuit is realized by adopting hardware, and logic resource consumption is reduced through register multiplexing; rearranging the assembly line and the whole algorithm time sequence, and disassembling the addition operation of the critical path into multi-stage assembly line addition tree operation, so that the maximum operation rate reaches 600MHz; the number of operations in a single clock period is increased through parallelization processing of independent operations; a 128-base multiplier is used as a basic calculation unit, only 3463 periods are needed for completing 4096-bit modular multiplication, consumed time is about 5.75 us, the number of cycles in the calculation process is remarkably reduced, the number of clocks needed by operation is reduced, and the calculation throughput rate in unit time is increased. According to the invention, the partial product generation circuit is improved, and the use of logic gates is further reduced. According to the method, the code length in the Montgomery modular multiplication algorithm is reduced through improvement, and the operation efficiency of the modular multiplication process is improved.

Owner:HANGZHOU DIANZI UNIV

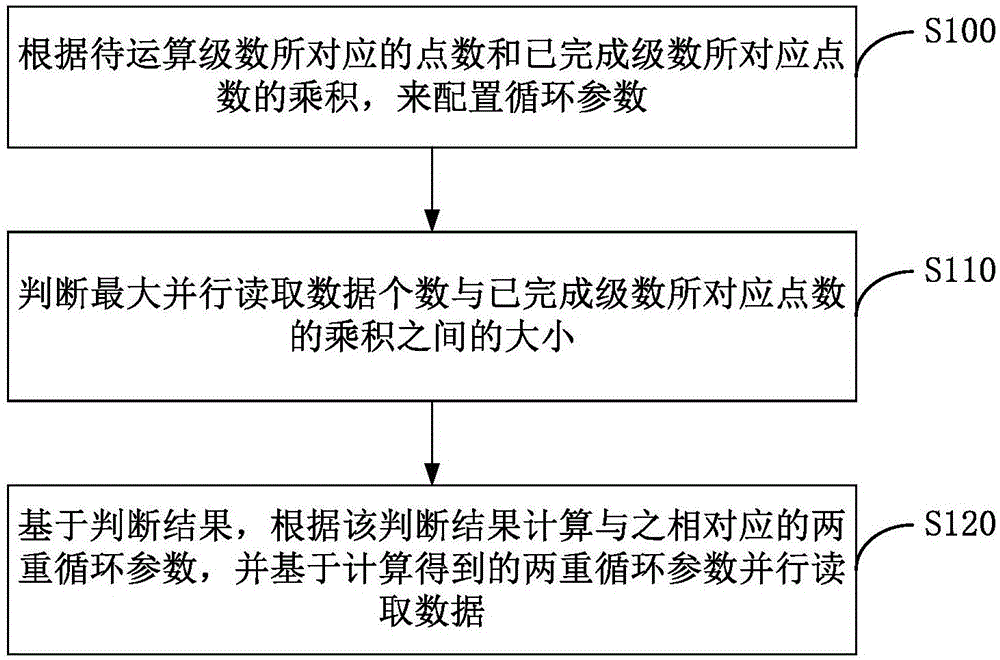

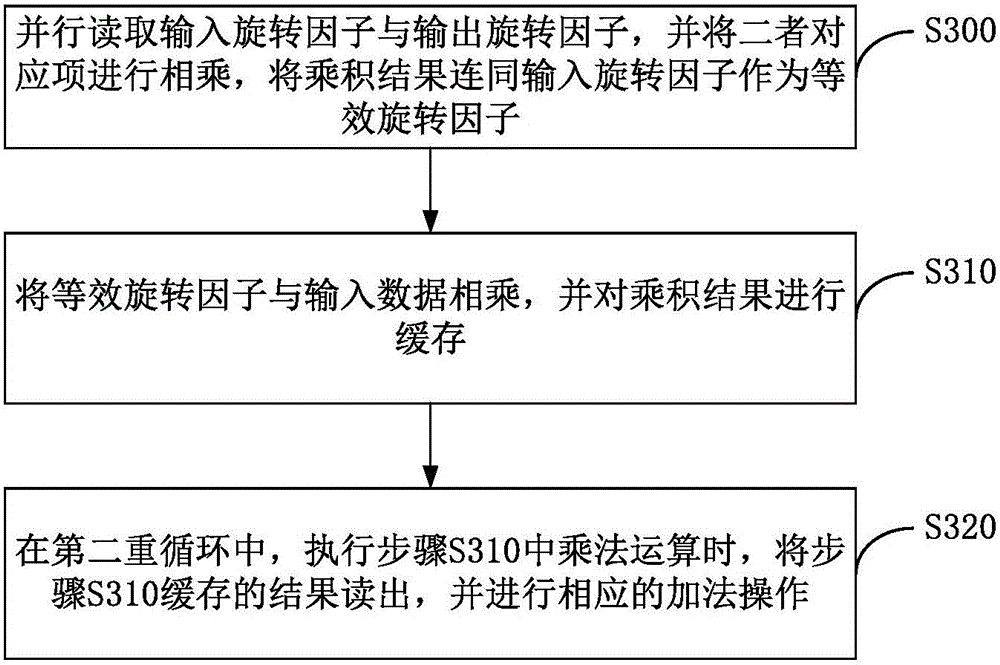

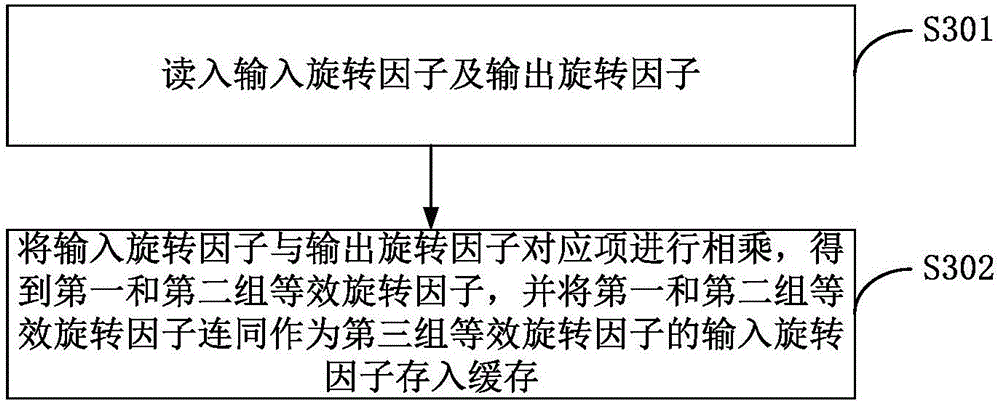

Mixed-radix DFT/IDFT (Discrete Fourier Transform/Inverse Discrete Fourier Transform) parallel reading and calculating methods and devices

ActiveCN106201999AIncrease processing parallelismShort operation cycleConcurrent instruction executionComplex mathematical operationsDegree of parallelismDual loop

The invention discloses a mixed-radix DFT / IDFT (Discrete Fourier Transform / Inverse Discrete Fourier Transform) data parallel reading method, a mixed-radix DFT / IDFT parallel calculating method, a mixed-radix DFT / IDFT data parallel reading device and a mixed-radix DFT / IDFT parallel calculating device, wherein the parallel reading method comprises the following steps of configuring a dual loop parameter according to a product of a point number corresponding to a to-be-operated series and a point number corresponding to a completed series; afterwards, judging a size between the number of maximum parallel read data and the product of the point number corresponding to the completed series; finally, based on a judgment result, calculating the dual loop parameter corresponding to the judgment result according to the judgment result, and reading the data in a parallel manner based on the dual loop parameter obtained by calculation. Thus, by using the mixed-radix DFT / IDFT data parallel reading method, the mixed-radix DFT / IDFT parallel calculating method, the mixed-radix DFT / IDFT data parallel reading device and the mixed-radix DFT / IDFT parallel calculating device, the processing degree of parallelism is improved; the relativity among the data is reduced; integral operational blank beats are reduced; the pipelining utilization rate is improved; further, the mixed-radix DFT / IDFT operating rate is effectively promoted.

Owner:INST OF AUTOMATION CHINESE ACAD OF SCI

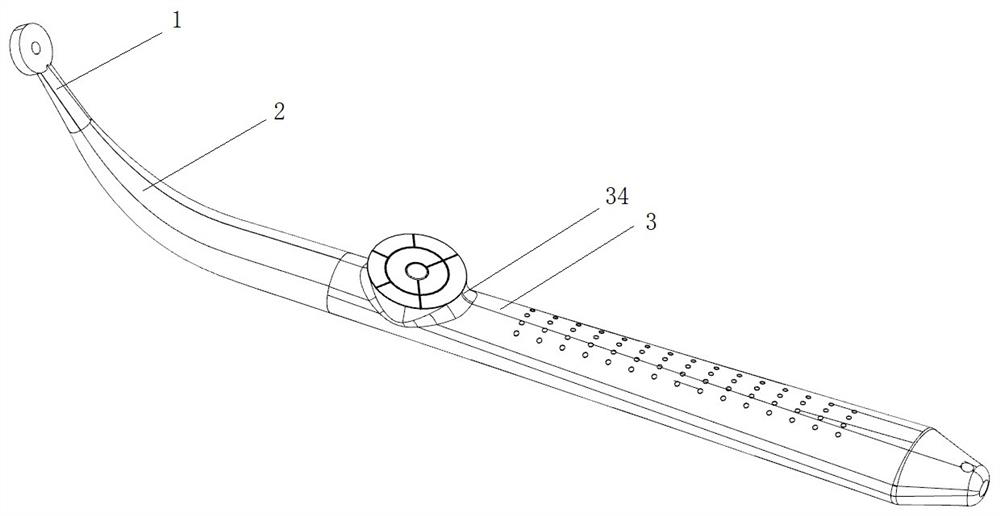

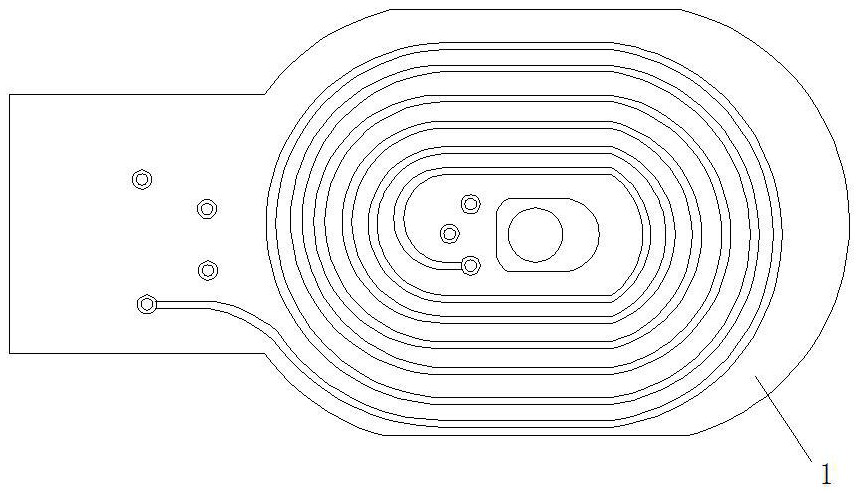

Oral implant detecting and positioning device and method based on constant current source

PendingCN112690773AImprove anti-interference abilityReduce distractionsDentistryDiagnostic recording/measuringFrequency conversionDentistry

The invention relates to an oral implant detecting and positioning device and method based on a constant current source, and belongs to the technical field of oral implant detecting and positioning devices. The oral implant detecting and positioning device comprises a detection sensor, a detection sensor socket and an implant positioning device, and two ends of the detection sensor socket are connected with the detection sensor and the implant positioning device respectively. The implant positioning device mainly comprises a CPU powered by a power supply, a constant voltage source module, a state display control module and a frequency conversion module. The constant voltage source module, the state display control module and the frequency conversion module are connected with the CPU, and a PCB is connected with the CPU through the detection sensor socket. The oral implant detecting and positioning device has the advantages of being high in sensitivity, convenient to operate and accurate in positioning, the problems that an existing method is long in period, inaccurate in positioning, low in positioning speed and the like are solved, it is guaranteed that a doctor rapidly and accurately finds the implant and implements an operation, and medical negligence is reduced.

Owner:CHANGSHA EASYINSMILE INTELLIGENCE TECH CO LTD

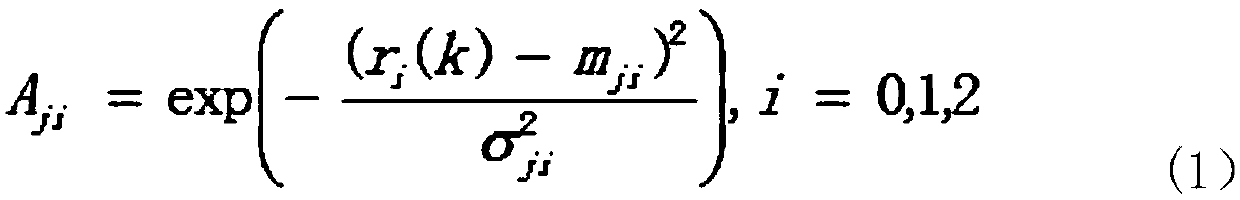

Control method for compartment intelligent service robot travelling based on neural network

InactiveCN108427283AWith learning functionIncrease travel distanceAdaptive controlTraining phaseSimulation

The invention discloses a control method for the compartment intelligent service robot traveling based on the neural network. The method is divided into a training phase and a learning phase, in the training phase, a positioning base station sensor is arranged in a compartment, a robot body is provided with a camera and an infrared detector, position parameters of the robot body are collected as input variables, an SCFNN model architecture is established in the form of at least two input nodes and one output node, and a four-layer operation in an SCFNN model is conducted to obtain an inferenceoutput value; in the learning phase, the input node is subjected to structural learning to generate new rules and subjected to parameter learning to obtain an inference value, a connection weight, the mean value of a member function and the modifier of a standard deviation are corrected, and when each input node enters the SCFNN model, correction is conducted until the SCFNN model is learned. Themethod has the following advantages that the application of the SCFNN neural network can shorten the calculation period and optimize the robot travel distance and speed to achieve the improvement ofartificial intelligence.

Owner:ZHEJIANG IND & TRADE VACATIONAL COLLEGE

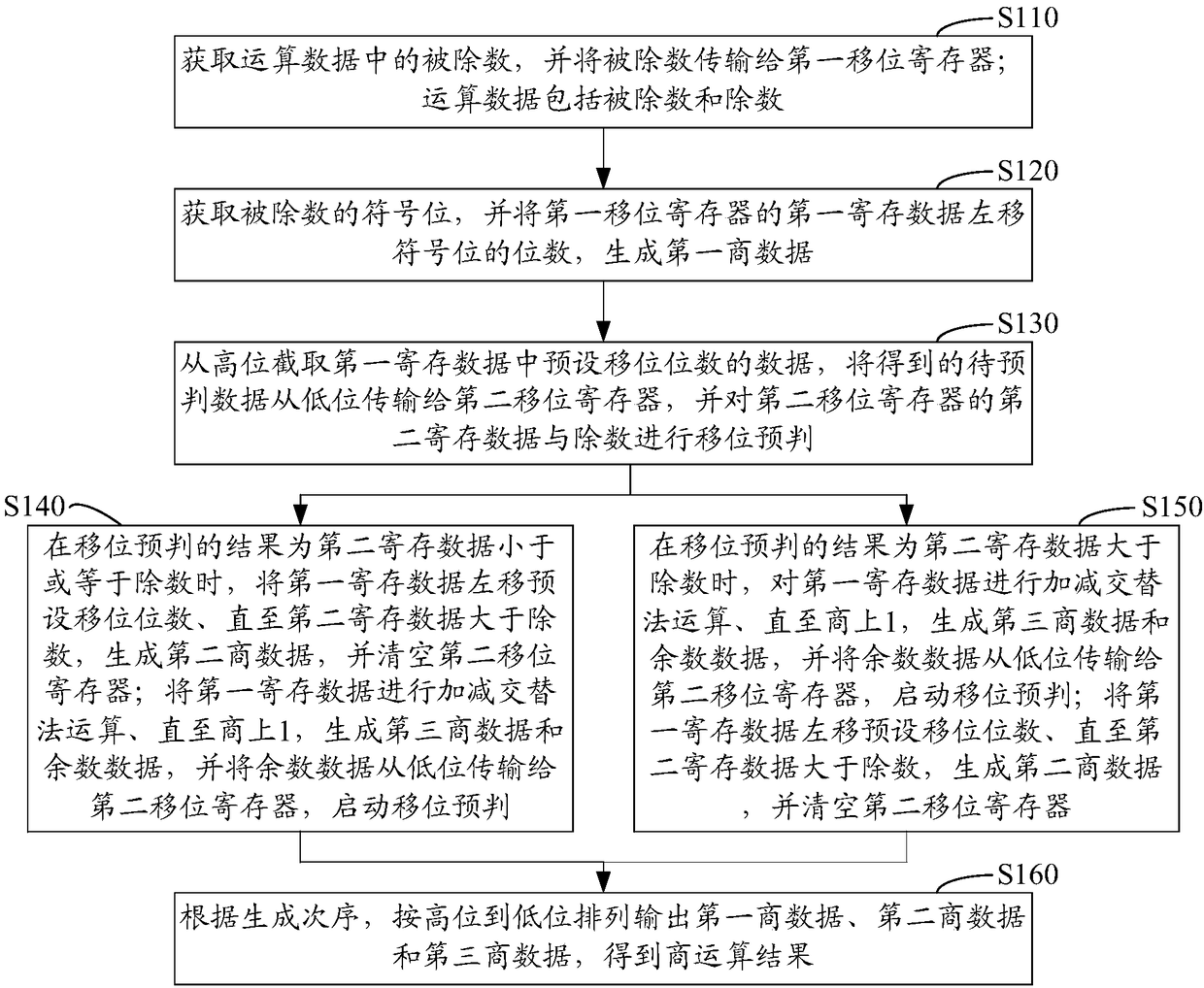

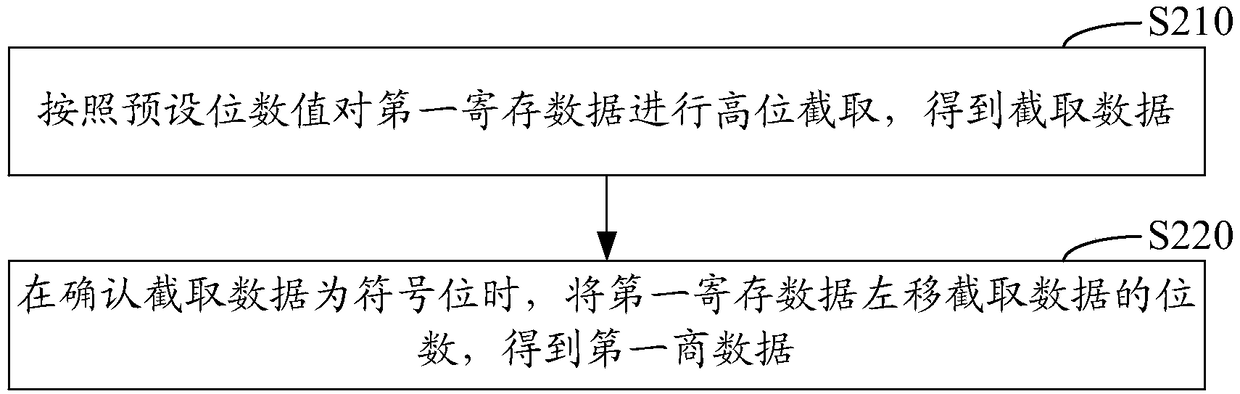

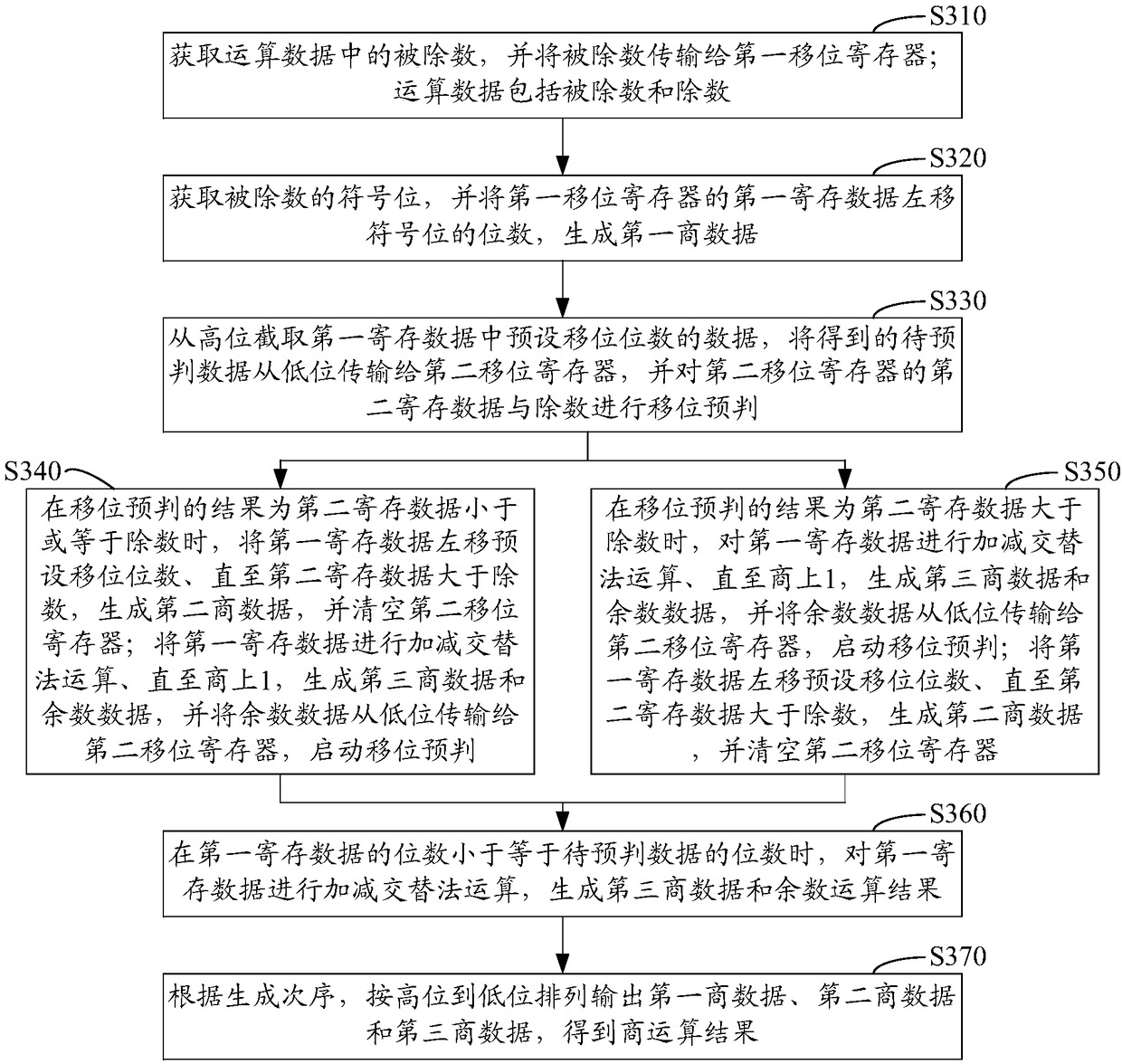

Division operation method, device and equipment

ActiveCN108595146AFast operationShort operation cycleDigital data processing detailsComputer scienceGeneration time

The invention relates to a division operation method, device and equipment. The division operation method comprises the following steps of: generating first quotient data through obtaining a sign bitof a dividend, carrying out shift prejudging on an intercepted to-be-prejudged data and a divisor, and when second register data is smaller than or equal to the divisor, shifting first register data leftwards for a preset shift number until the second register data is greater than the divisor so as to generate second quotient data; when the second register data is greater than the divisor, carrying out alternating addition and subtraction operations on the first register data until 1 is added to a quotient and the second register data is smaller than or equal to the divisor so as to generate third quotient data; and carrying out array output on the first quotient data, the second quotient data and the third quotient data according to generation time from high order to low order so as to obtain a quotient operation result. According to the method, the operation period is shortened, the division operation speed is greatly improved and then the division operation efficiency is improved.

Owner:ZHUHAI JIELI TECH

Self-propelled robot and control method thereof

PendingCN111949021AThe curvature is acquired in timeAvoid collisionCarpet cleanersFloor cleanersComputer visionControl theory

The invention provides a control method of a self-propelled robot, wherein the self-propelled robot is provided with an obstacle sensor. The control method comprises the following steps: detecting anobstacle through the obstacle sensor; extracting at least three feature points of the obstacle; fitting the curvature of at least part of the contour line of the corresponding obstacle based on the atleast three feature points; and controlling the self-propelled robot to advance according to the curvature. By means of the control method, the self-propelled robot can obtain the curvature of the obstacle in time, then the self-propelled robot can determine whether protrusions and recesses exist on the obstacle or not, so that the self-propelled robot can make corresponding strategies, and the self-propelled robot is prevented from colliding with the protrusions on the obstacle.

Owner:SHARKNINJA CHINA TECH CO LTD

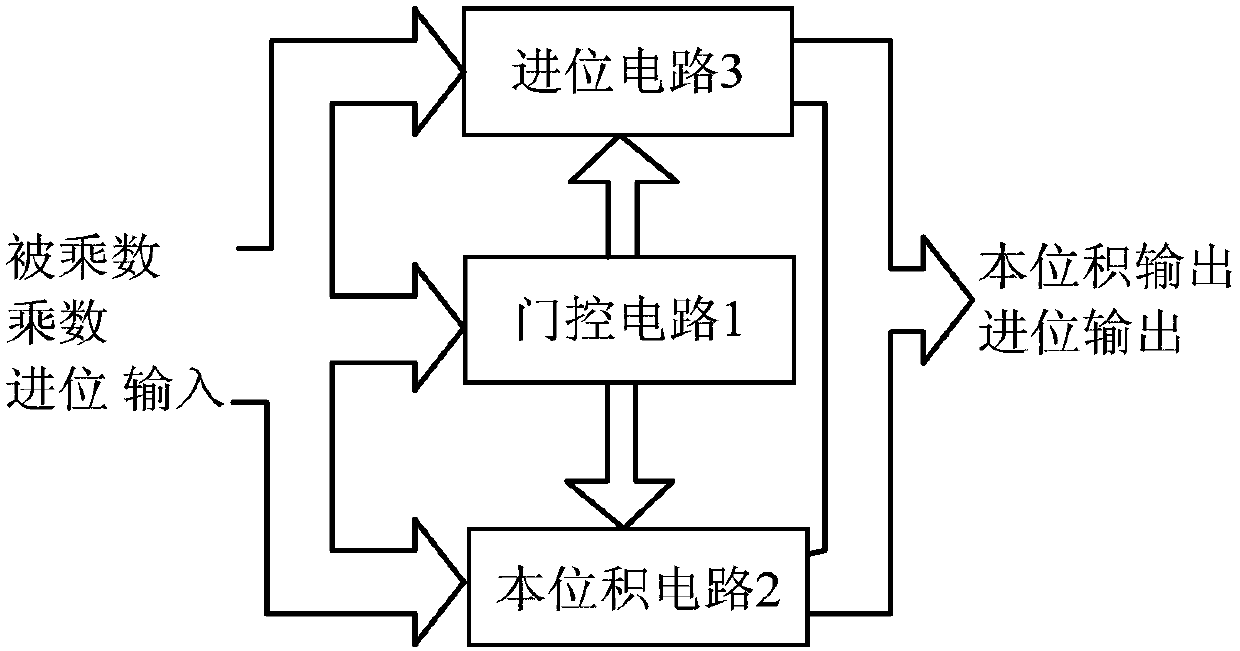

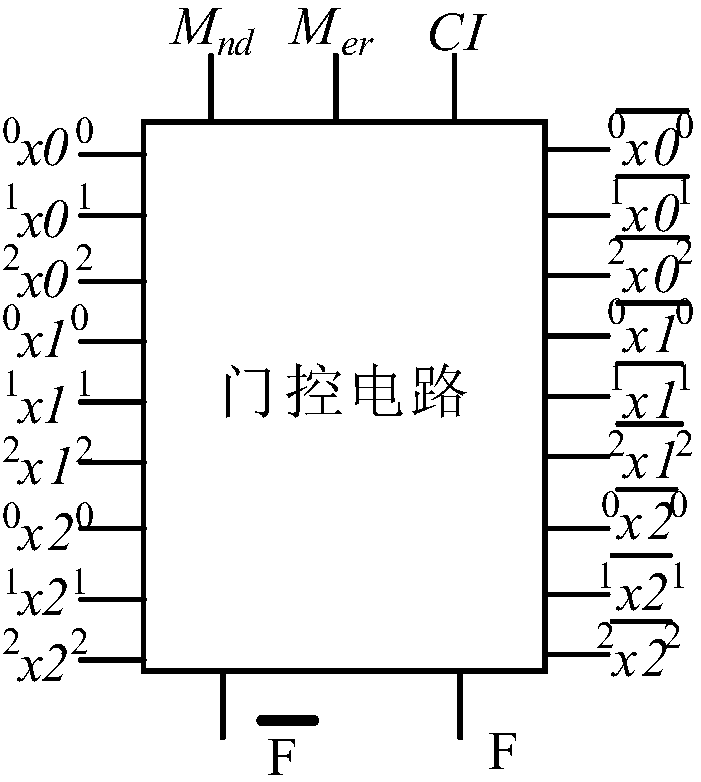

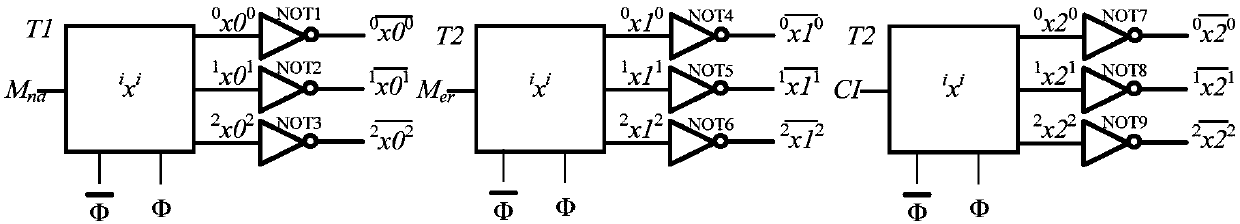

Multiple-valued heat-insulation multiplier unit circuit based on transmission gate structure

ActiveCN107688453AReduce power consumptionWork fasterDigital data processing detailsTransmission gateControl signal

The invention discloses a multiple-valued heat-insulation multiplier unit circuit based on a transmission gate structure. The multiple-valued heat-insulation multiplier unit circuit based on the transmission gate structure comprises a gating circuit, a standard integral circuit and a carry circuit, wherein the gating circuit is separately connected with the standard integral circuit and the carrycircuit; and two multiplicator and low carry signals are connected into the gating circuit, a character control signal is generated and is output to the standard integral circuit and the carry circuit, the standard integral circuit outputs a standard integral signal, and the carry circuit outputs a high carry signal. The multiple-valued heat-insulation multiplier unit circuit based on the transmission gate structure has the advantages that the standard integral circuit and the carry circuit are implemented by a full-heat-insulation mode, charge in the standard integral circuit and the carry circuit is recycled in a full heat-insulation recovery mode, power consumption of the circuit is reduced, meanwhile, multi-valued signals in the standard integral circuit and the carry circuit are implemented by a gating circuit switch controlled binary mode, the working speed of the circuit can be increased, the operation cycle is shortened, the hardware cost of the circuit is reduced, and the areais small.

Owner:NINGBO UNIV

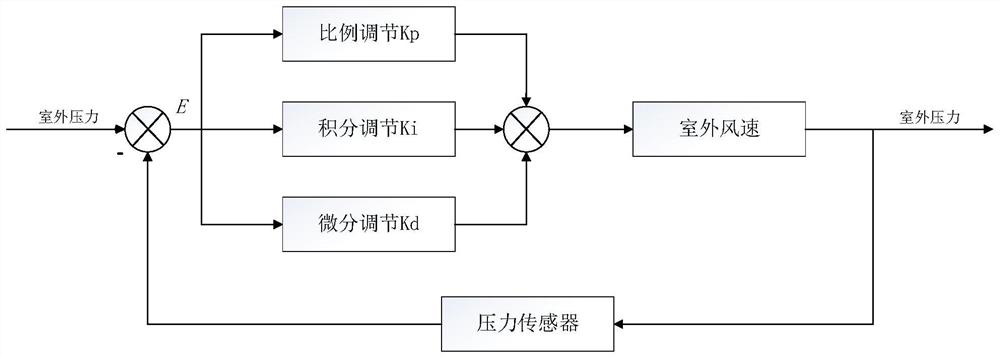

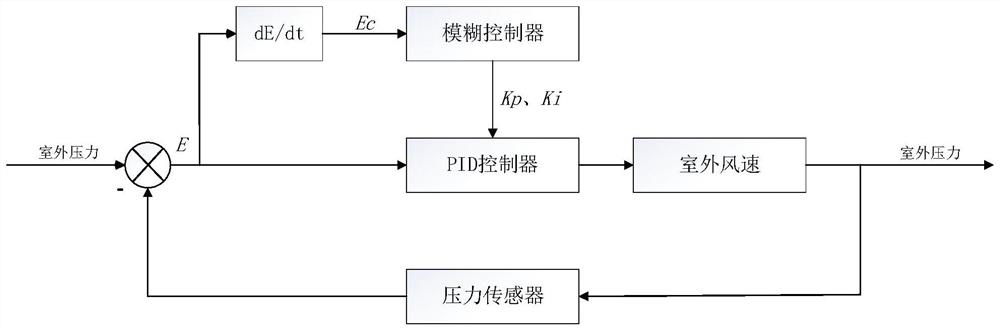

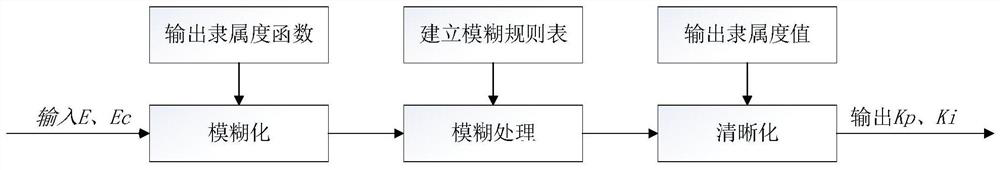

Air conditioner control method and air conditioner

ActiveCN112904709ATime-sensitiveBoth stableControllers with particular characteristicsDefuzzificationControl signal

The invention provides an air conditioner control method. The method comprises the steps of determining a pressure error value and a pressure error change value based on an actual pressure value and a target pressure value; defining a fuzzy subset, establishing a discrete domain, and calculating a pressure error value and a membership degree of a pressure error change value to the fuzzy subset; adaptively generating a fuzzy rule table according to system characteristics and environmental conditions; performing defuzzification according to a gravity center method, and determining a proportion parameter increment and an integral parameter increment; and based on a calculation formula of a PID controller, the proportion parameter increment and the integral parameter increment, obtaining a control signal of an outdoor fan, and then adjusting the speed of the outdoor fan. According to the air conditioner control method, the link of manual trial and error in the process of establishing the fuzzy rule table is omitted, resources and cost are saved, meanwhile, the operation period of the fuzzy rule table is effectively shortened, and the air conditioner operation process is more stable and reliable. The invention further provides the air conditioner adopting the method, and the air conditioner has the advantages of timeliness and stability.

Owner:QINGDAO HISENSE ELECTRONICS EQUIP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com