Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

40results about How to "Avoid electrical influence" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

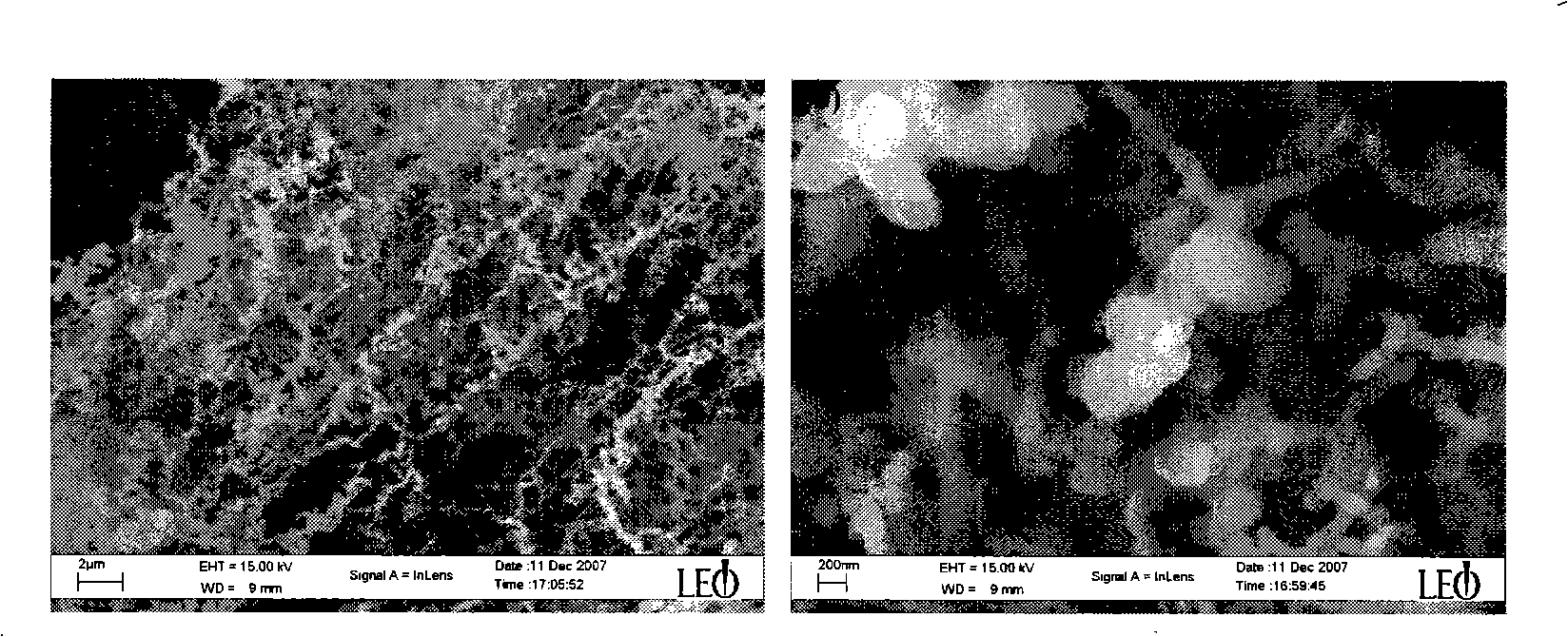

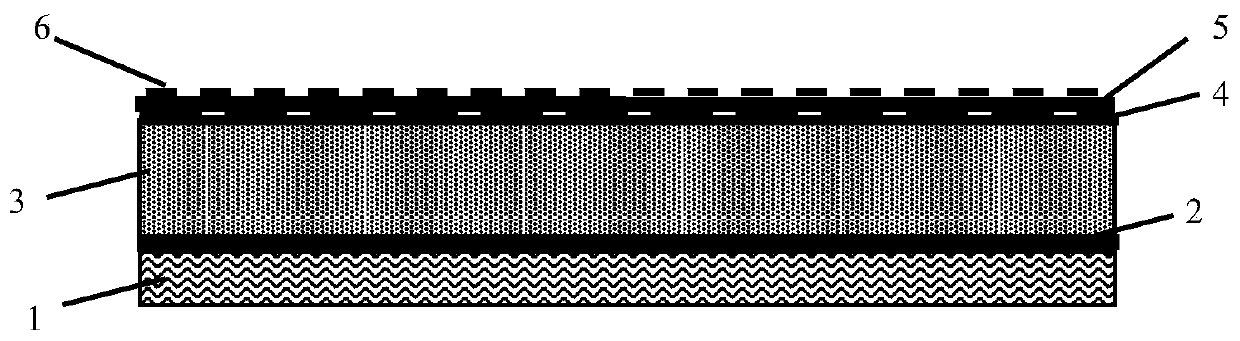

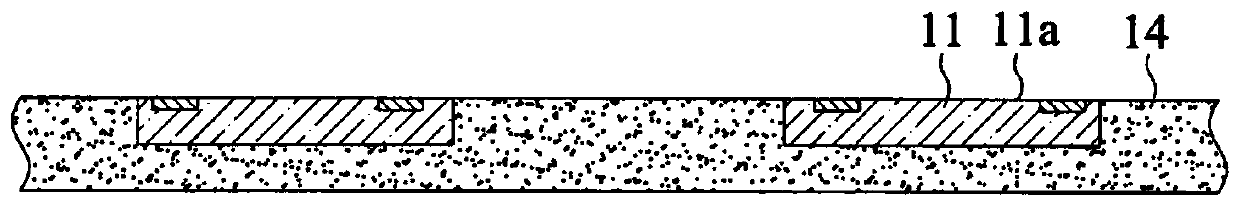

A radar/infrared compatible invisible coating resistant to 600 DEG C and a preparing method thereof

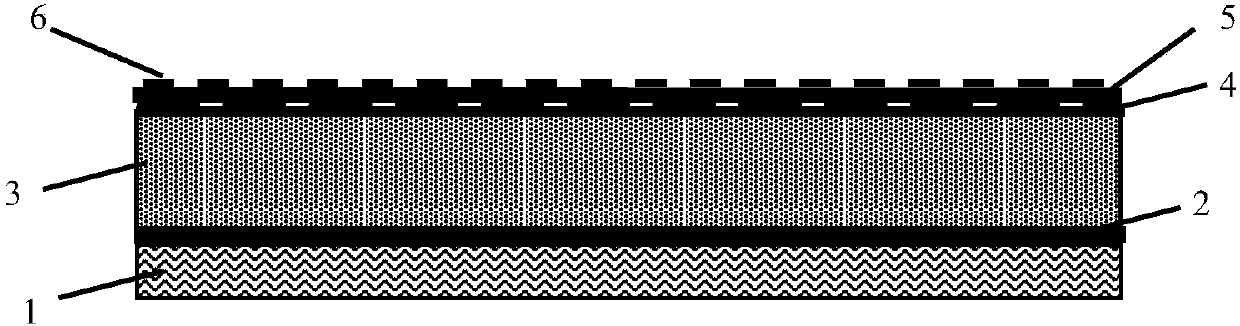

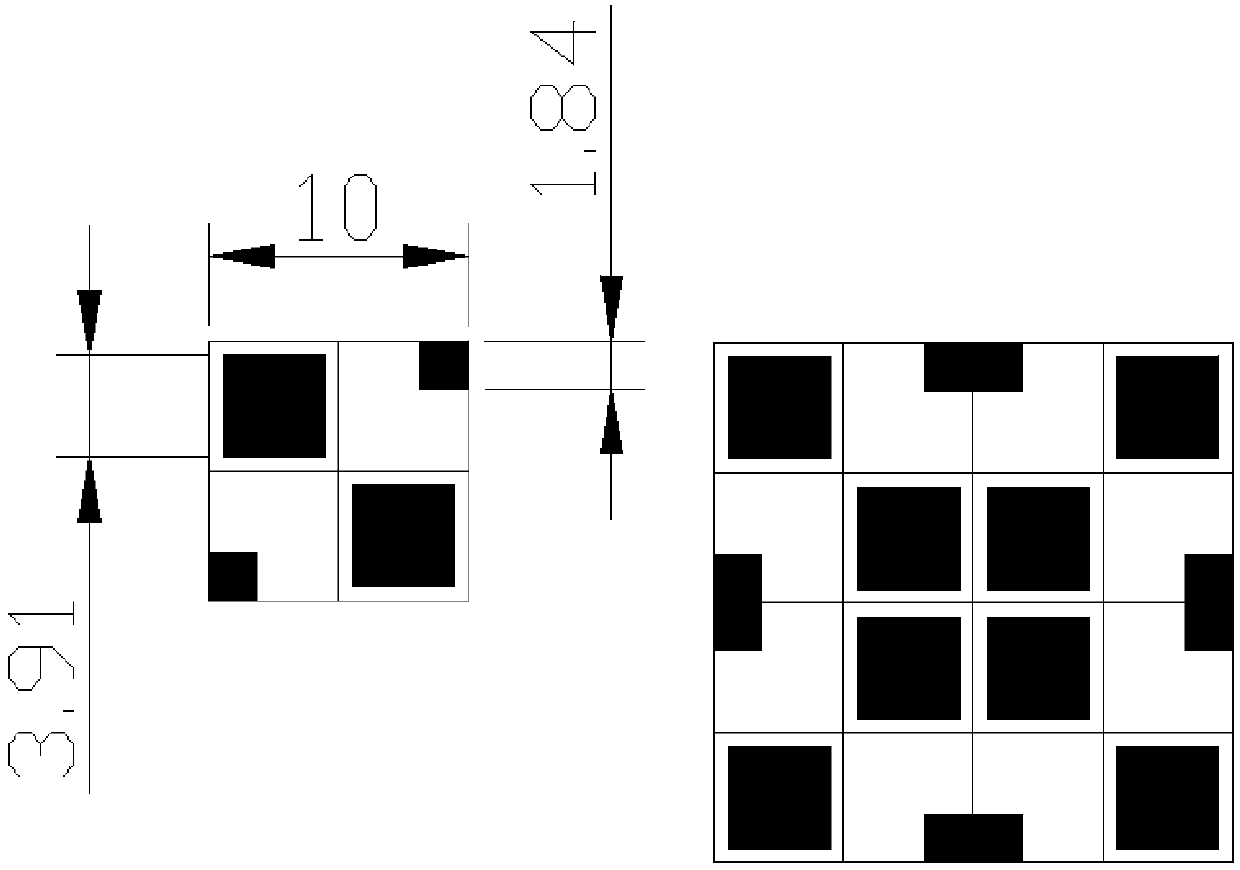

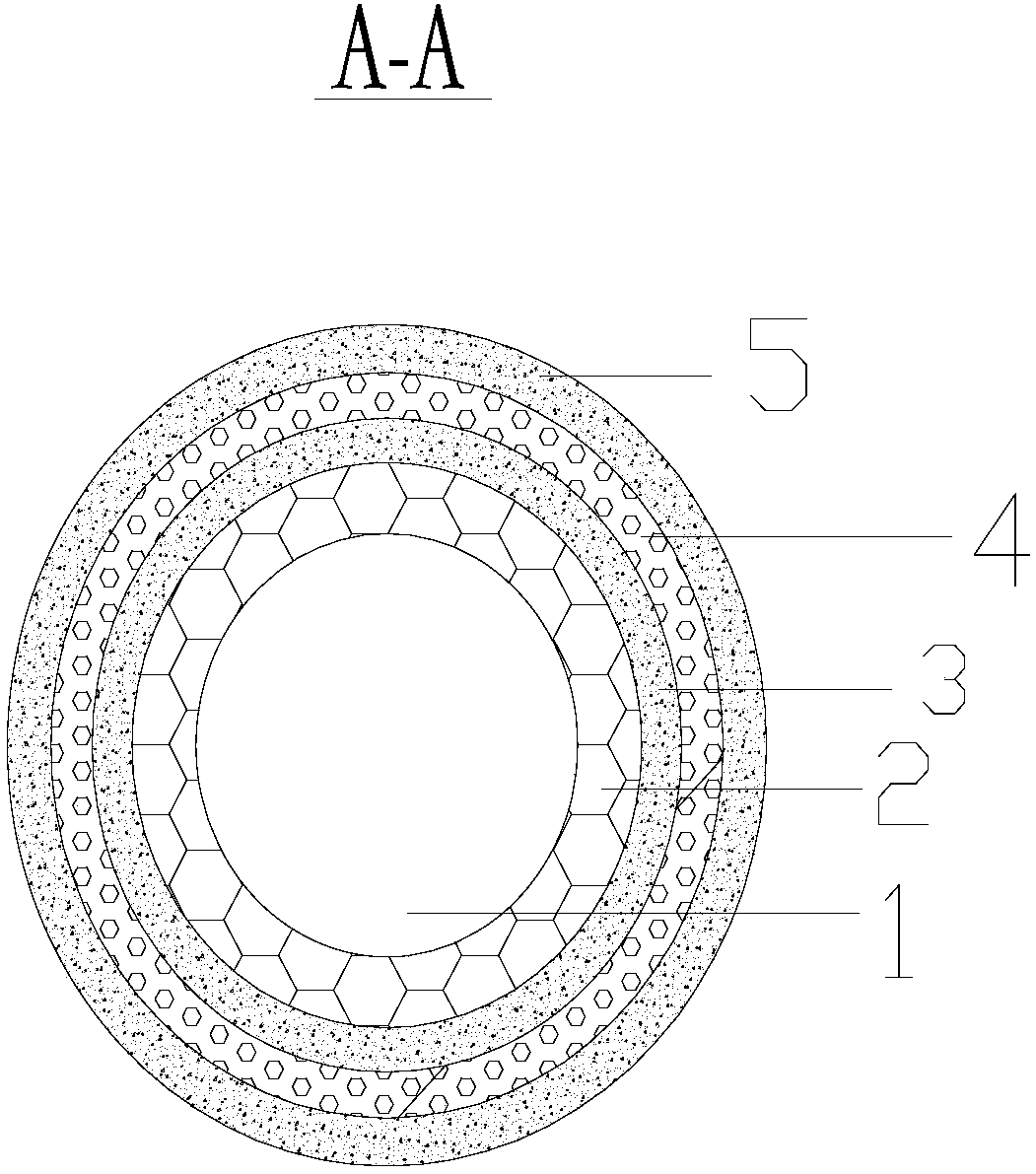

ActiveCN107747080AImprove absorbing performanceHigh radar bandMolten spray coatingMagnetic/electric field screeningElectrical conductorHigh reflectivity

A radar / infrared compatible invisible coating resistant to 600 DEG C is disclosed. The invisible coating is on the surface of a metal substrate, and includes an adhesive layer, a 8YSZ-Al2O3 ceramic bottom layer, a high-temperature resistance coating, a 8YSZ isolating layer and a high-temperature conductor coating in order from bottom to top form the surface of the metal substrate. The high-temperature resistance coating and the high-temperature conductor coating are in paster forms, and pasters are arranged periodically. A preparing method of the invisible coating is also disclosed. The structure of the invisible coating has a radar / infrared compatible stealth function. A resistance type periodic structure is introduced so that the invisible coating has a good wave absorbing function, anda defect that traditional wave absorbing coatings need absorbents so as to cause unsatisfied wave absorbing performance, big influences on processes and instable performance is solved. A conductor periodic structure is introduced to the surface layer, and the radar / infrared compatible stealth function is achieved by utilizing a high reflectivity characteristic for the infrared waveband and a hightransmittance characteristic for the radar waveband.

Owner:NAT UNIV OF DEFENSE TECH

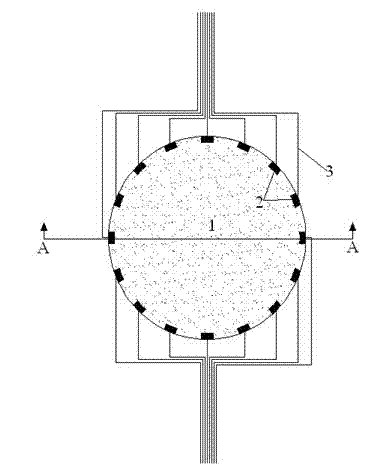

Interface pressure distribution testing sensing element

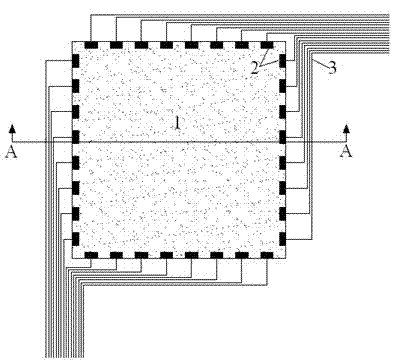

InactiveCN102410894AThin structureHigh precision of force sensitivityForce measurement using piezo-resistive materialsElectrical resistance and conductanceConductive polymer composite

The invention discloses an interface pressure distribution testing sensing element. The interface pressure distribution testing sensing element comprises a sensing film, electrodes uniformly arranged around the sensing film at intervals, a lead connected with the electrodes and an upper and lower insulating paint layer. The sensing film is made from a conductive polymer composite material provided with a piezo-resistive sensitivity characteristic, and the electrodes and the lead are used for outputting resistivity information of the sensing film in different positions. When in testing, the lead is connected with a testing instrument, the electrical impedance imaging technology is used for acquiring, testing and computing so as to obtain the resistivity distribution of the sensing film in different positions, and then the pressure distribution can be obtained through the relationship between the sensing film pressure and the resistivity. The interface pressure distribution testing sensing element can be used for measuring the interface pressure distribution and change, and has the advantages of simple structure, ultra-thin film, strong flexibility, high resolution and precision, large measuring range and low cost.

Owner:CHINA UNIV OF MINING & TECH

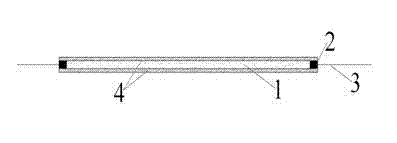

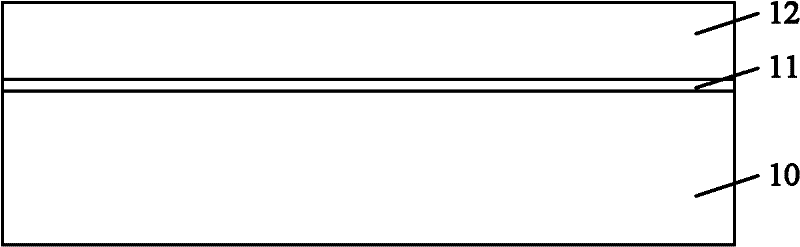

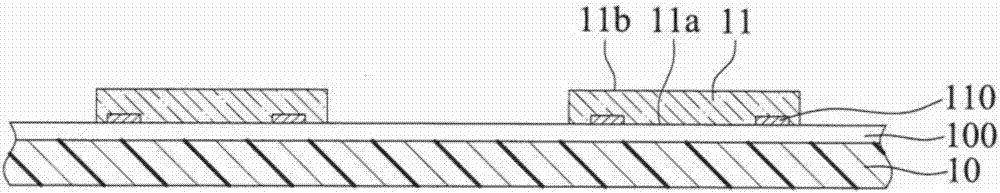

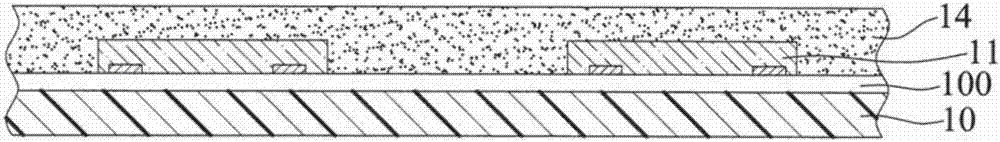

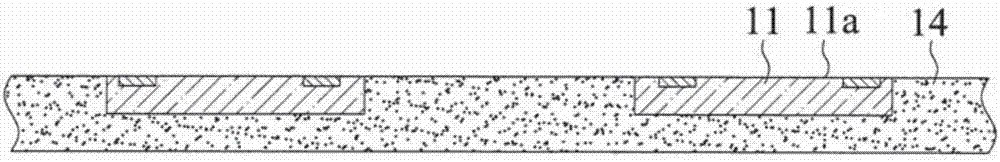

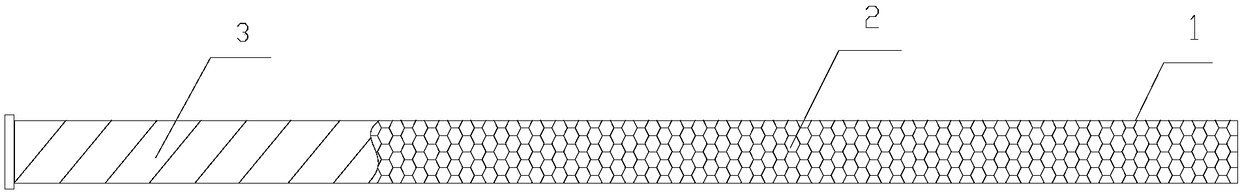

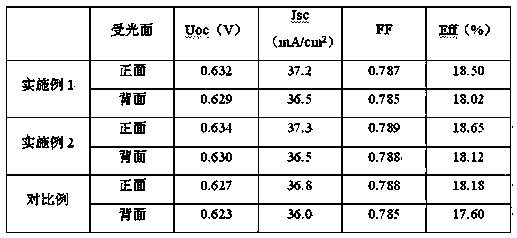

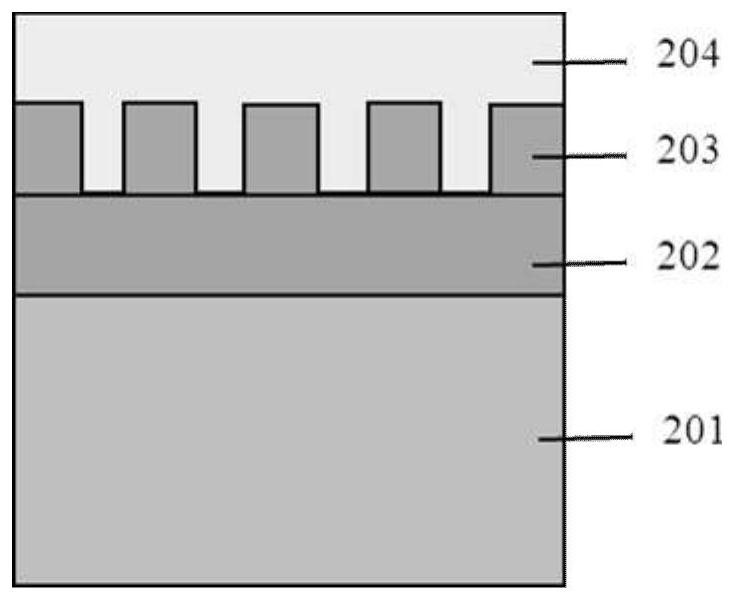

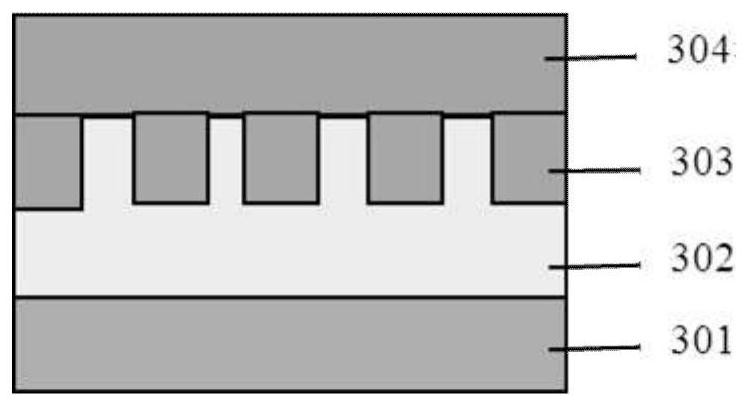

Manufacturing method for double-face illuminated crystalline silicon solar cell

ActiveCN102623563AAvoid electrical influenceEasy to operateFinal product manufactureSemiconductor devicesElectricityMetal electrodes

The invention discloses a manufacturing method for a double-face illuminated crystalline silicon solar cell. The method comprises the following steps of: (1) washing a raw silicon chip, and removing a damaged layer from the back face of the raw silicon chip; (2) performing single-face boron diffusion on the front face of the silicon chip in a back-to-back way, wherein the back face of the silicon chip is a diffusing face; (3) depositing a mask layer on the back face of the diffused silicon chip; (4) washing the front face of the silicon chip, removing a damaged layer, performing texturing, and removing a diffraction diffusion layer; (5) performing single-face phosphorus diffusion on the back face of the silicon chip in a back-to-back way, wherein the front face of the silicon chip is the diffused face; (6) removing a peripheral joint, impurity glass and a mask which are formed by the diffusion; (7) depositing an anti-reflection coating on each of the two faces of the silicon chip; and (8) printing a metal electrode on each of the two faces of the silicon chip, and performing sintering to obtain the double-face illuminated crystalline silicon solar cell. The influence of diffraction on the electrical properties of the cell is avoided, and the photoelectric efficiency of the cell can be improved by 0.3 to 0.5 percent; and the method has positive practical significance.

Owner:CSI CELLS CO LTD +1

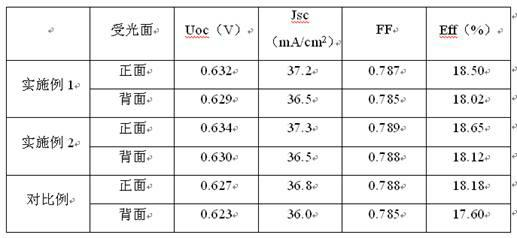

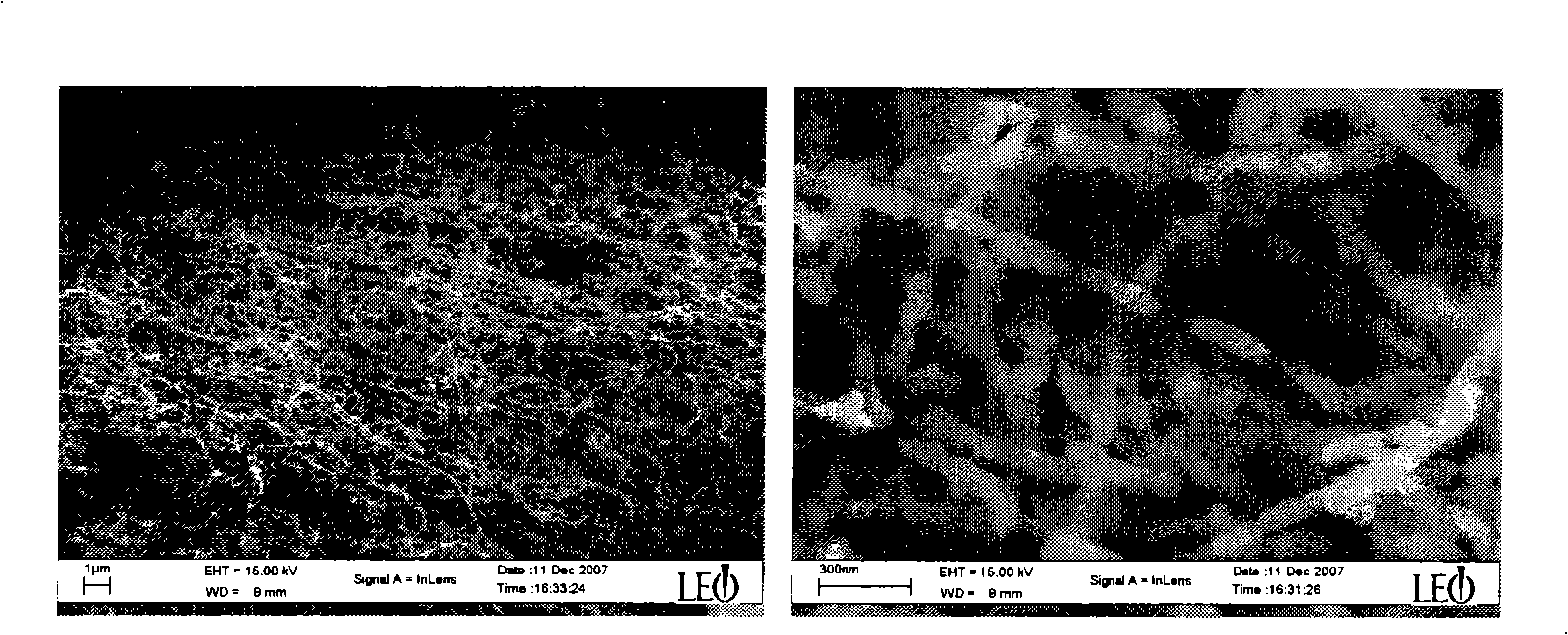

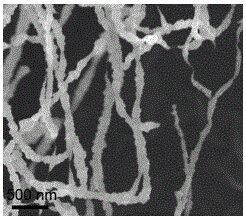

Method for synthesizing nano cable structure of silica-coated single-walled carbon nano tube

InactiveCN101513997ASimple processAvoid structureSilicaInsulated cablesInsulation layerCarbon nanotube

The invention relates to synthesis technology of nano cable, and in particular provides a preparation method for synthesizing the nano cable structure of the amorphous silica-coated single-walled carbon nano tube by an arc discharge method. The preparation method comprises the following steps: adopting a cathode and anode DC arc discharge mode to realize in-situ preparation; the anode is a consumptive anode formed by pressing graphite, silicon powder, catalyst and growth promoter; after arc starting discharge, carrying out coevaporation of raw materials including the graphite, the silicon powder, the catalyst and the growth promoter; and completing in-situ synthesis of the nano cable structure of one or more silica-coated single-walled carbon nano tubes. Silica has the characteristics of good thermal stability, high dielectric constant, small drain current and high compressive strength, and the like. and is an ideal material of insulation layers used in nano devices such as the nano cable and a field effect transistor; in addition, a core body of the developed nano cable consists of one or more single-walled carbon nano tubes, which is favorable for bringing into playing the nano size effect of the single-walled carbon nano tube and improving the performances such as efficiency and sensitivity of a fabricated nano device.

Owner:INST OF METAL RESEARCH - CHINESE ACAD OF SCI

A 600°C radar- and infrared-compatible stealth coating and its preparation method

ActiveCN107747080BImprove absorbing performanceHigh radar bandMolten spray coatingMagnetic/electric field screeningElectrical conductorEngineering

The invention discloses a radar- and infrared-compatible stealth coating capable of withstanding a temperature of 600°C. The stealth coating is located on the surface of a metal substrate, starting from the surface of the metal substrate, and sequentially including an adhesive layer, 8YSZ‑Al 2 o 3 Ceramic bottom layer, high-temperature resistance coating, 8YSZ isolation layer and high-temperature conductor coating; the high-temperature resistance coating and high-temperature conductor coating are all in the form of patches, and the patches are arranged periodically. The invention also discloses a specific preparation method of the stealth coating. The coating structure proposed by the present invention has radar and infrared compatible stealth functions. Due to the introduction of a resistive periodic structure, it can have better wave-absorbing performance, breaking through the unsatisfactory wave-absorbing performance caused by the addition of absorbents in traditional wave-absorbing coatings. , Insufficient impact on the process and unstable performance; the surface layer introduces a conductive periodic structure, and uses its high reflection in the infrared band and high transmission in the radar band to realize the radar and infrared compatible stealth function.

Owner:NAT UNIV OF DEFENSE TECH

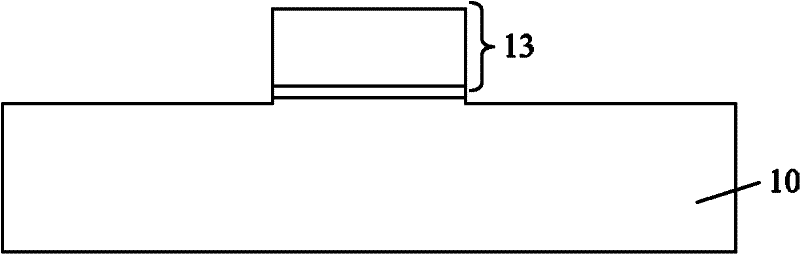

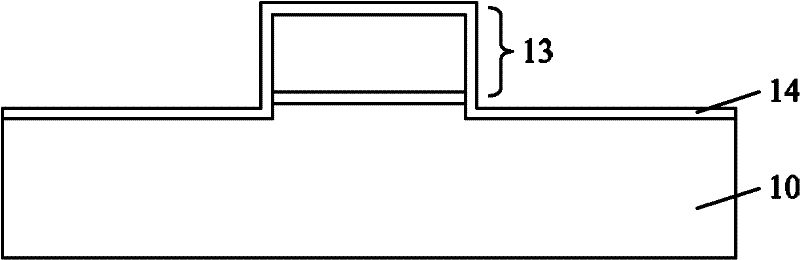

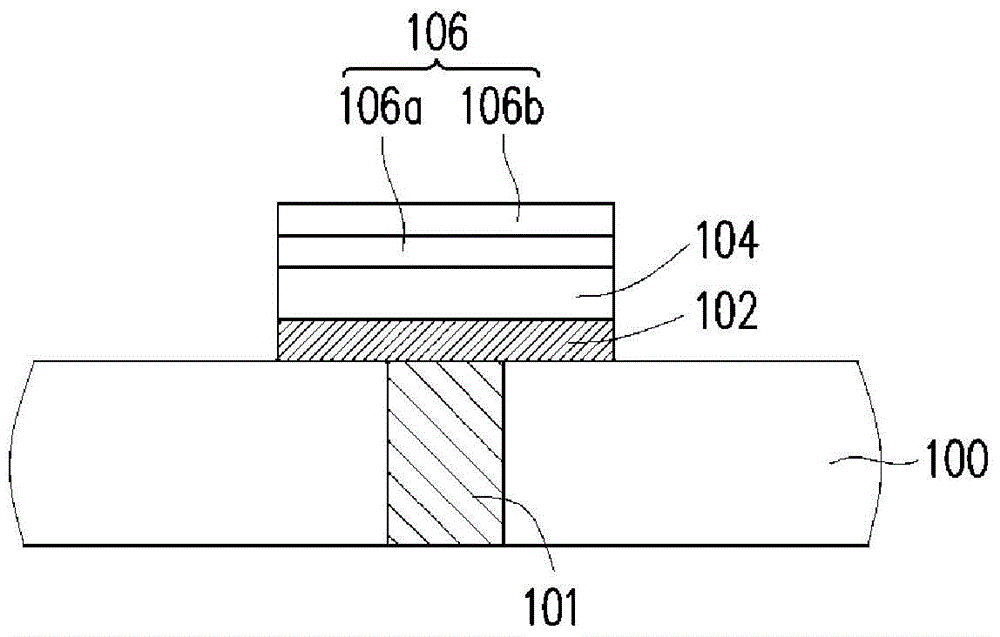

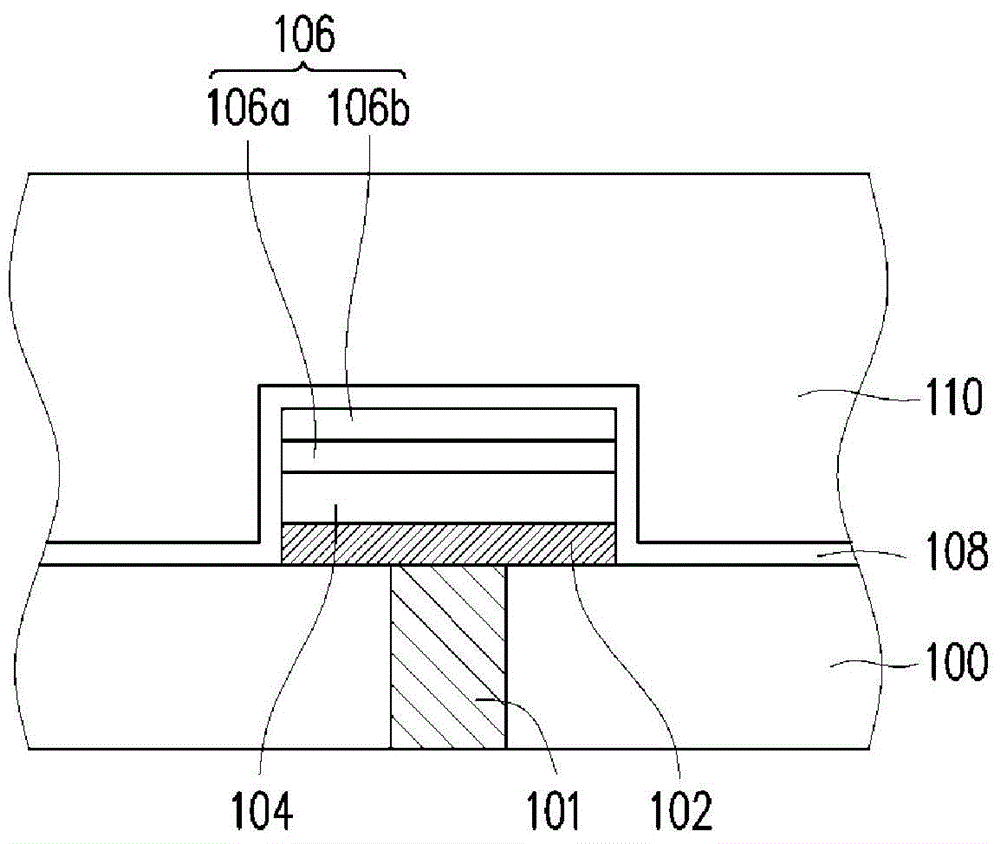

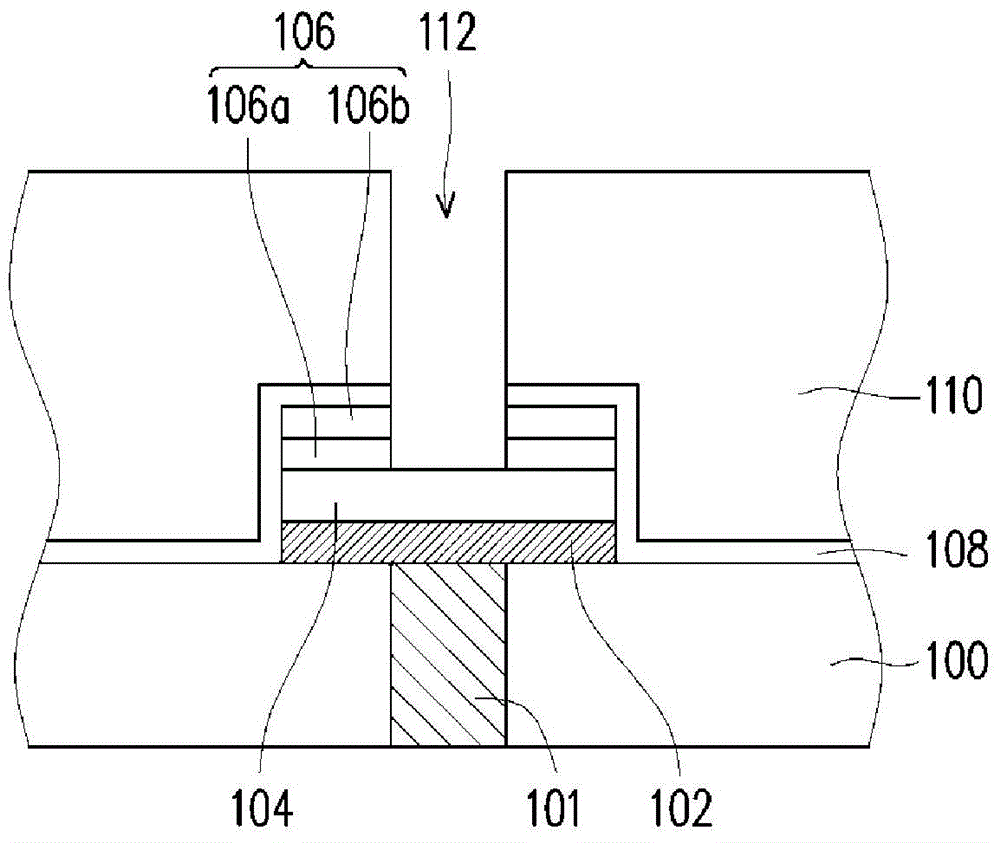

Manufacturing method of MOS (metal oxide semiconductor) device

InactiveCN102543743AEliminate spacingAvoid electrical influenceSemiconductor/solid-state device manufacturingGate dielectricHeight difference

The invention provides a manufacturing method of an MOS (metal oxide semiconductor) device. The manufacturing method comprises the following steps of: providing a semiconductor substrate and forming a hard mask layer on the surface of the semiconductor substrate; etching the hard mask layer and the semiconductor substrate to form a first groove, wherein the bottom surface of the first groove is lower than the surface of the semiconductor substrate, and the height difference exists between the two; forming a gate dielectric layer on the surface of the semiconductor substrate at the bottom of the first groove; filling the first groove to form a gate electrode; removing the hard mask layer; and forming a thin film oxidation layer on the surface of the semiconductor substrate through a heat oxidation process, wherein the bottom surface of the thin film oxidation layer is higher than or flush with that of the gate dielectric layer. According to the manufacturing method disclosed by the invention, the bottom of the gate electrode is lower than the surface of the semiconductor substrate, and the height difference exists between the two; and when the thin film oxidation layer is formed by heat oxidation, the thickness loss of the semiconductor substrate is not greater than the height difference, so that a spacing interval between the bottom of the gate electrode and a channel is further eliminated and a silicon recess can be further prevented from affecting the electrical properties of the MOS device.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

Electronic package and method of manufacture

ActiveCN107958894AImmune to electromagnetic interferenceElectrically functioning normallySemiconductor/solid-state device detailsSolid-state devicesElectromagnetic interferenceEngineering

Provided is an electronic package comprising a carrier structure, an electronic element and a shielding member disposed on the carrier structure, an encapsulating layer formed on the carrier structurefor encapsulating the electronic element and the shielding member, a metallic layer formed on the encapsulating layer and electrically connected to the shielding member, and an alignment member disposed at a side of the encapsulating layer, thereby allowing the periphery of the electronic element to be covered by the shielding member and the metallic layer to avoid external electromagnetic interference.

Owner:SILICONWARE PRECISION IND CO LTD

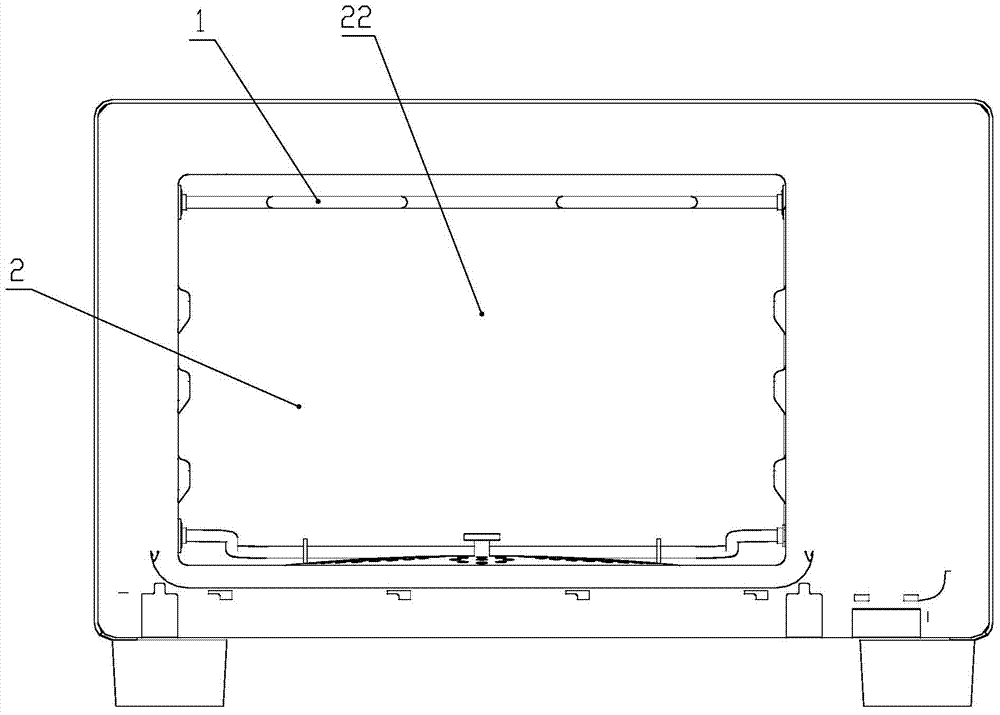

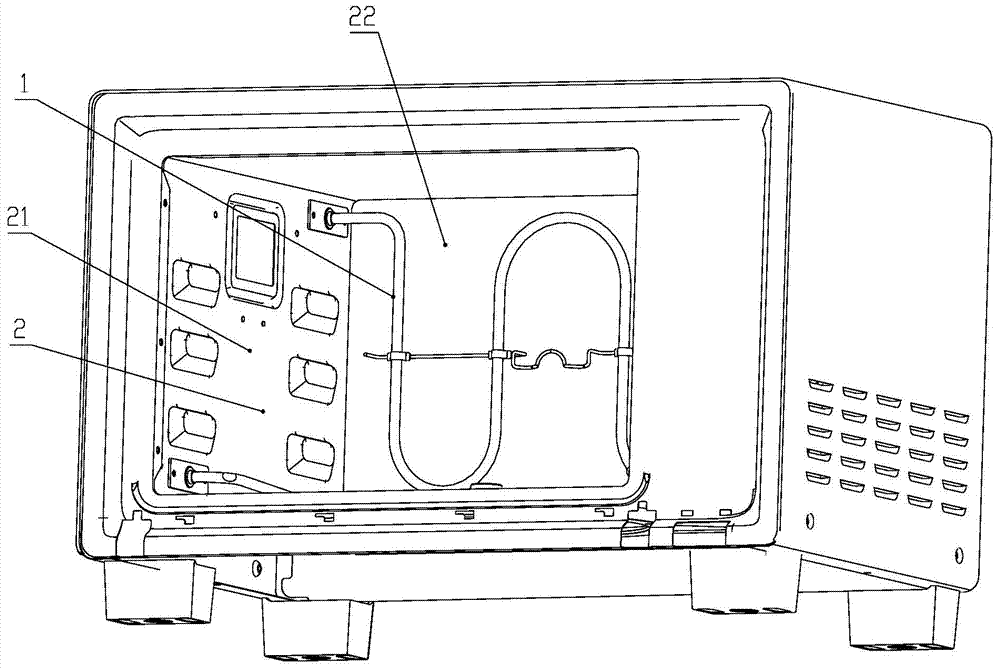

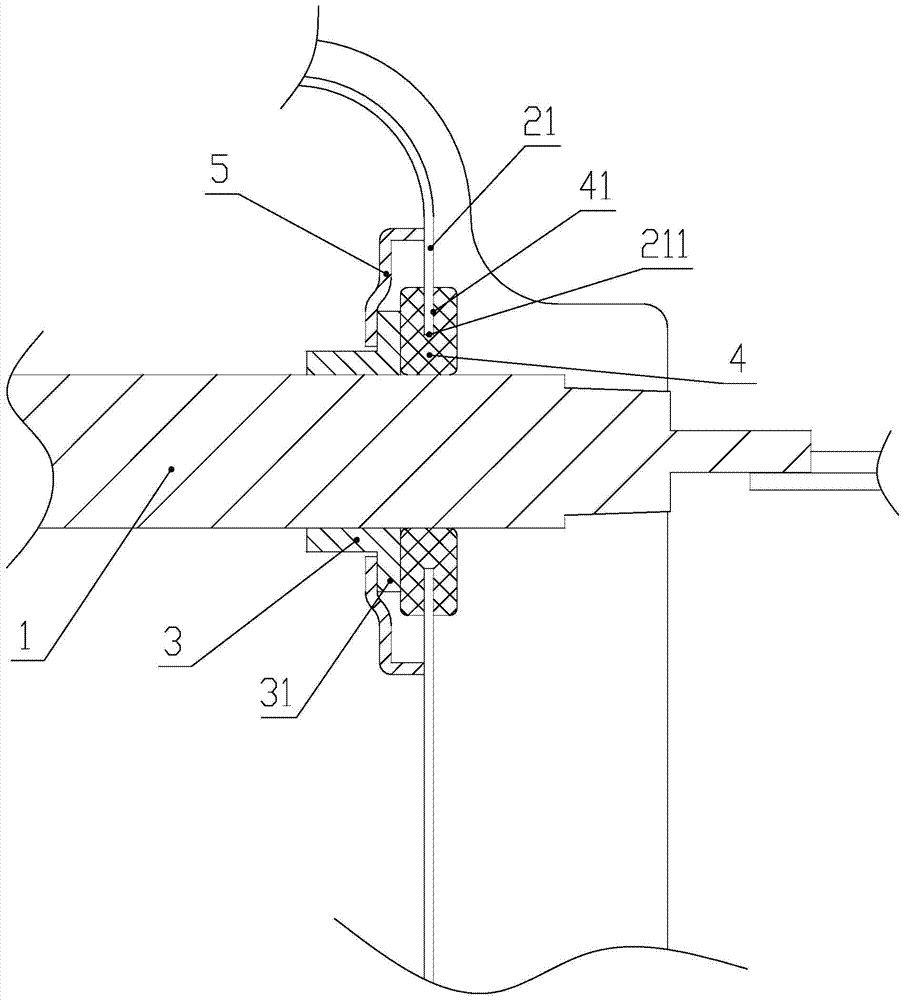

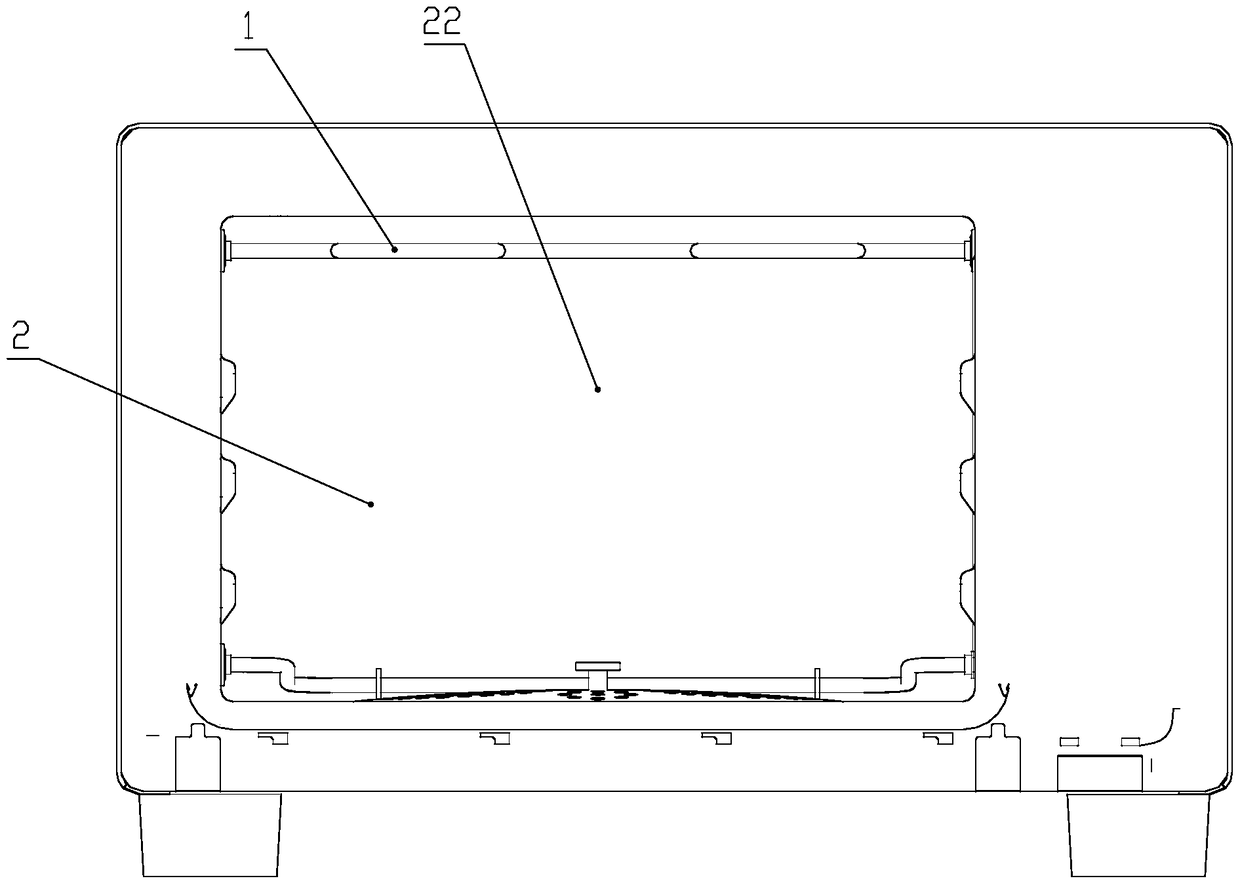

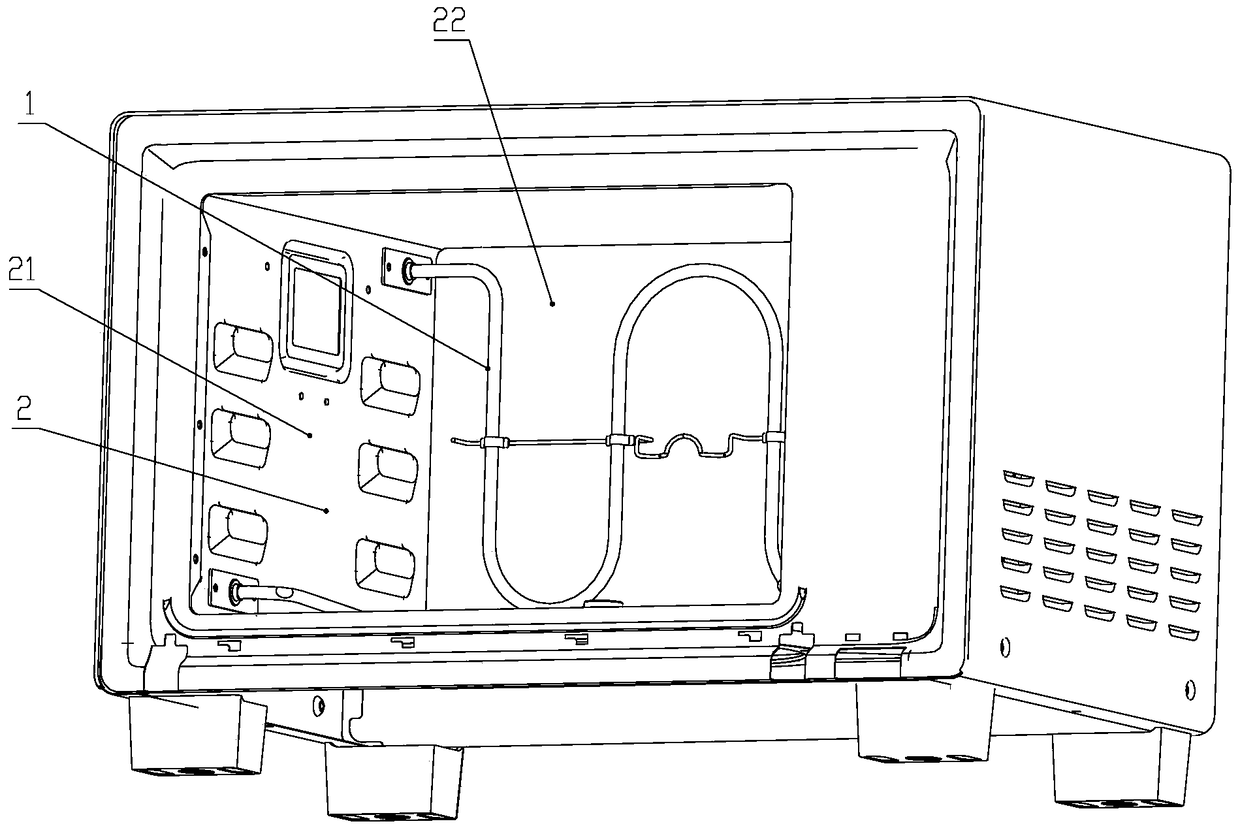

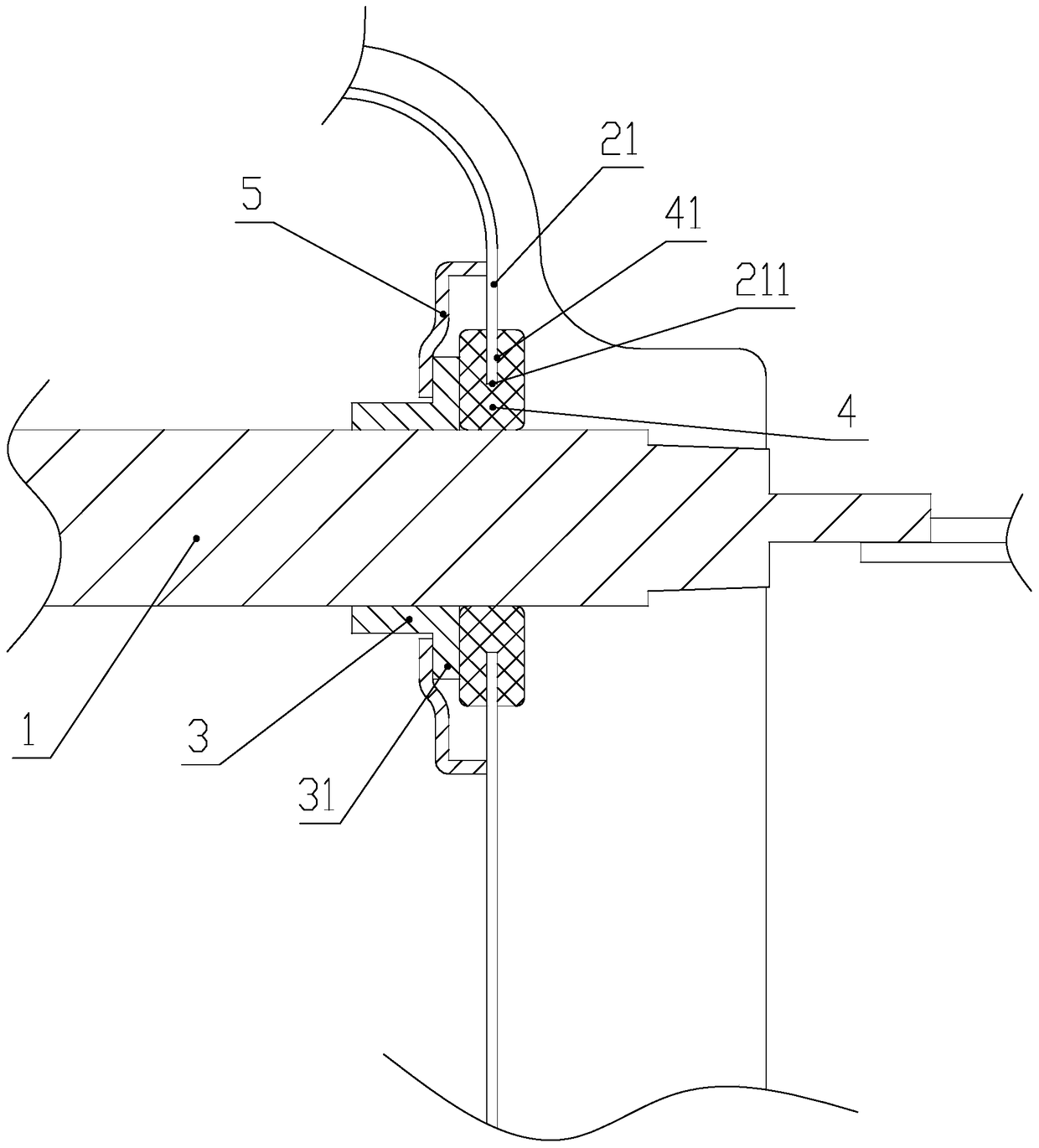

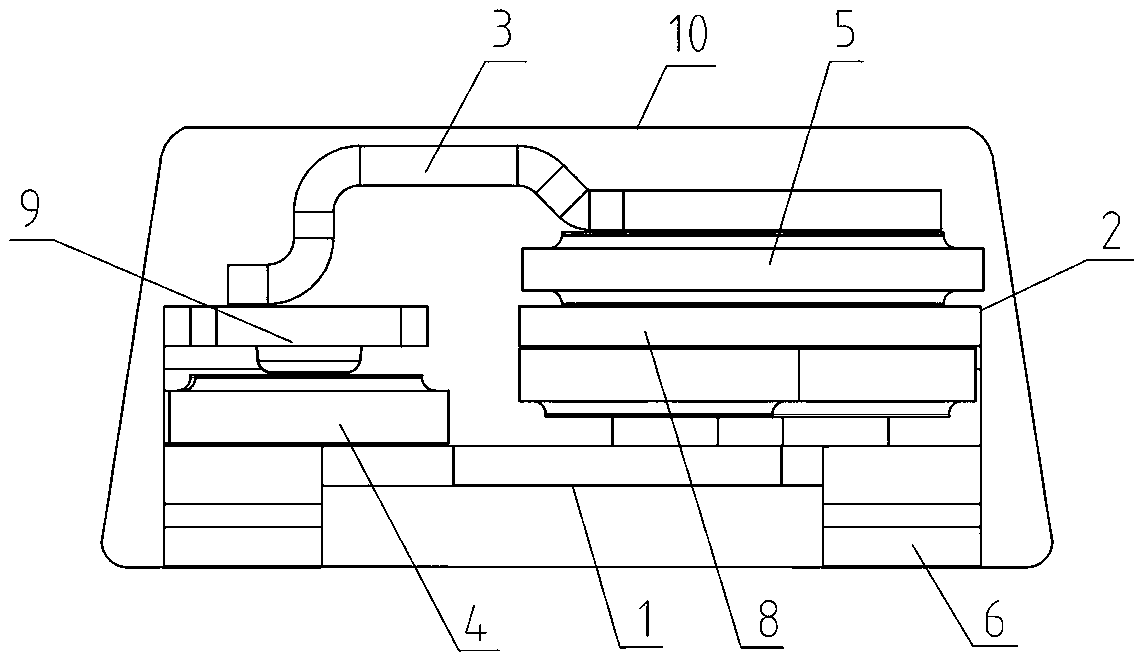

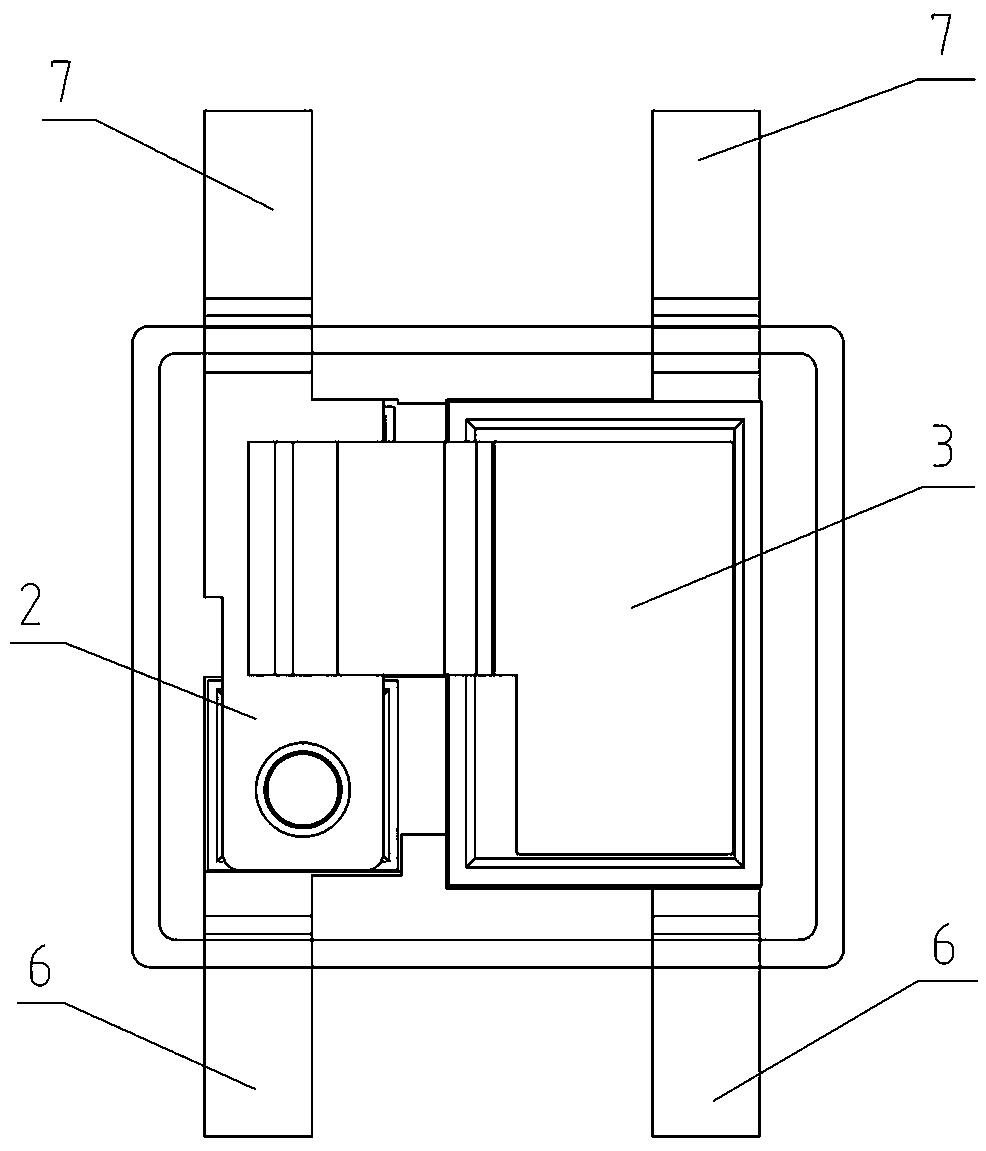

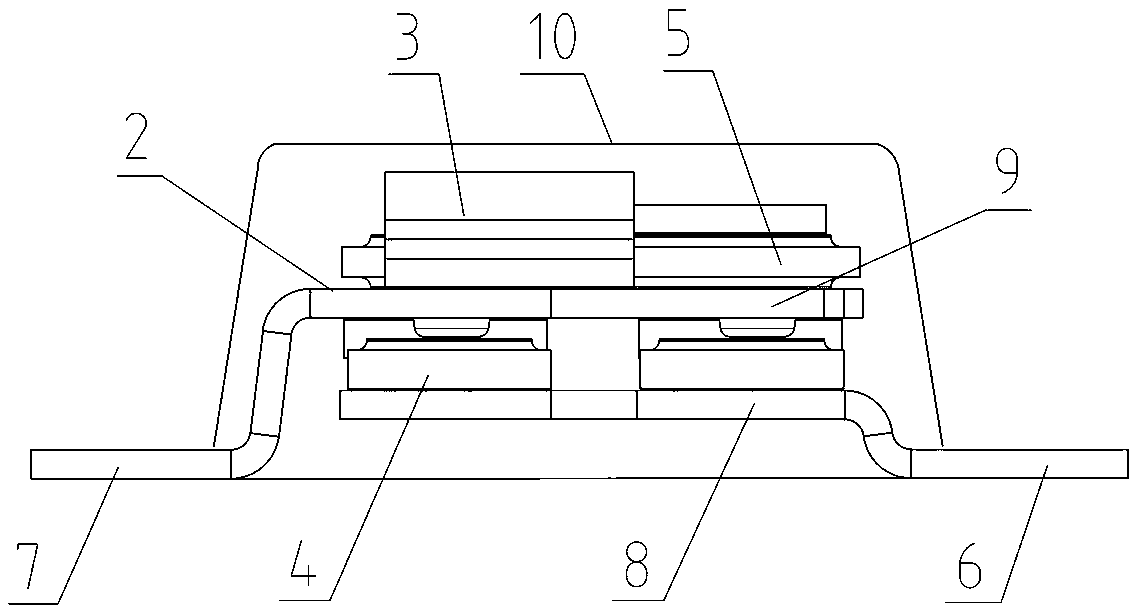

Turnable-heating-tube mounting structure and electric oven

Owner:HAIER GRP CORP +1

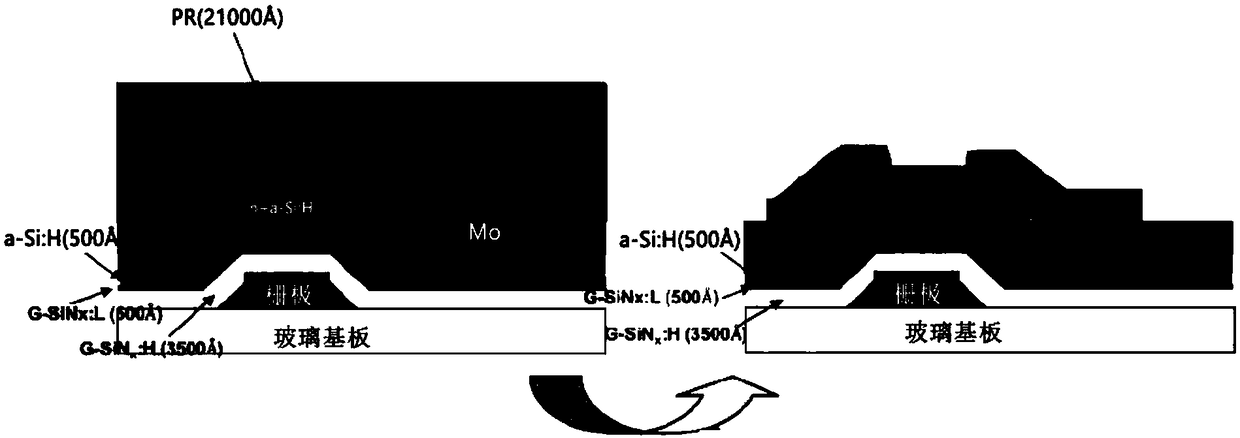

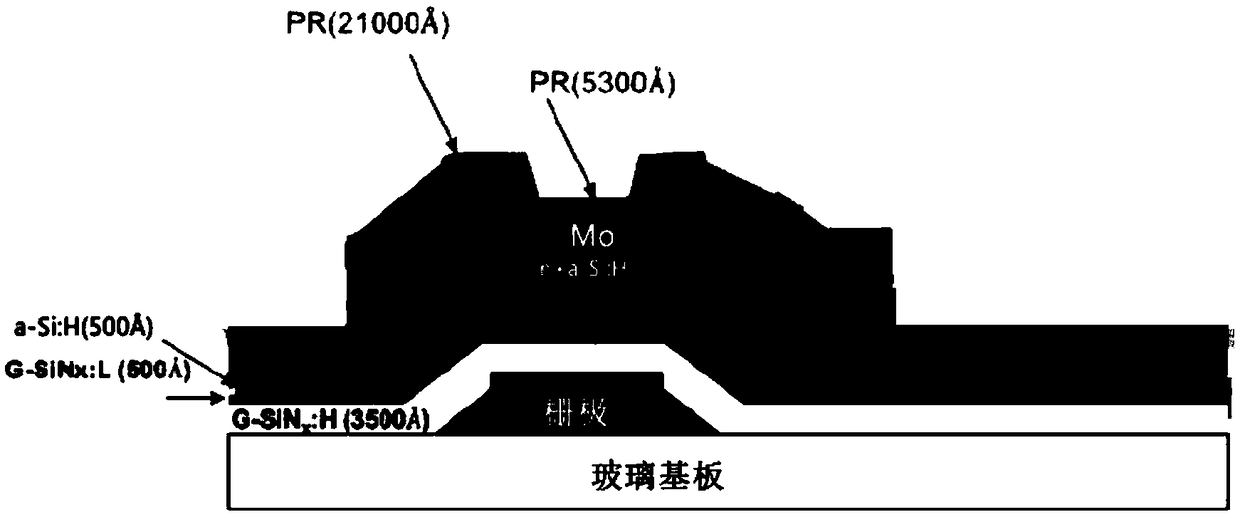

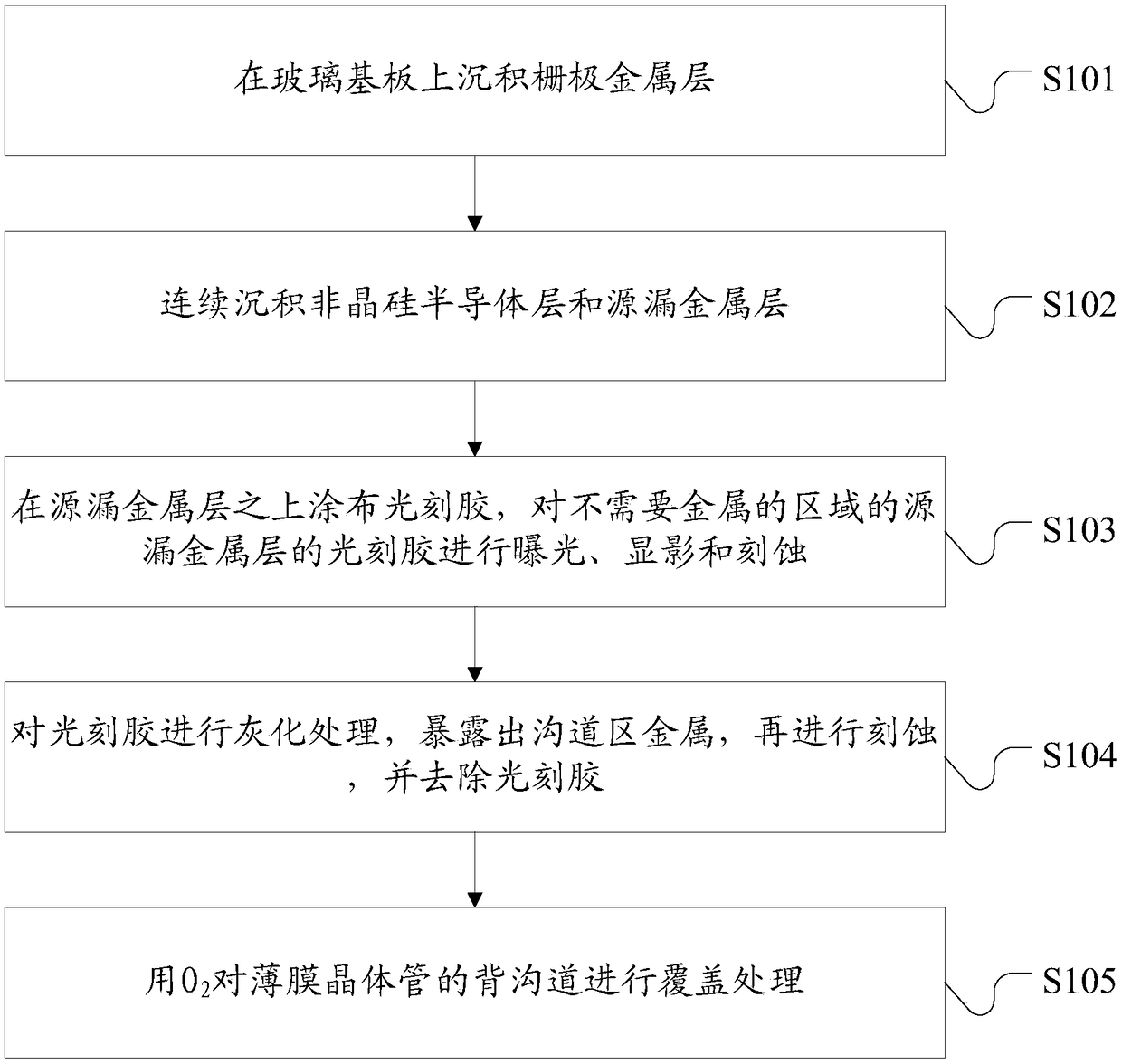

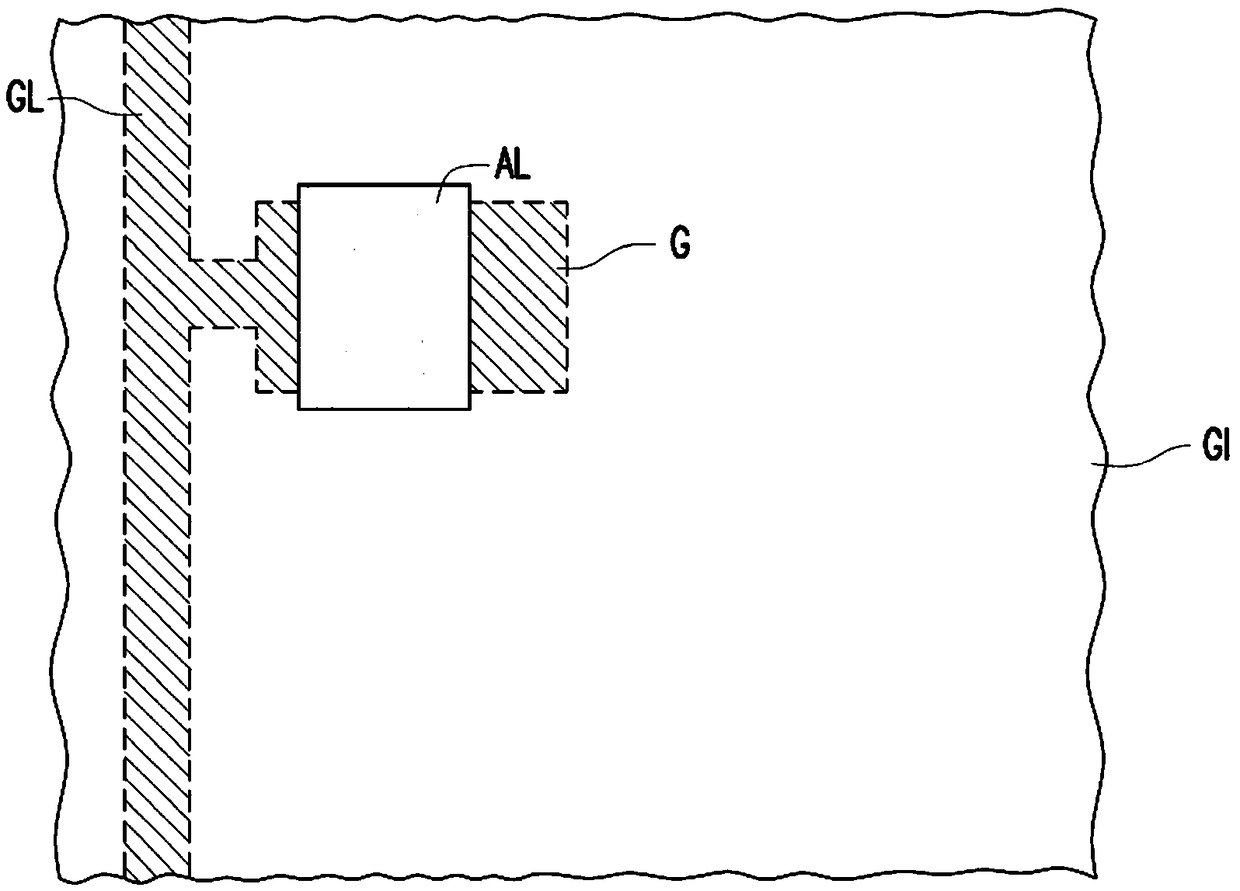

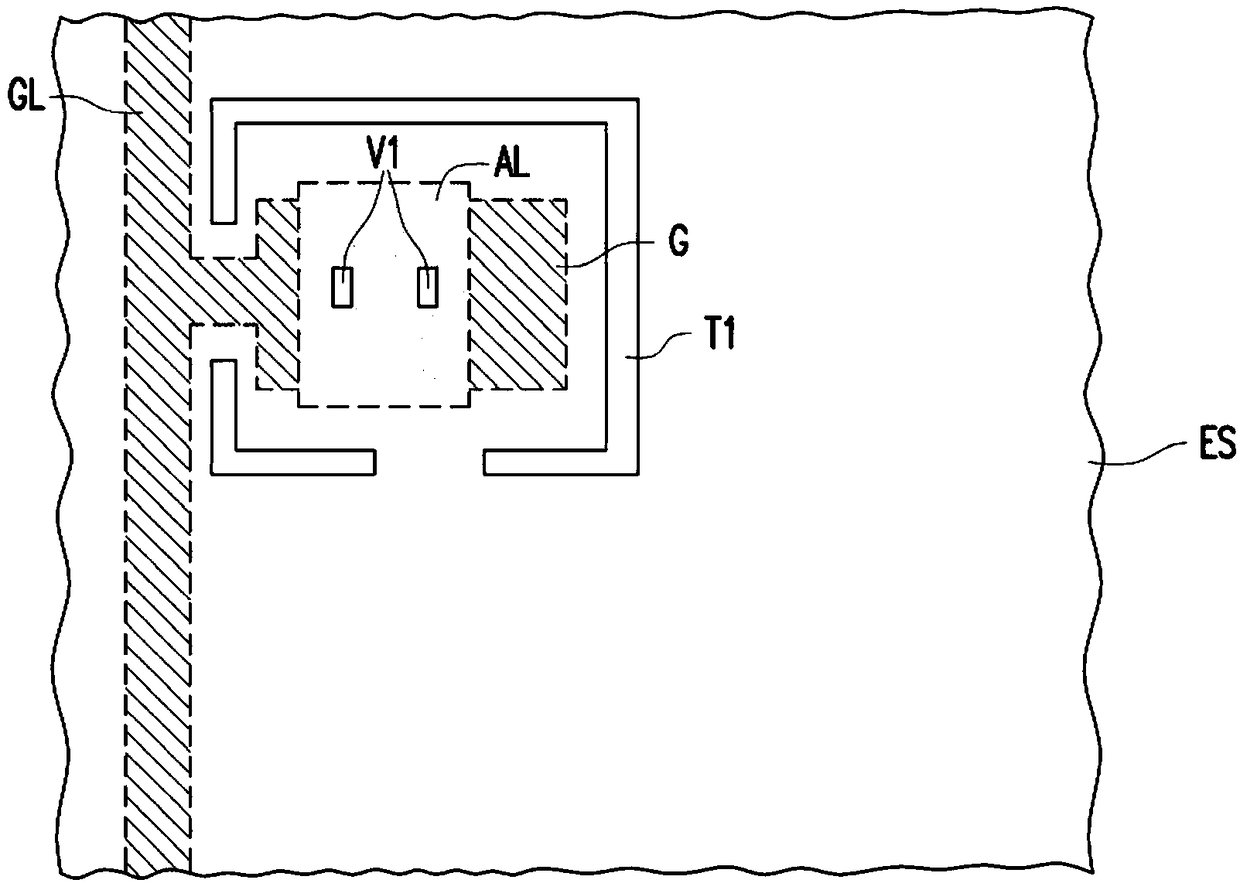

Thin film transistor and preparation method thereof

InactiveCN109461658AEfficient removalAvoid electrical influenceTransistorSemiconductor/solid-state device manufacturingPhotoresistMaterials science

The embodiment of the invention discloses a thin film transistor and a preparation method thereof. The preparation method of the thin film transistor comprises a step of performing mulching treatmenton a back channel of a thin film transistor by utilizing O2 after photoresist is finally removed. The preparation method disclosed by the embodiment of the invention comprises the step of performing the mulching treatment on the back channel of the thin film transistor by utilizing O2 after the photoresist is finally removed, not only good photoresist removal effect can be achieved, but also influence on electrical properties of the back channel of the thin film transistor is also avoided, and product performance is improved.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

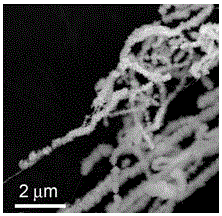

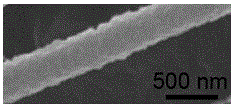

Metal sulfide-coated single-walled carbon nanotube cable and synthetic method thereof

ActiveCN106082166AThe process is simpleStrong maneuverabilityMaterial nanotechnologyEnergy inputSilica fumeCarbon nanotube

The invention relates to a cable and a synthetic method thereof, especially to a metal sulfide-coated single-walled carbon nanotube cable and a synthetic method thereof. The metal sulfide-coated single-walled carbon nanotube cable is prepared in situ by using a chemical vapor deposition (CVD) thermal reaction method. The synthetic method comprises the following steps: compacting graphite, a catalyst, a sulfur-containing growth promoter, silicon powder and metal powder or metal compound powder; with an inert atmosphere as a protective atmosphere and carrier gas, allowing the graphite, the catalyst, the sulfur-containing growth promoter and the silicon powder to undergo a reaction so as to produce a single-walled carbon nanotube; and reacting the sulfur-containing growth promoter with the metal powder or metal compound powder so as to produce a metal sulfide, and allowing the single-walled carbon nanotube and a metal sulfide cluster to depart from the surface of the raw material and to flow to a low-temperature zone, wherein the metal sulfide cluster coats the surface of the single-walled carbon nanotube in the process. The cable has excellent photoelectrochemical characteristics, and the core of the cable is composed of only one or a plurality of the single-walled carbon nanotubes, which facilitates performance of the nanoscale electric effect of the single-walled carbon nanotube and presence of more excellent novel characteristics.

Owner:SHENYANG INSTITUTE OF CHEMICAL TECHNOLOGY

Common-type radar antenna cover and winding forming method

InactiveCN108258412AGuaranteed structural strengthImprove rigidityRadiating element housingsElectricityGlass fiber

The invention provides a common-type radar antenna cover and a winding forming method and relates to the field of radar antennas. The radar antenna cover comprises an isolation medium, a glass fiberglass cloth tape, a waterproof film and a glass fiber winding tow, wherein an antenna array is coated with the isolation medium, the glass fiberglass cloth tape, the waterproof film and the glass fiberwinding tow from inside to outside in sequence. The radar antenna cover is characterized in that the effect of integrating the radar antenna cover with the antenna array in a common type is achieved.By means of the structure, not only is the structural strength of the thin-walled antenna cover ensured but also the rigidity and wind resistance of the antenna array are enhanced, and the electricalperformance of the antenna array can be ensured.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 38 RES INST

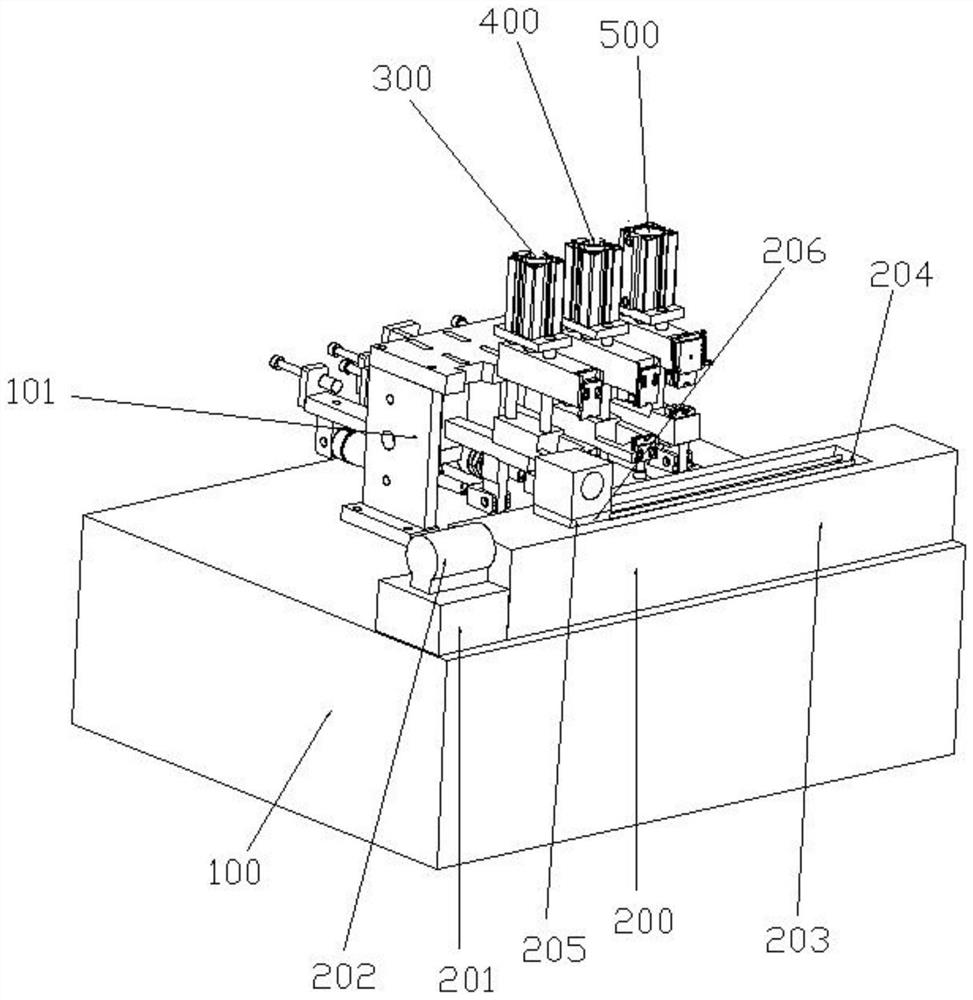

Method for low-pressure sintering hybrid power module by nano-silver solder paste

InactiveCN109378309AAvoid damageAvoid electrical influenceSemiconductor/solid-state device detailsSolid-state devicesNitrogen atmosphereNitrogen gas

The invention provides a method for low-pressure sintering a hybrid power module by nano-silver solder paste. The method can simultaneously sinter two chips with a large area difference and can obtaina solder paste layer having a high strength (>=30 MPa). The method comprises four processes including pre-drying, pressurizing, sintering, and reducing. The pre-drying process is to provide a certainviscosity for the solder paste to avoid the overflow of the excessive solder paste during the pressurizing process of a large-area chip. The pressurization process is to pressurize the large-area Sichip to promote the sintering, and not to pressurize the small-area SiC chip to avoid damage. The sintering process is carried out under a 50% air + 50% nitrogen atmosphere to ensure sufficient oxygen for the sintering of the solder paste and to avoid the oxide formation on the substrate surface. The reducing process is to reduce the surface oxide of the substrate by formic acid to remove copperoxide formed on the surface. The overall process flow of the invention is relatively simple, and is suitable for the manufacture of a hybrid power module having a large chip area difference.

Owner:TIANJIN UNIV

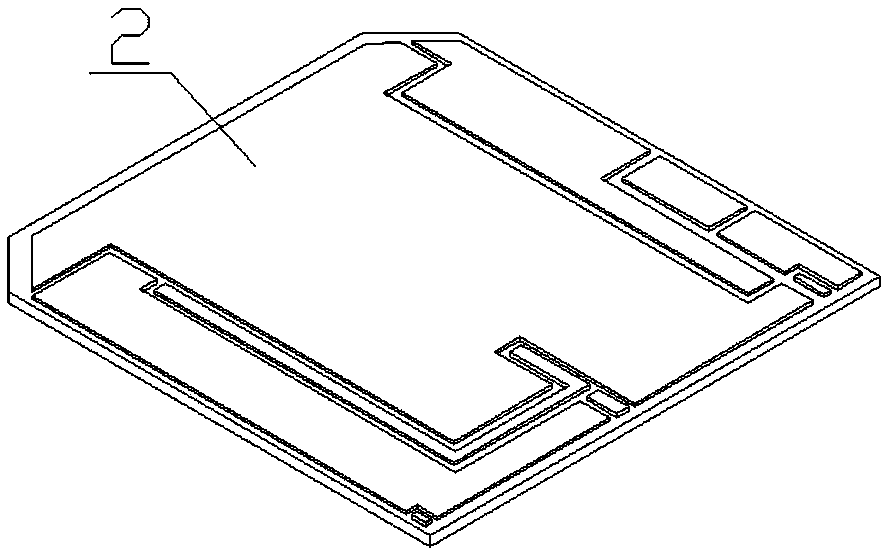

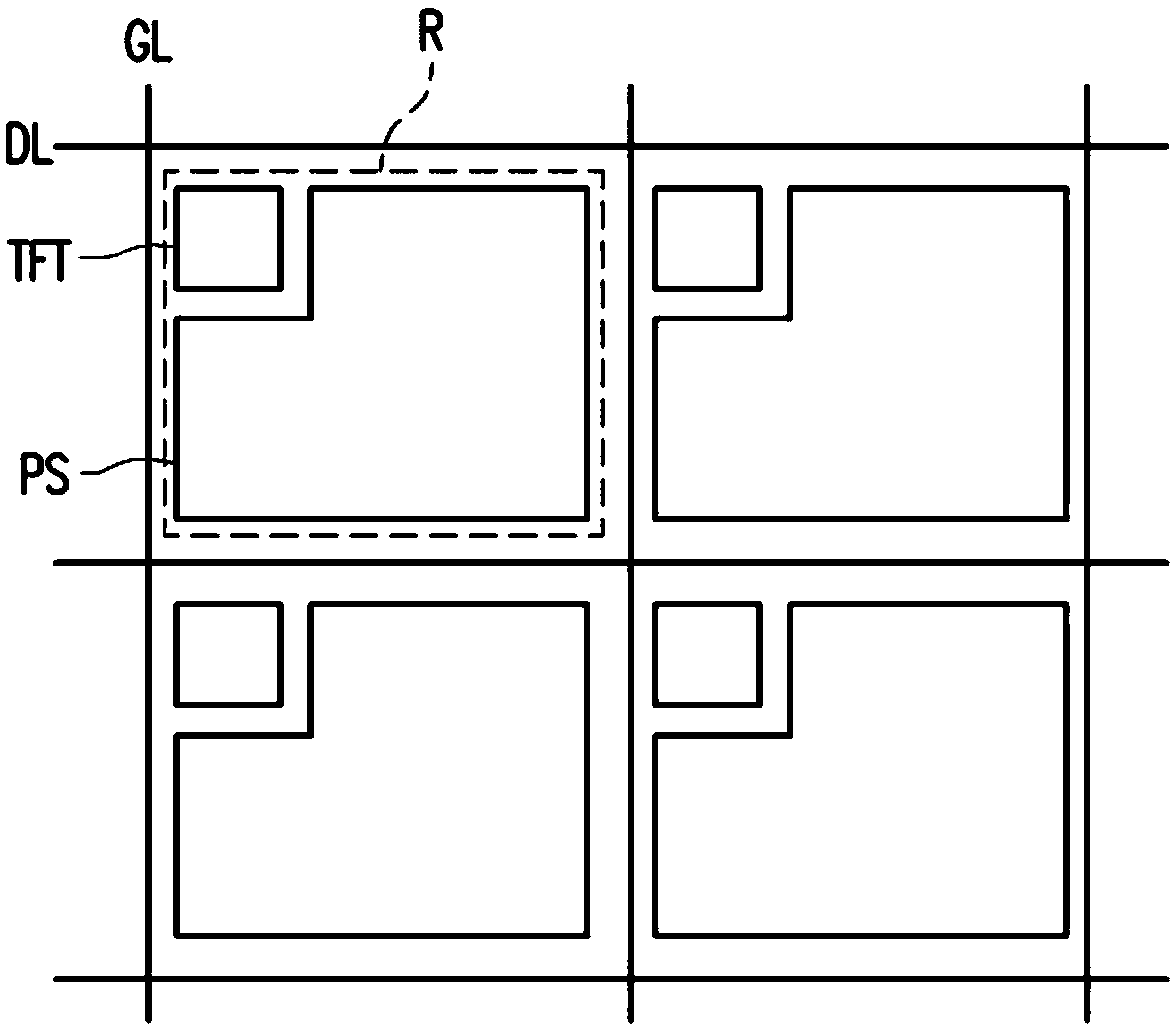

Display substrate and display device

ActiveCN104091819ASolve the problem of electrical driftAvoid electrical influenceSolid-state devicesSemiconductor devicesState of artEngineering

The embodiment of the invention provides a display substrate and a display device and relates to the technical field of organic electroluminescence displayers. The display substrate solves the problem that in the prior art, electrical property drift is generated due to changes of the threshold voltage in a thin film transistor when an organic electroluminescence displayer is manufactured, avoids the influence on electrical properties of the thin film transistor, improves the stability of performance of products and reduces production cost. The display substrate comprises the thin film transistor and is characterized by further comprising a grounding circuit, wherein one end of the grounding circuit is connected to the thin film transistor, and the other end of the grounding circuit is grounded; the grounding circuit and a conducting layer structure of the thin film transistor are formed simultaneously in the process of manufacturing the thin film transistor. The display substrate and the display device are applied to manufacturing of the organic electroluminescence displayers.

Owner:BOE TECH GRP CO LTD

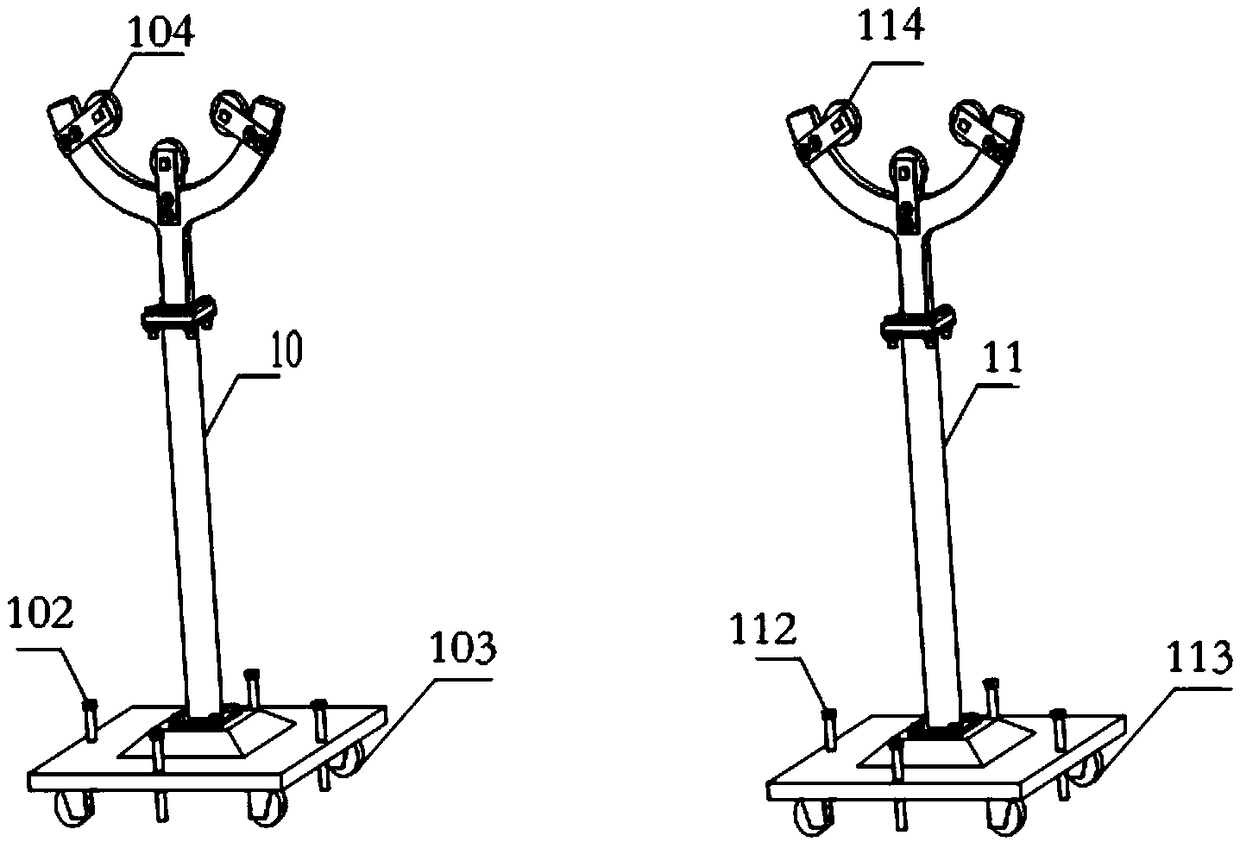

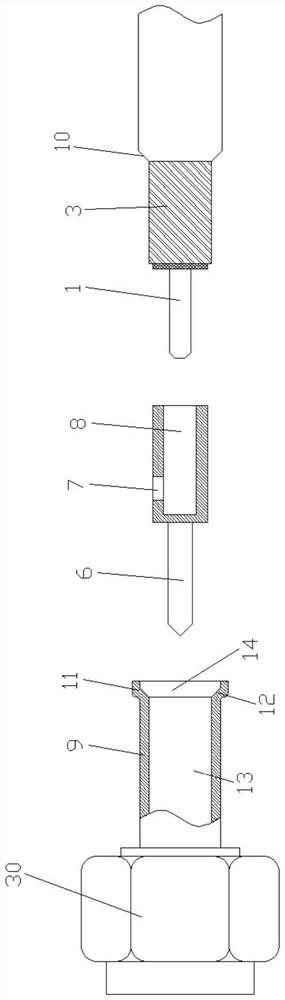

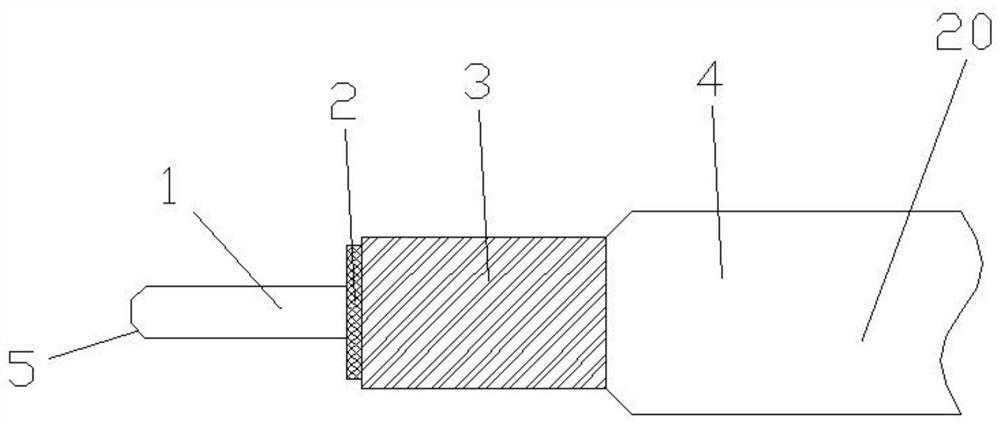

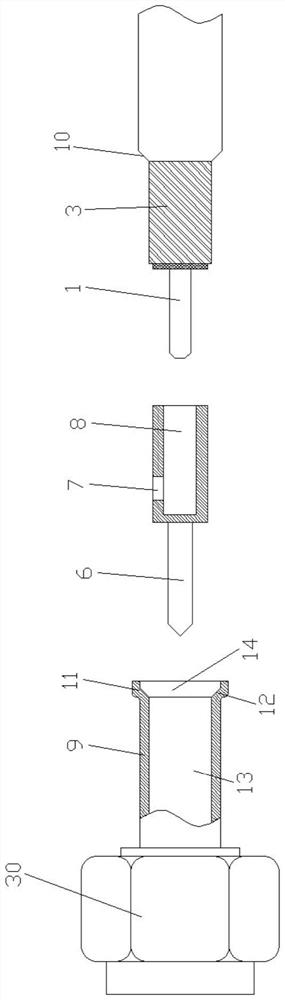

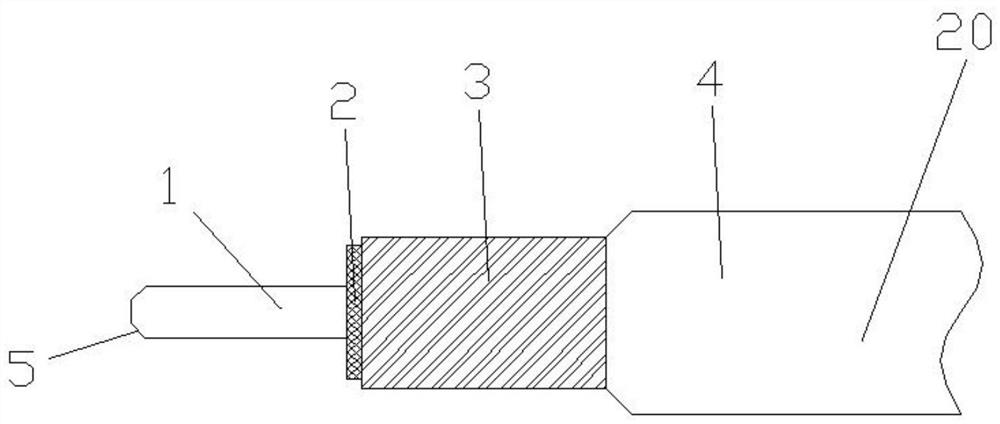

Low-loss low-standing-wave radio frequency cable assembly

ActiveCN112164906ASmall VSWREasy to assembleLine/current collector detailsElectrically conductive connectionsCoaxial cableElectrical conductor

The invention discloses a low-loss low-standing-wave radio frequency cable assembly. An coaxial cable comprises an inner conductor, an insulating medium layer is arranged outside the inner conductor,an outer conductor shielding layer is arranged outside the insulating medium layer, an insulating protective layer is arranged outside the outer conductor shielding layer, a first chamfer is arrangedat the end of the inner conductor. A second chamfer is arranged at the end of the insulation protection layer, a connector tail pipe is arranged on one side of the connector, a second welding cavity is formed in the connector tail pipe, a guide table is arranged at the head of the connector tail pipe, a guide cavity is formed in the guide table, and the guide cavity is communicated with the secondwelding cavity. A guide step is arranged at the joint of the guide cavity and the second welding cavity, a first welding cavity is formed in the tail end of the connector pin, and a welding observation hole is formed in the bottom end of the first welding cavity. By adopting the structure, the radio frequency cable assembly meets the requirements of low insertion loss, low standing wave and equalphase.

Owner:安徽新特华宇新材料科技有限公司

Manufacturing method for double-face illuminated crystalline silicon solar cell

ActiveCN102623563BAvoid electrical influenceEasy to operateFinal product manufactureSemiconductor devicesElectricityMetal electrodes

The invention discloses a manufacturing method for a double-face illuminated crystalline silicon solar cell. The method comprises the following steps of: (1) washing a raw silicon chip, and removing a damaged layer from the back face of the raw silicon chip; (2) performing single-face boron diffusion on the front face of the silicon chip in a back-to-back way, wherein the back face of the silicon chip is a diffusing face; (3) depositing a mask layer on the back face of the diffused silicon chip; (4) washing the front face of the silicon chip, removing a damaged layer, performing texturing, and removing a diffraction diffusion layer; (5) performing single-face phosphorus diffusion on the back face of the silicon chip in a back-to-back way, wherein the front face of the silicon chip is the diffused face; (6) removing a peripheral joint, impurity glass and a mask which are formed by the diffusion; (7) depositing an anti-reflection coating on each of the two faces of the silicon chip; and (8) printing a metal electrode on each of the two faces of the silicon chip, and performing sintering to obtain the double-face illuminated crystalline silicon solar cell. The influence of diffraction on the electrical properties of the cell is avoided, and the photoelectric efficiency of the cell can be improved by 0.3 to 0.5 percent; and the method has positive practical significance.

Owner:CSI CELLS CO LTD +1

Resistive memory and manufacture method thereof

The invention discloses a resistive memory and a manufacture method thereof. The method comprises: first of all, sequentially forming a first electrode, a variable resistance layer and a mask layer on a substrate; then, forming a dielectric layer covering the first electrode, the variable resistance layer and the mask layer on the substrate; next, performing an etching process to form an opening in the dielectric layer and the mask layer, the opening exposing a part of the variable resistance layer; afterwards, forming a second electrode in the opening, and afterwards, forming a conductive layer on the second electrode.

Owner:WINBOND ELECTRONICS CORP

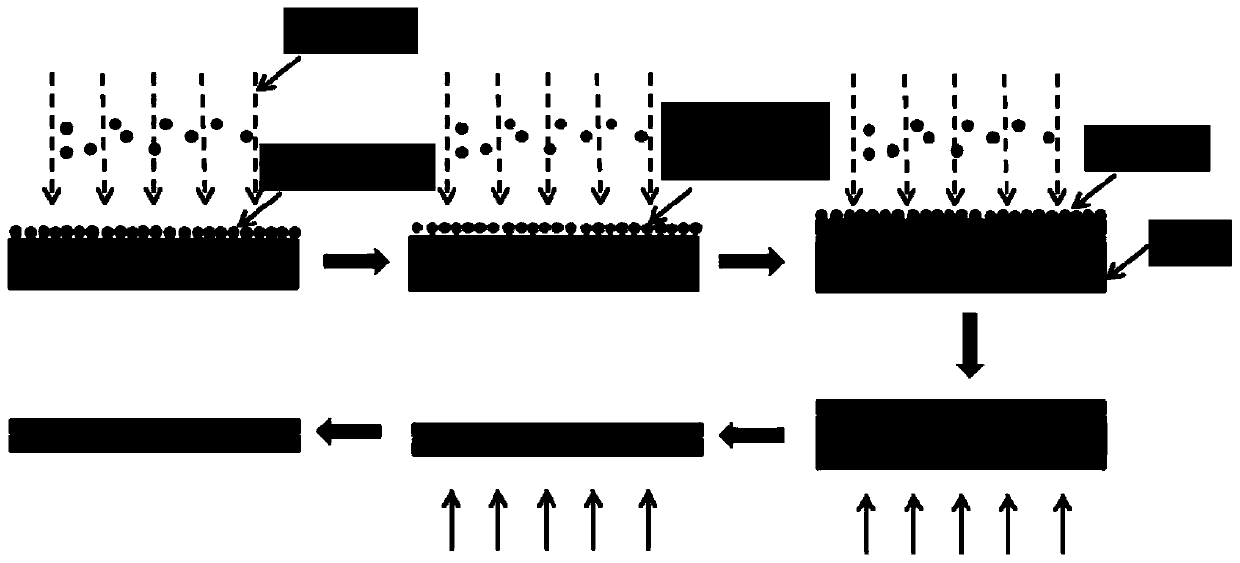

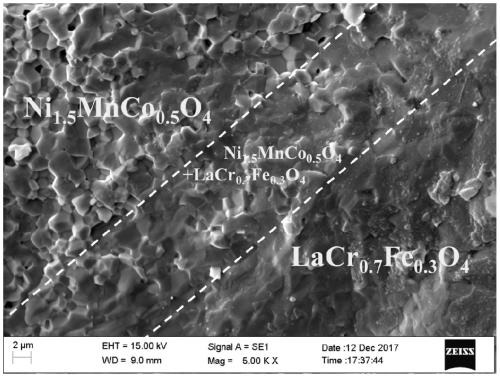

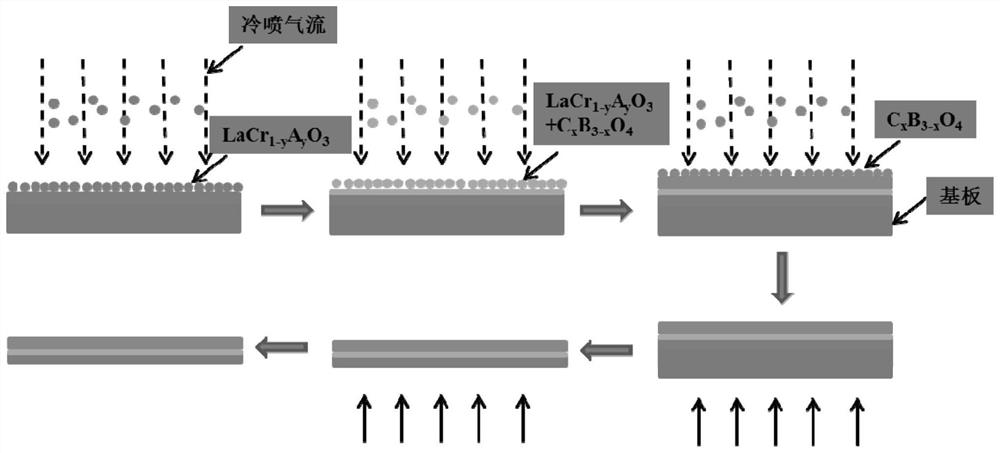

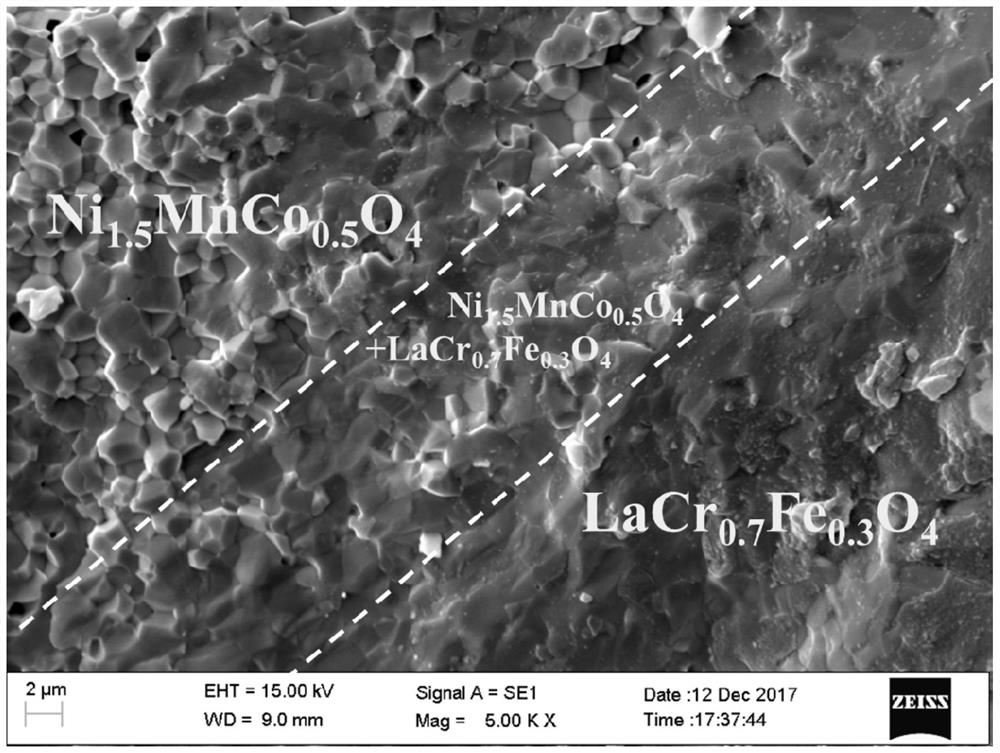

In-situ-generated layered composite negative-temperature-coefficient thermal-sensitive ceramic material, preparation method and application

ActiveCN109942285AGood conductivity and stabilityHigh interface shrinkage matchingLayered structureCeramic

The invention belongs to the technical field of negative-temperature-coefficient thermistors and particularly relates to an in-situ-generated layered composite negative-temperature-coefficient thermal-sensitive ceramic material, a preparation method and application. The thermal-sensitive ceramic material structurally comprises a base layer, a transition layer and a sensitive layer in sequence. Thecomposition of the base layer is a perovskite phase or a doped perovskite phase, the composition of the sensitive layer is a spinel phase or a doped spinel phase, and the composition of the transition layer is a mixture formed by mixing the perovskite phase or the doped perovskite phase with the spinel phase or the doped spinel phase in an isopyknic mode. A cold spraying technology is introducedinto preparation of layered-structure composite thermal-sensitive ceramics, the in-situ-generated layered composite negative-temperature-coefficient thermal-sensitive ceramic material is prepared, thedefect of a traditional method is overcome, the thickness of the sensitive layer and the microstructure of the material are effectively regulated and controlled, and the material has important significance on preparation of low-resistance-value, high-B-value and high-stability NTC thermal-sensitive ceramic materials for inhibiting the surge current.

Owner:UNIV OF JINAN

An in-situ-generated layered composite negative temperature coefficient thermosensitive ceramic material and its preparation method and application

ActiveCN109942285BImprove stabilityLower resistanceCeramic layered productsPerovskite (structure)Thermistor

The invention belongs to the technical field of negative temperature coefficient thermistors, and in particular relates to an in-situ-generated layered composite negative temperature coefficient thermosensitive ceramic material, a preparation method and an application thereof. The structure of the heat-sensitive ceramic material is a base layer, a transition layer, and a sensitive layer in sequence, wherein: the base layer is composed of a perovskite phase or a doped perovskite phase, and the sensitive layer is composed of a sharp Crystal phase or doped spinel phase, the composition of the transition layer is: perovskite phase or doped perovskite phase and spinel phase or doped spinel mixed in equal volumes mixture. Introducing the cold spraying technology into the preparation of layered structure composite heat-sensitive ceramics, the in-situ generation of layered composite negative temperature coefficient heat-sensitive ceramic materials was prepared, which overcomes the shortcomings of traditional methods and realizes the sensitivity to the thickness of the sensitive layer and the microstructure of the material. The effective control of NTC is of great significance for the preparation of NTC thermosensitive ceramic materials with low resistance, high B value and high stability for suppressing surge current.

Owner:UNIV OF JINAN

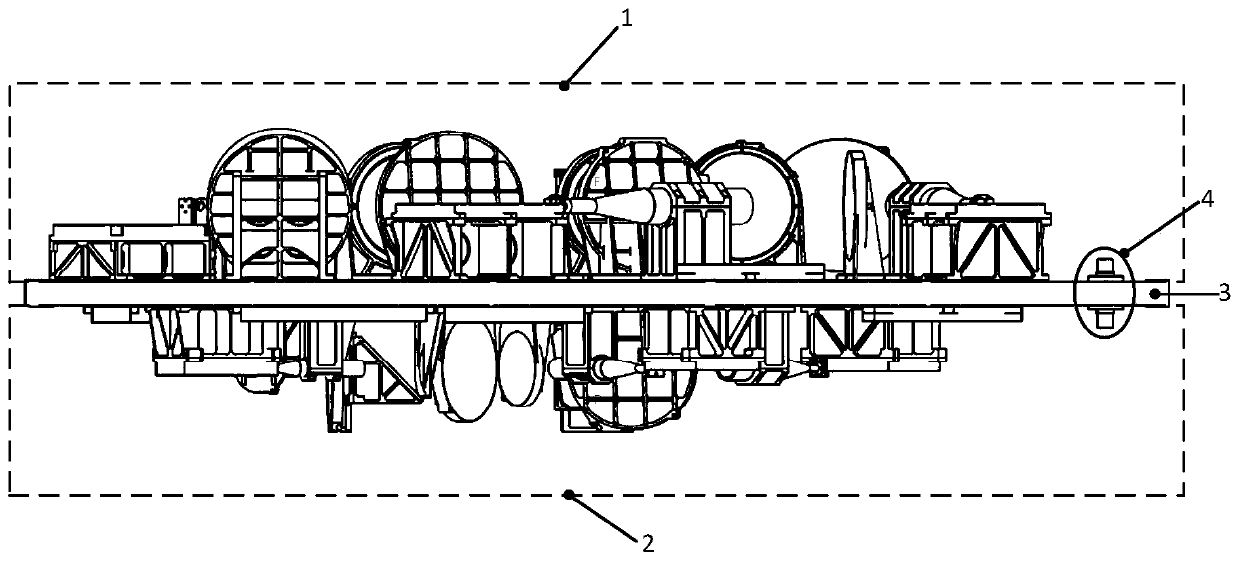

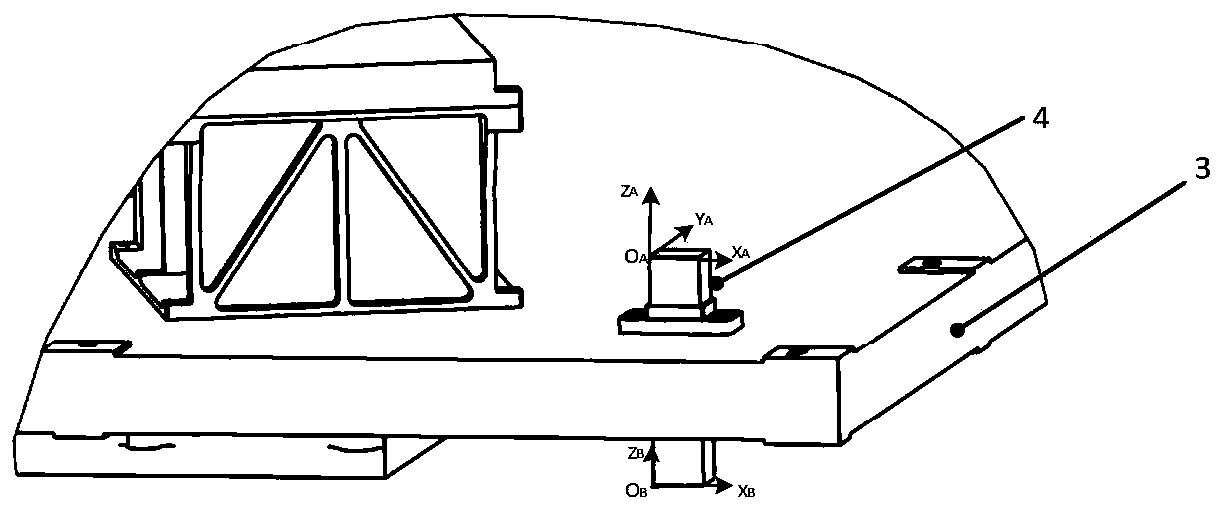

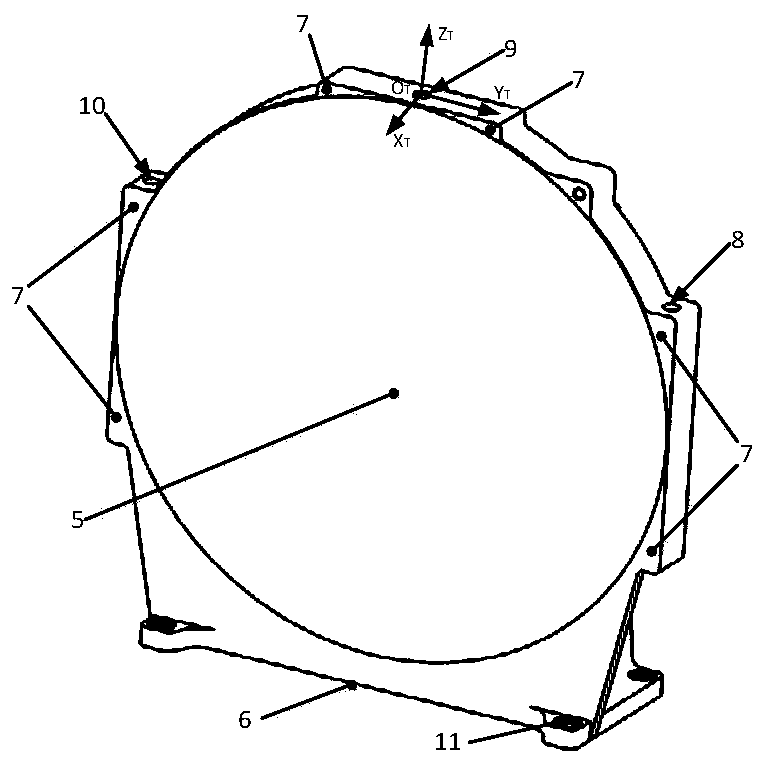

Laminated quasi-optical feed network structure and adjusting method thereof

ActiveCN111043955AAvoid electrical influenceElectrical testingUsing optical meansPlane mirrorNetworked system

The invention relates to a laminated quasi-optical feed network structure, which comprises a quasi-optical component mounting plate, an upper-layer feed system and a lower-layer feed system. The upper-layer feed system and the lower-layer feed system are arranged on the quasi-optical component mounting plate. Each of the upper-layer feed system and the lower-layer feed system at least comprises anellipsoidal mirror, a feed source horn, a frequency selective surface / polarization grid mesh and a plane mirror. The upper layer and the lower layer of the quasi-optical component mounting plate aresymmetrically provided with measuring reference pieces. The ellipsoidal mirror is provided with a measuring reference plane and at least one measuring reference hole. The frequency selective surface / polarization grid mesh is connected with the quasi-optical component mounting plate through a bracket; a mounting plane and a measurement reference hole are formed in the bracket According to the invention, for elimination of accumulated assembly errors of the laminated quasi-optical feed network system, the included angle between the mechanical axis direction and the electrical axis direction of each frequency band is calculated according to the planar near-field electrical performance test result of each frequency band link, and correction is carried out by adjusting the direction and orientation of a feed source horn by means of a multi-degree-of-freedom feed source horn adjusting and supporting tool.

Owner:SHANGHAI SPACEFLIGHT INST OF TT&C & TELECOMM

A display substrate and a display device

ActiveCN104091819BSolve the problem of electrical driftAvoid electrical influenceSolid-state devicesSemiconductor devicesThin membraneEngineering

Embodiments of the present invention provide a display substrate and a display device, which relate to the technical field of organic electroluminescent displays, and solve the problem that the threshold voltage of thin-film transistors in the prior art will change when making organic electroluminescent displays, resulting in electrical problems. The problem of drift avoids the influence on the electrical properties of the thin film transistor, improves the stability of the performance of the product, and reduces the production cost. The display substrate includes a thin film transistor, and it is characterized in that the display substrate further includes: a grounding line, wherein: one end of the grounding line is connected to the thin film transistor, and the other end of the grounding line is grounded; wherein, The grounding line is formed simultaneously with the conductive layer structure of the thin film transistor during the process of forming the thin film transistor. The invention is applied in the manufacture of organic electroluminescent displays.

Owner:BOE TECH GRP CO LTD

A reversible heating tube installation structure and electric oven

ActiveCN104757885BEasy to cleanAvoid destructionRoasters/grillsEngineeringElectrical and Electronics engineering

Owner:HAIER GRP CORP +1

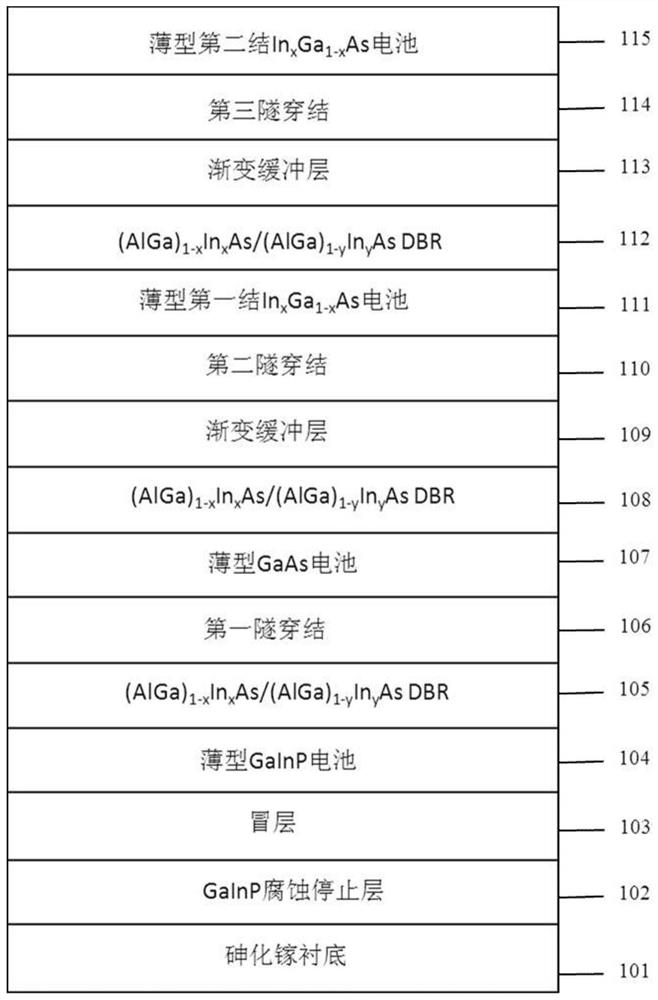

A four-junction solar cell structure with high radiation resistance and its preparation method

ActiveCN109920874BMeet the requirementsImprove radiation resistanceFinal product manufacturePhotovoltaic energy generationElectrical batterySolar cell

Owner:CHINA ELECTRONIC TECH GRP CORP NO 18 RES INST

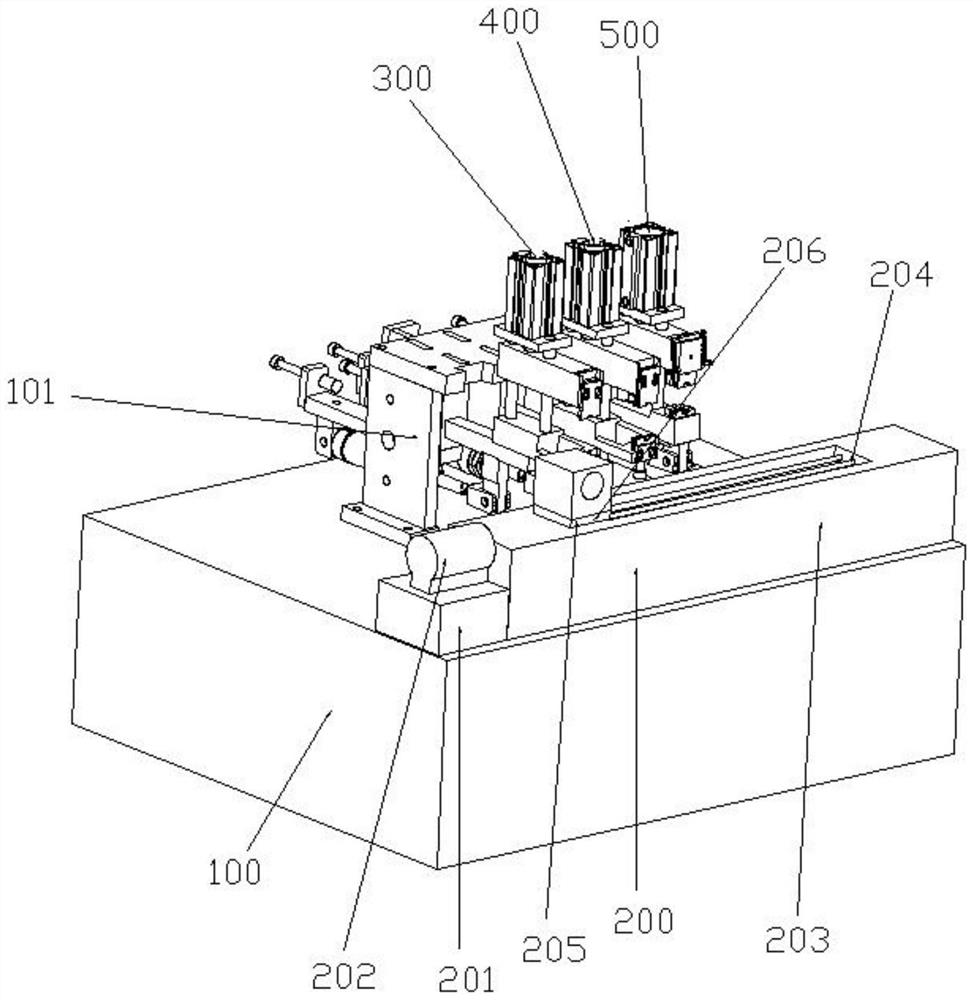

A low loss low standing wave radio frequency cable assembly and its cutting equipment

ActiveCN112164906BSmall VSWREasy to assembleLine/current collector detailsElectrically conductive connectionsElectrical conductorCoaxial cable

The invention discloses a low loss and low standing wave radio frequency cable assembly and its cutting equipment. The coaxial cable includes an inner conductor, an insulating medium layer is arranged outside the inner conductor, and an outer conductor is arranged outside the insulating medium layer. shielding layer, the outer conductor shielding layer is provided with an insulating protective layer, the end of the inner conductor is provided with a first chamfer, the end of the insulating protective layer is provided with a second chamfer, and one side of the connector is provided There is a joint tail pipe, a second welding cavity is opened inside the joint tail pipe, a guide platform is provided at the head of the joint tail pipe, a guide cavity is opened inside the guide platform, and the guide cavity communicates with the second welding cavity , and a guide step is provided at the connection between the guide cavity and the second welding cavity, a first welding cavity is opened inside the tail end of the connector pin, and a welding observation hole is opened at the bottom of the first welding cavity; the above structure makes The RF cable assembly meets the requirements of low insertion loss, low VSWR, and equal phase.

Owner:安徽新特华宇新材料科技有限公司

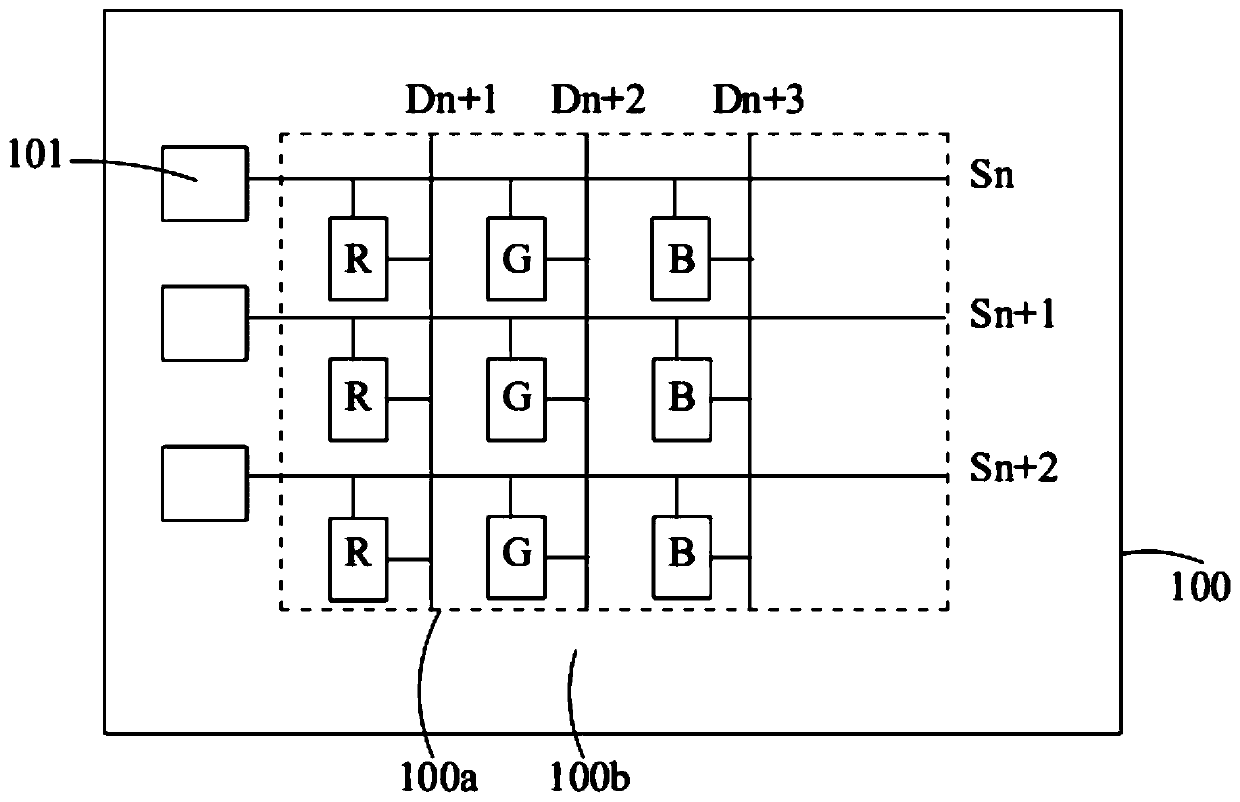

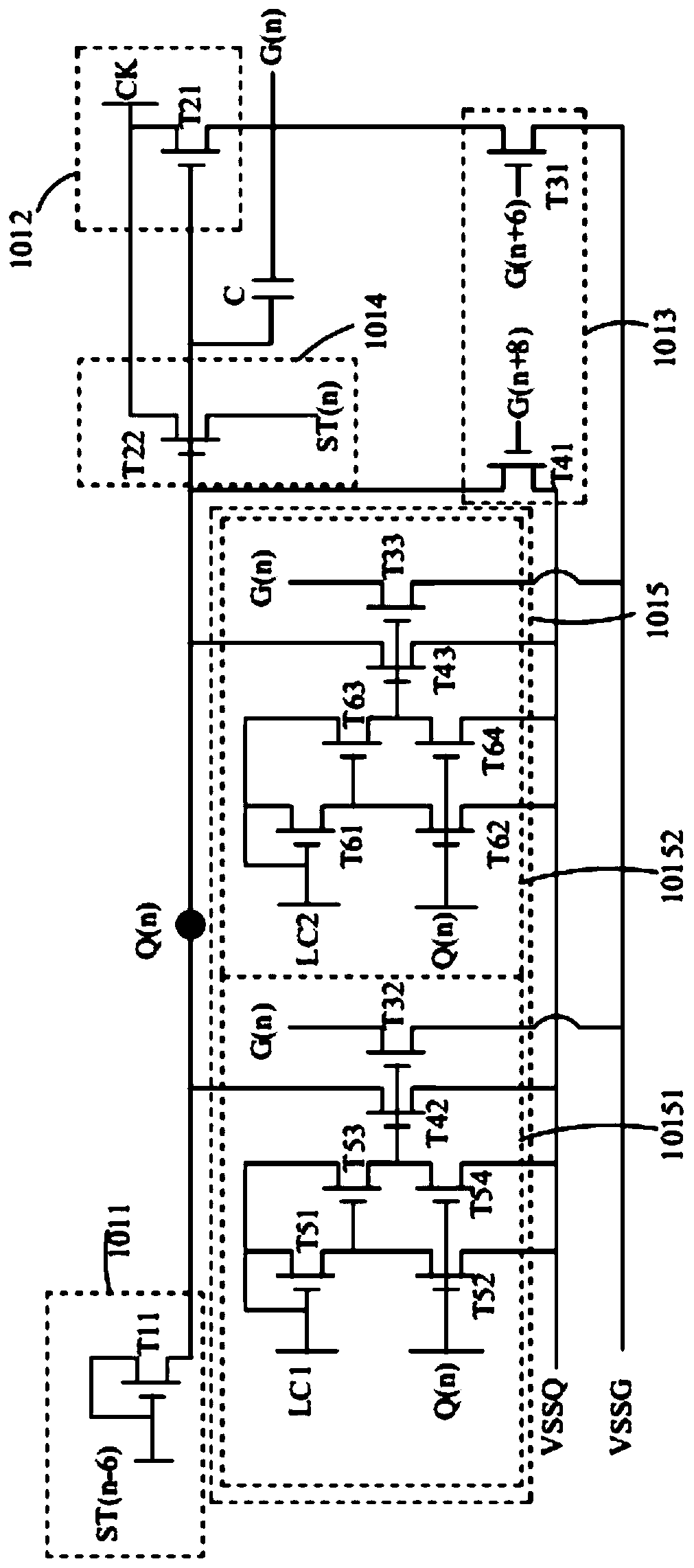

Drive circuit and display device

ActiveCN111445830AAvoid electrical influenceStatic indicating devicesDigital storageEtchingDisplay device

The invention provides a drive circuit and a display device, the drive circuit comprises a circuit unit, the circuit unit comprises a thin film transistor, and the thin film transistor comprises a patterning part; the capacitor is connected with at least one end of the thin film transistor in the circuit unit, and the capacitor comprises an electrode plate; and a redundant patterning part, the redundant patterning part, the electrode plate and the patterning part are located on the same conductive layer, and the redundant patterning part is connected between the patterning part and the electrode plate. The redundant patterning component is arranged between the patterning component forming the thin film transistor and the electrode plate of the capacitor, so that the problem that the electrical property of the thin film transistor of the circuit unit is affected due to uneven etching of the patterning component of the thin film transistor in the process of patterning the conductive layer is avoided.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Electronic package and its manufacturing method

ActiveCN107958894BImmune to electromagnetic interferenceElectrically functioning normallySemiconductor/solid-state device detailsSolid-state devicesElectromagnetic interferenceEngineering

Owner:SILICONWARE PRECISION IND CO LTD

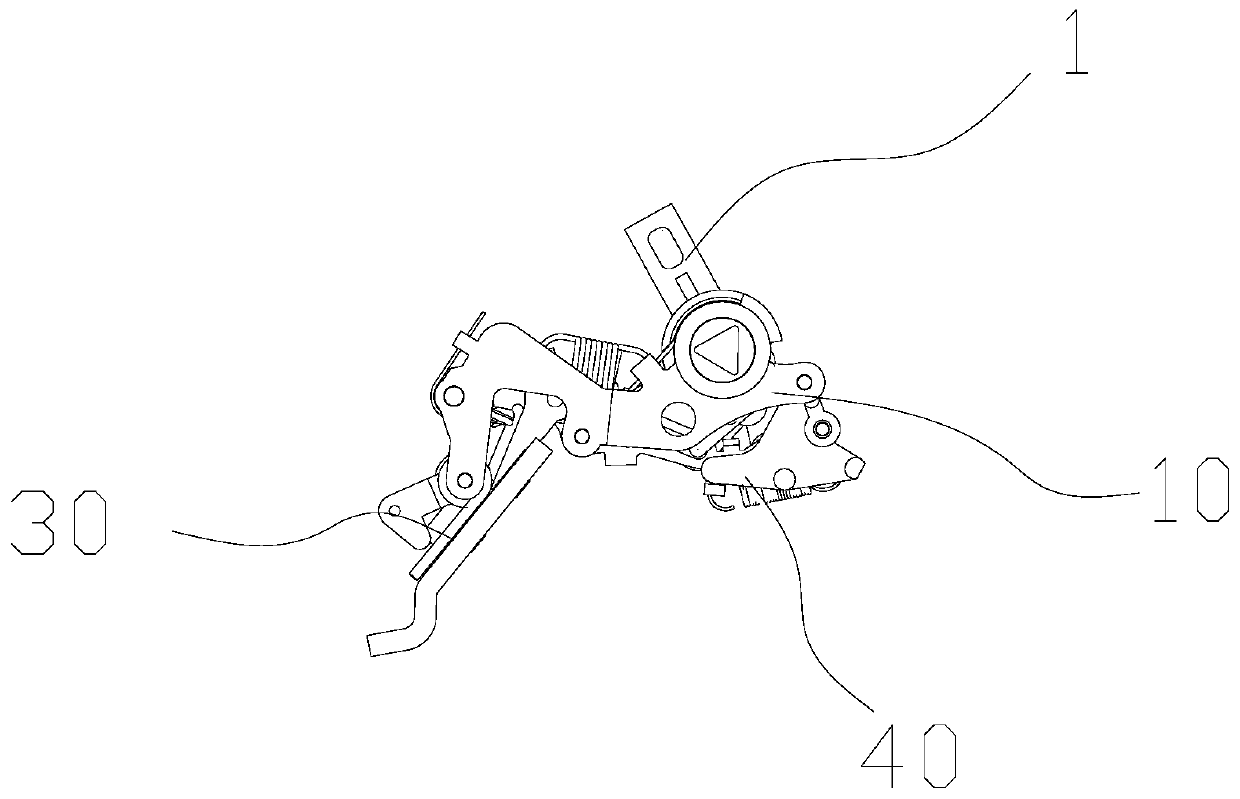

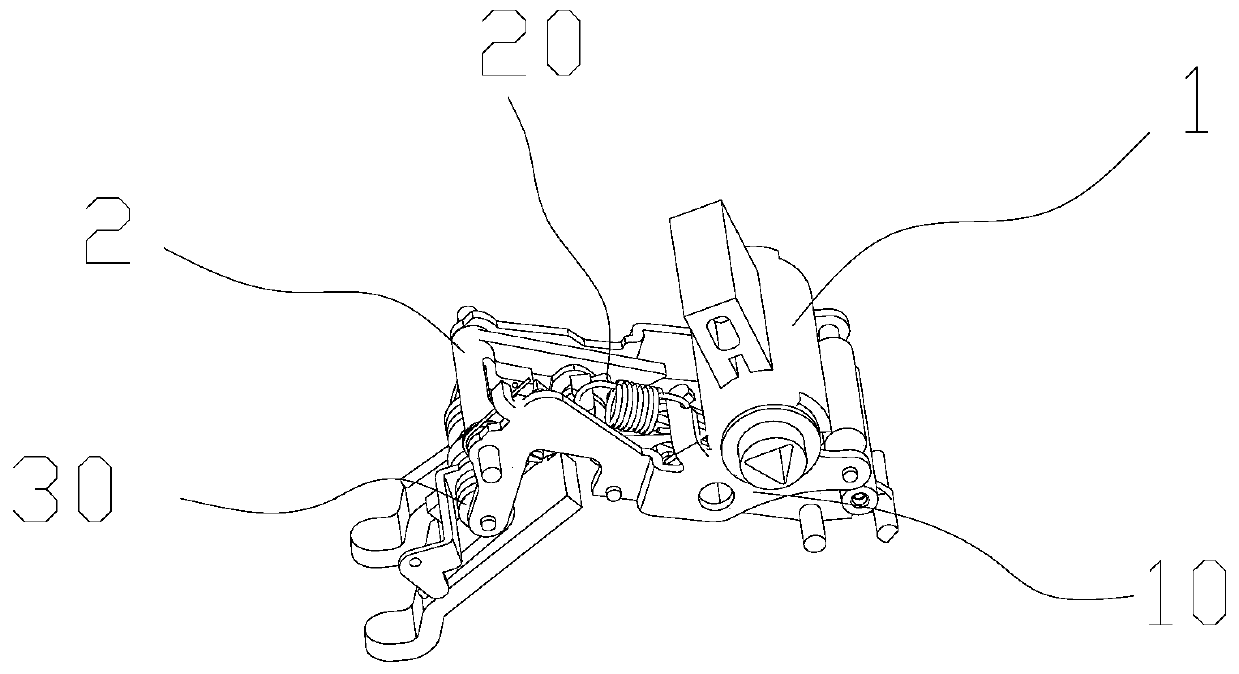

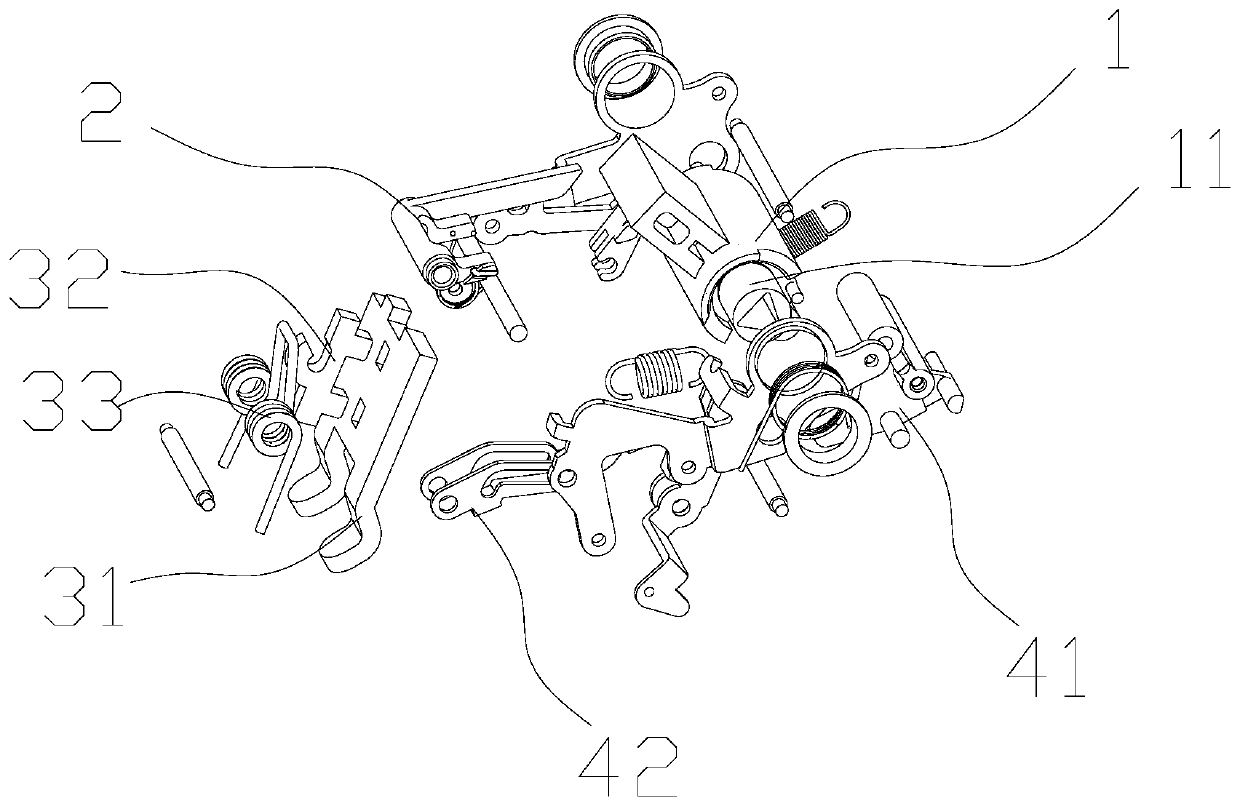

A moving contact quick-closing mechanism and a circuit breaker equipped with the moving contact quick-closing mechanism

ActiveCN106847630BAchieve integrationSimple structureProtective switch operating/release mechanismsControl theoryEnergy storage

The invention relates to a moving contact fast-operate mechanism and circuit breaker with the same. An energy storage rod and a stop piece are arranged on a support, an energy storage elastic piece is arranged between the energy storage rod and a moving contact, and the stop piece can abut against and limit the moving contact; meanwhile, the operating piece is connected to the energy storage rod, and is provided with a stir part to stir the stop piece; the operating piece can act on the moving contact through the energy storage rod, so that the purpose of integrating an energy storage mechanism and a moving contact linked mechanism is achieved, the structure of the moving contact fast-operate mechanism is simplified, and the assembly efficiency and the performance stability are improved; the purpose of integrating the energy storage mechanism and the moving contact linked mechanism is achieved, the energy storage elastic piece achieves the effect of dynamically compensating using loss of the moving contact, and the operating piece directly acts on the stop piece. According to the moving contact fast-operate mechanism and circuit breaker with the same, the structure is simpler, and stop and release of the moving contact is stabler and more reliable.

Owner:XIAMEN HONGFA ELECTRICAL SAFETY & CONTROLS CO LTD

Novel power supply power module structure with output protection

PendingCN108807305AReasonable space layout of package structureSave plane spaceSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor components

The invention provides a novel power supply power module structure with output protection and belongs to the field of semiconductor components. The novel power supply power module structure comprisesfour rectifier chips, an overvoltage protection chip, two input terminals, two output terminals and a plastic package body, and is characterized by further comprising a first frame unit, a second frame unit and a third frame unit which are arranged relatively in sequence; the four rectifier chips are arranged between the first frame unit and the second frame unit; the overvoltage protection chip is arranged between the second frame unit and the third frame unit to form a laminated structure; the two input terminals are led out of the first frame unit; the two output terminals are led out of the second frame unit; the four rectifier chips and the overvoltage protection chip are packaged integrally by the laminated structure, and a structure with the four rectifier chips laid flatly and integrated vertically with the overvoltage protection chip is formed, spatial arrangement of the package structure is more reasonable, the product occupies small planar space on a PCB, and the problem about space utilization rate of the PCB is solved.

Owner:SHANDONG JINGDAO MICROELECTRONICS

A metal sulfide-coated single-wall carbon nanotube nanocable and its synthesis method

ActiveCN106082166BSimple processAvoid structureMaterial nanotechnologyEnergy inputCarbon nanotubeMetallic sulfide

A metal sulfide-coated single-walled carbon nanotube nanocable and a synthesis method thereof, relating to a cable and a synthesis method thereof, which are prepared in situ by a chemical vapor deposition (CVD) thermal reaction method; graphite, catalyst, and Sulfur growth promoter, silicon powder, metal powder or metal compound powder are compressed; an inert atmosphere is used as a protective atmosphere and carrier gas, and graphite, catalyst, sulfur-containing growth promoter, and silicon powder are reacted to form single-walled carbon nanotubes; sulfur-containing growth promotion The agent reacts with metal powder or metal compound powder to form metal sulfide, and the single-walled carbon nanotubes and metal sulfide clusters leave the surface of the raw material and flow to the low temperature area; during this process, the metal sulfide clusters are coated on the single-walled carbon nanotubes. tube surface. The cable has excellent photoelectrochemical properties, and the core of the cable is only composed of one or several single-walled carbon nanotubes, which is conducive to the exertion of the nanoscale electrical effect of the single-walled carbon nanotubes, and reflects more excellent novel characteristics.

Owner:SHENYANG INSTITUTE OF CHEMICAL TECHNOLOGY

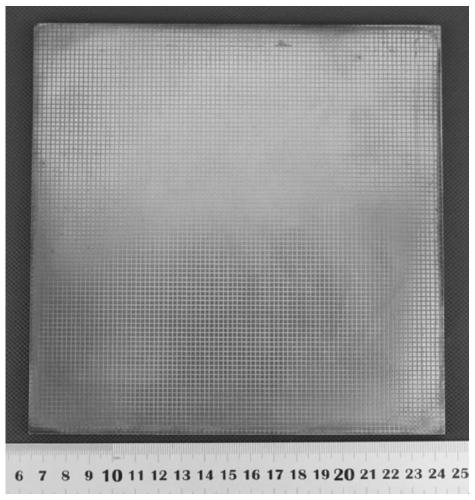

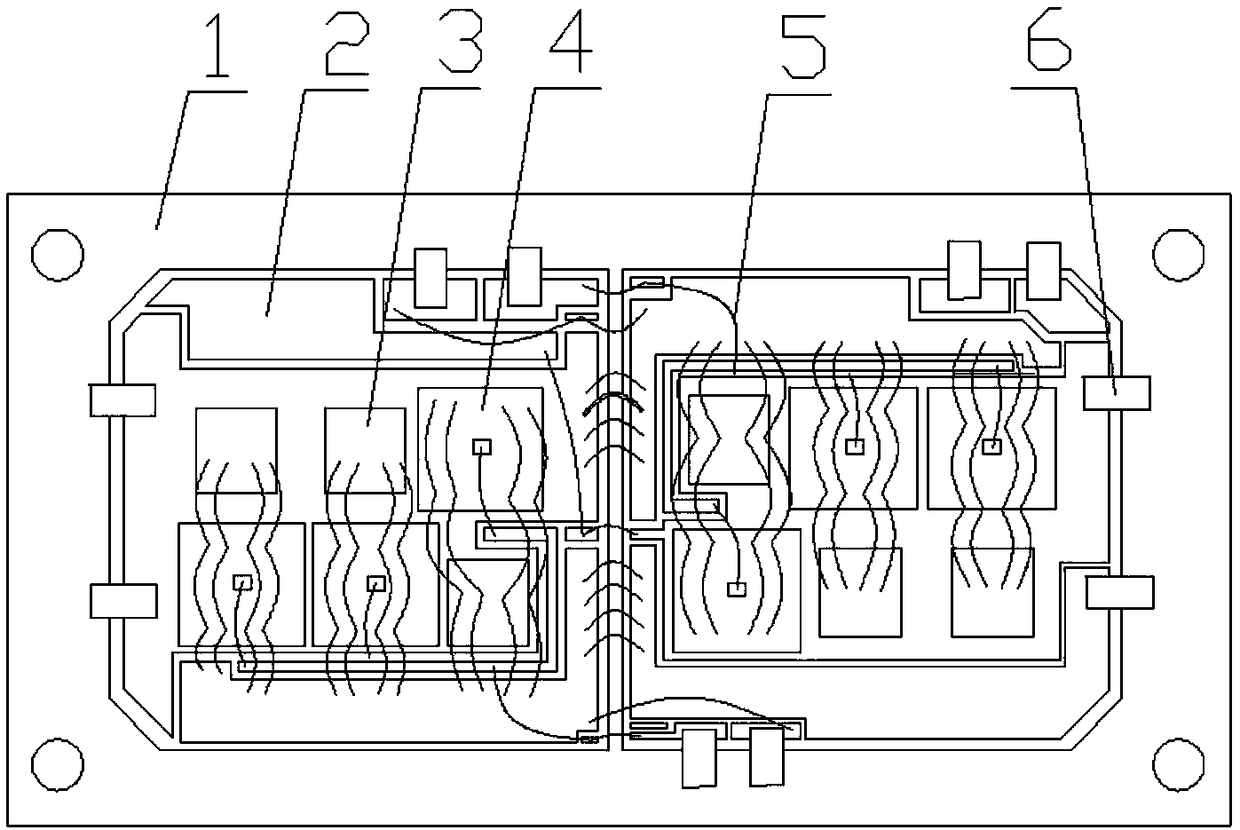

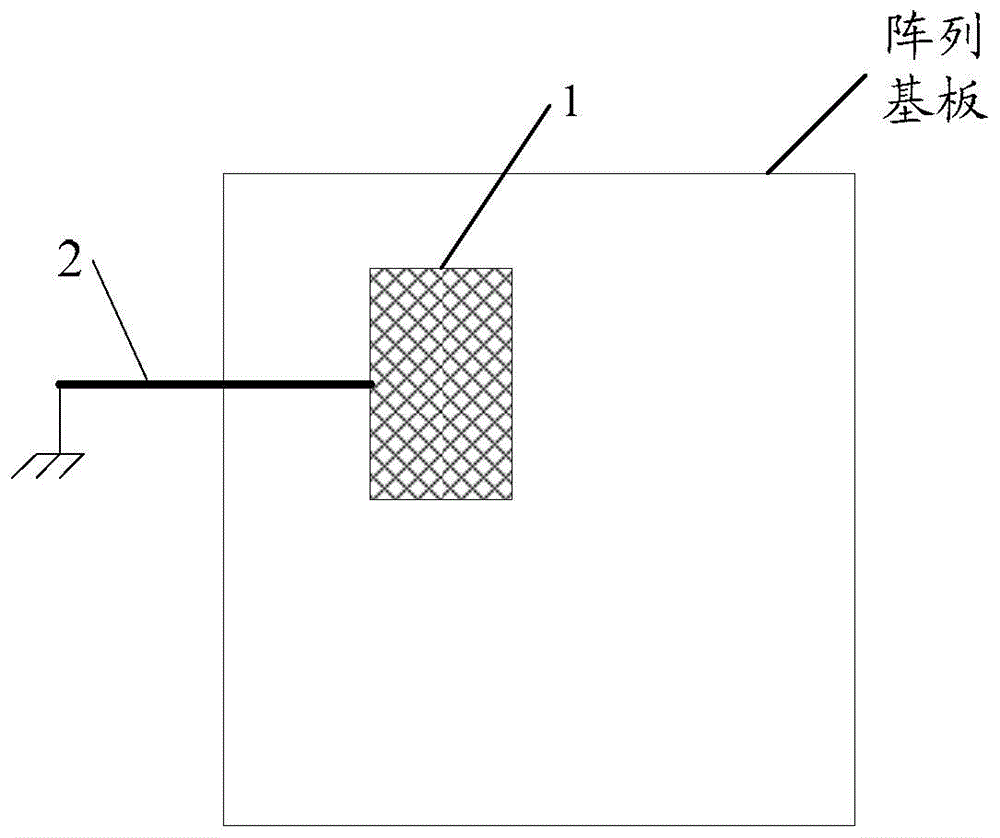

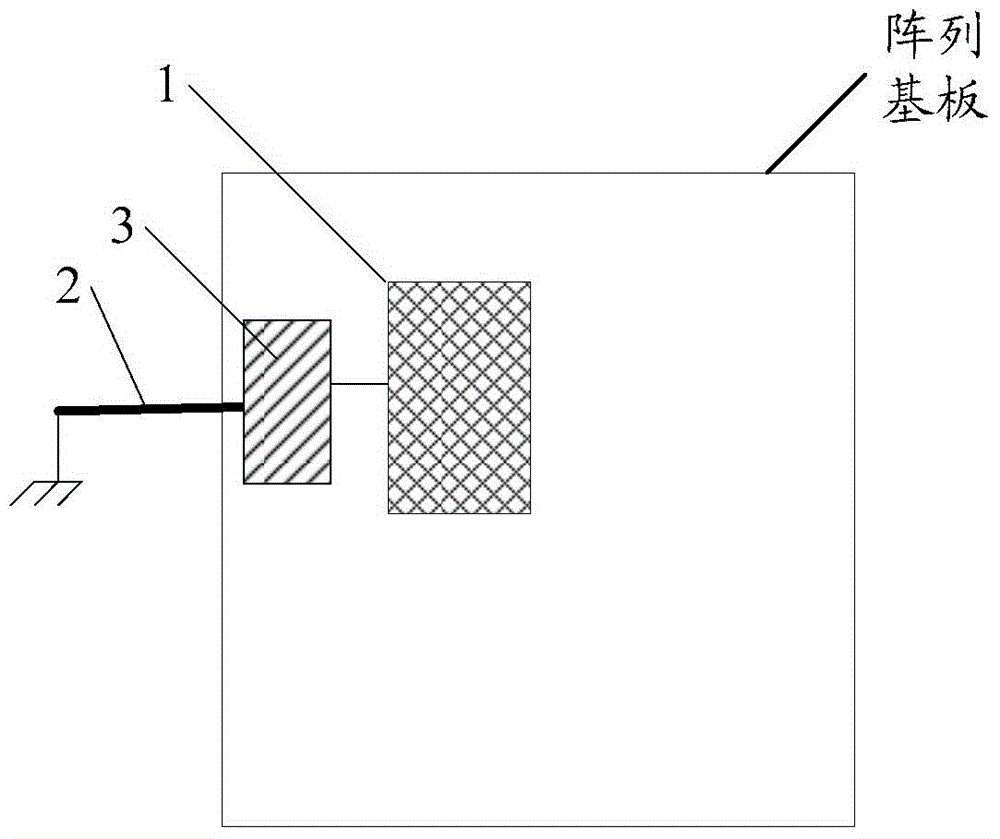

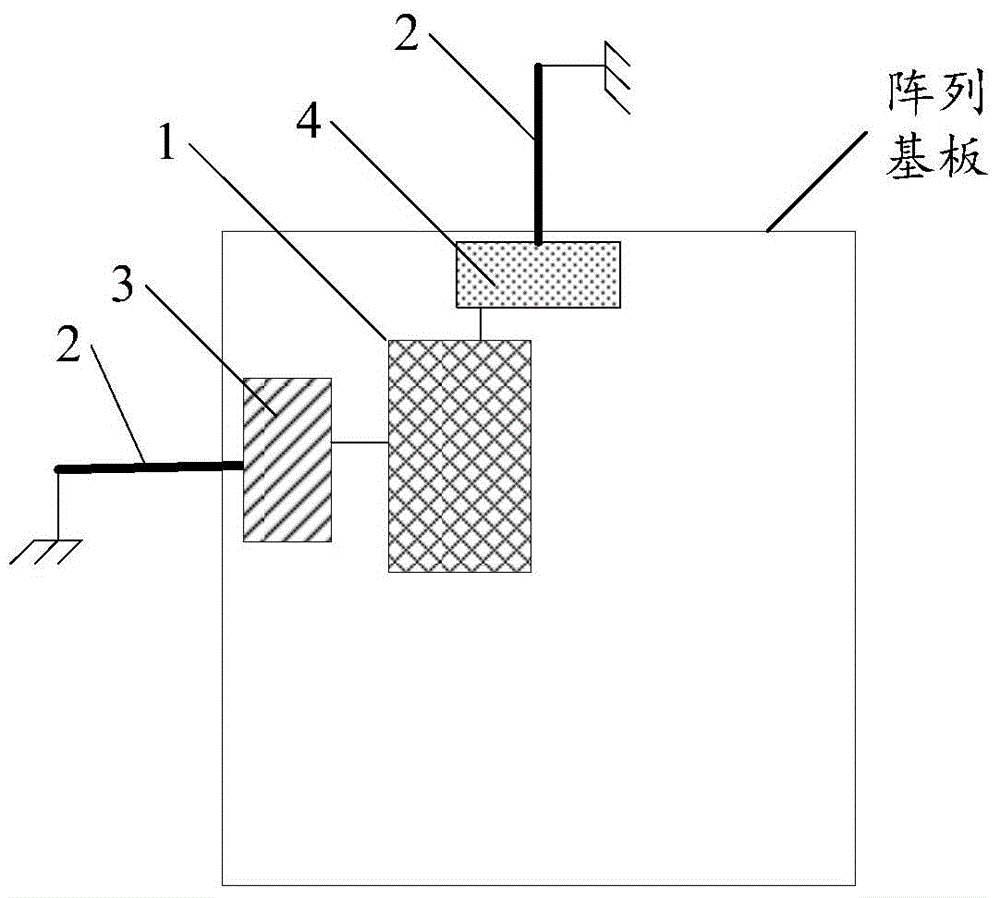

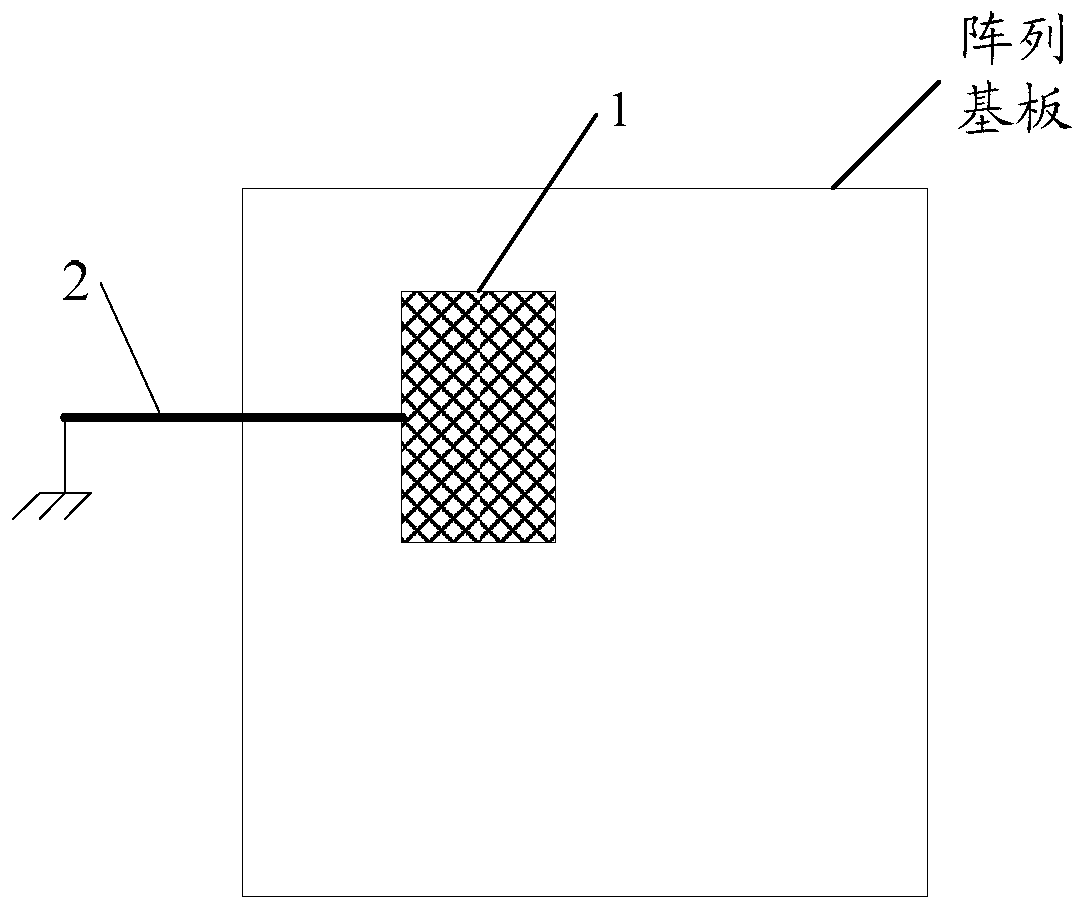

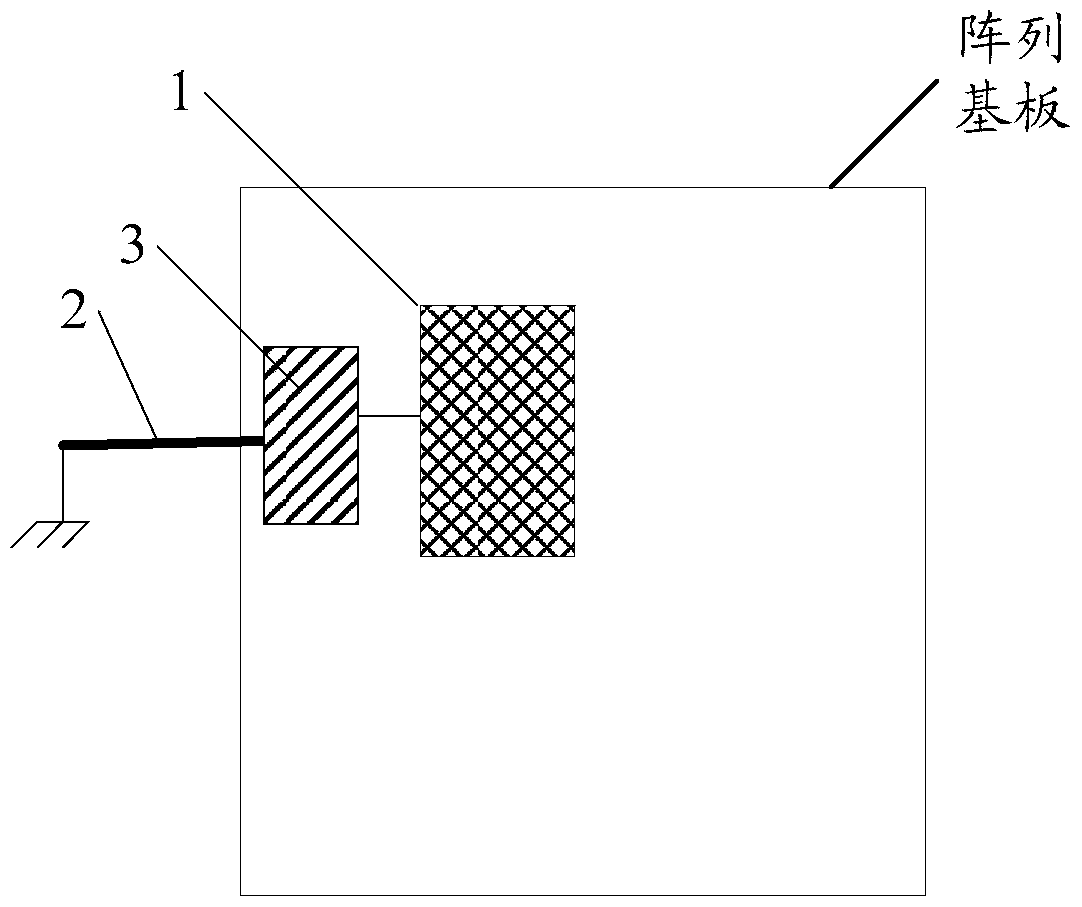

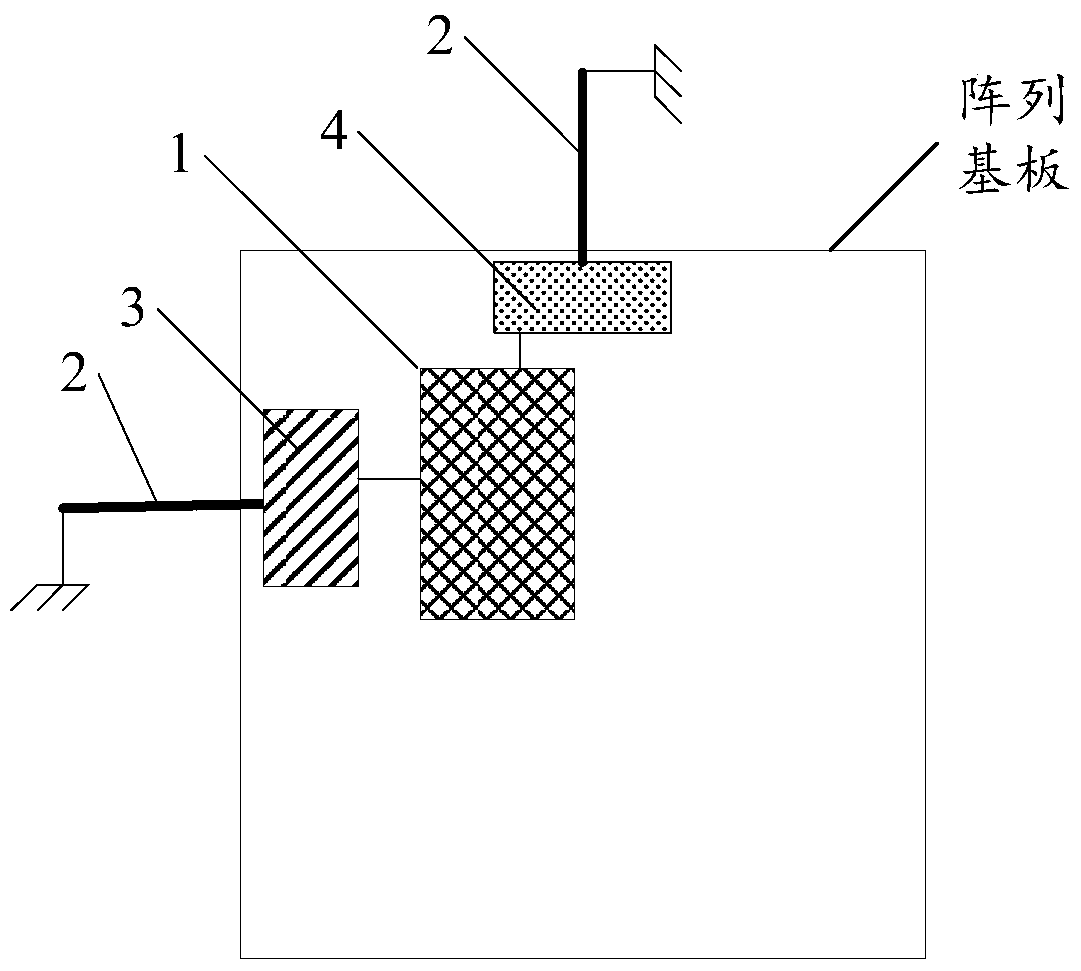

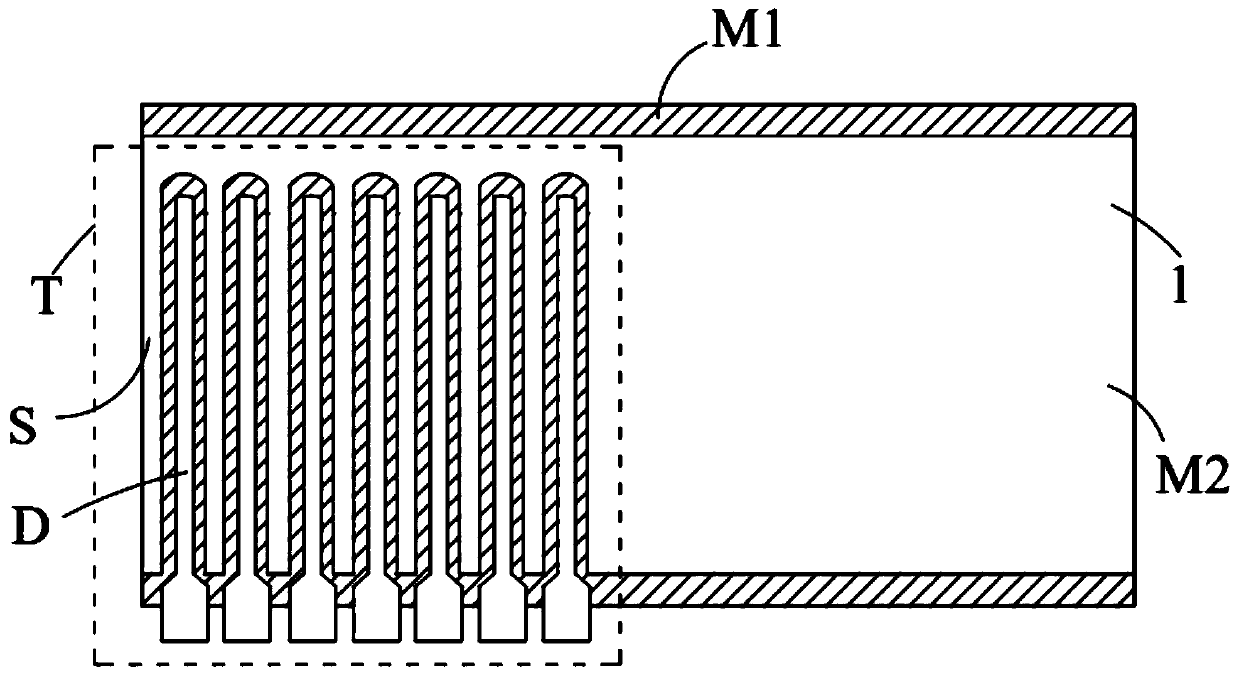

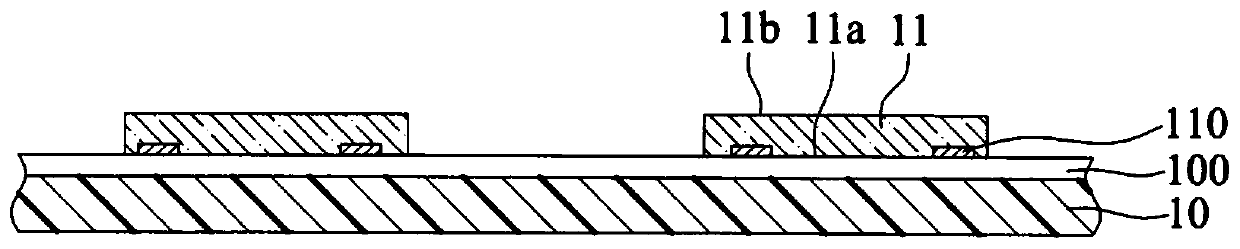

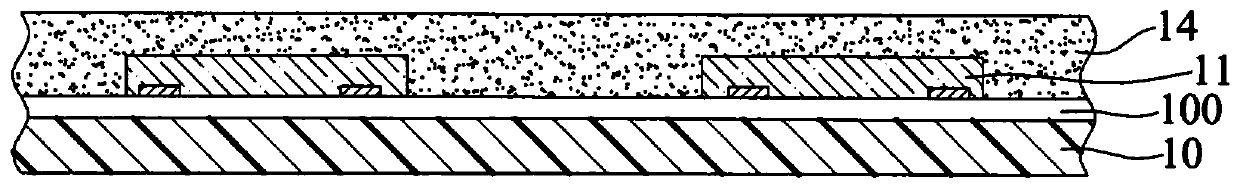

Manufacturing method and structure of light-sensing unit of light-sensing array

ActiveCN105762161BAvoid electrical influenceSolid-state devicesRadiation controlled devicesLight sensingEngineering

The invention discloses a production method of a light sensing unit of a light sensing array. The production method is characterized in that a substrate is provided, and an active element can be formed in the unit area of the substrate; a first electrode layer is formed in the unit area of the substrate, and the first electrode layer is electrically connected with the active element; the active element is provided with a protection layer; the protection layer is provided with a shielding layer to shield the active element; after the shielding layer is formed, the light sensing layer can be formed on the protection layer in the unit area; and the light sensing layer can be provided with a second electrode layer.

Owner:AU OPTRONICS CORP

Solar cell anaerobic annealing process

ActiveCN109427928AImprove performancePerformance impactFinal product manufacturePhotovoltaic energy generationInternal temperatureMetallurgy

The invention discloses a solar cell anaerobic annealing process. The solar cell anaerobic annealing process comprises the following steps of A. putting a cell into an annealing furnace; B. raising internal temperature of a furnace tube of the annealing furnace to a first temperature, and vacuumizing to a first pressure; C. keeping the first temperature and the first pressure; D. lowering internaltemperature of the furnace tube of the annealing furnace to a second temperature; E. raising pressure in the furnace tube of the annealing furnace to normal pressure; and F. discharging.

Owner:TONGWEI SOLAR ENERGY CHENGDU CO LID

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com