Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

48results about How to "Inhibition of current increase" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

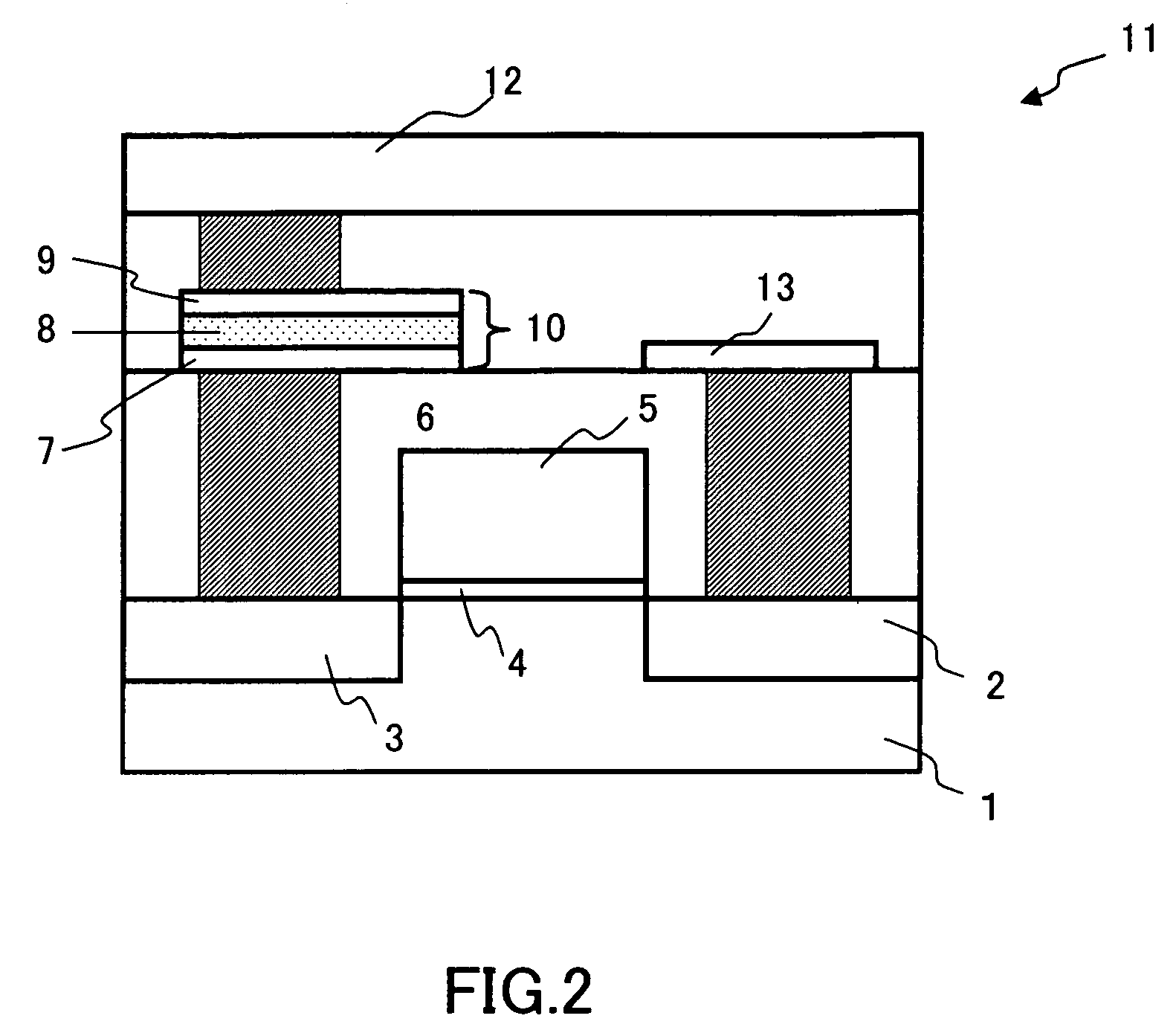

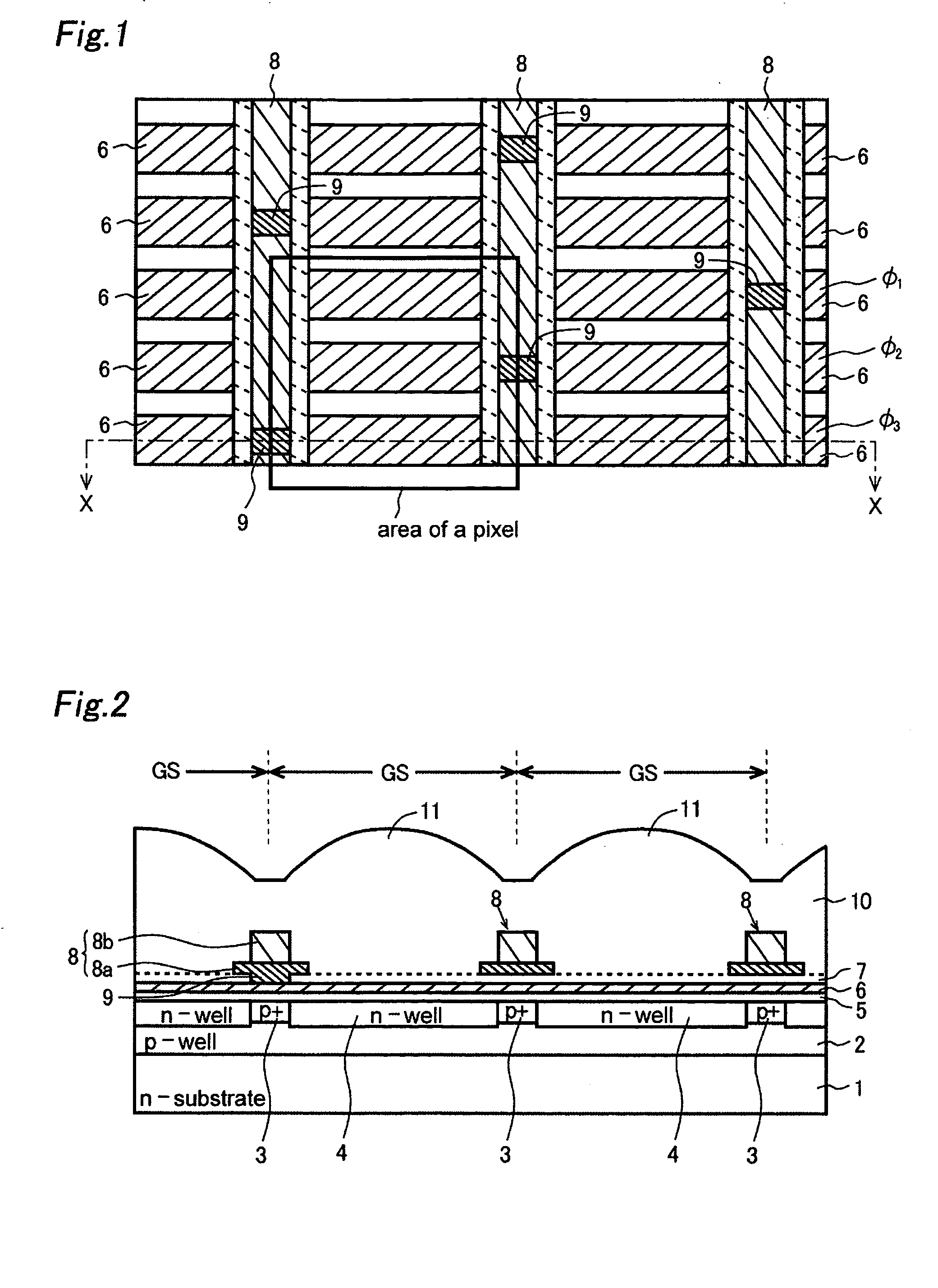

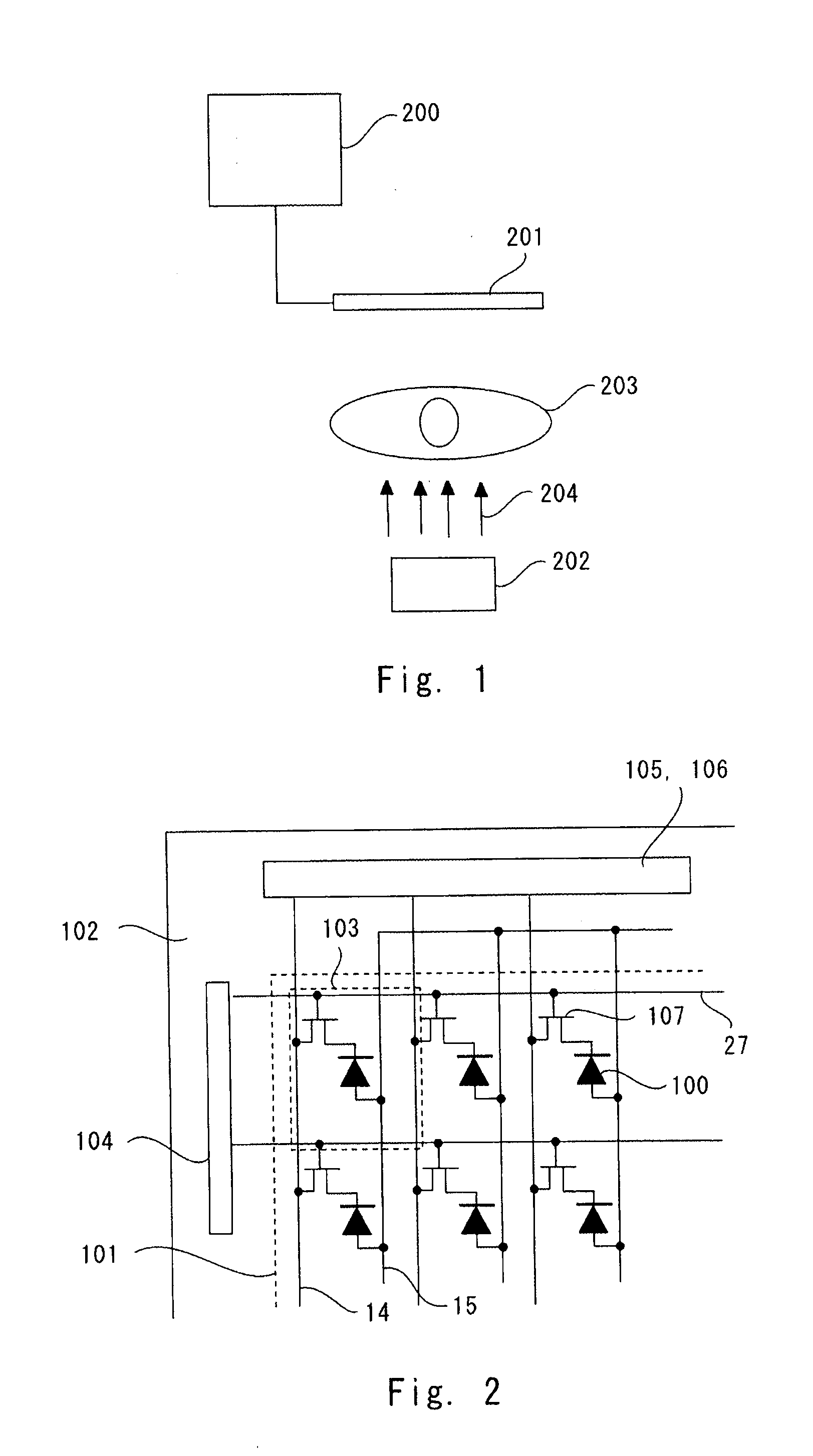

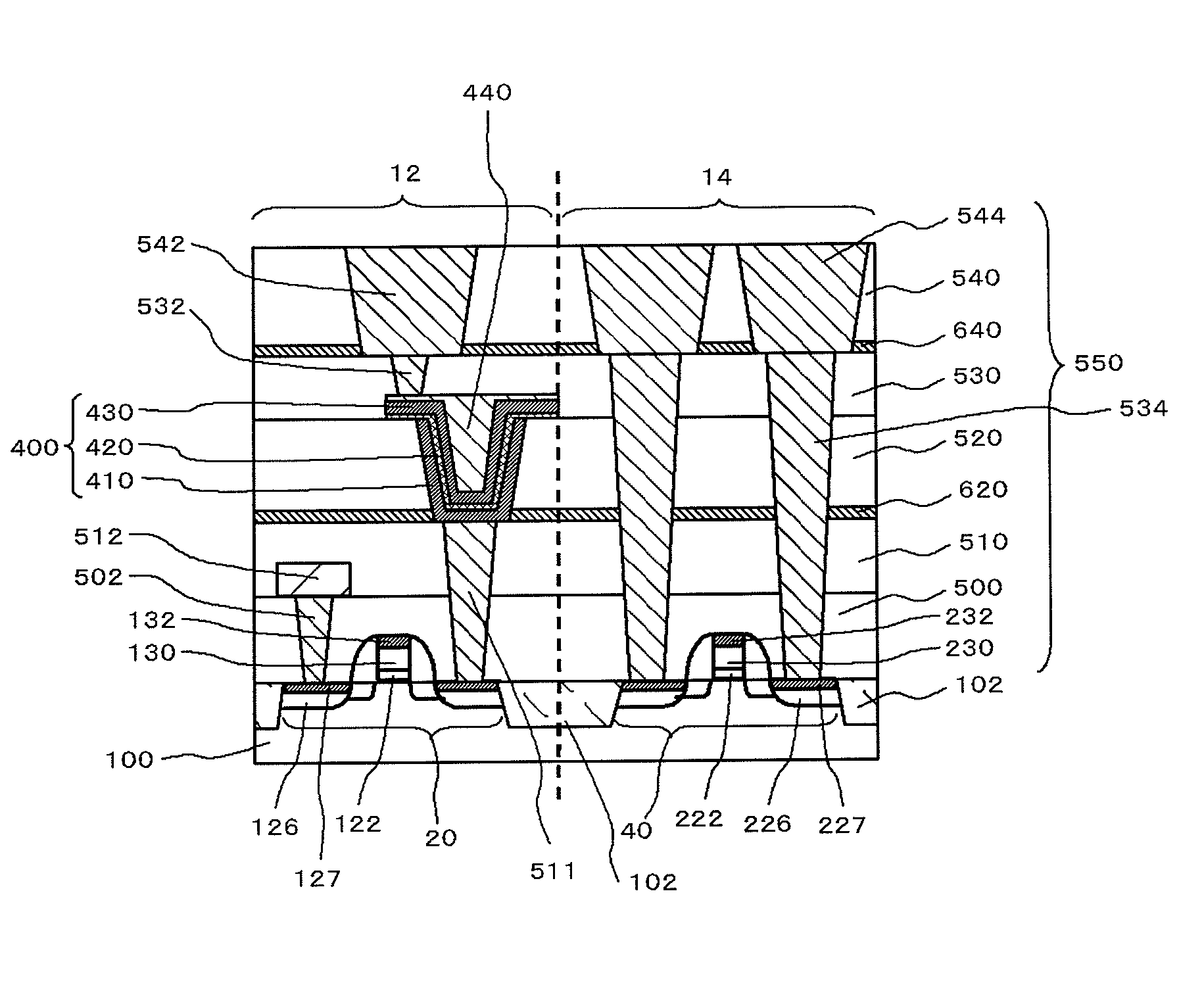

Photo-electric converting device and its driving method, and its manufacturing method, solid-state image pickup device and its driving method and its manufacturing method

ActiveUS20050040440A1High Sensitivity FeaturesIncrease currentTelevision system detailsThyristorEngineeringSolid-state

A photo-electric converting apparatus 100 has an arrangement in which a photo-electric converting apparatus 3 is formed on the surface of a substrate 1, an insulating film 11 is formed on the substrate 1, an uneven portion 18 having concavities and convexities in the thickness direction of the substrate 1 is formed on at least a part of the interface between the substrate 1 of the photo-electric converting portion 3 and the insulating film 11 and a recombination region 19 for decreasing a dark current is formed so as to contain the uneven portion 18 within the photo-electric converting portion 3. This photo-electric converting apparatus becomes able to obtain a high sensitivity characteristic and to suppress a dark current from being increased by a decrease of the interface states.

Owner:SONY SEMICON SOLUTIONS CORP

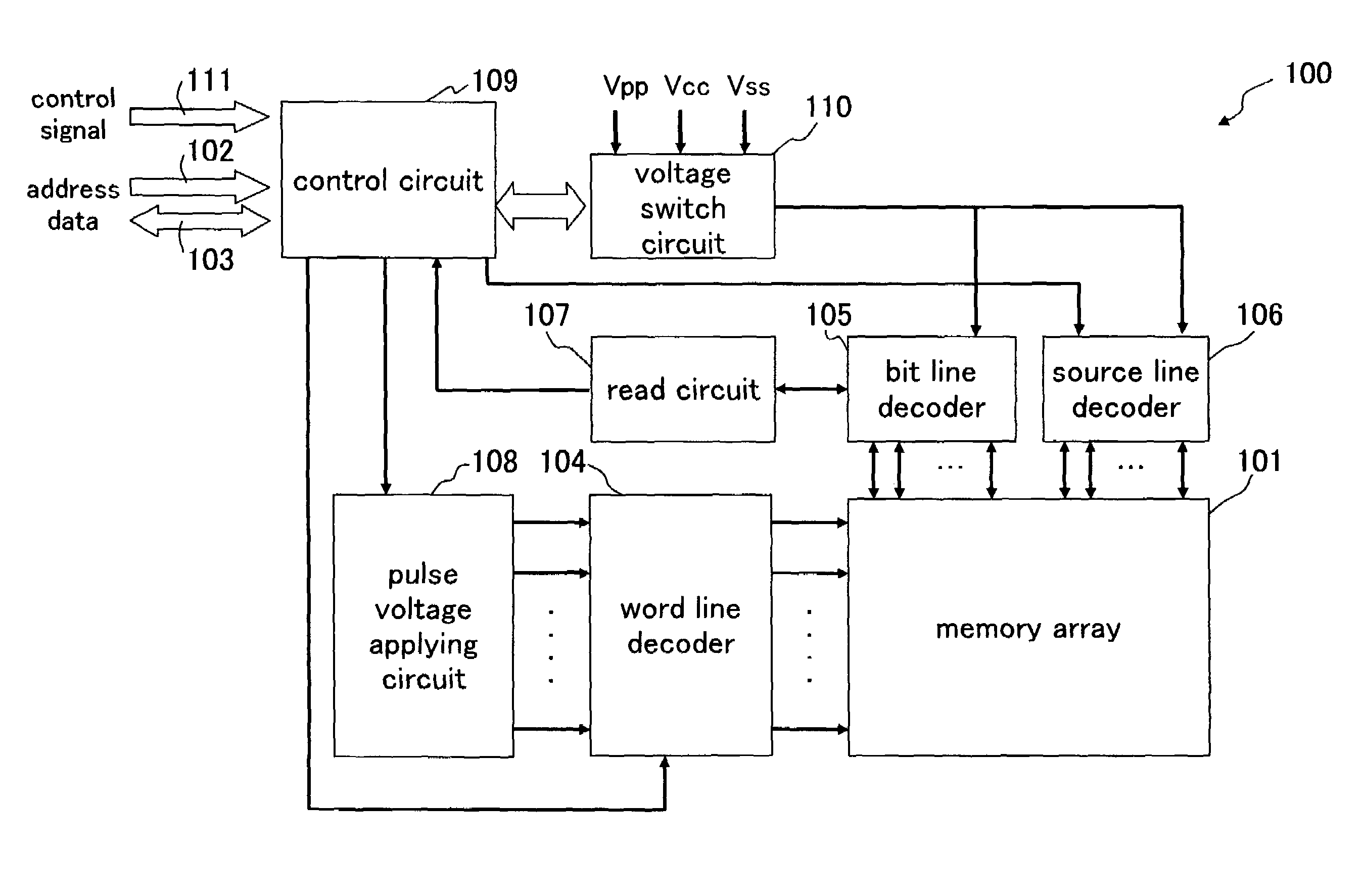

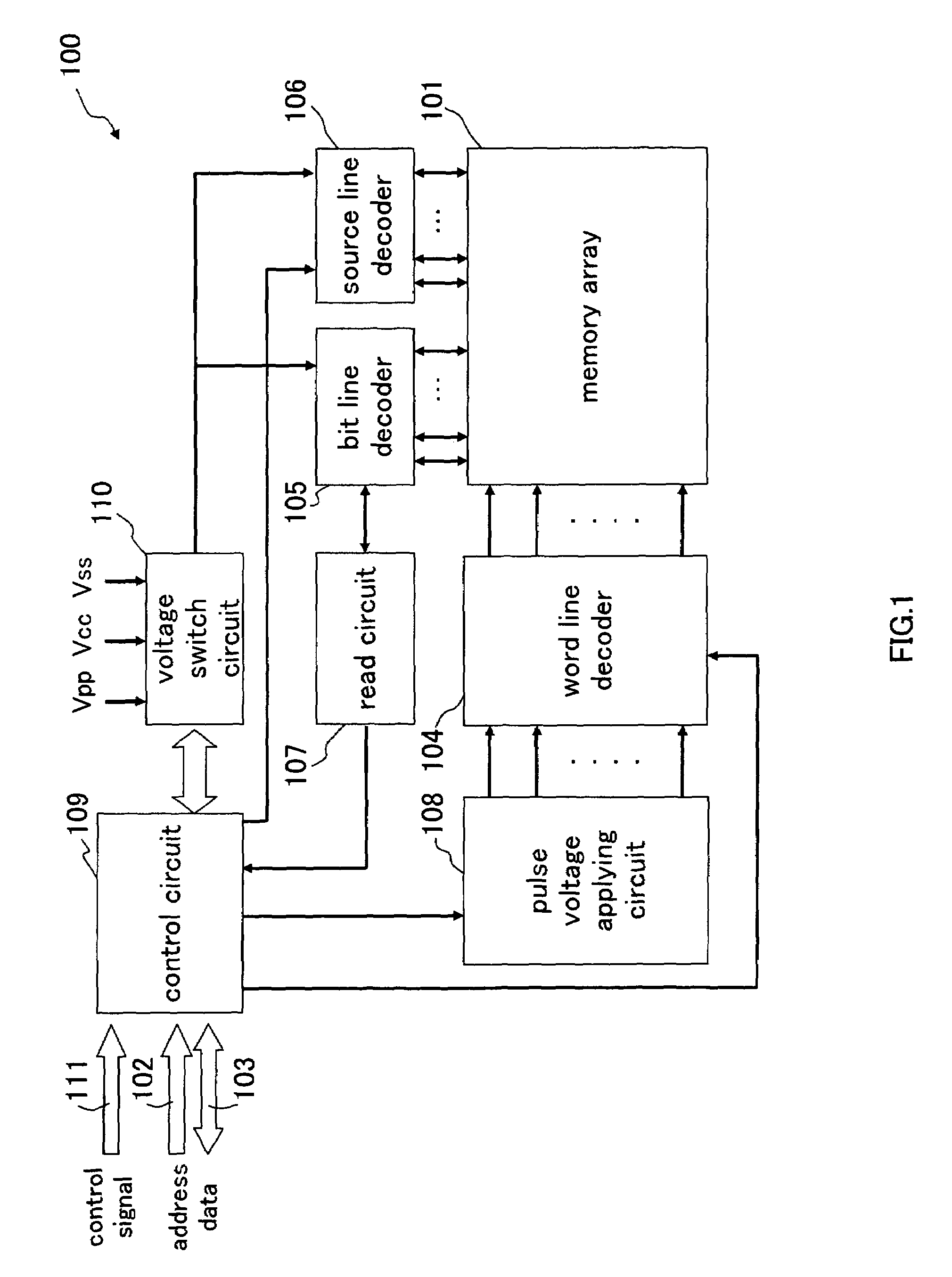

Nonvolatile semiconductor memory device and control method thereof

ActiveUS6995999B2Total current dropInhibition of current increaseSolid-state devicesRead-only memoriesBit lineVoltage pulse

A nonvolatile semiconductor memory device includes a memory array in which a plurality of memory cells are arranged in a row direction and a column direction, each of the memory cells being formed by connecting one end of a variable resistive element for storing information according to a change in electric resistance caused by an electric stress and a drain of a selection transistor to each other on a semiconductor substrate, a voltage switch circuit for switching among a program voltage, an erase voltage and a read voltage to be applied to the source line and the bit line connected to the memory cell, and a pulse voltage applying circuit. In the state where the program voltage or erase voltage corresponding to the bit line and the source line is applied to the bit line and the source line connected to a memory cell to be programmed or erased in the memory array via the voltage switch circuit, the pulse voltage applying circuit applies a voltage pulse for programming or erasing to the word line connected to the gate electrode of the selection transistor connected to the memory cell.

Owner:SAMSUNG ELECTRONICS CO LTD

Photo-electric converting device and its driving method, and its manufacturing method, solid-state image pickup device and its driving method and its manufacturing method

ActiveUS7511750B2Inhibition of current increaseHigh Sensitivity FeaturesTelevision system detailsThyristorEngineeringSolid-state

A photo-electric converting apparatus 100 has an arrangement in which a photo-electric converting apparatus 3 is formed on the surface of a substrate 1, an insulating film 11 is formed on the substrate 1, an uneven portion 18 having concavities and convexities in the thickness direction of the substrate 1 is formed on at least a part of the interface between the substrate 1 of the photo-electric converting portion and the insulating film 11 and a recombination region 19 for decreasing a dark current is formed so as to contain the uneven portion 18 within the photo-electric converting portion 3. This photo-electric converting apparatus becomes able to obtain a high sensitivity characteristic and to suppress a dark current from being increased by a decrease of the interface states.

Owner:SONY SEMICON SOLUTIONS CORP

Ink jet head

InactiveUS6984025B2Dimensionally stableReduce exposurePrintingEngineeringElectrical and Electronics engineering

An ink jet head includes a substrate provided with heat generating members for generating a bubble in ink on a surface of the substrate, a plurality of discharge ports for discharging the ink, the ports opposed to the surface of the substrate, and a plurality of ink flow passages communicating with the plurality of discharge ports to feed the ink. A plurality of the heat generating members is provided in each of the ink flow passages, and the discharge port is arranged on an extension line extending from a center of a pressure generating area composed of the plurality of heat generating members toward the surface of the substrate in a normal direction. Moreover, a distance dhc between centers of each of two heat generating members arranged most apart from each other among the plurality of heat generating members is set to be larger than a diameter do of an aperture of the discharge port. In the ink jet head, even if the center position of the discharge port and the center position of the pressure generating area are somewhat shifted from each other, main liquid droplets of the ink are discharged from the discharge port without generating no shift in their discharge directions.

Owner:CANON KK

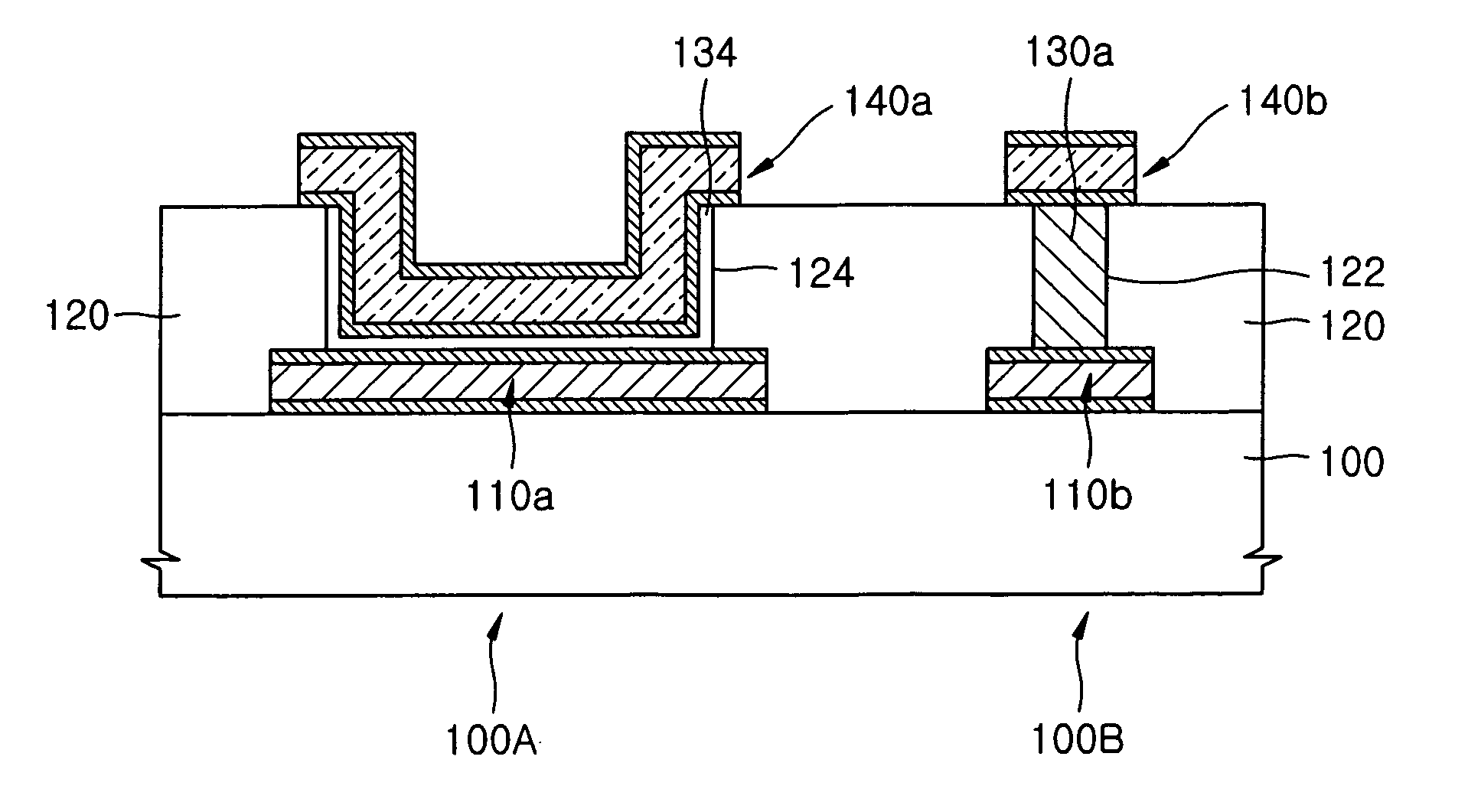

Semiconductor device including a trench-type metal-insulator-metal (MIM) capacitor and method of fabricating the same

InactiveUS20060006441A1Improve processing stabilityRelieve pressureTransistorSolid-state devicesDevice materialEngineering

In a semiconductor device, and a method of fabricating the same, the semiconductor device includes a bottom electrode and a first interconnection layer on a semiconductor substrate, an upper surface of the bottom electrode and an upper surface of the first interconnection layer being level, an interlayer insulating layer having a trench exposing the upper surface of the bottom electrode and a via hole exposing the upper surface of the first interconnection layer, a contact plug formed of a first material inside the via hole and connected to the first interconnection layer, an upper electrode formed of a second material inside the trench on the bottom electrode, the first material being exclusive of the second material, and a dielectric layer interposed between the bottom electrode and the upper electrode, and formed only inside the trench.

Owner:SAMSUNG ELECTRONICS CO LTD

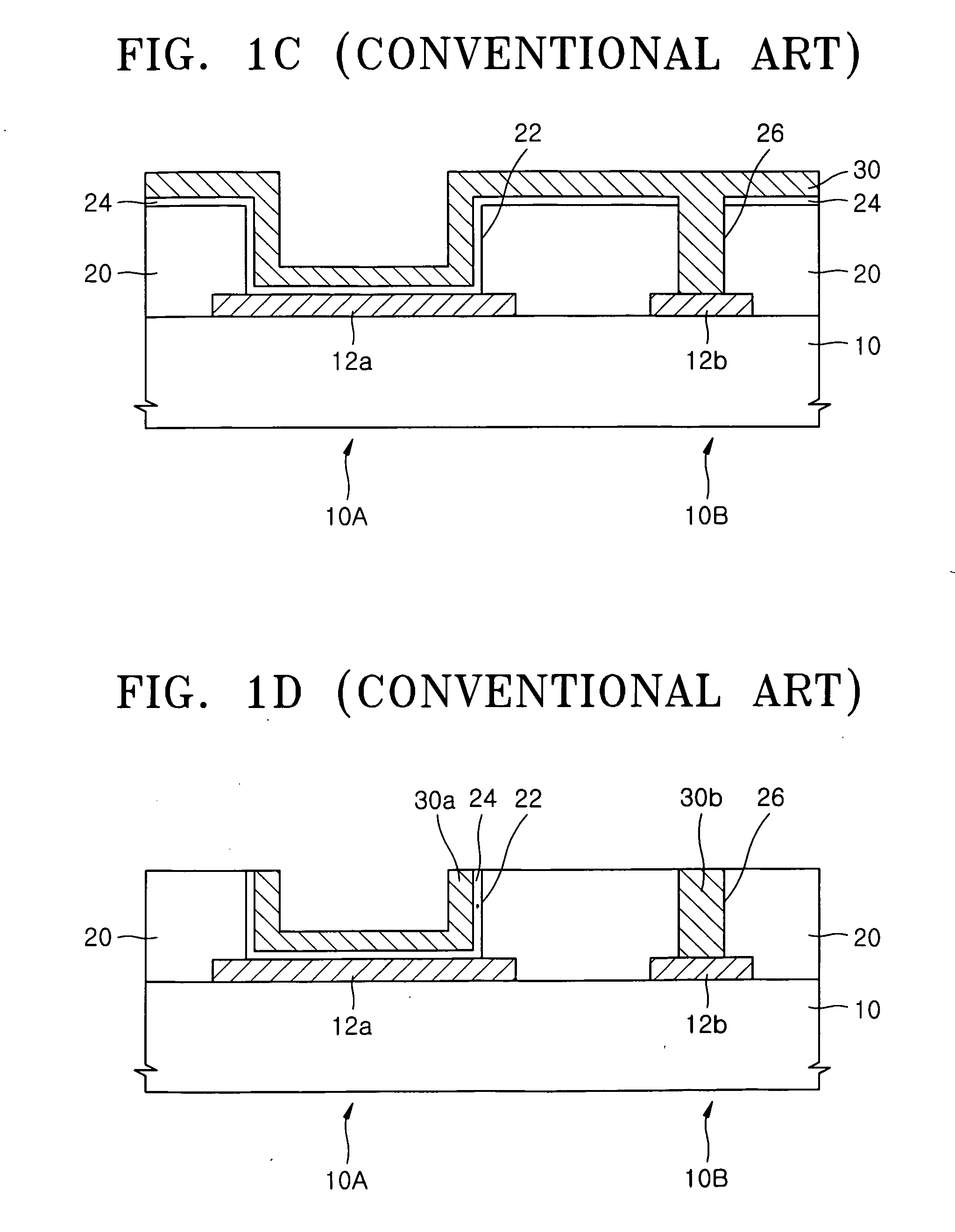

Semiconductor device and method of manufacturing semiconductor device

ActiveUS20140217407A1Suppress increase in on-voltageTotal current dropSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsPower semiconductor deviceHydrogen

A donor layer that is formed by performing a heat treatment for a crystal defect formed by proton radiation is provided in an n-type drift layer of an n− semiconductor substrate. The donor layer has an impurity concentration distribution including a portion with the maximum impurity concentration and a portion with a concentration gradient in which the impurity concentration is reduce to the same impurity concentration as that of the n-type drift layer in a direction from the portion with the maximum impurity concentration to both surfaces of the n-type drift layer. The crystal defect formed in the n-type drift layer is a composite crystal defect mainly caused by a vacancy, oxygen, and hydrogen.

Owner:FUJI ELECTRIC CO LTD

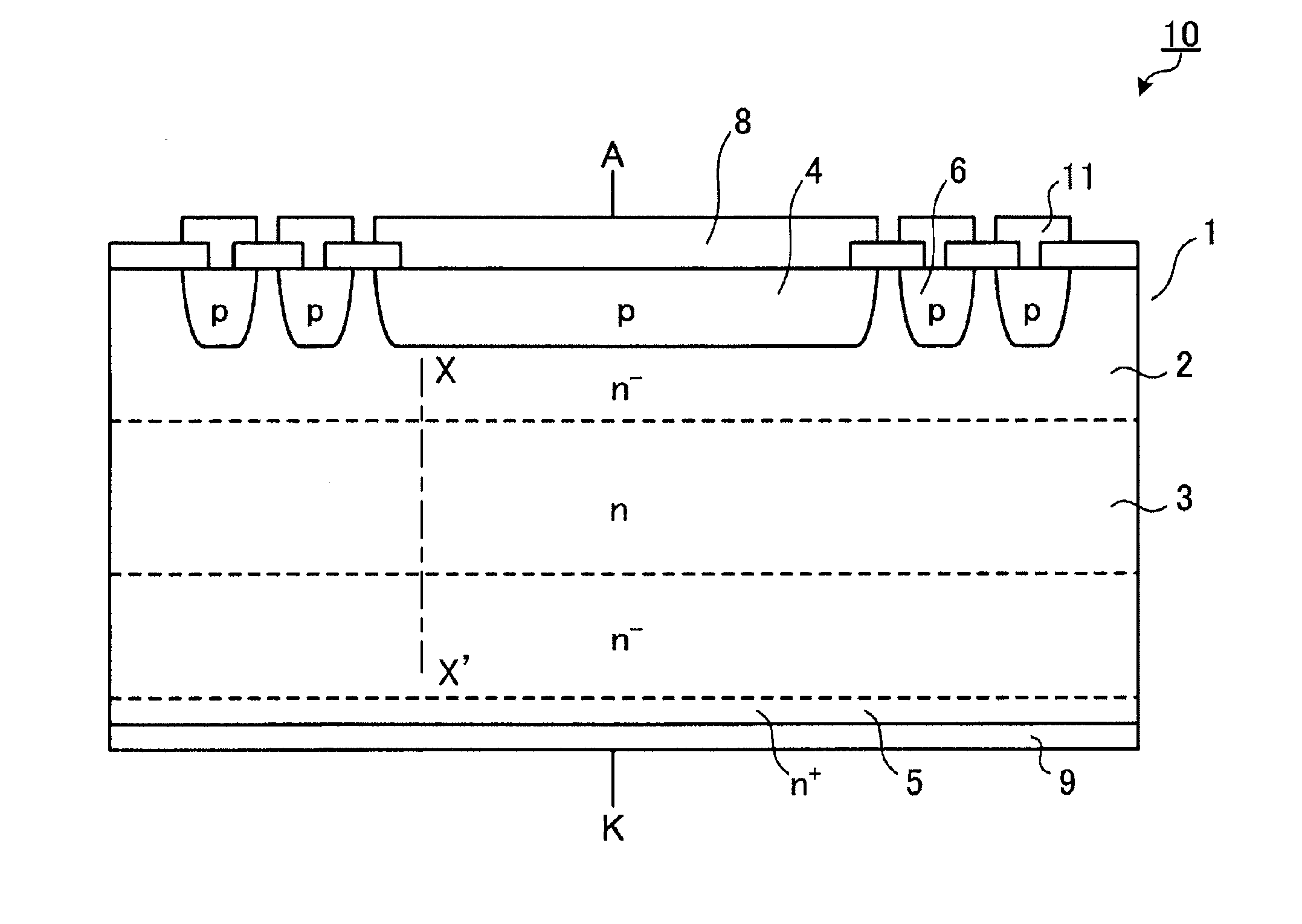

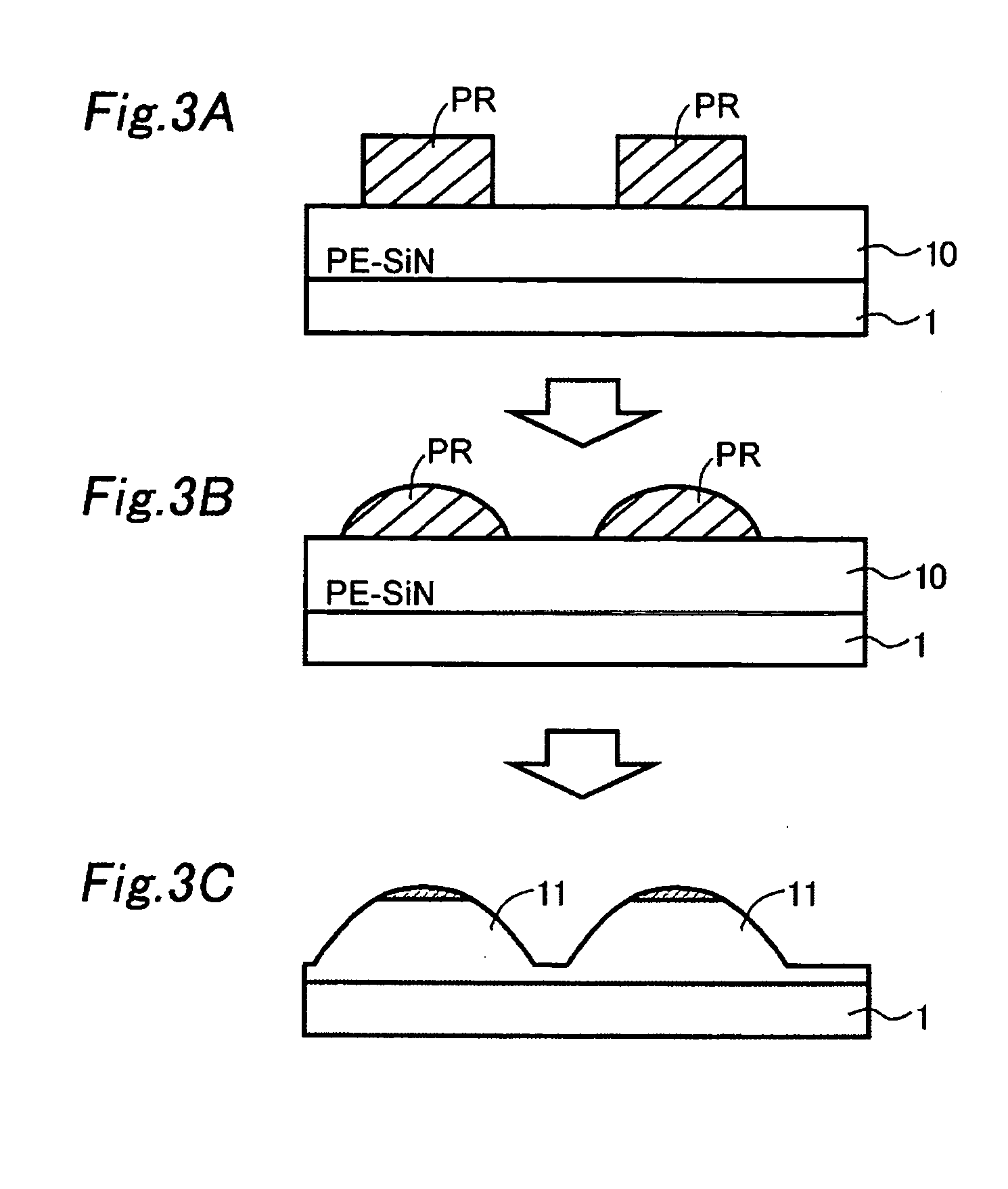

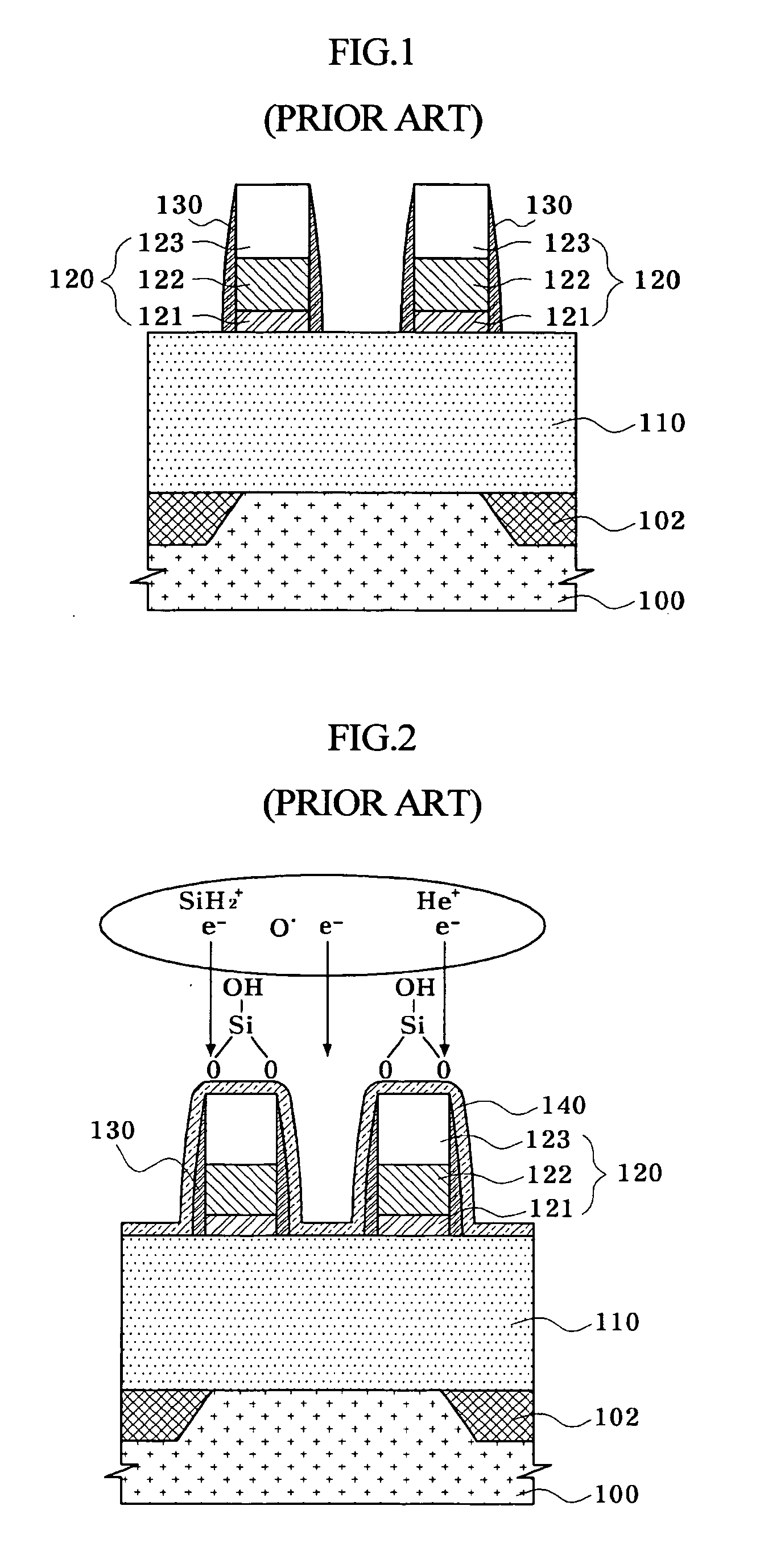

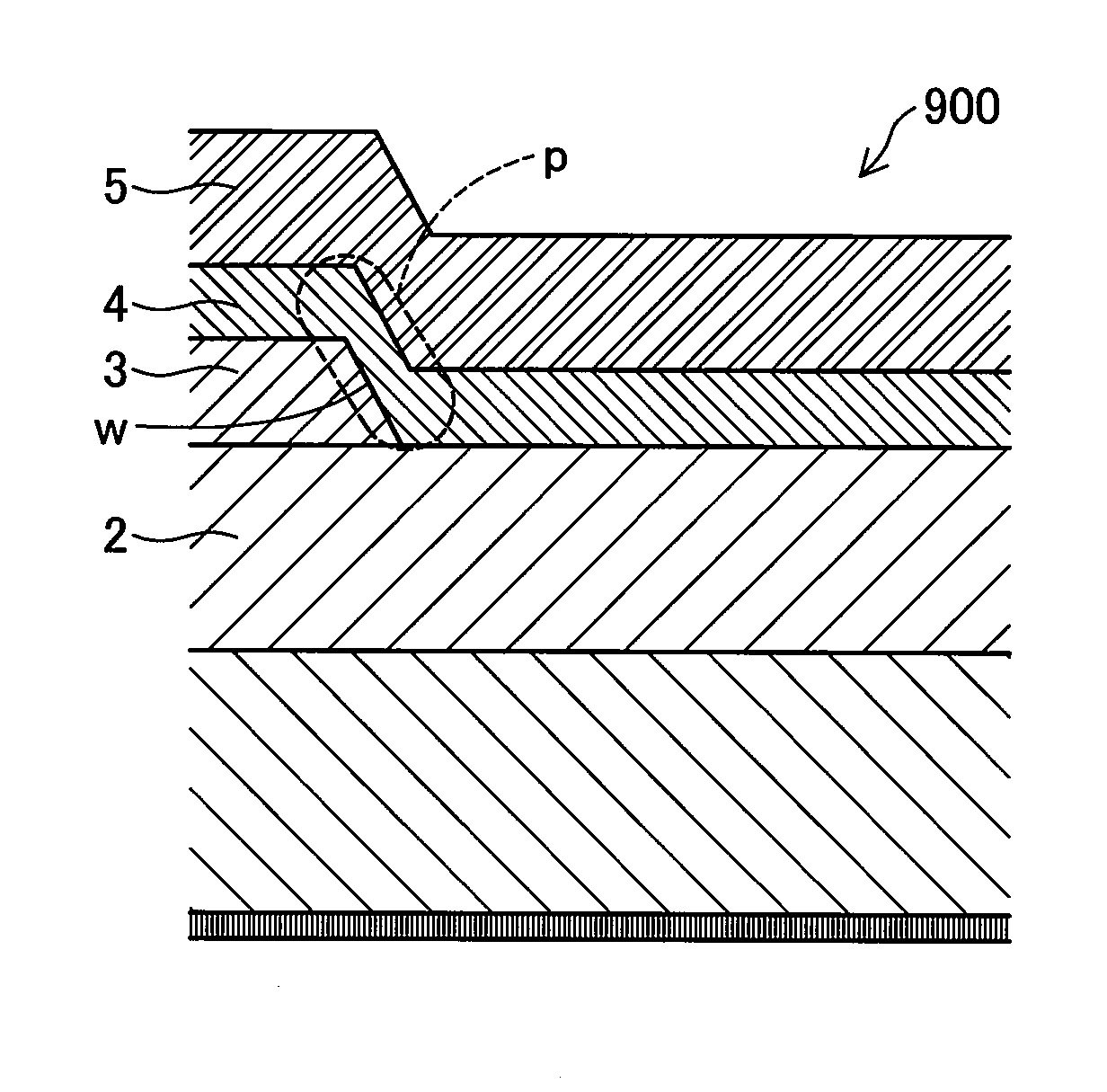

Plasma processing method, plasma etching method and manufacturing method of solid-state image sensor

InactiveUS20050085087A1Suppresses of interface stateInhibition of current increaseElectric discharge tubesSolid-state devicesPhotoresistMaterials science

A method of plasma processing is offered to suppress generation of interface states, specifically to suppress increase in the dark current of a solid-state image sensor by reducing the interface states. An interlayer insulation film made of silicon nitride film is formed over a silicon substrate by plasma CVD, and a photoresist layer is selectively formed on the interlayer insulation film. Subsequent heating process makes a profile of the photoresist layer round. Next, the interlayer insulation film is plasma-etched using the photoresist layer as a mask and a fluorocarbon gas as an etching gas to form micro lenses. Pulse-time-modulated plasma method in which RF power is supplied intermittently is used to suppress increase in the interface states at silicon-silicon dioxide interface due to an influence of UV light generated in the plasma etching.

Owner:SANYO ELECTRIC CO LTD +1

Photosensor and method of manufacturing the same

InactiveUS20100237250A1Inhibition of current increaseSolid-state devicesMaterial analysis by optical meansNitrogenTransparent conducting film

A photosensor includes a photodiode including a semiconductor layer. The semiconductor layer is made up of an n-type semiconductor layer, an i-type semiconductor layer and a p-type semiconductor layer, for example. The photosensor further includes a transparent electrode made of a transparent conductive film, and a nitrogen-containing semiconductor layer formed between the semiconductor layer and the transparent electrode.

Owner:MITSUBISHI ELECTRIC CORP

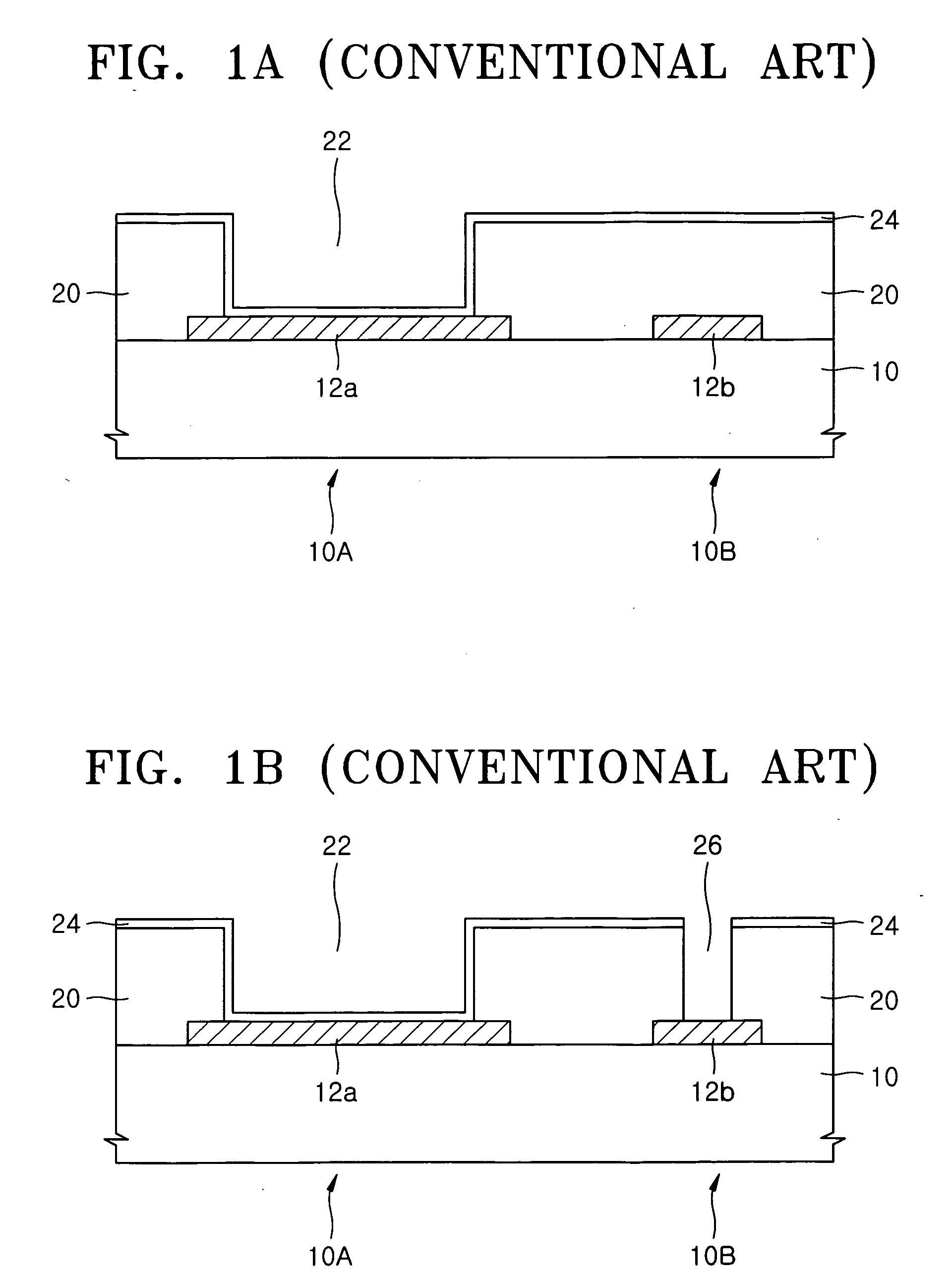

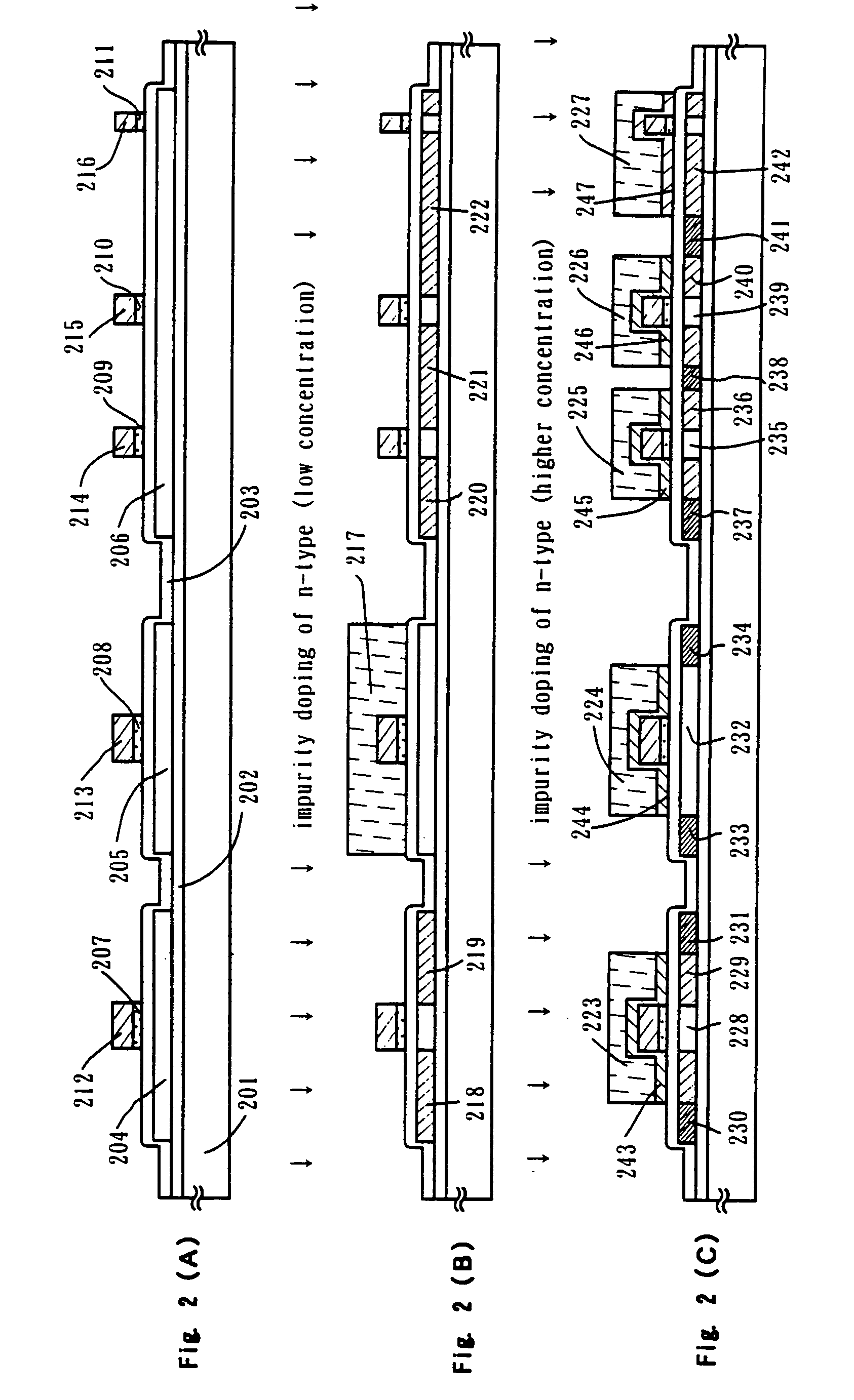

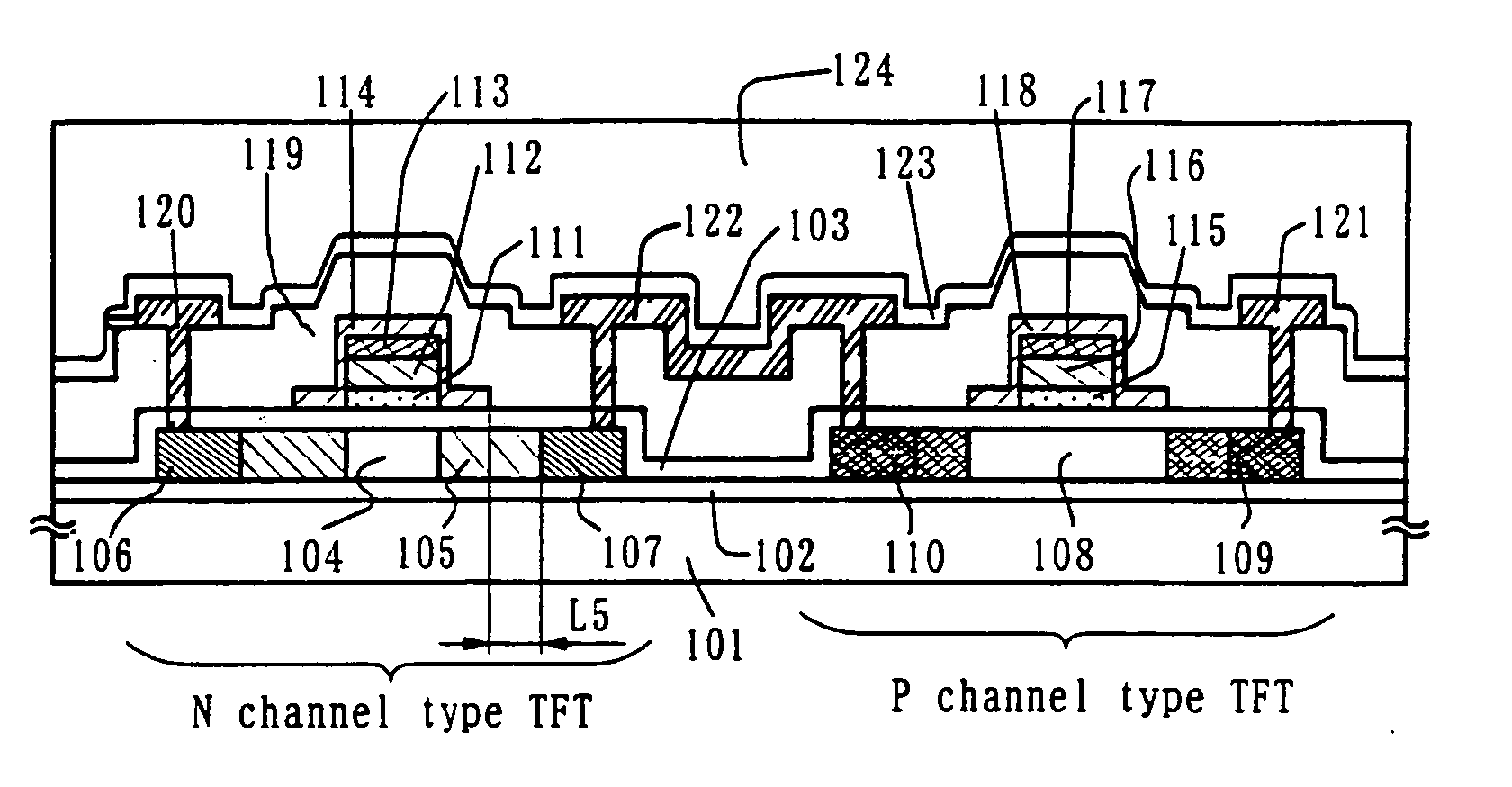

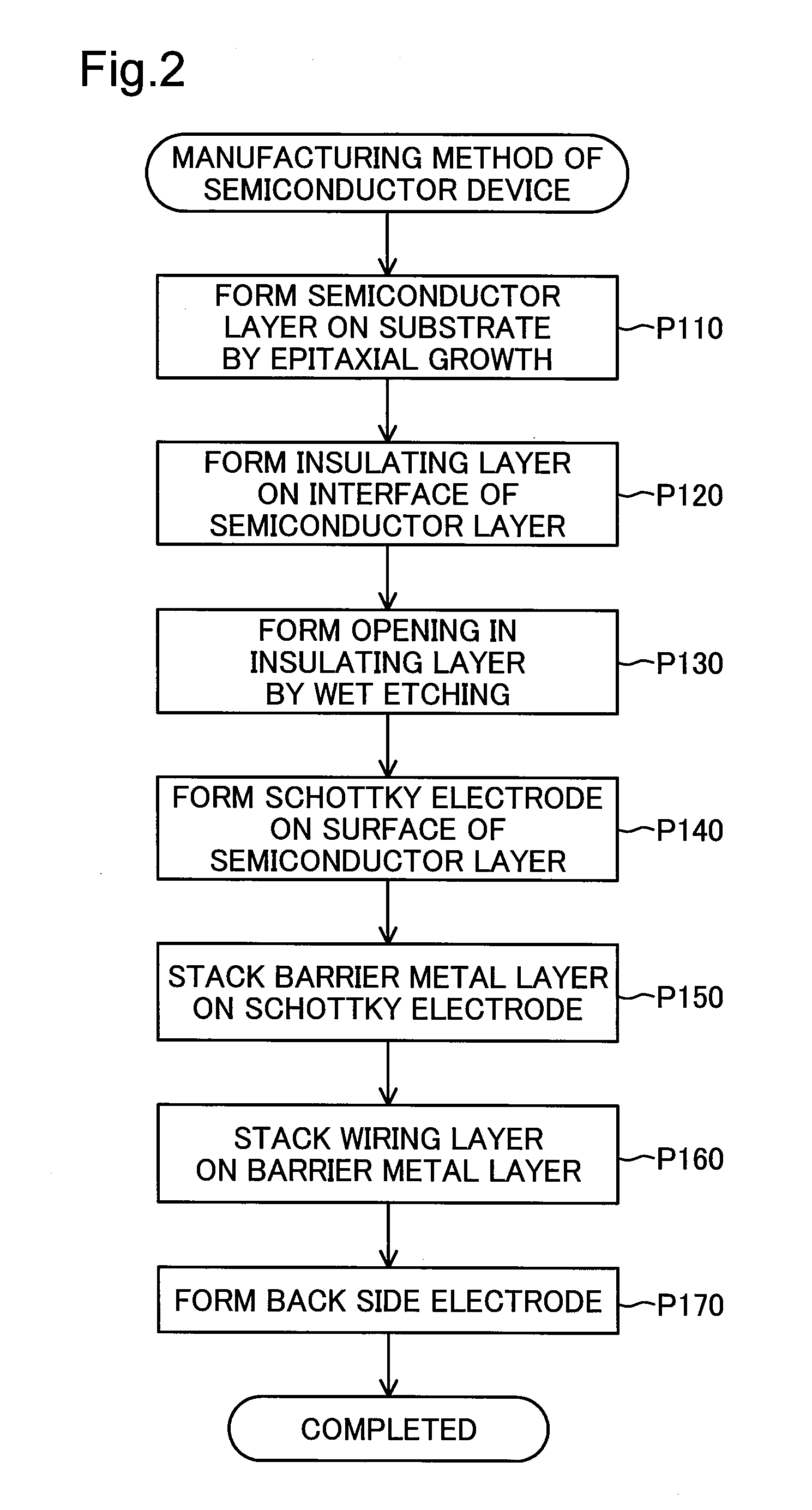

Method of manufacturing semiconductor devices

InactiveUS7244962B2Lower average currentInhibit deteriorationTransistorSolid-state devicesEngineeringSemiconductor

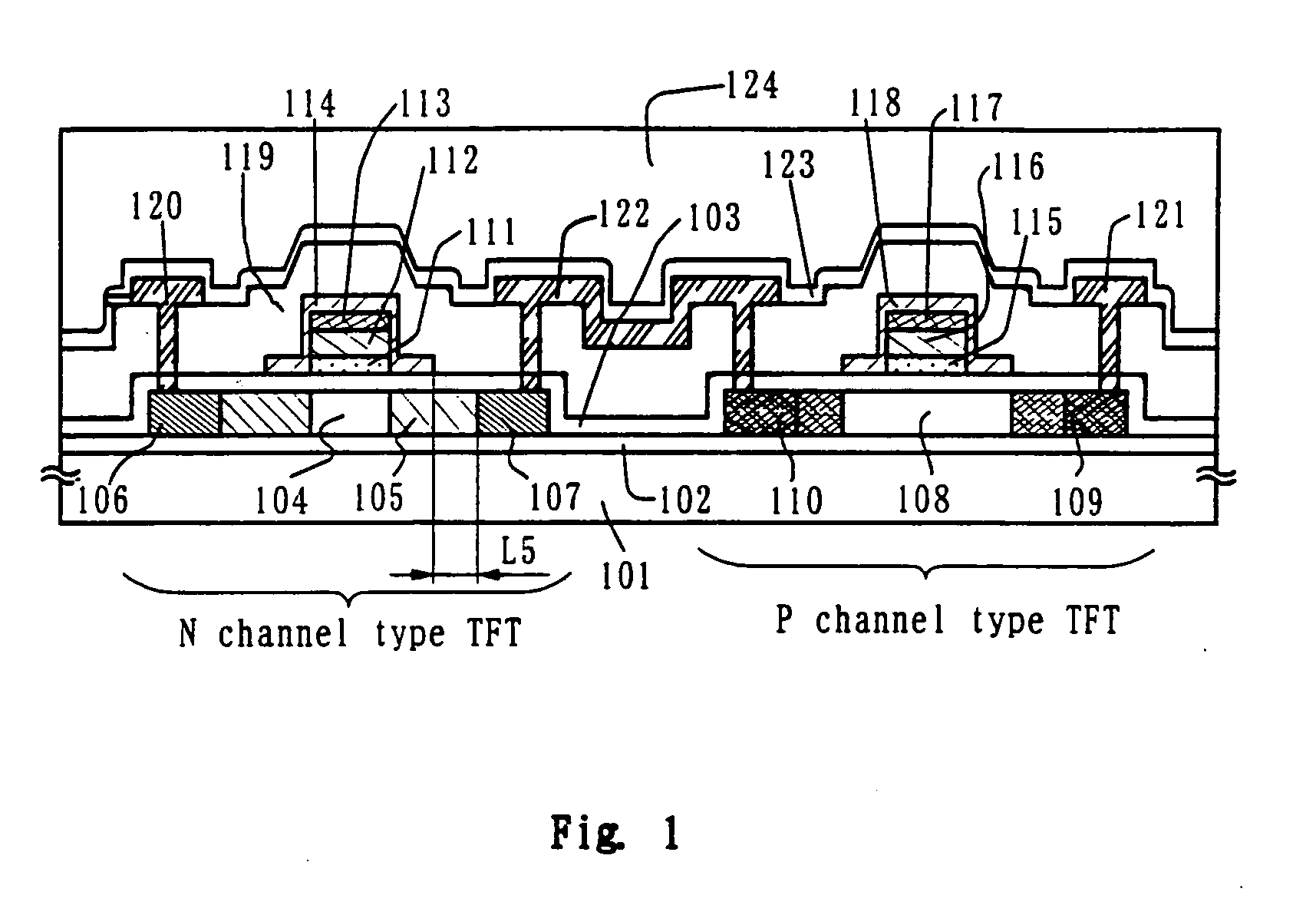

Subjected to obtain a crystalline TFT which simultaneously prevents increase of OFF current and deterioration of ON current. A gate electrode of a crystalline TFT is comprised of a first gate electrode and a second gate electrode formed in contact with the first gate electrode and a gate insulating film. LDD region is formed by using the first gate electrode as a mask, and a source region and a drain region are formed by using the second gate electrode as a mask. By removing a portion of the second gate electrode, a structure in which a region where LDD region and the second gate electrode overlap with a gate insulating film interposed therebetween, and a region where LDD region and the second gate electrode do not overlap, is obtained.

Owner:SEMICON ENERGY LAB CO LTD

Method of manufacturing semiconductor devices

InactiveUS20050067618A1Inhibit deteriorationTotal current dropTransistorSolid-state devicesDevice materialEngineering

Subjected to obtain a crystalline TFT which simultaneously prevents increase of OFF current and deterioration of ON current. A gate electrode of a crystalline TFT is comprised of a first gate electrode and a second gate electrode formed in contact with the first gate electrode and a gate insulating film. LDD region is formed by using the first gate electrode as a mask, and a source region and a drain region are formed by using the second gate electrode as a mask. By removing a portion of the second gate electrode, a structure in which a region where LDD region and the second gate electrode overlap with a gate insulating film interposed therebetween, and a region where LDD region and the second gate electrode do not overlap, is obtained.

Owner:SEMICON ENERGY LAB CO LTD

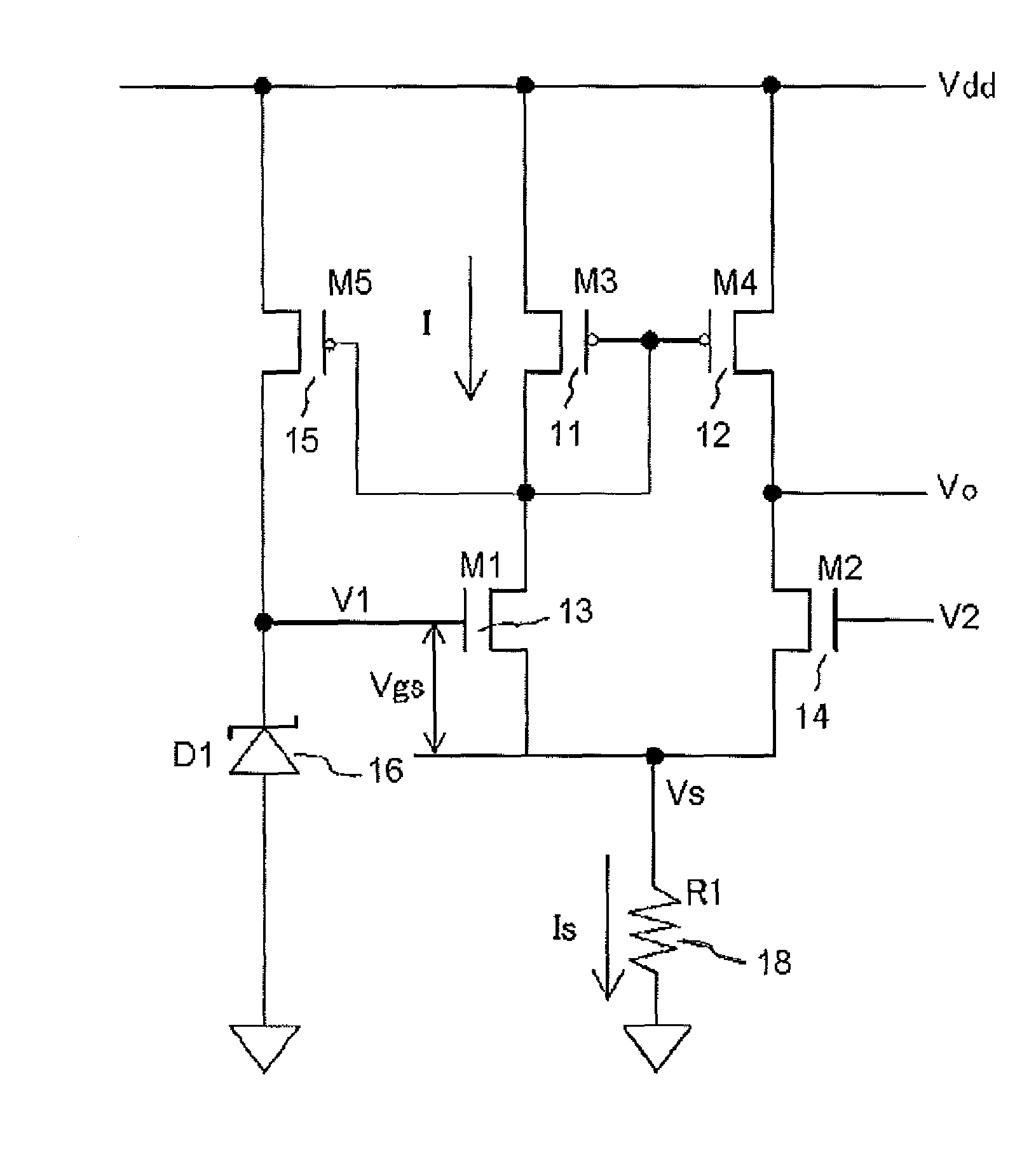

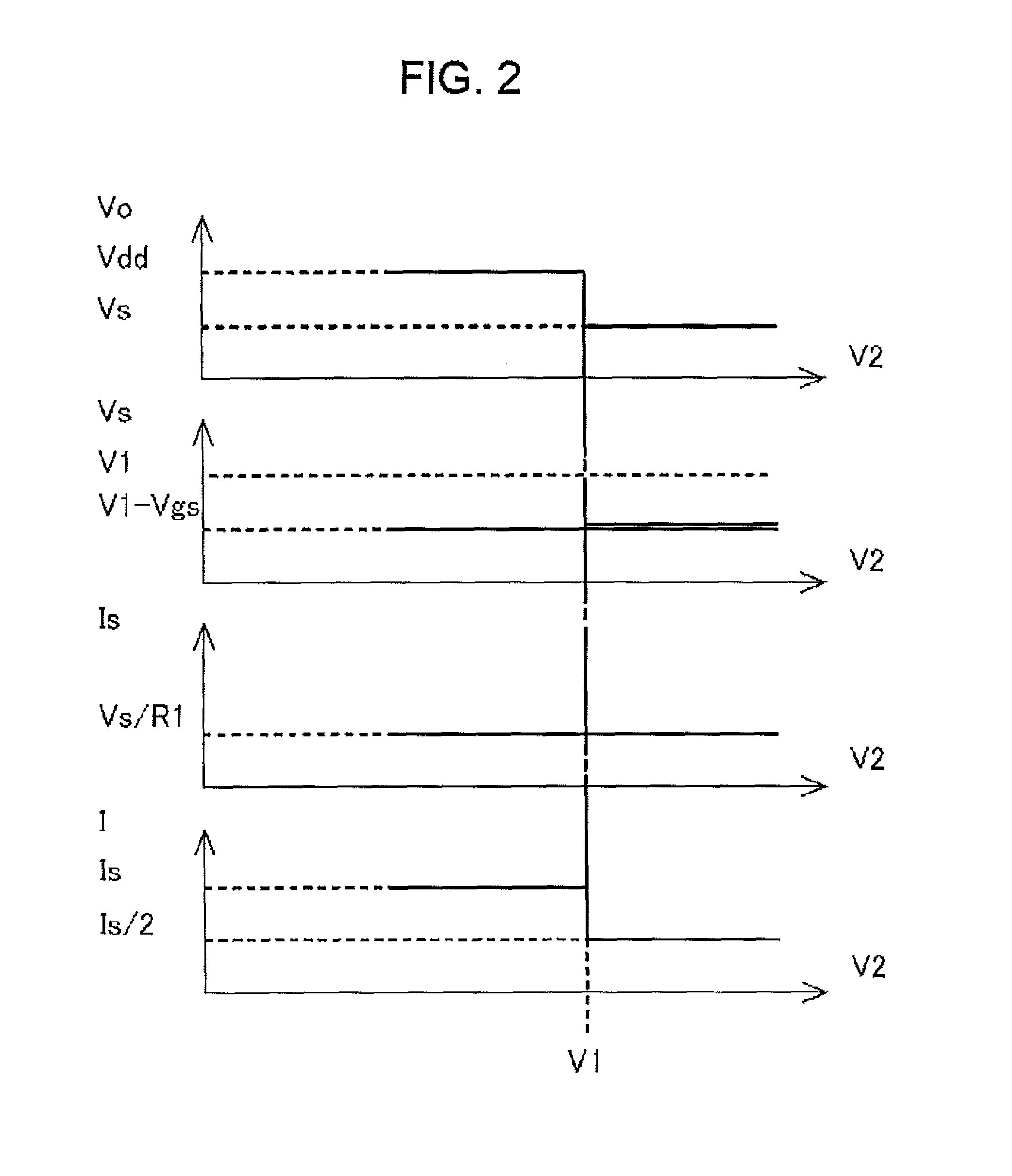

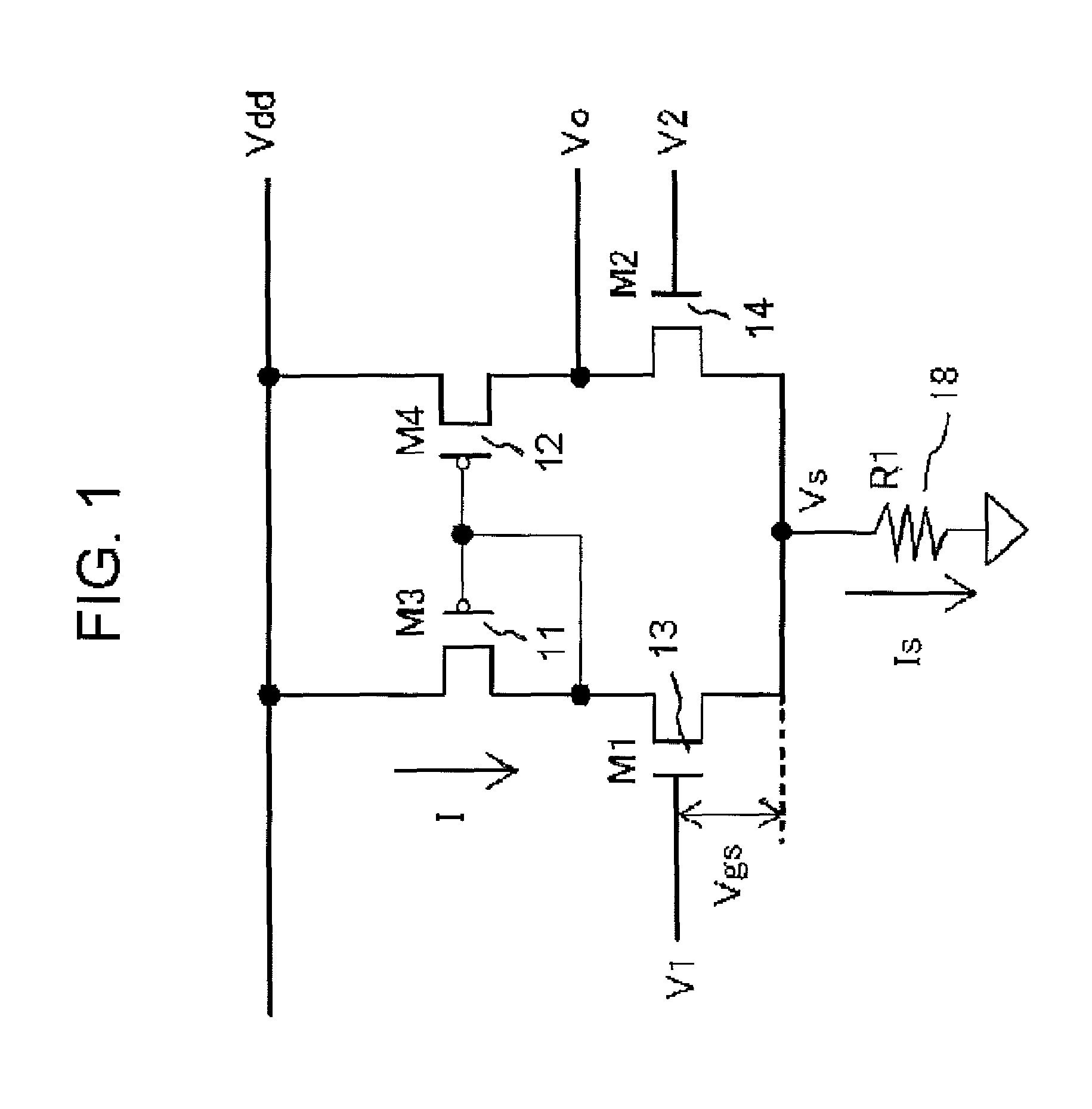

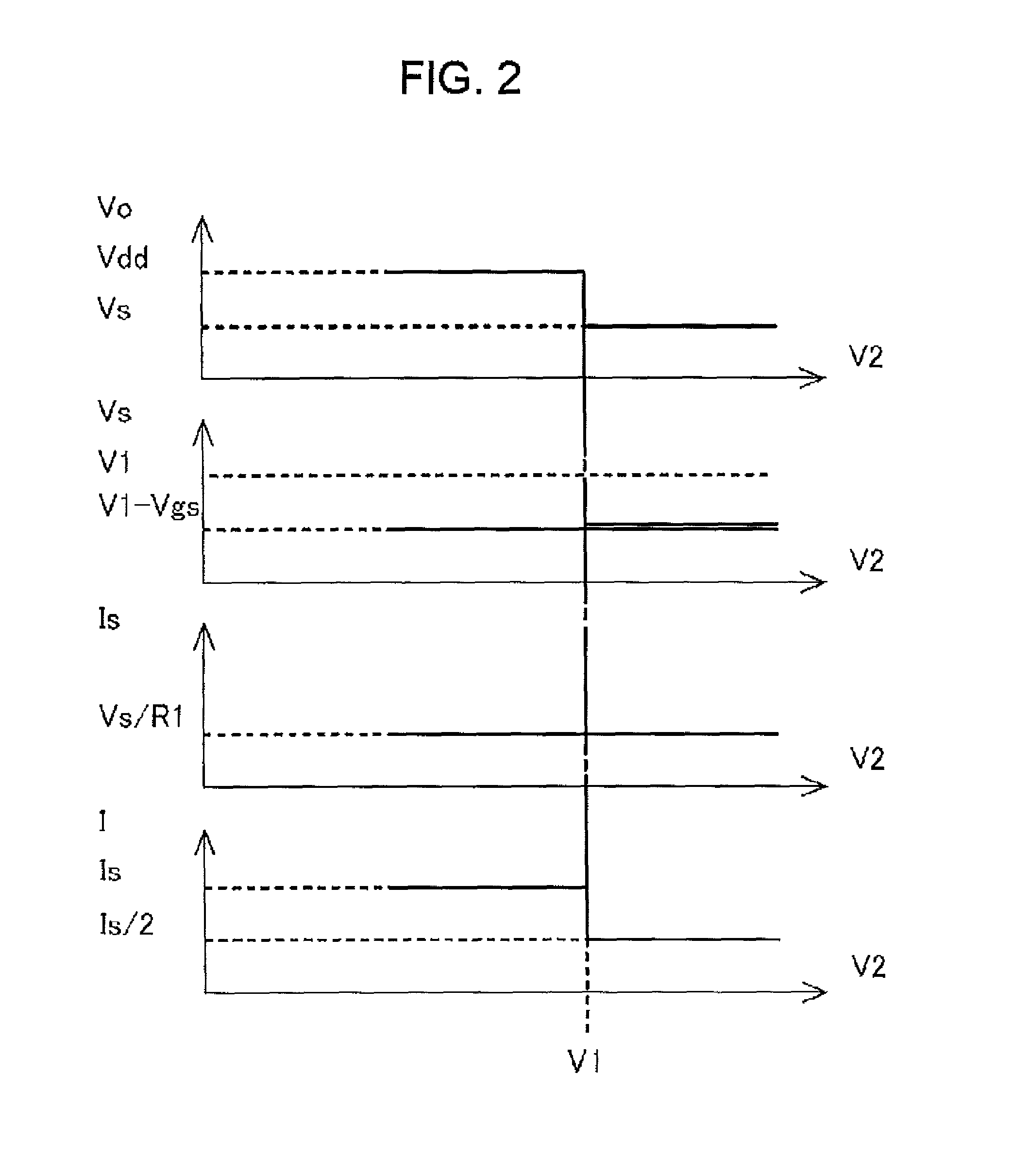

Comparator circuit

ActiveUS20110298497A1Eliminate currentReduce bias currentMultiple input and output pulse circuitsMOSFETPower flow

A comparator circuit can achieve a reduction in current consumption with a simple configuration, and can suppress an increase in current consumption accompanying a rise in power source voltage. A current mirror circuit is connected to a power source, and gates of MOSFETs of the circuit are interconnected. An input signal is applied to a gate of an NMOSFET of the circuit. By determining the value of the signal with a constant voltage device, the voltage across a tail resistor is constant, even in the event that the power source voltage and the input signal change.

Owner:FUJI ELECTRIC CO LTD

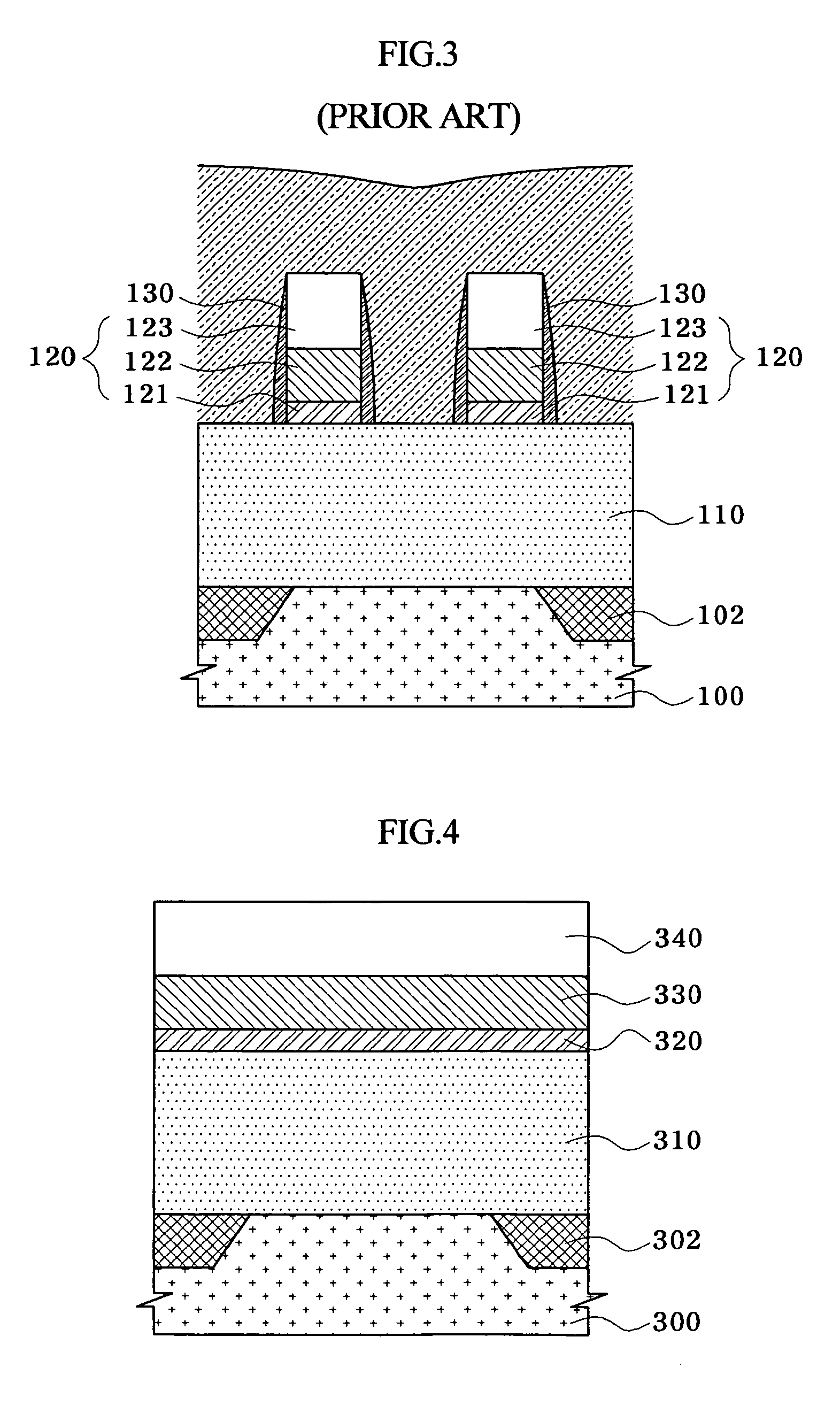

Method for forming interlayer dielectric film in semiconductor device

InactiveUS20060205202A1Increase currentImprove electrical performanceSemiconductor/solid-state device manufacturingChemical vapor deposition coatingBit lineDielectric

Disclosed herein is a method for forming an interlayer dielectric film in a semiconductor device. The method comprises the steps of preparing a semiconductor substrate having a dielectric film and conductive film patterns sequentially deposited thereon, and depositing a high plasma oxide film as the interlayer dielectric film on the conductive film patterns and the dielectric films by supplying H2 as an adding gas together with a source gas. A dangling bond in an interface of the semiconductor substrate is reduced by adding hydrogen into the dielectric film, thereby enhancing the uniformity of the deposition. Moreover, hydrogen in the dielectric film decreases current leakage occurring in the gate by preventing electrons in the plasma from flowing into a gate through the bit-line, thereby enhancing the refresh characteristics of the semiconductor device.

Owner:SK HYNIX INC

Semiconductor device and method of manufacturing semiconductor device

ActiveUS9443774B2Suppress increase in on-voltageInhibition of current increaseSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsPower semiconductor deviceHydrogen

A donor layer that is formed by performing a heat treatment for a crystal defect formed by proton radiation is provided in an n-type drift layer of an n− semiconductor substrate. The donor layer has an impurity concentration distribution including a portion with the maximum impurity concentration and a portion with a concentration gradient in which the impurity concentration is reduce to the same impurity concentration as that of the n-type drift layer in a direction from the portion with the maximum impurity concentration to both surfaces of the n-type drift layer. The crystal defect formed in the n-type drift layer is a composite crystal defect mainly caused by a vacancy, oxygen, and hydrogen.

Owner:FUJI ELECTRIC CO LTD

Electrode, method of producing electrode, and cell comprising the electrode

InactiveUS6399252B1Inhibition of current increaseHigh resistivityPrimary cell maintainance/servicingConductive materialConductive materialsEngineering

An electrode for a battery which increases resistivity with increasing temperature. The electrode has an electron conductive material containing a conductive filler and a resin so as to increase its resistivity with increasing temperature. This solves the problem of the prior art where the battery temperature rises above a temperature at which the separator melts and flows due to an internal short circuit, with a large short circuit current being generated between the positive and negative electrodes at portions where the separator flows to cause heat generation to further increase the battery temperature. As a result, the short circuit current increases further.

Owner:MITSUBISHI ELECTRIC CORP

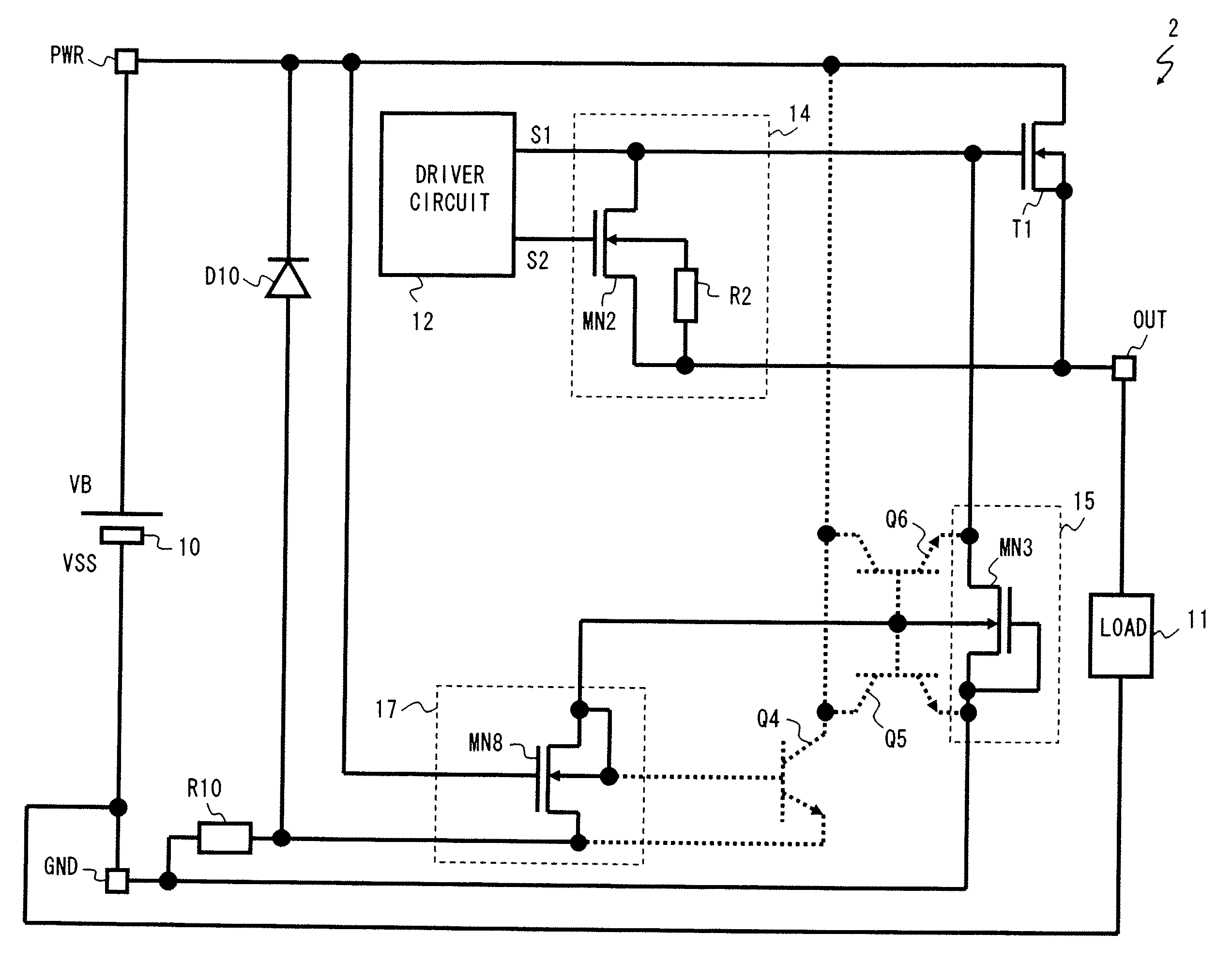

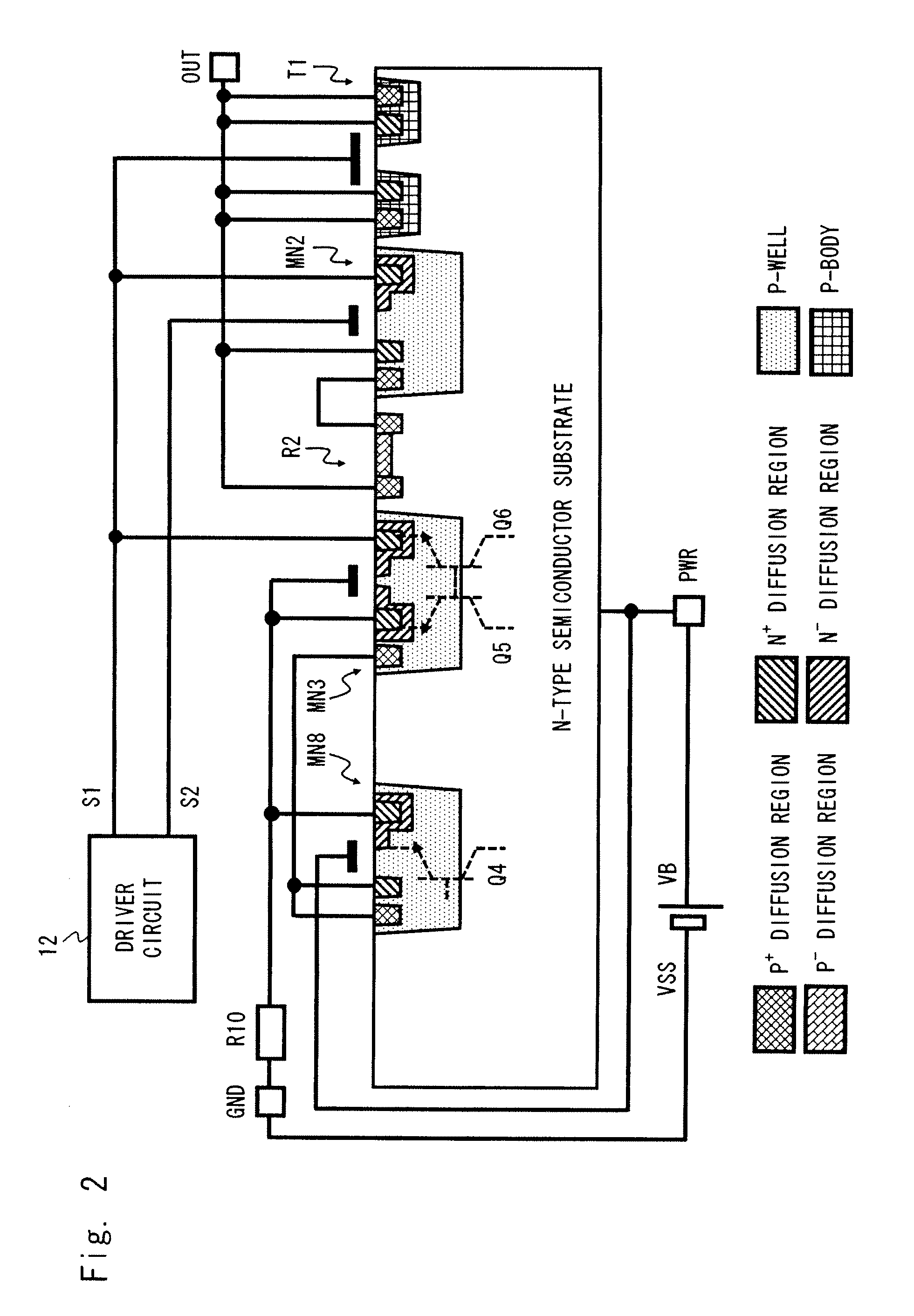

Load driving device

ActiveUS20110102956A1Suppress feverAvoid failureTransistorEmergency protective arrangements for automatic disconnectionElectrical polarityEngineering

A load driving device according to an exemplary aspect of the present invention includes: an output transistor coupled between a first power supply line and an output terminal, the output terminal being configured to be coupled with a load; a protection transistor that is provided between a gate of the output transistor and a second power supply line, and brings the output transistor into a conduction state when a polarity of a power supply coupled between the first power supply line and the second power supply line is reversed; and a back gate control circuit that controls the second power supply line and a back gate of the protection transistor to be brought into a conduction state in a standby mode when the polarity of the power supply is normal.

Owner:RENESAS ELECTRONICS CORP

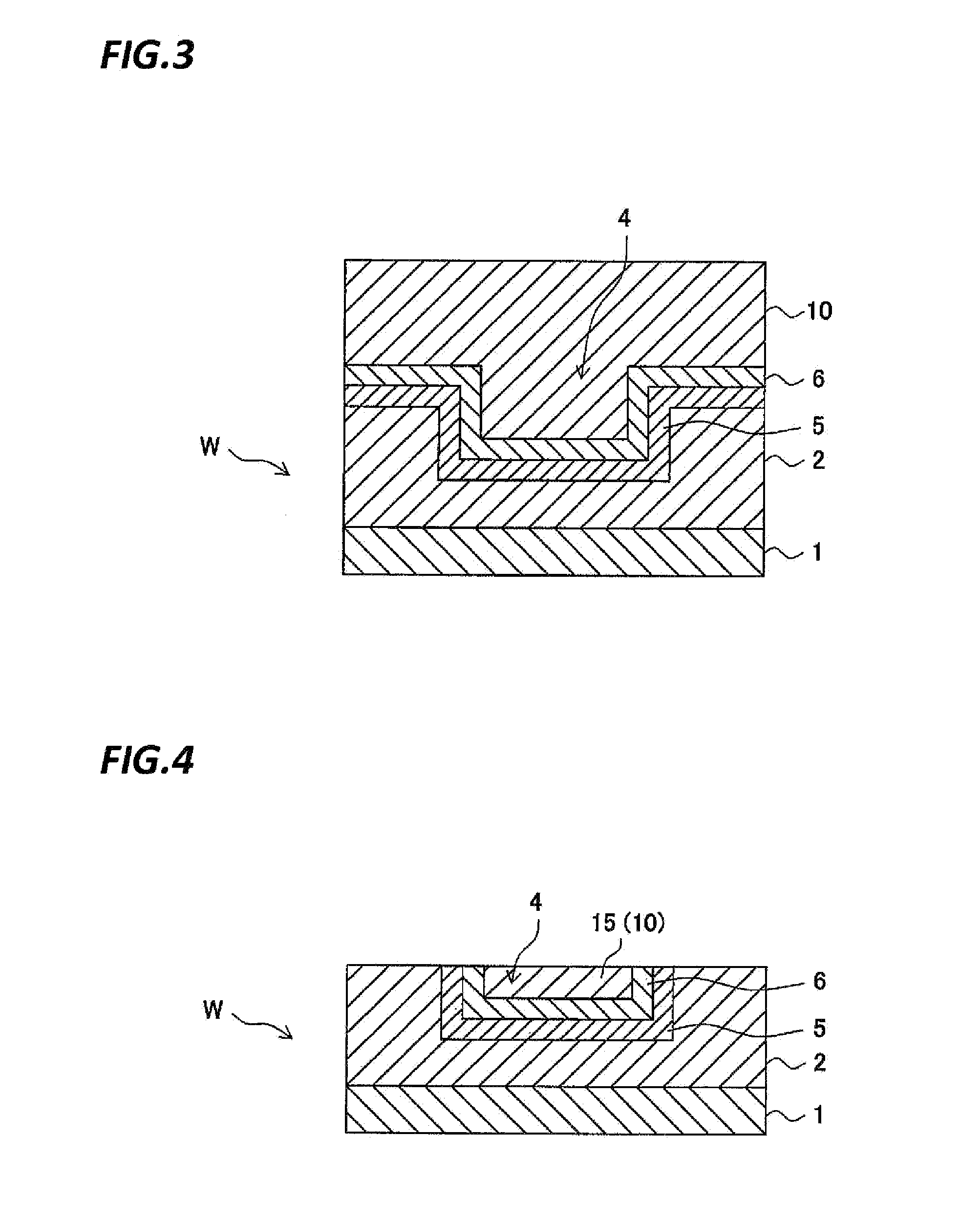

Semiconductor Device And Manufacturing Method Thereof

ActiveUS20150295096A1Increase currentEasy to manufactureSolid-state devicesSemiconductor/solid-state device manufacturingWork functionSemiconductor package

A technique of suppressing leak current in a semiconductor device is provided. A semiconductor device, comprises: a semiconductor layer made of a semiconductor; an insulating layer configured to have electric insulation property and formed to cover part of the semiconductor layer; a first electrode layer formed on the semiconductor layer, configured to have a work function of not less than 0.5 eV relative to electron affinity of the semiconductor layer and extended to surface of the insulating layer to form a field plate structure; and a second electrode layer configured to have electrical conductivity and formed to cover at least part of the first electrode layer. A distance between an edge of a part of the first electrode layer that is in contact with the semiconductor layer and the second electrode layer is equal to or greater than 0.2 μm.

Owner:TOYODA GOSEI CO LTD

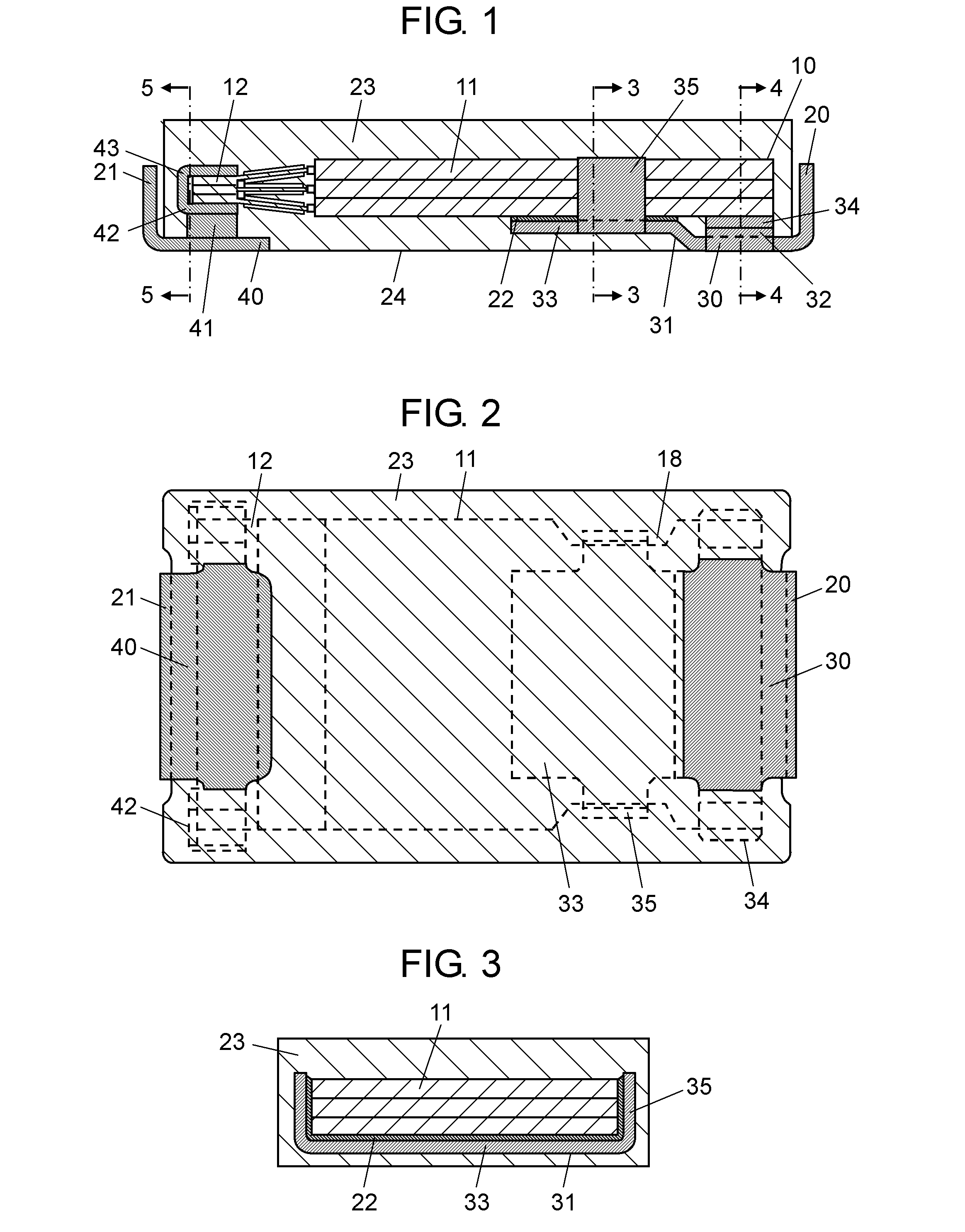

Solid electrolytic capacitor

ActiveUS20130222977A1Reduce physical stressLarge capacitanceSolid electrolytic capacitorsCapacitor electrolytes/absorbentsEngineeringAdhesive

A solid electrolytic capacitor includes a capacitor element including a cathode portion and an anode portion, a cathode terminal bonded to the cathode portion, an anode terminal bonded to the anode portion, and an enclosure resin covering the capacitor element. The cathode terminal includes a cathode lower surface portion, a cathode connection portion, and a cathode support portion. The cathode connection portion is connected to an end portion of the cathode lower surface portion on an anode side and bonded to the cathode portion through a conductive adhesive. The cathode support portion is connected to a side portion of the cathode lower surface and brought into contact with a lower surface of the cathode portion on an end portion side of the cathode portion without involving the conductive adhesive therebetween.

Owner:PANASONIC CORP

Power conversion device

ActiveUS20140321181A1Total current dropReduce lossesAc-dc conversionDc-dc conversionEngineeringDrain current

An increase in leakage current when a reverse voltage is applied to reverse-blocking insulated gate bipolar transistors is suppressed, thus reducing a loss resulting from the leakage current. A power conversion device includes a bidirectional switch formed by connecting two reverse-blocking insulated gate bipolar transistors having reverse breakdown voltage characteristics in reverse parallel. A control circuit is configured so as to output command signals for bringing the gates of the reverse-blocking insulated gate bipolar transistors, to which a reverse voltage is applied, into an on state.

Owner:FUJI ELECTRIC CO LTD

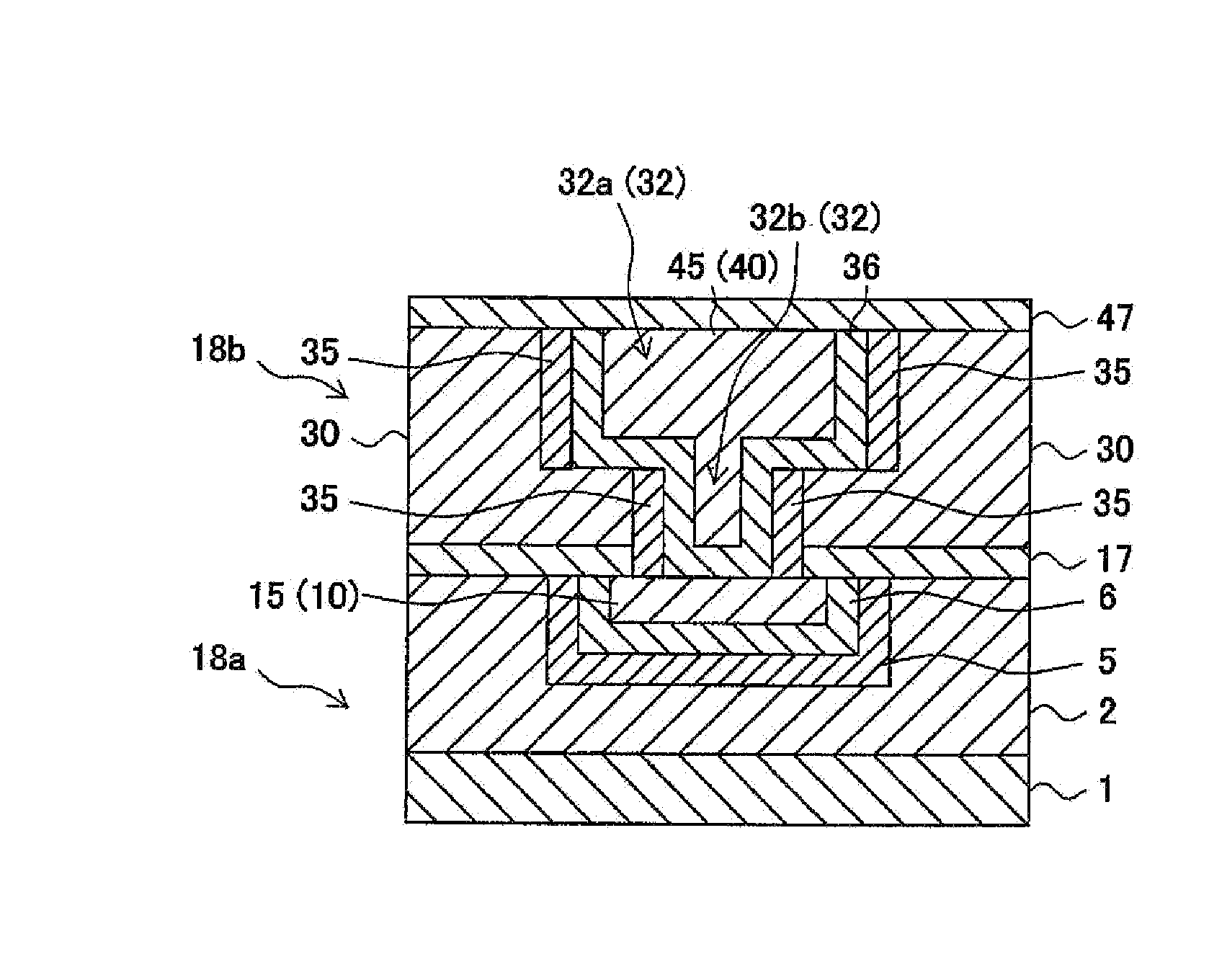

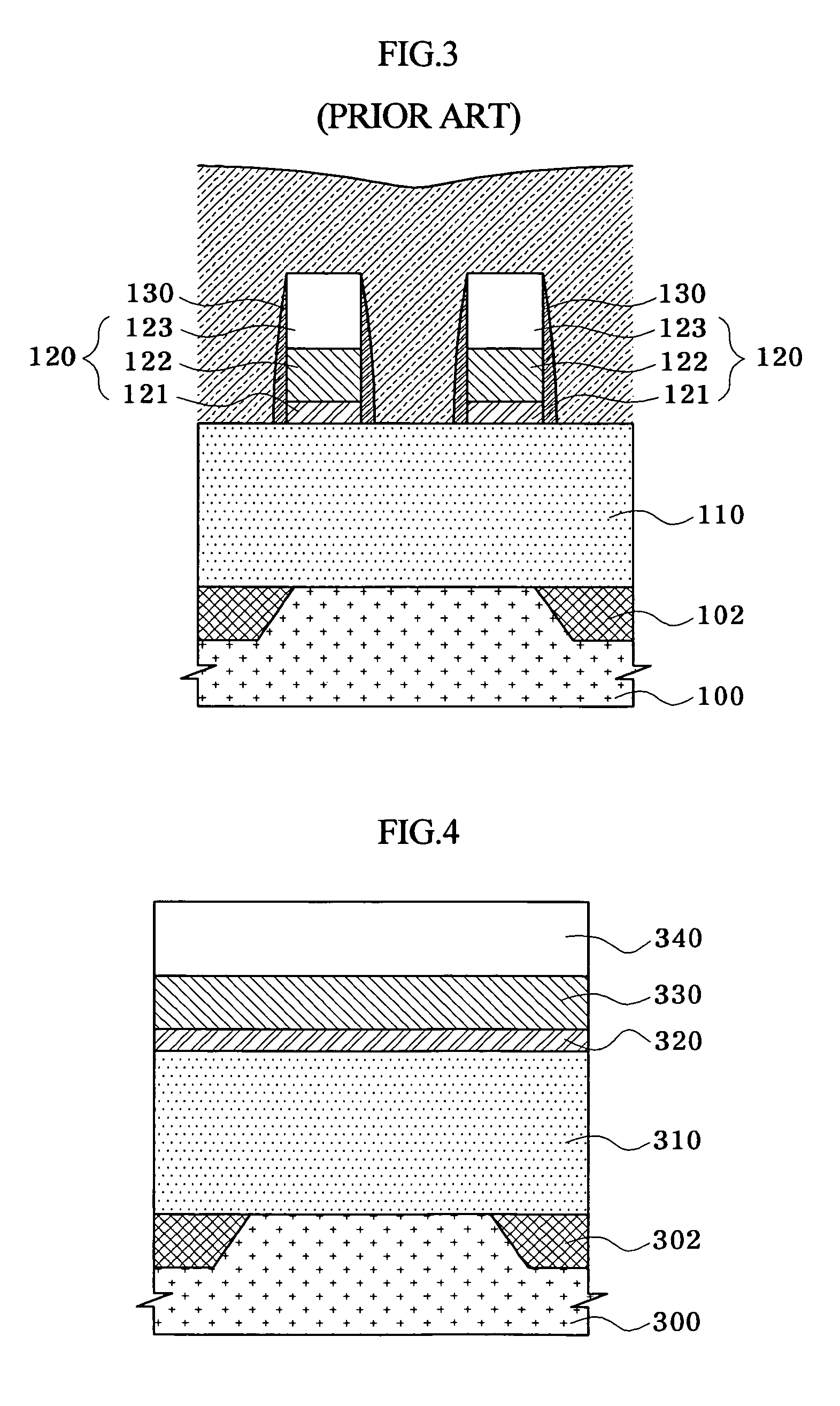

Semiconductor device and method for manufacturing semiconductor device

InactiveUS20140225263A1Total current dropSuppress DiffuseSemiconductor/solid-state device detailsSolid-state devicesCarbon filmEngineering

During the production of a semiconductor device having a Cu wiring line of a damascene structure, diffusion of fluorine from a CF film that serves as an interlayer insulating film is prevented in cases where a heat treatment is carried out, thereby suppressing increase in the leakage current. A semiconductor device of the present invention having a damascene wiring structure is provided with: an interlayer insulating film (2) that is formed of, for example, a fluorine-added carbon film; and a copper wiring line (4) that is embedded in the interlayer insulating film. A barrier metal layer (6) close to the copper wiring line and a fluorine barrier film (5) close to the interlayer insulating film are formed between the interlayer insulating film and the copper wiring line.

Owner:TOKYO ELECTRON LTD +1

Film forming method for depositing a plurality of high-k dielectric films

ActiveUS7041546B2Inhibition of current increaseImprove operationSolid-state devicesSemiconductor/solid-state device manufacturingMetal-insulator-metalDielectric

In a capacitor of an MIM (Metal-Insulator-Metal) structure, a silicon-containing high dielectric film (e.g., a hafnium silicate film) containing a silicon atom, as well as a silicon-free high dielectric film (e.g., a tantalum oxide film) containing no silicon atom is interposed between a lower electrode film and an upper electrode film which are made of metal or metal compound. By adding the silicon-containing high dielectric film, a leak current can be suppressed and the change in capacitor capacity accompanied with the change in applied voltage can be reduced.

Owner:TOKYO ELECTRON LTD

Method for forming interlayer dielectric film in semiconductor device

InactiveUS7462568B2Inhibition of current increaseImprove electrical performanceSemiconductor/solid-state device manufacturingChemical vapor deposition coatingDielectricBit line

Disclosed herein is a method for forming an interlayer dielectric film in a semiconductor device. The method comprises the steps of preparing a semiconductor substrate having a dielectric film and conductive film patterns sequentially deposited thereon, and depositing a high plasma oxide film as the interlayer dielectric film on the conductive film patterns and the dielectric films by supplying H2 as an adding gas together with a source gas. A dangling bond in an interface of the semiconductor substrate is reduced by adding hydrogen into the dielectric film, thereby enhancing the uniformity of the deposition. Moreover, hydrogen in the dielectric film decreases current leakage occurring in the gate by preventing electrons in the plasma from flowing into a gate through the bit-line, thereby enhancing the refresh characteristics of the semiconductor device.

Owner:SK HYNIX INC

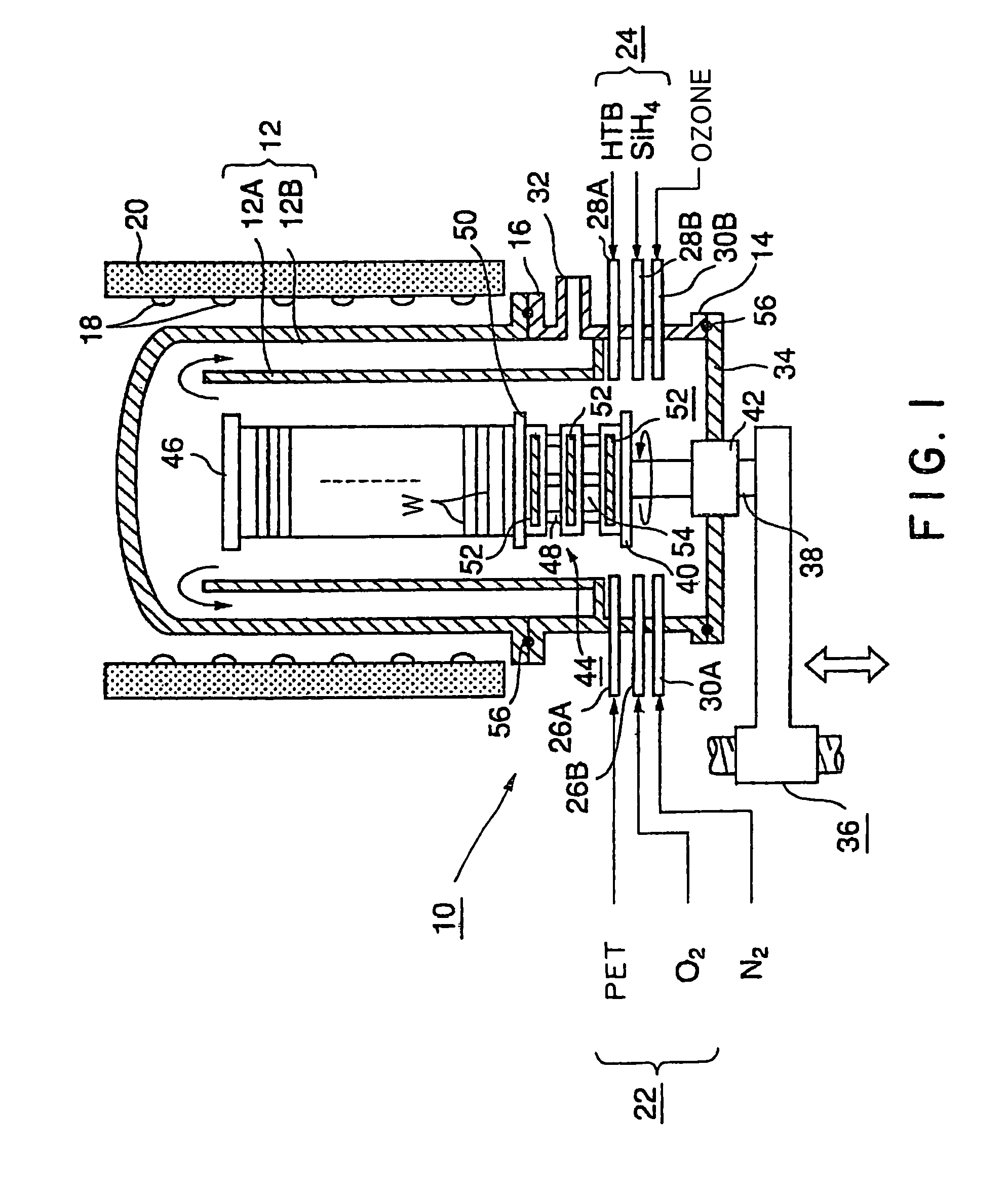

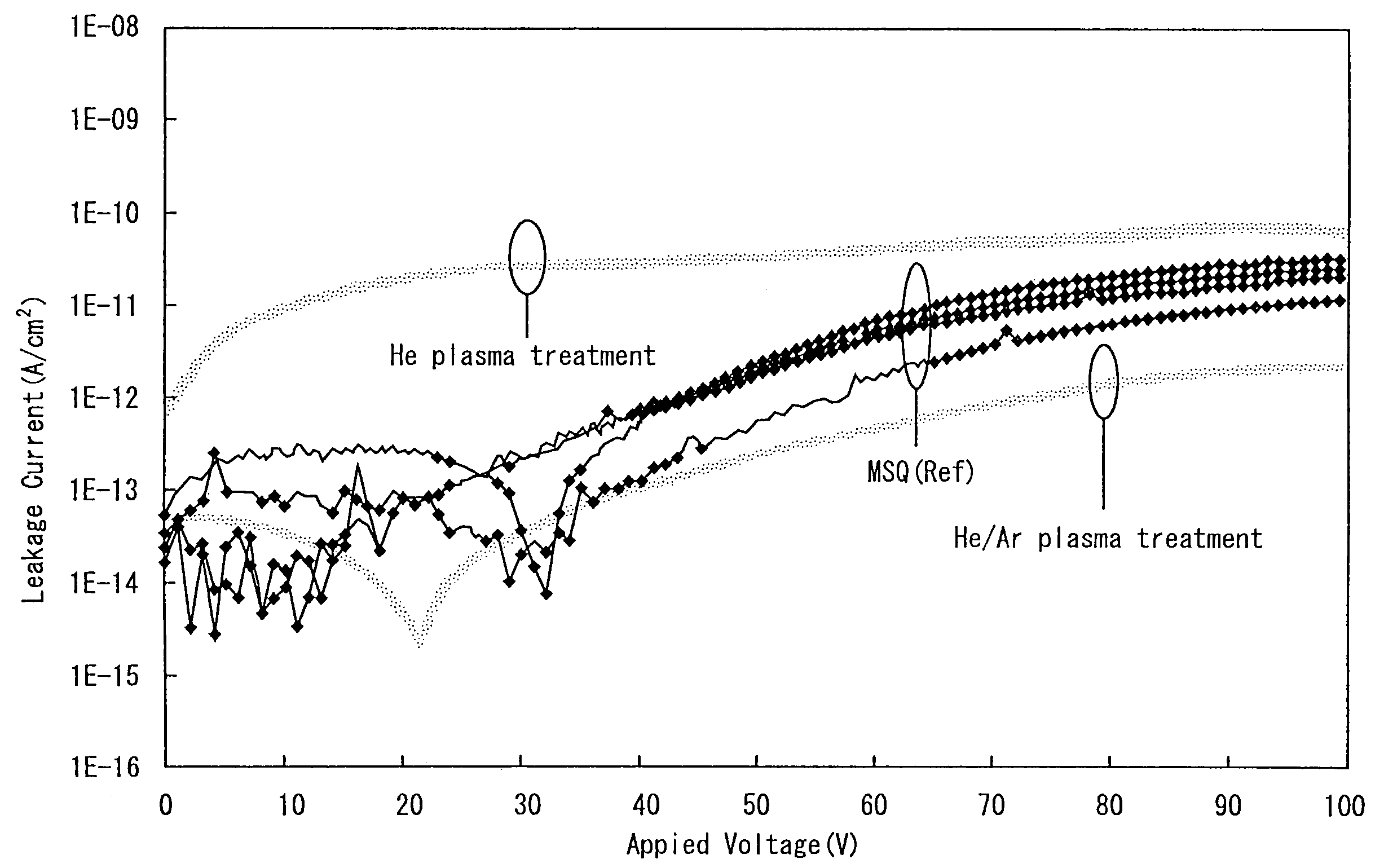

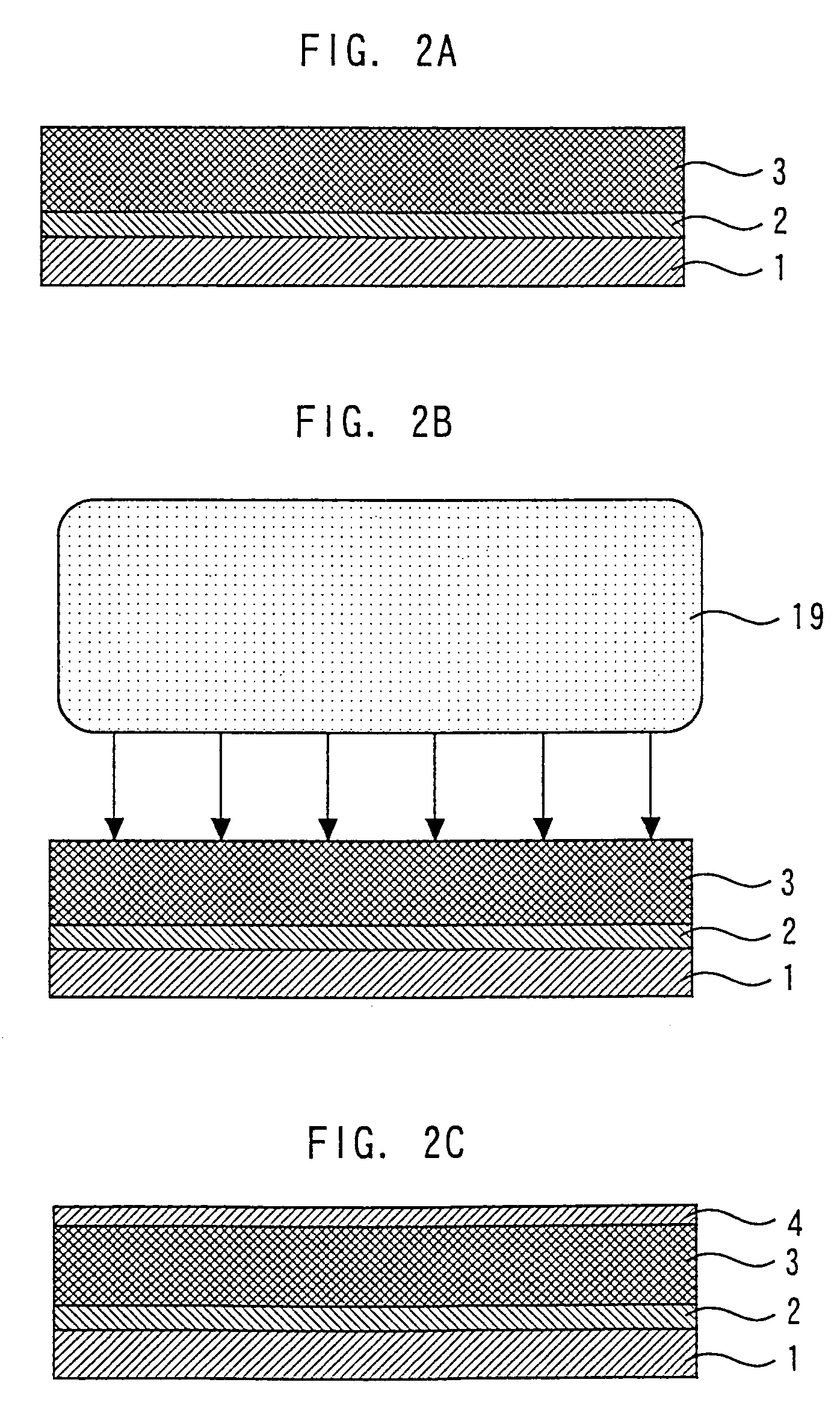

Method for manufacturing a semiconductor device that includes plasma treating an insulating film with a mixture of helium and argon gases

InactiveUS7056825B2Increase of dielectric constantIncrease of leakageSemiconductor/solid-state device manufacturingHeliumSemiconductor

In a method for manufacturing a semiconductor device having a multi-layer insulating film, a first insulating film is formed as one layer of the multi-layer insulating film, and a plasma treatment is performed on the surface of the first insulating film in an ambient of helium and argon, containing 5 to 31% Ar. After the plasma treatment, a second insulating film, different from the first insulating film, is formed on the first insulating film as another layer of the multi-layer insulating film.

Owner:RENESAS ELECTRONICS CORP

Comparator circuit with current mirror

ActiveUS8598914B2Simple configurationInhibition of current increaseInstant pulse delivery arrangementsMOSFETPower flow

A comparator circuit can achieve a reduction in current consumption with a simple configuration, and can suppress an increase in current consumption accompanying a rise in power source voltage. A current mirror circuit is connected to a power source, and gates of MOSFETs of the circuit are interconnected. An input signal is applied to a gate of an NMOSFET of the circuit. By determining the value of the signal with a constant voltage device, the voltage across a tail resistor is constant, even in the event that the power source voltage and the input signal change.

Owner:FUJI ELECTRIC CO LTD

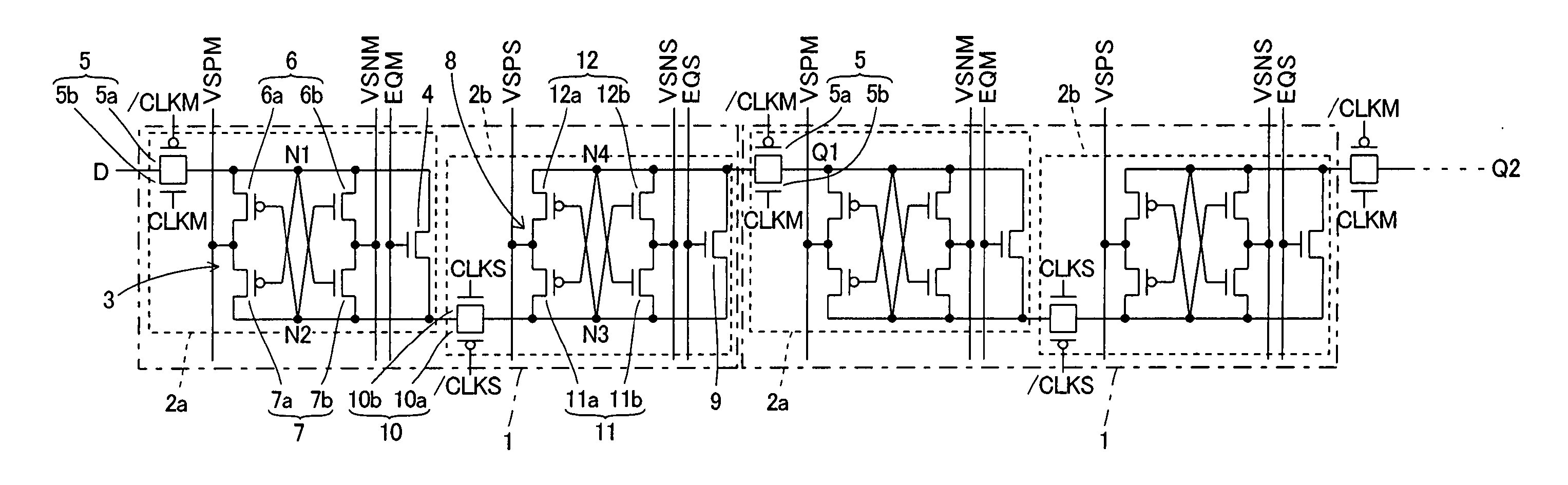

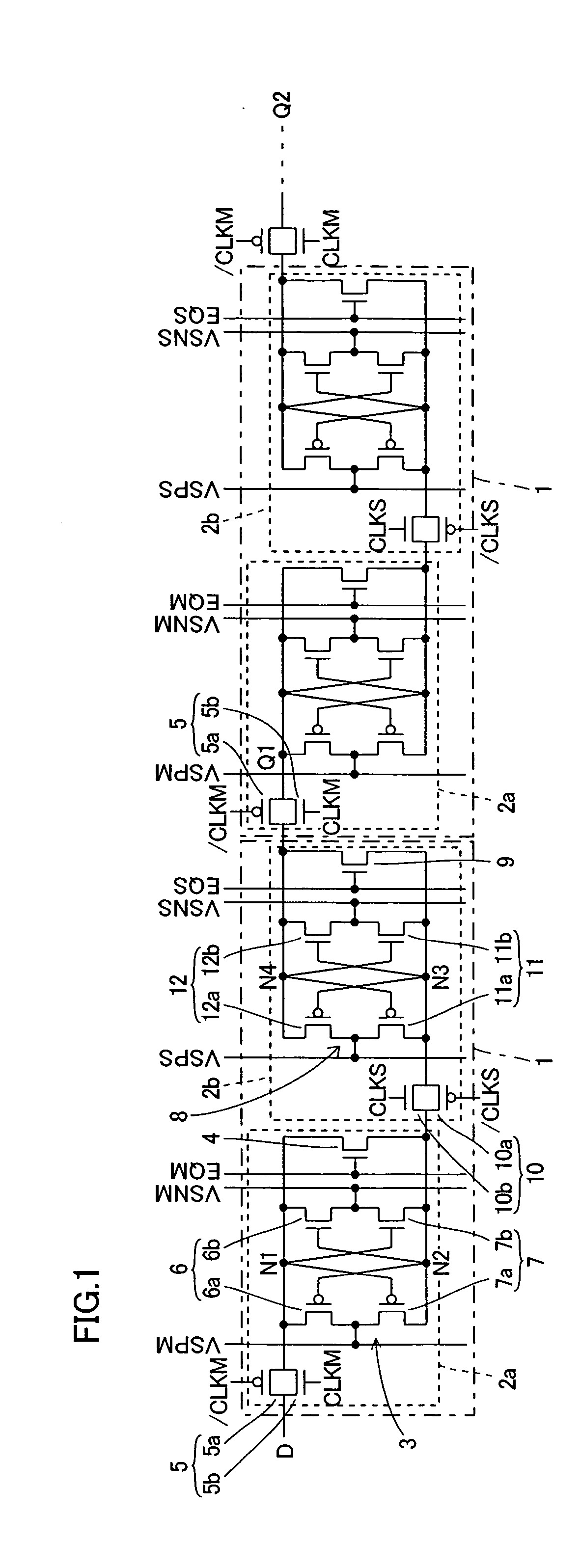

Flip-flop circuit

ActiveUS20060139077A1Total current dropReduce circuit sizeCurrent/voltage measurementDigital storageEngineeringCurrent consumption

A flip-flop circuit capable of inhibiting current consumption as well as the circuit scale from increase is provided. This flip-flop circuit comprises a first latch circuit including first and second inverter circuits. A first power supply line capable of switching a supplied potential between a fixing potential supplied for fixing the potentials of output nodes of the first and second inverter circuits and a floating potential supplied for floating the potentials of the output nodes of the first and second inverter circuits is connected to the first latch circuit.

Owner:SEMICON COMPONENTS IND LLC

Solid electrolytic capacitor and method for producing the same

InactiveUS20090015989A1Total current dropReduce leakage currentSolid electrolytic capacitorsFixed capacitor dielectricElectrolysisConductive polymer

The invention provides a solid electrolytic capacitor which can suppress increase of a leakage current due to a heat load, and a method for producing the solid electrolytic capacitor. The solid electrolytic capacitor includes an anode body, a dielectric layer formed on a surface of the anode body, a conductive polymer layer formed on the dielectric layer, and a cathode layer formed on the conductive polymer layer. The dielectric layer contains at least one metal element which is selected from the group consisting of tungsten (W), molybdenum (Mo), vanadium (V) and chromium (Cr) and which has a concentration distribution in a direction of the thickness of the dielectric layer (i.e. in a direction from the cathode side to the anode side of the dielectric layer) so that the concentration of the metal element is maximized at an interface between the dielectric layer and the conductive polymer layer.

Owner:SANYO ELECTRIC CO LTD

Semiconductor device and method of manufacturing semiconductor device

InactiveUS8368176B2High dielectric constantIncrease capacitanceTransistorSolid-state devicesPower semiconductor deviceSurface layer

A lower electrode includes a metal-containing oxide layer having a thickness of 2 nm or less on the surface layer. A metal-containing oxide layer is formed by oxidizing the surface of the lower electrode. A dielectric film includes a first phase appearing at room temperature in the bulk state and a second phase appearing at a higher temperature than that in the first phase in the bulk state. The second phase has a higher relative permittivity than that of the first phase.

Owner:RENESAS ELECTRONICS CORP

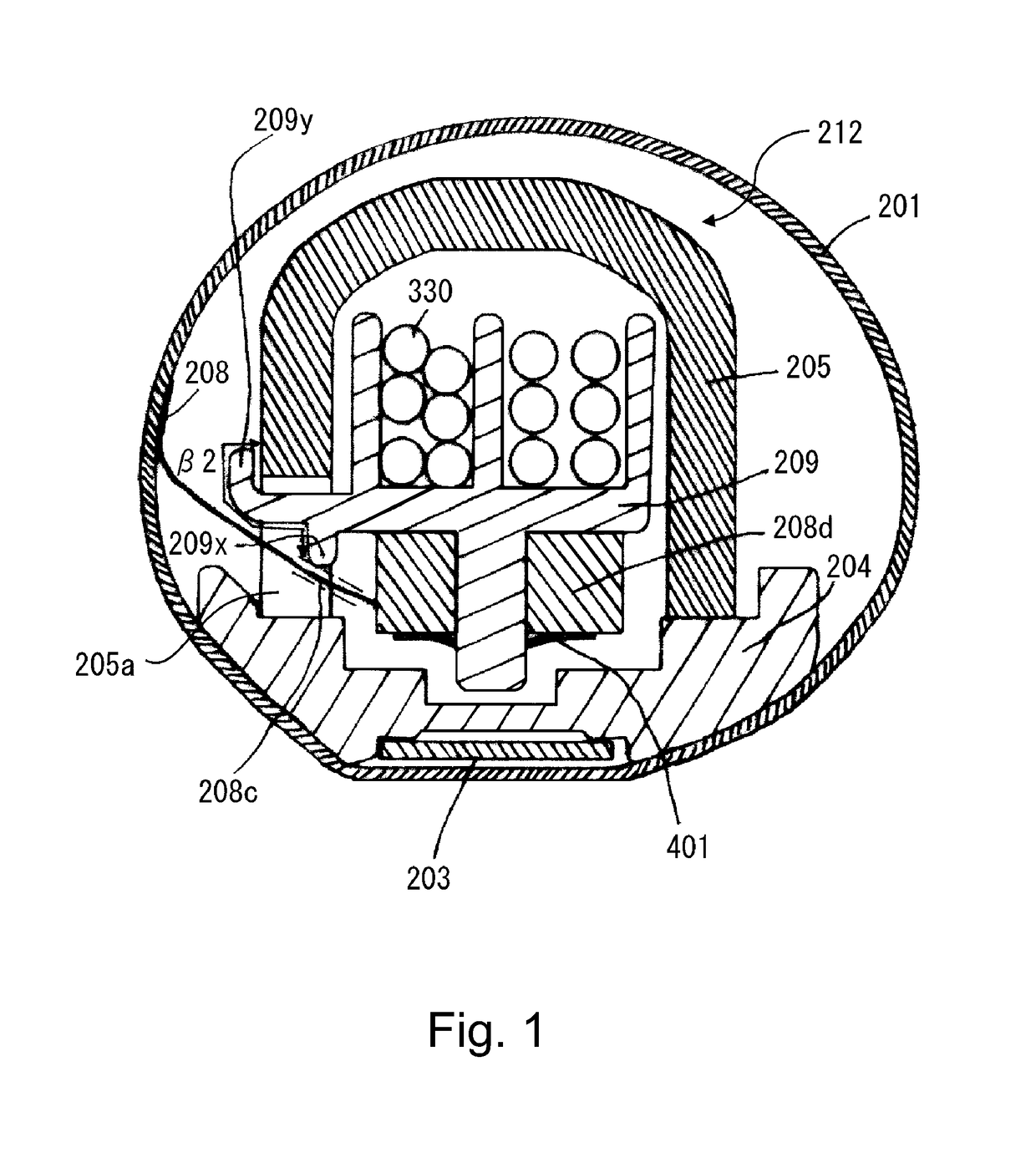

Permanent magnet motor and compressor

ActiveCN104025433AInhibition of current increaseInhibit overcurrent detectionPositive displacement pump componentsMagnetic circuit stationary partsPower flowOvercurrent

The present invention provides a permanent magnet motor that is capable of improving motor efficiency by minimizing a current increase by outputting a torque in accordance with pulsation of a load and of improving system reliability and redundancy by minimizing detection of an overcurrent, and a drive system that utilizes this permanent magnet motor. Of the permanent magnet motor and the drive system that utilizes the permanent magnet motor, the permanent magnet motor comprises a stator with multiple teeth and a rotor which is provided with a predetermined gap from the stator, and is characterized by being configured such that a pass-through flux in the gap direction is allowed to pass through more easily at least at one of the teeth than at the other teeth, and a pass-through flux in the gap direction is allowed to pass through more easily at least at one of poles of the rotor than at the other poles.

Owner:HITACHI JOHNSON CONTROLS AIR CONDITIONING INC

Semiconductor device and method of manufacturing semiconductor device

InactiveUS20110304017A1Increase capacitanceTotal current dropSolid-state devicesSemiconductor/solid-state device manufacturingDielectric membraneDevice material

A lower electrode includes a metal-containing oxide layer having a thickness of 2 nm or less on the surface layer. A metal-containing oxide layer is formed by oxidizing the surface of the lower electrode. A dielectric film includes a first phase appearing at room temperature in the bulk state and a second phase appearing at a higher temperature than that in the first phase in the bulk state. The second phase has a higher relative permittivity than that of the first phase.

Owner:RENESAS ELECTRONICS CORP

Belt unit and image heating apparatus

ActiveUS20180364623A1Increase currentInhibition of current increaseElectrographic process apparatusMetal leafEngineering

A belt unit includes an endless belt including a metal layer, a heater including a heat generating element, a nip forming member including the heater, a metal stay, a temperature detecting element, a metal leaf spring, an insulating supporting member positioned inside the stay, a cord, and an insulating holder portion including an interposed portion interposed between an exposed portion of the leaf spring and the stay so as to provide insulation therebetween and for holding the supporting member.

Owner:CANON KK

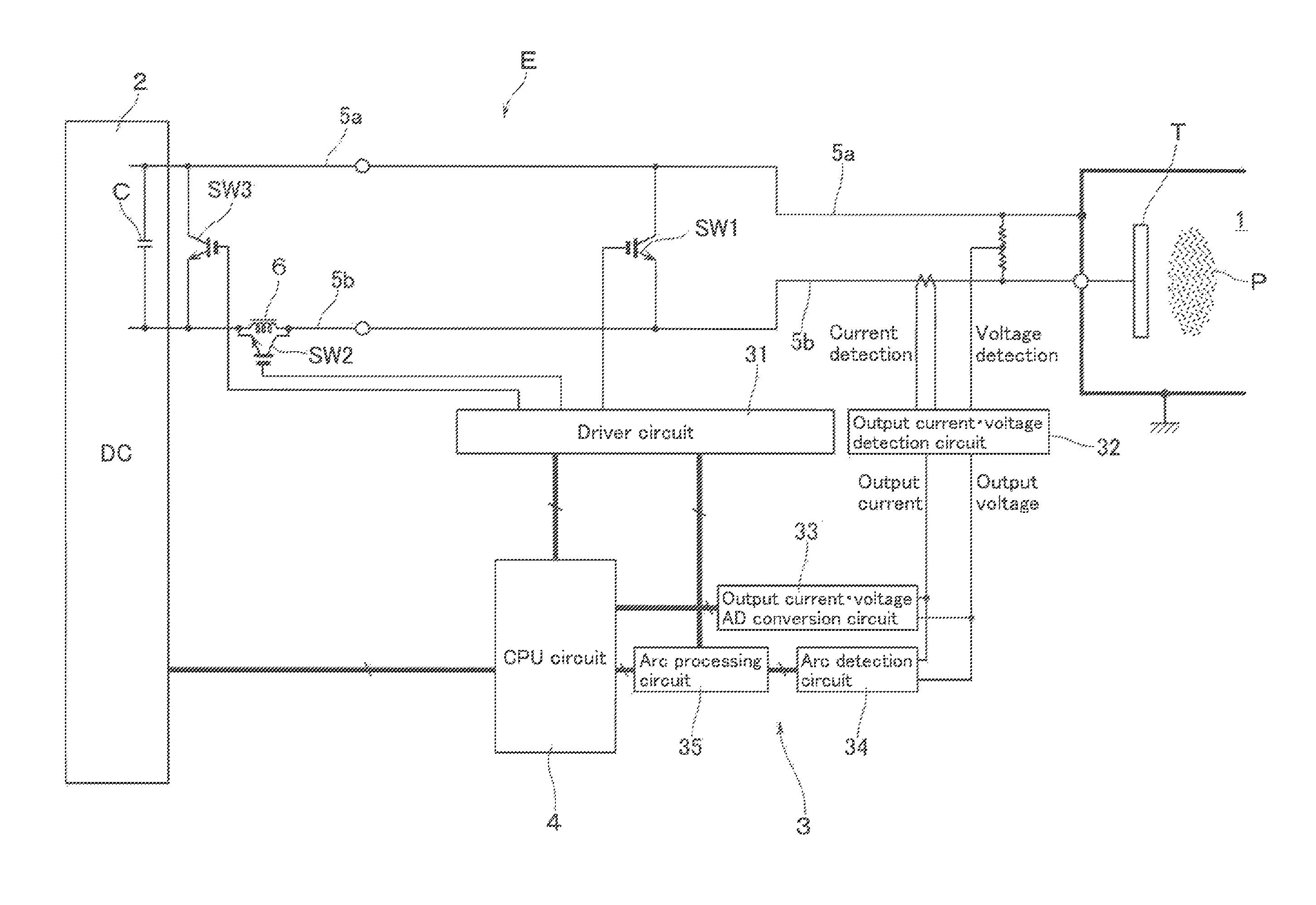

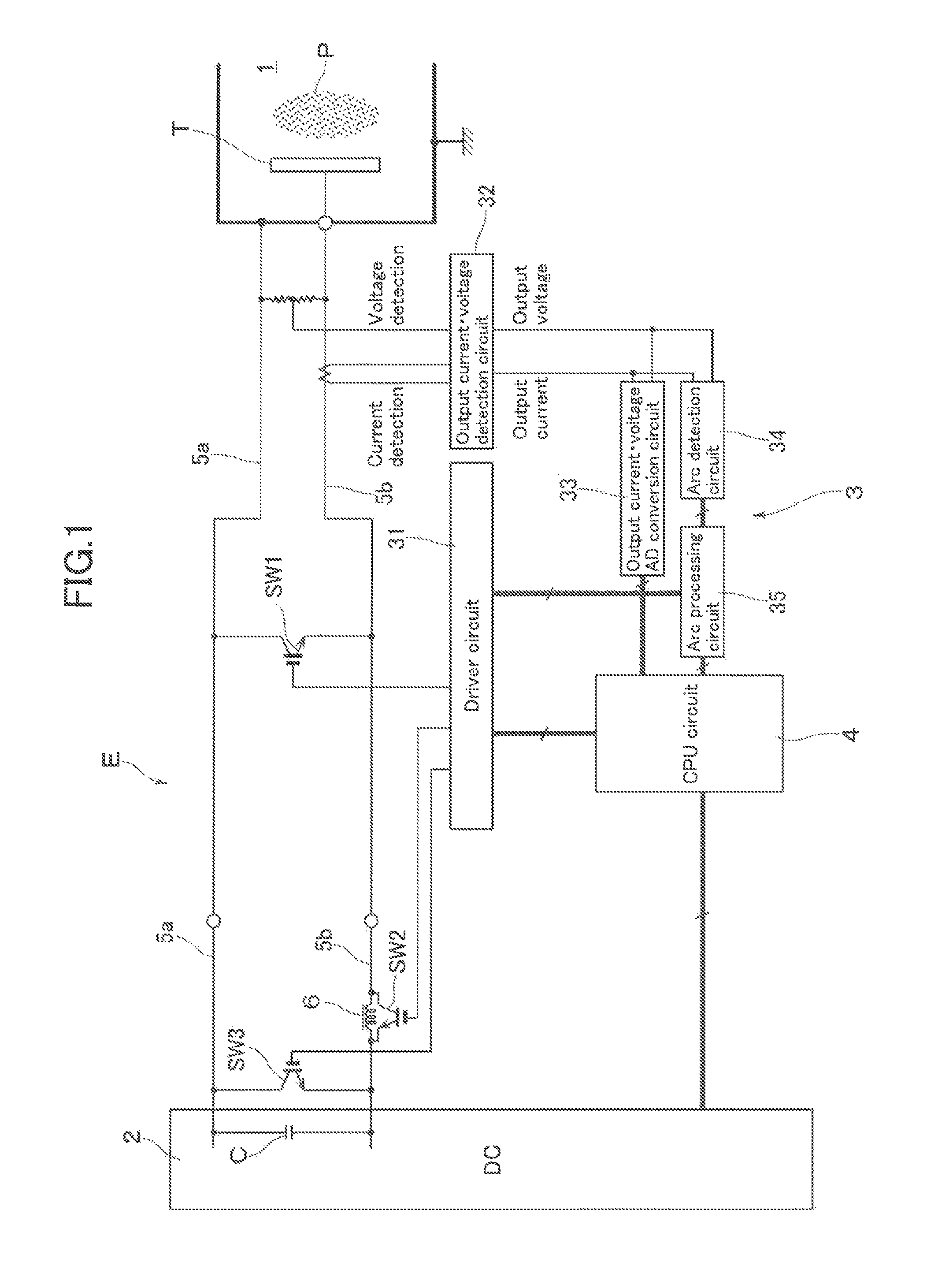

Power supply apparatus

Provided is a power supply apparatus which can effectively restrict the current rise at the time of occurrence of arc discharge that is directly related to the occurrence of splashes or particles, and which is also capable of preventing the discharge voltage from getting excessive at the time of finishing the arc processing. The power supply apparatus has: a DC power supply unit which applies a DC voltage to a target which comes into contact with a plasma; and an arc processing unit which can detect arc discharge generated in the electrode by positive and negative outputs from the DC power supply unit, and also which can perform arc discharge suppression processing. An output characteristics switching circuit switches the outputs such that the output to the electrode has constant-current characteristics and that the output to the electrode has constant-voltage characteristics by the time of completion of the arc suppressing processing.

Owner:ULVAC INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com