Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

38results about How to "High gettering capacity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

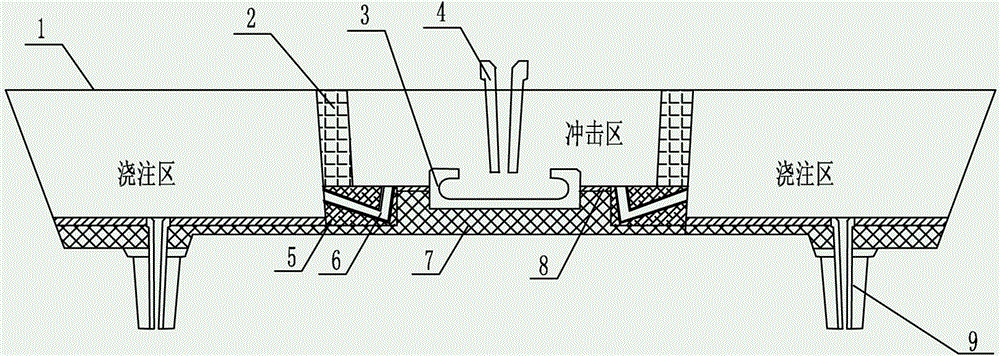

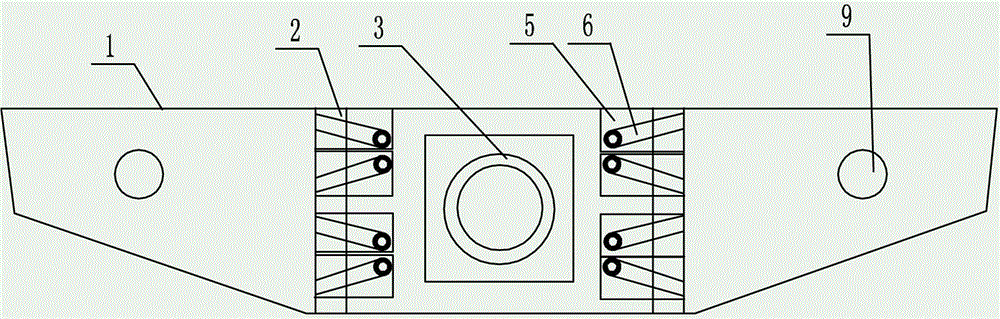

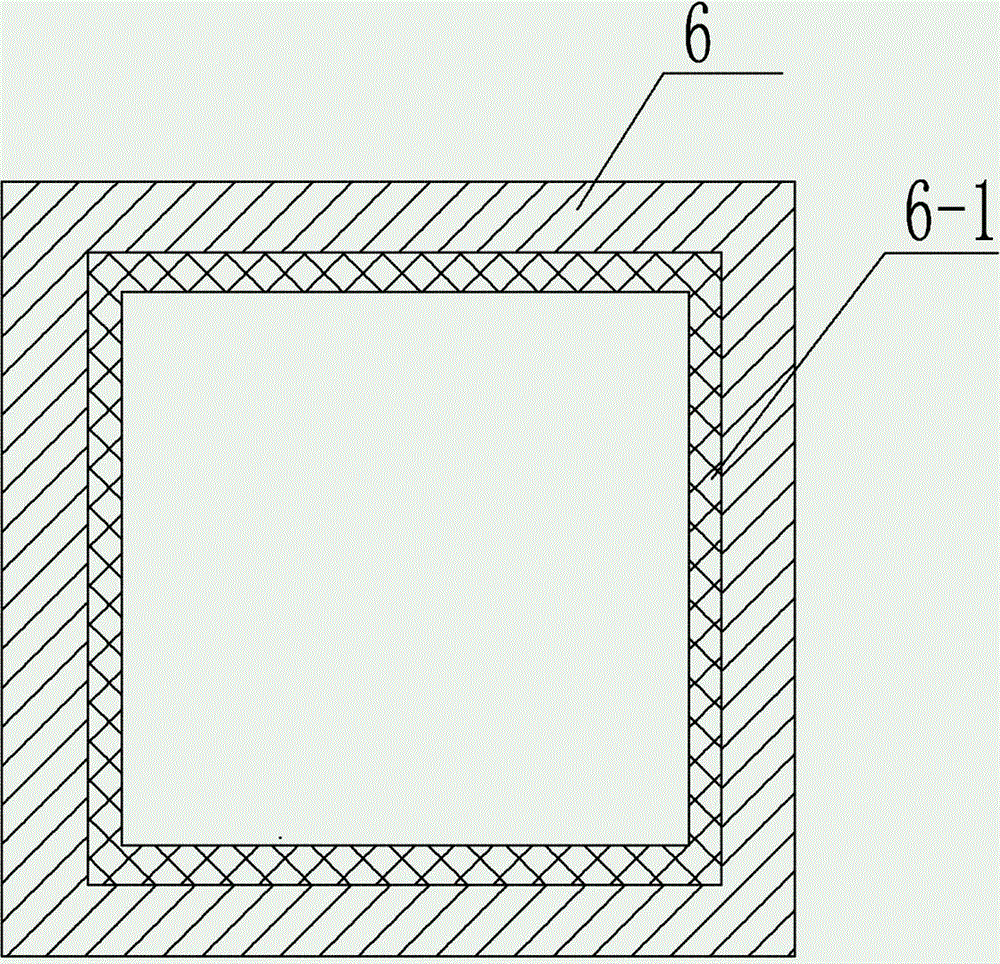

Impurity filtering and absorbing flow divider for tundish

InactiveCN104439136ACollision grows upIncreased chance of collisionEngineeringMechanical engineering

The invention relates to an impurity filtering and absorbing flow divider for a tundish. The impurity filtering and absorbing flow divider comprises a tundish body, a permanent layer, an operating layer, a tundish water port, an impurity baffle wall, a turbulence controller and a flow division filter. The impurity filtering and absorbing flow divider is characterized in that the flow division filter is arranged below the impurity baffle wall and comprises a flow division filter body and a plurality of 'V' or 'U'-shaped filter parts, the filter parts are embedded in the flow division filter body and provided with a plurality of through holes, and an adsorption layer is composited on the inner walls of the 'V' or 'U'-shaped filter parts. The impurity filtering and absorbing flow divider has the advantages that specific surface area of the unit size of the flow divider contacting with molten steel is increased to the greatest extent, and collision rate of the impurities and the flow divider is increased. In addition, flow state of the molten steel in the tundish is greatly improved, and the impurities in the molten steel can be further removed.

Owner:谢玉红

Phosphorus diffusion method of crystalline silicon solar cell

ActiveCN106057980AControl concentrationConcentration Control Concurrent Reduction of Phosphorus Doping Concentration Gradients in the BodyFinal product manufactureSemiconductor/solid-state device manufacturingConcentration gradientOxygen

The present invention discloses a phosphorus diffusion method of a crystalline silicon solar cell. The method comprises the steps of (1) entering into a boat, (2) adjusting temperature to be below 800 DEG C, introducing nitrogen carrying phosphorus source and dry oxygen, and forming a silicon dioxide layer containing phosphorus, (3) carrying out low temperature diffusion, (4) raising the temperature in a furnace and pushing with the rise of the temperature, (5) carrying out first time of high temperature diffusion, (6) raising the temperature in the furnace and pushing with the rise of the temperature, (7) carrying out second time of high temperature diffusion, (8) reducing the temperature in the furnace and pushing with the decrease of the temperature, and (9) reducing the temperature and going out of the boat, and completing a diffusion process. According to the method, an oxidation gettering effect is enhanced and the concentration gradient of the phosphorus doping is controlled, the separation and collection of carriers are facilitated, the open circuit voltage is raised, the temperature difference in a cooling process is controlled, and a crystal boundary gettering effect is enhanced.

Owner:CSI CELLS CO LTD +1

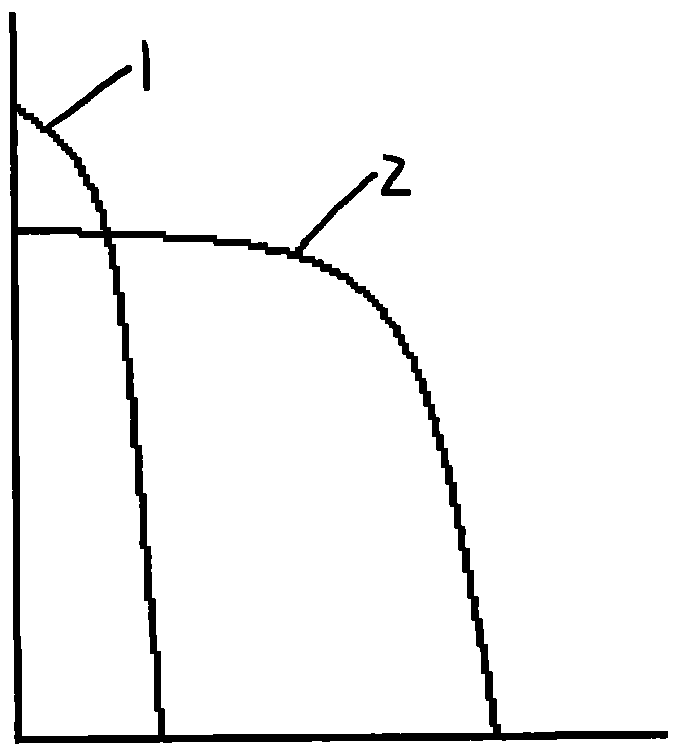

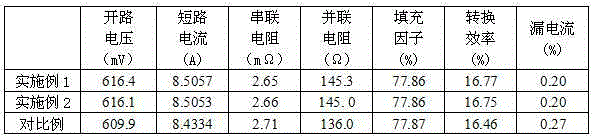

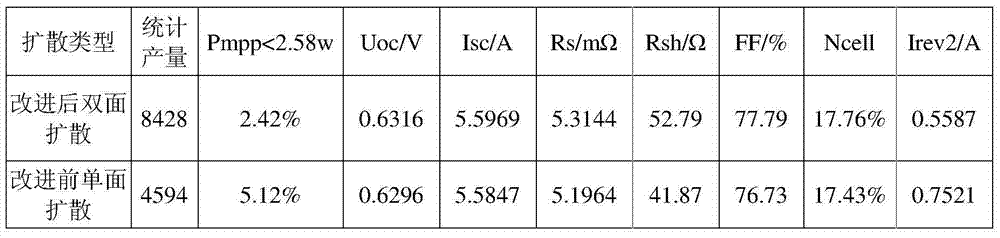

Diffusion method used for crystalline silicon solar battery

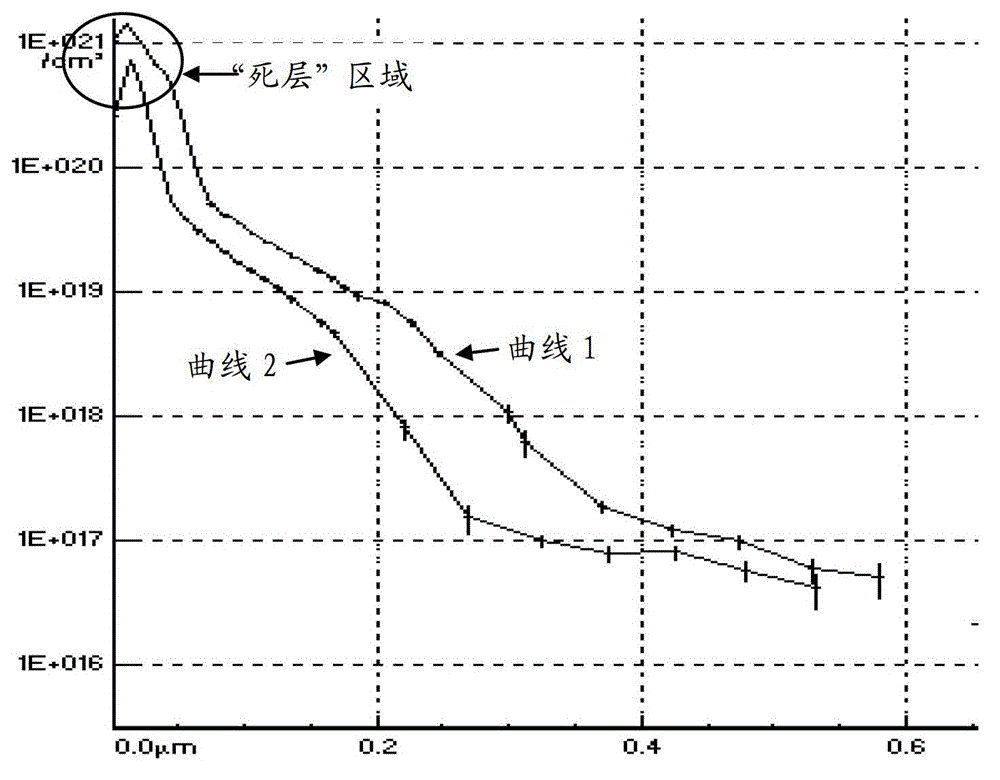

InactiveCN102157606AHigh gettering capacityIncrease short circuit currentFinal product manufactureDiffusion/dopingDiffusion methodsSurface concentration

The invention discloses a diffusion method used for a crystalline silicon solar battery. The method comprises the following steps of: (1) placing a silicon wafer into a diffusion furnace; rising the temperature from 780-810 DEG C to 840-860 DEG C; and simultaneously introducing POCL3+O2+N2 for 12 to 14 minutes; (2) simultaneously introducing O2+N2 when rising the temperature in the diffusion furnace to 840-860 DEG C and keeping the constant temperature for 2 to 5 minutes; simultaneously introducing the POCL3+O2+N2 for 8 to 12 minutes when rising the temperature from 840-860 DEG C to 870-890 DEG C; reducing the temperature from 870-890 DEG C to 800 DEG C; introducing the O2+N2 in the process of reducing the temperature; stabilizing for 2 minutes at the temperature of 800 DEG C; and introducing the POCL3+O2+N2; and (3) taking the silicon wafer out of the diffusion furnace. In the method, both the requirements on the doping concentration of an emitting region and the surface concentration of the emitting region in diffusion can be met at the same time; a gettering effect is good; and the distribution of a doping curve is more reasonable.

Owner:BAODING GUANGWEI GREEN ENERGY TECH CO LTD

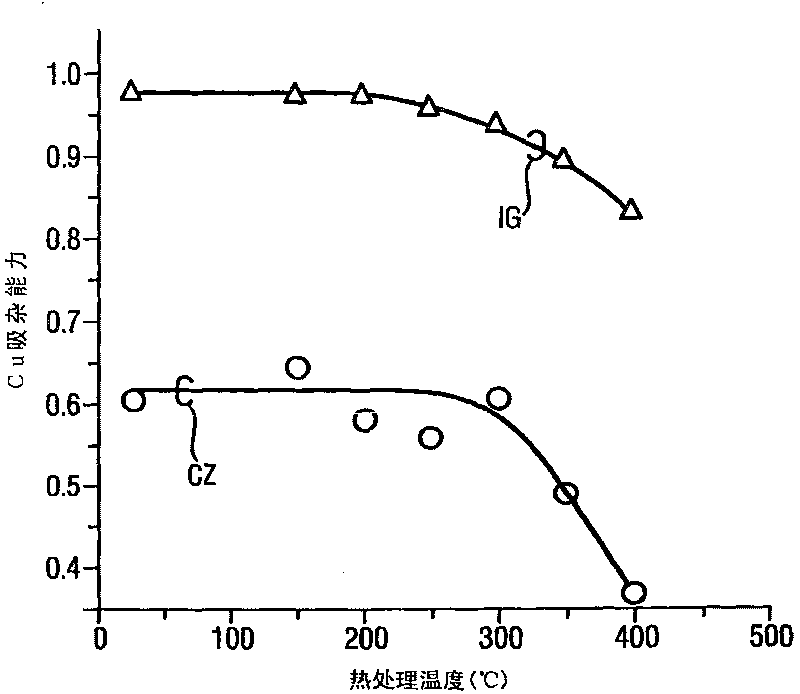

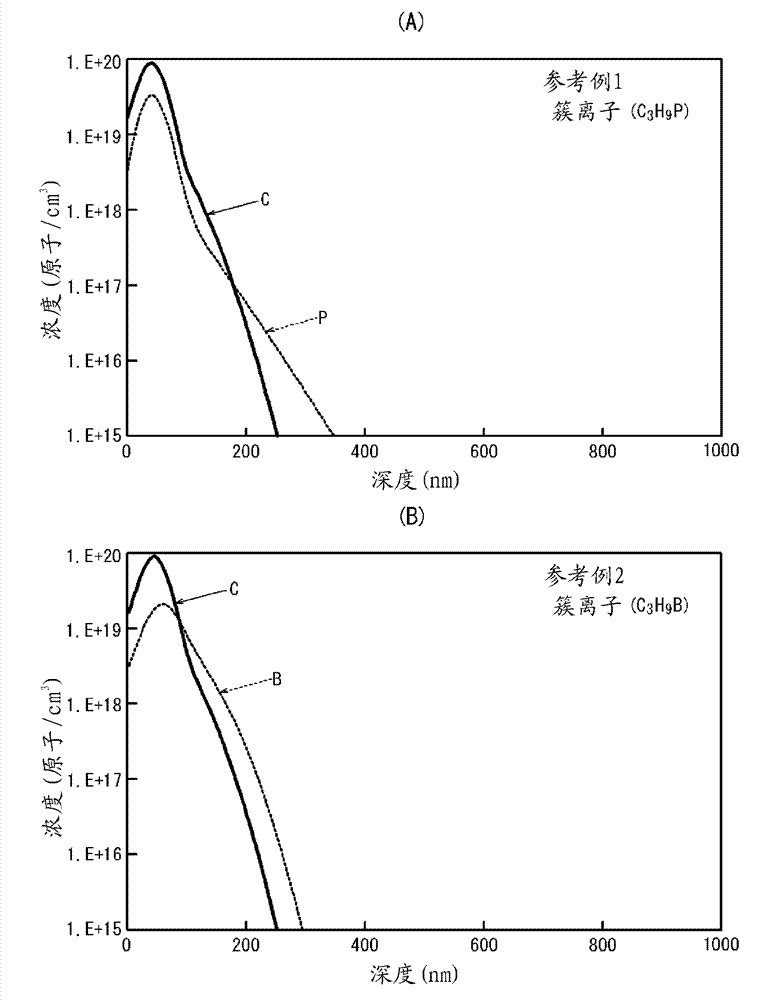

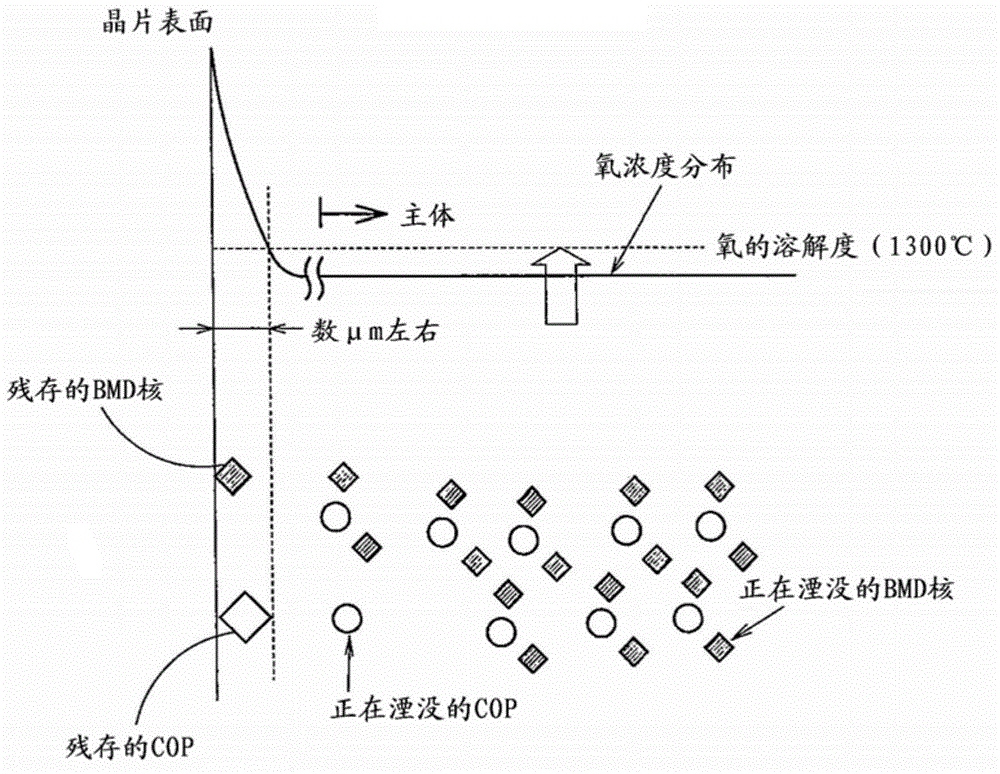

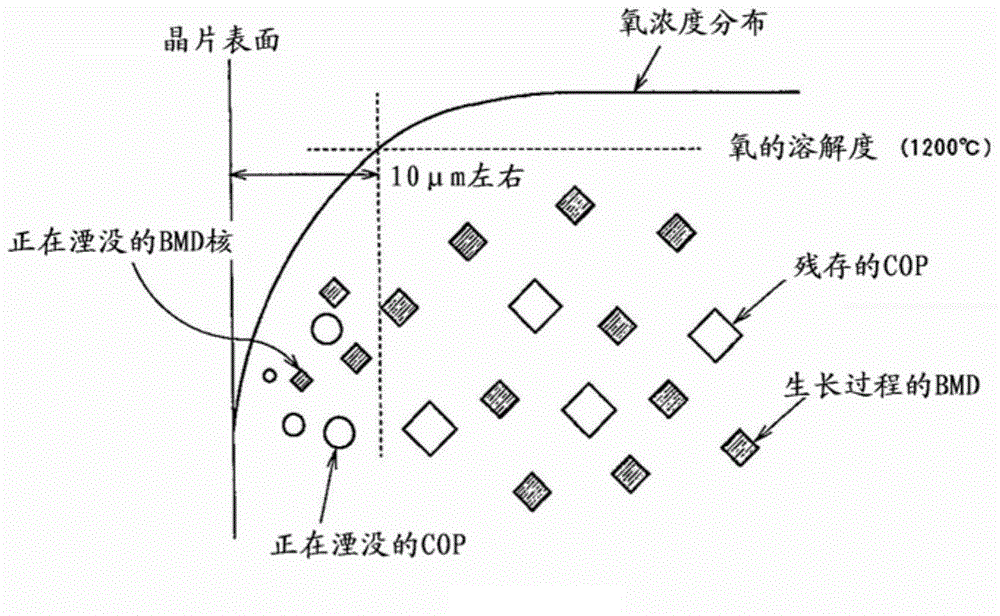

Annealed wafer and method for producing annealed wafer

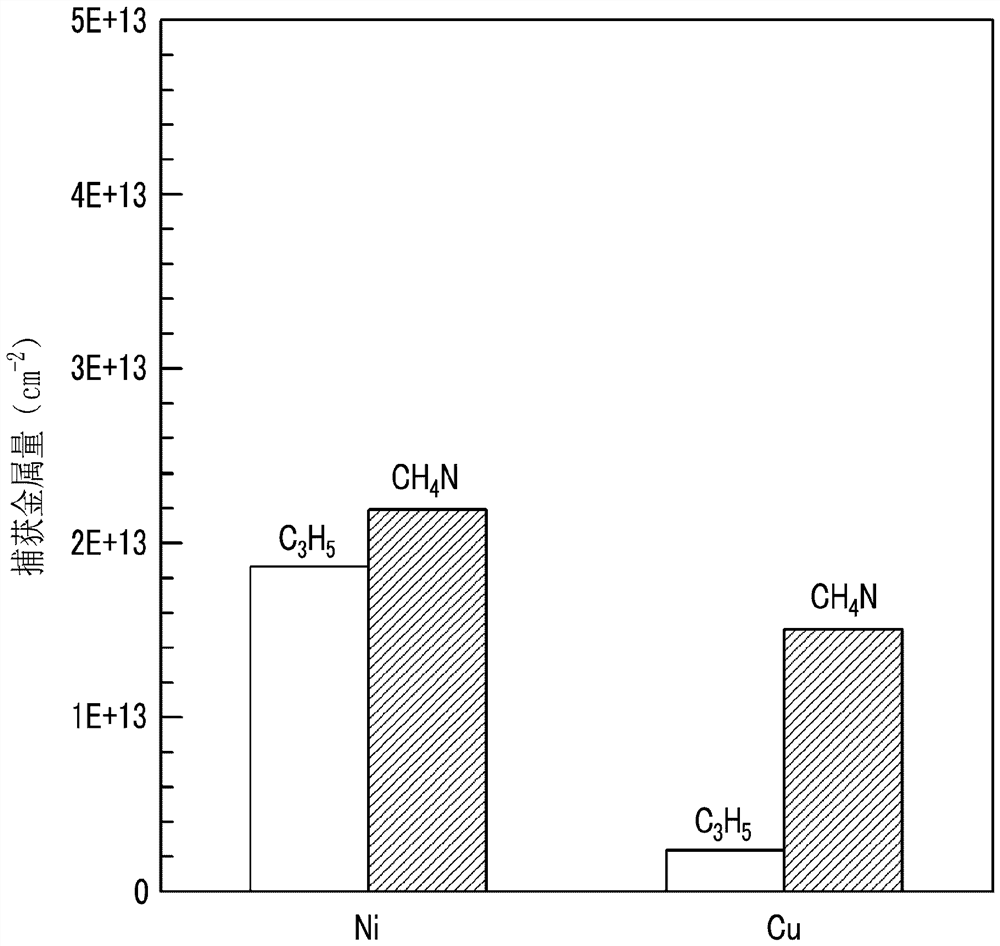

InactiveCN101748491AHigh gettering capacityInhibition of re-emissionPolycrystalline material growthAfter-treatment detailsStacking faultNitrogen

An annealed wafer having enhanced gettering effects for Cu is produced by heating a silicon substrate containing a nitrogen concentration of 5X1014 to 1X1016 / cm3, a carbon concentration of 1X1015 to 5X1016 / cm3, and an oxygen concentration of 6X1017 to 11X1017 / cm3 at a temperature of 650 to 800 DEG C. for a time >=4 hours, and subjecting the heated substrate to argon annealing at a temperature of 1100 to 1250 DEG C., wherein internal stacking fault density after annealing is >=5X108 / cm3.

Owner:SILTRONIC AG

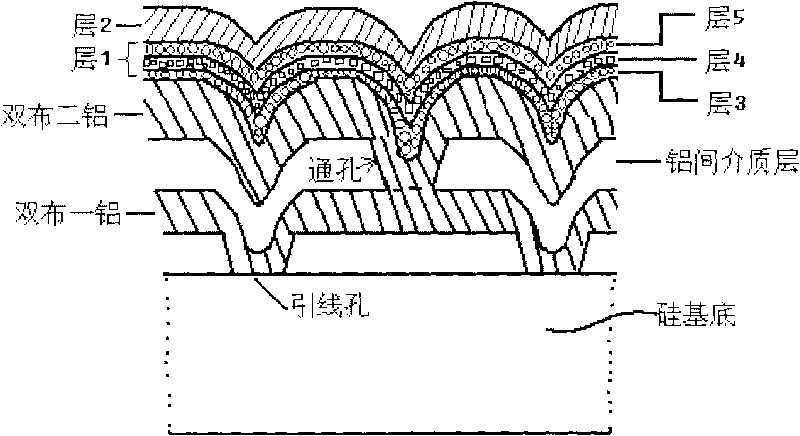

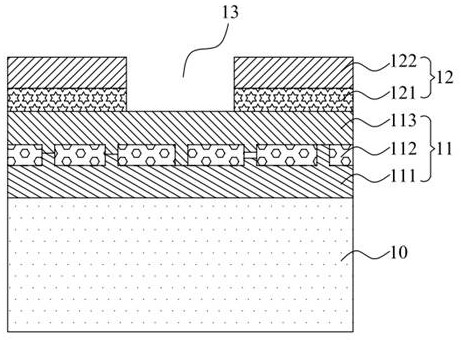

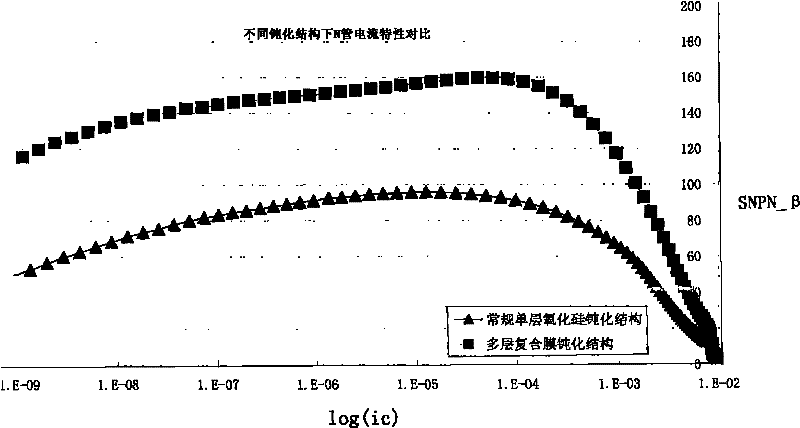

Multi-layer compound passivation layer structure of Bipolar circuit and manufacturing process thereof

InactiveCN101710580AReduce stressImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesHigh densitySilicon oxide

The invention provides a multi-layer compound passivation film structure of a Bipolar circuit, which comprises a bottom silicon oxide film layer and a silicon nitride film layer, wherein the silicon oxide film layer is deposited on the surface of a silicon substrate, and the silicon nitride film layer is deposited on the silicon oxide film layer; a certain proportion of phosphine is doped in the silicon oxide film layer; and the silicon oxide film layer sequentially comprises an undoped silicon oxide layer, a doped phosphorosilicate glass layer and an undoped silicon oxide layer. Meanwhile, the invention also provides a manufacturing process of the multi-layer compound passivation film of the Bipolar circuit. The multi-layer compound passivation film structure of the Bipolar circuit has scratch resistance, moisture resistance, high density, low film stress, higher impurity absorbing ability, better step covering ability and excellent photoelectric properties, electrical characteristics and heat stability, reduces the soft breakdown, and solves the problems of poor reliability, and the like.

Owner:HANGZHOU SILAN INTEGRATED CIRCUIT

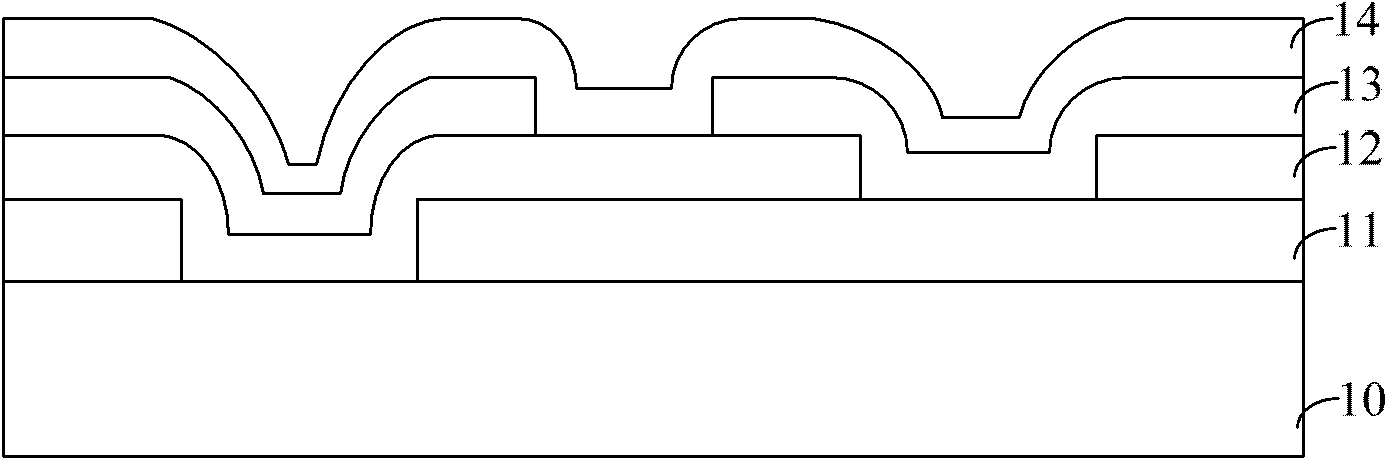

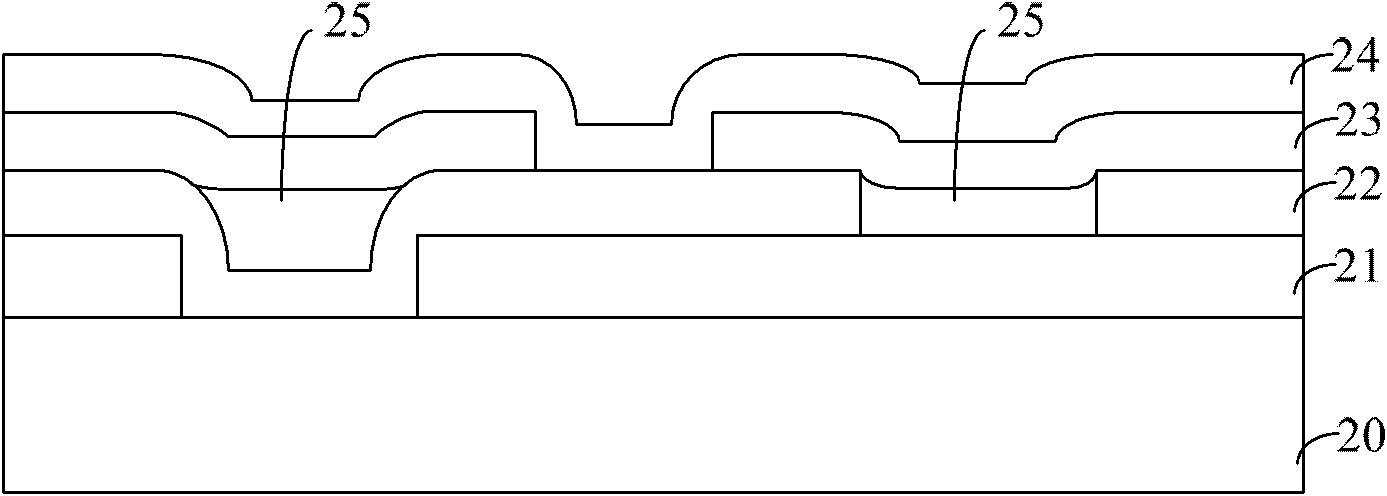

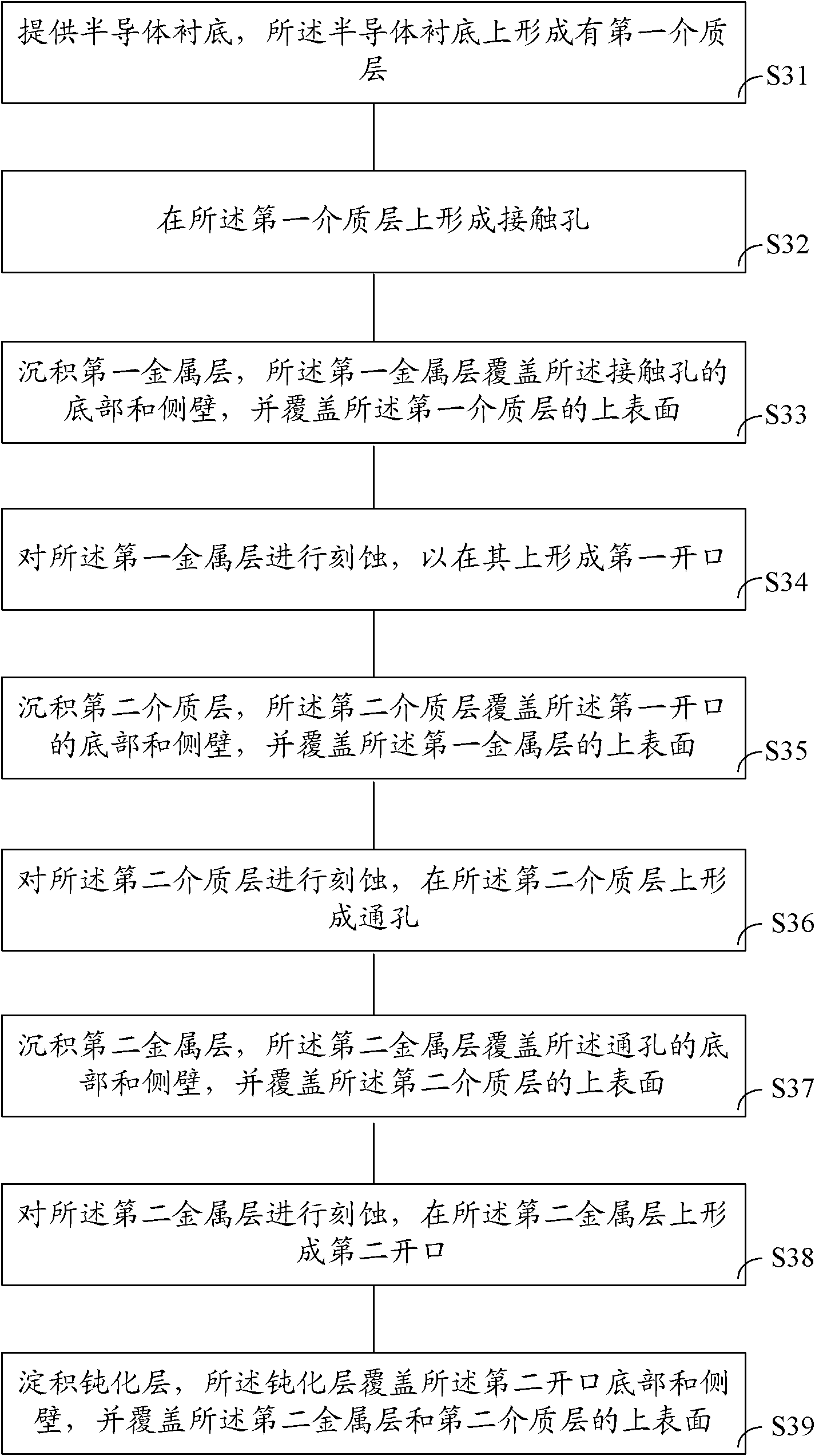

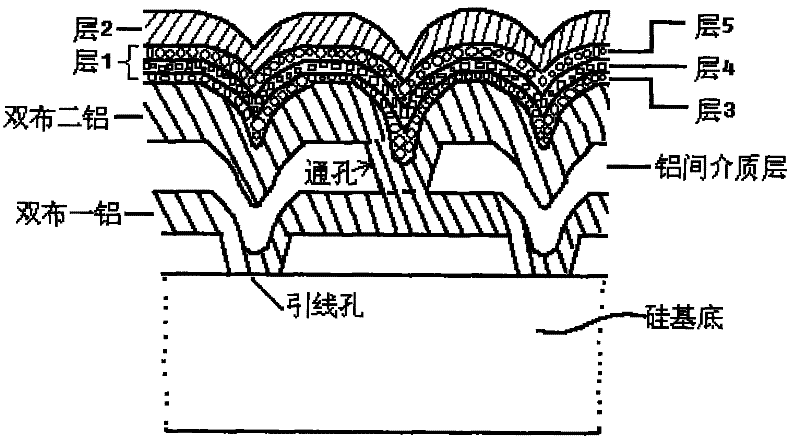

Wiring structure forming method

InactiveCN102354684AImprove the shape of the stepsPromote formationSemiconductor/solid-state device manufacturingEngineeringMedia layer

The invention provides a wiring structure forming method which comprises the following steps of: providing a semiconductor substrate, and forming a first medium layer thereon; forming a contact hole on the first medium layer; depositing a first metal layer, covering the bottom and side wall of the contact hole and covering the upper surface of the first medium layer; etching the first metal layer with a wet method, and etching with a dry method to form a bowl-mouth first opening; depositing a second medium layer, covering the bottom and side wall of the first opening and covering the upper surface of the first metal layer; etching the second medium layer to form an inverted trapezoidal through hole; depositing a second metal layer, covering the bottom and side wall of the through hole and covering the upper surface of the second medium layer; and etching the second metal layer with a wet method, and etching with a dry method to form a bowl-mouth second opening. Through the invention, the requirement on planarization of a process platform of near or below 1.5 microns is met without adopting SOG planarization, glue back-etching SOG planarization and the like.

Owner:HANGZHOU SILAN INTEGRATED CIRCUIT

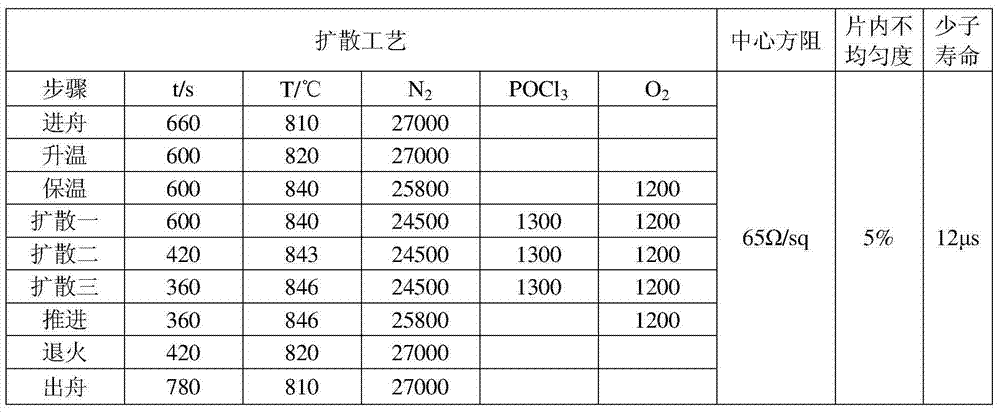

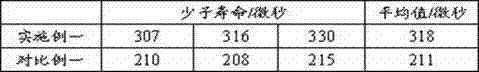

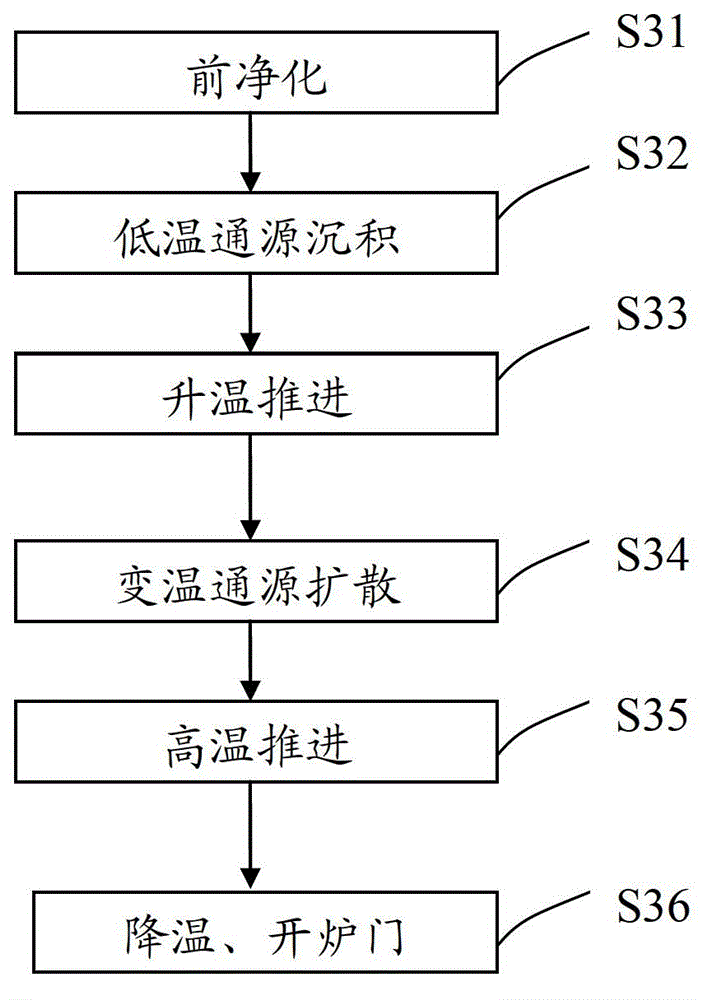

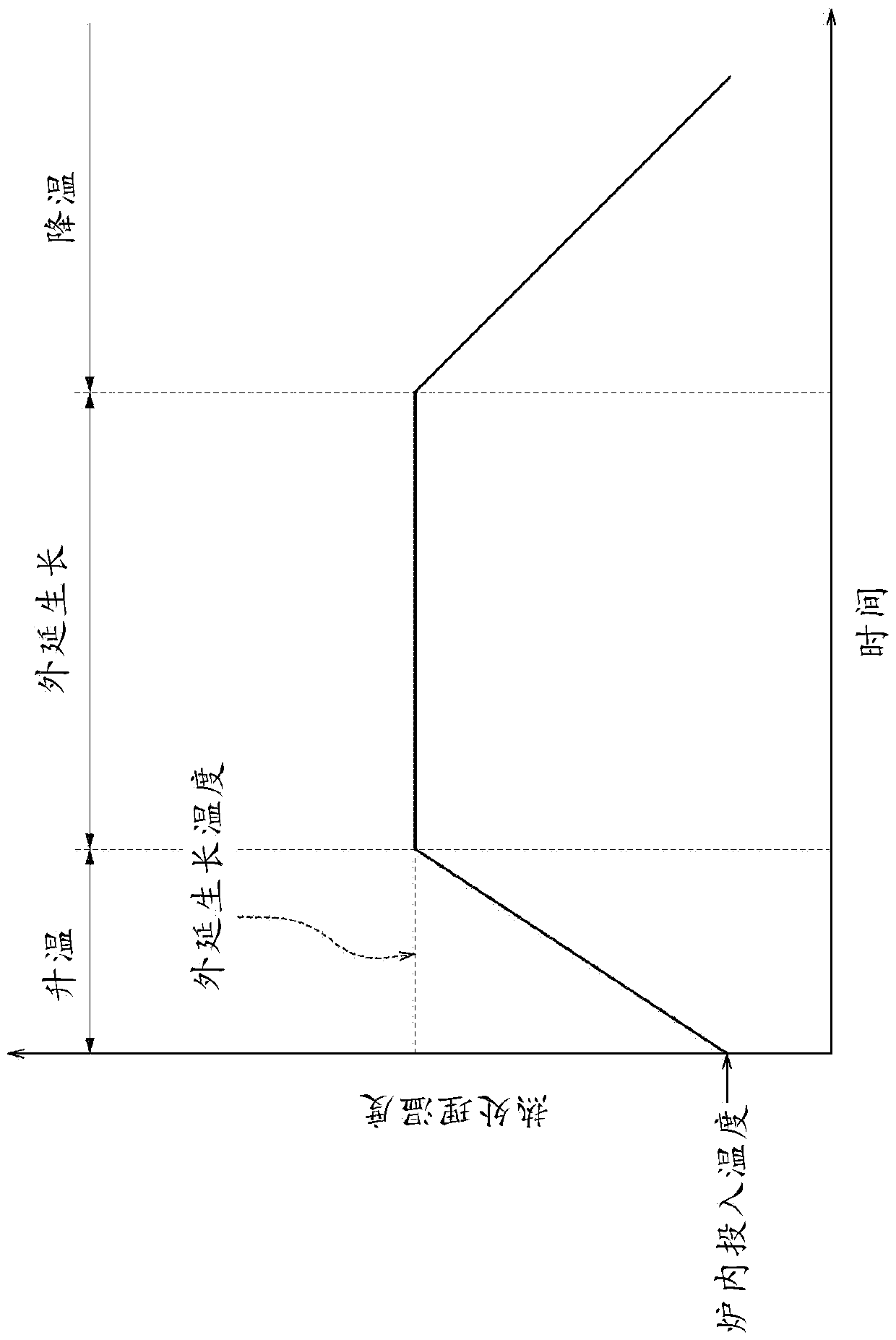

Warming junction-pushing diffusion technology

InactiveCN105118896AEasy to spreadOptimizing Diffusion ProcessFinal product manufactureSemiconductor devicesSurface concentrationIncrease temperature

The invention discloses warming junction-pushing diffusion technology comprising steps of: (1) boat in; (2) fast increasing temperature; (3) pre-oxidation; (4) warming deposition; (5) warming junction pushing; (6) cooling; and (7) boat out. Warming diffusion is carried out under a low-temperature condition and junction pushing is carried out under a high-temperature condition such that a deep junction with low surface concentration is formed and a conversion efficiency is increased by over 0.2 percent.

Owner:JIANGXI UNIEX NEW ENERGY CO LTD

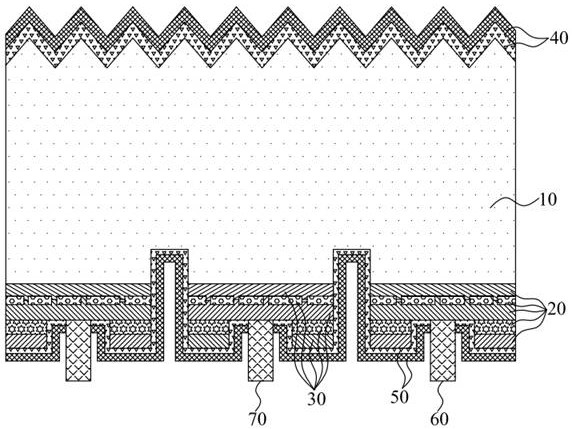

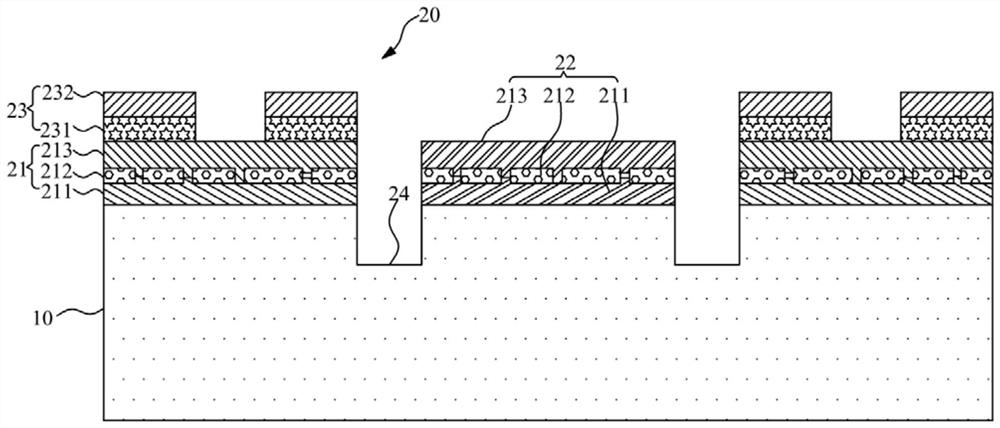

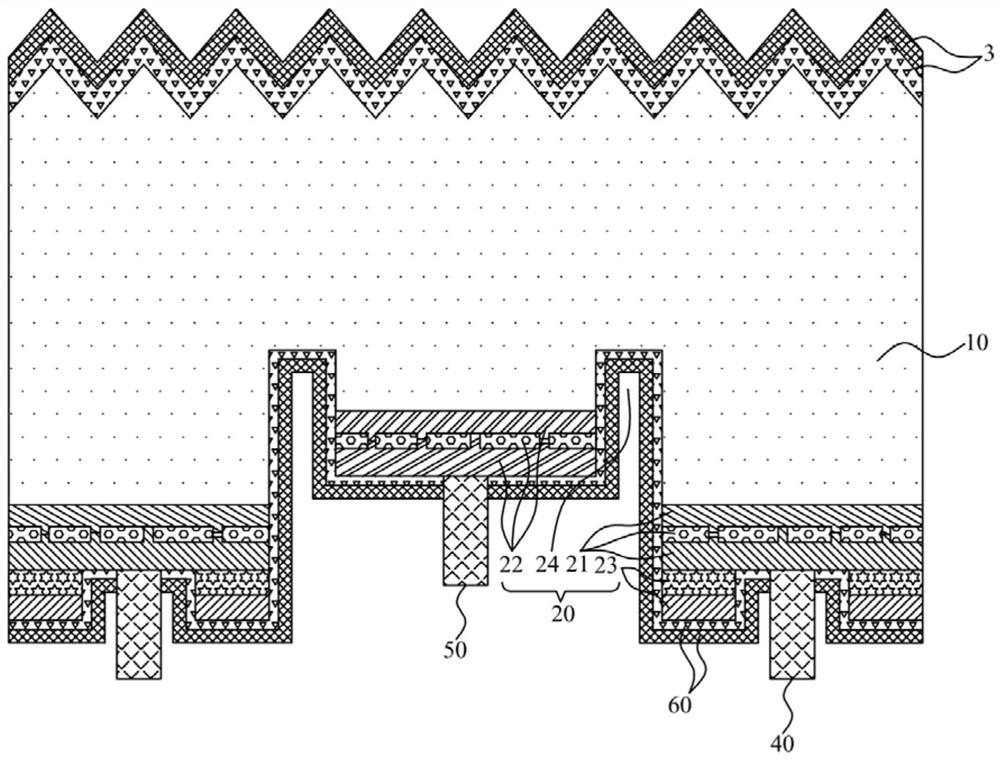

Solar cell and passivation contact structure thereof, cell assembly and photovoltaic system

The invention is suitable for the technical field of solar cells, and provides a solar cell and a passivation contact structure thereof, a cell assembly and a photovoltaic system, the passivation contact structure comprises a first passivation contact area arranged on a silicon substrate and a second passivation contact area arranged on the first passivation contact area; the second passivation contact area is provided with an opening, so that the conductive layer is connected with the first passivation contact area; the first passivation contact area comprises a first doping layer, a first passivation layer and a second doping layer, the second passivation contact area comprises a second passivation layer and a third doping layer, and the first passivation layer is of a porous structure with the first doping layer and / or the second doping layer in a hole region. According to the passivation contact structure provided by the invention, the problems that an existing conducting layer is poor in isolation effect, and recombination is increased and conversion efficiency is reduced due to the fact that the existing conducting layer is easily in direct contact with a silicon substrate are solved.

Owner:ZHEJIANG AIKO SOLAR ENERGY TECH CO LTD

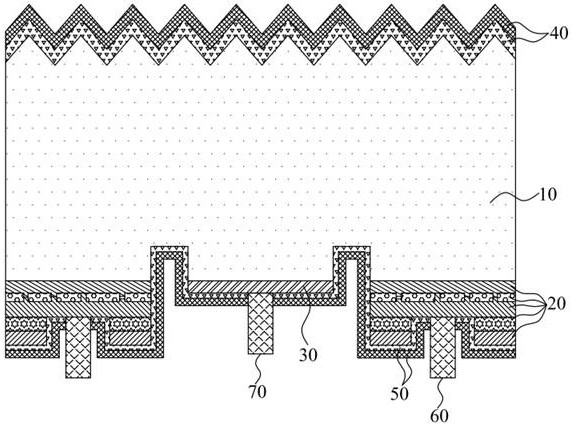

Solar cell, back contact structure thereof, cell assembly and photovoltaic system

PendingCN113394304AAvoid scratchesSolve the scratchPhotovoltaic energy generationSemiconductor devicesEngineeringSolar cell

The invention is applicable to the technical field of solar cells, and provides a solar cell and a back contact structure thereof, a cell assembly and a photovoltaic system, the back contact structure comprises first doped regions which are arranged on the back of a silicon substrate at intervals and have polarities opposite to the polarity of the silicon substrate, and second doped regions which have the same polarities as the polarity of the silicon substrate. Protection regions are arranged on the first doped regions; each of the first doped region and the second doped region comprises a first doped layer, a passivation layer and a second doped layer; each protection region comprises an insulating layer and a third doped layer with the same polarity as the second doped region; isolation regions are arranged between the first doped regions and the second doped regions; the protection regions are provided with openings, so that a first conductive layer is connected with the first doped region; and the heights of the first doped regions and the second doped regions are both higher than the heights of the isolation regions. According to the back contact structure provided by the invention, the problem of scratches caused by belt transmission in the existing battery preparation process is solved.

Owner:ZHEJIANG AIKO SOLAR ENERGY TECH CO LTD +3

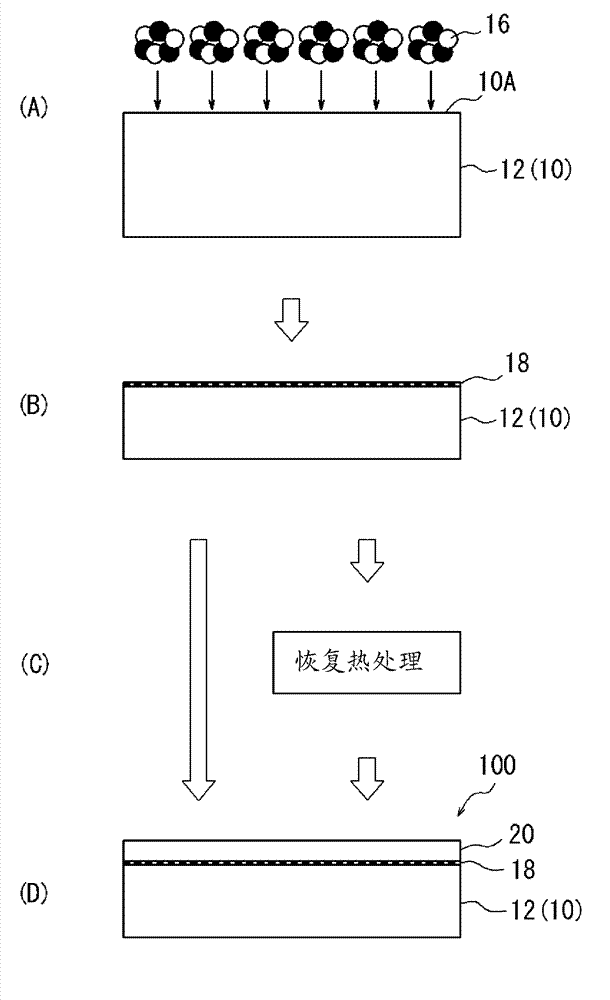

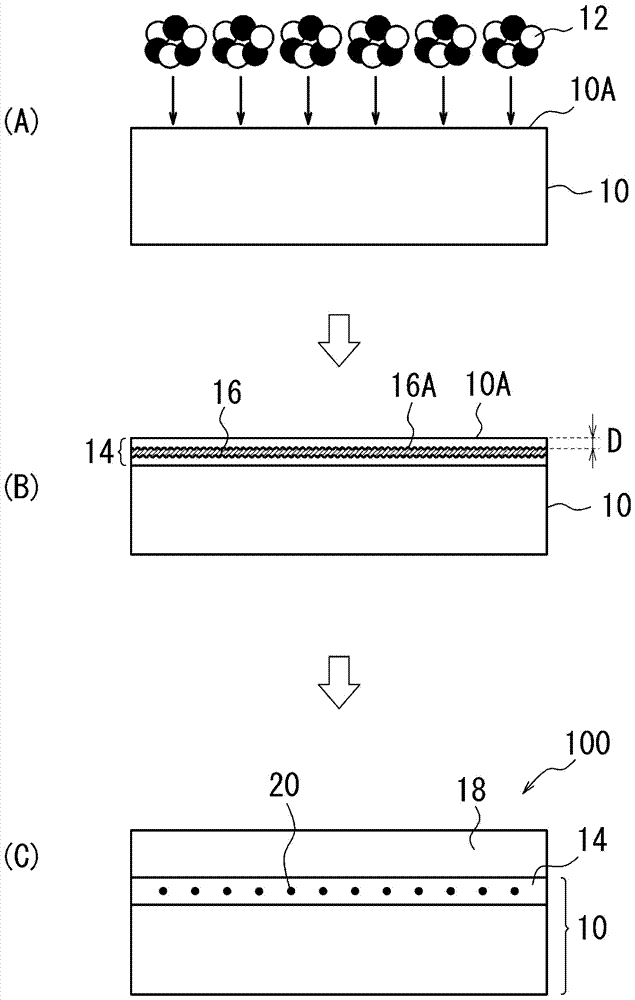

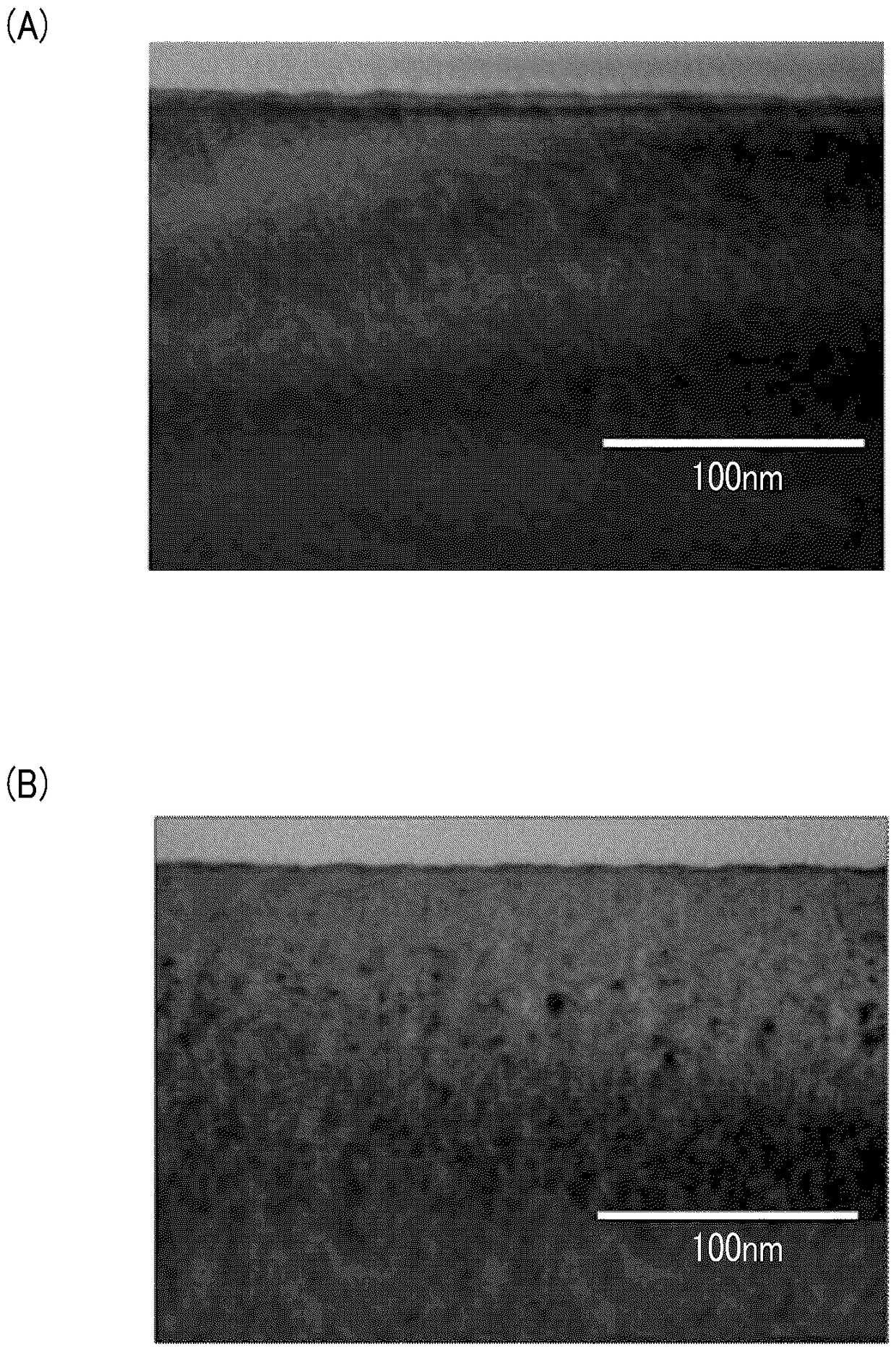

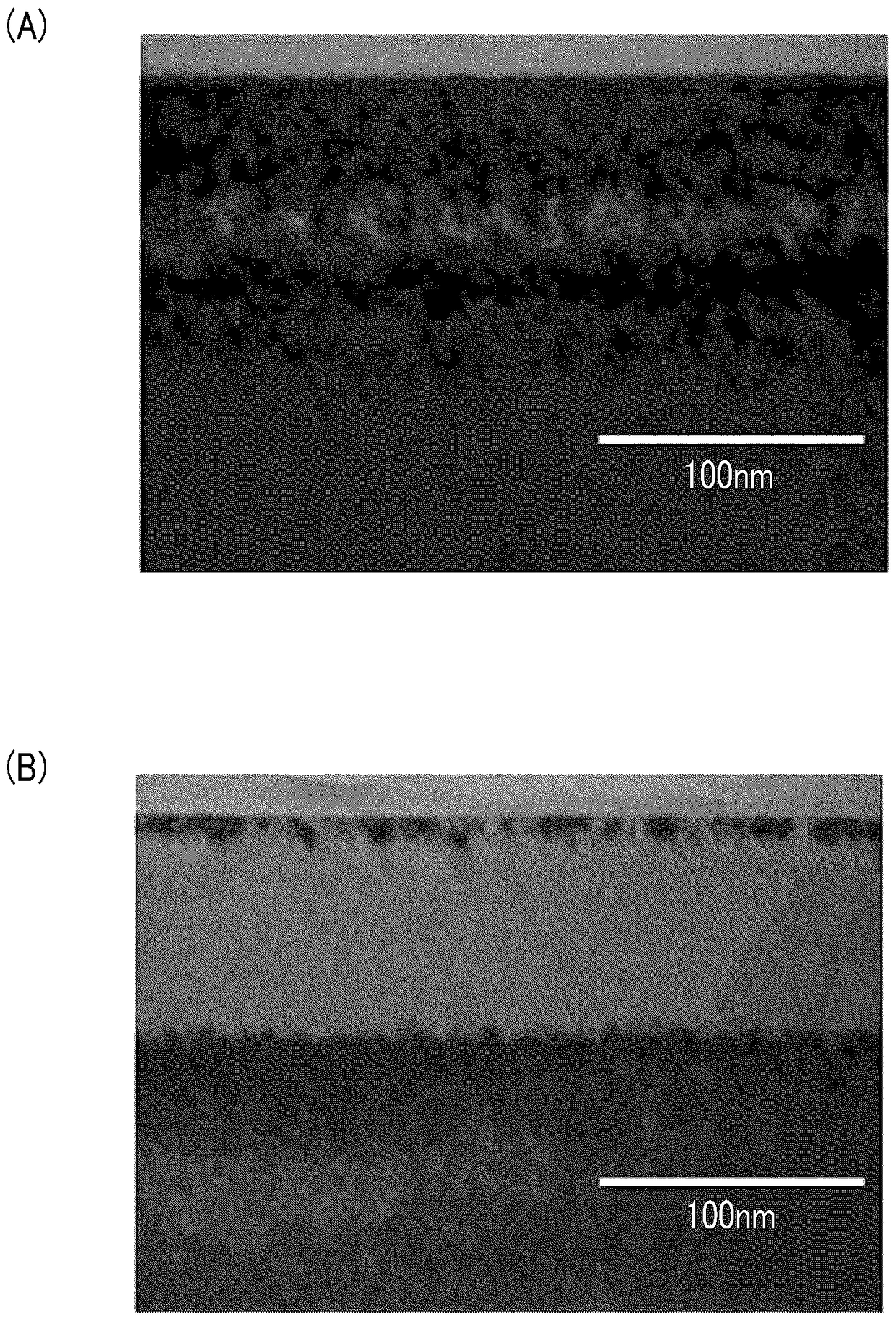

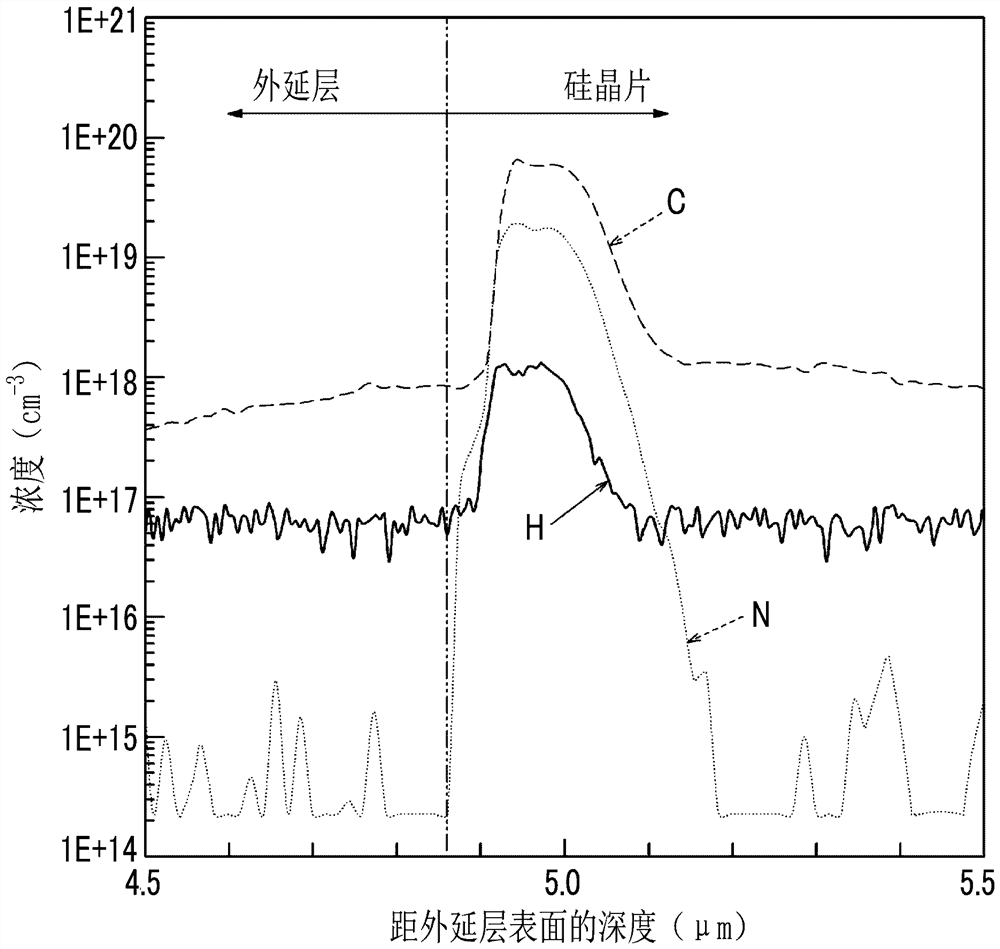

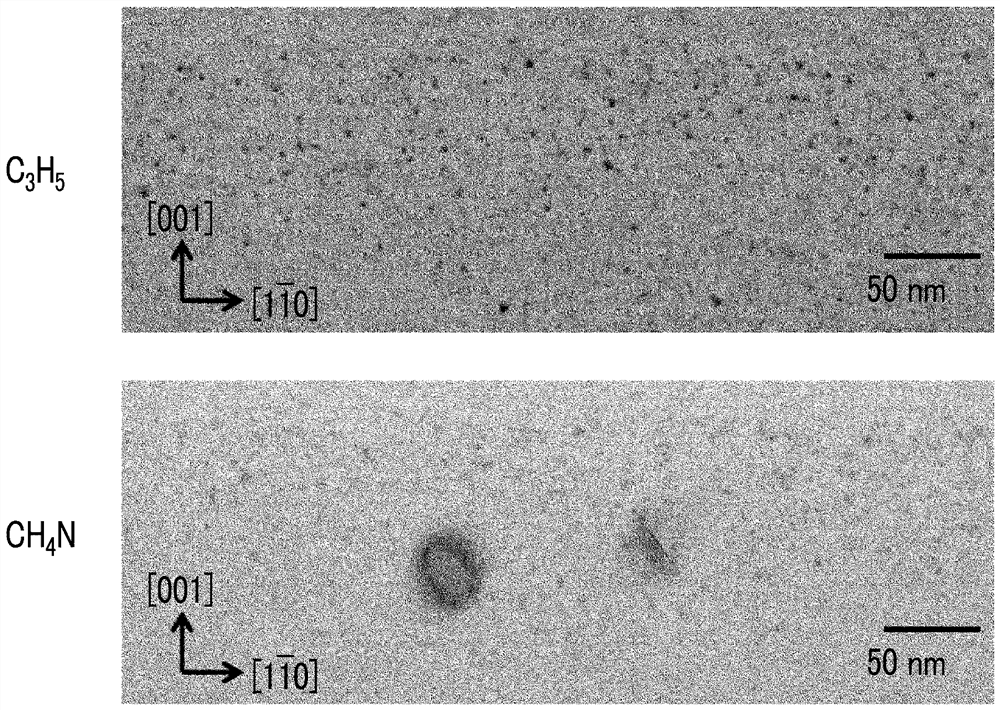

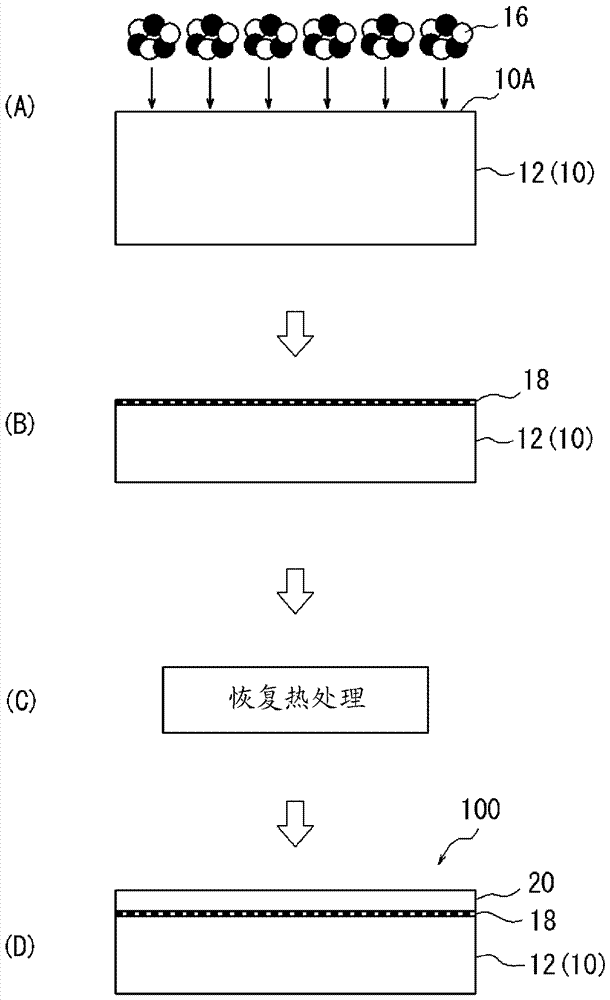

Production method for semiconductor epitaxial wafer, semiconductor epitaxial wafer, and production method for solid-state imaging element

ActiveCN104781919AImprove qualityPollution suppressionPolycrystalline material growthVacuum evaporation coatingWaferingMetal contamination

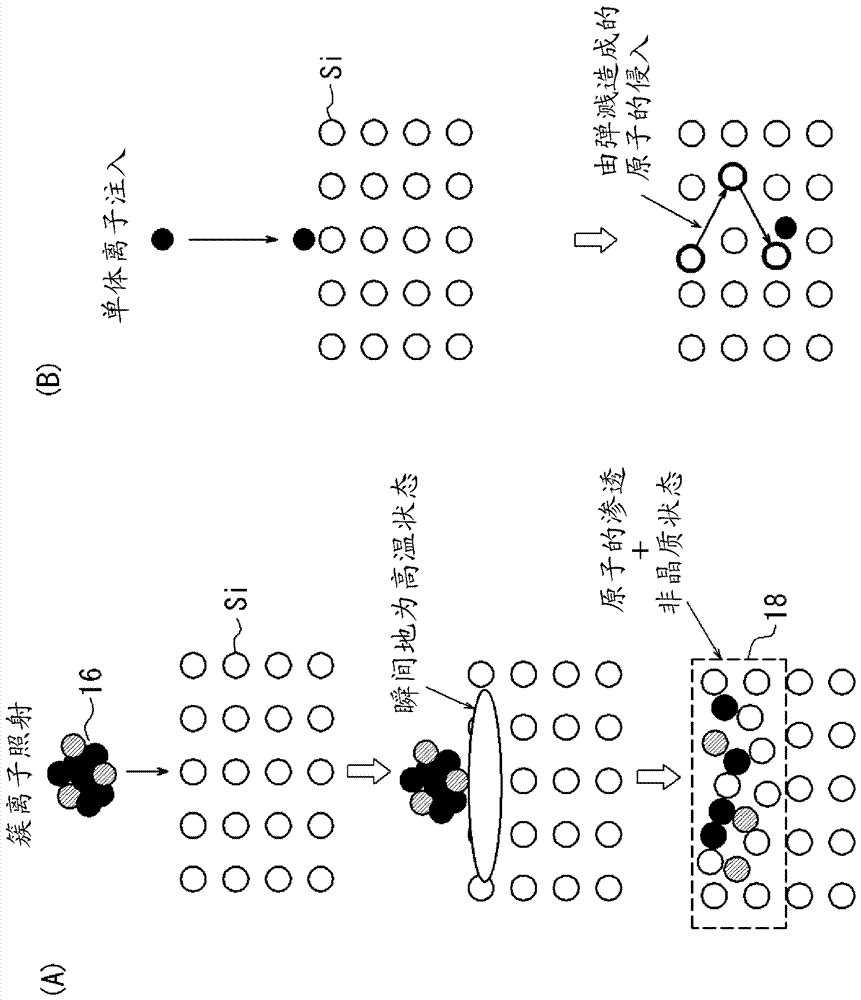

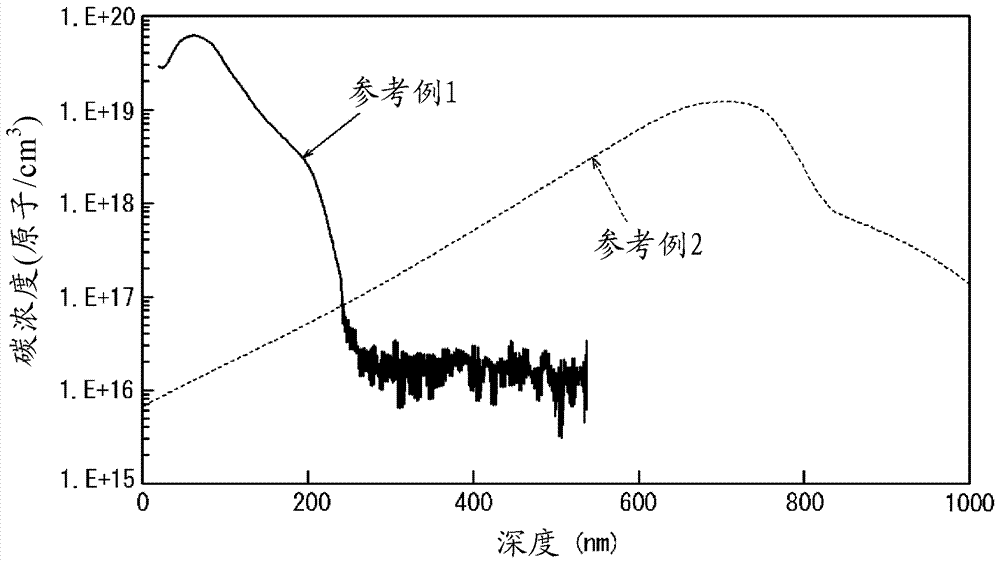

The present invention provides a production method for a semiconductor epitaxial wafer in which increased gettering properties enable metal contamination to be suppressed. In the present invention, the production method for the semiconductor epitaxial wafer is characterized in that the method includes: a first step, in which cluster ions (16) are irradiated on a surface (10A) of a semiconductor wafer (10) so as to form, on the surface (10A) of the semiconductor wafer, a modification layer (18) that is a solid solution of carbon and a dopant element, which are constituent elements of the cluster ions (16); and a second step in which an epitaxial layer (20), which has a lower dopant element concentration than the peak dopant element concentration in the modification layer (18), is formed upon the modification layer (18) of the semiconductor.

Owner:SUMCO CORP

Low-pressure diffusion and low-temperature oxidation gettering process

InactiveCN110323304AHigh gettering capacitySatisfy Diffusion NeedsFinal product manufacturePhotovoltaic energy generationLow temperature depositionPressure stabilization

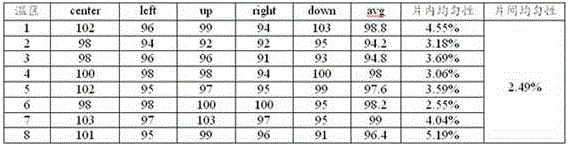

The invention provides a low-pressure diffusion and low-temperature oxidation gettering process, and belongs to the field of solar cell gettering processes. The method comprises the steps: low-temperature normal-pressure boat entry, rapid low-pressure heating, high-temperature normal-pressure stabilization, high-temperature low-pressure oxidation, four-step high-temperature low-pressure source communication and knot pushing, long-time cooling, oxidation and impurity absorption, rapid normal-pressure cooling and low-temperature deposition, and low-temperature boat exit. The furnace tube is rapidly cooled for a long time through the steps of cooling, oxidizing and gettering for a long time and controlling the oxygen flow, so that the uniformity and repeatability of diffusion sheet resistanceare improved, the surface doping concentration and junction depth are optimized, the internal defects of a silicon wafer are reduced, and the conversion efficiency of the solar cell is improved.

Owner:江苏润阳悦达光伏科技有限公司

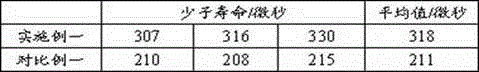

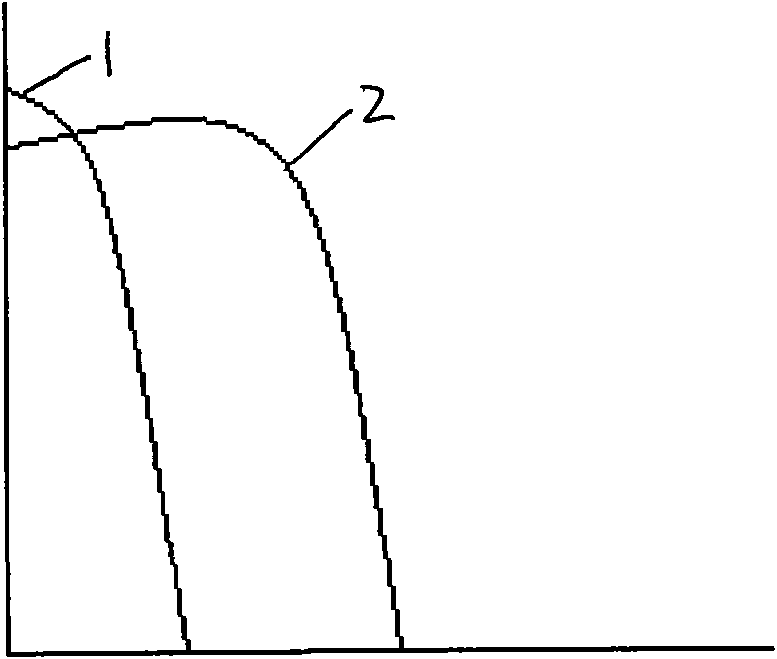

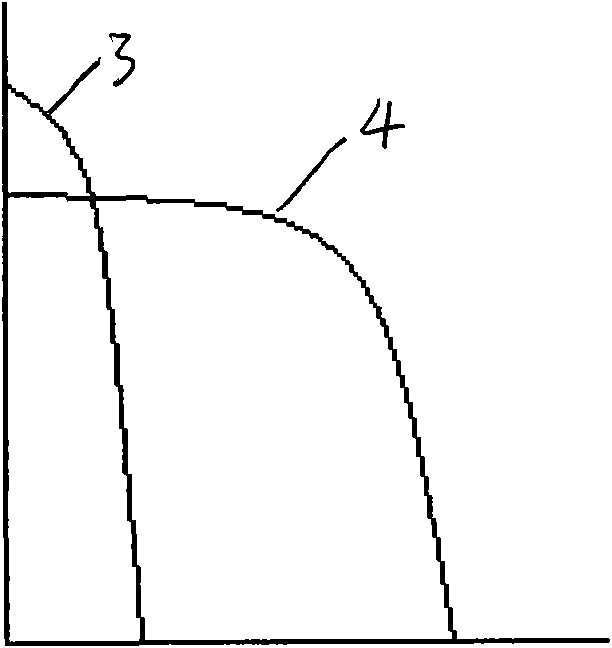

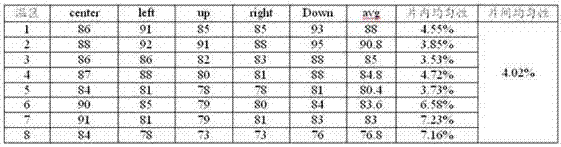

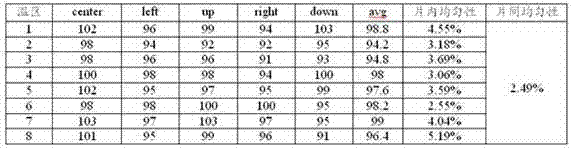

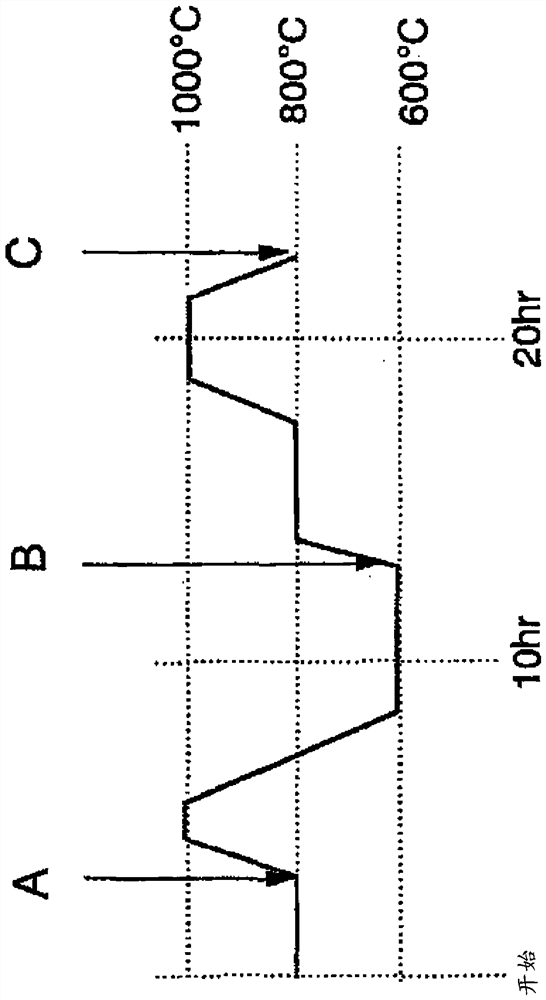

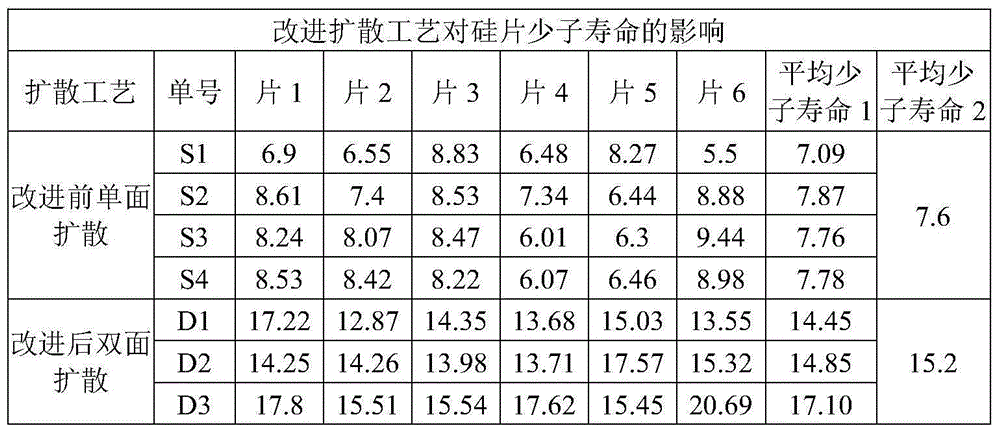

Diffusion technology for prolonging minority carrier lifetime of metallurgical silicon wafer

ActiveCN103531449AImprove conversion efficiencyImprove yieldFinal product manufactureSemiconductor/solid-state device manufacturingSilicon solar cellOxygen

The invention relates to a diffusion technology adopted in the process of manufacturing a physical metallurgical silicon solar cell, in particular to a diffusion technology for prolonging the minority carrier lifetime of a metallurgical silicon wafer. The diffusion technology is characterized by comprising the following steps: (1) propelling a quartz boat at the low temperature and raising the temperature preliminarily; (2) introducing nitrogen carried with phosphorus oxychloride and diffusing generated phosphorus atoms; (3) advancing at the constant temperature; (4) cooling and withdrawing the quartz boat. The technology has the benefits as follows: 1, spraying type diffusion is adopted, so as to save the phosphorus source as well as improve the uniformity of diffusion junction depth, and the technology is suitable for high sheet resistance; 2, according to the characteristics of physical metallurgical silicon, two-sided phosphorus is adopted in gettering to enhance the gettering effect and prolong the minority carrier lifetime of the silicon wafer; 3, the diffusion technology is effectively improved via the coordination of temperature and time; 4, the proportions of introduced oxygen and introduced raw material are controlled to reduce the defects caused by direct diffusion and improve the junction depth of a PN junction, the surface passivation effect can be further improved, and the short-circuit current and the open-circuit voltage are increased, so that the conversion efficiency and the yield of the metallurgical silicon solar cell are further improved.

Owner:NINGXIA YINXING ENERGY

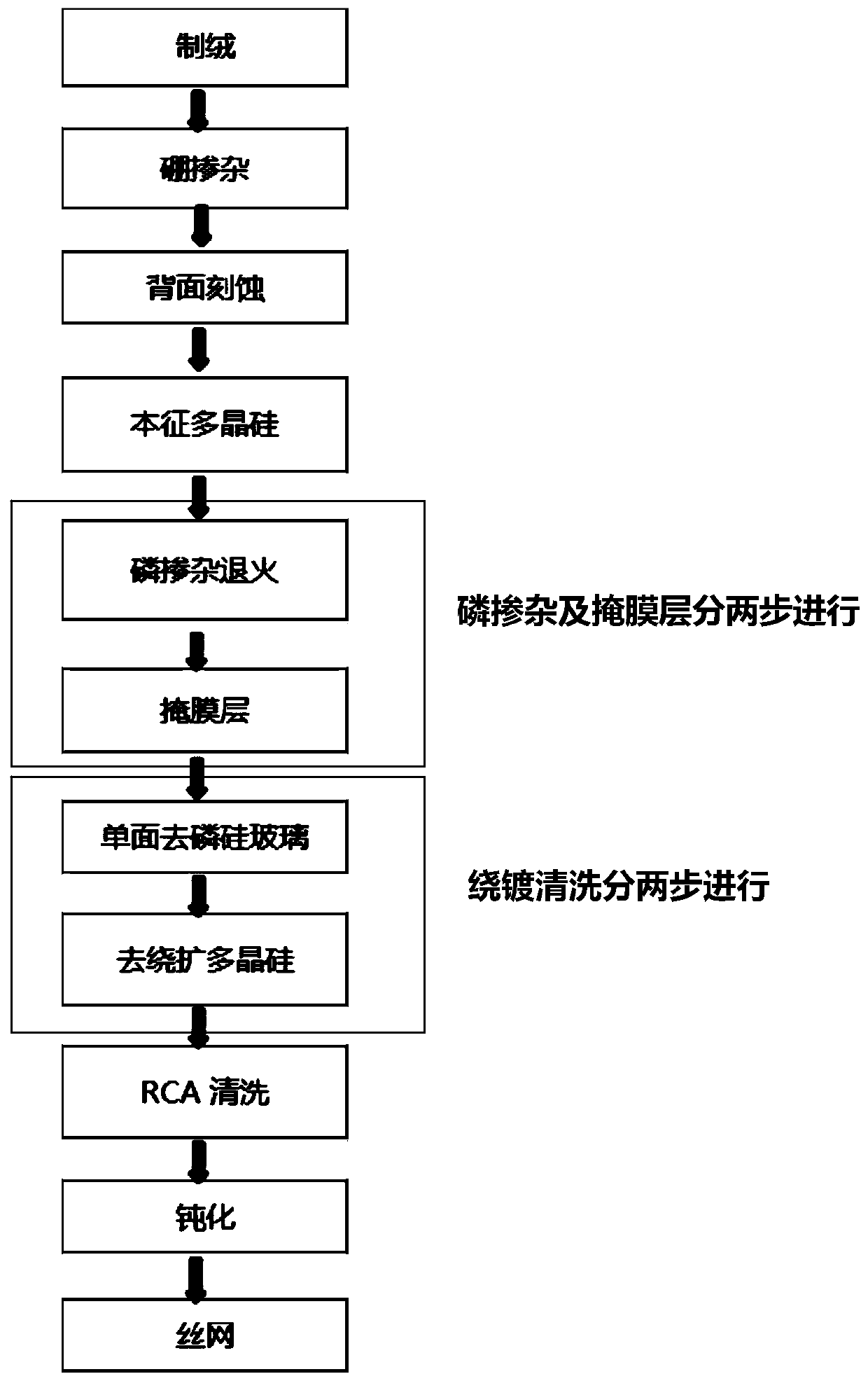

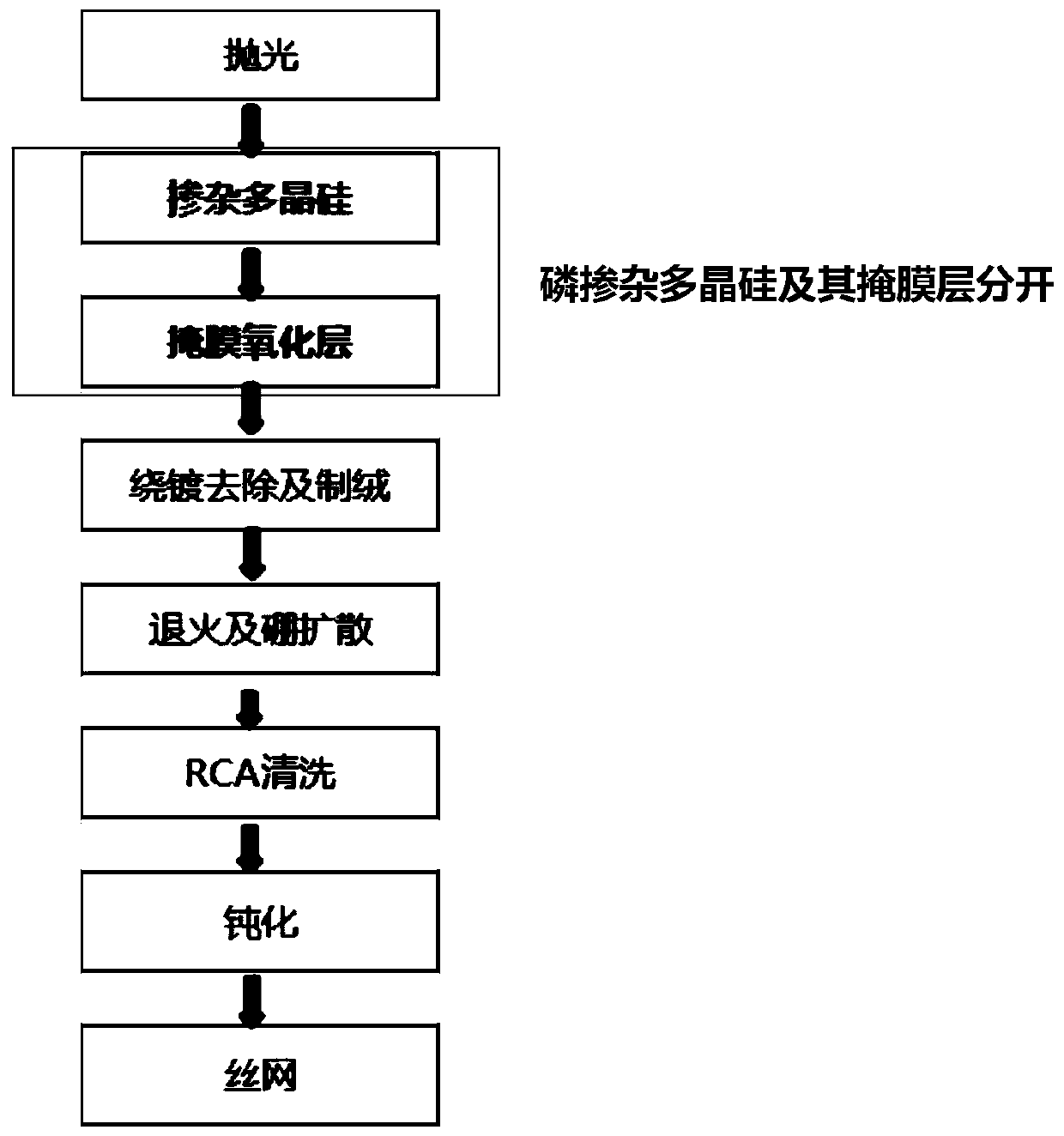

Preparation method of tunneling oxidation passivation battery

InactiveCN111524999AImprove production yieldSave machineFinal product manufacturePhotovoltaic energy generationPhysicsPolycrystalline silicon

The invention belongs to the field of solar photovoltaic industry and particularly relates to a preparation method of a tunneling oxidation passivation battery. The method is characterized in that a back surface adopts a polished surface structure so that the light utilization rate can be effectively improved, and the process steps are reduced by adopting one-step deposition of polycrystalline silicon phosphorus doping and growth of a thick oxidation mask layer; a whole surface of the coating is removed, the process window is enlarged, the defect of difficulty in removing the winding plating,namely the defect of difficulty in removing the winding plating due to the fact that boron diffusion is performed on a front surface and polycrystalline silicon is doped on a back surface in the conventional common process flow, is avoided, a certain mark is certainly caused even if the winding plating is completely removed, so the appearance yield is influenced. The method is advantaged in that an annealing and boron doping two-in-one mode is introduced into the method, so the process is simplified, the appearance is not poor, the process flow is short, energy consumption is low, the production yield is effectively increased, production quality is effectively improved, and the like.

Owner:CHANGZHOU UNIV +1

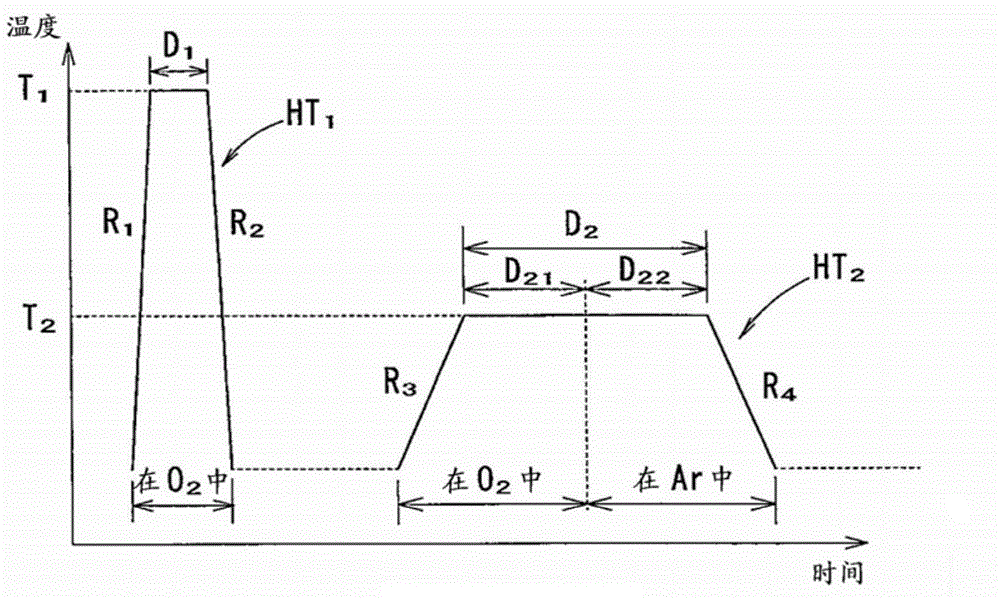

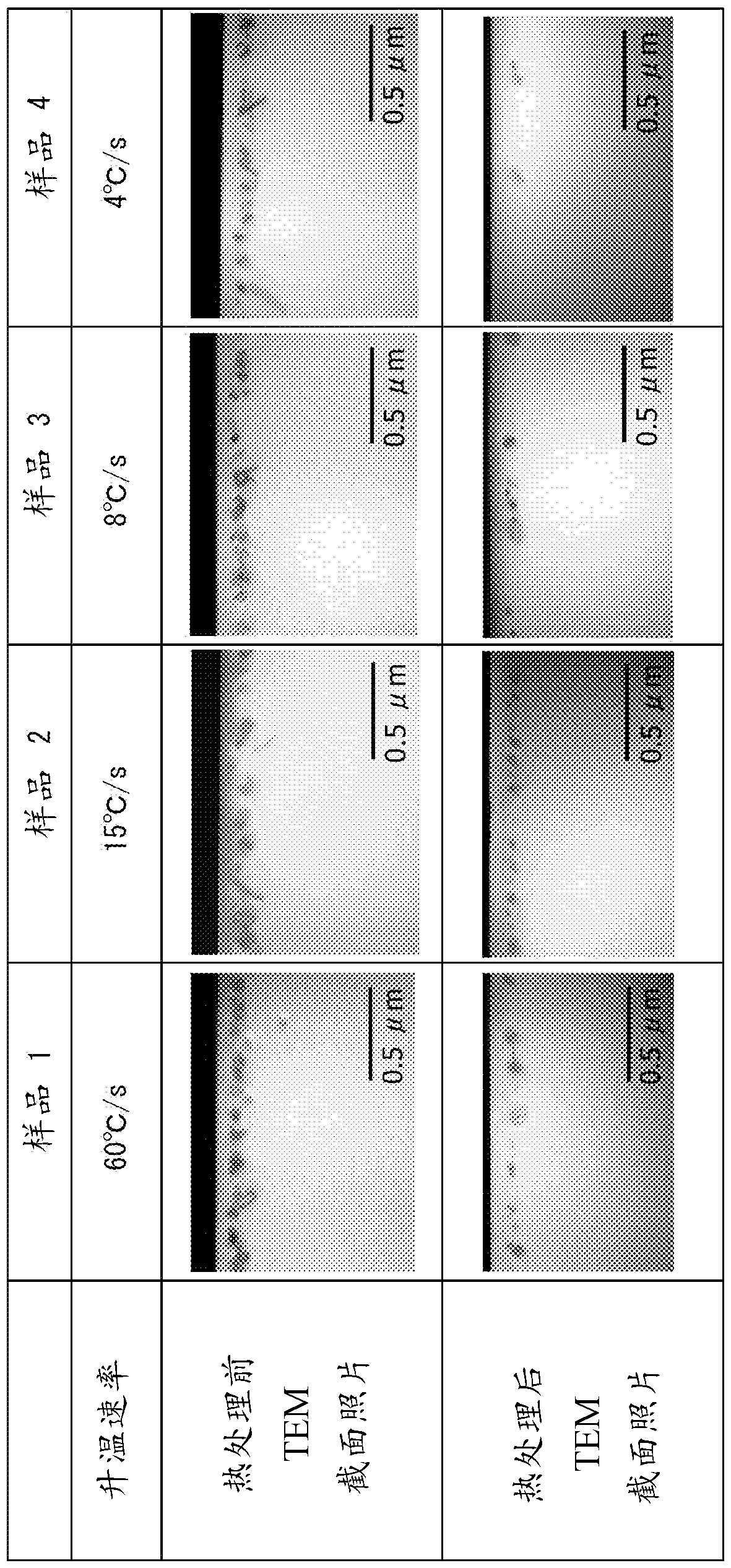

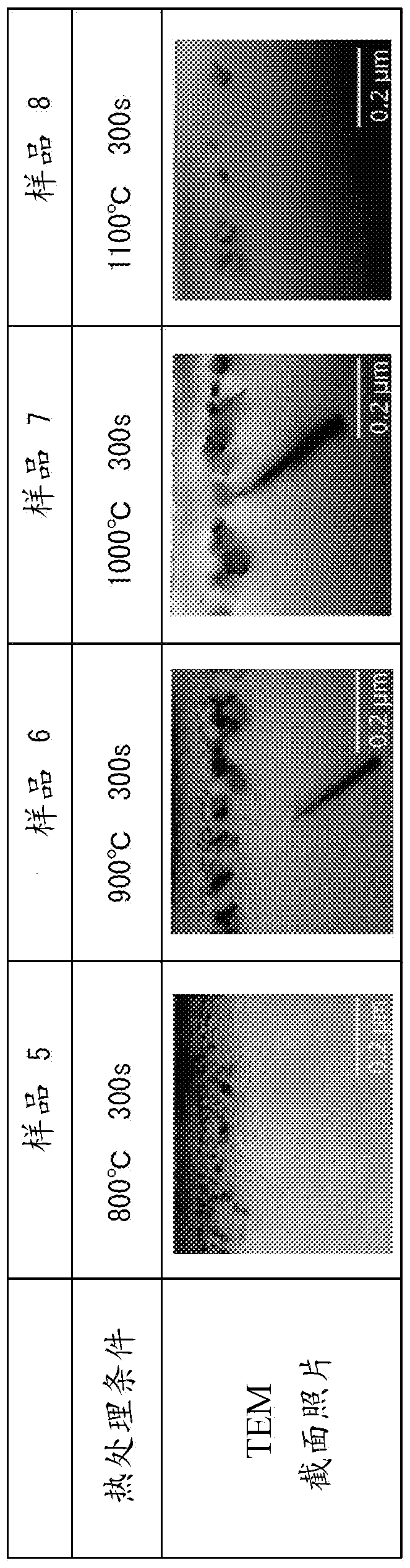

Method for heat treatment of silicon wafer and silicon wafer

ActiveCN104979191AHigh strengthGood effectPolycrystalline material growthAfter-treatment detailsIn planeSurface layer

The present invention aims to ensure the strength of a surface layer and a main body of a silicon wafer, and enhance the in-plane homogeneity of crystal quality. A method for heat treament of silicon wafer includes the steps as follows: firstly, heat treating silicon wafers in an oxidizing atmosphere in a temperature range between 1300 DEG C to 1400 DEG C; secondly, cooling the heat-treated silicon wafers at a speed of 10 DEG C per second to 150 DEG C per second; and thirdly, heat treating the cooled silicon wafers in the oxidizing atmosphere in a temperature range between 800 DEG C to 1250 DEG C for one hour to one hundred hours.

Owner:GLOBALWAFERS JAPAN

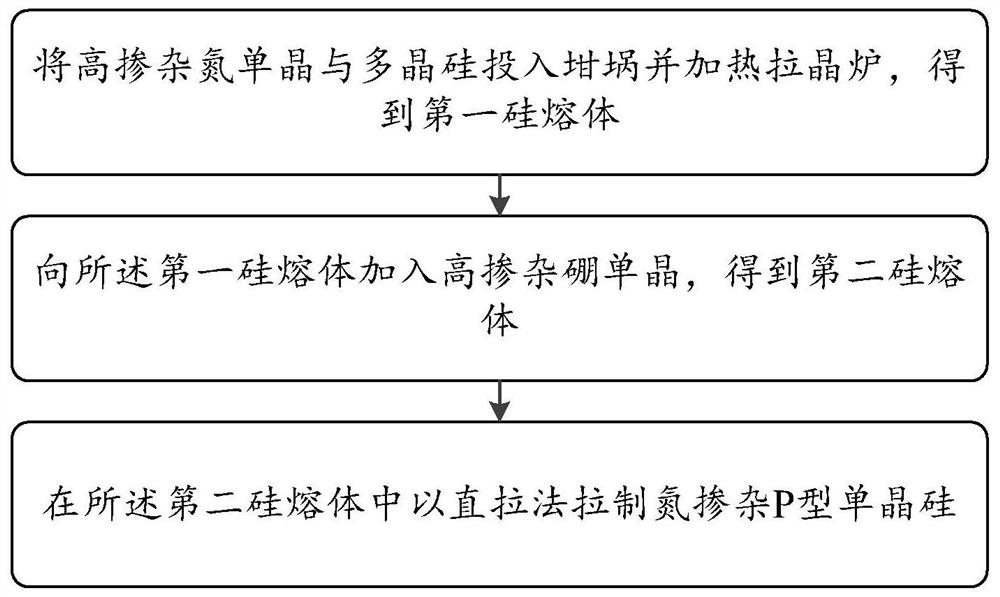

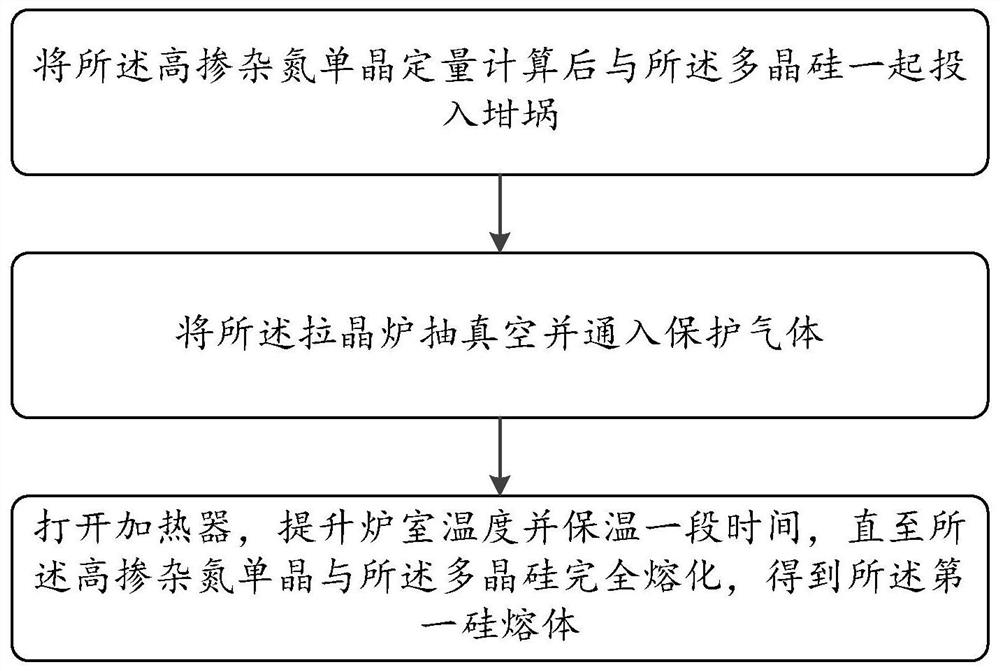

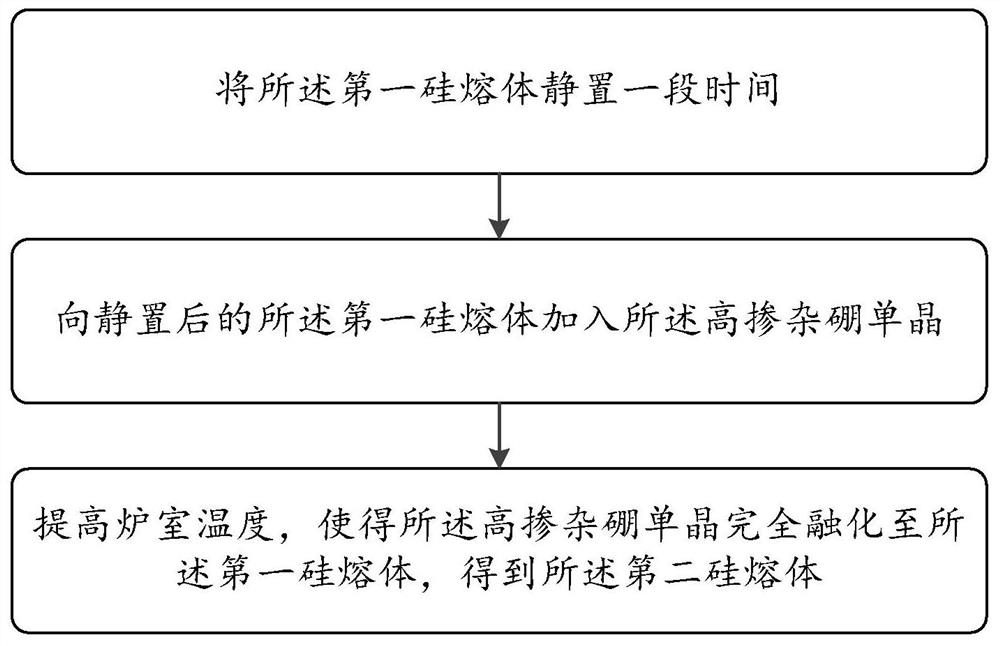

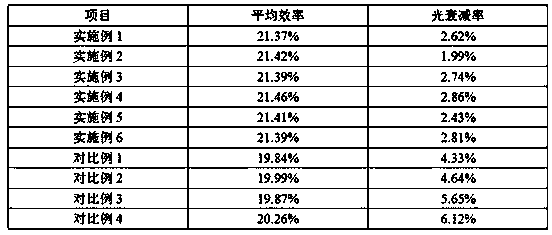

Nitrogen-doped P-type monocrystalline silicon manufacturing method

PendingCN113882016AImprove productivityLow costPolycrystalline material growthBy pulling from meltCzochralski methodPhysical chemistry

The embodiment of the invention discloses a nitrogen-doped P-type monocrystalline silicon manufacturing method which comprises the following steps: putting highly-doped nitrogen single crystal and polycrystalline silicon into a crucible, and heating a crystal pulling furnace to obtain a first silicon melt; adding a highly doped boron single crystal into the first silicon melt to obtain a second silicon melt; and drawing the nitrogen-doped P-type monocrystalline silicon in the second silicon melt by a czochralski method. According to the nitrogen-doped P-type monocrystalline silicon manufacturing method, the nitrogen and the boron are completely fused into the silicon melt at a relatively low furnace chamber temperature, and the technical problems of high furnace chamber temperature and long heating time are solved. Meanwhile, the melting sequence of the highly-doped boron single crystal and the highly-doped nitrogen single crystal is changed, so that the condition of crystal pulling failure caused by the formation of boron nitride (BN) is inhibited.

Owner:XIAN ESWIN MATERIAL TECH CO LTD

Light attenuation resistant PERC single crystalline silicon solar cell aluminum paste and preparation method thereof

ActiveCN108877989AReduce or avoid the formation ofIncrease the doping concentrationNon-conductive material with dispersed conductive materialCable/conductor manufactureAluminium powderSilicon solar cell

The invention discloses a light attenuation resistant PERC single crystalline silicon solar cell aluminum paste. The aluminum paste is prepared from the following components in parts by weight: 70 to86 parts of aluminum powder, 0.5 to 2.5 parts of an inorganic binder, 10 to 24 parts of an organic binder and 0.1 to 1.5 parts of an inorganic auxiliary agent. The invention also discloses a preparation method of the aluminum paste. The preparation method comprises the following steps: firstly uniformly stirring the organic binder and the inorganic auxiliary agent, then adding the inorganic binderand the aluminum powder in sequence to be stirred uniformly, and finally grinding to obtain the aluminum paste. An PERC single crystalline silicon solar cell obtained by using the aluminum paste hasthe characteristics of high photovoltaic conversion efficiency and light attenuation resistance.

Owner:JIANGXI NUCLEAR IND XINGZHONG NEW MATERIALS

Phosphorus diffusion method for crystalline silicon solar cells

ActiveCN106057980BIncrease growth rateEasy to separateFinal product manufactureSemiconductor/solid-state device manufacturingConcentration gradientNitrogen gas

Owner:CSI CELLS CO LTD +1

Method for improving diffusion quality by changing polycrystalline silicon slice phosphorus source components

InactiveCN103367125AImprove Diffusion QualityImprove life expectancySemiconductor/solid-state device manufacturingPolycrystalline siliconPhosphorus trichloride

The invention discloses a method for improving diffusion quality by changing polycrystalline silicon slice phosphorus source components, and relates to the technical field of methods for manufacturing semiconductor devices. The method includes the following steps that (1) phosphorus trichloride is added in phosphorus oxychloride and used as a phosphorus source; (2) oxidization: polycrystalline silicon slices with the manufactured suede are placed in a diffusion furnace, and oxygen is added in the diffusion furnace; (3) deposition: mixed gas of the phosphorus source and the oxygen is added in the diffusion furnace; (4) diffusion: the diffusion furnace is kept at a certain temperature, and then deposited phosphorus silicon slices are diffused in the diffusion furnace. Through the method, the service life of minority carriers in the polycrystalline silicon slices is prolonged, the diffusion gettering effect is beneficially improved, damage to crystal lattices in the high temperature process is reduced, and then photoelectric conversion efficiency is improved.

Owner:YINGLI ENERGY CHINA

Solar cell and diffusion method of solar cell

ActiveCN102925982BReduce phosphorus impurity concentrationMaximum solid solubility increaseDiffusion/dopingDiffusion methodsDiffusion

Owner:YINGLI ENERGY CHINA

Diffusion method used for crystalline silicon solar battery

InactiveCN102157606BHigh gettering capacityIncrease short circuit currentDiffusion/dopingRenewable energy productsPhysical chemistrySolar battery

The invention discloses a diffusion method used for a crystalline silicon solar battery. The method comprises the following steps of: (1) placing a silicon wafer into a diffusion furnace; rising the temperature from 780-810 DEG C to 840-860 DEG C; and simultaneously introducing POCL3+O2+N2 for 12 to 14 minutes; (2) simultaneously introducing O2+N2 when rising the temperature in the diffusion furnace to 840-860 DEG C and keeping the constant temperature for 2 to 5 minutes; simultaneously introducing the POCL3+O2+N2 for 8 to 12 minutes when rising the temperature from 840-860 DEG C to 870-890 DEG C; reducing the temperature from 870-890 DEG C to 800 DEG C; introducing the O2+N2 in the process of reducing the temperature; stabilizing for 2 minutes at the temperature of 800 DEG C; and introducing the POCL3+O2+N2; and (3) taking the silicon wafer out of the diffusion furnace. In the method, both the requirements on the doping concentration of an emitting region and the surface concentration of the emitting region in diffusion can be met at the same time; a gettering effect is good; and the distribution of a doping curve is more reasonable.

Owner:BAODING GUANGWEI GREEN ENERGY TECH CO LTD

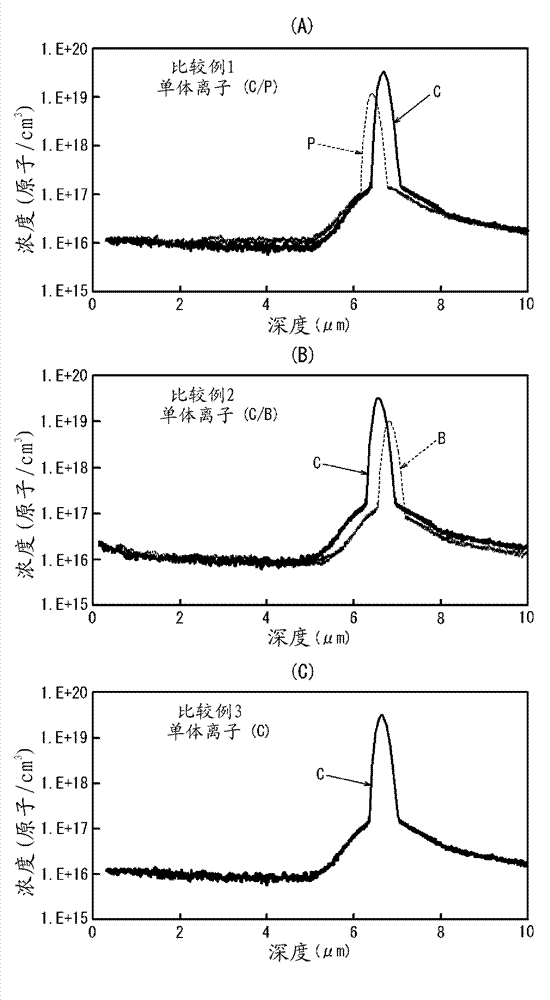

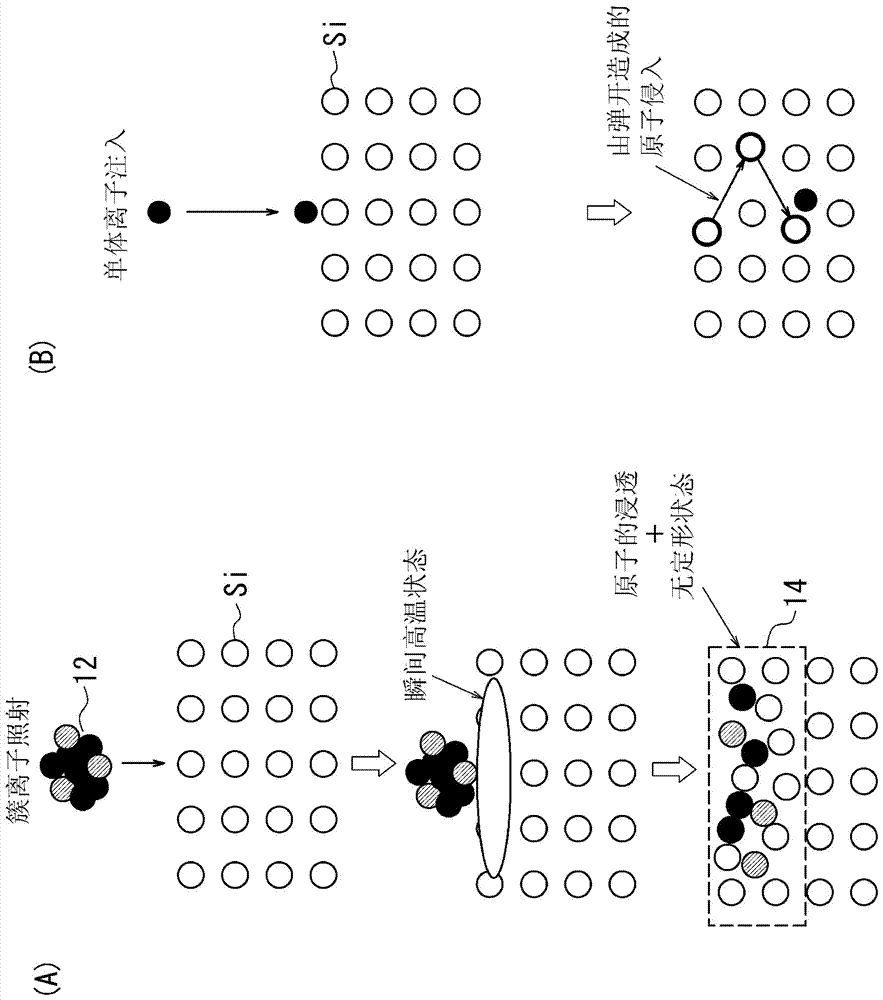

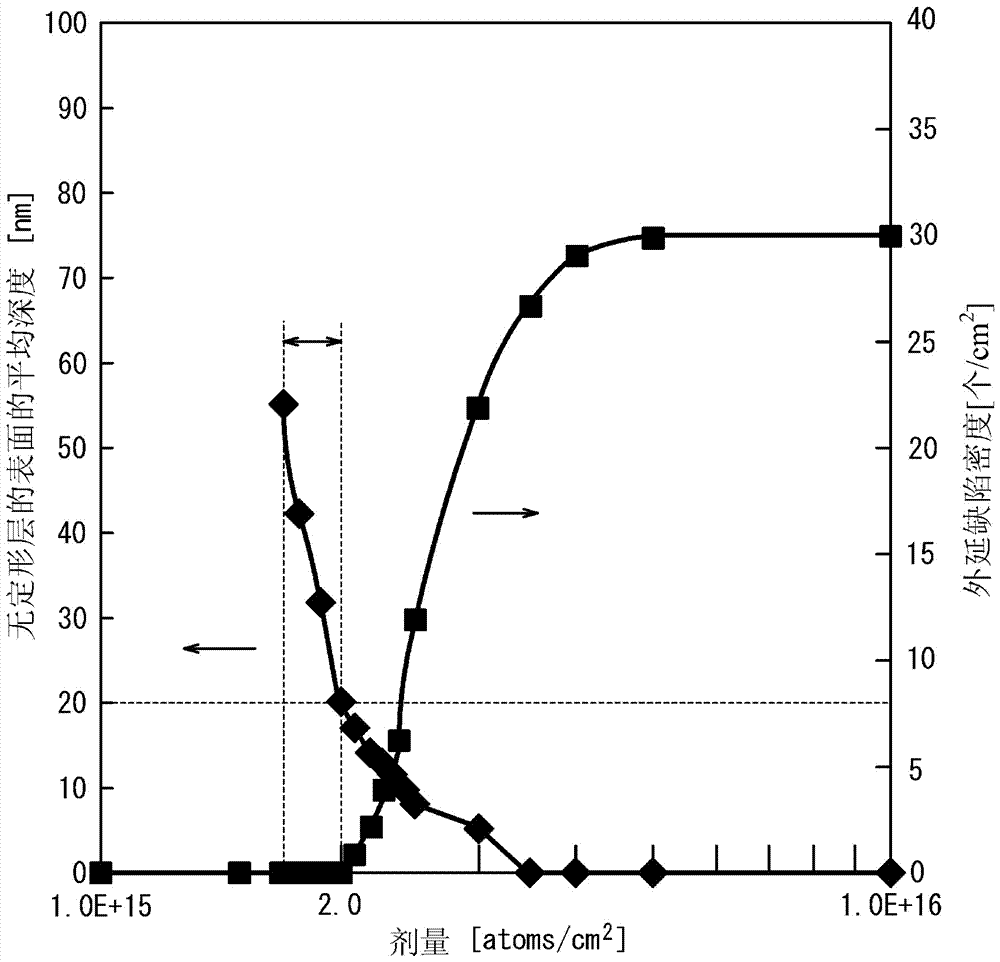

Method For Producing Semiconductor Epitaxial Wafer, Semiconductor Epitaxial Wafer, And Method For Manufacturing Solid-State Imaging Element

ActiveCN107452603AHigh gettering capacitySuppression of epitaxy defectsSolid-state devicesSemiconductor/solid-state device manufacturingOptoelectronicsSemiconductor

This method for producing a semiconductor epitaxial wafer (100) is characterized by comprising: a first step wherein a surface (10A) of a semiconductor wafer (10) is irradiated with cluster ions (12) so that a modified layer (14), in which the constituent element of the cluster ions is solid-solved, is formed in a surface portion of the semiconductor wafer; and a second step wherein an epitaxial layer (18) is formed on the modified layer (14) of the semiconductor wafer. This method for producing a semiconductor epitaxial wafer (100) is also characterized in that the first step is carried out so that a part of the modified layer (14) in the thickness direction forms an amorphous layer (16) and the average depth of the semiconductor wafer surface-side surface (16A) of the amorphous layer (16) is 20 nm or more from the semiconductor wafer surface (10A).

Owner:SUMCO CORP

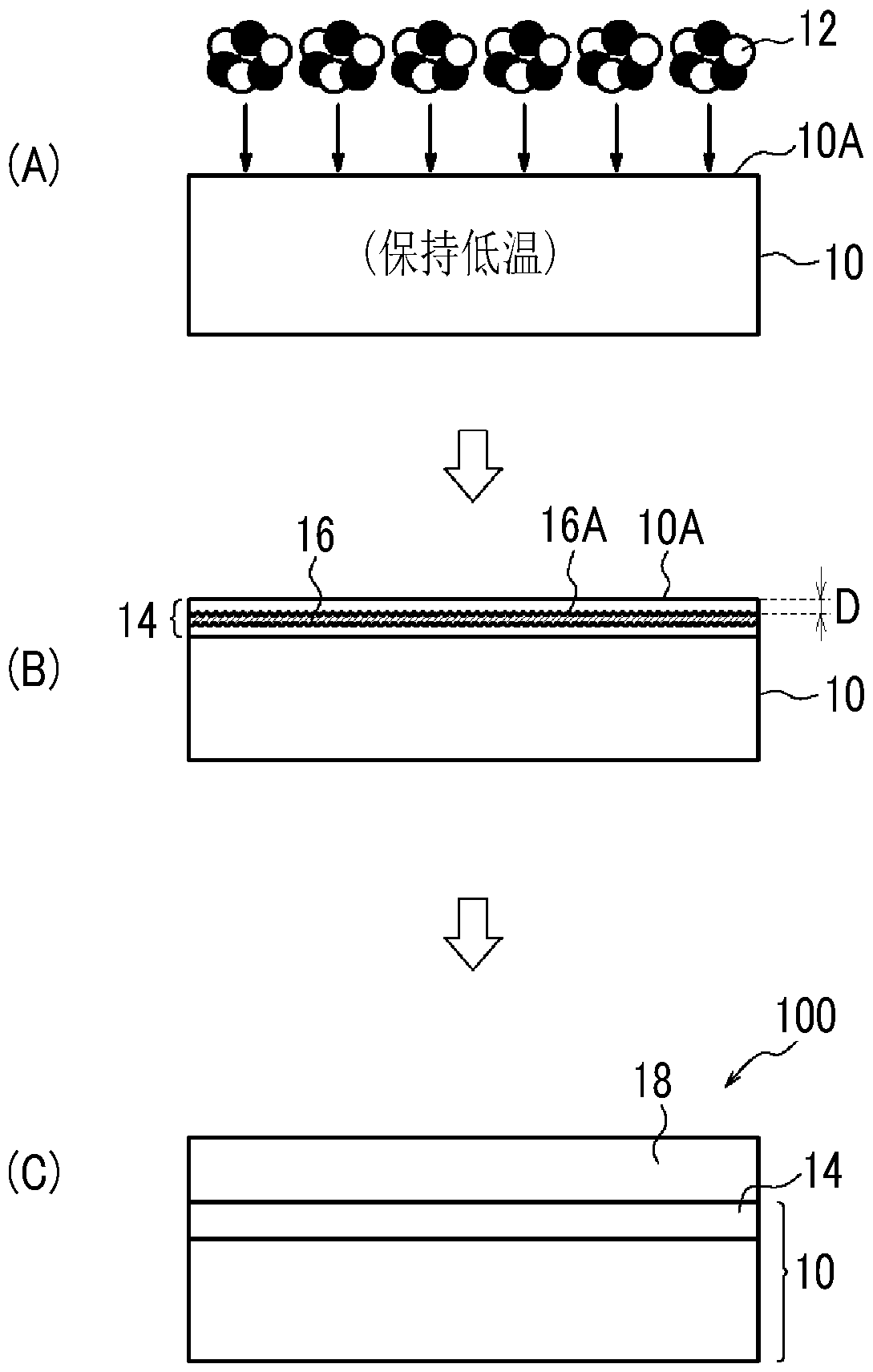

Method for manufacturing semiconductor epitaxial wafer and method for manufacturing solid-state imaging device

InactiveCN107431018BHigh gettering capacitySolid-state devicesSemiconductor/solid-state device manufacturingSolid solutionSemiconductor

Provided is a method of producing a semiconductor epitaxial wafer having enhanced gettering ability. The method of producing a semiconductor epitaxial wafer includes: a first step of irradiating a surface of a semiconductor wafer with cluster ions to form a modified layer that is located in a surface portion of the semiconductor wafer and that includes a constituent element of the cluster ions in solid solution; and a second step of forming an epitaxial layer on the modified layer of the semiconductor wafer. The first step is performed in a state in which a temperature of the semiconductor wafer is maintained at lower than 25° C.

Owner:SUMCO CORP

Semiconductor epitaxial wafer and method for manufacturing same

PendingCN113454756AHigh gettering capacitySemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsSemiconductor

The present invention provides a method for manufacturing a semiconductor epitaxial wafer having higher gettering capability. This method for manufacturing a semiconductor epitaxial wafer 100 is characterized by having: a first step in which the surface 10A of a semiconductor wafer 10 is irradiated with cluster ions 12 including carbon, oxygen, and nitrogen as constituent elements, and a modification layer 14 is formed on the surface part of the semiconductor wafer 10, the modification layer 14 being such that the constituent elements of the cluster ions are in solid solution; and a second step in which an epitaxial layer 16 is formed on the modification layer 14 of the semiconductor wafer 10.

Owner:SUMCO CORP

Method of producing semiconductor epitaxial wafer

ActiveCN110223907AHigh gettering capacitySemiconductor/solid-state device manufacturingRadiation controlled devicesWaferingPhysical chemistry

Provided is a method for manufacturing a semiconductor epitaxial wafer, which can have a higher gettering capability even if the conditions for cluster ion implantation are the same. A method for manufacturing a semiconductor epitaxial wafer according to the present invention includes: a first step of implanting multi-element cluster ions containing 3 elements of carbon, hydrogen, and oxygen as constituent elements into a surface of a semiconductor wafer to form a modified layer in which the constituent elements of the multi-element cluster ions are dissolved in a surface layer portion of thesemiconductor wafer; a second step of performing a defect formation heat treatment for increasing a defect density of the black-dot defects formed in the modified layer after the first step; and a third step of forming an epitaxial layer on the modified layer of the semiconductor wafer after the second step.

Owner:SUMCO CORP

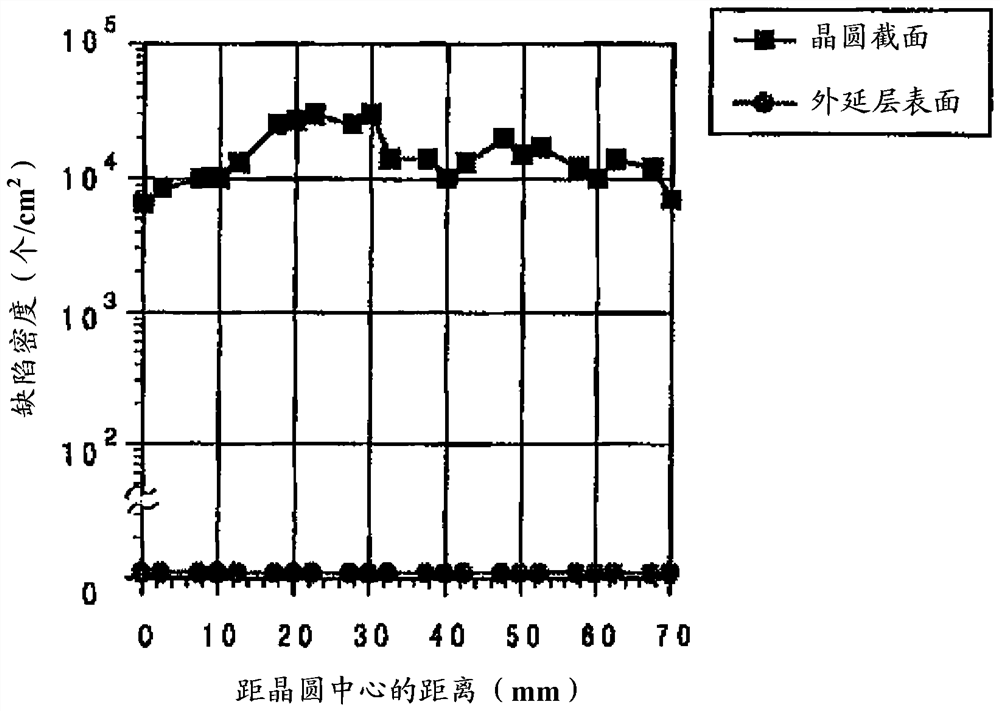

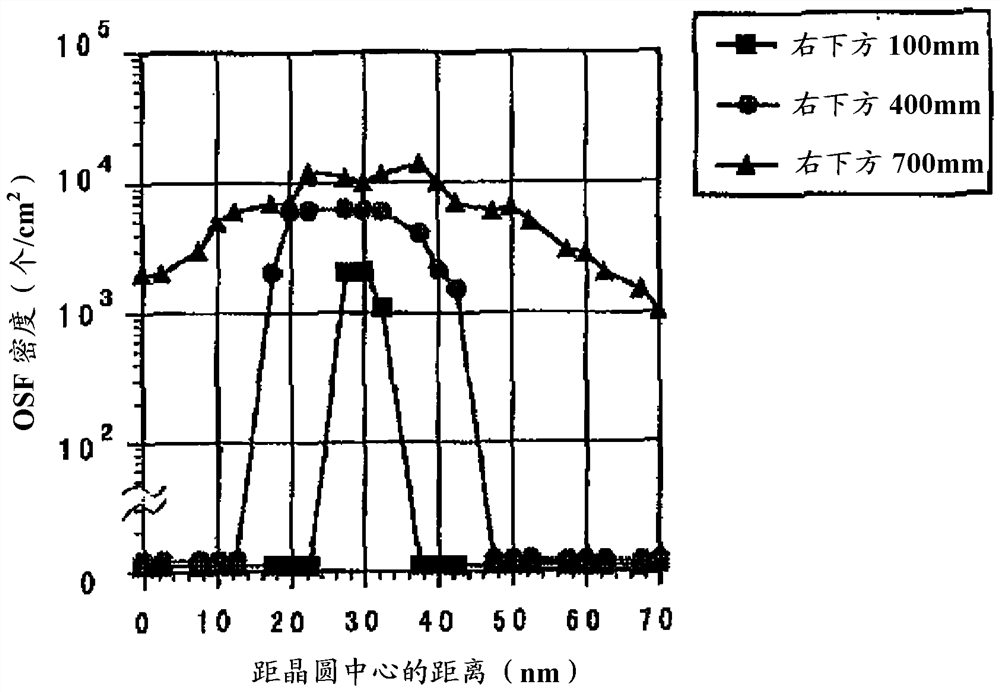

Epitaxial wafer manufacturing method and epitaxial wafer

ActiveCN108511317BHigh gettering capacitySemiconductor/solid-state device manufacturingWaferSingle crystal

The invention provides a method that can exert the gettering ability brought by crystal defects and has a defect density of 10 on the surface of the epitaxial layer. 2 piece / cm 2 The following epitaxial wafer manufacturing method. The manufacturing method of this epitaxial wafer is characterized in that it includes: a single crystal silicon growth step, and grows a doped silicon crystal by the Czochralski single crystal pulling method 11 atoms / cm 3 ~4.5×10 15 atoms / cm 3 single crystal silicon of nitrogen; a single crystal silicon cutting process, cutting out a silicon wafer from the single crystal silicon; and an epitaxial layer forming process, using the above silicon wafer as a substrate, and forming a single crystal silicon on the substrate by vapor phase growth The epitaxial layer is an epitaxial layer, and the epitaxial layer is formed at a temperature ranging from 1050° C. to 1200° C. in the step of forming the epitaxial layer.

Owner:SUMCO CORP

A Diffusion Process That Improves the Minority Carrier Lifetime of Metallurgical-Grade Silicon Wafers

ActiveCN103531449BImprove conversion efficiencyImprove yieldFinal product manufactureSemiconductor/solid-state device manufacturingSilicon solar cellOxygen

The invention relates to a diffusion technology adopted in the process of manufacturing a physical metallurgical silicon solar cell, in particular to a diffusion technology for prolonging the minority carrier lifetime of a metallurgical silicon wafer. The diffusion technology is characterized by comprising the following steps: (1) propelling a quartz boat at the low temperature and raising the temperature preliminarily; (2) introducing nitrogen carried with phosphorus oxychloride and diffusing generated phosphorus atoms; (3) advancing at the constant temperature; (4) cooling and withdrawing the quartz boat. The technology has the benefits as follows: 1, spraying type diffusion is adopted, so as to save the phosphorus source as well as improve the uniformity of diffusion junction depth, and the technology is suitable for high sheet resistance; 2, according to the characteristics of physical metallurgical silicon, two-sided phosphorus is adopted in gettering to enhance the gettering effect and prolong the minority carrier lifetime of the silicon wafer; 3, the diffusion technology is effectively improved via the coordination of temperature and time; 4, the proportions of introduced oxygen and introduced raw material are controlled to reduce the defects caused by direct diffusion and improve the junction depth of a PN junction, the surface passivation effect can be further improved, and the short-circuit current and the open-circuit voltage are increased, so that the conversion efficiency and the yield of the metallurgical silicon solar cell are further improved.

Owner:NINGXIA YINXING ENERGY

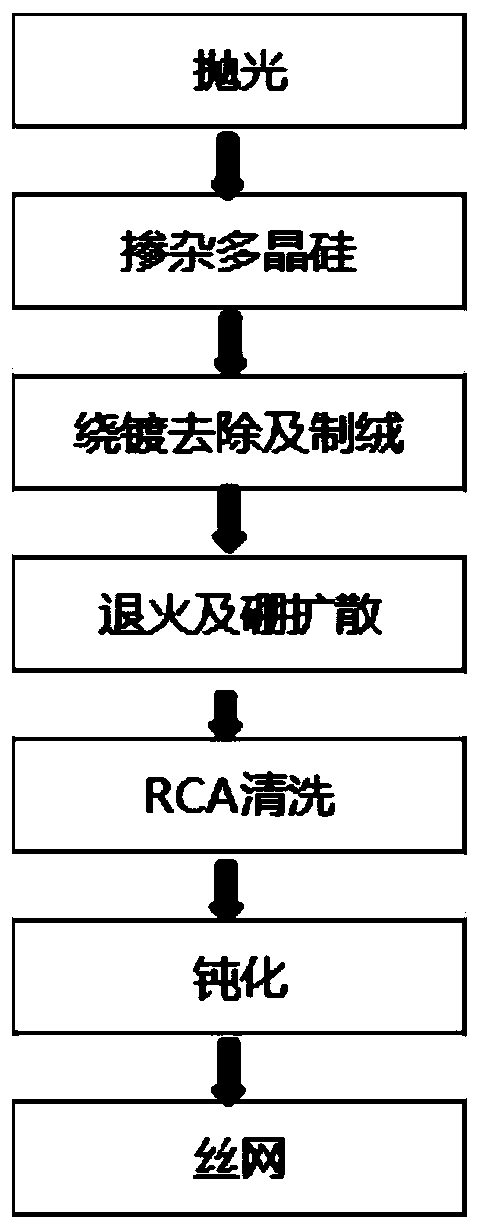

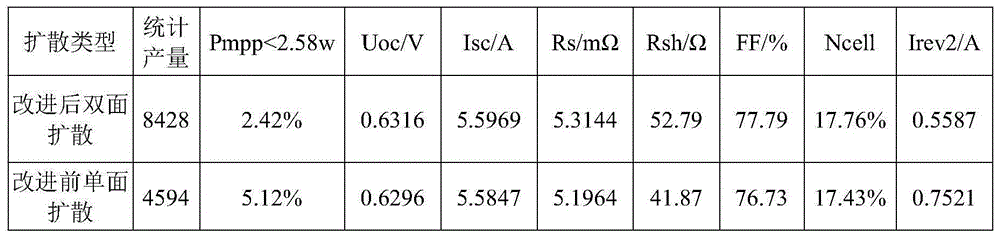

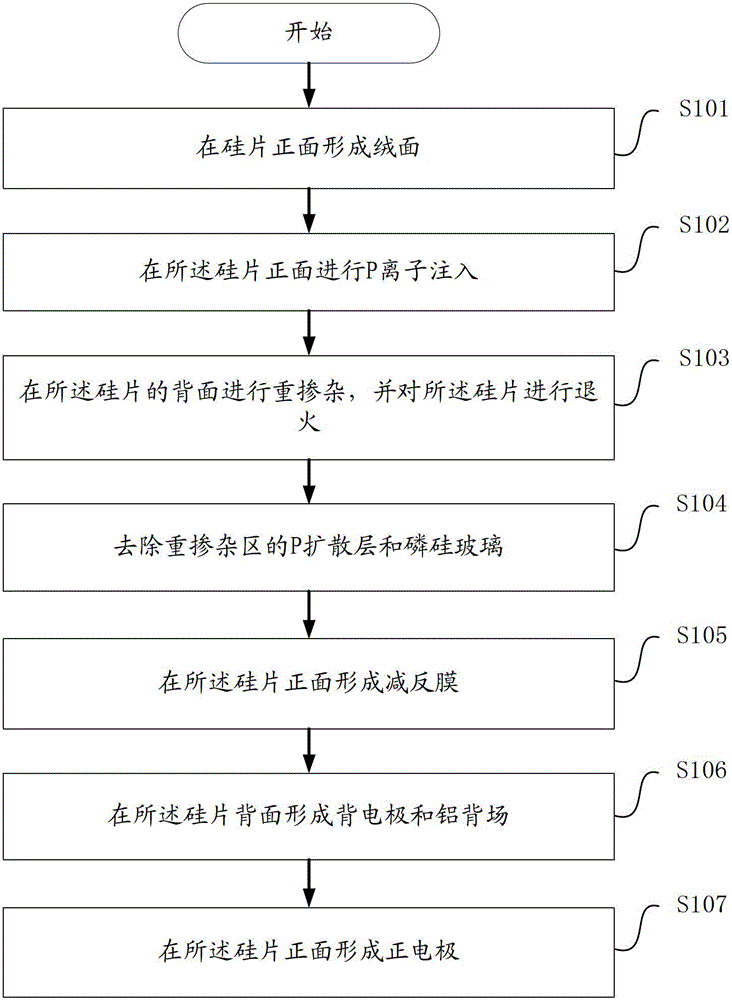

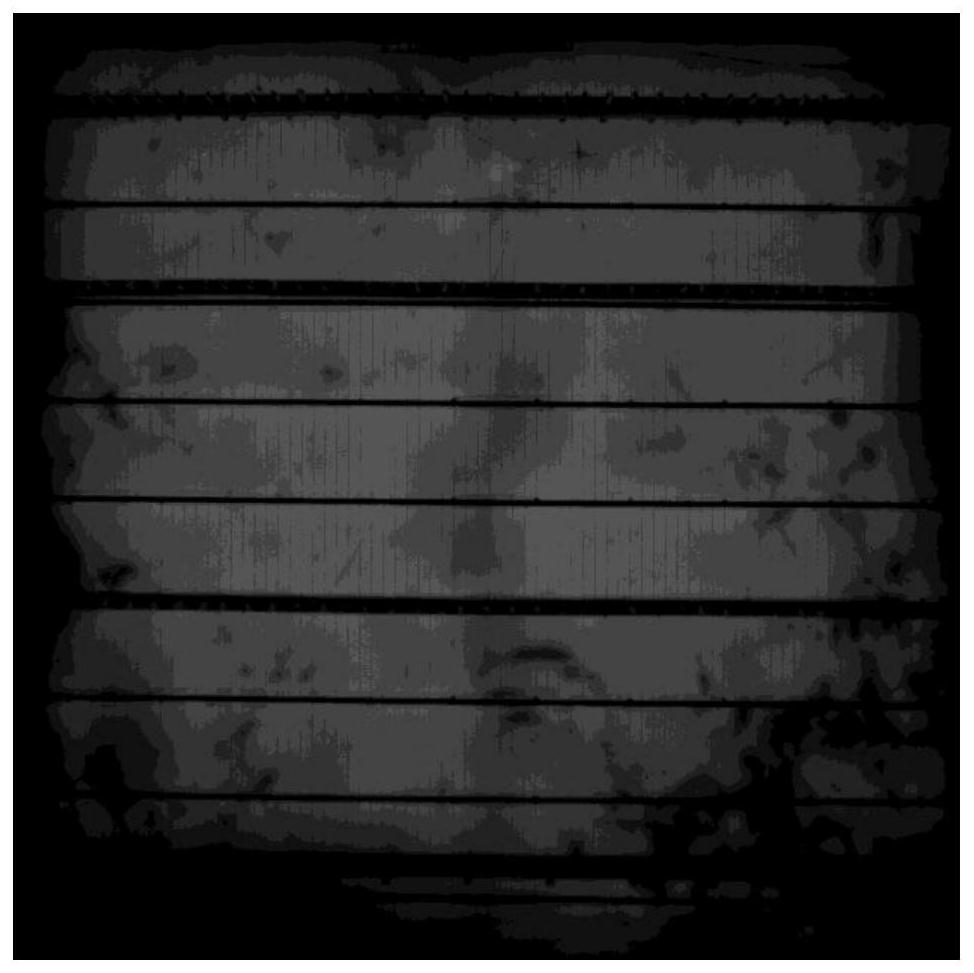

A kind of preparation method of crystalline silicon solar cell

ActiveCN103208564BIncrease production capacityImprove conversion efficiencyFinal product manufactureSemiconductor devicesP–n junctionCrystalline silicon

The invention discloses a method for preparing a crystalline silicon solar cell. The method comprises the following steps of: forming suede on the front surface of a silicon wafer; performing P ion implantation on the front surface of the silicon wafer; performing heavy doping on the back surface of the silicon wafer, and annealing the silicon wafer; removing a P diffusion layer and phosphorosilicate glass from a heavy doping region; forming an anti-reflection film on the front surface of the silicon wafer; forming a back electrode and an aluminum back field on the back surface of the silicon wafer; and forming a front electrode on the front surface of the silicon wafer. The solar cell prepared by using the method has an efficient p-n junction which is obtained by ion implantation, and has a good back gettering effect; and photoelectric conversion efficiency is remarkably improved.

Owner:CHINT NEW ENERGY TECH (HAINING) CO LTD

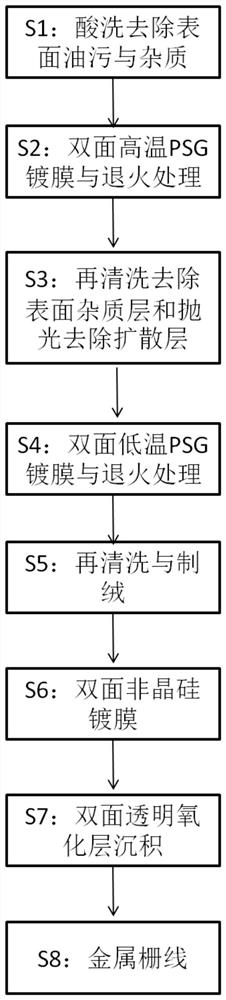

Two-step diffusion pretreatment method for casting single-crystal or polycrystal silicon wafers

PendingCN113161446ARelease fullyTo achieve the purpose of removing impuritiesFinal product manufactureSemiconductor/solid-state device manufacturingHigh cellSingle crystal

The invention relates to a two-step diffusion pretreatment method for casting single-crystal or polycrystal silicon wafers, which comprises the following steps of A, pickling, B, depositing PSG at high temperature, C, primary impurity removal, D, depositing PSG at low temperature, and E, secondary impurity removal. The invention aims to provide a two-step diffusion pretreatment method for casting single-crystal or polycrystalline silicon wafers, which is suitable for effective passivation of the cast single-crystal or polycrystalline silicon wafer, and can reduce defect density in and on the surface of the silicon wafer, reduce recombination of current carriers, improve passivation level and transmission level of the current carriers, therefore, solar cell production can be carried out on the cast single-crystal or polycrystal silicon wafer according to the existing high-efficiency cell piece manufacturing process, and high cell conversion efficiency is obtained.

Owner:XIFENG 2D FUJIAN MATERIAL TECH CO LTD

Multi-layer composite passivation layer structure of bipolar circuit and its production process

InactiveCN101710580BReduce stressImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesSilicon oxideSilicon dioxide

The present invention provides the multilayer composite passivation film structure of the Bipolar circuit, comprising the underlying silicon oxide film layer deposited on the surface of the silicon substrate and the silicon nitride film layer deposited on the silicon oxide film layer, the silicon oxide film layer A certain proportion of phosphine is doped in the layer, and the silicon oxide film layer is an undoped silicon dioxide layer, a doped phosphosilicate glass layer, and an undoped silicon dioxide layer in sequence. Simultaneously, the present invention also provides the multilayer composite passivation film production method of Bipolar circuit, utilizes the multilayer composite passivation film structure of Bipolar circuit realized by the present invention to have anti-scratch, anti-moisture, high density, low film stress, Higher gettering ability, better step coverage ability, excellent photoelectric performance, electrical characteristics and thermal stability, reducing soft breakdown and solving problems such as poor reliability.

Owner:HANGZHOU SILAN INTEGRATED CIRCUIT

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com