Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

55results about "Reliability increase in bipolar transistors" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

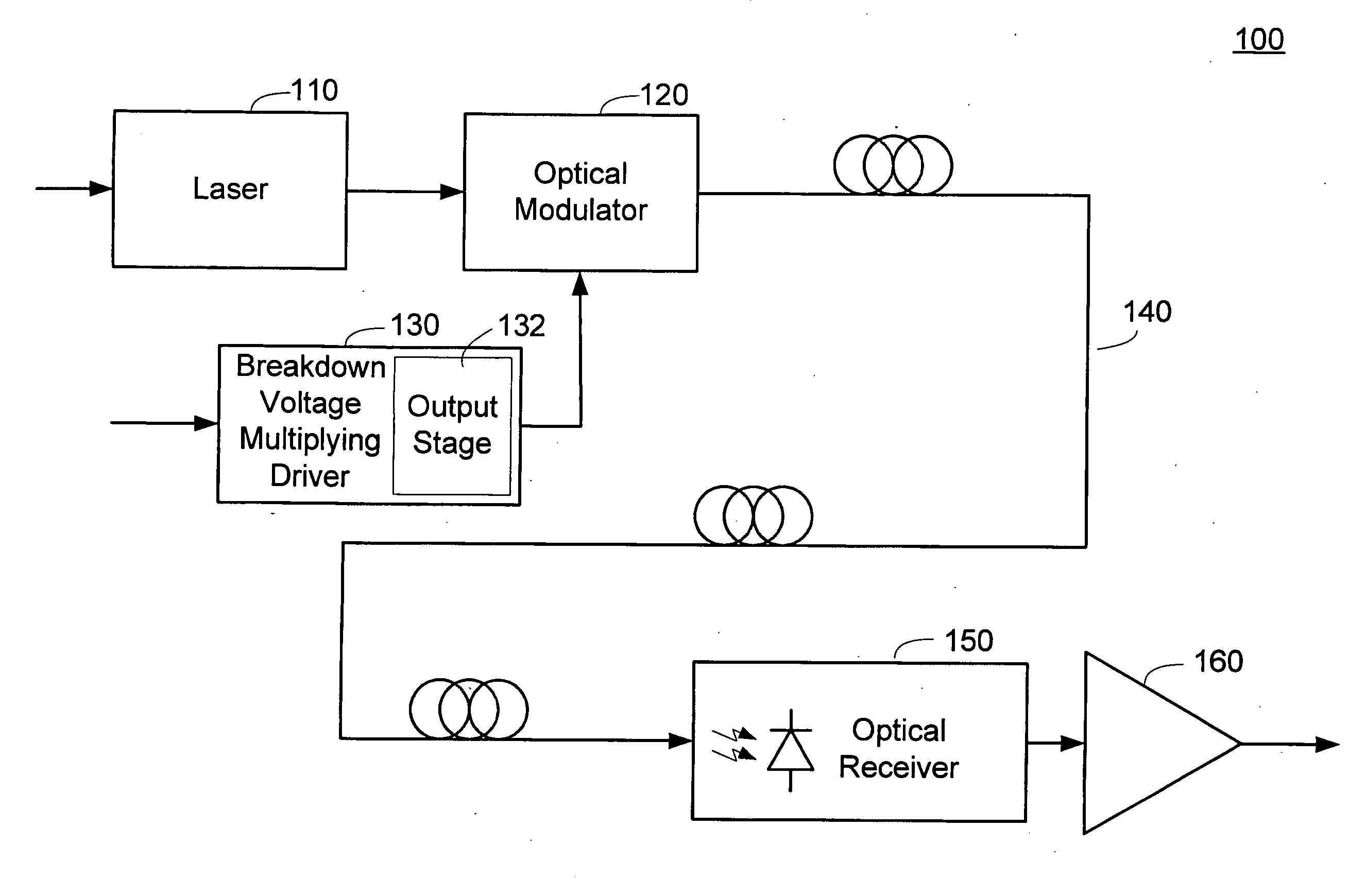

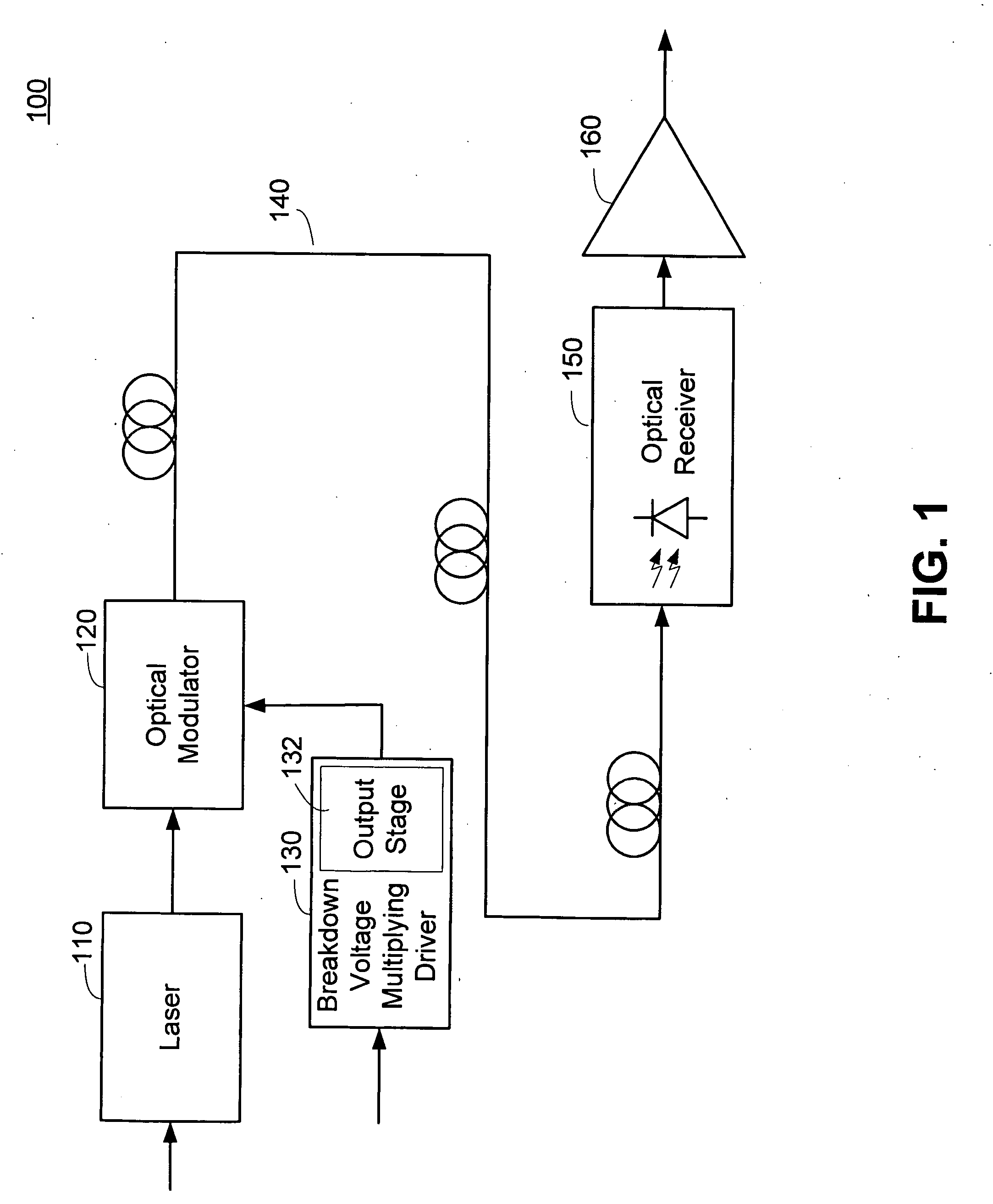

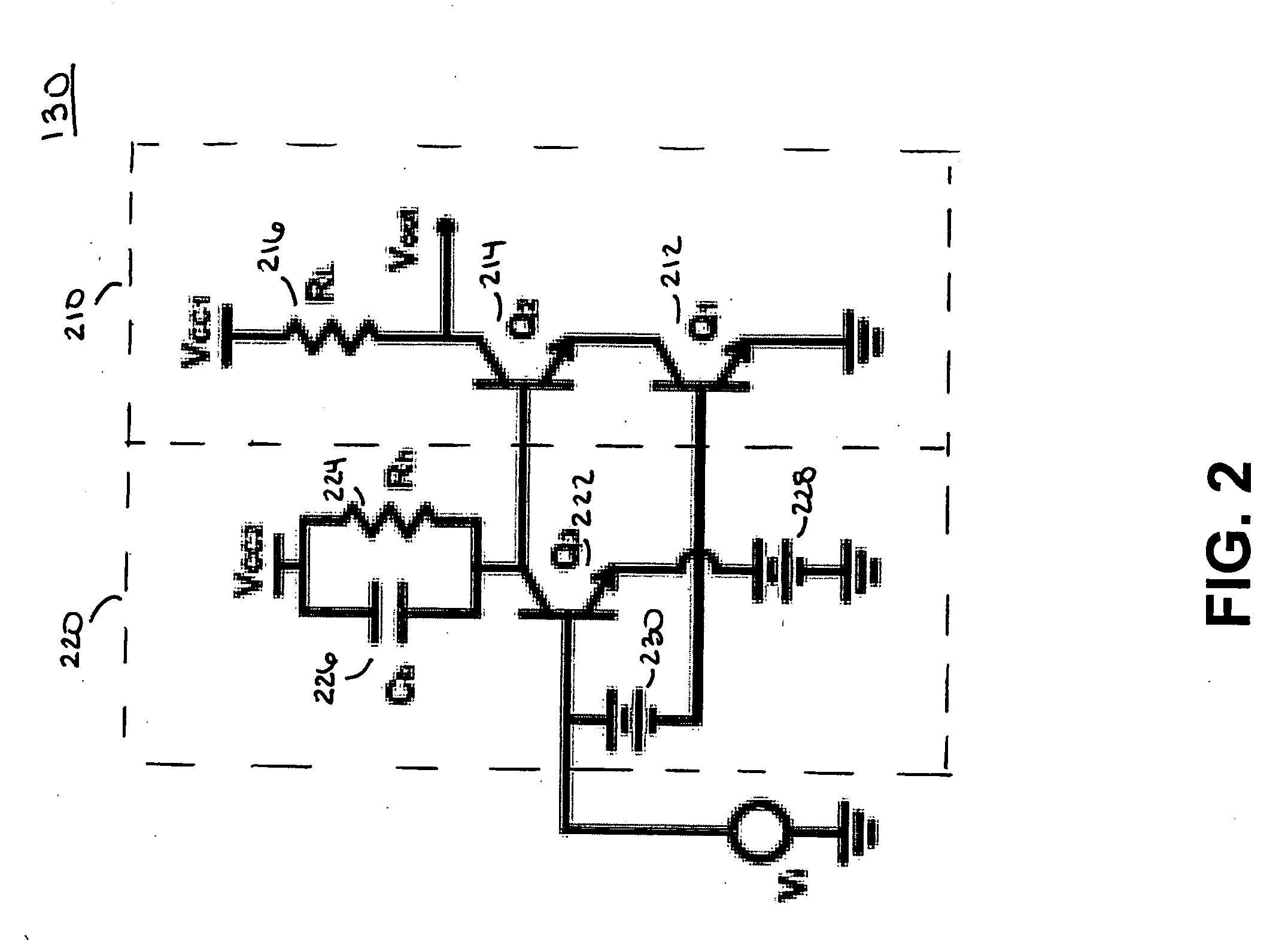

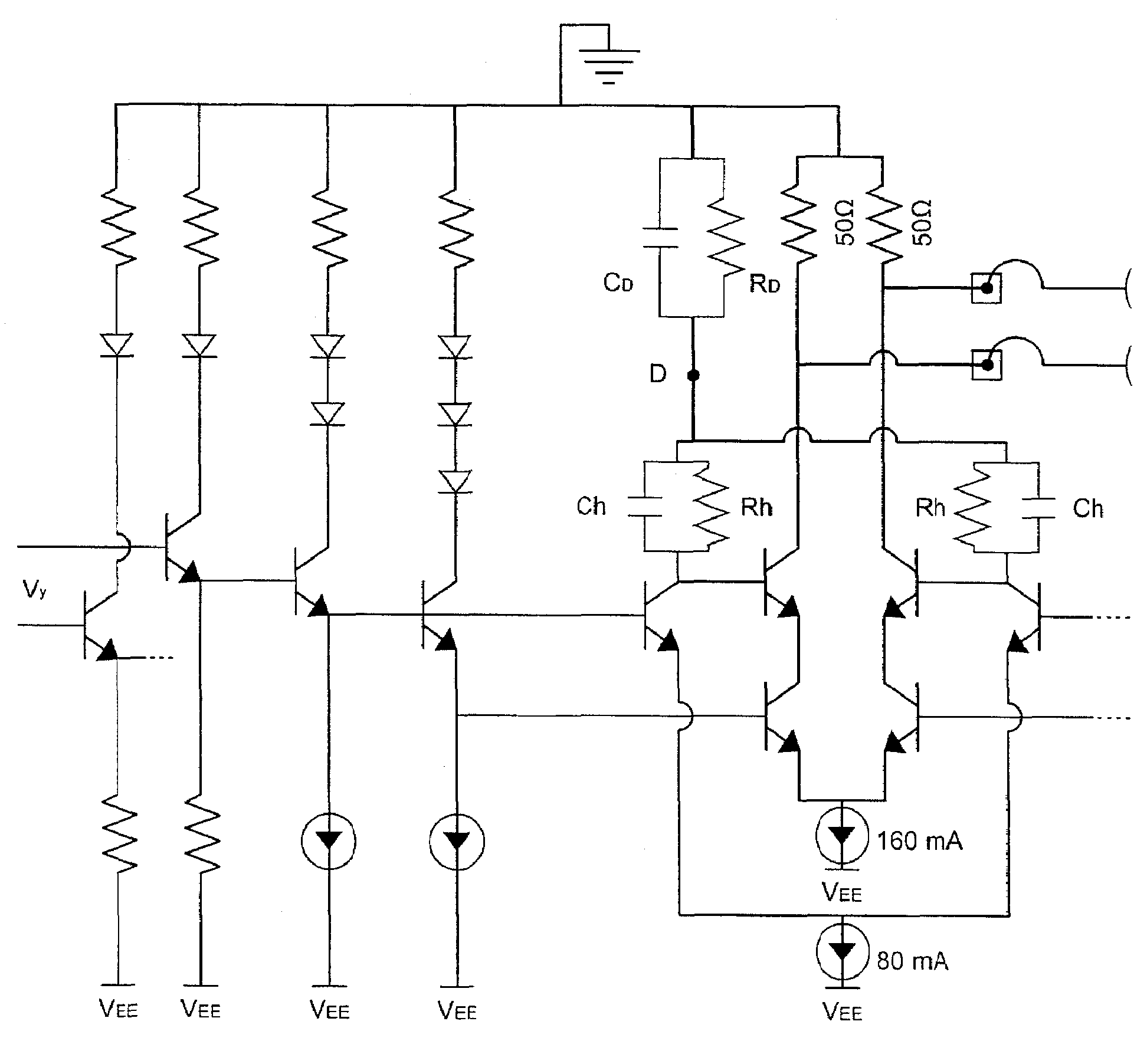

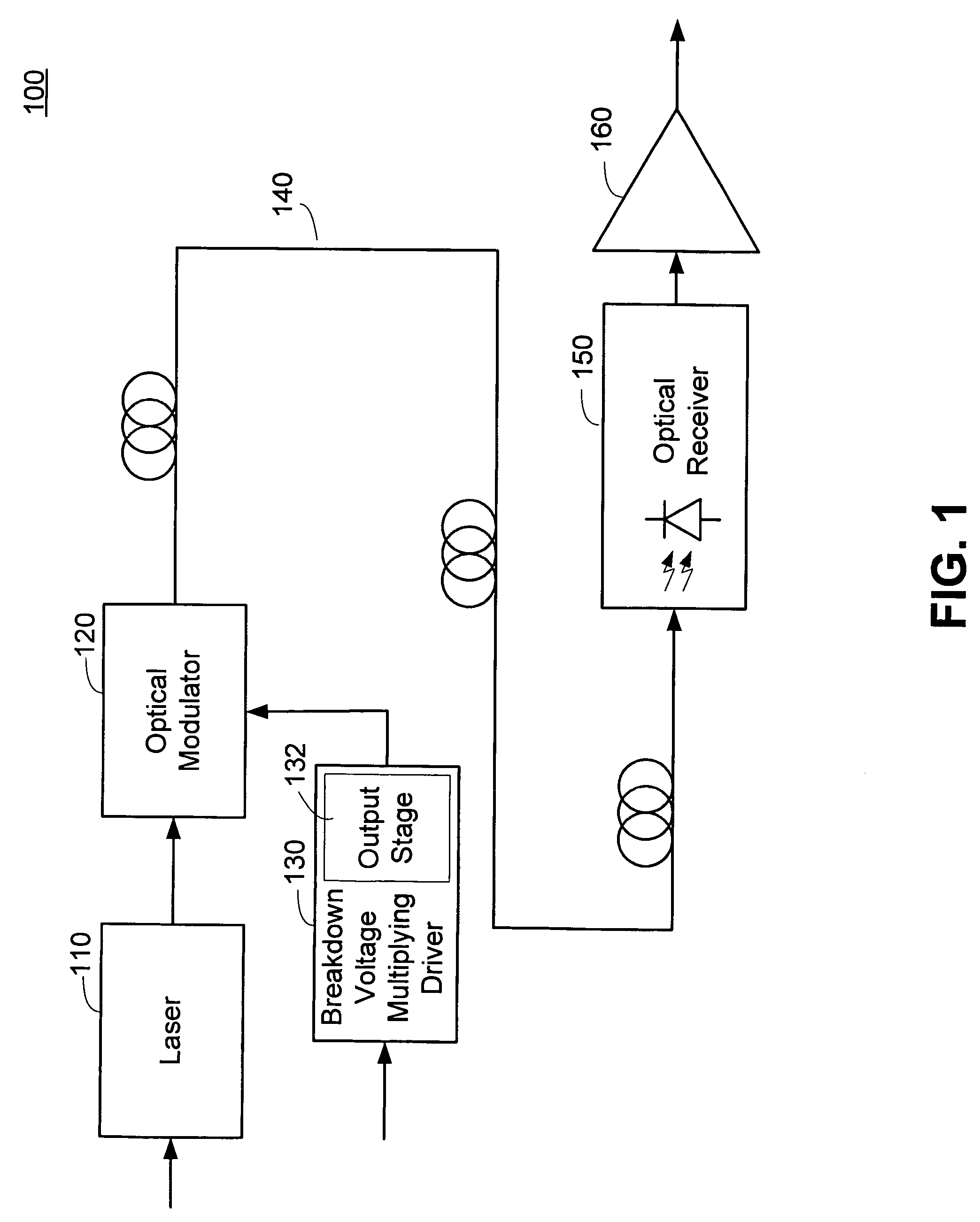

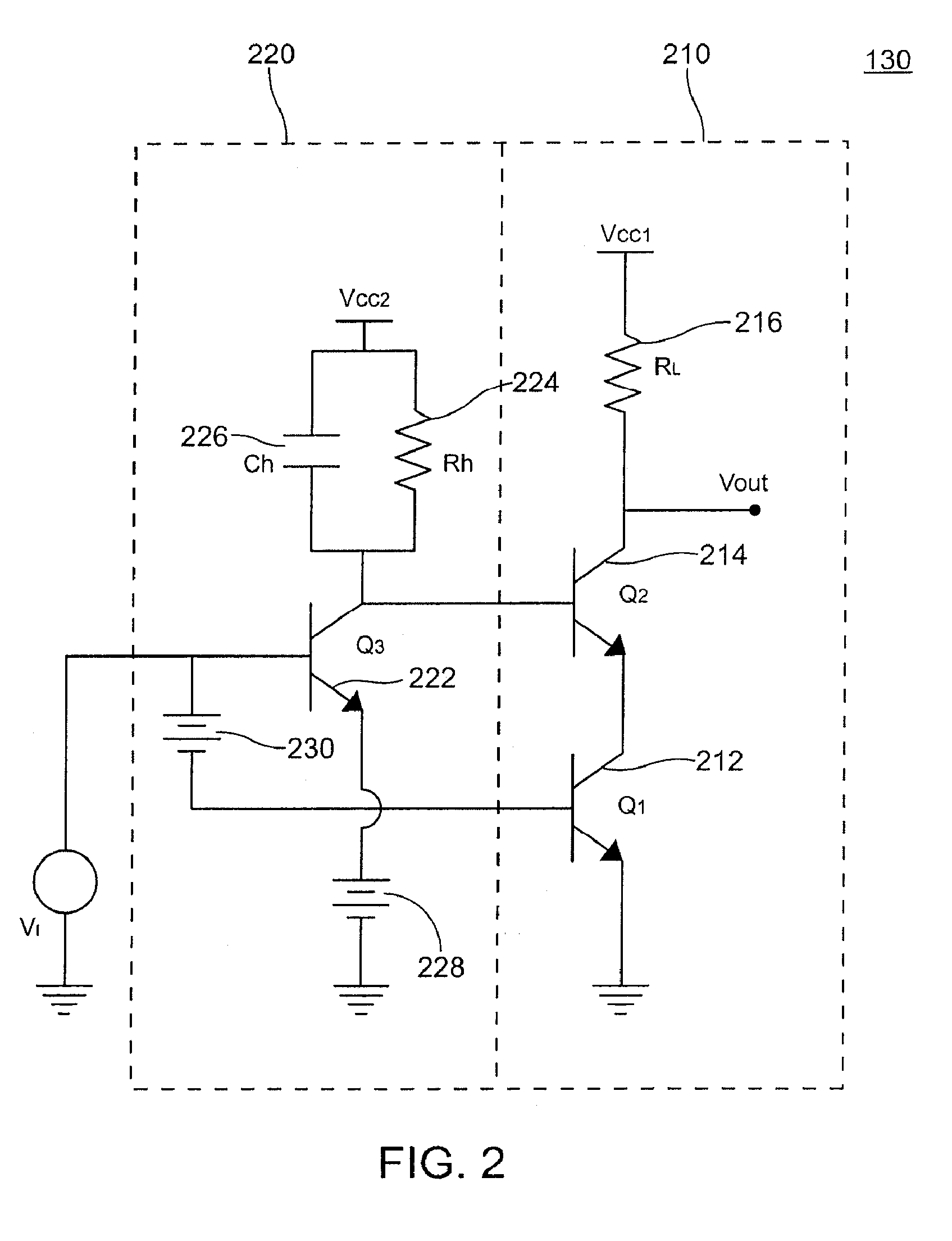

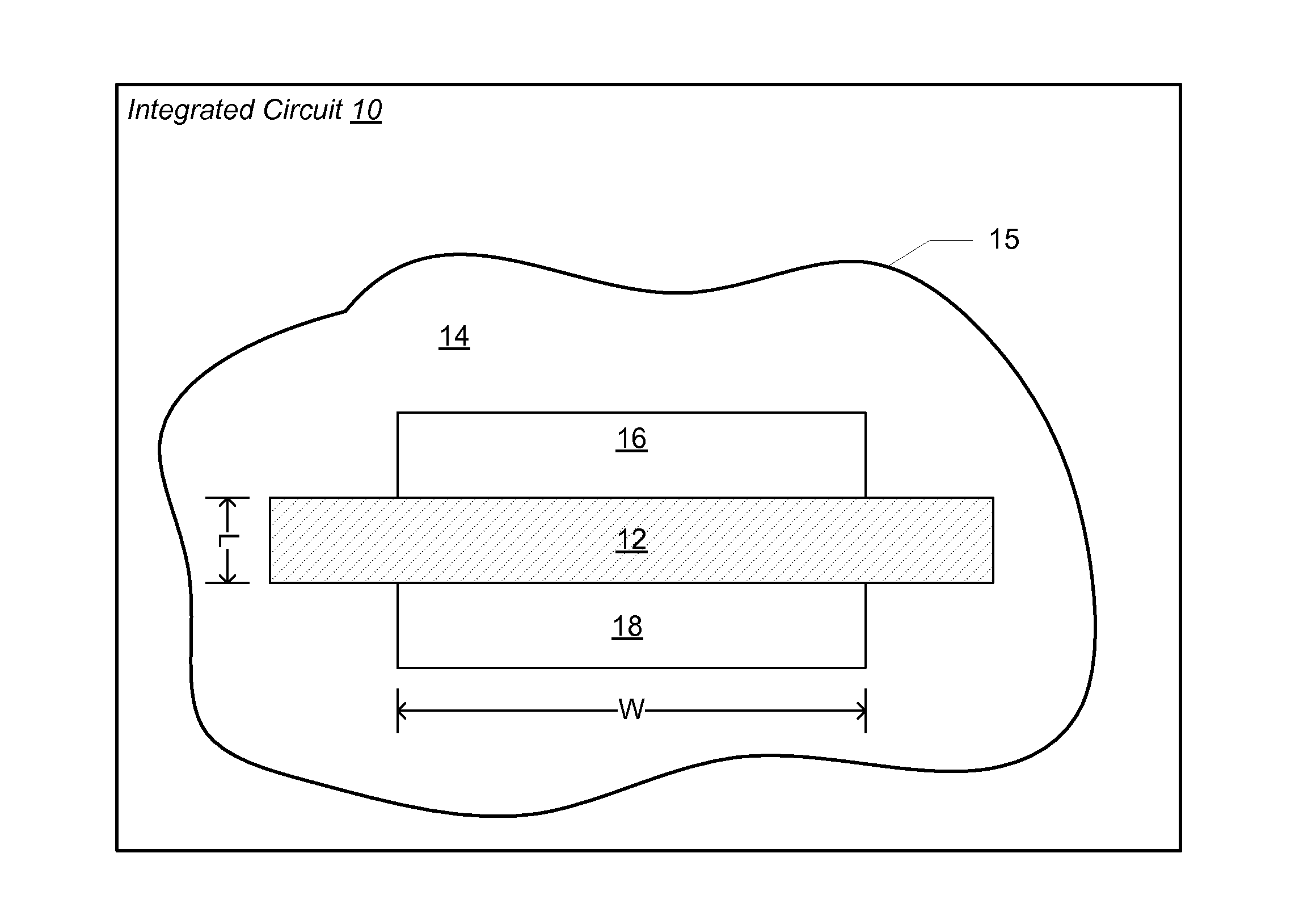

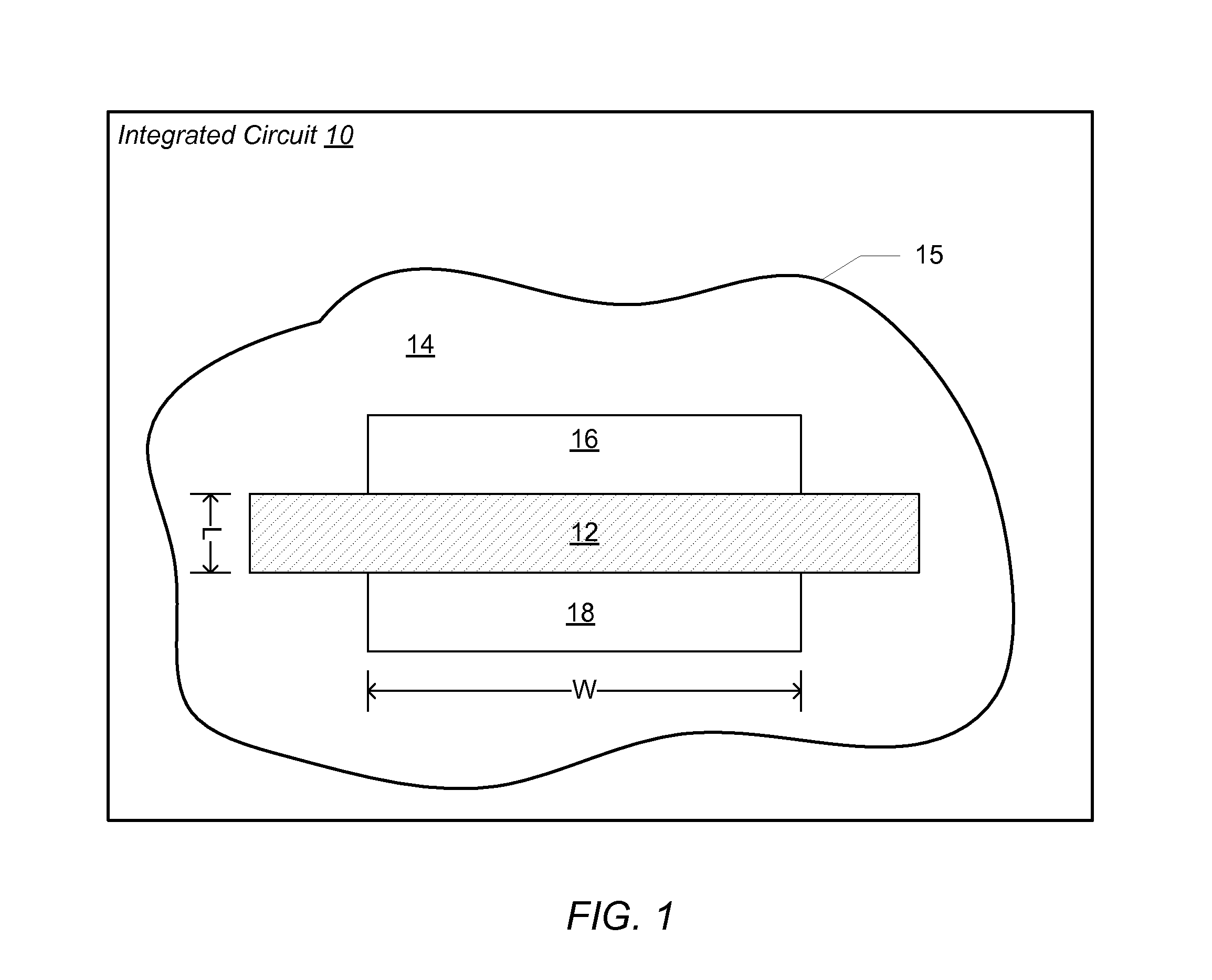

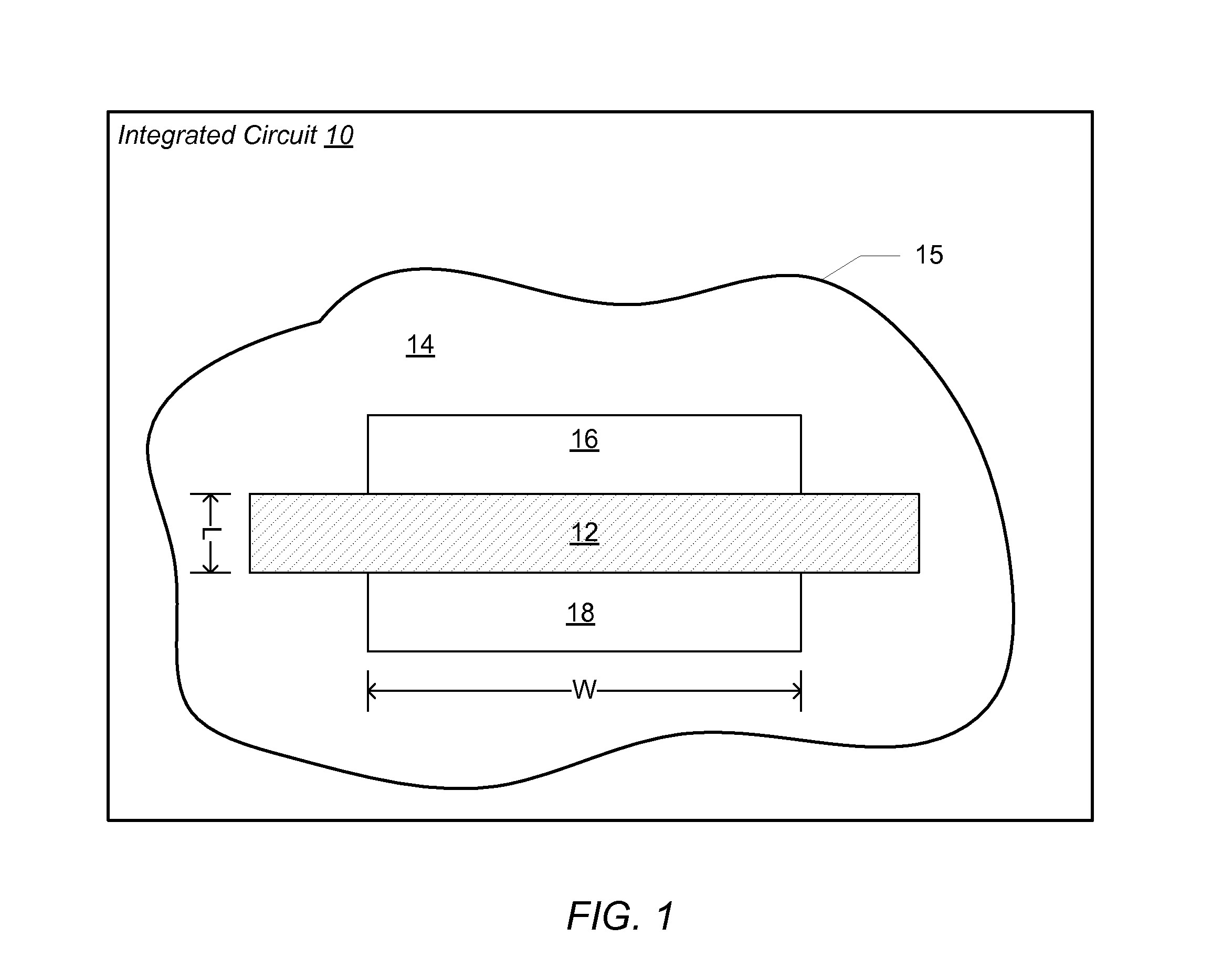

Integrated circuit with breakdown voltage multiplier

ActiveUS20050258866A1Reliability increase in bipolar transistorsReliability increase in field effect transistorsVoltage multiplierEngineering

An apparatus and method for driving an output signal in a high speed integrated circuit. The apparatus and methods enable the output voltage swing from the driver to exceed the breakdown voltage of any individual element in the output driver. A high speed driver can utilize one or more transistors in a stacked configuration, such that the breakdown voltage of the entire stacked configuration is based on the number of transistors in the stack. The driver is configured to distribute the output voltage substantially equally among each of the stacked transistors, such that the driver is able to source an output voltage swing that is greater than the breakdown voltage of any individual transistor in the driver.

Owner:CALIFORNIA INST OF TECH

Integrated circuit with breakdown voltage multiplier

ActiveUS7321242B2Reliability increase in bipolar transistorsReliability increase in field effect transistorsVoltage multiplierEngineering

An apparatus and method for driving an output signal in a high speed integrated circuit. The apparatus and methods enable the output voltage swing from the driver to exceed the breakdown voltage of any individual element in the output driver. A high speed driver can utilize one or more transistors in a stacked configuration, such that the breakdown voltage of the entire stacked configuration is based on the number of transistors in the stack. The driver is configured to distribute the output voltage substantially equally among each of the stacked transistors, such that the driver is able to source an output voltage swing that is greater than the breakdown voltage of any individual transistor in the driver.

Owner:CALIFORNIA INST OF TECH

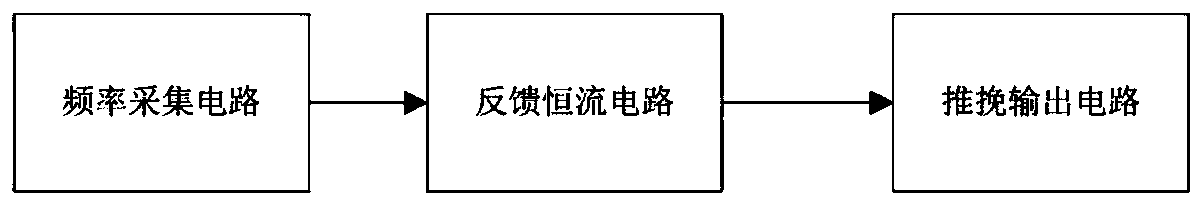

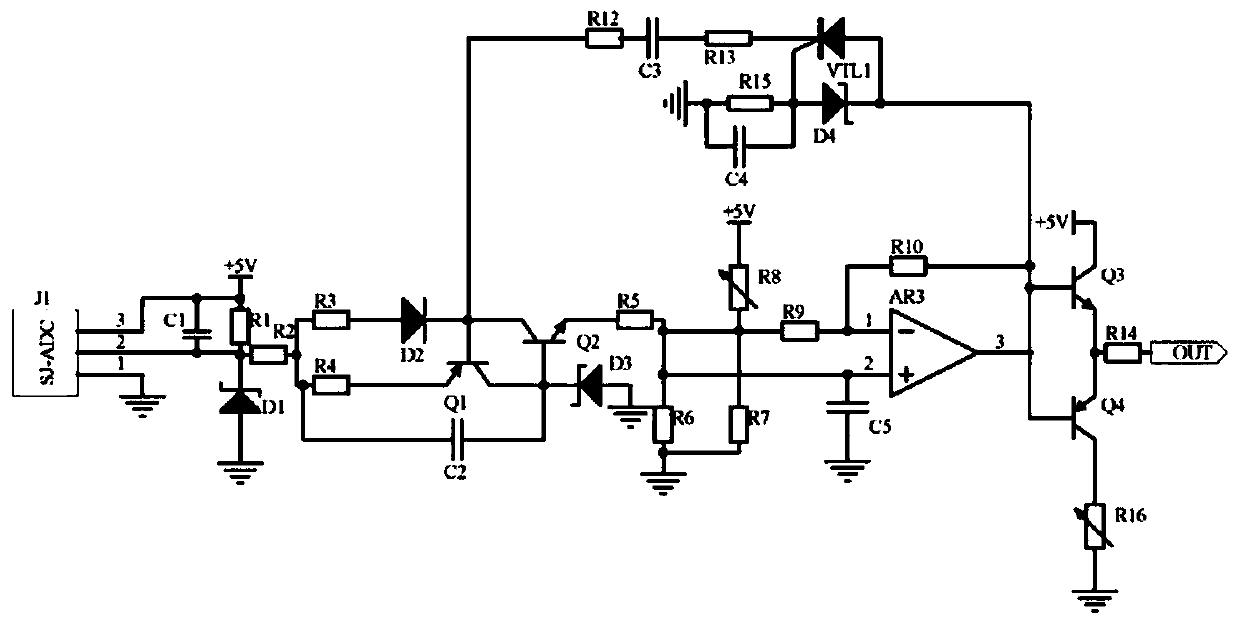

Electronic equipment analog signal calibration circuit

PendingCN110022146ARealize automatic calibrationReliability increase in bipolar transistorsSilicon-controlled rectifierLow voltage

The invention discloses an electronic equipment analog signal calibration circuit. The circuit comprises a frequency acquisition circuit, a feedback constant current circuit and a push-pull output circuit. The frequency acquisition circuit acquires signal frequency in an analog signal channel in the low-voltage electronic equipment control terminal; the feedback constant current circuit utilizes atriode Q1, a triode Q2 and a voltage stabilizing tube D3 to form a constant current source circuit stable signal potential. Meanwhile, a current-voltage conversion circuit composed of a variable resistor R8 and an operational amplifier AR3 is used for converting a current signal into a voltage signal and inputting the voltage signal into a push-pull output circuit; an abnormal signal detection circuit is composed of a silicon controlled rectifier VTL1 and a voltage-regulator tube D4 and feeds back abnormal signals to the collector electrode of a triode Q2. and finally, the push-pull output circuit uses a triode Q3, a triode Q4 and a variable resistor R16 to form a push-pull circuit to reduce signal conduction loss and then output the signal, so that the signal frequency can be converted into a compensation signal of a signal in an analog signal channel in a remote intelligent equipment control terminal.

Owner:WUXI CITY COLLEGE OF VOCATIONAL TECH

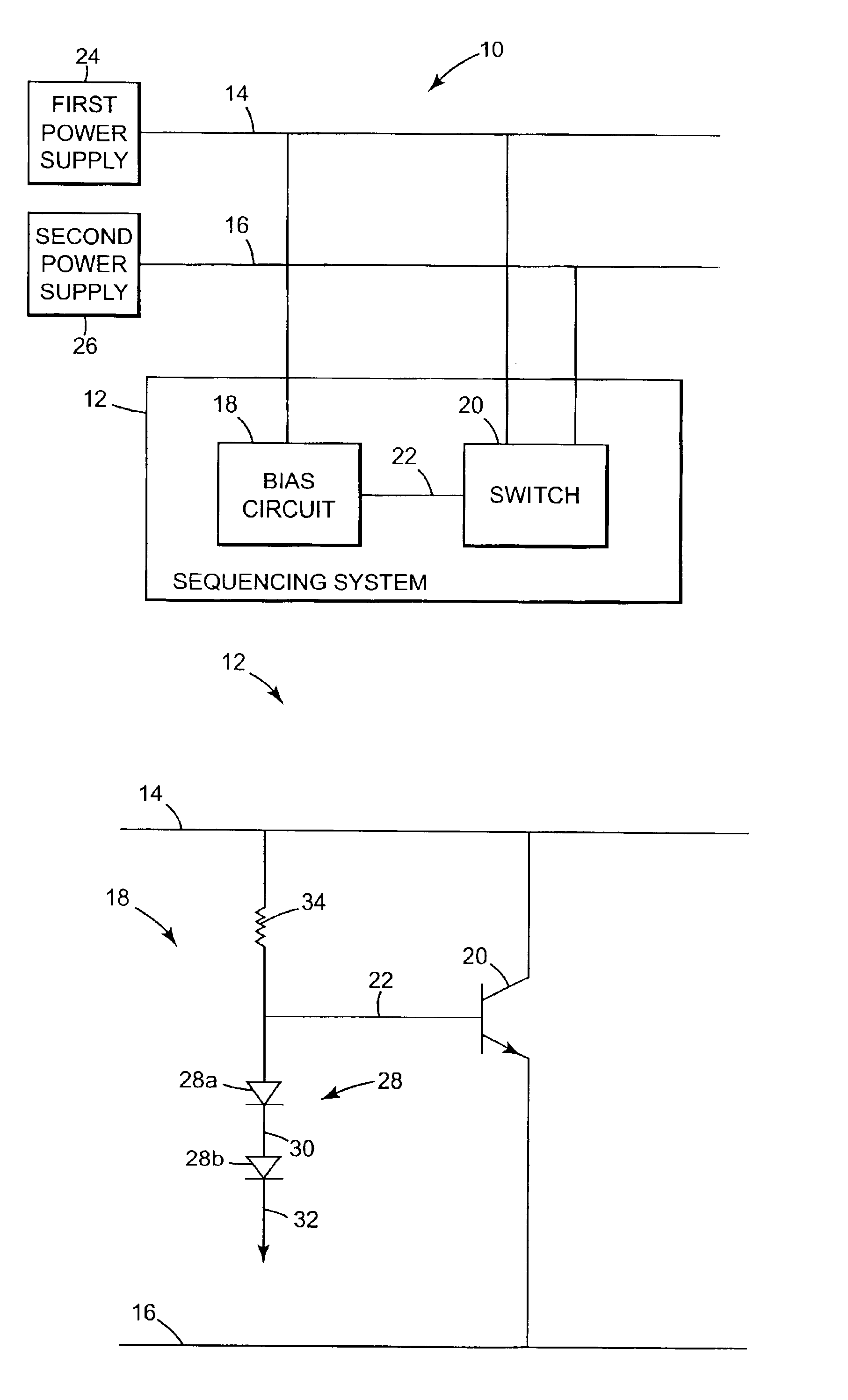

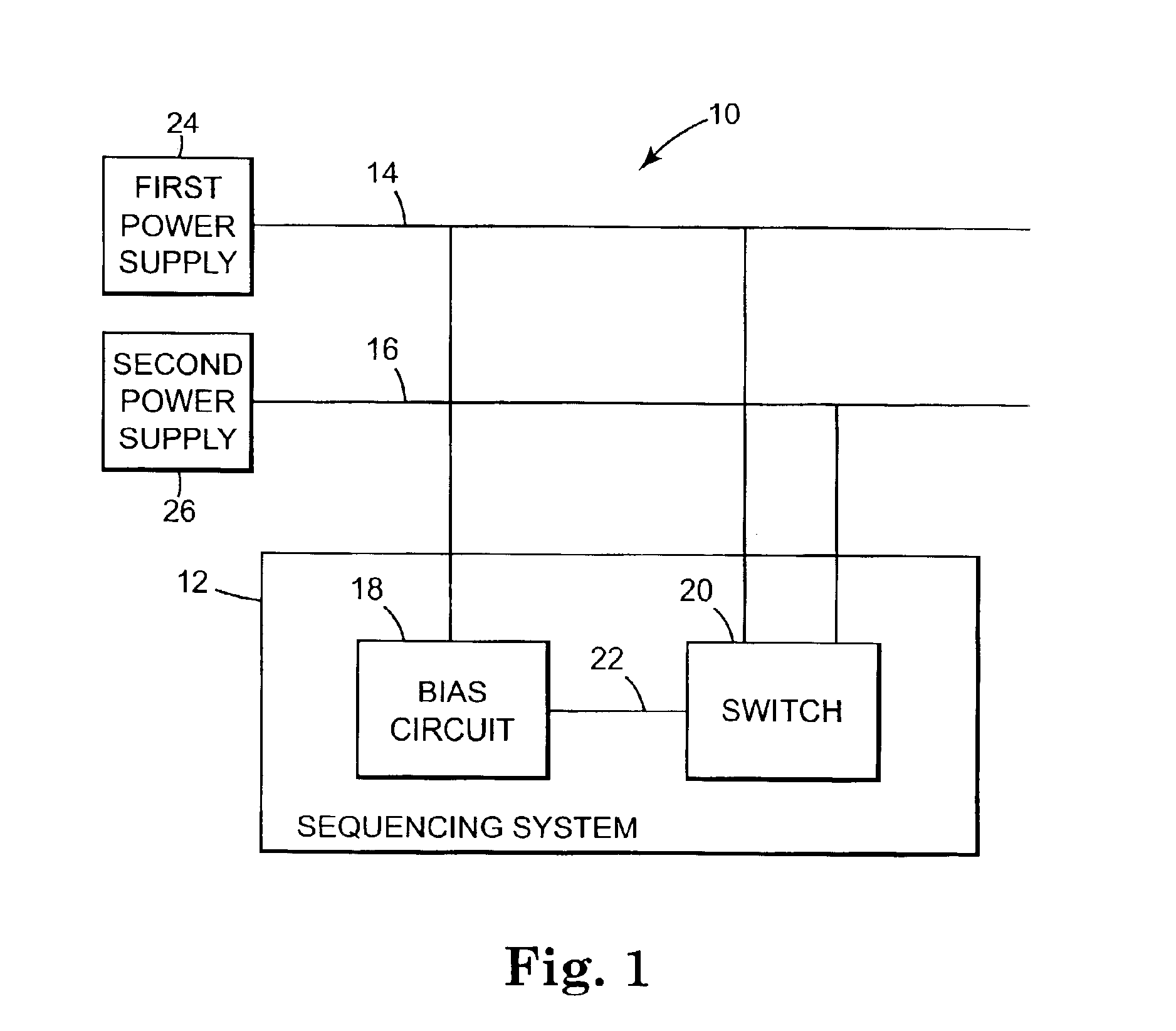

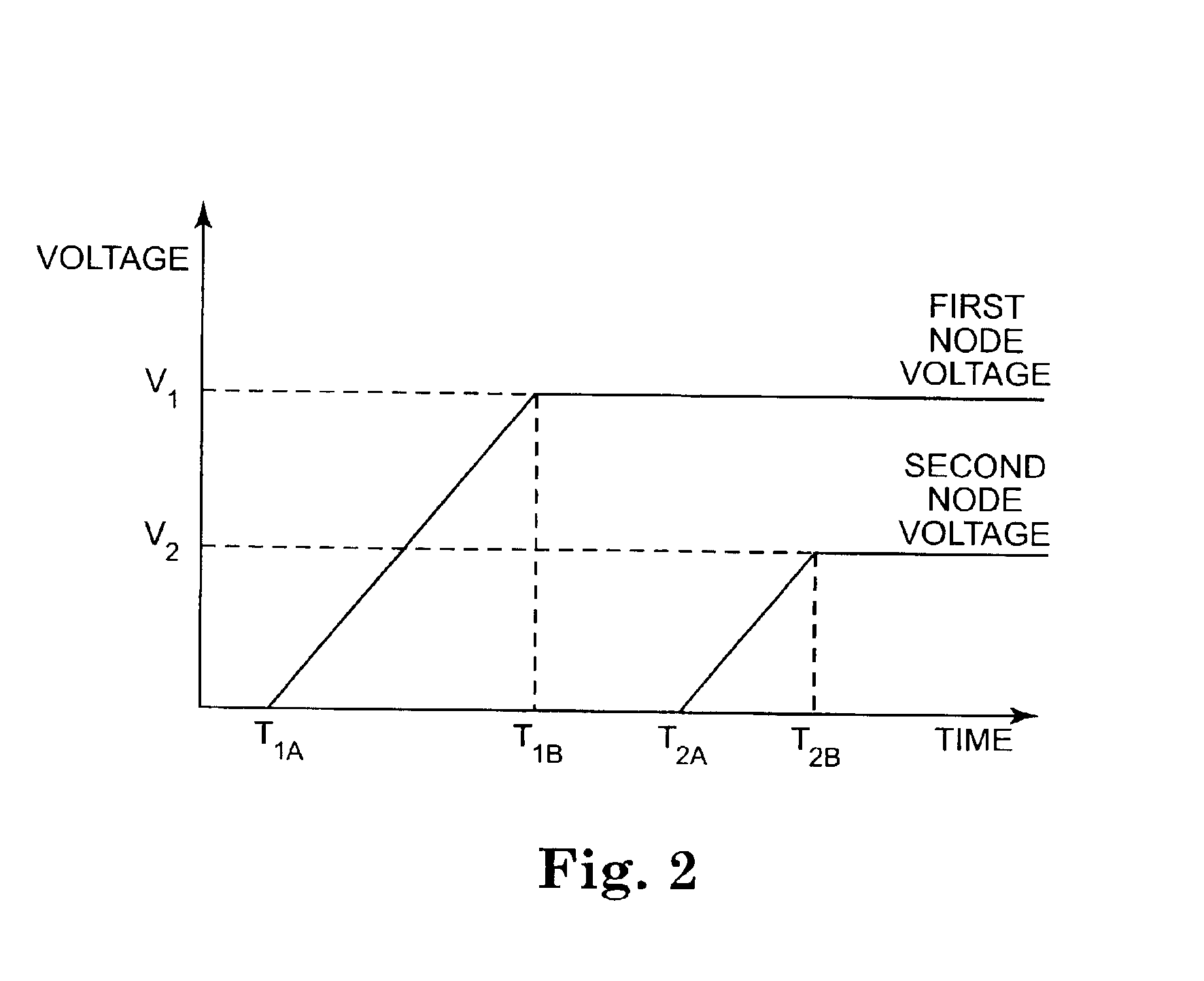

System for sequencing a first node voltage and a second node voltage

InactiveUS6909204B2High impedance pathBoards/switchyards circuit arrangementsProtective switchesEngineeringElectrical current

A sequencing system for sequencing a first node voltage at a first node and a second node voltage at a second node which is less than the first node voltage is disclosed. The sequencing system includes a bias circuit configured to provide a bias current in response to the first node voltage beginning to change to a first supply voltage. The sequencing system includes a switch configured to provide a low impedance path between the first node and the second node when the bias circuit is providing the bias current. The switch is configured to provide a high impedance path when the second node voltage is within a range of a second supply voltage which is less than the first supply voltage.

Owner:AVAGO TECH INT SALES PTE LTD

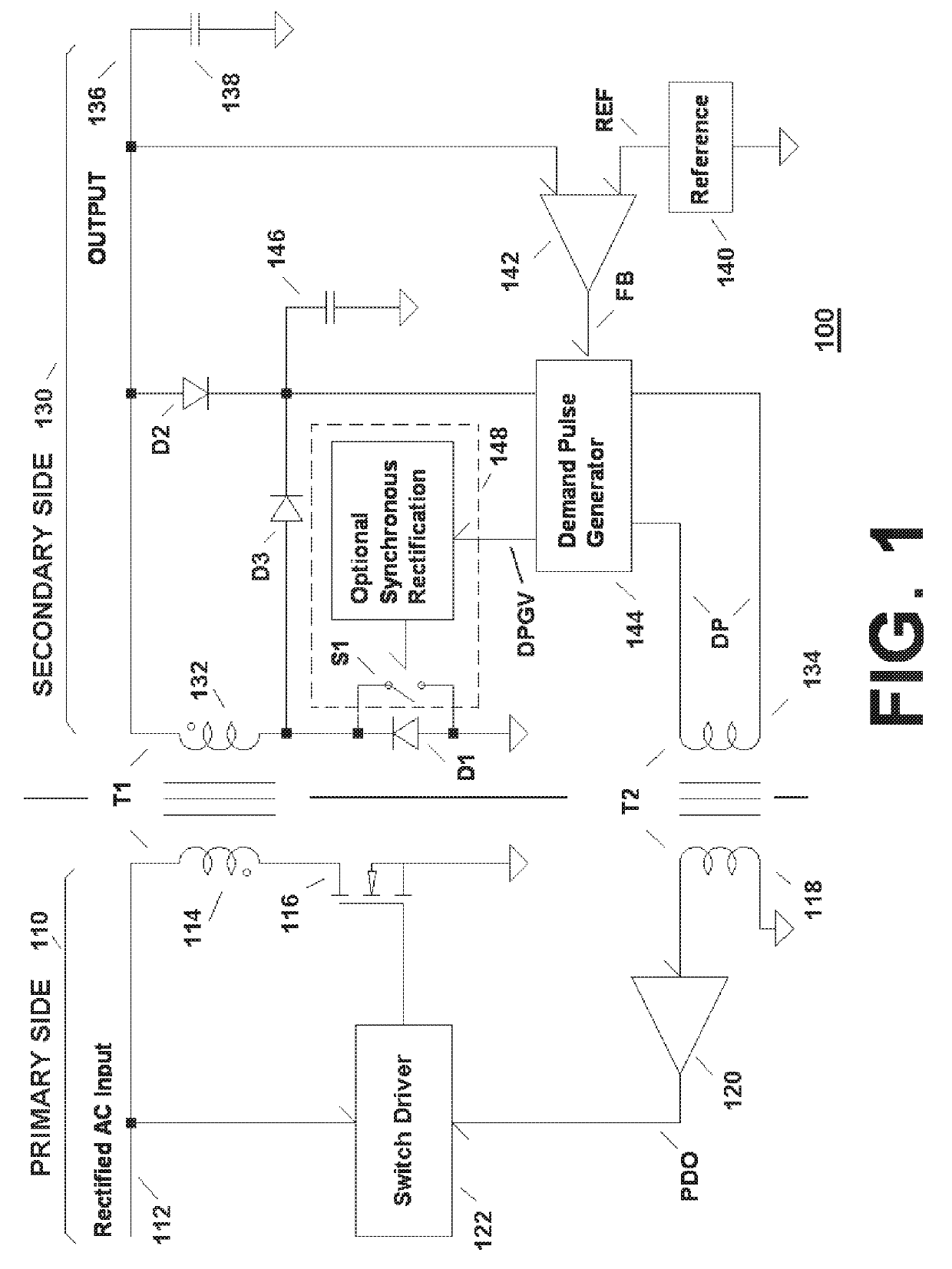

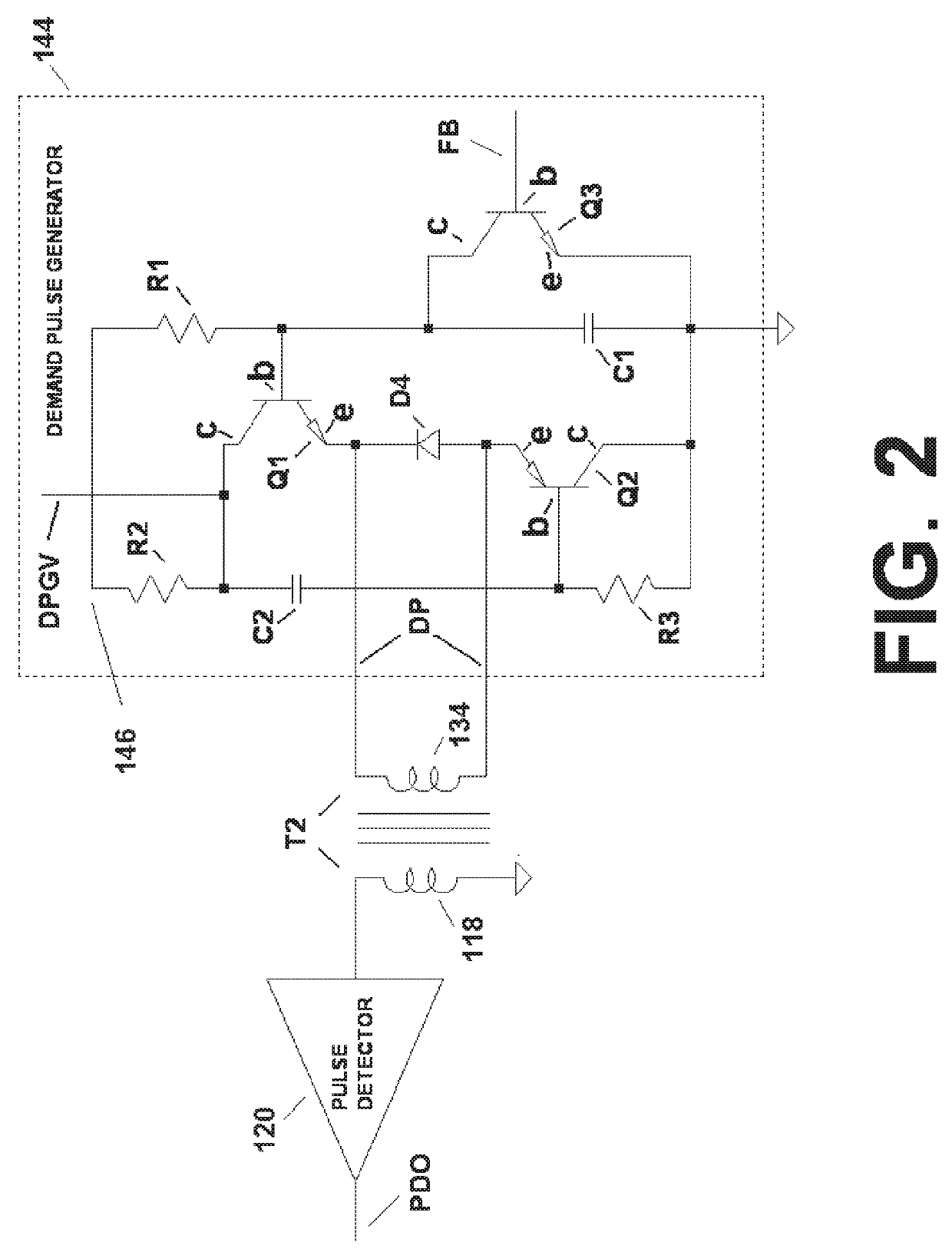

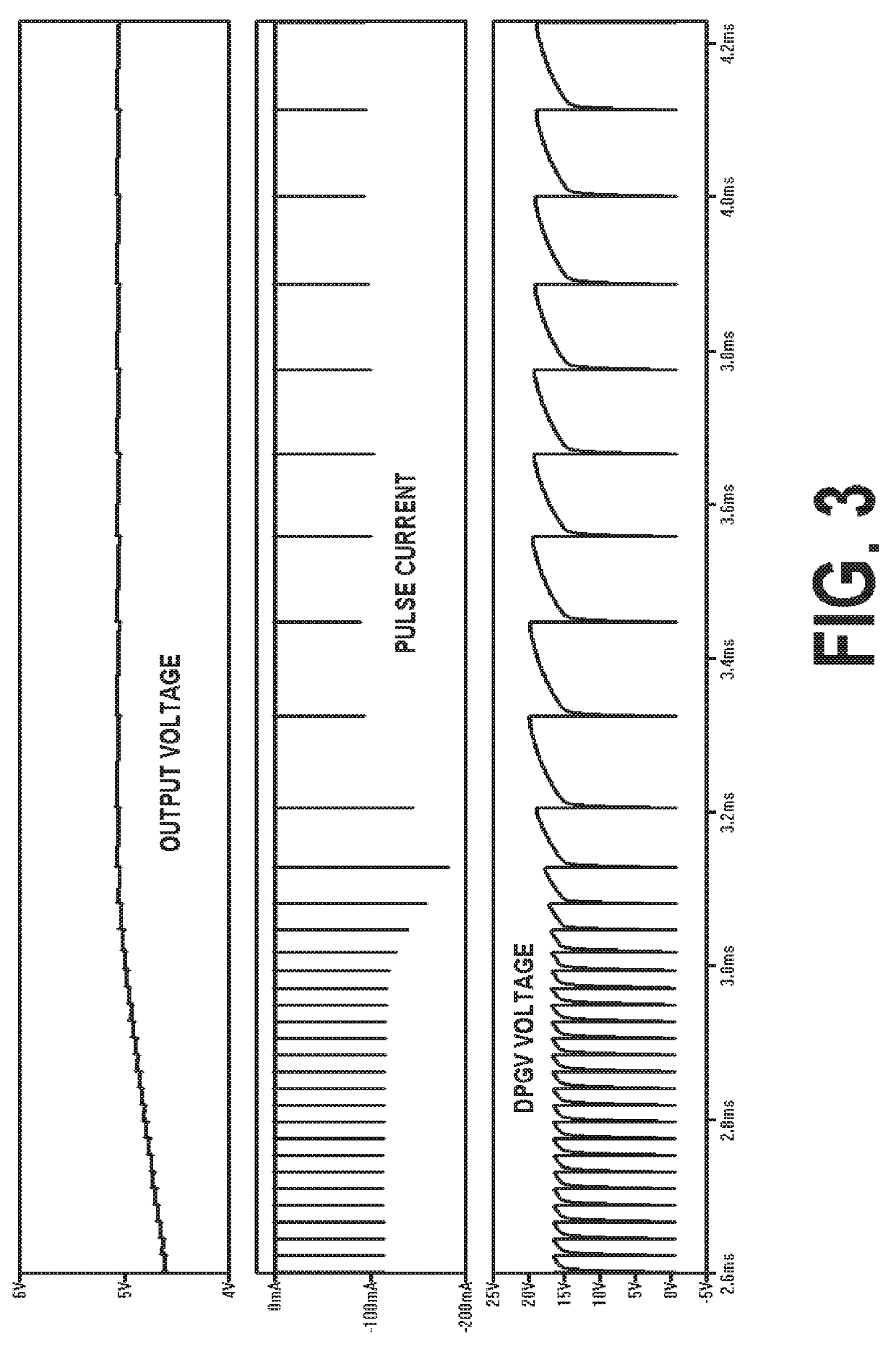

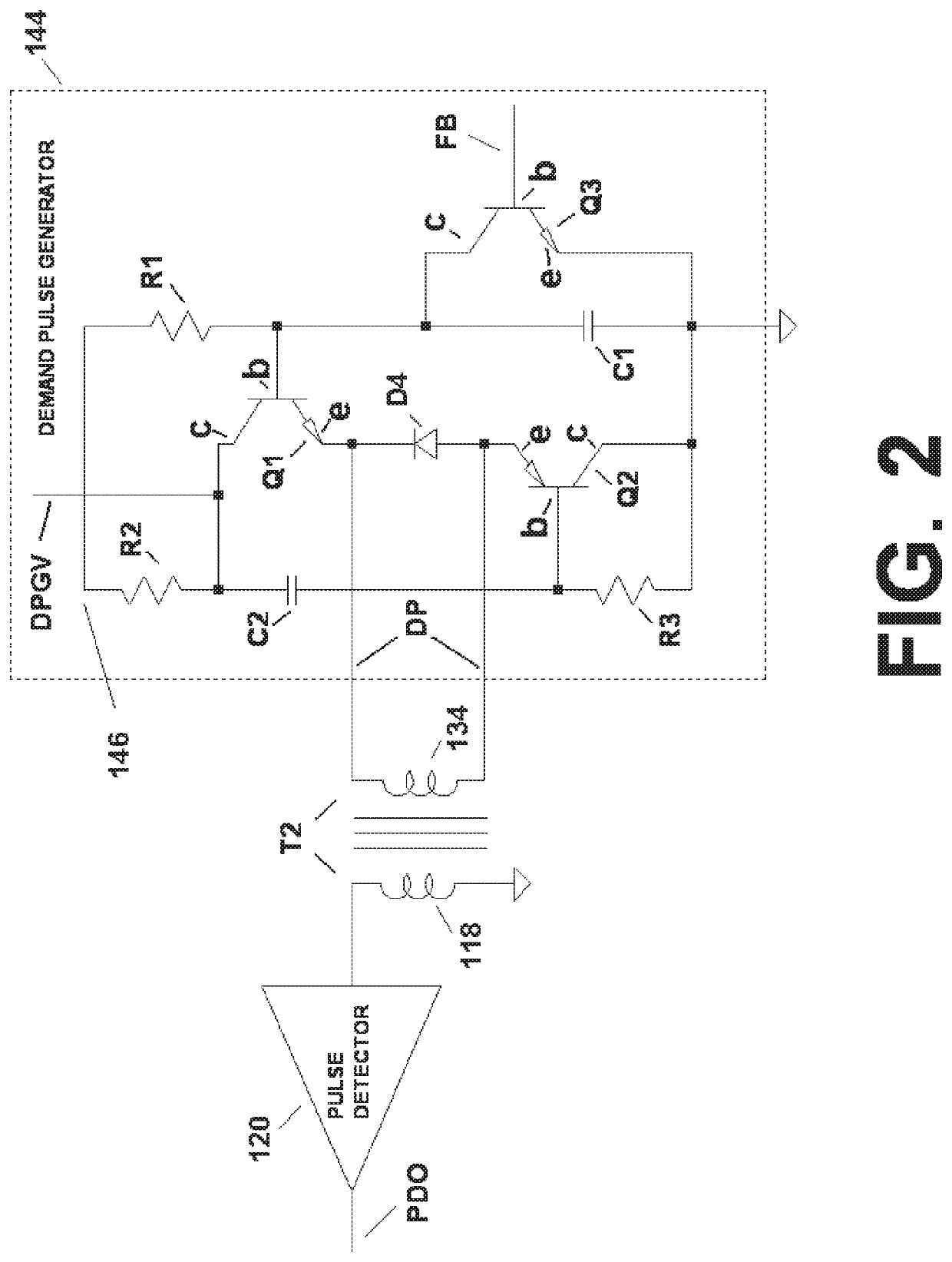

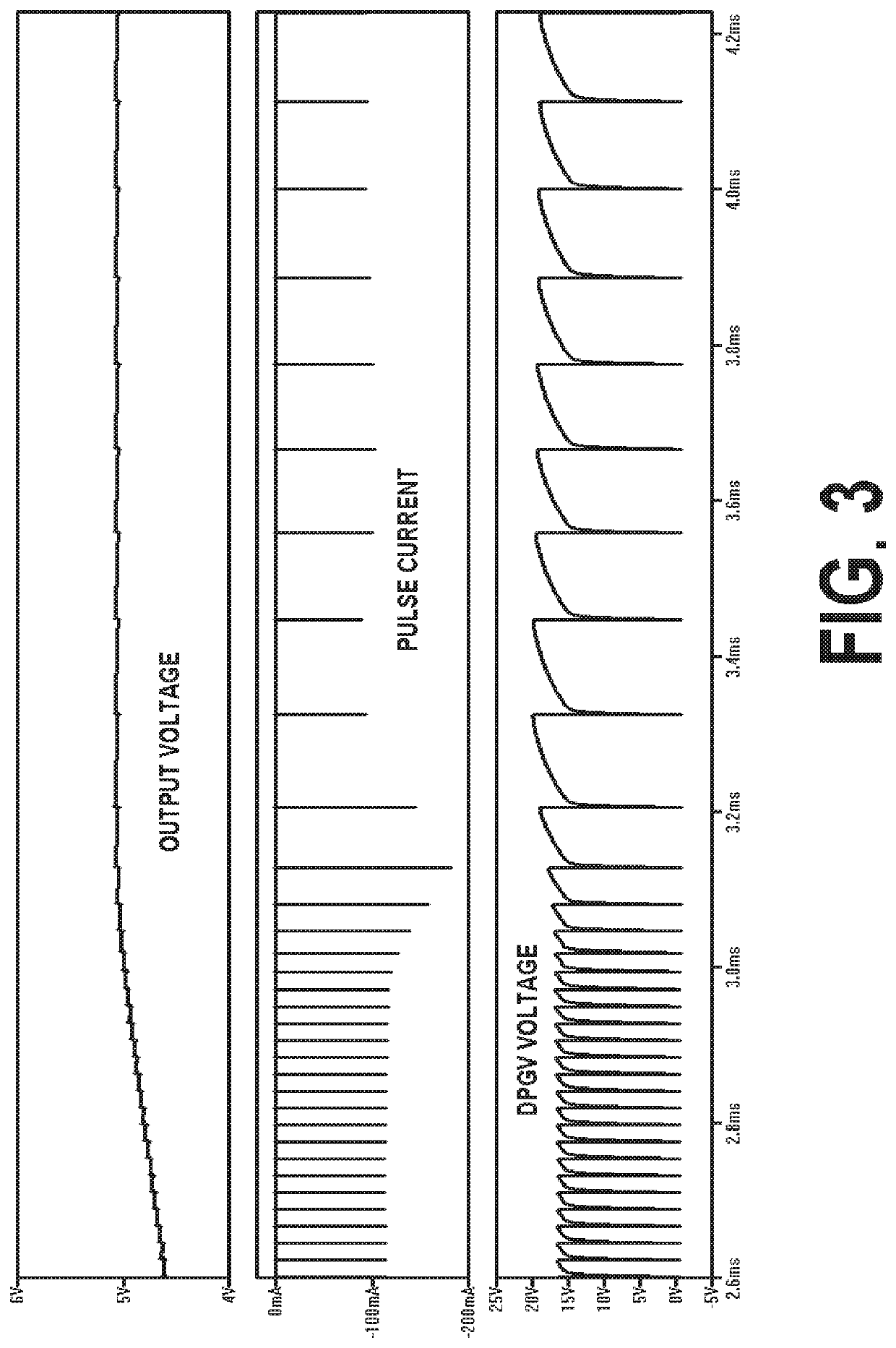

Trigger Circuitry for Fast, Low-Power State Transitions

ActiveUS20190267911A1Fast risingFast falling edgeAc-dc conversionDc-dc conversionCapacitanceControl circuit

An n-type transistor and a p-type transistor are connected in series such that, when the two transistors are turned on, current flows from the collector of the n-type transistor to the collector of the p-type transistor. A positive-feedback capacitor is connected between the collector of one transistor and the base of the other transistor. The two transistors turn on together when the base voltage of the n-type transistor exceeds the base voltage of the p-type transistor by at least the sum of the turn-on threshold voltages of the two transistors and (i) the two transistors turn off together when the base voltage of the n-type transistor fails to exceed the base voltage of the p-type transistor by at least that sum. The positive-feedback capacitor ensures that the two transistors turn fully on and off together. In certain embodiments, the circuitry can be controlled to operate as a current pulse generator.

Owner:COGNIPOWER

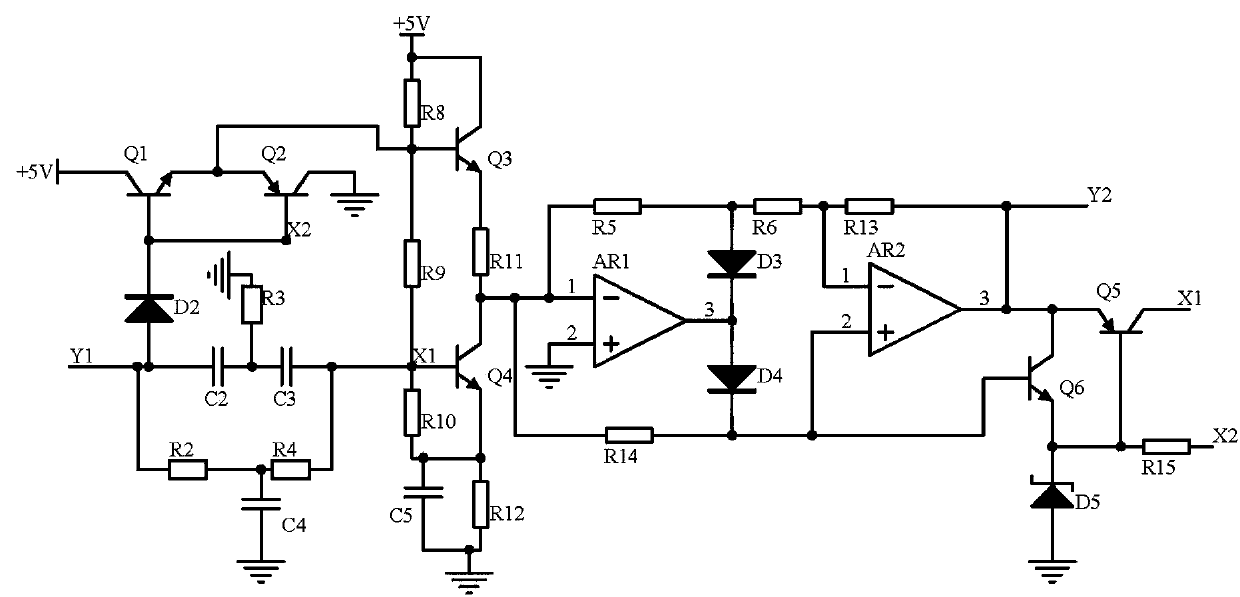

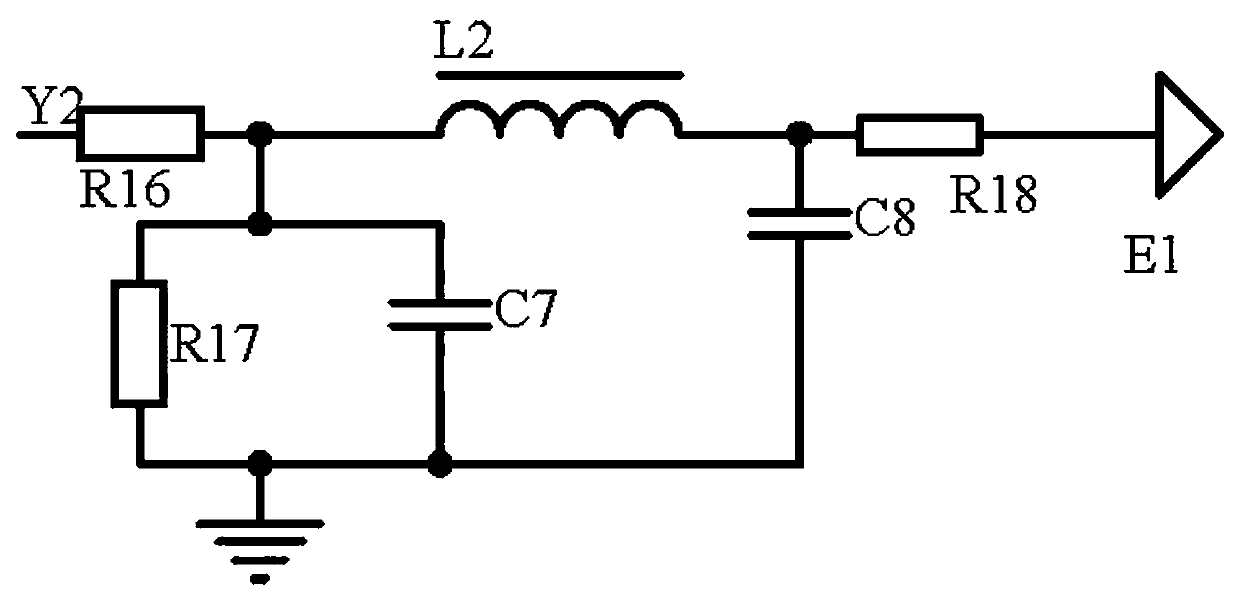

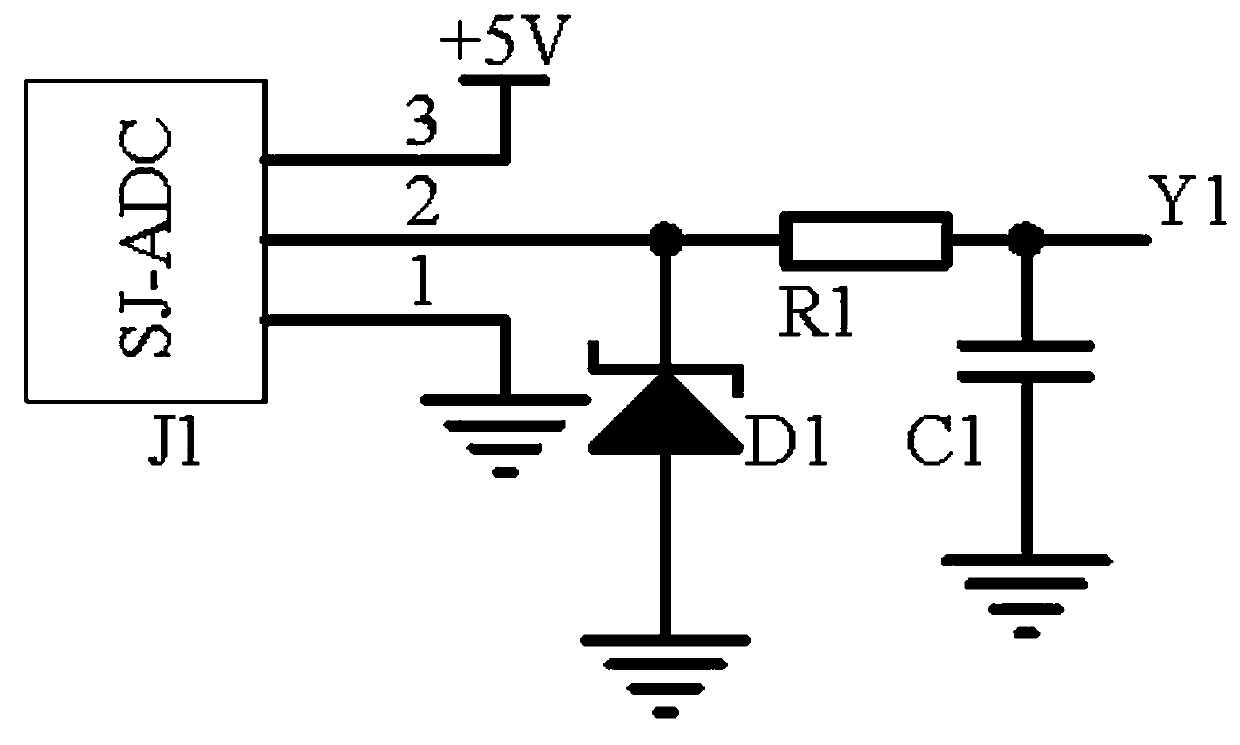

Water quality monitoring real-time early-warning system

InactiveCN110596335APrevent Crossover DistortionGuaranteed stabilityTransmission systemsReliability increase in bipolar transistorsCapacitanceWater quality

The invention discloses a water quality monitoring real-time early-warning system. The system includes a frequency collection circuit, a frequency modulation feedback circuit and a filter transmittingcircuit. The frequency collection circuit uses a frequency collector J1, of which a model is SJ-ADC, to detect water resource environment measurement data signal frequency received by a ground center. The frequency modulation feedback circuit receives output signals of the frequency collection circuit from two paths, a first path uses a triode Q1 and a triode Q 2 to form a push-pull circuit to prevent signal crossover distortion, a second path sues resistors R2- R4 and capacitors C2-C4 to form a frequency selection circuit to screen out single frequency signals, finally, a frequency modulation circuit formed by a triode Z3, a triode Z4 and resistors R8-R10 receives signals of the two paths and carries out frequency modulation, the filter transmitting circuit uses an inductor L2, a capacitor C7 and a capacitor C8 to form a filter circuit to filter out signal clutters. The water resource environment measurement data signal frequency received by the ground center can be detected in realtime, and converted into a water environment monitoring platform early-warning correction triggering signal.

Owner:河南沃海水务有限公司

CC pin circuit of USB Type-C

PendingCN110380721ARealize withstand voltage protectionSolve pressureReliability increase in bipolar transistorsReliability increase in field effect transistorsLow voltageEngineering

The invention provides a CC pin circuit of USB Type-C. In the Type-C interface circuit, a high-voltage NMOS is introduced for voltage isolation, and a first low-voltage region is generated. A pull-upresistor circuit, a CC connection detection circuit, a PD communication circuit and the like are placed in the first low-voltage region to realize high-voltage protection. The pull-down resistor circuit is directly connected to the CC pin, so that when the Type-C interface is in a Dead Battery state in a DRP or SNK mode, the CC connection can be normally realized by accessing the SRC or other DRPs(Data Redundancy Protocol). And a resistor in the pull-down resistor circuit is divided into a first resistor and a second resistor which are connected in series, and voltage clamping is performed ata middle series node to generate a second low-voltage region. And an enable control switch of the pull-down resistor circuit and the second resistor are placed in the second low-voltage region to realize high-voltage protection. The first resistor is placed in a high-voltage area and plays a role in current limiting when the voltage clamping circuit works. The withstand voltage design method andthe circuit structure can be applied to Type-of all modes. And in the C interface circuit, the voltage withstanding problem of the CC pin is solved.

Owner:ZHUHAI ISMARTWARE TECH CO LTD

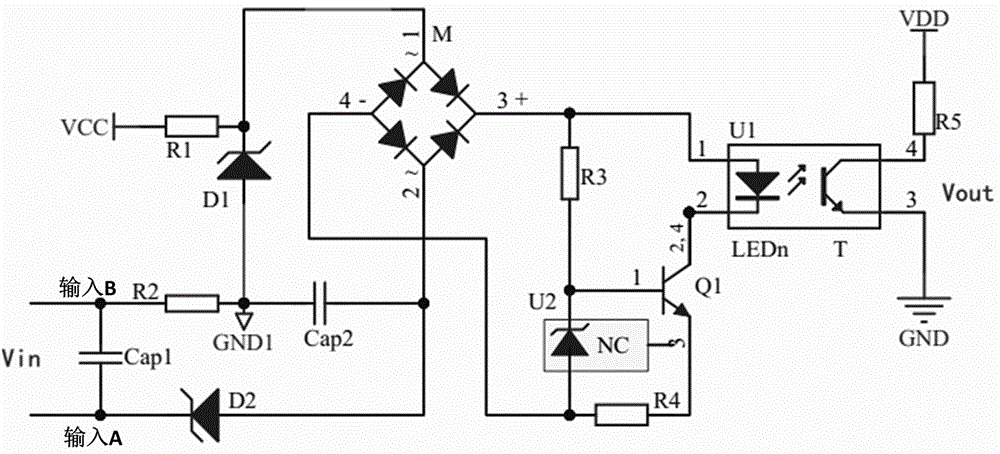

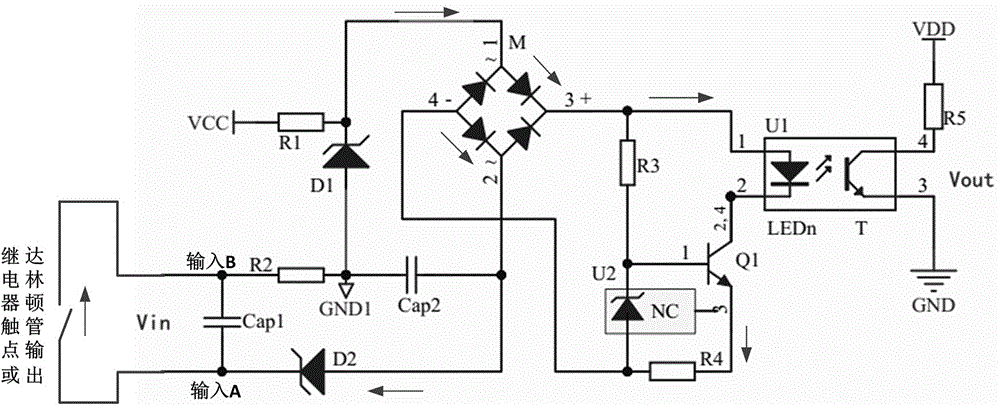

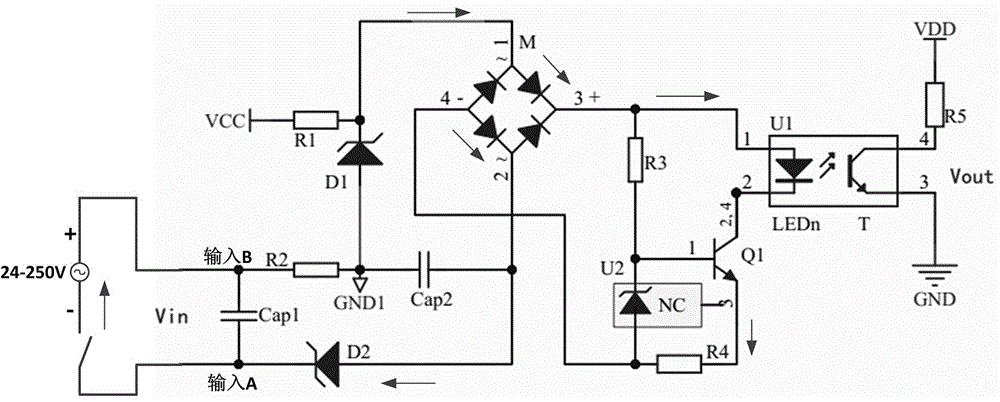

On-off input circuit for relay protection testing device

ActiveCN106788381AWill not pose a safety hazardReliability increase in bipolar transistorsTubing typesFilter capacitor

Owner:XIANGTAN UNIV

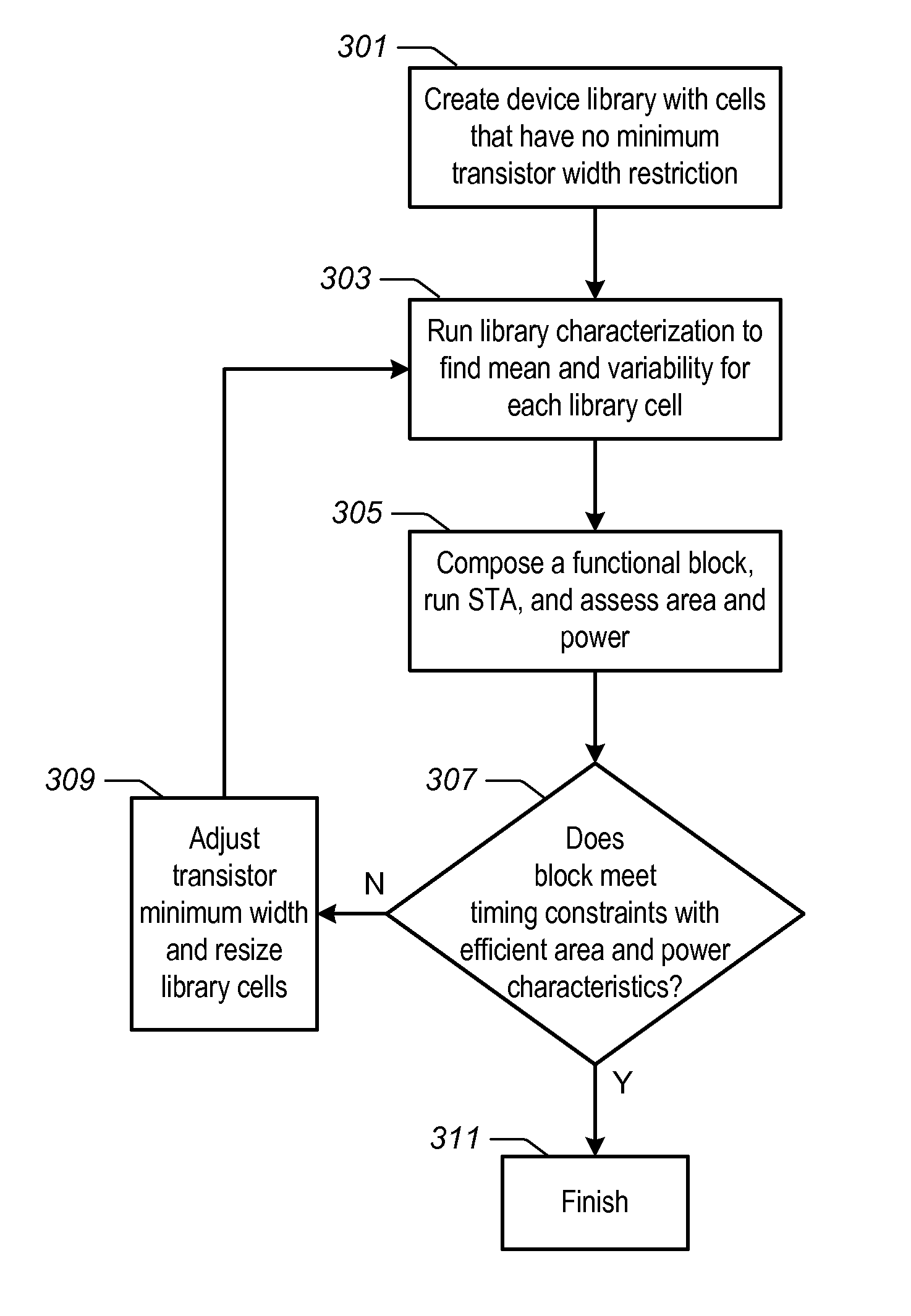

Reducing Narrow Gate Width Effects in an Integrated Circuit Design

InactiveUS20120274357A1Reducing narrow gate width effectReduce areaSolid-state devicesReliability increase in bipolar transistorsChannel widthCircuit design

A method for reducing narrow gate width effects in an integrated circuit includes finding the smallest transistor channel widths that are larger than the minimum width for the technology for library cells that produce logic blocks that meet timing constraints while using the least amount of power and have the smallest possible area. The method may include characterizing a device library while varying process, voltage and temperature parameters, and synthesizing an HDL representation of a functional logic block including cells from the device library. The method may also include determining whether timing, area, and power values of the functional logic block are within a predetermined range. In response to the timing, area, and power values not being within the predetermined range, iteratively increasing the channel width of at least a portion of the transistors of at least one of the cells in the device library.

Owner:APPLE INC

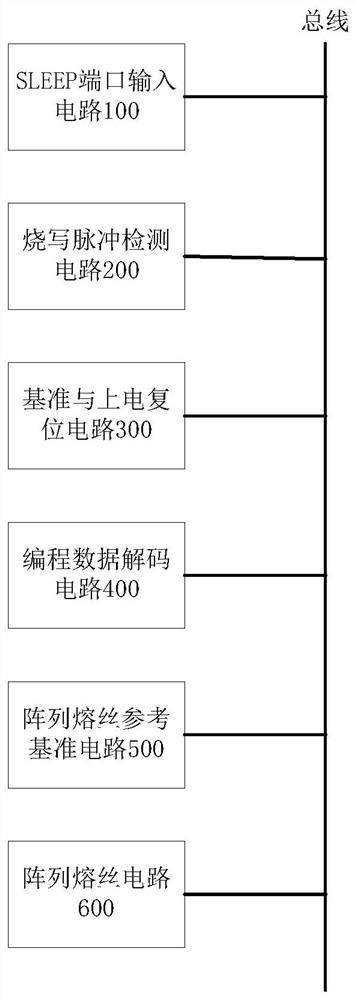

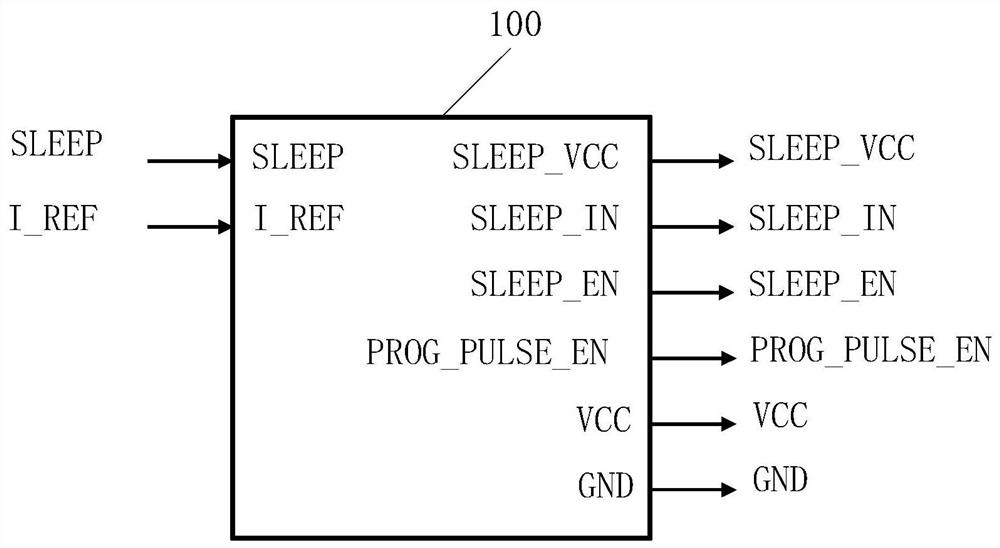

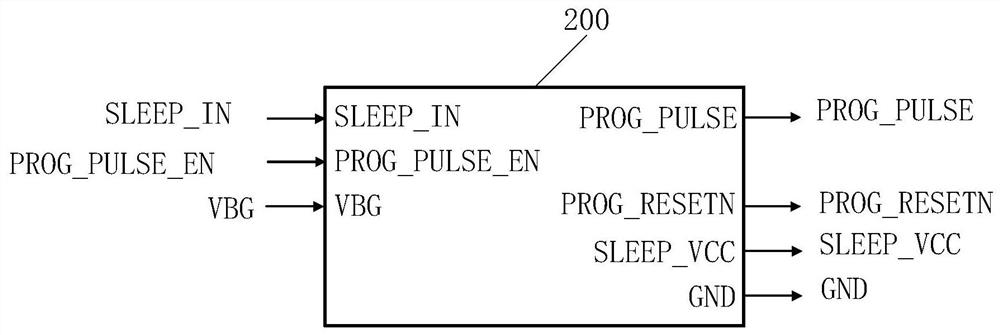

Programmable fuse trimming circuit system for IO port multiplexing

PendingCN111835336ALow costImprove reliabilityProgrammable logic circuit arrangementsReliability increase in bipolar transistorsPower-on resetMultiplexing

The invention provides a programmable fuse trimming circuit system for IO port multiplexing. The system is composed of an SLEEP port input circuit, a programming pulse detection circuit, a reference and power-on reset circuit, a programming data decoding circuit, an array fuse reference reference circuit and N M-bit array fuse circuits. The programmable fuse trimming circuit system is irrelevant to the operation of the chip after completing one-time programming, so that the programming data transmission port is selected to be multiplexed with the SLEEP dormancy control port, pulse sequences with different amplitudes and pulse widths are transmitted to the SLEEP port input circuit, the pulse sequences are decoded into programming address signals, programming data signals and programming enable signals through the programming pulse detection circuit and the programming data decoding circuit, and the programmable fuse trimming circuit system has the advantages of being low in cost, programmable, high in reliability and capable of achieving IO port multiplexing.

Owner:佛山中科芯蔚科技有限公司

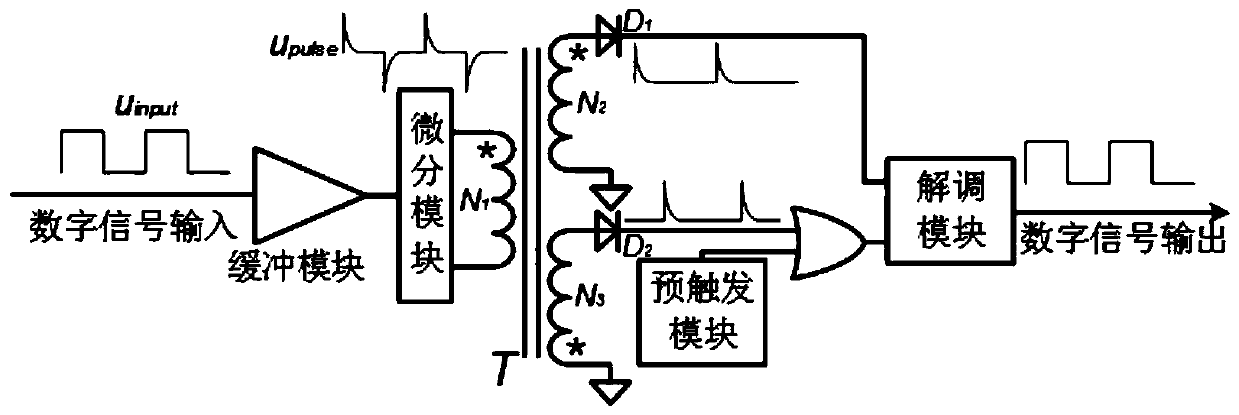

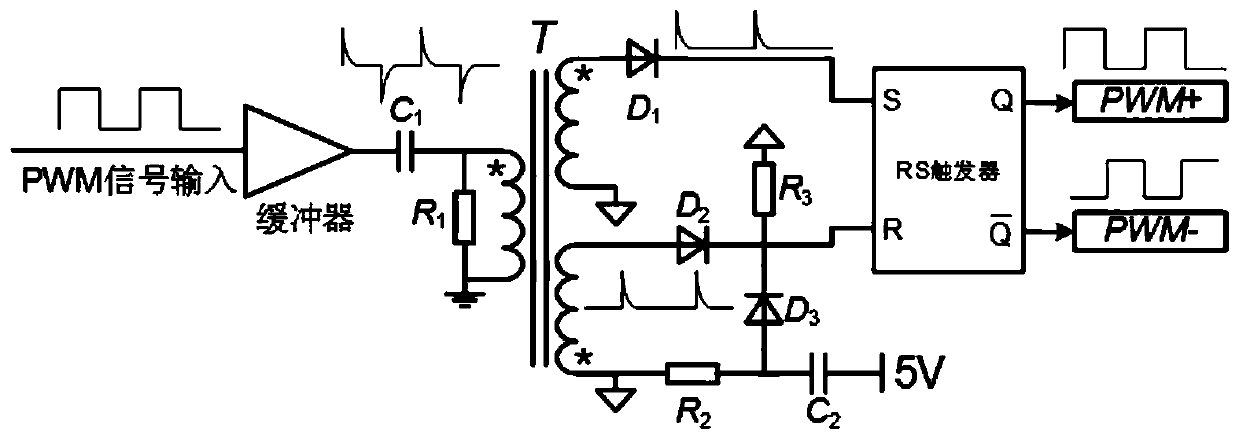

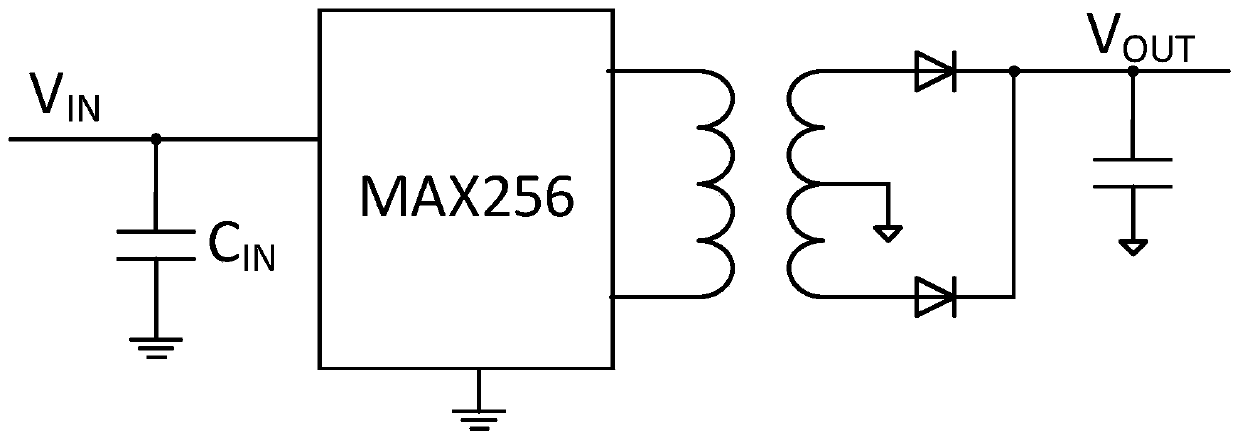

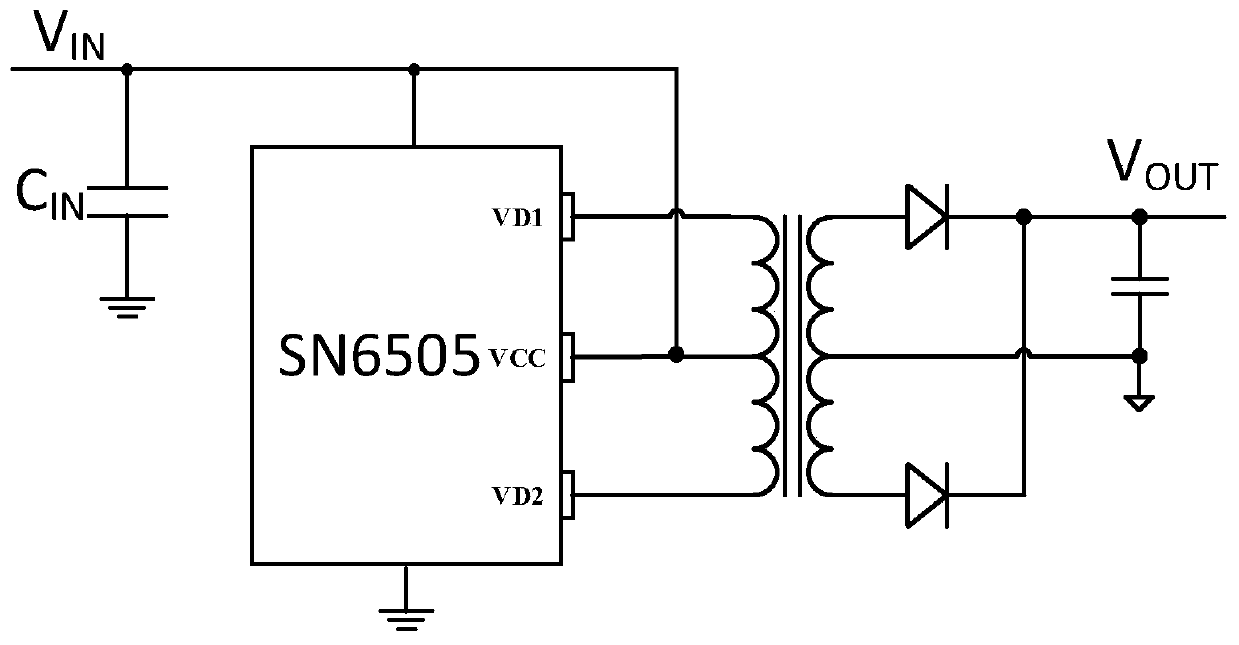

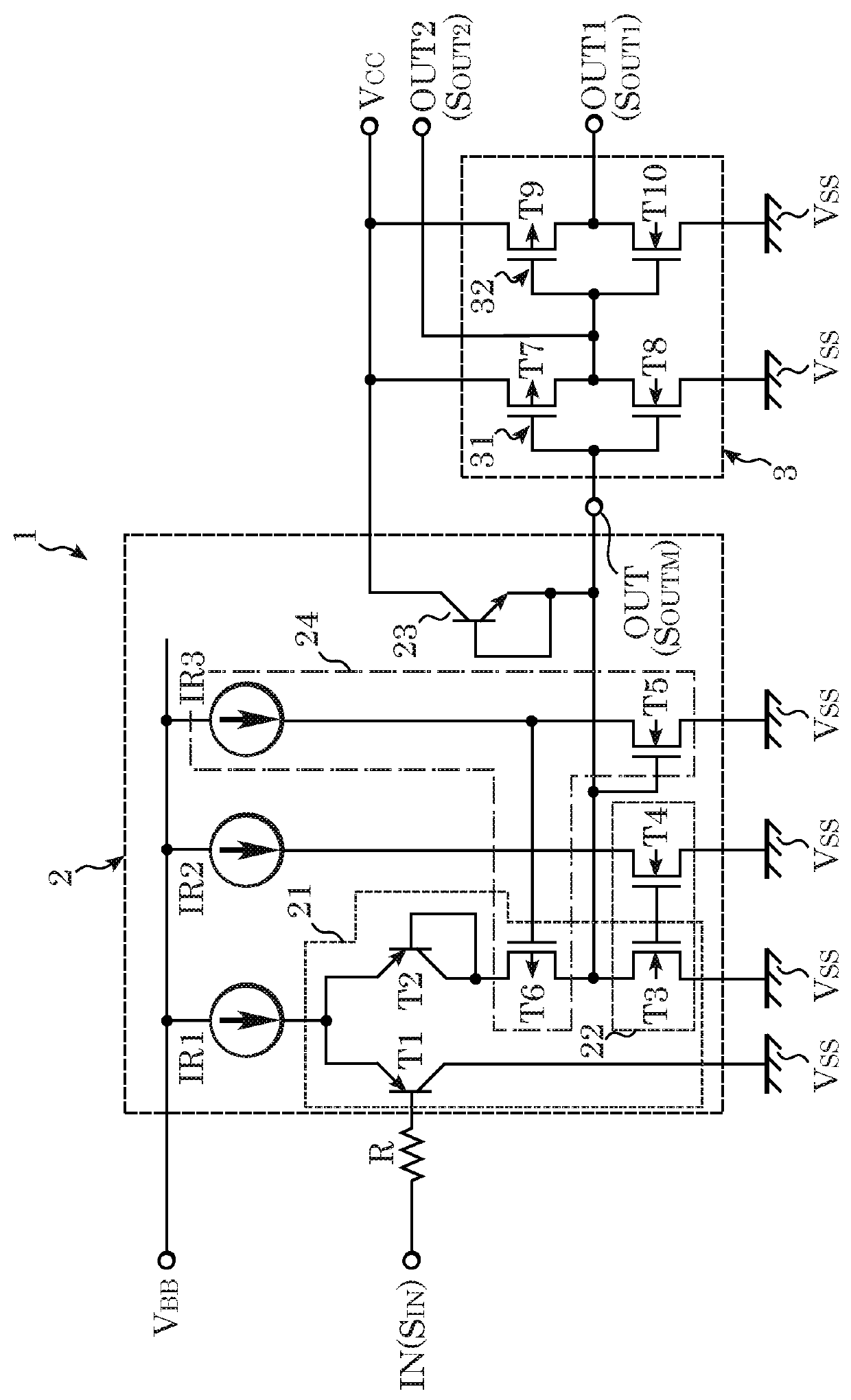

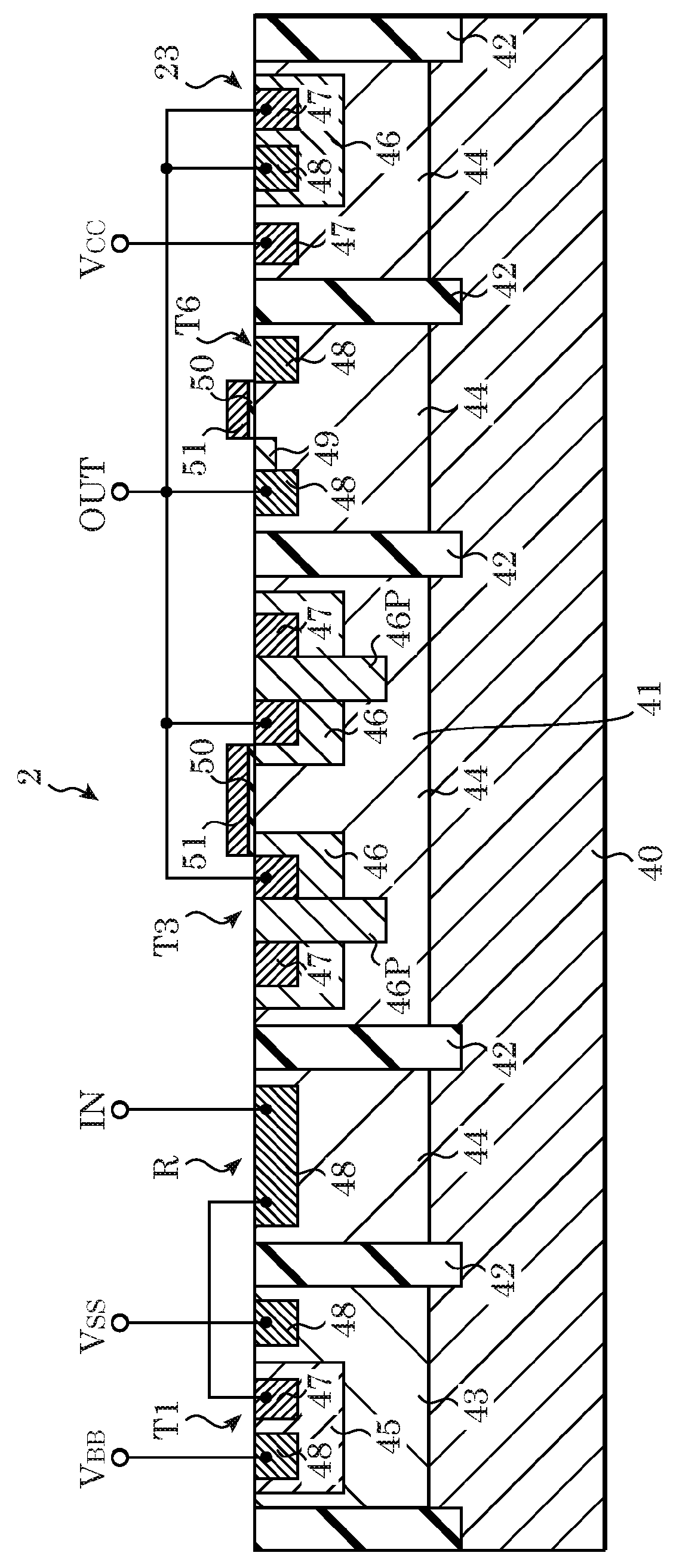

Miniaturized low-conduction delay digital signal isolation transmission system

InactiveCN111262573AImprove reliabilityExtended operating temperature rangeSwitching accelaration modificationsLogic circuit coupling arrangementsTransformerMiniaturization

The invention discloses a miniaturized low-conduction delay digital signal isolation transmission system. The system comprises a signal generation module for sending out an initial signal, a buffer module being connected with the signal generation module and being used for impedance matching, a differential module beings connected with the buffer module and being used for converting the initial signal into a modulation signal, a transformer module being connected with the differential module and being used for carrying out isolated transmission on the modulation signal, a trigger module beingconnected with the transformer module and being used for demodulating the modulation signal to obtain a final signal, a pre-triggering module being respectively connected with the transformer module and the trigger module and being used for generating and sending a pre-triggering pulse to the trigger module, and a signal receiving module being connected with the trigger module and being used for receiving the final signal. According to the invention, the requirement on the size of the transformer is low, the miniaturization design is facilitated, the working frequency range is wide, and the limitation on the duty ratio of the signal is small.

Owner:CHANGZHOU COLLEGE OF INFORMATION TECH

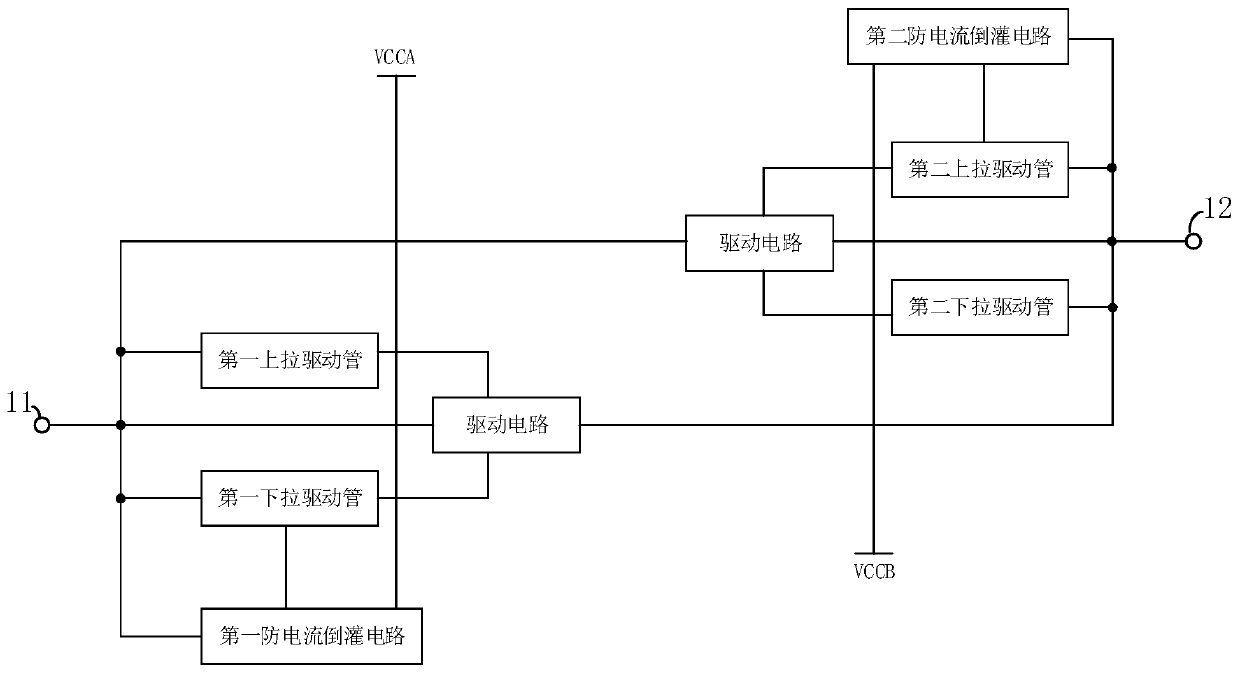

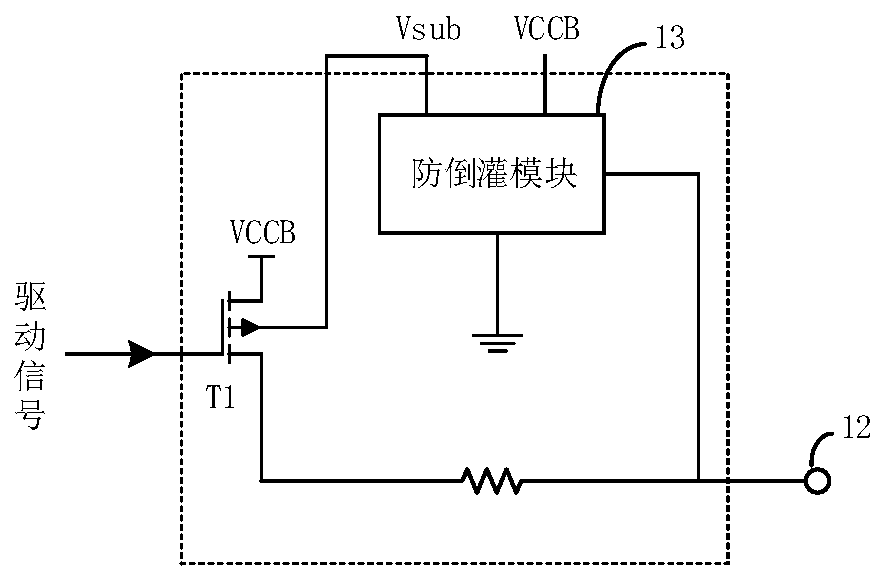

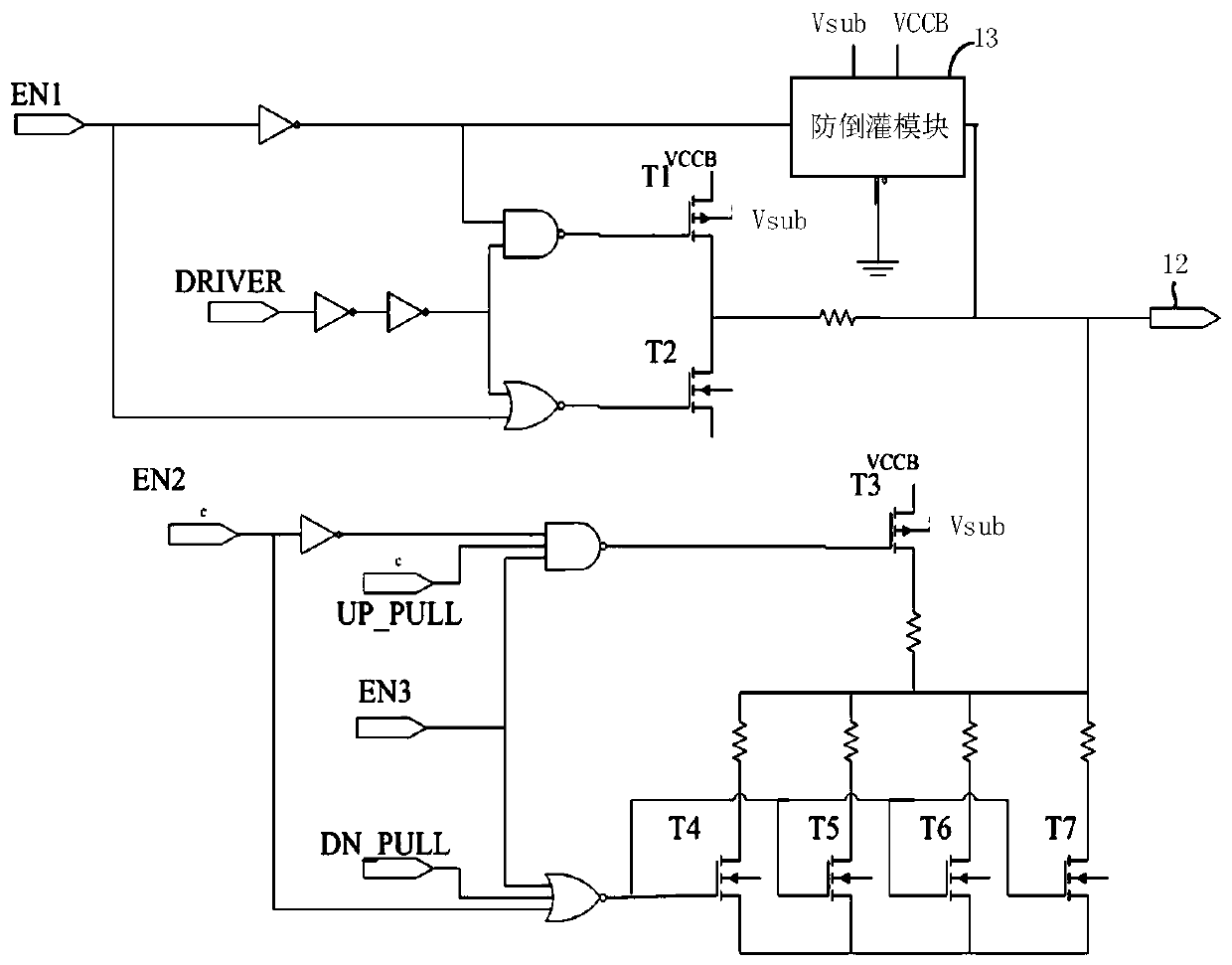

Anti-backflow circuit, bidirectional level converter and integrated circuit

PendingCN110868204ABurn out preventionReliability increase in bipolar transistorsConvertersHemt circuits

An anti-backflow circuit of a transistor is connected with a signal terminal and comprises: a driving transistor, awherein gate of the driving transistor is connected with a driving signal, a high-potential end of the driving transistor is connected with a power supply, and a low-potential end of the driving transistor is connected with the signal terminal; and an anti-backflow module which is electrically connected with the pull-up power supply, the signal terminal and the substrate of the driving transistor, and is configured to enable the power supply voltage to be loaded on the substrateof the driving transistor when the power supply is powered on, and enable the voltage of the signal terminal to be loaded on the substrate of the driving transistor when the pull-up power supply is powered off. According to the invention, the substrate voltage of the transistor tube can be adjusted to change along with the level of the signal terminal, so that the low-potential voltage of the transistor is not higher than the substrate voltage, and the transistor tube is effectively prevented from being burnt out due to backward flowing of current.

Owner:SHENZHEN STATE MICROELECTRONICS CO LTD

High-voltage PMOS drive circuit

PendingCN111245428AHighly integratedLow costPower reduction in field effect transistorsPower reduction by control/clock signalCapacitanceTerminal voltage

The invention discloses a high-voltage PMOS drive circuit. The circuit comprises a double-layer potential translation circuit, a clamper and a buffer. The double-layer potential translation circuit receives a low-end logic signal and a bias voltage provided by the clamper and outputs a high-end logic level to the buffer, and the buffer generates a high-end driving voltage as an output of the high-voltage PMOS drive circuit to control on and off of a high-voltage PMOS transistor. The output end of the clamper provides a negative end voltage for the buffer, so that the buffer works in a safe area, and the clamper provides a bias voltage for the double-layer potential translation circuit. Under the condition that an external capacitor is not needed, the voltages of a load element, a latch andthe buffer are all controlled within a safe working range, the integration level is high, and the cost is low. The voltage difference generated on the load element in the double-layer potential translation circuit is stable and reliable and is not easy to interfere with, and a latch required in the traditional technology can be omitted, so that the cost is saved.

Owner:苏州源特半导体科技有限公司

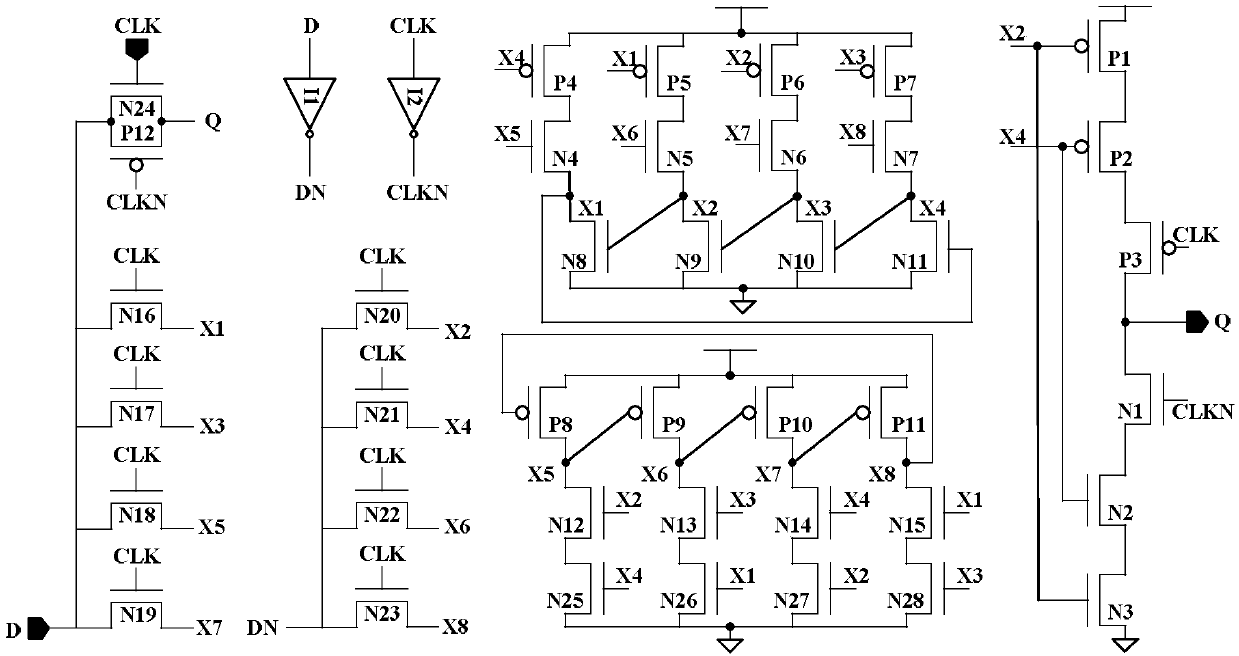

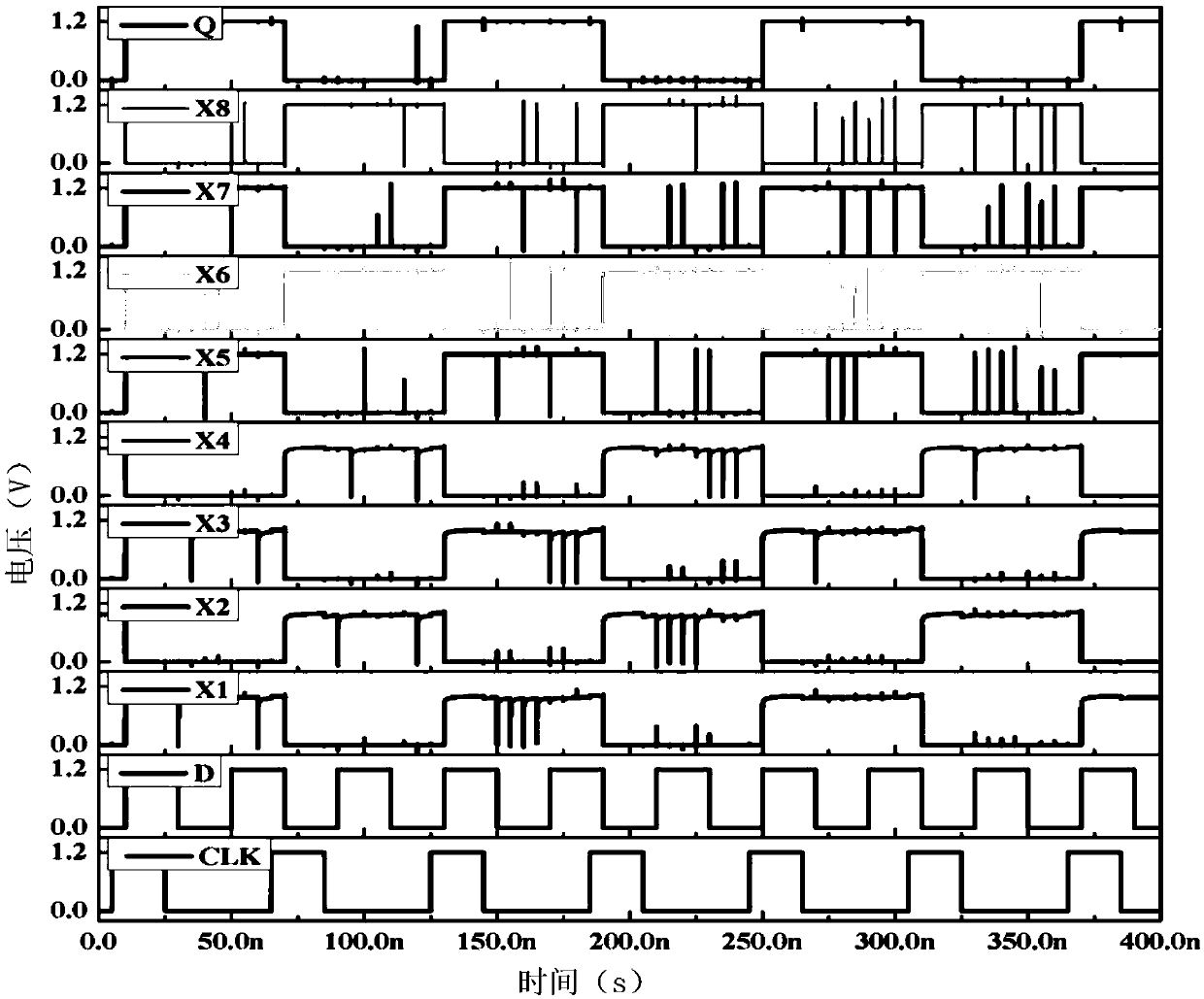

Nuclear hardening D-latch

PendingCN109547007ASensitive area reducedReduce areaReliability increase in bipolar transistorsFault toleranceTransmission gate

The invention discloses a nuclear hardening D-latch, and belongs to the field of anti-nuclear reinforcement in integrated circuit reliability. The problem that according to existing anti-radiation D-latches, more hardware is needed, power consumption is high, delay time is long, and fault tolerance for flipped double nodes cannot be realized is solved. The latch of the invention includes two inverters I1 and I2, 28 NMOS transistors N1 to N28, and 12 PMOS transistors P1 to P12. Used devices are few, volume is small, a structure is simple, and due to that the used devices are few, power consumption of the entire latch is reduced, and hardware overheads are lower. A signal at an input end of the latch can be transmitted to an output port simply through one transmission gate, data transmissiontime is short, fault tolerance for any-single-node and double-node flipping can also be realized, and thus fault tolerance protection against single-node and double-node flipping is realized. The latch of the invention can provide protection for application of integrated circuit chips in high-radiation environments (such as aerospace and terrestrial nuclear power plants).

Owner:ZHONGBEI UNIV +1

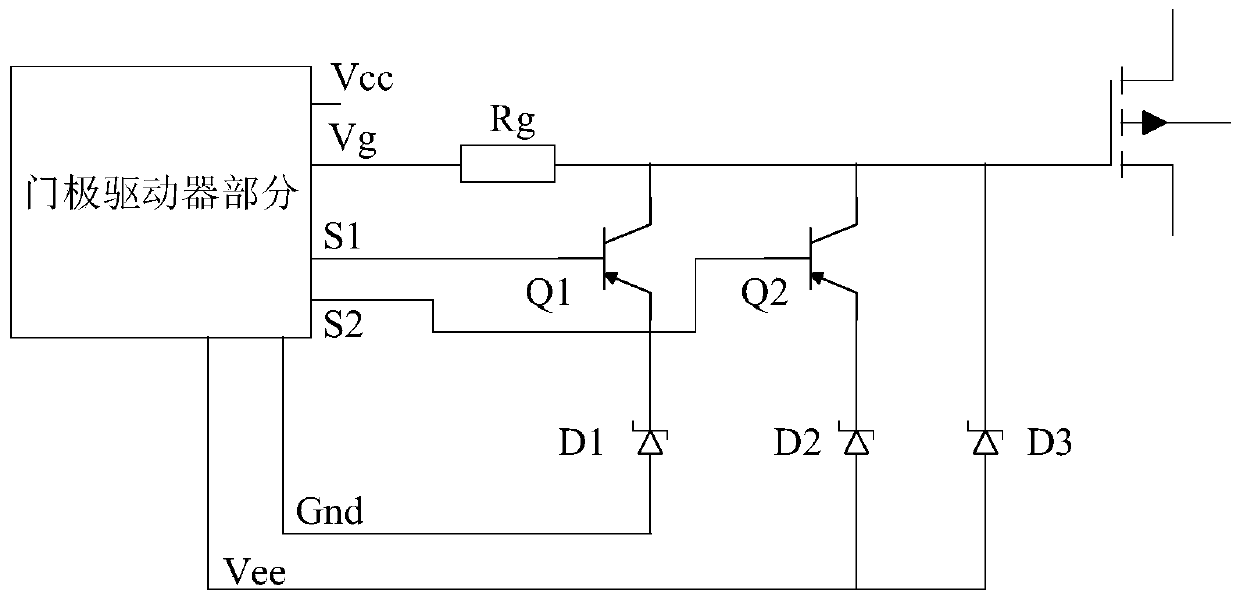

Driving protection circuit

ActiveCN110224696ASolve the problem of easy misleadingImprove stabilityReliability increase in bipolar transistorsReliability increase in field effect transistorsField-effect transistorGate driver

The invention discloses a driving protection circuit. The circuit includes: a gate driver; a first triode the gate electrode of which is connected with the first port of the gate electrode driver, andthe drain electrode of which is connected with the grounding end of the gate electrode driver; a second triode the gate electrode of which is connected with the second port of the gate electrode driver, and the drain electrode of which is connected with the third port of the gate electrode driver; a third voltage stabilizing diode the positive electrode of which is connected with the third port of the gate driver, and the negative electrode of which is connected with the fourth port of the gate driver; and a field effect transistor which is connected with the fourth port of the gate driver and the negative electrode of the third voltage stabilizing diode. According to the invention, the effect of improving the stability of the field effect transistor is achieved.

Owner:GREE ELECTRIC APPLIANCES INC

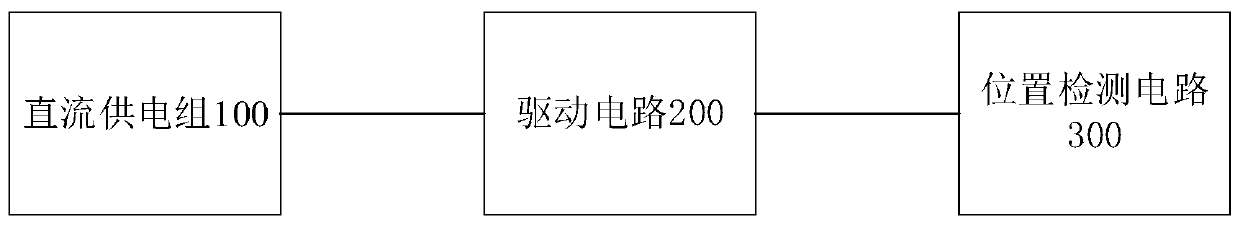

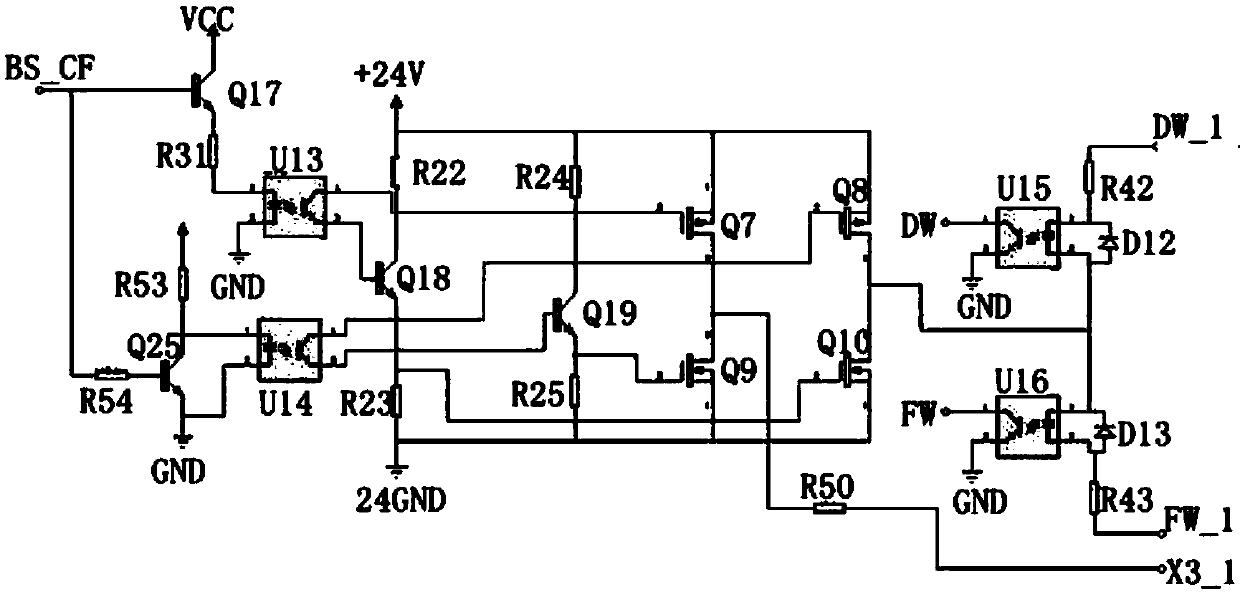

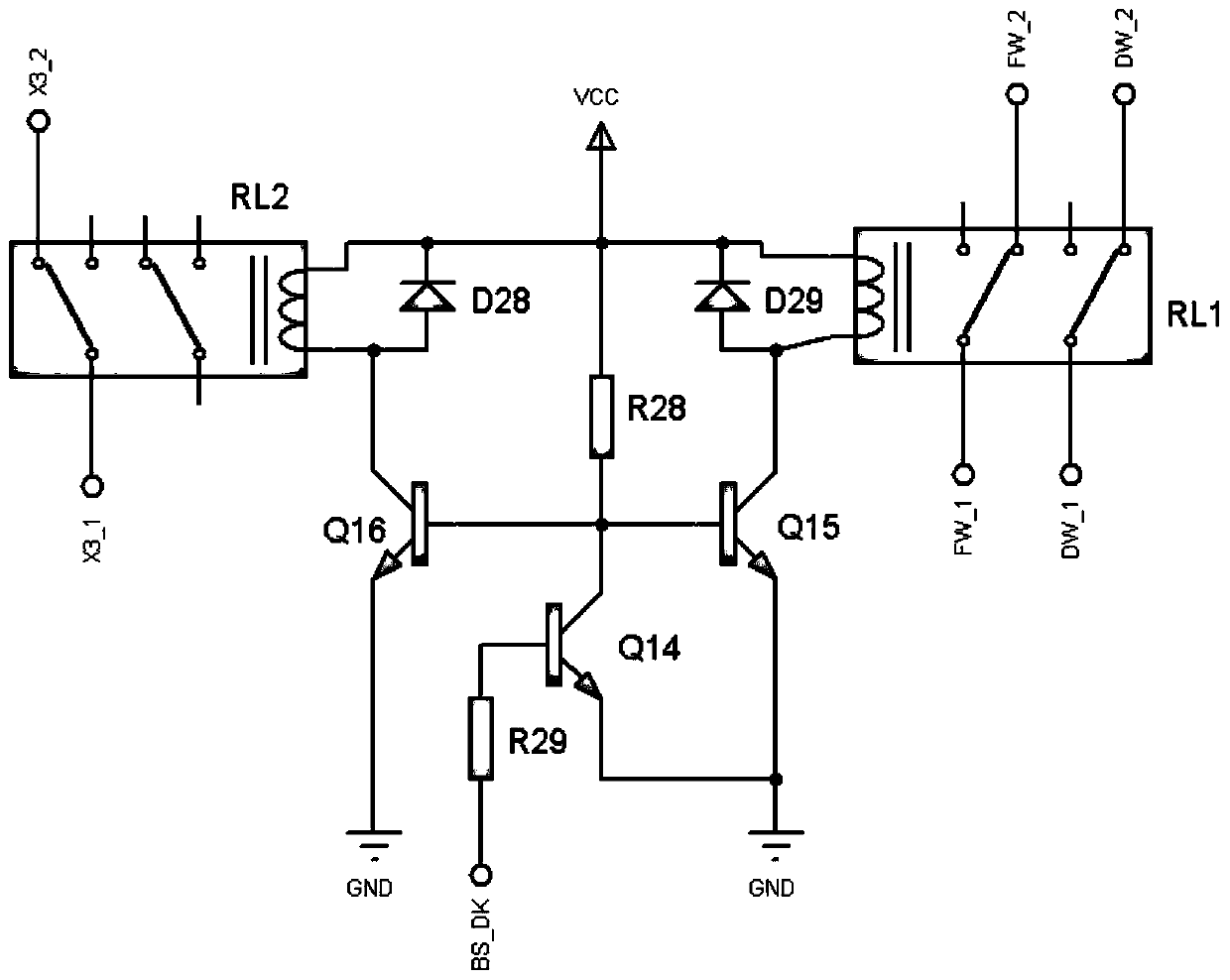

Turnout position detection device and system

PendingCN111426260ASmall footprintThe signal is stable and reliableProgrammable logic circuit arrangementsElectric/magnetic position measurementsControl theoryAlternate current

The embodiment of the invention provides a turnout position detection device and system, and relates to the field of railways, and the turnout position detection device comprises a DC power supply group, a drive circuit connected with the DC power supply group, and a position detection circuit connected with the drive circuit. Therefore, compared with the prior art that turnout position detectionis carried out by means of a polarization relay of an alternating-current power supply, the embodiment of the invention provides a technical scheme that uses A DC power supply group, the signal is more reliable and higher in safety, and the invention can improve the problems of lower safety coefficient and low reliability in the prior art, and improves the reliability and safety; the turnout position detection device realizes the function completed by a polarized relay in a point switch by adopting an electronic circuit, and also has the following advantages that the occupied space of electronic devices is smaller, the live plugging can be realized, and replacement is easy.

Owner:王先宏

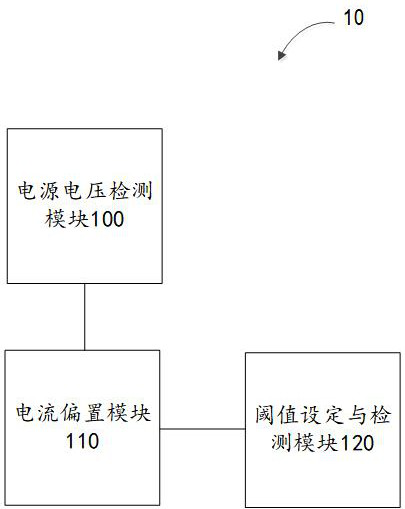

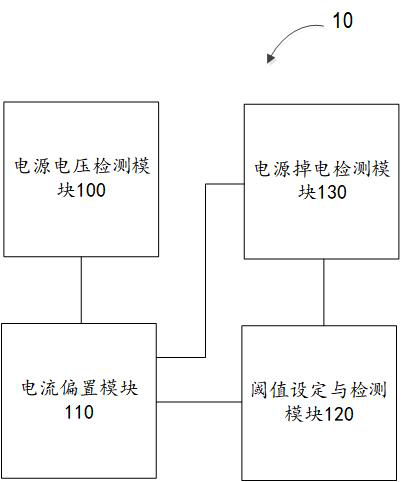

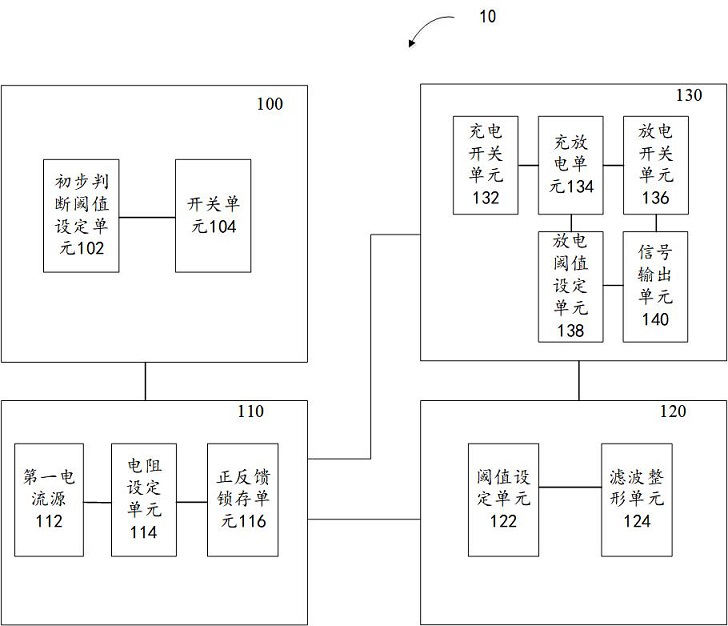

Power-on reset circuit for semiconductor integrated circuit

ActiveCN112073050AImprove reliabilityReliable power-on resetPower reduction in field effect transistorsReliability increase in bipolar transistorsPower-on resetReference current

An embodiment relates to a power-on reset circuit for a semiconductor integrated circuit, comprising: a power supply voltage detection module for detecting a power supply voltage and outputting a first indication signal indicating a magnitude of the power supply voltage; a current bias module coupled to the power supply voltage detection module and including: a first current source for outputtinga first reference current, and a resistance setting unit which is used for setting the bias resistance of the first current source based on the first indication signal, so that the bias resistance ismatched with the power supply voltage; a threshold value setting and detecting module which is coupled to the current bias module and comprises: a threshold value setting unit, the threshold value setting unit being used for setting a plurality of voltage threshold values based on the first reference current and outputting a second indication signal when the power supply voltage is greater than the maximum value of the plurality of voltage threshold values, and a filtering and shaping unit which is used for filtering and shaping the second indication signal so as to generate a power-on reset signal of the power supply. In this way, the power-on reset circuit of the power supply is low in power consumption and high in reliability.

Owner:HANGZHOU SDIC MICROELECTRONICS

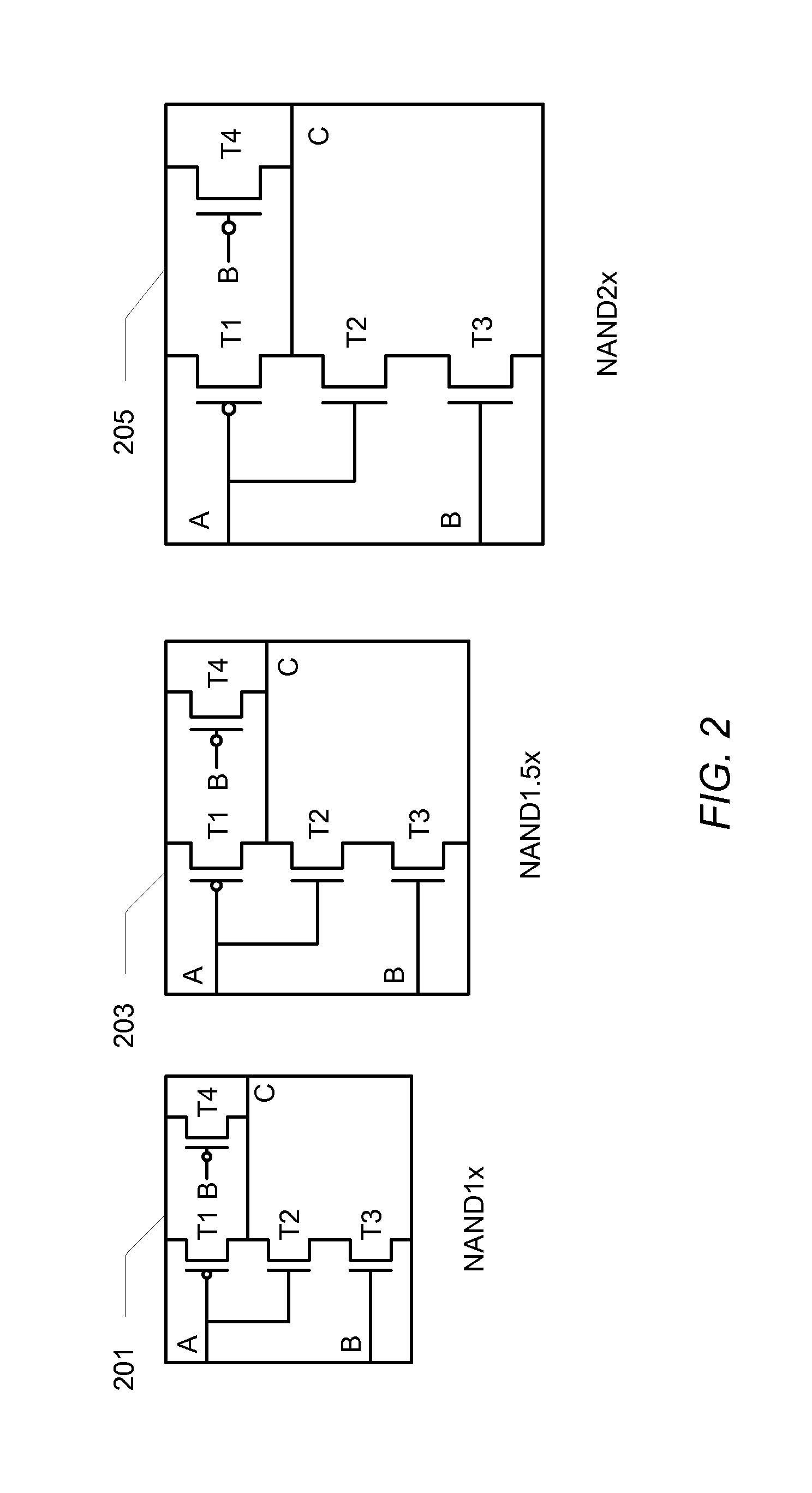

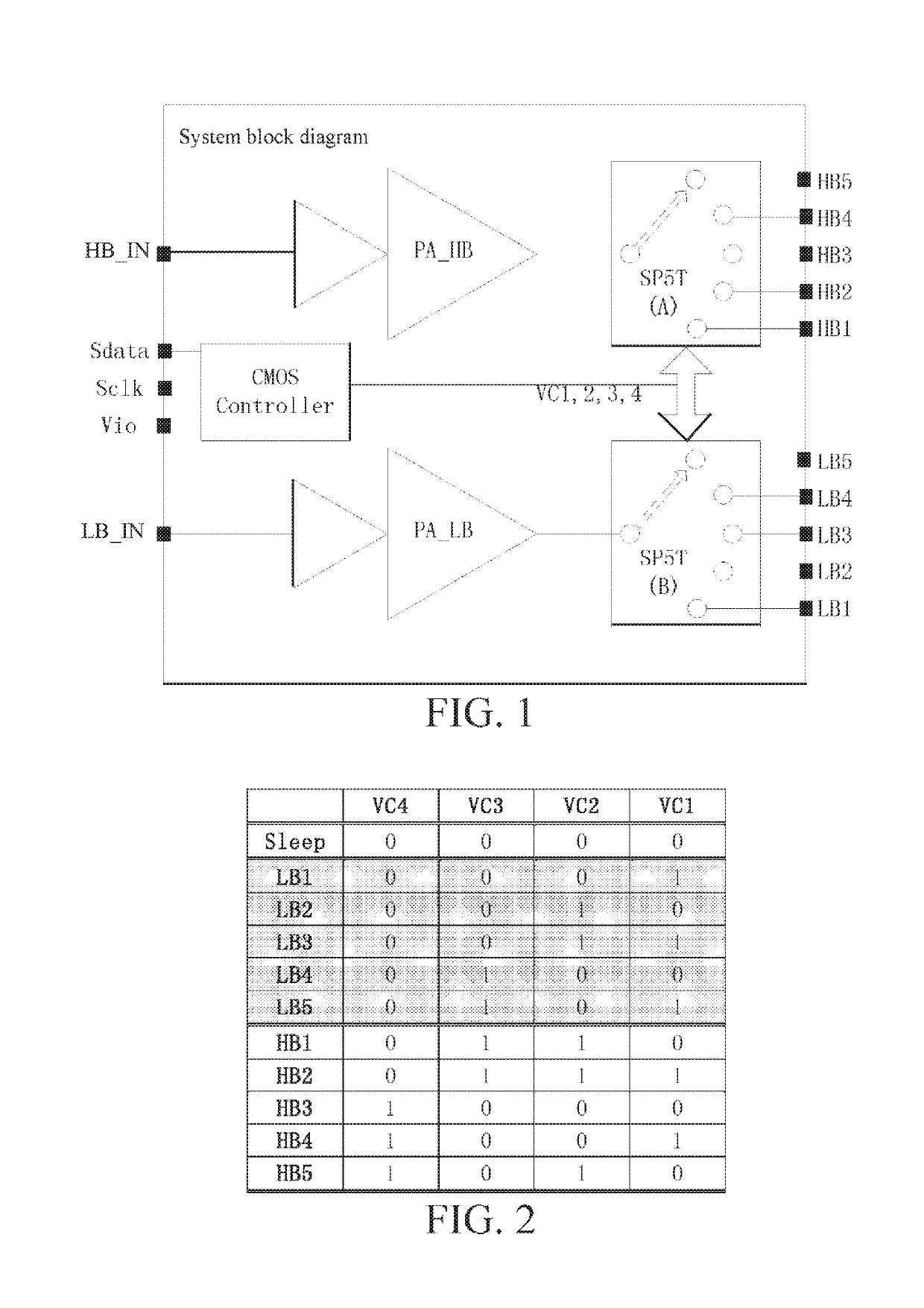

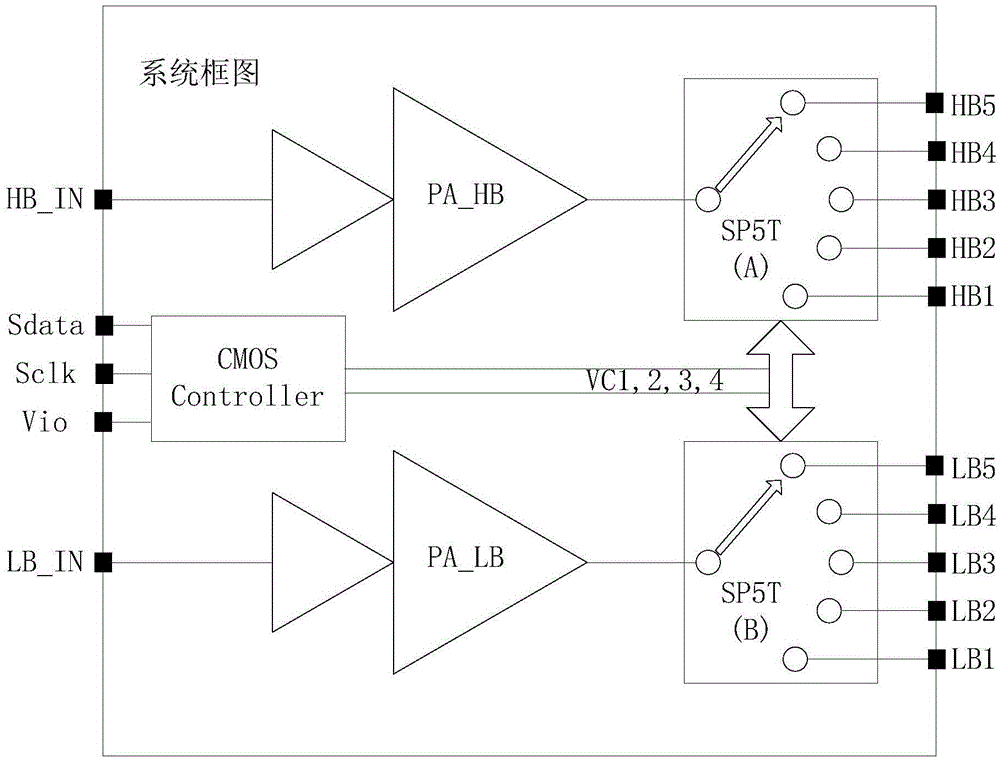

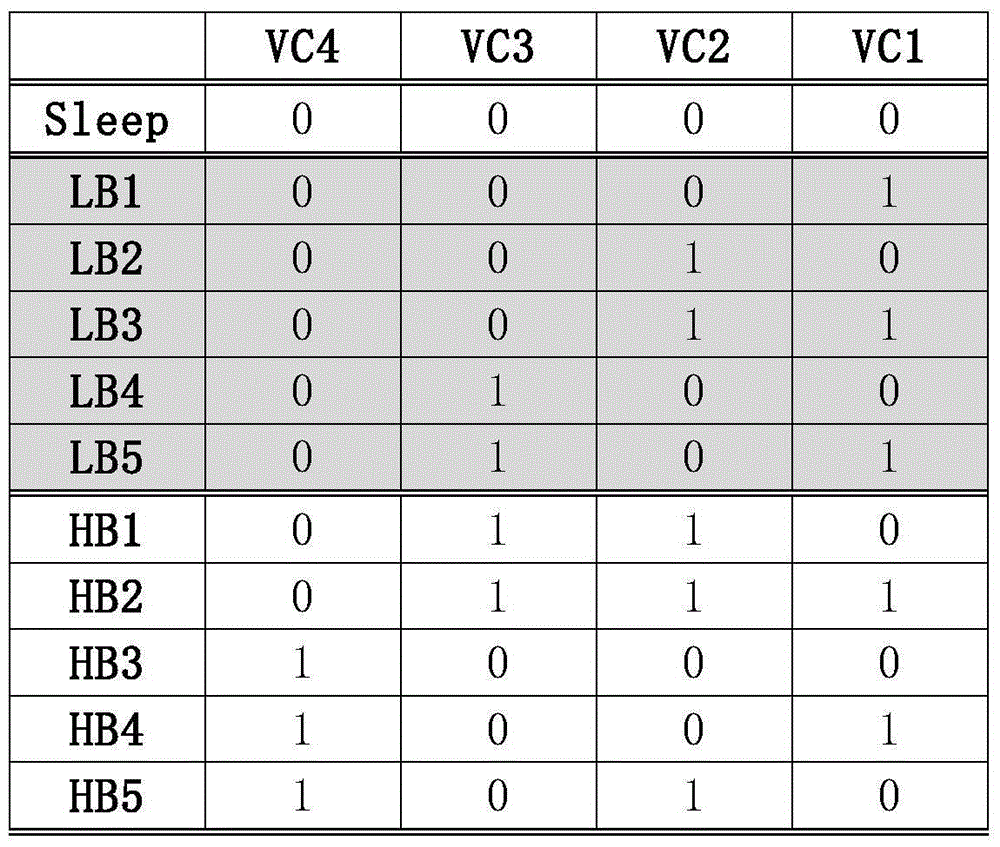

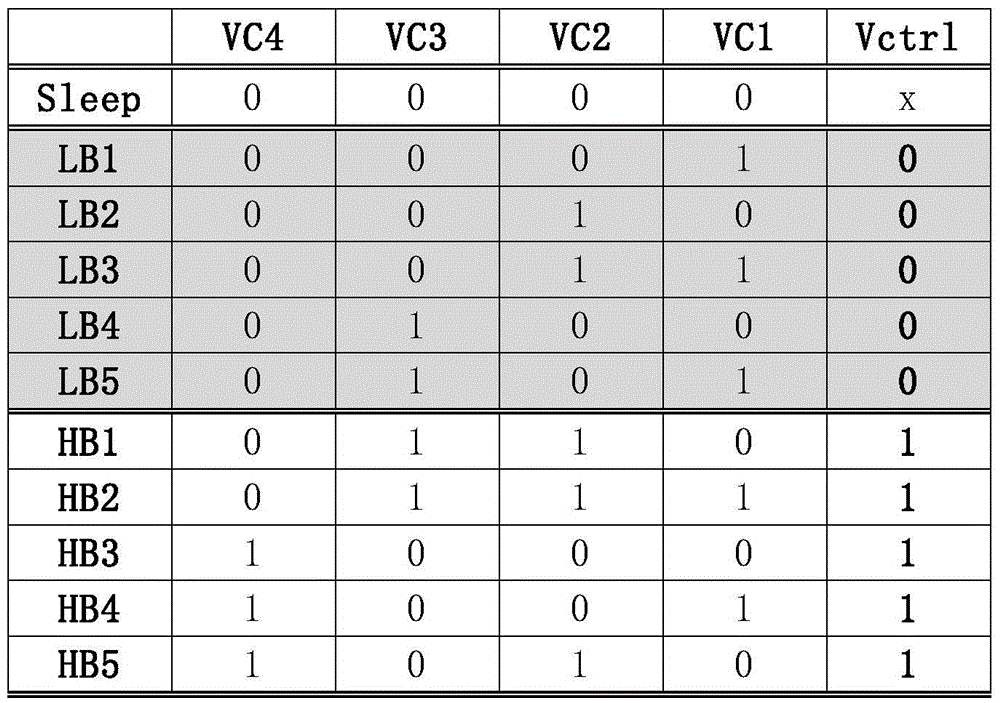

Variable coding method for realizing chip reuse and communication terminal therefor

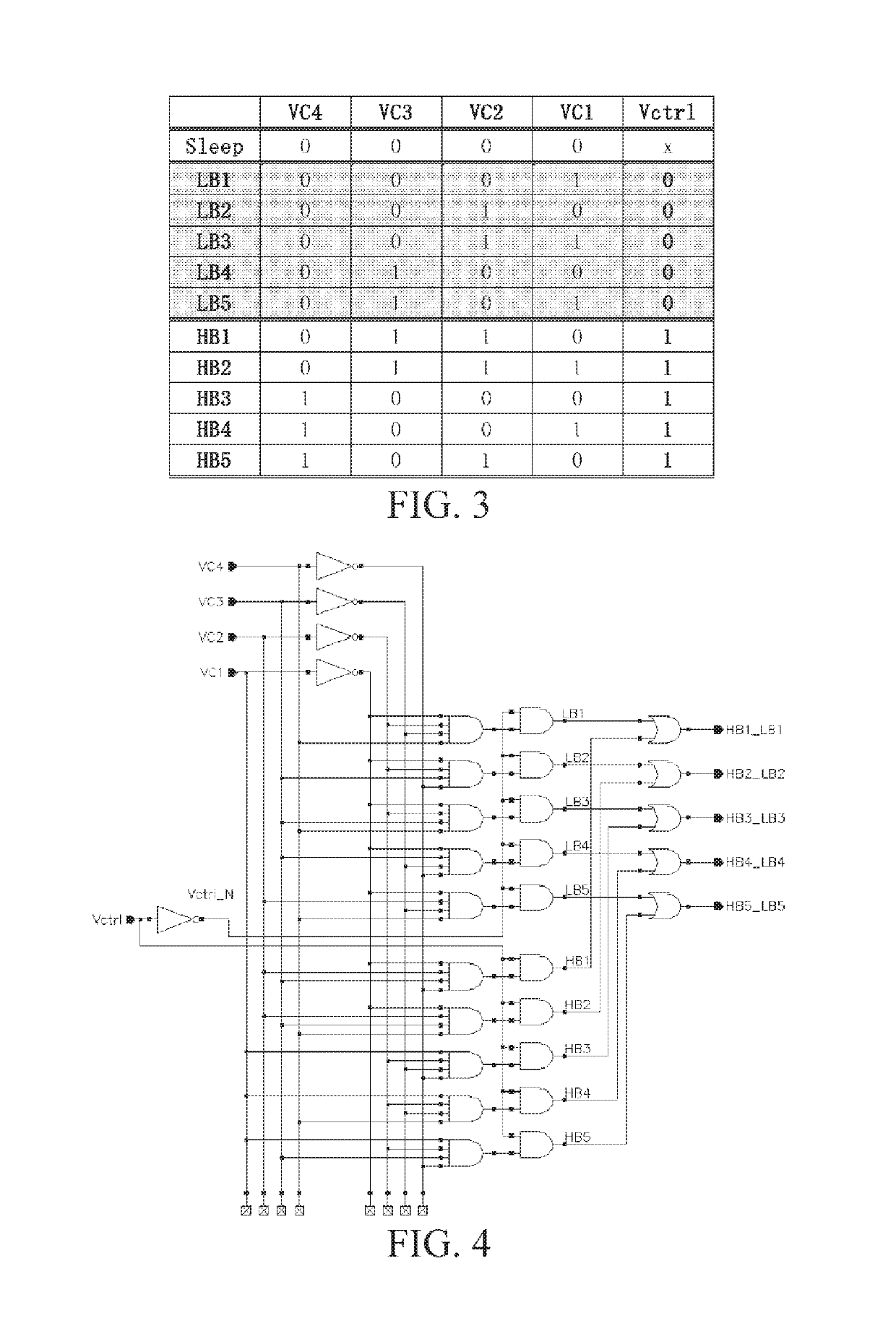

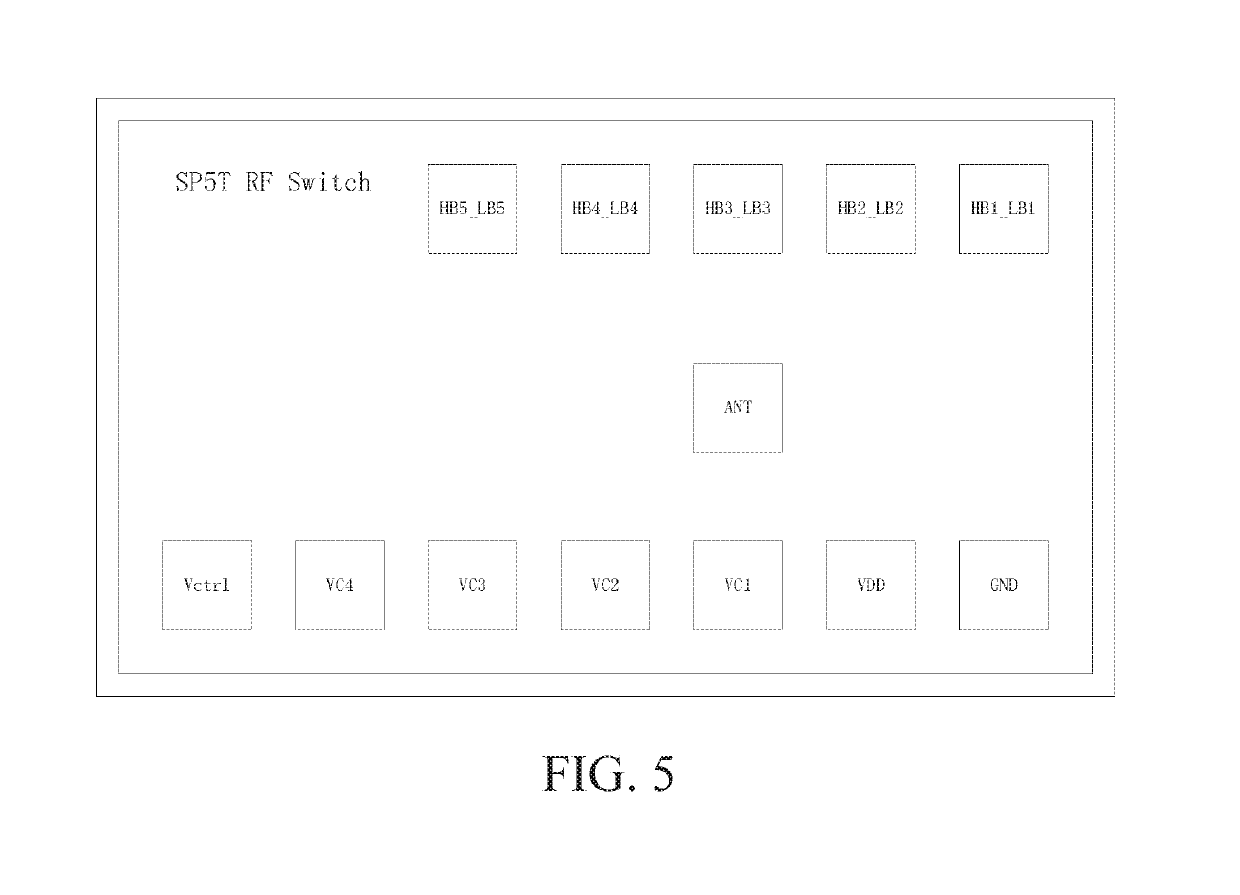

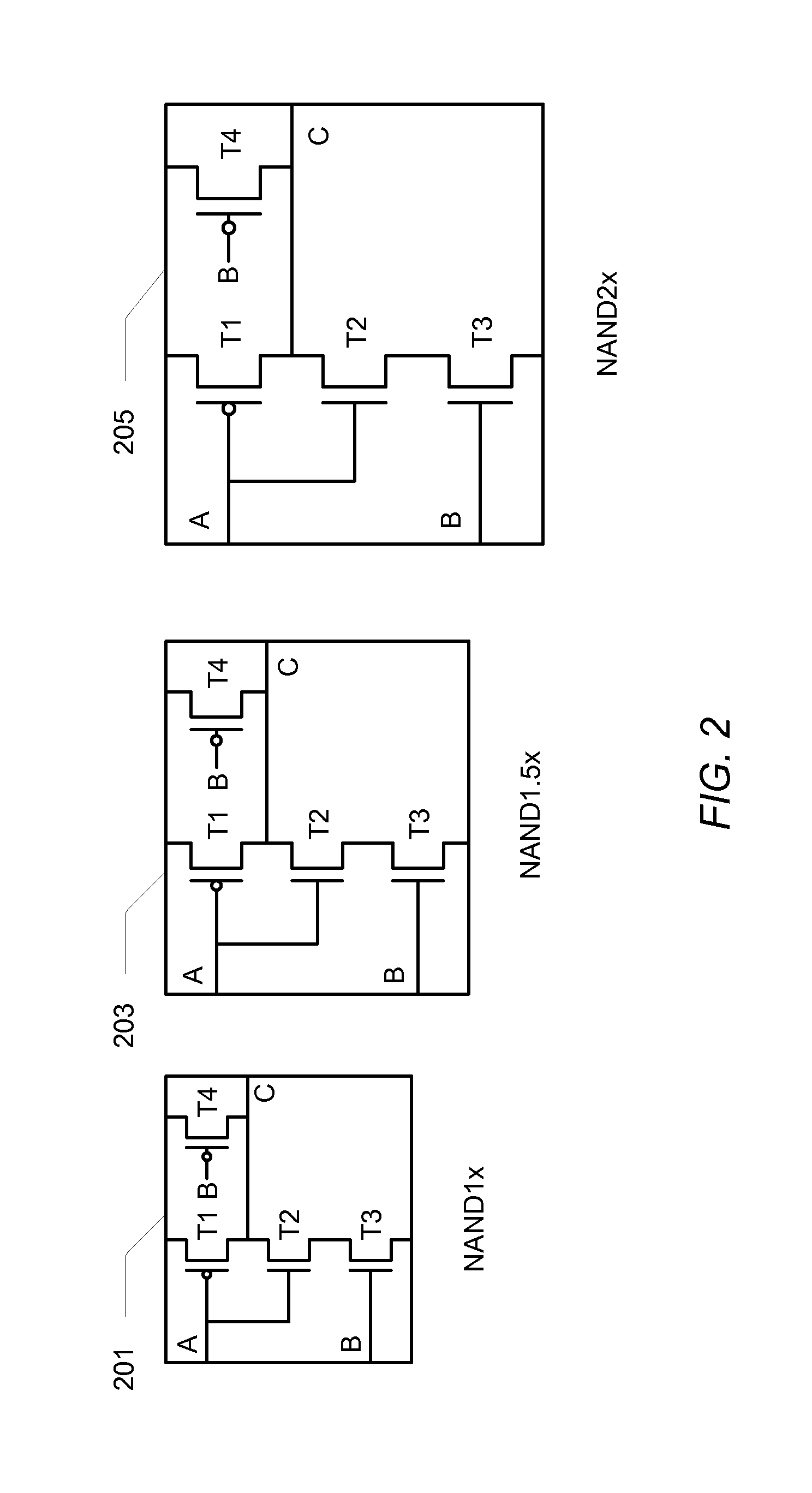

ActiveUS10320385B2Simplified typesReduce complexityExclusive-OR circuitsMultistate logicComputer architectureControl signal

Disclosed is a variable coding method for realizing chip reuse, comprising the following steps: using at least two identical integrated circuit chips, wherein each integrated circuit chip executes different control logic truth tables according to different gating signals; introducing at least one logical control signal as a gating signal; and controlling the logical control signal, so that each integrated circuit chip respectively executes a corresponding control logic truth table. Also disclosed is a communication terminal using the variable coding method for realizing chip reuse. Two or more completely identical integrated circuit chips can be used to realize different logical control functions, thereby simplifying the type of a chip for realizing a system function, and greatly reducing the development costs of an integrated circuit system and the management complexity of a mass production supply chain.

Owner:VANCHIP TIANJIN TECH

Level shifter

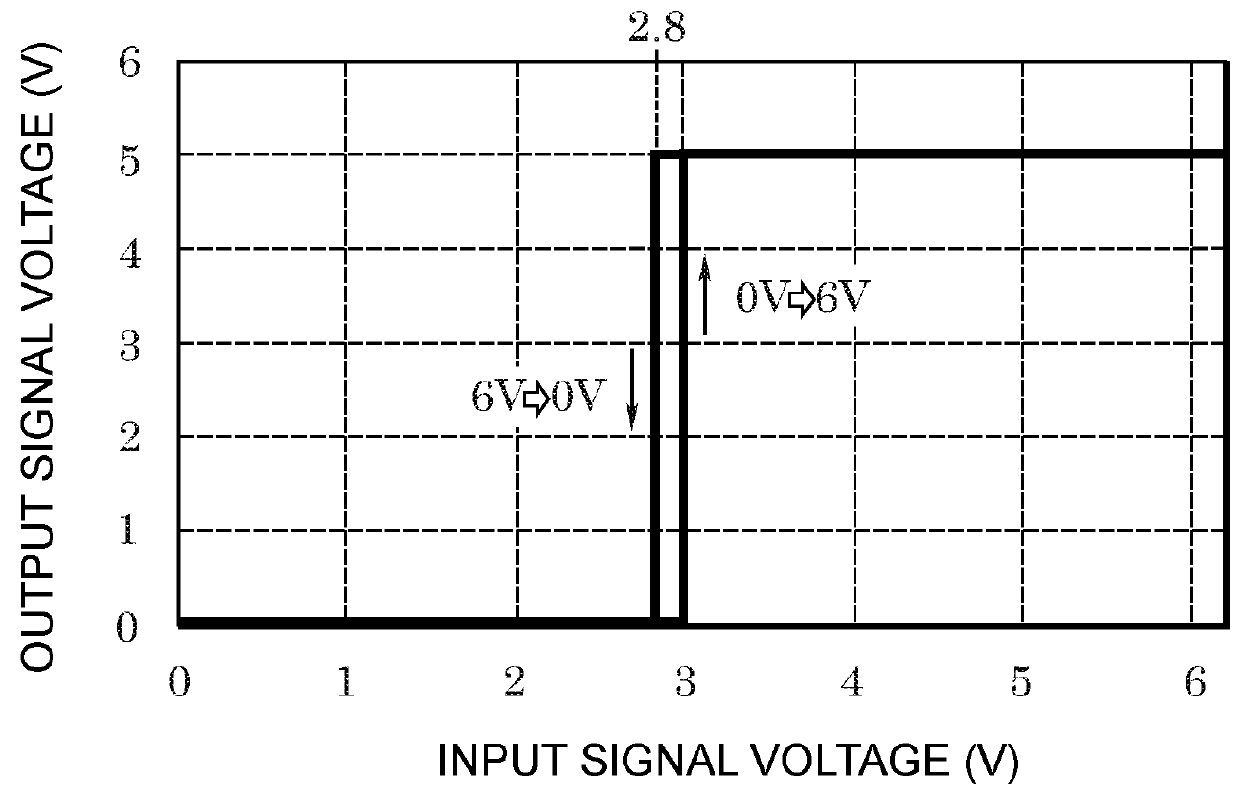

InactiveUS20180109260A1Improve noise marginAvoid failureReliability increase in bipolar transistorsLogic circuits using semiconductor devicesEngineeringThreshold voltage

The present disclosure provides a level shifter including: a level shifter section that is driven by a first power source voltage, and that, in accordance with switching of an input signal of a voltage lower than the first power source voltage, switches an output signal that has been level-shifted, from the first power source voltage to a voltage lower than the first power source voltage; and a threshold voltage changing circuit that, in accordance with a switching direction of the input signal, changes a threshold voltage of the input signal for switching the output signal.

Owner:KK TOKAI RIKA DENKI SEISAKUSHO

Variable coding method for implementing chip reuse and communication terminal thereof

ActiveCN106803756ASimplified typesReduce development costsMultistate logicReliability increase in bipolar transistorsComputer architectureControl signal

The invention discloses a variable coding method for implementing chip reuse. The method includes the following steps: using at least two same integrated circuit chips of which each controls logic truth tables based on the differences of gating signals; introducing at least one logical control signal as a gating signal; controlling the logic control signal, such that respective integrated circuit chip controls the logic truth table accordingly. The invention also discloses a communication terminal for implementing chip reuse by using the variable coding method. According to the invention, two completely identical integrated circuit chips or more are enabled to implement different logic control, so that chip types that implement system functions are reduced, development cost of an integrated circuit system is greatly reduced as well as supply chains for mass production.

Owner:VANCHIP TIANJIN TECH

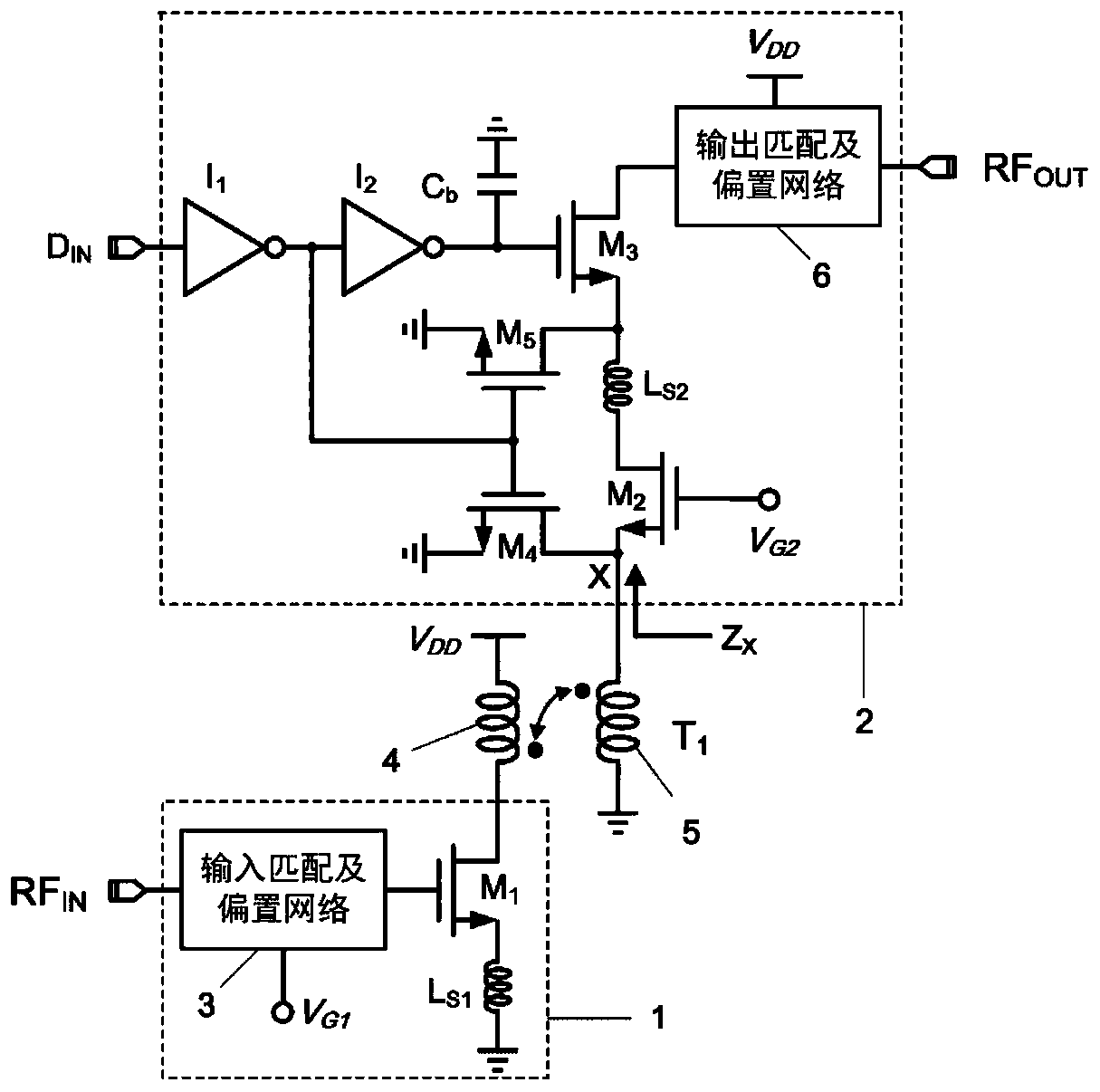

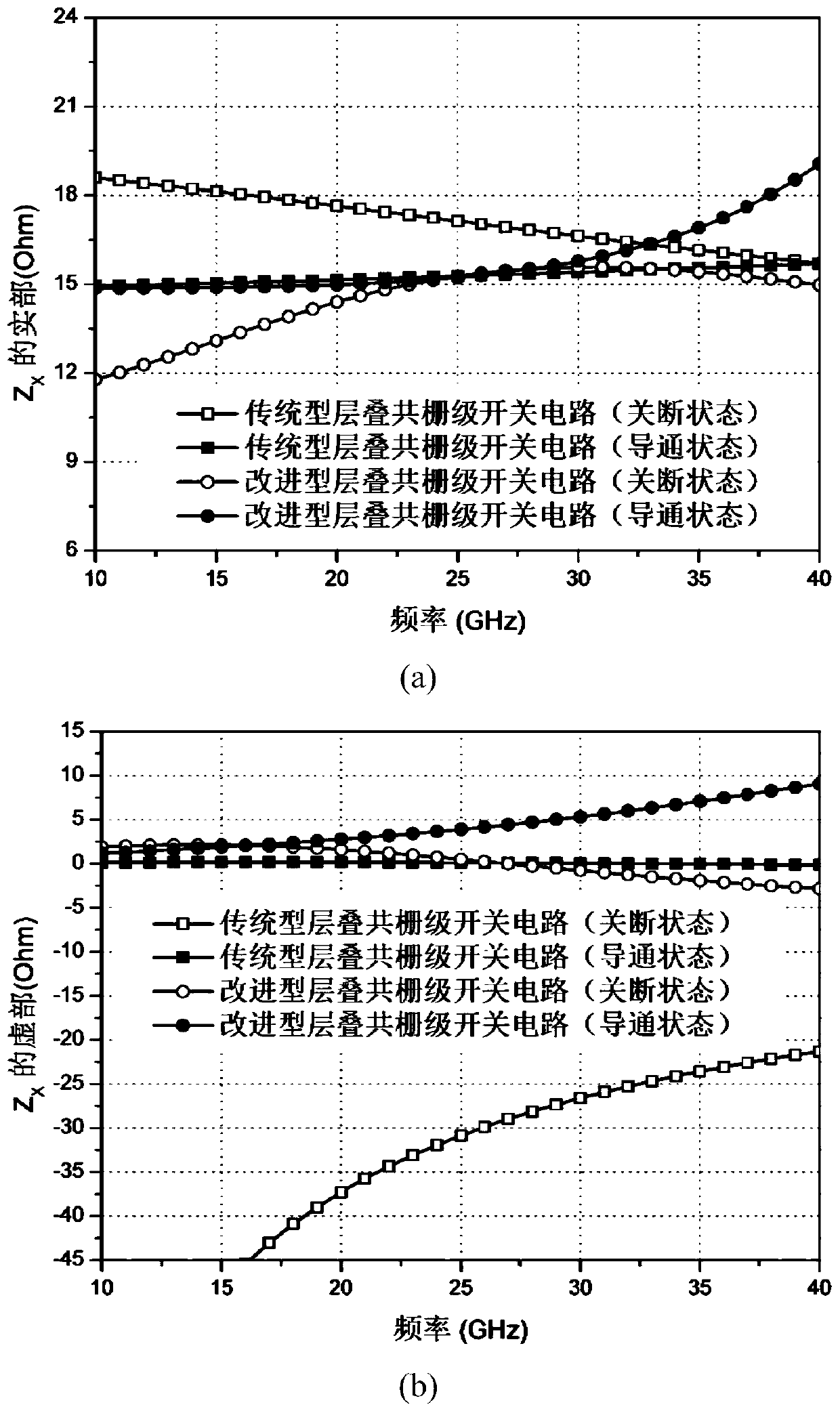

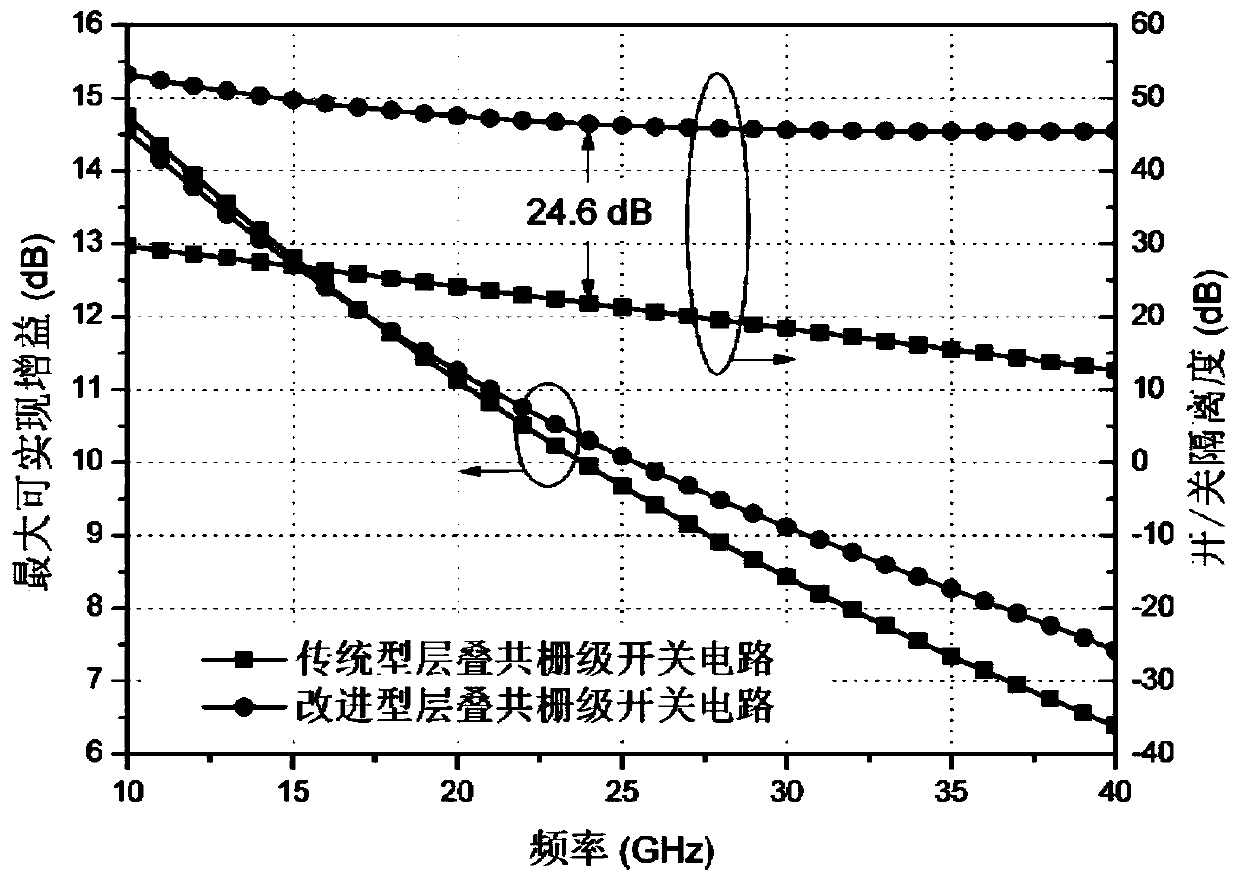

Millimeter wave on-off keying modulator with high isolation and stable input matching

ActiveCN111106823ASmall sizeRelieve stressLogic circuit coupling arrangementsReliability increase in bipolar transistorsTransformerLow voltage

The invention discloses a millimeter wave on-off keying modulator with high isolation and stable input matching. The modulator comprises a cascode circuit, a transformer and an improved stacked cascode switching circuit, according to the improved stacked common-gate switching circuit, a series inductor, a lower-layer switching transistor and an upper-layer switching transistor are added on the basis of a traditional stacked common-gate switching circuit; by optimizing the inductance value of the series inductor and the gate widths of the lower-layer switching transistor and the upper-layer switching transistor, the on / off isolation of the circuit can be improved under the condition that the circuit gain is not influenced, and the input impedance change of the circuit in an on / off state canalso be remarkably reduced; besides, the cascode circuit and the improved stacked common-gate switching circuit are coupled through the transformer, so that small size, low voltage and high gain arerealized, influence of the input impedance change of the improved stacked common-gate switching circuit in an on / off state on input matching of the modulator is further reduced, and more stable inputmatching is realized.

Owner:HANGZHOU DIANZI UNIV

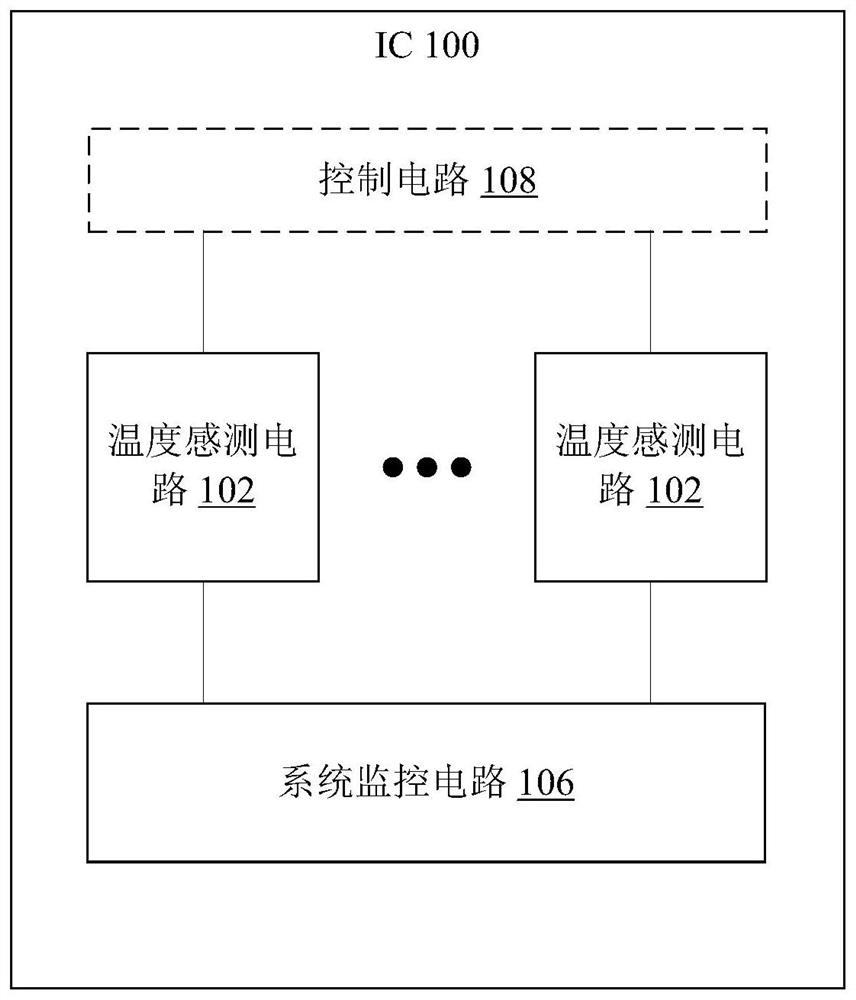

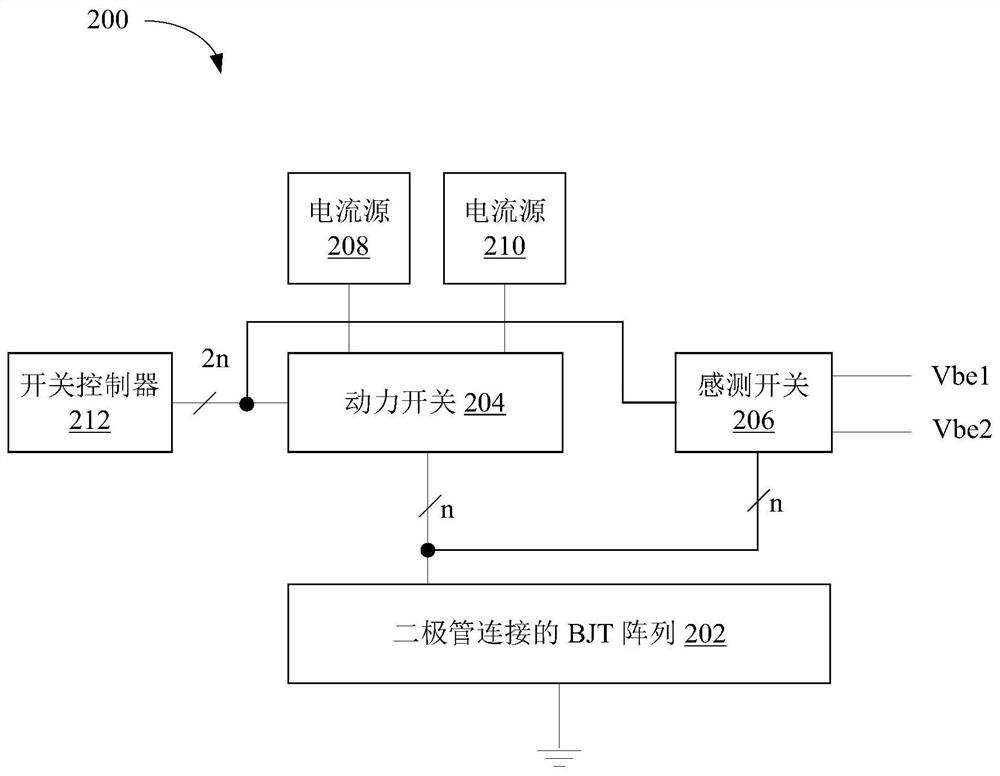

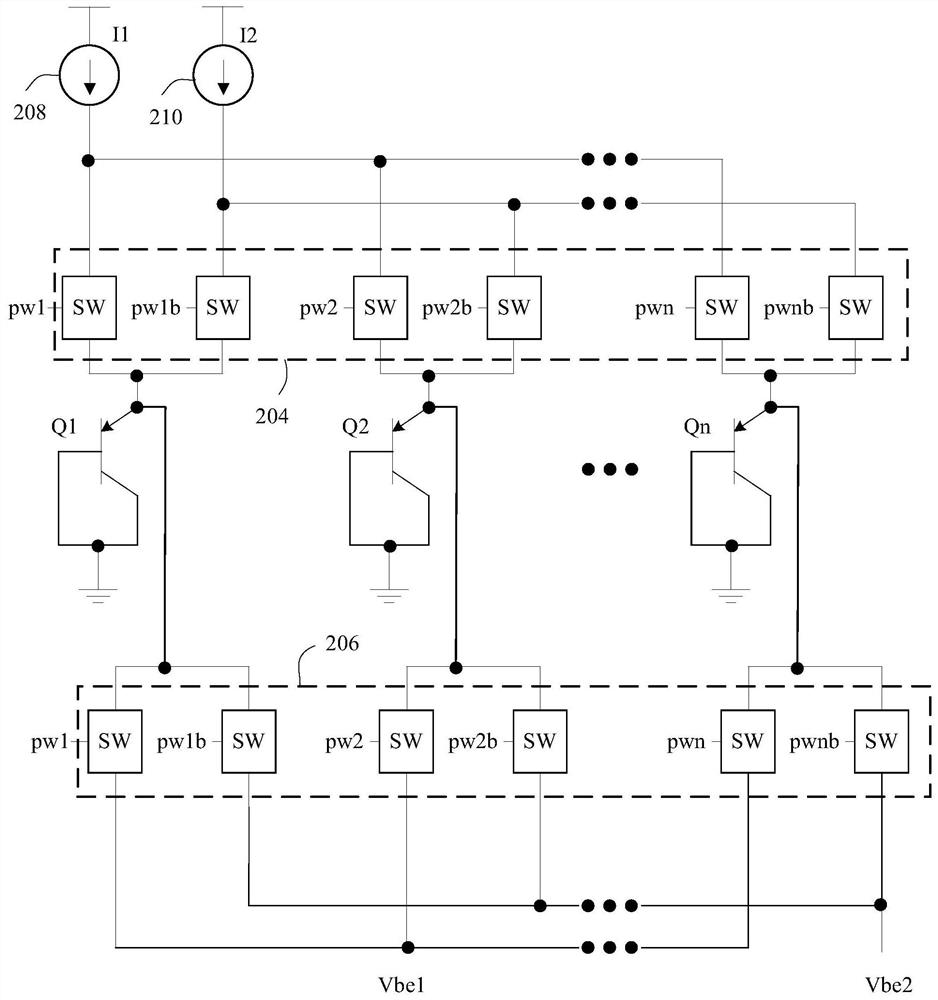

Dynamic Component Matching in Integrated Circuits

ActiveCN110892238BThermometer detailsProgrammable logic circuit arrangementsNode (circuits)Hemt circuits

An example dynamic element matching (DEM) circuit includes: a plurality of bipolar junction transistors (BJTs) (202), each of the plurality of BJTs having a base terminal and a collector terminal coupled to electrical ground; a plurality of power switch pairs (204), each power switch pair coupled to an emitter of a respective one of the plurality of BJTs; a plurality of sensing switch pairs (206), each sensing switch pair being respectively coupled to a plurality of BJTs The emitter of each of the BJTs, the first switch of each sense switch pair is coupled to the first node (Vbel), and the second switch of each sense switch pair is coupled to the second node (Vbe2); a first current source (208) coupled to the first switch in each power switch pair; and a second current source (210) coupled to the second switch in each power switch pair .

Owner:XILINX INC

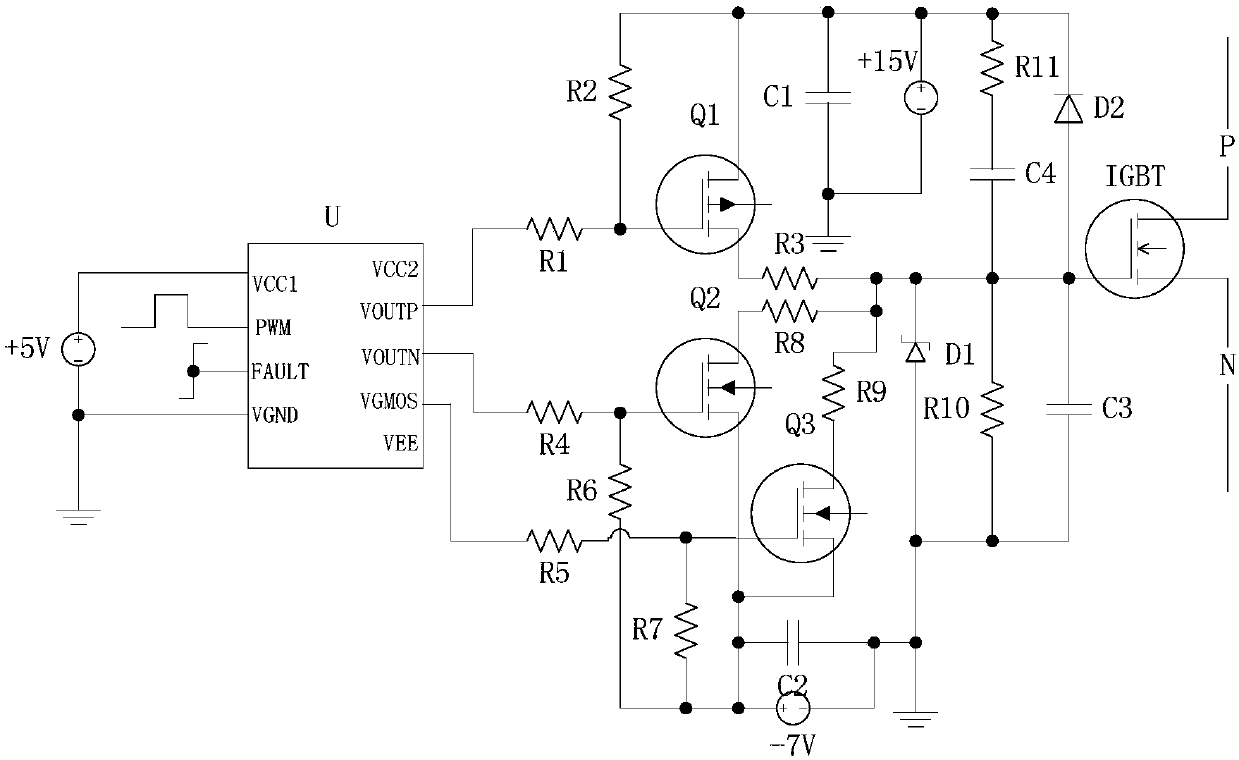

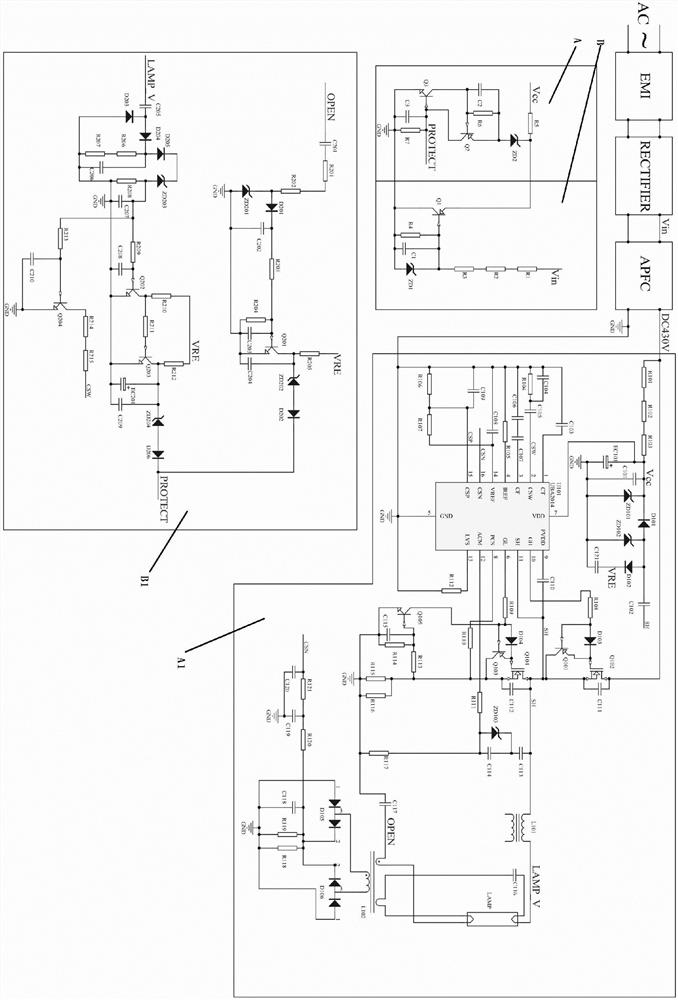

Insulated gate bipolar transistor (IGBT) driving circuit

ActiveCN107707242AProtection conductionSo as not to damageFail-safe circuitsReliability increase in bipolar transistorsOvervoltageEngineering

The invention provides an insulated gate bipolar transistor (IGBT) driving circuit. The IGBT driving circuit comprises a primary side power supply circuit, a secondary side power supply circuit and aprotection circuit, wherein the secondary side power supply circuit is connected with the primary side power supply circuit; the secondary side power supply circuit comprises a high side driving circuit and a low side driving circuit; the high side driving circuit and the low side driving circuit are connected with each other, and output an electric signal to a grid of an IGBT in a cooperative way; a first end of the protection circuit is connected to the grid of the IGBT; a second end of the protection circuit is connected to the high side driving circuit; and when the voltage of the first end of the protection circuit is higher than the voltage of the second end of the protection circuit, the protection circuit is switched on. In the embodiment of the invention, the protection circuit isarranged, and the voltage of the first end of the protection circuit is higher than the voltage of the second end of the protection circuit when the grid of the IGBT is in an overvoltage state to switch on the protection circuit, so that the voltage of the grid of the IGBT is fed back to the high side driving circuit, and the IGBT is protected from being damaged when the grid of the IGBT is in the overvoltage state.

Owner:BEIJING ELECTRIC VEHICLE

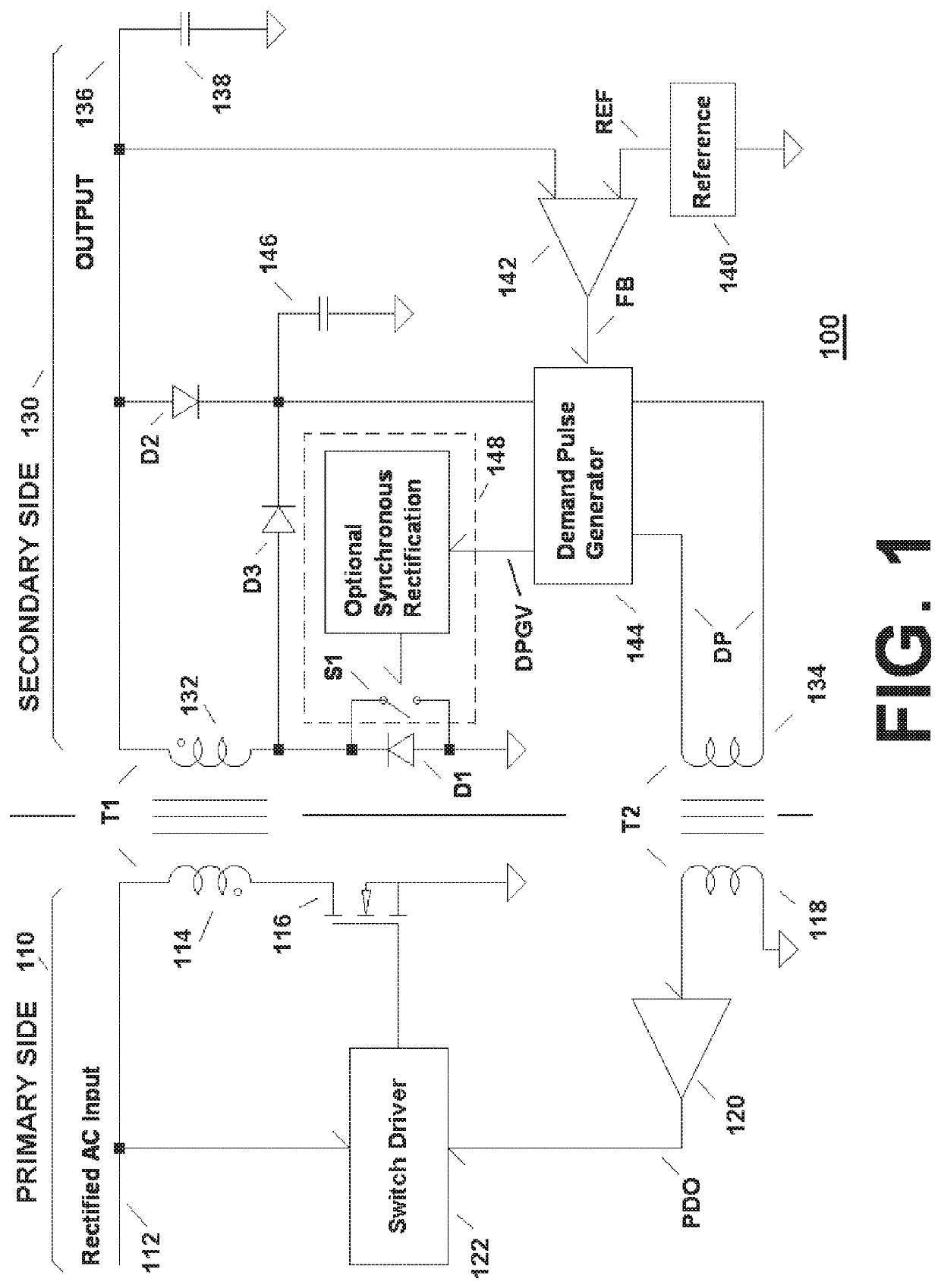

Trigger circuitry for fast, low-power state transitions

ActiveUS10554206B2Little powerFast rising and falling edgesElectronic switchingReliability increase in bipolar transistorsSoftware engineeringHemt circuits

An n-type transistor and a p-type transistor are connected in series such that, when the two transistors are turned on, current flows from the collector of the n-type transistor to the collector of the p-type transistor. A positive-feedback capacitor is connected between the collector of one transistor and the base of the other transistor. The two transistors turn on together when the base voltage of the n-type transistor exceeds the base voltage of the p-type transistor by at least the sum of the turn-on threshold voltages of the two transistors and (i) the two transistors turn off together when the base voltage of the n-type transistor fails to exceed the base voltage of the p-type transistor by at least that sum. The positive-feedback capacitor ensures that the two transistors turn fully on and off together. In certain embodiments, the circuitry can be controlled to operate as a current pulse generator.

Owner:COGNIPOWER

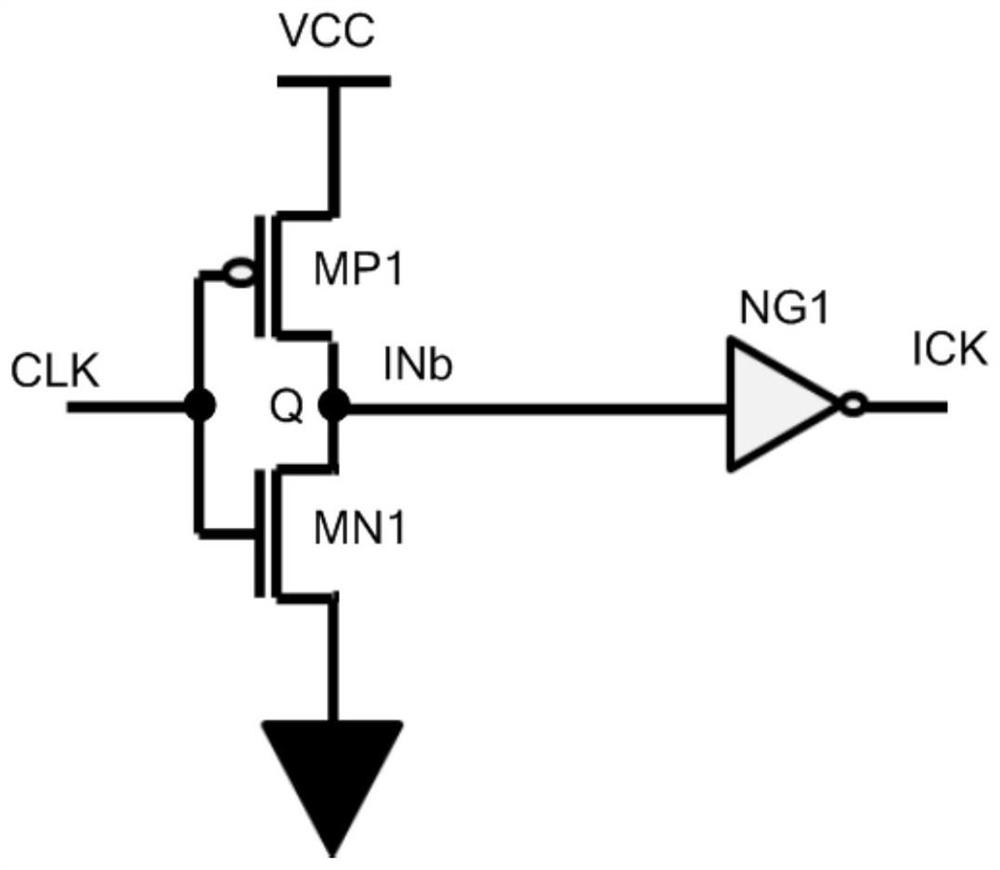

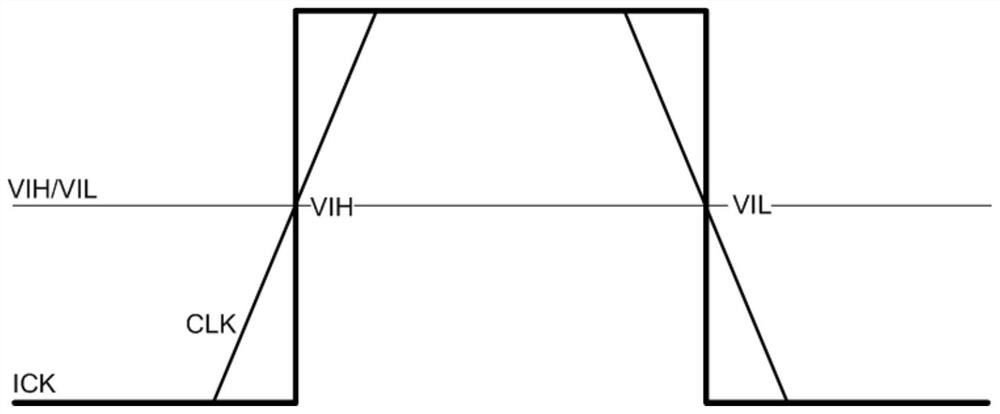

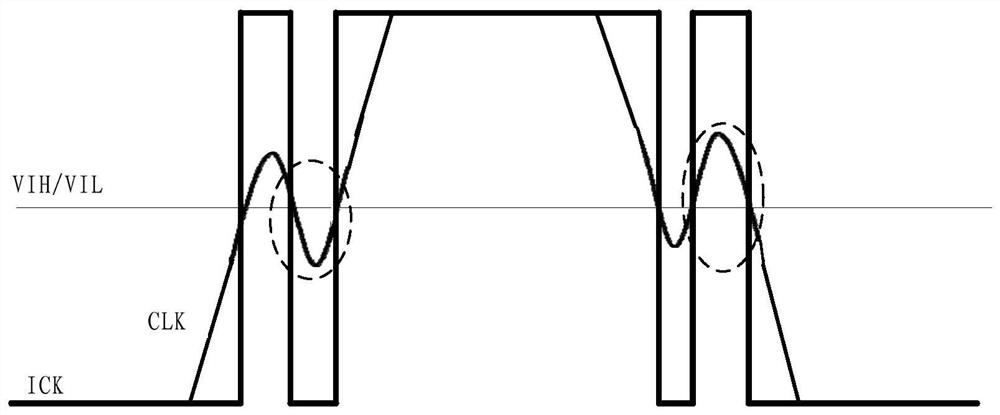

An input buffer circuit and memory

ActiveCN112349332BEliminate distractionsGuaranteed to workRead-only memoriesReliability increase in bipolar transistorsLow voltageHemt circuits

The application discloses an input buffer circuit and a memory. The input buffer circuit of this application, by configuring the input high voltage threshold to be different from the input low voltage threshold, when the input signal is between the input high voltage threshold and the input low voltage threshold, the logic output signal does not perform state switching, thereby eliminating noise on the input signal interference. That is, the present application can filter out the noise in the input signal, avoid the abnormal state of the logic output signal corresponding to the input signal, and ensure the normal operation of the device.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

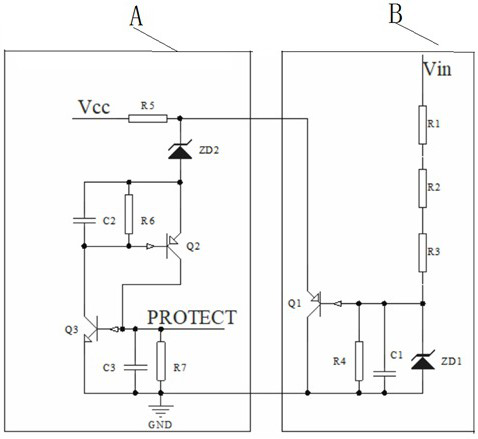

A self-locking circuit and its matched fast unlocking circuit after self-locking occurs

ActiveCN110944423BQuick unlockImprove performanceElectric lighting sourcesReliability increase in bipolar transistorsCapacitanceZener diode

The invention discloses a self-locking circuit and a matching fast unlocking circuit after self-locking, including a self-locking circuit and a fast unlocking circuit, the self-locking circuit is connected with the fast unlocking circuit, and the Vcc pin of the self-locking circuit The fifth resistor is connected to the negative electrode of the second zener diode, the anode of the second zener diode is connected to the emitter of the second switching transistor, and the second capacitor and the second capacitor are connected in parallel between the base and the emitter of the second switching transistor. Six resistors, the collector of the third switching transistor is connected to the base of the second switching transistor, the third capacitor and the seventh resistor are connected in parallel between the emitter and the base of the third switching transistor, and the base of the third switching transistor is also It is connected to the PROTECT pin, and the emitter of the third switching transistor is also connected to the GND pin; the invention not only retains the self-locking characteristic of the self-locking circuit, but also solves the problem caused by the long unlocking time of the self-locking circuit after the input power is cut off.

Owner:北京东方百士电子有限公司

Reducing narrow gate width effects in an integrated circuit design

InactiveUS8533645B2Solid-state devicesReliability increase in bipolar transistorsEngineeringChannel width

A method for reducing narrow gate width effects in an integrated circuit includes finding the smallest transistor channel widths that are larger than the minimum width for the technology for library cells that produce logic blocks that meet timing constraints while using the least amount of power and have the smallest possible area. The method may include characterizing a device library while varying process, voltage and temperature parameters, and synthesizing an HDL representation of a functional logic block including cells from the device library. The method may also include determining whether timing, area, and power values of the functional logic block are within a predetermined range. In response to the timing, area, and power values not being within the predetermined range, iteratively increasing the channel width of at least a portion of the transistors of at least one of the cells in the device library.

Owner:APPLE INC

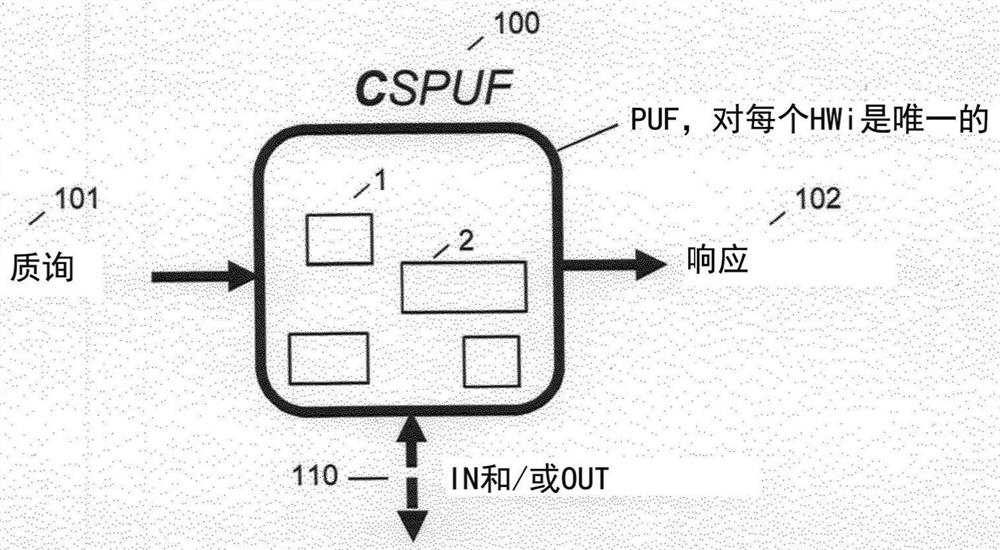

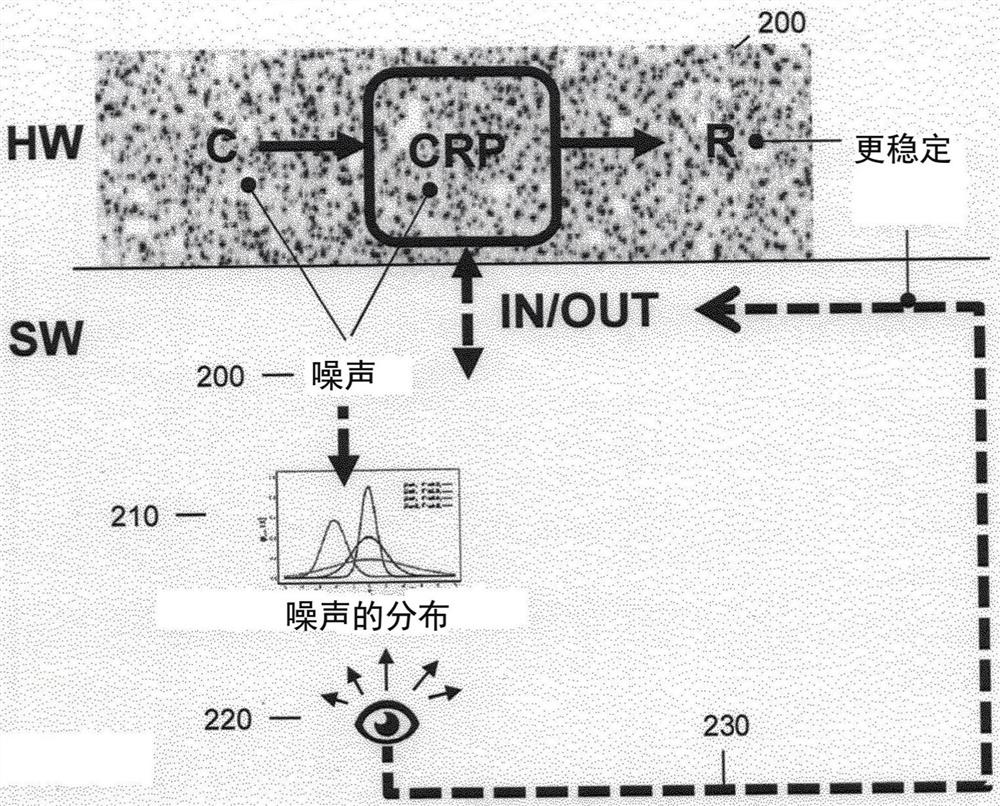

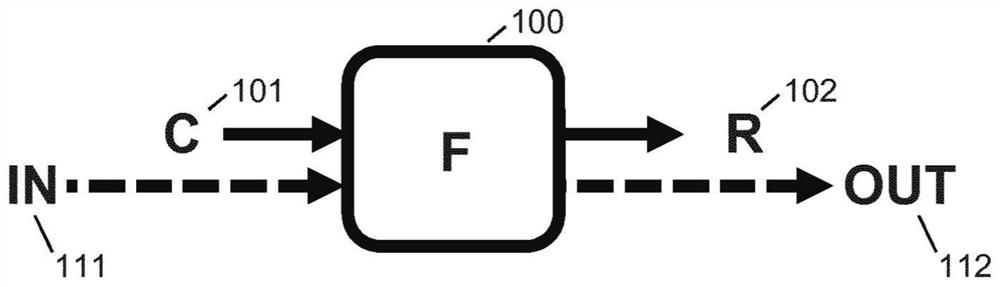

Connected synthetic physically unclonable function

PendingCN112805767AEnhanced unclonabilityManage agingReliability increase in bipolar transistorsCoding/ciphering apparatusDigital signatureExternal data

There is disclosed a connected synthetic physically unclonable function(acronym CSPUF) made of a circuit configured to receive signals of one or more sensors and / or actuators in / of a computer device; determine one or more statistical properties of the noise distribution of said selected one or more of said sensors and / or actuators; receive data IN from one or more external data sources; determine one or more digital signatures (responses) from said statistical properties and said selected external data. In one embodiment, along a response R when challenged by a challenge C, the circuit is configured to receive data IN and / or to communicate data OUT from one or more external data sources. Developments describe uses and advantages of data IN and data OUT channels, e.g. static or dynamic calibration, options to disable the circuit. Other embodiments consider variants of interconnections of two CSPUF circuits, providing self-cycled, iterative, cascaded and other blockchain arrangements.

Owner:SECURE IC

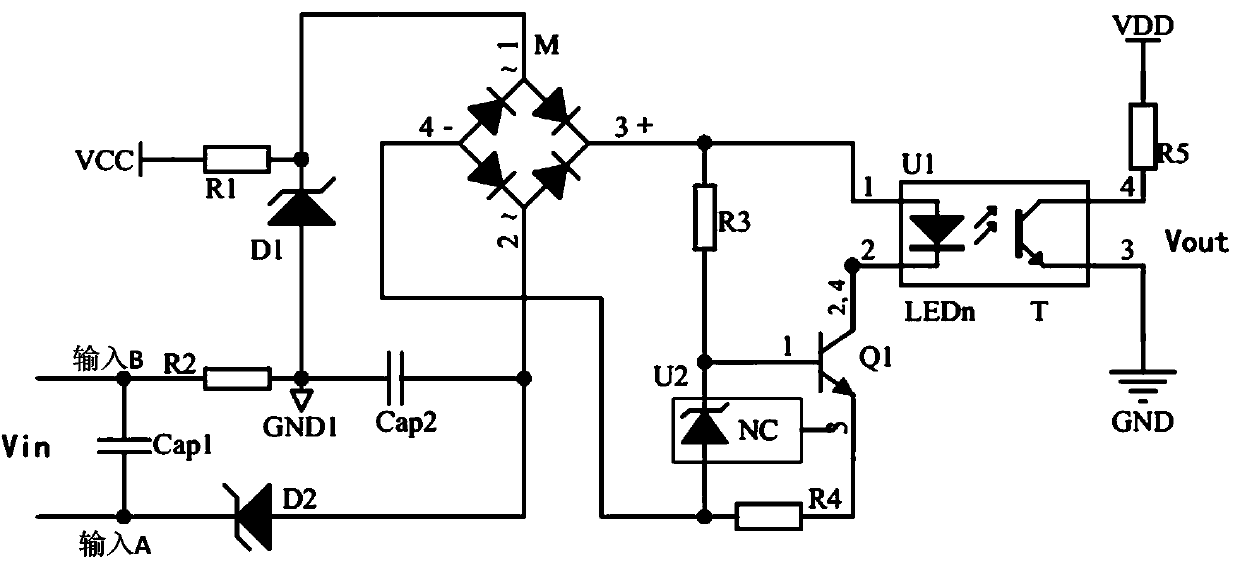

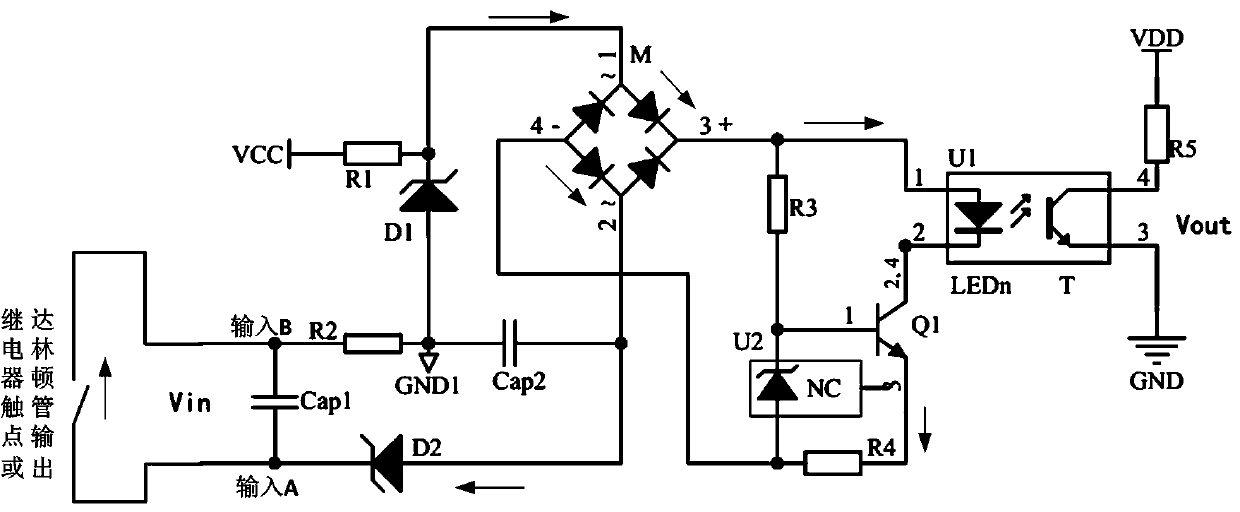

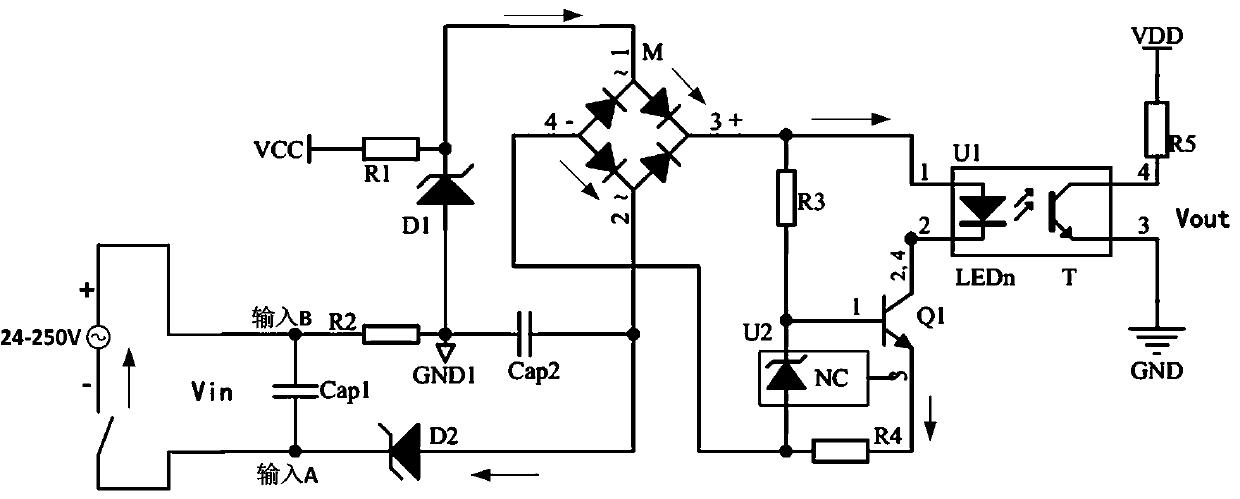

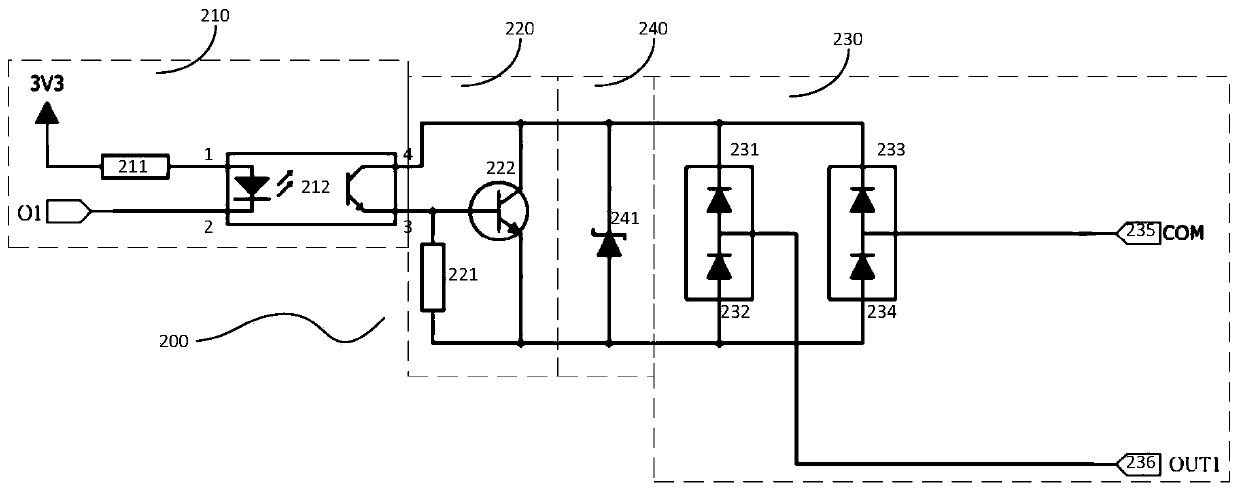

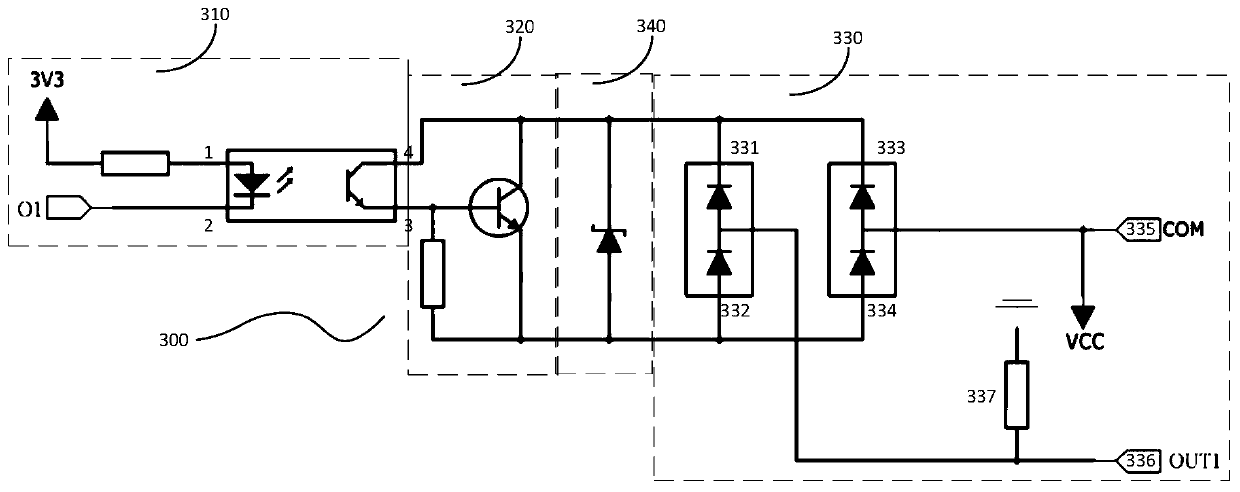

A switch input circuit for relay protection tester

ActiveCN106788381BWill not pose a safety hazardReliability increase in bipolar transistorsCapacitanceHemt circuits

The invention discloses an on-off input circuit for a relay protection testing device. The circuit consists of a voltage stabilizing diode, a rectification bridge circuit, a photoelectric coupler circuit, a triode switching circuit, a filter capacitor and a voltage stabilizing reference power circuit. The on-off input circuit for the relay protection testing device is self-adaptive about various types of the input patterns, and the pre-configuration does not need to be executed; and the on-off input circuit for the relay protection testing device is self-adaptive about the polarity of the active input, even the reverse connection can be correctly identified, and the potential safety hazard cannot be caused by the polarity of the input. The on-off input circuit for the relay protection testing device is provided with the potential output, and is capable of providing the power for the high-speed output of the Darlington tube type, and reducing the external connections.

Owner:XIANGTAN UNIV

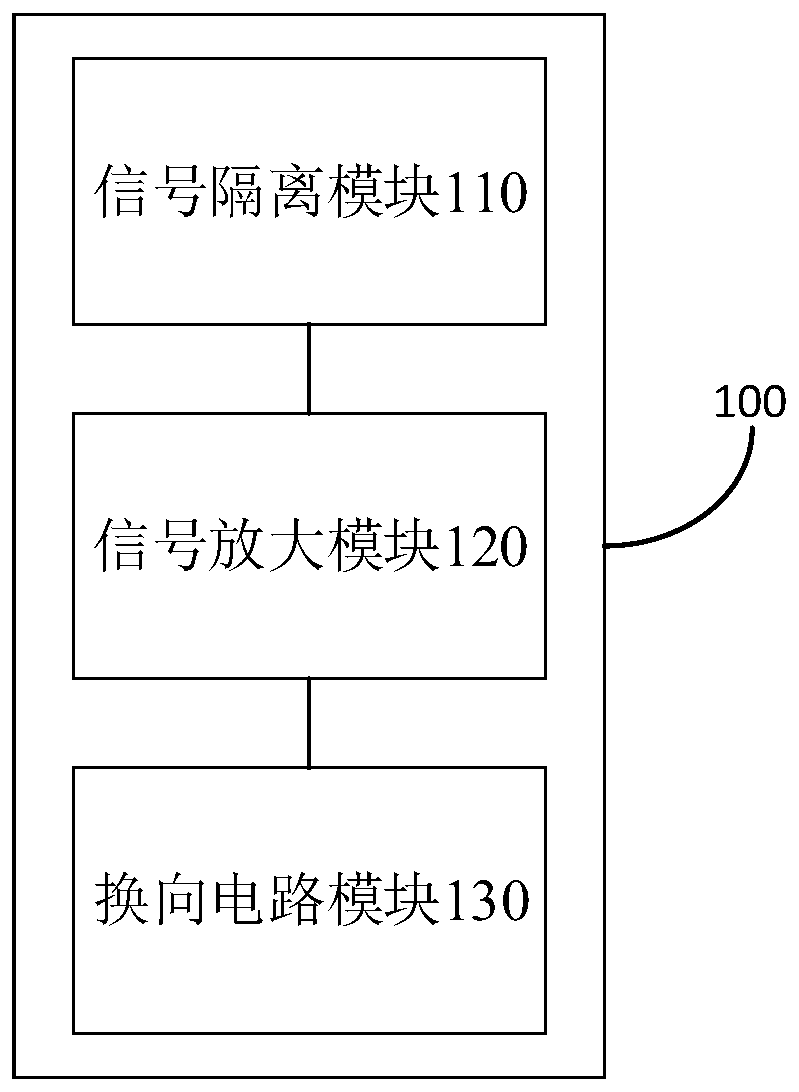

Output circuit and servo driver

PendingCN111064463AInput/output impedence modificationLogic circuit coupling arrangementsControl engineeringElectrical polarity

The invention provides an output circuit and a servo driver. The output circuit comprises a signal isolation module, a signal amplification module and a commutation circuit module, all of which are connected in sequence, the signal isolation module is used for connecting a control pin of the servo driver, receiving a state signal output by the servo driver, electrically isolating the state signaland transmitting the state signal to the signal amplification module; the signal amplification module is used for carrying out signal amplification processing on the state signal; and the commutationcircuit module is used for automatically adjusting the current direction of the state signal, so that the state signal after signal amplification is output according to a preset output polarity. According to the output circuit, electrical interference to the servo driver when the state signals are obtained can be reduced through electrical isolation, the load capacity of the circuit can be enhanced after the signals are amplified, and the preset output polarity can be selected so as to be compatible with output devices with different polarities.

Owner:深圳市嘉昱机电有限公司

Popular searches

Logic circuit coupling/interface arrangements Electric switches Emergency protective arrangements for automatic disconnection Relays Electric variable regulation Voltage/current interference elimination Synchronising arrangement Testing water Electric digital data processing Logic circuit interface arrangements

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com