Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

940 results about "8-bit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer architecture, 8-bit integers, memory addresses, or other data units are those that are 8 bits (1 octet) wide. Also, 8-bit CPU and ALU architectures are those that are based on registers, address buses, or data buses of that size. 8-bit is also a generation of microcomputers in which 8-bit microprocessors were the norm.

Multi-dimensional data protection and mirroring method for micro level data

ActiveUS7103824B2Detection errorLow common data sizeCode conversionCyclic codesData validationData integrity

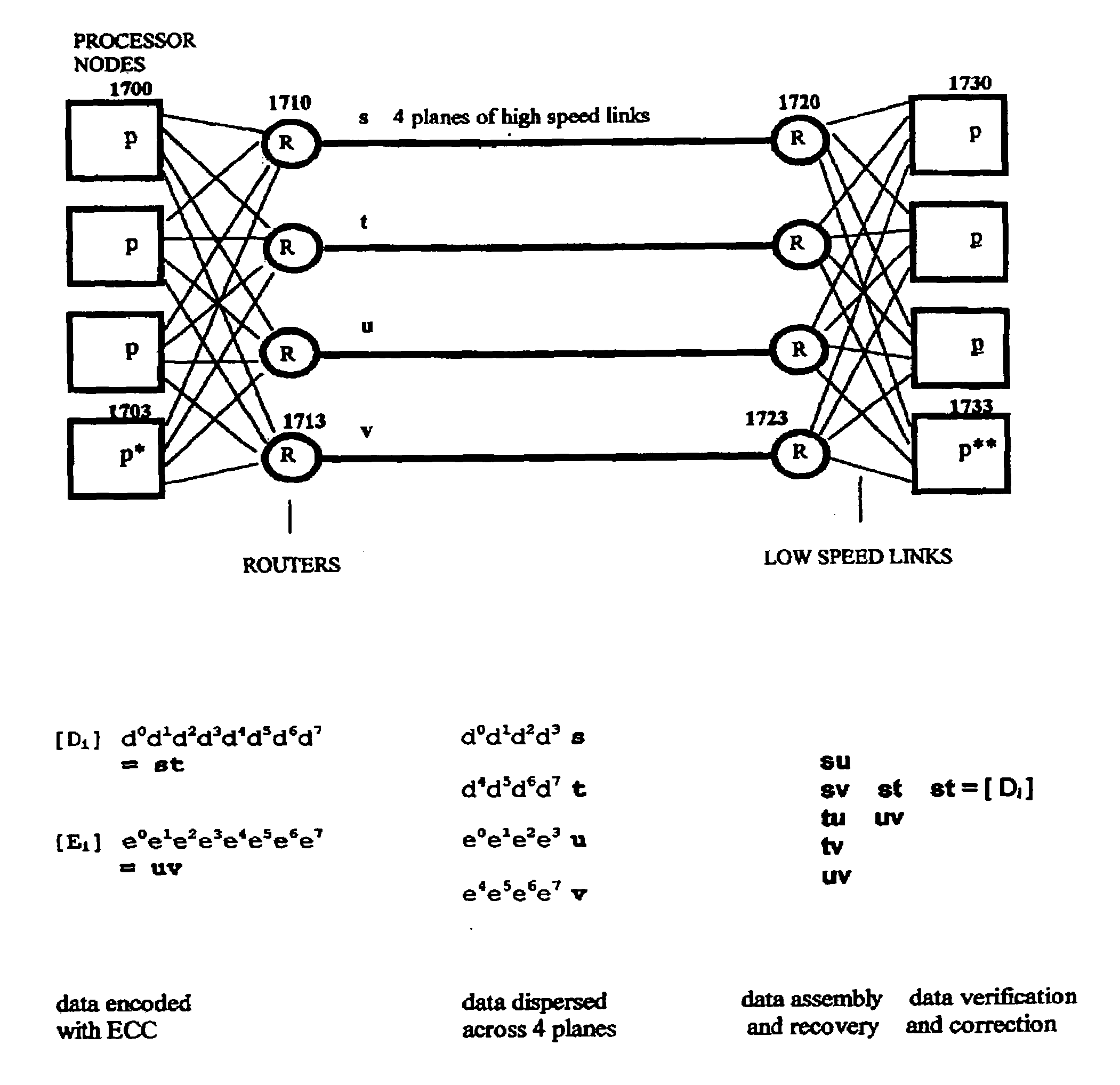

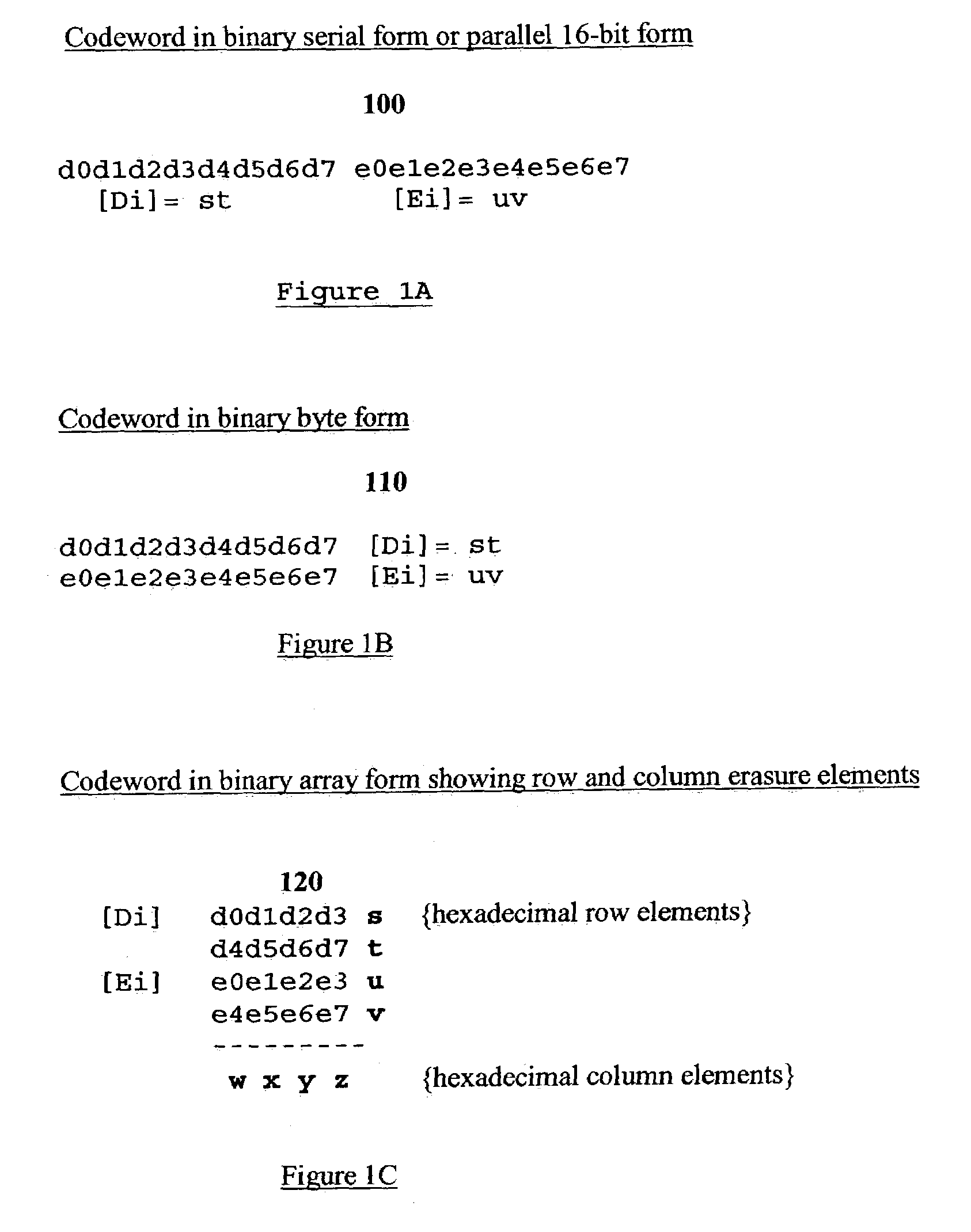

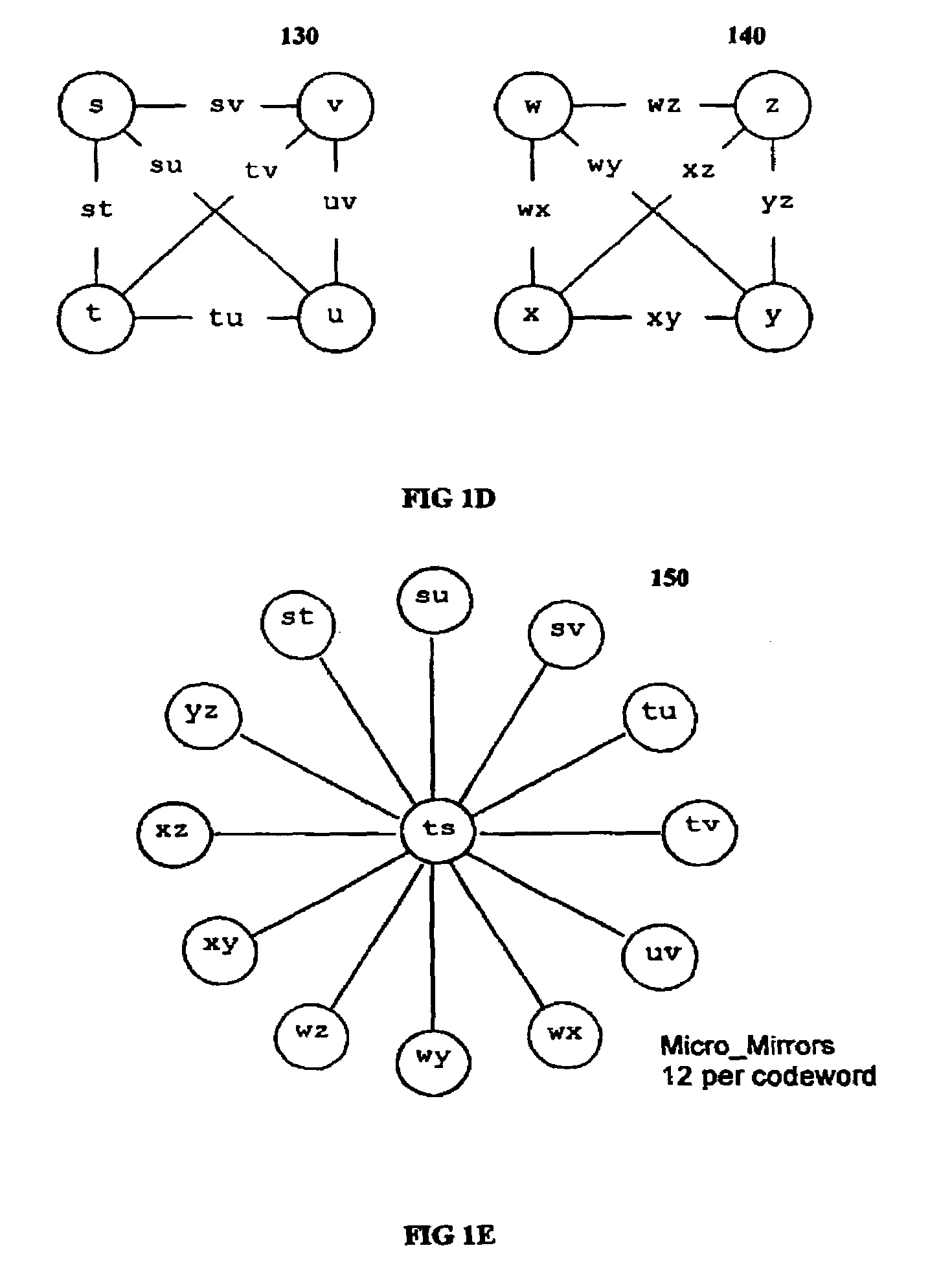

The invention discloses a data validation, mirroring and error / erasure correction method for the dispersal and protection of one and two-dimensional data at the micro level for computer, communication and storage systems. Each of 256 possible 8-bit data bytes are mirrored with a unique 8-bit ECC byte. The ECC enables 8-bit burst and 4-bit random error detection plus 2-bit random error correction for each encoded data byte. With the data byte and ECC byte configured into a 4 bit×4 bit codeword array and dispersed in either row, column or both dimensions the method can perform dual 4-bit row and column erasure recovery. It is shown that for each codeword there are 12 possible combinations of row and column elements called couplets capable of mirroring the data byte. These byte level micro-mirrors outperform conventional mirroring in that each byte and its ECC mirror can self-detect and self-correct random errors and can recover all dual erasure combinations over four elements. Encoding at the byte quanta level maximizes application flexibility. Also disclosed are fast encode, decode and reconstruction methods via boolean logic, processor instructions and software table look-up with the intent to run at line and application speeds. The new error control method can augment ARQ algorithms and bring resiliency to system fabrics including routers and links previously limited to the recovery of transient errors. Image storage and storage over arrays of static devices can benefit from the two-dimensional capabilities. Applications with critical data integrity requirements can utilize the method for end-to-end protection and validation. An extra ECC byte per codeword extends both the resiliency and dimensionality.

Owner:HALFORD ROBERT

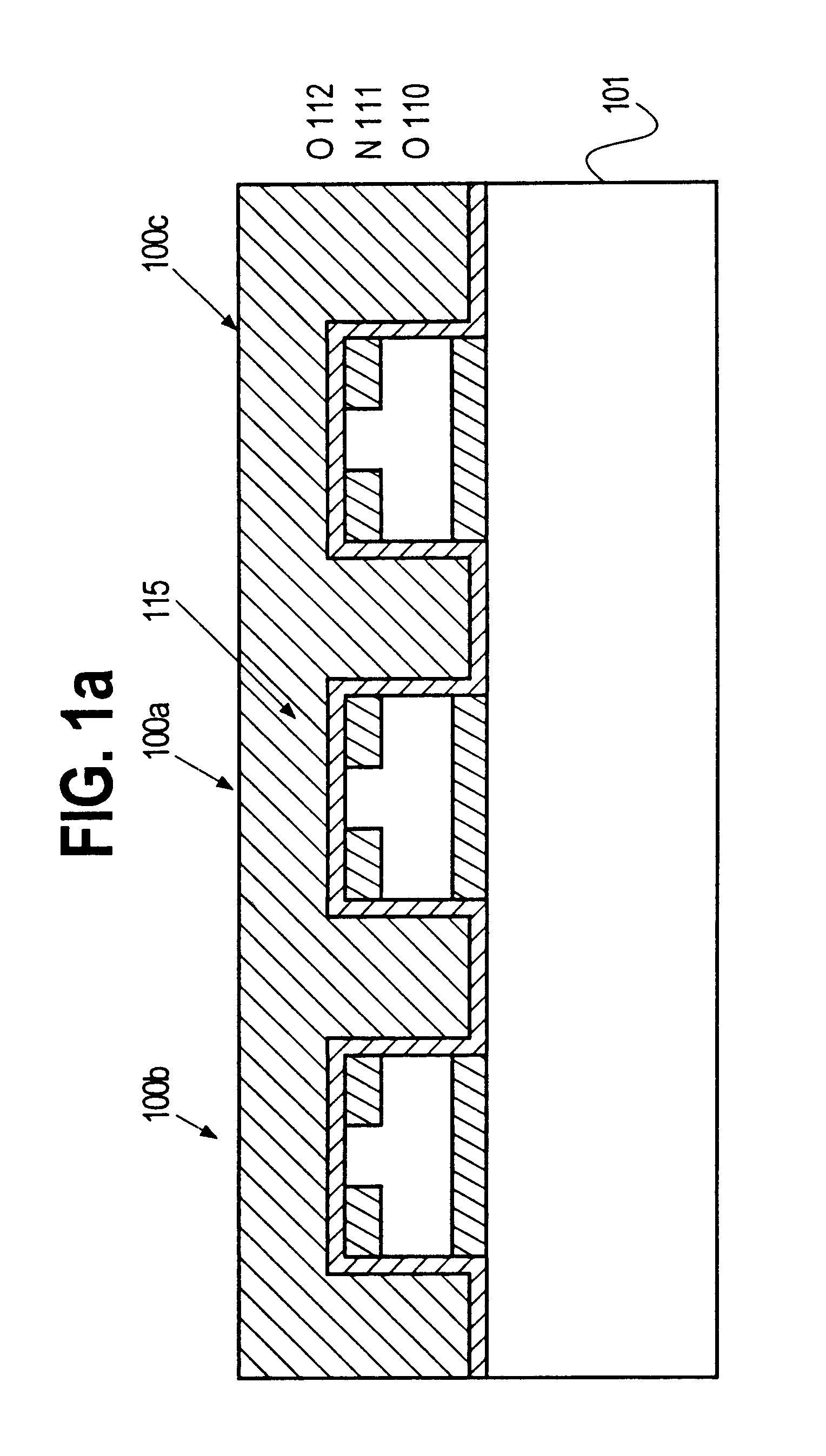

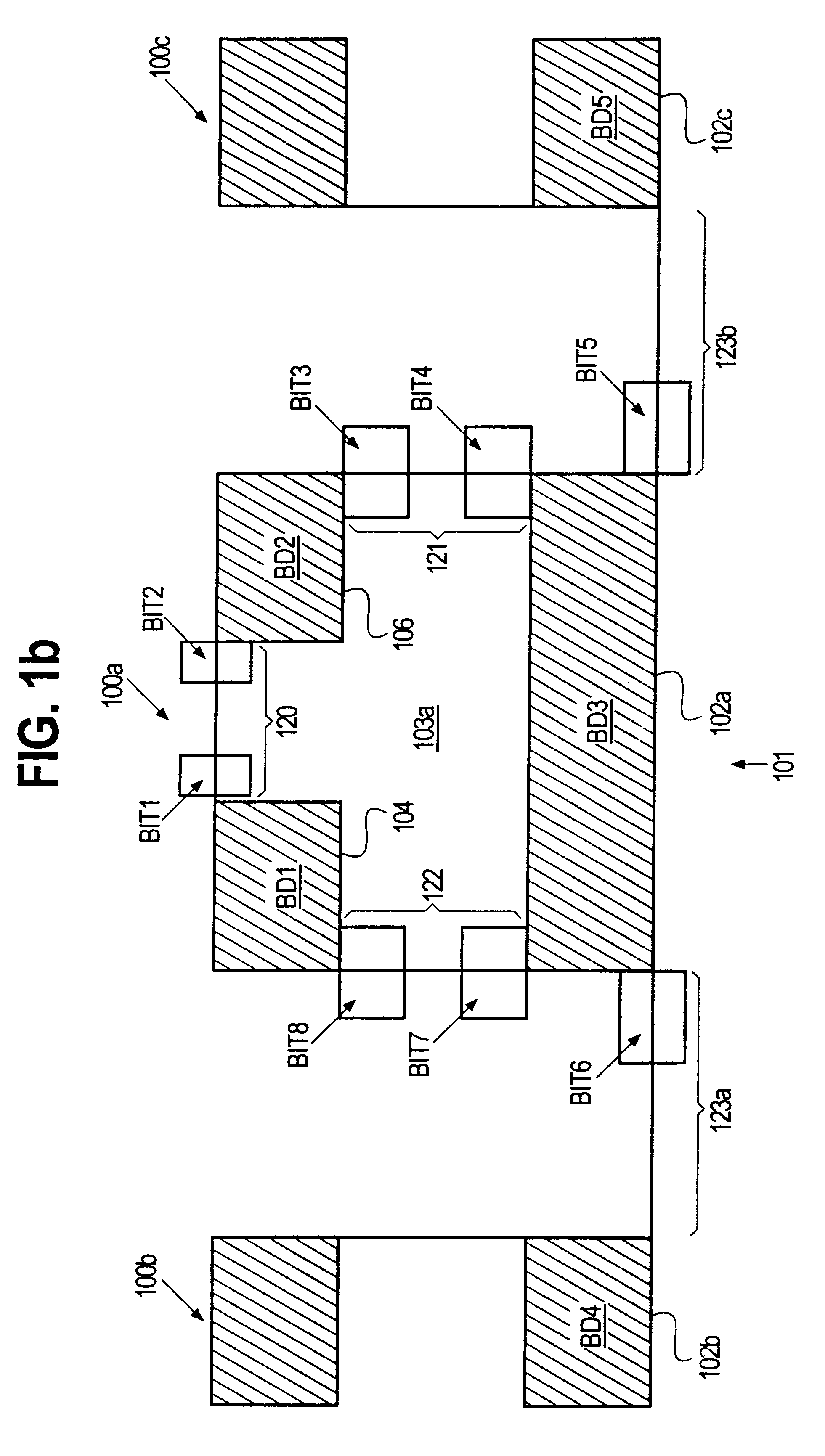

8 bit per cell non-volatile semiconductor memory structure utilizing trench technology and dielectric floating gate

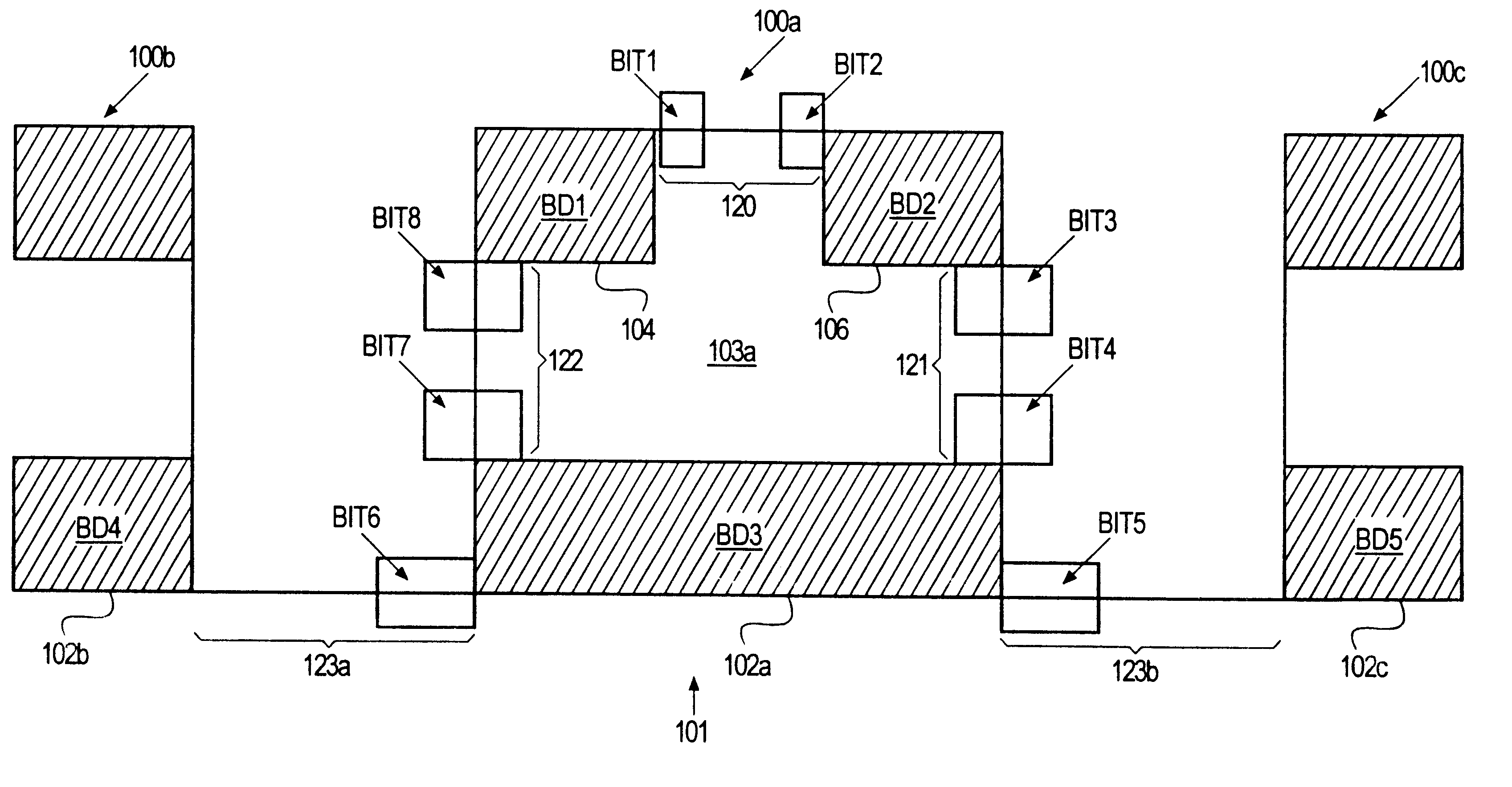

The present application discloses a non-volatile semiconductor memory device for storing up to eight-bits of information. The device has a semiconductor substrate of one conductivity type, a central bottom diffusion region on top of a portion of the semiconductor substrate, a second semiconductor layer on top of the bottom diffusion region, and left and right diffusion regions formed in the second semiconductor layer apart from the central bottom diffusion region thus forming a first vertical channel between the right and central bottom diffusion regions. The device further includes a trapping dielectric layer formed over exposed portions of the semiconductor substrate, left, central and right bottom diffusion regions and second semiconductor layer and a wordline formed over the trapping dielectric layer. A methods of fabricating this novel cell using trench technology is also disclosed.

Owner:MACRONIX INT CO LTD

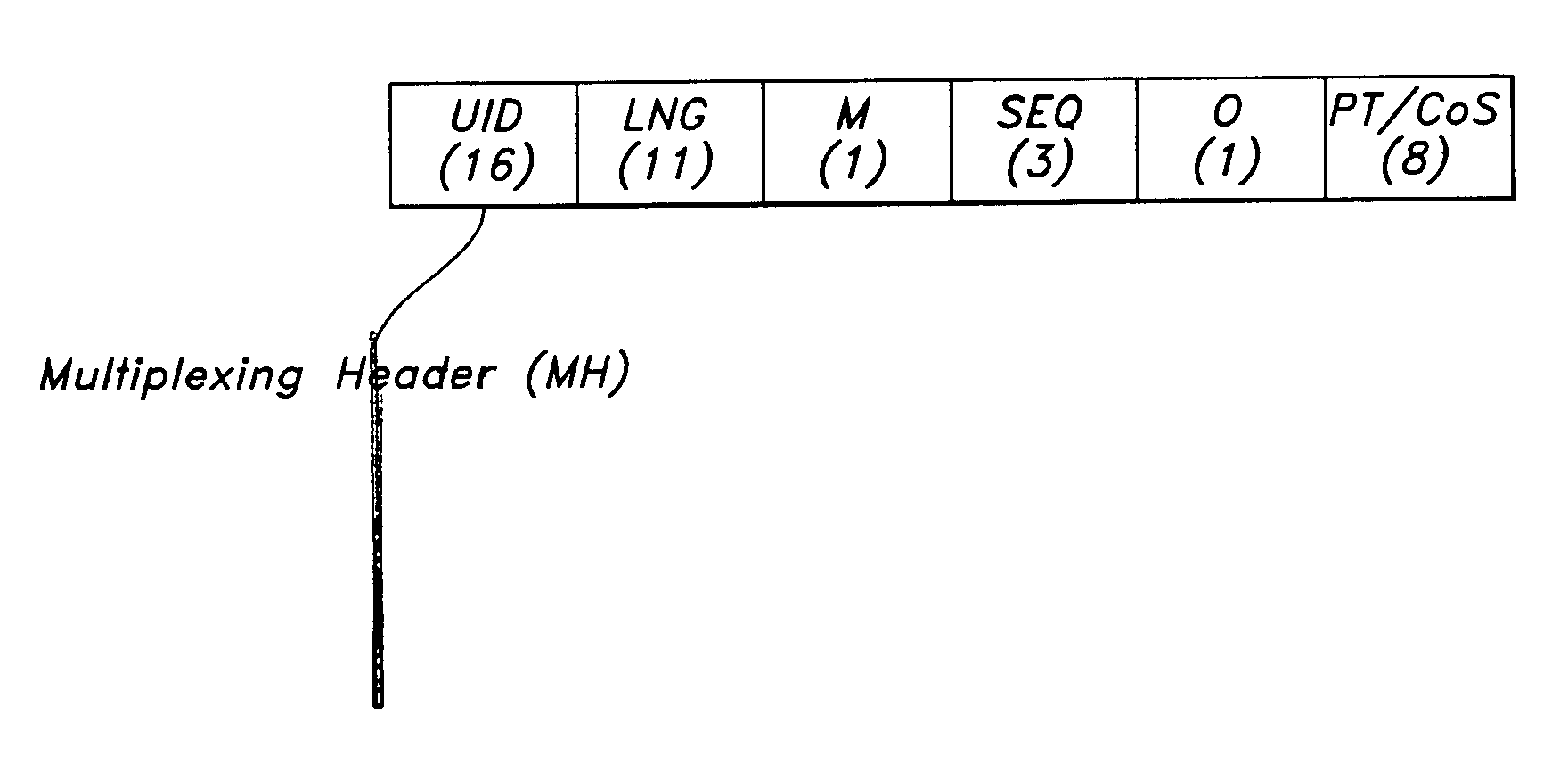

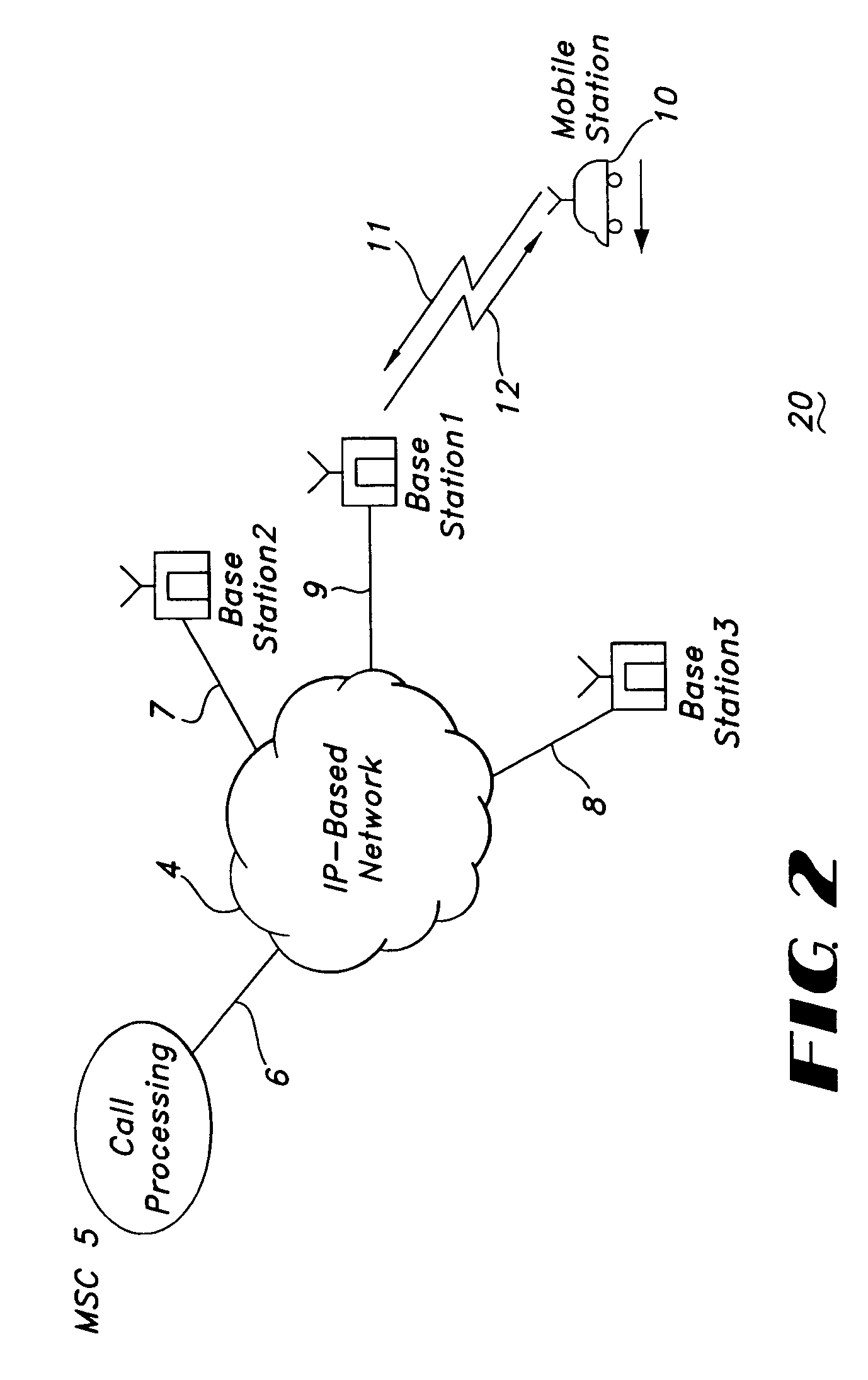

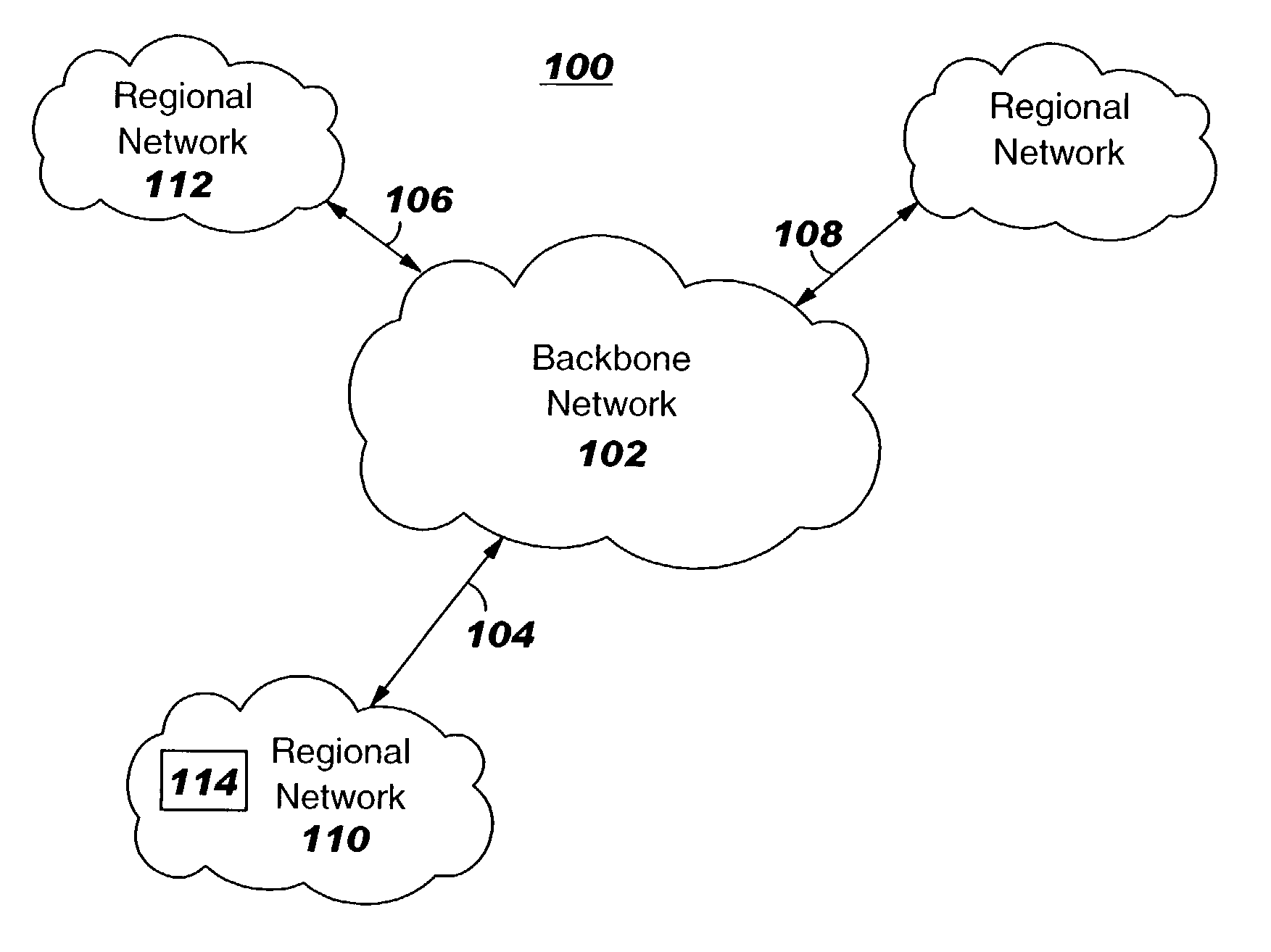

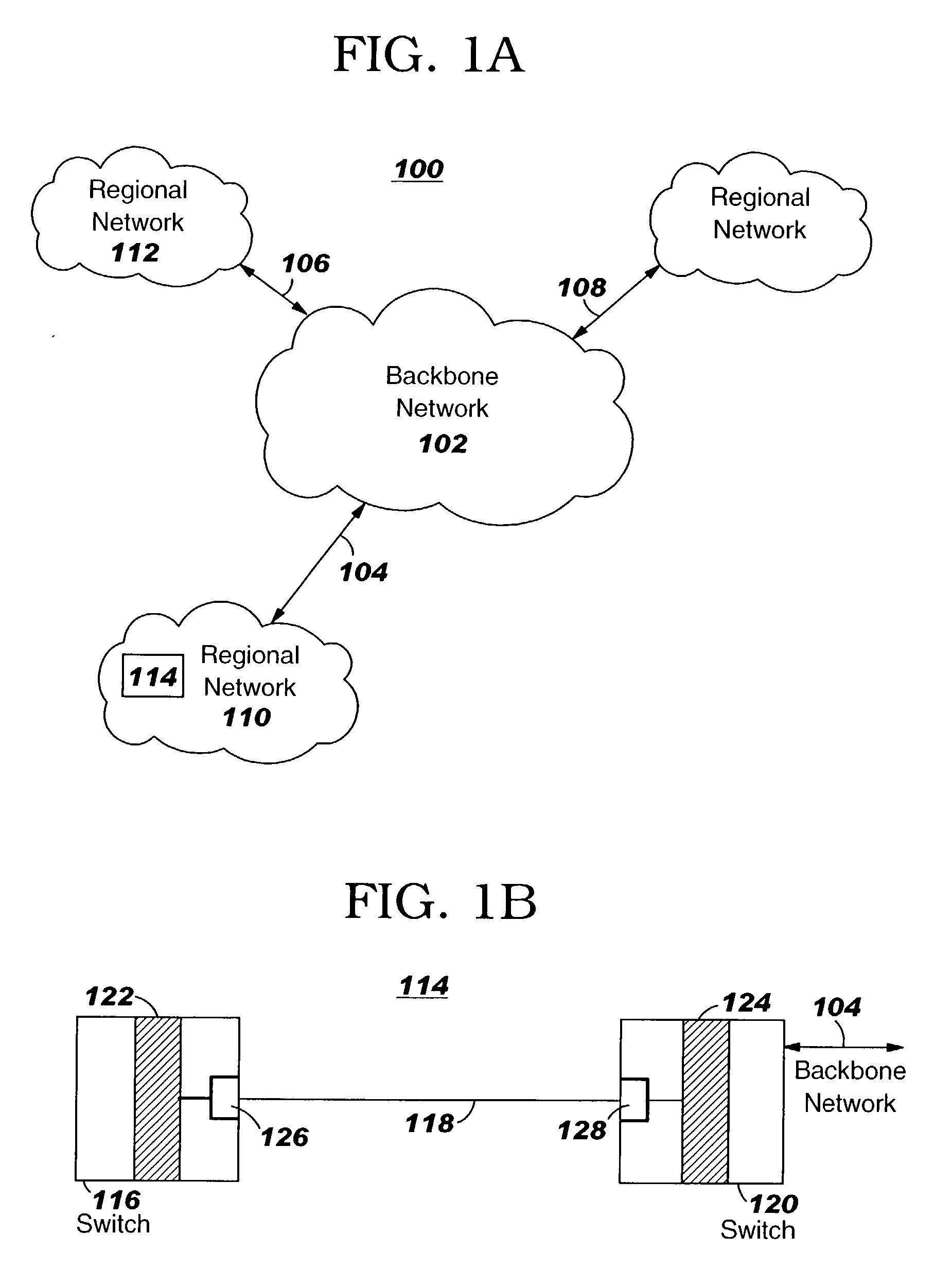

Lightweight internet protocol encapsulation (LIPE) scheme for multimedia traffic transport

InactiveUS6993021B1Increase in sizeTime-division multiplexData switching by path configurationTraffic capacityClass of service

A packet encapsulation scheme for multiplexing application sessions—Lightweight IP Encapsulation (LIPE)—is described. An LIPE packet comprises at least one multiplexing header (NH) and associated multimedia data packet (MDP). The LIPE packet uses UDP / IP as transport. An MH field further comprises a 16-bit a user identifier (UID) field, an 11 bit length indicator (LNG) field, a 1 bit “more” (M) field and an optional payload type / class of service (PT / CoS) field comprising 8 bits.

Owner:ALCATEL-LUCENT USA INC +1

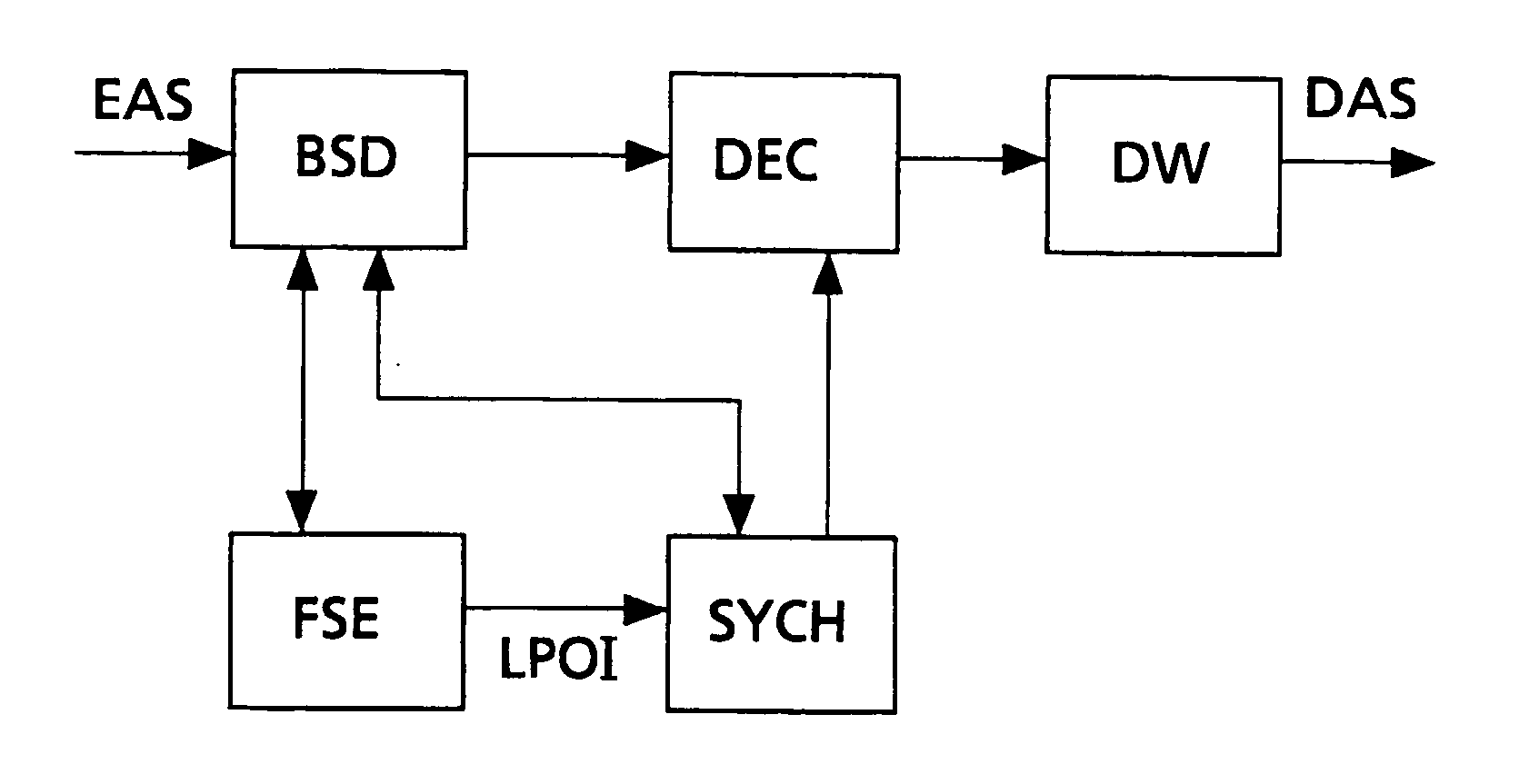

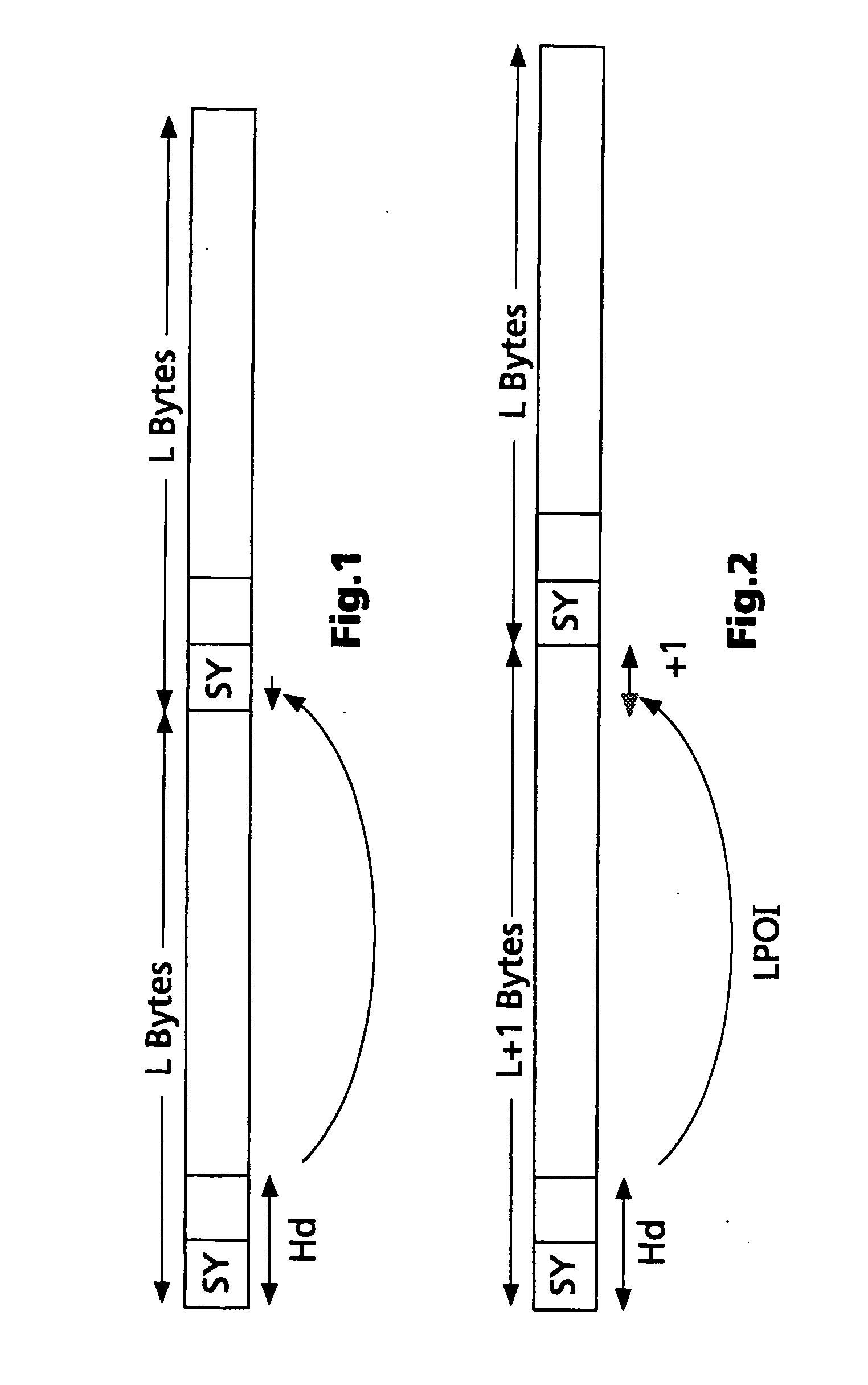

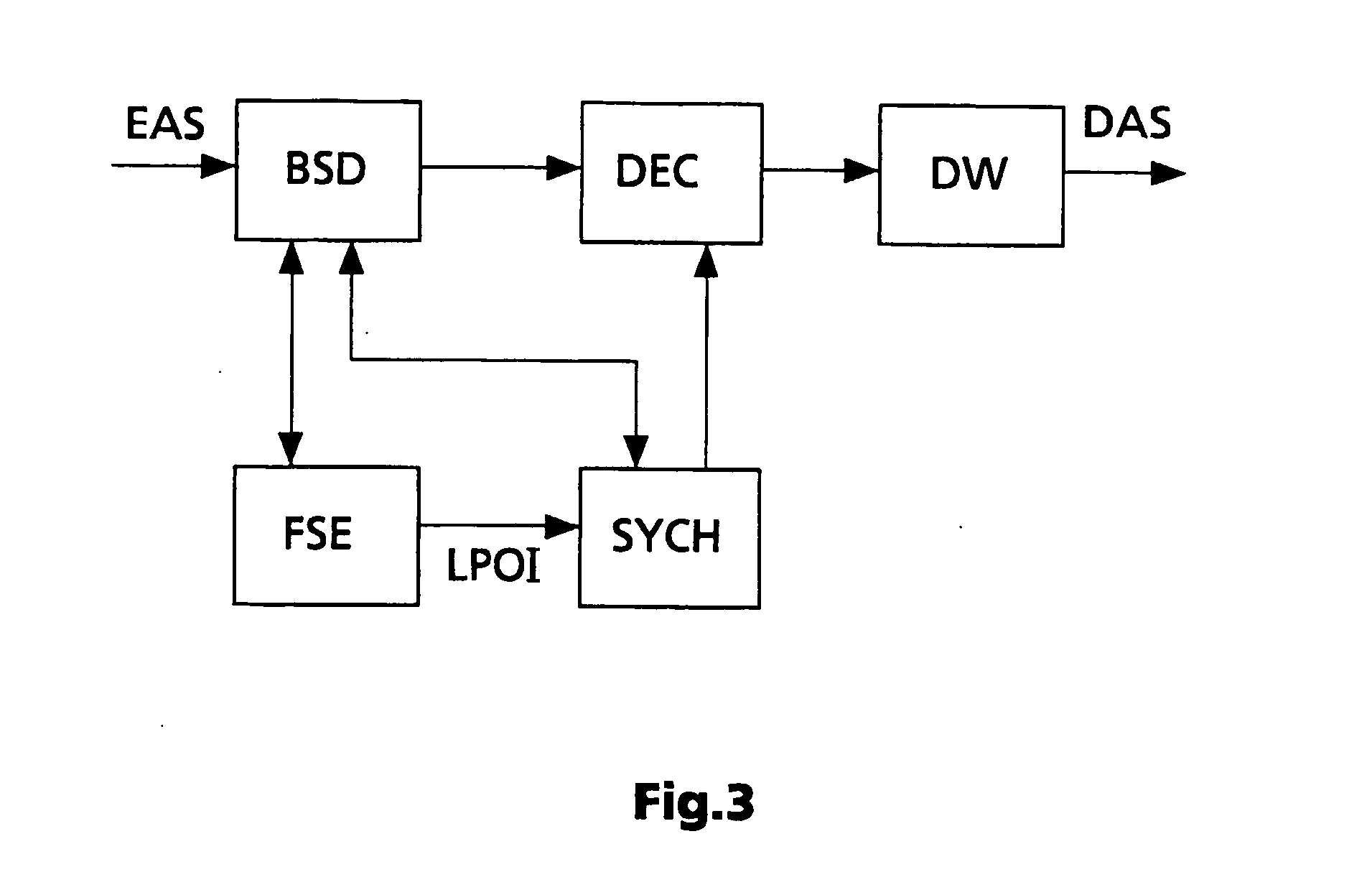

Method and apparatus for decoding a coded digital audio signal which is arranged in frames containing headers

With audio data reduction on the basis of ISO / IEC standard 11172-3, a frame length varying by 8 bits is used at a sampling frequency of 44.1 kHz in order to arrive, on average, at a particular fixed data rate. The lengthening of a data frame is signalled by a padding bit in the header of the frames. The invention dispenses with evaluation of the padding bit. Instead, the mean frame length L is calculated, L is rounded down to the next integer, for the subsequent frame it is first established whether the expected sync word for this frame appears, and, if this is so, this frame is decoded without taking into account the padding bit, but if the expected sync word for this frame does not appear, the decoding of the frame is started one 8-bit later without taking into account the padding bit.

Owner:INTERDIGITAL MADISON PATENT HLDG

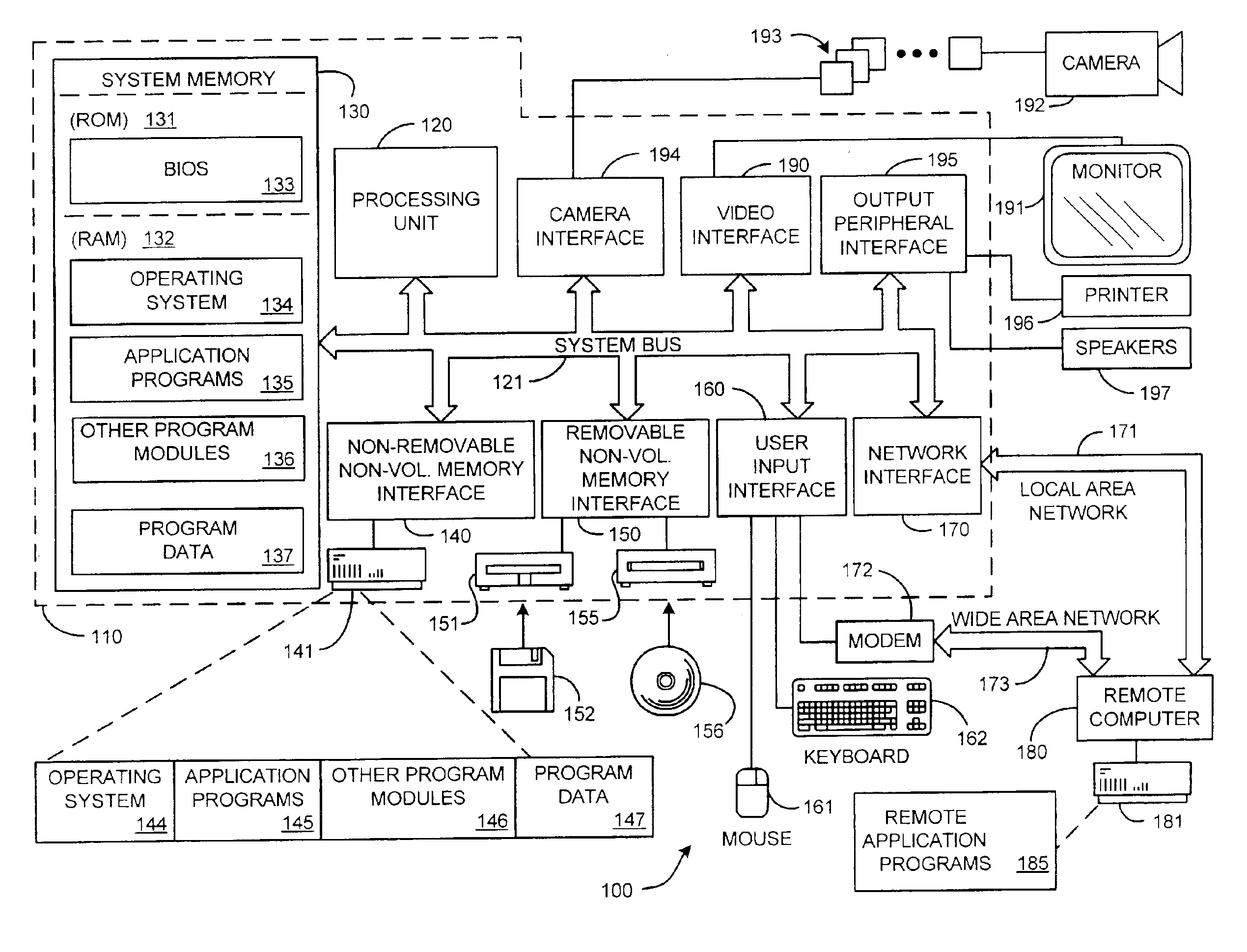

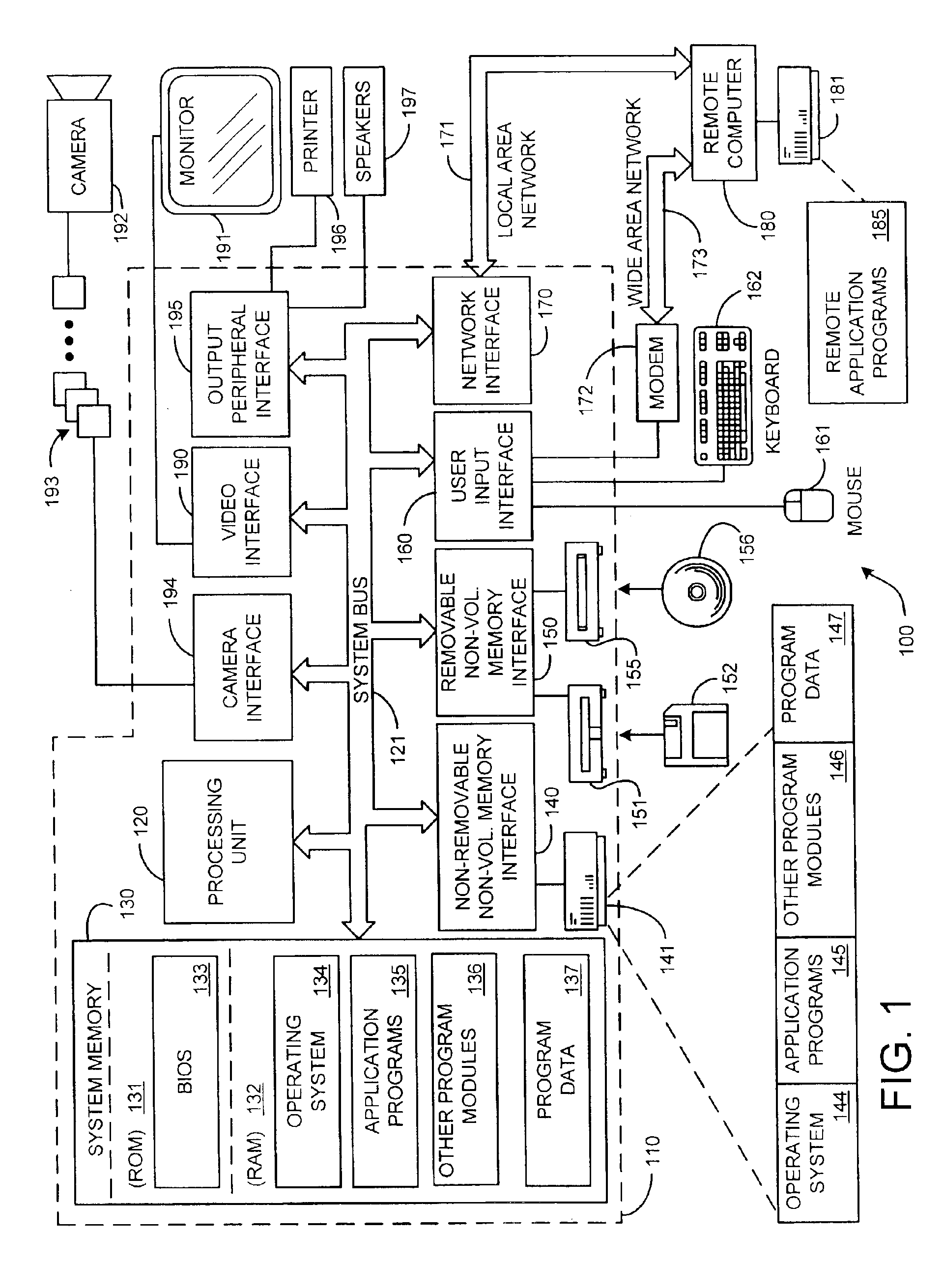

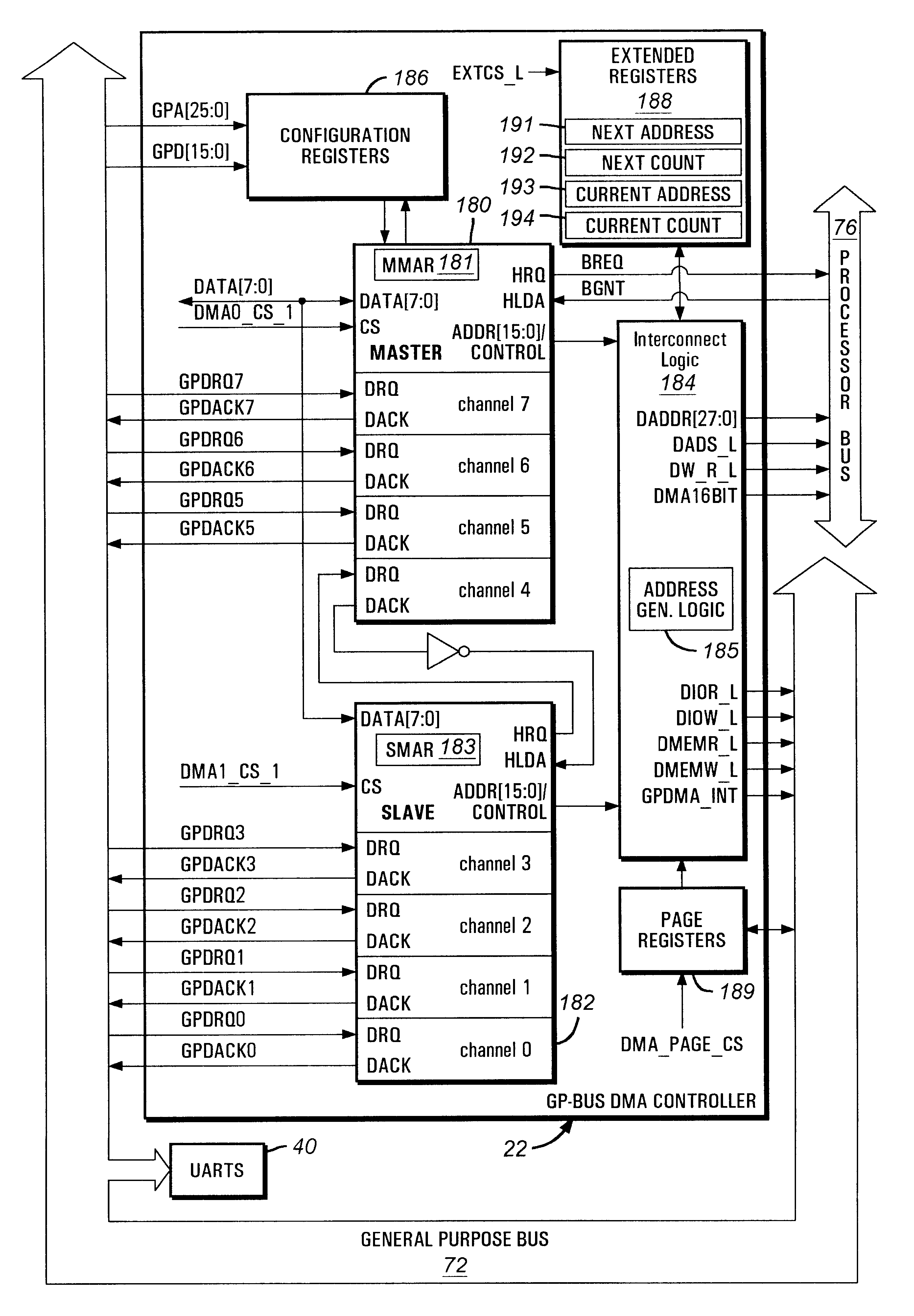

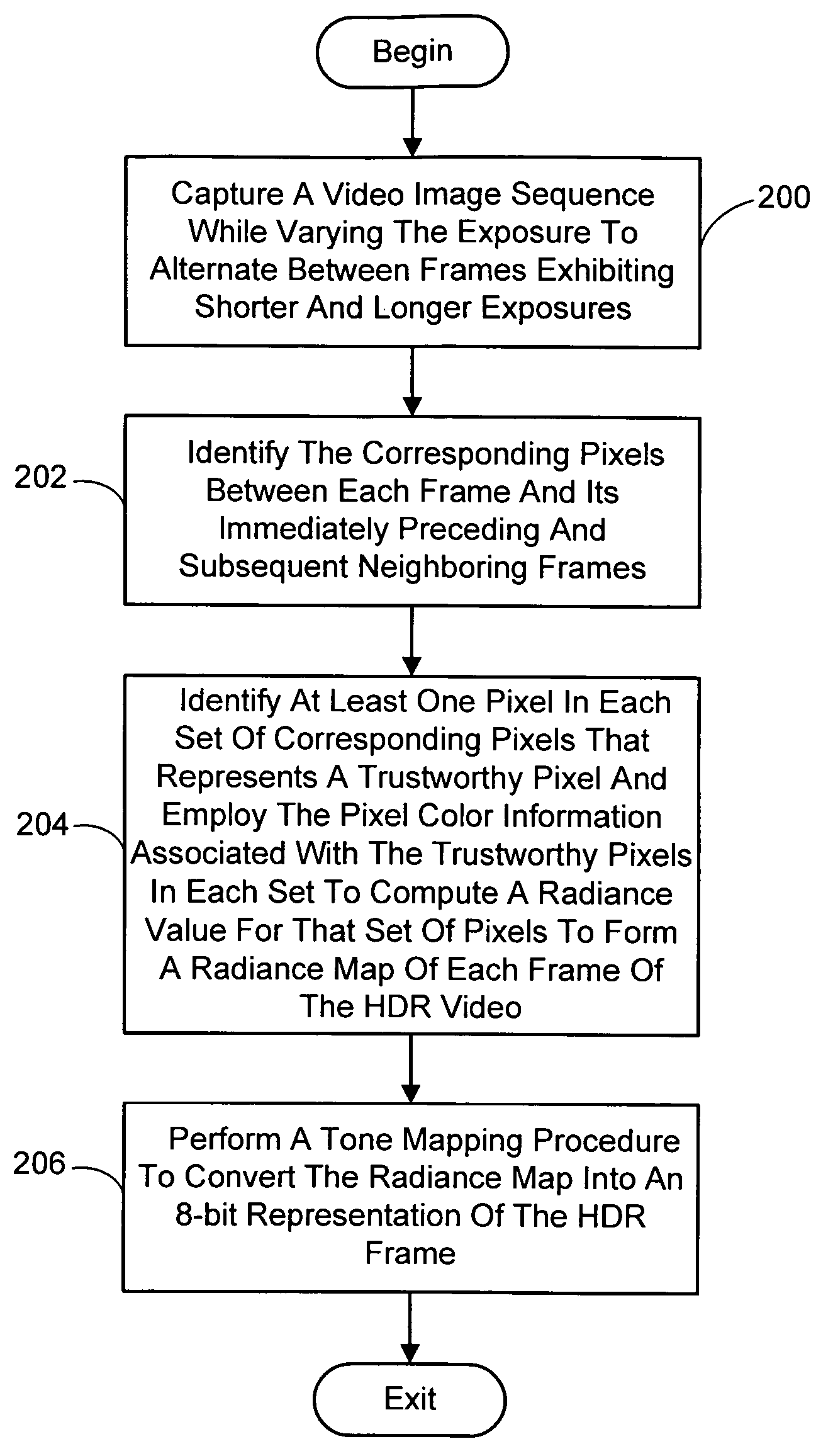

System and process for generating high dynamic range video

InactiveUS6879731B2Minimizing any discontinuityTelevision system detailsImage enhancementTone mappingRadiance

A system and process for generating High Dynamic Range (HDR) video is presented which involves first capturing a video image sequence while varying the exposure so as to alternate between frames having a shorter and longer exposure. The exposure for each frame is set prior to it being captured as a function of the pixel brightness distribution in preceding frames. Next, for each frame of the video, the corresponding pixels between the frame under consideration and both preceding and subsequent frames are identified. For each corresponding pixel set, at least one pixel is identified as representing a trustworthy pixel. The pixel color information associated with the trustworthy pixels is then employed to compute a radiance value for each pixel set to form a radiance map. A tone mapping procedure can then be performed to convert the radiance map into an 8-bit representation of the HDR frame.

Owner:MICROSOFT TECH LICENSING LLC

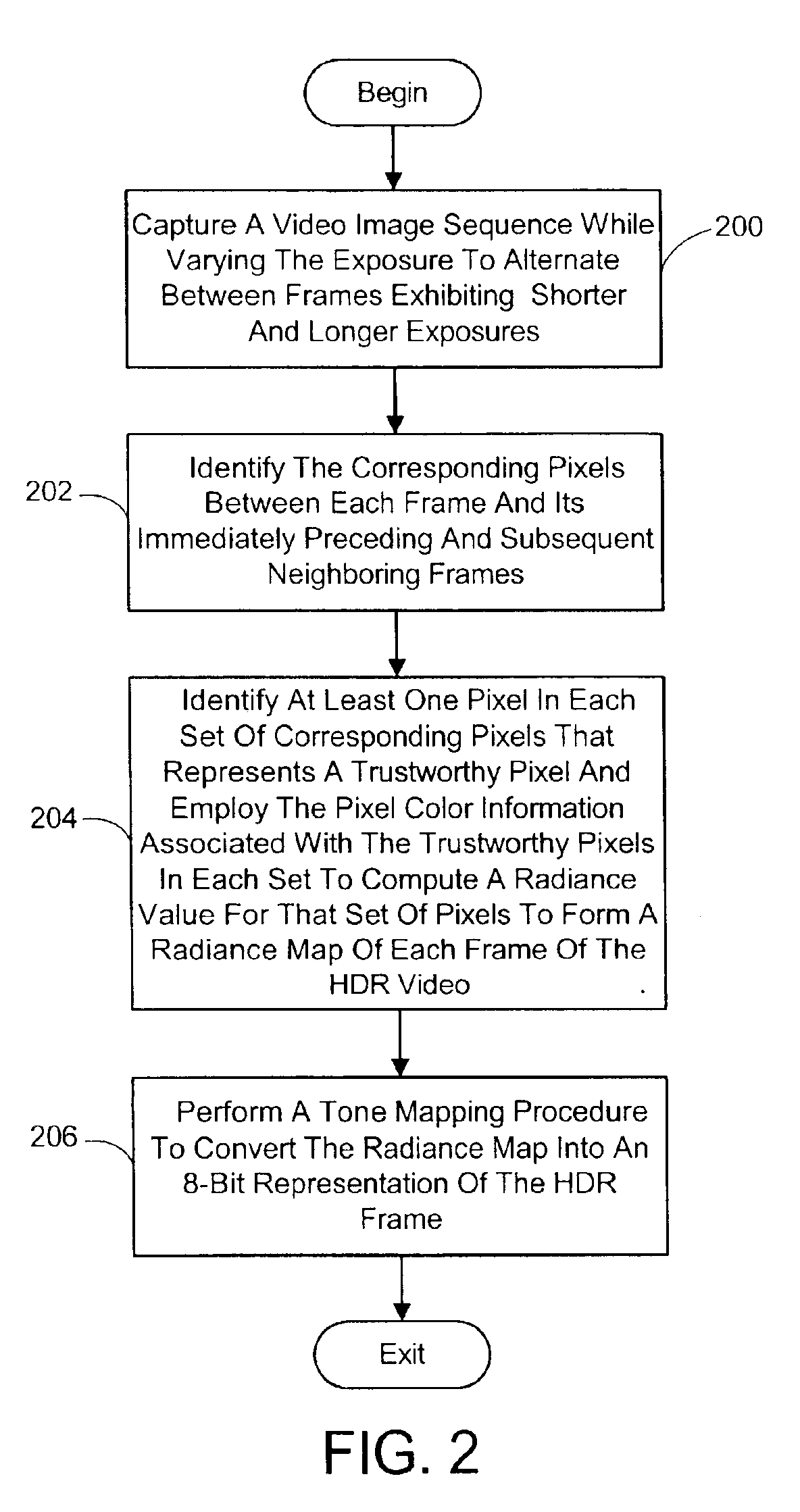

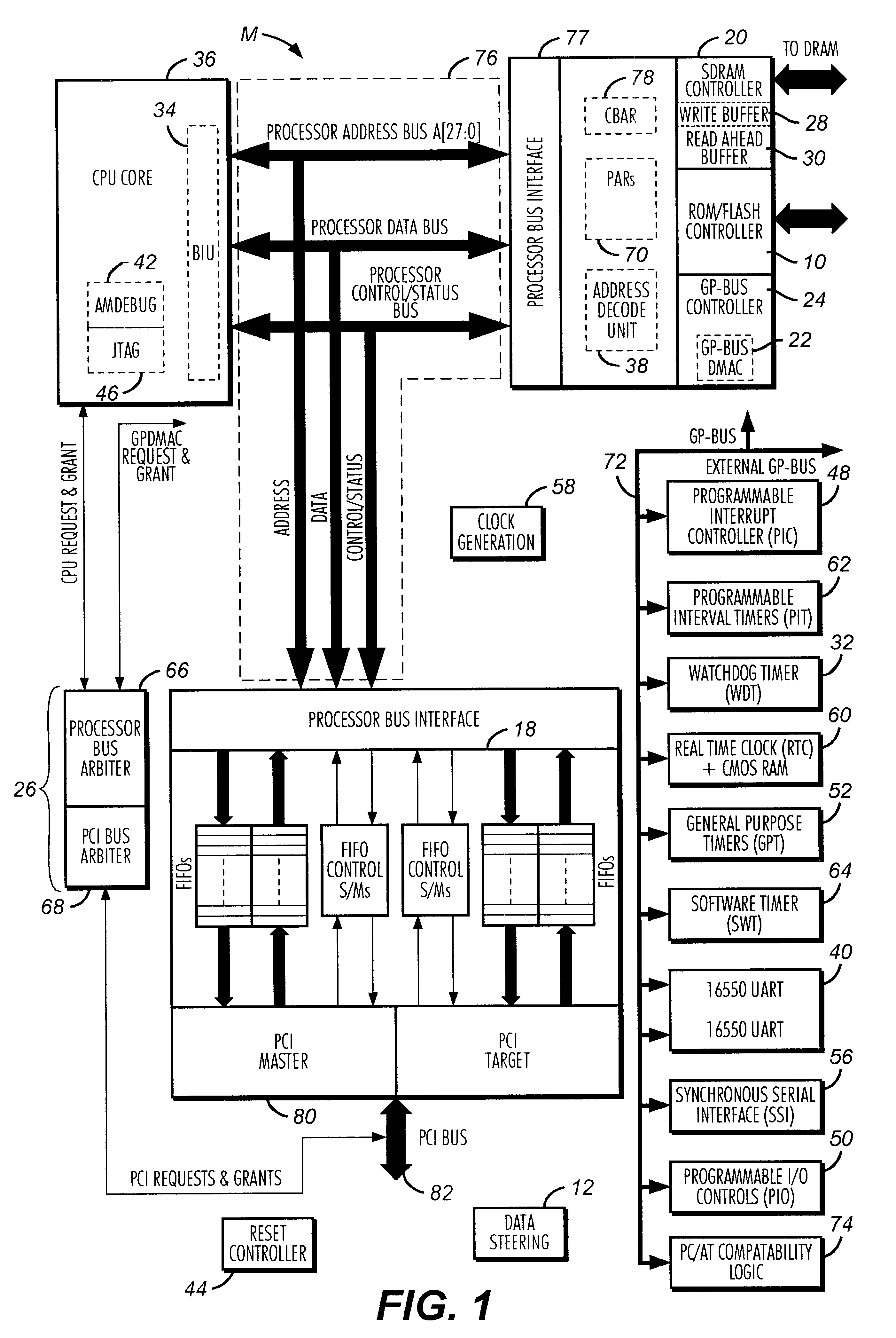

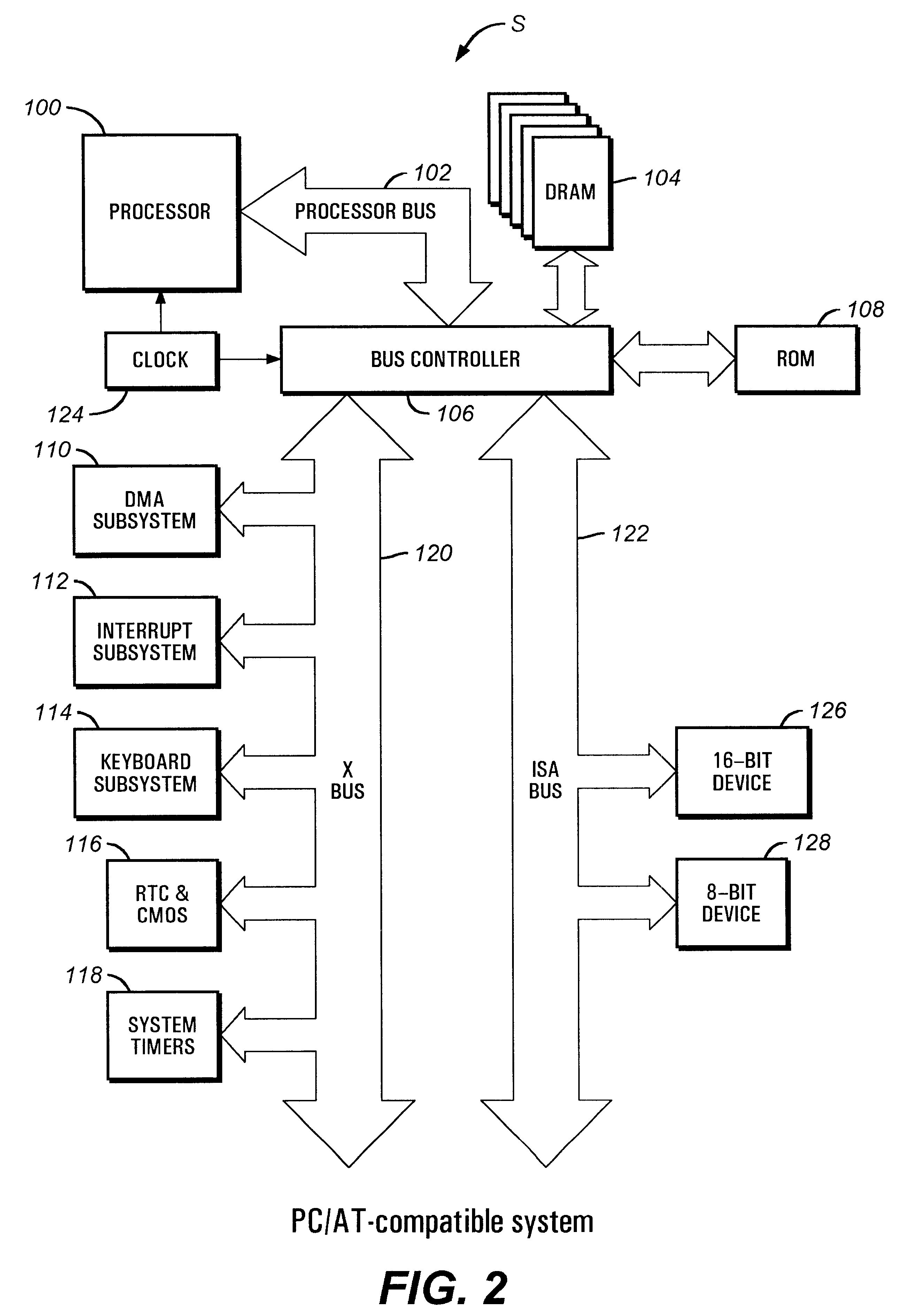

Direct memory access controller with channel width configurability support

A direct memory access (DMA) controller provides seven DMA channels configurable for a PC / AT compatible mode or an enhanced mode. In an enhanced mode of the DMA controller, three DMA master channels on a master DMA controller and a DMA channel on a slave DMA controller are individually configurable to be either 8-bit or 16-bit DMA channels. In addition, in the enhanced mode, a memory address can increment or decrement across a memory page boundary. The DMA controller includes a transfer count register selectively configured for 16-bit operation or 24-bit operation. The DMA controller also includes address generation logic selectively configured for 24-bit operation or 28-bit operation. In the PC / AT compatible mode, the DMA controller supports three 16-bit channels and four 8-bit channels. The DMA controller thus provides DMA channel width configurability.

Owner:GLOBALFOUNDRIES INC

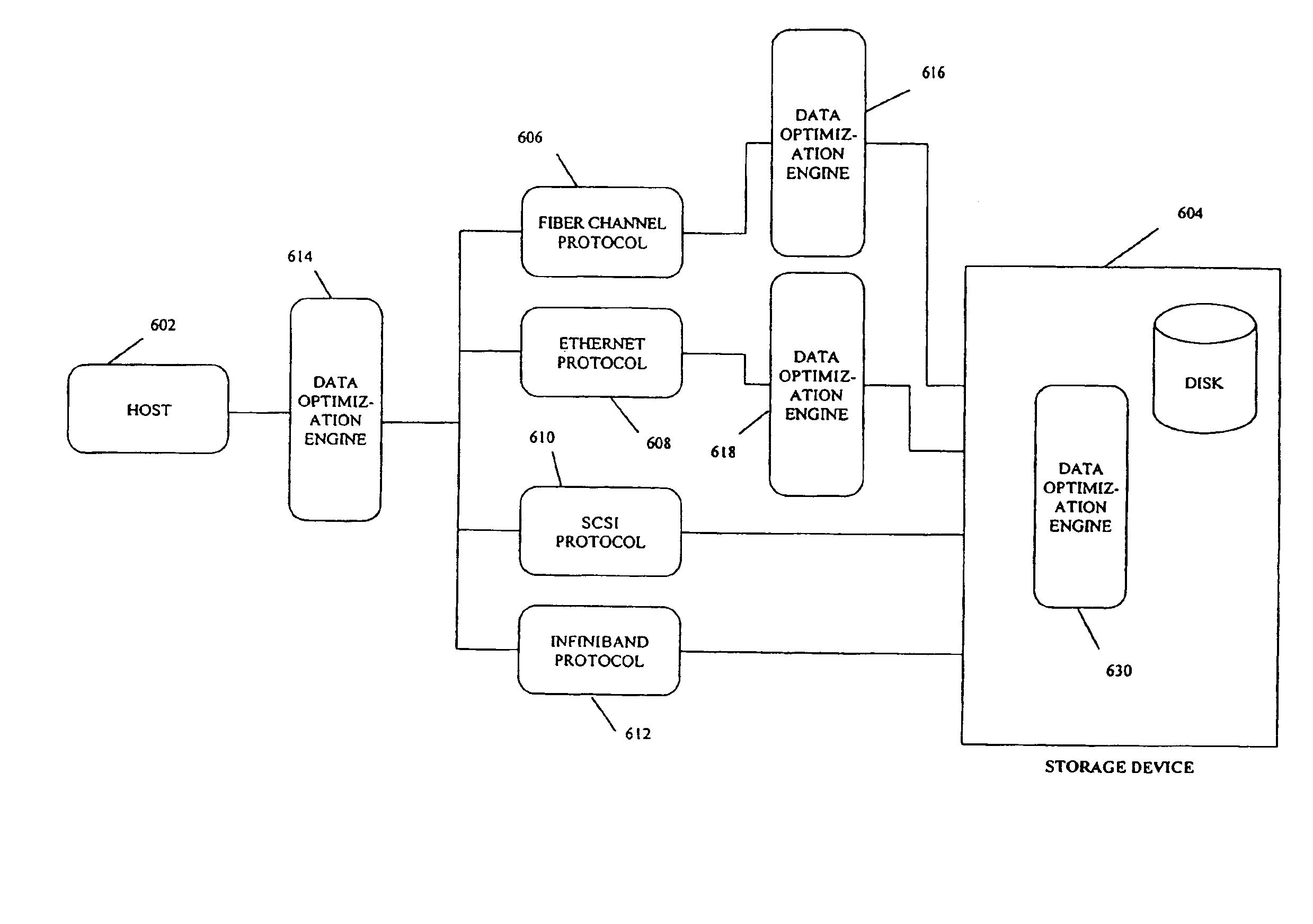

Architectures for a modularized data optimization engine and methods therefor

InactiveUS6920154B1Increase flexibilityEasy to compressMultiplex system selection arrangementsTime-division multiplexChannel dataFiber

A data optimization engine disposed inline with a first communication channel and a second communication channel. The data optimization engine comprises a transmit interface circuit configured to receive a first data stream from the first communication channel and to obtain a first data file from the first data stream. The data optimization engine further includes an optimization processor coupled to the transmit interface circuit for receiving a second data file from the transmit interface circuit. The second data file represents the first data file after the first data file has been processed by the transmit interface circuit into a format suitable for optimization by the optimization processor. The optimization processor performs one of a compression and an encryption on the second data file, thereby obtaining all optimized data file. In one embodiment, the first data file is a Fiber Channel data frame. In another embodiment, the first data file is encoded using 10-bit encoding, the format suitable for optimization by the optimization processor is an 8-bit encoding protocol.

Owner:MIND FUSION LLC

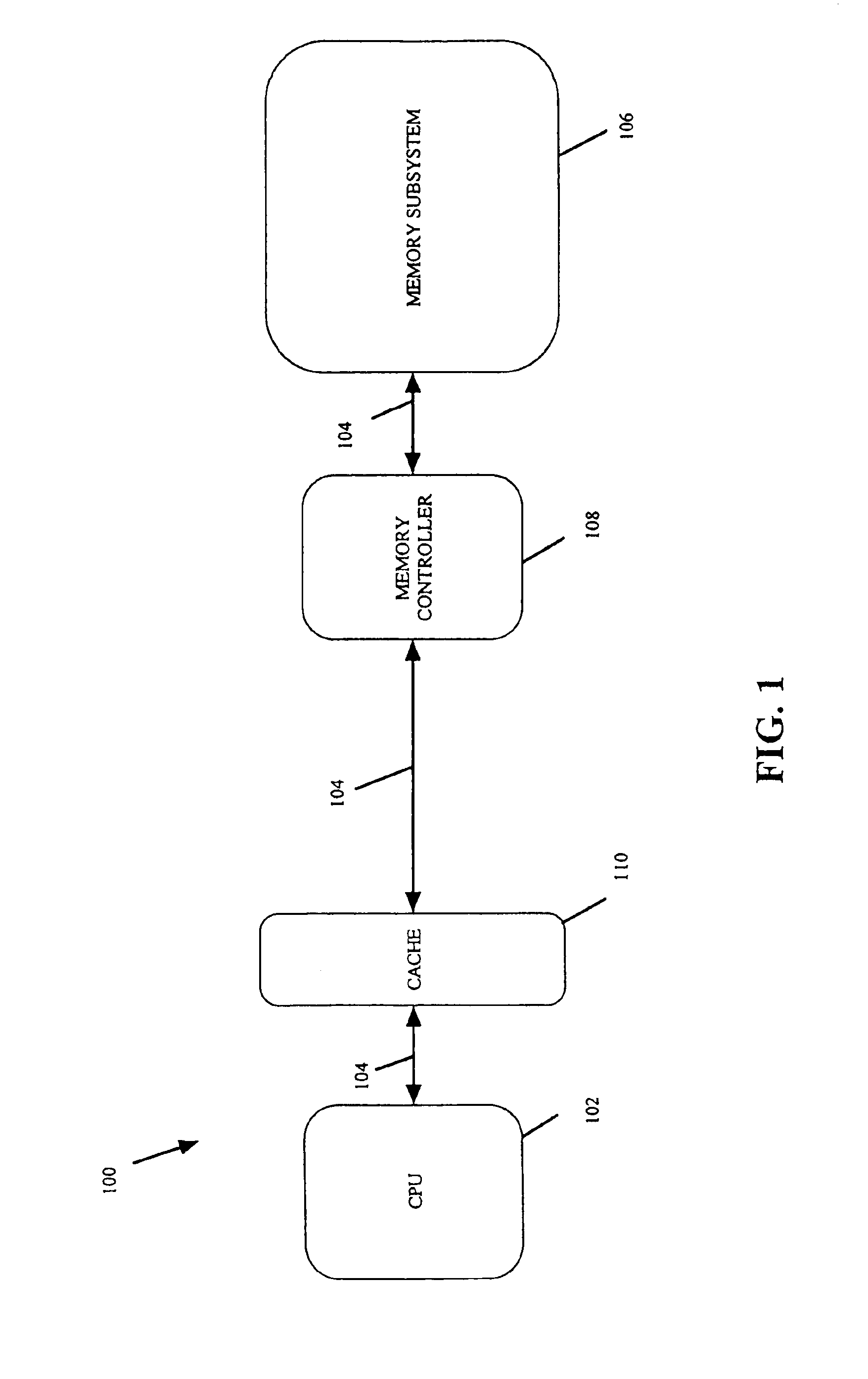

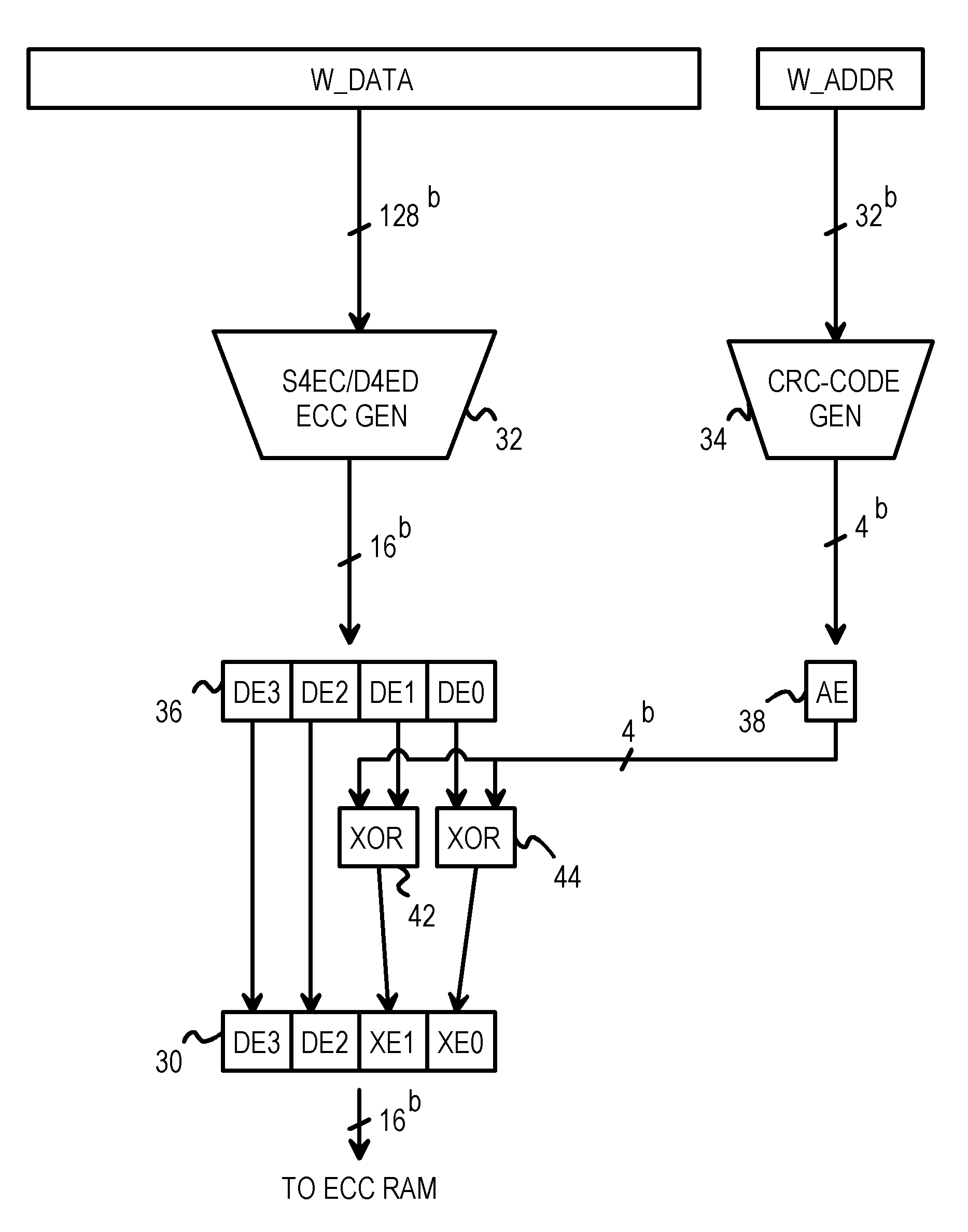

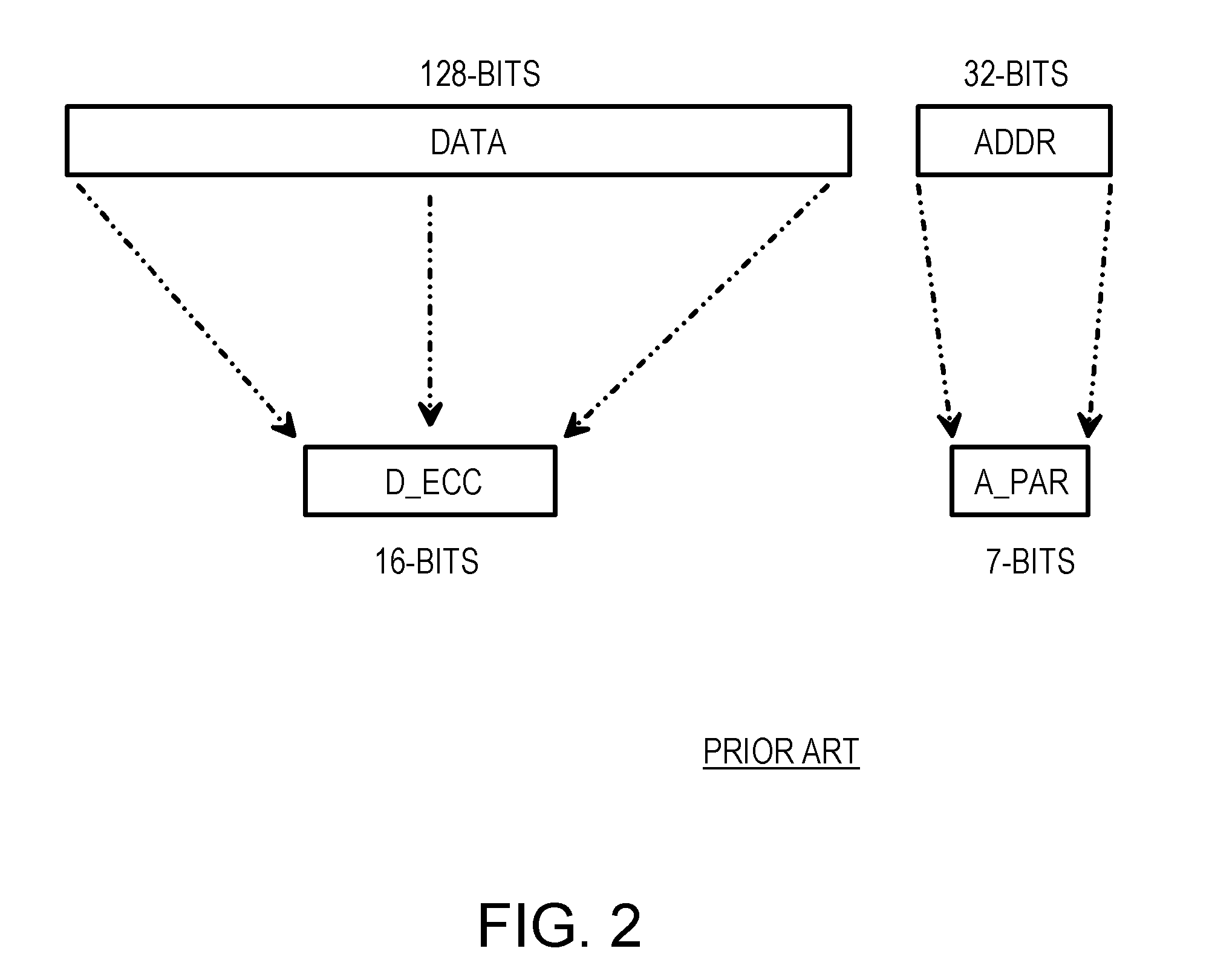

Address error detection by merging a polynomial-based CRC code of address bits with two nibbles of data or data ECC bits

A memory system provides data error detection and correction and address error detection. A Single-byte Error-Correcting / Double-byte Error-Detecting (SbEC / DbED) code with the byte being a 4-bit nibble is used to detect up to 8-bit errors and correct data errors of 4 bits or less. Rather than generating address parity, which is poor at detecting even numbers of errors, a cyclical-redundancy-check (CRC) code generates address check bits. A 32-bit address is compressed to just 4 address check bits using the CRC code. The 4 address check bits are merged (XOR'ed) with two 4-bit nibbles of the data SbEC / DbED code to generate a merged ECC codeword that is stored in memory. An address error causes a 2-nibble mis-match due to the redundant merging of the 4 address check bits with 2 nibbles of data correction code. The CRC code is ideal for detecting even numbers of errors common with multiplexed-address DRAMs.

Owner:AZUL SYSTEMS

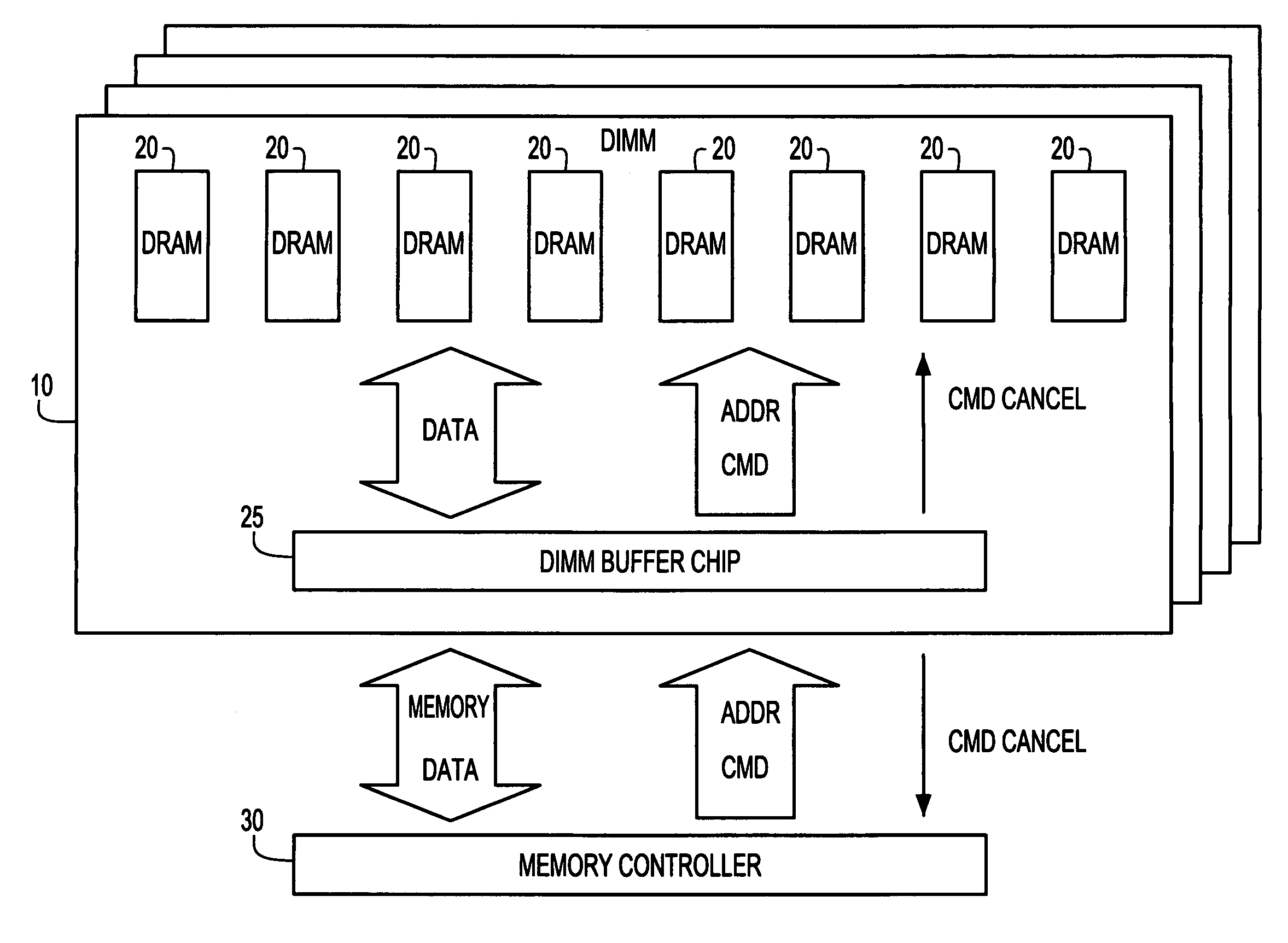

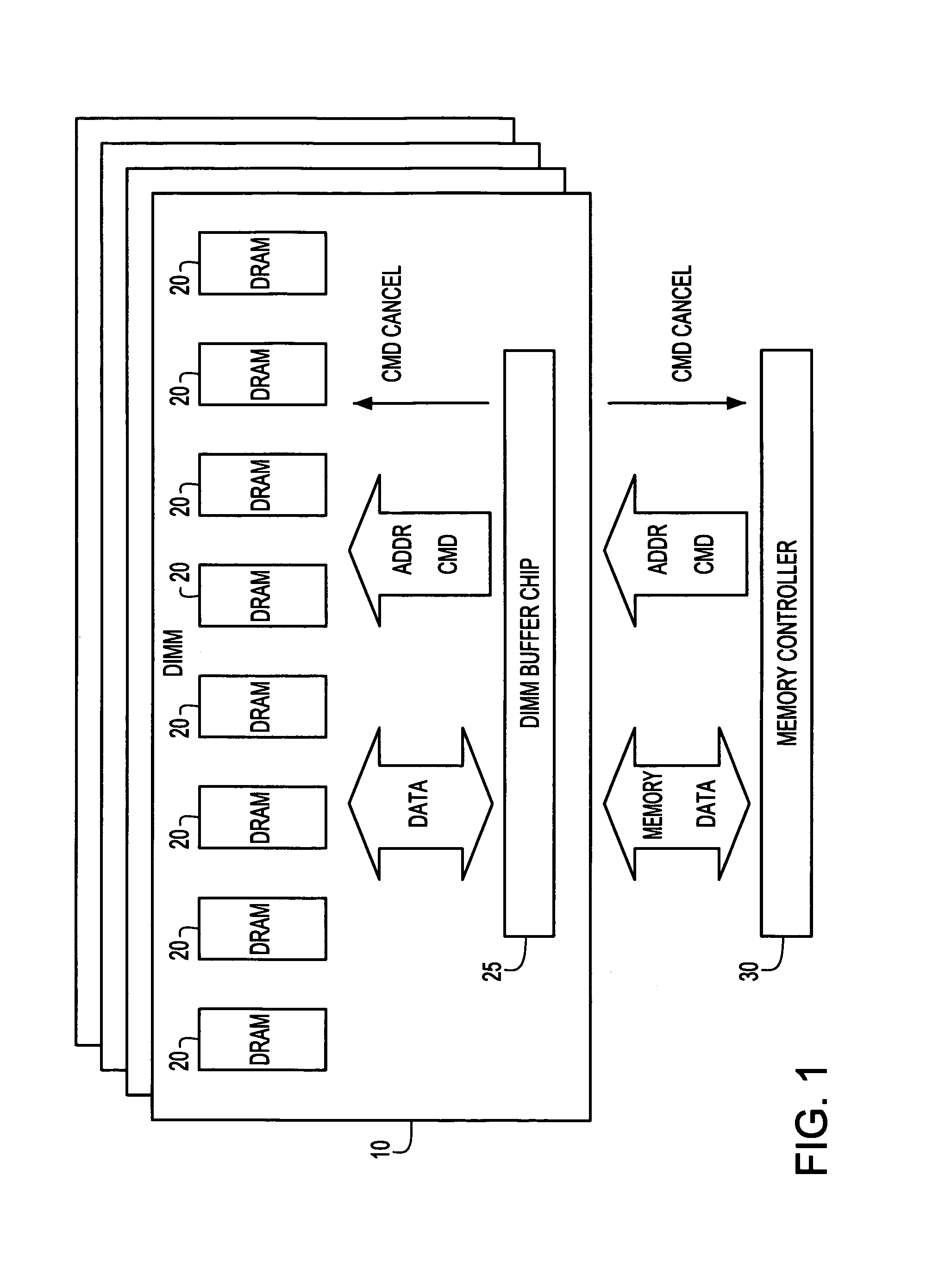

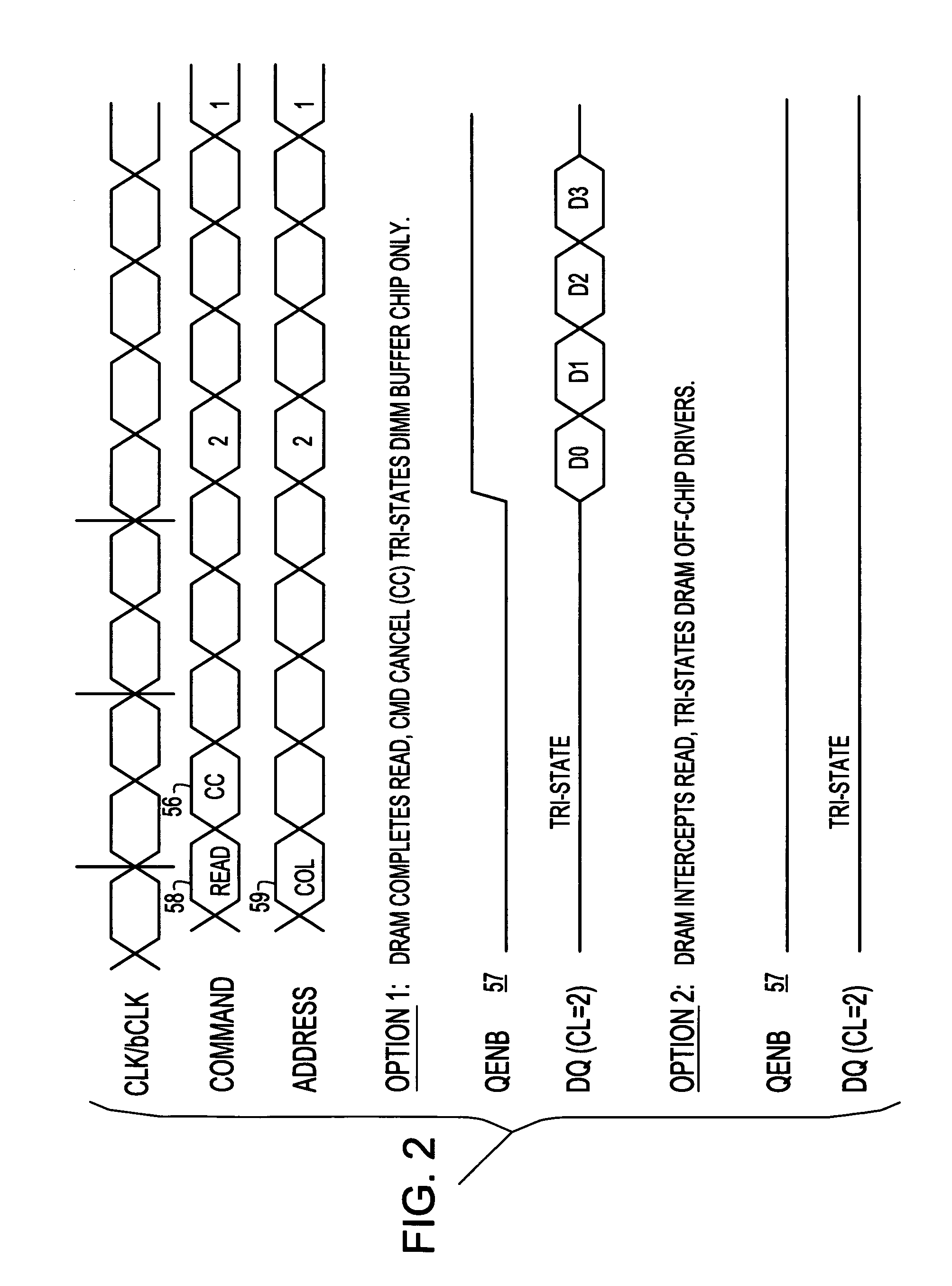

Method for performing a command cancel function in a DRAM

ActiveUS7480774B2Improve overall memory system reliabilityImprove system reliabilityOther printing matterMemory loss protectionClock rate8-bit

A method for performing a common cancel (CC) function on a dynamic random access memory (DRAM) semiconductor device to improve reliability and speed of a memory system. The CC function rakes advantage of the intrinsic delays associated wit memory read operations at high clock frequencies, and the increased write latency commensurate with increased read latencies where non-zero larencies for read and write operations are the norm by permitting address and command ECC structures to operate in parallel with the address and command re-drive circuitt The CC function is extendable to future DDR2 and DDR3 operating requirements in which latency of higher frequency modes will increase due to the shift from 2 bit pre-fetch to 4 and 8 bit pre-fetch architecture.

Owner:MARVELL ASIA PTE LTD

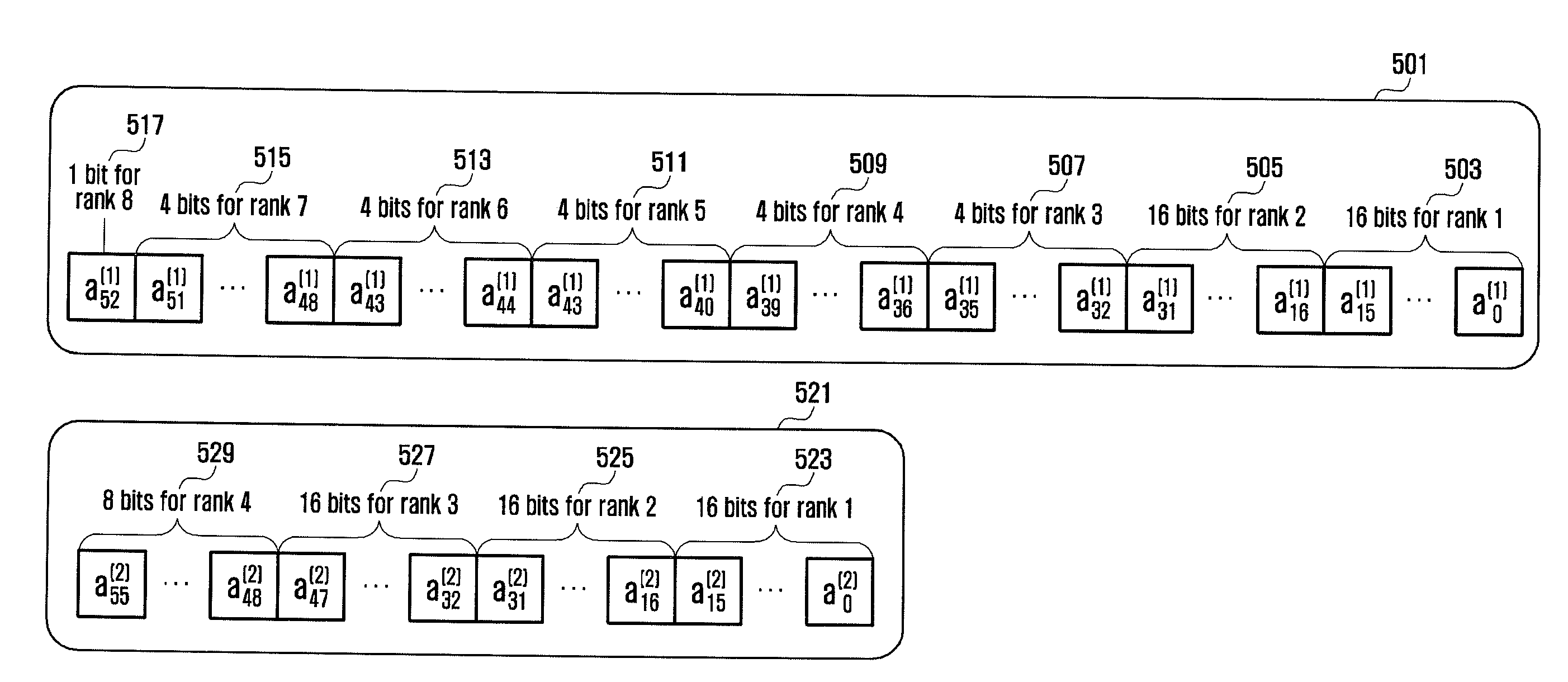

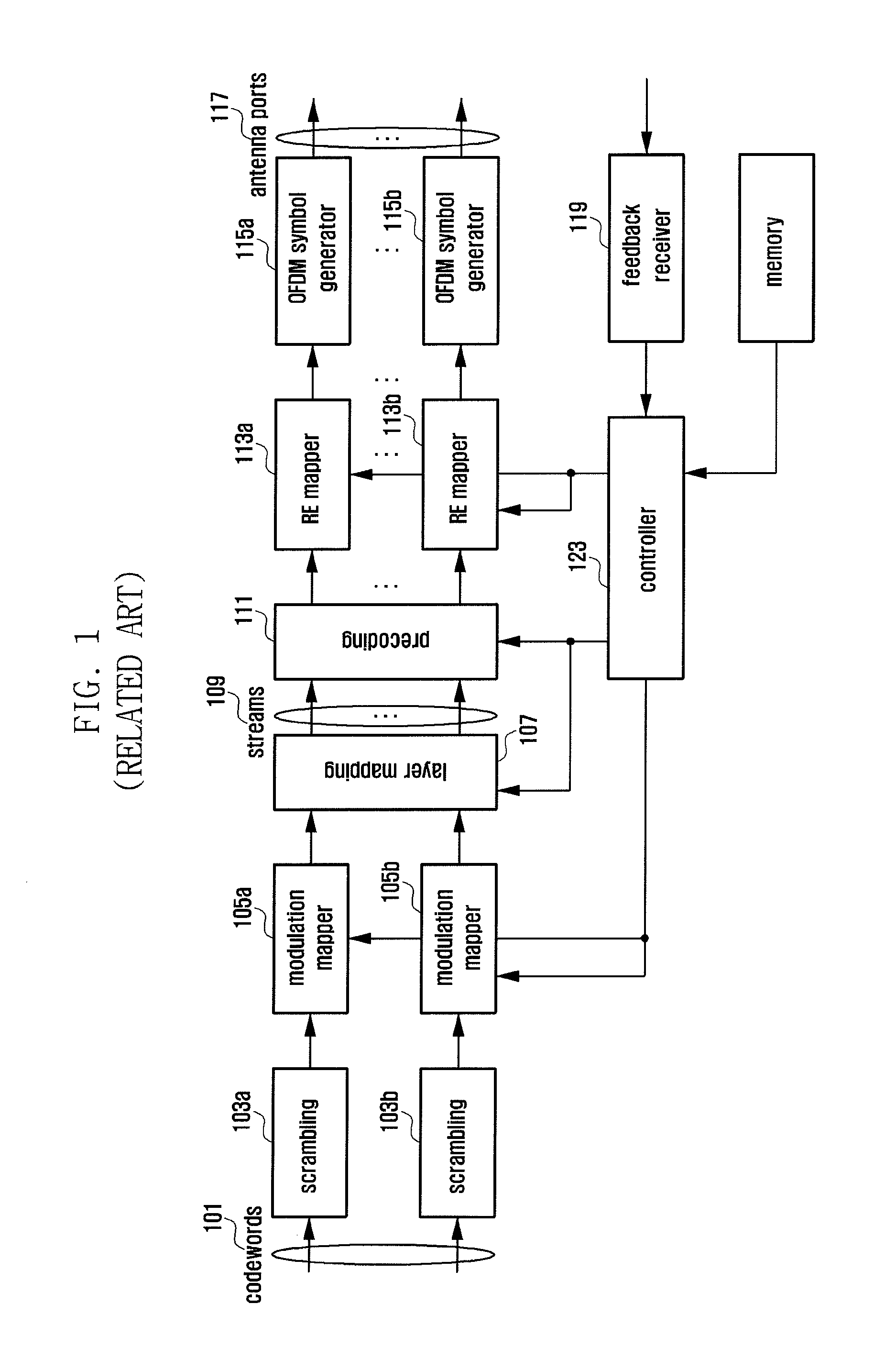

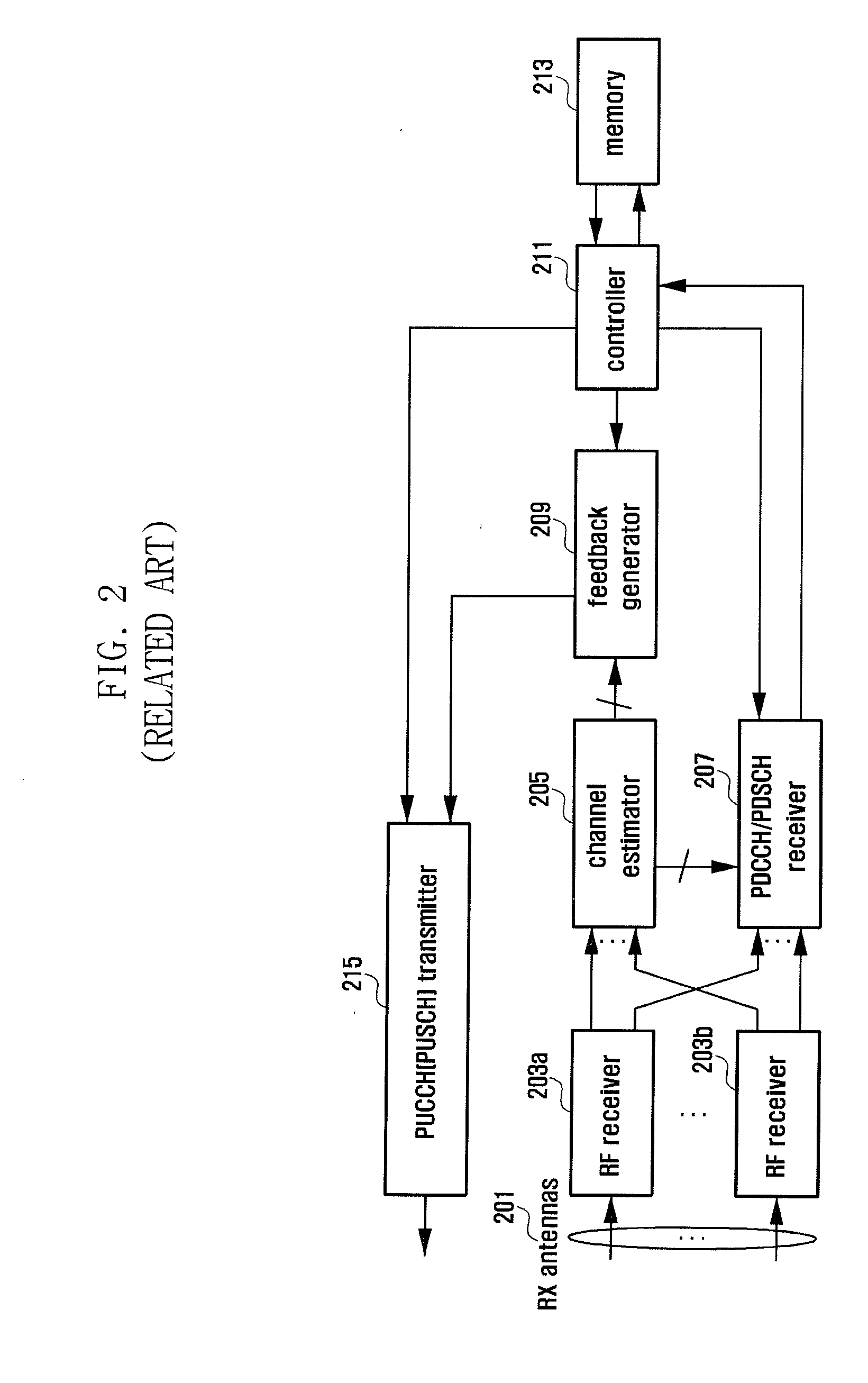

Method and apparatus for transmitting and receiving codebook subset restriction bitmap

ActiveUS20120082248A1Small sizeGuaranteed effective sizeError preventionModulated-carrier systemsTheoretical computer scienceEngineering

A method for transmitting and receiving a codebook subset restriction bitmap is provided. The Codebook Subset Restriction (CSR) bitmap transmission method of an evolved Node B (eNB) in transmission mode 9 for communication with 8 antenna ports includes generating a CSR bitmap including bits corresponding to restricted precoding matrix indicators and rank indicators that are not allowed for reporting and transmitting the CSR bitmap to a User Equipment (UE). The CSR bitmap comprises 53 bits corresponding to a first codebook and 56 bits corresponding to a second codebook, the 53 bits corresponding to a first codebook comprise 16, 16, 4, 4, 4, 4, and 1 bits for layers 1, 2, 3, 4, 5, 6, 7, and 8, respectively, and the 56 bits corresponding to a second codebook comprise 16, 16, 16 and 8 bits for layers 1, 2, 3, and 4, respectively.

Owner:SAMSUNG ELECTRONICS CO LTD

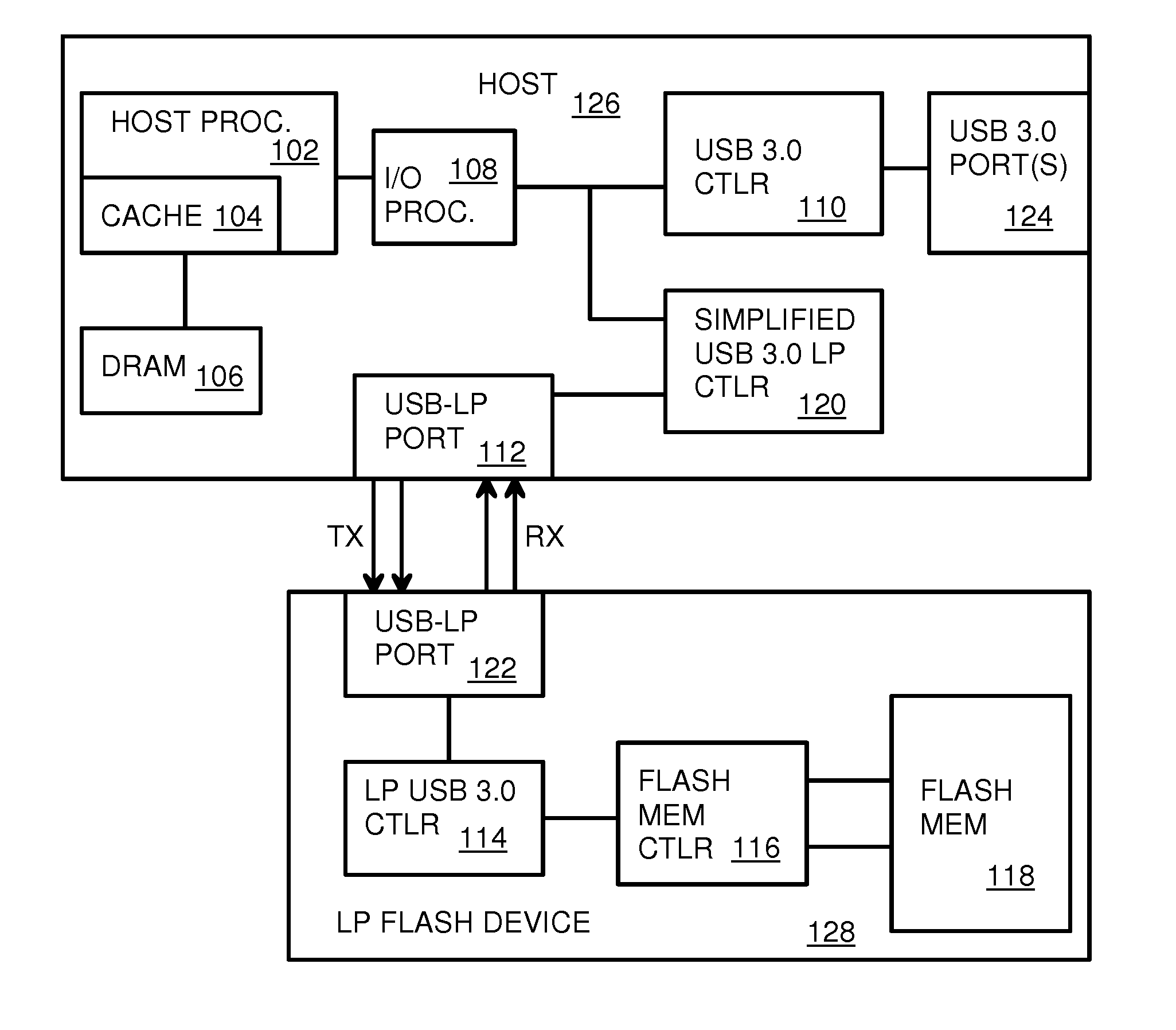

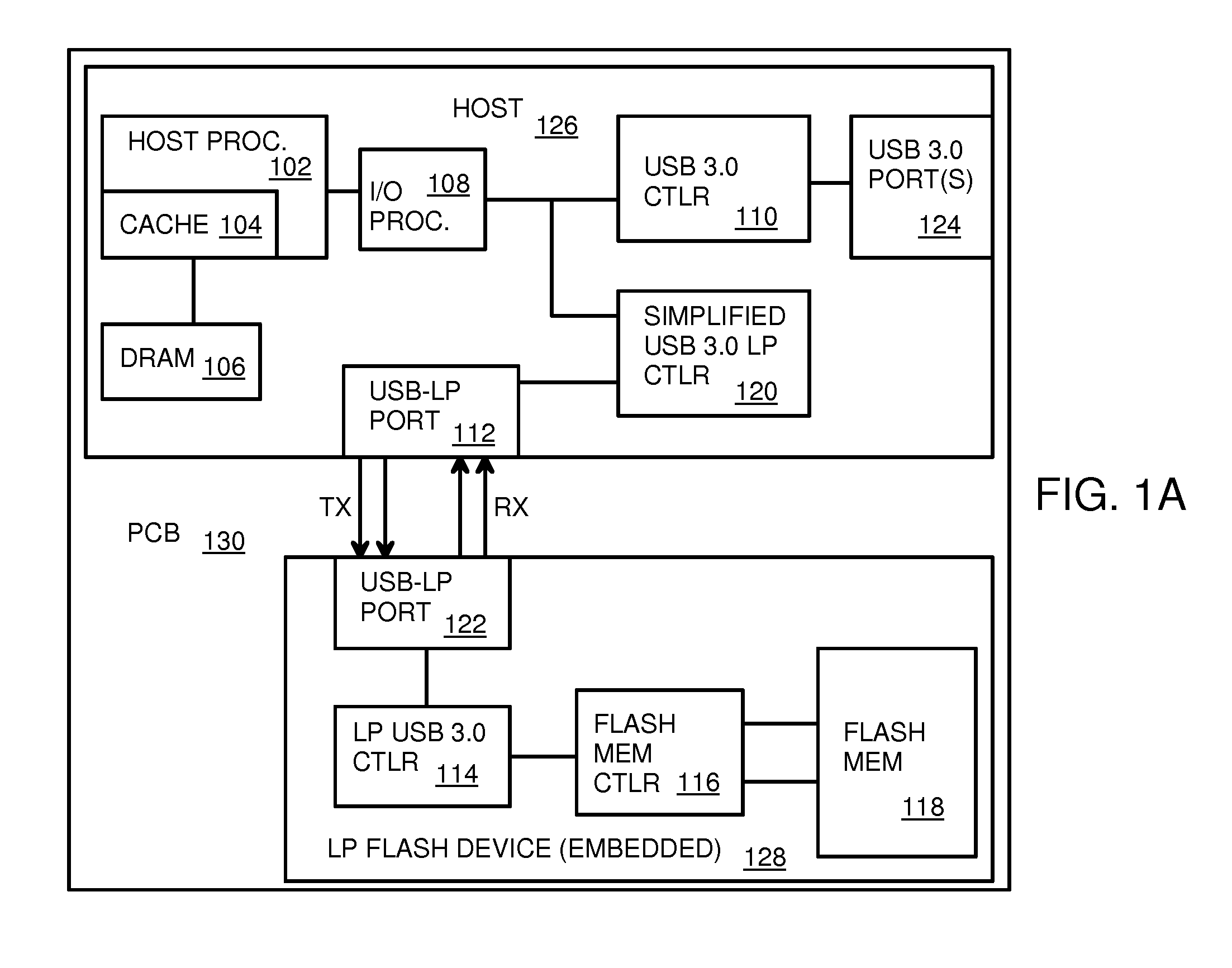

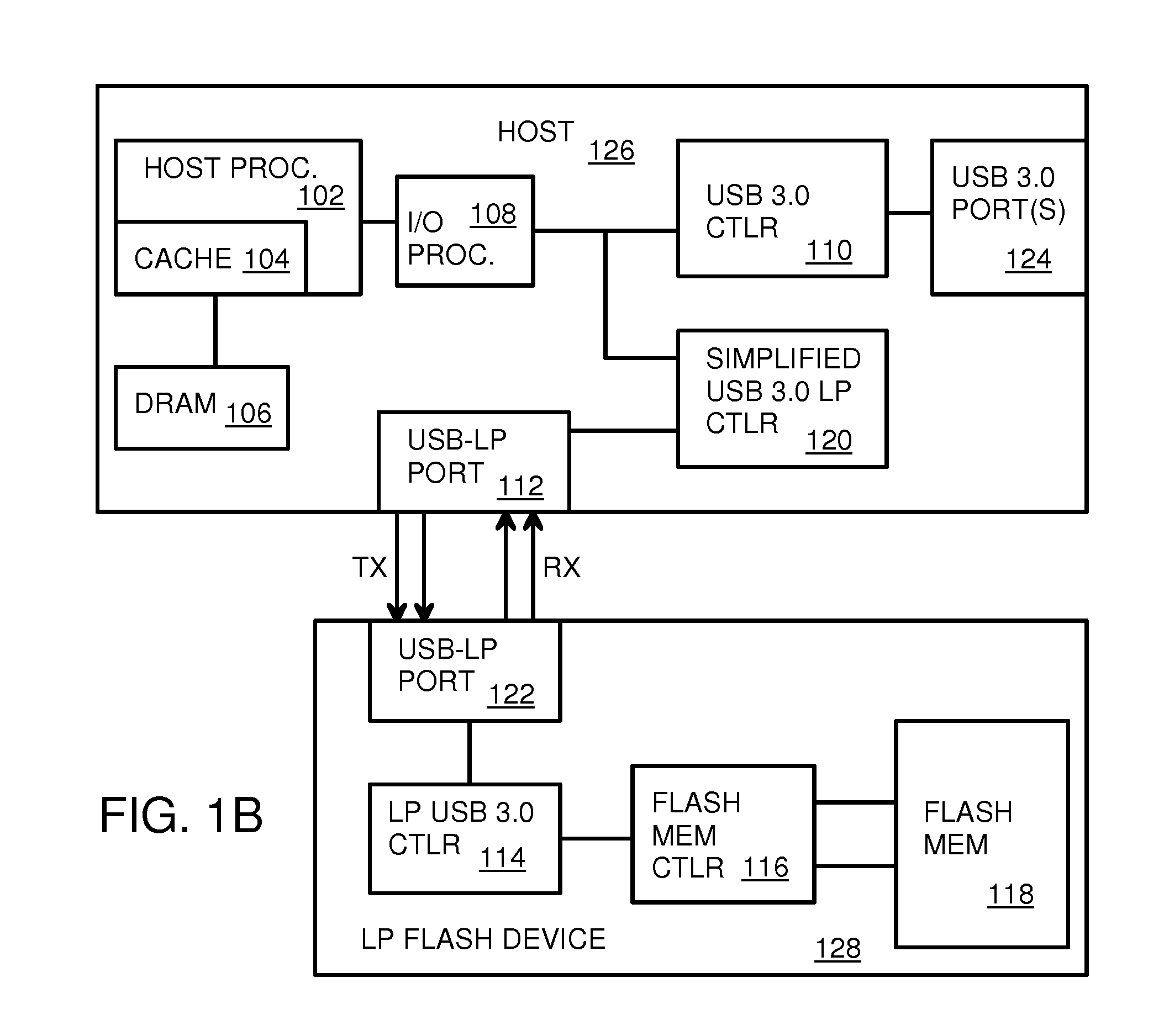

Low-Power USB SuperSpeed Device with 8-bit Payload and 9-bit Frame NRZI Encoding for Replacing 8/10-bit Encoding

A Low-power flash-memory device uses a modified Universal-Serial-Bus (USB) 3.0 Protocol to reduce power consumption. The bit clock is slowed to reduce power and the need for pre-emphasis when USB cable lengths are short in applications. Data efficiency is improved by eliminating the 8 / 10-bit encoder and instead encoding sync and framing bytes as 9-bit symbols. Data bytes are expanded by bit stuffing only when a series of six ones occurs in the data. Header and payload data is transmitted as nearly 8-bits per data byte while framing is 9-bits per symbol, much less than the standard 10 bits per byte. Low-power link layers, physical layers, and scaled-down protocol layers are used. A card reader converter hub allows USB hosts to access low-power USB devices. Only one flash device is accessed, reducing power compared with standard USB broadcasting to multiple devices.

Owner:SUPER TALENT TECH CORP

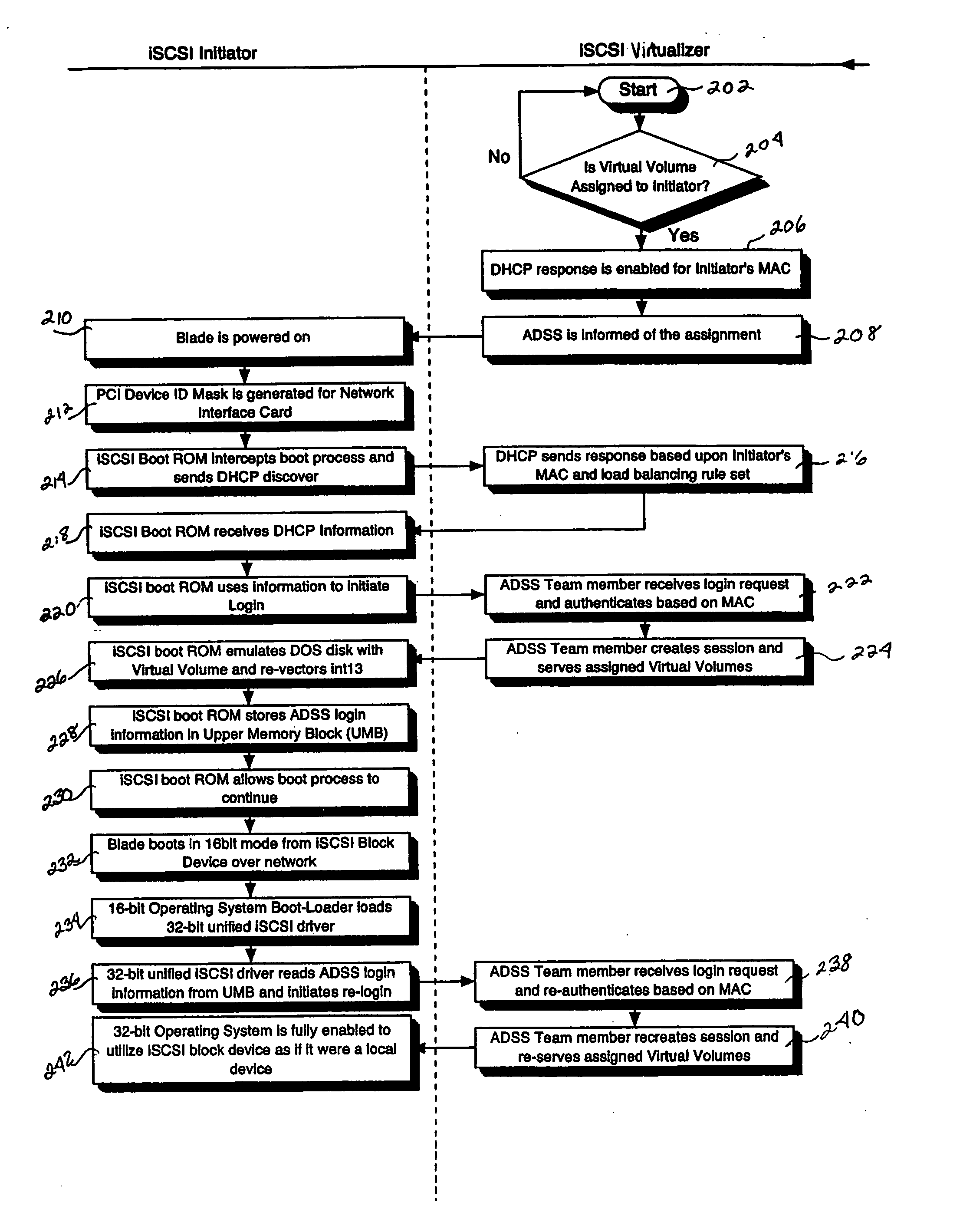

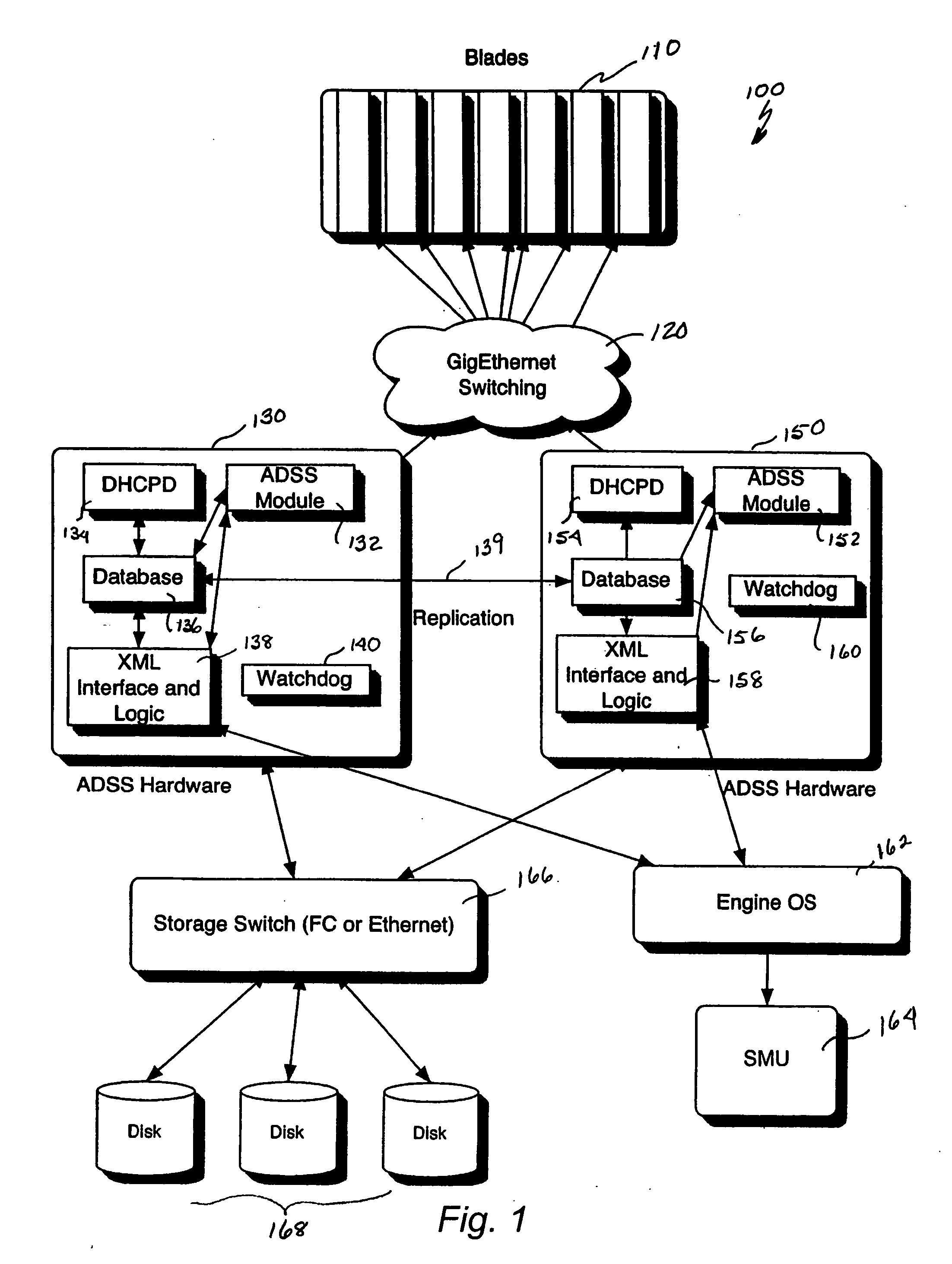

iSCSI boot drive system and method for a scalable internet engine

InactiveUS20050138346A1Digital computer detailsProgram loading/initiatingOperational systemThe Internet

A system for remote booting of a server generally includes a client initiator, an iSCSI virtualizer, and an iSCSI initiator. The client initiator requests access to the server and the iSCSI virtualizer receives the access request. Then, the iSCSI initiator acts upon the request received by the iSCSI virtualizer to initiate login to the server through use of an iSCSI Boot ROM on the server and to emulate a disk operating system through use of the iSCSI Boot ROM, which enables the server to boot. The server boots in both an 8-bit and a subsequent 32-bit mode. The iSCSI Boot ROM appears as a local device upon the completion of the server boot. The iSCSI virtualizer authenticates the login at least twice. The iSCSI virtualizer includes a pair of replicated active directory service servers (ADSS).

Owner:RPX CORP

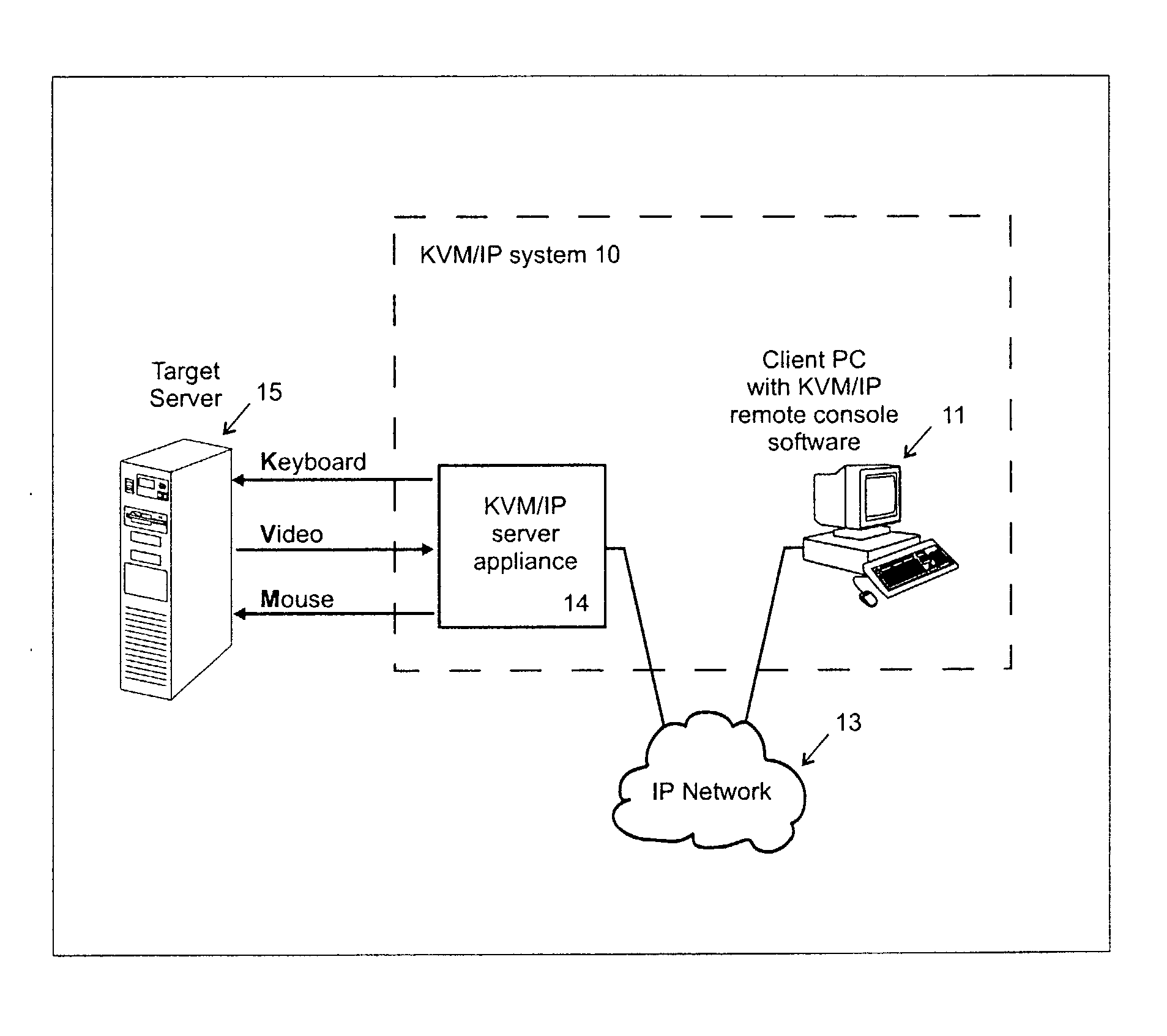

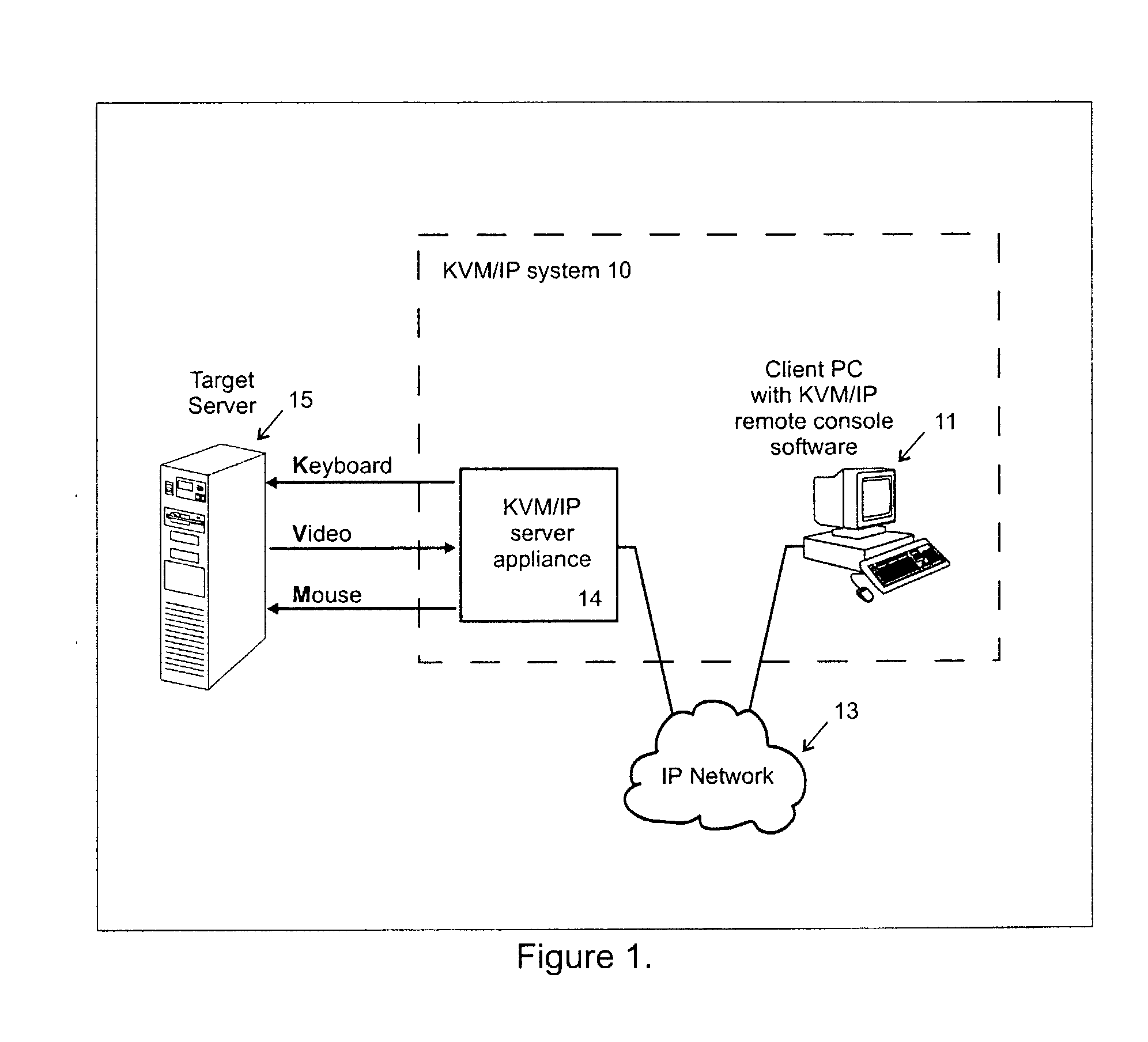

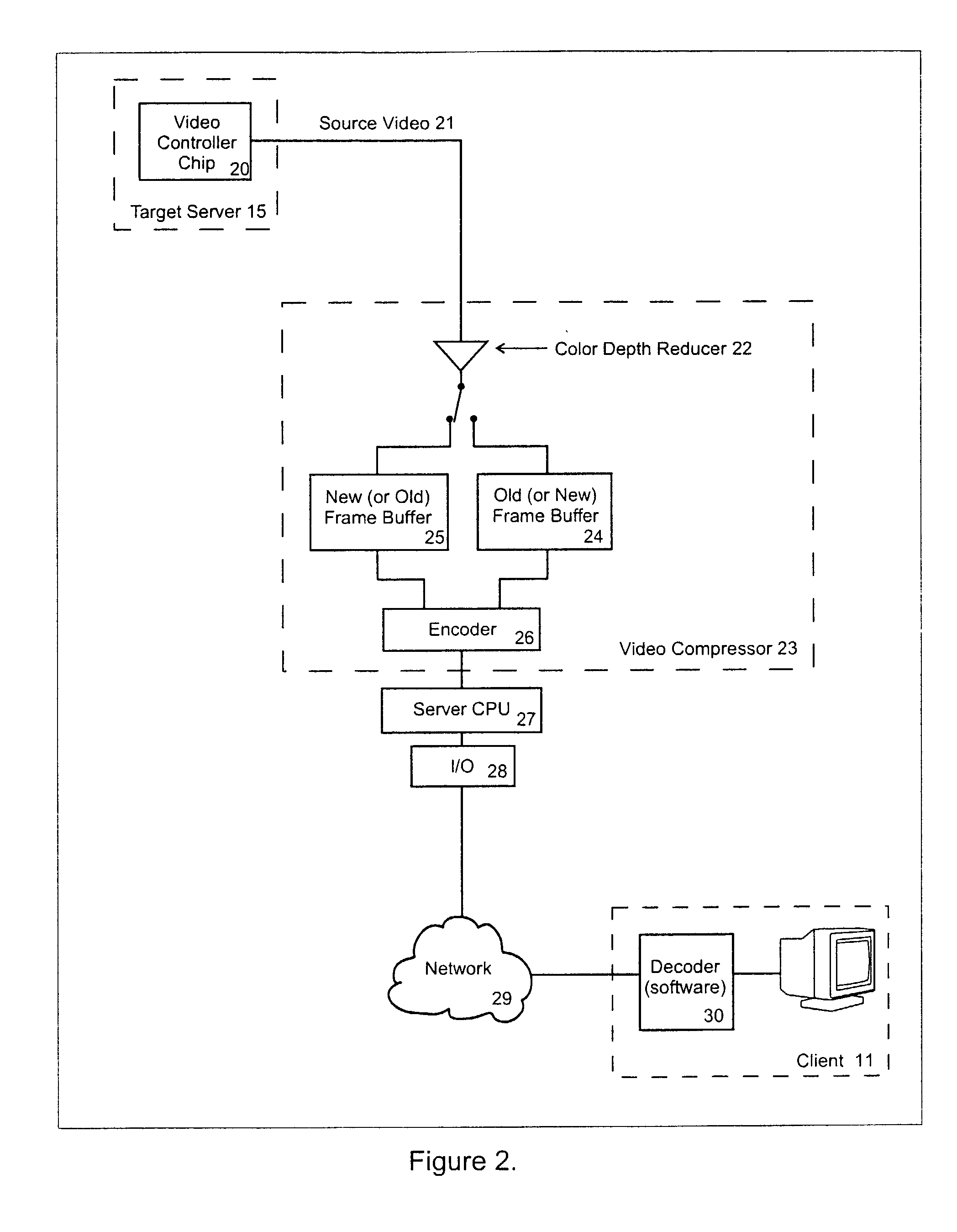

Video compression system

ActiveUS20050069034A1Efficient captureMinimum delayStatic indicating devicesPicture reproducers using cathode ray tubesComputer usersComputer graphics (images)

A video compression system is disclosed that is optimized to take advantage of the types of redundancies typically occurring on computer screens and the types of video loss acceptable to real time interactive computer users. It automatically adapts to a wide variety of changing network bandwidth conditions and can accommodate any video resolution and an unlimited number of colors. The disclosed video compression encoder can be implemented with either hardware or software and it compresses the source video into a series of data packets that are a fixed length of 8 bits or more. Sequences of one or more of these packets create unique encoding “commands” that can be sent over any network and easily decoded (decompressed) with either software or hardware. The commands include 3 dimensional copying (horizontal, vertical and time) and unique efficiencies for screen segments that are comprised of only two colors (such as text). Embodiments are also disclosed that improve the video compression depending on the popularity of pixel colors.

Owner:VERTIV IT SYST INC

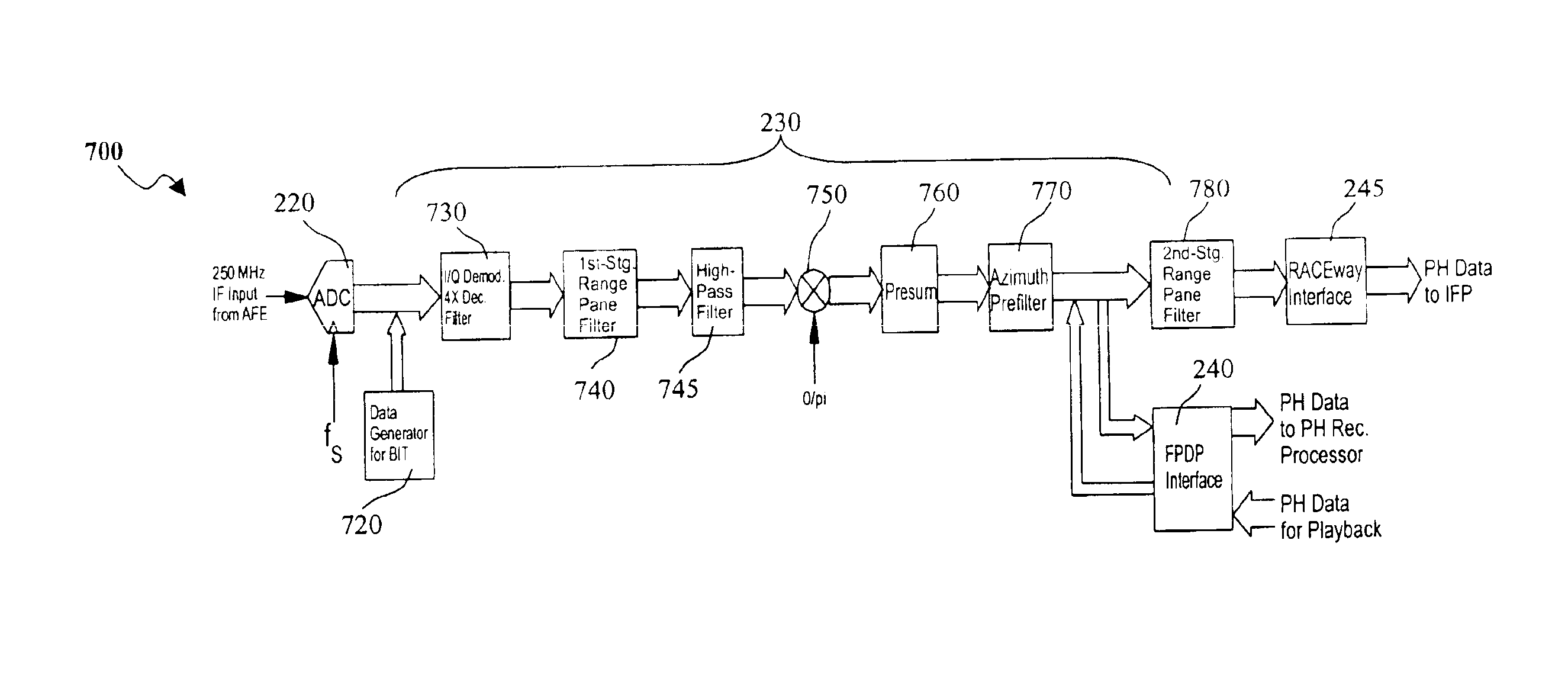

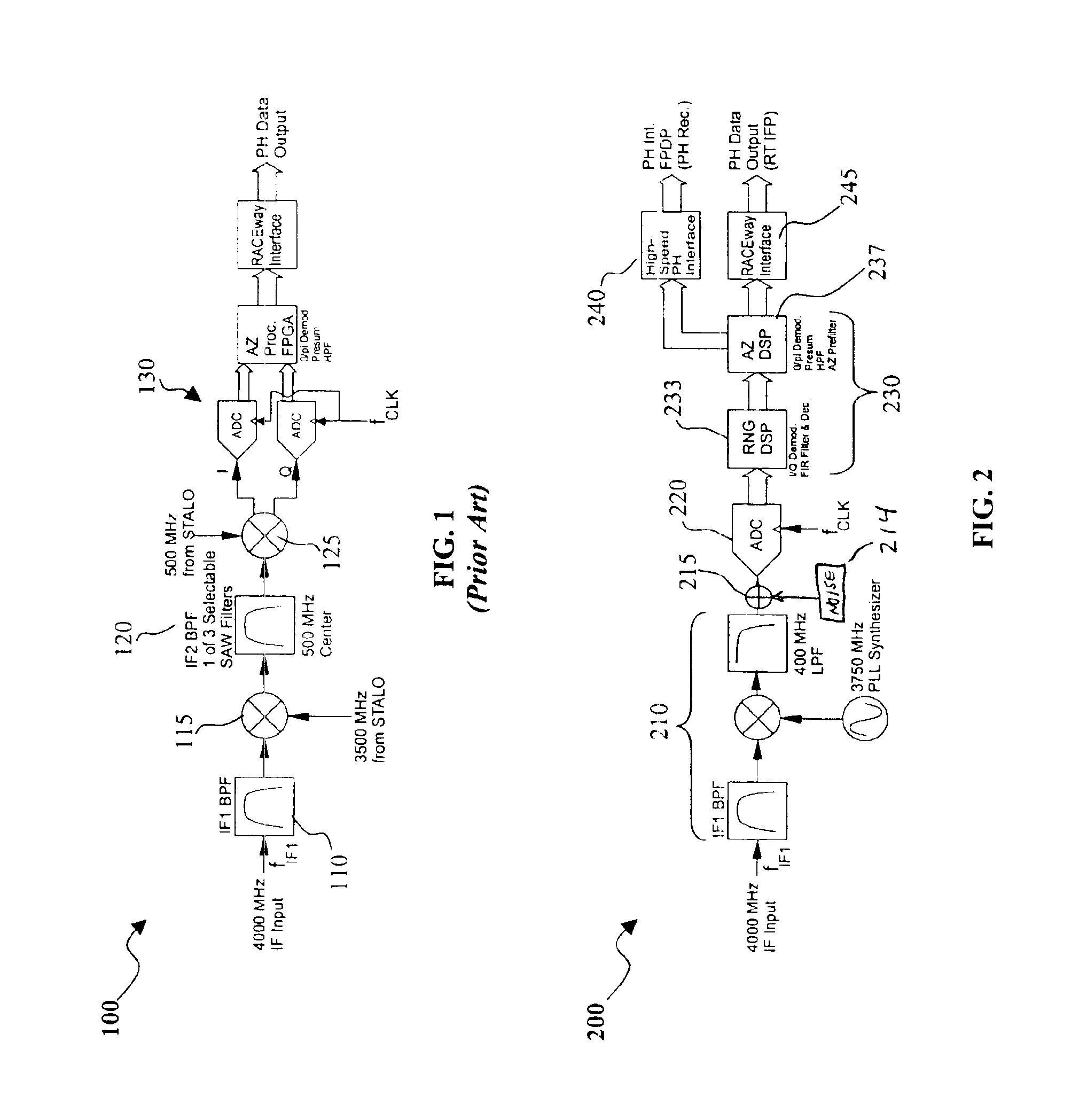

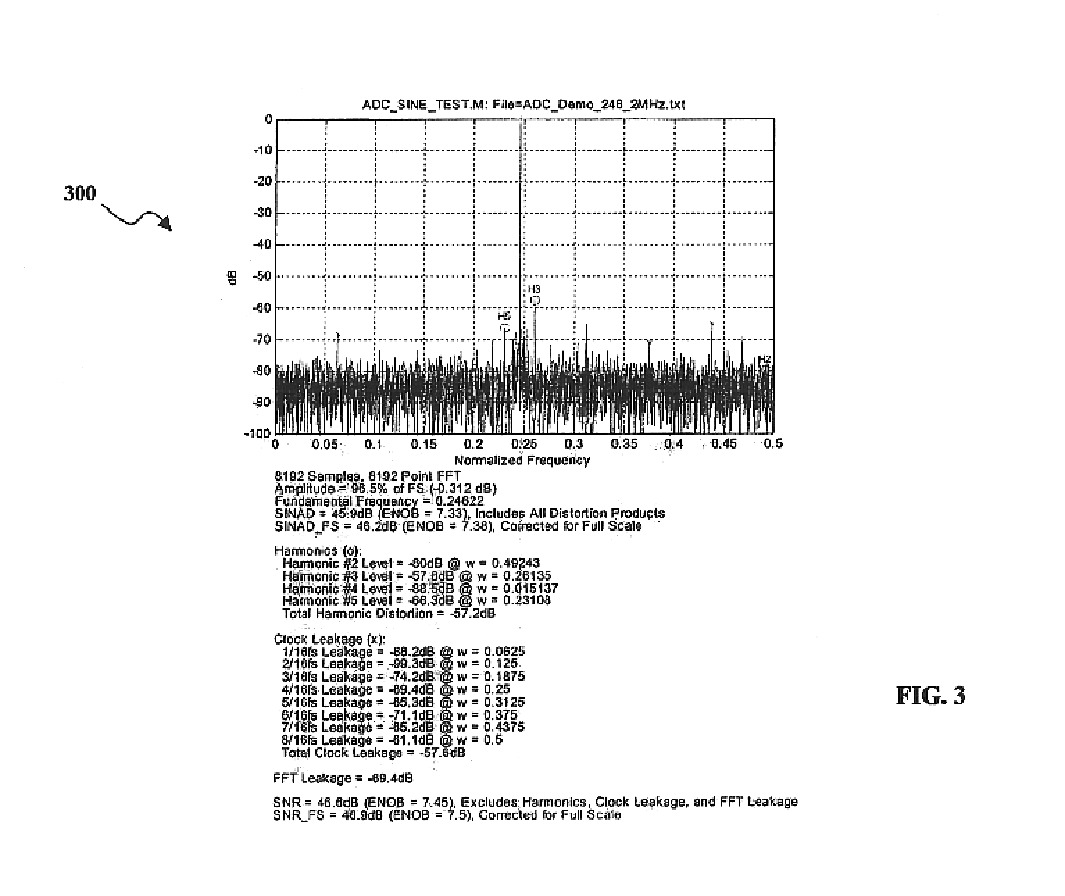

Digital intermediate frequency receiver module for use in airborne SAR applications

ActiveUS6864827B1Increase flexibilityIncrease spacingRadio wave reradiation/reflectionDigital signal processingRadar systems

A digital IF receiver (DRX) module directly compatible with advanced radar systems such as synthetic aperture radar (SAR) systems. The DRX can combine a 1 G-Sample / sec 8-bit ADC with high-speed digital signal processor, such as high gate-count FPGA technology or ASICs to realize a wideband IF receiver. DSP operations implemented in the DRX can include quadrature demodulation and multi-rate, variable-bandwidth IF filtering. Pulse-to-pulse (Doppler domain) filtering can also be implemented in the form of a presummer (accumulator) and an azimuth prefilter. An out of band noise source can be employed to provide a dither signal to the ADC, and later be removed by digital signal processing. Both the range and Doppler domain filtering operations can be implemented using a unique pane architecture which allows on-the-fly selection of the filter decimation factor, and hence, the filter bandwidth. The DRX module can include a standard VME-64 interface for control, status, and programming. An interface can provide phase history data to the real-time image formation processors. A third front-panel data port (FPDP) interface can send wide bandwidth, raw phase histories to a real-time phase history recorder for ground processing.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

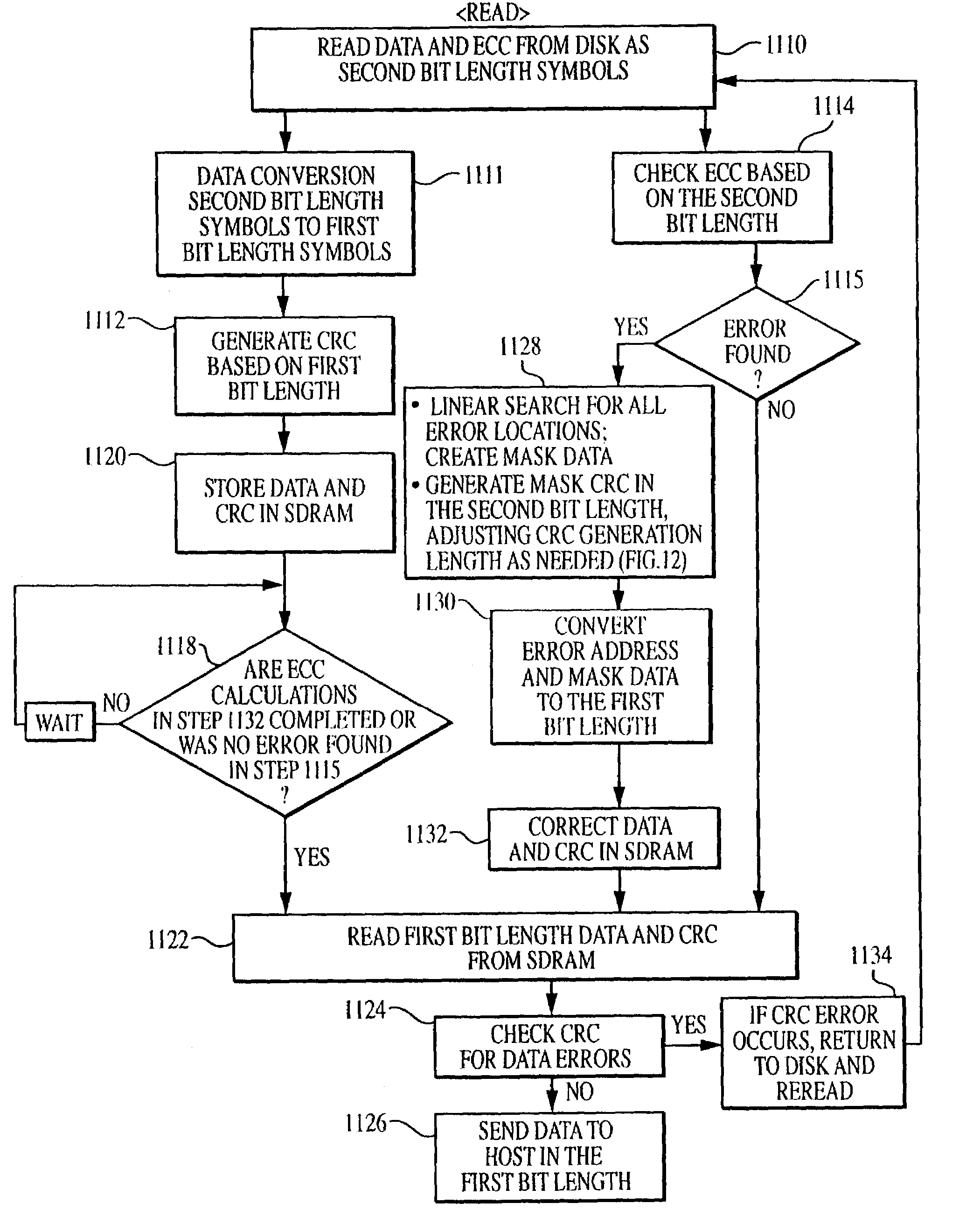

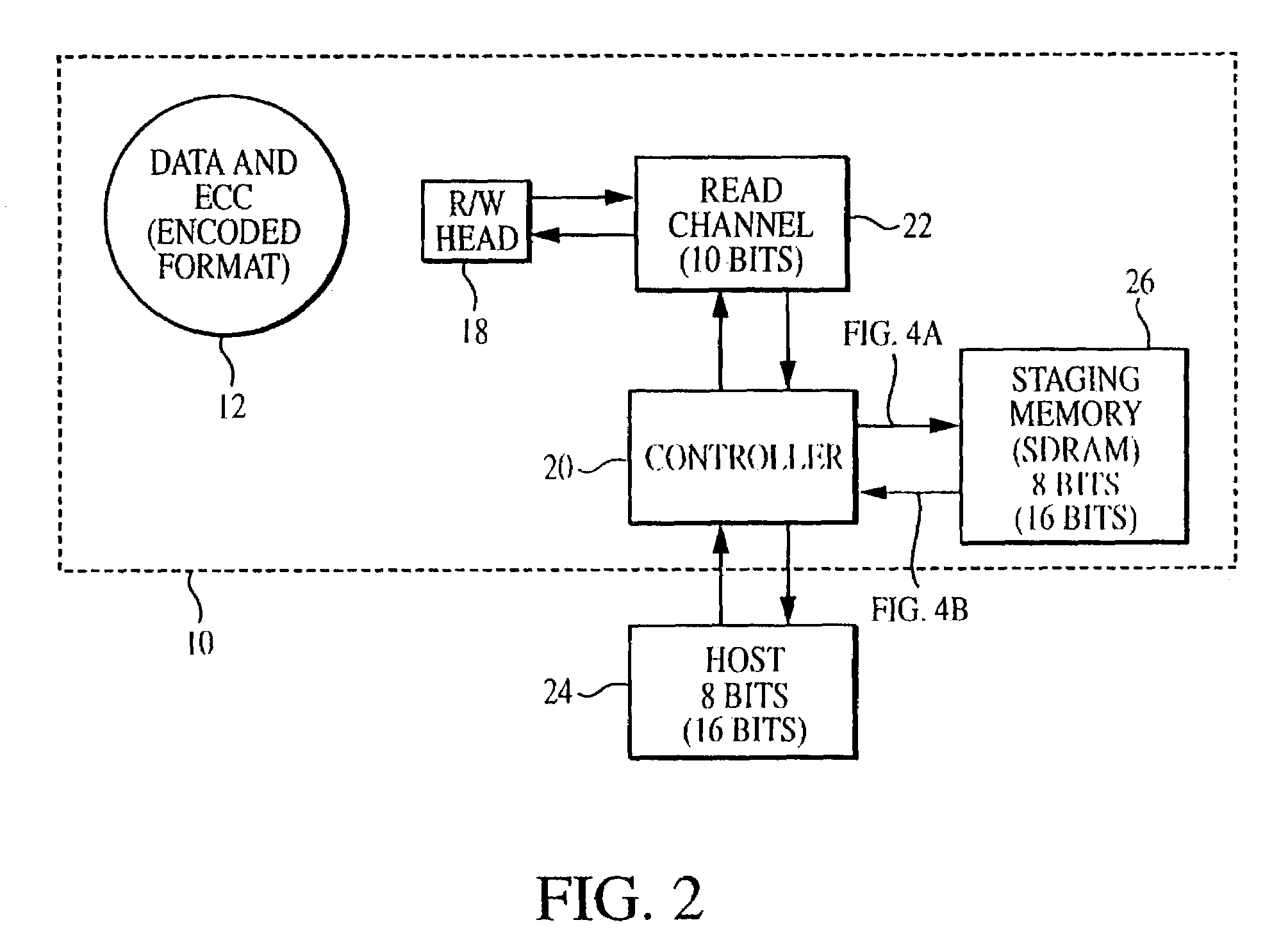

Methods and apparatus for correcting data and error detection codes on the fly

When data is read from a disk and stored in volatile memory, check bits are generated and stored in the memory using an algorithm such as cyclical redundancy check (CRC). The CRC algorithm operates on the basis of the bit length in which the data is organized, such as 8 bits. If the data has errors, an error correction code (ECC) algorithm is used to correct the data errors, but the ECC algorithm operates on the basis of symbols having a different bit length, such as 10 bits. To avoid having to re-read the data from the volatile memory to adjust the CRC value, the CRC algorithm is executed on selected mask data developed by the ECC algorithm, the CRC algorithm being executed on the basis of the second bit length to generate a CRC mask. The CRC mask corrects the stored CRC value.

Owner:TOSHIBA STORAGE DEVICE CORP

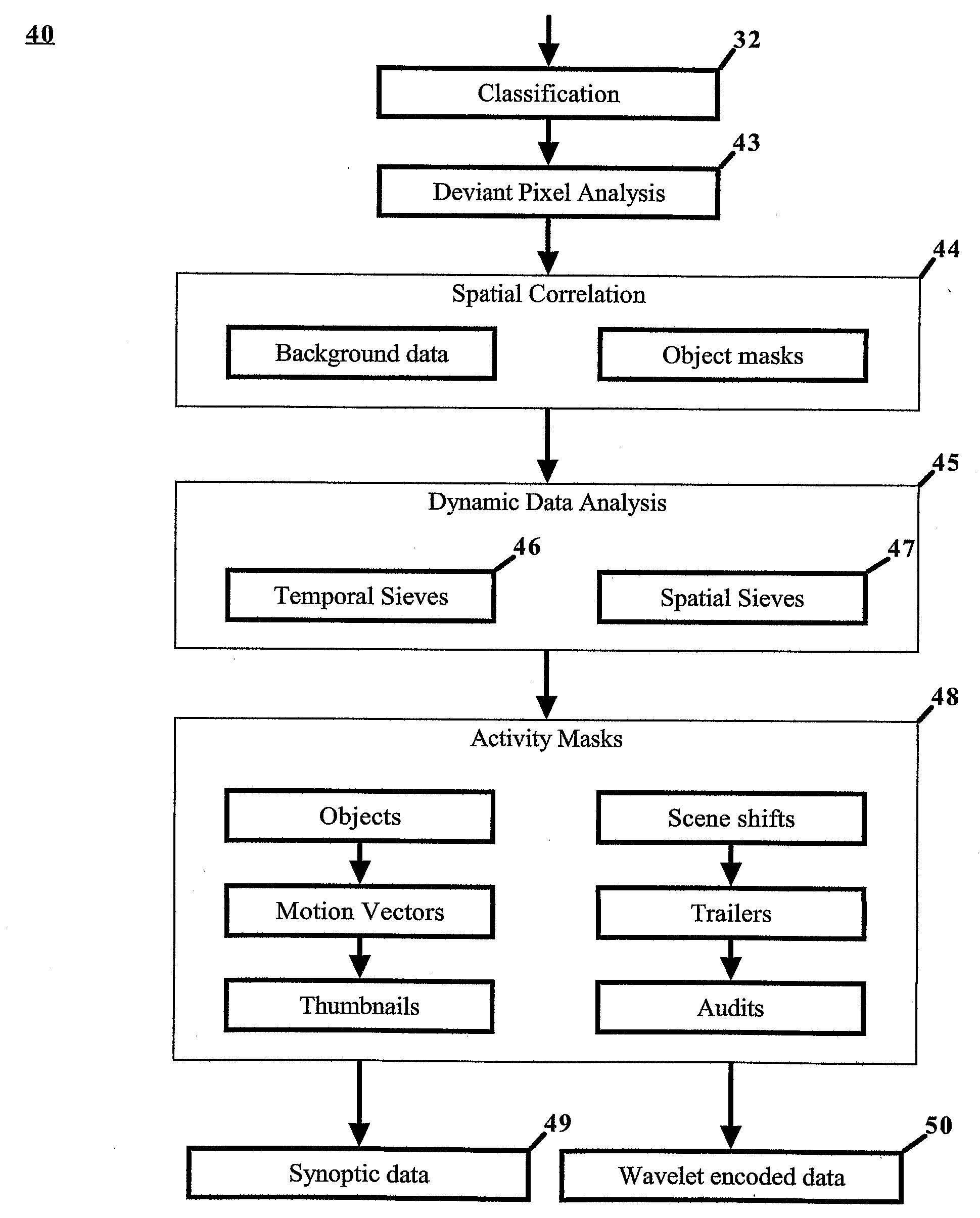

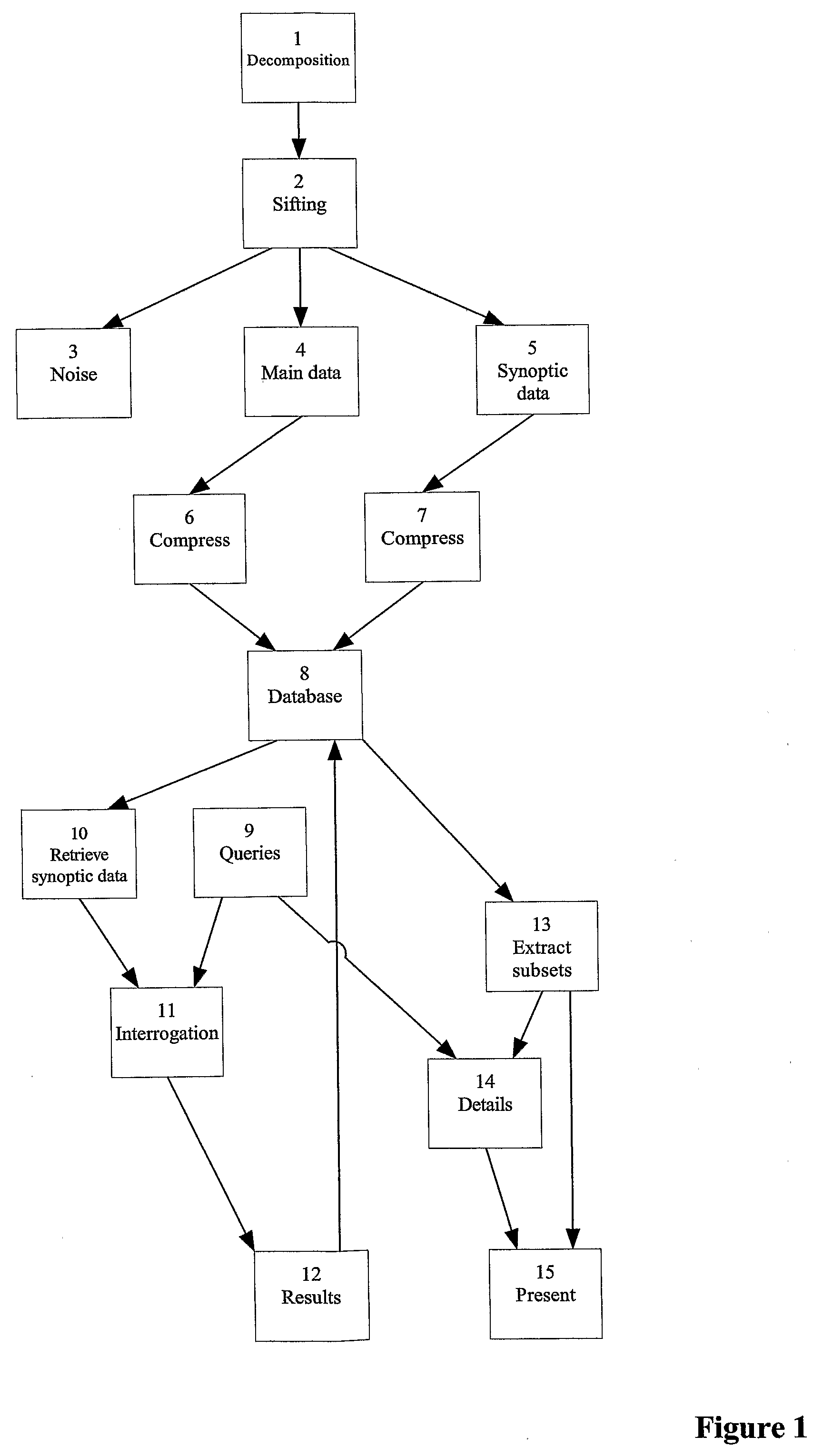

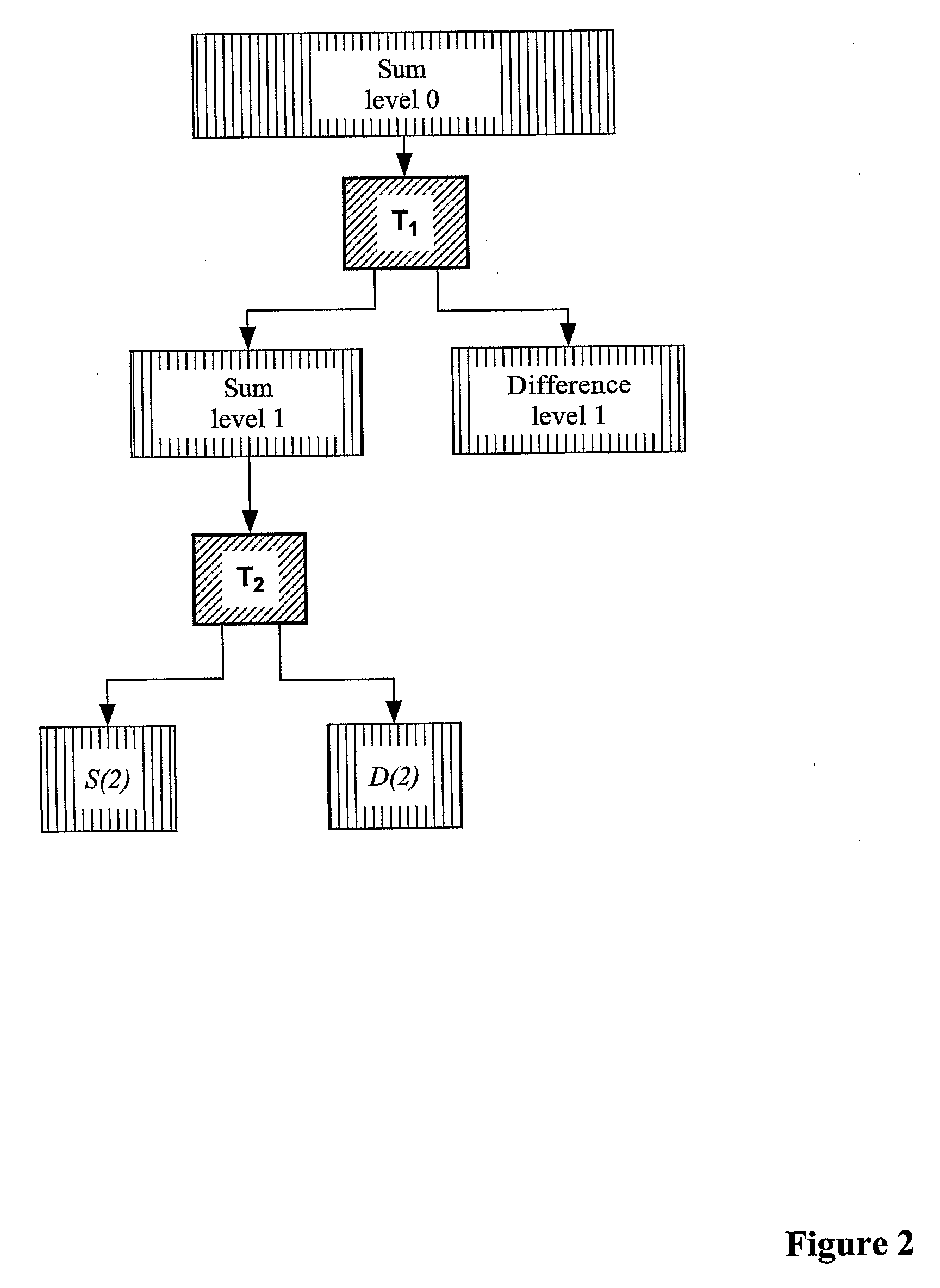

Post-Recording Data Analysis and Retrieval

InactiveUS20080263012A1Digital data information retrievalModulated-carrier systemsDigital dataData compression

When making digital data recordings using some form of computer or calculator, data is input in a variety of ways and stored on some form of electronic medium. During this process calculations and transformations are performed on the data to optimize it for storage. This invention involves designing the calculations in such a way that they include what is needed for each of many different processes, such as data compression, activity detection and object recognition. As the incoming data is subjected to these calculations and stored, information about each of the processes is extracted at the same time. Calculations for the different processes can be executed either serially on a single processor, or in parallel on multiple distributed processors. We refer to the extraction process as “synoptic decomposition”, and to the extracted information as “synoptic data”. The term “synoptic data” does not normally include the main body of original data. The synoptic data is created without any prior bias to specific interrogations that may be made, so it is unnecessary to input search criteria prior to making the recording. Nor does it depend upon the nature of the algorithms / calculations used to make the synoptic decomposition. The resulting data, comprising the (processed) original data together with the (processed) synoptic data, is then stored in a relational database. Alternatively, synoptic data of a simple form can be stored as part of the main data. After the recording is made, the synoptic data can be analyzed without the need to examine the main body of data. This analysis can be done very quickly because the bulk of the necessary calculations have already been done at the time of the original recording. Analyzing the synoptic data provides markers that can be used to access the relevant data from the main data recording if required. The nett effect of doing an analysis in this way is that a large amount of recorded digital data, that might take days or weeks to analyze by conventional means, can be analyzed in seconds or minutes. This invention also relates to a process for generating continuous parameterised families of wavelets. Many of the wavelets can be expressed exactly within 8-bit or 16-bit representations. This invention also relates to processes for using adaptive wavelets to extract information that is robust to variations in ambient conditions, and for performing data compression using locally adaptive quantisation and thresholding schemes, and for performing post recording analysis.

Owner:ASTRAGROUP AS

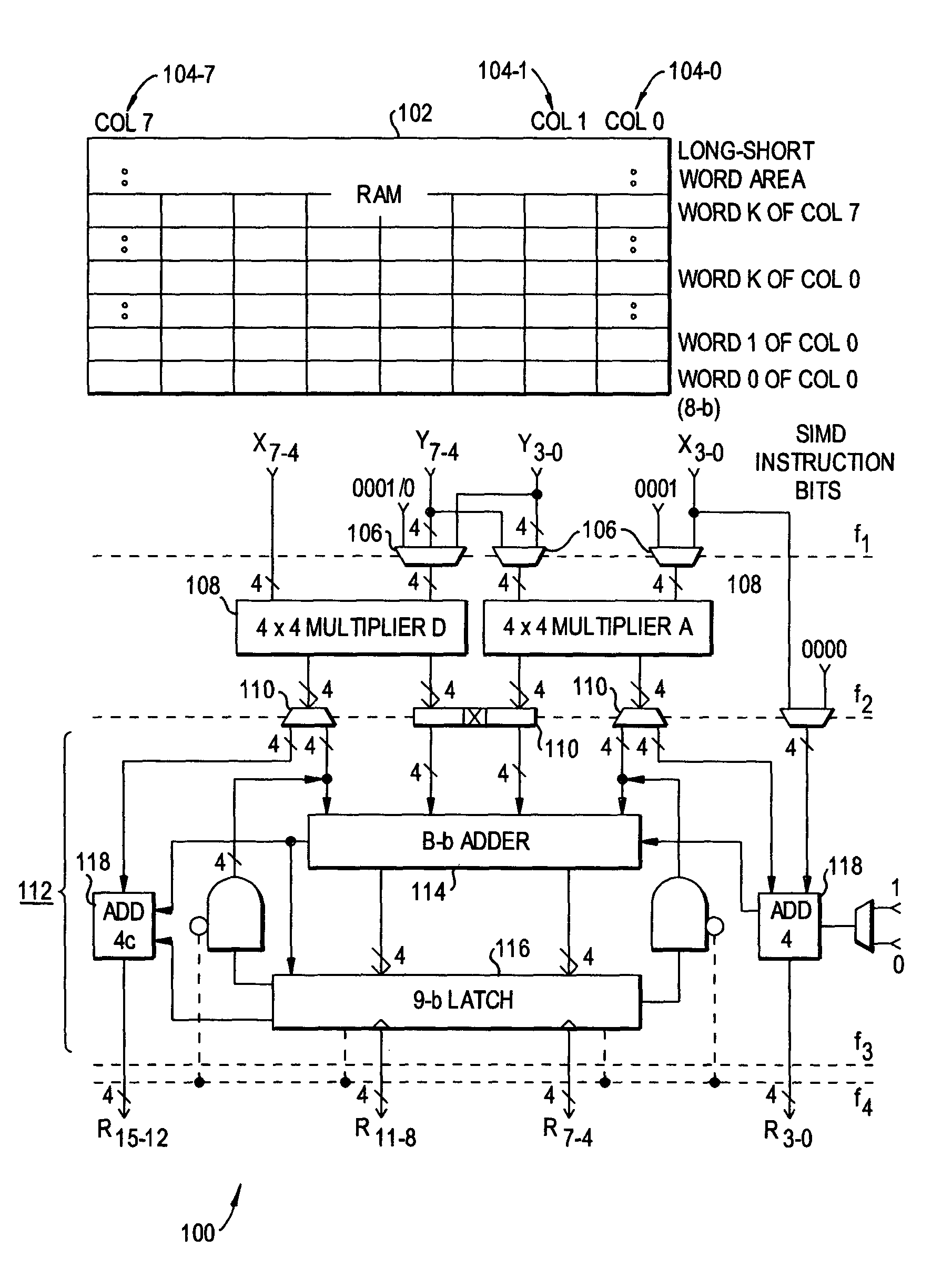

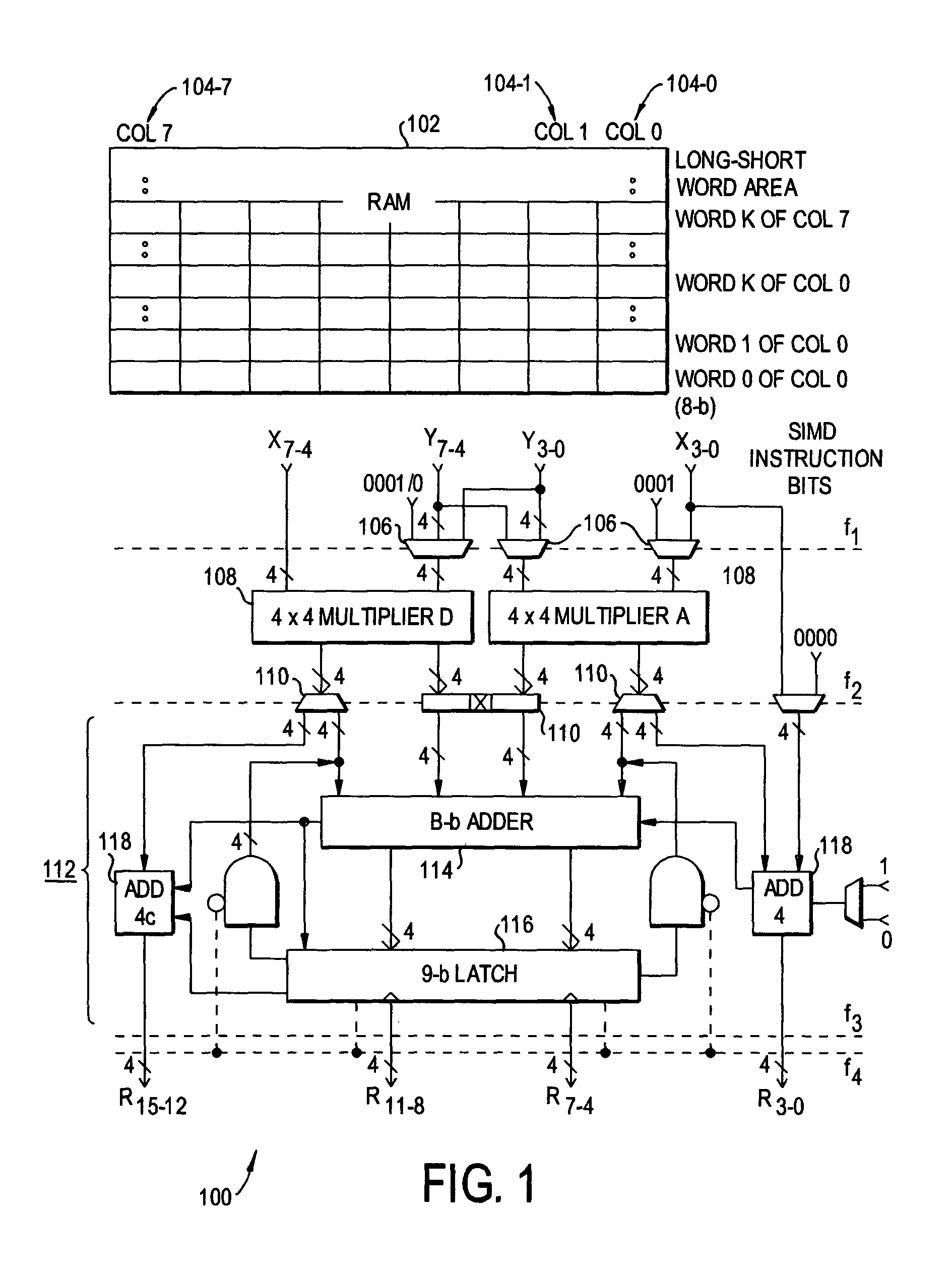

Multiplier-based processor-in-memory architectures for image and graphics processing

InactiveUS7167890B2Efficiently reconfiguredNegligible amountComputation using non-contact making devicesImage memory managementGraphicsComputational science

A Procesor-In-Memory (PIM) includes a digital accelerator for image and graphics processing. The digital accelerator is based on an ALU having multipliers for processing combinations of bits smaller than those in the input data (e.g., 4×4 adders if the input data are 8-bit numbers). The ALU implements various arithmetic algorithms for addition, multiplication, and other operations. A secondary processing logic includes adders in series and parallel to permit vector operations as well as operations on longer scalars. A self-repairing ALU is also disclosed.

Owner:UNIVERSITY OF ROCHESTER +2

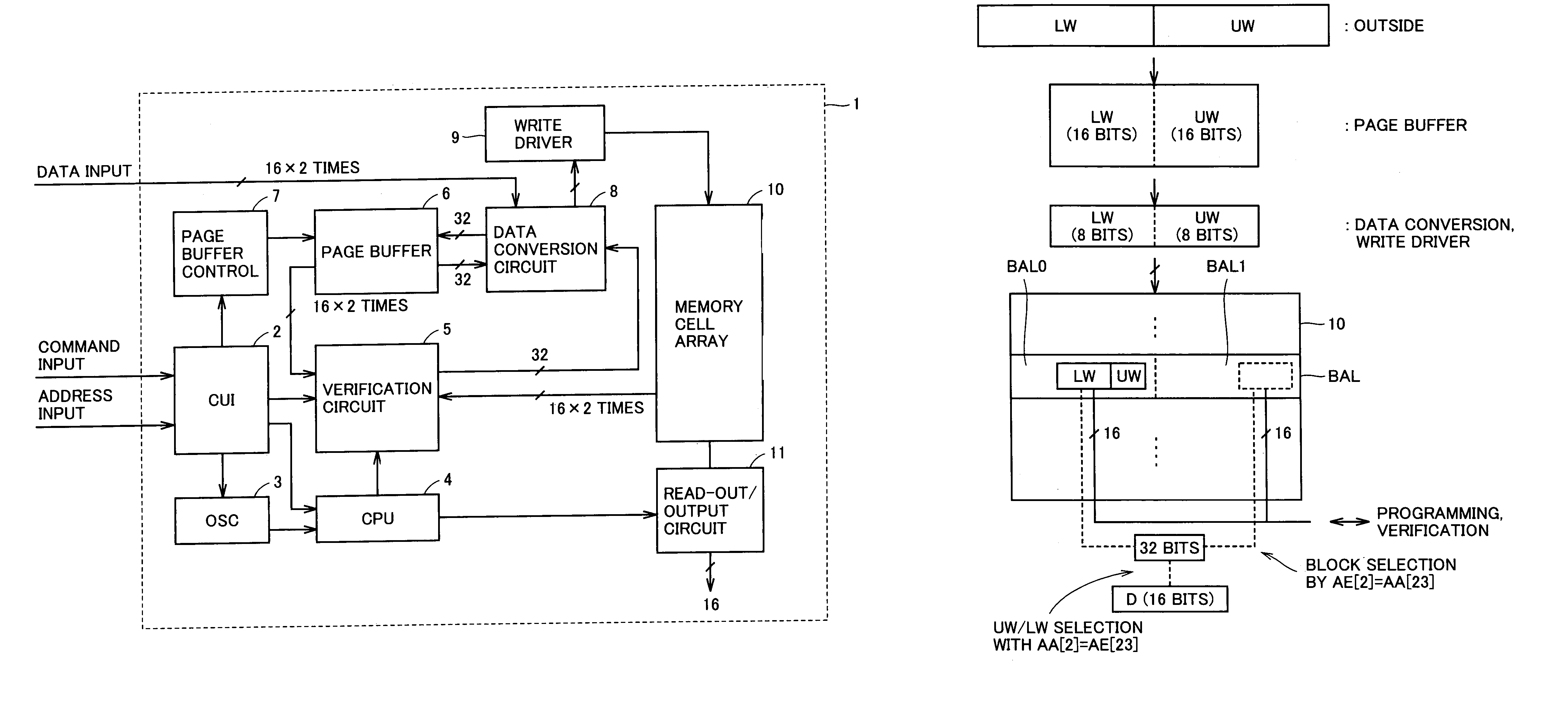

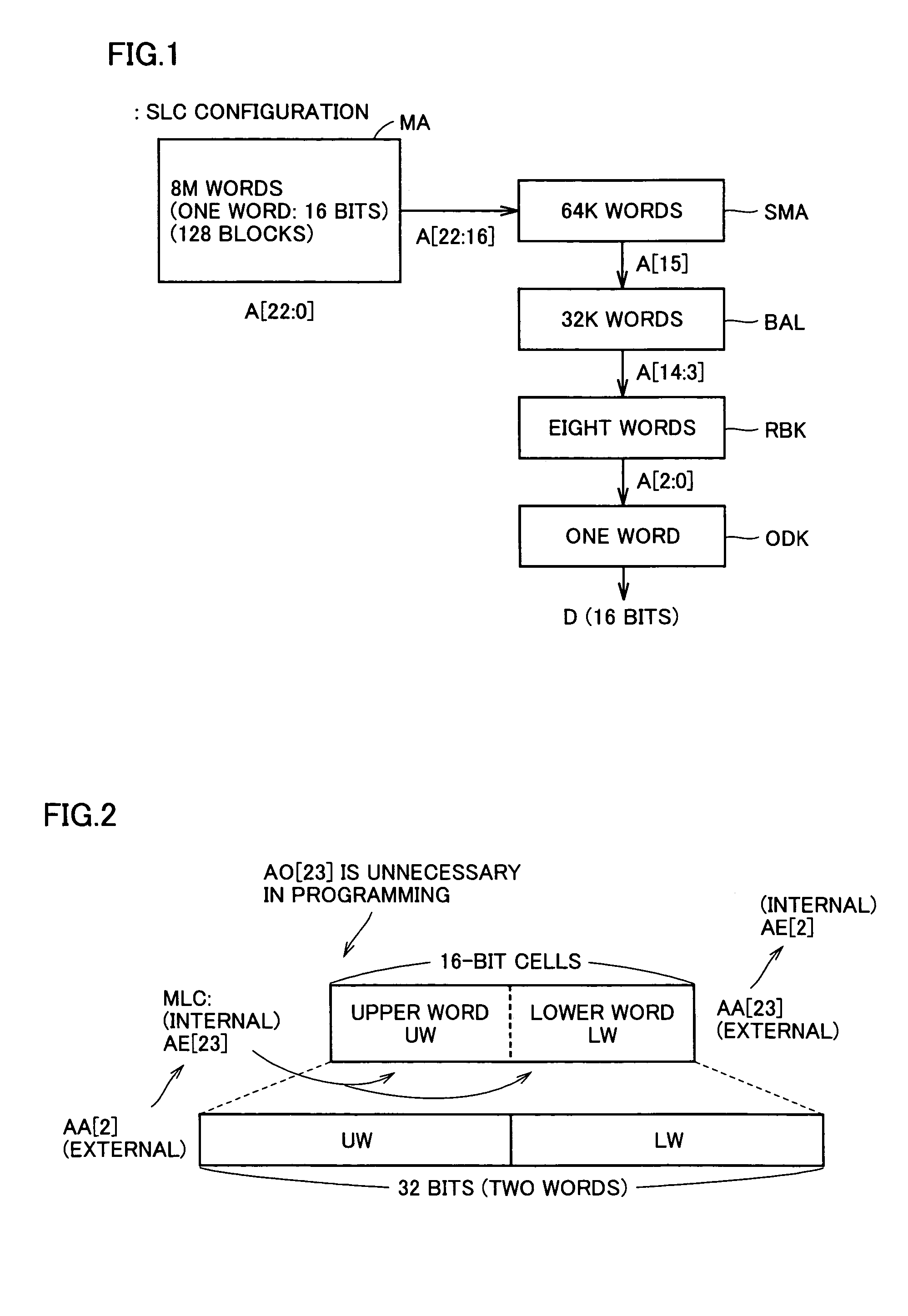

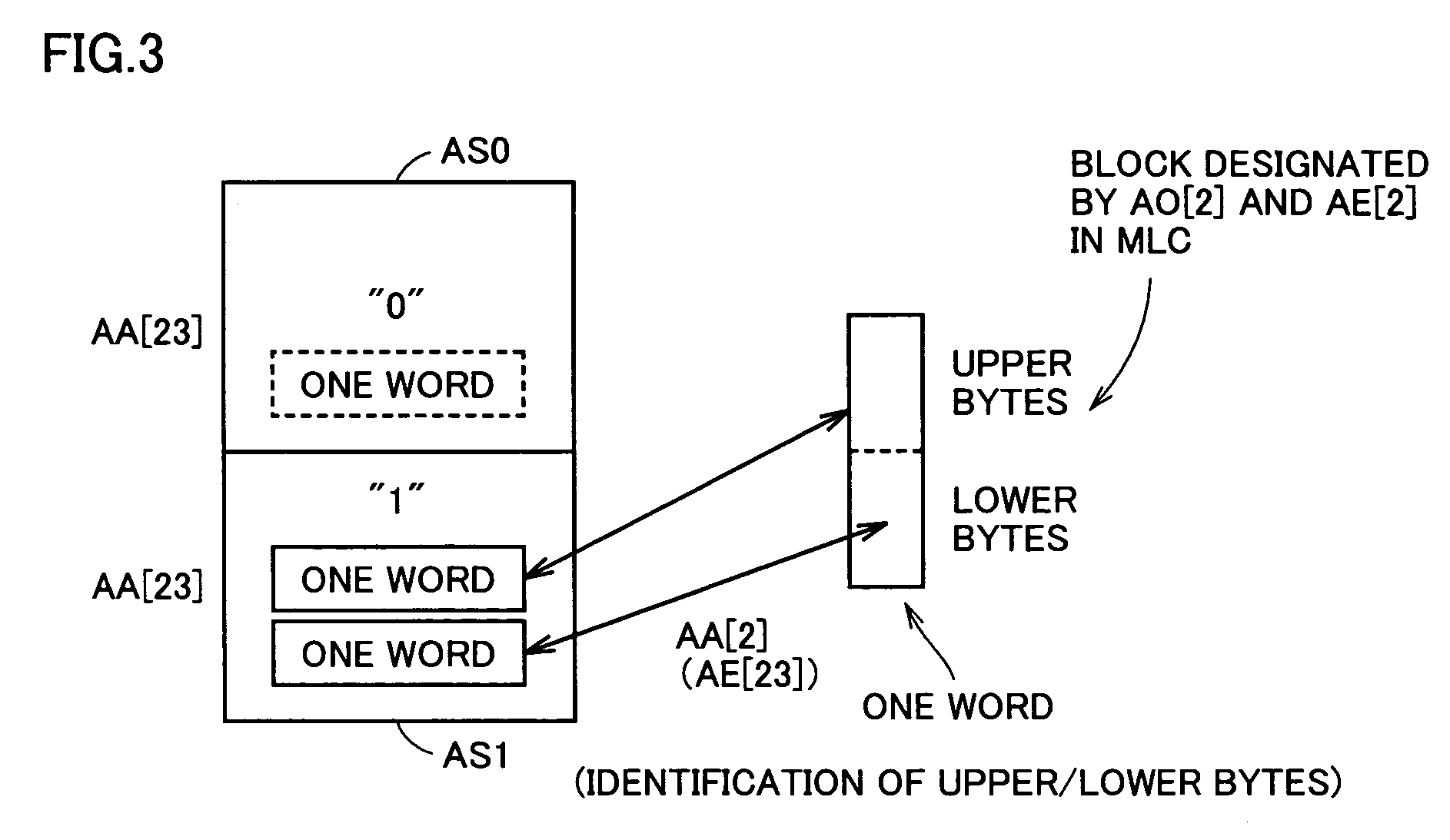

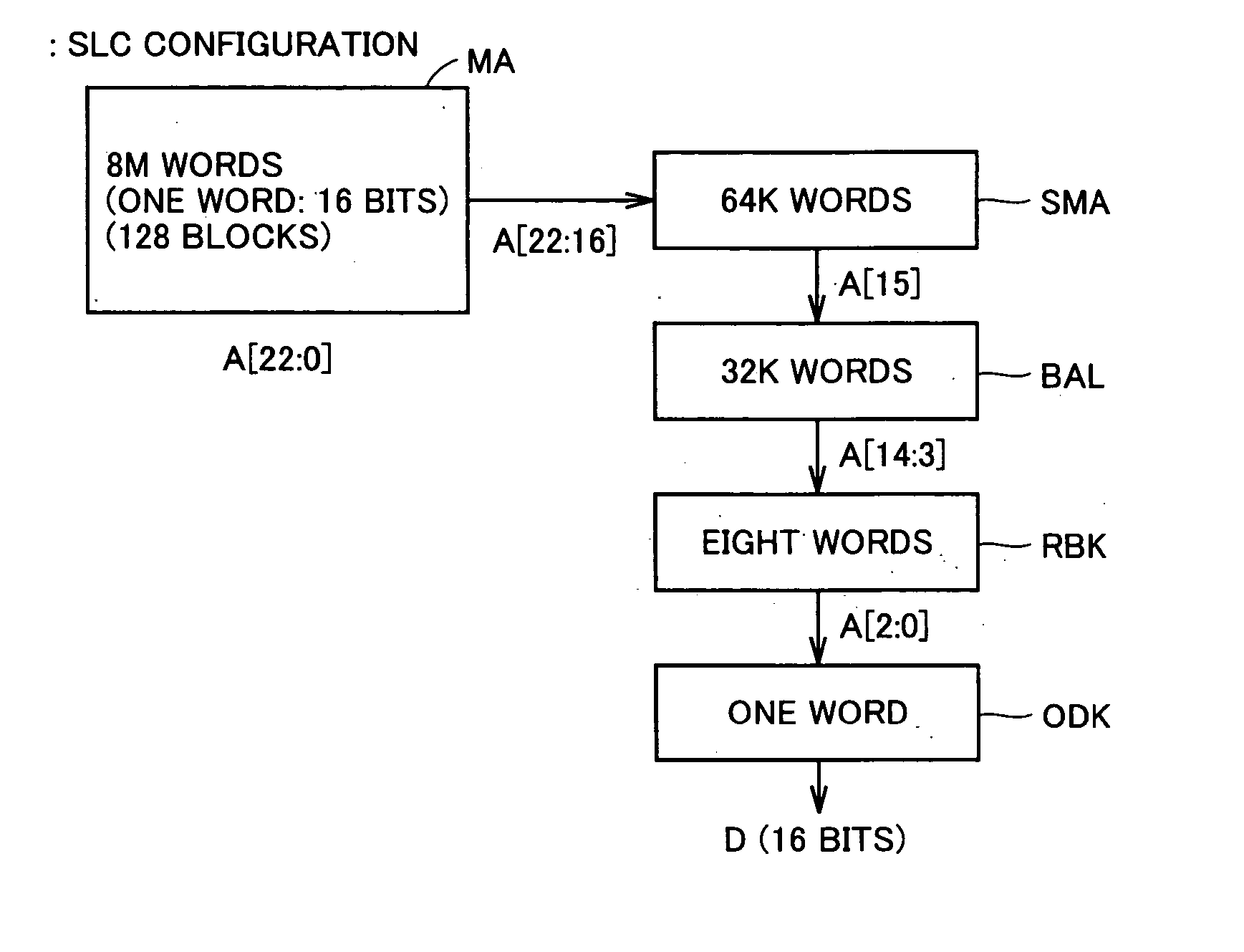

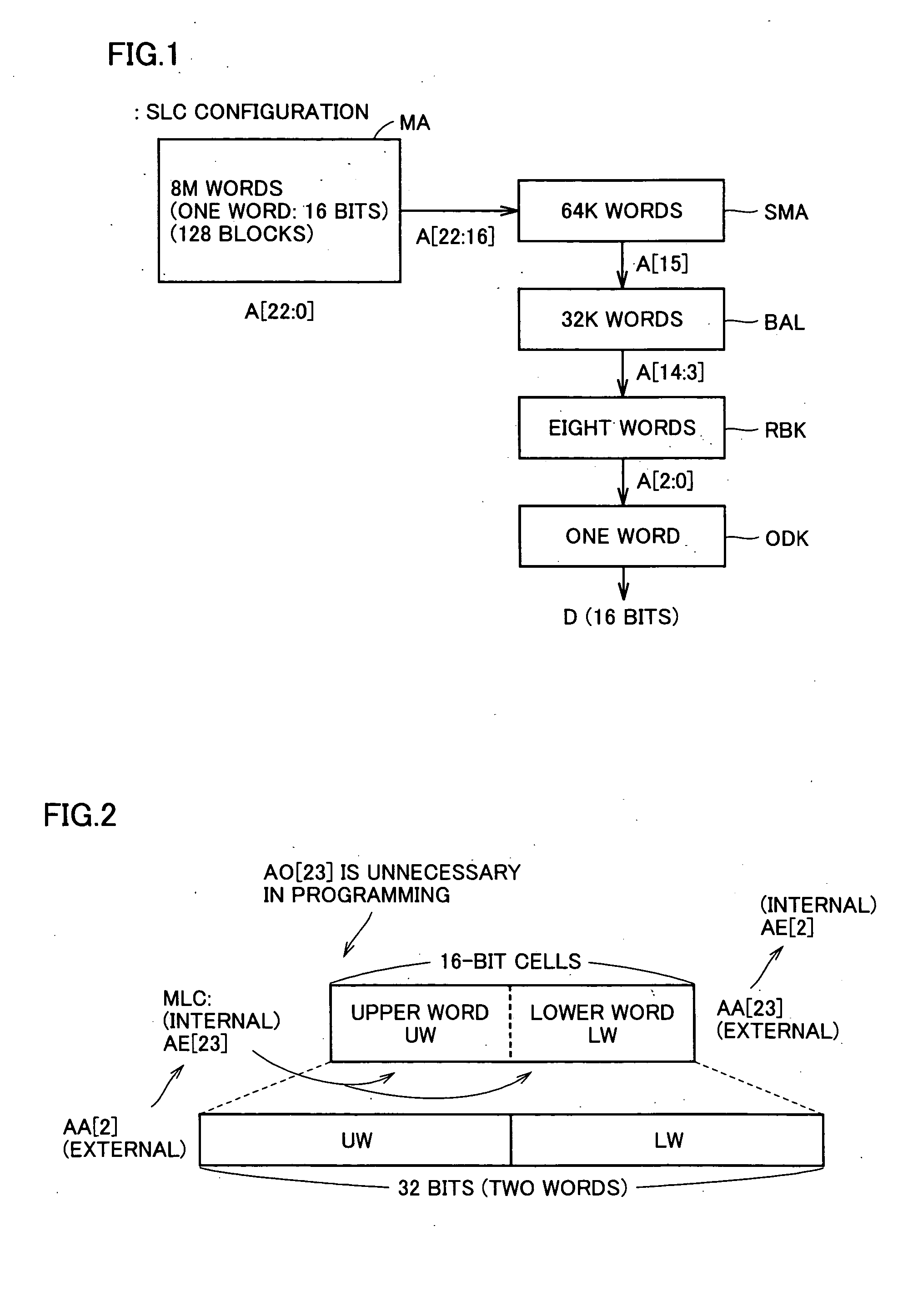

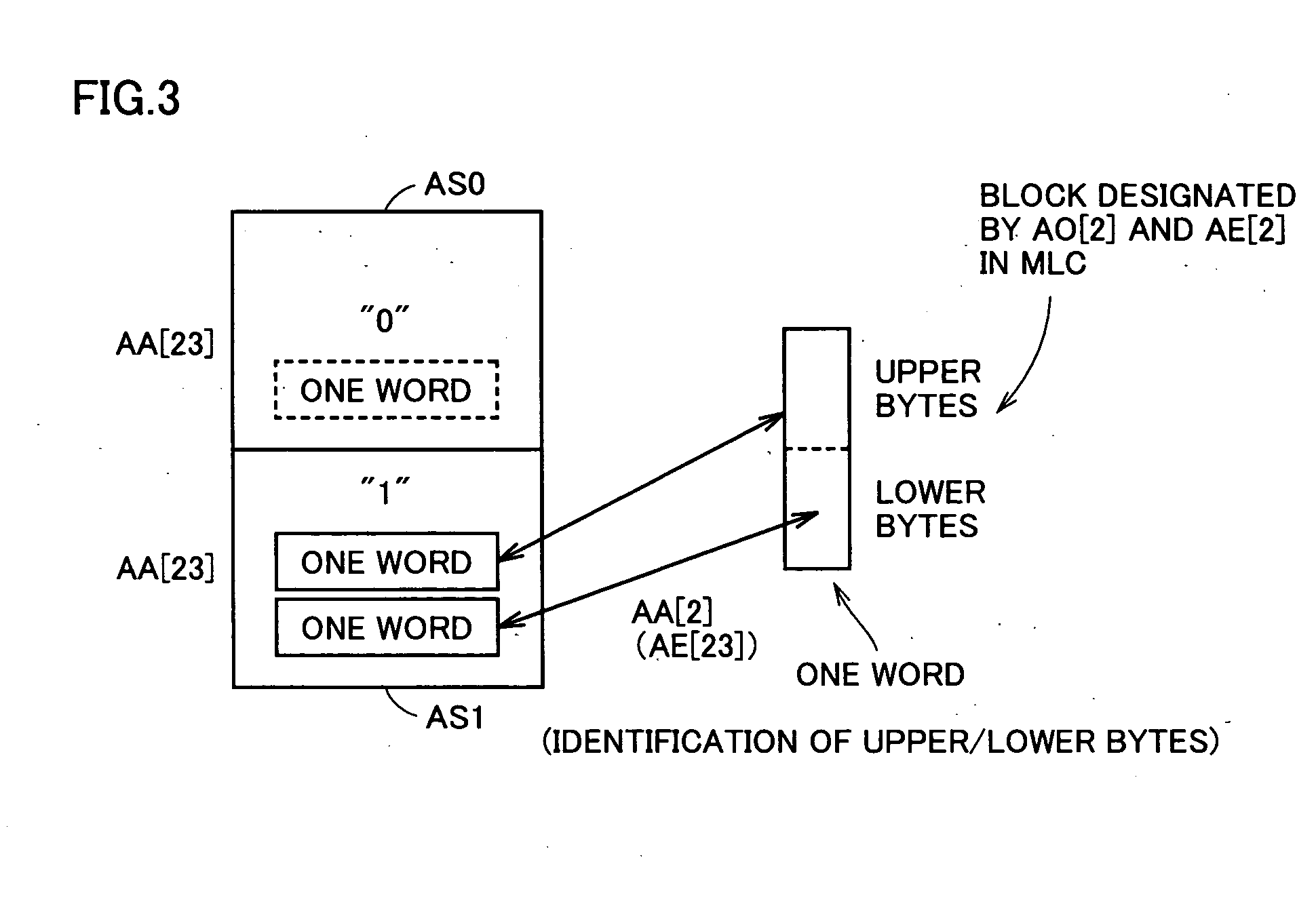

Multi-level nonvolatile semiconductor memory device utilizing a nonvolatile semiconductor memory device for storing binary data

A multi-level semiconductor memory device for storing multi-level data having three or more values is implemented by utilizing a nonvolatile memory device for storing 2-valued data. Identification of successive 16-bit data externally applied is performed with external address bit AA [2], and a storage block is selected with external address bit AA [23]. Upper word data LW and lower word data UW are compressed into byte data of 8 bits, respectively, and stored in a memory cell array.

Owner:RENESAS ELECTRONICS CORP

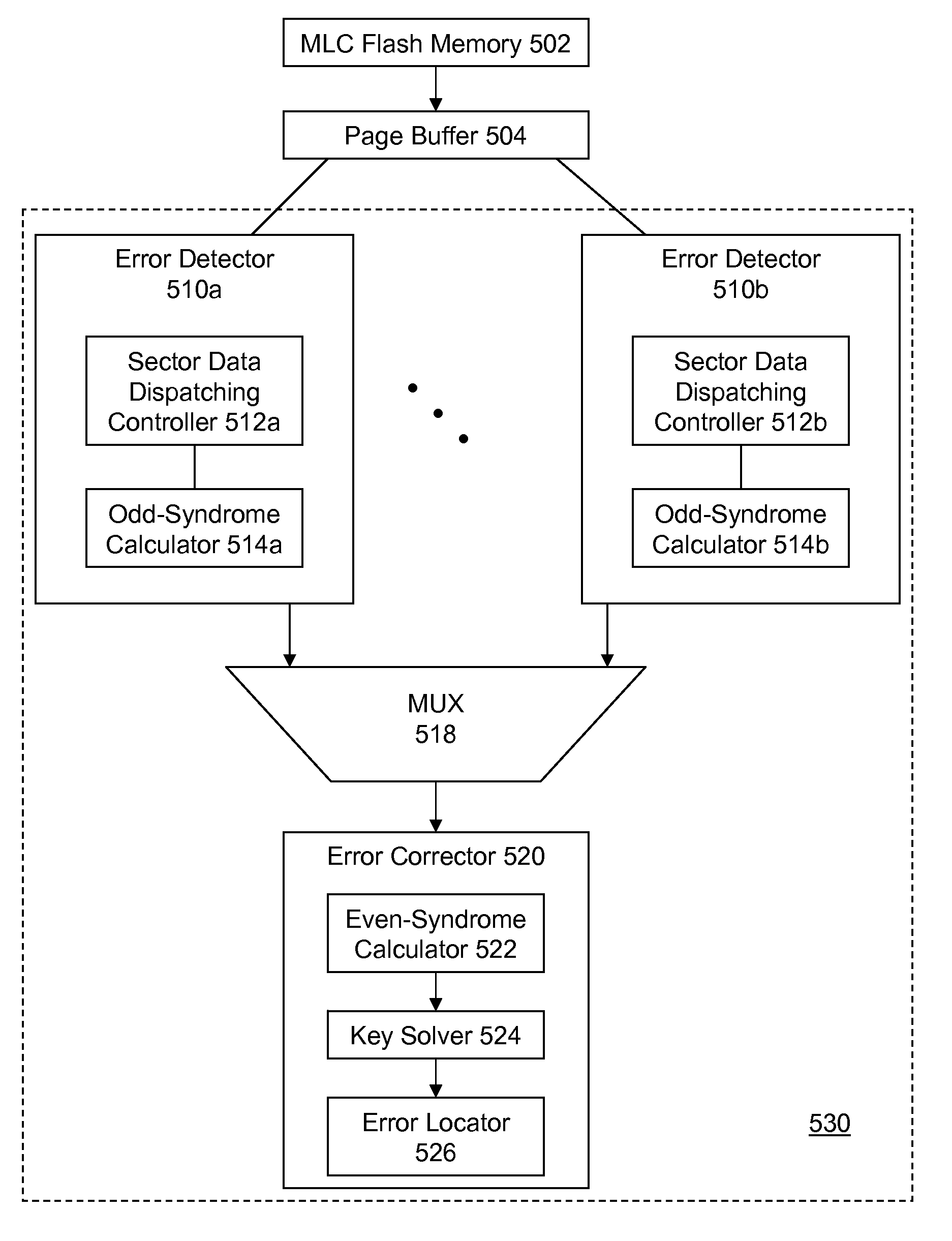

Data error detection and correction in non-volatile memory devices

Data error detection and correction in non-volatile memory devices are disclosed. Data error detection and correction can be performed with software, hardware or a combination of both. Generally an error corrector is referred to as an ECC (error correction code). One of the most relevant codes using in non-volatile memory devices is based on BCH (Bose, Ray-Chaudhuri, Hocquenghem) code. In order to correct reasonable number (e.g., up to 8-bit (eight-bit)) of random errors in a chunk of data (e.g., a codeword of 4200-bit with 4096-bit information data), a BCH(4200,4096,8) is used in GF(213). ECC comprises encoder and decoder. The decoder further comprises a plurality of error detectors and one error corrector. The plurality of error decoders is configured for calculating odd terms of syndrome polynomial for multiple channels in parallel, while the error corrector is configured for sequentially calculating even terms of syndrome polynomial, key solver and error location.

Owner:SUPER TALENT TECH CORP

System and process for generating high dynamic range video

InactiveUS20050047676A1Minimizing any discontinuityTelevision system detailsImage enhancementTone mappingRadiance

A system and process for generating High Dynamic Range (HDR) video is presented which involves first capturing a video image sequence while varying the exposure so as to alternate between frames having a shorter and longer exposure. The exposure for each frame is set prior to it being captured as a function of the pixel brightness distribution in preceding frames. Next, for each frame of the video, the corresponding pixels between the frame under consideration and both preceding and subsequent frames are identified. For each corresponding pixel set, at least one pixel is identified as representing a trustworthy pixel. The pixel color information associated with the trustworthy pixels is then employed to compute a radiance value for each pixel set to form a radiance map. A tone mapping procedure can then be performed to convert the radiance map into an 8-bit representation of the HDR frame.

Owner:MICROSOFT TECH LICENSING LLC

Semiconductor memory device

A multi-level semiconductor memory device for storing multi-level data having three or more values is implemented by utilizing a nonvolatile memory device for storing 2-valued data. Identification of successive 16-bit data externally applied is performed with external address bit AA [2], and a storage block is selected with external address bit AA [23]. Upper word data LW and lower word data UW are compressed into byte data of 8 bits; respectively, and stored in a memory cell array.

Owner:RENESAS ELECTRONICS CORP

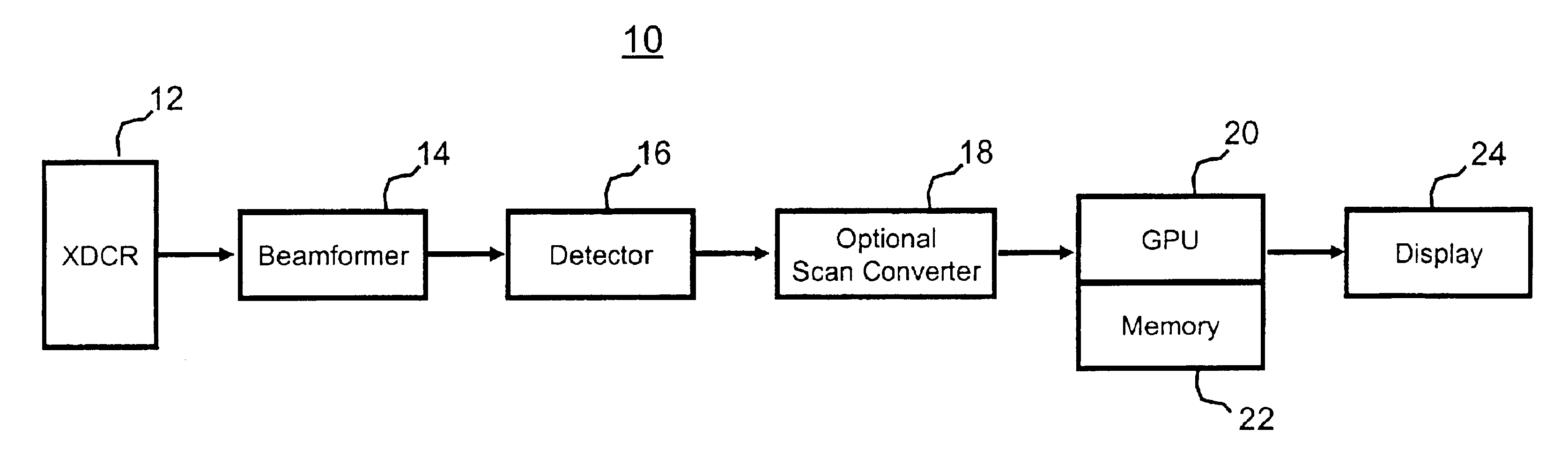

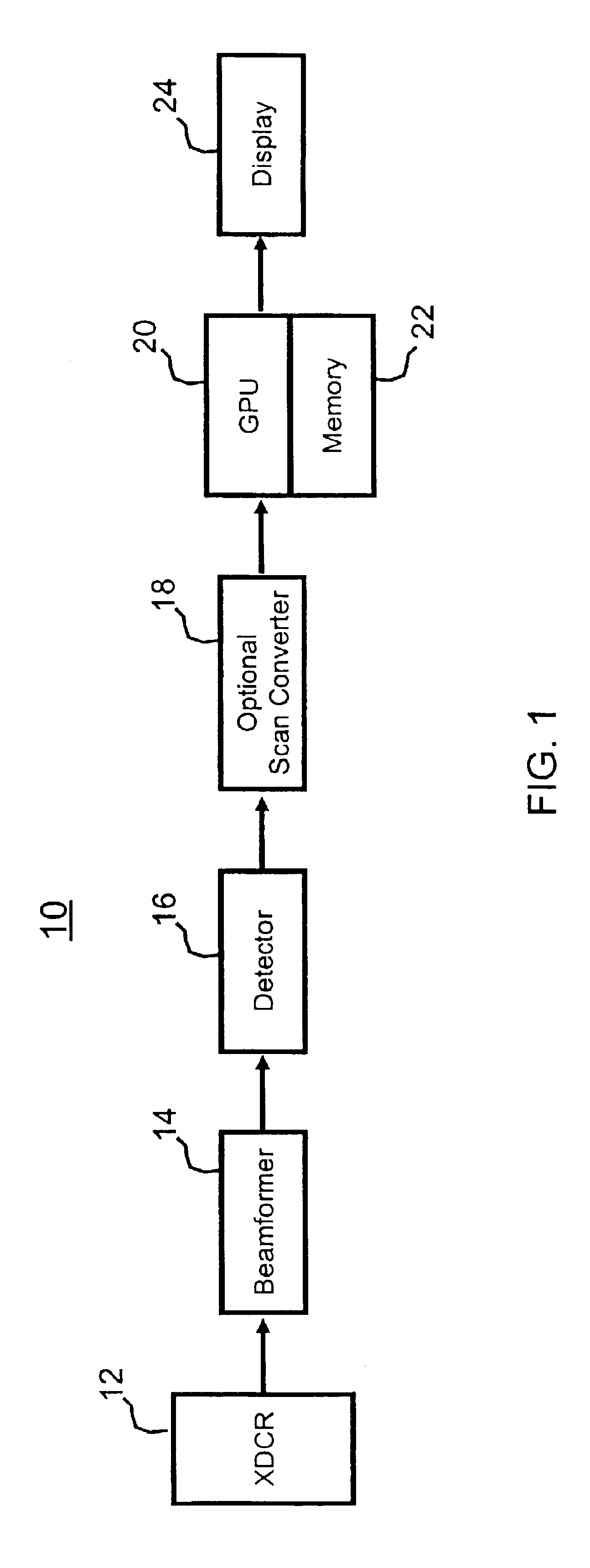

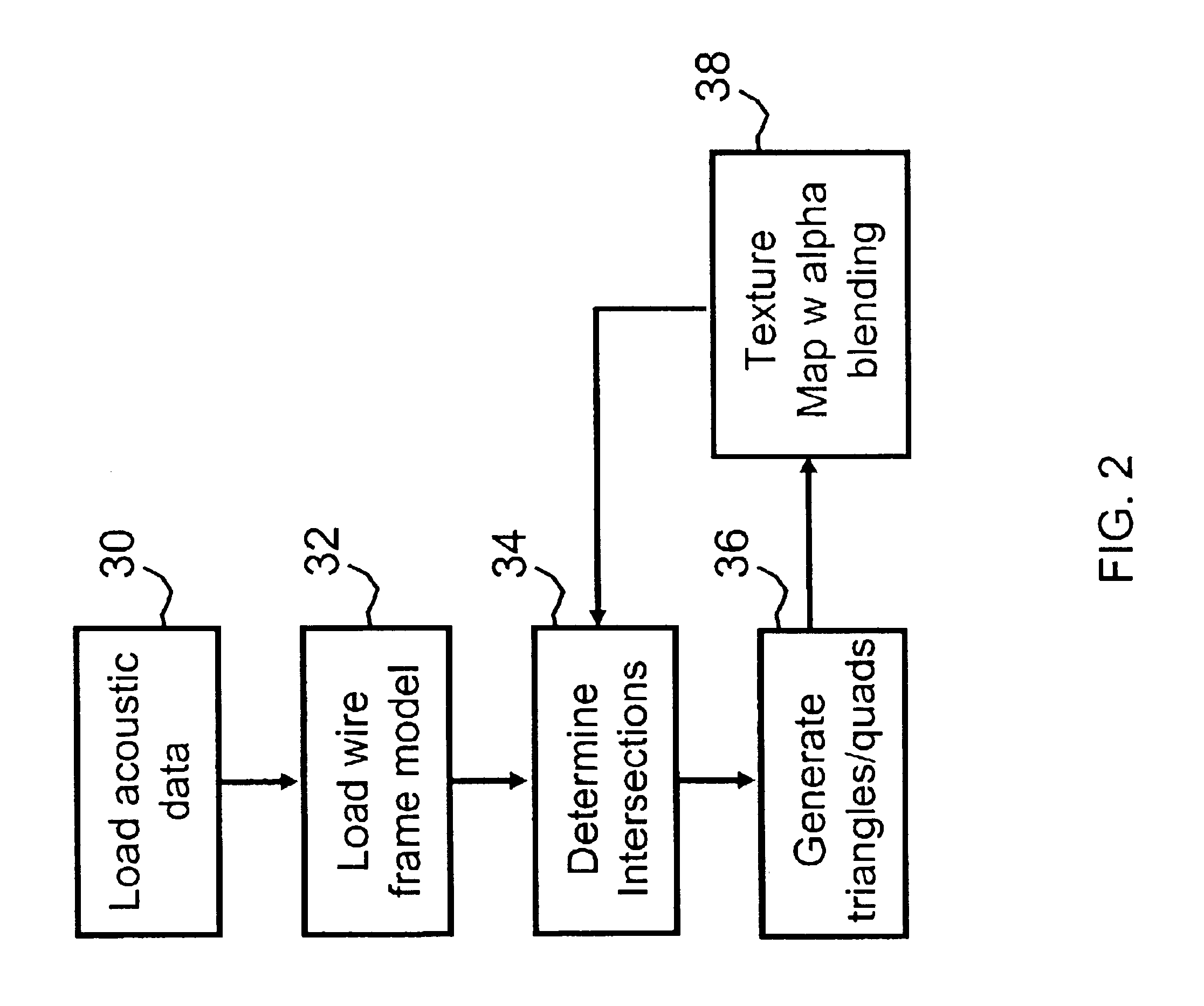

Volume rendering in the acoustic grid methods and systems for ultrasound diagnostic imaging

InactiveUS6852081B2Amount is reduced and eliminatedUltrasonic/sonic/infrasonic diagnosticsSurgeryData setSonification

Methods and systems for volume rendering three-dimensional ultrasound data sets in an acoustic grid using a graphics processing unit are provided. For example, commercially available graphic accelerators cards using 3D texturing may provide 256×, 256×128 8 bit volumes at 25 volumes per second or better for generating a display of 512×512 pixels using ultrasound data. By rendering from data at least in part in an acoustic grid, the amount of scan conversion processing is reduced or eliminated prior to the rendering.

Owner:SIEMENS MEDICAL SOLUTIONS USA INC

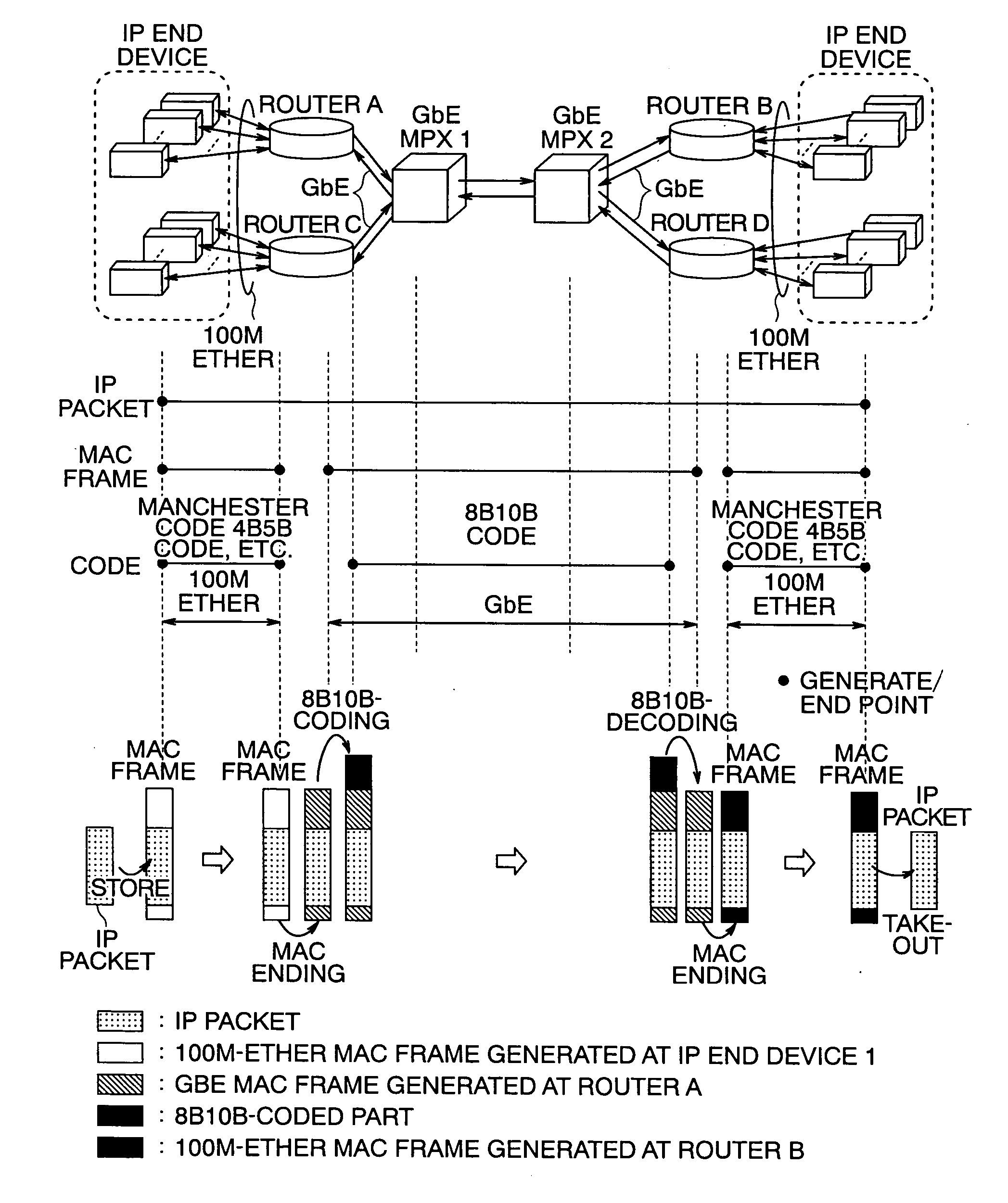

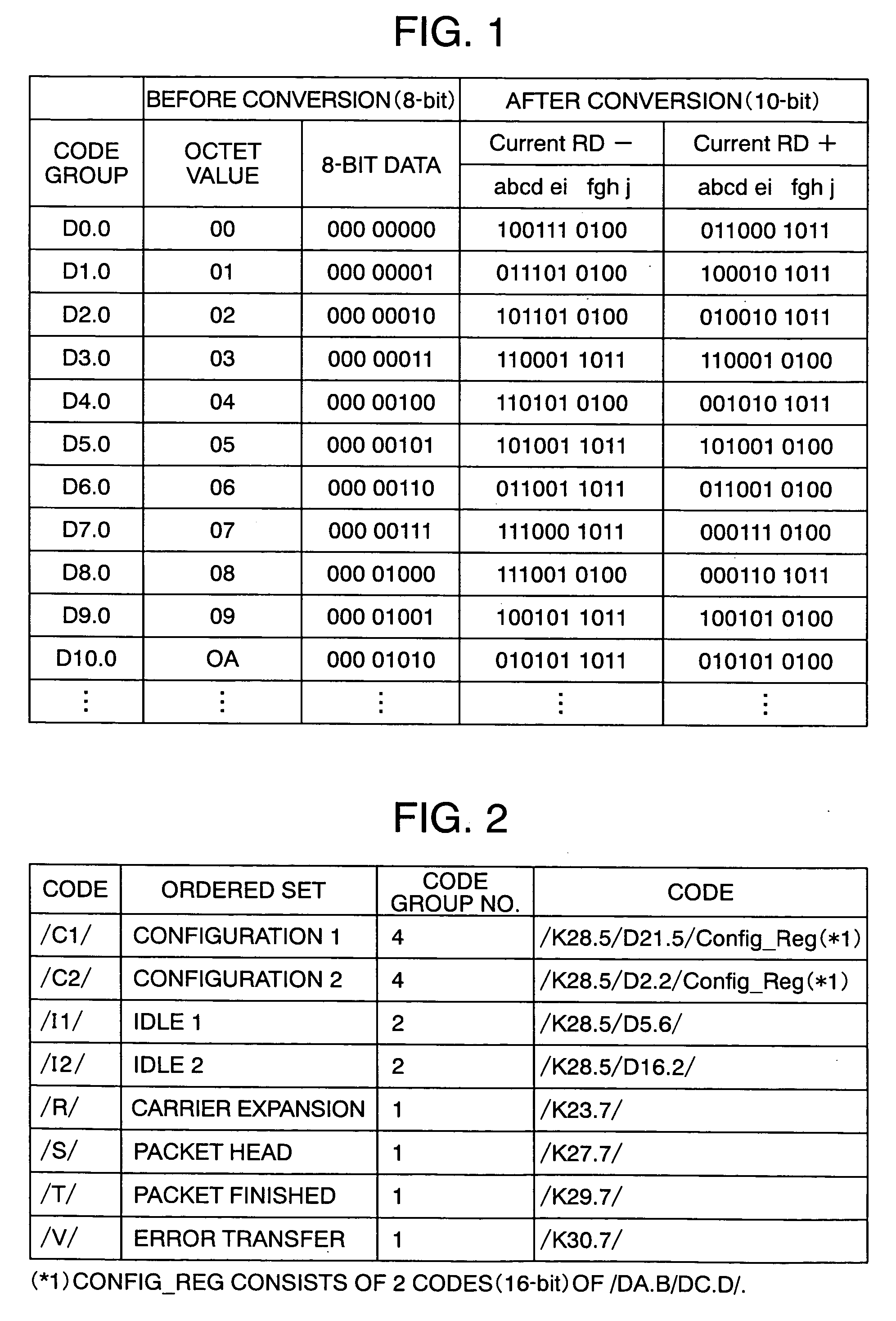

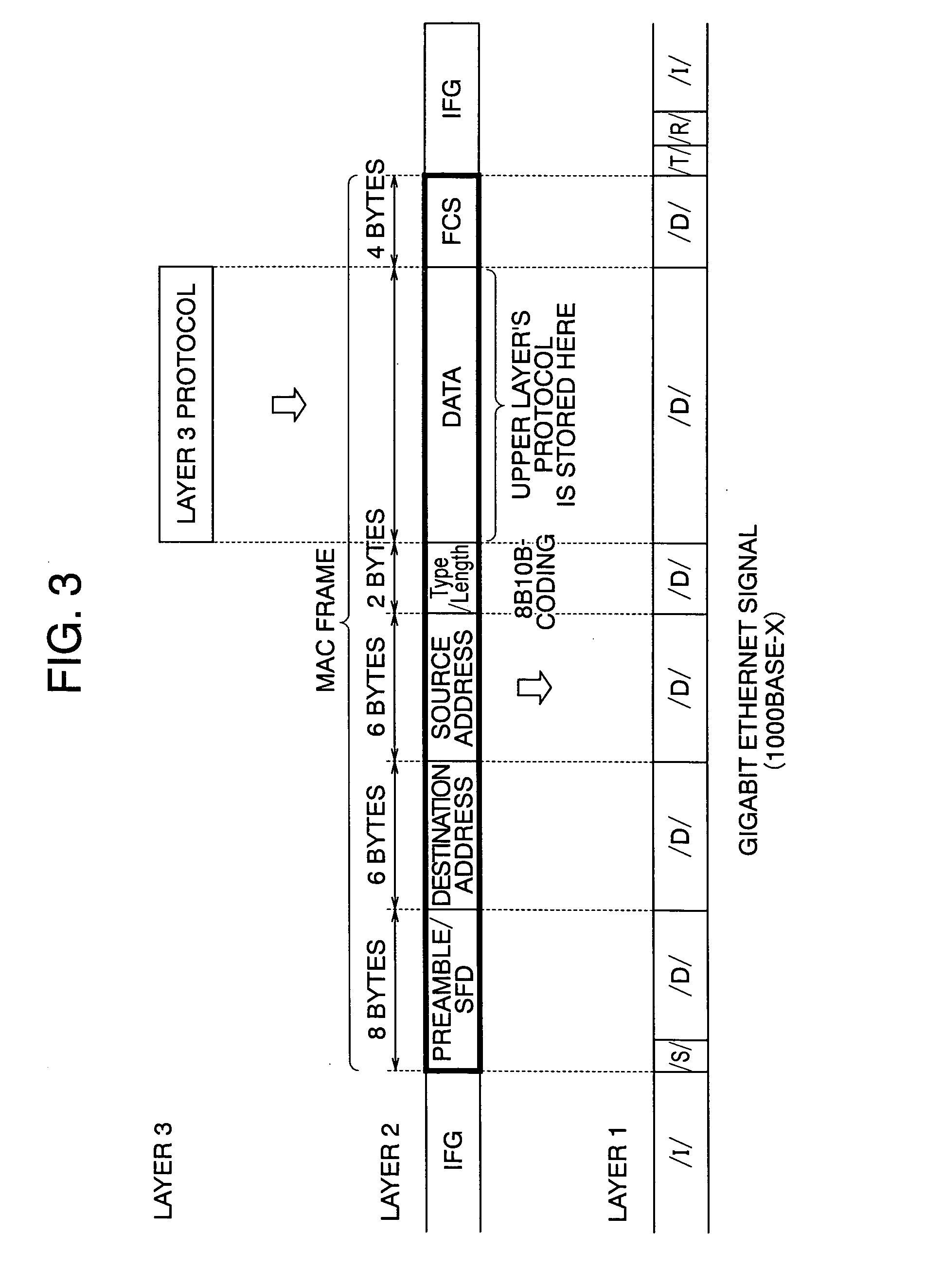

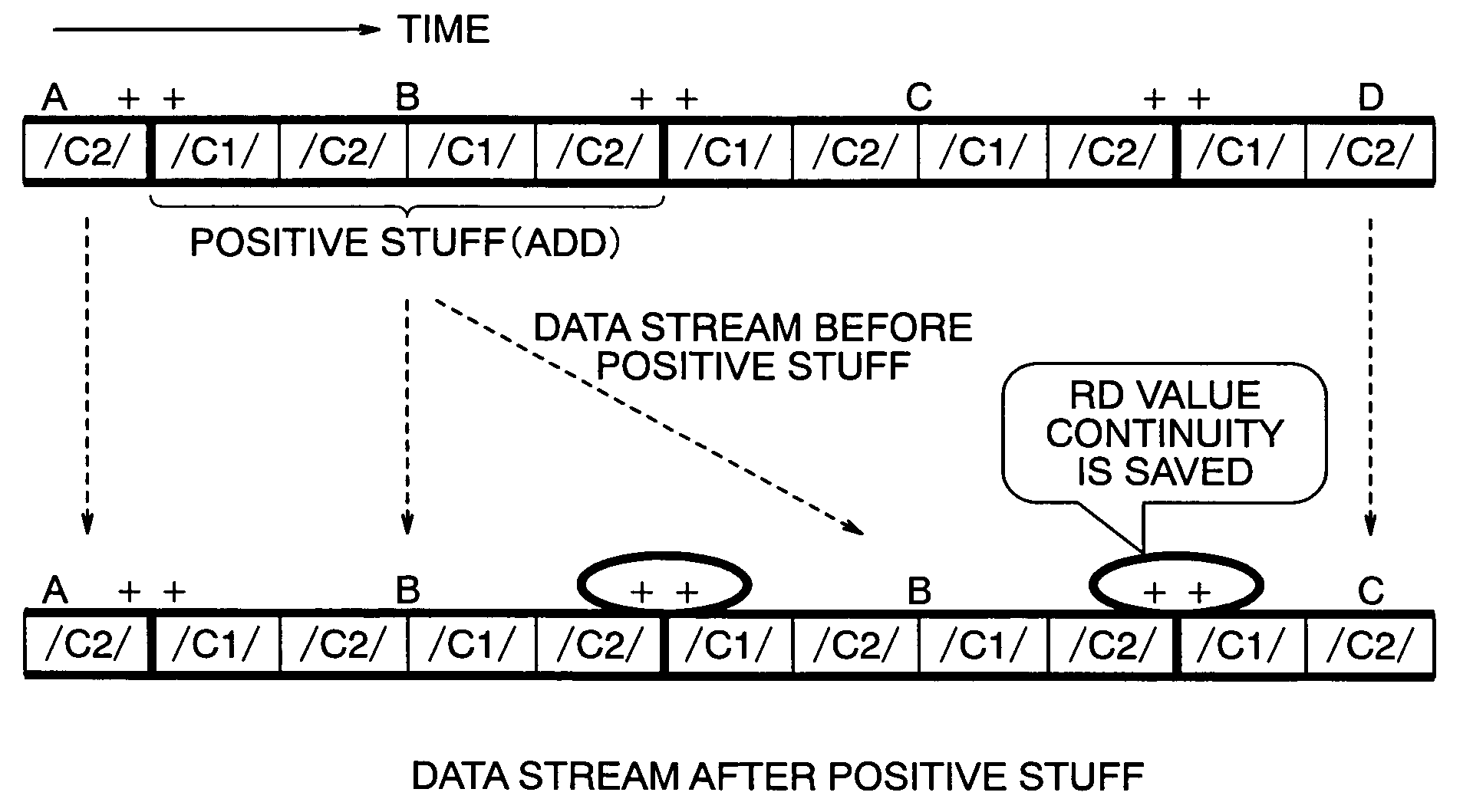

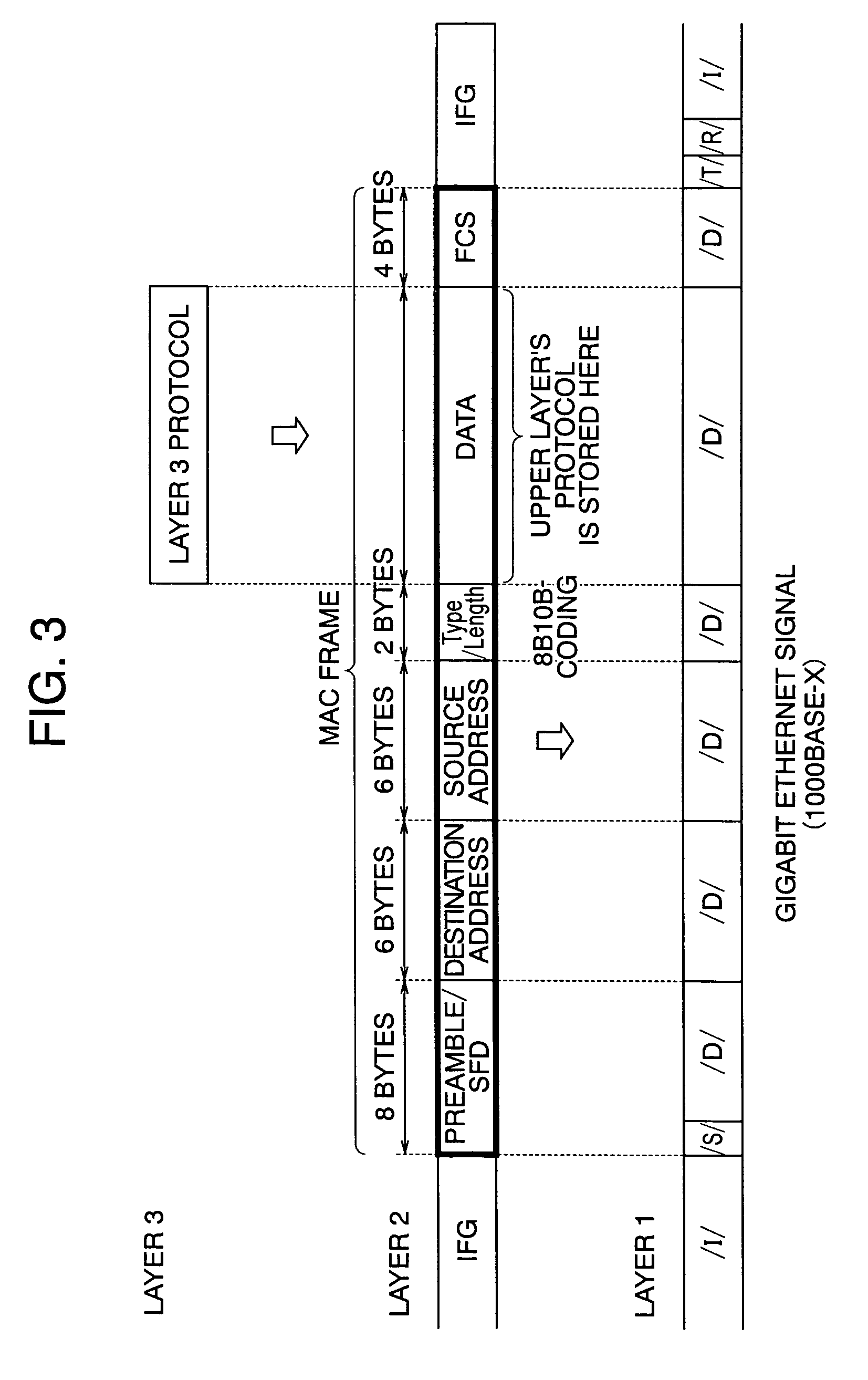

Transmission apparatus

InactiveUS20070116055A1Avoid it happening againTime-division multiplexBaseband systemsMultiplexingUser device

A transmission apparatus is disclosed, which performs positive / negative stuffing with 8-bit / 10-bit (8B / 10B) codes being kept intact while retaining the normality of 8B / 10B codes and the continuity of running disparity (RD) without termination of 8B / 10B codes of a plurality of Gigabit Ethernet (GbE) signals received. The apparatus then executes multiplexing and separation after synchronization of the plurality of signals, thereby achieving the “transparent” transport of management information which is contained in the 8B10B codes between user devices.

Owner:HITACHI LTD

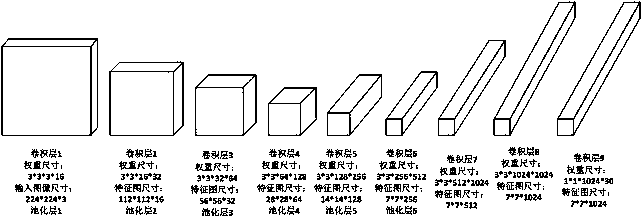

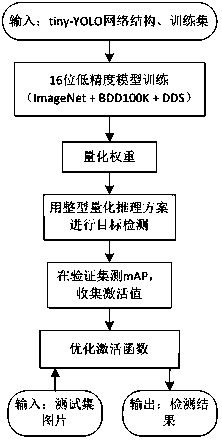

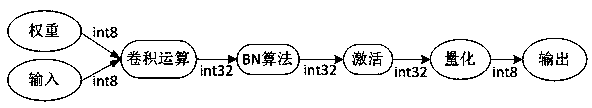

A CNN-based low-precision training and 8-bit integer quantitative reasoning method

InactiveCN109902745AReduce computing timeImprove computing efficiencyCharacter and pattern recognitionNeural architecturesAlgorithmFloating point

The invention provides a CNN-based low-precision training and 8-bit integer quantization reasoning method. The method mainly comprises the steps of carryin gout low-precision model training; Performing model training by using a 16-bit floating point type low-precision fixed point algorithm to obtain a model for target detection; Quantifying the weight; Proposing an 8-bit integer quantization scheme, and quantizing the weight parameters of the convolutional neural network from 16-bit floating point type to 8-bit integer according to layers; carrying out 8-bit integer quantitative reasoning; quantizing the activation value into 8-bit integer data, i.e., each layer of the CNN accepts an int8 type quantization input and generates an int8 quantization output. According to the invention, a 16-bit floating point type low-precision fixed point algorithm is used to train a model to obtain a weight; Compared with a 32-bit floating point type algorithm, the method has the advantages that the 8-bit integer quantization reasoning is directly carried out on the weight obtained by training the model, the reasoning process of the convolutional layer is optimized, and the precision loss caused by the low-bit fixed point quantization reasoning is effectively reduced.

Owner:成都康乔电子有限责任公司 +1

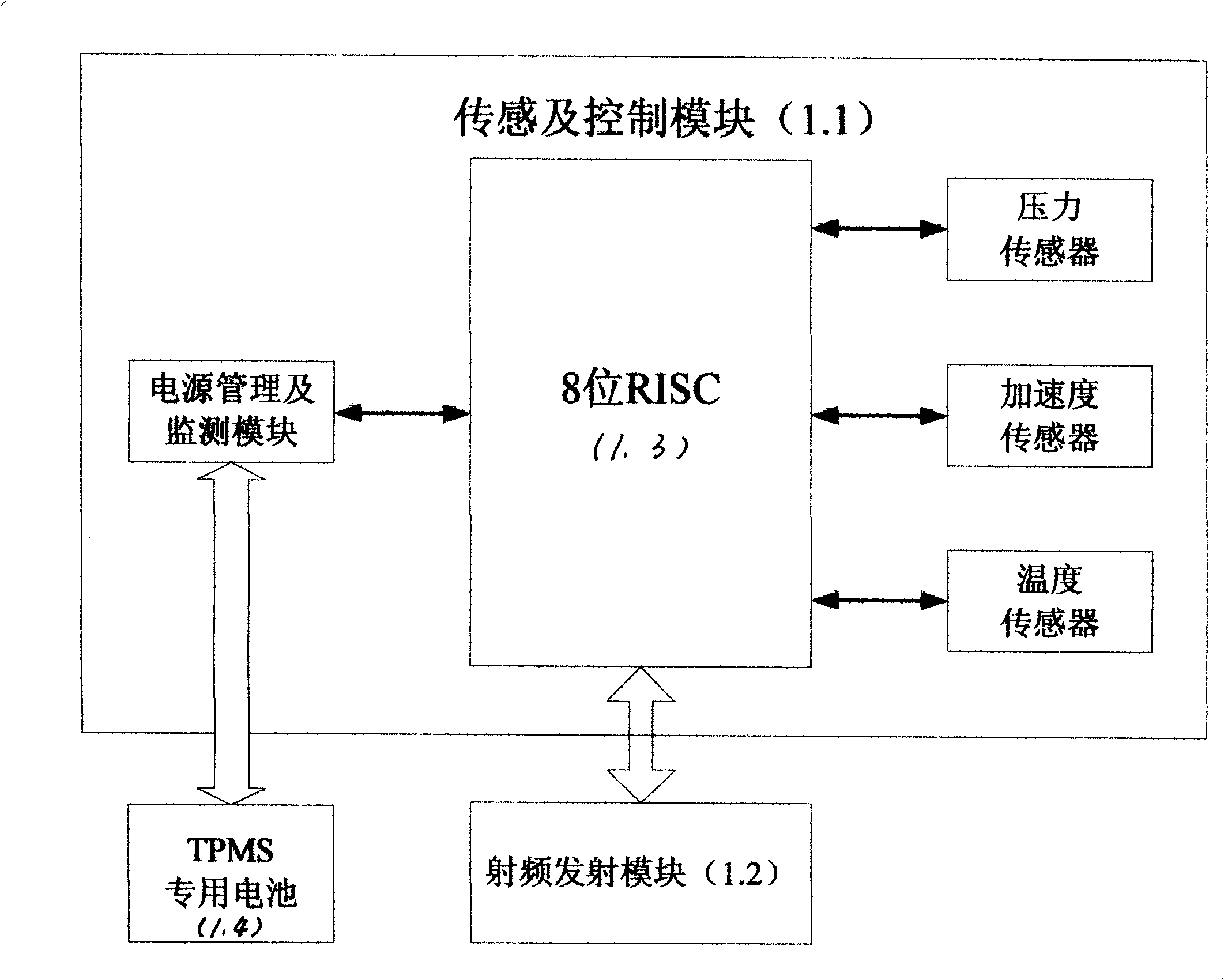

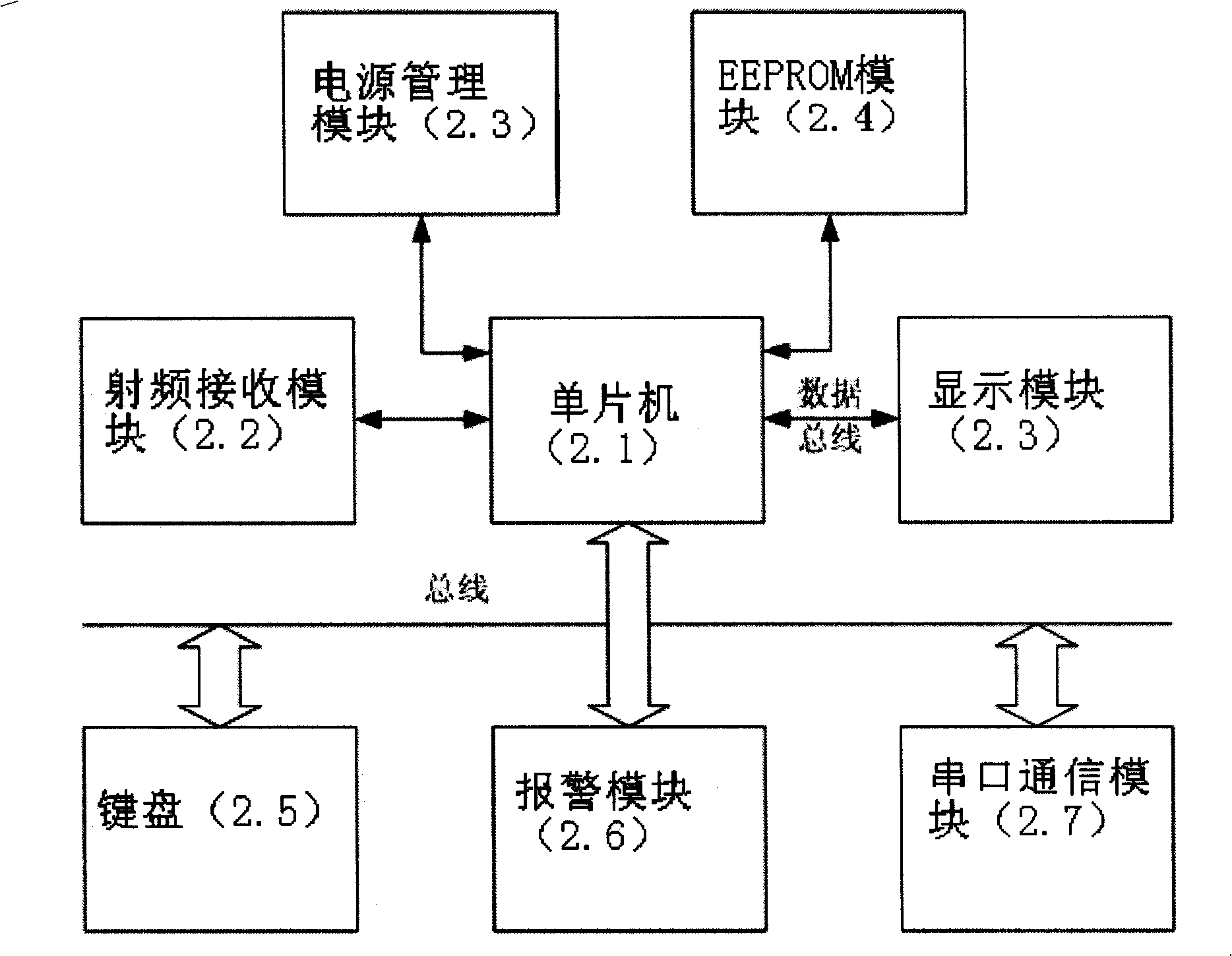

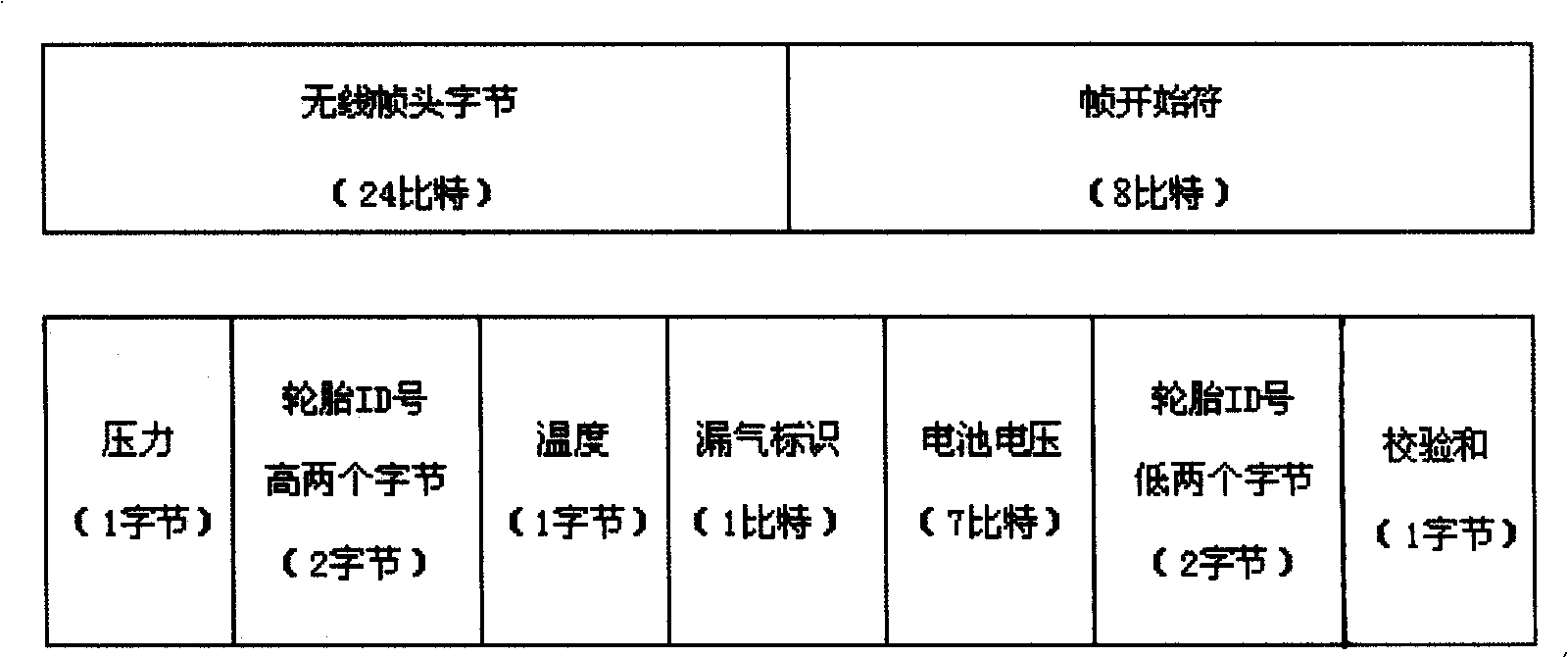

Monitoring method and device of vehicle tyre data

A vehicle tire data monitoring method and a monitoring device thereof relate to the technical field of wireless sensing and monitoring. The monitoring device comprises a tire monitoring module and a central module; the tire monitoring module is arranged in the tire; the central module is arranged in the vehicle; the tire monitoring module comprises sensors which comprise a pressure sensor, an acceleration sensor and a temperature sensor, a 8-bit RISC which centralizes the various data collected by the sensors and transmits the data to a RF emission module, the RF emission module and a TPMS special battery; the central module comprises a power management module which provides the central module with power for long time working, an EEPROM module, a RF receiving module, an SCM used for processing the data collected by the RF receiving module, a display module, a keyboard, an alarm module and a serial port communication module. The vehicle tire data monitoring method and a monitoring device thereof achieve to know the situation of the tire at any time, reinforce the safety of the vehicle during the running process and avoid a traffic accident from happening.

Owner:SOUTHEAST UNIV

Compact modular programmable logic controller

InactiveUS20070173960A1Programme control in sequence/logic controllersAdaptive controlElectrical resistance and conductanceProgrammable logic controller

A compact lower cost programmable logic controller with modular I / O is described. SPI bus is used for accessing multi-byte data from I / O modules, while 8 bit data bus is used to access single byte data from I / O modules. Compact I / O modules with use with the PLC are described. The include short circuit proof DC output modules, Relay output with built-in electromagnetic shield, analog modules with laser trimmed resistors, and high speed counter modules.

Owner:KUMAR SHALABH

Transmission apparatus

InactiveUS7916756B2Avoid it happening againTime-division multiplexBaseband systemsMultiplexingUser device

A transmission apparatus is disclosed, which performs positive / negative stuffing with 8-bit / 10-bit (8B / 10B) codes being kept intact while retaining the normality of 8B / 10B codes and the continuity of running disparity (RD) without termination of 8B / 10B codes of a plurality of Gigabit Ethernet (GbE) signals received. The apparatus then executes multiplexing and separation after synchronization of the plurality of signals, thereby achieving the “transparent” transport of management information which is contained in the 8B10B codes between user devices.

Owner:HITACHI LTD

Apparatus, method and program product to generate and use CRC in communications network

The CRC for the CPS Header of an ATM AAL2 cell is generated by a CRC generator which uses the 8 bits of the CID field to generate partial 5 bits CRCs which are loaded in a first table. The 6 bits LI field and 5 bits UUI field are added to the partial 5 bits CRC to form 16 bits. The CRC generator uses the 2<16 >bits to generate a second CRC table. The CRC for a particular CPS header is generated by correlating bits in the CID field, Li field and UUI field with the two tables.

Owner:META PLATFORMS INC

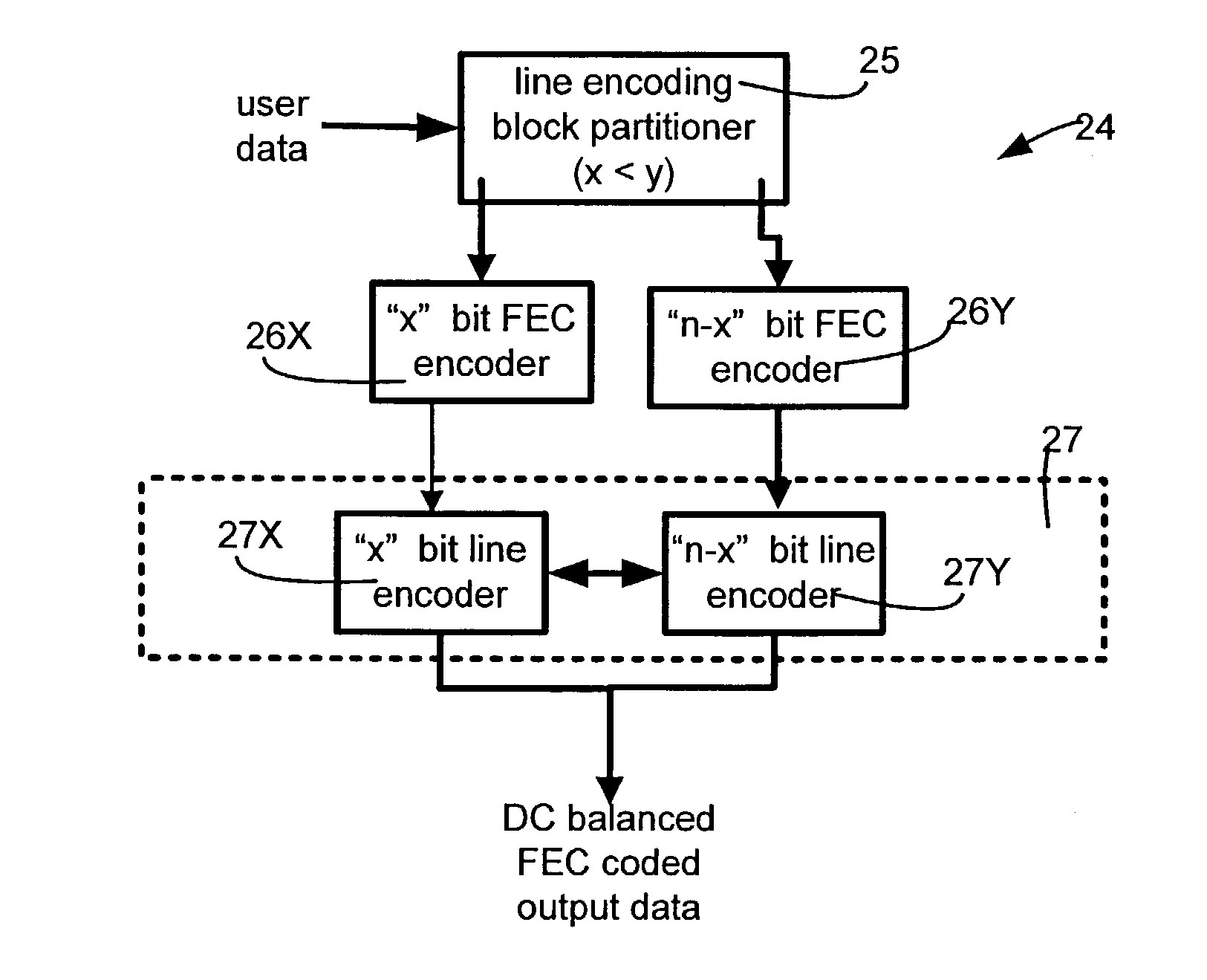

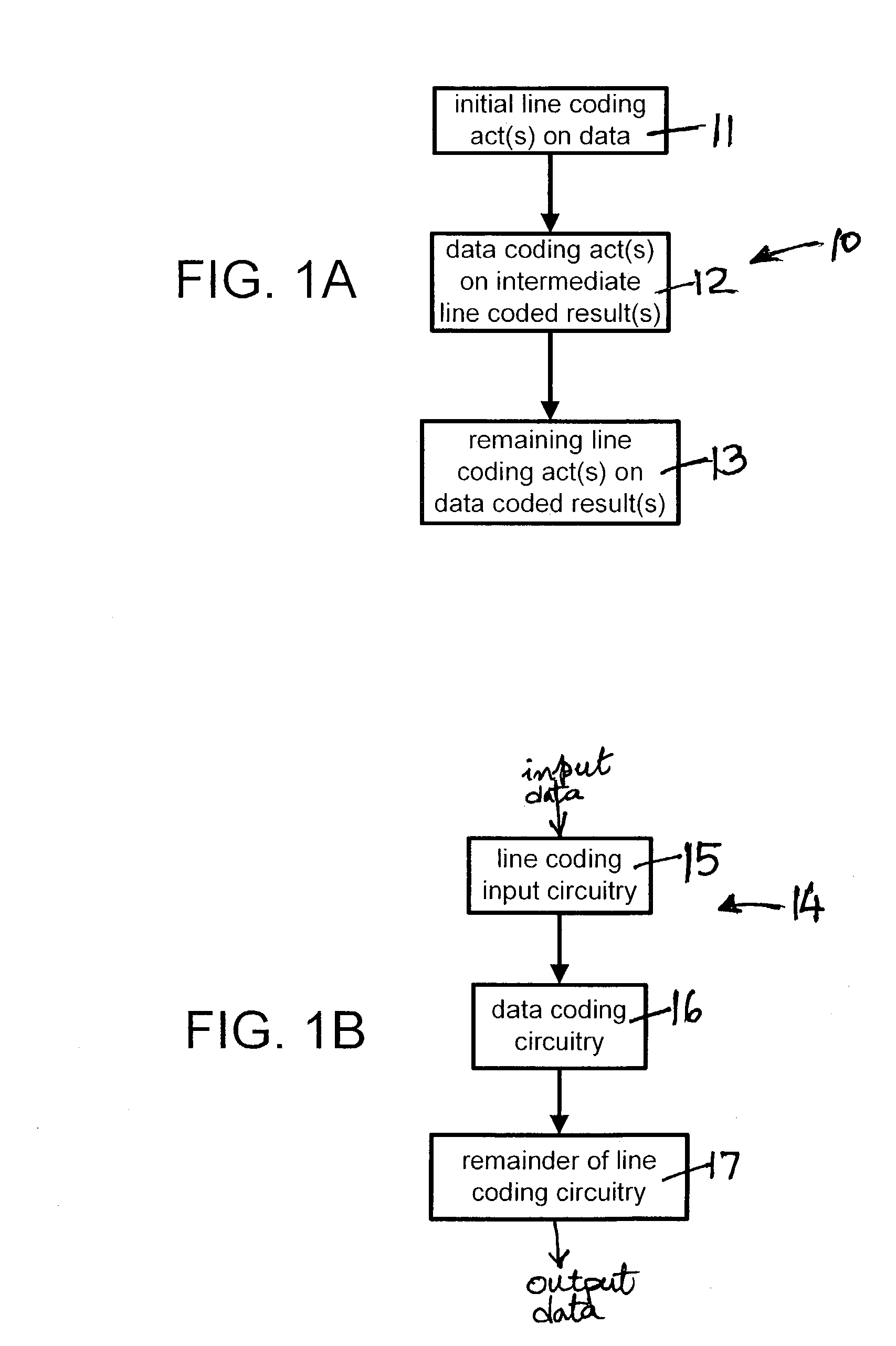

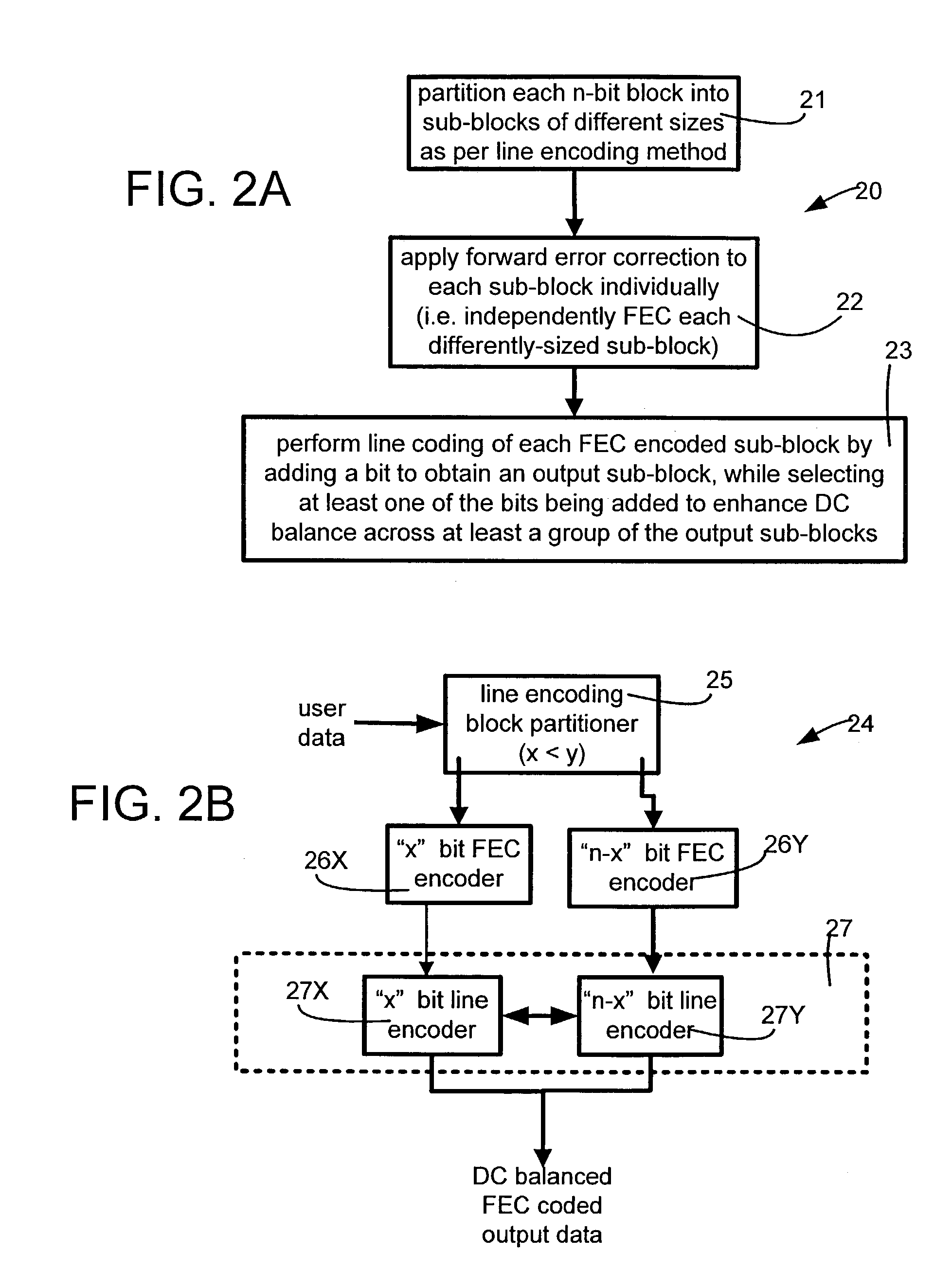

DC balanced error correction coding

ActiveUS7103830B1Simple processSmall circuitIndividual digits conversionError detection only8b/10b encodingData encoding

Two types of codings are integrated, instead of performing each coding independently. The two codings may be integrated by interleaving one or more acts of one coding method (e.g. data coding) between two or more acts of the other coding method (e.g. line coding). In some embodiments, partitioning of a block of data (e.g. a byte) for line coding (e.g. DC balance coding) is done prior to data coding (e.g. error correction coding). In such embodiments, the remaining acts of line coding may be performed after the data coding is completed. In one particular embodiment, an 8 bit byte is not directly used in error correction coding and instead, the 8 bit byte is initially partitioned into two sub-blocks (of 3 bits and 5 bits) as required by 8B / 10B encoding (which is an example of line coding). After partitioning, the 8B / 10B encoding is not continued, and instead Reed Solomon coding (which is an example of data coding) is then performed (to completion) on the individual sub-blocks (of 3 bits and 5 bits). The error correction coded sub-blocks (of 3 bits and 5 bits) are then used for the remainder of 8B / 10B encoding.

Owner:MACOM CONNECTIVITY SOLUTIONS LLC

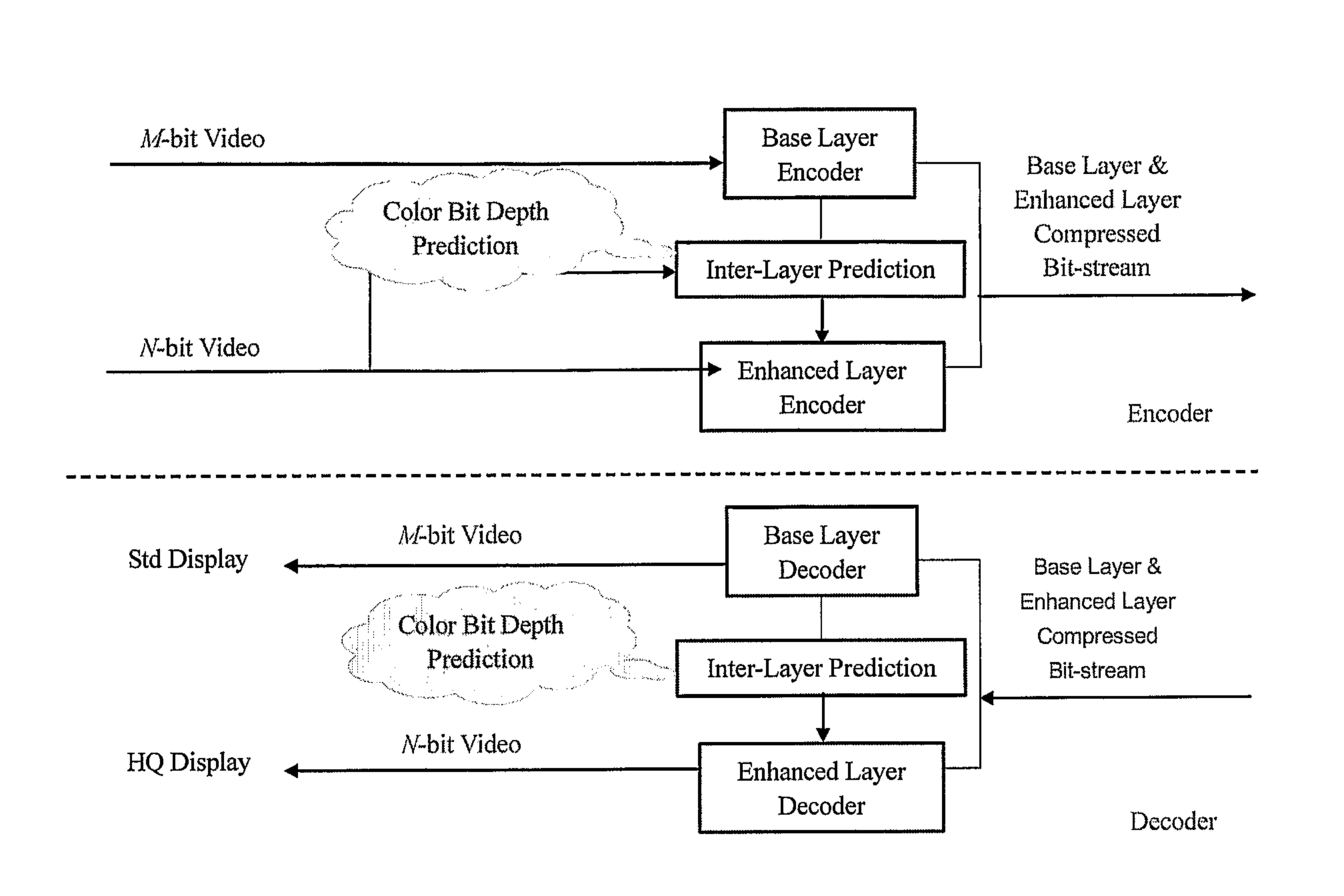

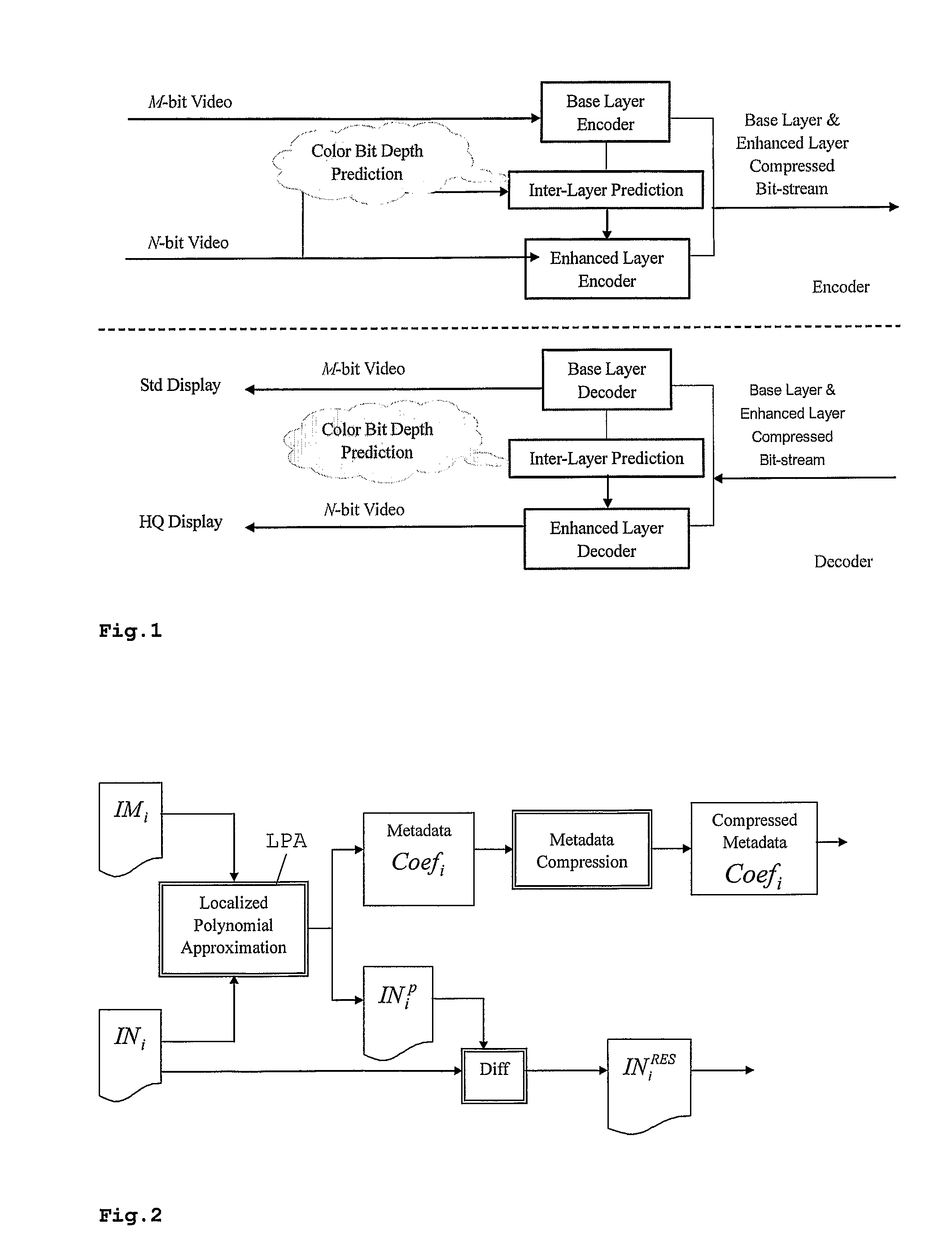

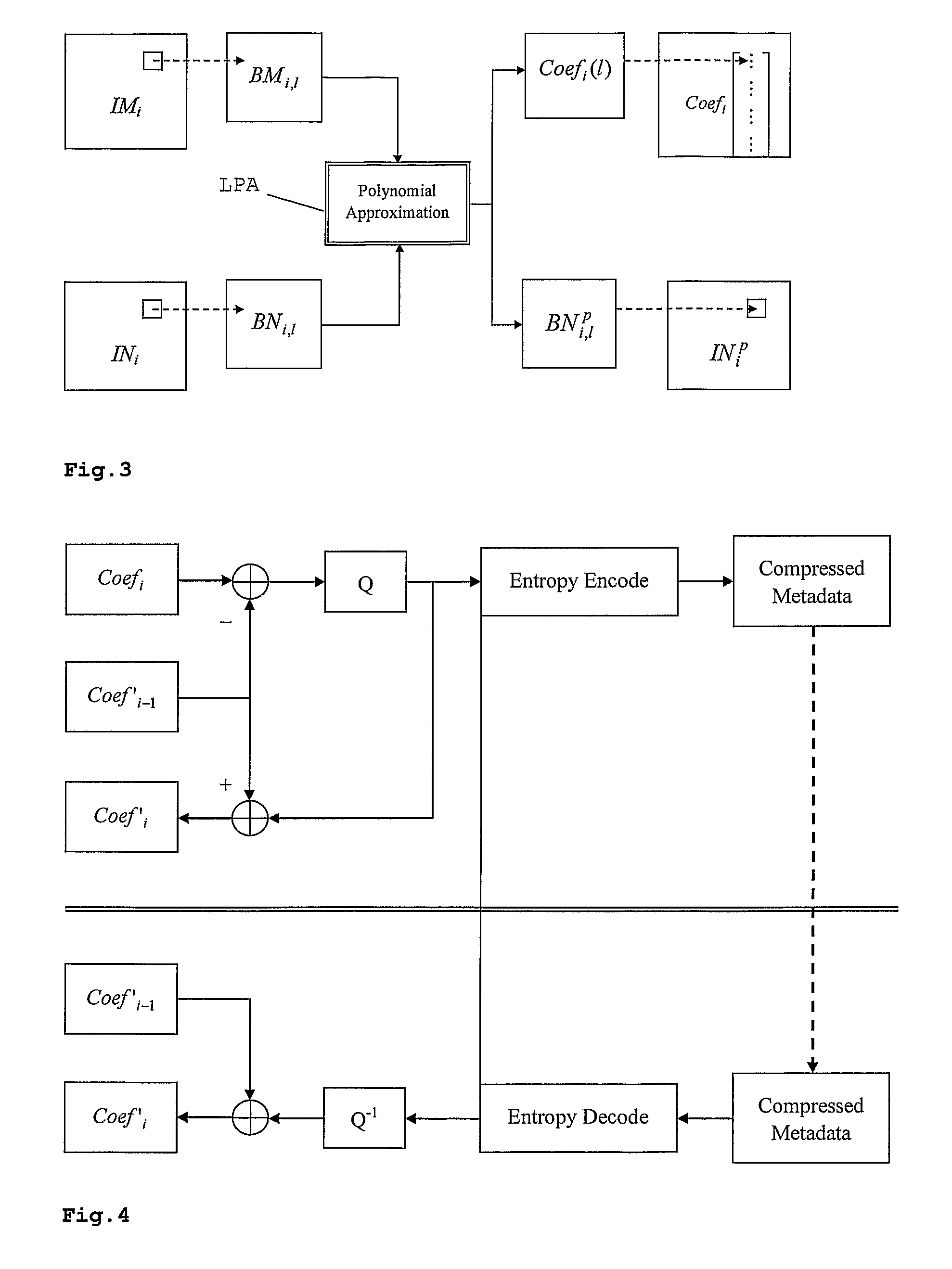

Method and device for encoding and decoding color enhancement layer for video

ActiveUS20100272185A1Easy to useColor television with pulse code modulationColor television with bandwidth reductionTemporal resolutionData stream

Enhanced dynamic range requires more than 8 bit representation for single color components of pixels. For this purpose, normal color resolution images and high color resolution images are available. Backward compatibility can be achieved by a layered approach using a color enhancement layer, and a conventional image as color base layer. Both have same spatial and temporal resolution. Encoding of the color enhancement layer uses prediction and residual. A methods for optimized color enhancement prediction is disclosed. Color bit depth prediction is done by constructing a polynomial that approximates for all pixels of one color component of a block the color enhancement layer from the color base layer. A predicted version of the high color resolution image and a residual are generated and updated by a residual. The coefficients are compressed and added as metadata to the data stream.

Owner:INTERDIGITAL VC HLDG INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com