Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

182results about How to "No performance loss" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

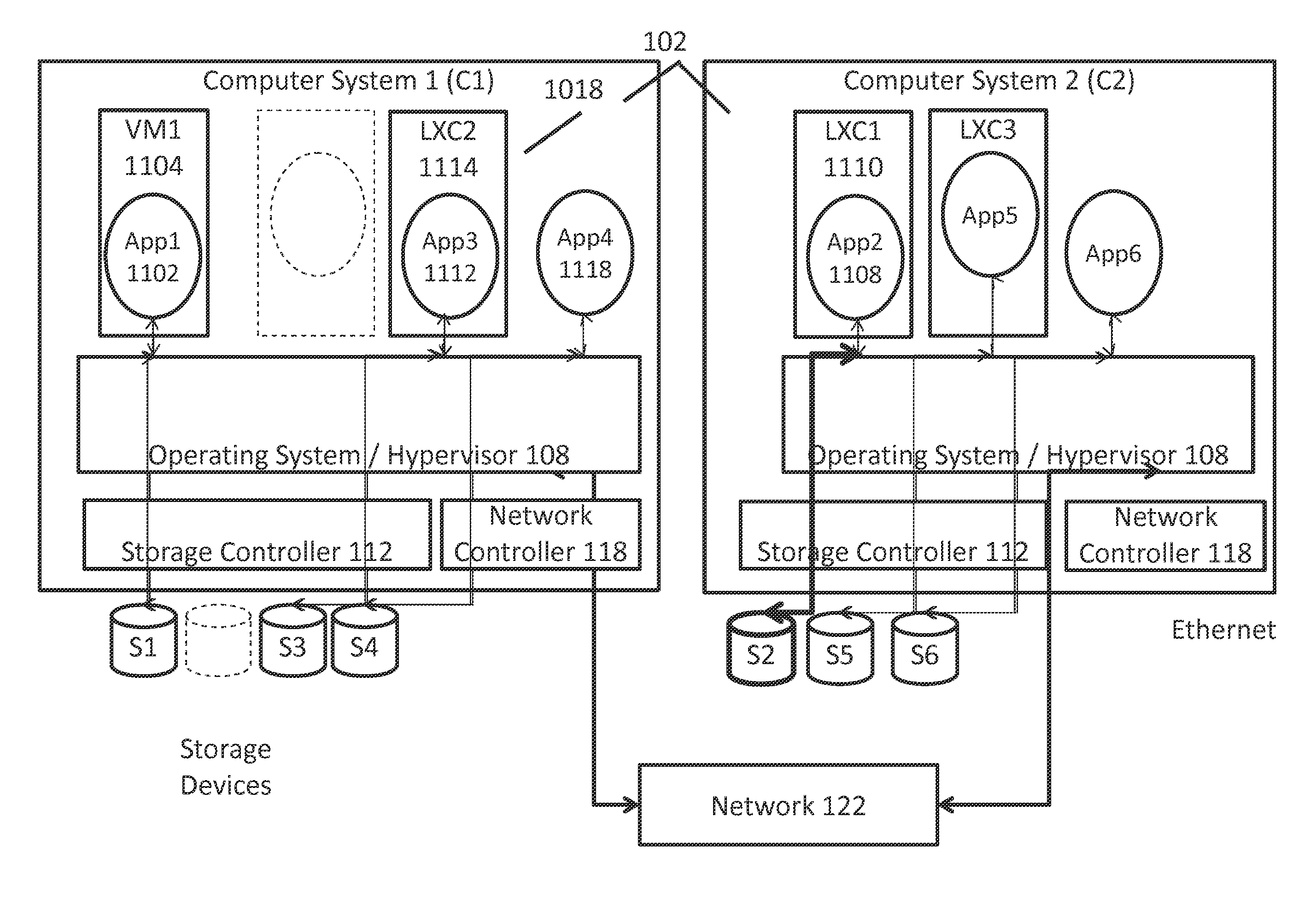

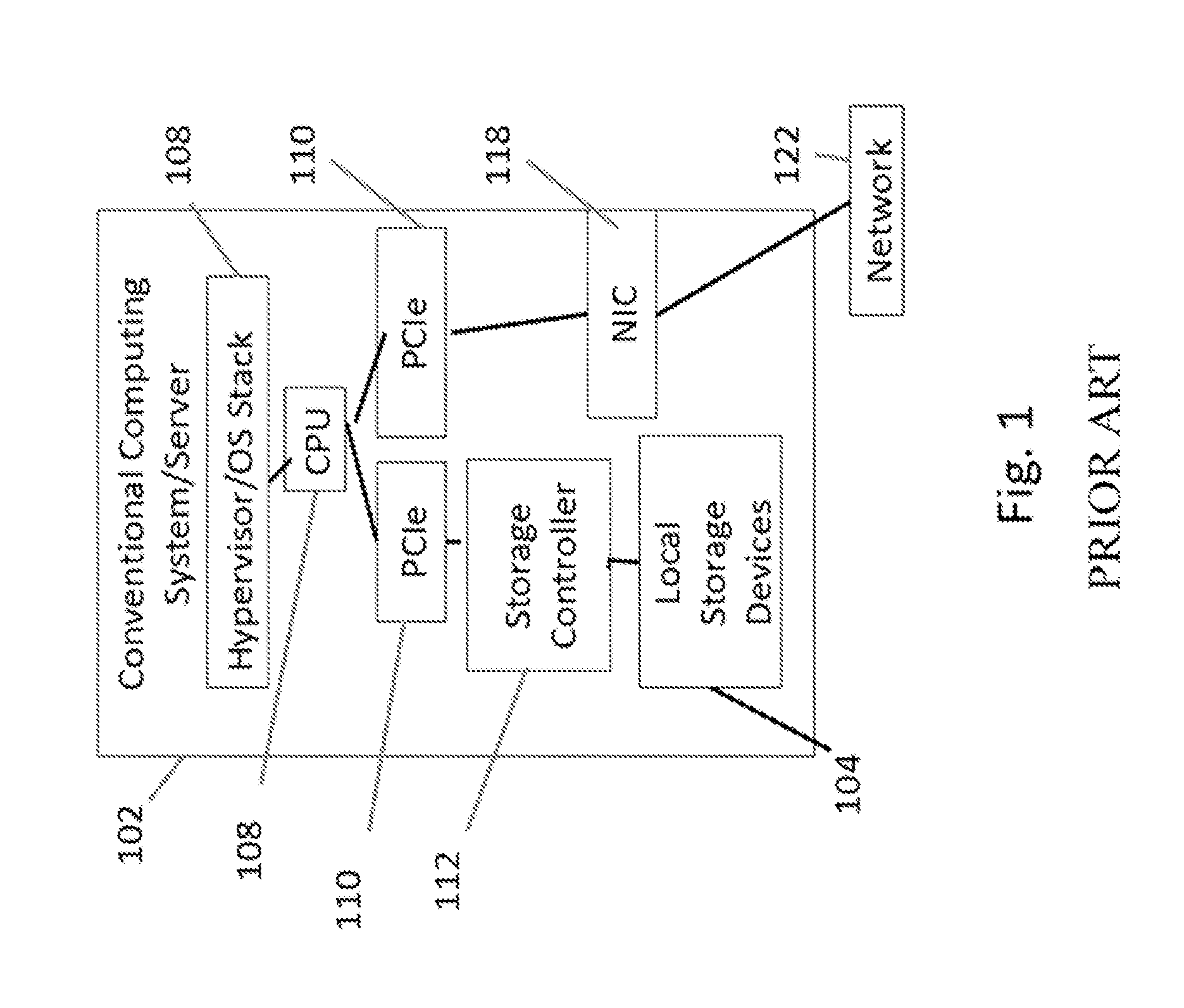

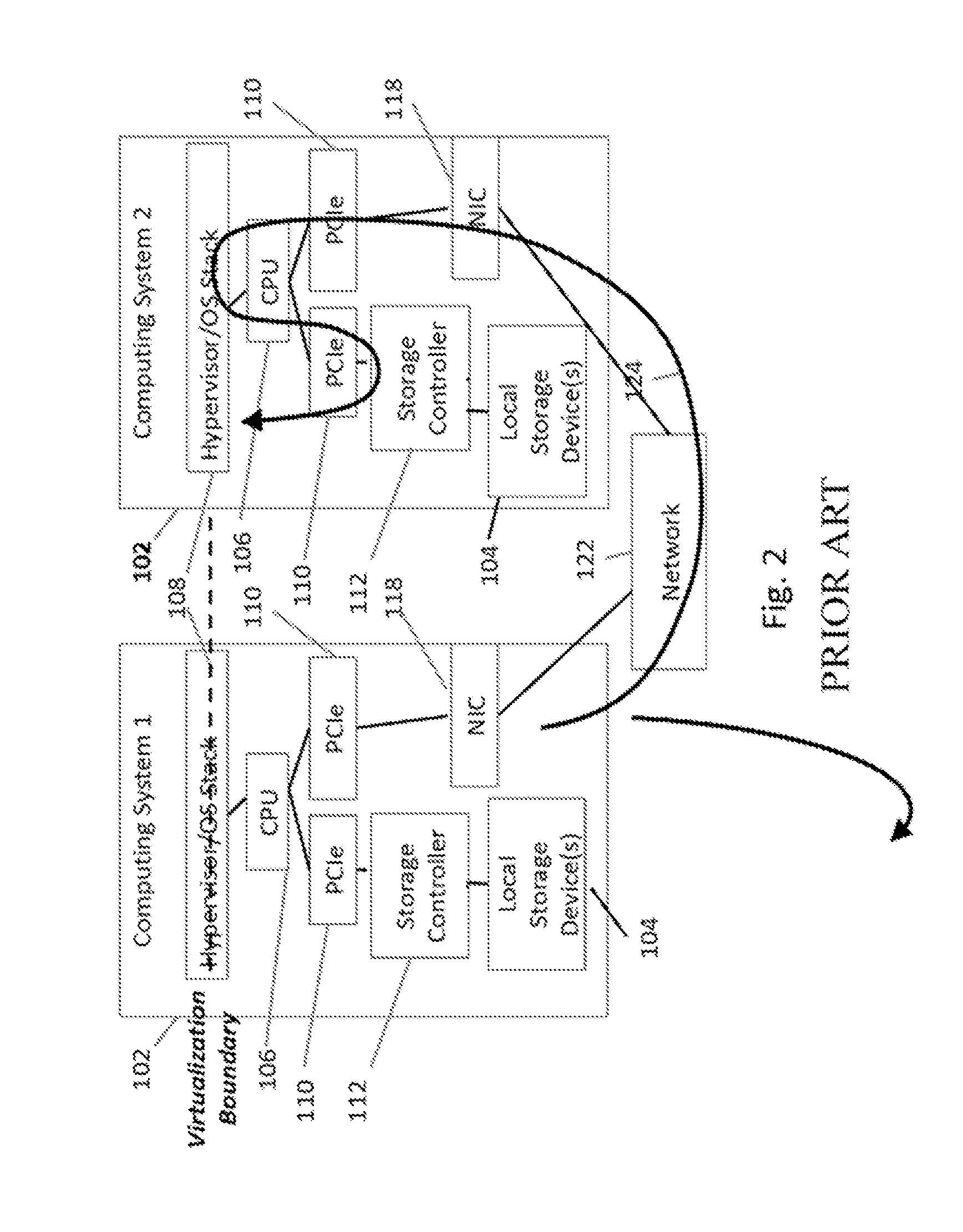

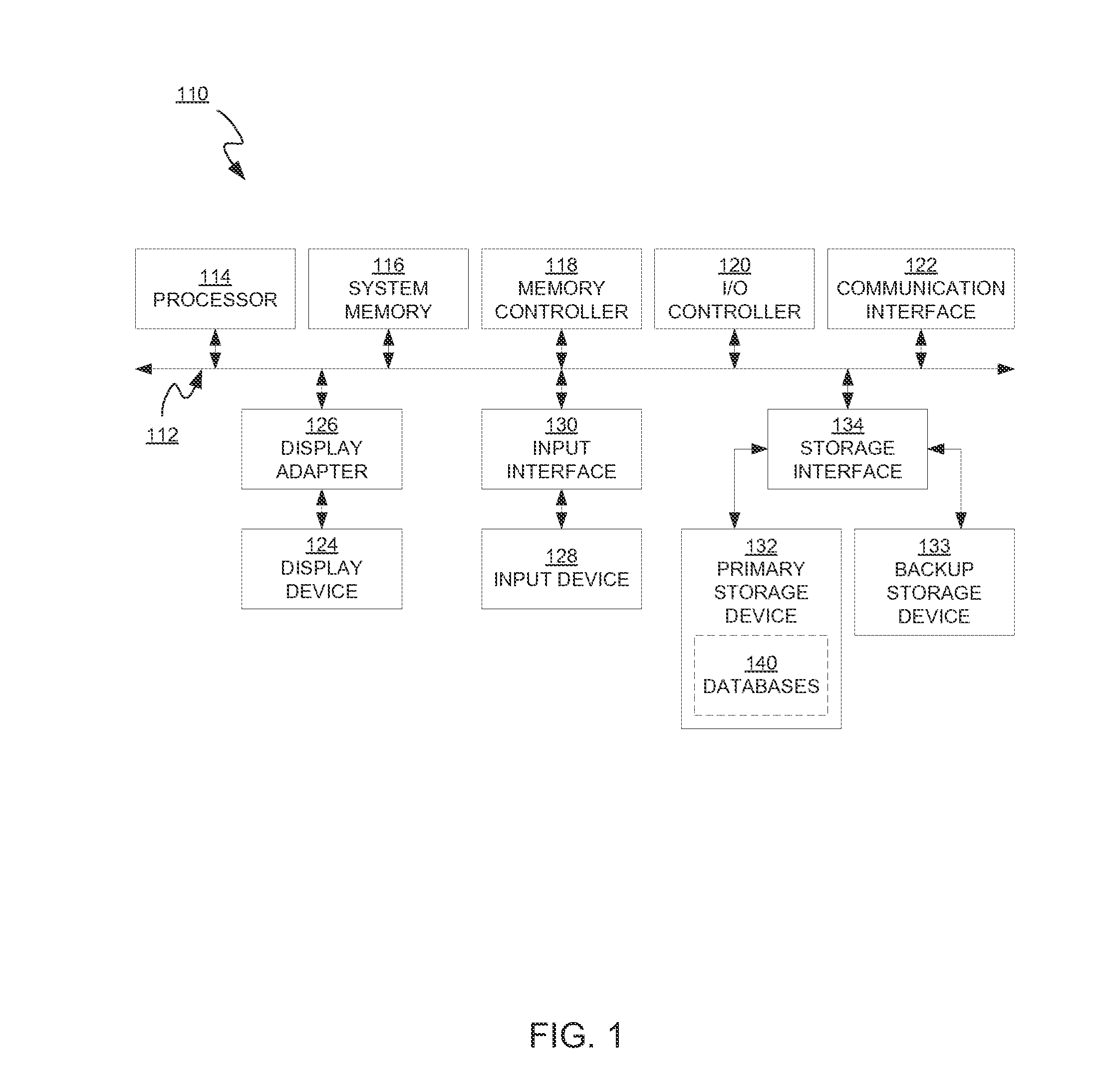

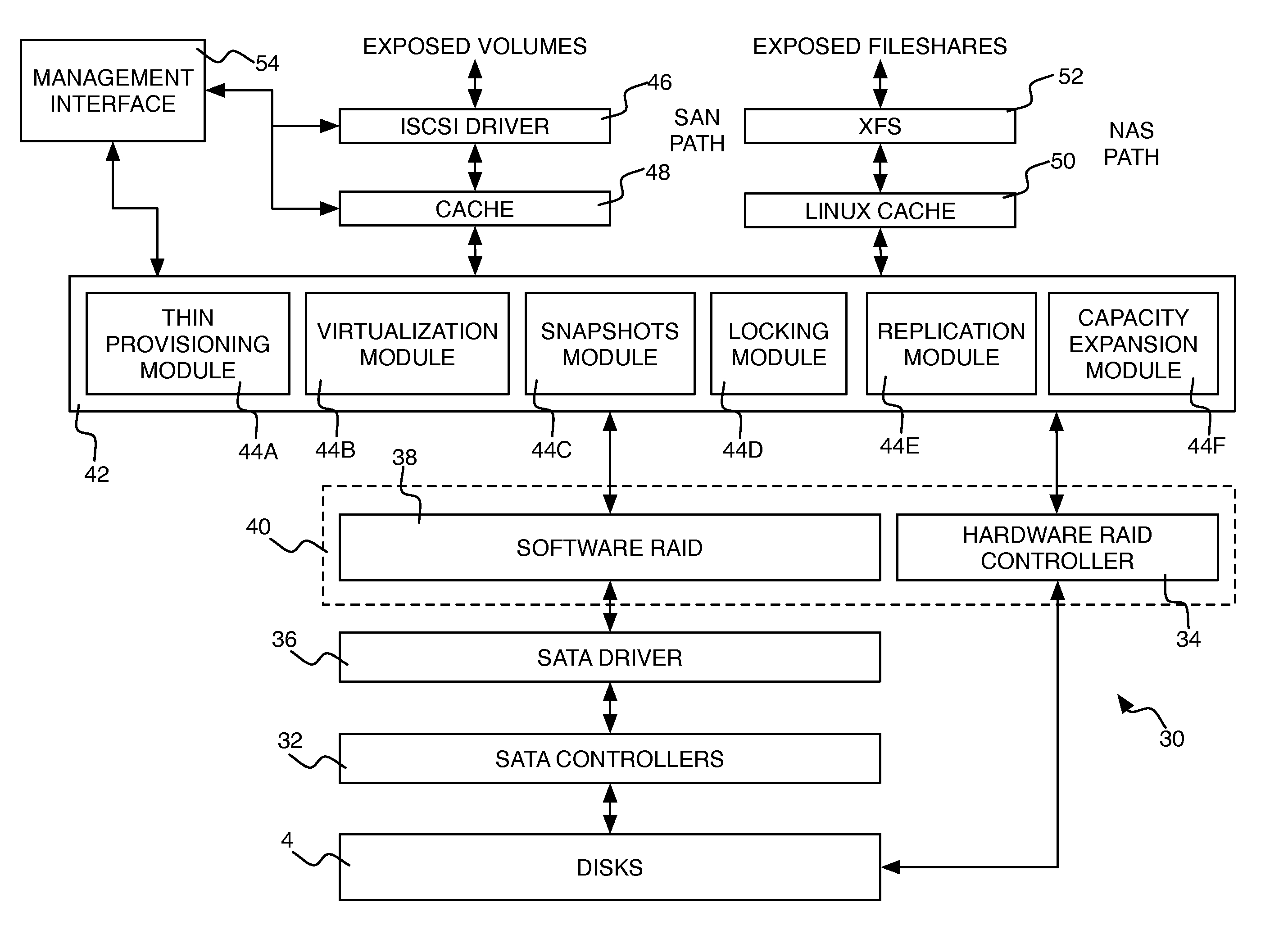

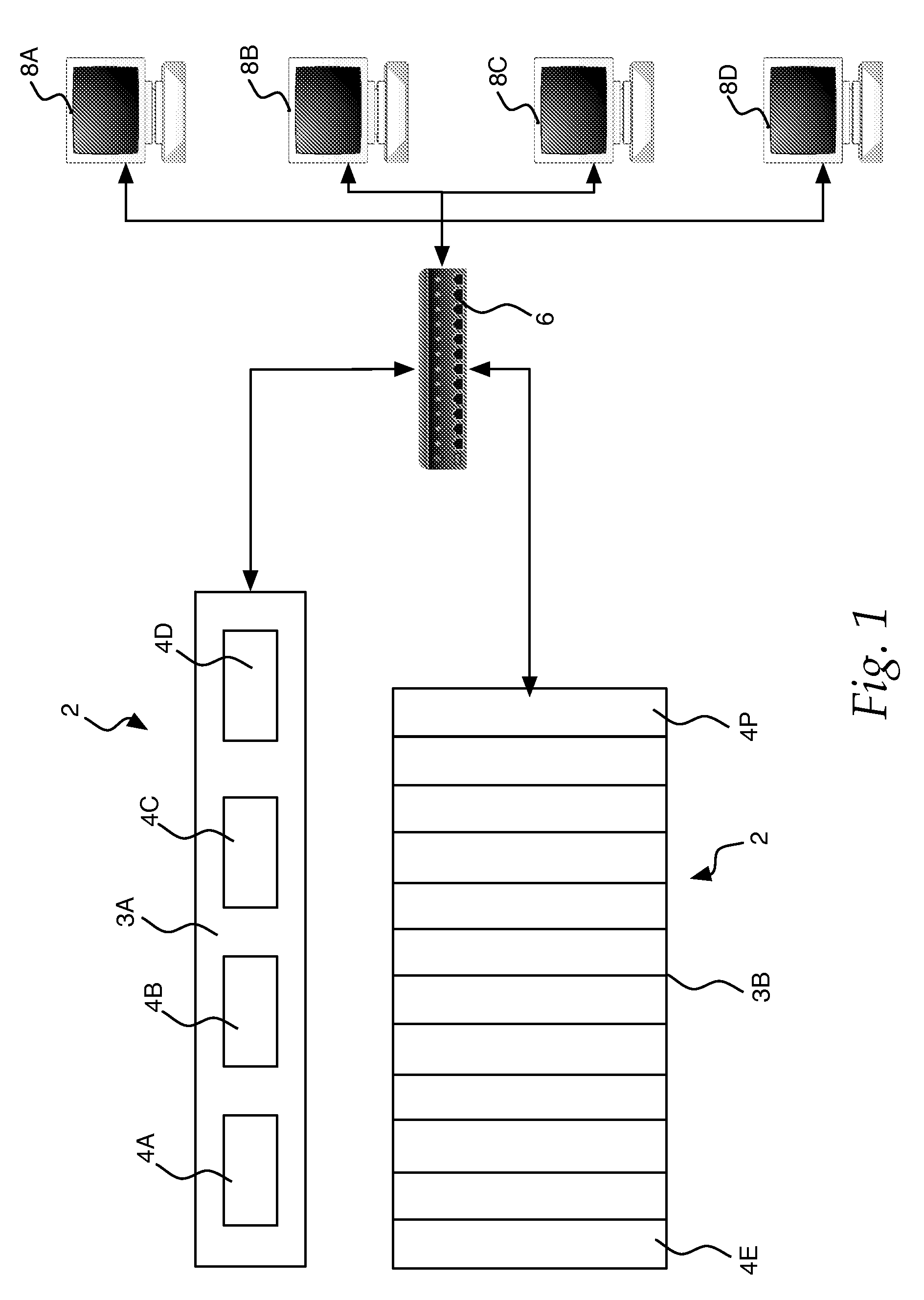

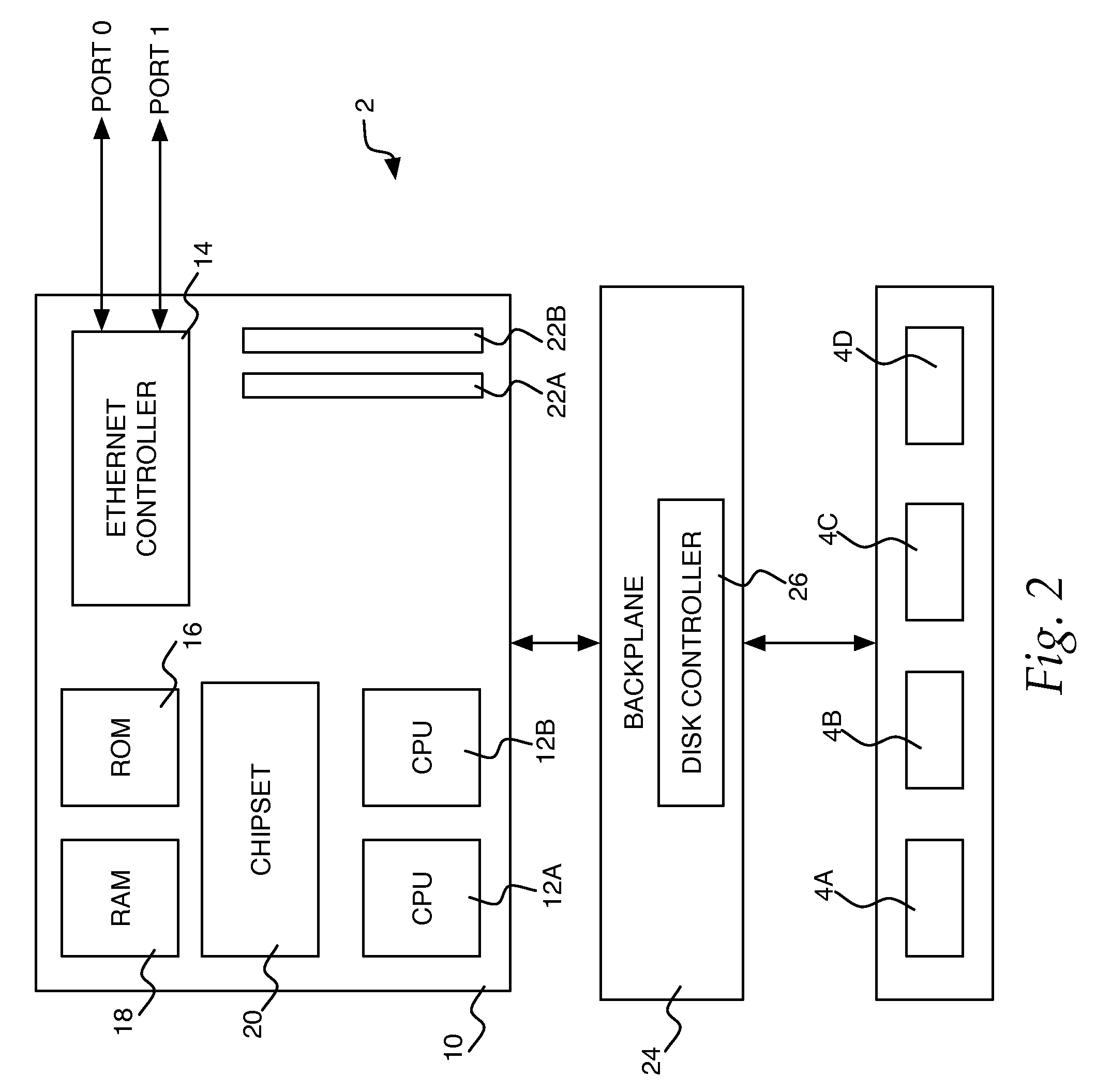

Methods and systems for converged networking and storage

InactiveUS20150254088A1Easy programmingImprove performanceResource allocationDigital computer detailsTraffic capacityNetwork interface controller

A device includes a converged input / output controller that includes a physical target storage media controller, a physical network interface controller and a gateway between the storage media controller and the network interface controller, wherein gateway provides a direct connection for storage traffic and network traffic between the storage media controller and the network interface controller.

Owner:DIAMANTI INC

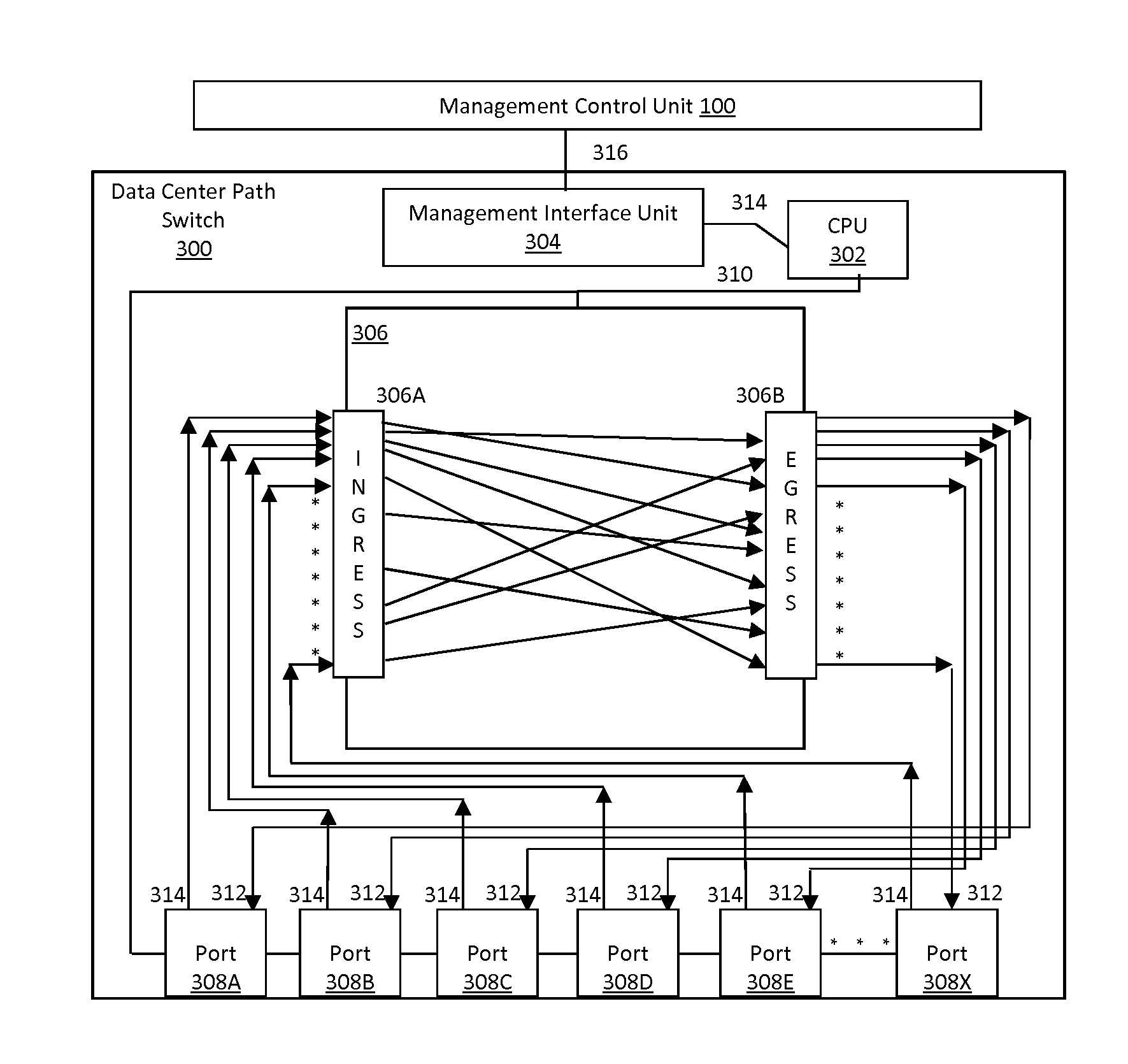

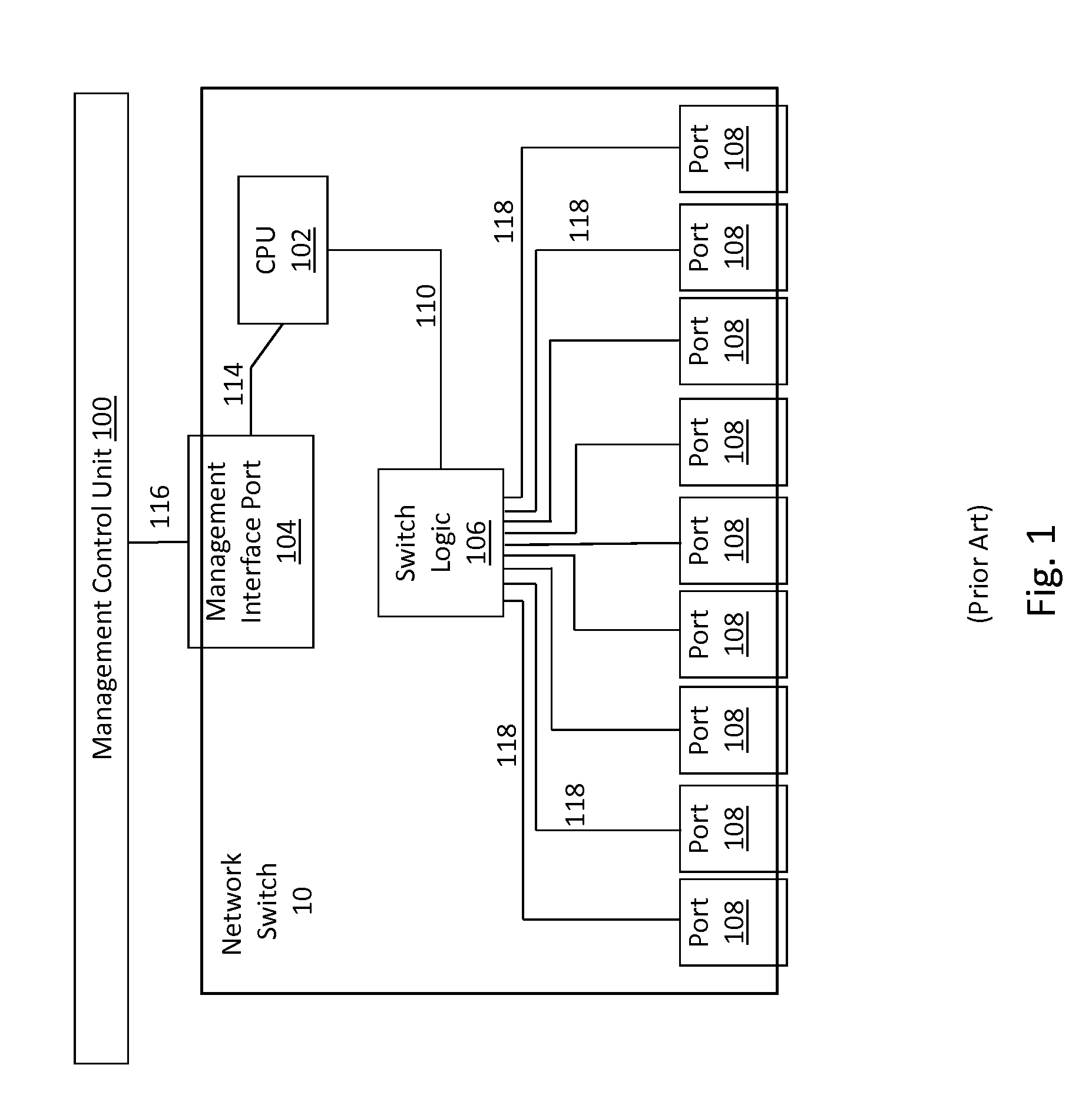

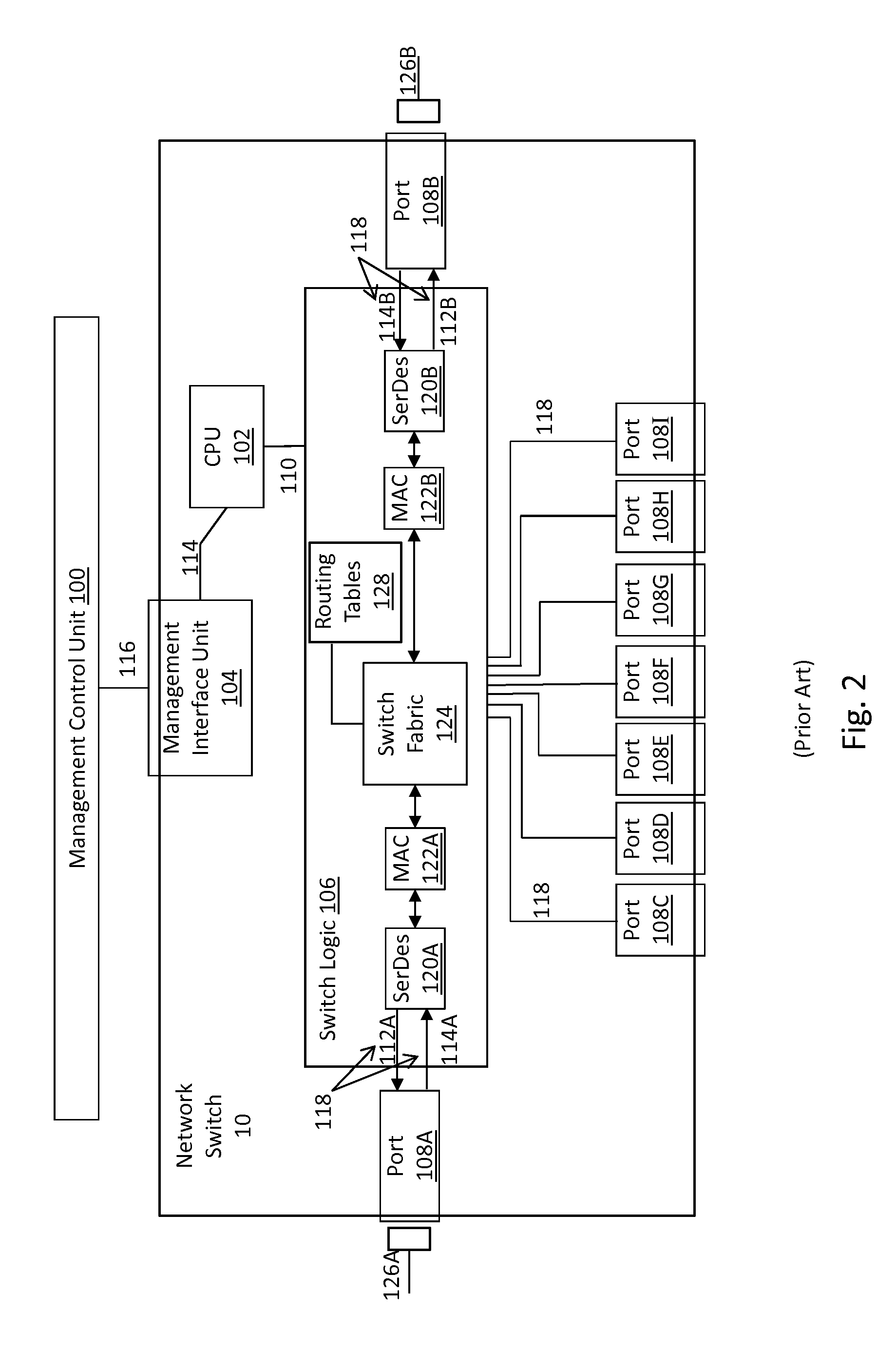

Data center path switch with improved path interconnection architecture

ActiveUS20160007102A1Easy to controlSimplifying interconnectionMultiplex system selection arrangementsOptical multiplexData centerSwitching signal

A data center path switch architecture permits path switching of the signal path of incoming signals to one or more output paths in real time without the need for manual intervention, and without delays associated with current data center network switches. In this architecture, a switching core capable of switching signals directly from the ingress of the switching core to alternate destination ports in real time, either under software or hardware control.

Owner:FIBER MOUNTAIN INC

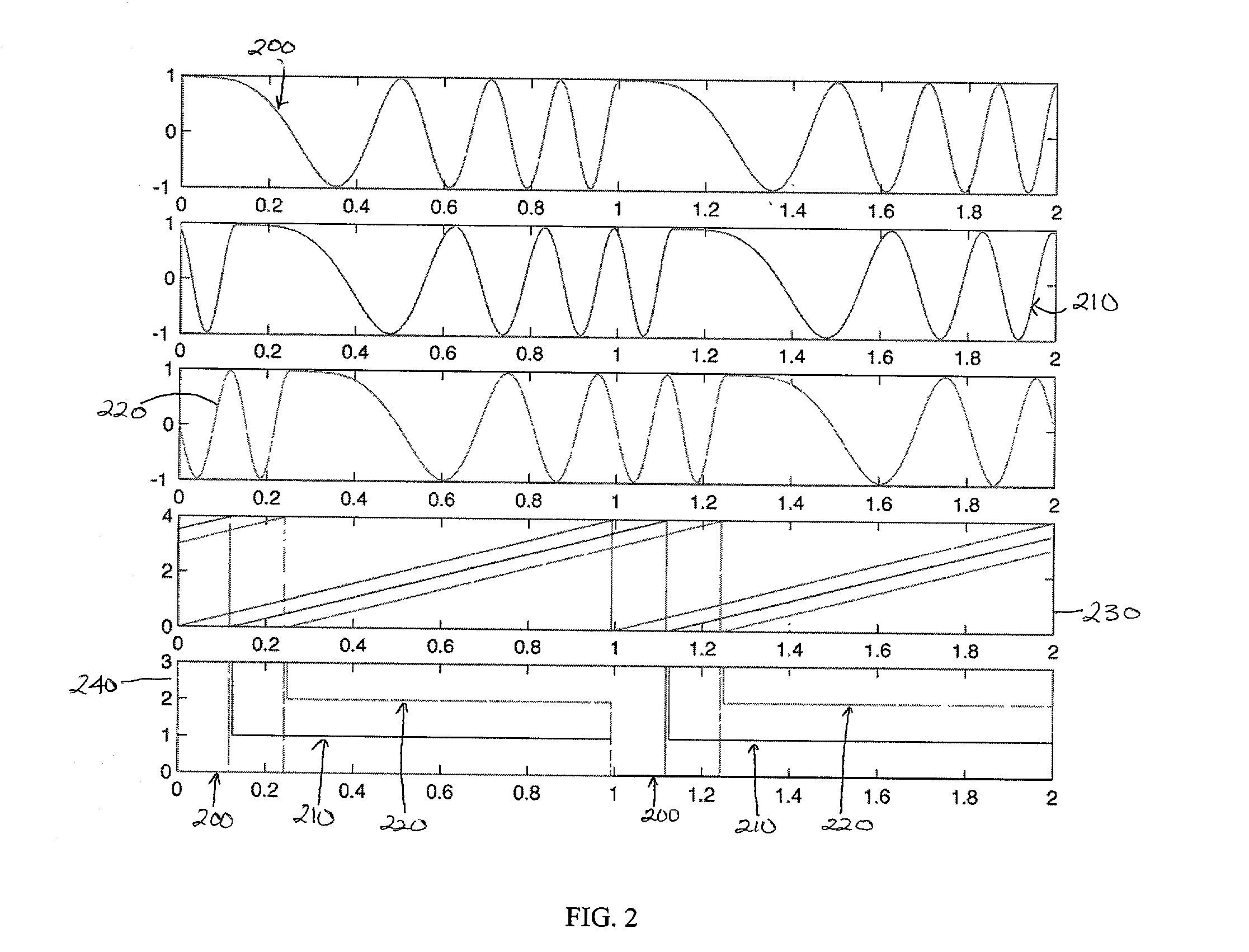

Multi-station HF FMCW radar frequency sharing with GPS time modulation multiplexing

InactiveUS20030025629A1No performance lossMulti-channel direction-finding systems using radio wavesPosition fixationTime informationDigital data

Systems and methods are described for HF radar frequency sharing with GPS time modulation multiplexing. A method is provided that includes generating clock signals from the time information contained in a GPS signal. Radio frequency signals are transmitted and received in a sequence whose start times are dictated by the clock signals. The clock signals also control the modulation of the radio frequency signals. The radio frequency signals are modulated by using a sweep modulation. An apparatus to implement the method includes a GPS receiver, a state machine, a clock generator, a microprocessor, a memory chip, a signal synthesizer, and a digital data output device. The GPS receiver extracts time information from GPS signals. The state machine controls radar functions versus time. The microprocessor performs modulation multiplexing on radar signals.

Owner:CODAR OCEAN SENSORS LTD

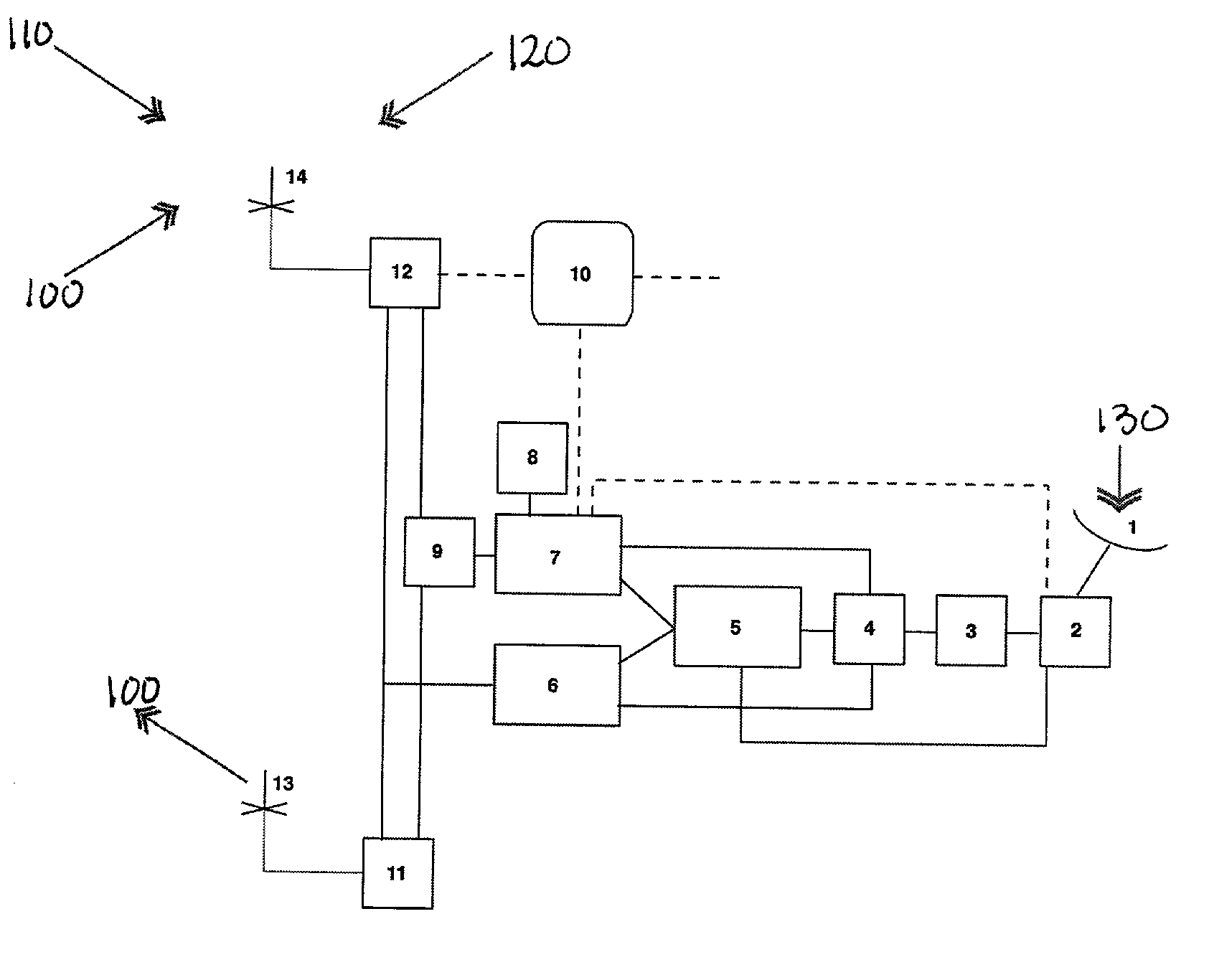

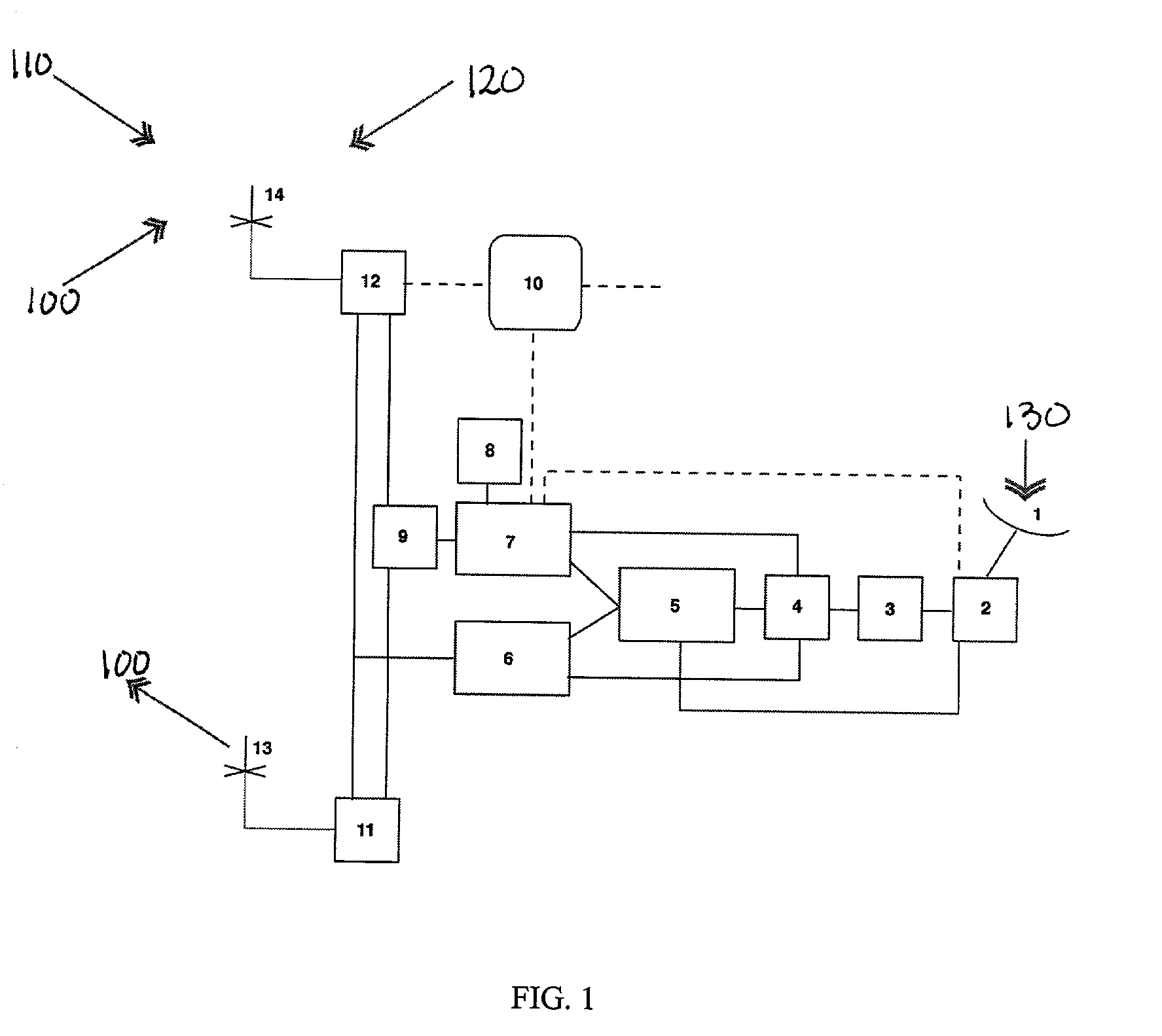

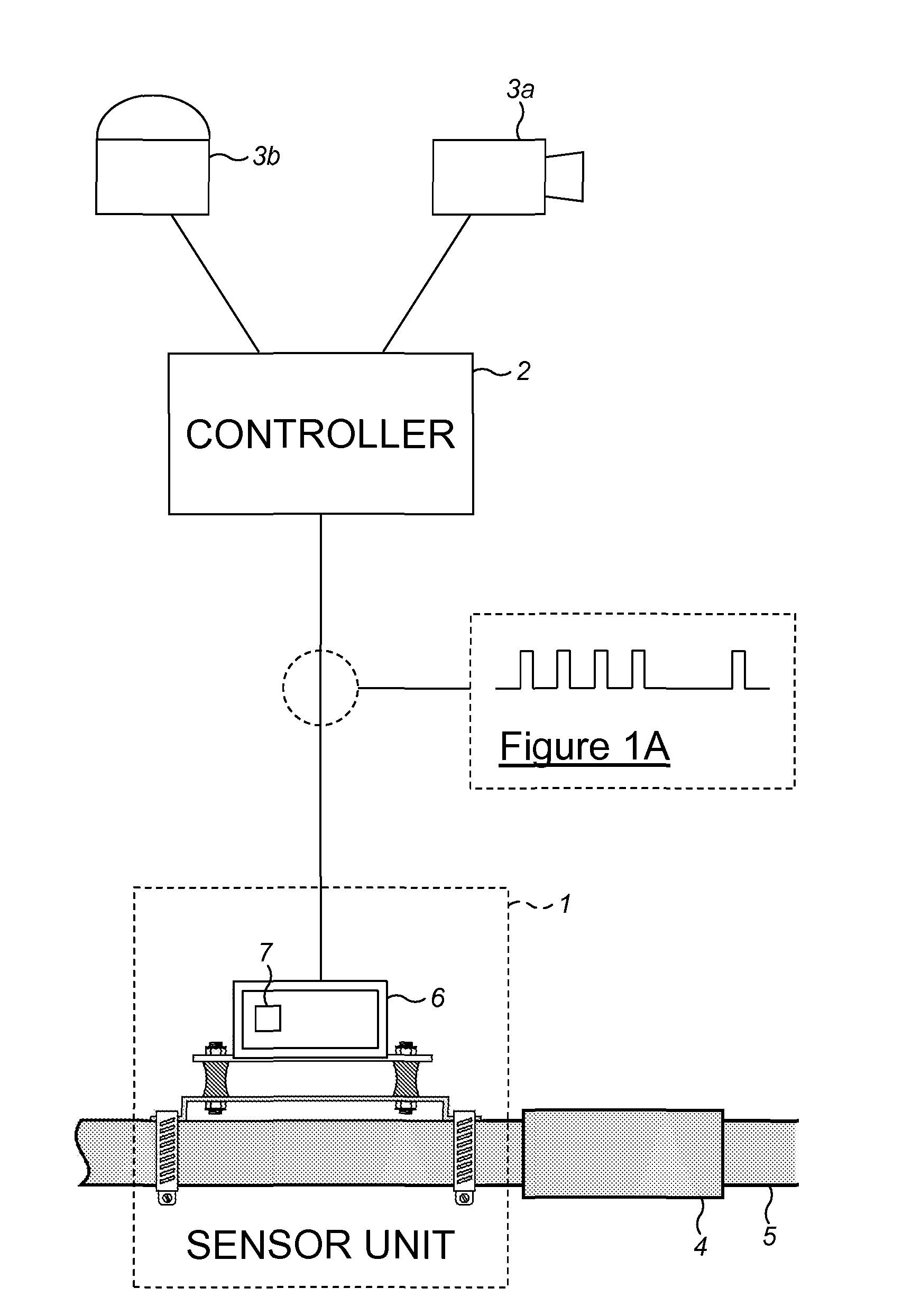

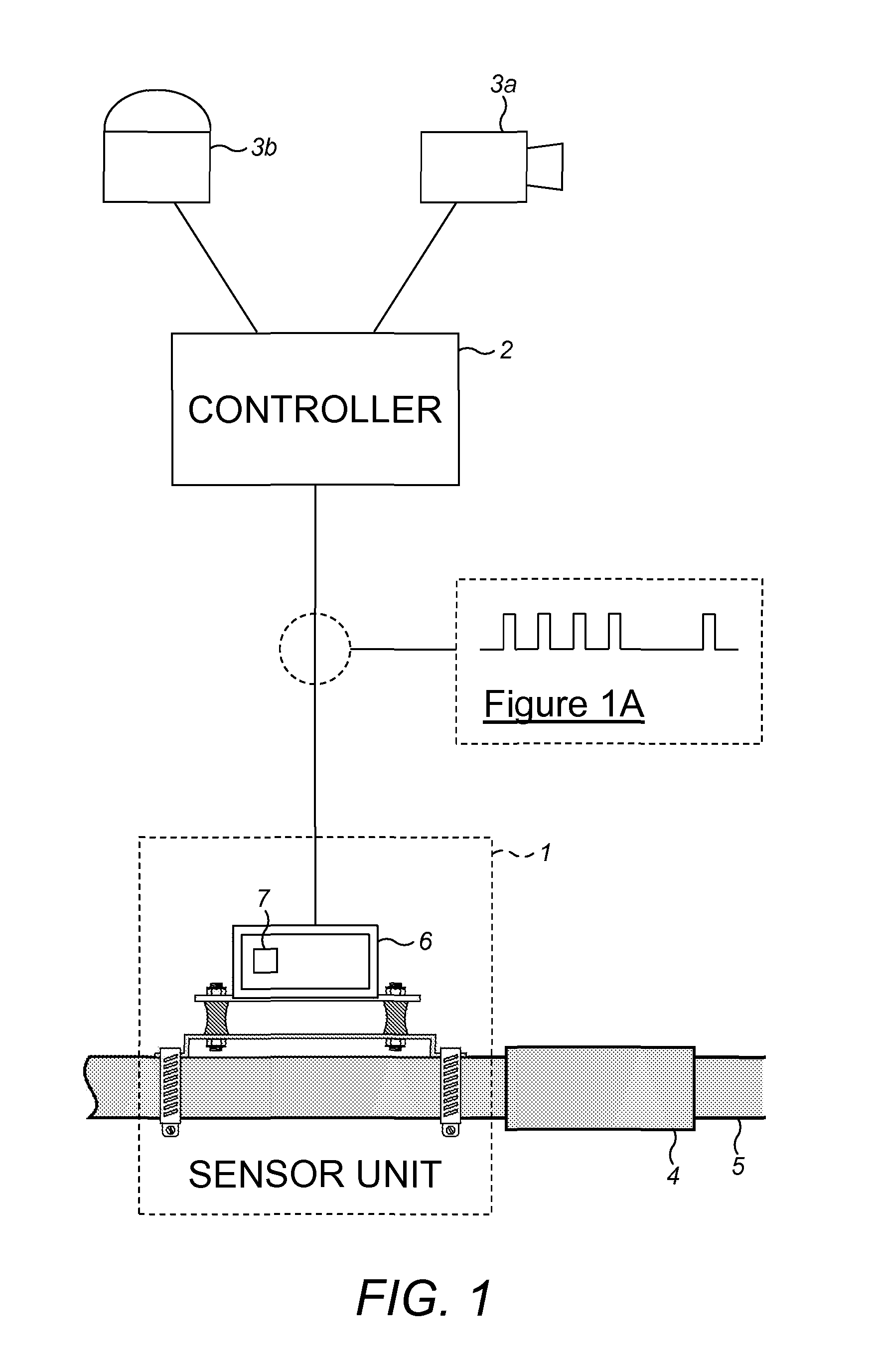

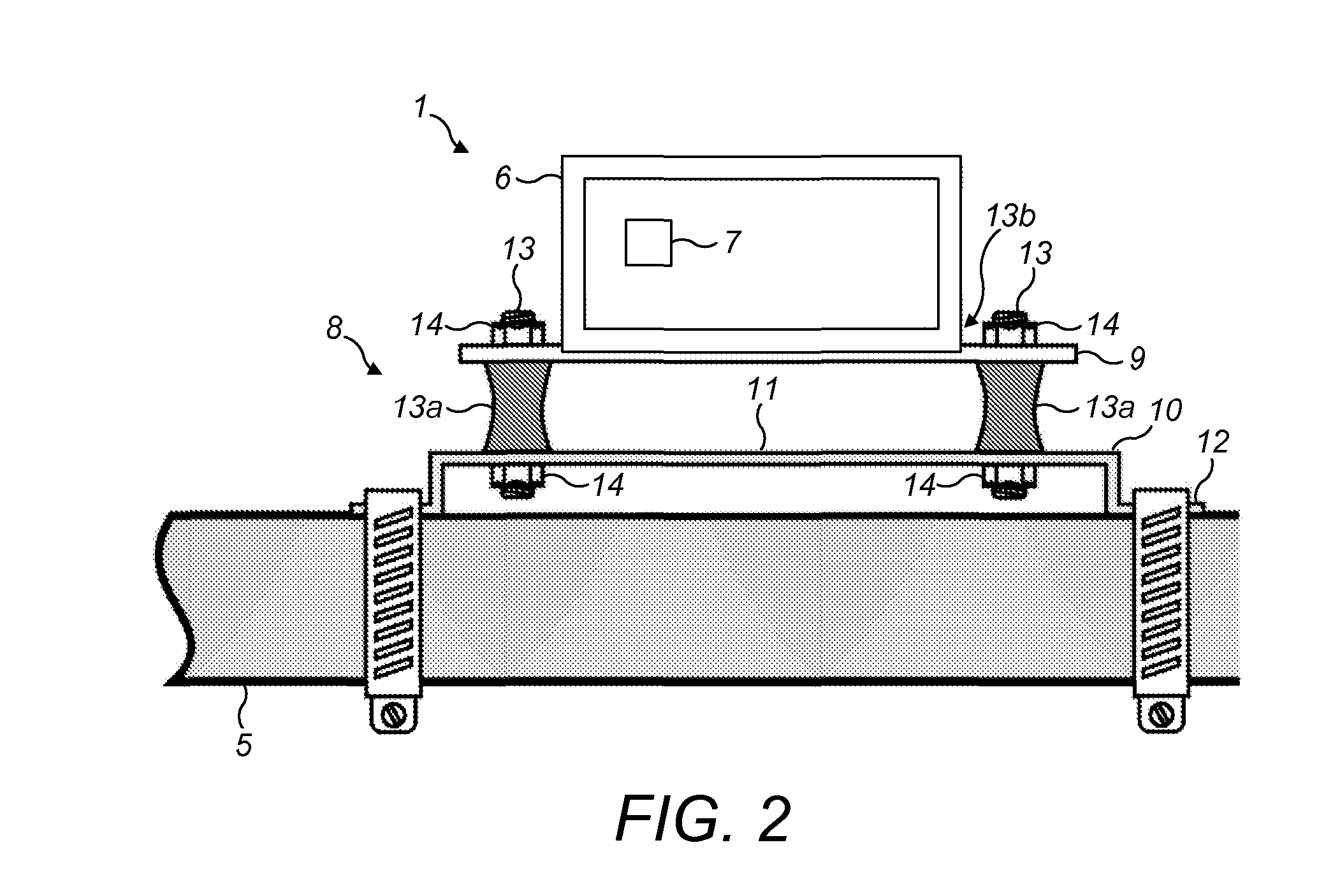

Anti-theft system for an automotive exhaust component

InactiveUS20140104048A1Difficult to controlNo performance lossInternal combustion piston enginesExhaust apparatusEngineeringAnti theft

An anti-theft system for protecting a vehicle exhaust component (4) is described. The system includes a sensor (1) configured to monitor vibrations associated with a vehicle exhaust system (5)and a controller (2) arranged to monitor a signal from the sensor (1). The controller (2) is configured to generate an alarm event if the signal from the sensor includes characteristics indicative of vibrations associated with an attempted theft of the vehicle exhaust component (4).

Owner:DE KOCK FILIP +1

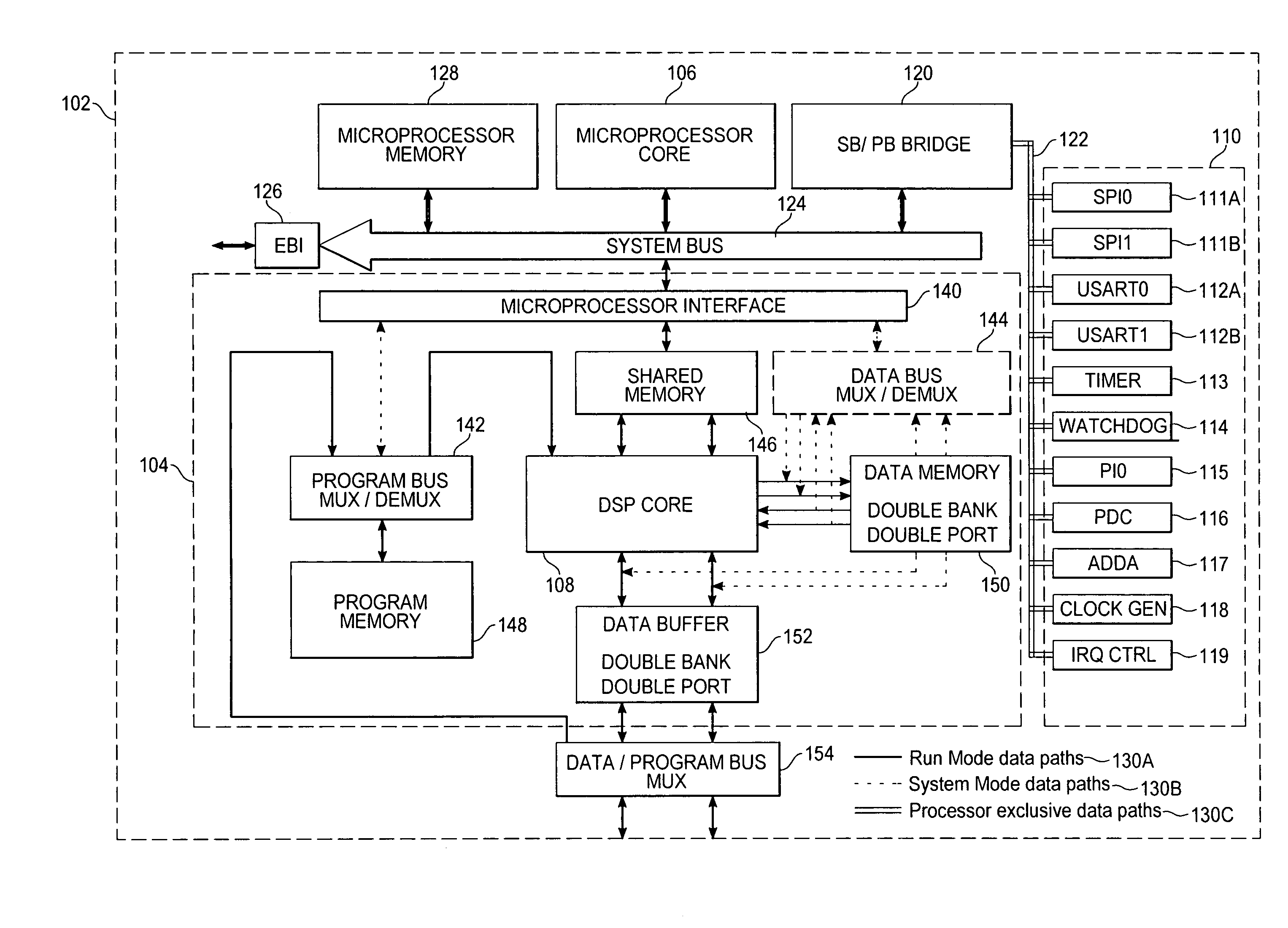

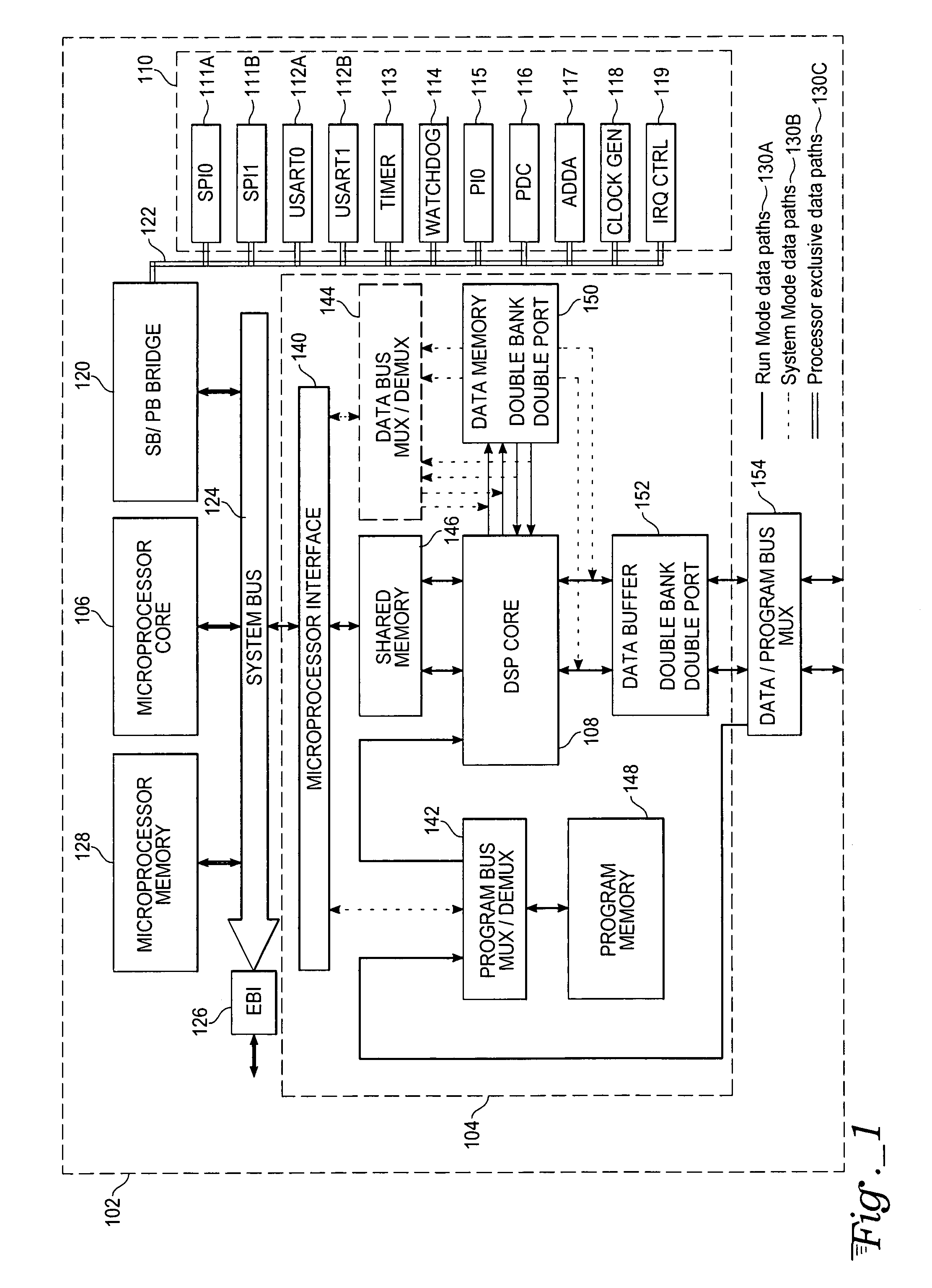

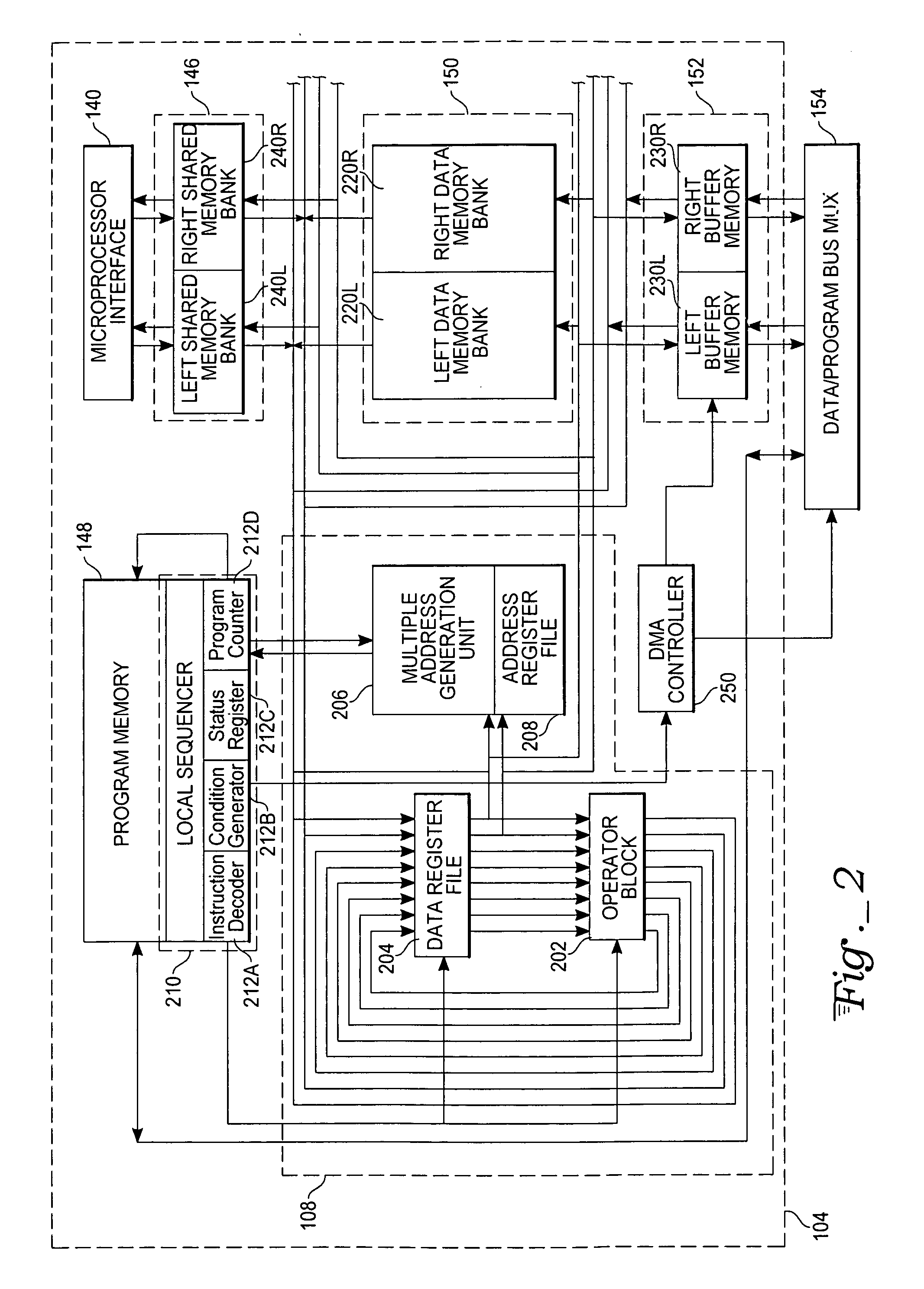

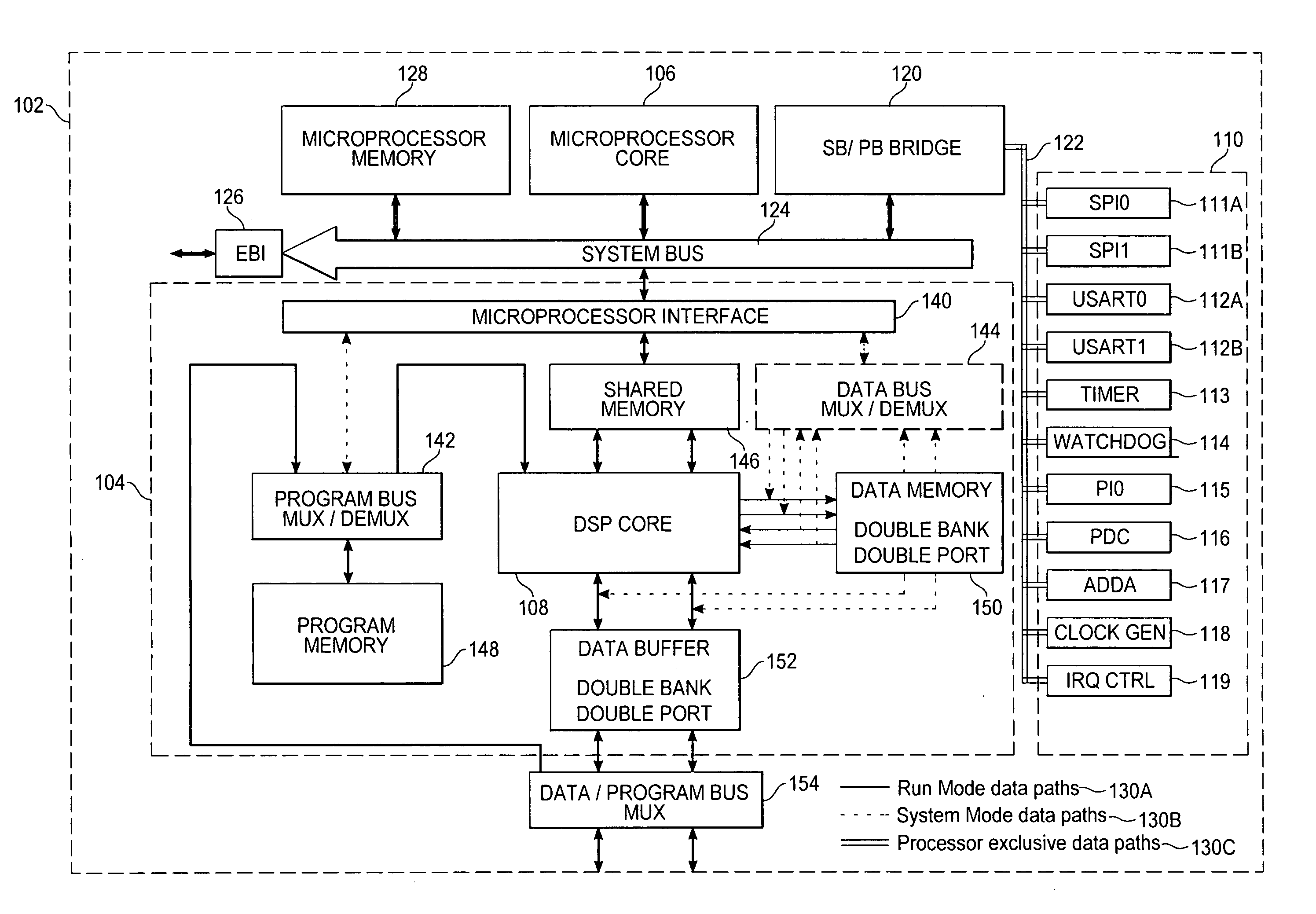

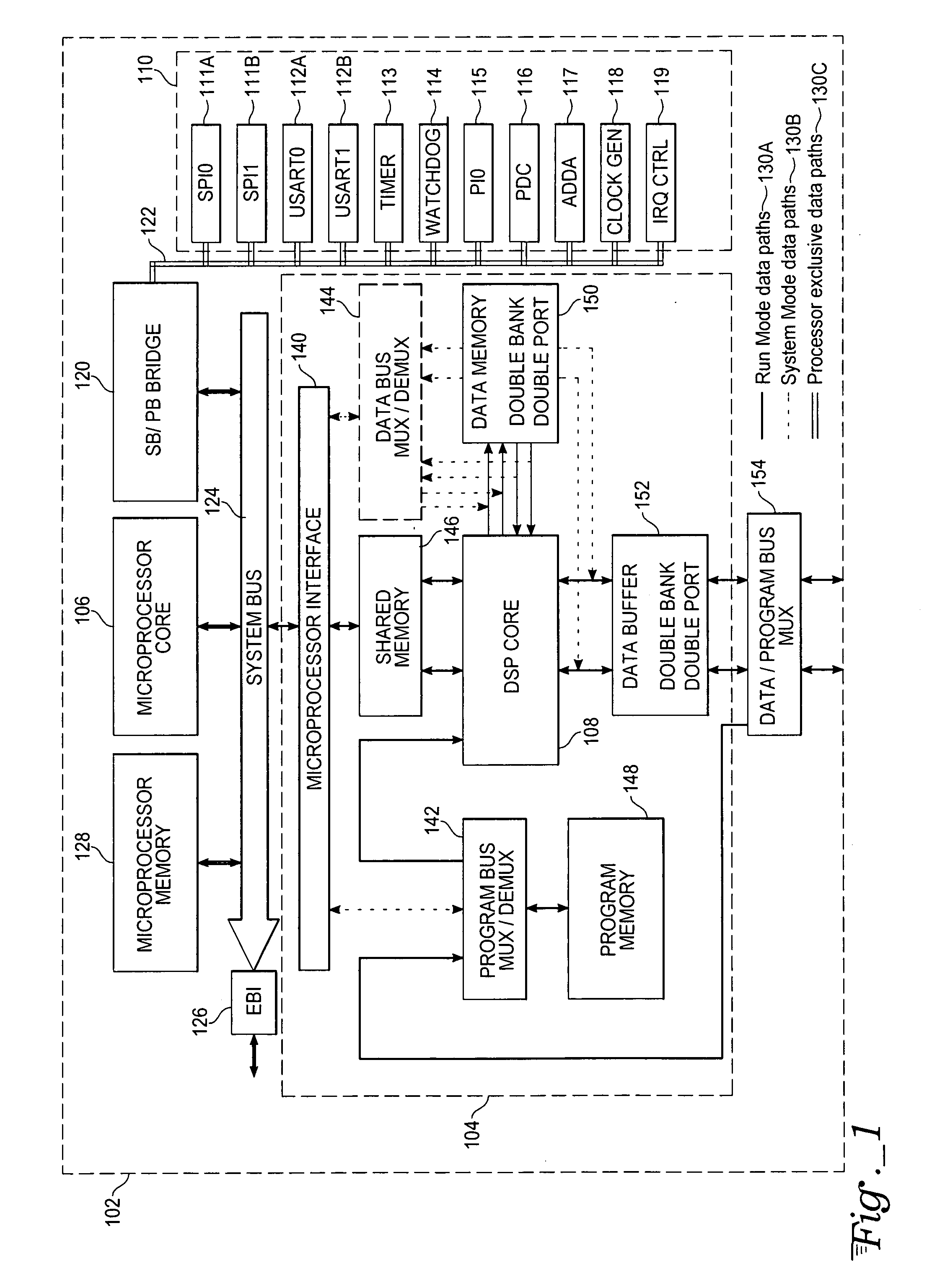

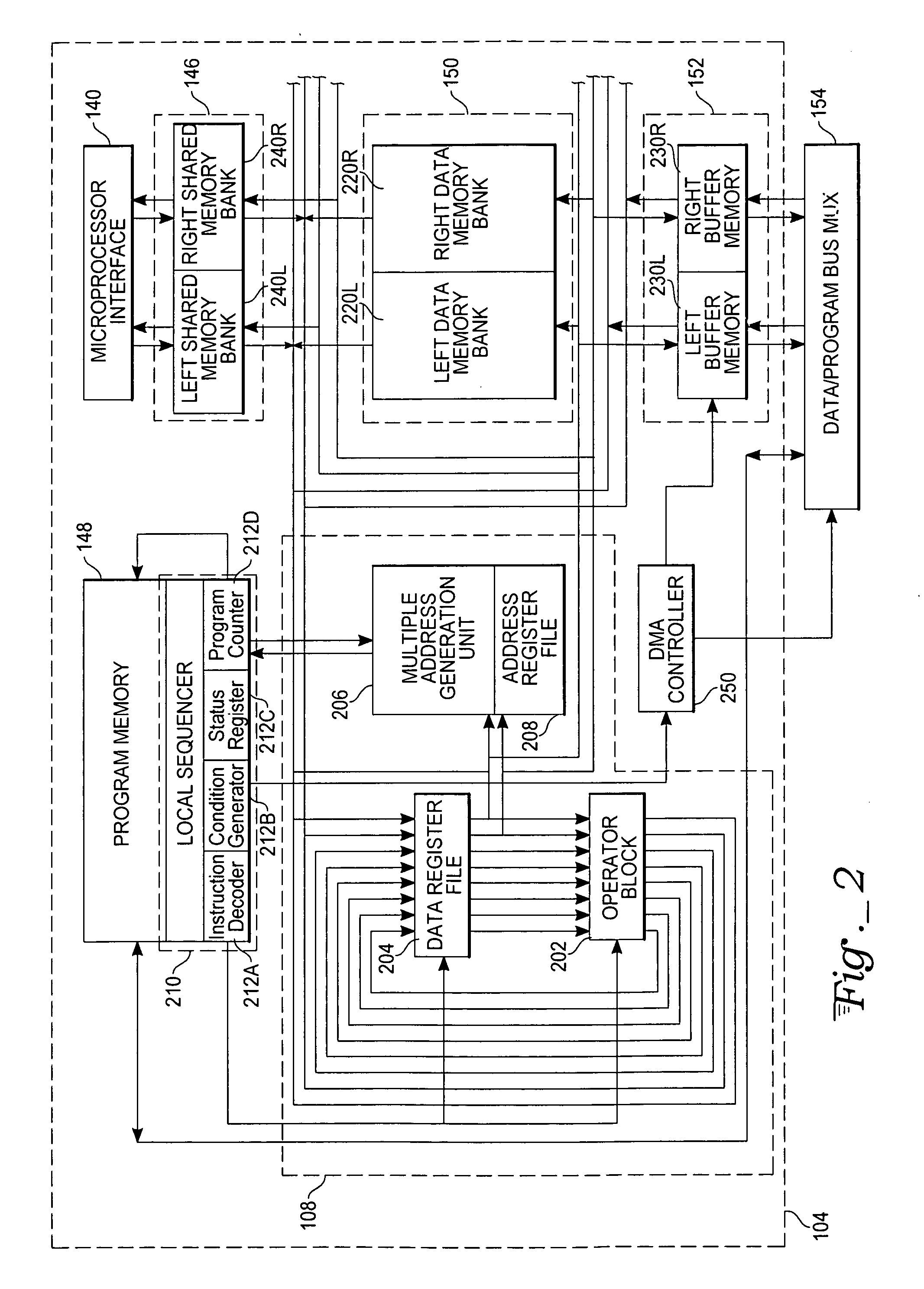

Complex domain floating point VLIW DSP with data/program bus multiplexer and microprocessor interface

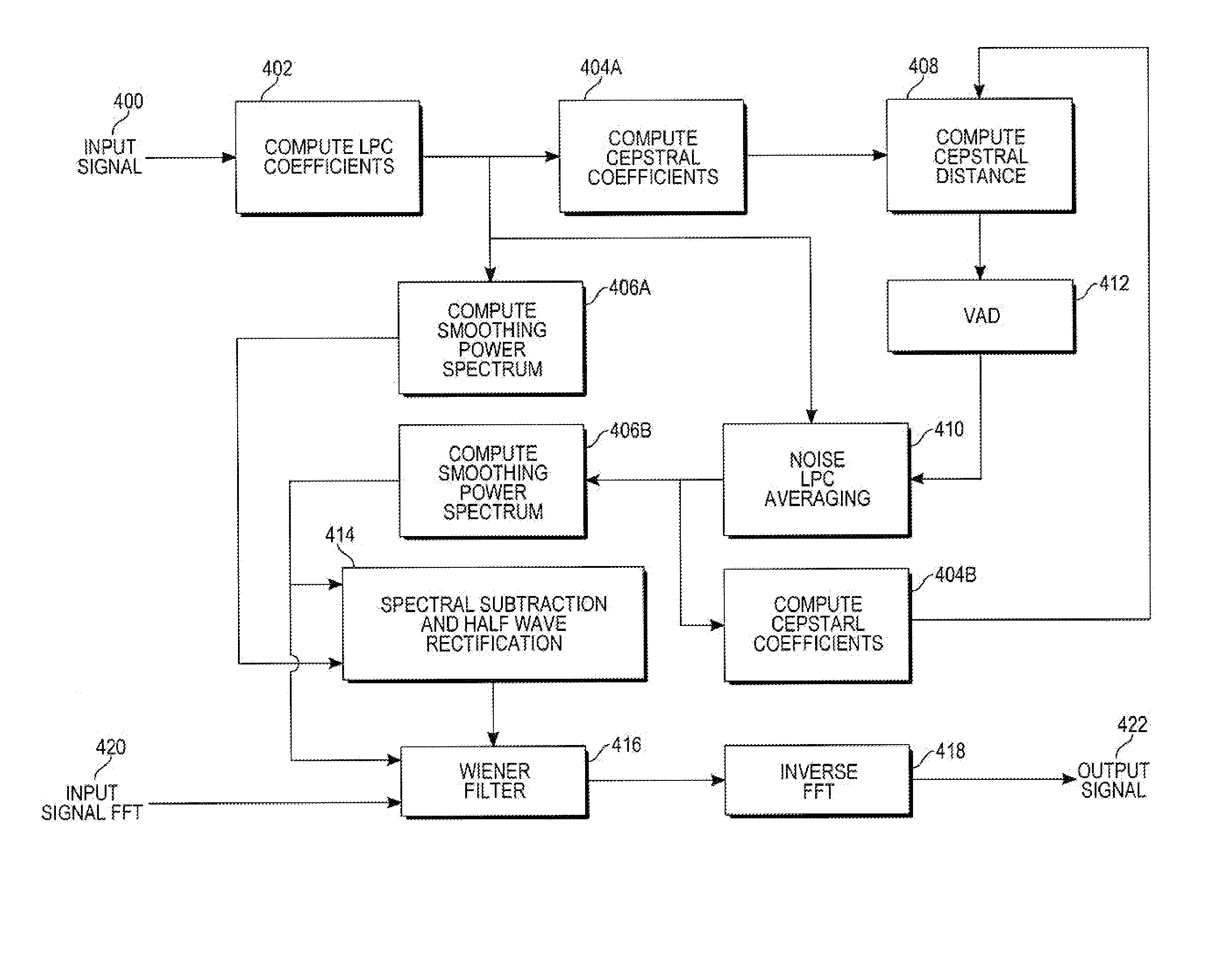

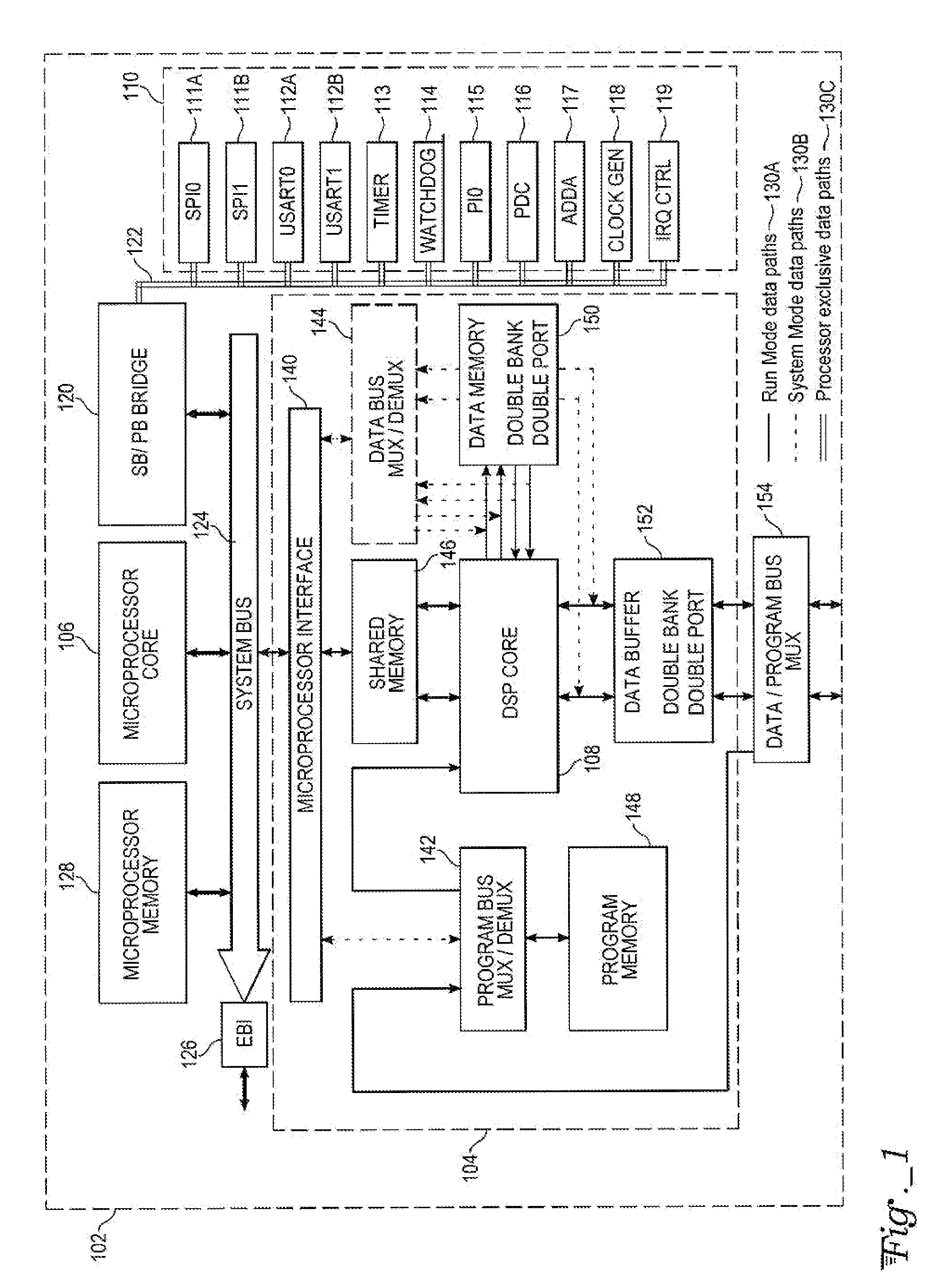

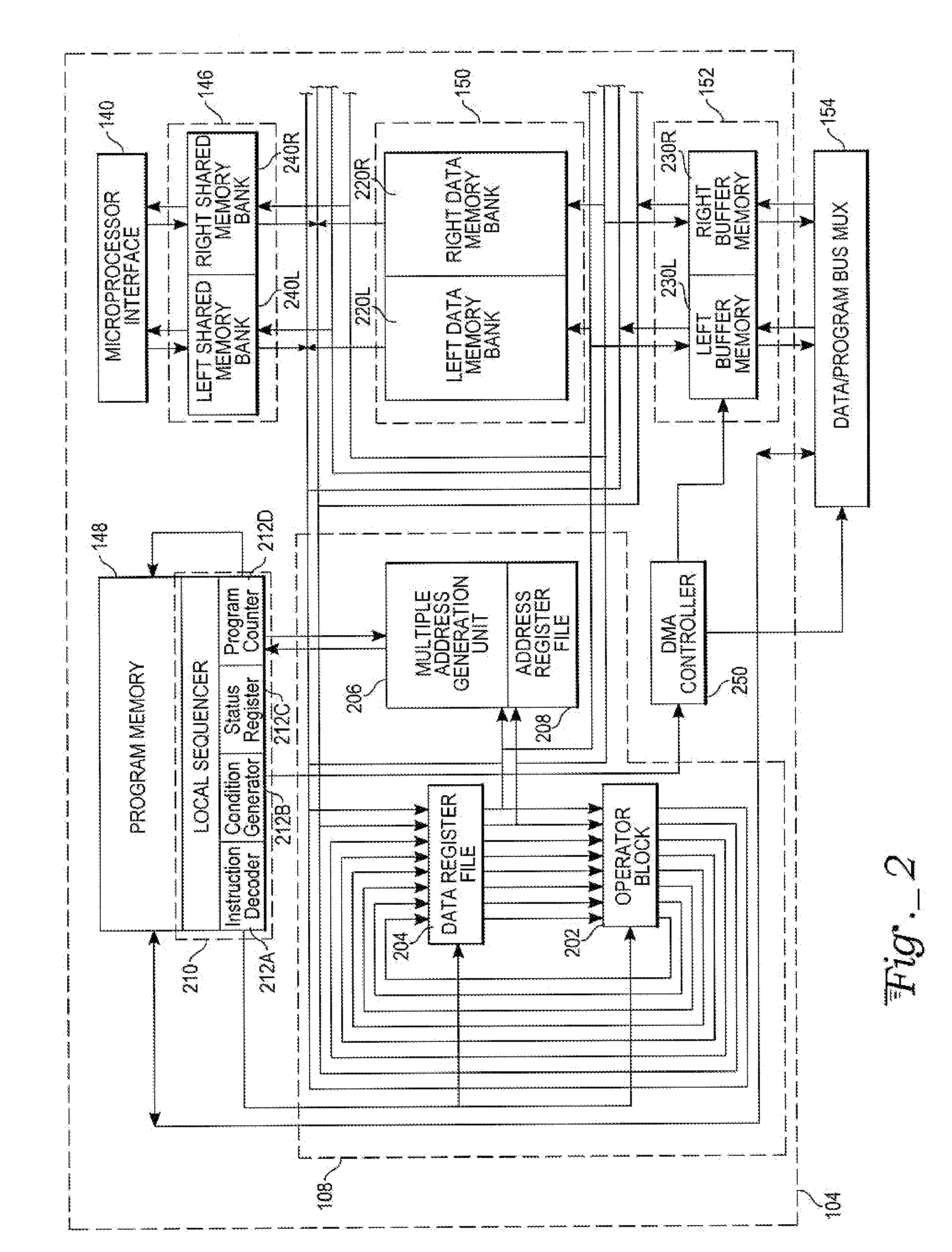

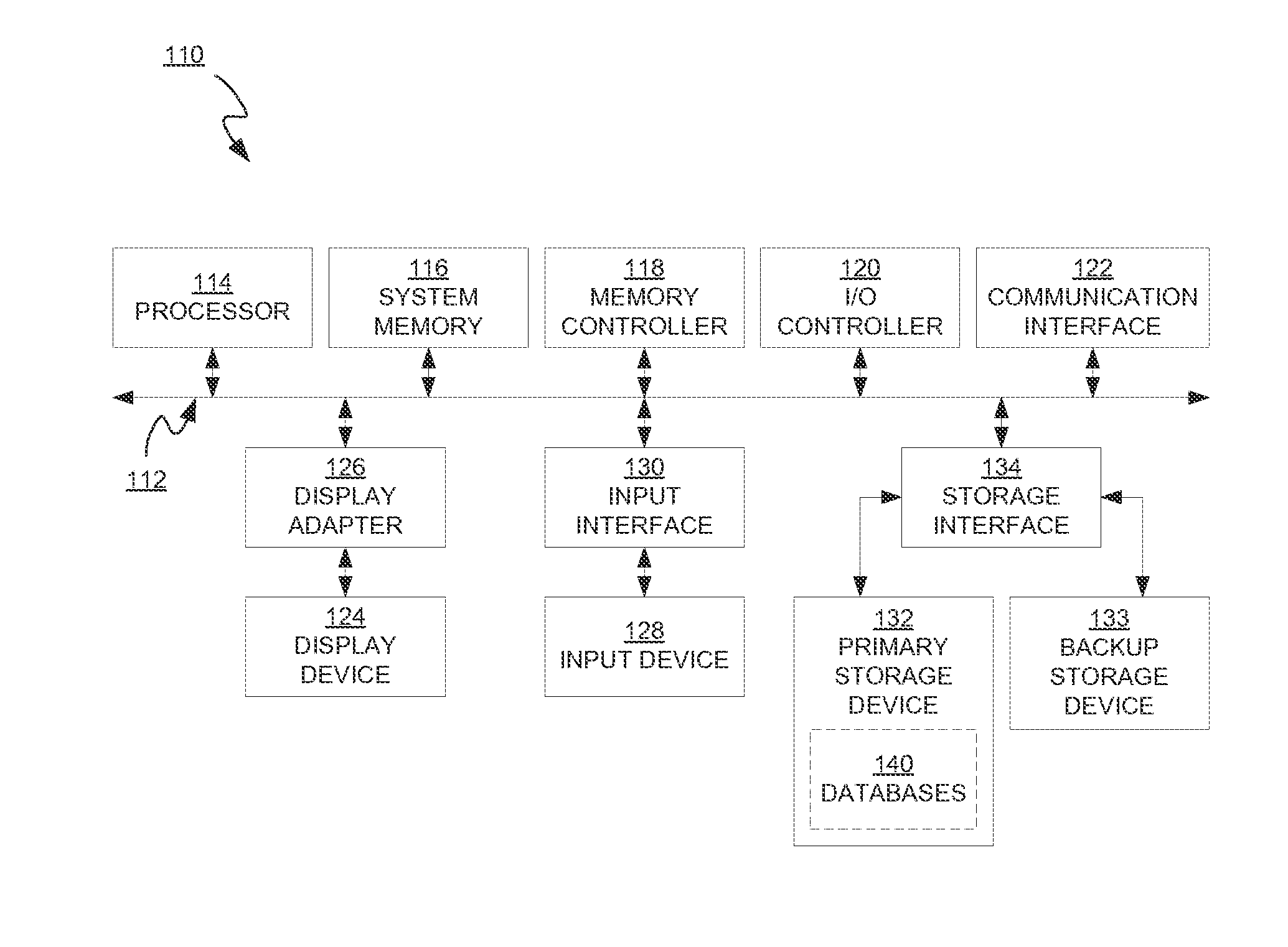

ActiveUS7437540B2No performance lossReduce in quantityArchitecture with single central processing unitSpecific program execution arrangementsDigital signal processingProcessing core

A system for digital signal processing, configured as a system on chip (SoC), combines a microprocessor core and digital signal processor (DSP) core with floating-point data processing capability. The DSP core can perform operations on floating-point data in a complex domain and is capable of producing real and imaginary arithmetic results simultaneously. This capability allows a single-cycle execution of, for example, FFT butterflies, complex domain simultaneous addition and subtraction, complex multiply accumulate (MULACC), and real domain dual multiply-accumulators (MACs). The SoC may be programmed entirely from a microprocessor programming interface, using calls from a DSP library to execute DSP functions. The cores may also be programmed separately. Capability for programming and simulating the entire SoC are provided by a separate programming environment. The SoC may have heterogeneous processing cores in which either processing core may act as master or slave, or both cores may operate simultaneously and independently.

Owner:ATMEL CORP

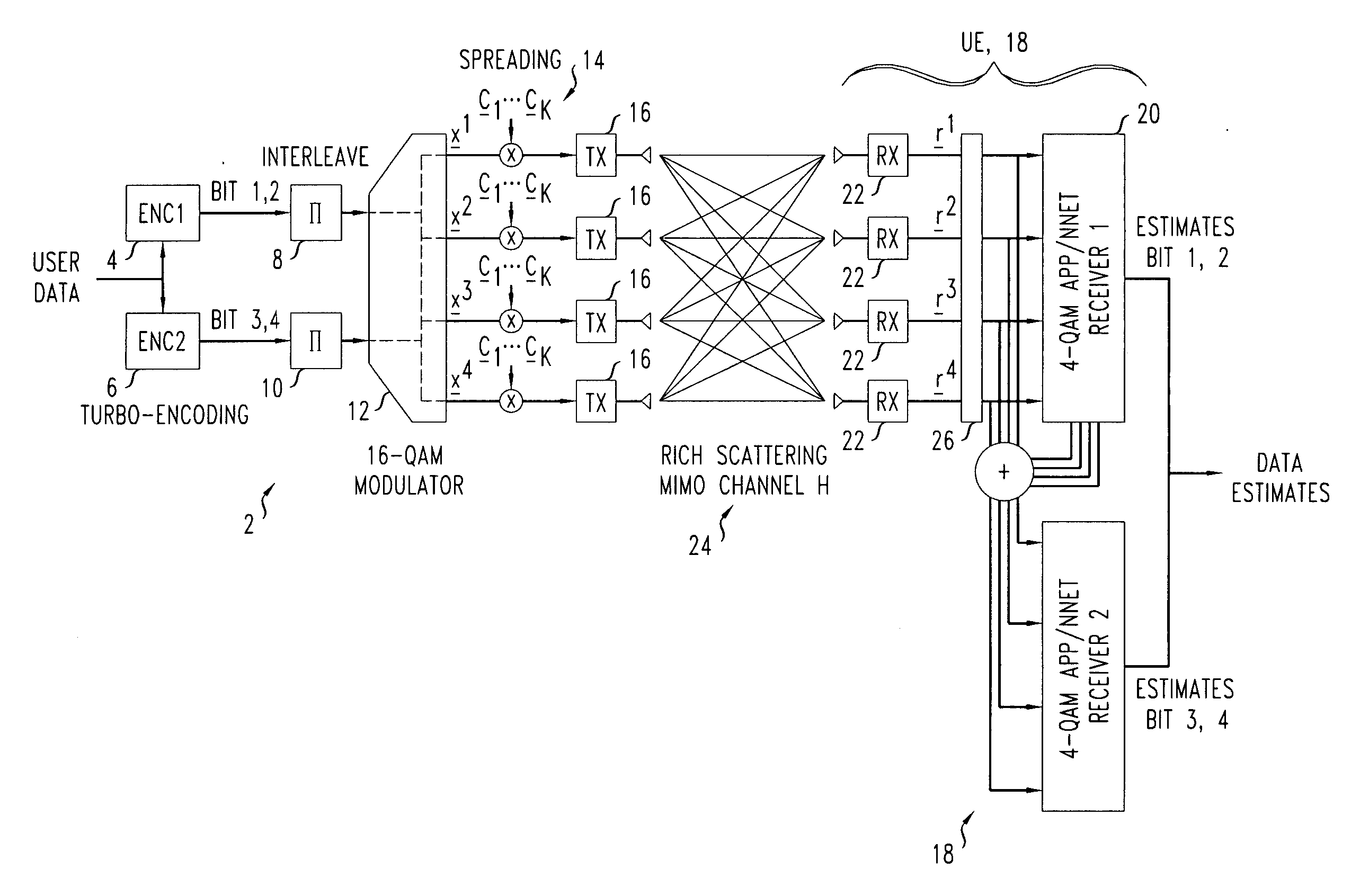

Modulation in a mobile telecommunications system

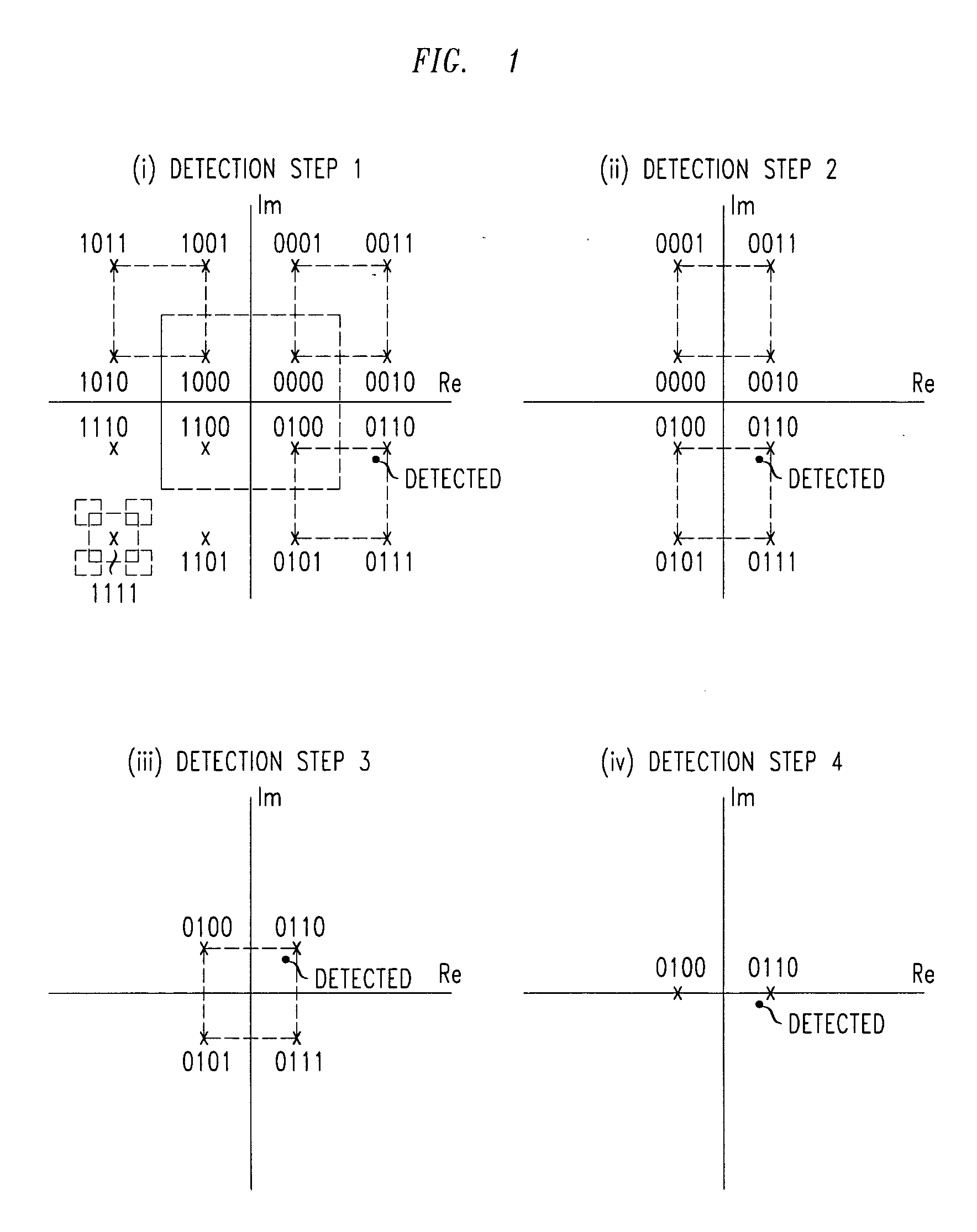

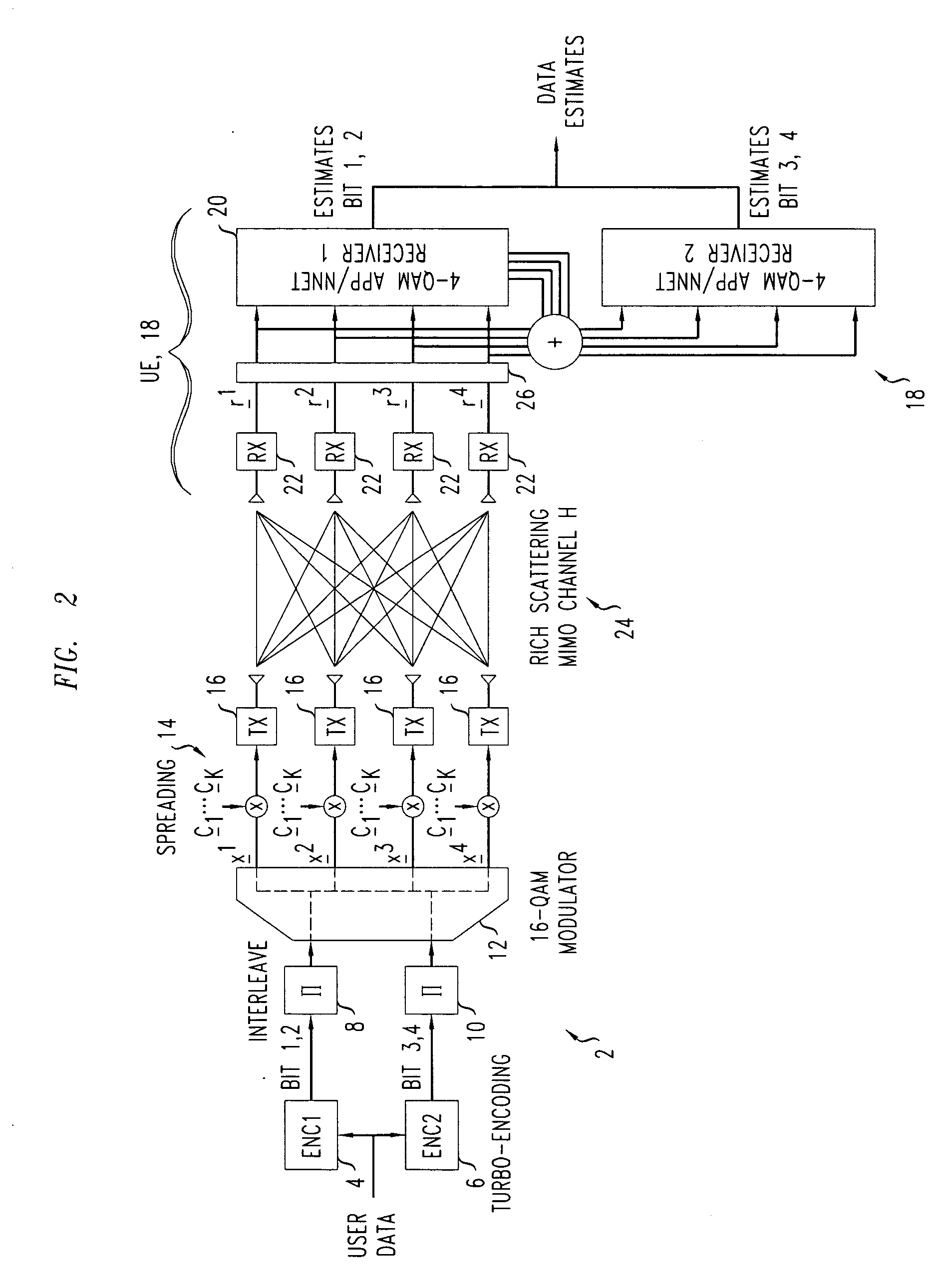

InactiveUS20050201478A1Reduce computational complexityWithout loss of performanceModulated-carrier systemsDiversity/multi-antenna systemsTelecommunications networkComputer science

A method of communication of data in a mobile telecommunications network involves at a transmitter first grouping the data into a first sequence of bits and a second sequence of bits. There is then a step of modulating a signal with the bits of the first sequence so that the bits of the first sequence have a first level of communication error protection provided by the modulation and with the bits of the second sequence so that the bits of the second sequence have a second level of communication error protection provided by the modulation less than the first level of communication error protection. The signal is then transmitted. At a receiver, estimates of the bits of the first sequence from the signal are detected and contributions to the signal corresponding to the estimates are determined and cancelled from the signal so as to produce a modified signal. Estimates of the bits of the second sequence are then detected from the modified signal.

Owner:LUCENT TECH INC

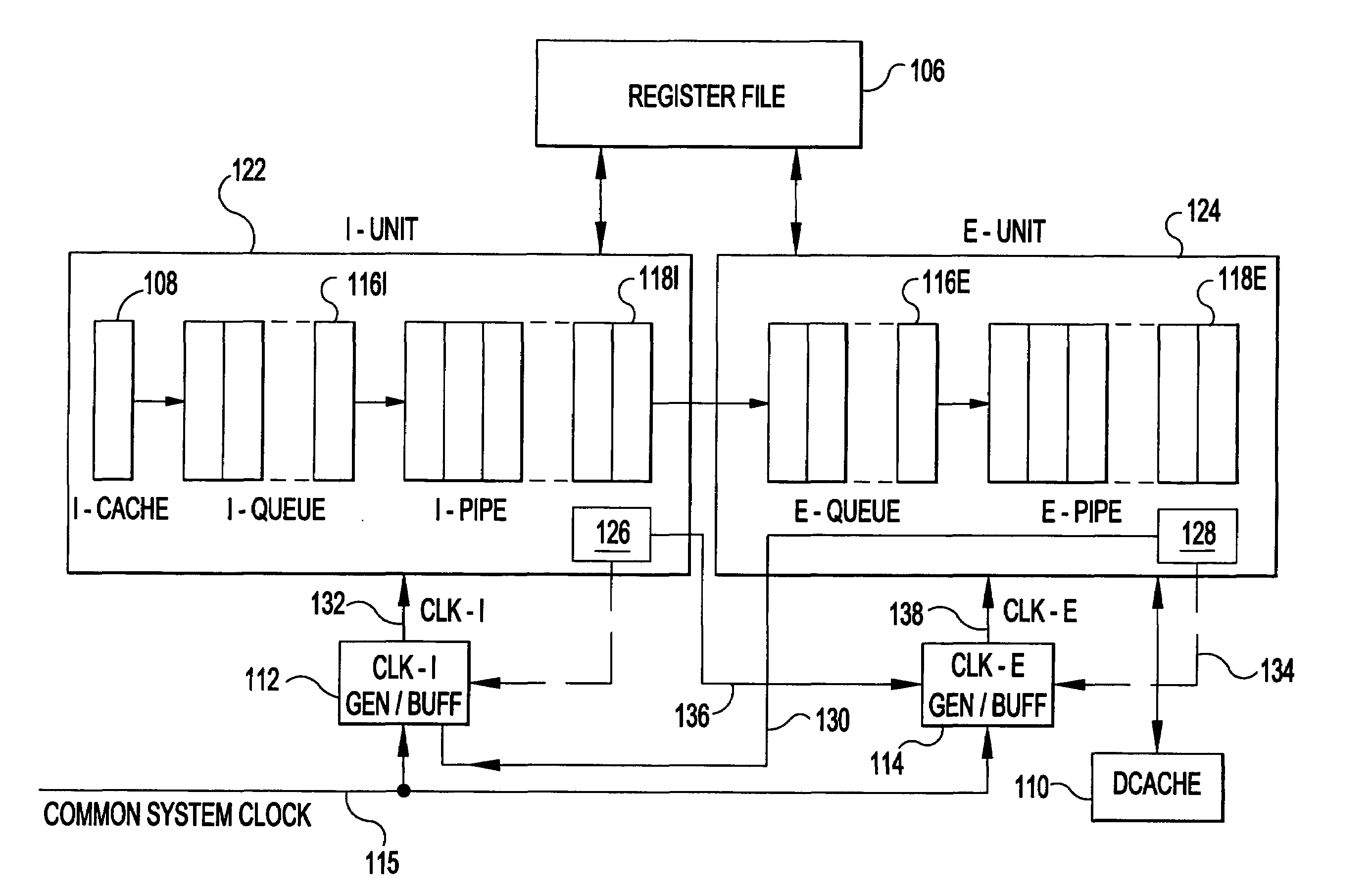

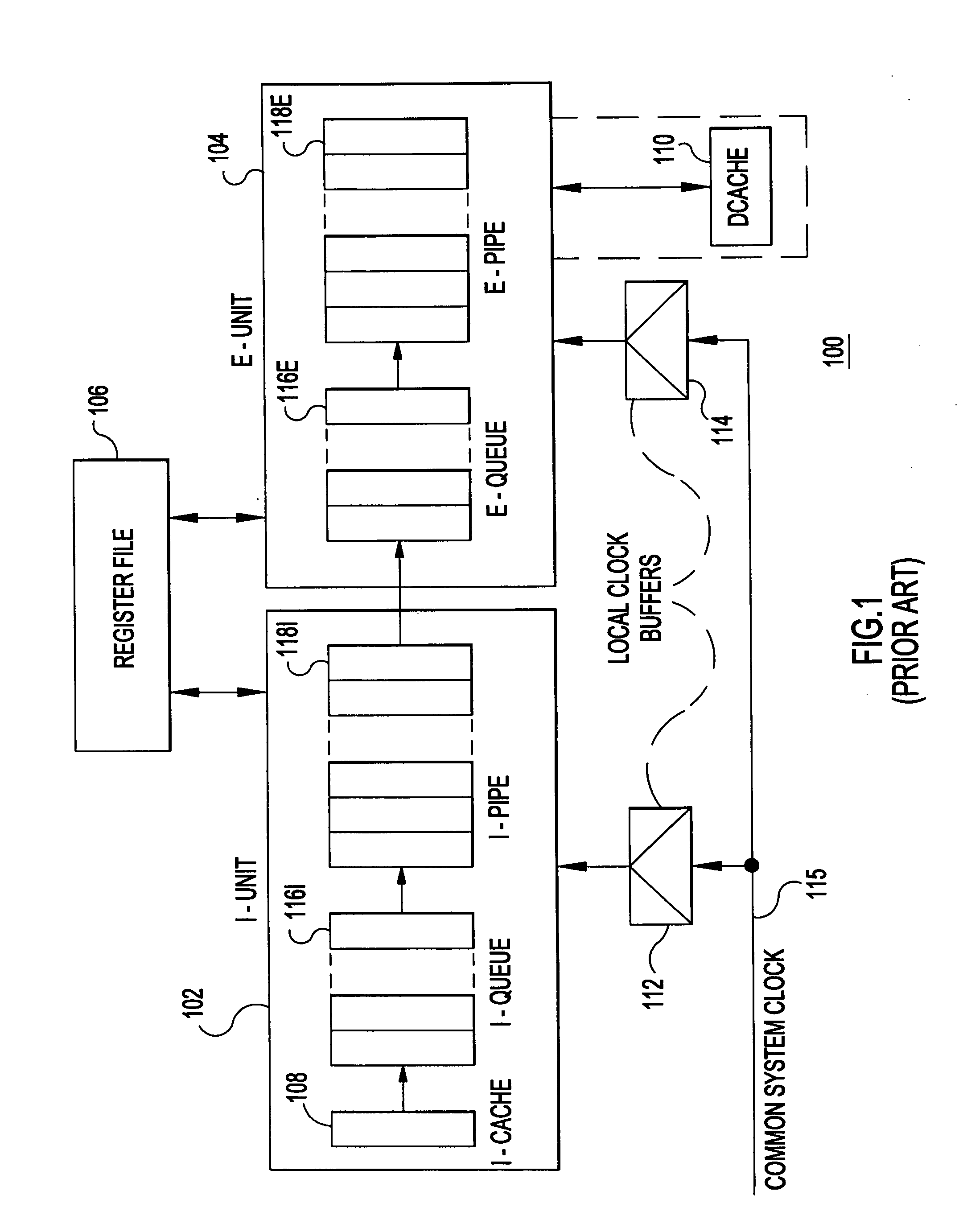

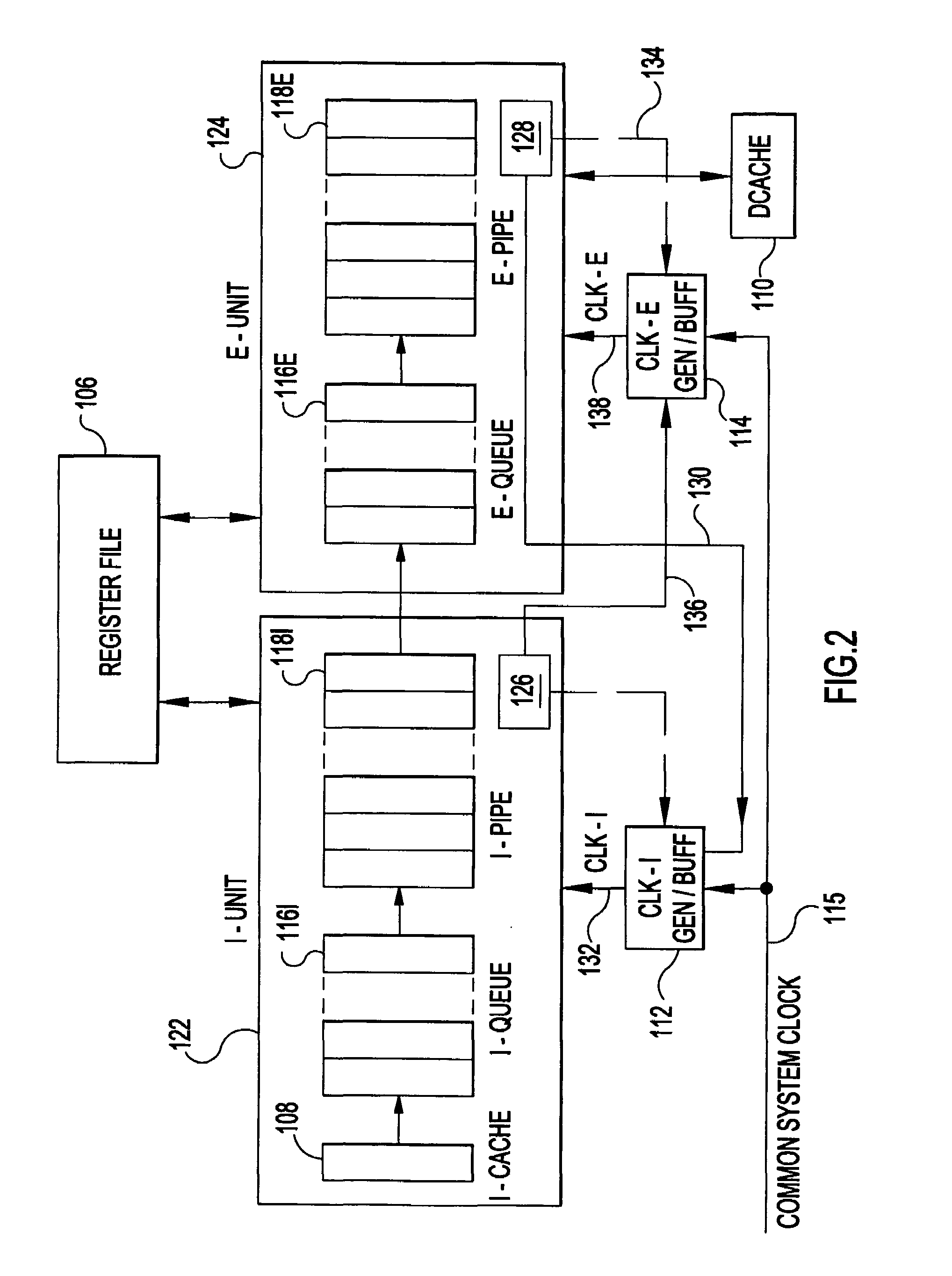

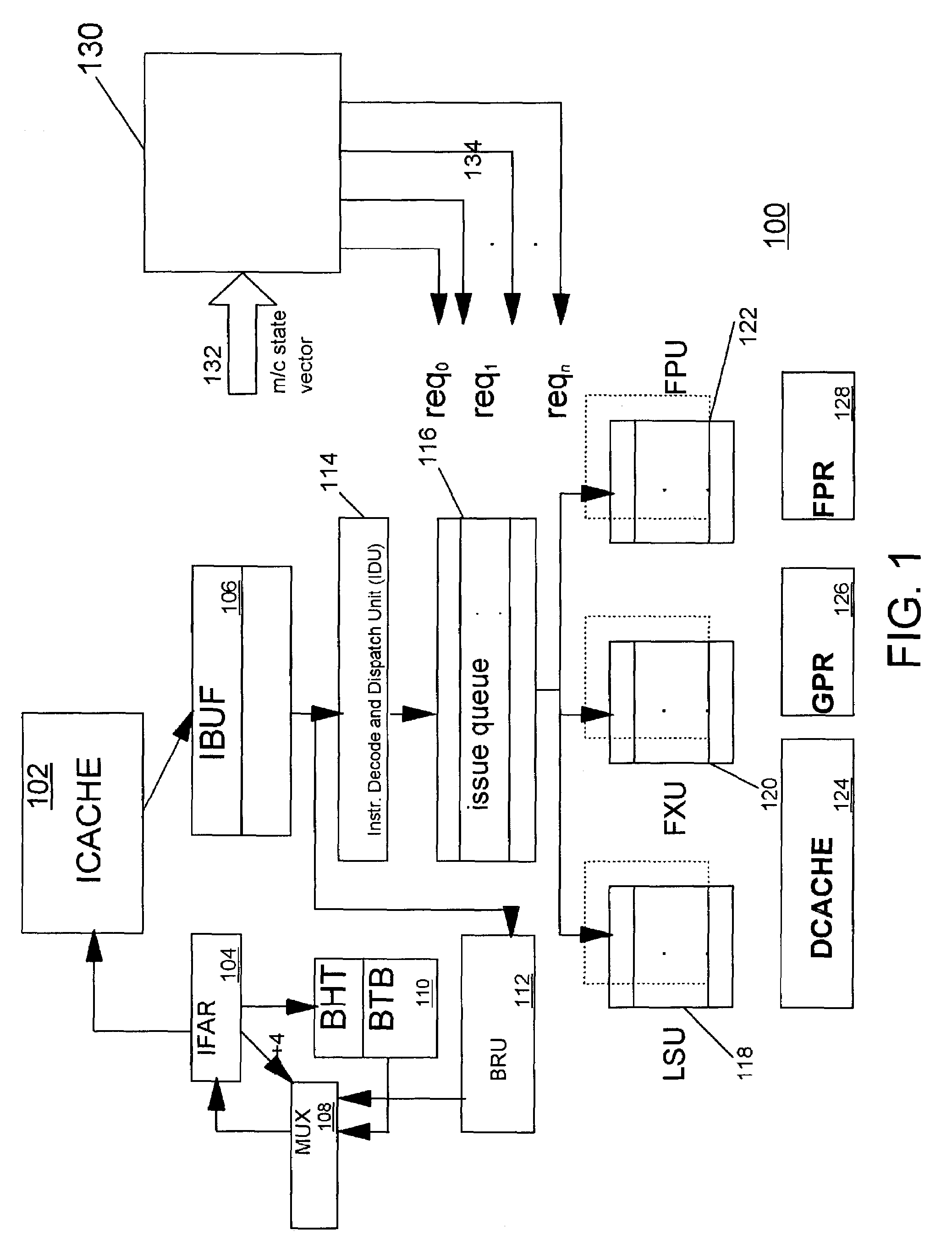

Processor with demand-driven clock throttling power reduction

InactiveUS7076681B2Reduce consumptionNo performance lossEnergy efficient ICTVolume/mass flow measurementScalar processorProcessor register

A synchronous integrated circuit such as a scalar processor or superscalar processor. Circuit components or units are clocked by and synchronized to a common system clock. At least two of the clocked units include multiple register stages, e.g., pipeline stages. A local clock generator in each clocked unit combines the common system clock and stall status from one or more other units to adjust register clock frequency up or down.

Owner:INT BUSINESS MASCH CORP

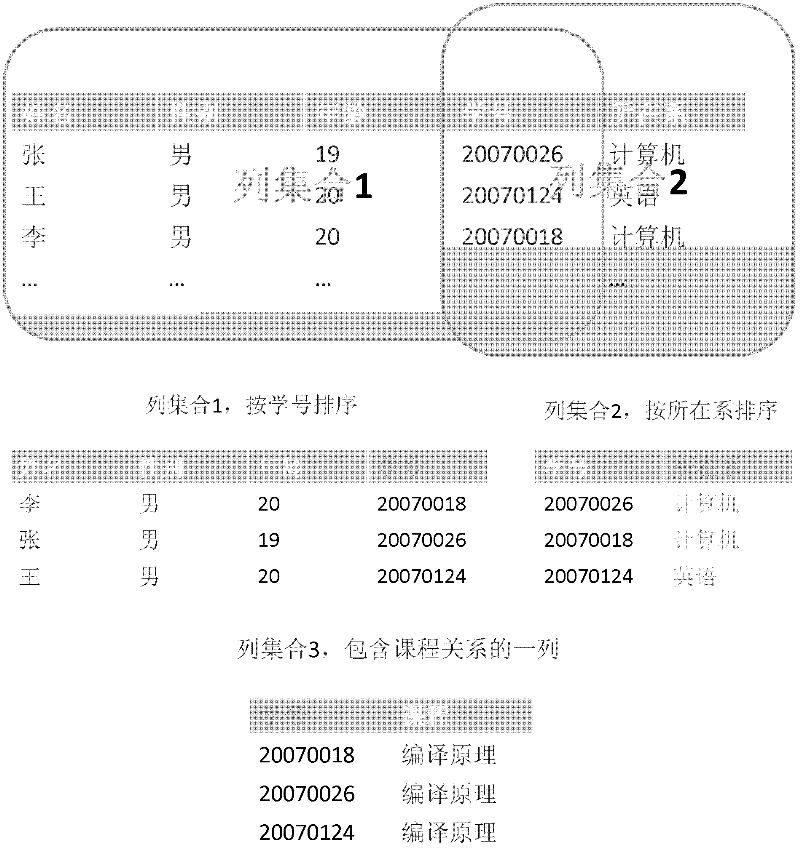

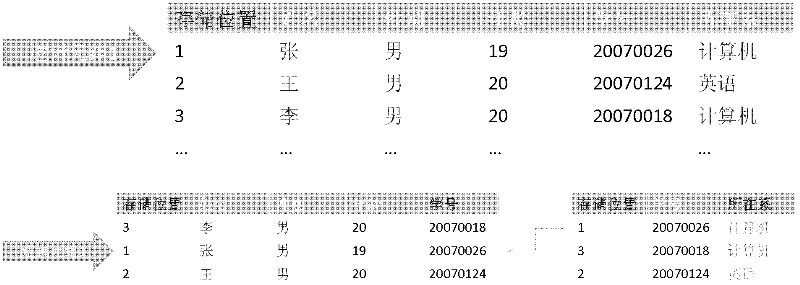

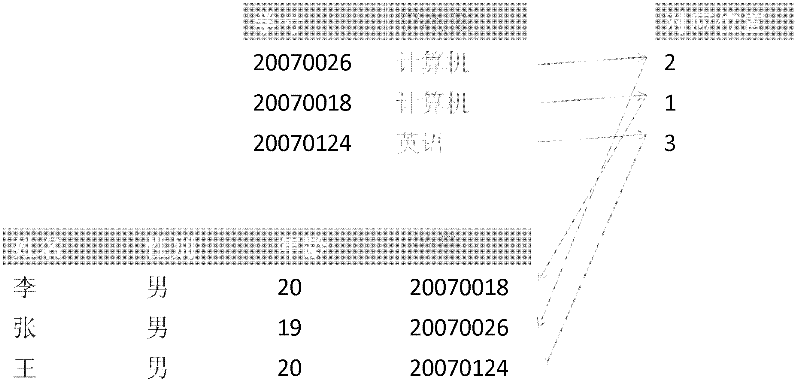

Single-table multi-column sequence storage method for column database

ActiveCN102521303AIncrease flexibilityImprove performanceSpecial data processing applicationsDatabaseData library

The invention discloses a single-table multi-column sequence storage method for a column database. The column database comprises a plurality of data tables formed by rows and columns, wherein the data tables are divided into a plurality of column sets, and the column set comprises one or more columns; and a union set of the column sets forms the data table, and a connection index is established between every two column sets and records the one-to-one corresponding relationship of storage positions of the columns of the same tuple belonging to the data table in the two column sets between which the connection index is established. The single-table multi-column sequence storage method provided by the invention can improve the query efficiency of the column database, and reduces the storage space.

Owner:北京人大金仓信息技术股份有限公司

Dual-processor complex domain floating-point DSP system on chip

ActiveUS20050216702A1No performance lossReduce in quantityArchitecture with single central processing unitSpecific program execution arrangementsProcessing coreReal arithmetic

A system for digital signal processing, configured as a system on chip (SoC), combines a microprocessor core and digital signal processor (DSP) core with floating-point data processing capability. The DSP core can perform operations on floating-point data in a complex domain and is capable of producing real and imaginary arithmetic results simultaneously. This capability allows a single-cycle execution of, for example, FFT butterflies, complex domain simultaneous addition and subtraction, complex multiply accumulate (MULACC), and real domain dual multiply-accumulators (MACs). The SoC may be programmed entirely from a microprocessor programming interface, using calls from a DSP library to execute DSP functions. The cores may also be programmed separately. Capability for programming and simulating the entire SoC are provided by a separate programming environment. The SoC may have heterogeneous processing cores in which either processing core may act as master or slave, or both cores may operate simultaneously and independently.

Owner:ATMEL CORP

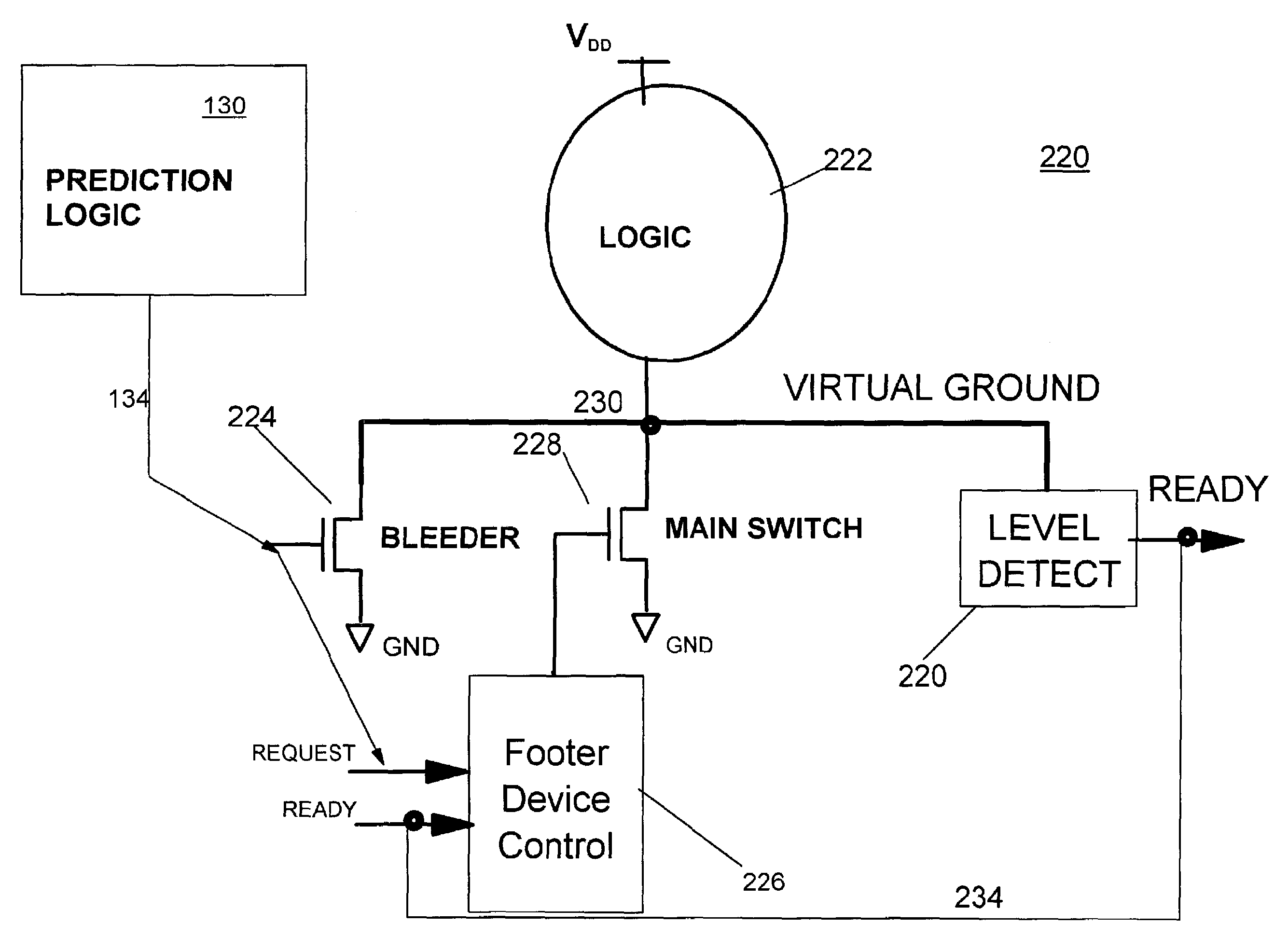

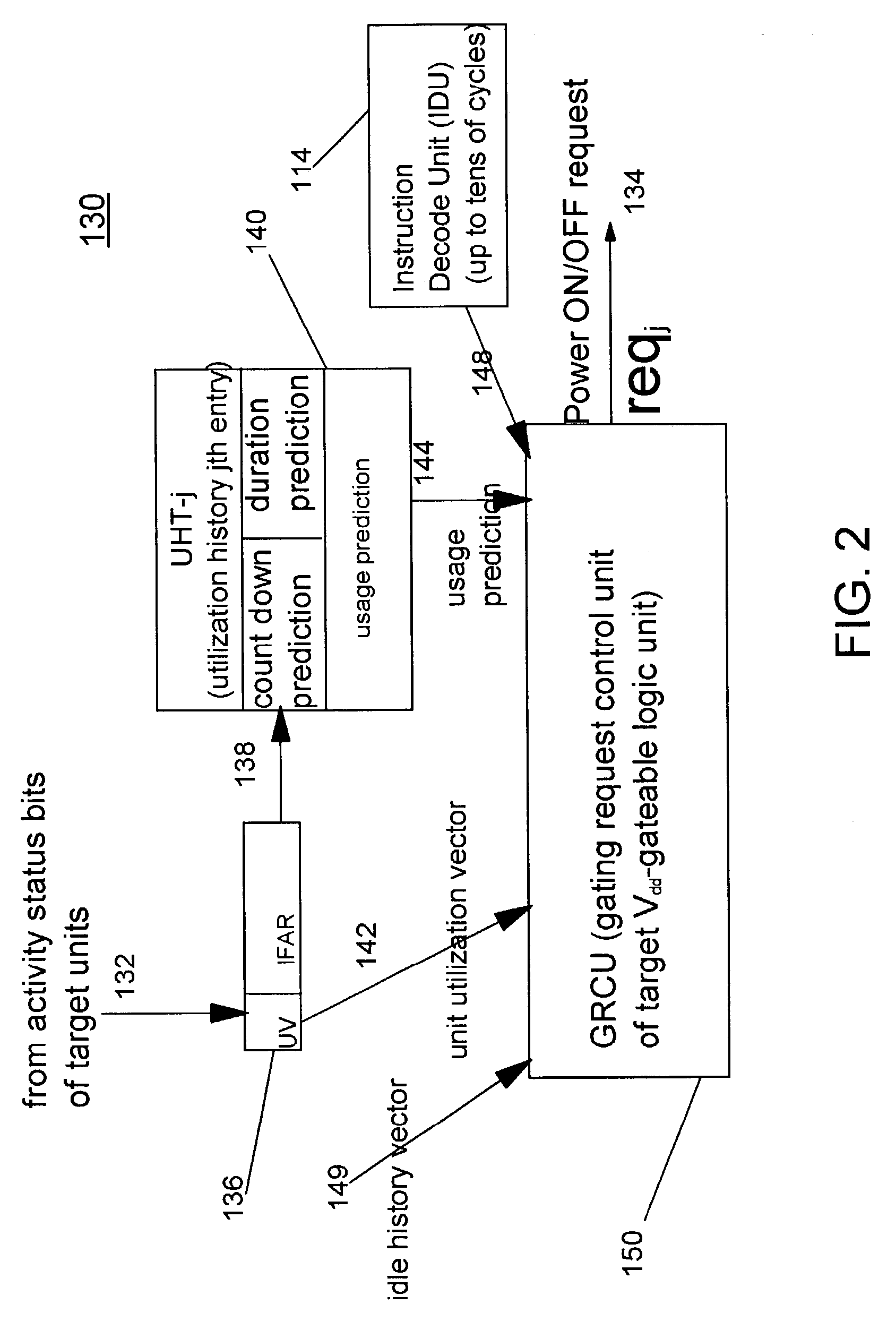

Processor with low overhead predictive supply voltage gating for leakage power reduction

ActiveUS7134028B2Decreasing processor power consumptionNo performance lossEnergy efficient ICTVolume/mass flow measurementTurn on timeLeakage power

An integrated circuit (IC) including unit power control, leakage reduction circuit for controllably reducing leakage power with reduced LdI / dt noise in the IC and, an activity prediction unit invoking active / dormant states in IC units. The prediction unit determines turn on and turn off times for each IC unit. The prediction unit controls a supply voltage select circuit selectively passing a supply voltage to a separate supply line at the predicted turn on time and selectively blocking the supply voltage at the predicted turn off time.

Owner:IBM CORP

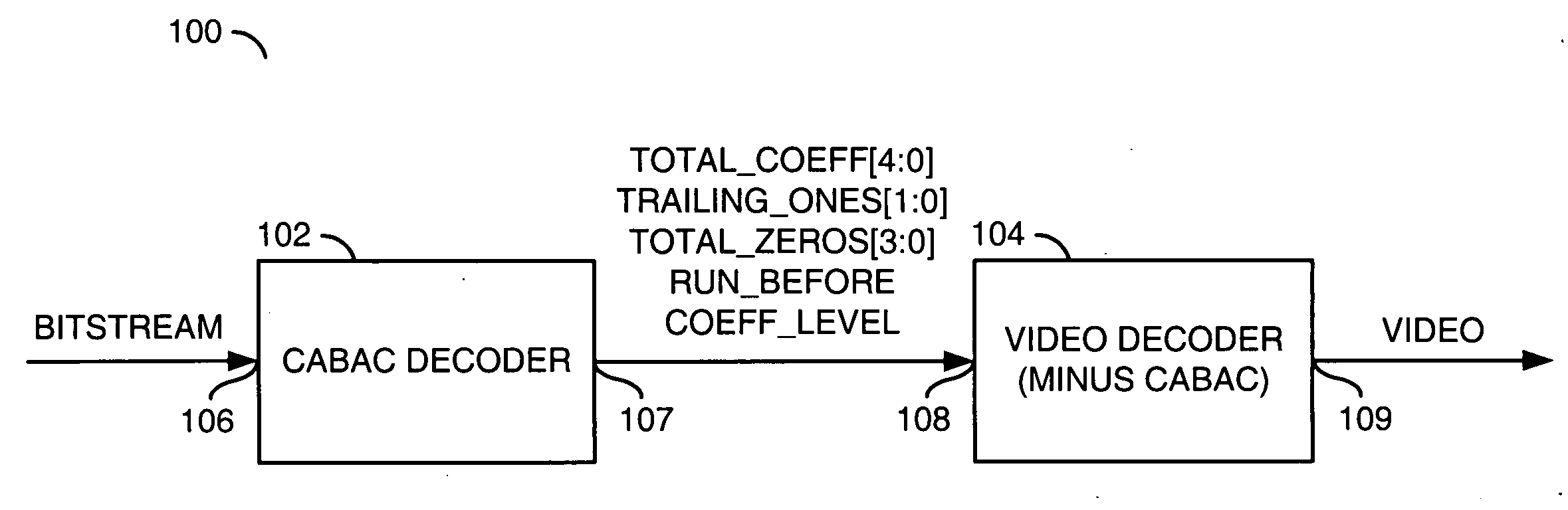

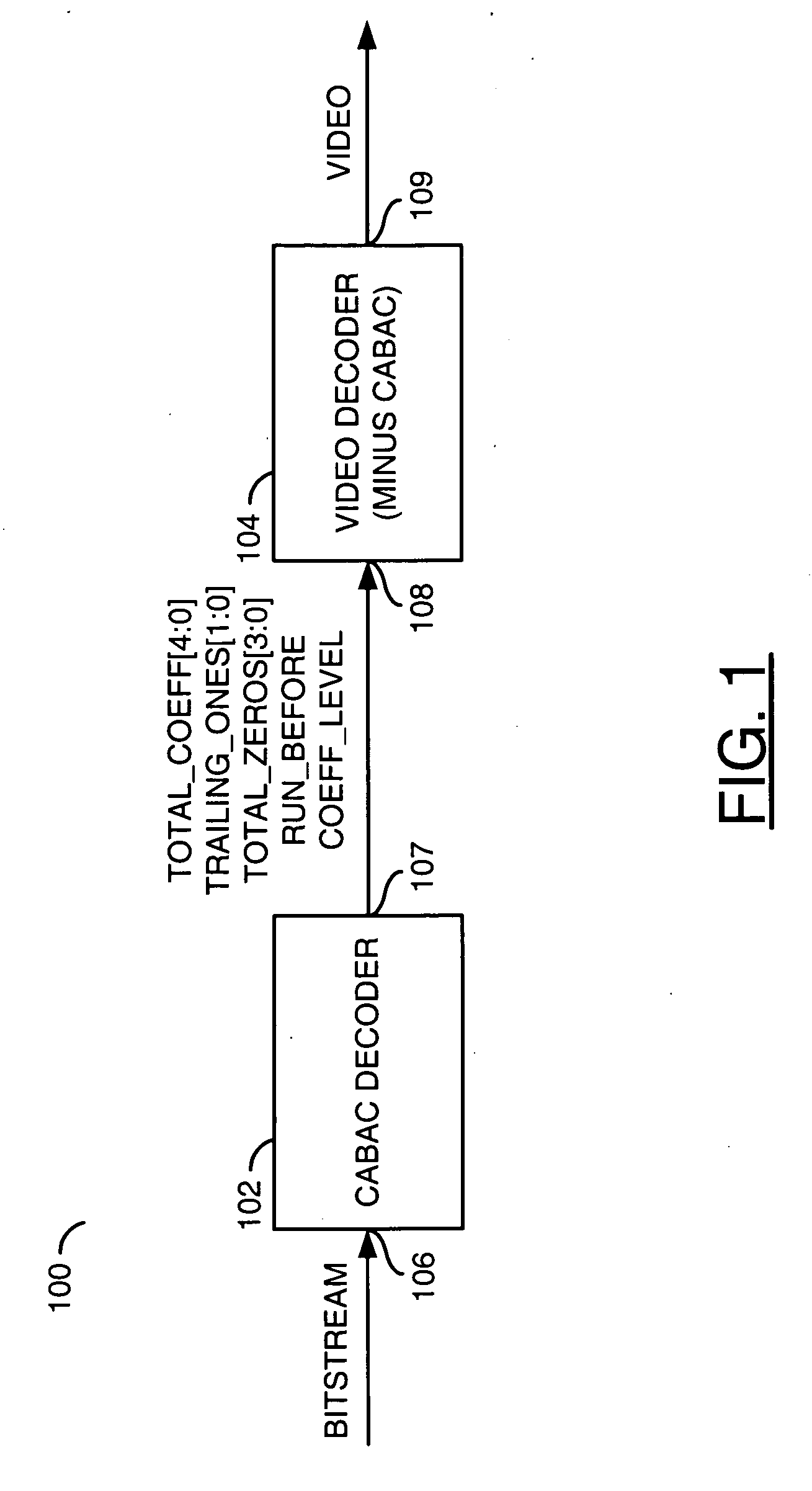

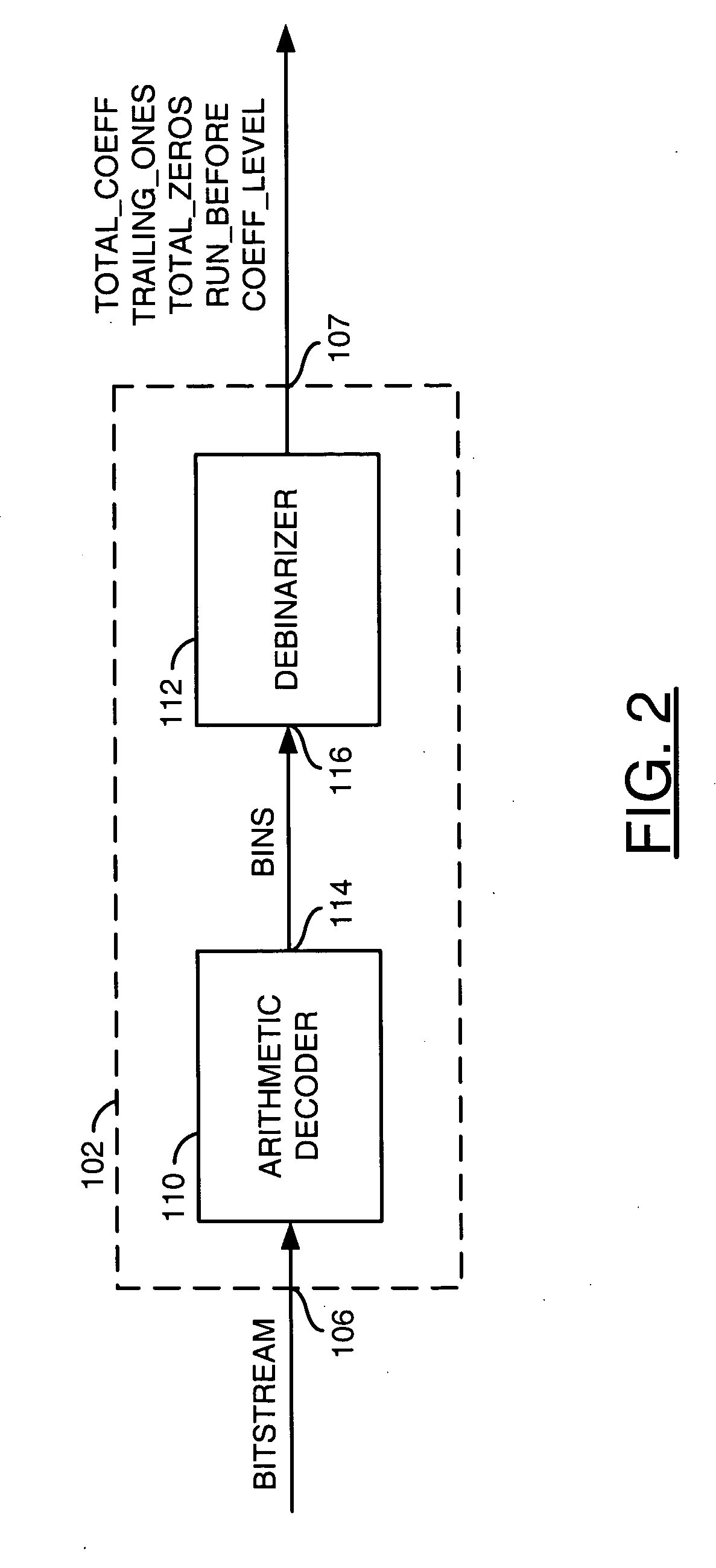

Efficient 8x8 CABAC residual block decode

InactiveUS20080152015A1Without loss of performanceLower latencyColor television with pulse code modulationColor television with bandwidth reductionVariable-length codeComputer architecture

A circuit generally having a first module, a second module and a third module is disclosed. The first module may be configured to (i) generate a plurality of parsed residual blocks by parsing an 8×8 CABAC (context-based adaptive binary arithmetic coding) residual block received in an input signal and (ii) generate a plurality of metric signals resulting from the parsing of the 8×8 CABAC residual block. The second module may be configured to generate a scanning position signal based on the metric signals. The third module may be configured to generating a plurality of 4×4 CAVLC (context-based adaptive variable length coding) residual blocks in an output signal by sub-sampling the parsed residual blocks based on the scanning position signal.

Owner:AVAGO TECH INT SALES PTE LTD

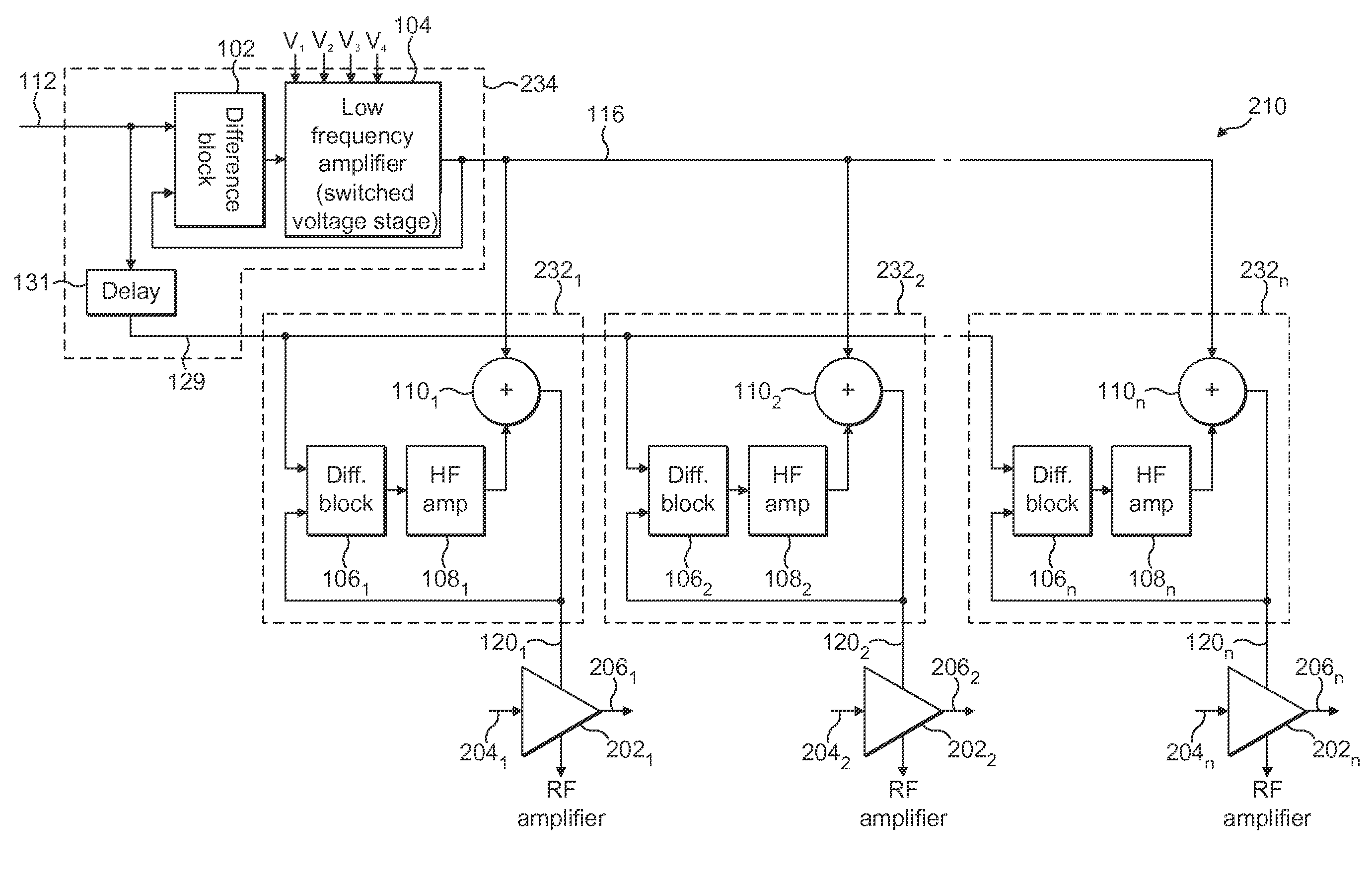

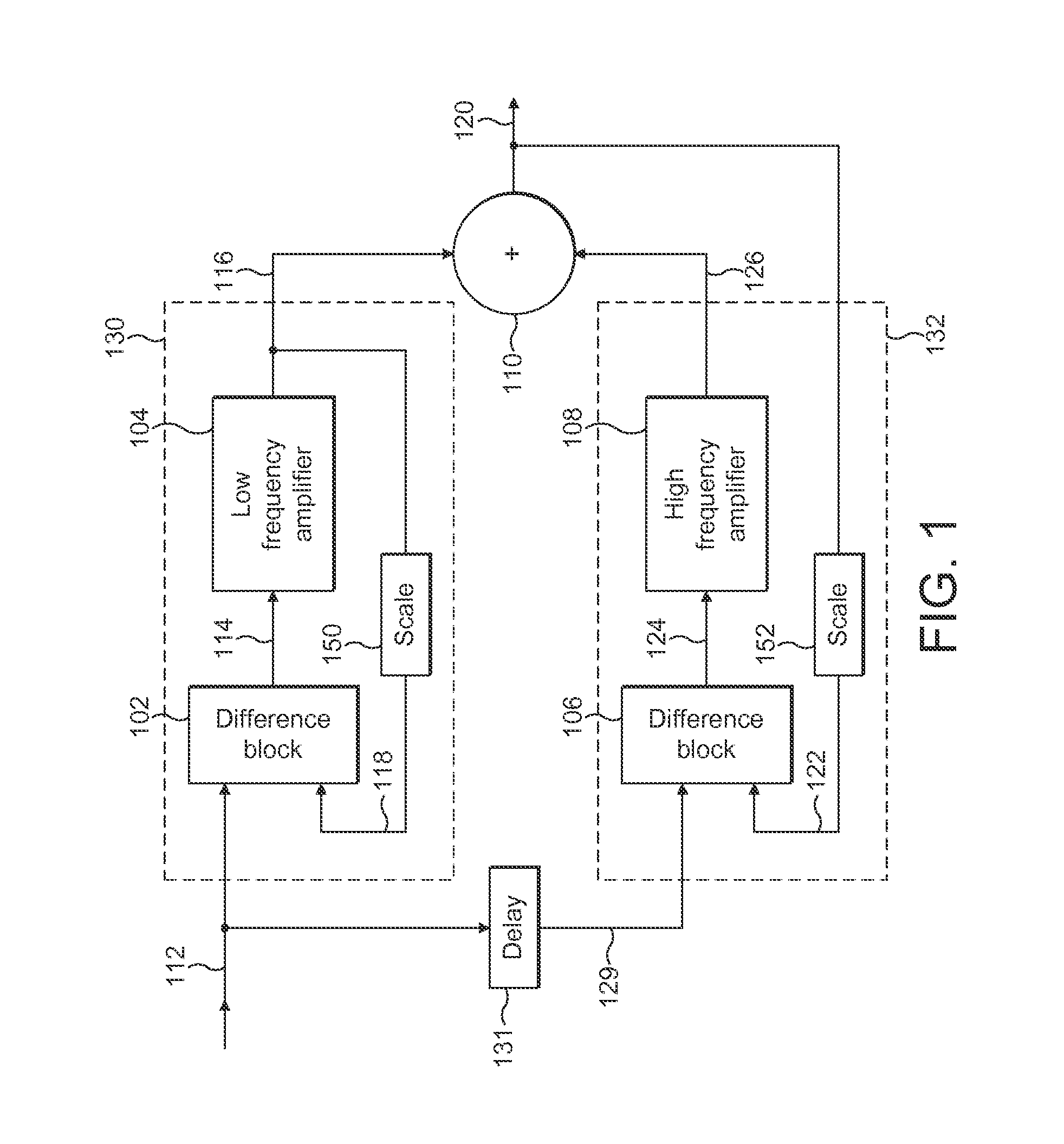

Multi-stage amplifier

ActiveUS8476976B2No performance lossWithout incurring significant overheads in consuming spaceSupply voltage varying controlAmplifier with semiconductor-devices/discharge-tubesAudio power amplifierEngineering

There is disclosed a power supply stage, and a corresponding method, comprising: a plurality of amplifiers for amplifying an input signal, each amplifier receiving a power supply voltage; a common selection means for selecting one of a plurality of power supply voltages in dependence on a reference signal representing a desired power supply voltage; and a plurality of adjusting means, corresponding to the plurality of amplifiers, adapted to generate an adjusted selected power supply voltage for a respective amplifier tracking the reference signal in dependence on the one selected power supply voltage and the reference signal.

Owner:SNAPTRACK

Dual-processor complex domain floating-point DSP system on chip

InactiveUS20070168908A1No performance lossReduce in quantityDigital data processing detailsDigital computer detailsReal arithmeticData processing

A system for digital signal processing, configured as a system on chip (SoC), combines a microprocessor core and digital signal processor (DSP) core with floating-point data processing capability. The DSP core can perform operations on floating-point data in a complex domain and is capable of producing real and imaginary arithmetic results simultaneously. This capability allows a single-cycle execution of, for example, FFT butterflies, complex domain simultaneous addition and subtraction, complex multiply accumulate (MULACC), and real domain dual multiply-accumulators (MACs). The SoC may be programmed entirely from a microprocessor programming interface, using calls from a DSP library to execute DSP functions. The cores may also be programmed separately. Capability for programming and simulating the entire SoC are provided by a separate programming environment. The SoC may have heterogeneous processing cores in which either processing core may act as master or slave, or both cores may operate simultaneously and independently.

Owner:ATMEL CORP

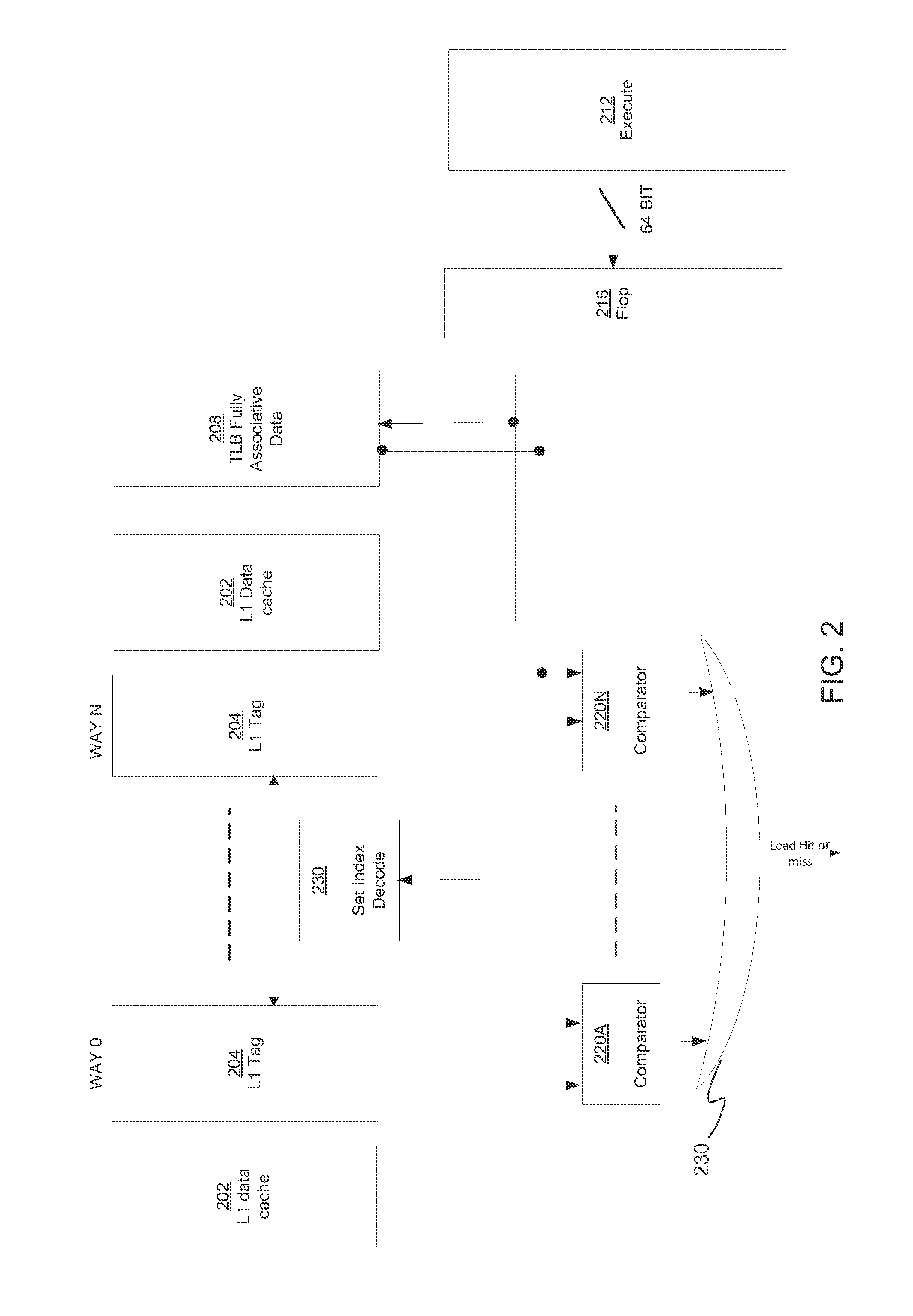

Method and Apparatus to Speed up the Load Access and Data Return Speed Path Using Early Lower Address Bits

InactiveUS20140281116A1Reduce latencyHigh frequencyMemory adressing/allocation/relocationProgram controlData cacheLoad instruction

A microprocessor implemented method for processing a load instruction is disclosed. The method comprises computing a virtual address corresponding to the load instruction. Next, it comprises performing a lookup of a set associative translation lookaside buffer (TLB) and a set associative data cache memory in parallel using early calculated lower address bits of the virtual address. Subsequently, it comprises retrieving a set of entries from the TLB corresponding to a first group of lower address bits transmitted to the TLB, wherein the set of entries comprise a plurality of virtual addresses and corresponding physical addresses. Further, it comprises finding a matching entry for the virtual address in the set of entries using upper bits of the virtual address, wherein the matching entry comprises a physical address corresponding to the virtual address. Finally, it comprises finding a matching entry in the data cache memory using the physical address.

Owner:INTEL CORP

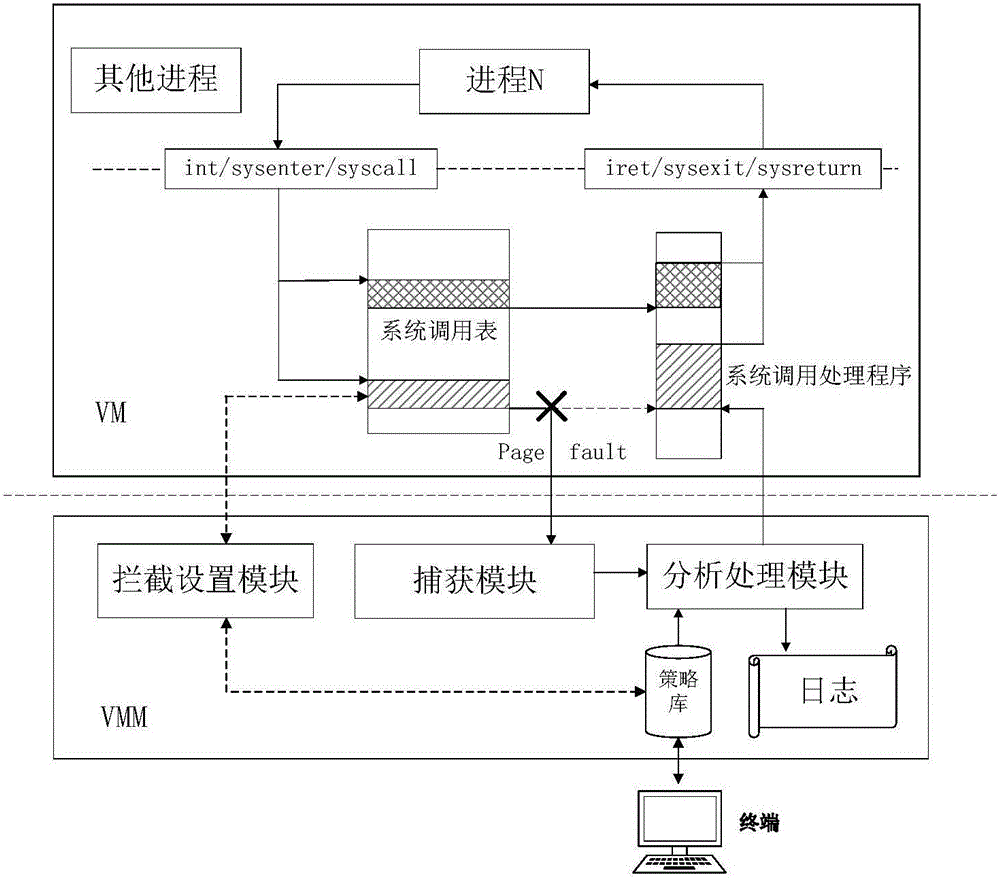

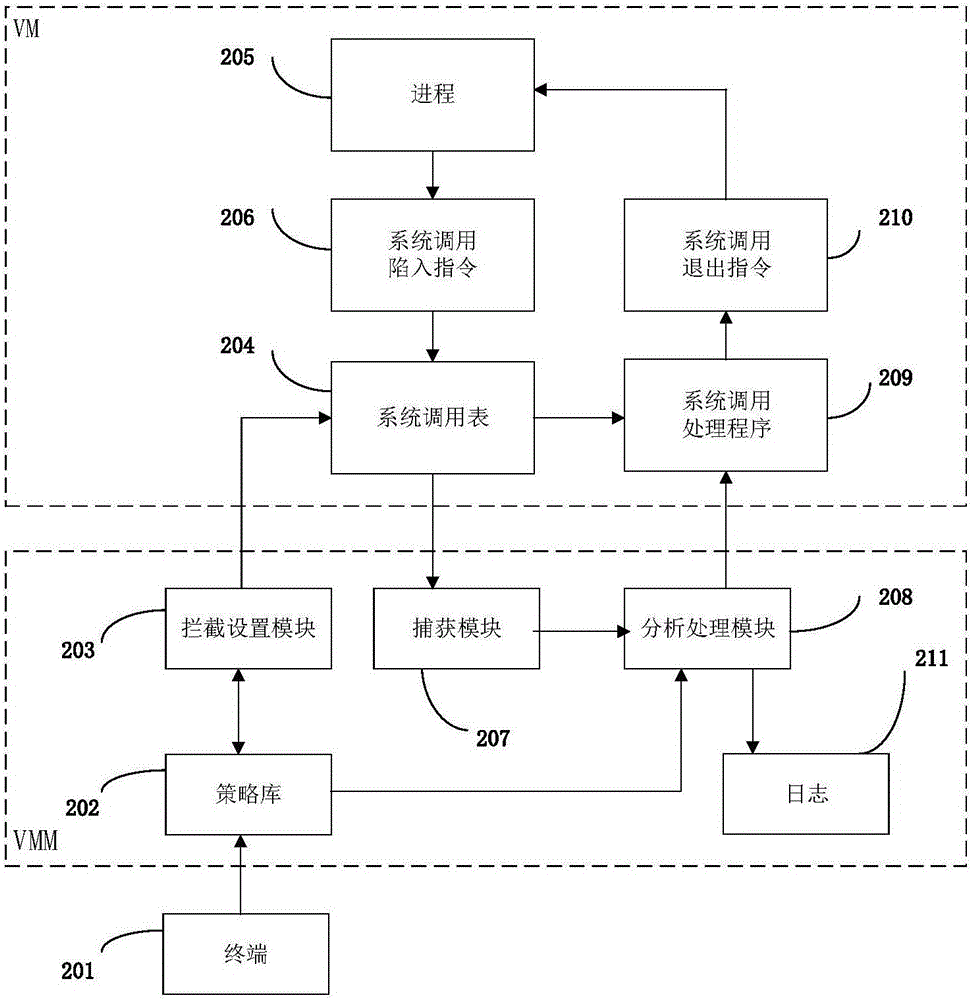

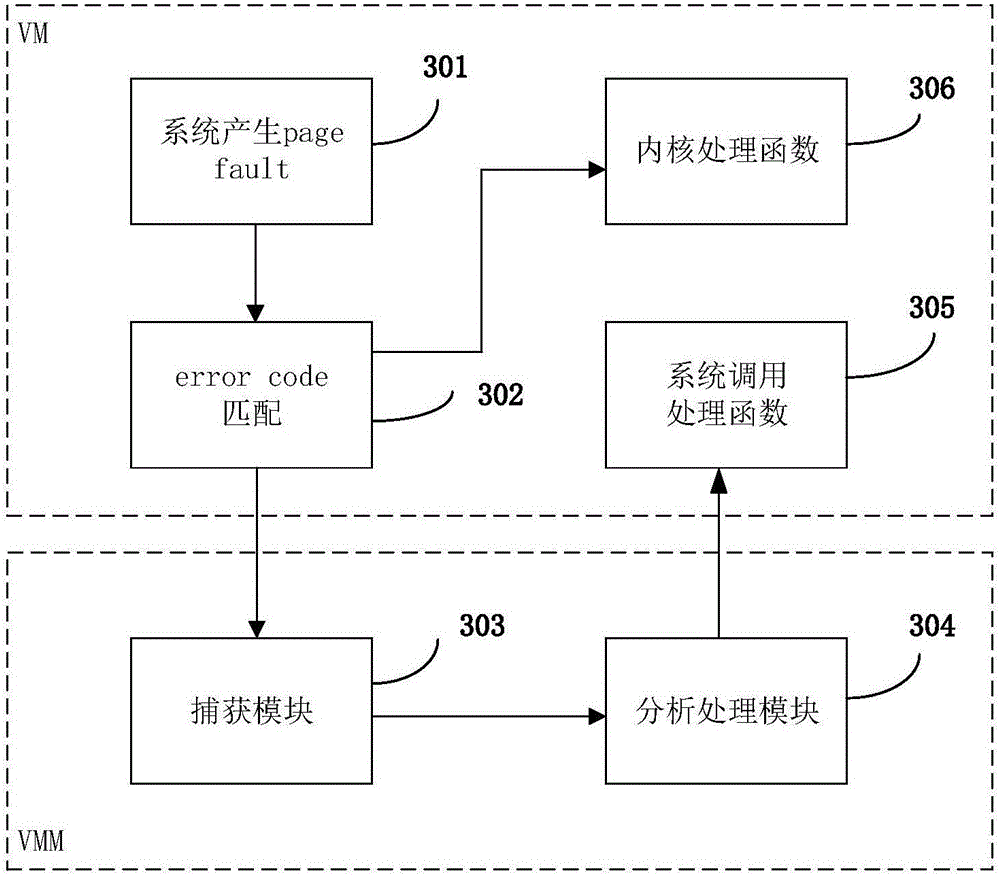

System and method for monitoring virtual machine process, and method for filtering page fault anomaly

ActiveCN106055385AIncrease flexibilityNo performance lossSoftware simulation/interpretation/emulationProcess systemsComputer module

The invention discloses a system and method for monitoring a virtual machine process, and a method for filtering page fault anomalies. The monitoring system comprises an interception setting module which modifies a virtual machine system call table dynamically in real time and intercepting virtual machine system call; a capturing module which captures anomalies generated when the virtual machine process is called by a monitoring system; an analysis processing module which analyzes a virtual machine process system call behavior is abnormal or not; a strategy library which stores virtual machine system call monitoring strategies, wherein abnormal system call behavior data in the virtual machine is stored in logs; and a terminal which updates the strategy library dynamically in real time. According to the system and methods, according to functions needing to be monitored, the monitoring strategies are configured dynamically in real time; the monitoring strategies can take effect instantly without rebooting the virtual machine or a cloud platform; extra performance consumption resulting from the fact that the virtual machine process is unnecessarily called by the monitoring system can be avoided; and the system and methods are compatible with system call processes initiated by all x86 instructions.

Owner:SICHUAN UNIV

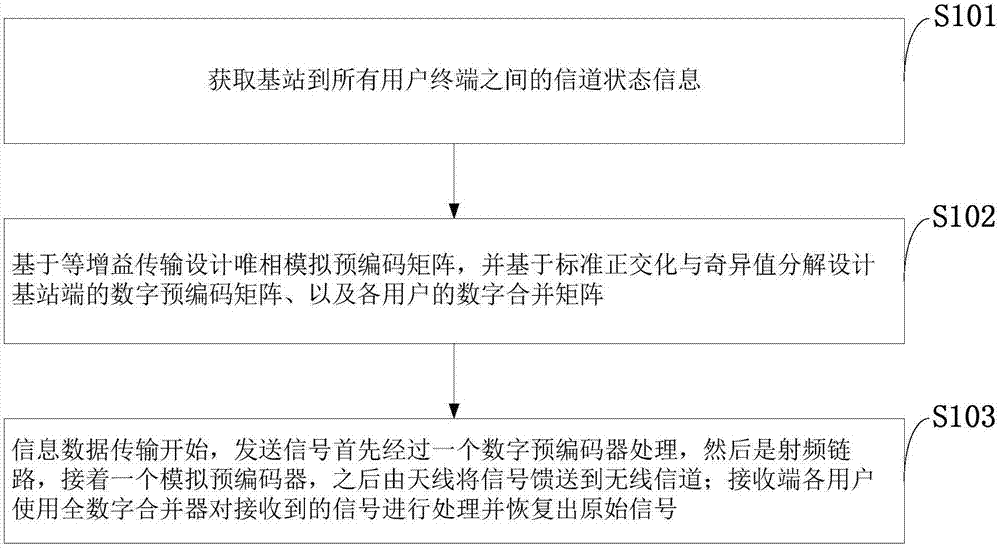

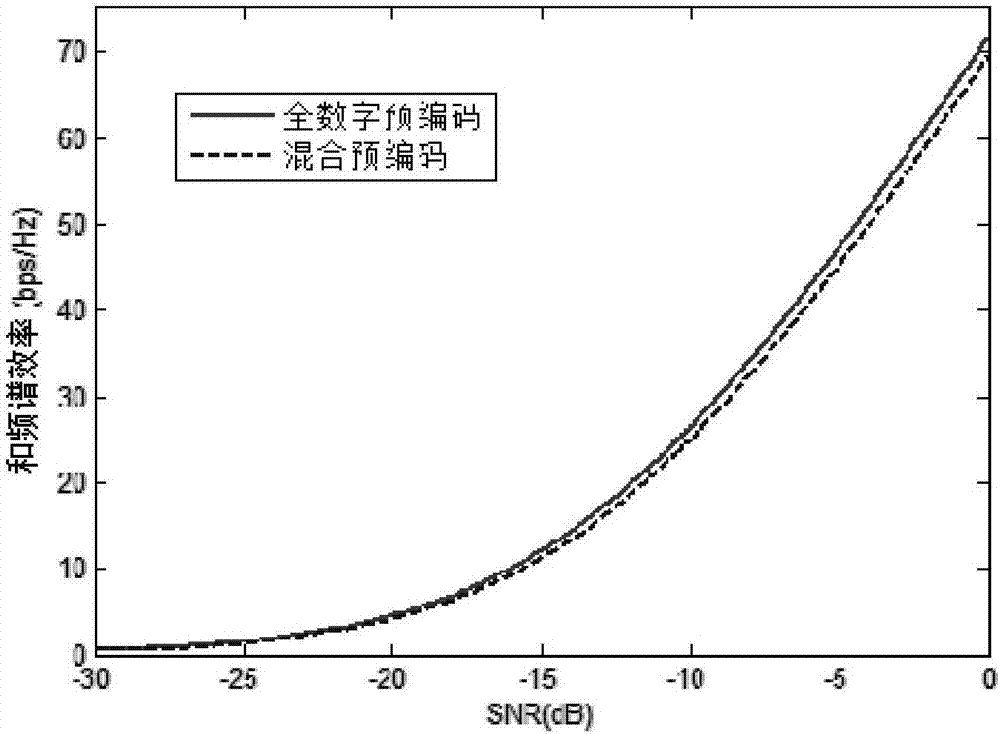

Standard-orthogonalization-based hybrid pre-coding method for large-scale MIMO system

ActiveCN107359921AReduce energy consumptionReduce complexityRadio transmissionSingular value decompositionMain diagonal

The invention belongs to the technical field of wireless communication and discloses a standard-orthogonalization-based hybrid pre-coding method for a large-scale MIMO system. Analog pre-coding design is based on equal-gain transmission. The phase of a main diagonal element of a baseband equivalent channel matrix is set to zero to obtain the maximum antenna array gain so as to reduce the total energy consumption and complexity of a transmitter. The design of a digital pre-coding matrix is based on standard orthogonalization and singular value decomposition. By mapping a desired user to other user null space, the interference between users is completely eliminated and the maximum spectral efficiency is obtained. A numerical result shows that the performance of the hybrid pre-coding method, when equipped with a small number of radiofrequency links, approaches that of an all-digital pre-coding solution that requires the same number of radiofrequency links as the antennas, and can obtain high spectral efficiency with low implementation complexity.

Owner:广州市埃特斯通讯设备有限公司

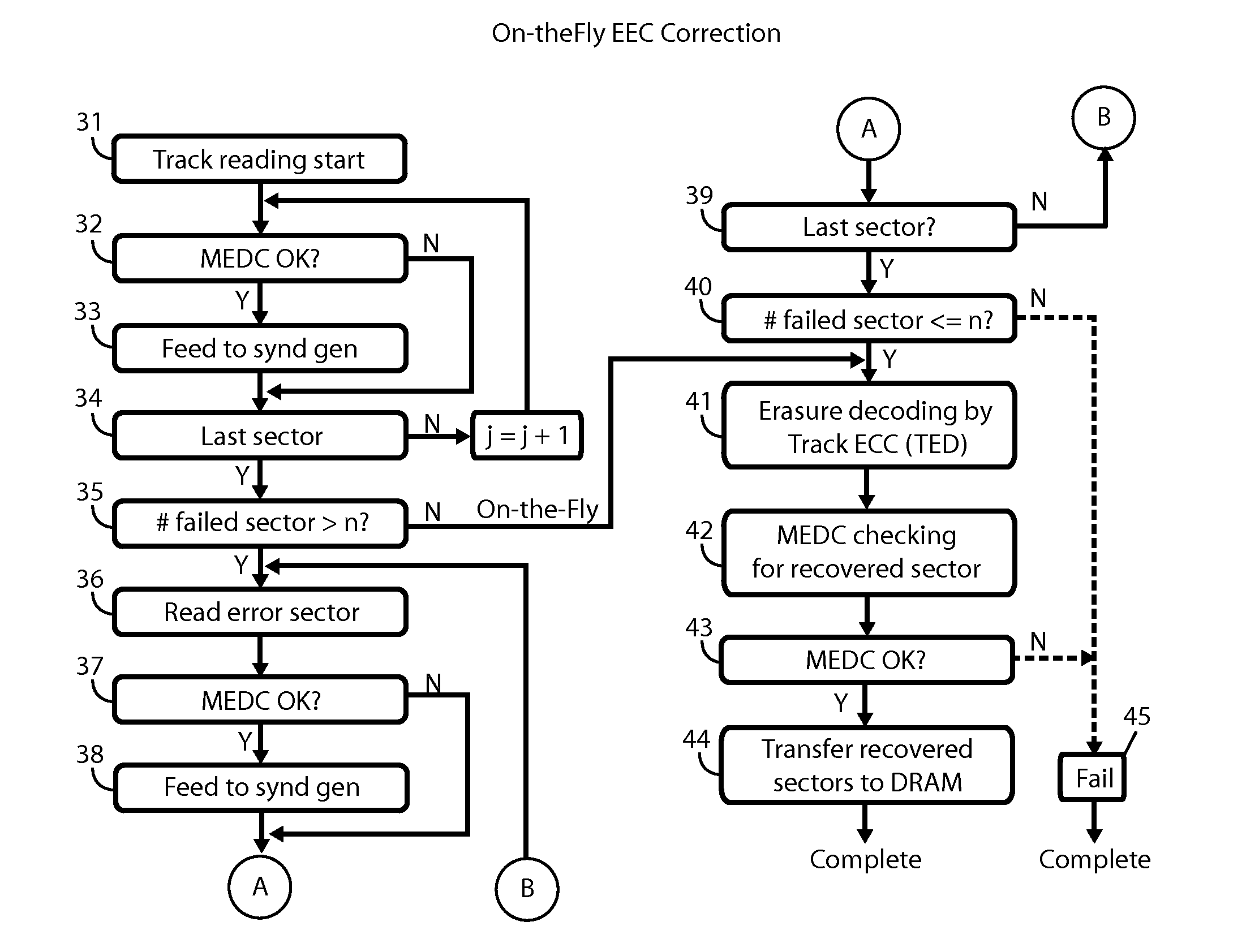

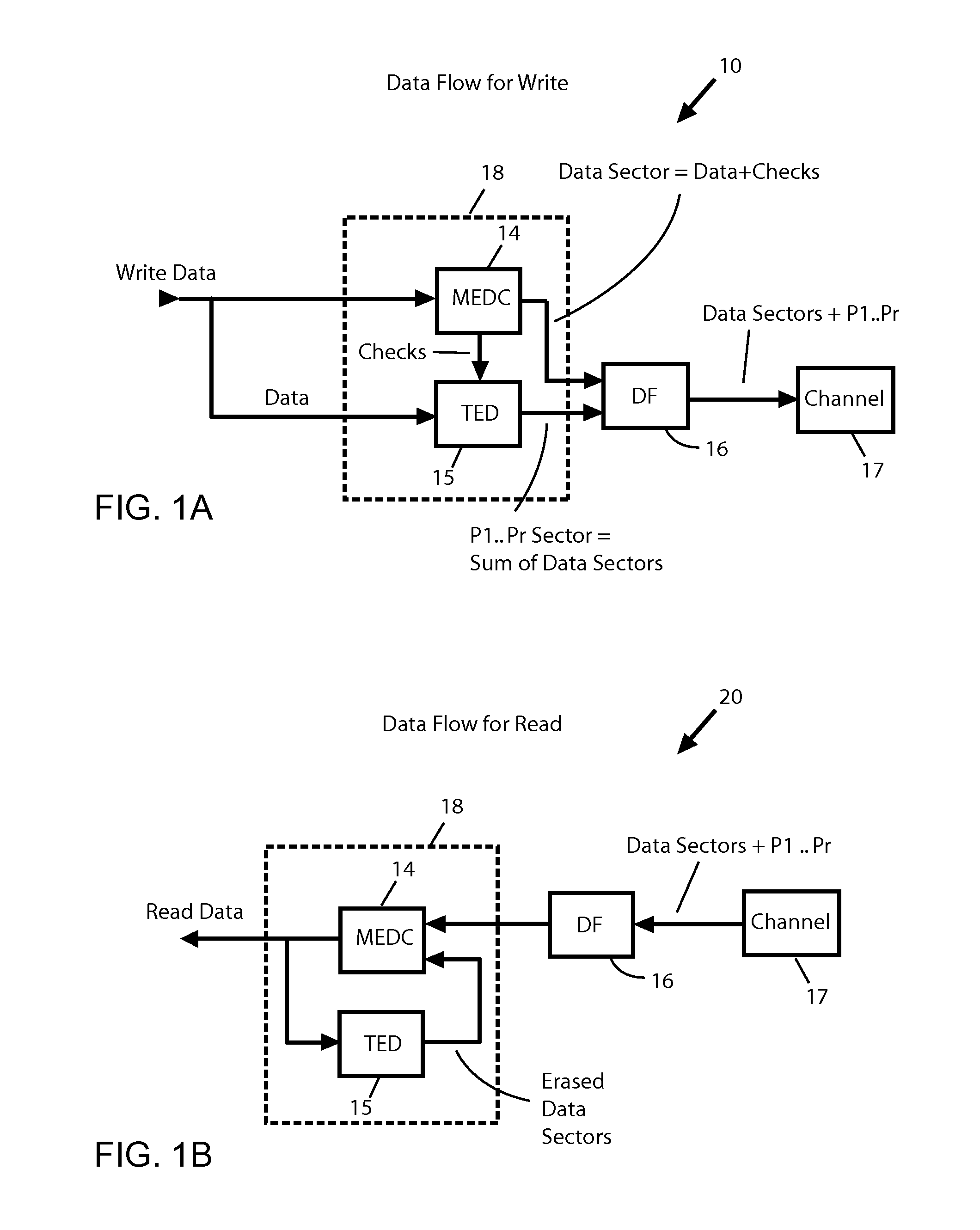

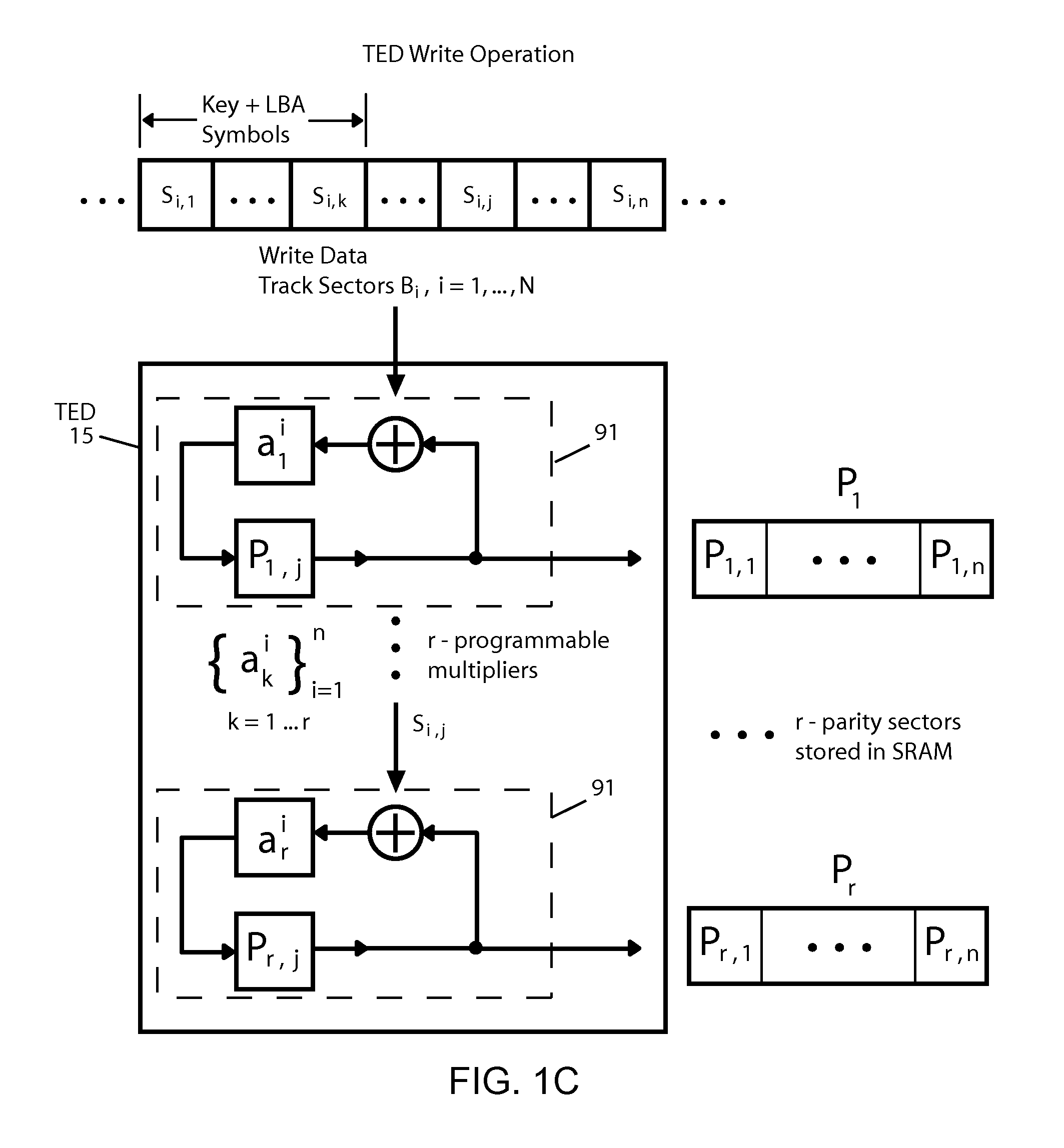

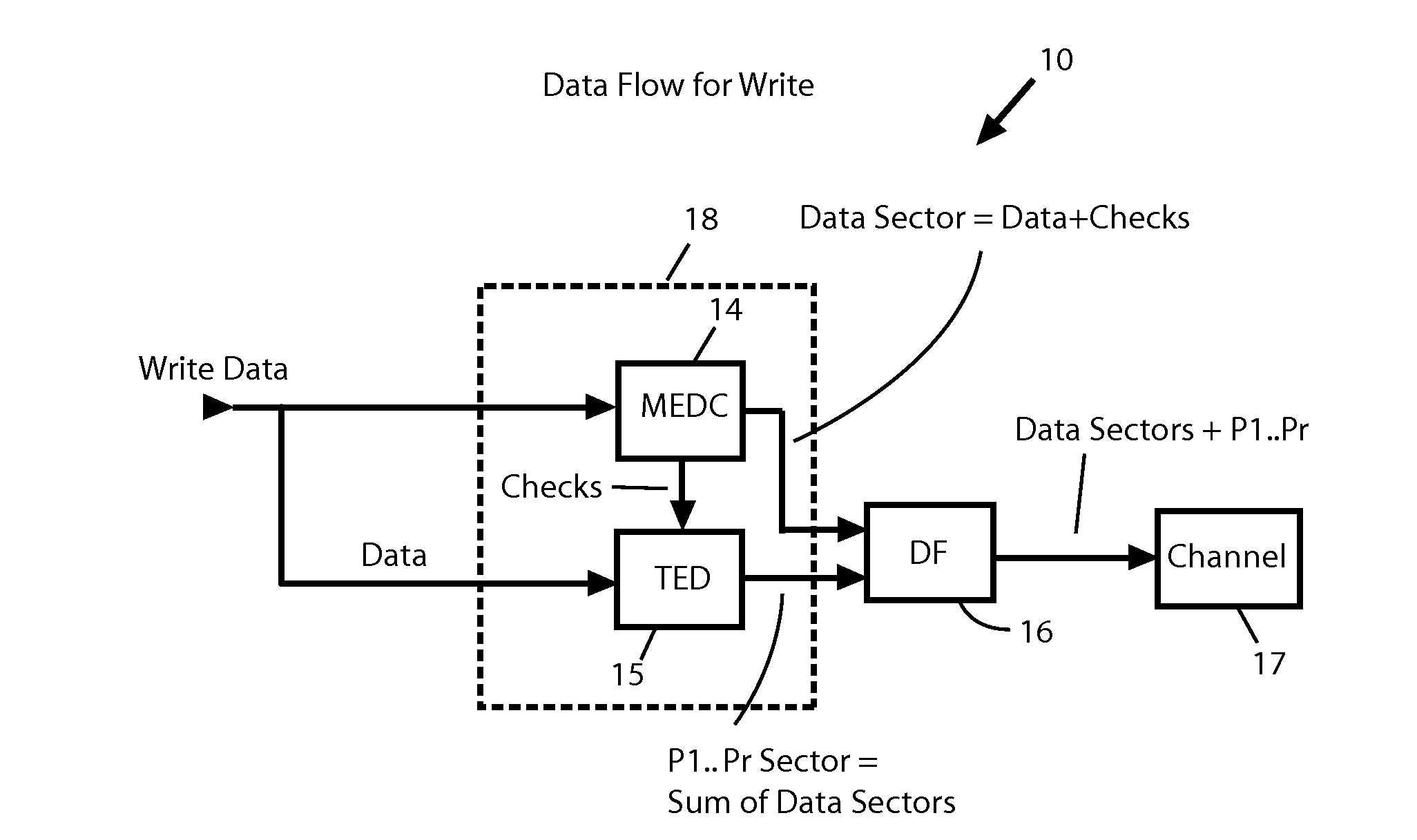

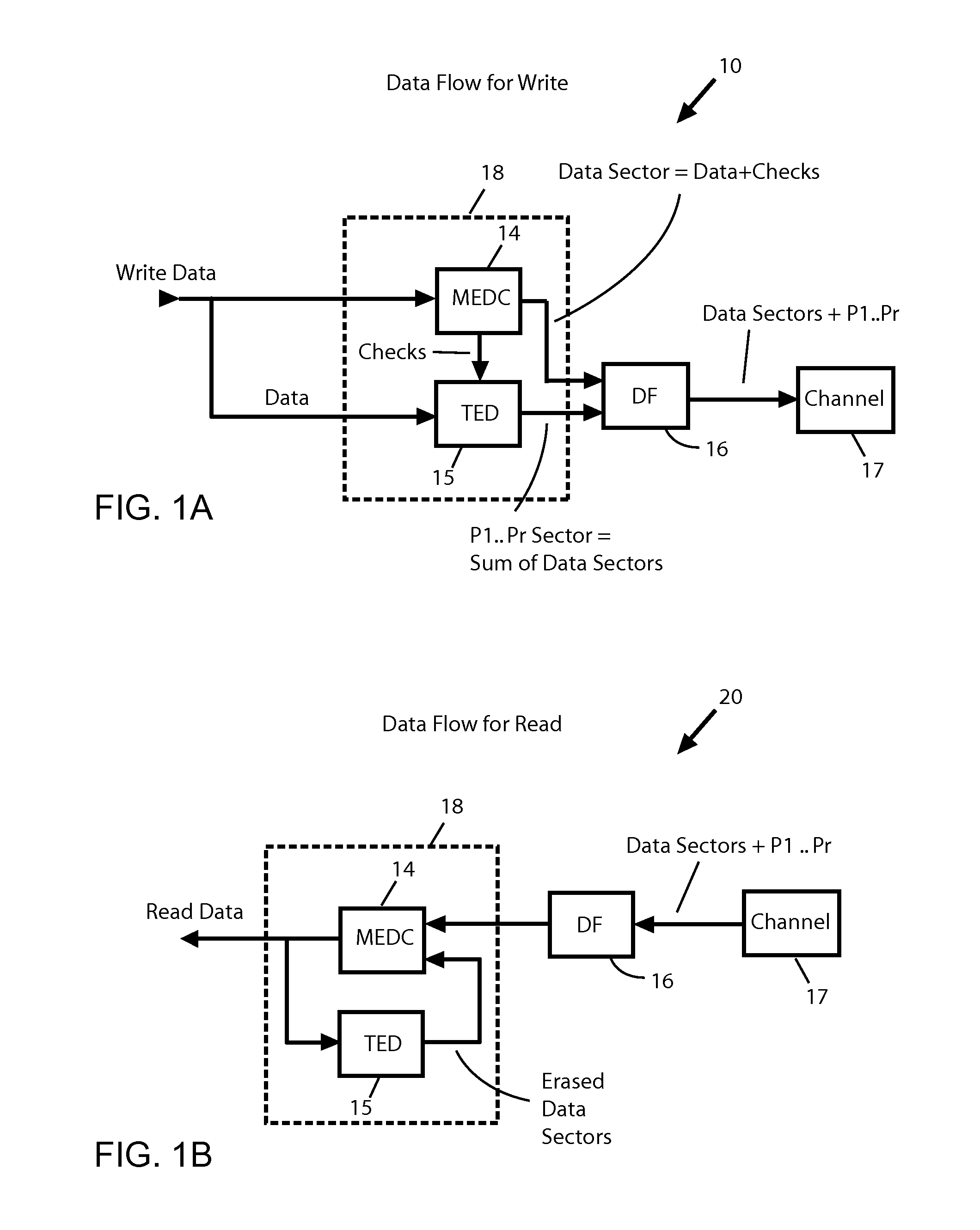

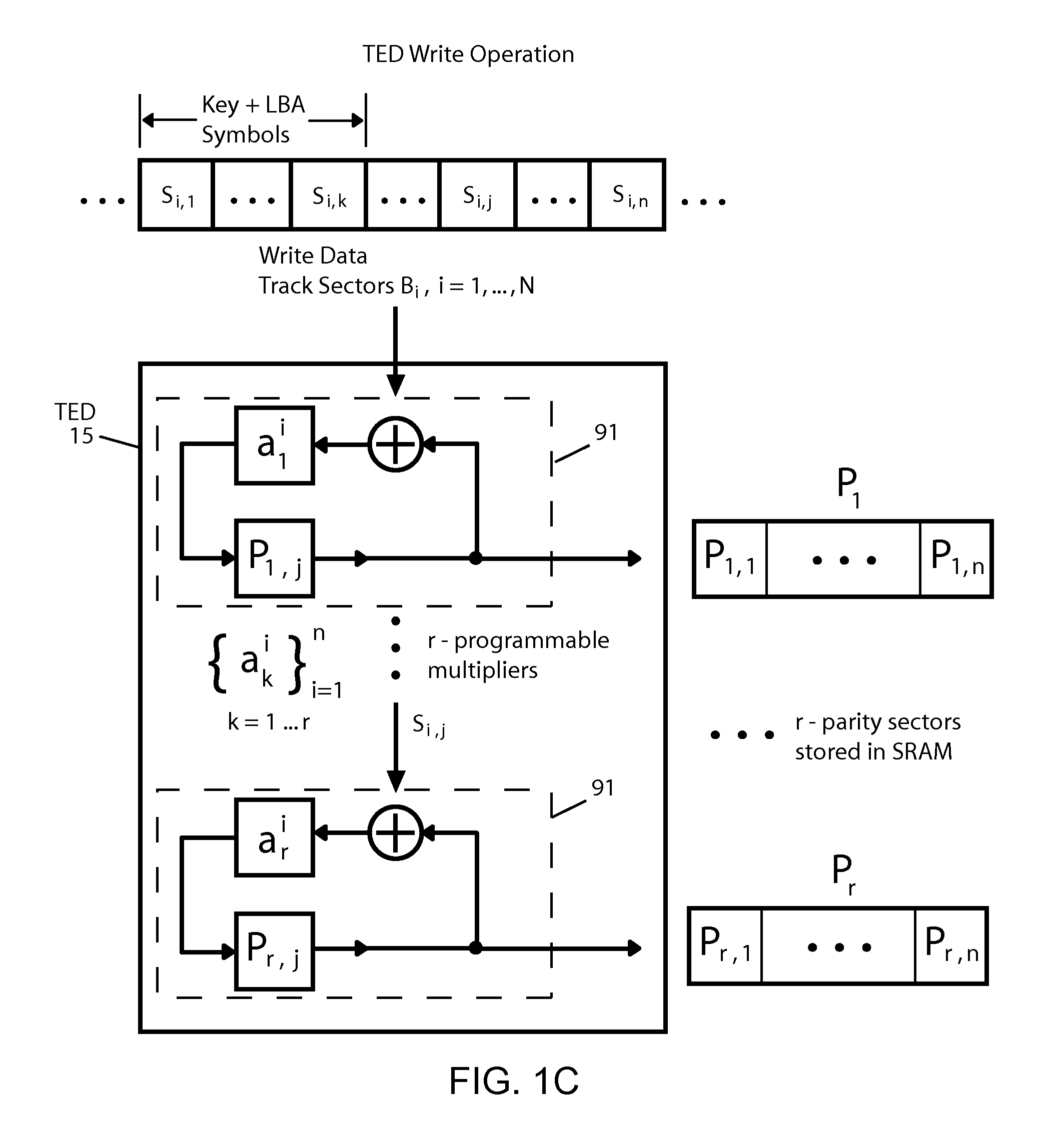

Scalable repair block error correction for sequential multiple data blocks in a magnetic data storage device

ActiveUS20140101515A1No performance lossIntegrity guaranteedRecord information storageError correction/detection using block codesShingled magnetic recordingOrbit

A technique for recovering of “squeezed” sectors in a set of sequential sectors such as are used in Shingled Magnetic Recording (SMR) is described. Embodiments of the invention use a programmable erased sector recovery scheme, which is a concatenation of a “Cauchy-type” track erasure correction code, together with a media-error correction code that generates N-weighted parity-sectors per track and is capable of replacing up to N-erased sectors per track in any possible combination.

Owner:WESTERN DIGITAL TECH INC

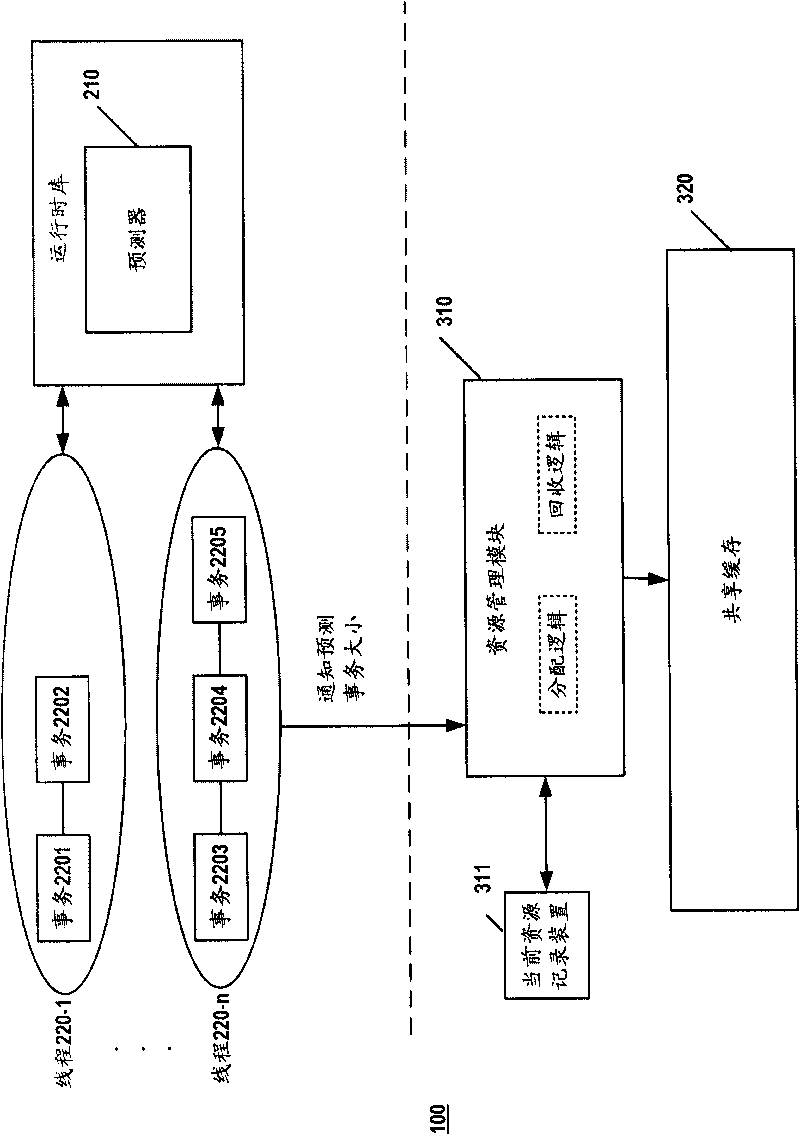

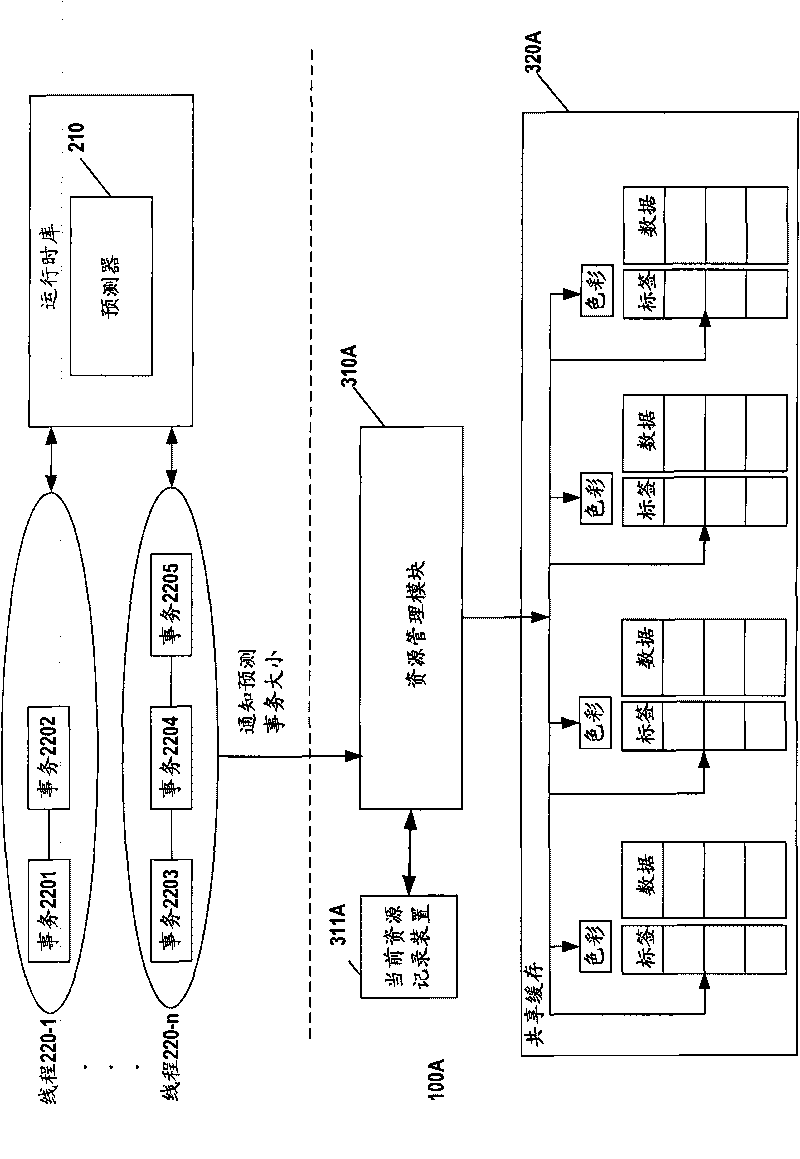

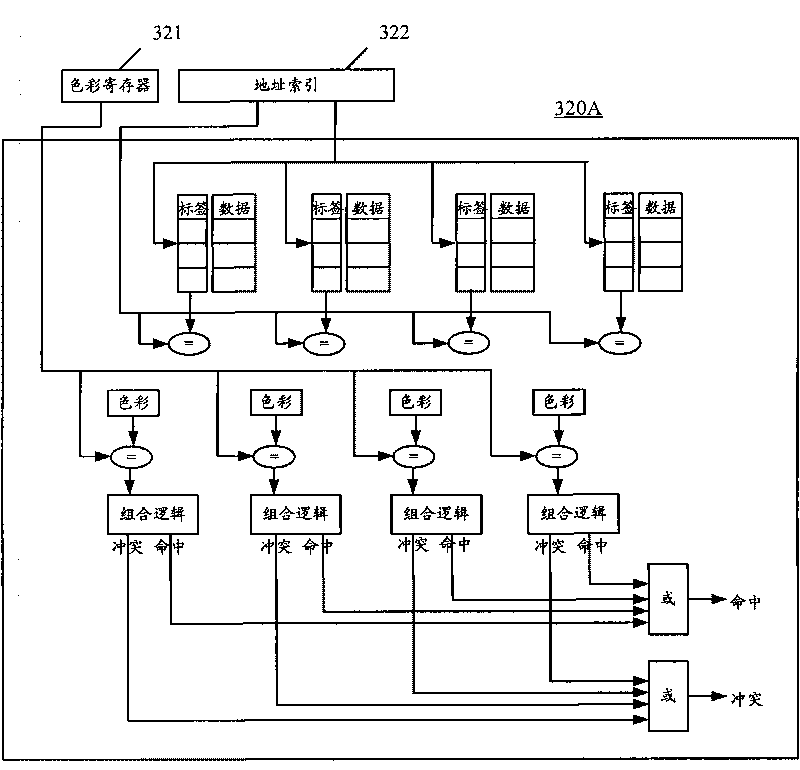

Shared cache management method and system

InactiveCN101739298AEasy to implementNo performance lossResource allocationMemory adressing/allocation/relocationTransaction dataResource management

The invention provides a shared cache management system which comprises a resource management module, wherein the resource management module is configured for responding to the start of a transaction, allocating shared cache resources to the transaction according to the predicted transaction data size, responding to the successful submission of the transaction and recording the shared cache size actually occupied by the transaction to update the historical information of the transaction, wherein the predicted transaction data size of the transaction is predicted by a predictor in the operating process according to the historical information of the transaction. The invention also provides a corresponding shared cache management method. The technical scheme of the invention can be used for dynamically allocating shared cache resources to a plurality of transactions by predicting the sizes of the cache needs of the transactions.

Owner:INT BUSINESS MASCH CORP

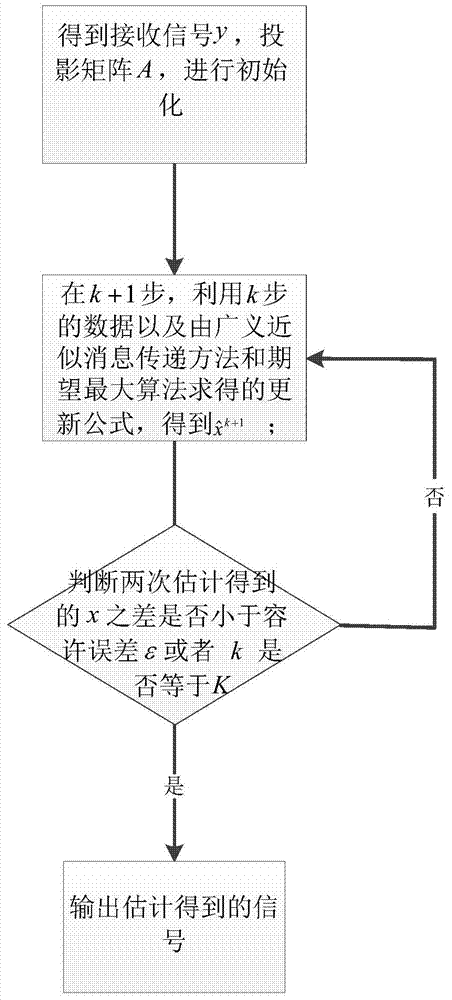

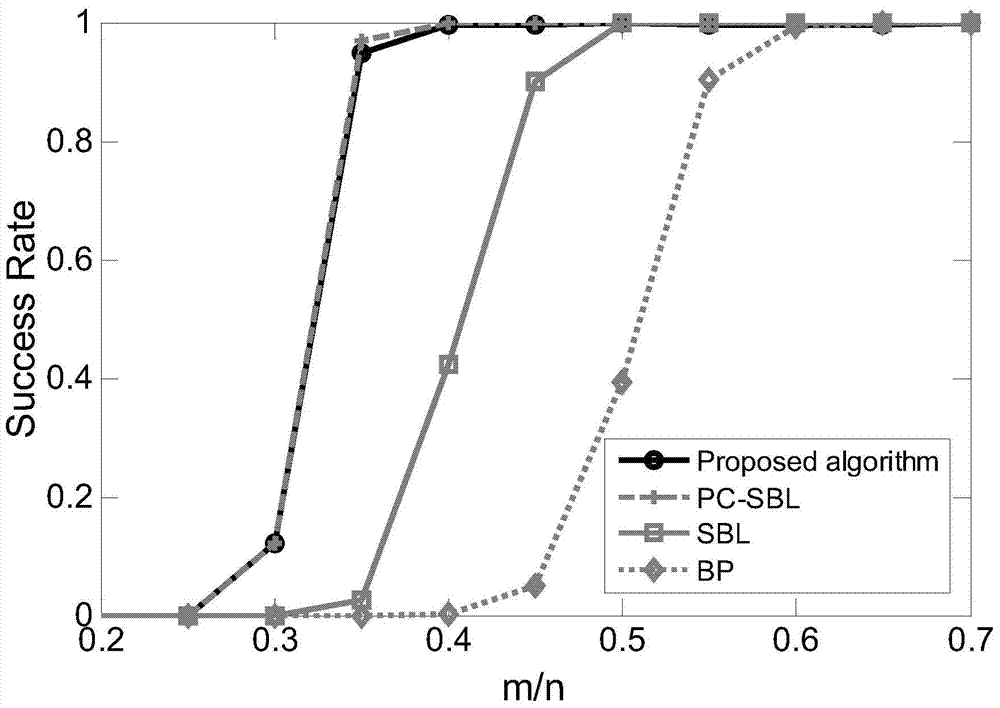

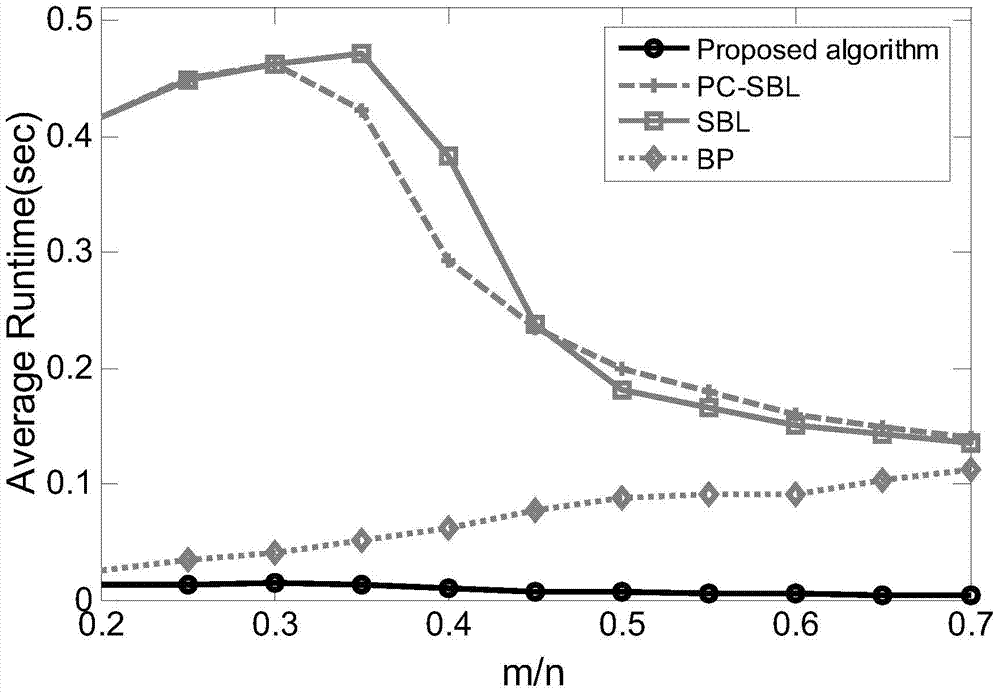

Low-complexity massive sparse signal reconstruction method

ActiveCN104767535ARelieve dealing with stressReduce computational complexityCode conversionComputation complexityRound complexity

The invention belongs to the technical field of sparse signal restoration, and particularly relates to a low-complexity massive sparse signal reconstruction method in signal receiving on the basis of generalized approximate message passing (GAMP). The low-complexity massive sparse signal reconstruction method includes the following steps that a receiving signal y=A*x is obtained through compressed sensing and sampling, initialization is carried out, loop iteration is conducted, and restored signals are input. Compared with a traditional restoration algorithm based on Bayes, a generalized approximate message passing method is used. The low-complexity massive sparse signal reconstruction method can effectively reduce computation complexity on the basis of keeping signal superior reconstruction performance. Computation time complexity is reduced from O(n3) to O(mn), namely cube complexity is reduced to linear time complexity, and signal processing pressure of the rear end is greatly reduced, wherein m and n refer to the dimension of an observed value and the dimension of original signals.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

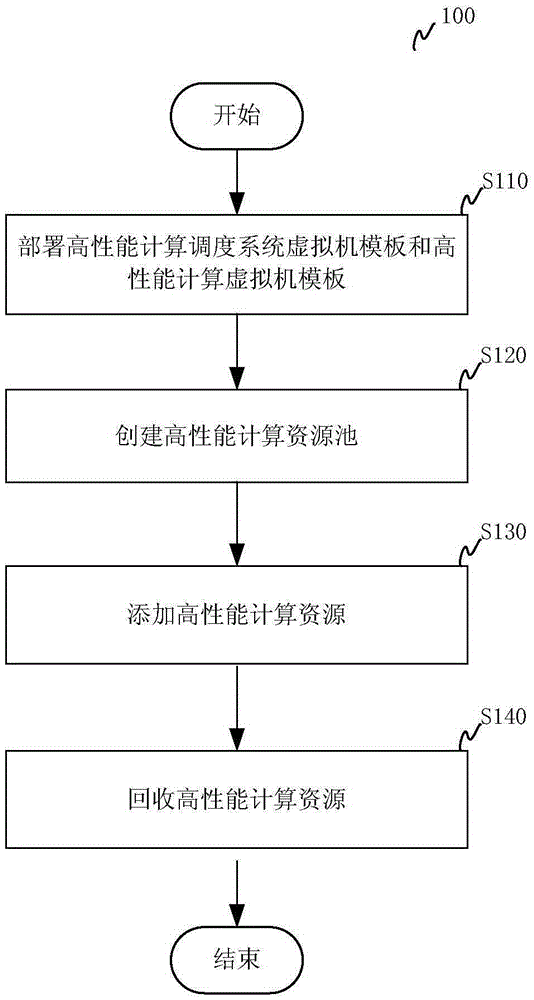

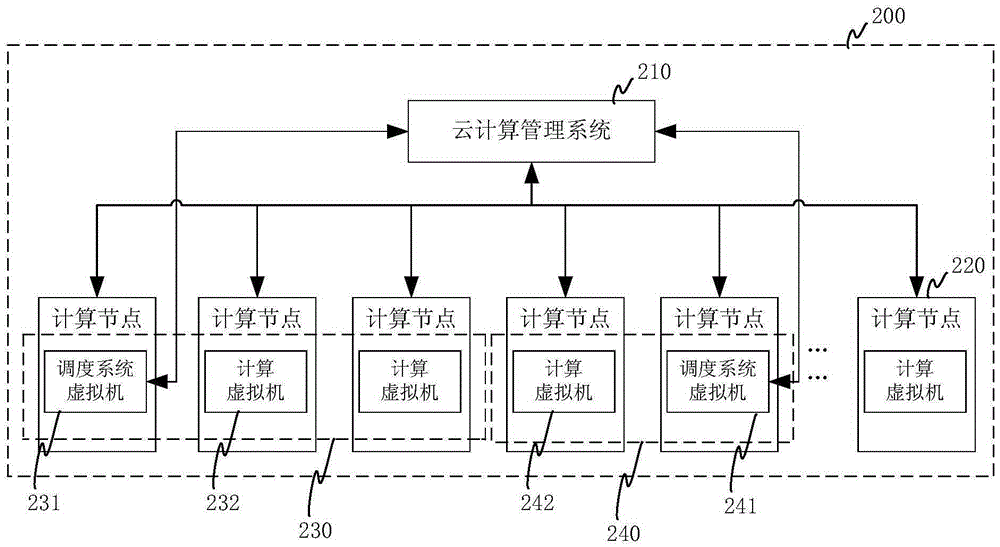

Cloud computing system and method for running high-performance computation in same

InactiveCN105404542AImprove resource utilizationAchieving dynamismTransmissionSoftware simulation/interpretation/emulationHigh performance computationVirtualization

The invention relates to a cloud computing system and a method for running high-performance computation in the same. The method comprises a step of creating a high-performance computation resource pool. The step of creating the high-performance computation resource pool specifically comprises: creating a scheduling system virtual machine in a computing node based on a high-performance computation operation demand by a cloud computing management system to run a high-performance computation scheduling system, creating computation virtual machines in a certain quantity of computing nodes, and returning information of the computation virtual machines to the high-performance computation scheduling system to form the high-performance computation resource pool. The created high-performance computation resource pool further can dynamically add and recover resources. According to the method, the high-performance computation resource pool is created in the cloud computing system; and by adopting a virtualization technology, the flexibility and elasticity brought by virtualization can be achieved in high-performance computation, and nearly no performance loss is caused. Therefore, the utilization rate of resources can be increased, the monopolization of a single business to the resources can be broken through, and the dynamicity of a whole computing service platform is realized.

Owner:国家超级计算深圳中心(深圳云计算中心)

Lower-energy process for preparing passivated inorganic nanoparticles

InactiveUS7276231B2Reduced tendency to form agglomerateNo performance lossCosmetic preparationsMaterial nanotechnologySodium aluminateSlurry

The disclosure is directed to a method for reducing the chemical activity and photo activity of titanium dioxide nanoparticles comprising adding an amorphous alumina-stabilizing agent, specifically an anion, such as citric acid, to an aqueous slurry of the titanium dioxide nanoparticles; treating the aqueous slurry with a source of alumina, such as a solution of sodium aluminate, to form alumina-treated titanium dioxide nanoparticles; recovering the alumina-treated inorganic nanoparticles, wherein the nanoparticles have a particle size of about 50 to about 300 nm; and milling the nanoparticles to form nanoparticles having a particle size about 15% smaller than silica-treated inorganic nanoparticles milled under similar conditions. The titanium dioxide nanoparticles described herein are useful in cosmetic, coating and thermoplastic compositions.

Owner:THE CHEMOURS CO TT LLC

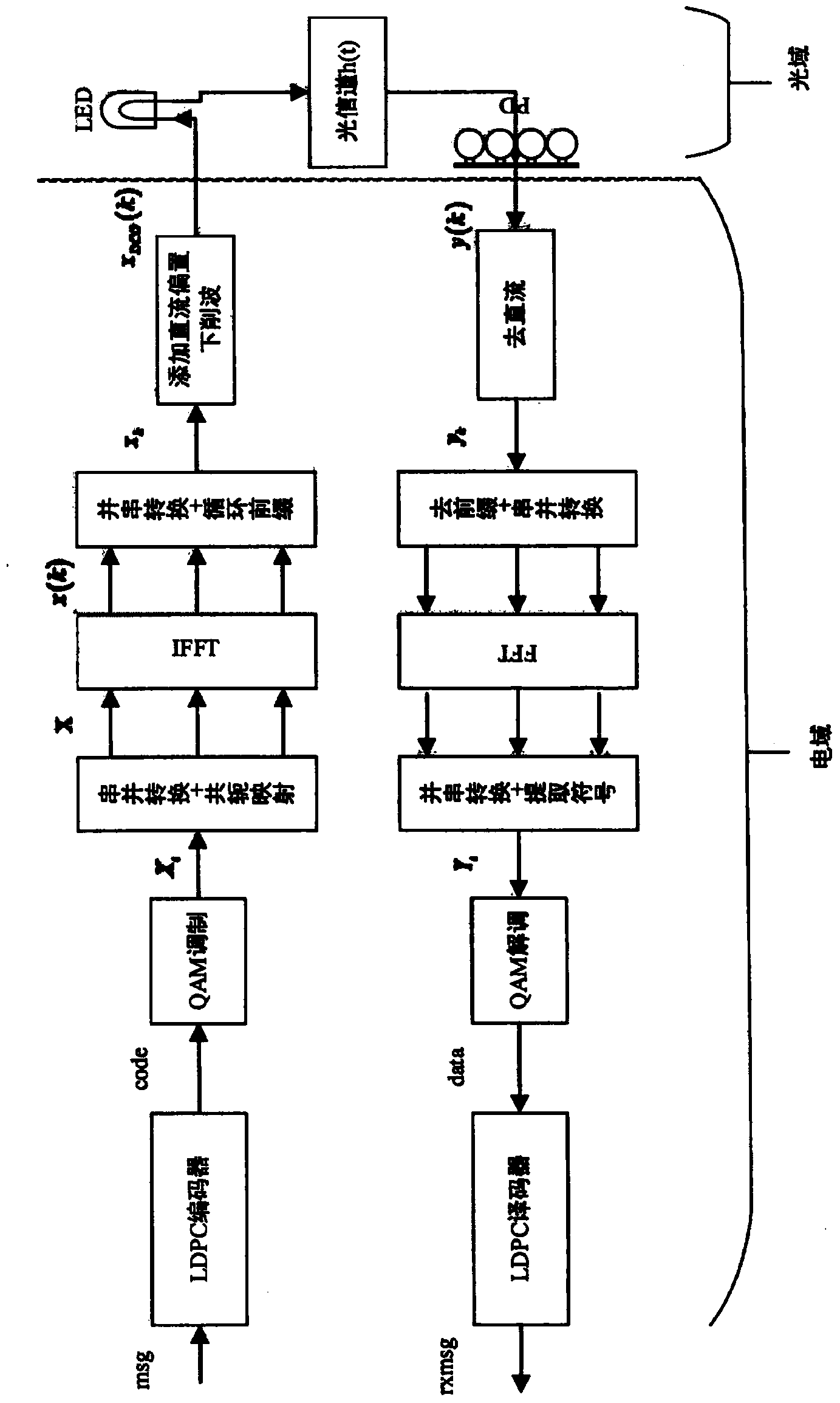

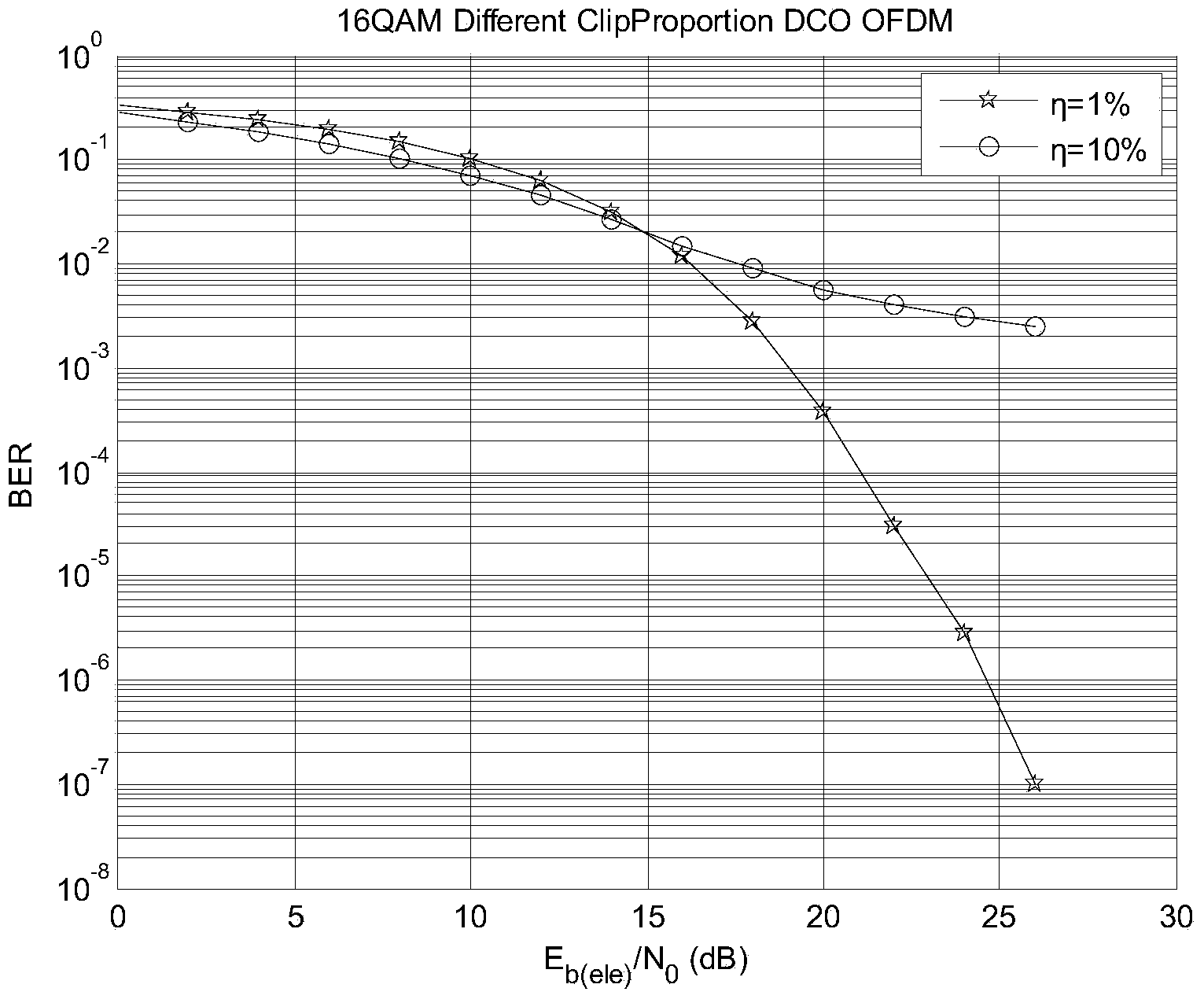

DCO-OFDM system direct current bias setting method applicable to visible light communication

ActiveCN104184693AImprove power utilizationIncrease brightness adjustment rangeDc level restoring means or bias distort correctionClose-range type systemsVisible light communicationCorrection code

The invention relates to the field of visible light communication, and provides a DCO-OFDM system direct current bias setting method applicable to visible light communication. Channel coding is carried out information source information before the information source information is modulated; good error correction and detection performance of an error correction code is utilized, reliability and power utilization of a system are taken into account comprehensively, the clipping proportion of a time-domain signal is appropriately added at a sending end, direct current bias required by the system is reduced, and therefore the power utilization rate of the system and the illuminating brightness adjustable range are improved. A receiving end compensates for clipping distortion of the sending end through error correction capacity of a channel code. The DCO-OFDM system direct current bias setting method reduces the magnitude of the direct current bias which needs to be added when DCO-OFDM modulation is carried out by the sending end, the power utilization rate of the system is improved, the brightness adjusting range on the aspect of illumination of visible light communication is expanded to a certain extent, and reliability and applicability of the system are enhanced.

Owner:SOUTHEAST UNIV

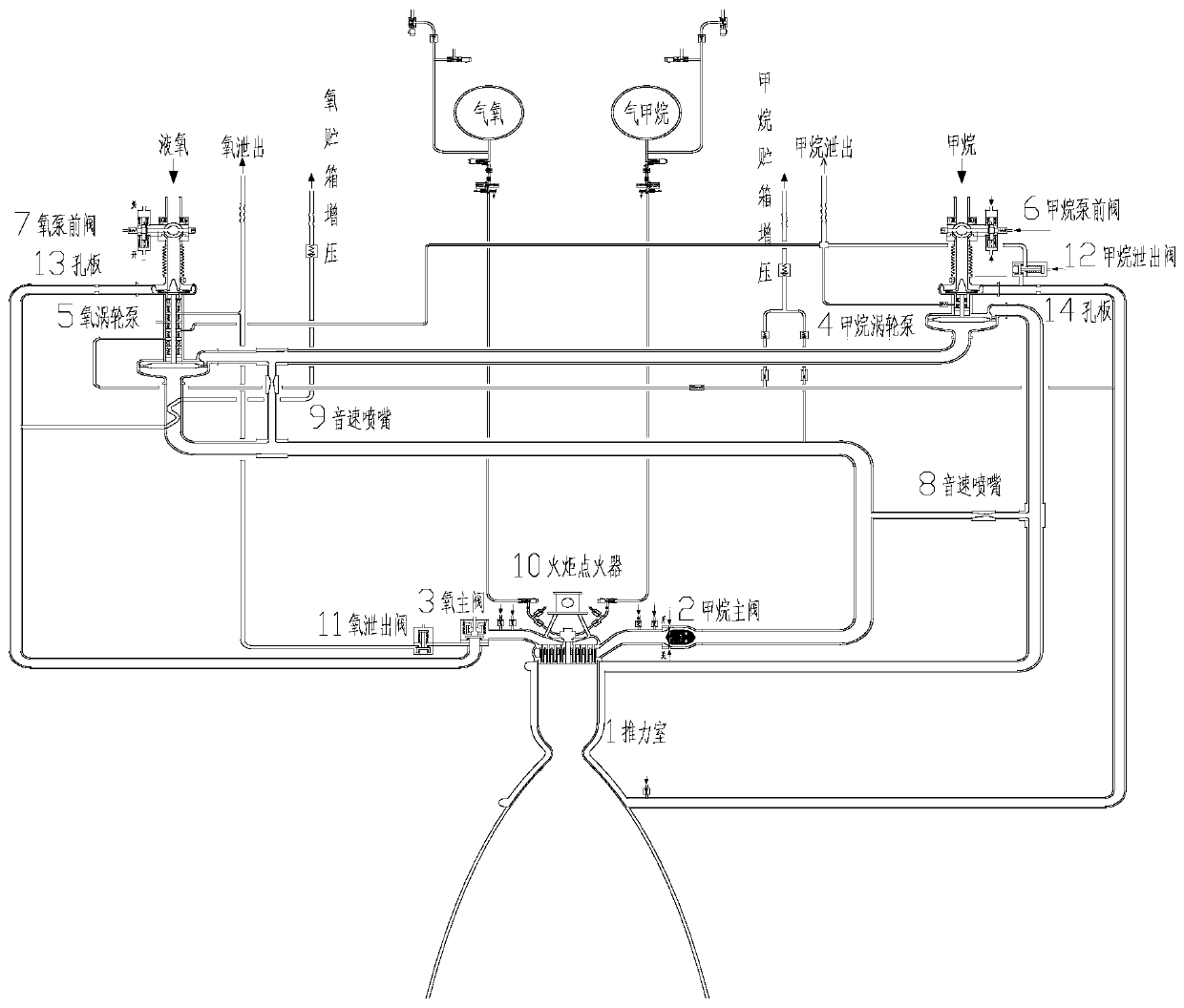

Expansion cycle liquid oxygen and methane upper-stage engine system

ActiveCN111005821ANo pollution in the processEasy to storeRocket engine plantsThrust chamberControl system

An expansion cycle liquid oxygen and methane upper-stage engine system comprises a propellant supply system, an ignition system and a thrust chamber. The propellant supply system comprises a methane supply system and a liquid oxygen supply system, the methane supply system pressurizes low-temperature liquid methane from an external storage tank and then supplies the low-temperature liquid methaneto the thrust chamber; the liquid oxygen supply system pressurizes the low-temperature liquid oxygen from the external storage tank and then supplies the low-temperature liquid oxygen to the thrust chamber; and the ignition system is located at the head of the thrust chamber and ignites under the control of a control system, liquid oxygen and methane entering the thrust chamber are ignited, and generated high-temperature gas is sprayed out of the nozzle of the thrust chamber to generate thrust force. The liquid oxygen and liquid methane are used as a propellant combination, and a closed expansion circulation system scheme is adopted, so the system is simple, the inherent reliability is high, the specific impulse performance is high, and repeated starting is easy to achieve.

Owner:BEIJING AEROSPACE PROPULSION INST

Method and system of logical volume dynamic allocation on shared storage

ActiveCN106656631ASave spaceAvoid wasting spaceData switching networksCloud computingHigh availability

The present invention discloses a method and a system of logical volume dynamic allocation on shared storage, relating to the technical field of cloud computing. The system comprises a plurality of servers, shared storage devices and network switches; each server is provided with a virtual disk drive program, a service program and a command line tool; one of the servers is used as a main node and the other servers are used as subordinate nodes. A user sends out a command of creating a virtual disk through the command line tool, and sends the command to the service program of the main node. The service program of the main node calls the drive program, creates the virtual disk, saves the corresponding configuration and mapping data in the reserved space of the virtual disk, and returns the result of creation to the command line tool; and the command line tool updates local data and loads the corresponding virtual disk locally by using the drive program. The present invention has the advantages of low cost, low consumption, high performance, and high availability without the need of purchasing expensive high-end storage devices, and achieves the dynamic allocation of the storage space according to needs.

Owner:WUHAN OPENKER COMPUTING

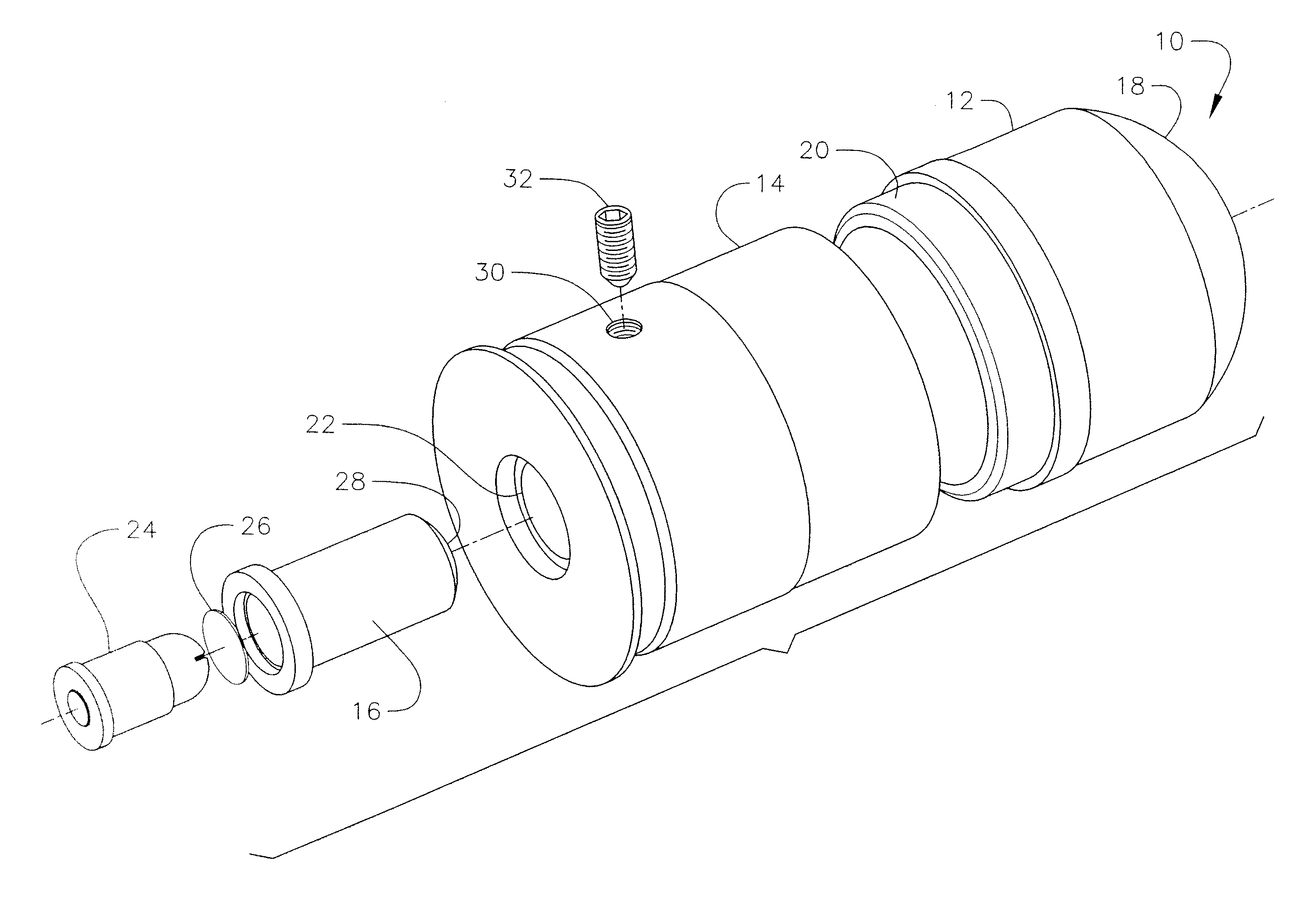

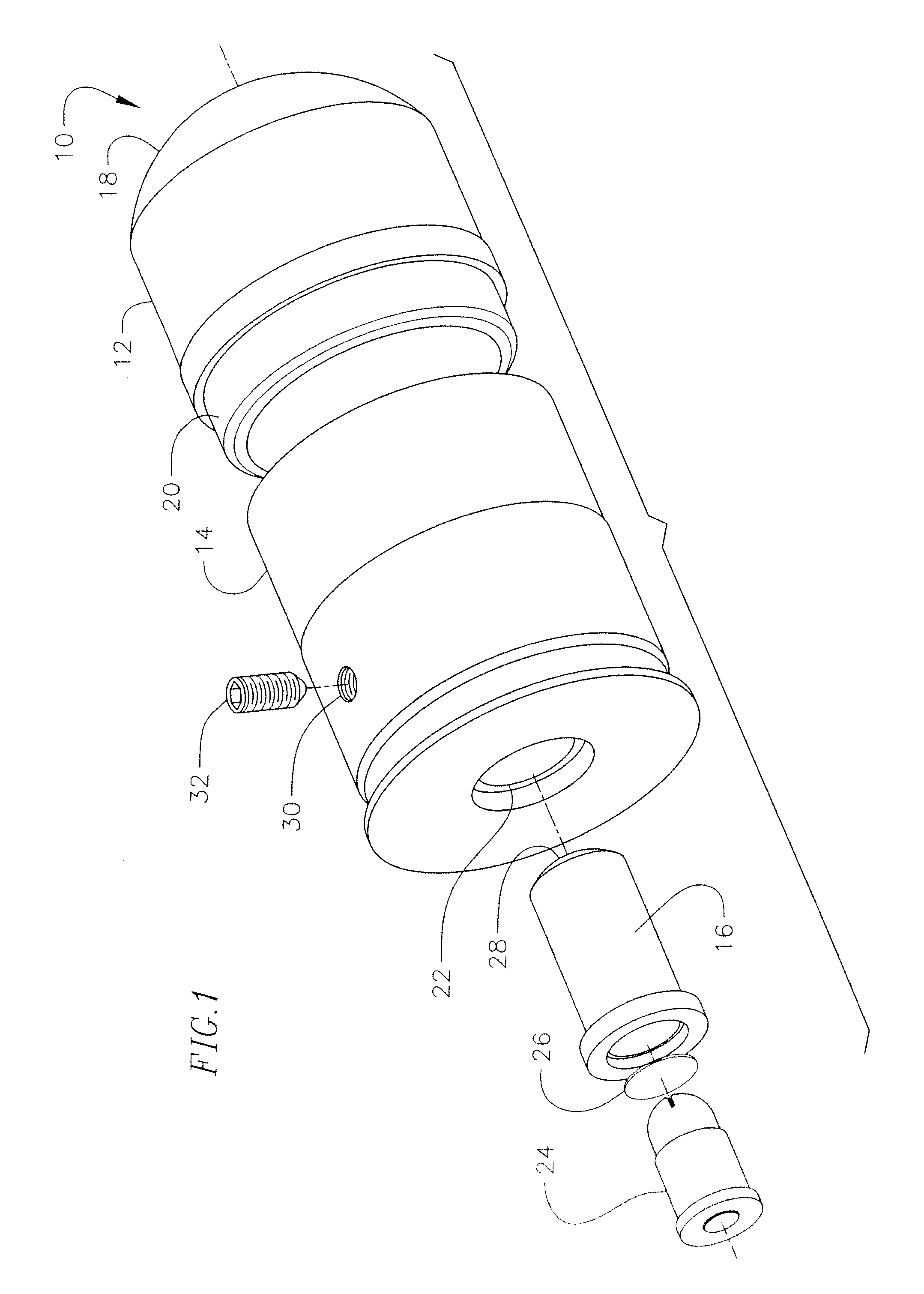

Single piece non-lethal projectile

ActiveUS20120210903A1Low costWithout loss of performanceAmmunition projectilesTraining ammunitionEngineeringMechanical engineering

A reloadable training munition having a reusable shell base having a propulsion system reload inserted into a hollow cavity of the shell base and a reusable single piece projectile inserted into the shell base, the projectile having a hollow body portion, a driving band adjacent the body portion, and a nose portion adjacent the driving band having void spaces for controlling both density and mass properties of the nose portion.

Owner:DEFENSE TECH

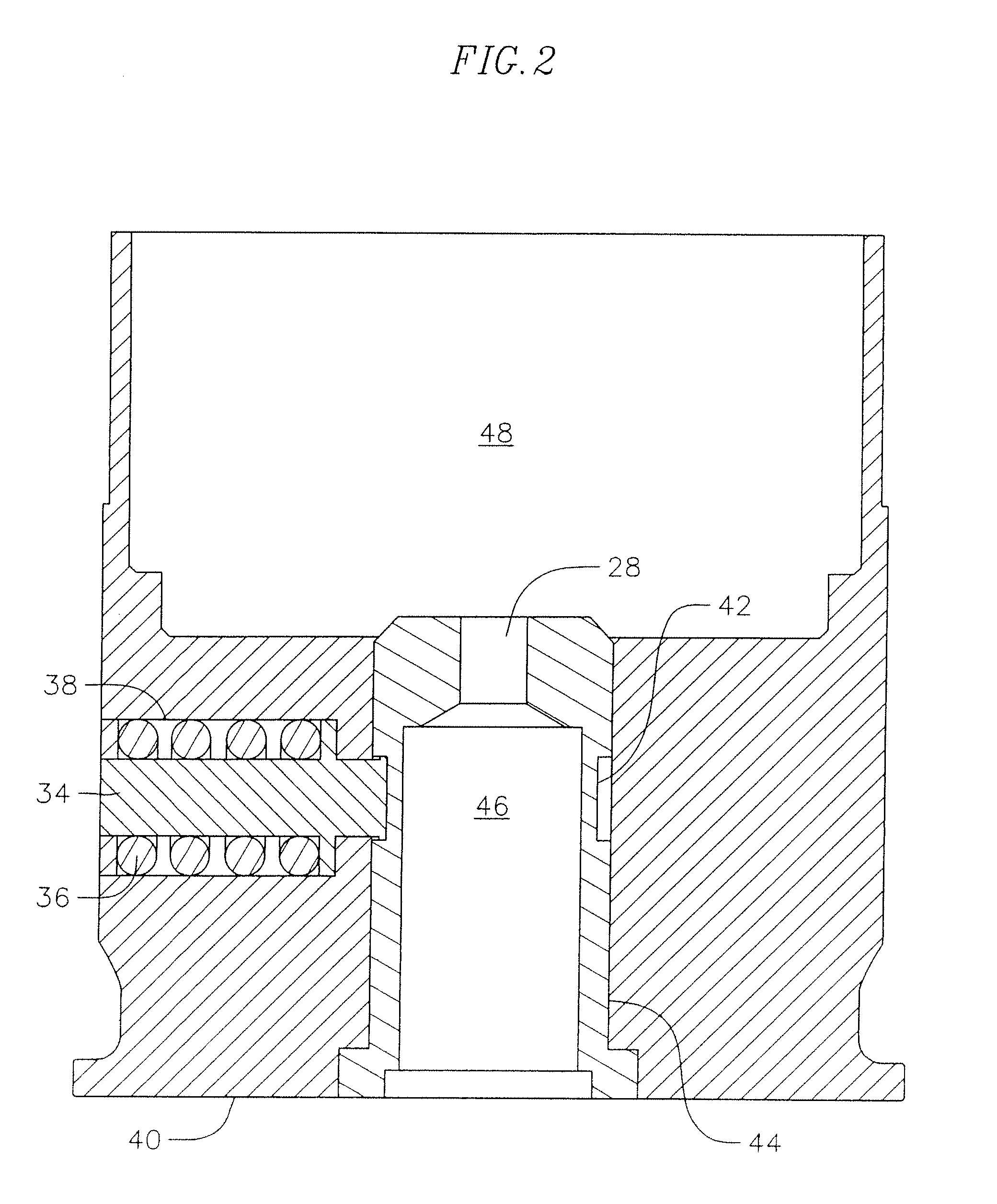

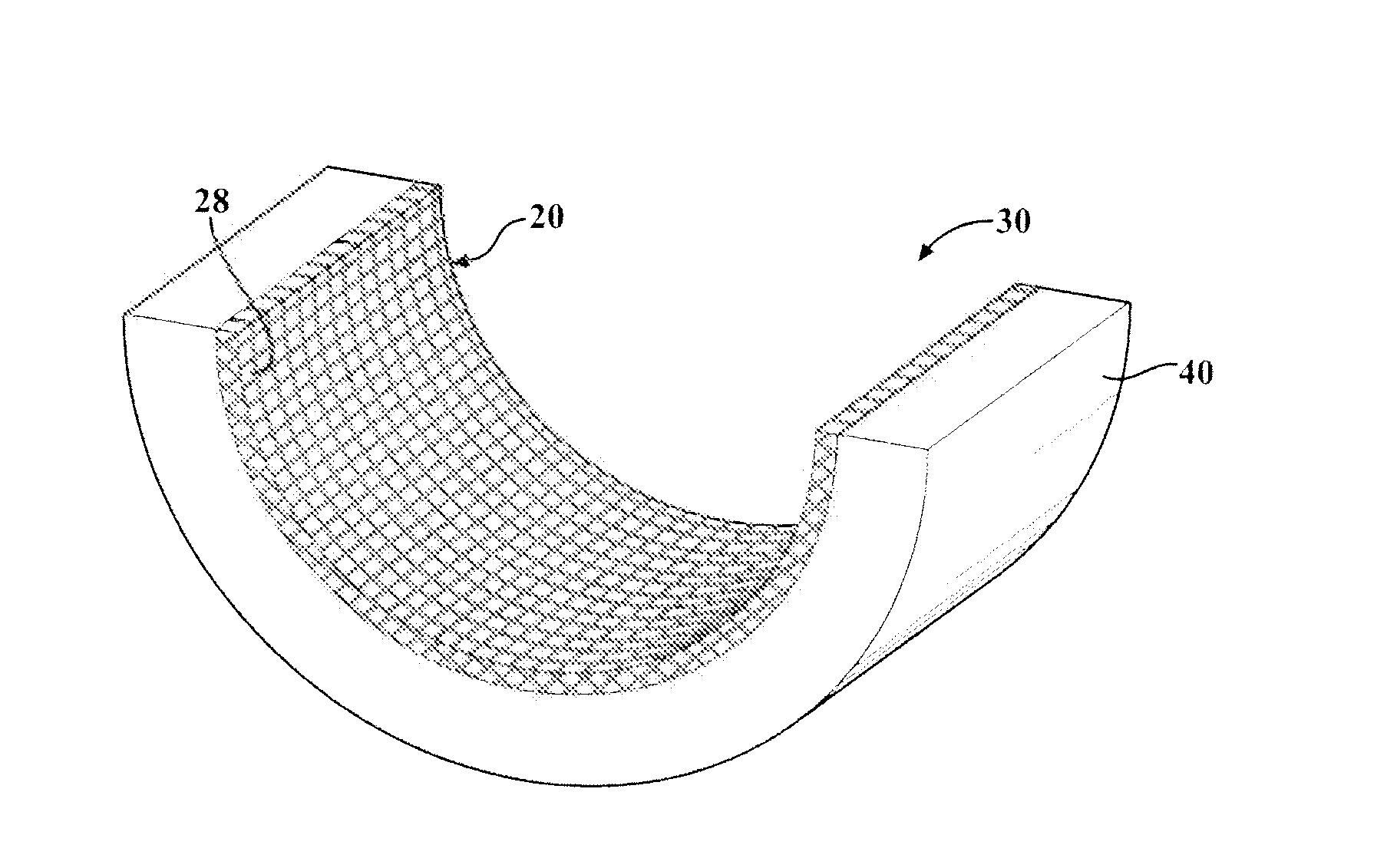

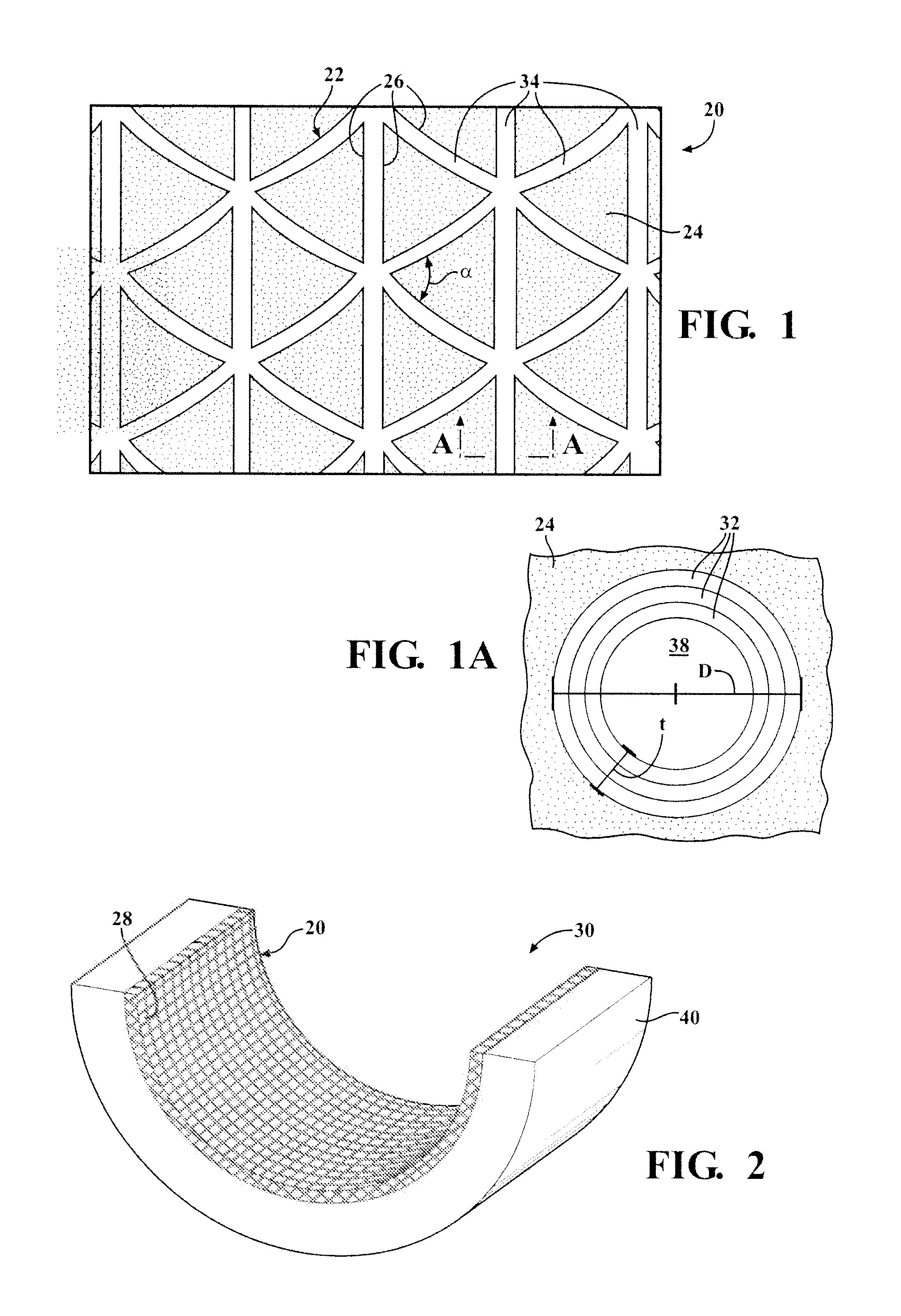

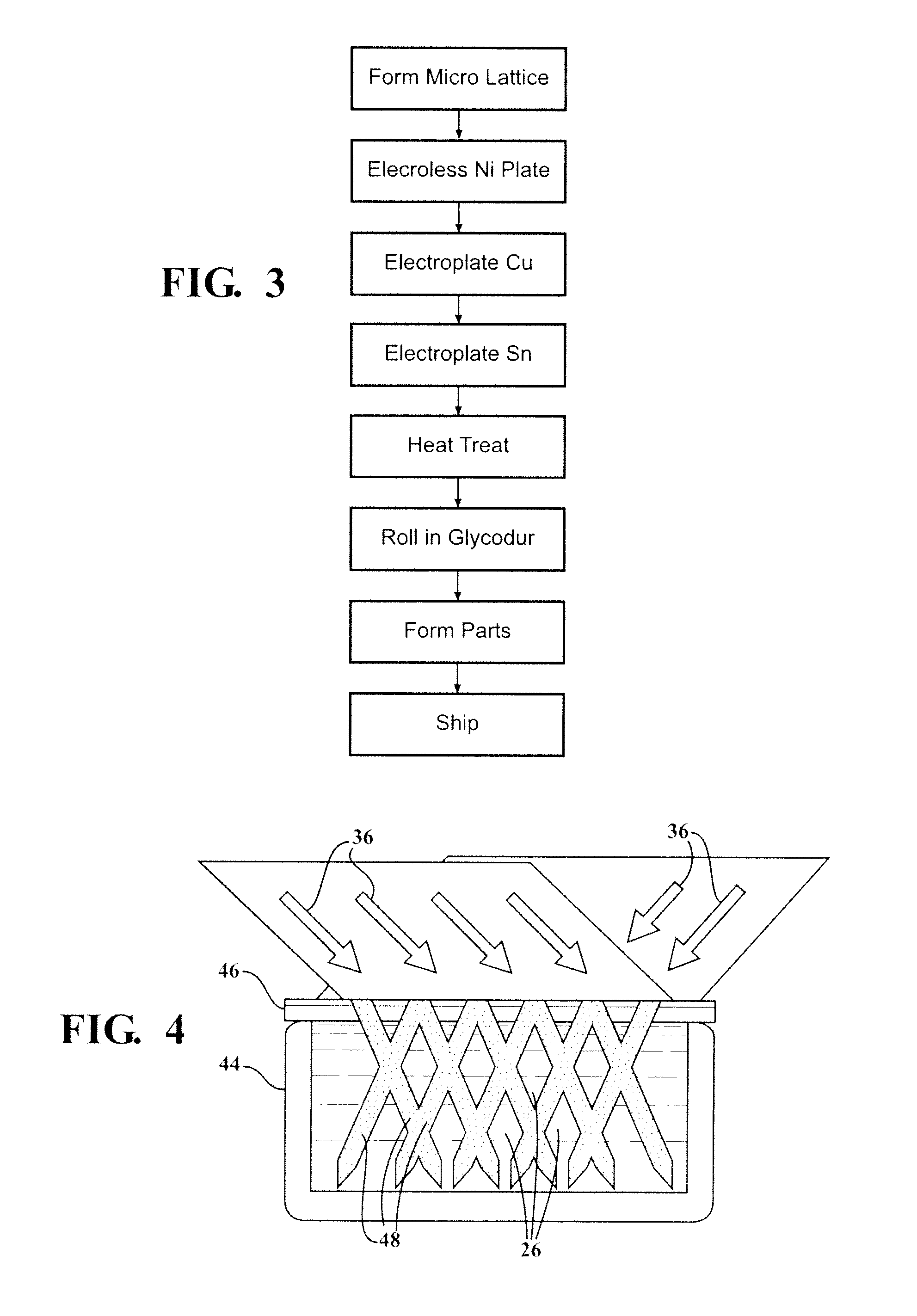

High strength low friction engineered material for bearings and other applications

ActiveUS20140140647A1Reduce frictionReduce forcePretreated surfaces3D object support structuresPolyamideFiller metal

A high strength, low friction engineered material includes a low friction material filling interstices of a metal microlattice. The metal typically comprises 5 volume % to 25 volume % and the interstices typically comprise 75 volume % to 95 volume %, based on the total volume of the metal microlattice and the interstices. The low friction material preferably fills 100 volume % of the interstices. The metal microlattice can be formed of a single layer, or multiple layers, for example layers of nickel, copper, and tin. The low friction material is typically a polymer, such as polytetrafluoroethylene (PTFE), polyamide (PAI), polyetheretherketone (PEEK), polyethylene (PE), or polyoxymethylene (POM). The low friction material can also include additive particles to modify the material properties. The engineered material can be used in various automotive applications, for example as a bearing, or non-automotive applications.

Owner:TENNECO

Method, system, apparatus, and computer-readable medium for taking and managing snapshots of a storage volume

ActiveUS7987156B1No performance lossScroll fastError detection/correctionDigital data processing detailsGranularityInvalid Data

A method, system, apparatus, and computer-readable medium are provided for taking snapshots of a storage volume. According to aspects of one method, each snapshot is represented as a unique sequence number. Every fresh write access to a volume in a new snapshot lifetime is allocated a new section in the disk, called a provision, which is labeled with the sequence number. Read-modify-write operations are performed on a sub-provision level at the granularity of a chunk. Because each provision contains chunks with valid data and chunks with invalid data, a bitmap is utilized to identify the valid and invalid chunks with each provision. Provisions corresponding to different snapshots are arranged in a linked list. Branches from the linked list can be created for storing writable snapshots. Provisions may also be deleted and rolled back by manipulating the contents of the linked lists.

Owner:AMZETTA TECH LLC

Scalable repair block error correction for sequential multiple data blocks in a magnetic data storage device

ActiveUS8856618B2No performance lossIntegrity guaranteedCode conversionRecord information storageShingled magnetic recordingConcatenation

A technique for recovering of “squeezed” sectors in a set of sequential sectors such as are used in Shingled Magnetic Recording (SMR) is described. Embodiments of the invention use a programmable erased sector recovery scheme, which is a concatenation of a “Cauchy-type” track erasure correction code, together with a media-error correction code that generates N-weighted parity-sectors per track and is capable of replacing up to N-erased sectors per track in any possible combination.

Owner:WESTERN DIGITAL TECH INC

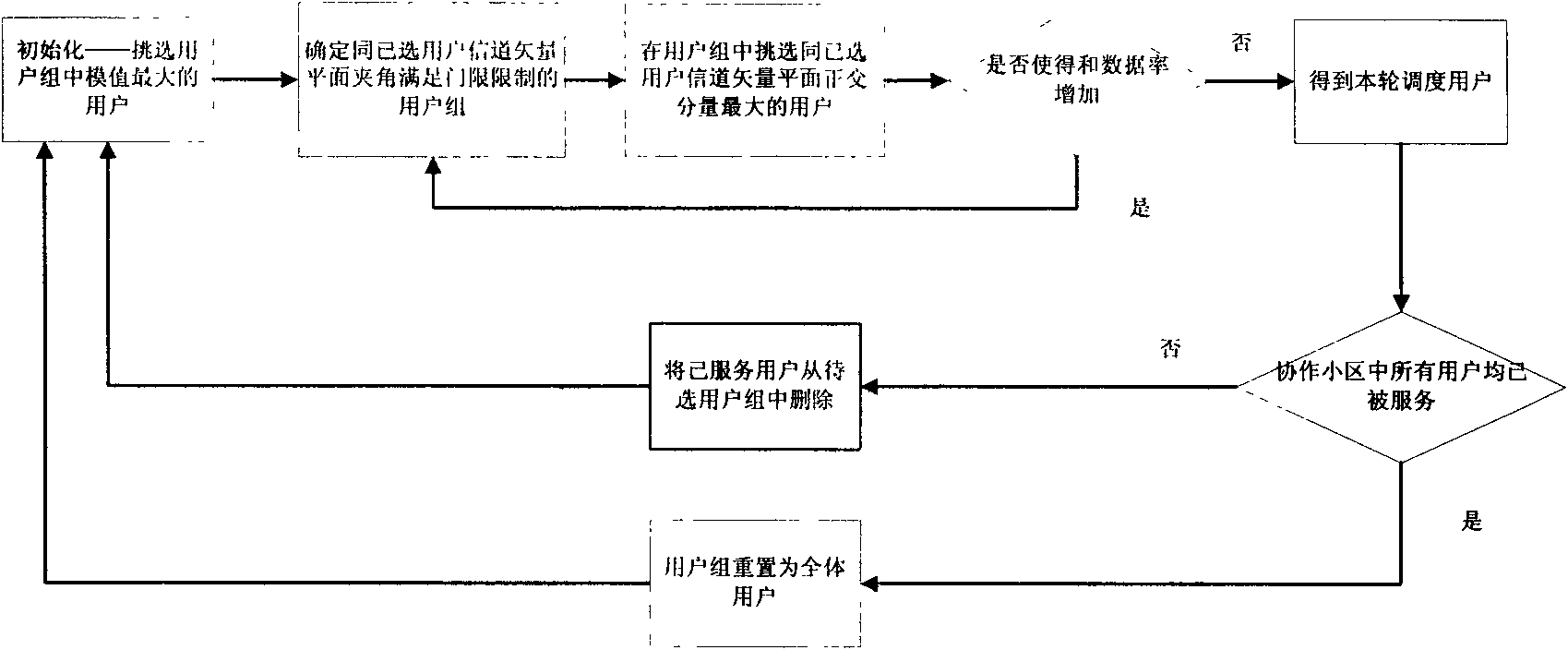

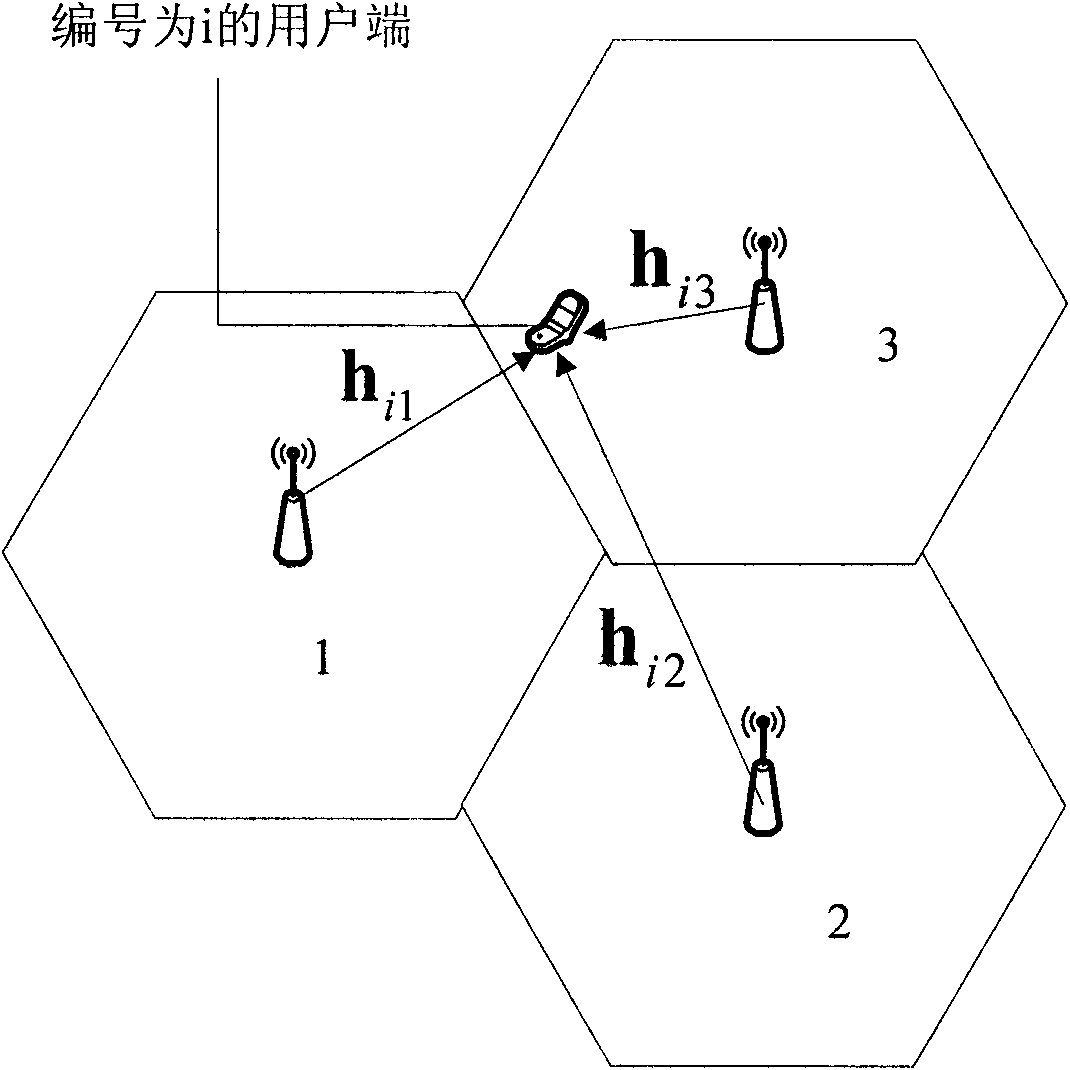

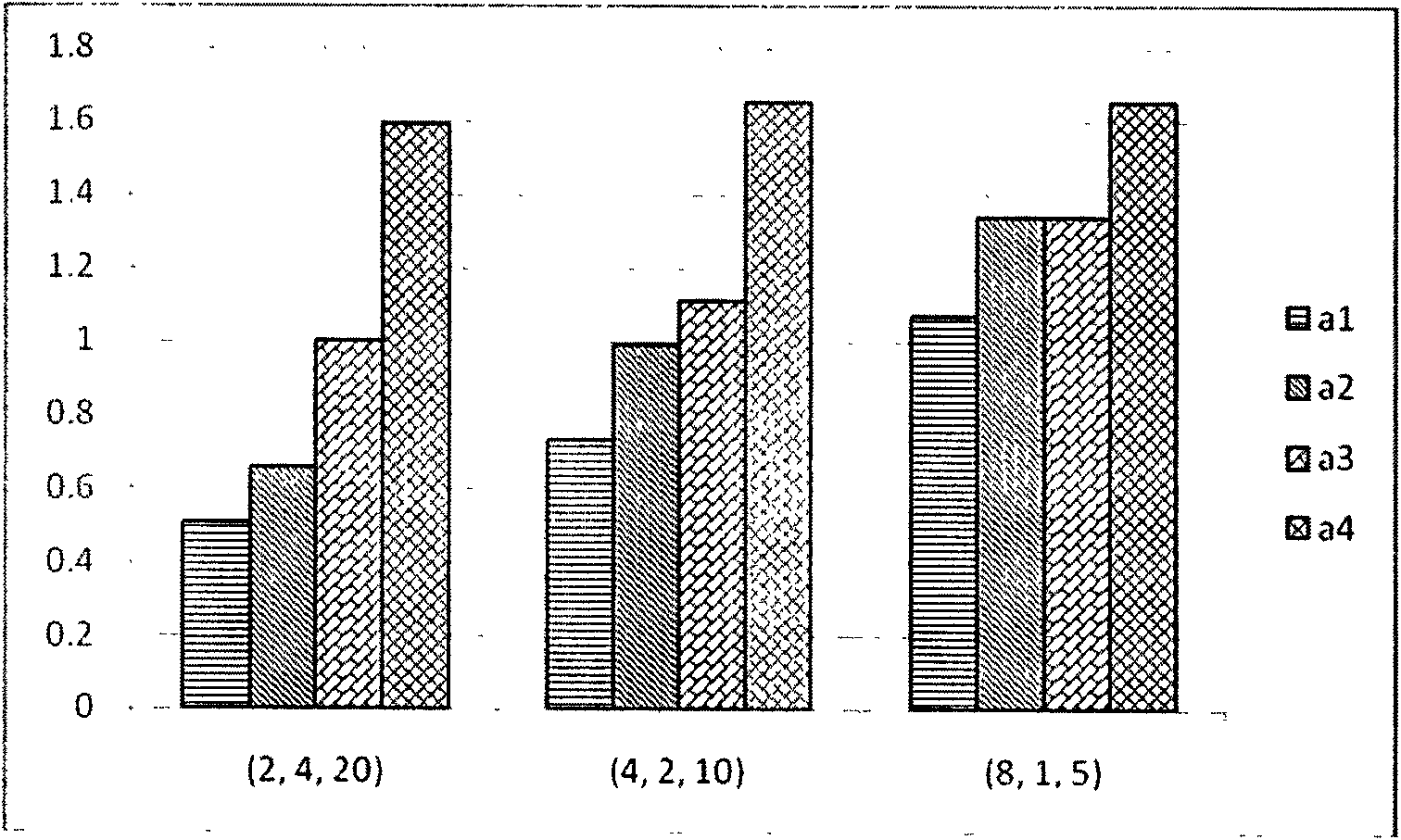

Low-feedback multi-user scheduling method in cooperative multicast MIMO transmission

InactiveCN101621322AReduce the amount of feedbackImprove throughput performanceSpatial transmit diversityDistributed allocationTime domainMimo transmission

The invention relates to a low-feedback multi-user scheduling method in cooperative multicast MIMO transmission. The method comprises the following four schemes: (1) NUS, (2) Large Scale, (3) Local-NUS and (4) Local-Large Scale; and the four schemes are respectively based on different channel feedback information and have a unified executive process. The method is a scheduling method for selecting a plurality of service users in the spatial domain, and ensures the fairness among different users by combining an opportunistic round-robin scheduling method on a time domain; the scheduling process is as follows: 1. initialization, the user with best channel condition is selected as a first user according to the feedback information; 2. a scheduling user set is iteratively selected from the rest users based on the selected user until the given stopping criterion is met; and 3. the selected user is eliminated based on the opportunistic round-robin scheduling method, and the step 1 and the step 2 are repeatedly carried out. Compared with the cooperative scheduling method based on the complete channel information, the method has no high performance loss but remarkably reduces the feedbackquantity of the system; and compared with the non-cooperative system, the invention can greatly improve the system performance.

Owner:BEIHANG UNIV

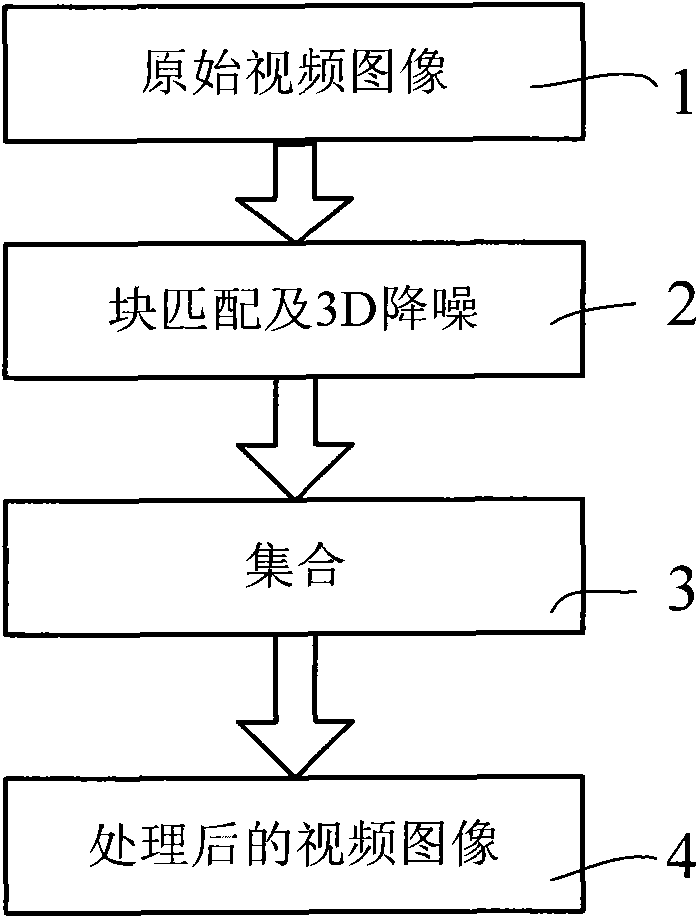

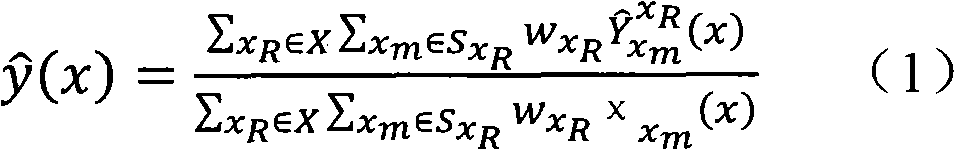

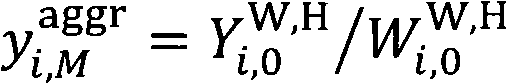

Integrated method suitable for real-time processing of BM3D

ActiveCN101895676AEliminate duplicate visitsSave bandwidthTelevision system detailsColor television detailsControl flowImaging processing

The technical problem to be solved by the invention is to provide a BM3D integration method. The method comprises the following steps: a, after 3D denoising processing, storing image processing information according to a line index or a column index; and b, reading the image processing information of a specific frame at a storing position from the storing position, reconstructing the image processing information of the specific frame and completing image reconstruction. The method realizes BM3D real-time integration processing by optimizing a BM3D integration process. In the method, the data structure and control flow are simple enough to be realized by software easily, and multiprocessor can be used for parallel processing. In addition, the method also makes the chip realization easy, is favorable for satisfying the high throughout needs for high-definition and multipath processing and realizes the video image BM3D real-time processing.

Owner:SHANGHAI FULLHAN MICROELECTRONICS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com