Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

33 results about "Wafer backgrinding" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

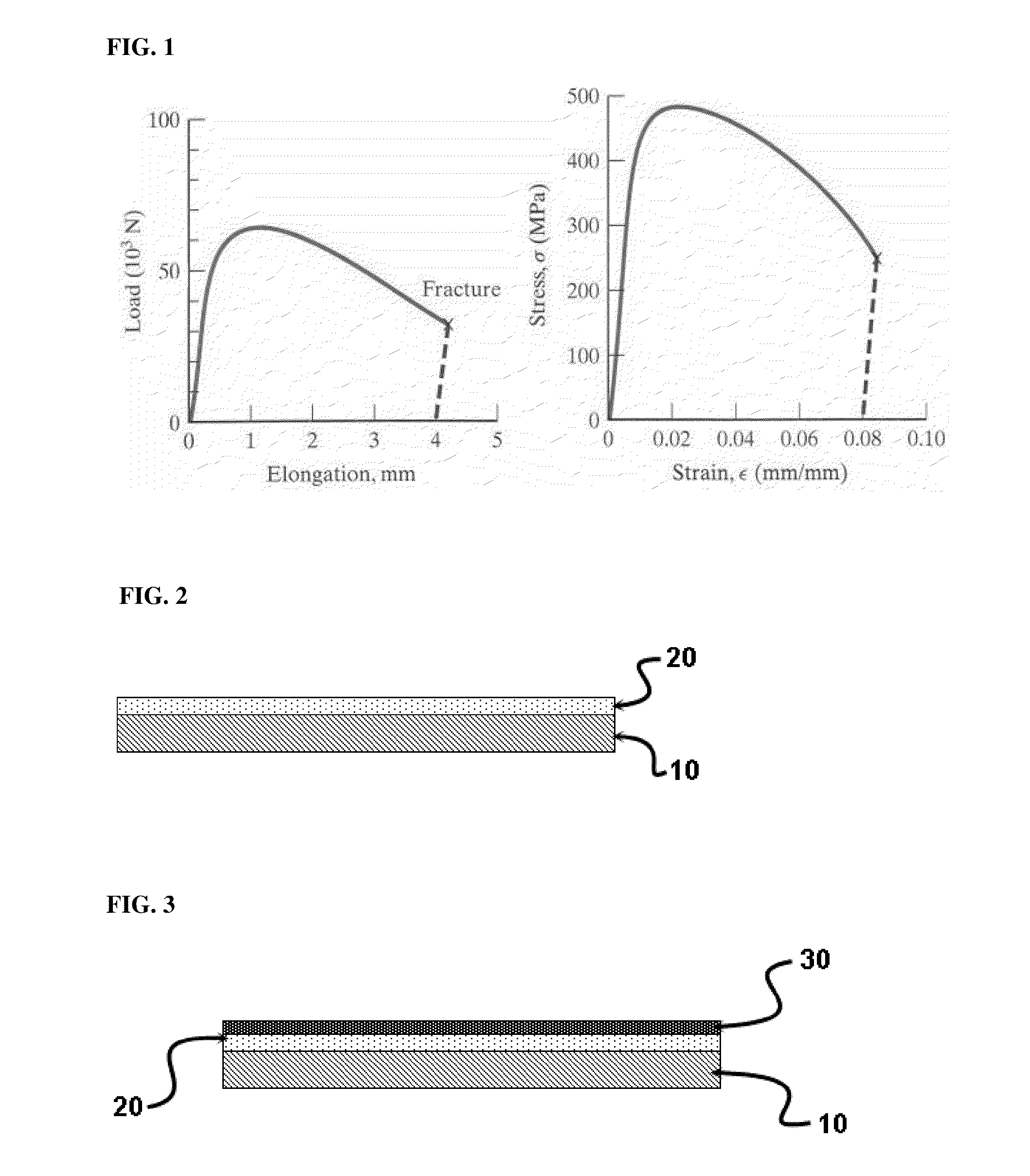

Wafer backgrinding is a semiconductor device fabrication step during which wafer thickness is reduced to allow stacking and high-density packaging of integrated circuits (IC). ICs are produced on semiconductor wafers that undergo a multitude of processing steps. The silicon wafers predominantly used today have diameters of 200 and 300 mm. They are roughly 750 μm thick to ensure a minimum of mechanical stability and to avoid warping during high-temperature processing steps.

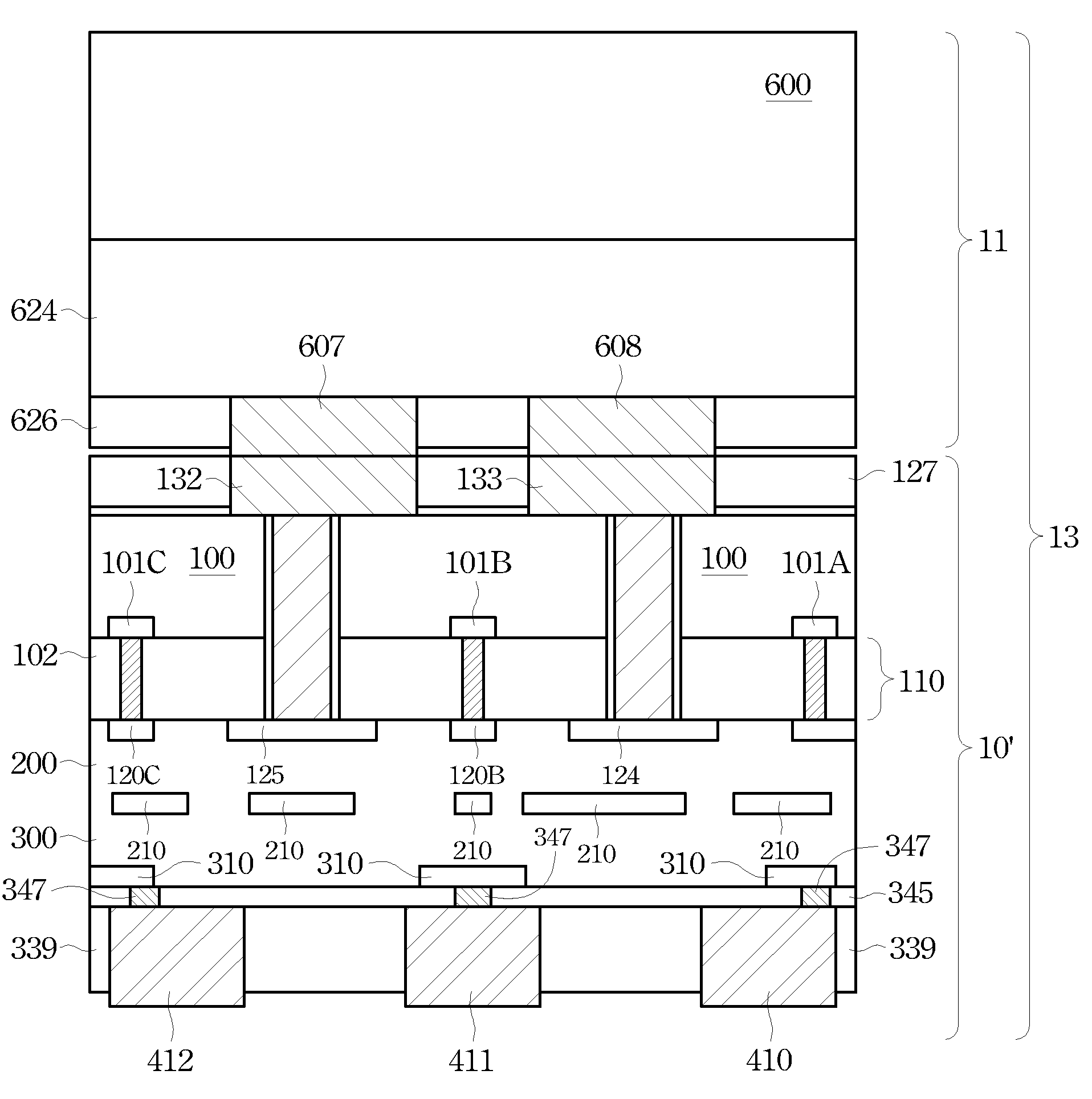

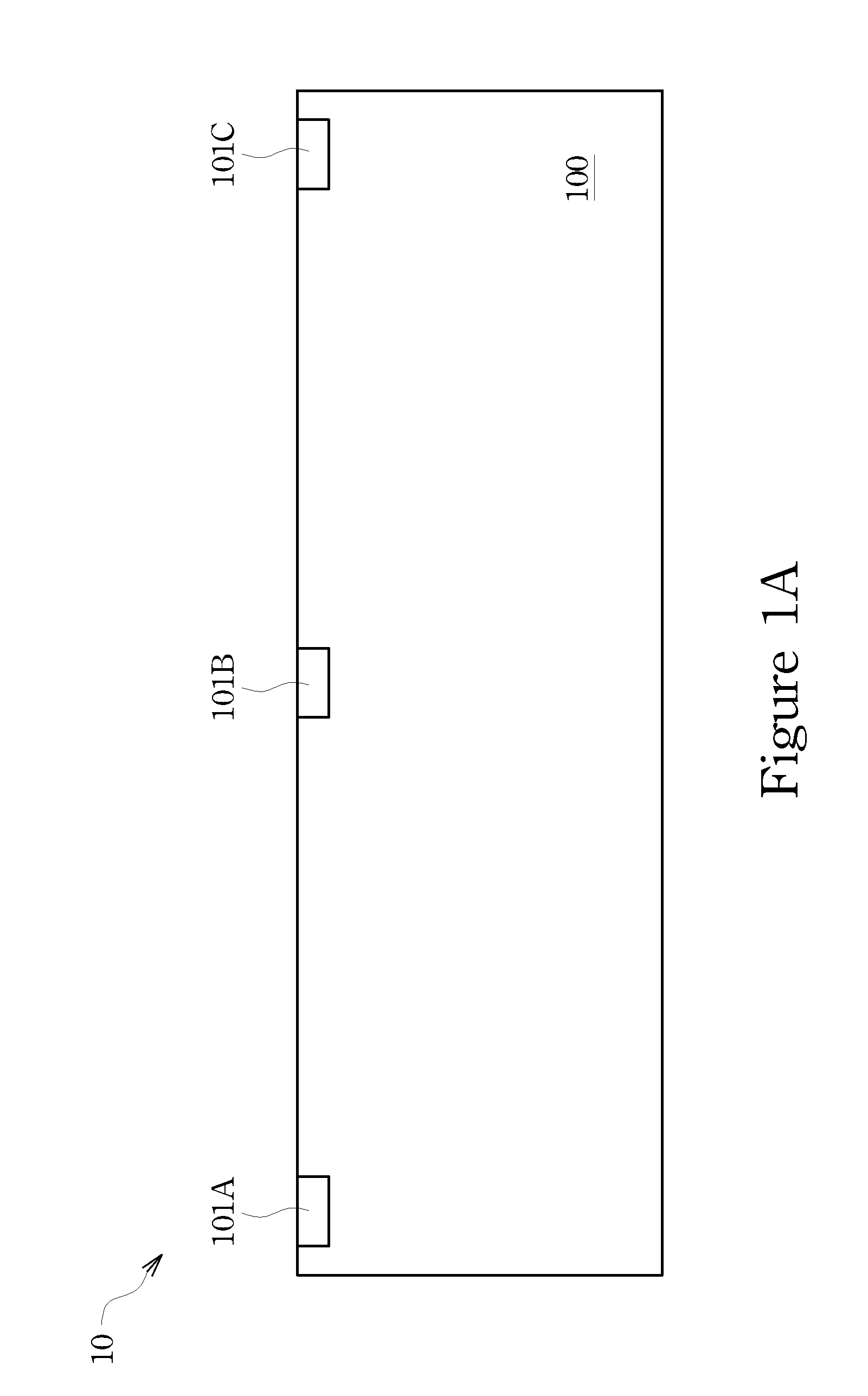

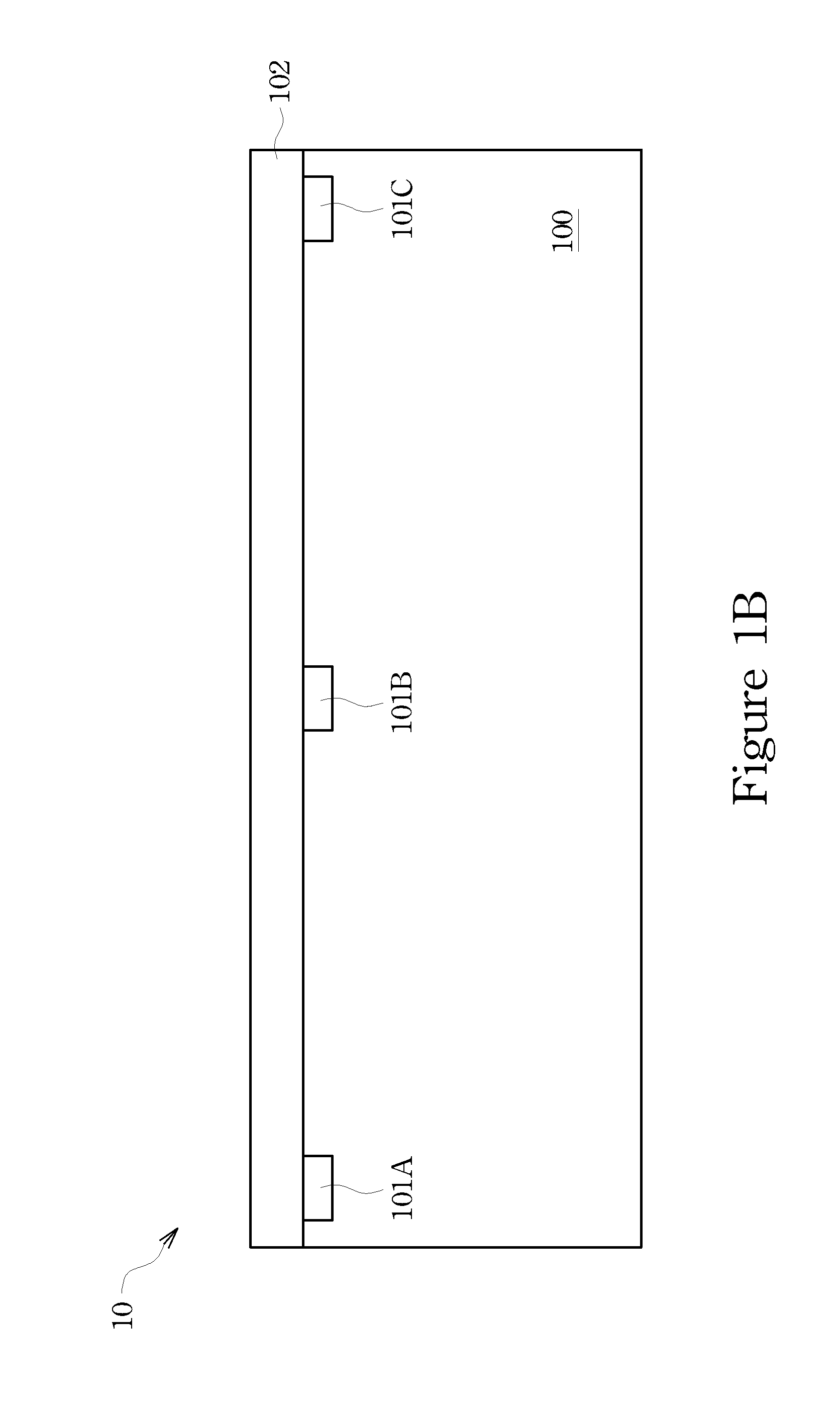

Method of forming stacked dies

ActiveUS8158456B2High aspect ratioReduce riskSolid-state devicesSemiconductor/solid-state device manufacturingWafer backgrindingSilicon

The formation of through silicon vias (TSVs) in an integrated circuit (IC) die or wafer is described in which the TSV is formed in the integration process prior to metallization processing. TSVs may be fabricated with increased aspect ratio, extending deeper in a wafer substrate. The method generally reduces the risk of overly-thinning a wafer substrate in a wafer back-side grinding process typically used to expose and make electrical contacts to the TSVs. By providing deeper TSVs and bonding pads, individual wafers and dies may be bonded directly between the TSVs and bonding pads on an additional wafer.

Owner:TAIWAN SEMICON MFG CO LTD

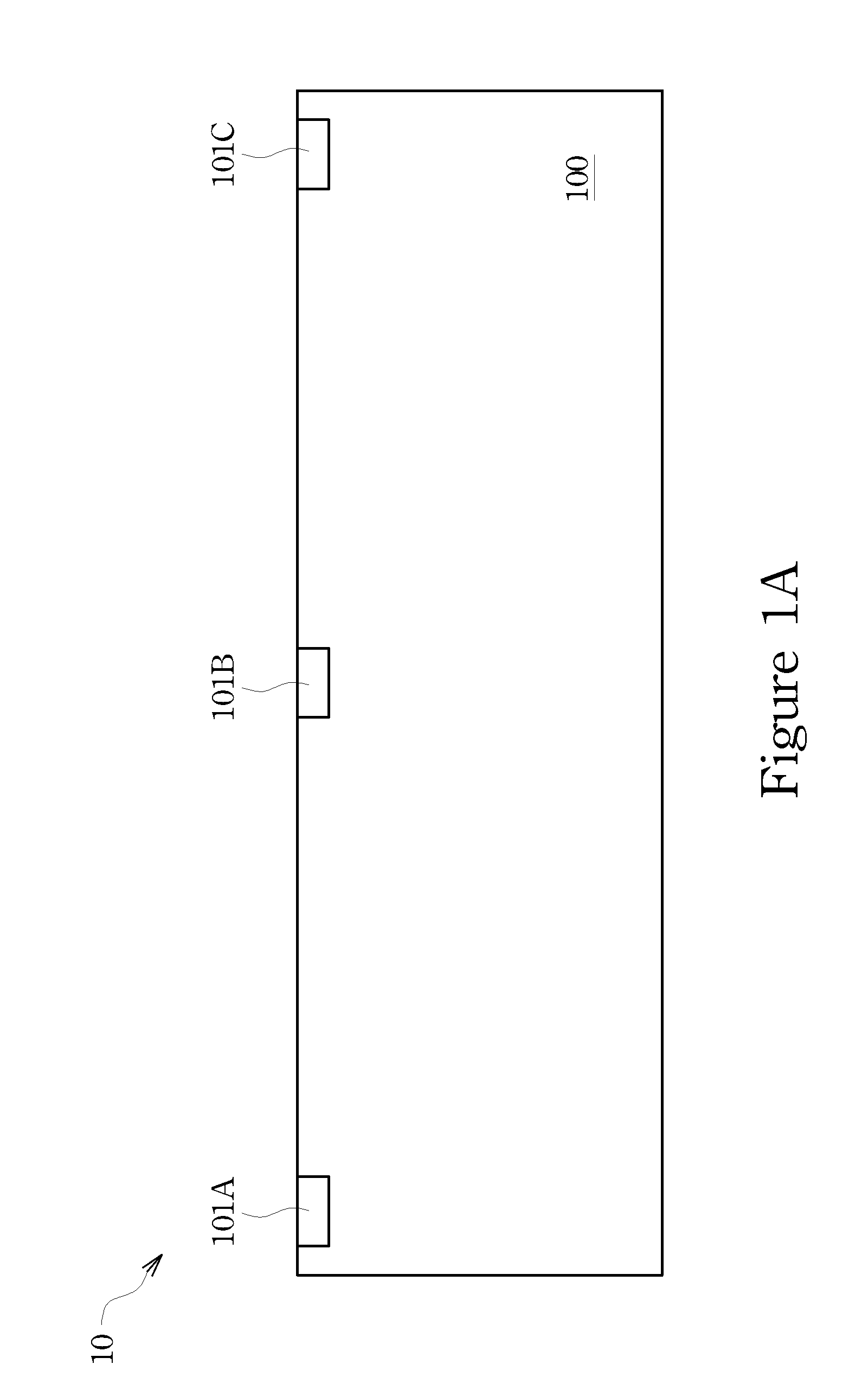

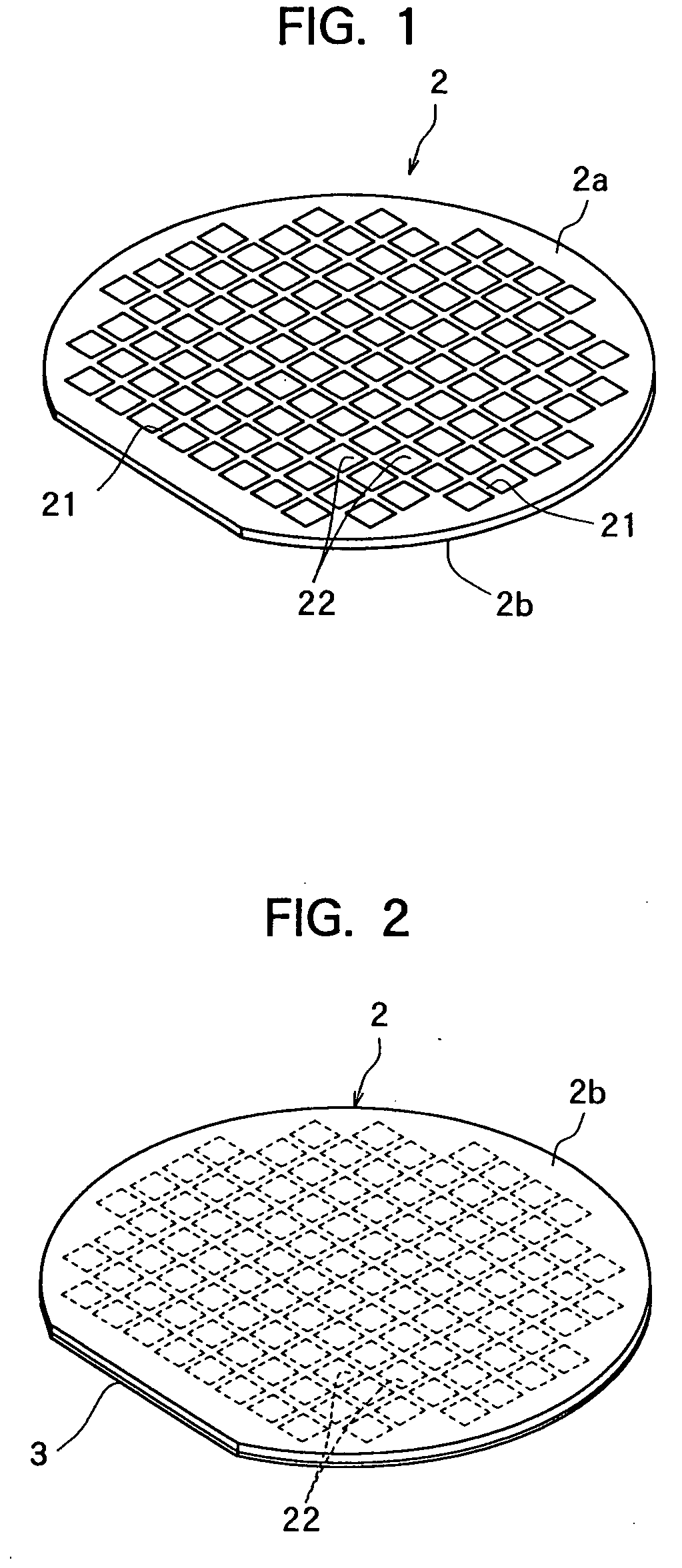

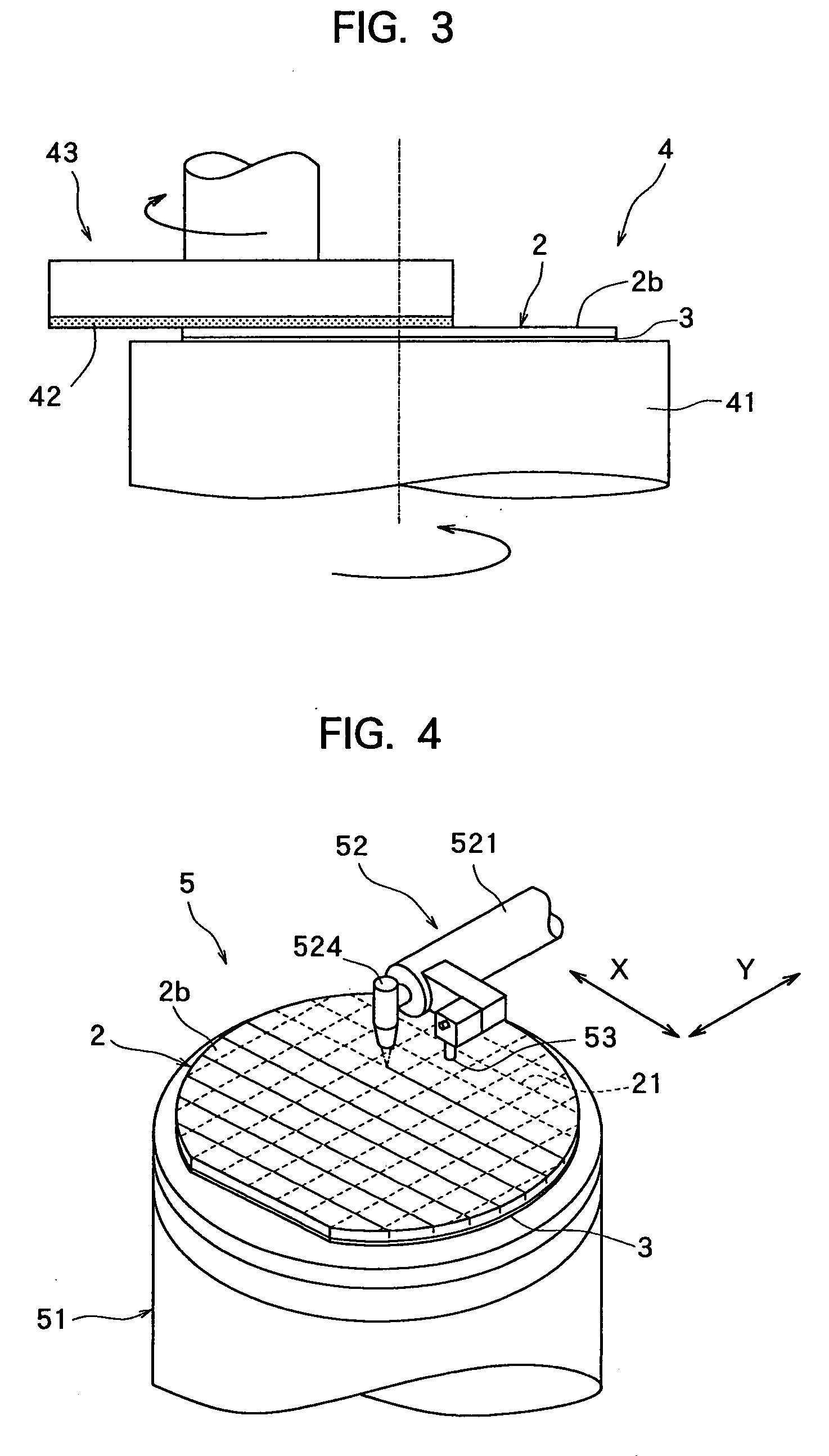

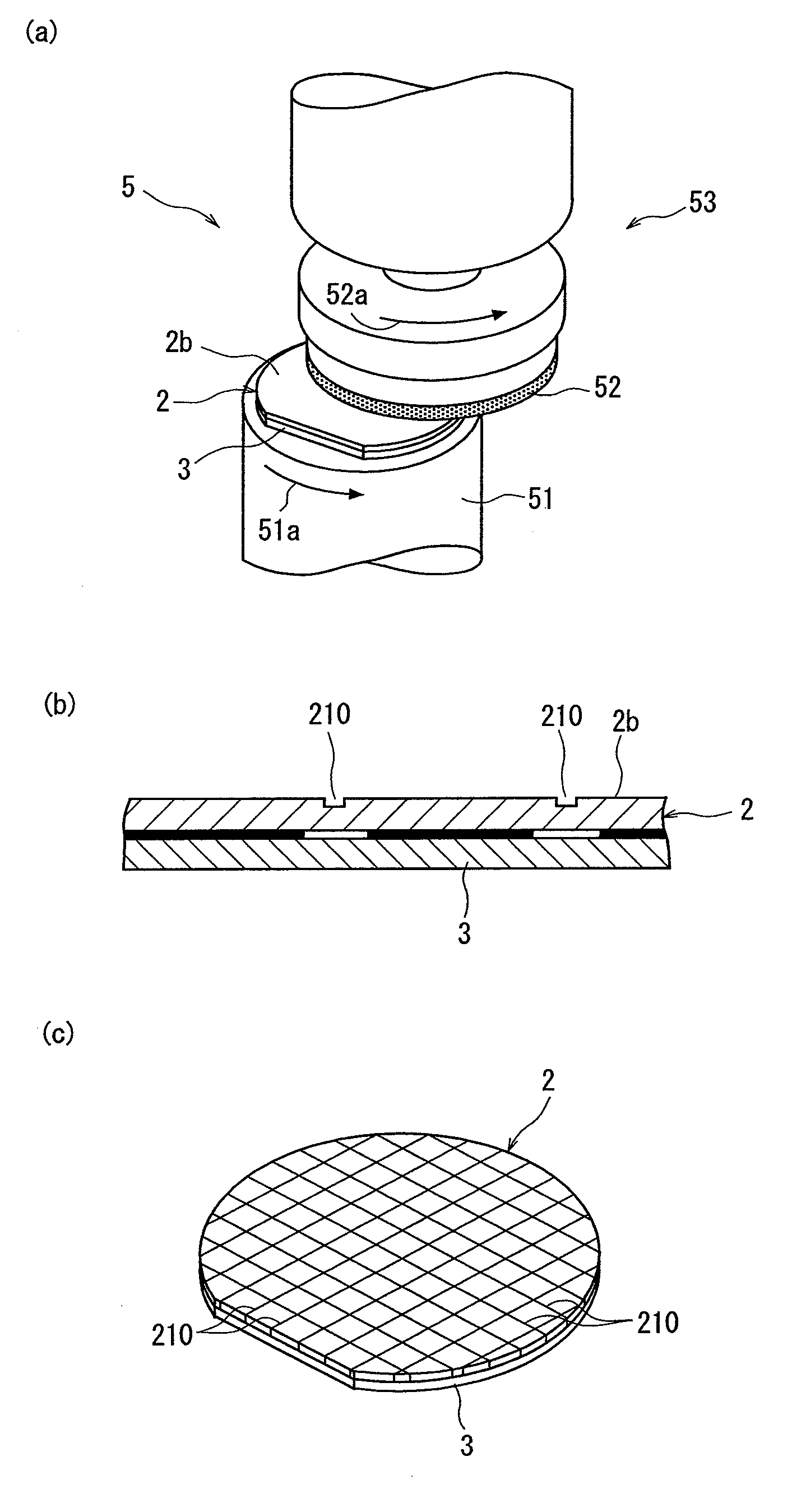

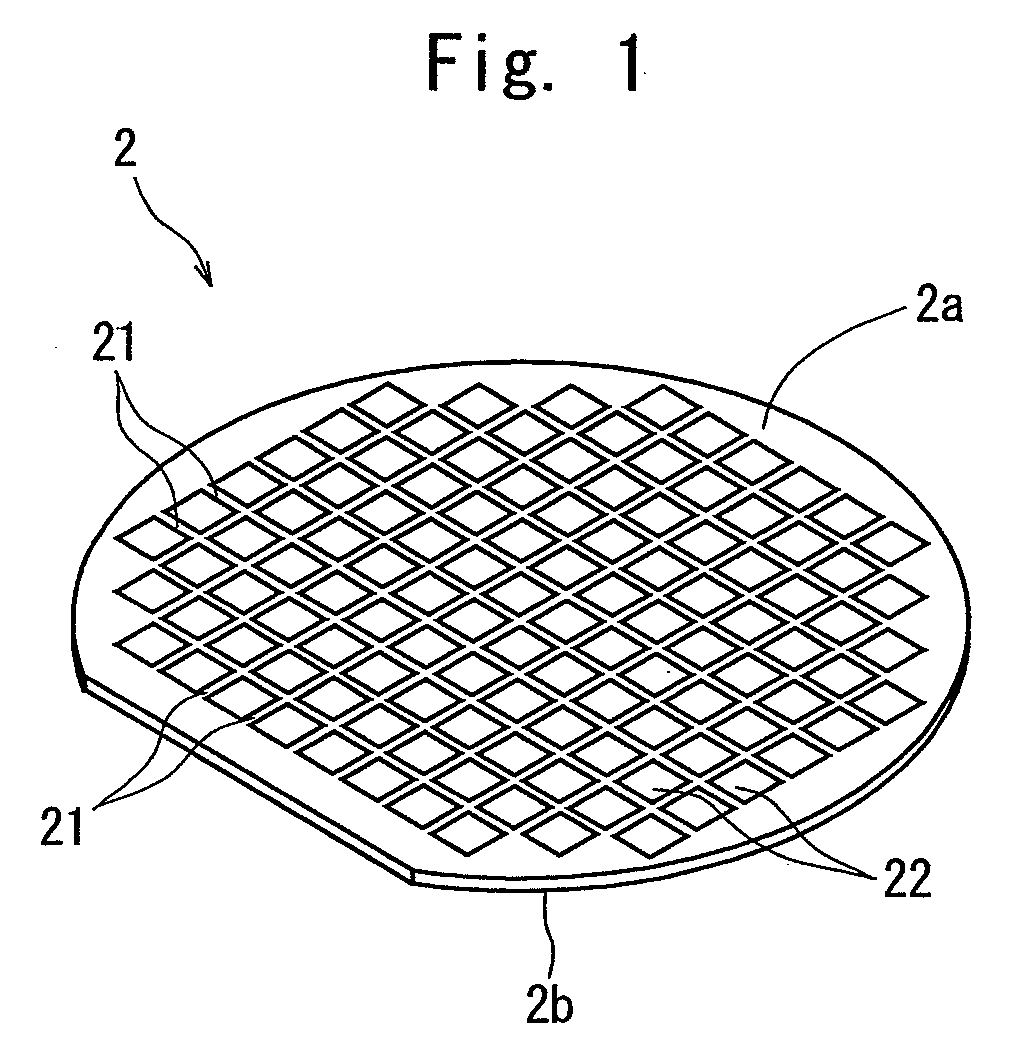

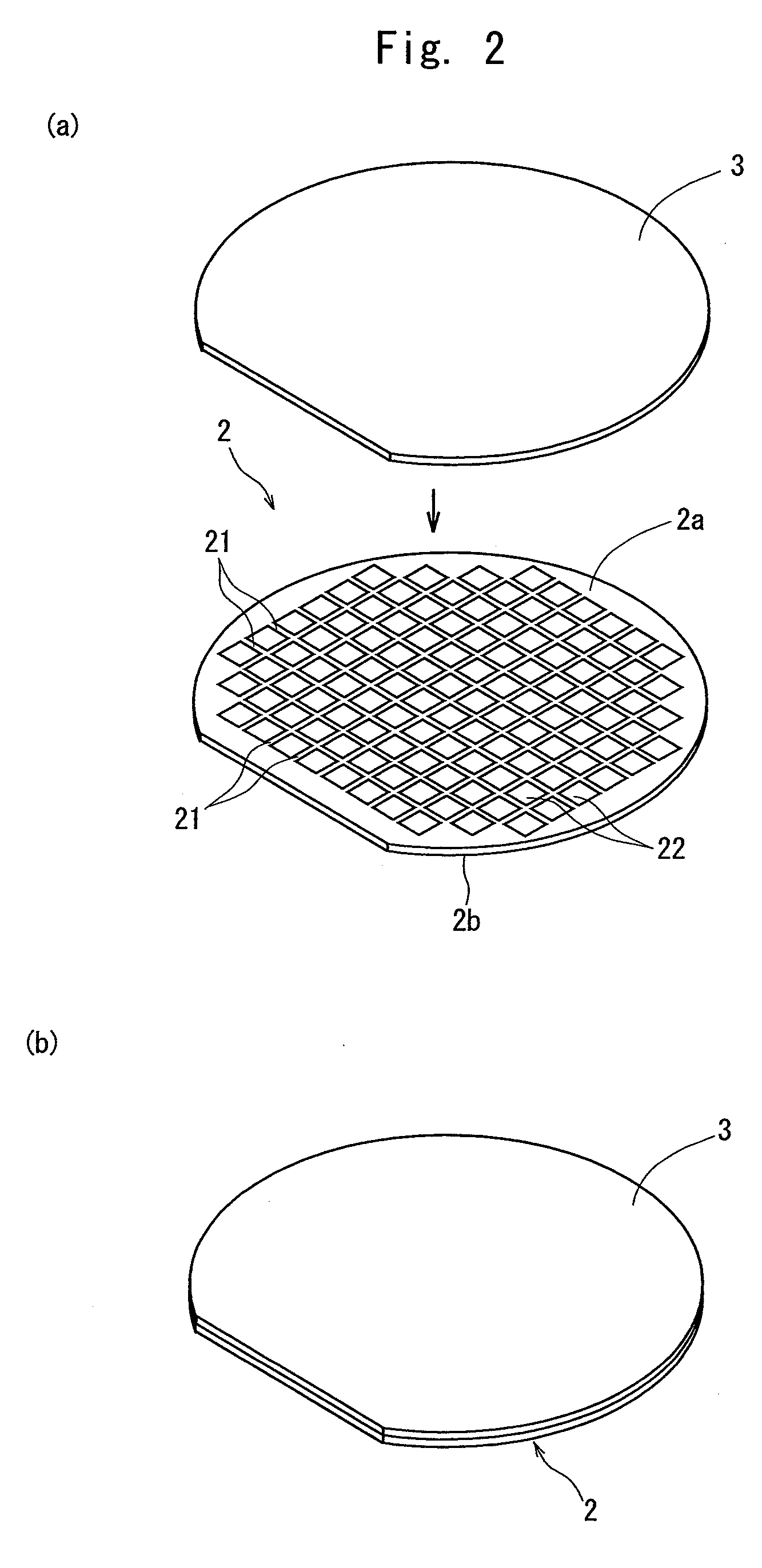

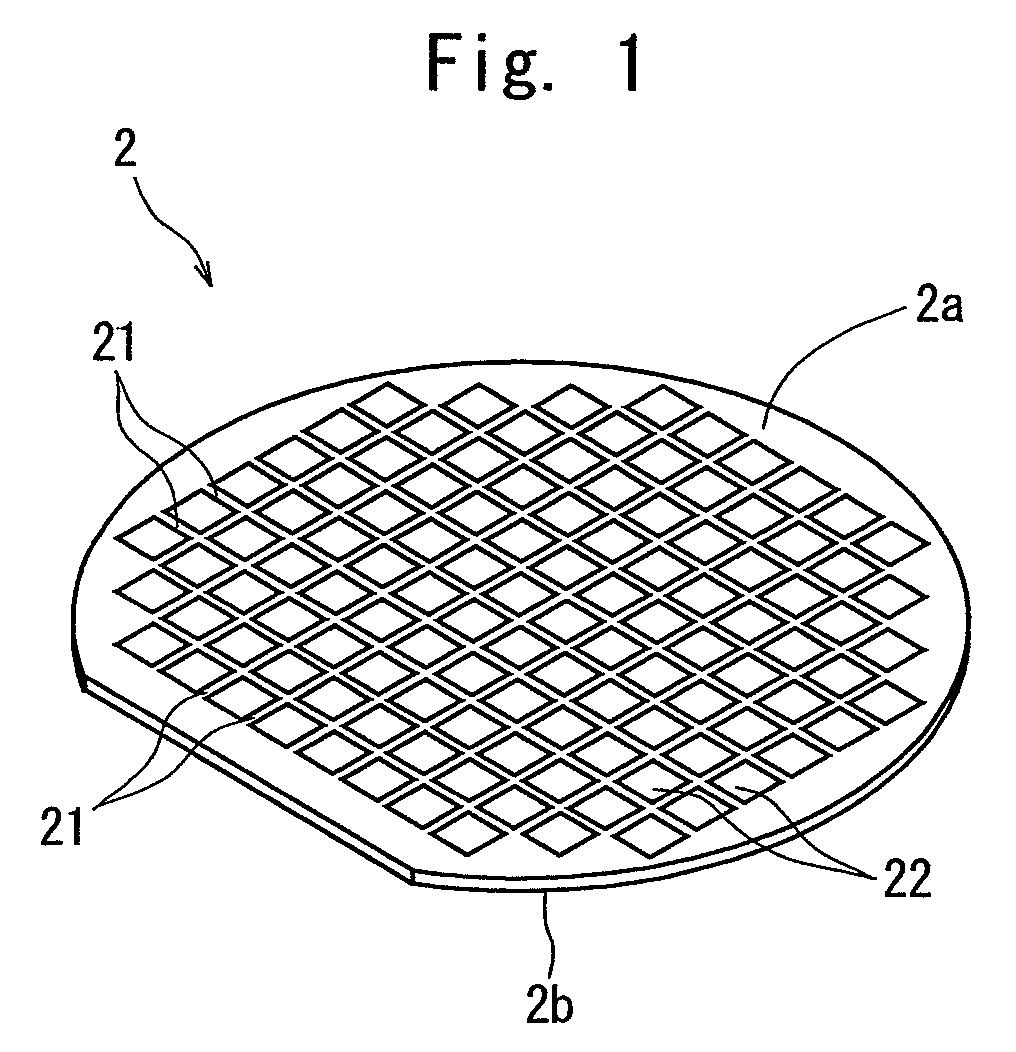

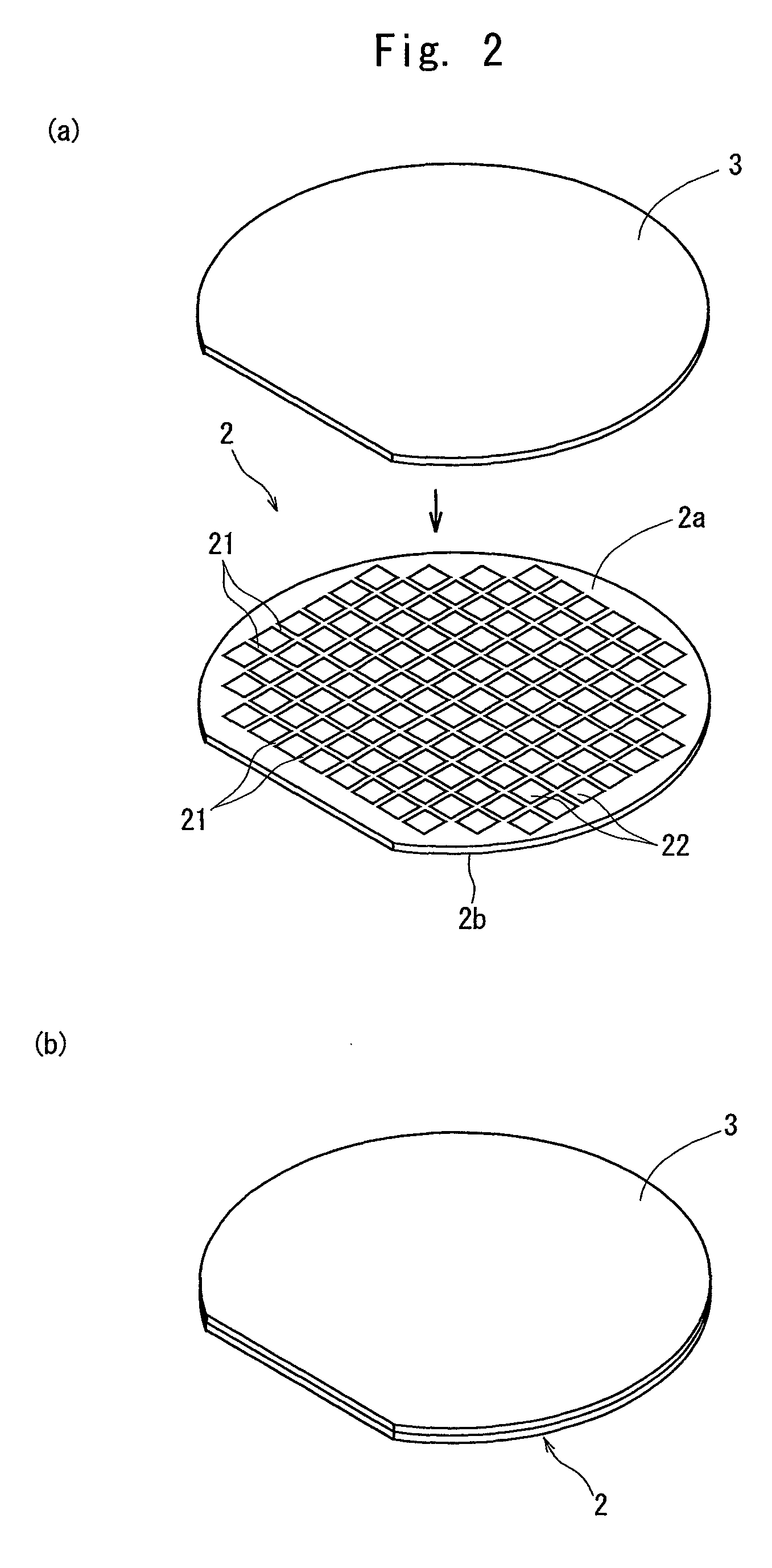

Wafer processing method

ActiveUS20050282359A1Transverse rupture strength of does not lowerHigh strengthSolid-state devicesSemiconductor/solid-state device manufacturingSplit linesWafer backgrinding

A wafer processing method for dividing a wafer having function elements in area sectioned by dividing lines formed on the front surface in a lattice pattern into individual chips along the dividing lines, comprising a deteriorated layer forming step for forming a deteriorated layer on the side of the back surface of a position at a distance corresponding to the final thickness of the chip from the front surface of the wafer by applying a laser beam capable of passing through the wafer along the dividing lines from the back surface of the wafer; a dividing step for dividing the wafer into individual chips along the dividing lines by applying external force to the wafer in which the deteriorated layer has been formed along the dividing lines; and a back surface grinding step for grinding the back surface of the wafer divided into individual chips to the final thickness of the chip.

Owner:DISCO CORP

Method of Forming Stacked Dies

ActiveUS20100144094A1High aspect ratioReduce riskSolid-state devicesSemiconductor/solid-state device manufacturingWafer backgrindingSilicon

The formation of through silicon vias (TSVs) in an integrated circuit (IC) die or wafer is described in which the TSV is formed in the integration process prior to metallization processing. TSVs may be fabricated with increased aspect ratio, extending deeper in a wafer substrate. The method generally reduces the risk of overly-thinning a wafer substrate in a wafer back-side grinding process typically used to expose and make electrical contacts to the TSVs. By providing deeper TSVs and bonding pads, individual wafers and dies may be bonded directly between the TSVs and bonding pads on an additional wafer.

Owner:TAIWAN SEMICON MFG CO LTD

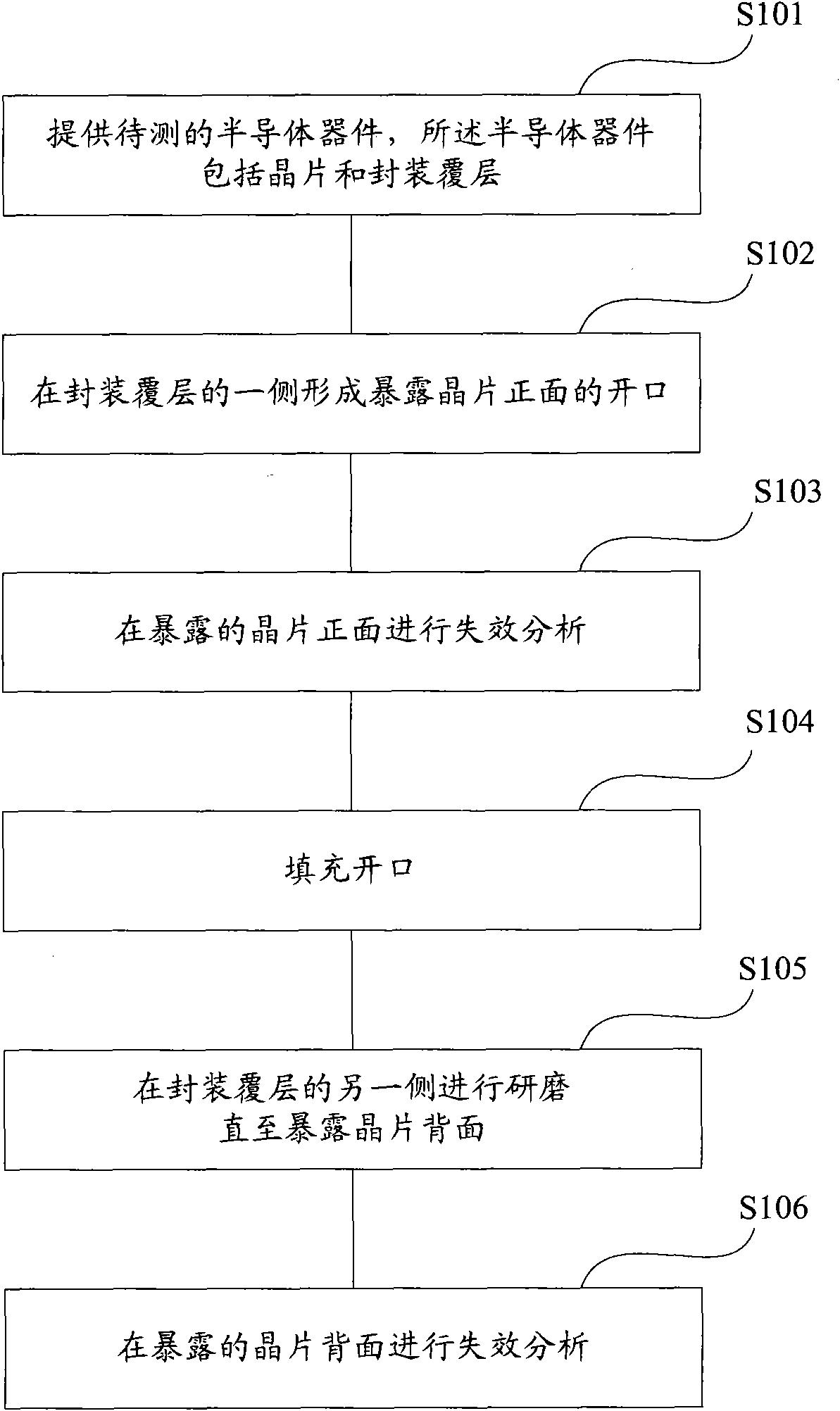

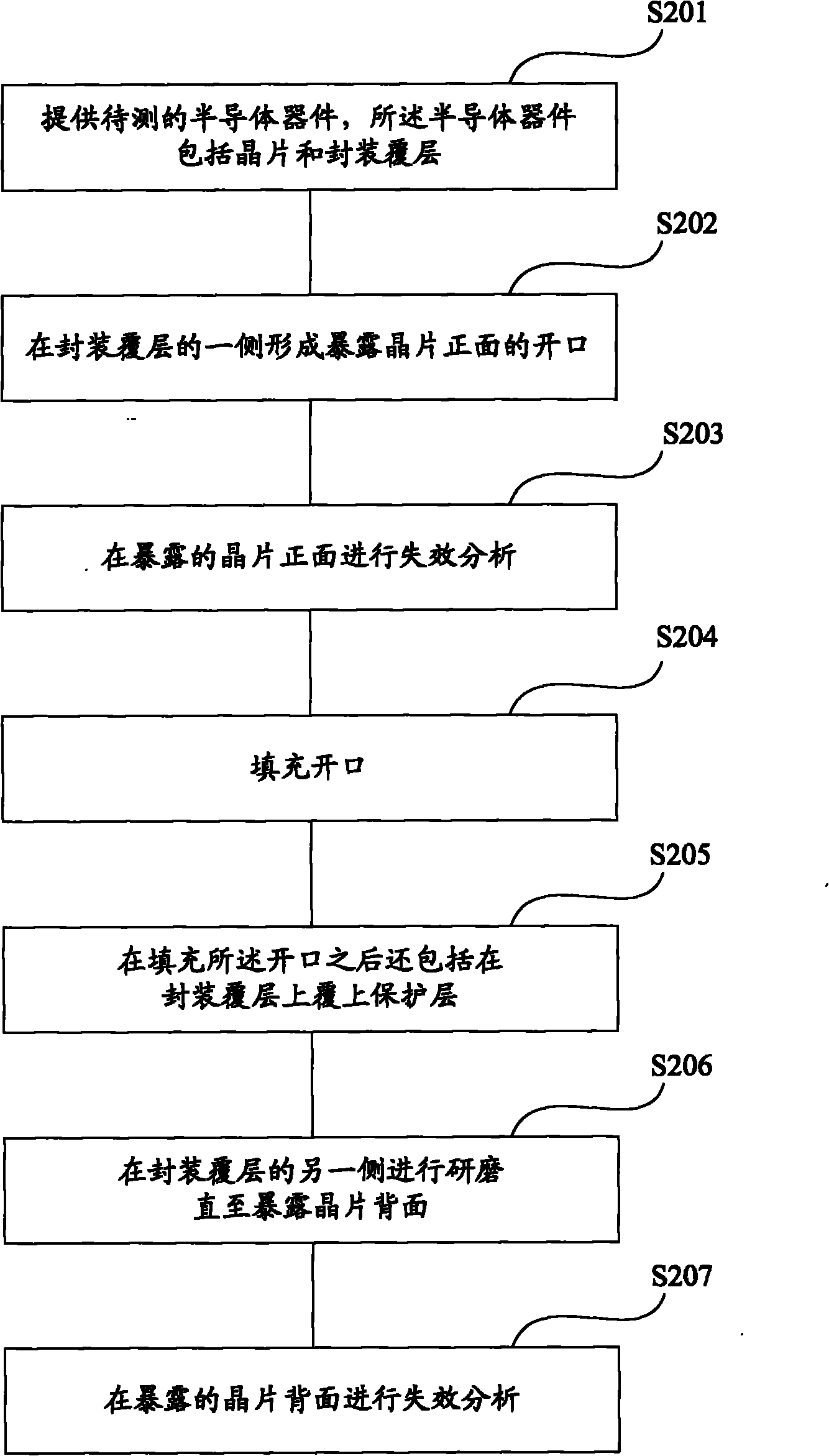

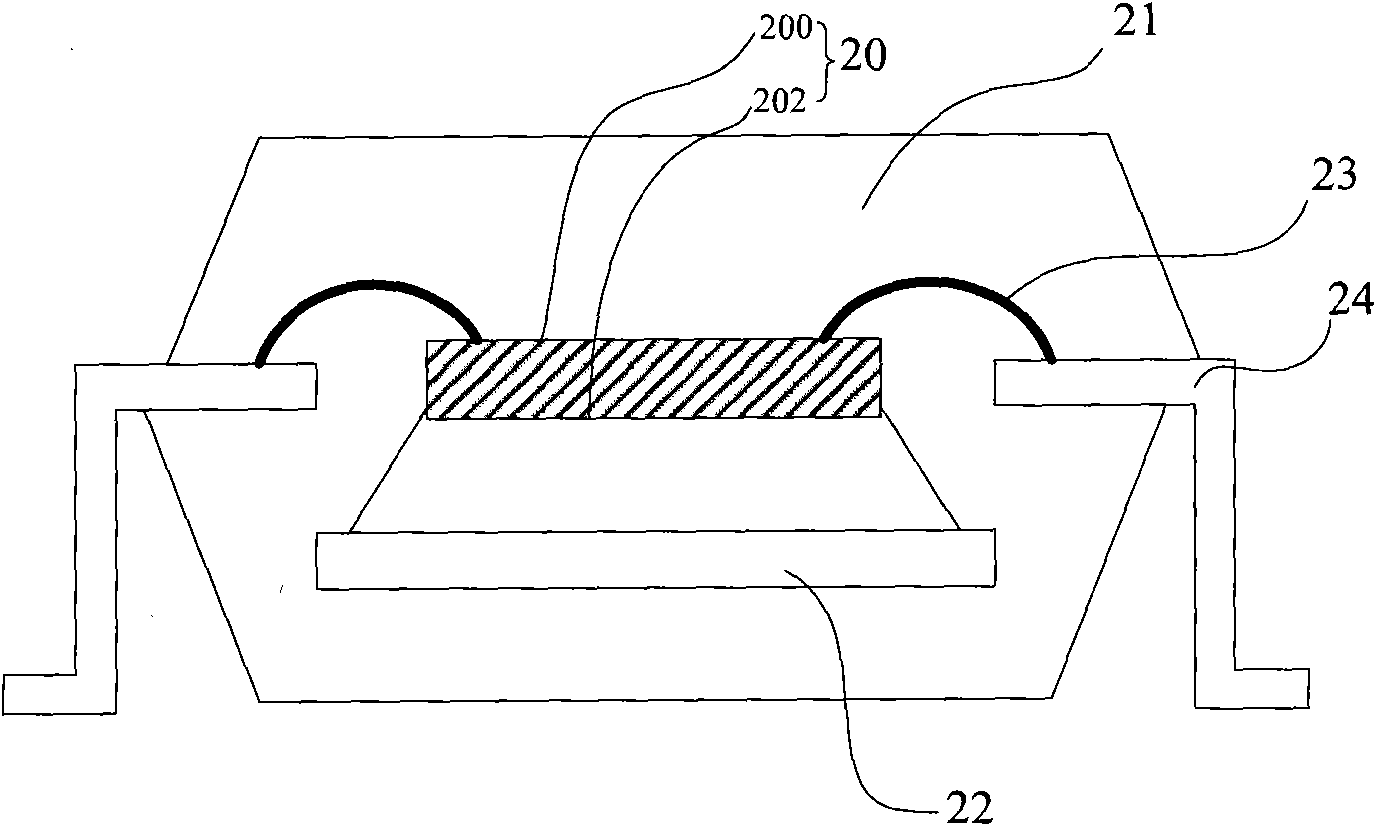

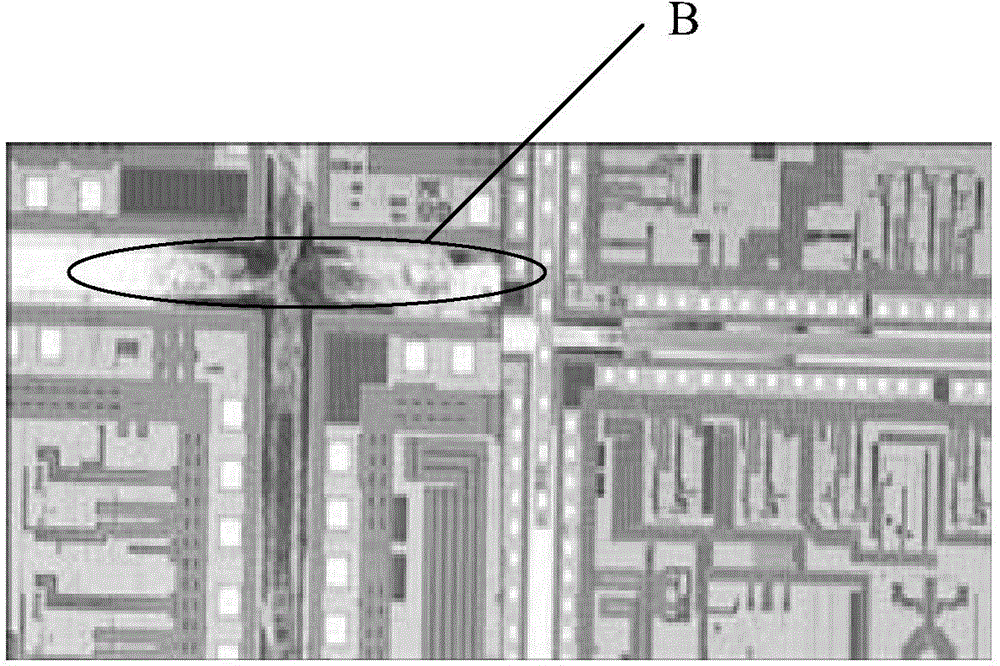

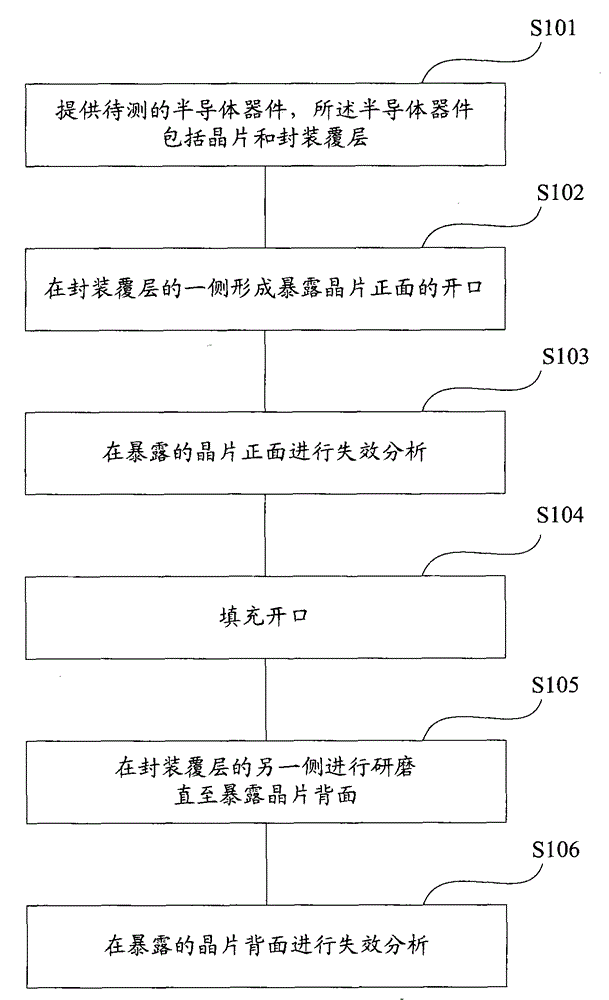

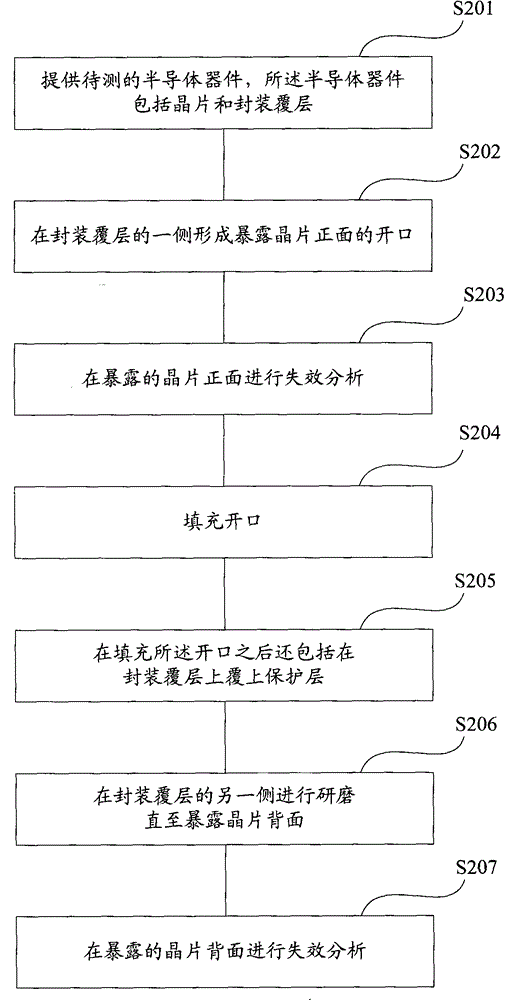

Method for carrying out failure analysis in semiconductor device

InactiveCN101769876AIncrease profitImprove accuracySurface/boundary effectOptically investigating flaws/contaminationWafer backgrindingFailure analysis

The invention relates to a method for carrying out failure analysis in a semiconductor device, which comprises the following steps: providing the semiconductor device to be tested, wherein the semiconductor device comprises a wafer and an encapsulation cladding; forming an opening which makes the front side of the wafer exposed on one side of the encapsulation cladding; carrying out failure analysis on the exposed front side of the wafer; filling the opening; carrying out grinding on the other side of the encapsulation cladding to expose the back of the wafer; and carrying out failure analysis on the exposed wafer back. Compared with the prior art, the invention adopts the method of opening on the front side of the wafer firstly and then grinding on the back of the wafer, realizes once failure analysis respectively on the front side and the back of the wafer, improves the accuracy of the failure analysis, strengthens the effect of the failure analysis and improves the utilization rate of the wafer.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

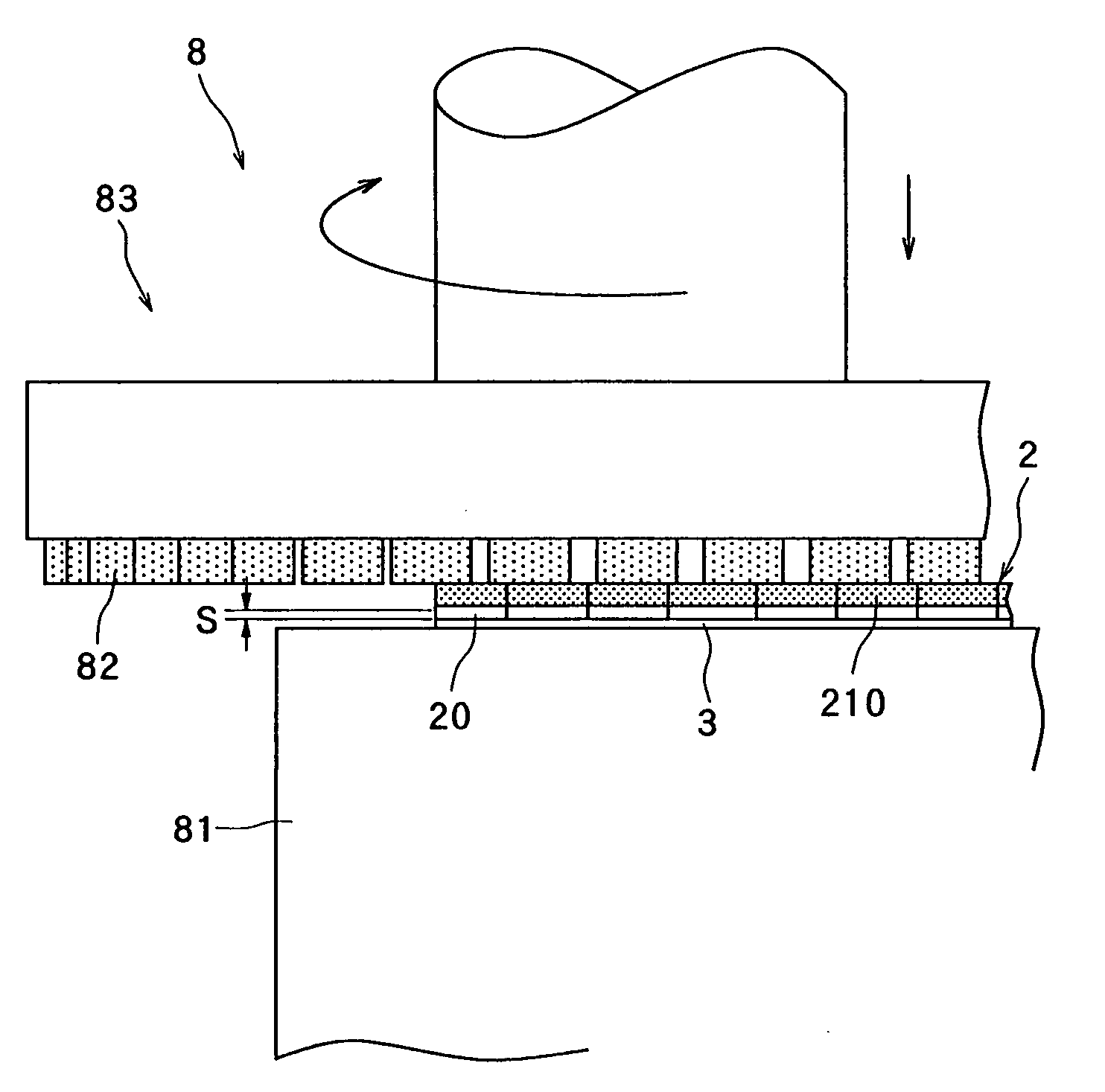

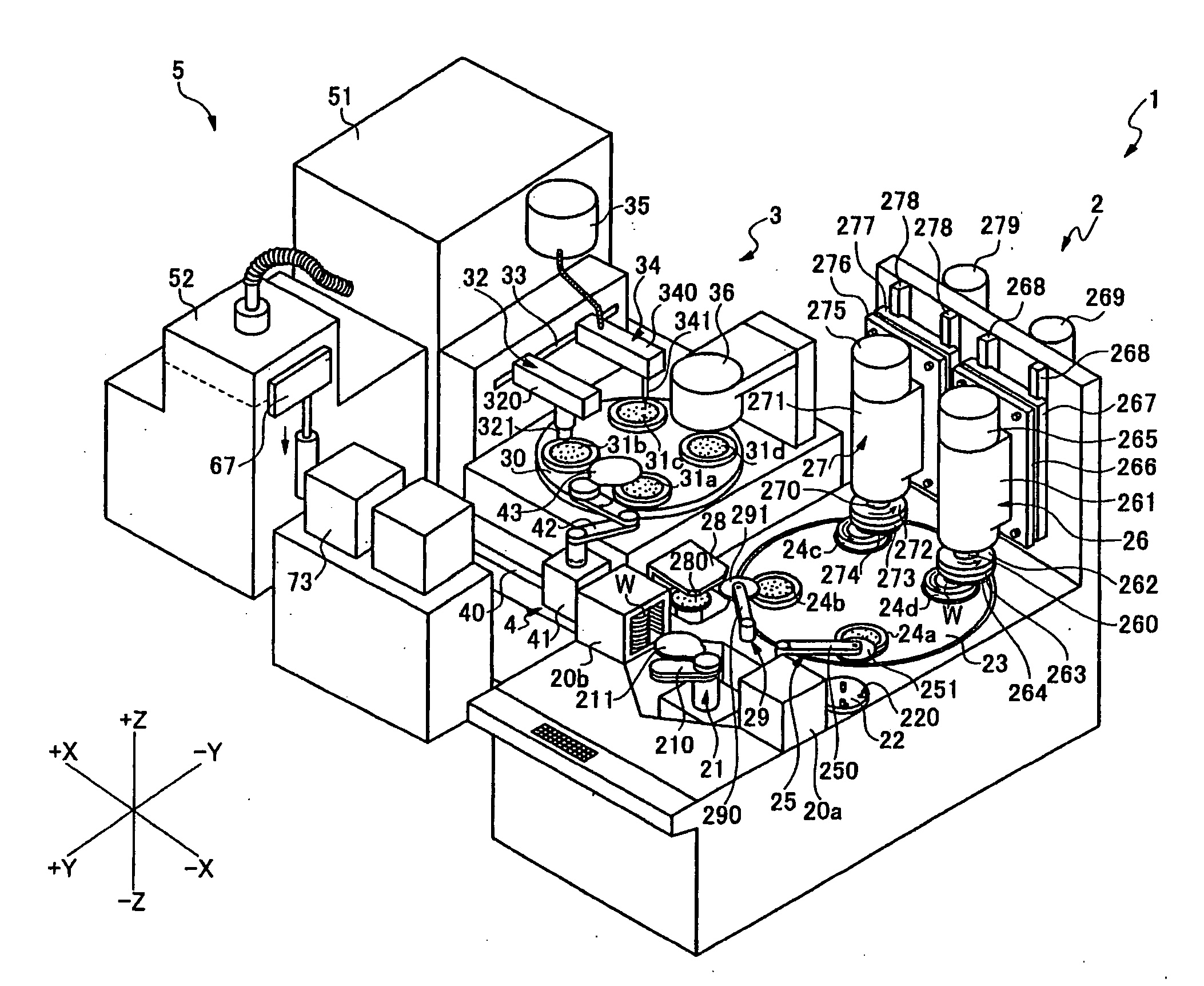

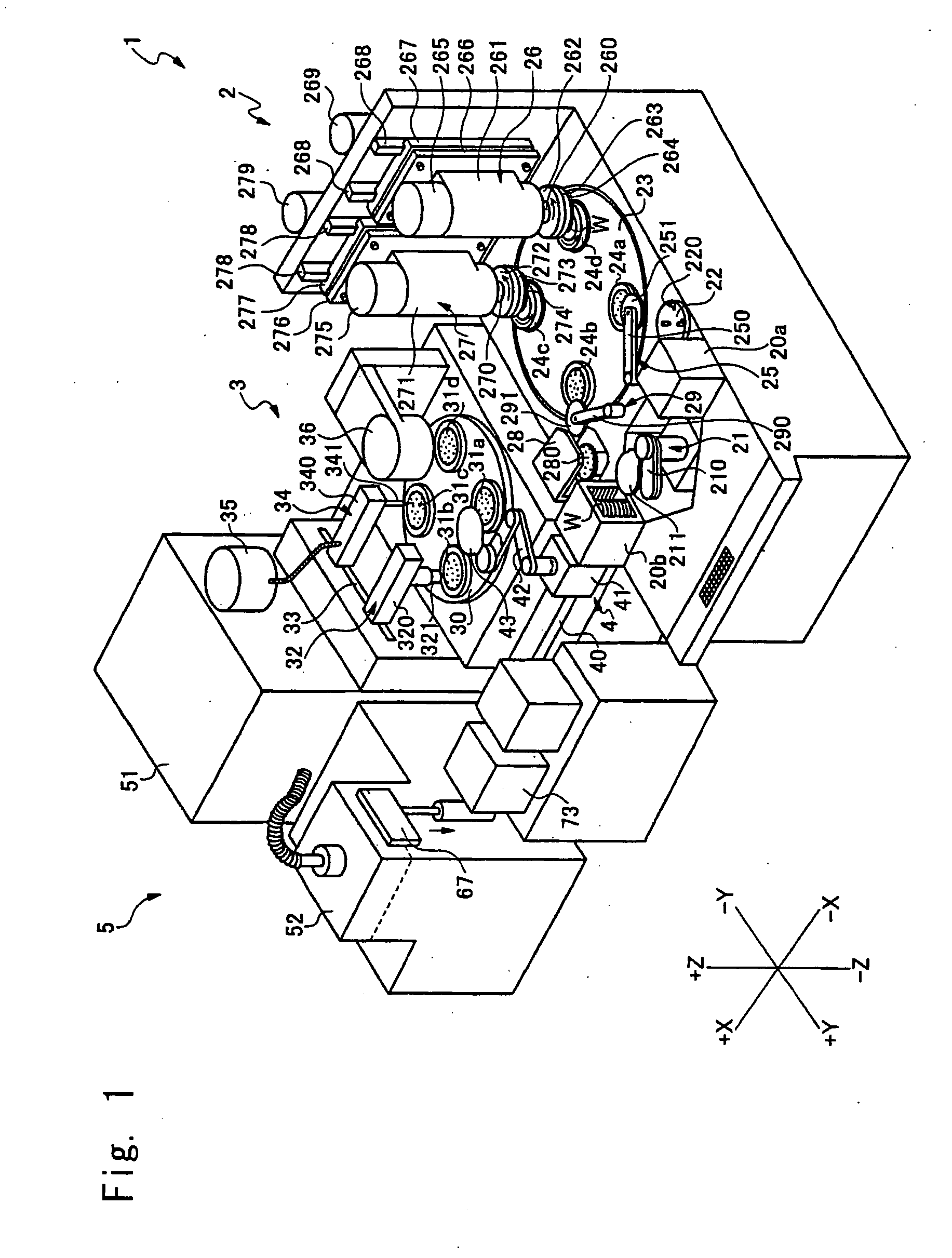

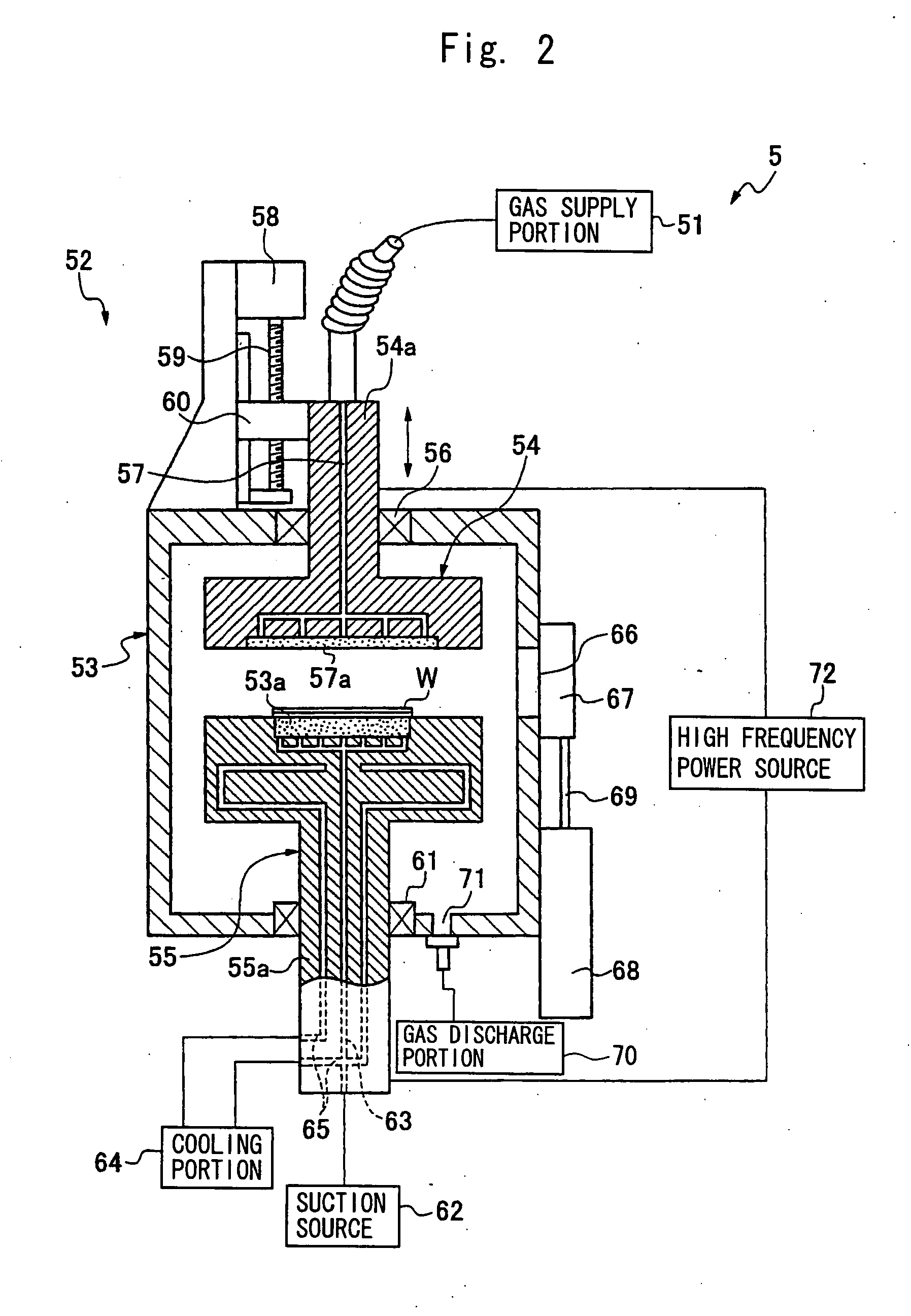

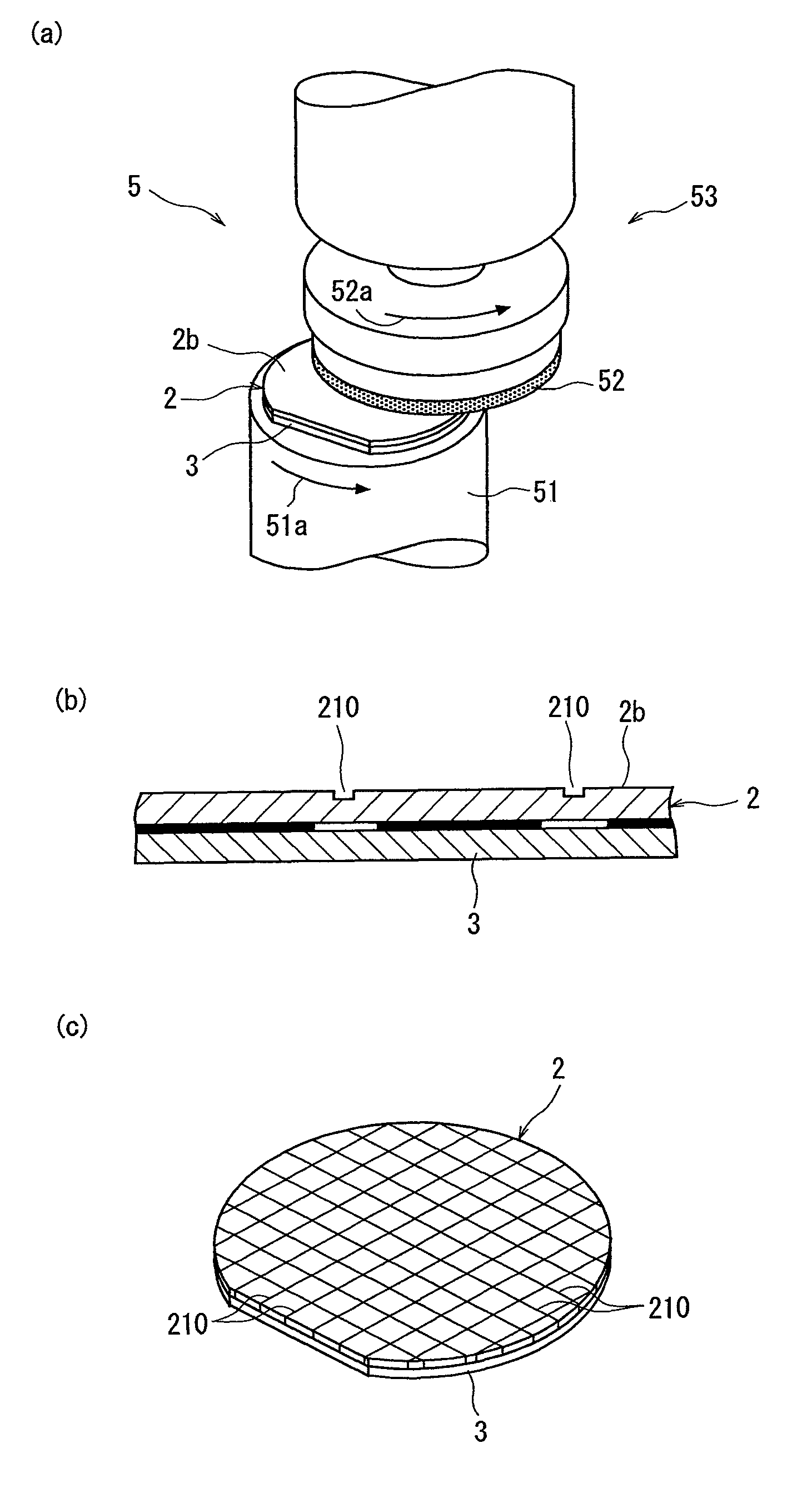

Wafer machining apparatus

InactiveUS20060130967A1Decrease productivityWithout deteriorating quality of deviceSolid-state devicesSemiconductor/solid-state device manufacturingResistWafer backgrinding

The present invention provides a wafer machining apparatus which can separate streets with high efficiency, without deteriorating the quality of devices, in dividing a wafer into individual devices. The wafer machining apparatus comprises grinding means for grinding the back of the wafer; resist film coating means for passing a radiation from the back side to the face side of the wafer to recognize the streets, and coating a resist film onto regions other than street-corresponding regions; and plasma etching means for etching away the street-corresponding regions in a range from the back to the face of the wafer to divide the wafer into individual devices, and thus can perform a procedure ranging from grinding of the back of the wafer to the division of the wafer into the devices. In the resist film coating means, the wafer is imaged from the back side by an infrared imaging portion to recognize the streets formed on the face side, and a liquid resist is jetted from a resist jetting portion toward the regions other than the street-corresponding regions, whereby only the street-corresponding regions can be exposed.

Owner:DISCO CORP

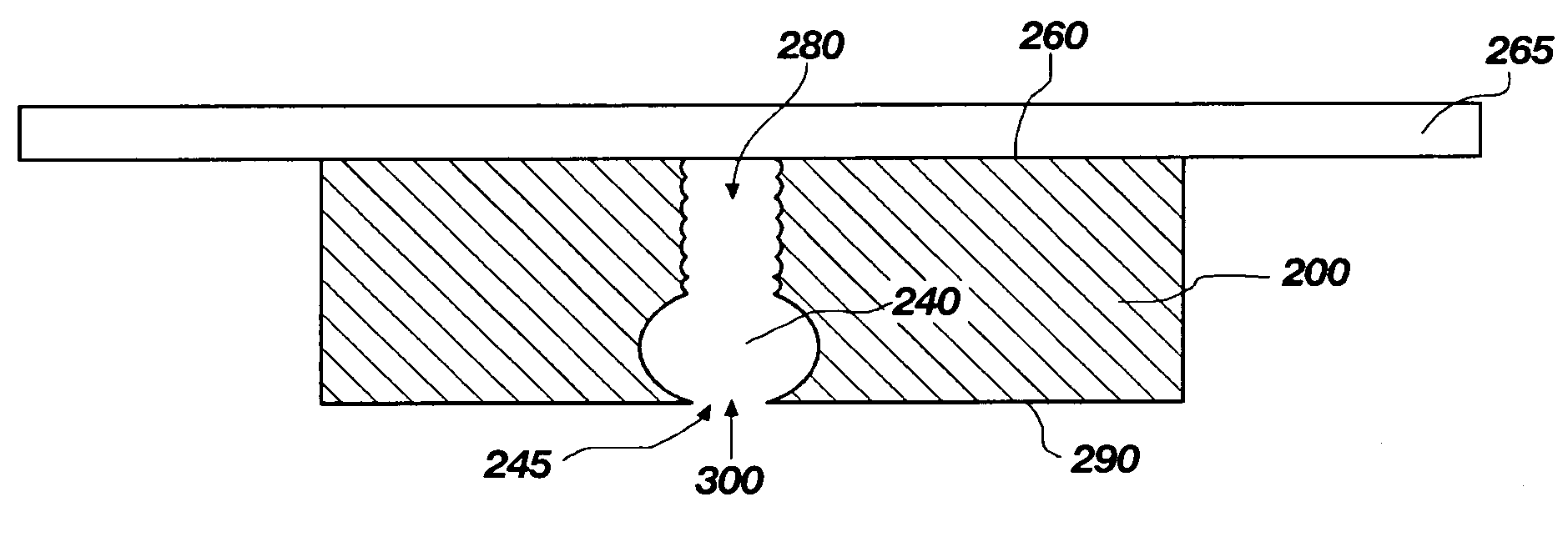

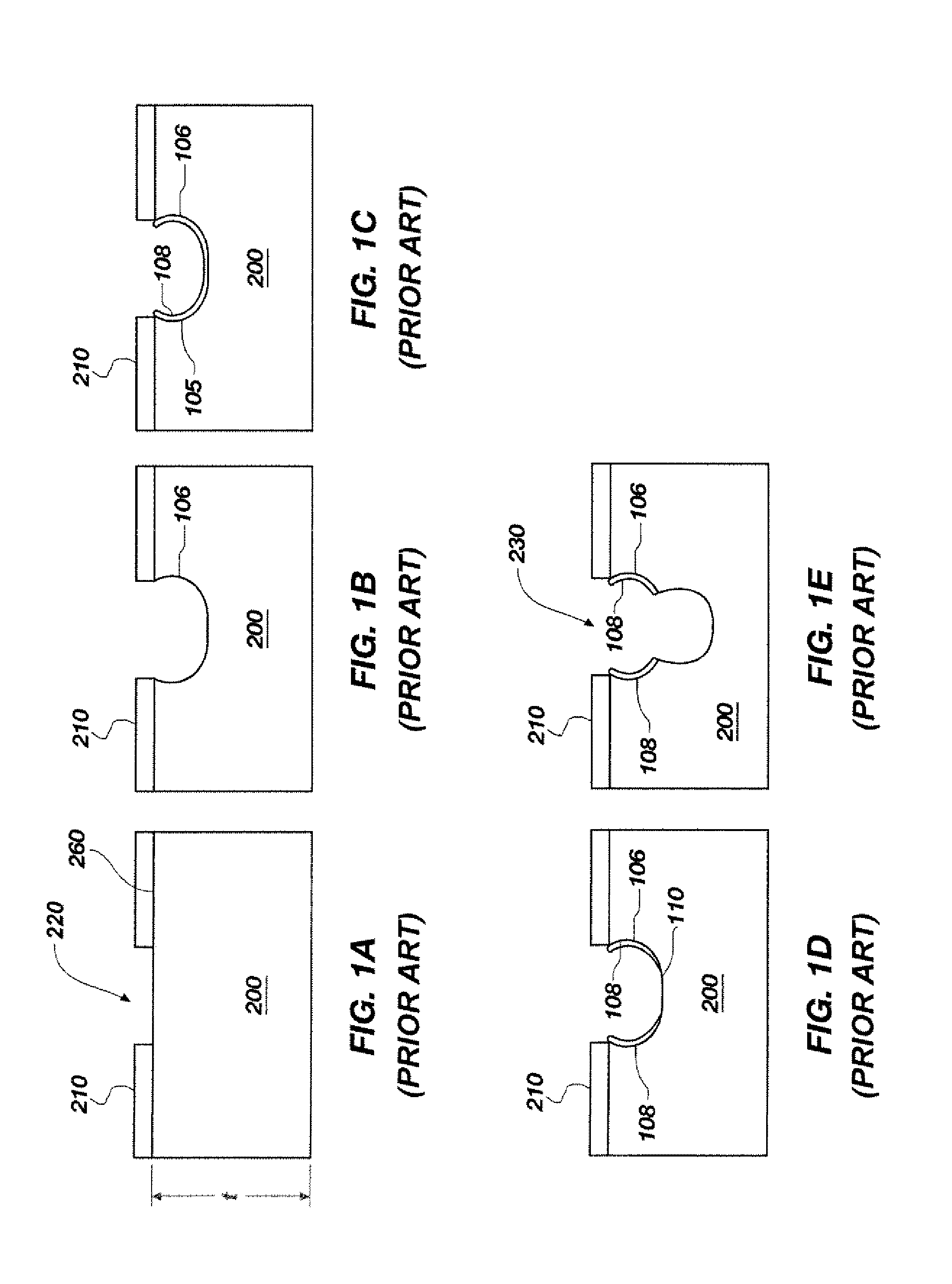

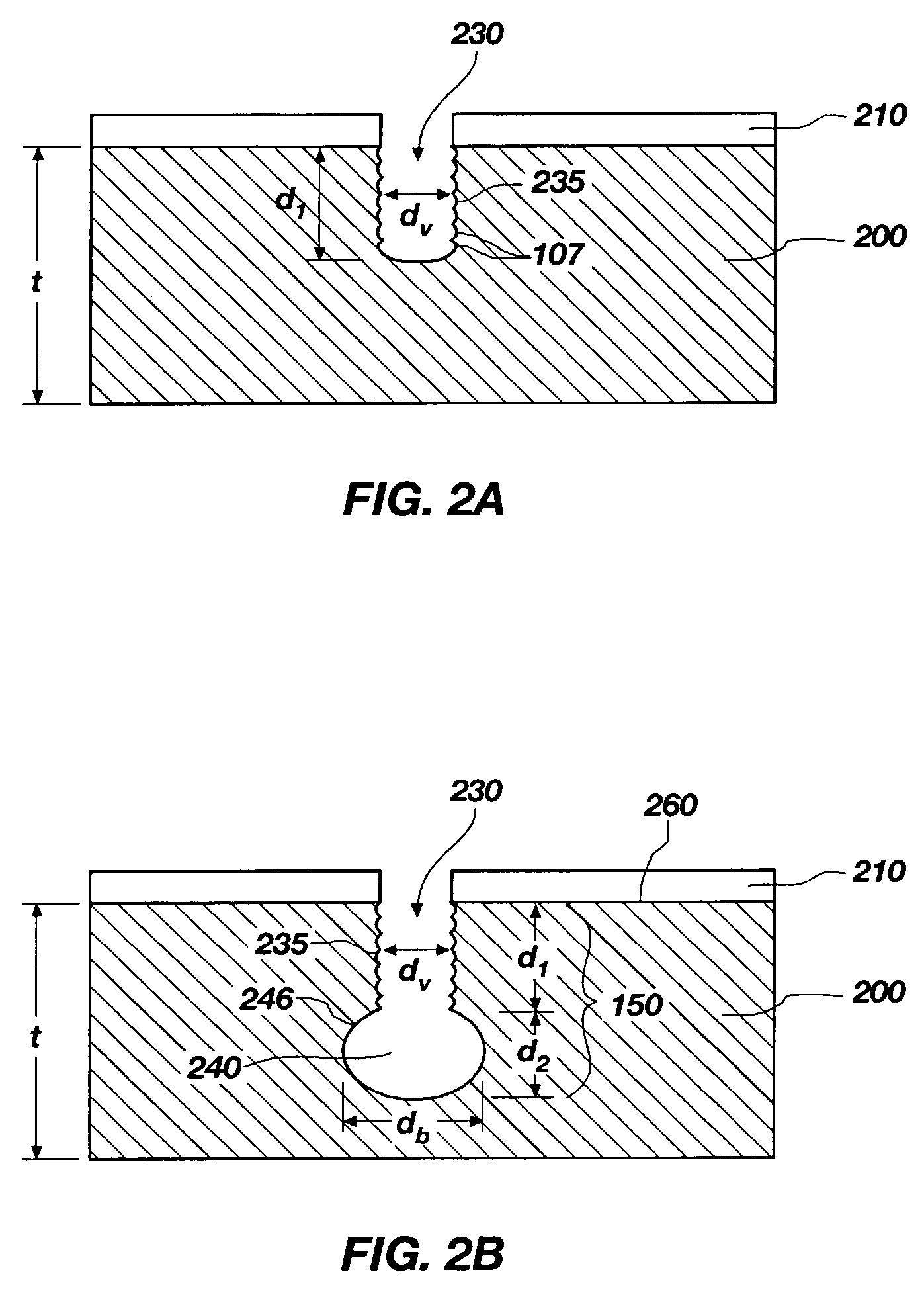

Semiconductor substrates including vias of nonuniform cross section, methods of forming and associated structures

ActiveUS7425507B2Semiconductor/solid-state device detailsSolid-state devicesWafer backgrindingConductive materials

Methods for forming a via and a conductive path are disclosed. The methods include forming a via within a wafer with cyclic etch / polymer phases, followed by an augmented etch phase. The resulting via may include a first portion having a substantially uniform cross section and a second portion in the form of a hollow ball, extending laterally further within the wafer than the first portion. Back-grinding the wafer to the second portion of the via may create a vent. A conductive path may be formed by filling the via with a conductive material, such as solder. Flux gases may escape through the vent. The wafer surrounding the second portion of the via may be removed, exposing a conductive element in the shape of a ball, the shape of the second portion of the via. Semiconductor devices including the conductive paths of the present invention are also disclosed.

Owner:MICRON TECH INC

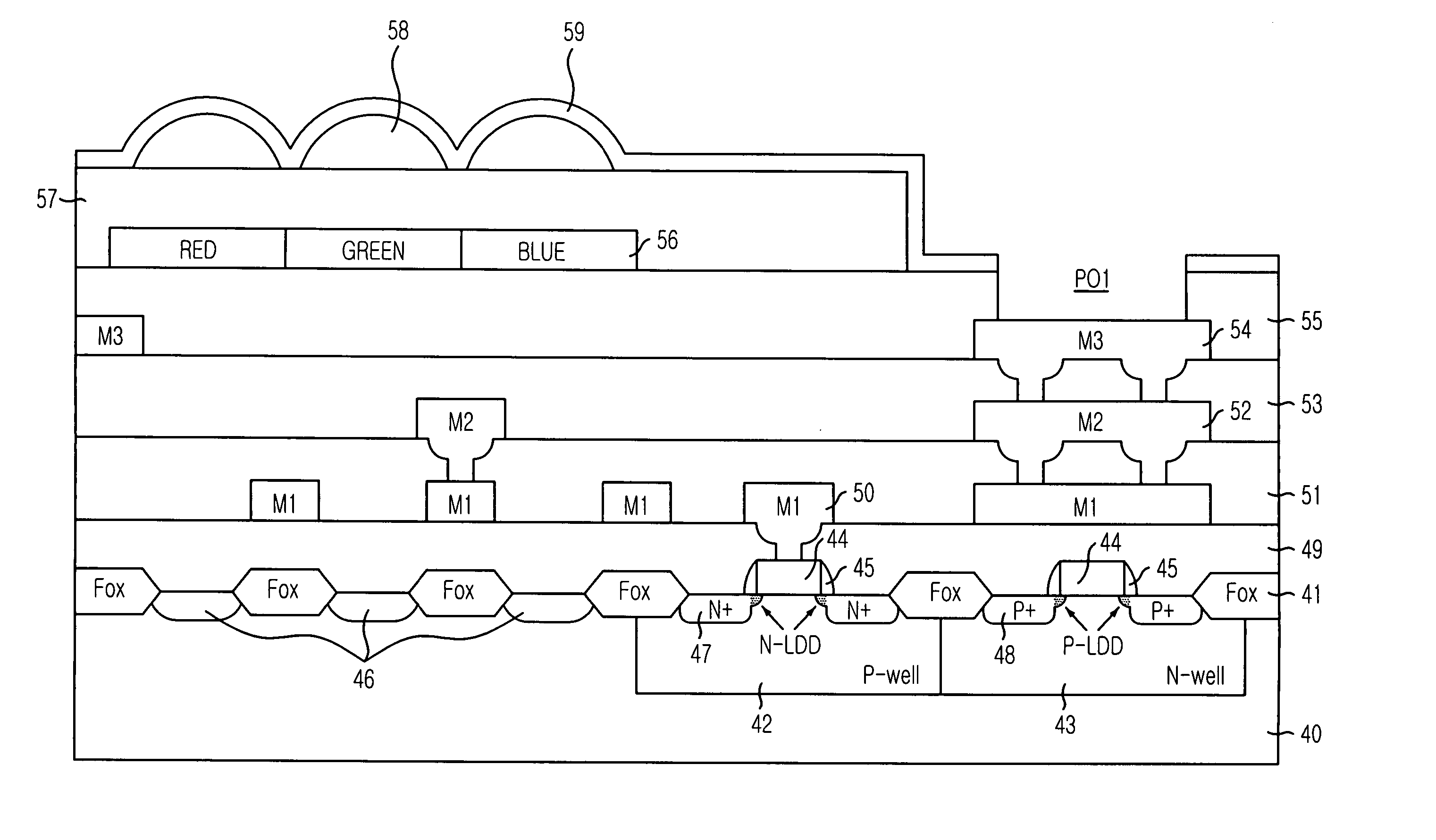

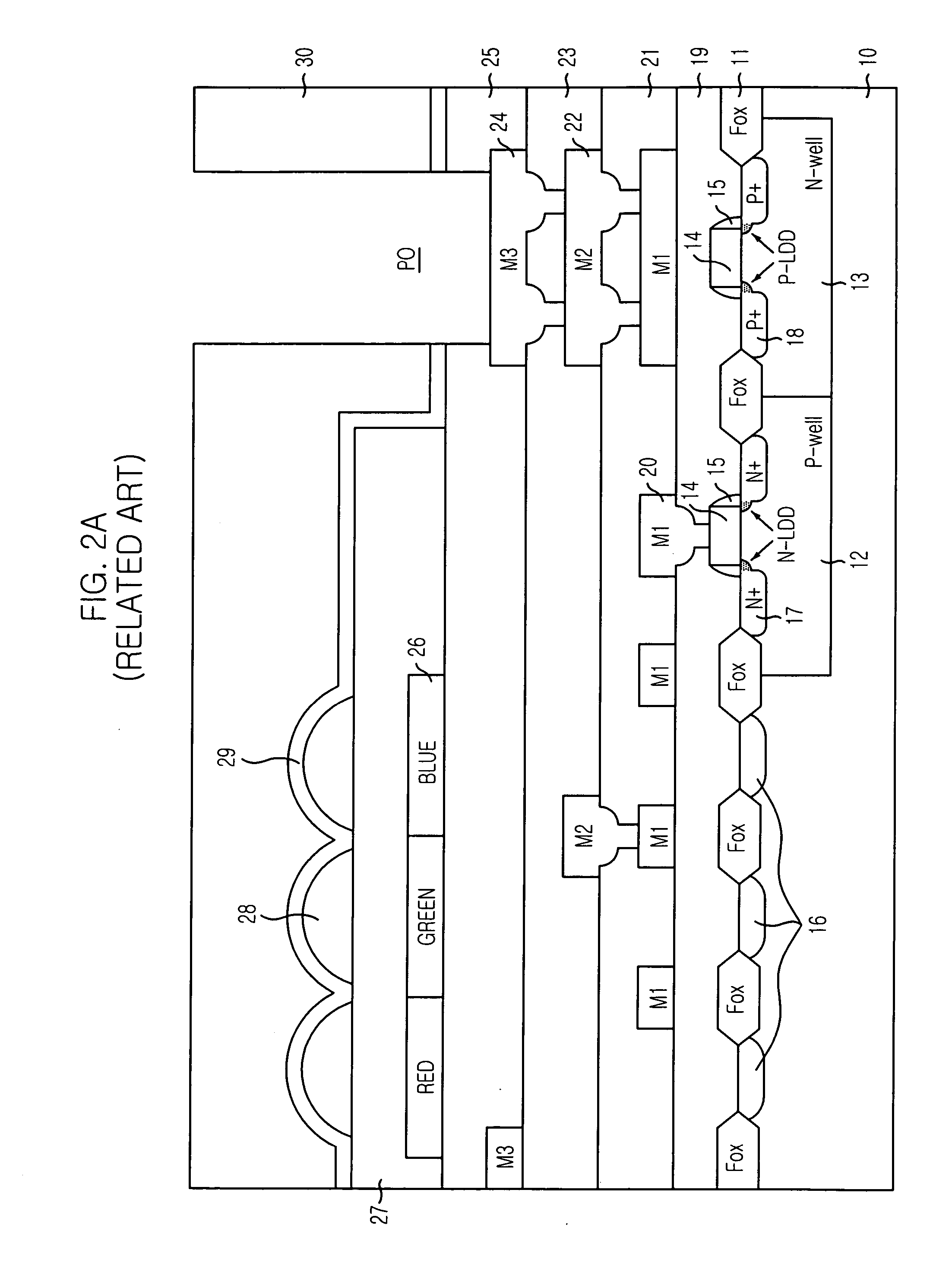

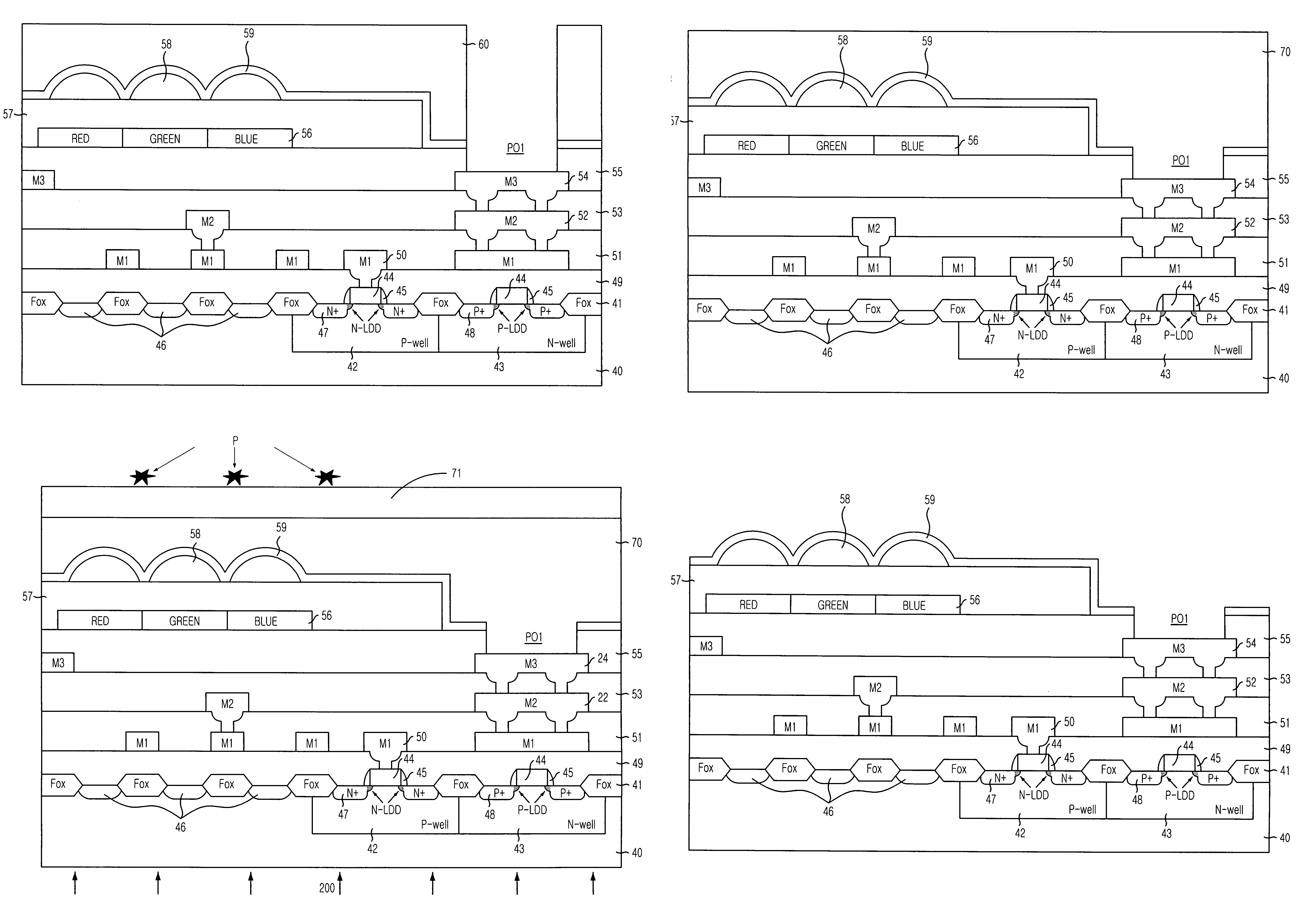

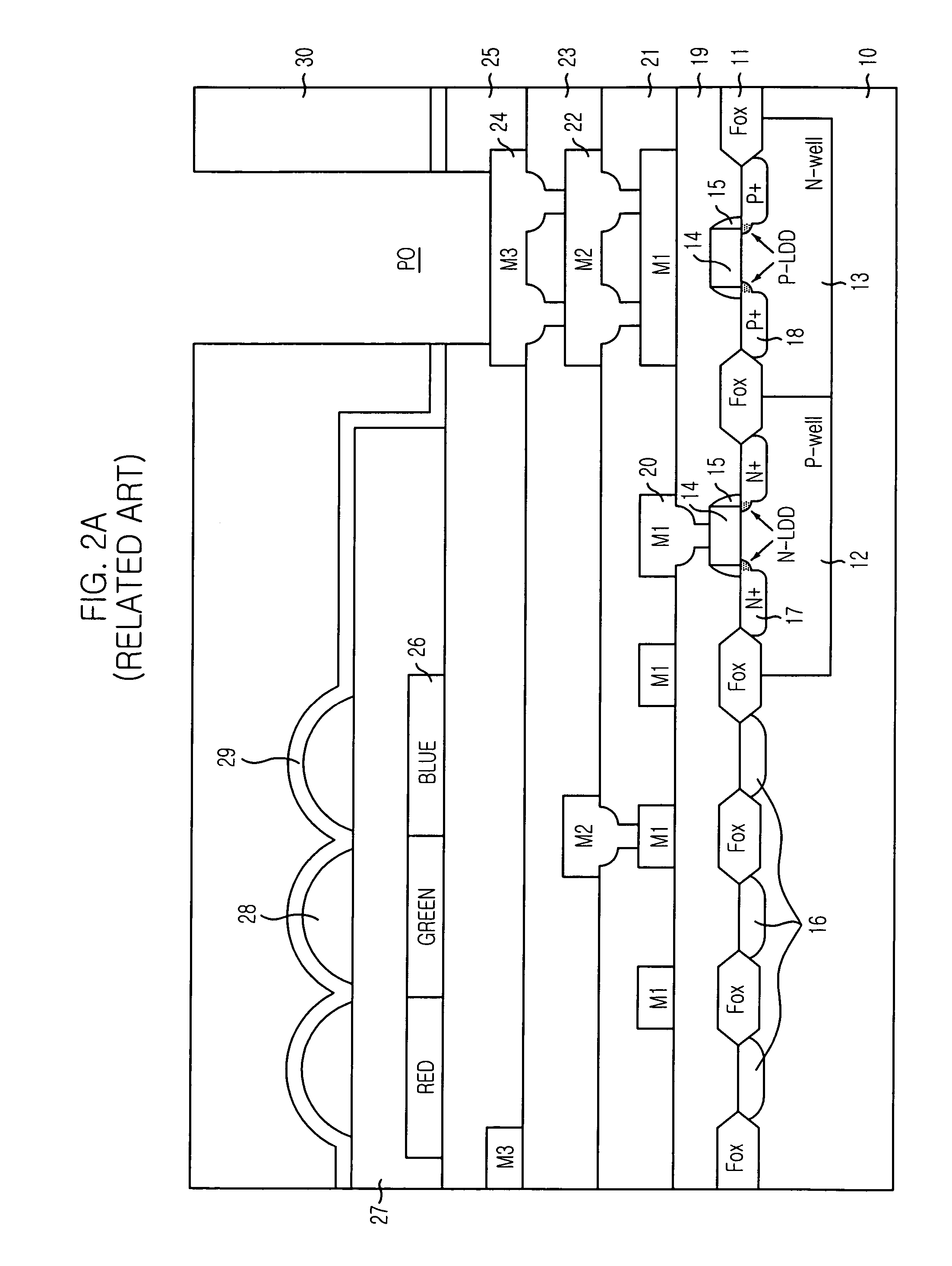

Method for fabricating image sensor using wafer back grinding

ActiveUS20060228826A1Reduce pollutionSolid-state devicesSemiconductor/solid-state device manufacturingLight sensingPhotodetector

Provided is a method for fabricating an image sensor using a wafer back grinding process. The method includes: forming a microlens protection layer over a substrate structure including a light sensing device and other associated devices; opening a pad open unit of the substrate structure using a mask; removing the mask; forming a photoresist layer over the substrate structure with the microlens protection layer; gluing a tape on the photoresist layer; performing a wafer back grinding process; and removing the tape and the photoresist layer.

Owner:INTELLECTUAL VENTURES II

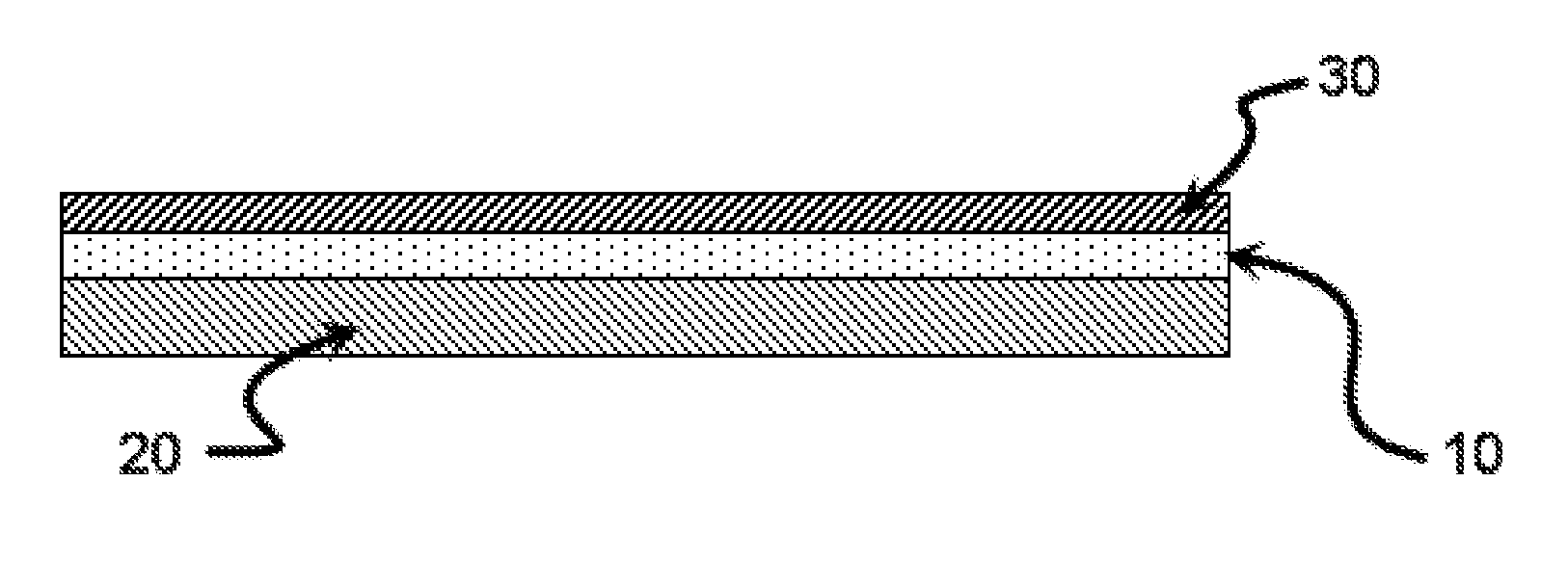

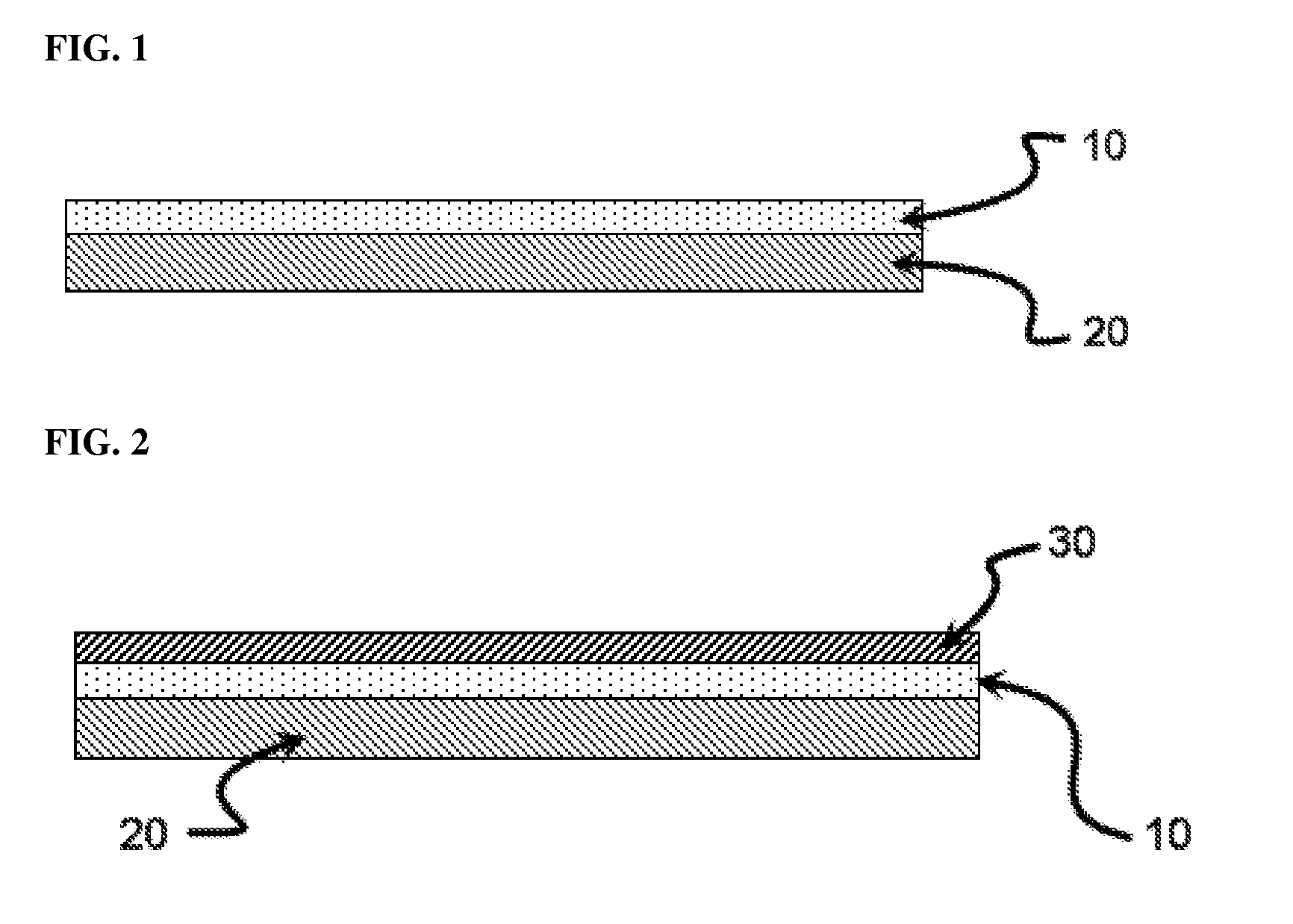

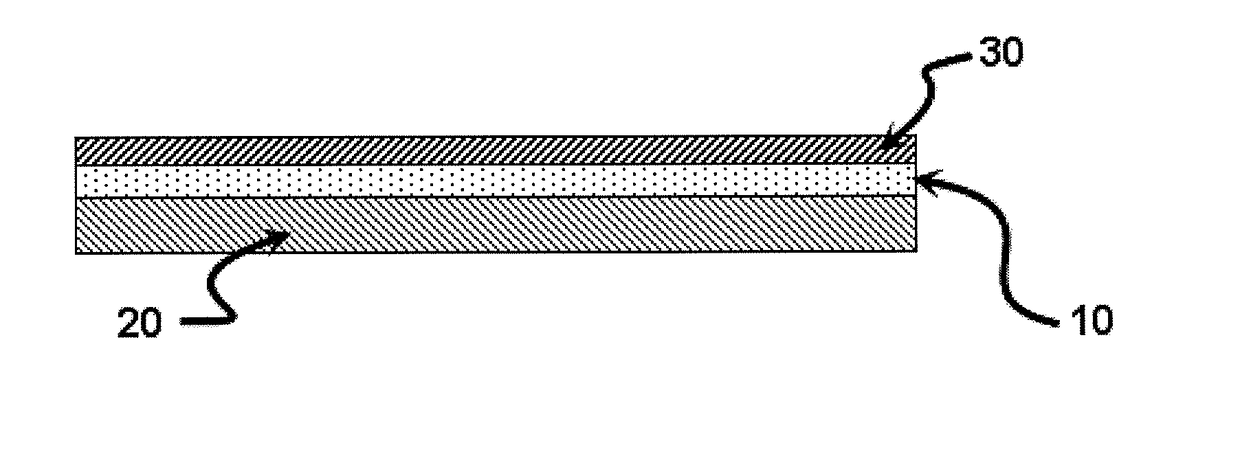

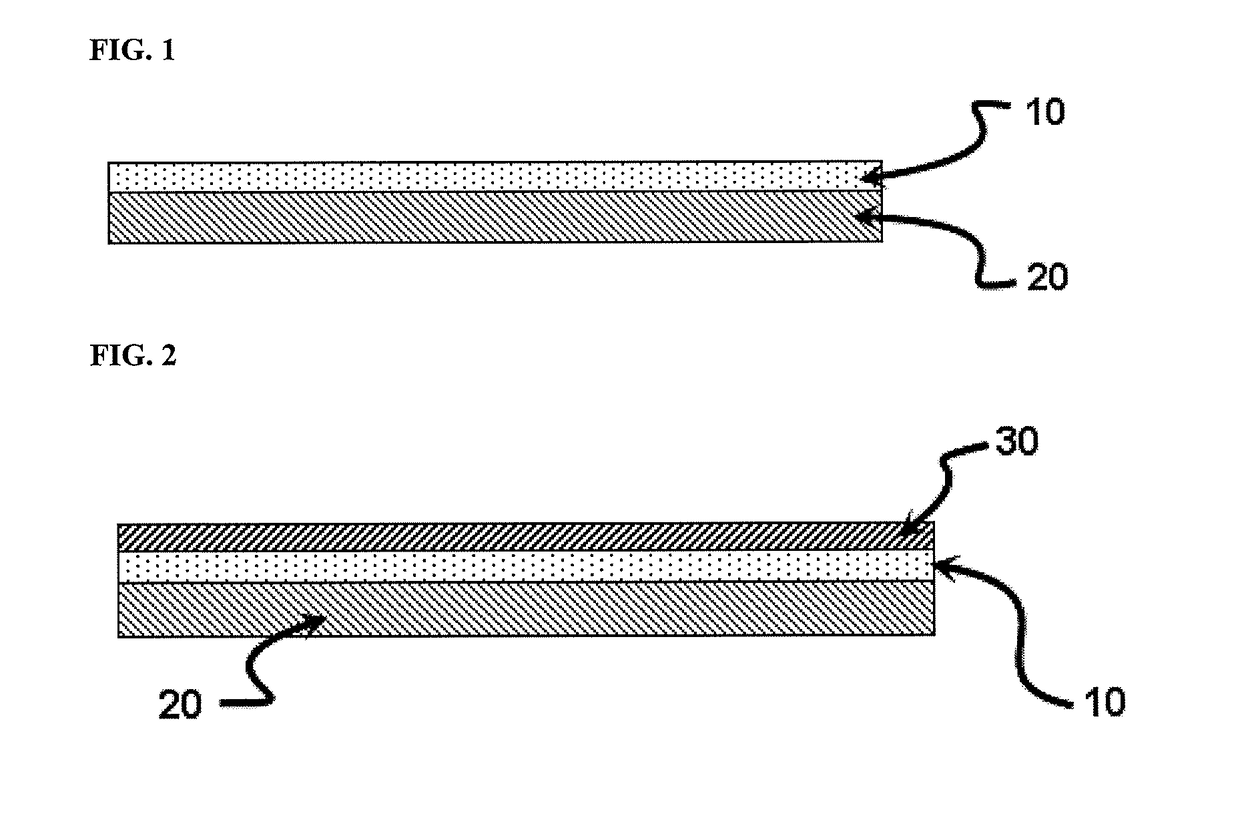

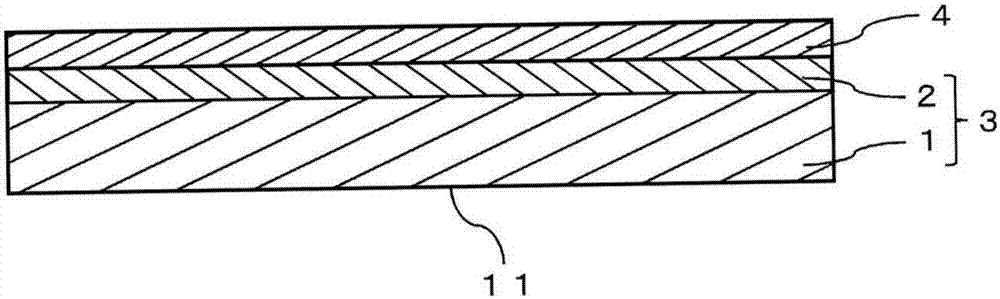

Adhesive composition, adhesive sheet, and back grinding method for semiconductor wafer

InactiveUS20110139347A1Reduce hydrophilicityExcellent wafer-proofing propertyLamination ancillary operationsSynthetic resin layered productsWafer backgrindingSemiconductor

The present invention relates to a pressure-sensitive adhesive composition including a polymer of a monomer mixture containing isobonyl (meth)acrylate, a pressure-sensitive adhesive sheet, and a semiconductor wafer backgrinding method. In the present invention, by using isobonyl (meth)acrylate which is a hard-type monomer and has a low hydrophilic property, a pressure-sensitive adhesive composition having superior releasing and re-releasing properties and wettability with respect to the wafer, and having an excellent wafer-proofing property; a pressure-sensitive adhesive sheet prepared by using the pressure-sensitive adhesive composition; and a backgrinding method using the pressure-sensitive adhesive sheet can be provided.

Owner:LG CHEM LTD

Method for fabricating image sensor using wafer back grinding

ActiveUS7449357B2Reduce pollutionSolid-state devicesSemiconductor/solid-state device manufacturingLight sensingWafer backgrinding

Owner:INTELLECTUAL VENTURES II

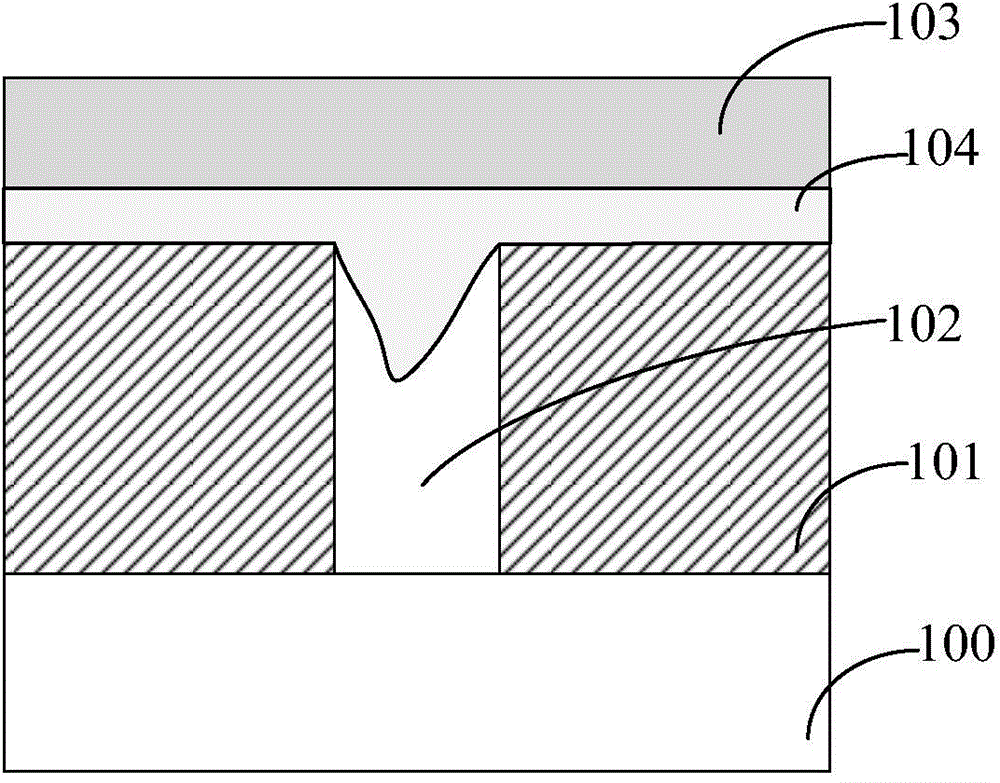

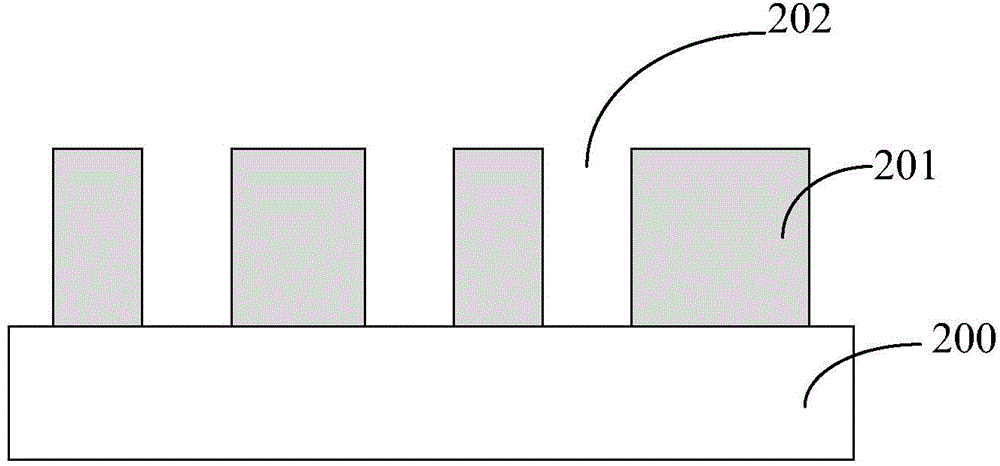

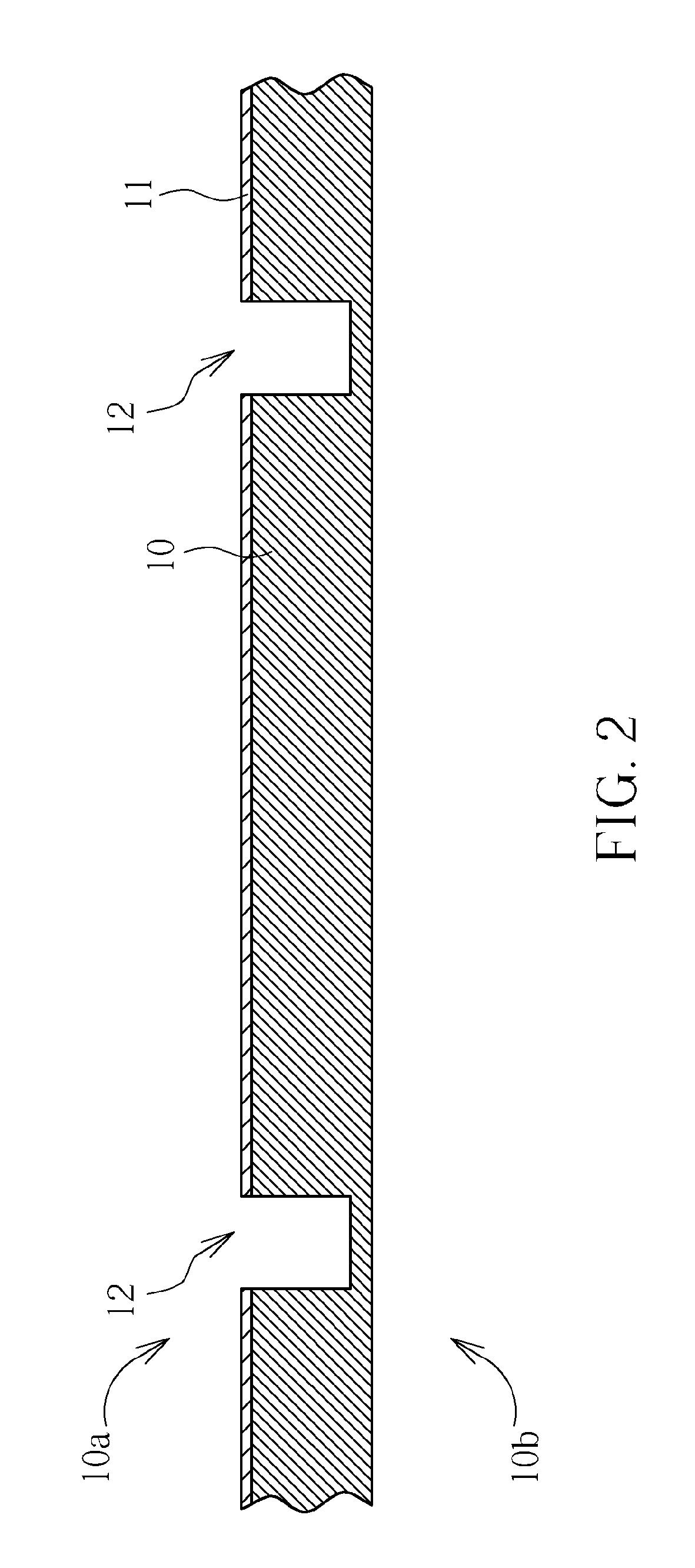

Thickness reduction method for wafer

ActiveCN106033708ASolve the problem of entering the chipSemiconductor/solid-state device manufacturingWafer backgrindingEngineering

The invention provides a thickness reduction method for wafer. The method comprises: a semiconductor wafer is provided, a passivation layer is formed on the front side of the semiconductor wafer, and the passivation layer is etched to form a groove; a filling layer covering the wafer edge, the groove and the passivation layer is formed; the part, beyond the wafer edge and the groove are, of the filling layer is removed; an adhesive tape is formed on the passivation layer; wafer backside grinding is carried out on the wafer; the adhesive tape is removed; and the filling layer is removed. According to the method, because the filling layer is formed at gaps like a cutting lane and the wafer edge, when wafer backside grinding is carried out, silicon powder that is caused during the grinding process can not enter the chip either from the side of the wafer or from the bottom based on filling by the filling layer at the gaps and the wafer edge, so that a problem of silicon powder entrance into the chip during the wafer backside grinding process can be solved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Process for the back-surface grinding of wafers

InactiveUS6958256B2AdhesionIncrease dampingNon-macromolecular adhesive additivesFilm/foil adhesivesWafer backgrindingSurface grinding

The present invention relates to a process for the back-surface grinding of wafers using films which have a support layer, which is known per se, and an adhesion layer which can be polymerized in steps, and to films which include such an adhesion layer which can be polymerized in steps, and to the use thereof.

Owner:POLARIS INNOVATIONS LTD

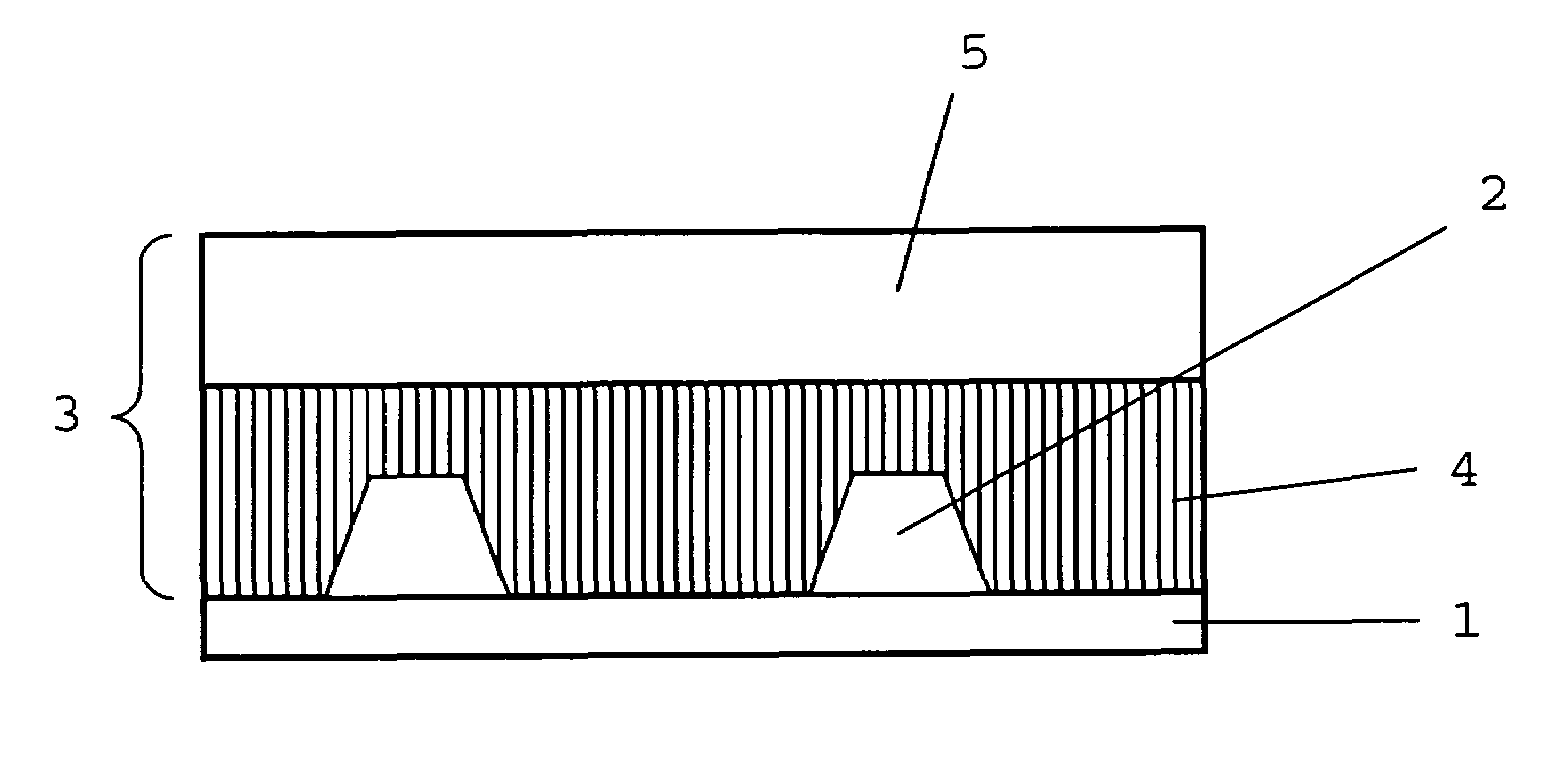

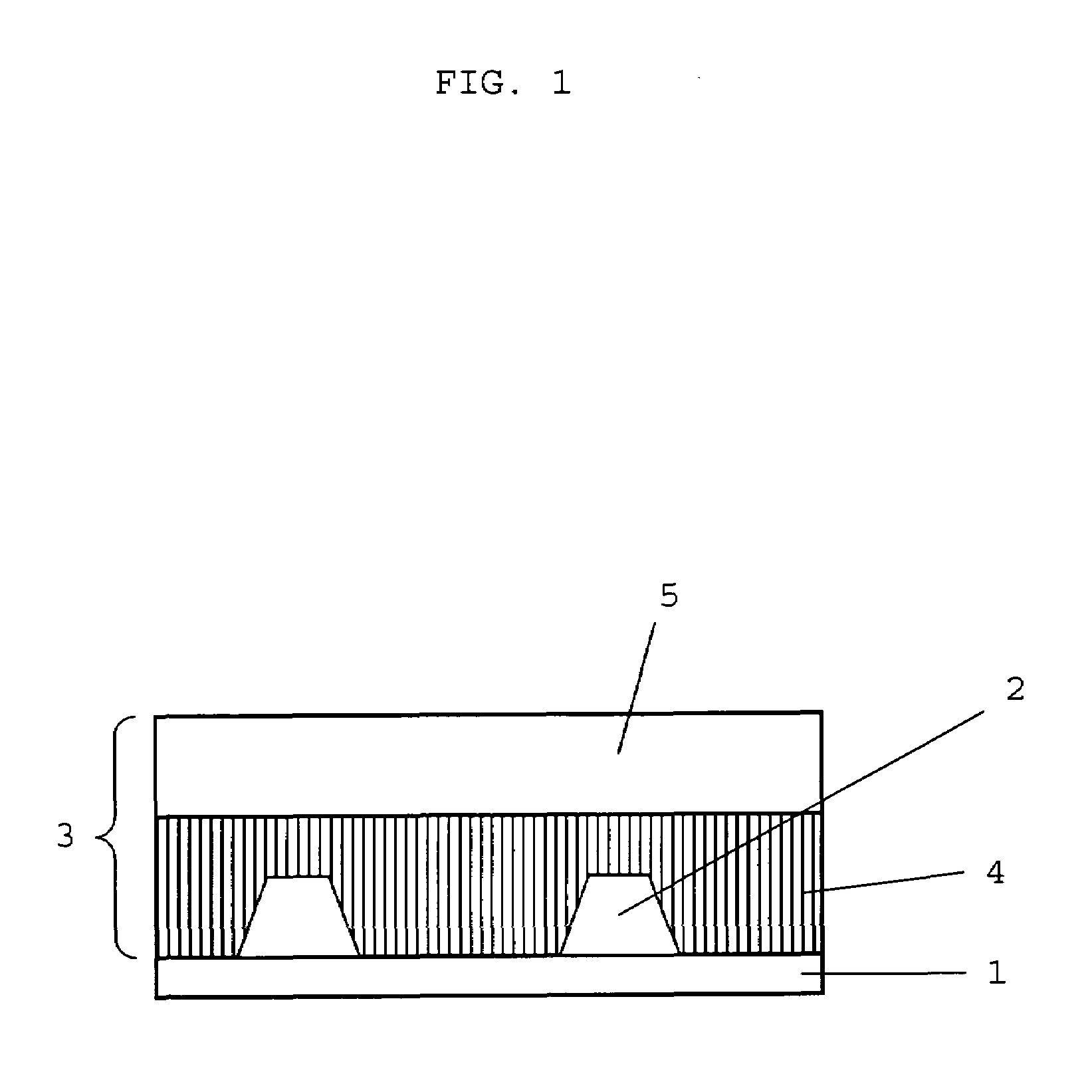

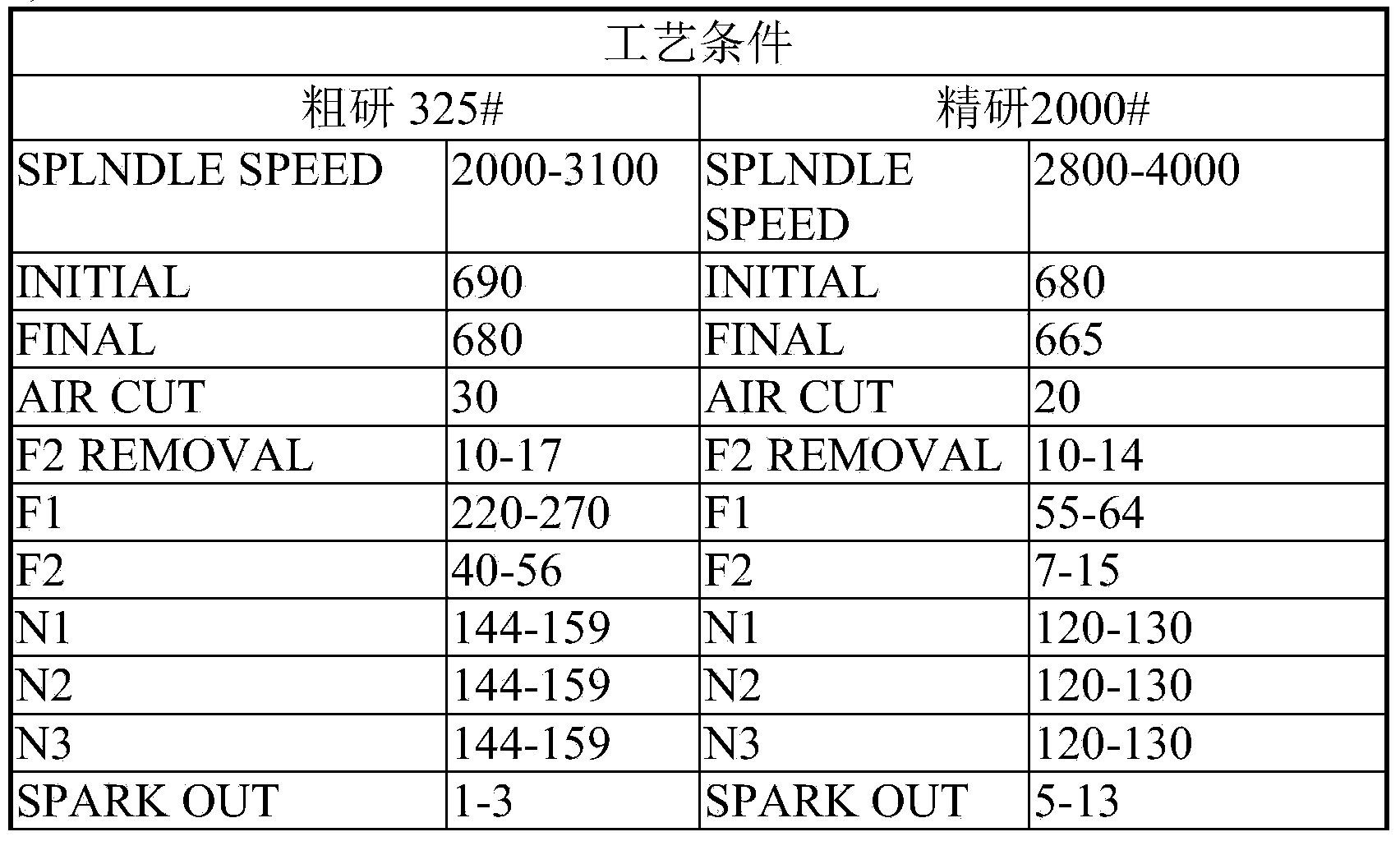

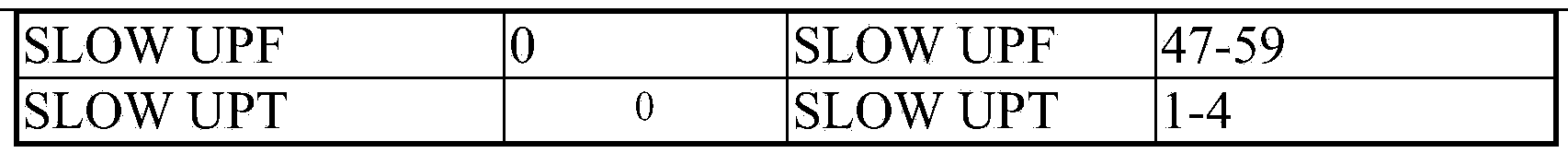

Machining method for high-yield monocrystalline silicon wafer for IGBT

ActiveCN103681298AIncrease production capacityReduced polishing removalSemiconductor/solid-state device manufacturingWaxWafer backgrinding

The invention provides a machining method for a high-yield monocrystalline silicon wafer for an IGBT. The method specifically comprises the steps of wafer grinding, grinding, acid corrosion, back damage, back sealing, trimming, polishing, examination and packing and is characterized in that the step of grinding is added between the step of wafer grinding and the step of acid corrosion. The technological process of the whole machining process is adjusted, a wax-free polishing device and a grinding device are matched for production, the damaged layer depth of a raw material grinding wafer is reduced, the polishing removed amount is reduced, and the machining time is shortened on the premise that product quality is ensured, so that productivity of the wax-free polishing process is improved, and earnings are increased.

Owner:ZHONGHUAN ADVANCED SEMICON MATERIALS CO LTD +1

Method for manufacturing device

ActiveUS20080251188A1Quality improvementChipping can be reliably preventedLamination ancillary operationsLaminationDevice formDicing tape

A method for manufacturing a device, in which a wafer having a plurality of devices formed on the face thereof is divided into the individual devices, and an adhesive film is mounted on the back side of each device. This method comprises: a cutting groove forming step of cutting the back side of the wafer along predetermined division lines by a cutting blade to form cutting grooves, while leaving an uncut portion, which is thinner than the target thickness of the device, on the front side of the wafer; a back side grinding step of grinding the back side of the wafer to the target thickness of the device, while allowing the cutting grooves to remain in the back side of the wafer; an adhesive film mounting step of mounting an adhesive film to the back side of the wafer; a wafer supporting step of sticking the adhesive film side of the wafer, on which the adhesive film has been mounted, to the surface of a dicing tape; a wafer severing step of cutting the front side of the wafer along the predetermined division lines by a cutting blade to sever the uncut portion, thereby dividing the wafer into the individual devices and cutting the adhesive film; and an adhesive film separating step of expanding the dicing tape to separate the adhesive film per device.

Owner:DISCO CORP

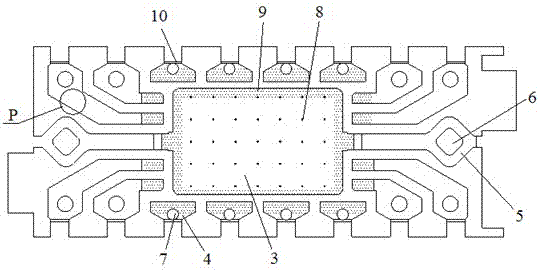

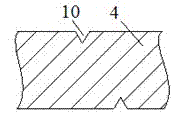

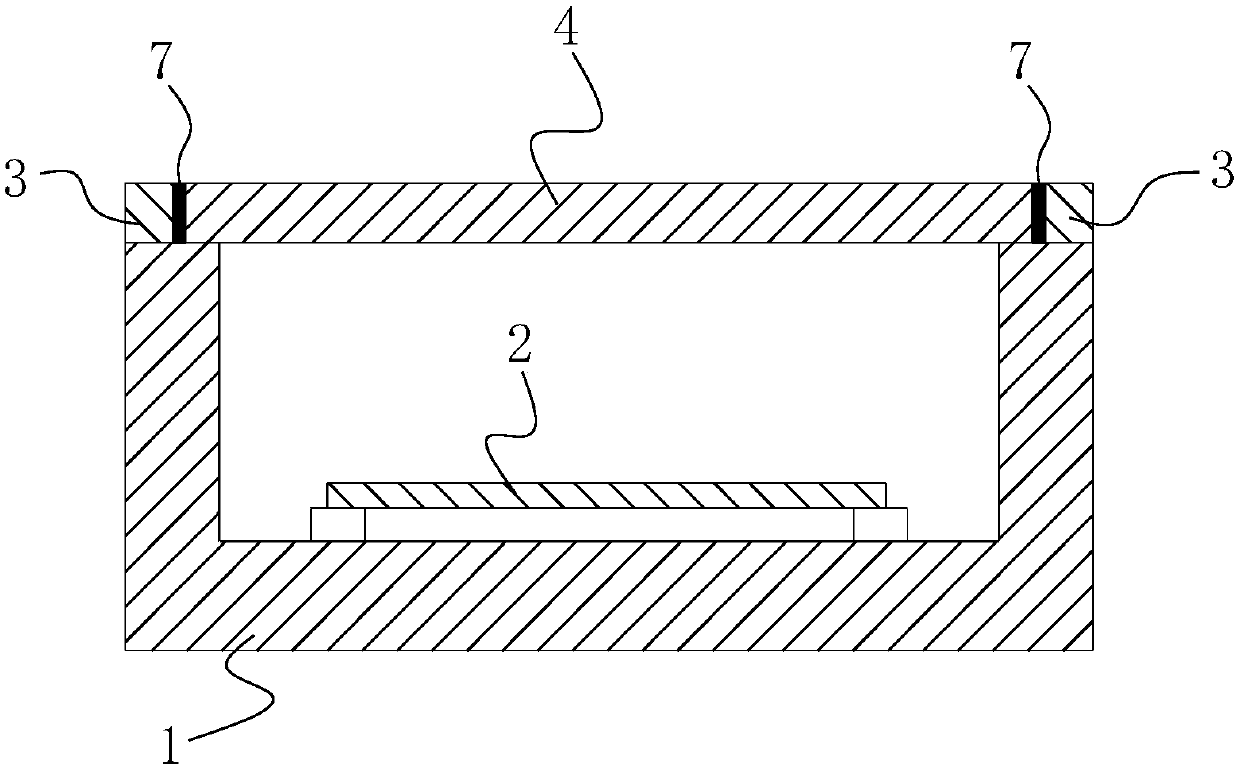

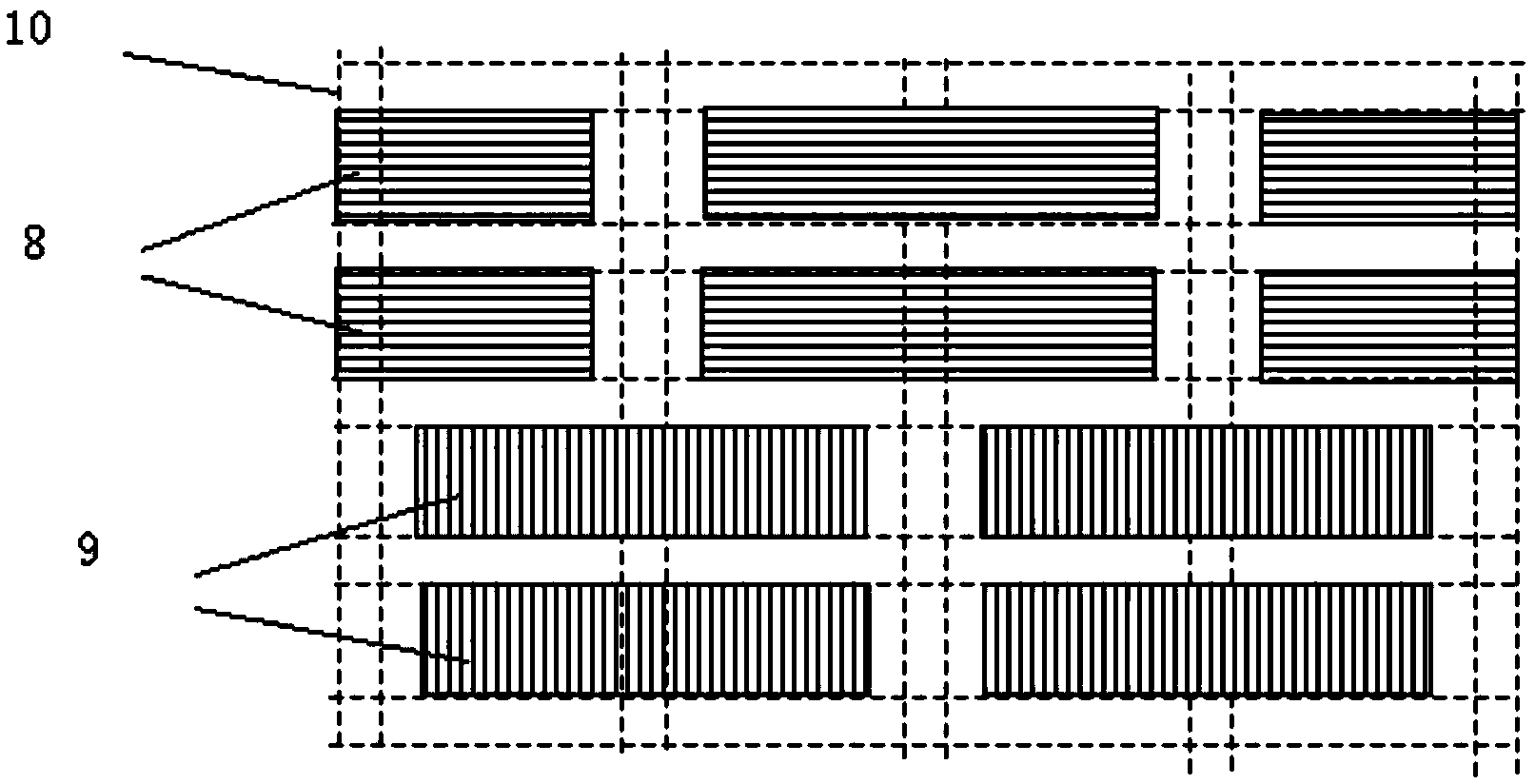

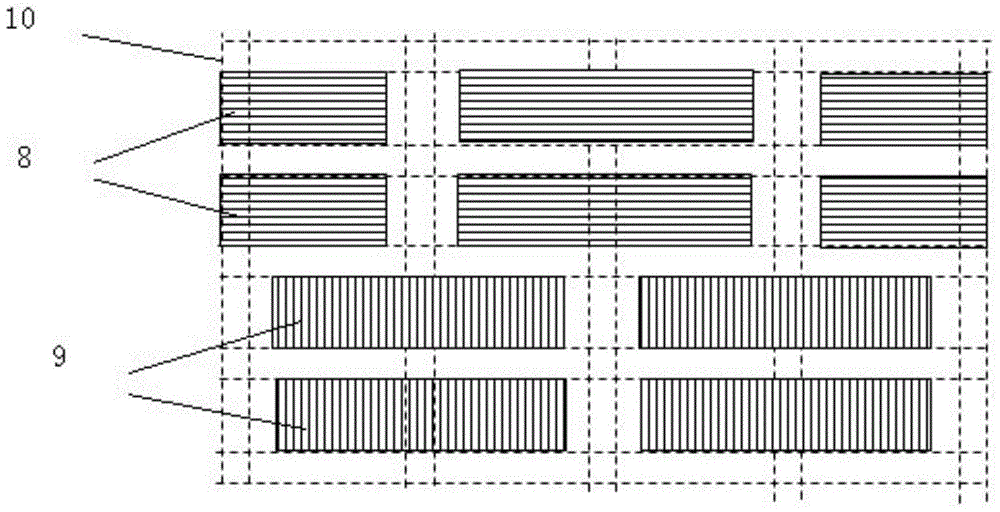

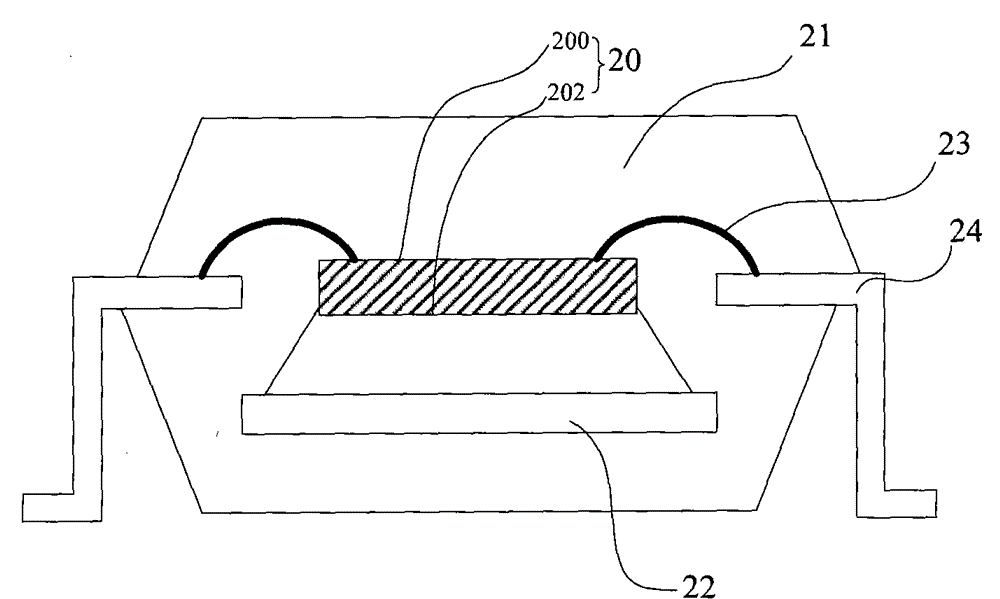

High reliability small outline package (SOP) lead frame and production method of packaging piece

ActiveCN104752386AImprove performanceImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesPlastic packagingWafer backgrinding

The invention provides a high reliability small outline package (SOP) lead frame and a production method of a packaging piece. The lead frame comprises a lead frame body with 240 packaging units in matrix arrangement. The packaging unit comprises a carrier. The back of the carrier is provided with a frame-shaped structure comprising a plurality of silver-plated rings. The frame-shaped structure is internally provided with a plurality of pits. Two sides of the carrier are provided with a plurality of inner pins with locking holes and waterproof grooves. The other two side edges of the carrier are respectively provided with a carrier connecting rod. One end of the carrier connecting rod is connected with the carrier. The other end of the carrier connecting rod is large in size and is provided with a stabilizing hole. Wafer backgrinding and scribing are performed according to an existing process; a chip is stuck on the lead frame; baking is performed through a rapid solidification anti-separation layer baking technique in seven different temperature areas; the steps of plasma cleaning, pressure welding, plastic packaging and tendon cutting are carried out; and then printing and testing are performed by a conventional SOP production technique so as to produce the SOP packaging piece. A frame material and a plastic packaging material are utilized to the greatest extent, the production efficiency and product quality are improved, error rate is lowered and safety risk is reduced.

Owner:广东韶华科技有限公司

Pressure-sensitive adhesive film and back-grinding method using the same

InactiveUS20110091676A1Increase productivityExcellent cuttabilityFilm/foil adhesivesSynthetic resin layered productsWafer backgrindingEngineering

The present invention relates to a pressure-sensitive adhesive film and a semiconductor wafer backgrinding method using the same. The present invention provides a pressure-sensitive adhesive film capable of remarkably improving production efficiency in a wafer backgrinding of a semiconductor manufacturing process due to its superior cutting and adherence properties in the semiconductor manufacturing process and an excellent cushioning property. Moreover, the present invention also provides a pressure-sensitive adhesive film having superior peeling and re-peeling properties and wettability to the wafer while providing excellent water resistance, and a backgrinding method using the pressure-sensitive adhesive film.

Owner:LG CHEM LTD

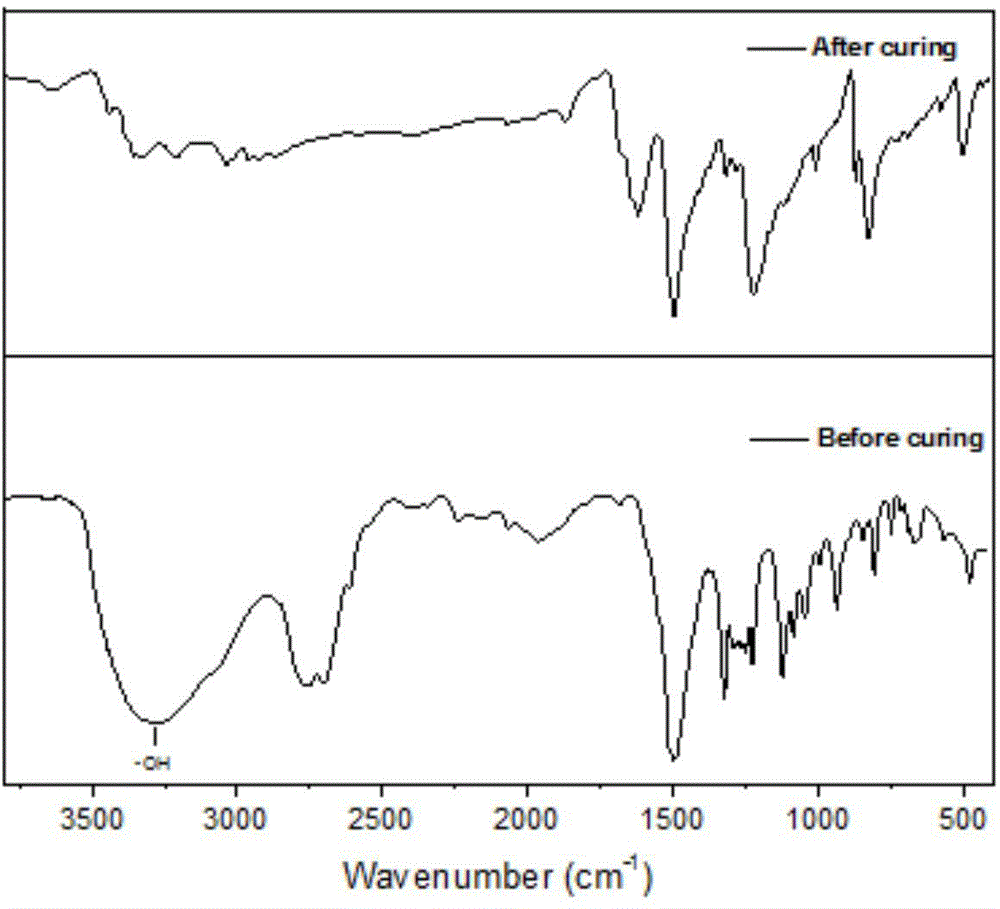

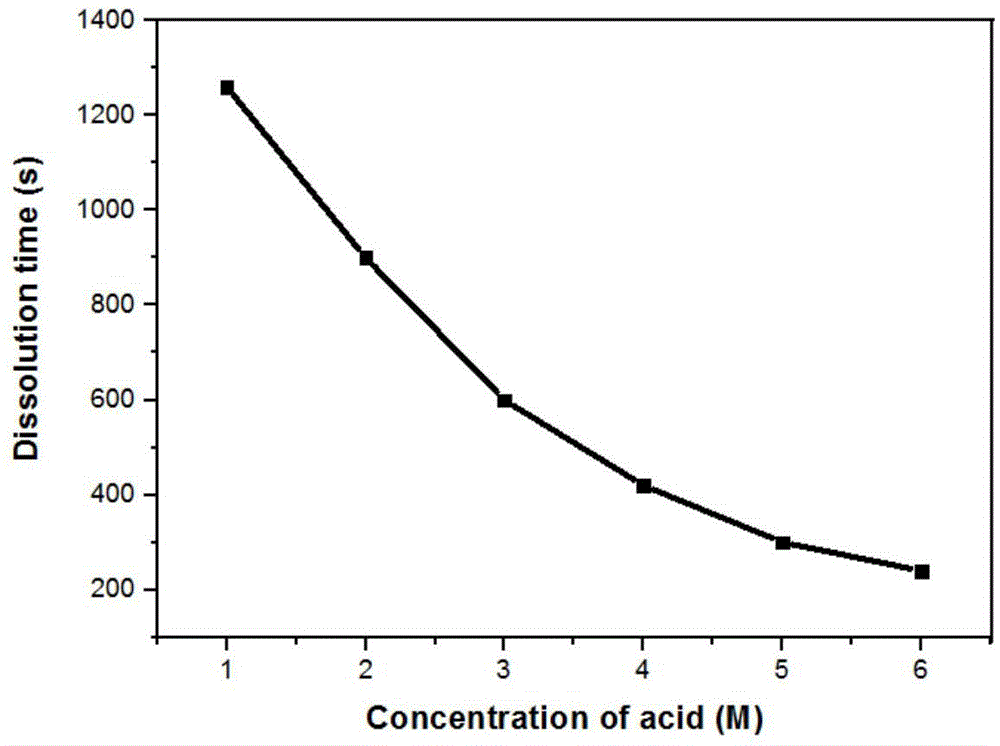

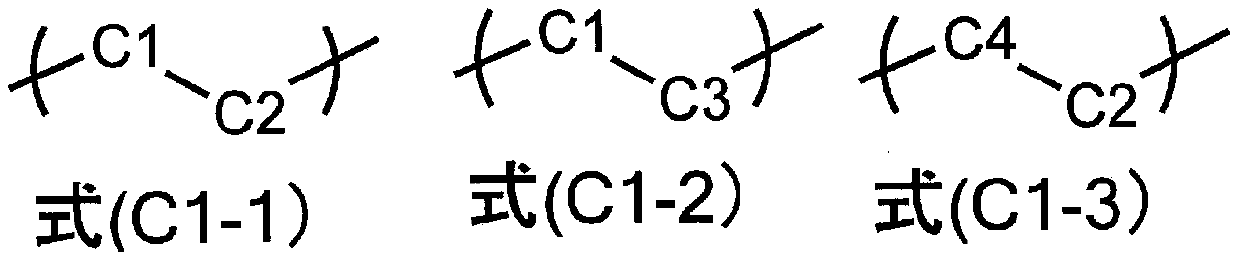

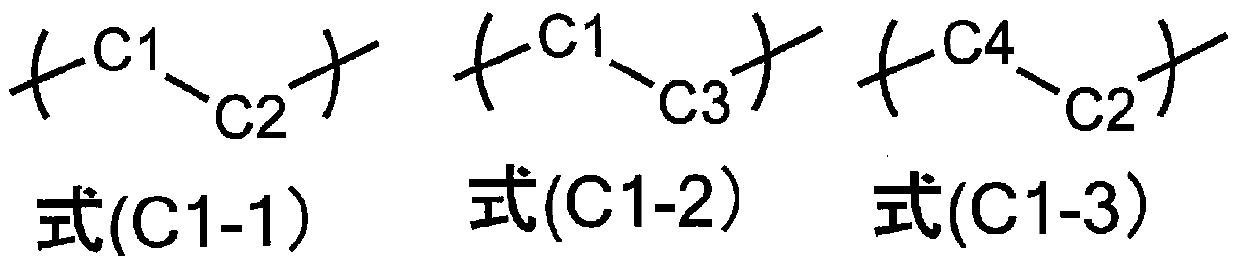

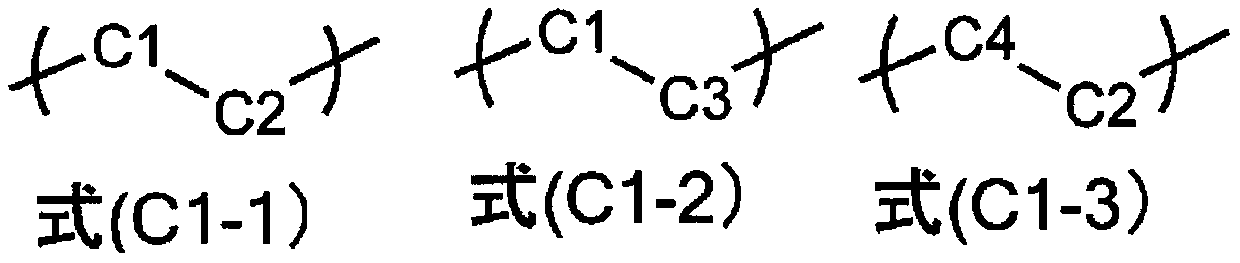

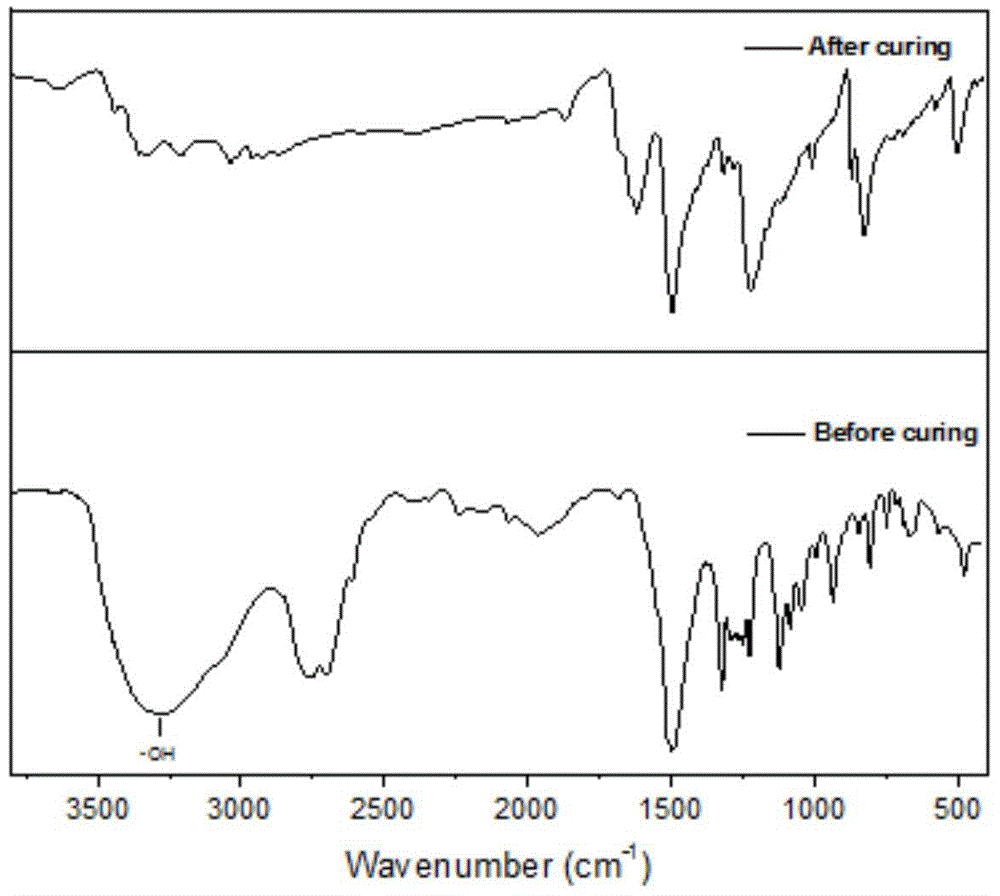

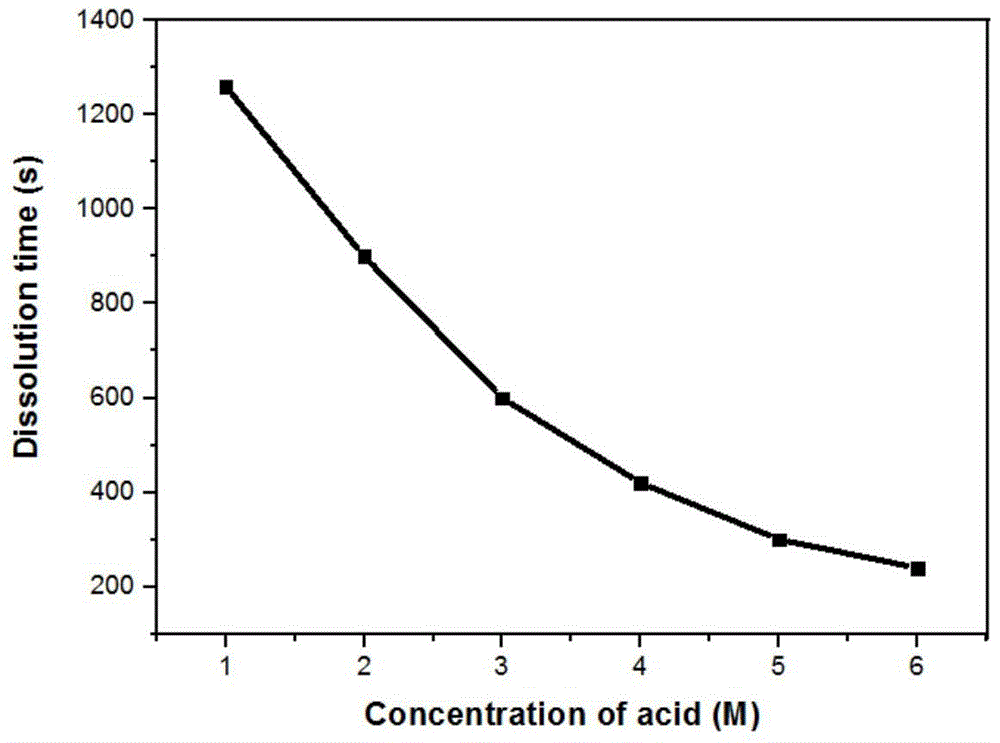

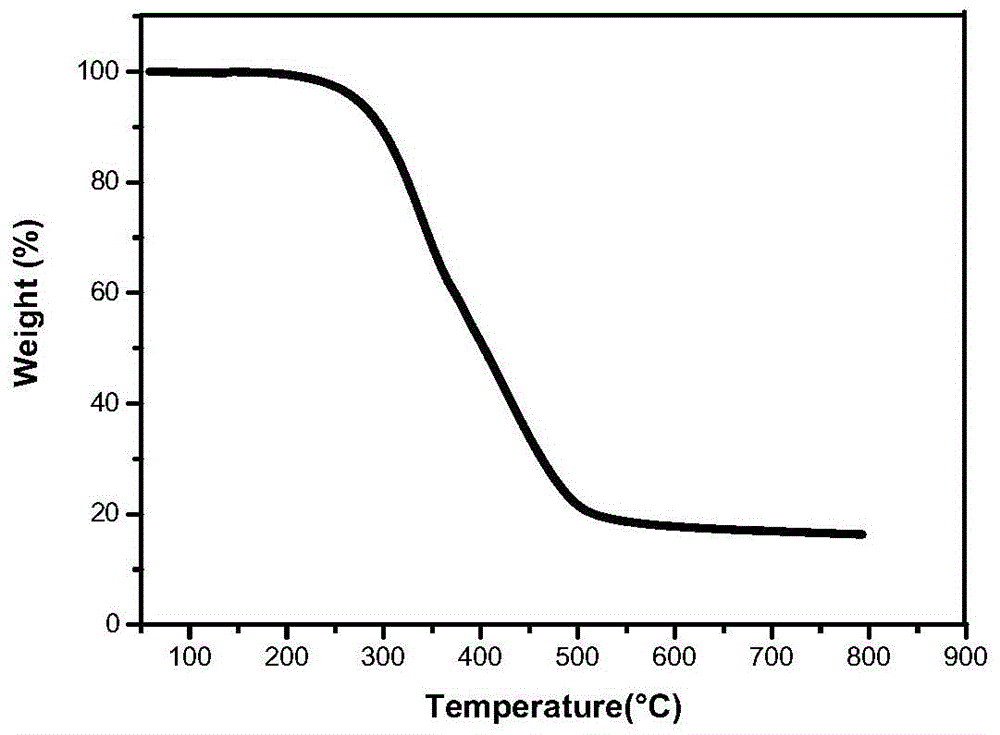

Temporary bonding glue for wafer backgrinding, preparation method of temporary bonding glue and bonding and de-bonding methods

ActiveCN104804682AImprove corrosion resistanceReduce manufacturing costAdhesive processes with adhesive heatingAldehyde/ketone condensation polymer adhesivesPolymer scienceDepolymerization

The invention discloses temporary bonding glue for wafer backgrinding, a preparation method of the temporary bonding glue and bonding and de-bonding methods. The temporary bonding glue comprises base resin for producing the adhesive effect, wherein the base resin can be depolymerized into a low molecular compound and / or a linear low polymer under the action of strong acid, so that an adhesive layer formed by the bonding glue has an obvious depolymerization reaction under the sufficient impregnation of acid liquor, that is, the structure of a three-dimensional polymer is damaged, the adhesive layer loses efficacy by means of the generated low molecular compound or linear low polymer, and the de-bonding efficiency is improved. Besides, the decomposition temperature of the high polymer is higher than 270 DEG C, so that the thermal stability of the adhesive layer is high; the corrosion resistance of the bonding glue is high, and the preparation cost is more economical.

Owner:深圳市化讯半导体材料有限公司

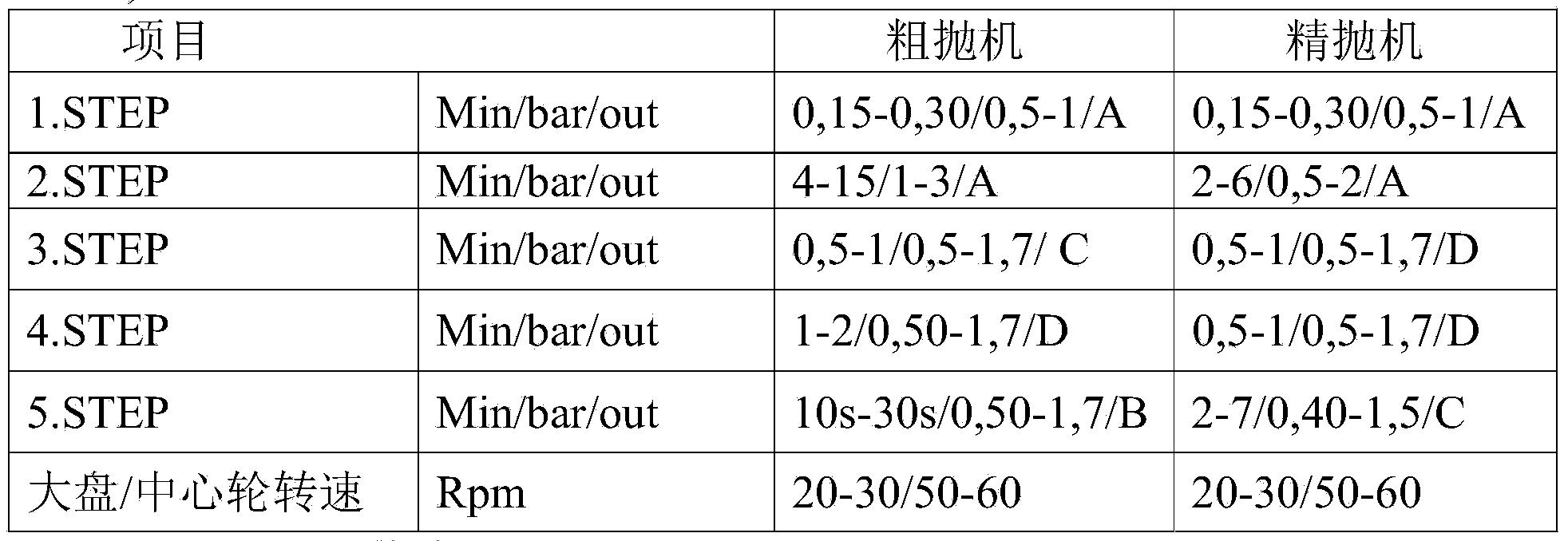

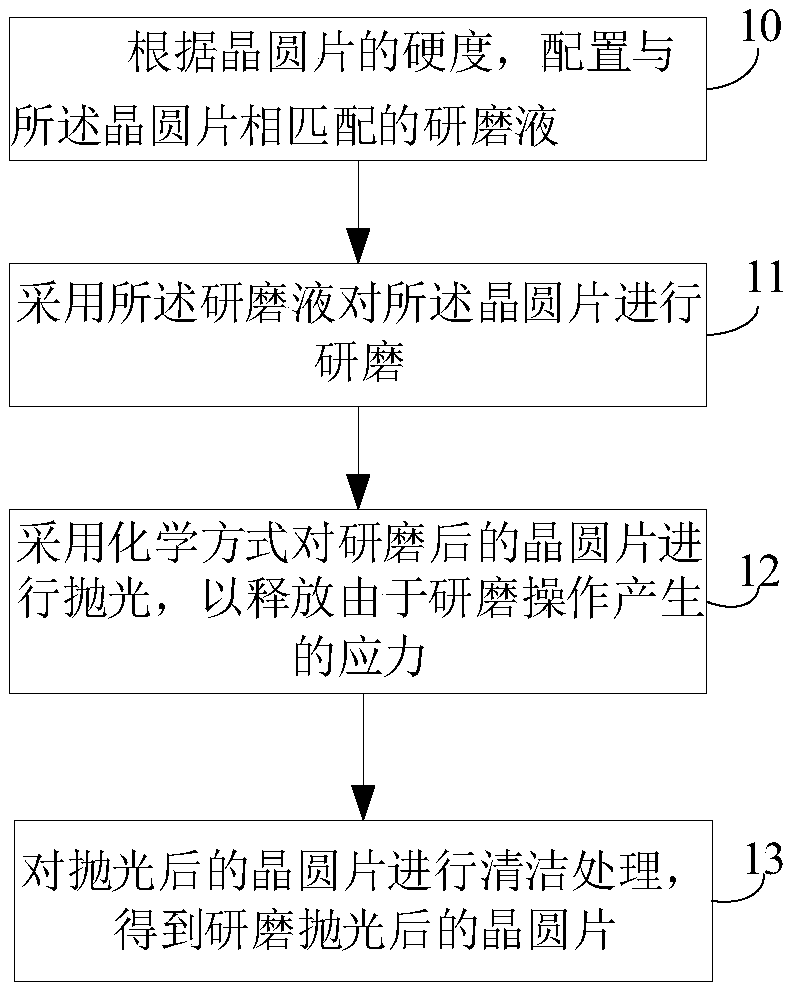

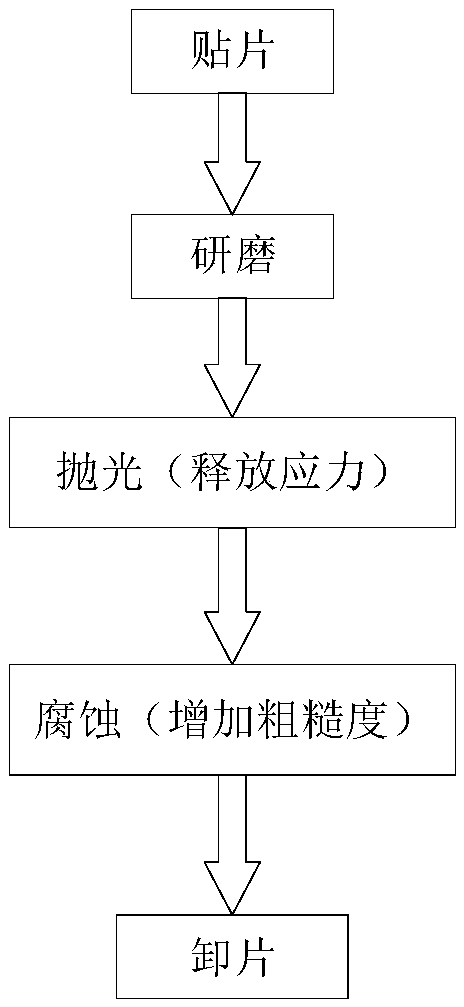

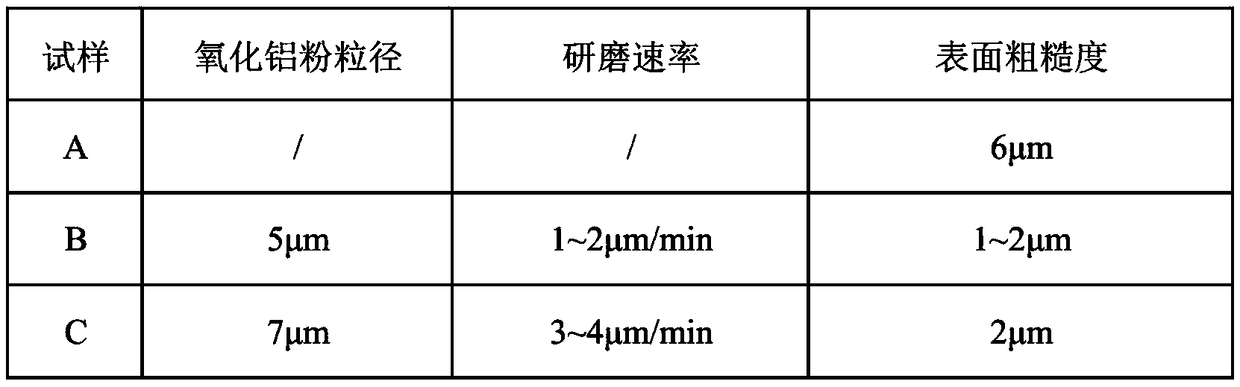

Wafer grinding and polishing method and corresponding wafer

ActiveCN109509701AEffective stress reliefAchieve the effect of thinningSemiconductor/solid-state device manufacturingLapping machinesWafer backgrindingHardness

The invention discloses a wafer grinding and polishing method and a corresponding wafer. The wafer grinding and polishing method comprises the steps: preparing a grinding fluid matching a wafer according to the hardness of the wafer; adopting the grinding liquid to grind the wafer; polishing the ground wafer in a chemical mode so as to release stress generated by grinding operation; and cleaning the polished wafer to obtain the ground and polished wafer. The proper grinding fluid is prepared according to the hardness of the wafer, so that the grinding removal rate is guaranteed, and the waferthinning effect is achieved; meanwhile, the wafer is polished in a chemical mode, stress generated in the grinding process is released, the flatness of the wafer is guaranteed, and the wafer is effectively prevented from cracking.

Owner:WUHAN TELECOMM DEVICES

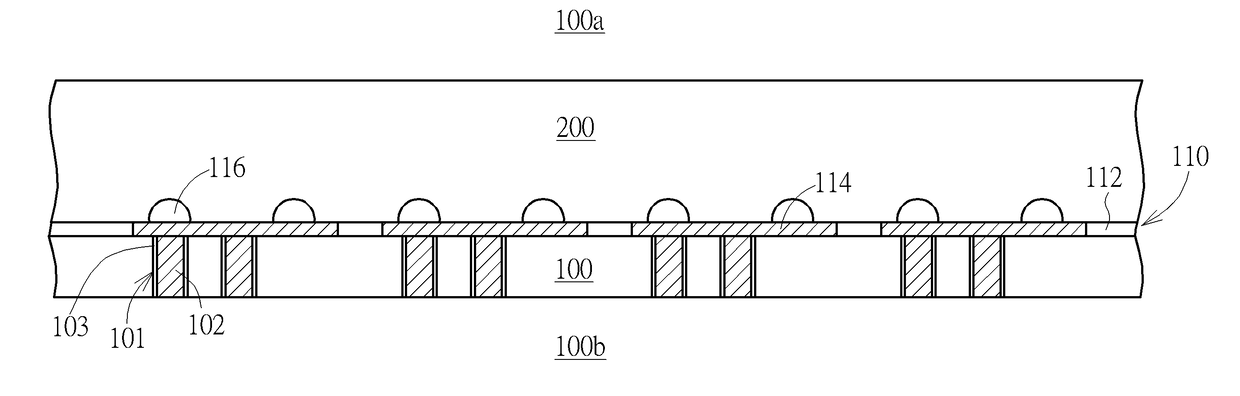

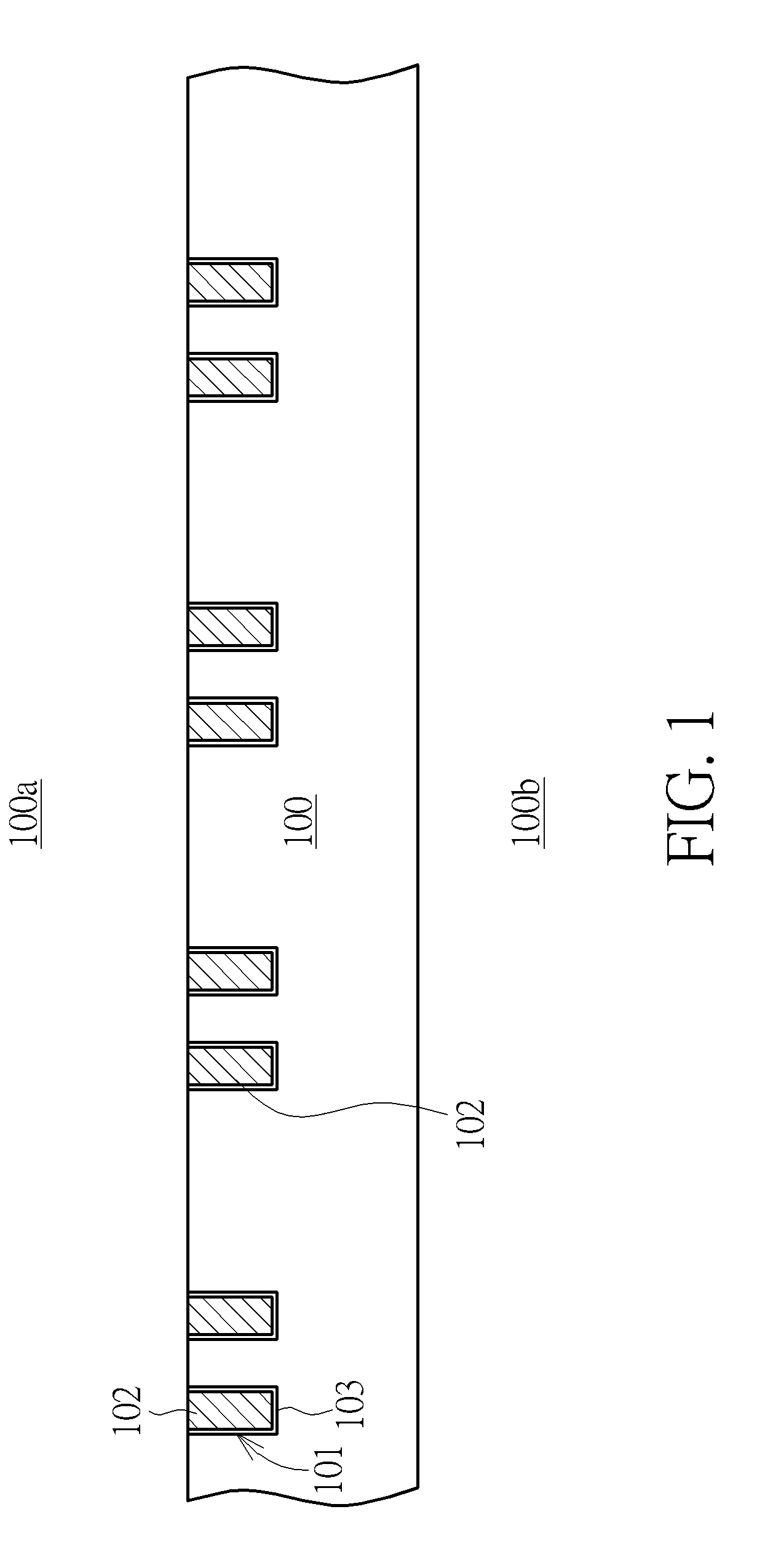

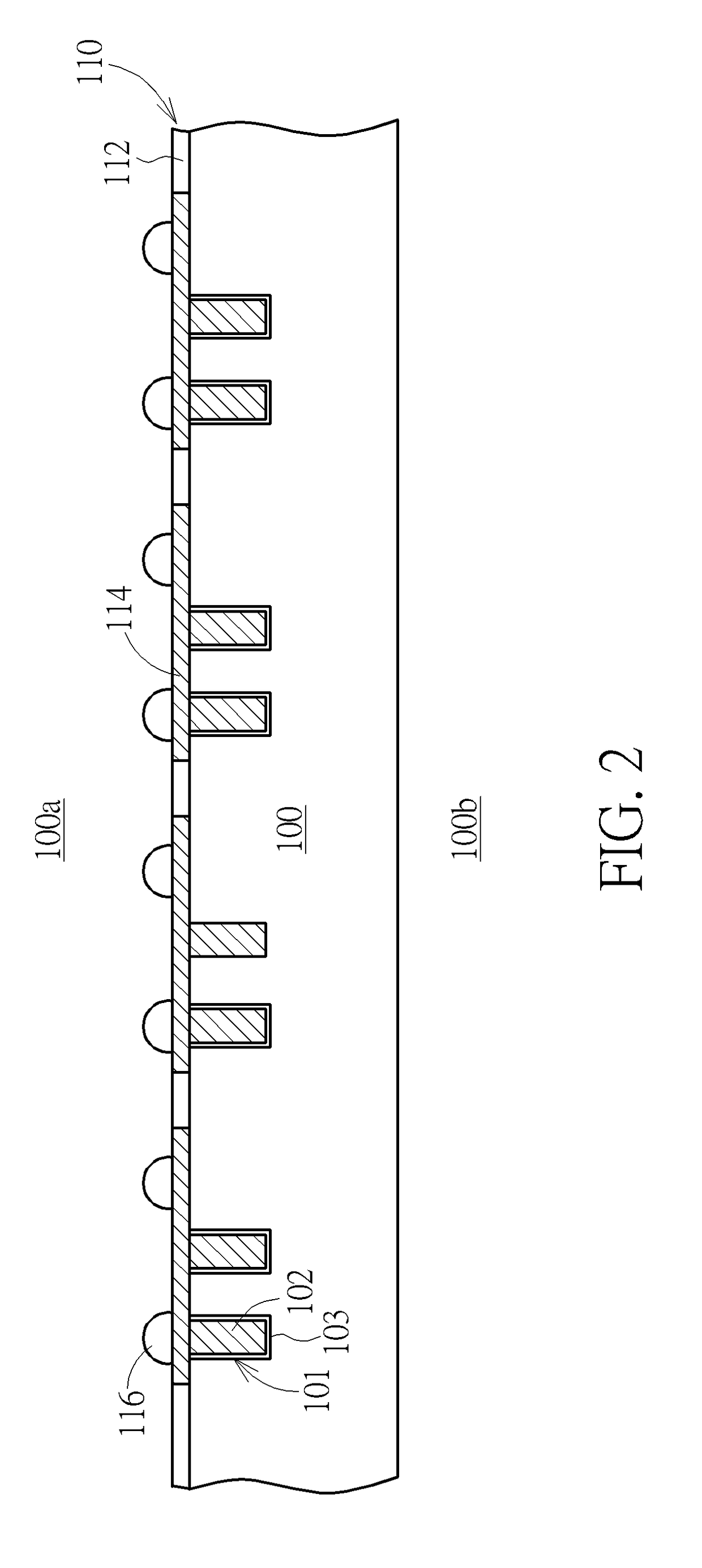

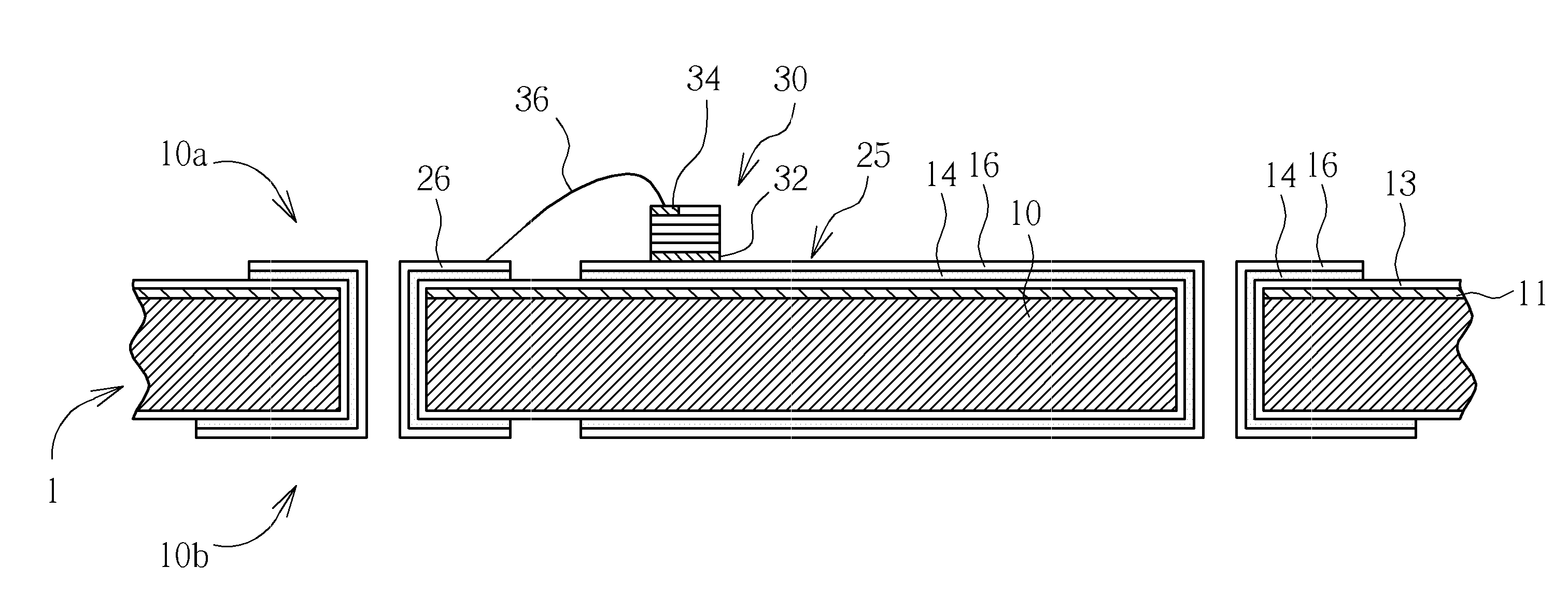

High-reflection submount for light-emitting diode package and fabrication method thereof

Owner:XINTEC INC

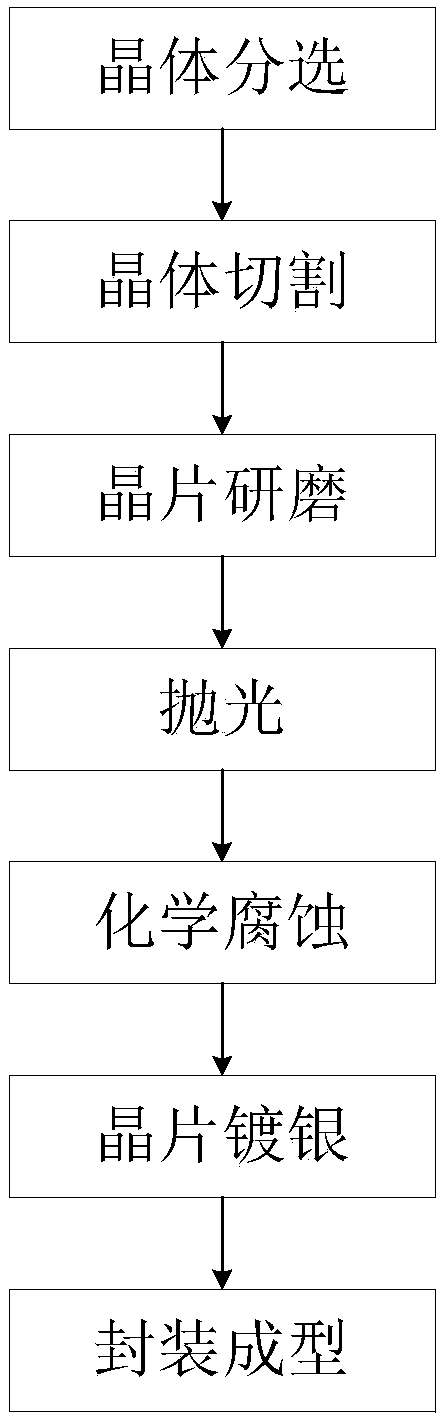

Method for machining quartz crystal resonator

ActiveCN107666296ASimple processImprove precision controlImpedence networksQuartz crystal resonatorSilver plate

The invention relates to a method for machining a quartz crystal resonator. The method comprises the following steps of S1, crystal sorting: sorting quartz crystals of the same angle and concentratingthe quartz crystals together; S2, crystal cutting: cutting the quartz crystals of the same angle obtained through sorting into wafers according to requirements; S3, wafer grinding: grinding the wafers till the thickness of the wafers is consistent with a required frequency by using a grinding machine; S4, polishing: polishing the ground wafers by using a polishing machine; S5, chemical corrosion:performing chemical corrosion on the polished wafers; S6, silver plating of wafers: dividing the surface of each chemically corroded wafer into a silver plating area and a non-silver plating area, plating the silver on the silver plating area and the non-silver plating area of the wafer firstly to obtain a silver-plated layer, and then etching away the silver-plated layer of the non-silver plating area by adopting an etching method; S7, packaging and forming. The machining method is low in machining difficulty, and the cleaning by acids is not required. Meanwhile, the method is high in environment-friendly degree, and the silver material can be recovered conveniently.

Owner:HEFEI JINGWEITE ELECTRONICS CO LTD

Method for fabricating a semiconductor device

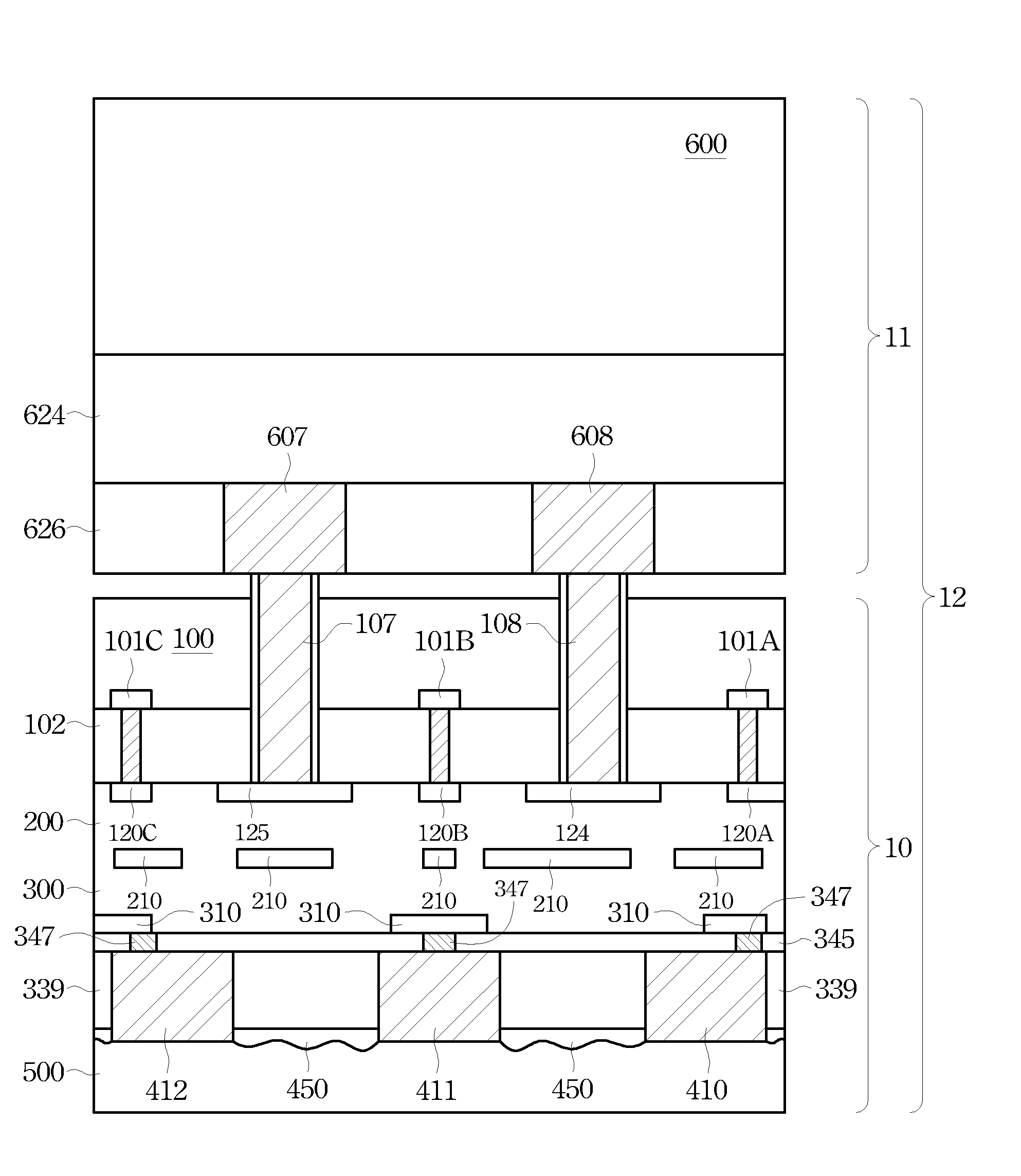

ActiveUS20170213764A1Semiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceRedistribution layer

A method of fabricating a semiconductor device. A wafer having a front side and a back side opposite to the front side is prepared. A plurality of through substrate vias (TSVs) is formed on the front side. A redistribution layer (RDL) is then formed on the TSVs. The wafer is bonded to a carrier. A wafer back side grinding process is performed to thin the wafer on the back side. An anneal process is performed to re-crystallize the TSVs. A chemical mechanical polishing (CMP) process is performed to polish the back side.

Owner:MICRON TECH INC

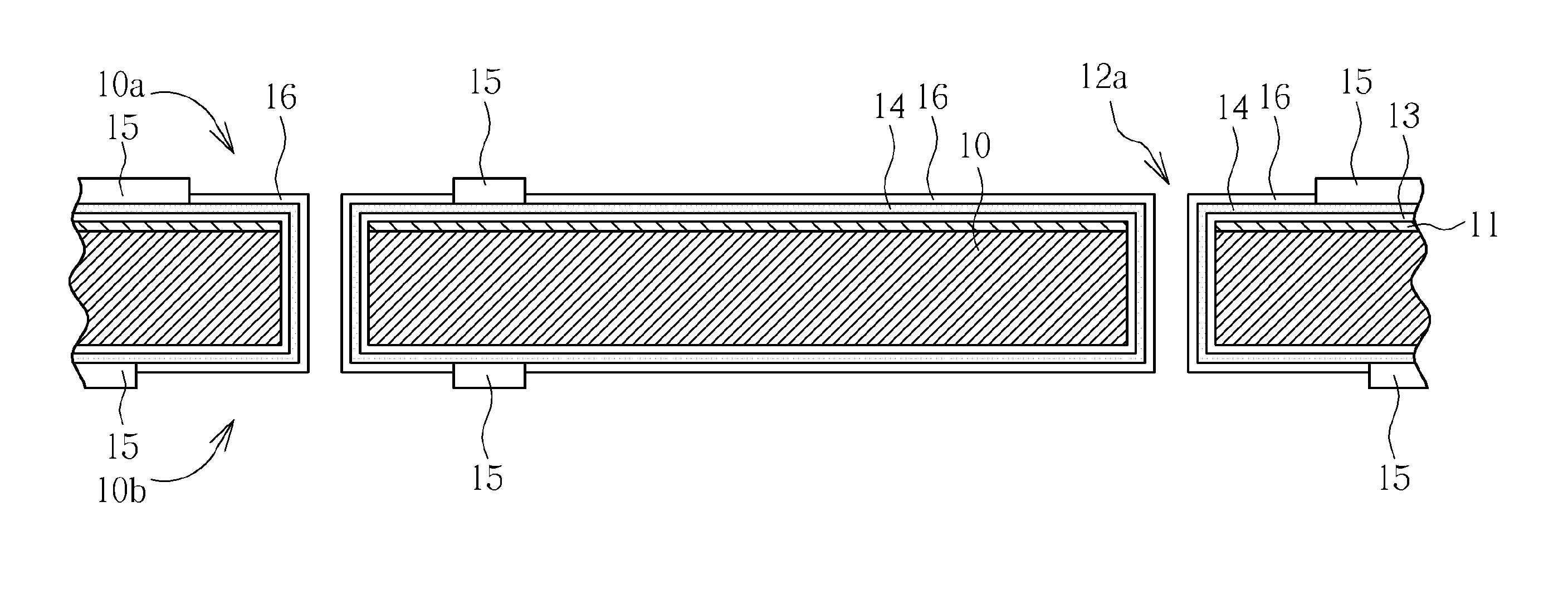

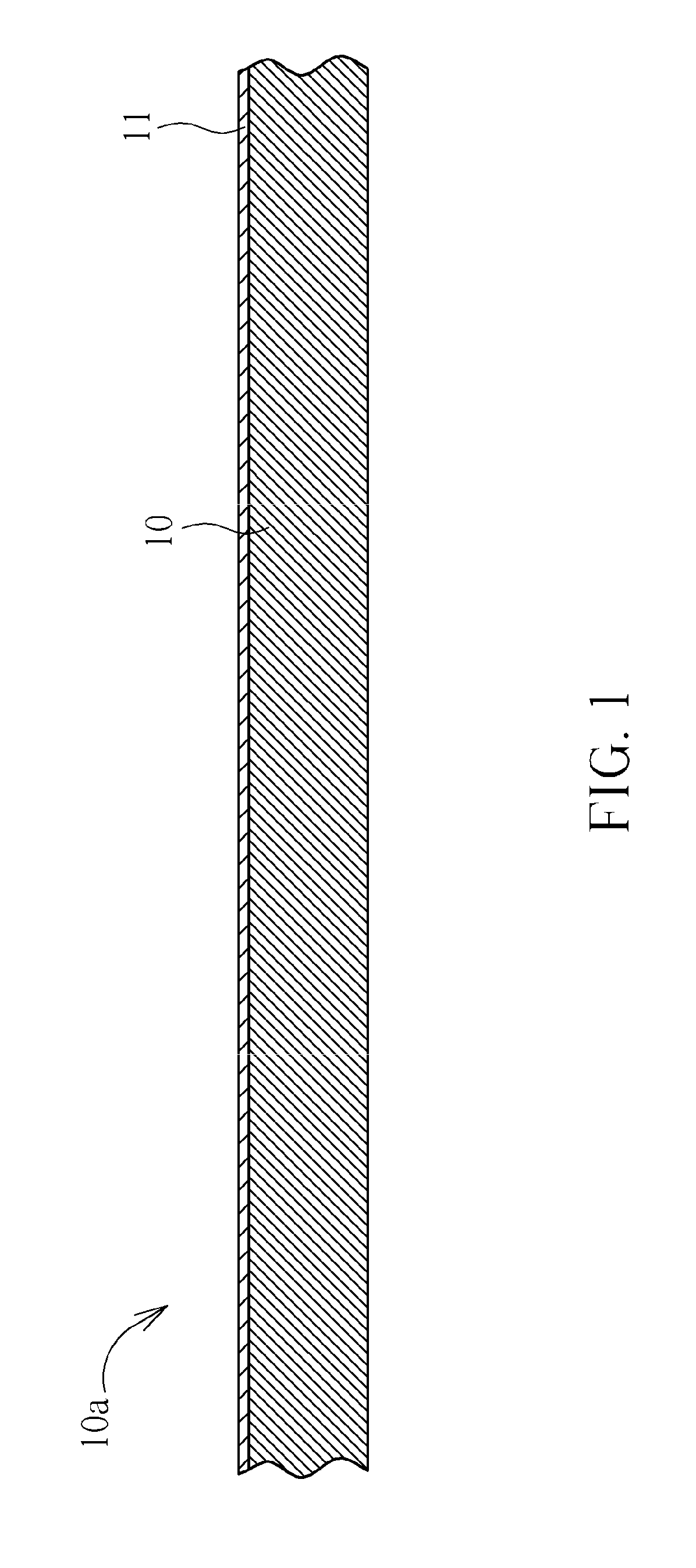

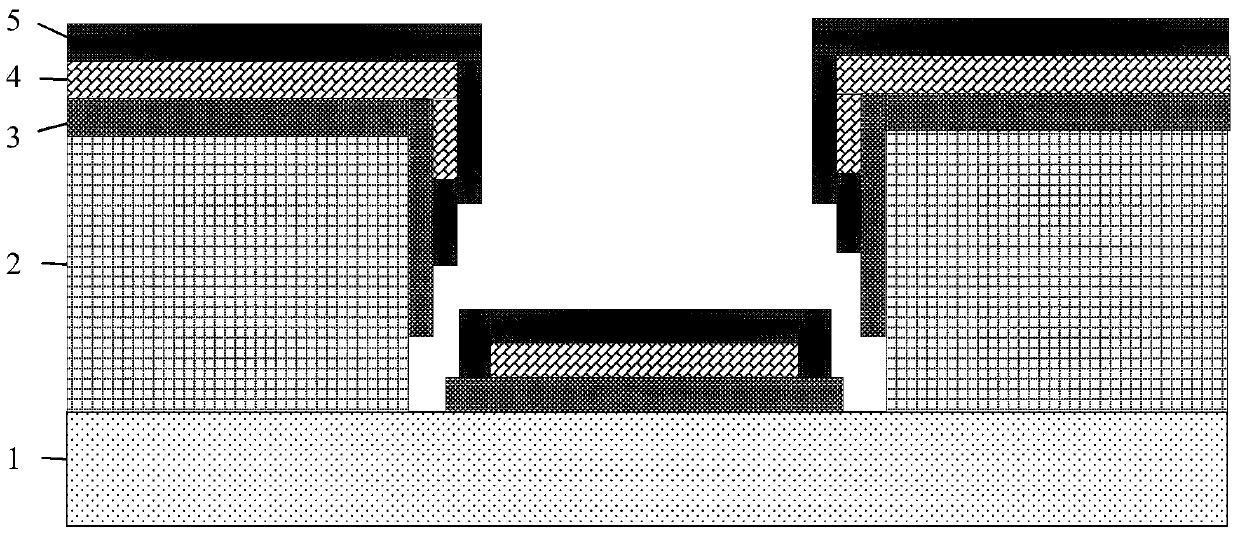

High-reflection submount for light-emitting diode package and fabrication method thereof

A method for fabricating a silicon submount for LED packaging. A silicon substrate is provided. A reflection layer is formed on the silicon substrate. Portions of the reflection layer and the silicon substrate are removed to form openings. A wafer backside grinding process is carried out to thin the silicon substrate thereby turning the openings into through silicon vias. An insulating layer is then deposited to cover the reflection layer and the silicon substrate. A seed layer is formed on the insulating layer. A resist pattern is then formed on the seed layer. A metal layer is formed on the seed layer not covered by the resist pattern. The resist pattern is then stripped. The seed layer not covered by the metal layer is then removed.

Owner:XINTEC INC

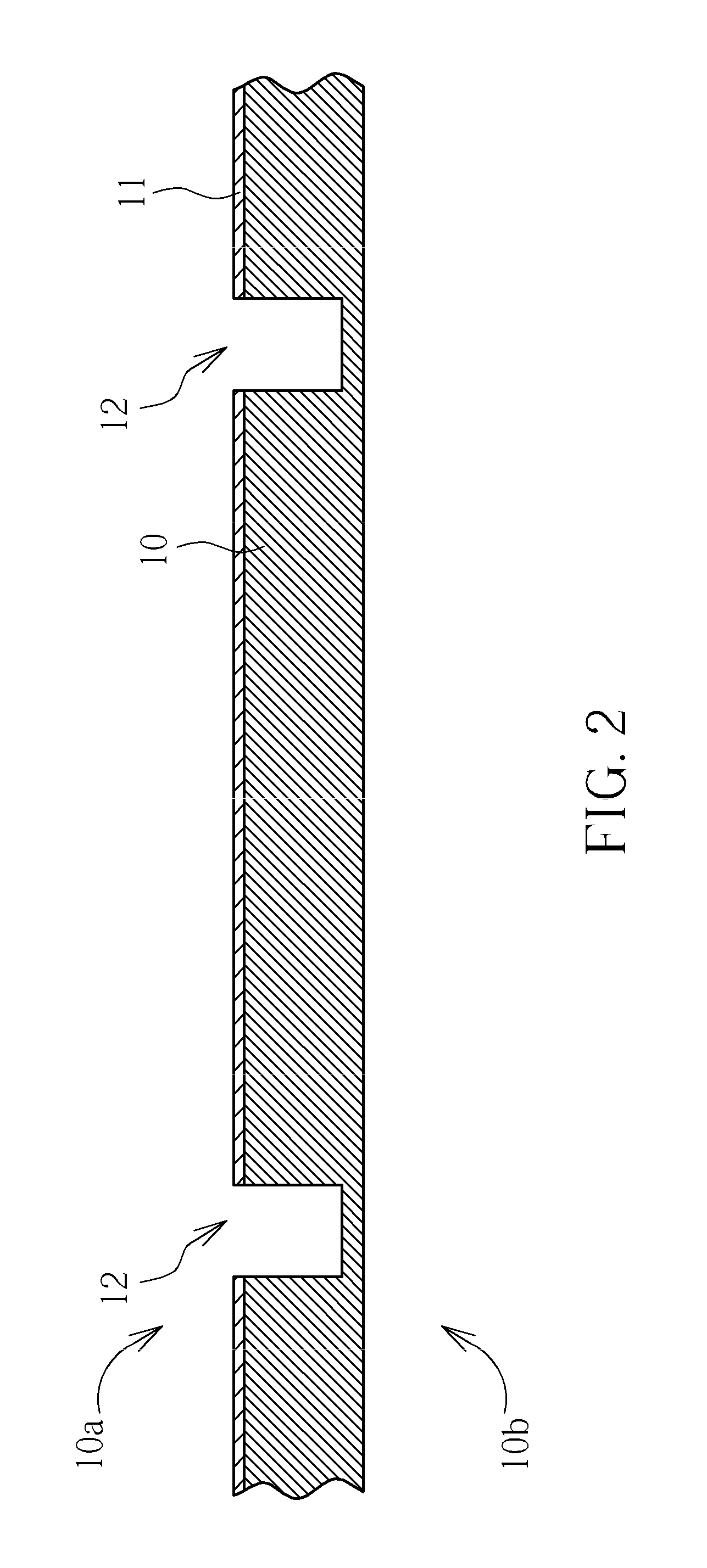

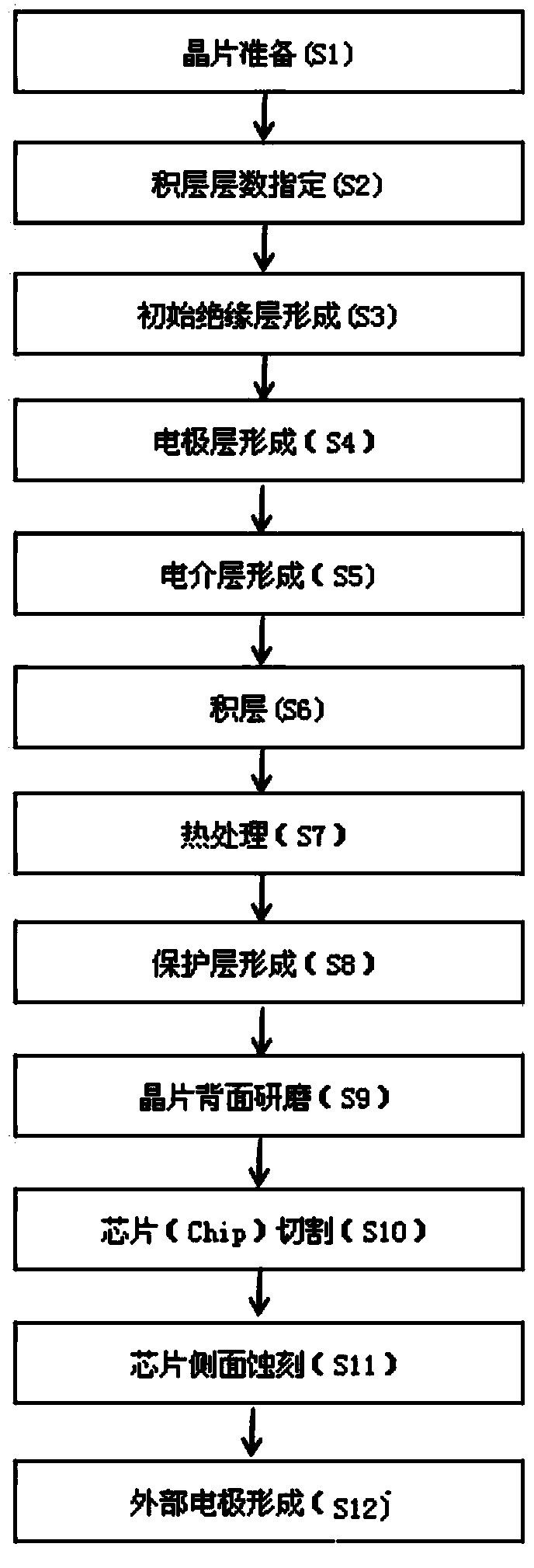

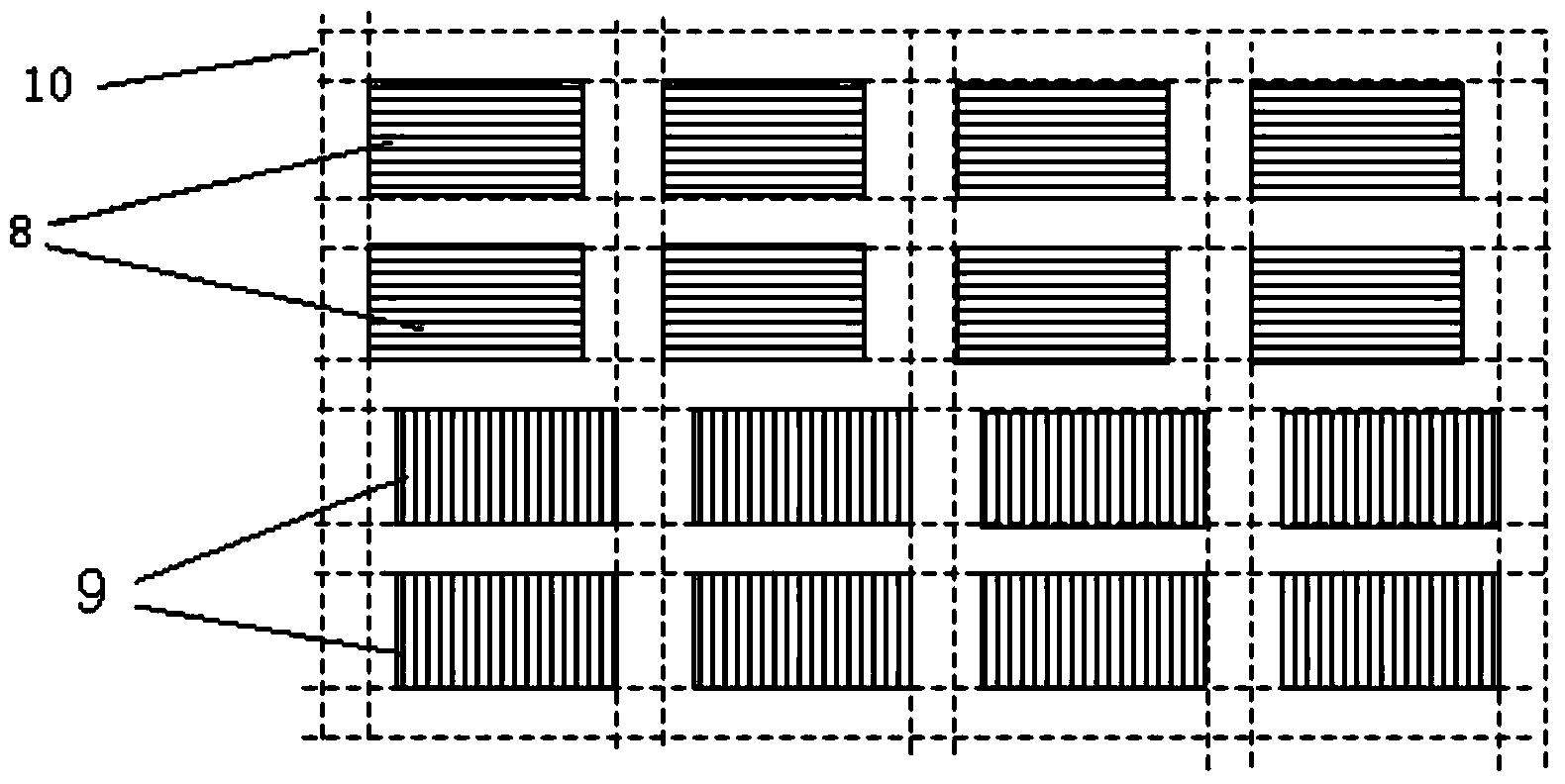

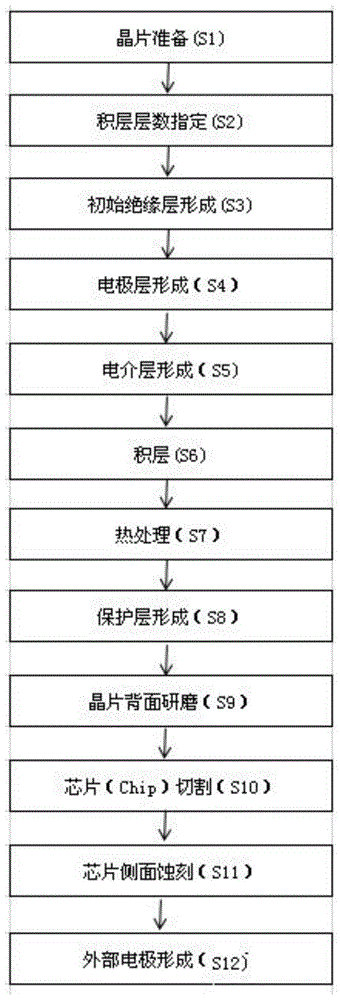

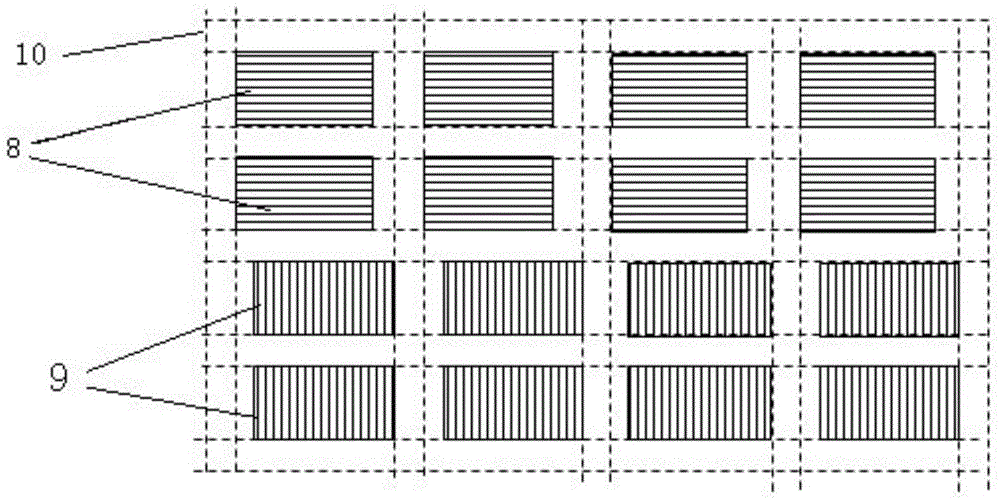

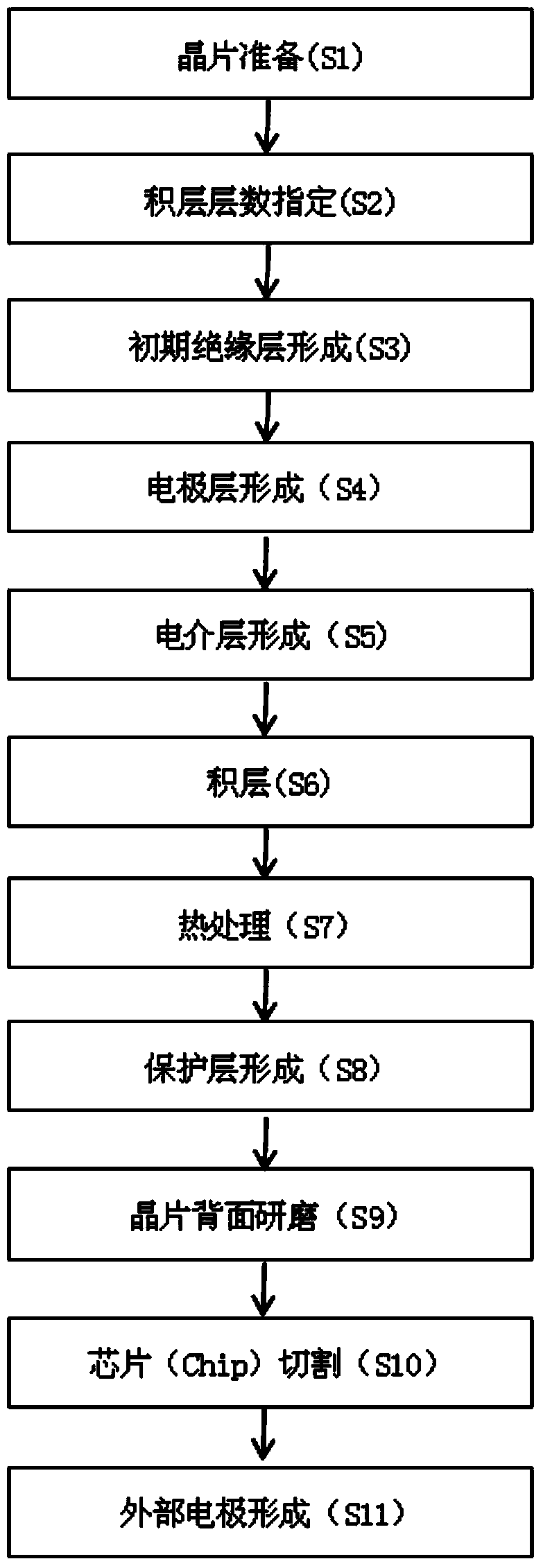

Method for manufacturing external electrode of dry type multilayer ceramic capacitor

InactiveCN103680951AImprove qualityImprove adhesionStacked capacitorsFixed capacitor terminalsWafer backgrindingCeramic capacitor

A method for manufacturing an external electrode of a dry type multilayer ceramic capacitor includes the steps of preparing a silicon wafer, determining the number of electrode layers and the number of electric medium layers, forming an initial insulating layer, forming the electrode layers, forming the electric medium layers, enabling the electrode layers and the electric medium layers to be layered repeatedly, conducting thermal processing on the electrode layers and the electric medium layers, forming a protective layer, grinding the back face of the silicon wafer, segmenting the multilayer wafer in the form of a chip (Chip), etching the side face of the chip, and forming an external electrode. According to the method related to the structure, a preset circuit is used in the electrode layer forming step, and the external electrode is manufactured by executing the etching process well determined between the chip cutting step and the external electrode forming step. After a preset electrode layer circuit pattern and the chip are cut, adhesiveness between the electrode layers and the external electrode is enhanced through the cutting face etching method, and finally, the high-quality MLCC can be obtained.

Owner:大连天壹电子有限公司

Adhesive composition, adhesive sheet, and back grinding method for semiconductor wafer

ActiveUS20170290217A1Reduce hydrophilicityMaintain good propertiesSolid-state devicesSemiconductor/solid-state device manufacturingMeth-Wafer backgrinding

The present invention relates to a pressure-sensitive adhesive composition including a polymer of a monomer mixture containing isobornyl (meth)acrylate, a pressure-sensitive adhesive sheet, and a semiconductor wafer backgrinding method. In the present invention, by using isobornyl (meth)acrylate which is a hard-type monomer and has a low hydrophilic property, a pressure-sensitive adhesive composition having superior releasing and re-releasing properties and wettability with respect to the wafer, and having an excellent wafer-proofing property; a pressure-sensitive adhesive sheet prepared by using the pressure-sensitive adhesive composition; and a backgrinding method using the pressure-sensitive adhesive sheet can be provided.

Owner:LG CHEM LTD

Method for manufacturing device

ActiveUS7960250B2Quality improvementChipping can be reliably preventedLamination ancillary operationsLaminationDevice formDicing tape

A method for manufacturing a device, in which a wafer having a plurality of devices formed on the face thereof is divided into the individual devices, and an adhesive film is mounted on the back side of each device. This method comprises: a cutting groove forming step of cutting the back side of the wafer along predetermined division lines by a cutting blade to form cutting grooves, while leaving an uncut portion, which is thinner than the target thickness of the device, on the front side of the wafer; a back side grinding step of grinding the back side of the wafer to the target thickness of the device, while allowing the cutting grooves to remain in the back side of the wafer; an adhesive film mounting step of mounting an adhesive film to the back side of the wafer; a wafer supporting step of sticking the adhesive film side of the wafer, on which the adhesive film has been mounted, to the surface of a dicing tape; a wafer severing step of cutting the front side of the wafer along the predetermined division lines by a cutting blade to sever the uncut portion, thereby dividing the wafer into the individual devices and cutting the adhesive film; and an adhesive film separating step of expanding the dicing tape to separate the adhesive film per device.

Owner:DISCO CORP

Method for manufacturing external electrode of dry-type multilayer ceramic capacitor

InactiveCN103680951BImprove qualityImprove adhesionStacked capacitorsFixed capacitor terminalsWafer backgrindingCeramic capacitor

A method for manufacturing an external electrode of a dry type multilayer ceramic capacitor includes the steps of preparing a silicon wafer, determining the number of electrode layers and the number of electric medium layers, forming an initial insulating layer, forming the electrode layers, forming the electric medium layers, enabling the electrode layers and the electric medium layers to be layered repeatedly, conducting thermal processing on the electrode layers and the electric medium layers, forming a protective layer, grinding the back face of the silicon wafer, segmenting the multilayer wafer in the form of a chip (Chip), etching the side face of the chip, and forming an external electrode. According to the method related to the structure, a preset circuit is used in the electrode layer forming step, and the external electrode is manufactured by executing the etching process well determined between the chip cutting step and the external electrode forming step. After a preset electrode layer circuit pattern and the chip are cut, adhesiveness between the electrode layers and the external electrode is enhanced through the cutting face etching method, and finally, the high-quality MLCC can be obtained.

Owner:大连天壹电子有限公司

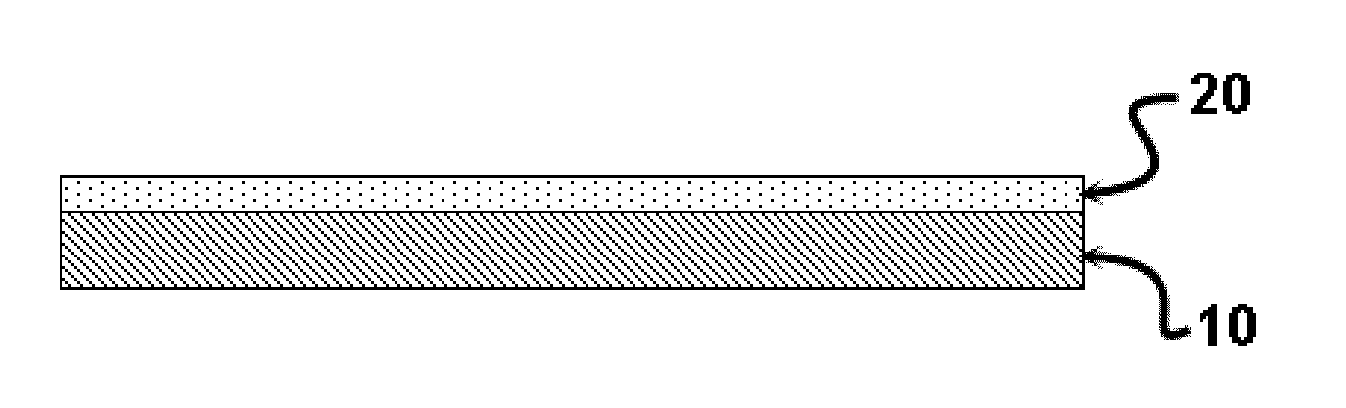

Laminated body including novolac resin as peeling layer

PendingCN111316401AEasy to removeLayered product treatmentSemiconductor/solid-state device detailsWaferingWafer backgrinding

Owner:NISSAN CHEM IND LTD

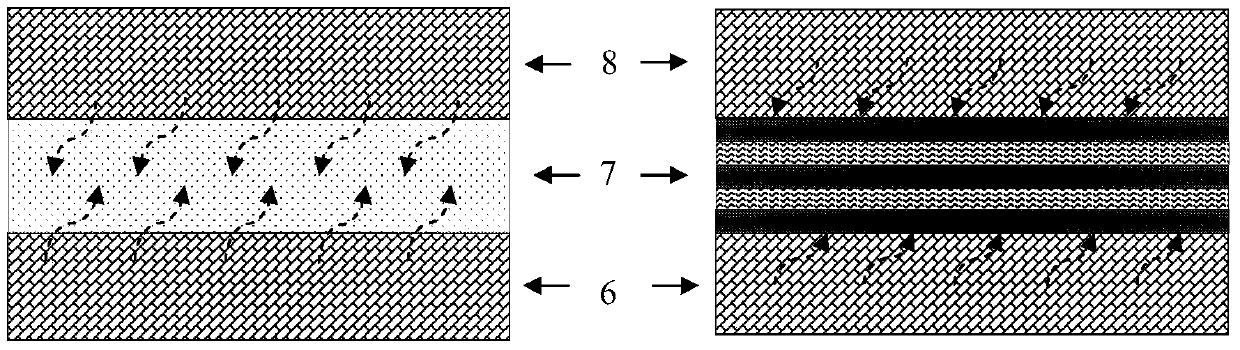

Leakage current characteristic improvement method of dry type lamination ceramic capacitor

InactiveCN103745828APrevent penetrationInhibited DiffusionFixed capacitor electrodesWafer backgrindingCeramic capacitor

Provided is a leakage current characteristic improvement method of a dry type lamination ceramic capacitor. The method comprises the following phases: preparing a wafer; specifying an electrode layer on the wafer and the lamination layer number of a dielectric layer; forming an initial insulating layer on the wafer; forming the electrode layer on the initial insulating layer; forming the dielectric layer on the electrode layer; repeatedly performing lamination on the electrode layer and the dielectric layer; after the lamination, performing heat treatment on the electrode layer and the dielectric layer; forming a protective layer after the heat treatment; grinding the back surface of the wafer after the protective layer is formed; performing cutting in the form of a chip after the back surface of the wafer is grinded; and forming an external electrode by the cut chip. According to the invention, a diffusion prevention membrane is formed during the phase of forming an internal electrode so that in case of change in external environment, internal electrode substances are prevented from being diffused into the dielectric layer. Besides, the dielectric layer is not crystallized, and proper heat treatment is carried out after an internal electrode layer and the dielectric layer are laminated, so that the method for manufacturing a high-quality capacitor with a higher leakage current characteristic is provided.

Owner:大连天壹电子有限公司

Surface protection adhesive tape for semiconductor wafer backgrinding, and semiconductor wafer grinding method

ActiveCN107431007AWith fit visibilitySensor-identifiableSolid-state devicesSemiconductor/solid-state device manufacturingAdhesiveWafer backgrinding

Owner:FURUKAWA ELECTRIC CO LTD

Methods for Failure Analysis in Semiconductor Devices

InactiveCN101769876BIncrease profitImprove accuracySurface/boundary effectOptically investigating flaws/contaminationWafer backgrindingFailure analysis

The invention relates to a method for carrying out failure analysis in a semiconductor device, which comprises the following steps: providing the semiconductor device to be tested, wherein the semiconductor device comprises a wafer and an encapsulation cladding; forming an opening which makes the front side of the wafer exposed on one side of the encapsulation cladding; carrying out failure analysis on the exposed front side of the wafer; filling the opening; carrying out grinding on the other side of the encapsulation cladding to expose the back of the wafer; and carrying out failure analysis on the exposed wafer back. Compared with the prior art, the invention adopts the method of opening on the front side of the wafer firstly and then grinding on the back of the wafer, realizes once failure analysis respectively on the front side and the back of the wafer, improves the accuracy of the failure analysis, strengthens the effect of the failure analysis and improves the utilization rate of the wafer.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Temporary bonding adhesive for wafer thinning, its preparation method, bonding and debonding method

ActiveCN104804682BImprove corrosion resistanceReduce manufacturing costAdhesive processes with adhesive heatingAldehyde/ketone condensation polymer adhesivesWafer backgrindingAdhesive

Disclosed are a temporary bonding glue for wafer backgrinding, a preparation method of the temporary bonding glue and bonding and de-bonding methods. The temporary bonding glue comprises a base resin for producing an adhesive effect, wherein the base resin can be depolymerised into a low molecular compound and / or a linear low polymer under the action of a strong acid, so that an adhesive layer formed by the bonding glue has an obvious depolymerisation reaction under the sufficient impregnation of an acid liquor, that is, the structure of a three-dimensional polymer is damaged, the adhesive layer loses efficacy by means of the generated low molecular compound or the linear low polymer, and the de-bonding efficiency is improved. In addition, the decomposition temperature of the high polymer is not less than 270°C, so that the thermal stability of the adhesive layer is high. In addition, the corrosion resistance of the bonding glue of the present invention is good, and the preparation cost is relatively economical.

Owner:深圳市化讯半导体材料有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com