Machining method for high-yield monocrystalline silicon wafer for IGBT

A processing method and technology of silicon wafers, which are applied in the fields of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of low wafer yield, large amount of polished wafer removal, and long polishing time, etc., so as to increase production capacity, The effect of reducing the amount of polishing removal and shortening the processing time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0020] This embodiment is a detailed description of the processing flow of a 6-inch 625 μm thick heavily doped sheet:

[0021] (1) Experimental silicon wafer: 6-inch Czochralski silicon abrasive disc, resistivity: 0.02-0.04Ω.cm, thickness 690±5μm, quantity: 120 pieces.

[0022] (2) Processing equipment: acid rot machine, grinding equipment, wax-free polishing machine.

[0023] (3) Auxiliary materials: 325# grinding wheel, 1500# grinding wheel, mixed acid, ceramic plate, rough polishing liquid, fine polishing liquid, template, INSERT (pad for polishing), DIW (deionized water).

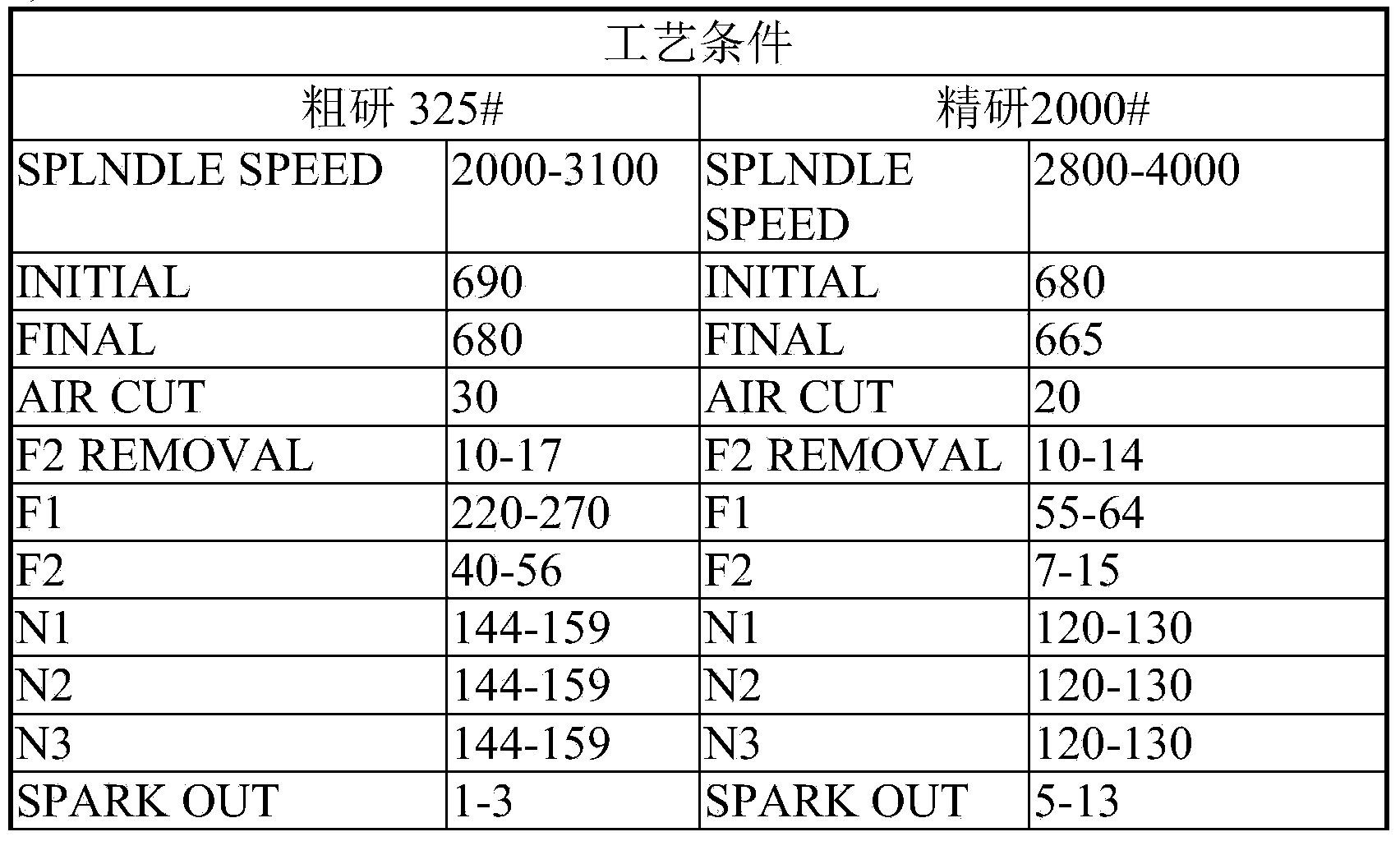

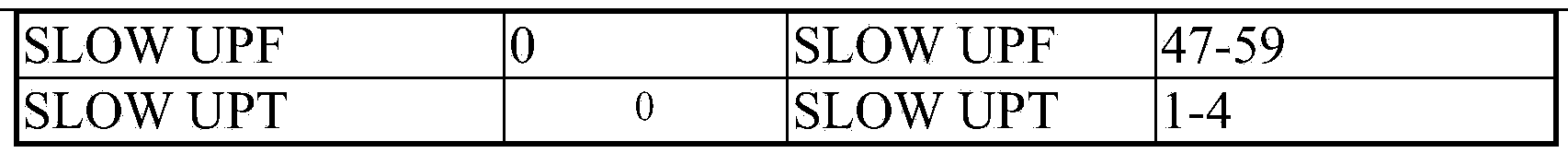

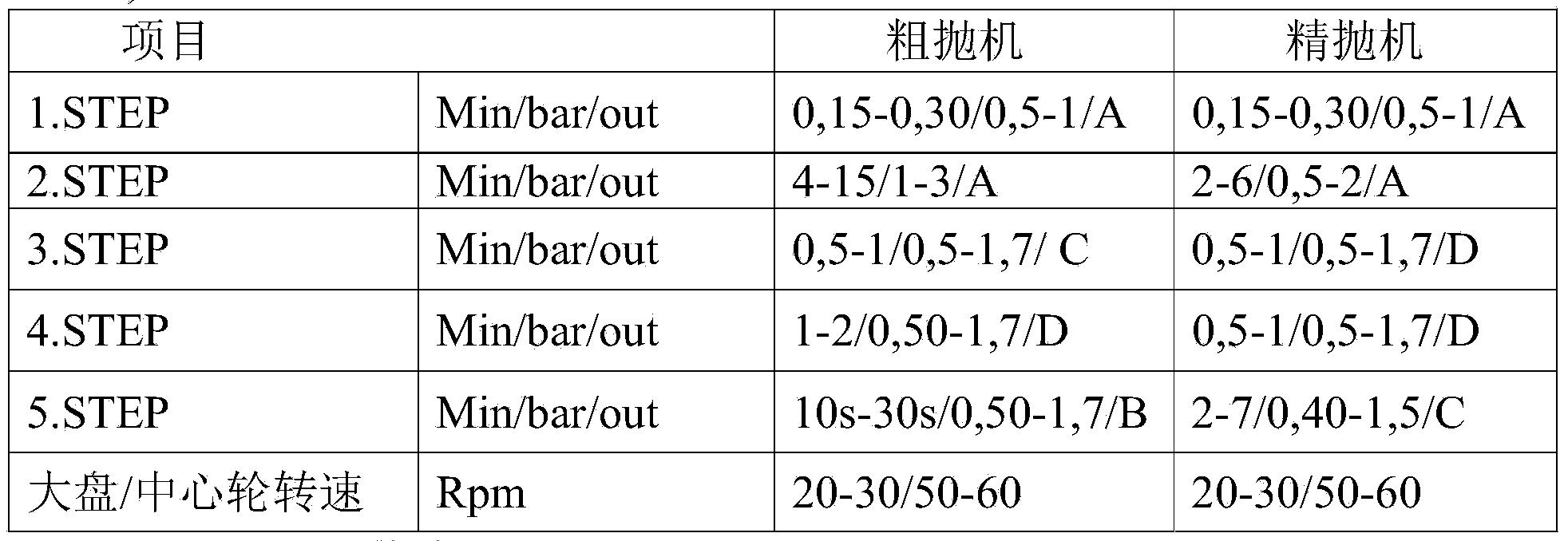

[0024] (4) Method parameter setting:

[0025] a) Grinding:

[0026]

[0027]

[0028] b) Sour rot: mixed acid ratio: HF:HNO 3 :HA C =1:1:2, corrosion time: 40s, washing time: 240s;

[0029] c) Back damage: use Al 2 o 3 , back damage density: ≥5×106ea / cm 2 ;

[0030] d) Back seal: Back seal film thickness: 5000±500A;

[0031] e) Edge removal: processed by automatic edge removal machine, t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com