Methods for Failure Analysis in Semiconductor Devices

A failure analysis and semiconductor technology, applied in the field of failure analysis, can solve problems such as primary failure analysis, achieve the effect of improving utilization rate, enhancing effect, and improving accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The inventors of the present invention have found that when using the traditional peeling technology to expose the wafer for failure analysis, since the peeling technology will destroy the chip itself or the electrical connection structure, only one failure analysis can be performed for a single chip, but one failure analysis can only be performed once. Analysis (whether on the front side of the die or the back side of the die) does not pinpoint the source of the failure in some cases.

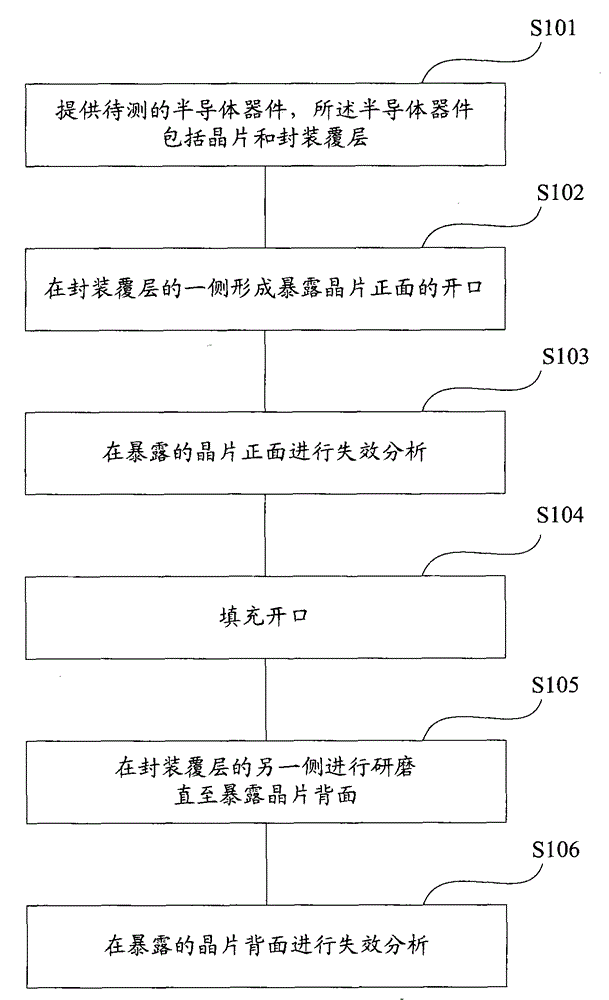

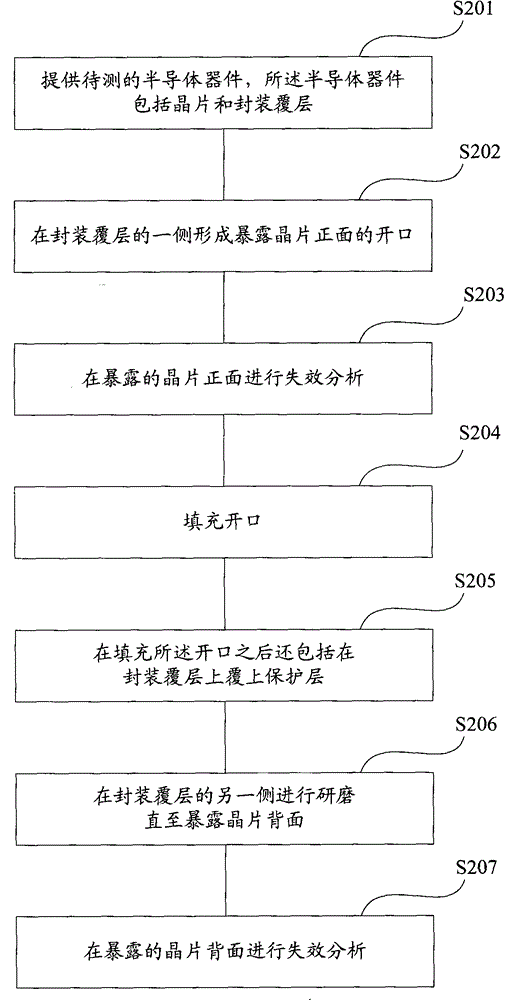

[0024] Therefore, in order to solve the above problems, such as figure 1 As shown, according to one embodiment of the present invention, a method for failure analysis in a semiconductor device is provided, comprising the steps of:

[0025] S101, providing a semiconductor device to be tested, the semiconductor device including a wafer and a packaging coating;

[0026] S102, forming an opening exposing the front surface of the chip on one side of the package coating;

[0027] S103, perf...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com