Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

50 results about "Quality gate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A Quality Gate is a special milestone in a software project. Quality Gates are located before a phase that is strongly dependent on the outcome of a previous phase. They are especially useful between phases in which breaches in disciplines must be overcome. Such a breach typically occurs, for example, when embedded software must be transferred to a hardware chip. Quality Gates are more general than Milestones; Quality Gates can be used in larger set of more or less similar projects, whereas milestones must be defined for each project from scratch. Each Quality Gate includes a check of documents relevant to the previous phase. Unlike a software review, this check is only formal; no deep check on the contents of applicable documents is conducted in a Quality Gate. A Quality Gate demands a set of documents and includes special requirements on these documents, both of which are detailed in a checklist. The check itself is performed in a session with decision makers and domain experts. Depending on their decision, the project can be canceled, put on hold, or approved to proceeded normally. Unfortunately, the term Quality Gate is not used consistently.

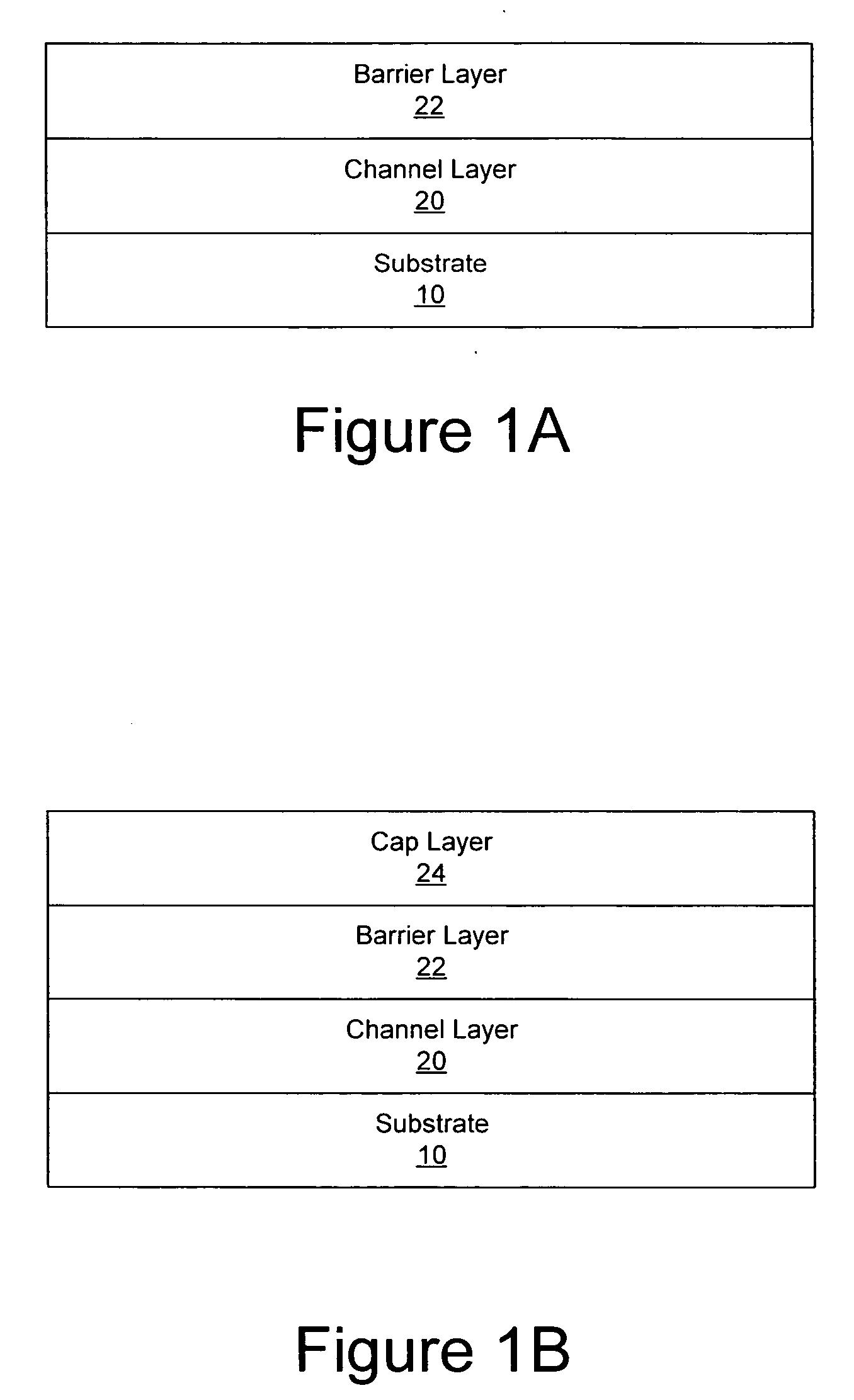

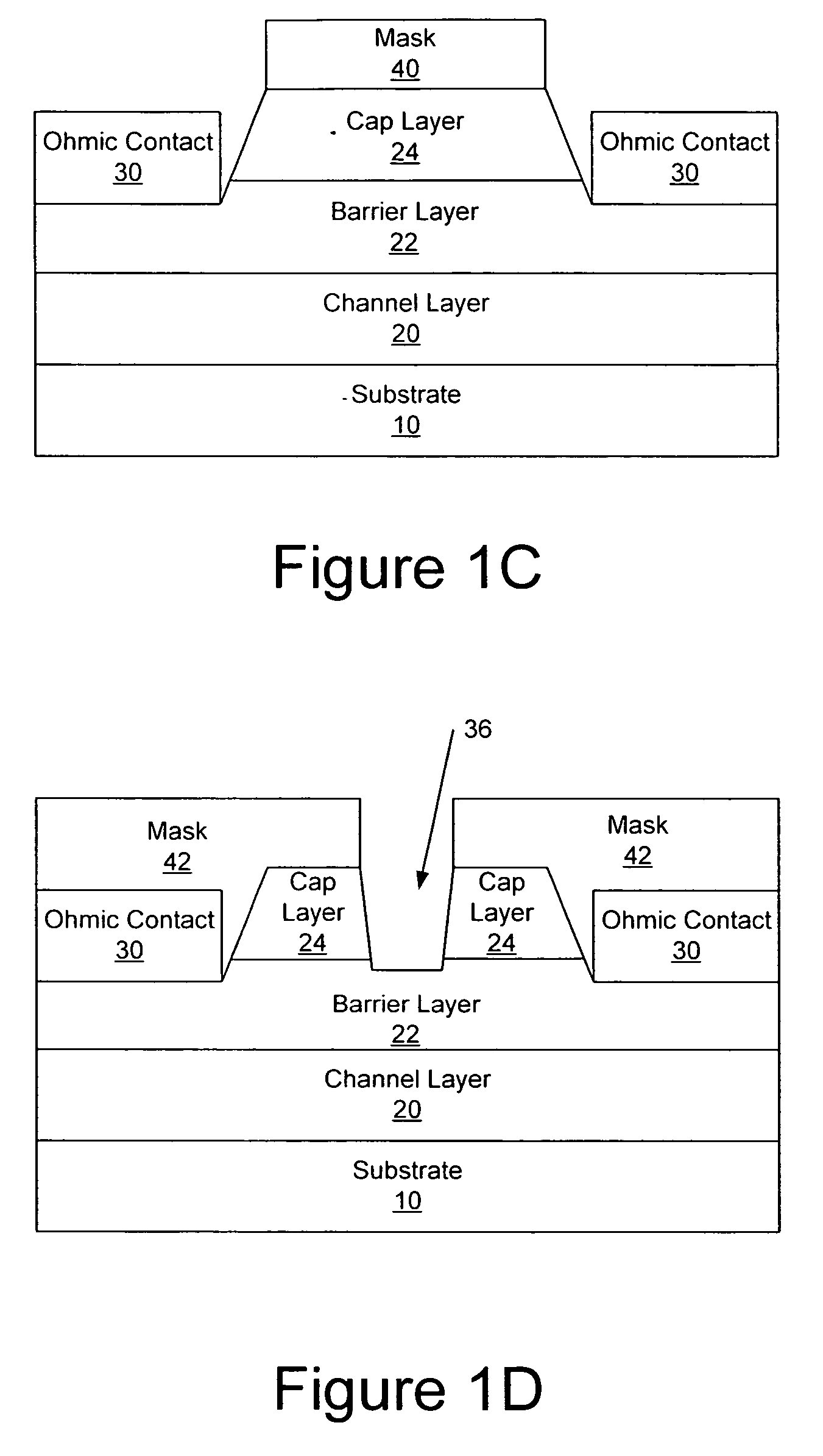

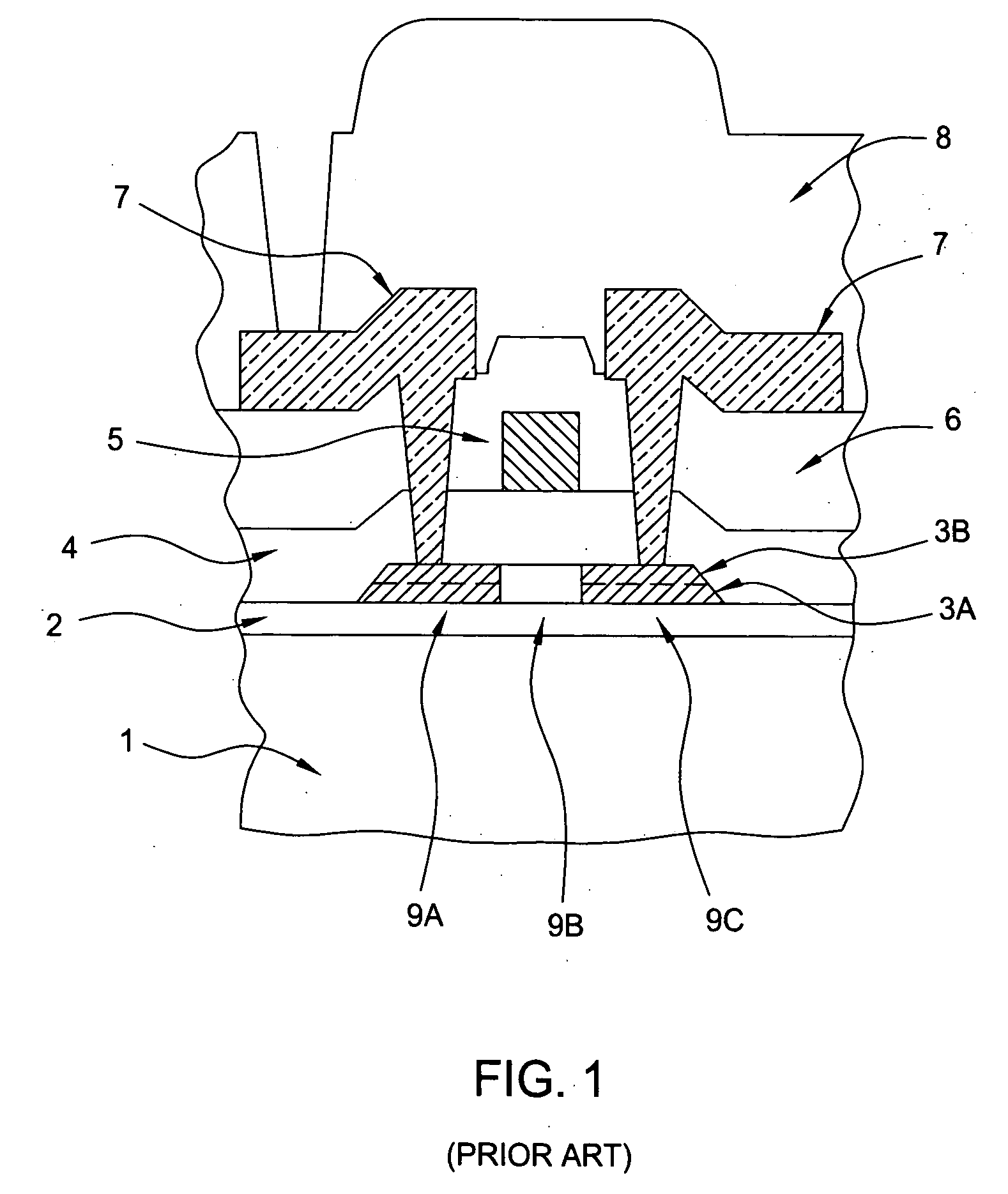

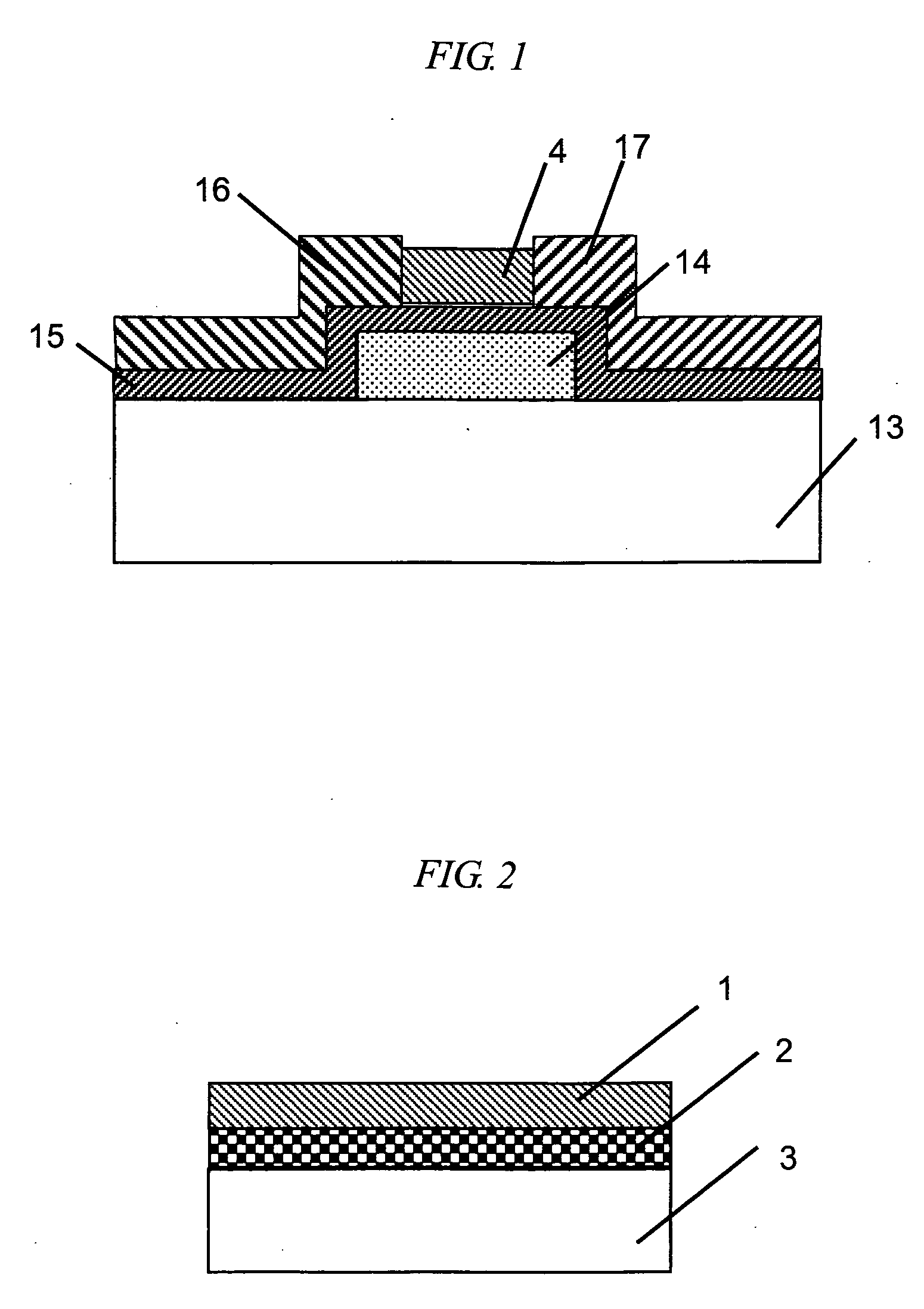

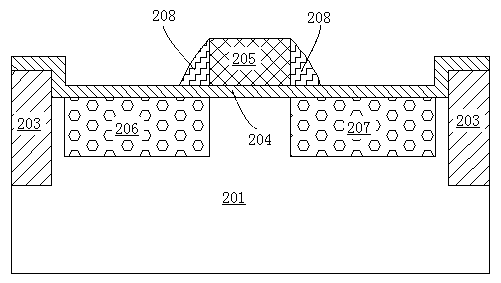

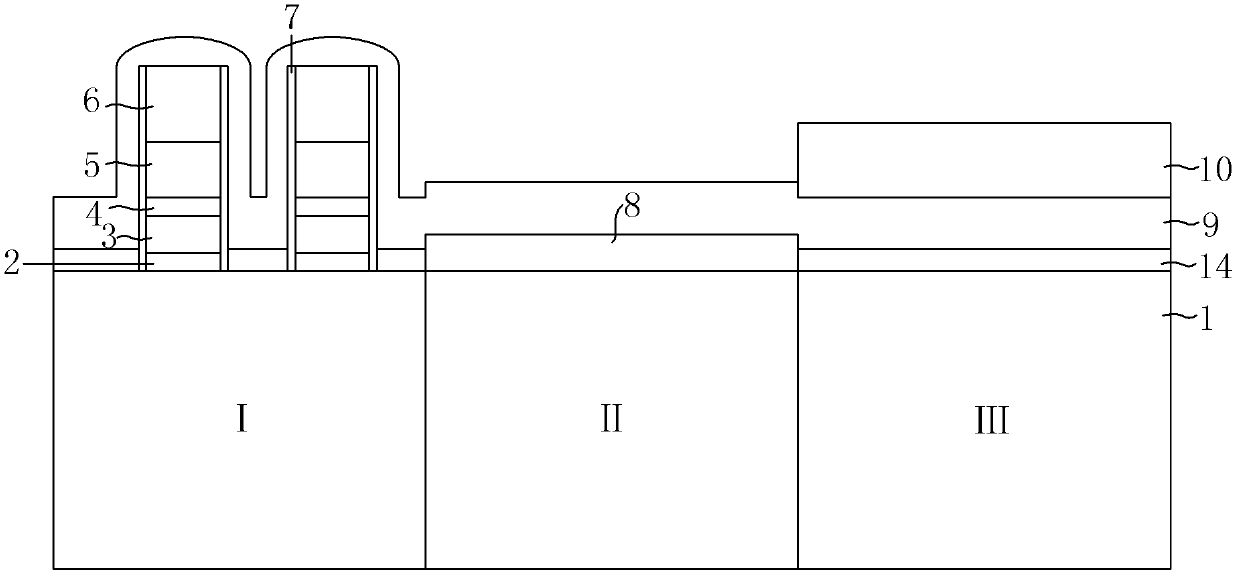

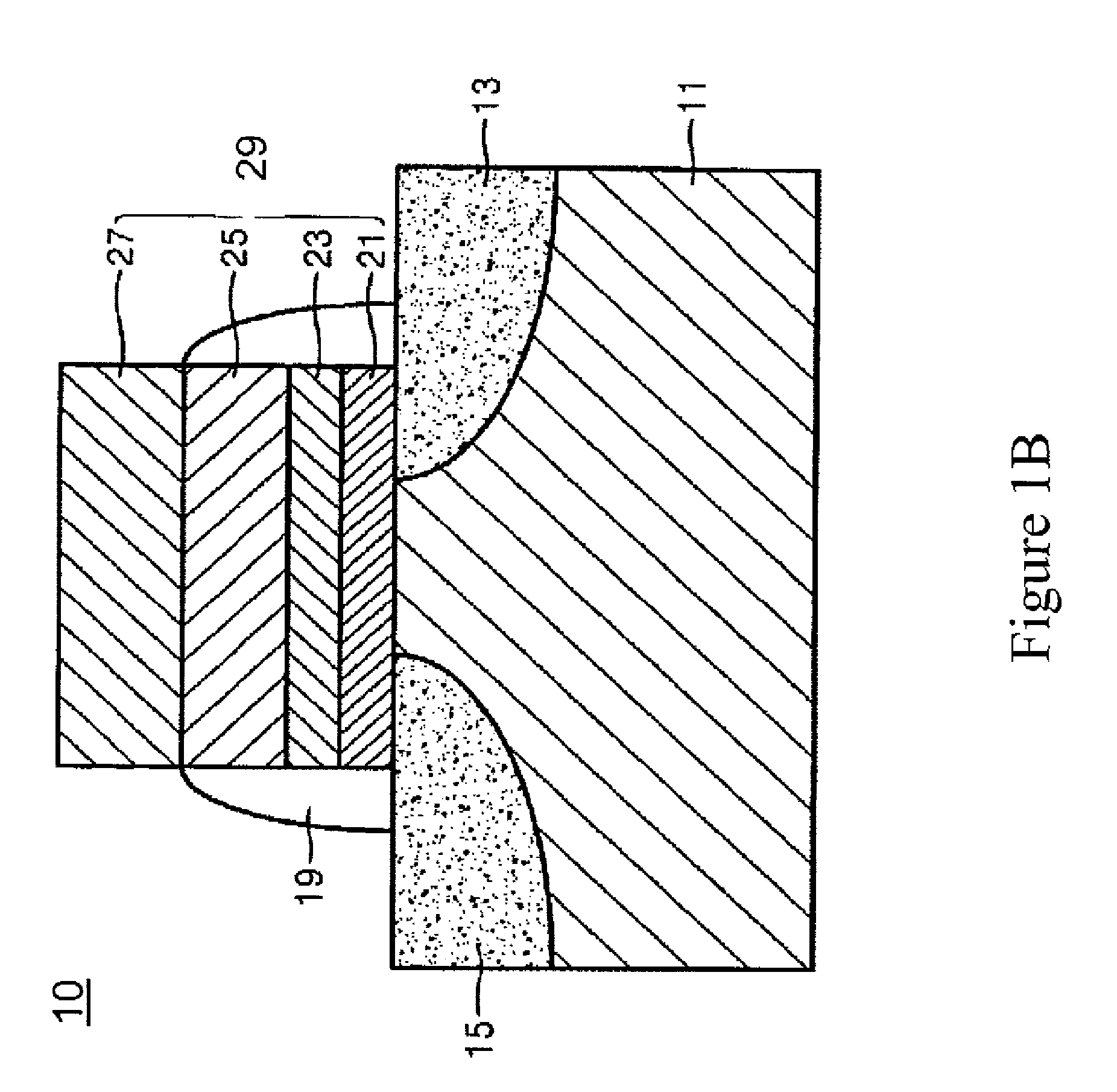

Methods of fabricating nitride-based transistors with a cap layer and a recessed gate

ActiveUS7238560B2Solid-state devicesSemiconductor/solid-state device manufacturingOhmic contactNitride

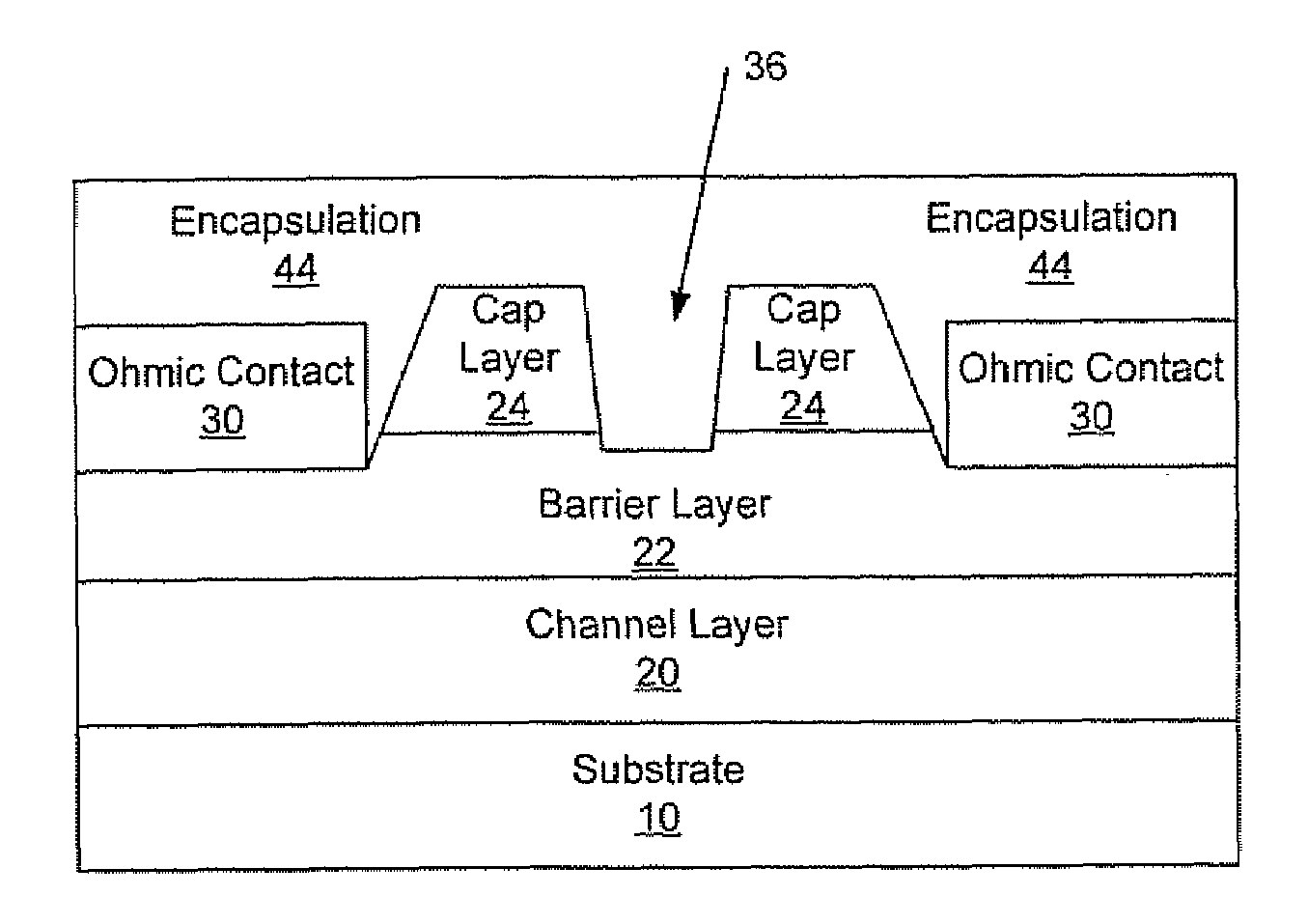

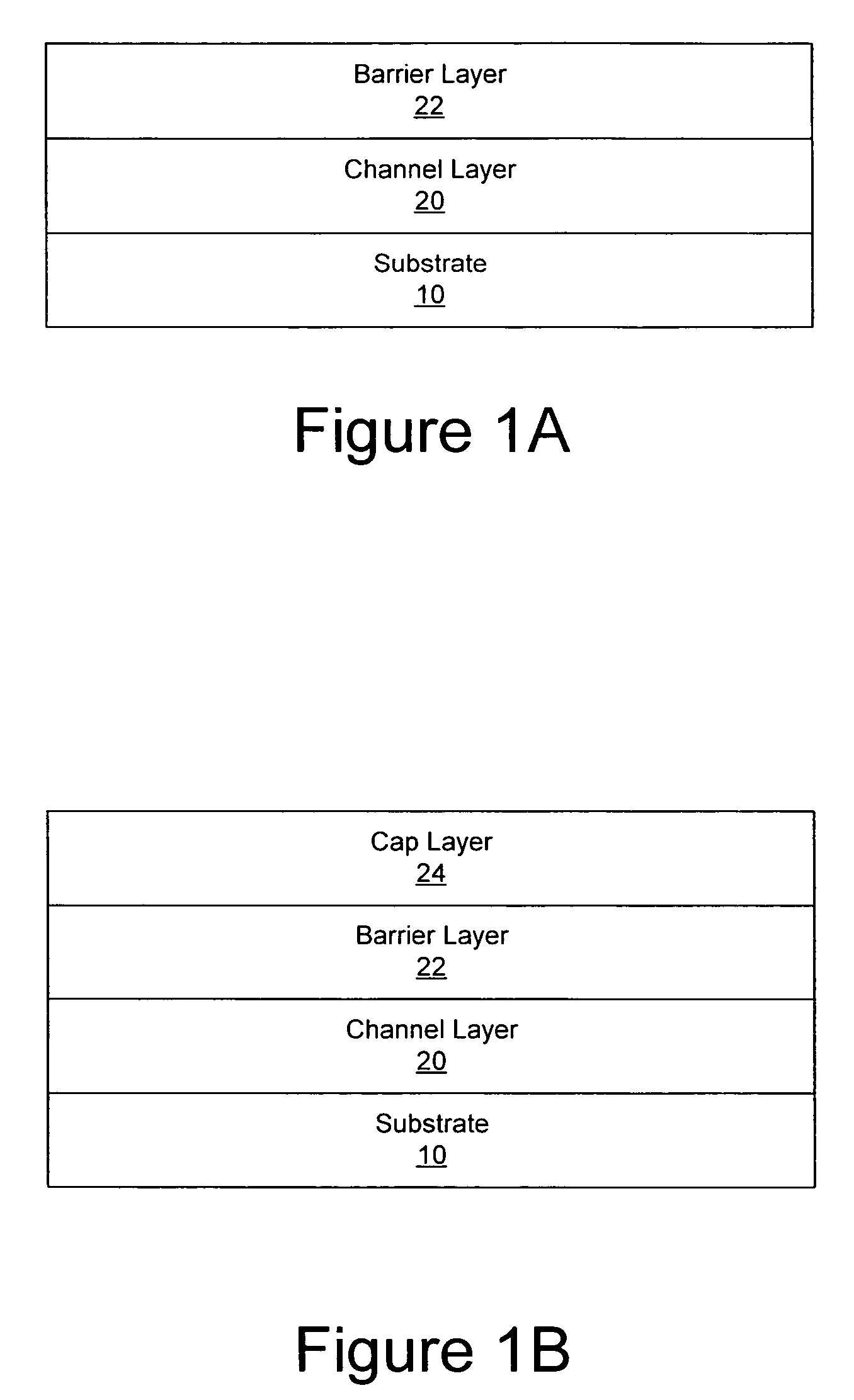

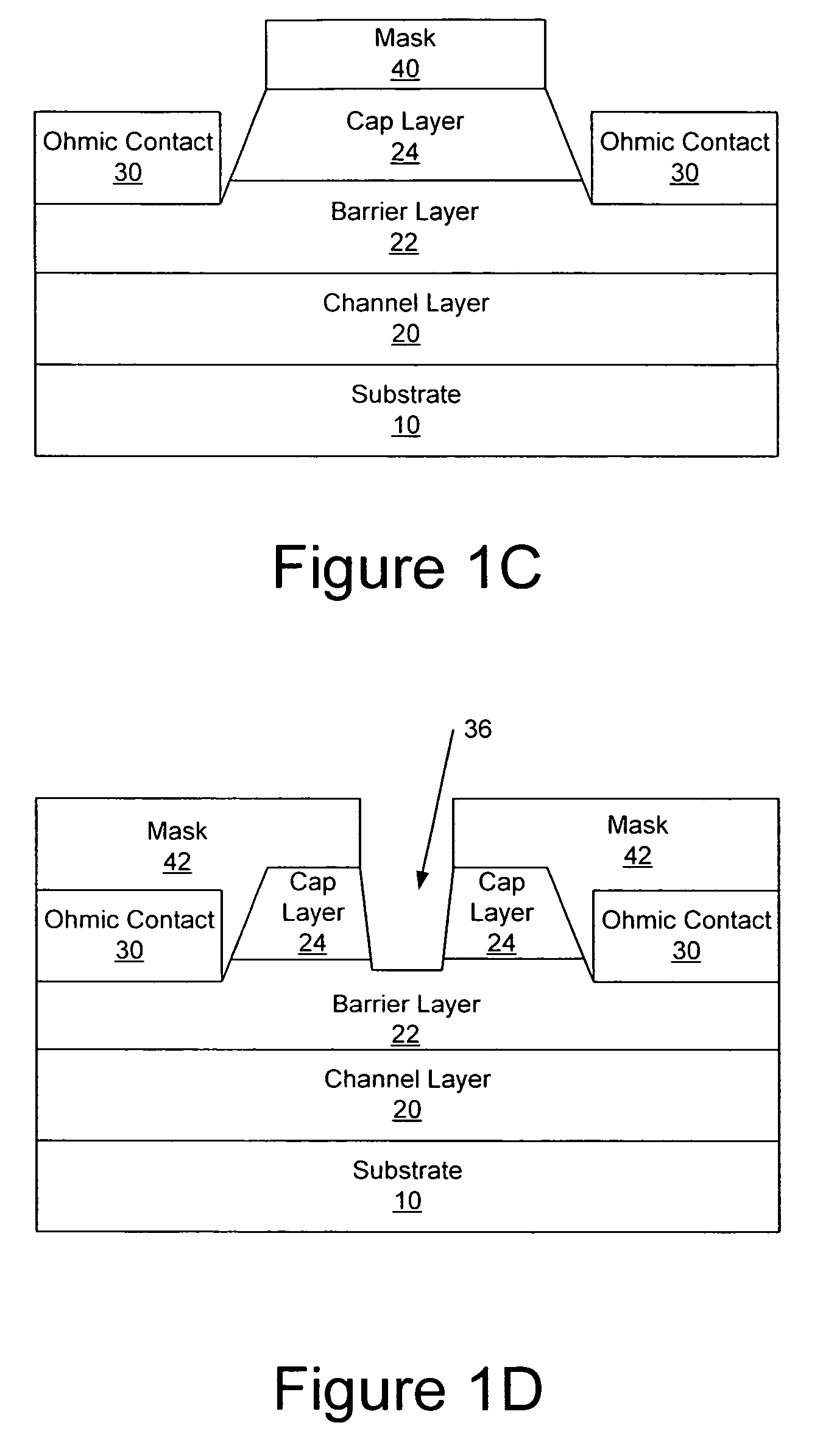

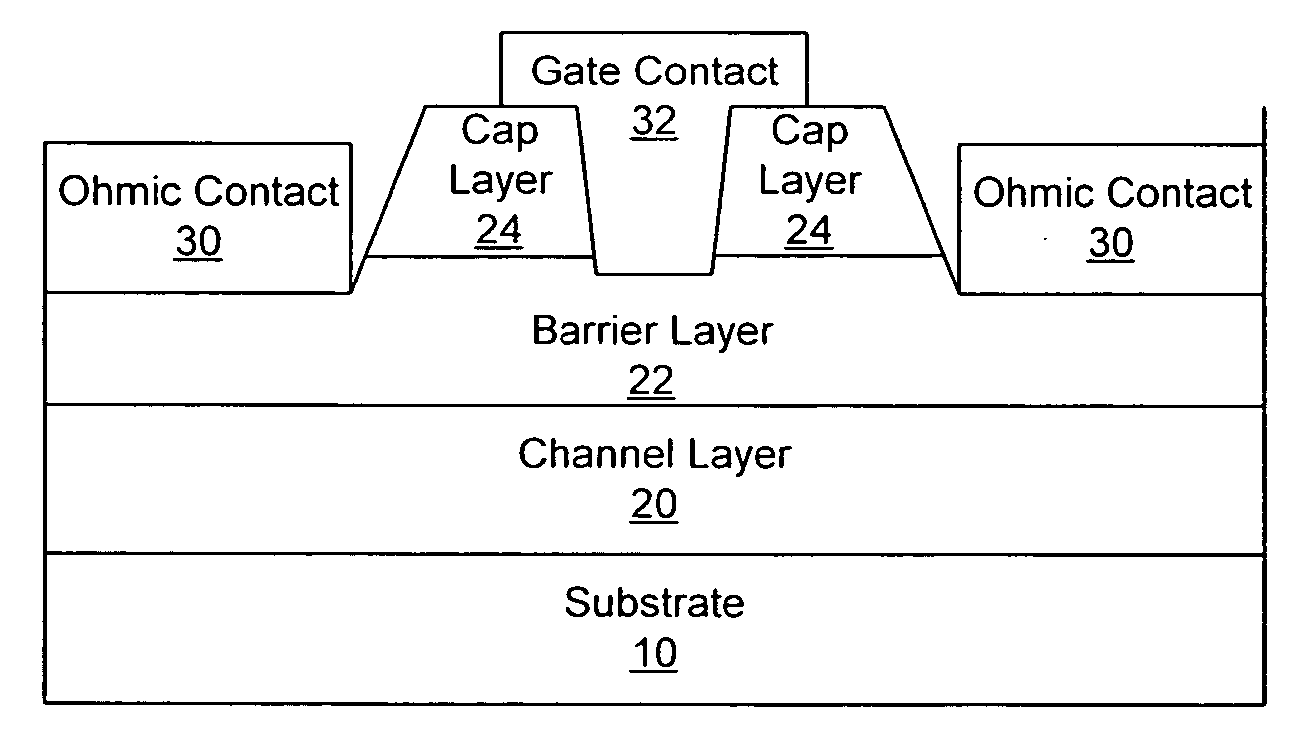

An anneal of a gate recess prior to formation of a gate contact, such as a Schottky contact, may reduce gate leakage and / or provide a high quality gate contact in a semiconductor device, such as a transistor. The use of an encapsulation layer during the anneal may further reduce damage to the semiconductor in the gate recess of the transistor. The anneal may be provided, for example, by an anneal of ohmic contacts of the device. Thus, high quality gate and ohmic contacts may be provided with reduced degradation of the gate region that may result from providing a recessed gate structure as a result of etch damage in forming the recess.

Owner:CREE INC

Methods of fabricating nitride-based transistors with a cap layer and a recessed gate

ActiveUS20060019435A1Solid-state devicesSemiconductor/solid-state device manufacturingOhmic contactDevice material

An anneal of a gate recess prior to formation of a gate contact, such as a Schottky contact, may reduce gate leakage and / or provide a high quality gate contact in a semiconductor device, such as a transistor. The use of an encapsulation layer during the anneal may further reduce damage to the semiconductor in the gate recess of the transistor. The anneal may be provided, for example, by an anneal of ohmic contacts of the device. Thus, high quality gate and ohmic contacts may be provided with reduced degradation of the gate region that may result from providing a recessed gate structure as a result of etch damage in forming the recess.

Owner:CREE INC

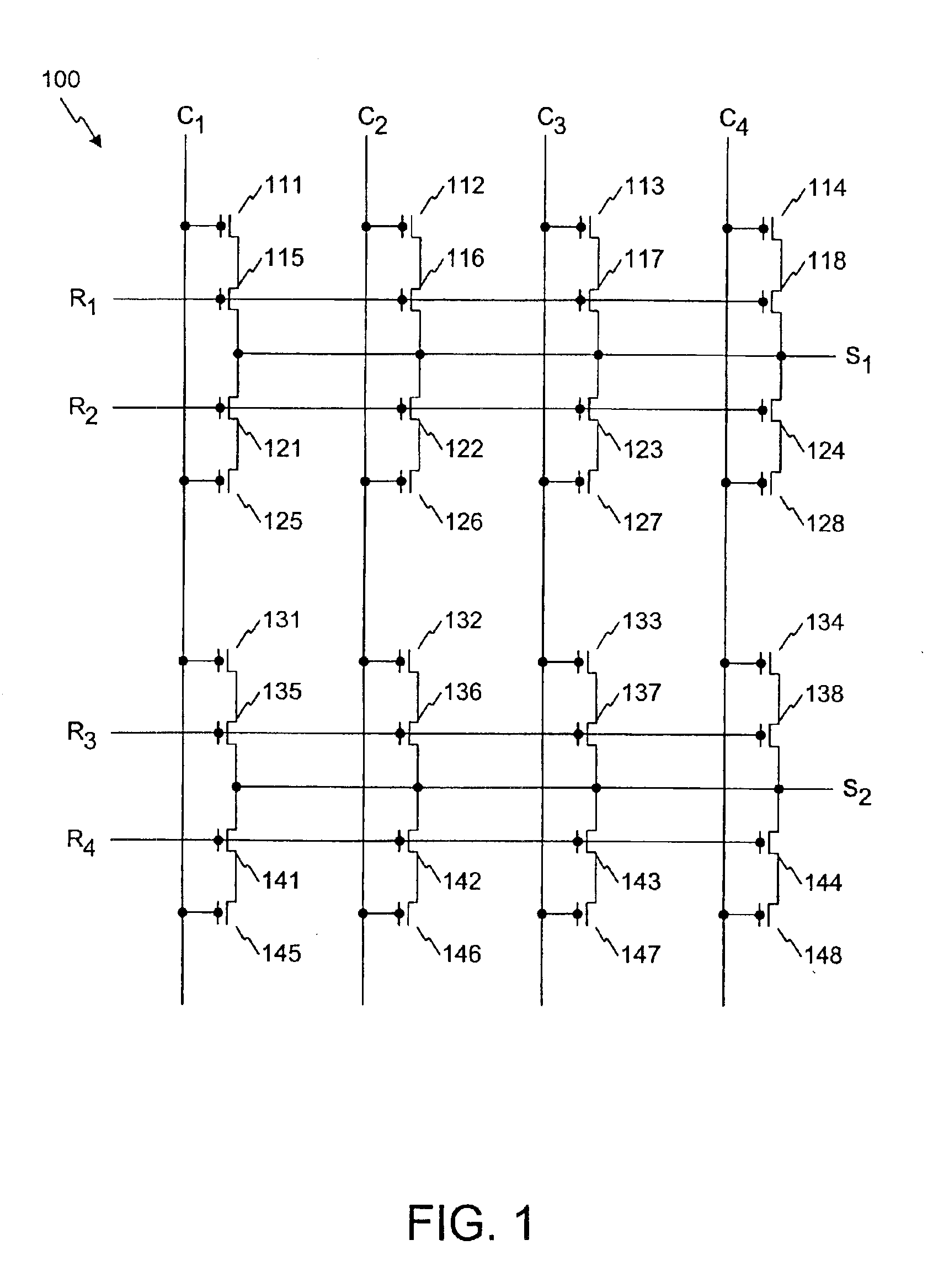

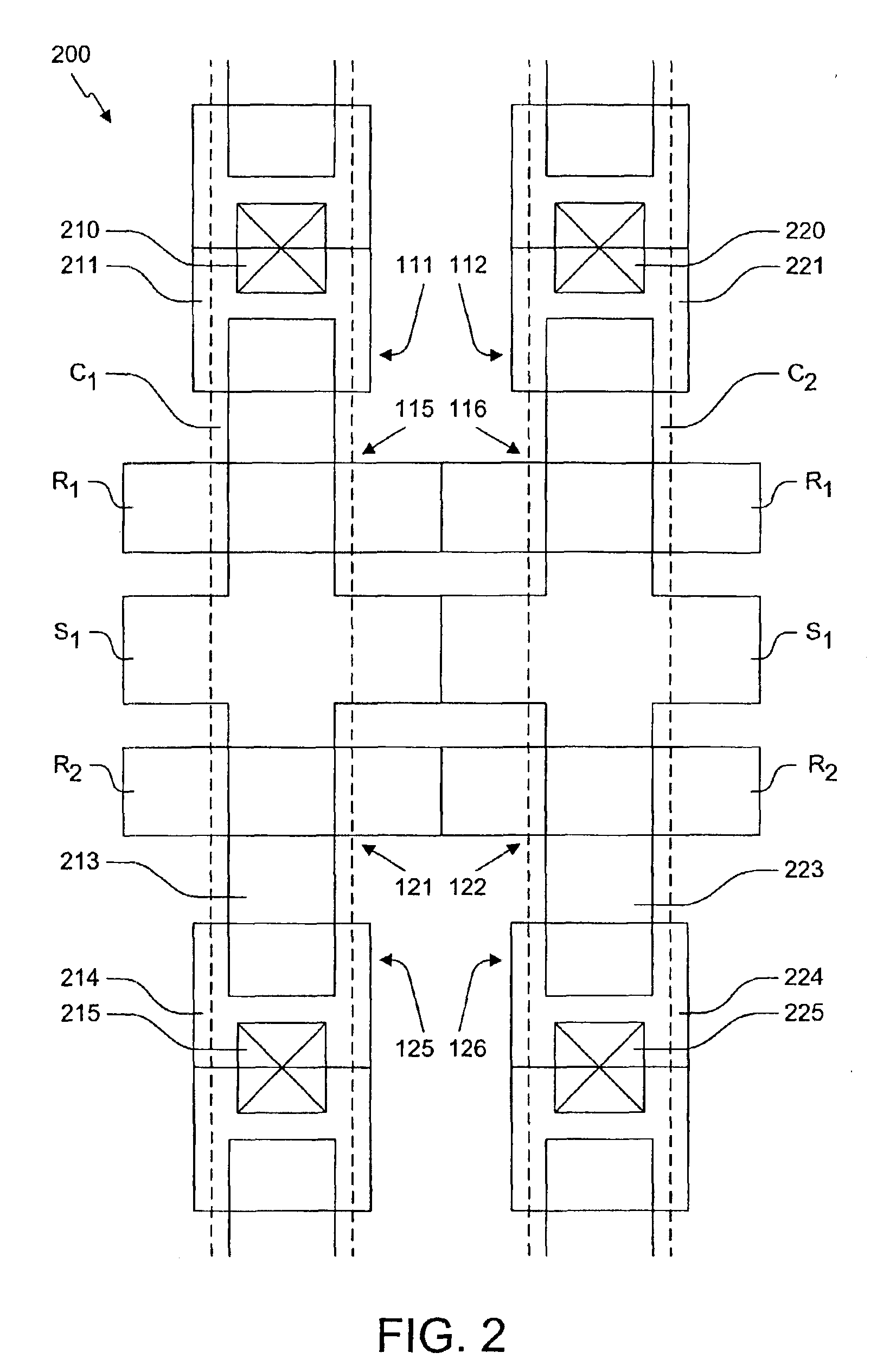

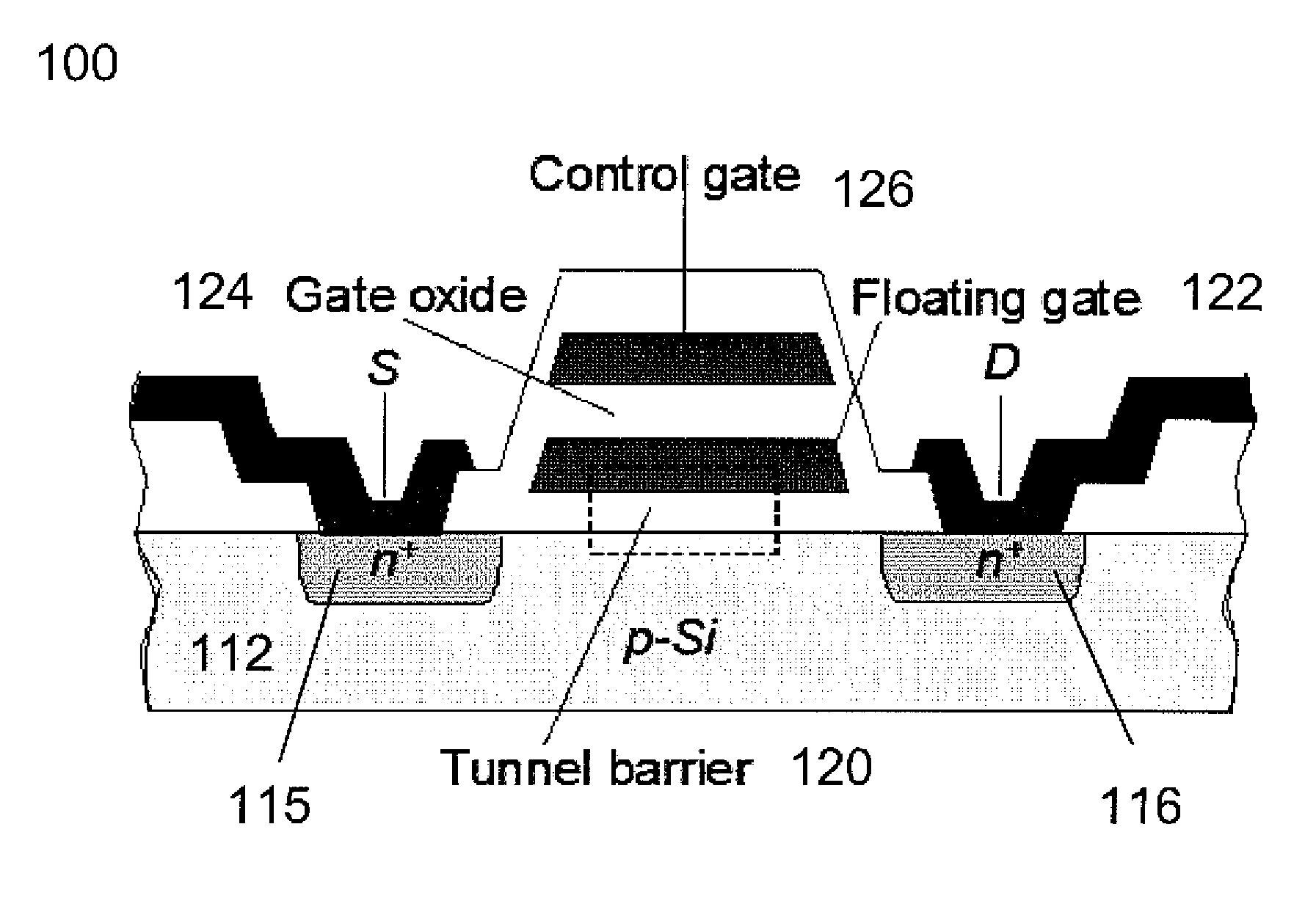

Reprogrammable non-volatile memory using a breakdown phenomena in an ultra-thin dielectric

A reprogrammable non-volatile memory array and constituent memory cells is disclosed. The semiconductor memory cells each have a data storage element constructed around an ultra-thin dielectric, such as a gate oxide. The gate oxide is used to store information by stressing the ultra-thin dielectric into breakdown (soft or hard breakdown) to set the leakage current level of the memory cell. The memory cell is read by sensing the current drawn by the cell. A suitable ultra-thin dielectric is high quality gate oxide of about 50 Å thickness or less, as commonly available from presently available advanced CMOS logic processes. The memory cells are first programmed by stressing the gate oxide until soft breakdown occurs. The memory cells are then subsequently reprogrammed by increasing the breakdown of the gate oxide.

Owner:SYNOPSYS INC

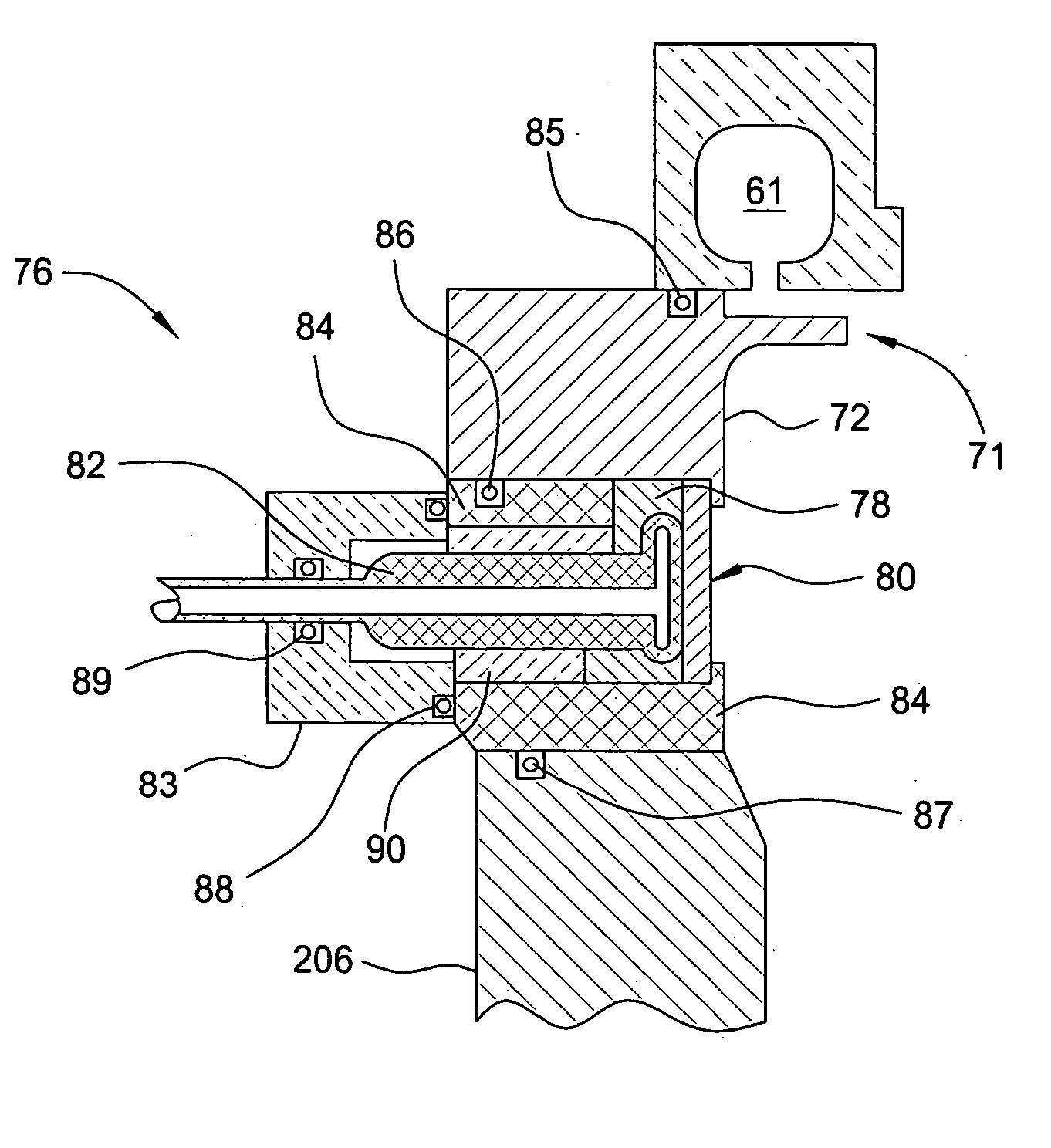

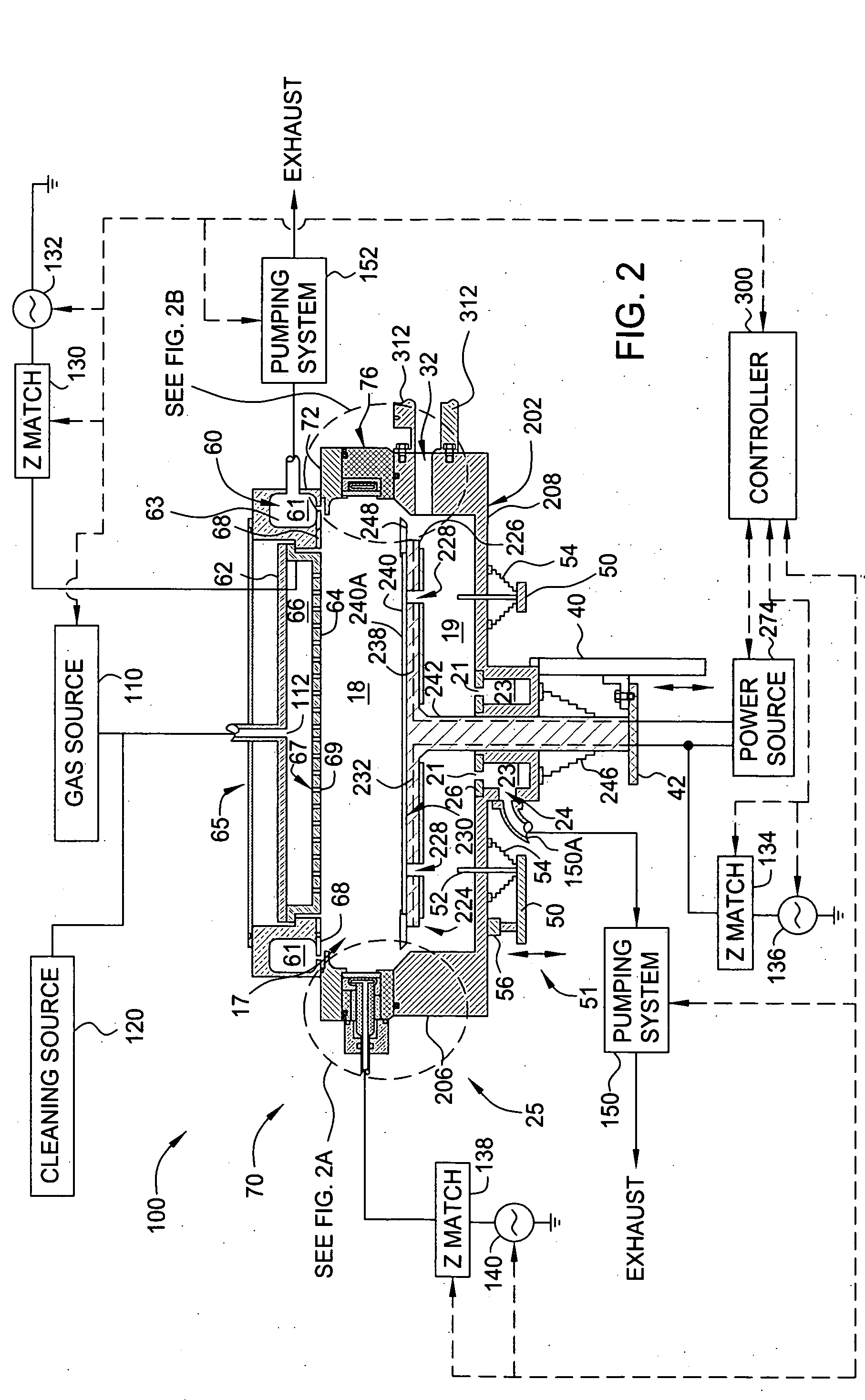

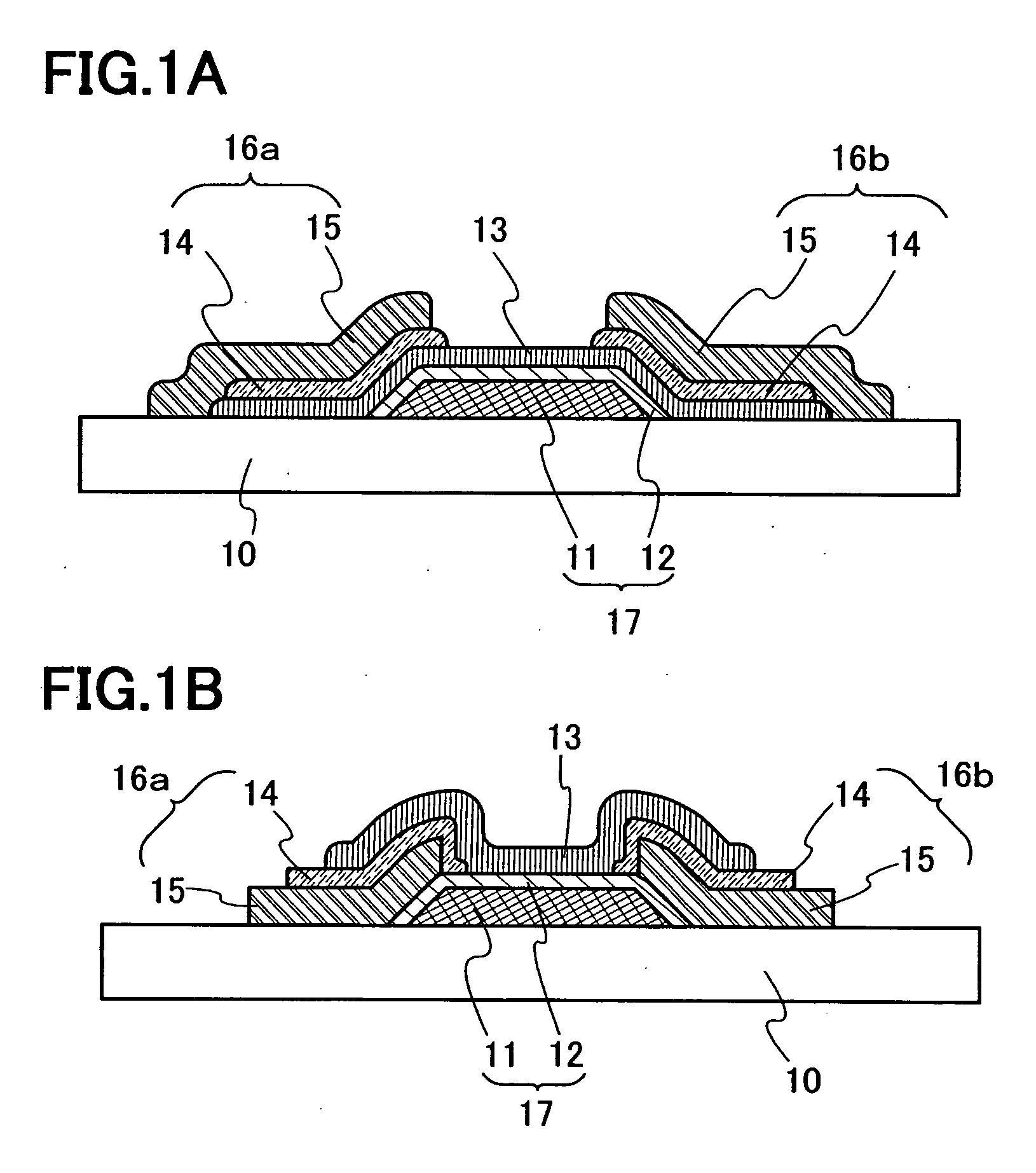

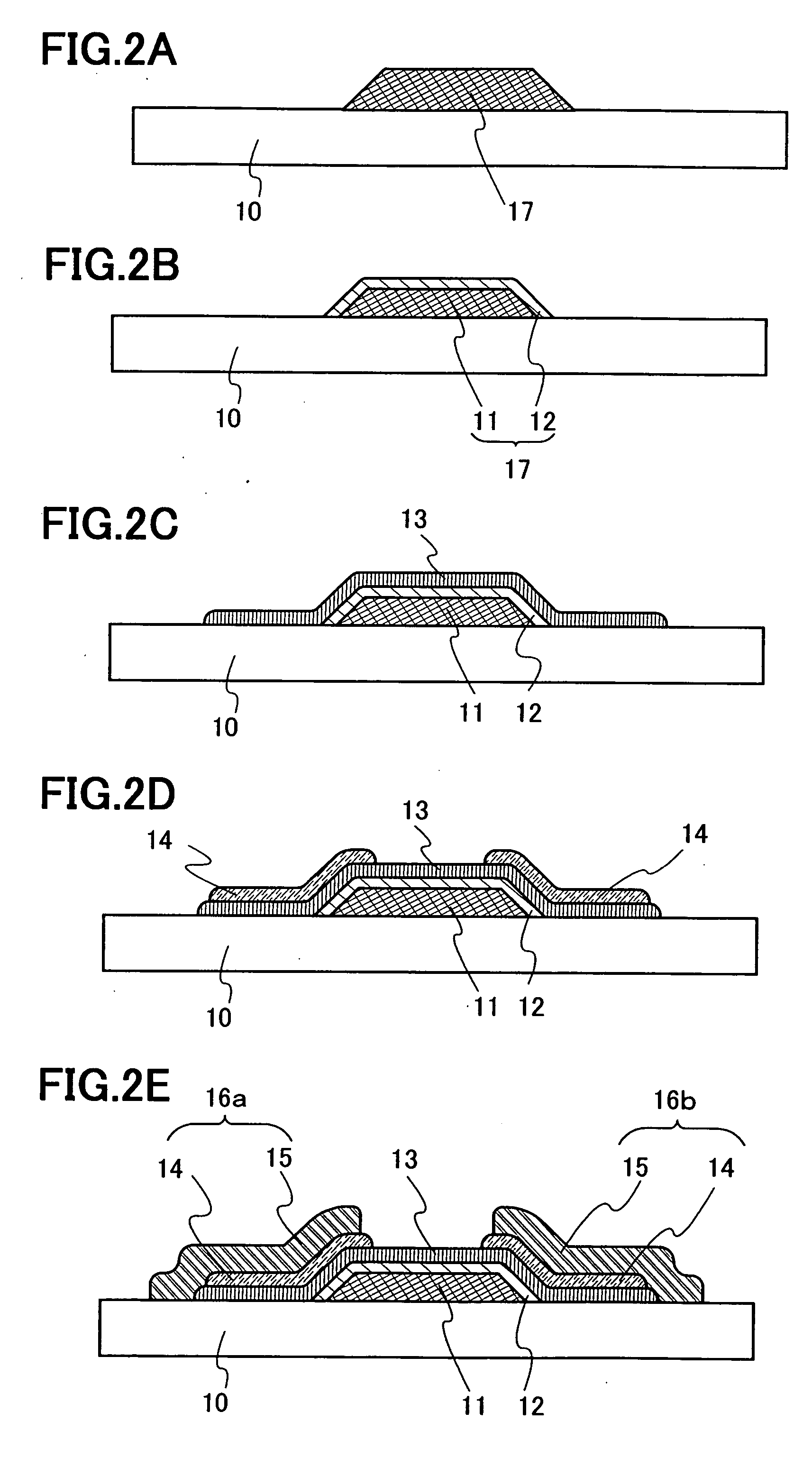

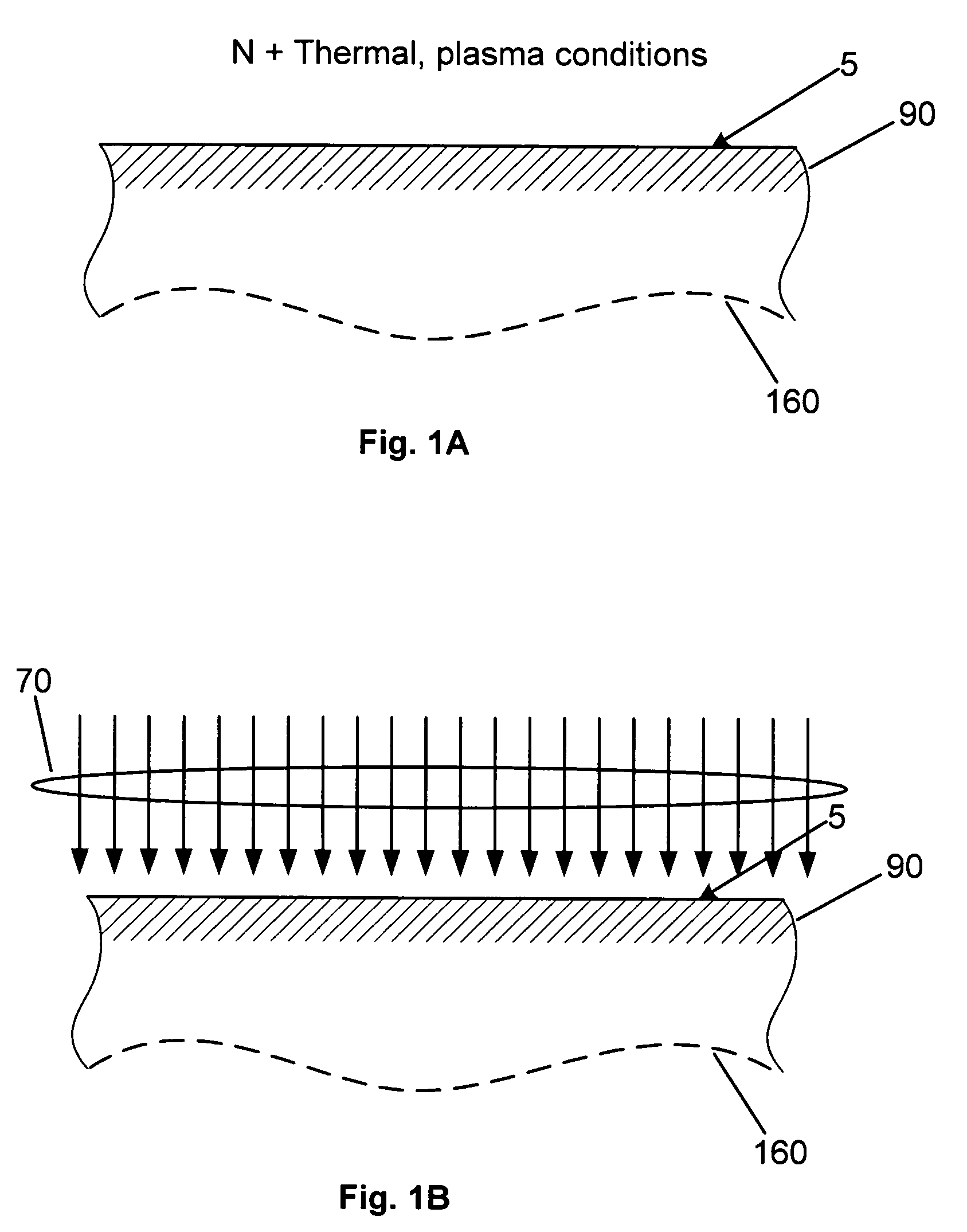

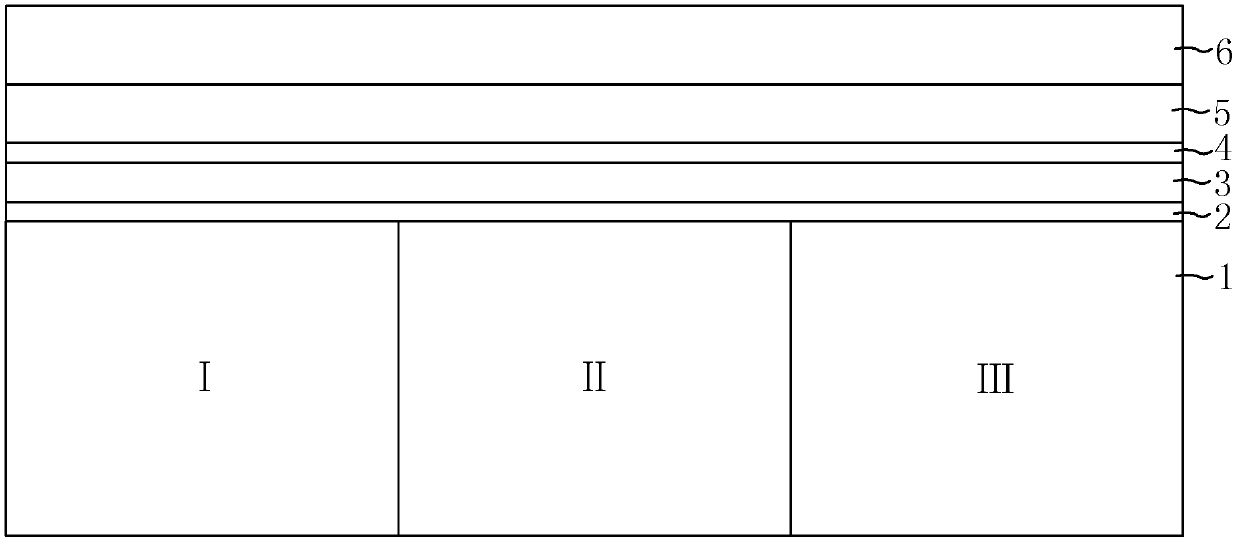

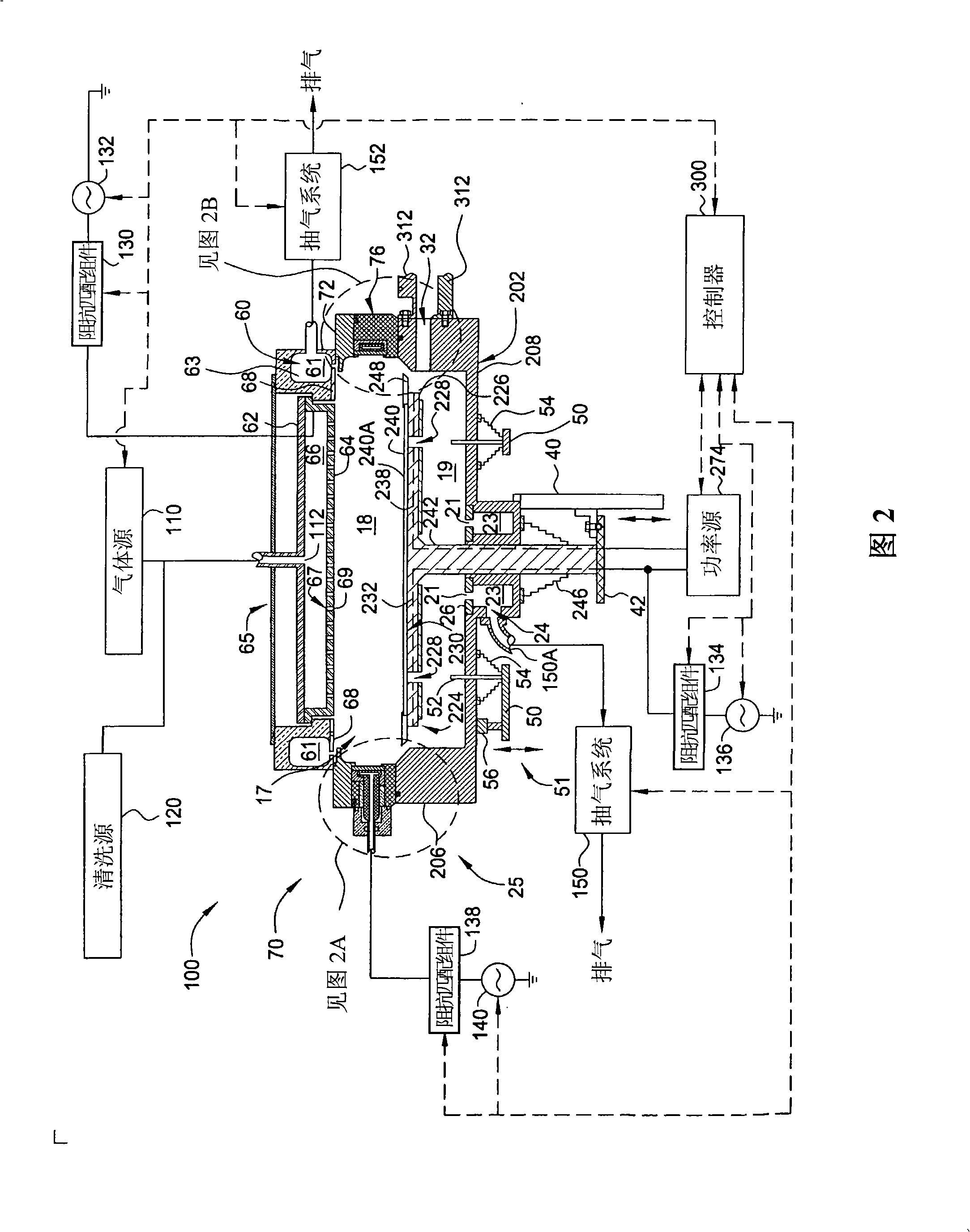

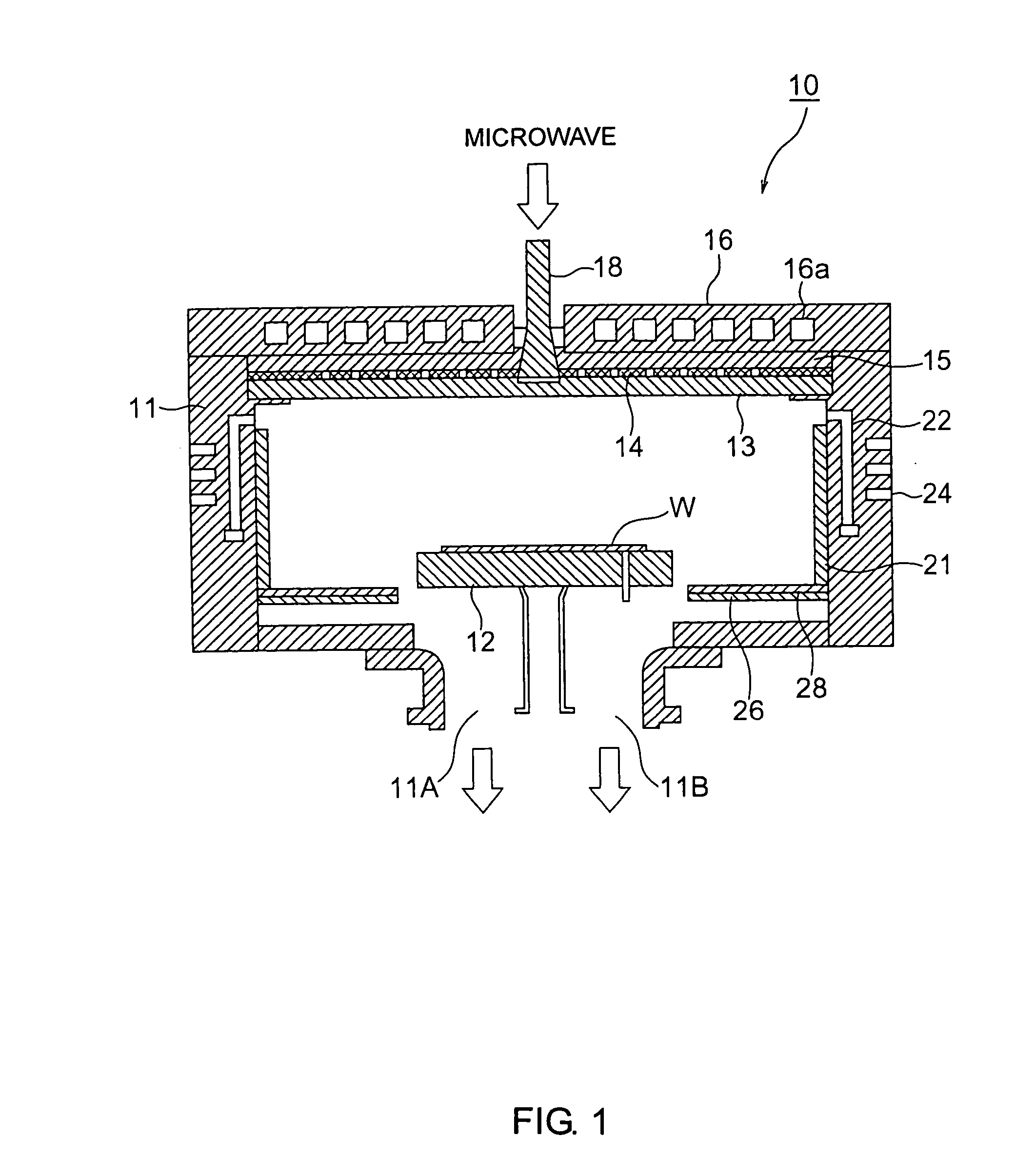

Multi-layer high quality gate dielectric for low-temperature poly-silicon TFTs

InactiveUS20060105114A1Quality improvementSolid state diffusion coatingChemical vapor deposition coatingCapacitanceEngineering

A method and apparatus that is useful for forming a high quality gate dielectric layer in MOS TFT devices using a high density plasma oxidation (HDPO) process. The HDPO process forms a good interface and then a second layer, which has good bulk electrical properties, is deposited at a higher deposition rate over the HDPO layer. In one embodiment a thin HDPO process layer is formed over the channel, source and drain regions to form a high quality dielectric interface and then one or more dielectric layers are deposited on the HDPO layer to form a high quality gate dielectric layer. The HDPO process generally entails using an inductively and / or capacitively coupled RF energy transmitting device to generate and control the plasma generated over the surface of the substrate and injecting a gas containing an oxidizing source to grow the interfacial layer. A second dielectric layer may then be deposited on the surface of the substrate using a CVD or plasma enhanced CVD deposition process. Aspects of the present invention also provide a cluster tool that contains at least one specialized plasma processing chamber that is capable of depositing a high quality gate dielectric layer. The cluster tool is advantageous because it supports both the pre-processing steps, such as, preheating the substrate, pre-cleaning the surface of the substrate prior to processing, and cool down after processing, all in a single controlled environment.

Owner:APPLIED MATERIALS INC

Organic transistor, manufacturing method of semiconductor device and organic transistor

InactiveUS20060270066A1Reduce leakage currentReduce tunnel leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingConductive polymerPlasma activation

It is an object to form a high quality gate insulating film which is dense and has a strong insulation resistance property, and to propose a high reliable organic transistor in which a tunnel leakage current is little. One mode of the organic transistor of the present invention has a step of forming the gate insulating film by forming the conductive layer which becomes the gate electrode activating oxygen (or gas including oxygen) or nitrogen (or gas including nitrogen) or the like using dense plasma in which density of electron is 1011 cm−3 or more, and electron temperature is a range of 0.2 eV to 2.0 eV with plasma activation, and reacting directly with a portion of the conductive layer which becomes the gate electrode to be insulated.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor material, field effect transistor and manufacturing method thereof

InactiveUS7109072B2Forming accuratelySolve the real problemNanoinformaticsSolid-state devicesResistSemiconductor materials

The silicon wires formed around metal particles by crystal growth have the problem of metal pollution. For its solution, in the present invention, a silicon bridge is formed through standard silicon processes such as the lithography and the wet etching using hydrofluoric acid performed to an SOI substrate. Thereafter, a thermal oxide film is desirably formed at a high temperature to form a high-quality gate insulating film. It is also desirable to form a coaxial gate electrode. Then, after burying the bridge sections of the silicon bridge in a resist film, the silicon on the bridge girders is removed, and thereafter, the silicon wires buried in the resist film are collected. In this manner, the silicon wires can be collected without dispersing into the hydrofluoric acid solution. Then, a transistor using the silicon wires as a channel is formed.

Owner:HITACHI LTD

Semiconductor material, field effect transistor and manufacturing method thereof

InactiveUS20060088960A1Forming accuratelySolve the real problemNanoinformaticsSolid-state devicesResistEtching

The silicon wires formed around metal particles by crystal growth have the problem of metal pollution. For its solution, in the present invention, a silicon bridge is formed through standard silicon processes such as the lithography and the wet etching using hydrofluoric acid performed to an SOI substrate. Thereafter, a thermal oxide film is desirably formed at a high temperature to form a high-quality gate insulating film. It is also desirable to form a coaxial gate electrode. Then, after burying the bridge sections of the silicon bridge in a resist film, the silicon on the bridge girders is removed, and thereafter, the silicon wires buried in the resist film are collected. In this manner, the silicon wires can be collected without dispersing into the hydrofluoric acid solution. Then, a transistor using the silicon wires as a channel is formed.

Owner:HITACHI LTD

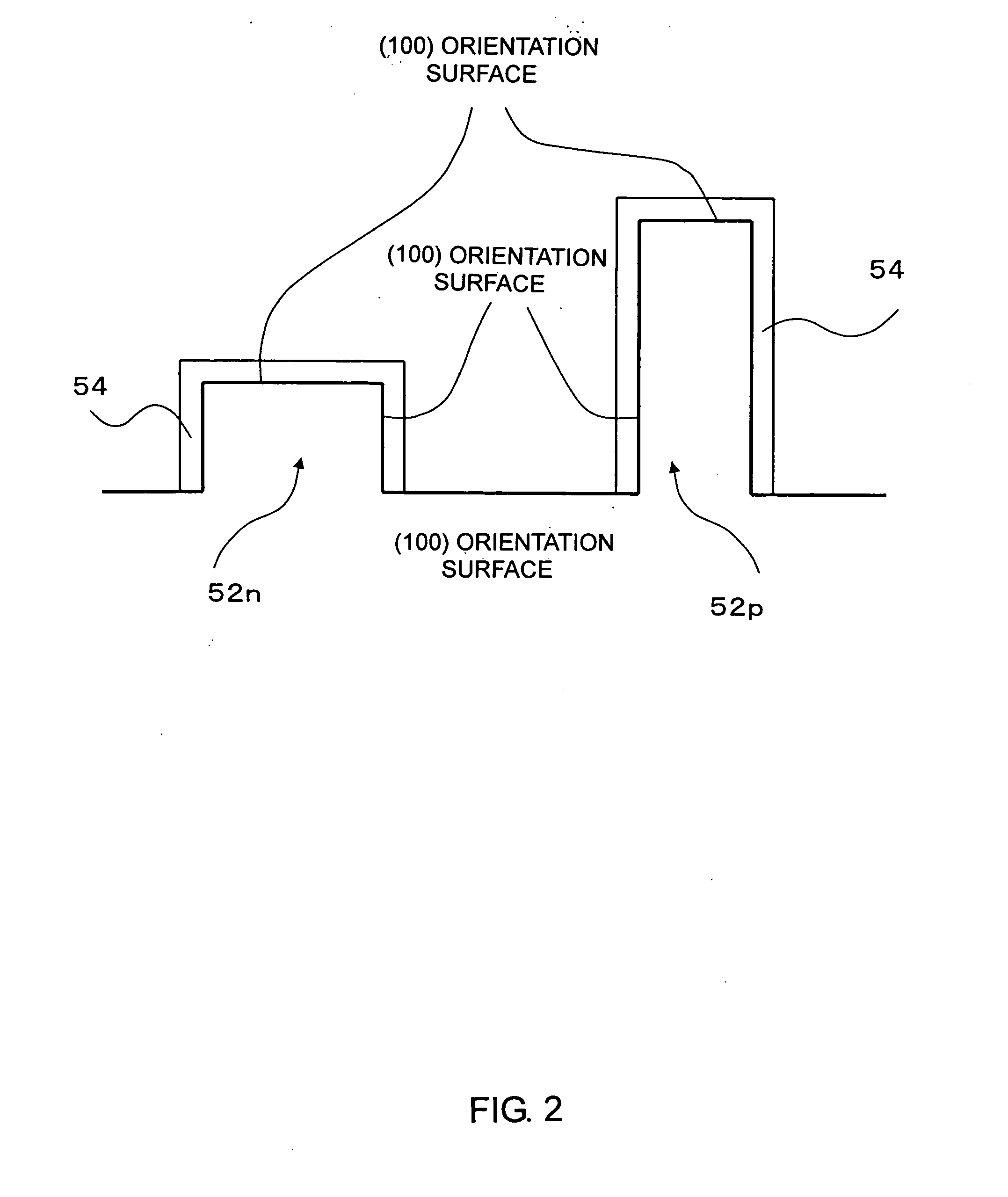

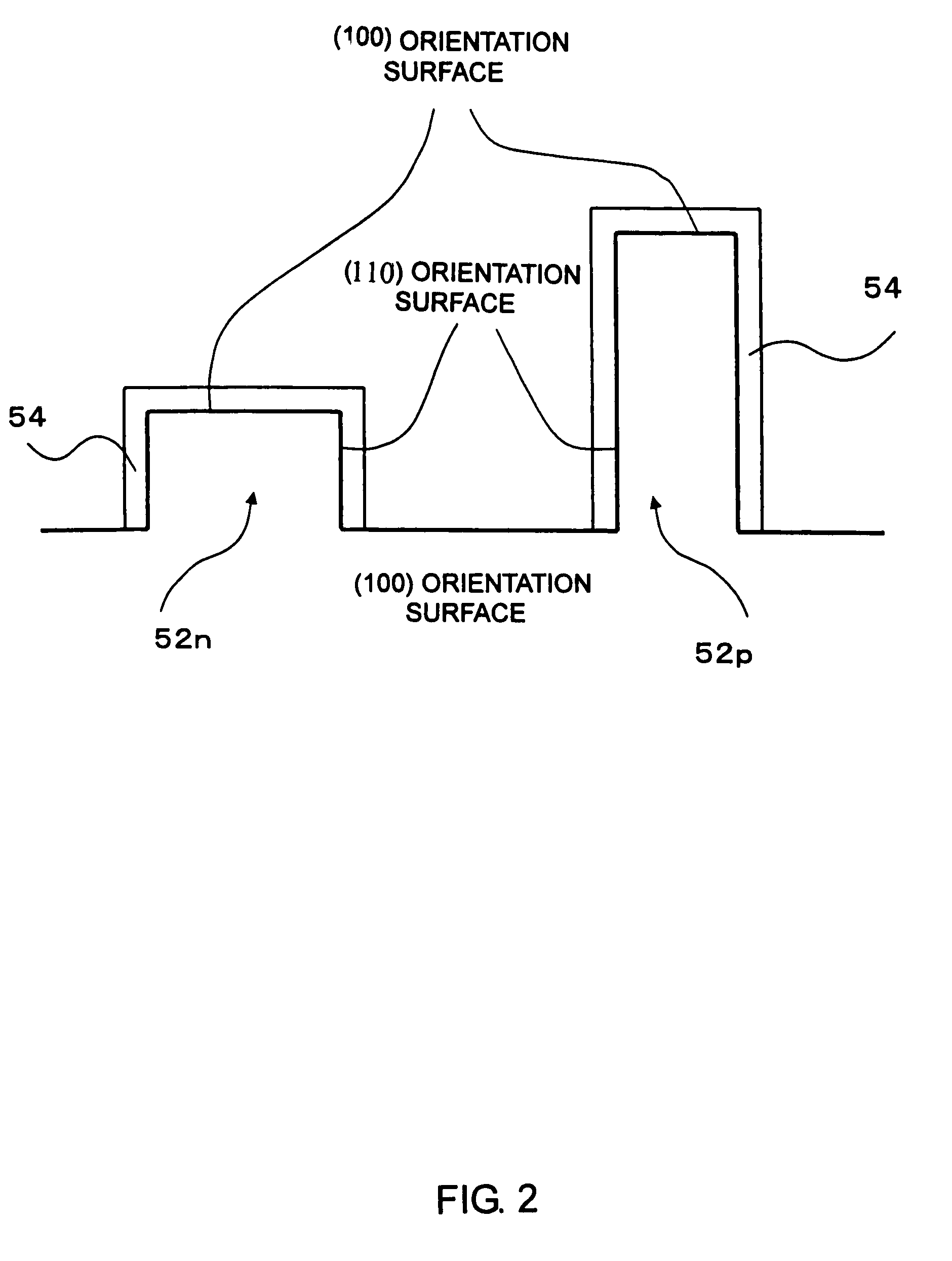

Complementary MIS device

A CMOS device includes a p-channel MOS transistor and an n-channel MOS transistor having a structure formed on a (100) surface of a silicon substrate and having a different crystal surface, a high-quality gate insulation film formed on such a structure by a microwave plasma process, and a gate electrode formed thereon, wherein the size and the shape of the foregoing structure is set such that the carrier mobility is balanced between the p-channel MOS transistor and the n-channel MOS transistor.

Owner:TOHOKU UNIV

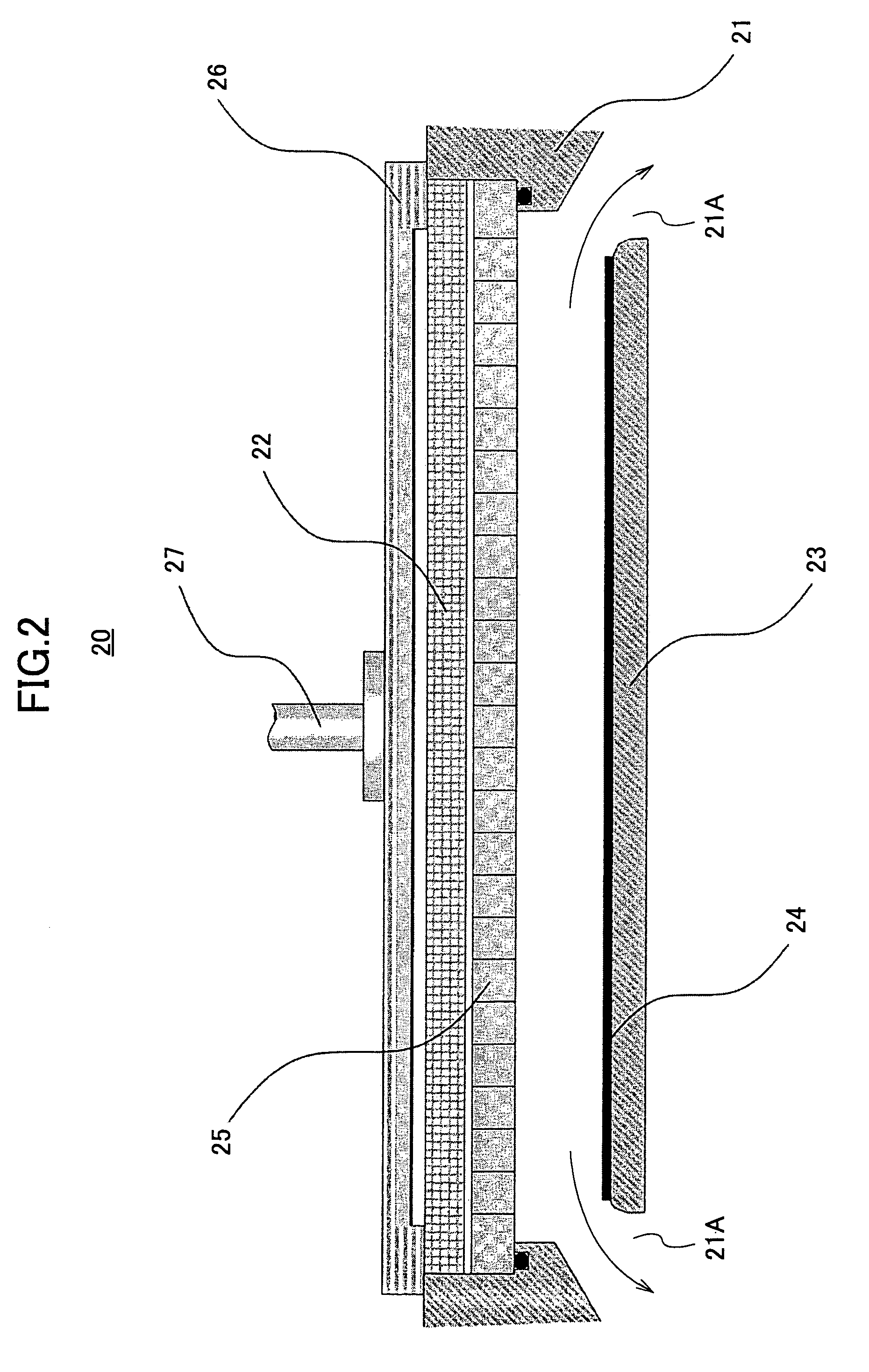

Integrated project management system

InactiveCN102855546AGuaranteed accuracyRealize explicitResourcesProject management information systemsServer-side

The invention discloses an integrated project management system comprising a plurality of clients, a database server and a plurality of functional systems which are all connected through a local area network. The system provided by the invention has the beneficial effects that a project is taken as the base point, so that a user can input the information such as progress plan, cost plan and quality gate into the system from the clients, and store the information in the database of the server end; the system provided by the invention has comprehensive management content and is added with the auxiliary systems of problem, contract, process, transaction, and organizational structure around three systems of progress, cost and quality. The information share, data accuracy and visualization, employee accountability expression, and approval process electronization in the project management controlling process are implemented, and the data accuracy is guaranteed through setting the organizational structure and permission, thereby avoiding the information isolated land caused by the fact that different departments are responsible for different contents.

Owner:TIANJIN BOXIN AUTOMOBILE PARTS

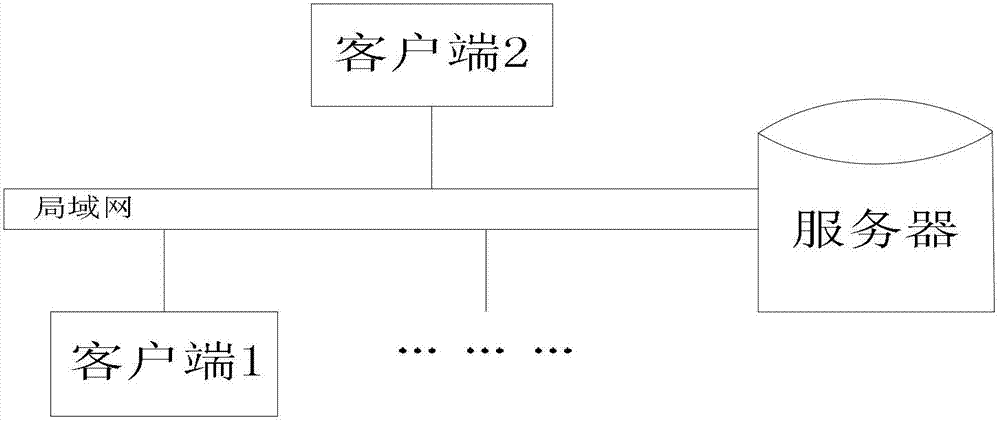

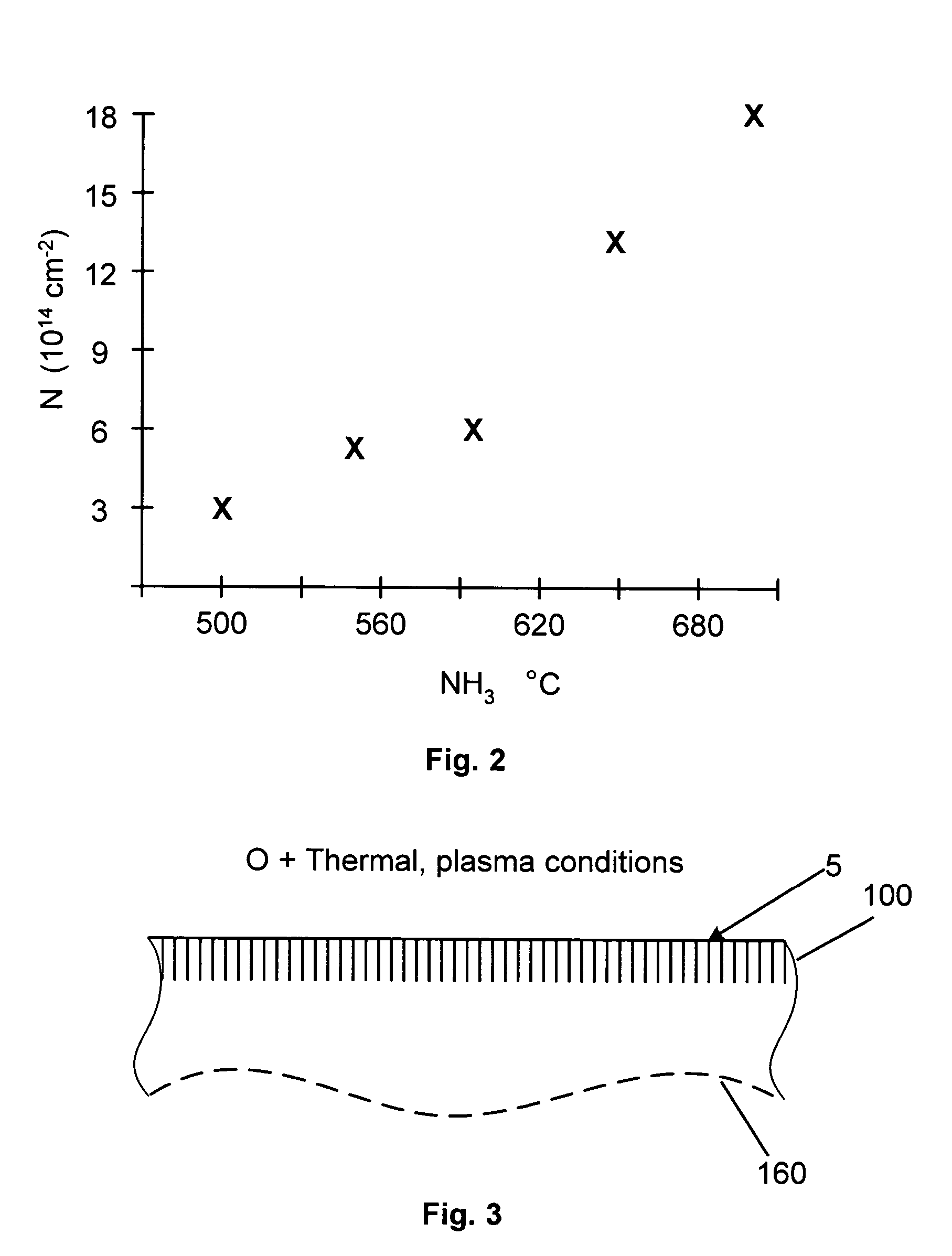

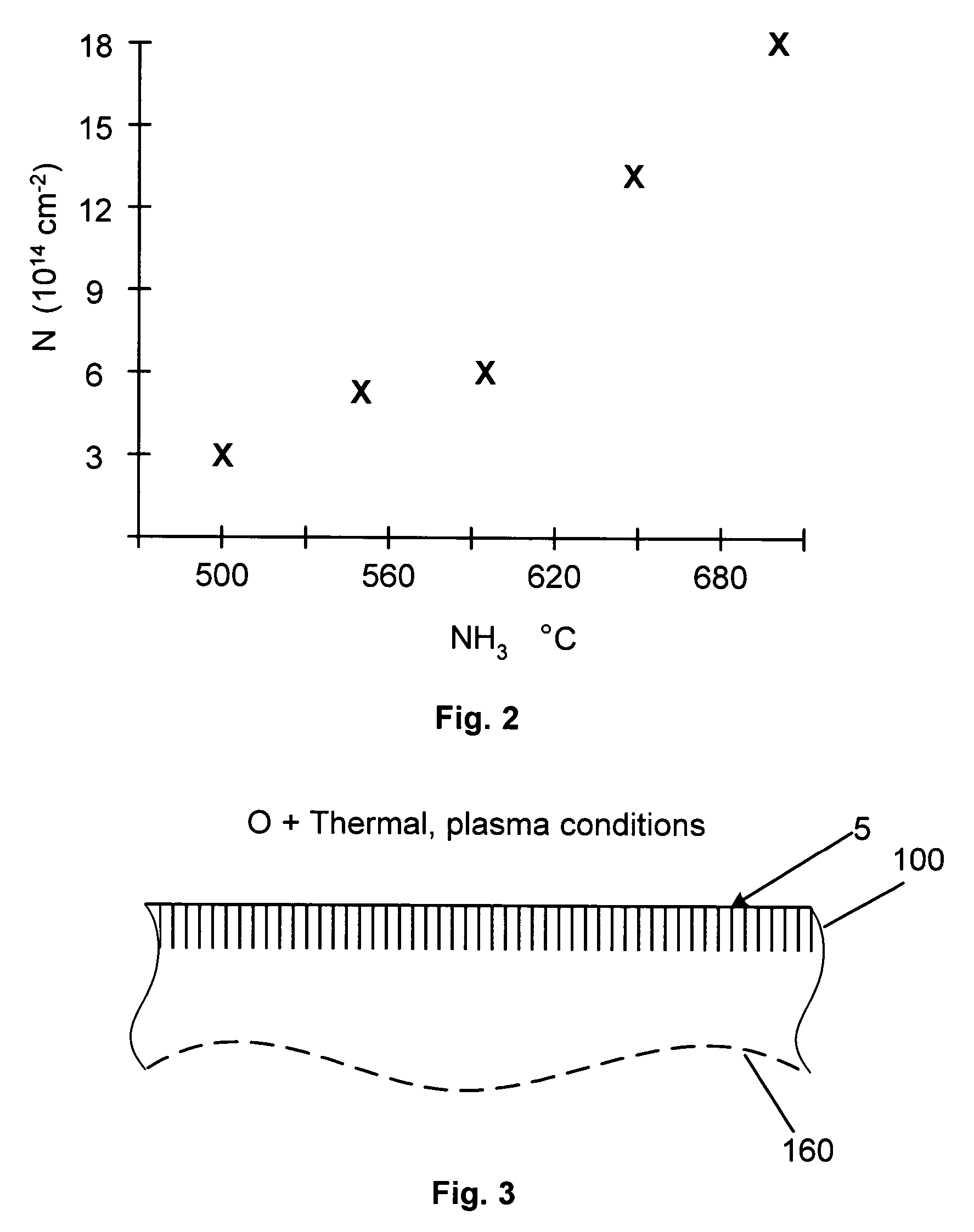

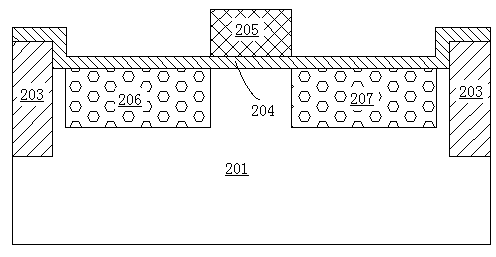

Thin germanium oxynitride gate dielectric for germanium-based devices

InactiveUS20050070122A1Improved propertyImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricEquivalent oxide thickness

A method for producing thin, below 6 nm of equivalent oxide thickness, germanium oxynitride layer on Ge-based materials for use as gate dielectric is disclosed. The method involves a two step process. First, nitrogen is incorporated in a surface layer of the Ge-based material. Second, the nitrogen incorporation is followed by an oxidation step. The method yields excellent thickness control of high quality gate dielectrics for Ge-based field effect devices, such as MOS transistors. Structures of devices having the thin germanium oxynitride gate dielectric and processors made with such devices are disclosed, as well.

Owner:GLOBALFOUNDRIES INC

Thin germanium oxynitride gate dielectric for germanium-based devices

InactiveUS7078300B2Improved propertyImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricEquivalent oxide thickness

Owner:GLOBALFOUNDRIES INC

Manufacturing method of MOS (Metal Oxide Semiconductor) transistor structure integrated with resistive random access memory

InactiveCN102709192AThe process steps are simpleSolid-state devicesSemiconductor/solid-state device manufacturingStatic random-access memoryEngineering

The invention belongs to the technical field of semiconductor memories below 20nmm and more particularly relates to a manufacturing method of an MOS (Metal Oxide Semiconductor) transistor structure integrated with a resistive random access memory. According to the manufacturing method disclosed by the invention, a source region and a drain region of the MOS transistor are formed by a self-aligned technology, a high-quality gate dielectric layer of the MOS transistor and a resistive random access memory layer of the resistive random access memory are deposited by a primary atomic layer deposition process, and the resistive random access memory and the MOS transistor are integrated together on the premise of not increasing extra process steps. The manufacturing method disclosed by the invention can be compatible with a shallow trench isolation process, or a field oxide layer isolation process and a source / drain ion implantation or diffusion process, is simple in process steps and provides convenience for process integration and devices to develop towards a miniaturization direction.

Owner:FUDAN UNIV

Manufacturing method for separated grid type flash memory embedded into logical circuit

ActiveCN103295967ASimple manufacturing processSemiconductor/solid-state device manufacturingComputer architectureHigh voltage transistors

The invention provides a manufacturing method for a separated grid type flash memory embedded into a logical circuit. According to the method, the separated grid type flash memory can be embedded into a peripheral circuit of a high-voltage circuit and the logical circuit, and the separated grid type flash memory, the high-voltage circuit and the logical circuit can be manufactured on a chip at the same time. After a stacking structure, comprising a floating gate oxide layer, a floating gate, a gate medium layer, a control gate and a hard mask layer, of the memory is formed, the thickness of a memory word line gate and the thickness of an erasing gate can be defined only through two-time polycrystalline silicon layer deposition and one-time photoetching glue line imaging treatment, and compared with three-time polycrystalline silicon layer deposition and two-time photoetching glue line imaging treatment in the prior art, the method greatly simplifies a manufacturing process. In addition, a gate medium layer of a high-voltage transistor is formed before the stacking structure of the memory is formed, and therefore the high-quality gate medium layer can be formed by means of a thermal oxidation growing method.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Multi-layer high quality gate dielectric for low-temperature poly-silicon tfts

A method and apparatus that is useful for forming a high quality gate dielectric layer in MOS TFT devices using a high density plasma oxidation (HDPO) process. In one embodiment a HDPO process layer is formed over the channel, source and drain regions to form a dielectric interface and then one or more dielectric layers are deposited on the HDPO layer to form a high quality gate dielectric layer. The HDPO process generally uses an inductively and / or capacitively coupled RF transmitting device to generate and control the plasma generated over the substrate and injecting a gas containing an oxidizing source to grow the interfacial layer. A second dielectric layer may then be deposited on the substrate using a CVD or PECVD deposition process. Aspects of the invention also provide a cluster tool that contains at least one specialized plasma processing chamber that is capable of depositing a high quality gate dielectric layer.

Owner:APPLIED MATERIALS INC

Organic transistor, manufacturing method of semiconductor device and organic transistor

InactiveUS20100297809A1Reduce leakage currentReduce tunnel leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialEngineering

It is an object to form a high quality gate insulating film which is dense and has a strong insulation resistance property, and to propose a high reliable organic transistor in which a tunnel leakage current is little. One mode of the organic transistor of the present invention has a step of forming the gate insulating film by forming the conductive layer which becomes the gate electrode activating oxygen (or gas including oxygen) or nitrogen (or gas including nitrogen) or the like using dense plasma in which density of electron is 1011 cm−3 or more, and electron temperature is a range of 0.2 eV to 2.0 eV with plasma activation, and reacting directly with a portion of the conductive layer which becomes the gate electrode to be insulated.

Owner:SEMICON ENERGY LAB CO LTD

Complementary MIS device

A CMOS device includes a p-channel MOS transistor and an n-channel MOS transistor having a structure formed on a (100) surface of a silicon substrate and having a different crystal surface, a high-quality gate insulation film formed on such a structure by a microwave plasma process, and a gate electrode formed thereon, wherein the size and the shape of the foregoing structure is set such that the carrier mobility is balanced between the p-channel MOS transistor and the n-channel MOS transistor.

Owner:TOHOKU UNIV

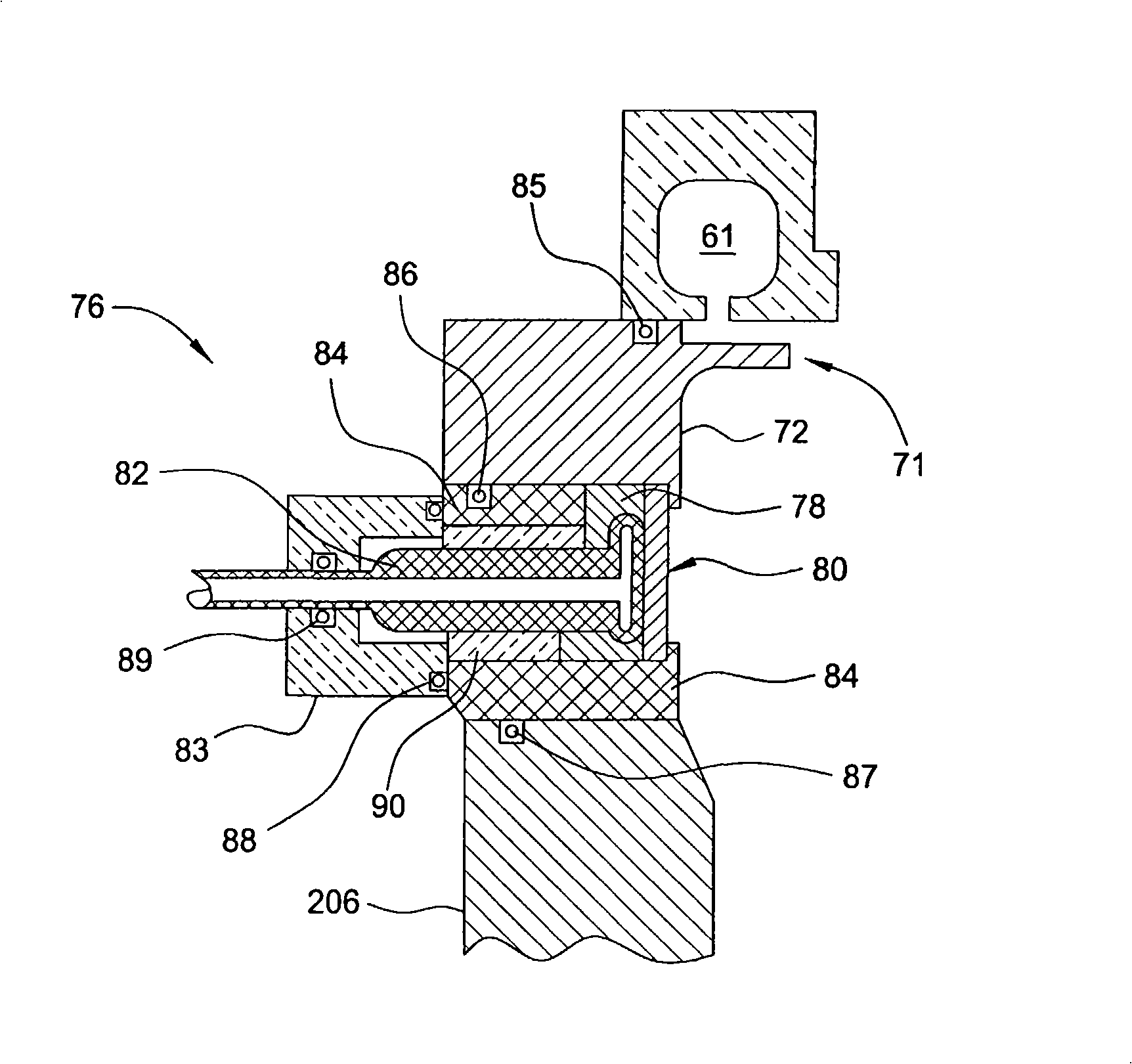

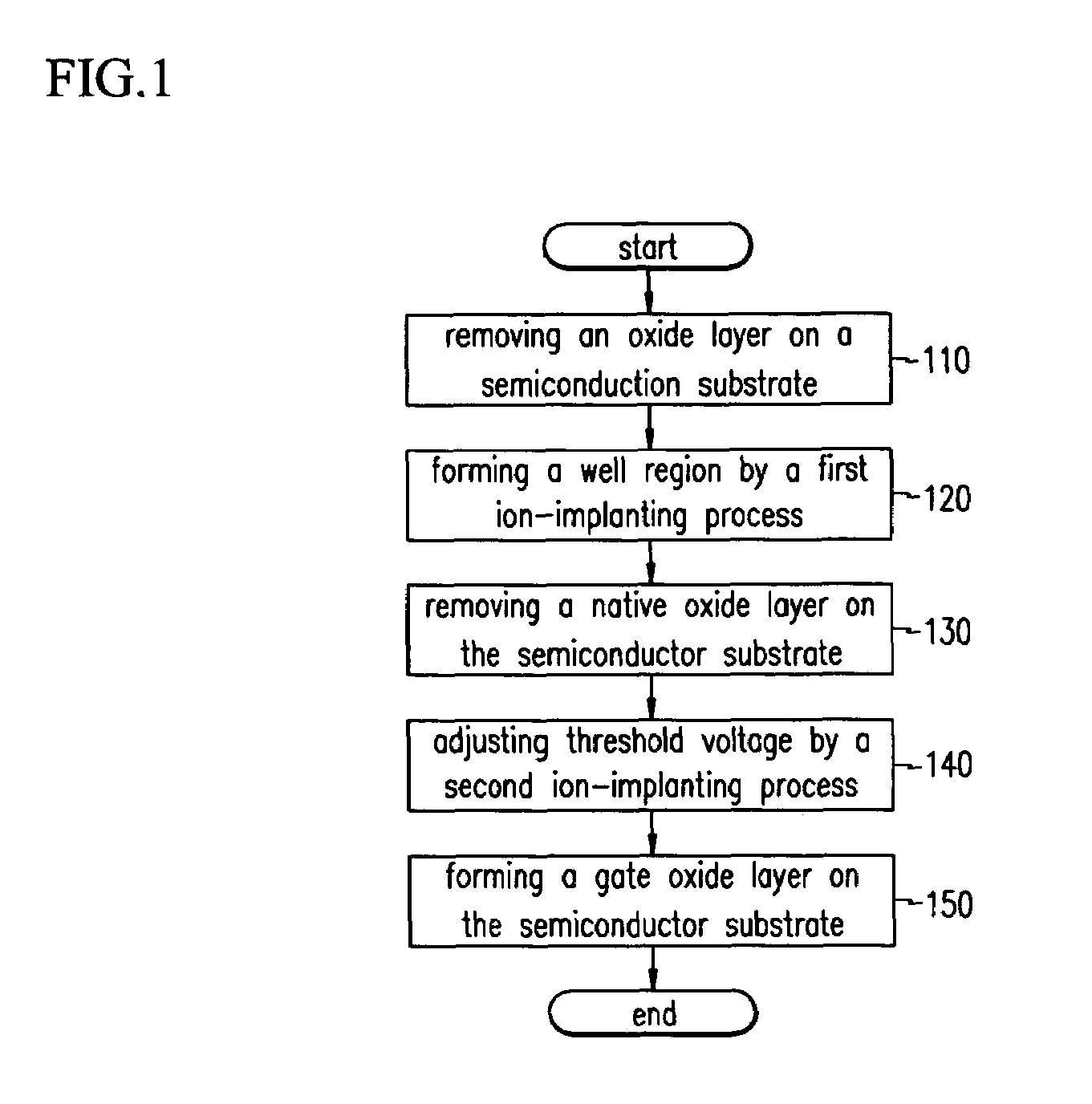

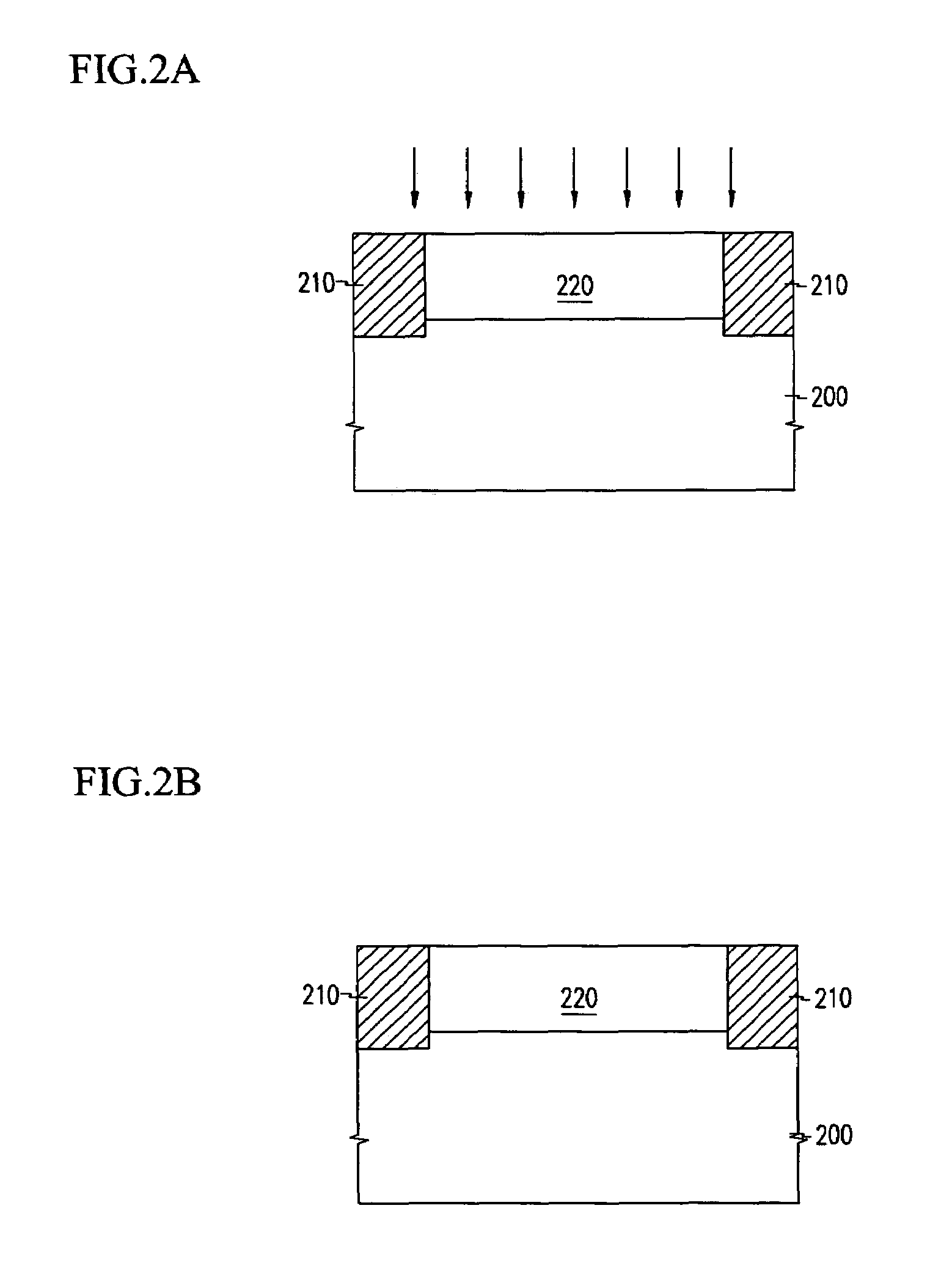

Method of manufacturing semiconductor device

ActiveUS7361562B2InhibitionSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringOxygen

Provided is a method of manufacturing a semiconductor device capable of forming a thin high-quality gate oxide layer by suppressing occurrence of recoiled oxygen due to ion implanting. The method of manufacturing a semiconductor device includes steps of: removing an oxide layer from a semiconductor substrate; forming a well region in the substrate by performing a first ion implanting process; removing a native oxide layer from the substrate; adjusting a threshold voltage by performing a second ion implanting process on the substrate; and forming a gate oxide layer on the substrate.

Owner:MARVELL ASIA PTE LTD +1

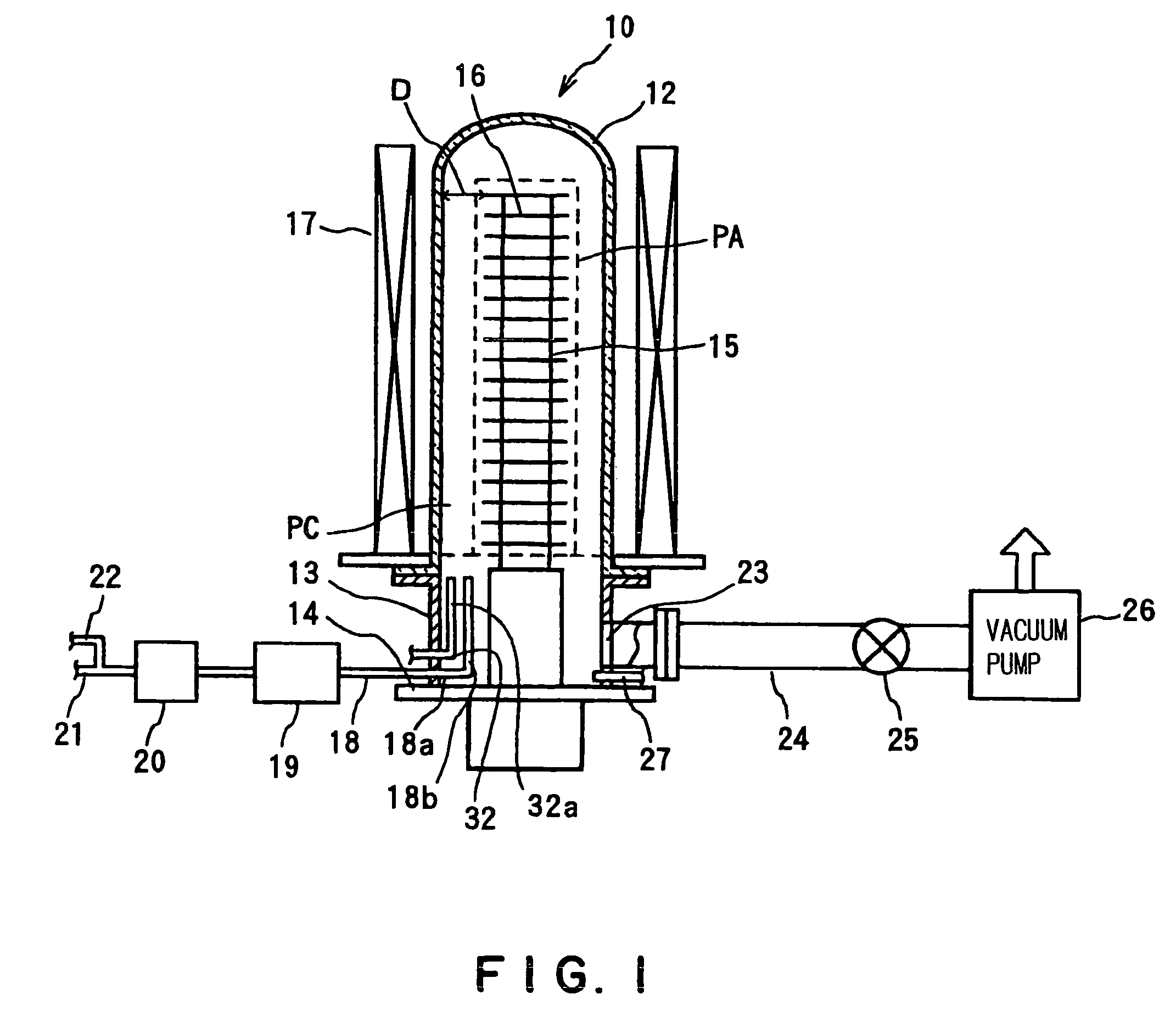

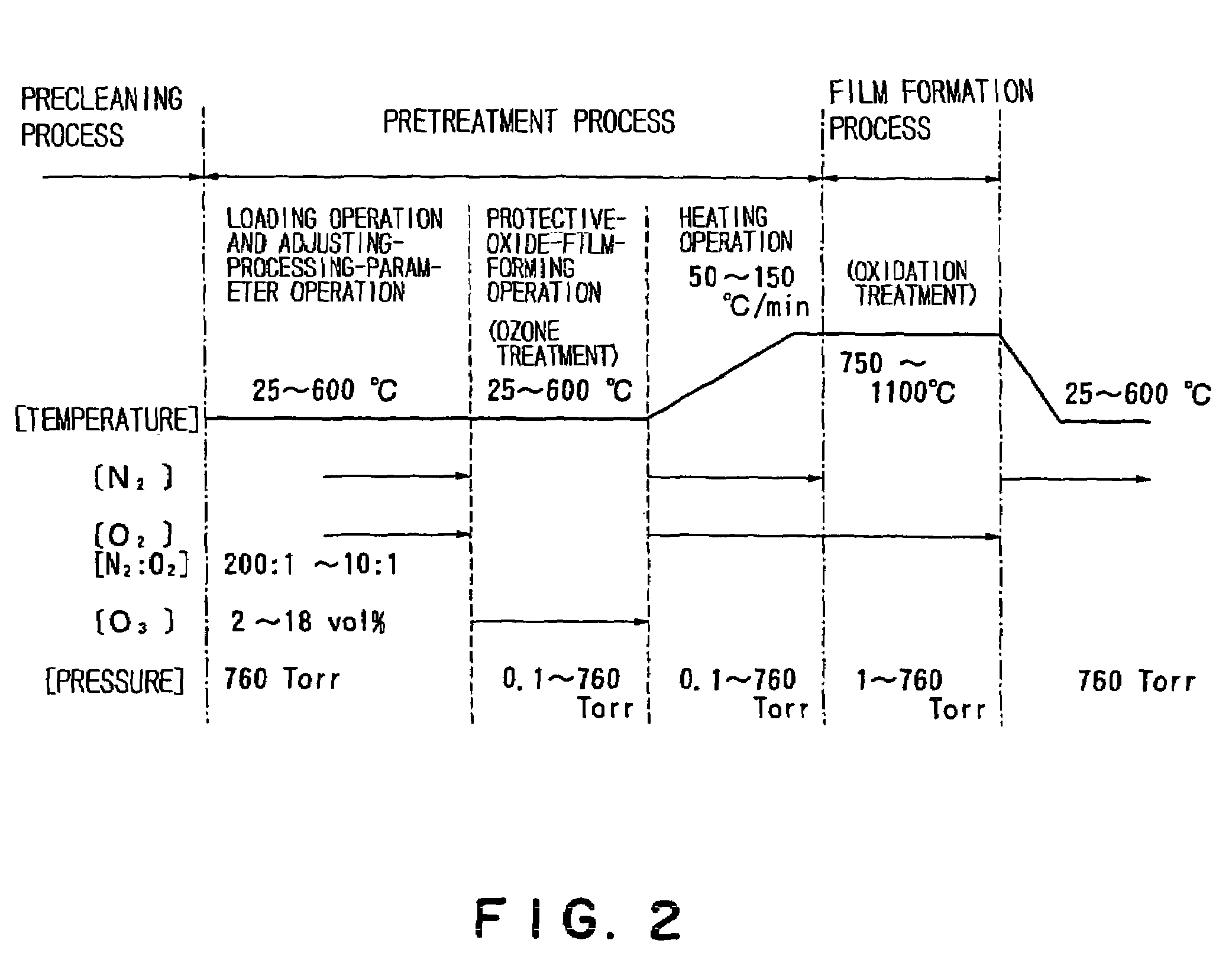

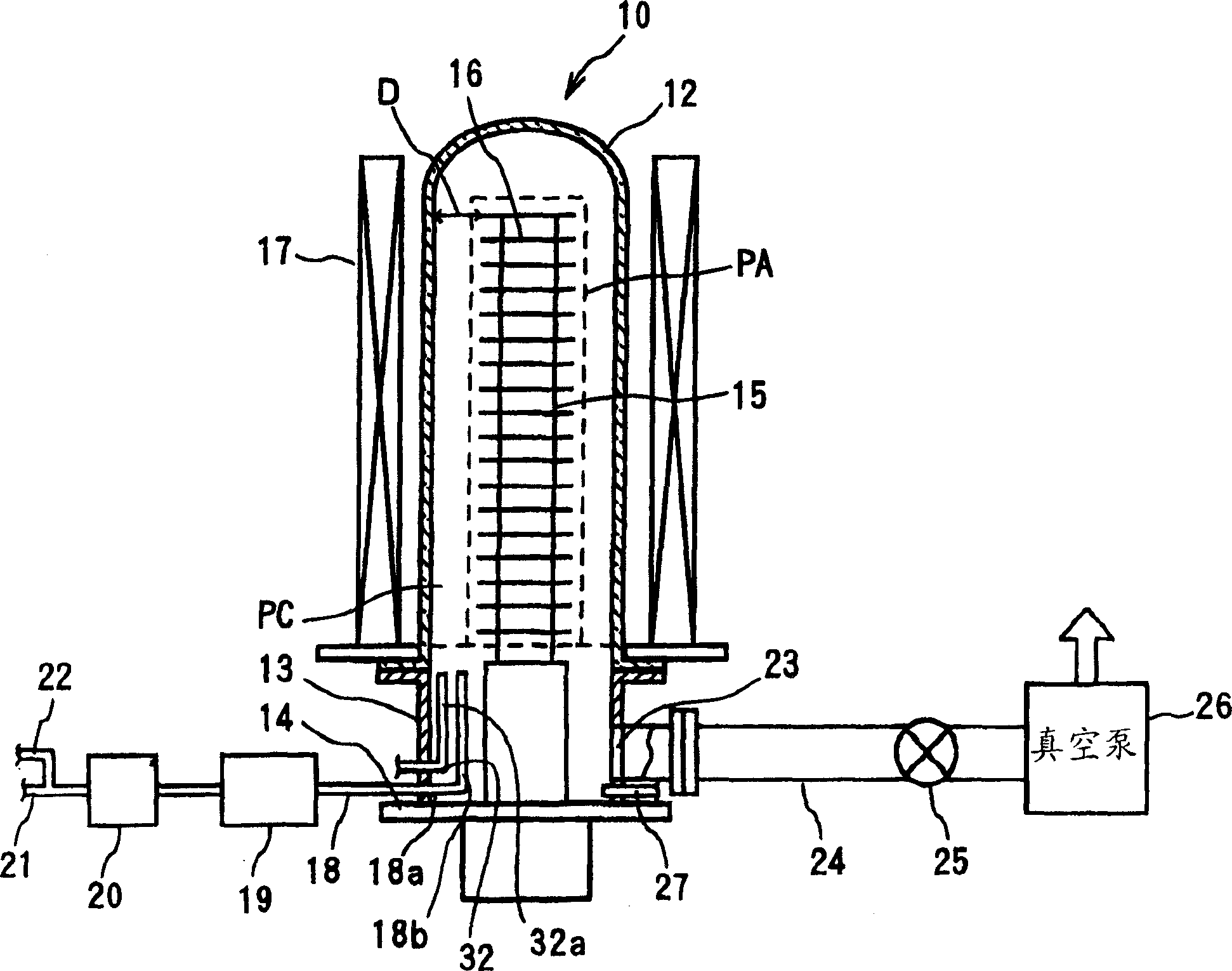

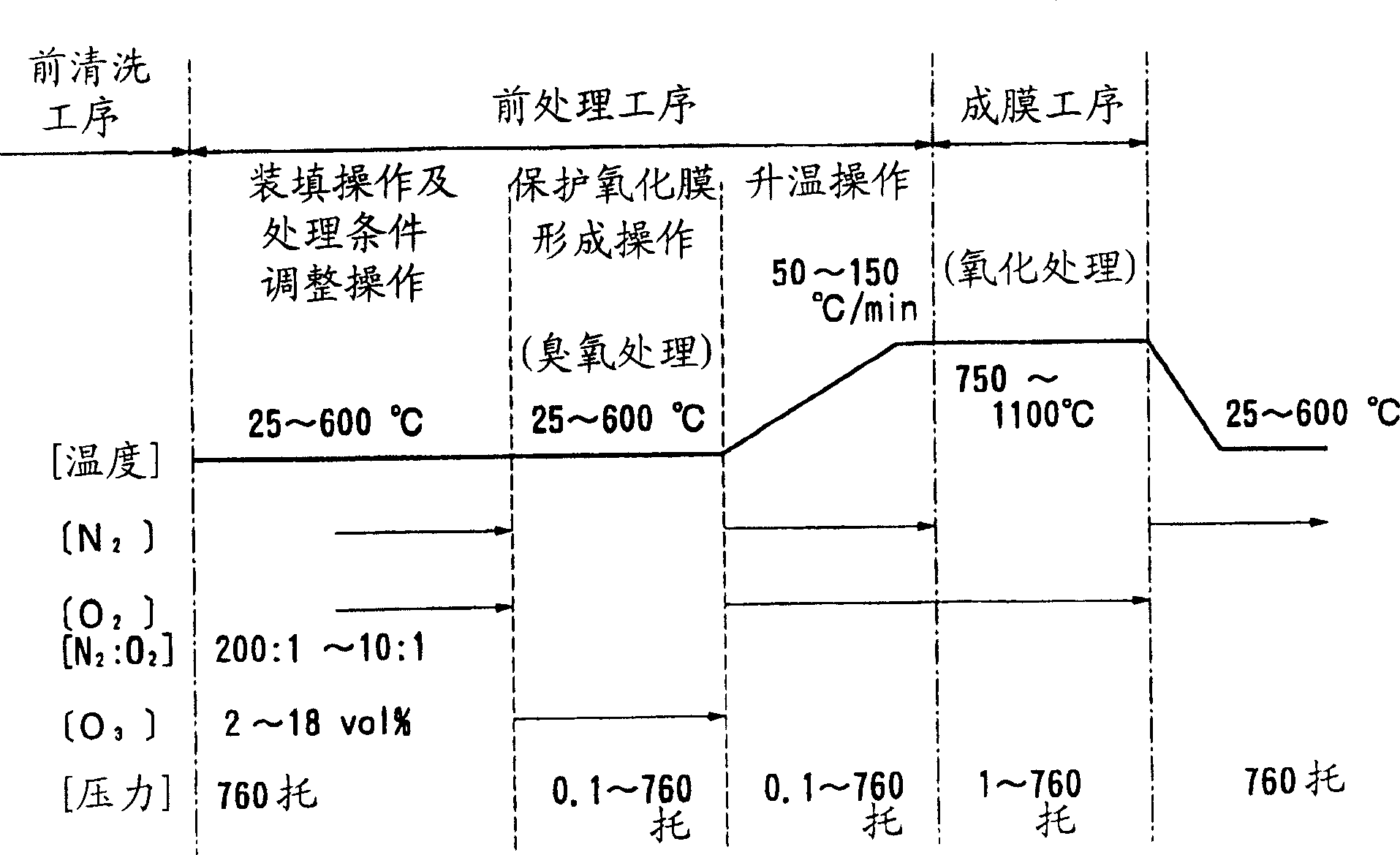

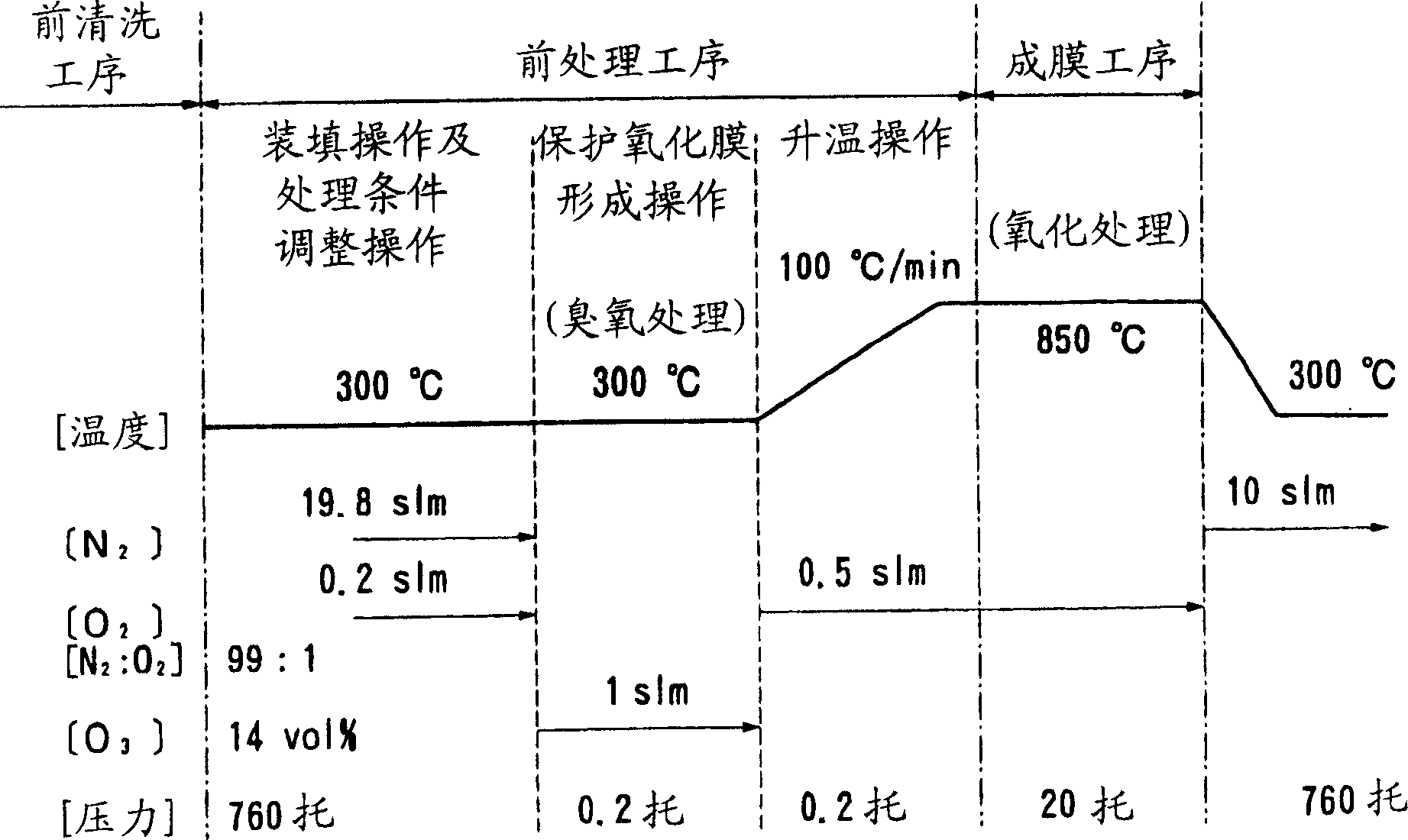

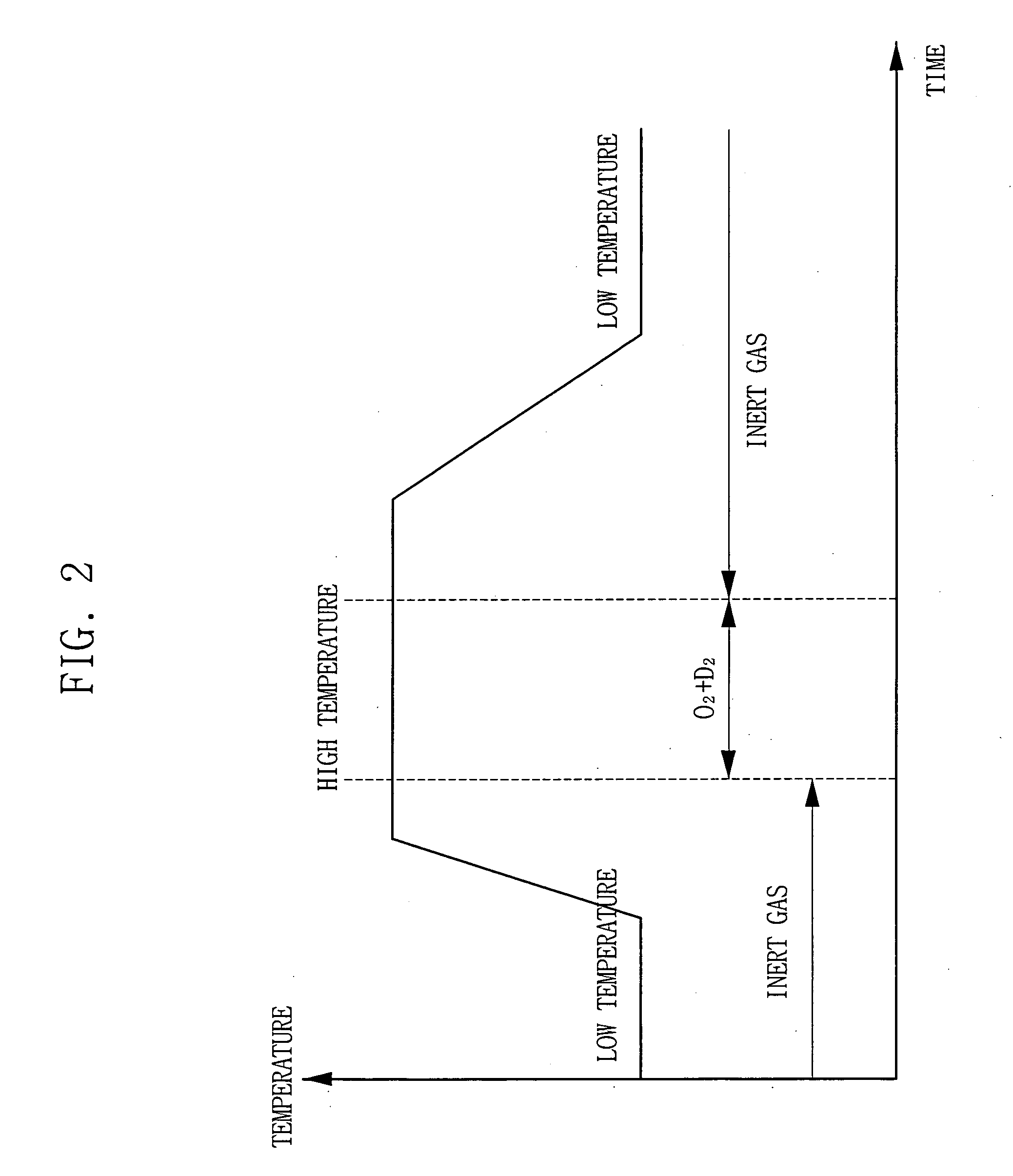

Oxide film forming method

InactiveUS7064084B2Improve featuresSolution to short lifeSemiconductor/solid-state device manufacturingSemiconductor devicesPre treatmentOxidative treatment

To provide a method for the formation of oxide films to form with advantage a high-quality oxide film having excellent uniformity in film thickness and film quality over the entire wafer. The method for the formation of oxide films comprises: the pretreatment process of forming a protective oxide film on the surface of a wafer positioned in a reaction vessel by performing oxidation treatment with radical oxidative species or an atmosphere containing radical oxidative species under depressurized conditions; and the oxide-film-formation process of forming an oxide film on the wafer by performing oxidation treatment at a predetermined temperature under depressurized conditions. The oxide-film-formation process is preferably performed following the pretreatment process in a continuous manner in the reaction vessel in which the pretreatment process is performed. The pretreatment process is preferably performed at a temperature lower than the temperature for the oxide-film-formation process and also preferably performed under depressurized conditions, the level of the depressurization being higher than the level for the oxide-film-formation process. A high-quality gate-insulating film for a transistor chip can be formed according to this method for the formation of oxide films.

Owner:TOKYO ELECTRON LTD

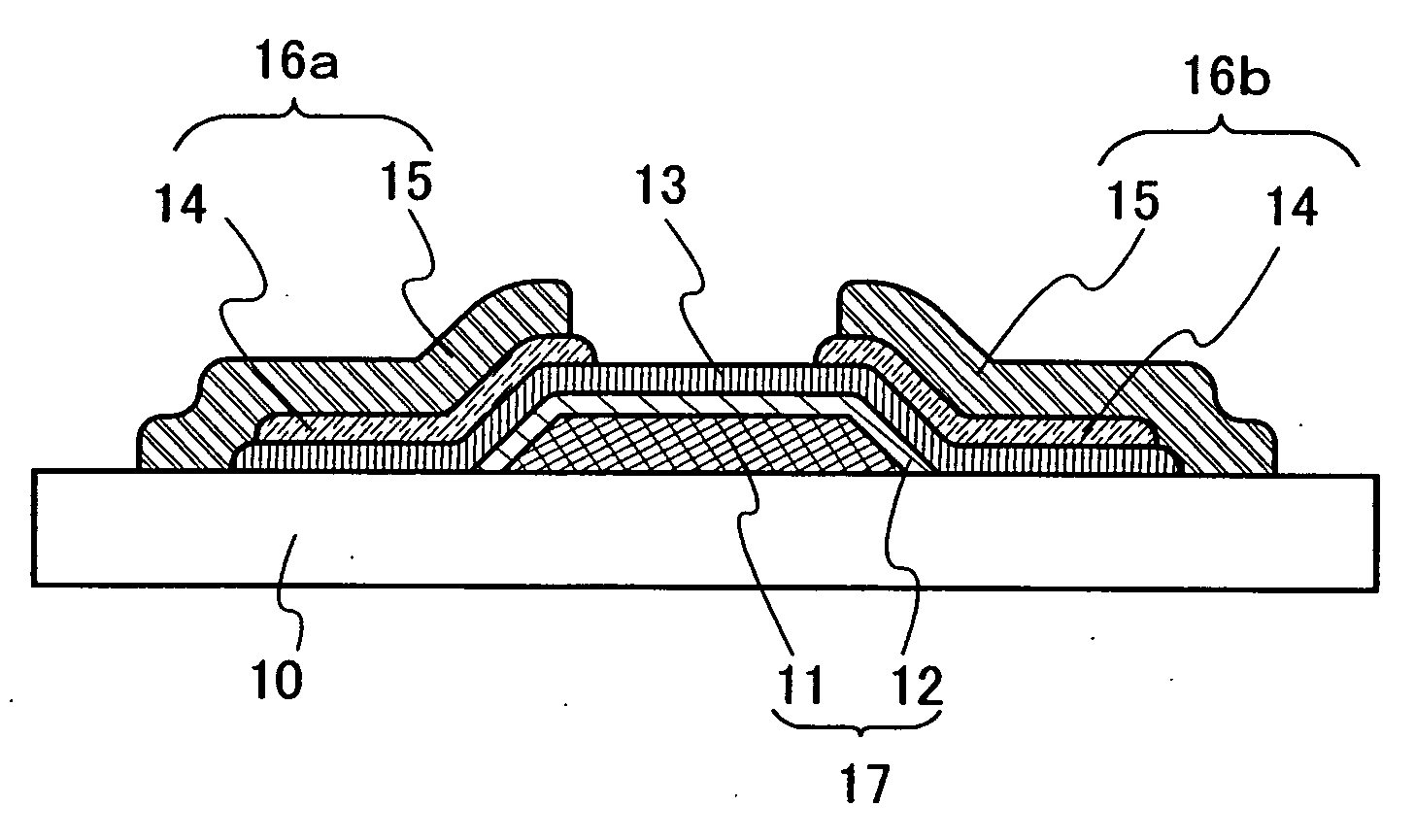

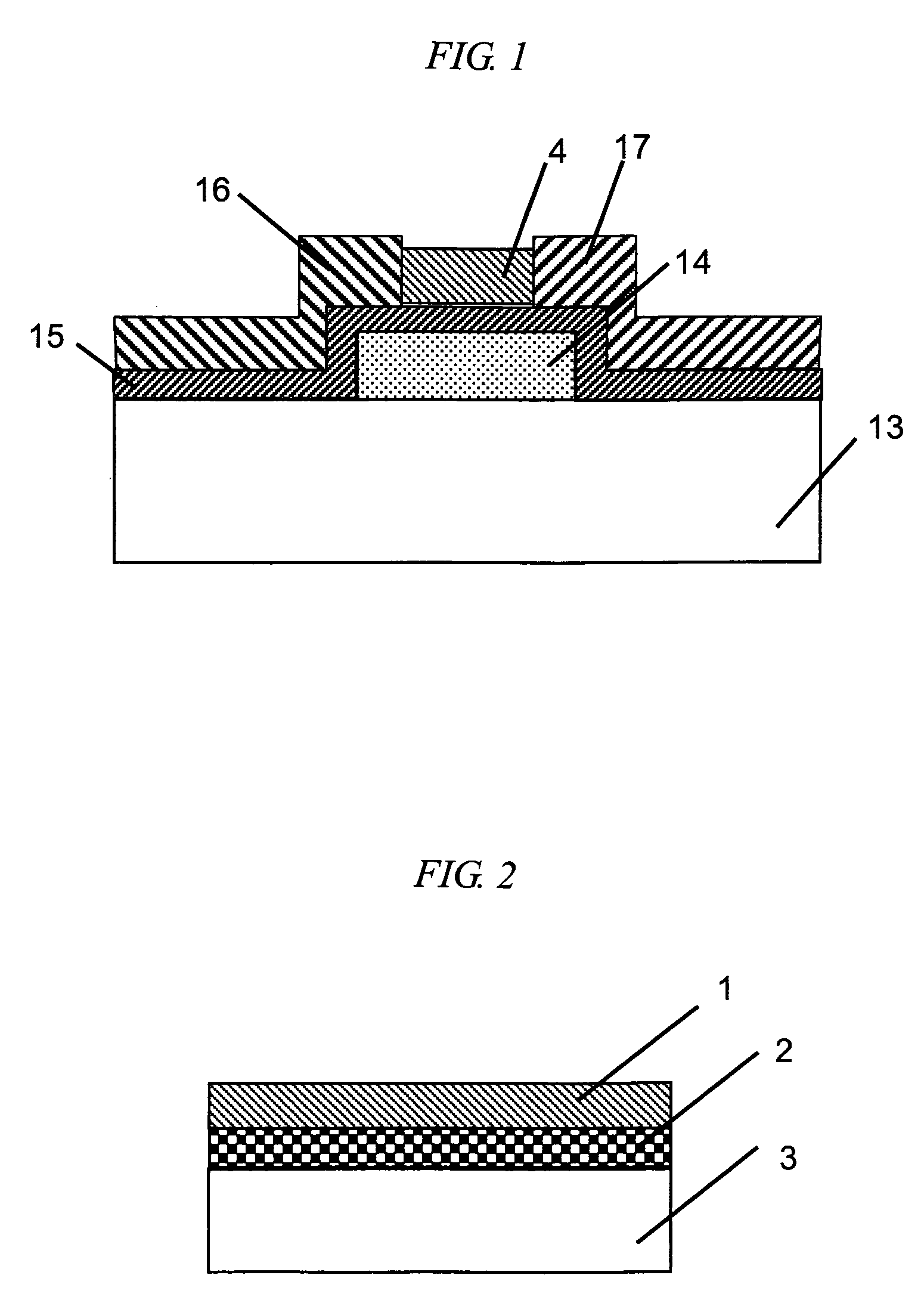

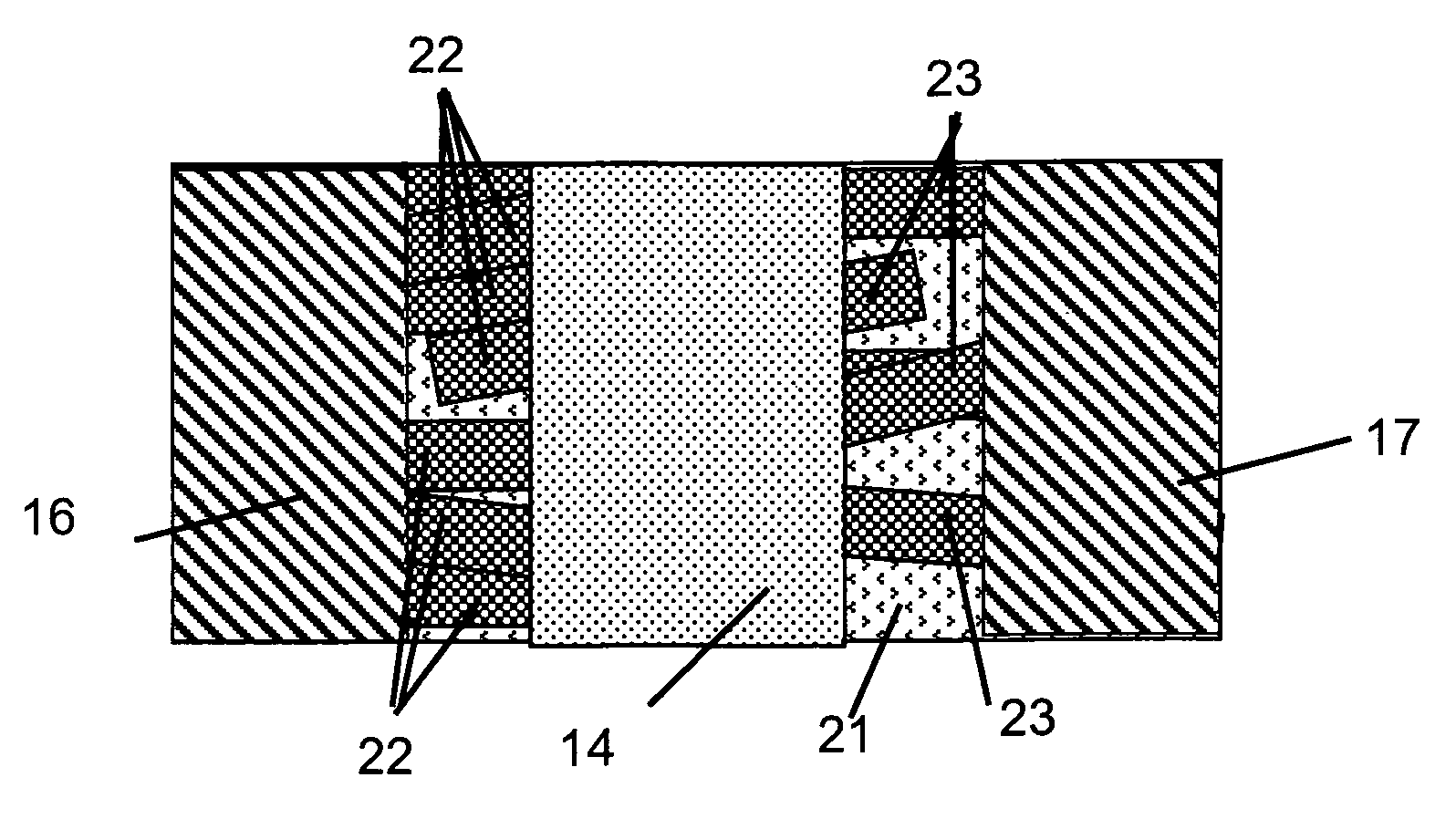

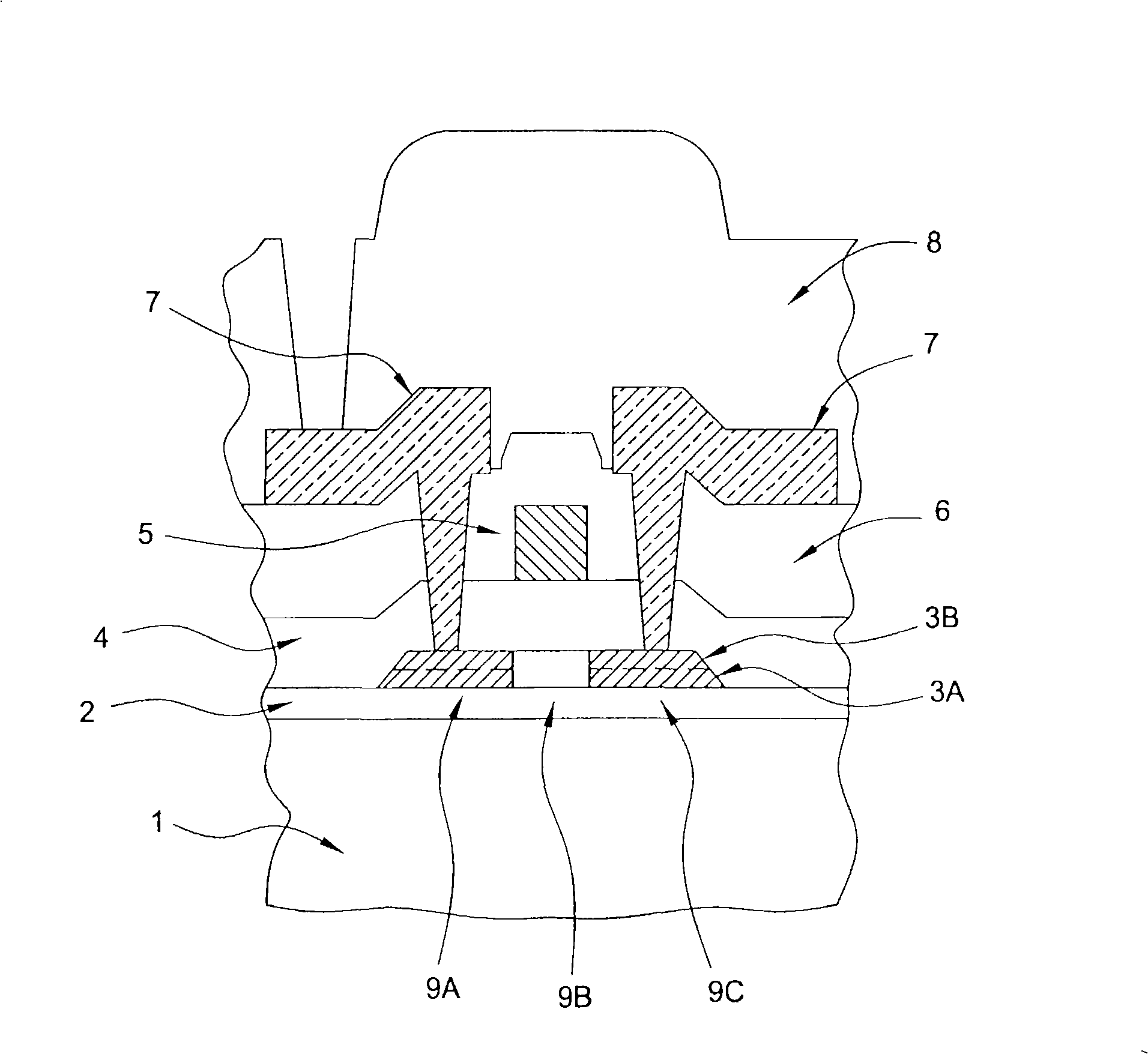

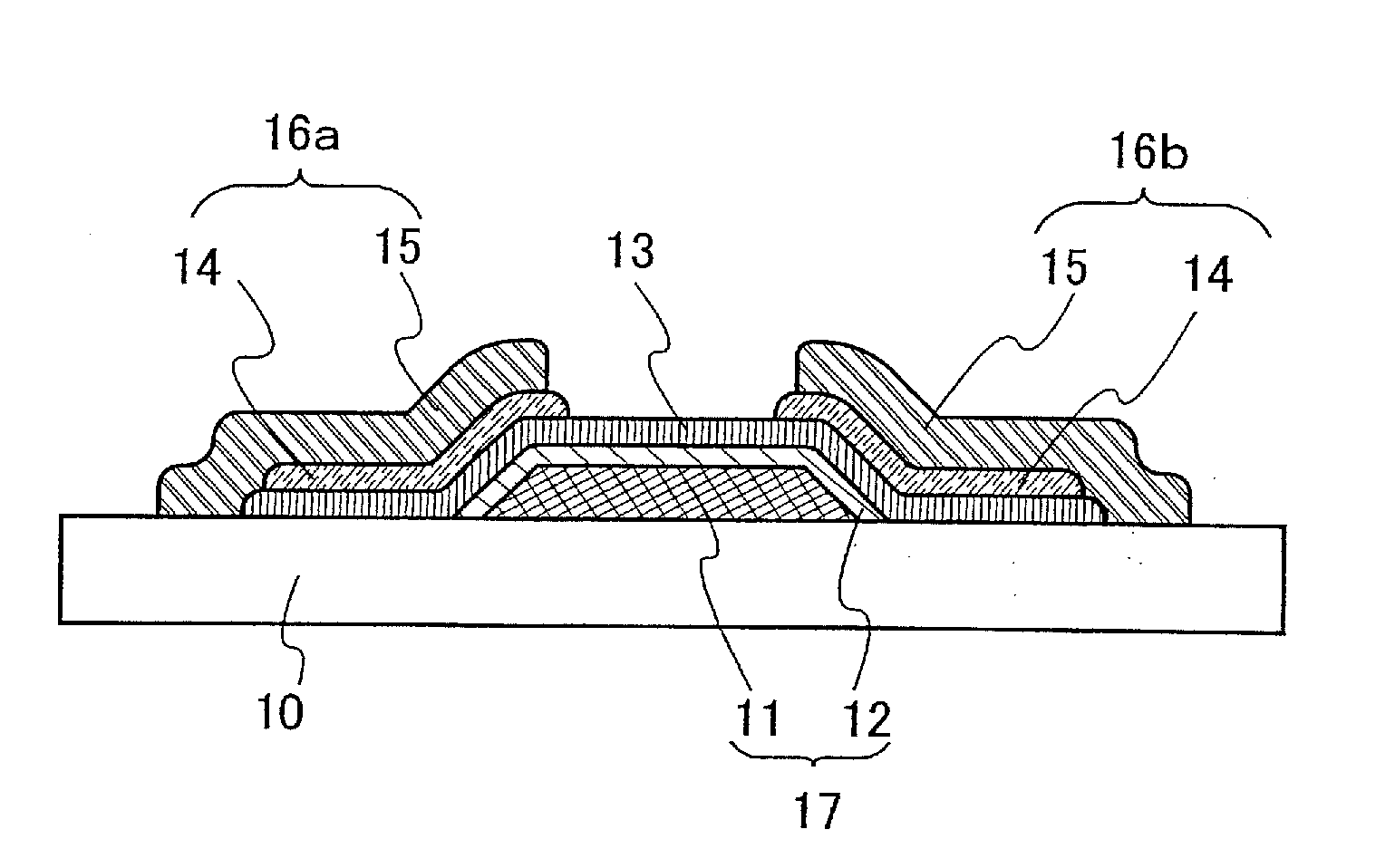

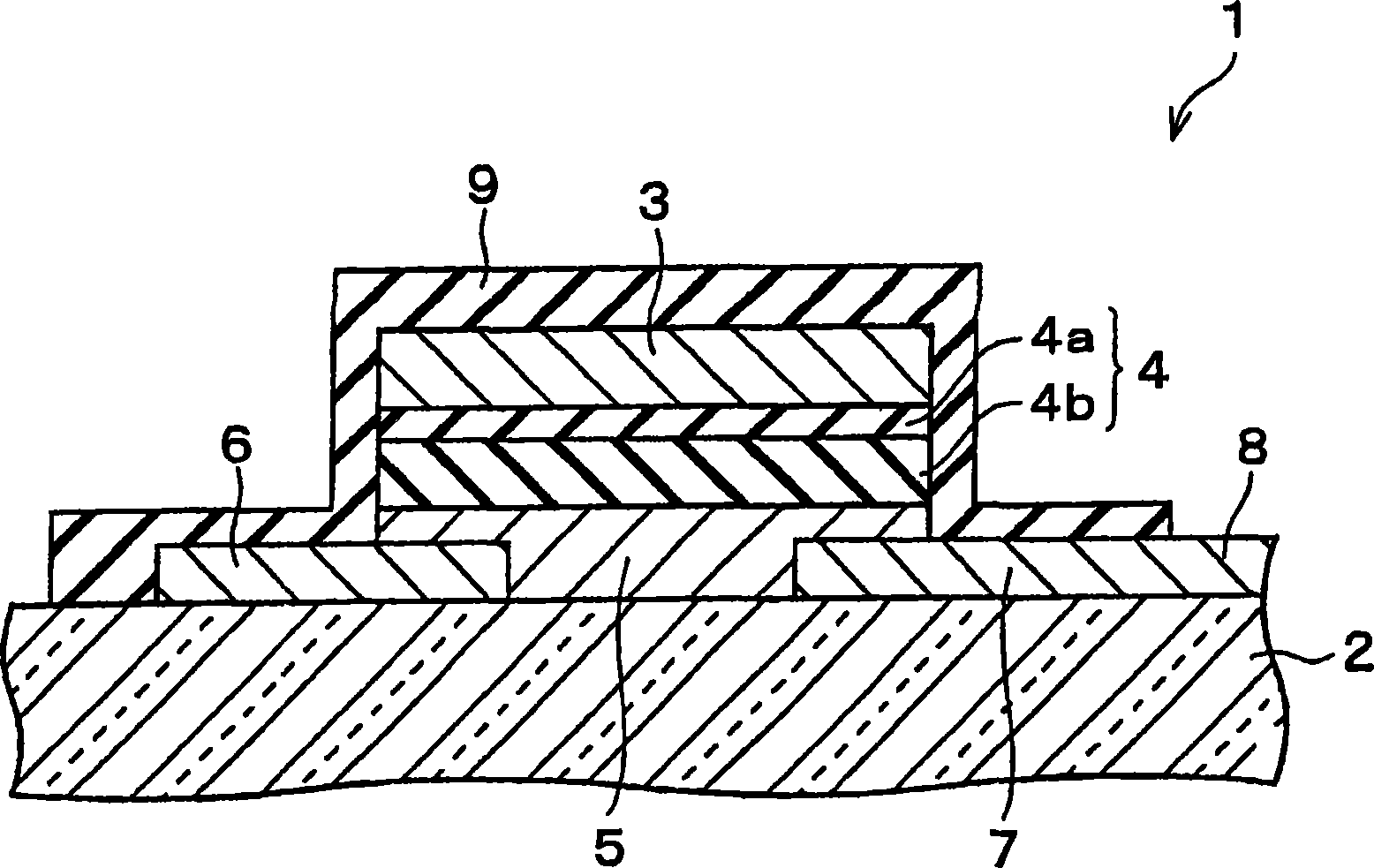

Thin film transistor and manufacturing method thereof, display apparatus, method for modifying oxide film, method for forming oxide film, semiconductor device, method for manufacturing semiconductor d

InactiveCN1918701AIncrease film thicknessImprove membrane qualityTransistorSemiconductor/solid-state device manufacturingEngineeringDielectric breakdown strength

In a method for manufacturing a thin film transistor (1), a substrate (2) to be processed, on which the gate oxide film (4) is to be formed on a front plane, is impregnated with an oxidizing solution including an active oxidation seed to directly oxidize polysilicon (51) on the substrate (2), and the gate oxide film (4) is formed. Thus, a silicon dioxide film (42) is formed by growing a silicon dioxide film (41) in a direction of the substrate (2). Thus, an interface between the polysilicon (51) and the gate oxide film (4) is kept clean and the high-quality gate oxide film (4) having excellent dielectric breakdown strength can be uniformly formed. Therefore, the thin film transistor (1) having excellent dielectric breakdown strength can be formed at a low temperature with a high-quality oxide film provided thereon.

Owner:SHARP KK +1

Method for growing gate dielectric on gallium nitride substrate and electrical performance testing method

ActiveCN103745923AImprove bindingSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingDielectricGate dielectric

The invention provides a method for growing gate dielectric on a gallium nitride substrate and an electrical performance testing method. The method for growing gate dielectric on the gallium nitride substrate comprises the steps of providing the gallium nitride substrate; performing in-situ ammonia plasma pretreatment to the gallium nitride substrate to compensate nitrogen onto the surface of gallium nitride; growing an aluminum oxide transition layer on the surface of the gallium nitride substrate; growing a gate dielectric thin film on the surface of the aluminum oxide transition layer. The method for growing gate dielectric on the gallium nitride substrate and the electrical performance testing method provided by the invention has the advantages that the high-quality gate dielectric can be grown on the gallium nitride substrate and the electrical performance of the gate dielectric can be simply and conveniently tested.

Owner:SHANGHAI SIMGUI TECH

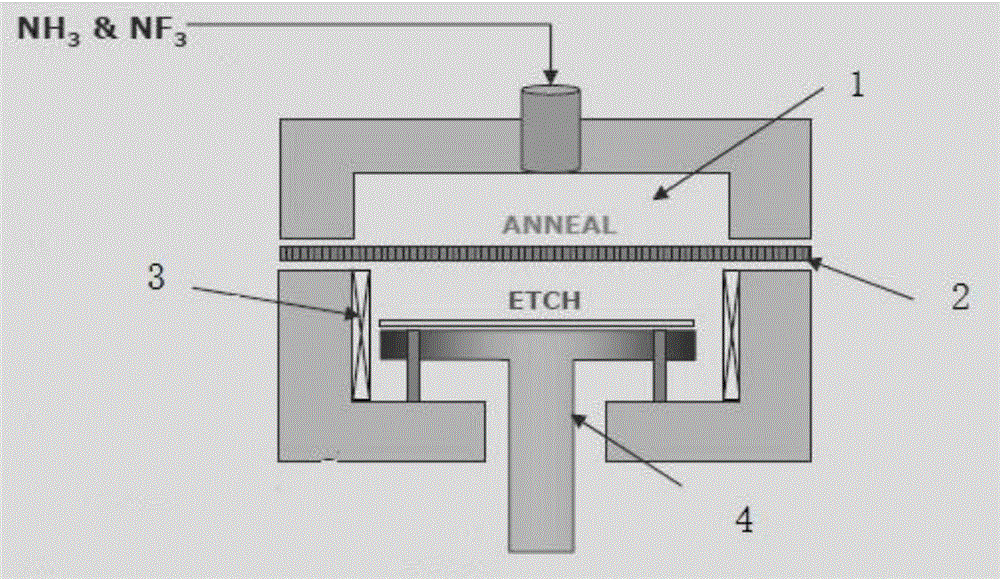

High-quality gate oxide forming method

ActiveCN104992903AQuality improvementAvoid exposureSemiconductor/solid-state device manufacturingSemiconductor devicesSilicon oxideWarming process

The invention provides a high-quality gate oxide forming method. The method comprises the following steps that a wafer already undergoing shallow trench isolation is provided; the wafer is placed in an iCoNi reaction chamber to remove a native silicon oxide layer on the silicon face; (NH4)2SiF6 will be formed on the wafer surface during a SiCoNi etching reaction process; in a normal temperature condition, the (NH4)2SiF6 layer will not be removed in the SiCoNi reaction chamber; instead, the (NH4)2SiF6 layer will be kept as a protective layer on the wafer surface to prevent silicon exposure and native oxide regeneration; then the wafer is placed in an oxidation furnace; after the wafer enters the oxidation furnace, the (NH4)2SiF6 protective layer will be decomposed and volatilized when the temperature of the oxidation furnace rises; and if the highest technical temperature of the oxidation furnace continuously rises to satisfy the temperature and technical condition required for gate oxide growing, then the gate oxide starts to grow. By means of the technical solution, the native silicon oxide can be prevented from being formed on the wafer surface again before the gate oxide is formed. The gate oxide quality is improved. Product performance improvement can be further facilitated.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

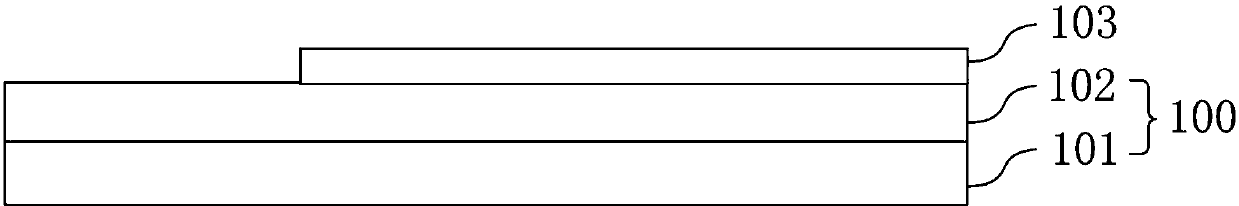

MOS (Metal Oxide Semiconductor) transistor structure integrated with resistive random access memory and manufacturing method of MOS transistor structure

InactiveCN102709308AThe process steps are simpleSolid-state devicesSemiconductor devicesStatic random-access memoryGate dielectric

The invention belongs to the technical field of semiconductor memories and more particularly relates to an MOS (Metal Oxide Semiconductor) transistor structure integrated with a resistive random access memory and a manufacturing method of the MOS transistor structure. The MOS transistor structure integrated with the resistive random access memory, provided by the invention, comprises an MOS transistor and the resistive random access memory which are formed on a substrate, wherein a gate dielectric layer of the MOS transistor extends onto the surface of a drain region of the MOS transistor, and a resistive random access memory layer of the resistive random access memory is formed on the gate dielectric layer part which extends onto the surface of the drain region of the MOS transistor. According to the invention, the high-quality gate dielectric layer of the MOS transistor and the resistive random access memory layer of the resistive random access memory are obtained by a primary atomic layer deposition process, the resistive random access memory and the MOS transistor are integrated together, and the process steps are simple; and in addition, the manufacturing method can be compatible with a shallow trench isolation process, or a field oxide layer isolation process and a source / drain ion implantation or diffusion process and is convenient for process integration.

Owner:FUDAN UNIV

Oxide film forming method

InactiveCN1518760AImprove uniformityUniform film thicknessSemiconductor/solid-state device manufacturingSemiconductor devicesProtective oxideOxidative treatment

To provide a method for the formation of oxide films to form with advantage a high-quality oxide film having excellent uniformity in film thickness and film quality over the entire wafer. The method for the formation of oxide films comprises: the pretreatment process of forming a protective oxide film on the surface of a wafer positioned in a reaction vessel by performing oxidation treatment with radical oxidative species or an atmosphere containing radical oxidative species under depressurized conditions; and the oxide-film-formation process of forming an oxide film on the wafer by performing oxidation treatment at a predetermined temperature under depressurized conditions. The oxide-film-formation process is preferably performed following the pretreatment process in a continuous manner in the reaction vessel in which the pretreatment process is performed. The pretreatment process is preferably performed at a temperature lower than the temperature for the oxide-film-formation process and also preferably performed under depressurized conditions, the level of the depressurization being higher than the level for the oxide-film-formation process. A high-quality gate-insulating film for a transistor chip can be formed according to this method for the formation of oxide films.

Owner:TOKYO ELECTRON LTD

Semiconductor device and method of manufacturing the same

ActiveUS20070023780A1Improve stateUniform thicknessTransistorSolid-state devicesCrystal orientationEngineering

A gate insulating film is formed using a plasma on a three-dimensional silicon substrate surface having a plurality of crystal orientations. The plasma gate insulating film experiences no increase in interface state in any crystal orientations as compared with tat in Si (100) crystal orientation and has a uniform thickness even at corner portions of the three-dimensional structure. By forming a high-quality gate insulating film using a plasma, there can be obtained a semiconductor device having good characteristics.

Owner:TOKYO ELECTRON LIMITED ONE HALF 50 OF ALL RIGHT TITLE & INTEREST +1

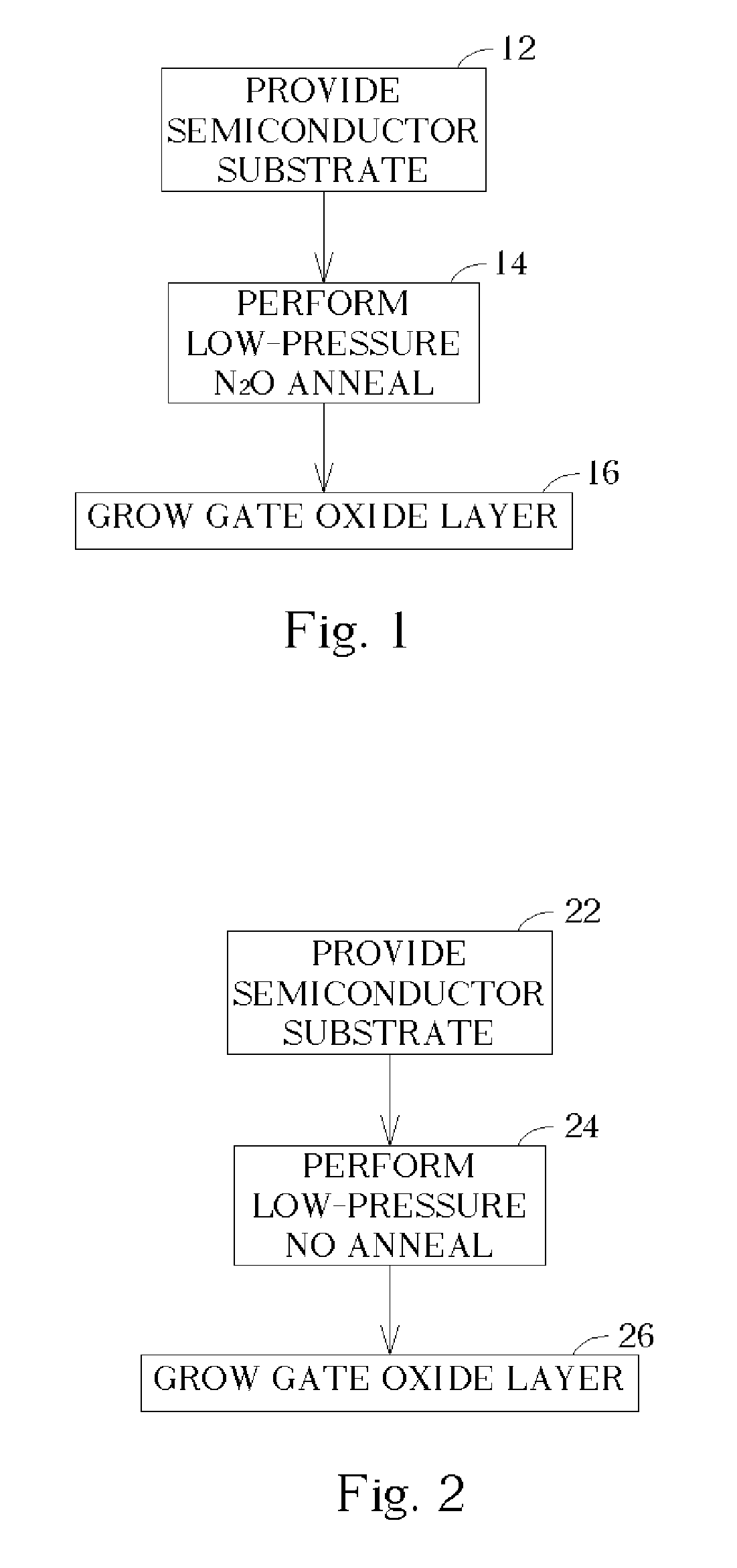

Method for growing a gate oxide layer on a silicon surface with preliminary n2o anneal

InactiveUS20050208775A1Excellent electrical propertiesImprove reliabilitySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingGate oxideSilicon

The present invention relates to a method for growing a robust, high-quality gate oxide layer on a silicon surface. The resultant gate oxide layer made according to the present invention can pass the standard 50K times 14V high-voltage stress testing. The preferred embodiment of this invention includes a step of preliminary low-pressure N2O annealing that is carried out in an air-tight chamber at a temperature of less than 1000° C., a pressure below 0.2 torr, and N2O flow rate of below 8000 sccm. The preliminary low-pressure N2O annealing of the silicon surface is performed prior to the growth of high-quality gate oxide layer. In another preferred embodiment, N2O may be replaced with NO.

Owner:NAN YA TECH

Method for manufacturing self-aligning graphene transistors by ion implantation oxidation

ActiveCN110137075AAvoid the problem of uncontrollable growthReduce parasitic resistanceTransistorSemiconductor/solid-state device manufacturingCvd grapheneFrequency characteristic

The invention discloses a method for manufacturing self-aligning graphene transistors by ion implantation oxidation. Self-aligning of transistors is realized by combining a composite metal film with the ion implantation technology. The oxidation of a gate medium and the alignment of transistor gate and source / drain are realized by means of region selective ion implantation based on the differencein oxidation performance between different metals and graphene. Parasitic resistance can be reduced, and the exposure of graphene is avoided. A high-quality gate medium can be prepared, and the frequency characteristic of graphene transistors can be enhanced.

Owner:南京中电芯谷高频器件产业技术研究院有限公司

High quality gate dielectric for semiconductor devices and method of formation thereof

Improved high quality gate dielectrics and methods of preparing such dielectrics are provided. Preferred dielectrics comprise a rare earth doped dielectric such as silicon dioxide or silicon oxynitride. In particular, cerium doped silicon dioxide shows an unexpectedly high charge-to-breakdown QBD, believed to be due to conversion of excess hot electron energy as photons, which reduces deleterious hot electron effects such as creation of traps or other damage. Rare earth doped dielectrics therefore have particular application as gate dielectrics or gate insulators for semiconductor devices such as floating gate MOSFETs, as used in as flash memories, which rely on electron injection and charge transfer and storage.

Owner:KIRSTEEN MGMT GRP

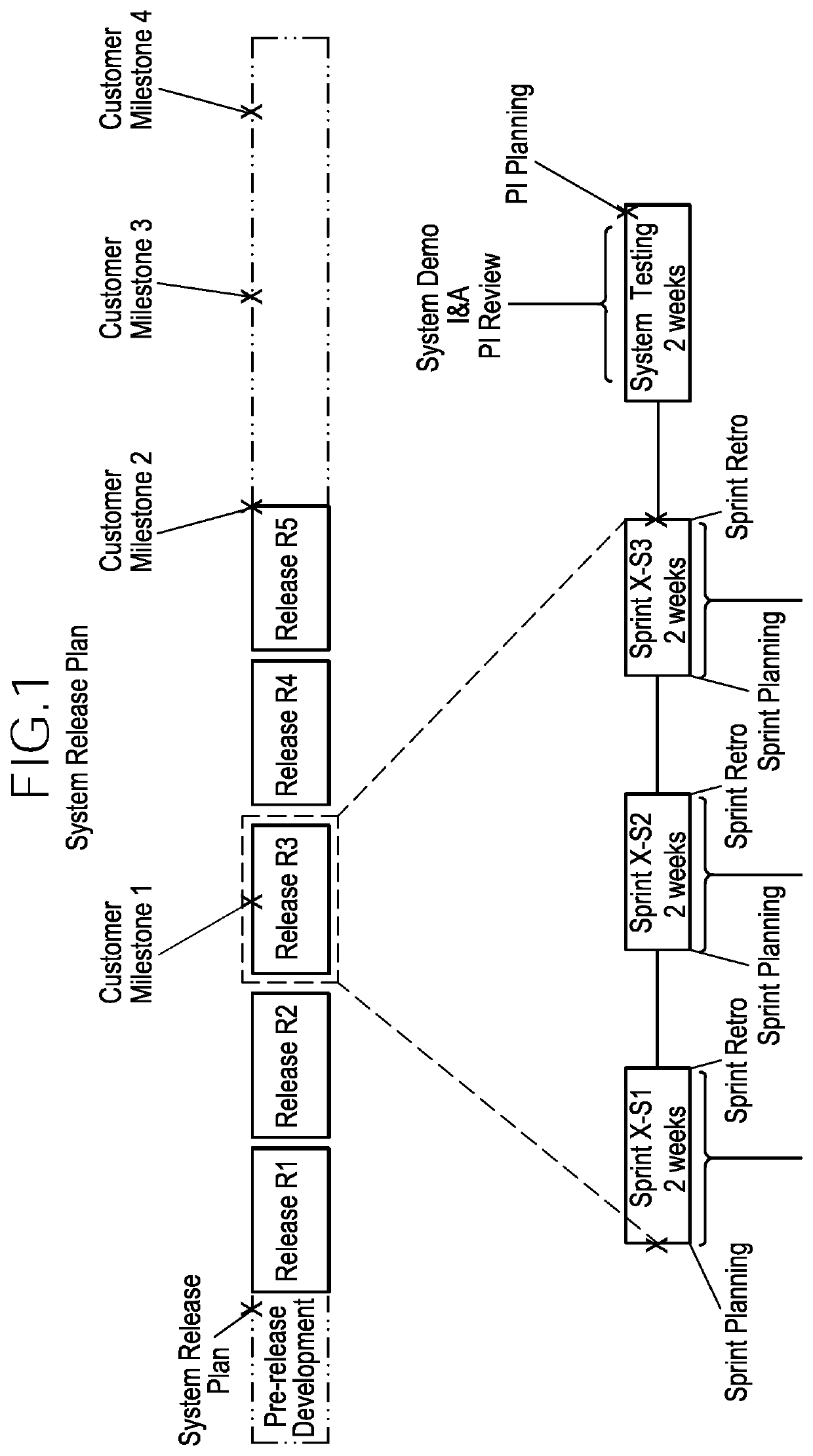

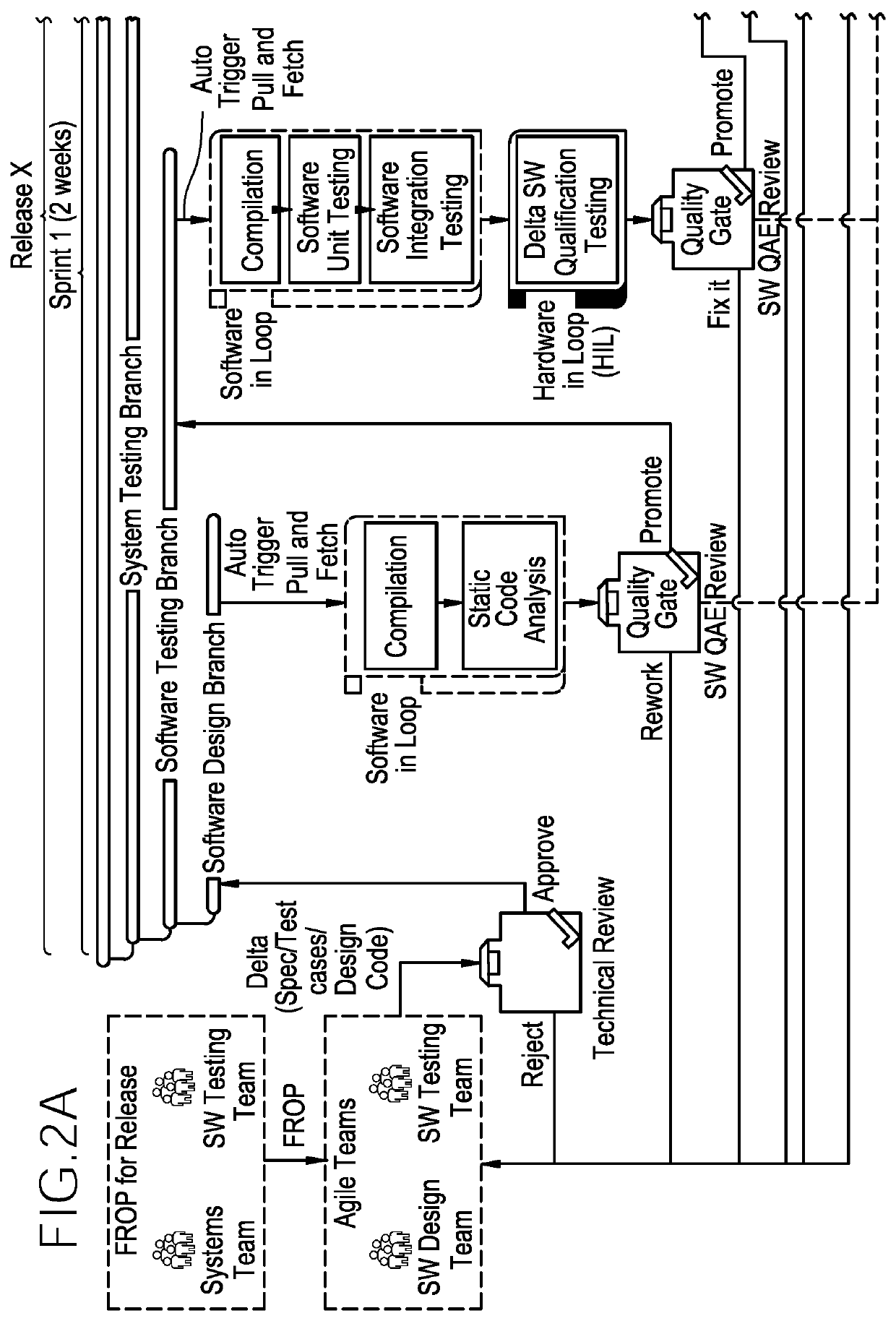

Agile, automotive spice, dev ops software development and release management system

PendingUS20220261240A1Promote collaborationVersion controlSoftware testing/debuggingCheck pointRelease management

An automated software development and release management system. The system includes and compounds multiple quality gates along various check points and includes Key Performance Indicators (KPIs) to monitor progress and measure software quality. The system puts members of the software development team in the same place in the development cycle, which allows better and more efficient collaboration. The system enables the review of work products (i.e., instead of merely the process).

Owner:N S INT LTD

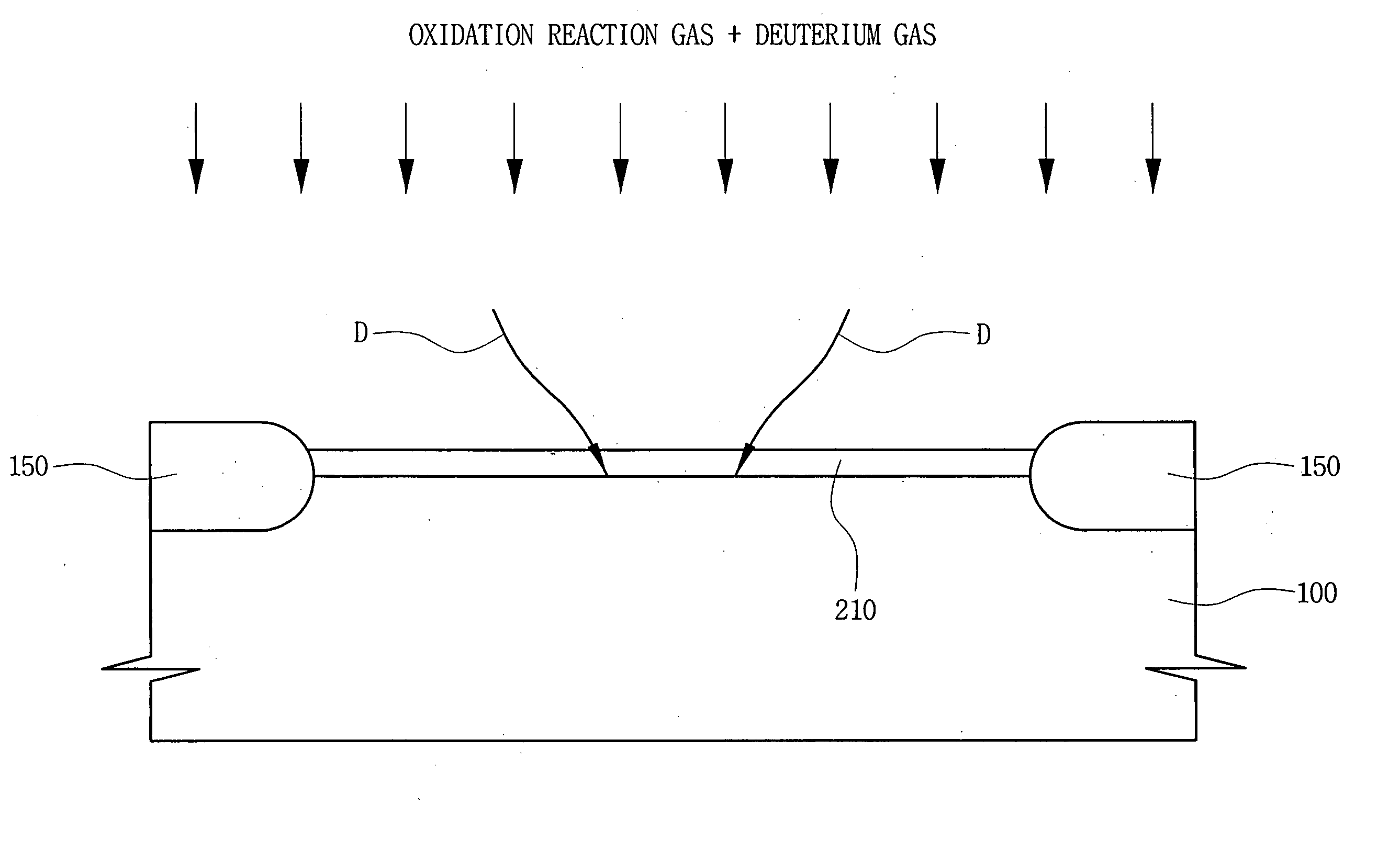

Method of forming a gate insulating layer of a semiconductor device using deuterium gas

InactiveUS20060134925A1Quality improvementImprove the immunitySemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEngineering

In an exemplary embodiment of the invention a method of forming a gate oxide layer of a semiconductor device uses deuterium gas. The method includes introducing a semiconductor substrate, and depositing an insulating layer on the semiconductor substrate by supplying an oxidation reaction gas and a deuterium gas to the semiconductor substrate. Thus, a high quality gate oxide layer can be formed and resistance to degradation from the hot carrier effect can be improved. Further, when the method is applied to a tunnel oxide layer process of a flash memory, problems such as an increasing dispersion of the threshold voltage can be mitigated.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor device and method of manufacturing the same

ActiveUS7449719B2Improve stateUniform thicknessTransistorSolid-state devicesCrystal orientationSubstrate surface

A gate insulating film is formed using a plasma on a three-dimensional silicon substrate surface having a plurality of crystal orientations. The plasma gate insulating film experiences no increase in interface state in any crystal orientations and has a uniform thickness even at corner portions of the three-dimensional structure. By forming a high-quality gate insulating film using a plasma, there can be obtained a semiconductor device having good characteristics.

Owner:TOKYO ELECTRON LIMITED ONE HALF 50 OF ALL RIGHT TITLE & INTEREST +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com