Multi-layer high quality gate dielectric for low-temperature poly-silicon tfts

A gate dielectric layer, dielectric layer technology, applied in the direction of coating, solid diffusion coating, metal material coating process, etc., can solve the problems of inapplicability, soft glass size, instability, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

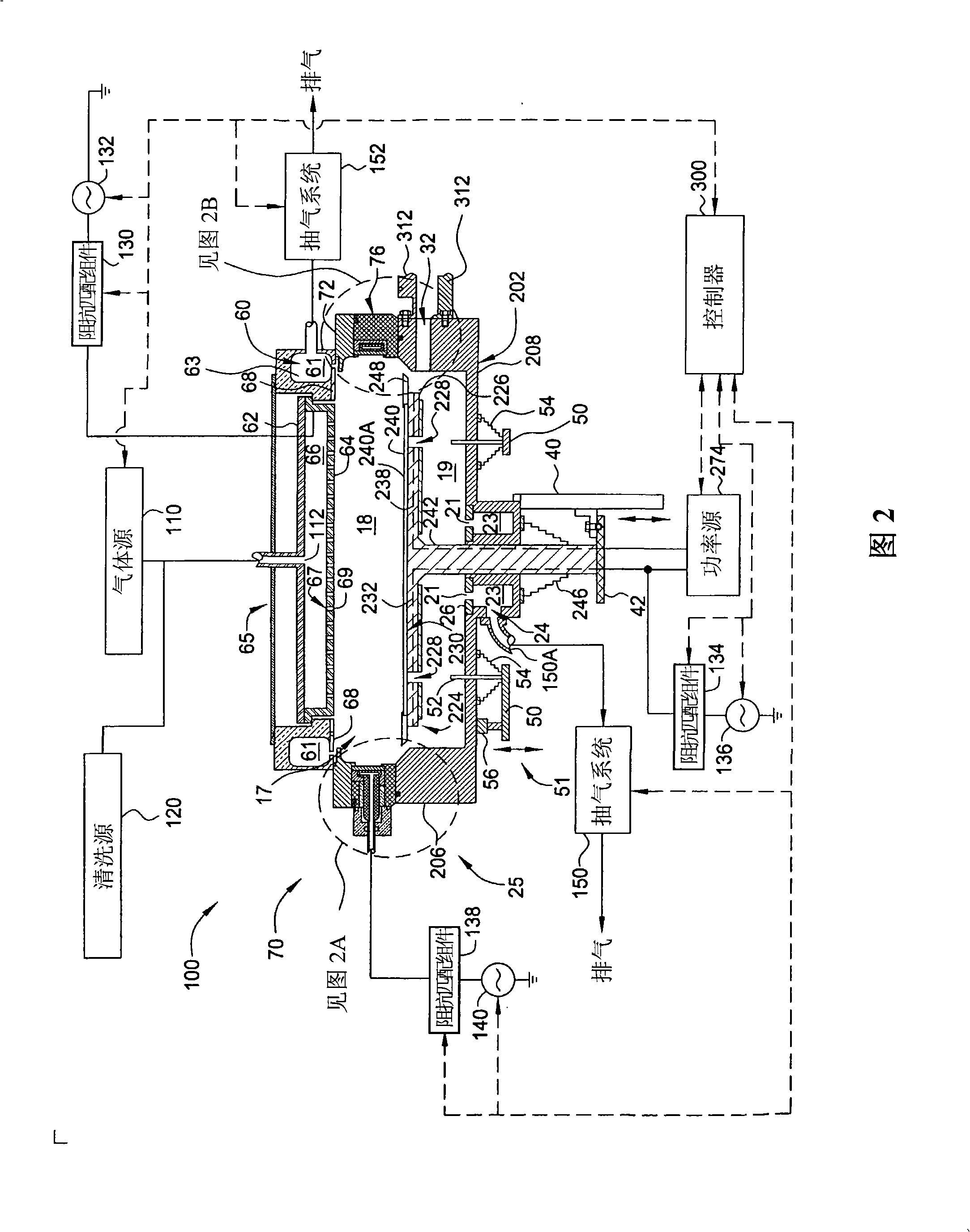

[0061] The invention provides a device and a method for treating the surface of a substrate by using inductively coupled high-density plasma. In general, the concepts of the present invention can be applied to flat panel display manufacturing processes, semiconductor manufacturing processes, solar cell manufacturing processes, or any other substrate manufacturing processes. The present invention will be described exemplarily with reference to a chemical vapor deposition system for processing large-area substrates, such as a plasma-enhanced chemical vapor deposition (PECVD) system available from AKT Corporation; AKT is located in Santa Maria, California. Monica's Applied Material company belongs to the unit. It should be understood, however, that the apparatus and method may also be applicable in other systems, including systems for processing circular substrates.

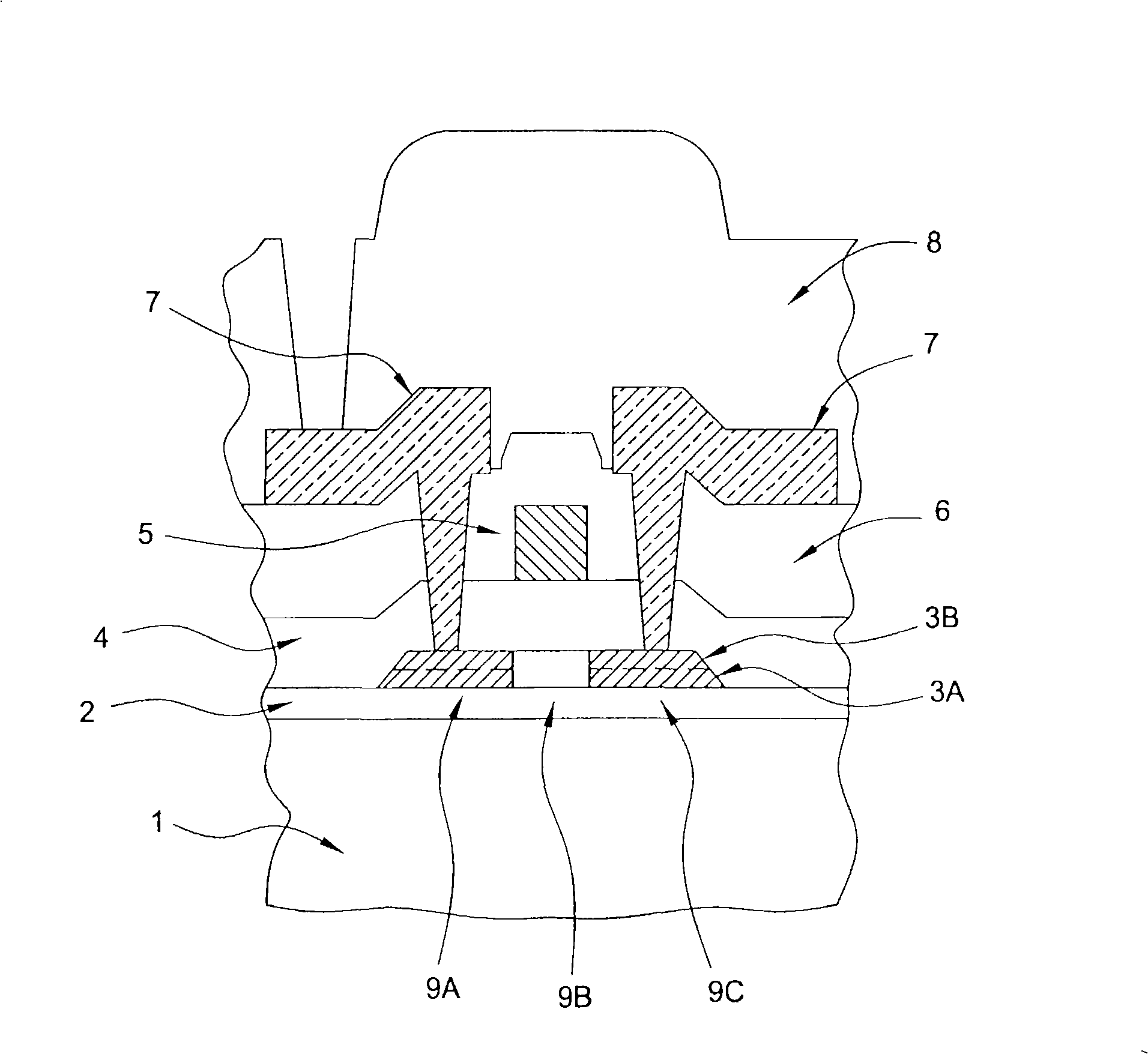

[0062] figure 1 A cross-sectional view showing a thin film transistor structure; the optically transparent subs...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com